ZHCS815A -MARCH 2012-REVISED MARCH 2012

## 具有可编程增益和偏移的单电源、自动置零传感器放大器

查询样品: PGA308-Q1

## 特性

- 符合汽车应用要求

- 具有符合 AEC-Q100 的下列结果:

RUMENTS

- 器件温度 **1** 级: **-40**<sup>℃</sup> 至 **+125**<sup>℃</sup> 的环境运行温度范围

- 器件人体模型 (HBM) 静电放电 (ESD) 分类等级 H2

- 器件充电器件模型 (CDM) ESD 分类等级 C3B

- 针对桥式传感器的数字校准

- 偏移选择: 粗略选择和精准选择

- 增益选择: 粗略选择和精准选择

- 桥式故障监控器

- 用于引线交换的输入复用器

- 过程量/欠程量限制

- D<sub>OUT</sub>/ V<sub>OUT</sub> 钳位功能

- 七插槽一次性可编程 (OTP) 内存

- 一线制数字通用异步收发器 (UART) 接口

- 运行电压: +2.7 V 至 +5.5 V

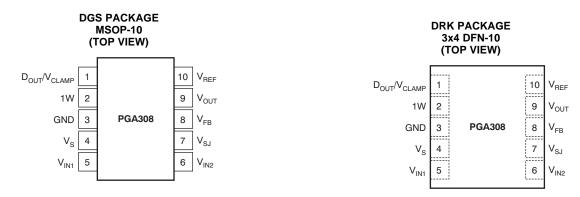

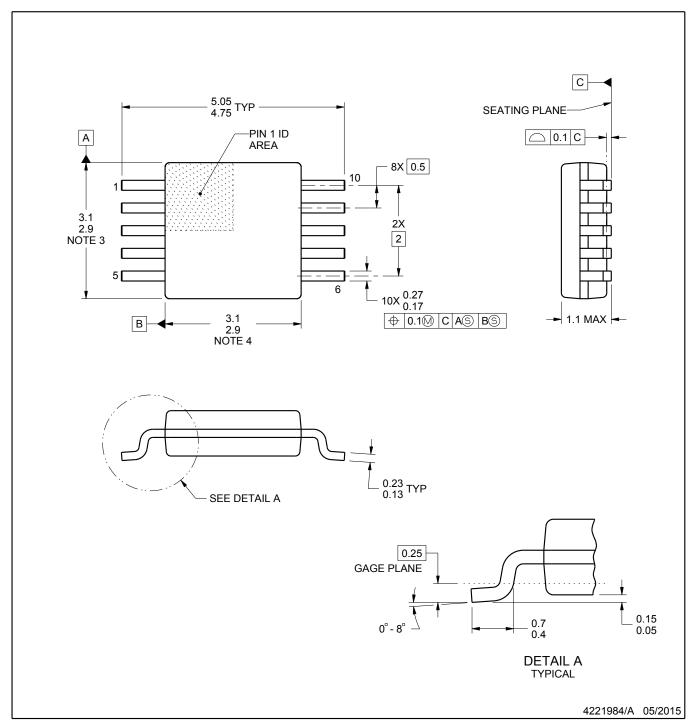

- MSOP-10 和 3mm x 4mm DFN-10 封装

## 应用范围

- 桥式传感器

- 远程 4-20 mA 发射器

- 应变、负载、衡器

- 车载传感器

## 评估工具

- PGA308EVM (硬件和软件)

- 校准和配置

- 传感器仿真

## 说明

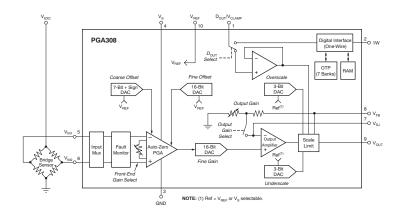

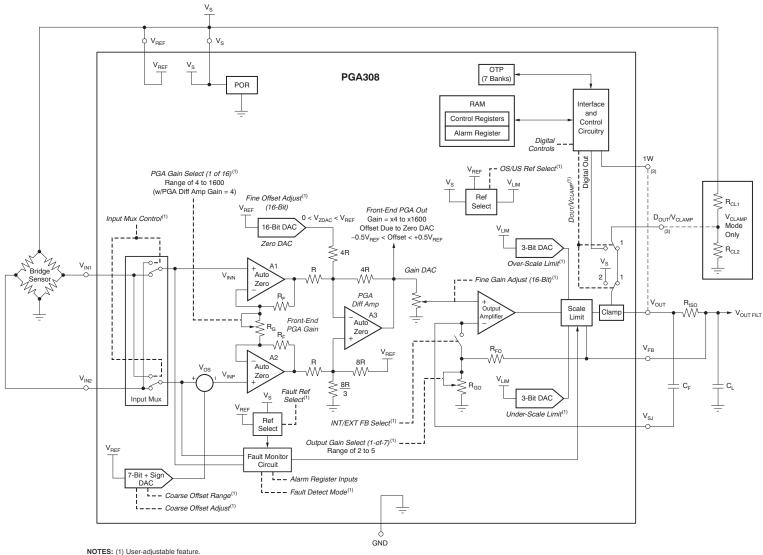

PGA308-Q1 是一款可编程模拟传感器信号调节器。 此模拟信号路径放大传感器信号并且为偏移和增益提供 数字校准。校准通过 1W 引脚、一个数字单线制 UART 兼容接口来完成。对于三端传感器模块,1W 可连接至 V<sub>OUT</sub> 并且此组件可通过 V<sub>OUT</sub> 引脚进行编 程。增益和偏移校准参数被存储在板载一次性可编程 (OTP) 内存的七个内存库中。加电复位 (POR) OTP 内存库总共可编程四次。

全模拟信号路径包含有一个 2 x 2 输入复用器 (mux) 以实现电子传感器引线交换、一个粗略偏移调整、一个自动置零可编程增益测量仪器放大器 (PGA)、一个精准增益调整、一个精准偏移调整、和一个可编程增益输出放大器。 故障监控电路检测并发出传感器烧断、过载、和系统故障状态信号。 过程量/欠程量限制为系统电平诊断提供额外了方法。 此两用 Dout/V<sub>CLAMP</sub> 引脚可被用作一个可编程数字输出或者一个 V<sub>OUT</sub> 过压钳位。

要获得详细的应用信息,请从网站 PGA308 用户指南 (SBOU069) 可供下载 www.ti.com。

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## PACKAGE/ORDERING INFORMATION(1)

| PRODUCT        | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | PACKAGE<br>MARKING |

|----------------|--------------|-----------------------|--------------------|

| PGA308AQDGSRQ1 | MSOP-10      | DGS                   | JAAQ               |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range, unless otherwise noted.

|                                                                                                    | PARAMETER                                                                                                               | PGA308-Q1                 | UNIT |  |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------|------|--|

| Supply Voltage, \                                                                                  | / <sub>S</sub>                                                                                                          | +5.5                      | V    |  |

| D <sub>OUT</sub> /V <sub>CLAMP</sub> Out                                                           | put Current Limit                                                                                                       | ±10 m                     |      |  |

|                                                                                                    | Input Current                                                                                                           | -10 to +10                | mA   |  |

|                                                                                                    | V <sub>IN1</sub> , V <sub>IN2</sub> , V <sub>REF</sub> , 1W, D <sub>OUT</sub> /V <sub>CLAMP</sub> , V <sub>SJ</sub> (2) | GND $-0.3$ to $V_S + 0.3$ | V    |  |

| Pin Protection                                                                                     | V <sub>FB</sub> Terminal Voltage                                                                                        | -30 to 30                 | V    |  |

|                                                                                                    | V <sub>FB</sub> Terminal Current                                                                                        | -10 to 10                 | mA   |  |

|                                                                                                    | V <sub>OUT</sub>                                                                                                        | -160 to 160               | mA   |  |

| Operating Tempe                                                                                    | erature Range                                                                                                           | -40 to +150               | °C   |  |

| Storage Tempera                                                                                    | ature Range                                                                                                             | -55 to +150               | °C   |  |

| Junction Tempera                                                                                   | ature                                                                                                                   | +165                      | °C   |  |

| Supply Voltage, V DOUT/VCLAMP Out Pin Protection Operating Temper Storage Tempera Junction Tempera | Human Body Model (HBM) AEC-Q100 Classification Level H2                                                                 | 2                         | kV   |  |

| ESD Kating                                                                                         | Charged Device Model (CDM) AEC-Q100 Classification Level C3B                                                            | 750                       | V    |  |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

<sup>(2)</sup> Terminals are diode-clamped to the power-supply rails, V<sub>S</sub> and GND. Limit current to 10mA or less.

### THERMAL INFORMATION

|                  |                                                             | PGA308-Q1 |      |

|------------------|-------------------------------------------------------------|-----------|------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | DGS       | UNIT |

|                  |                                                             | 10 PINS   |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance (2)                  | 154.6     |      |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 48.3      |      |

| $\theta_{JB}$    | Junction-to-board thermal resistance <sup>(4)</sup>         | 75.1      | °C/M |

| ΨЈТ              | Junction-to-top characterization parameter (5)              | 3.6       | °C/W |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(6)</sup> | 73.7      |      |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | n/a       |      |

- For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted

- from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). (6) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific

- JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## **ELECTRICAL CHARACTERISTICS**

|                                                                                                                  |                                                                                                                                                                                                |      | PGA308-Q1 <sup>(1)</sup> |                          |                    |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------|--------------------------|--------------------|

| PARAMETER                                                                                                        | CONDITIONS                                                                                                                                                                                     | MIN  | TYP                      | MAX                      | UNIT               |

| V <sub>OUT</sub> /V <sub>IN</sub> Differential Signal Gains <sup>(2)</sup><br>(Front-End PGA + Output Amplifier) | Front-End PGA gains (G <sub>F</sub> ): 4, 6, 8, 12, 16, 32, 64, 100, 200, 400, 480, 600, 800, 960, 1200, 1600  Output Amplifier gains: 2, 2.4, 3, 3.6, 4, 4.5, 6  Fine Gain Adjust = 0.33 to 1 | 2.67 |                          | 9600                     | V/V                |

| V <sub>OUT</sub> /V <sub>IN</sub> Slew Rate<br>(Front-End PGA + Output Amplifier)                                | CMP_SEL [CFG1 register] = 0                                                                                                                                                                    |      | 0.6                      |                          | V/µs               |

|                                                                                                                  | CMP_SEL [CFG1 register] = 1                                                                                                                                                                    |      | 0.3                      |                          | V/µs               |

| V <sub>OUT</sub> /V <sub>IN</sub> Settling Time (0.01%FSR)<br>(Front-End PGA + Output Amplifier)                 | $V_{OUT}/V_{IN}$ differential gain = 8,<br>$V_{OUT}$ = +0.5V to +4.5V step, comp off, no capacitive load                                                                                       |      | 13                       |                          | μs                 |

|                                                                                                                  | $V_{OUT}/V_{IN}$ differential gain = 200, $V_{OUT}$ = +0.5V to +4.5V step, comp off, no capacitive load                                                                                        |      | 15                       |                          | μs                 |

| FRONT-END PGA                                                                                                    |                                                                                                                                                                                                |      |                          |                          |                    |

| Auto-Zero Internal Frequency                                                                                     |                                                                                                                                                                                                |      | 40                       |                          | kHz                |

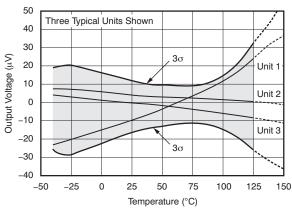

| Offset Voltage (RTI)(3)                                                                                          | Coarse Offset Adjust disabled                                                                                                                                                                  |      | ±5                       | ±40                      | μV                 |

| vs Temperature                                                                                                   | Coarse Offset Adjust disabled                                                                                                                                                                  |      | ±0.2                     |                          | μV/°C              |

| vs Supply Voltage, V <sub>S</sub>                                                                                | Coarse Offset Adjust disabled                                                                                                                                                                  |      | 2 + 150/G <sub>F</sub>   | 10 + 1000/G <sub>F</sub> | μV/V               |

| vs Common-Mode Voltage                                                                                           | $G_F$ = Front-End PGA gain,<br>Coarse Offset Adjust disabled                                                                                                                                   |      | 1 + 250/G <sub>F</sub>   | 10 + 2000/G <sub>F</sub> | μV/V               |

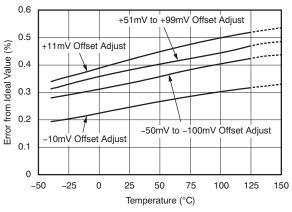

| Offset Voltage Programming Range (RTI) <sup>(3)</sup>                                                            | Coarse Offset Adjust enabled,<br>Coarse Offset Adjust controls offset                                                                                                                          | -100 |                          | 100                      | mV                 |

| vs Temperature                                                                                                   | Coarse Offset Adjust enabled                                                                                                                                                                   |      | ±0.2                     |                          | μV/°C              |

| vs Supply Voltage, V <sub>S</sub>                                                                                | Coarse Offset Adjust enabled                                                                                                                                                                   |      | 2 + 150/G <sub>F</sub>   |                          | μV/V               |

| vs Common-Mode Voltage                                                                                           | $G_F$ = Front-End PGA gain,<br>Coarse Offset Adjust enabled                                                                                                                                    |      | 1 + 250/G <sub>F</sub>   |                          | μV/V               |

| Linear Input Voltage Range <sup>(4)</sup>                                                                        |                                                                                                                                                                                                | 0.2  |                          | V <sub>S</sub> - 1.4     | V                  |

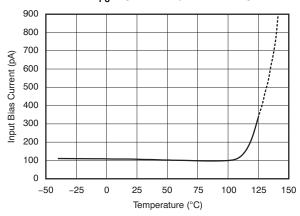

| Input Bias Current                                                                                               |                                                                                                                                                                                                |      | ±0.3                     | ±1.5                     | nA                 |

| vs Temperature                                                                                                   |                                                                                                                                                                                                |      | 10                       |                          | pA/°C              |

| Input Offset Current                                                                                             |                                                                                                                                                                                                |      | ±0.1                     | ±1.5                     | nA                 |

| vs Temperature                                                                                                   |                                                                                                                                                                                                |      | 10                       |                          | pA/°C              |

| Input Impedance: Differential                                                                                    |                                                                                                                                                                                                |      | 30    6                  |                          | GΩ ∥ pF            |

| Input Impedance: Common-Mode                                                                                     |                                                                                                                                                                                                |      | 50    20                 |                          | GΩ ∥ pF            |

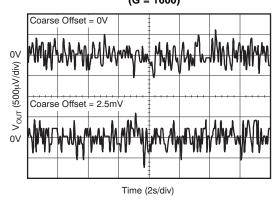

| Input Voltage Noise                                                                                              | RTI, dc to 10Hz, $G_F = 100$ , $R_S = 0\Omega$                                                                                                                                                 |      | 1.2                      |                          | $\mu V_{PP}$       |

| Input Voltage Noise Density                                                                                      | RTI, voltage noise density, f = 1kHz, Coarse Offset Adjust = 0V                                                                                                                                |      | 50                       |                          | nV/√Hz             |

|                                                                                                                  | RTI, voltage noise density, f = 1kHz,<br>Coarse Offset Adjust = 100mV                                                                                                                          |      | 80                       |                          | nV/√ <del>Hz</del> |

| Input EMI Filter Frequency PGA Gain <sup>(5)</sup>                                                               | $f_{\rm 3dB}$<br>Input EMI filter to GND, $V_{\rm IN1}$ and $V_{\rm IN2}$                                                                                                                      |      | 40                       |                          | MHz                |

| Gain Range Steps                                                                                                 | 4, 6, 8, 12, 16, 32, 64, 100, 200, 400, 480, 600, 800, 960, 1200, 1600                                                                                                                         | 4    |                          | 1600                     | V/V                |

| Initial Gain Error                                                                                               | G <sub>F</sub> ≤ 16                                                                                                                                                                            |      | ±0.03                    | ±0.25                    | %                  |

|                                                                                                                  | 32 ≤ G <sub>F</sub> ≤ 480                                                                                                                                                                      |      | ±0.1                     | ±0.4                     | %                  |

|                                                                                                                  | 600 ≤ G <sub>F</sub> ≤ 1600                                                                                                                                                                    |      | ±0.3                     | ±1                       | %                  |

| vs Temperature                                                                                                   |                                                                                                                                                                                                |      | 6                        |                          | ppm/°C             |

| Output Voltage Range                                                                                             |                                                                                                                                                                                                | 0.05 |                          | V <sub>S</sub> - 0.05    | V                  |

| Bandwidth                                                                                                        | G <sub>F</sub> = 4                                                                                                                                                                             |      | 400                      |                          | kHz                |

|                                                                                                                  | G <sub>F</sub> = 1600                                                                                                                                                                          |      | 10                       |                          | kHz                |

- External Sensor Output Sensitivity with condition  $V_S = V_{REF} = V_{CLAMP} = +5V$  has a range of 0.08mV/V to 296mV/V. This is based on a bridge sensor excitation voltage of +5V and PGA308-Q1 output voltage span of 4V. Individual applications must consider noise, smallsignal bandwidth, and required system error to assess if the PGA308-Q1 will work for a given sensor sensitivity.

- PGA308-Q1 total differential gain from input  $(V_{IN1} V_{IN2})$  to output  $(V_{OUT})$ :  $V_{OUT} / (V_{IN1} V_{IN2}) = (PGA gain) \times (output amplifier gain) \times (output amp$ (fine gain adjust) with output amplifier internal gains used.

- RTI = Referred-to-input.

- Linear input range is the allowed min/max voltage on the V<sub>IN1</sub> and V<sub>IN2</sub> pins for the front-end PGA to continue to operate in a linear region. The allowed common-mode and differential voltage depends on gain and offset settings. Refer to the PGA308 User's Guide (SBOU069), for more information.

- I<sub>REF</sub> current load is typically 100μA while in Shutdown mode. Although the output amplifier is disabled in Shutdown mode, RFO and RGO (180kΩ typical total) remain connected in series between V<sub>FB</sub> and GND while in Shutdown mode. See Figure 37, Detailed Block Diagram, for more information.

www.ti.com.cn

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                     |                 |                                                                 |                      |       |                       |        |

|---------------------------------------------------------------|-----------------|-----------------------------------------------------------------|----------------------|-------|-----------------------|--------|

| PARAMETER                                                     |                 | CONDITIONS                                                      | MIN                  | TYP   | MAX                   | UNIT   |

| Coarse Offset Adjust<br>(RTI of Front-End PGA) <sup>(6)</sup> |                 |                                                                 |                      |       |                       |        |

| Range                                                         |                 | $V_{REF} = +5V$                                                 | -100                 |       | +100                  | mV     |

| Resolution                                                    |                 | 7 bit + sign, $V_{REF} = +5V$                                   |                      | 1     |                       | mV     |

| PSRR                                                          |                 |                                                                 |                      | 2     |                       | μV/V   |

| CMRR                                                          |                 |                                                                 |                      | 1     |                       | μV/V   |

| Drift                                                         |                 | Coarse Offset Adjust = 100mV                                    |                      | 1.2   |                       | μV/°C  |

| Fine Offset Adjust (Zero DAC)                                 |                 |                                                                 |                      |       |                       |        |

| Programming Range                                             |                 | RTO of Front-End PGA                                            | -0.5V <sub>REF</sub> |       | +0.5V <sub>REF</sub>  | V      |

| Output Voltage Range                                          |                 |                                                                 | 0.1                  |       | V <sub>S</sub> - 0.1  | V      |

| Resolution                                                    |                 | 65,536 steps, 16-bit DAC, $V_{REF} = +5V$                       |                      | 76    |                       | μV     |

| Integral Nonlinearity                                         |                 |                                                                 |                      | ±6    |                       | LSB    |

| Differential Nonlinearity                                     |                 |                                                                 |                      | ±0.5  |                       | LSB    |

| Gain Error                                                    |                 |                                                                 |                      | ±0.5  |                       | %      |

| Gain Error Drift                                              |                 |                                                                 |                      | ±4    |                       | ppm/°C |

| Offset                                                        |                 |                                                                 |                      | ±4    |                       | mV     |

| Offset Drift                                                  |                 |                                                                 |                      | ±10   |                       | μV/°C  |

| PSRR                                                          |                 |                                                                 |                      | ±200  |                       | μV/V   |

| Output Amplifier                                              |                 |                                                                 |                      |       |                       |        |

| Output Fine Gain Adjust (Gain DAC)                            |                 |                                                                 |                      |       |                       |        |

| Range                                                         |                 |                                                                 | 0.33                 |       | 1                     | V/V    |

| Resolution                                                    |                 | 65,536 steps, 16-bit DAC                                        |                      | 10    |                       | μV/V   |

| Integral Nonlinearity                                         |                 |                                                                 |                      | ±6    |                       | LSB    |

| Differential Nonlinearity                                     |                 |                                                                 |                      | ±0.5  |                       | LSB    |

| Gain Error                                                    |                 |                                                                 |                      |       | ±0.2                  | %      |

| Gain Drift                                                    |                 |                                                                 |                      | 3     |                       | ppm/°C |

| Output Amplifier                                              |                 |                                                                 |                      |       |                       |        |

| Offset Voltage (RTI of Output Amplifier) <sup>(6)</sup>       |                 |                                                                 |                      | ±3    |                       | mV     |

| vs Temperature                                                |                 |                                                                 |                      | ±5    |                       | μV/°C  |

| vs Supply Voltage, V <sub>S</sub>                             |                 |                                                                 |                      | ±100  |                       | μV/V   |

| Common-Mode Input Range                                       |                 |                                                                 | 0                    |       | V <sub>S</sub> – 1.5  | V      |

| Input Bias Current                                            |                 |                                                                 |                      | ±100  |                       | pA     |

| Amplifier Internal Gain                                       |                 |                                                                 |                      |       |                       |        |

| Gain Range Steps                                              |                 | 2, 2.4, 3, 3.6, 4, 4.5, 6                                       | 2                    |       | 6                     | V/V    |

| Initial Gain Error                                            |                 |                                                                 |                      | ±0.05 | ±0.25                 | %      |

| vs Temperature                                                |                 |                                                                 |                      | ±1    |                       | ppm/°C |

| Output Voltage Range                                          |                 | $I_{OUT} = 0.5 \text{mA}^{(7)}$                                 | 0.03                 |       | V <sub>S</sub> - 0.06 | V      |

|                                                               |                 | $I_{OUT} = 4mA^{(7)}$                                           | 0.1                  |       | V <sub>S</sub> - 0.1  | V      |

| Output Short-Circuit Current                                  | I <sub>sc</sub> | Sourcing/sinking                                                | 10                   |       |                       | mA     |

| Open-Loop Gain at 0.1Hz                                       | -30             | <del> </del>                                                    |                      | 106   |                       | dB     |

| Gain-Bandwidth Product                                        |                 |                                                                 |                      | 2     |                       | MHz    |

| Phase Margin                                                  |                 | Gain = 2, C <sub>L</sub> = 200pF                                |                      | 45    |                       | deg    |

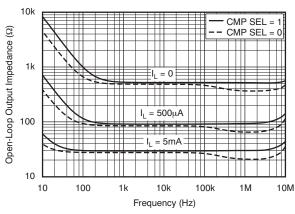

| Output Resistance                                             | Ro              | AC small-signal, open-loop, f = 1MHz, I <sub>OUT</sub> = 0, see |                      | 500   |                       | Ω      |

| Salpai Noticiano                                              | 1.0             | Figure 28                                                       |                      | 300   |                       | 32     |

RTI = Referred-to-input. Unless limited by the over/under-scale setting, or  $V_{CLAMP}$  pin.

| PARAMETER                                                      |                 |                                                                               |                           | PGA308-Q1 <sup>(1)</sup>           |                           |        |  |  |

|----------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------|---------------------------|------------------------------------|---------------------------|--------|--|--|

| PARAMETER                                                      |                 | CONDITIONS                                                                    | MIN                       | TYP                                | MAX                       | UNIT   |  |  |

| Over- and Under-Scale Limits                                   |                 |                                                                               |                           |                                    |                           |        |  |  |

| Over-Scale Thresholds                                          |                 | $V_{LIM} = 4V$ , register-selectable ratio of $V_{LIM}$                       |                           |                                    |                           |        |  |  |

|                                                                | OS0             | HL[2:0] (CFG1 register D[5:3]) = 000                                          | 0.97                      | 0.9805                             | 0.99                      | V/V    |  |  |

|                                                                | OS1             | HL[2:0] (CFG1 register D[5:3]) = 001                                          | 0.9588                    | 0.9688                             | 0.9788                    | V/V    |  |  |

|                                                                | OS2             | HL[2:0] (CFG1 register D[5:3]) = 010                                          | 0.9509                    | 0.9609                             | 0.9709                    | V/V    |  |  |

|                                                                | OS3             | HL[2:0] (CFG1 register D[5:3]) = 011                                          | 0.9392                    | 0.9492                             | 0.9492                    | V/V    |  |  |

|                                                                | OS4             | HL[2:0] (CFG1 register D[5:3]) = 100                                          | 0.8416                    | 0.8516                             | 0.8616                    | V/V    |  |  |

|                                                                | OS5             | HL[2:0] (CFG1 register D[5:3]) = 101                                          | 0.7673                    | 0.7773                             | 0.7873                    | V/V    |  |  |

|                                                                | OS6             | HL[2:0] (CFG1 register D[5:3]) = 110                                          | 0.6189                    | 0.6289                             | 0.6389                    | V/V    |  |  |

|                                                                | OS7             | HL[2:0] (CFG1 register D[5:3]) = 111                                          | 0.5603                    | 0.5703                             | 0.5803                    | V/V    |  |  |

| Over-Scale Threshold Tempco                                    |                 |                                                                               |                           | ±3                                 |                           | ppm/°C |  |  |

| Over-Scale Amplifier Offset                                    |                 |                                                                               |                           | ±9                                 |                           | mV     |  |  |

| Over-Scale Amplifier Offset Drift                              |                 |                                                                               |                           | ±10                                |                           | μV/°C  |  |  |

| Jnder-Scale Thresholds                                         |                 | $V_{LIM}$ = 5V, register-selectable ratio of $V_{LIM}$                        |                           |                                    |                           |        |  |  |

|                                                                | US7             | LL[2:0] (CFG1 register D[2:0]) = 111                                          | 0.0487                    | 0.0547                             | 0.0607                    | V/V    |  |  |

|                                                                | US6             | LL[2:0] (CFG1 register D[2:0]) = 110                                          | 0.04478                   | 0.05078                            | 0.05678                   | V/V    |  |  |

|                                                                | US5             | LL[2:0] (CFG1 register D[2:0]) = 101                                          | 0.04088                   | 0.04688                            | 0.05288                   | V/V    |  |  |

|                                                                | US4             | LL[2:0] (CFG1 register D[2:0]) = 100                                          | 0.03306                   | 0.03906                            | 0.04506                   | V/V    |  |  |

|                                                                | US3             | LL[2:0] (CFG1 register D[2:0]) = 011                                          | 0.02916                   | 0.03516                            | 0.04116                   | V/V    |  |  |

|                                                                | US2             | LL[2:0] (CFG1 register D[2:0]) = 010                                          | 0.02525                   | 0.03125                            | 0.03725                   | V/V    |  |  |

|                                                                | US1             | LL[2:0] (CFG1 register D[2:0]) = 001                                          | 0.01743                   | 0.02343                            | 0.02943                   | V/V    |  |  |

|                                                                | US0             | LL[2:0] (CFG1 register D[2:0]) = 000                                          | 0.01353                   | 0.01953                            | 0.02553                   | V/V    |  |  |

| Jnder-Scale Threshold Tempco                                   |                 |                                                                               |                           | ±3                                 |                           | ppm/°C |  |  |

| Inder-Scale Amplifier Offset                                   |                 |                                                                               |                           | ±9                                 |                           | mV     |  |  |

| Jnder-Scale Amplifier Offset Drift                             |                 |                                                                               |                           | ±10                                |                           | μV/°C  |  |  |

| Output Voltage Clamp                                           |                 |                                                                               |                           |                                    |                           |        |  |  |

| nput Voltage Range                                             |                 | $V_{CLAMP} \leq V_S, V_S = +5V$                                               | 1.25                      |                                    | 4.95                      | V      |  |  |

| nput Bias Current                                              |                 |                                                                               |                           | ±60                                |                           | nA     |  |  |

| / <sub>OUT</sub> Clamp Point                                   |                 |                                                                               | V <sub>CLAMP</sub> - 0.05 | V <sub>CLAMP</sub>                 | V <sub>CLAMP</sub> + 0.05 | V      |  |  |

| Fault Monitor Circuit                                          |                 |                                                                               |                           |                                    | 52                        |        |  |  |

| External Comparators)                                          |                 |                                                                               |                           |                                    |                           |        |  |  |

| NP_HI Comparator Threshold<br>NN_HI Comparator Threshold       |                 | Fault Detect Mode Select = 0 (bridge fault); see CFG1 register                | Smaller                   | of (V <sub>S</sub> – 1.2) or (0    | .65V <sub>FLT</sub> )     | V      |  |  |

| NP_LO Comparator Threshold<br>NN_LO Comparator Threshold       |                 | Fault Detect Mode Select = 0 (bridge fault); see CFG1 register                | Large                     | er of (0.1V) or (0.35              | 5V <sub>FLT</sub> )       | V      |  |  |

| Fault Monitor Reference                                        | $V_{FLT}$       | Fault Monitor Reference; see CFG1 register, FLT REF bit sets $V_{\text{FLT}}$ |                           | $V_{\text{S}}$ or $V_{\text{REF}}$ |                           | V      |  |  |

| NP_HI Comparator Threshold<br>NN_HI Comparator Threshold       |                 | Fault Detect Mode Select = 1 (common-mode fault); see<br>CFG1 register        |                           | V <sub>S</sub> – 1.2               |                           | V      |  |  |

| NP_LO Comparator Threshold<br>NN_LO Comparator Threshold       |                 | Fault Detect Mode Select = 1 (common-mode fault); see<br>CFG1 register        | 70                        | 100                                | 130                       | mV     |  |  |

| Comparator Hysteresis                                          |                 |                                                                               |                           | 7                                  |                           | mV     |  |  |

| Comparator Input Offset Voltage                                |                 |                                                                               |                           | ±10                                |                           | mV     |  |  |

| Fault Monitor Circuit<br>Internal Comparators)                 |                 |                                                                               |                           |                                    |                           |        |  |  |

| A1SAT_LO Comparator Threshold<br>A2SAT_LO Comparator Threshold |                 | Threshold is amplifier negative saturation voltage                            |                           | 100                                |                           | mV     |  |  |

| A1SAT_HI Comparator Threshold<br>A2SAT_HI Comparator Threshold |                 | Threshold is amplifier positive saturation voltage                            |                           | V <sub>S</sub> – 0.12              |                           | V      |  |  |

| A3SAT_LO Comparator Threshold                                  |                 | Threshold is amplifier negative saturation voltage                            |                           | 50                                 |                           | mV     |  |  |

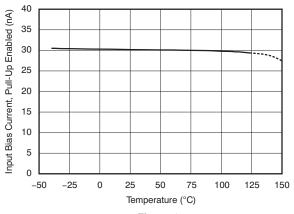

| / <sub>IN1</sub> , V <sub>IN2</sub> Pull-up Current Sources    |                 | -                                                                             |                           |                                    |                           |        |  |  |

| Pull-Up Current Source                                         | I <sub>PU</sub> | Register-selectable                                                           | 15                        | 30                                 | 45                        | nA     |  |  |

| Current Source Matching                                        |                 |                                                                               |                           | ±1.5                               | ±7                        | nA     |  |  |

| Current Source Tempco                                          |                 |                                                                               |                           | ±5                                 |                           | pA/°C  |  |  |

www.ti.com.cn

## **ELECTRICAL CHARACTERISTICS (continued)**

|                                        |                    |                                                                                                                                                |             | PGA308-Q1 <sup>(1)</sup> |      |          |

|----------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------|------|----------|

| PARAMETER                              |                    | CONDITIONS                                                                                                                                     | MIN         | TYP                      | MAX  | UNIT     |

| $V_{REF}$                              |                    |                                                                                                                                                |             |                          |      |          |

| Input Range                            |                    |                                                                                                                                                | 1.8         |                          | Vs   | V        |

| Input Resistance                       |                    |                                                                                                                                                |             | 43                       |      | kΩ       |

| Digital Interface                      |                    |                                                                                                                                                |             |                          |      |          |

| One-Wire                               |                    | Serial speed baud rate                                                                                                                         | 4.8k        |                          | 114k | bits/s   |

| Logic Levels                           |                    |                                                                                                                                                |             |                          |      |          |

| Logic Levels (1W pin)                  |                    | Low                                                                                                                                            |             |                          | 0.8  | V        |

|                                        |                    | High                                                                                                                                           | 2.0         |                          |      | V        |

|                                        |                    | Hysteresis                                                                                                                                     |             | 100                      |      | mV       |

| Output Low Level (1W pin)              |                    | Open drain, I <sub>SINK</sub> = 4mA                                                                                                            |             |                          | 0.5  | V        |

| Output Levels ( $D_{OUT}/V_{CLAMP}$ )  |                    | Low, D <sub>OUT</sub> mode selected, I <sub>SINK</sub> = 4mA and V <sub>S</sub> = +4.5V, or I <sub>SINK</sub> = 2mA and V <sub>S</sub> = +2.7V |             |                          | 0.4  | V        |

|                                        |                    | High, $D_{OUT}$ mode selected, $I_{SOURCE}$ = 4mA and $V_S$ = +4.5V, or $I_{SOURCE}$ = 2mA and $V_S$ = +2.7V                                   | $V_S - 0.4$ |                          |      | V        |

| POWER SUPPLY                           |                    | ISOURCE - ZITIA dild VS - +2.7 V                                                                                                               |             |                          |      |          |

| Supply Voltage                         | Vs                 |                                                                                                                                                | 2.7         |                          | 5.5  | V        |

| OTP Program Voltage                    | V <sub>S-PGM</sub> |                                                                                                                                                | 4.5         |                          | 5.5  | v        |

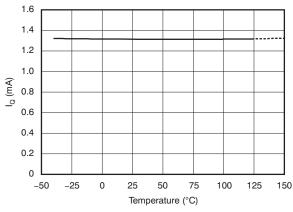

| Quiescent Current                      | V S-PGM            | $V_S = +5V$ , does not include $I_{REF}$                                                                                                       | 4.0         | 1.3                      | 1.6  | mA       |

| Shutdown Supply Current                | I <sub>SHDN</sub>  | $V_S = +5V$ , does not include $I_{REF}$ (8)                                                                                                   |             | 260                      | 1.0  | μA       |

| POWER-ON RESET (POR)                   | SHDN               | vs = 10v, does not mode 1 <sub>REF</sub>                                                                                                       |             | 200                      |      | μπ       |

| Power-Up Threshold                     |                    | V <sub>S</sub> rising                                                                                                                          |             | 2.1                      |      | V        |

| Power-Down Threshold                   |                    | V <sub>S</sub> falling                                                                                                                         |             | 1.7                      |      | v        |

| TEMPERATURE RANGE                      |                    | v S running                                                                                                                                    |             | 1                        |      | <u> </u> |

| Specified Performance Range            |                    |                                                                                                                                                | -40         |                          | +125 | °C       |

| Operational-Degraded Performance Range |                    |                                                                                                                                                | -40         |                          | +150 | °C       |

| Thermal Resistance                     |                    |                                                                                                                                                |             |                          |      |          |

| MSOP-10, Junction-to-Ambient           | $\theta_{JA}$      |                                                                                                                                                |             | 150                      |      | °C/W     |

$I_{REF}$  current load is typically 100μA while in Shutdown mode. Although the output amplifier is disabled in Shutdown mode, RFO and RGO (180k $\Omega$  typical total) remain connected in series between  $V_{FB}$  and GND while in Shutdown mode. See Figure 37, *Detailed Block* Diagram, for more information.

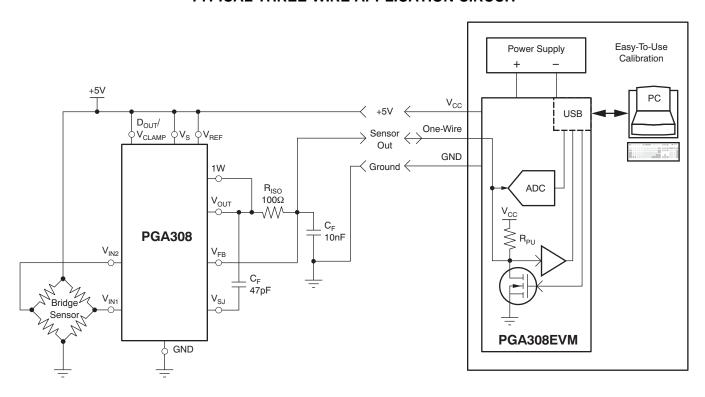

## TYPICAL THREE-WIRE APPLICATION CIRCUIT

## **PIN CONFIGURATIONS**

## **PIN DESCRIPTIONS**

| PIN# | NAME                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | D <sub>OUT</sub> /V <sub>CLAMP</sub> | Dual-use pin: Output voltage clamp limit for $V_{OUT}$ or programmable digital output. The output voltage clamp function is for use in multiple supply systems where the PGA308-Q1 may be at $V_S = +5V$ and the system analog-to-digital converter (ADC) is powered at $+3V$ . Setting $V_{CLAMP}$ to $+3.2V$ prevents over-voltage and latch-up on the system ADC input. $V_{CLAMP}$ may be set through a resistor divider from $V_S$ . If configured for digital output, the $D_{OUT}$ function allows for configuration plus calibration of a sensor module either through the One-Wire interface (1W pin) or as a permanently configured module through the power-on reset (POR) OTP memory setting. |

| 2    | 1W                                   | One-Wire interface program pin. UART interface for digital calibration of the PGA308-Q1 over a single wire. Can be connected to V <sub>OUT</sub> for a three terminal (V <sub>S</sub> , GND, V <sub>OUT</sub> ) programmable sensor assembly.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3    | GND                                  | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4    | Vs                                   | +Voltage supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5    | V <sub>IN1</sub>                     | Signal input voltage 1. Connect to + or – output of the sensor bridge. Internal multiplexer can change connection internally to front-end PGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6    | V <sub>IN2</sub>                     | Signal input voltage 2. Connect to + or – output of the sensor bridge. Internal multiplexer can change connection internally to front-end PGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7    | V <sub>SJ</sub>                      | Output amplifier summing junction. Use for output amplifier compensation when driving large capacitive loads (> 200pF) and/or for using external gain setting resistors for the output amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8    | V <sub>FB</sub>                      | $V_{OUT}$ feedback pin. Voltage feedback sense point for over-/under-scale limit circuitry. If internal gain set resistors for the output amplifier are used, this pin is also the voltage feedback sense point for the output amplifier. $V_{FB}$ in combination with $V_{SJ}$ allows for use of external filter and protection circuits without degrading the PGA308-Q1 $V_{OUT}$ accuracy. $V_{FB}$ must always be connected to either $V_{OUT}$ or the point of feedback for $V_{OUT}$ if external filtering is used.                                                                                                                                                                                 |

| 9    | V <sub>OUT</sub>                     | Analog output voltage of conditioned sensor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10   | V <sub>REF</sub>                     | Reference voltage input pin. $V_{REF}$ is used for coarse offset adjust and Zero DAC. $V_{REF}$ or $V_{S}$ may be individually selected for over-/under-scale threshold reference and fault monitor comparator reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

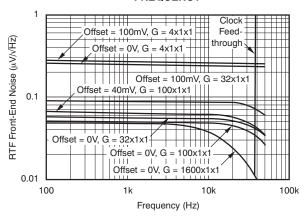

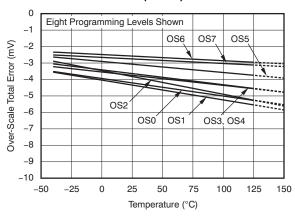

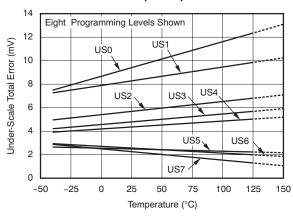

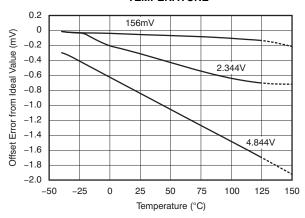

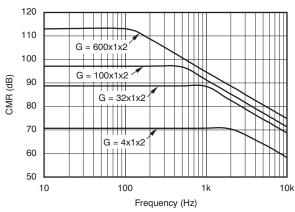

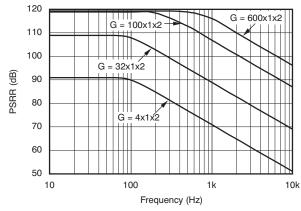

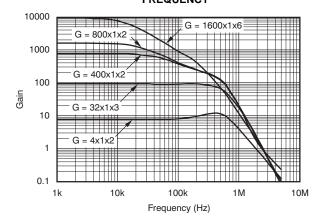

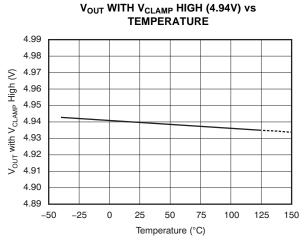

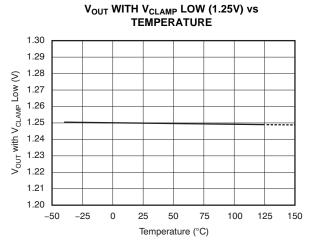

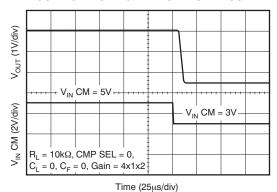

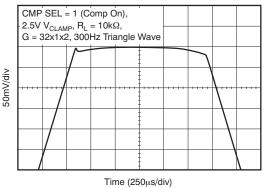

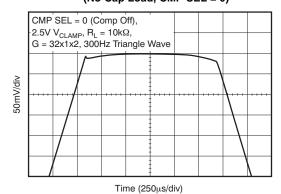

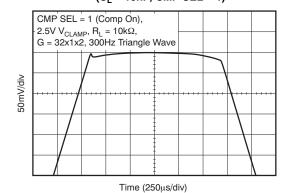

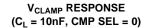

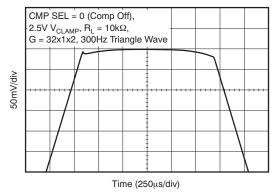

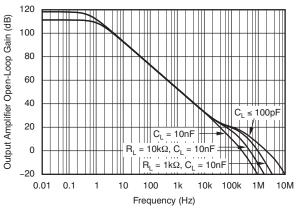

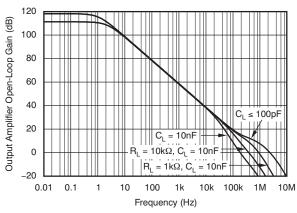

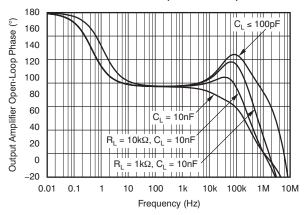

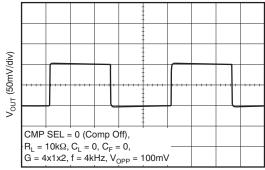

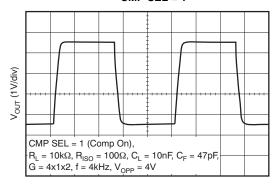

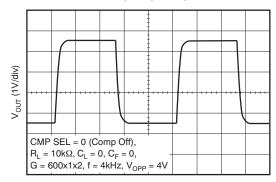

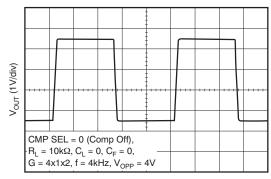

### TYPICAL CHARACTERISTICS

At  $T_A$  = +25°C,  $V_S$  =  $V_{REF}$  =  $D_{OUT}/V_{CLAMP}$  = +5V,  $R_L$  = 10k $\Omega$  and  $C_L$  = 100pF connected to GND, unless otherwise noted. Gain format is presented:  $G = FE-PGA \times Fine \ Gain \times Output \ Gain$ .

# FRONT-END PGA INPUT BIAS CURRENT WITH I<sub>PU</sub> ENABLED vs TEMPERATURE

Figure 1.

# FRONT-END PGA INPUT BIAS CURRENT WITH I<sub>PU</sub> DISABLED vs TEMPERATURE

Figure 2.

#### COARSE OFFSET ADJUST ERROR vs TEMPERATURE

Figure 3.

#### FRONT-END PGA OFFSET VOLTAGE vs TEMPERATURE

Figure 4.

## 0.1Hz TO 10Hz OUTPUT NOISE (G = 1600)

Figure 5.

# INPUT-REFERRED FRONT-END NOISE vs FREQUENCY

Figure 6.

At  $T_A$  = +25°C,  $V_S$  =  $V_{REF}$  =  $D_{OUT}/V_{CLAMP}$  = +5V,  $R_L$  = 10k $\Omega$  and  $C_L$  = 100pF connected to GND, unless otherwise noted.

Gain format is presented:  $G = FE-PGA \times Fine Gain \times Output Gain$ .

# OVER-SCALE TOTAL ERROR vs TEMPERATURE (5V Ref)

Figure 7.

# UNDER-SCALE TOTAL ERROR vs TEMPERATURE (4V Ref)

Figure 8.

### ZERO DAC OFFSET ERROR vs TEMPERATURE

Figure 9.

#### COMMON-MODE REJECTION (RTI) vs FREQUENCY

Figure 10.

#### POWER-SUPPLY REJECTION RATIO (RTI) vs FREQUENCY

Figure 11.

#### GAIN vs FREQUENCY

Figure 12.

At  $T_A = +25$ °C,  $V_S = V_{REF} = D_{OUT}/V_{CLAMP} = +5V$ ,  $R_L = 10k\Omega$  and  $C_L = 100pF$  connected to GND, unless otherwise noted.

Gain format is presented:  $G = FE-PGA \times Fine Gain \times Output Gain$ .

Figure 13.

Figure 14.

## **COMMON-MODE OVER-VOLTAGE RECOVERY**

Figure 15.

# $V_{CLAMP}$ RESPONSE (No Cap Load, CMP SEL = 1)

Figure 16.

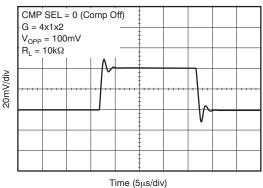

## V<sub>CLAMP</sub> RESPONSE (No Cap Load, CMP SEL = 0)

Figure 17.

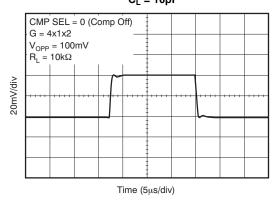

## V<sub>CLAMP</sub> RESPONSE (C<sub>L</sub> = 10nF, CMP SEL = 1)

Figure 18.

At  $T_A$  = +25°C,  $V_S$  =  $V_{REF}$  =  $D_{OUT}/V_{CLAMP}$  = +5V,  $R_L$  = 10k $\Omega$  and  $C_L$  = 100pF connected to GND, unless otherwise noted.

Gain format is presented: G = FE-PGA × Fine Gain × Output Gain.

Figure 19.

#### **OUTPUT VOLTAGE vs OUTPUT CURRENT** $V_{S} - 0.1$ $V_{S} - 0.2$ $V_S - 0.3$ Output Voltage (V) $V_{S} - 0.4$ $V_S = 3V$ $V_{s} = 2.7V$ $V_S = 5V$ $V_{S} = 5.5V$ GND + 0.4 GND + 0.3 GND + 0.2 GND + 0.1 **GND** 0 12 15 | Output Current | (mA)

Figure 20.

### QUIESCENT CURRENT vs TEMPERATURE

Figure 21.

### OUTPUT AMPLIFIER OPEN-LOOP GAIN vs FREQUENCY (CMP SEL = 1)

Figure 22.

## OUTPUT AMPLIFIER OPEN-LOOP GAIN vs FREQUENCY (CMP SEL = 0)

Figure 23.

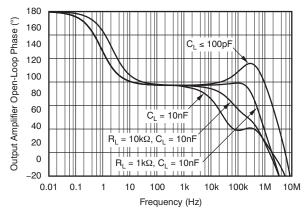

### OUTPUT AMPLIFIER OPEN-LOOP PHASE vs FREQUENCY (CMP SEL = 1)

Figure 24.

At  $T_A = +25$ °C,  $V_S = V_{REF} = D_{OUT}/V_{CLAMP} = +5V$ ,  $R_L = 10k\Omega$  and  $C_L = 100pF$  connected to GND, unless otherwise noted.

Gain format is presented:  $G = FE-PGA \times Fine Gain \times Output Gain$ .

Figure 25.

##

Figure 26.

# CAPACITIVE LOAD DRIVE $C_L = 10pF$

Figure 27.

### OPEN-LOOP OUTPUT IMPEDANCE vs FREQUENCY

Figure 28.

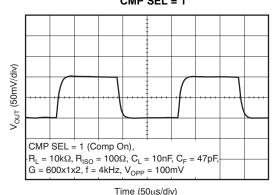

## SMALL-SIGNAL STEP RESPONSE CMP SEL = 1

Figure 29.

### LARGE-SIGNAL STEP RESPONSE CMP SEL = 1

Time (50µs/div)

Figure 30.

At  $T_A$  = +25°C,  $V_S$  =  $V_{REF}$  =  $D_{OUT}/V_{CLAMP}$  = +5V,  $R_L$  = 10k $\Omega$  and  $C_L$  = 100pF connected to GND, unless otherwise noted.

Gain format is presented:  $G = FE-PGA \times Fine Gain \times Output Gain$ .

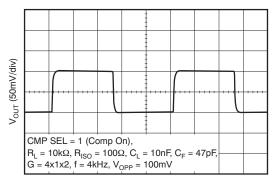

### SMALL-SIGNAL STEP RESPONSE CMP SEL = 1

Time (50µs/div)

Figure 31.

### SMALL-SIGNAL STEP RESPONSE CMP SEL = 0

Time (50 $\mu$ s/div)

Figure 33.

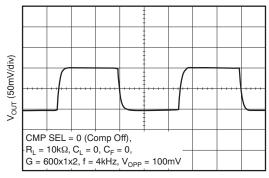

### SMALL-SIGNAL STEP RESPONSE CMP SEL = 0

Time (50µs/div)

Figure 35.

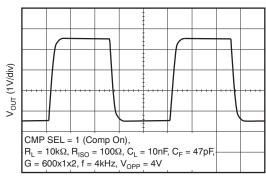

### LARGE-SIGNAL STEP RESPONSE CMP SEL = 1

Time (50µs/div)

Figure 32.

### LARGE-SIGNAL STEP RESPONSE CMP SEL = 0

Time (50 $\mu$ s/div)

Figure 34.

### LARGE-SIGNAL STEP RESPONSE CMP SEL = 0

Time (50µs/div)

Figure 36.

#### FUNCTIONAL DESCRIPTION

#### **OVERVIEW**

The PGA308-Q1 is an ideal building block for resistive bridge sensor conditioning and general data acquisition. Digitally-programmable coarse offset, fine offset, and gain may be controlled in real time or permanently programmed into the PGA308-Q1.

### SENSOR ERROR ADJUSTMENT RANGE

The PGA308-Q1 is designed to readily accommodate the following sensors:

Span<sub>25°C</sub>: 0.08mV/V to 296mV/V

Initial Offset: 20mV/V

Span and offset are based on a bridge sensor excitation voltage of +5V, a PGA308-Q1 output voltage span of 4V (+0.5V to +4.5V),  $V_{REF}$  of +5V, and a  $V_{OUT}/V_{IN}$  gain up to 9600. For proper PGA308-Q1 setup, consider noise, small-signal bandwidth,  $V_{OUT}/V_{IN}$  gain, and required system error.

## **AMPLIFICATION SIGNAL PATH**

The core of the PGA308-Q1 is a precision, low drift, and low noise front-end programmable gain amplifier (PGA). This front-end PGA has gain capabilities from x4 to x1600. The output amplifier has a gain range from x2 to x6. A fine gain adjust in front of the output amplifier offers a selectable x0.33 to x1.0 attenuation factor. This architecture yields a V<sub>OUT</sub>/V<sub>IN</sub> gain range for the PGA309 of x2.67 to x9600. Many applications use overall gains of ×1600 or less. The selection of gains in the front-end PGA and output amplifier, although capable of up to ×9600 overall gain, are intended to allow for gain distribution throughout the PGA308-Q1; this design enables optimum span and offset scaling from input to output. The polarity of the inputs can be switched through the input mux to accommodate sensors with unknown polarity output. Higher gains reduce bandwidth and require more analog filtering and/or system analog-to-digital converter (ADC) averaging to reject noise.

### COARSE AND FINE OFFSET ADJUSTMENT

The sensor offset adjustment is done in two stages. The input-referred Coarse Offset Adjust DAC has a  $\pm 100 \text{mV}$  offset adjustment range for a selected  $V_{\text{REF}}$  of +5V. Any residual input sensor offset is corrected and any desired  $V_{\text{OUT}}$  offset pedestal for zero-applied sensor strain input is set by a Fine Offset Adjust through the 16-bit Zero DAC that adds to the signal from the output of the front-end PGA.

#### **VOLTAGE REFERENCE**

The PGA308-Q1  $V_{REF}$  pin provides input from a reference voltage. The reference voltage is used by the Coarse Offset Adjust and Zero DACs. The fault monitor circuitry trip points, as well as the over- and under-scale limits, can be selected to be referenced to either  $V_S$  or  $V_{REF}$ . This flexibility accommodates absolute or ratiometric mode designs.

# FAULT MONITOR CIRCUIT SENSOR FAULT DETECTION

To detect sensor burnout and/or short, a set of four comparators (external fault comparators) are connected to the inputs of the front-end PGA. There are two fault-detect modes of operation for these comparators.

#### Common-Mode Fault

If either of the inputs are taken outside of the common-mode range of the amplifier [greater than  $(V_S - 1.2V),\,$  or less than  $100\text{mV}],\,$  then the corresponding comparator sets a sensor fault flag that can be programmed to drive the PGA308-Q1  $V_{\text{OUT}}$  to within 100mV ( $I_{\text{OUT}} < 4\text{mA}$ ) of either  $V_S$  (or  $V_{\text{CLAMP}}$  if  $V_{\text{CLAMP}}$  is used) or ground. This level is well above the set over-scale limit level or well below the set under-scale limit level. The state of the fault condition can be read in digital form in the ALRM register. If the over-scale/under-scale limiting is disabled, the PGA308-Q1 output voltage is also driven within 100mV ( $I_{\text{OUT}} < 4\text{mA}$ ) of either  $V_S$  (or  $V_{\text{CLAMP}}$  if  $V_{\text{CLAMP}}$  is used) or ground, depending on the selected fault polarity (high or low).

#### **Bridge Fault**

To assist in identifying mis-wiring, or open- or shortcircuit conditions, the PGA308-Q1 provides bridge fault monitoring. For bridge fault detection, either V<sub>S</sub> or V<sub>REF</sub> (whichever is used for bridge excitation) can be chosen as V<sub>FLT</sub>. If either of the inputs are taken to less than the larger of either 100mV or 0.35V<sub>FLT</sub>, then a fault is signaled. Also, if either of the inputs is taken to greater than the smaller of  $(V_S - 1.2V)$  or  $0.65V_{FLT}$ , then a fault is signaled. This fault detection allows for operation with bridge differential voltages of up to of the bridge excitation voltage. The corresponding comparator sets a sensor fault flag that can be programmed to drive the PGA308-Q1  $V_{OUT}$  to within 100mV ( $I_{OUT}$  < 4mA) of either  $V_{S}$  (or V<sub>CLAMP</sub> if V<sub>CLAMP</sub> is used) or ground. This level is well above the set over-scale limit level or well below the

www.ti.com.cn

set under-scale limit level. If over-scale/under-scale limiting is disabled, the PGA308-Q1 output voltage is driven within 100mV ( $I_{OUT}$  < 4mA) of either  $V_S$  or ground, depending on the selected fault polarity (high or low).

#### **Additional Fault Detection**

There are five additional fault detect comparators (internal fault comparators) that help detect subtle PGA308-Q1 front-end violations that could result in linear voltages at  $V_{\text{OUT}}$  and be interpreted as valid states. These comparators are especially useful during factory calibration and setup.

## **Alarm Register**

Each of nine fault conditions sets a corresponding bit in the Alarm register. The state of the fault condition can be read digitally from the Alarm register.

#### **OVER-SCALE AND UNDER-SCALE LIMITS**

The over-scale and under-scale limit circuitry provides a programmable upper and lower clip limit for the PGA308-Q1 output voltage. When combined with the fault monitor circuitry, system diagnostics can be performed to determine if a conditioned sensor is defective, or if the process being monitored by the sensor is out of range. The selected PGA308-Q1 V<sub>LIM</sub> is divided down by a precision resistor string to form the over- and under-scale trip points. These resistor ratios are extremely accurate and produce no significant initial or temperature errors. An over-scale amplifier driven by the over-scale threshold limits (clips) the maximum PGA308-Q1 output, V<sub>OUT</sub>. Similarly, an under-scale amplifier driven by the under-scale threshold limits (clips) the minimum PGA308-Q1 output, V<sub>OUT</sub>. The reference for the trip points,  $V_{LIM}$ , is register-selectable for either  $V_{REF}$  or  $V_S$ .

## D<sub>OUT</sub>/V<sub>CLAMP</sub> PIN

The dual-use  $D_{OUT}/V_{CLAMP}$  pin functions either as a  $V_{OUT}$  clamp or as a digital push-pull output. The voltage clamp function provides an output voltage clamp, which is external-resistor programmable. In mixed-voltage systems, where the PGA308-Q1 may run from +5V with its output scaled for 0.1V to 2.9V,  $V_{CLAMP}$  can be set to 3.0V to prevent an over-voltage lock-up/latch-up condition on a 3V system ADC or microcontroller input. When programmed as a digital output this pin can be used for sensor module configuration. The value may be pre-programmed in the one-time programmable (OTP) banks, or controlled through the One-Wire interface (1W pin).

# DIGITAL INTERFACE: ONE-WIRE PROGRAM PROTOCOL

The PGA308-Q1 can be configured through a single-wire, UART-compatible interface (1W pin). It is possible to connect this single-wire communication pin to the  $V_{\text{OUT}}$  pin in true three-terminal modules ( $V_{\text{S}}$ , ground, and sensor out) and continue to allow for calibration and configuration programming.

All communication transactions start with an initialization byte transmitted by the controller. This byte (55h) sets the baud rate used for the communication transaction. The baud rate is sensed during the initialization byte of every transaction, and is used throughout the entire transaction. Each transaction may use a different baud rate, if desired. Baud rates of 4.8k to 114k bits/second are supported.

Each communication consists of several bytes of data. Each byte consists of 10-bit periods. The first bit is the start bit and is always '0'. When idle, the 1W pin should always be high. The second through ninth bits are the eight data bits for the byte and are transferred LSB first. The 10th bit is the stop bit and is always '1'.