## 电压输出可编程传感器调节器

查询样片: PGA309-HT

#### 特性

- 完整的桥式传感器调节器

- 电压输出:成比例或绝对值

- 数字计算: 无电位器/传感器调整

- 传感器误差补偿

- 跨度、偏移和温度漂移

- 低误差、时间稳定

- 传感器线性化电路

- 温度感测:内部或外部

- 校准查询表逻辑

- 使用外部 EEPROM (小外形尺寸晶体管 (SOT)23-5 封装)

- 过量程/欠量程限制

- 传感器故障检测

- +2.7V 至 +5.5V 工作电压范围

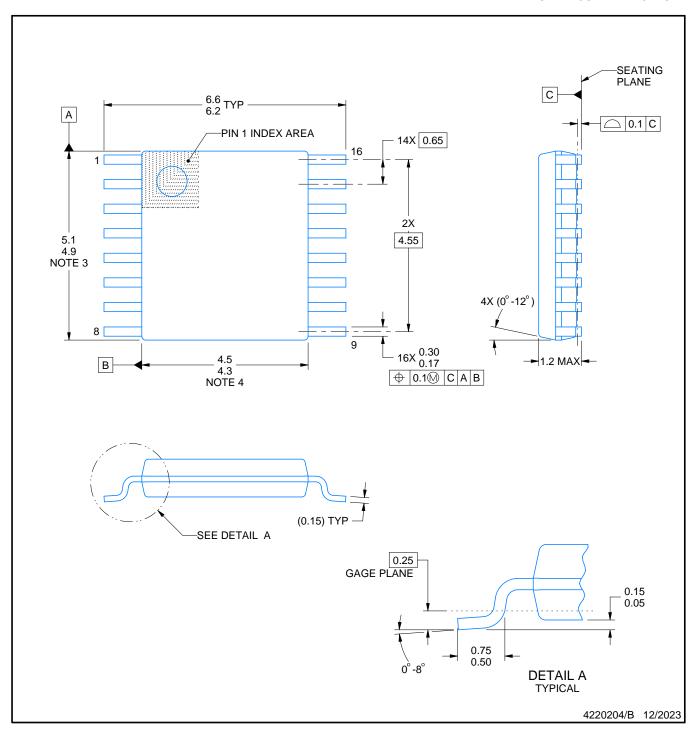

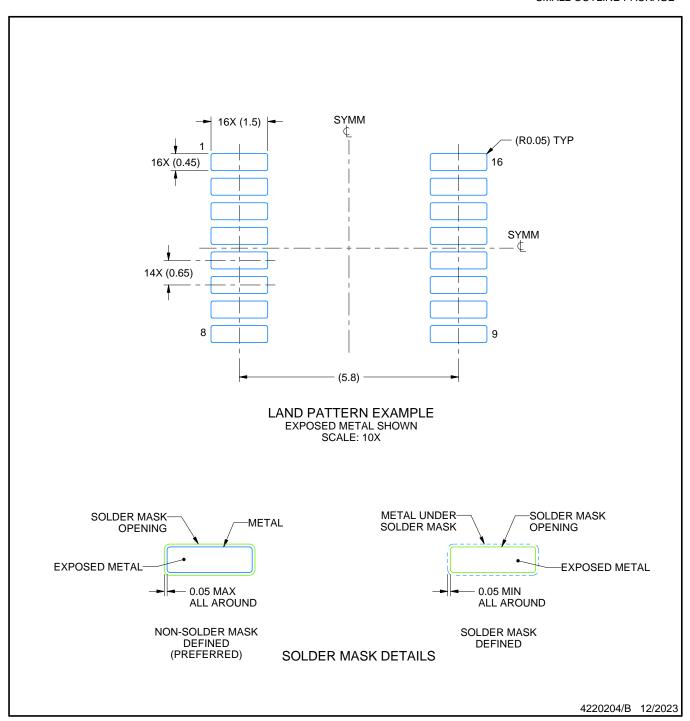

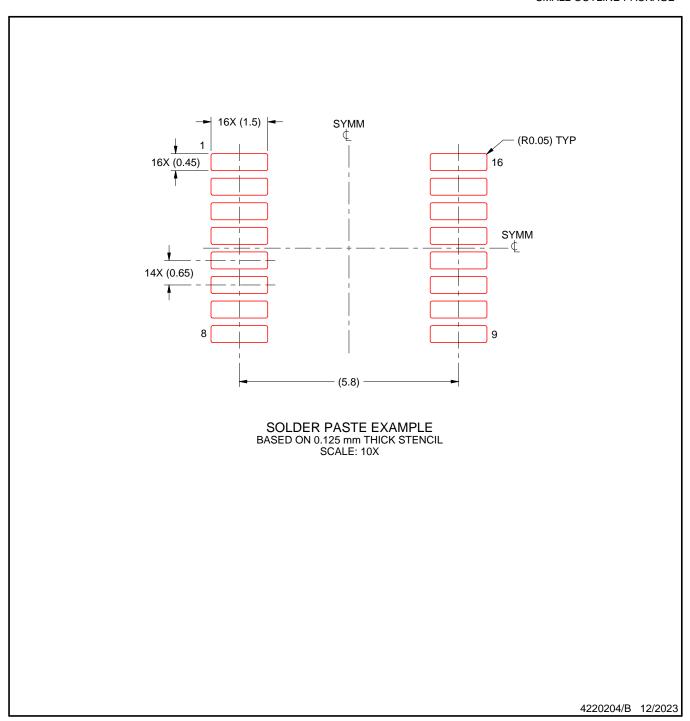

- 小型薄型小尺寸 (TSSOP)-16 封装

## 应用范围

- 桥式传感器

- 远程 4-20mA 发射器

- 应变、负载和衡器

- 车载传感器

## 支持极端温度环境下的应用

- 受控基线

- 同一组装和测试场所

- 同一制造场所

- 极端 (-55°C 至 150°C) 温度范围内可用 (1)

- 延长的产品生命周期

- 延长的产品变更通知

- 产品可追溯性

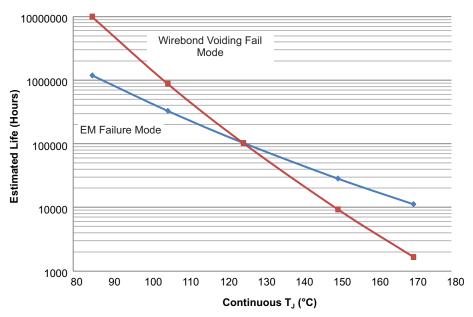

- 德州仪器 (TI) 高温产品利用高度优化的硅(芯片)解决方案,此解决方案对设计和制造工艺进行了提升以在拓展的温度范围内大幅提高性能。 在最大额定温度下,器件可连续正常运行 1000 小时。

## 评估工具

- 硬件设计人员套件 (PGA309EVM)

- PGA309 + 传感器的温度评估

- PGA309 完全编程

- 传感器补偿分析工具

- (1) 可定制工作温度范围

#### 说明

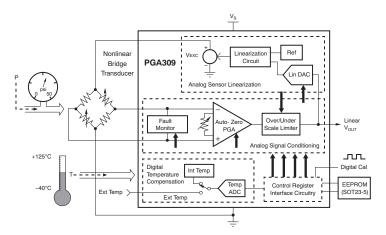

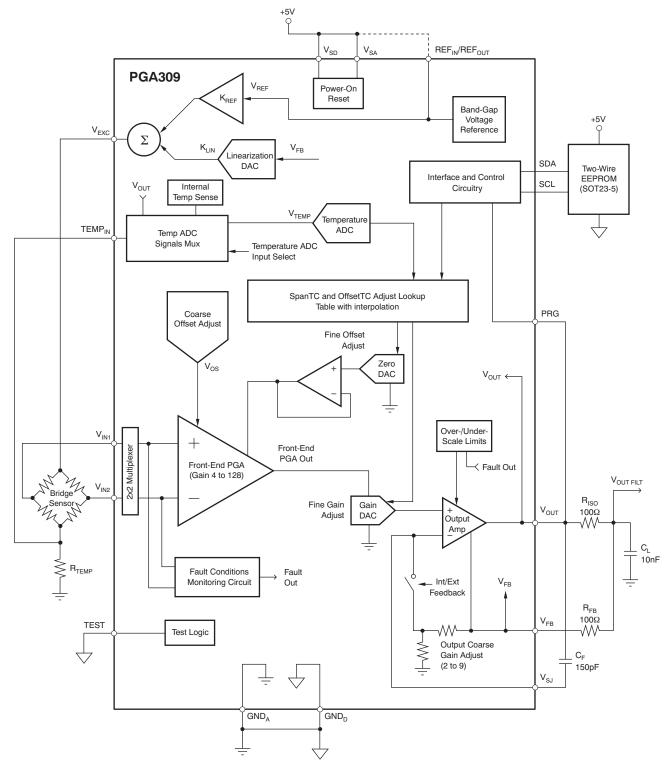

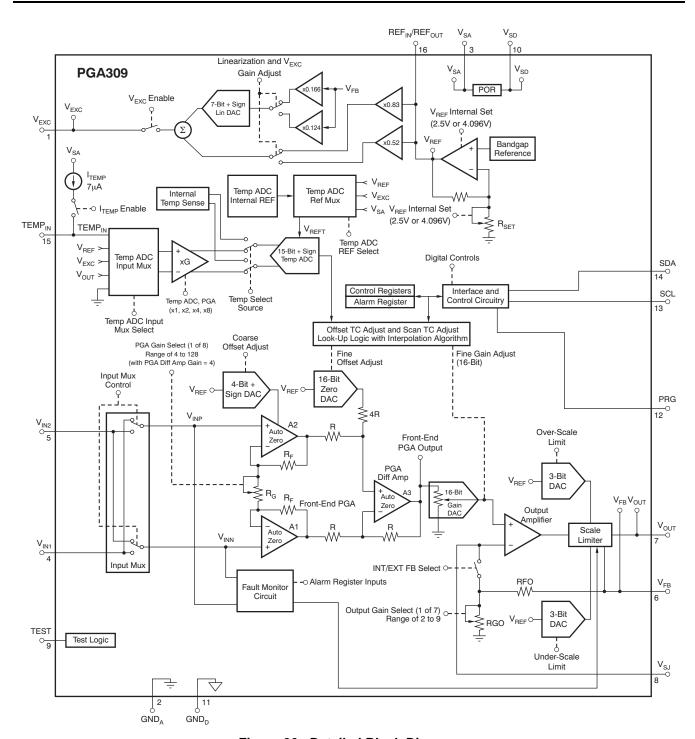

PGA309 是为电桥传感器设计的可编程模拟信号调节器。 模拟信号路径可以放大传感器信号,并通过外加应力(压力、应变等)为零、跨度、零漂移、跨度漂移和传感器线性化误差提供数字校准。 通过 1 线数字串行接口或 2 线行业标准连接进行校准。 校准参数存储在外部非易失性存储器(通常为 SOT23-5),无需手动修整并可以实现长期稳定性。

全部模拟信号路径包含一个 2 x 2 输入复用器 (mux),自动归零可编程增益仪表放大器,线性化电路,电压基准,内部振荡器,控制逻辑和一个输出放大器。可编程电平位移对传感器直流偏移做出补偿。

PGA309 的内核是精密、低漂移、无 1/f 噪声前端 PGA(可编程增益放大器)。 前端 PGA + 输出放大器的总体增益可在 2.7V/V 至 1152V/V 之间进行调节。可通过输入复用器来切换输入的极性,以使传感器适应未知的极性输出。 故障监控电路检测并发出传感器烧断、过载、和系统故障状态信号。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

ZHCSBQ8 – OCTOBER 2013 www.ti.com.cn

要获得参考应用信息,请参阅商用器件《PGA309 用户指南》(文献号: SBOU024),此文件可从www.ti.com 内下载。

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION(1)

| T <sub>J</sub> | PACKAGE       | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|---------------|-----------------------|------------------|

| –55°C to 150°C | TSSOP-16 (PW) | PGA309ASPWT           | PGA309AS         |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

website at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS(1)**

Over operating free-air temperature range, unless otherwise noted.

|                                    | PARAMETER                                        | PGA309                       | UNIT |

|------------------------------------|--------------------------------------------------|------------------------------|------|

| Supply Voltage,                    | V <sub>SD</sub> , V <sub>SD</sub>                | +7.0                         | V    |

| Input Voltage, V                   | <sub>IN1</sub> , V <sub>IN2</sub> <sup>(2)</sup> | -0.3 to V <sub>SA</sub> +0.3 | V    |

| Input Current, V                   | <sub>FB</sub> , V <sub>OUT</sub>                 | ±150                         | mA   |

| Input Current                      |                                                  | ±10                          | mA   |

| Output Current Limit               |                                                  | 50                           | mA   |

| Storage Temperature Range          |                                                  | -60 to +150                  | °C   |

| Operating Temperature Range        |                                                  | -55 to +150                  | °C   |

| Junction Temperature               |                                                  | +170                         | °C   |

| ESD Ratings Human Body Model (HBM) |                                                  | 4                            | kV   |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

#### THERMAL INFORMATION

|                         |                                                             | PGA309-HT |       |

|-------------------------|-------------------------------------------------------------|-----------|-------|

|                         | THERMAL METRIC <sup>(1)</sup>                               | PW        | UNITS |

|                         |                                                             | 16 PINS   |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance (2)                  | 95.3      |       |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance (3)               | 28.1      |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance (4)                    | 41.4      | 90044 |

| Ψлт                     | Junction-to-top characterization parameter <sup>(5)</sup>   | 1.4       | °C/W  |

| ΨЈВ                     | Junction-to-board characterization parameter <sup>(6)</sup> | 40.6      |       |

| $\theta_{JCbot}$        | Junction-to-case (bottom) thermal resistance (7)            | N/A       |       |

- (1) 有关传统和全新热度量的更多信息,请参阅 IC 封装热度量 应用报告 (文献号:ZHCA543)。

- (2) 在 JESD51-2a 描述的环境中,按照 JESD51-7 的规定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然对流条件下的结至环境热阻抗。

- (3) 通过在封装顶部模拟一个冷板测试来获得结至芯片外壳(顶部)的热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI 标准 G30-88 中找到内容接近的说明。

- (4) 按照 JESD51-8 中的说明,通过在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结至电路板的热阻。

- (5) 结至顶部的特征参数,( ψ<sub>JT</sub>),估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中描述的程序从仿真数据中提取出该 参数以便获得 θ<sub>JA</sub>。

- (6) 结至电路板的特征参数,(ψ<sub>JB</sub>),估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第7 章)中描述的程序从仿真数据中提取出该 参数以便获得 θ<sub>JA</sub> 。 (7) 通过在外露(电源)焊盘上进行冷板测试仿真来获得结至芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI

- (7) 通过在外露(电源)焊盘上进行冷板测试仿真来获得结至芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI 标准 G30-88 中找到了内容接近的说明。

<sup>(2)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5V beyond the supply rails should be current limited to 10mA or less.

ZHCSBQ8-OCTOBER 2013 www.ti.com.cn

### **ELECTRICAL CHARACTERISTICS**

**Boldface** limits apply over the specified temperature range,  $T_J = -55^{\circ}\text{C}$  to +150°C.

At  $T_J = +25$ °C,  $V_{SA} = V_{SD} = +5$ V ( $V_{SA} = V_{SUPPLY\ ANALOG}$ ,  $V_{SD} = V_{SUPPLY\ DIGITAL}$ ;  $V_{SA}$  must equal  $V_{SD}$ ),  $GND_D = GND_A = 0$ , and  $V_{REF} = V_{SUPPLY\ DIGITAL}$ = REF<sub>IN</sub>/REF<sub>OUT</sub> = +5V, unless otherwise noted.

|                                                                                 |                                                                            |     | PGA309                        |                       |                  |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|-------------------------------|-----------------------|------------------|

| PARAMETER                                                                       | CONDITIONS                                                                 | MIN | TYP                           | MAX                   | UNIT             |

| Front-End PGA + Output Amplifier                                                |                                                                            |     |                               |                       |                  |

| V <sub>OUT</sub> /V <sub>IN</sub> Differential Signal Gain Range <sup>(1)</sup> | Fine gain adjust = 1                                                       |     | 8 to 1152                     |                       | V/V              |

|                                                                                 | Front-End PGA Gains: 4, 8, 16, 23.27, 32, 42.67, 64, 128                   |     |                               |                       |                  |

|                                                                                 | Output Amplifier gains: 2, 2.4, 3, 3.6, 4.5, 6, 9                          |     |                               |                       |                  |

| Input Voltage Noise Density                                                     | f = 1kHz                                                                   |     | 210                           |                       | nV/√Hz           |

| V <sub>OUT</sub> Slew Rate                                                      |                                                                            |     | 0.5                           |                       | V/µs             |

| V <sub>OUT</sub> Settling Time (0.01%)                                          | $V_{OUT}/V_{IN}$ Differential gain = 8, $R_L = 5k\Omega$    200pF          |     | 6                             |                       | μs               |

| V <sub>OUT</sub> Settling Time (0.01%)                                          | $V_{OUT}/V_{IN}$ Differential gain = 191, $R_L = 5k\Omega \parallel 200pF$ |     | 4.1                           |                       | μs               |

| V <sub>OUT</sub> Nonlinearity                                                   |                                                                            |     | 0.002                         |                       | %FSR             |

| External Sensor Output Sensitivity                                              | $V_{SA} = V_{SD} = V_{EXC} = +5V$                                          |     | 1 to 245                      |                       | mV/V             |

| Front-End PGA                                                                   |                                                                            |     |                               |                       |                  |

| Auto-Zero Internal Frequency                                                    |                                                                            |     | 7                             |                       | kHz              |

| Offset Voltage (RTI) <sup>(2)</sup>                                             | Coarse offset adjust disabled                                              |     | ±3                            | ±70                   | μ۷               |

| vs Supply Voltage, V <sub>SA</sub>                                              |                                                                            |     | ±2                            |                       | μV/V             |

| vs Common-Mode Voltage                                                          | G <sub>F</sub> = Front-End PGA gain                                        |     | 1500/G <sub>F</sub>           | 6500/G <sub>F</sub>   | μV/V             |

| Linear Input Voltage Range <sup>(3)</sup>                                       |                                                                            | 0.2 |                               | V <sub>SA</sub> - 1.5 | v                |

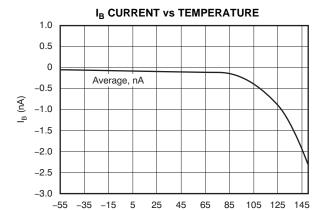

| Input Bias Current                                                              |                                                                            |     | 0.1                           | 1.5                   | nA               |

| Input Impedance: Differential                                                   |                                                                            |     | 30    6                       |                       | GΩ    pF         |

| Input Impedance: Common-Mode                                                    |                                                                            |     | 50    20                      |                       | GΩ    pF         |

| Input Voltage Noise                                                             | 0.1Hz to 10Hz, G <sub>F</sub> = 128                                        |     | 4                             |                       | μV <sub>PP</sub> |

| PGA Gain                                                                        |                                                                            |     |                               |                       |                  |

| Gain Range Steps                                                                | 4, 8, 16, 23.27, 32, 42.67, 64, 128                                        |     | 4 to 128                      |                       | V/V              |

| Initial Gain Error                                                              | G <sub>F</sub> = 4 to 42                                                   |     | 0.2                           | ±1.3                  | %                |

|                                                                                 | G <sub>F</sub> = 64                                                        |     | 0.25                          | ±1.3                  | %                |

|                                                                                 | G <sub>F</sub> = 128                                                       |     | 0.3                           | ±1.6                  | %                |

| vs Temperature                                                                  | '                                                                          |     | 10                            |                       | ppm/°C           |

| Output Voltage Range                                                            |                                                                            |     | 0.05 to V <sub>SA</sub> - 0.1 |                       | v                |

| Bandwidth                                                                       | Gain = 4                                                                   |     | 400                           |                       | kHz              |

|                                                                                 | Gain = 128                                                                 |     | 60                            |                       | kHz              |

| Coarse Offset Adjust                                                            | Sun = 120                                                                  |     |                               |                       | 10.12            |

| (RTI of Front-End PGA)                                                          |                                                                            |     |                               |                       |                  |

| Range                                                                           | ±(14)(V <sub>REF</sub> )(0.00085)                                          | ±56 | ±59.5                         | ±64                   | mV               |

| vs Temperature                                                                  |                                                                            |     | 0.004                         |                       | %/°C             |

| Drift                                                                           | ±14 steps, 4-bit + sign                                                    |     | 4                             |                       | mV               |

| Fine Offset Adjust (Zero DAC)<br>(RTO of the Front-End PGA) <sup>(2)</sup>      |                                                                            |     |                               |                       |                  |

| Programming Range                                                               |                                                                            | 0   |                               | $V_{REF}$             | V                |

| Output Voltage Range                                                            |                                                                            | 0.1 |                               | V <sub>SA</sub> - 0.1 | V                |

| Resolution                                                                      | 65,536 steps, 16-bit DAC                                                   |     | 73                            | -                     | μV               |

| Integral Nonlinearity                                                           |                                                                            |     | 20                            |                       | LSB              |

| Differential Nonlinearity                                                       |                                                                            |     | 0.5                           |                       | LSB              |

| Gain Error                                                                      |                                                                            |     | 0.1                           |                       | %                |

| Gain Error Drift                                                                |                                                                            |     | 10                            |                       | ppm/°C           |

| Offset                                                                          |                                                                            |     | 5                             |                       | mV               |

|                                                                                 |                                                                            |     | i                             |                       |                  |

<sup>(1)</sup> PGA309 total differential gain from input  $(V_{IN1} - V_{IN2})$  to output  $(V_{OUT})$ .  $V_{OUT} / (V_{IN1} - V_{IN2}) = (Front-end PGA gain) × (Output Amplifier$ gain) × (Gain DAC).

RTI = Referred-to-input. RTO = referred to output.

Linear input range is the allowed min/max voltage on the  $V_{IN1}$  and  $V_{IN2}$  pins for the input PGA to continue to operate in a linear region. The allowed common-mode and differential voltage depends on gain and offset settings. Refer to the Gain Scaling section for more information.

## **ELECTRICAL CHARACTERISTICS (continued)**

**Boldface** limits apply over the specified temperature range,  $T_J = -55^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ . At  $T_J = +25^{\circ}\text{C}$ ,  $V_{SA} = V_{SD} = +5\text{V}$  ( $V_{SA} = V_{SUPPLY \text{ ANALOG}}$ ,  $V_{SD} = V_{SUPPLY \text{ DIGITAL}}$ ;  $V_{SA}$  must equal  $V_{SD}$ ),  $GND_D = GND_A = 0$ , and  $V_{REF} = REF_{IN}/REF_{OUT} = +5\text{V}$ , unless otherwise noted.

| PARAMETER                                    | CONDITIONS                                                                                                         | MIN | TYP              | MAX                  | UNIT  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|------------------|----------------------|-------|

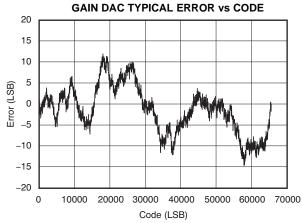

| Output Fine Gain Adjust (Gain DAC)           |                                                                                                                    |     |                  |                      |       |

| Range                                        |                                                                                                                    |     | 0.33 to 1        |                      | V/V   |

| Resolution                                   | 65,536 steps, 16-bit DAC                                                                                           |     | 10               |                      | μV/V  |

| Integral Nonlinearity                        |                                                                                                                    |     | 20               |                      | LSB   |

| Differential Nonlinearity                    |                                                                                                                    |     | 0.5              |                      | LSB   |

| Output Amplifier                             |                                                                                                                    |     |                  |                      |       |

| Offset Voltage (RTI of Output Amplifier) (4) |                                                                                                                    |     | 3                |                      | mV    |

| vs Temperature                               |                                                                                                                    |     | 5                |                      | μV/°C |

| vs Supply Voltage, $V_{SA}$                  |                                                                                                                    |     | 30               |                      | μV/V  |

| Common-Mode Input Range                      |                                                                                                                    | 0   |                  | V <sub>S</sub> – 1.5 | V     |

| Input Bias Current                           |                                                                                                                    |     | 100              |                      | pA    |

| Amplifier Internal Gain                      |                                                                                                                    |     |                  |                      |       |

| Gain Range Steps                             | 2, 2.4, 3, 3.6, 4.5, 6, 9                                                                                          |     | 2 to 9           |                      | V/V   |

| Initial Gain Error                           | 2, 2.4, 3.6                                                                                                        |     | 0.25             | ±1.1                 | %     |

|                                              | 4.5                                                                                                                |     | 0.3              | ±1.3                 | %     |

|                                              | 6                                                                                                                  |     | 0.4              | ±1.6                 | %     |

|                                              | 9                                                                                                                  |     | 0.6              | ±2.0                 | %     |

| vs Temperature                               | 2, 2.4, 3.6                                                                                                        |     | 5                |                      | ppm/° |

|                                              | 4.5                                                                                                                |     | 5                |                      | ppm/° |

|                                              | 6                                                                                                                  |     | 15               |                      | ppm/° |

|                                              | 9                                                                                                                  |     | 30               |                      | ppm/° |

| Output Voltage Range <sup>(5)</sup>          | $R_L = 10k\Omega$                                                                                                  | 0.1 |                  | 4.9                  | v     |

| Open-Loop Gain                               | -                                                                                                                  |     | 115              |                      | dB    |

| Gain-Bandwidth Product                       |                                                                                                                    |     | 2                |                      | MHz   |

| Phase Margin                                 | Gain = 2, C <sub>1</sub> = 200pF                                                                                   |     | 45               |                      | deg   |

| Output Resistance                            | AC Small-signal, open-loop, f = 1MHz, I <sub>O</sub> = 0                                                           |     | 675              |                      | Ω     |

| Over- and Under-Scale Limits                 | V <sub>RFF</sub> = 4.096                                                                                           |     |                  |                      |       |

| Over-Scale Thresholds                        | Ratio of V <sub>REF</sub> , Register 5—bits D5, D4, D3 = '000'                                                     |     | 0.9708           |                      |       |

|                                              | Ratio of V <sub>REF</sub> , Register 5—bits D5, D4, D3 = '001'                                                     |     | 0.9610           |                      |       |

|                                              | Ratio of V <sub>REF</sub> , Register 5—bits D5, D4, D3 = '010'                                                     |     | 0.9394           |                      |       |

|                                              | Ratio of V <sub>REF</sub> , Register 5—bits D5, D4, D3 = '011'                                                     |     | 0.9160           |                      |       |

|                                              | Ratio of $V_{REF}$ , Register 5—bits D5, D4, D3 = '100'                                                            |     | 0.9102           |                      |       |

|                                              | Ratio of V <sub>REF</sub> , Register 5—bits D5, D4, D3 = '101'                                                     |     | 0.7324           |                      |       |

|                                              | Ratio of V <sub>REF</sub> , Register 5—bits D5, D4, D3 = '110'                                                     |     | 0.5528           |                      |       |

| Over-Scale Comparator Offset                 |                                                                                                                    | +6  | +60              | +114                 | mV    |

| Over-Scale Comparator Offset Drift           |                                                                                                                    | 10  | +0.37            |                      | mV/°C |

| Under-Scale Thresholds                       | Ratio of V <sub>REF</sub> , Register 5—bits D2, D1, D0 = '111'                                                     |     | 0.0605           |                      |       |

| Chiasi Codio Tillesholds                     | -                                                                                                                  |     |                  |                      |       |

|                                              | Ratio of $V_{REF}$ , Register 5—bits D2, D1, D0 = '110'<br>Ratio of $V_{RFF}$ , Register 5—bits D2, D1, D0 = '101' |     | 0.0547<br>0.0507 |                      |       |

|                                              | · <del>-</del>                                                                                                     |     | 0.0507           |                      |       |

|                                              | Ratio of V <sub>REF</sub> , Register 5—bits D2, D1, D0 = '100'                                                     |     |                  |                      |       |

|                                              | Ratio of V <sub>REF</sub> , Register 5—bits D2, D1, D0 = '011'                                                     |     | 0.0391           |                      |       |

|                                              | Ratio of V <sub>REF</sub> , Register 5—bits D2, D1, D0 = '010                                                      |     | 0.0352           |                      |       |

|                                              | Ratio of V <sub>REF</sub> , Register 5—bits D2, D1, D0 = '001'                                                     |     | 0.0293           |                      |       |

|                                              | Ratio of V <sub>REF</sub> , Register 5—bits D2, D1, D0 = '000'                                                     |     | 0.0254           |                      |       |

| Under-Scale Comparator Offset                |                                                                                                                    | -7  | -50              | +93                  | mV    |

| Under-Scale Comparator Offset Drift          |                                                                                                                    |     | -0.15            |                      | mV/°0 |

<sup>(4)</sup> RTI = Referred-to-input. RTO = referred to output.

(5) Unless limited by the over/under-scale setting.

**ISTRUMENTS**

ZHCSBQ8-OCTOBER 2013 www.ti.com.cn

## **ELECTRICAL CHARACTERISTICS (continued)**

**Boldface** limits apply over the specified temperature range,  $T_J = -55^{\circ}\text{C}$  to +150°C.

At  $T_J$  = +25°C,  $V_{SA}$  =  $V_{SD}$  = +5V ( $V_{SA}$  =  $V_{SUPPLY\ ANALOG}$ ,  $V_{SD}$  =  $V_{SUPPLY\ DIGITAL}$ ;  $V_{SA}$  must equal  $V_{SD}$ ),  $GND_D$  =  $GND_A$  = 0, and  $V_{REF}$  =  $REF_{IN}/REF_{OUT}$  = +5V, unless otherwise noted.

| PARAMETER                                            | CONDITIONS                                                       | MIN      | TYP                                            | MAX                  | UNIT        |

|------------------------------------------------------|------------------------------------------------------------------|----------|------------------------------------------------|----------------------|-------------|

| Fault Monitor Circuit                                |                                                                  |          |                                                |                      |             |

| INP_HI, INN_HI Comparator Threshold                  | See (6)                                                          | ,        | V <sub>SA</sub> - 1.2 or V <sub>EXC</sub> - 0. | 1                    | V           |

| INP_LO, INN_LO Comparator Threshold                  |                                                                  | 40       | 100                                            |                      | mV          |

| A1SAT_HI, A2SAT_HI Comparator Threshold              |                                                                  |          | V <sub>SA</sub> - 0.12                         |                      | V           |

| A1SAT_LO, A2SAT_LO Comparator Threshold              |                                                                  |          | V <sub>SA</sub> - 0.12                         |                      | V           |

| A3_VCM Comparator Threshold                          |                                                                  |          | V <sub>SA</sub> - 1.2                          |                      | V           |

| Comparator Hysteresis                                |                                                                  |          | 20                                             |                      | mV          |

| Internal Voltage Reference                           |                                                                  |          |                                                |                      |             |

| V <sub>REF1</sub>                                    | Register 3, bit D9 = 1                                           | 2.43     | 2.5                                            | 2.53                 | V           |

|                                                      |                                                                  | 2.18     |                                                | 2.7                  | V           |

| V <sub>REF1</sub> Drift vs Temperature               |                                                                  |          | +10                                            |                      | ppm/°C      |

| $V_{REF2}$ $I_{PU}$                                  | Register 3, bit D9 = 0                                           | 4.0      | 4.096                                          | 4.14                 | V           |

|                                                      |                                                                  | 3.85     |                                                | 4.22                 | v           |

| V <sub>REF2</sub> Drift vs Temperature               |                                                                  |          | +10                                            |                      | ppm/°C      |

| Input Current REF <sub>IN</sub> /REF <sub>OUT</sub>  | Internal V <sub>REF</sub> disabled                               |          | 100                                            |                      | μA          |

| Output Current REF <sub>IN</sub> /REF <sub>OUT</sub> | $V_{SA} > 2.7V$ for $V_{REF} = 2.5V$                             |          | 1                                              |                      | mA          |

| ,                                                    | $V_{SA} > 4.3V$ for $V_{REF} = 4.096V$                           |          | 1                                              |                      | mA          |

| Temperature Sense Circuitry (ADC)                    | OA INCI                                                          |          |                                                |                      |             |

| Internal Temperature Measurement                     | Register 6, bit D9 = 1                                           |          |                                                |                      |             |

| Accuracy                                             | regions of the total                                             |          | ±2                                             |                      | °C          |

| Resolution                                           | 12-Bit + sign, twos complement data format                       |          | ±0.0625                                        |                      | °C          |

| Temperature Measurement Range                        | 12 Bit 1 sign, two complement data format                        | -55      | 10.0020                                        | +150                 | °C          |

| Conversion Rate                                      | R <sub>1</sub> , R <sub>0</sub> = '11', 12-bit + sign resolution | 33       | 24                                             | +130                 | ms          |

| Temperature ADC                                      | 11, 10 - 11, 12-01 + sign resolution                             |          | 24                                             |                      | 1115        |

| External Temperature Mode                            | Temp PGA + Temp ADC                                              |          | 1 to 8                                         |                      | V/V         |

|                                                      | G <sub>PGA</sub> = 1, 2, 4, 8                                    | GND -0.2 | 1 10 0                                         | V <sub>SA</sub> +0.2 | V           |

| Gain Range Steps                                     | Opga = 1, 2, 4, 0                                                | GND -0.2 |                                                | V <sub>SA</sub> +0.2 | V           |

| Analog Input Voltage Range                           | Deviator C hit D0 4                                              |          |                                                |                      |             |

| Temperature ADC Internal REF (2.048V)                | Register 6, bit D8 = 1                                           |          | 0.040/0                                        |                      |             |

| Full-Scale Input Voltage                             | (+Input) - (-Input)                                              |          | ±2.048/G <sub>PGA</sub>                        |                      | V           |

| Differential Input Impedance                         |                                                                  |          | 2.8/G <sub>PGA</sub>                           |                      | ΜΩ          |

| Common-Mode Input Impedance                          | $G_{PGA} = 1$                                                    |          | 3.5                                            |                      | ΜΩ          |

|                                                      | $G_{PGA} = 2$                                                    |          | 3.5                                            |                      | ΜΩ          |

|                                                      | $G_{PGA} = 4$                                                    |          | 1.8                                            |                      | ΜΩ          |

|                                                      | G <sub>PGA</sub> = 8                                             |          | 0.9                                            |                      | ΜΩ          |

| Resolution                                           | R1, R0 = '00', ADC2X = '0', conversion time = 8ms                |          | 11                                             |                      | Bits + Sigr |

|                                                      | R1, R0 = '01', ADC2X = '0', conversion time = 32ms               |          | 13                                             |                      | Bits + Sigr |

|                                                      | R1, R0 = '10', ADC2X = '0', conversion time = 64ms               |          | 14                                             |                      | Bits + Sigr |

|                                                      | R1, R0 = '11', ADC2X = '0', conversion time = 128ms              |          | 15                                             |                      | Bits + Sigr |

| Integral Nonlinearity                                |                                                                  |          | 0.004                                          |                      | %           |

| Offset Error                                         | G <sub>PGA</sub> = 1                                             |          | 1.2                                            |                      | mV          |

|                                                      | G <sub>PGA</sub> = 2                                             |          | 0.7                                            |                      | mV          |

|                                                      | G <sub>PGA</sub> = 4                                             |          | 0.5                                            |                      | mV          |

|                                                      | G <sub>PGA</sub> = 8                                             |          | 0.4                                            |                      | mV          |

| Offset Drift                                         | G <sub>PGA</sub> = 1                                             |          | 1.2                                            |                      | μV/°C       |

|                                                      | G <sub>PGA</sub> = 2                                             |          | 0.6                                            |                      | μV/°C       |

|                                                      | $G_{PGA} = 4$                                                    |          | 0.3                                            |                      | μV/°C       |

|                                                      | G <sub>PGA</sub> = 8                                             |          | 0.3                                            |                      | μV/°C       |

<sup>(6)</sup> When V<sub>EXC</sub> is enabled, a minimum reference selector circuit becomes the reference for the comparator threshold. This minimum reference selector circuit uses  $V_{EXC}$  – 100mV and  $V_{SA}$  – 1.2V and compares the  $V_{INX}$  pin to the lower of the two references. This configuration ensures accurate fault monitoring in conditions where  $V_{EXC}$  might be higher or lower than the input CMR of the PGA input amplifier relative to V<sub>SA</sub>.

## **ELECTRICAL CHARACTERISTICS (continued)**

**Boldface** limits apply over the specified temperature range,  $T_J = -55^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ . At  $T_J = +25^{\circ}\text{C}$ ,  $V_{SA} = V_{SD} = +5\text{V}$  ( $V_{SA} = V_{SUPPLY\ ANALOG}$ ,  $V_{SD} = V_{SUPPLY\ DIGITAL}$ ;  $V_{SA}$  must equal  $V_{SD}$ ),  $GND_D = GND_A = 0$ , and  $V_{REF} = REF_{IN}/REF_{OUT} = +5\text{V}$ , unless otherwise noted.

| PARAMETER                                                            | CONDITIONS                                          | MIN | TYP                                  | MAX  | UNIT        |

|----------------------------------------------------------------------|-----------------------------------------------------|-----|--------------------------------------|------|-------------|

| Temperature ADC. continued                                           |                                                     |     |                                      |      |             |

| Offset vs V <sub>SA</sub>                                            | G <sub>PGA</sub> = 1                                |     | 800                                  |      | μV/V        |

|                                                                      | G <sub>PGA</sub> = 2                                |     | 400                                  |      | μV/V        |

|                                                                      | $G_{PGA} = 4$                                       |     | 200                                  |      | μV/V        |

|                                                                      | G <sub>PGA</sub> = 8                                |     | 150                                  |      | μV/V        |

| Gain Error                                                           |                                                     |     | 0.05                                 | 0.50 | %           |

| Gain Error Drift                                                     |                                                     |     | 5                                    | 50   | ppm/°C      |

| Noise                                                                | All gains                                           |     | < 1                                  |      | LSB         |

| Gain vs V <sub>SA</sub>                                              |                                                     |     | 80                                   |      | ppm/V       |

| Common-Mode Rejection                                                | At dc and G <sub>PGA</sub> = 8                      |     | 105                                  |      | dB          |

|                                                                      | At dc and G <sub>PGA</sub> = 1                      |     | 100                                  |      | dB          |

| Temp ADC Ext. REF ( $V_{REFT} = V_{REF}$ , $V_{EXC}$ , or $V_{SA}$ ) | Register 6, bit D8 = 0                              |     |                                      |      |             |

| Full-Scale Input Voltage                                             | (+Input) - (-Input)                                 |     | ±V <sub>REFT</sub> /G <sub>PGA</sub> |      | V           |

| Differential Input Impedance                                         |                                                     |     | 2.4/G <sub>PGA</sub>                 |      | ΜΩ          |

| Common-Mode Input Impedance                                          | G <sub>PGA</sub> = 1                                |     | 8                                    |      | ΜΩ          |

|                                                                      | G <sub>PGA</sub> = 2                                |     | 8                                    |      | ΜΩ          |

|                                                                      | G <sub>PGA</sub> = 4                                |     | 8                                    |      | ΜΩ          |

|                                                                      | G <sub>PGA</sub> = 8                                |     | 8                                    |      | ΜΩ          |

| Resolution                                                           | R1, R0 = '00', ADC2X = '0', conversion time = 6ms   |     | 11                                   |      | Bits + Sigr |

|                                                                      | R1, R0 = '01', ADC2X = '0', conversion time = 24ms  |     | 13                                   |      | Bits + Sign |

|                                                                      | R1, R0 = '10', ADC2X = '0', conversion time = 50ms  |     | 14                                   |      | Bits + Sigr |

|                                                                      | R1, R0 = '11', ADC2X = '0', conversion time = 100ms |     | 15                                   |      | Bits + Sigr |

| Integral Nonlinearity                                                |                                                     |     | 0.01                                 |      | %           |

| Offset Error                                                         | G <sub>PGA</sub> = 1                                |     | 2.5                                  |      | mV          |

|                                                                      | G <sub>PGA</sub> = 2                                |     | 1.25                                 |      | mV          |

|                                                                      | G <sub>PGA</sub> = 4                                |     | 0.7                                  |      | mV          |

|                                                                      | G <sub>PGA</sub> = 8                                |     | 0.3                                  |      | mV          |

| Offset Drift                                                         | G <sub>PGA</sub> = 1                                |     | 1.5                                  |      | μV/°C       |

|                                                                      | G <sub>PGA</sub> = 2                                |     | 1.0                                  |      | μV/°C       |

|                                                                      | $G_{PGA} = 4$                                       |     | 0.7                                  |      | μV/°C       |

|                                                                      | G <sub>PGA</sub> = 8                                |     | 0.6                                  |      | μV/°C       |

| Gain Error                                                           |                                                     |     | -0.2                                 |      | %           |

| Gain Error Drift                                                     |                                                     |     | 2                                    |      | ppm/°C      |

| Gain vs V <sub>SA</sub>                                              |                                                     |     | 80                                   |      | ppm/V       |

| Common-Mode Rejection                                                | At dc and G <sub>PGA</sub> = 8                      |     | 100                                  |      | dB          |

|                                                                      | At dc and G <sub>PGA</sub> = 1                      |     | 85                                   |      | dB          |

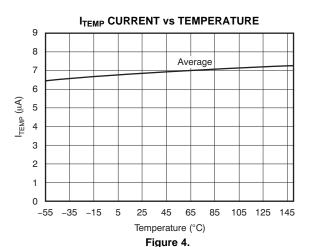

| External Temperature Current Excitation I <sub>TEMP</sub>            | Register 6, bit D11 = 1                             |     |                                      |      |             |

| Current Excitation                                                   |                                                     | 5.8 | 7                                    | 8    | μA          |

|                                                                      |                                                     | 5.2 |                                      | 8.3  | μA          |

| Temperature Drift                                                    |                                                     |     | 5                                    |      | nA/°C       |

| Voltage Compliance                                                   |                                                     |     | V <sub>SA</sub> -1.2                 |      | V           |

ZHCSBQ8-OCTOBER 2013 www.ti.com.cn

## **ELECTRICAL CHARACTERISTICS (continued)**

**Boldface** limits apply over the specified temperature range,  $T_J = -55^{\circ}\text{C}$  to +150°C. At  $T_J = +25^{\circ}\text{C}$ ,  $V_{SA} = V_{SD} = +5\text{V}$  ( $V_{SA} = V_{SUPPLY \ ANALOG}$ ,  $V_{SD} = V_{SUPPLY \ DIGITAL}$ ;  $V_{SA}$  must equal  $V_{SD}$ ),  $GND_D = GND_A = 0$ , and  $V_{REF} = REF_{IN}/REF_{OUT} = +5\text{V}$ , unless otherwise noted.

|                                                                 |                                               |                       | PGA309                |                       |        |

|-----------------------------------------------------------------|-----------------------------------------------|-----------------------|-----------------------|-----------------------|--------|

| PARAMETER                                                       | CONDITIONS                                    | MIN                   | TYP                   | MAX                   | UNIT   |

| Linearization Adjust and Excitation Voltage (V <sub>EXC</sub> ) |                                               |                       |                       |                       |        |

| Range 0                                                         | Register 3, bit D11 = 0                       |                       |                       |                       |        |

| Linearization DAC Range                                         | With respect to V <sub>FB</sub>               |                       | -0.166 to +0.166      |                       | V/V    |

| Linearization DAC Resolution                                    | ±127 steps, 7-bit + sign                      |                       | 1.307                 |                       | mV/V   |

| V <sub>EXC</sub> Gain                                           | With respect to V <sub>REF</sub>              |                       | 0.83                  |                       | V/V    |

| Gain Error Drift                                                |                                               |                       | 25                    |                       | ppm/°C |

| Range 1                                                         | Register 3, bit D11 = 1                       |                       |                       |                       |        |

| Linearization DAC Range                                         | With respect to V <sub>FB</sub>               |                       | -0.124 to +0.124      |                       | V/V    |

| Linearization DAC Resolution                                    | ±127 steps, 7-bit + sign                      |                       | 0.9764                |                       | mV/V   |

| V <sub>EXC</sub> Gain                                           | With respect to V <sub>REF</sub>              |                       | 0.52                  |                       | V/V    |

| Gain Error Drift                                                |                                               |                       | 25                    |                       | ppm/°C |

| V <sub>EXC</sub> Range Upper Limit                              | I <sub>EXC</sub> = 5mA                        |                       | V <sub>SA</sub> -0.5  |                       | V      |

| I <sub>EXC</sub> SHORT                                          | Short-circuit V <sub>EXC</sub> output current |                       | 50                    |                       | mA     |

| Digital Interface                                               |                                               |                       |                       |                       |        |

| Two-Wire Compatible                                             | Bus speed                                     | 1                     |                       | 400                   | kHz    |

| One-Wire                                                        | Serial speed baud rate                        | 4.8K                  |                       | 38.4K                 | Bits/s |

| Maximum Lookup Table Size(7)                                    |                                               |                       | 17 x 3 x 16           |                       | Bits   |

| Two-Wire Data Rate                                              | PGA309 to EEPROM (SCL frequency)              |                       | 65                    |                       | kHz    |

| Logic Levels                                                    |                                               |                       |                       |                       |        |

| Input Levels (SDA, SCL, PRG, TEST)                              | Low                                           |                       |                       | 0.2 • V <sub>SD</sub> | V      |

| (SDA, SCL, PRG, TEST)                                           | High                                          | 0.7 • V <sub>SD</sub> |                       |                       | V      |

| (SDA, SCL)                                                      | Hysteresis                                    |                       | 0.1 • V <sub>SD</sub> |                       | V      |

| Pull-Up Current Source (SDA, SCL)                               |                                               | 55                    | 85                    | 135                   | μΑ     |

| Pull-Down Current Source (TEST)                                 |                                               | 10.5                  | 25                    | 50                    | μΑ     |

| Output LOW Level (SDA, SCL, PRG)                                | Open drain, I <sub>SINK</sub> = 5mA           |                       |                       | 0.4                   | V      |

| Power Supply                                                    |                                               |                       |                       |                       |        |

| $V_{SA}$ , $V_{SD}$                                             |                                               | 2.7                   |                       | 5.5                   | V      |

| I <sub>SA</sub> + I <sub>SD</sub> , Quiescent Current           | $V_{SA} = V_{SD} = +5V$ , without bridge load |                       | 1.2                   | 1.6                   | mA     |

| Power-On Reset (POR)                                            |                                               |                       |                       |                       |        |

| Power-Up Threshold                                              | V <sub>s</sub> rising                         |                       | 2.2                   | 2.7                   | v      |

| Power-Down Threshold                                            | V <sub>s</sub> falling                        |                       | 1.7                   |                       | V      |

| Temperature Range                                               |                                               |                       |                       |                       |        |

| Specified Performance Range                                     |                                               | -55                   |                       | +150                  | °C     |

<sup>(7)</sup> Lookup table allows multislope compensation over temperature. Lookup table has access to 17 calibration points consisting of three adjustment values (Tx, Temperature, ZMx, Zero DAC, GMx, Gain DAC) that are stored in 16-bit data format (17x3x16 = Lookup table size).

- (1) See datasheet for absolute maximum and minimum recommended operating conditions.

- (2) Silicon operating life design goal is 10 years at 105°C junction temperature (does not include package interconnect life).

- (3) The predicted operating lifetime vs. junction temperature is based on reliability modeling using electromigration as the dominant failure mechanism affecting device wearout for the specific device process and design characteristics.

- (4) This device is qualified for 1000 hours of continuous operation at maximum rated temperature.

Figure 1. PGA309-HT Operating Life Derating Chart

ZHCSBQ8 – OCTOBER 2013 www.ti.com.cn

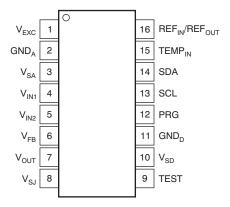

## **PIN CONFIGURATION**

## PW PACKAGE TSSOP-16 (TOP VIEW)

## **PIN DESCRIPTIONS**

| PIN NO. | NAME                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>EXC</sub>                      | Bridge sensor excitation. Connect to bridge if linearization and/or internal reference for bridge excitation is to be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2       | GND <sub>A</sub>                      | Analog ground. Connect to analog ground return path for V <sub>SA</sub> . Should be same as GND <sub>D</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3       | V <sub>SA</sub>                       | Analog voltage supply. Connect to analog voltage supply. To be within 200mV of V <sub>SD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4       | V <sub>IN1</sub>                      | Signal input voltage 1. Connect to + or – output of sensor bridge. Internal multiplexer can change connection internally to Front-End PGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5       | V <sub>IN2</sub>                      | Signal input voltage 2. Connect to + or – output of sensor bridge. Internal multiplexer can change connection internally to Front-End PGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6       | V <sub>FB</sub>                       | V <sub>OUT</sub> feedback pin. Voltage feedback sense point for over/under-scale limit circuitry. When internal gain set resistors for the output amplifier are used, this is also the voltage feedback sense point for the output amplifier. V <sub>FB</sub> in combination with V <sub>SJ</sub> allows for ease of external filter and protection circuits without degrading the PGA309 V <sub>OUT</sub> accuracy. V <sub>FB</sub> must always be connected to either V <sub>OUT</sub> or the point of feedback for V <sub>OUT</sub> , if external protection is used.                                                            |

| 7       | V <sub>OUT</sub>                      | Analog output voltage of conditioned sensor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8       | V <sub>SJ</sub>                       | Output amplifier summing junction. Use for output amplifier compensation when driving large capacitive loads (> 100pF) and/or for using external gain setting resistors for the output amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9       | TEST                                  | Test/External controller mode pin. Pull to GND <sub>D</sub> in normal mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10      | V <sub>SD</sub>                       | Digital voltage supply. Connect to digital voltage supply. To be within 200mV of V <sub>SA</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11      | GND <sub>D</sub>                      | Digital ground. Connect to digital ground return path for V <sub>SD</sub> . Should be same as GND <sub>A</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12      | PRG                                   | Single-wire interface program pin. UART-type interface for digital calibration of the PGA309 over a single wire. Can be connected to V <sub>OUT</sub> for a three-lead (V <sub>S</sub> , GND, V <sub>OUT</sub> ) digitally-programmable sensor assembly.                                                                                                                                                                                                                                                                                                                                                                            |

| 13      | SCL                                   | Clock input/output for Two-Wire, industry-standard compatible interface for reading and writing digital calibration and configuration from external EEPROM. Can also communicate directly to the registers in the PGA309 through the Two-Wire, industry-standard compatible interface.                                                                                                                                                                                                                                                                                                                                              |

| 14      | SDA                                   | Data input/output for Two-Wire, industry-standard compatible interface for reading and writing digital calibration and configuration from external EEPROM. Can also communicate directly to the registers in the PGA309 through the Two-Wire, industry-standard compatible interface.                                                                                                                                                                                                                                                                                                                                               |

| 15      | TEMP <sub>IN</sub>                    | External temperature signal input. PGA309 can be configured to read a bridge current sense resistor as an indicator of bridge temperature, or an external temperature sensing device such as diode junction, RTD, or thermistor. This input can be internally gained by 1, 2, 4, or 8. In addition, this input can be read differentially with respect to V <sub>GNDA</sub> , V <sub>EXC</sub> , or the internal/external V <sub>REF</sub> . There is also an internal, register-selectable, 7µA current source (I <sub>TEMP</sub> ) that can be connected to TEMP <sub>IN</sub> as an RTD, thermistor, or diode excitation source. |

| 16      | REF <sub>IN</sub> /REF <sub>OUT</sub> | Reference input/output pin. As an output, the internal reference (selectable as 2.5V or 4.096V) is available for system use on this pin. As an input, the internal reference may be disabled and an external reference can then be applied as the reference for the PGA309.                                                                                                                                                                                                                                                                                                                                                         |

ZHCSBQ8 - OCTOBER 2013 www.ti.com.cn

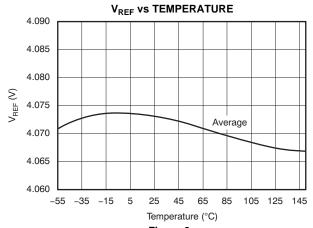

#### TYPICAL CHARACTERISTICS

$\text{At T}_{\text{A}} = +25 ^{\circ}\text{C}, \ V_{\text{SA}} = V_{\text{SD}} = +5 \text{V} \ (V_{\text{SA}} = V_{\text{SUPPLY ANALOG}}, \ V_{\text{SD}} = V_{\text{SUPPLY DIGITAL}}, \ V_{\text{SA}} \ \text{must equal V}_{\text{SD}}), \ \text{GND}_{\text{D}} = \text{GND}_{\text{A}} = 0, \ \text{and} \ V_{\text{REF}} = \text{REF}_{\text{IN}}/\text{REF}_{\text{OUT}} = +5 \text{V}, \ \text{unless otherwise noted}.$

Figure 2.

Figure 3.

Temperature (°C)

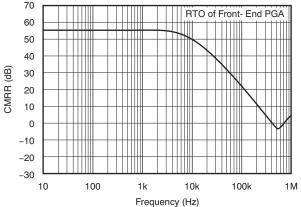

## **COMMON-MODE REJECTION RATIO vs FREQUENCY**

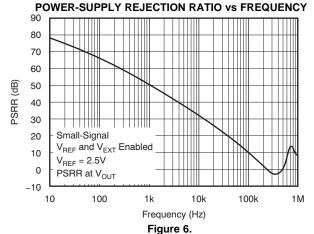

Figure 5.

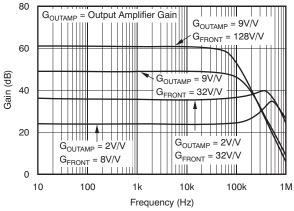

## **CLOSED-LOOP GAIN vs FREQUENCY**

Figure 7.

Instruments

ZHCSBQ8 – OCTOBER 2013 www.ti.com.cn

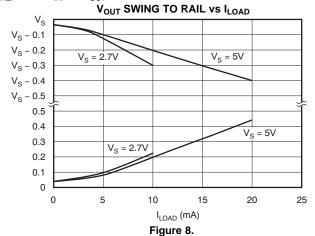

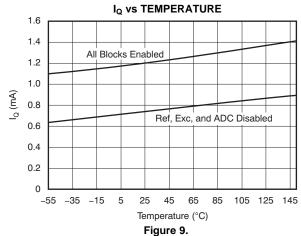

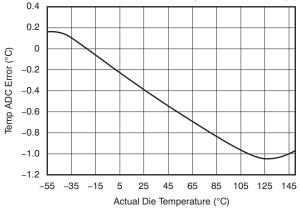

## TYPICAL CHARACTERISTICS (continued)

At  $T_A$  = +25°C,  $V_{SA}$  =  $V_{SD}$  = +5V ( $V_{SA}$  =  $V_{SUPPLY\ ANALOG}$ ,  $V_{SD}$  =  $V_{SUPPLY\ DIGITAL}$ ,  $V_{SA}$  must equal  $V_{SD}$ ),  $GND_D$  =  $GND_A$  = 0, and  $V_{REF}$  =  $REF_{IN}/REF_{OUT}$  = +5V, unless otherwise noted.

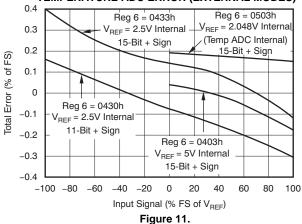

TEMPERATURE ADC ERROR (INTERNAL MODE)

TEMPERATURE ADC ERROR (EXTERNAL MODES)

Figure 10.

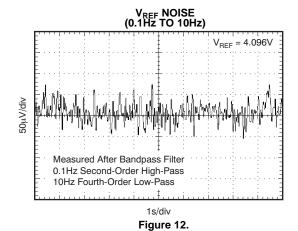

V<sub>OUT</sub> NOISE (0.1Hz TO 10Hz PEAK-TO-PEAK NOISE)

Figure 13.

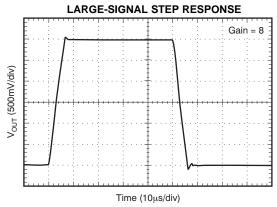

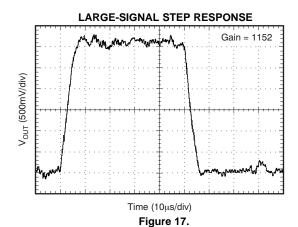

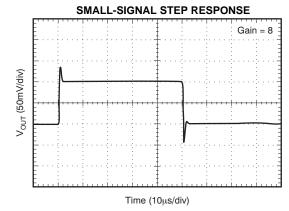

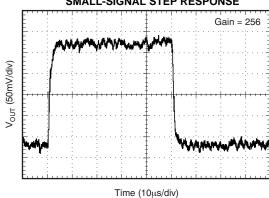

## **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25$ °C,  $V_{SA} = V_{SD} = +5$ V ( $V_{SA} = V_{SUPPLY\ ANALOG}$ ,  $V_{SD} = V_{SUPPLY\ DIGITAL}$ ,  $V_{SA}$  must equal  $V_{SD}$ ),  $GND_D = GND_A = 0$ , and  $V_{REF} = REF_{IN}/REF_{OUT} = +5$ V, unless otherwise noted.

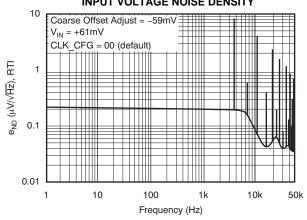

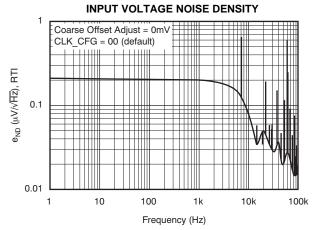

INPUT VOLTAGE NOISE DENSITY

INPUT VOLTAGE NOISE DENSITY

Figure 15.

Figure 16.

**SMALL-SIGNAL STEP RESPONSE**

Figure 18.

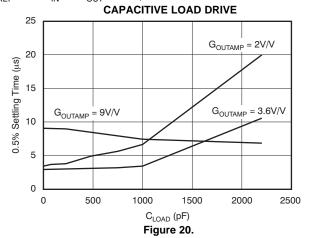

Figure 19.

ZHCSBQ8-OCTOBER 2013 www.ti.com.cn

**TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25$ °C,  $V_{SA} = V_{SD} = +5V$  ( $V_{SA} = V_{SUPPLY\ ANALOG}$ ,  $V_{SD} = V_{SUPPLY\ DIGITAL}$ ,  $V_{SA}$  must equal  $V_{SD}$ ),  $GND_D = GND_A = 0$ , and  $V_{REF} = REF_{IN}/REF_{OUT} = +5V$ , unless otherwise noted.

NSTRUMENTS

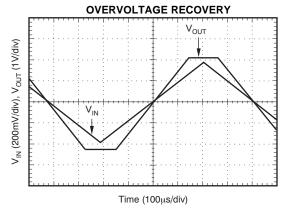

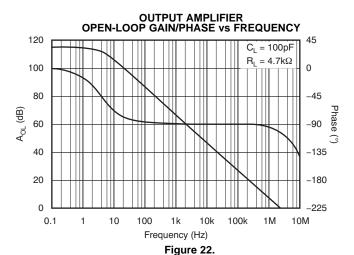

Figure 21.

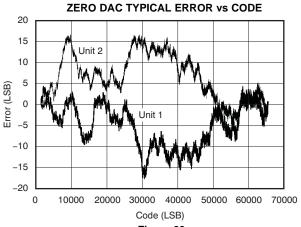

Figure 23.

Figure 24.

#### **FUNCTIONAL DESCRIPTION**

#### OVERVIEW

The PGA309 is a programmable analog signal conditioner designed for resistive bridge sensor applications. It is a complete signal conditioner with bridge excitation, initial span and offset adjustment, temperature adjustment of span and offset, internal/external temperature measurement capability, output over-scale and under-scale limiting, fault detection, and digital calibration. The PGA309, in a calibrated sensor module, can reduce errors to the level approaching the bridge sensor repeatability. See Figure 25 for a block diagram of the PGA309. Following is a brief overview of each major function.

#### SENSOR ERROR ADJUSTMENT RANGE

The adjustment capability of the PGA309 is summarized in Table 1.

**Table 1. PGA309 Adjustment Capability**

| FSS (full-scale sensitivity) | 1mV/V to 245mV/V                  |

|------------------------------|-----------------------------------|

| Span TC                      | Over ±3300ppmFS/°C <sup>(1)</sup> |

| Span TC nonlinearity         | ≥ 10%                             |

| Zero offset                  | ±200%FS <sup>(2)</sup>            |

| Zero offset TC               | Over ±3000ppmFS/°C <sup>(2)</sup> |

| Zero offset TC nonlinearity  | ≥ 10%                             |

| Sensor impedance             | Down to $200\Omega^{(3)}$         |

- 1. Depends on the temperature sensing scheme.

- 2. Combined coarse and fine offset adjust.

- 3. Lower impedance possible by using a dropping resistor in series with the bridge.

#### **GAIN SCALING**

The core of the PGA309 is the precision low-drift and no 1/f noise Front-End PGA. The overall gain of the Front-End PGA + Output Amplifier can be adjusted from 2.7V/V to 1152V/V. The polarity of the inputs can be switched through the 2x2 input mux to accommodate sensors with unknown polarity output.

The Front-End PGA provides initial coarse signal gain using a no 1/f noise, auto-zero instrumentation amplifier. The fine gain adjust is accomplished by the 16-bit attenuating Gain Digital-to-Analog Converter (Gain DAC). This Gain DAC is controlled by the data in the Temperature Compensation Lookup Table driven by the Temperature Analog-to-Digital

Converter (Temp ADC). In order to compensate for second-order and higher drift nonlinearity, the span drift can be fitted to piecewise linear curves during calibration with the coefficients stored in an external nonvolatile EEPROM lookup table.

Following the fine gain adjust stage is the Output Amplifier that provides additional programmable gain. Two key output amplifier connections,  $V_{FB}$  and  $V_{SJ}$ , are brought out on the PGA309 for application flexibility. These connections allow for an accurate conditioned signal voltage while also providing a means for PGA309 output overvoltage and large capacitive loading for RFI/EMI filtering required in many end applications.

#### **OFFSET ADJUSTMENT**

The sensor offset adjustment is performed in two stages. The input-referred Coarse Offset Adjust DAC has approximately a  $\pm 60 \text{mV}$  offset adjustment range for a selected  $V_{\text{REF}}$  of 5V. The fine offset and the offset drift are canceled by the 16-bit Zero DAC that sums the signal with the output of the front-end instrumentation amplifier. Similar to the Gain DAC, the input digital values of the Zero DAC are controlled by the data in the Temperature Compensation Lookup Table, stored in external EEPROM, driven by the Temp ADC. The programming range of the Zero DAC is 0V to  $V_{\text{REF}}$  with an output range of 0.1V to  $V_{\text{SA}}-0.1\text{V}$ .

#### **VOLTAGE REFERENCE**

The PGA309 contains a precision low-drift voltage reference (selectable for 2.5V or 4.096V) that can be used for external circuitry through the  $\text{REF}_{\text{IN}}/\text{REF}_{\text{OUT}}$  pin. This same reference is used for the Coarse Offset Adjust DAC, Zero DAC, Over/Under-Scale Limits and sensor excitation/linearization through the  $V_{\text{EXC}}$  pin. When the internal reference is disabled, the  $\text{REF}_{\text{IN}}/\text{REF}_{\text{OUT}}$  pin should be connected to an external reference or to  $V_{\text{SA}}$  for ratiometric-scaled systems.

#### SENSOR EXCITATION AND LINEARIZATION