# ADS5474-SP 五类 14 位 400MSPS 模数转换器

## 1 特性

- 采样率：400MSPS

- 14 位分辨率，10.9 位有效位数 (ENOB)

- 5962R13208：

- 耐辐射保障 (RHA)：高达 TID 100krad (Si)

- 电离辐射总剂量：100krad (Si)

- 无 ELDRS：100krad (Si)

- SEL/SEU 表征

- 输入带宽：1.28GHz

- 230MHz 和 400MSPS 时为 SFDR = 78dBc

- 230MHz 和 400MSPS 时为 SNR = 69.8dBFS

- 差分输入电压：2.2V<sub>PP</sub>

- 兼容 LVDS 的输出

- 总功率耗散：2.5W

- 断电模式：50mW

- 偏移二进制输出格式

- 输出数据在半速率输出时钟的上升沿及下降沿进行转换

- 片上模拟缓冲器、跟踪保持及基准电路

- 提供 84 针陶瓷非导电连接杆封装 (HFG)

- 军用级温度范围：-55°C 至 125°C T<sub>case</sub>

- 可提供工程评估 (/EM) 样片 <sup>1</sup>

- 引脚相似并与 12 位及 14 位系列兼容：[ADS5463-SP](#) 和 [ADS5444-SP](#)

## 2 应用

- 测试和测量仪表

- 软件定义无线电

- 数据采集

- 功率放大器线性化

- 通信仪表

- 雷达

## 3 说明

ADS5474 是一款 14 位 400MSPS 模数转换器 (ADC)，可由 5V 电源和 3.3V 电源供电，同时提供与 LVDS 兼容的数字输出。该 ADC 是 12 位、13 位、14 位 ADC 系列之一，运行速度为 210MSPS 至 500MSPS。ADS5474 输入缓冲器使板载跟踪和保持 (T&H) 功能的内部切换不会干扰信号源并提供一个高阻抗输入。此外，还提供了一个内部基准发生器，以简化系统设计。

ADS5474 具有 1.4GHz 的输入带宽，用于转换超过 400MSPS 输入频率 400MHz 的宽带宽信号，可在宽输入频率范围内提供出色的低噪声性能和无杂散动态范围。

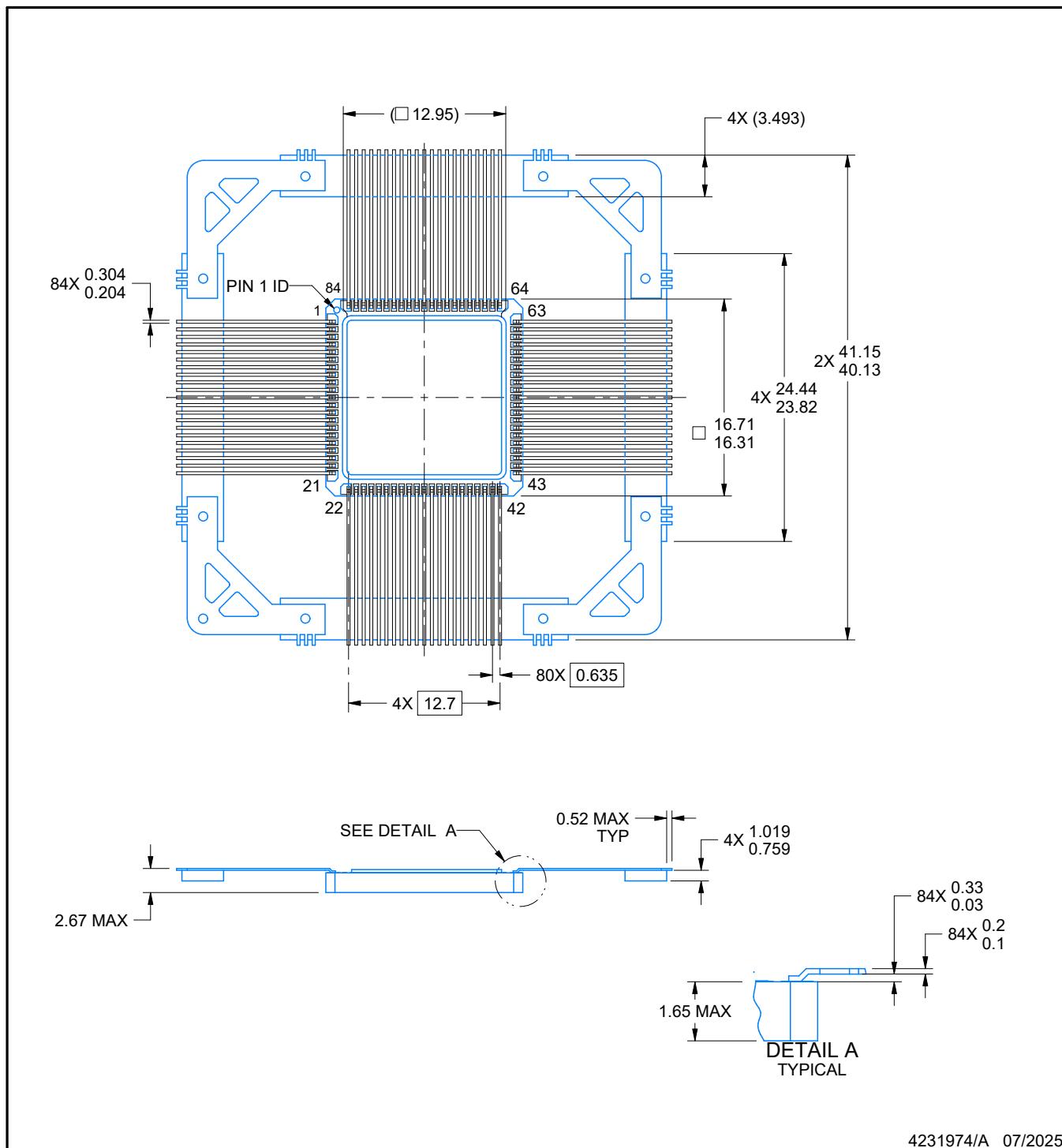

ADS5474 采用 84 针陶瓷非导电连接杆封装 (HFG)。该器件以德州仪器 (TI) 互补双极工艺 (BiCom3) 为基础，在整个军用温度范围内 (-55°C 至 125°C T<sub>case</sub>) 指定。

### 封装信息

| 器件型号       | 封装 <sup>(1)</sup> | 封装尺寸 <sup>(2)</sup> |

|------------|-------------------|---------------------|

| ADS5474-SP | CFP ( HFG , 84 )  | 19.05mm × 19.05mm   |

(1) 有关所有可用封装，请参阅节 10。

(2) 封装尺寸 (长 × 宽) 为标称值，并包括引脚 (如适用)。

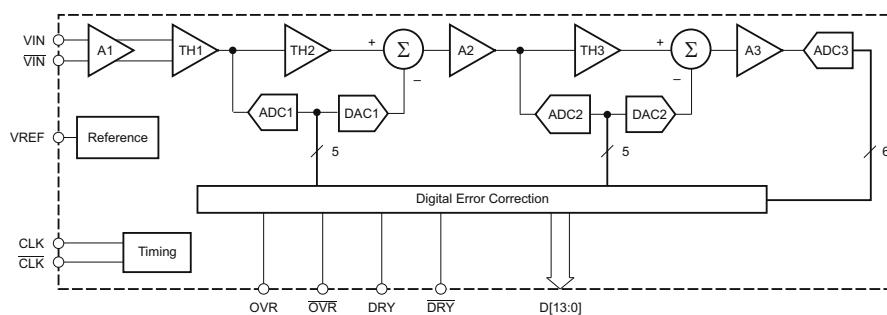

简化版原理图

<sup>1</sup> 这些器件仅适用于工程评估。以非合规性流程对其进行处理（例如，未进行老化处理），并且仅在 25°C 的额定温度下进行了测试。这些器件不适用于鉴定、量产、辐射测试或飞行用途。也不保证这些器件在 MIL 规定的 -55°C 至 125°C 完整温度范围内或运行寿命中的性能。

本资源的原文使用英文撰写。为方便起见，TI 提供了译文；由于翻译过程中可能使用了自动化工具，TI 不保证译文的准确性。为确认准确性，请务必访问 [ti.com](http://ti.com) 参考最新的英文版本（控制文档）。

## 内容

|                  |           |                       |           |

|------------------|-----------|-----------------------|-----------|

| <b>1 特性</b>      | <b>1</b>  | 6.1 概述                | <b>16</b> |

| <b>2 应用</b>      | <b>1</b>  | <b>7 应用和实施</b>        | <b>22</b> |

| <b>3 说明</b>      | <b>1</b>  | 7.1 电源相关建议            | <b>22</b> |

| <b>4 引脚配置和功能</b> | <b>3</b>  | <b>8 器件和文档支持</b>      | <b>24</b> |

| <b>5 规格</b>      | <b>5</b>  | 8.1 器件支持              | <b>24</b> |

| 5.1 绝对最大额定值      | 5         | 8.2 文档支持              | <b>25</b> |

| 5.2 ESD 等级       | 5         | 8.3 接收文档更新通知          | <b>25</b> |

| 5.3 建议运行条件       | 5         | 8.4 支持资源              | <b>25</b> |

| 5.4 热性能信息        | 6         | 8.5 商标                | <b>25</b> |

| 5.5 电气特性         | 6         | 8.6 静电放电警告            | <b>25</b> |

| 5.6 计时特点         | 10        | 8.7 术语表               | <b>25</b> |

| 5.7 典型特性         | 11        | <b>9 修订历史记录</b>       | <b>25</b> |

| <b>6 详细说明</b>    | <b>16</b> | <b>10 机械、封装和可订购信息</b> | <b>26</b> |

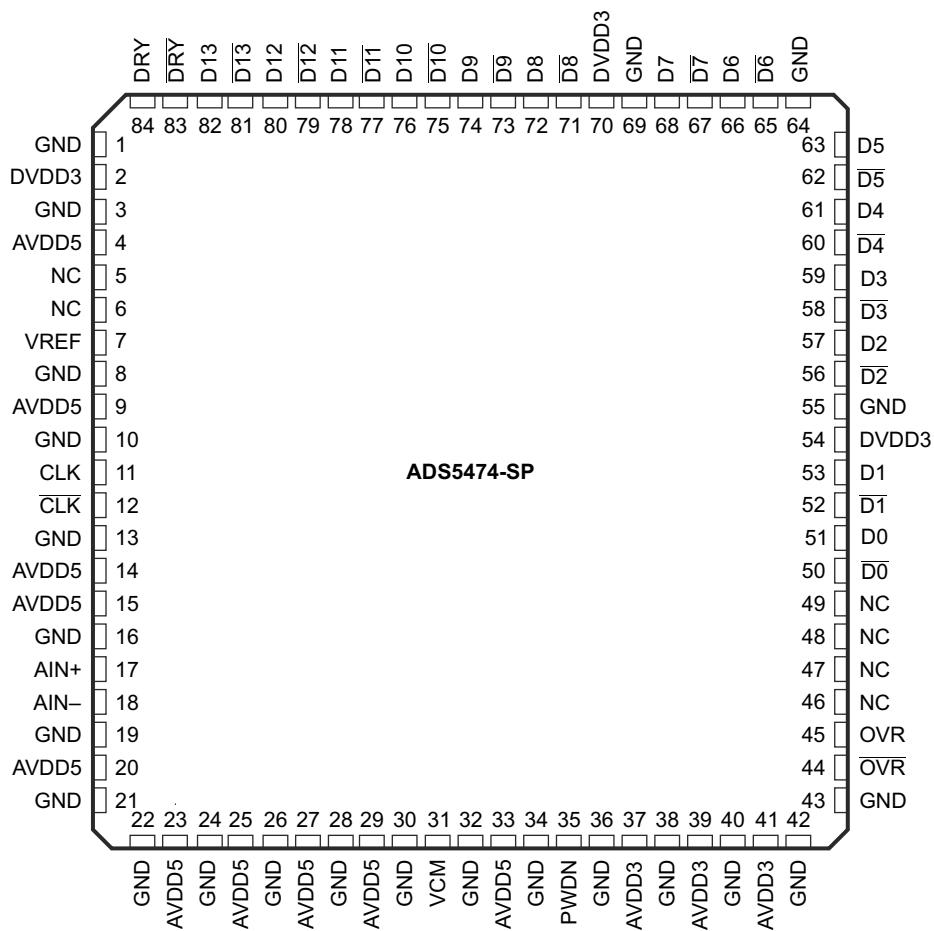

## 4 引脚配置和功能

图 4-1. HFG 封装，84 引脚 CFP (俯视图)

表 4-1. 引脚功能

| 引脚                                     |                                      | 类型 <sup>(1)</sup> | 说明                     |

|----------------------------------------|--------------------------------------|-------------------|------------------------|

| 名称                                     | 编号                                   |                   |                        |

| AIN                                    | 17                                   | I                 | 差分输入信号 (正)             |

| AIN                                    | 18                                   | I                 | 差分输入信号 (负)             |

| AVDD3                                  | 37、39、41                             | P                 | 模拟电源 (3.3V)            |

| AVDD5                                  | 4、9、14、15、<br>20、23、25、<br>27、29、33  | P                 | 模拟电源 (5V)              |

| CLK                                    | 11                                   | I                 | 差分输入时钟 (正)。在上升沿上启动转换。  |

| CLK                                    | 12                                   | I                 | 差分输入时钟 (负)             |

| D0、D0                                  | 50、51                                | O                 | LVDS 数字输出对、最低有效位 (LSB) |

| D1、D1、<br>D2 - D5、<br>D6-D7、<br>D8-D12 | 52、53、56 -<br>63、65 - 68、<br>71 - 82 | O                 | LVDS 数字输出对             |

| D13、D13                                | 81、82                                | O                 | LVDS 数字输出对，最高有效位 (MSB) |

| DRY、DRY                                | 84、83                                | O                 | 数据就绪 LVDS 输出对          |

| DVDD3                                  | 2、54、70                              | P                 | 数字和输出驱动器电源 (3.3V)      |

表 4-1. 引脚功能 (续)

| 引脚                  |                                                                                           | 类型 <sup>(1)</sup> | 说明                                                                                                          |

|---------------------|-------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------|

| 名称                  | 编号                                                                                        |                   |                                                                                                             |

| GND                 | 1、3、8、10、<br>13、16、19、<br>21、22、24、<br>26、28、30、<br>32、34、36、<br>38、40、42、<br>43、55、64、69 | GND               | 接地                                                                                                          |

| NC                  | 5、6、46、47、<br>48、49                                                                       | 不适用               | 无连接                                                                                                         |

| OVR、OV <sub>R</sub> | 45、44                                                                                     | O                 | 超范围指示器 LVDS 输出。逻辑高电平表示模拟输入超过满量程范围。                                                                          |

| PDWN                | 35                                                                                        | I                 | 断电 (高电平有效)。当 PDWN 引脚为逻辑高电平时，器件处于睡眠模式。当 PDWN 为逻辑低电平 (接地) 时，ADC 转换器唤醒。<br>(此引脚未在 ADS5463-SP 及 ADS5444-SP 上使用) |

| VCM                 | 31                                                                                        | O                 | 共模电压输出 (标称值为 3.1V)。通常用于直流耦合应用，可将输入信号设置为正确的共模电压。<br>(此引脚未在 ADS5463-SP 及 ADS5444-SP 上使用)                      |

| VREF                | 7                                                                                         | I/O               | 基准电压输入/输出 (标称 2.4V)                                                                                         |

(1) I = 输入、O = 输出、GND = 接地、P = 电源、I/O = 双向、N/A = 不适用

## 5 规格

### 5.1 绝对最大额定值

在自然通风条件下的工作温度范围内测得 (除非另有说明) <sup>(1)</sup>

|                   |                  | 最小值  | 最大值         | 单位 |

|-------------------|------------------|------|-------------|----|

| 电源电压              | AVDD5 至 GND      |      | 6           | V  |

|                   | AVDD3 至 GND      |      | 5           | V  |

|                   | DVDD3 至 GND      |      | 5           | V  |

| 模拟输入至 GND         |                  | -0.3 | AVDD5 + 0.3 | V  |

| 时钟输入至 GND         |                  | -0.3 | AVDD5 + 0.3 | V  |

| CLK 至 $\bar{CLK}$ |                  | -2.5 | 2.5         | V  |

| 数字数据输出至 GND       |                  | -0.3 | DVDD3 + 0.3 | V  |

| 工作外壳温度            | T <sub>C</sub>   | -55  | 125         | °C |

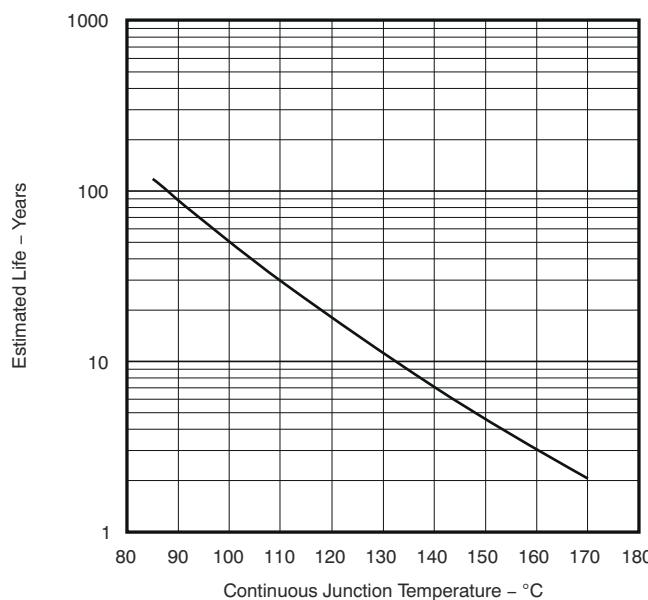

| 最大结温              | T <sub>J</sub>   |      | 150         | °C |

| 贮存温度              | T <sub>stg</sub> | -65  | 150         | °C |

- (1) 超出绝对最大额定值范围操作可能会导致器件永久损坏。绝对最大额定值并不表示器件在这些条件下或在建议的工作条件以外的任何其他条件下能够正常运行。如果超出建议运行条件但在绝对最大额定值范围内使用，器件可能不会完全正常运行，这可能影响器件的可靠性、功能和性能并缩短器件寿命。

### 5.2 ESD 等级

|                    |      | 值                                                        | 单位     |

|--------------------|------|----------------------------------------------------------|--------|

| V <sub>(ESD)</sub> | 静电放电 | 人体放电模型 (HBM)，符合 ANSI/ESDA/JEDEC JS-001 标准 <sup>(1)</sup> | 2000 V |

- (1) JEDEC 文档 JEP155 指出：500V HBM 时能够在标准 ESD 控制流程下安全生产。

### 5.3 建议运行条件

|                            |           | 最小值               | 标称值 | 最大值  | 单位              |

|----------------------------|-----------|-------------------|-----|------|-----------------|

| <b>电源</b>                  |           |                   |     |      |                 |

| AVDD5                      | 模拟电源电压    | 4.75              | 5   | 5.25 | V               |

| AVDD3                      | 模拟电源电压    | 3.1               | 3.3 | 3.6  | V               |

| DVDD3                      | 输出驱动器电源电压 | 3                 | 3.3 | 3.6  | V               |

| <b>模拟输入</b>                |           |                   |     |      |                 |

| 差分输入范围                     |           |                   | 2.2 |      | V <sub>PP</sub> |

| VCM                        | 输入共模      |                   | 3.1 |      | V               |

| <b>数字输出 (DRY、DATA、OVR)</b> |           |                   |     |      |                 |

| 最大差分输出负载                   |           |                   | 10  |      | pF              |

| <b>时钟输入 (CLK)</b>          |           |                   |     |      |                 |

| CLK 输入采样速率 (正弦波)           |           | 20 <sup>(1)</sup> |     | 400  | MSPS            |

| 时钟幅度，差分正弦波 <sup>(1)</sup>  |           | 0.5               |     | 5    | V <sub>PP</sub> |

| 时钟占空比 <sup>(1)</sup>       |           | 40%               | 50% | 60%  |                 |

| T <sub>C</sub>             | 工作外壳温度范围  | -55               |     | 125  | °C              |

- (1) 参数由特征确定，但未经过生产测试。

## 5.4 热性能信息

(1)

| 热指标                    | 测试条件                            | 典型值   | 单位                   |

|------------------------|---------------------------------|-------|----------------------|

| $R_{\theta JA}$ 结至大气热阻 | 结至外壳热阻<br>MIL-STD-883 测试方法 1012 | 21.81 | $^{\circ}\text{C/W}$ |

| $R_{\theta JC}$ 结至外壳热阻 |                                 | 0.849 |                      |

(1) 此 CQFP 封装具有内置过孔，可在电气和热方面将芯片底部连接到封装底部的焊盘。为了有效地散热并提供低阻抗接地路径，需要在 PCB 表面的正下方安装一个导热焊盘。在正常的表面贴装流动焊接操作中，封装底部的散热焊盘被焊接到该导热焊盘上，从而形成高效的散热路径。通常，PCB 散热焊盘内有多个散热过孔，内部覆铜区域（或 PCB 另一侧）提供散热路径，从而实现更高效的散热。TI 一般建议使用  $11.9\text{mm}^2$  板散散热焊盘。这样可实现更大的散热面积，同时使引线远离焊盘区域，以防止焊料桥接。必须包含足够数量的散热/电气过孔，以使器件保持在建议的工作条件下。此焊盘必须处在电气接地电位。

## 5.5 电气特性

典型值，除非另有说明，条件为  $T_C = 25^{\circ}\text{C}$ ，整个温度范围  $T_{C,\text{MIN}} = -55^{\circ}\text{C}$  至  $T_{C,\text{MAX}} = 125^{\circ}\text{C}$ 、采样率 = 400MSPS、50% 时钟占空比、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V、-1dBFS 差分输入，以及  $3V_{PP}$  差分时钟。

| 参数                                     | 测试条件                                                               | 最小值   | 典型值       | 最大值   | 单位                           |

|----------------------------------------|--------------------------------------------------------------------|-------|-----------|-------|------------------------------|

| 分辨率                                    |                                                                    |       | 14        |       | 位                            |

| <b>模拟输入</b>                            |                                                                    |       |           |       |                              |

| 差分输入范围                                 |                                                                    |       | 2.2       |       | $V_{PP}$                     |

| 模拟输入共模电压                               | 自偏置；请参阅下面的 VCM 规格                                                  |       | 3.1       |       | V                            |

| 输入电阻（直流）                               | 每个输入至 VCM                                                          |       | 500       |       | $\Omega$                     |

| 输入电容                                   | 每个输入至 GND                                                          |       | 2.8       |       | pF                           |

| 模拟输入带宽 (-3dB)                          |                                                                    |       | 1.28      |       | GHz                          |

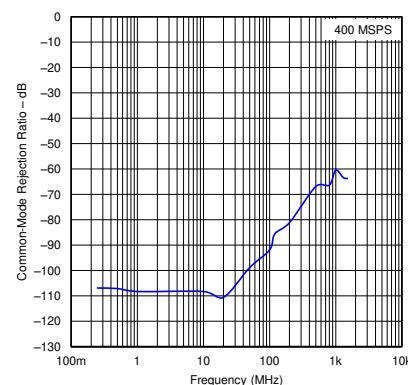

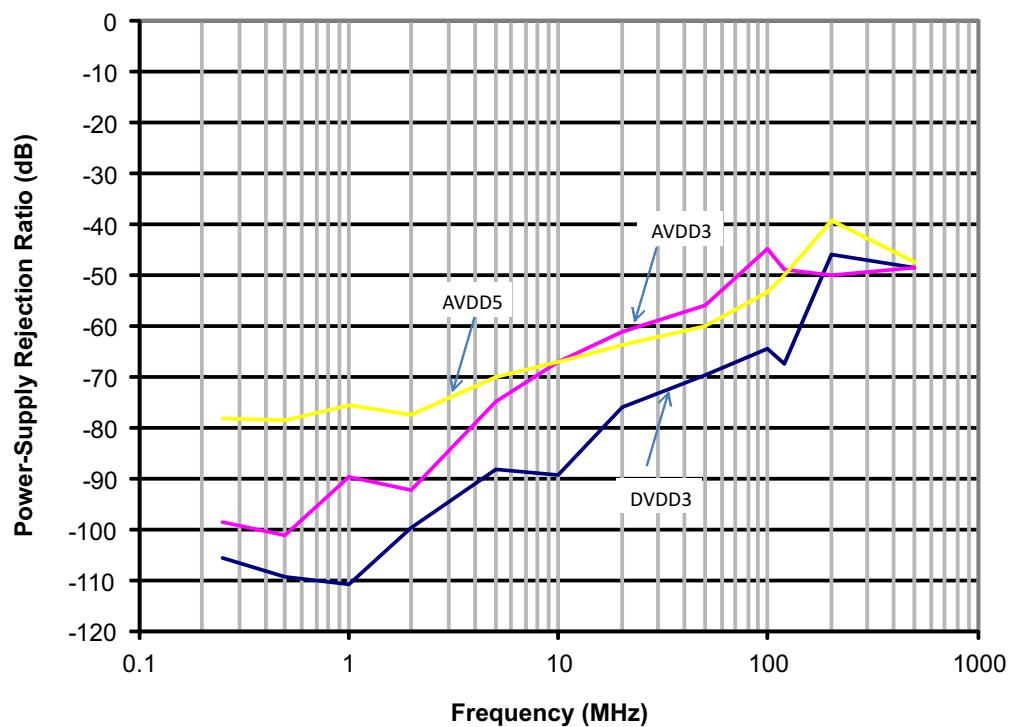

| CMRR 共模抑制比                             | 共模信号 < 50MHz<br>( 请参阅图 5-28 )                                      |       | 100       |       | dB                           |

| <b>内部基准电压</b>                          |                                                                    |       |           |       |                              |

| VREF 基准电压                              |                                                                    |       | 2.4       |       | V                            |

| VCM 模拟输入共模电压基准输出                       | 具有内部 VREF。通过 VCM 引脚提供作为输出，适用于直流耦合应用。                               | 2.9   | 3.1       | 3.3   | V                            |

| VCM 温度系数                               |                                                                    |       | -0.8      |       | $\text{mV}/^{\circ}\text{C}$ |

| <b>动态精度</b>                            |                                                                    |       |           |       |                              |

| 无丢码                                    |                                                                    |       |           | 保障式   |                              |

| DNL 微分线性误差                             | $f_{IN} = 10\text{MHz}$                                            | -0.99 | $\pm 0.7$ | 2.5   | LSB                          |

| INL 积分线性误差                             | $f_{IN} = 10\text{MHz}$                                            | -7.0  | $\pm 1.5$ | 7.0   | LSB                          |

| 偏移误差                                   |                                                                    | -16   |           | 16    | mV                           |

| 偏移温度系数                                 |                                                                    |       | 0.02      |       | $\text{mV}/^{\circ}\text{C}$ |

| 增益误差                                   |                                                                    | -5    |           | 5     | %FS                          |

| 增益温度系数                                 |                                                                    |       | -0.02     |       | %FS/ $^{\circ}\text{C}$      |

| <b>电源</b>                              |                                                                    |       |           |       |                              |

| $I_{AVDD5}$ 5V 模拟电源电流                  | $V_{IN} = \text{满量程}, f_{IN} = 70\text{MHz}, f_S = 400\text{MSPS}$ |       | 338       | 380   | mA                           |

| $I_{AVDD3}$ 3.3V 模拟电源电流                |                                                                    |       | 185       | 210   | mA                           |

| $I_{DVDD3}$ 3.3V 数字电源电流<br>( 包括 LVDS ) |                                                                    |       | 75        | 85    | mA                           |

| 总功率损耗                                  |                                                                    |       | 2.5       | 2.835 | W                            |

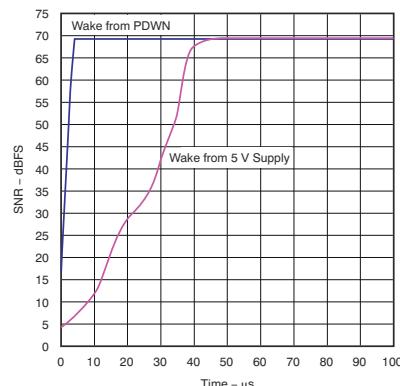

| 上电时间                                   | 自 AVDD5 导通                                                         |       | 50        |       | $\mu\text{s}$                |

| 唤醒时间                                   | 从 PDWN 引脚从高电平 ( PDWN 激活 ) 切换到低电平 ( ADC 唤醒 )<br>( 请参阅图 5-29 )       |       | 5         |       | $\mu\text{s}$                |

## 5.5 电气特性 (续)

典型值，除非另有说明，条件为  $T_C = 25^\circ\text{C}$ ，整个温度范围  $T_{C,\text{MIN}} = -55^\circ\text{C}$  至  $T_{C,\text{MAX}} = 125^\circ\text{C}$ 、采样率 = 400MSPS、50% 时钟占空比、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V、-1dBFS 差分输入，以及 3V<sub>PP</sub> 差分时钟。

| 参数                  | 测试条件                            | 最小值 | 典型值 | 最大值 | 单位 |

|---------------------|---------------------------------|-----|-----|-----|----|

| 断电功率耗散              | PDWN 引脚 = 逻辑高电平                 |     | 50  | 350 | mW |

| PSRR 电源抑制比，AVDD5 电源 |                                 |     | 75  |     | dB |

| PSRR 电源抑制比，AVDD3 电源 | 如果没有 0.1 μF 板电源电容器，且电源噪声 < 1MHz |     | 90  |     | dB |

| PSRR 电源抑制比，DVDD3 电源 |                                 |     | 110 |     | dB |

### 动态交流特性

|      |         |                                 |      |      |

|------|---------|---------------------------------|------|------|

| SNR  | 信噪比     | $f_{\text{IN}} = 30\text{MHz}$  | 70.5 | dBFS |

|      |         | $f_{\text{IN}} = 70\text{MHz}$  | 65   |      |

|      |         | $f_{\text{IN}} = 130\text{MHz}$ | 69.9 |      |

|      |         | $f_{\text{IN}} = 230\text{MHz}$ | 65   |      |

|      |         | $f_{\text{IN}} = 351\text{MHz}$ | 69.2 |      |

|      |         | $f_{\text{IN}} = 451\text{MHz}$ | 68.8 |      |

|      |         | $f_{\text{IN}} = 651\text{MHz}$ | 67.3 |      |

|      |         | $f_{\text{IN}} = 751\text{MHz}$ | 66.6 |      |

|      |         | $f_{\text{IN}} = 999\text{MHz}$ | 64.4 |      |

|      |         |                                 |      |      |

| SFDR | 无杂散动态范围 | $f_{\text{IN}} = 30\text{MHz}$  | 79.4 | dBc  |

|      |         | $f_{\text{IN}} = 70\text{MHz}$  | 69   |      |

|      |         | $f_{\text{IN}} = 130\text{MHz}$ | 78.8 |      |

|      |         | $f_{\text{IN}} = 230\text{MHz}$ | 64.5 |      |

|      |         | $f_{\text{IN}} = 351\text{MHz}$ | 74.3 |      |

|      |         | $f_{\text{IN}} = 451\text{MHz}$ | 70.5 |      |

|      |         | $f_{\text{IN}} = 651\text{MHz}$ | 58.6 |      |

|      |         | $f_{\text{IN}} = 751\text{MHz}$ | 54.3 |      |

|      |         | $f_{\text{IN}} = 999\text{MHz}$ | 46   |      |

|      |         |                                 |      |      |

| HD2  | 二次谐波    | $f_{\text{IN}} = 30\text{MHz}$  | 92   | dBc  |

|      |         | $f_{\text{IN}} = 70\text{MHz}$  | 87   |      |

|      |         | $f_{\text{IN}} = 130\text{MHz}$ | 87   |      |

|      |         | $f_{\text{IN}} = 230\text{MHz}$ | 84   |      |

|      |         | $f_{\text{IN}} = 351\text{MHz}$ | 77   |      |

|      |         | $f_{\text{IN}} = 451\text{MHz}$ | 75   |      |

|      |         | $f_{\text{IN}} = 651\text{MHz}$ | 68   |      |

|      |         | $f_{\text{IN}} = 751\text{MHz}$ | 64   |      |

|      |         | $f_{\text{IN}} = 999\text{MHz}$ | 53   |      |

|      |         |                                 |      |      |

## 5.5 电气特性 (续)

典型值，除非另有说明，条件为  $T_C = 25^\circ\text{C}$ ，整个温度范围  $T_{C,\text{MIN}} = -55^\circ\text{C}$  至  $T_{C,\text{MAX}} = 125^\circ\text{C}$ 、采样率 = 400MSPS、50% 时钟占空比、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V、-1dBFS 差分输入，以及 3V<sub>PP</sub> 差分时钟。

| 参数                          | 测试条件                            | 最小值  | 典型值  | 最大值 | 单位  |

|-----------------------------|---------------------------------|------|------|-----|-----|

| HD3 三次谐波                    | $f_{\text{IN}} = 30\text{MHz}$  | 81   |      |     | dBc |

|                             | $f_{\text{IN}} = 70\text{MHz}$  | 86   |      |     |     |

|                             | $f_{\text{IN}} = 130\text{MHz}$ | 80   |      |     |     |

|                             | $f_{\text{IN}} = 230\text{MHz}$ | 80   |      |     |     |

|                             | $f_{\text{IN}} = 351\text{MHz}$ | 76   |      |     |     |

|                             | $f_{\text{IN}} = 451\text{MHz}$ | 72   |      |     |     |

|                             | $f_{\text{IN}} = 651\text{MHz}$ | 60   |      |     |     |

|                             | $f_{\text{IN}} = 751\text{MHz}$ | 56   |      |     |     |

|                             | $f_{\text{IN}} = 999\text{MHz}$ | 48   |      |     |     |

| 最差谐波/杂散<br>( HD2 及 HD3 除外 ) | $f_{\text{IN}} = 30\text{MHz}$  | 93   |      |     | dBc |

|                             | $f_{\text{IN}} = 70\text{MHz}$  | 91   |      |     |     |

|                             | $f_{\text{IN}} = 130\text{MHz}$ | 91   |      |     |     |

|                             | $f_{\text{IN}} = 230\text{MHz}$ | 88   |      |     |     |

|                             | $f_{\text{IN}} = 351\text{MHz}$ | 87   |      |     |     |

|                             | $f_{\text{IN}} = 451\text{MHz}$ | 87   |      |     |     |

|                             | $f_{\text{IN}} = 651\text{MHz}$ | 91   |      |     |     |

|                             | $f_{\text{IN}} = 751\text{MHz}$ | 87   |      |     |     |

|                             | $f_{\text{IN}} = 999\text{MHz}$ | 80   |      |     |     |

| THD 总谐波失真                   | $f_{\text{IN}} = 30\text{MHz}$  | 77   |      |     | dBc |

|                             | $f_{\text{IN}} = 70\text{MHz}$  | 73.5 |      |     |     |

|                             | $f_{\text{IN}} = 130\text{MHz}$ | 74.9 |      |     |     |

|                             | $f_{\text{IN}} = 230\text{MHz}$ | 74.9 |      |     |     |

|                             | $f_{\text{IN}} = 351\text{MHz}$ | 71.3 |      |     |     |

|                             | $f_{\text{IN}} = 451\text{MHz}$ | 68.4 |      |     |     |

|                             | $f_{\text{IN}} = 651\text{MHz}$ | 57.8 |      |     |     |

|                             | $f_{\text{IN}} = 751\text{MHz}$ | 53.6 |      |     |     |

|                             | $f_{\text{IN}} = 999\text{MHz}$ | 45   |      |     |     |

| SINAD 信噪比和失真                | $f_{\text{IN}} = 30\text{MHz}$  | 69.8 |      |     | dBc |

|                             | $f_{\text{IN}} = 70\text{MHz}$  | 62.5 | 67.7 |     |     |

|                             | $f_{\text{IN}} = 130\text{MHz}$ | 68.9 |      |     |     |

|                             | $f_{\text{IN}} = 230\text{MHz}$ | 60.5 | 68.9 |     |     |

|                             | $f_{\text{IN}} = 351\text{MHz}$ | 67.5 |      |     |     |

|                             | $f_{\text{IN}} = 451\text{MHz}$ | 66.1 |      |     |     |

|                             | $f_{\text{IN}} = 651\text{MHz}$ | 58.2 |      |     |     |

|                             | $f_{\text{IN}} = 751\text{MHz}$ | 54.3 |      |     |     |

|                             | $f_{\text{IN}} = 999\text{MHz}$ | 45.9 |      |     |     |

## 5.5 电气特性 (续)

典型值，除非另有说明，条件为  $T_C = 25^\circ\text{C}$ ，整个温度范围  $T_{C,\text{MIN}} = -55^\circ\text{C}$  至  $T_{C,\text{MAX}} = 125^\circ\text{C}$ 、采样率 = 400MSPS、50% 时钟占空比、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V、-1dBFS 差分输入，以及 3V<sub>PP</sub> 差分时钟。

| 参数                               | 测试条件                                                                                         | 最小值   | 典型值   | 最大值 | 单位            |

|----------------------------------|----------------------------------------------------------------------------------------------|-------|-------|-----|---------------|

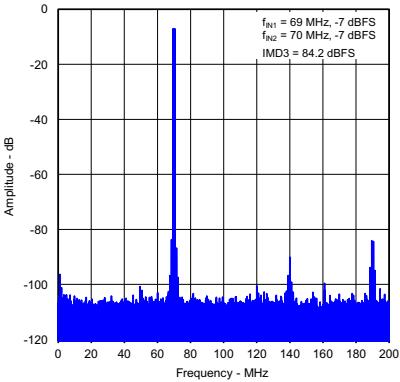

| 双音 SFDR                          | $f_{\text{IN}1} = 69\text{MHz}$ , $f_{\text{IN}2} = 70\text{MHz}$ ,<br>每个单音幅度为 -7dBFS        | 84.2  |       |     | dBFS          |

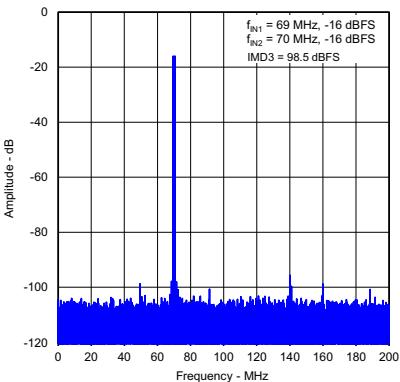

|                                  | $f_{\text{IN}1} = 69\text{MHz}$ , $f_{\text{IN}2} = 70\text{MHz}$ ,<br>每个单音幅度为 -16dBFS       | 98.5  |       |     |               |

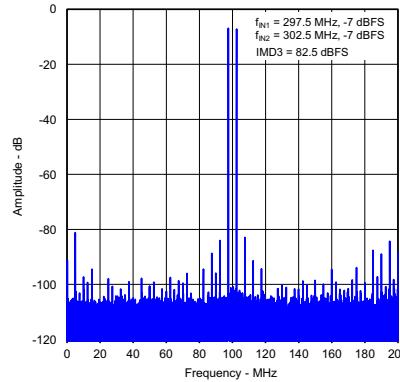

|                                  | $f_{\text{IN}1} = 297.5\text{MHz}$ , $f_{\text{IN}2} = 302.5\text{MHz}$ ,<br>每个单音幅度为 -7dBFS  | 82.5  |       |     |               |

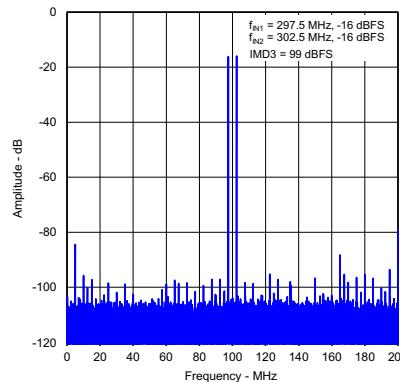

|                                  | $f_{\text{IN}1} = 297.5\text{MHz}$ , $f_{\text{IN}2} = 302.5\text{MHz}$ ,<br>每个单音幅度为 -16dBFS | 99    |       |     |               |

| ENOB 有效位数                        | $f_{\text{IN}} = 70\text{MHz}$                                                               | 10.1  | 10.9  |     | 位             |

|                                  | $f_{\text{IN}} = 230\text{MHz}$                                                              | 9.77  | 10.5  |     |               |

| RMS 空闲通道噪声                       | 连接到共模的输入                                                                                     | 1.8   |       |     | LSB           |

| <b>LVDS 数字输出</b>                 |                                                                                              |       |       |     |               |

| V <sub>OD</sub> 差分输出电压 ( $\pm$ ) |                                                                                              | 247   | 350   | 454 | mV            |

| V <sub>OC</sub> 共模输出电压           |                                                                                              | 1.115 | 1.375 |     | V             |

| <b>数字输入</b>                      |                                                                                              |       |       |     |               |

| V <sub>IH</sub> 高电平输入电压          | PWD ( 引脚 33 )                                                                                | 2.0   |       |     | V             |

| V <sub>IL</sub> 低电平输入电压          |                                                                                              | 0.8   |       |     | V             |

| I <sub>IH</sub> 高电平输入电流          |                                                                                              | 1     |       |     | $\mu\text{A}$ |

| I <sub>IL</sub> 低电平输入电流          |                                                                                              | -1    |       |     | $\mu\text{A}$ |

| C <sub>IN</sub> 输入电容             |                                                                                              | 2.2   |       |     | pF            |

图 5-1. 工作寿命降额表，电迁移失败模式

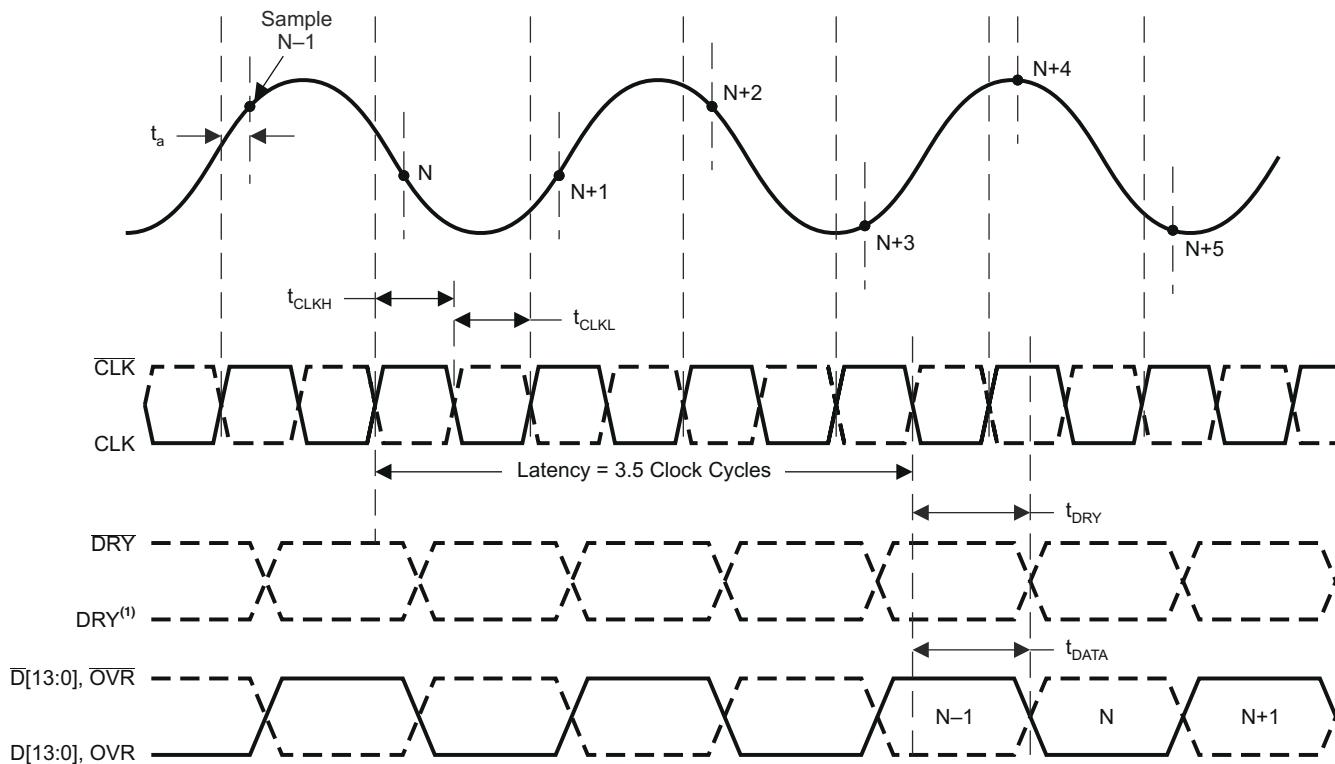

## 5.6 计时特点

典型值，除非另有说明，条件为  $T_C = 25^\circ\text{C}$ ，整个温度范围  $T_{C,\text{MIN}} = -55^\circ\text{C}$  至  $T_{C,\text{MAX}} = 125^\circ\text{C}$ 、采样率 = 400MSPS、50% 时钟占空比、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V、3V<sub>PP</sub> 差分时钟。

| 参数 <sup>(1)</sup>                                  | 测试条件                                                            | 最小值  | 典型值  | 最大值  | 单位 |

|----------------------------------------------------|-----------------------------------------------------------------|------|------|------|----|

| $t_a$ 孔径延迟                                         |                                                                 |      | 200  |      | ps |

| 孔径抖动, rms                                          | ADC 的内部抖动                                                       |      | 103  |      | fs |

| 延迟                                                 |                                                                 |      | 3.5  |      | 周期 |

| $t_{\text{CLK}}$ 时钟周期                              |                                                                 | 2.5  | 50   |      | ns |

| $t_{\text{CLKH}}$ 时钟脉冲持续时间, 高电平                    |                                                                 | 1    |      |      | ns |

| $t_{\text{CLKL}}$ 时钟脉冲持续时间, 低电平                    |                                                                 | 1    |      |      | ns |

| $t_{\text{DRY}}$ CLK 至 DRY 延迟 <sup>(2)</sup>       | 过零, 每个输出引脚上连接到 GND 的 10pF 寄生负载                                  | 700  | 1600 | 2500 | ps |

| $t_{\text{DATA}}$ CLK 至 DATA/OVR 延迟 <sup>(2)</sup> | 过零, 每个输出引脚上连接到 GND 的 10pF 寄生负载                                  | 650  | 1600 | 2600 | ps |

| $t_{\text{SKEW}}$ DATA 至 DRY 偏斜                    | $t_{\text{DATA}} - t_{\text{DRY}}$ , 每个输出引脚上连接到 GND 的 10pF 寄生负载 | -700 | 0    | 700  | ps |

| $t_{\text{RISE}}$ DRY/DATA/OVR 上升时间                | 每个输出引脚上连接到 GND 的 10pF 寄生负载                                      |      | 500  |      | ps |

| $t_{\text{FALL}}$ DRY/DATA/OVR 下降时间                | 每个输出引脚上连接到 GND 的 10pF 寄生负载                                      |      | 500  |      | ps |

(1) 时序参数由特征确定，但未经过生产测试。

(2) DRY、DATA 和 OVR 在 CLK 的下降沿上更新。必须将延迟与  $t_{\text{DATA}}$  相加，以确定总体传播延迟。

A. DRY 的极性不确定。有关更多信息，请参阅 [图 6.1.3](#)。

图 5-2. 时序图

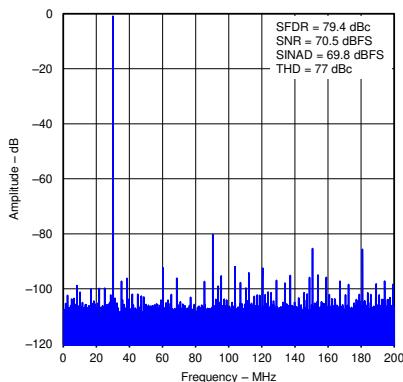

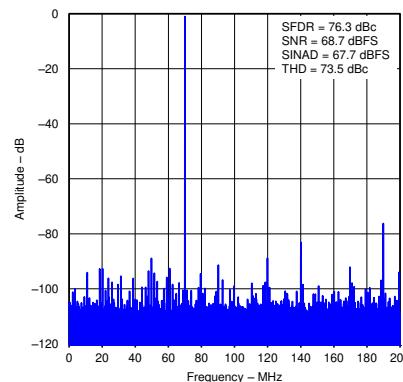

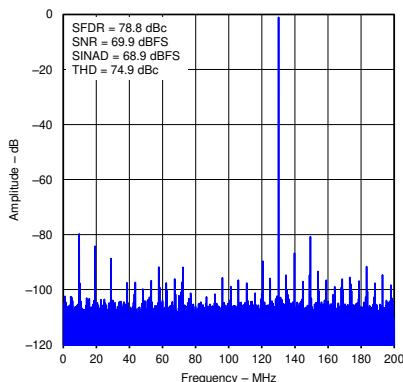

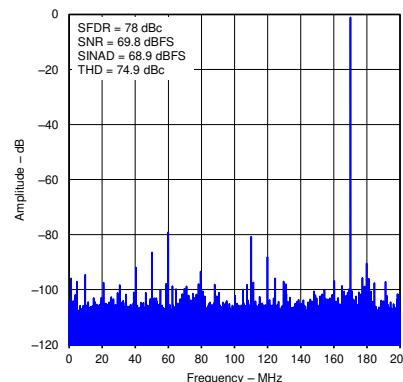

## 5.7 典型特性

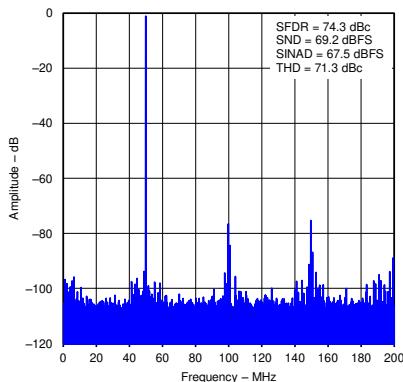

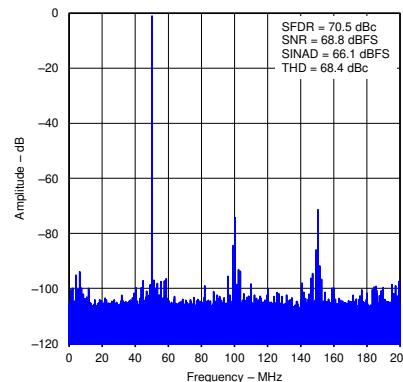

测量条件为除非另有说明，否则条件为  $T_A = 25^\circ\text{C}$ 、采样率 = 400MSPS、50% 时钟占空比、 $3\text{V}_{\text{PP}}$  差分正弦时钟、模拟输入振幅 = -1dBFS、AVDD5 = 5V、AVDD3 = 3.3V 且 DVDD3 = 3.3V。

图 5-3. 30MHz 输入信号的频谱性能 FFT

图 5-4. 70MHz 输入信号的频谱性能 FFT

图 5-5. 130MHz 输入信号的频谱性能 FFT

图 5-6. 230MHz 输入信号的频谱性能 FFT

图 5-7. 351MHz 输入信号的频谱性能 FFT

图 5-8. 451MHz 输入信号的频谱性能 FFT

## 5.7 典型特性 (续)

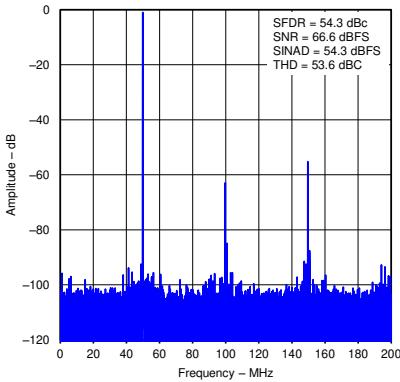

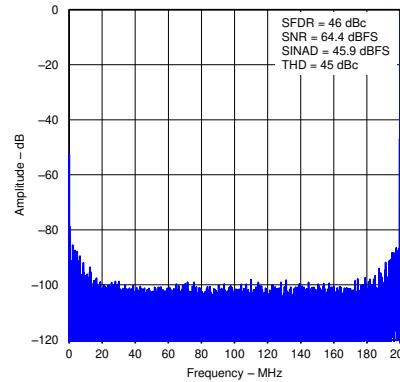

测量条件为除非另有说明，否则条件为  $T_A = 25^\circ\text{C}$ 、采样率 = 400MSPS、50% 时钟占空比、 $3\text{V}_{\text{PP}}$  差分正弦时钟、模拟输入振幅 = -1dBFS、AVDD5 = 5V、AVDD3 = 3.3V 且 DVDD3 = 3.3V。

图 5-9. 751MHz 输入信号的频谱性能 FFT

图 5-10. 999MHz 输入信号的频谱性能 FFT

图 5-11. 双音互调失真 (-7dBFS 条件下的 69MHz 和 70MHz 的 FFT )

图 5-12. 双音互调失真 (-7dBFS 条件下的 297.5MHz 和 302.5MHz 的 FFT )

图 5-13. 双音互调失真 (-16dBFS 条件下的 69MHz 和 70MHz 的 FFT )

图 5-14. 双音互调失真 (-16dBFS 条件下的 297.5MHz 和 302.5MHz 的 FFT )

## 5.7 典型特性 (续)

测量条件为除非另有说明，否则条件为  $T_A = 25^\circ\text{C}$ 、采样率 = 400MSPS、50% 时钟占空比、 $3V_{\text{PP}}$  差分正弦时钟、模拟输入振幅 = -1dBFS、AVDD5 = 5V、AVDD3 = 3.3V 且 DVDD3 = 3.3V。

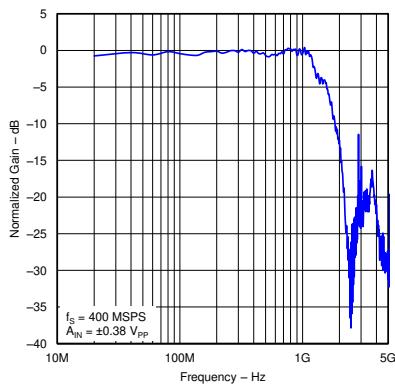

图 5-15. 归一化增益响应与输入频率间的关系

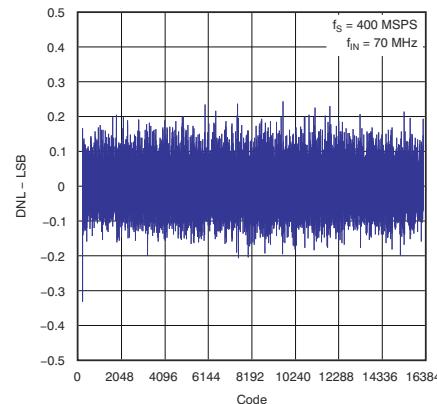

图 5-16. 微分非线性

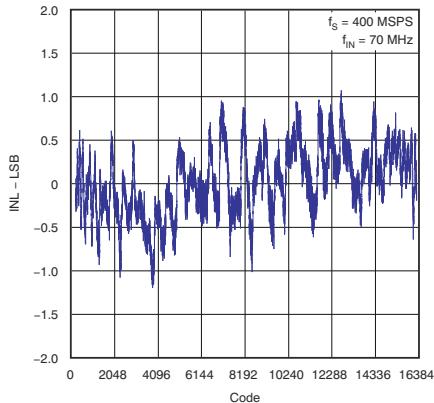

图 5-17. 积分非线性

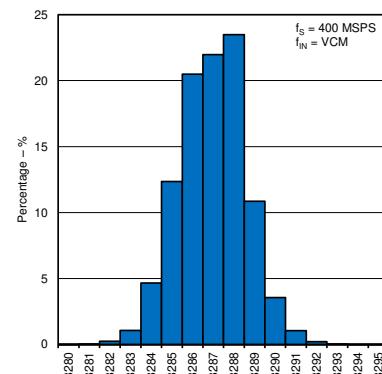

图 5-18. 输入短路时的噪声直方图

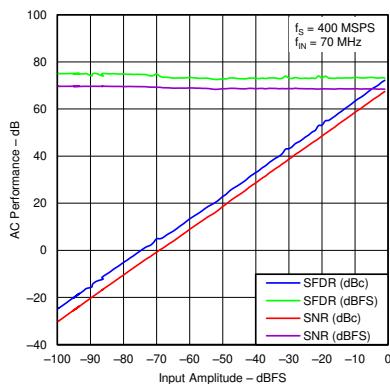

图 5-19. 交流性能与输入幅度间的关系 (70MHz 输入信号)

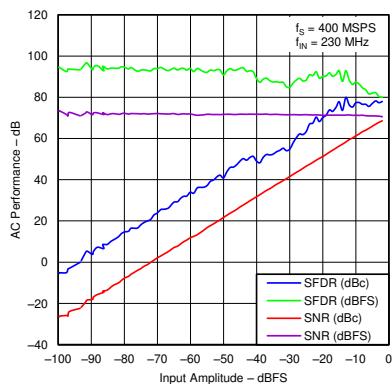

图 5-20. 交流性能与输入幅度间的关系 (230MHz 输入信号)

## 5.7 典型特性 (续)

测量条件为除非另有说明，否则条件为  $T_A = 25^\circ\text{C}$ 、采样率 = 400MSPS、50% 时钟占空比、 $3\text{V}_{\text{PP}}$  差分正弦时钟、模拟输入振幅 = -1dBFS、AVDD5 = 5V、AVDD3 = 3.3V 且 DVDD3 = 3.3V。

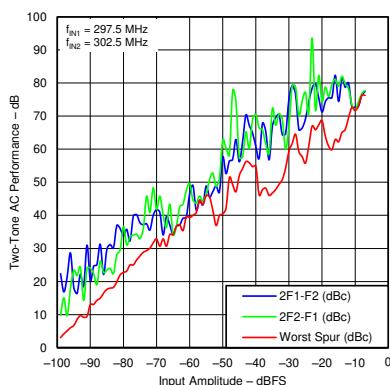

图 5-21. 双音性能与输入幅度间的关系 ( $F_1 = 297.5\text{MHz}$ ,  $F_2 = 302.5\text{MHz}$ )

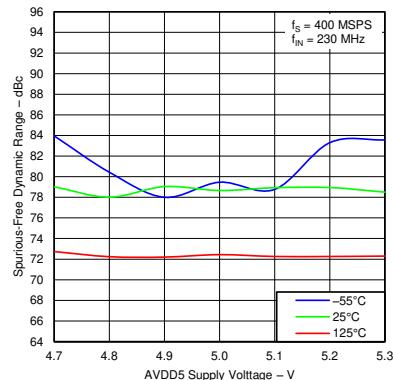

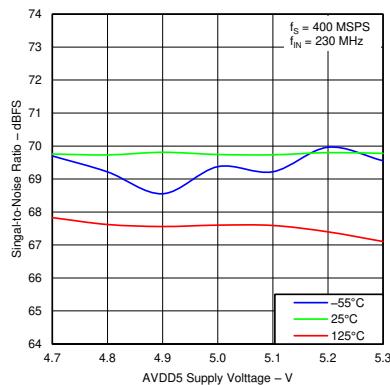

图 5-22. 过温条件下 SFDR 与 AVDD5 间的关系

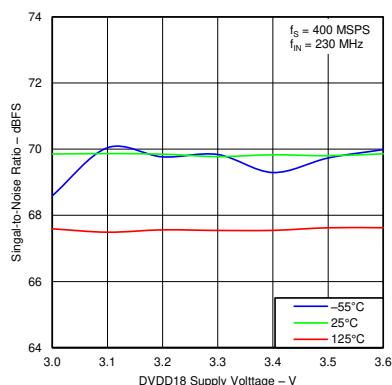

图 5-23. 过温条件下 SNR 与 AVDD5 间的关系

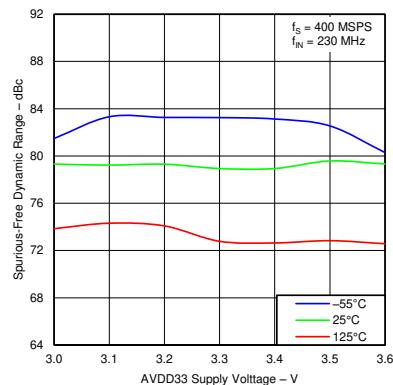

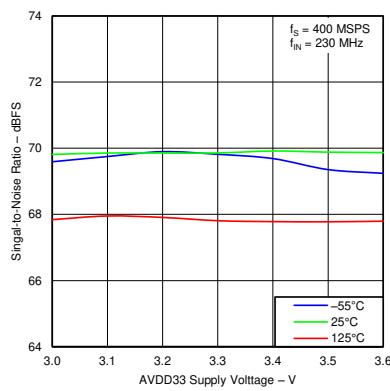

图 5-24. 过温条件下 SFDR 与 AVDD33 间的关系

图 5-25. 过温条件下 SNR 与 AVDD33 间的关系

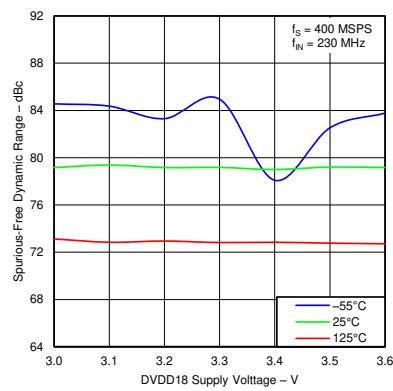

图 5-26. 过温条件下 SFDR 与 DVDD18 间的关系

## 5.7 典型特性 (续)

测量条件为除非另有说明，否则条件为  $T_A = 25^\circ\text{C}$ 、采样率 = 400MSPS、50% 时钟占空比、 $3V_{\text{PP}}$  差分正弦时钟、模拟输入振幅 = -1dBFS、AVDD5 = 5V、AVDD3 = 3.3V 且 DVDD3 = 3.3V。

图 5-27. 过温条件下 SNR 与 DVDD18 间的关系

图 5-28. CMRR 与共模输入频率间的关系

图 5-29. ADC 唤醒时间

## 6 详细说明

### 6.1 概述

ADS5474 是一个 14 位、400MSPS、单片流水线 ADC。双极模拟内核由 5V 和 3.3V 电源供电，而输出使用 3.3V 电源来提供与 LVDS 兼容的输出。外部输入时钟的上升沿启动转换过程。在转换过程的瞬间，输入跟踪保持(T&H)捕获差分输入信号，输入样本由一系列较低分辨率级按顺序进行转换，输出合并在一个数字校正逻辑块中。上升时钟沿及下降时钟沿每半个时钟周期通过流水线传播采样。该过程产生 3.5 个时钟周期的数据延迟，之后输出数据以偏移二进制格式编码的 14 位并行字的形式可用。

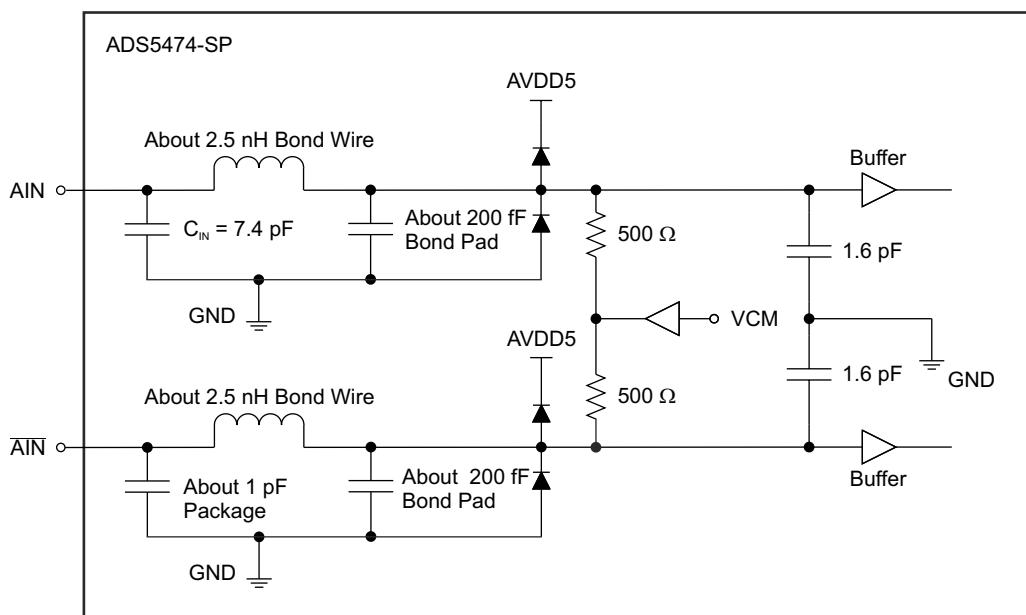

#### 6.1.1 输入配置

ADS5474 的模拟输入包含一个模拟伪差分缓冲器，后跟一个双极晶体管 T&H。模拟缓冲器将驱动 ADC 输入的源与任何内部开关隔离，并且与没有缓冲输入的 ADC 相比，提供在高输入频率下易于驱动的高阻抗。输入共模通过一个  $500\Omega$  电阻器在内部设置，该电阻器从 3.1V 连接到每个输入（在该系列的 12 位和 13 位成员上，共模为  $\approx 2.4V$ ）。该配置会产生  $1k\Omega$  差分输入阻抗。

图 6-1. 模拟输入等效电路

对于满量程差分输入，输入信号（引脚 16 和 17）的每条差分线路在  $(3.1V + 0.55V)$  和  $(3.1V - 0.55V)$  之间对称摆动。该范围意味着，对于总差分输入信号摆幅为  $2.2V_{PP}$  的情况，每个输入的最大信号摆幅为  $1.1V_{PP}$ 。允许在低于  $2.2V_{PP}$  的条件下运行，性能与输入振幅间的关系特性如图 5-19 和图 5-20 所示。例如，对于  $1.1V_{PP}$  而不是  $2.2V_{PP}$  时的性能，请参见  $-6\text{dBFS}$  ( $0\text{dBFS} = 2.2V_{PP}$ ) 时的 SNR 和 SFDR。最大摆幅由内部基准电压发生器决定，无需任何外部电路即可实现该目的。

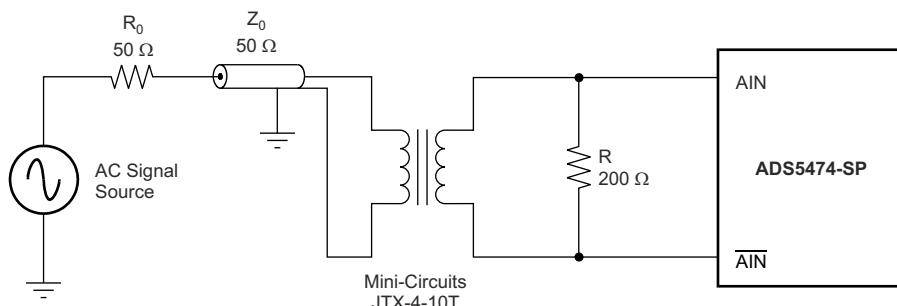

ADS5474 执行的最佳性能条件是以差分方式驱动模拟输入。图 6-2 中的电路显示了一种可能的配置，其使用射频变压器，在变压器的初级侧或次级侧都有终端。此外，评估模块的配置采用两个背对背变压器，进一步展示了良好的性能。如果需要电压增益，请使用升压变压器。

图 6-2. 使用射频变压器将单端输入转换成差分信号

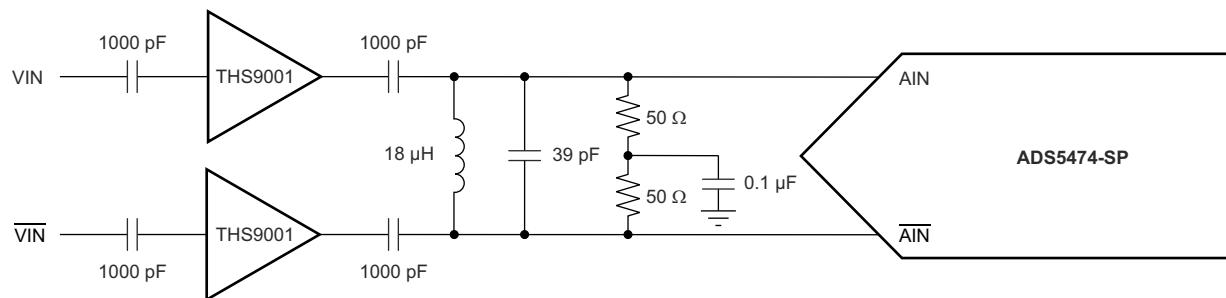

除了变压器配置外，德州仪器 (TI) 还提供了各种单端运算放大器，可根据应用进行选择。在高输入频率应用中使用射频增益块放大器（如 THS9001）。对于 50MHz 至 400MHz 范围内中频下较大的电压增益，使用图 6-3 所示的配置。针对不同的中间频率调整分量值。图 6-3 所示示例位于评估模块上，针对 IF 170MHz 进行了调优。有关此配置的更多信息，请参见 [ADS5474 EVM 用户指南](#) 和 [THS9001 50MHz 至 350MHz 级联放大器 数据表](#)。

图 6-3. 将 THS9001 中频放大器同 ADS5474 配合使用

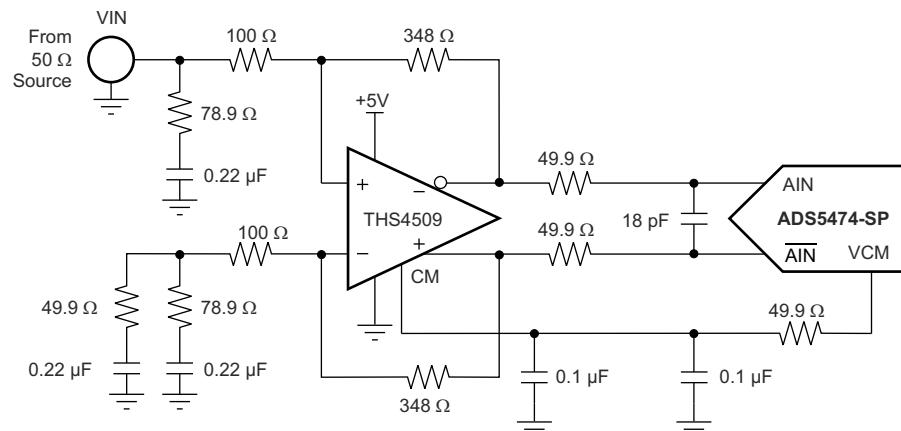

对于需要与信号源直流耦合的应用，差分输入或差分输出放大器（如 THS4509，如图 6-4 所示）可在宽频率范围内提供良好的谐波性能和低噪声。

图 6-4. 将 THS4509 或 THS4520 同 ADS5474 配合使用

在此配置中，THS4509 放大器电路提供 10dB 的增益，将单端输入转换为差分输入，并使用 ADC 的 VCM 输出引脚为 ADS5474 设置适当的输入共模电压。THS4509 输出和 ADS5474 输入之间的  $50\Omega$  电阻器和  $18\text{ pF}$  电容器（以及 ADC 的输入电容）将信号带宽限制在约 70MHz (-3dB)。输入端接通过  $78.9\Omega$  电阻器及  $0.22\mu\text{F}$  接地电容器以及放大器电路的输入阻抗实现。

为了平衡电路， $0.22 \mu F$  电容器和  $49.9 \Omega$  电阻器被插入备用输入端的  $78.9 \Omega$  电阻器和  $0.22 \mu F$  电容器接地。增益为源阻抗、端接和  $348 \Omega$  反馈电阻器的函数。请参阅 [THS4509 宽带、低噪声、低失真、全差分放大器 数据表](#)，了解用于为其他常见增益设置正确  $50 \Omega$  端接的更多分量值。

由于 ADS5474 建议的输入共模电压为  $3.1V$ ，因此 THS4509 由单一电源输入供电，其中  $V_{S+} = 5V$  且  $V_{S-} = 0V$ （接地）。由于 ADC 输入共模为  $3.1V$  和  $+0.55V$  满量程信号，该配置有可能略微超过 THS4509 的建议输出电压  $3.6V$ 。超过电压不会损害 THS4509，但可能会导致 THS4509 的谐波性能下降。

THS4520 是一款具有更宽建议输出电压范围的放大器，该放大器针对高达  $\approx 20MHz$  频率范围内的低噪声和低失真进行了优化。对谐波失真不敏感的应用可考虑使用较高频率下的任一器件。

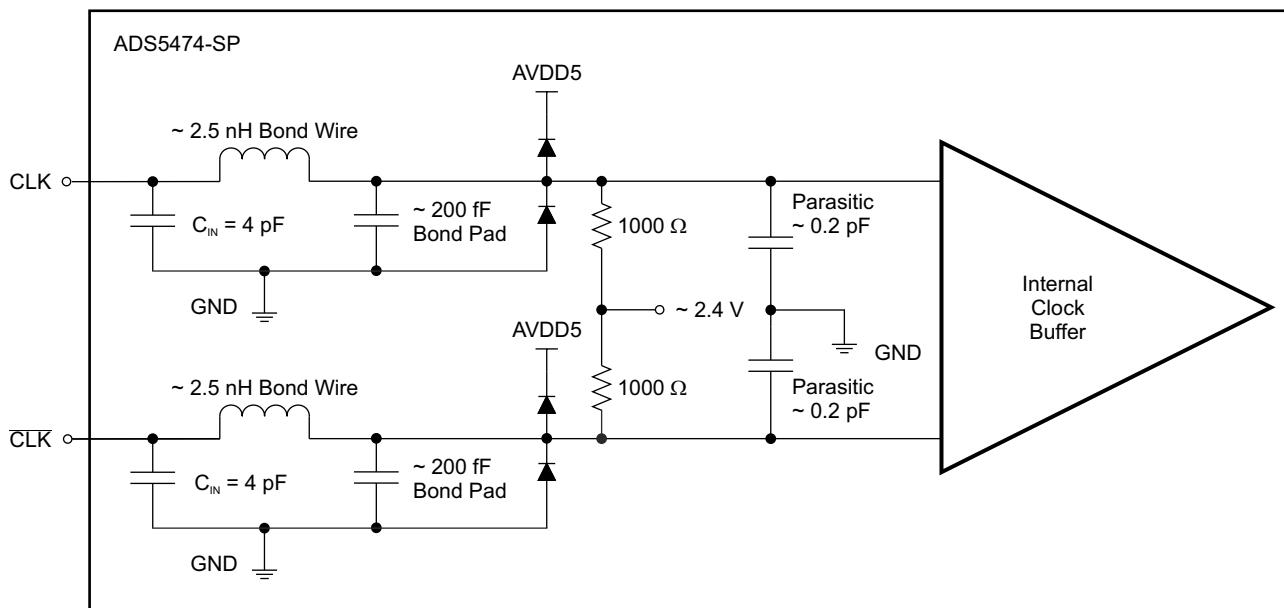

### 6.1.2 时钟输入

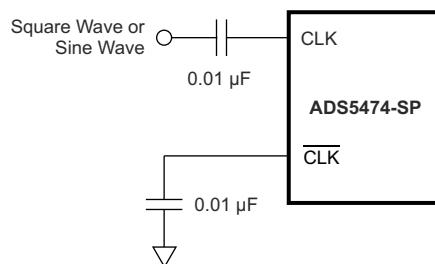

使用差分时钟信号或单端时钟输入来驱动 ADS5474 时钟输入。ADS5474 的特性通常是在  $3V_{PP}$  差分时钟下执行的，但 ADC 在差分时钟振幅低至  $\approx 0.5V_{PP}$  时表现良好。随着模拟输入频率的增加，时钟振幅成为影响性能的一个重要因素。在抖动可能不是大问题的低输入频率应用中，使用单端时钟可以节省成本和布板空间，而不会在性能上造成太大的折衷。使用此配置计时的情况下，TI 建议使用  $0.01 \mu F$  电容器将  $\overline{CLK}$  接地，而  $CLK$  通过  $0.01 \mu F$  电容器交流耦合到时钟源，如图 6-6 所示。

S0292-04

图 6-5. 时钟输入电路

图 6-6. 单端时钟

对于对抖动敏感的应用，使用差分时钟在系统层面具有一些优势。差分时钟可以在印刷电路板 (PCB) 级别实现共模噪声抑制。使用差分时钟时，由于板级时钟抖动更好，因此 ADC 的信噪比更适合抖动敏感的高频应用。

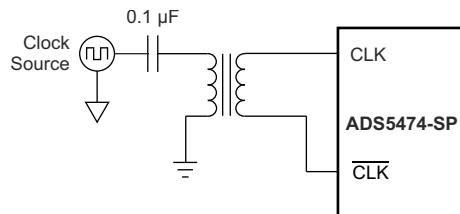

对于高模拟输入频率或慢时钟频率，建议使用更大的时钟振幅电平。对于正弦时钟，振幅越大，时钟压摆率越高，时钟噪声对抖动的影响就越小。在高模拟输入频率下，采样过程对抖动很敏感。在较慢的时钟频率下，小振幅正弦时钟具有较低的压摆率，并会导致与抖动相关的 SNR 下降。图 6-7 演示了将单端时钟源转换为差分时钟的推荐方法。该方法与评估板上的配置类似，用于大部分特性描述。有关更多详细信息，请参阅 [时钟高速数据转换器模拟设计期刊](#)。

图 6-7. 差分时钟

使用内部  $1\text{k}\Omega$  电阻器在内部将时钟输入的共模电压设置为 2.4V。TI 建议使用交流耦合。如果无法进行交流耦合，ADS5474 对时钟共模变化具有很好的容差。此外，内部 ADC 内核在转换过程中使用时钟的两个边沿。50% 占空比时钟信号是一个很好的选择。

ADS5474 能够在模拟输入频率的 350MHz 下实现 69.2dBFS SNR。要在 350MHz 下实现 SNR，请验证时钟源 RMS 抖动是否至少为 144fs，以便总 RMS 抖动为 177fs。[表 6-1](#) 中提供了作为模拟输入频率函数的最大建议 RMS 时钟抖动汇总。用于创建表格的[方程式 1](#) 和[方程式 2](#) 如下所示。

表 6-1. 建议的 RMS 时钟抖动

| 输入频率 (MHz) | 测得的 SNR (dBc) | 总抖动 (fsec RMS) | 最大时钟抖动 (fsec RMS) |

|------------|---------------|----------------|-------------------|

| 30         | 69.3          | 1818           | 1816              |

| 70         | 69.1          | 798            | 791               |

| 130        | 69.1          | 429            | 417               |

| 230        | 68.8          | 251            | 229               |

| 350        | 68.2          | 177            | 144               |

| 450        | 67.4          | 151            | 110               |

| 750        | 65.6          | 111            | 42                |

| 1000       | 63.7          | 104            | 14                |

使用[方程式 1](#) 和[方程式 2](#) 来估算所需的时钟源抖动。

$$\text{SNR(dBc)} = -20 \times \log_{10}(2 \times \pi \times f_{\text{IN}} \times j_{\text{TOTAL}}) \quad (1)$$

$$j_{\text{TOTAL}} = [j_{\text{ADC}}^2 + j_{\text{CLOCK}}^2]^{\frac{1}{2}} \quad (2)$$

其中

- $j_{\text{TOTAL}}$  = 时钟和 ADC 孔径抖动的 RMS 总和

- $f_{\text{IN}}$  = 模拟输入频率

- $j_{\text{ADC}}$  = ADC 内部孔径抖动，位于数据表中

- $j_{\text{CLOCK}}$  = ADC 时钟输入引脚上时钟的 RMS 抖动

SNR 是模拟输入频率（而非时钟频率）的强大函数。时钟源边沿的斜率也会对 SNR 产生轻微影响，这些估算中未考虑在内。因此，建议在 ADC 时钟输入处尽可能提高时钟源幅度，但并非必需（与抖动相关的 SNR 需要更高的斜率）。有关为高速 ADC 提供时钟的更多信息，请参阅 [为高速、高 IF ADC 器件实现 CDC7005 低抖动时钟解决方案应用手册](#)。推荐的时钟分配芯片 (CDC) 为 TI [CDC7005](#)、[CDCM7005-SP](#) 和 [CDCE72010](#)。

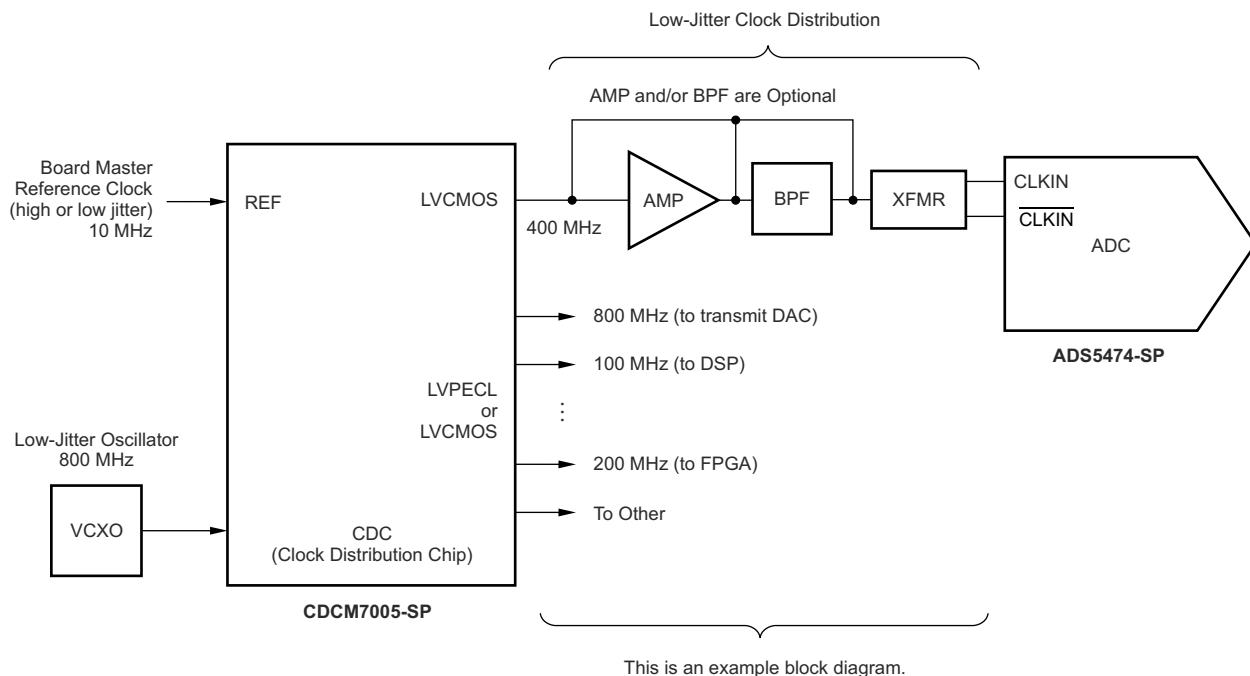

根据抖动要求，有时需要在 CDC 和 ADC 之间使用带通滤波器 (BPF)。如果 BPF 的插入损耗导致 ADC 的时钟振幅太低，或者时钟源振幅太低，不能开始，请在 CDC 和 BPF 之间放置一个成本不高的放大器。

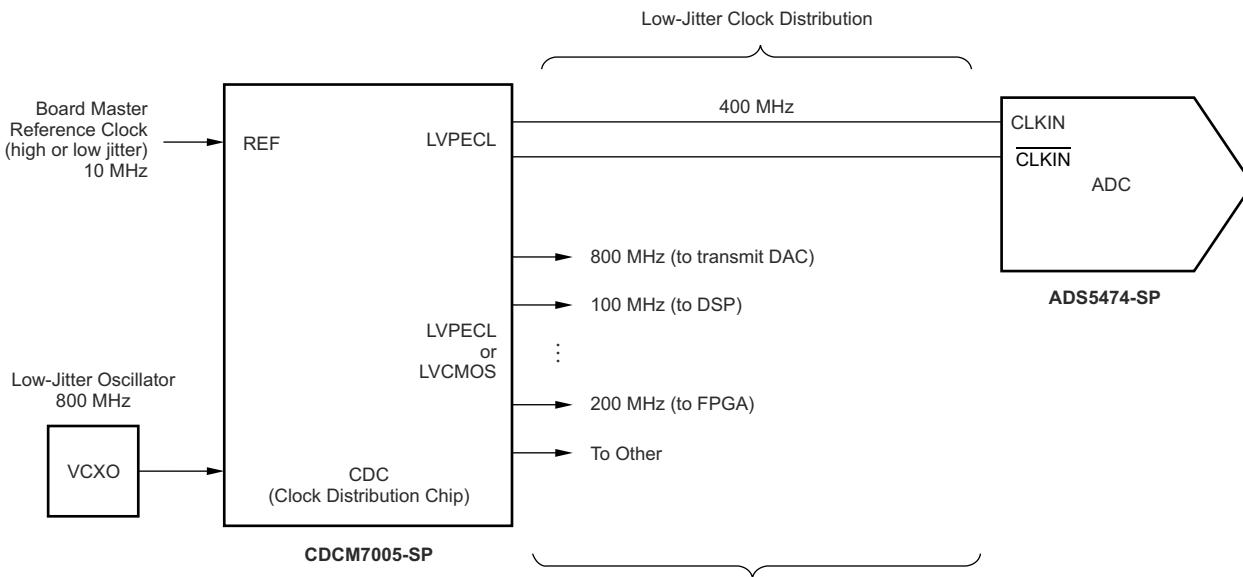

图 6-8 表示的场景为：使用 TI CDCM7005-SP 中的 LVCMOS 单端时钟输出，其中时钟信号路径针对最大幅度和最小抖动进行了优化。这种类型的调节很适合在输入频率大于 150MHz 的情况下使用。此设置的抖动很难估算，需要对时钟路径进行仔细的相位噪声分析。当 CDC 提供的抖动仍然不足时，BPF（可能是一个低成本放大器，因为 BPF 中存在插入损耗）可以改善 CDC 和 ADC 之间的抖动。CDCM7005-SP 输出端的总抖动在很大程度上取决于所选 VCXO 和 CDCM7005-SP 的相位噪声，并且通常具有 50fs 至 100fs 的 RMS 抖动。如果用户确定带有 VCXO 的 CDCM7005-SP 的抖动足以满足需求，无需进一步调节，则可以使用差分 LVPECL 输出直接从 CDCM7005-SP 为 ADS5474 提供时钟，如图 6-9 所示（有关确切的原理图，请参阅 [CDCM7005-SP 3.3V 高性能时钟同步器和抖动消除器数据表](#)）。在抖动并不那么重要的输入频率低于 150MHz 的条件下，这种情况是不错的选择。TI 建议在确定正确的方法之前仔细分析所需抖动。

有关允许的输入和输出频率以及振幅范围的正确原理图和规范，请参阅 [CDCM7005 3.3V 高性能时钟同步器和抖动消除器数据表](#)。

图 6-8. 最佳抖动时钟电路

This is an example block diagram.

有关允许的输入和输出频率以及振幅范围的正确原理图和规范，请参阅 [CDCM7005 3.3V 高性能时钟同步器和抖动消除器 数据表](#)。

**图 6-9. 可接受的抖动时钟电路**

### 6.1.3 数字输出

ADC 提供 14 个与 LVDS 兼容的偏移二进制数据输出 (D13 至 D0 ; D13 是 MSB、D0 是 LSB ) 、数据就绪信号 (DRY) 和一个超范围指示器 (OVR)。TI 建议使用 DRY 信号来采集 ADS5474 的输出数据。DRY 与数据/OVR 输出源同步，并以相同的频率运行，从而创建半速率 DDR 接口，用于更新 DRY 上升沿和下降沿上的数据。TI 建议尽可能地减少数字输出的容性负载。较高的电容会缩短数据有效时序窗口。通过在每条 LVDS 线路上测得的 10pF 接地寄生电路板电容 (或 5pF 差分寄生电容) 可获得给定的时序值 (请参阅 [图 5-2](#) )。在接收器件上设置 DRY 和数据之间的时间关系时，TI 建议尽可能地延长设置时间，但此时间在一定程度上取决于接收数字数据的器件 (例如 FPGA 或现场可编程现场阵列) 的建立时间和保持时间。由于 DRY 和数据是重合的，因此 TI 建议延迟 DRY 或数据，以更大限度地延长设置时间。

参考 [图 5-2](#)，DRY 相对于样本 N 数据输出转换的极性不确定，这是因为生成 DRY 信号的时钟分频器的未知启动逻辑电平 (DRY 是 CLK 的两分频频率)。DRY 的上升沿或下降沿与样本 N 重合，当下电上电或处于断电引脚周期时，DRY 的极性可能反转。建议从转换中采集数据，而不是从 DRY 的极性进行采集，但这不是必需的。如果需要同步多个 ADS5474 器件，则可能需要使用 CLKIN 信号的某种形式而不是 DRY，以便采集数据。

DRY 频率在 ADS5474 和 ADS5463 上相同 (其中 DRY 等于  $\frac{1}{2}$  CLK 频率)，但与在类似的 ADS5444 引脚上不同 (其中 DRY 等于 CLK 频率)。LVDS 输出都需要在每个输出对之间使用外部  $100\Omega$  负载，以满足预期的 LVDS 电压电平。对于较长的布线长度，可能需要在每个数字输出上尽可能靠近 ADS5474 放置一个  $100\Omega$  负载，并在 LVDS 传输线路末端放置另一个  $100\Omega$  差分负载，以提供匹配的阻抗并避免信号反射。在这种情况下，有效负载将 LVDS 电压电平降低了一半。

当 14 位输出字尝试超过全 0 或全 1 时，OVR 输出等于逻辑高电平。该标志用作模拟输入信号超过约  $2.2V_{PP}$  ( $\pm$  增益误差) 的满量程输入限值的指示器。OVR 指示灯适用于使用增益控制将模拟输入信号保持在可接受限制之内的系统。

## 7 应用和实施

### 备注

以下应用部分中的信息不属于 TI 元件规格，TI 不担保其准确性和完整性。TI 的客户应负责确定各元件是否适用于其应用。客户应验证并测试其设计是否能够实现，以确保系统功能。

### 7.1 电源相关建议

ADS5474 使用三个电源。对于设计的模拟部分，使用了 5V 和 3.3V 电源（AVDD5 和 AVDD3），而数字部分使用 3.3V 电源（DVDD3）。建议使用具备足够去耦能力的低噪声电源。线性电源优先于开关电源；开关电源往往会产生更多可耦合至 ADS5474 的噪声分量。用户或许能够使用不太理想的电源为器件供电，并且仍然可以实现良好的性能。对于所有系统的每种电源和去耦电平，都无法给出单一的建议。ADS5474 的功耗不会因架构和工艺而随时钟速率或输入频率发生实质性变化。

由于 AVDD3 和 DVDD3 之间在内部有两个二极管反向连接，因此建议采用上电序列。当这两个电源之间存在上电延迟时，滞后的电源在上电之前可能会通过内部二极管灌入电流。根据外部电源的阻抗，灌电流可能很大或很小，并可能损坏器件或影响电源。

理想的上电序列是以下选项之一（无论 AVDD5 上电时为何）：

1. 同时为 AVDD3 和 DVDD3 上电（最佳情况），或者

2. 在上电期间，将 AVDD3 和 DVDD3 之间的电压差保持在 0.8V 以下（0.8V 不是硬性规格 — 电源之间的差值越小越安全）。

如果上述序列不实用，则需要控制来自电源的灌电流或从外部添加保护。DVDD3 或 AVDD3 引脚的最大瞬态电流（以  $\mu\text{s}$  为时间单位）为 500mA，以避免对器件造成潜在损坏或缩短其寿命。

电源开启时，[节 5.1](#) 中给出的模拟和时钟输入值有效。当电源关闭且时钟或模拟输入仍然存在时，需要限制输入电压和电流以避免器件损坏。如果 ADC 电源关闭，则每个输入引脚（时钟或模拟）相对于接地的最大/最小连续直流电压为  $\pm 0.95\text{V}$ ，最大直流电流为 20mA。

图 7-1. PSRR 与电源注入频率间的关系

## 8 器件和文档支持

### 8.1 器件支持

#### 8.1.1 规范的定义

|                          |                                                                                                             |

|--------------------------|-------------------------------------------------------------------------------------------------------------|

| <b>模拟带宽</b>              | 基频功率相对于低频值而降低 3dB 时的模拟输入频率。                                                                                 |

| <b>孔径延迟</b>              | 输入采样时钟的上升沿到发生采样的实际时间之间的时间延迟。                                                                                |

| <b>孔径不确定性<br/>(抖动)</b>   | 孔径延迟的样本间变化。                                                                                                 |

| <b>时钟脉冲持续<br/>时间/占空比</b> | 时钟信号的占空比是时钟信号保持逻辑高电平的时间 ( 时钟脉冲持续时间 ) 与时钟信号的周期之比 , 以百分比表示。                                                   |

| <b>微分非线性<br/>(DNL)</b>   | 理想的 ADC 在模拟输入值实际相隔 1LSB 时表现出代码转换。DNL 是任何单个步进相对于此理想值的偏差 , 以 LSB 为单位。                                         |

| <b>共模抑制比<br/>(CMRR)</b>  | CMRR 可测量对同时呈现给两个模拟输入的信号进行抑制的能力。注入的共模频率电平转换为 dBFS , 输出 FFT 中的杂散以 dBFS 为单位进行测量 , 差值为 CMRR ( 以 dB 为单位 ) 。      |

| <b>有效位数<br/>(ENOB)</b>   | ENOB 是与基于量化噪声的理论极限相比以比特为单位的转换器性能度量 :                                                                        |

|                          | $\text{ENOB} = [\text{SINAD} - 1.76] \div 6.02 \quad (3)$                                                   |

| <b>增益误差</b>              | 增益误差是 ADC 实际输入满量程范围与其理想值的偏差 , 以理想输入满量程范围的百分比形式给出。                                                           |

| <b>积分非线性<br/>(INL)</b>   | INL 是 ADC 传递函数相对于通过该传递函数的最小二乘曲线拟合确定的最佳拟合线的偏差。每个模拟输入值上的 INL 是实际传递函数与该最佳拟合线之间的差值 , 以 LSB 为单位进行测量。             |

| <b>偏移误差</b>              | 偏移误差是当两个输入都连接到共模时输出代码与中间代码的偏差。                                                                              |

| <b>电源抑制比<br/>(PSRR)</b>  | PSRR 用于测量抑制电源频率的能力。注入的频率电平转换为 dBFS , 输出 FFT 中的杂散以 dBFS 为单位进行测量 , 差值为 PSRR ( 以 dB 为单位 ) 。测量可校准电路板电源去耦电容器的优势。 |

| <b>信噪比 (SNR)</b>         | SNR 是基频功率 ( $P_S$ ) 与噪底功率 ( $P_N$ ) 的比值 , 不包括直流和前五次谐波的功率。                                                   |

$$\text{SNR} = 10\log_{10} \frac{P_S}{P_N} \quad (4)$$

当基频的绝对功率用作基准时 , SNR 以 dBc ( 相对于载波的分贝数 ) 为单位 ; 当基频功率被外推至转换器满量程范围时 , 则以 dBFS ( 相对于满量程的分贝数 ) 为单位。

|                           |                                                                                     |

|---------------------------|-------------------------------------------------------------------------------------|

| <b>信噪比和失真<br/>(SINAD)</b> | SINAD 是指基频功率 ( $P_S$ ) 与所有其他频谱分量 ( 包括噪声 ( $P_N$ ) 和失真 ( $P_D$ ) , 但不包括 dc ) 的功率的比值。 |

|---------------------------|-------------------------------------------------------------------------------------|

$$\text{SINAD} = 10\log_{10} \frac{P_S}{P_N + P_D} \quad (5)$$

当基频的绝对功率用作基准时 , SINAD 以 dBc ( 相对于载波的分贝数 ) 为单位 ; 当基频功率被外推至转换器满量程范围时 , 则以 dBFS ( 相对于满量程的分贝数 ) 为单位。

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| <b>温漂</b> | 温漂 ( 关于增益误差及偏移误差 ) 指定从标称温度下的值到 $T_{MIN}$ 或 $T_{MAX}$ 下的值的变化。它的计算方法是将整个温度范围内参数的最大变化除以 $T_{MIN} - T_{MAX}$ 。 |

|-----------|------------------------------------------------------------------------------------------------------------|

|                        |                                               |

|------------------------|-----------------------------------------------|

| <b>总谐波失真<br/>(THD)</b> | THD 是指基频功率 ( $P_S$ ) 与前五个谐波的功率 ( $P_D$ ) 的比值。 |

|------------------------|-----------------------------------------------|

$$\text{THD} = 10\log_{10} \frac{P_S}{P_D} \quad (6)$$

THD 通常以 dBc ( 相对于载波的分贝数 ) 为单位。

**双音互调失真 (IMD3)** IMD3 是基频功率 ( 频率  $f_1$ 、 $f_2$  ) 与频率  $2f_1 - f_2$  或  $2f_2 - f_1$  下最差频谱分量功率之比。当基频的绝对功率用作基准时 , IMD3 以 dBc ( 相对于载波的分贝数 ) 为单位 ; 当基频功率被外推至转换器满量程范围时 , 则以 dBFS ( 相对于满量程的分贝数 ) 为单位。

## 8.2 文档支持

### 8.2.1 相关文档

- 德州仪器 (TI) , [50MHz 至 750MHz 可级联放大器 数据表](#)

- 德州仪器 (TI) , [ADS5440/44/63/74 EVM 用户指南](#)

- 德州仪器 (TI) , [CDCM7005 3.3V 高性能时钟同步器和抖动消除器 数据表](#)

- 德州仪器 (TI) , [CDCM7005-SP 3.3V 高性能抗辐射五类时钟同步器和抖动消除器 数据表](#)

- 德州仪器 (TI) , [时钟高速数据转换器 模拟设计期刊](#)

- 德州仪器 (TI) , [为高速、高中频 ADC 器件实现 CDC7005 低抖动时钟解决方案 应用手册](#)

- 德州仪器 (TI) , [THS4509 宽带、低噪声、低失真、全差分放大器 数据表](#)

## 8.3 接收文档更新通知

要接收文档更新通知 , 请导航至 [ti.com](#) 上的器件产品文件夹。点击 [通知](#) 进行注册 , 即可每周接收产品信息更改摘要。有关更改的详细信息 , 请查看任何已修订文档中包含的修订历史记录。

## 8.4 支持资源

[TI E2E™ 中文支持论坛](#) 是工程师的重要参考资料 , 可直接从专家处获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题 , 获得所需的快速设计帮助。

链接的内容由各个贡献者 “按原样” 提供。这些内容并不构成 TI 技术规范 , 并且不一定反映 TI 的观点 ; 请参阅 TI 的 [使用条款](#)。

## 8.5 商标

TI E2E™ is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

## 8.6 静电放电警告

静电放电 (ESD) 会损坏这个集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理和安装程序 , 可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级 , 大至整个器件故障。精密的集成电路可能更容易受到损坏 , 这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

## 8.7 术语表

[TI 术语表](#) 本术语表列出并解释了术语、首字母缩略词和定义。

## 9 修订历史记录

注 : 以前版本的页码可能与当前版本的页码不同

| <b>Changes from Revision A (December 2013) to Revision B (November 2025)</b> | <b>Page</b> |

|------------------------------------------------------------------------------|-------------|

| • 标题自 : 五类 14 位 400MSPS 模数转换器更改为 : ADS5474-SP 五类 14 位 400MSPS 模数转换器.....     | 1           |

| • 更新了整个文档中的表格、图和交叉参考的编号格式.....                                               | 1           |

| • 将引脚配置图中的引脚 1、22、43 和 64 自 : AGND 更改为 : GND.....                            | 3           |

| • 移动了 规格 部分之前的 引脚配置和功能 部分.....                                               | 3           |

| • 添加了 <i>ESD</i> 等级 部分.....                                                  | 5           |

| • 将 ESD 数据从 绝对最大额定值 等级 部分移至 <i>ESD</i> 等级 部分.....                            | 5           |

|                                                                                                         |    |

|---------------------------------------------------------------------------------------------------------|----|

| • 将建议运行条件部分移到 <i>ESD</i> 等级部分之后.....                                                                    | 5  |

| • 标题自：热特性更新为：热性能信息.....                                                                                 | 6  |

| • 将热性能信息部分移到建议运行条件部分之后.....                                                                             | 6  |

| • 将 $R_{\theta JA}$ 从 : $21.81^{\circ}\text{C}/\text{W}$ 更改为 : $19^{\circ}\text{C}/\text{W}$ .....      | 6  |

| • 将 $R_{\theta JC}$ 从 : $0.849^{\circ}\text{C}/\text{W}$ 更改为 : $1.8^{\circ}\text{C}/\text{W}$ .....     | 6  |

| • 将模拟输入下的输入电容的典型值从 : $7.4\text{pF}$ 更改为 : $2.8\text{pF}$ .....                                          | 6  |

| • 将工作寿命降额表的电迁移失败模式从热特性部分移至电气特性部分.....                                                                   | 6  |

| • 将时序图移至时序特性部分.....                                                                                     | 10 |

| • 将章节标题从“应用程序信息”更新为“详细说明”.....                                                                          | 16 |

| • 将小节标题从工作原理更新为概述.....                                                                                  | 16 |

| • 将图 6-1 中的电容更改为“约 $1\text{pF}$ 封装”.....                                                                | 16 |

| • 将数字输出中的(其中 $\text{DRY}$ 等于 $\text{CLK}$ 频率)更改为(其中 $\text{DRY}$ 等于 $\frac{1}{2}$ $\text{CLK}$ 频率)..... | 21 |

| • 添加了应用和实施部分.....                                                                                       | 22 |

| • 将标题从“电源”更新为“电源建议”.....                                                                                | 22 |

| • 将电源相关建议部分移到了应用和实施部分.....                                                                              | 22 |

| • 将静电放电注意事项移至器件和文档支持部分.....                                                                             | 24 |

| <b>Changes from Revision * (September 2013) to Revision A (December 2013)</b> | <b>Page</b> |

|-------------------------------------------------------------------------------|-------------|

| • 向特性列表中添加了项目符号工程评估 (/EM).....                                                | 1           |

## 10 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件可用的最新数据。数据如有变更，恕不另行通知，且不会对此文档进行修订。有关此数据表的浏览器版本，请查阅左侧的导航栏。

---

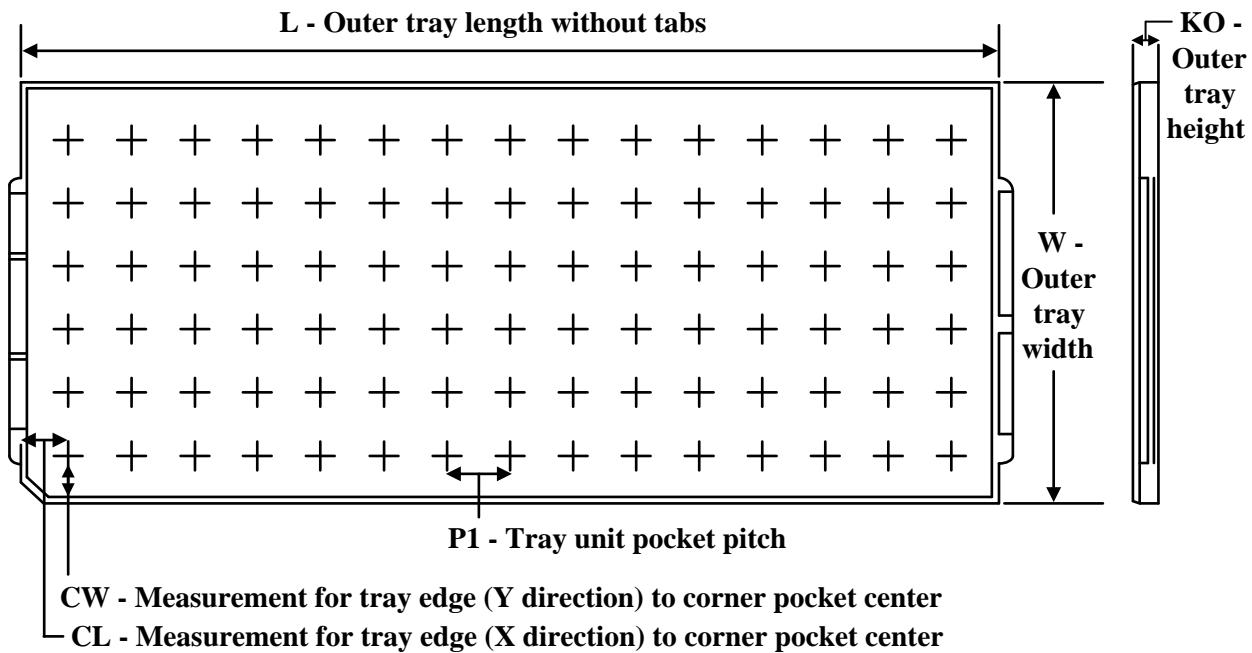

**TRAY**

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | Unit array matrix | Max temperature (°C) | L (mm) | W (mm) | KO (µm) | P1 (mm) | CL (mm) | CW (mm) |

|---------------|--------------|--------------|------|-----|-------------------|----------------------|--------|--------|---------|---------|---------|---------|

| ADS5474HFG/EM | HFG          | CFP          | 84   | 1   | 2 x 5             | 150                  | 315    | 135.9  | 7620    | 57      | 43.5    | 39.45   |

# DATA BOOK PACKAGE OUTLINE

|                   |

|-------------------|

| SUBSTRATE EXAMPLE |

| 4041137           |

|                |               |       |            |                                                                                                                                                                              |                           |         |                                                 |

|----------------|---------------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------|-------------------------------------------------|

| DRAFTER:       | ANIS FAUZI    | DATE: | 07/10/2025 |                                                                                                                                                                              | DIMENSIONS IN MILLIMETERS |         |                                                 |

| DESIGNER:      |               | DATE: |            |  <b>TEXAS INSTRUMENTS</b><br>SEMICONDUCTOR OPERATIONS<br>CODE IDENTITY<br>NUMBER<br>01295 |                           |         | ePOD, HFG0084B / CFP,<br>84 PIN, 0.635 MM PITCH |

| CHECKER:       | K. SINCERBOX  | DATE: | 07/10/2025 |                                                                                                                                                                              |                           |         |                                                 |

| ENGINEER:      | LI JIANG      | DATE: | 07/10/2025 |                                                                                                                                                                              |                           |         |                                                 |

| APPROVED:      | NICK CHU      | DATE: | 07/10/2025 |                                                                                                                                                                              |                           |         |                                                 |

| RELEASED:      | ANIS FAUZI    | DATE: | 07/10/2025 |                                                                                                                                                                              |                           |         |                                                 |

| TEMPLATE INFO: | EDGE# 4218519 | DATE: | 03/20/2013 | SCALE                                                                                                                                                                        | SIZE                      | 4231974 | REV A PAGE 1 OF 3                               |

# PACKAGE OUTLINE

HFG0084B

CFP - 2.67 mm max height

CFP

4231974/A 07/2025

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This package is hermetically sealed with a metal lid.

- The lid and the heat sink are connected to ground leads.

- The leads are gold plated and can be solder dipped.

## REVISIONS

| REV | DESCRIPTION         | ECR     | DATE       | ENGINEER / DRAFTSMAN  |

|-----|---------------------|---------|------------|-----------------------|

| A   | RELEASE NEW DRAWING | 2213474 | 07/10/2025 | LI JIANG / ANIS FAUZI |

SCALE

SIZE

A

4231974

REV

APAGE

3 OF 3

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#))、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025 , 德州仪器 (TI) 公司

最后更新日期 : 2025 年 10 月