**DAC11001B**

ZHCSPG5 - DECEMBER 2021

# DAC11001B 20 位低噪声、超低谐波失真、 快速稳定、高电压输出数模转换器 (DAC)

# 1 特性

20 位单调性: 1LSB DNL (最大值) • 积分线性: 1LSB INL (最大值)

• 低噪声:7nV/√Hz

• 独立于代码的低干扰:1nV-s

• 出色的 THD:

在 20kHz fout、1MHz foac 下为 - 118dB

• 快速稳定:1µs

• 灵活的输出范围: V<sub>REFPF</sub> 至 V<sub>REFNF</sub>

集成式精密反馈电阻器

• 50MHz、4 线 SPI 兼容接口

- 读同

- 菊花链

• 温度范围: -40°C 至 +125°C

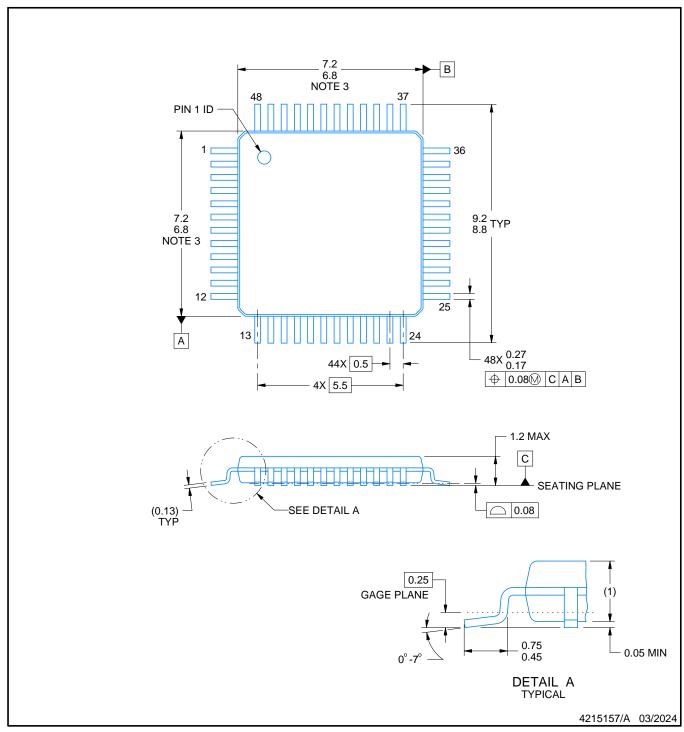

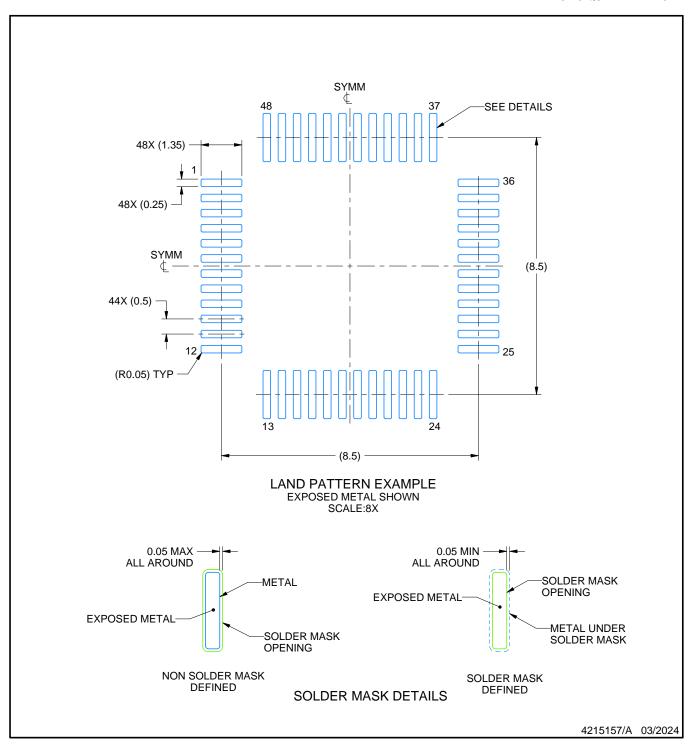

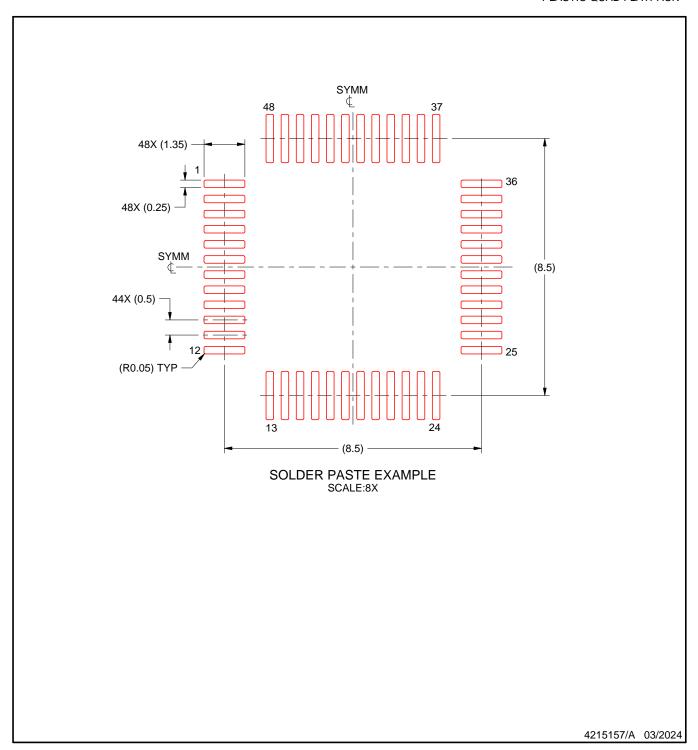

封装:48 管脚 TQFP

### 2 应用

实验室和现场仪表

光谱仪

模拟输出模块

电池测试

半导体测试

• 任意波形发生器 (AWG)

MRI

X射线系统

专业音频放大器(机架式)

### 3 说明

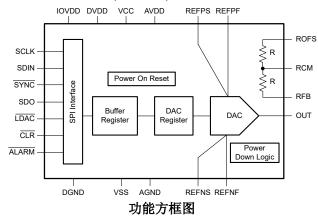

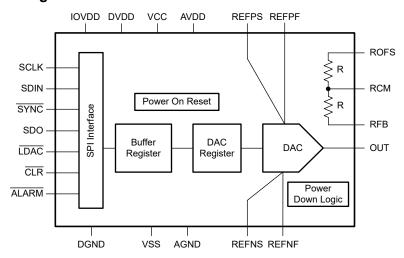

20 位 DAC11001B 是一款高精度、低噪声、电压输 出、单通道数模转换器 (DAC)。DAC11001B 根据设计 具有单调性,并可在所有输出范围内提供出色的线性 度。

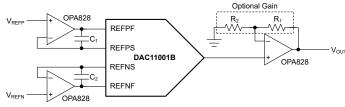

非缓冲电压输出可提供低噪声性能 (7nV/√Hz) 和快速 稳定时间 (1µs), 因此这款器件非常适合低噪声、快速 控制环路和波形生成应用。DAC11001B 兼具增强型抗 尖峰脉冲电路以及独立于代码的超低干扰 (1nV-s),可 实现干净的波形斜坡和超低总谐波失真 (THD)。

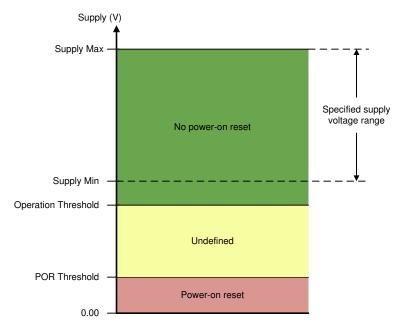

DAC11001B 器件包含上电复位电路, 因此 DAC 上电 时使用寄存器中的已知值。使用外部基准,可以实现 V<sub>REFPF</sub> 到 V<sub>REFNF</sub> 的 DAC 输出,包括非对称输出范

DAC11001B 使用一个以高达 50MHz 的时钟速率运行 的多功能 4 线制串行接口。

### 器件信息

| 器件型号      | 封装 <sup>(1)</sup> | 封装尺寸 ( 标称值 )    |

|-----------|-------------------|-----------------|

| DAC11001B | TQFP (48)         | 7.00mm × 7.00mm |

要了解所有可用封装,请参见数据表末尾的封装选项附录。

任意波形发生电路

本文档旨在为方便起见,提供有关 TI 产品中文版本的信息,以确认产品的概要。有关适用的官方英文版本的最新信息,请访问 www.ti.com,其内容始终优先。TI 不保证翻译的准确性和有效性。在实际设计之前,请务必参考最新版本的英文版本。

English Data Sheet: SLASF03

# **Table of Contents**

| 1 特性                                                          | 1 7.4 Device Functional Modes       | 28 |

|---------------------------------------------------------------|-------------------------------------|----|

| .                                                             |                                     | 29 |

|                                                               | 1 7.6 Register Map                  |    |

| 4 Revision History                                            | 2 8 Application and Implementation  |    |

| 5 Pin Configuration and Functions                             | 3 8.1 Application Information       |    |

| 6 Specifications                                              |                                     | 36 |

| 6.1 Absolute Maximum Ratings                                  | <sub>5</sub> 8.3 System Examples    |    |

| 6.2 ESD Ratings                                               | 0 4 \                               | 43 |

| 6.3 Recommended Operating Conditions                          |                                     | 43 |

| 6.4 Thermal Information                                       | A D A I . D                         | 44 |

| 6.5 Electrical Characteristics                                | 0.4.0 0 1.0 .                       | 46 |

| 6.6 Timing Requirements: Write, 4.5 V ≤ DV <sub>DD</sub> ≤    | 10 Layout                           |    |

| 5.5 V                                                         | 10.1 Layout Guidelines              |    |

| 6.7 Timing Requirements: Write, 2.7 V ≤ DV <sub>DD</sub> <    | 10.2 Layout Example                 |    |

| 4.5 V                                                         | 11 Device and Documentation Support |    |

| 6.8 Timing Requirements: Read and Daisy-Chain                 | 11.1 Device Support                 | 49 |

| Write, $4.5 \text{ V} \leq \text{DV}_{DD} \leq 5.5 \text{ V}$ | 11.2 Documentation Support          |    |

| 6.9 Timing Requirements: Read and Daisy-Chain                 | 12 11.3 接收文档更新通知                    | 49 |

| Write, $2.7 \text{ V} \leq \text{DV}_{DD} < 4.5 \text{ V}$    | 11.4 支持资源                           | 49 |

| 6.10 Timing Diagrams                                          | 11.5 Trademarks                     |    |

| 6.11 Typical Characteristics                                  |                                     | 49 |

| 7 Detailed Description                                        |                                     | 49 |

| 7.1 Overview                                                  |                                     |    |

| 7.2 Functional Block Diagram                                  | Information                         | 49 |

| 7.3 Feature Description                                       |                                     |    |

| 7.0 / Gataro Docomption                                       |                                     |    |

# **4 Revision History**

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2021 | *        | Initial Release |

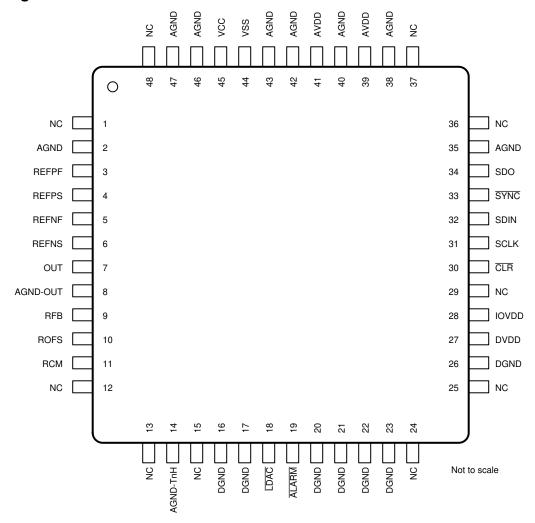

# **5 Pin Configuration and Functions**

图 5-1. PFB Package, 48-Pin TQFP, Top View

# 表 5-1. Pin Functions

| Р        | IN                                             |                   | 2 3-1. Fill 1 dilctions                                                                                                                                                          |

|----------|------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.                                            | TYPE              | DESCRIPTION                                                                                                                                                                      |

| AGND     | 2, 35, 38,<br>40, 42, 43,<br>46, 47            | Analog<br>ground  | Connect to 0 V.                                                                                                                                                                  |

| AGND-OUT | 8                                              | Analog<br>ground  | Connect to 0 V. Measure DAC output voltage with respect to this node.                                                                                                            |

| AGND-TnH | 14                                             | Analog<br>ground  | Connect to 0 V. Integrated deglitcher clock ground.                                                                                                                              |

| ALARM    | 19                                             | Output            | Alarm output                                                                                                                                                                     |

| AVDD     | 39, 41                                         | Power             | Positive low voltage analog power supply                                                                                                                                         |

| CLR      | 30                                             | Input             | DAC registers clear pin, active low                                                                                                                                              |

| DGND     | 16, 17, 20,<br>21, 22, 23,<br>26               | Digital<br>ground | Connect to 0 V.                                                                                                                                                                  |

| DVDD     | 27                                             | Power             | Digital power supply pin                                                                                                                                                         |

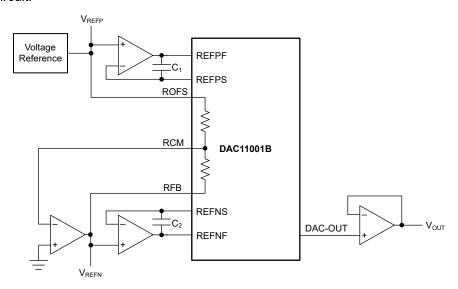

| RFB      | 9                                              | Input             | Integrated precision resistor feedback node                                                                                                                                      |

| IOVDD    | 28                                             | Power             | Interface power supply pin                                                                                                                                                       |

| LDAC     | 18                                             | Input             | Load DAC pin, active low                                                                                                                                                         |

| NC       | 1, 12, 13,<br>15, 24, 25,<br>29, 36, 37,<br>48 | _                 | No connection, leave floating                                                                                                                                                    |

| OUT      | 7                                              | Output            | Unbuffered voltage output                                                                                                                                                        |

| RCM      | 11                                             | Input             | Integrated precision resistor common-mode node                                                                                                                                   |

| REFNF    | 5                                              | Input             | External negative reference input. Connect to 0 V for unipolar DAC output.                                                                                                       |

| REFNS    | 6                                              | Input             | External negative reference sense node                                                                                                                                           |

| REFPF    | 3                                              | Input             | External positive reference input                                                                                                                                                |

| REFPS    | 4                                              | Input             | External positive reference sense node                                                                                                                                           |

| ROFS     | 10                                             | Input             | Integrated precision resistor offset node                                                                                                                                        |

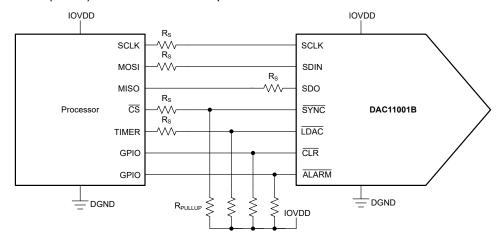

| SCLK     | 31                                             | Input             | Serial clock input of serial peripheral interface (SPI). Schmitt-trigger logic input. Data are transferred at rates of up to 50 MHz.                                             |

| SDIN     | 32                                             | Input             | Serial data input. Schmitt-trigger logic input.  Data are clocked into the input shift register on the falling edge of the serial clock input.                                   |

| SDO      | 34                                             | Output            | Serial data output. Data are valid on the falling edge of SCLK.                                                                                                                  |

| SYNC     | 33                                             | Input             | SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC is low. When SYNC is high, the SDO pin is in high-impedance status. |

| VCC      | 45                                             | Power             | Analog positive power supply                                                                                                                                                     |

| VSS      | 44                                             | Power             | Analog negative power supply                                                                                                                                                     |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                      | ·                                            | MIN                   | MAX                     | UNIT |

|------------------|--------------------------------------|----------------------------------------------|-----------------------|-------------------------|------|

|                  |                                      | AV <sub>DD</sub> to AGND                     | - 0.3                 | 7                       |      |

|                  | Positive supply voltage              | V <sub>CC</sub> to V <sub>SS</sub>           | - 0.3                 | 40                      | V    |

|                  |                                      | V <sub>CC</sub> to AGND                      | - 0.3                 | 40                      |      |

|                  | Negative supply voltage              | V <sub>SS</sub> to AGND                      | - 19                  | 0.3                     | V    |

|                  | Digital and IO supply voltage        | DV <sub>DD</sub> , IOV <sub>DD</sub> to DGND | - 0.3                 | 7                       | V    |

|                  |                                      | V <sub>REFPF</sub> to V <sub>REFNF</sub>     | - 0.3                 | 40                      |      |

|                  | Positive reference voltage           | V <sub>REFPF</sub> to V <sub>CC</sub>        | - 0.3                 | V <sub>CC</sub> + 0.3   | V    |

|                  |                                      | V <sub>REFPF</sub> to AGND                   | - 0.3                 | 40                      |      |

|                  | No matical professional contractions | V <sub>REFNF</sub> to AGND                   | - 19                  | 0.3                     | V    |

|                  | Negative reference voltage           | V <sub>REFNF</sub> to V <sub>SS</sub>        | V <sub>SS</sub> - 0.3 | 0.3                     | V    |

|                  | Digital input(s) to DGND             | 1                                            | DGND - 0.3            | IOV <sub>DD</sub> + 0.3 | V    |

|                  | OUT DED DOM DOES nin voltage         | to AGND (V <sub>SS</sub> = AGND)             | V <sub>SS</sub>       | V <sub>CC</sub>         | V    |

|                  | OUT, RFB, RCM, ROFS pin voltage      | to V <sub>SS</sub>                           | 0                     | V <sub>CC</sub>         | V    |

|                  | Alarm pin voltage, ALARM to DGND     |                                              | - 0.3                 | DV <sub>DD</sub> + 0.3  | V    |

|                  | Digital output, SDO to DGND          |                                              | - 0.3                 | DV <sub>DD</sub> + 0.3  | V    |

|                  | Current into any pin                 |                                              | - 10                  | 10                      | mA   |

| ГЈ               | Junction temperature                 |                                              |                       | 150                     | °C   |

| Γ <sub>stg</sub> | Storage temperature                  |                                              | - 65                  | 150                     | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 6.2 ESD Ratings

|                    |                          |                                                                                 | VALUE | UNIT |

|--------------------|--------------------------|---------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±1000 | V    |

| V <sub>(ESD)</sub> | Liectiostatic discriarge | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±250  | v    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                |                                            | MIN                     | NOM MAX                 | UNIT |

|----------------|--------------------------------------------|-------------------------|-------------------------|------|

|                | AV <sub>DD</sub> to AGND                   | 4.5                     | 5.5                     | V    |

|                | V <sub>SS</sub> to AGND                    | - 18                    | - 3                     | V    |

|                | V <sub>CC</sub> to AGND                    | 8                       | 33                      | V    |

|                | V <sub>CC</sub> to V <sub>SS</sub>         | 11                      | 36                      | V    |

|                | DV <sub>DD</sub> to DGND                   | 2.7                     | 5.5                     | V    |

|                | IOV <sub>DD</sub> to DGND                  | 1.7                     | 5.5                     | V    |

|                | AGND to DGND                               | - 0.3                   | 0.3                     | V    |

|                | V <sub>IH</sub> digital input high voltage | 0.7 × IOV <sub>DD</sub> |                         | V    |

|                | V <sub>IL</sub> digital input low voltage  |                         | 0.3 × IOV <sub>DD</sub> | V    |

|                | V <sub>REFPF</sub> to AGND                 | 3                       | 15                      | V    |

|                | V <sub>REFNF</sub> to AGND                 | - 15                    | 0                       | V    |

|                | V <sub>REFPF</sub> to V <sub>REFNF</sub>   | 3                       | 30                      | V    |

| T <sub>A</sub> | Operating temperature                      | - 40                    | 125                     | °C   |

# **6.4 Thermal Information**

|                        |                                              | DAC11001B  |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PFB (TQFP) | UNIT |

|                        |                                              | 48 PINS    |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 51.0       | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 10.3       | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 16.2       | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 0.3        | °C/W |

| Ψ ЈВ                   | Junction-to-board characterization parameter | 16.0       | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: DAC11001B

# 6.5 Electrical Characteristics

at  $T_A$  =  $-40^{\circ}$ C to +125°C,  $V_{CC}$  = +15 V,  $V_{SS}$  = -15 V,  $AV_{DD}$  = 5.5 V,  $DV_{DD}$  = 3.3 V,  $IOV_{DD}$  = 1.8 V, see note<sup>(1)</sup> for  $V_{REFPF}$  and  $V_{REFNF}$ , OUT pin buffered with unity gain OPA827, ROFS, RCM, RFB unconnected, and all typical specifications at  $T_A$  = 25°C, (unless otherwise noted)

|       | PARAMETER                                        | TEST CONDITIONS                                                                                                                 | MIN    | TYP   | MAX  | UNIT         |

|-------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------|-------|------|--------------|

| STATI | C PERFORMANCE                                    |                                                                                                                                 |        |       |      |              |

|       | Resolution                                       |                                                                                                                                 | 20     |       |      | Bits         |

| INL   | Relative accuracy <sup>(2) (3)</sup>             | $T_A = 0$ °C to $70$ °C <sup>(4)</sup><br>$V_{REFPF} = 10$ V and $V_{REFNF} = 0$ V<br>$V_{REFPF} = +5$ V and $V_{REFNF} = -5$ V | - 1    |       | 1    | LSB          |

|       | Troiding desards,                                | T <sub>A</sub> = 0°C to 70°C <sup>(4)</sup>                                                                                     | - 1.25 |       | 1.25 |              |

|       |                                                  | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                                  | - 2    |       | 2    |              |

|       | Relative accuracy drift over time <sup>(2)</sup> | T <sub>A</sub> = 25°C, 1000 hrs                                                                                                 |        | ±0.1  |      | LSB          |

| DNL   | Differential nonlinearity <sup>(2) (3)</sup>     | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                                  | - 1    |       | 1    | LSB          |

|       |                                                  | T <sub>A</sub> = 0°C to 70°C, code 0d into DAC, unipolar ranges only                                                            | - 4    |       | 4    |              |

|       | Zero code error <sup>(4)</sup>                   | $T_A = -40$ °C to +125°C, code 0d into DAC, unipolar ranges only                                                                | - 4    |       | 4    | LSB          |

|       |                                                  | T <sub>A</sub> = 25°C, unipolar ranges only                                                                                     |        | ±2    |      |              |

|       | Zero code error temperature coefficient          | T <sub>A</sub> = 0°C to 70°C, code 0d into DAC, unipolar ranges only                                                            |        | ±0.04 |      | ppm          |

|       | Zero code error temperature coemicient           | $T_A = -40$ °C to +125°C, code 0d into DAC, unipolar ranges only                                                                |        | ±0.04 |      | FSR/°C       |

|       |                                                  | T <sub>A</sub> = 0°C to 70°C                                                                                                    | - 8    |       | 8    |              |

|       | Gain error <sup>(2) (4)</sup>                    | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                                  | - 10   |       | 10   | ppm o<br>FSR |

|       |                                                  | T <sub>A</sub> = 25°C                                                                                                           |        | ±2    |      |              |

|       | Cain arror temperature coefficient               | T <sub>A</sub> = 0°C to 70°C                                                                                                    |        | ±0.04 |      | ppm          |

|       | Gain error temperature coefficient               | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                                  |        | ±0.04 |      | FSR/°0       |

|       |                                                  | T <sub>A</sub> = 0°C to 70°C, code 1048575d into DAC                                                                            | - 8    |       | 8    |              |

|       | Positive full-scale error <sup>(4)</sup>         | $T_A = -40$ °C to +125°C, code 1048575d into DAC                                                                                | - 10   |       | 10   | LSB          |

|       |                                                  | T <sub>A</sub> = 25°C, code 1048575d into DAC                                                                                   |        | ±2    |      |              |

|       | Full cools arror tomporature coefficient         | T <sub>A</sub> = 0°C to 70°C                                                                                                    |        | ±0.04 |      | ppm          |

|       | Full-scale error temperature coefficient         | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                                  |        | ±0.04 |      | FSR/°0       |

| OUTP  | UT CHARACTERISTICS                               |                                                                                                                                 |        |       |      |              |

|       | Headroom                                         | From V <sub>REFPF</sub> to V <sub>CC</sub>                                                                                      | 5      |       |      | V            |

|       | Footroom                                         | From V <sub>REFNF</sub> to V <sub>SS</sub>                                                                                      | 5      |       |      | V            |

|       | DC impedance                                     | From ROFS to RCM                                                                                                                |        | 5     |      | kΩ           |

|       | DO Impedance                                     | From RCM to RFB                                                                                                                 |        | 5     |      | K 52         |

| Zo    | DC output impedance                              |                                                                                                                                 |        | 2.5   |      | kΩ           |

|       | Power supply rejection ratio (dc)                | $V_{CC} = 15 \text{ V} \pm 20\%, V_{SS} = -15 \text{ V}$                                                                        |        | 1.5   |      | μV/V         |

|       | rower supply rejection ratio (uc)                | $V_{CC} = 15 \text{ V}, V_{SS} = -15 \text{ V} \pm 20\%$                                                                        |        | 1     |      | μν/ν         |

|       | Output voltage drift over time                   | T <sub>A</sub> = 25°C, V <sub>OUT</sub> = midscale, 1000 hr                                                                     |        | 1     |      | ppm o<br>FSR |

| VOLTA | AGE REFERENCE INPUT                              |                                                                                                                                 |        |       |      |              |

|       | Reference input impedance (REFPF)                | DAC at midscale,<br>V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                         |        | 5.5   |      | ko           |

|       | Reference input impedance (REFNF)                | DAC at midscale,<br>V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                         |        | 7     |      | kΩ           |

|       |                                                  | - I                                                                                                                             |        |       |      |              |

# **6.5 Electrical Characteristics (continued)**

at  $T_A$  =  $-40^{\circ}$ C to +125°C,  $V_{CC}$  = +15 V,  $V_{SS}$  = -15 V,  $AV_{DD}$  = 5.5 V,  $DV_{DD}$  = 3.3 V,  $IOV_{DD}$  = 1.8 V, see note<sup>(1)</sup> for  $V_{REFPF}$  and  $V_{REFNF}$ , OUT pin buffered with unity gain OPA827, ROFS, RCM, RFB unconnected, and all typical specifications at  $T_A$  = 25°C, (unless otherwise noted)

| - , (          | unless otherwise noted)  PARAMETER          | TEST CONDITIONS                                                                                                                                                  | MIN TYP N     | IAX UNIT    |

|----------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|

| DVNA           |                                             | TEST CONDITIONS                                                                                                                                                  | IVIIIV IIF IV | IAX UNII    |

| DYNAN          | MIC PERFORMANCE                             |                                                                                                                                                                  |               |             |

|                |                                             | Full-scale settling to 0.1%FSR,<br>V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                                           | 1             |             |

| t <sub>s</sub> | Output voltage settling time <sup>(5)</sup> | Full-scale settling to ±1 LSB,<br>V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                                            | 3             | μs          |

|                |                                             | 1-mV step settling to ±1 LSB,<br>V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                                             | 2.5           |             |

| SR             | Slew rate <sup>(6)</sup>                    | Full-scale step, measured at OUT pin,<br>V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                                     | 30            | V/µs        |

|                | Power-on glitch magnitude                   | Measured at unbuffered DAC voltage output, V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                                   | - 0.2         | V           |

|                |                                             | 0.1-Hz to 10-Hz, DAC at midscale,<br>V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                                         | 0.4           | μVpp        |

| V <sub>n</sub> | Output noise                                | 100-kHz bandwidth, DAC at midscale,<br>V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                                       | 3             | μVrms       |

|                | Output noise density                        | Measured at 1 kHz, 10 kHz, 100 kHz, DAC at mid scale, V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                        | 7             | nV/ √<br>Hz |

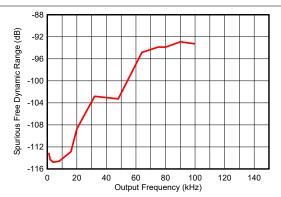

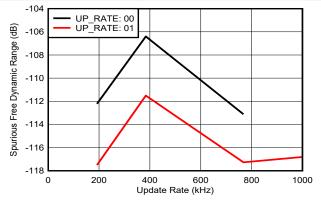

|                | Spurious free dynamic range <sup>(6)</sup>  | DAC update rate = 768 kHz, $f_{OUT}$ = 1 kHz, $V_{REFPF}$ = 4.5 V, $V_{REFNF}$ = -4.5 V, sixth-order, low-pass, 30-kHz output filter                             | - 120         |             |

| SFDR           |                                             | DAC update rate = 768 kHz, $f_{OUT}$ = 20 kHz, $V_{REFPF}$ = 4.5 V, $V_{REFNF}$ = -4.5 V, sixth-order, low-pass, 30-kHz output filter                            | - 114         | dB          |

|                |                                             | DAC update rate = 1 MHz, f <sub>OUT</sub> = 100 kHz,<br>V <sub>REFPF</sub> = 4.5 V, V <sub>REFNF</sub> = -4.5 V,<br>sixth-order, low-pass, 150-kHz output filter | - 92          |             |

|                | Total harmonic distortion <sup>(6)</sup>    | DAC update rate = 768 kHz, f <sub>OUT</sub> = 1 kHz,<br>V <sub>REFPF</sub> = 4.5 V, V <sub>REFNF</sub> = -4.5 V,<br>sixth-order, low-pass, 30-kHz output filter  | - 118         |             |

| THD            |                                             | DAC update rate = 768 kHz, $f_{OUT}$ = 20 kHz, $V_{REFPF}$ = 4.5 V, $V_{REFNF}$ = -4.5 V, sixth-order, low-pass, 30-kHz output filter                            | - 118         | dB          |

|                |                                             | DAC update rate = 1 MHz, f <sub>OUT</sub> = 100 kHz,<br>V <sub>REFPF</sub> = 4.5 V, V <sub>REFNF</sub> = -4.5 V,<br>sixth-order, low-pass, 150-kHz output filter | - 96          |             |

|                | Dayyar aunnly rejection ratio (ac)          | 200-mV, 50-Hz or 60-Hz sine wave superimposed on $V_{SS}$ , $V_{CC}$ = 15 V                                                                                      | 95            | dB          |

|                | Power supply rejection ratio (ac)           | 200-mV, 50 Hz or 60 Hz sine wave superimposed on V <sub>CC</sub> , V <sub>SS</sub> = -15 V                                                                       | 95            | ив          |

|                | Code change glitch impulse                  | ±1 LSB change around mid code (including feedthrough), V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V, measured at output of buffer op amp                  | 1             | nV-s        |

|                | Code change glitch impulse magnitude        | ±1 LSB change around mid code (including feedthrough), V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V, measured at output of buffer op amp                  | 5             | mV          |

|                | Deference foodthrough                       | V <sub>REFPF</sub> = 10 V ± 10%, V <sub>REFNF</sub> = 0 V,<br>frequency = 100 Hz, DAC at zero scale                                                              | - 90          | -10         |

|                | Reference feedthrough                       | V <sub>REFNF</sub> = -10 V ± 10%, V <sub>REFPF</sub> = 10 V,<br>frequency = 100 Hz, DAC at full scale                                                            | - 90          | dB          |

|                | Digital feedthrough                         | SCLK = 1 MHz, DAC static at midscale,<br>V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V                                                                     | 1             | nV-s        |

### **6.5 Electrical Characteristics (continued)**

at  $T_A = -40^{\circ}\text{C}$  to +125°C,  $V_{CC} = +15 \text{ V}$ ,  $V_{SS} = -15 \text{ V}$ ,  $AV_{DD} = 5.5 \text{ V}$ ,  $DV_{DD} = 3.3 \text{ V}$ ,  $IOV_{DD} = 1.8 \text{ V}$ , see note<sup>(1)</sup> for  $V_{REFPF}$  and  $V_{REFNF}$ , OUT pin buffered with unity gain OPA827, ROFS, RCM, RFB unconnected, and all typical specifications at  $T_A = 25^{\circ}\text{C}$ , (unless otherwise noted)

|                                                                                                                                                                                                                                 | PARAMETER                                     | TEST CONDITIONS                                                                                                        | MIN | TYP | MAX | UNIT |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|

| Input current  Pin capacitance  Per pin  DIGITAL OUTPUTS  V <sub>OL</sub> Low-level output voltage  Sinking 200 μA  V <sub>OH</sub> High-level output voltage  Sourcing 200 μA  IOV <sub>DD</sub> - 0.5  High impedance leakage |                                               |                                                                                                                        |     |     |     |      |  |  |

|                                                                                                                                                                                                                                 | Hysteresis voltage                            |                                                                                                                        |     | 0.4 |     | V    |  |  |

|                                                                                                                                                                                                                                 | Input current                                 |                                                                                                                        |     | ±5  |     | μΑ   |  |  |

|                                                                                                                                                                                                                                 | Pin capacitance                               | Per pin                                                                                                                |     | 10  |     | pF   |  |  |

| DIGITA                                                                                                                                                                                                                          | LOUTPUTS                                      |                                                                                                                        |     |     | '   |      |  |  |

| V <sub>OL</sub>                                                                                                                                                                                                                 | Low-level output voltage                      | Sinking 200 μA                                                                                                         |     |     | 0.4 | V    |  |  |

| V <sub>OH</sub>                                                                                                                                                                                                                 | High-level output voltage                     | Sourcing 200 μA                                                                                                        |     |     |     | V    |  |  |

|                                                                                                                                                                                                                                 | High impedance leakage                        |                                                                                                                        |     | ±5  |     | μΑ   |  |  |

|                                                                                                                                                                                                                                 | High impedance output capacitance             |                                                                                                                        |     | 10  |     | pF   |  |  |

| POWE                                                                                                                                                                                                                            | R                                             |                                                                                                                        |     |     | '   |      |  |  |

| I <sub>AVDD</sub>                                                                                                                                                                                                               | Current flowing into AV <sub>DD</sub>         | V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V, midscale code                                                     |     |     | 2.5 | mA   |  |  |

| I <sub>VCC</sub>                                                                                                                                                                                                                | Current flowing into V <sub>CC</sub>          | V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V, midscale code                                                     |     |     | 15  | mA   |  |  |

| I <sub>VSS</sub>                                                                                                                                                                                                                | Current flowing into V <sub>SS</sub>          | V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V, midscale code                                                     |     |     | 15  | mA   |  |  |

| I <sub>DVDD</sub>                                                                                                                                                                                                               | Current flowing into DV <sub>DD</sub>         | V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V, midscale code                                                     |     | 0.5 |     | mA   |  |  |

| I <sub>IOVDD</sub>                                                                                                                                                                                                              | Current flowing into IOV <sub>DD</sub>        | V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V, midscale code, all digital input pins static at IOV <sub>DD</sub> |     | 0.1 |     | mA   |  |  |

| I <sub>REFPF</sub>                                                                                                                                                                                                              | Reference input current (V <sub>REFPF</sub> ) | V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V, midscale code                                                     |     |     | 7   | mA   |  |  |

| I <sub>REFNF</sub>                                                                                                                                                                                                              | Reference input current (V <sub>REFNF</sub> ) | V <sub>REFPF</sub> = 10 V, V <sub>REFNF</sub> = 0 V, midscale code                                                     |     |     | 7   | mA   |  |  |

<sup>(1)</sup> Specified for the following pairs: V<sub>REFPF</sub> = 5 V and V<sub>REFNF</sub> = 0 V; V<sub>REFPF</sub> = 10 V and V<sub>REFNF</sub> = 0 V; V<sub>REFPF</sub> = 5 V and V<sub>REFNF</sub> = -5 V; V<sub>REFPF</sub> = 10 V and V<sub>REFNF</sub> = -10 V.

- (2) Calculated between code 0d to 1048575d.

- (3) With device temperature calibration mode enabled and used.

- (4) Specified by design, not production tested.

- (5) Adaptive TnH mode. TnH action is disabled for large code steps. For small steps, TnH action happens with a hold time of 1.2 μs.

- (6) OUT pin buffered with unity gain OPA828.

Copyright © 2022 Texas Instruments Incorporated

# 6.6 Timing Requirements: Write, 4.5 V $\leq$ DV<sub>DD</sub> $\leq$ 5.5 V

all input signals are specified with  $t_R$  =  $t_F$  = 1 ns/V (10% to 90% of IOV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2, SDO loaded with 20 pF, and  $T_A$  =  $-40^{\circ}$ C to +125°C (unless otherwise noted)

|                       |                                                                                                                                                                            | MIN | NOM MA | UNIT  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-------|

| f                     | SCLK frequency, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                                                                                                     |     | 3      | 3 MHz |

| f <sub>SCLK</sub>     | SCLK frequency, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                                                                |     | 5      |       |

| +                     | SCLK high time, 1.7 V $\leq$ IOV <sub>DD</sub> $<$ 2.7 V                                                                                                                   | 15  |        | no    |

| <sup>t</sup> SCLKHIGH | SCLK high time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                                                                | 10  |        | ns    |

| •                     | SCLK low time, 1.7 V $\leq$ IOV <sub>DD</sub> $<$ 2.7 V                                                                                                                    | 15  |        | no    |

| tsclklow              | SCLK low time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                                                                 | 10  |        | ns    |

| +                     | SDI setup, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                                                                                               | 13  |        | ns    |

| t <sub>SDIS</sub>     | SDI setup, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                                                                     | 8   |        | 115   |

| <b>t</b>              | SDI hold, 1.7 V $\leq$ IOV <sub>DD</sub> $<$ 2.7 V                                                                                                                         | 13  |        | ne    |

| t <sub>SDIH</sub>     | SDI hold, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                                                                      | 8   |        | ns    |

| t <sub>CSS</sub>      | SYNC falling edge to SCLK falling edge, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                                                                  | 23  |        | no    |

|                       | $\overline{\overline{\text{SYNC}}}$ falling edge to SCLK falling edge, 2.7 V $\leqslant$ IOV <sub>DD</sub> $\leqslant$ 5.5 V                                               | 18  |        | ns    |

| t <sub>CSH</sub>      | SCLK falling edge to $\overline{\text{SYNC}}$ rising edge, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                                                          | 15  |        | ns    |

|                       | SCLK falling edge to $\overline{\text{SYNC}}$ rising edge, 2.7 V $\leqslant$ IOV $_{\text{DD}} \leqslant$ 5.5 V                                                            | 10  |        | 113   |

| t                     | $\overline{\text{SYNC}}$ high time, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                                                                                 | 55  |        | ne    |

| tcshigh               | $\overline{\overline{\text{SYNC}}}$ high time, 2.7 V $\leqslant$ IOV <sub>DD</sub> $\leqslant$ 5.5 V                                                                       | 50  |        | ns    |

| +                     | SCLK falling edge to $\overline{\text{SYNC}}$ ignore, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                                                               | 10  |        | no    |

| tcsignore             | SCLK falling edge to $\overline{\text{SYNC}}$ ignore, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                          | 5   |        | ns    |

| t                     | Synchronous update: $\overline{\text{SYNC}}$ rising edge to $\overline{\text{LDAC}}$ falling edge, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                  | 50  |        | ne    |

| t <sub>LDACSL</sub>   | $\frac{\text{Synchronous update:}}{\text{SYNC rising edge to }\overline{\text{LDAC}} \text{ falling edge, 2.7 V} \leqslant \text{IOV}_{\text{DD}} \leqslant 5.5 \text{ V}$ | 50  |        | ns    |

| +                     | $\overline{\text{LDAC}}$ low time, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                                                                                  | 20  |        | no    |

| t <sub>LDACW</sub>    | $\overline{\overline{\text{LDAC}}}$ low time, 2.7 V $\leqslant$ IOV <sub>DD</sub> $\leqslant$ 5.5 V                                                                        | 20  |        | ns    |

| 4                     | $\overline{\text{CLR}}$ low time, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                                                                                   | 20  |        | no    |

| t <sub>CLRW</sub>     | $\overline{\text{CLR}}$ low time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                                              | 20  |        | ns    |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 6.7 Timing Requirements: Write, 2.7 V $\leqslant$ DV $_{DD}$ < 4.5 V

all input signals are specified with  $t_R$  =  $t_F$  = 1 ns/V (10% to 90% of IOV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2, SDO loaded with 20 pF, and  $T_A$  =  $-40^{\circ}$ C to +125°C (unless otherwise noted)

|                     |                                                                                                                                           | MIN | NOM | MAX | UNIT  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| f                   | SCLK frequency, 1.7 V $\leq$ IOV <sub>DD</sub> $<$ 2.7 V                                                                                  |     |     | 20  | MHz   |

| f <sub>SCLK</sub>   | SCLK frequency, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                               |     |     | 25  | IVITZ |

| 4                   | SCLK high time, 1.7 V $\leq$ IOV <sub>DD</sub> $<$ 2.7 V                                                                                  | 25  |     |     |       |

| tsclkhigh           | SCLK high time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                               | 20  |     |     | ns    |

| +                   | SCLK low time, 1.7 V $\leq$ IOV <sub>DD</sub> $<$ 2.7 V                                                                                   | 25  |     |     | no    |

| tsclklow            | SCLK low time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                                | 20  |     |     | ns    |

| +                   | SDI setup, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                                                              | 21  |     |     | no    |

| t <sub>SDIS</sub>   | SDI setup, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                                    | 16  |     |     | ns    |

| •                   | SDI hold, 1.7 V $\leq$ IOV <sub>DD</sub> $<$ 2.7 V                                                                                        | 21  |     |     | no    |

| t <sub>SDIH</sub>   | SDI hold, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                                                     | 16  |     |     | ns    |

| •                   | SYNC falling edge to SCLK falling edge, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                                 | 41  |     |     | no    |

| tcss                | $\overline{\overline{\text{SYNC}}}$ falling edge to SCLK falling edge, 2.7 V $\leqslant$ IOV <sub>DD</sub> $\leqslant$ 5.5 V              | 36  |     |     | ns    |

| +                   | SCLK falling edge to $\overline{\text{SYNC}}$ rising edge, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                         | 25  |     |     | ne    |

| t <sub>CSH</sub>    | SCLK falling edge to $\overline{\text{SYNC}}$ rising edge, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                    | 20  |     |     | ns    |

| •                   | SYNC high time, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                                                         | 100 |     |     | no    |

| tcshigh             | $\overline{\overline{\text{SYNC}}}$ high time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                | 100 |     |     | ns    |

|                     | SCLK falling edge to $\overline{\text{SYNC}}$ ignore, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                              | 10  |     |     |       |

| tcsignore           | SCLK falling edge to $\overline{\text{SYNC}}$ ignore, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                         | 5   |     |     | ns    |

| t                   | Synchronous update: $\overline{\text{SYNC}}$ rising edge to $\overline{\text{LDAC}}$ falling edge, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V | 100 |     |     | ns    |

| t <sub>LDACSL</sub> |                                                                                                                                           | 100 |     |     | 115   |

|                     | $\overline{\text{LDAC}}$ low time, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                                                 | 40  |     |     |       |

| t <sub>LDACW</sub>  | $\overline{\overline{\text{LDAC}}}$ low time, 2.7 V $\leqslant$ IOV <sub>DD</sub> $\leqslant$ 5.5 V                                       | 40  |     |     | ns    |

| +                   | $\overline{\text{CLR}}$ low time, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                                                                  | 40  |     |     | no    |

| t <sub>CLRW</sub>   | $\overline{\text{CLR}}$ low time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                                                             | 40  |     |     | ns    |

# 6.8 Timing Requirements: Read and Daisy-Chain Write, 4.5 V $\leq$ DV $_{DD}$ $\leq$ 5.5 V

all input signals are specified with  $t_R$  =  $t_F$  = 1 ns/V (10% to 90% of IOV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2, SDO loaded with 20 pF, and  $T_A$  =  $-40^{\circ}$ C to +125°C (unless otherwise noted)

|                       |                                                                               |                                                                                           | MIN | NOM | MAX | UNIT   |  |

|-----------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|--------|--|

|                       |                                                                               | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 0                                               |     |     | 10  |        |  |

| faaru                 | SCLK frequency                                                                | $1.7 \text{ V} \leq \text{IOV}_{\text{DD}} < 2.7 \text{ V}, \text{ FSDO} = 1$             |     |     | 20  | MHz    |  |

| f <sub>SCLK</sub>     | SCEN frequency                                                                | $2.7 \text{ V} \leqslant \text{IOV}_{\text{DD}} \leqslant 5.5 \text{ V, FSDO} = 0$        |     |     | 15  | IVIIIZ |  |

|                       |                                                                               | 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V, FSDO = 1                                               |     |     | 30  |        |  |

|                       |                                                                               | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 0                                               | 50  |     |     |        |  |

| 4                     | SCI K high time                                                               | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 1                                               | 25  |     |     |        |  |

| <sup>t</sup> sclkhigh | SCLK high time                                                                | 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V, FSDO = 0                                               | 33  |     |     | ns     |  |

|                       |                                                                               | 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V, FSDO = 1                                               | 16  |     |     |        |  |

|                       |                                                                               | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 0                                               | 50  |     |     |        |  |

|                       | CCL K law time                                                                | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 1                                               | 25  |     |     |        |  |

| <sup>t</sup> SCLKLOW  | SCLK low time                                                                 | 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V, FSDO = 0                                               | 33  |     |     | ns     |  |

|                       |                                                                               | 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V, FSDO = 1                                               | 16  |     |     |        |  |

| 1                     | SDI setup, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                  |                                                                                           | 13  | ,   |     |        |  |

| t <sub>SDIS</sub>     | SDI setup, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                  |                                                                                           | 8   |     |     | ns     |  |

|                       | SDI hold, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V                              |                                                                                           | 13  |     |     |        |  |

| t <sub>SDIH</sub>     | SDI hold, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                         |                                                                                           | 8   | ,   |     | ns     |  |

|                       | SYNC falling edge to SCLK falling edge                                        | 30                                                                                        |     |     |     |        |  |

| t <sub>CSS</sub>      | SYNC falling edge to SCLK falling edge                                        | ge, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                                     | 20  |     |     | ns     |  |

|                       | SCLK falling edge to SYNC rising edg                                          | e, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                      | 15  | ,   |     |        |  |

| t <sub>CSH</sub>      | SCLK falling edge to SYNC rising edg                                          | e, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                                      | 10  |     |     | ns     |  |

|                       | SYNC high time, 1.7 V ≤ IOV <sub>DD</sub> < 2.7                               | · V                                                                                       | 55  |     |     |        |  |

| <sup>t</sup> CSHIGH   | $\overline{\text{SYNC}}$ high time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.  | 5 V                                                                                       | 50  |     |     | ns     |  |

| 1                     | SCLK falling edge to SYNC ignore, 1.                                          | 7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                           | 10  |     |     |        |  |

| <sup>t</sup> CSIGNORE | SCLK falling edge to SYNC ignore, 2.                                          | $7 \text{ V} \leq \text{IOV}_{\text{DD}} \leq 5.5 \text{ V}$                              | 5   |     |     | ns     |  |

|                       | Synchronous update: SYNC rising edge to LDAC falling edge                     | ge, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                     | 50  |     |     | 200    |  |

| t <sub>LDACSL</sub>   | Synchronous update: SYNC rising edge to LDAC falling edge                     | ge, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                                     | 50  |     |     | ns     |  |

| 4                     | $\overline{\text{LDAC}}$ low time, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7       | V                                                                                         | 20  |     |     | no     |  |

| t <sub>LDACW</sub>    | $\overline{\text{LDAC}}$ low time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5  | i V                                                                                       | 20  |     |     | ns     |  |

| 4                     | $\overline{\text{CLR}}$ low time, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V      |                                                                                           | 20  |     |     |        |  |

| t <sub>CLRW</sub>     | $\overline{\text{CLR}}$ low time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V | /                                                                                         | 20  |     |     | ns     |  |

|                       | SCLK rising edge to SDO valid data,                                           | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 0                                               | 0   |     | 35  |        |  |

|                       | SCLK rising edge to SDO valid data, 2                                         | SCLK rising edge to SDO valid data, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V, FSDO = 0 |     |     |     |        |  |

| t <sub>SDODLY</sub>   | SCLK falling edge to SDO valid data,                                          | 0                                                                                         |     | 35  | ns  |        |  |

|                       | SCLK falling edge to SDO valid data,                                          | 0                                                                                         |     | 25  |     |        |  |

|                       | SYNC rising edge to SDO HiZ, 1.7 V                                            | ≤ IOV <sub>DD</sub> < 2.7 V                                                               | 0   |     | 20  |        |  |

| t <sub>SDOZ</sub>     | SYNC rising edge to SDO HiZ, 2.7 V                                            | ≤ IOV <sub>DD</sub> ≤ 5.5 V                                                               | 0   |     | 20  | ns     |  |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 6.9 Timing Requirements: Read and Daisy-Chain Write, 2.7 V $\leqslant$ DV $_{DD}$ < 4.5 V

all input signals are specified with  $t_R$  =  $t_F$  = 1 ns/V (10% to 90% of IOV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>) / 2, SDO loaded with 20 pF, and  $T_A$  =  $-40^{\circ}$ C to +125°C (unless otherwise noted)

|                       |                                                                               |                                                                                    | MIN | NOM | MAX | UNIT    |

|-----------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----|-----|---------|

|                       |                                                                               | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 0                                        |     |     | 8   |         |

| faaru                 | SCLK frequency                                                                | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 1                                        |     |     | 16  | MHz     |

| f <sub>SCLK</sub>     | SCEN frequency                                                                | $2.7 \text{ V} \leqslant \text{IOV}_{\text{DD}} \leqslant 5.5 \text{ V, FSDO} = 0$ |     |     | 10  | IVII IZ |

|                       |                                                                               | $2.7 \text{ V} \leqslant \text{IOV}_{\text{DD}} \leqslant 5.5 \text{ V, FSDO} = 1$ |     |     | 20  |         |

|                       |                                                                               | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 0                                        | 62  |     |     |         |

| 4                     | SCLK high time                                                                | $1.7 \text{ V} \leq \text{IOV}_{\text{DD}} < 2.7 \text{ V}, \text{ FSDO} = 1$      | 31  |     |     |         |

| <sup>t</sup> sclkhigh | SCLK high time                                                                | $2.7 \text{ V} \le \text{IOV}_{\text{DD}} \le 5.5 \text{ V}, \text{FSDO} = 0$      | 50  |     |     | ns      |

|                       |                                                                               | $2.7 \text{ V} \leq \text{IOV}_{\text{DD}} \leq 5.5 \text{ V, FSDO} = 1$           | 25  |     |     |         |

|                       |                                                                               | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 0                                        | 62  |     |     |         |

|                       | CCL K law time                                                                | 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 1                                        | 31  |     |     |         |

| <sup>t</sup> SCLKLOW  | SCLK low time                                                                 | $2.7 \text{ V} \le \text{IOV}_{\text{DD}} \le 5.5 \text{ V, FSDO} = 0$             | 50  |     |     | ns      |

|                       |                                                                               | 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V, FSDO = 1                                        | 25  |     |     |         |

| 1                     | SDI setup, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                  |                                                                                    | 21  | ,   |     |         |

| t <sub>SDIS</sub>     | SDI setup, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                        |                                                                                    | 16  |     |     | ns      |

|                       | SDI hold, 1.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 2.7 V                         |                                                                                    | 21  |     |     |         |

| t <sub>SDIH</sub>     | SDI hold, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V                         |                                                                                    | 16  | ,   |     | ns      |

|                       | SYNC falling edge to SCLK falling edg                                         | 41                                                                                 |     |     |     |         |

| t <sub>CSS</sub>      | SYNC falling edge to SCLK falling edg                                         | e, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                               | 36  |     |     | ns      |

|                       | SCLK falling edge to SYNC rising edge                                         | e, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                               | 25  | ,   |     |         |

| t <sub>CSH</sub>      | SCLK falling edge to SYNC rising edge                                         | $e, 2.7 \text{ V} \leqslant \text{IOV}_{\text{DD}} \leqslant 5.5 \text{ V}$        | 20  |     |     | ns      |

| 4                     | SYNC high time, 1.7 V ≤ IOV <sub>DD</sub> < 2.7                               | V                                                                                  | 100 |     |     |         |

| <sup>T</sup> CSHIGH   | $\overline{\text{SYNC}}$ high time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 | 5 V                                                                                | 100 |     |     | ns      |

|                       | SCLK falling edge to SYNC ignore, 1.7                                         | $V \leq IOV_{DD} \leq 2.7 V$                                                       | 10  |     |     |         |

| <sup>T</sup> CSIGNORE | SCLK falling edge to SYNC ignore, 2.7                                         | $V \leq IOV_{DD} \leq 5.5 V$                                                       | 5   |     |     | ns      |

|                       | Synchronous update: SYNC rising edge to LDAC falling edge                     | e, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                               | 100 |     |     |         |

| t <sub>LDACSL</sub>   | Synchronous update: SYNC rising edge to LDAC falling edge                     | e, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                               | 100 |     |     | ns      |

|                       | $\overline{\text{LDAC}}$ low time, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 \     | 1                                                                                  | 40  | ,   |     |         |

| t <sub>LDACW</sub>    | $\overline{\text{LDAC}}$ low time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5  | V                                                                                  | 40  |     |     | ns      |

|                       | $\overline{\text{CLR}}$ low time, 1.7 V $\leq$ IOV <sub>DD</sub> < 2.7 V      |                                                                                    | 40  |     |     |         |

| t <sub>CLRW</sub>     | $\overline{\text{CLR}}$ low time, 2.7 V $\leq$ IOV <sub>DD</sub> $\leq$ 5.5 V |                                                                                    | 40  |     |     | ns      |

|                       | SCLK rising edge to SDO valid data, 1                                         | .7 V ≤ IOV <sub>DD</sub> < 2.7 V, FSDO = 0                                         | 0   |     | 40  |         |

|                       | SCLK rising edge to SDO valid data, 2                                         | .7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V, FSDO = 0                                         | 0   |     | 30  |         |

| t <sub>SDODLY</sub>   | SCLK rising edge to SDO valid data, 1                                         | 0                                                                                  |     | 40  | ns  |         |

|                       | SCLK rising edge to SDO valid data, 2                                         | 0                                                                                  |     | 30  |     |         |

|                       | SYNC rising edge to SDO HiZ, 1.7 V ≤                                          |                                                                                    | 0   |     | 20  |         |

| t <sub>SDOZ</sub>     | SYNC rising edge to SDO HiZ, 2.7 V                                            | -<br>≤ IOV <sub>DD</sub> ≤ 5.5 V                                                   | 0   |     | 20  | ns      |

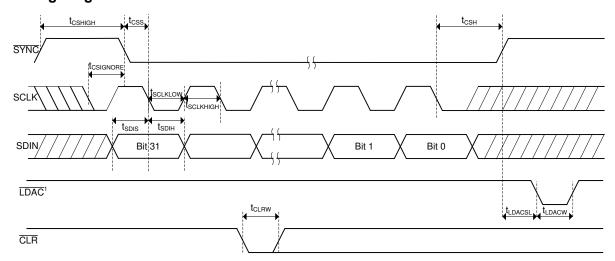

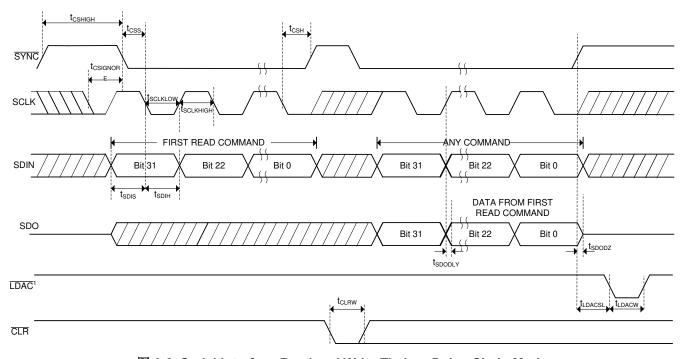

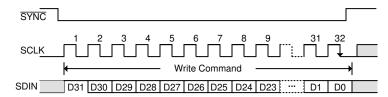

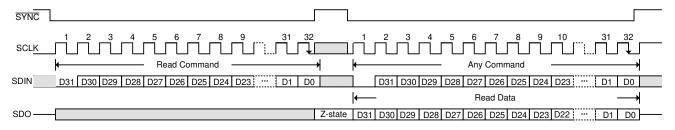

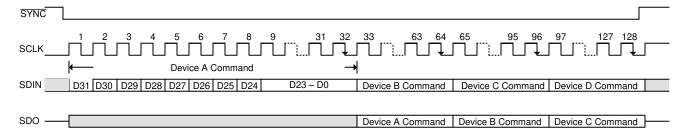

### 6.10 Timing Diagrams

图 6-1. Serial Interface Write Timing: Standalone Mode

图 6-2. Serial Interface Read and Write Timing: Daisy-Chain Mode

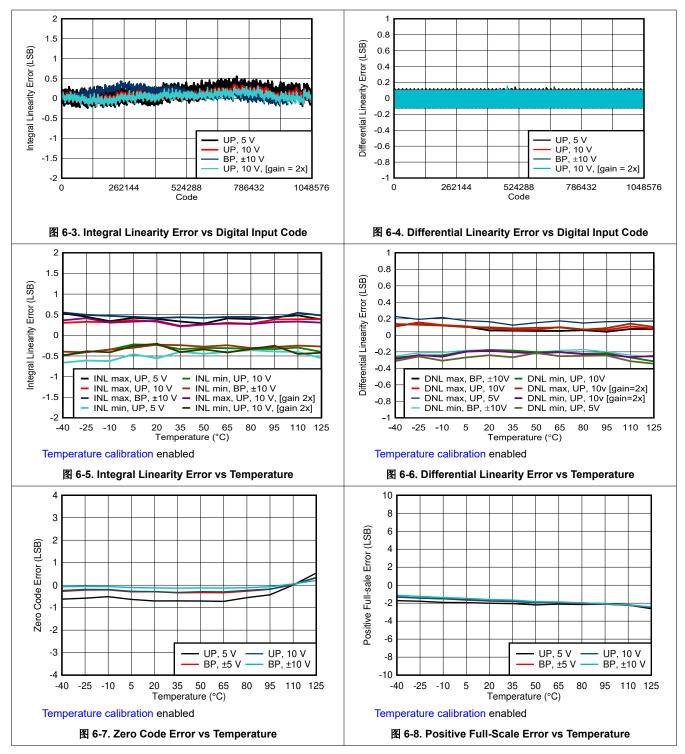

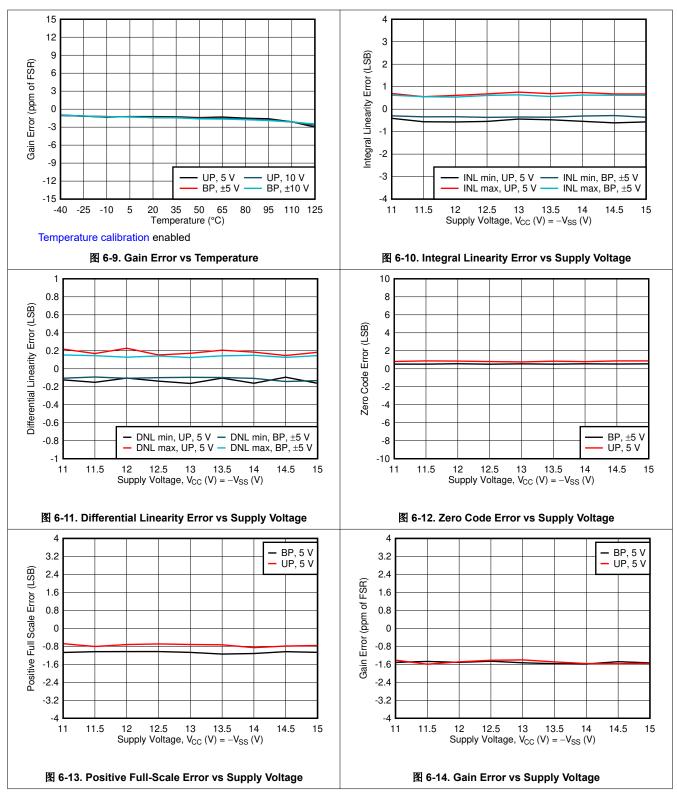

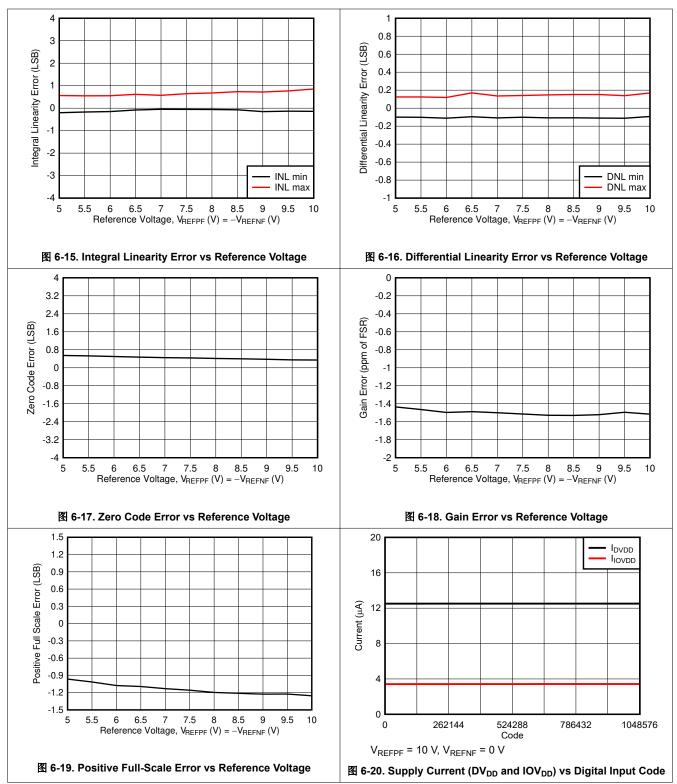

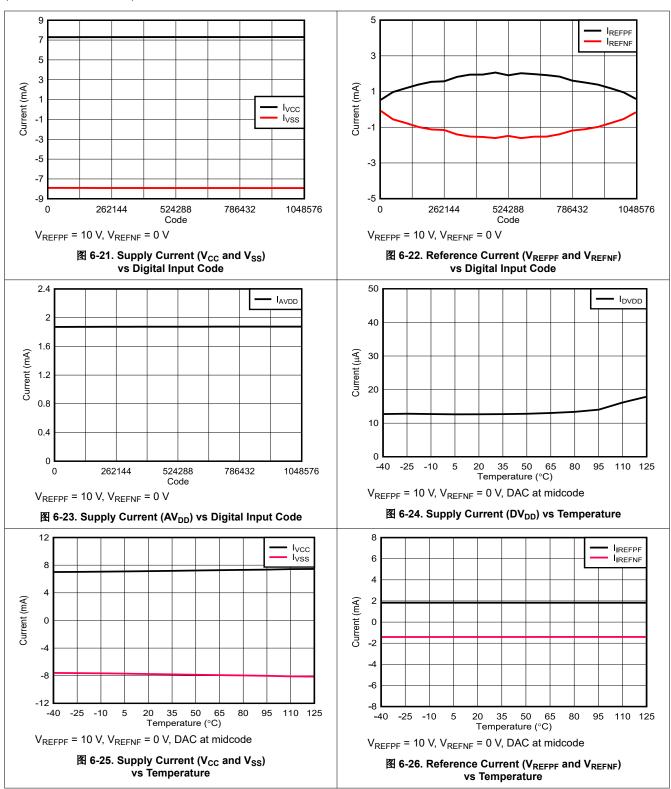

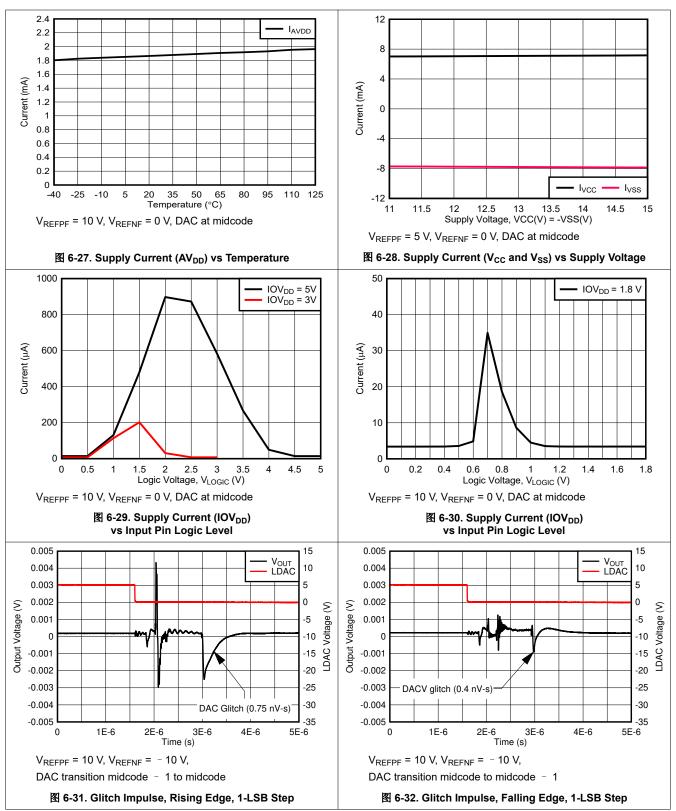

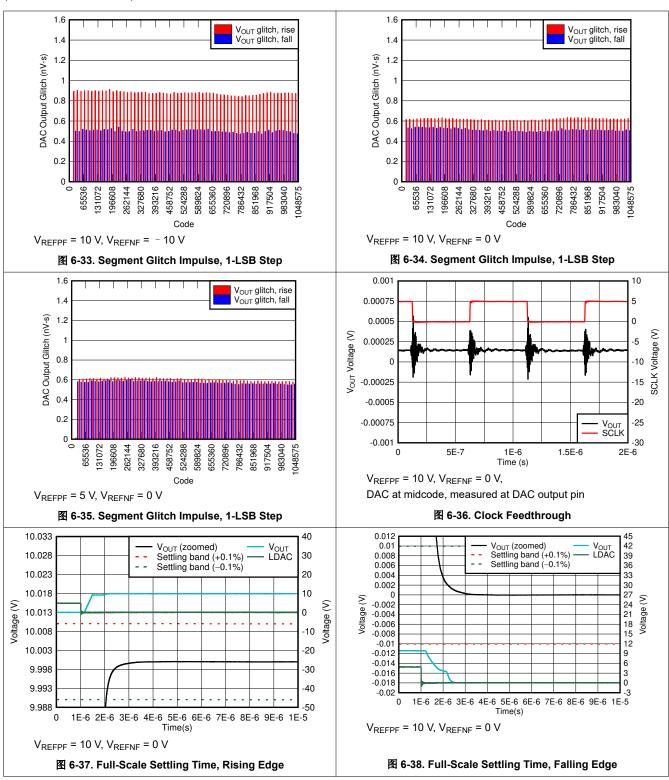

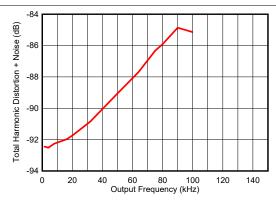

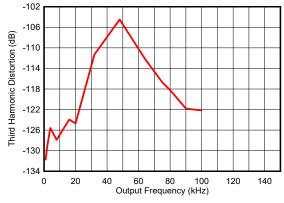

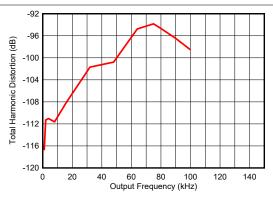

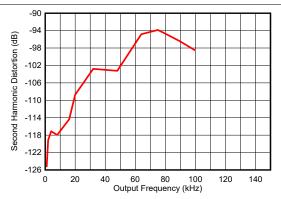

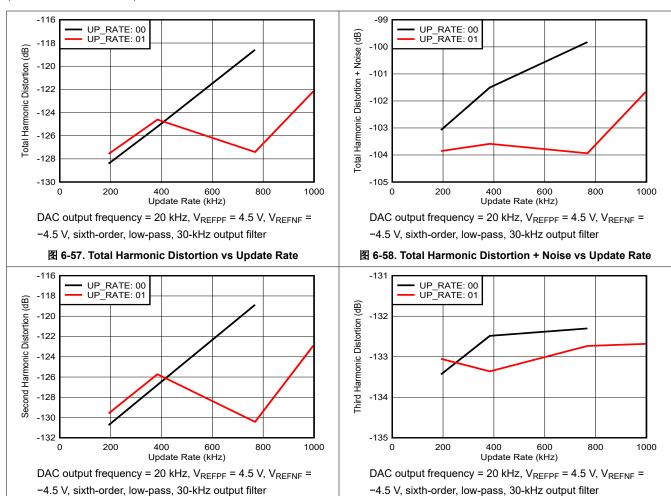

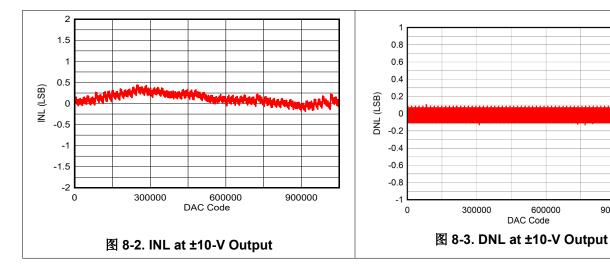

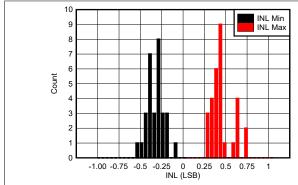

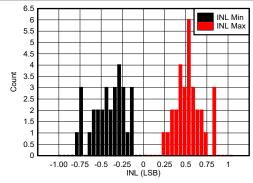

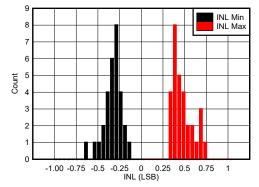

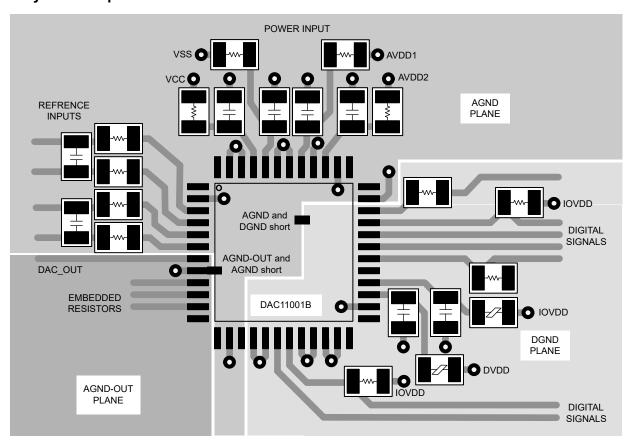

### 6.11 Typical Characteristics

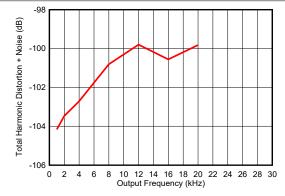

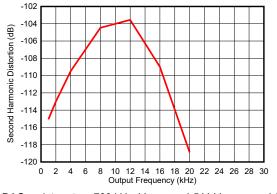

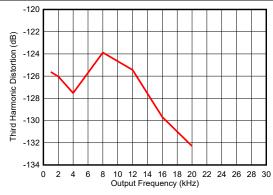

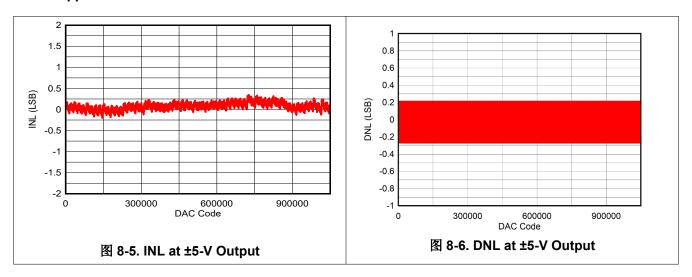

at  $T_A = 25$ °C,  $V_{CC} = 15$  V,  $V_{SS} = -15$  V,  $AV_{DD} = 5$  V,  $IOV_{DD} = 1.8$  V, gain resistors unconnected (gain = 1x), OPA827 used as reference amplifier, OPA828 used as output amplifier, UP = unipolar, BP = bipolar, and temperature calibration disabled (unless otherwise noted)

at  $T_A = 25$ °C,  $V_{CC} = 15$  V,  $V_{SS} = -15$  V,  $AV_{DD} = 5$  V,  $IOV_{DD} = 1.8$  V, gain resistors unconnected (gain = 1x), OPA827 used as reference amplifier, OPA828 used as output amplifier, UP = unipolar, BP = bipolar, and temperature calibration disabled (unless otherwise noted)

at  $T_A$  = 25°C,  $V_{CC}$  = 15 V,  $V_{SS}$  =  $^-$  15 V,  $AV_{DD}$  = 5 V,  $IOV_{DD}$  = 1.8 V, gain resistors unconnected (gain = 1x), OPA827 used as reference amplifier, OPA828 used as output amplifier, UP = unipolar, BP = bipolar, and temperature calibration disabled (unless otherwise noted)

at  $T_A = 25$ °C,  $V_{CC} = 15$  V,  $V_{SS} = -15$  V,  $AV_{DD} = 5$  V,  $IOV_{DD} = 1.8$  V, gain resistors unconnected (gain = 1x), OPA827 used as reference amplifier, OPA828 used as output amplifier, UP = unipolar, BP = bipolar, and temperature calibration disabled (unless otherwise noted)

at  $T_A$  = 25°C,  $V_{CC}$  = 15 V,  $V_{SS}$  = - 15 V,  $AV_{DD}$  = 5 V,  $IOV_{DD}$  = 1.8 V, gain resistors unconnected (gain = 1x), OPA827 used as reference amplifier, OPA828 used as output amplifier, UP = unipolar, BP = bipolar, and temperature calibration disabled (unless otherwise noted)

at  $T_A = 25^{\circ}$ C,  $V_{CC} = 15$  V,  $V_{SS} = -15$  V,  $AV_{DD} = 5$  V,  $IOV_{DD} = 1.8$  V, gain resistors unconnected (gain = 1x), OPA827 used as reference amplifier, OPA828 used as output amplifier, UP = unipolar, BP = bipolar, and temperature calibration disabled (unless otherwise noted)

at  $T_A$  = 25°C,  $V_{CC}$  = 15 V,  $V_{SS}$  = - 15 V,  $AV_{DD}$  = 5 V,  $IOV_{DD}$  = 1.8 V, gain resistors unconnected (gain = 1x), OPA827 used as reference amplifier, OPA828 used as output amplifier, UP = unipolar, BP = bipolar, and temperature calibration disabled (unless otherwise noted)

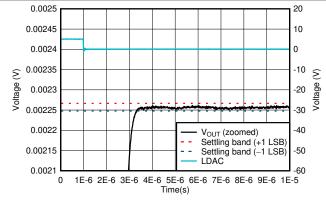

$V_{REFPF} = 10 \text{ V}, V_{REFNF} = 0 \text{ V},$

DAC transitions 100 codes around midscale

#### 图 6-39. 100 Codes Settling Time, Rising Edge

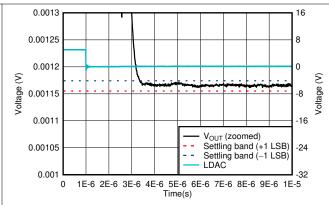

$V_{\mathsf{REFPF}}$  = 10 V,  $V_{\mathsf{REFNF}}$  = 0 V,

DAC transitions 100 codes around midscale

#### 图 6-40. 100 Codes Settling Time, Falling Edge

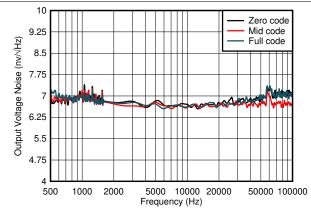

V<sub>REFPF</sub> = 10 V, V<sub>REFNF</sub> = 0 V, measured at DAC output

图 6-41. DAC Output Noise Spectral Density

Time (TS/L

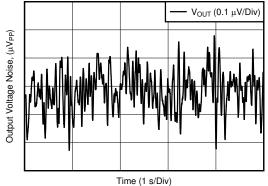

V<sub>REFPF</sub> = 10 V, V<sub>REFNF</sub> = 0 V, DAC at midcode, measured at DAC output pin

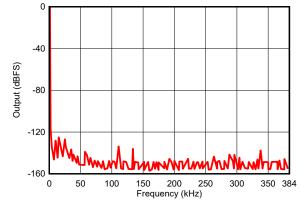

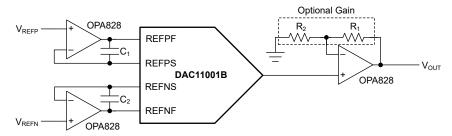

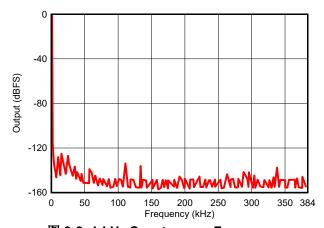

DAC update rate = 768 kHz,  $V_{REFPF}$  = 4.5 V,  $V_{REFNF}$  = -4.5 V, sixth-order, low-pass, 30-kHz output filter

图 6-43. 1-kHz Spectrum vs Frequency

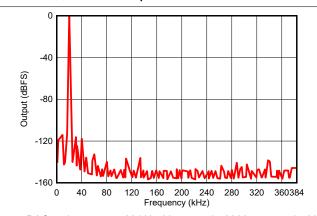

DAC update rate = 768 kHz,  $V_{REFPF}$  = 4.5 V,  $V_{REFNF}$  = -4.5 V, sixth-order, low-pass, 30-kHz output filter

图 6-44. 20-kHz Spectrum vs Frequency

at  $T_A$  = 25°C,  $V_{CC}$  = 15 V,  $V_{SS}$  = - 15 V,  $AV_{DD}$  = 5 V,  $IOV_{DD}$  = 1.8 V, gain resistors unconnected (gain = 1x), OPA827 used as reference amplifier, OPA828 used as output amplifier, UP = unipolar, BP = bipolar, and temperature calibration disabled (unless otherwise noted)

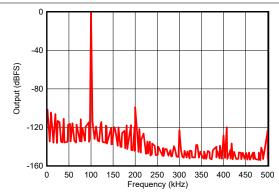

DAC update rate = 1 MHz,  $V_{REFPF}$  = 4.5 V,  $V_{REFNF}$  = -4.5 V, sixth-order, low-pass, 150-kHz output filter

图 6-45. 100-kHz Spectrum vs Frequency

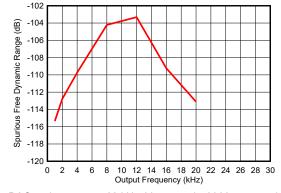

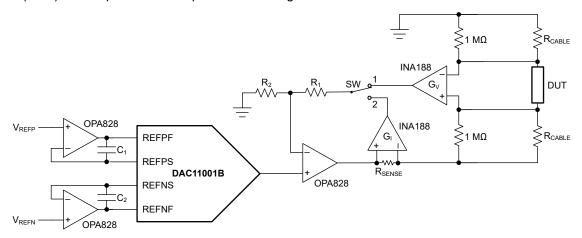

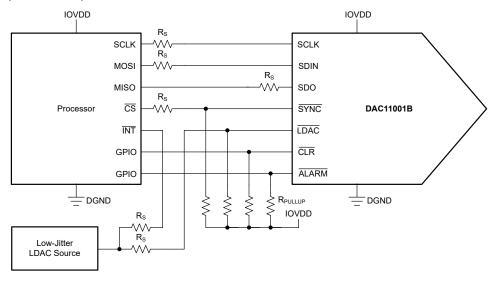

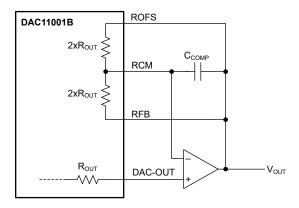

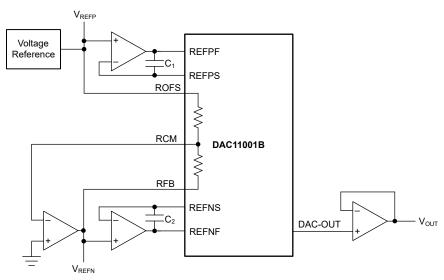

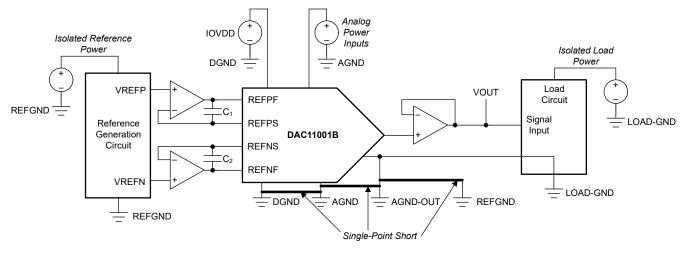

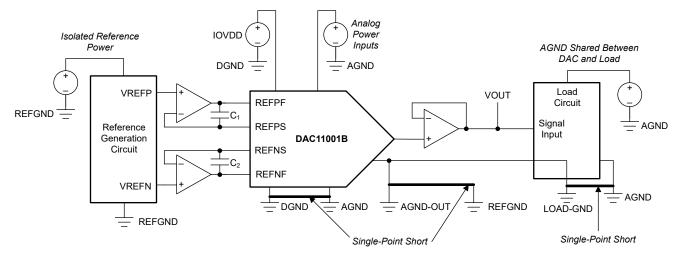

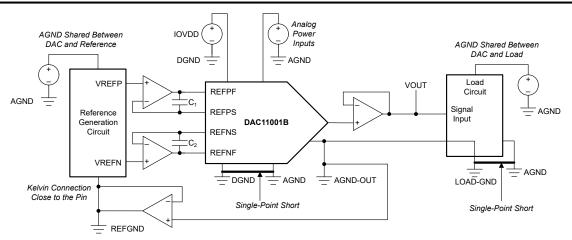

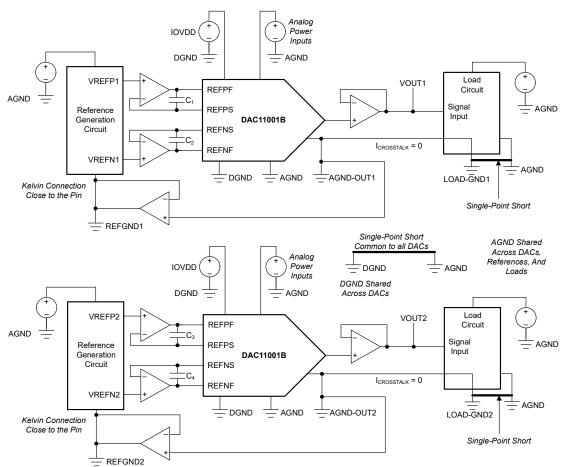

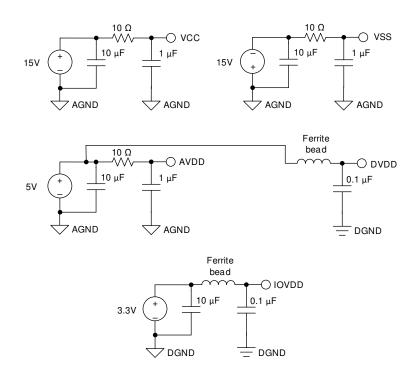

DAC update rate = 768 kHz,  $V_{REFPF}$  = 4.5 V,  $V_{REFNF}$  = -4.5 V, sixth-order, low-pass, 30-kHz output filter