🕳 Order

Now

# **DLPA2000**

ZHCSCO5B-JUNE 2014-REVISED FEBRUARY 2018

# DLPA2000 电源管理和 LED/灯驱动器 IC

#### 特性 1

Texas

INSTRUMENTS

- 高效 RGB LED/灯驱动器,在小型芯片级封装中集 成了降压/升压直流/直流转换器、DMD 电源、DPP 内核电源、1.8V 负载开关以及测量系统

- 三个用于通道选择的低阻抗(27°C时典型值为 30mΩ)金属氧化物半导体场效应晶体管 (MOSFET) 开关

- 每个通道具有独立的 10 位电流控制 •

- 针对 DLPA2000 嵌入式应用的最大 LED 电流为 750mA

- 片上电机驱动器

- DMD 调节器

- 仅需一个电感器

- VOFS: 10V

- VBIAS: 18V

- VRST: –14V

- 当禁用时对接地 (GND) 被动放电

- DPP 1.1V 内核电源

- 具有集成开关 FET 的同步降压转换器

- 支持高达 600mA 的输出电流

- VLED 降压/升压转换器

- 轻负载电流状态下的省电模式

- 低阻抗负载开关

- V<sub>IN</sub>范围: 1.8V 至 3.6V

- 支持高达 200mA 的电流

- 当禁用时对接地 (GND) 被动放电

- DMD 复位信号生成和电源排序

- 33MHz 串行外设接口 (SPI)

- 用于测量模拟信号的多路复用器

- 电池电压

- \_ LED 电压, LED 电流

- 光传感器(用于白点修正)

- 内部基准电压

- 外部(热敏电阻)温度传感器

- 监控和保护电路

- 热模警告和热关断

- 低电池电压警告

- 可编程的电池欠压闭锁 (UVLO)

- 负载开关 UVLO

- 过流和欠压保护

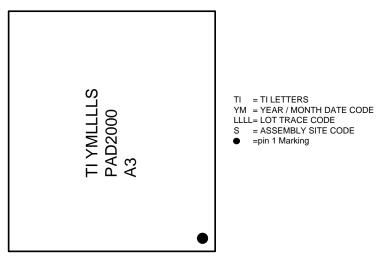

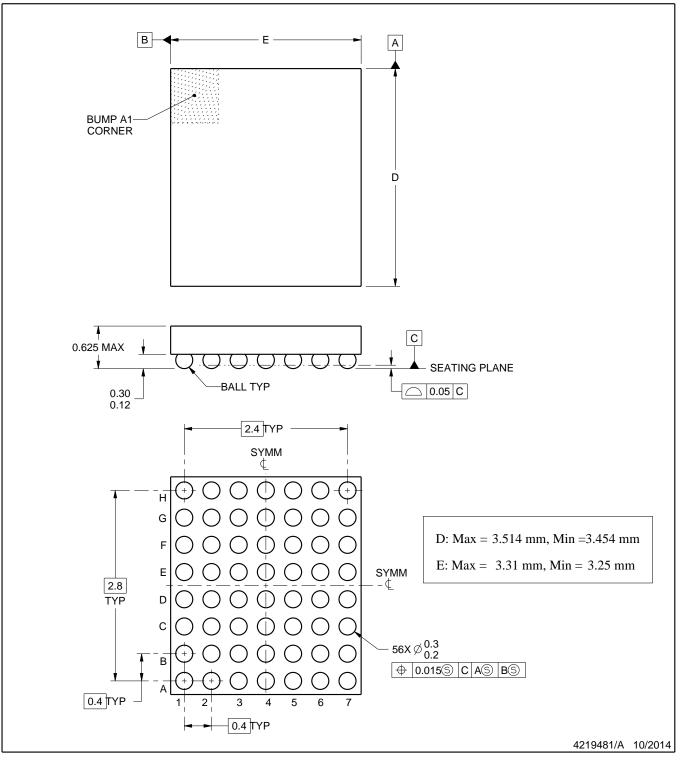

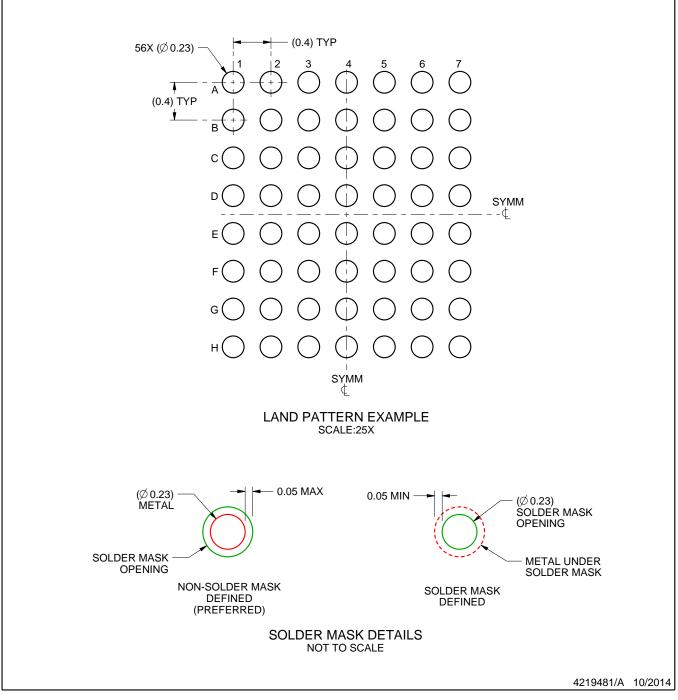

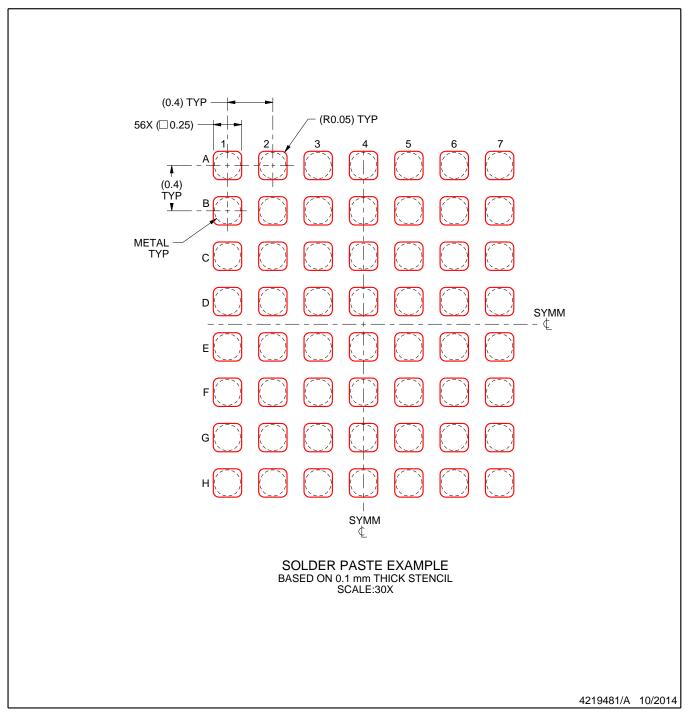

- DLPA2000 芯片级球栅阵列 (DSBGA) 封装

- 56 球 0.4mm 间距

- 裸片尺寸: 3.280mm × 3.484mm ± 0.03mm

# 2 应用

DLP™显示投影仪 DLP™移动传感

3 说明

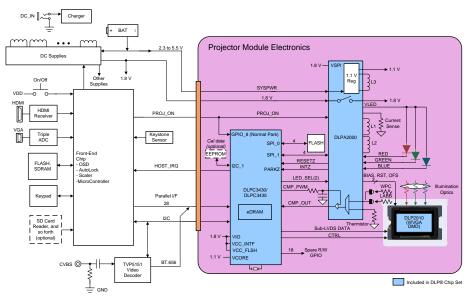

DLPA2000 是一款专用于 DLP2010 和 DLP2010NIR 数字微镜器件 (DMD) 的 PMIC/RGB LED/灯驱动器, 与 DLPC3430、DLPC3435 或 DLPC150 数字控制器 搭配使用。为确保这些芯片组可靠运行,必须搭配 **DLPA2000**使用。

#### 器件信息(1)

| 器件型号     | 封装         | 封装尺寸(标称值)                   |  |  |  |

|----------|------------|-----------------------------|--|--|--|

| DLPA2000 | DSBGA (56) | 3.28mm × 3.48mm ±<br>0.03mm |  |  |  |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

#### + BAT I നന്ന Module Electronics 1.81 HDMI Receiver VGA Triple ADC Keystone Sensor FLASH, SDRAM LOST ID OSD AutoLock Scaler Keypad SD Card Reader, ar so forth I2C 18 Spare R/ GPIO Included in I

# 图 1. 简化电路原理图

# 目录

| 特性   | 1                                                                                                          |

|------|------------------------------------------------------------------------------------------------------------|

| 应用   |                                                                                                            |

| 说明   | 1                                                                                                          |

| 修订   | 历史记录                                                                                                       |

| Pin  | Configuration and Functions 3                                                                              |

| Spe  | cifications5                                                                                               |

| 6.1  | Absolute Maximum Ratings 5                                                                                 |

| 6.2  | Storage Conditions 5                                                                                       |

| 6.3  | ESD Ratings5                                                                                               |

| 6.4  | Recommended Operating Conditions5                                                                          |

| 6.5  | Thermal Information 6                                                                                      |

| 6.6  | Electrical Characteristics 6                                                                               |

| 6.7  | Motor Driver Timing Requirements 11                                                                        |

| 6.8  | Data Transmission Timing Requirements 12                                                                   |

| 6.9  | Typical Characteristics 13                                                                                 |

| Deta | ailed Description 14                                                                                       |

| 7.1  | Overview 14                                                                                                |

| 7.2  | Functional Block Diagram 15                                                                                |

| 7.3  | Feature Description 16                                                                                     |

|      | 应说修 <b>Pin</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br><b>Deta</b><br>7.1<br>7.2 |

|    | 7.4  | Device Functional Modes 27            |

|----|------|---------------------------------------|

|    | 7.5  | Register Maps 29                      |

| 8  | Appl | ication and Implementation 41         |

|    | 8.1  | Application Information 41            |

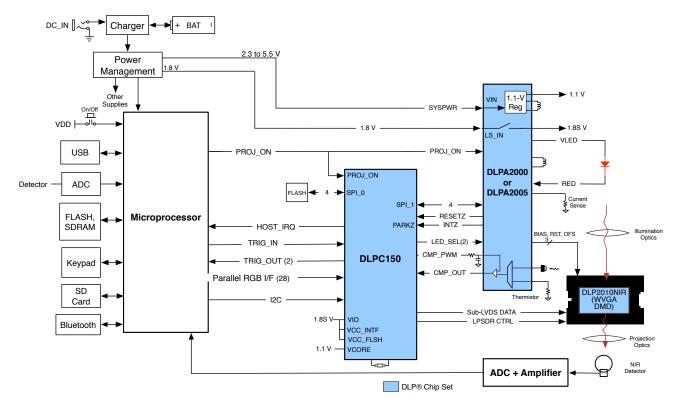

|    | 8.2  | Typical Projector Application 41      |

|    | 8.3  | Typical Mobile Sensing Application 43 |

| 9  | Powe | er Supply Recommendations 46          |

| 10 | Layo | out                                   |

|    | 10.1 | Layout Guidelines 47                  |

|    | 10.2 | Layout Example 48                     |

| 11 | 器件   | 和文档支持 49                              |

|    | 11.1 | 器件支持 49                               |

|    | 11.2 | 相关链接 49                               |

|    | 11.3 | 社区资源 49                               |

|    | 11.4 | 商标                                    |

|    | 11.5 | 静电放电警告 49                             |

|    | 11.6 | Glossary 50                           |

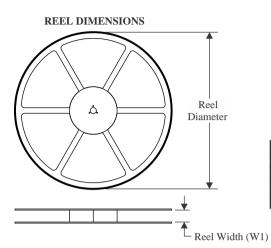

| 12 | 机械   | 、封装和可订购信息51                           |

# 4 修订历史记录

| C | hanges from Revision A (August 2015) to Revision B                                          | Page |

|---|---------------------------------------------------------------------------------------------|------|

| • | 修正了器件信息中的封装尺寸的拼写错误,将 3.48mm <sup>2</sup> 更正为 3.48mm                                         | 1    |

| • | 已添加 在修订版本 A 中添加先前缺失的历史记录标记                                                                  | 1    |

| • | Corrected package family to 'DSBGA' in Pin Functions Diagram, originally labeled as 'DSGBA' | 3    |

| • | Added mechanical package designator YFF to Thermal Information                              | 6    |

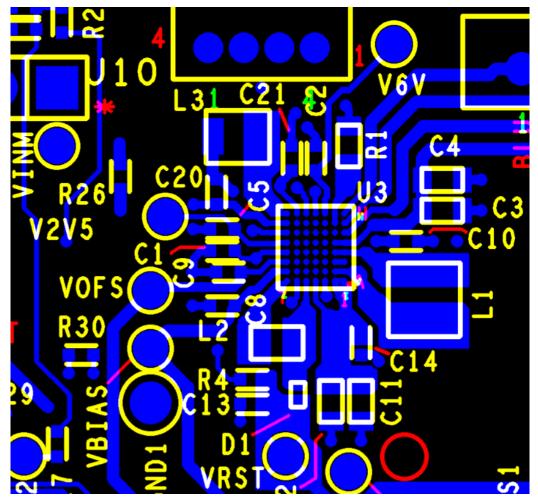

| • | Changed layout example to show correct image in Figure 46                                   | 48   |

|   |                                                                                             |      |

# Changes from Original (June 2014) to Revision A

| • | 已更改 将最大电流更改为 <b>750mA</b>                                                                         | . 1 |

|---|---------------------------------------------------------------------------------------------------|-----|

| • | 已添加 移动传感应用                                                                                        | . 1 |

| • | Added typical Mobile sensing application                                                          | 43  |

| • | Updated the Power Supply Recommendations to remove information that did not apply to the DLPA2000 | 46  |

# www.ti.com.cn

# Page

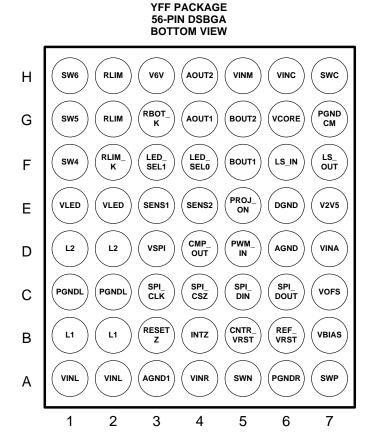

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN       |        | 1/0 | DESCRIPTION                                                                                                         |  |  |

|-----------|--------|-----|---------------------------------------------------------------------------------------------------------------------|--|--|

| NAME      | NUMBER | 1/0 | DESCRIPTION                                                                                                         |  |  |

| N/INII    | A1     |     |                                                                                                                     |  |  |

| VINL      | A2     |     | Power supply input for VLED BUCK-BOOST power stage. Connect to system power.                                        |  |  |

| AGND1     | A3     | GND | Analog ground. Connect to ground plane.                                                                             |  |  |

| VINR      | A4     | I   | Power supply input for DMD switch mode power supply (SMPS). Connect to system power.                                |  |  |

| SWN       | A5     | I   | Connection for the DMD SMPS-inductor (high-side switch).                                                            |  |  |

| PGNDR     | A6     | GND | Power ground for DMD SMPS. Connect to ground plane.                                                                 |  |  |

| SWP       | A7     | 0   | Connection for the DMD SMPS-inductor (low-side switch).                                                             |  |  |

| 1.4       | B1     | 0   | Connection for VILED DUCK DOOST industor                                                                            |  |  |

| L1        | B2     | 0   | Connection for VLED BUCK-BOOST inductor.                                                                            |  |  |

| RESETZ    | B3     | 0   | Reset output to the DLP system (active low). Pin is held low to reset DLP system.                                   |  |  |

| INTZ      | B4     | 0   | Interrupt output signal (open drain). Connect to pull-up resistor or short to ground.                               |  |  |

| CNTR_VRST | B5     | 0   | Connection to V <sub>RST</sub> for fast discharge function.                                                         |  |  |

| REF_VRST  | B6     | I   | Reference pin for the V <sub>RST</sub> regulator. Connect to V <sub>RST</sub> rail through 100-k $\Omega$ resistor. |  |  |

| VBIAS     | B7     | 0   | V <sub>BIAS</sub> output rail. Connect to ceramic capacitor.                                                        |  |  |

| DONIDI    | C1     |     |                                                                                                                     |  |  |

| PGNDL     | C2     | GND | Power ground for VLED BUCK-BOOST. Connect to ground plane.                                                          |  |  |

| SPI_CLK   | C3     | I   | Clock input for SPI interface.                                                                                      |  |  |

| SPI_CSZ   | C4     | I   | SPI chip select (active low).                                                                                       |  |  |

| SPI_DIN   | C5     | I   | SPI data input.                                                                                                     |  |  |

DLPA2000 ZHCSCO5B – JUNE 2014 – REVISED FEBRUARY 2018

www.ti.com.cn

NSTRUMENTS

Texas

# Pin Functions (continued)

| PIN      |        |       |                                                                                                                                                                                                                                                        |  |  |  |

|----------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NUMBER | I/O   | DESCRIPTION                                                                                                                                                                                                                                            |  |  |  |

| SPI_DOUT | C6     | 0     | SPI data output.                                                                                                                                                                                                                                       |  |  |  |

| VOFS     | C7     | 0     | V <sub>OFS</sub> output rail. Connect to ceramic capacitor.                                                                                                                                                                                            |  |  |  |

| D1       |        | - 1   | Connection for VLED BUCK-BOOST inductor.                                                                                                                                                                                                               |  |  |  |

| L2       | D2     |       |                                                                                                                                                                                                                                                        |  |  |  |

| VSPI     | D3     | Ι     | Power supply input for SPI interface. Connect to system I/O voltage.                                                                                                                                                                                   |  |  |  |

| CMP_OUT  | D4     | 0     | Analog-comparator output.                                                                                                                                                                                                                              |  |  |  |

| PWM_IN   | D5     | Ι     | Reference voltage input for analog comparator.                                                                                                                                                                                                         |  |  |  |

| AGND     | D6     | GND   | Analog ground. Connect to ground plane.                                                                                                                                                                                                                |  |  |  |

| VINA     | D7     | POWER | Power supply input for sensitive analog circuitry.                                                                                                                                                                                                     |  |  |  |

|          | E1     | 0     |                                                                                                                                                                                                                                                        |  |  |  |

| VLED     | E2     | 0     | VLED BUCK-BOOST converter output pin.                                                                                                                                                                                                                  |  |  |  |

| SENS1    | E3     | Ι     | Input signal from light sensor.                                                                                                                                                                                                                        |  |  |  |

| SENS2    | E4     | Ι     | Input signal from temperature sensor.                                                                                                                                                                                                                  |  |  |  |

| PROJ_ON  | E5     | Ι     | Input signal to enable or disable the IC and DLP projector.                                                                                                                                                                                            |  |  |  |

| DGND     | E6     | GND   | Digital ground. Connect to ground plane.                                                                                                                                                                                                               |  |  |  |

| V2V5     | E7     | 0     | Internal supply filter pin for digital logic; typical 2.5 V.                                                                                                                                                                                           |  |  |  |

| SW4      | F1     | 0     | Low-side MOSFET switch for LED cathode. Connect to RGB LED assembly.                                                                                                                                                                                   |  |  |  |

| RLIM_K   | F2     | I     | Kelvin sense connection to top side of LED current sense resistor.<br>For best accuracy, route this trace directly to the top of the current sense resistor and<br>separate it from the normal trace from the current sense resistor to the RLIM pins. |  |  |  |

| LED_SEL1 | F3     | I     | Digital input to the RGB STROBE DECODER.                                                                                                                                                                                                               |  |  |  |

| LED_SEL0 | F4     | Ι     | Digital input to the RGB STROBE DECODER.                                                                                                                                                                                                               |  |  |  |

| BOUT1    | F5     | 0     | Motor driver B phase output1.                                                                                                                                                                                                                          |  |  |  |

| LS_IN    | F6     | Ι     | Load switch.                                                                                                                                                                                                                                           |  |  |  |

| LS_OUT   | F7     | 0     | Load switch.                                                                                                                                                                                                                                           |  |  |  |

| SW5      | G1     | 0     | Low-side MOSFET switch for LED cathode. Connect to RGB LED assembly.                                                                                                                                                                                   |  |  |  |

| RLIM     | G2     | 0     | Connection to LED 'current sense' resistor.<br>Bottom side of sense resistor is connected to GND.                                                                                                                                                      |  |  |  |

| RBOT_K   | G3     | Ι     | Kelvin sense connection to ground side of LED current sense resistor.                                                                                                                                                                                  |  |  |  |

| AOUT1    | G4     | 0     | Motor driver A phase output1.                                                                                                                                                                                                                          |  |  |  |

| BOUT2    | G5     | 0     | Motor driver B phase output2.                                                                                                                                                                                                                          |  |  |  |

| VCORE    | G6     | I     | VCORE BUCK converter feedback pin.                                                                                                                                                                                                                     |  |  |  |

| PGNDCM   | G7     | GND   | Power ground for VCORE BUCK and motor driver.                                                                                                                                                                                                          |  |  |  |

| SW6      | H1     | 0     | Low-side MOSFET switch for LED cathode. Connect to RGB LED assembly.                                                                                                                                                                                   |  |  |  |

| RLIM     | H2     | 0     | Connection to LED current sense resistor.<br>Bottom side of sense resistor is connected to GND.                                                                                                                                                        |  |  |  |

| V6V      | H3     | 0     | Internal supply filter pin for gate driver circuitry. Typical 6.25 V.                                                                                                                                                                                  |  |  |  |

| AOUT2    | H4     | 0     | Motor driver A phase output2.                                                                                                                                                                                                                          |  |  |  |

| VINM     | H5     | I     | Power supply input for motor driver power stage. Connect to system power.                                                                                                                                                                              |  |  |  |

| VINC     | H6     | I     | Power supply input for VCORE BUCK power stage. Connect to system power.                                                                                                                                                                                |  |  |  |

| SWC      | H7     | I/O   | Connection for 1.1-V BUCK inductor.                                                                                                                                                                                                                    |  |  |  |

#### DLPA2000 ZHCSCO5B – JUNE 2014 – REVISED FEBRUARY 2018

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted) <sup>(1)</sup>

|    |                                                                                                               | MIN                        | MAX       | UNIT |

|----|---------------------------------------------------------------------------------------------------------------|----------------------------|-----------|------|

|    | Input voltage at V <sub>INL</sub> , V <sub>INA</sub> , V <sub>INR</sub> , V <sub>INC</sub> , V <sub>INM</sub> | -0.3                       | 7         | V    |

|    | Ground pins to system ground                                                                                  | -0.3                       | 0.3       | V    |

|    | Voltage at SWN                                                                                                | -18.0                      | 7         | V    |

|    | Voltage at SWP, V <sub>BIAS</sub>                                                                             | -0.3                       | 20        | V    |

|    | Voltage at V <sub>OFS</sub>                                                                                   | -0.3                       | 12        | V    |

|    | Voltage at V <sub>6V</sub> , V <sub>LED</sub> , L1, L2, SWC, SW4, SW5, SW6, INTZ, PROJ_ON                     | -0.3                       | 7         | V    |

|    | Voltage at all pins, unless noted otherwise                                                                   | -0.3                       | 3.6       | V    |

|    | Source current RESETZ, CMP_OUT                                                                                |                            | 1         | mA   |

|    | Source current SPI_DOUT                                                                                       |                            | 5.5       | mA   |

|    | Sink current RESETZ, CMP_OUT                                                                                  |                            | 1         | mA   |

|    | Sink current SPI_DOUT, INTZ                                                                                   |                            | 5.5       | mA   |

|    | Peak output current                                                                                           | Internally                 | / limited |      |

|    | Continuous total power dissipation                                                                            | Internally limite<br>shute |           |      |

| TJ | Operating junction temperature                                                                                | -30                        | 150       | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 Storage Conditions

applicable before the DMD is installed in the final product.

|                  |                         | MIN | MAX | UNIT |

|------------------|-------------------------|-----|-----|------|

| ENVIRONMENTAL    |                         |     |     |      |

| T <sub>stg</sub> | DMD Storage Temperature | -65 | 150 | °C   |

# 6.3 ESD Ratings

|                    |                                                                             |                                                                                          | VALUE | UNIT |

|--------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2000                                                                                    |       |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                                     | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                                                                                     |                                                          | MIN  | NOM | MAX | UNIT |

|----------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|-----|-----|------|

|                | Input voltage range at $V_{\text{INL}},V_{\text{INA}},V_{\text{INR}},V_{\text{INC}},V_{\text{INM}}$ | Full functional and parametric performance               | 2.7  | 3.6 | 6   |      |

|                |                                                                                                     | Extended operating range, limited parametric performance | 2.3  | 3.6 | 6   | V    |

|                | Voltage range at V <sub>SPI</sub>                                                                   |                                                          | 1.65 | 1.8 | 3.6 | V    |

| T <sub>A</sub> | Operational ambient temperature                                                                     |                                                          | -10  |     | 85  | °C   |

| TJ             | Operational junction temperature                                                                    |                                                          | -10  |     | 120 | °C   |

EXAS

# 6.5 Thermal Information

|                                          | THERMAL METRIC <sup>(1)</sup>   | DLPA2000    | UNIT |

|------------------------------------------|---------------------------------|-------------|------|

|                                          |                                 | YFF (DSBGA) | UNIT |

|                                          |                                 | 56 PINS     |      |

| R <sub>0JA</sub> Junction-to-ambient the | ermal resistance <sup>(2)</sup> | 45          | °C/W |

For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

Estimated when mounted on high K JEDEC board per JESD 51-7 with thickness of 1.6 mm, 4 layers, size of 76.2 mm × 114.3 mm, and 2-oz. copper for top and bottom plane. Actual thermal impedance will depend on PCB used in the application.

# 6.6 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted) (see (1)(2))

| PARAMETER              |                                             | TEST CONDITIONS                                                                                                                     | MIN TYP | MAX | UNIT |

|------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| SUPPLIES               | 3                                           |                                                                                                                                     |         |     |      |

| INPUT VO               | LTAGE                                       |                                                                                                                                     |         |     |      |

| 、 <i>i</i>             | Input voltage range                         |                                                                                                                                     | 2.7 3.6 | 6   | .,   |

| VI                     | Extended input voltage range <sup>(1)</sup> | V <sub>INA</sub> , V <sub>INR</sub> , V <sub>INL</sub> , V <sub>INC</sub>                                                           | 2.3 3.6 | 6   | V    |

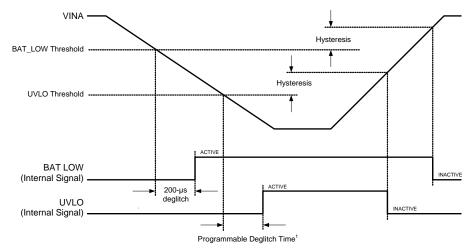

| .,                     | Low-battery warning threshold               | V <sub>INA</sub> falling                                                                                                            | 3       |     | V    |

| V <sub>LOW_BAT</sub>   | Hysteresis                                  | V <sub>INA</sub> rising                                                                                                             | 100     |     | mV   |

| .,                     | Undervoltage lockout threshold              | V <sub>INA</sub> falling (through 5-bit trim function)                                                                              | 2.3     | 4.5 | V    |

| V <sub>hys(UVLO)</sub> | Hysteresis                                  | V <sub>INA</sub> rising                                                                                                             | 100     |     | mV   |

| V <sub>STARTUP</sub>   | Startup voltage                             | V <sub>BIAS</sub> , V <sub>OFS</sub> , V <sub>RST</sub> ; loaded with 2 mA                                                          | 2.5     |     | V    |

| INPUT CU               | RRENT                                       |                                                                                                                                     |         |     |      |

| l <sub>Q</sub>         | ACTIVE mode                                 | Motor current excluded                                                                                                              | 15      |     | mA   |

| I <sub>STD</sub>       | STANDBY mode                                |                                                                                                                                     | 900     |     | μA   |

| I <sub>IDLE</sub>      | IDLE mode                                   |                                                                                                                                     | 10      |     | μA   |

| INTERNAL               | L SUPPLIES                                  |                                                                                                                                     |         |     |      |

| V <sub>V6V</sub>       | Internal supply, analog                     |                                                                                                                                     | 6.25    |     | V    |

| C <sub>LDO_V6V</sub>   | Filter capacitor for V6V LDO                |                                                                                                                                     | 100     |     | nF   |

| V <sub>V2V5</sub>      | Internal supply, logic                      |                                                                                                                                     | 2.5     |     | V    |

| C <sub>LDO_V2V5</sub>  | Filter capacitor for V2V5 LDO               |                                                                                                                                     | 2.2     |     | μF   |

| DMD REG                | ULATOR                                      |                                                                                                                                     |         |     |      |

| D                      |                                             | Switch E (from V <sub>INR</sub> to SWN)                                                                                             | 1000    |     |      |

| R <sub>DS(ON)</sub>    | MOSFET ON-resistance                        | Switch F (from SWP to PGNDR)                                                                                                        | 320     |     | mΩ   |

| M                      |                                             | Switch G <sup>(2)</sup> (from SWP to V <sub>BIAS</sub> )<br>V <sub>INR</sub> = 5 V, V <sub>SWP</sub> = 2 V, I <sub>F</sub> = 100 mA | 1.3     |     | V    |

| V <sub>FW</sub>        | Forward voltage drop                        | Switch H (from SWP to V <sub>OFS</sub> ) $V_{INR} = 5 V$ , $V_{SWP} = 2 V$ , $I_F = 100 mA$                                         | 1.3     |     | V    |

| t <sub>DIS</sub>       | Rail discharge time                         | V <sub>IN</sub> = 2.9 V; C <sub>OUT</sub> = 110 nF                                                                                  |         | 40  | μs   |

| t <sub>PG</sub>        | Power-good timeout                          | Not tested in production                                                                                                            | 6       |     | ms   |

| I <sub>LIMIT</sub>     | Switch current limit                        |                                                                                                                                     | 312     |     | mA   |

| L                      | Inductor value                              |                                                                                                                                     | 10      |     | μH   |

| V <sub>OFS</sub> REG   | ULATOR                                      |                                                                                                                                     |         |     |      |

|                        | Output voltage                              |                                                                                                                                     | 10      |     | V    |

|                        | DC output voltage accuracy                  | I <sub>OUT</sub> = 2 mA                                                                                                             | -2%     | 2%  |      |

| V <sub>OFS</sub>       | DC load regulation                          | $V_{IN} = 3.6 \text{ V}, I_{OUT} = 0 \text{ to } 2 \text{ mA}$                                                                      | -19     |     | V/A  |

|                        | DC line regulation                          | VINA, VINL, VINR, VINC 2.7 to 6.0 V, $I_{OUT} = 2 \text{ mA}$                                                                       | 35      |     | mV/V |

| V <sub>RIPPLE</sub>    | Output ripple                               | $V_{IN}$ = 3.6 V, $I_{OUT}$ = 2 mA, $C_{OUT}$ = 440 nF <sup>(3)</sup>                                                               | 375     |     | mVpp |

| I <sub>OUT</sub>       | Output current                              |                                                                                                                                     | 0       | 3   | mA   |

(1) Fully functional but limited parametric performance

(2) Including rectifying diode

(3) To reduce ripple the C<sub>OUT</sub> can be increased. V<sub>RIPPLE</sub> is inversely proportional to C<sub>OUT</sub>.

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted) (see <sup>(1)(2)</sup>)

|                  | PARAMETER                            | TEST CONDITIONS                                                                            | MIN TYP | MAX | UNIT |

|------------------|--------------------------------------|--------------------------------------------------------------------------------------------|---------|-----|------|

| 50               | Power-good threshold                 | V <sub>OFS</sub> rising                                                                    | 86%     |     |      |

| PG               | (fraction of nominal output voltage) | V <sub>OFS</sub> falling                                                                   | 66%     |     |      |

| R <sub>DIS</sub> | Output discharge resistor            | Active when rail is disabled                                                               | 100     |     | Ω    |

| C <sub>OUT</sub> | Output capacitor                     | Recommended value (output capacitors for $V_{\text{OFS}}\!/V_{\text{BIAS}}$ must be equal) | 110 220 |     | nF   |

|                  |                                      | t <sub>DISCHARGE</sub> < 40 μs at 2.9 V                                                    | 100     | 110 | nF   |

Texas Instruments

www.ti.com.cn

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted) (see <sup>(1)(2)</sup>)

|                       | PARAMETER                            | TEST CONDITIONS                                                                                      | MIN | TYP    | MAX | UNIT       |  |

|-----------------------|--------------------------------------|------------------------------------------------------------------------------------------------------|-----|--------|-----|------------|--|

| V <sub>BIAS</sub> REG | ULATOR                               | · · · · · ·                                                                                          |     |        | I   |            |  |

|                       | Output voltage                       |                                                                                                      |     | 18     |     | V          |  |

|                       | DC output voltage accuracy           | I <sub>OUT</sub> = 2 mA                                                                              | -2% |        | 2%  |            |  |

| V <sub>BIAS</sub>     | DC load regulation                   | $V_{IN} = 3.6 \text{ V}, I_{OUT} = 0 \text{ to } 2 \text{ mA}$                                       |     | -14    |     | V/A        |  |

|                       | DC line regulation                   | $V_{INA}$ , $V_{INL}$ , $V_{INR}$ , $V_{INC}$ 2.7 to 6 V,<br>$I_{OUT} = 2 \text{ mA}$                |     | 18     |     | mV/V       |  |

| V <sub>RIPPLE</sub>   | Output ripple                        | V <sub>IN</sub> = 3.6 V, I <sub>OUT</sub> = 2 mA, C <sub>OUT</sub> = 440 nF<br>(see <sup>(3)</sup> ) |     | 375    |     | mVpp       |  |

| IOUT                  | Output current                       |                                                                                                      | 0   |        | 4   | mA         |  |

| 001                   | Power-good threshold                 | V <sub>BIAS</sub> rising                                                                             | -   | 86%    |     |            |  |

| PG                    | (fraction of nominal output voltage) | V <sub>BIAS</sub> falling                                                                            |     | 66%    |     |            |  |

| R <sub>DIS</sub>      | Output discharge resistor            | Active when rail is disabled                                                                         |     | 100    |     | Ω          |  |

| C <sub>OUT</sub>      | Output capacitor                     | Recommended value (output capacitors for V <sub>OFS</sub> / V <sub>BIAS</sub> must be equal)         | 110 | 220    |     | nF         |  |

| 0001                  |                                      | t <sub>DISCHARGE</sub> < 40 μs at 2.9 V                                                              | 100 |        | 110 |            |  |

| V <sub>RST</sub> REGI | JLATOR                               |                                                                                                      |     |        | -   |            |  |

| NOT                   | Output voltage                       |                                                                                                      |     | -14    |     | V          |  |

| V <sub>RST</sub>      | DC output voltage accuracy           | I <sub>OUT</sub> = 2 mA                                                                              | -3% |        | 3%  |            |  |

|                       | DC load regulation                   | $V_{IN} = 3.6 \text{ V}, I_{OUT} = 0 \text{ to } 2 \text{ mA}$                                       |     | 13     |     | V/A        |  |

|                       | DC line regulation                   | $V_{INA}$ , $V_{INL}$ , $V_{INR}$ , $V_{INC}$ 2.7 to 6 V,<br>$I_{OUT} = 2 \text{ mA}$                | -21 |        |     | mV/V       |  |

| V <sub>RIPPLE</sub>   | Output ripple                        | V <sub>IN</sub> = 3.6 V, I <sub>OUT</sub> = 2 mA, C <sub>OUT</sub> = 440 nF<br>(see <sup>(3)</sup> ) |     | 375    |     | mVpp       |  |

| V <sub>REF_VRST</sub> | Reference voltage                    |                                                                                                      |     | 500    |     | mV         |  |

|                       | Output current                       |                                                                                                      | 0   |        | 4   | mA         |  |

| 001                   | Power-good threshold (fraction of    | V <sub>RST</sub> rising                                                                              |     | 90%    |     |            |  |

| PG                    | nominal output voltage)              | V <sub>RST</sub> falling                                                                             |     | 90%    |     |            |  |

| R <sub>DIS</sub>      | Output discharge resistor            | Active when rail is disabled                                                                         |     | ±150   |     | Ω          |  |

| 11015                 |                                      |                                                                                                      | 110 | 220    |     |            |  |

| C <sub>OUT</sub>      | Output capacitor                     | t <sub>DISCHARGE</sub> < 70 µs at V <sub>BAT</sub> ≥ 2.7 V                                           | 100 | 220    | 110 | nF         |  |

| LED DRIVE             | =P                                   | DISCHARGE VIO DO UN VBAT - 2.7 V                                                                     | 100 |        | 110 |            |  |

| VLED BUC              |                                      |                                                                                                      |     |        |     |            |  |

|                       | Output voltage range                 |                                                                                                      | 1.2 |        | 5.5 |            |  |

| V <sub>LED</sub>      | Default output voltage               | SW4, SW5, SW6 in OPEN position                                                                       | 1.2 | 3.5    | 0.0 | V          |  |

| V <sub>OVP</sub>      | Output overvoltage protection        | Clamps buck-boost output                                                                             | 5.5 | 0.0    | 7   | V          |  |

| VOVP                  | Fault detection threshold            | Triggers VLED_OVP interrupt                                                                          | 5.5 | 5.4    |     | V          |  |

|                       | Switch current limit                 |                                                                                                      | 3.5 | 4.0    | 4.5 | A          |  |

| I <sub>SW</sub>       | Switch current limit                 | Switch A (from V <sub>INL</sub> to L1)                                                               | 0.0 | 50     | 4.5 | ~          |  |

|                       |                                      | Switch B (from L1 to PGNDL)                                                                          |     | 50     |     |            |  |

| R <sub>DS(ON)</sub>   | MOSFET ON-resistance                 |                                                                                                      |     | 50     |     | mΩ         |  |

|                       |                                      | Switch C (from L2 to PGNDL)<br>Switch D (from L2 to VLED)                                            |     | 50     |     |            |  |

| f                     | Switching frequency                  |                                                                                                      |     | 2.25   |     | MHz        |  |

| f <sub>sw</sub>       | Switching frequency                  |                                                                                                      |     |        |     |            |  |

|                       |                                      |                                                                                                      |     | 2 × 22 |     | μF         |  |

| _                     | DECONTROLLER SWITCHES                | SIMA SIME SIME                                                                                       |     | 20     | 75  | <b>m</b> 0 |  |

| R <sub>DS(ON)</sub>   | Drain-source ON-resistance           | SW4, SW5, SW6                                                                                        |     | 30     | 75  | mΩ         |  |

| I <sub>LEAK</sub>     | OFF-state leakage current            | V <sub>DS</sub> = 5.0 V                                                                              |     |        | 1   | μA         |  |

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted) (see  $^{(1)(2)}$ )

|                     | PARAMETER                          | TEST CONDITIONS                                                                                                                                                                                                                                                                                                           | MIN   | ТҮР  | MAX  | UNIT       |

|---------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------------|

| LED CUR             | RENT CONTROL                       |                                                                                                                                                                                                                                                                                                                           |       |      |      |            |

| V <sub>f</sub>      | LED forward voltage                |                                                                                                                                                                                                                                                                                                                           |       |      | 4.8  | V          |

|                     | DLPA2000 LED currents              | $ \begin{array}{l} V_{IN} \geq 2.3 \ V, \ V_{LED} \leq 4.8 \ V \\ R_{LIM} = 100 \ m\Omega, \ 0.1\%, \ T_{A} = 25^{\circ}C \ (\text{see} \\ \text{register settings}) \\ Current at minimum code  0x00Ch for SWx \\ IDAC[9:0]. \end{array} $                                                                               |       | 25   |      | mA         |

| I <sub>LED</sub>    |                                    | $ \begin{array}{l} V_{\text{IN}} \geq 2.3 \ \text{V}, \ V_{\text{LED}} \leq 4.8 \ \text{V} \\ R_{\text{LIM}} = 100 \ \text{m}\Omega, \ 0.1\%, \ T_{\text{A}} = 25^{\circ}\text{C} \ (\text{see} \\ \text{register settings}) \\ \text{Current at maximum code } 0x307\text{h for} \\ \text{SWx\_IDAC[9:0]}. \end{array} $ |       | 750  |      | ША         |

|                     | DC current accuracy, SW4, 5, 6     | R <sub>LIM</sub> = 100 mΩ                                                                                                                                                                                                                                                                                                 |       | 25   |      | mA         |

|                     |                                    | ILIM[3:0] = 0000 at $R_{LIM}$ = 100 m $\Omega$                                                                                                                                                                                                                                                                            |       | 130  |      | <b>س</b> ۸ |

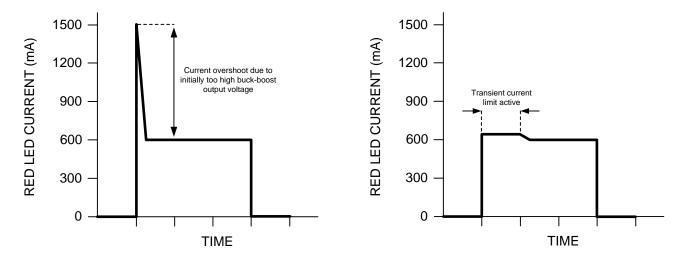

|                     | Transient LED current limit range  | ILIM[3:0] = 1111 at $R_{LIM}$ = 100 m $\Omega$                                                                                                                                                                                                                                                                            |       | 1500 |      | mA         |

| t <sub>rise</sub>   | Current rise time                  | $I_{LED}$ from 5% to 95%, $I_{LED}$ = 300 mA,<br>Transient current limit disabled<br>Not tested in production                                                                                                                                                                                                             |       |      | 50   | μs         |

| 1.1-V RE0           | GULATOR                            |                                                                                                                                                                                                                                                                                                                           |       |      |      |            |

| VCORE (             | BUCK)                              |                                                                                                                                                                                                                                                                                                                           |       |      |      |            |

| V <sub>IN</sub>     | Input voltage                      |                                                                                                                                                                                                                                                                                                                           | 2.3   |      | 6    | V          |

|                     | Nominal fixed output voltage       |                                                                                                                                                                                                                                                                                                                           |       | 1.1  |      | V          |

| V <sub>OUT</sub>    | DC output voltage accuracy         | 0 mA $\leq$ I <sub>OUT</sub> $\leq$ 600 mA at V <sub>IN</sub> > 2.5 V<br>V <sub>OUT</sub> = 1.1 V                                                                                                                                                                                                                         | -1.5% |      | 1.5% |            |

| d                   | Maximum duty cycle                 |                                                                                                                                                                                                                                                                                                                           |       |      | 100% |            |

| R <sub>DS(ON)</sub> | Low-side MOSFET on-resistance      | V 0.0.V/ T 0700                                                                                                                                                                                                                                                                                                           |       | 185  | 380  | mΩ         |

|                     | High-side MOSFET on-resistance     | V <sub>IN</sub> = 3.6 V, T <sub>J</sub> = 27°C                                                                                                                                                                                                                                                                            |       | 240  | 480  | mΩ         |

| I <sub>OUT</sub>    | Output current                     | V <sub>IN</sub> > 2.3 V                                                                                                                                                                                                                                                                                                   |       | 300  | 600  | mA         |

| I <sub>LIMIT</sub>  | Switch current limit               |                                                                                                                                                                                                                                                                                                                           |       | 1    |      | А          |

| T <sub>SS</sub>     | Soft-start time                    | Time to ramp from 10% to 90% of V <sub>OUT</sub> , V <sub>IN</sub> = 3.6 V                                                                                                                                                                                                                                                |       | 250  |      | μs         |

| C <sub>OUT</sub>    | Output capacitance                 |                                                                                                                                                                                                                                                                                                                           |       | 10   |      | μF         |

| L                   | Nominal Inductance                 |                                                                                                                                                                                                                                                                                                                           |       | 2.2  |      | μH         |

| LOAD SV             | VITCH                              |                                                                                                                                                                                                                                                                                                                           |       |      |      |            |

| V <sub>IN</sub>     | Input voltage range                | LS_IN                                                                                                                                                                                                                                                                                                                     | 1.8   |      | 3.6  | V          |

| R <sub>DS(ON)</sub> | P-channel MOSFET on-<br>resistance | $V_{IN}$ = 1.8 V, over full temperature range                                                                                                                                                                                                                                                                             |       | 385  | 505  | mΩ         |

| C                   | Output capacitor                   | Ceramic                                                                                                                                                                                                                                                                                                                   | 4.7   | 10   | 12   | μF         |

| C <sub>OUT</sub>    | ESR of output capacitor            | Ceramic                                                                                                                                                                                                                                                                                                                   | 5     | 20   | 500  | mΩ         |

| MEASUR              | EMENT SYSTEM (AFE)                 |                                                                                                                                                                                                                                                                                                                           |       |      |      |            |

|                     |                                    | AFE_GAIN[1:0] = 01                                                                                                                                                                                                                                                                                                        |       | 1.0  |      |            |

| G                   | Amplifier gain (PGA)               | AFE_GAIN[1:0] = 10                                                                                                                                                                                                                                                                                                        |       | 9.5  |      | V/V        |

|                     |                                    | AFE_GAIN[1:0] = 11                                                                                                                                                                                                                                                                                                        |       | 18   |      |            |

| V <sub>OFS</sub>    | Input referred offset voltage      | PGA, AFE_CAL_DIS = 1<br>Not tested in production                                                                                                                                                                                                                                                                          | -1    |      | 1    | mV         |

| - 053               |                                    | Comparator<br>Not tested in production                                                                                                                                                                                                                                                                                    | -1.5  |      | 1.5  |            |

| t <sub>settle</sub> | Settling time                      | To 1% of final value<br>(not tested in production)                                                                                                                                                                                                                                                                        |       |      | 15   | μs         |

| -selle              |                                    | To 0.1% of final value<br>(not tested in production)                                                                                                                                                                                                                                                                      |       |      | 52   | 20         |

TEXAS INSTRUMENTS

www.ti.com.cn

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted) (see (1)(2))

|                       | PARAMETER                                                   | TEST CONDITIONS                                               | MIN                  | TYP | MAX                    | UNIT |

|-----------------------|-------------------------------------------------------------|---------------------------------------------------------------|----------------------|-----|------------------------|------|

| f <sub>sample</sub>   | Sampling rate                                               | Not tested in production                                      |                      |     | 19                     | kHz  |

| •                     | VELS AND TIMING CHARACTERIS                                 | STICS                                                         |                      |     | L                      |      |

| M                     | Output low-level                                            | I <sub>O</sub> = 0.5-mA sink current<br>(RESETZ, CMP_OUT)     | 0                    |     | 0.3                    | V    |

| V <sub>OL</sub>       |                                                             | I <sub>O</sub> = 5-mA sink current<br>(SPI_DOUT, INTZ)        | 0                    |     | 0.3 × V <sub>SPI</sub> | v    |

| V <sub>OH</sub>       | Output high lovel                                           | I <sub>O</sub> = 0.5-mA source current<br>(RESETZ, CMP_OUT)   | 1.3                  |     | 2.5                    | V    |

| VOH                   | Output high-level                                           | I <sub>O</sub> = 5-mA source current<br>(SPI_DOUT)            | $0.7 \times V_{SPI}$ |     | V <sub>SPI</sub>       | v    |

| V                     | Input low lovel                                             | PROJ_ON, LED_SEL0, LED_SEL1                                   | 0                    |     | 0.4                    | V    |

| V <sub>IL</sub>       | Input low-level                                             | SPI_CSZ, SPI_CLK, SPI_DIN                                     | 0                    |     | 0.3 × V <sub>SPI</sub> | v    |

| N/                    | langet bink laval                                           | PROJ_ON, LED_SEL0, LED_SEL1                                   | 1.2                  |     |                        |      |

| VIH                   | Input high-level                                            | SPI_CSZ, SPI_CLK, SPI_DIN                                     | $0.7 \times V_{SPI}$ |     | V <sub>SPI</sub>       | V    |

| I <sub>BIAS</sub>     | Input bias current                                          | V <sub>IO</sub> = 3.3 V, any input pin                        |                      |     | 0.5                    | μA   |

|                       | De alitata tima                                             | PROJ_ON,<br>(not tested in production)                        |                      | 1   |                        | ms   |

| t <sub>DEGLITCH</sub> | Deglitch time                                               | LED_SEL0, LED_SEL1 pins<br>(not tested in production)         |                      | 300 |                        | ns   |

| INTERNAL              | OSCILLATOR                                                  |                                                               |                      |     |                        |      |

| (                     | Oscillator frequency                                        |                                                               |                      | 9   |                        | MHz  |

| fosc                  | Frequency accuracy                                          | $T_{A} = -30 \text{ to } 85^{\circ}\text{C}$                  | -10%                 |     | 10%                    |      |

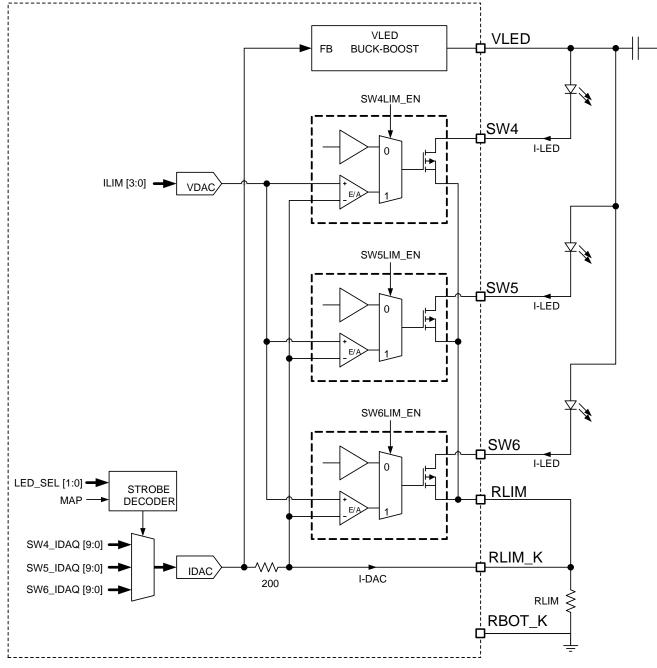

| THERMAL               | SHUTDOWN                                                    |                                                               |                      |     |                        |      |

| <b>-</b>              | Thermal warning (HOT threshold)                             |                                                               |                      | 120 |                        |      |

| T <sub>WARN</sub>     | Hysteresis                                                  |                                                               |                      | 10  |                        | °C   |

| T <sub>SHTDWN</sub>   | Thermal shutdown (TSD threshold)                            |                                                               |                      | 150 |                        | °C   |

| SITUM                 | Hysteresis                                                  |                                                               |                      | 15  |                        | -    |

| MOTOR DI              | RIVER                                                       |                                                               |                      |     |                        |      |

| POWER S               | UPPLY                                                       |                                                               |                      |     |                        |      |

| V <sub>INM</sub>      | Operating motor supply voltage                              |                                                               | 2                    |     | 6                      | V    |

| I <sub>M</sub>        | Operating motor current                                     |                                                               |                      |     | 500 <sup>(4)</sup>     | mA   |

| H-BRIDGE              | FETS                                                        | I                                                             |                      |     |                        |      |

| R <sub>DS(ON)</sub>   | HS + LS FET on resistance                                   | $V_{V2V5}$ = 2.5 V, $V_M$ = 3 V, $I_O$ = 200 mA, $T_J$ = 25°C |                      | 1.9 | 2.1                    | Ω    |

| I <sub>OFF</sub>      | Off-state leakage current                                   |                                                               |                      |     | ±200                   | nA   |

|                       | RIVER PROTECTION CIRCUITS                                   | •                                                             |                      |     |                        |      |

| I <sub>OCP</sub>      | Overcurrent protection trip level<br>per A-out or B-out pin |                                                               | 0.53                 |     | 1.16                   | А    |

|                       | por / out of B out pin                                      |                                                               |                      |     |                        |      |

(4) Power dissipation and thermal limits must be observed

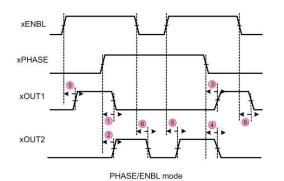

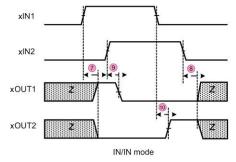

# 6.7 Motor Driver Timing Requirements

The table lists the timing numbers to drive the motor voltages correctly, while Figure 2 shows the timing sequences.

| NUMBER |                 |                                       | MIN | MAX | UNIT |

|--------|-----------------|---------------------------------------|-----|-----|------|

| 1      | t <sub>1</sub>  | Delay time, xPHASE high to xOUT1 low  |     | 300 | ns   |

| 2      | t <sub>2</sub>  | Delay time, xPHASE high to xOUT2 high |     | 200 | ns   |

| 3      | t <sub>3</sub>  | Delay time, xPHASE low to xOUT1 high  |     | 200 | ns   |

| 4      | t <sub>4</sub>  | Delay time, xPHASE low to xOUT1 low   |     | 300 | ns   |

| 5      | t <sub>5</sub>  | Delay time, xENBL high to xOUTx high  |     | 200 | ns   |

| 6      | t <sub>6</sub>  | Delay time, xENBL high to xOUTx low   |     | 300 | ns   |

| 7      | t <sub>7</sub>  | Output enable time                    |     | 300 | ns   |

| 8      | t <sub>8</sub>  | Output disable time                   |     | 300 | ns   |

| 9      | t <sub>9</sub>  | Delay time, xINx high to xOUTx high   |     | 160 | ns   |

| 10     | t <sub>10</sub> | Delay time, xINx low to xOUTx low     |     | 160 | ns   |

| 11     | t <sub>R</sub>  | Output rise time                      | 30  | 188 | ns   |

| 12     | t <sub>F</sub>  | Output fall time                      | 30  | 188 | ns   |

Figure 2. Bridge Control

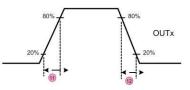

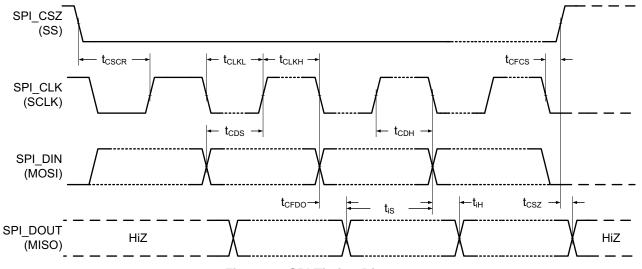

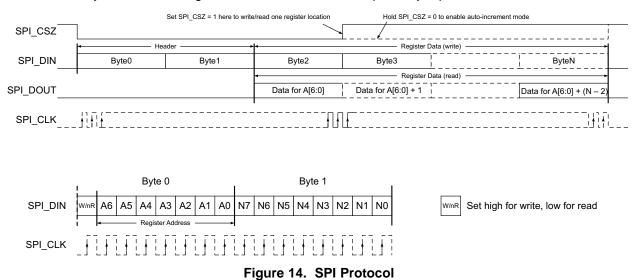

# 6.8 Data Transmission Timing Requirements

VBAT = 3.6  $\pm$  5%, T<sub>A</sub> = 25 °C, C<sub>L</sub> = 10 pF (unless otherwise noted)

|                   |                                                     | MIN | NOM MAX | UNIT |

|-------------------|-----------------------------------------------------|-----|---------|------|

| fclk              | Serial clock frequency                              | 0   | 36      | MHz  |

| t <sub>CLKL</sub> | Pulse width low, SPI_CLK, 50% level                 | 10  |         | ns   |

| t <sub>CLKH</sub> | Pulse width high, SPI_CLK, 50% level                | 10  |         | ns   |

| tt                | Transition time, 20% to 80% level, all signals      | 0.2 | 4       | ns   |

| t <sub>CSCR</sub> | SPI_CSZ falling to SPI_CLK rising, 50% level        | 8   |         | ns   |

| t <sub>CFCS</sub> | SPI_CLK falling to SPI_CSZ rising, 50% level        |     | 1       | ns   |

| t <sub>CDS</sub>  | SPI_DIN data setup time, 50% level                  | 7   |         | ns   |

| t <sub>CDH</sub>  | SPI_DIN data hold time, 50% level                   | 6   |         | ns   |

| t <sub>iS</sub>   | SPI_DOUT data setup time <sup>(1)</sup> , 50% level | 10  |         | ns   |

| t <sub>iH</sub>   | SPI_DOUT data hold time <sup>(1)</sup> , 50% level  | 0   |         | ns   |

| t <sub>CFDO</sub> | SPI_CLK falling to SPI_DOUT data valid, 50% level   |     | 13      | ns   |

| t <sub>CSZ</sub>  | SPI_CSZ rising to SPI_DOUT HiZ                      |     | 6       | ns   |

(1) The DPPxxxx processors send and receive data on the falling edge of the clock.

Figure 3. SPI Timing Diagram

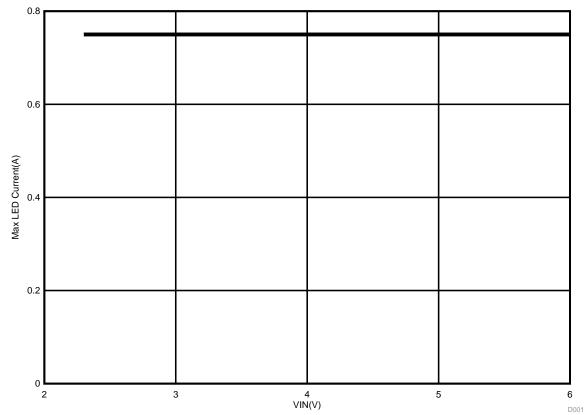

# 6.9 Typical Characteristics

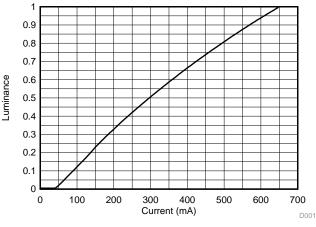

The maximum output current of the buck-boost is a function of input voltage ( $V_{IN}$ ) and output voltage ( $V_{LED}$ ). The relationship between  $V_{IN}$ ,  $V_{LED}$ , and MAX I<sub>LED</sub> is shown in Figure 4. Note that  $V_{LED}$  is the output of the buck-boost regulator, which includes the voltage drop across the sense resistor R<sub>LIM</sub> (100 m $\Omega$  typical), internal strobe control switch (75 m $\Omega$  max), and the forward voltage of the LED.

Gamma Curves

$2.3 \text{ V} < \text{V}_{\text{LED}} < 4.8 \text{ V}$

Figure 4. Maximum LED Output Current as a Function of Input Voltage ( $V_{IN}$ ) and Buck-Boost Output Voltage ( $V_{LED}$ )

# 7 Detailed Description

### 7.1 Overview

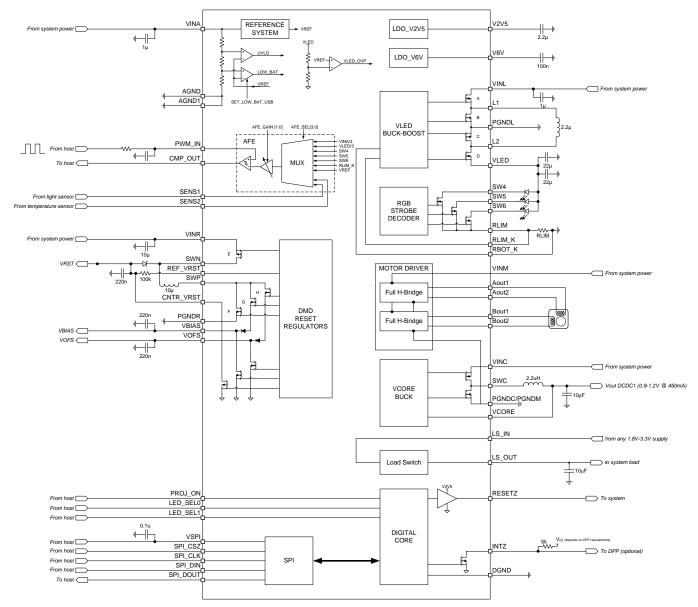

The DLPA2000 is a power management and LED driver IC optimized for DLP video and data display systems and meant for use in either embedded or accessory projector applications. DLPA2000 is part of the chipset comprising of either DLP2010 (0.2 WVGA) DMD and DLPC3430/DLPC3435 controller or the DLP2010NIR (0.2 WVGA NIR) DMD and DLPC150 controller. The DLPA2000 contains a complete LED driver including high efficiency power convertors. The DLPA2000 can supply up to 750 mA per LED. Integrated high-current switches are included for sequentially selecting R, G, and B LEDs. The DLPA2000 also contains three regulated DC supplies for the DMD reset circuitry:  $V_{BIAS}$ ,  $V_{RST}$  and  $V_{OFS}$ , as well as a regulated DC supply of 1.1 V and a load switch for the 1.8 V to support the DLPC3430 or DLPC3435 controller. The DLPA2000 also contains a motor driver which can be used to drive the focus lens motor. The DLPA2000 has a SPI used for setting the configuration. Using SPI, currents can be set independently for each LED with 10-bit resolution. Other features included are the generation of the system reset, power sequencing, input signals for sequentially selecting the active LED, IC self-protections, and an analog MUX for routing analog information to an external ADC.

# 7.2 Functional Block Diagram

A. Pin names refer to DLPA2000 pinout

B. Pins connected to 'system power' can be locally decoupled with the capacity as indicated in the block diagram. At least adequate decoupling capacity (50 μF or more) should be connected at the location the supply is entering the board.

DLPA2000 ZHCSCO5B – JUNE 2014 – REVISED FEBRUARY 2018

www.ti.com.cn

#### 7.3 Feature Description

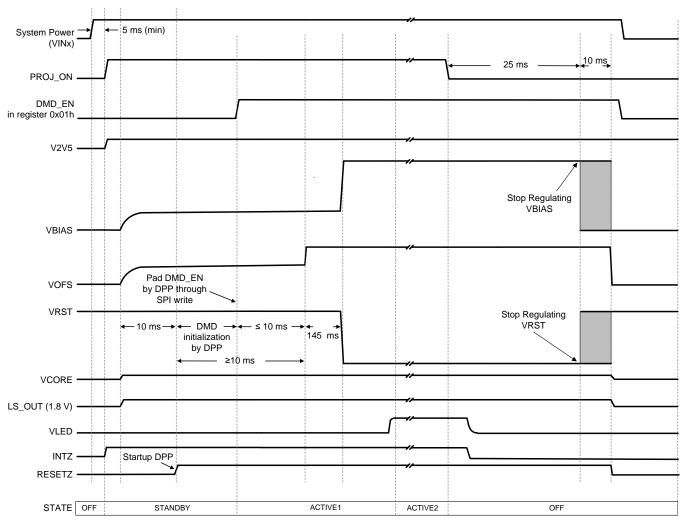

#### 7.3.1 DMD Regulators

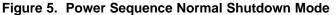

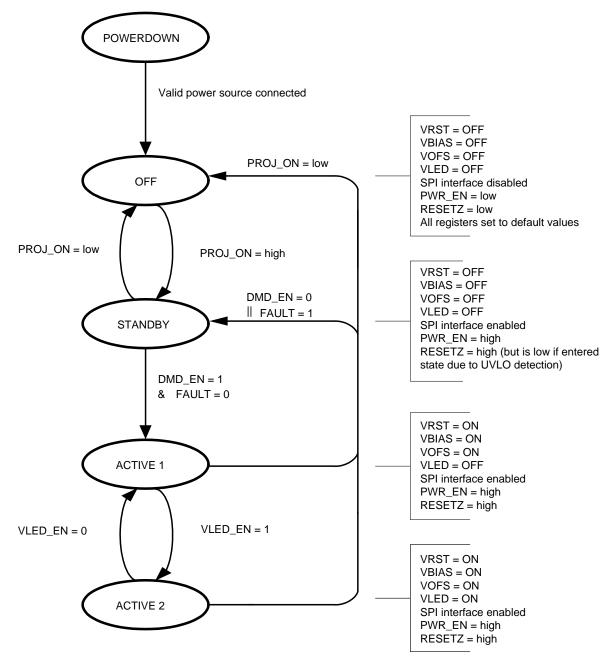

DLPA2000 contains three switch-mode power supplies that power the DMD. These rails are  $V_{OFS}$ ,  $V_{BIAS}$ , and  $V_{RST}$ . After pulling the PROJ\_ON pin high, the DMD is first initialized followed by a power-up of the  $V_{OFS}$  line after a small delay of less than 10 ms followed by  $V_{BIAS}$  and  $V_{RST}$  with an additional delay of 145 ms. The LED driver and STROBE DECODER circuit can only be enabled after all three rails are enabled. There are two power-down sequences, the normal power-down timing initiated after pulling the PROJ\_ON pin low, and a fast power-down mode where if any one of the rails encounters a fault such as an output short, all three rails are discharged simultaneously. The detailed power-up and power-down diagrams are shown in Figure 5 and Figure 6.

#### NOTE

All values are typical (unless otherwise noted).

# Feature Description (continued)

A. If the FAULT condition happens and its associated interrupt is masked in the interrupt mask register (0Dh), the If does not go low, but all other timing shown in the diagram is unaffected.

Figure 6. Power Sequence Fault Shutdown Mode

#### NOTE

All values are typical (unless otherwise noted).

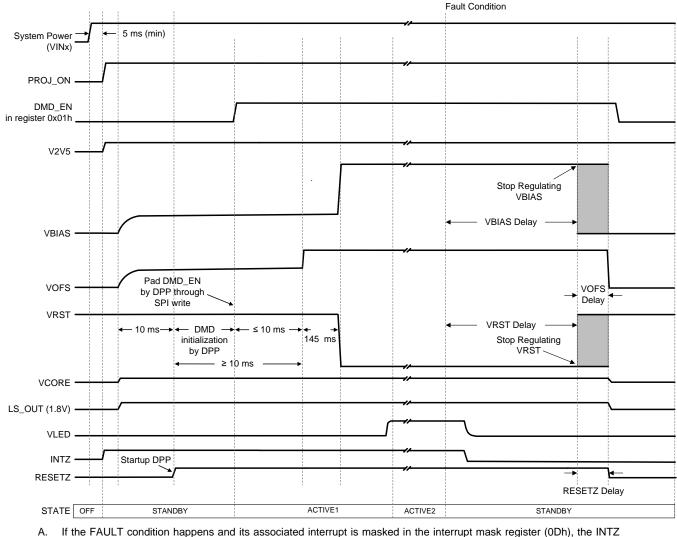

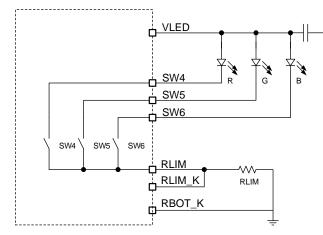

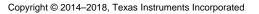

#### 7.3.2 RGB Strobe Decoder

DLPA2000 contains RGB color-sequential circuitry that is composed of three NMOS switches, the LED driver, the strobe decoder, and the LED current control. The NMOS switches are connected to the terminals of the external LED package and turn the currents through the LEDs on and off. Package connections are shown in Figure 7 and Figure 10 and the corresponding switch map is in Table 1.