Support & training

LDC5072-Q1

ZHCSJ59C - DECEMBER 2018 - REVISED JULY 2023

## LDC5072-Q1 具有 Sin/Cos 接口的电感式位置传感器前端

## 1 特性

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 0: 40°C 至 +160°C 的工作环 境温度范围

- 集成模拟前端 IC,适用于 0°至 360°绝对旋转位置 的非接触式电感式位置传感器

- 无需磁体,可降低系统成本

- 支持在恶劣环境中运行;不受杂散磁场、污垢和污 染的影响

- 高分辨率,在高达 480,000RPM 的转速下具有 ≤1 度的精度

- 具有正弦和余弦输出的差分信号路径,支持宽动态 输入范围

- 5V和 3.3V输入电源工作模式

- 集成 2.4MHz 至 5MHz 频段的 LC 振荡器,用于激 励电感式传感器线圈

- 具有高电压保护功能和大容性负载能力的差分输出 驱动器

- 自动和手动增益控制,能够尽可能地提高输出驱动 器的动态范围

- 符合功能安全标准

- 专为功能安全应用开发

- 有助于进行 ISO 26262 系统设计的文档

- 系统可满足 ASIL C(D) 级要求

- 硬件可满足 ASIL C 级要求

- 全面的 IC、传感器输入、输出和电源引脚诊断功能

- 输入电源和输出引脚具有 15V 至 30V 的反向电 压和过压保护功能

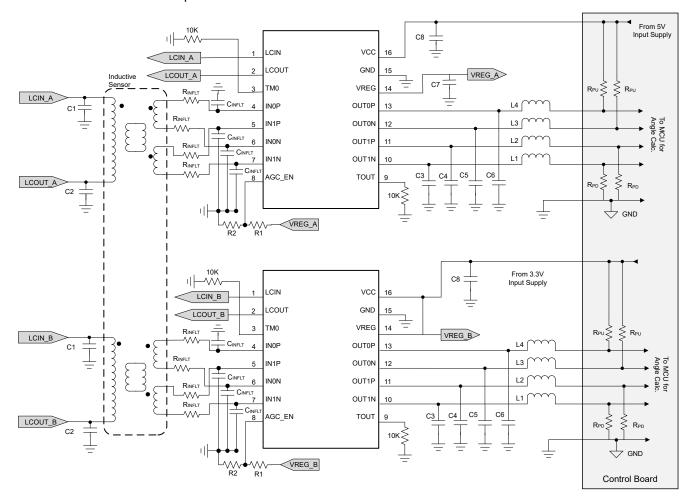

- 支持冗余模式,可实现功能安全

## 2 应用

- 旋转位置传感器,适用于:

- 电动汽车/混合动力汽车牵引电机逆变器

- 电动助力转向

- 制动助力电机

- 集成式起动发电机

- 小型角度传感器或弧形运动传感器,适用于:

- 踏板位置

- 阀门和执行器

- 机器人

## 3 说明

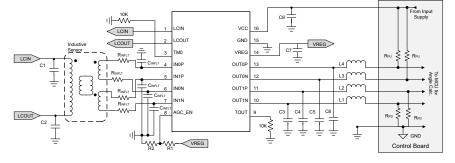

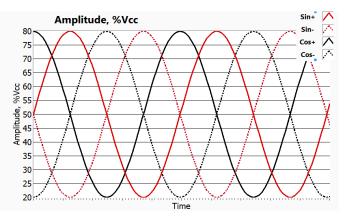

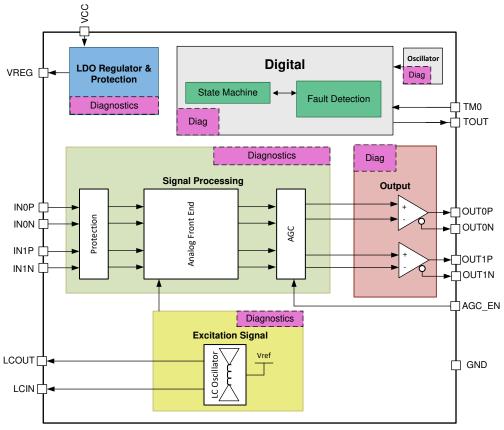

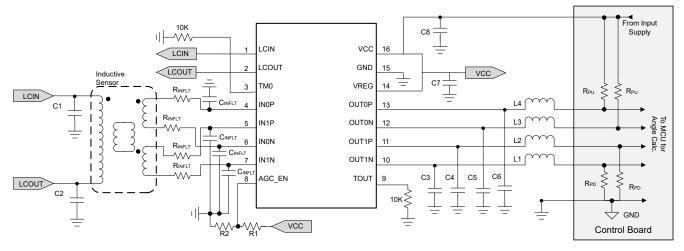

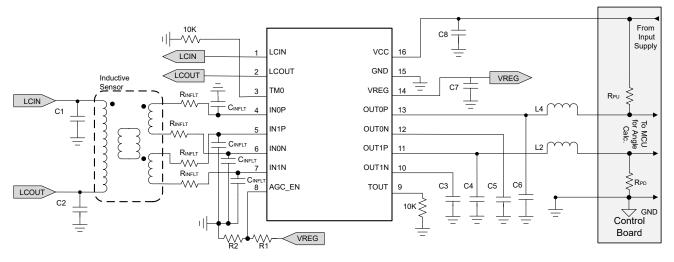

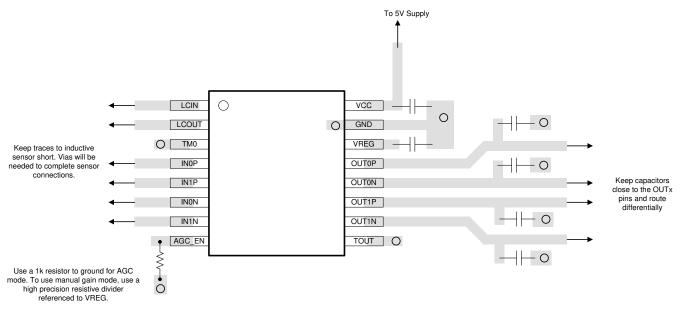

LDC5072-Q1 IC 是一款模拟前端,适用于面向汽车和 工业应用中绝对旋转位置检测的非接触式电感式位置传 感器。LDC5072-Q1 用于激励通常印刷在印刷电路板 (PCB) 上的线圈。该激励会通过靠近 PCB 的导电目标 耦合回同一 PCB 上的两组接收器线圈。导电目标也可 以是印刷在另一个 PCB 上的图案。线圈 PCB 保持静 止,目标随电机、执行器或阀门移动。激励线圈会根据 目标相对于接收器线圈的位置,在接收器线圈上产生次 级电压。通过从接收器线圈中读取电压、对其进行处理 并给出表示目标位置的正弦和余弦分量的模拟输出,可 以获得位置的信号表示。

#### 器件信息(1)

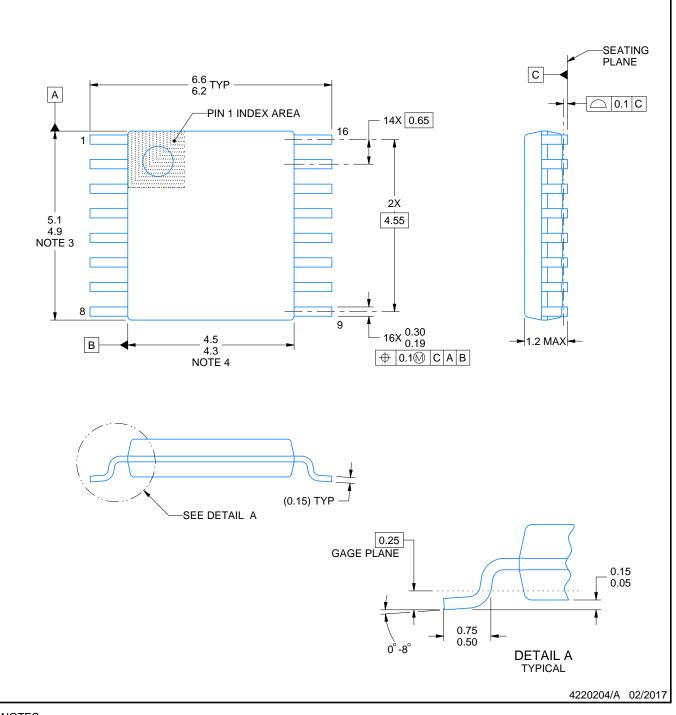

| 器件型号       | 封装         | 封装尺寸(标称值)       |

|------------|------------|-----------------|

| LDC5072-Q1 | TSSOP (16) | 5.00mm × 4.40mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

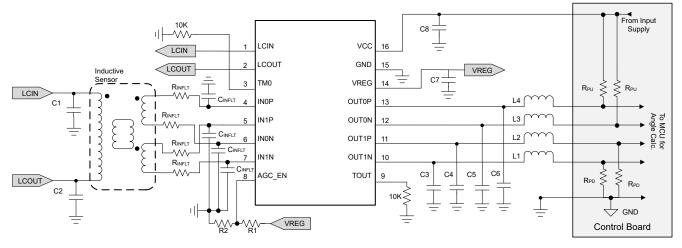

LDC5072-Q1 典型应用图

## **Table of Contents**

| 1 | 特性                                   | 1  |

|---|--------------------------------------|----|

| 2 | 应用                                   | 1  |

| 3 | 说明                                   | 1  |

|   | Revision History                     |    |

|   | 说明(续)                                |    |

| 6 | Pin Configuration and Functions      | .5 |

| 7 | Specifications                       | 6  |

|   | 7.1 Absolute Maximum Ratings         | 6  |

|   | 7.2 ESD Ratings                      | 6  |

|   | 7.3 Recommended Operating Conditions |    |

|   | 7.4 Thermal Information              |    |

|   | 7.5 Electrical Characteristics       |    |

|   | 7.6 Diagnostics                      | 11 |

|   | 7.7 Switching Characteristics1       | 12 |

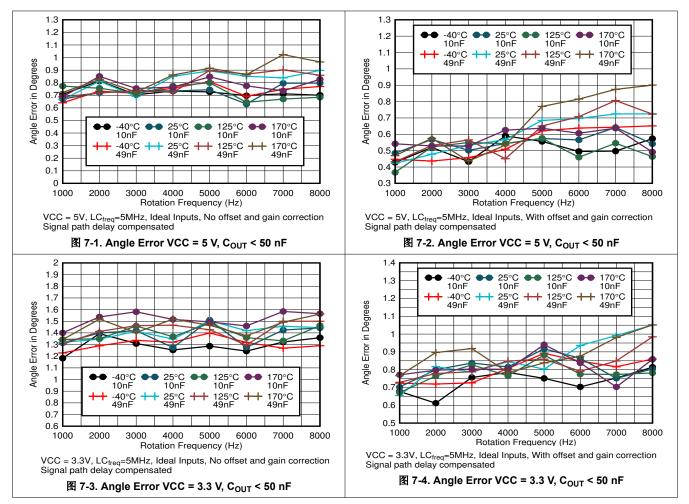

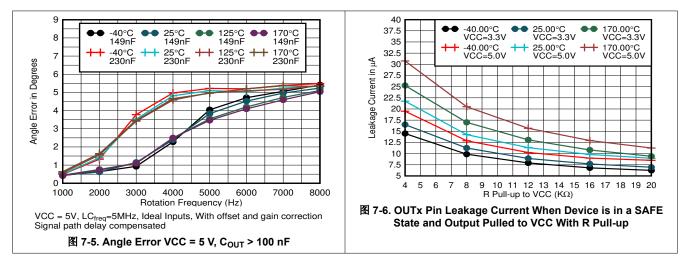

|   | 7.8 Typical Characteristics1         |    |

| 8 | Detailed Description1                |    |

|   | 8.1 Overview1                        | 15 |

|   | 8.2 Functional Block Diagram1        |    |

|   | 8.3 Feature Description1             | 6  |

| 9.4 Device Eurotional Madea                  | 24                        |

|----------------------------------------------|---------------------------|

| 8.4 Device Functional Modes                  |                           |

| 9 Application and Implementation             |                           |

| 9.1 Application Information                  | <mark>27</mark>           |

| 9.2 Typical Applications                     | 27                        |

| 10 Power Supply Recommendations              | 34                        |

| 10.1 Mode 1: VCC = 5 V, VREG = 3.3 V         |                           |

| 10.2 Mode 2: VCC = VREG = 3.3 V              |                           |

| 11 Layout                                    | 35                        |

| 11.1 Layout Guidelines                       |                           |

| 11.2 Layout Example                          | 35                        |

| 12 Device and Documentation Support          |                           |

| 12.1 Receiving Notification of Documentation | n Updates <mark>36</mark> |

| 12.2 支持资源                                    | 36                        |

| 12.3 Trademarks                              |                           |

| 12.4 静电放电警告                                  | 36                        |

| 12.5 术语表                                     |                           |

| 13 Mechanical, Packaging, and Orderable      |                           |

| Information                                  |                           |

|                                              |                           |

|                                              |                           |

## 4 Revision History

注:以前版本的页码可能与当前版本的页码不同

| Cł | hanges from Revision B (August 2021) to Revision C (July 2023)                                                                                                                                                            | Page  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| •  | 将数据表状态可见性更改为公开发布                                                                                                                                                                                                          | 1     |

| Cł | hanges from Revision A (September 2020) to Revision B (August 2021)                                                                                                                                                       | Page  |

| •  | 更新了整个文档中的表格、图和交叉参考的编号格式                                                                                                                                                                                                   | 1     |

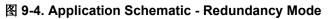

|    | 更新了"说明"部分中的应用图以及图 9-1、图 9-3、图 9-4 和图 9-5。                                                                                                                                                                                 |       |

| •  | Separated output comparator short into positive and negative limits                                                                                                                                                       | 11    |

| •  | The tPRWR_ON_DT in the "Switching Characteristics" is incorrectly specified. The values "360/400/440" will be changed to "302/336/370"                                                                                    | 12    |

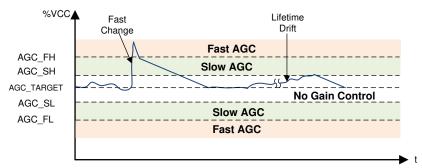

| •  | The AGC rate change is imprecisely specified in <i>Automatic Gain Control</i> : "1 code each second" was updated to "one code approximately every 840mS". Added eight codes every 3.2uS during start-up i fast AGC region | n the |

| •  | Updated application diagram in 5-V Supply Mode and updated 表 9-1 to include connection instructions the AGC_EN pin                                                                                                        | s for |

| •  | The resistor R2 in the example design in AGC Mode was updated to $1.5 \text{K} \Omega$ .                                                                                                                                  |       |

| •  | Changed 图 9-3                                                                                                                                                                                                             |       |

|   | evision A (September 2020))                                                                                             | Page           |

|---|-------------------------------------------------------------------------------------------------------------------------|----------------|

| • | 将器件最高环境工作温度更新为 160°C                                                                                                    | 1              |

| • | 更新了"功能安全能力"文本。                                                                                                          | 1              |

|   | Updated pin description for better clarity replacing inverted and non-inverted with negative and positive respectively. |                |

|   | Updated T <sub>A</sub> to 160℃ in <i>Absolute Maximum Ratings</i>                                                       |                |

| • | Updated T <sub>J</sub> to 170°C in Absolute Maximum Ratings                                                             | <mark>6</mark> |

| • | Added 4000V HBM ESD information to ESD Ratings                                                                          | 6              |

TEXAS INSTRUMENTS www.ti.com.cn

| • | Changed INL to Err <sub>INL</sub> and updated definition and values in Signal Path section of <i>Electrical</i> Characteristics                                                   | 7        |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| • | Changed maximum value of t <sub>PROP_CH</sub> over temperature and changed maximum T <sub>A</sub> to 160°C in Signal Pat section of <i>Electrical Characteristics</i>             | th<br>7  |

|   |                                                                                                                                                                                   |          |

|   | Changed maximum value of t <sub>PROP_DIFF</sub> in Signal Path section of <i>Electrical Characteristics</i>                                                                       | /        |

|   | Added V <sub>OUT_SE</sub> in Signal Path section of <i>Electrical Characteristics</i>                                                                                             | ···· /   |

| • | Changed maximum value of V <sub>OUT_DIFF_TC</sub> over temperature and changed maximum T <sub>A</sub> to 160°C in Signal Path section of <i>Electrical Characteristics</i>        | 7        |

| • | Added G <sub>MIS_SIG_PATH</sub> parameter in Signal Path section of <i>Electrical Characteristics</i>                                                                             |          |

| • | Added V <sub>in_off</sub> parameter in Signal Path section of <i>Electrical Characteristics</i>                                                                                   |          |

| • | Added n <sub>SIG_PATH_SE</sub> parameter in Signal Path section of <i>Electrical Characteristics</i>                                                                              |          |

| • | Added n <sub>SIG_PATH_DIFF</sub> parameter in Signal Path section of <i>Electrical Characteristics</i>                                                                            | 7        |

| • | Split V <sub>AMP_LC</sub> between 25°C and over temperature and specified values wnen VREG is below regulation voltage in Excitation section of <i>Electrical Characteristics</i> | 7        |

| • | Split V <sub>DC LC</sub> between 25°C and over temperature and specified values wnen VREG is below regulation                                                                     |          |

|   | voltage in Excitation section of <i>Electrical Characteristics</i>                                                                                                                | 7        |

| • | Changed limits and test conditions for I <sub>LIM LC</sub> in Excitation section of <i>Electrical Characteristics</i>                                                             |          |

| • | Added Internal Pull Up resistor parameter $R_{PU LCx}$ in Excitation section of <i>Electrical Characteristics</i>                                                                 |          |

| • | Added Internal Pull down resistor parameter $R_{PD LCx}$ in Excitation section of <i>Electrical Characteristics</i>                                                               |          |

|   |                                                                                                                                                                                   | /        |

| • | Expanded limits for input differential input signal amplitude V <sub>DIFF_REC</sub> in Receiver section of<br><i>Electrical Characteristics</i>                                   | 7        |

| • | Added Internal pull-up resistor parameter RPU_INxN in Receiver section of Electrical Characteristics                                                                              | 7        |

| • | Added Internal pull-down resistor parameter RPD_INXP in Receiver section of Electrical Characteristics                                                                            | 7        |

| • | Split R <sub>ACG_EN_AUTO</sub> parameter into R <sub>AGC_EN_MIN</sub> and R <sub>AGC_EN_MAX</sub> in AGC section of<br><i>Electrical Characteristics</i>                          | 7        |

| • | Added internal pull-up resistor R <sub>PU_AGC_EN</sub> parameter in AGC section of <i>Electrical Characteristics</i>                                                              | 7        |

| • | Updated definition of AGC_Target, AGC_FH, AGC_SH, AGC_SL and AGC_FL for clarity and                                                                                               |          |

|   | split parameter across temperature and VCC in AGC section of <i>Electrical Characteristics</i>                                                                                    | 7        |

| • | Changed V <sub>ILIM OUT</sub> to I <sub>ILIM OUT</sub> for clarity in Output Stage section of <i>Electrical Characteristics</i>                                                   |          |

| • | Removed required conditions for VCC and GND connection to be valid and added min, and max values for                                                                              |          |

|   | R <sub>PD OUT</sub> and R <sub>PU OUT</sub> parameters in Output Stage section of <i>Electrical Characteristics</i>                                                               |          |

| • | Added I <sub>OUT_NOVCC_*</sub> and I <sub>OUT_NOGND_*</sub> parameters in Output Stage section of <i>Electrical Characteristics</i>                                               |          |

| • | Removed required conditions for VCC and GND connection to be valid and added test conditions for                                                                                  |          |

|   | $V_{OUT_{FLT}LOW}$ and $V_{OUT_{FLT}_{HIGH}}$ parameters in Output Stage section of <i>Electrical Characteristics</i>                                                             | 7        |

| • | Split $V_{OUT_FLT_HIGH}$ and $V_{OUT_FLT_LOW}$ parameters across temperature and VCC in Output Stage section of                                                                   | of       |

|   | Electrical Characteristics                                                                                                                                                        | 7        |

| • | Added I <sub>OUT LK PU</sub> parameter in Output Stage section of <i>Electrical Characteristics</i>                                                                               |          |

| • | Added internal impedance parameters I <sub>PD_INx*_BIST</sub> in <i>Diagnostics</i>                                                                                               |          |

| • | Added pin BIST comparator thresholds V <sub>TH_FALL_INx*_BIST</sub> in <i>Diagnostics</i>                                                                                         |          |

| • | Added internal impedance parameter I <sub>PU_AGC_EN_BIST</sub> on AGC_EN pin in <i>Diagnostics</i>                                                                                |          |

| • | Added value for VREG capacitor loss C <sub>LOSS VREG</sub> in <i>Diagnostics</i>                                                                                                  |          |

| • | Moved V <sub>POR_VREG xth</sub> to <i>Diagnostics</i>                                                                                                                             |          |

| • | Added LC Frequency fault detection parameter f <sub>FLTH LC</sub> in <i>Diagnostics</i>                                                                                           |          |

| • | Added internal impedance on LCV ping parameters L in Diagnostics                                                                                                                  | 11<br>   |

|   | Added internal impedance on LCx pins parameters, $\bar{I}_{Px\_LCx\_BIST}$ in <i>Diagnostics</i>                                                                                  | 11<br>14 |

| • | Added t <sub>MIN_PH_IMB</sub> in <i>Diagnostics</i>                                                                                                                               |          |

| • | Added AGC fault limits, VAL <sub>AGC_INP_OOR_x</sub> in <i>Diagnostics</i>                                                                                                        | ۲۲<br>مە |

| • | Added input out-of-range pin and low-pass filter parameters, V <sub>OOR_H_INx_x</sub> in <i>Diagnostics</i>                                                                       |          |

| • | Added common mode fault parmeters for output pin, V <sub>CM_x_OUTx_PIN</sub> in <i>Diagnostics</i>                                                                                |          |

| • | Added V <sub>OUTx_SHRT_CMP_OFF</sub> in <i>Diagnostics</i>                                                                                                                        | 11       |

| • | Added internal regulator under voltage parameter, V <sub>UV_DVDD</sub> in <i>Diagnostics</i>                                                                                      |          |

| • | Added V <sub>TOGGLE AGC EN</sub> in <i>Diagnostics</i>                                                                                                                            | 11       |

| • | Added thermal shutdown parameters T <sub>TSD x</sub> in <i>Diagnostics</i>                               | 11 |

|---|----------------------------------------------------------------------------------------------------------|----|

| • | Combined VCC out of range fault degltich times in t <sub>VCC FLT DT</sub> and updated value in Switching |    |

|   | Characteristics                                                                                          | 12 |

| • | Added VREG over voltage deglitch time t <sub>VREG OV DT</sub> in Switching Characteristics               | 12 |

| • | Added LC amplitude fault deglitch times in Switching Characteristics                                     | 12 |

| • | Updated values for t <sub>AGC EN x DT</sub> parameters Switching Characteristics                         | 12 |

| • | Added input pin and low pass filter fault deglitch times in Switching Characteristics                    | 12 |

| • | Added and updated outpin fault deglitch times tout x DT in Switching Characteristics                     | 12 |

| • | Added AGC deglitch times t <sub>AGC x DT</sub> in <i>Switching Characteristics</i>                       | 12 |

| • | Renamed t <sub>FLT_SIGNAL</sub> to t <sub>FLT_RECOV</sub> in <i>Switching Characteristics</i>            | 12 |

| • | Added power on degltich time t <sub>PWR ON DT</sub> in Switching Characteristics                         | 12 |

| • | Added 🛽 7-6 for OUTx leakage current                                                                     | 13 |

| • | Updated text in Signal Processing Block for clarity                                                      |    |

| • | Updated Fixed Gain Control section based on new design                                                   | 19 |

| • | Updated variable name in 方程式 8 for clarity                                                               | 19 |

| • | Updated text in Automatic Gain Control to add information on time-step of the AGC block                  | 19 |

| • | Added details on output pin diagnostics and output ratiometricity to VCC in Output Stage                 | 20 |

| • | Added Undervoltage Diagnostics, Initialization Diagnostics, Normal State Diagnostics and Fault State     |    |

|   | Diagnostics to list details on the diagnsostics available in LDC5072-Q1                                  |    |

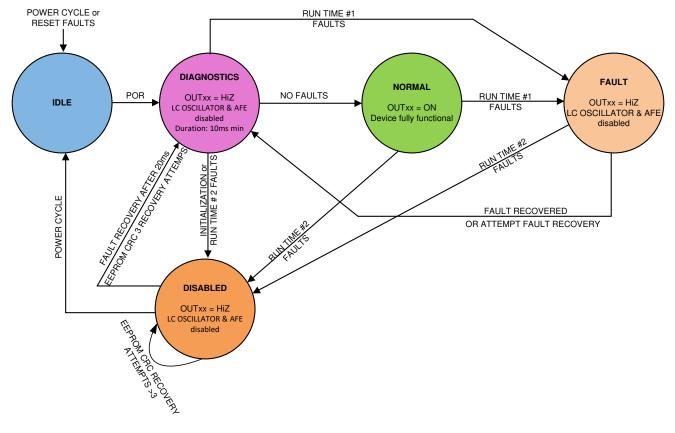

| • | Added details for device functional modes. Added 8 8-5 and described each of the states in LDC5072-C     |    |

|   |                                                                                                          | 24 |

| • | Updated application diagram in 5-V Supply Mode and updated 表 9-1 with new optional component value       |    |

|   | EMC robustness                                                                                           | 27 |

| • | Updated application diagram in 3.3-V Supply Mode with new optional component values for                  |    |

|   | EMC robustness.                                                                                          |    |

| • | Updated application diagram in <sup>†</sup> 9.2.3 with new optional component values for EMC robustness  | 32 |

|   |                                                                                                          |    |

## 5 说明(续)

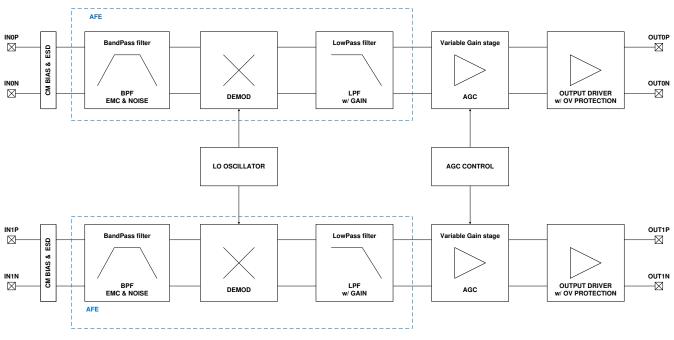

LDC5072-Q1 可以采用 3.3V 或 5V 输入,而模拟正弦和余弦输出可以连接到 MCU 以计算角度。该器件提供 ESD 保护、EMC/EMI 抗扰能力、电池反向保护,以及输出引脚上短路至高电压的反向电流保护。电源引脚和输出引脚 均符合高电压标准。该器件具有抗电机噪声干扰能力,并可以滤除带外低频和高频噪声。LDC5072-Q1 具有全面 的诊断功能,可检测短路和开路等传感器故障,并且具有电流限制、过压和欠压检测等内部诊断功能。LDC5072-Q1 根据面向功能安全应用的 ISO 26262 规范要求进行设计。

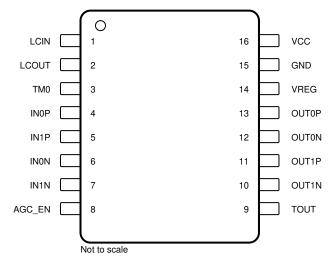

## **6** Pin Configuration and Functions

#### 表 6-1. Pin Functions

| PIN |        | TYPE <sup>(1)</sup> | DESCRIPTION                                          |  |

|-----|--------|---------------------|------------------------------------------------------|--|

| NO. | NAME   |                     | DESCRIPTION                                          |  |

| 1   | LCIN   | I/O                 | LC oscillator input                                  |  |

| 2   | LCOUT  | I/O                 | LC oscillator output                                 |  |

| 3   | TM0    | I/O                 | Test Mode Input                                      |  |

| 4   | IN0P   | I                   | Input channel 0 positive                             |  |

| 5   | IN1P   | I                   | Input channel 1 positive                             |  |

| 6   | INON   | I                   | Input channel 0 negative                             |  |

| 7   | IN1N   | I                   | put channel 1 negative                               |  |

| 8   | AGC_EN | I                   | Automatic Gain Control Enable and Fixed Gain Setting |  |

| 9   | TOUT   | I/O                 | Test Mode Output                                     |  |

| 10  | OUT1N  | 0                   | Output channel 1 negative                            |  |

| 11  | OUT1P  | 0                   | Output channel 1 positive                            |  |

| 12  | OUTON  | 0                   | Output channel 0 negative                            |  |

| 13  | OUT0P  | 0                   | Output channel 0 positive                            |  |

| 14  | VREG   | I/O                 | Regulated 3.3-V Supply output                        |  |

| 15  | GND    | G                   | Ground                                               |  |

| 16  | VCC    | Р                   | Input Voltage Supply                                 |  |

(1) I = input, O = output, I/O = input and output, G = ground, P = power

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                           |                                | MIN  | MAX | UNIT |

|-------------------------------------------|--------------------------------|------|-----|------|

| VCC                                       | Input Supply voltage           | -15  | 30  |      |

| OUT0P, OUT0N, OUT1P, OUT1N                | Output pin voltage             | -15  | 30  |      |

| VREG                                      | Regulator output voltage       | -0.3 | 5.5 | V    |

| GND                                       | Ground Pin voltage             | -0.3 | 0.3 | v    |

| LCOUT, LCIN                               | LC Oscillator pin voltage      | -0.3 | 5.5 |      |

| AGC_EN, TM0, TOUT, IN0P, IN0N, IN1P, IN1N | All other pin voltage          | -0.3 | 5.5 |      |

| T <sub>A</sub>                            | Operating free air temperature | -40  | 160 |      |

| TJ                                        | Operating junction temperature | -40  | 170 | °C   |

| T <sub>stg</sub>                          | Storage temperature range      | -65  | 150 |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |     |                                              |                                              |                                                              | VALUE | UNIT |

|--------------------|-----|----------------------------------------------|----------------------------------------------|--------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> |     |                                              | Human-body model (HBM), per AEC Q100-002     | All pins                                                     | ±2000 | v    |

|                    | SD) | Electrostatic discharge                      | (1)                                          | OUT0x, OUT1x, IN0x, IN1x,<br>LCIN, LCOUT, VCC to GND<br>only | ±4000 |      |

|                    |     |                                              | Charged-device model (CDM), per AEC All pins | ±500                                                         |       |      |

|                    |     | Q100-011<br>CDM ESD Classification Level C4B | Corner pins (1, 8, 9, 16)                    | ±750                                                         |       |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                    |                                                                               | MIN  | NOM | MAX | UNIT |

|--------------------|-------------------------------------------------------------------------------|------|-----|-----|------|

| V <sub>CC_50</sub> | V <sub>CC</sub> input voltage (5V input mode)                                 | 4.5  | 5   | 5.6 | V    |

| V <sub>CC_33</sub> | V <sub>CC</sub> and V <sub>REG</sub> input voltage (3.3V input mode)          | 3.15 | 3.3 | 3.6 | v    |

| IQ                 | During startup and in operation (excluding LC oscillator load and OUTxx load) |      |     | 22  | mA   |

#### 7.4 Thermal Information

|                        |                                              | LDC5072-Q1 |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | UNIT |

|                        |                                              | 16 PINS    |      |

| R <sub>0JA</sub>       | Junction-to-ambient thermal resistance       | 93.2       | °C/W |

| R <sub>0 JC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.1       | °C/W |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 39.7       | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 0.9        | °C/W |

| ψ <sub>JB</sub>        | Junction-to-board characterization parameter | 39.1       | °C/W |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report, SPRA953.

#### 7.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted) over recommended  $V_{cc}$  range (unless otherwise noted)

|                            | PARAMETER                                                                                                                                                                                                                                                      | TEST CONDITIONS                                                                                                                                                                                      | MIN   | TYP | MAX   | UNIT       |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------------|--|

| Input Supply               |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                      |       |     |       |            |  |

| VCC <sub>Ramp</sub>        | Allowed VCC ramp up rate                                                                                                                                                                                                                                       |                                                                                                                                                                                                      | 0.17  |     | 100e6 | V/s        |  |

| C <sub>EXT_VCC</sub>       | External VCC decoupling capacitor range                                                                                                                                                                                                                        |                                                                                                                                                                                                      | 80    | 100 |       | nF         |  |

| nternal LDO Regula         | tor VREG                                                                                                                                                                                                                                                       |                                                                                                                                                                                                      |       |     |       |            |  |

| / <sub>VREG</sub>          | Internal LDO output voltage                                                                                                                                                                                                                                    |                                                                                                                                                                                                      | 3.15  | 3.3 | 3.6   |            |  |

| VPOR_VREG_UTH              | VREG power-on upper threshold                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |       |     | 3.15  | V          |  |

| VPOR_VREG_LTH              | VREG power-on lower thershold                                                                                                                                                                                                                                  |                                                                                                                                                                                                      | 2.91  |     |       |            |  |

| LOAD_REG_EXT               | Maximum external load on VREG (used<br>for setting voltage on AGC_EN pin<br>externally) (Information Only)                                                                                                                                                     |                                                                                                                                                                                                      |       |     | 1     | mA         |  |

| LIM_VREG                   | VREG current limit                                                                                                                                                                                                                                             |                                                                                                                                                                                                      | 40    |     | 90    |            |  |

| C <sub>EXT_VREG</sub>      | External VREG decoupling capacitor                                                                                                                                                                                                                             |                                                                                                                                                                                                      | 180   |     | 2000  | nF         |  |

| Signal Path                |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                      |       |     | I     |            |  |

| Err <sub>iNL</sub>         | Integral Non-Linearity error <sup>(3)</sup> of the signal<br>path transfer function for each channel<br>measured as:<br>Maximum % deviation of output from a<br>best fit line through measured outputs<br>when input is swept from minium to<br>maximum value. | For static inputs; VCC=5V;<br>-3.5V $\leq$ (V <sub>OUTxP</sub> -V <sub>OUTxN</sub> )<br>$\leq$ 3.5V                                                                                                  |       | 1%  | 2.5   | %          |  |

|                            | Propagation Delay through receive stage at room temperature.                                                                                                                                                                                                   | Measured as zero crossing of diffrential input (INx) to                                                                                                                                              | 3.3   |     | 4.6   |            |  |

| <sup>t</sup> PROP_CH       | Propagation Delay through receive stage across temperature (-40 $^\circ\!\mathrm{C}$ to 160 $^\circ\!\mathrm{C}$ ).                                                                                                                                            | zero crossing of differential<br>output (OUTx)<br>C <sub>OUT</sub> on each pin = 10nF                                                                                                                | 3     |     | 5     | μ <b>s</b> |  |

| PROP_DIFF                  | Propagation Delay difference between two channels across temperature                                                                                                                                                                                           | Measured as delay<br>between the zero crossings<br>of the diffrential outputs.                                                                                                                       |       |     | 500   | ns         |  |

| V <sub>OUT_SE</sub>        | Difference between single ended outputs calculated at V <sub>OUT0P</sub> -V <sub>OUT1P</sub>                                                                                                                                                                   | $\begin{array}{l} \mbox{Measured for static inputs} \\ \mbox{only for VCC=5V; -1.75V} \leqslant \\ \mbox{(} \ \mbox{V}_{OUT0P}\mbox{-} \mbox{V}_{OUT1P}\mbox{)} \leqslant 1.75 \mbox{V} \end{array}$ |       | 50  | 65    | mV         |  |

| Vout_diff                  | Difference between differential output calculated as $(V_{OUT0P}-V_{OUT0N}) - (V_{OUT1P}-V_{OUT1N})$ at room temperature                                                                                                                                       | Measured for static inputs                                                                                                                                                                           |       |     | 100   |            |  |

| M                          | Deviation of V <sub>OUT_DIFF</sub> at -40 ℃ from room temperature                                                                                                                                                                                              | only for VCC=5V; -3.5V $\leq$<br>( V <sub>OUTxP</sub> -V <sub>OUTxN</sub> ) $\leq$ 3.5V                                                                                                              |       |     | 20    | mV         |  |

| Vout_diff_tc               | Deviation of $V_{OUT\_DIFF}$ at 160 $^{\rm \odot}$ from room temperature                                                                                                                                                                                       |                                                                                                                                                                                                      |       |     | 38    |            |  |

|                            | Gain mismatch between Channel 1 and<br>Channel 2 signal path calculated as                                                                                                                                                                                     | Fixed Gain Mode;<br>VCC=3.3V 4.55%VREG <<br>V <sub>AGC_EN</sub> < 95.45%VREG<br>-40 $^\circ\!\!C \leqslant T_A \leqslant 160^\circ\!\!C$                                                             | -0.4  |     | 0.4   | %          |  |

| G <sub>MIS_SIG_PATH</sub>  | (Gain <sub>out1</sub> -Gain <sub>out0</sub> )/<br>((Gain <sub>out1</sub> +Gain <sub>out0</sub> )*0.5) <sup>(2)</sup>                                                                                                                                           | Fixed Gain Mode;<br>VCC=5.0V; 4.55%VREG <<br>V <sub>AGC_EN</sub> < 95.45%VREG<br>-40 $^\circ\!C \leqslant T_A \leqslant 160^\circ\!C$                                                                | -0.35 |     | 0.55  | 70         |  |

| V:                         | Input referred offset for IN0 channel <sup>(2)</sup><br>measured with input shorted and exciter<br>coil connected                                                                                                                                              | VCC=3.3V, 5.0V;<br>Fixed Gain Mode;<br>30%VREG < V <sub>AGC EN</sub> <                                                                                                                               |       | 150 | 170   | μV         |  |

| Vin_off                    | Input referred offset for IN1 channel <sup>(2)</sup><br>measured with input shorted and exciter<br>coil connected                                                                                                                                              | $95.45\% VREG -40°C \leqslant T_A \leqslant 160°C$                                                                                                                                                   |       | 50  | 100   | μV         |  |

| N <sub>SIG_PATH_SE</sub>   | Input referred noise for the complete signal path for single ended output for each channel <sup>(2)</sup>                                                                                                                                                      |                                                                                                                                                                                                      |       | 25  |       | nV/ √ Hz   |  |

| <sup>1</sup> SIG_PATH_DIFF | Input referred noise for the complete<br>signal path for differential output for each<br>channel <sup>(2)</sup>                                                                                                                                                |                                                                                                                                                                                                      |       | 36  |       | nV/ √ Hz   |  |

Copyright © 2023 Texas Instruments Incorporated

# over operating free-air temperature range (unless otherwise noted) over recommended $V_{cc}$ range (unless otherwise noted)

|                                     | PARAMETER                                                                                                                  | TEST CONDITIONS                                                                                                             | MIN  | TYP  | MAX  | UNIT  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

|                                     | LC oscillator differential amplitude                                                                                       | $\begin{array}{l} 3.15 V \leqslant V_{VREG} \leqslant 3.6; \\ T_{A} \mbox{=} 25^{\circ} \mbox{C} \end{array}$               | 70   | 75.8 | 81.5 |       |  |

|                                     |                                                                                                                            | $\begin{array}{l} 3.15 V \leqslant V_{VREG} \leqslant 3.6; \\ -40^{\circ} C < T_{A} < 160^{\circ} C \end{array}$            | 64   |      | 87   |       |  |

| V <sub>AMP_LC</sub>                 |                                                                                                                            | $\begin{array}{l} V_{POR\_VREG\_LTH} \leqslant V_{VREG} \leqslant \\ V_{POR\_VREG\_UTH}; \ T_{A} = 25^{\circ}C \end{array}$ | 69.5 |      | 82.5 | %Vreg |  |

|                                     | LC oscillator differential amplitude when<br>V <sub>VREG</sub> is below regulation voltage                                 |                                                                                                                             | 63   |      | 88   |       |  |

|                                     |                                                                                                                            | $\begin{array}{l} 3.15 V \leqslant V_{VREG} \leqslant 3.6; \\ T_A \!=\! 25^\circ \! C \end{array}$                          | 47   | 50   | 52.5 |       |  |

|                                     | DC operating point for LC oscillator                                                                                       | $3.15V \leqslant V_{VREG} \leqslant 3.6; -40^{\circ}C < T_A < 160^{\circ}C$                                                 | 43.5 |      | 56.5 |       |  |

| V <sub>DC_LC</sub>                  | DC anarating point for LC appillator when                                                                                  | $V_{POR_VREG_LTH} \leqslant V_{VREG} \leqslant V_{POR_VREG_UTH}; T_A=25^{\circ}C$                                           | 47.5 |      | 53   | %VREG |  |

|                                     | DC operating point for LC oscillator when V <sub>VREG</sub> is below regulation voltage                                    |                                                                                                                             | 42.5 |      | 57.5 |       |  |

| I <sub>LIM_LC</sub> <sup>(2)</sup>  | RMS value of LC oscillator current limit                                                                                   |                                                                                                                             | 13   |      | 30   | mA    |  |

| f <sub>OSC_LC</sub> <sup>(2)</sup>  | LC oscillator resonant frequency                                                                                           |                                                                                                                             | 2.4  |      | 5    | MHz   |  |

| THD <sub>LC</sub> <sup>(2)</sup>    | Total harmonic distortion of oscillator output (V <sub>LCIN</sub> -V <sub>LCOUT</sub> )                                    |                                                                                                                             |      |      | -30  | dB    |  |

| R <sub>PU_LCx</sub>                 | Internal pull up resistance to VREG on LCIN and LCOUT pins                                                                 |                                                                                                                             | 220  |      | 330  | KΩ    |  |

| R <sub>PD_LCx</sub>                 | Internal pull down resistance to GND on LCIN and LCOUT pins                                                                |                                                                                                                             | 220  |      | 330  | KΩ    |  |

| Rp                                  | Allowed range for equivalent parallel resistance of LC oscillator coil                                                     |                                                                                                                             | 167  |      | 5000 | Ω     |  |

| L                                   | Allowed range of inductance of excitation coil resonator                                                                   |                                                                                                                             |      | 5    |      | μH    |  |

| C <sub>LC1</sub> , C <sub>LC2</sub> | Allowed range for capacitors for excitation coil                                                                           |                                                                                                                             | 100  | 370  |      | pF    |  |

| C <sub>MIS</sub>                    | Allowed capacitor mismatch (between $C_{LC1}$ and $C_{LC2}$ )                                                              |                                                                                                                             | -10  |      | 10   | %     |  |

| Receiver                            |                                                                                                                            |                                                                                                                             |      |      |      |       |  |

| V <sub>DIFF_REC</sub>               | Allowed range for differential input signal amplitude                                                                      | In fixed gain mode, voltage<br>on AGC_EN pin adjusted to<br>set gain to avoid clipping                                      | 5    |      | 400  | mVp-p |  |

| V <sub>COM_REC</sub>                | Common mode voltage forced on input signals                                                                                |                                                                                                                             | 45   | 50   | 55   | %VREG |  |

| f <sub>LF_BPF_REC</sub>             | Bandpass filter lower cutoff frequency <sup>(1)</sup>                                                                      |                                                                                                                             | 430  | 600  | 760  | kHz   |  |

| f <sub>UF_BPF_REC</sub>             | Bandpass filter upper cutoff frequency <sup>(1)</sup>                                                                      |                                                                                                                             | 12   | 20   | 26   | MHz   |  |

| f <sub>LPF_REC</sub>                | Low pass filter (after demodulation)                                                                                       |                                                                                                                             | 65   | 100  | 125  | kHz   |  |

| $V_{N\_DIFF\_REC}$                  | Amplitude of differential noise on input<br>rejected by receive path for fundamental<br>frequency between 10KHz to 20KHz   | Differential input signal<br>>20mVpp, VCC=5V,<br>Sqaure wave noise signal<br>ramp time = 8µs                                |      |      | 1    | Vpp   |  |

| Vn_com_rec                          | Amplitude of common mode noise on<br>input rejected by receive path for<br>fundamental frequency between 10KHz to<br>20KHz | Differential input signal<br>>20mVpp, VCC=5V,<br>Sqaure wave noise signal<br>ramp time = 8µs                                |      |      | 1    |       |  |

| R <sub>PU_INxN</sub>                | Internal pull up resistor to VREG on each of the INxN pins                                                                 |                                                                                                                             | 0.8  | 1    | 1.2  | Mo    |  |

| R <sub>PD_INxP</sub>                | Internal pull down resistor to GND on each of the INxP pins                                                                |                                                                                                                             | 0.8  | 1    | 1.2  | MΩ    |  |

| L <sub>REC</sub>                    | Typical Receiver coil inductance<br>(Information only)                                                                     |                                                                                                                             |      | 0.2  |      | μH    |  |

# over operating free-air temperature range (unless otherwise noted) over recommended $V_{cc}$ range (unless otherwise noted)

|                           | PARAMETER                                                                                                   | TEST CONDITIONS                                                       | MIN  | TYP  | MAX   | UNIT    |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|-------|---------|--|

| R <sub>REC</sub>          | Typical Receiver coil resistance (Information only)                                                         |                                                                       |      | 6    |       | Ω       |  |

| Automatic Gain Cont       | rol                                                                                                         |                                                                       |      |      |       |         |  |

| VAGC_EN_AUTO              | Voltage on AGC_EN pin to set AGC in auto mode                                                               |                                                                       |      |      | 2     | %VREG   |  |

| Vagc_en_manual            | Voltage range on AGC_EN pin to<br>manually set different AGC gains                                          |                                                                       | 4.55 |      | 95.45 |         |  |

| Ragc_en_min               | Minimum value of required external<br>resistor on AGC_EN to ground to enable<br>AGC mode (Information Only) |                                                                       | 1    |      |       | KΩ      |  |

| R <sub>AGC_EN_MAX</sub>   | Maximum value of required external<br>resistor on AGC_EN to ground to enable<br>AGC mode (Information Only) |                                                                       |      |      | 16.3  | KΩ      |  |

| R <sub>PU_AGC_EN</sub>    | Internal pull up resistor to VREG on AGC_EN                                                                 |                                                                       | 0.8  | 1    | 1.2   | MΩ      |  |

|                           |                                                                                                             | V <sub>CC</sub> = V <sub>CC_33</sub> ; T <sub>A</sub> =25°C           | 54.5 | 59.5 | 64.5  |         |  |

| ACC Torget(4)             | $\lambda_{1}$                                                                                               | V <sub>CC</sub> = V <sub>CC_33</sub> ;<br>-40°C≪T <sub>A</sub> ≪160°C | 53.5 |      | 65    | 8/\\/CC |  |

| AGC_Target <sup>(4)</sup> | Value of √ (OUT0 <sup>2</sup> + OUT1 <sup>2</sup> )                                                         | V <sub>CC</sub> = V <sub>CC_50</sub> ; T <sub>A</sub> =25°C           | 55   | 60   | 65    | %VCC    |  |

|                           |                                                                                                             | V <sub>CC</sub> = V <sub>CC_50</sub> ;<br>-40°C≪T <sub>A</sub> ≪160°C | 54   |      | 66    |         |  |

|                           |                                                                                                             | V <sub>CC</sub> = V <sub>CC_33</sub> ; T <sub>A</sub> =25°C           | 75.5 | 78.9 | 83    |         |  |

| AGC_FH                    | Automatic gain control - fast regulation region high threshold.                                             | V <sub>CC</sub> = V <sub>CC_33</sub> ;<br>-40°C≪T <sub>A</sub> ≪160°C | 75   |      | 83.5  | 94VCC   |  |

|                           |                                                                                                             | $V_{CC} = V_{CC_{50}}; T_A = 25^{\circ}C$                             | 77   | 80.1 | 84    | %VCC    |  |

|                           |                                                                                                             | V <sub>CC</sub> = V <sub>CC_50</sub> ;<br>-40°C≪T <sub>A</sub> ≪160°C | 76   |      | 85    |         |  |

|                           | Automatic gain control - slow regulation region high threshold.                                             | V <sub>CC</sub> = V <sub>CC_33</sub> ; T <sub>A</sub> =25°C           | 66   | 68.8 | 73.5  |         |  |

|                           |                                                                                                             | V <sub>CC</sub> = V <sub>CC_33</sub> ;<br>-40°C≪T <sub>A</sub> ≪160°C | 65.5 |      | 74    | %VCC    |  |

| AGC_SH                    |                                                                                                             | $V_{CC} = V_{CC_{50}}; T_A = 25^{\circ}C$                             | 67   | 70   | 74    |         |  |

|                           |                                                                                                             | $V_{CC} = V_{CC_{50}};$<br>-40°C $\ll$ T <sub>A</sub> $\ll$ 160°C     | 66.5 |      | 74.8  |         |  |

|                           |                                                                                                             | V <sub>CC</sub> = V <sub>CC_33</sub> ; T <sub>A</sub> =25°C           | 45   | 48.6 | 52    |         |  |

| AGC SL                    | Automatic gain control - slow regulation                                                                    | V <sub>CC</sub> = V <sub>CC_33</sub> ;<br>-40°C≪T <sub>A</sub> ≪160°C | 44.5 |      | 52.5  | %VCC    |  |

| A00_0L                    | region low threshold.                                                                                       | $V_{CC} = V_{CC_{50}}; T_A = 25^{\circ}C$                             | 46.5 | 49.8 | 53    |         |  |

|                           |                                                                                                             | V <sub>CC</sub> = V <sub>CC_50</sub> ;<br>-40°C≪T <sub>A</sub> ≪160°C | 46   |      | 53.5  |         |  |

|                           |                                                                                                             | V <sub>CC</sub> = V <sub>CC_33</sub> ; T <sub>A</sub> =25°C           | 34.5 | 38.3 | 42.5  |         |  |

|                           | Automatic gain control - fast regulation                                                                    | V <sub>CC</sub> = V <sub>CC_33</sub> ;<br>-40°C≪T <sub>A</sub> ≪160°C | 34   |      | 43    | %VCC    |  |

| AGC_FL                    | region low threshold.                                                                                       | $V_{CC} = V_{CC_{50}}; T_A = 25^{\circ}C$                             | 36.7 | 39.9 | 42.7  |         |  |

|                           |                                                                                                             | V <sub>CC</sub> = V <sub>CC_50</sub> ;<br>-40°C≪T <sub>A</sub> ≪160°C | 36   |      | 43.5  |         |  |

| Output Stage              |                                                                                                             | ·                                                                     |      |      |       |         |  |

| V <sub>OUT</sub>          | Output signal range                                                                                         | OUTxy pins single-ended measurement                                   | 7    |      | 93    | %VCC    |  |

| V <sub>REF_OUT</sub>      | Output reference voltage                                                                                    |                                                                       | 48   | 50   | 52    |         |  |

| IILIM_OUT                 | Current limit source or sink on output pins                                                                 |                                                                       | 3    |      | 20    | mA      |  |

| I <sub>OUT</sub>          | Load current on output pins                                                                                 |                                                                       |      |      | 1.5   | 1.5 mA  |  |

# over operating free-air temperature range (unless otherwise noted) over recommended $V_{cc}$ range (unless otherwise noted)

|                           | PARAMETER                                                                                                                                                  | TEST CONDITIONS                                                                                                                                                                                                             | MIN | TYP MAX | UNIT |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|--|

| R <sub>PD_OUT</sub>       | Allowed range for resistor on OUT pins to<br>GND for output pins during a detected<br>fault condition. Refer to V <sub>OUT_FLT_LOW</sub> for<br>error band |                                                                                                                                                                                                                             | 4   | 20      | kΩ   |  |

| R <sub>PU_OUT</sub>       | Allowed range for resistor on OUT pins to VCC for output pin during a detected fault condition. Refer to V <sub>OUT_FLT_HIGH</sub> for error band          |                                                                                                                                                                                                                             | 4   | 20      | K22  |  |

| C <sub>OUT</sub>          | Capacitors on OUT pins (Information Only)                                                                                                                  | R <sub>PD_OUT</sub> = R <sub>PU_OUT</sub> =<br>10k Ω , 8kHz rotation speed                                                                                                                                                  | 1   | 8       | nF   |  |

| C <sub>OUT</sub>          | Capacitors on OUT pins (Information Only)                                                                                                                  | Maximum rotational speed limited                                                                                                                                                                                            | 8   | 200     |      |  |

| SCB_OUT                   | Short circuit current into OUT pins when shorted to voltage higher than VCC                                                                                | V <sub>OUT</sub> >8V; VCC=5V                                                                                                                                                                                                |     | 5       | mA   |  |

|                           | Leakage current in to each OUT pin when<br>VCC is lost; Outputs used in differential                                                                       | VCC pin open; R <sub>PU_OUT</sub><br>=5K on each OUTx pin;<br>VCC=3.3V                                                                                                                                                      |     | 12      |      |  |

| OUT_NOVCC_DIFF            | mode.                                                                                                                                                      | VCC pin open; R <sub>PU_OUT</sub><br>=5K on each OUTx pin;<br>VCC=5.0V                                                                                                                                                      |     | 25      |      |  |

|                           | Leakage current in to each OUT pin when<br>VCC is lost; Outputs used in single-ended                                                                       | VCC pin open; R <sub>PU_OUT</sub><br>=5K on each OUTxP pins;<br>VCC=3.3V                                                                                                                                                    |     | 17      | μΑ   |  |

| OUT_NOVCC_SE              | mode.                                                                                                                                                      | VCC pin open; R <sub>PU_OUT</sub><br>=5K on each OUTxP pins;<br>VCC=5.0V                                                                                                                                                    |     | 35      |      |  |

|                           | Leakage current out of each OUT pin                                                                                                                        | GND pin open; R <sub>PD_OUT</sub> =<br>5K on each OUTx pin;<br>VCC=3.3V                                                                                                                                                     |     | 30      |      |  |

| IOUT_NOGND_DIFF           | when GND is lost; Outputs used in differential mode.                                                                                                       | GND open; R <sub>PD_OUT</sub> = 5K<br>on each OUTx pin;<br>VCC=5.0V                                                                                                                                                         |     | 50      |      |  |

|                           | Leakage current out of each OUT pin                                                                                                                        | GND pin open; R <sub>PD_OUT</sub> =<br>5K on each OUTxP pin;<br>VCC=3.3V                                                                                                                                                    |     | 35      | μA   |  |

| OUT_NOGND_SE              | when GND is lost; Outputs used in single-<br>ended mode.                                                                                                   | GND pin open; R <sub>PD_OUT</sub> =<br>5K on each OUTxP pin;<br>VCC=5.0V                                                                                                                                                    |     | 60      |      |  |

| Vout_flt_low              | Voltage on OUT pins in fault state with<br>external pulldown resistors to ground on<br>OUT pins                                                            | $\begin{array}{l} 4K\Omega \leqslant R_{PD} \ _{OUT} \leqslant 20 K\Omega \\ \text{on each } OUTx \ pin; \\ VCC{=}3.3V; 5.0V; \\ \text{-}40^\circC \leqslant TA \leqslant 160^\circC \end{array}$                           |     | 4       | %VCC |  |

|                           | Voltage on OUT pins in fault state with                                                                                                                    | $\begin{array}{l} 4K\Omega \leqslant R_{PU\_OUT} \leqslant 5K\Omega \text{ on} \\ \text{each OUTx pin; VCC=3.3V;} \\ -40^{\circ}\text{C} \leqslant \text{T}_{\text{A}} \leqslant 160^{\circ}\text{C} \end{array}$           | 96  |         |      |  |

| V <sub>OUT_FLT_HIGH</sub> | external pullup resistors to VCC on OUT pins                                                                                                               | $\begin{array}{l} 4K\Omega \leqslant R_{PU\_OUT} \leqslant 10K\Omega \\ \text{on each OUTx pin;} \\ \text{VCC=}5.0\text{V;} \\ \text{-40°C} \leqslant T_A \leqslant 160^\circ\text{C} \end{array}$                          | 96  |         | %VCC |  |

|                           | Leakge current on OUT pins in fault state                                                                                                                  | $\begin{array}{l} 5 K\Omega \leqslant R_{PU} _{OUT} \leqslant 20 K\Omega \\ \text{on each OUTx pin;} \\ VCC=3.3V; \\ -40^\circC \leqslant T_A \leqslant 160^\circC \end{array}$                                             |     | 30      |      |  |

| Iout_lk_pu <sup>(2)</sup> | with external pullup resistors to VCC on<br>OUT pins when V <sub>OUTx</sub> > V <sub>OUT_FLT_HIGH</sub>                                                    | $\begin{array}{l} 10K\Omega \leqslant R_{\text{PU_OUT}} \leqslant 20K\Omega \\ \text{on each OUTx pin;} \\ \text{VCC=5.0V;} \\ -40^{\circ}\text{C} \leqslant \text{T}_{\text{A}} \leqslant 160^{\circ}\text{C} \end{array}$ |     | 20      | μΑ   |  |

(1) Guaranteed by design

(2) Not tested in production

(3) This INL error is not same as INL error in calculated angle in the external MCU

(4) (AGC\_SH-AGC\_TARGET) and (AGC\_TARGET-AGC\_SL)  $\ge$  3% across temperature and allowed VCC range

## 7.6 Diagnostics

over operating free-air temperature range (unless otherwise noted)

|                                        | PARAMETER                                                                                                                                                                | TEST CONDITIONS  | MIN  | TYP  | MAX  | UNIT       |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|------------|--|

| I <sub>PD_INXN_BIST</sub>              | Pull down current to GND during startup<br>on INxN pins for sensor BIST                                                                                                  |                  | 150  | 200  | 270  | μ <b>Α</b> |  |

| IPU_INXP_BIST                          | Pull up current from VREG during startup<br>on INxP pins for sensor BIST                                                                                                 |                  | 150  | 200  | 270  | μų         |  |

| V <sub>TH_FALL_INxP_BIST</sub>         | Falling threshold of window comparator for sensor BIST on INxP pins                                                                                                      |                  | 22.7 | 25   | 30   |            |  |

| V <sub>TH_FALL_INxN_BIST</sub>         | Falling threshold of window comparator<br>for sensor BIST on INxN pins                                                                                                   |                  | 70   | 75   | 77.3 | %VREG      |  |

| I <sub>PU_AGC_EN_BIST</sub>            | Pull up current from VREG during startup<br>BIST on AGC_EN pin to check short to<br>ground                                                                               |                  | 200  | 250  | 350  | μA         |  |

| V <sub>UVUTH_VCC</sub>                 | VCC under voltage upper threshold <sup>(1)</sup>                                                                                                                         |                  |      |      | 4.5  |            |  |

| V <sub>UVLTH_VCC</sub>                 | VCC under voltage lower threshold <sup>(1)</sup>                                                                                                                         |                  | 3.6  |      |      | V          |  |

| V <sub>OVUTH_VCC</sub>                 | VCC over voltage upper threshold                                                                                                                                         |                  |      |      | 6.5  | v          |  |

| V <sub>OVLTH_VCC</sub>                 | VCC over voltage lower threshold                                                                                                                                         |                  | 5.6  |      |      |            |  |

| C <sub>LOSS_VREG</sub>                 | VREG external capacitor loss check.<br>Capacitor values below this will trigger a<br>fault.                                                                              | 5V VCC mode only | 1    |      |      | nF         |  |

| V <sub>OVUTH_VREG</sub> <sup>(3)</sup> | VREG overvoltage upper threshold                                                                                                                                         |                  |      |      | 4.2  | V          |  |

| V <sub>OVLTH_VREG</sub>                | VREG overvoltage lower threshold                                                                                                                                         |                  | 3.6  |      |      | V          |  |

| V <sub>POR_VREG_uth</sub>              | VREG power-on upper threshold                                                                                                                                            |                  |      |      | 3.15 |            |  |

| VPOR VREG Ith                          | VREG power-on lower thershold                                                                                                                                            |                  | 2.91 |      |      | V          |  |

| f <sub>flth_lc</sub>                   | LC oscillator frequency too high fault detection                                                                                                                         |                  | 5.3  |      | 6.2  | N41        |  |

| ffltl_lC                               | LC oscillator frequency too low fault detection                                                                                                                          |                  | 2.0  |      | 2.4  | MHz        |  |

| I <sub>PU_LCx_BIST</sub>               | Pull up current from VREG during startup<br>on LCOUT and LCIN pins for sensor BIST                                                                                       |                  | 1.7  | 2.6  | 4.0  | mA         |  |

| IPD_LCx_BIST                           | Pull down current to GND during startup<br>on LCOUT and LCIN pins for sensor BIST                                                                                        |                  | 1.7  | 2.6  | 4.0  | ША         |  |

| t <sub>min_ph_imb</sub>                | Minimum time between zero crossing of sine output and the following zero crossing of cosine output and vice versa to not signal a phase imbalance fault <sup>(2)</sup> . |                  | 8.5  | 10   | 11.5 | μ <b>S</b> |  |

| VALAGC_INP_OOR_L                       | AGC quantized step out of 256 (min to<br>max gain) in auto gaib mode to signal<br>FAULT when input signal is very low<br>amplitude                                       |                  | 251  |      |      | AGC code   |  |

| VAL <sub>AGC_INP_OOR_H</sub>           | AGC quantized step out of 256 (min to<br>max gain) in auto gain modet o signal<br>FAULT when input signal is very high<br>amplitude                                      |                  |      |      | 4    |            |  |

| V <sub>OOR_H_INX_PIN</sub>             | Out of range single ended fault threshold voltage for each IN pin - High                                                                                                 |                  | 70   | 75   | 77.3 | %VREG      |  |

| V <sub>OOR_L_INX_PIN</sub>             | Out of range single ended fault threshold voltage for each IN pin - Low                                                                                                  |                  | 22.7 | 25   | 30   | %VREG      |  |

| V <sub>OOR_H_INX_LPF</sub>             | Out of range single ended fault threshold voltage at low pass filter output - High                                                                                       |                  | 87.5 | 92.5 | 98   | %VREG      |  |

| V <sub>OOR_L_INx_LPF</sub>             | Out of range single ended fault threshold voltage at low pass filter output - Low                                                                                        |                  | 1    | 7.5  | 12   | %VREG      |  |

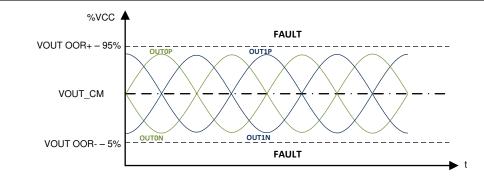

| V <sub>OOR_H_OUTX_PIN</sub>            | Out of range single ended fault threshold voltage for each OUT pin - High                                                                                                |                  | 93   | 95   | 97   | %VCC       |  |

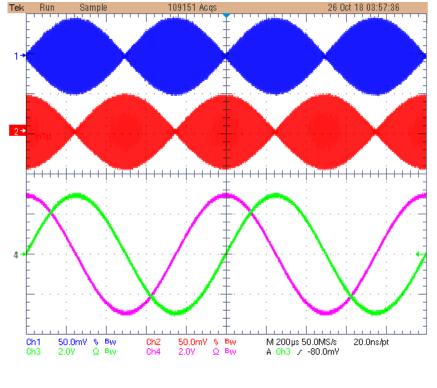

| V <sub>OOR_L_OUTx_PIN</sub>            | Out of range single ended fault threshold voltage for each OUT pin - Low                                                                                                 |                  | 3    | 5    | 7    | %VCC       |  |