LM25122-Q1

ZHCSEL4A - DECEMBER 2015 - REVISED DECEMBER 2015

# LM25122-Q1 具有多相功能的宽输入同步升压控制器

## 特性

- 符合 AEC-Q100 1 级标准 (T<sub>A</sub> = -40°C 至 125°C)

- 最高输入电压: 42V

- 最低输入电压: 3V(启动时为 4.5V)

- 输出电压最高可达 50V

- 旁路 (V<sub>OUT</sub> = V<sub>IN</sub>) 运行

- 精度为 ±1.0% 的 1.2V 基准

- 自由运行和同步开关频率最高可达 600 kHz

- 峰值电流模式控制

- 稳健耐用的 3A 集成栅极驱动器

- 自适应死区时间控制

- 可选二极管仿真模式

- 可编程逐周期电流限制

- 断续模式过载保护

- 可编程线路欠压闭锁 (UVLO)

- 可编程软启动

- 热关断保护

- 低关断静态电流: 9µA

- 可编程斜率补偿

- 可编程跳周模式减少待机功耗

- 允许使用外部 VCC 电源

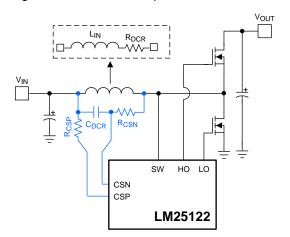

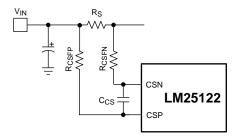

- 电感器分布式直流电阻 (DCR) 电流感应功能

- 多相位功能

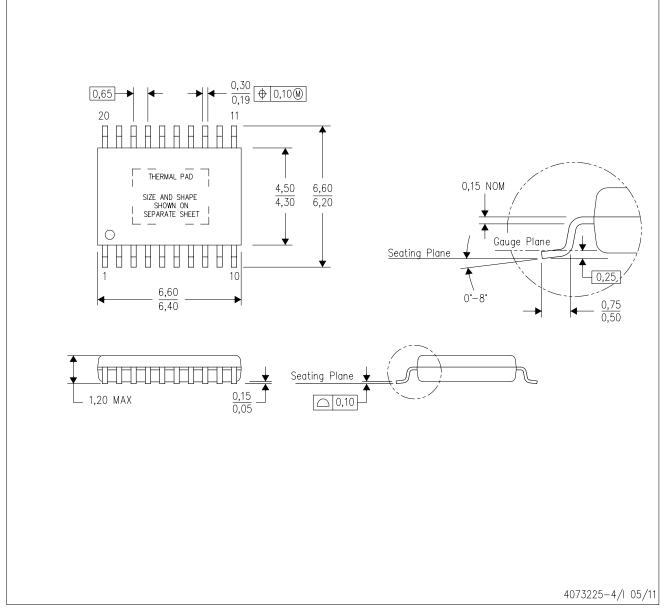

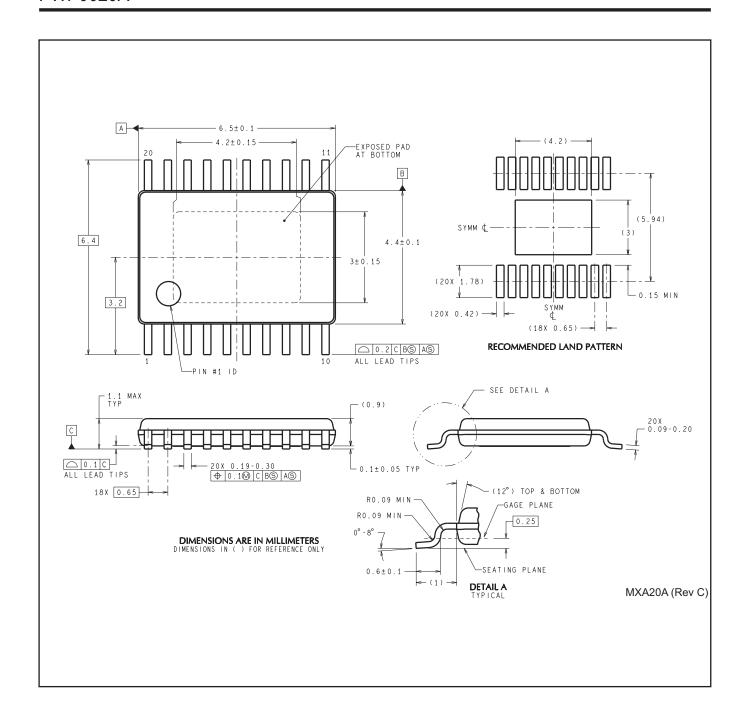

- 耐热增强型 20 引脚散热薄型小外形尺寸封装 (HTSSOP)

## 2 应用

- 12V、24V 和 48V 电源系统

- 汽车启停

- 音频电源

- 高电流升压电源

## 3 说明

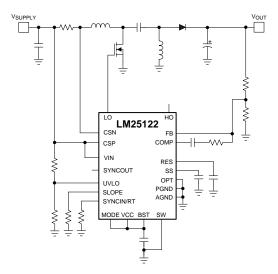

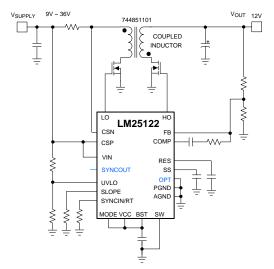

LM25122 是一款支持多相位的同步升压控制器,面向 高效同步升压稳压器 应用。此控制方法基于峰值电流 模式控制。电流模式控制可提供内部线路前馈、逐周期 电流限制和简化的环路补偿。

开关频率最高可通过编程设定为 600kHz。通过两个支 持自适应死区时间控制的稳健耐用 N 通道金属氧化物 半导体场效应晶体管 (MOSFET) 栅极驱动器来实现更 高效率。一个用户可选二极管仿真模式还可实现断续模 式运行,以提高轻负载时的效率。

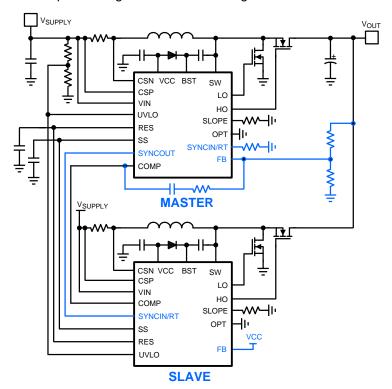

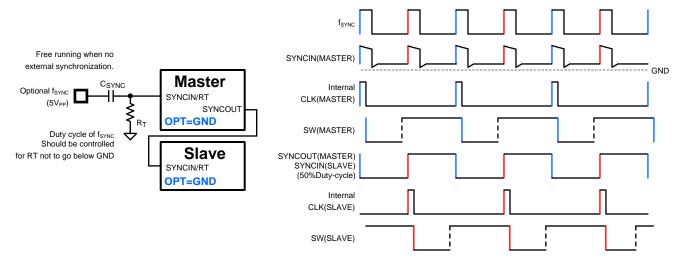

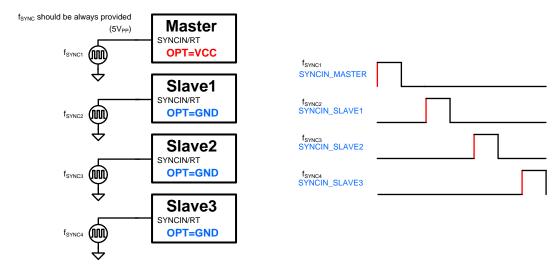

一个内部电荷泵可针对高侧同步开关实现 100% 占空 比(旁路运行)。一个 180° 相移时钟输出可实现简单 多相位交叉配置。其他 功能 包括: 热关断、频率同 步、断续模式电流限制和可调线路欠压锁定。

## 器件信息<sup>(1)</sup>

| 器件型号       | 封装          | 封装尺寸 (标称值)      |

|------------|-------------|-----------------|

| LM25122-Q1 | HTSSOP (20) | 6.50mm x 4.40mm |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

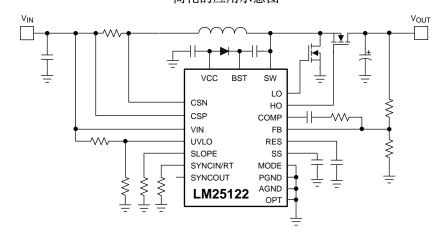

## 简化的应用示意图

|   | 目录                                   |    |                                |    |

|---|--------------------------------------|----|--------------------------------|----|

| 1 | 特性 1                                 |    | 7.3 Feature Description        | 13 |

| 2 | 应用 1                                 |    | 7.4 Device Functional Modes    | 20 |

| 3 | 说明1                                  | 8  | Application and Implementation | 23 |

| 4 | 修订历史记录 2                             |    | 8.1 Application Information    | 23 |

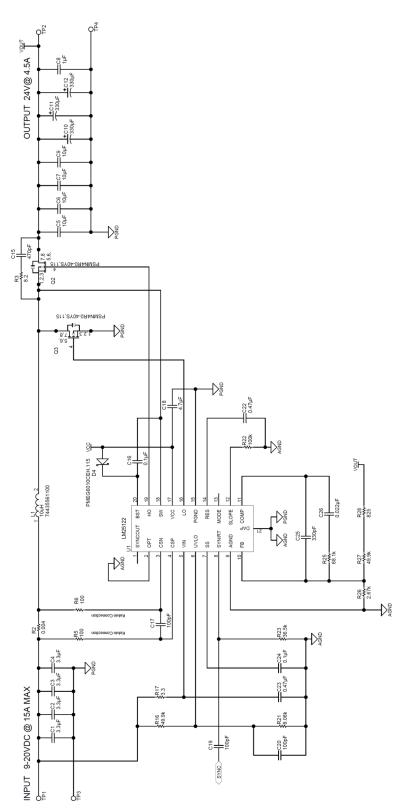

| 5 | Pin Configuration and Functions      |    | 8.2 Typical Application        | 32 |

| 6 | Specifications4                      | 9  | Power Supply Recommendations   | 40 |

| · | 6.1 Absolute Maximum Ratings         | 10 | Layout                         | 40 |

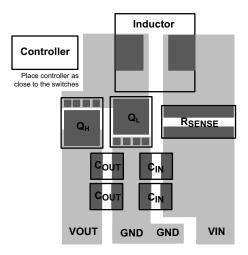

|   | 6.2 ESD Ratings                      |    | 10.1 Layout Guidelines         | 40 |

|   | 6.3 Recommended Operating Conditions |    | 10.2 Layout Example            |    |

|   | 6.4 Thermal Information              | 11 | 器件和文档支持                        | 41 |

|   | 6.5 Electrical Characteristics       |    | 11.1 社区资源                      | 41 |

|   | 6.6 Typical Characteristics9         |    | 11.2 商标                        | 41 |

| 7 | Detailed Description 12              |    | 11.3 静电放电警告                    |    |

|   | 7.1 Overview 12                      |    | 11.4 Glossary                  |    |

|   | 7.2 Functional Block Diagram         | 12 | 机械、封装和可订购信息                    | 41 |

|   |                                      |    |                                |    |

# 4 修订历史记录

| Changes from Original (December 2015) to Revision A | Page |

|-----------------------------------------------------|------|

| <ul><li>产品预览至量产数据版本</li></ul>                       | 1    |

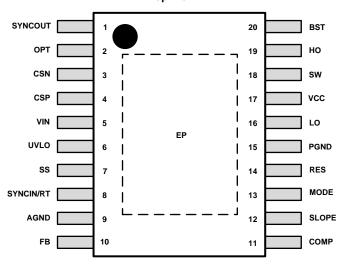

# 5 Pin Configuration and Functions

#### PWP Package 20-Pin HTSSOP With Exposed Pad Top View

#### **Pin Functions**

| PIN      |    | TYPE <sup>(1)</sup> | DECODINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------|----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME NO. |    | IYPE                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| AGND     | 9  | G                   | Analog ground connection. Return for the internal voltage reference and analog circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| BST      | 20 | Р                   | High-side driver supply for bootstrap gate drive. Connect to the cathode of the external bootstrap diode and to the bootstrap capacitor. The bootstrap capacitor supplies current to charge the high-side N-channel MOSFET gate and should be placed as close to controller as possible. An internal BST charge pump will supply 200-µA current into bootstrap capacitor for bypass operation.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| COMP     | 11 | 0                   | Output of the internal error amplifier. The loop compensation network should be connected between this pin and the FB pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| CSN      | 3  | I                   | Inverting input of current sense amplifier. Connect to the negative-side of the current sense resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| CSP      | 4  | 1                   | Non-inverting input of current sense amplifier. Connect to the positive-side of the current sense resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| FB       | 10 | I                   | Feedback. Inverting input of the internal error amplifier. A resistor divider from the output to this pin sets the output voltage level. The regulation threshold at the FB pin is 1.2 V. The controller is configured as slave mode if the FB pin voltage is above 2.7 V at initial power-on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| НО       | 19 | 0                   | High-side N-channel MOSFET gate drive output. Connect to the gate of the high-side synchronous N-channel MOSFET switch through a short, low inductance path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| LO       | 16 | 0                   | Low-side N-channel MOSFET gate drive output. Connect to the gate of the low-side N-channel MOSFET switch through a short, low inductance path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

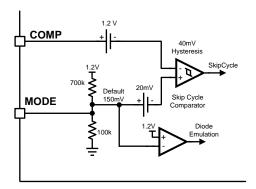

| MODE     | 13 | I                   | Switching mode selection pin. $700\text{-}k\Omega$ pullup and $100\text{-}k\Omega$ pulldown resistor internal hold MODE pin to $0.15\text{ V}$ as a default. By adding external pullup or pulldown resistor, MODE pin voltage can be programmed. When MODE pin voltage is greater than $1.2\text{ V}$ diode emulation mode threshold, forced PWM mode is enabled, allowing current to flow in either direction through the high-side N-channel MOSFET switch. When MODE pin voltage is less than $1.2\text{ V}$ , the controller works in diode emulation mode. Skip cycle comparator is activated as a default. If MODE pin is grounded, the controller still operates in diode emulation mode, but the skip cycle comparator will not be triggered in normal operation, this enables pulse skipping operation at light load. |  |  |  |

| ОРТ      | 2  | I                   | Clock synchronization selection pin. This pin also enables/disables SYNCOUT related with master/slave configuration. The OPT pin should not be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| PGND     | 15 | G                   | Power ground connection pin for low-side N-channel MOSFET gate driver. Connect directly to the source terminal of the low-side N-channel MOSFET switch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

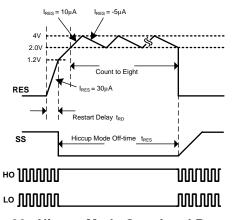

| RES 14   |    | 0                   | The restart timer pin for an external capacitor that configures hiccup mode off-time and restart delay during over load conditions. Connect directly to the AGND when hiccup mode operation is not required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

#### (1) G = Ground, I = Input, O = Output, P = Power

## Pin Functions (continued)

| PIN NAME NO.                                                                                                                                                                                       |    | TYPE <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                    |    | I TPE'                                                                                                                                                                                                                                                                                                                                                                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| SLOPE                                                                                                                                                                                              | 12 | I                                                                                                                                                                                                                                                                                                                                                                     | Slope compensation is programmed by a single resistor between SLOPE and the AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| SS                                                                                                                                                                                                 | 7  | I                                                                                                                                                                                                                                                                                                                                                                     | Soft-start programming pin. An external capacitor and an internal 10-µA current source set the ramp rate of the internal error amplifier reference during soft-start.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SW                                                                                                                                                                                                 | 18 | I/O                                                                                                                                                                                                                                                                                                                                                                   | Switching node of the boost regulator. Connect to the bootstrap capacitor, the source terminal of the high-side N-channel MOSFET switch and the drain terminal of the low-side N-channel MOSFET switch through short, low inductance paths.                                                                                                                                                                                                                                                                                                                                      |  |  |

| SYNCIN/RT 8 I The internal oscillator can be synchronized to an external clock by applying a positive purint into this SYNCIN pin. The recommended maximum internal oscillator frequency in master |    | The internal oscillator frequency is programmed by a single resistor between RT and the AGND. The internal oscillator can be synchronized to an external clock by applying a positive pulse signal into this SYNCIN pin. The recommended maximum internal oscillator frequency in master configuration is 1.2 MHz which leads to 600 kHz maximum switching frequency. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SYNCOUT                                                                                                                                                                                            | 1  | 0                                                                                                                                                                                                                                                                                                                                                                     | Clock output pin. SYNCOUT provides 180° shifted clock output for an interleaved operation. SYNCOUT pin can be left floating when it is not used. See <i>Slave Mode and SYNCOUT</i> section.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| UVLO                                                                                                                                                                                               | 6  | I                                                                                                                                                                                                                                                                                                                                                                     | Undervoltage lockout programming pin. If the UVLO pin is below 0.4 V, the regulator is in the shutdown mode with all functions disabled. If the UVLO pin voltage is greater than 0.4 V and below 1.2 V, the regulator is in standby mode with the VCC regulator operational and no switching at the HO and LO outputs. If the UVLO pin voltage is above 1.2 V, the startup sequence begins. A 10-µA current source at UVLO pin is enabled when UVLO exceeds 1.2 V and flows through the external UVLO resistors to provide hysteresis. The UVLO pin should not be left floating. |  |  |

|                                                                                                                                                                                                    |    | P/O/I                                                                                                                                                                                                                                                                                                                                                                 | VCC bias supply pin. Locally decouple to PGND using a low ESR/ESL capacitor located as close to controller as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                                                                                                                                                                                                    |    | P/I                                                                                                                                                                                                                                                                                                                                                                   | Supply voltage input source for the VCC regulator. Connect to input capacitor and source power supply connection with short, low impedance paths.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| EP EP                                                                                                                                                                                              |    | N/A                                                                                                                                                                                                                                                                                                                                                                   | Exposed pad of the package. No internal electrical connections. Should be soldered to the large ground plane to reduce thermal resistance.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings(1)

Over operating free-air temperature range (unless otherwise noted)

|                       |                                         | MIN         | MAX           | UNIT |

|-----------------------|-----------------------------------------|-------------|---------------|------|

| Input                 | VIN, CSP, CSN                           | -0.3        | 50            | V    |

|                       | BST to SW, FB, MODE, UVLO, OPT, VCC (2) | -0.3        | 15            | V    |

|                       | SW                                      | -5.0        | 60            | V    |

|                       | BST                                     | -0.3        | 75            | ٧    |

|                       | SS, SLOPE, SYNCIN/RT                    | -0.3        | 7             | ٧    |

|                       | CSP to CSN, PGND                        | -0.3        | 0.3           | V    |

|                       | HO to SW                                | -0.3        | BST to SW+0.3 | ٧    |

| Output <sup>(3)</sup> | LO                                      | -0.3        | VCC+0.3       | ٧    |

|                       | COMP, RES, SYNCOUT                      | -0.3        | 7             | ٧    |

| Thermal               | Junction Temperature                    | -40         | 150           | °C   |

| T <sub>stg</sub>      | Storage temperature                     | <b>-</b> 55 | 150           | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* are not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. Unless otherwise specified, all voltages are referenced to AGND pin.

<sup>(2)</sup> See Application Information when input supply voltage is less than the VCC voltage.

<sup>(3)</sup> All output pins are not specified to have an external voltage applied.

## 6.2 ESD Ratings

|                    |                         |                                              |                                 | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------|---------------------------------|-------|------|

|                    |                         | Human body model (HBM), per AEC Q100         | )-002 <sup>(1)</sup>            | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per AEC Q100-011 | Corner pins (1, 10, 11, and 20) | ±1000 | V    |

|                    |                         | Q100-011                                     | Other pins                      | ±1000 |      |

<sup>(1)</sup> AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                |                | MIN | NOM MAX | UNIT |

|------------------------------------------------|----------------|-----|---------|------|

| Input supply voltage (2)                       | VIN            | 4.5 | 42      | V    |

| Low-side driver bias voltage                   | VCC            |     | 14      | V    |

| High-side driver bias voltage                  | BST to SW      | 3.8 | 14      | V    |

| Current sense common mode range <sup>(2)</sup> | CSP, CSN       | 3   | 42      | V    |

| Switch node voltage                            | SW             |     | 50      | V    |

| Junction temperature                           | T <sub>J</sub> | -40 | 125     | ۰C   |

<sup>(1)</sup> Recommended Operating Conditions are conditions under which operation of the device is intended to be functional, but does not guarantee specific performance limits.

## 6.4 Thermal Information

|                      |                                              | LM25122-Q1      |      |

|----------------------|----------------------------------------------|-----------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | PWP<br>(HTSSOP) | UNIT |

|                      |                                              | 20 PINS         |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 36.0            | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 20.1            | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 16.8            | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.4             | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 16.7            | °C/W |

| ΨJCbot               | Junction-to-case (bottom) thermal resistance | 1.7             | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> Minimum VIN operating voltage is always 4.5 V. The minimum input power supply voltage can be 3.0 V after start-up, assuming VIN voltage is supplied from an available external source.

## 6.5 Electrical Characteristics

Unless otherwise specified, these specifications apply for  $-40^{\circ}\text{C} \le T_{J} \le +125^{\circ}\text{C}$ ,  $V_{VIN} = 12 \text{ V}$ ,  $V_{VCC} = 8.3 \text{ V}$ ,  $R_{T} = 20 \text{ k}\Omega$ , no load on LO and HO. Typical values represent the most likely parametric norm at  $T_{J} = 25^{\circ}\text{C}$ , and are provided for reference purposes only.

|                      | PARAMETER                                                    | TEST CONDITIONS                                      | MIN   | TYP   | MAX   | UNIT |

|----------------------|--------------------------------------------------------------|------------------------------------------------------|-------|-------|-------|------|

| /IN SUPPL            | .Y                                                           |                                                      |       |       |       |      |

| SHUTDOWN             | VIN shutdown current                                         | V <sub>UVLO</sub> = 0 V                              |       | 9     | 17    | μA   |

| I <sub>BIAS</sub>    | VIN operating current (exclude the current into RT resistor) | V <sub>UVLO</sub> = 2 V, non-switching               |       | 4     | 5     | mA   |

| CC REGU              | ILATOR                                                       |                                                      | *     |       |       |      |

| V <sub>CC(REG)</sub> | VCC regulation                                               | No load                                              | 6.9   | 7.6   | 8.3   | V    |

|                      |                                                              | V <sub>VIN</sub> = 4.5 V, no external load           |       |       | 0.25  | V    |

|                      | VCC dropout (VIN to VCC)                                     | V <sub>VIN</sub> = 4.5 V, I <sub>VCC</sub> = 25 mA   |       | 0.28  | 0.5   | V    |

|                      | VCC sourcing current limit                                   | V <sub>VCC</sub> = 0 V                               | 50    | 62    |       | mA   |

|                      | VCC operating current (exclude                               | V <sub>VCC</sub> = 8.3 V                             |       | 3.5   | 5     | mA   |

| I <sub>VCC</sub>     | the current into RT resistor)                                | V <sub>VCC</sub> = 12 V                              |       | 4.5   | 8     | mA   |

|                      | V00 1 1 1 1 1 1                                              | VCC rising, V <sub>VIN</sub> = 4.5 V                 | 3.9   | 4.0   | 4.1   | V    |

|                      | VCC undervoltage threshold                                   | VCC falling, V <sub>VIN</sub> = 4.5 V                |       |       | 3.7   | V    |

|                      | VCC undervoltage hysteresis                                  | -                                                    |       | 0.385 |       | V    |

| JNDERVO              | LTAGE LOCKOUT                                                |                                                      | !     |       | ļ     |      |

|                      | UVLO threshold                                               | UVLO rising                                          | 1.17  | 1.20  | 1.23  | V    |

|                      | UVLO hysteresis current                                      | V <sub>UVLO</sub> = 1.4 V                            | 7     | 10    | 13    | μA   |

|                      | UVLO standby enable threshold                                | UVLO rising                                          | 0.3   | 0.4   | 0.5   | V    |

|                      | UVLO standby enable hysteresis                               | -                                                    |       | 0.1   | 0.125 | V    |

| MODE                 |                                                              |                                                      | +     |       |       |      |

|                      | Diode emulation mode threshold                               | MODE rising                                          | 1.20  | 1.24  | 1.28  | V    |

|                      | Diode emulation mode hysteresis                              |                                                      |       | 0.1   |       | V    |

|                      | Default MODE voltage                                         |                                                      | 145   | 155   | 170   | mV   |

|                      |                                                              | COMP rising, measured at COMP                        |       | 1.290 |       | V    |

|                      | Default skip cycle threshold                                 | COMP falling, measured at COMP                       |       | 1.245 |       | V    |

|                      | Skip cycle hysteresis                                        | Measured at COMP                                     |       | 40    |       | mV   |

| RROR AN              |                                                              |                                                      |       |       |       |      |

| V <sub>REF</sub>     | FB reference voltage                                         | Measured at FB, V <sub>FB</sub> = V <sub>COMP</sub>  | 1.188 | 1.200 | 1.212 | V    |

| IXEI                 | FB input bias current                                        | V <sub>FB</sub> = V <sub>REF</sub>                   |       | 5     |       | nA   |

|                      | ·                                                            | I <sub>SOURCE</sub> = 2 mA, V <sub>VCC</sub> = 4.5 V | 2.75  |       |       | V    |

| $V_{OH}$             | COMP output high voltage                                     | I <sub>SOURCE</sub> = 2 mA, V <sub>VCC</sub> = 12 V  | 3.40  |       |       | V    |

| V <sub>OL</sub>      | COMP output low voltage                                      | I <sub>SINK</sub> = 2 mA                             |       |       | 0.25  | V    |

| A <sub>OL</sub>      | DC gain                                                      | O. T.                                                |       | 80    |       | dB   |

| f <sub>BW</sub>      | Unity gain bandwidth                                         |                                                      |       | 3     |       | MHz  |

|                      | Slave mode threshold                                         | FB rising                                            |       | 2.7   | 3.4   | V    |

| OSCILLAT             | OR                                                           | -                                                    | I     |       | I .   |      |

| f <sub>SW1</sub>     | Switching frequency 1                                        | $R_T = 20 \text{ k}\Omega$                           | 400   | 450   | 500   | kHz  |

|                      | RT output voltage                                            |                                                      |       | 1.2   |       | V    |

|                      | RT sync rising threshold                                     | RT rising                                            |       | 2.5   | 2.9   | V    |

|                      | RT sync falling threshold                                    | RT falling                                           | 1.6   | 2.0   |       | V    |

|                      | Minimum sync pulse width                                     |                                                      | 100   |       |       | ns   |

| SYNCOUT              | , ,                                                          | 1                                                    | IL.   |       | I     |      |

|                      | SYNCOUT high-state voltage                                   | I <sub>SYNCOUT</sub> = -1 mA                         | 3.3   | 4.3   |       | V    |

|                      | SYNCOUT low-state voltage                                    | I <sub>SYNCOUT</sub> = 1 mA                          |       | 0.15  | 0.25  | V    |

|                      | z z z z                                                      | STROUGH                                              | 1     | 5.10  | 5.20  | •    |

## **Electrical Characteristics (continued)**

Unless otherwise specified, these specifications apply for  $-40^{\circ}\text{C} \le T_{\text{J}} \le +125^{\circ}\text{C}$ ,  $V_{\text{VIN}} = 12 \text{ V}$ ,  $V_{\text{VCC}} = 8.3 \text{ V}$ ,  $R_{\text{T}} = 20 \text{ k}\Omega$ , no load on LO and HO. Typical values represent the most likely parametric norm at  $T_{\text{J}} = 25^{\circ}\text{C}$ , and are provided for reference purposes only.

|                             | PARAMETER                                           | TEST CONDITIONS                                                                           | MIN   | TYP   | MAX   | UNIT   |

|-----------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-------|-------|--------|

|                             | Synchronization selection threshold                 | OPT rising                                                                                | 2.0   | 3.0   | 4.0   | V      |

| SLOPE CO                    | MPENSATION                                          |                                                                                           |       |       |       |        |

|                             | SLOPE output voltage                                |                                                                                           | 1.17  | 1.20  | 1.23  | V      |

| V                           | Slope compensation amplitude                        | $R_{SLOPE}$ = 20 k $\Omega$ , $f_{SW}$ = 100 kHz, 50% duty cycle, $T_J$ = -40°C to +125°C | 1.375 | 1.650 | 1.925 | V      |

| V <sub>SLOPE</sub>          | Slope compensation amplitude                        | $R_{SLOPE}$ = 20 k $\Omega$ , $f_{SW}$ = 100 kHz, 50% duty cycle, $T_J$ = 25°C            | 1.400 | 1.650 | 1.900 | V      |

| SOFT-STA                    | RT                                                  |                                                                                           |       |       |       |        |

| SS-SOURCE                   | SS current source                                   | V <sub>SS</sub> = 0 V                                                                     | 7.5   | 10    | 12    | μΑ     |

|                             | SS discharge switch R <sub>DS-ON</sub>              |                                                                                           |       | 13    |       | Ω      |

| PWM COM                     | PARATOR                                             |                                                                                           |       |       |       |        |

|                             | Forced LO off-time                                  | V <sub>VCC</sub> = 5.5 V                                                                  |       | 330   | 400   | ns     |

| t <sub>LO-OFF</sub>         | Forced LO on-time                                   | V <sub>VCC</sub> = 4.5 V                                                                  |       | 560   | 750   | ns     |

|                             | Minimum I O on time                                 | $R_{SLOPE} = 20 \text{ k}\Omega$                                                          |       | 150   |       | ns     |

| t <sub>ON-MIN</sub>         | Minimum LO on-time                                  | $R_{SLOPE} = 200 \text{ k}\Omega$                                                         |       | 300   |       | ns     |

|                             | COMP : DWM :                                        | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                      | 0.95  | 1.10  | 1.25  | V      |

|                             | COMP to PWM voltage drop                            | $T_{\rm J} = 25^{\rm o}{\rm C}$                                                           | 1.00  | 1.10  | 1.20  | V      |

| CURRENT                     | SENSE / CYCLE-BY-CYCLE CUR                          | RENT LIMIT                                                                                |       |       |       |        |

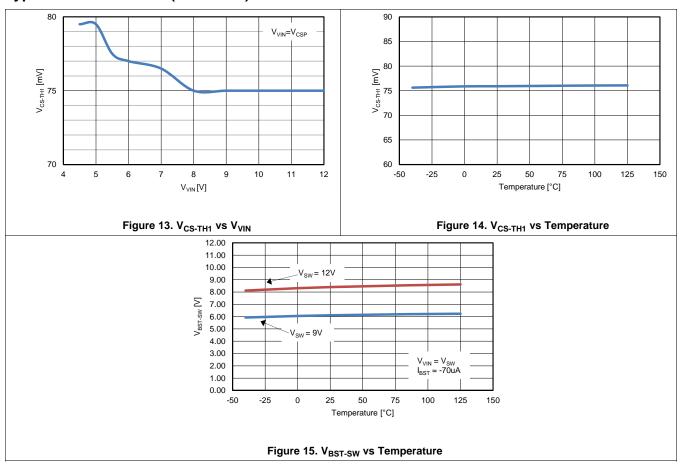

|                             | Cycle-by-cycle current limit                        | CSP to CSN, $T_J = -40^{\circ}$ C to +125°C                                               | 65.5  | 75.0  | 87.5  | mV     |

| V <sub>CS-TH1</sub>         | threshold                                           | CSP to CSN, T <sub>J</sub> = 25°C                                                         | 67.0  | 75.0  | 86.0  | mV     |

|                             |                                                     | CSP to CSN, rising                                                                        |       | 7     |       | mV     |

| $V_{CS-ZCD}$                | Zero cross detection threshold                      | CSP to CSN, falling                                                                       | 0.5   | 6     | 12    | mV     |

|                             | Current sense amplifier gain                        | and the confirming                                                                        |       | 10    |       | V/V    |

| I <sub>CSP</sub>            | CSP input bias current                              |                                                                                           |       | 12    |       | μA     |

| I <sub>CSN</sub>            | CSN input bias current                              |                                                                                           |       | 11    |       | μA     |

| ·CSIN                       | Bias current matching                               | I <sub>CSP</sub> - I <sub>CSN</sub>                                                       | -1.75 | 1     | 3.75  | μA     |

|                             | CS to LO delay                                      | Current sense / current limit delay                                                       | 1.10  | 150   | 0.70  | ns     |

| HICCLIP M                   | ODE RESTART                                         | Carrent series / carrent innit delay                                                      |       | 100   |       | 110    |

| V <sub>RES</sub>            | Restart threshold                                   | RES rising                                                                                | 1.15  | 1.20  | 1.25  | V      |

| V RES                       | Restart tireshold                                   | RES rising                                                                                | 1.10  | 4.2   | 1.20  | V      |

| $V_{HCP}$                   | Hiccup counter upper threshold                      | RES rising.                                                                               |       | 4.2   |       | V      |

| UPPER                       | ,                                                   | $V_{VIN} = V_{VCC} = 4.5 \text{ V}$                                                       |       | 3.6   |       | V      |

|                             |                                                     | RES falling                                                                               |       | 2.15  |       | V      |

| V <sub>HCP</sub> -<br>LOWER | Hiccup counter lower threshold                      | RES falling,<br>V <sub>VIN</sub> = V <sub>VCC</sub> = 4.5 V                               |       | 1.85  |       | V      |

| I <sub>RES</sub> -          | RES current source1                                 | Fault-state charging current                                                              | 20    | 30    | 40    | μΑ     |

| I <sub>RES-SINK1</sub>      | RES current sink1                                   | Normal-state discharging current                                                          |       | 5     |       | μΑ     |

| I <sub>RES</sub> -          | RES current source2                                 | Hiccup mode off-time charging current                                                     |       | 10    |       | μΑ     |

| I <sub>RES-SINK2</sub>      | RES current sink2                                   | Hiccup mode off-time discharging current                                                  |       | 5     |       | μA     |

|                             | Hiccup cycle                                        |                                                                                           |       | 8     |       | Cycles |

|                             | RES discharge switch R <sub>DS-ON</sub>             |                                                                                           |       | 40    |       | Ω      |

|                             | Ratio of hiccup mode off-time to restart delay time |                                                                                           |       | 122   |       |        |

| HO GATE I                   | DRIVER                                              |                                                                                           |       |       |       |        |

## **Electrical Characteristics (continued)**

Unless otherwise specified, these specifications apply for  $-40^{\circ}\text{C} \le T_{\text{J}} \le +125^{\circ}\text{C}$ ,  $V_{\text{VIN}} = 12 \text{ V}$ ,  $V_{\text{VCC}} = 8.3 \text{ V}$ ,  $R_{\text{T}} = 20 \text{ k}\Omega$ , no load on LO and HO. Typical values represent the most likely parametric norm at  $T_{\text{J}} = 25^{\circ}\text{C}$ , and are provided for reference purposes only.

|                  | PARAMETER                        | TEST CONDITIONS                                                         | MIN | TYP  | MAX  | UNIT |

|------------------|----------------------------------|-------------------------------------------------------------------------|-----|------|------|------|

| $V_{OHH}$        | HO high-state voltage drop       | $I_{HO} = -100 \text{ mA}, V_{OHH} = V_{BST} - V_{HO}$                  |     | 0.15 | 0.24 | V    |

| $V_{OLH}$        | HO low-state voltage drop        | $I_{HO}$ = 100 mA, $V_{OLH}$ = $V_{HO}$ $-V_{SW}$                       |     | 0.1  | 0.18 | V    |

|                  | HO rise time (10% to 90%)        | C <sub>LOAD</sub> = 4700 pF, V <sub>BST</sub> = 12 V                    |     | 25   |      | ns   |

|                  | HO fall time (90% to 10%)        | C <sub>LOAD</sub> = 4700 pF, V <sub>BST</sub> = 12 V                    |     | 20   |      | ns   |

|                  | Peak HO source current           | $V_{HO} = 0 \text{ V}, V_{SW} = 0 \text{ V}, V_{BST} = 4.5 \text{ V}$   |     | 0.8  |      | Α    |

| Іонн             | reak no source current           | $V_{HO} = 0 \text{ V}, V_{SW} = 0 \text{ V}, V_{BST} = 7.6 \text{ V}$   |     | 1.9  |      | Α    |

|                  | Dook LIO sink surrent            | $V_{HO} = V_{BST} = 4.5 \text{ V}$                                      |     | 1.9  |      | Α    |

| I <sub>OLH</sub> | Peak HO sink current             | $V_{HO} = V_{BST} = 7.6 \text{ V}$                                      |     | 3.2  |      | Α    |

| I <sub>BST</sub> | BST charge pump sourcing current | $V_{VIN} = V_{SW} = 9.0 \text{ V}$ , $V_{BST} - V_{SW} = 5.0 \text{ V}$ | 100 | 200  |      | μΑ   |

|                  | DCT shows number regulation      | $B_{ST}$ to SW, $I_{BST}$ = -70 $\mu$ A, $V_{VIN}$ = $V_{SW}$ = 9.0 $V$ | 5.3 | 6.2  | 6.75 | V    |

|                  | BST charge pump regulation       | $B_{ST}$ to SW, $I_{BST} = -70 \mu A$ , $V_{VIN} = V_{SW} = 12 V$       | 7   | 8.5  | 9    | V    |

|                  | BST to SW undervoltage           |                                                                         | 2.0 | 3.0  | 3.5  | V    |

|                  | BST DC bias current              | V <sub>BST</sub> - V <sub>SW</sub> = 12 V, V <sub>SW</sub> = 0 V        |     | 30   | 45   | μΑ   |

| LO GATE          | DRIVER                           |                                                                         |     |      |      |      |

| $V_{OHL}$        | LO high-state voltage drop       | $I_{LO} = -100 \text{ mA}, V_{OHL} = V_{VCC} - V_{LO}$                  |     | 0.15 | 0.25 | V    |

| V <sub>OLL</sub> | LO low-state voltage drop        | $I_{LO}$ = 100 mA, $V_{OLL}$ = $V_{LO}$                                 |     | 0.1  | 0.17 | V    |

|                  | LO rise time (10% to 90%)        | C <sub>LOAD</sub> = 4700 pF                                             |     | 25   |      | ns   |

|                  | LO fall time (90% to 10%)        | C <sub>LOAD</sub> = 4700 pF                                             |     | 20   |      | ns   |

|                  | Peak LO source current           | $V_{LO} = 0 \text{ V}, V_{VCC} = 4.5 \text{ V}$                         |     | 8.0  |      | Α    |

| I <sub>OHL</sub> | reak LO Source current           | $V_{LO} = 0 V$                                                          |     | 2.0  |      | Α    |

|                  | Peak LO sink current             | $V_{LO} = V_{VCC} = 4.5 \text{ V}$                                      |     | 1.8  |      | Α    |

| I <sub>OLL</sub> | Peak LO SINK Current             | $V_{LO} = V_{VCC}$                                                      |     | 3.2  |      | Α    |

| SWITCHIN         | NG CHARACTERISTICS               |                                                                         |     |      |      |      |

| t <sub>DLH</sub> | LO fall to HO rise delay         | No load, 50% to 50%                                                     | 50  | 80   | 115  | ns   |

| t <sub>DHL</sub> | HO fall to LO rise delay         | No load, 50% to 50%                                                     | 60  | 80   | 105  | ns   |

| THERMAI          |                                  |                                                                         |     |      |      |      |

| $T_{SD}$         | Thermal shutdown                 | Temperature rising                                                      |     | 165  |      | °C   |

|                  | Thermal shutdown hysteresis      |                                                                         |     | 25   |      | °С   |

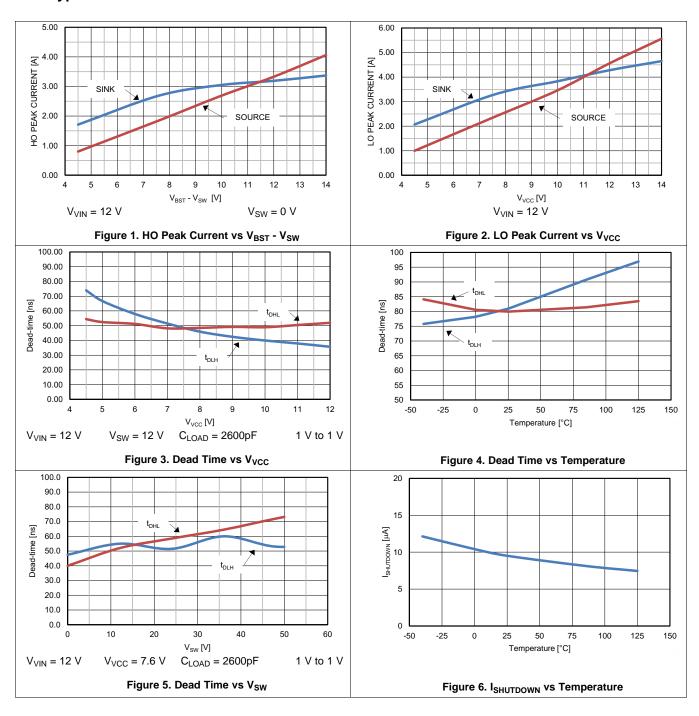

## 6.6 Typical Characteristics

# TEXAS INSTRUMENTS

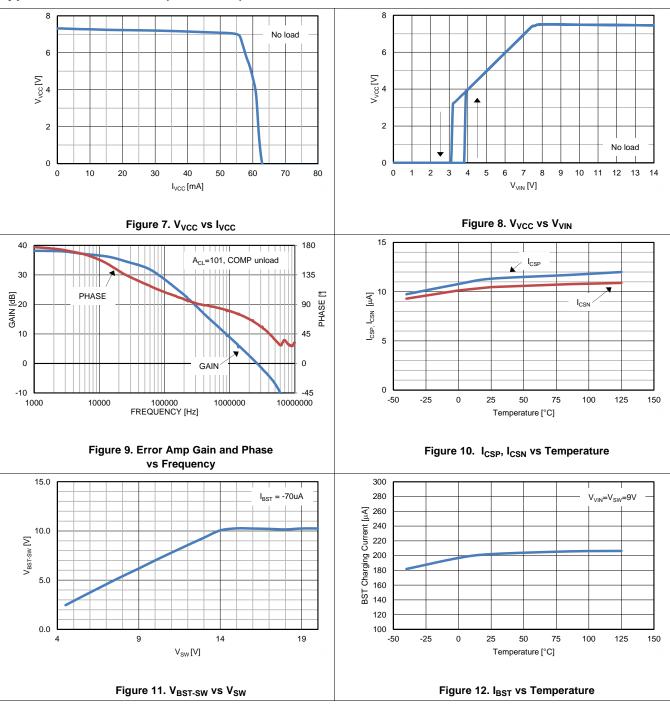

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

## 7 Detailed Description

#### 7.1 Overview

The LM25122 wide input range synchronous boost controller features all of the functions necessary to implement a highly efficient synchronous boost regulator. The regulator control method is based upon peak current mode control. Peak current mode control provides inherent line feed-forward and ease of loop compensation. This highly integrated controller provides strong high-side and low-side N-channel MOSFET drivers with adaptive dead-time control. The switching frequency is user programmable up to 600 kHz set by a single resistor or synchronized to an external clock. The LM25122's 180° shifted clock output enables easy multi-phase configuration.

The control mode of high-side synchronous switch can be configured as either forced PWM (FPWM) or diode emulation mode. Fault protection features include cycle-by-cycle current limiting, hiccup mode over load protection, thermal shutdown and remote shutdown capability by pulling down the UVLO pin. The UVLO input enables the controller when the input voltage reaches a user selected threshold, and provides a tiny 9 µA shutdown quiescent current when pulled low. The device is available in 20-pin HTSSOP package featuring an exposed pad to aid in thermal dissipation.

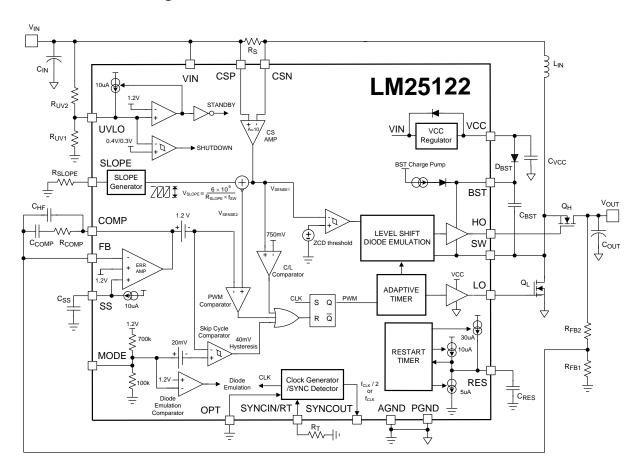

## 7.2 Functional Block Diagram

#### 7.3 Feature Description

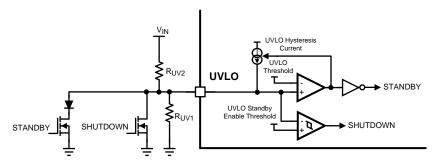

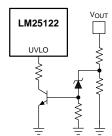

### 7.3.1 Undervoltage Lockout (UVLO)

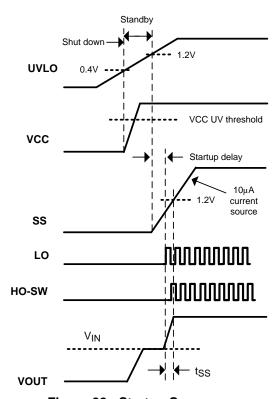

The LM25122 features a dual level UVLO circuit. When the UVLO pin voltage is less than the 0.4-V UVLO standby enable threshold, the LM25122 is in the shutdown mode with all functions disabled. The shutdown comparator provides 0.1 V of hysteresis to avoid chatter during transition. If the UVLO pin voltage is greater than 0.4 V and below 1.2 V during power up, the controller is in standby mode with the VCC regulator operational and no switching at the HO and LO outputs. This feature allows the UVLO pin to be used as a remote shutdown function by pulling the UVLO pin down below the UVLO standby enable threshold with an external open collector or open drain device.

Figure 16. UVLO Remote Standby and Shutdown Control

If the UVLO pin voltage is above the 1.2-V UVLO threshold and VCC voltage exceeds the VCC UV threshold, a startup sequence begins. UVLO hysteresis is accomplished with an internal 10-μA current source that is switched on or off into the impedance of the UVLO setpoint divider. When the UVLO pin voltage exceeds 1.2 V, the current source is enabled to quickly raise the voltage at the UVLO pin. When the UVLO pin voltage falls below the 1.2-V UVLO threshold, the current source is disabled causing the voltage at the UVLO pin to quickly fall. In addition to the UVLO hysteresis current source, a 5-μs deglitch filter on both rising and falling edge of UVLO toggling helps preventing chatter upon power up or down.

An external UVLO setpoint voltage divider from the supply voltage to AGND is used to set the minimum input operating voltage of the regulator. The divider must be designed such that the voltage at the UVLO pin is greater than 1.2 V when the input voltage is in the desired operating range. The maximum voltage rating of the UVLO pin is 15 V. If necessary, the UVLO pin can be clamped with an external zener diode. The UVLO pin should not be left floating. The values of  $R_{\text{UV}1}$  and  $R_{\text{UV}2}$  can be determined from Equation 1 and Equation 2.

$$R_{UV2} = \frac{V_{HYS}}{10\mu A} \left[\Omega\right] \tag{1}$$

$$R_{UV1} = \frac{1.2V \times R_{UV2}}{V_{IN(STARTUP)} - 1.2V} [\Omega]$$

(2)

where

- V<sub>HYS</sub> is the desired UVLO hysteresis

- V<sub>IN(STARTUP)</sub> is the desired startup voltage of the regulator during turn-on.

Typical shutdown voltage during turn-off can be calculated as follows:

$$V_{IN(SHUTDOWN)} = V_{IN(STARTUP)} - V_{HYS}[V]$$

(3)

#### 7.3.2 High Voltage VCC Regulator

The LM25122 contains an internal high voltage regulator that provides typical 7.6 V VCC bias supply for the controller and N-channel MOSFET drivers. The input of VCC regulator, VIN, can be connected to an input voltage source as high as 42 V. The VCC regulator turns on when the UVLO pin voltage is greater than 0.4 V. When the input voltage is below the VCC setpoint level, the VCC output tracks VIN with a small dropout voltage. The output of the VCC regulator is current limited at 50 mA minimum.

Upon power-up, the VCC regulator sources current into the capacitor connected to the VCC pin. The recommended capacitance range for the VCC capacitor is 1.0  $\mu$ F to 47  $\mu$ F and is recommended to be at least 10 times greater than C<sub>BST</sub> value. When operating with a VIN voltage less than 6 V, the value of VCC capacitor should be 4.7  $\mu$ F or greater.

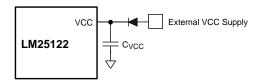

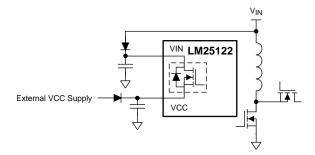

The internal power dissipation of the LM25122 device can be reduced by supplying VCC from an external supply. If an external VCC bias supply exists and the voltage is greater than 9 V and below 14.5 V. The external VCC bias supply can be applied to the VCC pin directly through a diode, as shown in Figure 17.

Figure 17. External Bias Supply when 9 V<V<sub>EXT</sub><14.5 V

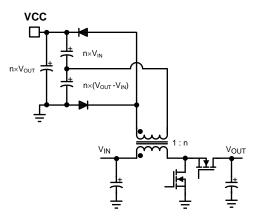

Shown in Figure 18 is a method to derive the VCC bias voltage with an additional winding on the boost inductor. This circuit must be designed to raise the VCC voltage above VCC regulation voltage to shut off the internal VCC regulator.

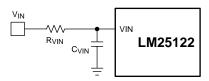

Figure 18. External Bias Supply using Transformer

The VCC regulator series pass transistor includes a diode between VCC and VIN that should not be fully forward biased in normal operation, as shown in Figure 19. If the voltage of the external VCC bias supply is greater than the VIN pin voltage, an external blocking diode is required from the input power supply to the VIN pin to prevent the external bias supply from passing current to the input supply through VCC. The need for the blocking diode should be evaluated for all applications when the VCC is supplied by the external bias supply. Especially, when the input power supply voltage is less than 4.5 V, the external VCC supply should be provided and the external blocking diode is required.

Figure 19. VIN Configuration when  $V_{VIN} < V_{VCC}$

#### 7.3.3 Oscillator

The LM25122 switching frequency is programmable by a single external resistor connected between the RT pin and the AGND pin. The resistor should be located very close to the device and connected directly to the RT pin and AGND pin. To set a desired switching frequency ( $f_{SW}$ ), the resistor value can be calculated from Equation 4.

$$R_{T} = \frac{9 \times 10^{9}}{f_{SW}} \left[\Omega\right] \tag{4}$$

#### 7.3.4 Slope Compensation

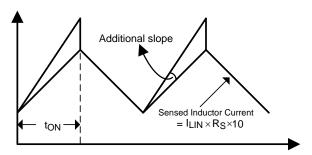

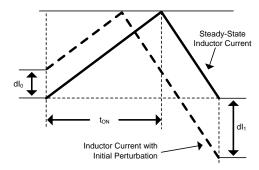

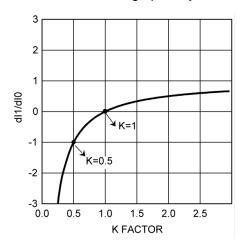

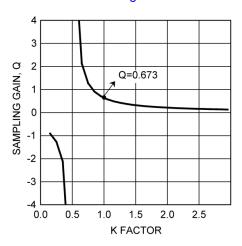

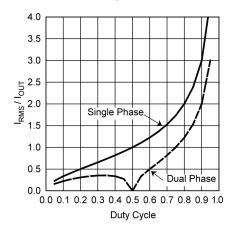

For duty cycles greater than 50%, peak current mode regulators are subject to sub-harmonic oscillation. Sub-harmonic oscillation is normally characterized by observing alternating wide and narrow duty cycles. This sub-harmonic oscillation can be eliminated by a technique, which adds an artificial ramp, known as slope compensation, to the sensed inductor current.

Figure 20. Slope Compensation

The amount of slope compensation is programmable by a single resistor connected between the SLOPE pin and the AGND pin. The amount of slope compensation can be calculated as follows:

$$V_{SLOPE} = \frac{6 \times 10^9}{f_{SW} \times R_{SLOPE}} \times D \quad [V]$$

where

$$D = 1 - \frac{V_{IN}}{V_{OUT}}$$

(5)

R<sub>SLOPE</sub> value can be determined from the following equation at minimum input voltage:

$$R_{SLOPE} = \frac{L_{IN} \times 6 \times 10^{9}}{\left[K \times V_{OUT} - V_{IN(MIN)}\right] \times R_{S} \times 10} \left[\Omega\right]$$

where

From the previous equation, K can be calculated over the input range as follows:

$$K = \left(1 + \frac{L_{IN} \times 6 \times 10^9}{V_{IN} \times R_S \times 10 \times R_{SLOPE}}\right) \times D^{'}$$

where

$$D' = \frac{V_{IN}}{V_{OUT}}$$

(7)

In any case, K should be greater than at least 0.5. At higher switching frequency over 500 kHz, K factor is recommended to be greater than or equal to 1 because the minimum on-time affects the amount of slope compensation due to internal delays.

The sum of sensed inductor current and slope compensation should be less than COMP output high voltage  $(V_{OH})$  for proper startup with load and proper current limit operation. This limits the minimum value of  $R_{SLOPE}$  to be:

$$R_{SLOPE} > \frac{5.7 \times 10^9}{f_{SW}} \times \left(1.2 - \frac{V_{IN(MIN)}}{V_{OUT}}\right) \left[\Omega\right]$$

This equation can be used in most cases

$$R_{SLOPE} > \frac{8 \times 10^9}{f_{SW}} \left[\Omega\right]$$

• This conservative selection should be considered when  $V_{IN(MIN)}$  < 5.5 V

The SLOPE pin cannot be left floating.

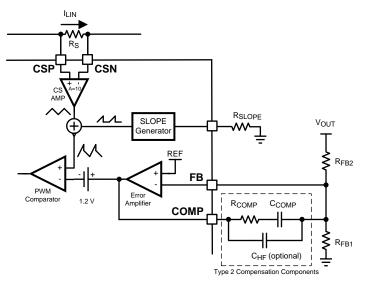

#### 7.3.5 Error Amplifier

The internal high-gain error amplifier generates an error signal proportional to the difference between the FB pin voltage and the internal precision 1.2-V reference. The output of the error amplifier is connected to the COMP pin allowing the user to provide a Type 2 loop compensation network.

$R_{COMP}$ ,  $C_{COMP}$  and  $C_{HF}$  configure the error amplifier gain and phase characteristics to achieve a stable voltage loop. This network creates a pole at DC, a mid-band zero ( $f_{Z\_EA}$ ) for phase boost, and a high frequency pole ( $f_{P\_EA}$ ). The minimum recommended value of  $R_{COMP}$  is 2 k $\Omega$ . See the *Feedback Compensation* section.

$$f_{Z\_EA} = \frac{1}{2\pi \times R_{COMP} \times C_{COMP}} [Hz]$$

$$f_{P\_EA} = \frac{1}{2\pi \times R_{COMP} \times \left(\frac{C_{COMP} \times C_{HF}}{C_{COMP} + C_{HF}}\right)} [Hz]$$

(9)

#### 7.3.6 PWM Comparator

The PWM comparator compares the sum of sensed inductor current and slope compensation ramp to the voltage at the COMP pin through a 1.2-V internal COMP to PWM voltage drop, and terminates the present cycle when the sum of sensed inductor current and slope compensation ramp is greater than  $V_{COMP}$  –1.2 V.

Figure 21. Feedback Configuration and PWM Comparator

#### 7.3.7 Soft-Start

The soft-start feature helps the regulator to gradually reach the steady state operating point, thus reducing startup stresses and surges. The LM25122 regulates the FB pin to the SS pin voltage or the internal 1.2-V reference, whichever is lower. The internal 10- $\mu$ A soft-start current source gradually increases the voltage on an external soft-start capacitor connected to the SS pin. This results in a gradual rise of the output voltage starting from the input voltage level to the target output voltage. Soft-start time ( $t_{SS}$ ) varies by the input supply voltage, is calculated from Equation 11.

$$t_{SS} = \frac{C_{SS} \times 1.2V}{10\mu A} \times \left(1 - \frac{V_{IN}}{V_{OUT}}\right) [sec]$$

(11)

When the UVLO pin voltage is greater than the 1.2-V UVLO threshold and VCC voltage exceeds the VCC UV threshold, an internal 10- $\mu$ A soft-start current source turns on. At the beginning of this soft-start sequence, V<sub>SS</sub> should be allowed to fall down below 25 mV by the internal SS pulldown switch. The SS pin can be pulled down by external switch to stop switching, but pulling up to enable switching is not allowed. The startup delay (see Figure 22) should be long enough for high-side boot capacitor to be fully charged up by internal BST charge pump.

The value of C<sub>SS</sub> should be large enough to charge the output capacitor during soft-start time.

$$C_{SS} > \frac{10\mu A \times V_{OUT}}{1.2V} \times \frac{C_{OUT}}{I_{OUT}} [F]$$

(12)

Figure 22. Startup Sequence

#### 7.3.8 HO and LO Drivers

The LM25122 contains strong N-channel MOSFET gate drivers and an associated high-side level shifter to drive the external N-channel MOSFET switches. The high-side gate driver works in conjunction with an external boot diode  $D_{BST}$ , and bootstrap capacitor  $C_{BST}$ . During the on-time of the low-side N-channel MOSFET driver, the SW pin voltage is approximately 0 V and the  $C_{BST}$  is charged from VCC through the  $D_{BST}$ . A 0.1- $\mu$ F or larger ceramic capacitor, connected with short traces between the BST and SW pin, is recommended.

The LO and HO outputs are controlled with an adaptive dead-time methodology which insures that both outputs are never enabled at the same time. When the controller commands LO to be enabled, the adaptive dead-time logic first disables HO and waits for HO-SW voltage to drop. LO is then enabled after a small delay (HO Fall to LO Rise Delay). Similarly, the HO turn-on is delayed until the LO voltage has discharged. HO is then enabled after a small delay (LO Fall to HO Rise Delay). This technique insures adequate dead-time for any size N-channel MOSFET device, especially when VCC is supplied by a higher external voltage source. Be careful when adding series gate resistors, as this may decrease the effective dead-time.

Care should be exercised in selecting the N-channel MOSFET devices threshold voltage, especially if the VIN voltage range is below the VCC regulation level or a bypass operation is required. If the bypass operation is required, especially when output voltage is less than 12 V, a logic level device should be selected for the high-side N-channel MOSFET. During startup at low input voltages, the low-side N-channel MOSFET switch's gate plateau voltage should be sufficient to completely enhance the N-channel MOSFET device. If the low-side N-channel MOSFET drive voltage is lower than the low-side N-channel MOSFET device gate plateau voltage during startup, the regulator may not start up properly and it may stick at the maximum duty cycle in a high power dissipation state. This condition can be avoided by selecting a lower threshold N-channel MOSFET switch or by increasing V<sub>IN(STARTUP)</sub> with the UVLO pin voltage programming.

## 7.3.9 Bypass Operation $(V_{OUT} = V_{IN})$

The LM25122 allows 100% duty cycle operation for the high-side synchronous switch when the input supply voltage is equal to or greater than the target output voltage. An internal 200 µA BST charge pump maintains sufficient high-side driver supply voltage to keep the high-side N-channel MOSFET switch on without the power stage switching. The internal BST charge pump is enabled when the UVLO pin voltage is greater than 1.2 V and the VCC voltage exceeds the VCC UV threshold. The BST charge pump generates 5.3-V minimum BST to SW voltage when SW voltage is greater than 9 V. This requires minimum 9 V boost output voltage for proper bypass operation. The leakage current of the boot diode should be always less than the BST charge pump sourcing current to maintain a sufficient driver supply voltage at both low and high temperatures. Forced PWM mode is the recommended PWM configuration when bypass operation is required.

#### 7.3.10 Cycle-by-Cycle Current Limit

The LM25122 features a peak cycle-by-cycle current limit function. If the CSP to CSN voltage exceeds the 75-mV cycle-by-cycle current limit threshold, the current limit comparator immediately terminates the LO output.

For the case where the inductor current may overshoot, such as inductor saturation, the current limit comparator skips pulses until the current has decayed below the current limit threshold. Peak inductor current in current limit can be calculated as follows:

$$I_{PEAK(CL)} = \frac{75mV}{R_{S}} [A]$$

(13)

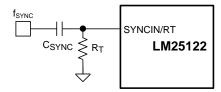

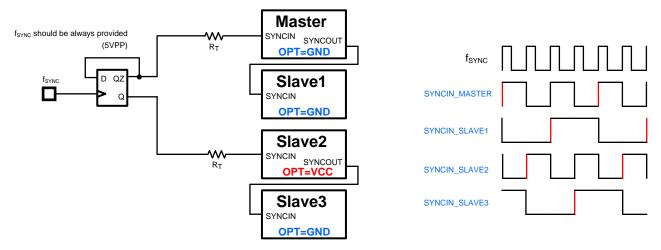

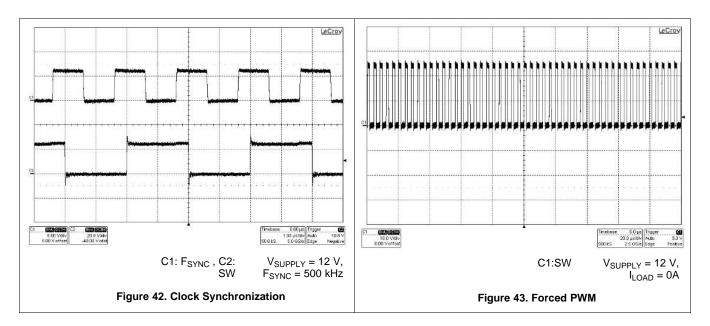

## 7.3.11 Clock Synchronization

The SYNCIN/RT pin can be used to synchronize the internal oscillator to an external clock. A positive going synchronization clock at the RT pin must exceed the RT sync rising threshold and negative going synchronization clock at RT pin must exceed the RT sync falling threshold to trip the internal synchronization pulse detector.

In Master1 mode, two types of configurations are allowed for clock synchronization. With the configuration in Figure 23, the frequency of the external synchronization pulse is recommended to be within +40% and -20% of the internal oscillator frequency programmed by the RT resistor. For example, 900-kHz external synchronization clock and 20-k $\Omega$  RT resistor are required for 450-kHz switching in master1 mode. The internal oscillator can be synchronized by AC coupling a positive edge into the RT pin. A 5-V amplitude pulse signal coupled through 100-pF capacitor is a good starting point. The RT resistor is always required with AC coupling capacitor with the Figure 23 configuration, whether the oscillator is free running or externally synchronized.

Care should be taken to guarantee that the RT pin voltage does not go below -0.3 V at the falling edge of the external pulse. This may limit the duty cycle of external synchronization pulse. There is approximately 400-ns delay from the rising edge of the external pulse to the rising edge of LO.

Figure 23. Oscillator Synchronization Through AC Coupling in Master1 Mode

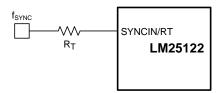

With the configuration in Figure 24, the internal oscillator can be synchronized by connecting the external synchronization clock into the RT pin through RT resistor with free of the duty cycle limit. The output stage of the external clock source should be a low impedance totem-pole structure. Default logic state of f<sub>SYNC</sub> should be low.

Figure 24. Oscillator Synchronization Through a Resistor in Master1 Mode

In master2 and slave modes, this external synchronization clock should be directly connected to the RT pin and always provided continuously. The internal oscillator frequency can be either of two times faster than switching frequency or the same as the switching frequency by configuring the combination of FB and OPT pins (see Table 1).

#### 7.3.12 Maximum Duty Cycle

When operating with a high PWM duty cycle, the low-side N-channel MOSFET device is forced off each cycle. This forced LO off-time limits the maximum duty cycle of the controller. When designing a boost regulator with high switching frequency and high duty cycle requirements, a check should be made of the required maximum duty cycle. The minimum input supply voltage which can achieve the target output voltage is estimated from Equation 14.

$$V_{IN(MIN)} = f_{SW} \times V_{OUT} \times (750ns + margin) \quad [V]$$

(14)

In normal operation, about 100 ns of margin is recommended.

#### 7.3.13 Thermal Protection

Internal thermal shutdown circuitry is provided to protect the controller in the event the maximum junction temperature is exceeded. When activated, typically at 165°C, the controller is forced into a low-power shutdown mode, disabling the output drivers, disconnection switch and the VCC regulator. This feature is designed to prevent overheating and destroying the device.

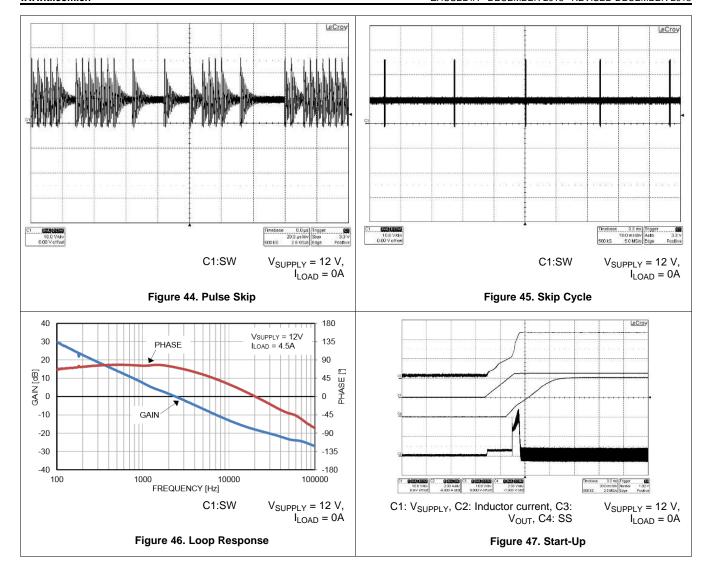

#### 7.4 Device Functional Modes

#### 7.4.1 MODE Control (Forced PWM Mode and Diode Emulation Mode)

A fully synchronous boost regulator implemented with a high-side switch rather than a diode has the capability to sink current from the output in certain conditions such as light load, overvoltage or load transient. The LM25122 can be configured to operate in either forced PWM mode or diode emulation mode.

In forced PWM mode (FPWM), reverse current flow in high-side N-channel MOSFET switch is allowed and the inductor current conducts continuously at light or no load conditions. The benefit of the forced PWM mode is fast light load to heavy load transient response and constant frequency operation at light or no load conditions. To enable forced PWM mode, connect the MODE pin to VCC or tie to a voltage greater than 1.2 V. In FPWM mode, reverse current flow is not limited.