LM25148-Q1

ZHCSNB5A - JUNE 2021 - REVISED FEBRUARY 2023

LM25148-Q1 42V、汽车类、具有超低 I<sub>Q</sub> 和双随机展频的同步降压直流/直流控制器

# 1 特性

TEXAS

INSTRUMENTS

- 符合面向汽车应用的 AEC-Q100 标准:

器件温度等级 1: -40°C 至 +125°C 环境工作温 度范围

- 功能安全型

有助于进行功能安全系统设计的文档

- 集成式 EMI 缓解

- 一可选双随机展频 (DRSS) 特性,可在低频和高频频带上增强 EMI 降低性能

- 针对 CISPR 25 5 级要求进行了优化

- 多功能同步降压直流/直流控制器

- 宽输入电压范围为 3.5V 至 42V

- 1% 精度、固定 3.3V/5V/12V 或 0.8V 至 36V 可 调输出电压

- 150°C 最大结温

- 无损 DCR 或分流电流检测

- 关断时的静态电流为 2.3μA(典型值)

- 9.5µA 低漏电流

- 3ms 的内部软启动斜坡

- 最多可堆叠两个相位

- 内部自举二极管

- 开关频率范围为 100kHz 至 2.2MHz

- 同步输入和同步输出功能

- 可选 PFM 或 FPWM 模式

- 固有保护特性,可实现稳健设计

- 内部断续模式过流保护

- 使能和 PGOOD 功能

- VCC、VDDA 和栅极驱动 UVLO 保护

- 内部或外部环路补偿

- 具有迟滞功能的热关断保护

- 使用 LM25148-Q1 并借助 WEBENCH<sup>®</sup> Power Designer 创建定制设计方案

# 2 应用

- 汽车电子系统

- 高级驾驶辅助系统 (ADAS)

- 信息娱乐系统与仪表组

- 车身电子装置

### 3 说明

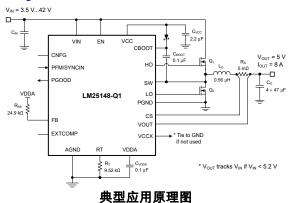

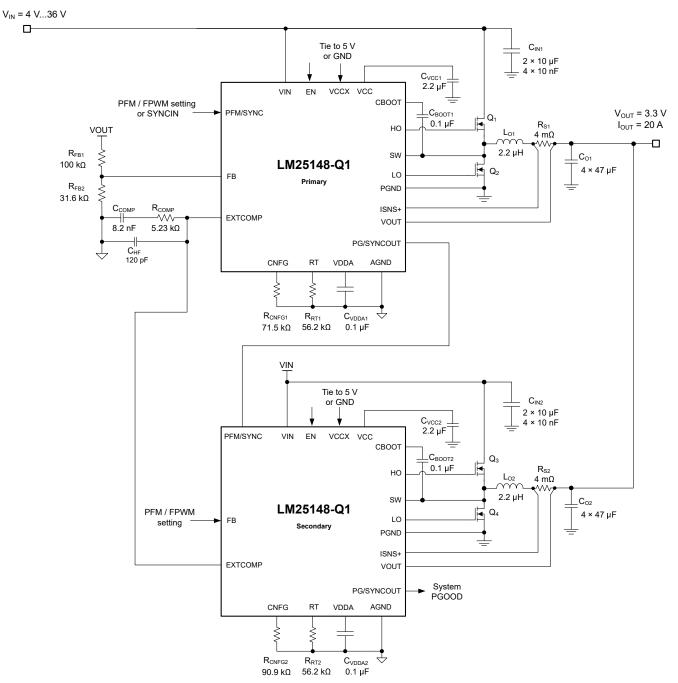

LM25148-Q1 是一款 42V 超低 I<sub>Q</sub> 同步降压直流/直 流控制器,适合高电流单输出应用。该控制器使用峰值 电流模式控制架构,可实现简单环路补偿、快速瞬态响 应和出色的负载和线路调节性能。LM25148-Q1 可设 置为以交错模式(并联输出)运行,实现精确的电流共 享,适合高电流应用。它可在低至 3.5V 的输入电压和 接近 100% 的占空比(如果需要)下运行。

LM25148-Q1 具有一种独特的 EMI 降低特性,称为双 随机展频 (DRSS)。将低频三角调制与高频随机调制相 结合,可分别在低频和高频频带上降低 EMI 干扰。此 项混合技术符合业界通用的 EMC 测试中指定的多种分 辨率带宽 (RBW) 设置。

封装信息

|      |            | 피카티카                     |                 |  |  |

|------|------------|--------------------------|-----------------|--|--|

| 器件型号 |            | <b>封装</b> <sup>(1)</sup> | 封装尺寸(标称值)       |  |  |

|      | LM25148-Q1 | RGY (VQFN, 24)           | 3.50mm × 5.50mm |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录

# **Table of Contents**

| 1 特性                                 | 1              |

|--------------------------------------|----------------|

| 2 应用                                 |                |

| 3 说明                                 |                |

| 4 Revision History                   | 2              |

| 5 说明 (续)                             | <mark>2</mark> |

| 6 Pin Configuration and Functions    | 3              |

| 6.1 Wettable Flanks                  | 4              |

| 7 Specifications                     | <mark>5</mark> |

| 7.1 Absolute Maximum Ratings         | <mark>5</mark> |

| 7.2 ESD Ratings                      | 5              |

| 7.3 Recommended Operating Conditions | 5              |

| 7.4 Thermal Information              | <mark>6</mark> |

| 7.5 Electrical Characteristics       | <mark>6</mark> |

| 7.6 Typical Characteristics          | 10             |

| 8 Detailed Description               | 14             |

| 8.1 Overview                         | 14             |

| 8.2 Functional Block Diagram         |                |

| 8.3 Feature Description                 | 16 |

|-----------------------------------------|----|

| 8.4 Device Functional Modes             |    |

| 9 Application and Implementation        | 27 |

| 9.1 Application Information             |    |

| 9.2 Typical Applications                |    |

| 9.3 Power Supply Recommendations        |    |

| 9.4 Layout                              |    |

| 10 Device and Documentation Support     |    |

| 10.1 Device Support                     |    |

| 10.2 Documentation Support              |    |

| 10.3 接收文档更新通知                           |    |

| 10.4 支持资源                               | 57 |

| 10.5 Trademarks                         |    |

| 10.6 静电放电警告                             |    |

| 10.7 术语表                                |    |

| 11 Mechanical, Packaging, and Orderable |    |

| Information                             |    |

|                                         |    |

## **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| С | Changes from Revision * (June 2021) to Revision A (February 2023) |   |  |

|---|-------------------------------------------------------------------|---|--|

| • | 将文档状态从"预告信息"更改为"量产数据"                                             | 1 |  |

# 5 说明(续)

LM25148-Q1 的其他特性包括 150°C 最大工作结温、可在轻负载条件下降低电流消耗的用户可选二极管仿真功 能、用于故障报告和输出监控的开漏电源正常标志、精密使能输入、单调启动至预偏置负载、集成 VCC 偏置电源 稳压器、3ms 内部软启动时间和带自动恢复功能的热关断保护。

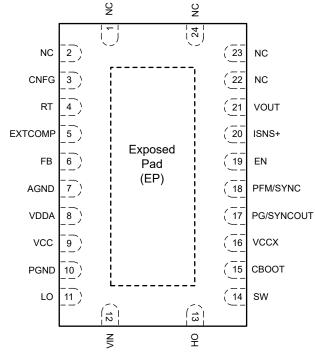

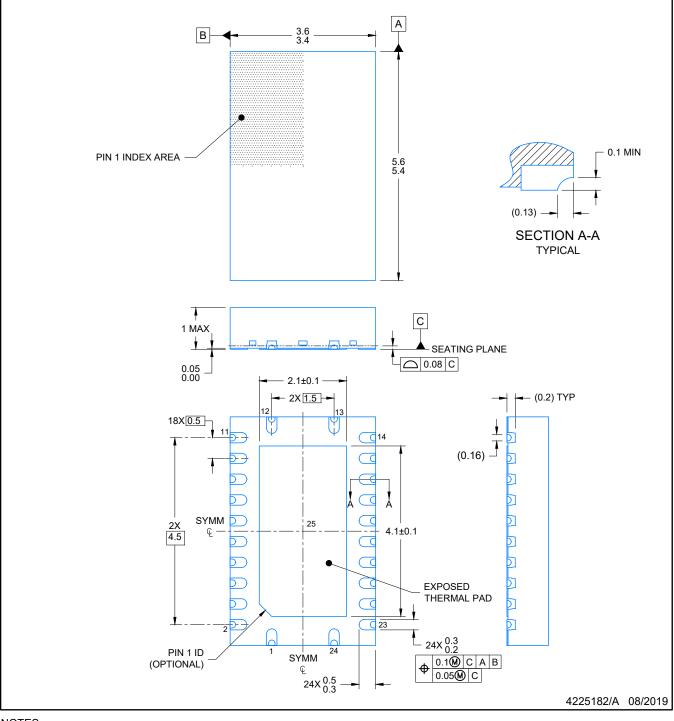

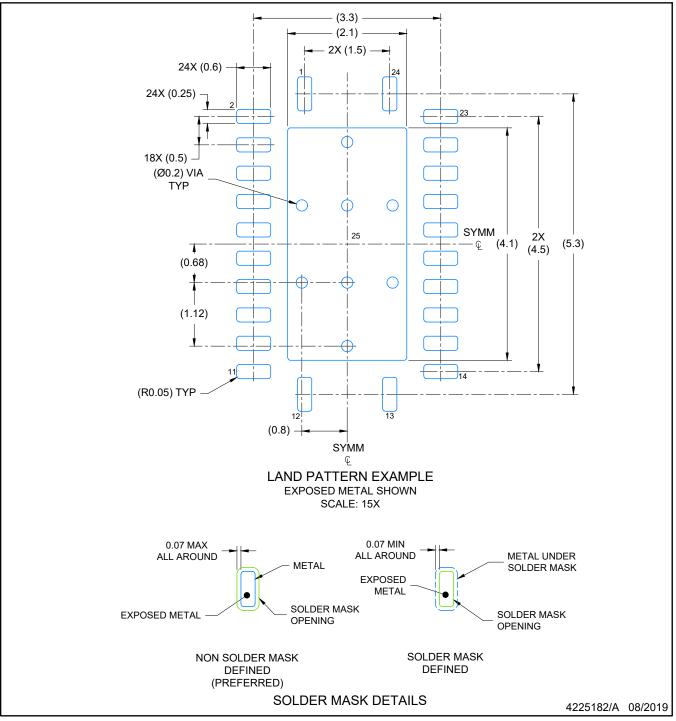

LM25148-Q1 控制器采用 3.5mm × 5.5mm 热增强型 24 引脚 VQFN 封装,该封装具有可湿性侧面引脚,便于在 制造期间进行光学检测。

# **6** Pin Configuration and Functions

Connect the exposed pad to AGND and PGND on the PCB.

## 图 6-1. 24-Pin VQFN RGY Package with Wettable Flanks (Top View)

#### 表 6-1. Pin Functions

| PIN                                                                                                                        |                                                                                                                                                                                                                                                                                                             | I/O <sup>(1)</sup>                                                                                               | DESCRIPTION                                                                                                                                                                                            |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. NAME                                                                                                                   |                                                                                                                                                                                                                                                                                                             |                                                                                                                  | DESCRIPTION                                                                                                                                                                                            |  |  |  |

| 1                                                                                                                          | NC                                                                                                                                                                                                                                                                                                          | _                                                                                                                | Connect to GND at the exposed pad to improve heat spreading.                                                                                                                                           |  |  |  |

| 2                                                                                                                          | NC                                                                                                                                                                                                                                                                                                          | -                                                                                                                | Connect to GND at the exposed pad to improve heat spreading.                                                                                                                                           |  |  |  |

| 3                                                                                                                          | CNFG                                                                                                                                                                                                                                                                                                        | Connect a resistor to ground to set primary/secondary, spread spectrum enable/disable, or interleaved operation. |                                                                                                                                                                                                        |  |  |  |

| 4 RT I Frequency programming pin. A resistor from RT to AGND sets the oscillator frequency between 10 and 2.2 MHz.         |                                                                                                                                                                                                                                                                                                             |                                                                                                                  |                                                                                                                                                                                                        |  |  |  |

| 5 EXTCOMP O Transconductance error amplifier output. If used, connect the compensation network from EXTCOMP AGND.          |                                                                                                                                                                                                                                                                                                             |                                                                                                                  |                                                                                                                                                                                                        |  |  |  |

| 6                                                                                                                          | 6FBIConnect FB to VDDA to set the output voltage to 3.3 V. Connect FB using a 24.9 kΩ or 49.9 kΩ to V<br>to set the output voltage to 5 V or 12 V, respectively. Install a resistor divider from VOUT to AGND to<br>the output voltage setpoint between 0.8 V and 36 V. The FB regulation voltage is 0.8 V. |                                                                                                                  |                                                                                                                                                                                                        |  |  |  |

| 7                                                                                                                          | 7 AGND G Analog ground connection. Ground return for the internal voltage reference and analog circuits                                                                                                                                                                                                     |                                                                                                                  | Analog ground connection. Ground return for the internal voltage reference and analog circuits                                                                                                         |  |  |  |

| 8         VDDA         O         Internal analog bias regulator. Connect a ceramic decoupling capacitor from VDDA to AGND. |                                                                                                                                                                                                                                                                                                             | Internal analog bias regulator. Connect a ceramic decoupling capacitor from VDDA to AGND.                        |                                                                                                                                                                                                        |  |  |  |

| 9                                                                                                                          | VCC                                                                                                                                                                                                                                                                                                         | Р                                                                                                                | VCC bias supply pin. Connect a ceramic capacitor between VCC and PGND.                                                                                                                                 |  |  |  |

| 10                                                                                                                         | PGND                                                                                                                                                                                                                                                                                                        | G                                                                                                                | Power ground connection pin for low-side MOSFET gate driver                                                                                                                                            |  |  |  |

| 11                                                                                                                         | LO                                                                                                                                                                                                                                                                                                          | 0                                                                                                                | Low-side power MOSFET gate driver output                                                                                                                                                               |  |  |  |

| 12                                                                                                                         | VIN                                                                                                                                                                                                                                                                                                         | Р                                                                                                                | Supply voltage input source for the VCC regulator                                                                                                                                                      |  |  |  |

| 13                                                                                                                         | НО                                                                                                                                                                                                                                                                                                          | 0                                                                                                                | High-side power MOSFET gate driver output                                                                                                                                                              |  |  |  |

| 1//     SW/     P     Switching node of the buck regulator and high-side gate                                              |                                                                                                                                                                                                                                                                                                             | Р                                                                                                                | Switching node of the buck regulator and high-side gate driver return. Connect to the bootstrap capacitor, the source terminal of the high-side MOSFET, and the drain terminal of the low-side MOSFET. |  |  |  |

| 15                                                                                                                         | CBOOT                                                                                                                                                                                                                                                                                                       | Р                                                                                                                | High-side driver supply for bootstrap gate drive                                                                                                                                                       |  |  |  |

| 16                                                                                                                         | VCCX                                                                                                                                                                                                                                                                                                        | Р                                                                                                                | Optional input for an external bias supply. If $V_{VCCX} > 4.3$ V, VCCX is internally connected to VCC and the internal VCC regulator is disabled.                                                     |  |  |  |

Copyright © 2023 Texas Instruments Incorporated

| PIN<br>NO. NAME                                                      |            | I/O <sup>(1)</sup>                                                                                                                                                                                                       | DESCRIPTION                                                                                                                                                                                                                                                                                     |  |

|----------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                      |            |                                                                                                                                                                                                                          | DESCRIPTION                                                                                                                                                                                                                                                                                     |  |

| 17                                                                   | PG/SYNCOUT | 0                                                                                                                                                                                                                        | An open-collector output that goes low if VOUT is outside the specified regulation window. The PG/<br>SYNCOUT pin of the primary controller in dual-phase mode provides a 180° phase-shifted SYNCOUT signal.                                                                                    |  |

| 18                                                                   | PFM/SYNC   | I                                                                                                                                                                                                                        | Connect PFM/SYNC to VDDA to enable diode emulation mode. Connect PFM to AGND to operate the LM25148-Q1 in forced PWM (FPWM) mode with continuous conduction at light loads. PFM can also be used as a synchronization input to synchronize the internal oscillator to an external clock signal. |  |

|                                                                      |            | An active-high precision input with rising threshold of 1 V and hysteresis current of 10 $\mu$ A. If the EN voltage is less than 0.5 V, the LM25148-Q1 is in shutdown mode, unless a SYNC signal is present on PFM/SYNC. |                                                                                                                                                                                                                                                                                                 |  |

| 20                                                                   | ISNS+      | I                                                                                                                                                                                                                        | Current sense amplifier input. Connect this pin to the inductor side of the external current sense resistor (or to the relevant sense capacitor terminal if inductor DCR current sensing is used) using a low-current Kelvin connection.                                                        |  |

| 21 VOUT                                                              |            | I                                                                                                                                                                                                                        | Output voltage sense and the current sense amplifier input. Connect VOUT to the output side of the current sense resistor (or to the relevant sense capacitor terminal if inductor DCR current sensing is used).                                                                                |  |

| 22 NC — Connect to GND at the exposed pad to improve heat spreading. |            | Connect to GND at the exposed pad to improve heat spreading.                                                                                                                                                             |                                                                                                                                                                                                                                                                                                 |  |

| 23                                                                   | NC         | _                                                                                                                                                                                                                        | Connect to GND at the exposed pad to improve heat spreading.                                                                                                                                                                                                                                    |  |

| 24                                                                   | NC         | _                                                                                                                                                                                                                        | Connect to GND at the exposed pad to improve heat spreading.                                                                                                                                                                                                                                    |  |

表 6-1. Pin Functions (continued)

(1) P = Power, G = Ground, I = Input, O = Output

## 6.1 Wettable Flanks

100% automated visual inspection (AVI) post-assembly is typically required to meet reliability and robustness standards. Standard quad-flat no-lead (QFN) packages do not have solderable or exposed pins and terminals that are easily viewed. It is therefore difficult to visually determine whether or not the package is successfully soldered onto the printed-circuit board (PCB). The wettable-flank process was developed to resolve the issue of side-lead wetting of leadless packaging. The LM25148-Q1 is assembled using a 24-pin VQFN package with wettable flanks to provide a visual indicator of solderability, which reduces the inspection time and manufacturing costs1.

# **7** Specifications

### 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise noted). ((1))

|                    |                                                        | MIN  | MAX                    | UNIT |

|--------------------|--------------------------------------------------------|------|------------------------|------|

|                    | VOUT, ISNS+ to AGND                                    | -0.3 | 36                     | V    |

| Output voltage     | VOUT to ISNS+                                          | -0.3 | 0.3                    | V    |

|                    | VIN to PGND                                            | -0.3 | 47                     | V    |

| -                  | SW to PGND                                             | -0.3 | 47                     | V    |

|                    | SW to PGND, transient < 20 ns                          | -5   |                        | V    |

|                    | CBOOT to SW                                            | -0.3 | 6.5                    | V    |

|                    | CBOOT to SW, transient < 20 ns                         | -2   |                        | V    |

| Input voltage      | HO to SW                                               | -0.3 | V <sub>HB</sub> + 0.3  | V    |

| Input voltage      | HO to SW, transient < 20ns                             | -5   |                        | V    |

|                    | LO to PGND                                             | -0.3 | V <sub>VCC</sub> + 0.3 | V    |

|                    | LO to PGND, transient < 20 ns                          | -1.5 |                        | V    |

|                    | EN to PGND                                             | -0.3 | 47                     | V    |

|                    | VCC, VCCX, VDDA, PG, FB, PFM/SYNC, RT, EXTCOMP to AGND | -0.3 | 6.5                    | V    |

|                    | CNFG to AGND                                           | -0.3 | 5.5                    | V    |

| Operating junction | n temperature, T <sub>J</sub>                          | -40  | 150                    | °C   |

| Storage temperat   | ure, T <sub>stg</sub>                                  | -55  | 150                    | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 7.2 ESD Ratings

|                    |                         |                                                                                  |                                | VALUE                                                                                                           | UNIT |

|--------------------|-------------------------|----------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------|------|

|                    |                         | Human body model (HBM), per AEC Q100-002 <sup>((1))</sup> H                      | IBM ESD classification level 2 | ±2000                                                                                                           |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per AEC Q100-011<br>CDM ESD_classification level C4A |                                | 00-002 <sup>((1))</sup> HBM ESD classification level 2 ±2000<br>Corner pins (1, 2, 11, 12, 13, 14, 23, and ±750 |      |

|                    |                         |                                                                                  | Other pins                     | ±500                                                                                                            |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

Over the operating junction temperature range of -40°C to 150°C (unless otherwise noted). ((1))

|                  |                                | MIN  | NOM | MAX  | UNIT |

|------------------|--------------------------------|------|-----|------|------|

| V <sub>IN</sub>  | Input supply voltage range     | 3.5  |     | 42   | V    |

| V <sub>OUT</sub> | Output voltage range           | 0.8  |     | 36   | V    |

|                  | SW to PGND                     | -0.3 |     | 42   | V    |

|                  | CBOOT to SW                    | -0.3 | 5   | 5.25 | V    |

|                  | FB, EXTCOMP, RT, CNFG to AGND  | -0.3 |     | 5.25 | V    |

|                  | EN to PGND                     | -0.3 |     | 42   | V    |

|                  | VCC, VCCX, VDDA, to PGND       | -0.3 | 5   | 5.25 | V    |

|                  | VOUT, ISNS+ to PGND            | -0.3 |     | 36   | V    |

|                  | PGND to AGND                   | -0.3 |     | 0.3  | V    |

|                  | CNFG to AGND                   | -0.3 |     | 5.5  | V    |

| TJ               | Operating junction temperature | -40  |     | 150  | °C   |

(1) Recommended operating conditions are conditions under which the device is intended to be functional. For specifications and test conditions, see the *Electrical Characteristics*.

## 7.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | RGY (VQFN)<br>24 PINS | UNIT |

|-----------------------|----------------------------------------------|-----------------------|------|

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 37.3                  | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 32                    | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 15.5                  | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 1.2                   | °C/W |

| Ψ <sub>ЈВ</sub>       | Junction-to-board characterization parameter | 15.5                  | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 5.6                   | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics

# 7.5 Electrical Characteristics

$T_J$  = -40°C to 125°C. Typical values are at  $T_J$  = 25°C and  $V_{IN}$  = 12 V (unless otherwise noted).

|                            | PARAMETER                                | TEST CONDITIONS                                                                                                                                                               | MIN   | TYP | MAX  | UNIT |

|----------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

| SUPPLY (VIN)               |                                          |                                                                                                                                                                               |       |     | •    |      |

| I <sub>Q-VIN1</sub>        | VIN shutdown current                     | V <sub>EN</sub> = 0 V                                                                                                                                                         |       | 2.3 | 3.8  | μA   |

| I <sub>Q-VIN2</sub>        | VIN standby current                      | Non-switching, $0.5 \text{ V} \le \text{V}_{EN} \le 1 \text{ V}$                                                                                                              |       | 124 |      | μA   |

| I <sub>SLEEP1</sub>        | Sleep current, 3.3 V                     | 1.03 V $\leq$ V <sub>EN</sub> $\leq$ 42 V, V <sub>VOUT</sub> $=$ 3.3 V, in regulation, no-load, not switching, V <sub>PFM/SYNC</sub> $=$ VDDA                                 |       | 9.5 | 19.7 | μA   |

| I <sub>SLEEP2</sub>        | Sleep current, 5 V                       | $\begin{array}{l} 1.03 \; V \leq V_{EN} \leq \; 42 \; V, \; V_{VOUT} = 5.0 \\ V, \; in \; regulation, \; no-load, \; not \; switching, \\ V_{PFM}/_{SYNC} = VDDA \end{array}$ |       | 9.9 | 19.9 | μA   |

| ENABLE (EN)                |                                          |                                                                                                                                                                               |       |     |      |      |

| V <sub>SDN</sub>           | Shutdown to standby threshold            | V <sub>EN</sub> rising                                                                                                                                                        |       | 0.5 |      | V    |

| V <sub>EN-HIGH</sub>       | Enable voltage rising threshold          | V <sub>EN</sub> rising, enable switching                                                                                                                                      | 0.95  | 1.0 | 1.05 | V    |

| I <sub>EN-HYS</sub>        | Enable hysteresis                        | V <sub>EN</sub> = 1.1 V                                                                                                                                                       | -12   | -10 | -8   | μA   |

| INTERNAL LDO               | (vcc)                                    |                                                                                                                                                                               |       |     | I    |      |

| V <sub>VCC-REG</sub>       | VCC regulation voltage                   | I <sub>VCC</sub> = 0 mA to 100 mA                                                                                                                                             | 4.7   | 5   | 5.3  | V    |

| V <sub>VCC-UVLO</sub>      | VCC UVLO rising threshold                |                                                                                                                                                                               | 3.3   | 3.4 | 3.5  | V    |

| V <sub>VCC-HYST</sub>      | VCC UVLO hysteresis                      |                                                                                                                                                                               |       | 148 |      | mV   |

| I <sub>VCC-REG</sub>       | Internal LDO short-circuit current limit |                                                                                                                                                                               | 115   | 170 |      | mA   |

| INTERNAL LDO               | (VDDA)                                   |                                                                                                                                                                               |       |     | I    |      |

| V <sub>VDDA-REG</sub>      | VDDA regulation voltage                  |                                                                                                                                                                               | 4.75  | 5   | 5.25 | V    |

| V <sub>VDDA-UVLO</sub>     | VDDA UVLO rising                         | V <sub>VCC</sub> rising, V <sub>VCCX</sub> = 0 V                                                                                                                              | 3     | 3.2 | 3.3  | V    |

| V <sub>VDDA-HYST</sub>     | VDDA UVLO hysteresis                     | V <sub>VCCX</sub> = 0 V                                                                                                                                                       |       | 120 |      | mV   |

| R <sub>VDDA</sub>          | VDDA resistance                          | V <sub>VCCX</sub> = 0 V                                                                                                                                                       |       | 5.5 |      | Ω    |

| EXTERNAL BIAS              | s (VCCX)                                 |                                                                                                                                                                               |       |     | I    |      |

| V <sub>VCCX-ON</sub>       | VCCX rising threshold                    |                                                                                                                                                                               | 4.1   | 4.3 | 4.4  | V    |

| V <sub>VCCX-HYST</sub>     | VCCX hysteresis voltage                  |                                                                                                                                                                               |       | 130 |      | mV   |

| R <sub>VCCX</sub>          | VCCX resistance                          |                                                                                                                                                                               |       | 2   |      | Ω    |

| REFERENCE VO               | LTAGE                                    |                                                                                                                                                                               |       |     | I    |      |

| V <sub>REF</sub>           | Regulated FB voltage                     |                                                                                                                                                                               | 795   | 800 | 808  | mV   |

| OUTPUT VOLTA               | GE (VOUT)                                |                                                                                                                                                                               |       |     | I    |      |

| V <sub>OUT-3.3V</sub> –INT | 3.3-V output voltage setpoint            | $R_{FB}$ = 0 $\Omega, V_{IN}$ = 3.8 V to 42 V, internal compensation                                                                                                          | 3.267 | 3.3 | 3.33 | V    |

| V <sub>OUT-3.3V-EXT</sub>  | 3.3-V output voltage setpoint            | $R_{FB}$ = 0 $\Omega$ , $V_{IN}$ = 3.8 V to 42 V, external compensation                                                                                                       | 3.267 | 3.3 | 3.33 | V    |

| V <sub>OUT-5V-INT</sub>    | 5-V output voltage setpoint              | $R_{FB}$ = 24.9 kΩ, $V_{IN}$ = 5.5 V to 42 V, internal compensation                                                                                                           | 4.95  | 5.0 | 5.05 | V    |

| V <sub>OUT-5V-EXT</sub>    | 5-V output voltage setpoint              | $R_{FB}$ = 24.9 kΩ, $V_{IN}$ = 5.5 V to 42 V, external compensation                                                                                                           | 4.95  | 5.0 | 5.05 | V    |

# 7.5 Electrical Characteristics (continued)

$T_J = -40^{\circ}C$  to 125°C. Typical values are at  $T_J = 25^{\circ}C$  and  $V_{IN} = 12$  V (unless otherwise noted).

|                          | PARAMETER                                              | TEST CONDITIONS                                                             | MIN   | TYP  | MAX   | UNIT  |

|--------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------|-------|------|-------|-------|

| V <sub>OUT-12V-INT</sub> | 12-V output setpoint                                   | $R_{FB}$ = 48.7 k $\Omega$ , $V_{IN}$ = 24 V to 42 V, internal compensation | 11.88 | 12   | 12.12 | V     |

| V <sub>OUT-12V-EXT</sub> | 12-V output setpoint                                   | $R_{FB}$ = 48.7 kΩ, $V_{IN}$ = 24 V to 42 V, external compensation          | 11.88 | 12   | 12.12 | V     |

| R <sub>FB-OPT1</sub>     | 5-V output select                                      |                                                                             | 23    | 25   | 27    | kΩ    |

| R <sub>FB-OPT2</sub>     | 12-V output select                                     |                                                                             | 47    | 50   | 53    | kΩ    |

| ERROR AMPLIFI            | ER (COMP)                                              |                                                                             |       |      |       |       |

| gm-external              | EA transconductance, external compensation             | FB to COMP                                                                  | 1020  | 1200 |       | μS    |

| g <sub>m-INTERNAL</sub>  | EA transconductance, internal compensation             | EXTCOMP 10 kΩ to VDDA                                                       |       | 30   |       | μS    |

| I <sub>FB</sub>          | Error amplifier input bias current                     |                                                                             |       |      | 75    | nA    |

| V <sub>COMP-CLAMP</sub>  | COMP clamp voltage                                     | V <sub>FB</sub> = 0 V                                                       |       | 2.1  |       | V     |

| I <sub>COMP-SRC</sub>    | EA source current                                      | V <sub>EXTCOMP</sub> = 1 V, V <sub>FB</sub> = 0.6 V                         |       | 180  |       | μA    |

| I <sub>COMP-SINK</sub>   | EA sink current                                        | V <sub>EXTCOMP</sub> = 1 V, V <sub>FB</sub> = 1 V                           |       | 180  |       | μA    |

| R <sub>COMP</sub>        | Internal compensation                                  | EXTCOMP 10 kΩ to VDDA                                                       |       | 400  |       | kΩ    |

| C <sub>COMP</sub>        | Internal compensation                                  | EXTCOMP 10 kΩ to VDDA                                                       |       | 50   |       | pF    |

| C <sub>COMP-HF</sub>     | Internal compensation                                  | EXTCOMP 10 kΩ to VDDA                                                       |       | 1    |       | pF    |

| PULSE FREQUE             | NCY MODULATION (PFM/SYNC)                              |                                                                             |       |      |       |       |

| V <sub>PFM-LO</sub>      | PFM detection threshold low                            |                                                                             | 0.8   |      |       | V     |

| V <sub>PFM-HI</sub>      | PFM decection threshold high                           |                                                                             |       |      | 2.0   | V     |

| V <sub>ZC-SW</sub>       | Zero-cross threshold                                   |                                                                             |       | -5.5 |       | mV    |

| V <sub>ZC-DIS</sub>      | Zero-cross threshold disable                           | PFM/SYNC = 0 V, 1000 SW cycles after first<br>HO pulse                      |       | 100  |       | mV    |

| F <sub>SYNCIN</sub>      | Frequency sync range                                   | $R_{RT}$ = 9.52 k $\Omega$ , ±20% of the nominal oscillator frequency       | 1.74  |      | 2.7   | MHz   |

| t <sub>SYNC-MIN</sub>    | Minimum pulse-width of external synchronization signal |                                                                             | 20    |      | 250   | ns    |

| tsyncin-ho               | Delay from PFM faling edge to HO rising edge           |                                                                             |       | 45   |       | ns    |

| t <sub>PFM-FILTER</sub>  | SYNCIN to PFM mode                                     |                                                                             | 13    |      | 45    | μs    |

| DUAL RANDOM              | SPREAD SPECTRUM (DRSS)                                 |                                                                             |       |      |       |       |

| Δf <sub>C</sub>          | Switching frequency percentage change                  |                                                                             |       | 7    |       | %     |

| f <sub>m</sub>           | Modulation frequency                                   |                                                                             | 8.2   |      | 16.2  | kHz   |

| SWITCHING FRE            | QUENCY                                                 |                                                                             |       |      |       |       |

| V <sub>RT</sub>          | RT pin regulation voltage                              | 10 kΩ < R <sub>RT</sub> < 100 kΩ                                            |       | 0.5  |       | V     |

| F <sub>SW1</sub>         | Switching frequency 1                                  | R <sub>RT</sub> = 97.6 kΩ to AGND                                           |       | 0.22 |       | MHz   |

| F <sub>SW2</sub>         | Switching frequency 2                                  | $V_{IN}$ = 12 V, $R_{RT}$ = 9.52 k $\Omega$ to AGND                         | 1.98  | 2.2  | 2.42  | MHz   |

| F <sub>SW3</sub>         | Switching frequency 3                                  | R <sub>RT</sub> = 220 kΩ to AGND                                            |       | 100  |       | kHz   |

| SLOPE1                   | Internal slope compensation 1                          | R <sub>RT</sub> = 9.52 kΩ                                                   |       | 600  |       | mV/µs |

| SLOPE <sub>2</sub>       | Internal slope compensation 2                          | R <sub>RT</sub> = 97.6 kΩ                                                   |       | 50   |       | mV/µs |

| t <sub>ON(min)</sub>     | Minimum on-time                                        |                                                                             |       | 50   |       | ns    |

| t <sub>OFF(min)</sub>    | Minimum off-time                                       |                                                                             |       | 90   |       | ns    |

| POWER GOOD (F            | PG)                                                    | , I                                                                         |       |      | I     |       |

| V <sub>PG-UV</sub>       | Power Good UV trip level                               | Falling with respect to the regulated voltage                               | 90%   | 92%  | 94%   |       |

| V <sub>PG-OV</sub>       | Power Good OV trip level                               | Rising with respect to the regulation voltage                               | 108%  | 110% | 112%  |       |

| V <sub>PG-UV-HYST</sub>  | Power Good UV hysteresis                               | Rising with respect to the regulated output                                 |       | 3.6% |       |       |

| V <sub>PG-OV-HYST</sub>  | Power Good OV hysteresis                               | Rising with respect to the regulation voltage                               |       | 3.4% |       |       |

| t <sub>OV-DLY</sub>      | OV filter time                                         | V <sub>OUT</sub> rising                                                     |       | 25   |       | μs    |

| t <sub>UV-DLY</sub>      | UV filter time                                         | V <sub>OUT</sub> falling                                                    |       | 25   |       | μs    |

| V <sub>PG-OL</sub>       | PG voltage                                             | Open collector, PG/SYNC = 2 mA                                              |       |      | 0.8   | V     |

# 7.5 Electrical Characteristics (continued)

$T_J = -40^{\circ}C$  to 125°C. Typical values are at  $T_J = 25^{\circ}C$  and  $V_{IN} = 12$  V (unless otherwise noted).

|                             | PARAMETER                                                         | TEST CONDITIONS                                                      | MIN  | TYP   | MAX  | UNIT   |

|-----------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------|------|-------|------|--------|

| SYNCHRONIZATIO              | ON OUTPUT (PG/SYNCOUT)                                            |                                                                      |      |       |      |        |

| V <sub>SYNCOUT-LO</sub>     | SYNCOUT-LO low-state voltage                                      | $R_{CNFG}$ = 54.9 kΩ or 71.5 kΩ to GND<br>(primary), PFM/SYNC = 2 mA |      |       | 0.8  | V      |

| V <sub>SYNCOUT-HO</sub>     | SYNCO-HO high-state voltage                                       | $R_{CNFG}$ = 54.9 kΩ, or 71.5 kΩ to GND<br>(primary) PFM/SYNC = 2 mA | 2.0  |       |      | V      |

| t <sub>SYNCOUT</sub>        | Delay from HO rising edge to SYNCOUT (PG/SYNCOUT in primary mode) | $V_{PFM}$ = 0 V, $F_{SW}$ set by $R_{RT}$ = 97.6 k $\Omega$          |      | 2.1   |      | μs     |

| STARTUP (Soft Sta           | art)                                                              |                                                                      |      |       |      |        |

| t <sub>SS-INT</sub>         | Internal fixed soft-start time                                    |                                                                      | 1.9  | 3     | 4.6  | ms     |

| BOOT CIRCUIT                | ·                                                                 |                                                                      |      |       |      |        |

| V <sub>BOOT-DROP</sub>      | Internal diode forward drop                                       | I <sub>CBOOT</sub> = 20 mA, VCC to CBOOT                             | 0.63 | 0.8   |      | V      |

| I <sub>BOOT</sub>           | CBOOT to SW quiescent current, not switching                      | V <sub>EN</sub> = 5 V, V <sub>CBOOT-SW</sub> = 5 V                   | 2.88 |       | 4.3  | μA     |

| V <sub>BOOT-SW-UV-R</sub>   | CBOOT to SW UVLO rising threshold                                 | V <sub>CBOOT-SW</sub> rising                                         |      | 2.83  |      | V      |

| V <sub>BOOT-SW-UV-F</sub>   | CBOOT to SW UVLO falling threshold                                | V <sub>CBOOT-SW</sub> falling                                        |      | 2.5   |      | V      |

| V <sub>BOOT-SW-UV-HYS</sub> | CBOOT to SW UVLO hysteresis                                       |                                                                      |      | 0.05  |      | V      |

| HIGH-SIDE GATE I            | DRIVER (HO)                                                       |                                                                      |      |       | 1    |        |

| V <sub>HO-HIGH</sub>        | HO high-state output voltage                                      | $I_{HO}$ = -100 mA, $V_{HO-HIGH}$ = $V_{CBOOT} - V_{HO}$             |      | 106   |      | mV     |

| V <sub>HO-LOW</sub>         | HO low-state output voltage                                       | I <sub>HO</sub> = 100 mA                                             |      | 50    |      | mV     |

| t <sub>HO-RISE</sub>        | HO rise time (10% to 90%)                                         | C <sub>LOAD</sub> = 2.7 nF                                           |      | 7     |      | ns     |

| t <sub>HO-FALL</sub>        | HO fall time (90% to 10%)                                         | C <sub>LOAD</sub> = 2.7 nF                                           |      | 7     |      | ns     |

| I <sub>HO-SRC</sub>         | HO peak source current                                            | $V_{HO} = V_{SW} = 0 V, V_{CBOOT} = V_{VCC} = 5 V$                   |      | 2.2   |      | А      |

| I <sub>HO-SINK</sub>        | HO peak sink current                                              | V <sub>VCC</sub> = 5 V                                               |      | 3.2   |      | А      |

| LOW-SIDE GATE               | DRIVER (LO)                                                       |                                                                      |      |       | ·    |        |

| V <sub>LO-LOW</sub>         | LO low-state output voltage                                       | I <sub>LO</sub> = 100 mA                                             |      | 50    |      | mV     |

| V <sub>LO-HIGH</sub>        | LO high-state output voltage                                      | I <sub>LO</sub> = -100 mA                                            |      | 130   |      | mV     |

| t <sub>LO-RISE</sub>        | LO rise time (10% to 90%)                                         | C <sub>LOAD</sub> = 2.7 nF                                           |      | 7     |      | ns     |

| t <sub>LO-FALL</sub>        | LO fall time (90% to 10%)                                         | C <sub>LOAD</sub> = 2.7 nF                                           |      | 7     |      | ns     |

| I <sub>LO-SRC</sub>         | LO peak source current                                            | V <sub>LO</sub> = V <sub>SW</sub> = 0 V, V <sub>VCC</sub> = 5 V      |      | 2.2   |      | А      |

| I <sub>LO-SINK</sub>        | LO peak sink current                                              | V <sub>VCC</sub> = 5 V                                               |      | 3.2   |      | А      |

| ADAPTIVE DEADT              | IME CONTROL                                                       |                                                                      |      |       |      |        |

| t <sub>DEAD1</sub>          | HO off to LO on deadtime                                          |                                                                      |      | 20    |      | ns     |

| t <sub>DEAD2</sub>          | LO off to HO on deadtime                                          |                                                                      |      | 20    |      | ns     |

| INTERNAL HICCU              | P MODE                                                            |                                                                      |      |       | 1    |        |

| HIC <sub>DLY</sub>          | Hiccup mode activation delay                                      | V <sub>ISNS+</sub> -V <sub>VOUT</sub> > 60 mV                        |      | 512   |      | cycles |

| HIC <sub>CYCLES</sub>       | HICCUP mode fault                                                 | V <sub>ISNS+</sub> -V <sub>VOUT</sub> > 60 mV                        |      | 16384 |      | cycles |

| OVERCURRENT P               | ROTECTION                                                         |                                                                      |      |       |      |        |

| V <sub>CS-TH</sub>          | Current limit threshold                                           | Measured from ISNS+ to VOUT                                          | 49   | 60    | 73   | mV     |

| t <sub>DELAY-ISNS+</sub>    | ISNS+ delay to output                                             |                                                                      |      | 65    |      | ns     |

| G <sub>CS</sub>             | CS amplifier gain                                                 |                                                                      | 9    | 10    | 10.8 | V/V    |

| IBIAS-ISNS+                 | CS amplifier input bias current                                   |                                                                      |      | 15    |      | nA     |

| CONFIGURATION               |                                                                   |                                                                      |      |       |      |        |

| R <sub>CONF-OPT1</sub>      | Primary, no spread spectrum                                       |                                                                      | 28.7 | 29.4  | 31   | kΩ     |

| R <sub>CONF-OPT2</sub>      | Primary, with spread spectrum                                     |                                                                      | 40.2 | 41.2  | 43.2 | kΩ     |

| R <sub>CONF-OPT3</sub>      | Primary, interleaved, no spread spectrum                          |                                                                      | 53.6 | 54.9  | 57.6 | kΩ     |

| R <sub>CONF-OPT4</sub>      | Primary, interleaved, with spread spectrum                        |                                                                      | 69.8 | 71.5  | 73.2 | kΩ     |

| R <sub>CONF-OPT5</sub>      | Secondary                                                         |                                                                      | 87   | 90.9  | 93.1 | kΩ     |

| THERMAL SHUTD               | OWN                                                               |                                                                      |      |       |      |        |

| T <sub>J-SD</sub>           | Thermal shutdown threshold <sup>(1)</sup>                         | Temperature rising                                                   |      | 175   |      | °C     |

# 7.5 Electrical Characteristics (continued)

$T_J$  = -40°C to 125°C. Typical values are at  $T_J$  = 25°C and  $V_{IN}$  = 12 V (unless otherwise noted).

|                    | PARAMETER                                  | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|--------------------------------------------|-----------------|-----|-----|-----|------|

| T <sub>J-HYS</sub> | Thermal shutdown hysteresis <sup>(1)</sup> |                 |     | 15  |     | °C   |

(1) Specified by design. Not production tested.

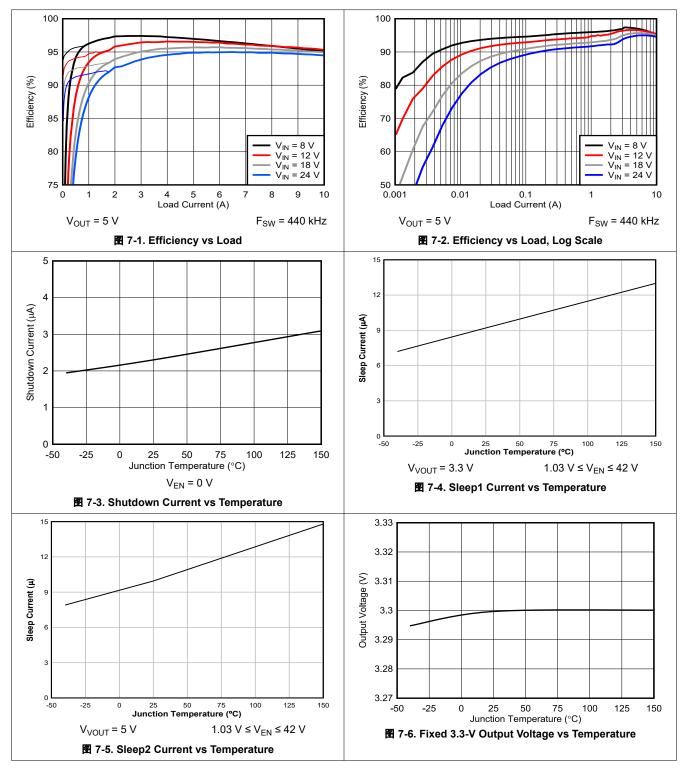

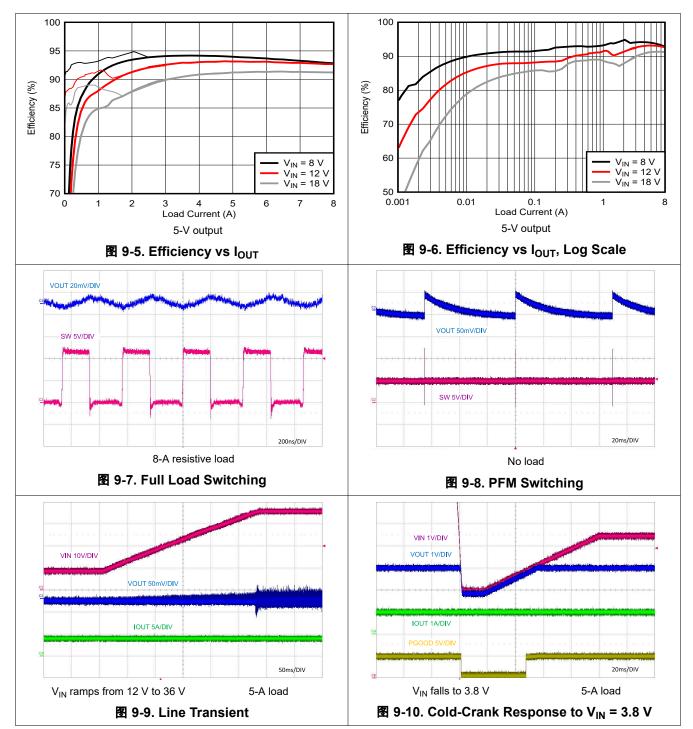

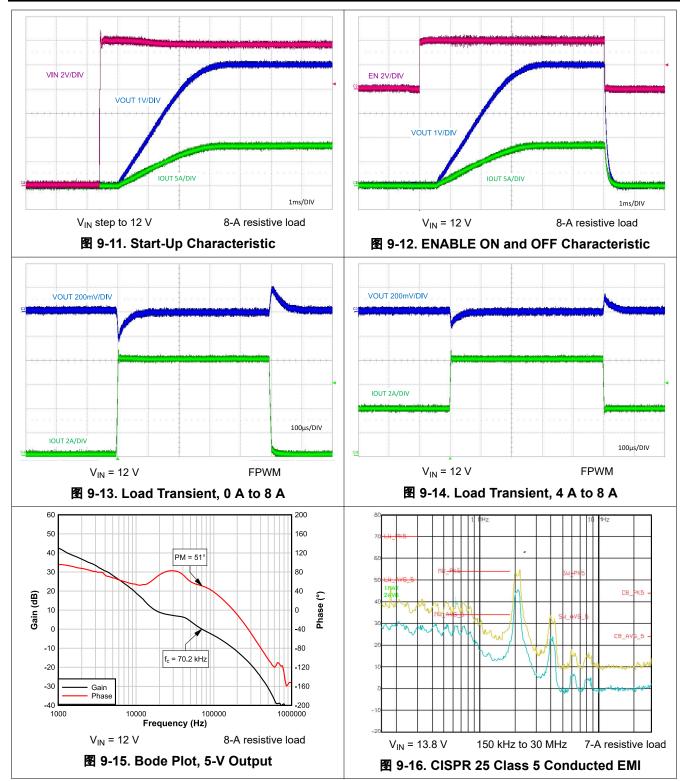

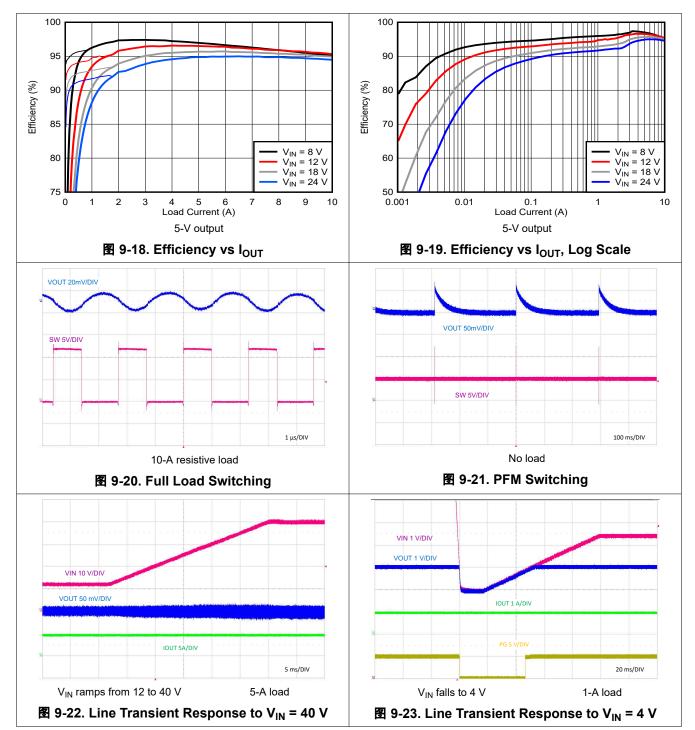

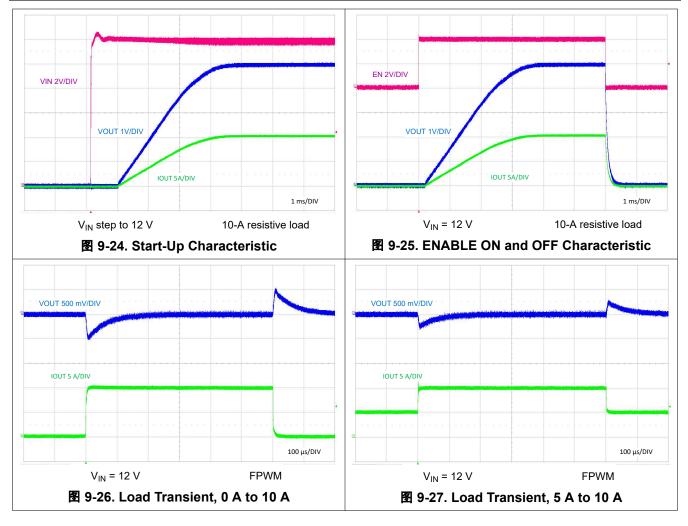

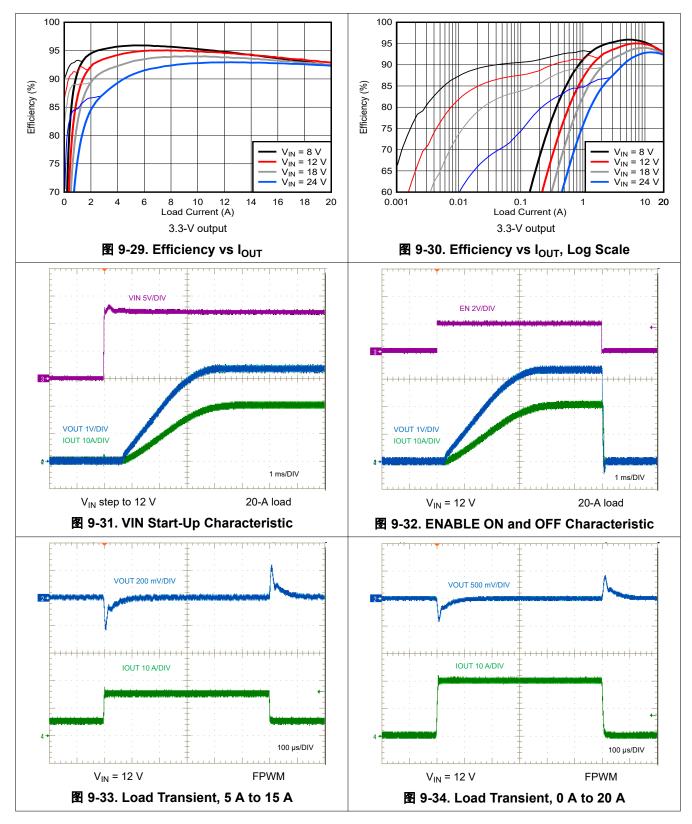

# 7.6 Typical Characteristics

$V_{IN}$  = 12 V, unless otherwise specified

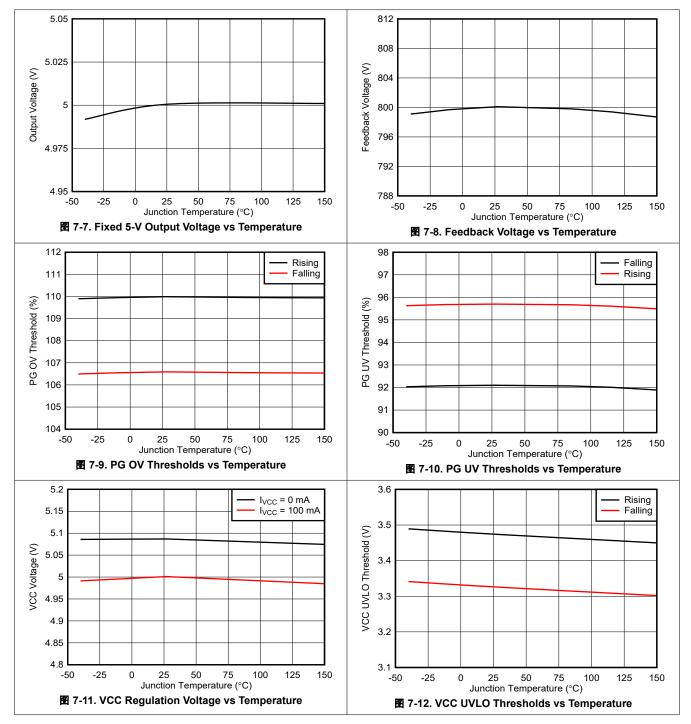

# 7.6 Typical Characteristics (continued)

V<sub>IN</sub> = 12 V, unless otherwise specified

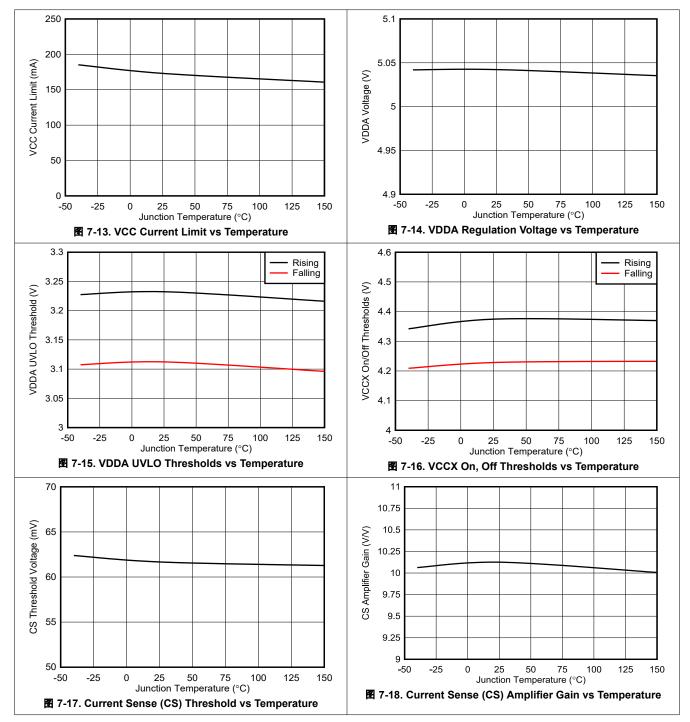

# 7.6 Typical Characteristics (continued)

V<sub>IN</sub> = 12 V, unless otherwise specified

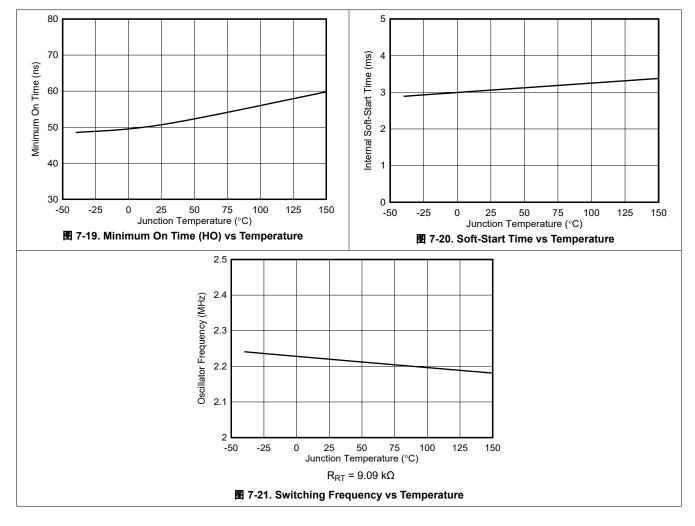

# 7.6 Typical Characteristics (continued)

V<sub>IN</sub> = 12 V, unless otherwise specified

# 8 Detailed Description

## 8.1 Overview

The LM25148-Q1 is a switching DC/DC controller that features all of the functions necessary to implement a high-efficiency synchronous buck power supply operating over a wide input voltage range from 3.5 V to 42 V. The LM25148-Q1 is configured to provide a fixed 3.3-V, 5-V, or 12-V output, or an adjustable output from 0.8 V to 36 V. This easy-to-use controller integrates high-side and low-side MOSFET gate drivers capable of sourcing and sinking peak currents of 2.2 A and 3.2 A, respectively. Adaptive dead-time control is designed to minimize body diode conduction during switching transitions.

Current-mode control using a shunt resistor or inductor DCR current sensing provides inherent line feedforward, cycle-by-cycle peak current limiting, and easy loop compensation. Current-mode control using a shunt resistor or inductor DCR current sensing also supports a wide duty cycle range for high input voltage and low-dropout applications as well as when application require a high step-down conversion ratio (for example, 10-to-1). The oscillator frequency is user-programmable between 100 kHz to 2.2 MHz, and the frequency can be synchronized as high as 2.5 MHz by applying an external clock to the PFM/SYNC pin.

An external bias supply can be connected to VCCX to maximize efficiency in high input voltage applications. A user-selectable diode emulation feature enables discontinuous conduction mode (DCM) operation to further improve efficiency and reduce power dissipation during light-load conditions. Fault protection features include current limiting, thermal shutdown, UVLO, and remote shutdown capability.

The LM25148-Q1 incorporates features to simplify the compliance with various EMI standards, for example CISPR 25 Class 5 automotive EMI requirements. DRSS techniques reduce the peak harmonic EMI signature.

The LM25148-Q1 is provided in a 24-pin VQFN package with a wettable flank pinout and an exposed pad to aid in thermal dissipation.

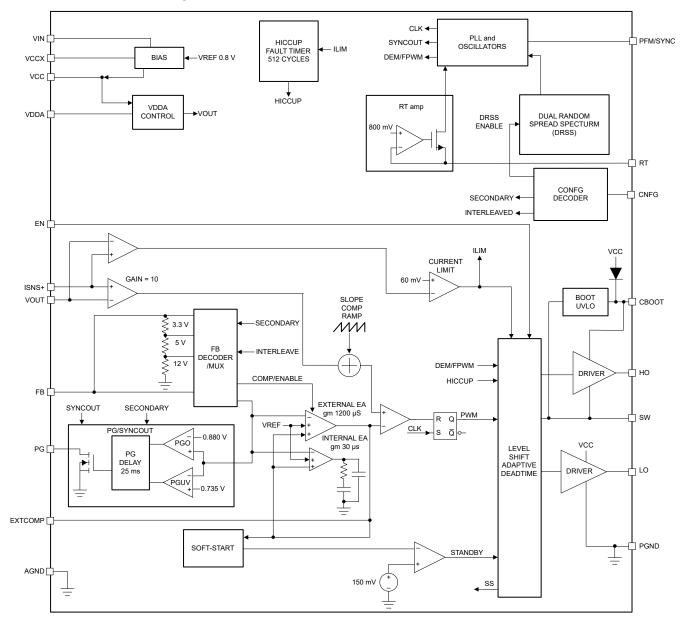

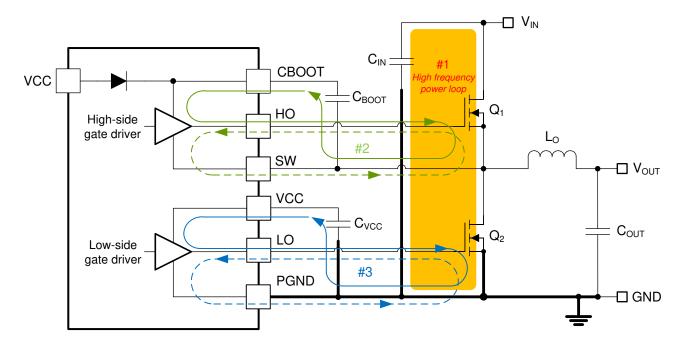

## 8.2 Functional Block Diagram

## 8.3 Feature Description

## 8.3.1 Input Voltage Range (VIN)

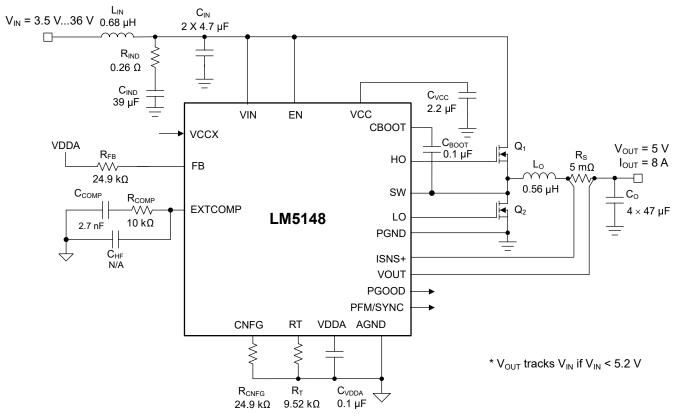

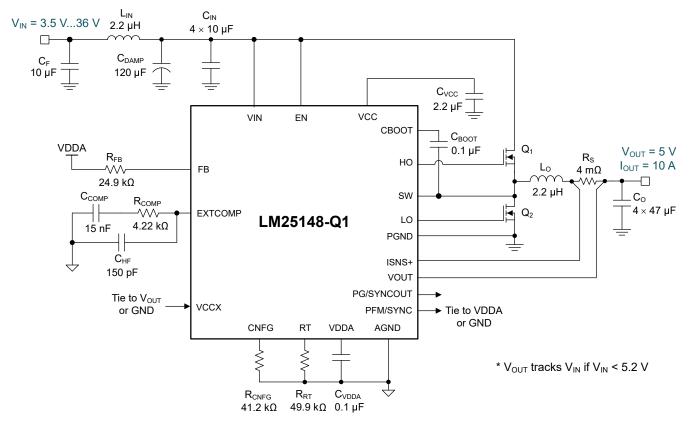

The LM25148-Q1 operational input voltage range is from 3.5 V to 42 V. The device is intended for step-down conversions from 12-V, 24-V, and 48-V supply rails. The application circuit in  $\mathbb{R}$  9-4 shows all the necessary components to implement an LM25148-Q1 based wide-V<sub>IN</sub> single-output step-down regulator using a single supply. The LM25148-Q1 uses an internal LDO to provide a 5-V VCC bias rail for the gate drive and control circuits (assuming the input voltage is higher than 5 V with additional voltage margin necessary for the subregulator dropout specification).

In high input voltage applications, take extra care to ensure that the VIN and SW pins do not exceed their absolute maximum voltage rating of 47 V during line or load transient events. Voltage excursions that exceed the applicable voltage specifications can damage the device.

Care must be taken in applications where there are fast input transients that cause the voltage at VIN to suddenly drop more than 2 V below the VOUT setpoint. The LM25148-Q1 has an internal ESD diode from the VOUT to the VIN pins that can conduct under such conditions causing the output to discharge. To prevent damage to the internal ESD diode under the said conditions, TI recommends adding a Schottky diode in series with the VIN pin of the LM25148-Q1 to prevent reverse current flow from VOUT to VIN.

As  $V_{IN}$  approaches  $V_{OUT}$ , the LM25148-Q1 skips  $t_{OFF}$  cycles to allow the controller to extend its duty cycle up to approximately 99%. Refer to Dropout Mode.

Use 方程式 1 to calculate when the LM25148-Q1 enters dropout mode.

$$V_{\rm IN} = V_{\rm OUT} \times \left(\frac{t_{\rm P}}{t_{\rm P} - t_{\rm OFF}}\right) \tag{1}$$

- t<sub>P</sub> is the oscillator period

- t<sub>OFF</sub> is the minimum off time, typical 90 ns

图 8-1. Dropout Mode Operation

## 8.3.2 High-Voltage Bias Supply Regulator (VCC, VCCX, VDDA)

The LM25148-Q1 contains an internal high-voltage VCC bias regulator that provides the bias supply for the PWM controller and the gate drivers for the external MOSFETs. The input voltage pin (VIN) can be connected directly to an input voltage source up to 42 V. However, when the input voltage is below the VCC setpoint level, the VCC voltage tracks  $V_{IN}$  minus a small voltage drop.

The VCC regulator output current limit is 115 mA (minimum). At power up, the controller sources current into the capacitor connected at the VCC pin. When the VCC voltage exceeds 3.3 V and the EN pin is connected to a voltage greater than 1 V, the soft-start sequence begins. The output remains active unless the VCC voltage falls

below the VCC UVLO falling threshold of 3.1 V (typical) or EN is switched to a low state. Connect a ceramic capacitor from VCC to PGND. The recommended range of the VCC capacitor is from 2.2  $\mu$ F to 10  $\mu$ F.

An internal 5-V linear regulator generates the VDDA bias supply. Bypass VDDA with a 100-nF or higher ceramic capacitor to achieve a low-noise internal bias rail. Normally, VDDA is 5 V. However, there is one condition where VDDA regulates at 3.3 V. This is in PFM mode with a light or no-load on the output.

Minimize the internal power dissipation of the VCC regulator by connecting VCCX to a 5-V output or to an external 5-V supply. If the VCCX voltage is above 4.3 V, VCCX is internally connected to VCC and the internal VCC regulator is disabled. Tie VCCX to PGND if it is unused. Never connect VCCX to a voltage greater than 6.5 V. If an external supply is connected to VCCX to power the LM25148-Q1, V<sub>IN</sub> must be greater than the external bias voltage during all conditions to avoid damage to the controller.

### 8.3.3 Precision Enable (EN)

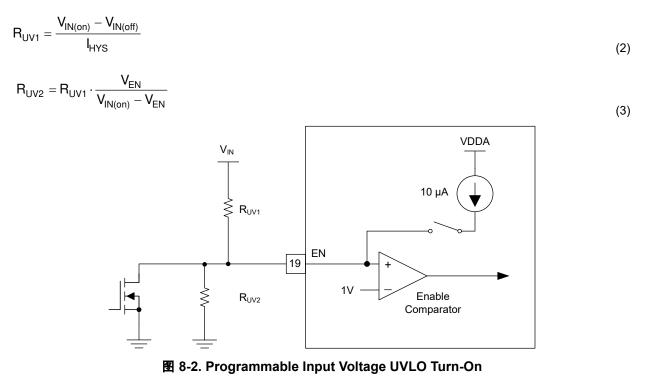

The EN pin can be connected to a voltage as high as 42 V. The LM25148-Q1 has a precision enable. When the EN voltage is greater than 1 V, controller switching is enabled. If the EN pin is pulled below 0.5 V, the LM25148-Q1 is in shutdown with an  $I_Q$  of 2.3  $\mu$ A (typical) current consumption from  $V_{IN}$ . When the enable voltage is between 0.5 V and 1 V, the LM25148-Q1 is in standby mode with the VCC regulator active but the controller is not switching. In standby mode, the non-switching input quiescent current is 124- $\mu$ A typical. The LM25148-Q1 is enabled with a voltage greater than 1.0 V. However, many applications benefit from using a resistor divider  $R_{UV1}$  and  $R_{UV2}$ , as shown in  $\mathbb{R}$  8-2, to establish a precision UVLO level. TI does not recommend leaving the EN pin floating.

Use 方程式 2 and 方程式 3 to calculate the UVLO resistors given the required input turn-on and turn-off voltages.

#### 8.3.4 Power-Good Monitor (PG)

The LM25148-Q1 includes an output voltage monitoring signal for  $V_{OUT}$  to simplify sequencing and supervision. The power-good signal is used for start-up sequencing of downstream converters, fault protection, and output monitoring. The power-good output (PG) switches to a high impedance open-drain state when the output voltage is in regulation. The PG switches low when the output voltage drops below the lower power-good threshold (92% typical) or rises above the upper power-good threshold (110% typical). A 25-µs deglitch filter prevents false

Copyright © 2023 Texas Instruments Incorporated

tripping of the power-good signal during transients. TI recommends a pullup resistor of 100 k $\Omega$  (typical) from PG to the relevant logic rail. PG is asserted low during soft start and when the buck regulator is disabled.

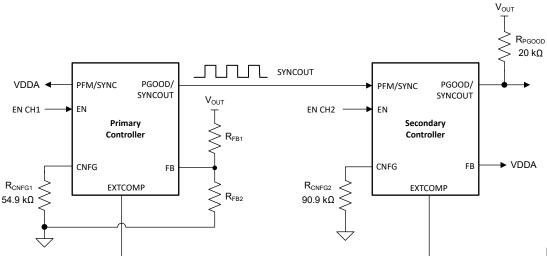

When the LM25148-Q1 is configured as a primary controller, the PG/SYNC pin becomes a synchronization clock output for the secondary controller. The synchronization signal is 180° out-of-phase with the primary HO driver output.

### 8.3.5 Switching Frequency (RT)

Program the LM25148-Q1 oscillator with a resistor from RT to AGND to set an oscillator frequency from 100 kHz and 2.2 MHz. Calculate the RT resistance for a given switching frequency using 方程式 4.

$$R_{T}(k\Omega) = \frac{\frac{10^{6}}{F_{SW}(kHz)} - 53}{45}$$

(4)

Under low  $V_{IN}$  conditions when the on time of the high-side MOSFET exceeds the programmed oscillator period, the LM25148-Q1 extends the switching period until the PWM latch is reset by the current sense ramp exceeding the controller compensation voltage.

The approximate input voltage level at which this occurs is given by 方程式 5.

$$V_{IN(min)} = V_{OUT} \cdot \frac{t_{SW}}{t_{SW} - t_{OFF(min)}}$$

where

- t<sub>SW</sub> is the switching period.

- t<sub>OFF(min)</sub> is the minimum off time of 90 ns.

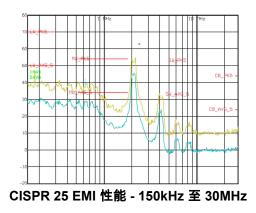

## 8.3.6 Dual Random Spread Spectrum (DRSS)

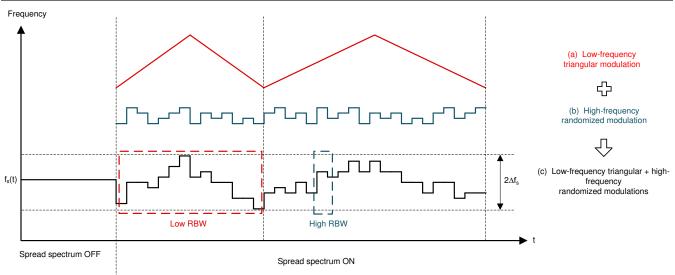

The LM25148-Q1 provides a digital spread spectrum, which reduces the EMI of the power supply over a wide frequency range. DRSS combines a low-frequency triangular modulation profile with a high frequency cycle-by-cycle random modulation profile. The low-frequency triangular modulation improves performance in lower radio-frequency bands, while the high-frequency random modulation improves performance in higher radio frequency bands.

Spread spectrum works by converting a narrowband signal into a wideband signal that spreads the energy over multiple frequencies. Because industry standards require different EMI receiver resolution bandwidth (RBW) settings for different frequency bands, the RBW has an impact on the spread spectrum performance. DRSS is able to simultaneously improve the EMI performance in the low and high RBWs using its low-frequency triangular modulation profile and at high frequency cycle-by-cycle random modulation, respectively. DRSS can reduce conducted emissions up to 15 dB $\mu$ V in the low-frequency band (150 kHz to 30 MHz) and 5 dB $\mu$ V in the high-frequency band (30 MHz to 108 MHz).

To enable DRSS, connect either a 41.2-k $\Omega$  or 71.5-k $\Omega$  resistor from CNFG to AGND. DRSS is disabled when an external clock is applied to the PFM/SYNC pin.

(5)

图 8-3. Dual Random Spread Spectrum Implementation

## 8.3.7 Soft Start

The LM25148-Q1 has an internal 3-ms soft-start timer (typical). The soft-start feature allows the regulator to gradually reach the steady-state operating point, thus reducing start-up stresses and surges.

## 8.3.8 Output Voltage Setpoint (FB)

The LM25148-Q1 output can be independently configured for one of three fixed output voltages without external feedback resistors, or adjusted to a desired voltage using an external resistor divider. Set the output to 3.3 V by connecting FB directly to VDDA. Alternatively, set the output to either 5 V or 12 V by installing a 24.9-k $\Omega$  or 49.9-k $\Omega$  resistor between FB and VDDA, respectively. See  $\frac{1}{2}$  8-1.

Copyright © 2023 Texas Instruments Incorporated

| 表 8-1. Feedback Cor | ifiguration Resistors |

|---------------------|-----------------------|

|                     |                       |

| PULLUP RESISTOR TO VDDA | V <sub>OUT</sub> SETPOINT   |  |  |

|-------------------------|-----------------------------|--|--|

| 0 Ω                     | 3.3 V                       |  |  |

| 24.9 kΩ                 | 5 V                         |  |  |

| 49.9 kΩ                 | 12 V                        |  |  |

| Not installed           | External FB divider setting |  |  |

The configuration settings are latched and cannot be changed until the LM25148-Q1 is powered down (with the VCC voltage decreasing below its falling UVLO threshold) and then powered up again (VCC rises above 3.4-V typical). Alternatively, set the output voltage with an external resistor divider from the output to AGND. The output voltage adjustment range is between 0.8 V and 36 V. The regulation voltage at FB is 0.8 V ( $V_{RFF}$ ). Use  $\overline{f}$ 程式 6 to calculate the upper and lower feedback resistors, designated as R<sub>FB1</sub> and R<sub>FB2</sub>, respectively.

$$\mathbf{R}_{\mathsf{FB1}} = \left(\frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{REF}}} - 1\right) \cdot \mathbf{R}_{\mathsf{FB2}} \tag{6}$$

The recommended starting value for  $R_{FB2}$  is between 10 k $\Omega$  and 20 k $\Omega$ .

If low-I<sub>Q</sub> operation is required, take care when selecting the external feedback resistors. The current consumption of the external divider adds to the LM25148-Q1 sleep current (9.5 µA typical). The divider current reflected to  $V_{IN}$  is scaled by the ratio of  $V_{OUT} / V_{IN}$ .

#### 8.3.9 Minimum Controllable On Time

There are two limitations to the minimum output voltage adjustment range: the LM25148-Q1 voltage reference of 0.8 V and the minimum controllable switch-node pulse width, tON(min).

t<sub>ON(min)</sub> effectively limits the voltage step-down conversion ratio V<sub>OUT</sub> / V<sub>IN</sub> at a given switching frequency. For fixed-frequency PWM operation, the voltage conversion ratio must satisfy 方程式 7.

$$\frac{V_{OUT}}{V_{IN}} > t_{ON(min)} \cdot F_{SW}$$

(7)

where

- t<sub>ON(min)</sub> is 50 ns (typical).

- F<sub>SW</sub> is the switching frequency.

If the desired voltage conversion ratio does not meet the above condition, the LM25148-Q1 transitions from fixed switching frequency operation to a pulse-skipping mode to maintain output voltage regulation. For example, if the desired output voltage is 5 V with an input voltage of 24 V and switching frequency of 2.1 MHz, use 方程式 8 to check the conversion ratio.

$$\frac{5V}{24V} > 50 \text{ ns} \cdot 2.1 \text{ MHz}$$

0.208 > 0.105 (8)

For wide V<sub>IN</sub> applications and low output voltages, an alternative is to reduce the LM25148-Q1 switching frequency to meet the requirement of 方程式 7.

## 8.3.10 Error Amplifier and PWM Comparator (FB, EXTCOMP)

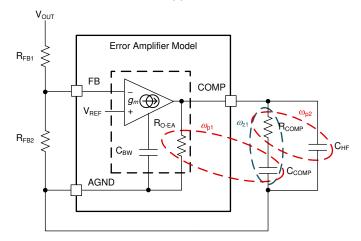

The LM25148-Q1 has a high-gain transconductance amplifier that generates an error current proportional to the difference between the feedback voltage and an internal precision reference (0.8 V). The control loop

compensation is configured two ways. The first is using the internal compensation amplifier, which has a transconductance of 30  $\mu$ S. Internal compensation is configured by connecting the EXTCOMP pin through a 10-k $\Omega$  resistance to VDDA. If a 10-k $\Omega$  resistor is not detected, the LM25148-Q1 defaults to the external loop compensation network. The transconductance of the amplifier for external compensation is 1200  $\mu$ S. This is latched and cannot be reconfigured after programmed unless power to the device is recycled. Use an external compensation network if higher performance is required to meet a stringent transient response specification. To reconfigure the compensation (internal or external), remove power and allow VCC to drop below its VCC<sub>UVLO</sub> threshold, which is 3.3 V (typical).

TI generally recommends a type-II compensation network for peak current-mode control.

### 8.3.11 Slope Compensation

The LM25148-Q1 provides internal slope compensation for stable operation with peak current-mode control and a duty cycle greater than 50%. Calculate the buck inductance to provide a slope compensation contribution equal to one times the inductor downslope using 方程式 9.

$$L_{O-IDEAL}(\mu H) = \frac{V_{OUT}(V) \cdot R_{S}(m\Omega)}{24 \cdot F_{SW}(MHz)}$$

(9)

- A lower inductance value generally increases the peak-to-peak inductor current, which minimizes size and cost, and improves transient response at the cost of reduced light-load efficiency due to higher cores losses and peak currents.

- A higher inductance value generally decreases the peak-to-peak inductor current, reducing switch peak and RMS currents at the cost of requiring larger output capacitors to meet load-transient specifications.

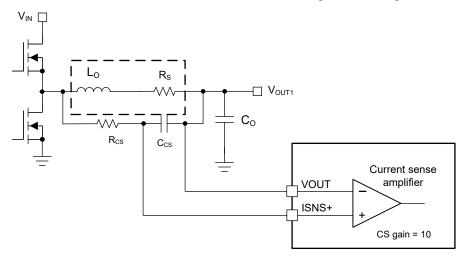

## 8.3.12 Inductor Current Sense (ISNS+, VOUT)

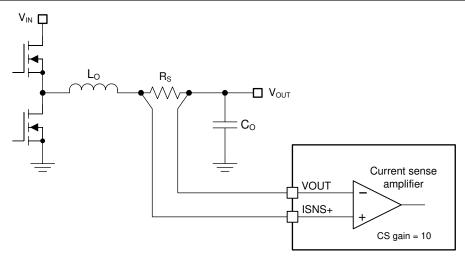

There are two methods to sense the inductor current of the buck power stage. The first uses a current sense resistor (also known as a shunt) in series with the inductor, and the second avails of the DC resistance of the inductor (DCR current sensing).

#### 8.3.12.1 Shunt Current Sensing

If the peak voltage signal sensed from ISNS+ to VOUT exceeds the current limit threshold of 60 mV, the current limit comparator immediately terminates the HO output for cycle-by-cycle current limiting. Calculate the shunt resistance using 方程式 10.

$$R_{S} = \frac{V_{CS-TH}}{I_{OUT(CL)} + \frac{\Delta I_{L}}{2}}$$

(10)

- where

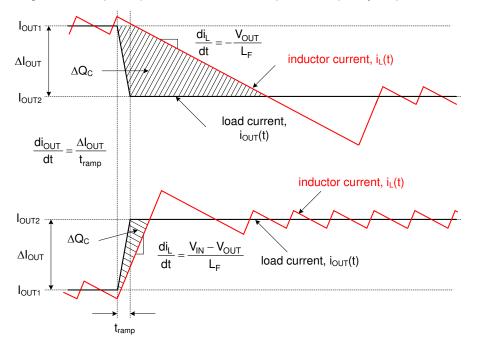

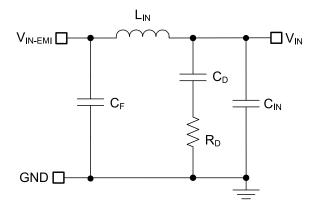

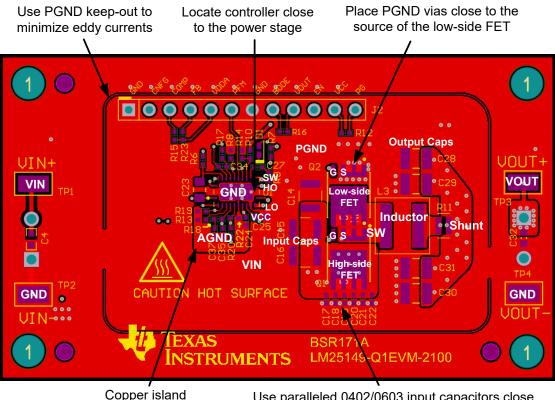

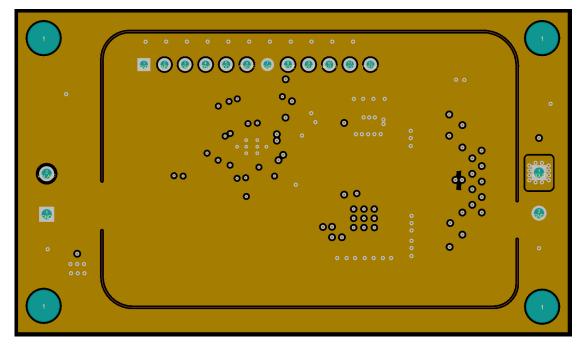

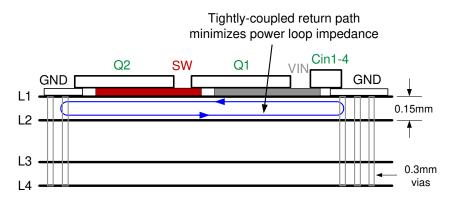

- V<sub>CS-TH</sub> is current sense threshold of 60 mV.