🕳 Sample &

Buy

UCC28063A

ZHCSDH6B – DECEMBER 2014 – REVISED MARCH 2015

UCC28063A 具有改进的可闻噪声和输入浪涌噪声抑制性能的 Natural Interleaving<sup>™</sup> 转换模式 PFC 控制器

#### 特性 1

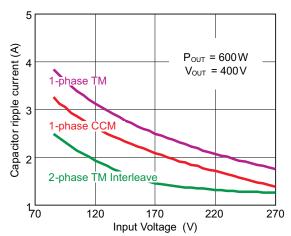

- 输入滤波器和输出电容纹波电流消除

- 减少了电流纹波,可提高系统可靠性并降低电容 容量需求

- 减小了电磁干扰 (EMI) 滤波器的尺寸

- 相位管理能力

- 双路故障安全过压保护 (OVP),可防止出现电压感 测故障所导致的输出过压情况

- 采用无传感器电流整形技术,可简化电路板布局并 提高效率

- 高级可闻噪声性能

- 非线性误差放大器增益

- 过压软恢复

- 集成欠压和压降处理

- 降低了偏置电流

- 相比传统的单相连续导通模式 (CCM), 提升了效率 和设计灵活性

- 浪涌安全电流限制:

- 在浪涌期间防止金属氧化物半导体场效应晶体管 (MOSFET) 导通

- 消除输出整流器中的反向恢复事件

- 无需大量的缓冲器电路,使用低成本二极管即可

- 提高了轻负载时的效率

- 快速且平滑的瞬态响应

- 扩展了系统级保护功能

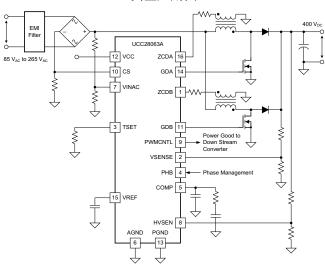

典型应用图

- 1A 拉电流/1.8A 灌电流栅极驱动器

- 工作温度范围为 -40°C 至 125°C,采用 16 引脚小 外形尺寸集成电路 (SOIC) 封装

- 2 应用

- 100W 至 800W 电源 •

- 游戏机

- 数模转换机顶盒 •

- 适配器 ٠

- 液晶电视、等离子电视以及 DLP™ 电视 •

- 家用音频系统

# 3 说明

该器件的特性与 UCC28063 几乎相同, 只不过删除了 TSET 引脚开路/短路故障检测和 CS 引脚开路故障检 测特性。 在某些应用中,当交流电源上出现快速瞬 变、浪涌或脉冲噪声时,会有大量电压噪声耦合到 TSET 或 CS 引脚上。而删除上述两个故障检测特性可 提升噪声抑制性能,从而为这类应用提供更强的"承受 能力"。

## 器件信息(1)

| 器件型号      | 封装        | 封装尺寸(标称值)       |

|-----------|-----------|-----------------|

| UCC28063A | SOIC (16) | 9.90mm x 3.91mm |

|           |           |                 |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

# 通过 Natural Interleaving 技术降低输入纹波电流

#### **Ripple Current Reduction**

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

# 目录

| 1 | 特性   | 1                                  |

|---|------|------------------------------------|

| 2 | 应用   |                                    |

| 3 | 说明   | 1                                  |

| 4 | 修订   | 历史记录                               |

| 5 | 说明   | (继续)3                              |

| 6 | Pin  | Configuration and Functions 3      |

| 7 | Spe  | cifications 4                      |

|   | 7.1  | Absolute Maximum Ratings 4         |

|   | 7.2  | ESD Ratings 4                      |

|   |      | Recommended Operating Conditions 5 |

|   | 7.4  | Thermal Information 5              |

|   | 7.5  | Electrical Characteristics 5       |

|   | 7.6  | Typical Characteristics 9          |

| 8 | Deta | ailed Description 13               |

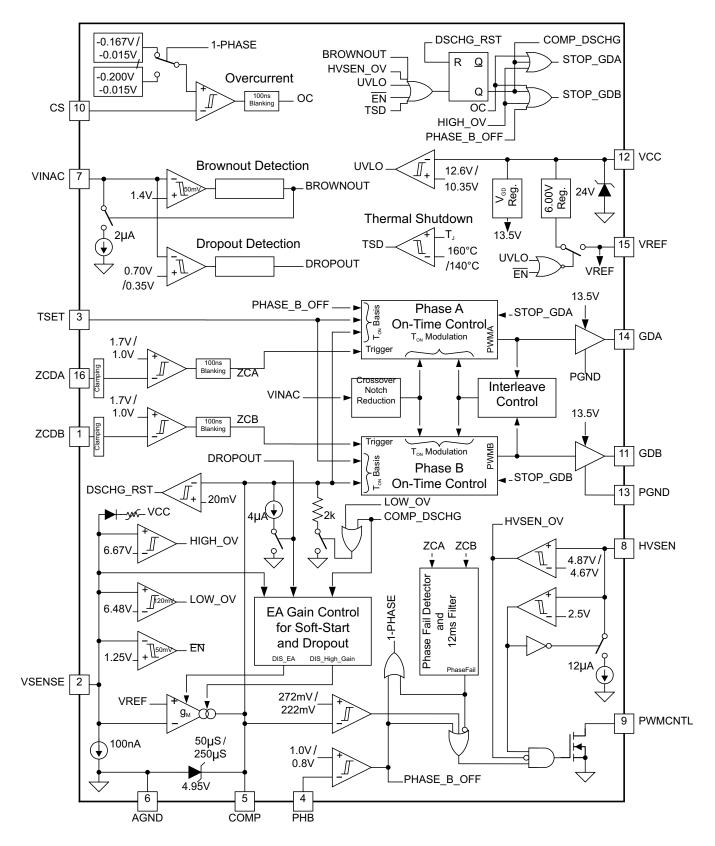

|   | 8.1  | Overview 13                        |

|   | 8.2  | Functional Block Diagram 14        |

# 4 修订历史记录

2

#### Changes from Revision A (February 2015) to Revision B

|    | 8.3  | Feature Description 15       |

|----|------|------------------------------|

|    | 8.4  | Device Functional Modes 27   |

| 9  | App  | lications and Implementation |

|    | 9.1  | Application Information      |

|    | 9.2  | Typical Application          |

| 10 | Pow  | ver Supply Recommendations   |

| 11 | Lay  | out                          |

|    | 11.1 | Layout Guidelines            |

|    | 11.2 | Layout Example               |

| 12 | 器件   | 和文档支持 37                     |

|    | 12.1 | 器件支持                         |

|    | 12.2 | 文档支持                         |

|    | 12.3 | 商标                           |

|    | 12.4 | 静电放电警告 39                    |

|    | 12.5 | 术语表 39                       |

| 13 | 机械   | 、封装和可订购信息 39                 |

|    |      |                              |

www.ti.com.cn

Page

## 5 说明(继续)

这套解决方案针对消费类应用在可闻噪声抑制方面的需求进行了优化,不仅保留了转换模式的高效率与低元件成本两大优势,还提高了额定功率。利用 Natural Interleaving ™ 技术,可使两个通道均作为主通道运行(即,没有从通道),而且这两个通道同步至同一频率。此方案本身可提供高匹配度的快速响应、并确保每个通道都运行在转换模式下。

该器件具有扩展系统级保护,其中包括输入欠压和压降恢复、输出过压、开环、过载、软启动、相位故障检测以及 热关断保护。附加故障安全过压保护 (OVP) 特性可防止发生中间电压短路,如果未成功检测到此类短路,则可能 会导致灾难性的器件故障。 该器件具有高级非线性增益,可针对线路和负载瞬态事件提供快速而更为平滑的响应。 并且偏置电流较小,提高了待机功率效率。 该器件还具备特殊的线路压降处理特性,可防止出现明显的电流中断并 以最大限度抑制可闻噪声的产生。

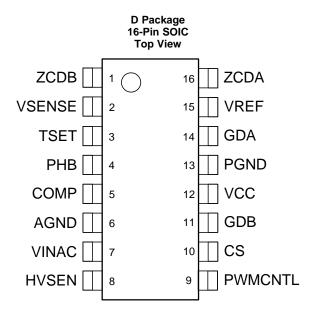

# 6 Pin Configuration and Functions

#### **Pin Functions**

| P       | IN  | I/O           | DESCRIPTION                                 |

|---------|-----|---------------|---------------------------------------------|

| NAME    | NO. | _ <i>1</i> /O | DESCRIPTION                                 |

| AGND    | 6   | -             | Analog Ground                               |

| COMP    | 5   | 0             | Error Amplifier Output                      |

| CS      | 10  | I             | Current Sense Input                         |

| GDA     | 14  | 0             | Channel A and Channel B. Cata Drive Quitaut |

| GDB     | 11  | 0             | Channel A and Channel B Gate Drive Output   |

| HVSEN   | 8   | I             | High Voltage Output Sense                   |

| PHB     | 4   | I             | Phase-B Enable/Disable                      |

| PWMCNTL | 9   | 0             | PWM-Control Output                          |

| TSET    | 3   | I             | Timing Set                                  |

| VCC     | 12  | -             | Bias Supply Input                           |

| VINAC   | 7   | I             | Input AC Voltage Sense                      |

| VREF    | 15  | 0             | Voltage Reference Output                    |

| VSENSE  | 2   | I             | Output DC Voltage Sense                     |

| ZCDA    | 16  | I             | Zero Current Detection Innute               |

| ZCDB    | 1   | I             | - Zero Current Detection Inputs             |

# 7 Specifications

## 7.1 Absolute Maximum Ratings<sup>(1)</sup>

All voltages are with respect to GND, -40 °C <  $T_J = T_A < 125$  °C, currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                  |                                |                                                                                                | MIN  | MAX | UNIT |

|------------------|--------------------------------|------------------------------------------------------------------------------------------------|------|-----|------|

|                  |                                | VCC <sup>(2)</sup>                                                                             | -0.5 | 21  |      |

|                  |                                | PWMCNTL                                                                                        | -0.5 | 20  |      |

|                  | Continuous input voltage range | COMP <sup>(3)</sup> , PHB, HVSEN <sup>(4)</sup> , VINAC <sup>(4)</sup> , VSENSE <sup>(4)</sup> | -0.5 | 7   | V    |

|                  |                                | ZCDA, ZCDB                                                                                     | -0.5 | 4   |      |

|                  |                                | CS <sup>(5)</sup>                                                                              | -0.5 | 3   |      |

|                  |                                | VCC                                                                                            |      | 20  |      |

|                  | Continuous input current       | PWMCNTL                                                                                        |      | 10  |      |

|                  |                                | ZCDA, ZCDB                                                                                     |      | ±5  | mA   |

|                  | Peak input current             | CS                                                                                             |      | -30 | mA   |

|                  | Output current                 | VREF                                                                                           |      | -10 |      |

|                  | Continuous gate current        | GDA, GDB <sup>(6)</sup>                                                                        |      | ±25 |      |

| т                | lunction Towns roture          | Operating                                                                                      | -40  | 125 |      |

| ΤJ               | Junction Temperature           | Storage                                                                                        | -65  | 150 | °C   |

| T <sub>SOL</sub> | Lead Temperature               | Soldering, 10s                                                                                 |      | 260 | U    |

| T <sub>stg</sub> | Storage temperature            |                                                                                                | -40  | 125 |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those included under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods of time may affect device reliability.

(2) Voltage on VCC is internally clamped. VCC may exceed the continuous absolute maximum input voltage rating if the source is current limited below the absolute maximum continuous VCC input current level.

(3) In normal use, COMP is connected to capacitors and resistors and is internally limited in voltage swing.

(4) In normal use, VINAC, VSENSE, and HVSEN are connected to high-value resistors and are internally limited in negative-voltage swing. Although not recommended for extended use, VINAC, VSENSE, and HVSEN can survive input currents as high as -10mA from negative voltage sources, and input currents as high as +0.5mA from positive voltage sources.

(5) In normal use, CS is connected to a series resistor to limit peak input current during brief system line-inrush conditions. In these situations, negative voltage on CS may exceed the continuous absolute maximum rating.

(6) No GDA or GDB current limiting is required when driving a power MOSFET gate. However, a small series resistor may be required to damp resonant ringing due to stray inductance.

# 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

All voltages are with respect to GND, -40 °C <  $T_J = T_A < 125$  °C, currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                                                | MIN  | MAX | UNIT |

|------------------------------------------------|------|-----|------|

| VCC input voltage from a low-impedance source  | 14   | 21  | V    |

| VCC input current from a high-impedance source | 8    | 18  | ~ ^  |

| VREF load current                              | 0    | -2  | mA   |

| VINAC input voltage                            | 0    | 6   | V    |

| ZCDA, ZCDB series resistor                     | 20   | 80  | kΩ   |

| TSET resistor to program PWM on-time           | 66.5 | 400 | K12  |

| HVSEN input voltage                            | 0.8  | 4.5 | V    |

## 7.4 Thermal Information

|                       |                                                             | UCC28063A |      |

|-----------------------|-------------------------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                               | SOIC (D)  | UNIT |

|                       |                                                             | 16 PINS   |      |

| $R_{	extsf{	heta}JA}$ | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 91.6      |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 52.1      |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance <sup>(4)</sup>         | 48.6      | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter <sup>(5)</sup>   | 14.9      |      |

| $\Psi_{JB}$           | Junction-to-board characterization parameter <sup>(6)</sup> | 48.3      |      |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

(2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>0JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{\theta JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

# 7.5 Electrical Characteristics

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V, R<sub>TSET</sub> = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded, -40 °C < T<sub>J</sub> = T<sub>A</sub> < 125 °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                        | PARAMETER                        | TEST CONDITIONS                               | MIN  | TYP   | MAX  | UNIT |

|------------------------|----------------------------------|-----------------------------------------------|------|-------|------|------|

| VCC BIAS SU            | JPPLY                            |                                               |      |       |      |      |

| VCC <sub>SHUNT</sub>   | VCC shunt voltage <sup>(1)</sup> | I <sub>VCC</sub> = 10 mA                      | 22   | 24    | 26   | V    |

| I <sub>VCC(ULVO)</sub> | VCC current, UVLO                | VCC = 11.4 V prior to turn-on                 |      | 95    | 200  |      |

| I <sub>VCC(stby)</sub> | VCC current, disabled            | VSENSE = 0 V                                  |      | 100   | 200  | μA   |

| I <sub>VCC(on)</sub>   | VCC current, enabled             | VSENSE = 2 V                                  |      | 5     | 8    | mA   |

| UNDERVOLT              | AGE LOCKOUT (UVLO)               |                                               |      |       |      |      |

| VCC <sub>ON</sub>      | VCC turn-on threshold            | VCC rising                                    | 11.5 | 12.6  | 13.5 |      |

| VCC <sub>OFF</sub>     | VCC turn-off threshold           | VCC falling                                   | 9.5  | 10.35 | 11.5 | V    |

|                        | UVLO Hysteresis                  |                                               | 1.85 | 2.15  | 2.45 |      |

| REFERENCE              |                                  |                                               |      |       |      |      |

| V <sub>REF</sub>       | VREF output voltage, no load     | I <sub>VREF</sub> = 0 mA                      | 5.82 | 6.00  | 6.18 | V    |

|                        | VREF change with load            | $0 \text{ mA} \le I_{VREF} \le -2 \text{ mA}$ |      | -1    | -6   |      |

|                        | VREF change with VCC             | 12 V ≤ VCC ≤ 20 V                             |      | 2     | 10   | mV   |

(1) Excessive VCC input voltage and current will damage the device. This clamp will not protect the device from an unregulated bias supply. If an unregulated bias supply is used, a series-connected Fixed Positive-Voltage Regulator such as the UA78L15A is recommended. See the Absolute Maximum Ratings table for the limits on VCC voltage, current, and junction temperature.

ZHCSDH6B-DECEMBER 2014-REVISED MARCH 2015

www.ti.com.cn

# Electrical Characteristics (接下页)

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V, R<sub>TSET</sub> = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded, -40 °C < T<sub>J</sub> = T<sub>A</sub> < 125 °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                       | PARAMETER                                                                   | TEST CONDITIONS                                           | MIN    | TYP   | MAX    | UNIT |

|-----------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------|--------|-------|--------|------|

| ERROR AMPLI           | FIER                                                                        |                                                           |        |       |        |      |

| VSENSEreg25           | VSENSE input regulation voltage                                             | $T_A = 25 \text{ °C}$                                     | 5.85   | 6     | 6.15   | V    |

| VSENSEreg             | VSENSE input regulation voltage                                             |                                                           | 5.82   | 6     | 6.18   | V    |

| VSENSE                | VSENSE input bias current                                                   | In regulation                                             | 50     | 100   | 150    | nA   |

| V <sub>ENAB</sub>     | VSENSE enable threshold, rising                                             |                                                           | 1.15   | 1.25  | 1.35   |      |

|                       | VSENSE enable hysteresis                                                    |                                                           | 0.02   | 0.07  | 0.15   | V    |

| V <sub>COMPCLMP</sub> | COMP high voltage, clamped                                                  | VSENSE = VSENSEreg – 0.3 V                                | 4.70   | 4.95  | 5.10   |      |

|                       | COMP low voltage, saturated                                                 | VSENSE = VSENSEreg + 0.3 V                                |        | 0.03  | 0.125  |      |

| 9м                    | VSENSE to COMP<br>transconductance, small signal                            | 0.99(VSENSEreg) < VSENSE <<br>1.01(VSENSEreg), COMP = 3 V | 40     | 55    | 70     | μS   |

|                       | VSENSE high-going threshold<br>to enable COMP large signal<br>gain, percent | Relative to VSENSEreg, COMP = 3 V                         | 3.25%  | 5%    | 6.75%  |      |

|                       | VSENSE low-going threshold to<br>enable COMP large signal gain,<br>percent  | Relative to VSENSEreg, COMP = 3 V                         | -3.25% | -5%   | -6.75% |      |

|                       | VSENSE to COMP<br>transconductance, large signal                            | VSENSE = VSENSEreg - 0.4 V ,<br>COMP = 3 V                | 210    | 290   | 370    | μS   |

|                       | VSENSE to COMP<br>transconductance, large signal                            | VSENSE = VSENSEreg + 0.4 V,<br>COMP = 3 V                 | 210    | 290   | 370    | μο   |

|                       | COMP maximum source current                                                 | VSENSE = 5 V, COMP = 3 V                                  | -80    | -125  | -170   | μA   |

| R <sub>COMPDCHG</sub> | COMP discharge resistance                                                   | HVSEN = 5.2 V, COMP = 3 V                                 | 1.6    | 2     | 2.4    | kΩ   |

| IDODCHG               | COMP discharge current during<br>Dropout                                    | VSENSE = 5 V, VINAC = 0.3 V                               | 3.2    | 4     | 4.8    | μA   |

| V <sub>LOW_OV</sub>   | VSENSE over-voltage threshold, rising                                       | Relative to VSENSEreg                                     | 7%     | 8%    | 10%    |      |

|                       | VSENSE over-voltage<br>hysteresis                                           | Relative to V <sub>LOW_OV</sub>                           | -1.5%  | -2%   | -3%    |      |

| V <sub>HIGH_OV</sub>  | VSENSE 2nd over-voltage threshold, rising                                   | Relative to VSENSEreg                                     | 10.5%  | 11.3% | 14%    |      |

| SOFT START            |                                                                             |                                                           |        |       |        |      |

| V <sub>SSTHR</sub>    | COMP Soft-Start threshold, falling                                          | VSENSE = 1.5 V                                            | 15     | 23    | 30     | mV   |

| SS,FAST               | COMP Soft-Start current, fast                                               | SS-state, V <sub>ENAB</sub> < VSENSE < VREF/2             | -80    | -125  | -170   |      |

| SS,SLOW               | COMP Soft-Start current, slow                                               | SS-state, VREF/2 < VSENSE < 0.88VREF                      | -11.5  | -16   | -20    | μA   |

| K <sub>EOSS</sub>     | VSENSE End-of-Soft-Start<br>threshold factor                                | Percent of VSENSEreg                                      | 96.5%  | 98.3% | 99.8%  |      |

| OUTPUT MONI           | TORING                                                                      |                                                           |        |       |        |      |

| V <sub>PWMCNTL</sub>  | HVSEN threshold to PWMCNTL                                                  | HVSEN rising                                              | 2.35   | 2.50  | 2.65   | V    |

| I <sub>HVSEN</sub>    | HVSEN input bias current, high                                              | HVSEN = 3 V                                               |        | ±0.03 | ±0.5   |      |

| I <sub>HV_HYS</sub>   | HVSEN hysteresis bias current, low                                          | HVSEN = 2 V                                               | 9.2    | 11.4  | 14     | μΑ   |

# Electrical Characteristics (接下页)

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V, R<sub>TSET</sub> = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded, -40 °C < T<sub>J</sub> = T<sub>A</sub> < 125 °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                           | PARAMETER                                           | TEST CONDITIONS                                                           | MIN    | TYP    | MAX    | UNIT |

|---------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|--------|--------|--------|------|

| V <sub>HV_OV_FLT</sub>    | HVSEN threshold to over-<br>voltage fault           | HVSEN rising                                                              | 4.64   | 4.87   | 5.1    |      |

| $V_{\rm HV\_OV\_CLR}$     | HVSEN threshold to over-<br>voltage clear           | HVSEN falling                                                             | 4.45   | 4.67   | 4.8    |      |

| V <sub>COMP_PHFOFF</sub>  | Phase Fail monitoring-disable threshold             | COMP falling                                                              | 0.21   | 0.225  | 0.25   | V    |

| V <sub>COMP_PHFHYS</sub>  | Phase Fail monitoring<br>hysteresis                 | COMP rising                                                               |        | 0.051  |        |      |

|                           | PWMCNTL output voltage low                          | HVSEN = 3 V, I <sub>PWMCNTL</sub> = 5 mA,<br>COMP = 0 V                   |        | 0.2    | 0.5    |      |

| t <sub>PHFDLY</sub>       | Phase Fail filter time to<br>PWMCNTL high           | PHB = 5 V, ZCDA switching,<br>ZCDB = 0.5 V, COMP = 3 V                    | 7.9    | 12     | 17     | ms   |

| I <sub>PWMCNTL_LEAK</sub> | PWMCNTL leakage current, high                       | HVSEN = 2 V, PWMCNTL = 15 V                                               |        | ±0.03  | ±0.5   | μA   |

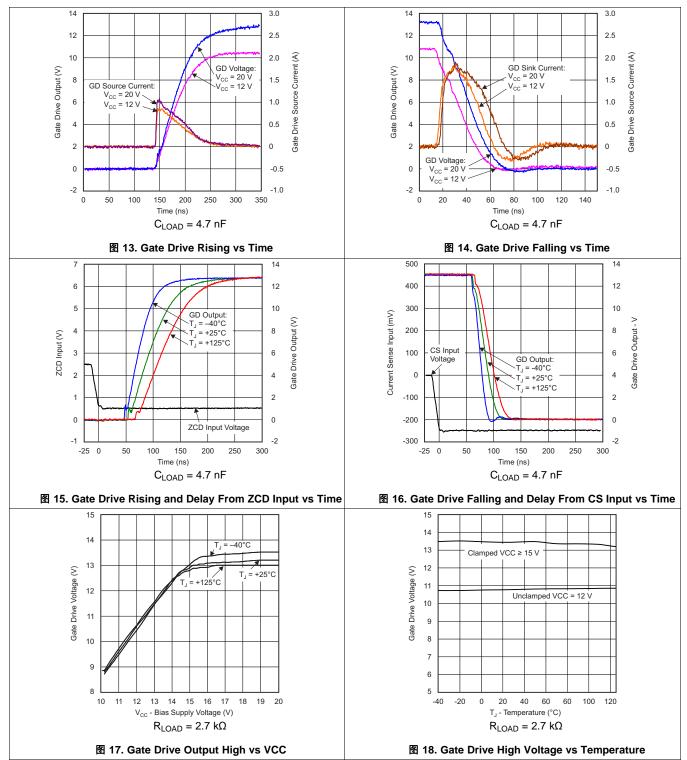

| GATE DRIVE <sup>(2</sup>  |                                                     | ·                                                                         |        |        |        |      |

|                           | GDA, GDB output voltage, high                       | $I_{GDA}$ , $I_{GDB} = -100 \text{ mA}$                                   | 11.5   | 12.4   | 15     | V    |

|                           | GDA, GDB on-resistance, high                        | $I_{GDA}$ , $I_{GDB} = -100 \text{ mA}$                                   |        | 8.8    | 14     | Ω    |

|                           | GDA, GDB output voltage, low                        | $I_{GDA}$ , $I_{GDB} = 100 \text{ mA}$                                    |        | 0.18   | 0.32   | V    |

|                           | GDA, GDB on-resistance, low                         | $I_{GDA}$ , $I_{GDB} = 100 \text{ mA}$                                    |        | 2      | 3.2    | Ω    |

|                           | GDA, GDB output voltage high, clamped               | VCC = 20 V, $I_{GDA}$ , $I_{GDB}$ = -5 mA                                 | 12     | 13.5   | 15     |      |

|                           | GDA, GDB output voltage high, low VCC               | VCC = 12 V, $I_{GDA}$ , $I_{GDB}$ = -5 mA                                 | 10     | 10.5   | 11.5   | V    |

|                           | Rise time                                           | 1 V to 9 V, C <sub>LOAD</sub> = 1 nF                                      |        | 18     | 30     |      |

|                           | Fall time                                           | 9 V to 1 V, C <sub>LOAD</sub> = 1 nF                                      |        | 12     | 25     | ns   |

|                           | GDA, GDB output voltage,<br>UVLO                    | VCC = 3.0 V, $I_{GDA}$ , $I_{GDB}$ = 2.5 mA                               |        | 100    | 200    | mV   |

| ZERO CURRE                | NT DETECTOR                                         | ·                                                                         |        |        |        |      |

|                           | ZCDA, ZCDB voltage threshold, falling               |                                                                           | 0.8    | 1      | 1.2    |      |

|                           | ZCDA, ZCDB voltage threshold, rising                |                                                                           | 1.5    | 1.7    | 1.9    | V    |

|                           | ZCDA, ZCDB clamp, high                              | $I_{ZCDA} = +2 \text{ mA}, I_{ZCDB} = +2 \text{ mA}$                      | 2.6    | 3      | 3.4    |      |

|                           | ZCDA, ZCDB clamp, low                               | $I_{ZCDA} = -2 \text{ mA}, I_{ZCDB} = -2 \text{ mA}$                      | 0      | -0.2   | -0.4   |      |

|                           | ZCDA, ZCDB input bias current                       | ZCDA = 1.4 V, ZCDB = 1.4 V                                                |        | ±0.03  | ±0.5   | μA   |

|                           | ZCDA, ZCDB delay to GDA, GDB outputs <sup>(2)</sup> | From ZCDx input falling to 1 V to respective gate drive output rising 10% |        | 50     | 100    |      |

|                           | ZCDA blanking time <sup>(3)</sup>                   | From GDA rising and GDA falling                                           |        | 100    |        | ns   |

|                           | ZCDB blanking time <sup>(3)</sup>                   | From GDB rising and GDB falling                                           |        | 100    |        |      |

| CURRENT SE                | NSE                                                 |                                                                           | .1     |        |        |      |

|                           | CS input bias current, dual-<br>phase               | At rising threshold                                                       | -120   | -166   | -200   | μA   |

|                           | CS current-limit rising threshold, dual-phase       | PHB = 5 V                                                                 | -0.18  | -0.2   | -0.22  |      |

|                           | CS current-limit rising threshold, single-phase     | PHB = 0 V                                                                 | -0.149 | -0.166 | -0.183 | V    |

|                           | CS current-limit reset falling threshold            |                                                                           | -0.003 | -0.015 | -0.025 |      |

(2) Refer to 🛐 13, 🛐 14, 🛐 15, and 🖺 16 of the Typical Characteristics for typical gate drive waveforms.

(3) ZCD blanking times are ensured by design.

ZHCSDH6B-DECEMBER 2014-REVISED MARCH 2015

www.ti.com.cn

# Electrical Characteristics (接下页)

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded, -40 °C <  $T_J$  =  $T_A$  < 125 °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                    | PARAMETER                                            | TEST CONDITIONS                                                           | MIN   | ТҮР   | MAX  | UNIT |

|--------------------|------------------------------------------------------|---------------------------------------------------------------------------|-------|-------|------|------|

|                    | CS current-limit response time <sup>(2)</sup>        | From CS exceeding threshold-0.05 V to GDx dropping 10%                    |       | 60    | 100  | ns   |

|                    | CS blanking time                                     | From GDx rising and falling edges                                         |       | 100   |      |      |

| VINAC INPU         | т                                                    |                                                                           |       |       |      |      |

| I <sub>VINAC</sub> | VINAC input bias current, above brownout             | VINAC = 2 V                                                               |       | ±0.03 | ±0.5 | μA   |

| V <sub>BODET</sub> | VINAC brownout detection threshold                   | VINAC falling                                                             | 1.33  | 1.39  | 1.44 | V    |

| t <sub>BODLY</sub> | VINAC brownout filter time                           | VINAC below the brownout detection threshold for the brownout filter time | 340   | 440   | 540  | ms   |

| V <sub>BOHYS</sub> | VINAC brownout threshold<br>hysteresis               | VINAC rising                                                              | 30    | 62    | 75   | mV   |

| I <sub>BOHYS</sub> | VINAC brownout hysteresis<br>current                 | $VINAC = 1 V \text{ for } > t_{BODLY}$                                    | 1.6   | 2     | 2.5  | μA   |

| V <sub>DODET</sub> | VINAC dropout detection threshold                    | VINAC falling                                                             | 0.315 | 0.35  | 0.38 | V    |

| t <sub>DODLY</sub> | VINAC dropout filter time                            | VINAC below the dropout detection threshold for the dropout filter time   | 3.5   | 5     | 7    | ms   |

| V <sub>DOCLR</sub> | VINAC dropout clear threshold                        | VINAC rising                                                              | 0.67  | 0.71  | 0.75 | V    |

| PULSE-WID          | TH MODULATOR                                         |                                                                           |       |       |      |      |

| Κ <sub>T</sub>     | On-time factor, phases A and B                       | VSENSE = 5.8 V <sup>(4)</sup>                                             | 3.6   | 4.0   | 4.4  | µs/V |

| K <sub>TS</sub>    | On-time factor, single-phase, A                      | VSENSE = 5.8 V, PHB = 0 $V^{(4)}$                                         | 7.2   | 8.0   | 8.9  | µs/v |

|                    | Phase B to phase A on-time<br>matching error         | VSENSE = 5.8 V                                                            |       | ±2%   | ±6%  |      |

|                    | Zero-crossing distortion                             | COMP = 0.25 V, VINAC = 1 V                                                | 1.2   | 2     | 2.8  |      |

|                    | correction additional on time                        | COMP = 0.25 V, VINAC = 0.1 V                                              | 12.6  | 20    | 29   | μs   |

| V <sub>PHBF</sub>  | PHB threshold falling, to single-<br>phase operation | To GDB output shutdown, VINAC = 1.5 V                                     | 0.7   | 0.8   | 0.9  | V    |

| V <sub>PHBR</sub>  | PHB threshold rising, to two-<br>phase operation     | To GDB output running, VINAC = 1.5 V                                      | 0.9   | 1     | 1.1  | v    |

| T <sub>MIN</sub>   | Minimum switching period                             | $R_{TSET} = 133 \text{ k}\Omega^{(4)}$                                    | 1.7   | 2.2   | 3    | 110  |

| T <sub>START</sub> | PWM restart time                                     | $ZCDA = ZCDB = 2 V^{(5)}$                                                 | 165   | 210   | 265  | μs   |

| THERMAL S          | HUTDOWN                                              |                                                                           |       |       |      |      |

| TJ                 | Thermal shutdown temperature                         | Temperature rising <sup>(6)</sup>                                         |       | 160   |      | °C   |

| TJ                 | Thermal restart temperature                          | Temperature falling <sup>(6)</sup>                                        |       | 140   |      | C    |

|                    |                                                      |                                                                           |       |       |      |      |

Gate drive on-time is proportional to (V<sub>COMP</sub> - 0.125 V). The on-time proportionality factor, K<sub>T</sub>, scales linearly with the value of R<sub>TSET</sub> (4) and is different in two-phase and single-phase modes. The minimum switching period is proportional to  $R_{TSET}$ . An output on-time is generated at both GDA and GDB if both ZCDA and ZCDB negative-going edges are not detected for the restart

(5)time. In single-phase mode, the restart time applies for the ZCDA input and the GDA output.

Thermal shutdown occurs at temperatures higher than the normal operating range. Device performance above the normal operating (6) temperature is not specified or assured.

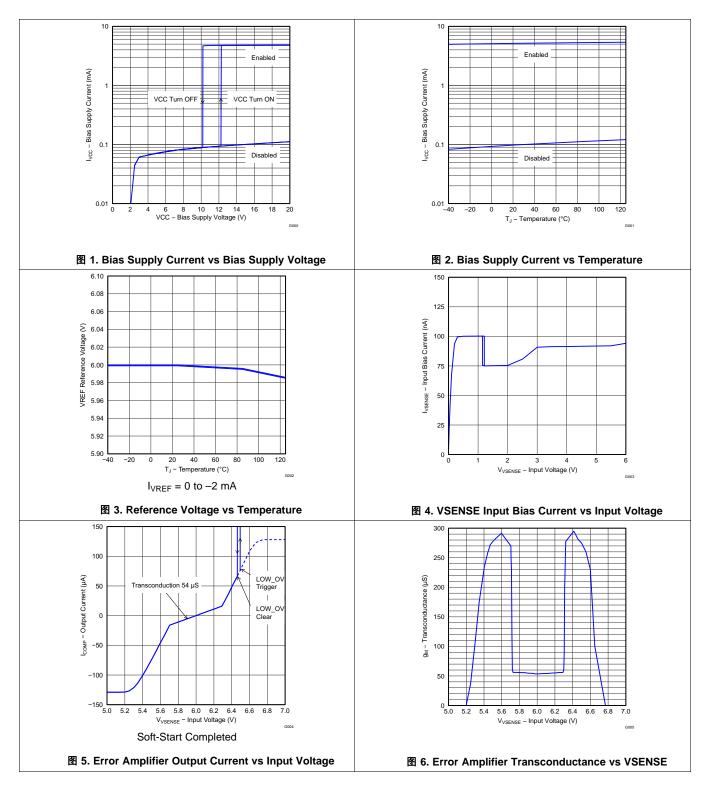

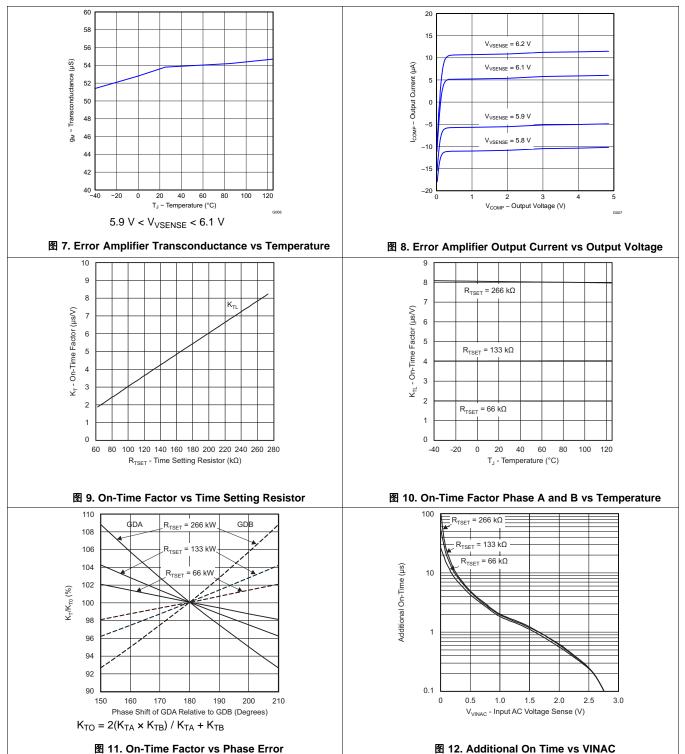

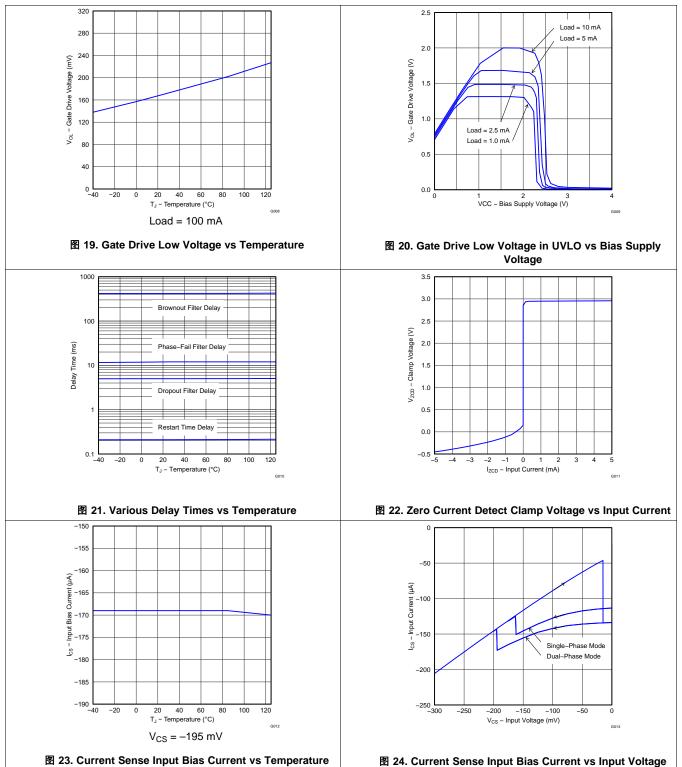

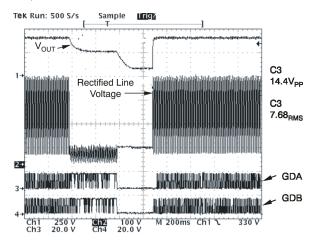

## 7.6 Typical Characteristics

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25$  °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

ZHCSDH6B-DECEMBER 2014-REVISED MARCH 2015

www.ti.com.cn

# Typical Characteristics (接下页)

# Typical Characteristics (接下页)

ZHCSDH6B-DECEMBER 2014-REVISED MARCH 2015

www.ti.com.cn

# Typical Characteristics (接下页)

# 8 Detailed Description

## 8.1 Overview

This part is identical to UCC28063 with the exception that the TSET pin Open/ Short Fault Detect and the CS pin Open Fault Detect features are removed. Removal of these fault detect mechanisms provides a higher degree of noise immunity for applications where significant voltage noise could be coupled onto the TSET or CS pins during conditions of extreme fast transient, surge or impulse noise events. The Soft Re-Start fault protection which would be triggered on the UCC28063 will not occur with the UCC28063A. The system will continue to provide power delivery through such events, albeit with the possibility of some dynamic regulation irregularity.

Transition Mode Control is the most popular choice for the Boost Power Factor Correction topology at lower power levels because of its lower complexity in achieving high power factor while at the same time not placing demanding requirements on the power component specifications. A lower cost boost diode with higher reverse recovery current specification may be used, for instance, in the Transition Mode Boost. Interleaved Transition Mode Control retains this benefit and generally extends the applicability up to much higher power levels while simultaneously conferring the interleaving benefits of reduced input and output ripple, phase management for light load efficiency enhancement, redundancy, system thermal optimization and low profile or planar solutions.

The UCC28063A enables a very cost effective solution with a particular focus on ruggedness, fault management, fault recovery, efficiency and higher end performance in areas such as acoustic management and fast transient response. It may be regarded as an enhanced and new generation UCC28061.

Interleaving control and phase management facilitates 80+ and Energy Star designs with reduced input and output ripple. The Natural Interleaving method allows TM operation and achieves 180 degrees between the phases by On-time management and does not rely on tight tolerance requirements on the inductors. The Crossover Notch Reduction block implements a non-linear current shaping characteristic on the instantaneous voltage sense (VINAC) in order to reduce distortion and increase Power Factor. Negative current sensing is implemented on the total input current instead of just the MOSFET current which prevents MOSFET switching during inrush surges or in any mode where the inductor current may become substantially continuous (CCM). This prevents reverse recovery conduction events between the MOSFET and output rectifier. Downstream power stage management is facilitated by the PWMCNTL signal. This open drain signal provides an enable with hysteresis for a downstream converter when the PFC stage voltage is above an operating threshold, FailSafe OV protection is not in operation and there is no PhaseFail fault.

Independent output voltage sense chains with their separate fault management behaviors provide a high degree of redundancy against PFC stage overvoltage. Brown-Out, HVSENSE OV, UVLO, and IC Overtemperature will all cause a complete Soft-Start cycle. Other faults such as short duration AC Drop-Out, minor overvoltage or cycle-by-cycle overcurrent cause a live recovery process to initiate by pulling down on the COMP pin or by terminating the pulses early.

In general IC operation is designed to ensure smooth and acoustic noise free start-up, good transient response behavior and well behaved recovery from faults. The Error amplifier transconductance is designed to allow smaller compensation components and optimum transient response for larger deviations. The Soft-Start process is carefully optimized. A complete Soft Start is implemented on recovery from every fault, for consistency. The Soft Start speed is dependent on the output voltage sense to speed up start-up from low AC line and to minimize the effect of excessive "COMP" during start-up into no-load. This complete discharge of COMP aids with preventing excessive currents on recovery from an AC Brown-Out event. UCC28063A ZHCSDH6B – DECEMBER 2014–REVISED MARCH 2015

www.ti.com.cn

## 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Principles of Operation

The UCC28063A contains the control circuits for two parallel-connected boost pulse-width modulated (PWM) power converters. The boost PWM power converters ramp current in the boost inductors for a time period proportional to the voltage on the error amplifier output. Each power converter then turns off the power MOSFET until current in the boost inductor decays to zero, as sensed on the zero current detection inputs (ZCDA and ZCDB). Once the inductor is demagnetized, the power converter starts another cycle. This on/off cycling produces a triangle wave of current, with peak current set by the on-time and instantaneous power mains input voltage, V<sub>IN</sub>(t), as shown in 公式 1.

$$I_{\mathsf{PEAK}}(t) = \frac{V_{\mathsf{IN}}(t) \times \mathsf{T}_{\mathsf{ON}}}{\mathsf{L}}$$

(1)

The average line current is exactly equal to half of the peak line current, as shown in 公式 2.

$$I_{AVG}(t) = \frac{V_{IN}(t) \times T_{ON}}{2 \times L}$$

<sup>(2)</sup>

With T<sub>ON</sub> and L being essentially constant during an AC-line period, the resulting triangular current waveform during each switching cycle will have an average value proportional to the instantaneous value of the rectified AC-line voltage. This architecture results in a resistive input impedance characteristic at the line frequency and a near-unity power factor.

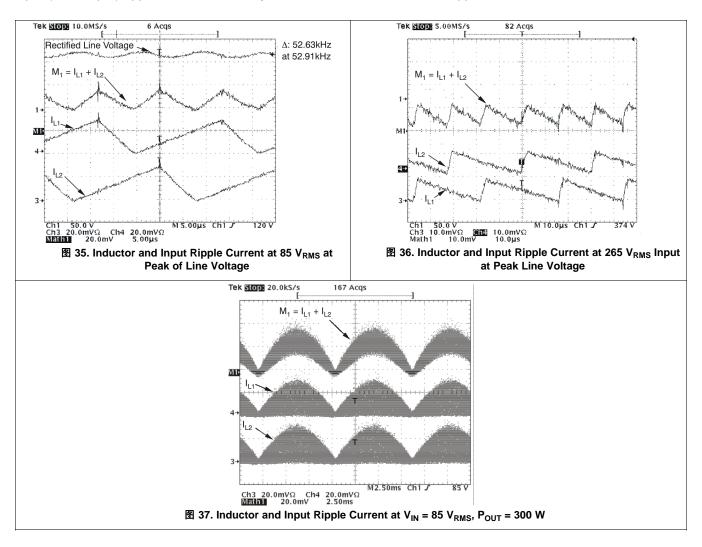

#### 8.3.2 Natural Interleaving

Under normal operating conditions, the UCC28063A regulates the relative phasing of the channel A and channel B inductor currents to be very close to 180°. This greatly reduces the switching-frequency ripple currents seen at the line-filter and output capacitors, compared to the ripple current of each individual converter. This design allows a reduction in the size and cost of input and output filtering. The phase-control function differentially modulates the on-times of the A and B channels based on their phase and frequency relationship. The Natural Interleaving method allows the converter to achieve 180° phase-shift and transition-mode operation for both phases without tight requirements on boost inductor tolerance.

Ideally, the best current-sharing is achieved when both inductors are exactly the same value. Typically the inductances are not the same, so the current-sharing of the A and B channels is proportional to the inductor tolerance. Also, switching delays and resonances of each channel typically differ slightly, and the controller allows some necessary phase-error deviation from 180° to maintain equal switching frequencies. Optimal phase balance occurs if the individual power stages and the on-times are well matched. Mismatches in inductor values do not affect the phase relationship.

#### 8.3.3 On-Time Control, Maximum Frequency Limiting, and Restart Timer

Gate-drive on-time varies proportionately with the error-amplifier output voltage by a factor called  $K_T$  (in units of µs/V), as shown in 公式 3.

$$T_{ON} = K_T \left( V_{COMP} - 125 mV \right)$$

Where:

V<sub>COMP</sub> is the output voltage of the error amplifier and 125 mV is a modulator offset voltage.

The maximum output of the error amplifier is limited to 4.95 V. This value, minus the 125-mV modulator offset, limits maximum on-time as determined by 公式 4.

$$T_{ON(max)} = K_T \times 4.825 V$$

This on-time limit sets the maximum power that can be delivered by the converter at a given input voltage.

At lower power, one boost channel (phase) may be turned off to achieve efficiency benefits (see Phase Management section, below). To provide a smooth transition between two-phase and single-phase operation,  $K_{T}$ increases by a factor of two in single-phase mode:

$K_{TS} = 2 \times K_T$ ; active during single-phase operation

(3)

(4)

(5)

15

## Feature Description (接下页)

The maximum switching frequency of each phase is limited by minimum-period timers. If inductor current decays to zero before the minimum-period timer elapses, the next turn-on will be delayed, resulting in discontinuous phase current.

A restart timer ensures starting under all circumstances by restarting both phases if the ZCD input of either phase has not transitioned from high-to-low within approximately 200 µs. To prevent the circuit from operating in continuous conduction mode (CCM), the restart timer does not trigger turn-on until both phase-currents return to zero.

The on-time factors (K<sub>T</sub>, K<sub>TS</sub>) and the minimum switching period, T<sub>(MIN)</sub>, are proportional to the time-setting resistor R<sub>TSET</sub> (the resistor from the TSET pin to ground), and these factors can be calculated by  $\Delta \pm 5$ ,  $\Delta \pm 6$  and  $\Delta \pm 7$ :

$$K_{T} = \frac{R_{TSET}}{133 k\Omega} \times 4.0 \frac{\mu s}{\text{volt}}$$

$$T_{(MIN)} = \frac{R_{TSET}}{133 k\Omega} \times 2.2 \mu s \text{ ; Minimum Switching Period}$$

(6)

(7)

The proper value of R<sub>TSET</sub> will result in the clamped maximum on-time, T<sub>ON(max)</sub>, required by the converter operating at the minimum input line voltage and maximum load.

#### 8.3.4 Distortion Reduction

Due to the parasitic resonance between the drain-source capacitance of the switching MOSFET and the boost inductor, conventional transition-mode PFC circuits may not be able to absorb power from the input line when the input voltage is near zero. This limitation increases total harmonic distortion as a result of ac-line current waveform distortion in the form of flat spots. To help reduce line-current distortion, the UCC28063A increases switching MOSFET on-time when the input voltage is near 0 V to improve the power absorption capability and compensate for this effect.

#### 8.3.5 Zero-Current Detection and Valley Switching

In transition-mode PFC circuits, the MOSFET turns on when the boost inductor current reaches zero. Because of the resonance between the boost inductor and the parasitic capacitance at the MOSFET drain node, part of the energy stored in the MOSFET junction capacitor can be recovered, reducing switching losses. Furthermore, when the rectified input voltage is less than half of the output voltage, all the energy stored in the MOSFET junction capacitor can be recovered and zero-voltage switching (ZVS) can be realized. By adding an appropriate delay, the MOSFET can be turned on at the valley of its resonating drain voltage (valley-switching). In this way, the energy recovery can be maximized and switching loss is minimized.

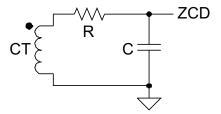

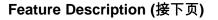

The optimal time delay is generally derived empirically, but a good starting point is a value equal to 25% of the resonant period of the drain circuit. The delay can be realized by a simple RC filter, as shown in 25, but the delay time increases slightly as the input voltage nears the output voltage. Because the ZCD pin is internally clamped, a more accurate delay can also be realized by using the circuit shown in 26.

图 25. Simple RC Delay Circuit

图 26. More Accurate Time Delay Circuit

#### 8.3.6 Phase Management and Light-Load Operation

Under light-load conditions, switching losses may dominate over conduction losses and efficiency may be improved if one phase (channel) is turned off. At a certain power level, the reduction of switching losses is greater than the increase in conduction losses. Turning off one phase at light load is especially valuable for meeting light-load efficiency standards. This is one of the major benefits of interleaved PFC and it is especially valuable for waluable for meeting 80+ design requirements.

The PHB input can be used to force the UCC28063A to operate in single-phase mode. When PHB is driven below 0.8 V, channel B will stop switching and channel A on-time will automatically double to compensate. The device will resume dual-phase mode when PHB is raised above 1.0 V. For customized phase management, an external circuit can detect the conditions for switching to single-phase operation and drive PHB accordingly. To operate continuously in two-phase mode (normal mode) when phase management is not desired, simply connect PHB to VREF.

As load current decreases, the error amplifier commands less ac-line input current by lowering COMP voltage. In applications where the ac-line is limited to the low-voltage range only, it may be advantageous to connect PHB directly to COMP to allow automatic selection of single-phase operation without additional external circuitry.

#### 8.3.7 External Disable

The UCC28063A can be externally disabled by purposefully grounding the VSENSE pin with an open-drain or open-collector driver. When disabled, the device supply current drops significantly and COMP is actively pulled low. This disable method forces the device into standby mode and minimizes its power consumption. This is particularly useful when standby power is a key design aspect. When VSENSE is released, the device enters soft-start mode.

#### 8.3.8 Improved Error Amplifier

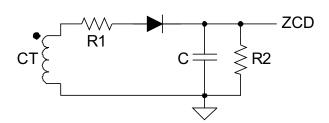

The voltage-error amplifier is a transconductance amplifier. Voltage-loop compensation is connected from the error amplifier output, COMP, to analog ground, AGND. The recommended Type-II compensation network is shown in  $\mathbb{E}$  27. For loop-stability purposes, the compensation network values are calculated based on small-signal perturbations of the output voltage using the nominal transconductance (gain) of 55  $\mu$ S.

ZHCSDH6B-DECEMBER 2014-REVISED MARCH 2015

www.ti.com.cn

## Feature Description (接下页)

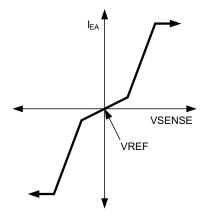

To improve the transient response to large perturbations, the error amplifier gain increases by a factor of  $\sim$ 5X when the error amp input deviates more than ±5% from the nominal regulation voltage, VSENSEreg. This increase allows faster charging and discharging of the compensation components following sudden load-current increases or decreases (also refer to  $\mathbb{R}$  5 in the *Typical Characteristics*).

Basic voltage-error amplifier transconductance curve showing small-signal and large-signal gain sections, with maximum current limitations.

#### 图 28. Basic Voltage-Error Amplifier Transconductance Curve

### 8.3.9 Soft Start

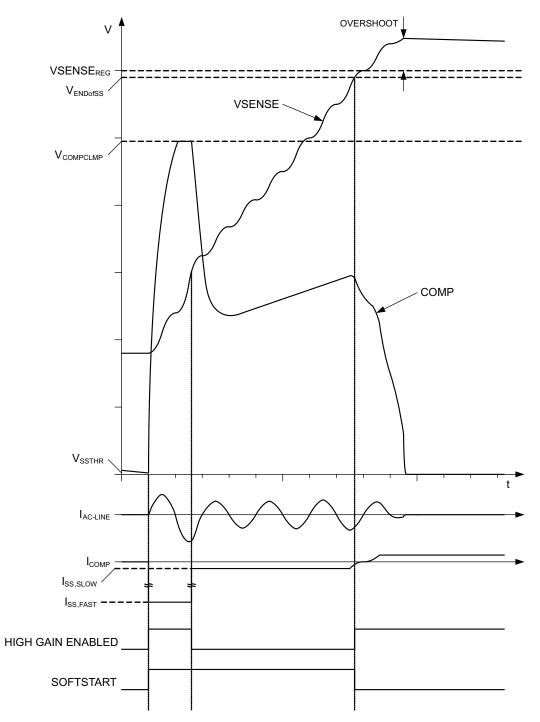

Soft-start is a process for boosting the output voltage of the PFC converter from the peak of the ac-line input voltage to the desired regulation voltage under controlled conditions. Instead of a dedicated soft-start pin, the UCC28063A uses the voltage error amplifier as a controlled current source to increase the PWM duty-cycle by way of increasing the COMP voltage. To avoid excessive start-up time-delay when the ac-line voltage is low, a higher current is applied until VSENSE exceeds 3 V at which point the current is reduced to minimize the tendency for excess COMP voltage at no-load start-up.

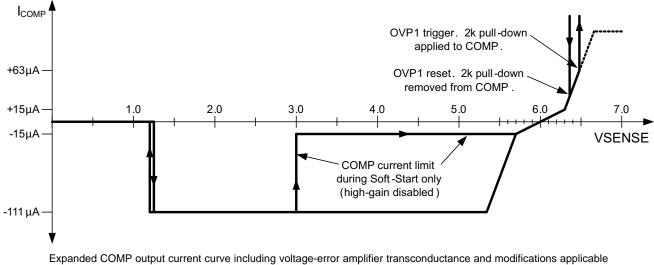

The PWM gradually ramps from zero on-time to normal on-time as the compensation capacitor from COMP to AGND charges from zero to near its final value. This process implements a soft-start, with timing set by the output current of the error amplifier and the value of the compensation capacitors. In the event of a HVSEN FailSafe OVP, brownout, external-disable, UVLO fault, or other protection faults, COMP is actively discharged and the UCC28063A will soft-start after the triggering event is cleared. Even if a fault event happens very briefly, the fault is latched into the soft-start state and soft-start is delayed until COMP is fully discharged to 20 mV and the fault is cleared. See 29 for details on the COMP current. See 30 which illustrates an example of typical system behavior during soft-start.

UCC28063A ZHCSDH6B – DECEMBER 2014 – REVISED MARCH 2015

#### www.ti.com.cn

# Feature Description (接下页)

Expanded COMP output current curve including voltage-error amplifier transconductance and modifications applicab to soft-start and overvoltage conditions.

图 29. Expanded Comp Output Current Curve

# Feature Description (接下页)

图 30. Soft-Start Timing With Illustrative System Behavior

### Feature Description (接下页)

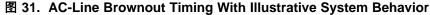

#### 8.3.10 Brownout Protection

As the power line RMS voltage decreases, RMS input current must increase to maintain a constant output

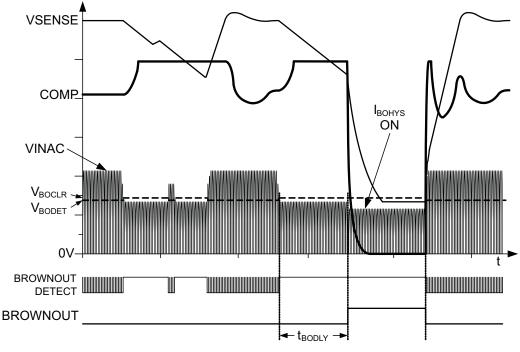

voltage for a specific load. Brownout protection helps prevent excess system thermal stress (due to the higher RMS input current) from exceeding a safe operating level. Power-line voltage is sensed at VINAC. When the VINAC fails to exceed the brownout threshold for the brownout filter time, a brownout condition is detected and both gate drive outputs are turned off. During brownout, COMP is actively pulled low and a soft-start condition is initiated. Hysteresis is built into the brownout detection circuit to avoid chatter around the threshold. When VINAC rises above the brownout threshold, the power stage soft-starts as COMP rises with controlled current.

The brownout detection threshold and its hysteresis are set by the voltage-divider ratio and resistor values. Brownout protection is based on VINAC peak voltage; the threshold and hysteresis are also based on the line peak voltage. Major hysteresis is provided by a 2-µA current-sink (IBOHYS) enabled whenever VINAC falls below the brownout detection threshold. Minor hysteresis is also present in the form of a 50-mV offset (V<sub>BOHYS</sub>) between the VINAC detection and clear thresholds. The peak VINAC voltage can be easily translated into an RMS value. Example resistor values for the voltage divider are 8.61 M $\Omega$  ±1% from the rectified input voltage to VINAC and 133 k $\Omega$  ±1% from VINAC to ground. These resistors set the typical thresholds for RMS line voltages, as shown in 表 1.

#### 表 1. Brownout Thresholds (For Conditions Stated in the Text)

| THRESHOLD | AC-LINE VOLTAGE (RMS) |

|-----------|-----------------------|

| Falling   | 66 V                  |

| Rising    | 78 V                  |

公式 8 and 公式 9 can be used to calculate the VINAC divider-resistor values based on desired brownout detection and brownout clear voltage levels. V<sub>AC OK</sub> is the desired RMS turn-on voltage, V<sub>AC BO</sub> is the desired RMS turn-off brownout voltage, and  $V_{LOSS}$  is total series voltage drop due to wiring, EMI-filter, and bridge-rectifier impedances at  $V_{AC\_BO}$ .  $V_{BODET}$ ,  $V_{BOHYS}$  and  $I_{BOHYS}$  are found in the data-tables of this datasheet.

$$R_{A} = \left(\frac{\sqrt{2}(V_{AC\_OK} - V_{AC\_BO}) - V_{BOHYS}}{I_{BOHYS}}\right) \left(1 + \frac{V_{BOHYS}}{V_{BODET}}\right)$$

$$R_{B} = \frac{RA}{\left(\frac{\sqrt{2}V_{AC\_BO} - V_{LOSS}}{V_{BODET}} - 1\right)}$$

(8)

(9)

Once standard values for the VINAC divider-resistors R<sub>A</sub> and R<sub>B</sub> are selected, the actual turn-on and brownout threshold RMS voltages for the ac-line can be back-calculated with 公式 10 and 公式 11:

$$V_{AC\_BO} = \left(1 + \frac{R_A}{R_B}\right) \frac{V_{BODET}}{\sqrt{2}} + \frac{V_{LOSS}}{\sqrt{2}}$$

(10)

$$V_{AC\_OK} = V_{AC\_BO} + \frac{R_A I_{BOHYS}}{\sqrt{2}} + \frac{V_{BOHYS}}{\sqrt{2}} \frac{V_{BOHYS}}{\sqrt{2}}$$

(11)

An example of the timing for the brownout function is illustrated in **3**1.

For a quick estimation of the turn-on and brownout voltages, simplify the foregoing equations by setting the VLOSS and V<sub>BOHYS</sub> terms to zero.

#### UCC28063A

ZHCSDH6B-DECEMBER 2014-REVISED MARCH 2015

#### 8.3.11 Dropout Detection

It is often the case that the ac-line voltage momentarily drops to zero or nearly zero, due to transient abnormal events affecting the local ac power distribution network. Referred to as ac-line dropouts (or sometimes as linedips) the duration of such events usually extends to only 1 or 2 line cycles. During a dropout, the down-stream power conversion stages depend on sufficient energy storage in the PFC output capacitance, which is sized to provide the ride-through energy for a specified hold-up time. Typically while the PFC output voltage is falling, the voltage-loop error amplifier output rises in an attempt to maintain regulation. As a consequence, excess duty-cycle is commanded when the ac-line voltage returns and high peak current surges may saturate the boost inductors with possible overstress and audible noise.

The UCC28063A incorporates a dropout detection feature which suspends the action of the error amplifier for the duration of the dropout. If the VINAC voltage falls below 0.35 V for longer than 5 ms, a dropout condition is detected and the error amplifier output is turned off. In addition, a 4- $\mu$ A pull-down current is applied to COMP to gently discharge the compensation network capacitors. In this way, when the ac-line voltage returns, the COMP voltage (and corresponding duty-cycle setting) remains very near or even slightly below the level it was before the dropout occurred. Current surges due to excess duty-cycle, and their undesired attendant effects, are avoided. The dropout condition is cancelled and the error amplifier resumes normal operation when VINAC rises above 0.71 V.

Based on the VINAC divider-resistor values calculated for brownout in the previous section, the input RMS voltage thresholds for dropout detection  $V_{AC_{DO}}$  and dropout clearing  $V_{DO_{CLR}}$  can be determined using  $\Delta \pm 12$  and  $\Delta \pm 13$ , below.

$$V_{AC\_DO} = \frac{V_{DODET} \left( \frac{R_A}{R_B} + 1 \right) + V_{LOSS}}{\sqrt{2}}$$

$$V_{DO\_CLR} = \frac{V_{DOCLR} \left( \frac{R_A}{R_B} + 1 \right) + V_{LOSS}}{\sqrt{2}}$$

(12)

(13)

Avoid excessive filtering of the VINAC signal, or dropout detection may be delayed or defeated. An RC timeconstant of  $\leq$  100-µs should provide good performance. An example of the timing for the dropout function is illustrated in  $\mathbb{R}$  32.

VSENSE VINAC COMP VDOCLR VDOCLR

图 32. AC-Line Dropout Timing With Illustrative System Behavior

► t<sub>DODLY</sub>

## 8.3.12 VREF

VREF is an output which supplies a well-regulated reference voltage to circuits within the device as well as serving as a limited source for external circuits. This output must be bypassed to GND with a low-impedance 0.1- $\mu$ F or larger capacitor placed as close to the VREF and GND pins as possible. Current draw by external circuits should not exceed a few milli-amperes and should not be pulsing.

The VREF output is disabled under the following conditions: when VCC is in UVLO, or when VSENSE is below the Enable threshold. This output can only source current and is unable to accept current into the pin.

## 8.3.13 VCC

VCC is usually connected to a bias supply of between 13 V and 21 V. To minimize switching ripple voltage on VCC, it should be by-passed with a low-impedance capacitor as close to the VCC and GND pins as possible. The capacitance should be sized to adequately decouple the peak currents due to gate-drive switching at the highest operating frequency. When powered from a poorly-regulated low-impedance supply, an external zener diode is recommended to prevent excessive current into VCC.

The undervoltage-lockout (UVLO) condition is when VCC voltage has not yet reached the turn-on threshold or has fallen below the turn-off threshold, having already been turned on. While in UVLO, the VREF output and most circuits within the device are disabled and VCC current falls significantly below the normal operating level. The same situation applies when VSENSE is below its Enable threshold. This helps minimize power loss during pre-powerup and standby conditions.

## 8.3.14 Control of Downstream Converter

In the UCC28063A, the PWMCNTL pin can be used to coordinate the PFC stage with a downstream converter. Through the HVSEN pin, the PFC output voltage is monitored. A 12- $\mu$ A current source (I<sub>HV\_HYS</sub>) is enabled as long as the output voltage remains below a programmed threshold. When the output voltage exceeds that threshold, PWMCNTL pin is pulled to ground internally and can be used to enable a downstream converter. At the same time the current source is disabled, providing hysteresis for a lower threshold at which the downstream converter should be turned off. The enable/disable hysteresis is adjusted through the HVSEN voltage-divider ratio and resistor values. The HVSEN pin is also used for the FailSafe over-voltage protection (OVP). When designing the voltage divider, make sure this FailSafe OVP level is set above normal VSENSE OVP levels.

Because there are two thresholds associated with the HVSEN input detected through a single resistor divider, the PWMCNTL turn-off voltage,  $V_{PWM-OFF}$ , is linked to the FailSafe OVP voltage,  $V_{FLSF_OV}$ , as shown by  $\Delta \pm 14$ :

UCC28063A ZHCSDH6B-DECEMBER 2014-REVISED MARCH 2015

www.ti.com.cn

**NSTRUMENTS**

**EXAS**

$$\frac{V_{\mathsf{PWM}-\mathsf{OFF}}}{2.5\,\mathsf{V}} = \frac{V_{\mathsf{FLSF}}_{\mathsf{OV}}}{4.87\,\mathsf{V}} \tag{14}$$

Choosing either one first arbitrarily determines the other, so a trade-off may be necessary. The PWMCNTL turnon voltage,  $V_{PWM-ON}$ , is programmed by choosing the upper divider resistor value in consideration with the HVSEN hysteresis current, as shown in 公式 15 and 公式 16. The lower divider resistor is then calculated as shown in 公式 17.

$$V_{PWM-ON} = V_{PWM-OFF} + I_{HV}_{HYS}R_{HV}_{UPPER}$$

(15)

$$R_{HV}_{UPPER} = \frac{V_{PWM-ON} - V_{PWM-OFF}}{I_{HV}_{HYS}}$$

(16)

$$R_{HV}_{UPPER} = \frac{R_{HV}_{UPPER}}{I_{HV}_{UPPER}}$$

(17)

$$\frac{V_{\text{PWM}-\text{OFF}}}{2.5 \text{ V}} - 1$$

(17)

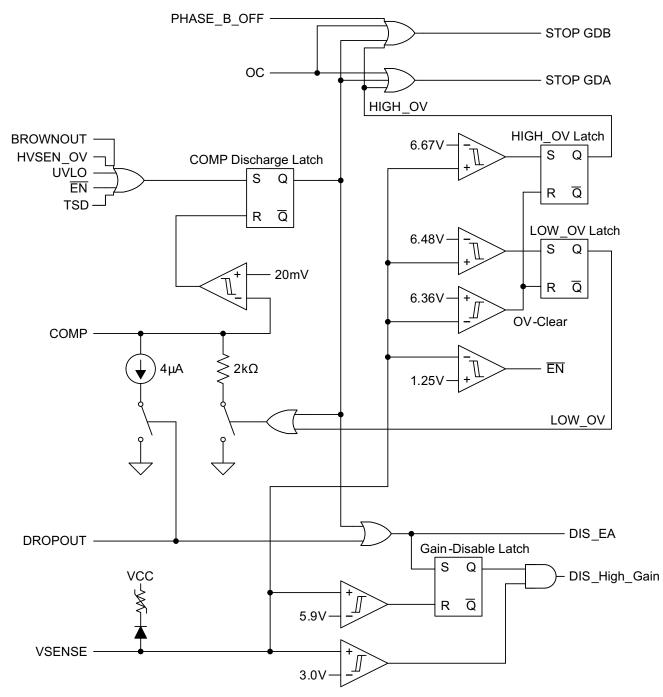

#### 8.3.15 System Level Protections

#### 8.3.15.1 Failsafe OVP - Output Overvoltage Protection

FailSafe OVP prevents any single failure from allowing the output to boost above safe levels. Redundant paths for output voltage sensing provide additional protection against output over-voltage. Over-voltage protection is implemented through two independent paths: VSENSE and HVSEN. The converter shuts down if either input senses a severe over-voltage condition. The output voltage can still remain below a safe limit if either sense path fails. The device is re-enabled when both sense inputs fall back into their normal ranges. At that time, the gate drive outputs will resume switching under PWM control. A low-level over-voltage on VSENSE does not trigger soft-start, but the COMP pin is discharged by an internal 2-k $\Omega$  resistance until the output voltage falls below the 2% hysteresis OV-clear threshold. A higher-level over-voltage on VSENSE additionally shuts off the gate-drive outputs until the OV clears, but still does not trigger a soft-start. However, an overvoltage detected on HVSEN does trigger a full soft-start and the COMP pin is fully discharged to 20 mV before the soft-start can begin.

#### 8.3.15.2 Overcurrent Protection

Under certain conditions (such as inrush, brownout-recovery, and output over-load) the PFC power stage sees large currents. It is critical that the power devices be protected from switching during these conditions.

The conventional current-sensing method uses a shunt resistor in series with each MOSFET source leg to sense the converter currents, resulting in multiple ground points and high power dissipation. Furthermore, since no current information is available when the MOSFETs are off, the source-resistor current-sensing method results in repeated turn-on of the MOSFETs during overcurrent (OC) conditions. Consequently, the converter may temporarily operate in continuous conduction mode (CCM) and may experience failures induced by excessive reverse-recovery currents in the boost diodes or other abnormal stresses.

The UCC28063A uses a single resistor to continuously sense the combined total inductor (input) current. This way, turn-on of the MOSFETs is completely avoided when the inductor currents are excessive. The gate drive to the MOSFETs is inhibited until total inductor current drops to near zero, precluding reverse-recovery-induced failures (these failures are most likely to occur when the ac-line recovers from a brownout condition).

The nominal OC threshold voltage during two-phase operation is -200 mV, which helps minimize losses. This threshold is automatically reduced to -166 mV during single-phase operation, either by detection of a phase failure or because PHB is driven below 0.8 V. Note that the single-phase threshold is not simply 1/2 of the dual-phase threshold, because the ratio of the single-phase peak current to the interleaved peak current is higher than 1/2.

An OC condition immediately turns off both gate-drive outputs, but does not trigger a soft-start and does not modify the error amplifier operation. The over-current condition is cleared when the total inductor current-sense voltage falls below the OC-clear threshold (-15 mV).

Following an over-current condition, both MOSFETs are turned on simultaneously once the input current drops to near zero. Because the two phase currents are temporarily operating in-phase, the current-sense resistance should be chosen so that OC protection is not triggered with twice the maximum current peak value of either phase in order to allow quick return to normal operation after an over-current event. Automatic phase-shift control will re-establish interleaving within a few switching cycles.

#### 8.3.15.3 Open-Loop Protection

If the feedback loop is disconnected from the device, a 100-nA current source internal to the UCC28063A pulls the VSENSE pin voltage towards ground. When VSENSE falls below 1.20 V, the device becomes disabled. When disabled, the bias supply current decreases, both gate-drive outputs and COMP are actively pulled low, and a soft-start condition is initiated. The device is re-enabled when VSENSE rises above 1.25 V. At that time, the gate drive outputs will begin switching under soft-start PWM control.

If the feedback loop is disconnected from ground, the VSENSE voltage will be pulled high. When VSENSE rises above the 2nd-level over-voltage protection threshold, both gate drive outputs are shut off and COMP is actively pulled low. The device is re-enabled when VSENSE falls below the OV-clear threshold. The VSENSE input can tolerate a limited amount of current into the device under abnormally high input voltage conditions. Refer to the Absolute Maximum Ratings table near the beginning of this datasheet for details.

#### 8.3.15.4 VCC Undervoltage Lock-Out (UVLO) Protection

VCC must rise above the turn-on threshold for the PWM to begin functioning. If VCC drops below the UVLO threshold during operation, both gate-drive outputs are actively pulled low, COMP is actively pulled low, and a soft-start condition is triggered. VCC must again rise above the turn-on threshold for the PWM function to restart in soft-start mode.

#### 8.3.15.5 Phase-Fail Protection

The UCC28063A detects failure of either of the phases by monitoring the sequence of ZCD pulses. During normal two-phase operation, if one ZCD input remains idle for longer than approximately 12 ms while the other ZCD input switches normally, the over-current threshold is reduced and PWMCNTL goes to a high-impedance state, indicating that the PFC power stage is not operating correctly. During normal single-phase operation (PHB < 0.8 V), phase failure is not monitored. Also on the UCC28063A, phase failure is not monitored when COMP is below approximately 222 mV.

#### 8.3.15.6 Thermal Shutdown Protection

Overloading of the gate-drive outputs, VREF, or both can dissipate excess power within the device which may raise the internal temperature of the circuits beyond a safe level. Even normal power dissipation can generate excess heat if the thermal impedance is too high or the ambient temperature is too high. When the UCC28063A detects an internal over-temperature condition it will shutdown the outputs and trigger a full soft-start condition. When the internal device junction temperature has cooled below the thermal hysteresis temperature, operation will resume under soft-start control.

#### 8.3.15.7 AC-Line Brownout and Dropout Protections

See specific discussions for each topic in previous sections of this data sheet.

#### 8.3.15.8 Fault Logic Diagram

图 33 depicts the fault-handling logic involving VSENSE, COMP, and several internal states.

图 33. Fault Logic With VSENSE Detections and Error Amplifier Control

#### 8.4 Device Functional Modes

The controller is primarily intended for set up as a dual phase interleaved PFC which utilizes inductor demagnetization information based on inductor sense winding voltages which are routed to ZCDA and ZCDB to trigger the start of a switching cycle.

The functionality may be extended in a couple of ways:

- Phase-B Enable and Disable: Phase-B may be *shed* by explicit user control or it may be set up as an automatic light load efficiency management feature. When the voltage applied to the PHB pin is below VPHBF threshold, Phase B and the Phase Fail Detector will be disabled. The commanded On-time for Phase-A will be doubled to minimize the output voltage transient which would otherwise occur. When the voltage on the PHB pin is greater than the VPHBR threshold, two phase mode is continuously enabled. Tie PHB to VREF pin for this mode. Alternatively PHB may be tied to the COMP pin for *automatic* phase shedding at light load.

- **PFC Stage Enable and Disable Control:** Controller operation is enabled when VSENSE voltage exceeds the 1.25-V enable threshold. The primary disable method should be by pulling VSENSE low by an open drain or open collector logic output. This will disable the outputs and significantly reduce VCC current. Releasing VSENSE will initiate a Soft-Start. Avoid any PCB traces which would couple any noise into this node.

# **9** Applications and Implementation

#### 注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

This control IC is generally applicable to the control of AC-DC power supplies which require Active Power Factor Correction off Universal AC line. Applications using this IC will generally meet the Class D equipment input current harmonics standards per EN61000-3-2. This standard applies to equipment with rated Powers higher than 75W. The IC brings two phase interleaved control capability to the Transition Mode Boost and hence will be generally a very good choice for cost optimized applications in the 150W to 800W space, or to even lower powers that wish to exploit the interleaving benefits of reduced filtering component size, lower profile solutions and distributed thermal management.

The UCC28063EVM-723 300-W Interleaved PFC Pre-Regulator User's Guide (SLUU512) describes an EVM design for a 300W Application.

This EVM has an associated Excel file to help automate calculations for its component choices available at SLUC292.

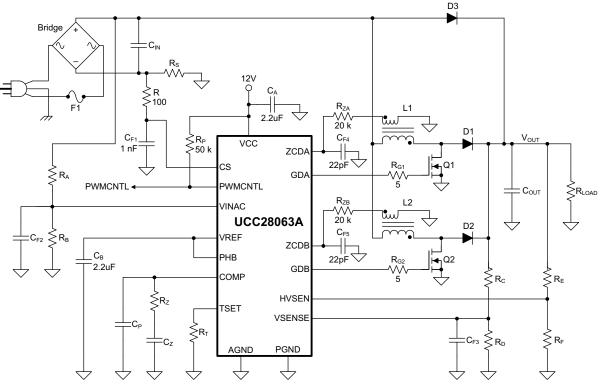

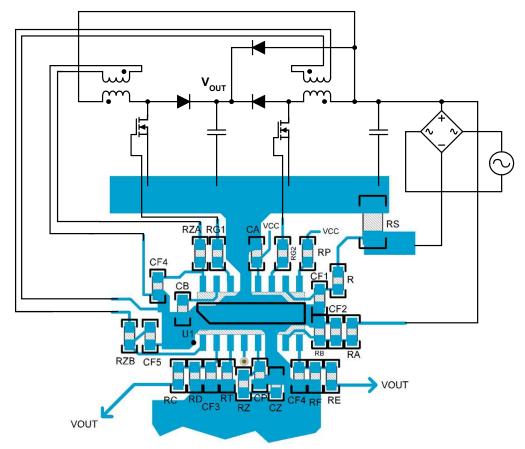

# 9.2 Typical Application

An example of the UCC28063A PFC controller in a two-phase interleaved, transition-mode PFC pre-regulator is shown in .

图 34. Typical Interleaved Transition-Mode PFC Pre-Regulator

#### Typical Application (接下页)

#### 9.2.1 Design Requirements

The specifications for this design were chosen based on the power requirements of a typical 300-W LCD TV. These specifications are shown in 表 2.

|                   | DESIGN PARAMETER             | MIN             | ТҮР | MAX              | UNIT |

|-------------------|------------------------------|-----------------|-----|------------------|------|

| V <sub>IN</sub>   | RMS input voltage            | 85<br>(VIN_MIN) |     | 265<br>(VIN_MAX) | VRMS |

| V <sub>OUT</sub>  | Output voltage               |                 | 390 |                  | V    |

| f <sub>LINE</sub> | AC-line frequency            | 47              |     | 63               | Hz   |

| PF                | Power factor at maximum load | 0.90            |     |                  |      |

| P <sub>OUT</sub>  |                              |                 |     | 300              | W    |

| η                 | Full-load efficiency         | 92%             |     |                  |      |

| f <sub>MIN</sub>  | Minimum switching frequency  | 45              |     |                  | kHz  |

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Inductor Selection

The boost inductor is selected based on the inductor ripple current requirements at the peak of low line. Selecting the inductor requires calculating the boost converter duty cycle at the peak of low line (D<sub>PEAK LOW LINE</sub>), as shown in 公式 18.

$$D_{\text{PEAK}\_LOW\_LINE} = \frac{V_{\text{OUT}} - V_{\text{IN}\_MIN}\sqrt{2}}{V_{\text{OUT}}} = \frac{390 \text{ V} - 85 \text{ V}\sqrt{2}}{390 \text{ V}} \approx 0.69$$

(18)

The minimum switching frequency of the converter (f<sub>MIN</sub>) under low line conditions occurs at the peak of low line and is set between 25 kHz and 50 kHz to avoid audible noise. For this design example, f<sub>MIN</sub> is set to 45 kHz. For a 2-phase interleaved design, L1 and L2 are determined as shown in 公式 19.

$$L1 = L2 = \frac{\eta \times V_{IN} MIN^{2} \times D_{PEAK} LOW LINE}{P_{OUT} \times f_{MIN}} = \frac{0.92(85 \text{ V})^{2} 0.69}{300 \text{ W} \times 45 \text{ kHz}} \approx 340 \,\mu\text{H}$$

(19)

The inductor for this design would have a peak current (I<sub>LPEAK</sub>) of 5.4 A, as shown in 公式 20, and an RMS current (I<sub>LRMS</sub>) of 2.2 A, as shown in 公式 21.

$$I_{LPEAK} = \frac{P_{OUT}\sqrt{2}}{V_{IN\_MIN} \times \eta} = \frac{300 \,\text{W}\sqrt{2}}{85 \,\text{V} \times 0.92} \approx 5.4 \,\text{Apk}$$

$$I_{LRMS} = \frac{I_{LPEAK}}{\sqrt{6}} = \frac{5.4 \,\text{A}}{\sqrt{6}} \approx 2.2 \,\text{Arms}$$

(20)

This converter uses constant on time (T<sub>ON</sub>) and zero-current detection (ZCD) to set up the converter timing. Auxiliary windings on L1 and L2 detect when the inductor currents are zero. Selecting the turns ratio using 公式 22 ensures that there will be at least 2 V at the peak of high line to reset the ZCD comparator after every switching cycle.

The turns-ratio of each auxiliary winding is:

$$\frac{N_{P}}{N_{s}} = \frac{V_{OUT} - V_{IN}_{MAX}\sqrt{2}}{2V} = \frac{390V - 265V\sqrt{2}}{2V} \approx 8$$

(22)

#### 9.2.2.2 ZCD Resistor Selection (R<sub>ZA</sub>, R<sub>ZB</sub>)

The minimum value of the ZCD resistors is selected based on the internal clamps maximum current ratings of 3 mA, as shown in 公式 23.

(21)

$R_{ZA} = R_{ZB} \ge \frac{V_{OUT}N_S}{N_P \times 3mA} = \frac{390 V}{8 \times 3mA} \approx 16.3 k\Omega$

In this design the ZCD resistors are set to 20 k $\Omega$ , as shown in  $\Delta \pm 24$ .  $R_{ZA} = R_{ZB} = 20 k\Omega$

# 9.2.2.3 HVSEN

The HVSEN pin programs the PWMCNTL output of the UCC28063A. The PWMCNTL open-drain output can be used to disable a downstream converter while the PFC output capacitor is charging. PWMCNTL starts high impedance and pulls to ground when HVSEN increases above 2.5 V. Setting the point where PWMCNTL becomes active requires a voltage divider from the boost voltage to the HVSEN pin to ground. 公式 25 to 公式 30 show how to set the PWMCNTL pin to activate when the output voltage is within 90% of its nominal value.

$$V_{OUT_OK} = V_{OUT} \times 0.90 \approx 351 \text{ V}$$

(25)

Resistor R<sub>E</sub> sets up the high side of the voltage divider and programs the hysteresis of the PWMCNTL signal. For this example, R<sub>F</sub> was selected to provide 99 V of hysteresis, as shown in 公式 26. Three resistors in series were used to meet voltage requirements.

$$R_{E} = \frac{\text{Hysteresis}}{12\,\mu\text{A}} = \frac{99\,\text{V}}{12\,\mu\text{A}} = 8.25\,\text{M}\Omega \approx 3 \times 2.74\,\text{M}\Omega \tag{26}$$

Resistor R<sub>F</sub> is used to program the PWMCNTL active threshold, as shown in 公式 27.

$$R_{F} = \frac{2.5V}{\frac{V_{OUT}_{OK} - 2.5V}{R_{E}} - 12\mu A} = \frac{2.5V}{\frac{351V - 2.5V}{8.22M\Omega} - 12\mu A} = 82.25k\Omega$$

(27)

Select a standard resistor value for R<sub>F</sub>.

$R_F = 82.5 k\Omega$ This PWMCNTL output will remain active until a minimum output voltage (VOUT MIN) is reached, as shown in 公式 29.

$$V_{OUT\_MIN} = \frac{2.5 \, V \left( R_E + R_F \right)}{R_F} = \frac{2.5 \, V \left( 8.22 \, M \Omega + 82.5 \, k \Omega \right)}{82.5 \, k \Omega} \approx 252 \, V$$

(29)

According to these resistor values, the FailSafe OVP threshold will be set according to 公式 30

$$V_{OV\_FAILSAFE} = \frac{4.87 \, V \left(R_E + R_F\right)}{R_F} = \frac{4.87 \, V \left(8.22 M \Omega + 82.5 k \Omega\right)}{82.5 k \Omega} \approx 490 \, V$$

(30)

# 9.2.2.4 Output Capacitor Selection

The output capacitor ( $C_{OUT}$ ) is selected based on holdup requirements, as shown in  $\Delta \vec{x}$  31.