# UCC2895x-Q1 汽车级 适用于宽输入电压范围应用的 相移全桥控制器

# 1 特性

- 符合汽车应用要求

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 1: -40°C 至 +125°C 环境工作 温度范围

- 器件 HBM ESD 分类等级 H2

- 器件 CDM ESD 分类等级 C3B

- 增强型零电压开关 (ZVS) 范围

- 直接同步整流器 (SR) 控制

- 轻负载效率管理包括:

- 突发模式运行

- 不连续导通模式 (DCM), 动态 SR 开/关控制

- 支持可编程斜坡补偿和电压模式控制的平均或者峰 值电流模式控制

- 闭环路软启动和使能功能

- 支持双向同步的高达 1MHz 的可编程开关频率

- (±3%) 支持断续模式的逐周期电流限制保护

- 150µA 启动电流

- V<sub>DD</sub> 欠压锁定

- 宽温度范围:-40°C至+125°C

## 2 应用

- 电动汽车逆变器

- 电动汽车车载充电器

- 光伏逆变器

- **UPS**

# 3 说明

UCC28951-Q1 控制器是 UCC28950-Q1 的增强版 本。它是 UCC28950-Q1 完全兼容的快插替代器件。 请参阅应用手册做出正确选择: UCC28950-Q1 或 UCC28951-Q1 以确定要使用的控制器。 UCC2895x-Q1 器件采用全桥高级控制,并对同步整流器 (SR) 输 出级进行主动控制。

ZVS 运行在各种工作条件下均可实现,而负载电流可 自动调节次级侧同步整流器 (SR) 的开关延迟。此功能 可更大程度地提高系统整体效率。

借助 UCC2895x-Q1 600W 相移全桥设计评审/应用手 册 (SLUA560),可轻松开始使用该器件。

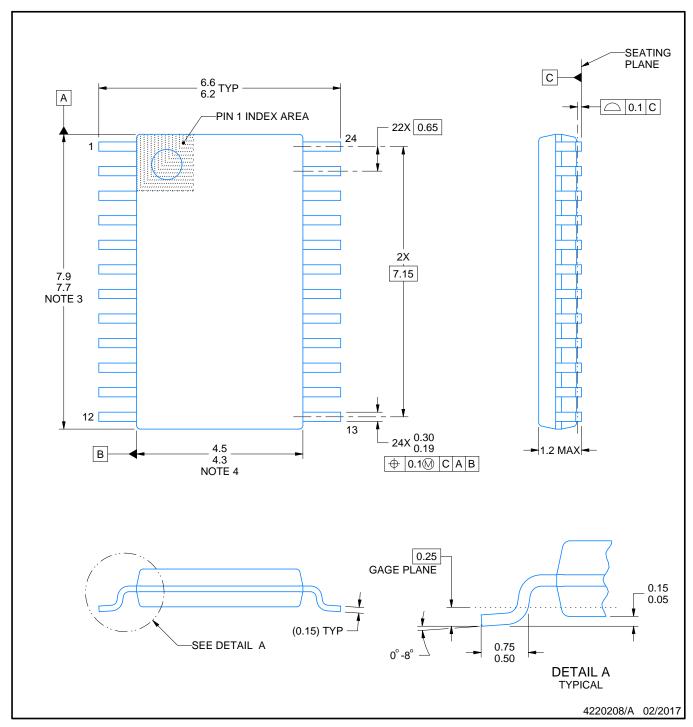

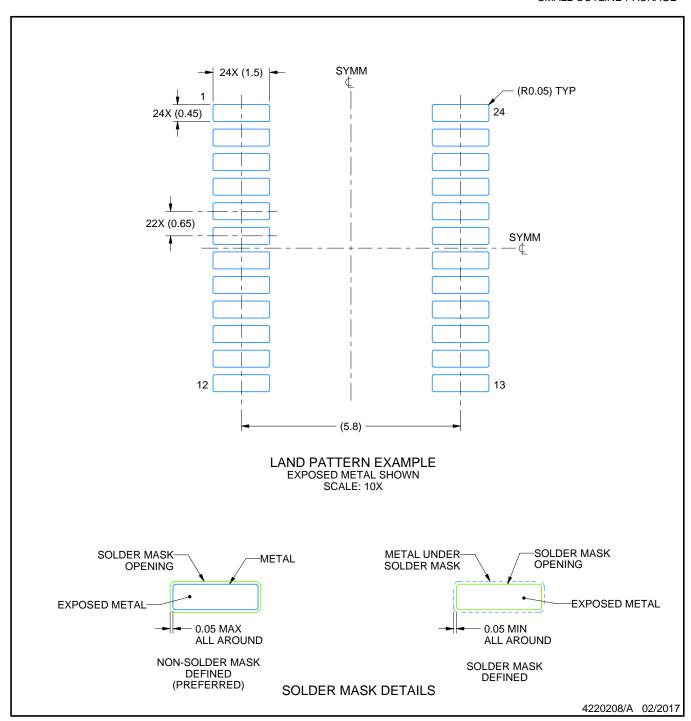

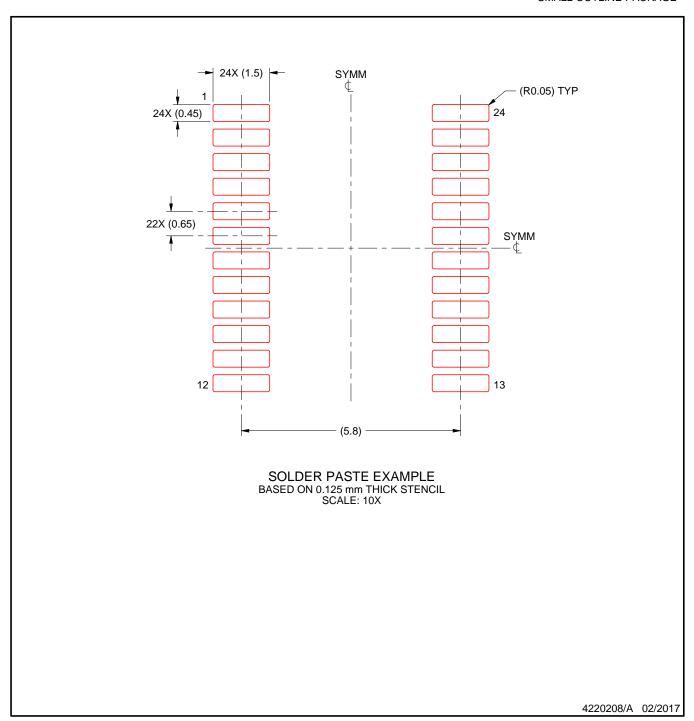

24 引脚 TSSOP 封装符合 RoHS 要求。

# 器件信息

| 器件型号        | 封装 <sup>(1)</sup> | 封装尺寸(标称值)       |

|-------------|-------------------|-----------------|

| UCC2895x-Q1 | TSSOP (24)        | 7.80mm × 4.40mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

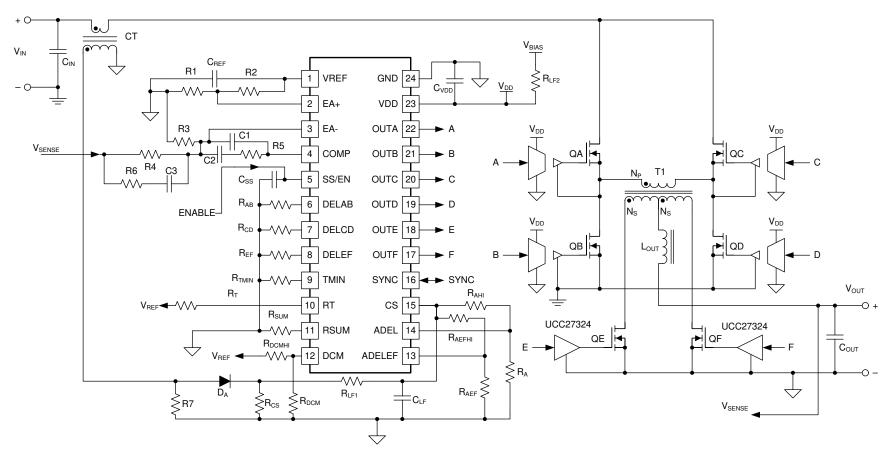

简化版应用

# **Table of Contents**

| 1 特性                                 | 1 | 6.3 Feature Description                            | 19 |

|--------------------------------------|---|----------------------------------------------------|----|

| 2 应用                                 |   | 6.4 Device Functional Modes                        | 36 |

|                                      |   | 7 Application and Implementation                   | 37 |

| 4 Pin Configuration and Functions    |   | 7.1 Application Information                        |    |

| 5 Specifications                     |   | 7.2 Typical Application                            | 40 |

| 5.1 Absolute Maximum Ratings         |   | 7.3 Power Supply Recommendations                   |    |

| 5.2 ESD Ratings                      |   | 7.4 Layout                                         | 69 |

| 5.3 Recommended Operating Conditions |   | 8 Device and Documentation Support                 | 7  |

| 5.4 Thermal Information              |   | 8.1 Device Support                                 | 7° |

| 5.5 Electrical Characteristics       |   | 8.2 Documentation Support                          | 7  |

| 5.6 Timing Requirements              |   | 8.3 Receiving Notification of Documentation Update | s7 |

| 5.7 Dissipation Ratings              |   | 8.4 Community Resources                            | 7° |

| 5.8 Typical Characteristics          |   | 8.5 Trademarks                                     | 7  |

| 6 Detailed Description               |   | 9 Revision History                                 | 7° |

| 6.1 Overview                         |   | 10 Mechanical, Packaging, and Orderable            |    |

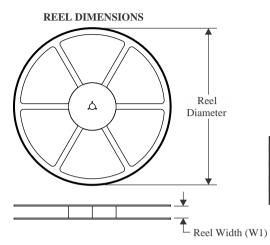

| 6.2 Functional Block Diagram         |   | Information                                        | 73 |

# **4 Pin Configuration and Functions**

图 4-1. PW Package, 24-Pin TSSOP (Top View)

# **Pin Functions**

| P      | IN  | TYPE | DESCRIPTION                                                                                                                               |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | ITPE | DESCRIPTION                                                                                                                               |

| ADEL   | 14  | I    | Dead-time programming for the primary switches over CS voltage range, t <sub>ABSET</sub> and t <sub>CDSET</sub> . See 节 6.3.6             |

| ADELEF | 13  | I    | Delay-time programming between primary side and secondary side switches, $t_{\text{AFSET}}$ and $t_{\text{BESET}}$ . See $\ddagger$ 6.3.7 |

| COMP   | 4   | I/O  | Error amplifier output and input to the PWM comparator. See 节 6.3.3                                                                       |

| cs     | 15  | I    | Current sense for cycle-by-cycle overcurrent protection and adaptive delay functions. See † 6.3.14                                        |

| DCM    | 12  | I    | DCM threshold setting. See 节 6.3.12                                                                                                       |

| DELAB  | 6   | I    | Dead-time delay programming between OUTA and OUTB. See 节 6.3.6                                                                            |

| DELCD  | 7   | I    | Dead-time delay programming between OUTC and OUTD. See 节 6.3.6                                                                            |

| DELEF  | 8   | I    | Delay-time programming between OUTA to OUTF, and OUTB to OUTE. See 节 6.3.7                                                                |

| EA+    | 2   | I    | Error amplifier noninverting input. See 节 6.3.3                                                                                           |

| EA -   | 3   | I    | Error amplifier inverting input. See ‡ 6.3.3                                                                                              |

| GND    | 24  | _    | Ground. All signals are referenced to this node.                                                                                          |

| OUTA   | 22  | 0    |                                                                                                                                           |

| OUTB   | 21  | 0    |                                                                                                                                           |

| OUTC   | 20  | 0    | 0.2A sink and source primary switching output.                                                                                            |

| OUTD   | 19  | 0    | 0.2A sink and source printary switching output.                                                                                           |

| OUTE   | 18  | 0    |                                                                                                                                           |

| OUTF   | 17  | 0    |                                                                                                                                           |

| RSUM   | 11  | I    | Slope compensation programming. Voltage mode or peak current mode setting. See 节 6.3.11                                                   |

| RT     | 10  | I    | Oscillator frequency set. leader or follower mode setting. See 节 6.3.10                                                                   |

| SS/EN  | 5   | I    | Soft-start programming, device enable and hiccup mode protection circuit. See # 6.3.4                                                     |

| SYNC   | 16  | I/O  | Synchronization out from leader controller to input of follower controller. See 节 6.3.15                                                  |

| TMIN   | 9   | I    | Minimum duty cycle programming in burst mode. See † 6.3.9                                                                                 |

| VDD    | 23  | I    | Bias supply input. See 节 6.3.17                                                                                                           |

# Pin Functions (续)

| Р        | IN   | TYPE        | DESCRIPTION                                           |

|----------|------|-------------|-------------------------------------------------------|

| NAME NO. | ITPE | DESCRIPTION |                                                       |

| VREF     | 1    | 0           | 5V, ±1.5%, 20mA reference voltage output. See 节 6.3.2 |

# 5 Specifications

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                                                                                                          | MIN   | MAX        | UNIT |

|----------------------------------------------------------------------------------------------------------|-------|------------|------|

| Input supply voltage, V <sub>DD</sub> <sup>(3)</sup>                                                     | - 0.4 | 20         | V    |

| OUTA, OUTB, OUTC, OUTD, OUTE, OUTF                                                                       | - 0.4 | VDD + 0.4  | V    |

| Input voltage on DELAB, DELCD, DELEF, SS/EN, DCM, TMIN, RT, SYNC, RSUM, EA+, EA-, COMP, CS, ADEL, ADELEF | - 0.4 | VREF + 0.4 | V    |

| Output voltage on VREF                                                                                   | - 0.4 | 5.6        | V    |

| Continuous total power dissipation                                                                       |       | See # 5.7  | •    |

| Operating virtual junction temperature, T <sub>J</sub>                                                   | - 40  | 150        | °C   |

| Operating ambient temperature, T <sub>A</sub>                                                            | - 40  | 125        | °C   |

| Lead temperature (soldering, 10 s)                                                                       |       | 300        | °C   |

| Storage temperature, T <sub>stg</sub>                                                                    | - 65  | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under #5.3 is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 5.2 ESD Ratings

|                   |             |                                                                                | VALUE | UNIT |

|-------------------|-------------|--------------------------------------------------------------------------------|-------|------|

| V                 |             | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD</sub> | ) discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

# **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                                                                                                          | MIN  | TYP MAX | UNIT |

|--------------------------------------------------------------------------------------------------------------------------|------|---------|------|

| Supply voltage, V <sub>DD</sub>                                                                                          | 8    | 12 17   | V    |

| Operating junction temperature                                                                                           | - 40 | 125     | °C   |

| Converter switching frequency setting, F <sub>SW(nom)</sub>                                                              | 50   | 1000    | kHz  |

| Programmable delay between OUTA, OUTB and OUTC, OUTD set by resistors DELAB and DELCD and parameter $\rm K_A$ $^{(1)}$   | 30   | 1000    | ns   |

| UCC28950-Q1, D <sub>MAX</sub>                                                                                            |      | 90      | %    |

| UCC28951-Q1, D <sub>MAX</sub>                                                                                            |      | 92      | %    |

| Programmable delay between OUTA, OUTF and OUTB, OUTE set by resistor DELEF, and parameter $K_{\text{EF}}$ <sup>(1)</sup> | 30   | 1400    | ns   |

| Programmable DCM as percentage of voltage at CS <sup>(1)</sup>                                                           | 5%   | 30%     |      |

| Programmable T <sub>MIN</sub>                                                                                            | 100  | 800     | ns   |

Verified during characterization only.

<sup>(2)</sup> These devices are sensitive to electrostatic discharge; follow proper device handling procedures.

<sup>(3)</sup> All voltages are with respect to GND unless otherwise noted. Currents are positive into, negative out of the specified terminal. See # 10 for thermal limitations and considerations of packages.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

# **5.4 Thermal Information**

|                        |                                              | UCC2895x-Q1 |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP)  | UNIT |

|                        |                                              | 24 PINS     |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 93.3        | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.2        | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 47.9        | °C/W |

| ψJT                    | Junction-to-top characterization parameter   | 0.7         | °C/W |

| <sup>ψ</sup> ЈВ        | Junction-to-board characterization parameter | 47.4        | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **5.5 Electrical Characteristics**

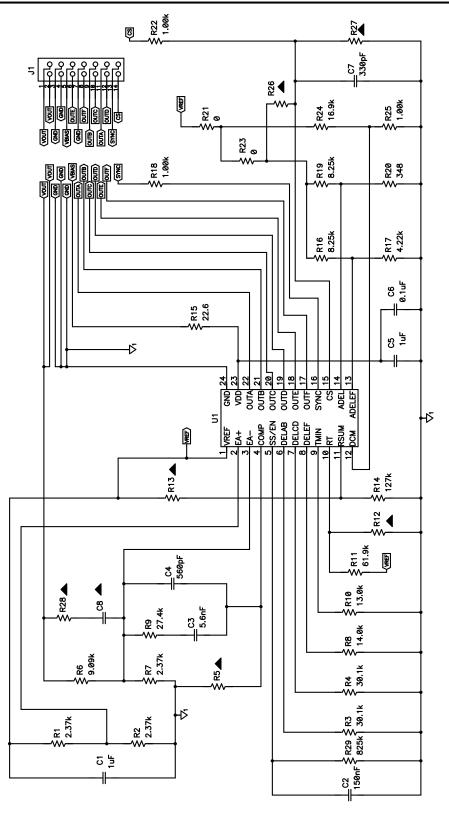

$V_{DD}$  = 12V,  $T_A$  =  $T_J$  =  $-40^{\circ}$ C to +125 $^{\circ}$ C,  $C_{VDD}$  = 1μF,  $C_{REF}$  = 1μF,  $R_{AB}$  = 22.6k  $\Omega$ ,  $R_{CD}$  = 22.6k  $\Omega$ ,  $R_{EF}$  = 13.3k  $\Omega$ ,  $R_{SUM}$  = 124k  $\Omega$ ,  $R_{TMIN}$  = 88.7k  $\Omega$ ,  $R_T$  = 59k  $\Omega$  connected between RT pin and 5V voltage supply to set  $F_{SW}$  = 100kHz ( $F_{OSC}$  = 200kHz) (unless otherwise noted). All component designations are from  $\Xi$  7-3.

|                      | PARAMETER                 | TEST CONDITIONS                                                                                           | MIN   | TYP | MAX   | UNIT |

|----------------------|---------------------------|-----------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

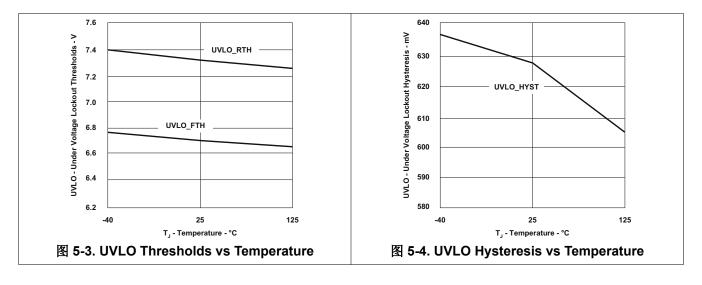

| UNDERVOLT            | AGE LOCKOUT (UVLO)        |                                                                                                           |       |     |       |      |

| UVLO RTH             | Ctart threehold           |                                                                                                           | 6.75  |     | 7.9   | V    |

| UVLO_KIH             | Start threshold           | T <sub>A</sub> = 25°C                                                                                     |       | 7.3 |       | V    |

| UVLO_FTH             | Minimum operating voltage |                                                                                                           | 6.15  |     | 7.2   | V    |

| OVLO_FIH             | after start               | T <sub>A</sub> = 25°C                                                                                     |       | 6.7 |       | V    |

| UVLO HYST            | Hyetoroeie                |                                                                                                           | 0.53  |     | 0.75  | V    |

| OVLO_III31           | Tysteresis                | T <sub>A</sub> = 25°C                                                                                     |       | 0.6 |       | V    |

| SUPPLY CUF           | RRENTS                    |                                                                                                           |       |     |       |      |

| I                    | Startup current           | V <sub>DD</sub> = 5.2V                                                                                    |       |     | 270   | μA   |

| I <sub>DD(off)</sub> | Startup current           | V <sub>DD</sub> = 5.2V, T <sub>A</sub> = 25°C                                                             |       | 150 |       | μΑ   |

| I                    | Operating supply current  |                                                                                                           |       |     | 10    | mA   |

| I <sub>DD</sub>      | Operating supply current  | T <sub>A</sub> = 25°C                                                                                     |       | 5   | "     | ША   |

| VREF OUTP            | UT VOLTAGE                |                                                                                                           |       |     |       |      |

|                      |                           | $0 \leqslant I_{R} \leqslant 20 mA,  8V \leqslant V_{DD} \leqslant 17V$                                   | 4.925 |     | 5.075 |      |

| $V_{REF}$            | VREF total output range   | $0 \leqslant I_{R} \leqslant 20$ mA, $8$ V $\leqslant$ V $_{DD} \leqslant 1$ 7V, $T_{A}$ = $25^{\circ}$ C |       | 5   |       | V    |

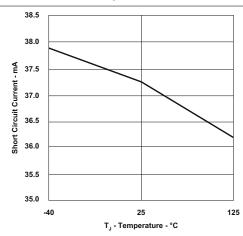

| I <sub>SCC</sub>     | Short circuit current     | V <sub>REF</sub> = 0V                                                                                     | - 53  | ,   | - 23  | mA   |

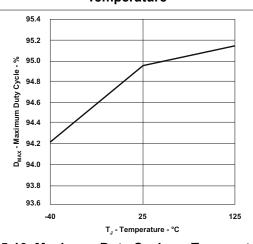

| SWITCHING            | FREQUENCY (1/2 OF INTERNA | AL OSCILLATOR FREQUENCY Fosc)                                                                             |       |     |       |      |

| _                    | T                         |                                                                                                           | 92    |     | 108   |      |

| F <sub>SW(nom)</sub> | Total range               | T <sub>A</sub> = 25°C                                                                                     |       | 100 |       | kHz  |

| Б.                   | Mandana data anala        |                                                                                                           |       |     | 97%   |      |

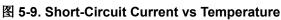

| D <sub>MAX</sub>     | Maximum duty cycle        | T <sub>A</sub> = 25°C                                                                                     |       | 95% |       |      |

| SYNCHRONI            | ZATION                    |                                                                                                           |       |     |       |      |

| DU                   | Total range               | $R_T$ = 59k $Ω$ between RT and GND, Input pulses 200kHz, D = 0.5 at SYNC                                  | 85    |     | 95    | °PH  |

| PH <sub>SYNC</sub>   | Total range               | $R_T$ = 59k $Ω$ between RT and GND, Input pulses 200kHz, D = 0.5 at SYNC, $T_A$ = 25°C                    |       | 90  |       | РΠ   |

| F <sub>SYNC</sub>    | Total range               | R <sub>T</sub> = 59k $\Omega$ between RT and 5V; -40 °C $\leq$ T <sub>J</sub> $\leq$ 125°C                | 180   |     | 220   | kHz  |

|                      | -                         | T <sub>A</sub> = 25°C                                                                                     |       | 200 |       |      |

| <b>-</b>             | D. I                      |                                                                                                           | 2.2   |     | 2.8   |      |

| $T_PW$               | Pulse width               | T <sub>A</sub> = 25°C                                                                                     |       | 2.5 |       | μs   |

$V_{DD}$  = 12V,  $T_A$  =  $T_J$  =  $-40^{\circ}$ C to +125°C,  $C_{VDD}$  = 1μF,  $C_{REF}$  = 1μF,  $R_{AB}$  = 22.6k  $\Omega$ ,  $R_{CD}$  = 22.6k  $\Omega$ ,  $R_{EF}$  = 13.3k  $\Omega$ ,  $R_{SUM}$  = 124k  $\Omega$ ,  $R_{TMIN}$  = 88.7k  $\Omega$ ,  $R_T$  = 59k  $\Omega$  connected between RT pin and 5V voltage supply to set  $F_{SW}$  = 100kHz ( $F_{OSC}$  = 200kHz) (unless otherwise noted). All component designations are from  $\Xi$  7-3.

|                     | PARAMETER                           | TEST CONDITIONS                                                                                                                                      | MIN  | TYP    | MAX   | UNIT     |

|---------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|-------|----------|

| ERROR AI            | MPLIFIER                            |                                                                                                                                                      |      |        |       |          |

| V <sub>ICM</sub>    | Common-mode input voltage range     | V <sub>ICM</sub> range ensures parameters, the functionality ensured for 3.6V < V <sub>ICM</sub> < VREF + 0.4V, and - 0.4V < V <sub>ICM</sub> < 0.5V | 0.5  |        | 3.6   | V        |

| V <sub>IO</sub>     | Offset voltage                      |                                                                                                                                                      | - 7  |        | 7     | mV       |

| I <sub>BIAS</sub>   | Input bias current                  |                                                                                                                                                      | - 1  |        | 1     | μA       |

|                     |                                     | V <sub>(EA+)</sub> - V <sub>(EA-)</sub> = 500mV, I <sub>EAOUT</sub> = -0.5mA                                                                         | 3.9  |        |       |          |

| EA <sub>HIGH</sub>  | High-level output voltage           | $V_{(EA+)} - V_{(EA-)} = 500$ mV, $I_{EAOUT} = -0.5$ mA, $I_{A} = 25$ °C                                                                             |      | 4.25   |       | V        |

|                     |                                     | $V_{(EA+)} - V_{(EA-)} = -500$ mV, $I_{EAOUT} = 0.5$ mA                                                                                              |      |        | 0.35  |          |

| EA <sub>LOW</sub>   | Low-level output voltage            | $V_{(EA+)} - V_{(EA-)} = -500$ mV, $I_{EAOUT} = 0.5$ mA, $T_A = 25$ °C                                                                               |      | 0.25   |       | V        |

|                     | - va                                |                                                                                                                                                      | - 8  |        | - 0.5 |          |

| ISOURCE             | Error amplifier source current      | T <sub>A</sub> = 25°C                                                                                                                                |      | - 3.75 |       | mA       |

|                     |                                     |                                                                                                                                                      | 2.7  |        | 5.75  | 4        |

| I <sub>SINK</sub>   | Error amplifier sink current        | T <sub>A</sub> = 25°C                                                                                                                                |      | 4.6    |       | mA       |

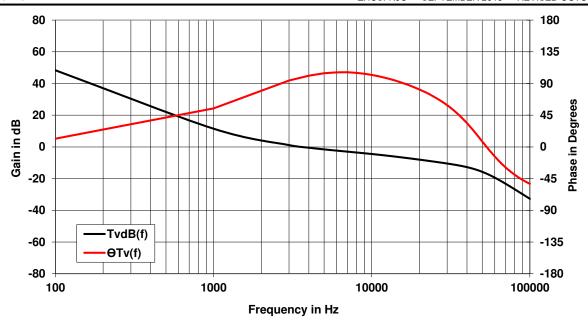

| I <sub>VOL</sub>    | Open-loop DC gain                   | T <sub>A</sub> = 25°C                                                                                                                                |      | 100    |       | dB       |

| GBW                 | Unity gain bandwidth <sup>(1)</sup> | T <sub>A</sub> = 25°C                                                                                                                                |      | 3      |       | MHz      |

| CYCLE-BY            | Y-CYCLE CURRENT LIMIT               |                                                                                                                                                      |      |        | '     |          |

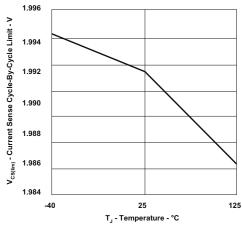

| V                   | CS pin cycle-by-cycle               |                                                                                                                                                      | 1.94 |        | 2.06  | V        |

| V <sub>CS_LIM</sub> | threshold                           | T <sub>A</sub> = 25°C                                                                                                                                |      | 2      |       | V        |

| INTERNAL            | HICCUP MODE SETTINGS                |                                                                                                                                                      |      |        |       |          |

| I <sub>DS</sub>     | Discharge current to set cycle-     | V <sub>CS</sub> = 2.5V, V <sub>VSS</sub> = 4V                                                                                                        | 15   |        | 25    | μΑ       |

| טי<br>8טי           | by-cycle current limit duration     | V <sub>CS</sub> = 2.5V, V <sub>VSS</sub> = 4V, T <sub>A</sub> = 25°C                                                                                 |      | 20     |       | μπ       |

| V <sub>HCC</sub>    | Hiccup OFF time threshold           |                                                                                                                                                      | 3.2  |        | 4.2   | V        |

| * HCC               | Though of Familia and onloid        | T <sub>A</sub> = 25°C                                                                                                                                |      | 3.6    |       | <u> </u> |

| I <sub>HCC</sub>    | Discharge current to set            |                                                                                                                                                      | 1.9  |        | 3.2   | μΑ       |

|                     | Hiccup Mode OFF Time                | T <sub>A</sub> = 25°C                                                                                                                                |      | 2.55   |       | <b>I</b> |

| SOFT STA            | RT/ENABLE                           |                                                                                                                                                      |      |        |       |          |

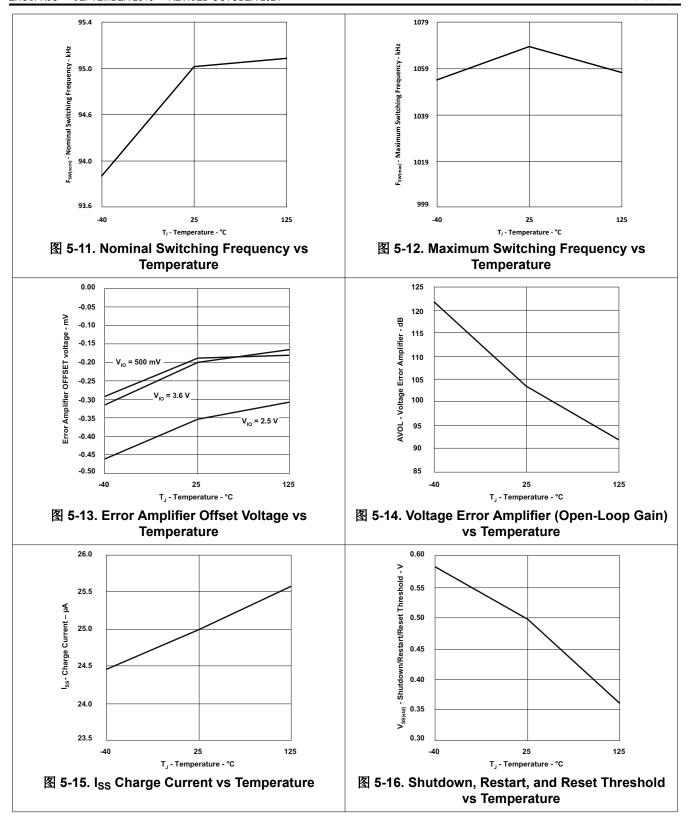

| I <sub>SS</sub>     | Charge current                      | V <sub>SS</sub> = 0V                                                                                                                                 | 20   |        | 30    | μA       |

|                     |                                     | T <sub>A</sub> = 25°C                                                                                                                                |      | 25     |       |          |

| V <sub>SS_STD</sub> | Shutdown, restart threshold         |                                                                                                                                                      | 0.25 |        | 0.7   | V        |

|                     |                                     | T <sub>A</sub> = 25°C                                                                                                                                |      | 0.5    |       |          |

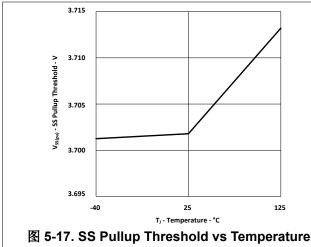

| V <sub>SS PU</sub>  | Pullup threshold                    |                                                                                                                                                      | 3.3  |        | 4.3   | V        |

|                     | •                                   | T <sub>A</sub> = 25°C                                                                                                                                |      | 3.7    |       |          |

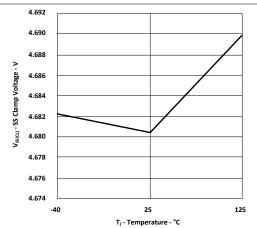

| V <sub>SS_CL</sub>  | Clamp voltage                       |                                                                                                                                                      | 4.2  |        | 4.95  | V        |

| 55_52               |                                     | T <sub>A</sub> = 25°C                                                                                                                                |      | 4.65   |       | V        |

200kHz) (unless otherwise noted). All component designations are from \$\bigsep\$ 7-3.

|                       | PARAMETER                                   | TEST CONDITIONS                                                                                                                  | MIN   | TYP  | MAX   | UNIT |

|-----------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| LIGHT-LOA             | AD EFFICIENCY CIRCUIT                       |                                                                                                                                  |       |      |       |      |

|                       |                                             | V <sub>DCM</sub> = 0.4V, Sweep CS confirm there are OUTE and OUTF pulses, T <sub>A</sub> = 25°C                                  | 0.37  | 0.39 | 0.41  | V    |

| $V_{DCM}$             | DCM threshold                               | $V_{DCM}$ = 0.4V, Sweep CS, confirm there are OUTE and OUTF pulses, 0°C $\leq$ T <sub>A</sub> $\leq$ 85°CDCM threshold, $^{(6)}$ | 0.364 | 0.39 | 0.416 | V    |

|                       |                                             | $V_{DCM}$ = 0.4V, Sweep CS, confirm there are OUTE and OUTF pulses, $-40^{\circ}C \leqslant T_{A} \leqslant 125^{\circ}C^{(6)}$  | 0.35  | 0.39 | 0.43  | V    |

| 1                     | DCM Sourcing Current                        | CS < DCM threshold                                                                                                               | 14    |      | 26    |      |

| I <sub>DCM_SRC</sub>  | DCM Sourcing Current                        | CS < DCM threshold, T <sub>A</sub> = 25°C                                                                                        |       | 20   |       | μA   |

| OUTPUTS               | OUTA, OUTB, OUTC, OUTD, O                   | OUTE, OUTF                                                                                                                       |       |      | -     |      |

| I <sub>SINK/SRC</sub> | Sink and source peak current <sup>(6)</sup> | T <sub>A</sub> = 25°C                                                                                                            |       | 0.2  |       | Α    |

| D                     | Output source resistance                    | I <sub>OUT</sub> = 20mA                                                                                                          | 10    |      | 35    | 0    |

| R <sub>SRC</sub>      | Output source resistance                    | I <sub>OUT</sub> = 20mA, T <sub>A</sub> = 25°C                                                                                   |       | 20   |       | Ω    |

| D                     | Output aink registence                      | I <sub>OUT</sub> = 20mA                                                                                                          | 5     |      | 30    | 0    |

| R <sub>SINK</sub>     | Output sink resistance                      | I <sub>OUT</sub> = 20mA, T <sub>A</sub> = 25°C                                                                                   |       | 10   |       | Ω    |

| THERMAL               | SHUTDOWN                                    |                                                                                                                                  |       |      | 1     |      |

|                       | Rising threshold <sup>(6)</sup>             | T <sub>A</sub> = 25°C                                                                                                            |       | 160  |       | °C   |

|                       | Falling threshold <sup>(6)</sup>            | T <sub>A</sub> = 25°C                                                                                                            |       | 140  |       | °C   |

|                       | Hysteresis                                  |                                                                                                                                  |       | 20   |       | °C   |

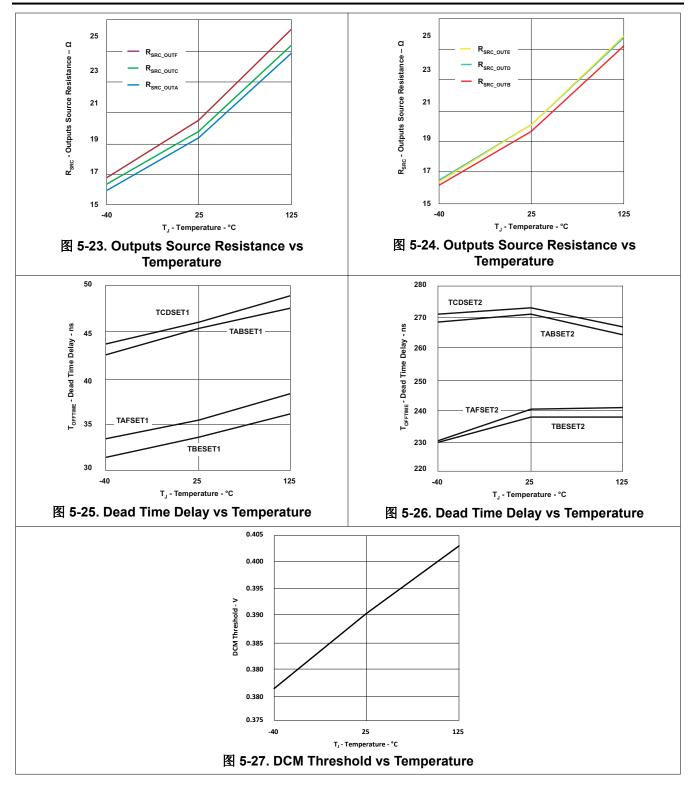

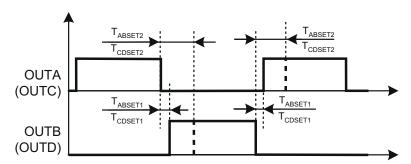

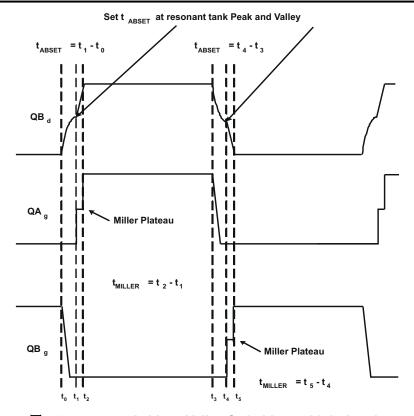

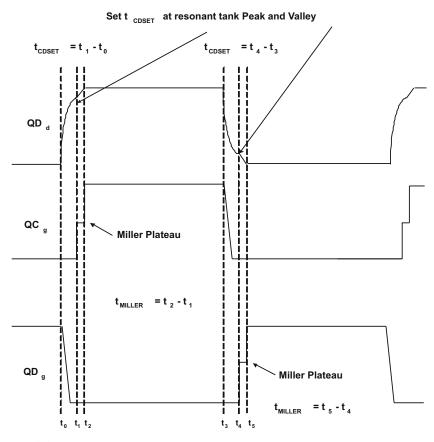

- (1) See  $\boxtimes$  6-1 for timing diagram and T<sub>ABSET1</sub>, T<sub>ABSET2</sub>, T<sub>CDSET1</sub>, T<sub>CDSET2</sub> definitions.

- See

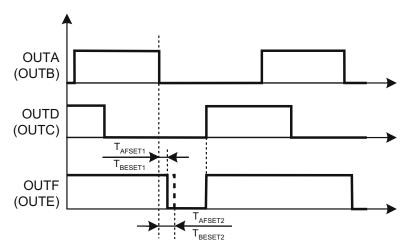

6-4 for timing diagram and T<sub>AFSET1</sub>, T<sub>AFSET2</sub>, T<sub>BESET1</sub>, T<sub>BESET2</sub> definitions. Pair of outputs OUTC, OUTE and OUTD, OUTF always going high simultaneously. (3)

- Outputs A or B are never allowed to go high if both outputs OUTE and OUTF are high.

- All delay settings are measured relative to 50% of pulse amplitude. (5)

- Verified during characterization only.

# **5.6 Timing Requirements**

|                     |                                                                                                                  | MIN  | NOM | MAX | UNIT |

|---------------------|------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| CYCLE-BY-CYC        | LE CURRENT LIMIT                                                                                                 |      |     |     |      |

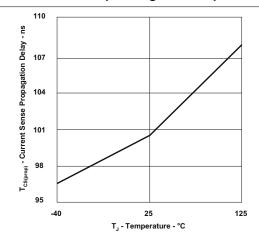

| T <sub>CS</sub>     | Propagation delay from CS to OUTC and OUTD outputs Input pulse between CS and GND from zero to 2.5 V             |      | 100 |     | ns   |

| PROGRAMMAB          | LE DELAY TIME SET ACCURACY AND RANGE(1) (2) (3) (4) (5)                                                          |      |     |     |      |

| T <sub>ABSET1</sub> | Short delay time set accuracy between OUTA and OUTB CS = ADEL = ADELEF = 1.8 V                                   | 32   | 45  | 56  | ns   |

| T <sub>ABSET2</sub> | Long delay time set accuracy between OUTA and OUTB CS = ADEL = ADELEF = 0.2 V                                    | 216  | 270 | 325 | ns   |

| T <sub>CDSET1</sub> | Short delay time set accuracy between OUTC and OUTD CS = ADEL = ADELEF = 1.8 V                                   | 32   | 45  | 56  | ns   |

| T <sub>CDSET2</sub> | Long delay time set accuracy between OUTC and OUTD CS = ADEL = ADELEF = 0.2 V                                    | 216  | 270 | 325 | ns   |

| T <sub>AFSET1</sub> | Short delay time set accuracy between falling OUTA, OUTF CS = ADEL = ADELEF = 0.2 V                              | 22   | 35  | 48  | ns   |

| T <sub>AFSET2</sub> | Long delay time set accuracy between falling OUTA, OUTF CS = ADEL = ADELEF = 1.8 V                               | 190  | 240 | 290 | ns   |

| T <sub>BESET1</sub> | Short delay time set accuracy between falling OUTB, OUTE CS = ADEL = ADELEF = 0.2 V                              | 22   | 35  | 48  | ns   |

| T <sub>BESET2</sub> | Long delay time set accuracy between falling OUTB, OUTE CS = ADEL = ADELEF = 1.8 V                               | 190  | 240 | 290 | ns   |

| Δ T <sub>ADBC</sub> | Pulse matching between OUTA rise, OUTD fall and OUTB rise, OUTC fall CS = ADEL = ADELEF = 1.8 V, COMP = 2 V      | - 50 | 0   | 50  | ns   |

| Δ T <sub>ABBA</sub> | Half cycle matching between OUTA rise, OUTB rise and OUTB rise, OUTA rise CS = ADEL = ADELEF = 1.8 V, COMP = 2 V | - 50 | 0   | 50  | ns   |

| ΔT <sub>EEFF</sub>  | Pulse matching between OUTE fall, OUTE rise and OUTF fall, OUTF rise CS = ADEL = ADELEF = 0.2 V, COMP = 2 V      | - 60 | 0   | 60  | ns   |

| ΔT <sub>EFFE</sub>  | Pulse matching between OUTE fall, OUTF rise and OUTF fall, OUTE rise CS = ADEL = ADELEF = 0.2 V, COMP = 2 V      | - 60 | 0   | 60  | ns   |

| LIGHT-LOAD EF       | FICIENCY CIRCUIT                                                                                                 |      |     |     |      |

| T <sub>MIN</sub>    | Total range, R <sub>TMIN</sub> = 88.7 k Ω                                                                        | 425  | 525 | 625 | ns   |

| OUTPUTS OUT         | A, OUTB, OUTC, OUTD, OUTE, OUTF                                                                                  |      |     |     |      |

| T <sub>R</sub>      | Rise time, C <sub>LOAD</sub> = 100 pF                                                                            |      | 9   | 25  | ns   |

| T <sub>F</sub>      | Fall time, C <sub>LOAD</sub> = 100 pF                                                                            |      | 7   | 25  | ns   |

# 5.7 Dissipation Ratings

over operating free-air temperature range (unless otherwise noted)

| PACKAGE | DERATING FACTOR             | POWER RATING          |                       |                       |

|---------|-----------------------------|-----------------------|-----------------------|-----------------------|

|         | ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> < 25°C | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

| PW      | 10.7mW/°C                   | 1.07W                 | 0.59W                 | 0.429W                |

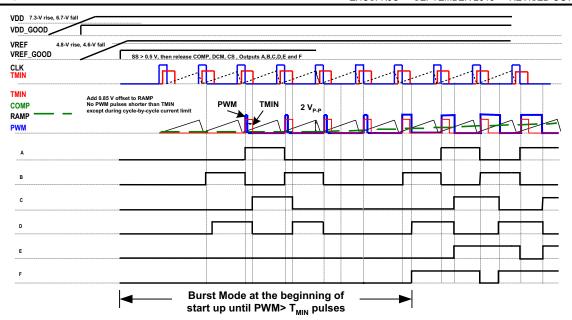

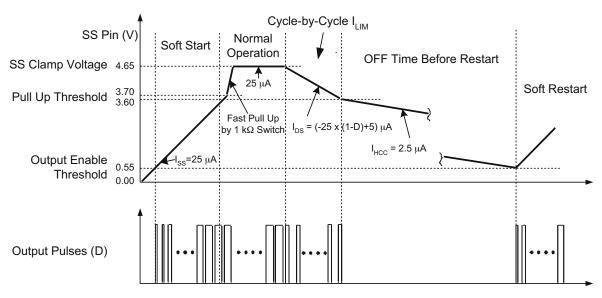

No output delay shown, COMP-to-RAMP offset not included.

There is no pulse on OUTE during burst mode at start-up. Two falling edge PWM pulses are required before enabling the synchronous rectifier outputs. Narrower pulse widths (less than 50% duty cycle) may be observed in the 1st OUTD pulse of a burst. The user must design the bootstrap capacitor charging circuit of the gate driver device so that the first OUTC pulse is transmitted to the MOSFET gate in all cases. Transformer based gate driver circuits are not affected. This behavior is described in more detail in the Gate Drive Outputs on the UCC28950 and UCC2895x-Q1 During Burst Mode Operation (SLAU787) application note.

图 5-1. UCC2895x-Q1 Start-Up Timing

11

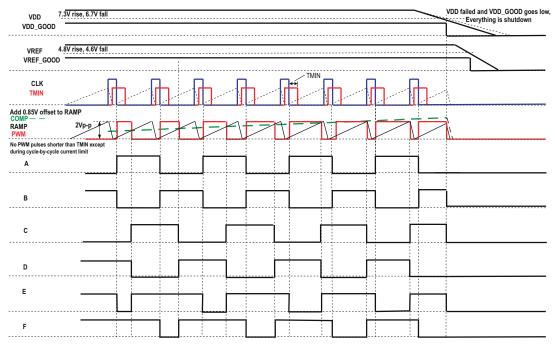

No output delay shown, COMP-to-RAMP offset not included.

图 5-2. UCC2895x-Q1 Steady-State and Shutdown Timing Diagram

# 5.8 Typical Characteristics

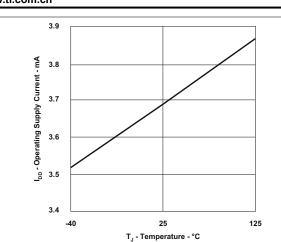

图 5-5. Supply Current vs Temperature

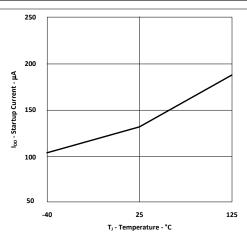

图 5-6. Start-Up Current vs Temperature

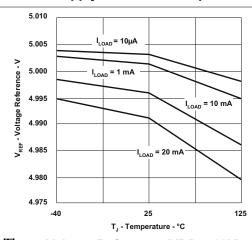

图 5-7. Voltage Reference (VDD = 12V) vs **Temperature**

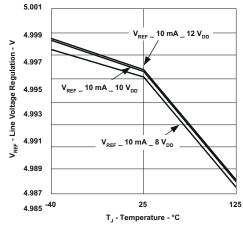

图 5-8. Line Voltage Regulation ( $I_{LOAD} = 10$ mA) vs **Temperature**

图 5-10. Maximum Duty Cycle vs Temperature

English Data Sheet: SLUSCK4

图 5-18. SS Clamp Voltage vs Temperature

图 5-19. Current Sense Cycle-by-Cycle Limit vs **Temperature**

图 5-20. Current Sense Propagation Delay vs **Temperature**

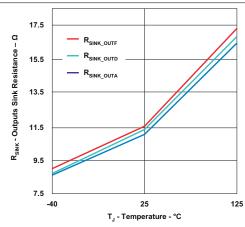

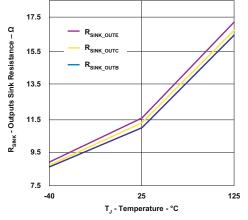

图 5-21. Outputs Sink Resistance vs Temperature

图 5-22. Outputs Sink Resistance vs Temperature

# 6 Detailed Description

## 6.1 Overview

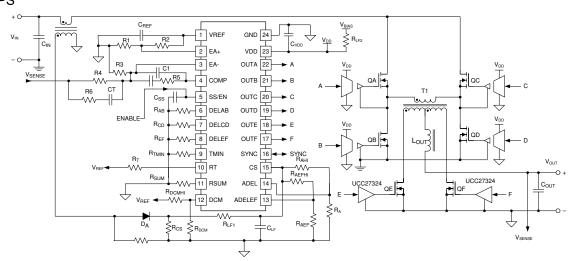

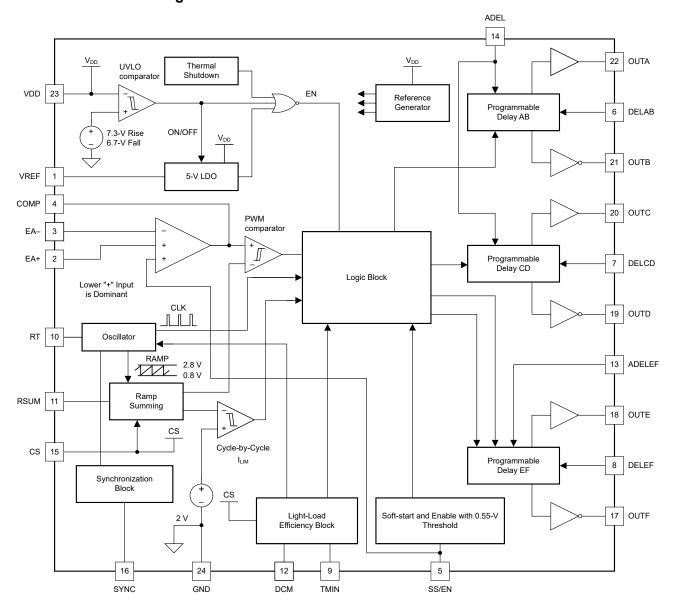

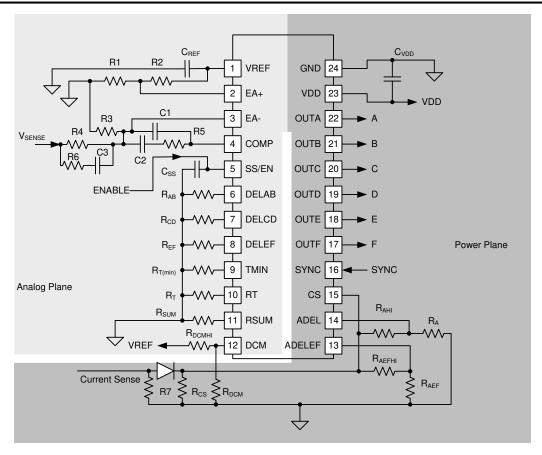

The UCC2895x-Q1 controllers combine all the functions necessary to control a phase-shifted, full-bridge, power stage in a 24-pin TSSOP package. The controller includes two synchronous-rectifier (SR), gate-drive outputs as well as the outputs needed to drive all four switches in the full-bridge circuit. The dead times between the upper and lower switches in the full bridge may be set using the DELAB and DELCD inputs. Further, this dead time may be dynamically adjusted according to the load level using the ADEL pin. This adjustment allows the user to optimize the dead time for their particular power circuit and to achieve ZVS over the entire operating range. In a similar manner, the dead times between the full-bridge switches and the secondary SRs may be optimized using the DELEF input. This dead time may also be dynamically adjusted according to the load, using the ADELEF input to the controller. A DCM (discontinuous conduction mode) option disables the SRs at a user settable light load to improve power circuit efficiency. The controller enters a light-load-burst mode if the feedback loop demands a conduction time less than a user settable level (TMIN).

At higher-power levels, two or more UCC2895x-Q1 controllers may be easily synchronized in a leader/follower configuration. A SS/EN input may be used to set the length of the soft start process and to turn the controller on and off. The controller may be configured for voltage mode or current mode control. Cycle-by-cycle current limiting is provided in voltage mode and peak current mode. Users can set the switching frequency over a wide range making this controller suited to both IGBT and MOSFET based designs.

17

# 6.2 Functional Block Diagram

## **6.3 Feature Description**

### 6.3.1 Start-Up Protection Logic

Before the UCC2895x-Q1 controllers will start up, the following conditions must be met:

- VDD voltage exceeds rising UVLO threshold 7.3V typical.

- The 5V reference voltage is available.

- Junction temperature is below the thermal shutdown threshold of 140°C.

- The voltage on the soft-start capacitor is not below 0.55V typical.

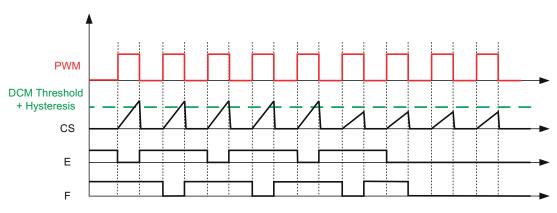

If all those conditions are met, an internal enable signal EN is generated that initiates the soft-start process. The duty cycle during the soft start is defined by the voltage at the SS pin, and cannot be lower than the duty cycle set by TMIN, or by cycle-by-cycle current limit circuit depending on load conditions.

### 6.3.2 Voltage Reference (VREF)

The accurate (±1.5%) 5V reference voltage regulator with a short-circuit protection circuit supplies internal circuitry and provides up to 20mA external output current. Place a low ESR and ESL, preferably ceramic decoupling capacitor C<sub>RFF</sub> in 1µF to 2.2µF range from this pin to GND as close to the related pins as possible for best performance. The only condition where the reference regulator is shut down internally is during undervoltage lockout.

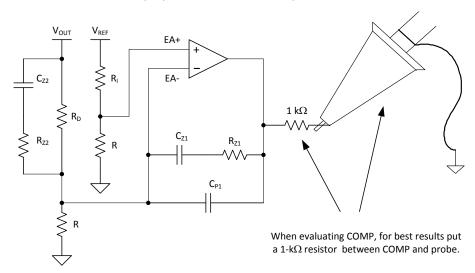

### 6.3.3 Error Amplifier (EA+, EA -, COMP)

The error amplifier has two uncommitted inputs, EA+ and EA - , with a 3MHz unity gain bandwidth, which allows flexibility in closing the feedback loop. The EA+ is a noninverting input, the EA - is an inverting input and the COMP is the output of the error amplifier. The input voltage common-mode range, where the parameters of the error amplifier are ensured, is from 0.5V to 3.6V. The output of the error amplifier is connected internally to the noninverting input of the PWM comparator. The range of the error amplifier output of 0.25V to 4.25V far exceeds the PWM comparator input ramp-signal range, which is from 0.8V to 2.8V. The soft-start signal serves as an additional noninverting input of the error amplifier. The lower of the two noninverting inputs of the error amplifier is the dominant input and sets the duty cycle where the output signal of the error amplifier is compared with the internal ramp at the inputs of the PWM comparator.

Product Folder Links: UCC28950-Q1 UCC28951-Q1

Copyright © 2024 Texas Instruments Incorporated

提交文档反馈

### 6.3.4 Soft-Start and Enable (SS/EN)

The soft-start pin (SS/EN) is a multi-function pin used for the following operations:

- Closed-loop soft start with the gradual duty cycle increase from the minimum set by TMIN up to the steadystate duty cycle required by the regulated output voltage.

- Setting hiccup mode conditions during cycle-by-cycle overcurrent limit.

- On/off control for the converter.

During the soft-start sequence, one of the voltages at the SS/EN or EA+ pins, whichever is lower (SS/EN - 0.55 V) or EA+ voltage (see # 6.2), sets the reference voltage for a closed feedback loop. Both SS/EN and EA+ signals are noninverting inputs of the error amplifier with the COMP pin being its output. Thus the soft-start time always goes under the closed feedback loop and the voltage at COMP pin sets the duty cycle. The duty cycle defined by the COMP pin voltage can not be shorter than TMIN pulse width set by the user. However, if the shortest duty cycle is set by the cycle-by-cycle current limit circuit, then it becomes dominant over the duty cycle defined by the COMP pin voltage or by the TMIN block.

The soft-start duration is defined by an external capacitor C<sub>SS</sub>, connected between the SS/EN pin and ground, and the internal charge current that has a typical value of 25 µA. Pulling the soft-start pin externally below 0.55 V shuts down the controller. The release of the soft-start pin enables the controller to start, and if there is no current limit condition, the duty cycle applied to the output inductor gradually increases until it reaches the steady-state duty cycle defined by the regulated output voltage of the converter. This increase happens when the voltage at the SS/EN pin reaches and then exceeds by 0.55 V, the voltage at the EA+ pin. Thus for the given soft-start time T<sub>SS</sub>, the C<sub>SS</sub> value can be defined by 方程式 1 or 方程式 2:

$$C_{SS(leader)} = \frac{T_{SS} \times 25 \,\mu\text{A}}{\left(0.55 + V_{(EA +)}\right)} \tag{1}$$

$$C_{SS(follower)} = \frac{T_{SS} \times 25 \,\mu\text{A}}{825 \,\text{k}\Omega \times \ln\left(\frac{20.6}{20.6 - 0.55 - \text{V}(\text{EA} + )}\right)} \tag{2}$$

For example, in 方程式 1, if the soft-start time T<sub>SS</sub> is 10 ms, and the EA+ pin is 2.5 V, then the soft-start capacitor C<sub>SS</sub> is equal to 82 nF.

#### 备注

If the converter is configured to operate in follower mode, connect a 825-k Ω (±5%) resistor from the SS pin to ground.

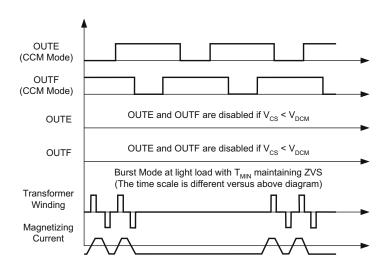

## 6.3.5 Light-Load Power Saving Features

The UCC2895x-Q1 offers four different light-load management techniques for improving the efficiency of a power converter over a wide load current range.

- 1. Adaptive Delay,

- a. ADEL, which sets and optimizes the dead-time control for the primary switches over a wide load current

- b. ADELEF, which sets and optimizes the delay-time control between the primary side switches and the secondary side switches.

- 2. TMIN, sets the minimum pulse width as long as the part is not in current limit mode.

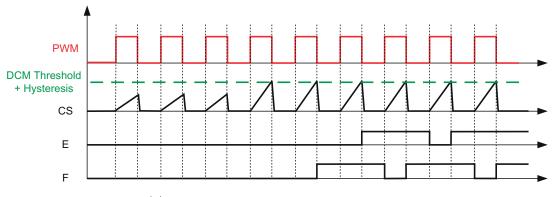

- 3. Dynamic synchronous rectifier on/off control in DCM Mode, For increased efficiency at light loads. The DCM Mode starts when the voltage at CS pin is lower than the threshold set by the user. In DCM Mode, the synchronous output drive signals OUTE and OUTF are brought down low.

- 4. Burst Mode, for maximum efficiency at very light loads or no load. Burst Mode has an even number of PWM TMIN pulses followed by off time. Transition to the Burst Mode is defined by the TMIN duration set by the user.

Copyright © 2024 Texas Instruments Incorporated

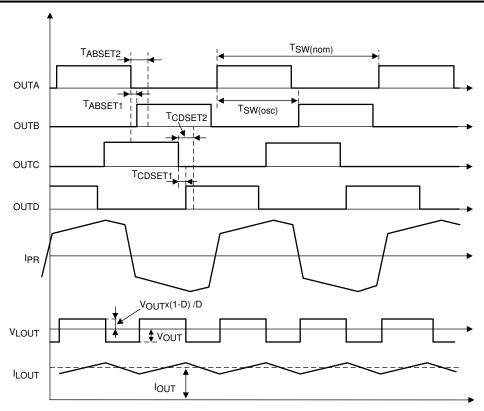

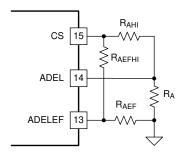

### 6.3.6 Adaptive Delay, (Delay Between OUTA and OUTB, OUTC and OUTD (DELAB, DELCD, ADEL))

The resistor  $R_{AB}$  from the DELAB pin, DELAB to GND, along with the resistor divider  $R_{AHI}$  from CS pin to ADEL pin and  $R_A$  from ADEL pin to GND sets the delay  $T_{ABSET}$  between one of outputs OUTA or OUTB going low and the other output going high 86-1. The total resistance of this resistor divider should be in the range between  $10k\Omega$  and  $20k\Omega$

图 6-1. Delay Definitions Between OUTA and OUTB, OUTC and OUTD

This delay gradually increases as a function of the CS signal from  $T_{ABSET1}$ , which is measured at  $V_{CS} = 1.8V$ , to  $T_{ABSET2}$ , which is measured at the  $V_{CS} = 0.2V$ . This approach ensures there will be no shoot-through current during the high-side and low-side MOSFET switching and optimizes the delay for acheiving ZVS condition over a wide load current range. The ratio between the longest and shortest delays is set by the resistor divider  $R_{AHI}$  and  $R_{A}$ . The maximum ratio is achieved by tying the CS and ADEL pins together. If ADEL is connected to GND, then the delay is fixed, defined only by the resistor  $R_{AB}$  from DELAB to GND. The delay  $T_{CDSET1}$  and  $T_{CDSET2}$  settings and their behaviour for outputs OUTC and OUTD are very similar to the one described for OUTA and OUTB. The difference is that resistor  $R_{CD}$  connected between DELCD pin and GND sets the delay  $T_{CDSET}$ . The ratio between the longest and shortest delays is set by the resistor divider  $R_{AHI}$  and  $R_{A}$ .

The delay time  $T_{ABSET}$  is defined by the following 方程式 3 .

$$T_{ABSET} = \frac{R_{AB} \times 5V}{CS \times K_A \times 0.927 + 0.22V} \times 1pF - 12.6ns$$

(3)

where

- the CS, which is the voltage at pin CS, is in volts

- K<sub>A</sub> is a numerical gain factor of CS voltage from 0 to 1

The same equation is used to define the delay time  $T_{CDSET}$  in another leg, except  $R_{AB}$  is replaced by  $R_{CD}$  (see 方程式 4).

$$T_{CDSET} = \frac{R_{CD} \times 5V}{CS \times K_{A} \times 0.927 + 0.22V} \times 1pF - 12.6ns$$

(4)

where

- the CS, which is the voltage at pin CS, is in volts

- K<sub>A</sub> is a numerical gain factor of CS voltage from 0 to 1

These equations are empirical and they are approximated from measured data. Thus, there is no unit agreement in the equations. As an example, assume  $R_{AB}$  = 15k  $\Omega$ , CS = 1V and  $K_A$  = 0.5. Then the  $T_{ABSET}$  is approximately 90ns.

In 方程式 5, KA is the same and is defined as 方程式 5:

$$K_{A} = \frac{R_{A}}{R_{A} + R_{AHI}} \tag{5}$$

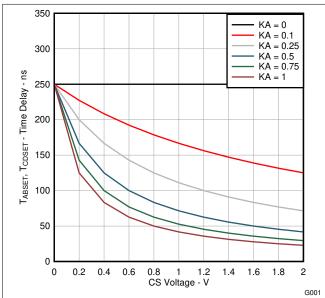

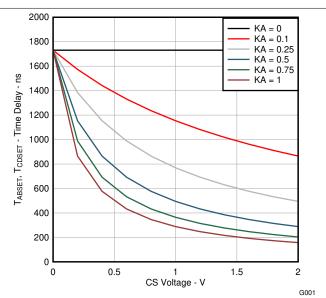

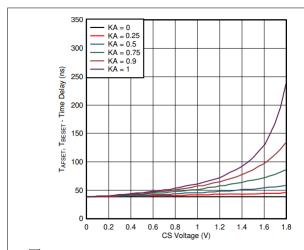

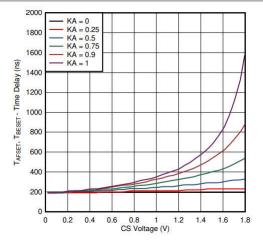

K<sub>A</sub> sets how the delay varies with the CS pin voltage as shown in 图 6-2 and 图 6-3.

TI recommends starting by setting  $K_A = 0$  and set  $T_{ABSET}$  and  $T_{CDSET}$  relatively large using equations or plots in this data sheet to avoid hard switching or even shoot through current. The delay between outputs A, B and C, D set by resistors  $R_{AB}$  and  $R_{CD}$  accordingly. Program the optimal delays at light load first. Then by changing  $K_A$  set the optimal delay for the outputs A, B at maximum current.  $K_A$  for outputs C, D is the same as for A, B. Usually outputs C, D always have ZVS if sufficient delay is provided.

### 备注

The allowed resistor range on DELAB and DELCD,  $R_{AB}$  and  $R_{CD}$  is  $13k\Omega$  to  $90k\Omega$ .

$R_A$  and  $R_{AHI}$  define the portion of voltage at pin CS applied to the pin ADEL (see  $\[ \]$  7-3).  $K_A$  defines how significantly the delay time depends on CS voltage.  $K_A$  varies from 0, where ADEL pin is shorted to ground ( $R_A$  = 0) and the delay does not depend on CS voltage, to 1, where ADEL is tied to CS ( $R_{AHI}$  = 0). Setting  $K_A$ ,  $R_{AB}$ , and  $R_{CD}$  provides the ability to maintain optimal ZVS conditions of primary switches over load current because the voltage at CS pin includes the load current reflected to the primary side through the current-sensing circuit. The plots in  $\[ \]$  6-2 and  $\[ \]$  6-3 show the delay time settings as a function of CS voltage and  $K_A$  for two different conditions:  $R_{AB} = R_{CD} = 13k\Omega$  ( $\[ \]$  6-2) and  $R_{AB} = R_{CD} = 90k\Omega$  ( $\[ \]$  6-3).

图 6-2. Delay Time Set  $T_{ABSET}$  and  $T_{CDSET}$  (Over CS Voltage Variation and selected  $K_A$  for  $R_{AB}$  and  $R_{CD}$  Equal 13k  $\Omega$ )

图 6-3. Delay Time set  $T_{ABSET}$  and  $T_{CDSET}$  (Over CS Voltage Variation and Selected  $K_A$  for  $R_{AB}$  and  $R_{CD}$  Equal 90  $k\Omega$ )

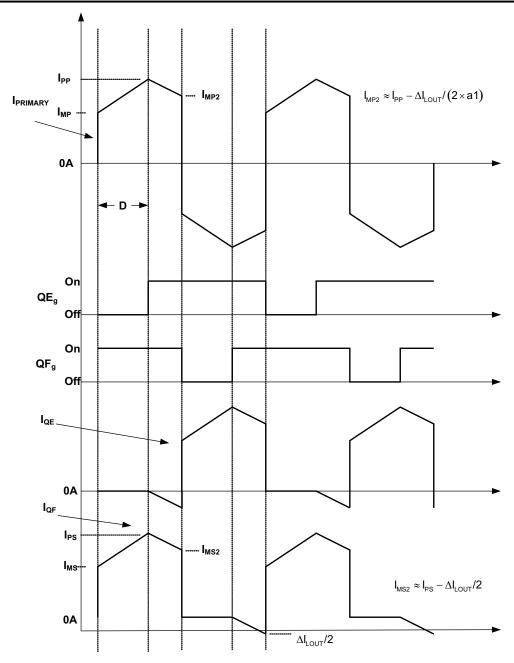

### 6.3.7 Adaptive Delay (Delay Between OUTA and OUTF, OUTB and OUTE (DELEF, ADELEF)

The resistor R<sub>EF</sub> from the DELEF pin to GND along with the resistor divider R<sub>AEFHI</sub> from CS pin to ADELEF pin and RAEF from ADELEF pin to GND sets equal delays TAFSET and TBESET between outputs OUTA or OUTB going low and related output OUTF or OUTE going low 8 6-4. The total resistance of this resistor divider should be in the range between  $10k\Omega$  and  $20k\Omega$ .

图 6-4. Delay Definitions Between OUTA and OUTF, OUTB and OUTE

These delays gradually increase as function of the CS signal from  $T_{AFSET1}$ , which is measured at  $V_{CS} = 0.2V$ , to T<sub>AESET2</sub>, which is measured at V<sub>CS</sub> = 1.8V. This is opposite to the DELAB and DELCD behavior and this delay is longest (T<sub>AFSET2</sub>) when the signal at CS pin is maximized and shortest (T<sub>AFSET1</sub>) when the CS signal is minimized. This approach will reduce the synchronous rectifier MOSFET body diode conduction time over a wide load current range thus improving efficiency. The ratio between the longest and shortest delays is set by the resistor divider RAFFHI and RAFF. If CS and ADELEF are tied, the ratio is maximized. If ADELEF is connected to GND, then the delay is fixed, defined only by resistor R<sub>FF</sub> from DELEF to GND.

The delay time T<sub>AFSET</sub> is defined by the following 方程式 6. 方程式 6 also defines the delay time T<sub>BESET</sub>.

$$T_{AFSET} = T_{BESET} = \frac{R_{EF} \times 5V}{-CS \times K_{EF} \times 0.993 + 2.063V} \times 1pF - 1.3ns$$

(6)

where

- · the CS, which is the voltage at pin CS, is in volts

- K<sub>FF</sub> is a numerical gain factor of CS voltage from 0 to 1

方程式 7 is an empirical approximation of measured data, thus, there is no unit agreement in it. As an example, assume R<sub>EF</sub> = 15k  $\Omega$ , CS = 1V and K<sub>EF</sub> = 0.5. Then the T<sub>AFSET</sub> is going to be 41.7ns. K<sub>EF</sub> is defined as 方程式 7:

$$K_{EF} = \frac{R_{AEF}}{R_{AEF} + R_{AEF(hi)}}$$

(7)

R<sub>AEF</sub> and R<sub>AEFHI</sub> define the portion of voltage at pin CS applied to the pin ADELEF (see <a>8</a> 7-3). K<sub>EF</sub> defines how significantly the delay time depends on CS voltage.  $K_{\text{EF}}$  varies from 0, where ADELEF pin is shorted to ground (R<sub>AFF</sub> = 0) and the delay does not depend on CS voltage, to 1, where ADELEF is tied to CS (R<sub>AFFHI</sub> = 0).

Product Folder Links: UCC28950-Q1 UCC28951-Q1

### 备注

The allowed resistor range on DELEF,  $R_{EF}$  is  $13k \Omega$  to  $90k \Omega$ .

The plots in  $\boxtimes$  6-5 and  $\boxtimes$  6-6 show delay time settings as function of CS voltage and  $K_{EF}$  for two different conditions:  $R_{EF} = 13k\Omega$  ( $\boxtimes$  6-5) and  $R_{EF} = 90k\Omega$  ( $\boxtimes$  6-6)

图 6-5. Delay Time  $T_{AFSET}$  and  $T_{BESET}$  (Over CS Voltage and Selected  $K_{EF}$  for  $R_{EF}$  Equal  $13k\Omega$ )

图 6-6. Delay Time T<sub>AFSET</sub> and T<sub>BESET</sub> (Over CS Voltage and Selected K<sub>EF</sub> for R<sub>EF</sub> Equal 90kΩ)

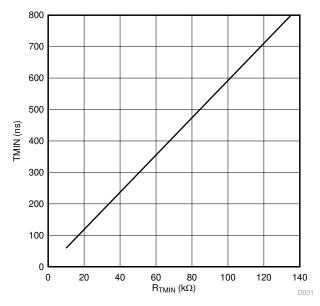

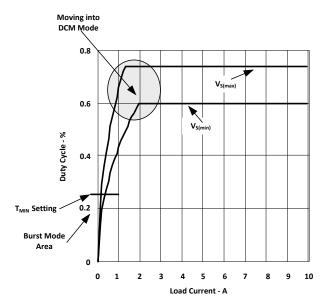

# 6.3.8 Minimum Pulse (TMIN)

The resistor  $R_{\mathsf{TMIN}}$  from the TMIN pin to GND sets a fixed minimum pulse width. This pulse is applied to the transformer and enables ZVS at light load. If the output PWM pulse demanded by the feedback loop is shorter than TMIN, then the controller proceeds to burst mode operation where an even number of TMIN pulses are followed by the off time dictated by the feedback loop. The proper selection of the TMIN duration is dictated by the time it takes to raise sufficient magnetizing current in the power transformer to maintain ZVS. The TMIN pulse is measured from the rising edge of OUTA to the falling edge of OUTD - or from the rising edge of OUTB to the falling edge of OUTC. The minimum pulse TMIN is then defined by  $\hbar$ 8.

$$TMIN = (5.92 \times R_{TMIN}) \, ns$$

(8)

where

- TMIN is in ns

- R<sub>TMIN</sub> is in kΩ

Various propagation and response time delays in the power circuit modify (usually increase) the pulse width that is measured at the transformer. Select the correct TMIN setting using an iterative process due to the propagation and response time delays in the power circuit.

备注

The minimum allowed resistance on the TMIN pin,  $R_{TMIN}$  is 10k  $\Omega$ .

The related plot is shown in <a>\bar{8}</a> 6-7.

图 6-7. Minimum Time TMIN Over Setting Resistor R<sub>TMIN</sub>

The value of minimum duty cycle D<sub>MIN</sub> is determined by 方程式 9.

$$DMIN = \left(TMIN \times F_{SW(osc)} \times 10^{-4}\right)\%$$

(9)

#### where

- F<sub>SW(osc)</sub> is oscillator frequency in kHz

- TMIN is the minimum pulse in ns

- and DMIN is in percent

### 6.3.9 Burst Mode

If the converter is commanding a duty cycle lower than TMIN, then the controller will go into Burst Mode. The controller will always deliver an even number of power cycles to the power transformer. The controller always stops its bursts with an OUTB and an OUTC power delivery cycle. If the controller is still demanding a duty cycle less than TMIN, then the controller goes into shut down mode. Then it waits until the converter is demanding a duty cycle equal or higher than TMIN before the controller puts out TMIN or a PWM duty cycle as dictated by COMP voltage pin.

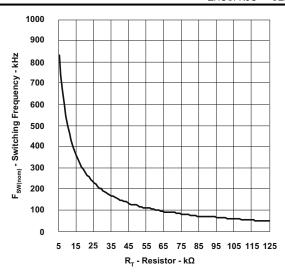

### 6.3.10 Switching Frequency Setting

Connecting an external resistor  $R_T$  between the RT pin and VREF pins sets the fixed frequency operation and configures the controller as a leader providing synchronization output pulses at SYNC pin with 0.5 duty cycle and frequency equal to the internal oscillator. Connect an external resistor RT between the RT and GND pins to configure the controller as a follower. When the controller is used in follower mode, connect a  $825k\Omega$  ±5% resistor from the SS pin to the ground pin in parallel with the SS\_EN capacitor. The follower controller operates with 90° phase shift relative to the leader converter if their SYNC pins are tied together. The switching frequency of the converter is equal to the frequency of output pulses.

方程式 10 defines the nominal switching frequency of the converter configured as a leader (resistor R $_{ extsf{T}}$  between the RT pin and VREF). On the UCC2895x-Q1 there is an internal clock oscillator frequency which is twice as that of the controller's output frequency.

$$F_{\text{SW(nom)}} = \left( \frac{2.5 \times 10^3}{\left( \frac{R_{\text{T}}}{V_{\text{REF}} - 2.5 \, \text{V}} + 1 \times \frac{\text{k}\Omega}{\text{V}} \right)} \right) \text{kHz}$$

(10)

#### where

- $R_T$  is in  $k \Omega$

- VREF is in volts

- F<sub>SW(nom)</sub> is in kHz

This is also an empirical approximation and thus, there is no unit agreement. Assume for example, VREF = 5V,  $R_T = 65k\Omega$ . Then the switching frequency  $F_{SW(nom)}$  is going to be 92.6kHz.

方程式 11 defines the nominal switching frequency of converter if the converter configured as a follower and the resistor R<sub>T</sub> is connected between the RT pin and GND.

$$F_{SW(nom)} = \left(\frac{2.5 \times 10^{3}}{\left(\frac{R_{T}}{2.5 \text{ V}} + 1 \times \frac{k\Omega}{\text{V}}\right)}\right) \text{kHz}$$

(11)

#### where

- $R_T$  is in  $k \Omega$

- F<sub>SW(nom)</sub> is in kHz

Notice that for VREF = 5V, 方程式 10 and 方程式 11 yield the same results.

The plot in 86-8 shows how  $F_{SW(nom)}$  depends on the resistor  $R_T$  value when the VREF = 5V. As it is seen from 方程式 10 and 方程式 11, the switching frequency F<sub>SW(nom)</sub> is set to the same value for either leader or follower configuration provided the same resistor value R<sub>T</sub> is used.

图 6-8. Converter Switching Frequency F<sub>SW(nom)</sub> Over Resistor R<sub>T</sub> Value

### 6.3.11 Slope Compensation (R<sub>SUM</sub>)

Slope compensation prevents a sub-harmonic oscillation in the controller during in peak current mode (PCM) control operation or during cycle-by-cycle current limit at duty cycles above 50% (some publications suggest it may happen at D < 50%). Slope compensation in the controller adds an additional ramp signal to the CS signal and is applied to:

- the PWM comparator in the case of peak current mode control

- the input of the cycle-by-cycle comparator

At low duty cycles and light loads, the slope compensation ramp reduces the noise sensitivity during peak current mode control operation.

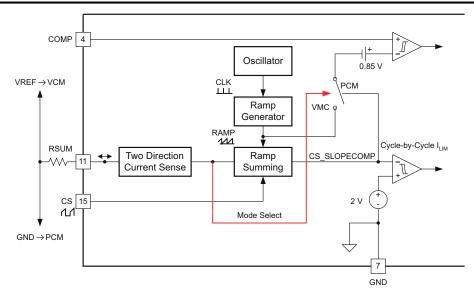

Placing a resistor from the R<sub>SUM</sub> pin to ground allows the controller to operate in PCM control. Connecting a resistor from R<sub>SUM</sub> to VREF switches the controller to voltage mode control (VMC) with the internal PWM ramp. In VMC the resistor at R<sub>SUM</sub> provides CS signal slope compensation for operation in cycle-by-cycle current limit. That is, in VMC, the slope compensation is applied only to the cycle-by-cycle comparator while in PCM the slope compensation is applied to both the PWM and cycle-by-cycle current limit comparators. The operation logic of the slope compensation circuit is shown in \overline{8} 6-9.

27

图 6-9. The Operation Logic of Slope Compensation Circuit

Too much slope compensation reduces the benefits of PCM control. In the case of cycle-by-cycle current limit, the average current limit becomes lower and this might reduce the start-up capability into large output capacitances.

The optimum compensation ramp varies, depending on duty cycle, L<sub>OUT</sub> and L<sub>MAG</sub>. A good starting point in selecting the amount of slope compensation is to set the slope compensation ramp to be half the inductor current ramp downslope (inductor current ramp during the off time). The inductor current ramp downslope (as seen at the CS pin input, and neglecting the effects of any filtering at the CS pin) is calculated in 方程式 12:

$$m_{o} = \frac{V_{OUT}}{L_{OUT}} \times \frac{R_{CS}}{a1 \times CT_{RAT}}$$

(12)

#### where

- V<sub>OUT</sub> is the output voltage of the converter

- L<sub>OUT</sub> is the output inductor value

- a1 is the transformer turns ratio (N<sub>P</sub>/N<sub>S</sub>)

- CT<sub>RAT</sub> is the current transformer ratio (I<sub>P</sub>/I<sub>S</sub>, typically 100:1)

Selection of L<sub>OUT</sub>, a1 and CT<sub>RAT</sub> are described later in this document. The total slope compensation is 0.5m<sub>0</sub>. Some of this ramp is due to magnetizing current in the transformer, the rest is added by an appropriately chosen resistor from RSUM to ground.

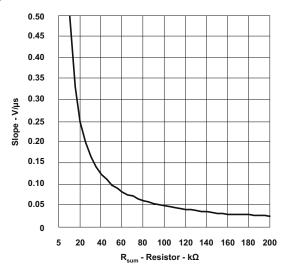

The slope of the additional ramp, me, added to the CS signal by placing a resistor from RSUM to ground is defined by 方程式 13.

$$me = \left(\frac{2.5}{0.5 \times R_{SUM}}\right) \frac{V}{\mu s}$$

(13)

### where

- $R_{SUM}$  is in  $k\Omega$

- me is in V/  $\mu$  s

If the resistor from the RSUM pin is connected to the VREF pin, then the controller operates in voltage mode control, still having the slope compensation ramp added to the CS signal used for cycle-by-cycle current limit. In this case the slope is defined by 方程式 14.

$$me = \left(\frac{(V_{REF} - 2.5 V)}{0.5 \times R_{SUM}}\right) \frac{V}{\mu s}$$

(14)

where

- · VREF is in volts

- R<sub>SUM</sub> is in kΩ

- me is in V/ μ s

图 6-10. Slope of the Added Ramp Over Resistor R<sub>SUM</sub>

备注

The recommended resistor range for  $R_{SUM}$  is  $10k \Omega$  to  $1M \Omega$ .

## 6.3.12 Dynamic SR ON/OFF Control (DCM Mode)

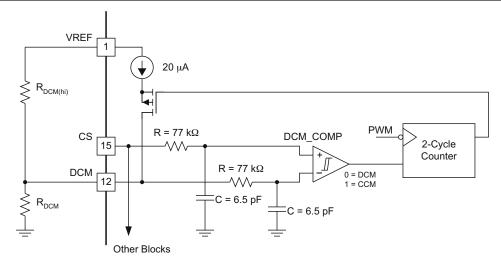

The voltage at the DCM pin provided by the resistor divider  $R_{\text{DCMHI}}$  between VREF pin and DCM, and  $R_{\text{DCM}}$  from DCM pin to GND, sets the percentage of 2V current limit threshold for the Current Sense pin, (CS). If the CS pin voltage falls below the DCM pin threshold voltage, then the controller initiates the light load power saving mode, and shuts down the synchronous rectifiers, OUTE and OUTF. If the CS pin voltage is higher than the DCM pin threshold voltage, then the controller runs in CCM mode. Connecting the DCM pin to VREF makes the controller run in DCM mode and shuts both Outputs OUTE and OUTF. Shorting the DCM pin to GND disables the DCM feature and the controller runs in CCM mode under all conditions.

图 6-11. DCM Functional Block

图 6-12. Duty Cycle Change Over Load Current Change

$$\Delta V = 2 \times 10^{-5} \frac{R_{\text{DCMHI}} \times R_{\text{DCM}}}{R_{\text{DCMHI}} + R_{\text{DCM}}}$$

(15)

图 6-13. Moving From DCM to CCM Mode

图 6-14. Moving From CCM to DCM Mode

DCM must be used to prevent reverse current in the output inductor which could cause the synchronous FETS to fail.

The controller must switch to DCM mode at a level where the output inductor current is positive. If the output inductor current is negative when the controller switches to DCM mode then the synchronous FETs will see a large V<sub>DS</sub> spike and may fail.

## 6.3.13 Current Sensing (CS)

The signal from the current sense pin is used for cycle-by-cycle current limit, peak-current mode control, light-load efficiency management and setting the delay time for outputs OUTA, OUTB, OUTC, OUTD and delay time for outputs OUTE, OUTF. Connect the current sense resistor  $R_{CS}$  between CS and GND. Depending on layout, to prevent a potential electrical noise interference, TI recommends pulling a small R-C filter between the  $R_{CS}$  resistor and the CS pin. There is a 200  $\Omega$  pulldown at the CS pin which is turned on after the PWM comparator has tripped. This helps to reset the CS signal prior to the following switching cycle.

# 6.3.14 Cycle-by-Cycle Current Limit Current Protection and Hiccup Mode

$$I_{DS(leader)} = (-25 \times (1 - D) + 5) \,\mu A$$

(16)

$$I_{DS(follower)} = (-25 \times (1 - D)) \mu A \tag{17}$$

The soft-start capacitor value also determines the so-called hiccup mode off-time duration. The behavior of the converter during different modes of operation, along with related soft-start capacitor charge and discharge currents are shown in § 6-15.

图 6-15. Timing Diagram of Soft-Start Voltage V<sub>SS</sub>

The largest discharge current of  $20\mu A$  is when the duty cycle is close to zero. This current sets the shortest operation time during the cycle-by-cycle current limit and is defined in 方程式 18 and 方程式 19

$$T_{CL(on\_leader)} = \frac{C_{SS} \times (4.65 \text{ V} - 3.7 \text{ V})}{20 \,\mu\text{A}}$$

(18)

$$T_{CL(on\_follower)} = \frac{C_{SS} \times (4.65 \text{ V} - 3.7 \text{ V})}{25 \text{ µA}}$$

(19)

Thus, if the soft-start capacitor  $C_{SS}$  = 100nF is selected, then the  $T_{CL(on)}$  time is 5ms.

To calculate the hiccup off time T<sub>CL(off)</sub> before the restart, use 方程式 20 or 方程式 21.

$$T_{CL(off\_leader)} = \frac{C_{SS} \times (3.6V - 0.55V)}{2.5\mu A}$$

(20)

$$T_{\text{CL(off\_follower)}} = \frac{C_{\text{SS}} \times (3.6V - 0.55V)}{4.9\mu\text{A}}$$

(21)

With the same soft-start capacitor value at 100nF, the off-time before the restart is 122ms. If the overcurrent condition occurs before the soft-start capacitor voltage reaches the 3.7V threshold during start-up, the controller limits the current but the soft-start capacitor continues to be charged. As soon as the 3.7V threshold is reached, the soft-start voltage is quickly pulled up to the 4.65V threshold by an internal  $1k\Omega$   $R_{DS(on)}$  switch and the cycle-by-cycle current limit duration timing starts by discharging the soft-start capacitor. Depending on specific design requirements, the user can override this default behavior by applying external charge or discharge currents to the soft-start capacitor. The whole cycle-by-cycle current limit and hiccup operation is shown in  $\mathbb{R}$  6-15. In this example, the cycle-by-cycle current limit lasts about 5ms followed by 122ms of off-time.

Similarly to the overcurrent condition, the hiccup mode with the restart can be disabled by the user if a pullup resistor of  $261k\Omega$  is connected between the SS and VREF pins. The controller remains in the latch-off mode if an

overcurrent condition occurs. In this case, calculate an external soft-start capacitor value with the additional pullup current taken into account. The latch-off mode can be reset externally if the soft-start capacitor is forcibly discharged below 0.55V or the V<sub>DD</sub> voltage is lowered below the UVLO threshold.

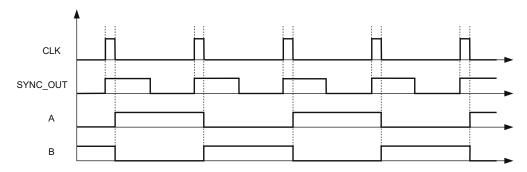

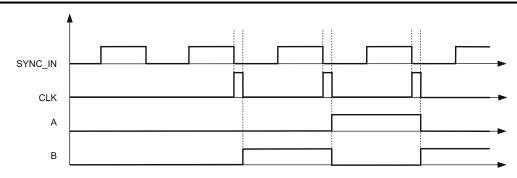

### 6.3.15 Synchronization (SYNC)

The UCC2895x-Q1 allows flexible configuration of converters operating in synchronized mode by connecting all SYNC pins together and by configuration of the controllers as leader and/or followers. The controller configured as leader (resistor between RT and VREF) provides synchronization pulses at the SYNC pin with the frequency equal to 2X the converter frequency F<sub>SW(nom)</sub> and 0.5 duty cycle. The controller configured as a follower (resistor between RT and GND and 825-k  $\Omega$  resistor between SS EN pin to GND) does not generate the synchronization pulses. The follower controller synchronizes its own clock to the falling edge of the synchronization signal thus operating 90° phase shifted versus the leader converter's frequency F<sub>SW(nom)</sub>.

The output inductor in a full bridge converter sees a switching frequency which is twice that seen by the transformer. In the case of the UCC2895x-Q1 this means that the output inductor operates at 2 × F<sub>SW(nom)</sub>. This means that the 90° phase shift between leader and follower controllers gives a 180° phase shift between the currents in the output inductors and hence maximum ripple cancellation. For more information about synchronizing more than two UCC2895x-Q1 devices, see Synchronizing Three or More UCC28950 Phase-Shifted, Full-Bridge Controllers (SLUA609).

If the synchronization feature is not used then the SYNC pin may be left floating, but connecting the SYNC pin to GND through a  $10k\Omega$  resistor will reduce noise pickup and switching frequency jitter.

- If any converter is configured as a follower, the SYNC frequency must be greater than or equal to 1.8 times the converter frequency.

- follower converter does not start until at least one synchronization pulse has been received.

- If any or all converters are configured as followers, then each converter operates at its own frequency without synchronization after receiving at least one synchronization pulse. Thus, If there is an interruption of synchronization pulses at the follower converter, then the controller uses its own internal clock pulses to maintain operation based on the R<sub>T</sub> value that is connected to GND in the follower converter.

- In leader mode, SYNC pulses start after SS pin passes its enable threshold which is 0.55 V.

- follower starts generating SS/EN voltage even though synchronization pulses have not been received.

- TI recommends that the SS on the leader controller starts before the SS on the follower controller; therefore SS/EN pin on leader converter must reach its enable threshold voltage before SS/EN on the follower converter starts for proper operation. On the same note, TI also recommends that the T<sub>MIN</sub> resistors on both leader and follower are set at the same value.

图 6-16. SYNC OUT (leader Mode) Timing Diagram

33

图 6-17. SYNC\_IN (follower Mode) Timing Diagram

# 6.3.16 Outputs (OUTA, OUTB, OUTC, OUTD, OUTE, OUTF)

- All MOSFET control outputs have 0.2A drive capability.

- The control outputs are configured as P-MOS and N-MOS totem poles with typical  $R_{DS(on)}$  20  $\Omega$  and 10  $\Omega$ , accordingly.

- The control outputs are capable of charging 100pF capacitor within 12ns and discharge within 8ns.

- The amplitude of output control pulses is equal to V<sub>DD</sub>.

- Control outputs are designed to be used with external gate MOSFET/IGBT drivers.

- The design is optimized to prevent the latch-up of outputs and verified by extensive tests.

### 6.3.17 Supply Voltage (VDD)

Connect this pin to a bias supply in the range from 8V to 17V. Place high-quality, low ESR and ESL and at least 1 $\mu$ F ceramic bypass capacitor  $C_{VDD}$  from this pin to GND. TI recommends using a 10  $\Omega$  resistor in series from the bias supply to the VDD pin to form an RC filter with the  $C_{VDD}$  capacitor.

# 6.3.18 Ground (GND)

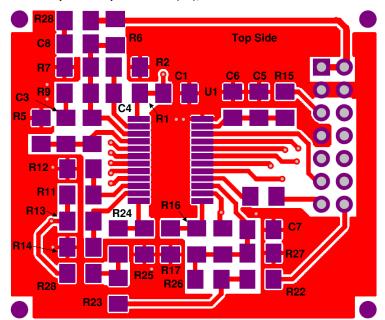

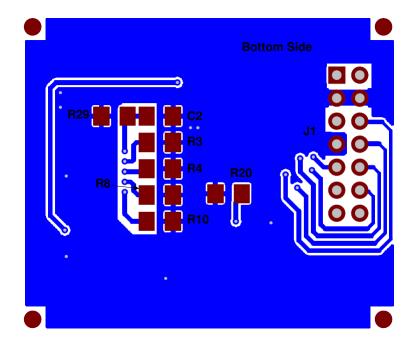

All signals are referenced to this node. TI recommends having a separate quiet analog plane connected in one place to the power plane. The analog plane connects the components related to the pins VREF, EA+, EA-, COMP, SS/EN, DELAB, DELCD, DELEF, TMIN, RT, RSUM. The power plane connects the components related to the pins DCM, ADELEF, ADEL, CS, SYNC, OUTF, OUTE, OUTD, OUTC, OUTB, OUTA, and VDD. 🖺 6-18 shows an example of layout and ground planes connection.

图 6-18. Layout Recommendation for Analog and Power Planes

#### 6.4 Device Functional Modes

The UCC2895x-Q1 controllers offer many operational modes. These modes are described in detail in #6.3.

- Current mode<sup>1</sup>. The UCC2895x-Q1 controller operates in current mode control when the RSUM pin is connected to GND through a resistor (R<sub>SUM</sub>) . The resistor sets the amount of slope compensation.

- Voltage mode<sup>1</sup>. The controller operates in voltage mode control when the RSUM pin is connected to VREF through a resistor (R<sub>SUM</sub>). The chosen resistor value gives the correct amount of slope compensation for operation in current limit mode (cycle-by-cycle current limit).

- DCM mode. The controller enters DCM mode when the signal at the CS pin falls below the level set by the resistor at the DCM pin. The SR drives (OUTE and OUTF) turn off and secondary rectification occurs through the body diodes of the SRs.

- Burst mode. The controllers enter burst mode when the pulse width demanded by the feedback signal falls below the width set by the resistor at the TMIN pin.

- Leader mode. This is the default operation mode of the controller and is used when there is only one UCC2895x-Q1 controller in the system. Connect the timing resistor (R<sub>T</sub>) from the RT pin to VREF. In a system with more than one UCC2895x-Q1 controller, configure one as the leader and the others as followers<sup>1</sup>.

- Follower mode. The follower controller operates with a 90° phase shift relative to the leader (providing their SYNC pins are tied together). Connect the timing resistor (R<sub>T</sub>) from the RT pin to GND and connect an 825k  $\Omega$  ±5% resistor from the SS/EN pin to GND<sup>1</sup>.

- Synchronized mode. When a UCC2895x-Q1 controller is configured as a follower, its SYNC pin is used as an input. The follower synchronizes its internal oscillator at 90° to the signal at its SYNC pin. The application note, Synchronizing Three or More UCC28950 Phase-Shifted, Full-Bridge Controllers, discusses how multiple follower controllers may be synchronized to a single leader oscillator.

- Hiccup mode. This mode provides overload protection to the power circuit. The UCC2895x-Q1 controller stops switching after a certain time in current limit. It starts again (soft-start) after a delay time. The user can control the time spent in current limit before switching is stopped and the delay time before the soft start

- Current-limit mode. The UCC2895x-Q1c ontroller provides cycle-by-cycle current limiting when the signal at the CS pin reaches 2V.

- Latch-off mode. Connect a resistor between the SS pin and VREF. The UCC2895x-Q1 controller then latches off when the controller enterscurrent-limit mode. 1

Copyright © 2024 Texas Instruments Incorporated Product Folder Links: UCC28950-Q1 UCC28951-Q1

Current mode control and voltage mode control are mutually exclusive as are leader and follower modes.

# 7 Application and Implementation

#### 备注

以下应用部分中的信息不属于 TI 元件规格,TI 不担保其准确性和完整性。TI 的客户负责确定元件是否 适合其用途,以及验证和测试其设计实现以确认系统功能。

# 7.1 Application Information

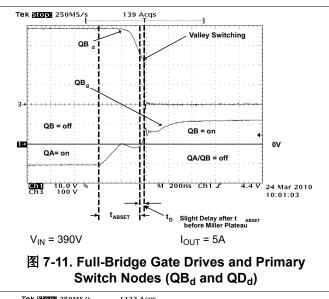

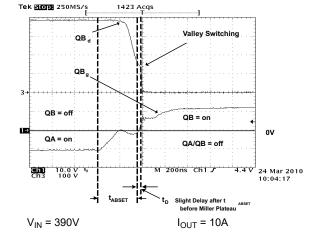

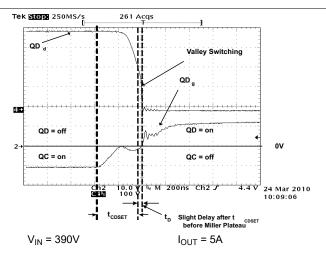

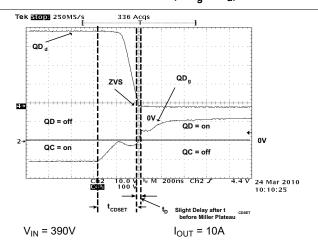

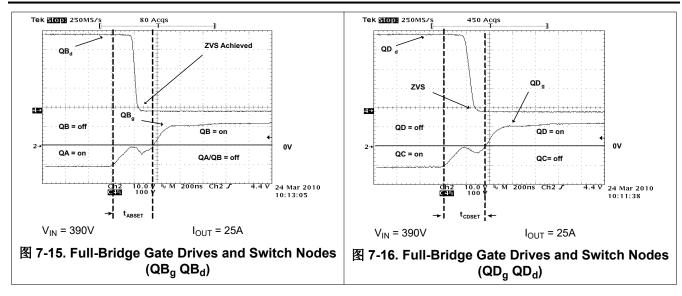

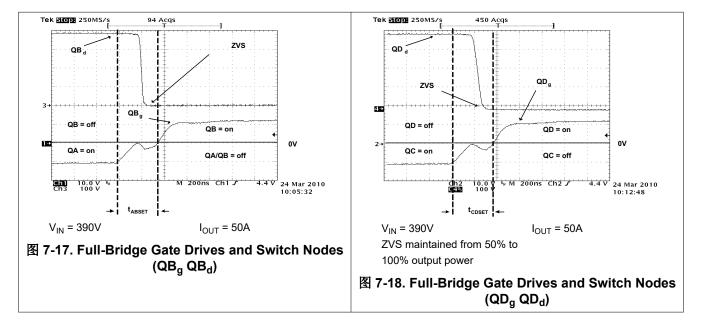

The high efficiency of a phase-shifted full-bridge DC-DC converter using the UCC2895x-Q1 is achieved by using synchronous rectification, a control algorithm providing ZVS condition over the entire load current range, accurate adaptive timing of the control signals between primary and secondary FETs and special operating modes at light load. A simplified electrical diagram of this converter is shown in 🗵 7-3. The UCC2895x-Q1controller is located on the secondary side of converter, although it could be placed on the primary side as well. The secondary side lication allows easy power system level communication and better handling of some transient conditions that require fast direct control of the synchronous rectifier MOSFETs. The power stage includes primary side MOSFETs, QA, QB, QC, QD and secondary side synchronous rectifier MOSFETs, QE and QF. For example, for the 12-V output converters in server power supplies use of the center-tapped rectifier scheme with L-C output filter is a popular choice.

To maintain high efficiency at different output power conditions, the converter operates in synchronous rectification mode at mid and high output power levels, transitioning to diode rectifier mode at light load and then into burst mode as the output power becomes even lower. All of these transitions are based on current sensing on the primary side using a current sense transformer in this specific case.