# TI Designs: TIDA-00522 Reference Guide Stabilizing Differential Amplifiers as Attenuators

# 🦊 Texas Instruments

### **TI Designs**

TI Designs are analog solutions created by TI's analog experts. Reference designs offer the theory, component selection, and simulation of useful circuits. Circuit modifications that help to meet alternate design goals are also discussed.

#### **Design Resources**

Design Page TINA-TI™ LMH5401

All Design files SPICE Simulator Product Folder

#### **Circuit Description**

This design provides a reference for using a fully differential amplifier (FDA) at a gain lower than what is specified in the datasheet. In this example the LMH5401 which is specified at a gain of 4V/V is used as an attenuator with a gain of 0.5V/V.

Ask The Analog Experts WEBENCH® Design Center TI Precision Designs Library

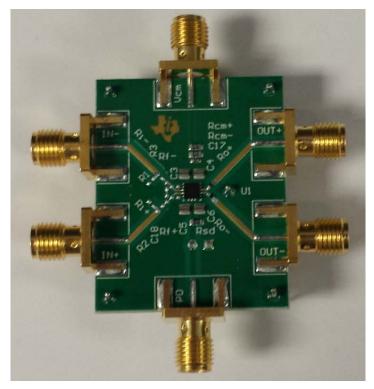

Figure 1 Reference Design Board

## 1 Design Summary

Flexible Gain

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

TINA-TI is a trademark of Texas Instruments WEBENCH is a registered trademark of Texas Instruments

- Noise Shaping

- Supply Voltage: +5V or +-2.5V

- Supply Current: 60 mA

Although amplifiers are often used with large voltage gains there are times when the amplifier is used for other purposes, including attenuating a signal while providing source isolation. This reference design will show how to configure the LMH5401 for gains less than the 4V/V recommended in the datasheet.

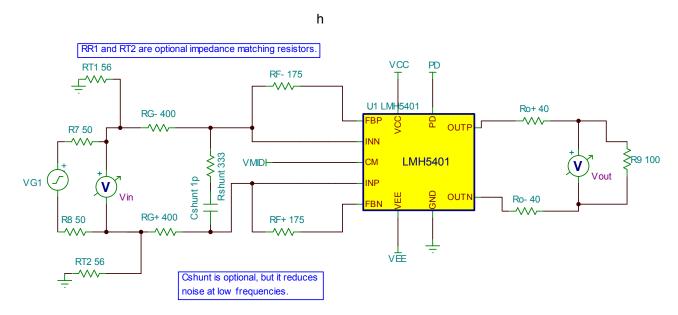

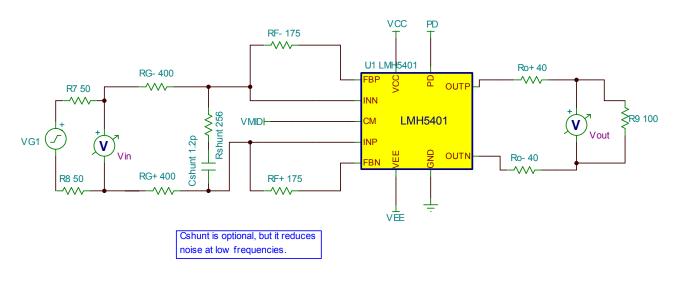

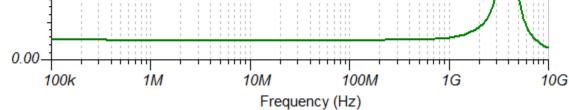

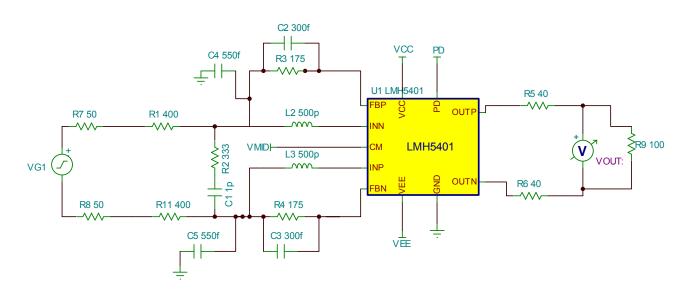

Figure 2 LMH5401 Basic Schematic (Note: Rf total = 200  $\Omega$ , there is 25  $\Omega$  on chip).

#### 2 Theory of Operation

The LMH5401 as implemented on the standard EVM is not stable for gains less than 4V/V (Rf = 200, Rg = 50). Because amplifier stability is based on noise gain rather than signal gain, we can increase the noise gain to stabilize the amplifier while keeping the signal gain low. The method shown in this reference design uses the addition of a resistor and (optionally) a capacitor between the amplifier input pins to accomplish this increase in noise gain, while leaving the signal gain unchanged.

#### 2.1 Equations

Fully differential amplifiers have a noise gain that is equal to  $1 + \left(\frac{RF}{RG+RSeq}\right)$ . Where RF is the feedback resistance, RG is the gain set resistance and RSeq is the equivalent source and termination resistance. To simplify we will combine RG + RSeq = RGT. Adding a resistor between the amplifier input pins essentially adds another phantom input that also contributes to noise gain. Using superposition the new noise gain equation is equal to  $1 + \left(\frac{RF}{RGT||0.5*RS}\right)$  where the extra resistor Rs is the shunt resistor added between the amplifier input pins.

For the standard configuration where the source resistance is 50 Ohms and RG is 50 Ohms and RF is equal to 200 Ohms the EVM measured gain is 4V/V while the net gain is 2V/V due to the loss in the source resistance. The noise gain is 3V/V for this configuration. In order to implement this noise gain, use the values shown in the table below. Because the shunt resistor is applied to both inputs the value in the table is 2x the valued required for each input. If using two shunt resistors (one for each input) connect them to ground and use half of the table value on each input.

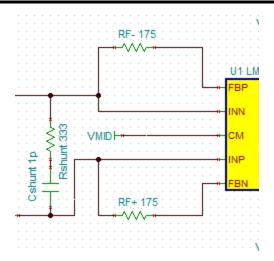

Figure 3 Stabilizing shunt resistor shown as Rshunt

Table 1 Shunt Resistor Selection for Various Gain Settings (Rf = 200 Ohms, Source = 50 Ohms)

| 1 | 1 | 1 |  |

|---|---|---|--|

| • |   | ) |  |

|   |   |   |  |

| Closed Loop<br>Gain V/V* | Gain Set Resistor (Rg) Value | Shunt Resistor Value (Rs) | Shunt Capacitor Value<br>(Cs) |

|--------------------------|------------------------------|---------------------------|-------------------------------|

| 4                        | 50                           | Not Required              | Not Required                  |

| 2                        | 100                          | 600                       | 0.5p                          |

| 1                        | 200                          | 333                       | 1p                            |

| 0.5                      | 400                          | 256                       | 1.2p                          |

| 0.1                      | 2000                         | 210                       | 1.5p                          |

| *Closed Loop Ga          | Rs,Cs Corner                 |                           |                               |

|                          |                              |                           | Frequency = ~500MHz           |

These resistor values are set for a noise gain of 3V/V. For a flatter frequency response, use smaller resistance values. This will result in higher noise levels, but will give much flatter response.

#### 3 Designing for Low Gain Operation

The LMH5401 is a high speed amplifier which is compensated for stability for differential gain of 4V/V or higher as well as single ended gains of 2V/V or higher. Stability is based on the noise gain of the amplifier which must be above the minimum stable value stated above. In the simplest case noise gain is equal to  $1 + \frac{RF}{RG}$ . Some applications require the isolation and buffering of an amplifier, but do not require voltage gain. These applications are the subject of this reference design.

The method that this paper proposes to add stability to low gain circuits is to directly increase the amplifier noise gain with a shunt resistor between the amplifier input pins. The resistive element can be placed across the input pins of the amplifier which are a virtual short circuit. Being a virtual short circuit with very little delta V is the primary reason that parasitic reactance has minimal influence on the circuit. This also means that a resistor added to this node adds only noise gain. There is no signal present at this node to amplify. This resistor also has very little impact on the amplifier input impedance because the voltage difference between the pins is kept close to 0V by the amplifier feedback loop.

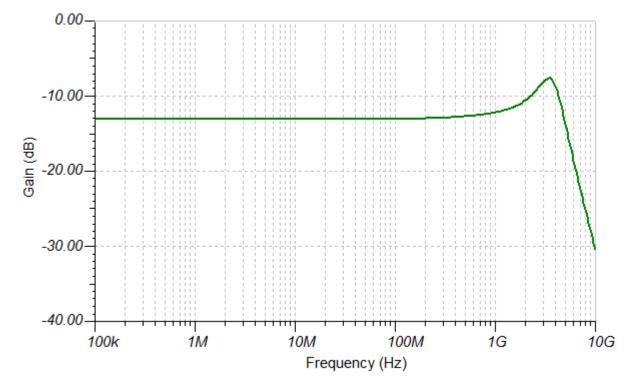

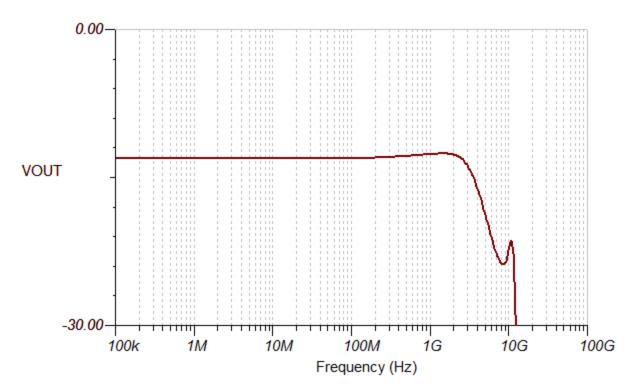

Figure 4 Gain = 0.5 V/V Frequency response, noise gain = 3V/V

Figure 5 Gain = 0.5V/V, Noise Gain = 3V/V

#### 4 Simulation

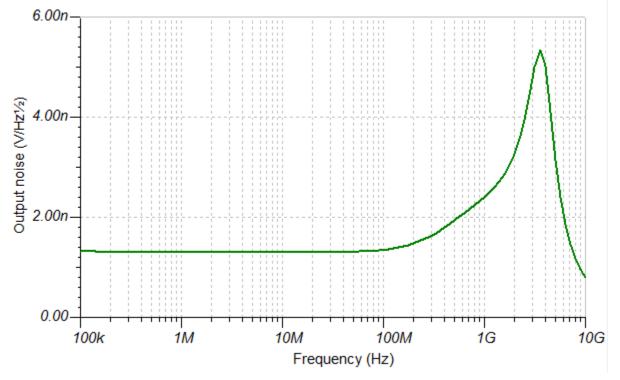

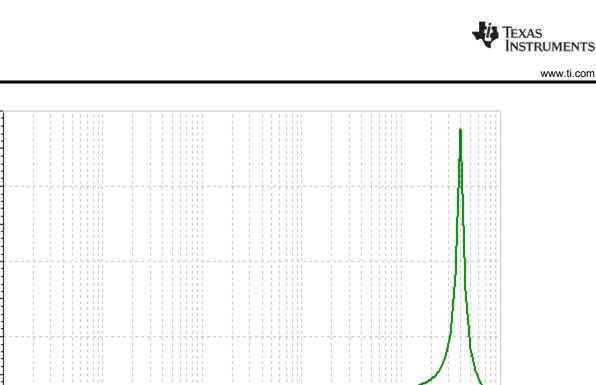

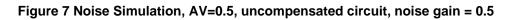

The plot in Figure 4 is the simulated frequency response for the circuit shown in Figure 5. Adding noise gain to the amplifier adds noise. This is shown in Figure 6. The increase in noise is obvious when compared to a noise plot from an uncompensated circuit; this is shown in Figure 7. The narrow and sharp noise spike in Figure 7 is also a strong indicator that the circuit is unstable. The extreme peak in noise corresponds with a frequency of instability for the amplifier. Testing in the lab has confirmed that the simulation results are accurate with regard to the amplifier instability.

Figure 6 TINA-TI Noise Simulation, Av =0.5, Rs=255 Ohms, Noise Gain = 3

20.00n

15.00n

10.00n

5.00n

Output noise (V/Hz1/2)

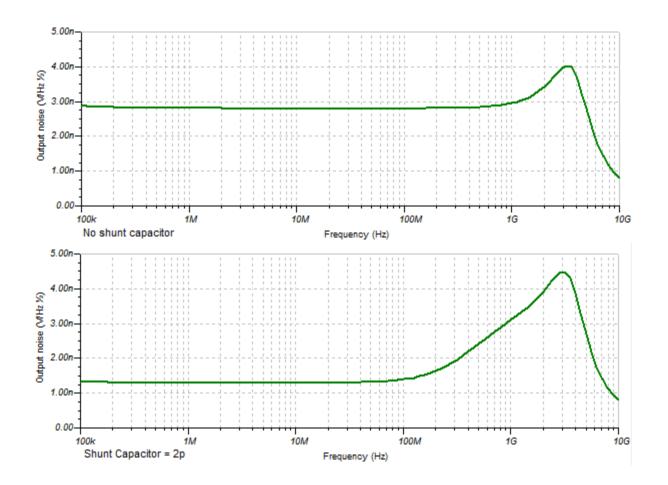

Figure 8. The LMH5401 has excess phase margin at low frequencies. We can use this fact to reduce noise at lower frequencies. The shunt resistor is 255 Ohms and the shunt capacitor is 1.2p. The frequency corner for the series RC circuit is  $\frac{1}{2*\pi*R*c}$  which is equal to 520 MHz. This is almost one order of magnitude lower in frequency than the noise spike at ~3.7GHz shown in Figure 7 which means that the additional capacitor will have minimal impact on stability while significantly reducing noise gain at lower frequencies where stability is not a problem. Note that figure 8 (bottom) low frequency (~1.3nV) matches the uncompensated value of Figure 7.

Figure 8 TINA-TI Noise Simulation, Av =0.5, Rs=154 Ohms, noise gain = 4 (Top plot no Cshunt, Bottom plot, Cshunt = 2p)

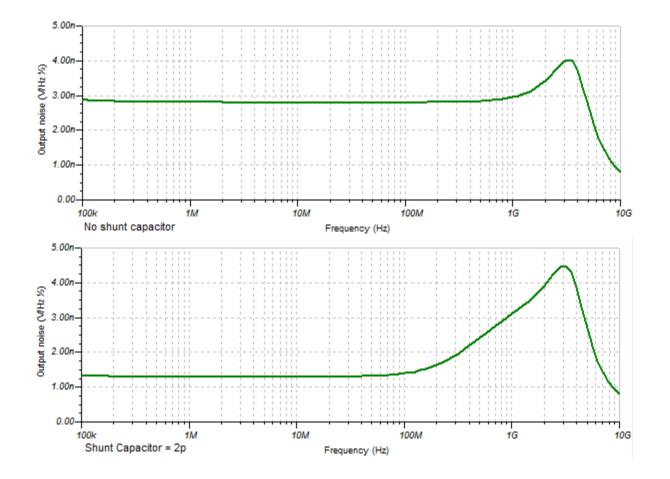

#### 5 Measured Results

Figure 9 Measured frequency response for various gains

Using the component values in Table 1 we made measurements of different gains. The frequency response curves are shown in Figure 9. These results show that while the amplifier can be configured for arbitrarily low gain settings there is a point of diminishing returns when the gain is set to a gain of less than 1V/V (net gain of - 6dB). The frequency response of the curves with gain of less than 1V/V is not flat and has undesirable peaking. This is an artifact of the feedback network which reduces the ability of the amplifier to provide large amounts of attenuation.

Since the frequency response did not agree with initial TINA simulations it would be instructive to find possible causes of the discrepancy. In order to match the measured results there are only small changes needed to be made to the TINA models. For a Gain of 2 the model changes are shown below in Figure 10. What is clear from these adjustments is that at frequencies above 1GHz very small parasitic reactance can have measurable impacts on the circuit.

The added elements in the adjusted model are capacitors C2 and C3. The physical structures on the design board responsible for this capacitance is the section of trace from the FBP pin to the INN pin and also from the FBN pin to the INP pin. The other elements in the adjusted model are inductors L2 and L3. These represent the trace inductance on the amplifier input pins.

Figure 10 Adjusted TINA Schematic

Figure 11 Simulation Results for Av =0.5 V/V, Approximating Measured Results (see schematic in Figure 10)

The results shown in Figure 11 match fairly well with the measured results shown in Figure 9. The model does not agree exactly, though. This indicates there are other circuit elements that are not completely modeled. This is common when working at frequencies above 1GHz. Every circuit element has small reactances that will impact behavior at these frequencies. This is one reason that it is very important to build prototype circuits to test performance.

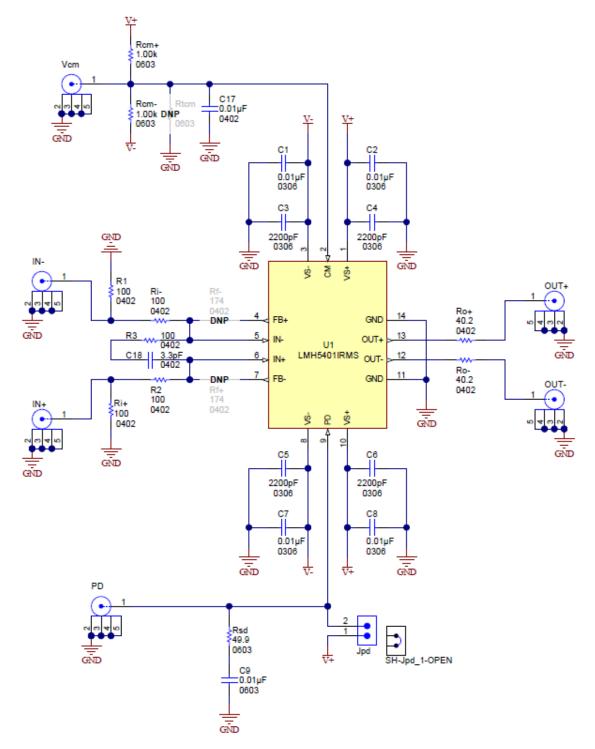

#### 6 Board Schematics

The schematics for the reference design are shown below in Figure 12.

## 7 BOM

| Designator                             | Quantity | Value  | Description                                                            | Size                                | PartNumber         | Manufacturer          |

|----------------------------------------|----------|--------|------------------------------------------------------------------------|-------------------------------------|--------------------|-----------------------|

| !PCB                                   | 1        |        | Printed Circuit<br>Board                                               |                                     | XX####             | Any                   |

| C1, C2, C7,<br>C8                      | 4        | 0.01uF | CAP, CERM,<br>0.01uF, 25V, +/-<br>20%, X7R, 0306                       | 0306                                | LLL185R71E103MA01L | MuRata                |

| C3, C4, C5,<br>C6                      | 4        | 2200pF | CAP, CERM,<br>2200pF, 50V, +/-<br>20%, X7R, 0306                       | 0306                                | LLL185R71H222MA01L | MuRata                |

| C9                                     | 1        | 0.01uF | CAP, CERM,<br>0.01uF, 16V, +/-<br>10%, X7R, 0603                       | 0603                                | GRM188R71C103KA01D | MuRata                |

| C10, C13,<br>C14                       | 3        | 10uF   | CAP, TA, 10uF,<br>10V, +/-10%, 0.9<br>ohm, SMD                         | 3216-18                             | TPSA106K010R0900   | AVX                   |

| C11                                    | 1        | 0.1uF  | CAP, CERM, 0.1uF,<br>10V, +/-10%, X5R,<br>0402                         | 0402                                | C1005X5R1A104K     | TDK                   |

| C12, C17                               | 2        | 0.01uF | CAP, CERM,<br>0.01uF, 25V, +/-<br>10%, X7R, 0402                       | 0402                                | C1005X7R1E103K     | TDK                   |

| C18                                    | 1        | 3.3pF  | CAP, CERM, 3.3<br>pF, 25 V, +/- 5%,<br>C0G/NP0, 0402                   | 0402                                | GRM1555C1E3R3CA01D | MuRata                |

| GND,<br>TPG1,<br>TPG2                  | 3        | Black  | Test Point, TH,<br>Multipurpose, Black                                 |                                     | 5011               | Keystone Electronics  |

| IN+, IN-,<br>OUT+,<br>OUT-, PD,<br>Vcm | 6        |        | Connector, SMT,<br>End launch SMA 50<br>ohm                            | SMA End<br>Launch                   | 142-0701-851       | Emerson Network Power |

| Jpd                                    | 1        |        | Header, TH, 100mil,<br>2x1, Gold plated,<br>230 mil above<br>insulator | TSW-102-<br>07-G-S                  | TSW-102-07-G-S     | Samtec, Inc.          |

| R1, R2, R3,<br>Ri+, Ri-                | 5        | 100    | RES, 100, 1%,<br>0.063 W, 0402                                         | 0402                                | CRCW0402100RFKED   | Vishay-Dale           |

| Rcm+,<br>Rcm-                          | 2        | 1.00k  | RES, 1.00k ohm,<br>1%, 0.1W, 0603                                      | 0603                                | CRCW06031K00FKEA   | Vishay-Dale           |

| Ro+, Ro-                               | 2        | 40.2   | RES, 40.2 ohm, 1%, 0.063W, 0402                                        | 0402                                | CRCW040240R2FKED   | Vishay-Dale           |

| Rsd                                    | 1        | 49.9   | RES, 49.9 ohm, 1%, 0.1W, 0603                                          | 0603                                | CRCW060349R9FKEA   | Vishay-Dale           |

| SH-Jpd_1-<br>OPEN                      | 1        | 1x2    | Shunt, 100mil, Gold plated, Black                                      |                                     | 382811-6           | AMP                   |

| U1                                     | 1        |        | 8GHz Ultra<br>Wideband Fully<br>Differential<br>Amplifier,<br>RMS0014A | RMS0014A                            | LMH5401IRMS        | Texas Instruments     |

| V+                                     | 1        | Red    | Test Point, TH,<br>Multipurpose, Red                                   |                                     | 5010               | Keystone Electronics  |

| V-                                     | 1        | Yellow | Test Point,<br>Multipurpose,<br>Yellow, TH                             | Yellow<br>Multipurpose<br>Testpoint | 5014               | Keystone              |

| C15, C16                               | 0        |        | CAP, CERM, xxxF,<br>xxV, [TempCo],<br>xx%,<br>[PackageReference]       | 0603                                | Used in BOM report | Used in BOM report    |

| RB+, RB-,<br>Rtcm                      | 0        |        | RES, xxx ohm, x%,<br>xW,<br>[PackageReference]                         | 0603                                | Used in BOM report | Used in BOM report    |

| Designator | Quantity | Value | Description                    | Size | PartNumber       | Manufacturer |

|------------|----------|-------|--------------------------------|------|------------------|--------------|

| Rf+, Rf-   | 0        | 174   | RES, 174, 1%,<br>0.063 W, 0402 | 0402 | CRCW0402174RFKED | Vishay-Dale  |

#### 8 About the Author

Loren Siebert has been an applications engineer with National Semiconductor and Texas Instruments since 2000. Loren has supported high speed amplifiers in a wide array of applications ranging from video buffers to communications devices. Prior to working in the semiconductor industry Loren was an RF engineer for Cellular One, McCaw Cellular, Nextel and AT&T Wireless.

References:

AN-1719 Noise Figure Analysis Fully Differential Amplifier

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated