# Application Brief

## 了解 SPI 总线

Younghua Pan

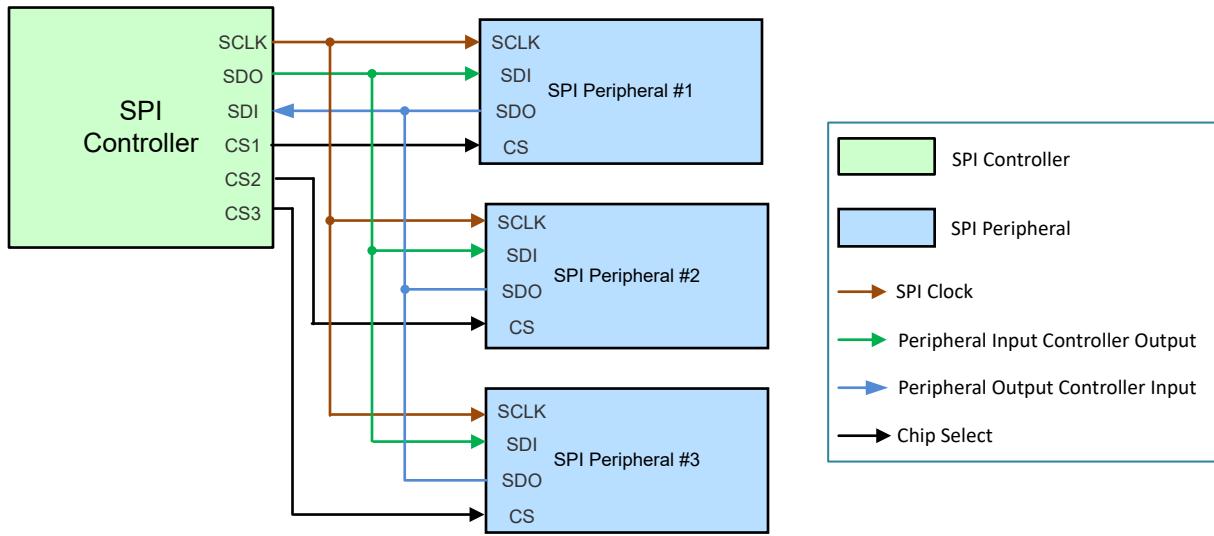

串行外设接口 (SPI) 总线是一种广泛使用的同步通信协议，可在控制器器件与一个或多个外设之间实现高速、全双工数据传输。SPI 由 Motorola 于 20 世纪 80 年代开发，现已成为嵌入式系统中外设连接的标准接口。由于其简单性、多功能性和高效性，SPI 已成为工程师设计可靠、高速通信系统时的重要工具。图 1 展示了总线上 SPI 连接的典型示意图。

图 1. SPI 总线示例

SPI 通信通过共享时钟信号实现同步，从而确保数据传输时序的精确性。与集成电路总线 (I2C) 等其他串行协议不同，串行外设接口 (SPI) 没有规定标准的通信格式，因此开发者可根据具体应用需求灵活定制协议参数。表 1 展示了 SPI、I2C 与通用异步收发传输器 (UART) 之间的差异。

表 1. 与其他协议的比较

| 功能     | SPI       | I2C  | UART |

|--------|-----------|------|------|

| 通信类型   | 同步        | 同步   | 异步   |

| 数据传输模式 | 全双工       | 半双工  | 全双工  |

| 时钟信号   | 是         | 是    | 否    |

| 寻址     | 片选 (CS) 线 | 寻址协议 | 不适用  |

| 速度     | 高         | 中    | 低    |

## SPI 基础知识

SPI 支持全双工通信、这意味着可以同时发送和接收数据。SPI 支持全双工通信，这意味着可以同时发送和接收数据。协议采用一组基本信号来建立通信连接，而这些信号可能因 SPI 配置的不同有所变化。

**表 2. SPI 总线信号**

| 信号名称                    | 用途                          |

|-------------------------|-----------------------------|

| PICO ( 控制器 SDO、外设 SDI ) | 将数据从控制器发送到外设                |

| POCI ( 控制器 SDI、外设 SDO ) | 将数据从外设发送到控制器                |

| SCLK ( 串行时钟 )           | 由控制器生成，用于同步数据传输             |

| CS ( 片选 )               | 一种由控制器用于选择并启用特定外设设备的低电平有效信号 |

## SPI 总线架构

SPI 总线的架构较为简单，由一个**控制器**和一个或多个**外设**组成。控制器负责发起通信、控制时钟以及选择与之通信的外设。该架构支持三种主要配置：

- **单控制器、单外设：**

- 最简单的设置、其中控制器仅与一个外设通信。

- 需要四条线路 ( PICO、POCI、SCLK 和 CS )。

- **单控制器、多外设 ( 独立片选 )：**

- 每个外设都有一条专用的片选 (CS) 线。

- 控制器激活目标外设的 CS 线，而其他外设的 CS 线保持未激活状态。

- **菊花链配置：**

- 外设串联，一个器件的输出馈入为下一个器件的输入。

- 可减少 CS 线路数量，整个链路仅需一条 CS 线。

- 在每个时钟周期内，数据通过链中的所有器件移位。

- **3 线 SPI 配置：**

- 将 PICO 和 POCI 线路合并为一条双向数据线路，通常称为**数据输入/输出 (DIO)**。

- 该配置将所需线缆减少至三条：SCLK、CS 和 DIO。

## 数据传输模式

SPI 支持四种工作模式，具体由时钟极性 (CPOL) 和时钟相位 (CPHA) 决定。表 3 所示的这些模式定义了时钟信号的特性以及数据采样的时序。

**表 3. SPI 数据传输模式**

| 模式   | CPOL | CPHA | 说明                         |

|------|------|------|----------------------------|

| 模式 0 | 0    | 0    | 数据会在时钟的上升沿进行采样，且时钟空闲时为低电平。 |

| 模式 1 | 0    | 1    | 数据会在时钟的下降沿进行采样，且时钟空闲时为低电平。 |

| 模式 2 | 1    | 0    | 数据会在时钟的下降沿进行采样，且时钟空闲时为高电平。 |

| 模式 3 | 1    | 1    | 数据会在时钟的上升沿进行采样，且时钟空闲时为高电平。 |

SPI 数据传输

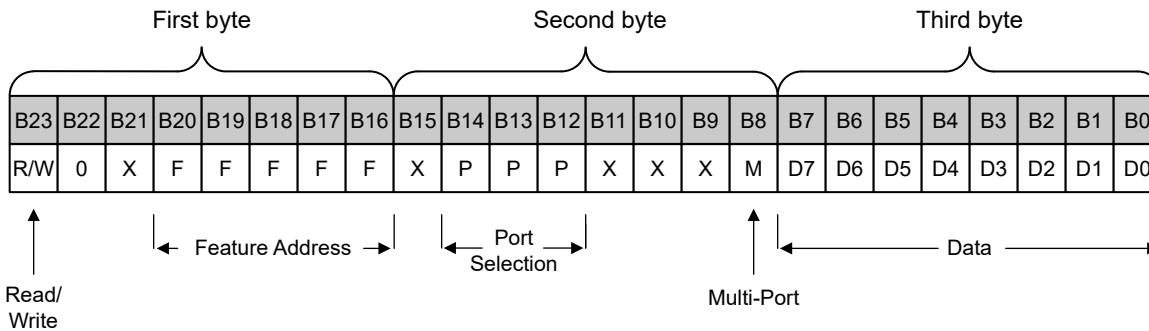

由于 SPI 是一种同步全双工通信协议，能够实现控制器与一个或多个外设之间的数据交换。TI 的 TXE8116/24 器件采用固定的 24 位 SPI 事务格式，按高位优先 (MSB first) 的方式传输，且工作于 SPI 模式 0 ( 时钟极性 CPOL=0，时钟相位 CPHA=0 )。该器件支持全双工操作，可同时交换输入的命令帧与输出的数据或状态帧。每次 SPI 事务必须以 CS 信号拉低开始，并在整个 24 位序列期间保持低电平。[图 2](#) 展示了 TXE8116/24 器件中的 SPI 数据帧。

图 2. TXE8116/24 SPI 数据帧

写入外设

要向寄存器写入数据，控制器需传输一个 24 位字，且 MSB（第 23 位）需设为 0。寄存器地址编码在第 [22:16] 位中，第 [15:8] 位用于选择目标 GPIO 端口或配置多端口模式。最后 8 位 [7:0] 则携带实际要写入的数据。

- 示例：将端口 0 配置为输出

- 寄存器地址：0x04 ( 方向寄存器 )

- 端口选择：0x00 ( 端口 0 )

- Data: 0xFF ( 所有引脚均设为输出模式 )

- PICO：

- 第 [23] 位 ( 读写位 , R/W ) = 0 ( 写入 )

- 第 [22:16] 位 ( 地址位 ) = 0x04

- 第 [15:8] 位 ( 端口位 ) = 0x00

- 第 [7:0] 位 ( 数据位 ) = 0xFF

- 最终帧 = 0x0400FF

- POCI 响应：

- 第 [23:22] 位 = 0x3 ( 表示其为状态段 )

- 第 [21:16] 位：故障状态寄存器

- 第 [15:8] 位：全为 0

- 第 [7:0] 位：先前的寄存器数据

## 从外设读取数据

要从寄存器读取数据，主机需将第 23 位设为 1 并传输目标寄存器地址。低 16 位可填充虚拟数据。在同一传输过程中，TXE8124 会通过 POCI 线返回所寻址寄存器的当前值。

- 示例：从端口 1 读取 GPIO 输入状态

- 寄存器地址：0x02 (输入端口寄存器)

- 端口选择：0x01 (端口 1)

- Data: 0x00 (虚拟数据)

- PICO：

- 第 [23] 位 (读写位, R/W) = 1 (读取)

- 第 [22:16] 位 (地址位) = 0x02

- 第 [15:8] 位 (端口位) = 0x01

- 第 [7:0] 位 (虚拟数据位) = 0x00

- 最终帧 = 0x820100

- **POCI 响应：**

- 第 [23:22] 位 = 0x3 ( 表示其为状态段 )

- 第 [21:16] 位：故障状态寄存器

- 第 [15:8] 位：全为 0

- 第 [7:0] 位：读取数据

#### TXE8116/24 的关键时序要求

| 参数                                | 说明                           | 典型值           |

|-----------------------------------|------------------------------|---------------|

| t <sub>SCLK</sub>                 | SPI 时钟周期 (3.3V < VCC < 5.5V) | 100ns (10MHz) |

| t <sub>CS</sub> /t <sub>CSH</sub> | CS 设置保持时间                    | ≥50ns         |

| t <sub>V(SDO)</sub>               | POCI 在 SCLK 边沿之后有效           | ≤27ns         |

| t <sub>DIS(SDO)</sub>             | CS 置为无效后，POCI 线呈高阻态          | ≤50ns         |

所有 SPI 事务都必须满足《[具有中断输出、复位输入和 I/O 配置寄存器的 TXE81xx-Q1 汽车级 24 位 SPI 总线 I/O 扩展器数据手册](#)》中规定的最低时序约束，以确保通信正常。

#### 注释

- 所有事务均为全双工模式；每个 SPI 时钟周期内，PICO 和 POCI 线上各传输 1 位数据。

- 数据会在 SCLK 的上升沿进行采集，并在下降沿被驱动输出。

- 始终确保在 24 位帧传输期间 CS 信号保持低电平；在帧传输过程中切换 CS 信号可能会导致事务出错。

- 可通过 [15:8] 位中的特定端口位实现多端口寻址。

#### 商标

所有商标均为其各自所有者的财产。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，TI 对此概不负责。

TI 提供的产品受 [TI 的销售条款](#) 或 [ti.com](#) 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

版权所有 © 2025 , 德州仪器 (TI) 公司