## Design Guide: TIDA-00176

# 具有高分辨率位置内插的正弦/余弦编码器接口

## 说明

此参考设计是针对正弦/余弦位置编码器且符合 EMC 标准的工业接口。其应用场景包括需要精确速度和位置控制的工业驱动器。该设计使用 16 位双路采样 ADC，并提供了可直接替换的 14 位或 12 位版本，从而允许在性能和成本之间进行优化。此外，TIDA-00176 还支持通过 SPI 和 QEP 接口轻松连接外部处理器，并支持使用可选的嵌入式 ADC。为实现快速评估，本设计提供适用于 Piccolo™ F28069M MCU LaunchPad™ 的示例固件。该固件可输出来自正弦/余弦编码器的实测角，同时可通过 MCU 的 USB 虚拟 COM 端口提供高达 28 位的分辨率。

## 资源

|                               |       |

|-------------------------------|-------|

| TIDA-00176                    | 设计文件夹 |

| ADS8354、THS4531A              | 产品文件夹 |

| TLV3202、OPA2365               | 产品文件夹 |

| REF2033、TPS54040A             | 产品文件夹 |

| TIPD117                       | 工具文件夹 |

| Piccolo F28069M MCU LaunchPad | 工具文件夹 |

请咨询我司 TI E2E™ 支持专家

## 特性

- 符合 EMC 标准的工业接口设计适用于带  $1\text{-}V_{PP}$  差分输出（2.5V 偏移）以及高达 500kHz 输入频率的正弦/余弦编码器

- 高分辨率插值位置，分辨率高达 28 位，电缆长度测试可达 70 米

- 双路模拟信号链支持同时使用 16 位双路 SAR ADC 和 MCU 嵌入式 ADC，允许评估两条路径和优化一条路径以提高防噪性能并降低带宽

- 易于通过 SPI 和 QEP 接口连接到 MCU，并且根据分辨率要求，可以通过使用可直接替换的 14 位或 12 位 ADC 来实现成本优化

- 为 C2000™ MCU 提供的示例固件，能够在 16kHz 频率下计算高分辨率角度，并通过 USB 虚拟 COM 端口发送角度数据，以便于性能评估

- 经测试符合 IEC61000-4-2、4-4 和 4-5 要求（ESD、EFT 和浪涌 EMC 抗扰度要求）

## 应用

- 交流驱动器

- 精密变速驱动器

- 伺服驱动

## 1 系统说明

### 1.1 设计概述

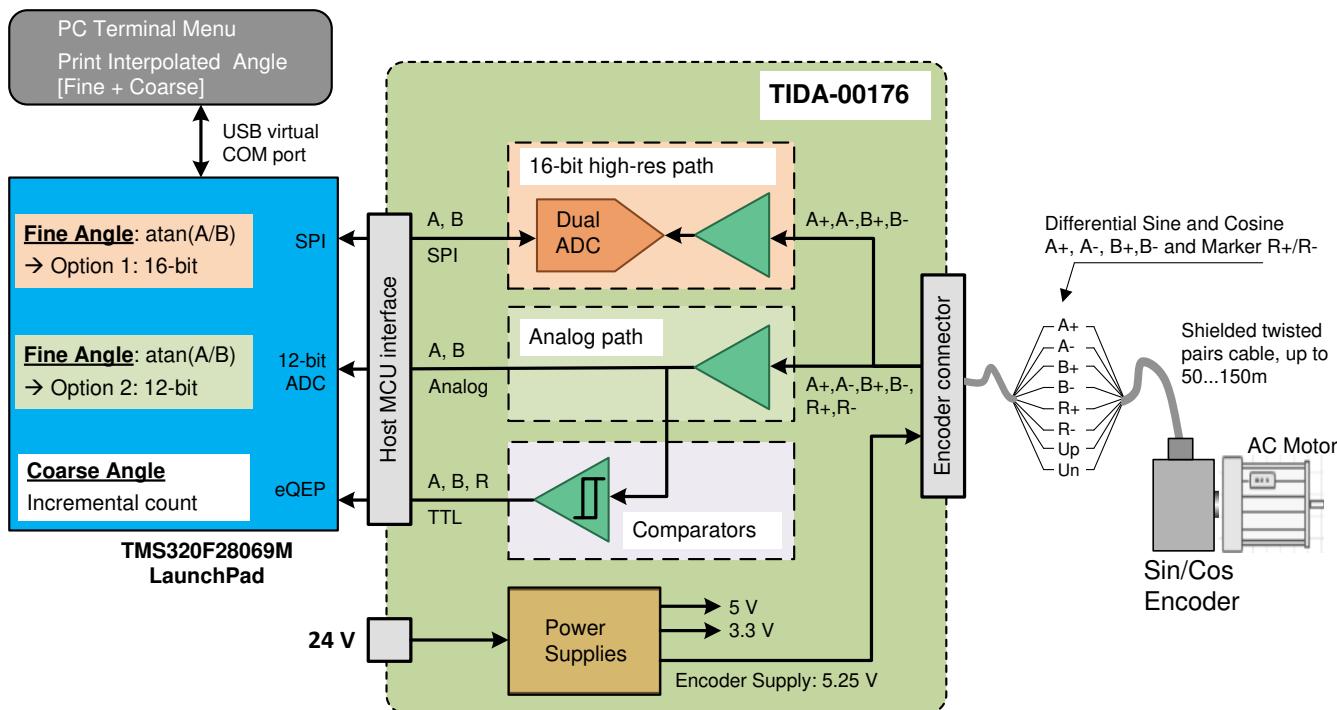

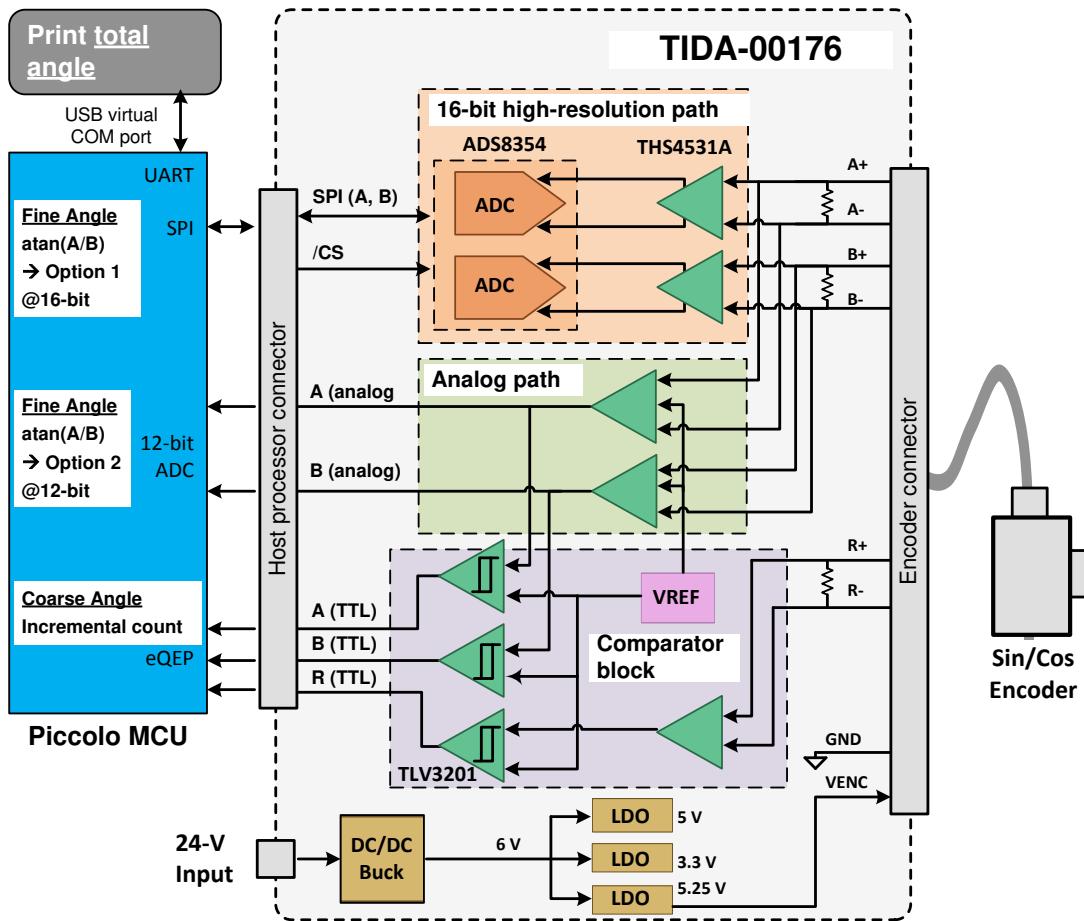

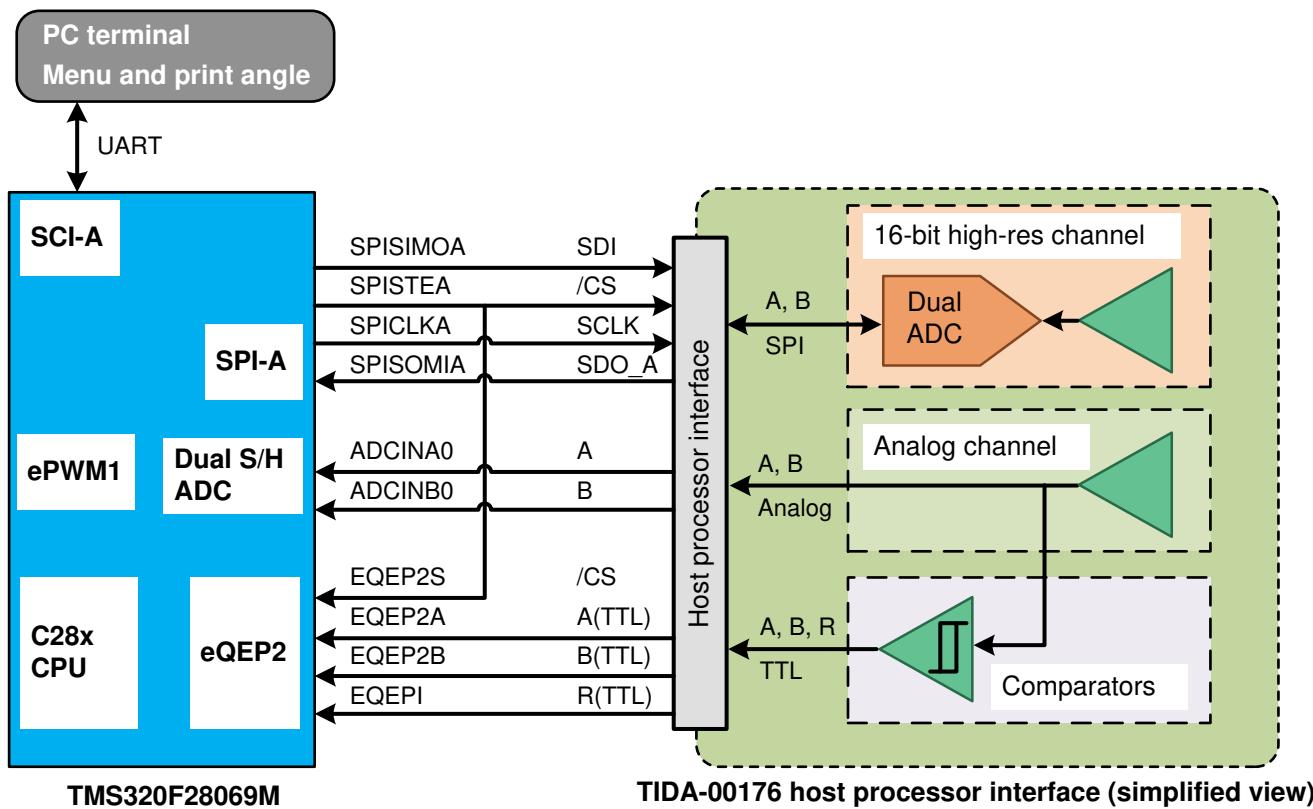

德州仪器 (TI) 的这一设计符合工业温度要求和 EMC 标准，该设计下的接口适用于具有  $1 V_{PP}$  差分模拟输出信号、频率高达 500kHz 且采用 5V 电源电压的正弦/余弦增量式位置编码器。这一 TI 设计的主要组成模块包括双路径模拟信号链、高速比较器模块、电源管理模块、正弦/余弦编码器接口，以及用于数字信号处理和高分辨率位置计算的主机微控制器接口。图 1-1 中所示为简化的系统方框图，其中 TI 硬件设计用浅绿色框表示。

为便于对此设计指南进行评估，我们为 TMS320F28069M InstaSPIN™-MOTION LaunchPad 提供了示例固件。TMS320F28069M 可为两条模拟信号路径计算高分辨率角度位置。一条路径通过 SPI 利用外部 16 位双 ADC。另一条路径则使用 F28069M 嵌入式双路 S/H 12 位 ADC。角度计算的分辨率最高可达 28 位，并通过 USB 虚拟串口输出以便进行评估。

图 1-1. 采用 Piccolo F28069M LaunchPad 的 TIDA-00176 简化系统方框图

模拟信号链提供具有 EMC 保护功能的  $120 \Omega$  终端。差分  $1 V_{PP}$  正弦和余弦输入信号将分别进行放大和电平转换。该设计提供了双信号路径选项，板载了一个高速、高分辨率的双路 16 位同步采样 ADC，支持 SPI 接口，同时还具有双路模拟单端输出，输出偏置电压为 1.65V，可与如 C2000™ Piccolo 实时微控制器系列这类嵌入式双路 S/H ADC 的微控制器连接。

比较器块具有速度快，传播延迟低，迟滞可调的特点，可提高防噪性能。比较器块可将模拟信号 A，B 及标记 R 转换为具有 3.3V TTL 电平的数字信号，可连接至正交编码器脉冲模块，如 C2000 Piccolo MCU 上的 QEP 模块。

板载的宽输入范围 24V 电源为模拟信号链提供必要的电压，同时为正弦/余弦编码器提供 5.25V 的电源电压。

正弦/余弦编码器可连接至 15 引脚屏蔽 Sub-D 连接器或 8 引脚插头。与主机处理器连接的接口可提供模拟单端信号 A 和 B，这两个信号的电压在 0 到 3.3V 之间变化，并且带有 1.65V 的偏置电压；同时，该接口还会提供用于串行外设接口 (SPI) 的数字信号；以及 A、B 和 R 这几个数字信号，它们的输入输出 (I/O) 电压为 3.3V。数字输出信号 A、B 和 R 通常称为 ABZ 信号。

该设计按照 IEC 61800-3 标准中针对可调速电力驱动系统的电磁兼容性 (EMC) 抗扰度要求以及特定测试方法，依据 IEC61000-4-2、4-4 和 4-5 标准，进行了 ESD、EFT 和浪涌方面的测试。

## 1.2 模拟正弦/余弦增量编码器

增量旋转编码器或线性位置编码器在许多应用中用于测量角度或线性位置及速度。根据应用的不同，会使用具有 TTL/HTL 输出信号或模拟正弦输出信号的编码器。后者通常称为正弦/余弦编码器。模拟正弦/余弦增量编码器可实现高分辨率位置测量。正弦增量信号的质量很高，可实现用于数字速度控制的高插值因子。应用领域包括电机、机床、印刷机、木工机床、纺织机、机器人、装卸装置以及各种类型的测量、测试和检验设备。

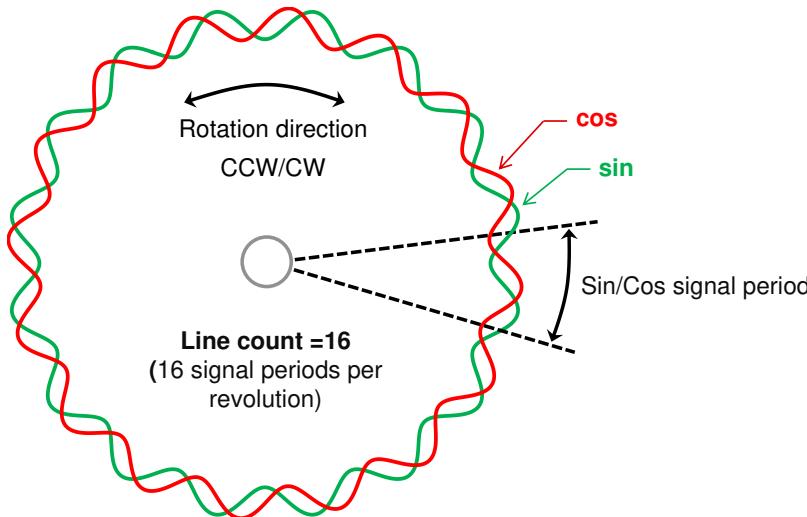

### 1.2.1 正弦/余弦编码器输出信号

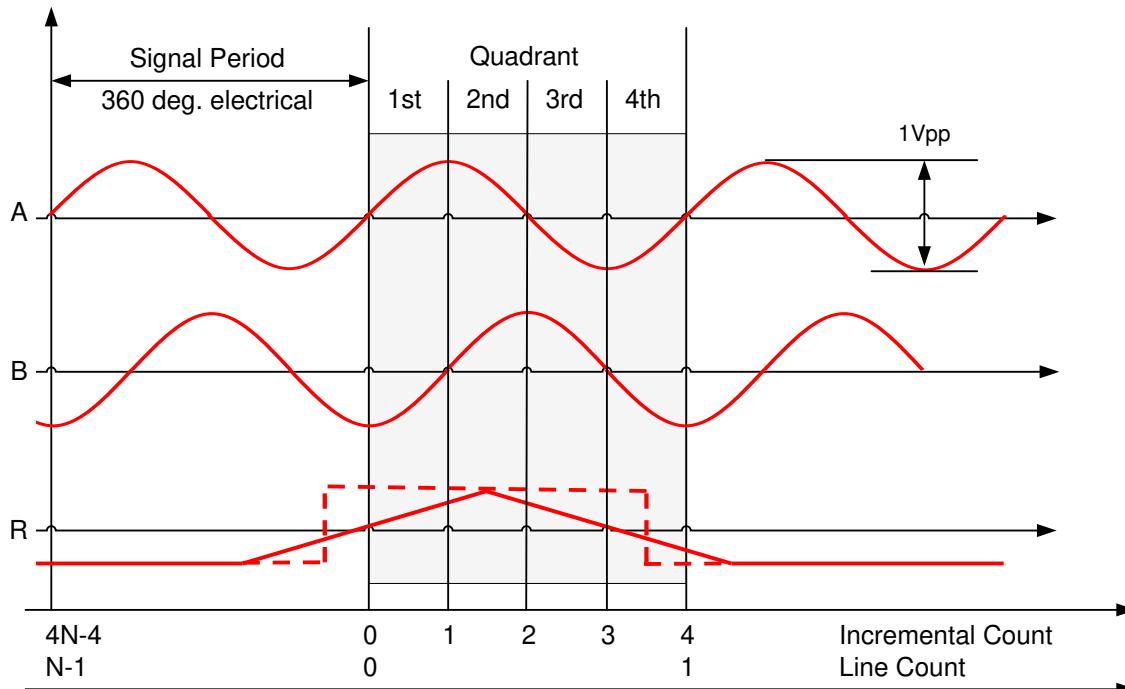

利用编码器通常可实现两种感测方法：光学感测或电感感测。在光学旋转编码器中，编码器圆盘对可以被光电管感测到强度的光束进行调制。这样会产生两个 90 度相移正弦增量信号 A 和 B。从编码器转轴角度看，顺时针旋转时，B 滞后于 A。在一个机械旋转周期，信号 A 和 B 的周期数等于编码器线数 N。较远的轨道能承载参考标记 R，每个机械旋转周期出现一次。借助参考标记可测量绝对角位置。

图 1-2. 线数为 16 的正弦/余弦编码器在一个机械旋转周期中的简化正弦和余弦信号

带有  $1V_{PP}$  接口的正弦/余弦编码器可以提供差分模拟输出信号 A ( $A_+$ 、 $A_-$ ) 和 B ( $B_+$ 、 $B_-$ )，该信号附有  $1V_{PP}$  及通常为 2.5V 的 DC 偏移。差分参考标记信号 R ( $R_+$ 、 $R_-$ ) 的振幅通常略低，每个旋转周期仅出现一个峰值。图 1-3 所示为差分输出信号 A、B 和 R。请注意，A、B 和 R 分别代表  $A_+$  减  $A_-$ 、 $B_+$  减  $B_-$  及  $R_+$  减  $R_-$  的差分信号。

图 1-3. 线数为 N 的正弦/余弦编码器在每个旋转周期的输出电压信号 A、B 和标记 R

正弦/余弦编码器差分输出信号的频率取决于编码器的线数及机械速度，如方程式 1 所示：

$$f_{A,B} [\text{Hz}] = N \times v[\text{rpm}] \times \frac{1}{60} \quad (1)$$

N 代表正弦/余弦编码器线数，v 代表编码器转轴的机械速度，单位为 rpm。

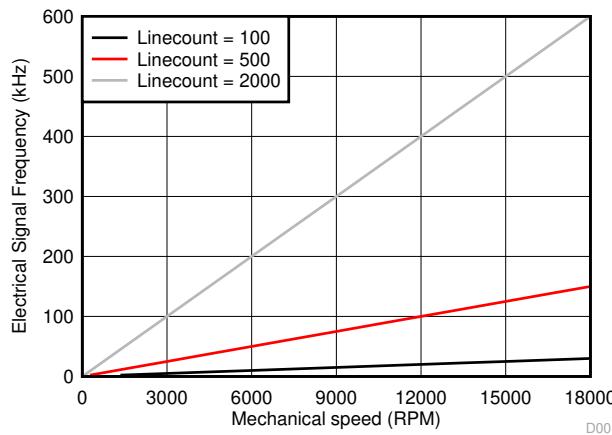

图 1-4 概述了线数 N 为 100、1000 和 2000 时编码器输出频率与机械速度的关系。

图 1-4. 正弦/余弦编码器输出信号 A 和 B 的电频率与机械速度和线数

例如，线数 N 为 2000 时，以 12000rpm 的机械速度运行的正弦/余弦编码器将输出频率为 400KHz 的信号 A 和 B。

### 1.2.2 正弦/余弦编码器电气参数示例

为了了解正弦/余弦编码器电气接口模块的要求，我们对一些工业正弦/余弦编码器模型示例进行了分析。表 1-1 中列出了相应地参数。

**表 1-1. 编码器电源电压示例**

| 正弦/余弦编码器模型 | 电源电压         | 电流消耗         |

|------------|--------------|--------------|

| 1          | 5V ± 0.5V DC | < 120mA      |

| 2          | 5V ± 10%     | 150mA        |

| 3          | 5V ± 5%      | 70mA ( 最小值 ) |

正弦/余弦编码器的电源需要在该规格范围内。

模拟信号链需要至少满足表 1-2 中列出的信号振幅、偏移和最大频率要求。

**表 1-2. 编码器输出信号 A , B 示例**

| 正弦/余弦编码器模型 | 信号电平 A , B                                        | 直流偏移        | 线数 N        | 限制频率 ( -3dB) |

|------------|---------------------------------------------------|-------------|-------------|--------------|

| 1          | 0.6 至 1.2 V <sub>PP</sub> , 1 V <sub>PP</sub> 典型值 | 2.5V ±0.5V  | 50 至 5000   | ≥180 kHz     |

| 2          | 1 V <sub>PP</sub> (+20%, -40%)                    | 2.5V ±0.5V  |             | 120kHz       |

| 3          | 1 V <sub>PP</sub> (±10%)                          | 2.5V ±100mV | 1024 或 2048 | 400kHz       |

**表 1-3. 编码器输出信号标记 R 示例**

| 正弦/余弦编码器模型 | 参考标记处的可用分量 G                                      | 参考标记外的静态值 H | 直流偏移 |

|------------|---------------------------------------------------|-------------|------|

| 1          | 0.5 V <sub>PP</sub> 典型值 , 0.2 V <sub>PP</sub> 最小值 | -1.7V       | 2.5V |

**表 1-4. 编码器机械参数示例**

| 正弦/余弦编码器模型 | 系统精度       | 轴机械速度       |

|------------|------------|-------------|

| 1          | 光栅周期的 1/20 | < 16000 rpm |

## 1.3 通过正弦/余弦编码器计算高分辨率位置的方法

### 1.3.1 理论方法

#### 1.3.1.1 概述

从硬件的角度而言，通常可采用两种方法，这两种方法主要影响 A/D 转换器的要求。

在"过采样方法"中，正弦和余弦信号的采样频率至少应为最大正弦和余弦频率的四倍。增量计数及相位计算由主机处理器上的后续数字信号处理来完成。在该方法中，不需要比较器，而是需要高速双采样 ADC。

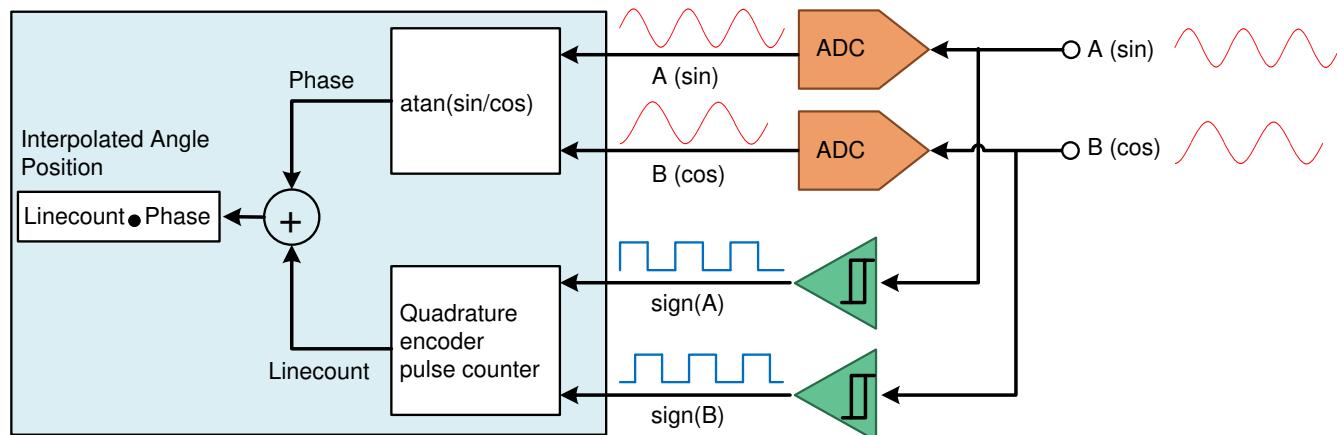

常用的"欠采样"方法使用单独的硬件块来计算增量计数和插值增量相位。与第一种方法相比，该方法的优点是 ADC 的采样频率和带宽更低，因为它不会影响增量计数，而仅影响插值相位。但是，欠采样方法需要为每个正弦和余弦各使用一个比较器，以便生成数字正交编码信号 A 和 B，这两个信号会驱动方向递增递减计数器，通常称为正交编码脉冲计数器。双采样 ADC 的模拟带宽至少需要等于最大正弦/余弦频率。图 1-5 中概述了欠采样方法。

图 1-5. 用于插值角度计算的信号处理方框图

总插值角位置由粗略角和精确角组成。插值角由实际增量线数及该增量线范围内的相位决定。增量线范围内的相位源自任何特定时刻的模拟正弦和余弦信号 A 和 B。实际增量计数和实际模拟正弦和余弦信号都必须同时锁存，因此二者应同步。增量线数提供粗略角，而该增量线范围内正弦和余弦的相位提供精确角。总插值角由粗略角和精确角构成，如图 1-5 中的简化方框图所示。下一段将介绍相应的方程式 2 至方程式 4。

### 1.3.1.2 粗略分辨率角度计算

增量计数及其确定的增量粗略角可由计数器决定，当 A 信号序列超前时，计数器进行递增计数；当 B 信号序列超前时，计数器进行递减计数。当进行数字化处理时，A 信号和 B 信号的上升沿和下降沿都会被计数。因此，一个增量计数相当于信号 A 和 B 均产生了  $90^\circ$  的相移，参见 图 1-3。增量计数从 0 开始，每个 方程式 2 的最大增量计数为  $\text{incr}_{\text{MAX}}$ ，其中 N 为线数：

$$\text{incr}_{\text{MAX}} = (4 \times N) - 1 \quad (2)$$

增量位置  $\Phi_{\text{incr}}$  的计算公式为：

$$\Phi_{\text{incr}} [\text{deg}] = \frac{360}{4 \times N} \times \text{incr} + \Phi_0 \quad (3)$$

其中，incr 是实际增量计数，N 是总线数， $\Phi_0$  是零度角，由参考标记 R ( 如果使用 ) 确定。

### 1.3.1.3 精确分辨率角度计算

正弦信号 A 和 B 的相位  $\phi_{A,B}$  用于在两个连续的线计数或四个增量步进 ( 二者相当 ) 之间对角度进行插值。相位  $\phi_{A,B}$  可以使用 方程式 4 进行计算：

$$\phi_{A,B} [\text{deg}] = \begin{cases} 90^\circ + \tan^{-1}\left(\frac{B}{A}\right) & \text{if } A \geq 0 \\ 270^\circ + \tan^{-1}\left(\frac{B}{A}\right) & \text{if } A < 0 \end{cases} \quad (4)$$

由于在计算中仅使用了信号 A 和信号 B 幅值的比值，而这两个信号的幅值都同时取决于编码器的转速和电源电压，所以编码器转速和电源电压的变化不会影响最终的计算结果。

### 1.3.1.4 插值高分辨率角度计算

在根据 表 1-5 将增量计数 incr 与相位  $\phi_{A,B}$  匹配时，总插值角  $\Phi_{\text{TOTAL}}$  可通过线数 N 计算，公式如下：

$$\Phi_{\text{TOTAL}} [\text{deg}] = \frac{360^\circ}{N} \left( (\text{incr} \gg 2) + \left( \times \frac{\phi_{A,B}}{360^\circ} \right) \right) + \Phi_0 \quad (5)$$

#### 小心

正弦信号 A 和 B 与增量计数 incr 必须同时锁存。

表 1-5. 增量计数与相位及相位象限间关系的示例

| 增量计数 | PHASE                      | 象限 |

|------|----------------------------|----|

| 0    | $0 \leq \text{相位} < 90$    | 1  |

| 1    | $90 \leq \text{相位} < 180$  | 2  |

| 2    | $180 \leq \text{相位} < 270$ | 3  |

| 3    | $270 \leq \text{相位} < 360$ | 4  |

| 4    | $0 \leq \text{相位} < 90$    | 1  |

### 1.3.1.5 非理想同步条件下的实际实施情况

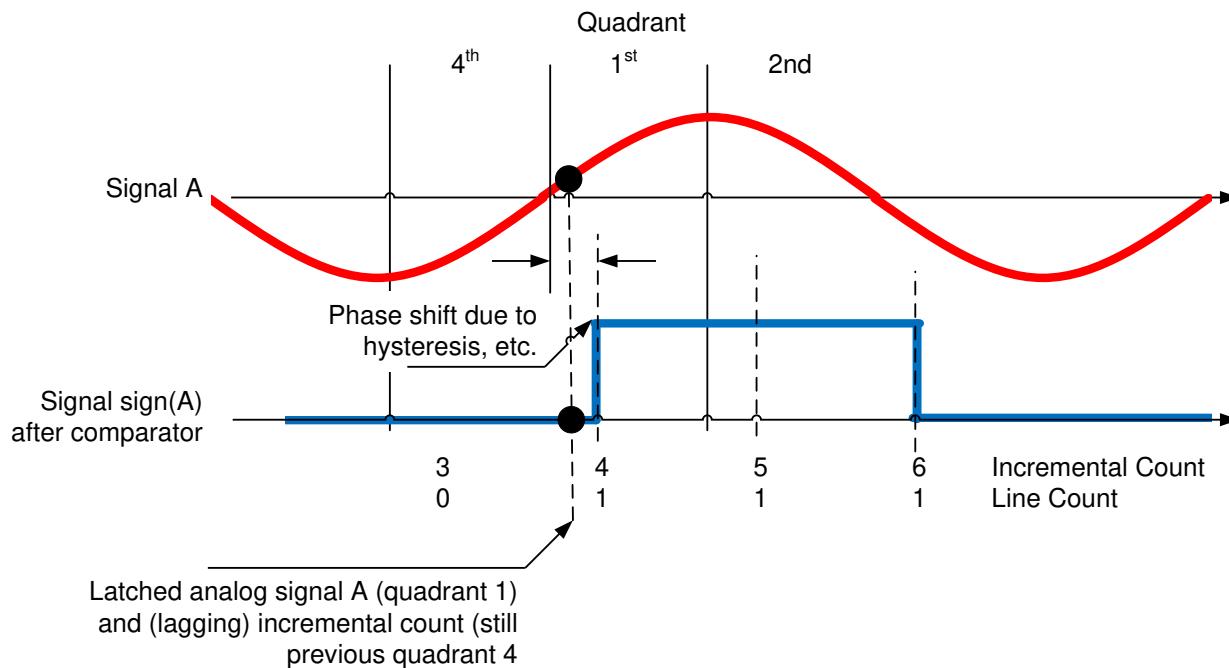

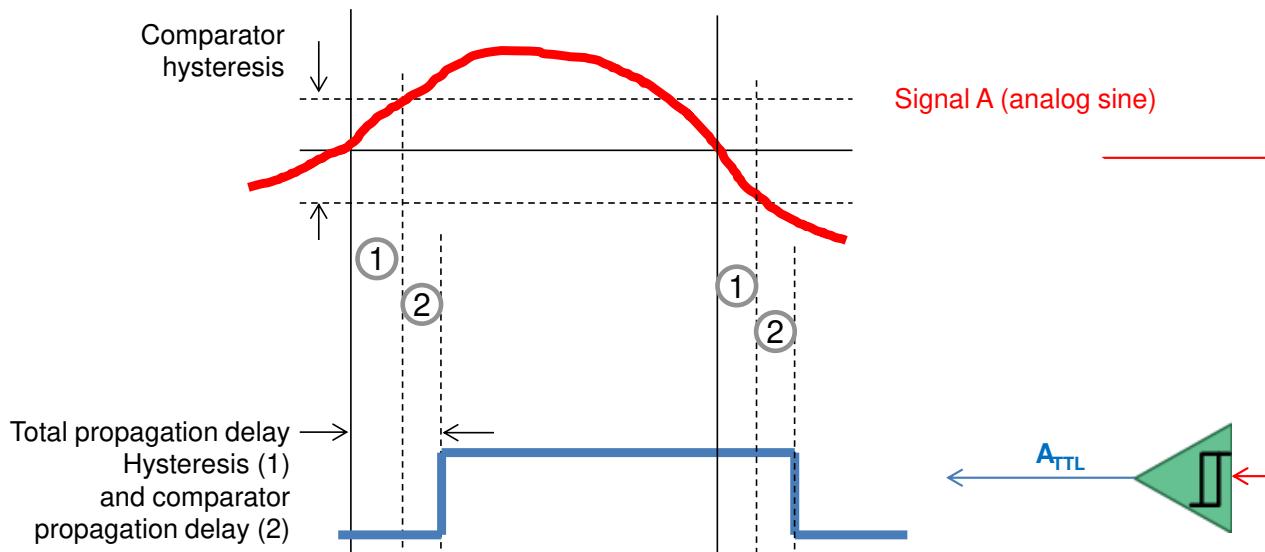

实际上，与模拟信号相比，输入正交编码器脉冲计数器的数字化信号  $A_{TTL}$  和  $B_{TTL}$  通常都有相移。造成这种现象的主要原因是比较器的迟滞和传播延迟，以及锁存增量计数和采样模拟输入  $A$  和  $B$  之间的同步不理想。

迟滞对相移的影响几乎与信号频率无关，但几乎与信号振幅成反比。传播延迟及采样模拟信号与锁存增量计数之间的不理想同步所产生的影响与振幅几乎无关，但与频率成正比。因此，最大相移出现在正弦/余弦编码器频率最大和振幅最小的位置。

这意味着每次转换到下一象限时，由于相位滞后，增量计数器不会立即更新，如图 1-6 中第一象限所示。

图 1-6.  $A_{TTL}$  与模拟信号  $A$  因相位滞后产生的相移

上述因素不容忽视，因此需要采用一种方法来检测并校正这些极端情况。由于增量线数的低两位和模拟相位具有不确定性，因此只要相移保持小于  $\pm 90^\circ$ ，就可以应用表 1-6 中所述的校正方法。

由于仅使用相位信息来识别象限，因此只有两种例外情况需要考虑，即从象限 4 转换到象限 1 或从象限 1 转换到象限 4 期间发生的情况，具体取决于旋转方向。

表 1-6. 校正方法

| 增量计数 [incr]     | 相位 $\Phi_{A,B}$                  | 校正方法                                                            |

|-----------------|----------------------------------|-----------------------------------------------------------------|

| $incr \% 4 = 3$ | $0 \leqslant$ 相位 $< 90^\circ$    | $incr = incr + 1$<br>, 如果 $incr > 4 \times N - 1$ ，则 $incr = 0$ |

| $INCR \% 4 = 0$ | $270 \leqslant$ 相位 $< 360^\circ$ | $incr = incr - 1$<br>, 如果 $incr < 0$ ，则 $incr = 4 \times N - 1$ |

#### 小心

仅当模拟信号  $A$  和  $B$  与数字信号  $A_{TTL}$  和  $B_{TTL}$  之间的相移小于  $\pm 90^\circ$  时，此校正方法才有效。

在节 1.4 中列出了此项设计中最坏情况下的计算值。

### 1.3.1.6 分辨率、精度和速度注意事项

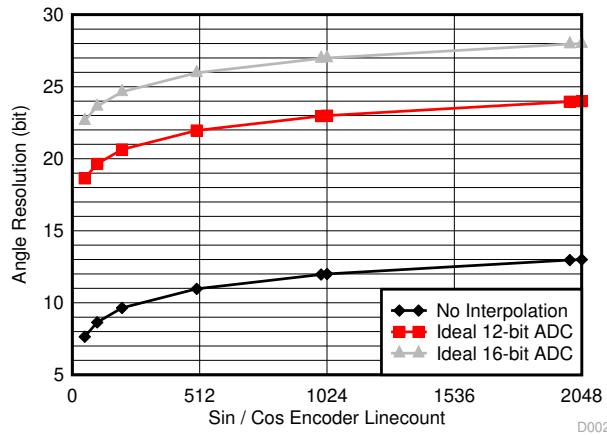

理想的插值角分辨率是正弦/余弦编码器的线数与双路 ADC 分辨率的函数。等效的插值角分辨率的计算公式为：

$$\Phi_{\text{RESOLUTION}}[\text{bit}] = \log_2(2 \times N) + \text{ADC}_{\text{RESOLUTION}}[\text{bit}] \quad (6)$$

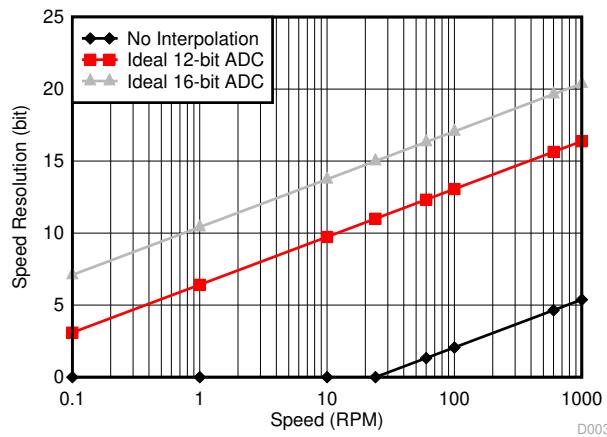

图 1-7 展示了在没有插值、使用理想 12 位双路 ADC 和 16 位双路 ADC 的情况下，可实现的插值角分辨率，其能用作线数的函数。

图 1-7. 理想插值角分辨率、线数和 ADC 分辨率间的关系

如果使用 ADC 的满量程输入范围，则使用 16 位双路 ADC 时，线数为 2048 的正弦/余弦编码器的理想分辨率等于 28 位。

位置控制通常不需要高分辨率，但在进行非常精确的速度控制时，尤其是在机械速度较低的情况下，需要高分辨率。图 1-8 所述的是，在采样速率为 1.6kHz，无低通滤波条件下得出的理想速度分辨率曲线。此时假设在 16kHz 条件下工业驱动系统速度闭环控制的运行比当前闭环控制和 PWM 低 10 倍。

图 1-8. 采样速率为 1.6kHz 且编码器线数为 1000 时的理想速度分辨率与机械速度间的关系

在实践中，将进行低通滤波并提高分辨率和抗扰度，但会出现滤波器特定的传播（组）延迟或延时。

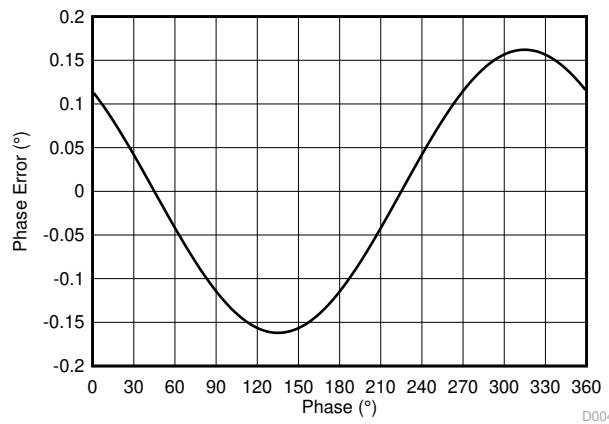

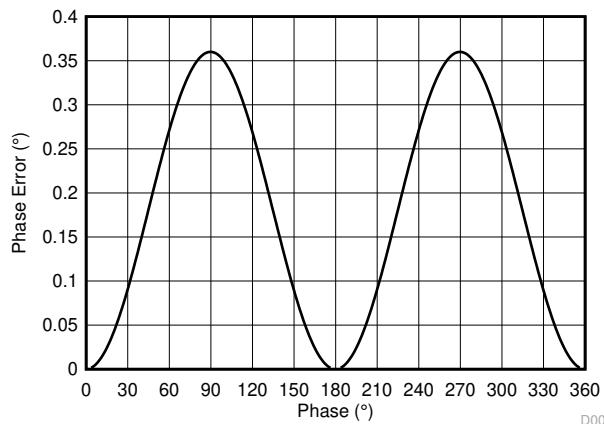

根据理想分辨率、表 1-7、图 1-9，且图 1-10 概述了量化、偏移、增益或相位误差对插值角的影响。

表 1-7. 相位误差示例分析

| 误差源              | 示例                        | 相位误差 [最大值]      |

|------------------|---------------------------|-----------------|

| 信号 A 和 B 的量化     | 12 位                      | 0.012% [0.045°] |

| 信号 A 和 B 的偏移误差   | 0.1%                      | 0.05% [0.18°]   |

| 信号 A 和 B 的增益误差   | 0.1%                      | 0.04% [0.15°]   |

| 输入信号 A 和 B 之间的相移 | $90 + 0.36^\circ [0.1\%]$ | 0.1% [0.36°]    |

图 1-9. 偏移为 +0.1% 时信号 A 和 B 的相位误差

图 1-10. 信号 A 和 B 之间的相移为  $(90 + 0.36^\circ)$  时的相位误差

请注意，由于输入信号 A 和 B 之间的相移引起的相位误差显示了两个周期。可利用此特征和信号处理算法检测和校正恒定相移。但这超出了本设计指南的讨论范围。

#### 1.4 正弦/余弦编码器参数对模拟电路规范的影响

为确定模拟电路，如节 4 中所述，我们考虑了以下正弦/余弦编码器信号参数（包括支持更长的电缆）。

- 正弦/余弦最小和最大峰值间振幅：差分 0.3 至 1.2 V<sub>PP</sub>，满量程输入范围，至少 50% 的余量 (1.8 V<sub>PP</sub>)

- 正弦/余弦偏移电压范围：2.5V ±1V

- 正弦/余弦最大频率：500kHz

- 正弦/余弦最大压摆率：>2 V/μs

- 正弦/余弦线路端接：120-Ω ±1%

- 编码器电源电压和电流：5V ±5%，200mA

### 1.4.1 相位插值的模拟信号链设计注意事项

高分辨率模拟信号链应支持 16 位分辨率，以便提供高插值角分辨率，这尤其适用于精确速度控制。

差分模拟放大器的 AC 本底噪声和失真应匹配 16 位分辨率。对于  $1-V_{PP}$  输入，该值约等于  $15 \mu V$ 。

- 输入电压噪声： $15\mu V/SQRT(1 MHz) = 15nV/SQRT(Hz)$

- 输入电流噪声：对于  $R_{INPUT} = 1k$ ， $15\mu V/SQRT(1MHz)/R_{INPUT}$  等于  $15pA/SQRT(Hz)$

增益和失调属于直流参数，其漂移通常极为缓慢，主要与温度或老化相关。初始失调和增益可在初始化时校准，借助特定算法甚至能在运行期间校准。因此，对这些参数的要求可以稍微放宽。增益和失调随温度的漂移均应在  $10LSB$  的范围内。对于  $1V_{PP}$  输入信号，该值约等于  $150 \mu V$ 。

- 失调漂移 [0 至  $85^{\circ}C$ ]： $150\mu V/85^{\circ}C \sim 2\mu V/^{\circ}C$

- 增益漂移：[0 至  $85^{\circ}C$ ]： $160ppm/85^{\circ}C \sim 2ppm/^{\circ}C$

对于增益设置，建议使用匹配的电阻器（相同封装）。

### 1.4.2 增量计数的比较器功能系统设计

回顾图 1-5：在  $500kHz$  时模拟信号与数字信号 ATT 和 BTTL 之间的总传播延迟应小于  $90^{\circ}$ ，相当于  $500ns$ 。硬件造成的延迟不应超过约 50% 到 70%，相当于  $250$  到  $350ns$ ，以便为硬件相关的失调和温度漂移、因模拟低通/去耦滤波器引起的相移以及后续主机处理器中的非理想同步等情况留出余量。

当比较器的输入信号最小值为  $0.3-V_{PP}V$ ，且存在  $160mV (\pm 80 mV)$  的迟滞电压时，迟滞效应所造成的延迟，从角度来看约为 32 度，换种说法，在  $500kHz$  的信号频率下，这种延迟对应的时长相当于  $180ns$ 。

此外，还要加上比较器自身的传播延迟。比较器传播延迟越小，就有越多余量来增大迟滞，或采用其他方式来提高系统的防噪性能。

图 1-11. 带迟滞的比较器上的信号延迟

## 2 设计特性

如节 1 中所述，此 TI 设计符合工业温度范围要求和 EMC 标准，该设计下的接口适用具有  $1V_{PP}$  差分模拟输出信号 A、B 和索引标记信号 R、输入频率高达 500kHz 且采用 5V 电源电压的正弦/余弦增量式位置编码器。这一 TI 设计的主要组成模块包括双路径模拟信号链、高速比较器模块、电源管理模块、正弦/余弦编码器接口以及用于数字信号处理和高分辨率位置计算的主机微控制器接口。

为便于对此 TI 设计进行评估，我们为 TMS320F28069M InstaSPIN-MOTION LaunchPad 提供了示例固件。

TMS320F28069M 利用 SPI 接口连接的外部 16 位 ADC 以及内部双通道 S/H 12 位 ADC 的模拟通道，为两条信号路径计算高分辨率角度位置，并通过 USB 虚拟 COM 端口输出分辨率最高可达 28 位的角度位置数据。

### TIDA-00176 特性概述

- 宽输入电压范围：具有反极性保护的 24V ( 17 到 36V ) 可为模拟信号链提供必要的电压，并为正弦/余弦编码器提供 5.25V 电压。

- 编码器接口：适用于 5V 正弦/余弦编码器的 Sub-D 15 或 8 引脚插头接口，具有差分输出信号 A、B 和标记 R，电压范围为 0.3V 到  $1.2V_{PP}$ ，偏移量为  $2.5V \pm 1V$ ，输入带宽高达 500kHz。

- 双路模拟信号处理：双路选项，包含板载高速高分辨率双路 16 位同步采样 ADC，支持 SPI 接口，以及具备双路模拟输出，偏置电压为 1.65V，可连接外部双通道 S/H ADC。具有 160mV 可调迟滞特性的高速、低传播延迟比较器，可实现更好的防噪性能，可将模拟信号 A、B 和 R 转换为 3.3V TTL 信号（通常称为 ABZ 信号）。

- 可实现高分辨率插值角度位置计算，分辨率最高可达 28 位，经测试，电缆长度测试可达 70 米。

- EMC 抗扰度：该设计按照 IEC 61800-3 中针对可调速电力驱动系统的电磁兼容性 (EMC) 抗扰度要求以及特定测试方法，依据 IEC61000-4-2、4-4 和 4-5 标准，进行了 ESD、EFT 和浪涌方面的测试。

- 可连接主机处理器，具有用于 MCU QEP 和 SPI 的 3.3V 数字接口信号输出，以及提供可选的单端模拟输出，输出电压范围为 0 至 3.3V，可用于 MCU 嵌入式双通道 S/H ADC。

- 评估固件：适用于 Piccolo F28069M MCU 的示例固件可在 16kHz 频率下进行高分辨率双角位置计算。用户界面通过 USB 虚拟 COM 端口输出，方便进行性能评估。

### 2.1 正弦/余弦编码器接口

此设计提供与 HEIDENHAIN 编码器测试设备兼容的屏蔽式 Sub-D15 插座或 8 引脚接头连接器，可连接到具有差分输出信号 A、B 和标记 R 的 5V 正弦/余弦编码器。

**表 2-1. 正弦/余弦编码器接口**

| 参数                       | 典型值                                      | 注释                                                                     |

|--------------------------|------------------------------------------|------------------------------------------------------------------------|

| 编码器电源电压                  | 5.25V [ $\pm 5\%$ ]，200 mA               | 选择 5.25V 电压是为了获得额外的 0.25V 裕度，以补偿长距离电缆上的电压降。<br>可通过更改反馈电阻器进行调整，例如调整为 5V |

| 输入信号                     | A+、A-、B+、B-、R+、R-                        | $120\Omega$ 差动线路端接                                                     |

| A+、A-、B+、B- 的输入电平和共模电压范围 | 0.3V - $1.2V_{PP}$ ， $2.5V \pm 1.0V$ 共模  |                                                                        |

| R+、R- 的输入电平和共模电压范围       | 0.2V - $0.85V_{PP}$ ， $2.5V \pm 1.0V$ 共模 |                                                                        |

## 2.2 主机处理器接口

针对 A+、A- 以及 B+、B- 信号的高分辨率路径采用了一款高速、高分辨率的 16 位双通道同步采样 ADC，具备差分输入和 SPI 输出。该功能模块的主要特性如 表 2-2 中所述。

**表 2-2. 带 ADC 和 SPI 输出的 16 位高分辨率通道**

| 参数              | 典型值                         | 注释                                         |

|-----------------|-----------------------------|--------------------------------------------|

| 增益 A、B          | 5.0 (0.1%)                  | 匹配的单封装内增益设置寄存器 ( 精度 0.1% )                 |

| 增益漂移 A、B        | 2ppm//°C                    | 匹配的单封装内电阻器                                 |

| 偏移 , A、B        | < 10 LSB ( 16 位 )           | 未校准                                        |

| 失调漂移 , A、B      | < 0.15LSB//°C               |                                            |

| 带宽 (-3dB)       | ≥500kHz                     |                                            |

| 量化              | 16 位                        | 提供 FSR =±5V (ADS8354)<br>插接式兼容 14 或 12 位版本 |

| 采样频率            | 高达 700kSPS                  |                                            |

| 数据输出格式 A、B      | 16 位二进制补码                   |                                            |

| 串行接口 ( SPI 从机 ) | 3.3 V , 频率高达 24MHz 的 SPI 时钟 | 每个 SPI 帧双路 16 位数据                          |

针对信号 A+、A- 和 B+ 的并行第二条路径，为信号 A 和 B 提供单端模拟输出，该输出带有 1.65V 的偏置电压，可连接至嵌入到 C2000 Piccolo 等微控制器中的外部双通道 S/H ADC。

**表 2-3. 具有单端模拟输出的模拟通道**

| 参数           | 典型值                           | 注释                                                      |

|--------------|-------------------------------|---------------------------------------------------------|

| 单端模拟输出 A 和 B | 0-3.3V , 1.65V 偏置电压 [50ppm/K] | 有插接式且兼容的 1.5V 基准电压可供选择，以匹配输入范围为 0 - 3V 且偏置为 1.5V 的 ADC。 |

| 增益 ( A、B )   | 1.66 (0.1%)                   | 可调，建议使用精度为 0.1% 的电阻器                                    |

| 失调 ( A、B )   | < 1mV                         | 未校准                                                     |

| 失调漂移 ( A、B ) | < 2μV//°C                     |                                                         |

| 带宽 (-3dB)    | ~ 500kHz                      | 适用于带宽调节的可调低通滤波器                                         |

具有 100mV 可调迟滞特性的高速、低传播延迟比较器，具有更好的防噪性能，可将模拟信号 A、B 和 R 转换为 3.3V TTL。

**表 2-4. 比较器**

| 参数                 | 典型值            | 注释                             |

|--------------------|----------------|--------------------------------|

| 数字输出信号 A、B 和 R     | 3.3V TTL       |                                |

| 迟滞                 | ~160mV (±80mV) | 要提高防噪性能，可通过更改反馈电阻器进行调节         |

| 传播延迟               | ~ 40ns         | 低传播延迟                          |

| 最大相位延迟 ( 传播延迟和迟滞 ) | < 60°          | 0.3 V <sub>PP</sub> 500kHz 输入下 |

## 2.3 评估固件

为快速评估 TIDA-00176 参考设计，我们提供了适用于 Piccolo F28069M MCU 的示例固件，该固件可针对 16 位双 ADC ADS8354 和 F28069M MCU 的嵌入式双路 S/H 12 位 ADC 分别计算插值高分辨率角度。通过波特率为 115000 的 USB 虚拟 COM 端口的用户界面，能够轻松进行性能评估。

该波特率为 115000 的虚拟 COM 端口用户界面具备以下功能：

- 选择正弦/余弦编码器线数：最大 32000

- 通过 SPI 对外部双路采样 16 位 ADC、内部 12 位双路 S/H ADC 和增量计数器进行硬件和软件同步采样，同步延迟小于 100ns

- 采用 32 位小数 Q28 格式输出高分辨率角。角度按单位进行缩放，范围从 0 到 0.9999999，具备高达 28 位的插值角度分辨率

- 首次出现索引标记 R 后会自动初始化绝对位置

- 菜单有两种模式可供选择。一种是显示模式，更新频率为 10Hz，能展示 TIDA-00176 设计里 16 位双通道 ADC (ADS8354) 和 C2000 片上 12 位双通道 S/H ADC 所测的总角度、角度增量和相位数据。另一种是数据转储模式，更新频率为 200Hz，同样也会呈现上述两个 ADC 测得的这些数据

- 当编码器未连接或差分输入电压低于 0.3V<sub>PP</sub> 时，将显示诊断错误消息

## 2.4 电源管理

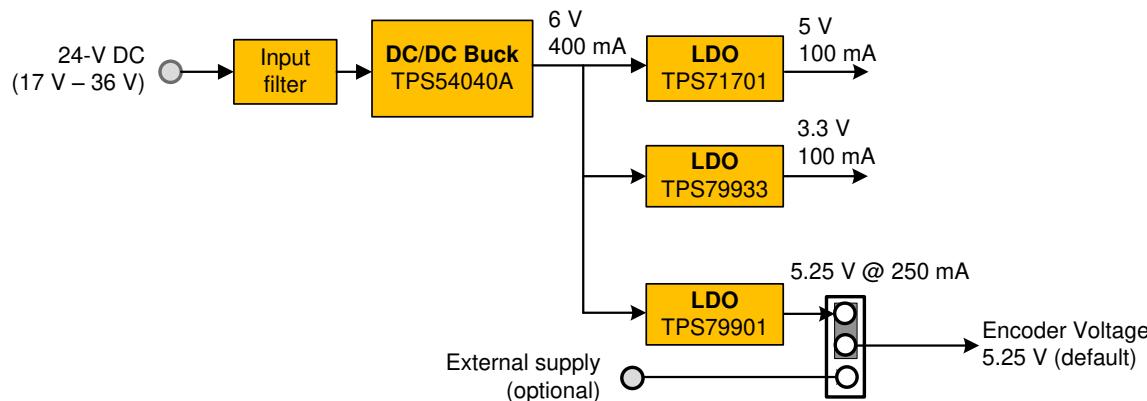

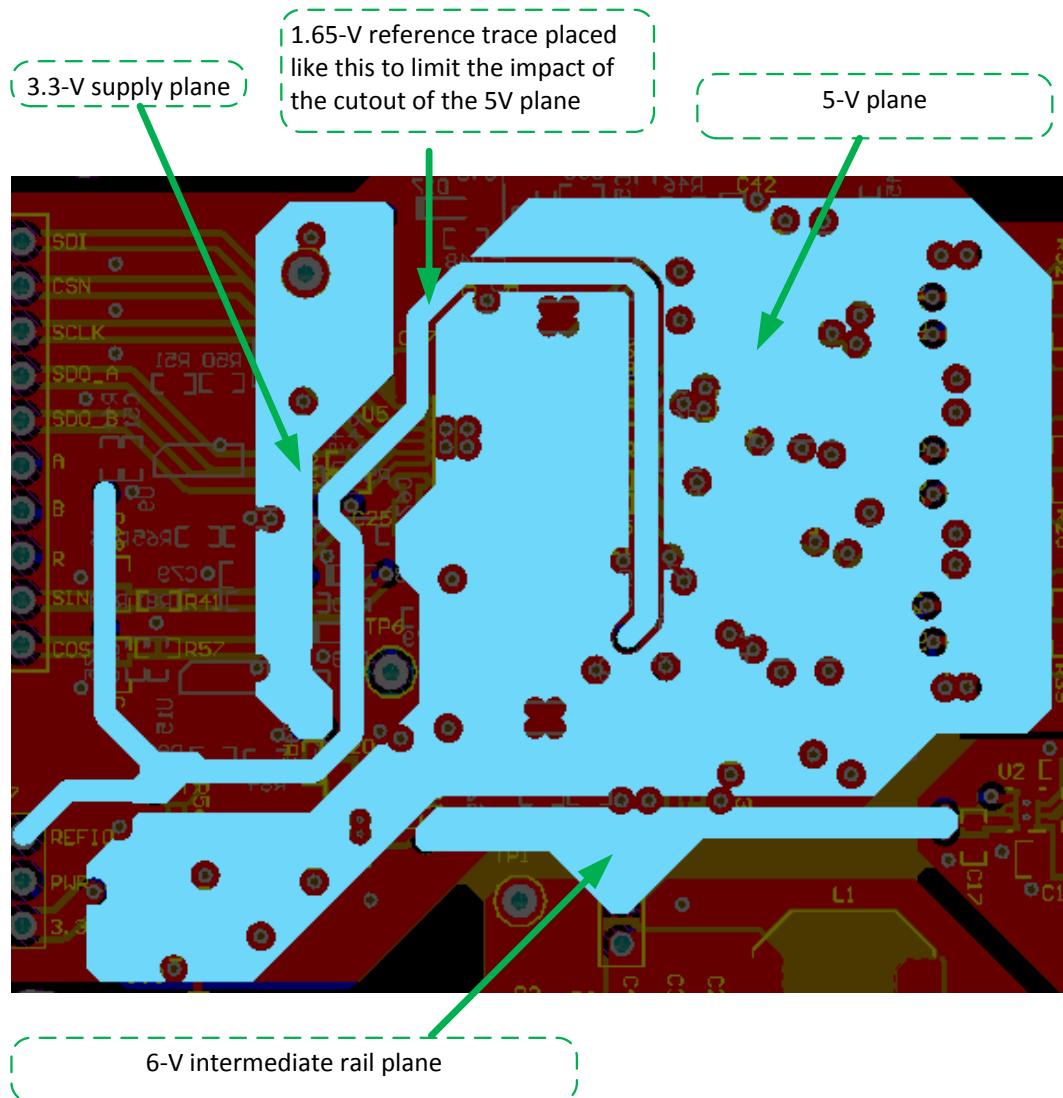

本 TI 参考设计采用 24V DC 输入，输入电压范围宽，从 17 到 36V，并具有反极性保护功能。板载电源管理分为 DC/DC 降压，可生成中间的 6V 电源轨和三个 LDO，而这三个 LDO 又能生成相应的 3.3V、5V 和 5.25V 电源轨。

5.25V 编码器电源配噪声极低的 LDO 及使能引脚。因此，如有需要，可通过主机处理器切断正弦/余弦编码器的电源电压。

表 2-5. TIDA-00176 电压轨

| 参数       | 电压                 | 电流    | 注释                                                                 |

|----------|--------------------|-------|--------------------------------------------------------------------|

| 输入       | 24V [17 至 36V]     | 150mA | 宽输入电压，具有反极性保护功能                                                    |

| 中间轨      | 6V [ $\pm 5\%$ ]   | 500mA | 中间轨。高效 (>80%) DC/DC 降压电源                                           |

| 编码器电源    | 5V [ $\pm 5\%$ ]   | 250mA | 选择 5.25V 电压是为了获得额外的 0.25V 裕度，以补偿长距离电缆上的电压降。可通过更改反馈电阻器进行调整，例如调整为 5V |

| 5V 电源轨   | 5V [ $\pm 5\%$ ]   | 100mA | 高精度信号链电源                                                           |

| 3.3V 电源轨 | 3.3V [ $\pm 5\%$ ] | 100mA | 低精度信号链电源                                                           |

## 2.5 EMC 抗扰度

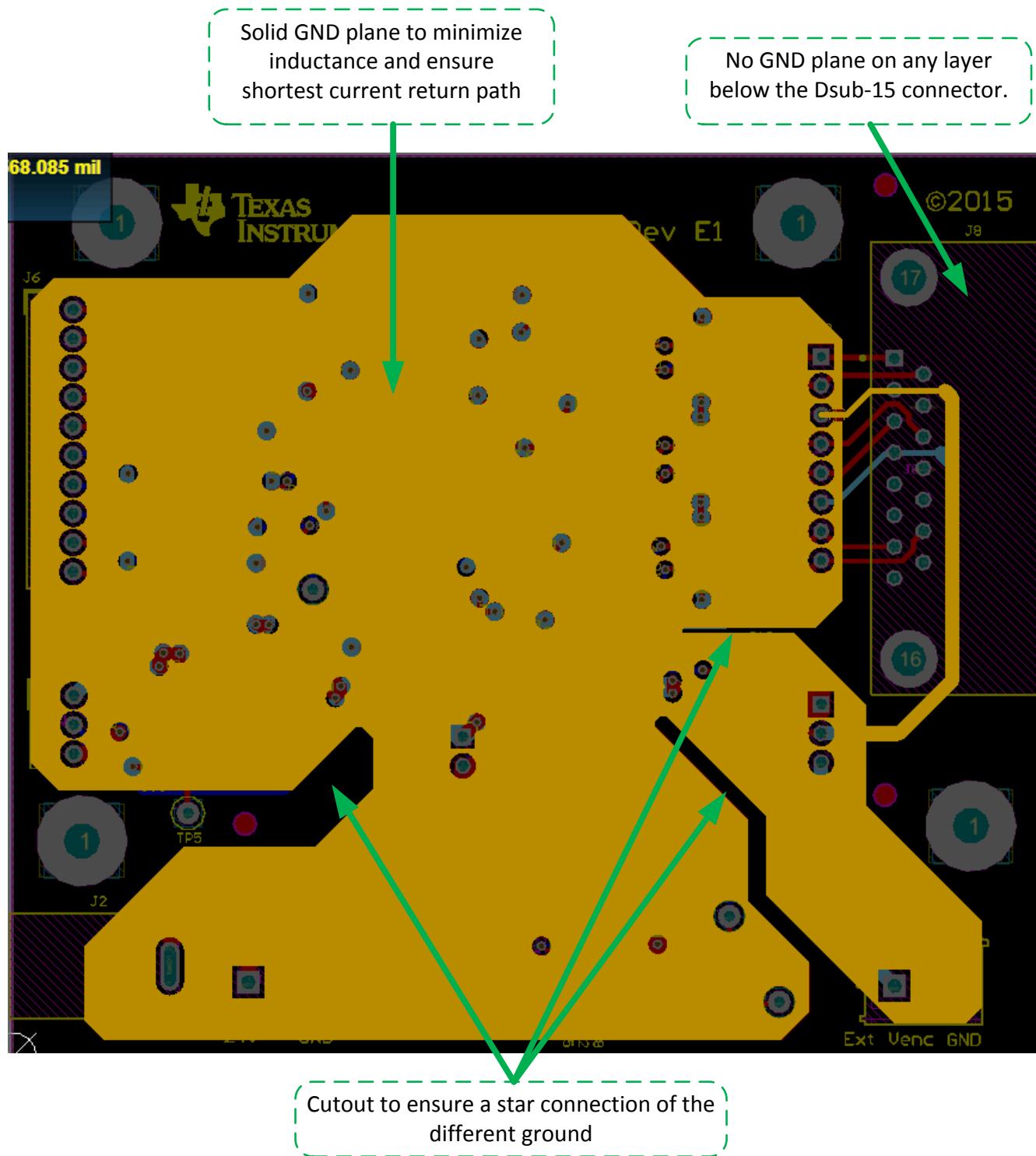

该设计符合 IEC61000-4-2 , 4-4 及 4-5 针对 ESD、EFT 和浪涌的要求，具体的要求等级则依据 IEC 61800-3 标准“可调速电力驱动系统的电磁兼容性 (EMC) 抗扰度要求”中规定的等级。假定仅能使用连接位置编码器的 subD-15 连接器，并通过编码器屏蔽电缆来连接编码器。由于编码器电缆长度可能会超过 30m，因此需参照 表 2-6 所示的 2 类环境要求实施 ESD、EFT 和浪涌。

**表 2-6. EMC 抗扰度要求**

| 端口            | EMC 测试              | EMC 标准       | 等级                                      | 性能(验收)标准 |

|---------------|---------------------|--------------|-----------------------------------------|----------|

| 正弦/余弦编码器接口连接器 | ESD                 | IEC61000-4-2 | ±4kV CD 或 CD 无法实现时 8kV AD               | B        |

|               | 快速瞬变脉冲群 (EFT)       | IEC61000-4-4 | ±2kV/5kHz, 电容钳位                         | B        |

|               | 浪涌 1.2/50μs, 8/20μs | IEC61000-4-5 | ±1kV。由于屏蔽电缆长度超过 20m，因此需直接耦合屏蔽层 (2Ω 源阻抗) | B        |

性能(验收)标准定义如下：

**表 2-7. 性能标准**

| 性能(验收)标准 | 说明                                                          |

|----------|-------------------------------------------------------------|

| A        | 模块应按预期连续工作。甚至测试过程中无功能或性能损失                                  |

| B        | 可接受出现性能暂时下降。测试完成后，模块在无人工干预的情况下应能够按预期继续工作。                   |

| C        | 在测试期间，允许出现功能丧失，但不得损坏硬件或软件。测试完成后，模块经手动重启、断电或上电后应能够自动按预期继续工作。 |

### 3 方框图

图 3-1 中展示了该设计的系统方框图。这一 TI 设计的主要组成模块包括双路径模拟信号链、高速比较器模块、电源管理模块、正弦/余弦编码器接口以及用于数字信号处理和高分辨率位置计算的主机微控制器接口。为方便评估 TIDA-00176 设计，我们提供了适用于 F28069M Piccolo LaunchPad 的示例固件，用于通过虚拟 COM 端口输出角位置。

图 3-1. 采用 Piccolo F28069M LaunchPad 的 TIDA-00176 系统方框图

模拟信号链提供具有 EMC 保护功能的  $120\Omega$  终端，并分别对差分  $1V_{PP}$  正弦和余弦输入信号进行放大和电平转换。该设计提供了双信号路径选项，其中一路采用板载的 ADS8354 高速、16 位双通道同步采样模数转换器（ADC），它支持 SPI 接口；另一路为模拟信号路径，具备两个模拟输出端，偏置电压为  $1.65V$ ，可用于连接外部的双通道 S/H ADC，比如 C2000 Piccolo 系列这类 MCU 上所嵌入的 ADC。

高速、低传播延迟比较器块具有迟滞可调的特点，可提高抗扰度，并且将模拟信号 A, B 和标记 R 转换为  $3.3V$  TTL 电平数字信号，可连接至正交编码器脉冲模块，如 C2000™ Piccolo MCU 上的 QEP 模块。

板载的宽输入范围  $24V$  电源为模拟信号链提供必要的电压，同时为正弦/余弦编码器提供  $5.25V$  电压。

正弦/余弦编码器接口可连接至 15 引脚屏蔽 Sub-D 连接器或 8 引脚插头。与主机 MCU 连接的接口可提供符合  $3.3-V$  TTL 标准的数字信号，用于串行外设接口 (SPI) 通信，以及数字信号 A、B 和 R；同时，该接口还提供模拟信号 A 和 B，这些模拟信号经缩放后电压范围在  $0$  至  $3.3V$  之间，且带有  $1.65V$  的偏置电压。

## 4 电路设计和元件选型

### 4.1 模拟信号链

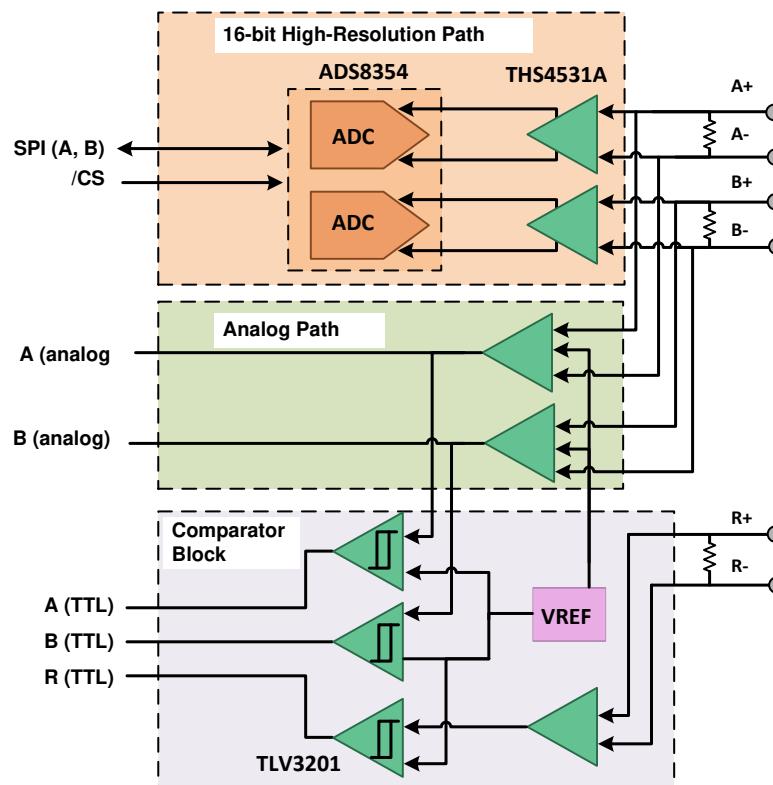

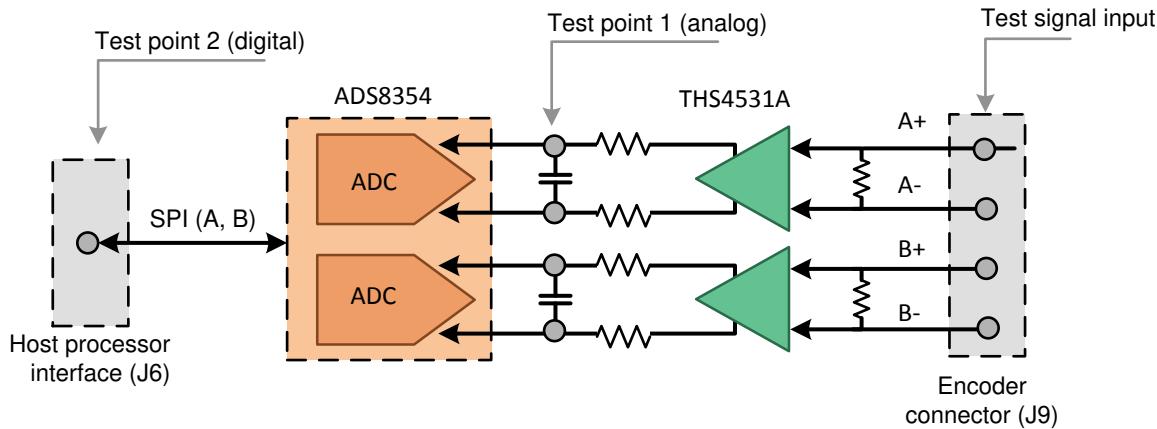

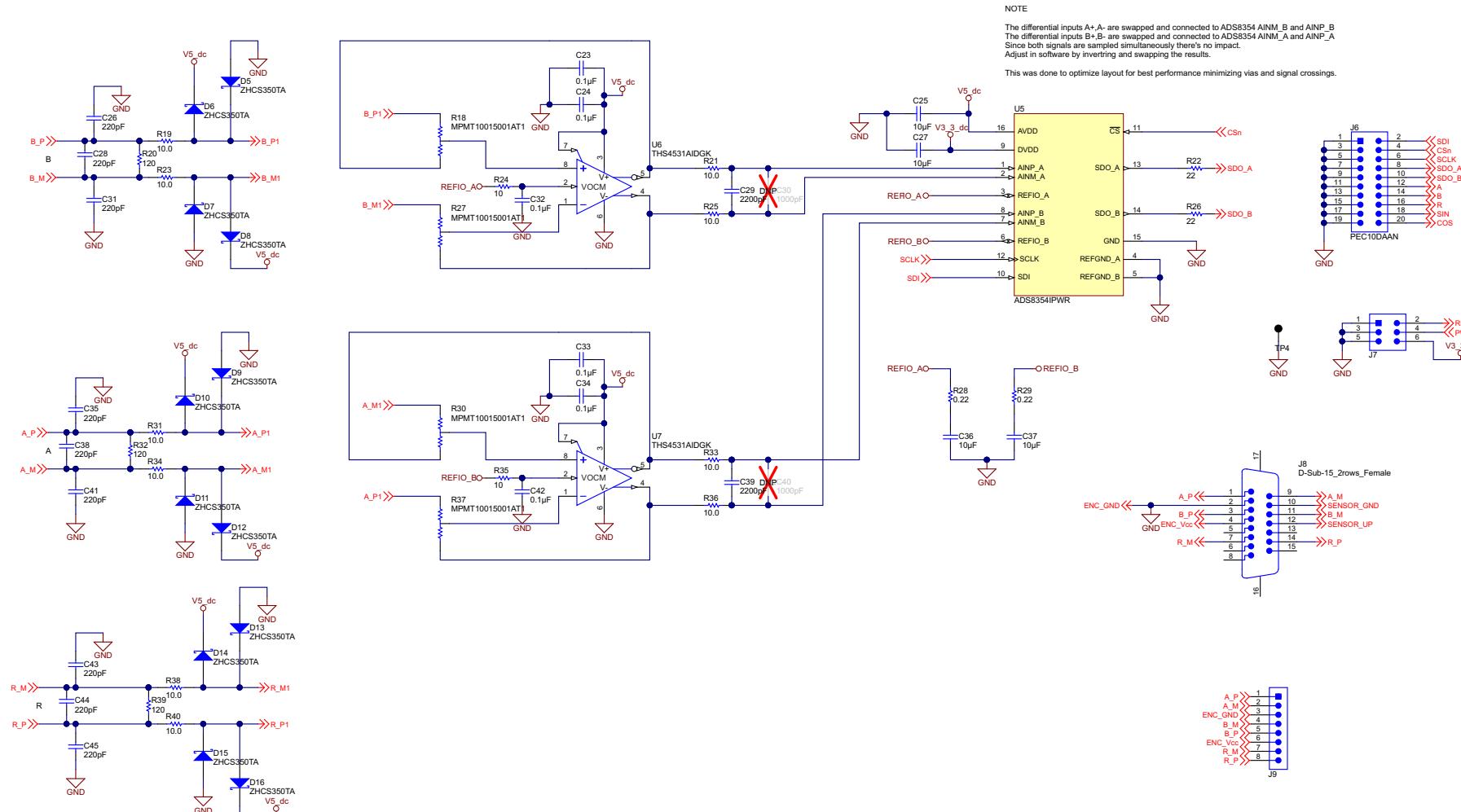

图 4-1 概述了模拟信号链子系统和比较器子系统。模拟信号链的实施分为两条路径：

- 高分辨率信号路径，具有更高的共模防噪性能，采用全差分放大器，搭配带 SPI 输出的全差分 16 位双通道 ADC

- 模拟路径，输入为差分信号，输出为单端模拟信号，可驱动比较器，并可连接至带有嵌入式 ADC 的主机处理器

双模拟路径有两种选择：其一，可借助板载 16 位双路 ADC，将其作为高分辨率路径的一部分，对设计进行测试；其二，可启用模拟差分转单端路径，将其与带有嵌入式 ADC 的 MCU 相连。此外，由于模拟路径通过高分辨率路径的缓冲器去耦，因此可确保比较器路径实现理想的去耦合效果。这样在正弦和余弦过零期间切换输出电平时，可避免对高分辨率模拟路径产生串扰。

另一种情况是同时使用这两条路径。一条路径通过降低带宽来滤除高频噪声，从而提高防噪性能，而另一条路径则提供标准带宽，直至达到最大速度。低带宽通路的防噪性能强，用于高分辨率

16 位 ADC，而另一条标准带宽路径则连接到带有嵌入式 ADC 的 MCU。当电机转速较低（低于所配置的截止频率）时，从高分辨率通路获取插值相位（反切）；而当电机转速较高时，从另一通路获取插值相位。主机处理器将根据电机转速决定使用的角度。

比较器子系统将以极短的传播延迟生成信号 A、B 和 R 的 TTL 电平输出。以下各节将对每个子系统进行说明。

图 4-1. 模拟信号链

#### 4.1.1 带有 16 位双路采样 ADC 的高分辨率信号路径

##### 4.1.1.1 元件选型

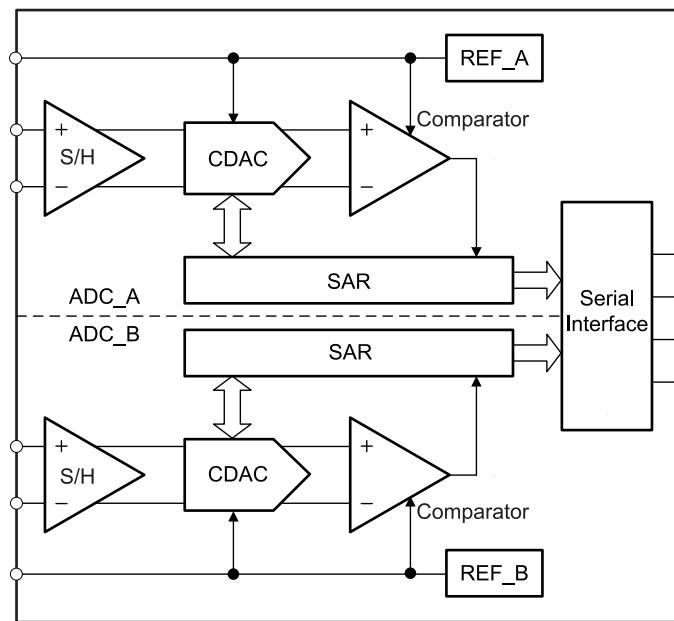

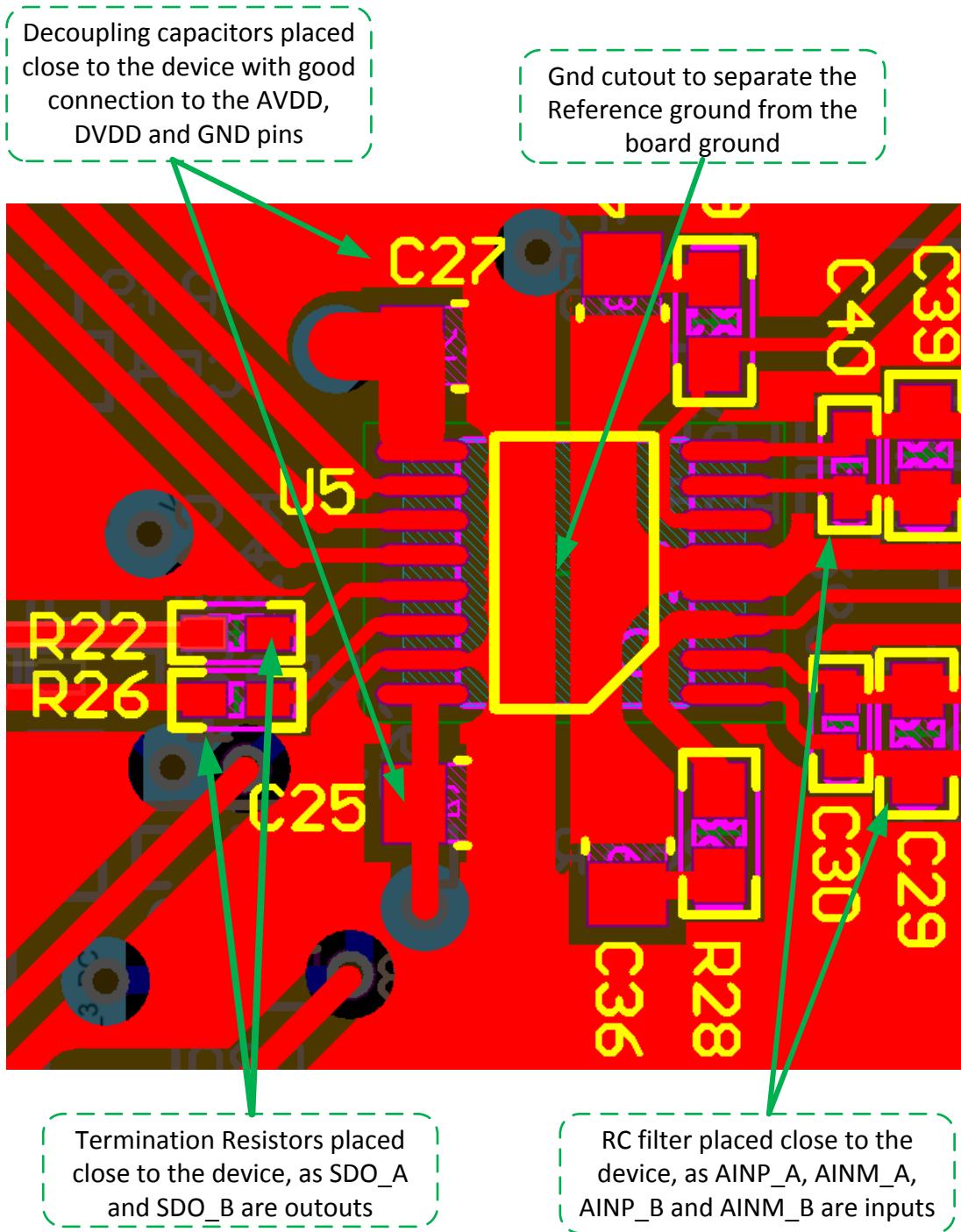

为满足设计要求，需采用高精度双通道 ADC。选择 ADS8354 的原因如下：

- 高分辨率（16 位），高精度（出色的 THD 和 SNR 性能：-93dB SNR，-100dB THD）

- 插接式引脚兼容的 14 位和 12 位版本可供选择，可根据所需分辨率和成本优化情况灵活搭配

- 速度快 (700kSPS) 且带宽高，能够支持至少 500kHz 的模拟输入信号

- 双通道具有真差分输入及双/独立基准电压，可提升对共模噪声的抗干扰能力

- 双通道，两通道同步采样，确保正弦与余弦输入信号 A 和 B 之间零相移

- 硬件触发采样点(ICS 下降沿)，使主机处理器能够将采样点与增量计数器锁存精确同步。

- 采样保持电路在完成转换过程后会返回采样模式，因此有相对较长的采样时间，以确保达到 16 位的转换精度

- 2.5V 双路可编程缓冲内部基准，可为放大器提供共模偏置电压，几乎能完全消除与失调及失调漂移相关的误差。

- 连接主机处理器采用串行接口（双路数据），时钟频率最高可达 24 MHz，可将延时降至最低

- 可在更大的工业温度范围内正常工作：-40°C 至 125°C

- 小型封装

图 4-2. ADS8354 方框图

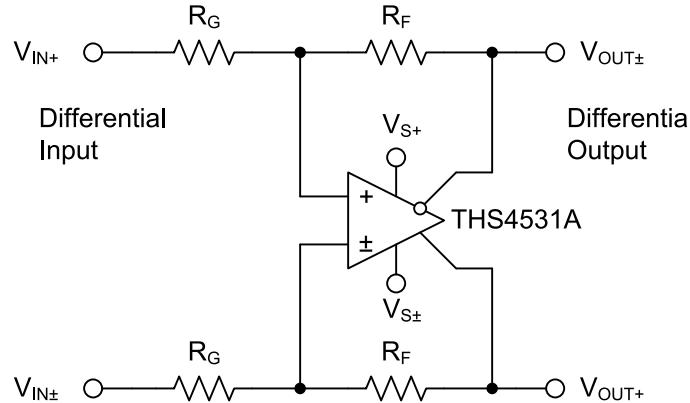

要发挥 ADS8354 的性能，需借助具备可配置输出共模电压的全差分高速放大器，如 THS45xx 系列。

图 4-3. 差分输入至差分输出放大器

信号在整个处理过程中保持全差分状态，其增益和可选的滤波功能由输入和反馈的电阻器和电容器共同决定。增益由  $RF/RG$  比值决定，而输出共模电压由输入信号  $V_{OCM}$  设定。

选择 THS4531A 的原因在于，它符合电路拓扑结构要求，能够驱动 ADS8354，并且满足 节 1.4 中规定的交流和直流性能要求。为了提高设计的灵活性并简化 PCB 的布线，采用了每个封装一个单放大器的拓扑结构，而非像 THS4532 那样每个封装包含两个差分放大器的结构。

在本设计中，THS4531A 的关键参数如下：

- 完全差分架构，输出共模电压可调

- 高增益带宽：27MHz ( 在  $G = 5$  时为 6MHz )

- 低失真，1kHz 时 THD 为  $-120\text{dBc}$  ( $1\text{V}_{\text{RMS}}, R_L = 2\text{k}\Omega$  )

- 低输入电压噪声： $10\text{nV}/\sqrt{\text{Hz}}$  ( $f = 1\text{kHz}$ )

- 极低的失调电压， $V_{OS} : \pm 100\text{\mu V}$

- 极低的失调漂移， $V_{OS}$  漂移： $\pm 2\text{\mu V}/^\circ\text{C}$  ( 工业温度范围 )

- 采用单路 5 V 电源供电，与 ADS8354 使用相同的电源

- 轨到轨输出 (RRO) 与负电源轨输入 (NRI)，可最大限度增大输入和输出信号摆幅

#### 4.1.1.2 输入信号端接与保护

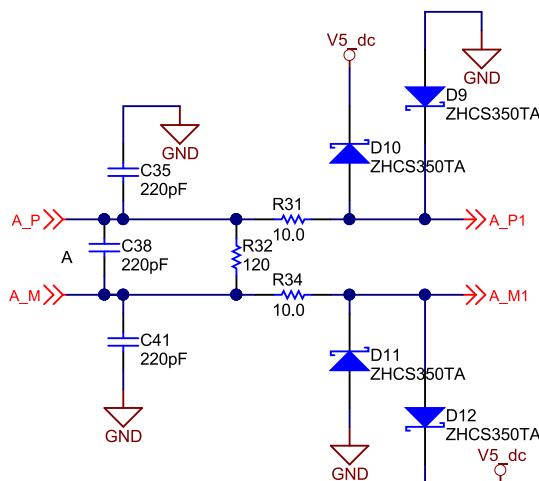

每个差分输入信号都与  $120\Omega$  电阻器端接。为实现差模及共模 HF 噪声抑制，增加了 COG 电容。差分低通滤波器的截止频率 ( $-3\text{dB}$ ) 约为  $6\text{MHz}$ 。 $10\Omega$  (1%) 防脉冲电阻器与肖特基二极管共同作用，钳位至  $5\text{V}$  电源轨或 GND，通过限制输入电流实现 ESD 保护。图 4-4 所示为 TIDA-00176 编码器差分信号 A+ ( 正弦 ) 和 A- ( 余弦 ) 输入级的原理图。

图 4-4. 模拟输入端接

从左到右查看编码器信号 A+/A- ( 原理图中名为 "A\_P - A\_M" ) 信号调节原理框图，可以看出其包含以下部分/功能：

- HF 噪声抑制 COG 电容：C35、C38 和 C41。若要提高共模抑制，可在每个差分输入端与 GND 之间增加  $2\text{nF}$  COG 电容，该电容与  $220\text{ pF}$  电容并联。低通截止频率 ( $-3\text{dB}$ ) 在  $6\text{MHz}$  附近。

- 阻抗匹配/端接电阻器  $120\Omega$  : R32

- 耐脉冲限流电阻 : R31, R34

- $5\text{V}$  电源轨和 GND 钳位二极管/运算放大器保护 ( D9 至 D12 )

LP 滤波器设计用于在系统规范所规定的速度下确保功能和性能正常。

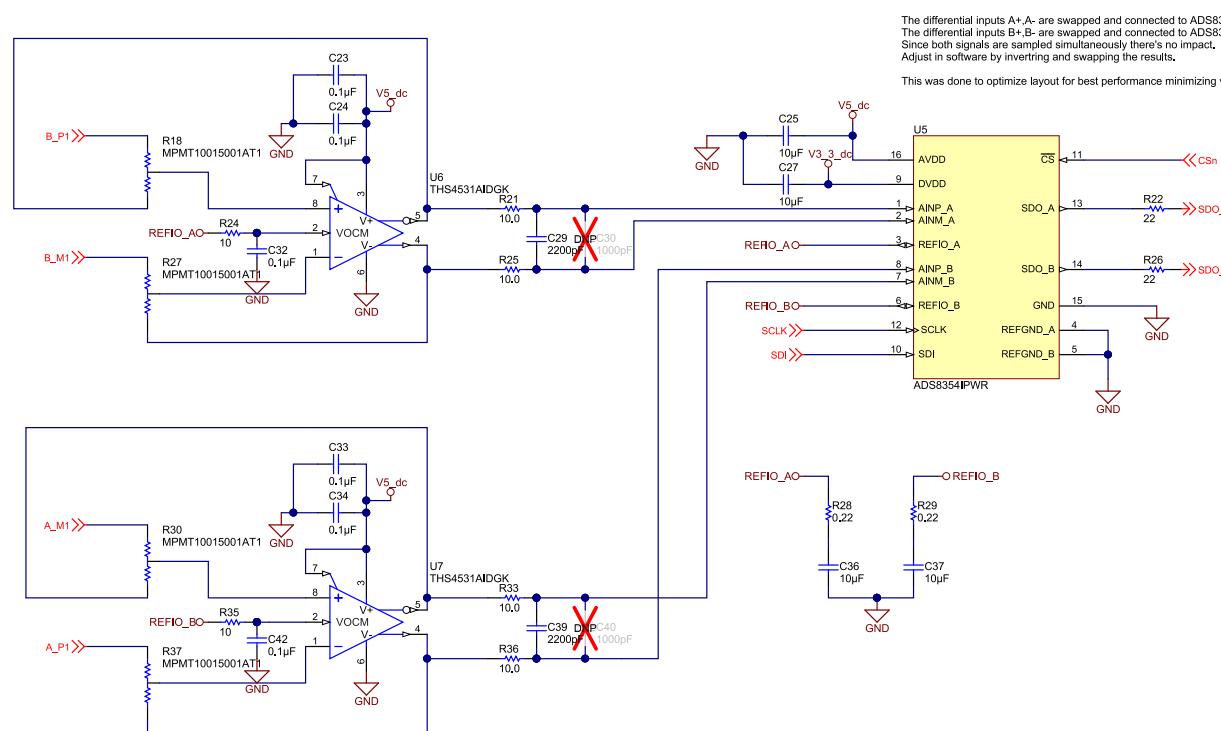

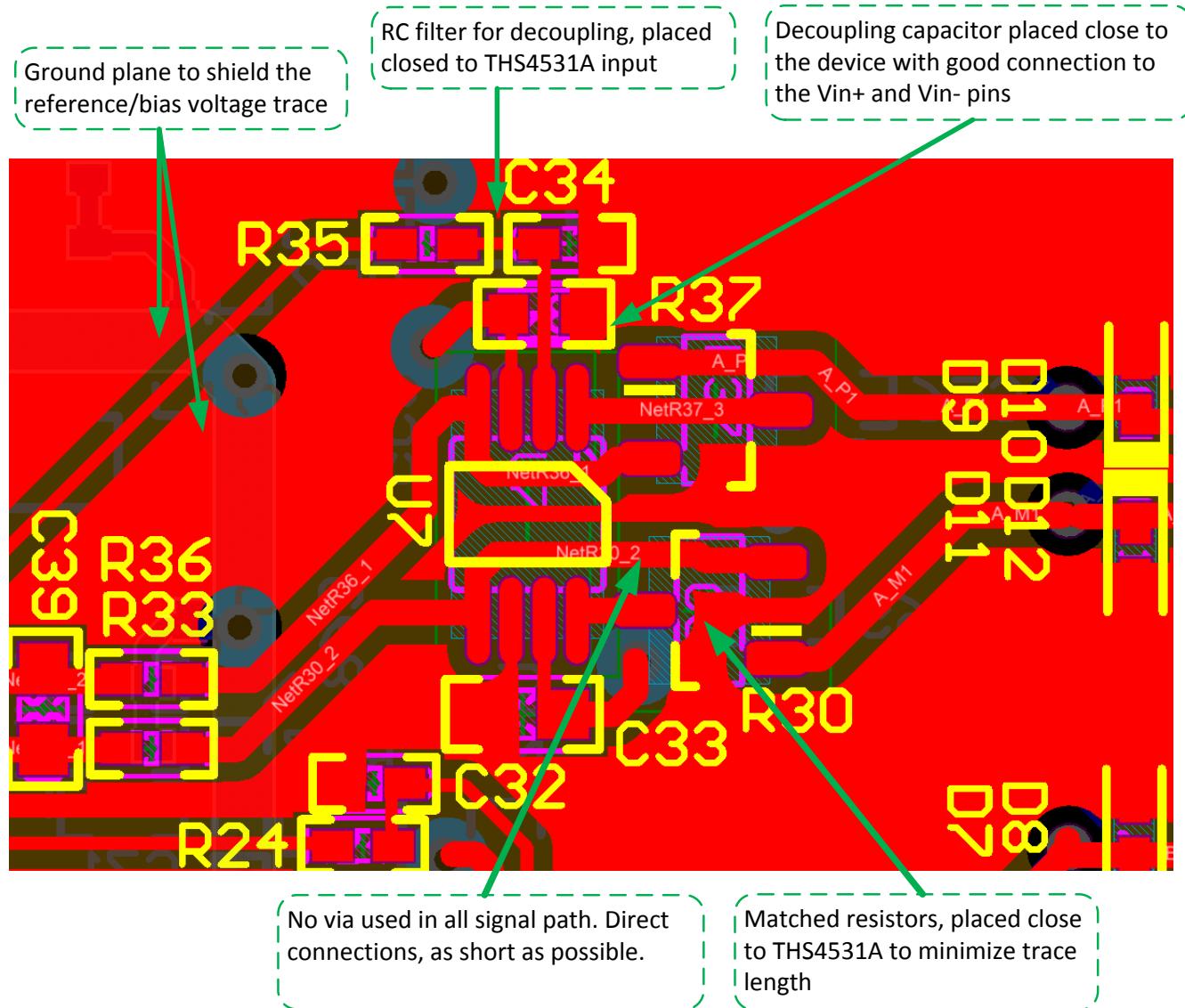

#### 4.1.1.3 差分放大器 THS4531A 和 16 位 ADC ADS8354

更大限度地提高高精度连续逼近型寄存器 (SAR) (ADC) 性能所需的两个主要电路是输入驱动器和基准驱动器电路。有关选用放大器的详细信息，请参阅 **ADS8354** 数据表第 9.1 节。

**THS4531A** 是专门设计与 **ADS8354** 搭配使用的。实际上，输入信号的共模电压或直流电平（标称值为 2.5V）直接由 **ADS8354** 自身的基准电压输出端提供给 **THS4531A**，这样做是为了尽可能减小潜在的失调和漂移误差。

**ADS8354** 的差分输入满标量程配置为  $\pm 2 \times V_{REF}$ 。如果基准电压  $V_{REF} = 2.5V$ ，则 FSR 为  $\pm 5V$ 。正弦/余弦编码器最大差分输入电压为  $1.2V_{PP}$ 。当电压高于  $1.35V_{PP}$  时，仍应被检测为故障情况。最大峰值间电压加上 50% 的安全裕度，即  $1.8V_{PP}$ 。为与 ADC 满标量程输入范围匹配，**THS4531A** 的增益应为 5.5。但是，要在 5V 电源电压下保持 **THS4531A** 的线性输出电压范围（至少 0.25 至 4.8V），增益应降低约 10%，因此理想的差分放大器增益应为 5。

为确保最大限度降低增益误差，尤其是通道间的漂移，需使用 0.1% 精度，2ppm/K 温度漂移的高精度匹配电阻器。为了将噪声降至最低，反馈电阻器应选择在较低的千欧 ( $k\Omega$ ) 范围内（请参见 [节 1.4](#)）。

使用高精度匹配电阻分压器来尽可能降低潜在增益误差。有关详细信息，请参阅 **MPMT10015001AT1** 数据表。

由于增益为 5，典型的  $1V_{PP}$  输入信号大约会用到 ADC 满标量程范围 (FSR) 的 50%，这会导致精度损失 1 位，因此等效分辨率为 15 位。当输入电压低至  $0.6V_{PP}$  时，约用到 FSR 的 25%，通常相当于 14 位分辨率。

**图 4-5** 所示为高精度模拟信号路径原理图；匹配的增益设置电阻器为 R18、R27、R30 和 R37。

串联抗混叠滤波器的  $10\ \Omega$  电阻器 R21、R25 与  $2.2nF$  电容器 C29（对于 **ADS8354** 通道 B，分别为 R33、R36 与 C39）。跨接 ADC 输入的滤波器电容器 C29 (C39) 将过滤前端驱动电路噪声，减少采样电荷注入，并提供一个电荷桶，可在采集过程中快速给保持电容充电。通常，该电容器的值应至少为 ADC 采样电容指定值的 10 倍。对于这些器件，输入采样电容等于  $40pF$ 。应采用 COG 或 NPO 类型电容器，因为这两种类型的电容器具有电荷量大，温度系数低的特点，且在电压、频率及时间变化的情况下依然能保持稳定的电气特性。为避免出现放大器稳定性问题，在放大器输出端使用了  $10-\Omega$  串联隔离电阻器 R21、R25 ( R31、R39 )。有关详细信息，请参阅 **ADS8354** 数据表的第 9.1 节。

为最大限度降低 ADC 基准电压 **REFIO\_A** 和 **REFIO\_B** 的失调漂移的影响，设计中采用 ADC 基准来偏置 **THS4531A** 的共模输出电压。为对 **THS4531A** 的  $V_{OCM}$  信号进行缓冲并去耦，在每个引脚附近添加了小型 RC 滤波器，如 R24/C32 和 R35/C42，以及 R28、R29、C36 和 C37。

**ADS8354** 基准电压 **REFIO\_A** 和 **REFIO\_B** 分别通过  $10-\mu F$  电容器 C36 和 C37 去耦，同时串联一个  $0.22\Omega$  电阻器，以避免高频振荡。

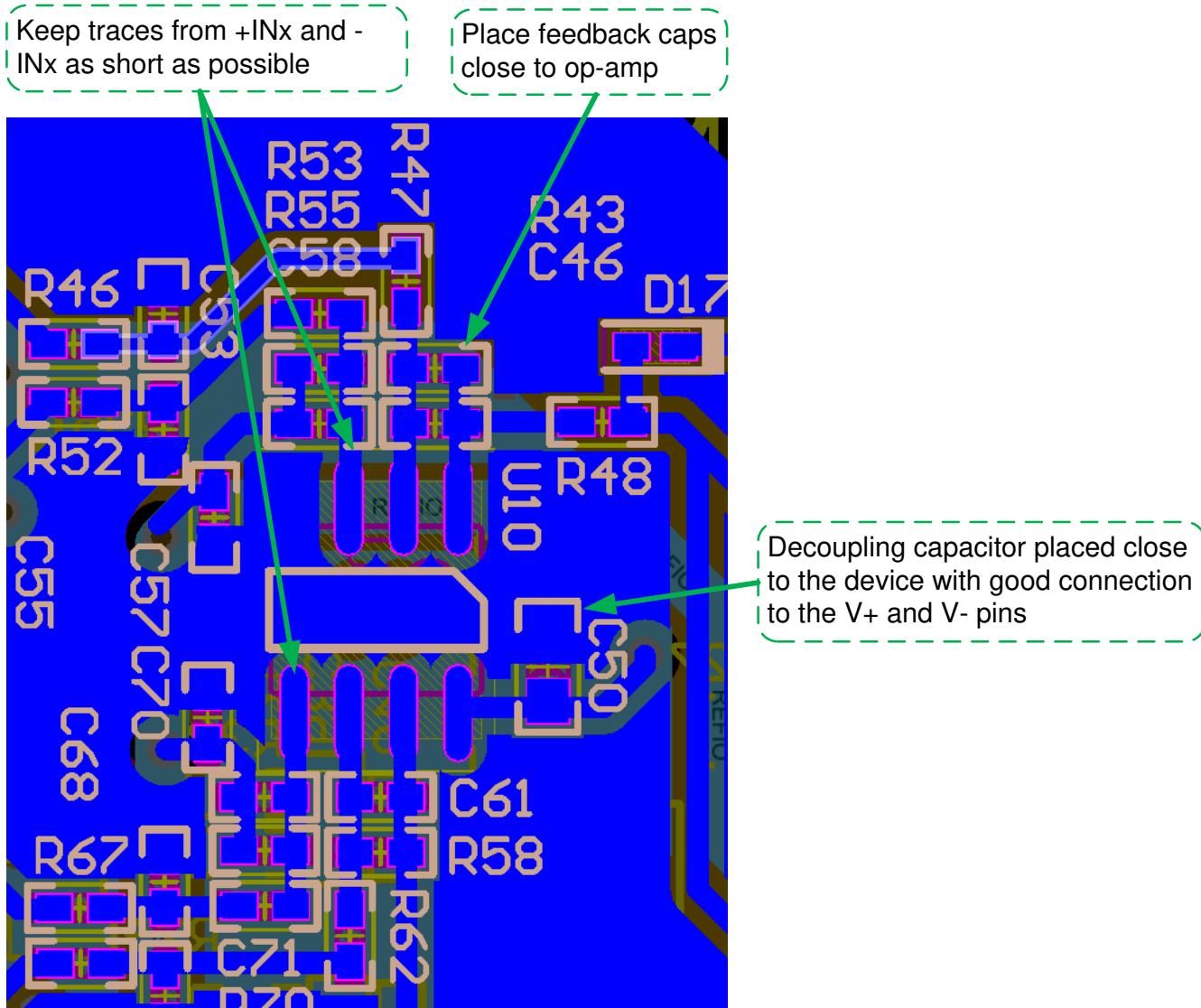

为了优化布局，减少关键信号 A+、A- 和 B+、B- 之间的串扰，并且尽量减少过孔的使用，进行了如下连接。

1. 差分输入信号 A (A+, A-) 在 **THS4531A** 的输入端反相，然后馈入 **ADS8354** 输入通道 B。

2. **THS4531A** 的差分输出信号 B+ 和 B- 反相连接至 **ADS8354** 输入引脚，其中 **AINP\_A** 连接 B-，而 **AINM\_A** 连接 B+

这就产生了如下的硬件关系：**ADS8354** 通道 B 等同于反相后的正弦/余弦编码器信号 A；**ADS8354** 通道 A 等同于反相后的正弦/余弦编码器信号 B。

图 4-5. 双通道 THS4531A 和 ADS8354 的正弦和余弦信号链

### 备注

通道进行反相和交换是为了实现最佳性能布局，并最大程度地减少过孔数量。

为了在降低带宽的情况下实现更高的防噪性能，建议在与  $5\text{k}\Omega$  并联的反馈路径中使用  $10\text{pF}$  ( 1% 或更高 ) 或更高的电容器。具体请参阅节 4.5。

有关通过串行接口配置 ADS8354 寄存器的说明，请参见节 4.3。

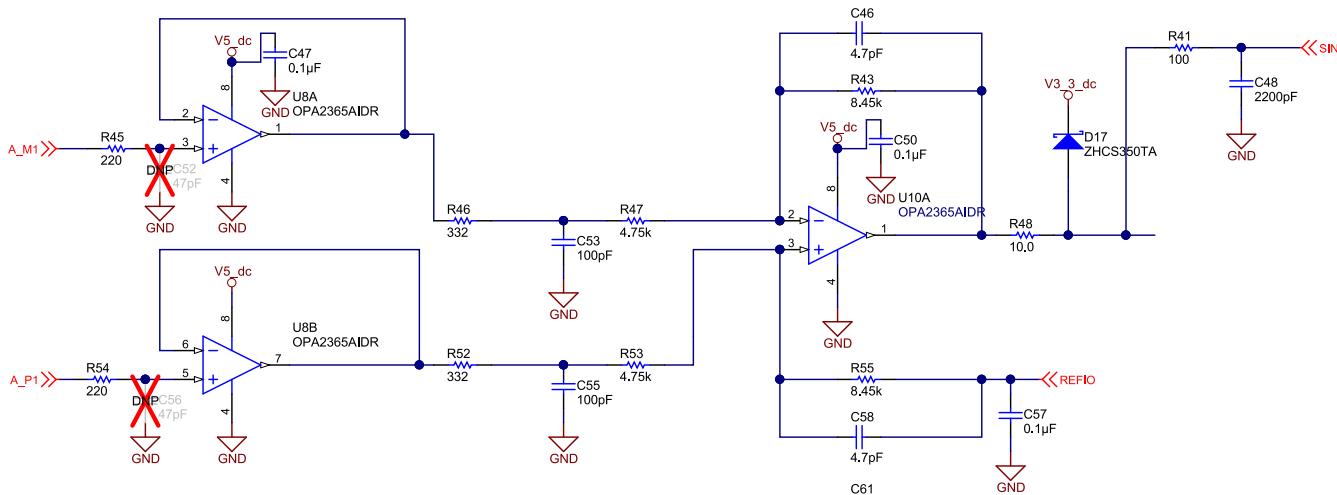

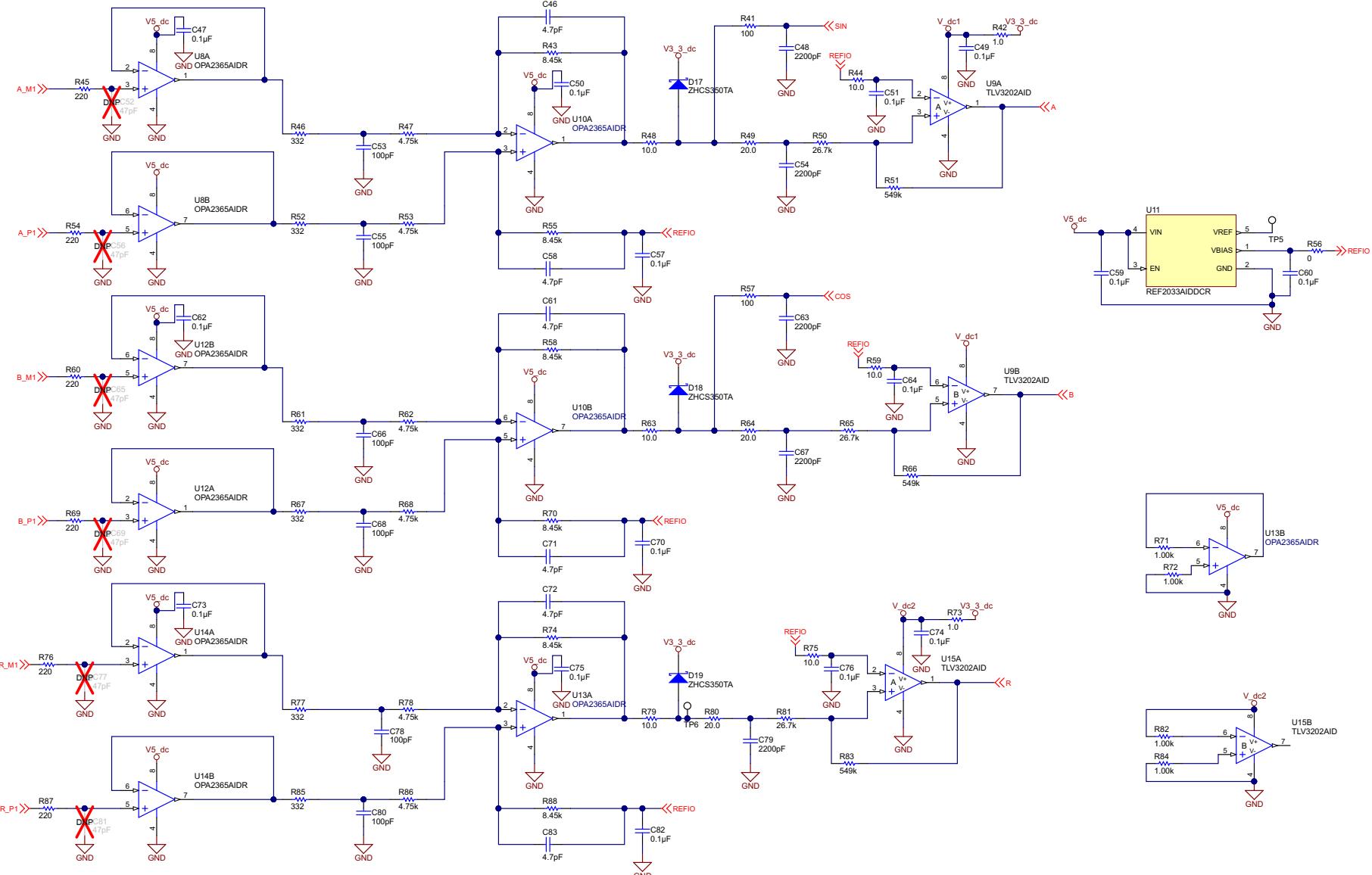

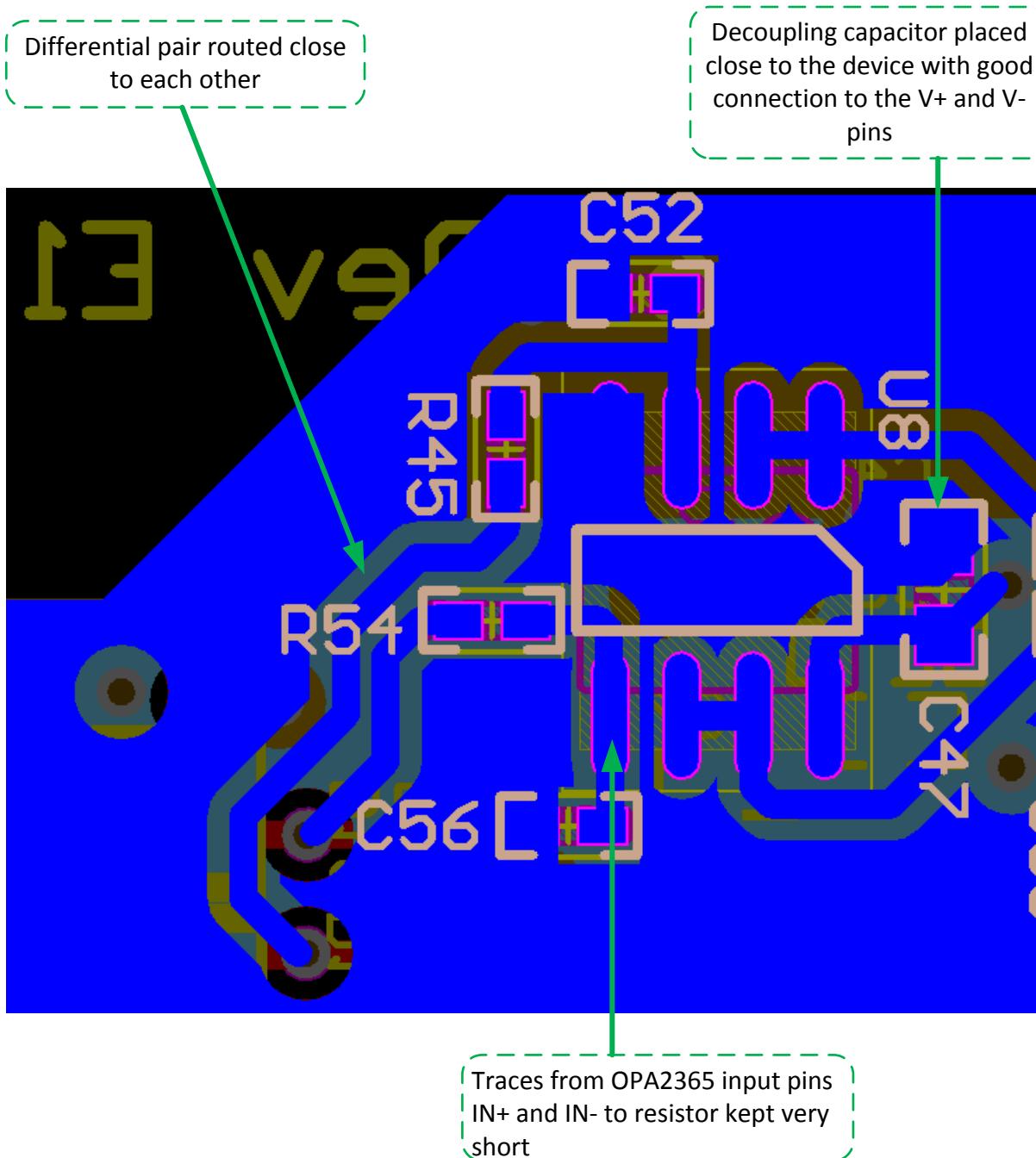

#### 4.1.2 面向嵌入式 ADC 的 MCU 的单端输出模拟信号路径

并行模拟信号路径不应影响高分辨率路径，尤其是差分放大器。因此，差分信号 A+、A-、B+ 和 B- 在输入终端接电阻并完成保护处理后被引出，然后使用失调电压极低、失调电压漂移极小的单位增益放大器进行缓冲。接下来的放大器应将差分信号转换为单端信号。最小带宽至少应为  $500\text{kHz}$ ，理想情况下应高到能够支持输出信号高于

$500\text{kHz}$  的增量编码器。通向比较器的信号路径的相位延迟应与高分辨率路径相似，以最大限度减小模拟信号相移。

电源电压应为  $5\text{V}$  单电源。

为匹配高分辨率通道，两个运算放大器漂移的总和应至少达到相当于 12 位的精度，从而与高分辨率通道的模拟性能完美匹配。选择 OPA2365 执行输入缓冲及差分到单端转换，原因如下：

- 工作电压范围为 2.2V 至 5.5V，可利用 5V 电源轨

- 轨到轨 I/O

- 失调电压和失调电压漂移极低：200 $\mu$ V (最大值) 和 1 $\mu$ V/K (典型值)

- 电压噪声和电流噪声低：4.5nV/SQRT(Hz) 和 0.004pA/SQRT(Hz)

- 出色的 THD+N：0.0004%

- 高共模抑制，CMRR：100dB (最小值)

- 压摆率：25V/ $\mu$ s

- 快速稳定：300ns 内达到 0.01%，可驱动外部 ADC

另一个选择是成本更低的替代产品 OPA2322，其偏移电压为 2mV，会使交流和直流性能略微下降。

模拟输出电压范围应为 0 至 3.3V，共模电压 1.65V。在最大输入电压为 1.8V<sub>PP</sub> 的情况下，采用 [节 4.1.1](#) 中所述相同标准，并考虑到 3.3V FSR 留 10% 的余量，计算得出增益为 1.66。

[图 4-6](#) 中展示了通道 A 的模拟信号链，通道 B 与之相同。

**图 4-6. 信号 A (正弦) 的差分输入转单端输出模拟信号路径，信号 B (余弦) 未展示**

差分信号 A\_P 和 A\_N 通过一个 220 $\Omega$  的电阻器连接到 OPA2365 (U8A 和 U8B) 的同相输入端。OPA2365 (U8A 和 U8B) 被配置为单位增益缓冲器，以避免对信号源造成负载影响并引入失真。在过压或欠压情况下，220 $\Omega$  串联电阻器可限制流入 OPA2365 同相输入端的电流。每个缓冲器的输出都采用一个小型可调 RC 滤波器，例如上图中的 R46 和 C53，其 -3dB 截止频率约为 5MHz，用于降低高频噪声。

后面的 OPA2365 (U10A) 配置为差分转单端放大器及电平转换器。其采用低漂移电压基准 REF2033，增益设置为 1.66，输出共模电压为 1.65V。可调 5.6 pF 反馈电容器与反馈电阻器并联，用于滤除 HF 噪声(f-3dB ~ 3.5 MHz)，非常适合 THS4531A 带宽。具体请参阅 [节 4.5](#)。

由于 OPA2365 采用 5V 电源，放大器输出借助一个串联 10 $\Omega$  限流电阻器 (R48) 锯齿至 3.3V (D17)。这是为了保护后续的比较器 (TLV3202/1) 和外部 ADC (通常为 3.3V I/O)。

增加抗混叠去耦合 RC 网络(R41/C48)，用于驱动外部 ADC。滤波器经过优化，可与 C2000 Piccolo MCU 系列中嵌入式的 12 位双通道 S/H ADC 配合使用。对于其他 ADC，必须相应地调整滤波器。

1.65V 偏置电压采用 100n 电容器 (C57) 进行去耦。此外，添加了 LP RC 滤波器以减少越来越多的 HF 噪声组件，尤其是开关 TPS54040A 可能产生的噪声组件。

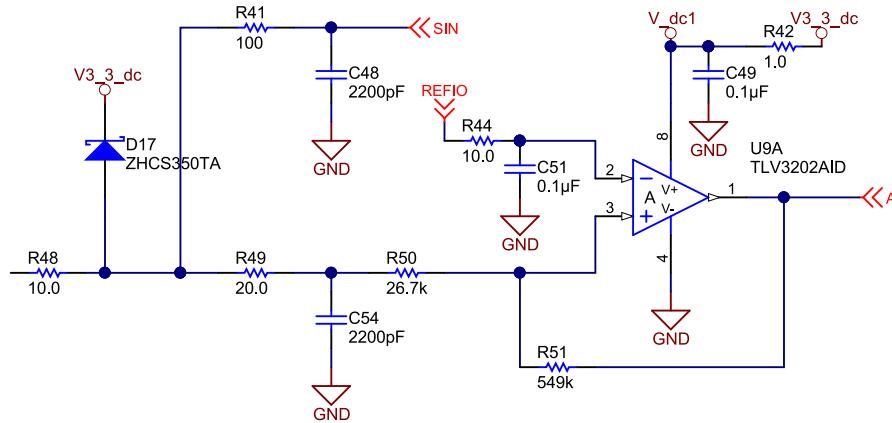

#### 4.1.3 数字信号 A、B 和 R 的比较器子系统

比较器需要检测模拟信号 A 和 B 的过零，以及标记 R 的零索引脉冲，并生成相应的数字 3.3V TTL 兼容信号 A<sub>TTL</sub>、B<sub>TTL</sub> 和 R<sub>TTL</sub> (通常称为 ABZ)。如 [节 1.4](#) 中所述，低传播延迟的比较器可以为系统提供额外的裕度。

所选用的比较器分别是 TLV3201 (单路) 和 TLV3202 (双路)，为 40ns 微功耗推挽式输出比较器，主要具备以下特性：

- 低传播延迟，典型值为 40ns

- 低输入失调电压（典型值为 1mV），可更大限度地降低开关阈值的漂移

- 推挽式输出，可驱动 3.3V I/O 主机处理器的输入

- 工业温度范围

具有 250ns 传播延迟的 TLC372 双路比较器的成本更为低廉，具体选型取决于总系统传播延迟及最大频率。

TLV320x 系列的优势在于：它允许其他元件增加更多的延迟，同时在 500kHz 的频率下仍能保持所需的最大 500ns 的延迟。例如，较大的迟滞会增加传播延迟，同时能提高防噪性能。

#### 4.1.3.1 具有迟滞功能的同相比较器

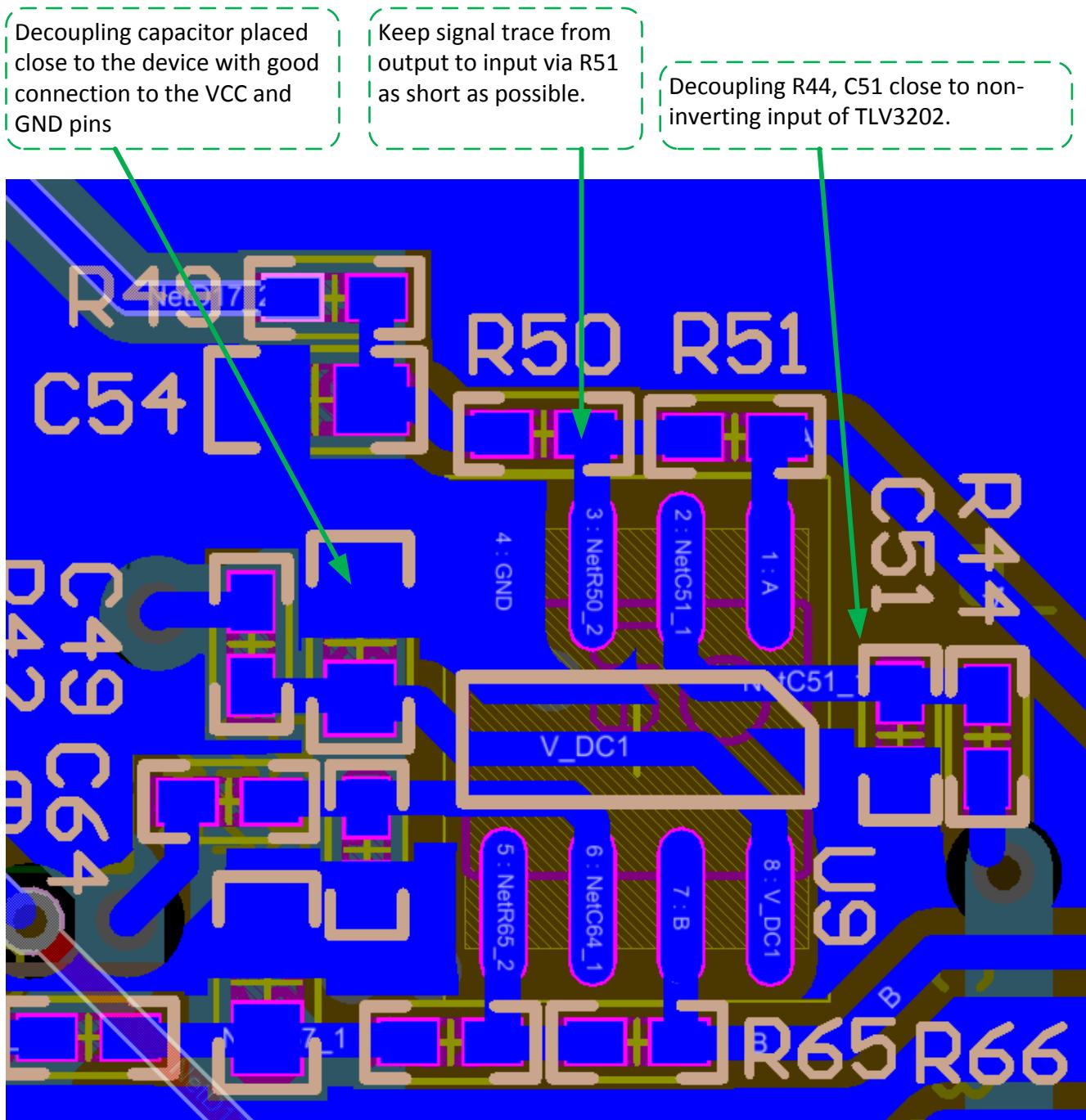

所有比较器的输入信号均源自单端至差分放大器的输出。如前文所述，输出信号钳位到 3.3V，并通过 RC 网络（例如，图 19 中信号 A 的 R49 和 C54）去耦，以避免分别与模拟单端信号 A 和 B 发生串扰。

这与高分辨率路径和该路径之间的相位匹配，比较器输入端的 RC 去耦网络与 THS4531A 输出端的 RC 滤波器（ $2 \times 10\Omega$  和  $2.2nF$ ）匹配。

TLV370x 配置为同相比较器，用于模拟正弦信号和余弦信号 A 和 B 的过零检测，以及索引脉冲 R 检测。图 4-7 所示为信号 A 对应的原理图。

开关阈值的设置取决于基准电压  $V_{REF} = 1.65V$  (REF2033)，基准电压还能为差分放大器到单端放大器的单端模拟信号提供偏置。在每个比较器中，基准输入源自 REF2033，并通过  $10\Omega$  串联电阻和  $100n$  电容实现去耦。

为提升抗扰度，我们增加了迟滞。 $(V_{TH+} - V_{TH-})$  可以根据方程式 7 计算：

$$V_{Hysteresis} = (V_{Out\_High} - V_{Out\_Low}) \times \frac{R_G}{R_F} \quad (7)$$

$V_{Out\_High}$  为高电平、 $V_{Out\_Low}$  为低电平比较器输出电压、 $R_F$  为反馈电阻且  $R_G$  为同相比较器输入端的输入电阻器。

在图 4-7 中所述的设计配置中，已根据方程式 8 将迟滞设置为大约 160mV。由于 R49 和 R48 的量级低于 R50，因此可忽略。

$$V_{Hysteresis} = 3.3 V \times \frac{R_{50}}{R_{51}} \sim 160 mV \quad (8)$$

上限和下限开关阈值  $V_{TH+}$  和  $V_{TH-}$  根据方程式 10 和方程式 9 定义，其中基准电压  $V_{REF} = 1.65V$ 。

$$V_{TH+} = 1.65 V \times \left(1 + \frac{R50}{R51}\right) = 1.73 V \quad (9)$$

$$V_{TH-} = (3.3 V - 1.65 V) \times \left(1 - \frac{R50}{R51}\right) = 1.57 V \quad (10)$$

### 小心

下限阈值是电源电压的一个函数。但是，在此项设计中电源电压容差为 5%，此值为大多数设计的典型值。3.3V 电源电压  $\pm 5\%$  的容差仅会对下限阈值产生  $\pm 16mV$  的影响，因此  $V_{TH-}$  范围约为 1.56 至 1.59V，仍然可以接受。

图 4-7. 具有迟滞功能的信号 A 比较器

每个比较器 3.3V 电源通过  $1\Omega$  串联电阻器和  $100nF$  电容器去耦，以尽可能减少 3.3V 电源轨到其他比较器之间的串扰。增加由 R49 和 C54 组成的 RC 低通滤波器，将比较器开关节点从 A/正弦模拟信号处去耦，该节点将连接至外部 ADC。

迟滞功能可避免在过零点附近因噪声而快速切换，从而获得干净的数字信号。但迟滞会引入额外的传播延迟，延时时间的长短取决于比较器输入端模拟信号振幅  $V_{IN\_PEAK-PEAK}$ 。

$$f_{Hysteresis} \sim \sin^{-1} \left( \pm \frac{160 mV}{V_{IN\_PEAK-PEAK}} \right) \quad (11)$$

假设最小输入电压为  $0.3 V_{PP}$ ：差分放大器至单端放大器（增益= 1.66）的输出振幅为  $0.5V_{PP}$ （0 至  $100kHz$ ），在  $500kHz$  时由于低通滤波器衰减，振幅约为  $0.32 V_{PP}$ 。当比较器输入为  $0.32 V_{PP}$  时，数字信号 A、B 和 R 的迟滞对应相位延迟约为 30 度。在  $500kHz$  时，将转化为比较器的总传播延迟，约为  $170ns + 40ns = 210ns$ 。

由于 TLV3201 传播延迟低，只有  $40ns$ ，因此当频率达到  $500kHz$  时，比较器块的总延迟始终低于 45 度。

信号 B 和 R 的比较器具有相同的设置。同样，索引标记 R 的缓冲和增益级也与信号 A 和 B 相同。这样可确保当信号频率达到  $500kHz$  时，索引标记 R 的相位与信号 A 和 B 精确同步。这样可确保零索引标记 R 按预期出现，出现时间早于信号 A 和 B 的上升沿。索引标记 R 定义绝对零位，因此需要与信号 A 和 B 精确相关才能避免任何位置偏移。

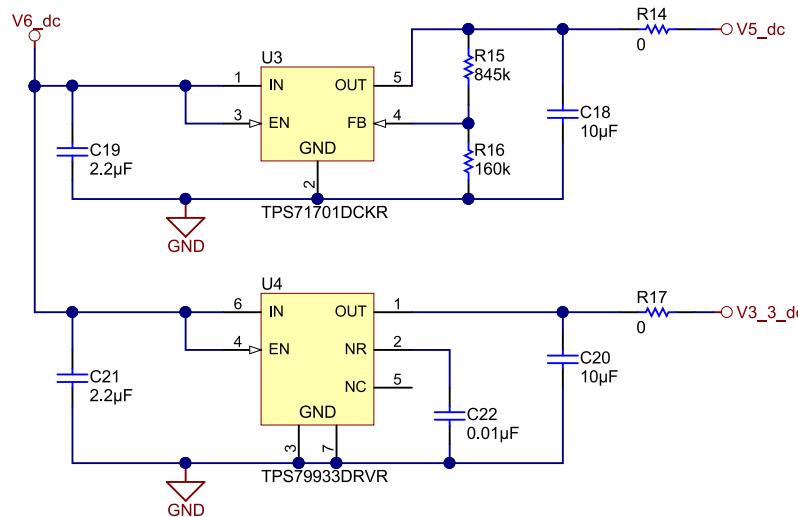

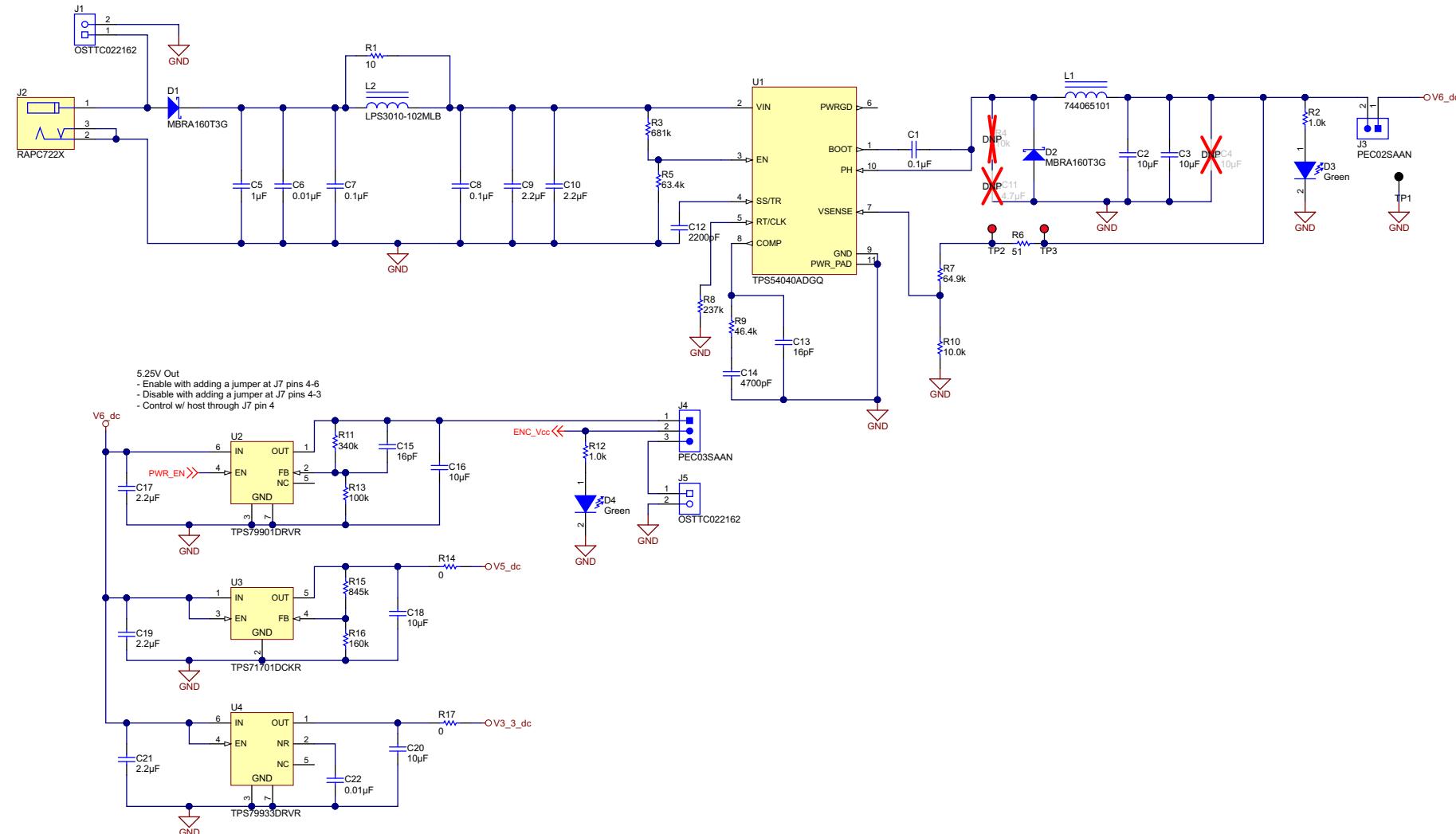

## 4.2 电源管理

电源管理部分有 DC/DC 降压功能，能从  $24V$  输入电压生成  $6V$  中间电源轨。编码器电源电压以及  $5V$  和  $3.3V$  电源轨均由中间电压生成，如图 4-8 所示。

图 4-8. 电源管理解决方案

由于系统及解决方案的高性能要求，大部分电源轨均由低噪声 LDO 提供。其缺点是效率有限且输出电流能力低。由于功率损耗较高，热性能会限制最大输出电流。

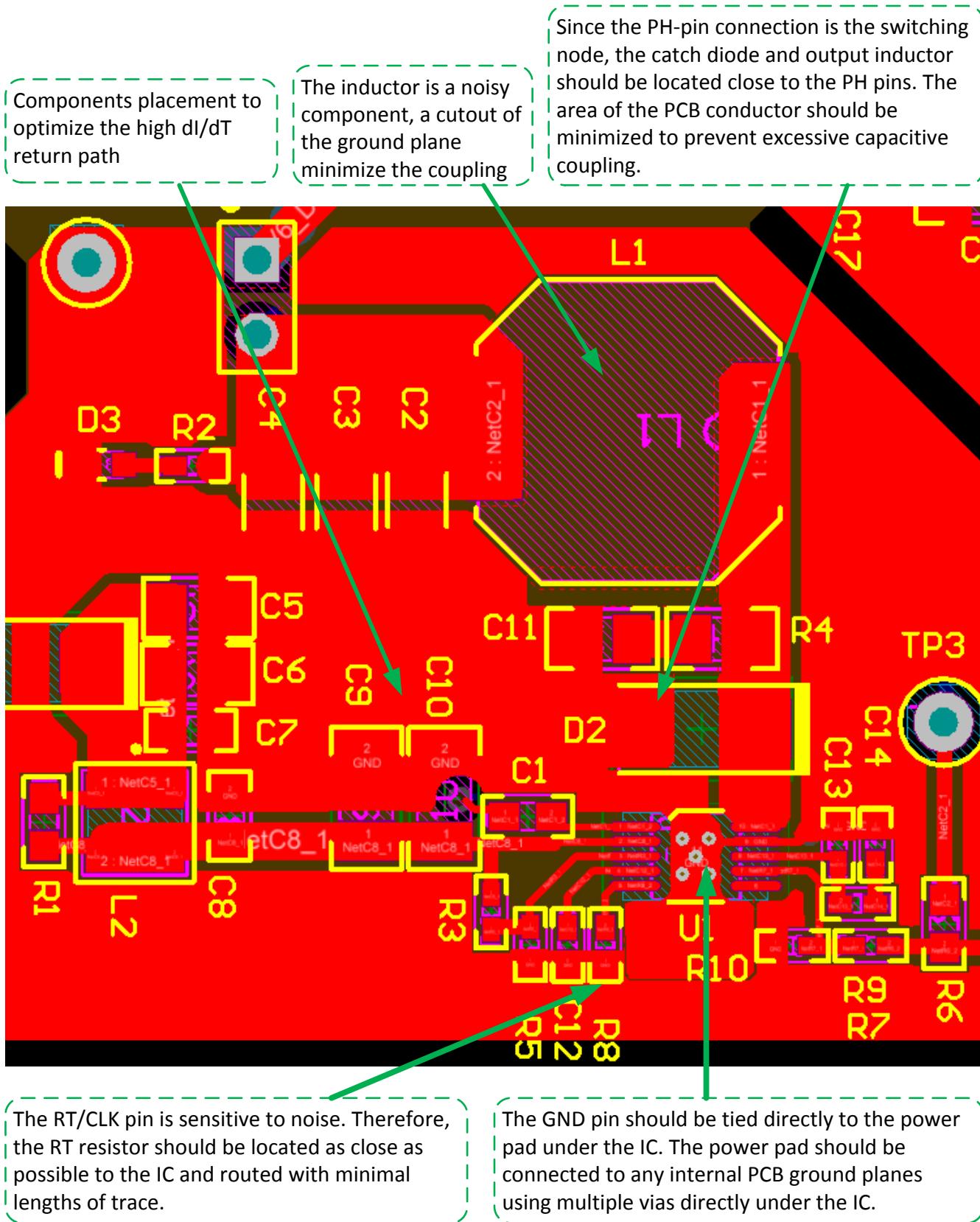

为降低 LDO 两端的压降，使用了高效的 DC/DC 开关转换器，可由 24V 输入生成 6V 中间电源轨。通过适当的布局和元件选择来最大程度地降低开关解决方案引起的噪声。

#### 4.2.1 24V 输入转换为 6V 中间电压轨

使用一个开关式 DC-DC 转换器来产生 6V 的中间电压轨，为三个 LDO 供电。这基本上是一个必然的选择，因为在  $V_{IN}/V_{OUT}$  比率较高的情况下，任何 LDO 均不适用于进行电源转换。事实上，任何 LDO 的效率都可以简单地计算为  $V_{OUT}/V_{IN}$ ，在最坏情况下（最大  $V_{IN}$ ），效率将为  $5.25V/36V \approx 14\%$ 。剩余 86% 的功耗会被 LDO 封装消耗掉：实际上，如果最大电流为 200mA，那么 LDO 封装上消耗的功率将为  $36V \times 200mA \times 86\% = 6.2W$ ，这会轻易且迅速地烧毁任何合理的封装。

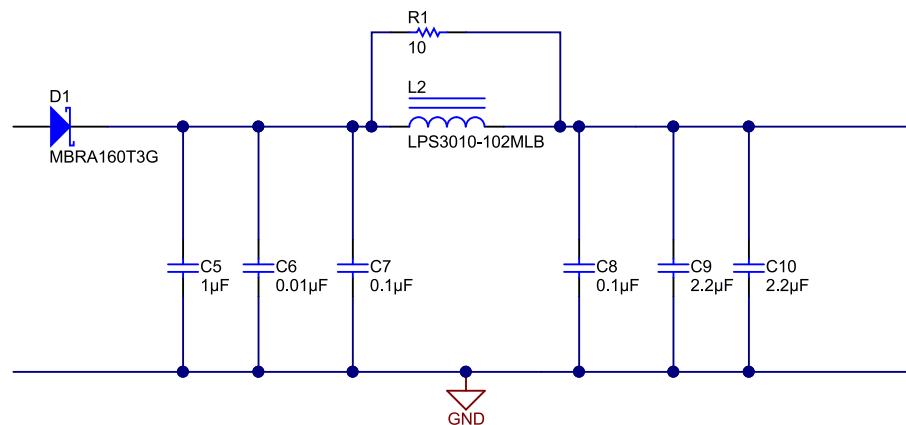

众所周知，从输入滤波器开始，开关电路的正常运行会产生传导性 EMI。电源开关快速的导通和关断会产生很大的不连续电流。在降压拓扑中，转换器的输入端存在较大的不连续电流（高  $di/dt$ ）。输入滤波器的选定值如 图 4-9 中所示。

有关如何设计输入 EMI 滤波器的详细信息，请参阅 [AN-2162 DC/DC 转换器传导 EMI 的简易解决方案 \(SNVA489\)](#) 应用报告。

图 4-9. 带反极性保护的输入滤波器

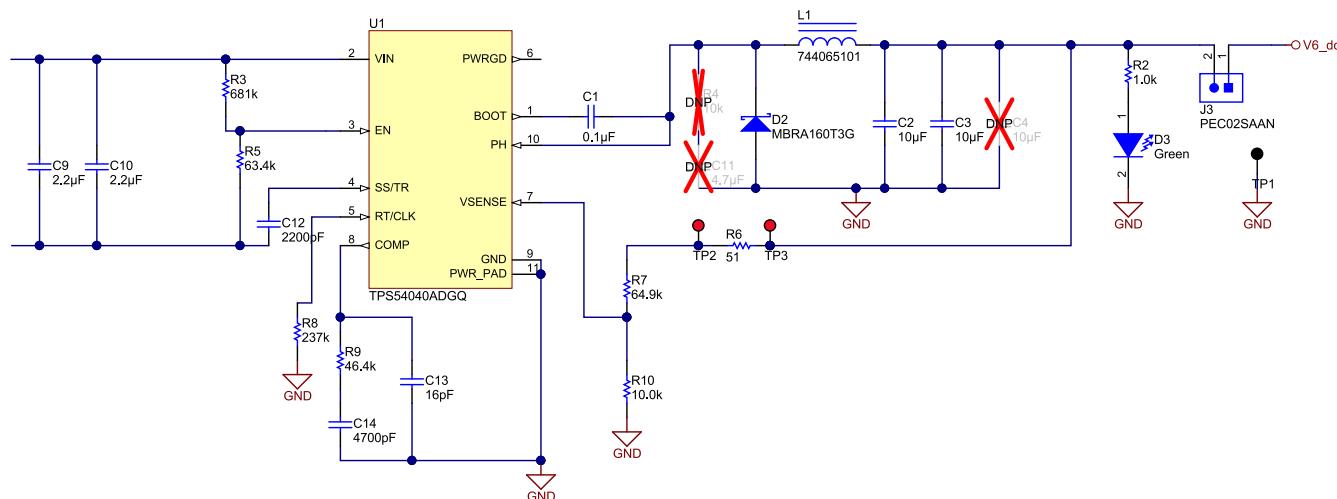

DC/DC 降压转换器的设计满足以下规格：

- 输入电压： $V_{IN} = 17$  至  $36V$ ，标称值为  $24V$

- 输出电压： $6V @ 500mA$

- 开关频率： $500kHz$  标称值

- 输出电压纹波：最大值  $25 mV_{PP}$

- 效率：满负载时  $>80\%$

- 非隔离拓扑

选用 TPS54040A 的目的在于：该降压转换器具有集成 FET，其输入电压范围为  $3.5$  至  $42V$ ，输出电压范围为  $0.8$  至  $39V$ ，输出电流为  $500mA$ 。其频率可在  $100kHz$  至  $2.5MHz$  之间调节，也可与外部时钟同步。此外，它还可以被启用和禁用。这些特点使得 TPS54040A 非常适合上述要求/规范。

请注意，TPS54040A 与其低成本版本 TPS5401 引脚对引脚兼容，它与 TPS54040A 性能类似，但输出电压精度较低，启用阈值也不同。

还要注意，TPS54040A 也与 TPS54140A、TPS54240、TPS54340 和 TPS54540 具有引脚对引脚兼容：这拓宽了器件选择范围，并为在未来系统升级时调整成本和功率级别提供了可能性。

图 4-10. 采用 TPS54040A 的 24V 转 6V DC-DC 降压转换器原理图

有关设计过程的详细介绍，请参阅 TPS54040A 数据表或 TI 参考设计 TIDA-00180。

在典型应用中，通过简单的电阻分压器网络设置输出电压。方程式 12 根据输出电压、基准电压（TPS54040A 为 0.8V）和下电阻器（通常情况下，R10 固定为 10kΩ）计算上电阻器的阻值。

$$R7 = R10 \times \frac{V_{OUT} - 0.8 \text{ V}}{0.8 \text{ V}} \quad (12)$$

当  $V_{OUT} = 6\text{V}$  且  $R10 = 10\text{k}\Omega$  时，R7 得出  $65\text{k}\Omega$ 。

6V 输出电压的容差为  $6\text{V}\pm4\%$ 。此容差是基于反馈电阻 1% 的容差，以及 TPS54040A 内部带隙  $\pm2\%$  的容差计算得出。

开关频率在  $R8 = 237\text{k}\Omega$  时设置为 500kHz。

在 TPS54040A 原理图中，某些元件标记为不安装 (DNP)。对于由 R4 和 C11 构成的缓冲器网络便是如此。

TPS54040A 的设计无需该缓冲器网络。缓冲器网络可减少开关节点上的振铃以及 MOSFET 过冲（如需）。有关如何使用和计算缓冲器网络的详细信息，请参阅针对 *NexFET™ 高性能 MOSFET 的振铃减少技术 (SLPA010)* 应用说明。

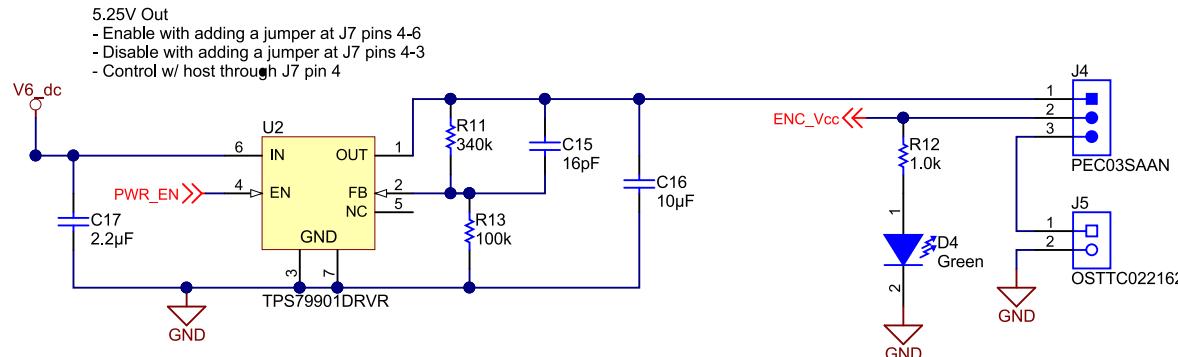

#### 4.2.2 编码器电源

为满足典型值 5V ( $\pm5\%$ ) 的编码器电源规范，本设计选用 5.25V 编码器电源，同时留出 0.25V 的额外裕量，以补偿连接编码器的较长电缆上的电压降。

为编码器提供 5.25V 的 LDO 还必须带有使能引脚。这样，可以根据需要从主机处理器断开或启动编码器电源，例如，在未连接编码器时断开编码器连接器端的电压。

除出于稳定性考虑所规定的输出电容/ESR 允许范围需要特别关注外，这些 LDO 本身并不需要进行特别的说明；设计中主要关注对象是 SMPS，它会影响所有主要性能（噪声、EMI、效率、成本和布板空间）。

TPS79901 经设计可提供稍高于标称 5V 的电压 (5.25V)，通过 LDO 较高精度的一部分特性，来降低自身所承受的热应力。简而言之， $5.25\text{V}\pm2\%$  在编码器允许的电源电压范围 ( $5\text{V}\pm5\%$ ) 内。这样，它必须耗散的功率是

$$P_{LDO,MAX} = (V_{LDO,IN} - V_{LDO,OUT}) \times i_{LDO,MAX} = (6 \text{ V} - 5.25 \text{ V}) \times 250 \text{ mA} = 187 \text{ mW} \quad (13)$$

对于 5V 编码器电压，最大功耗将增加至 250mW。

实际上，如果  $R_{thja} \approx 180^\circ\text{C/W}$ ，这意味着当 TPS79901 在 250 mA 的最大负载电流下工作时，其结温相对于环境温度的升高幅度会小于 34°C。例如，在 85°C 环境条件下，结温将是 120°C。

TPS79901 LDO 的输出电压通过精度为 1% 的反馈电阻器 R11 和 R13，依据 方程式 13 来设置，其中 1.193V 是 TPS79901 参考电压的标称值：

$$V_{ENC\_VCC} = 1.193 \text{ V} \times \left(1 + \frac{R11}{R13}\right) = 1.193 \times \left(1 + \frac{340\text{k}}{100\text{k}}\right) = 5.25 \text{ V} \quad (14)$$

图 4-11. 编码器电源 5.25V LDO 原理图

如果有需要，可以通过跳线在 5.25-V LDO 输出和可选的外部电源之间进行选择。信号 PWR\_EN 默认为上拉，但可以通过主机微控制器将其置为低电平来禁用或重新启动编码器电源电压（参见 [节 4.3](#)）。

#### 4.2.3 信号链电源 5V 和 3.3V

如[节 4.1](#)中所述，由于模拟信号链需要低电流，并且要实现高性能和极低噪声，因此必须同样选择 LDO。实际上，由于 TI LDO 具有 PSRR 高的特性，因此能够阻隔开关产生的交流噪声，不会对 ADC、输入缓冲器和放大器等对噪声敏感的器件产生任何影响。

5V 电源轨能为模拟缓冲器和放大器供电，并同时为 ADS8354 ADC 提供模拟电源电压。3.3V 能为 ADS8354 和比较器提供数字电源，从而确保在无需 I/O 电平移位器的情况下，用于连接主机处理器的接口电压为 3.3V。由于所选元件均为低功耗产品，因此为 3.3V 和 5V 电源轨选用的 LDO 的标称输出电流为 100 mA。

3.3V 电源轨采用固定的 3.3V LDO TPS79933，5V 电源轨则采用 TPS71701。原理图如[图 4-12](#) 所示。5V 输出电压由反馈电阻器 R15 和 R16 设定，当 TPS71701 V<sub>REF</sub> = 0.8V 时，其计算公式为[方程式 15](#)。

$$V_{5V} = V_{REF} \times \left(1 + \frac{R15}{R16}\right) = 0.8 \text{ V} \times \left(1 + \frac{845\text{k}}{160\text{k}}\right) = 5.02 \text{ V} \quad (15)$$

图 4-12. 信号链 5V 和 3.3V POL 的原理图

## 4.3 主机处理器接口

### 4.3.1 信号描述

可使用 10 引脚插头接口连接主机处理器。该插头可提供必要的信号来为两条信号路径计算高分辨率插值角，这两条路径分别使用 ADS8354 双路 16 位 ADC 和内置的双路 S/H ADC（如果提供）。

该接口与 3.3V I/O 系统兼容。为实现可靠的 GND 连接，所有奇数引脚均分配给 GND。表 4-1 列出了可用信号。

**表 4-1. 连接主 MCU 的 TIDA-00176 接口连接器**

| 功能                                           | 信号        | I/O (3.3V)                     | 注释                                                                                  |

|----------------------------------------------|-----------|--------------------------------|-------------------------------------------------------------------------------------|

| 用于 A 和 B 的 16 位高分辨率输出通道，配有 ADS8354 和 SPI（从机） | SDI (I)   | 数字输入                           | 串行通信的数据输入。用于双采样模式配置                                                                 |

|                                              | /CS (I)   | 数字输入                           | 片选信号；低电平有效。/CS 下降沿将锁存模拟输入（保持）并启动新的转换。采用 /CS 下降沿同步锁存主处理器（如 Piccolo MCU）上的 QEP 计数器    |

|                                              | SCLK (I)  | 数字输入，最高 24MHz                  | 串行通信的时钟                                                                             |

|                                              | SDO_A (O) | 数字输出                           | 串行通信通道 A 和通道 B 的数据输出。通道 A 和通道 B 均采用 16 位 2's 补码数据。输入到输出信号增益 = 5。                    |

|                                              | SDO_B (O) | 数字输出                           | 串行通信通道 B 的数据输出                                                                      |

| 数字正交编码信号 A，B 以及索引标记 R                        | ATTL (O)  | 数字输出                           | A、B 和 R 的 160mV 迟滞，可配置                                                              |

|                                              | BTTL (O)  | 数字输出                           |                                                                                     |

|                                              | RTTL (O)  | 数字输出                           |                                                                                     |

| A 和 B 的模拟单端输出通道                              | A/sin (O) | 模拟输出：0 至 3.3V，<br>1.65V 偏置（单端） | 标称输出范围：<br>1 V <sub>PP</sub> 时，0.82V - 2.48V<br>(1.65±0.83V)、增益 = 1.66、偏置电压 = 1.65V |

|                                              | B/cos (O) | 模拟输出：0 至 3.3V，<br>1.65V 偏置（单端） | 标称输出范围：<br>1 V <sub>PP</sub> 时，0.82V - 2.48V<br>(1.65±0.83V)、增益 = 1.66、偏置电压 = 1.65V |

有关连接器引脚分配的详细信息，请参见节 6。

#### 小心

若要同步 ADS8354 16 位双路采样 ADC 的模拟输入信号样本与 QEP 增量计数器模块，可向 ADS8354 发送 /CS 信号，同时锁定 QEP 计数器。在 MCU（如 Piccolo）中，需将 /CS 连接至 eQEP 选通输入引脚 EPEPxS，其中 x 代表模块编号。可将 Piccolo eQEPx 模块配置为在 EQEPxS 引脚的下降沿锁存 QEP 计数器。

### 4.3.2 采用具有串行输出的 16 位双路 ADC ADS8354 的高分辨率路径

本节介绍通过串行接口对 ADS8354 进行配置的情况。这分为两个方面，一是利用 ADS8354 内部基准来对满标度输入电压范围进行编程，二是进行串行数据传输。

#### 4.3.2.1 ADS8354 输入满标量程输出数据格式

在本设计中，ADS8354 拟配置为  $\pm 2 \times V_{REF}$  输入范围。内部基准电压  $V_{REF}$  应设置为 2.5V，从而获得  $\pm 5V$  FSR。

表 4-2. ADS8354 针对 TIDA-00176 的传输特性

| 输入电压：<br>AINP_x - AINM_x | 模式                        | 输入电压         | 输出代码（十六进制） |

|--------------------------|---------------------------|--------------|------------|

| < -5V                    | $\pm 2 \times V_{REF}$ 范围 | NFSC         | 8000       |

| - 5V + 1 LSB             |                           | NFSR         | 8001       |

| -1 LSB                   |                           | -1 LSB       | FFFF       |

| 0                        |                           | 0            | 0000       |

| > 5V - 1 LSB             |                           | PFSR - 1 LSB | 7FFF       |

通道 A 和 B 的输出数据格式为 16 位有符号整数输出（二进制补码）。

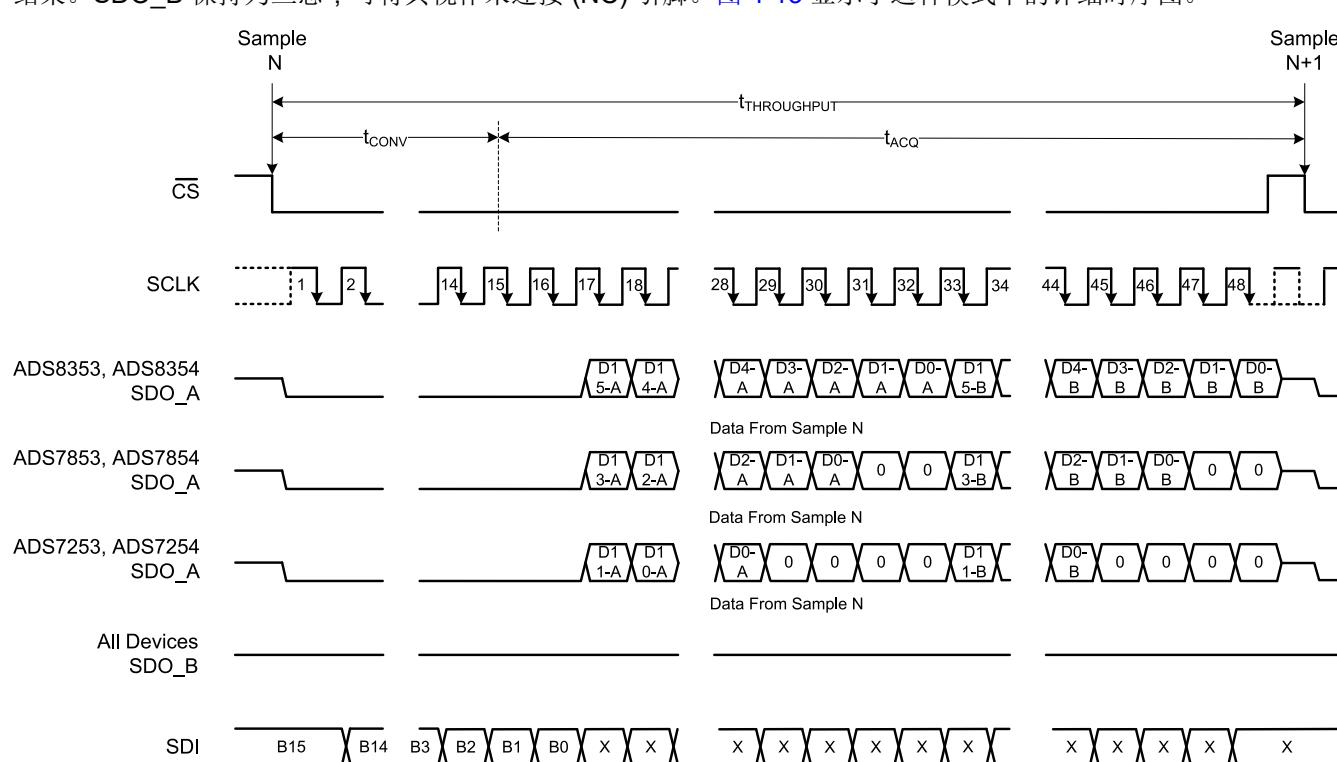

#### 4.3.2.2 ADS8354 串行接口

DS8354 使用串行时钟 (SCLK) 来同步器件的数据输入与输出传输。CS 信号界定一次转换和串行传输帧。一个帧从 CS 信号的下降沿起始，至 CS 信号的上升沿结束。在帧的起点和终点之间，必须提供最少 N 个 SCLK 下降沿，才能确保读写操作有效。如 表 4-3 中所示，N 的数值取决于读取转换结果所采用的接口模式。当出现 N 个 SCLK 下降沿时，该帧内尝试的写操作即被认定有效，并在随后的 CS 上升沿更新内部用户可编程寄存器。该 CS 上升沿同时也标志着该帧的结束。若在提供 N 个 SCLK 下降沿之前将 CS 信号置为高电平，那么该帧内尝试的写操作将无效。

表 4-3. 有效写操作所需的 ADS8354 SCLK 下降沿数量

| 接口模式                | 使写操作有效的最小 SCLK 下降沿数量 N |

|---------------------|------------------------|

| 32-CLK，双 SDO 模式（默认） | 32                     |

| 32-CLK，单 SDO 模式     | 48                     |

| 16-CLK，双 SDO 模式     | 16                     |

| 16-CLK，单 SDO 模式     | 32                     |

F28069M Piccolo MCU 中的示例固件以 32-CLK 单 SDO 模式初始化 ADS8354。

有关串行接口模式和读写操作的详细信息，请参阅 ADxx54 数据表。

#### 4.3.2.3 ADS8354 转换数据读取

如表 4-3 中所述，该器件为用户提供了四种不同的接口模式。这些模式也适用于读取转换结果。借助这些模式，可实现灵活的硬件连接和固件编程。在 32-CLK 接口模式下，器件使用内部时钟转换模拟采样信号。转换在前 16 个 SCLK 周期完成，然后在后续 SCLK 下降沿读取转换结果。该系列的所有器件（即 ADS8354，ADS7854 和 ADS7254）均支持 32-CLK 接口模式。除 32-CLK 接口模式外，ADS7854 和 ADS7254 还支持 16-CLK 接口模式。通过使用 16-CLK 接口模式，在低得多的 SCLK 速度下也能够实现相同的数据吞吐量。

F28069M Piccolo MCU 中的示例固件以 32-CLK 单 SDO 模式初始化 ADS8354。

在 32 位时钟单 SDO 模式下，可以仅使用一个 SDO 引脚 (SDO\_A) 读取两个 ADC (ADC\_A 和 ADC\_B) 的转换结果。SDO\_B 保持为三态，可将其视作未连接 (NC) 引脚。图 4-13 显示了这种模式下的详细时序图。

图 4-13. 32-CLK 单 SDO 模式时序图

CS 下降沿会使串行数据总线脱离三态，并且还会在 SDO\_A 引脚上输出 0。该器件在转换时间 ( $t_{CONV}$ ) 内对采样的模拟输入进行转换。在此期间，SDO\_A 读取到的数值为 0。转换过程完成后，采样保持电路会重新回到采样模式。在第 16 个 SCLK 下降沿时，器件会在 SDO\_A 引脚上输出 ADC\_A 的 MSB。后续 SCLK 下降沿用于依次将 ADC\_A 的转换结果以及 ADC\_B 的转换结果从 SDO\_A 引脚上移出。此模式下，必须至少提供 48 个 SCLK 下降沿，才能验证读写帧的有效性。CS 上升沿会结束该帧，并将串行总线置于三态。

有关更多详细信息，请参阅 ADSxx54 数据表。

#### 4.3.2.4 ADS8354 寄存器配置

要选择前面部分所述的模式，需按如下方式对 ADS8354 寄存器 REFDAC\_A、REFDAC\_B 和 CFR 进行编程。

REFDAC\_X 和 CFR 为 16 位寄存器，编程方式如 [表 4-4](#) 中所示，其中高 4 位用于选择写/读模式及其对应的寄存器。

**表 4-4. ADS8354 寄存器配置**

| 寄存器      | 数据 (十六进制) | 注释                                                                                         |

|----------|-----------|--------------------------------------------------------------------------------------------|

| REFDAC_A | 9FF8      | REFDAC_A 写入模式，选择 VREF_A = 2.5V                                                             |

| REFDAC_B | AFF8      | REFDAC_B 写入模式，选择 VREF_B = 2.5V                                                             |

| CFR      | 8640      | CFR 写入模式，SDO_A 上的 A 和 B 均选择 32-CLK 双路 SDO 模式， $FSR = \pm 2 \times V_{REF}$ ，选择内部 $V_{REF}$ |

有关更多详细信息，请参阅 [ADSxx54](#) 数据表。

#### 4.4 编码器连接器

连接正弦/余弦编码器有两种连接器选项。默认的连接器是一种带屏蔽功能的 SubD-15 插座。另一个选项是 8 引脚接头。有关连接器分配的更多详细信息，请参阅 [节 6](#)。

#### 4.5 设计升级

高分辨率路径：为进一步提高高分辨率通道的防噪性能，建议对差分放大器 THS4531A 使用一阶低通滤波器。要使用高达 500kHz 的高分辨率通道，建议在 THS4531A 反馈路径中与  $5k\Omega$  匹配电阻器并联各增加一个  $33pF$  1% NPO/COG 电容器。要降低截止频率，电容器值应相应增大。

通过信号 PWR\_EN 实现具有输出使能的 5.25V LDO：虽然连接器 J-7 的引脚 4 可用于确保输入始终通过上拉（跳线：J7 4-6）或下拉（跳线：J7 4-3）的方式进行端接，但仍建议从 U2 的引脚 4 连接到 3.3 V (V3\_3\_dc) 的线路上额外添加一个  $10k$  的上拉电阻。

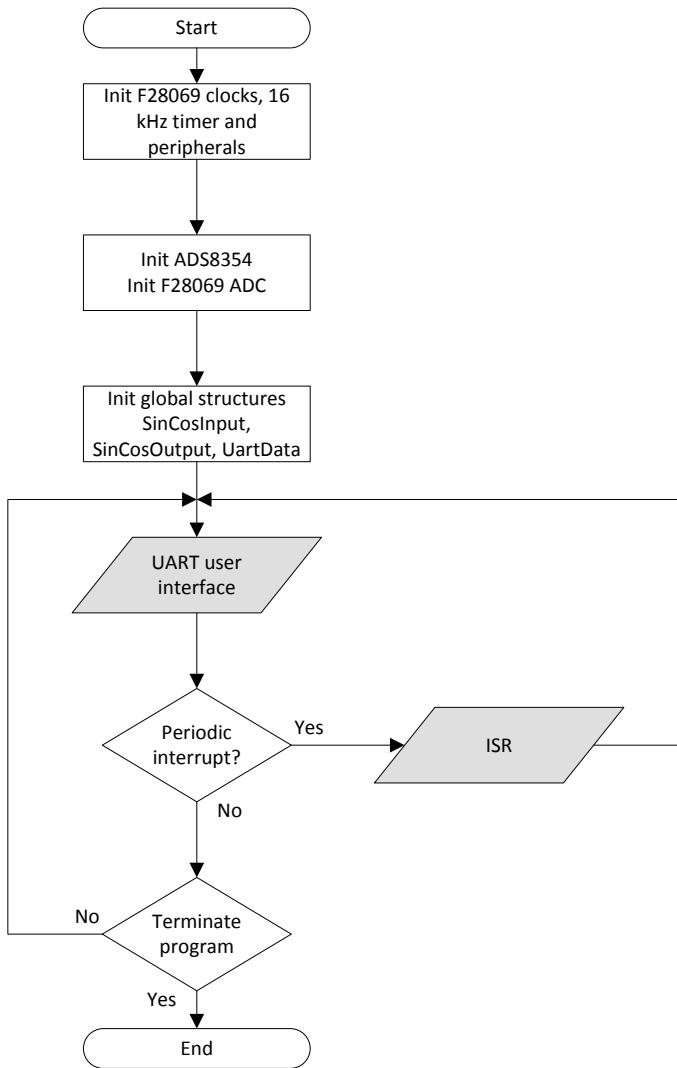

## 5 软件设计

### 5.1 概述

TIDA-00176 硬件设计可与任何带嵌入式正交编码脉冲计数器和 SPI 的嵌入式处理器或微控制器搭配使用。

但为简化 TIDA-00176 硬件参考设计的评估，我们提供了适用于 C2000 F28069M Piccolo LaunchPad 的示例固件，以便对采用正弦/余弦增量位置编码器的 TIDA-00176 进行评估。将通过 USB 虚拟 COM 端口提供用户菜单，以初始化所选正弦/余弦编码器的线数并显示计算得出的高分辨率角度信息及其他用户可选数据。

F28069M 采用的主要外设包括 SPI-A 外设，能读取双路高分辨率 16 位数据信号  $A_{16\text{-bit}}$  和  $B_{16\text{-bit}}$ 。嵌入式双路 S/H ADC 用于转换单端模拟信号  $A_{12\text{-bit}}$  和  $B_{12\text{-bit}}$ 。正交编码器脉冲 (eQEP2) 模块根据信号  $A_{\text{TTL}}$  和  $B_{\text{TTL}}$  以及绝对位置初始化的零索引标记  $R_{\text{TTL}}$ ，执行方向增量减量计数。ePWM1 计时器能生成周期性中断，触发新的角度测量。选择 16kHz 的周期。SCI-A 外设用于通过虚拟 COM 端口以 115000 波特实现基于 UART 的用户界面。

图 5-1. TMS320F28069M 外设模块及 TIDA-00176 主机处理器接口的引脚分配

## 5.2 C2000 Piccolo 固件

我们针对 Piccolo TMS320F28069M 开发和编译了示例固件，并将使用图 5-1 中所述的外设模块。

该固件将使用 C2000 controlSUITETM。固件主要由三个功能模块组成。F28069M 框架（如图 5-2 中所述）、用于同步采样所需数据并计算插值角度的算法，以及基于 UART 终端的用户界面。

图 5-2. 正弦/余弦编码器框架流程图

TMS320F28069M 框架可初始化 TMS320F28069M CPU 时钟至 80MHz，对 GPIO 多路复用器以及各种外设，例如 SPI-A、SCI-A (UART)、基于 ePWM1 的周期性计时器和中断，嵌入式 12 位双路 S/H ADC 进行初始化设置。它还通过 SPI-A 配置外部 16 位双路 ADC ADS8354，如节 4.3.2.4 中所述。SPI-A 被配置为 SPI 主设备，串行时钟设置为 10MHz。对于 Piccolo F28069M，这是最大的 SPI 时钟。对于其他处理器（如 Sitara AM437x 或 Delfino F287x），SPI 时钟可高达 24 MHz。

初始化完成后，程序将调用基于 UART 的用户界面并运行周期中断服务例程 (ISR)。周期 ISR 将基于外部 16 位 ADC ADS8354 和内部 12 位 ADC，实施同步数据捕获、计算中间相位及总插值角。它遵循中节 1 概述的算法。这些编码利用 TI IQmath 库，采用 32 位整数分数 Q28 格式编写。与 32 位 IEEE 浮点数相比，32 位小数的优势在于，无论数据范围如何，分辨率都能保持恒定。由于角度数据（按单位计）的取值范围被限定在 0 到 1.0 之间，ADC 的输入数据经缩放后最大值为  $\pm 5$  (V)，而整数范围为  $\pm 8.0$  的 Q28 数据格式能够提供充足的余量，同时对于所有数据都能保持稳定的精度。

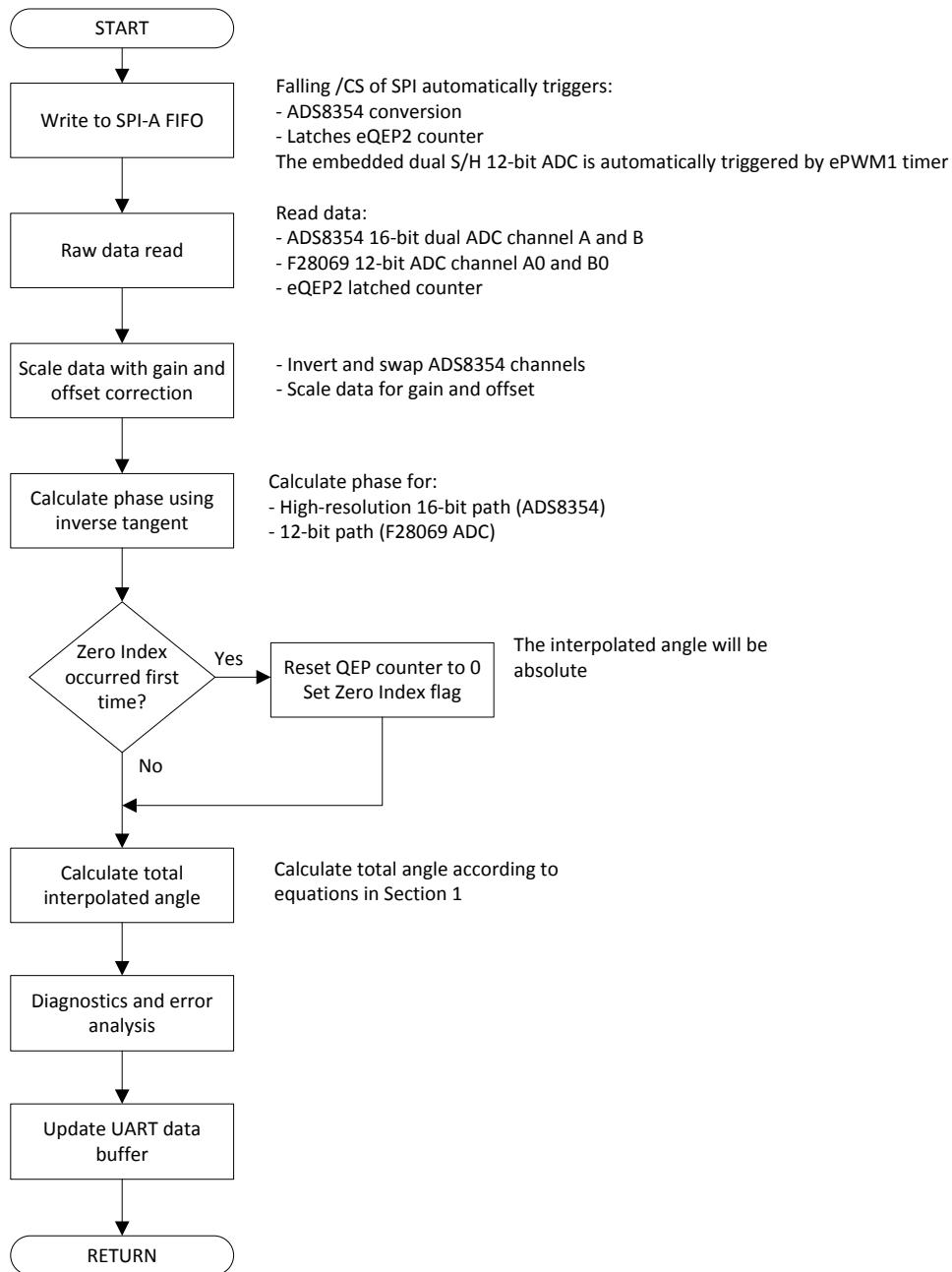

图 5-3 中所示为 ISR 的流程图。

图 5-3. 带插值角度计算的正弦/余弦编码器主 ISR 流程图

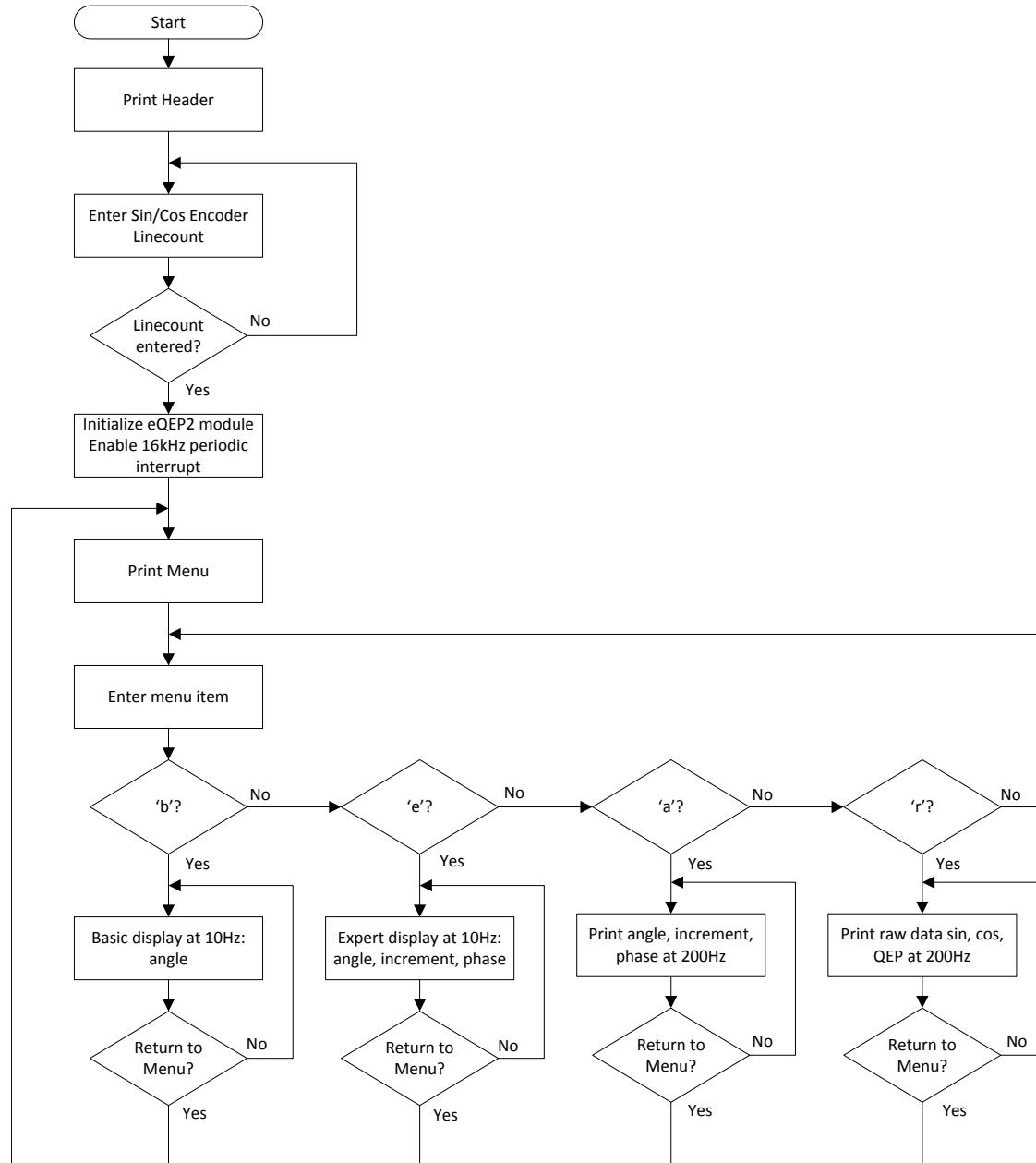

## 5.3 用户界面

为快速完成评估，我们实施了基于虚拟 COM 端口的用户界面。可使用任何采用 115000 波特的终端接口，如 Tera Term。

用户可在程序到达主菜单前，借助用户界面输入连接正弦/余弦编码器的线数。用户可通过菜单中提供的菜单项选项，选择基本显示模式（仅显示高分辨率角度）或专业显示模式，二者的更新速率均为 10Hz。后续的菜单项可选择数据转储模式，更新速率为 200Hz，这样可将数据写入文件中以便进行事后分析。

图 5-4 展示了用户界面的流程图。

图 5-4. UART 终端用户界面流程图

表 5-1 至表 5-4 所示分别为四个菜单项的数据输出格式。在数据转储模式下，每行数据之间会以 "tab" 符号作为分隔符。

**表 5-1. 基本显示模式输出格式和数据定标**

| 菜单       | COLUMN 1              | COLUMN 2 | COLUMN 3 | COLUMN 4 | COLUMN 5 |

|----------|-----------------------|----------|----------|----------|----------|

| "b" 基本显示 | 采用 ADS8354 时的总角度 (定标) | —        | —        | —        | —        |

| 数据格式     | 浮点 (0 至 360 度)        | —        | —        | —        | —        |

**表 5-2. 专业显示模式输出格式和数据定标**

| 菜单       | COLUMN 1              | COLUMN 2 | COLUMN 3 | COLUMN 4        | COLUMN 5            |

|----------|-----------------------|----------|----------|-----------------|---------------------|

| "e" 专业显示 | 采用 ADS8354 时的总角度 (定标) | 出现标记索引 R | 增量计数     | 相位 ADS8354 (定标) | 相位 F28069M ADC (定标) |

| 数据格式     | 浮点 (0 至 360 度)        | 标志 (是/否) | 整数       | 浮点 (0 至 1.0)    | 浮点 (0 至 1.0)        |

**表 5-3. 角度数据转储菜单格式及定标**

| 菜单       | COLUMN 1              | COLUMN 2                 | COLUMN 3 | COLUMN 4        | COLUMN 5            | COLUMN 6   |

|----------|-----------------------|--------------------------|----------|-----------------|---------------------|------------|

| "d" 角度转储 | 采用 ADS8354 时的总角度 (定标) | 采用 F28069 ADC 时的总角度 (定标) | 增量计数     | 相位 ADS8354 (定标) | 相位 F28069M ADC (定标) | 周期性节拍 (定标) |

| 数据格式     | 浮点 (0 至 360 度)        | 浮点 (0 至 360 度)           | 整数       | 浮点 (0 至 1.0)    | 浮点 (0 至 1.0)        | 整数 (66 μs) |

**表 5-4. 原始数据转储菜单格式及定标**

| 菜单       | COLUMN 1  | COLUMN 2        | COLUMN 3                | COLUMN 4                | COLUMN 5               | COLUMN 6               | COLUMN 7   |

|----------|-----------|-----------------|-------------------------|-------------------------|------------------------|------------------------|------------|

| "r" 原始数据 | 增量计数 (SW) | 增量计数 (锁定在 /CS ) | 输入 A+/A- , ADS8354 (定标) | 输入 B+/B- , ADS8354 (定标) | 输入 A+/A- , F28069 (定标) | 输入 A+/A- , F28069 (定标) | 周期性节拍 (定标) |

|          | 整数        | 整数              | 悬空 (V <sub>PP</sub> )   | 悬空 (V <sub>PP</sub> )   | 悬空 (V <sub>PP</sub> )  | 悬空 (V <sub>PP</sub> )  | 整数 (66 μs) |

## 6 入门

### 6.1 TIDA-00176 PCB 概览

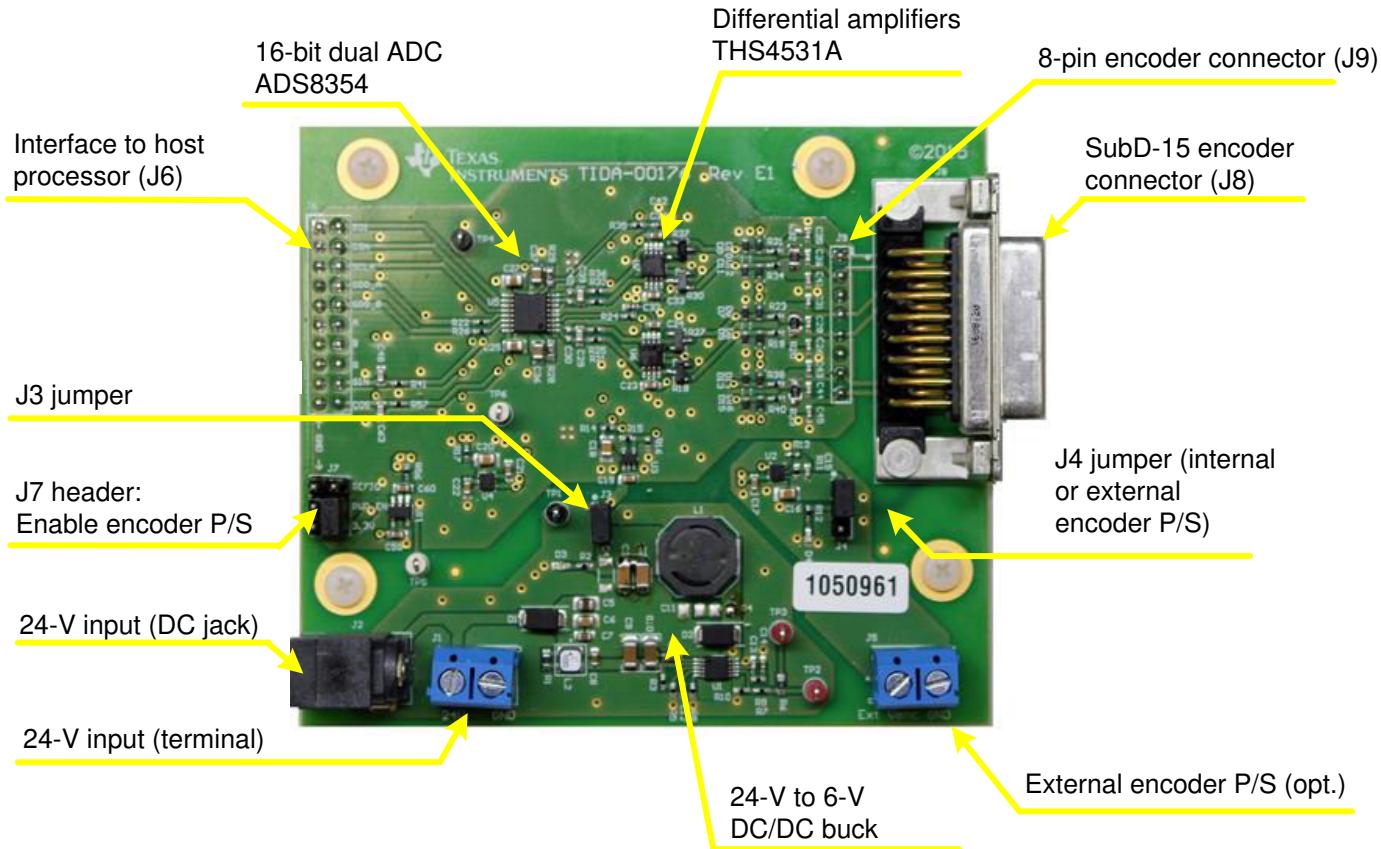

图 6-1 所示为搭载 TIDA-00176 PCB 的顶面图。在节 6.2 中介绍了其接头和默认跳线设置。

图 6-1. TIDA-00176 电路板图

## 6.2 连接器和跳线设置

### 6.2.1 连接器和跳线概述

连接器分配和跳线设置在 表 6-1 到 表 6-4 中有详细说明。

可通过连接器 J1 或 J2 提供 24V 标称输入电压。

**表 6-1. 连接器分配和跳线设置 ( J1 至 J4 )**

| 连接器和引脚分配                     | 说明                     |

|------------------------------|------------------------|

| <b>24V 输入 ( 端子 ; J1 )</b>    |                        |

| 1                            | 24V 输入电压 ( 17 至 36V )  |

| 2                            | GND                    |

| <b>24V 输入 ( DC 插孔 ; J2 )</b> |                        |

| 内部                           | 24V 输入电压 ( 17 至 36V )  |

| 外部                           | GND                    |

| <b>J3</b>                    |                        |

| 1                            | TPS54040A 输出 ( 默认 6V ) |

| 2                            | 6V 电源导轨                |

| <b>J4</b>                    |                        |

| 1                            | 5.25V 电源 ( 默认 )        |

| 2                            | V_ENC ( 编码器电源电压 )      |

| 3                            | 外部电源                   |

如有必要，也可不使用 5.25V 编码器电源电压，而是通过连接器 J5 提供外部电源电压。

**表 6-2. 外部编码器电源连接器 (J5)**

| 引脚 | 说明        |

|----|-----------|

| 1  | 编码器电源 VCC |

| 2  | 编码器电源 GND |

**表 6-3. 主机处理器接口 (J6)**

| 引脚 | 说明  | 引脚 | 说明 (3.3V I/O)       |

|----|-----|----|---------------------|

| 1  | GND | 2  | SDI (ADS8354)       |

| 3  | GND | 4  | /CS (ADS8354)       |

| 5  | GND | 6  | SCLK (ADS8354)      |

| 7  | GND | 8  | SDO_A (ADS8354)     |

| 9  | GND | 10 | SDO_B (ADS8354)     |

| 11 | GND | 12 | A (TTL)             |

| 13 | GND | 14 | B (TTL)             |

| 15 | GND | 16 | R (TTL)             |

| 17 | GND | 18 | A ( 单端模拟 0 至 3.3V ) |

| 19 | GND | 20 | B ( 单端模拟 0 至 3.3V ) |

有关主机处理器接口信号的详细说明，请参阅[节 4.3](#)。

**表 6-4. 连接器分配和跳线设置 ( J7 至 J9 )**

| 引脚                          | 说明        | 引脚 | 说明                     |

|-----------------------------|-----------|----|------------------------|

| <b>带编码器电源使能的接头 J7 (J7)</b>  |           |    |                        |

| 1                           | GND       | 2  | REFIO (1.65V)          |

| 3                           | GND       | 4  | 使能编码器电源电压 (5.25V)      |

| 5                           | GND       | 6  | 3.3V                   |

| <b>编码器 DSUB15 连接器 (J8)</b>  |           |    |                        |

| 1                           | A+        | 2  | 编码器电源 GND              |

| 3                           | B+        | 4  | 编码器电源 VCC ( 默认 5.25V ) |

| 5                           | NC        | 6  | NC                     |

| 7                           | R -       | 8  | NC                     |

| 9                           | A -       | 10 | 保留                     |

| 11                          | B -       | 12 | 保留                     |

| 13                          | NC        | 14 | R+                     |

| 15                          | NC        | —  | —                      |

| <b>编码器 8SIL100 连接器 (J9)</b> |           |    |                        |

| 1                           | A+        | 2  | A -                    |

| 3                           | 编码器电源 GND | 4  | B -                    |

| 5                           | B+        | 6  | 编码器电源 VCC ( 默认 5.25V ) |

| 7                           | R -       | 8  | R+                     |

### 6.2.2 默认跳线配置

在使用 TIDA-00176 电路板之前，请确保已设置为以下默认跳线配置。参阅板图 [图 6-1](#)。

**表 6-5. 默认跳线设置**

| 接头 | 跳线设置                                           |

|----|------------------------------------------------|

| J3 | 在 J3 引脚 1-2 之间插入跳线，以启用连接三个 LDO 的 6V 中间电源轨      |

| J4 | 在 J4 引脚 1 和 2 之间插入跳线，以将板载 5.25V 编码器电源连接至编码器连接器 |

| J7 | 在 J7 引脚 4 和 6 之间插入跳线，以启用 5.25V 编码器电源。          |

## 6.3 设计评估

### 6.3.1 先决条件

为全面评估 TIDA-00176

TI 参考设计，需要以下硬件设备和软件。

**表 6-6. 先决条件**

| 设备                                 | 注释                                                              |

|------------------------------------|-----------------------------------------------------------------|

| 24V 电源                             | 具有至少 250mA 输出电流的 24V 输出电源模块<br>输出连接器 2.1mm 内径×5.5mm 外径×9.5mm 母头 |

| TIDA-00176 硬件                      | 有关默认跳线设置信息，请参见第 6.2 节。                                          |

| 用于设置电路板的三个跳线                       | 2 引脚，100mil                                                     |

| TIDA-00176 固件                      | 从 TIDA-00176 设计文件夹下载                                            |

| InstaSPIN-MOTION F28069M LaunchPad | 可从 TI eStore 购买                                                 |

| USB 线缆                             | 微型 A 型 USB 至 A 型 USB 电缆                                         |

| TIDA-00176 至 LaunchPad 适配器         | 内部 TI ( 可选 )                                                    |

| Code Composer Studio 6             | 从 <a href="http://www.ti.com">www.ti.com</a> 下载                 |

| PC 终端程序                            | 任何终端程序，例如 Tera Term                                             |

| 带 1V <sub>PP</sub> 输出信号的正弦/余弦编码器   | 例如，ROD480                                                       |

### 6.3.2 硬件设置

需在 TIDA-00176 与 InstaSPIN-MOTION LaunchPad 之间进行如下连接。

**表 6-7. TIDA-00176 主机处理器接口 (J6) 与 InstaSPIN-LaunchPad 之间的连接**

| TIDA-00176 主机处理器接口 (J6) |                     | 连接到<br>→ | InstaSPIN-MOTION LAUNCHPAD |                                   |

|-------------------------|---------------------|----------|----------------------------|-----------------------------------|

| J6-PIN                  | 说明                  |          | 接头引脚                       | 说明 (3.3V I/O)                     |

| 1                       | GND                 |          | J3 引脚 22                   | GND                               |

| 19                      | GND                 |          | J2 引脚 20                   | GND                               |

| 2                       | SDI (ADS8354)       |          | J2 引脚 15                   | GPIO16/SPISIMOA                   |

| 4                       | /CS (ADS8354)       |          | J2 引脚 19<br>J6 引脚 59       | GPIO27/eQEP2S 和<br>GPIO19/SPISTEA |

| 6                       | SCLK (ADS8354)      |          | J1 引脚 7                    | GPIO18/SPICLKA                    |

| 8                       | SDO_A (ADS8354)     |          | J2 引脚 14                   | GPIO17/SPISOMIA                   |

| 10                      | SDO_B (ADS8354)     | NC       | NC                         | NC                                |

| 12                      | A (TTL)             |          | J6 引脚 55                   | GPIO24/eQEP2A                     |

| 14                      | B (TTL)             |          | J6 引脚 54                   | GPIO25/eQEP2B                     |

| 16                      | R (TTL)             |          | J6 引脚 58                   | GPIO26/eQEP2I                     |

| 18                      | A ( 单端模拟 0 至 3.3V ) |          | J3 引脚 27                   | ADCIN_A0                          |

| 20                      | B ( 单端模拟 0 至 3.3V ) |          | J3 引脚 28                   | ADCIN_B0                          |

请按照以下步骤来设置硬件：

1. 使用适当的连接器或适配器连接 TIDA-00176 电路板和 InstaSPIN-MOTION LaunchPad。

---

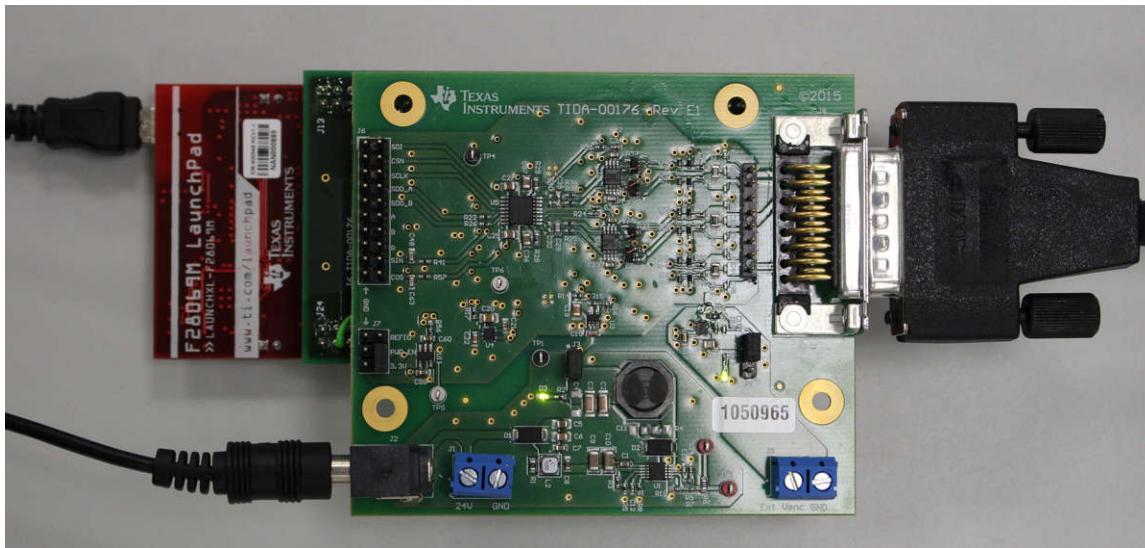

#### 备注

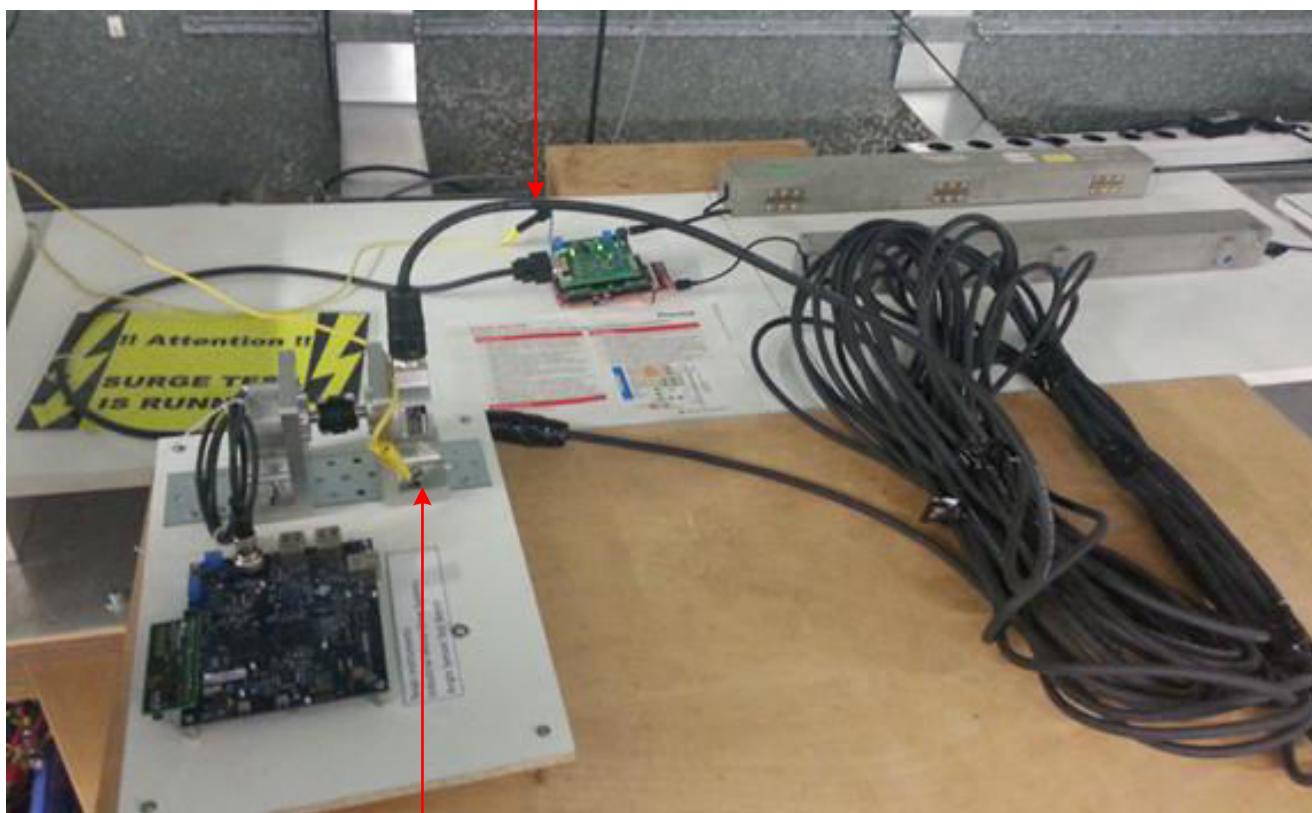

为进行内部测试，已设计了一块适配板，用于实现 TIDA-00176 与 InstaSPIN-MOTION LaunchPad 之间的连接，如 图 6-2 中所示。

2. 按照 节 6.2.2，验证 TIDA-00176 是否已配置为默认的三个跳线设置。

3. 通过 SubD-15 连接器 (J8) 或 SIL-8 连接器 (J9) 将正弦/余弦编码器连接至电路板。

4. 将电源模块的 24V 输入端插入 J1 连接器，若使用外部电源（17 至 36V），则使用 J2 连接器。

5. 使用 USB 迷你电缆将 InstaSPIN-MOTION LaunchPad 连接至 PC。

图 6-2. InstaSPIN-MOTION LaunchPad 上安装的 TIDA-00176 电路板

另请参阅 InstaSPIN-MOTION LaunchPad 的先决条件，网址为：<http://www.ti.com/tool/launchxl-f28069m>

确保 F28069 LaunchPad 上的以下跳线已设置：JP1、JP2、JP3 和 JP7。请勿设置 JP4、JP5 和 JP6；这些跳线不得连接。

### 6.3.3 软件设置

按照以下步骤安装软件：

1. 如果尚未下载，请从 TIDA-00176 设计文件夹下载 TIDA-00176 SinCosEncoder 固件并解压至文件夹，如 c:\ti\tida-00176\bin。

2. 调用一个可连接至虚拟 COM 端口的终端程序，如 Tera Term。

3. 将终端程序设置为串行控制台模式，并将参数设置为：

- 波特率= 115200、数据= 8 位、奇偶校验=无、停止位= 1 位和流控制=无

4. 启动 Code Composer Studio (CCS)。

5. 在 CCS 中，将 XDS100 JTAG 目标设置为 InstaSPIN-MOTION F28069M LaunchPad。

6. 在 CCS 中，连接 TMS320F28069M 并下载 TIDA-00176 二进制输出文件。运行→加载程序→TIDA-00176\_SinCosEncoder\_Firmware\_rev1\_0.out

7. 在 CCS 中运行目标。

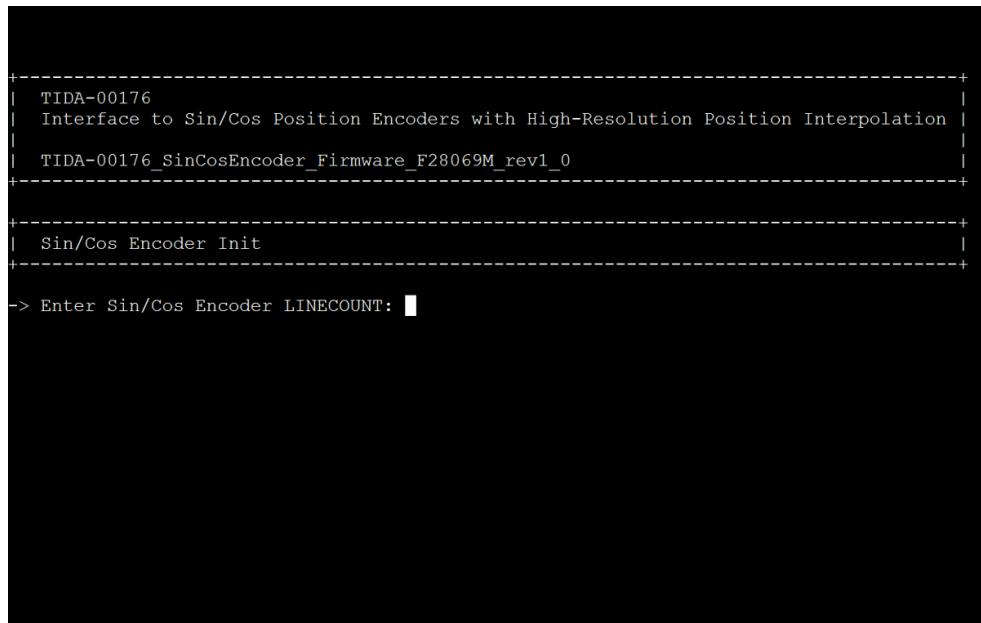

终端程序应显示 TIDA-00176 的开始屏幕，如图 6-3 所示。

#### 备注

二进制文件加载至 F28069M 后，便无需再执行步骤 4 至 7。只需重置 LaunchPad 即可重新启动程序。确保 F28069M 配置为从内部闪存启动。请参考 InstaSPIN-MOTION LaunchPad 文档。

故障排除：如果未建立连接，则需要在 Windows® 7 Device Manager 中启用 USB 虚拟 Com 端口 TI XDS100 通道 B 的 VCP 驱动器。有关更多详细信息，请参阅 InstaSPIN-MOTION LaunchPad 文档。

```

+-----+

| TIDA-00176

| Interface to Sin/Cos Position Encoders with High-Resolution Position Interpolation |

| TIDA-00176_SinCosEncoder_Firmware_F28069M_rev1_0

+-----+

+-----+

| Sin/Cos Encoder Init

+-----+

-> Enter Sin/Cos Encoder LINECOUNT: |

```

图 6-3. TIDA-00176 启动时的用户界面

### 6.3.4 用户界面

启动后，用户需在用户界面中输入十进制的正弦/余弦编码器线数。输入线数后，将显示主菜单，如图 6-4 所示。

```

Interface to Sin/Cos Position Encoders with High-Resolution Position Interpolation |

| TIDA-00176_SinCosEncoder_Firmware_F28069M_rev1_0 |

+-----+

| Sin/Cos Encoder Init |

+-----+

-> Enter Sin/Cos Encoder LINECOUNT: 2000

LINECOUNT entered: 2000

+-----+

| Main Menu |

+-----+

key mode format

--- -----

b basic display mode [angle]

e expert display mode [angle index incr phase16 phase12 tick]

r raw data dump at 200Hz [QEP QEPL sin16 cos16 sin12 cos12 tick]

a angle dump at 200Hz [angle incr phase16 phase12 tick]

x reserved

--- -----

any any other key returns to this main menu

-> press key

```

图 6-4. TIDA-00176 用户界面主菜单

能提供四个菜单。可通过按下字符 **b**、**e**、**r** 或 **a** 来选择每个选项。菜单项 **x** 为软件开发期间的内部测试模式而保留。

按下 "**b**" 或 "**e**" 可选择基本显示模式或专业显示模式，从而以度为单位显示插值角或其它信息。请注意，最初由于尚未出现索引，因此总角度不是绝对角度值。这可以通过专业显示模式中 **Increments Marker** 设置为"否"来识别。沿顺时针方向缓慢转动编码器，直至增量标记变为"是"。此时，插值角是相对于索引标记位置的绝对值。若要返回主菜单，请按任意键。

```

+-----+

| High-resolution angle [degree] |

+-----+

359.9804

+-----+

| Main Menu |

+-----+

key mode format

--- -----

b basic display mode [angle]

e expert display mode [angle index incr phase16 phase12 tick]

r raw data dump at 200Hz [QEP QEPL sin16 cos16 sin12 cos12 tick]

a angle dump at 200Hz [angle incr phase16 phase12 tick]

x reserved

--- -----

any any other key returns to this main menu

-> press key

+=====+

| Expert display mode [10Hz update rate] |

+=====+

+=====+

| High-resolution angle | Increments | Phase/atan [PU] |

| [degree] | Marker Count | ADS8354 F28069 |

+=====+

359.9804 No 0 0.8914 0.8926

```

图 6-5. 基本角度显示及专业显示模式

按下 "a" 可启动角度数据转储，其更新速率为 200Hz。数据格式如节 5 中所述。屏幕截图如图 6-6 所示。按任意键停止并返回主菜单。

| Angle16PU  | Angle12PU  | Incr | Phase16PU | Phase12PU | Tick[32kHz] |

|------------|------------|------|-----------|-----------|-------------|

| 0.85510715 | 0.85510683 | 7005 | 0.25946   | 0.25879   | 9190        |

| 0.85510674 | 0.85510638 | 7005 | 0.25862   | 0.25788   | 9270        |

| 0.85510715 | 0.85510668 | 7005 | 0.25945   | 0.25851   | 9350        |

| 0.85510679 | 0.85510661 | 7005 | 0.25871   | 0.25835   | 9430        |

| 0.85510692 | 0.85510671 | 7005 | 0.25898   | 0.25854   | 9510        |

| 0.85510753 | 0.85510694 | 7005 | 0.26022   | 0.25902   | 9590        |

| 0.85510702 | 0.85510659 | 7005 | 0.25919   | 0.25830   | 9670        |

| 0.85510717 | 0.85510682 | 7005 | 0.25949   | 0.25878   | 9750        |

| 0.85510726 | 0.85510671 | 7005 | 0.25967   | 0.25857   | 9830        |

| 0.85510681 | 0.85510660 | 7005 | 0.25876   | 0.25833   | 9910        |

| 0.85510682 | 0.85510658 | 7005 | 0.25877   | 0.25829   | 9990        |

| 0.85510727 | 0.85510681 | 7005 | 0.25970   | 0.25877   | 10070       |

| 0.85510728 | 0.85510672 | 7005 | 0.25972   | 0.25858   | 10150       |

| 0.85510755 | 0.85510694 | 7005 | 0.26027   | 0.25902   | 10230       |

图 6-6. 更新速率为 200Hz 的角度转储模式

按下 "r" 可启动原始数据转储，更新速率为 200Hz。数据格式如节 5 中所述。屏幕截图如图 6-7 所示。按任意键停止并返回主菜单。

| Raw data dump at 200 Hz |      |        |        |        |        |             |

|-------------------------|------|--------|--------|--------|--------|-------------|

| QEP                     | QEPL | Vsin16 | Vcos16 | Vsin12 | Vcos12 | Tick[32kHz] |

| 7005                    | 7005 | 1.0044 | 0.0631 | 1.0280 | 0.0583 | 1542        |

| 7005                    | 7005 | 1.0108 | 0.0631 | 1.0280 | 0.0583 | 1622        |

| 7005                    | 7005 | 1.0069 | 0.0616 | 1.0280 | 0.0583 | 1622        |

| 7005                    | 7005 | 1.0150 | 0.0662 | 1.0309 | 0.0597 | 1702        |

| 7005                    | 7005 | 1.0089 | 0.0627 | 1.0324 | 0.0612 | 1782        |

| 7005                    | 7005 | 1.0083 | 0.0643 | 1.0280 | 0.0597 | 1862        |

| 7005                    | 7005 | 1.0101 | 0.0680 | 1.0295 | 0.0612 | 1942        |

| 7005                    | 7005 | 1.0066 | 0.0636 | 1.0265 | 0.0597 | 2022        |

| 7005                    | 7005 | 1.0072 | 0.0666 | 1.0265 | 0.0597 | 2102        |

| 7005                    | 7005 | 1.0083 | 0.0595 | 1.0295 | 0.0568 | 2182        |

| 7005                    | 7005 | 1.0047 | 0.0605 | 1.0251 | 0.0554 | 2262        |

| 7005                    | 7005 | 1.0032 | 0.0610 | 1.0251 | 0.0583 | 2342        |

| 7005                    | 7005 | 1.0040 | 0.0671 | 1.0280 | 0.0612 | 2422        |

| 7005                    | 7005 | 1.0110 | 0.0643 | 1.0324 | 0.0597 | 2502        |

图 6-7. 更新速率为 200Hz 的原始数据转储模式

## 7 测试结果

为了解每个功能块及整个电路板的特性，我们进行了相关测试。具体来说，进行了如下测试。

- 模拟信号链

- 电源管理

- 带正弦/余弦编码器信号仿真和正弦/余弦编码器的整个系统

- EMC 抗扰度 ( ED、EFT 和浪涌 )

在室温约 22 至 23 度或 75 或 85 度时进行测试。除非具体说明，否则均在室温条件下进行。

将下述设备用于测试 TIDA-00176 会话：

**表 7-1. TIDA-00176 性能测试的测试设备**

| 测试设备                                                                     | 器件型号                                |

|--------------------------------------------------------------------------|-------------------------------------|

| 可编程 16 位波形发生器                                                            | Keysight (Agilent) 33600A           |

| 低速示波器 ( 适用于电源测试 )                                                        | Tektronix TDS2024B                  |

| 高速示波器 ( 适用于模拟信号测试 )                                                      | Tektronix TDS784C                   |

| 可调节 SMPS                                                                 | Knuerr-Heinzinger Polaris 125-5     |

| 24V @ 2.5A SMPS ( 电源模块 )                                                 | V-infinity 3A-621DN24               |

| 准确的 RMS 万用表                                                              | Fluke 179                           |

| 差分探头                                                                     | Tektronix P6630                     |

| 单端探头                                                                     | Tektronix P6139A                    |

| 可编程热处理室                                                                  | Voetsch VT 4002                     |

| 可编程电子负载模块                                                                | Chroma 63103                        |

| 电子负载模块的控制模块                                                              | Chroma 6314                         |

| 热像仪                                                                      | Fluke TI40                          |

| 控制系统环路分析仪                                                                | Venable 3120                        |

| HEIDENHAIN 屏蔽电缆 , PUR M23 插头/插座 (4 × 2 × 0.14mm ; 4 × 0.5mm)、10m、20m、50m | 298399-10,-20,-50                   |

| HEIDENHAIN M23/Sub-D15 插头适配器电缆 , 1m                                      | 310196-01                           |

| HEIDENHAIN 正弦/余弦编码器                                                      | ROD480-2000、ROD480-1024、ROD486-2048 |

## 7.1 模拟性能测试

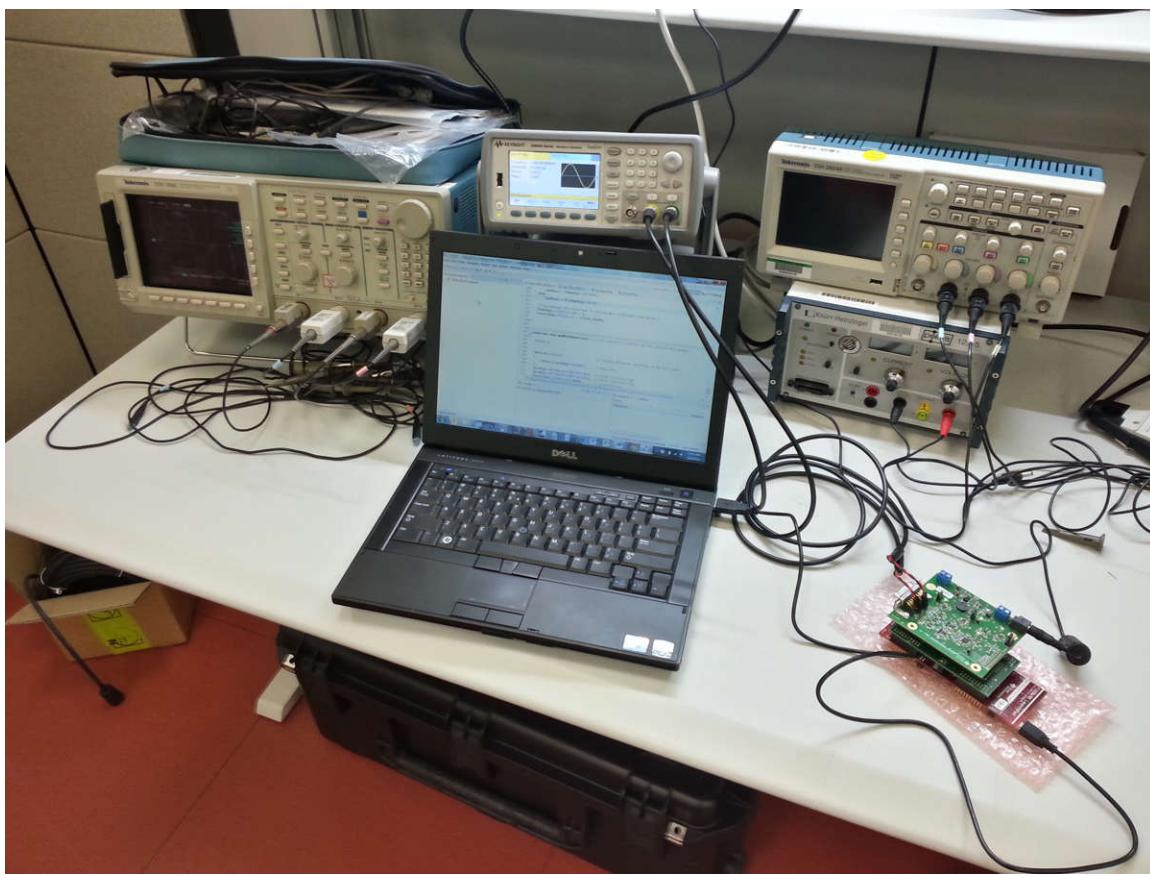

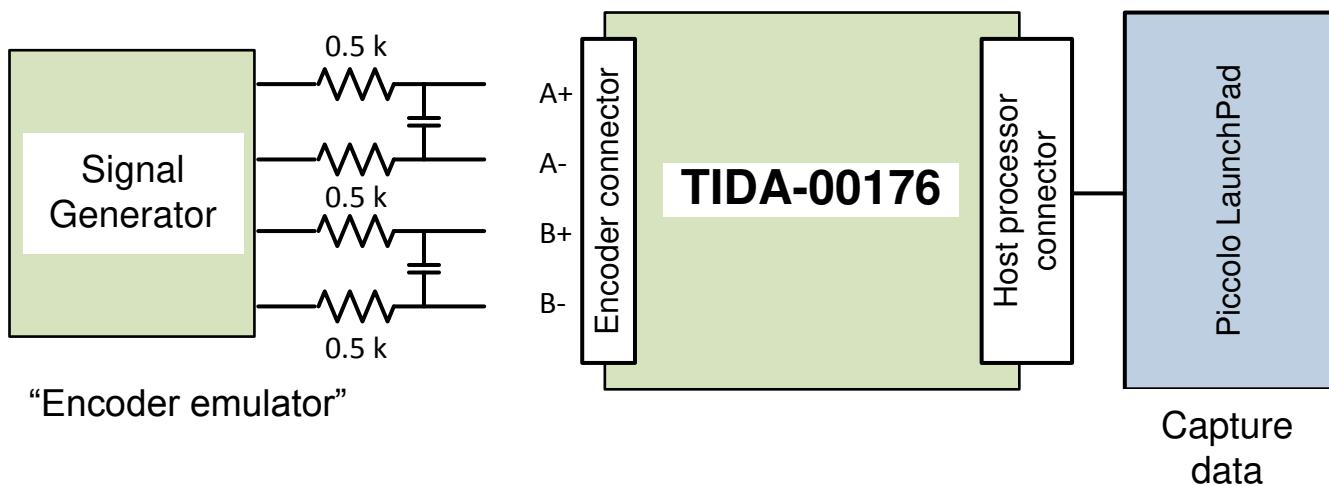

图 7-1 所示为 TIDA-00176 模拟信号链测试图。

图 7-1. TIDA-00176 模拟信号链性能测试的测试设置

我们对高分辨率 16 位信号路径（包含全差分放大器 THS4531A 和双路 16 位 ADC ADS8353）及差分转单端模拟信号路径进行了测试。测试中使用了双路输出可编程函数发生器。在连接器 J8 上施加输入信号（差分输入 A、B 和 R）。然后在不同的探测点采集输出波形，测试点取决于所分析的信号路径。

### 7.1.1 高分辨率信号路径

我们在高精度、高分辨率信号路径上进行测量。在编码器连接器 J8 输入 A+、A- 和 B+、B- 注入  $1V_{PP}$  正弦信号，然后在 ADS8354 差分输入端测量差分模拟信号。图 7-2 概述了为测试所测量的输入和输出信号。

图 7-2. 高分辨率信号链测量点

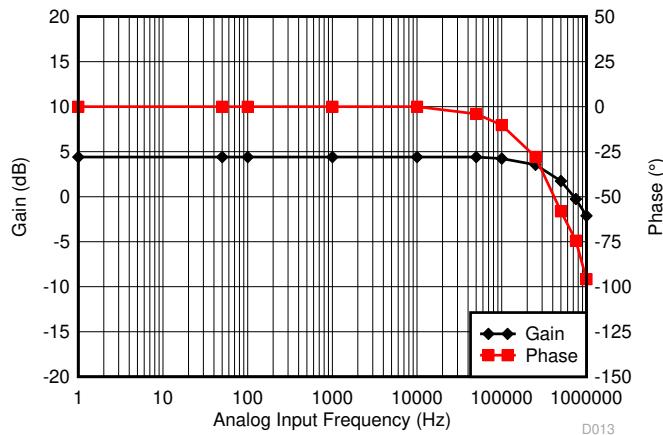

#### 7.1.1.1 编码器连接器至 ADS8354 输入端的模拟路径波德图

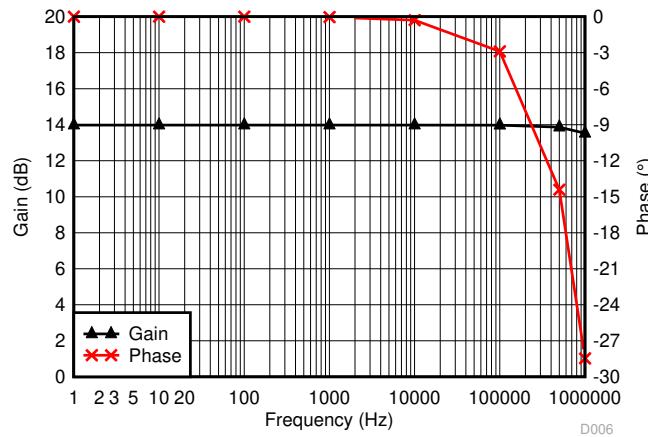

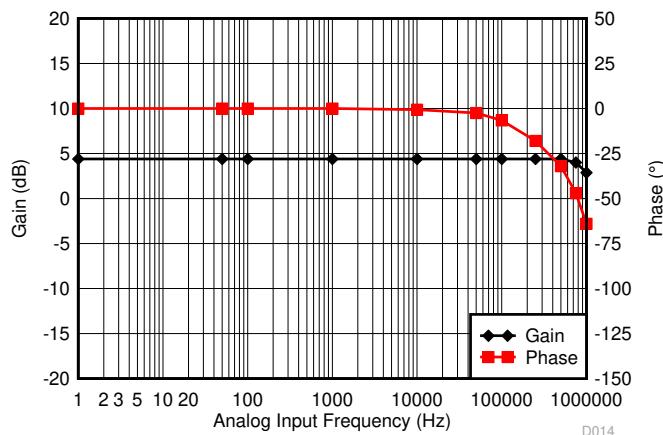

图 7-3 所示为幅值和相位响应，主要取决于 THS4531A 增益设置 2 以及由两个  $10\Omega$  串联电阻器和  $2.2nF$  并联电容器组成的一阶无源低通滤波器。

图 7-3. 从编码器差分输入至 ADS8354 差分输入的高分辨率模拟信号波德图

### 7.1.1.2 整个高分辨率信号路径的性能曲线图 (DFT)

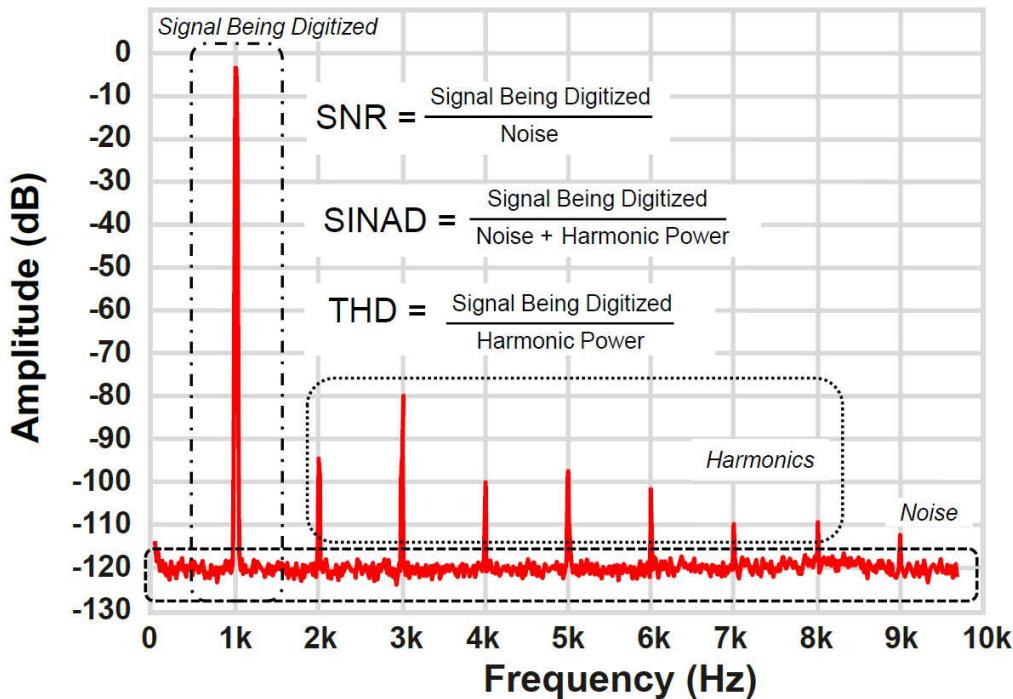

在以下测试中，我们测试了整个高分辨率信号链，包括经 RC 滤波器连接的差分放大器 THS4531A 到双路 16 位 ADC ADS8354。在编码器差分输入引脚注入正弦测试信号，然后对 16 位数字数据进行分析。

在频域中进行分析，以评估信噪比 (SNR)、总谐波失真 (THD)、信纳比 (SINAD) 和有效位数 (ENOB) 等性能。本质上，所有这些参数都是基于快速傅里叶变换 (FFT) 分析，利用不同的方式来量化 ADC 的噪声和失真性能。在本节的结尾处简要介绍了 ADC 信噪测量的原理。

在测试中，使用了两种输入信号：

- 1.8V 的超低噪声直流电源

- 振幅为 0.6 V<sub>PP</sub> 时的 1kHz 正弦波代表正弦/余弦编码器的低输出

每次在 A+，A- 或 B+，B- 其中一组输入通道上施加输入信号时，另一通道则处于未连接状态。这样做的目的是测量和突出两个通道 A 和 B（或分别为正弦和余弦）的超低串扰电平。

为了确保最佳噪声性能，使用了直流输入（因为输入/源不会产生噪声）。采用 1kHz 正弦波测量两个并联通道的有效位数。

以 32kHz 的频率对通道 A 和 B 进行采样，并分别采集 8192 个连续 16 位样本。针对所采集的数据计算 DFT，以测量 SNR 和 THD。

结果如下图所示。

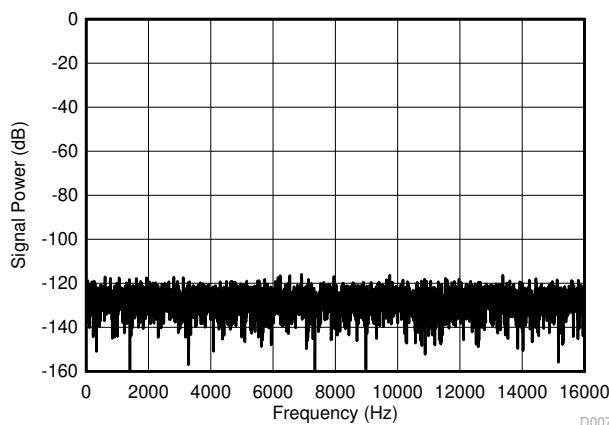

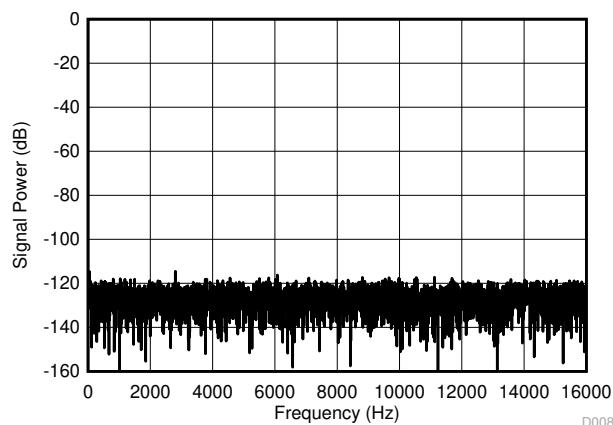

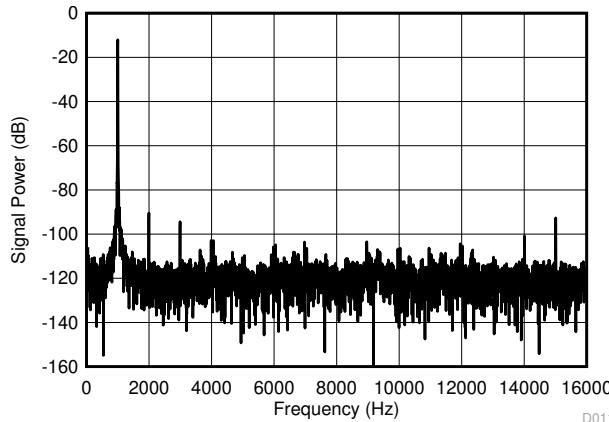

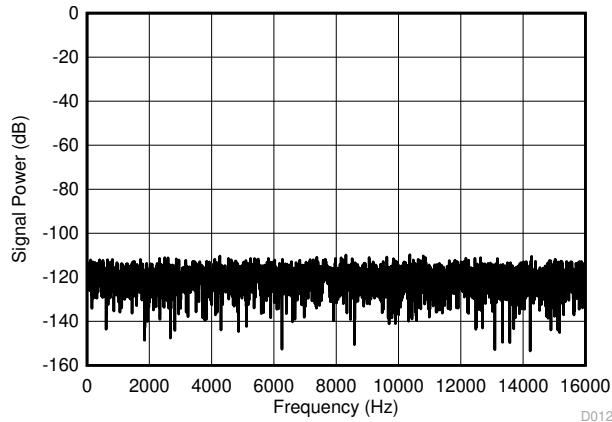

图 7-4. 在 A 输入端施加 1.8V 直流时 16 位通道 A 输出的 DFT

图 7-5. 在 B 输入端施加 1.8V 直流时 16 位通道 B 输出的 DFT

在前面的图中，所测量的噪底低于 120dB，这意味着这是可实现的最佳性能。此外，还需注意的是，这些图均采用满量程输入范围，即最大振幅。0dB 对应于 ADS8354 最大可能输入，在此配置中，该值将为 2 V<sub>PP</sub>。

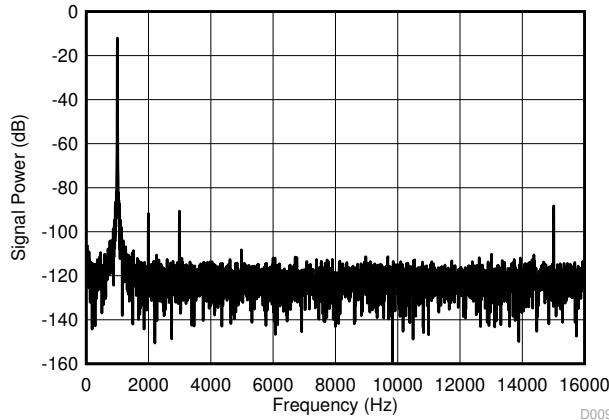

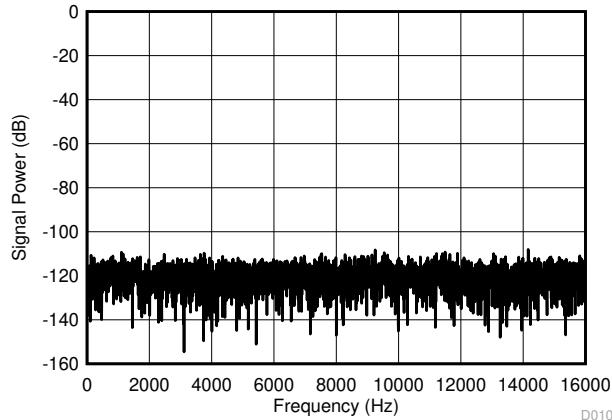

下图所示为整个高分辨率通道的 DFT，其中正弦输入电压振幅为 0.6V<sub>PP</sub>，频率为 1KHz。这约等于理论满标量程输入范围内的 -6dB 输入电平。

输入信号可施加到通道 A 或通道 B。另一通道保持开路状态，以便测量串扰。

图 7-6. 在 A 输入端施加 600mV<sub>PP</sub>, 1KHz 正弦波输入时，16 位通道 A 输出的 DFT

图 7-7. 在 A 输入端施加 600mV<sub>PP</sub>, 1KHz 正弦波输入时，16 位通道 B 输出的 DFT

图 7-8. 在 B 输入端施加 600mV<sub>PP</sub>, 1KHz 正弦波输入时，16 位通道 B 输出的 DFT

图 7-9. 在 B 输入端施加 600mV<sub>PP</sub>, 1KHz 正弦波输入时，16 位通道 A 输出的 DFT

这些图均采用理论上的满量程输入范围。注意，1kHz 正弦信号的第一个和第二个谐波源于信号源本身（通常采用极其严格的陷波滤波器来隔离测试信号的频率；相关示例，另请参阅 [SLAU515](#)）。

另请注意，1kHz 信号存在轻微的扩频。这与 TIDA-00176 硬件无关，而是由于 F28069 软件实施中出现抖动，触发了 SPI 传输，从而启动了 ADS8354 转换（保持模式），引起相当于 12.5ns 的、一个 CPU 时钟周期的抖动。

从上图中还可知，两个正弦（信号 A+，A-）和余弦（B+，B-）模拟通道之间基本不存在串扰。频谱（DFT）为采样频率的一半（另一半频谱是前半部分高光复制品，因此图表中未显示）。Hann 函数 ([http://en.wikipedia.org/wiki/Hann\\_function](http://en.wikipedia.org/wiki/Hann_function)) 用于对数据进行窗口化，以获得频域中更干净的图。

然后可以计算本设计在满量程信号下的 THD、SNR 和 ENOB，并且列举在表 7-2 中。

**表 7-2. 高分辨率信号路径 ( THS4531A 和 ADS8354 ) 的典型性能**

| 参数    | 值 ( 测量值 )        |

|-------|------------------|

| SNR   | 89.1dB           |

| SINAD | 88.5dB           |

| ENOB  | 14.4 位           |

| 串扰    | - 107 至 - 109 dB |

### 7.1.1.3 ADC 交流性能定义的背景信息

ADC 的典型 FFT 绘图如 图 7-10 中所示。

图 7-10. 性能定义

通过 SNR 可深入了解系统的总计噪声。数据采集系统的总计噪声是前端放大器噪声和 ADC 噪声的平方和根 (rss)。此 ADC 噪声包括量化噪声，以及由 ADC 内部电路产生的噪声。所有这些噪声源引入的噪声成分总和表示为  $V_{n\_TOT\_RMS}$ ，是指用于计算系统总 SNR 的 ADC 输入：

$$\text{SNR} = \frac{V_{\text{SIGNAL\_RMS}}}{V_{\text{NOISE\_RMS}}} \quad (16)$$

THD 的定义是所有谐波分量的平方和根 (一般采用九个谐波分量) 与基波信号频率功率的比值。它通常由一个接近满标度 (FS) 的输入信号确定，但是在这个设计中，输入保持在比 FS 低 0.5dB 的水平上以防止削波失真。

如果输入信号的均方根 (rms) 值表示为  $V_{\text{SIGNAL\_RMS}}$ ，且前九个谐波 (基波除外) 的总功率表示为  $V_{\text{HARMONICS\_RMS}}$ ，则 THD 计算公式如下：

$$\text{THD} = \frac{V_{\text{SIGNAL\_RMS}}}{V_{\text{HARMONICS\_RMS}}} \quad (17)$$

SINAD 将失真和噪声的影响组合在一起，为系统的整体动态性能提供了一个累计的衡量指标。

$$\text{SINAD} = \frac{V_{\text{SIGNAL\_RMS}}}{\sqrt{V_{\text{NOISE\_RMS}}^2 + V_{\text{HARMONICS\_RMS}}^2}} \quad (18)$$

最后但同样重要的是，由于 ENOB 指定了高于本底噪声的位数，因此是 ADC 数字化信号质量的一个有效衡量指标。其计算公式如下（从以 dB 表示的 SINAD 开始）：

$$\text{ENOB} = \frac{\text{SINAD}_{\text{dB}} - 1.76 \text{ dB}}{6.02 \text{ dB}} \quad (19)$$

有关各个参数计算方式的详细信息，请参阅 [SLAU515](#)。

### 7.1.2 差分转单端模拟信号路径

使用双通道信号发生器产生两个耦合的正弦波（振幅相同、频率相同且两者之间相移 90 度），并通过 J9 连接器将其施加到模拟差分信号 A+、A- 和 B+ 和 B- 上。使用两个差分探头采集输入端的差分信号，同时两个单端探头分别连接模拟路径中的单端模拟输出 A 和 B，即连接器 J6 的引脚 18 和引脚 20。

通过这种方式测量输出与输入的振幅，同时测量差分输入与相应单端输出之间的相移。通过这种方式，可以计算出模拟信号调节路径的波特图。

图 7-11. 差分转单端模拟信号路径的传递函数 - 通道 A 和 B

我们对标记信号 (R+/R-) 进行了相同的测量。注意，由于在比较器的输入端测量 R 信号的输出，因此 R 信号的相位小于 A 和 B 的相位。此处去耦滤波器的截止频率 (R = 20 Ω, C = 2.2nF) 比 A 和 B 输出滤波器 (R = 100 Ω, C = 2.2nF) 高五倍。

图 7-12. 差分转单端索引标记 R 的传递函数

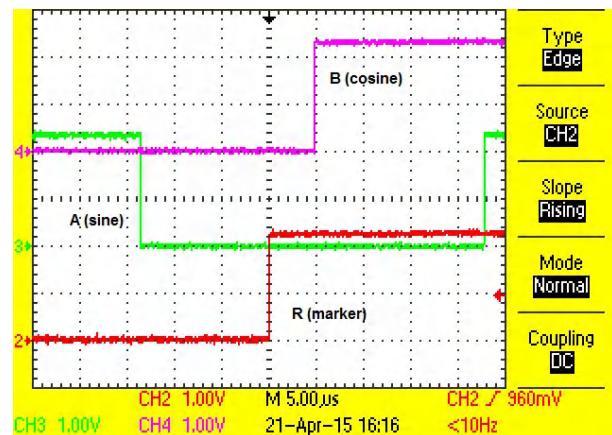

### 7.1.3 带数字输出信号 A<sub>TTL</sub>、B<sub>TTL</sub> 和 R<sub>TTL</sub> 的比较器子系统

本节对用于将单端模拟信号 A、B 和 R 转换为数字信号且带有迟滞的比较器进行性能测试。

测试重点在于比较器输出信号  $A_{TTL}$ 、 $B_{TTL}$  和  $R_{TTL}$  在主机连接器 J6 处的传播延迟，与高分辨率路径 ADS8354 处的模拟输入信号输入以及模拟路径的单端模拟信号的对比情况。

测试的目的是测量比较器路径相对于模拟路径的整体信号延迟，同时考虑迟滞带来的延迟、低通滤波导致的相移以及比较器自身的传播延迟。

由于 A, B 和 R 三个通道在比较器输出方面完全对称，因此仅对通道 A 进行了测量。

模拟信号均采用单端探头进行测量，因此在 ADS8354 的差分输入中，仅测量对地正差分信号。

测试中，在编码器连接器 J9 的 A\_P, A\_M ( 正弦 ) 和 B\_P, B\_M ( 余弦 ) 以及 P\_M 和 R\_P 引脚注入正弦信号。

对于高分辨率路径，将幅值设置为  $1.0V_{PP}$  ( 典型值 ) 和  $0.3V_{PP}$  ( 最小值 )，频率为  $100Hz$  和  $500kHz$  ( 最大值 )，以测试传播延迟的最坏情况。对于模拟路径，在  $0.3V_{PP}$  下，分别以  $100Hz$  和  $500kHz$  的频率作为临界情况进行了测量。

测试结果如下图所示。注意，高分辨率路径 ( ADS8354 差分输入 ) 和单端模拟路径 ( 连接器 J6 引脚 12 ) 均与比较器输出 ( 连接器 J6 引脚 18 ) 进行了对比。

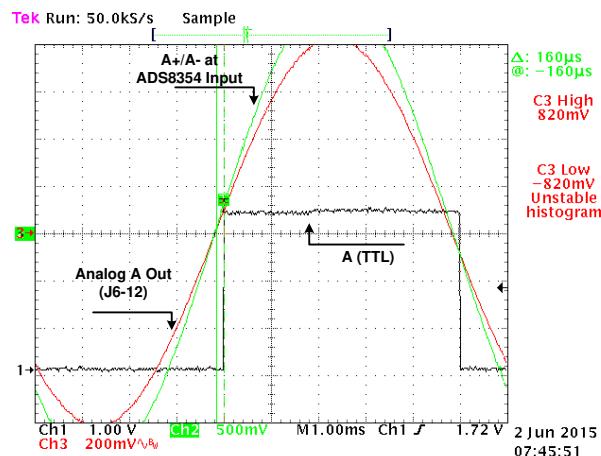

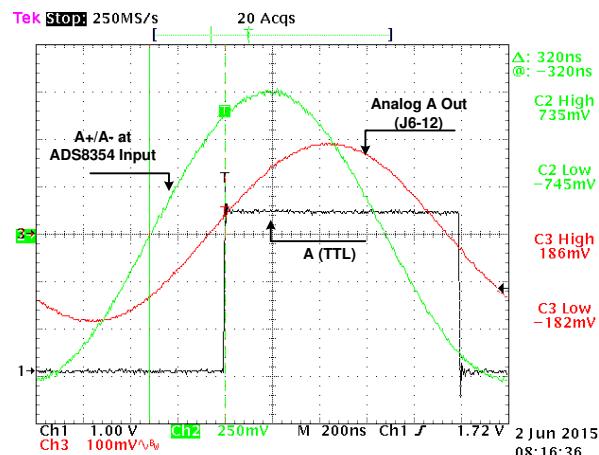

图 7-13. 当编码器连接器 J9-1、J9-2 处输入为  $1.0V_{PP}$ 、频率为  $100 Hz$  时，比较器输出  $A_{TTL}$  与 ADS8354 差分输入以及模拟输出 A (J6-12) 的对比情况

图 7-14. 当编码器连接器 J9-1、J9-2 处输入为  $0.3V_{PP}$ 、频率为  $100 Hz$  时，比较器输出  $A_{TTL}$  与 ADS8354 差分输入以及模拟输出 A (J6-12) 的对比情况

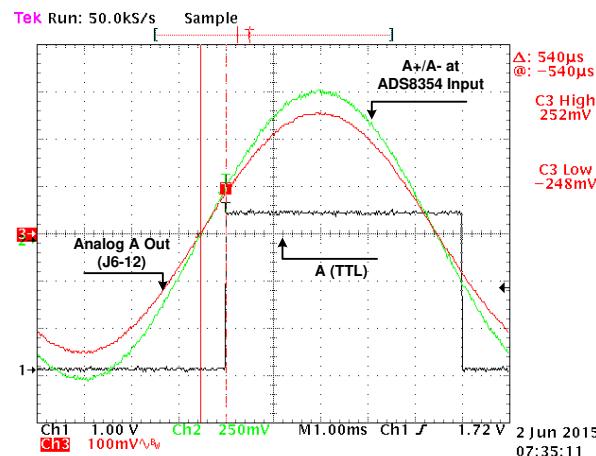

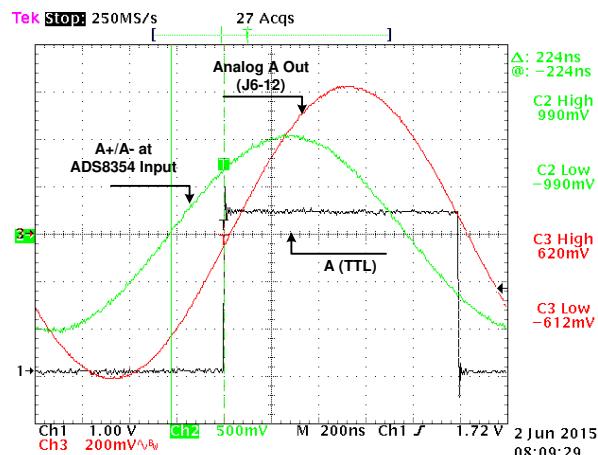

图 7-15. 当编码器连接器 J9-1、J9-2 处输入为 1.0 V<sub>PP</sub>、频率为 500kHz 时，比较器输出 A<sub>TTL</sub> 与 ADS8354 差分输入以及模拟输出 A (J6-12) 的对比情况

图 7-16. 当编码器连接器 J9-1、J9-2 处输入为 0.3 V<sub>PP</sub>、频率为 500 kHz 时，比较器输出 A<sub>TTL</sub> 与 ADS8354 差分输入以及模拟输出 A (J6-12) 的对比情况

正如预期的那样，包含 RC 滤波器去耦合网络的最大整体相移出现在频率为 500kHz 且输入振幅最低的情况下，总计约为 320ns，相当于 57 度，这远低于 90 度，并且在 [节 2](#) 规定的 60 度范围之内。之所以能有如此低的相移数值，TLV3201 极低的传播延迟（典型值为 40ns）起到了关键作用。这也为补偿诸如低通滤波器等影响相移延迟量的参数中所有可能的偏差留出了很大的余量。

由于较低频率下的延迟取决于与振幅相关的迟滞，因此 100Hz 时的传播延迟与高分辨率通道几乎相同。

在单端模拟路径中，尽管带有迟滞功能的比较器自身有 250ns 的传播延迟，但在 500kHz 下几乎没有延迟。这是因为单端模拟输出端配有强大的低通滤波器( $R = 100 \Omega$ ,  $C = 4.7nF$ )，可驱动 Piccolo MCU 等微控制器中的嵌式开关电容器 ADC。这种与频率相关的相位延迟在较高频率下略微补偿了比较器带来的延迟。

在第二步中，仅测量了与带有迟滞功能的比较器相关的延迟。该延迟指的是比较器的输入（R50 处的模拟信号）与比较器的输出之间的时间差。注意，由于前一级放大器的增益为 1.66，编码器输入端 0.3V<sub>PP</sub> 的信号在比较器输入端约等于 0.5V<sub>PP</sub>。

我们测量了仅由比较器块引入的延迟（迟滞和比较器传播延迟），如 [表 7-3](#) 中所示。

表 7-3. 迟滞比较器子系统延迟

| 编码器连接器处的输入                   | 比较器输入端的电压（例如，R50 处） | 传播延迟  | 相位延迟   |

|------------------------------|---------------------|-------|--------|

| 1.0 V <sub>PP</sub> , 100Hz  | 1.66V               | 170μs | 6.1 度  |

| 0.3 V <sub>PP</sub> , 100Hz  | 0.5V                | 560μs | 20.1 度 |

| 1.0 V <sub>PP</sub> , 500kHz | 1.52V               | 120ns | 21 度   |

| 0.3 V <sub>PP</sub> , 500kHz | 0.46V               | 200ns | 36 度   |

与 [图 7-13](#) 至 [图 7-16](#) 中整体延迟的差异是由模拟路径中的低通噪声滤波器造成的，在 500kHz 的频率下，对于高分辨率信号路径，该滤波器额外贡献了约 22 度的相移。但是，该延迟仍然远低于 90 度。

如果需要理想的相位匹配，可以按照 [节 4.5](#) 中所述，使用 THS4531A 来实现相应的低通滤波器。

## 7.2 电源测试

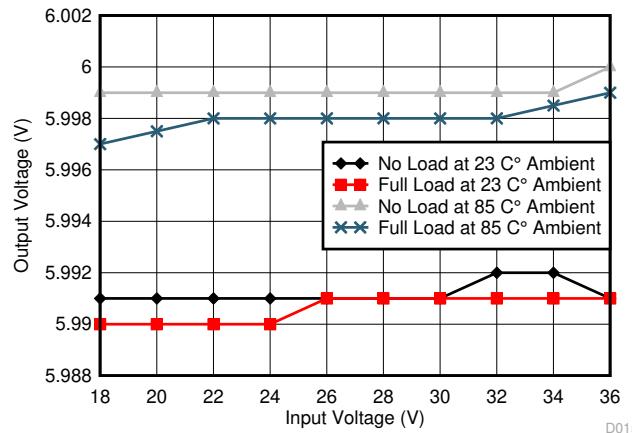

### 7.2.1 24V DC/DC 输入电源

为了确定这款将 24V 转换为 6V 中间电压轨的 DC/DC 降压转换器的特性，进行了以下测试。

#### 7.2.1.1 负载-线路调整

图 7-17. 负载-线路调整

注释：在完全工作状态下，线路负载调整范围在  $\pm 10\text{mV}$  内。 $V_{\text{OUT}}$  等于预期  $6\text{V}\pm 2\%$  ( 稳压器精度 ) 加上电阻分压器 R7/R10 的精度。

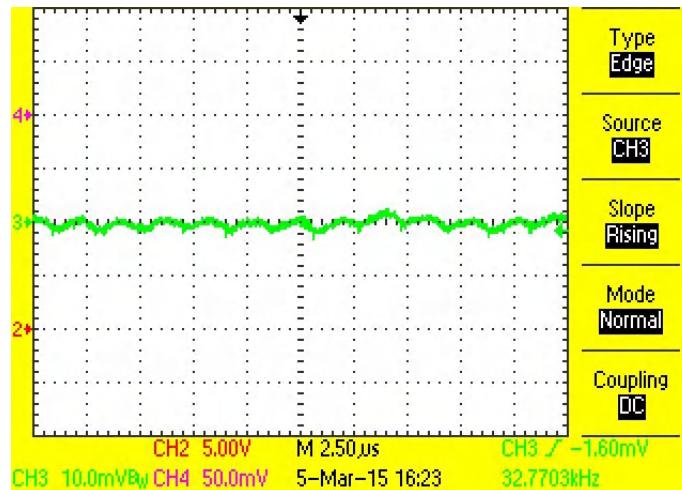

#### 7.2.1.2 输出电压纹波

图 7-18. 在 24V 输入、空载、@ 22°C 环境温度条件下的输出电压纹波

评价： $V_{\text{OUT}}$  纹波远低于所需的  $20\text{mV}_{\text{PP}}$ 。

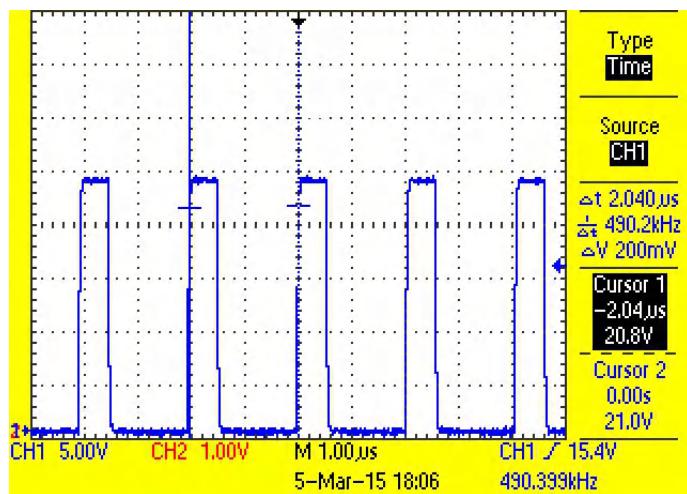

### 7.2.1.3 开关节点和开关频率

图 7-19. 开关频率测量 ( 满载、24V 输入、Troom )

评价: 开关频率处于预期范围内  $500\text{KHz} \pm 23\%$ 。SMPS 处于稳定状态，无抖动、无不规则开关且无电压尖峰。

### 7.2.1.4 效率

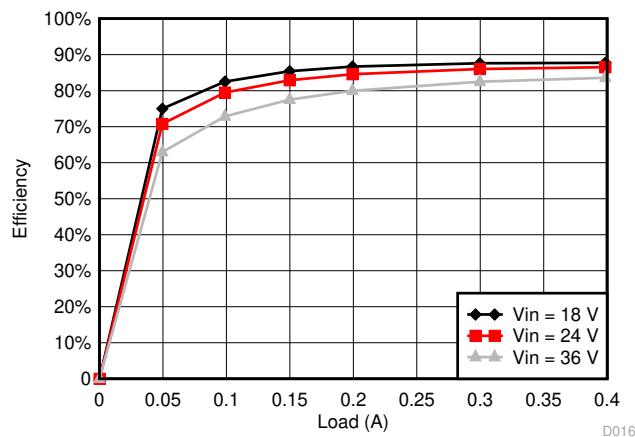

图 7-20. 在  $22^\circ\text{C}$  时有反极性保护二极管情况下的效率

评价: 二极管的反极性保护对直流/直流转换器效率的影响可以忽略不计。在任何规定的输入电压下，满负载时 80% 的效率目标都已完全达到。

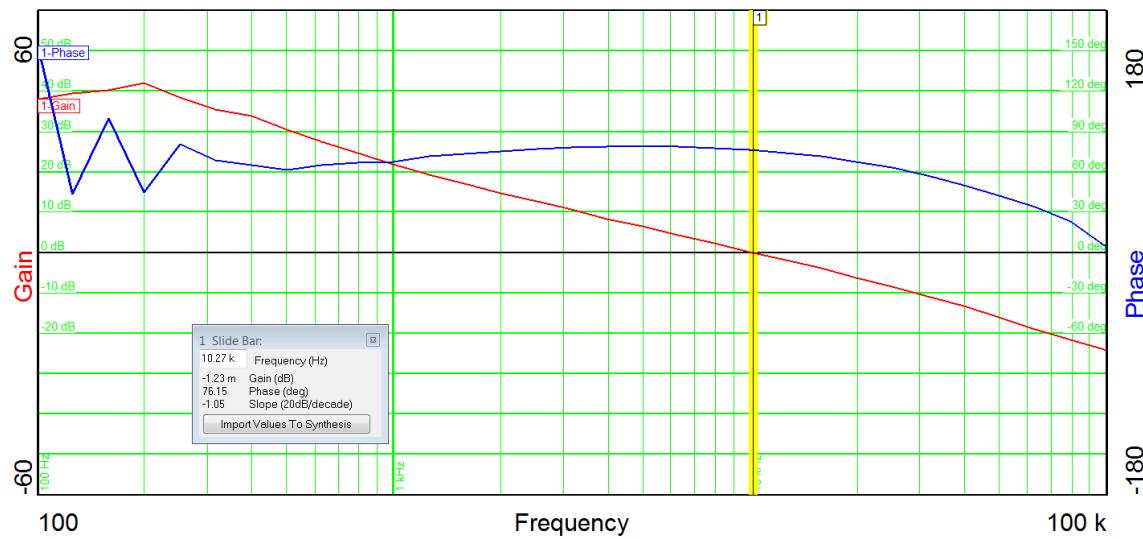

### 7.2.1.5 波特图

图 7-21. 24V 输入的满负载条件下的波特图

表 7-4. 相位和增益裕度

| 输入电压 | 相位裕度 | 频率交叉点   |

|------|------|---------|

| 36V  | 78 度 | 10.3KHz |

| 24V  | 76 度 | 10.3KHz |

| 17V  | 74 度 | 10.2KHz |

评价: 增益环路分析显示, 在任何工作条件下系统带宽为 10kHz, 且具有非常好的相位裕度 (> 60 度)。

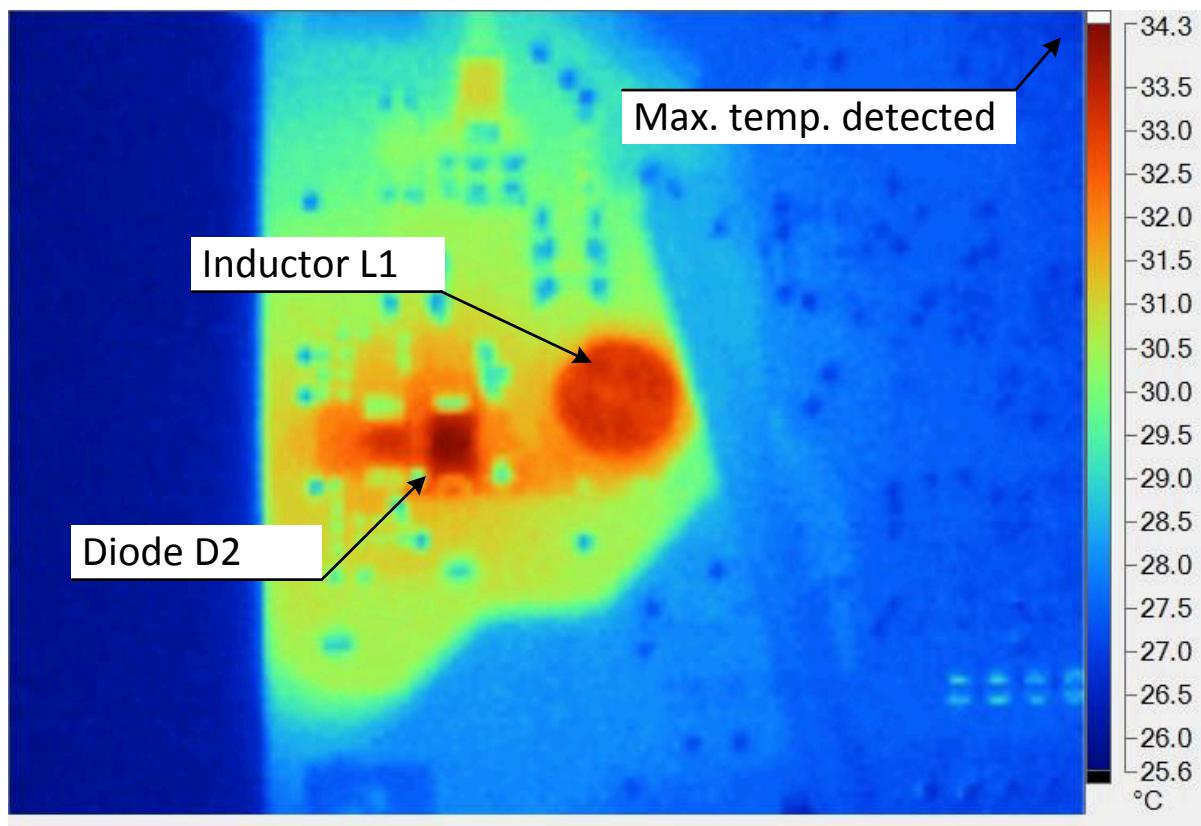

### 7.2.1.6 热像图

为确定在最大负载条件下电路板上的热点，获取了热像图。

图 7-22. 热像图、24V 输入、满载、22°C 环境温度

评价：检测到电路板上的热点对应于 TPS54040A 电路中的非同步整流器或二极管。从图中可知，T<sub>room</sub> 测试时 11°C 的温度上升幅度取决于输入电压和输出电流。此器件检测到的最高温度为 34°C。

在 85°C 时进行的测试未表示性能上有明显漂移（请参考图 7-17，负载线路调节 @ 85°C）。

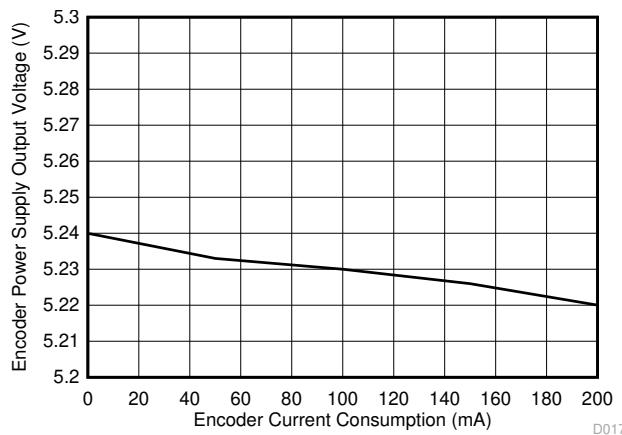

### 7.2.2 编码器电源输出电压

负责为编码器供电的 LDO 的输出电压具有良好的稳压效果，符合执行以下测量所规定的规格要求。

图 7-23. 编码器电源输出电压与负载电流 (0 至 200mA) 间的关系

### 7.2.3 5V 和 3.3V 负载点

两个 LDO 负责给信号链模块供电，它们输出的电压很稳定，完全符合规格要求。测量结果如表 7-5 中所示。我们在连接正弦/余弦编码器的情况下测量了 3.3V 和 5V 电源轨的标称电流消耗，并且 F28069M LaunchPad 以 16kHz 的频率触发新的测量。

表 7-5. 输出电压测量值

| 规定的输出电压 | 标称负载时测得的电压 | 标称电流   |

|---------|------------|--------|

| 5V      | 5.02V      | 49.9mA |

| 3.3V    | 3.34V      | 0.2mA  |

## 7.3 系统性能

### 7.3.1 正弦/余弦编码器输出信号仿真

为实现这一目的，采用了 16 位可编程双路输出信号发生器 Keysight (Agilent) 33600A 来仿真编码器输出信号。将来自 DC 的正弦测试信号（最高 500kHz）注入差分输入 A+/A- 和 B+/B-。

本节将介绍系统级性能的测量。特别是，

- 一个电周期（相位）内的精度

- 在最大输入频率为 500kHz 时旋转一周的精度。此时，编码器仿真的一周旋转相当于 2000 个信号周期

测试均在室温条件下完成，并在 70 度温度条件下重复执行，以检查误差漂移与温度之间的关系。

图 7-24. 编码器信号仿真的测试设置

#### 7.3.1.1 一个周期（增量相位）测试

根据前几次测试所示，双路输出信号发生器引发的误差远高于 TIDA-00176 精度所应达到的水平，完全背离了测试的目的。噪声和误差源可以“简单”概括为：

- 增益误差（A 的振幅不等于 B 的振幅）

- 相移误差（未按预期精确达到恒定的 90 度）

- 偏移误差（A 或 B 信号的平均值不等于 0）

- 由函数发生器的量化误差导致的 HF 噪声

- 频率误差（即使信号已“耦合”，A 的频率也不等于 B 的频率）

#### 小心

为了减少函数发生器引入的量化误差和噪声，在信号发生器与 TIDA-00176 输入端之间插入一个 1K 至 1- $\mu$ F LP 滤波器（实际上，为保持网络平衡，1K 电阻器由两个 500  $\Omega$  电阻器串联）。

为了消除两个通道之间的增益、偏移、相移和频率误差，应用了以下设置：在 TIDA-00176 编码器连接器 J8 上，只有一个输入信号按上述要求进行滤波后，再施加于输入 A 和 B，馈送相同信号。这样可以消除函数发生器的局限性。此外，也可以更好地评估 ADS8354 两条通道（及其各自信号调节路径）之间的任何不匹配。

实际上，在理想状况下，从 ADS8354 采集的数据应显示出两个相同的原始数据流，而这一级别的任何不匹配均源于两条通道之间的不匹配，而非输入本身。这也可用于校准系统，因为可以执行偏移和增益误差校正以实现 A 通道和 B 通道的完全平衡。

使用连接至 TIDA-00176 的 F28069M LaunchPad 以 32kHz 的采样率采集数据，如节 6 所述。

F28069M 采集到 ADS8354 通道 A 和 B 的数据后，将 16 位原始数据转储到 Excel 文件中。然后，将通道 B 的原始数据精确相移

90 度。然后，使用原始数据 A 和经过 90 度相移的原始数据 B 的反正切值计算相位。

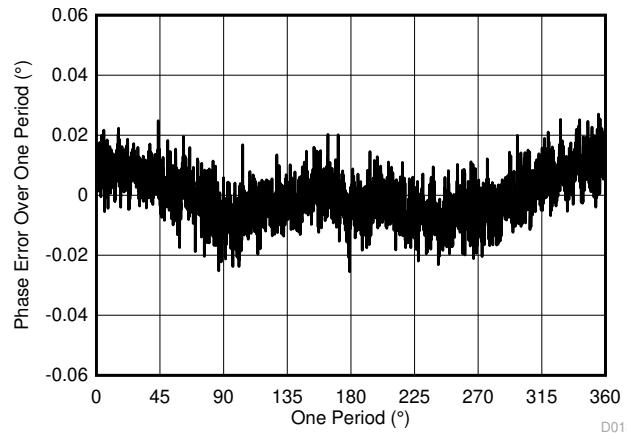

在  $1.0V_{PP}$  振幅和 10Hz 至 500Hz 频率范围内多次重复执行此测试。结果如下图所示。

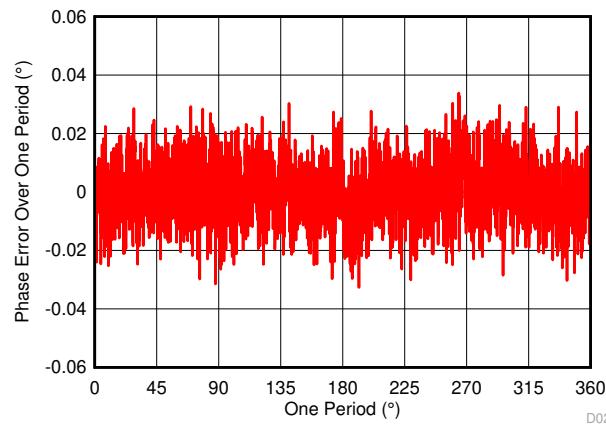

图 7-25. 施加  $1.0V_{PP}$  10Hz 输入时一个信号周期内的相位误差

在一个增量线内（一个信号周期= 360 度），相位误差保持在  $\pm 0.02$  度范围内。该值对应于误差  $\pm 0.02/360 = 0.0055\%$ 。分辨率为 16 位时，该值仅约等于  $\pm 3$  LSB。

噪声分布甚至在  $\pm 0.01$  ( $\pm 1.5$  LSB) 范围内。两个周期的相位误差是由于两个信号 A 和 B 之间存在非理想的 90 度相移，如节 1 所述。

注意，一个信号周期内  $\pm 0.02$  度误差对于线数为 2000 的编码器而言，相当于总误差为  $\pm 10$  微度 ( 0.036 角秒 )。

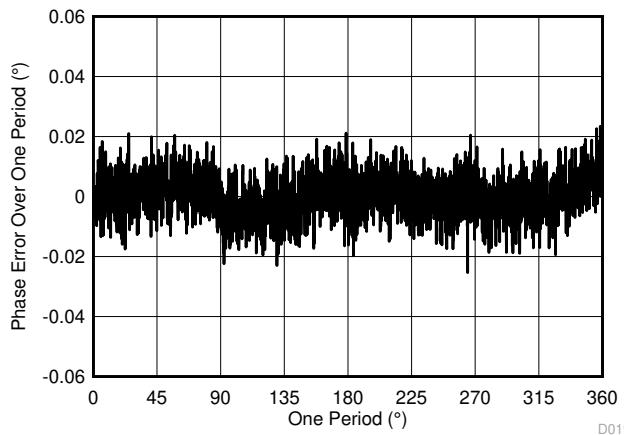

标称  $70^{\circ}\text{C}$  下在热处理室中执行了相同测试，以评估系统性能漂移，尤其是角度位置的绝对误差。

同样，两个输入信号的非完全匹配（90度相移等）会导致双频调制。

图 7-26. 施加  $1.0V_{PP}$  10Hz 输入时，在  $70^{\circ}\text{C}$  下，一个信号周期内的相位误差

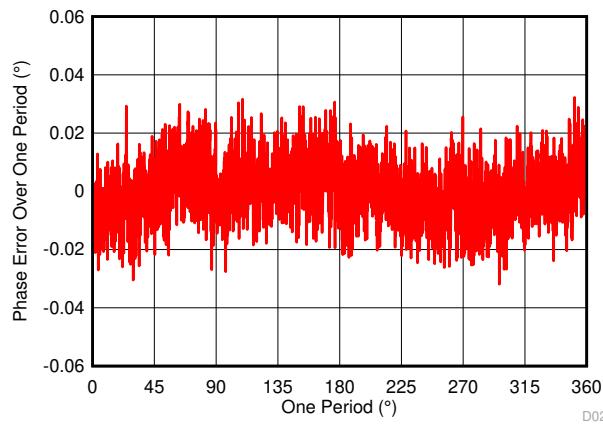

在输入为  $0.6V_{PP}$  时执行相同测试，此时可以看到更高的噪声/更低的 SNR：

图 7-27. 施加  $0.6V_{PP}$  10Hz 输入时，在  $23^{\circ}\text{C}$  环境温度下，一个信号周期内的相位误差

图 7-28. 施加  $0.6V_{PP}$  10Hz 输入时，在  $70^{\circ}\text{C}$  下，一个信号周期（旋转一周/2000）内的环境相位误差

相对于温度的超低漂移符合预期，这同样也是因为所选运算放大器和用于模拟信号调节的匹配电阻器的特性。

### 7.3.1.2 最大速度时机械旋转一周的测试

为完成本测试，我们计算了 Piccolo F28069M LaunchPad 所连 TIDA-00176 中机械旋转一周的高分辨率插值角。在 CPU 时钟频率为 80-MHz 时，采样率设置为 32kHz。

此测试的目的在于，验证插值算法在最大输入信号频率

500kHz 下有效，例如，不会因模拟样本与 QEP 计数器锁存产生的不匹配而导致任何增量计数缺失，或插值相位（反切）与相应线数（QEP）不匹配。这将转化为比节 7.3.1.1 中测量的量化噪声更大的误差。

为此，采用双路信号发生器模拟编码器 360 旋转。使用双路输出信号发生器以下述方式执行该测试：两个输出信号在振幅和频率上进行耦合，相移为 90 度。然后，两个信号作为输入施加到 TIDA-00176 编码器连接器的 J9 A+/A- 和 B+/B- 引脚。

总插值角存储在 F28069M RAM 中，通过 CCS 内存转储进行读取。

将计算得出的高分辨率角度与编码器线数为 2000 时的理想相位进行比较。因此，在 500K kHz 时，2000 个信号周期等于一周的仿真旋转。总角相位以  $360 \text{ 度} \times 500\text{kHz}/2000 = 90,000\text{deg/s}$  的速率斜升。[表 7-6](#) 提供了

1 $\mu$ s 和 100ns 的时序，它们等于 80MHz 处的一个 F28069M CPU 时钟。

**表 7-6. 线数为 2000 时的正弦/余弦编码器以 15000rpm 运行时的角速度**

| 理想角速度       | 1 $\mu$ s 中的角度变化 | 12.5 (CPU 时钟) 内的角度变化 |

|-------------|------------------|----------------------|

| 90,000deg/s | 0.09             | 0.0011               |

信号发生器及处理器时钟的抖动，乃至主机处理器通过 SPI/CS 采样模拟信号时的 CPU 时钟抖动均无法避免。假设角度以理想状态斜升（由于缺少参照值），测得的角度将出现相应的相位滞后或相位超前，进而导致与速度相关的角度误差。

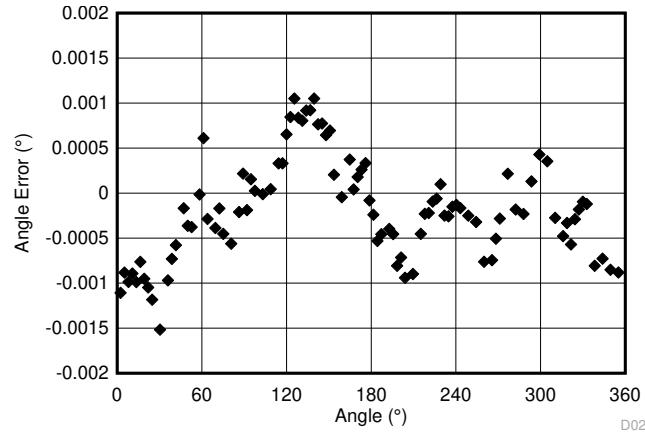

图 7-29 所示为理想斜升 (500kHz，每转 2000 个信号周期) 情况下在 32kHz (每转产生 128 个连续样本) 时测得的插值角误差。

**图 7-29. 使用编码器仿真一周内插值角度的误差 (1V<sub>PP</sub>, 500kHz 输入@ 32kHz 采样)**

如前所述，此测试的目的不是测试精度，而是验证增量是否丢失。在 2000 线数仿真中，一个增量线数相当于  $360/2000 = 0.18$  度。理想直线的角度误差（差异）始终保持在  $\pm 0.001$  度内；因此，在 500kHz 时插值运算仍然有效，未丢失增量。

从图中可知，误差在  $\pm 0.0015$  度以内。其原因是 CPU 时钟抖动以及其他抖动，例如来自信号发生器源的抖动，CPU 时钟抖动决定了最小精度。

这样分布的原因在于 F28069 软件的抖动，抖动触发了一个或两个 CPU 时钟周期的 SPI 传输/CS。/CS 下降沿能锁存模拟输入。仅仅 12.5ns 的抖动就会转换为约  $12.5\text{ns}/2000\text{ns} \times 360/2000$  度  $\sim 0.0011$  度的相位差。因此，角度差实际上是一项与速度相关角度误差（速度）滞后。

## 7.4 正弦/余弦编码器系统测试

系统测试中采用正弦/余弦编码器 ROD480-2000 和 ROD480-1024，电缆长度分别为 1m 和 71m。

### 7.4.1 零索引标记 R

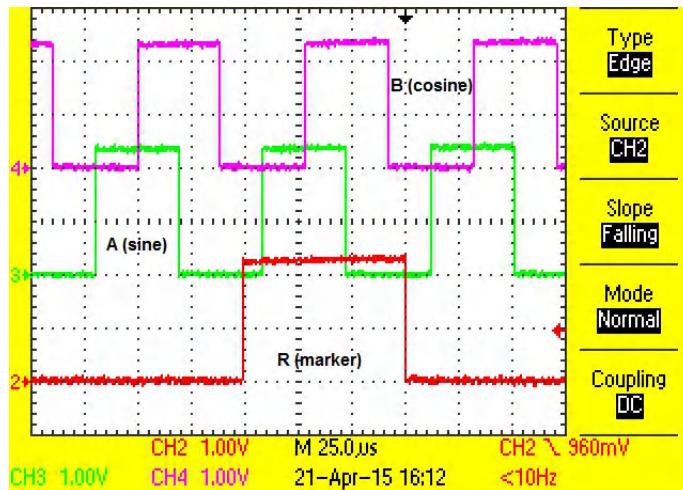

第一项测试用于验证 TIDA-00176 主机处理器接口连接器 J6、引脚 12 ( $A_{TTL}$ )、引脚 14 ( $B_{TTL}$ ) 和引脚 16 ( $R_{TTL}$ ) 上可用的数字输出信号 A、B 和 R 之间的同步或偏移。通过此项测试可验证 TIDA-00176 比较器子系统的配置是否正确。

图 7-30. 在 TIDA-00176 比较器输出 J6-12、14 和 18 端测得的 TTL 信号 A、B 和 R

仅当 A 和 B 均为低电平时，比较器输出信号 R 才发生转换，这符合预期。这意味着 A、B 和 R 信号之间的序列取决于正弦/余弦编码器转轴的旋转方向。在图 7-30 中，B 的上升沿出现在 A 的上升沿之后，因此编码器为顺时针旋转。

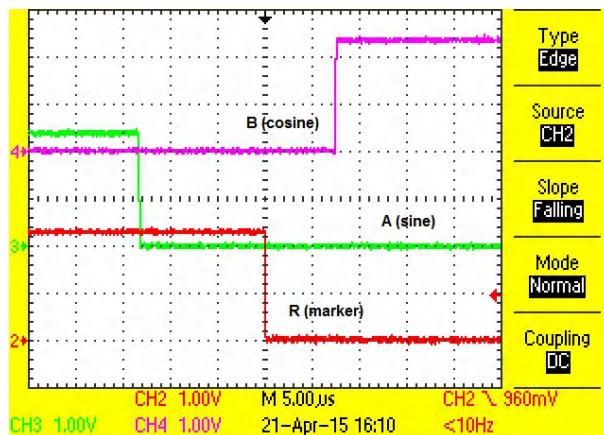

我们对约 400rpm 更高速度下 R 上升沿与下降沿之间 A、B 与 R 的偏移进行了更为详细的研究。R 的上升沿和下降沿仍出现在信号 A 和 B 均为低电平时。

注意，图 7-31 和图 7-32 的旋转方向为逆时针方向 (CCW)。

图 7-31. CCW 方向时索引信号 R 下降沿与 A 和 B 之间的关系

图 7-32. CCW 方向时索引信号 R 上升沿与 A 和 B 之间的关系

### 7.4.2 功能性系统测试

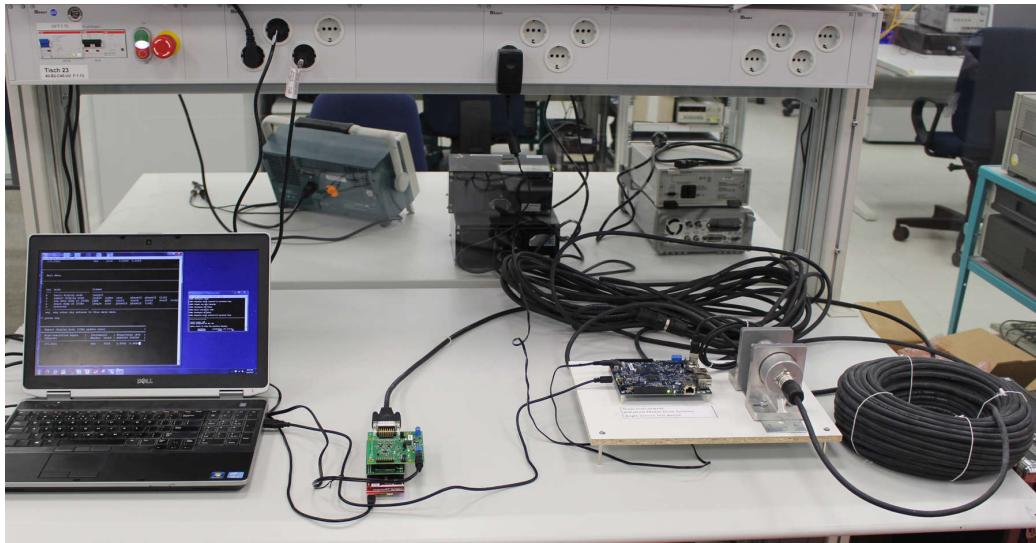

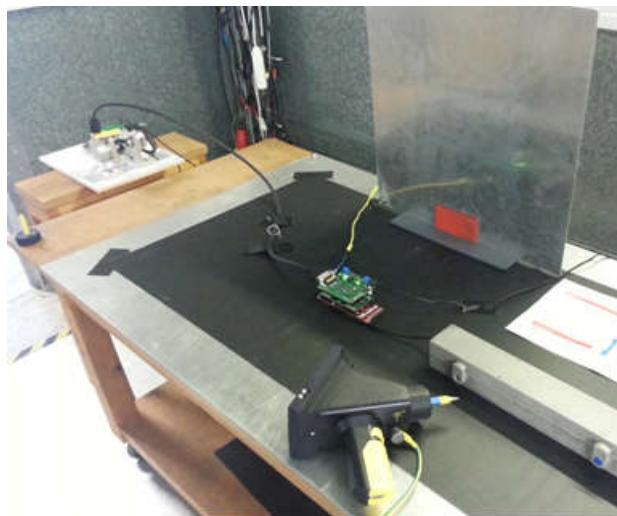

以下静态角度测试采用 ROD480-1024 正弦/余弦编码器，电缆长度为 1m 和 71m。由于编码器测试台的机械精度不足，因此无法进行高于 0.003 度 ( 10 角秒 ) 的总精度测量。图 7-33 中显示了测试设置图片。

图 7-33. TIDA-00176 测试设置，采用 70m 电缆 (20m + 50m) 和 ROD4800-1024 正弦/余弦编码器

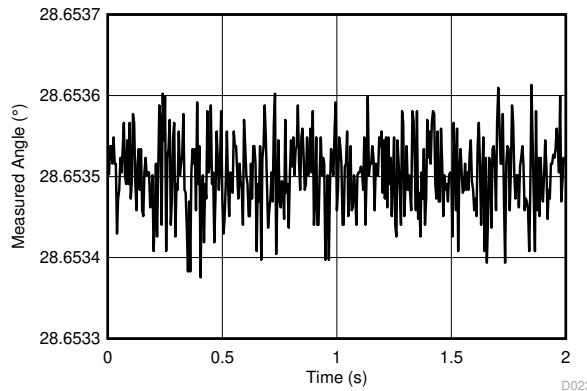

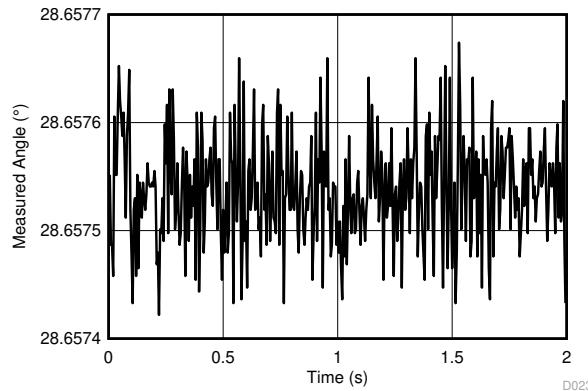

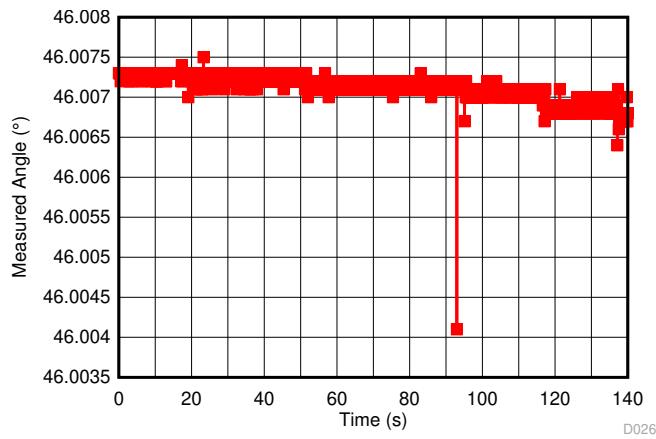

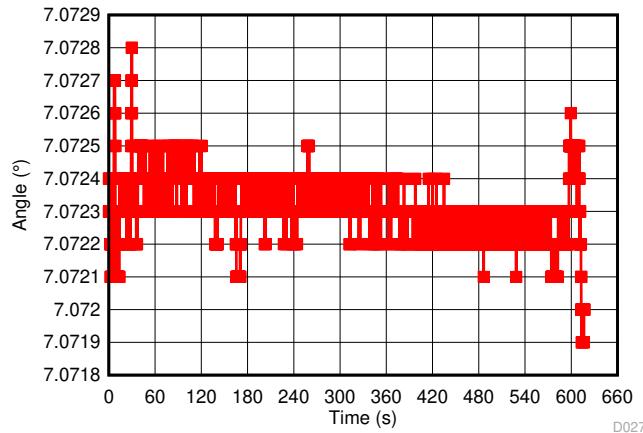

图 7-34 和 图 7-35 相应地展示在电缆长度分别为 1m 和 70m 的情况下，针对静态角度，使用 ROD480-1024 ( 线数为 1024 ) 所测得的角度随时间变化的情况。转轴未固定。

请注意，由于从编码器拆除 1m 电缆而改为安装 70m 电缆时发生机械振动，1m 和 71m 测量的绝对角度略有变化。

图 7-34. 系统测试，ROD480-1024 连接 1m 电缆时测量角度分布

图 7-35. 系统测试，ROD480-1024 连接 71m 电缆时测量角度分布

使用 ROD480-1024 编码器测量得到的角度，其噪声分布为  $\pm 0.0001$  度 ( 0.36 角秒 )。由于 0Hz 时电缆衰减约为 -1.5dB，因此 1m 和 70m 测量之间没有显著差异。

为验证 TIDA-00176 设计与正弦/余弦编码器配合使用时的基本精度和重复性，将 ROD480-1024 正弦/余弦编码器与 EnDat 2.2 编码器 ROQ437 进行了机械耦合。ROD480-1024 通过 70m 电缆连接。图 7-37 中显示了测试设置图片。

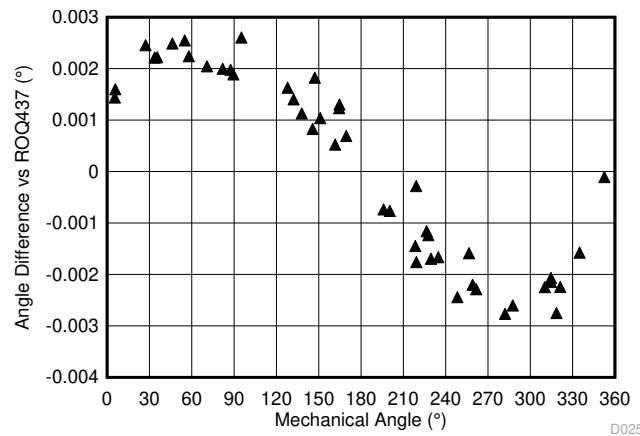

图 7-36 所示为 TIDA-00176 连接 ROD480-1024 正弦/余弦编码器与连接 ROQ437 EnDat 2.2 绝对值编码器时的角度差异，其中绝对角度是通过 Sitara AM437x EnDat 2.2 Master 读取。绝对角度呈现余弦波形误差，造成该误差的原因是带有小幅偏转的两个转轴之间存在不理想的非中心耦合。

为了检查可重复性，我们多次旋转编码器并捕获相应的角度。

然而，正如所预期的那样，该机械装置的精度和准度不足以对整个系统的绝对精度得出结论。因此，在 节 7.3 中基于编码器仿真所进行的测试更能体现 TIDA-00176 参考设计的预期性能。

图 7-36. 正弦/余弦编码器连接 70m 电缆时的基本系统精度测试

## 7.5 EMC 测试结果

TIDA-00176 TI 设计已按照 IEC 61800-3 “可调速电力驱动系统的电磁兼容性 (EMC) 抗扰度要求以及特定测试方法” 标准中规定的测试等级和性能准则，依据 IEC61000-4-2、4-4 和 4-5 标准，进行了 ESD、EFT 和浪涌方面的测试。

本设计符合这些标准并优于

IEC61800-3 EMC 抗扰度的电压要求。下表为概要介绍，后续章节将提供更多详细信息。

性能标准 A 通常因客户而异，预期精度取决于系统要求。有关测试规范的详细信息，请参阅节 7.5.1。

**表 7-7. IEC61800-3 针对第二环境的电磁兼容性抗扰度要求以及测量电压等级和类别**

| 要求                     |                                            |              |                                                                                |          | TIDA-00176 测量       |                         |        |

|------------------------|--------------------------------------------|--------------|--------------------------------------------------------------------------------|----------|---------------------|-------------------------|--------|

| 端口                     | 现象                                         | 基本标准         | 等级                                                                             | 性能(验收)标准 | 等级                  | 性能(实现)标准 <sup>(1)</sup> | 测试     |

| 外壳端口                   | ESD                                        | IEC61000-4-2 | $\pm 4\text{kV}$ CD 或 CD 无法实现时 $8\text{kV}$ AD                                 | B        | $\pm 8\text{kV}$ CD | B                       | 通过(超出) |

| 控制线端口及低于 60V 的直流辅助电源端口 | 快速瞬变脉冲群 (EFT)                              | IEC61000-4-4 | $\pm 2\text{kV}/5\text{kHz}$ , 电容钳位                                            | B        | $\pm 4\text{kV}$    | B                       | 通过(超出) |

|                        | 浪涌 $1.2/50\mu\text{s}$ , $8/20\mu\text{s}$ | IEC61000-4-5 | $\pm 1\text{kV}$ 。由于屏蔽电缆超过 $20\text{m}$ , 因此直接耦合到屏蔽层 ( $2\Omega/500\text{A}$ ) | B        | $\pm 1\text{kV}$    | B                       | 通过     |

- (1) 当 EMC 事件期间所测角度与初始机械参考位置之间的差值始终低于增量角度精度时，可判定为达到 A 类性能。增量线精度为  $360/\text{N}$  度。测试中，采用线数为 2000 的正弦/余弦编码器 (HEIDENHAIN ROD480)，其增量分辨率等于  $0.18$  度。

性能(验收)标准定义如下：

**表 7-8. 性能标准**

| 性能(验收)标准 | 说明                                                          |

|----------|-------------------------------------------------------------|

| A        | 模块应按预期连续工作。甚至测试过程中无功能或性能损失。                                 |

| B        | 可接受出现性能暂时下降。测试完成后，模块在无人工干预的情况下应能够按预期继续工作。                   |

| C        | 在测试期间，允许出现功能丧失，但不得损坏硬件或软件。测试完成后，模块经手动重启、断电或上电后应能够自动按预期继续工作。 |

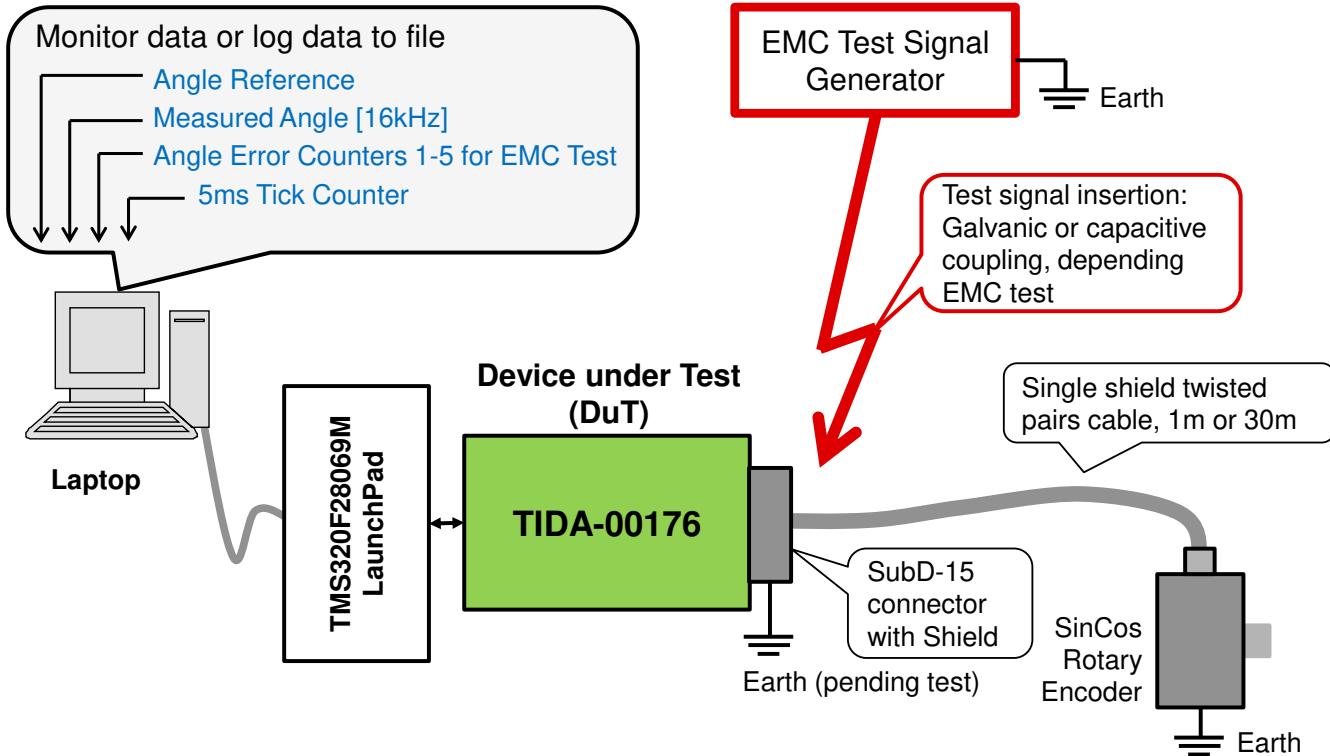

### 7.5.1 测试设置

该 TIDA-00176 TI 参考设计已经在德国 Strasskirchen 的 CSA Group Bayern 测试实验室进行过测试。图 7-37 中所示为 TIDA-00176 设计的基本设置。

图 7-37. 配有 Piccolo F2069M LaunchPad 的 TIDA-00176 的简化系统方框图

为验证 EMC 测试期间及测试完成后插值角信号的完整性，在 EMC 测试过程中使用正弦/余弦编码器初始角位置（静止）作为参考，且编码器未旋转。

每隔 16kHz 频率测量一次插值角，测量结果与初始参考角位置进行比较。由于具有非常高的分辨率和模拟输入信号，角度误差分为六个范围，如表 7-9 所示。每次在特定范围内出现误差时，相应误差计数器加 1。

表 7-9. TIDA-00176 高分辨率角度误差范围的定义

| 误差计数器  | 角度误差范围 (度)          | 角度误差范围 (角秒)   | 注释         |

|--------|---------------------|---------------|------------|

| 误差范围 1 | >1.0                |               |            |

| 误差范围 2 | 0.18 ≤ 误差 < 1.0     |               |            |

| 误差范围 3 | 0.1 ≤ 误差 < 0.18     |               | 仍然没有增量线数误差 |

| 误差范围 4 | 0.01 ≤ 误差 < 0.1     |               |            |

| 误差范围 5 | 0.001 ≤ 误差 < 0.01   | 3.6 ≤ 误差 < 36 |            |