# TI 设计: TIDA-01444 适用于服务器 PSU 的 180W、双通道、效率为 97% 的降压转 换器参考设计

# TEXAS INSTRUMENTS

#### 说明

TIDA-01444 设计 利用 12V 稳压直流输入电压实施了一款 180W 降压、双通道直流/直流转换器,旨在为终端负载电压提供 97% 以上的效率和良好的热性能,该设计适用于服务器 PSU、PC PSU 和其他降压转换器等应用。可轻松实现双通道间的开关频率同步。双输出的真差分遥感可补偿线路压降,为终端负载提供更精确的电压。为实现更高的功率密度和低厚度设计,此集成电路参考设计使用平面电感器代替传统的分立式电感器。此TI 设计具有全面保护和温度传感功能。

#### 资源

TIDA-01444

设计文件夹

TPS543C20

产品文件夹

LM20BIM7

产品文件夹

TL431BQDBZR

产品文件夹

咨询我们的 E2E 专家

# 特性

- 设计采用了 TPS543C20,器件具有集成高侧和低侧 MOSFET

- 低 BOM 数目

- 输入电压: 11.4V、12V 和 12.6V

- 效率: 在 180W 负载下为 96% (典型值); 在 83W 负载下为 97% (典型值)

- 适用于两个输出通道的差分遥感

- 轻松实现双通道间的开关频率同步

- 带热补偿功能的无损低侧 MOSFET 电流感应

- 保护:输出 OVP、UVP 和 OCP

- 以平面电感器作为输出电感器

- 外形紧凑 (47mm x 59mm), 可与服务器 PSU 应用 兼容

#### 应用范围

- 服务器 PSU

- PC PSU

- 非隔离式直流/直流模块

- 工业用电源

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

System Description www.ti.com.cn

## 1 System Description

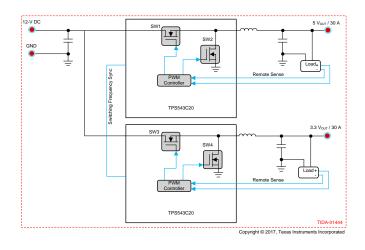

In server power supply units (PSUs) and PC PSU applications, the outputs are always configured with three groups of output voltage: 12-V DC, 5-V DC, and 3.3-V DC. Generally, in order to realize the high efficiency and excellent cross voltage regulation performance, 12-V DC is obtained from the front-end PFC stage and isolated DC-DC stage, and 5-V DC or 3.3-V DC is obtained through the dual-channel buck converter from 12-V DC. A typical block diagram of a server PSU system is shown in 8.1.

图 1. Typical Block Diagram of Server Power Supply

High efficiency, high power density, and excellent performance are the most important pursues of a switching power supply as well as in server and PC PSU applications. A high efficiency requirement means excellent component properties and excellent design capability; a high power density requirement means higher component integration; and a high performance requirement means reasonable design specification. The TIDA-01444 reference design is exactly based on this design thought. The high efficiency, high power density, and excellent performance of the TIDA-01444 design can meet the requirements for server and PC PSU applications.

The TIDA-01444 design is a 180-W buck module that converts the typical input voltage of 12-V DC to dual outputs 3.3  $V_{OUT}$  and 5  $V_{OUT}$ . This TI Design is designed specially to meet a high efficiency of > 97% at a typical load of 83 W and > 96% at a full load of 180 W, fewer BoM components, low profile requirement, true differential remote sense function, and switching frequency synchronization between dual-channel and excellent output voltage regulation of < 1%. It is important that each of these two outputs has a maximum 30-A output current capability. This reference design is a simple construction, low-component, dual-output buck converter implemented using the TPS543C20 device with integrated high-side and low-side MOSFETs with low-loss switching to facilitate high efficiency and deliver up to 40 A in a 5-mm×7-mm PowerStack<sup>TM</sup> package with a layout friendly thermal pad. The design operates the typical 12-V DC input voltage, delivering a total power of 180 W.

www.ti.com.cn System Description

# 1.1 Key System Specifications

# 表 1. Key System Specifications

| DADAMETED                                    | COMPITIONS                                           | SPI  | ECIFICATION | 1     | LINUTO |

|----------------------------------------------|------------------------------------------------------|------|-------------|-------|--------|

| PARAMETER                                    | CONDITIONS                                           | MIN  | TYP         | MAX   | UNITS  |

| INPUT CHARACTERISTICS                        |                                                      | 1    | <u> </u>    | 1     |        |

| Input voltage (V <sub>IN</sub> )             | _                                                    | 11.4 | 12.00       | 12.6  | V      |

| Maximum input current (I <sub>IN_MAX</sub> ) | _                                                    | 15.5 | 15.95       | 16.5  | Α      |

| OUTPUT CHARACTERISTICS                       |                                                      |      |             |       |        |

| Output voltage                               | Output channel 1                                     | _    | 3.3         | _     | V      |

| Output voltage                               | Output channel 2                                     | _    | 5           | _     | V      |

| Output voltage set point                     | Both for 3.3 V <sub>OUT</sub> and 5 V <sub>OUT</sub> | 1    | 0           | 1     | %      |

| Maximum output current                       | Both for 3.3 V <sub>OUT</sub> and 5 V <sub>OUT</sub> | _    | _           | 30    | Α      |

| Load regulation                              | Both for 3.3 V <sub>OUT</sub> and 5 V <sub>OUT</sub> | 1    | 0           | 1     | %      |

| Pinnle and naine                             | V <sub>OUT</sub> = 5-V DC                            | 5    | 30          | 50    | mV     |

| Ripple and noise                             | V <sub>OUT</sub> = 3.3-V DC                          | 5    | 20          | 30    | mV     |

| 0.1                                          | 5 V <sub>OUT</sub> : 30-A step, 0.5 A/μs             | -250 | 0           | 250   | mV     |

| Output transient response                    | 3.3 V <sub>OUT</sub> : 30-A step, 0.5 A/µs           | -165 | 0           | 165   | mV     |

| Start-up time                                | Both for 3.3 V <sub>OUT</sub> and 5 V <sub>OUT</sub> | 8    | 12          | 20    | ms     |

| Output OVP                                   | Both for 3.3 $V_{\text{OUT}}$ and 5 $V_{\text{OUT}}$ | 113  | 117         | 121   | %      |

| Output UVP                                   | Both for 3.3 V <sub>OUT</sub> and 5 V <sub>OUT</sub> | 79   | 83          | 87    | %      |

| Output OCP                                   | Both for 3.3 V <sub>OUT</sub> and 5 V <sub>OUT</sub> | 35   | 40          | 45    | Α      |

| SYSTEM CHARACTERISTICS                       | •                                                    | •    | *           |       |        |

| Maximum output power                         | Any combination                                      |      |             | 180.0 | W      |

|                                              | $I_{OUT}$ = 10 A for 3.3 $V_{OUT}$ and 5 $V_{OUT}$   | 96.5 | 97.0        | 97.5  | %      |

| Efficiency                                   | I <sub>OUT</sub> = 21.7 A for 3.3 V and 5 V          | 96   | 96.4        | 97.0  | %      |

| Switching frequency (f <sub>SW</sub> )       | _                                                    | _    | 500.0       | _     | kHz    |

| Operating ambient temperature                | 200FLM Airflow                                       | -10  | _           | 65.0  | °C     |

| EMI/CE                                       | EN55032 Class A                                      | 6    | 10.0        | _     | dB     |

System Overview www.ti.com.cn

# 2 System Overview

# 2.1 Block Diagram

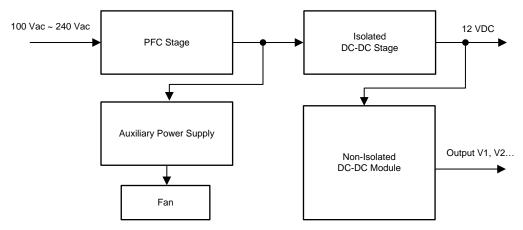

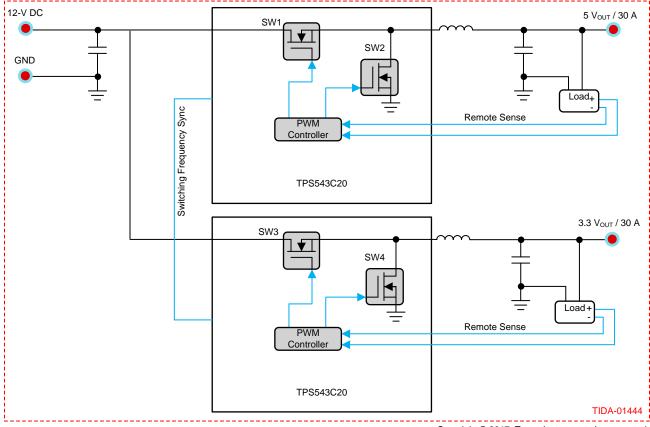

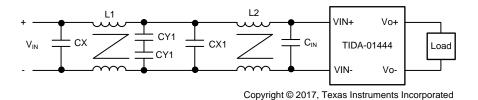

Copyright © 2017, Texas Instruments Incorporated

图 2. Block Diagram of 180-W Dual Buck Module

www.ti.com.cn System Overview

## 2.2 Highlighted Products

The following subsections detail the highlighted products used in this reference design, including the key features for their selection. See their respective product datasheet for complete details on any highlighted device.

#### 2.2.1 TPS543C20

To implement the high-performance, small form factor, dual-channel buck design of 180 W of power, the TPS543C20 is the preferred converter as it is a synchronous buck converter with two integrated N-channel NexFET<sup>TM</sup> power MOSFETs, enabling high power density and small PCB layout area. The TPS543C20 employs an internally compensated emulated peak current mode control, with a clock with a synchronizable, fixed frequency modulator for EMI sensitive point-of-load (POL). The internal integrator and directly amplifying ramp tracking loop eliminate the need for external compensation over a wide range of frequencies thereby making the system design flexible, dense, and simple. Optional asynchronous pulse injection (API) and Body Braking help improve transient performance by significantly reducing undershoot and overshoot, respectively. Integrated NexFET MOSFETs with low-loss switching facilitate high efficiency and deliver up to 40 A in a 5-mm×7-mm PowerStack package with a layout friendly thermal pad. Two TPS543C20 devices can be stacked together to provide up to 80-A POL.

The key features that make this device unique are:

- Integrated 3.0/0.9-mΩ Stacked NexFET Power

- Internally-compensated advanced current mode control 40-A POL

- Input voltage range: 4 to 16 V

- Output voltage range: 0.6- to 5.5-V stage with lossless low-side current sensing

- Fixed frequency: Synchronization to an external clock or sync out

- Stack 2x for up to 80 A with current share, voltage share, and CLK sync

- Pin strapping programmable switching frequency:

- 300 kHz to 2 MHz for standalone

- 300 kHz to 1 MHz for stackable

- Pin strapping programmable reference from 0.6 to 1.1 V with 0.5% accuracy

- Differential remote sensing

- Safe start-up into pre-biased output

- · High accuracy hiccup current limit

- Asynchronous pulse injection (API) and body braking

- 40-pin, 5-mm×7-mm LQFN Package with a 0.5-mm pitch and a single thermal pad

#### 2.2.2 TL431BQDBZR

The TL431 is a three-terminal adjustable shunt regulator with specified ranges for thermal stability over temperature. The output voltage can be set to any value between  $V_{REF}$  (approximately 2.5 V) and 36 V with two external resistors. Active output circuitry provides a very sharp turnon characteristic, making these devices excellent replacements for Zener diodes in many applications. The "B-grade" version comes with initial tolerances (at 25°C) of 0.5% and TL431BQ devices are characterized to operate from -40°C to 125°C.

The key features that make this device unique are:

System Overview www.ti.com.cn

I<sub>OUT</sub>: 300 mA

Low-power I<sub>O</sub>: 31 μA

V<sub>OUT</sub>: 2% accurate

Low output noise: 48 mV<sub>RMS</sub> (no bypass capacitor required)

High PSRR: 68 dB at 1 kHz

#### 2.2.3 LM20BIM7

The LM20 is a precision analog output CMOS integrated-circuit temperature sensor that operates over  $-55^{\circ}$ C to  $130^{\circ}$ C. The power supply operating range is 2.4 to 5.5 V. The transfer function of LM20 is predominately linear, yet has a slight predictable parabolic curvature. The accuracy of the LM20 when specified to a parabolic transfer function is  $\pm 1.5^{\circ}$ C at an ambient temperature of  $30^{\circ}$ C. The temperature error increases linearly and reaches a maximum of  $\pm 2.5^{\circ}$ C at the temperature range extremes. The temperature range is affected by the power supply voltage. At a power supply voltage of 2.7 to 5.5 V, the temperature range extremes are  $130^{\circ}$ C and  $-55^{\circ}$ C. Decreasing the power supply voltage to 2.4 V changes the negative extreme to  $-30^{\circ}$ C, while the positive extreme remains at  $130^{\circ}$ C.

The LM20 quiescent current is less than 10  $\mu$ A. Therefore, self-heating is less than 0.02°C in still air. Shutdown capability for the LM20 is intrinsic because its inherent low-power consumption allows it to be powered directly from the output of many logic gates or does not necessitate shutdown.

The key features that make this device unique are:

- Rated for -55°C to 130°C

- Available in SC70 and DSBGA package

- · Predictable curvature error

- · Suitable for remote applications

- Accuracy at 30°C ±1.5°C to 4°C (maximum)

- Accuracy at 130°C and -55°C ±2.5°C to 5°C (maximum)

- Power supply voltage range: 2.4 to 5.5 V

- Current drain: 10 μA (maximum)

- Nonlinearity: ±0.4% (typical)

- Output impedance: 160 Ω (maximum)

- Load Regulation: 0 μA < IL < 16 μA –2.5 mV (maximum)</li>

# 2.3 System Design Theory

This reference design is a dual-channel output 180-W buck module, operating at a regulated DC input voltage of 12-V DC. The design has two buck power stages implemented using two pieces of the TPS543C20 integrated a with high-side MOSFET and low-side MOSFET to deliver two different outputs: 3.3 V<sub>OUT</sub>/30 A and 5 V<sub>OUT</sub>/30 A. The overall system efficiency is over 96% with a 12-V DC input under full load conditions. The design has protection built-in for output overcurrent protection (OCP), output short-current protection (OSCP), undervoltage protection (UVP), and overvoltage protection (OVP). The true differential remote sensing compensates the line voltage drop and provides more accurate voltage for terminal load.

www.ti.com.cn System Overview

In this TI Design, there would be no  $\pi$  frequency issue for the switching frequency difference between the dual-channel converter. Because of the switching frequency, synchronization is accomplished easily between dual-channel as the customer's expectation, which can resolve the  $\pi$  frequency noise issue for EMI. However, it could decrease the filter inductor and capacitor, which are needed for resolving the  $\pi$  frequency issue. So from this point, the switching frequency synchronization can decrease the total cost and improve the whole efficiency and power density.

System Overview www.ti.com.cn

# 2.3.1 Buck Circuit Component Design

This section details the design process and component selection a designer must follow to complete a buck converter using the TPS543C20.

#### 2.3.1.1 Design Goal Parameters

表 2 states the design goal parameters for this TI Design. These parameters are used in further calculation to select components.

| PARAMETER                                    | CONDITIONS                                           | SP   | UNITS    |          |       |

|----------------------------------------------|------------------------------------------------------|------|----------|----------|-------|

| PARAMETER                                    | CONDITIONS                                           | MIN  | TYP      | MAX      | UNITS |

| INPUT CHARACTERISTICS                        |                                                      | '    | <u>'</u> |          |       |

| Input voltage (V <sub>IN</sub> )             | _                                                    | 11.4 | 12.00    | 12.6     | V     |

| Maximum input current (I <sub>IN_MAX</sub> ) | _                                                    | 15.5 | 15.95    | 16.5     | Α     |

| OUTPUT CHARACTERISTICS                       |                                                      |      | <u>.</u> | <u> </u> |       |

| Output voltage                               | Output channel 1                                     | _    | 3.3      | _        | V     |

| Output voltage                               | Output channel 2                                     | _    | 5.0      | _        | V     |

| Output voltage set point                     | Both for 3.3 V <sub>OUT</sub> and 5 V <sub>OUT</sub> | 1.0  | 0        | 1.0      | %     |

| Maximum output current                       | For both channels                                    | 0    | _        | 30.0     | Α     |

| Maximum output power                         | Any combination                                      | _    | _        | 180.0    | W     |

|                                              | $I_{OUT}$ = 10 A for 3.3 $V_{OUT}$ and 5 $V_{OUT}$   | 96.5 | 97.0     | 97.5     | %     |

| Efficiency                                   | $I_{OUT}$ = 21.7 A for 3.3 $V_{OUT}$ and 5 $V_{OUT}$ | 96.0 | 96.4     | 97.0     | %     |

表 2. Design Goal Parameter

#### 2.3.1.2 Output Inductor Selection

The inductor is typically sized for approximately 30% peak-to-peak ripple current ( $I_{RIPPLE}$ ). Given this target ripple current, the required inductor value can be calculated by  $\triangle \exists 1$ :

$$L_{O} = \frac{V_{IN} - V_{OUT}}{I_{RIPPLE}} \times \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{SW}}$$

(1)

In this TI Design, in order to decrease the design profile and save cost, the output inductor uses the planner inductor to replace the traditional finished inductor.

Based on the calculation and analysis, the output inductor typical value can be set as 0.65  $\mu$ H for dual-channel, using RM7 size core with DMR95 material, and the inductor winding are two turns. The RMS current through the inductor is calculated by  $\triangle$ 式 2. The 3.3-V channel and 5-V channel RMS current through inductor are approximated by  $\triangle$ 式 3 and  $\triangle$ 式 4, respectively:

$$I_{L(RMS)} = \sqrt{I_{L(AVG)}^{2} + \frac{1}{12} \times I_{RIPPLE}^{2}} = \sqrt{I_{OUT}^{2} + \frac{1}{12} \times I_{RIPPLE}^{2}}$$

(2)

$$I_{3.3V_L(RMS)} = \sqrt{30^2 + \frac{1}{12} \times 7.362^2} \approx 30.074 \text{ A}$$

(3)

$$I_{5V_L(RMS)} = \sqrt{30^2 + \frac{1}{12} \times 8.974^2} \approx 30.109 \text{ A}$$

(4)

Also, this inductor design can ensure the inductor will not be saturated before the setting OCP.

www.ti.com.cn System Overview

#### 2.3.1.3 Switching Frequency Selection

Select a switching frequency for the TPS543C20. There is a trade-off between higher and lower switching frequencies. A higher switching frequency may produce a smaller solution size using lower-valued inductors and smaller output capacitors compared to a power supply that switches at a lower frequency. However, the higher switching frequency causes extra switching losses, which decrease efficiency and impact thermal performance.

This TI Design features a switching frequency of 500 kHz achieves both a small solution size and a high efficiency operation. The device supports continuous switching frequency programming (see 公式 5).

$$R_{Rt} = \frac{20 \times 10^9}{f_{SW}} - 2 \times \frac{f_{SW}}{2000}$$

(5)

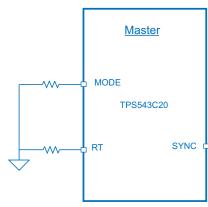

In this case, considering the frequency setting tolerance, a standard resistor value of 43.2 k $\Omega$  is selected. The switching frequency configuration for a standalone device is shown in  $\boxtimes$  3; the MODE pin keeps no external resistor, and the RT pin sets the switching frequency.

Copyright © 2017, Texas Instruments Incorporated

图 3. Stand-alone: RT Pin Sets Switching Frequency

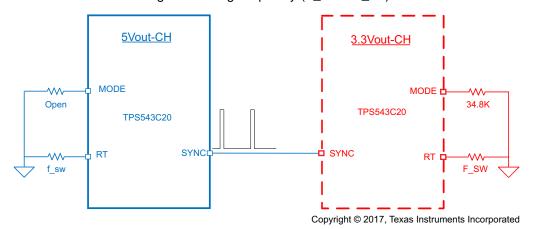

#### 2.3.1.4 Switching Frequency Synchronization Configuration

Many applications require synching the switching frequency for multiple outputs to resolve some unexpected issues. In this TI Design, the dual outputs are configured with the same frequency through the frequency synchronization function.

The TPS543C20 device can synchronize to an external clock, which must be equal to or higher than internal frequency setting. For a standalone device, the external clock must be applied to the SYNC pin. A sudden change in synchronization clock frequency causes an associated control loop response, resulting in an overshoot or undershoot on the output voltage.

System Overview www.ti.com.cn

The switching frequency synchronization configuration is accomplished through MODE and RT pin, as shown in 表 3:

| 表 3. MODE Pin-Strapping Sel | ection |

|-----------------------------|--------|

|-----------------------------|--------|

| CONTROL MODE SELECTION | API OR BODY BRAKE                    | RESISTOR VALUE $(k\Omega)^{(1)}$ | NOTE                       |

|------------------------|--------------------------------------|----------------------------------|----------------------------|

|                        | API OFF                              | Open                             |                            |

|                        | BB OFF                               | Open                             |                            |

|                        | API ON                               | 15.4                             |                            |

| Ctand alana            | BB OFF                               | 15.4                             | Sync pin to receive clock  |

| Stand-alone            |                                      | 121 (1×)                         | RT pin to set frequency    |

|                        | API ON, BB OFF API threshold setting | 187 (2×)                         |                            |

|                        |                                      | 8.66 (3×)                        |                            |

|                        |                                      | 78.7 (4×)                        |                            |

| (Master sync out)      |                                      | 23.7                             | Sync pin to send out clock |

| ` , ,                  |                                      |                                  | RT pin to set frequency    |

| (Master sync in)       | Master sync in) API OFF, BB OFF      | 34.8                             | Sync pin to receive clock  |

| ,                      | ·                                    |                                  | RT pin to set sync point   |

| (Slave sync out)       |                                      | 51.1                             | Sync pin to receive clock  |

|                        |                                      |                                  | RT pin to set sync point   |

<sup>&</sup>lt;sup>(1)</sup> The E48 series resistors with a tolerance of 1% or less are recommended.

For this application, the configuration principle is as follows: set one output channel as Stand-alone control mode, and set the other output as Master Sync In control mode. In this TI Design, the 5-V output channel is configured as the Stand-alone control mode to generate a switching frequency of 500 kHz, and then the 3.3-V output channel is configured as Master Sync In control mode to be synchronized with the 5-V output channel.

The detail configuration for MODE pin and RT pin is as follows:

- 1. 5-V output channel (5Vout-CH): Set the MODE pin to be open. Set the RT pin to be a 43.2-kΩ resistor;

- 2. 3.3-V output channel (3.3Vout-CH): Set the MODE pin to be a 34.8-k $\Omega$  resistor. Set the RT pin to be a resistor higher than 43.2 k $\Omega$ . This resistor selection is used to generate the switching frequency, which should be lower than the target switching frequency (F SW < f sw).

图 4. Switching Frequency Synchronization Configuration for Dual-Channel Converter

www.ti.com.cn System Overview

表 4 shows the configuration for these two pins of the converter:

表 4. MODE and RT Pin Configuration on TIDA-01444

| CONFIGURATION                | MODE PIN RESISTOR | RT PIN RESISTOR                            | NOTES                        |

|------------------------------|-------------------|--------------------------------------------|------------------------------|

| 5-V <sub>OUT</sub> channel   | Open              | 43.2K                                      | Set real switching frequency |

| 3.3-V <sub>OUT</sub> channel | 34.8K             | Higher than 43.2 kΩ (for example, 68.1 kΩ) | Set as master sync in        |

#### 2.3.1.5 Output Capacitor Selection

There are three primary considerations for selecting the value of the output capacitor. The output capacitor affects these three criteria:

- Stability

- Regulator response to a change in load current or load transient

- · Output voltage ripple

These three considerations are important when designing regulators that must operate where the electrical conditions are unpredictable. The output capacitance needs to be selected based on the most stringent of these three criteria.

This TI Design features the following:

- 5-V output channel: 13pcs 16-V/22-μF X7R ceramic capacitor and 1pcs 16-V/1000-μF OSCON capacitor

- 3.3-V output channel: 14pcs 16-V/22-μF X7R ceramic capacitor and 1pcs 16-V/1000-μF OSCON capacitor

#### 2.3.1.6 Feedback Loop Compensation

The RAMP pin sets internal ramp amplitude for the control loop compensation. RAMP amplitude is determined by internal RC, selected by the resistor connected from the MODE pin to GND, to optimize the control loop (see 表 5).

表 5. RAMP Pin-Strapping Selection

| CRAMP (pF) | RESISTOR VALUE $(k\Omega)^{(1)}$ |

|------------|----------------------------------|

| 1.00       | 0                                |

| 1.42       | 8.66                             |

| 1.94       | 15.40                            |

| 2.58       | 23.70                            |

| 3.43       | 34.80                            |

| 4.57       | 51.10                            |

| 6.23       | 78.70                            |

| 8.91       | 121.00                           |

| 14.10      | 187.00                           |

| 29.10      | Open                             |

<sup>(1)</sup> The E48 series resistors with a tolerance of 1% or less are recommended.

System Overview www.ti.com.cn

A certain criteria is recommended for the TPS543C20 to achieve optimized loop stability, bandwidth, and switching jitter performance. The internal ramp voltage should be two to four times bigger than the output capacitor ripple (capacitive ripple only). The TPS543C20 is defined to be ease-of-use, for most applications, we recommend ramp resistor to be 187 k $\Omega$  to achieve the optimized jitter and loop response. For a detailed design procedure, see the WEBENCH® Power Designer.

Through debugging results, this TI Design uses 187 k $\Omega$  for the 5-V<sub>OUT</sub> channel and 51.1 k $\Omega$  for the 3.3-V<sub>OUT</sub> channel at the RAMP pin.

#### 2.3.1.7 BP and VDD

Bypass the BP pin to PGND with 4.7  $\mu$ F of capacitance. In order for the regulator to function properly, it is important that these capacitors be localized to the TPS543C20 with low-impedance return paths.

For VDD decoupling capacitor, the TPS543C20 device requires a high-quality, ceramic, type X7R, input decoupling capacitor with a value of at least 1  $\mu$ F of effective capacitance on the VDD pin, relative to AGND.

This TI Design uses a 4.7-µF ceramic capacitor for BP and 2.2-µF ceramic capacitor for VDD.

For more information, see the TPS543C20 datasheet[1].

# 2.3.1.8 Voltage Reference

The VSEL pin strap is used to program initial boot voltage value from 0.6 to 1.1 V by the resistor connected from VSEL to AGND. The initial boot voltage is used to program the main loop voltage reference point. VSEL voltage settings provide TI designated discrete internal reference voltages. 表 6 lists internal reference voltage selections.

This TI Design uses 1 V as its reference voltage, so the VSEL pin keeps open.

DEFAULT V<sub>REF</sub> (V) RESISTOR VALUE  $(k\Omega)^{(1)}$ 0.60 0.70 8.66 0.75 15.40 0.80 23.70 0.85 34.80 0.90 51.10 0.95 78.70 1.00 Open 1.05 121.00 1.10 187.00

表 6. VSEL Pin Configuration

<sup>(1)</sup> The E48 series resistors with a tolerance of 1% or less are recommended.

www.ti.com.cn System Overview

#### 2.3.1.9 RSP/RSN Remote Sense Function

RSP and RSN pins are used for remote sensing purpose. If feedback resistors are required for output voltage programming, the RSP pin should be connected to the mid-point of the resistor divider and the RSN pin should always be connected to the load return.

In a lower output voltage application, as the VSEL programs the output voltage set point, the feedback resistors are not required. Because of this, the RSP pin could be connected to the positive sensing point of the load and the RSN pin could be connected to the load return.

RSP and RSN pins are extremely high-impedance input terminals of the true differential remote sense amplifier. The feedback resistor divider should use resistor values much less than 100 k $\Omega$ . A standard is to use a 10-k $\Omega$  lower divider resistor and then size the upper resistor to achieve the desired ratio.

图 5. Remote Sensing With Feedback Resistors

图 6. Remote Sensing Without Feedback Resistors

#### 2.3.1.10 Auxiliary Power Supply

VDD is the controller power supply input and can be connected to PVIN directly to obtain the power supply easily. In this TI Design, in order to decrease the power loss, instead of from PVIN directly, VDD is configured with an external auxiliary power supply circuit which is mainly composed by TL431BQDBZR.

The operation principle is that after the PVIN is built, this auxiliary power supply circuit will produce a voltage that is just lower a bit than 5 V to provide the start-up voltage for the TPS543C20. When the 5-V output voltage is built successfully, this 5-V output voltage will take control for providing the energy for the TPS543C20 internal circuit operation.

As a result, this auxiliary power supply only provides the operation current for the TPS543C20 during the start-up process. After the 5-V output voltage is built, this auxiliary power supply circuit will be kept at a standby state.

System Overview www.ti.com.cn

#### 2.3.1.11 Low-Side MOSFET Overcurrent Protection

The TPS543C20 uses the ILIM pin to set the OCP level. The ILIM pin should be connected to AGND through the ILIM voltage setting resistor,  $R_{\text{ILIM}}$ . The ILIM terminal sources  $I_{\text{ILIM}}$  current, which is around 11.2  $\mu$ A typically at room temperature, and the ILIM level is set to the OCP ILIM voltage,  $V_{\text{ILIM}}$ . In order to provide both good accuracy and a cost-effective solution, the TPS543C20 supports temperature compensated MOSFET  $R_{DS(on)}$  sensing. Also, the TPS543C20 performs both positive and fixed negative inductor current limiting. The inductor current is monitored by the voltage between GND pin and SW pin during the OFF time. ILIM has 1200 ppm/°C temperature slope to compensate the temperature dependency of the  $R_{DS(on)}$ . The GND pin is used as the positive current sensing node. The device has cycle-by-cycle overcurrent limiting control. The inductor current is monitored during the OFF state, and the controller maintains the OFF state during the period that the inductor current is larger than the overcurrent ILIM level.  $V_{\text{ILIM}}$  sets the peak level of the inductor current. Thus, the load current at the overcurrent threshold,  $I_{OCP}$ , can be calculated as shown in  $\triangle$ 式 6:

$$I_{OCP} = \frac{V_{ILIM}}{16 \times R_{DS(on)}} - \frac{I_{IND(ripple)}}{2} = \frac{V_{ILIM}}{16 \times R_{DS(on)}} - \frac{1}{2 \times L \times f_{SW}} \times \frac{\left(V_{IN} - V_{OUT}\right) \times V_{OUT}}{V_{IN}}$$

$$\tag{6}$$

Where

•  $R_{DS(on)}$  is the on-resistance of the low-side MOSFET.  $R_{DS(on)}$  must be 0.68 m $\Omega$  to calculate OCP  $\triangle$ 式 6 is valid for VDD ≥ 5 V.

If an overcurrent event is detected in a given switching cycle, the device increments an overcurrent counter. When the device detects three consecutive overcurrent (either high-side or low-side) events, the converter responds, entering continuous restart hiccup. In continuous hiccup mode, the device implements a 7 soft-start cycle time-out, followed by a normal soft-start attempt. When the overcurrent fault clears, normal operation resumes; otherwise, the device detects overcurrent and the process repeats.

#### 2.3.1.12 High-Side MOSFET Overcurrent Protection

The device also implements a fixed high-side MOSFET OCP to limit the peak current at 60 A and prevent inductor saturation in the event of a short circuit. The device detects an overcurrent event by sensing the voltage drop across the high-side MOSFET during ON state. If the peak current reaches the IHOSC level on any given cycle, the cycle terminates to prevent the current from increasing any further. High-side MOSFET overcurrent events are counted. If the devices detect three consecutive overcurrent events (high-side or low-side), the converter responds by entering continuous restart hiccup.

#### 2.3.1.13 Output Overvoltage and Undervoltage Protection

The TPS543C20 device configures with both output OVP and output UVP capabilities. The device compares the RSP pin voltage to internal selectable pre-set voltages. If the RSP voltage with respect to RSN voltage rises above the output OVP threshold, the device terminates normal switching and activates the low-side MOSFET to discharge the output capacitor and prevent further increases in the output voltage. Then, the device enters continuous restart hiccup.

If the RSP pin voltage falls below the UVP level, after soft-start has completed, the device terminates normal switching and forces both the high-side and low-side MOSFETs off, then enters hiccup timeout delay prior to restart.

www.ti.com.cn System Overview

# 2.3.1.14 Temperature Sensing

In this TI Design, the temperature sensing is accomplished through the LM20BIM7 device, which provides a continuous analog voltage respecting the temperature information. A pin from the LM20BIM7 is used to connect with the system board to deliver temperature information to the customer's system.

An internal temperature sensor in the TPS543C20 protects the devices from thermal runaway. The internal thermal shutdown threshold, TSD, is fixed at 165°C typical. When the devices sense a temperature above TSD, power conversion stops until the sensed junction temperature falls by the thermal shutdown hysteresis amount. Then, the part starts up again.

## 3 Hardware, Testing Requirements, and Test Results

#### 3.1 Test Equipment Needed to Validate Board

The required test equipment include:

- DC source

- Digital oscilloscope

- True RMS multimeter (x4)

- Electronic load (x2)

- Thermal imager

#### 3.2 Test Conditions

For the input feature, the DC source must be capable of providing 12-V DC, and the total output power must be high than 360 W. Set the input current limit to 30 A.

For the output feature, connect an electronic load to each channel output. The load must be variable and capable of 45 A for both the 3.3-V and 5-V output channels.

#### 3.3 Test Procedure

- 1. Solder wires from the DC input terminals of the reference boards, and then connect to an adjustable DC source, maintaining correct polarity. The input line should be capable of enduring a 20-A current.

- Solder wires from output terminals of the reference boards, and then connect them to the electronic load, maintaining correct polarity. The output line should be capable of enduing higher than a 30-A current.

- 3. Set the limit input DC source current 0.2 A with open load for the first time power on.

- 4. Turn on the input DC source with 12-V DC.

- 5. Observe the startup conditions for smooth switching waveforms.

- 6. Increase the input current limit to 30 A, and then increase the output load current for the 3.3-V and 5-V output channels.

- 7. Observe the output voltage waveform to verify it works normally. The user can check the performance of power supply by electronic load for each output channel, specified as < 30 A.

- 8. Cool the module with a fan to prevent the module from overheating.

# 3.4 Testing and Results

The test results are divided into multiple sections that cover the performance data, performance curve, functional waveforms, transient performance waveforms, and thermal measurements.

#### 3.4.1 Performance Data

# 3.4.1.1 Efficiency and Regulation with Load Variation

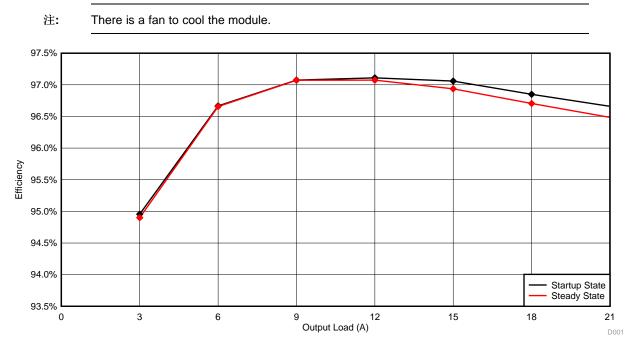

表 7 and 表 8 show the efficiency performance data at start-up and steady state.

注: There is an external fan to cool the module.

#### 表 7. Efficiency Performance at Start-up State

| V <sub>IN</sub> (V) | I <sub>IN</sub> (A) | V <sub>OUT1</sub> (V) | I <sub>OUT1</sub> (A) | VOUT2 (V) | I <sub>OUT2</sub> (A) | P <sub>IN</sub> (W) | P <sub>OUT</sub> (W) | EFF (%)  |

|---------------------|---------------------|-----------------------|-----------------------|-----------|-----------------------|---------------------|----------------------|----------|

| 11.94               | 2.201171            | 5.020                 | 2.9943                | 3.325     | 2.985                 | 26.28198            | 24.95651             | 94.95674 |

| 11.91               | 4.334387            | 5.019                 | 5.9887                | 3.324     | 5.970                 | 51.62255            | 49.90157             | 96.66621 |

| 11.88               | 6.489858            | 5.018                 | 8.9850                | 3.323     | 8.955                 | 77.09951            | 74.84420             | 97.07480 |

| 11.85               | 8.679107            | 5.018                 | 11.9770               | 3.322     | 11.973                | 102.84740           | 99.87489             | 97.10977 |

| 11.81               | 10.886640           | 5.017                 | 14.9740               | 3.321     | 14.955                | 128.57120           | 124.79010            | 97.05917 |

| 11.78               | 13.122780           | 5.016                 | 17.9700               | 3.321     | 17.940                | 154.58630           | 149.71630            | 96.84962 |

| 11.73               | 15.919640           | 5.015                 | 21.6560               | 3.320     | 21.630                | 186.73740           | 180.41640            | 96.61504 |

### 表 8. Efficiency Performance at Steady State

| V <sub>IN</sub> (V) | I <sub>in</sub> (A) | V <sub>OUT1</sub> (V) | I <sub>OUT1</sub> (A) | V <sub>OUT2</sub> (V) | I <sub>OUT2</sub> (A) | P <sub>IN</sub> (W) | P <sub>OUT</sub> (W) | EFF (%)  |

|---------------------|---------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------------|----------------------|----------|

| 11.94               | 2.204350            | 5.025                 | 2.9906                | 3.325                 | 2.9925                | 26.26775            | 24.97783             | 94.90078 |

| 11.91               | 4.337169            | 5.024                 | 5.9868                | 3.323                 | 5.9737                | 51.60835            | 49.92829             | 96.65595 |

| 11.89               | 6.487871            | 5.024                 | 8.9812                | 3.322                 | 8.9587                | 77.14078            | 74.88235             | 97.07232 |

| 11.86               | 8.677517            | 5.023                 | 11.9730               | 3.320                 | 11.9770               | 102.91540           | 99.90402             | 97.07397 |

| 11.83               | 10.885050           | 5.022                 | 14.9700               | 3.319                 | 14.9580               | 128.77010           | 124.82490            | 96.93628 |

| 11.80               | 13.122380           | 5.021                 | 17.9660               | 3.318                 | 17.9430               | 154.84410           | 149.74220            | 96.70512 |

| 11.75               | 15.926400           | 5.021                 | 21.6500               | 3.317                 | 21.6330               | 187.13520           | 180.46130            | 96.43366 |

#### 3.4.1.2 Load Regulation

This reference design configures with a remote sense function. Comparing the output test results of load regulation shows the excellent performance when implements the remote sense function.

注: The output voltage is based on the test point of the terminal load voltage.

# 表 9. Load Regulation Performance between Local and Remote Sense

| LOAD CONDITION | 3.3 V <sub>OUT</sub> |              | 5 V         | оит          |

|----------------|----------------------|--------------|-------------|--------------|

| LOAD CONDITION | LOCAL SENSE          | REMOTE SENSE | LOCAL SENSE | REMOTE SENSE |

| 0 A            | 3.325                | 3.308        | 5.027       | 5.008        |

| 15 A           | 3.252                | 3.306        | 4.948       | 5.007        |

| 30 A           | 3.176                | 3.305        | 4.870       | 5.006        |

| Regulation     | 149 mV               | 3 mV         | 187 mV      | 2 mV         |

#### 3.4.2 Performance Curves

#### 3.4.2.1 Efficiency With Load Variation

▼ 7 shows the efficiency curve of this reference design. For the efficiency test, 3.3 V<sub>OUT</sub> and 5 V<sub>OUT</sub> have the same load current, and the total maximum output power is 180 W. This test shows the overall unit efficiency feature at the start-up state and steady state separately.

图 7. Overall Unit Efficiency Curve versus Output Load Current

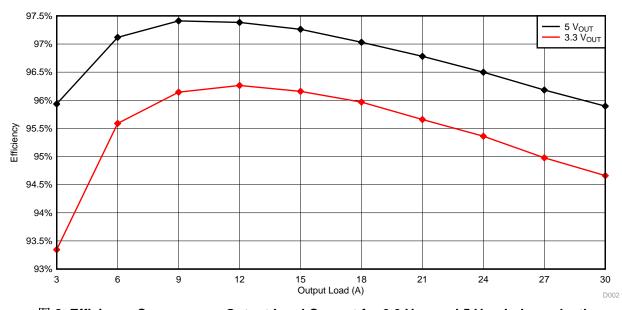

$\boxtimes$  8 shows the efficiency curve, which is based on 3.3  $V_{OUT}$  and 5  $V_{OUT}$  independently at the start-up state with a maximum output current of 30 A for each channel.

図 8. Efficiency Curve versus Output Load Current for 3.3 V<sub>OUT</sub> and 5 V<sub>OUT</sub> Independently

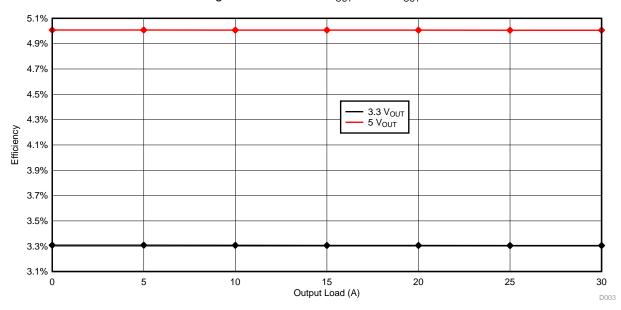

# 3.4.2.2 Load Regulation

${\ensuremath{\mathbb R}}$  9. Output Voltage Regulation With Load Current for 3.3 V $_{\ensuremath{\text{OUT}}}$  and 5 V $_{\ensuremath{\text{OUT}}}$

# 3.4.3 Functional Waveforms

# 3.4.3.1 Output Voltage Ripple

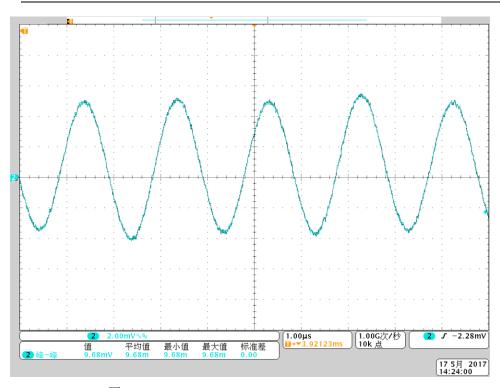

The output voltage ripple performance is observed for 3.3-V and 5-V output voltage and a half load of 15 A at 12-V DC inputs, as shown in 图 10 and 图 11.

注: CH2: 3.3-V output voltage ripple (bandwidth: 20 MHz) Test condition:  $V_{IN}$  = 12-V DC;  $I_{OUT}$  = 15 A (2 mV/div, 1  $\mu$ s/div) Test result: 9.68 mV peak to peak

图 10. 3.3-V Output Voltage Ripple and Noise

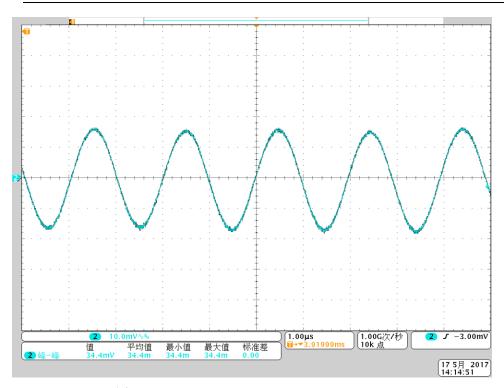

注: CH2: 5-V output voltage ripple (bandwidth: 20 MHz)

Test condition:  $V_{IN}$  = 12-V DC;  $I_{OUT}$  = 15 A (10 mV/div, 1  $\mu$ s/div)

Test result: 34.4mV peak to peak

图 11. 5-V Output Voltage Ripple and Noise

#### 3.4.4 Transient Performance Waveforms

#### 3.4.4.1 Turnon Transient

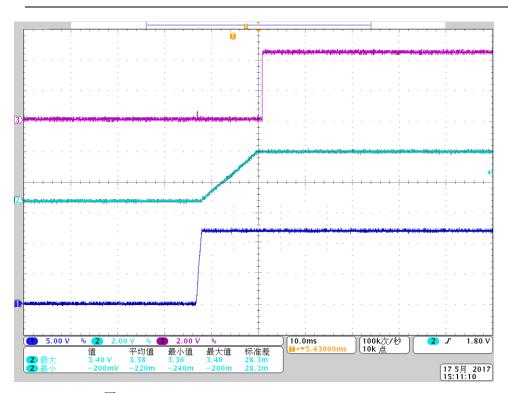

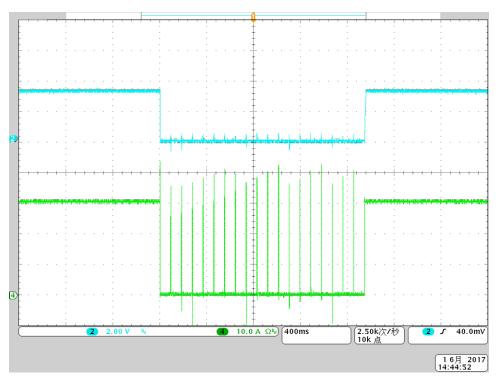

The turnon transient performance is observed for 3.3-V and 5-V output voltages and a half load of 15 A at 12-V DC inputs, as shown in

■ 12 and ■ 13.

注: CH1:  $V_{IN}$ ; CH2: 3.3  $V_{OUT}$ ; CH3: PGOOD\_3.3Vout Test condition:  $V_{IN}$  = 12-V DC;  $I_{OUT}$  = 15 A

Test result: Start-up time = 12 ms

图 12. 3.3-V Output Turnon Transient Waveform

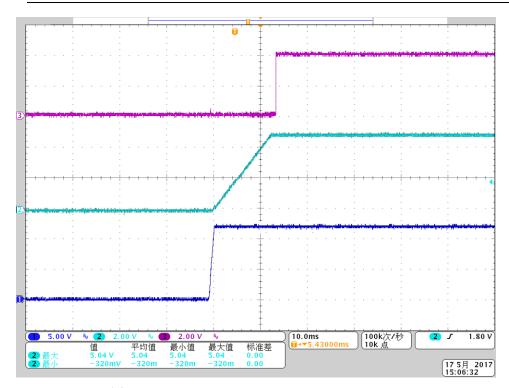

注: CH1:  $V_{IN}$ ; CH2: 5  $V_{OUT}$ ; CH3: PGOOD\_5Vout Test condition:  $V_{IN}$  = 12-V DC;  $I_{OUT}$  = 15 A Test result: Start-up time = 12 ms

图 13. 5-V Output Turnon Transient Waveform

# 3.4.4.2 Output Load Transient

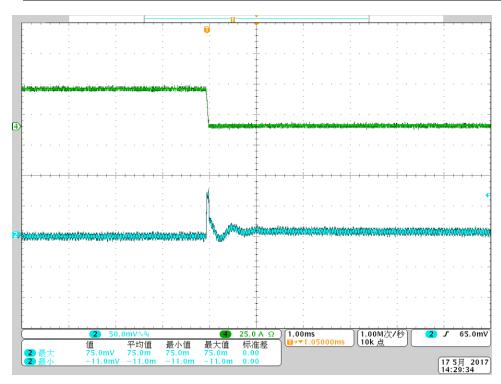

The load transient performance is observed for 3.3-V and 5-V output voltage at 12-V DC inputs, as shown in 图 14, 图 15, 图 16, and 图 17.

注: CH2:  $3.3~V_{OUT}$ ; CH4: lout\_3.3V (bandwidth: 20 MHz) Test condition:  $V_{IN}=12\text{-V}$  DC;  $I_{OUT}=30~A$  to 0~A,  $di/dt=0.5~A/\mu s$  Test result: 75 mV for negative step change

图 14. 3.3-V Output Load Transient From 30 A to 0 A

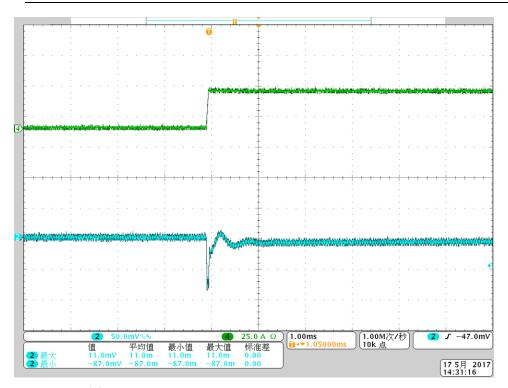

注: 3.3 V<sub>OUT</sub>; CH4: lout\_3.3V (bandwidth: 20 MHz)

Test condition:  $V_{IN} = 12-V$  DC;  $I_{OUT} = 0$  A to 30 A, di/dt = 0.5 A/ $\mu$ s

Test result: 87 mV for positive step change

图 15. 3.3-V Output Load Transient From 0 A to 30 A

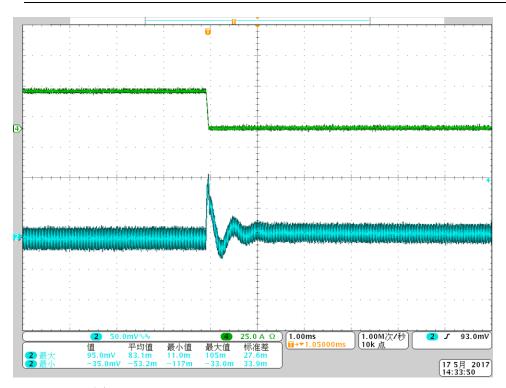

注: 5 V<sub>OUT</sub>; CH4: lout\_5V (bandwidth: 20 MHz)

Test condition:  $V_{IN} = 12$ -V DC;  $I_{OUT} = 30$  A to 0 A, di/dt = 0.5 A/ $\mu$ s

Test result: 95 mV for negative step change

图 16. 5-V Output Load Transient From 30 A to 0 A

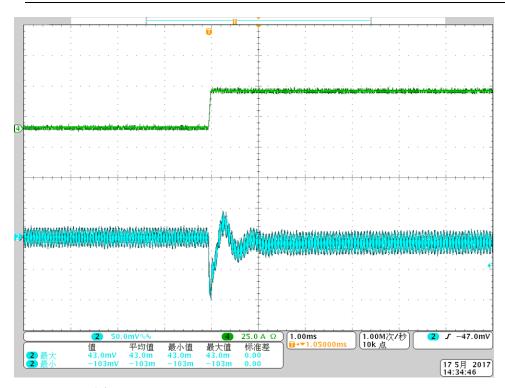

注: 5 V<sub>OUT</sub>; CH4: lout\_5V (bandwidth: 20 MHz)

Test condition:  $V_{IN}$  = 12-V DC;  $I_{OUT}$  = 0 A to 30 A, di/dt = 0.5 A/ $\mu$ s

Test result: 103 mV for positive step change

图 17. 5-V Output Load Transient From 0 A to 30 A

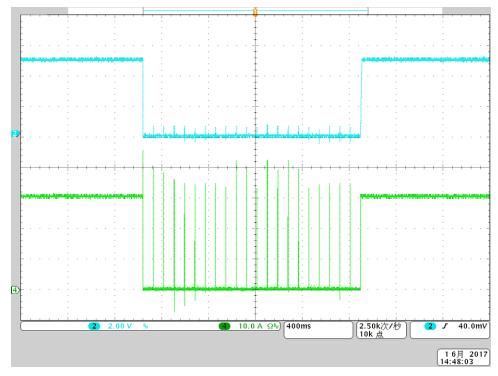

#### 3.4.4.3 Overload and Overcurrent Response

The overcurrent response was recorded by applying an overcurrent condition in load from 30- to 45-A operation.

■ 18 and ■ 19 show that during the interval when the overcurrent condition is present, the converter goes into hiccup mode; when the overcurrent condition is removed, the converter recovers back to the normal operation.

图 18. 3.3-V Output Voltage Response During Overcurrent and Recovery

图 19. 5-V Output Voltage Response During Overcurrent and Recovery

# 3.4.4.4 Output Undervoltage and Overvoltage Protection

Due to the output OVP and UVP, sample the RSP voltage with respect to RSN voltage. As a result, the conventional trimming method through a external adjustable resistor to change the voltage divide network is not effective for this type of design because the RSP voltage with respect to RSN voltage is permanent during the trimming process.

To check the output UVP:

- 1. Have a resistor (1  $\Omega$  is fine) in series with the output inductor.

- 2. Turn on the electronic load with 5 A or 10 A.

The output capacitor delivers the energy to the load, and then the output voltage decreases to trigger the undervoltage threshold. The purpose of the resistor in series with the output inductor is to block the current feed to the output capacitor.

To check the output OVP:

- 1. Use an external power supply, which sets higher than 1.2 x V<sub>REF</sub>.

- 2. When the module is powered on and enters into stable state, touch the RSP pin with the external voltage to trigger the overvoltage threshold.

#### 3.4.5 Thermal Measurements

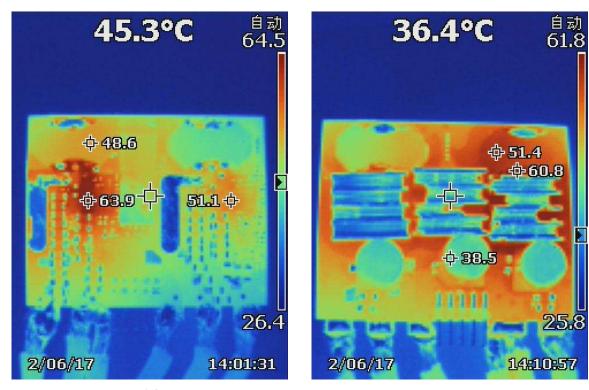

In this section, two sets of thermal images are provided. Based on the design requirements, each channel of the multiple outputs has a 30-A output current capability, and the total output power is 180 W. Therefore, check the two worst cases:

- 1. The 3.3-V output channel is with 30 A, and the total output power is 180 W.

- 2. The 5-V output channel is with 30 A, and the total output power is 180 W.

These two sets of thermal images are provided under room temperature with 100 LFM airflow measured at the board.

$\boxtimes$  20 shows the thermal image for both the top and bottom side of the board. The input voltage is 12-V DC, and the loads are 30 A for 3.3 V<sub>OUT</sub> and 16.2 A for 5 V<sub>OUT</sub>.

图 20. Thermal Performance at Worst Condition 1

# 表 10. Highlighted Image Makers at Worst Condition 1

| PARAMETER           | VALUE   |

|---------------------|---------|

| Input voltage       | 12-V DC |

| Output power        | 180 W   |

| Ambient temperature | 25°C    |

| Inductor_Core       | 51.4°C  |

| Inductor_Winding    | 60.8°C  |

| TPS543C20_3.3Vout   | 63.9°C  |

| TPS543C20_5Vout     | 51.1°C  |

| Input capacitor     | 38.5°C  |

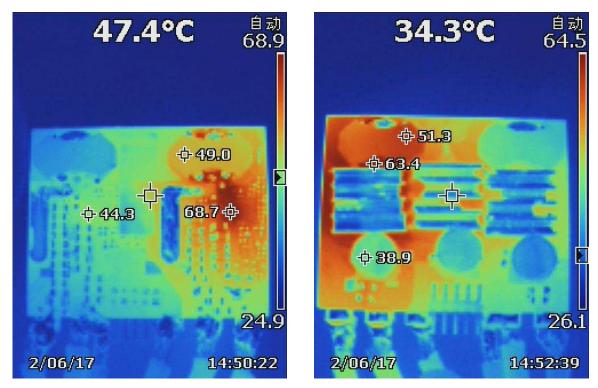

$\boxtimes$  21 shows the thermal images for both the top and bottom sides of the board. The input voltage is 12-V DC, and the loads are 9 A for 3.3  $V_{OUT}$  and 30 A for 5  $V_{OUT}$ .

图 21. Thermal Performance at Worst Condition 2

| 表 11. Highlighted Image M | akers at Worst Condition 2 |

|---------------------------|----------------------------|

| DADAMETED                 | \/A1.11E                   |

| PARAMETER           | VALUE   |

|---------------------|---------|

| Input voltage       | 12-V DC |

| Output power        | 180 W   |

| Ambient temperature | 25°C    |

| Inductor_Core       | 51.3°C  |

| Inductor_Winding    | 63.4°C  |

| TPS543C20_3.3Vout   | 44.3°C  |

| TPS543C20_5Vout     | 68.7°C  |

| Output capacitor    | 38.9°C  |

#### 3.4.6 Conducted Emissions

The TIDA-01444 design is a DC-DC module. The CE test setup is based on the module category. This test has the external EMI filter components based on the output power.

図 22 shows the external EMI filter configuration:

图 22. External EMI Filter Configuration

#### Where:

- CX is a 4.7-µF ceramic capacitor

- CX1 is a 4.7-µF ceramic capacitor

- CY1 is a 4.7-nF ceramic capacitor

- Cin is a 100-µF electrolytic capacitor

- L1 is a common-mode inductor, L1 = 0.08 mH

- L2 is a common-mode inductor, L2 = 0.24 mH

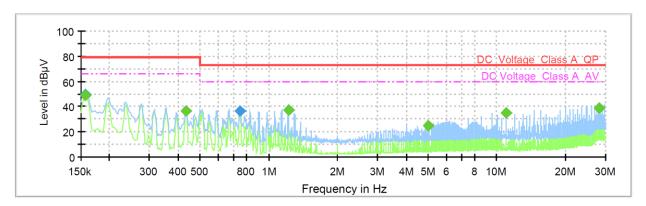

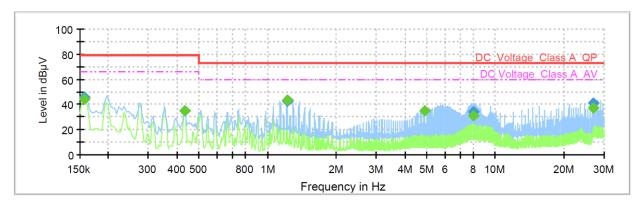

The conducted emissions were measured with a 12-V DC input voltage at a 21.7-A load for each output channel in a standard setup and were compared against EN55032 Class-A limits. (EN55032 standard has replaced EN55022/EN55013/EN55103-1 after March 2, 2017).

图 23. CE as per EN55032 Class A, Positive Line

# 表 12. CE Quasi-Peak And Average Margins Test Result, Positive Line

| FREQ<br>(MHz) | QUASIPEAK<br>(dBµV) | AVERAGE<br>(dBμV) | LIMIT<br>(dBµV) | MARGIN<br>(dB) | MEAS TIME<br>(ms) | BANDWIDTH<br>(kHz) | LINE | PE  |

|---------------|---------------------|-------------------|-----------------|----------------|-------------------|--------------------|------|-----|

| 0.15675       | _                   | 48.47             | 66.00           | 17.53          | 1000              | 9.000              | L    | GND |

| 0.15675       | 49.42               | _                 | 79.00           | 29.58          | 1000              | 9.000              | L    | GND |

| 0.43350       | _                   | 36.48             | 66.00           | 29.52          | 1000              | 9.000              | L    | GND |

| 0.74625       | 36.19               | _                 | 73.00           | 36.81          | 1000              | 9.000              | L    | GND |

| 1.21875       | 37.05               | _                 | 73.00           | 35.95          | 1000              | 9.000              | L    | GND |

| 1.21875       | _                   | 37.07             | 60.00           | 22.93          | 1000              | 9.000              | L    | GND |

| 5.00500       | 24.51               | _                 | 73.00           | 48.49          | 1000              | 9.000              | L    | GND |

| 5.00500       | _                   | 24.59             | 60.00           | 35.41          | 1000              | 9.000              | L    | GND |

| 11.01075      | _                   | 34.89             | 60.00           | 25.11          | 1000              | 9.000              | L    | GND |

| 11.01300      | 35.19               | _                 | 73.00           | 37.81          | 1000              | 9.000              | L    | GND |

| 28.02750      | 39.08               | _                 | 73.00           | 33.92          | 1000              | 9.000              | L    | GND |

| 28.02975      | _                   | 38.97             | 60.00           | 21.03          | 1000              | 9.000              | L    | GND |

图 24. CE as per EN55032 Class A, Negative Line

# 表 13. CE Quasi-Peak And Average Margins Test Result, Negative Line

| FREQ<br>(MHz) | QUASIPEAK<br>(dBµV) | AVERAGE<br>(dBμV) | LIMIT<br>(dBµV) | MARGIN<br>(dB) | MEAS TIME<br>(ms) | BANDWIDTH<br>(kHz) | LINE | PE  |

|---------------|---------------------|-------------------|-----------------|----------------|-------------------|--------------------|------|-----|

| 0.15675       | 45.79               | _                 | 79.00           | 33.21          | 1000              | 9.000              | N    | GND |

| 0.15675       |                     | 44.12             | 66.00           | 21.88          | 1000              | 9.000              | N    | GND |

| 0.43125       |                     | 34.69             | 66.00           | 31.31          | 1000              | 9.000              | N    | GND |

| 0.43125       | 34.81               | _                 | 79.00           | 44.19          | 1000              | 9.000              | N    | GND |

| 0.43350       | 34.8                | _                 | 79.00           | 44.20          | 1000              | 9.000              | N    | GND |

| 1.21650       | 42.32               | _                 | 73.00           | 30.68          | 1000              | 9.000              | N    | GND |

| 1.21875       |                     | 43.13             | 60.00           | 16.87          | 1000              | 9.000              | N    | GND |

| 4.91100       |                     | 34.53             | 60.00           | 25.47          | 1000              | 9.000              | N    | GND |

| 7.97325       | 34.17               | _                 | 73.00           | 38.83          | 1000              | 9.000              | N    | GND |

| 7.97325       |                     | 31.3              | 60.00           | 28.70          | 1000              | 9.000              | N    | GND |

| 27.03300      | _                   | 36.92             | 60.00           | 23.08          | 1000              | 9.000              | N    | GND |

| 27.03525      | 41.18               | _                 | 73.00           | 31.82          | 1000              | 9.000              | N    | GND |

www.ti.com.cn Design Files

# 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01444.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01444.

# 4.3 PCB Layout Recommendations

# 4.3.1 Power Stage Specific Guidelines

Follow these key guidelines to route power stage components:

- Minimize the loop area and trace length of the power path circuits, which contain high-frequency switching currents. This helps to reduce EMI and improve converter overall performance.

- Keep the switch node as short as possible. A compact switch node reduces common-mode noise associated with the high dV/dt.

- Keep traces with high dV/dt and high di/dt away or shielded from sensitive signal traces with adequate clearance or ground shielding.

- It is absolutely critical that all TPS543C20 GND pins, including AGND (pin 29), GND (pin 27), and PGND (pins 13, 14, 15, 16, 17, 18, 19, and 20) are connected directly to the thermal pad underneath the device via traces or plane. The number of thermal vias needed to support 40-A thermal operation should be as many as possible.

- Place protection devices such as snubbers, capacitors, or diodes physically close to the device they are intended to protect, and route them with short traces to reduce inductance.

- Place the input capacitor close to the high-side MOS drain and low-side MOS source to reduce AC current loop in buck topology.

- Choose the width of PCB traces based on acceptable temperature rise at the rated current as per IPC2152 as well as acceptable DC and AC impedances. Also, the traces should withstand the fault currents (such as short-circuit current) before the activation of electronic protection.

- Adapt thermal management to fit the end-equipment requirements.

#### 4.3.2 Controller Specific Guidelines

Follow these key guidelines to route controller components and signal circuits:

- Place VDD and BP decoupling capacitors as close to the device pins as possible. Do not use PVIN

plane connection for VDD. VDD needs to be tapped off from PVIN with separate trace connection.

Ensure to provide GND vias for each decoupling capacitor and make the loop as small as possible.

- Place all sensitive analog traces and components such as RAMP, RSP, RSN, ILIM, MODE, VSEL, and RT away from any high-voltage switch node (itself and others), such as SW and BOOT to avoid noise coupling. In addition, Place the MODE, VSEL, ILIM, RAMP, and RT programming resistors near the device or pins.

- See the placement and routing guidelines and layout examples presented in the TPS543C20 datasheet[1].

Design Files www.ti.com.cn

# 4.3.3 Layout Prints

To download the layer plots, see the design files at TIDA-01444.

# 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01444.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01444.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01444.

# 4.7 Design Calculator Spreadsheet

To download the design spreadsheet calculator for this reference design, see the link at TIDA-01444.

#### 5 Related Documentation

Texas Instruments, TPS543C20 4 Vin to 16 Vin, 40-A Stackable, Synchronous Step-down SWIFT™ Converter with Adaptive Internal Compensation, TPS543C20 Datasheet (SLUSCD4)

# 5.1 商标

PowerStack, NexFET are trademarks of Texas Instruments. WEBENCH is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 6 About the Author

**CHENG LIU** is a systems engineer at Texas Instruments, where he is responsible for developing reference design solutions for the industrial segment. Cheng brings to this role his extensive experience in power electronics, high frequency high power density DC-DC and analog circuit design. Cheng earned his masters of electrical machinery and apparatus from Wuhan University of Technology in 2012.

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2017 德州仪器半导体技术(上海)有限公司