# Programmer's Guide

## TPS65215Q1 NVM 编程指南

### 摘要

TPS65215 系列电源管理集成电路 (PMIC) 包含一个可配置的非易失性存储器 (NVM) 空间。本编程人员指南详细介绍了定义 PMIC 默认配置的分步编程说明以及如何对 NVM 重新编程。

### 内容

|                                 |    |

|---------------------------------|----|

| <b>1 简介</b>                     | 3  |

| <b>2 NVM 编程的硬件要求</b>            | 4  |

| <b>3 典型 NVM 流程</b>              | 4  |

| <b>4 TPS65215 与 TPS65219EVM</b> | 6  |

| <b>5 编程指令</b>                   | 7  |

| 5.1 配置使能设置                      | 8  |

| 5.2 配置降压转换器                     | 9  |

| 5.3 配置 LDO                      | 10 |

| 5.4 配置 GPIO                     | 11 |

| 5.5 配置序列                        | 12 |

| 5.6 配置多功能引脚                     | 16 |

| 5.7 配置 EN/PB/VSENSE 引脚          | 18 |

| 5.8 更改 I <sub>2</sub> C 地址      | 18 |

| 5.9 配置屏蔽设置                      | 19 |

| 5.10 NVM 重新编程                   | 20 |

| <b>A 非 NVM 寄存器</b>              | 22 |

| <b>B 将 NVM 配置文件加载到 PMIC</b>     | 22 |

| <b>C PMIC 可配置字段</b>             | 22 |

| <b>参考资料</b>                     | 23 |

| <b>E 修订历史记录</b>                 | 24 |

### 插图清单

|                                          |    |

|------------------------------------------|----|

| 图 1-1. 供应选项                              | 3  |

| 图 2-1. NVM 编程的硬件设置                       | 4  |

| 图 3-1. 插槽式 EVM                           | 5  |

| 图 3-2. 原型示例                              | 5  |

| 图 3-3. TPS65215-GUI                      | 6  |

| 图 4-1. 将 TPS65215 与 TPS65219EVM 配合使用     | 7  |

| 图 5-1. NVM 编程                            | 8  |

| 图 5-2. 使用 TPS65215-GUI 的使能设置             | 8  |

| 图 5-3. 使用 TPS65215-GUI 的降压转换器设置          | 9  |

| 图 5-4. 使用 TPS65215-GUI 的 LDO 设置          | 11 |

| 图 5-5. GPIO 配置                           | 12 |

| 图 5-6. 上电序列配置                            | 13 |

| 图 5-7. 断电序列配置                            | 14 |

| 图 5-8. 使用 TPS65215-GUI 的多功能配置            | 17 |

| 图 5-9. 使用 TPS65215-GUI 的 EN/PB/VSENSE 配置 | 18 |

| 图 5-10. I <sub>2</sub> C_ADDRESS_REG     | 19 |

| 图 5-11. 器件 I <sub>2</sub> C 地址           | 19 |

| 图 5-12. TPS65215-GUI 中的屏蔽设置              | 20 |

| 图 5-13. 使用 TPS65215-GUI 重新对 NVM 进行编程     | 21 |

|                                        |    |

|----------------------------------------|----|

| 图 5-14. 使用 TPS65215-GUI 导出 NVM 设置..... | 21 |

| 图 B-1. 加载 NVM 配置文件.....                | 22 |

| 图 C-1. NVM 可编程字段.....                  | 23 |

## 表格清单

|                                                             |    |

|-------------------------------------------------------------|----|

| 表 1-1. TPS65215 用户可编程型号.....                                | 3  |

| 表 2-1. NVM 编程的最低硬件要求.....                                   | 4  |

| 表 5-1. 用于使能设置的 NVM 寄存器.....                                 | 9  |

| 表 5-2. 用于 Buck1 配置的 NVM 寄存器.....                            | 10 |

| 表 5-3. 用于 Buck2 配置的 NVM 寄存器.....                            | 10 |

| 表 5-4. 用于 Buck3 配置的 NVM 寄存器.....                            | 10 |

| 表 5-5. 用于开关模式的 NVM 寄存器 ( 仅在 BUCK_FF_ENABLE = 1h 时适用 ) ..... | 10 |

| 表 5-6. 用于 LDO1 设置的 NVM 寄存器.....                             | 11 |

| 表 5-7. 用于 LDO2 设置的 NVM 寄存器.....                             | 11 |

| 表 5-8. 用于 GPIO 设置的 NVM 寄存器.....                             | 12 |

| 表 5-9. 用于多 PMIC 配置的 NVM 寄存器.....                            | 12 |

| 表 5-10. 上电序列 - 时隙分配.....                                    | 14 |

| 表 5-11. 上电序列 - 时隙持续时间.....                                  | 15 |

| 表 5-12. 下电序列 - 时隙分配.....                                    | 15 |

| 表 5-13. 下电序列 - 时隙持续时间.....                                  | 16 |

| 表 5-14. 用于 VSEL_SD/VSEL_DDR 的 NVM 寄存器.....                  | 17 |

| 表 5-15. 用于 MODE/STBY 的 NVM 寄存器.....                         | 17 |

| 表 5-16. 用于 MODE/RESET 的 NVM 寄存器.....                        | 17 |

| 表 5-17. 用于 EN/PB/VSENSE 的 NVM 寄存器.....                      | 18 |

| 表 5-18. I2C_ADDRESS_REG.....                                | 19 |

| 表 5-19. 寄存器 0x1E 上的屏蔽设置.....                                | 20 |

| 表 5-20. 寄存器 0x1E 上的屏蔽设置.....                                | 20 |

| 表 5-21. 寄存器 0x1E 上的屏蔽设置.....                                | 20 |

| 表 5-22. 用以将寄存器设置保存到 NVM 中的 I2C 写入.....                      | 21 |

## 商标

所有商标均为其各自所有者的财产。

## 1 简介

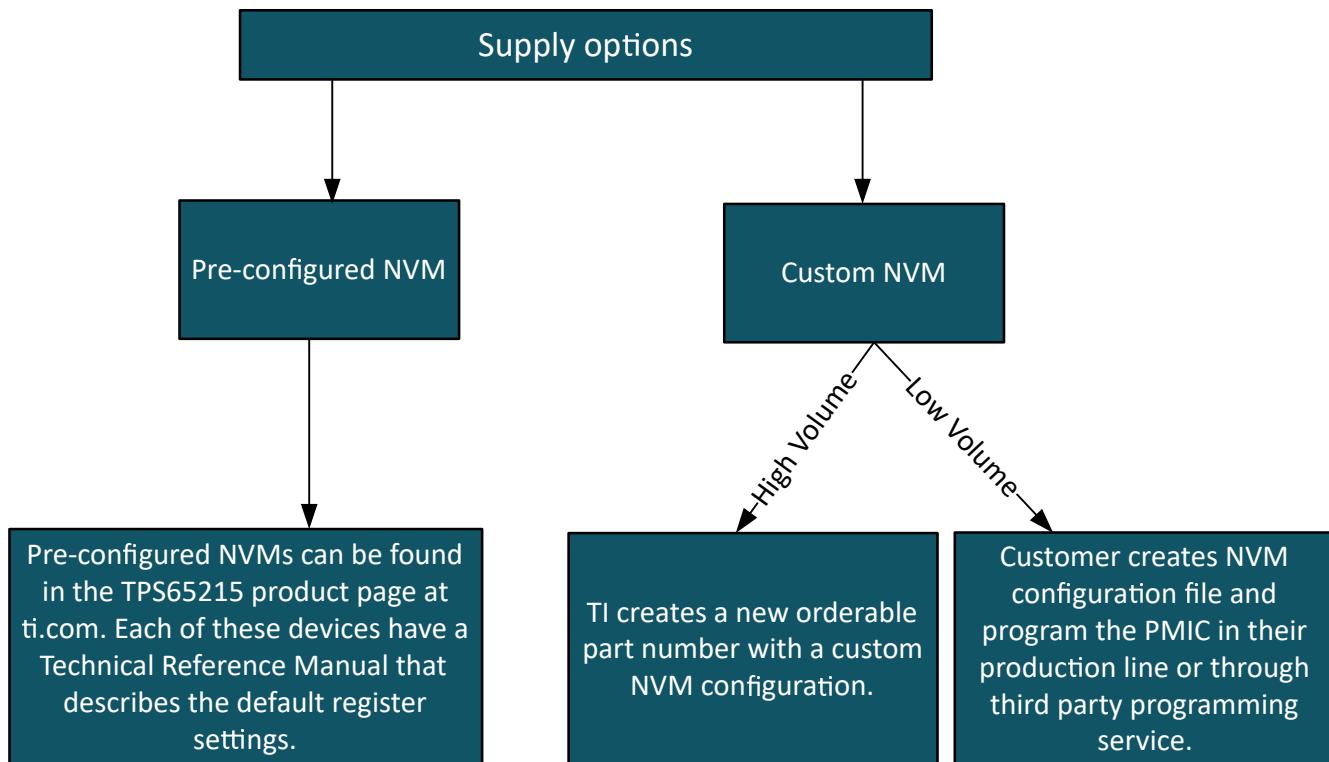

本文档中描述的配置过程写入 NVM 空间，旨在用于生产线或原型板。该机制不适用于最终应用，因为该过程会影响稳压器输出和数字引脚功能。TPS6521505 属于 TPS65215 系列，是专为支持定制 NVM 配置而创建的可订购器件型号。表 1-1 显示了用户可编程型号以及支持的封装尺寸、温度和开关模式。图 1-1 介绍了针对预配置 NVM 和基于容量的定制 NVM 的供应选项。设计资源不仅可用于预配置的 NVM 和大容量 NVM，还可用于小容量定制 NVM。这些资源包括应用手册、用户指南、技术参考手册以及可立即加载到 PMIC NVM 中的 NVM 配置文件。访问 [ti.com](http://ti.com) 上的 TPS6521505-Q1 产品页面或使用我们的 [PMIC E2E 论坛](#)，查看可用资源。

### 备注

为了支持 NVM 编程，TI 提供了一个插槽式 EVM。TPS65219EVM-SKT 是插槽式 EVM 的可订购器件型号。

TPS65215 可与 TPS65219EVM-SKT 配合使用。

**表 1-1. TPS65215 用户可编程型号**

| OPN               | 封装                              | 温度                                                               | 支持的开关频率                                   |

|-------------------|---------------------------------|------------------------------------------------------------------|-------------------------------------------|

| TPS6521505WRHBRQ1 | RHB - 5x5 ( 0.5mm 间距 )<br>可湿性侧面 | T <sub>a</sub> = -40°C 至 125°C<br>T <sub>j</sub> = -40°C 至 150°C | 开关频率<br>( 自动 PFM 或强制 PWM )                |

| 可应要求提供            | RHB - 5x5 ( 0.5mm 间距 )<br>可湿性侧面 | T <sub>a</sub> = -40°C 至 125°C<br>T <sub>j</sub> = -40°C 至 150°C | 固定频率<br>( 推荐用于需要最佳 EMI 控制的应用。可提供展频和异相开关 ) |

**图 1-1. 供应选项**

## 2 NVM 编程的硬件要求

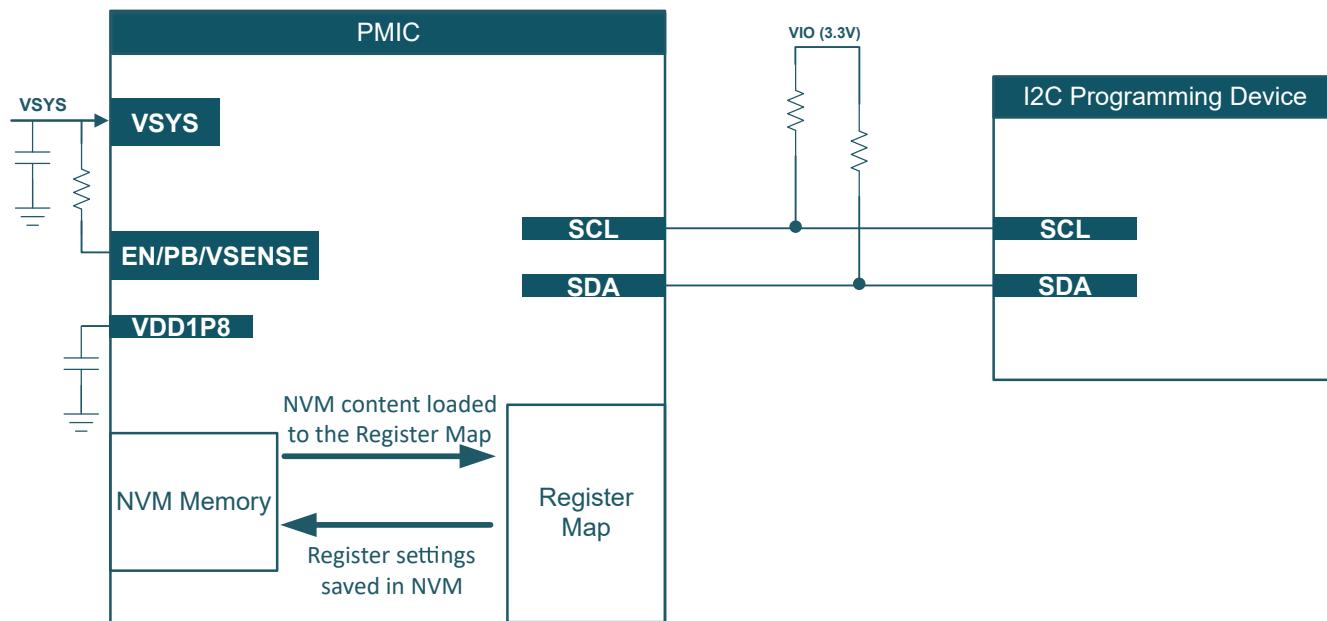

PMIC 有两个存储器空间：寄存器映射空间和 NVM 空间。对 NVM 重新编程的方法是：首先通过串行接口 (I2C) 写入寄存器映射，然后将寄存器设置保存到 NVM 中。由于配置首先需要写入控制稳压器和数字引脚的寄存器映射，因此必须对 PMIC 资源没有依赖或使用需求。例如，在重新对 NVM 进行编程时，必须使用外部电源为 I2C 引脚的上拉电阻供电，而不是使用其中一个 PMIC 电源器件。表 2-1 和图 2-1 显示了在 PMIC 和编程器件之间进行硬件设置的最低硬件要求。

### 备注

在初始化状态下重新对 NVM 进行编程时，不需要其他外部元件，如电感器、电容器等。但是，在活动状态下运行 PMIC 并验证 NVM 设置需要这些元件。

**表 2-1. NVM 编程的最低硬件要求**

| 器件引脚         | 所需的连接                                                    |

|--------------|----------------------------------------------------------|

| VSYS         | VSYS 电压必须为 3.3V 或更高，并且不得超过规格中建议的最大电压。                    |

|              | VSYS 必须具有至少 $2.2 \mu F$ 的电容。                             |

| VDD1P8       | VDD1P8 必须具有 $2.2 \mu F$ 的电容                              |

|              | I2C 引脚上的上拉电阻 (SDA/SCL) 必须由外部 3.3V 电源供电。                  |

| EN/PB/VSENSE | PMIC 的 I2C 引脚必须由外部 I2C 器件驱动，该器件可以与 PMIC 通信并写入寄存器。        |

| AGND         | EN/PB/VSENSE 引脚必须通过上拉电阻连接到 VSYS。                         |

| 散热焊盘         | AGND (引脚编号 15) 必须通过过孔连接到 PCB 接地层。使 AGND 引脚与 VIA 之间的布线较短。 |

| 散热焊盘         | 封装散热焊盘必须通过至少九个过孔连接到 PCB 接地层。                             |

**图 2-1. NVM 编程的硬件设置**

## 3 典型 NVM 流程

本节介绍了典型的 NVM 定义流程，其中包括以下步骤：系统要求、硬件设置、NVM 编程和测试/验证。

### 1. 系统要求

确定系统要求并构建配电网络 (PDN)。电压/电流、上电/下电序列、低功耗模式和负载瞬态是处理器、SoC 和外设的典型要求。

### 2. 硬件设置

TPS65215 可使用 PMIC 插槽式 EVM、客户原型板（电路内编程）或生产线进行编程。

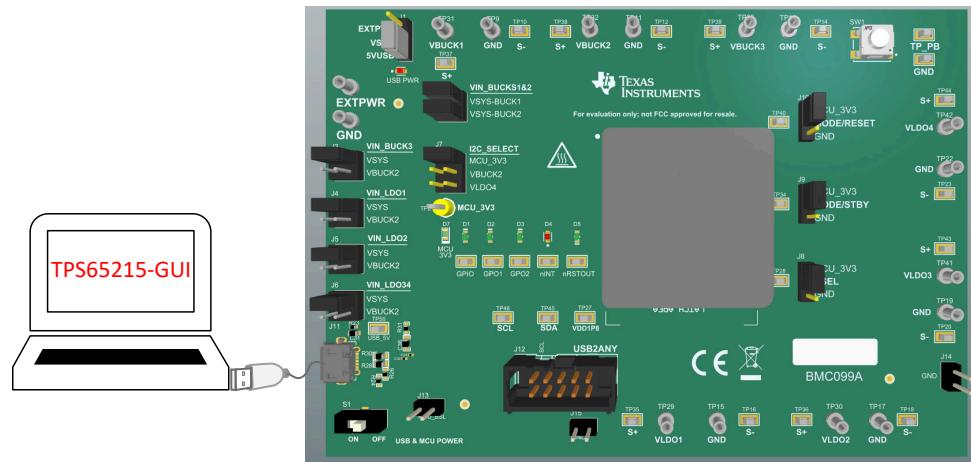

- a. **插槽式 EVM**：PMIC 插槽式 EVM 附带板载 MSP340，后者可通过 I2C 与 PMIC 通信，以对 NVM 存储器进行重新编程。此硬件还集成了一个分立式 3.3V LDO，当 PMIC 电源轨在初始化状态下关断时，该 LDO 可以为 I2C 上拉电阻供电。

图 3-1. 插槽式 EVM

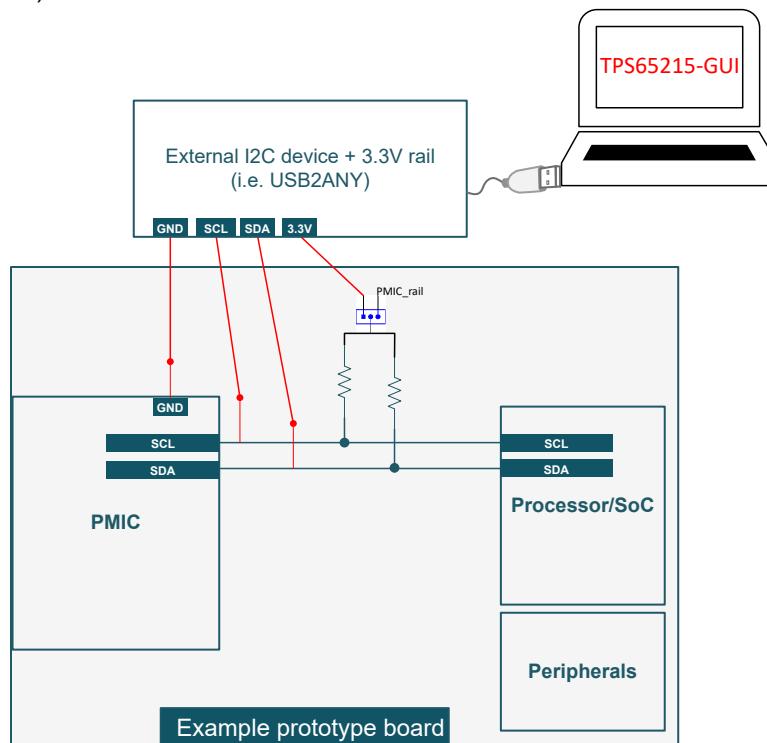

- b. **原型板**：默认情况下，用户可编程的 TPS6521505 NVM 附带的所有电源资源均处于非活动状态，并且 EN/PB/VSENSE 引脚配置为“Push-Button”，FSD 处于禁用状态 ( $\text{PU\_ON\_FSD} = 0x0$ )。如果此引脚上拉至 VSYS，当有效电源连接到 VSYS 时，PMIC 会保持关闭状态（初始化状态）。此配置允许在执行上电序列之前重新对 NVM 进行编程。图 3-2 展示了客户需要在原型板中包含哪些内容来重新对 PMIC NVM 进行编程。所需的元件包括 GND、SCL、SDA 上的三个测试点，以及一个 1x3 单排接头连接器，该连接器会在外部 3.3V 和 PMIC 电源轨（在正常应用中为 I2C 引脚供电）之间选择上拉电源。USB2ANY（可在 TI.com 上获取）可用于与 PMIC 通信并对 NVM 设置重新编程。

图 3-2. 原型示例

**备注**

有关推荐的外部元件（如电感器、输出电容等）的更多信息，请参阅器件特定数据表中的规格和详细设计过程部分。

c. 生产线：在将器件焊接到最终 PCB 之前，还可以根据 [图 2-1](#) 在生产线上重新对 PMIC NVM 进行编程。

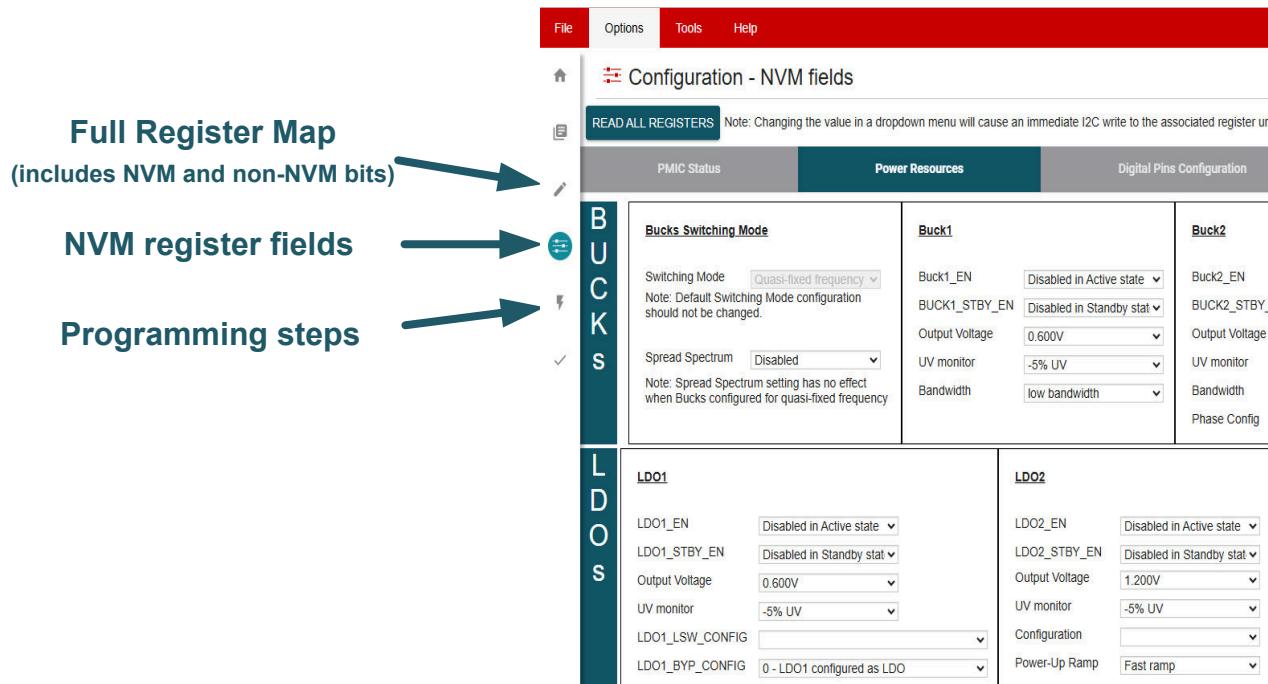

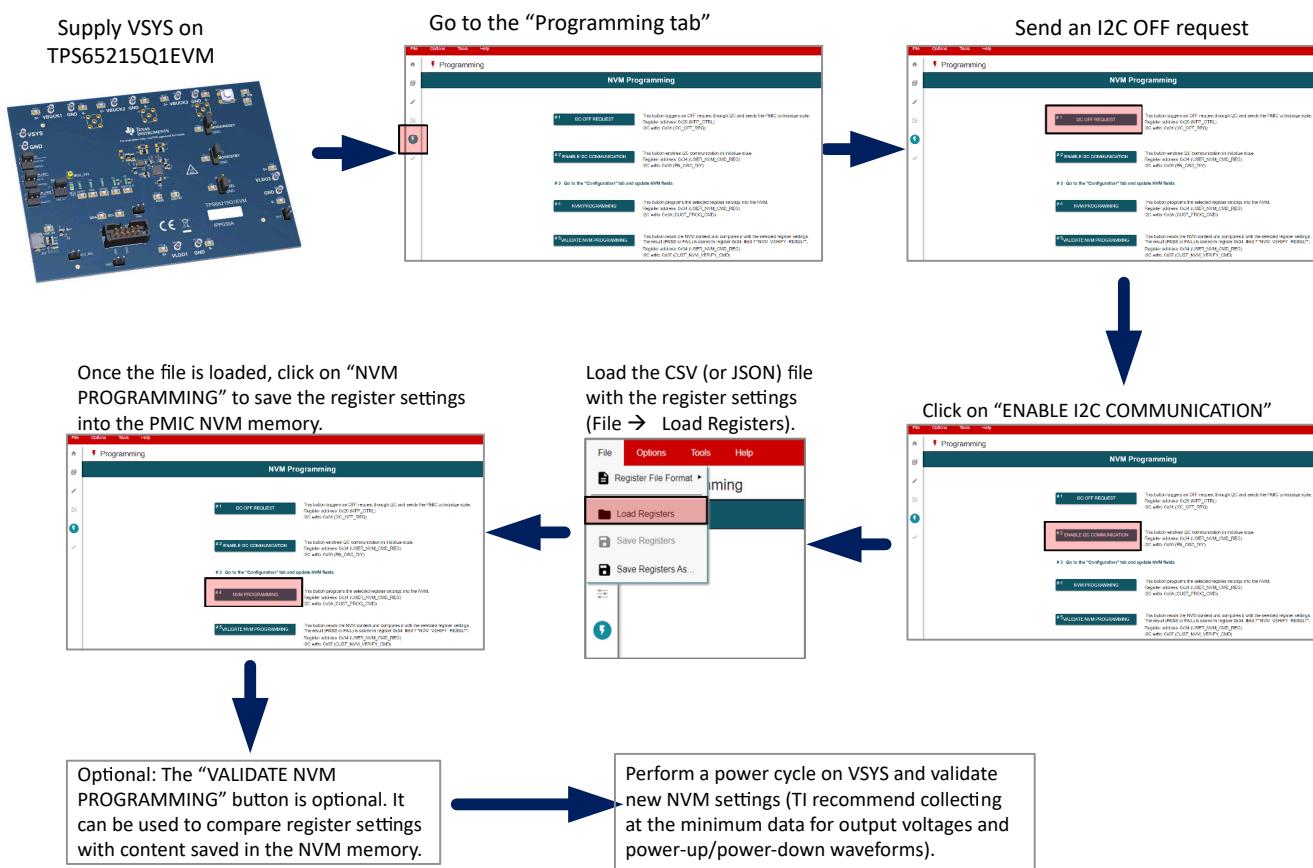

### 3. NVM 编程

按照 [节 5](#) 中的编程说明更改寄存器设置，并将新值保存到 NVM 存储器中。[TPS65215-GUI](#) 可与插座式 EVM（或原型板加外部 USB2ANY）配合使用。或者，客户可以使用他们首选的 I2C 调试器工具，在不使用 [TPS65215-GUI](#) 的情况下写入每个 NVM 寄存器。重新对 NVM 进行编程后，建议执行下电上电以确认新的寄存器设置是否已保存到 NVM 存储器中。

**图 3-3. TPS65215-GUI**

### 4. NVM 测试

必须测试 NVM 设置以确认预期的 PMIC 行为。下面的列表显示了建议的最低测试。这些测试可以在插座式 EVM 或原型板上执行。如果使用插座式 EVM 对 PMIC 重新编程，则可以将器件焊接到客户原型板中，以测试和验证系统级功能。或者，可以替换焊接在 [TPS65215Q1EVM](#) 上的 PMIC，以测试定制 NVM 配置。

- 测量所有输出电压

- 为上电序列收集示波器波形（包括 GPIO [若已启用] 和 nRSTOUT）

- 为下电序列收集示波器波形（包括 GPIO [若已启用] 和 nRSTOUT）

- 测试 EN/PB/VSENSE 引脚功能和极性以触发 ON 和 OFF 请求。

- 测试每个多功能引脚（VSEL、MODE/STBY、MODE/RESET）的配置和极性。将此引脚拉至高电平或低电平，并根据配置的引脚功能验证 PMIC 行为是否发生变化。

**备注**

该插槽式 EVM 可用于重新编程和基本测试（例如：测量输出电压以及收集上电序列波形等），但不得用于测试负载瞬态和效率等特定性能参数，因为插座弹簧针和布局放置会引入不代表应用设计的更高寄生效应。

## 4 TPS65215 与 TPS65219EVM

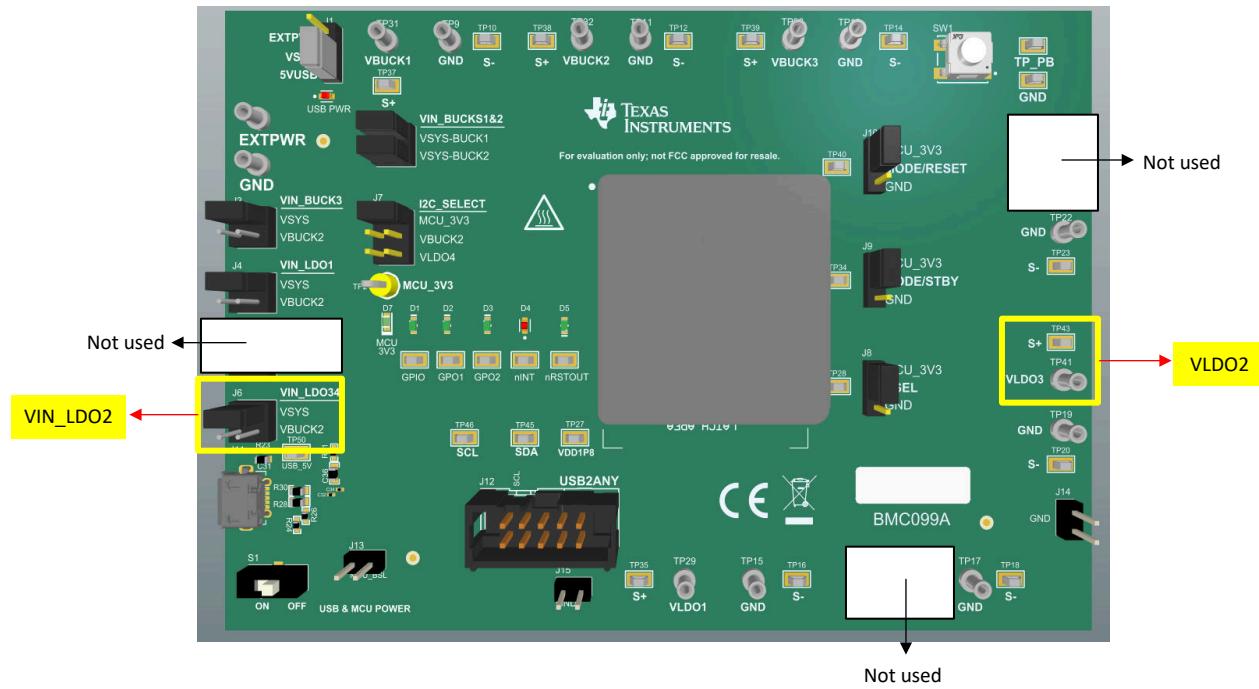

与 TPS65219 相比，TPS65215 器件的 LDO 减少了两个。[图 4-1](#) 展示了 TPS65215 与 TPS65219EVM 配合使用时 LDO2 的连接。

图 4-1. 将 TPS65215 与 TPS65219EVM 配合使用

## 5 编程指令

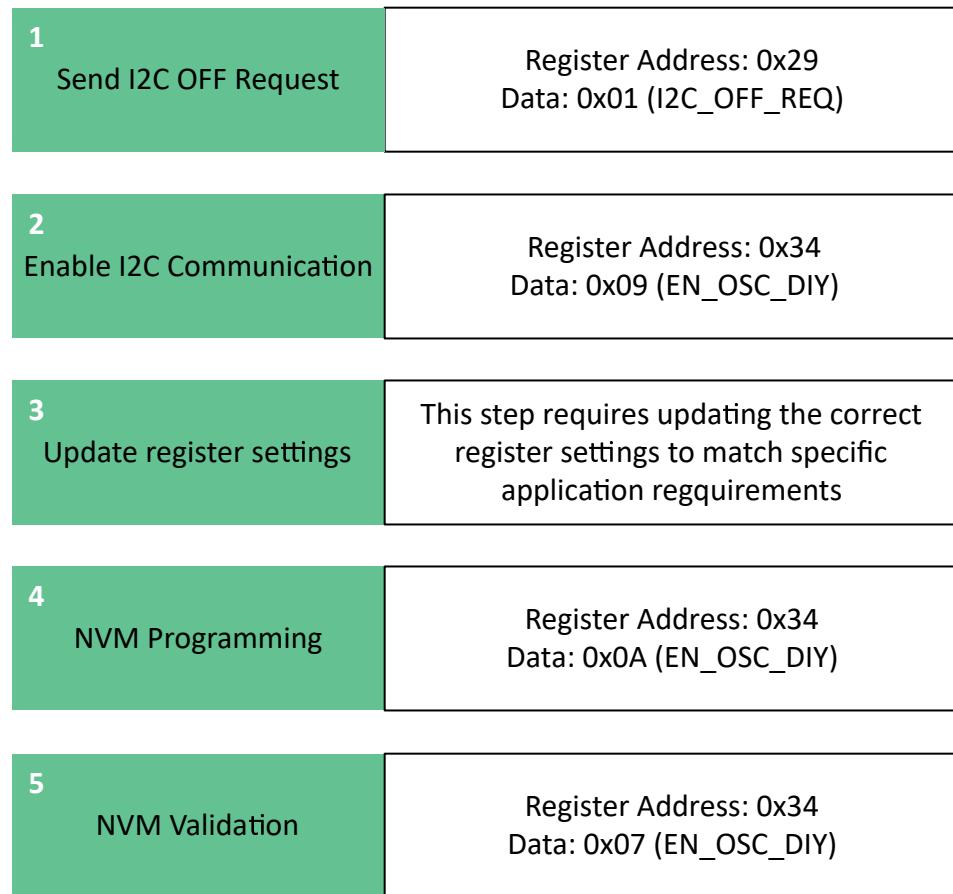

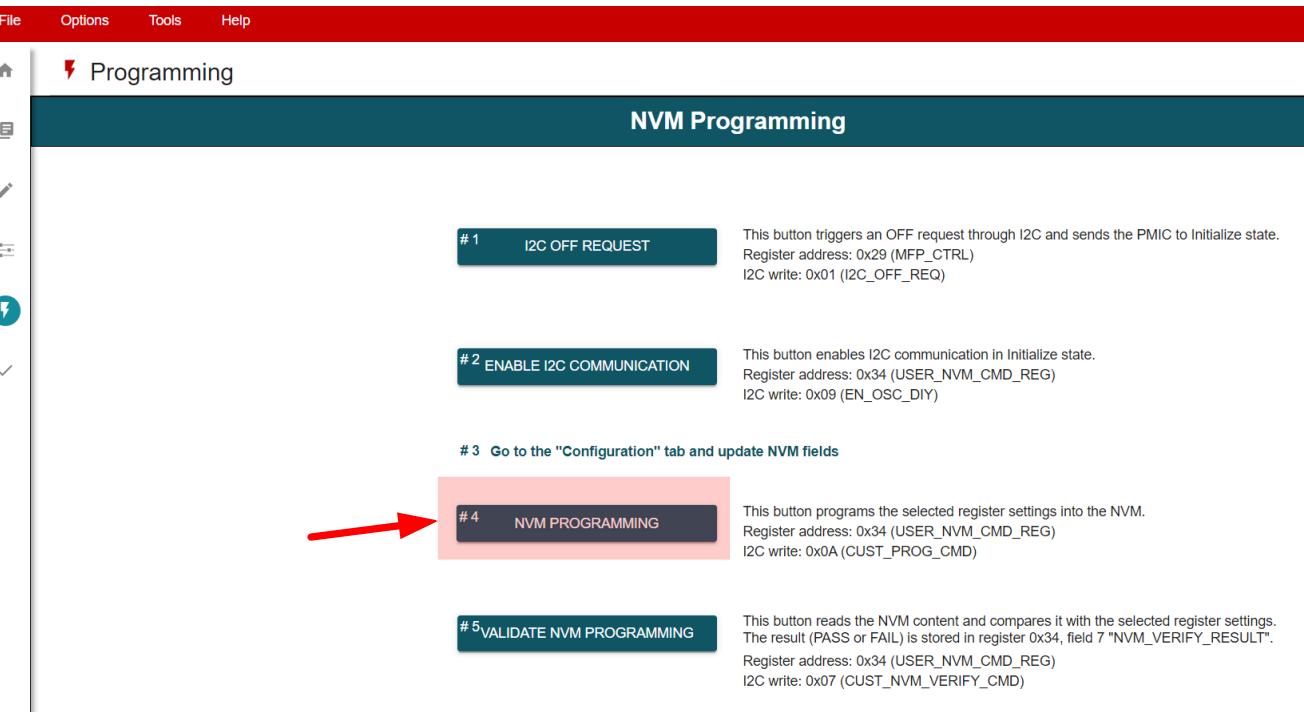

本节介绍了对 PMIC NVM 进行编程所需的步骤。编程过程主要包括两个步骤：更改寄存器设置和将新值保存到 NVM 存储器中。TI 建议在初始化状态下对 NVM 进行编程，在这种状态下，为 VSYS 供电，但所有 PMIC 输出和监视器都关闭。

图 5-1 展示了对器件重新编程的步骤。第一条命令包含将器件发送到初始化状态的 I<sub>2</sub>C OFF 请求。仅当器件未处于初始化状态时才需要此命令。第二个 I<sub>2</sub>C 命令用于启用内部振荡器进行 I<sub>2</sub>C 通信，并禁用电源轨放电。第三步需要按照编程说明更新寄存器设置，以匹配特定的应用要求。更新寄存器设置后，可以通过将 0x0A 写入寄存器地址 0x34 而将新值保存到 NVM 中。最后一步“验证”是可选的，包含一条将寄存器设置与 NVM 内容进行比较的 I<sub>2</sub>C 命令。

### 备注

仅当 PMIC 未处于初始化状态时，才需要第一个 I<sub>2</sub>C 命令（I<sub>2</sub>C OFF 请求）。默认情况下，用户可编程的 OPN TPS6521505 的 EN/PB/VSENSE 引脚配置为“Push-Button”，且 FSD 功能处于禁用状态。当配置为 PB 时，该器件会在引脚被拉低时检测到 ON 请求。如果该引脚上拉至 VSYS，则在为 VSYS 供电后，PMIC 保持初始化状态。为了验证在初始化状态下是否支持 I<sub>2</sub>C 通信，建议读取地址 0x01 上的 NVM ID 寄存器。回读操作与器件型号中“TPS65215”后面的两位数字匹配。例如，当使用 TPS6521505 时，寄存器 0x01 读取 05。

图 5-1. NVM 编程

## 5.1 配置使能设置

PMIC 具有活动和待机状态，可以在这两个状态下启用或禁用电源轨。当配置为 STBY 时，可以通过 MODE/STBY 引脚触发状态变化。

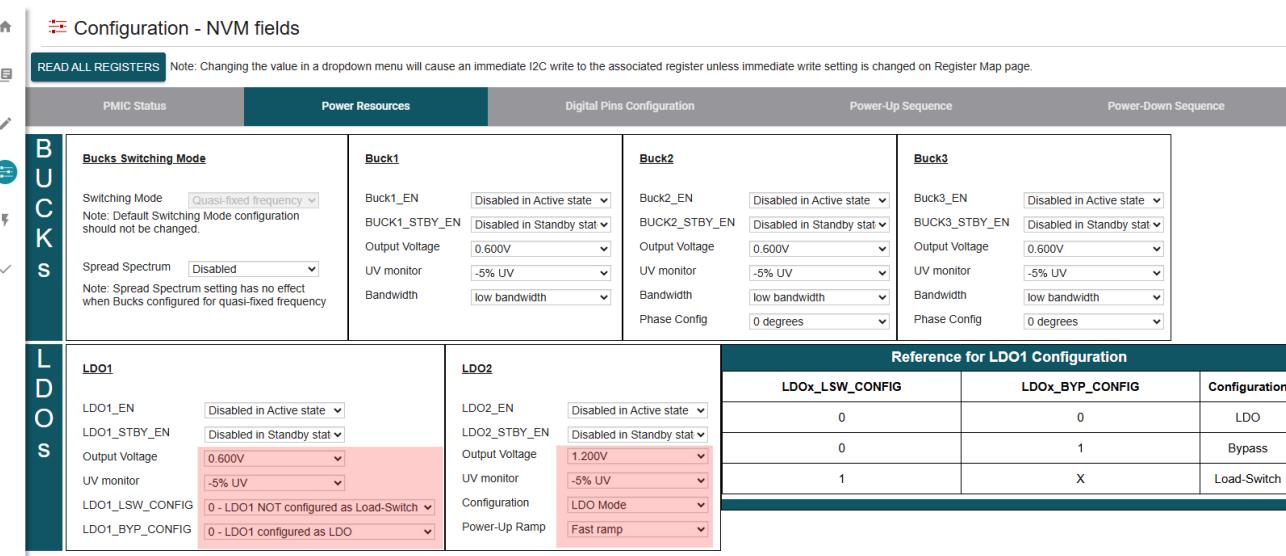

- 图 5-2 显示了使用 TPS65215-GUI 时需要更改的设置。

- 表 5-1 显示了不使用 TPS65215-GUI 时要写入的寄存器字段。

The screenshot shows the TPS65215-GUI configuration interface for NVM fields. The left sidebar lists sections: BUCKS, LDOs, and Sensors. The main area has tabs for Power Resources, Digital Pins Configuration, Power-Up Sequence, and Power-Down Sequence. Under Power Resources, Buck1, Buck2, and Buck3 configurations are shown with various enable and configuration options. A table titled 'Reference for LDO1 Configuration' provides a mapping between LDOx\_LSW\_CONFIG and LDOx\_BYP\_CONFIG values and their meanings (LDO, Bypass, Load-Switch).

| Reference for LDO1 Configuration |                 |               |

|----------------------------------|-----------------|---------------|

| LDOx_LSW_CONFIG                  | LDOx_BYP_CONFIG | Configuration |

| 0                                | 0               | LDO           |

| 0                                | 1               | Bypass        |

| 1                                | X               | Load-Switch   |

图 5-2. 使用 TPS65215-GUI 的使能设置

表 5-1. 用于使能设置的 NVM 寄存器

|             | 寄存器地址 | 位 | 字段名称          | 设置                 |

|-------------|-------|---|---------------|--------------------|

| 在活动状态下启用电源轨 | 0x02  | 5 | LDO2_EN       | 0h = 禁用<br>1h = 启用 |

|             |       | 3 | LDO1_EN       | 0h = 禁用<br>1h = 启用 |

|             |       | 2 | BUCK3_EN      | 0h = 禁用<br>1h = 启用 |

|             |       | 1 | BUCK2_EN      | 0h = 禁用<br>1h = 启用 |

|             |       | 0 | BUCK1_EN      | 0h = 禁用<br>1h = 启用 |

| 在待机状态下启用电源轨 | 0x21  | 5 | LDO2_STBY_EN  | 0h = 禁用<br>1h = 启用 |

|             |       | 3 | LDO1_STBY_EN  | 0h = 禁用<br>1h = 启用 |

|             |       | 2 | BUCK3_STBY_EN | 0h = 禁用<br>1h = 启用 |

|             |       | 1 | BUCK2_STBY_EN | 0h = 禁用<br>1h = 启用 |

|             |       | 0 | BUCK1_STBY_EN | 0h = 禁用<br>1h = 启用 |

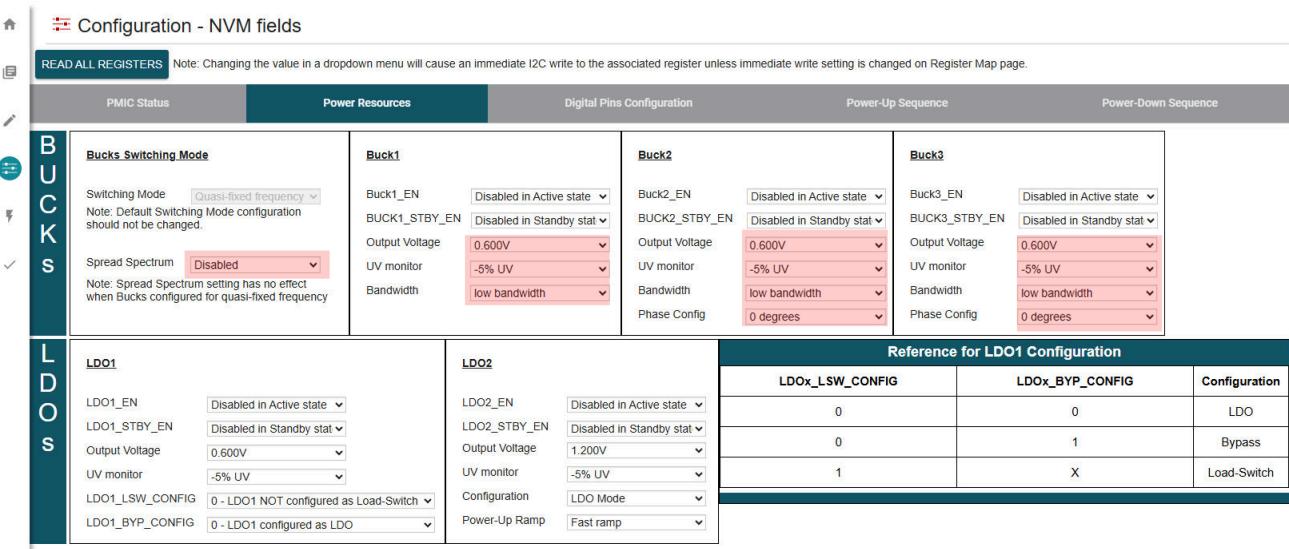

## 5.2 配置降压转换器

可以为降压转换器设定多项设置，其中包括输出电压、欠压 (UV) 监控和带宽等。

- 图 5-3 显示了使用 TPS65215-GUI 时需要更改的设置。

- 表 5-2、表 5-3、表 5-4 和表 5-5 显示了不使用 TPS65215-GUI 时要写入的寄存器字段。

The screenshot shows the TPS65215-GUI software interface. The top navigation bar includes 'File', 'Edit', 'Configuration - NVM fields', 'Read All Registers' (disabled), and 'Note: Changing the value in a dropdown menu will cause an immediate I2C write to the associated register unless immediate write setting is changed on Register Map page'. The main window has tabs for 'PMIC Status', 'Power Resources' (selected), 'Digital Pins Configuration', 'Power-Up Sequence', and 'Power-Down Sequence'. On the left, there are vertical tabs for 'BUCKS' and 'LDOES'. Under 'BUCKS', the 'Bucks Switching Mode' section shows 'Switching Mode: Quasi-fixed frequency' and 'Note: Default Switching Mode configuration should not be changed'. The 'Buck1' and 'Buck2' sections show configuration for Buck1\_EN, BUCK1\_STBY\_EN, Output Voltage (0.600V), UV monitor (-5% UV), Bandwidth (low bandwidth), and Phase Config (0 degrees). Under 'LDOES', the 'LDO1' and 'LDO2' sections show configuration for LDO1\_EN, LDO1\_STBY\_EN, Output Voltage (0.600V), UV monitor (-5% UV), LDO1\_LSW\_CONFIG (0 - LDO1 NOT configured as Load-Switch), and LDO1\_BYP\_CONFIG (0 - LDO1 configured as LDO). To the right, a 'Reference for LDO1 Configuration' table maps LDOx\_LSW\_CONFIG values (0, 1, X) to LDOx\_BYP\_CONFIG values (0, 1) and Configuration types (LDO, Bypass, Load-Switch).

| Reference for LDO1 Configuration |                 |               |

|----------------------------------|-----------------|---------------|

| LDOx_LSW_CONFIG                  | LDOx_BYP_CONFIG | Configuration |

| 0                                | 0               | LDO           |

| 0                                | 1               | Bypass        |

| 1                                | X               | Load-Switch   |

图 5-3. 使用 TPS65215-GUI 的降压转换器设置

**表 5-2. 用于 Buck1 配置的 NVM 寄存器**

| 寄存器地址               | 位   | 字段名称             | 设置                                     |

|---------------------|-----|------------------|----------------------------------------|

| 带宽<br>UV 监视<br>输出电压 | 7   | BUCK1_BW_SEL     | 0h = 低带宽<br>1h = 高带宽                   |

|                     | 6   | BUCK1_UV_THR_SEL | 0h = -5% UV 检测电平<br>1h = - 10% UV 检测电平 |

|                     | 5-0 | BUCK1_VSET       | 有关更多信息，请参阅器件数据表中的寄存器映射。                |

**表 5-3. 用于 Buck2 配置的 NVM 寄存器**

| 寄存器地址               | 位   | 字段名称             | 设置                                     |

|---------------------|-----|------------------|----------------------------------------|

| 带宽<br>UV 监视<br>输出电压 | 7   | BUCK2_BW_SEL     | 0h = 低带宽<br>1h = 高带宽                   |

|                     | 6   | BUCK2_UV_THR_SEL | 0h = -5% UV 检测电平<br>1h = - 10% UV 检测电平 |

|                     | 5-0 | BUCK2_VSET       | 有关更多信息，请参阅器件数据表中的寄存器映射。                |

**表 5-4. 用于 Buck3 配置的 NVM 寄存器**

| 寄存器地址               | 位   | 字段名称             | 设置                                     |

|---------------------|-----|------------------|----------------------------------------|

| 带宽<br>UV 监视<br>输出电压 | 7   | BUCK3_BW_SEL     | 0h = 低带宽<br>1h = 高带宽                   |

|                     | 6   | BUCK3_UV_THR_SEL | 0h = -5% UV 检测电平<br>1h = - 10% UV 检测电平 |

|                     | 5-0 | BUCK3_VSET       | 有关更多信息，请参阅器件数据表中的寄存器映射。                |

**表 5-5. 用于开关模式的 NVM 寄存器 ( 仅在 BUCK\_FF\_ENABLE = 1h 时适用 )**

| 寄存器地址                          | 位   | 字段名称               | 设置                                                |

|--------------------------------|-----|--------------------|---------------------------------------------------|

| 展频<br>开关模式<br>Buck2/Buck3 相位配置 | 5   | BUCK_SS_ENABLE     | 0h = 已禁用展频<br>1h = 已启用展频                          |

|                                | 4   | BUCK_FF_ENABLE     | 请勿更改此位                                            |

|                                | 3-2 | BUCK3_PHASE_CONFIG | 0h = 0 度<br>1h = 90 度<br>2h = 180 度<br>3h = 270 度 |

|                                | 1-0 | BUCK2_PHASE_CONFIG | 0h = 0 度<br>1h = 90 度<br>2h = 180 度<br>3h = 270 度 |

### 5.3 配置 LDO

可以为 LDO 稳压器设定多项设置，其中包括输出电压、欠压 (UV) 监控等。

- 图 5-4 显示了使用 TPS65215-GUI 时需要更改的设置。

- 表 5-6 和 表 5-7 显示了不使用 TPS65215-GUI 时要写入的寄存器字段。

图 5-4. 使用 TPS65215-GUI 的 LDO 设置

表 5-6. 用于 LDO1 设置的 NVM 寄存器

|       | 寄存器地址 | 位   | 字段名称            | 设置                                                                     |  |

|-------|-------|-----|-----------------|------------------------------------------------------------------------|--|

| 输出电压  | 0x07  | 5-0 | LDO1_VSET       | 请参阅器件特定数据表中的寄存器映射。                                                     |  |

| 配置    |       | 7   | LDO1_LSW_CONFIG | 0h = LDO1 未配置为负载开关<br>1h = LDO1 配置为负载开关                                |  |

|       |       | 6   | LDO1_BYP_CONFIG | 0h = LDO1 配置为 LDO<br>1h = LDO1 配置为旁路<br>( 仅在 LDO1_LSW_CONFIG 0x0 时适用 ) |  |

| UV 监视 | 0x1E  | 3   | LDO1_UV_THR     | 0h = -5% UV<br>1h = -10% UV                                            |  |

表 5-7. 用于 LDO2 设置的 NVM 寄存器

|       | 寄存器地址 | 位   | 字段名称              | 设置                          |

|-------|-------|-----|-------------------|-----------------------------|

| 输出电压  | 0x05  | 5-0 | LDO2_VSET         | 请参阅器件特定数据表中的寄存器映射。          |

| 配置    |       | 6   | LDO2_LSW_CONFIG   | 0h = LDO 模式<br>1h = LSW 模式  |

| 斜坡    |       | 7   | LDO2_SLOW_PU_RAMP | 0h = 上电快速斜坡<br>1h = 上电慢速斜坡  |

| UV 监测 | 0x1E  | 5   | LDO2_UV_THR       | 0h = -5% UV<br>1h = -10% UV |

## 5.4 配置 GPIO

GPIO 可用于启用外部分立元件。GPIO 还可用于多 PMIC 配置，以同步两个 TPS65215 器件之间的上电和断电序列。

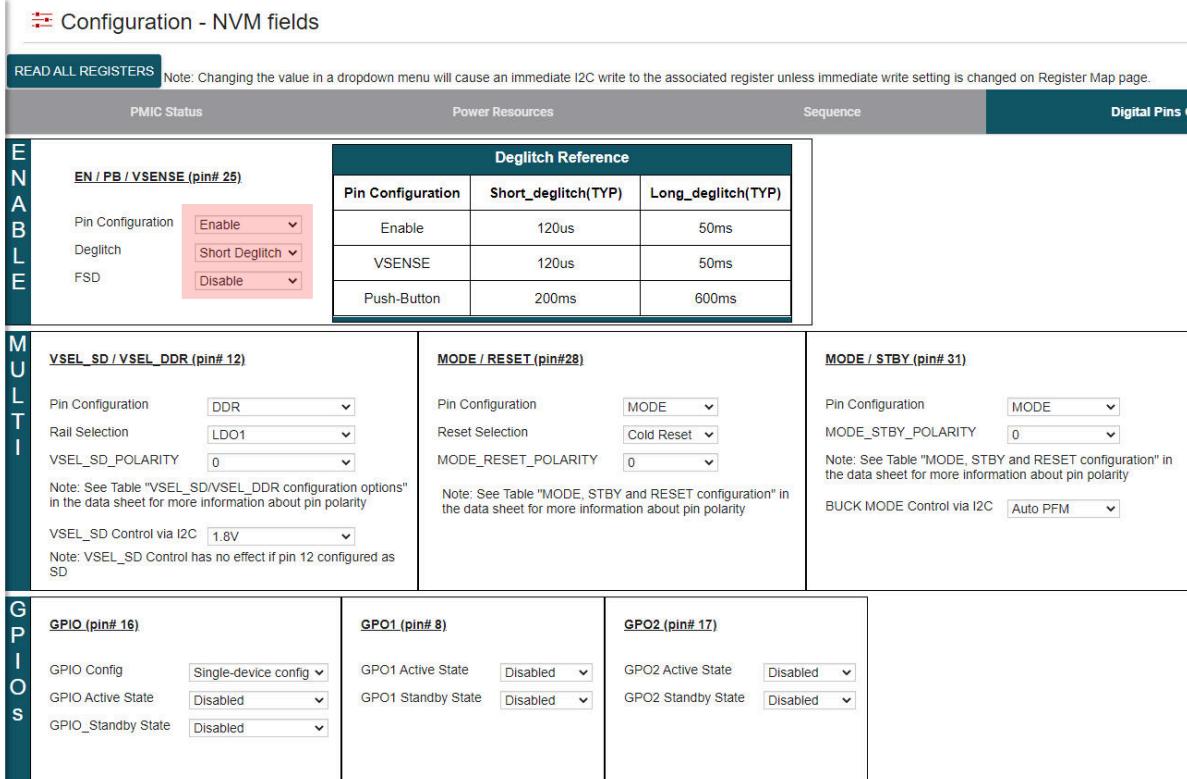

- 图 5-5 显示了使用 TPS65215-GUI 时需要更改的设置。

- 表 5-8 和 表 5-9 显示了不使用 TPS65215-GUI 时要写入的寄存器字段。

Configuration - NVM fields

READ ALL REGISTERS Note: Changing the value in a dropdown menu will cause an immediate I2C write to the associated register unless immediate write setting is changed on Register Map page.

| PMIC Status                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                               | Power Resources                                                |                              | Sequence   | Digital Pins Configuration                                                                                     |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------|------------|----------------------------------------------------------------------------------------------------------------|--------------------|--|--|-------------------|---------------------|--------------------|--------|-------|------|--------|-------|------|-------------|-------|-------|

| <b>E<br/>N<br/>A<br/>B<br/>L<br/>E</b>                                                                             | <table border="1"> <thead> <tr> <th colspan="3">Deglitch Reference</th> </tr> <tr> <th>Pin Configuration</th> <th>Short_deglitch(TYP)</th> <th>Long_deglitch(TYP)</th> </tr> </thead> <tbody> <tr> <td>Enable</td> <td>120us</td> <td>50ms</td> </tr> <tr> <td>VSENSE</td> <td>120us</td> <td>50ms</td> </tr> <tr> <td>Push-Button</td> <td>200ms</td> <td>600ms</td> </tr> </tbody> </table> |                                                                |                              |            |                                                                                                                | Deglitch Reference |  |  | Pin Configuration | Short_deglitch(TYP) | Long_deglitch(TYP) | Enable | 120us | 50ms | VSENSE | 120us | 50ms | Push-Button | 200ms | 600ms |

|                                                                                                                    | Deglitch Reference                                                                                                                                                                                                                                                                                                                                                                            |                                                                |                              |            |                                                                                                                |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

|                                                                                                                    | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                             | Short_deglitch(TYP)                                            | Long_deglitch(TYP)           |            |                                                                                                                |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

|                                                                                                                    | Enable                                                                                                                                                                                                                                                                                                                                                                                        | 120us                                                          | 50ms                         |            |                                                                                                                |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

| VSENSE                                                                                                             | 120us                                                                                                                                                                                                                                                                                                                                                                                         | 50ms                                                           |                              |            |                                                                                                                |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

| Push-Button                                                                                                        | 200ms                                                                                                                                                                                                                                                                                                                                                                                         | 600ms                                                          |                              |            |                                                                                                                |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

| <b>M<br/>U<br/>L<br/>T<br/>I</b>                                                                                   | <b>VSEL_SD / VSEL_DDR (pin# 12)</b>                                                                                                                                                                                                                                                                                                                                                           |                                                                | <b>MODE / RESET (pin#28)</b> |            | <b>MODE / STBY (pin# 31)</b>                                                                                   |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

|                                                                                                                    | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                             | DDR                                                            | Pin Configuration            | MODE       | Pin Configuration                                                                                              | MODE               |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

|                                                                                                                    | Rail Selection                                                                                                                                                                                                                                                                                                                                                                                | LDO1                                                           | Reset Selection              | Cold Reset | MODE_STBY_POLARITY                                                                                             | 0                  |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

|                                                                                                                    | VSEL_SD_POLARITY                                                                                                                                                                                                                                                                                                                                                                              | 0                                                              | MODE_RESET_POLARITY          | 0          | Note: See Table "MODE, STBY and RESET configuration" in the data sheet for more information about pin polarity |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

| Note: See Table "VSEL_SD/VSEL_DDR configuration options" in the data sheet for more information about pin polarity |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                |                              |            |                                                                                                                |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

| VSEL_SD Control via I2C                                                                                            | 1.8V                                                                                                                                                                                                                                                                                                                                                                                          | Note: VSEL_SD Control has no effect if pin 12 configured as SD |                              |            |                                                                                                                |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

| BUCK MODE Control via I2C Auto PFM                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                |                              |            |                                                                                                                |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

| <b>G<br/>P<br/>I<br/>O<br/>S</b>                                                                                   | <b>GPIO (pin# 16)</b>                                                                                                                                                                                                                                                                                                                                                                         |                                                                | <b>GPO1 (pin# 8)</b>         |            | <b>GPO2 (pin# 17)</b>                                                                                          |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

|                                                                                                                    | GPIO Config                                                                                                                                                                                                                                                                                                                                                                                   | Single-device config                                           | GPO1 Active State            | Disabled   | GPO2 Active State                                                                                              | Disabled           |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

|                                                                                                                    | GPIO Active State                                                                                                                                                                                                                                                                                                                                                                             | Disabled                                                       | GPO1 Standby State           | Disabled   | GPO2 Standby State                                                                                             | Disabled           |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

|                                                                                                                    | GPIO_Standby State                                                                                                                                                                                                                                                                                                                                                                            | Disabled                                                       |                              |            |                                                                                                                |                    |  |  |                   |                     |                    |        |       |      |        |       |      |             |       |       |

图 5-5. GPIO 配置

表 5-8. 用于 GPIO 设置的 NVM 寄存器

|            | 寄存器地址 | 位 | 字段名称          | 设置                                      |

|------------|-------|---|---------------|-----------------------------------------|

| 活动状态下的使能设置 | 0x1E  | 2 | GPIO_EN       | 0h = 禁用。输出状态为低电平。<br>1h = 已启用。输出状态为高阻态。 |

|            |       | 1 | GPO2_EN       | 0h = 禁用。输出状态为低电平。<br>1h = 已启用。输出状态为高阻态。 |

|            |       | 0 | GPO1_EN       | 0h = 禁用。输出状态为低电平。<br>1h = 已启用。输出状态为高阻态。 |

| 待机状态下的使能设置 | 0x22  | 2 | GPIO_STBY_E_N | 0h = 禁用。输出状态为低电平。<br>1h = 已启用。输出状态为高阻态。 |

|            |       | 1 | GPO2_STBY_E_N | 0h = 禁用。输出状态为低电平。<br>1h = 已启用。输出状态为高阻态。 |

|            |       | 0 | GPO1_STBY_E_N | 0h = 禁用。输出状态为低电平。<br>1h = 已启用。输出状态为高阻态。 |

表 5-9. 用于多 PMIC 配置的 NVM 寄存器

|         | 寄存器地址 | 位 | 字段名称                | 设置                       |

|---------|-------|---|---------------------|--------------------------|

| GPO2 配置 | 0x1F  | 3 | MULTI_DEVICE_ENABLE | 0h = 单器件配置<br>1h = 多器件配置 |

## 5.5 配置序列

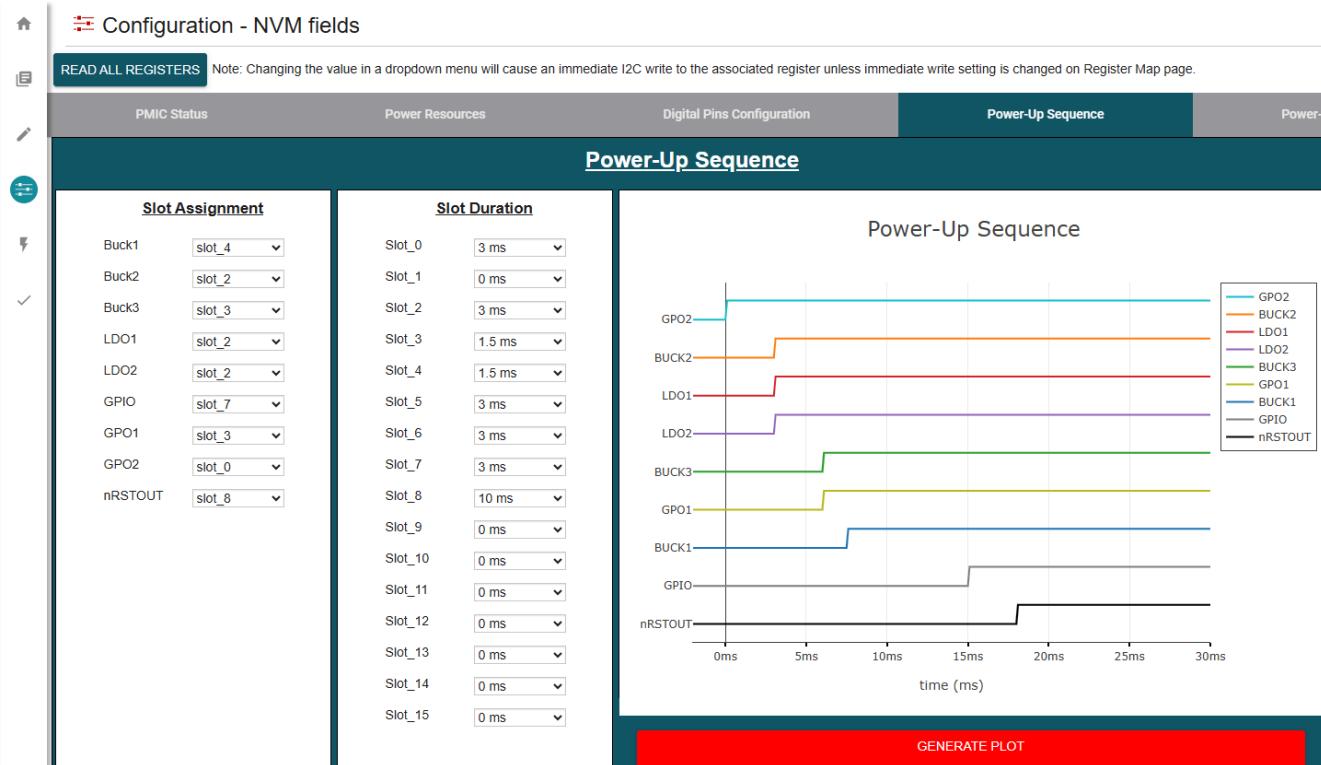

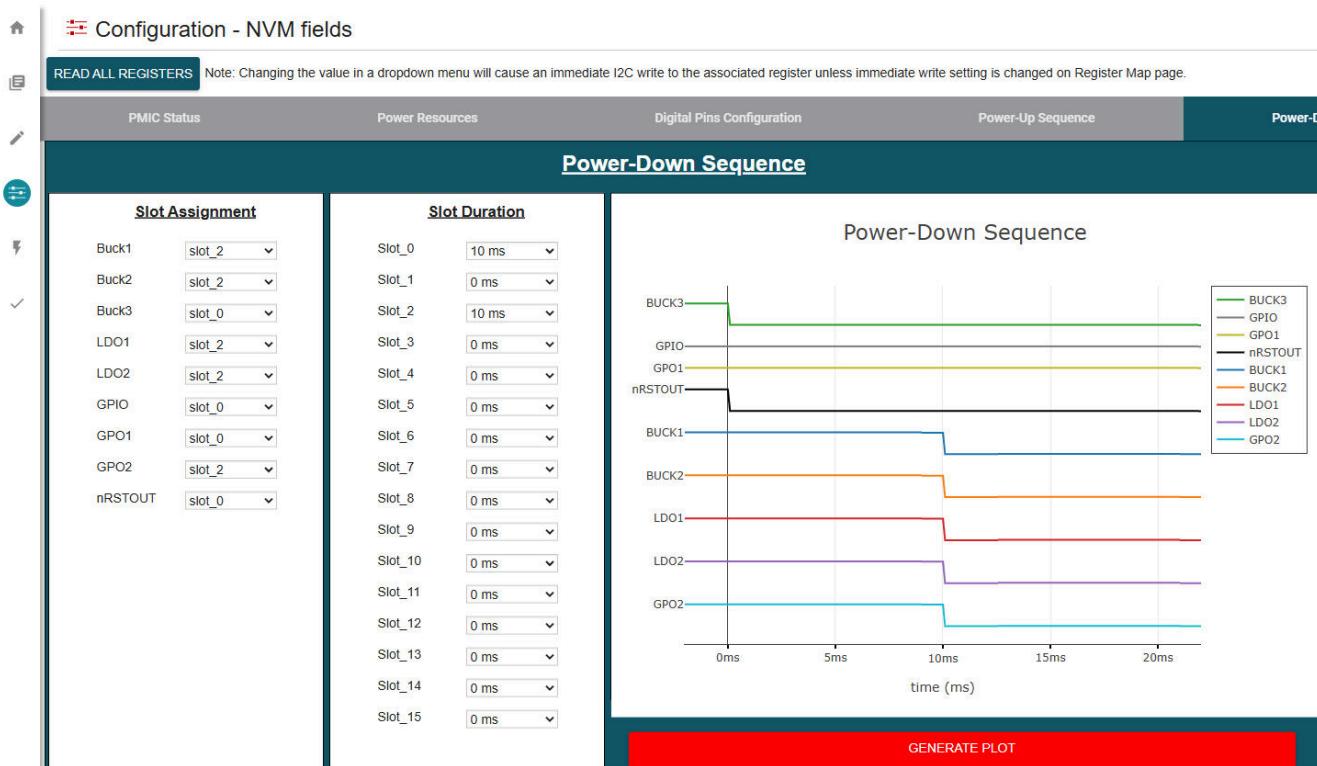

配置 PMIC 序列的过程包括以下两个步骤：

1. 上电/下电时隙分配：时隙分配定义了电源轨的开启或关闭顺序。每个 PMIC 电源轨必须分配一个时隙。有 16 个可用时隙 (0-15)。可将多个电源轨 (包括 GPIO) 分配到同一时隙，以便同时启用它们。

2. 上电/下电时隙持续时间：时隙持续时间是指从一个时隙开始到下一时隙开始所隔的时间。例如，如果 Buck1 被分配至持续时间为 3ms 的 slot0，Buck2 被分配至时隙 1，则 Buck2 在 Buck1 后 3ms 开启。

#### 备注

时隙持续时间不能决定电源轨斜升所需的时间。时隙持续时间仅指定 PMIC 在启用（或禁用）分配给下一个时隙的电源轨之前等待的时间。

- 图 5-6 和 图 5-7 显示了使用 TPS65215-GUI 时需要更改的设置。

- 表 5-10、表 5-11、表 5-12 和表 5-13 显示了不使用 TPS65215-GUI 时要写入的寄存器字段。

图 5-6. 上电序列配置

图 5-7. 断电序列配置

表 5-10. 上电序列 - 时隙分配

|              | 寄存器地址 | 位   | 字段名称                   | 设置                 |

|--------------|-------|-----|------------------------|--------------------|

| 上电序列<br>时隙分配 | 0x11  | 7-4 | BUCK1_SEQUENCE_ON_SLOT | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0x10  | 7-4 | BUCK2_SEQUENCE_ON_SLOT | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0xF   | 7-4 | BUCK3_SEQUENCE_ON_SLOT | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0xE   | 7-4 | LDO1_SEQUENCE_ON_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0xC   | 7-4 | LDO2_SEQUENCE_ON_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0x15  | 7-4 | GPO1_SEQUENCE_ON_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0x14  | 7-4 | GPO2_SEQUENCE_ON_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0x13  | 7-4 | GPIO_SEQUENCE_ON_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0x12  | 7-4 | nRST_SEQUENCE_ON_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

表 5-11. 上电序列 - 时隙持续时间

|                | 寄存器地址 | 位   | 字段名称                      | 设置                 |

|----------------|-------|-----|---------------------------|--------------------|

| 上电序列<br>时隙持续时间 | 0x16  | 7-6 | POWER_UP_SLOT_0_DURATION  | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 5-4 | POWER_UP_SLOT_1_DURATION  | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 3-2 | POWER_UP_SLOT_2_DURATION  | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 1-0 | POWER_UP_SLOT_3_DURATION  | 请参阅器件特定数据表中的寄存器映射。 |

|                | 0x17  | 7-6 | POWER_UP_SLOT_4_DURATION  | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 5-4 | POWER_UP_SLOT_5_DURATION  | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 3-2 | POWER_UP_SLOT_6_DURATION  | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 1-0 | POWER_UP_SLOT_7_DURATION  | 请参阅器件特定数据表中的寄存器映射。 |

|                | 0x18  | 7-6 | POWER_UP_SLOT_8_DURATION  | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 5-4 | POWER_UP_SLOT_9_DURATION  | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 3-2 | POWER_UP_SLOT_10_DURATION | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 1-0 | POWER_UP_SLOT_11_DURATION | 请参阅器件特定数据表中的寄存器映射。 |

|                | 0x19  | 7-6 | POWER_UP_SLOT_12_DURATION | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 5-4 | POWER_UP_SLOT_13_DURATION | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 3-2 | POWER_UP_SLOT_14_DURATION | 请参阅器件特定数据表中的寄存器映射。 |

|                |       | 1-0 | POWER_UP_SLOT_15_DURATION | 请参阅器件特定数据表中的寄存器映射。 |

表 5-12. 下电序列 - 时隙分配

|              | 寄存器地址 | 位   | 字段名称                    | 设置                 |

|--------------|-------|-----|-------------------------|--------------------|

| 下电序列<br>时隙分配 | 0x11  | 7-4 | BUCK1_SEQUENCE_OFF_SLOT | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0x10  | 7-4 | BUCK2_SEQUENCE_OFF_SLOT | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0xF   | 7-4 | BUCK3_SEQUENCE_OFF_SLOT | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0xE   | 7-4 | LDO1_SEQUENCE_OFF_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0xC   | 7-4 | LDO2_SEQUENCE_OFF_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0x15  | 7-4 | GPO1_SEQUENCE_OFF_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0x14  | 7-4 | GPO2_SEQUENCE_OFF_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0x13  | 7-4 | GPIO_SEQUENCE_OFF_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

|              | 0x12  | 7-4 | nRST_SEQUENCE_OFF_SLOT  | 请参阅器件特定数据表中的寄存器映射。 |

**表 5-13. 下电序列 - 时隙持续时间**

| 寄存器地址          | 位    | 字段名称 | 设置                                                |

|----------------|------|------|---------------------------------------------------|

| 下电序列<br>时隙持续时间 | 0x1A | 7-6  | POWER_DOWN_SLOT_0_DURATION<br>请参阅器件特定数据表中的寄存器映射。  |

|                |      | 5-4  | POWER_DOWN_SLOT_1_DURATION<br>请参阅器件特定数据表中的寄存器映射。  |

|                |      | 3-2  | POWER_DOWN_SLOT_2_DURATION<br>请参阅器件特定数据表中的寄存器映射。  |

|                |      | 1-0  | POWER_DOWN_SLOT_3_DURATION<br>请参阅器件特定数据表中的寄存器映射。  |

|                | 0x1B | 7-6  | POWER_DOWN_SLOT_4_DURATION<br>请参阅器件特定数据表中的寄存器映射。  |

|                |      | 5-4  | POWER_DOWN_SLOT_5_DURATION<br>请参阅器件特定数据表中的寄存器映射。  |

|                |      | 3-2  | POWER_DOWN_SLOT_6_DURATION<br>请参阅器件特定数据表中的寄存器映射。  |

|                |      | 1-0  | POWER_DOWN_SLOT_7_DURATION<br>请参阅器件特定数据表中的寄存器映射。  |

|                | 0x1C | 7-6  | POWER_DOWN_SLOT_8_DURATION<br>请参阅器件特定数据表中的寄存器映射。  |

|                |      | 5-4  | POWER_DOWN_SLOT_9_DURATION<br>请参阅器件特定数据表中的寄存器映射。  |

|                |      | 3-2  | POWER_DOWN_SLOT_10_DURATION<br>请参阅器件特定数据表中的寄存器映射。 |

|                |      | 1-0  | POWER_DOWN_SLOT_11_DURATION<br>请参阅器件特定数据表中的寄存器映射。 |

|                | 0x1D | 7-6  | POWER_DOWN_SLOT_12_DURATION<br>请参阅器件特定数据表中的寄存器映射。 |

|                |      | 5-4  | POWER_DOWN_SLOT_13_DURATION<br>请参阅器件特定数据表中的寄存器映射。 |

|                |      | 3-2  | POWER_DOWN_SLOT_14_DURATION<br>请参阅器件特定数据表中的寄存器映射。 |

|                |      | 1-0  | POWER_DOWN_SLOT_15_DURATION<br>请参阅器件特定数据表中的寄存器映射。 |

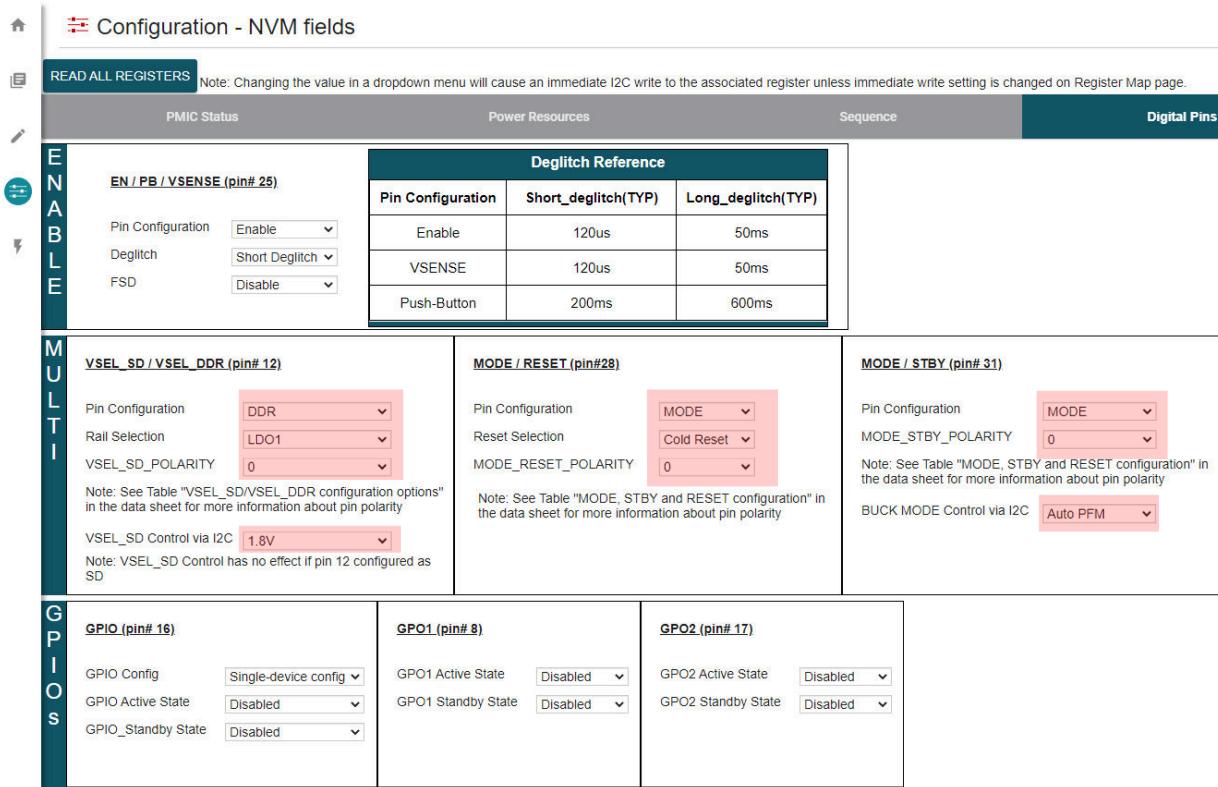

## 5.6 配置多功能引脚

TPS65215 PMIC 有三个可配置多功能引脚。MODE/STBY 和 MODE/RESET 可配置为 MODE ( 以选择开关 ) 、 STBY ( 以触发至待机状态的转换 ) , 或配置为 RESET ( 以触发冷复位或热复位 ) 。可将 VSEL\_SD/VSEL\_DDR 引脚配置为设置 LDO1 上的输出电压或设置 Buck3 上的输出电压。有关引脚极性的信息 , 请参阅器件特定数据表。

### 备注

如果 VSEL\_SD/VSEL\_DDR 未用于设置 LDO1 上的输出电压 , 则必须将其配置为 DDR , 并使用原理图中的下拉电阻将其拉至 GND 。此外 , VSEL\_SD\_I2C\_CTRL 必须编程为 1h 。

- 图 5-8 显示了使用 TPS65215-GUI 时需要更改的设置

- 图 5-8 显示了不使用 TPS65215-GUI 时要写入的寄存器字段。

The screenshot shows the TPS65215-GUI software interface. The top navigation bar includes 'Configuration - NVM fields', 'READ ALL REGISTERS', and a note about immediate I2C writes. The main area is divided into several sections:

- Digital Pins Configuration:** Contains a 'Deglitch Reference' table with columns for Pin Configuration, Short\_deglitch(TYP), and Long\_deglitch(TYP). It includes rows for EN / PB / VSENSE (pin# 25) and Push-Button.

- VSEL\_SD / VSEL\_DDR (pin# 12):** Includes Pin Configuration (DDR), Rail Selection (LDO1), and VSEL\_SD\_POLARITY (0).

- MODE / RESET (pin#28):** Includes Pin Configuration (MODE), Reset Selection (Cold Reset), and MODE\_RESET\_POLARITY (0).

- MODE / STBY (pin# 31):** Includes Pin Configuration (MODE), MODE\_STBY\_POLARITY (0), and a note about pin polarity.

- GPIOs:** Contains sections for GPIO (pin# 16), GPO1 (pin# 8), and GPO2 (pin# 17), each with Active and Standby State configurations.

图 5-8. 使用 TPS65215-GUI 的多功能配置

表 5-14. 用于 VSEL\_SD/VSEL\_DDR 的 NVM 寄存器

|      | 寄存器地址 | 位 | 字段名称             | 设置                                                                                                 |

|------|-------|---|------------------|----------------------------------------------------------------------------------------------------|

| 引脚功能 | 0x1F  | 0 | VSEL_DDR_SD      | 0h = VSEL 引脚配置为 DDR , 以设置 Buck3 上的电压<br>1h = VSEL 引脚配置为 SD , 以设置 VSEL_RAIL 上的电压                    |

| 引脚极性 |       | 1 | VSEL_SD_POLARITY | 0h =<br>• 低电平 : 1.8V<br>• 高电平 : LDOx_VOUT 寄存器<br><br>1h =<br>• 高电平 : 1.8V<br>• 低电平 : LDOx_VOUT 寄存器 |

表 5-15. 用于 MODE/STBY 的 NVM 寄存器

|      | 寄存器地址 | 位   | 字段名称               | 设置                                                      |

|------|-------|-----|--------------------|---------------------------------------------------------|

| 引脚功能 | 0x20  | 1-0 | MODE_STBY_CONFIG   | 0h = MODE<br>1h = STBY<br>2h = MODE 和 STBY<br>3h = MODE |

| 引脚极性 | 0x1F  | 4   | MODE_STBY_POLARITY | 有关更多信息 , 请参阅器件数据表中的 寄存器映射。                              |

表 5-16. 用于 MODE/RESET 的 NVM 寄存器

|          | 寄存器地址 | 位 | 字段名称                   | 设置                                 |

|----------|-------|---|------------------------|------------------------------------|

| 引脚功能     | 0x20  | 2 | MODE_RESET_CONFIG      | 0h = MODE<br>1h = RESET            |

| RESET 配置 |       | 6 | WARM_COLD_RESET_CONFIG | 0h = COLD RESET<br>1h = WARM RESET |

表 5-16. 用于 MODE/RESET 的 NVM 寄存器 (续)

|      | 寄存器地址 | 位 | 字段名称                | 设置                      |

|------|-------|---|---------------------|-------------------------|

| 引脚极性 | 0x1F  | 5 | MODE_RESET_POLARITY | 有关更多信息，请参阅器件数据表中的寄存器映射。 |

## 5.7 配置 EN/PB/VSENSE 引脚

PMIC 的使能引脚可配置为“Enable”、“Push-Button”或“VSENSE”。除此功能外，还可以配置抗尖峰脉冲。此外，该引脚还具有首次电源检测 (FSD) 选项，从而在首次上电期间忽略 EN/PB/VSENSE 引脚的状态。

- 图 5-9 显示了使用 TPS65215-GUI 时需要更改的设置。

- 表 5-17 显示了不使用 TPS65215-GUI 时要写入的寄存器字段。

图 5-9. 使用 TPS65215-GUI 的 EN/PB/VSENSE 配置

表 5-17. 用于 EN/PB/VSENSE 的 NVM 寄存器

|        | 寄存器地址 | 位   | 字段名称                | 设置                                           |

|--------|-------|-----|---------------------|----------------------------------------------|

| 首次电源检测 | 0x20  | 7   | PU_ON_FSD           | 0h = FSD 禁用<br>1h = FSD 启用                   |

| 引脚配置   |       | 5-4 | EN_PB_VSENSE_CONFIG | 0h = 启用<br>1h = 按钮<br>2h = VSENSE<br>3h = 启用 |

| 抗尖峰脉冲  |       | 3   | EN_PB_VSENSE_DEGL   | 请参阅器件特定数据表中的寄存器映射。                           |

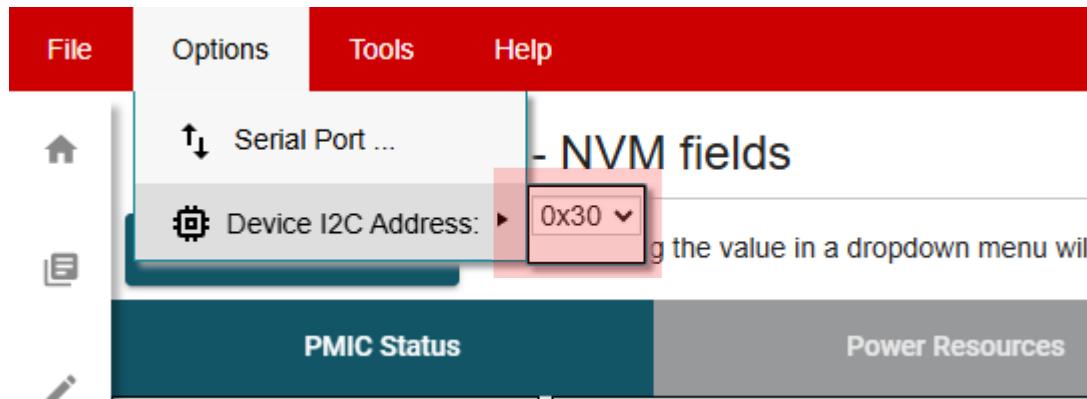

## 5.8 更改 I2C 地址

TPS6521505 的默认 I2C 地址配置为 0x30。如果需要，可以通过在 TPS65215-GUI 的寄存器映射中搜索寄存器 I2C\_ADDRESS\_REG 并更改默认的 0x30 地址来更改此配置，如图 5-10 所示。由于对此寄存器的任何写入都会

立即作出反应，因此您必须将设备 I<sub>2</sub>C 地址更改为新值，如 图 5-11 所示。一旦更改了寄存器，必须通过将 0x0A 写入寄存器 0x34 来将新值保存到 NVM 中。器件现在开始与器件 I<sub>2</sub>C 地址中设置的新地址通信。

#### 备注

在多 PMIC 配置中使用多个 TPS65215 器件时，每个器件必须具有唯一的 I<sub>2</sub>C 地址。第 2 个、第 3 个和其他 PMIC 的 I<sub>2</sub>C 地址必须从默认值 0x30 更改为新值。

图 5-10. I<sub>2</sub>C\_ADDRESS\_REG

表 5-18. I<sub>2</sub>C\_ADDRESS\_REG

| 寄存器地址 | 位   | 字段名称                         |

|-------|-----|------------------------------|

| 0x26  | 6-0 | I <sub>2</sub> C_ADDRESS_REG |

图 5-11. 器件 I<sub>2</sub>C 地址

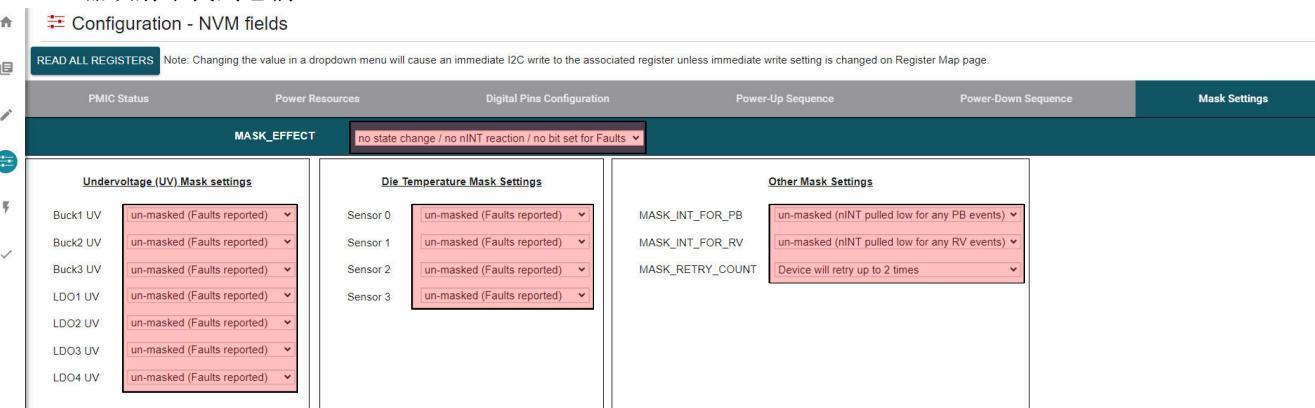

## 5.9 配置屏蔽设置

有多种中断设置可被屏蔽，从而绕过特定 PMIC 监控功能或修改 PMIC 在检测到中断时的反应方式。可以屏蔽的中断包括欠压监测、温度监测等。图 5-12 显示了 GUI 配置选项卡中的屏蔽设置。

**备注**

如果任何屏蔽寄存器未显示在 TPS65215-GUI 的配置选项卡中，则可以在包含完整寄存器列表的寄存器映射中找到它们。

图 5-12. TPS65215-GUI 中的屏蔽设置

表 5-19. 寄存器 0x1E 上的屏蔽设置

| 寄存器地址 | 位 | 字段名称                         |

|-------|---|------------------------------|

| 0x1E  | 7 | BYPASS_RAILS_DISCHARGE_CHECK |

表 5-20. 寄存器 0x1E 上的屏蔽设置

| 寄存器地址 | 位 | 字段名称             |

|-------|---|------------------|

| 0x24  | 7 | MASK_RETRY_COUNT |

|       | 6 | BUCK3_UV_MASK    |

|       | 5 | BUCK2_UV_MASK    |

|       | 4 | BUCK1_UV_MASK    |

|       | 2 | LDO2_UV_MASK     |

|       | 0 | LDO1_UV_MASK     |

表 5-21. 寄存器 0x1E 上的屏蔽设置

| 寄存器地址 | 位   | 字段名称               |

|-------|-----|--------------------|

| 0x25  | 7   | MASK_INT_FOR_PB    |

|       | 6-5 | MASK_EFFECT        |

|       | 4   | MASK_INT_FOR_RV    |

|       | 3   | SENSOR_0_WARM_MASK |

|       | 2   | SENSOR_1_WARM_MASK |

|       | 1   | SENSOR_2_WARM_MASK |

|       | 0   | SENSOR_3_WARM_MASK |

## 5.10 NVM 重新编程

更新寄存器设置后，可以通过将 0x0A 写入寄存器地址 0x34 而将新值保存到 NVM 中。

- 图 5-13 显示了使用 TPS65215-GUI 时用于将寄存器设置保存到 NVM 的按钮。

- 表 5-22 显示了不使用 TPS65215-GUI 时要写入的寄存器字段。

图 5-13. 使用 TPS65215-GUI 重新对 NVM 进行编程

表 5-22. 用以将寄存器设置保存到 NVM 中的 I2C 写入

| 寄存器地址 | 位   | 字段名称         | 数据   |

|-------|-----|--------------|------|

| 0x34  | 3-0 | USER_NVM_CMD | 0x0A |

#### 备注

建议使用 TPS65215-GUI 将所选的寄存器设置导出到 CSV 和 JSON 文件中。图 5-14 展示了如何导出 NVM 设置。使用“Save Registers As”之前，必须在“Register File Format”中选择文件格式。

图 5-14. 使用 TPS65215-GUI 导出 NVM 设置

## A 非 NVM 寄存器

PMIC 寄存器映射包含 NVM 和非 NVM 位。寄存器地址 0x00 至 0x27 包含由 EEPROM 备份的 NVM 位。该寄存器设置可通过 I2C 进行更改，并且可按照编程指南中所述对默认值重新编程。每个 NVM 位的复位值在器件特定数据表寄存器映射中标记为“X”，因为这些值可以重新进行编程，并且对于每个可订购器件型号都是唯一的。

非 NVM 位位于寄存器地址 0x28 至 0x41 中。这些寄存器设置可由 I2C 更改，但默认值无法重新进行编程。下电上电后以及每次 PMIC 进入初始化状态时，非 NVM 位的寄存器设置都会恢复为其默认值。可以在器件特定数据表寄存器映射中的“复位”列下找到非 NVM 位的默认值。

## B 将 NVM 配置文件加载到 PMIC

图 B-1 描述了将预配置的 NVM 文件 (.CSV 或 .JSON 扩展名) 加载到 PMIC NVM 中的过程。焊接 EVM (TPS65215EVM) 可用作参考，但也可使用插槽式 EVM。TPS6521505 产品页面包含多个 NVM 文件，这些文件经过预先配置，可满足特定处理器或 SoC 的要求。TI 的客户可以重复使用这些文件，在其生产线上或通过与经销商联系来对 PMIC 重新编程。

### 备注

如果预先配置的 NVM 文件无法满足所有应用要求，则仍可使用 TPS65215-GUI 将这些文件加载到 PMIC NVM、进行必要的更改并生成新的 NVM 文件。

图 B-1. 加载 NVM 配置文件

## C PMIC 可配置字段

本节展示了每个 PMIC 电源和数字资源的可编程 NVM 字段列表。一些寄存器字段带有“x”以简化列表。将“x”替换为相应的电源轨编号，即可在器件设定数据表或编程指南中找到正确的寄存器字段。同样，对于序列时隙持续时间，使用“y”来简化列表，但可将其替换为特定的时隙编号。

| PMIC rail           | Configurable Setting                   | Register Field                                                              |

|---------------------|----------------------------------------|-----------------------------------------------------------------------------|

| Bucks               | Enable settings                        | Active State: Buck $x$ _EN<br>Standby State: BUCK $x$ _STBY_EN              |

|                     | Output voltage                         | BUCK $x$ _VSET                                                              |

|                     | Under-voltage monitoring               | BUCK $x$ _UV_THR_SEL                                                        |

|                     | Bandwidth                              | BUCK $x$ _BW_SEL                                                            |

|                     | Power-up sequence                      | Slot#: BUCK $x$ _SEQUENCE_ON_SLOT<br>Duration: POWER_UP_SLOT_y_DURATION     |

|                     | Power-down sequence                    | Slot#: BUCK $x$ _SEQUENCE_OFF_SLOT<br>Duration: POWER_DOWN_SLOT_y_DURATION  |

| LDOs                | Enable settings                        | Active State: LDO $x$ _EN<br>Standby State: LDO $x$ _STBY_EN                |

|                     | Output voltage                         | LDO $x$ _VSET                                                               |

|                     | Under-voltage monitoring               | LDO $x$ _UV_THR_SEL                                                         |

|                     | Rail config (LDO, load-switch, bypass) | LDO $x$ _LSW_CONFIG<br>LDO $x$ _BYP_CONFIG (LDO1 only)                      |

|                     | Ramp                                   | LDO $x$ _SLOW_PU_RAMP (LDO2 only)                                           |

|                     | Power-up sequence                      | Slot#: LDO $x$ _SEQUENCE_ON_SLOT<br>Duration: POWER_UP_SLOT_y_DURATION      |

|                     | Power-down sequence                    | Slot#: LDO $x$ _SEQUENCE_OFF_SLOT<br>Duration: POWER_DOWN_SLOT_y_DURATION   |

| GPIOs               | Enable settings GPIO                   | Active State: GPI/O $x$ _EN<br>Standby State: GPI/O $x$ _STBY_EN            |

|                     | Pin Function                           | MULTI_DEVICE_ENABLE (GPIO only)                                             |

|                     | Power-up sequence                      | Slot#: GPI/O $x$ _SEQUENCE_ON_SLOT<br>Duration: POWER_UP_SLOT_y_DURATION    |

|                     | Power-down sequence                    | Slot#: GPI/O $x$ _SEQUENCE_OFF_SLOT<br>Duration: POWER_DOWN_SLOT_y_DURATION |

| Enable pin          | Pin Function                           | EN_PB_VSENSE_DEGL                                                           |

|                     | Deglitch                               | EN_PB_VSENSE_CONFIG                                                         |

|                     | First Supply Detection (FSD)           | PU_ON_FSD                                                                   |

| VSEL_SD<br>VSEL_DDR | Pin Function                           | VSEL_DDR_SD                                                                 |

|                     | Rail Selection                         | VSEL_RAIL                                                                   |

|                     | Pin Polarity                           | VSEL_SD_POLARITY                                                            |

| MODE/STBY           | Pin Function                           | MODE_STBY_CONFIG                                                            |

|                     | Pin Polarity                           | MODE_STBY_POLARITY                                                          |

| MODE/RESET          | Pin Function                           | MODE_RESET_CONFIG                                                           |

|                     | RESET selection                        | WARM_COLD_RESET_CONFIG                                                      |

|                     | Pin Polarity                           | MODE_RESET_POLARITY                                                         |

| nRSTOUT             | Power-up sequence                      | Slot#: nRST_SEQUENCE_ON_SLOT<br>Duration: POWER_UP_SLOT_y_DURATION          |

|                     | Power-down sequence                    | Slot#: nRST_SEQUENCE_OFF_SLOT<br>Duration: POWER_DOWN_SLOT_y_DURATION       |

图 C-1. NVM 可编程字段

## 参考资料

- 德州仪器 (TI) , [TPS6521505-Q1 适用于 ARM Cortex—A53 处理器和 FPGA 的集成电源管理 IC 数据表](#)

- 德州仪器 (TI) , [TPS65219EVM-SKT 用户指南](#)

## 9 修订历史记录

注：以前版本的页码可能与当前版本的页码不同

| 日期         | 修订版本 | 注释    |

|------------|------|-------|

| 2025 年 9 月 | *    | 初始发行版 |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#))、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025 , 德州仪器 (TI) 公司

最后更新日期 : 2025 年 10 月