SLPS384D March 2013 – April 2015 CSD87588N

PRODUCTION DATA.

- 1Features

- 2Applications

- 3Description

- 4Revision History

- 5Specifications

- 6Application and Implementation

- 7Layout

- 8Device and Documentation Support

- 9Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- MPA|5

Thermal pad, mechanical data (Package|Pins)

Orderable Information

1 Features

2 Applications

- Synchronous Buck Converters

- High-Current, Low Duty Cycle Applications

- Multiphase Synchronous Buck Converters

- POL DC-DC Converters

3 Description

The CSD87588N NexFET™ power block II is a highly-optimized design for synchronous buck applications offering high current and high efficiency capability in a small 5 mm × 2.5 mm outline. Optimized for 5 V gate drive applications, this product offers an efficient and flexible solution capable of providing a high density power supply when paired with any 5 V gate driver from an external controller/driver.

Ordering Information(1)

| Device | Media | Qty | Package | Ship |

|---|---|---|---|---|

| CSD87588N | 13-Inch Reel | 2500 | 5 x 2.5 LGA | Tape and Reel |

| CSD87588NT | 7-Inch Reel | 250 |

- For all available packages, see the orderable addendum at the end of the data sheet.

Typical Circuit |

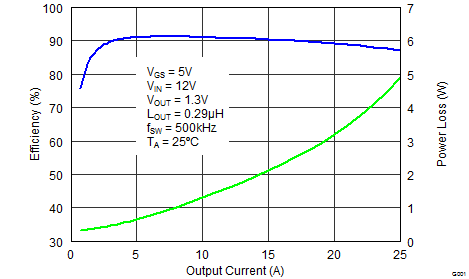

Typical Power Block Efficiency and Power Loss |