# ADC12DJ5200-SP 10.4GSPS シングルチャネルまたは 5.2GSPS デュアルチャネル、12 ビット、RF サンプリング A/D コンバータ (ADC)

## 1 特長

- 耐放射線特性:

- 吸収線量 (TID): 300krad (Si)

- シングル イベント ラッチアップ (SEL): 120MeV $\cdot$ cm<sup>2</sup>/mg

- シングル イベント アップセット(SEU)耐性レジスタ

- ADC コア:

- 12 ビット分解能

- シングル チャネル モードで最大 10.4GSPS

- デュアル チャネル モードで最大 5.2GSPS

- 性能仕様:

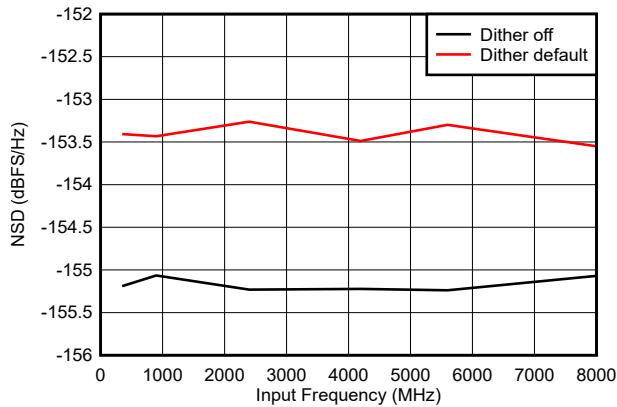

- ノイズフロア (-20dBFS、V<sub>FS</sub> = 1V<sub>PP-DIFF</sub>):

- デュアル チャネル モード:-151.8dBFS/Hz

- シングル チャネル モード:-154.4dBFS/Hz

- ENOB (デュアル チャネル、F<sub>IN</sub> = 2.4GHz): 8.6 ビット

- バッファ付きアナログ入力、V<sub>CMI</sub> = 0V:

- アナログ入力帯域幅 (-3dB): 8GHz

- 使用可能な入力周波数範囲:> 10GHz

- フルスケール入力電圧 (V<sub>FS</sub>、デフォルト): 0.8V<sub>PP</sub>

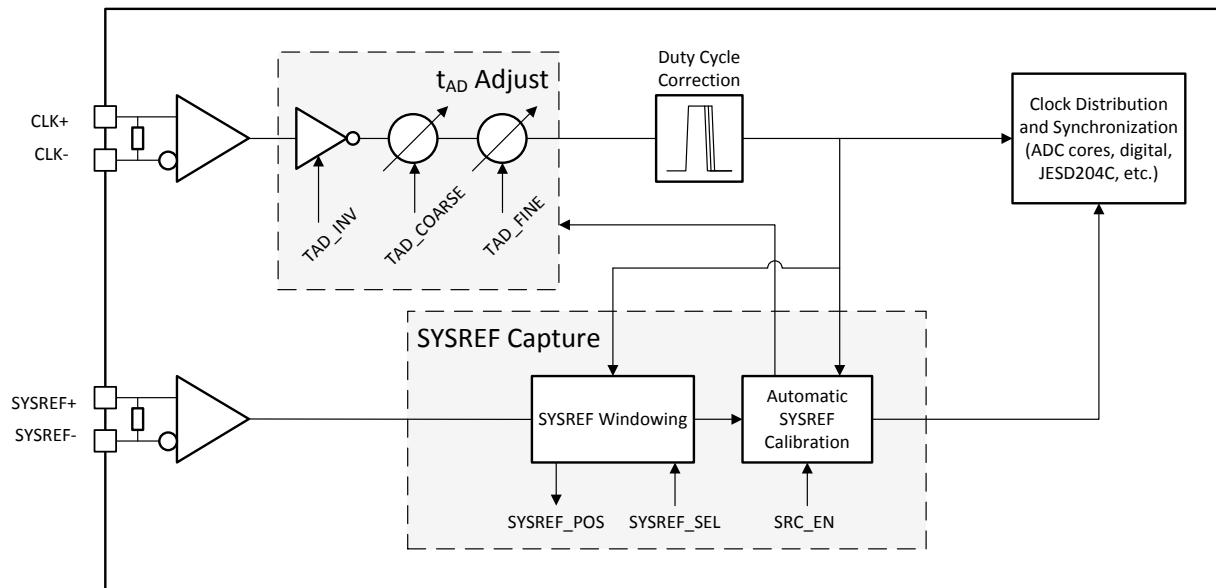

- ノイズなしのアーチャ遅延 (t<sub>AD</sub>) 調整:

- 高精度サンプリング制御: 19fs ステップ

- 同期およびインターリーブ動作を簡素化

- 遅延は温度および電圧に対して不変

- 使いやすい同期機能:

- SYSREF タイミングの自動較正

- サンプル マーキング用タイム スタンプ

- JESD204C シリアル データ インターフェイス

- 最大レーン速度: 17.16Gbps

- 64b/66b および 8b/10b エンコードのサポート

- 8b/10b モードは JESD204B 互換

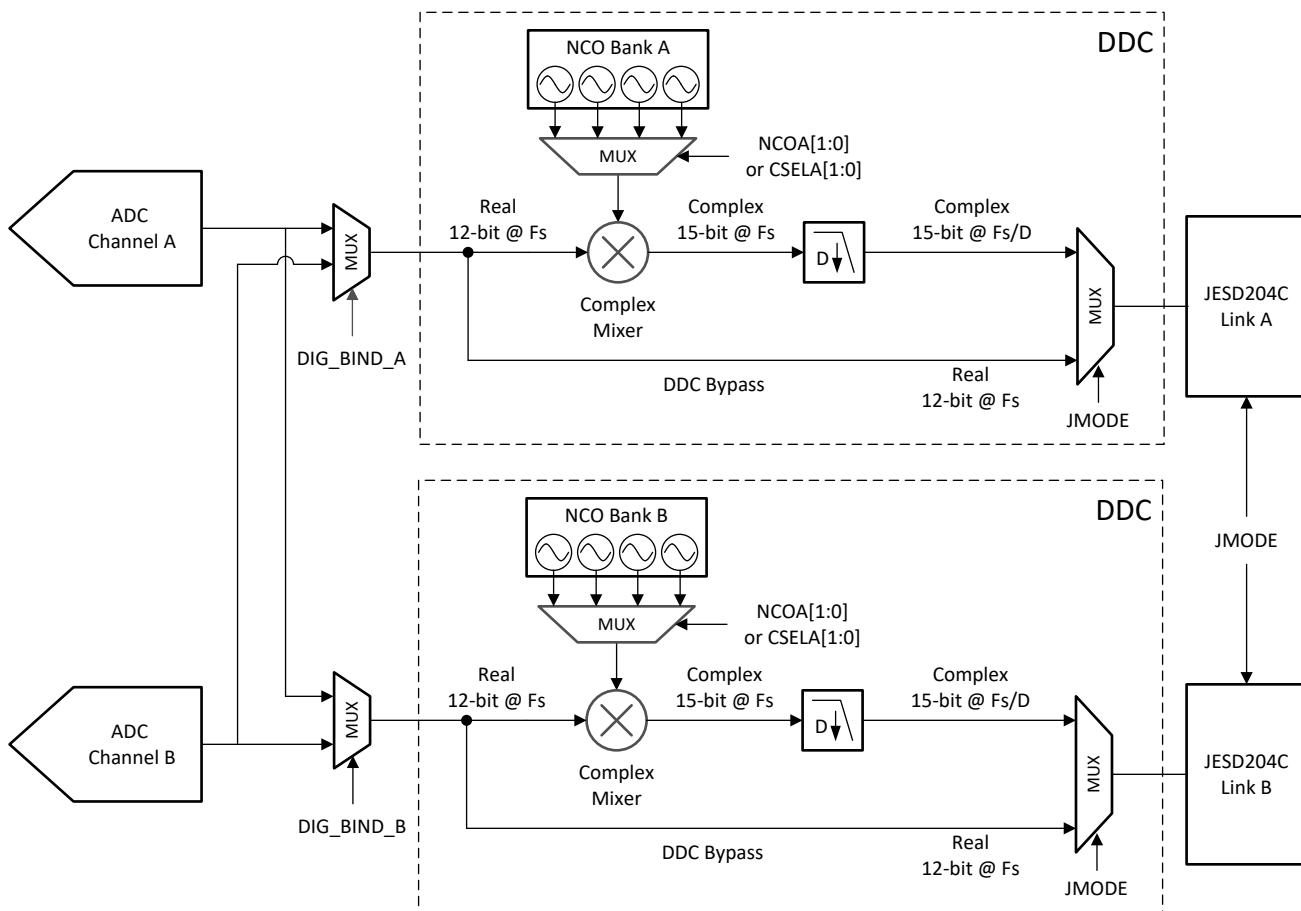

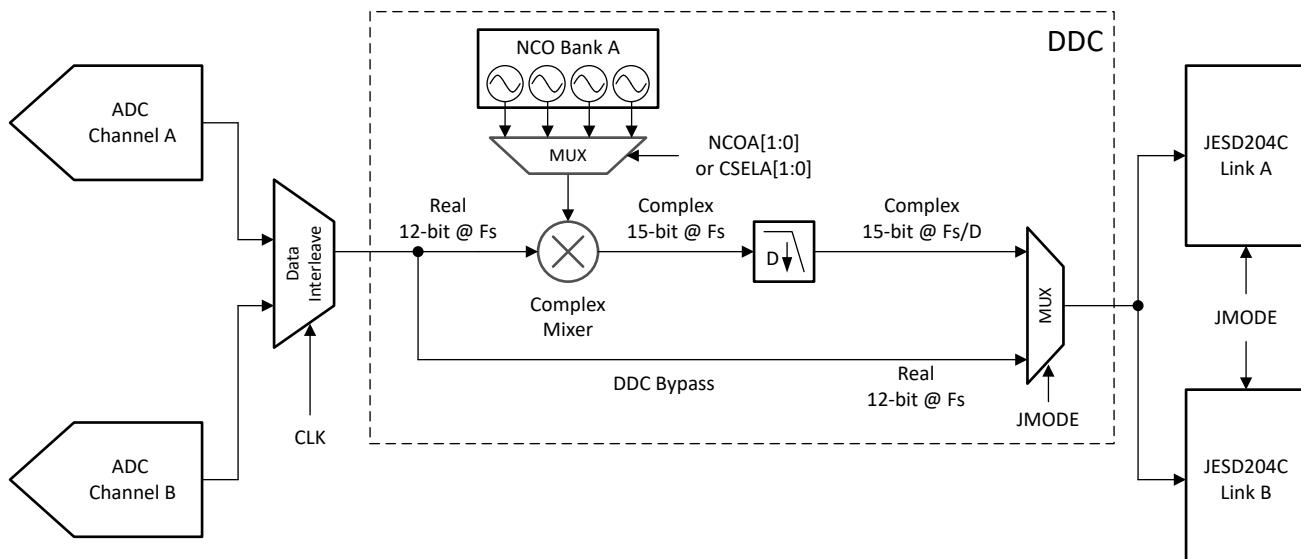

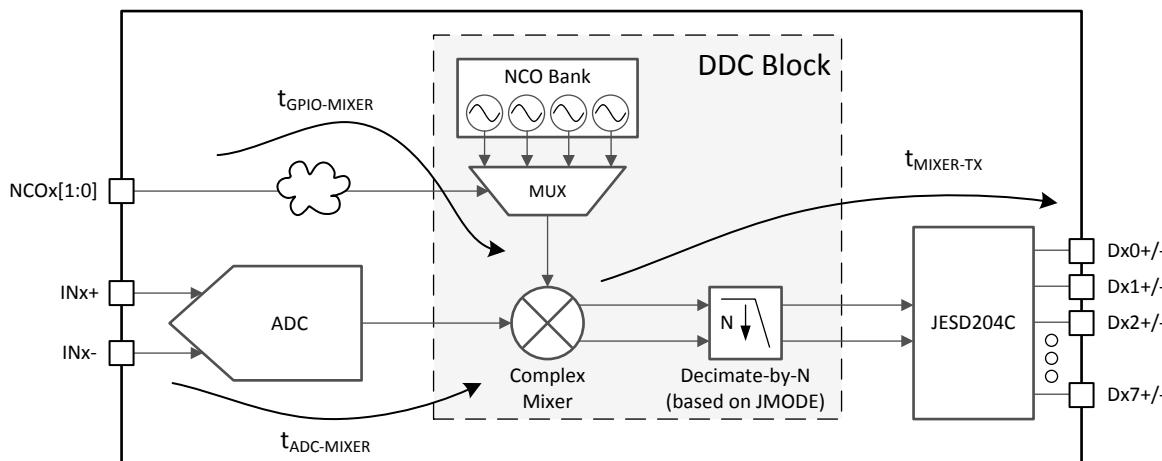

- オプションのデジタル ダウン コンバータ (DDC):

- 4x、8x、16x および 32x の複素数間引き

- DDC ごとに 4 つの独立した 32 ビット NCO

- ピーク RF 入力電力 (差動): +26.5dBm

(+27.5dBFS、560x フルスケール電力)

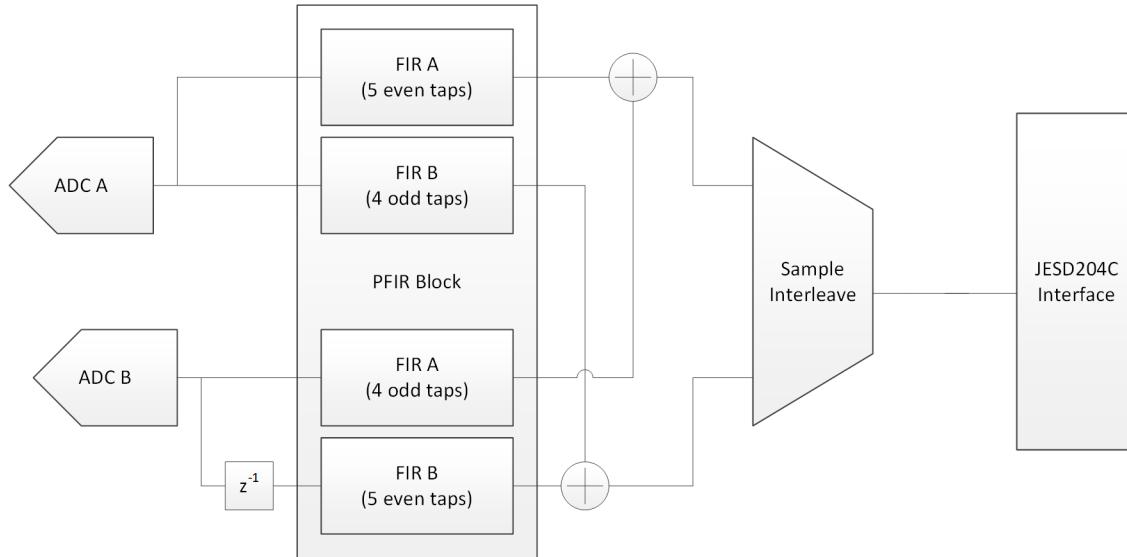

- 「イコライゼーション用のプログラム可能な FIR フィルタ」を追加

- 消費電力: 4W

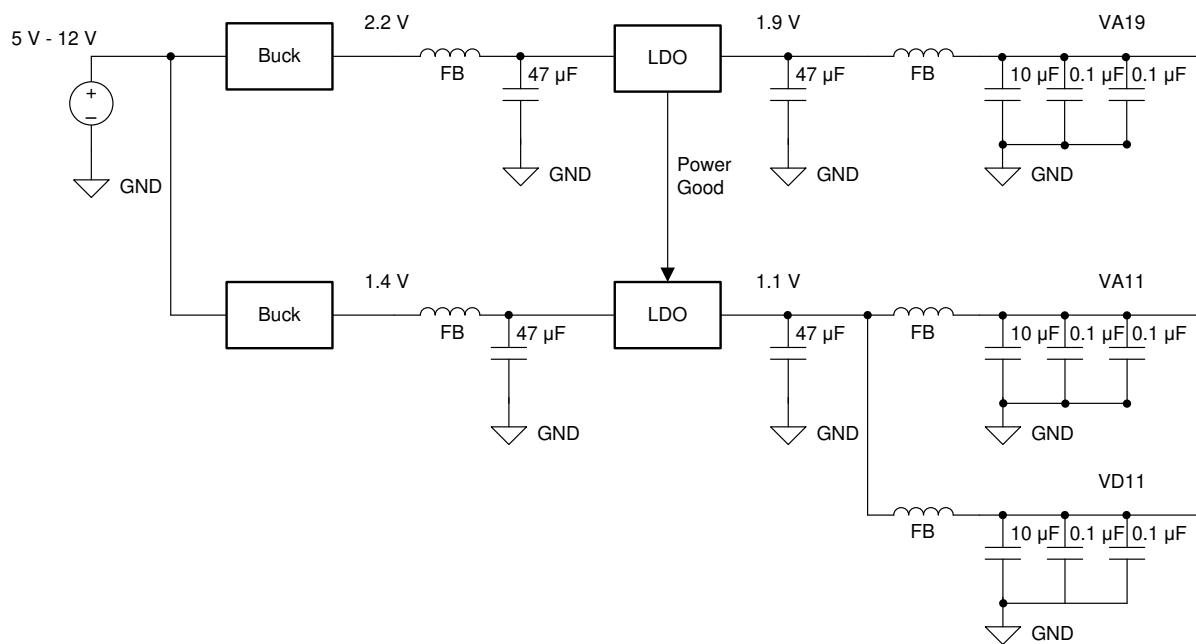

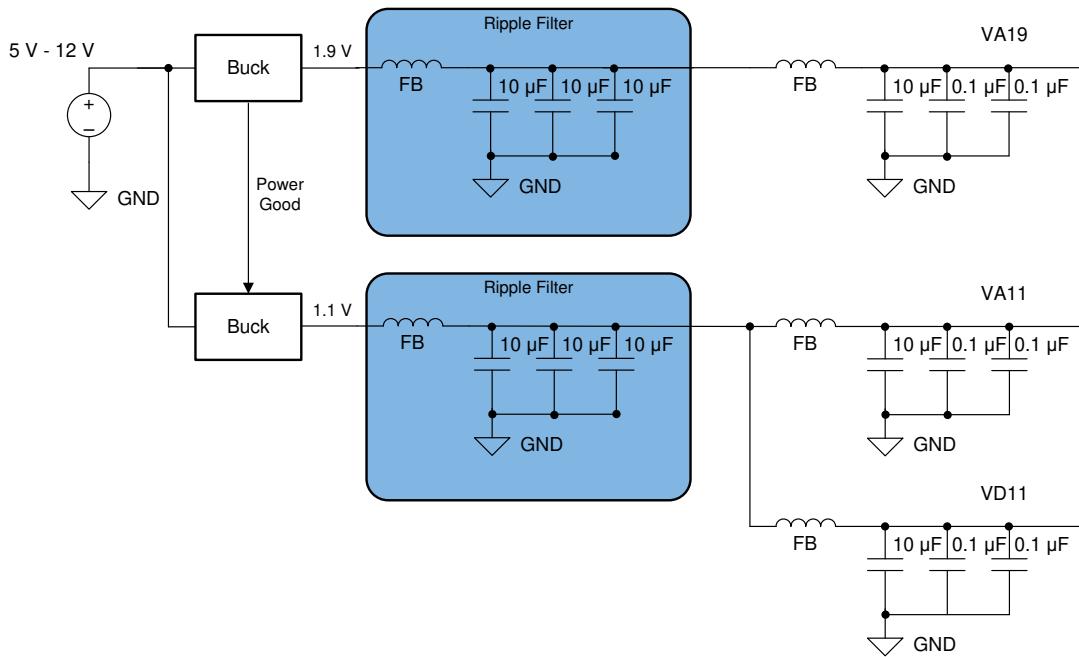

- 電源: 1.1V、1.9V

## 2 アプリケーション

- 広帯域 デジタイザ

- 電子諜報活動 (SIGINT、ELINT)

- 衛星通信 (SATCOM)

- RF サンプリングのソフトウェア無線 (SDR)

## 3 説明

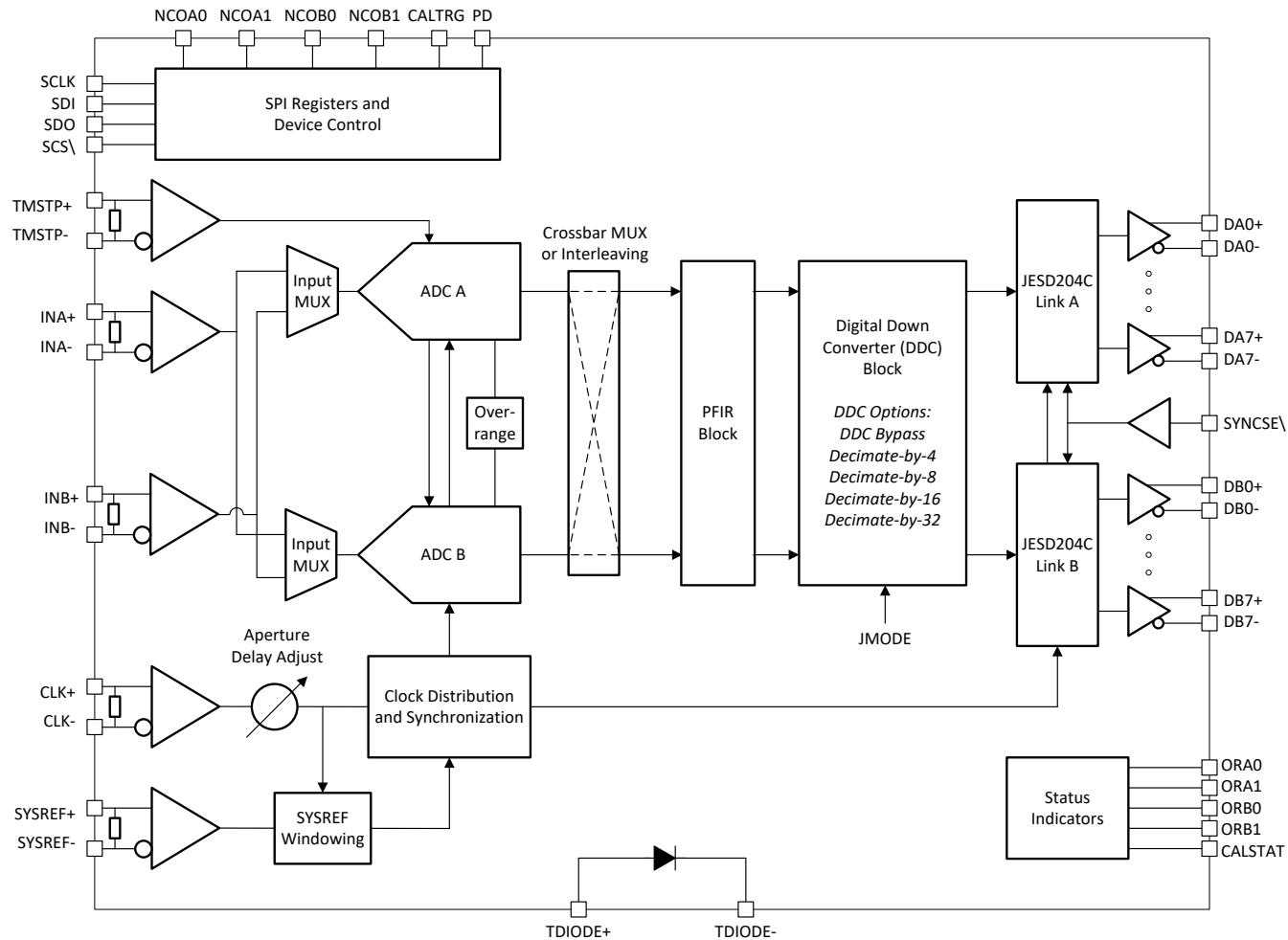

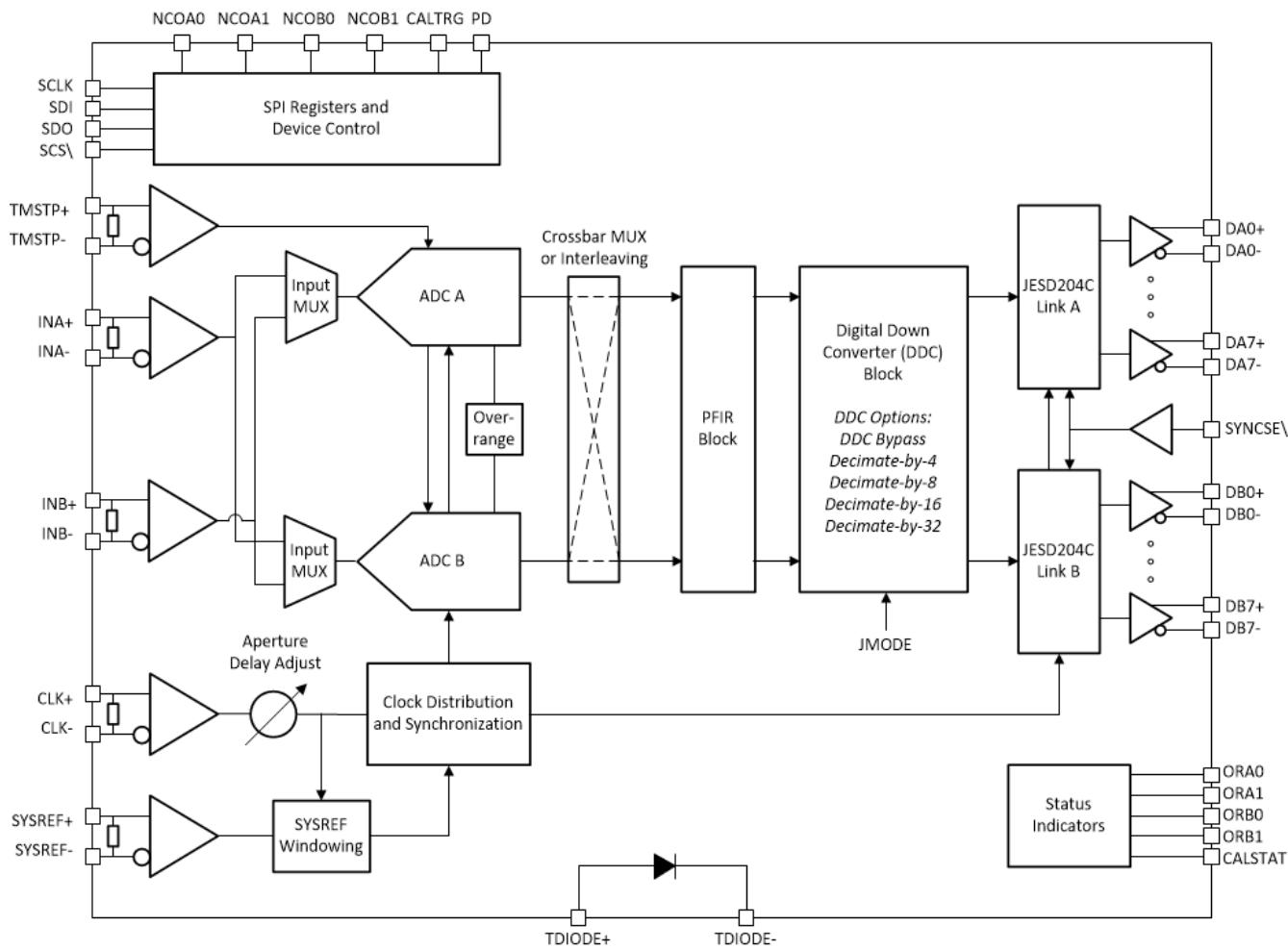

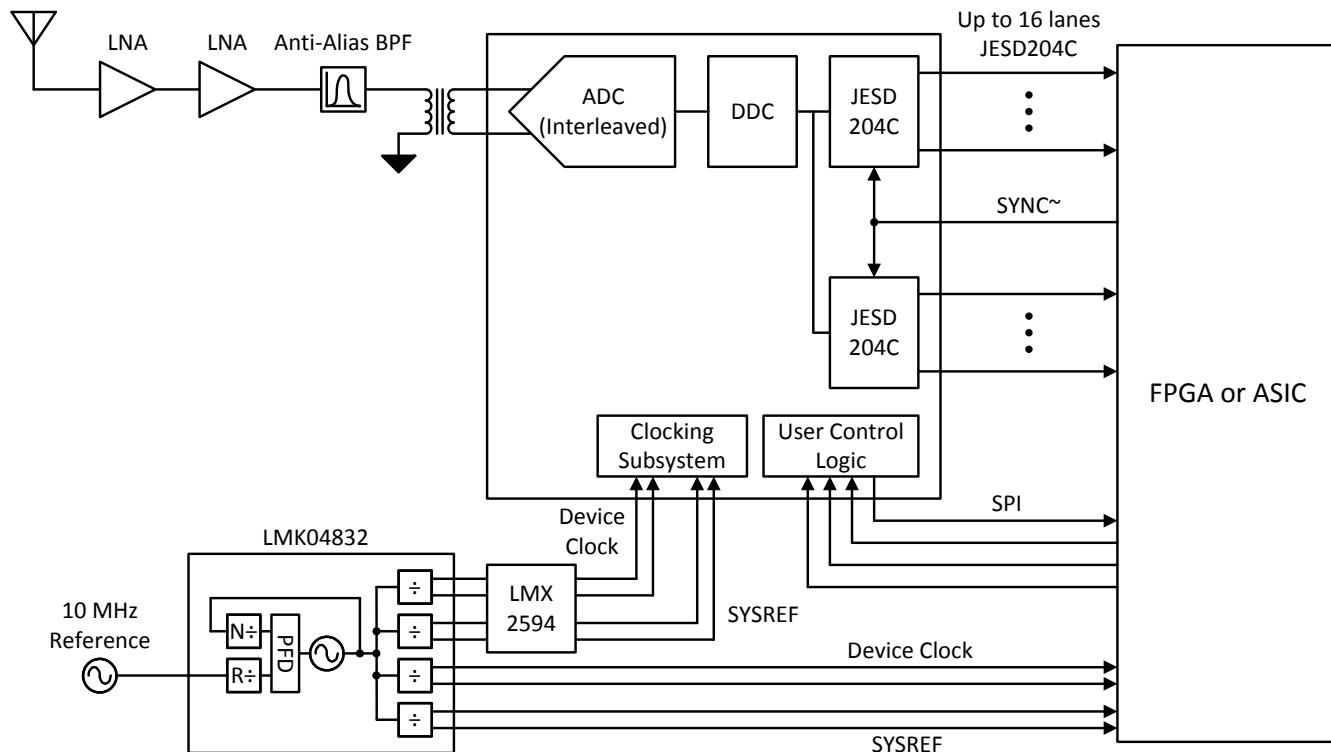

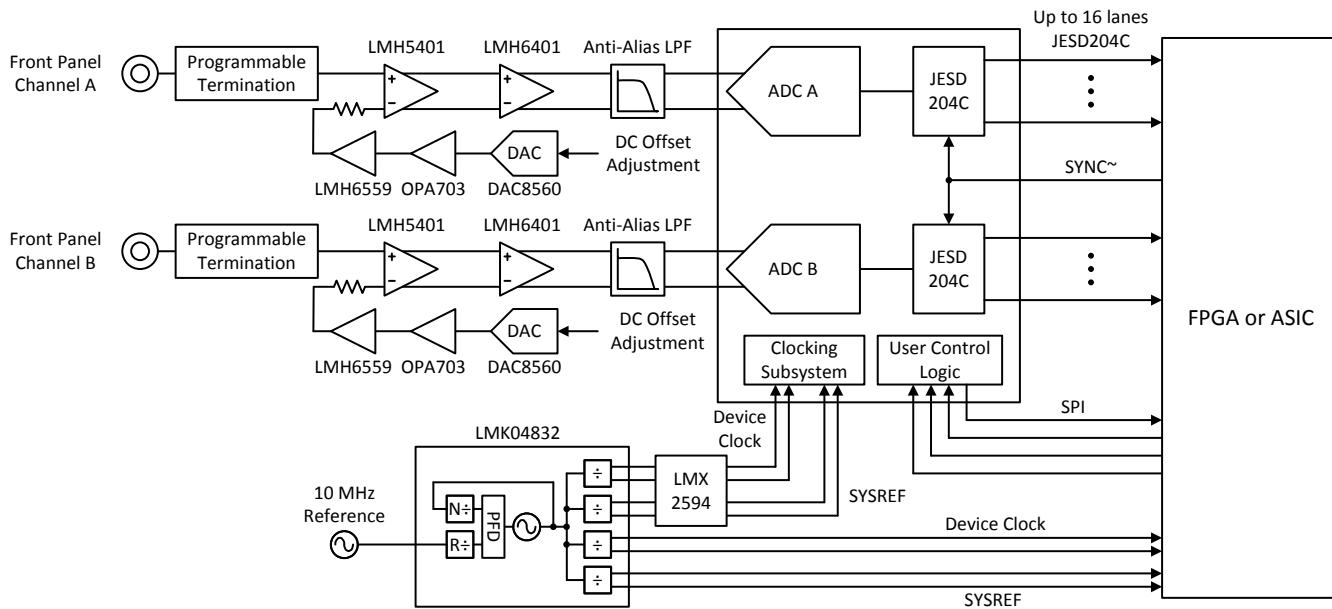

ADC12DJ5200-SP デバイスは、RF サンプリング、ギガサンプルの A/D コンバータ (ADC) で、DC から 10GHz 超までの入力周波数を直接サンプリングできます。ADC12DJ5200-SP はデュアル チャネル 5.2GSPS の ADC、またはシングル チャネル 10.4GSPS の ADC として構成できます。使用可能な入力周波数帯域が最高 10GHz であるため、L バンド、S バンド、C バンド、X バンドを直接 RF サンプリングでき、多様な周波数に対応したシステムを実現できます。

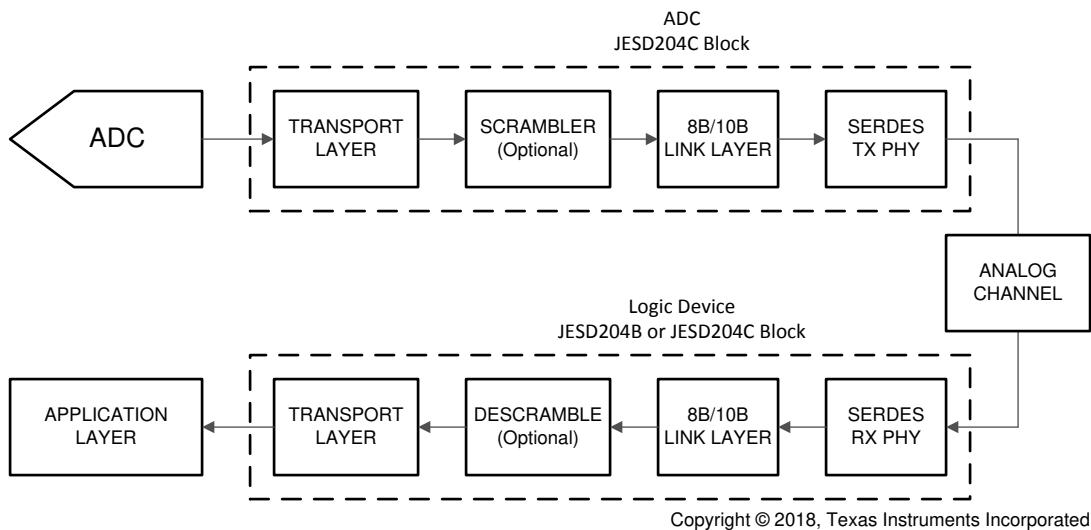

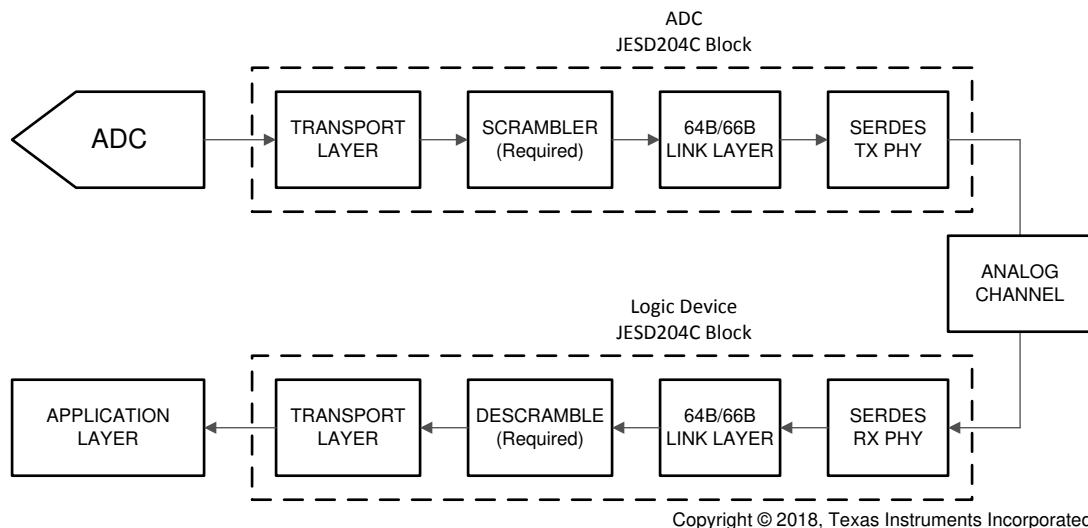

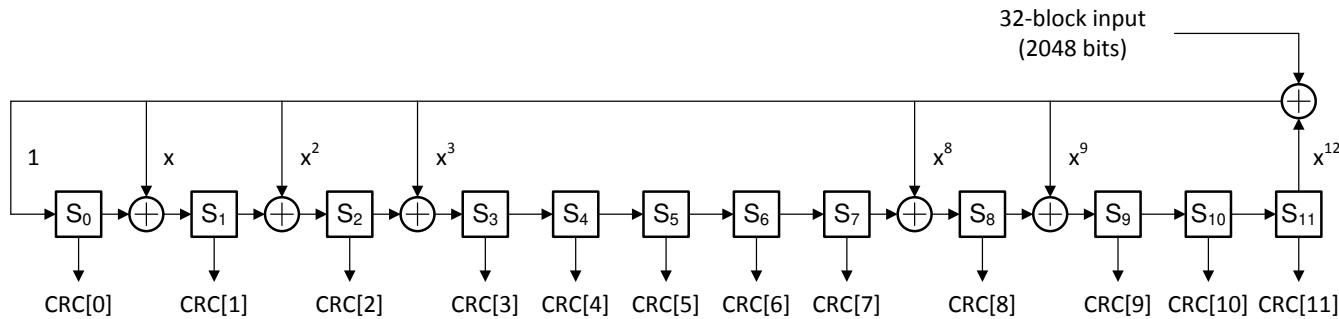

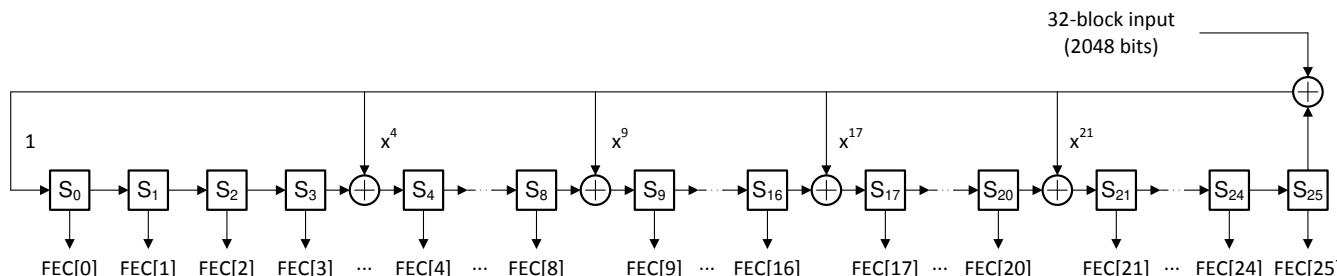

ADC12DJ5200-SP は、最大 17.16Gbps のライン速度をサポートする最大 16 個のシリアル化されたレーンを備えた、高速な JESD204C 出力インターフェイスを使っています。JESD204C subclass-1 により、決定論的レイテンシおよびマルチデバイス同期をサポートしています。JESD204C インターフェイスは、ライン速度とレーン数との間でトレードオフのバランスを取るように構成できます。8b/10b と 64b/66b の両方のデータ エンコードをサポートしています。64B/66B エンコードでは、前方エラー訂正 (FEC) によるビット エラー率の改善をサポートしています。このインターフェイスは、JESD204B レシーバと下位互換性があります。

ノイズなしのアーチャ遅延調整や、SYSREF ウィンドウ処理などの革新的な同期機能により、マルチ チャネル アプリケーションのシステム設計を簡素化できます。オプションのデジタル ダウン コンバータ (DDC) を使用すると、ベースバンドへのデジタル変換を実行でき、またインターフェイス速度を低減できます。プログラム可能な FIR フィルタにより、オンチップのイコライゼーションが可能です。

### パッケージ情報

| 部品番号           | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------------|----------------------|--------------------------|

| ADC12DJ5200-SP | FCBGA (144)          | 10mm × 10mm              |

(1) 詳細については、[セクション 10](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

ADC12DJ5200-SP ブロック図

## 目次

|                                  |    |                        |     |

|----------------------------------|----|------------------------|-----|

| 1 特長                             | 1  | 6.4 デバイスの機能モード         | 101 |

| 2 アプリケーション                       | 1  | 6.5 プログラミング            | 125 |

| 3 説明                             | 1  | 6.6 SPI レジスタ マップ       | 127 |

| 4 ピン構成および機能                      | 4  | 7 アプリケーション情報に関する免責事項   | 195 |

| 5 仕様                             | 11 | 7.1 アプリケーション情報         | 195 |

| 5.1 絶対最大定格                       | 11 | 7.2 代表的なアプリケーション       | 195 |

| 5.2 ESD 定格                       | 11 | 7.3 初期化セットアップ          | 199 |

| 5.3 推奨動作条件                       | 12 | 7.4 電源に関する推奨事項         | 199 |

| 5.4 熱に関する情報                      | 12 | 7.5 レイアウト              | 201 |

| 5.5 電気的特性: DC の仕様                | 13 | 8 デバイスおよびドキュメントのサポート   | 206 |

| 5.6 電気的特性: 消費電力                  | 15 | 8.1 デバイス サポート          | 206 |

| 5.7 電気的特性: AC 仕様 (デュアル チャネル モード) | 16 | 8.2 ドキュメントのサポート        | 206 |

| 5.8 電気的特性: AC 仕様 (シングル チャネル モード) | 21 | 8.3 ドキュメントの更新通知を受け取る方法 | 207 |

| 5.9 タイミング要件                      | 27 | 8.4 サポートリソース           | 207 |

| 5.10 スイッチング特性                    | 29 | 8.5 商標                 | 207 |

| 5.11 代表的特性                       | 34 | 8.6 静電気放電に関する注意事項      | 207 |

| 6 詳細説明                           | 67 | 8.7 用語集                | 207 |

| 6.1 概要                           | 67 | 9 改訂履歴                 | 207 |

| 6.2 機能ブロック図                      | 68 | 10 メカニカル、パッケージ、および注文情報 | 208 |

| 6.3 機能説明                         | 69 |                        |     |

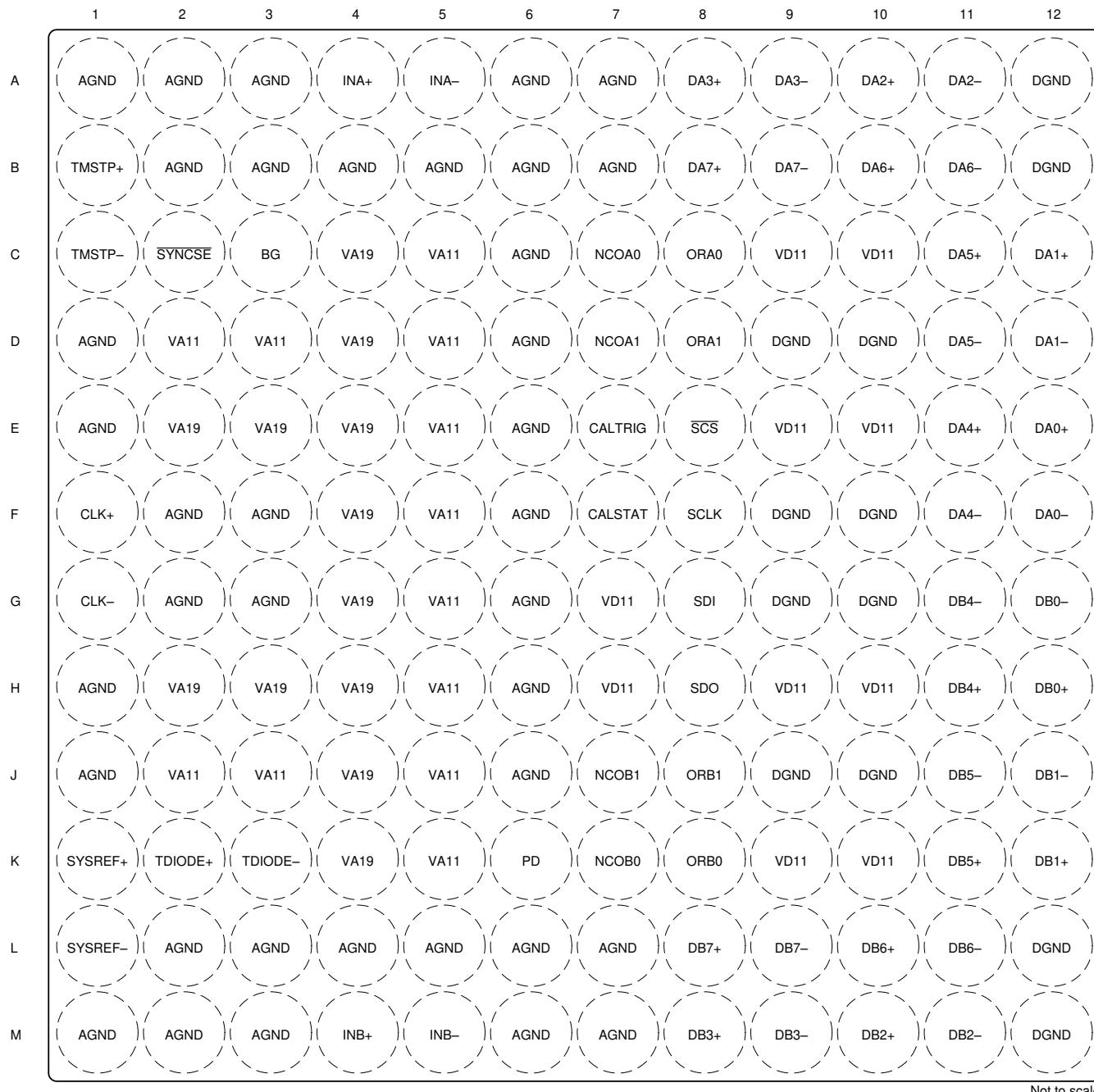

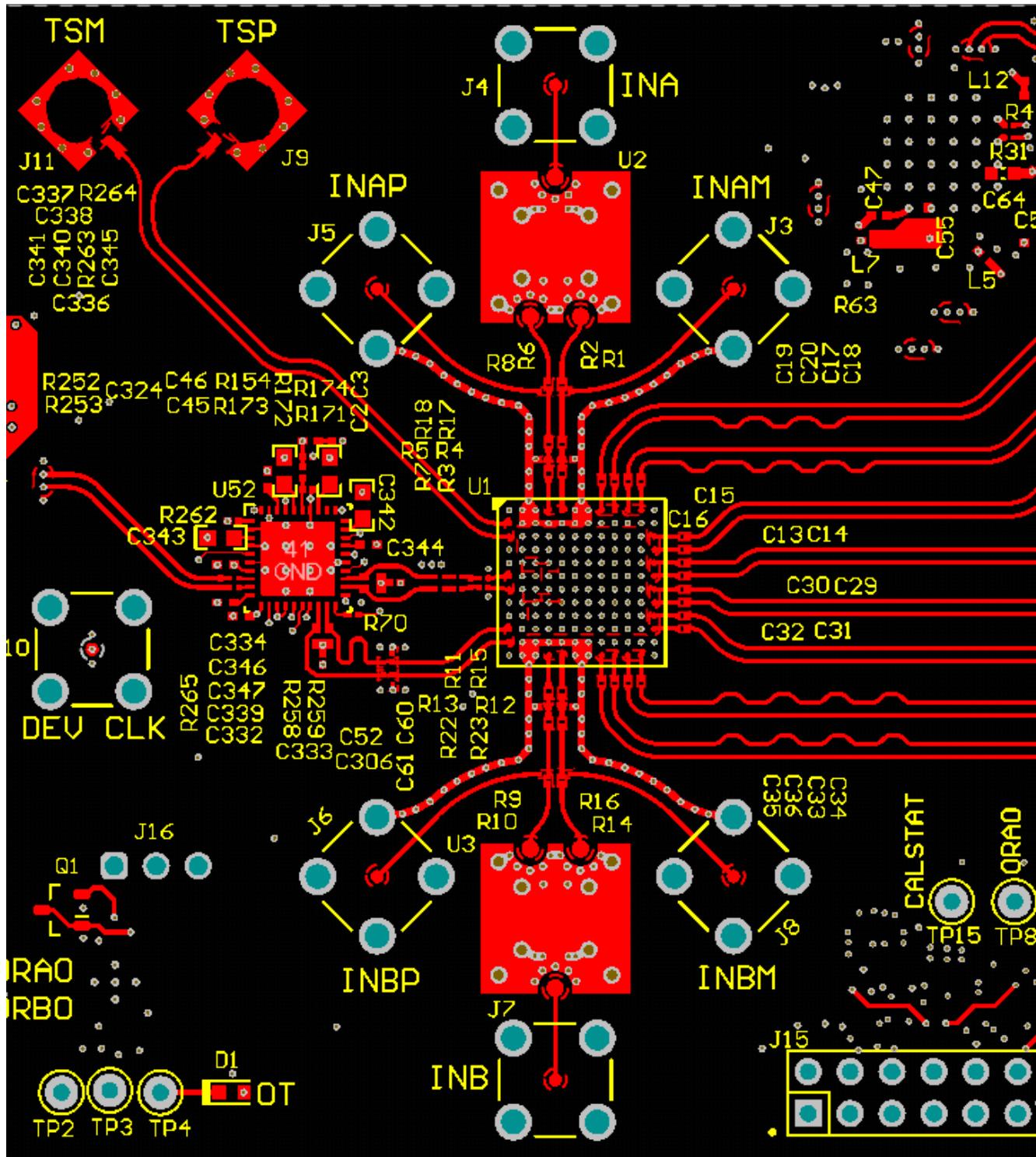

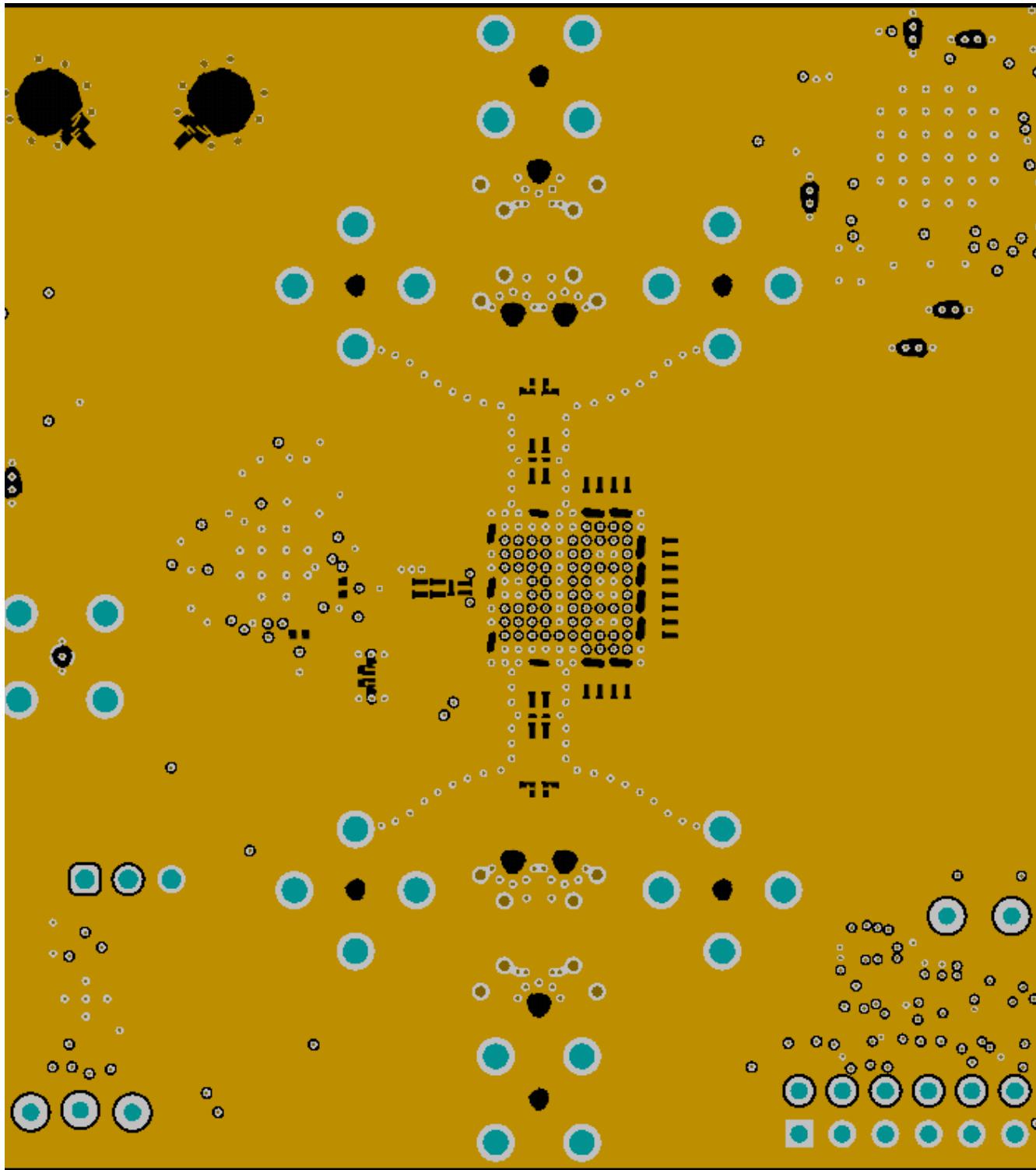

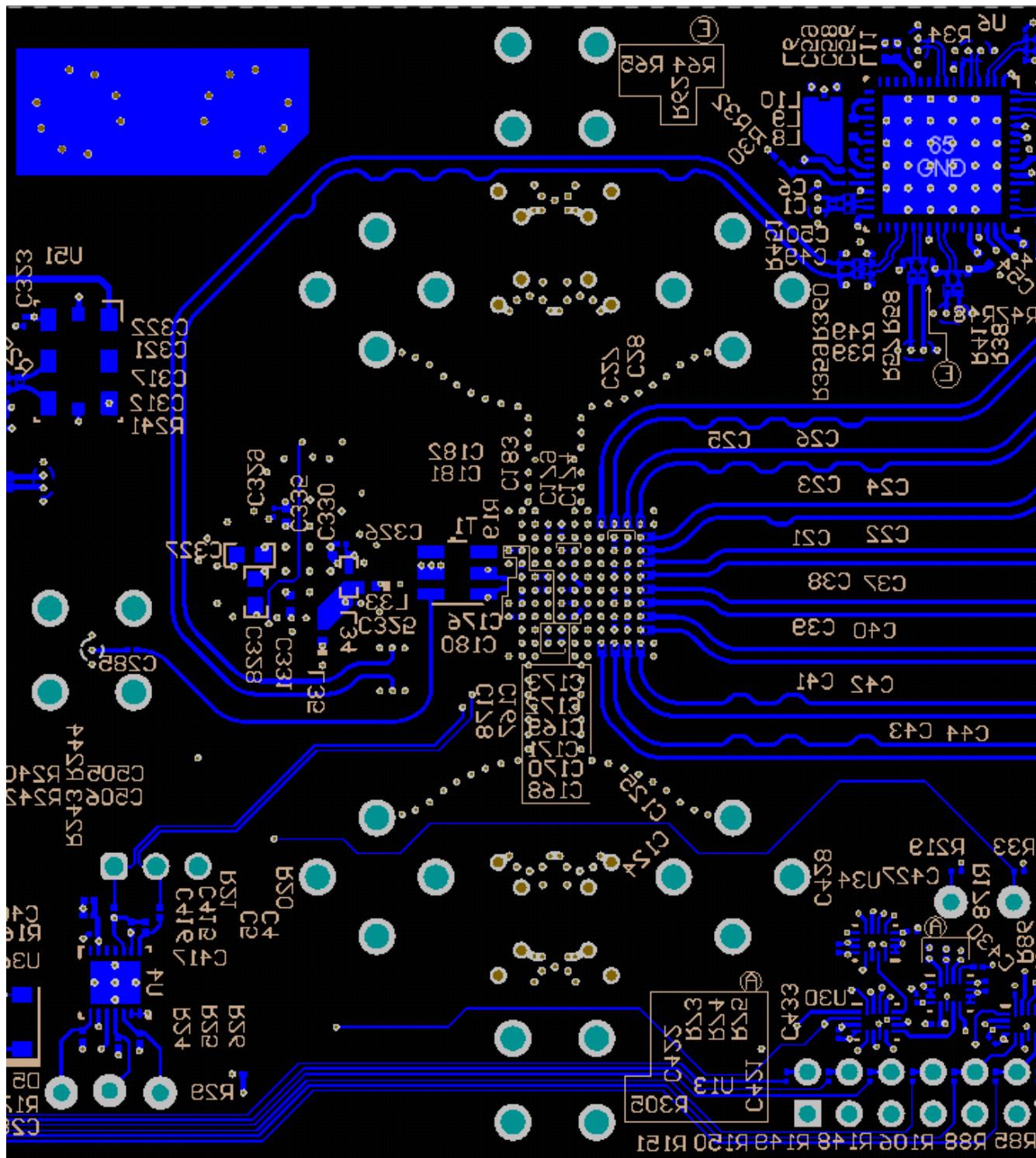

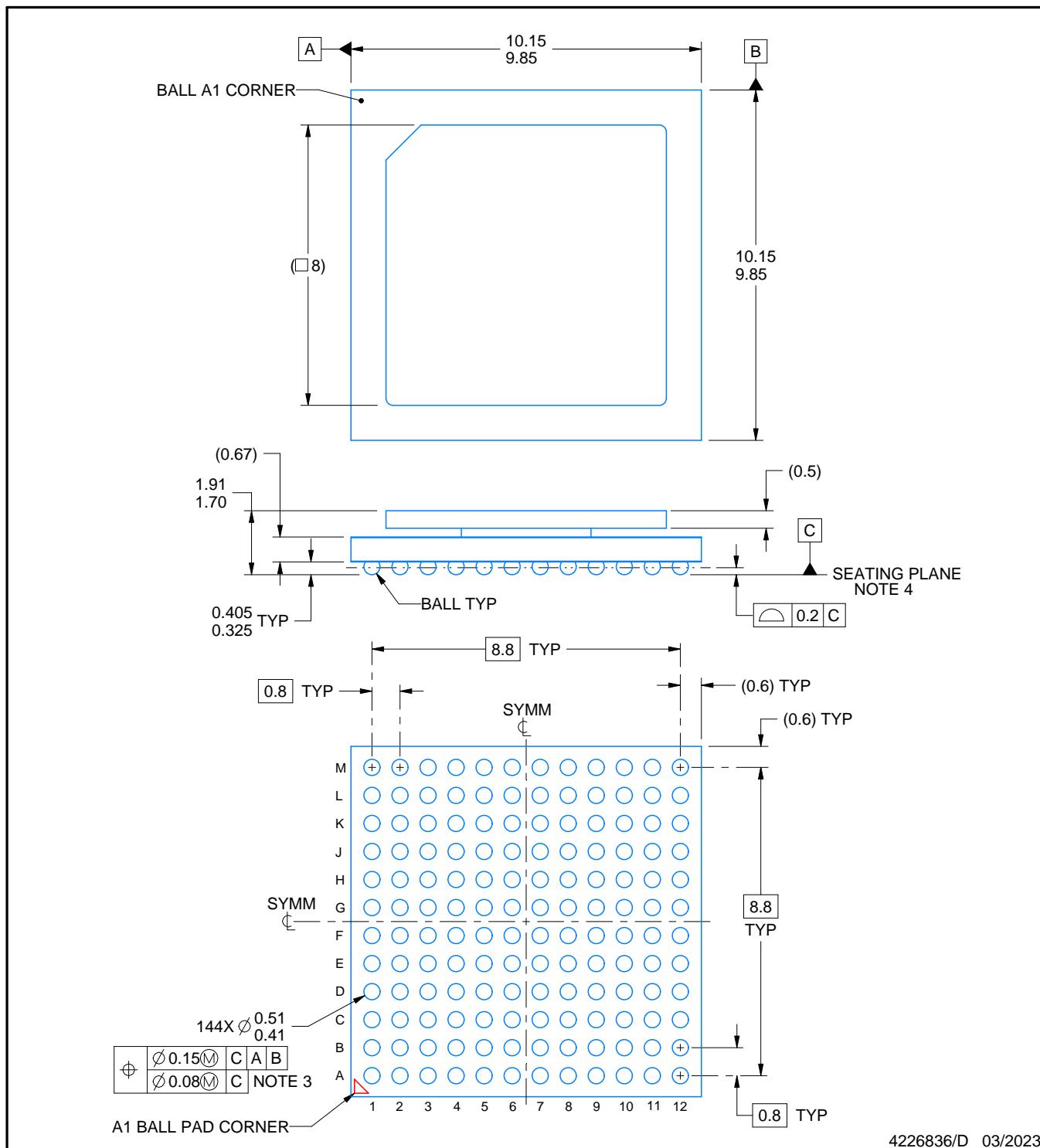

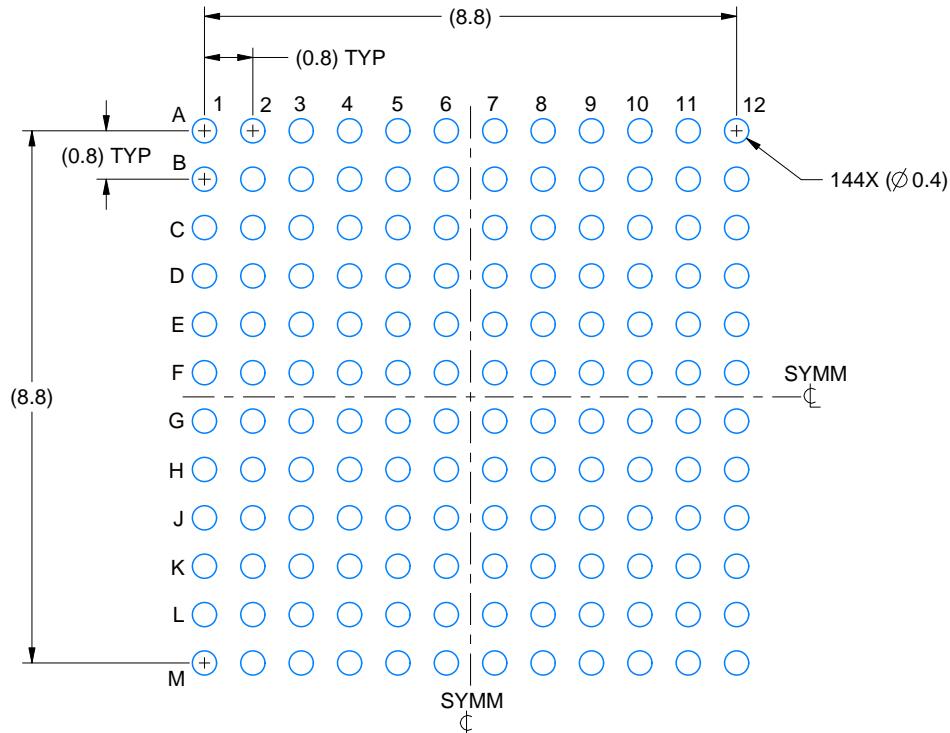

## 4 ピン構成および機能

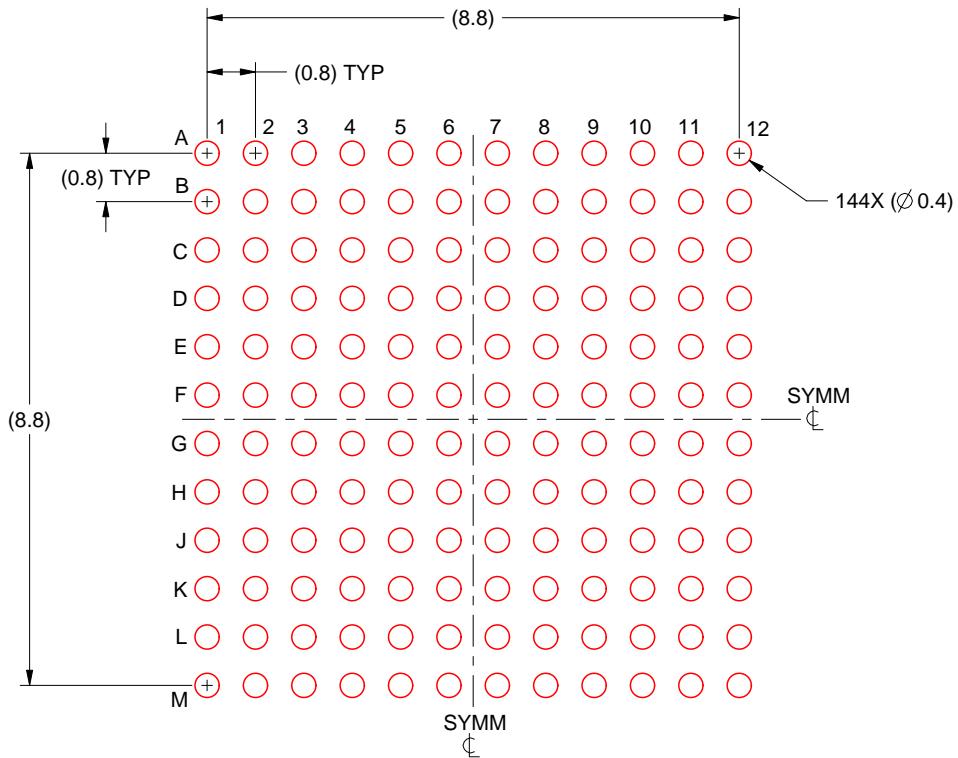

**図 4-1. ALR パッケージ、144 ボール フリップチップ BGA

(上面図)**

**表 4-1. ピンの機能**

| ピン      |                                                                                                                                                                | タイプ | 説明                                                                                                                                                                                                                                                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 番号                                                                                                                                                             |     |                                                                                                                                                                                                                                                                           |

| AGND    | A1、A2、A3、<br>A6、A7、B2、<br>B3、B4、B5、<br>B6、B7、C6、<br>D1、D6、E1、<br>E6、F2、F3、<br>F6、G2、G3、<br>G6、H1、H6、<br>J1、J6、L2、<br>L3、L4、L5、<br>L6、L7、M1、<br>M2、M3、M6、<br>M7 | —   | アナログ電源の接地。AGND および DGND を回路基板の共通グランドプレーン (GND) に接続します。                                                                                                                                                                                                                    |

| BG      | C3                                                                                                                                                             | O   | バンドギャップ電圧出力。このピンは、 <a href="#">推奨動作条件</a> 表に規定されているように、小さな電流のみを供給し、制限された容量性負荷を駆動できます。このピンは、使用しない場合は接続解除できます。                                                                                                                                                              |

| CALSTAT | F7                                                                                                                                                             | O   | フォアグラウンド キャリブレーション ステータス出力またはデバイス アラーム出力。機能は <b>CAL_STATUS_SEL</b> によってプログラムされます。このピンは、使用しない場合は接続解除できます。                                                                                                                                                                  |

| CALTRIG | E7                                                                                                                                                             | I   | フォアグラウンド キャリブレーショントリガ入力。このピンは、 <b>CAL_TRIG_EN</b> でハードウェア キャリブレーショントリガが選択されている場合にのみ使用されます。それ以外の場合は、 <b>CAL_SOFT_TRIG</b> を使用してソフトウェアトリガが実行されます。使用しない場合は、このピンを <b>GND</b> に接続してください。                                                                                       |

| CLK+    | F1                                                                                                                                                             | I   | デバイス (サンプリング) クロックの正の入力。最高の性能を得るために、この入力にクロック信号を AC 結合することを強く推奨します。シングル チャネル モードでは、立ち上がりエッジと立ち下がりエッジの両方でアナログ入力信号がサンプリングされます。デュアル チャネル モードでは、立ち上がりエッジでアナログ信号がサンプリングされます。この差動入力はトリムされない $100\Omega$ の差動終端を内蔵し、 <b>DEVCLK_LVPECL_EN</b> が 0 に設定されている限り、最適な入力同相電圧に自己バイアスされます。 |

| CLK-    | G1                                                                                                                                                             | I   | デバイス (サンプリング) クロックの負の入力。TI では、最高の性能を得るために AC 結合を強く推奨します。                                                                                                                                                                                                                  |

| DA0+    | E12                                                                                                                                                            | O   | チャネル A、レーン 0、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して <b>GND (0V)</b> と <b>VD11 (1.1V)</b> の間の任意の電圧レベルに接続できます。                                                           |

| DA0-    | F12                                                                                                                                                            | O   | チャネル A、レーン 0、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して <b>GND (0V)</b> と <b>VD11 (1.1V)</b> の間の任意の電圧レベルに接続できます。                                                                                                                             |

| DA1+    | C12                                                                                                                                                            | O   | チャネル A、レーン 1、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して <b>GND (0V)</b> と <b>VD11 (1.1V)</b> の間の任意の電圧レベルに接続できます。                                                           |

| DA1-    | D12                                                                                                                                                            | O   | チャネル A、レーン 1、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して <b>GND (0V)</b> と <b>VD11 (1.1V)</b> の間の任意の電圧レベルに接続できます。                                                                                                                             |

| DA2+    | A10                                                                                                                                                            | O   | チャネル A、レーン 2、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して <b>GND (0V)</b> と <b>VD11 (1.1V)</b> の間の任意の電圧レベルに接続できます。                                                           |

| DA2-    | A11                                                                                                                                                            | O   | チャネル A、レーン 2、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して <b>GND (0V)</b> と <b>VD11 (1.1V)</b> の間の任意の電圧レベルに接続できます。                                                                                                                             |

| DA3+    | A8                                                                                                                                                             | O   | チャネル A、レーン 3、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して <b>GND (0V)</b> と <b>VD11 (1.1V)</b> の間の任意の電圧レベルに接続できます。                                                           |

表 4-1. ピンの機能 (続き)

| ピン   |     | タイプ | 説明                                                                                                                                                                                                |

|------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号  |     |                                                                                                                                                                                                   |

| DA3- | A9  | O   | チャネル A、レーン 3、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                   |

| DA4+ | E11 | O   | チャネル A、レーン 4、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。 |

| DA4- | F11 | O   | チャネル A、レーン 4、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                   |

| DA5+ | C11 | O   | チャネル A、レーン 5、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。 |

| DA5- | D11 | O   | チャネル A、レーン 5、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                   |

| DA6+ | B10 | O   | チャネル A、レーン 6、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、常にレシーバで $100\Omega$ の差動終端で終端するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続する必要があります。このピンは、使用しない場合は接続解除できます。     |

| DA6- | B11 | O   | チャネル A、レーン 6、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                   |

| DA7+ | B8  | O   | チャネル A、レーン 7、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。 |

| DA7- | B9  | O   | チャネル A、レーン 7、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                   |

| DB0+ | H12 | O   | チャネル B、レーン 0、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。 |

| DB0- | G12 | O   | チャネル B、レーン 0、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                   |

| DB1+ | K12 | O   | チャネル B、レーン 1、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンは、使用しない場合は接続解除できます。                                                                           |

| DB1- | J12 | O   | チャネル B、レーン 1、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                   |

| DB2+ | M10 | O   | チャネル B、レーン 2、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。 |

| DB2- | M11 | O   | チャネル B、レーン 2、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                   |

**表 4-1. ピンの機能 (続き)**

| ピン   |                                                             | タイプ | 説明                                                                                                                                                                                                                                                                                                                                 |

|------|-------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号                                                          |     |                                                                                                                                                                                                                                                                                                                                    |

| DB3+ | M8                                                          | O   | チャネル B、レーン 3、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                                                                                  |

| DB3- | M9                                                          | O   | チャネル B、レーン 3、負接続の高速シリアル化データ出力。このピンは、使用しない場合は接続解除できます。                                                                                                                                                                                                                                                                              |

| DB4+ | H11                                                         | O   | チャネル B、レーン 4、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                                                                                  |

| DB4- | G11                                                         | O   | チャネル B、レーン 4、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                                                                                                                                                    |

| DB5+ | K11                                                         | O   | チャネル B、レーン 5、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                                                                                  |

| DB5- | J11                                                         | O   | チャネル B、レーン 5、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                                                                                                                                                    |

| DB6+ | L10                                                         | O   | チャネル B、レーン 6、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                                                                                  |

| DB6- | L11                                                         | O   | チャネル B、レーン 6、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                                                                                                                                                    |

| DB7+ | L8                                                          | O   | チャネル B、レーン 7、正接続の高速シリアル化データ出力。この差動出力は AC 結合する必要があります、レシーバに接続された $100\Omega$ の差動終端で常に終端する必要があります。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                                                                                  |

| DB7- | L9                                                          | O   | チャネル B、レーン 7、負接続の高速シリアル化データ出力。このピンを使用しない場合は接続解除するか、 $0\Omega \sim 1M\Omega$ の抵抗を使用して GND (0V) と VD11 (1.1V) の間の任意の電圧レベルに接続できます。                                                                                                                                                                                                    |

| DGND | A12、B12、<br>D9、D10、F9、<br>F10、G9、<br>G10、J9、J10、<br>L12、M12 | —   | デジタル電源の接地。AGND および DGND を回路基板の共通グランドプレーン (GND) に接続します。                                                                                                                                                                                                                                                                             |

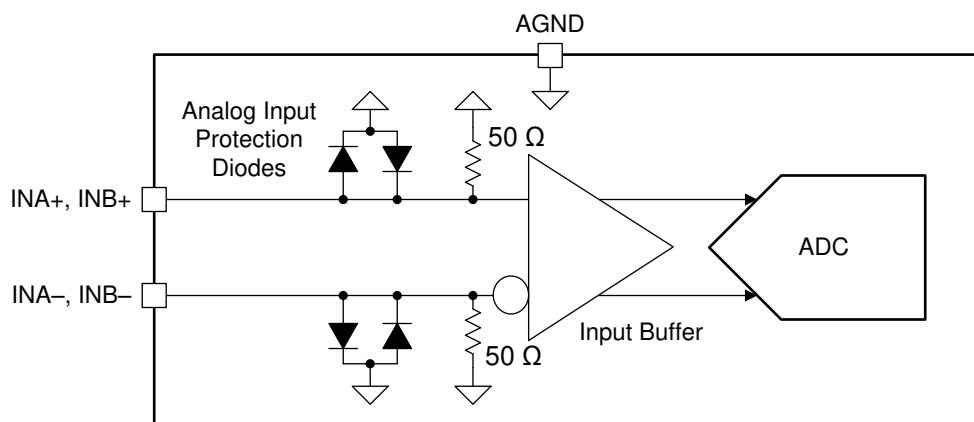

| INA+ | A4                                                          | I   | チャネル A アナログ入力の正接続。最適な性能を得るために、シングル チャネル モードで <b>INA<math>\pm</math></b> を使用することを推奨します。差動フルスケール入力電圧は、 <b>FS_RANGE_A</b> レジスタによって決定されます (「 <a href="#">フルスケール電圧 (V<sub>FS</sub>) の調整</a> 」セクション)。この入力は、 $50\Omega$ の終端抵抗を経由してグランドに終端されます。入力同相電圧は通常 0V (GND) に設定され、「 <a href="#">推奨動作条件</a> 」表の推奨事項に従う必要があります。このピンは、使用しない場合は接続解除できます。 |

| INA- | A5                                                          | I   | チャネル A アナログ入力の負接続。最適な性能を得るために、シングル チャネル モードで <b>INA<math>\pm</math></b> を使用することを推奨します。詳細については、 <a href="#">INA+ (ピン A4)</a> を参照してください。この入力は、 $50\Omega$ の終端抵抗を経由してグランドに終端されます。このピンは、使用しない場合は接続解除できます。                                                                                                                              |

| INB+ | M4                                                          | I   | チャネル B アナログ入力の正接続。最適な性能を得るために、シングル チャネル モードで <b>INA<math>\pm</math></b> を使用することを推奨します。差動フルスケール入力電圧は、 <b>FS_RANGE_B</b> レジスタによって決定されます (「 <a href="#">フルスケール電圧 (V<sub>FS</sub>) の調整</a> 」セクション)。この入力は、 $50\Omega$ の終端抵抗を経由してグランドに終端されます。入力同相電圧は通常 0V (GND) に設定して、「 <a href="#">推奨動作条件</a> 」表の推奨事項に従う必要があります。このピンは、使用しない場合は接続解除できます。 |

表 4-1. ピンの機能 (続き)

| ピン    |    | タイプ | 説明                                                                                                                                                                                                                                                                                                                                    |

|-------|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称    | 番号 |     |                                                                                                                                                                                                                                                                                                                                       |

| INB–  | M5 | I   | チャネル B アナログ入力の負接続。最適な性能を得るために、シングルチャネルモードで $INA_{\pm}$ を使用することを推奨します。詳細については、INB+を参照してください。この入力は、 $50\Omega$ の終端抵抗を経由してグランドに終端されます。このピンは、使用しない場合は接続解除できます。                                                                                                                                                                            |

| NCOA0 | C7 | I   | NCO の LSB の選択により DDC A が制御されます。JMODE を使用する際、NCOA0 および NCOA1 は、可能な 4 つの NCO のうち、デジタルミキシングに使用される NCO を選択します。残りの未選択の NCO は、位相コヒーレントを維持するため引き続き動作し、NCOA0 と NCOA1 の値を変更することで交換できます (CMODE = 1 のとき)。このピンは非同期入力です。詳細については、「 <a href="#">NCO 高速周波数ホッピング (FFH)</a> 」および「 <a href="#">NCO の選択</a> 」セクションを参照してください。使用しない場合は、このピンを GND に接続してください。 |

| NCOA1 | D7 | I   | NCO の MSB の選択により DDC A が制御されます。使用しない場合、このピンを GND に接続します。                                                                                                                                                                                                                                                                              |

| NCOB0 | K7 | I   | NCO の LSB の選択により DDC B が制御されます。JMODE を使用する際、NCOB0 および NCOB1 は、可能な 4 つの NCO のうち、デジタルミキシングに使用される NCO を選択します。残りの未選択の NCO は、位相コヒーレントを維持するため引き続き動作し、NCOB0 と NCOB1 の値を変更することで交換できます (CMODE = 1 のとき)。このピンは非同期入力です。詳細については、「 <a href="#">NCO 高速周波数ホッピング (FFH)</a> 」および「 <a href="#">NCO の選択</a> 」セクションを参照してください。使用しない場合は、このピンを GND に接続してください。 |

| NCOB1 | J7 | I   | NCO の MSB の選択により DDC B が制御されます。使用しない場合、このピンを GND に接続します。                                                                                                                                                                                                                                                                              |

| ORA0  | C8 | O   | OVR_T0 スレッショルドのチャネル A の高速オーバーレンジ検出ステータス。アナログ入力が OVR_T0 にプログラムされたスレッショルドを超えると、このステータス インジケータが High になります。最小パルス幅は OVR_N によって設定されます。詳細については、「 <a href="#">ADC オーバーレンジ検出</a> 」セクションを参照してください。このピンは、使用しない場合は接続解除できます。                                                                                                                      |

| ORA1  | D8 | O   | OVR_T1 スレッショルドのチャネル A の高速オーバーレンジ検出ステータス。アナログ入力が OVR_T1 にプログラムされたスレッショルドを超えると、このステータス インジケータが High になります。最小パルス幅は OVR_N によって設定されます。詳細については、「 <a href="#">ADC オーバーレンジ検出</a> 」セクションを参照してください。このピンは、使用しない場合は接続解除できます。                                                                                                                      |

| ORB0  | K8 | O   | OVR_T0 スレッショルドのチャネル B の高速オーバーレンジ検出ステータス。アナログ入力が OVR_T0 にプログラムされたスレッショルドを超えると、このステータス インジケータが High になります。最小パルス幅は OVR_N によって設定されます。詳細については、「 <a href="#">ADC オーバーレンジ検出</a> 」セクションを参照してください。このピンは、使用しない場合は接続解除できます。                                                                                                                      |

| ORB1  | J8 | O   | OVR_T1 スレッショルドのチャネル B の高速オーバーレンジ検出ステータス。アナログ入力が OVR_T1 にプログラムされたスレッショルドを超えると、このステータス インジケータが High になります。最小パルス幅は OVR_N によって設定されます。詳細については、「 <a href="#">ADC オーバーレンジ検出</a> 」セクションを参照してください。このピンは、使用しない場合は接続解除できます。                                                                                                                      |

| PD    | K6 | I   | このピンを High に設定すると、温度ダイオードのキャリブレーションのため、またはデバイスを使用していないときに消費電力を低減するため、すべてのアナログ回路とシリアル出力がディセーブルになります。使用しない場合は、このピンを GND に接続してください。                                                                                                                                                                                                      |

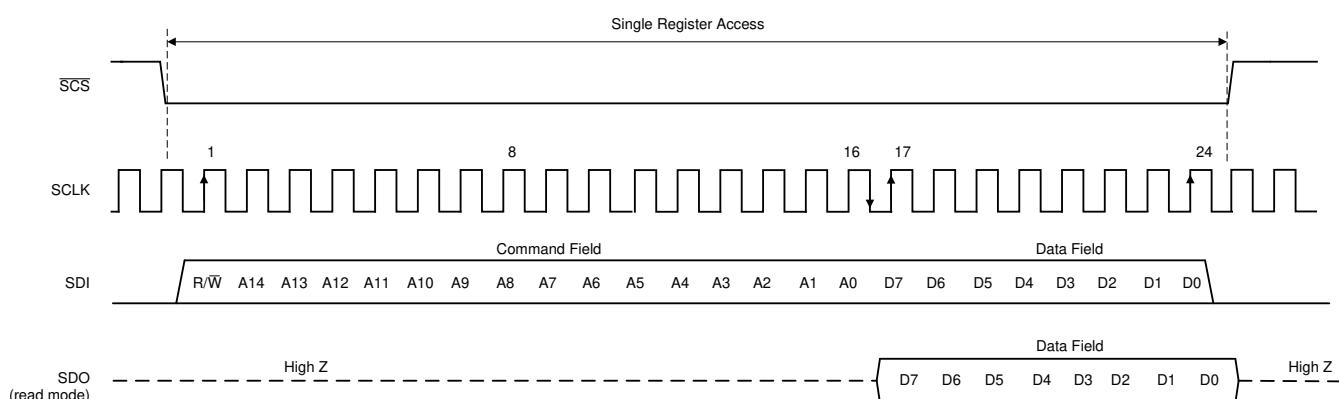

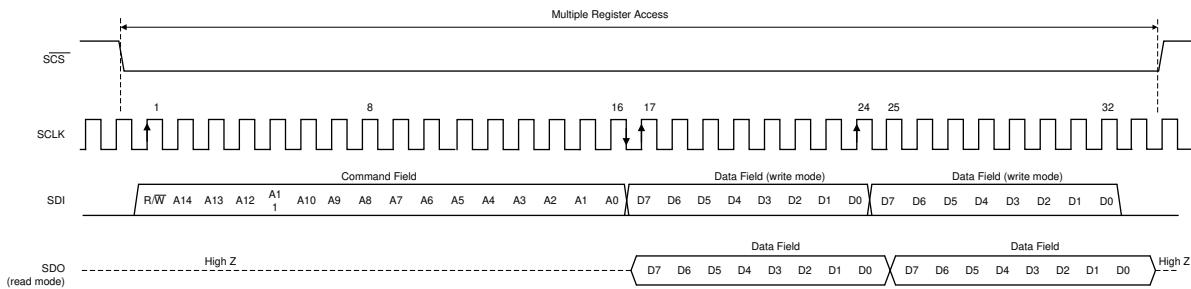

| SCLK  | F8 | I   | シリアル インターフェイス クロック。このピンはシリアル・プログラミング・データの入出力をクロックするシリアル・インターフェイス・クロック入力として機能します。シリアルインターフェイスの使い方 セクションでは、シリアルインターフェイスについて詳しく説明しています。1.1V と 1.8V の CMOS レベルをサポート。                                                                                                                                                                      |

| SCS   | E8 | I   | シリアル インターフェイスのチップ セレクトのアクティブ Low 入力。シリアルインターフェイスの使い方 セクションでは、シリアルインターフェイスについて詳しく説明しています。1.1V と 1.8V の CMOS レベルをサポート。このピンには、VD11 への $82\text{k}\Omega$ のプルアップ抵抗が搭載されています。                                                                                                                                                              |

| SDI   | G8 | I   | シリアル インターフェイスのデータ入力。シリアルインターフェイスの使い方 セクションでは、シリアルインターフェイスについて詳しく説明しています。1.1V と 1.8V の CMOS レベルをサポート。                                                                                                                                                                                                                                  |

**表 4-1. ピンの機能 (続き)**

| ピン      |                                                | タイプ | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 番号                                             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDO     | H8                                             | O   | シリアル インターフェイス データ出力。シリアルインターフェイスの使い方 セクションでは、シリアルインターフェイスについて詳しく説明しています。このピンは、デバイス通常動作中はハイインピーダンスになります。このピンは、シリアルインターフェイスの読み取り動作時に 1.9V CMOS レベルを出力します。このピンは、使用しない場合は接続解除できます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SYNCSE  | C2                                             | I   | シングルエンド JESD204C SYNC 信号。この入力はアクティブ Low 入力であり、SYNC_SEL が 0 に設定されているときに、8B/10B モードで JESD204C シリアルリンクを初期化するために使用されます。64B/66B モードでは初期化に SYNC 信号を使用しませんが、NCO 同期には使用できます。8B/10B モードで Low に切り替えると、この入力により、コード・グループ同期が開始されます（コード・グループ同期（CGS）を参照）。コード・グループ同期後に、最初のレーン・アライメント・シーケンスを開始するには、この入力を High に切り替える必要があります（初期レーン・アライメント・シーケンス（ILAS）セクションを参照）。代わりに、SYNC_SEL を 1 に設定し、TMSTP $\pm$ を差動 SYNC 入力として使用することで、差動 SYNC 信号を使用できます。差動 SYNC (TMSTP $\pm$ ) を JESD204C SYNC 信号として使用する場合は、このピンを GND に接続します。                                                                                                                                                                                                                                                                                                                  |

| SYSREF+ | K1                                             | I   | SYSREF の正入力は、JESD204C インターフェイス全体で同期と決定論的レイテンシを実現するため使用されます。この差動入力 (SYSREF+ ~ SYSREF-) には、トリムされていない 100 $\Omega$ 差動終端が内蔵されており、SYSREF_LVPECL_EN が 0 に設定されているときは AC 結合できます。SYSREF_LVPECL_EN が 0 に設定されると、この入力は自己バイアスされます。終端は、各入力ピン (SYSREF+ と SYSREF-) のグランドに対して 50 $\Omega$ に変化し、SYSREF_LVPECL_EN が 1 に設定されているときは DC 結合できます。SYSREF_LVPECL_EN が 1 に設定されている場合、この入力は自己バイアスではなく、推奨動作条件表に記載されている入力同相電圧範囲に外部でバイアスする必要があります。                                                                                                                                                                                                                                                                                                                                                                                             |

| SYSREF- | L1                                             | I   | SYSREF 負入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TDIODE+ | K2                                             | I   | 温度ダイオードの正（アノード）接続。外部温度センサを TDIODE+ および TDIODE- に接続して、デバイスの接合部温度を監視できます。このピンは、使用しない場合は接続解除できます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TDIODE- | K3                                             | I   | 温度ダイオードの負（カソード）接続。このピンは、使用しない場合は接続解除できます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TMSTP+  | B1                                             | I   | タイムスタンプ入力の正接続または差動 JESD204C SYNC の正接続。この入力はタイムスタンプ入力であり、TIMESTAMP_EN が 1 に設定されているときに、特定のサンプルをマークするために使用されます。SYNC_SEL が 1 にセットされている場合、この差動入力は JESD204C SYNC 信号入力として使用されます。この入力は、タイムスタンプと差動 SYNC 入力の両方として同時に使用でき、タイムスタンプメカニズムを使用して SYNC 信号をフィードバックできます。JESD204C SYNC として使用する場合、TMSTP $\pm$ はアクティブ Low 信号を用います。使用法の詳細については、タイムスタンプセクションを参照してください。この入力を使用するには、TMSTP_RECV_EN を 1 に設定する必要があります。この差動入力 (TMSTP+ ~ TMSTP-) には、トリムされていない 100 $\Omega$ 差動終端が内蔵されており、TMSTP_LVPECL_EN が 0 に設定されているときは AC 結合できます。終端は、各入力ピン (TMSTP+ および TMSTP-) のグランドに対して 50 $\Omega$ に変化し、TMSTP_LVPECL_EN が 1 に設定されているときは DC 結合も可能です。このピンは自己バイアスではないため、AC 結合および DC 結合の両方の構成では、外部バイアスを印加する必要があります。AC 結合と DC 結合の両方について、同相電圧は推奨動作条件表に記載されている範囲内である必要があります。SYNCSE を JESD204C SYNC に使用し、タイムスタンプが不要な場合、このピンを切断したままにして無効化 (TMSTP_RECV_EN = 0) できます。 |

| TMSTP-  | C1                                             | I   | タイムスタンプ入力の正接続または差動 JESD204C SYNC の負接続。SYNCSE を JESD204C SYNC に使用し、タイムスタンプが不要な場合、このピンを切断したままにして無効化 (TMSTP_RECV_EN = 0) できます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VA11    | C5, D2, D3, D5, E5, F5, G5, H5, J2, J3, J5, K5 | I   | 1.1V アナログ電源                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VA19    | C4, D4, E2, E3, E4, F4, G4, H2, H3, H4, J4, K4 | I   | 1.9V アナログ電源                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

**表 4-1. ピンの機能 (続き)**

| ピン   |                                               | タイプ | 説明          |

|------|-----------------------------------------------|-----|-------------|

| 名称   | 番号                                            |     |             |

| VD11 | C9、C10、E9、<br>E10、G7、H7、<br>H9、H10、K9、<br>K10 | I   | 1.1V デジタル電源 |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                |                                                  |                                                                                                       | 最小値   | 最大値                       | 単位  |

|----------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|---------------------------|-----|

| $V_{DD}$       | 電源電圧範囲                                           | VA19 <sup>(2)</sup>                                                                                   | -0.3  | 2.35                      | V   |

|                |                                                  | VA11 <sup>(2)</sup>                                                                                   | -0.3  | 1.32                      |     |

|                |                                                  | VD11 <sup>(3)</sup>                                                                                   | -0.3  | 1.32                      |     |

|                |                                                  | VD11 と VA11 の間の電圧                                                                                     | -1.32 | 1.32                      |     |

| $V_{GND}$      | AGND と DGND の間の電圧                                |                                                                                                       | -0.1  | 0.1                       | V   |

| $V_{PIN}$      | ピン電圧範囲                                           | DA[7:0]+、DA[7:0]-、DB[7:0]+、DB[7:0]-、TMSTP+、TMSTP- <sup>(3)</sup>                                      | -0.5  | VD11 + 0.5 <sup>(5)</sup> | V   |

|                |                                                  | CLK+、CLK-、SYSREF+、SYSREF- <sup>(2)</sup>                                                              | -0.5  | VA11 + 0.5 <sup>(4)</sup> |     |

|                |                                                  | BG、TDIODE+、TDIODE- <sup>(2)</sup>                                                                     | -0.5  | VA19 + 0.5 <sup>(6)</sup> |     |

|                |                                                  | INA+、INA-、INB+、INB- <sup>(2)</sup>                                                                    | -1    | 1                         |     |

|                |                                                  | CALSTAT、CALTRIG、NCOA0、NCOA1、NCOB0、NCOB1、ORA0、ORA1、ORB0、ORB1、PD、SCLK、SCS、SDI、SDO、SYNCSE <sup>(2)</sup> | -0.5  | VA19 + 0.5 <sup>(6)</sup> |     |

| $I_{MAX(ANY)}$ | ピーク入力電流 (INA+、INA-、INB+、INB- を除く任意の入力)           |                                                                                                       | -25   | 25                        | mA  |

| $I_{MAX(INx)}$ | ピーク入力電流 (INA+、INA-、INB+、INB-)                    |                                                                                                       | -50   | 50                        | mA  |

| $P_{MAX(INx)}$ | ピーク RF 入力電力 (INA+、INA-、INB+、INB-)                | $Z_{S-DIFF} = 100 \Omega$ での差動、最大 21 日 <sup>(7)</sup>                                                 |       | 26.5                      | dBm |

|                |                                                  | $Z_{S-SE} = 50 \Omega$ のシングルエンド                                                                       |       | 16.4                      | dBm |

| $I_{MAX(ALL)}$ | ピーク合計入力電流 (電源電流を含まない、強制的に流入または流出するすべての電流の絶対値の合計) |                                                                                                       | 100   | mA                        |     |

| $T_j$          | 接合部温度                                            |                                                                                                       | 150   | 150                       | °C  |

| $T_{stg}$      | 保存温度                                             |                                                                                                       | -65   | 150                       | °C  |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。セクション 5.1 これらはストレス定格に限られたものであり、「[推奨動作条件](#)」に示されている条件を超える当該の条件またはその他のいかなる条件も、このデバイスが正常に動作することを默示するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) AGND に対して測定。

- (3) DGND に対して測定。

- (4) 最大電圧が VA11 の絶対最大定格を超えてはいけません。

- (5) 最大電圧が VD11 の絶対最大定格を超えてはいけません。

- (6) 最大電圧が VA19 の絶対最大定格を超えてはいけません。

- (7) 標準的なデバイスを使用し、 $F_{IN} = 1.2\text{GHz}$  で 21 日間連続テスト。テストの最後でも、デバイスは損傷していません。オーバードライブ中、ADC は入力信号を適切に変換していますが、入力フルスケールを超える電圧では飽和します。

### 5.2 ESD 定格

|             |      |                                                         | 値          | 単位 |

|-------------|------|---------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | $\pm 2000$ | V  |

|             |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | $\pm 500$  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|            |                   |                                                  | 最小値  | 公称値 | 最大値                | 単位            |

|------------|-------------------|--------------------------------------------------|------|-----|--------------------|---------------|

| $V_{DD}$   | 電源電圧範囲            | VA19、アナログ 1.9V 電源 <sup>(2)</sup>                 | 1.8  | 1.9 | 2.0                | V             |

|            |                   | VA11、アナログ 1.1V 電源 <sup>(2)</sup>                 | 1.05 | 1.1 | 1.15               |               |

|            |                   | VD11、デジタル 1.1V 電源 <sup>(3)</sup>                 | 1.05 | 1.1 | 1.15               |               |

| $V_{CMII}$ | 入力同相電圧            | INA+、INA-、INB+、INB- <sup>(2)</sup>               | -50  | 0   | 100                | mV            |

|            |                   | CLK+、CLK-、SYSREF+、SYSREF- <sup>(2) (4)</sup>     | 0    | 0.3 | 0.55               | V             |

|            |                   | TMSTP+、TMSTP- <sup>(3) (5)</sup>                 | 0    | 0.3 | 0.55               |               |

| $V_{ID}$   | 入力電圧、ピーク ツー ピーク差動 | CLK+から CLK-へ、SYSREF+から SYSREF-へ、TMSTP+から TMSTP-へ | 0.4  | 1.0 | 2.0                | $V_{PP-DIFF}$ |

|            |                   | INA+ から INA- へ、INB+ から INB- へ                    |      |     | 0.8 <sup>(6)</sup> |               |

| $I_{C_TD}$ | 温度ダイオード入力電流       | TDIODE+ から TDIODE- へ                             |      | 100 |                    | $\mu$ A       |

| $C_L$      | BG 最大負荷容量         |                                                  |      |     | 50                 | pF            |

| $I_O$      | BG 最大出力電流         |                                                  |      |     | 100                | $\mu$ A       |

| DC         | 入力クロック デューティ サイクル |                                                  | 30   | 50  | 70                 | %             |

| $T_A$      | 自由空気での動作温度        |                                                  | -55  |     | 125                | °C            |

| $T_J$      | 動作時接合部温度          |                                                  |      |     | 150 <sup>(1)</sup> | °C            |

- (1) ダイは、 $T_J = 150^{\circ}\text{C}$  動作と、 $T_J = 125^{\circ}\text{C}$  でのデバイスおよびダイのメタライゼーション劣化で最大 150,000POH で連続動作するように設計されています。 $T_J = 105^{\circ}\text{C}$  の接合部温度を超えて長時間使用すると、パッケージの FIT 率 (Failure-In-Time、故障率) が上昇する可能性があります。

- (2) AGND に対して測定。

- (3) DGND に対して測定。

- (4) 最高の性能を得るために、CLK $\pm$ を最適な入力同相電圧に自己バイアスできるように、DEVCLK\_LVPECL\_EN を 0 に設定して CLK $\pm$ AC 結合することを強く推奨します。DC 結合が必要な場合を除き、SYSREF $\pm$ の AC 結合を推奨します。この場合、LVPECL 入力モードを使用する (SYSREF\_LVPECL\_EN = 1) 必要があります。

- (5) TMSTP $\pm$ には内部バイアスがないため、AC 結合で TMSTP\_LVPECL\_EN = 0、DC 結合で TMSTP\_LVPECL\_EN = 1 のいずれであっても、TMSTP $\pm$ を外部バイアスする必要があります。

- (6) INA $\pm$ または INB $\pm$ の  $V_{ID}$ 、INA $\pm$ の場合は FS\_RANGE\_A で設定されたプログラムされたフルスケール電圧 ( $V_{FS}$ ) を超えると、ADC 出力コードが飽和します。

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | 10mm x 10mm FC-BGA |  | 単位   |

|----------------------|---------------------|--------------------|--|------|

|                      |                     | 144 ピン             |  |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 23.9               |  | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 0.8                |  | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 8.4                |  | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 0.23               |  | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 8.4                |  | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性 : DC の仕様

標準値は、 $T_J = 50^\circ\text{C}$ 、 $\text{VA19} = 1.9\text{V}$ 、 $\text{VA11} = 1.1\text{V}$ 、 $\text{VD11} = 1.1\text{V}$ 、デフォルトのフルスケール電圧、 $f_{IN} = 347\text{MHz}$ 、 $A_{IN} = -1\text{dBFS}$ 、 $f_{CLK} = 5.12\text{GHz}$ 、フィルタ処理された 1- $V_{PP}$  正弦波クロック、 $\text{JMODE} = 1$ 、デフォルト設定でディザイナーイネーブル、 $\text{VA11}$ 、 $\text{VD11}$  および  $\text{VS11}$  ノイズ抑制オン ( $\text{EN\_VA11\_NOISE\_SUPPR} = \text{EN\_VD11\_NOISE\_SUPPR} = \text{EN\_VS11\_NOISE\_SUPPR} = 1$ )、バックグラウンドキャリブレーションにおける値(特に記述のない限り)。最小値および最大値は、「[推奨動作条件](#)」表に記載された公称電源電圧および動作温度範囲での値。

| パラメータ                                  | テスト条件                  |                                                                                                                                                                     | 最小値        | 標準値    | 最大値                          | 単位                              |

|----------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------------------------------|---------------------------------|

| <b>DC 精度</b>                           |                        |                                                                                                                                                                     |            |        |                              |                                 |

|                                        | 分解能                    | ミッシング コードなしの分解能                                                                                                                                                     | 12         |        |                              | ビット                             |

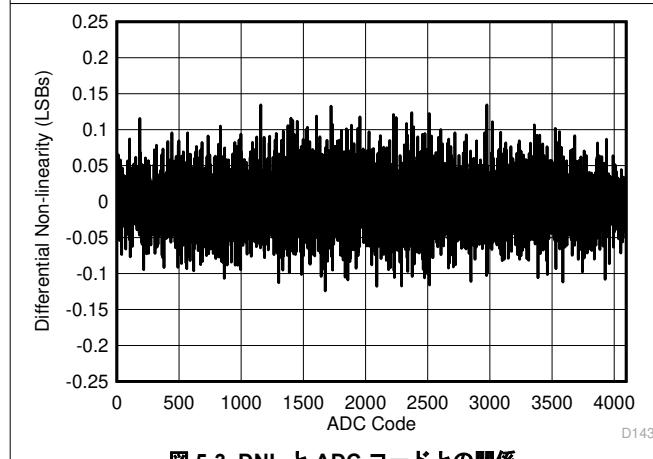

| DNL                                    | 微分非直線性                 | 理想的なステップ サイズからの正の最大変位                                                                                                                                               | 0.14       |        |                              | LSB                             |

|                                        |                        | 理想的なステップ サイズからの負の最大変位                                                                                                                                               | -0.13      |        |                              |                                 |

| INL                                    | 積分非直線性                 | 理想的な伝達関数からの正の最大変位                                                                                                                                                   | 2.0        |        |                              | LSB                             |

|                                        |                        | 理想的な伝達関数からの負の最大変位                                                                                                                                                   | -2.4       |        |                              | LSB                             |

| <b>アナログ入力 (INA+, INA-, INB+, INB-)</b> |                        |                                                                                                                                                                     |            |        |                              |                                 |

| $V_{OFF}$                              | オフセット エラー              | $\text{CAL\_OS} = 0$                                                                                                                                                | $\pm 0.50$ |        | mV                           |                                 |

|                                        |                        | $\text{CAL\_OS} = 1$                                                                                                                                                | $\pm 0.15$ |        | mV                           |                                 |

| $V_{OFF\_ADJ}$                         | 入力オフセット電圧の調整範囲         | 利用可能なオフセット補正範囲 ( $\text{OS\_CAL}$ または $\text{OADJ\_X\_INx}$ を参照)                                                                                                    | $\pm 50$   |        | mV                           |                                 |

| $V_{OFF\_DRIFT}$                       | オフセットのドリフト             | 公称温度のみでのフォアグラウンドキャリブレーション                                                                                                                                           | 18         |        | $\mu\text{V}/^\circ\text{C}$ |                                 |

|                                        |                        | 各温度でのフォアグラウンドキャリブレーション                                                                                                                                              | -5.5       |        |                              |                                 |

|                                        |                        | 各温度でのフォアグラウンドおよび FGOS キャリブレーション                                                                                                                                     | 0          |        |                              |                                 |

| $V_{FS}$                               | アナログ差動入力フルスケールレンジ      | デフォルトのフルスケール電圧 ( $\text{FS\_RANGE\_A} = \text{FS\_RANGE\_B} = 0xA000$ )                                                                                             | 750        | 825    | 910                          | $\text{mV}_{PP}$                |

|                                        |                        | 最大フルスケール電圧 ( $\text{FS\_RANGE\_A} = \text{FS\_RANGE\_B} = 0xFFFF$ )                                                                                                 | 975        | 1060   |                              |                                 |

|                                        |                        | 最小フルスケール電圧 ( $\text{FS\_RANGE\_A} = \text{FS\_RANGE\_B} = 0x2000$ )                                                                                                 |            | 500    | 560                          |                                 |

| $V_{FS\_DRIFT}$                        | アナログ差動入力フルスケールレンジドリフト  | デフォルトの $\text{FS\_RANGE\_A}$ および $\text{FS\_RANGE\_B}$ 設定、各温度でのフォアグラウンドキャリブレーション、 $50\Omega$ ソースで駆動される入力、 $R_{IN}$ ドリフトの影響を含む                                       |            | 0.033  |                              | $\text{%/}^\circ\text{C}$       |

| $V_{FS\_MATCH}$                        | アナログ差動入力フルスケールレンジマッチング | $\text{INA}_\pm$ と $\text{INB}_\pm$ とのマッチング、デフォルト設定、デュアル チャネル モード                                                                                                   |            | 0.625% |                              |                                 |

| $R_{IN}$                               | AGND へのシングルエンド入力抵抗     | 各入力ピンは AGND に終端、 $T_A = 25^\circ\text{C}$ で測定                                                                                                                       | 48         | 50     | 52                           | $\Omega$                        |

| $R_{IN\_TEMPCO}$                       | 入力終端の線形温度係数            |                                                                                                                                                                     |            | 14.7   |                              | $\text{m}\Omega/^\circ\text{C}$ |

| $C_{IN}$                               | シングルエンド入力容量            | DC で測定されたシングルチャネルモード                                                                                                                                                |            | 0.4    |                              | $\text{pF}$                     |

|                                        |                        | DC で測定されたデュアルチャネルモード                                                                                                                                                |            | 0.4    |                              |                                 |

| <b>温度ダイオードの特性 (TDIODE+, TDIODE-)</b>   |                        |                                                                                                                                                                     |            |        |                              |                                 |

| $\Delta V_{BE}$                        | 温度ダイオードの電圧スローパ         | 100 $\mu\text{A}$ の強制順方向電流、オフセット電圧 ( $0^\circ\text{C}$ で約 0.792V) はプロセスによって変化するため、各部品で測定する必要があります。デバイスの電源がオフのとき、または PD ピンがアサートされた状態でオフセット測定を実行し、デバイスの自己発熱を最小限に抑えます。 |            | -1.65  |                              | $\text{mV}/^\circ\text{C}$      |

## 5.5 電気的特性 : DC の仕様 (続き)

標準値は、 $T_J = 50^\circ\text{C}$ 、 $VA19 = 1.9\text{V}$ 、 $VA11 = 1.1\text{V}$ 、 $VD11 = 1.1\text{V}$ 、デフォルトのフルスケール電圧、 $f_{IN} = 347\text{MHz}$ 、 $A_{IN} = -1\text{dBFS}$ 、 $f_{CLK} = 5.12\text{GHz}$ 、フィルタ処理された 1-V<sub>PP</sub> 正弦波クロック、 $JMODE = 1$ 、デフォルト設定でディザイナーイネーブル、 $VA11$ 、 $VD11$  および  $VS11$  ノイズ抑制オン ( $EN_{VA11\_NOISE\_SUPPR} = EN_{VD11\_NOISE\_SUPPR} = EN_{VS11\_NOISE\_SUPPR} = 1$ )、パッケージラウンドキャリブレーションにおける値 (特に記述のない限り)。最小値および最大値は、「[推奨動作条件](#)」表に記載された公称電源電圧および動作温度範囲での値。

| パラメータ                                                                                                       | テスト条件             | 最小値                                                                                                             | 標準値      | 最大値      | 単位                           |

|-------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|----------|----------|------------------------------|

| <b>バンドギャップ電圧出力 (BG)</b>                                                                                     |                   |                                                                                                                 |          |          |                              |

| $V_{BG}$                                                                                                    | リファレンス出力電圧        | $I_L \leq 100\mu\text{A}$                                                                                       | 1.1      |          | V                            |

| $V_{BG\_DRIFT}$                                                                                             | リファレンス出力の温度ドリフト   | $I_L \leq 100\mu\text{A}$                                                                                       | -64      |          | $\mu\text{V}/^\circ\text{C}$ |

| <b>クロック入力 (CLK+, CLK-, SYSREF+, SYSREF-, TMSTP+, TMSTP-)</b>                                                |                   |                                                                                                                 |          |          |                              |

| $Z_T$                                                                                                       | 内部終端              | DEVCLK_LVPECL_EN = 0, SYSREF_LVPECL_EN = 0, TMSTP_LVPECL_EN = 0 による差動終端                                         | 100      | $\Omega$ |                              |

|                                                                                                             |                   | DEVCLK_LVPECL_EN = 0, SYSREF_LVPECL_EN = 0, TMSTP_LVPECL_EN = 0 での GND へのシングルエンド終端 (ピンごと)                       | 50       |          |                              |

| $V_{CM}$                                                                                                    | 入力同相電圧、自己バイアス     | AC 結合されている場合の $CLK\pm$ の自己バイアス同相電圧 (DEVCLK_LVPECL_EN を 0 に設定する必要があります)                                          | 0.3      | V        |                              |

|                                                                                                             |                   | AC 結合されており (SYSREF_LVPECL_EN を 0 に設定する必要があります)、レシーバがイネーブル (SYSREF_RECV_EN = 1) の場合における SYSREF $\pm$ の自己バイアス同相電圧 | 0.28     |          |                              |

|                                                                                                             |                   | AC 結合されている場合 (SYSREF_LVPECL_EN を 0 に設定する必要があります)、レシーバがディセーブル (SYSREF_RECV_EN = 0) のとき、SYSREF $\pm$ の自己バイアス同相電圧  | 0.28     |          |                              |

| $C_{L\_DIFF}$                                                                                               | 差動入力容量            | 正と負の差動入力ピン間に接続されています                                                                                            | 0.04     |          | pF                           |

| $C_{L\_SE}$                                                                                                 | シングルエンド入力容量       | 各入力からグランドへ                                                                                                      | 0.5      |          | pF                           |

| <b>SERDES 出力 (DA[7:0]+, DA[7:0]-, DB[7:0]+, DB[7:0]-)</b>                                                   |                   |                                                                                                                 |          |          |                              |

| $V_{OD}$                                                                                                    | 差動出力電圧、ピーク ツー ピーク | 100- $\Omega$ の負荷                                                                                               | 540      | 600      | 650 mV <sub>PP-DIFF</sub>    |

| $V_{CM}$                                                                                                    | 出力同相電圧            | AC 結合                                                                                                           | VD11 / 2 |          | V                            |

| $Z_{DIFF}$                                                                                                  | 差動出力インピーダンス       |                                                                                                                 | 100      |          | $\Omega$                     |

| <b>CMOS インターフェイス:SCLK、SDI、SDO、SCS、PD、NCOA0、NCOA1、NCOB0、NCOB1、CALSTAT、CALTRIG、ORA0、ORA1、ORB0、ORB1、SYNCSE</b> |                   |                                                                                                                 |          |          |                              |

| $V_{IH}$                                                                                                    | High レベル入力電圧      | 必須入力電圧                                                                                                          | 0.7      |          | V                            |

| $V_{IL}$                                                                                                    | Low レベル入力電圧       | 必須入力電圧                                                                                                          |          | 0.45     | V                            |

| $I_{IH}$                                                                                                    | High レベル入力電流      |                                                                                                                 |          | 40       | $\mu\text{A}$                |

| $I_{IL}$                                                                                                    | Low レベル入力電流       |                                                                                                                 | -40      |          | $\mu\text{A}$                |

| $C_I$                                                                                                       | 入力容量              |                                                                                                                 |          | 3.4      | pF                           |

| $V_{OH}$                                                                                                    | 高レベル出力電圧          | $I_{LOAD} = -400\mu\text{A}$                                                                                    | 1.65     |          | V                            |

| $V_{OL}$                                                                                                    | Low レベル出力電圧       | $I_{LOAD} = 400\mu\text{A}$                                                                                     |          | 150      | mV                           |

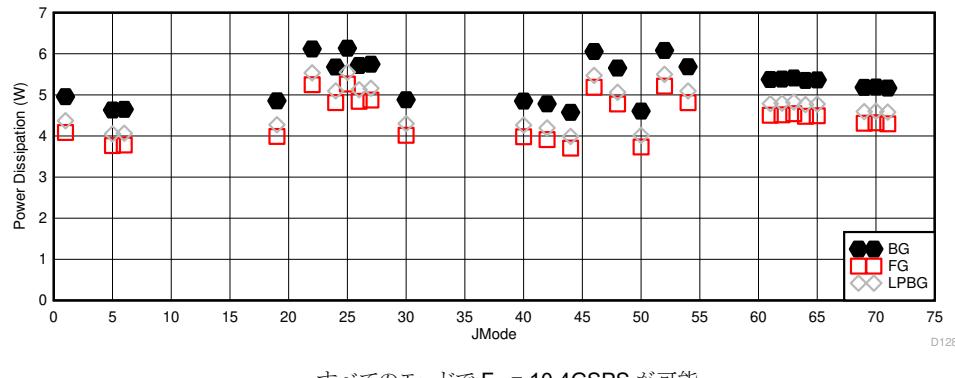

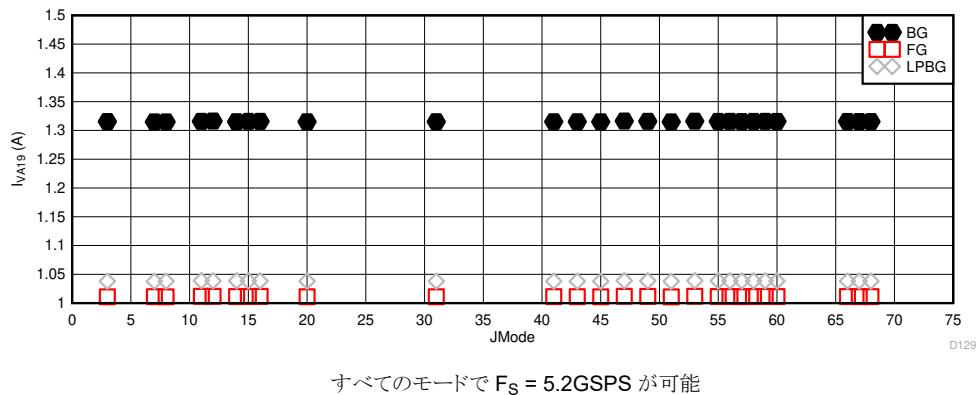

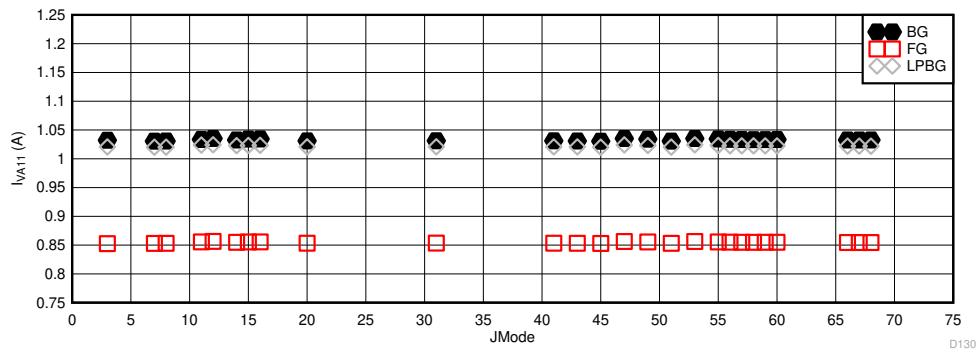

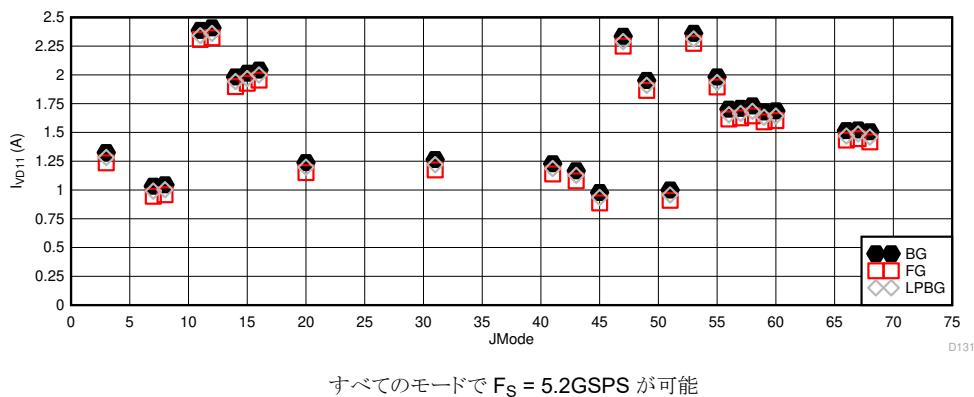

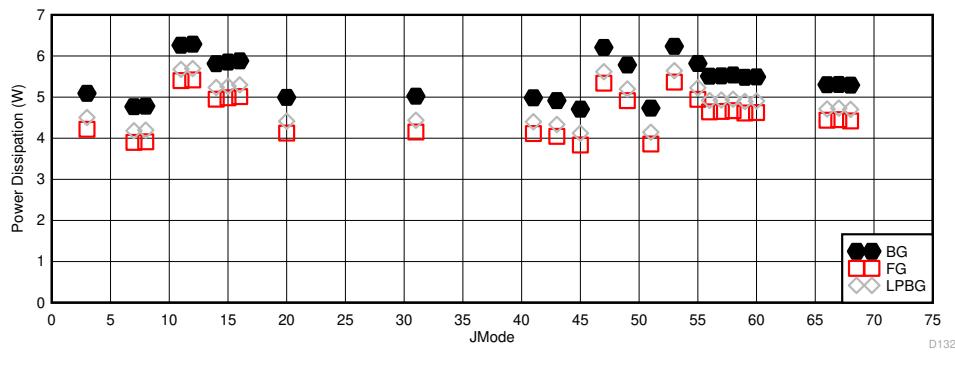

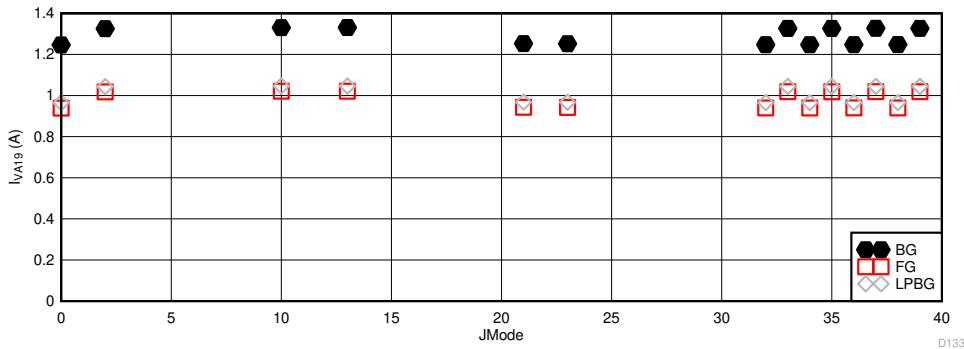

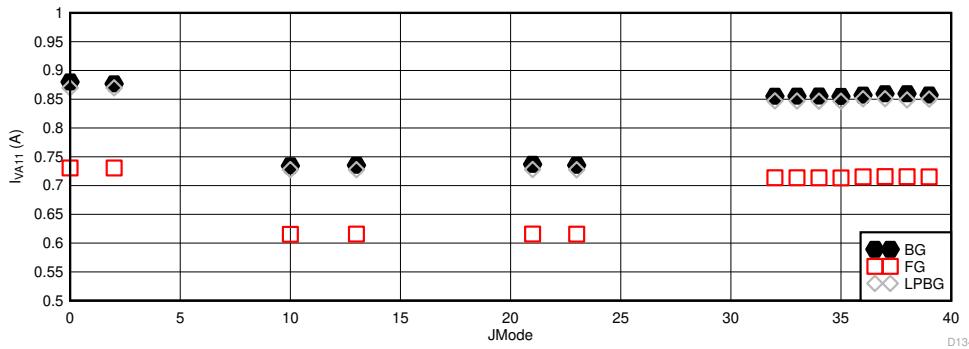

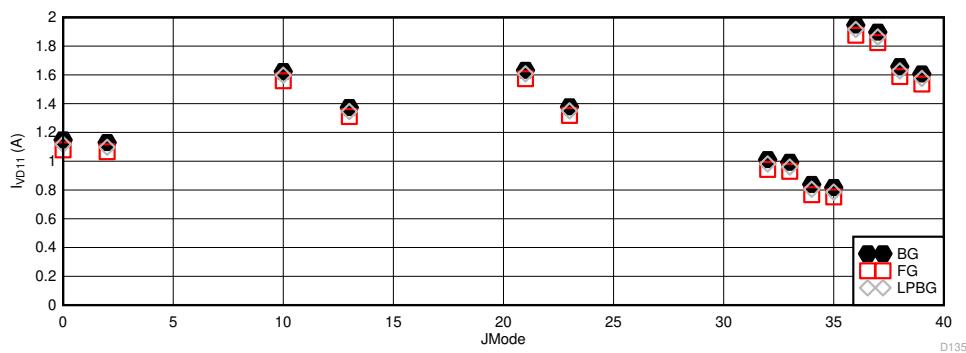

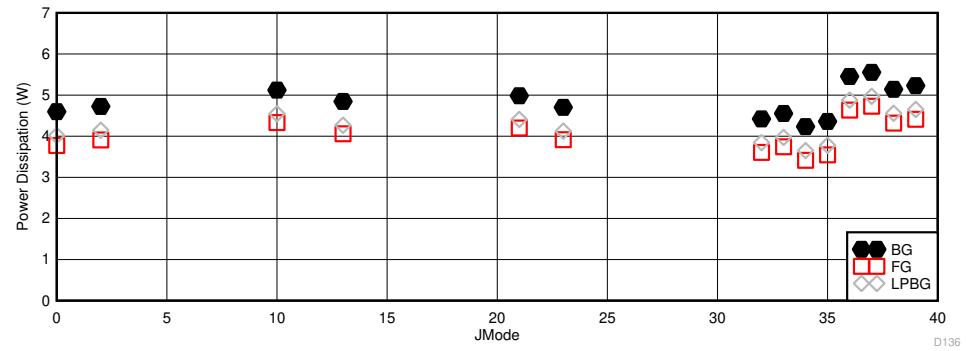

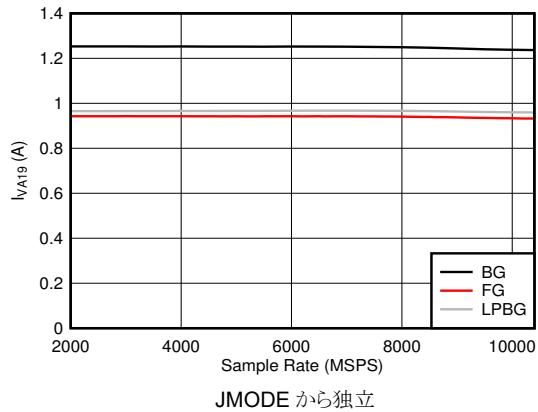

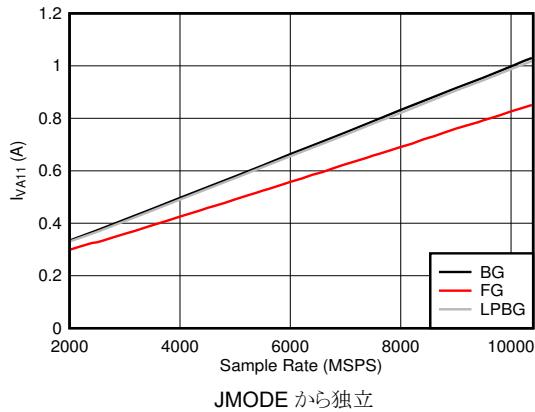

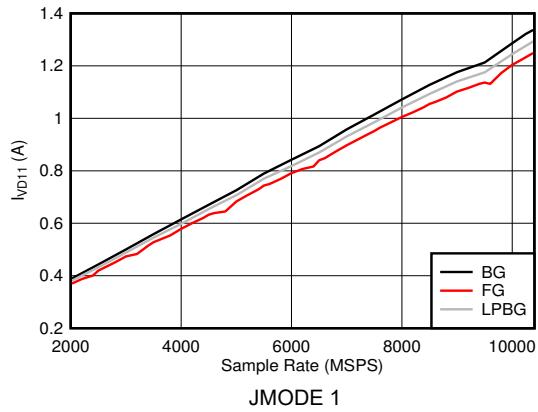

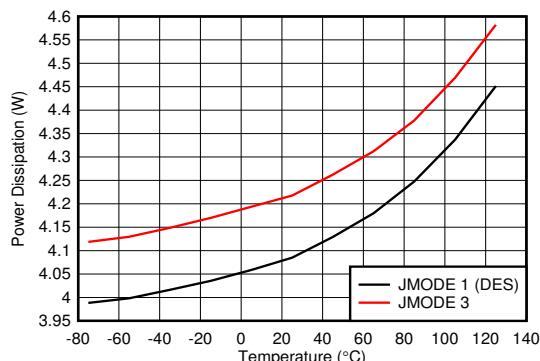

## 5.6 電気的特性：消費電力

標準値は、 $T_J = 50^\circ\text{C}$ 、 $\text{VA19} = 1.9\text{V}$ 、 $\text{VA11} = 1.1\text{V}$ 、 $\text{VD11} = 1.1\text{V}$ 、デフォルトのフルスケール電圧、 $f_{IN} = 347\text{MHz}$ 、 $A_{IN} = -1\text{dBFS}$ 、 $f_{CLK} = 5.12\text{GHz}$ 、フィルタ処理された 1-V<sub>PP</sub> 正弦波クロック、JMODE = 1、デフォルト設定でディザイナーイネーブル、VA11、VD11 および VS11 ノイズ抑制オン ([EN\\_VA11\\_NOISE\\_SUPPR = EN\\_VD11\\_NOISE\\_SUPPR = EN\\_VS11\\_NOISE\\_SUPPR = 1](#))、バックグラウンドキャリブレーションにおける値(特に記述のない限り)。最小値および最大値は、「[推奨動作条件](#)」表に記載された公称電源電圧および動作温度範囲での値。

| パラメータ      | テスト条件         | 最小値  | 標準値  | 最大値 | 単位 |

|------------|---------------|------|------|-----|----|

| $I_{VA19}$ | 1.9V アナログ電源電流 |      | 934  |     | mA |

| $I_{VA11}$ | 1.1V アナログ電源電流 |      | 845  |     | mA |

| $I_{VD11}$ | 1.1V デジタル電源電流 |      | 1170 |     | mA |

| $P_{DIS}$  | 消費電力          |      | 4.01 |     | W  |

| $I_{VA19}$ | 1.9V アナログ電源電流 | 935  | 1050 |     | mA |

| $I_{VA11}$ | 1.1V アナログ電源電流 | 850  | 1000 |     | mA |

| $I_{VD11}$ | 1.1V デジタル電源電流 | 1195 | 1650 |     | mA |

| $P_{DIS}$  | 消費電力          | 4.0  | 4.98 |     | W  |

| $I_{VA19}$ | 1.9V アナログ電源電流 | 1242 |      |     | mA |

| $I_{VA11}$ | 1.1V アナログ電源電流 | 1030 |      |     | mA |

| $I_{VD11}$ | 1.1V デジタル電源電流 | 1265 |      |     | mA |

| $P_{DIS}$  | 消費電力          | 4.90 |      |     | W  |

| $I_{VA19}$ | 1.9V アナログ電源電流 | 1320 |      |     | mA |

| $I_{VA11}$ | 1.1V アナログ電源電流 | 1030 |      |     | mA |

| $I_{VD11}$ | 1.1V デジタル電源電流 | 1250 |      |     | mA |

| $P_{DIS}$  | 消費電力          | 5.03 |      |     | W  |

| $I_{VA19}$ | 1.9V アナログ電源電流 | 936  |      |     | mA |

| $I_{VA11}$ | 1.1V アナログ電源電流 | 845  |      |     | mA |

| $I_{VD11}$ | 1.1V デジタル電源電流 | 2350 |      |     | mA |

| $P_{DIS}$  | 消費電力          | 5.3  |      |     | W  |

| $I_{VA19}$ | 1.9V アナログ電源電流 | 1014 |      |     | mA |

| $I_{VA11}$ | 1.1V アナログ電源電流 | 845  |      |     | mA |

| $I_{VD11}$ | 1.1V デジタル電源電流 | 2260 |      |     | mA |

| $P_{DIS}$  | 消費電力          | 5.34 |      |     | W  |

| $I_{VA19}$ | 1.9V アナログ電源電流 | 44   |      |     | mA |

| $I_{VA11}$ | 1.1V アナログ電源電流 | 30   |      |     | mA |

| $I_{VD11}$ | 1.1V デジタル電源電流 | 56   |      |     | mA |

| $P_{DIS}$  | 消費電力          | 0.18 |      |     | W  |

## 5.7 電気的特性 : AC 仕様 (デュアルチャネルモード)

標準値は、 $T_J = 50^\circ\text{C}$ 、 $VA19 = 1.9\text{V}$ 、 $VA11 = 1.1\text{V}$ 、 $VD11 = 1.1\text{V}$ 、デフォルトのフルスケール電圧、 $f_{IN} = 347\text{MHz}$ 、 $A_{IN} = -1\text{dBFS}$ 、 $f_{CLK} = 5.12\text{GHz}$ 、フィルタ処理された 1-V<sub>PP</sub> 正弦波クロック、JMODE = 3、デフォルト設定でディザイナーイネーブル、VA11、VD11 および VS11 ノイズ抑制オン ([EN\\_VA11\\_NOISE\\_SUPPR = EN\\_VD11\\_NOISE\\_SUPPR = EN\\_VS11\\_NOISE\\_SUPPR = 1](#))、バックグラウンドキャリブレーションにおける値 (特に記述のない限り)。最小値および最大値は、「[推奨動作条件](#)」表に記載された公称電源電圧および動作温度範囲での値。

| パラメータ               |                                                      | テスト条件                                                                     | 最小値                                                 | 標準値         | 最大値    | 単位   |

|---------------------|------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------|-------------|--------|------|

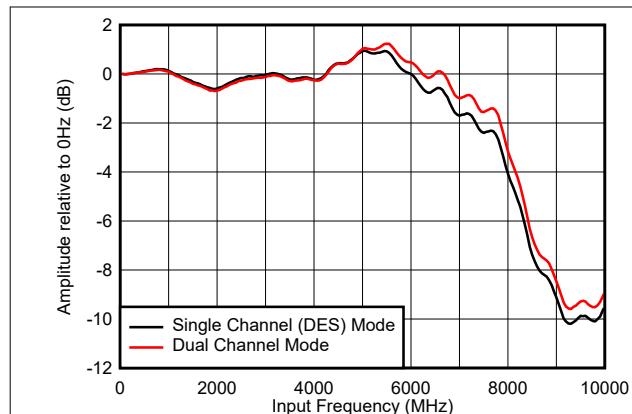

| FPBW                | 最大出力入力帯域幅 (-3dB)<br>(1)                              | フォアグラウンドキャリブレーション                                                         | 8.1                                                 | GHz         | 8.1    |      |

|                     |                                                      | バックグラウンドキャリブレーション                                                         | 8.1                                                 |             |        |      |

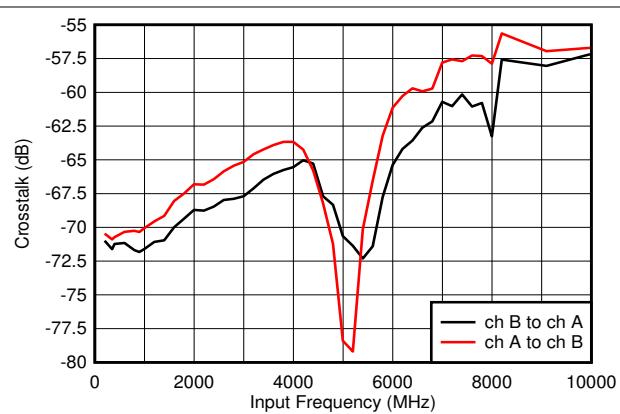

| XTALK               | チャネル間クロストーク                                          | アグレッサー = 1GHz, -1dBFS                                                     | -77                                                 | dB          | -71    |      |

|                     |                                                      | アグレッサー = 3GHz, -1dBFS                                                     | -71                                                 |             |        |      |

|                     |                                                      | アグレッサー = 6GHz, -1dBFS                                                     | -63                                                 |             |        |      |

| CER                 | コードエラーレート                                            | 最大 CER、JESD204C インターフェイス BER は付属していません                                    | $10^{-18}$                                          | エラー / サンプル  |        |      |

| NOISE <sub>DC</sub> | DC 入力ノイズの標準偏差                                        | 入力なし、フォアグラウンドキャリブレーション。DC オフセットを除く。固定のインターリーブスプリアス ( $f_S/2$ スプリアス) を含む   | 2.3                                                 |             |        |      |

| NSD                 | ノイズスペクトル密度、固定インターリーブスプリアス ( $f_S/2$ スプリアス) を除く       | 最大フルスケール電圧 ( $V_{FS} = 1.0\text{V}_{PP}$ )、 $A_{IN} = -20\text{dBFS}$     | -152.0                                              | dBFS/<br>Hz | -150.4 |      |

|                     |                                                      | デフォルトのフルスケール電圧 ( $V_{FS} = 0.8\text{V}_{PP}$ )、 $A_{IN} = -20\text{dBFS}$ | -150.4                                              |             |        |      |

| NF                  | ノイズ指数、 $Z_S = 100\Omega$                             | 最大フルスケール電圧 ( $V_{FS} = 1.0\text{V}_{PP}$ )、 $A_{IN} = -20\text{dBFS}$     | 23.0                                                | dB          | 22.6   |      |

|                     |                                                      | デフォルトのフルスケール電圧 ( $V_{FS} = 0.8\text{V}_{PP}$ )、 $A_{IN} = -20\text{dBFS}$ | 22.6                                                |             |        |      |

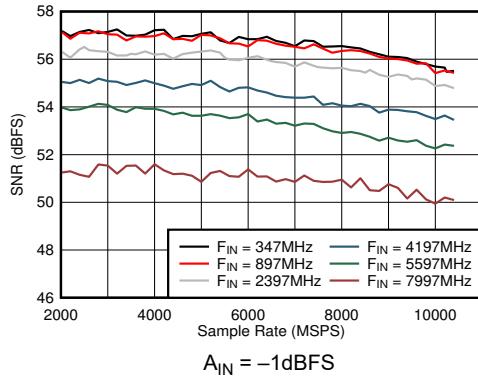

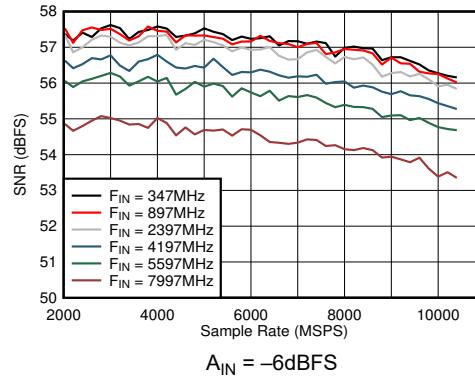

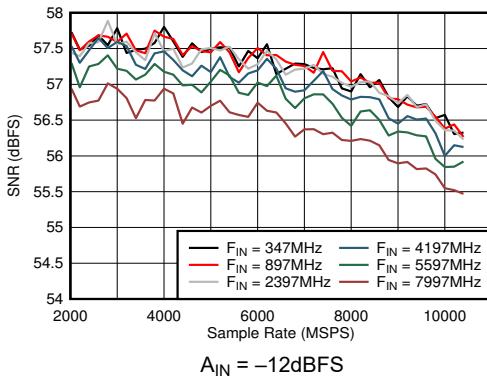

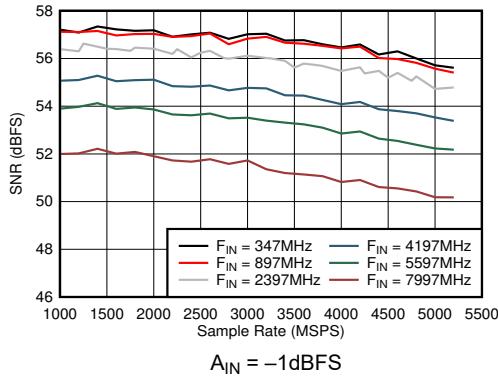

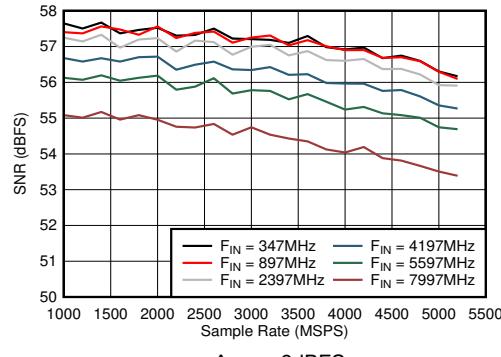

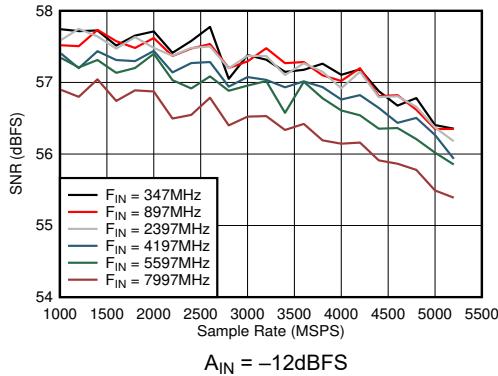

| SNR                 | 信号対雑音比、DC、HD2 ~ HD9、 $f_S/2$ 、 $f_S/2 - f_{IN}$ を除く、 | $f_{IN} = 347\text{MHz}$                                                  | $A_{IN} = -1\text{dBFS}$                            | dBFS        | 55.6   |      |

|                     |                                                      |                                                                           | $A_{IN} = -3\text{dBFS}$                            |             | 55.9   |      |

|                     |                                                      |                                                                           | $A_{IN} = -12\text{dBFS}$                           |             | 56.3   |      |

|                     |                                                      |                                                                           | $A_{IN} = -3\text{dBFS}, V_{FS} = 1.0\text{V}_{PP}$ |             | 57.2   |      |

|                     |                                                      | $f_{IN} = 997\text{MHz}$                                                  | $A_{IN} = -1\text{dBFS}$                            |             | 55.4   |      |

|                     |                                                      |                                                                           | $A_{IN} = -3\text{dBFS}$                            |             | 55.8   |      |

|                     |                                                      |                                                                           | $A_{IN} = -12\text{dBFS}$                           |             | 56.3   |      |

|                     |                                                      | $f_{IN} = 2397\text{MHz}$                                                 | $A_{IN} = -1\text{dBFS}, T_A = -55^\circ\text{C}$   |             | 48     |      |

|                     |                                                      |                                                                           | $A_{IN} = -1\text{dBFS}, T_A = 25^\circ\text{C}$    |             | 52     | 54.7 |

|                     |                                                      |                                                                           | $A_{IN} = -1\text{dBFS}, T_A = 125^\circ\text{C}$   |             | 51     |      |

|                     |                                                      |                                                                           | $A_{IN} = -3\text{dBFS}$                            |             | 55.2   |      |

|                     |                                                      |                                                                           | $A_{IN} = -12\text{dBFS}$                           |             | 56.2   |      |

|                     |                                                      |                                                                           | $A_{IN} = -3\text{dBFS}, V_{FS} = 1.0\text{V}_{PP}$ |             | 56.3   |      |

|                     |                                                      | $f_{IN} = 4197\text{MHz}$                                                 | $A_{IN} = -1\text{dBFS}$                            |             | 53.0   |      |

|                     |                                                      |                                                                           | $A_{IN} = -3\text{dBFS}$                            |             | 54.0   |      |

|                     |                                                      |                                                                           | $A_{IN} = -12\text{dBFS}$                           |             | 56.0   |      |

|                     |                                                      | $f_{IN} = 5997\text{MHz}$                                                 | $A_{IN} = -1\text{dBFS}$                            |             | 51.4   |      |

|                     |                                                      |                                                                           | $A_{IN} = -3\text{dBFS}$                            |             | 52.6   |      |

|                     |                                                      |                                                                           | $A_{IN} = -12\text{dBFS}$                           |             | 55.6   |      |

|                     |                                                      | $f_{IN} = 7997\text{MHz}$                                                 | $A_{IN} = -1\text{dBFS}$                            |             | 49.6   |      |

|                     |                                                      |                                                                           | $A_{IN} = -3\text{dBFS}$                            |             | 51.1   |      |

|                     |                                                      |                                                                           | $A_{IN} = -12\text{dBFS}$                           |             | 55.2   |      |

## 5.7 電気的特性 : AC 仕様 (デュアル チャネル モード) (続き)

標準値は、 $T_J = 50^\circ\text{C}$ 、 $VA19 = 1.9\text{V}$ 、 $VA11 = 1.1\text{V}$ 、 $VD11 = 1.1\text{V}$ 、デフォルトのフルスケール電圧、 $f_{IN} = 347\text{MHz}$ 、 $A_{IN} = -1\text{dBFS}$ 、 $f_{CLK} = 5.12\text{GHz}$ 、フィルタ処理された  $1\text{-}V_{PP}$  正弦波クロック、 $JMODE = 3$ 、デフォルト設定でディザイナーイネーブル、 $VA11$ 、 $VD11$  および  $VS11$  ノイズ抑制オン ( $EN\_VA11\_NOISE\_SUPPR = EN\_VD11\_NOISE\_SUPPR = EN\_VS11\_NOISE\_SUPPR = 1$ )、パックグラウンド キャリブレーションにおける値 (特に記述のない限り)。最小値および最大値は、「[推奨動作条件](#)」表に記載された公称電源電圧および動作温度範囲での値。

| パラメータ |                                          | テスト条件                     | 最小値                                               | 標準値  | 最大値  | 単位   |

|-------|------------------------------------------|---------------------------|---------------------------------------------------|------|------|------|

| SINAD | 信号対雑音比および歪み比、DC および $f_S / 2$ 固定スプリアスを除く | $f_{IN} = 347\text{MHz}$  | $A_{IN} = -1\text{dBFS}$                          | 54.5 |      | dBFS |

|       |                                          |                           | $A_{IN} = -3\text{dBFS}$                          | 55.3 |      |      |

|       |                                          |                           | $A_{IN} = -12\text{dBFS}$                         | 56.1 |      |      |

|       |                                          |                           | $A_{IN} = -3\text{dBFS}, V_{FS} = 1\text{V}_{PP}$ | 56.3 |      |      |

|       |                                          | $f_{IN} = 997\text{MHz}$  | $A_{IN} = -1\text{dBFS}$                          | 54.4 |      |      |

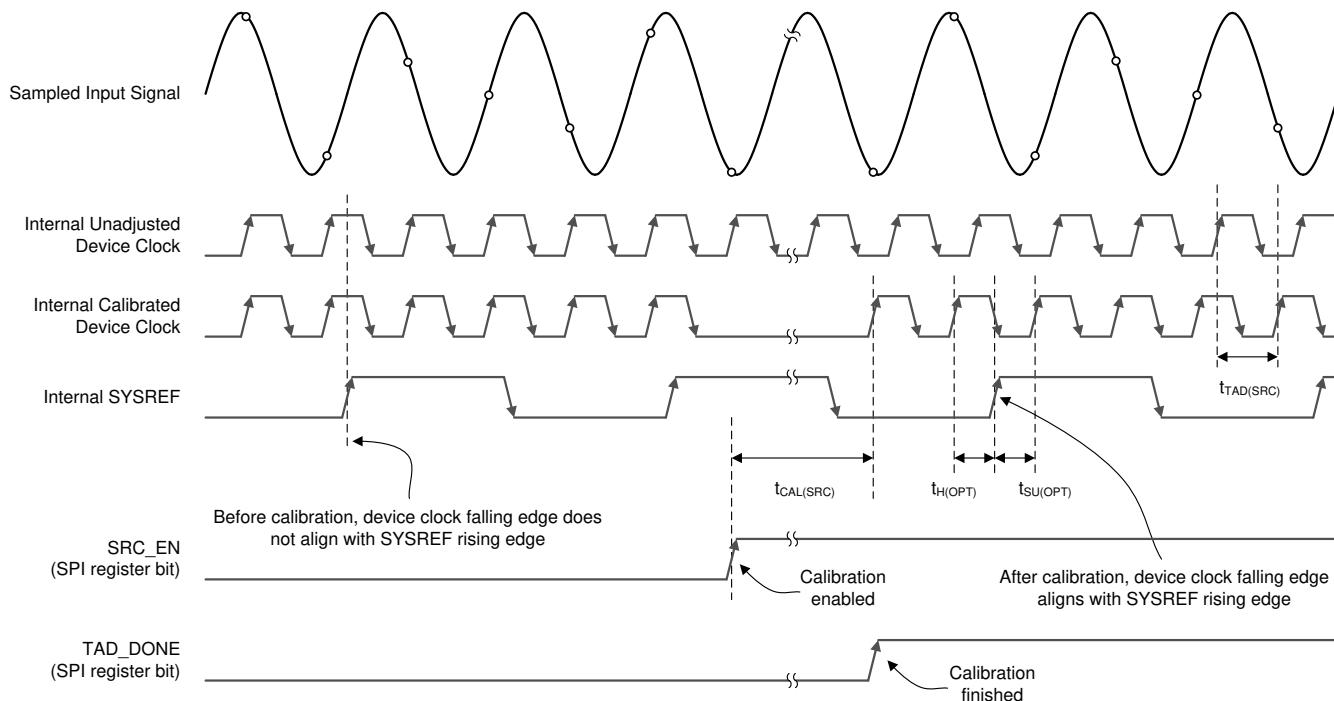

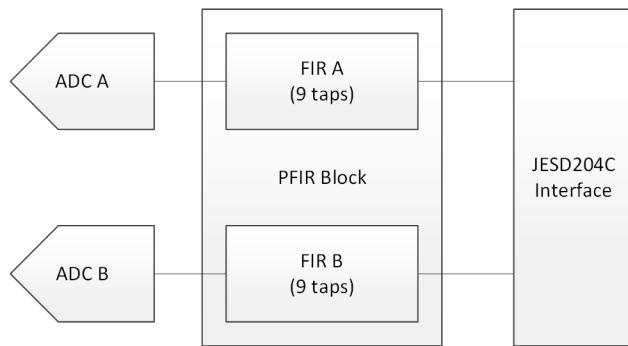

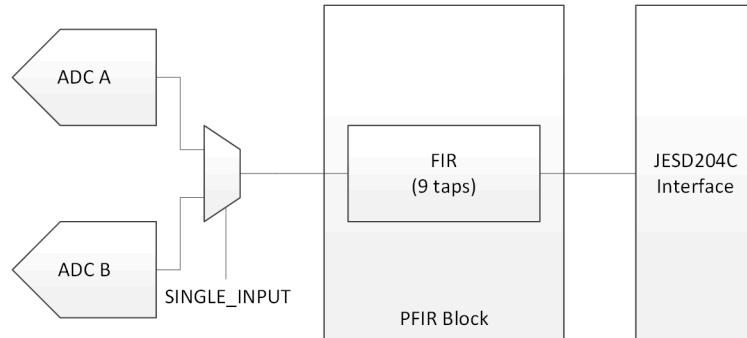

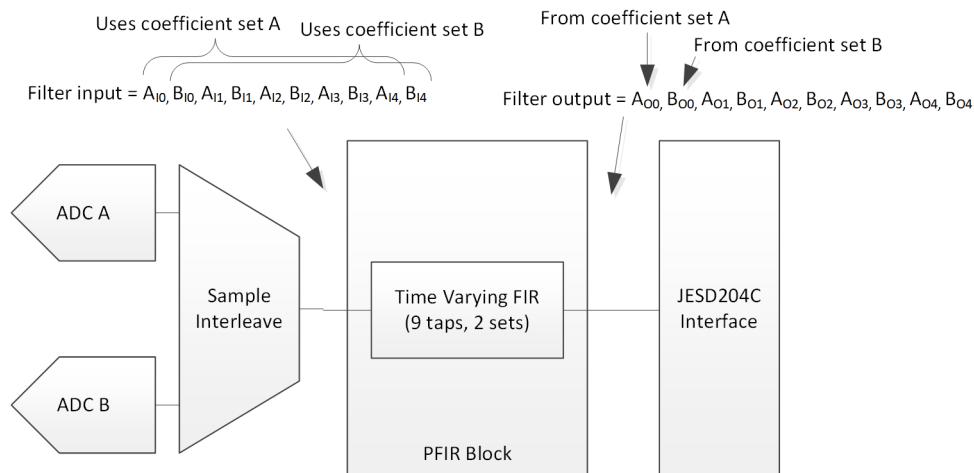

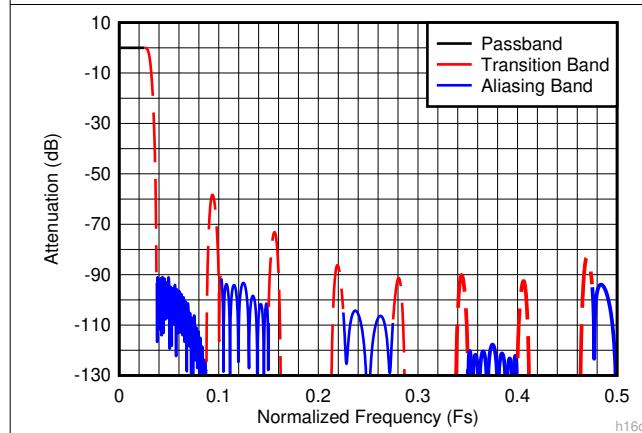

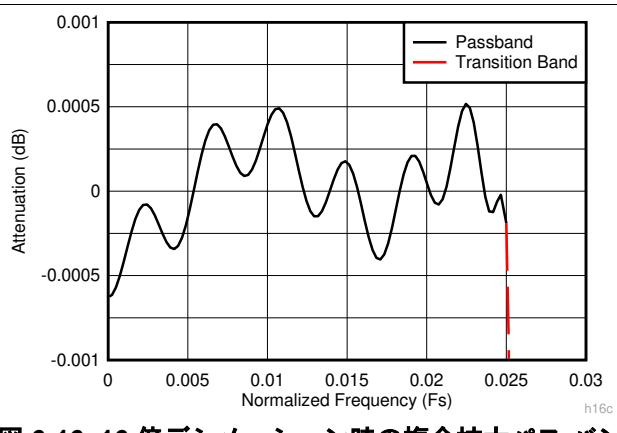

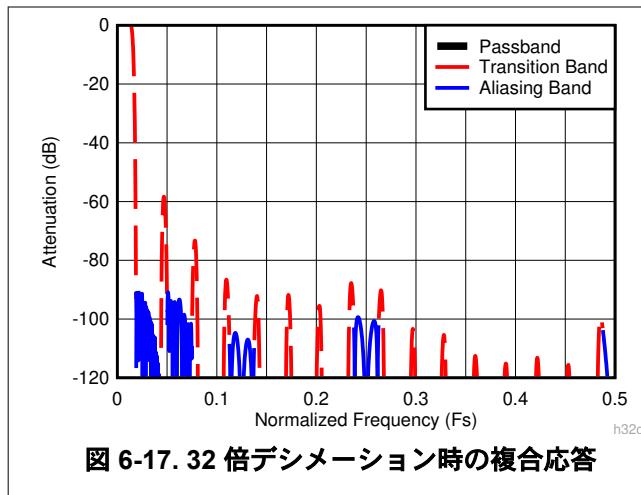

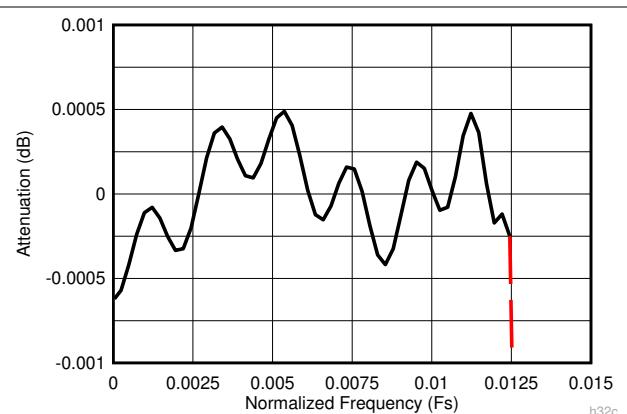

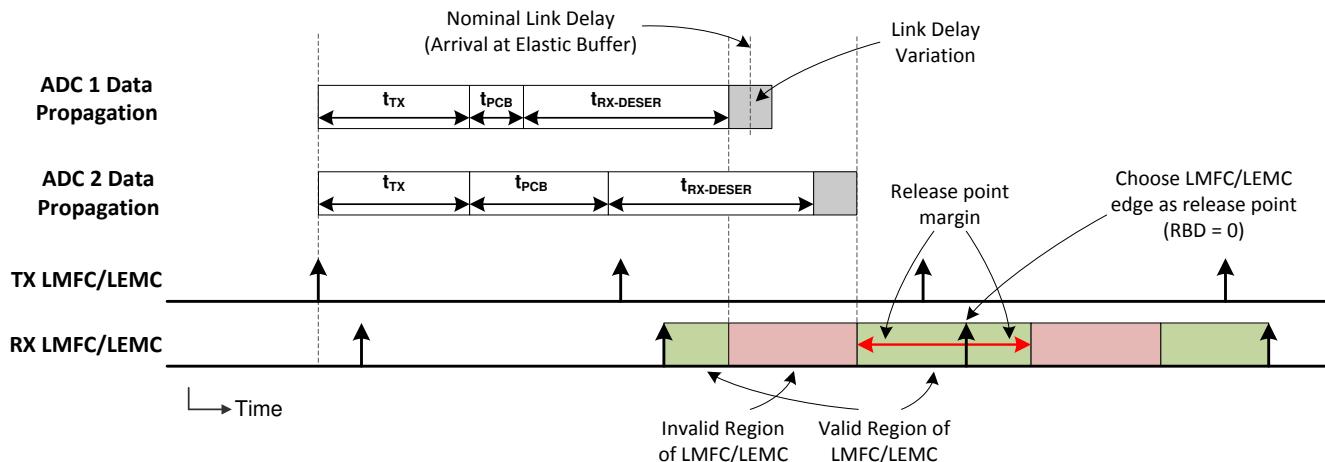

|       |                                          |                           | $A_{IN} = -3\text{dBFS}$                          | 55.3 |      |      |