# ADS1x2C14 低消費電力 16 ビット/24 ビット、8 チャネル、64kSPS、PGA、電圧リファレンス、および I<sup>2</sup>C インターフェイスを搭載した ADC

## 1 特長

- 低消費電力 (最小 57 $\mu$ A)

- 広い電源電圧範囲:

- アナログ: 1.74V ~ 3.6V

- デジタル: 1.65V ~ 3.6V

- ゲインをプログラム可能: 0.5 ~ 256

- 消費電力とノイズ性能のトレードオフを行うための、プログラマブルなデータレート (最大 64kSPS) および速度モード

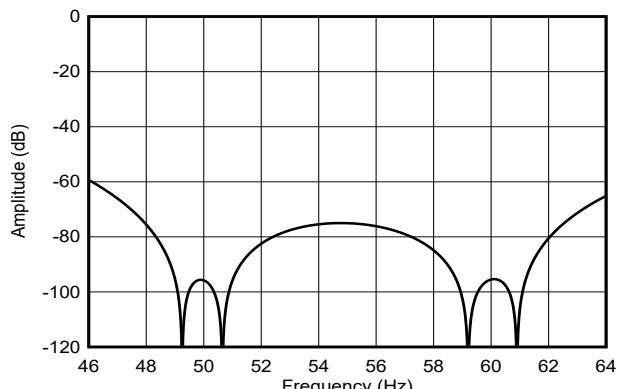

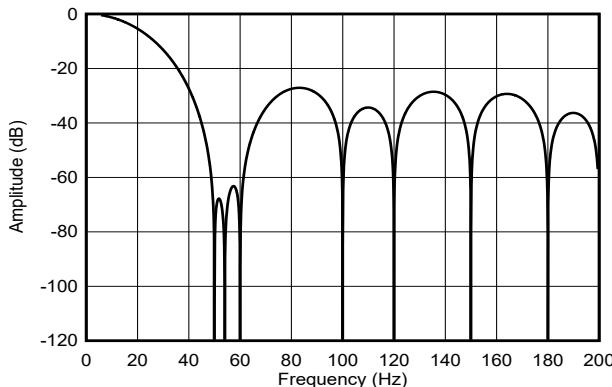

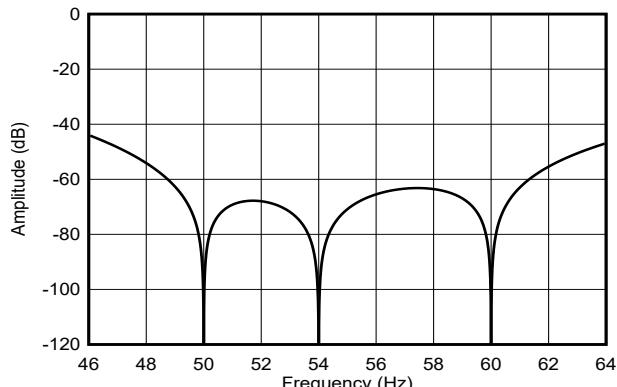

- 単一サイクル整定のデジタルフィルタにより、20 または 25SPS で 50Hz と 60Hz を同時に除去

- 8 の独立して選択可能な入力を備えたアナログマルチプレクサ

- デュアルマッチドプログラマブル電流源

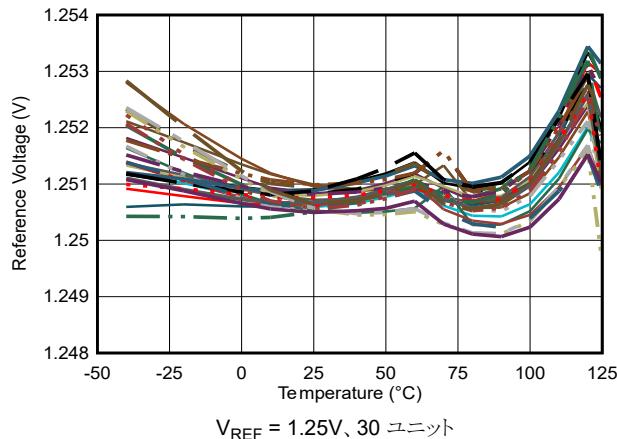

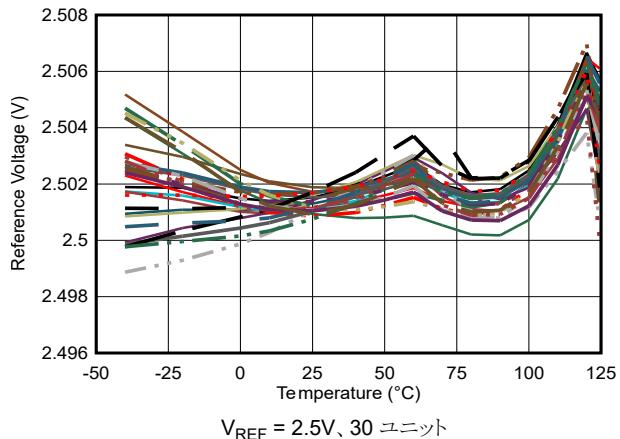

- 内部プログラム可能な電圧リファレンス: 25ppm/ $^{\circ}$ C (最大) のドリフト特性を持つ 1.25V または 2.5V

- 1% (max) 精度の内部発振器

- 内部温度センサ

- 4 つの汎用 I/O (プッシュプル出力またはオープンドレイン出力)

- オプションの CRC を備えた I<sup>2</sup>C 互換インターフェイス

- サポートされている I<sup>2</sup>C バス速度: Sm, Fm, Fm+

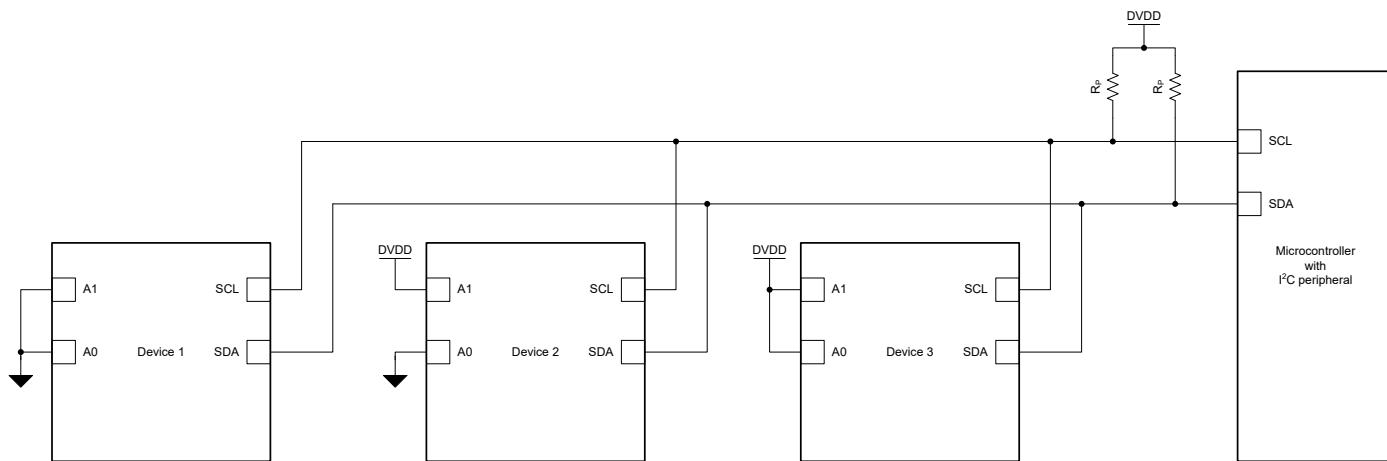

- ピンによりプログラム可能な 8 つの I<sup>2</sup>C アドレス

## 2 アプリケーション

- フィールドトランシミッタ:

- 温度、圧力、歪み、フロー

- PLC および DCS アナログ入力モジュール

- 温度コントローラ

- 患者モニタリングシステム:

- 体温、血圧

## 3 説明

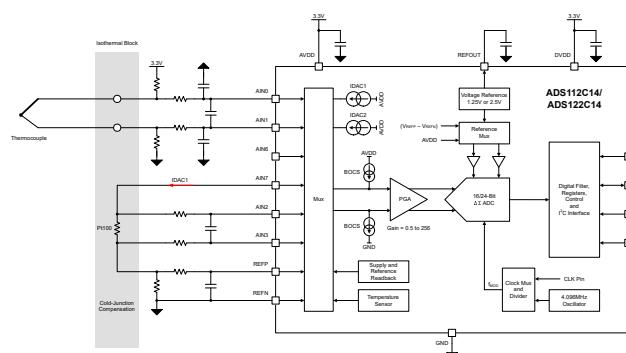

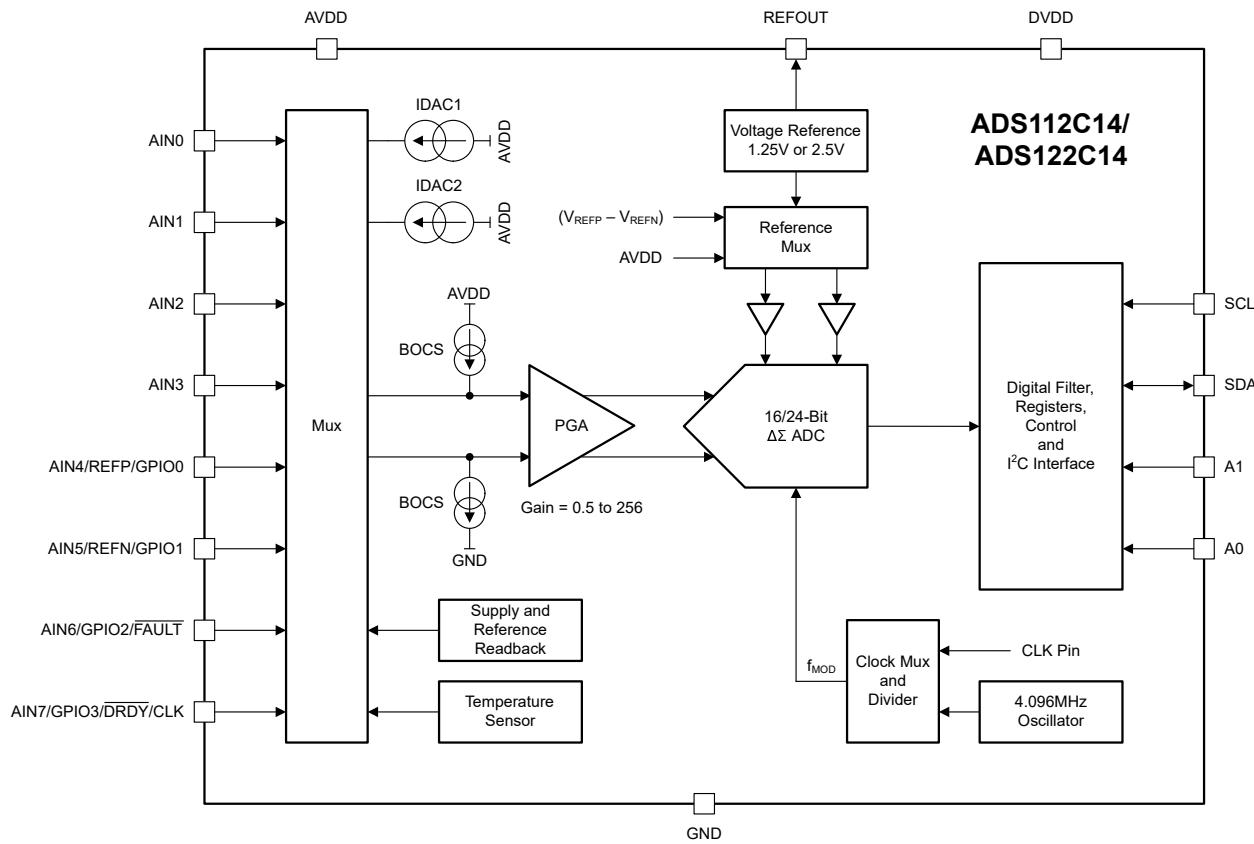

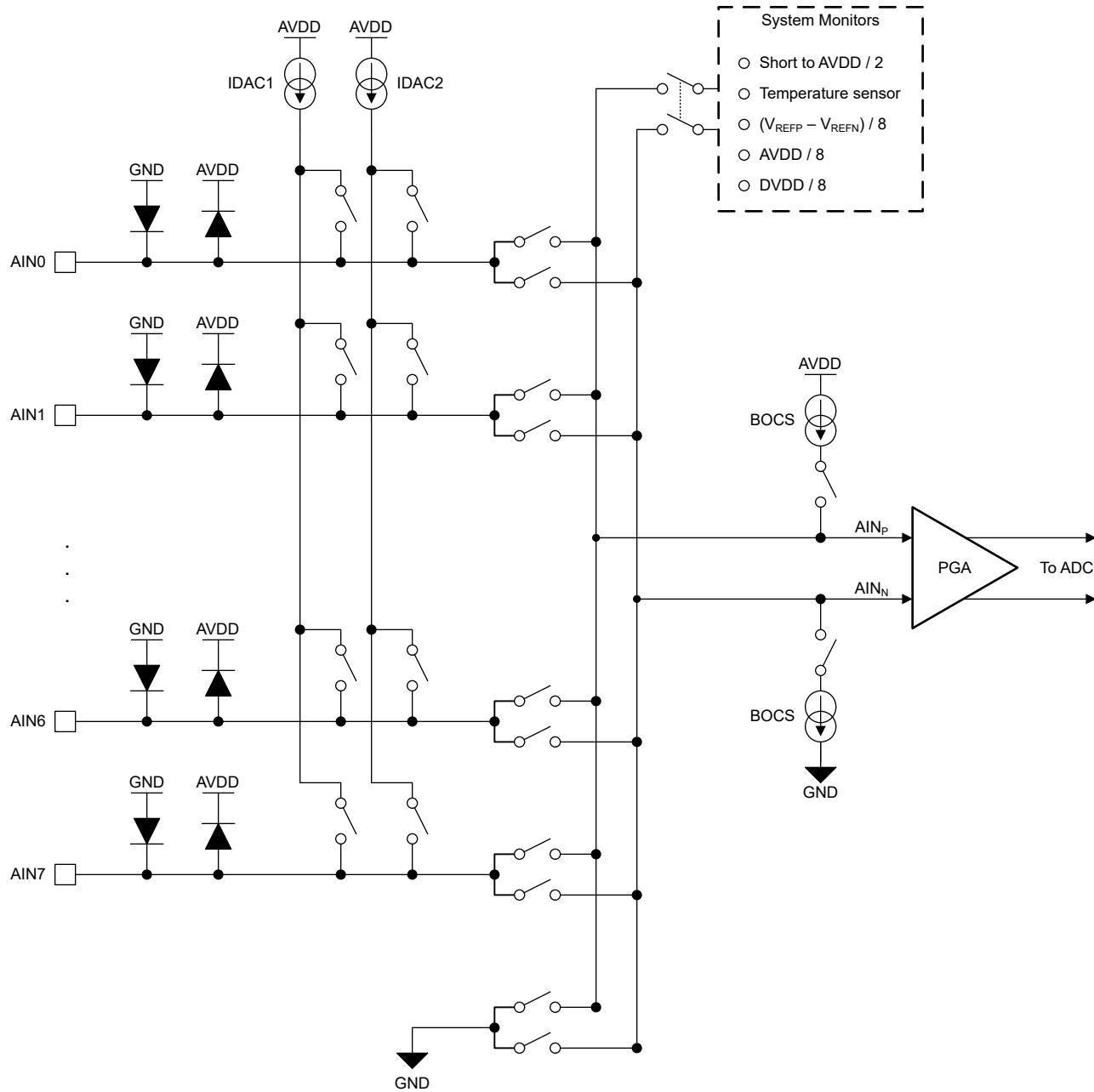

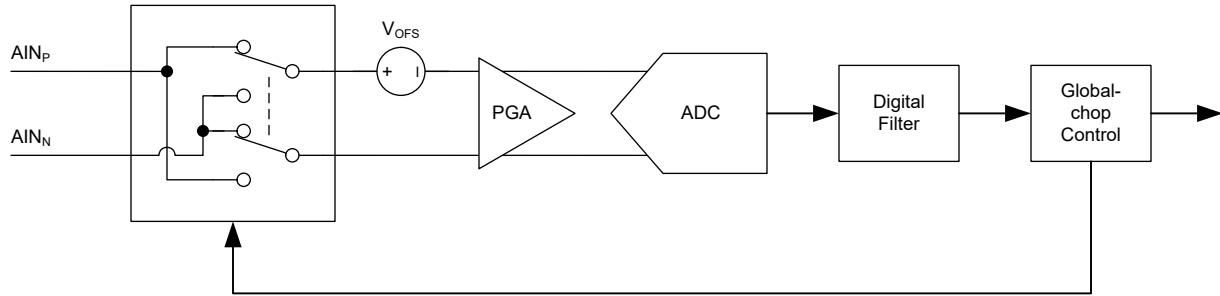

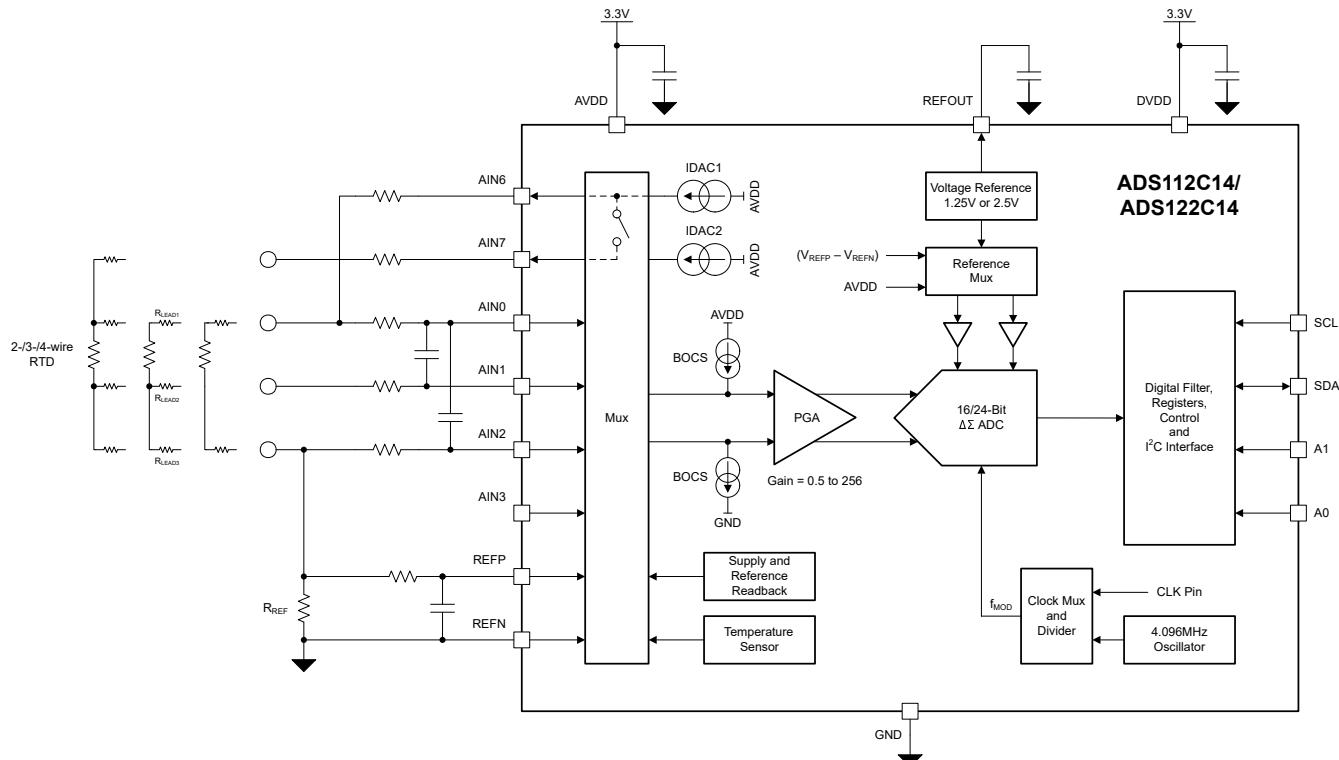

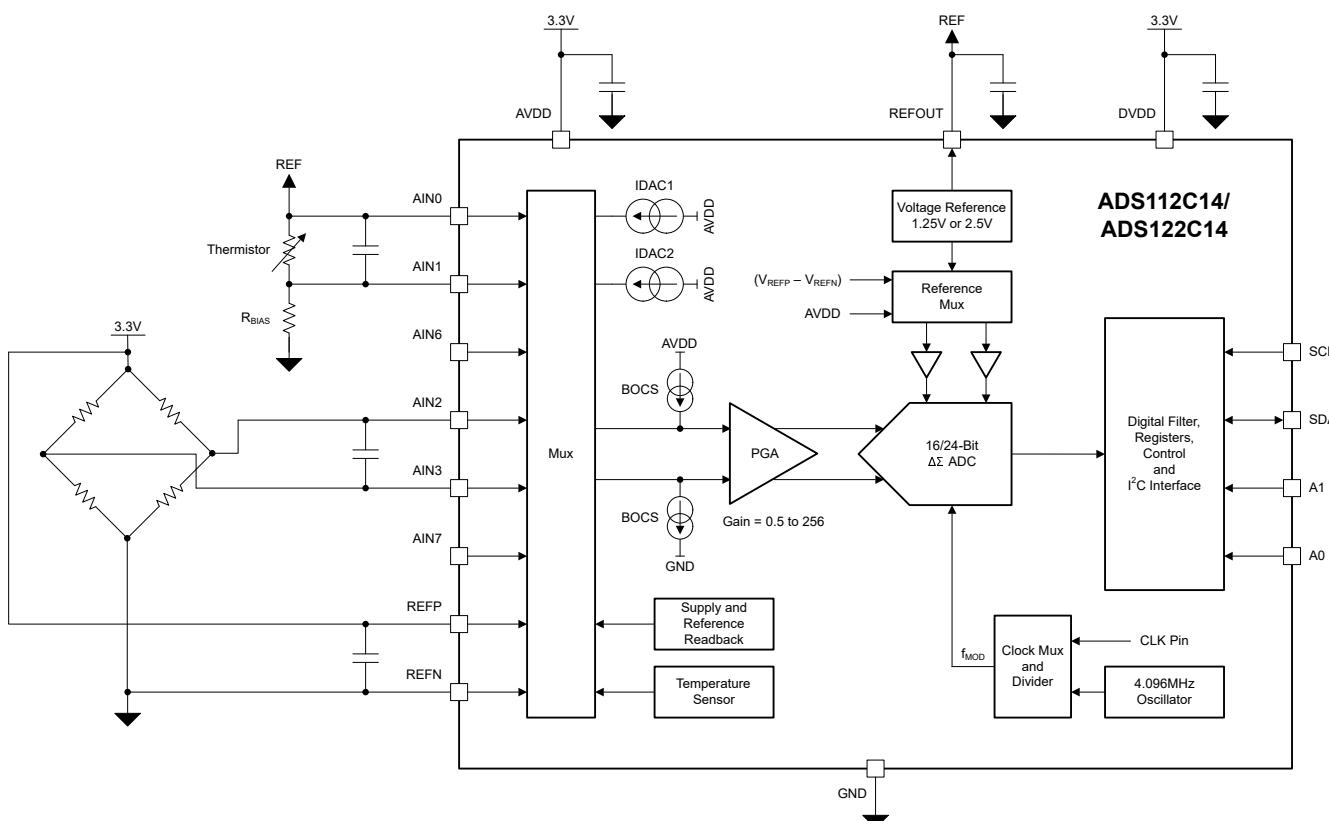

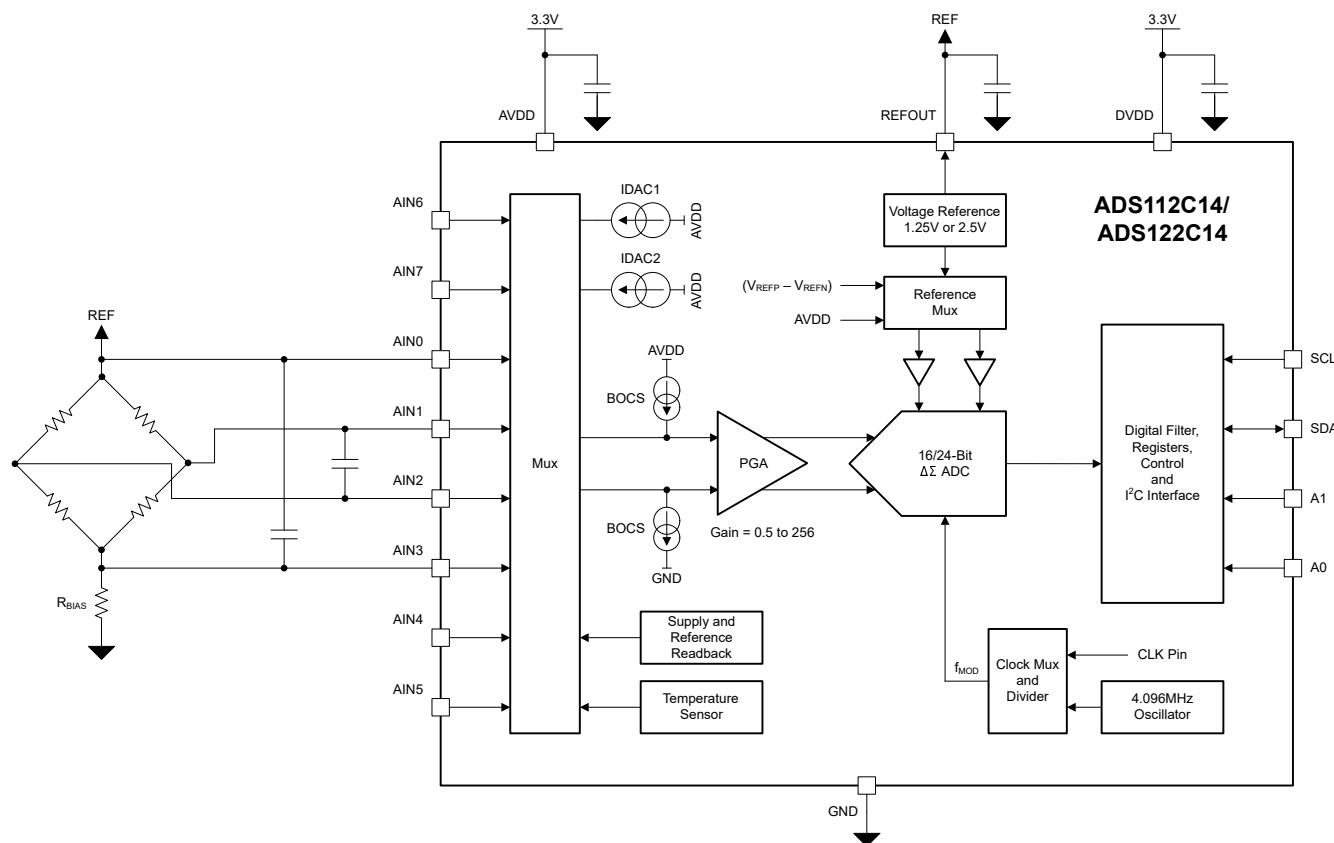

ADS1x2C14 は、高精度・低消費電力の 16 ビットおよび 24 ビットの A/D コンバータ (ADC) で、一般的なセンサ測定アプリケーションにおいて、システムコストと部品点数を削減するための多くの統合機能を備えています。このデバイスは、柔軟な入力マルチプレクサ (MUX) を介した eight のアナログ入力、低ノイズのプログラマブルゲインアンプ (PGA)、プログラム可能な低ドリフト電圧リファレンス、2 系統のプログラム可能な励起電流源、オシレータ、および温度センサを備えています。

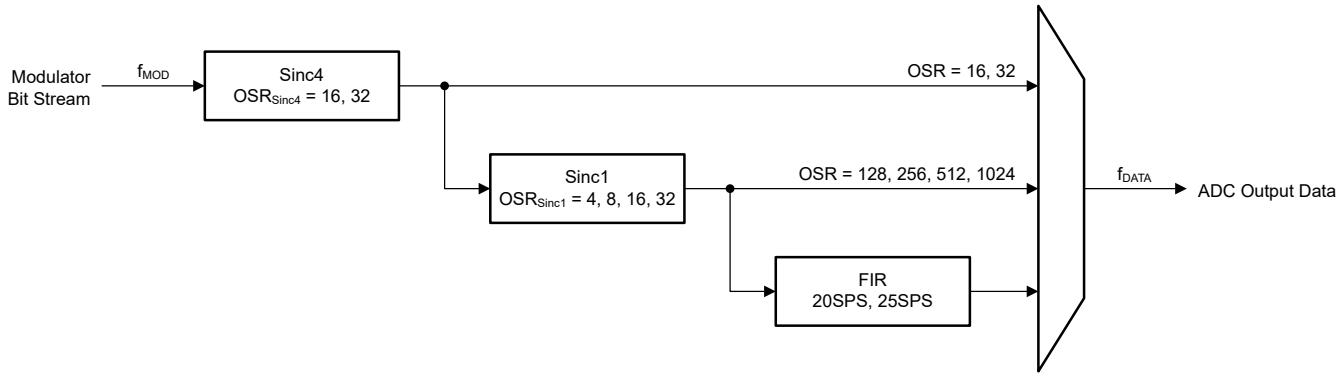

20SPS から最大 64kSPS までプログラム可能な出力データレートを備えた 4 種類の速度モードにより、各アプリケーションに応じて消費電力とノイズ性能を最適化できます。出力データレートが 20SPS および 25SPS の場合、内蔵デジタルフィルタは、1 サイクルで整定しつつ、50Hz と 60Hz のラインサイクルノイズを同時に除去します。

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------|----------------------|--------------------------|

| ADS1x2C14 | RTE (WQFN, 16)       | 3.00mm × 3.00mm          |

|           | YBH (DSBGA, 16)      | 1.87mm × 1.97mm          |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージサイズ (長さ × 幅) は公称値であり、。

### 表 3-1. 製品情報

| 部品番号      | 分解能    | アナログ入力 |

|-----------|--------|--------|

| ADS112C14 | 16 ビット | 8      |

| ADS122C14 | 24 ビット | 8      |

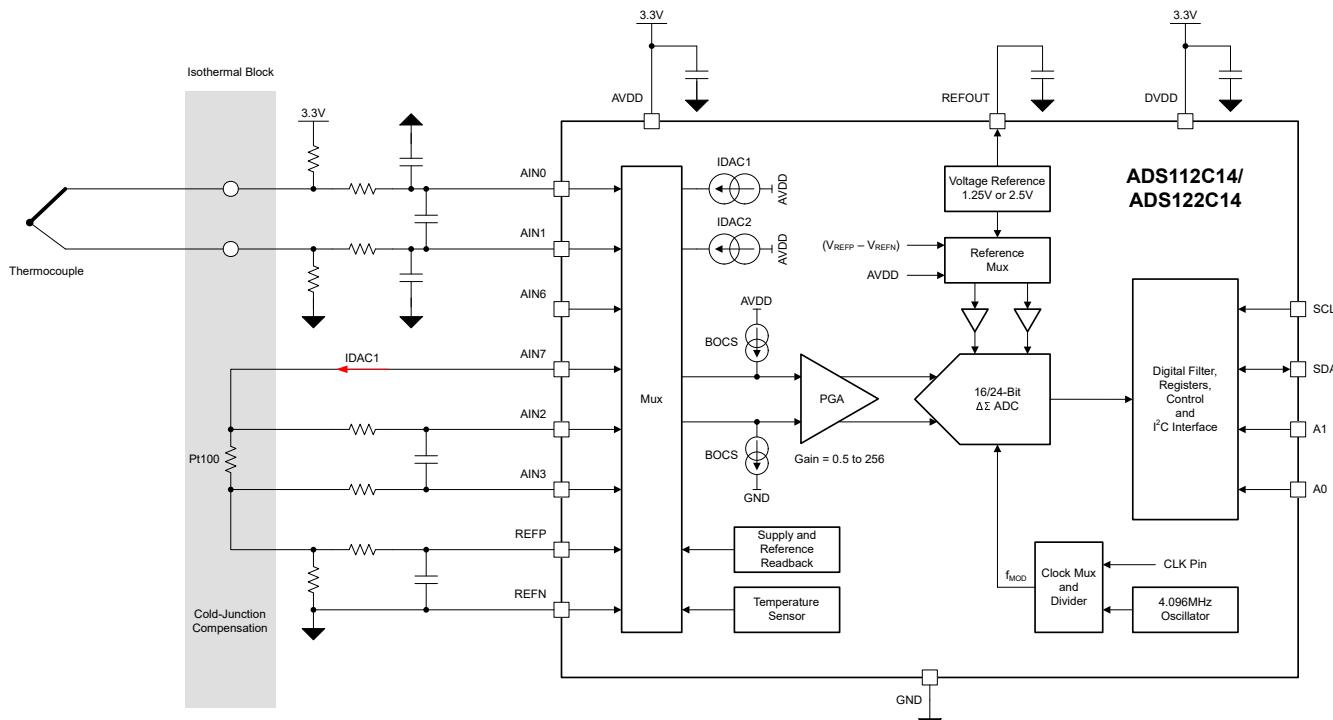

### 2 線式 Pt100 RTD を用いた 冷接点補償付き K タイプ熱電対測定

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: **SBASAW5**

## 目次

|                                   |    |                                              |    |

|-----------------------------------|----|----------------------------------------------|----|

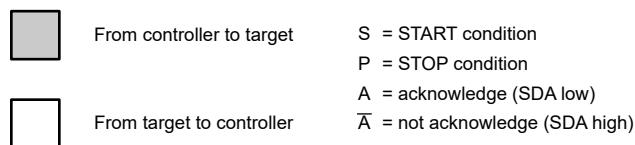

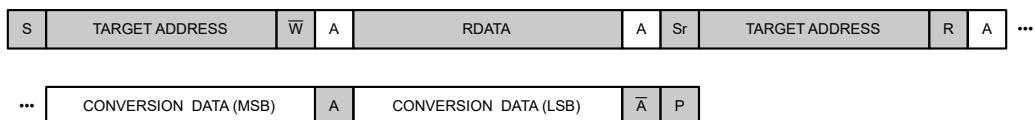

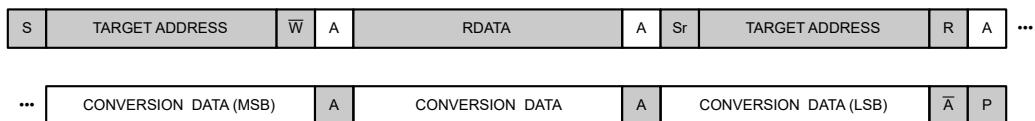

| 1 特長                              | 1  | 7.5.5 I <sup>2</sup> C データ転送プロトコル            | 42 |

| 2 アプリケーション                        | 1  | 7.5.6 I <sup>2</sup> C ゼネラル コール (ソフトウェアリセット) | 42 |

| 3 説明                              | 1  | 7.5.7 I <sup>3</sup> C 互換性                   | 42 |

| 4 ピン構成および機能                       | 3  | 7.5.8 コマンド                                   | 43 |

| 5 仕様                              | 5  | 7.5.9 ステータス ヘッダ                              | 45 |

| 5.1 絶対最大定格                        | 5  | 7.5.10 I <sup>2</sup> C CRC 故障               | 45 |

| 5.2 ESD 定格                        | 5  | 7.5.11 レジスタ マップ CRC                          | 46 |

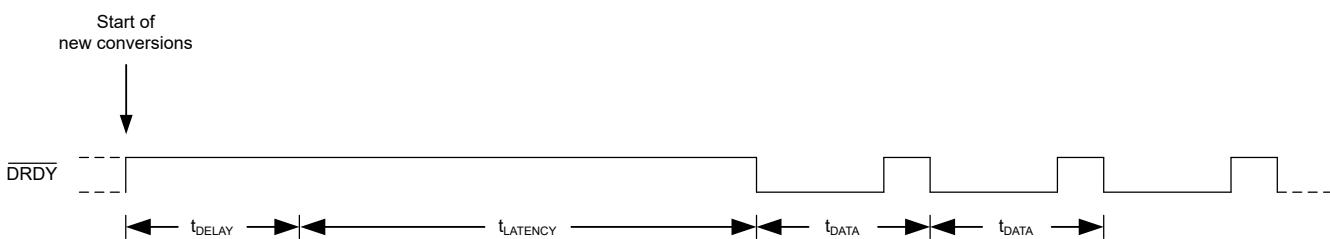

| 5.3 推奨動作条件                        | 6  | 7.5.12 データ準備完了 (DRDY) ピン                     | 48 |

| 5.4 熱に関する情報                       | 6  | 7.5.13 新しい変換データの監視                           | 49 |

| 5.5 電気的特性                         | 7  | 7.5.14 変換データの形式                              | 50 |

| 5.6 I <sup>2</sup> C のタイミング要件     | 15 | 8 レジスタ                                       | 51 |

| 5.7 I <sup>2</sup> C スイッチング特性     | 16 | 9 アプリケーションと実装                                | 68 |

| 5.8 タイミング図                        | 16 | 9.1 アプリケーション情報                               | 68 |

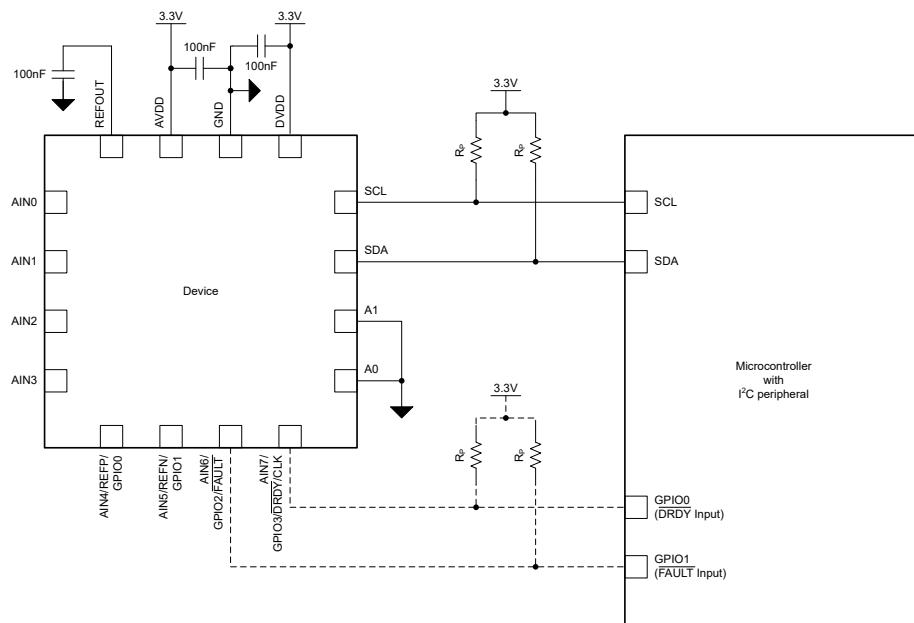

| 5.9 代表的特性                         | 17 | 9.1.1 シリアル インターフェイスの接続                       | 68 |

| 6 パラメータ測定情報                       | 18 | 9.1.2 複数のデバイスを同じ I <sup>2</sup> C バス上に搭載     | 69 |

| 6.1 ノイズ性能                         | 18 | 9.1.3 未使用入出力                                 | 69 |

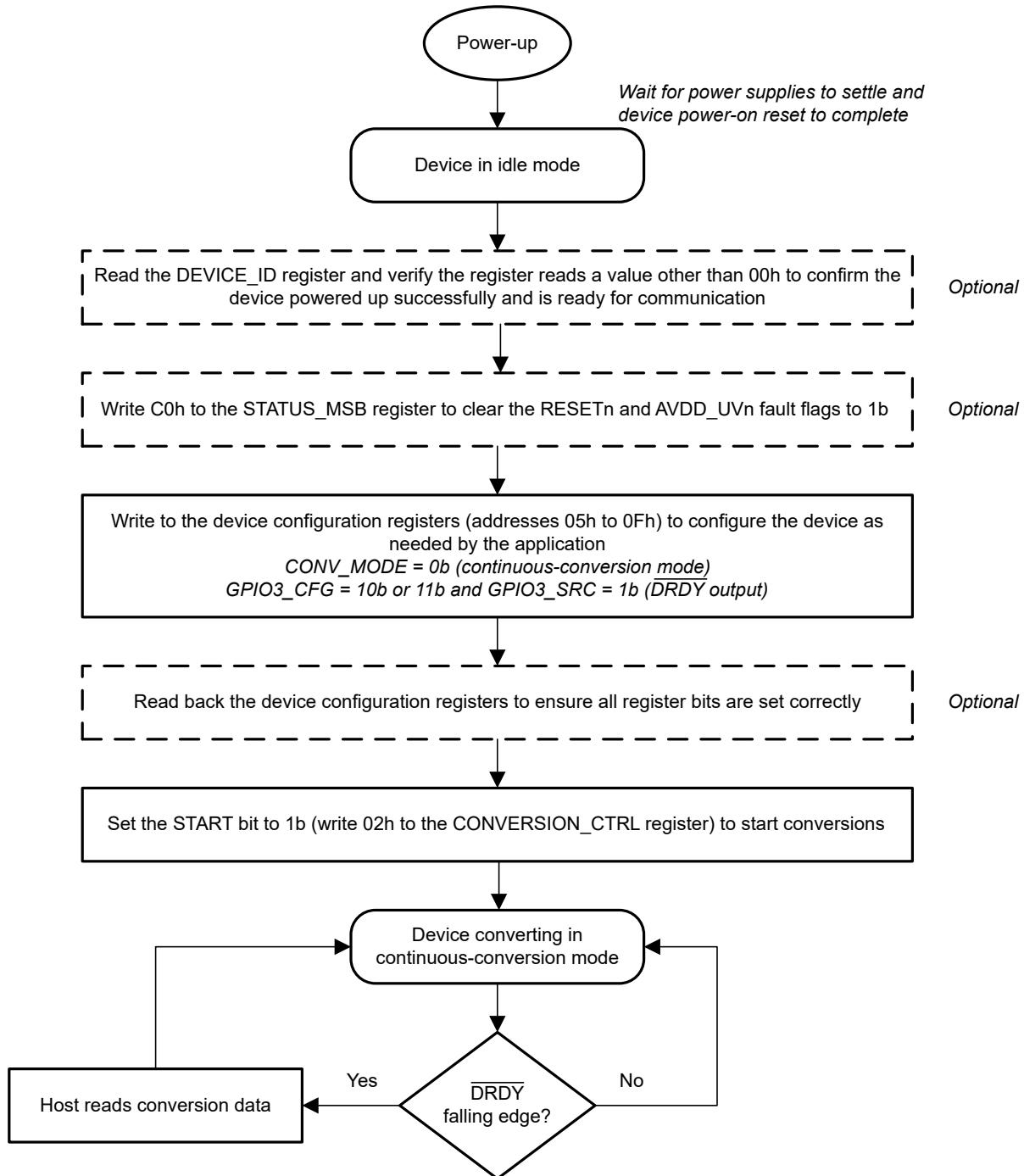

| 7 詳細説明                            | 22 | 9.1.4 デバイスの初期化                               | 70 |

| 7.1 概要                            | 22 | 9.2 代表的なアプリケーション                             | 71 |

| 7.2 機能ブロック図                       | 23 | 9.2.1 ソフトウェアで構成可能な RTD 測定入力                  | 71 |

| 7.3 機能説明                          | 23 | 9.2.2 線式 RTD を使用した冷接点補償による熱電                 |    |

| 7.3.1 アナログ入力およびマルチプレクサ            | 23 | 対測定                                          | 76 |

| 7.3.2 プログラマブル ゲイン アンプ (PGA)       | 25 | 9.2.3 溫度補償付き抵抗ブリッジ センサ測定                     | 77 |

| 7.3.3 電圧リファレンス                    | 26 | 9.3 電源に関する推奨事項                               | 79 |

| 7.3.4 クロック ソース                    | 26 | 9.3.1 電源                                     | 79 |

| 7.3.5 デルタシグマ変調器                   | 27 | 9.3.2 電源シーケンス                                | 79 |

| 7.3.6 デジタル フィルタ                   | 27 | 9.3.3 電源のデカッピング                              | 79 |

| 7.3.7 励起電流源 (IDAC)                | 32 | 9.4 レイアウト                                    | 80 |

| 7.3.8 バーンアウト電流源の電流 (BOCS)         | 33 | 9.4.1 レイアウトのガイドライン                           | 80 |

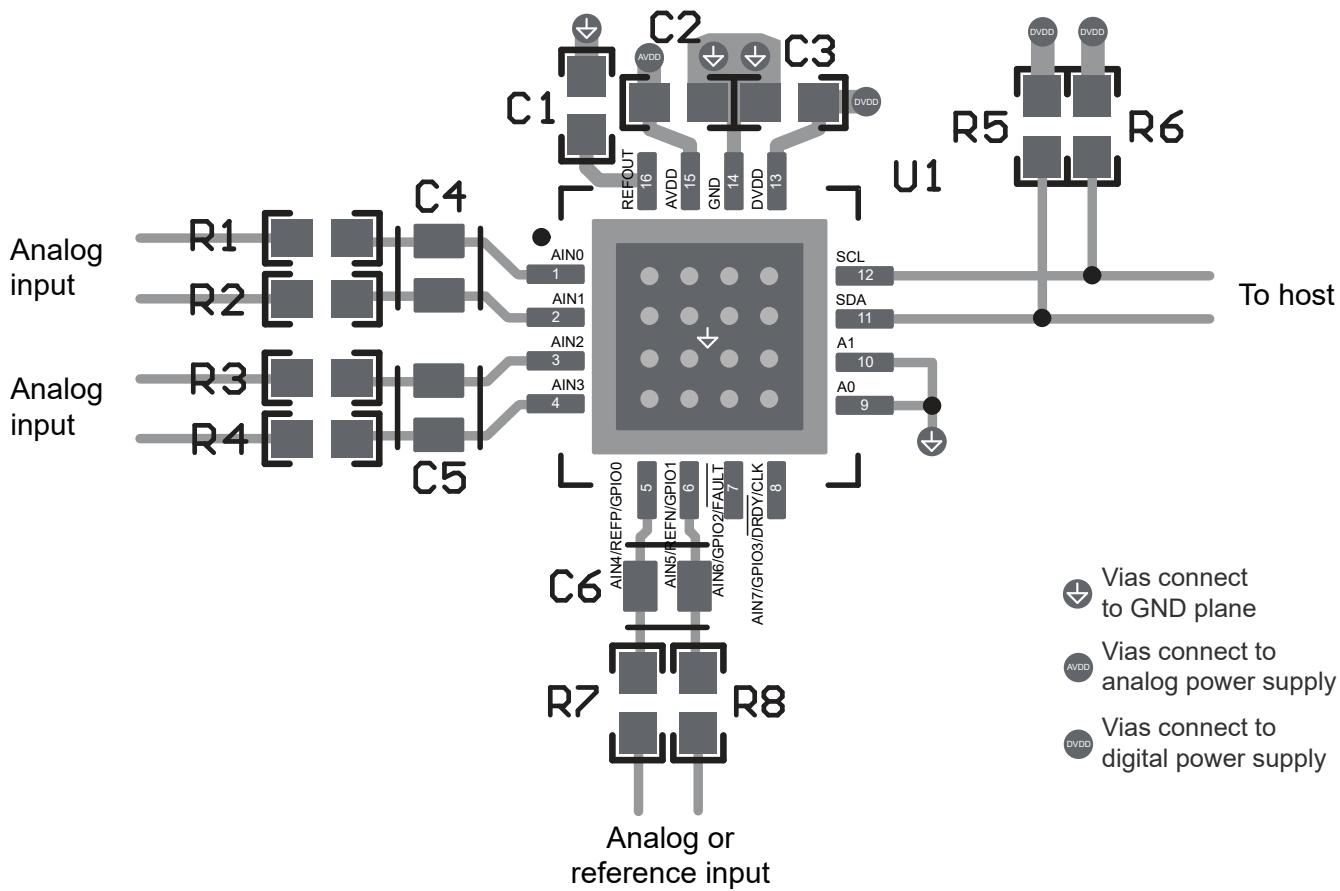

| 7.3.9 汎用インターフェイス (GPIO)           | 33 | 9.4.2 レイアウト例                                 | 81 |

| 7.3.10 システム モニタ                   | 34 | 10 デバイスおよびドキュメントのサポート                        | 82 |

| 7.3.11 モニタおよびステータス フラグ            | 36 | 10.1 ドキュメントのサポート                             | 82 |

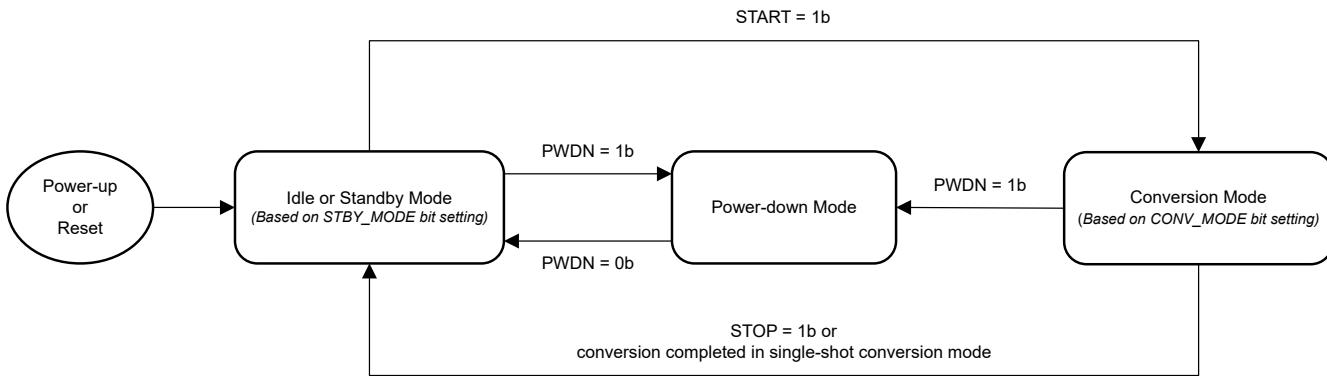

| 7.4 デバイスの機能モード                    | 38 | 10.1.1 関連資料                                  | 82 |

| 7.4.1 パワーアップとリセット                 | 38 | 10.2 ドキュメントの更新通知を受け取る方法                      | 82 |

| 7.4.2 動作モード                       | 39 | 10.3 サポート・リソース                               | 82 |

| 7.5 プログラミング                       | 41 | 10.4 商標                                      | 82 |

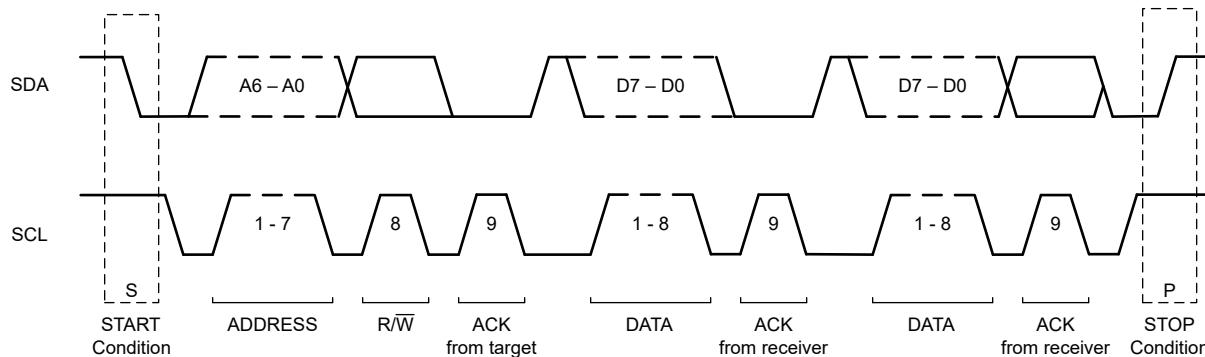

| 7.5.1 I <sup>2</sup> C インターフェイス   | 41 | 10.5 静電気放電に関する注意事項                           | 82 |

| 7.5.2 I <sup>2</sup> C アドレス       | 41 | 10.6 用語集                                     | 82 |

| 7.5.3 シリアル クロック (SCL) およびシリアル データ |    | 11 改訂履歴                                      | 82 |

| (SDA)                             | 41 | 12 メカニカル、パッケージ、および注文情報                       | 83 |

| 7.5.4 I <sup>2</sup> C バスの速度      | 42 |                                              |    |

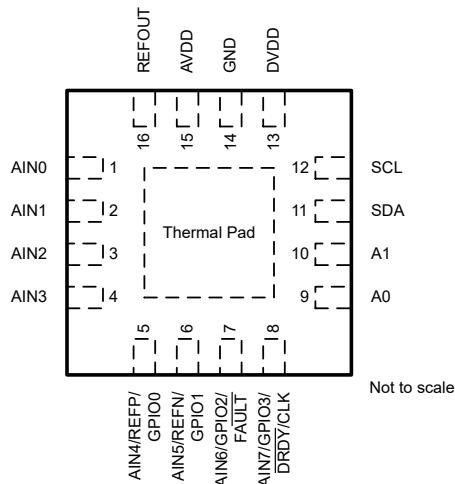

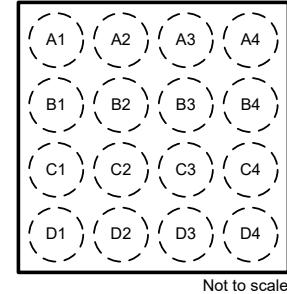

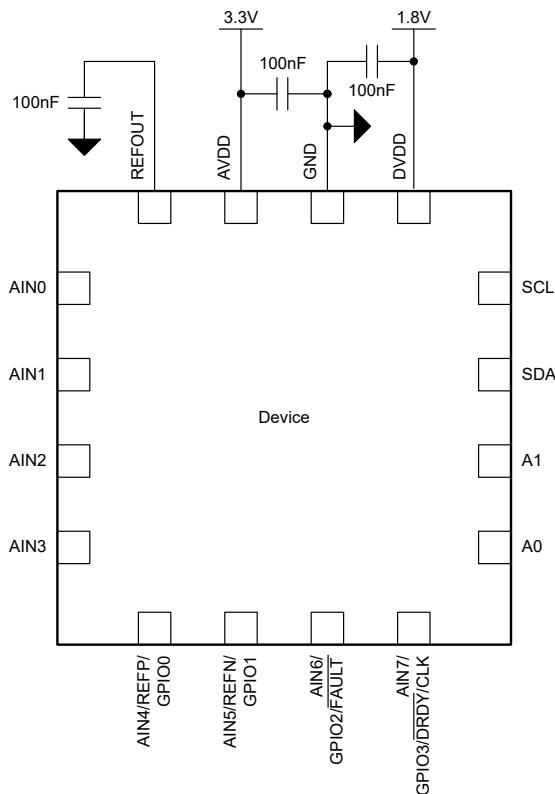

## 4 ピン構成および機能

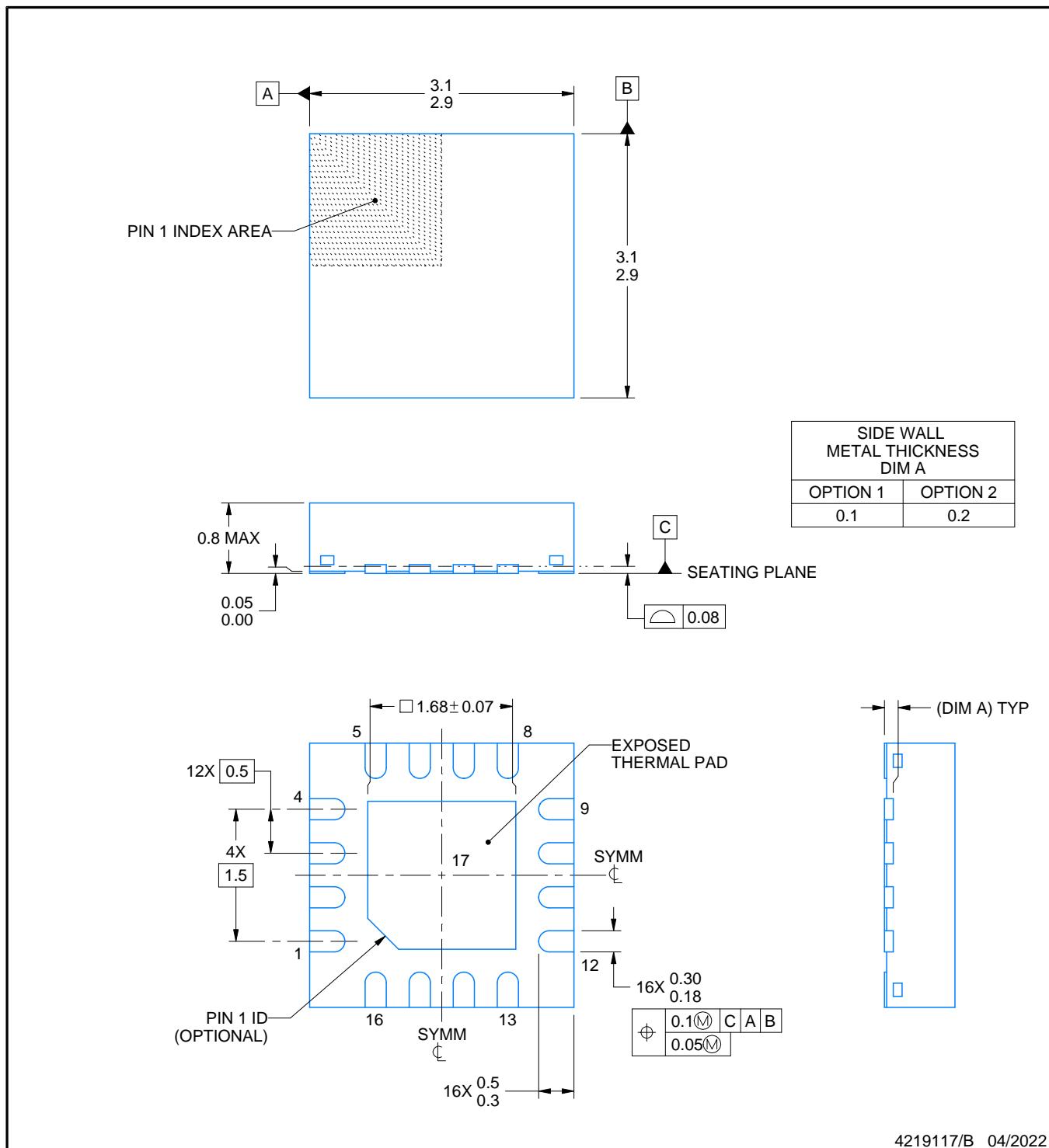

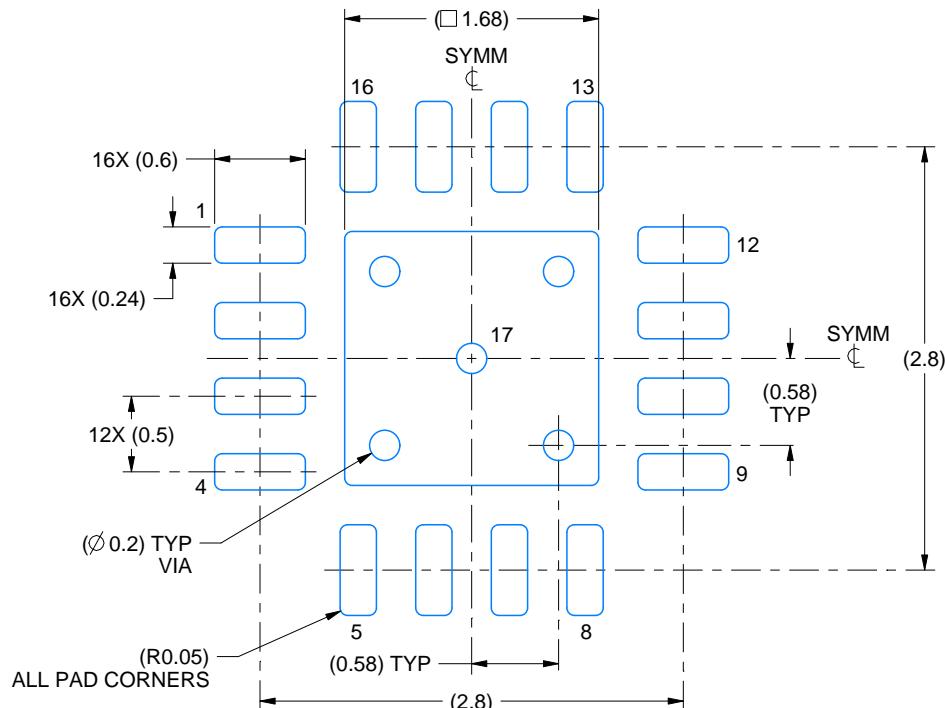

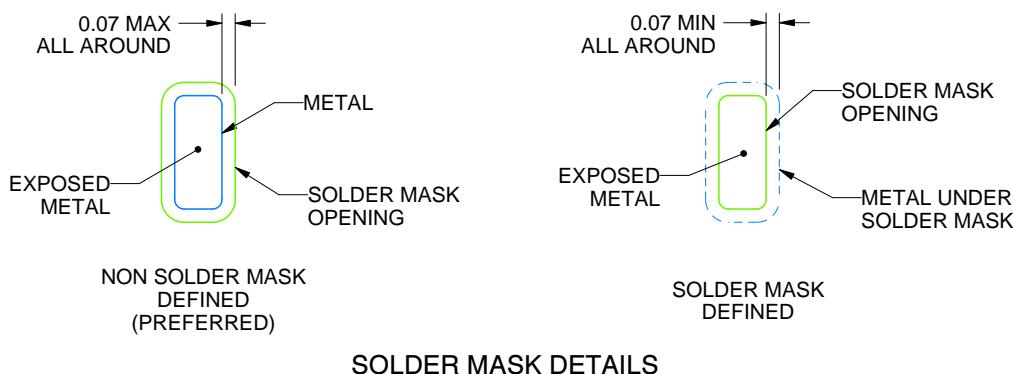

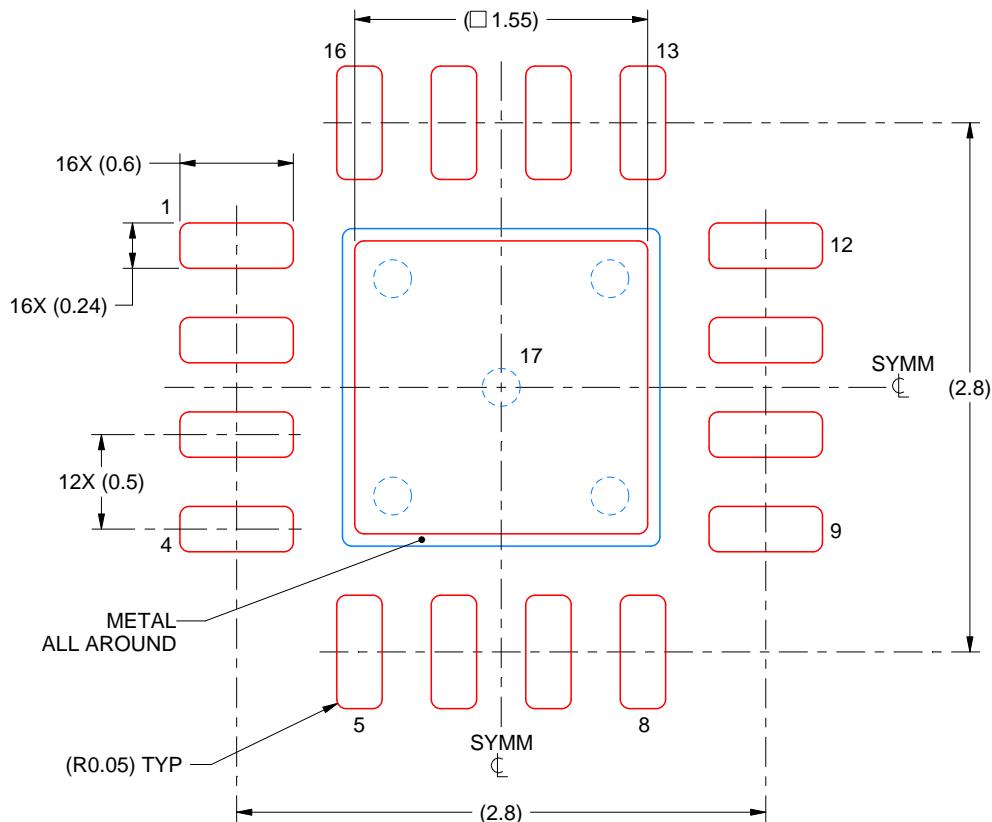

図 4-1. ADS1x2C14、RTE パッケージ、

16 ピン WQFN、上面図

図 4-2. ADS1x2C14、YBH パッケージ、

16 ピン DSBGA、上面図

表 4-1. ADS1x2C14 のピンの機能

| ピン                      |     |     | タイプ                | 説明 <sup>(1)</sup>                                                                                            |

|-------------------------|-----|-----|--------------------|--------------------------------------------------------------------------------------------------------------|

| 名称                      | RTE | YBH |                    |                                                                                                              |

| A0                      | 9   | C2  | デジタル入力             | I <sup>2</sup> C ターゲットアドレス選択ピン 0。詳細については、 <a href="#">I<sup>2</sup>C アドレスセクション</a> を参照してください。 <sup>(5)</sup> |

| A1                      | 10  | D1  | デジタル入力             | I <sup>2</sup> C ターゲットアドレス選択ピン 1。詳細については、 <a href="#">I<sup>2</sup>C アドレスセクション</a> を参照してください。 <sup>(5)</sup> |

| AIN0                    | 1   | A4  | アナログ入力             | アナログ入力 0                                                                                                     |

| AIN1                    | 2   | B4  | アナログ入力             | アナログ入力 1                                                                                                     |

| AIN2                    | 3   | C4  | アナログ入力             | アナログ入力 2                                                                                                     |

| AIN3                    | 4   | D4  | アナログ入力             | アナログ入力 3                                                                                                     |

| AIN4/REFP/<br>GPIO0     | 5   | B3  | アナログ入力/<br>デジタル IO | アナログ入力 4。正の外部リファレンス入力。<br>汎用デジタル入力/出力 0。 <sup>(2) (4)</sup>                                                  |

| AIN5/REFN/<br>GPIO1     | 6   | C3  | アナログ入力/<br>デジタル IO | アナログ入力 5。負の外部リファレンス入力。<br>汎用 デジタル入力/出力 1。 <sup>(2) (4)</sup>                                                 |

| AIN6/<br>GPIO2/FAULT    | 7   | D3  | アナログ入力/<br>デジタル IO | アナログ入力 6。<br>汎用デジタル入出力 2。 <sup>(2) (4)</sup><br>ピンは、専用の故障出力として構成できます。                                        |

| AIN7/<br>GPIO3/DRDY/CLK | 8   | D2  | アナログ入力/<br>デジタル IO | アナログ入力 7。<br>汎用デジタル入出力 3。 <sup>(2) (4)</sup><br>このピンは、専用の DRDY 出力または外部クロック入力として構成できます。                       |

| AVDD                    | 15  | A2  | アナログ電源             | 正のアナログ電源。100nF のデカップリングコンデンサを GND に接続してください。                                                                 |

| DVDD                    | 13  | A1  | デジタル電源             | デジタル電源。100nF のデカップリングコンデンサを GND に接続してください。                                                                   |

| GND                     | 14  | B2  | グランド               | グランド                                                                                                         |

| REFOUT                  | 16  | A3  | アナログ出力             | 内部電圧リファレンス出力。100nF のデカップリングコンデンサを GND に接続してください。                                                             |

| SCL                     | 12  | B1  | デジタル入力             | シリアル クロック入力。プルアップ抵抗を介して DVDD に接続します。 <sup>(5)</sup>                                                          |

| SDA                     | 11  | C1  | デジタル出力             | シリアル データ入力および出力。プルアップ抵抗を介して DVDD に接続します。 <sup>(3) (5)</sup>                                                  |

表 4-1. ADS1x2C14 のピンの機能 (続き)

| ピン       |     |      | タイプ | 説明 <sup>(1)</sup>     |

|----------|-----|------|-----|-----------------------|

| 名称       | RTE | YBH  |     |                       |

| サーマル パッド | -   | 該当なし | -   | サーマル パワー パッド。GND に接続。 |

(1) 未使用ピンの接続方法の詳細については、[未使用入出力](#) セクションを参照してください。

(2) ブッシュプル出力またはオープンドレイン出力として設定可能。

(3) オープンドレイン出力。

(4) AVDD を基準とするロジック レベル。

(5) DVDD を基準とするロジック レベル。

## 5 仕様

### 5.1 絶対最大定格

動作時周囲温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|          |                                           |  | 最小値       | 最大値        | 単位 |

|----------|-------------------------------------------|--|-----------|------------|----|

| 電源電圧     | AVDD から GND                               |  | -0.3      | 5          | V  |

|          | DVDD から GND                               |  | -0.3      | 5.5        | V  |

| アナログ入力電圧 | AINx, REFP, REFN                          |  | GND - 0.3 | AVDD + 0.3 | V  |

| デジタル入力電圧 | GPIO0, GPIO1, GPIO2/FAULT, GPIO3/DRDY/CLK |  | GND - 0.3 | AVDD + 0.3 | V  |

| デジタル入力電圧 | SCL, SDA, A0                              |  | GND - 0.3 | 5.5        | V  |

|          | A1                                        |  | GND - 0.3 | DVDD + 0.3 | V  |

| 入力電流     | 連続、電源ピンを除く任意のピン                           |  | -10       | 10         | mA |

| 温度       | 接合部、 $T_J$                                |  |           | 140        | °C |

|          | 保存、 $T_{stg}$                             |  | -60       | 150        | °C |

- (1) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能性、性能に影響を及ぼし、デバイスの寿命を短縮する可能性があります。

### 5.2 ESD 定格

|             |      |                                                          | 値     | 単位 |

|-------------|------|----------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠 <sup>(1)</sup>    | ±2000 | V  |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±750  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.3 推奨動作条件

動作時周囲温度範囲内 (特に記述のない限り)

|                                |                       |                                                               | 最小値                     | 公称値                    | 最大値  | 単位  |

|--------------------------------|-----------------------|---------------------------------------------------------------|-------------------------|------------------------|------|-----|

| <b>電源</b>                      |                       |                                                               |                         |                        |      |     |

| アナログ電源                         |                       | AVDD から GND、<br>$I_{IDAC} \leq 500\mu A$                      | 1.74                    | 3.6                    |      | V   |

|                                |                       | AVDD から GND、<br>$I_{IDAC} > 500\mu A$ 、または内部 $V_{REF} = 2.5V$ | 2.7                     | 3.6                    |      |     |

| デジタル電源                         |                       | DVDD から GND                                                   | 1.65                    | 3.6                    |      | V   |

| <b>アナログ入力<sup>(1)</sup></b>    |                       |                                                               |                         |                        |      |     |

| $V_{AINx}$                     | 絶対入力電圧                | ゲイン = 0.5 ~ 10                                                | GND                     | AVDD - 0.35            |      | V   |

|                                |                       | ゲイン = 16 ~ 256                                                | GND + 0.35              | AVDD - 0.4             |      |     |

| $V_{IN}$                       | 差動入力電圧 <sup>(2)</sup> | ユニポーラストレートバイナリ符号化                                             | 0                       | $V_{REF} / \text{ゲイン}$ |      | V   |

|                                |                       | 2の補数バイナリ符号化                                                   | $-V_{REF} / \text{ゲイン}$ | $V_{REF} / \text{ゲイン}$ |      |     |

| <b>電圧リファレンス入力</b>              |                       |                                                               |                         |                        |      |     |

| $V_{REF}$                      | 差動リファレンス入力電圧          | $V_{REF} = (V_{REFP} - V_{REFN})$                             | 0.5                     | AVDD                   |      | V   |

| $V_{REFN}$                     | 絶対負リファレンス電圧           | 負のリファレンスバッファが無効                                               | GND - 0.05              |                        |      | V   |

|                                |                       | 負のリファレンスバッファが有効                                               | GND + 0.1               |                        |      | V   |

| $V_{REFP}$                     | 絶対正リファレンス電圧           | 正のリファレンスバッファが無効                                               |                         | AVDD + 0.05            |      | V   |

|                                |                       | 正のリファレンスバッファが有効                                               |                         | AVDD - 0.1             |      | V   |

| <b>外部クロックソース<sup>(3)</sup></b> |                       |                                                               |                         |                        |      |     |

| $f_{CLK}$                      | 外部クロック周波数設定           |                                                               | 3                       | 4.096                  | 4.15 | MHz |

|                                |                       | デューティサイクル                                                     | 40%                     | 50%                    | 60%  |     |

| <b>汎用入力(GPIO)</b>              |                       |                                                               |                         |                        |      |     |

|                                | 入力電圧                  |                                                               | GND                     | AVDD                   |      | V   |

| <b>デジタル入力(GPIO以外)</b>          |                       |                                                               |                         |                        |      |     |

|                                | 入力電圧                  | SCL、SDA、A0                                                    | GND                     | 5.5                    |      | V   |

|                                |                       | A1                                                            | GND                     | DVDD                   |      | V   |

| <b>温度範囲</b>                    |                       |                                                               |                         |                        |      |     |

|                                | 規定周囲温度                |                                                               | -40                     | 125                    |      | °C  |

| $T_A$                          | 動作時周囲温度               |                                                               | -50                     | 125                    |      | °C  |

- (1)  $AIN_P$  および  $AIN_N$  は、PGA の正と負の入力を示します。利用可能なアナログ入力 ( $AINx$ ) はいずれも、入力マルチプレクサにより  $AIN_P$  または  $AIN_N$  のいずれかを選択できます。

- (2)  $V_{IN} = (V_{AINP} - V_{AINN})$ 。オフセットとゲイン誤差の影響を除外したものです。

- (3) 内部発振器を使用する場合、外部クロックは不要です。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                   | WQFN (RTE) | DSBGA (YBH) | 単位   |

|-----------------------------|-------------------|------------|-------------|------|

|                             |                   | 16 ピン      | 16 ピン       |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗      | 59.3       | 86.4        | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 | 40.2       | 0.2         | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗      | 31.6       | 22.9        | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 0.8        | 0.2         | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 31.5       | 22.9        | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース(底面)への熱抵抗 | 27.2       | 該当なし        | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションノートを参照してください。

## 5.5 電気的特性

最小値および最大値の仕様は、 $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  の範囲に適用されます。代表値の仕様は  $T_A = 25^\circ\text{C}$  での値です。すべての仕様は、AVDD = 1.74V ~ 3.6V、DVDD = 1.65V ~ 3.6V、内部リファレンス、内部発振器、すべての速度モード、すべてのデータレート、すべてのゲイン設定、ならびにグローバル チョップ無効の条件下で規定されています (特に記述のない限り)

| パラメータ                     | テスト条件                                                                                                                                                                                            | 最小値                                                                                                                                           | 標準値        | 最大値       | 単位                          |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|-----------------------------|

| <b>アナログ入力</b>             |                                                                                                                                                                                                  |                                                                                                                                               |            |           |                             |

| 絶対入力電流 <sup>(1)</sup>     | すべてのゲイン、 $f_{\text{DATA}} = 20\text{SPS}$ または $25\text{SPS}$ 、<br>グローバル チョップ無効またはディスエーブル、<br>$V_{\text{AINx(MIN)}} \leq V_{\text{AINx}} \leq V_{\text{AINx(MAX)}}$ , $V_{\text{IN}} = 0\text{V}$ | -2                                                                                                                                            | $\pm 0.3$  | 2         | nA                          |

| 絶対入力電流ドリフト <sup>(1)</sup> | すべてのゲイン、 $f_{\text{DATA}} = 20\text{SPS}$ または $25\text{SPS}$ 、<br>グローバル チョップ無効またはディスエーブル、<br>$V_{\text{AINx(MIN)}} \leq V_{\text{AINx}} \leq V_{\text{AINx(MAX)}}$ , $V_{\text{IN}} = 0\text{V}$ |                                                                                                                                               | 2          |           | $\text{pA}/^\circ\text{C}$  |

| 差動入力電流 <sup>(1)</sup>     | すべてのゲイン、 $f_{\text{DATA}} = 20\text{SPS}$ または $25\text{SPS}$ 、<br>グローバル チョップが有効または無効、<br>$V_{\text{CM}} = \text{AVDD}/2, -V_{\text{REF}}$ ゲイン $\leq V_{\text{IN}} \leq V_{\text{REF}}$ ゲイン       | -2                                                                                                                                            | $\pm 0.1$  | 2         | nA                          |

| 差動入力電流ドリフト <sup>(1)</sup> | すべてのゲイン、 $f_{\text{DATA}} = 20\text{SPS}$ または $25\text{SPS}$ 、<br>グローバル チョップが有効または無効、<br>$V_{\text{CM}} = \text{AVDD}/2, -V_{\text{REF}}$ ゲイン $\leq V_{\text{IN}} \leq V_{\text{REF}}$ ゲイン       |                                                                                                                                               | 2          |           | $\text{pA}/^\circ\text{C}$  |

| <b>PGA</b>                |                                                                                                                                                                                                  |                                                                                                                                               |            |           |                             |

| ゲイン設定                     |                                                                                                                                                                                                  | 0.5, 1, 2, 4, 5,<br>8, 10, 16, 20,<br>32, 50, 64,<br>100, 128, 200,<br>256                                                                    |            |           |                             |

| <b>システム性能</b>             |                                                                                                                                                                                                  |                                                                                                                                               |            |           |                             |

| 分解能 (欠落コードなし)             | ADS112C14                                                                                                                                                                                        | 16                                                                                                                                            |            |           | ビット                         |

|                           | ADS122C14                                                                                                                                                                                        | 24                                                                                                                                            |            |           |                             |

| $f_{\text{DATA}}$         | 出力データレート                                                                                                                                                                                         | 速度モード 0 ( $f_{\text{MOD}} = 32\text{kHz}$ )                                                                                                   | 20         | 2k        | SPS                         |

|                           |                                                                                                                                                                                                  | 速度モード 1 ( $f_{\text{MOD}} = 256\text{kHz}$ )                                                                                                  | 20         | 16k       |                             |

|                           |                                                                                                                                                                                                  | 速度モード 2 ( $f_{\text{MOD}} = 512\text{kHz}$ )                                                                                                  | 20         | 32k       |                             |

|                           |                                                                                                                                                                                                  | 速度モード 3 ( $f_{\text{MOD}} = 1024\text{kHz}$ )                                                                                                 | 20         | 64k       |                             |

| INL                       | 積分非直線性                                                                                                                                                                                           | $V_{\text{CM}} = \text{AVDD}/2$ 、最適なフィット                                                                                                      | 5          | 15        | $\text{ppm}_{\text{FSR}}$   |

| $V_{\text{IO}}$           | 入力オフセット電圧                                                                                                                                                                                        | $T_A = 25^\circ\text{C}$ 、ゲイン = 0.5、グローバル チョップ無効                                                                                              | -250       | $\pm 50$  | 250                         |

|                           |                                                                                                                                                                                                  | $T_A = 25^\circ\text{C}$ 、ゲイン = 1 ~ 10、グローバル チョップ無効                                                                                           | -150       | $\pm 20$  | 150                         |

|                           |                                                                                                                                                                                                  | $T_A = 25^\circ\text{C}$ 、ゲイン $\geq 16$ 、グローバル チョップ無効                                                                                         | -50        | $\pm 10$  | 50                          |

|                           |                                                                                                                                                                                                  | $T_A = 25^\circ\text{C}$ 、ゲイン = 0.5、グローバル チョップ有効                                                                                              | -5         | $\pm 0.5$ | 5                           |

|                           |                                                                                                                                                                                                  | $T_A = 25^\circ\text{C}$ 、ゲイン $\geq 1$ 、グローバル チョップ有効                                                                                          | -2         | $\pm 0.2$ | 2                           |

| オフセットのドリフト                | ゲイン $\leq 10$ 、グローバル チョップ無効                                                                                                                                                                      |                                                                                                                                               | 60         | 300       | $\mu\text{V}$               |

|                           |                                                                                                                                                                                                  |                                                                                                                                               | 20         | 125       |                             |

|                           |                                                                                                                                                                                                  |                                                                                                                                               | 10         | 50        |                             |

| ゲイン誤差                     | $T_A = 25^\circ\text{C}$ 、すべてのゲイン、外部リファレンス                                                                                                                                                       | -0.3                                                                                                                                          | $\pm 0.08$ | 0.3       | %                           |

| ゲインドリフト                   | すべてのゲイン、外部リファレンス                                                                                                                                                                                 |                                                                                                                                               | 0.5        | 2.5       | $\text{ppm}/^\circ\text{C}$ |

| ノイズ (入力換算)                |                                                                                                                                                                                                  | 詳細については、ノイズ性能セクションを参照してください                                                                                                                   |            |           |                             |

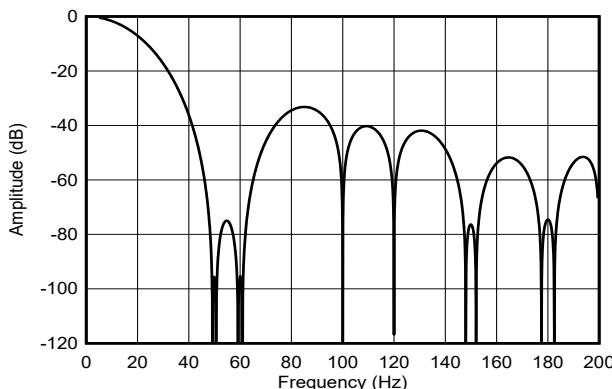

| NMRR                      | ノーマル モード除去比                                                                                                                                                                                      | $f_{\text{IN}} = 50\text{Hz}$ または $60\text{Hz}$ ( $\pm 1\text{Hz}$ )、 $f_{\text{DATA}} = 20\text{SPS}$                                        | 82         | 95        | dB                          |

|                           |                                                                                                                                                                                                  | $f_{\text{IN}} = 50\text{Hz}$ または $60\text{Hz}$ ( $\pm 1\text{Hz}$ )、 $f_{\text{DATA}} = 20\text{SPS}$ 、外部 $f_{\text{CLK}} = 4.096\text{MHz}$ | 95         |           |                             |

|                           |                                                                                                                                                                                                  | $f_{\text{IN}} = 50\text{Hz}$ または $60\text{Hz}$ ( $\pm 1\text{Hz}$ )、 $f_{\text{DATA}} = 25\text{SPS}$                                        | 57         | 62        |                             |

|                           |                                                                                                                                                                                                  | $f_{\text{IN}} = 50\text{Hz}$ または $60\text{Hz}$ ( $\pm 1\text{Hz}$ )、 $f_{\text{DATA}} = 25\text{SPS}$ 、外部 $f_{\text{CLK}} = 4.096\text{MHz}$ | 62         |           |                             |

| CMRR                      | 同相除去比                                                                                                                                                                                            | DC 時                                                                                                                                          |            | 120       | dB                          |

|                           |                                                                                                                                                                                                  | $f_{\text{CM}} = 50\text{Hz}$ または $60\text{Hz}$ ( $\pm 1\text{Hz}$ )、 $f_{\text{DATA}} = 20\text{SPS}$ または $25\text{SPS}$                     |            | 130       |                             |

|                           |                                                                                                                                                                                                  | $f_{\text{CM}} = 50\text{Hz}$ または $60\text{Hz}$ ( $\pm 1\text{Hz}$ )、 $f_{\text{DATA}} > 25\text{SPS}$                                        |            | 120       |                             |

最小値および最大値の仕様は、 $T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  の範囲に適用されます。代表値の仕様は  $T_A = 25^{\circ}\text{C}$  での値です。すべての仕様は、AVDD = 1.74V ~ 3.6V、DVDD = 1.65V ~ 3.6V、内部リファレンス、内部発振器、すべての速度モード、すべてのデータレート、すべてのゲイン設定、ならびにグローバル チョップ無効の条件下で規定されています (特に記述のない限り)

| パラメータ |       | テスト条件      | 最小値 | 標準値 | 最大値 | 単位 |

|-------|-------|------------|-----|-----|-----|----|

| PSRR  | 電源除去比 | dc での AVDD |     | 110 |     | dB |

|       |       | dc での DVDD |     | 115 |     |    |

最小値および最大値の仕様は、 $T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  の範囲に適用されます。代表値の仕様は  $T_A = 25^{\circ}\text{C}$  での値です。すべての仕様は、AVDD = 1.74V ~ 3.6V、DVDD = 1.65V ~ 3.6V、内部リファレンス、内部発振器、すべての速度モード、すべてのデータレート、すべてのゲイン設定、ならびにグローバル チョップ無効の条件下で規定されています (特に記述のない限り)

| パラメータ               | テスト条件                                                                | 最小値         | 標準値         | 最大値  | 単位                |

|---------------------|----------------------------------------------------------------------|-------------|-------------|------|-------------------|

| <b>電圧リファレンス入力</b>   |                                                                      |             |             |      |                   |

| 絶対入力電流              | REF バッファがディスエーブル、速度モード 0 <sup>(2)</sup>                              | -1.5        | ±1          | 1.5  | µA/V              |

|                     | REF バッファがディスエーブル、速度モード 1 <sup>(2)</sup>                              | -7          | ±6          | 7    |                   |

|                     | REF バッファがディスエーブル、速度モード 2 <sup>(2)</sup>                              | -8          | ±7          | 8    |                   |

|                     | REF バッファがディスエーブル、速度モード 3 <sup>(2)</sup>                              | -9          | ±8          | 9    |                   |

|                     | REF バッファがイネーブル、速度モード 0                                               | -2          | ±0.2        | 2    | nA                |

|                     | REF バッファがイネーブル、速度モード 1                                               |             | 3           | 7    |                   |

|                     | REF バッファがイネーブル、速度モード 2                                               |             | 10          | 12   |                   |

|                     | REF バッファがイネーブル、速度モード 3                                               |             | 17          | 23   |                   |

| <b>内部基準電圧</b>       |                                                                      |             |             |      |                   |

| V <sub>REF</sub>    | 出力電圧                                                                 | AVDD < 2.7V | 1.25        |      | V                 |

|                     |                                                                      | AVDD ≥ 2.7V | 1.25, 2.5   |      |                   |

| 精度                  | $T_A = 25^{\circ}\text{C}$                                           | -0.15       | ±0.05       | 0.15 | %                 |

| 温度ドリフト              |                                                                      |             | 10          | 25   | ppm/°C            |

| 出力電流                | V <sub>REF</sub> = 1.25V、シンクまたはソース                                   | -5          |             | 5    | mA                |

|                     | V <sub>REF</sub> = 2.5V、AVDD ≥ 2.75V、シンクまたはソース                       | -10         |             | 5    |                   |

| 回路短絡時の電流制限          | シンクまたはソース                                                            |             | ±25         |      | mA                |

| PSRR                | 電源除去比                                                                | dc での AVDD  | 90          |      | dB                |

| 負荷レギュレーション          | 負荷電流 = -5mA ~ 0mA (ソース)                                              |             | 100         |      | µV/mA             |

| 容量性負荷および安定性         |                                                                      | 50          | 100         | 1300 | nF                |

| リファレンス ノイズ          | f = 0.1Hz ~ 10Hz、REFOUT に 100nF のコンデンサを接続                            |             | 4           |      | ppm <sub>PP</sub> |

| 起動時間                | パワーダウン モードから、REFOUT に 100nF コンデンサを接続、0.01% セトリング                     |             |             | 10   | ms                |

| <b>内部発振器</b>        |                                                                      |             |             |      |                   |

| f <sub>osc</sub>    | 周波数                                                                  |             | 4.096       |      | MHz               |

|                     | 精度                                                                   | -1          |             | 1    | %                 |

| <b>励起電流源 (IDAC)</b> |                                                                      |             |             |      |                   |

| 電流設定                | IDAC ユニット電流 = 1µA                                                    | 1 ~ 100     |             |      | µA                |

|                     |                                                                      | 10 ~ 500    |             |      |                   |

|                     |                                                                      | 10 ~ 1000   |             |      |                   |

| コンプライアンス電圧          | I <sub>IDAC</sub> < 100µA、(AVDD - 1V) から 1% 未満で電流が変化                 | GND         | AVDD - 0.3  |      | V                 |

|                     | I <sub>IDAC</sub> = 100µA ~ 700µA へ、電流は (AVDD - 1V) から 1% 未満で変化      | GND         | AVDD - 0.4  |      |                   |

|                     | I <sub>IDAC</sub> 電流 ≥ 800µA、(AVDD - 1V) から 1% 未満で電流が変化              | GND         | AVDD - 0.45 |      |                   |

| 精度                  | I <sub>IDAC</sub> = 1µA、T <sub>A</sub> = 25°C                        | -6          | ±0.4        | 6    | %                 |

|                     | I <sub>IDAC</sub> = 10µA ~ 1mA、T <sub>A</sub> = 25°C                 | -3          | ±0.4        | 3    |                   |

| IDAC 間の電流ミスマッチ      | I <sub>IDAC</sub> ≤ 10µA、IDAC1 と IDAC2 は同一値に設定、T <sub>A</sub> = 25°C |             | 0.5         | 2    | %                 |

|                     | I <sub>IDAC</sub> ≥ 20µA、IDAC1 と IDAC2 は同一値に設定、T <sub>A</sub> = 25°C |             | 0.05        | 0.5  |                   |

| 温度ドリフト              | I <sub>IDAC</sub> = 1µA                                              |             | 50          | 300  | ppm/°C            |

|                     | I <sub>IDAC</sub> ≥ 10µA                                             |             | 25          | 110  |                   |

| 温度ドリフト マッチング        | I <sub>IDAC</sub> ≤ 10µA、IDAC1、IDAC2 は同じ値に設定されます                     |             | 12          | 70   | ppm/°C            |

|                     | I <sub>IDAC</sub> ≥ 20µA、IDAC1、IDAC2 は同じ値に設定されます                     |             | 1           | 10   |                   |

最小値および最大値の仕様は、 $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  の範囲に適用されます。代表値の仕様は  $T_A = 25^\circ\text{C}$  での値です。すべての仕様は、AVDD = 1.74V ~ 3.6V、DVDD = 1.65V ~ 3.6V、内部リファレンス、内部発振器、すべての速度モード、すべてのデータレート、すべてのゲイン設定、ならびにグローバル チョップ無効の条件下で規定されています (特に記述のない限り)

| パラメータ                   | テスト条件                                     | 最小値                                                         | 標準値       | 最大値      | 単位                           |

|-------------------------|-------------------------------------------|-------------------------------------------------------------|-----------|----------|------------------------------|

| <b>バーンアウト電流源 (BOCS)</b> |                                           |                                                             |           |          |                              |

| 電流設定                    |                                           | 0.2, 1, 10                                                  |           |          | $\mu\text{A}$                |

| 精度                      | シンクおよびソース                                 | $\pm 2$                                                     |           |          | %                            |

| <b>温度センサ</b>            |                                           |                                                             |           |          |                              |

| TS <sub>Offset</sub>    | 出力電圧                                      | $T_A = 25^\circ\text{C}$                                    | 119.5     |          | mV                           |

| TS <sub>TC</sub>        | 温度係数                                      |                                                             | 405       |          | $\mu\text{V}/^\circ\text{C}$ |

| <b>モニタ</b>              |                                           |                                                             |           |          |                              |

| TH <sub>DVDD_POR</sub>  | DVDD POR スレッショルド                          |                                                             | 1.55      |          | V                            |

| TH <sub>AVDD_UV</sub>   | AVDD 低電圧スレッショルド <sup>(3)</sup>            |                                                             | 1.2       | 1.5      | V                            |

| TH <sub>REF_UV</sub>    | リファレンス低電圧スレッショルド <sup>(3)</sup>           |                                                             | 0.5       | 0.6      | V                            |

| システム監視電圧リードバック精度        | $(V_{\text{REFP}} - V_{\text{REFN}}) / 8$ |                                                             | $\pm 0.5$ |          | %                            |

|                         | AVDD / 8                                  |                                                             | $\pm 1$   |          |                              |

|                         | DVDD / 8                                  |                                                             | $\pm 1$   |          |                              |

| <b>汎用入出力 (GPIO)</b>     |                                           |                                                             |           |          |                              |

| V <sub>IL</sub>         | ロジック入力レベル、Low                             |                                                             | GND       | 0.3 AVDD | V                            |

| V <sub>IH</sub>         | ロジック入力レベル、High                            |                                                             | 0.7 AVDD  | AVDD     | V                            |

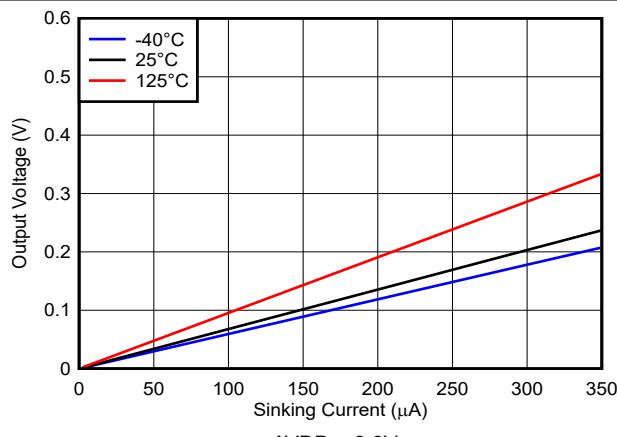

| V <sub>OL</sub>         | ロジック出力レベル、Low                             | $I_{OL} = 100\mu\text{A}$ 、オープンドレインまたはプッシュプル出力              | GND       | 0.2 AVDD | V                            |

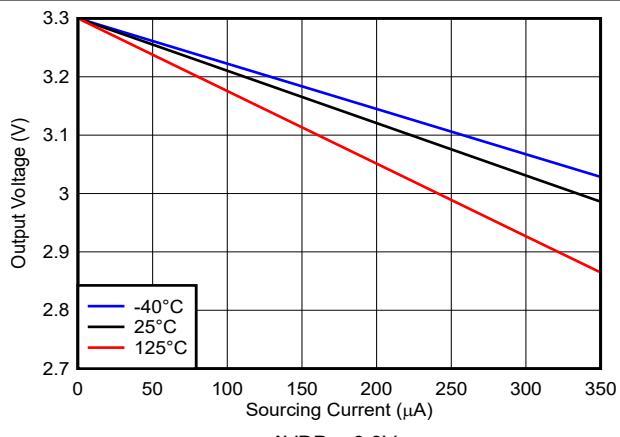

| V <sub>OH</sub>         | ロジック出力レベル、High                            | $I_{OH} = -100\mu\text{A}$ 、プッシュプル出力                        | 0.8 AVDD  | AVDD     | V                            |

|                         | 入力ヒステリシス                                  |                                                             |           | 10       | mV                           |

| <b>デジタル入出力</b>          |                                           |                                                             |           |          |                              |

| V <sub>IL</sub>         | ロジック入力レベル、Low                             |                                                             | GND       | 0.3 DVDD | V                            |

| V <sub>IH</sub>         | ロジック入力レベル、High                            |                                                             | 0.7 DVDD  | 5.5      | V                            |

| V <sub>hys</sub>        | シュミットトリガ入力のヒステリシス                         |                                                             |           | 180      | mV                           |

| V <sub>OL</sub>         | ロジック出力レベル、Low                             | $I_{OL} = 3\text{mA}$                                       | GND       | 0.3      | V                            |

| I <sub>OL</sub>         | Low レベル出力電流                               | $V_{OL} = 0.4\text{V}$ 、ファーストモード プラス、DVDD = 1.65V ~ 2V      | 12        |          | mA                           |

|                         |                                           | $V_{OL} = 0.4\text{V}$ 、ファーストモード プラス、DVDD = 2V ~ 3.6V       | 20        |          |                              |

|                         |                                           | $V_{OL} = 0.6\text{V}$ 、ファーストモード                            | 6         |          |                              |

| C <sub>i</sub>          | 容量                                        | 各ピン                                                         |           | 10       | pF                           |

|                         | 入力電流                                      | $\text{GND} \leq V_{\text{Digital Input}} \leq \text{DVDD}$ | -1        | 1        | $\mu\text{A}$                |

最小値および最大値の仕様は、 $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  の範囲に適用されます。代表値の仕様は  $T_A = 25^\circ\text{C}$  での値です。すべての仕様は、AVDD = 1.74V ~ 3.6V、DVDD = 1.65V ~ 3.6V、内部リファレンス、内部発振器、すべての速度モード、すべてのデータレート、すべてのゲイン設定、ならびにグローバル チョップ無効の条件下で規定されています (特に記述のない限り)

| パラメータ                                                                                               | テスト条件    | 最小値                                         | 標準値  | 最大値  | 単位            |

|-----------------------------------------------------------------------------------------------------|----------|---------------------------------------------|------|------|---------------|

| アナログ電源電流 (AVDD = 3.3V、外部リファレンス、リファレンス バッファがディスエーブル、IDAC がディスエーブル、すべてのデータレート、 $V_{IN} = 0\text{V}$ ) |          |                                             |      |      |               |

| $I_{AVDD}$                                                                                          | アナログ電源電流 | パワーダウン モード                                  | 0.2  | 2    | $\mu\text{A}$ |

|                                                                                                     |          | スタンバイ モード                                   | 10   | 16   |               |

|                                                                                                     |          | 変換モード、速度モード 0、ゲイン = 0.5 ~ 2                 | 52   | 59   |               |

|                                                                                                     |          | 変換モード、速度モード 0、ゲイン = 4 および 5                 | 55   | 63   |               |

|                                                                                                     |          | 変換モード、速度モード 0、ゲイン = 8 ~ 50                  | 61   | 68   |               |

|                                                                                                     |          | 変換モード、速度モード 0、ゲイン = 64 ~ 256                | 57   | 64   |               |

|                                                                                                     |          | 変換モード、速度モード 1、ゲイン = 0.5 ~ 2                 | 135  | 145  |               |

|                                                                                                     |          | 変換モード、速度モード 1、ゲイン = 4 および 5                 | 155  | 170  |               |

|                                                                                                     |          | 変換モード、速度モード 1、ゲイン = 8 ~ 50                  | 205  | 220  |               |

|                                                                                                     |          | 変換モード、速度モード 1、ゲイン = 64 ~ 256                | 255  | 275  |               |

|                                                                                                     |          | 変換モード、速度モード 2、ゲイン = 0.5 ~ 2                 | 315  | 335  |               |

|                                                                                                     |          | 変換モード、速度モード 2、ゲイン = 4 および 5                 | 360  | 380  |               |

|                                                                                                     |          | 変換モード、速度モード 2、ゲイン = 8 ~ 50                  | 450  | 480  |               |

|                                                                                                     |          | 変換モード、速度モード 2、ゲイン = 64 ~ 256                | 670  | 705  |               |

|                                                                                                     |          | 変換モード、速度モード 3、ゲイン = 0.5 ~ 2                 | 540  | 570  |               |

|                                                                                                     |          | 変換モード、速度モード 3、ゲイン = 4 および 5                 | 640  | 680  |               |

|                                                                                                     |          | 変換モード、速度モード 3、ゲイン = 8 ~ 50                  | 870  | 920  |               |

|                                                                                                     |          | 変換モード、速度モード 3、ゲイン = 64 ~ 256                | 1090 | 1140 |               |

| 機能ごとに追加のアナログ電源電流 (AVDD = 3.3V、 $V_{REF} = 2.5\text{V}$ )                                            |          |                                             |      |      |               |

| $I_{AVDD}$                                                                                          | アナログ電源電流 | 内部電圧リファレンス、速度モード 0                          | 4.5  | 6    | $\mu\text{A}$ |

|                                                                                                     |          | 内部電圧リファレンス、速度モード 1                          | 25   | 28   |               |

|                                                                                                     |          | 内部電圧リファレンス、速度モード 2                          | 35   | 40   |               |

|                                                                                                     |          | 内部電圧リファレンス、速度モード 3                          | 65   | 75   |               |

|                                                                                                     |          | REFP または REFN バッファがイネーブル、速度モード 0            | 4.5  | 6    |               |

|                                                                                                     |          | REFP または REFN バッファがイネーブル、速度モード 1            | 25   | 28   |               |

|                                                                                                     |          | REFP または REFN バッファがイネーブル、速度モード 2            | 35   | 40   |               |

|                                                                                                     |          | REFP または REFN バッファがイネーブル、速度モード 3            | 65   | 75   |               |

|                                                                                                     |          | REFP バッファと REFN バッファの両方がイネーブル、速度モード 0       | 6.5  | 9    |               |

|                                                                                                     |          | REFP バッファと REFN バッファの両方がイネーブル、速度モード 1       | 33   | 39   |               |

|                                                                                                     |          | REFP バッファと REFN バッファの両方がイネーブル、速度モード 2       | 51   | 60   |               |

|                                                                                                     |          | REFP バッファと REFN バッファの両方がイネーブル、速度モード 3       | 106  | 124  |               |

|                                                                                                     |          | IDAC オーバーヘッド、IDAC ユニット電流 = 1 $\mu\text{A}$  | 4    | 6    |               |

|                                                                                                     |          | IDAC オーバーヘッド、IDAC ユニット電流 = 10 $\mu\text{A}$ | 16   | 28   |               |

| デジタル電源電流 (DVDD = 3.3V、すべてのデータレート、 $\text{I}^2\text{C}$ はアクティブではありません)                               |          |                                             |      |      |               |

最小値および最大値の仕様は、 $T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  の範囲に適用されます。代表値の仕様は  $T_A = 25^{\circ}\text{C}$  での値です。すべての仕様は、AVDD = 1.74V ~ 3.6V、DVDD = 1.65V ~ 3.6V、内部リファレンス、内部発振器、すべての速度モード、すべてのデータレート、すべてのゲイン設定、ならびにグローバル チョップ無効の条件下で規定されています (特に記述のない限り)

| パラメータ      | テスト条件             | 最小値 | 標準値 | 最大値 | 単位            |

|------------|-------------------|-----|-----|-----|---------------|

| $I_{DVDD}$ | パワーダウン モード        |     | 1.6 | 6.5 | $\mu\text{A}$ |

|            | スタンバイ モード、速度モード 0 |     | 8   | 13  |               |

|            | スタンバイ モード、速度モード 1 |     | 20  | 26  |               |

|            | スタンバイ モード、速度モード 2 |     | 26  | 33  |               |

|            | スタンバイ モード、速度モード 3 |     | 40  | 47  |               |

|            | 変換モード、速度モード 0     |     | 9   | 16  |               |

|            | 変換モード、速度モード 1     |     | 30  | 38  |               |

|            | 変換モード、速度モード 2     |     | 48  | 56  |               |

|            | 変換モード、速度モード 3     |     | 82  | 92  |               |

最小値および最大値の仕様は、 $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  の範囲に適用されます。代表値の仕様は  $T_A = 25^\circ\text{C}$  での値です。すべての仕様は、AVDD = 1.74V ~ 3.6V、DVDD = 1.65V ~ 3.6V、内部リファレンス、内部発振器、すべての速度モード、すべてのデータレート、すべてのゲイン設定、ならびにグローバル チョップ無効の条件下で規定されています (特に記述のない限り)

| パラメータ                                                                                                               | テスト条件    | 最小値                                         | 標準値  | 最大値  | 単位            |

|---------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------|------|------|---------------|

| <b>アナログ電源電流 (AVDD = 1.8V、外部リファレンス、リファレンス バッファがディスエーブル、IDAC がディスエーブル、すべてのデータレート、<math>V_{IN} = 0\text{V}</math>)</b> |          |                                             |      |      |               |

| $I_{AVDD}$                                                                                                          | アナログ電源電流 | パワーダウン モード                                  | 0.2  | 2    | $\mu\text{A}$ |

|                                                                                                                     |          | スタンバイ モード                                   | 8    | 14   |               |

|                                                                                                                     |          | 変換モード、速度モード 0、ゲイン = 0.5 ~ 2                 | 48   | 55   |               |

|                                                                                                                     |          | 変換モード、速度モード 0、ゲイン = 4 および 5                 | 51   | 58   |               |

|                                                                                                                     |          | 変換モード、速度モード 0、ゲイン = 8 ~ 50                  | 57   | 64   |               |

|                                                                                                                     |          | 変換モード、速度モード 0、ゲイン = 64 ~ 256                | 53   | 60   |               |

|                                                                                                                     |          | 変換モード、速度モード 1、ゲイン = 0.5 ~ 2                 | 120  | 130  |               |

|                                                                                                                     |          | 変換モード、速度モード 1、ゲイン = 4 および 5                 | 140  | 155  |               |

|                                                                                                                     |          | 変換モード、速度モード 1、ゲイン = 8 ~ 50                  | 190  | 205  |               |

|                                                                                                                     |          | 変換モード、速度モード 1、ゲイン = 64 ~ 256                | 240  | 260  |               |

|                                                                                                                     |          | 変換モード、速度モード 2、ゲイン = 0.5 ~ 2                 | 285  | 305  |               |

|                                                                                                                     |          | 変換モード、速度モード 2、ゲイン = 4 および 5                 | 325  | 345  |               |

|                                                                                                                     |          | 変換モード、速度モード 2、ゲイン = 8 ~ 50                  | 420  | 445  |               |

|                                                                                                                     |          | 変換モード、速度モード 2、ゲイン = 64 ~ 256                | 635  | 670  |               |

|                                                                                                                     |          | 変換モード、速度モード 3、ゲイン = 0.5 ~ 2                 | 485  | 515  |               |

|                                                                                                                     |          | 変換モード、速度モード 3、ゲイン = 4 および 5                 | 580  | 620  |               |

|                                                                                                                     |          | 変換モード、速度モード 3、ゲイン = 8 ~ 50                  | 810  | 860  |               |

|                                                                                                                     |          | 変換モード、速度モード 3、ゲイン = 64 ~ 256                | 1020 | 1080 |               |

| <b>機能ごとに追加のアナログ電源電流 (AVDD = 1.8V、<math>V_{REF} = 1.25\text{V}</math>)</b>                                           |          |                                             |      |      |               |

| $I_{AVDD}$                                                                                                          | アナログ電源電流 | 内部電圧リファレンス、速度モード 0                          | 3.5  | 5    | $\mu\text{A}$ |

|                                                                                                                     |          | 内部電圧リファレンス、速度モード 1                          | 16   | 20   |               |

|                                                                                                                     |          | 内部電圧リファレンス、速度モード 2                          | 26   | 31   |               |

|                                                                                                                     |          | 内部電圧リファレンス、速度モード 3                          | 56   | 66   |               |

|                                                                                                                     |          | REFP または REFN バッファがイネーブル、速度モード 0            | 3.5  | 5    |               |

|                                                                                                                     |          | REFP または REFN バッファがイネーブル、速度モード 1            | 16   | 20   |               |

|                                                                                                                     |          | REFP または REFN バッファがイネーブル、速度モード 2            | 26   | 31   |               |

|                                                                                                                     |          | REFP または REFN バッファがイネーブル、速度モード 3            | 56   | 66   |               |

|                                                                                                                     |          | REFP バッファと REFN バッファの両方がイネーブル、速度モード 0       | 5.5  | 8    |               |

|                                                                                                                     |          | REFP バッファと REFN バッファの両方がイネーブル、速度モード 1       | 25   | 30   |               |

|                                                                                                                     |          | REFP バッファと REFN バッファの両方がイネーブル、速度モード 2       | 43   | 53   |               |

|                                                                                                                     |          | REFP バッファと REFN バッファの両方がイネーブル、速度モード 3       | 100  | 120  |               |

|                                                                                                                     |          | IDAC オーバーヘッド、IDAC ユニット電流 = 1 $\mu\text{A}$  | 4    | 6    |               |

|                                                                                                                     |          | IDAC オーバーヘッド、IDAC ユニット電流 = 10 $\mu\text{A}$ | 16   | 28   |               |

| <b>デジタル電源電流 (DVDD = 1.8V、すべてのデータレート、<math>\text{I}^2\text{C}</math> はアクティブではありません)</b>                              |          |                                             |      |      |               |

最小値および最大値の仕様は、 $T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  の範囲に適用されます。代表値の仕様は  $T_A = 25^{\circ}\text{C}$  での値です。すべての仕様は、 $\text{AVDD} = 1.74\text{V} \sim 3.6\text{V}$ 、 $\text{DVDD} = 1.65\text{V} \sim 3.6\text{V}$ 、内部リファレンス、内部発振器、すべての速度モード、すべてのデータレート、すべてのゲイン設定、ならびにグローバル チョップ無効の条件下で規定されています (特に記述のない限り)

| パラメータ             | テスト条件             | 最小値 | 標準値 | 最大値 | 単位            |

|-------------------|-------------------|-----|-----|-----|---------------|

| $I_{\text{DVDD}}$ | パワーダウン モード        |     | 1.6 | 6.5 | $\mu\text{A}$ |

|                   | スタンバイ モード、速度モード 0 |     | 7   | 13  |               |

|                   | スタンバイ モード、速度モード 1 |     | 19  | 26  |               |

|                   | スタンバイ モード、速度モード 2 |     | 25  | 33  |               |

|                   | スタンバイ モード、速度モード 3 |     | 39  | 47  |               |

|                   | 変換モード、速度モード 0     |     | 9   | 16  |               |

|                   | 変換モード、速度モード 1     |     | 30  | 38  |               |

|                   | 変換モード、速度モード 2     |     | 48  | 56  |               |

|                   | 変換モード、速度モード 3     |     | 82  | 92  |               |

- (1) 入力電流は、速度モード、データレート、ゲイン、グローバル チョップ モード設定によってスケーリングされます。

- (2) 電流は **REFP** に流れ込み、**REFN** から流れ出します。

- (3) 低電圧モニタは常に、指定された最小値を下回るようトリップし、指定された最大値を超えるようにはトリップしません。

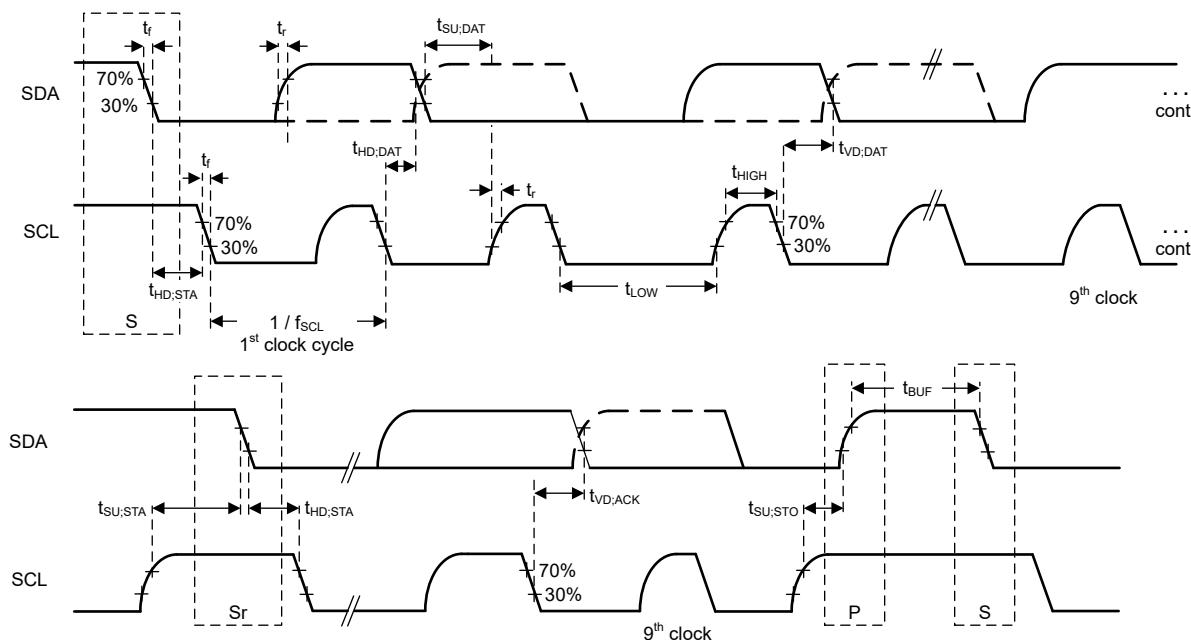

## 5.6 I<sup>2</sup>C のタイミング要件

動作時周囲温度範囲全体、DVDD = 1.65V ~ 3.6V(特に記述のない限り)

|                          |                                                           | 最小値  | 最大値  | 単位  |

|--------------------------|-----------------------------------------------------------|------|------|-----|

| <b>標準モード (Sm)</b>        |                                                           |      |      |     |

| $f_{SCL}$                | SCL クロック周波数                                               | 0    | 100  | kHz |

| $t_{HD:STA}$             | ホールド時間、(繰り返し) START 条件。<br>この時間が経過すると、最初のクロック パルスが生成されます。 | 4    |      | μs  |

| $t_{LOW}$                | パルス幅、SCL low                                              | 4.7  |      | μs  |

| $t_{HIGH}$               | パルス幅、SCL high                                             | 4.0  |      | μs  |

| $t_{SU:STA}$             | セットアップ時間、反復開始条件                                           | 4.7  |      | μs  |

| $t_{HD:DAT}$             | ホールド時間、データ                                                | 0    |      | μs  |

| $t_{SU:DAT}$             | セットアップ時間、データ                                              | 250  |      | ns  |

| $t_r$                    | 立ち上がり時間、SCL、SDA                                           |      | 1000 | ns  |

| $t_f$                    | 立ち下がり時間、SCL、SDA                                           |      | 250  | ns  |

| $t_{SU:STO}$             | セットアップ時間、STOP 条件                                          | 4.0  |      | μs  |

| $t_{BUF}$                | バス開放時間、STOP 条件と START 条件間                                 | 4.7  |      | μs  |

| $t_{VD:DAT}$             | 有効時間、データ                                                  |      | 3.45 | μs  |

| $t_{VD:ACK}$             | 有効時間、アクリッジ                                                |      | 3.45 | μs  |

| <b>ファストモード (Fm)</b>      |                                                           |      |      |     |

| $f_{SCL}$                | SCL クロック周波数                                               | 0    | 400  | kHz |

| $t_{HD:STA}$             | ホールド時間、(繰り返し) START 条件。<br>この時間が経過すると、最初のクロック パルスが生成されます。 | 0.6  |      | μs  |

| $t_{LOW}$                | パルス幅、SCL low                                              | 1.3  |      | μs  |

| $t_{HIGH}$               | パルス幅、SCL high                                             | 0.6  |      | μs  |

| $t_{SU:STA}$             | セットアップ時間、反復開始条件                                           | 0.6  |      | μs  |

| $t_{HD:DAT}$             | ホールド時間、データ                                                | 0    |      | μs  |

| $t_{SU:DAT}$             | セットアップ時間、データ                                              | 100  |      | ns  |

| $t_r$                    | 立ち上がり時間、SCL、SDA                                           | 20   | 300  | ns  |

| $t_f$                    | 立ち下がり時間、SCL、SDA                                           |      | 250  | ns  |

| $t_{SU:STO}$             | セットアップ時間、STOP 条件                                          | 0.6  |      | μs  |

| $t_{BUF}$                | バス開放時間、STOP 条件と START 条件間                                 | 1.3  |      | μs  |

| $t_{VD:DAT}$             | 有効時間、データ                                                  |      | 0.9  | μs  |

| $t_{VD:ACK}$             | 有効時間、アクリッジ                                                |      | 0.9  | μs  |

| $t_{SP}$                 | 入力フィルタで抑制しなければならないスパイクのパルス幅                               | 0    | 50   | ns  |

| <b>ファストモード プラス (Fm+)</b> |                                                           |      |      |     |

| $f_{SCL}$                | SCL クロック周波数                                               | 0    | 1000 | kHz |

| $t_{HD:STA}$             | ホールド時間、(繰り返し) START 条件。<br>この時間が経過すると、最初のクロック パルスが生成されます。 | 0.26 |      | μs  |

| $t_{LOW}$                | パルス幅、SCL low                                              | 0.5  |      | μs  |

| $t_{HIGH}$               | パルス幅、SCL high                                             | 0.26 |      | μs  |

| $t_{SU:STA}$             | セットアップ時間、反復開始条件                                           | 0.26 |      | μs  |

| $t_{HD:DAT}$             | ホールド時間、データ                                                | 0    |      | μs  |

| $t_{SU:DAT}$             | セットアップ時間、データ                                              | 50   |      | ns  |

| $t_r$                    | 立ち上がり時間、SCL、SDA                                           |      | 120  | ns  |

| $t_f$                    | 立ち下がり時間、SCL、SDA                                           |      | 120  | ns  |

| $t_{SU:STO}$             | セットアップ時間、STOP 条件                                          | 0.26 |      | μs  |

| $t_{BUF}$                | バス開放時間、STOP 条件と START 条件間                                 | 0.5  |      | μs  |

| $t_{VD:DAT}$             | 有効時間、データ                                                  |      | 0.45 | μs  |

| $t_{VD:ACK}$             | 有効時間、アクリッジ                                                |      | 0.45 | μs  |

| $t_{SP}$                 | 入力フィルタで抑制しなければならないスパイクのパルス幅                               | 0    | 50   | ns  |

動作時周囲温度範囲全体、DVDD = 1.65V ~ 3.6V(特に記述のない限り)

|            |                                                                  | 最小値 | 最大値 | 単位 |

|------------|------------------------------------------------------------------|-----|-----|----|

| リセット       |                                                                  |     |     |    |

| $t_d(RST)$ | 遅延時間、RESET[5:0] ビット フィールドを使用したソフトウェアリセットから I <sup>2</sup> C 通信開始 | 500 |     | μs |

| $t_d(POR)$ | 遅延時間、DVDD が最小 DVDD 電圧を超えてから I <sup>2</sup> C 通信開始                | 5   |     | ms |

## 5.7 I<sup>2</sup>C スイッチング特性

動作周囲温度範囲全体において、DVDD = 1.65V~3.6V(特に記述のない限り)

| パラメータ      | テスト条件          | 最小値 | 標準値 | 最大値 | 単位        |

|------------|----------------|-----|-----|-----|-----------|

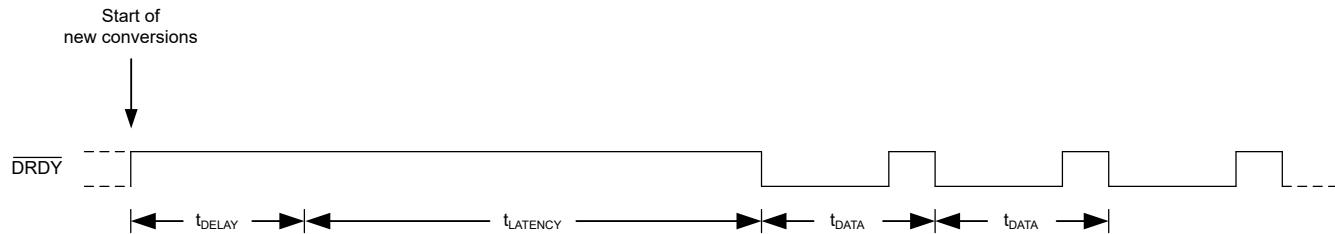

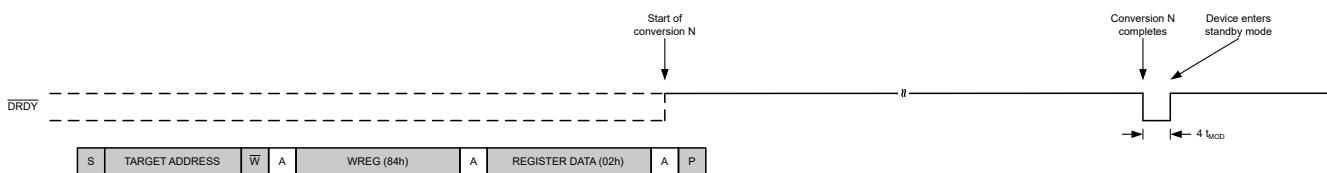

| $t_w(DRH)$ | パレス幅、DRDY High | 2   |     |     | $t_{MOD}$ |

## 5.8 タイミング図

図 5-1. I<sup>2</sup>C のタイミング要件

## 5.9 代表的特性

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

図 5-2. 内部基準電圧と温度との関係

図 5-3. 内部基準電圧と温度との関係

図 5-4. GPIO ピン出力電圧とシンク電流との関係

図 5-5. GPIO デピンの出力電圧とソース電流との関係

## 6 パラメータ測定情報

### 6.1 ノイズ性能

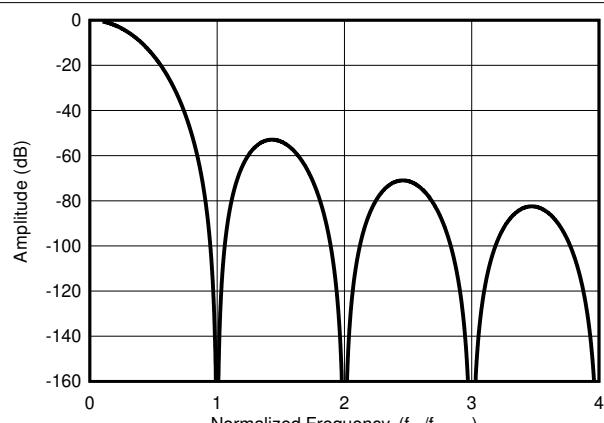

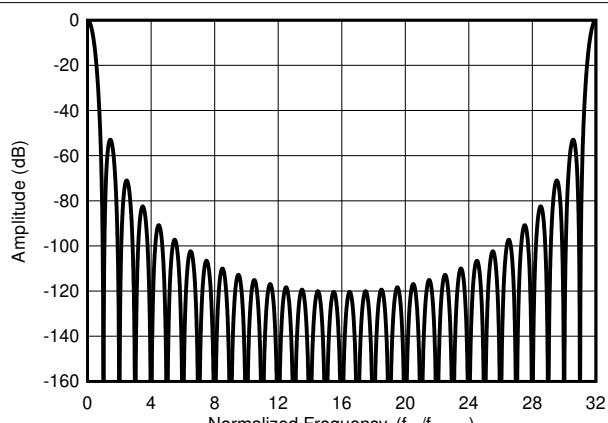

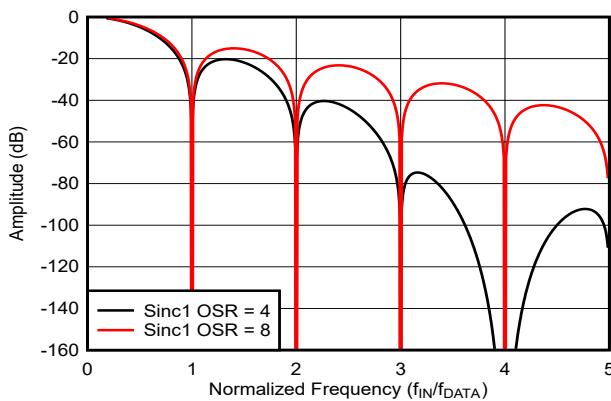

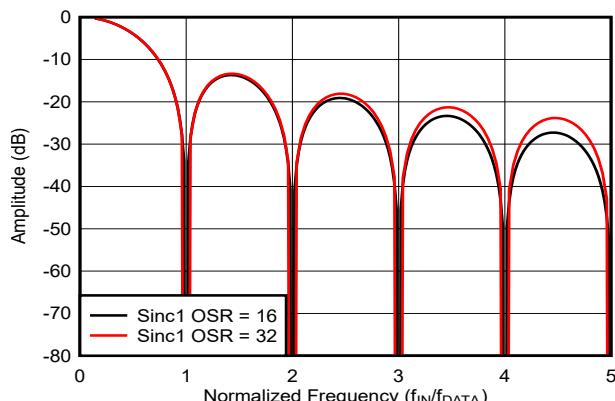

デルタシグマ ( $\Delta\Sigma$ ) 方式の A/D コンバータ (ADC) は、オーバーサンプリングの原理に基づいています。 $\Delta\Sigma$  ADC の入力信号は高い周波数 (変調器周波数) でサンプリングされ、その後、デジタル領域でフィルタ処理およびデシメーションが行われ、対応する出力データ レートでの変換結果が得られます。変調器周波数と出力データ レートの比は、オーバーサンプリング比 (OSR) と呼ばれます。OSR を高くし、それによって出力データ レートを低下させることで、ADC のノイズ性能を最適化できます。言い換えると、内部変調器のより多くのサンプルが平均化されて一つの変換結果が得られるため、出力データ レートを下げるに伴い入力換算ノイズは低下します。ゲインを大きくすると、入力換算ノイズも減少し、低レベル信号を測定する場合に特に役立ちます。

表 6-1～表 6-3 は、 $T_A = 25^\circ\text{C}$ 、 $f_{\text{CLK}} = 4.096\text{MHz}$  における代表的なデバイスのノイズ性能を要約しています。示されているデータは、アナログ入力を短絡した状態で測定した、 $\mu\text{V}_{\text{RMS}}$  単位の代表的な入力換算ノイズ ( $e_n$ ) 結果です。RMS ノイズの測定には、連続した 1,000 回の変換、または連続 10 秒間の変換のいずれか先に到達した方が使用されます。ノイズの統計的な性質から、繰り返しノイズを測定すると、ノイズの結果は大きく、または小さくなる可能性があります。

選択したコーディング方式に応じて、提供される  $\mu\text{V}_{\text{RMS}}$  の数値によって有効分解能を計算するには、式 2 または式 1 を使用します。

$$\text{Binary two's complement coding: Effective Resolution} = \ln[(2 \times V_{\text{REF}} / \text{Gain}) / e_{n(\text{RMS})}] / \ln(2) \quad (1)$$

$$\text{Unipolar straight binary coding: Effective Resolution} = \ln[(V_{\text{REF}} / \text{Gain}) / e_{n(\text{RMS})}] / \ln(2) \quad (2)$$

$\mu\text{V}_{\text{PP}}$  単位の入力換算ノイズ ( $e_n$ ) は、 $e_{n(\text{PP})} = 6.6 \times e_{n(\text{RMS})}$  と推定できます。選択したコーディング方式に応じて、推定  $\mu\text{V}_{\text{PP}}$  値からノイズフリー分解能を計算するには、式 4 または式 3 を使用します。

$$\text{Binary two's complement coding: Noise-free Resolution} = \ln[(2 \times V_{\text{REF}} / \text{Gain}) / e_{n(\text{PP})}] / \ln(2) \quad (3)$$

$$\text{Unipolar straight binary coding: Noise-free Resolution} = \ln[(V_{\text{REF}} / \text{Gain}) / e_{n(\text{PP})}] / \ln(2) \quad (4)$$

入力を短絡した状態での入力換算ノイズ性能は、基準電圧によってほとんど変化しません。つまり表 6-1～表 6-3 は、他のリファレンス電圧値にも適用されます。

グローバル チョップ モードでは、入力を入れ替えた状態で行った ADC の 2 回の測定結果をデバイスが平均化します。グローバル チョップ モードでは、デバイスの入力オフセットが大幅に低減され、ノイズは  $\sqrt{2}$  の係数で低減されます。

ノイズ データは、デバイスの 24 ビットバージョンを使用して測定します。16 ビット デバイスの場合は、ノイズ データを LSB サイズでクリップします。

**表 6-1. 入力換算ノイズ ( $\mu\text{V}_{\text{RMS}}$ 、

AVDD = 3.3V、グローバルチョップモード無効、内部 2.5V リファレンス、ゲイン = 0.5 ~ 8)**

| OSR                                        | データレート<br>(SPS) <sup>(1)</sup> | ゲイン  |      |      |      |      |      |

|--------------------------------------------|--------------------------------|------|------|------|------|------|------|

|                                            |                                | 0.5  | 1    | 2    | 4    | 5    | 8    |

| <b>速度モード 0 (f<sub>MOD</sub> = 32kHz)</b>   |                                |      |      |      |      |      |      |

| 1600                                       | 20                             | 8.06 | 3.91 | 2.20 | 1.44 | 1.37 | 0.99 |

| 1280                                       | 25                             | 8.44 | 4.36 | 2.46 | 1.51 | 1.50 | 1.10 |

| 1024                                       | 31.25                          | 8.27 | 4.22 | 3.32 | 1.46 | 1.44 | 1.07 |

| 512                                        | 62.5                           | 11.5 | 5.82 | 3.27 | 2.09 | 2.00 | 1.47 |

| 256                                        | 125                            | 16.1 | 8.18 | 4.44 | 2.91 | 2.91 | 2.08 |

| 128                                        | 250                            | 21.6 | 10.9 | 6.20 | 3.80 | 3.80 | 2.75 |

| 32                                         | 1000                           | 33.1 | 16.5 | 9.24 | 5.80 | 5.80 | 4.13 |

| 16                                         | 2000                           | 51.7 | 26.0 | 14.1 | 8.37 | 8.37 | 5.81 |

| <b>速度モード 1 (f<sub>MOD</sub> = 256kHz)</b>  |                                |      |      |      |      |      |      |

| 12800                                      | 20                             | 2.46 | 1.32 | 0.80 | 0.57 | 0.57 | 0.49 |

| 10240                                      | 25                             | 2.64 | 1.41 | 0.82 | 0.61 | 0.59 | 0.54 |

| 1024                                       | 250                            | 7.34 | 3.87 | 2.33 | 1.69 | 1.69 | 1.53 |

| 512                                        | 500                            | 10.4 | 5.41 | 3.23 | 2.37 | 2.37 | 2.15 |

| 256                                        | 1000                           | 14.4 | 7.44 | 4.51 | 3.31 | 3.31 | 2.98 |

| 128                                        | 2000                           | 19.5 | 10.2 | 6.08 | 4.39 | 4.39 | 3.93 |

| 32                                         | 8000                           | 29.4 | 15.2 | 9.10 | 6.56 | 6.56 | 5.76 |

| 16                                         | 16000                          | 49.4 | 25.3 | 14.5 | 9.78 | 9.77 | 8.26 |

| <b>速度モード 2 (f<sub>MOD</sub> = 512kHz)</b>  |                                |      |      |      |      |      |      |

| 25600                                      | 20                             | 1.74 | 0.90 | 0.51 | 0.33 | 0.33 | 0.28 |

| 20480                                      | 25                             | 1.85 | 0.99 | 0.55 | 0.35 | 0.35 | 0.30 |

| 1024                                       | 500                            | 7.36 | 3.75 | 2.11 | 1.42 | 1.40 | 1.18 |

| 512                                        | 1000                           | 10.2 | 5.16 | 2.93 | 1.97 | 1.97 | 1.65 |

| 256                                        | 2000                           | 14.3 | 7.16 | 4.13 | 2.73 | 2.73 | 2.27 |

| 128                                        | 4000                           | 19.3 | 9.82 | 5.55 | 3.66 | 3.65 | 3.04 |

| 32                                         | 16000                          | 29.0 | 14.8 | 8.34 | 5.40 | 5.40 | 4.45 |

| 16                                         | 32000                          | 49.4 | 25.1 | 13.6 | 8.31 | 8.31 | 6.48 |

| <b>速度モード 3 (f<sub>MOD</sub> = 1024kHz)</b> |                                |      |      |      |      |      |      |

| 51200                                      | 20                             | 1.27 | 0.67 | 0.39 | 0.28 | 0.28 | 0.26 |

| 40960                                      | 25                             | 1.36 | 0.70 | 0.41 | 0.30 | 0.30 | 0.27 |

| 1024                                       | 1000                           | 7.43 | 3.86 | 2.27 | 1.64 | 1.63 | 1.55 |

| 512                                        | 2000                           | 10.4 | 5.42 | 3.18 | 2.29 | 2.29 | 2.18 |

| 256                                        | 4000                           | 14.5 | 7.47 | 4.43 | 3.17 | 3.17 | 3.02 |

| 128                                        | 8000                           | 19.6 | 10.2 | 5.93 | 4.27 | 4.26 | 4.03 |

| 32                                         | 32000                          | 29.5 | 15.2 | 8.89 | 6.31 | 6.30 | 5.93 |

| 16                                         | 64000                          | 50.1 | 25.6 | 14.3 | 9.56 | 9.56 | 8.52 |

(1) f<sub>CLK</sub> = 4.096MHz を使用

表 6-2. 入力換算ノイズ ( $\mu\text{V}_{\text{RMS}}$ 、

AVDD = 3.3V、グローバル チョップ モード無効、内部 2.5V リファレンス、ゲイン = 10 ~ 64)

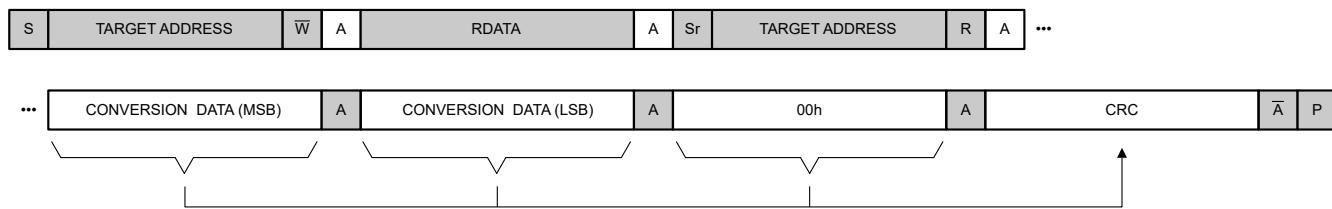

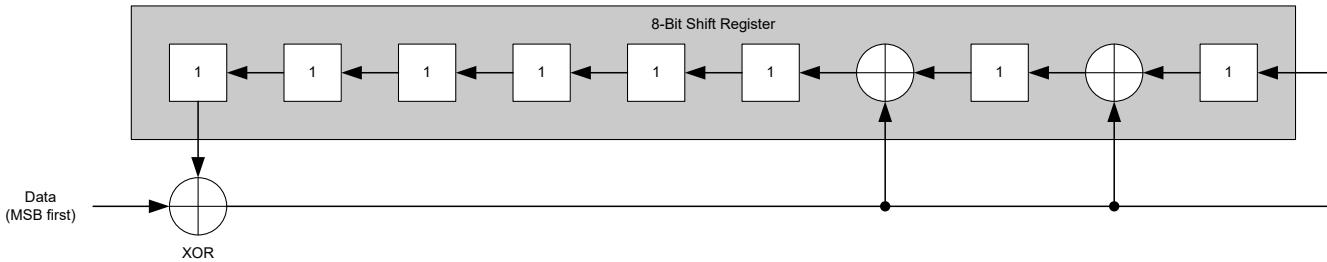

| OSR                                        | データレート<br>(SPS) <sup>(1)</sup> | ゲイン  |      |      |      |      |      |