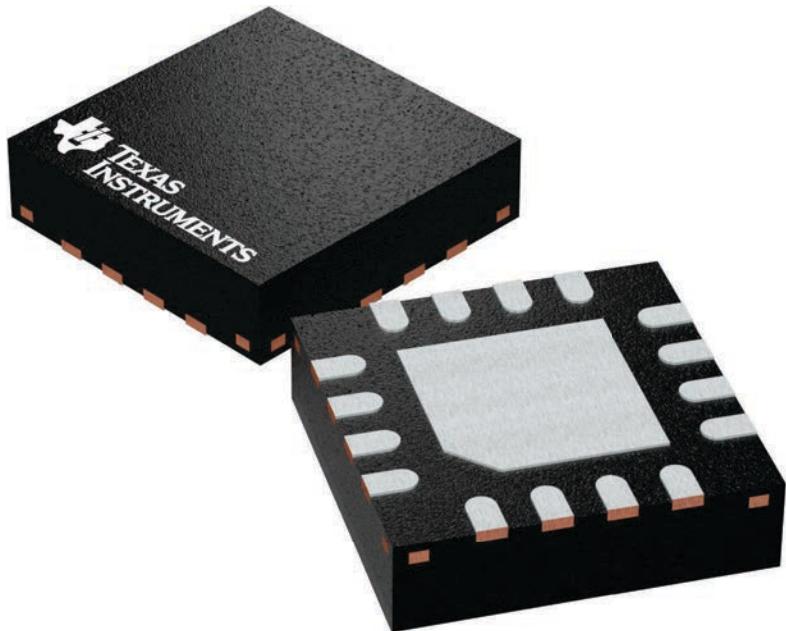

# ADS7067 小型、8 チャネル、16 ビット、800kSPS SAR ADC、GPIO 付き

## 1 特長

- パッケージオプション:

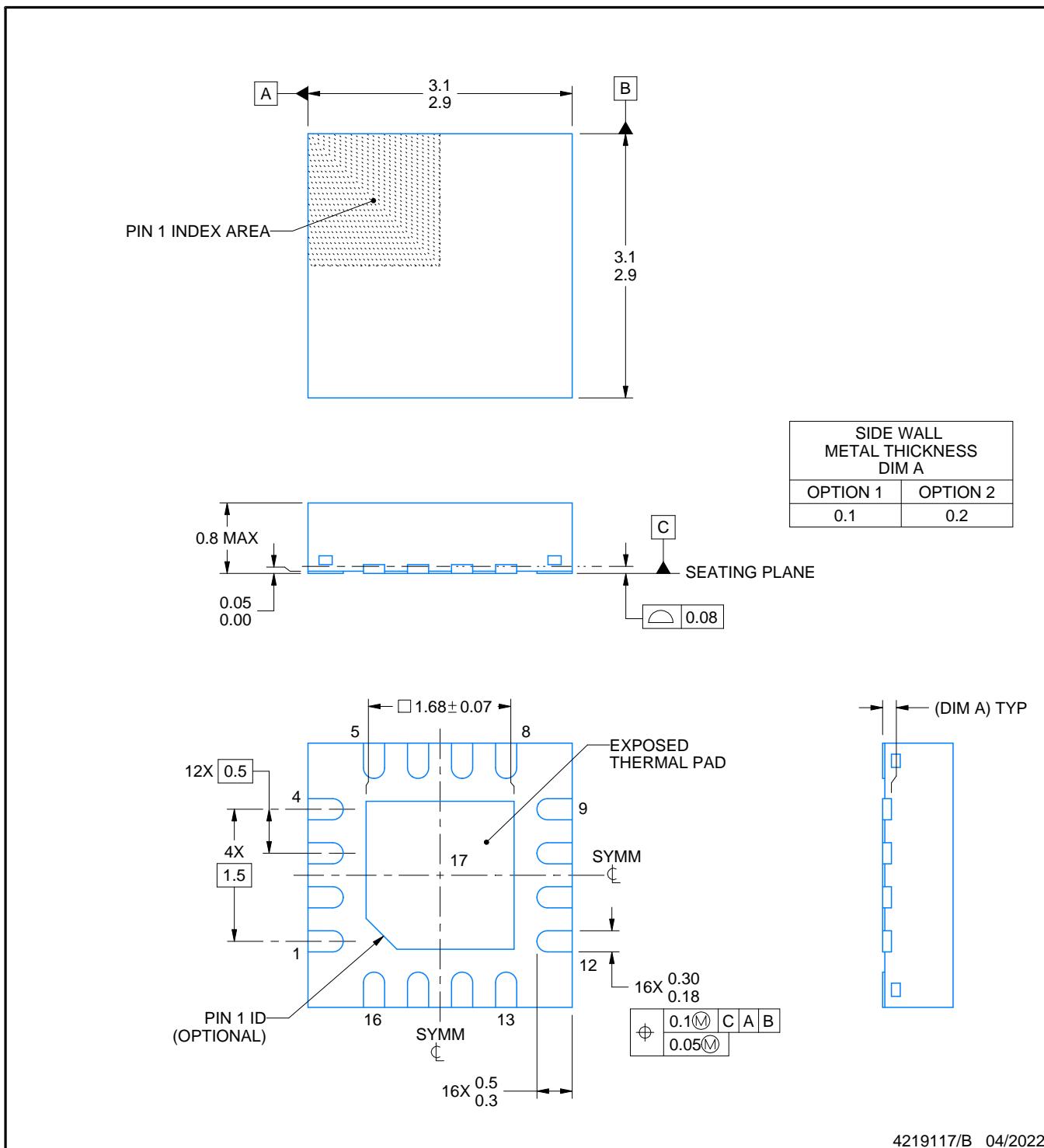

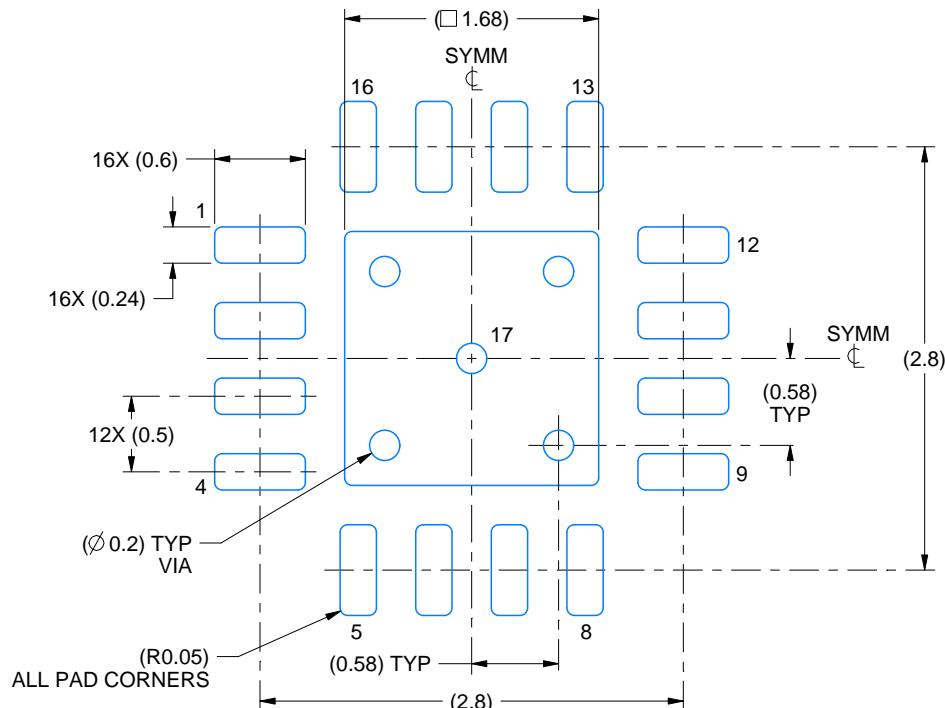

- 1.636mm × 1.636mm DSBGA と 3mm × 3mm WQFN

- 省スペース、コンデンサ不要、2.5V 内部基準電圧

- 8 つのチャネルを次の任意の組み合わせに構成可能:

- 最大 8 つのアナログ入力、デジタル入力、またはデジタル出力

- 平均化フィルタをプログラム可能

- 平均化のサンプル サイズをプログラム可能

- 内部変換による平均化

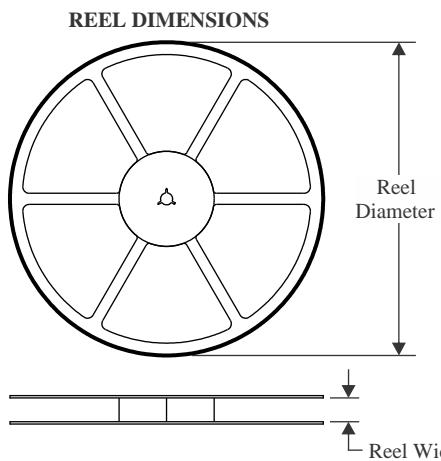

- 平均出力の分解能:20 ビット

- チャネルシーケンサ付きの低リーケ マルチプレクサ:

- マニュアル モード

- オンザフライ モード

- 自動シーケンス モード

- 優れた AC および DC 性能:

- 信号対雑音比:90dB、THD:-100 dB

- プログラム可能な平均化フィルタによる SNR の向上

- INL:±1LSB、16 ビット、ノーミッシング コード

- 内部的な較正によりオフセットとドリフト係数が改善

- 高いサンプリング レートとレイテンシなしの出力 800kSPS

- 広い動作範囲:

- ADC 入力範囲:0V~V<sub>REF</sub> および 2 × V<sub>REF</sub>

- アナログ電源:3V~5.5V

- デジタル電源:1.65V~5.5V

- 温度範囲:-40°C~+125°C

- 拡張 SPI デジタル インターフェイス

- 60MHz の高速 SPI インターフェイス

## 2 アプリケーション

- 光モジュール

- 光ライン・カード

- マルチパラメータ・メディカル・モニタ

## 3 概要

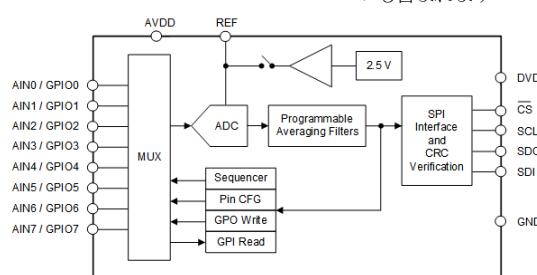

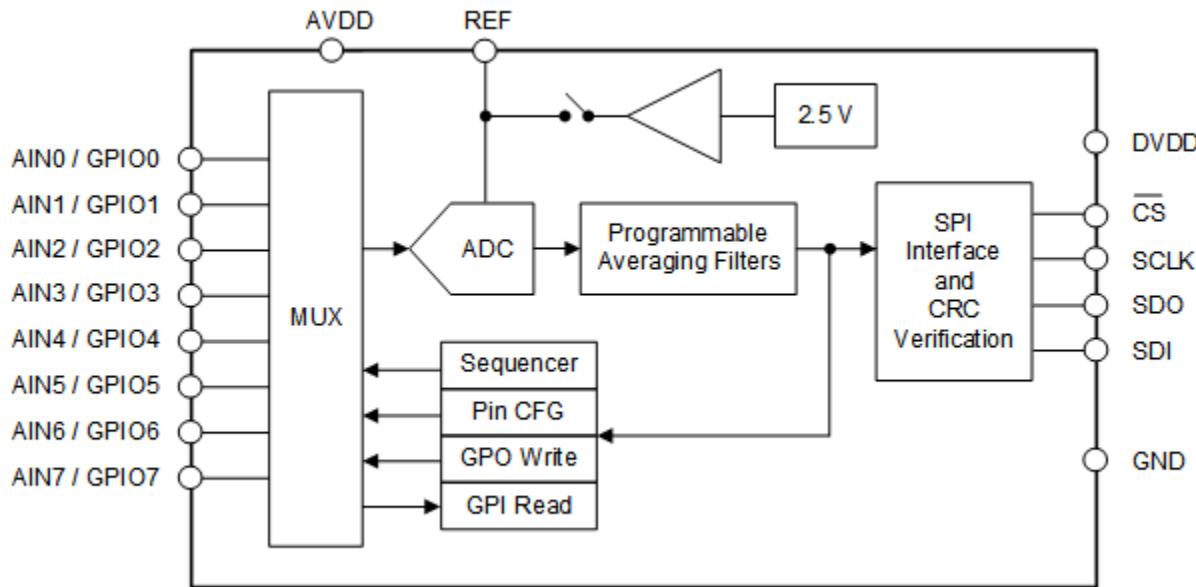

ADS7067 は小型、16 ビット、8 チャネル、高精度の逐次比較型 (SAR) アナログ / デジタル コンバータ (ADC) です。ADS7067 はコンデンサ不要の基準電圧と基準電圧 バッファを内蔵し、必要な外付け部品が少ないとからソリューションの小型化に役立ちます。ウェハー レベル チップ スケール パッケージを採用していることと、外付け部品の少なさにより、このデバイスはスペースの制約が厳しいアプリケーションに適した設計になっています。このデバイス ファミリには、ADS7067 (800kSPS) と ADS7066 (250kSPS) の速度バリアントが含まれます。

ADS7067 はオフセット較正機能を備えているため、幅広いシステム動作条件にわたって精度を高めることができます。プログラム可能な平均化フィルタにより、高分解能測定が可能です。ADS7067 の 8 つのチャネルはアナログ入力、デジタル入力、デジタル出力として個別に構成できるため、システムの小型化が可能になり、ミクスト シグナル 帰還やデジタル制御の回路設計を簡素化できます。

ADS7067 は、拡張 SPI により低いクロック速度で高いスループットを達成できるため、基板レイアウトを簡素化し、システムコストを低減できます。ADS7067 は、データの読み書き動作と起動時の構成のための巡回冗長検査 (CRC) 機能を備えています。

## パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| ADS7067 | YBH (DSBGA, 16)      | 1.636mm × 1.636mm        |

|         | RTE (WQFN, 16)       | 3mm × 3mm                |

(1) 詳細については、「[メカニカル、パッケージ、および注文情報](#)」を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はビンも含まれます

ADS7067 のブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

## Table of Contents

|                                      |    |                                         |    |

|--------------------------------------|----|-----------------------------------------|----|

| 1 特長                                 | 1  | 6.4 Device Functional Modes             | 25 |

| 2 アプリケーション                           | 1  | 6.5 ADS7067 Registers                   | 28 |

| 3 概要                                 | 1  | 7 Application and Implementation        | 37 |

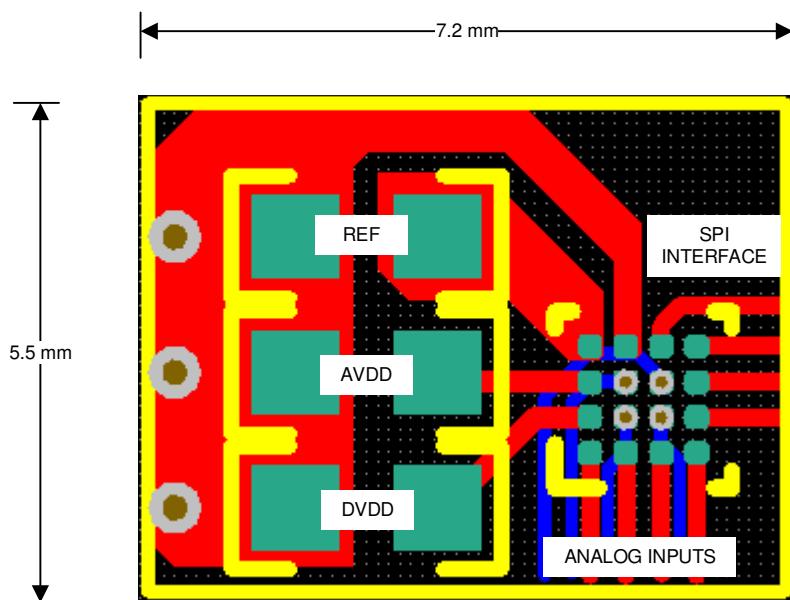

| 4 Pin Configuration and Functions    | 3  | 7.1 Application Information             | 37 |

| 5 Specifications                     | 5  | 7.2 Typical Application                 | 37 |

| 5.1 Absolute Maximum Ratings         | 5  | 7.3 Power Supply Recommendations        | 39 |

| 5.2 ESD Ratings                      | 5  | 7.4 Layout                              | 40 |

| 5.3 Recommended Operating Conditions | 5  | 8 Device and Documentation Support      | 41 |

| 5.4 Thermal Information              | 6  | 8.1 Device Support                      | 41 |

| 5.5 Electrical Characteristics       | 7  | 8.2 Documentation Support               | 41 |

| 5.6 Timing Requirements              | 8  | 8.3 ドキュメントの更新通知を受け取る方法                  | 41 |

| 5.7 Switching Characteristics        | 8  | 8.4 サポート・リソース                           | 41 |

| 5.8 Timing Diagrams                  | 9  | 8.5 Trademarks                          | 41 |

| 5.9 Typical Characteristics          | 10 | 8.6 静電気放電に関する注意事項                       | 41 |

| 6 Detailed Description               | 14 | 8.7 用語集                                 | 41 |

| 6.1 Overview                         | 14 | 9 Revision History                      | 41 |

| 6.2 Functional Block Diagram         | 14 | 10 Mechanical, Packaging, and Orderable |    |

| 6.3 Feature Description              | 15 | Information                             | 42 |

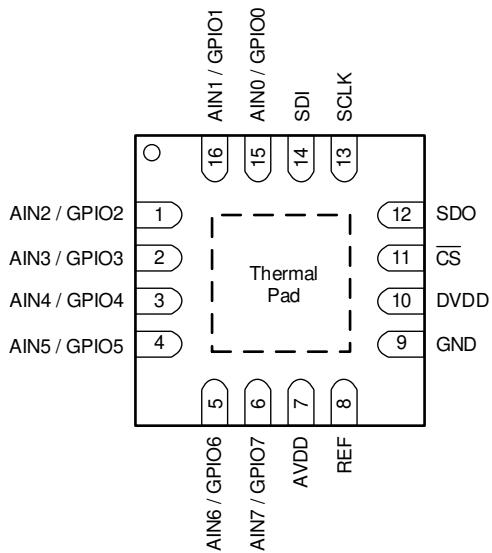

## 4 Pin Configuration and Functions

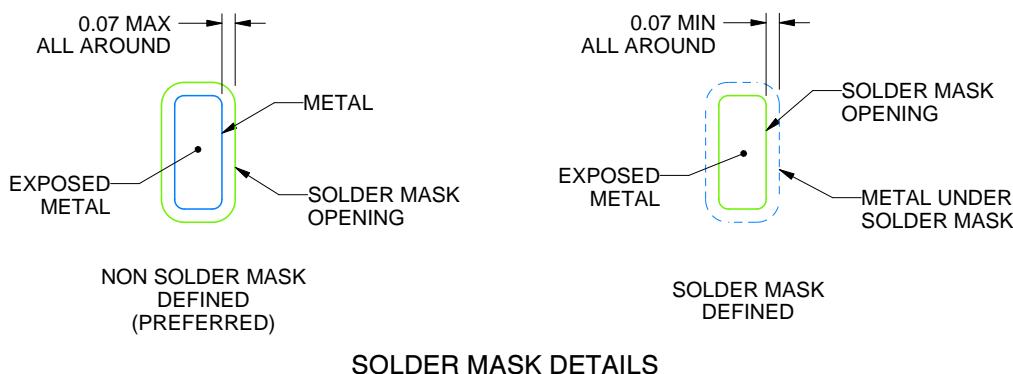

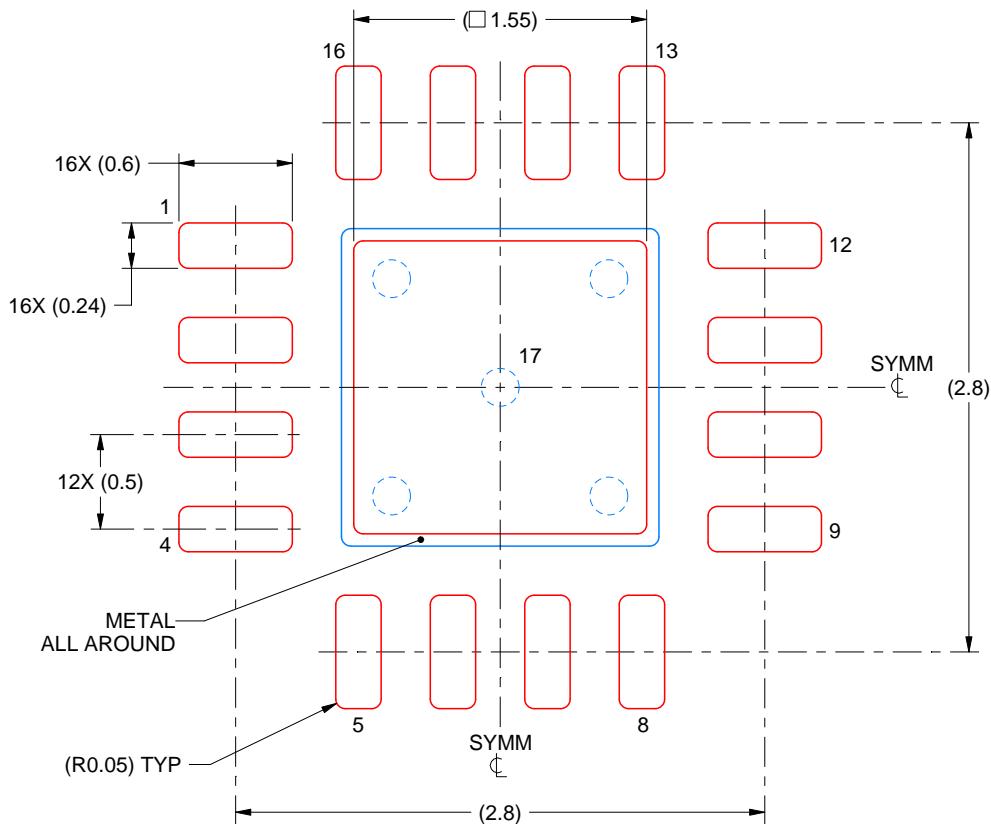

図 4-1. RTE Package, 16-Pin WQFN (Top View)

表 4-1. Pin Functions: RTE Package

| PIN         |     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                              |

|-------------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | RTE |                     |                                                                                                                                          |

| AIN0/GPIO0  | 15  | AI, DI, DO          | Channel 0; configurable as either an analog input (default) or general-purpose input/output (GPIO).                                      |

| AIN1/GPIO1  | 16  | AI, DI, DO          | Channel 1; configurable as either an analog input (default) or GPIO.                                                                     |

| AIN2/GPIO2  | 1   | AI, DI, DO          | Channel 2; configurable as either an analog input (default) or GPIO.                                                                     |

| AIN3/GPIO3  | 2   | AI, DI, DO          | Channel 3; configurable as either an analog input (default) or GPIO.                                                                     |

| AIN4/GPIO4  | 3   | AI, DI, DO          | Channel 4; configurable as either an analog input (default) or GPIO.                                                                     |

| AIN5/GPIO5  | 4   | AI, DI, DO          | Channel 5; configurable as either an analog input (default) or GPIO.                                                                     |

| AIN6/GPIO6  | 5   | AI, DI, DO          | Channel 6; configurable as either an analog input (default) or GPIO.                                                                     |

| AIN7/GPIO7  | 6   | AI, DI, DO          | Channel 7; configurable as either an analog input (default) or GPIO.                                                                     |

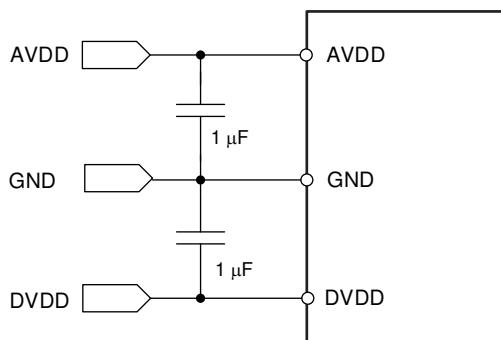

| AVDD        | 7   | P                   | Analog supply voltage. Connect a 1 $\mu$ F capacitor to GND.                                                                             |

| CS          | 11  | DI                  | Chip-select input pin; active low.<br>The device takes control of the data bus when CS is low.<br>The SDO pin goes Hi-Z when CS is high. |

| DVDD        | 10  | P                   | Digital I/O supply voltage. Connect a 1 $\mu$ F capacitor to GND.                                                                        |

| GND         | 9   | P                   | Ground for power supply, all analog and digital signals are referred to this pin.                                                        |

| REF         | 8   | P                   | Internal reference buffer output; external reference input. Connect a 1 $\mu$ F capacitor to GND.                                        |

| SCLK        | 13  | DI                  | Clock input pin for the SPI interface.                                                                                                   |

| SDI         | 14  | DI                  | Serial data input pin for the SPI interface.                                                                                             |

| SDO         | 12  | DO                  | Serial data output pin for the SPI interface.                                                                                            |

| Thermal Pad | Pad | P                   | Exposed thermal pad. Connect to ground.                                                                                                  |

(1) AI = analog input, DI = digital input, DO = digital output, P = power supply.

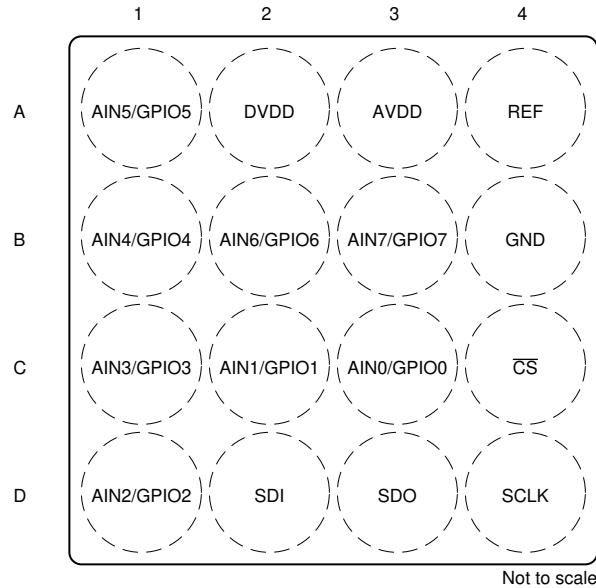

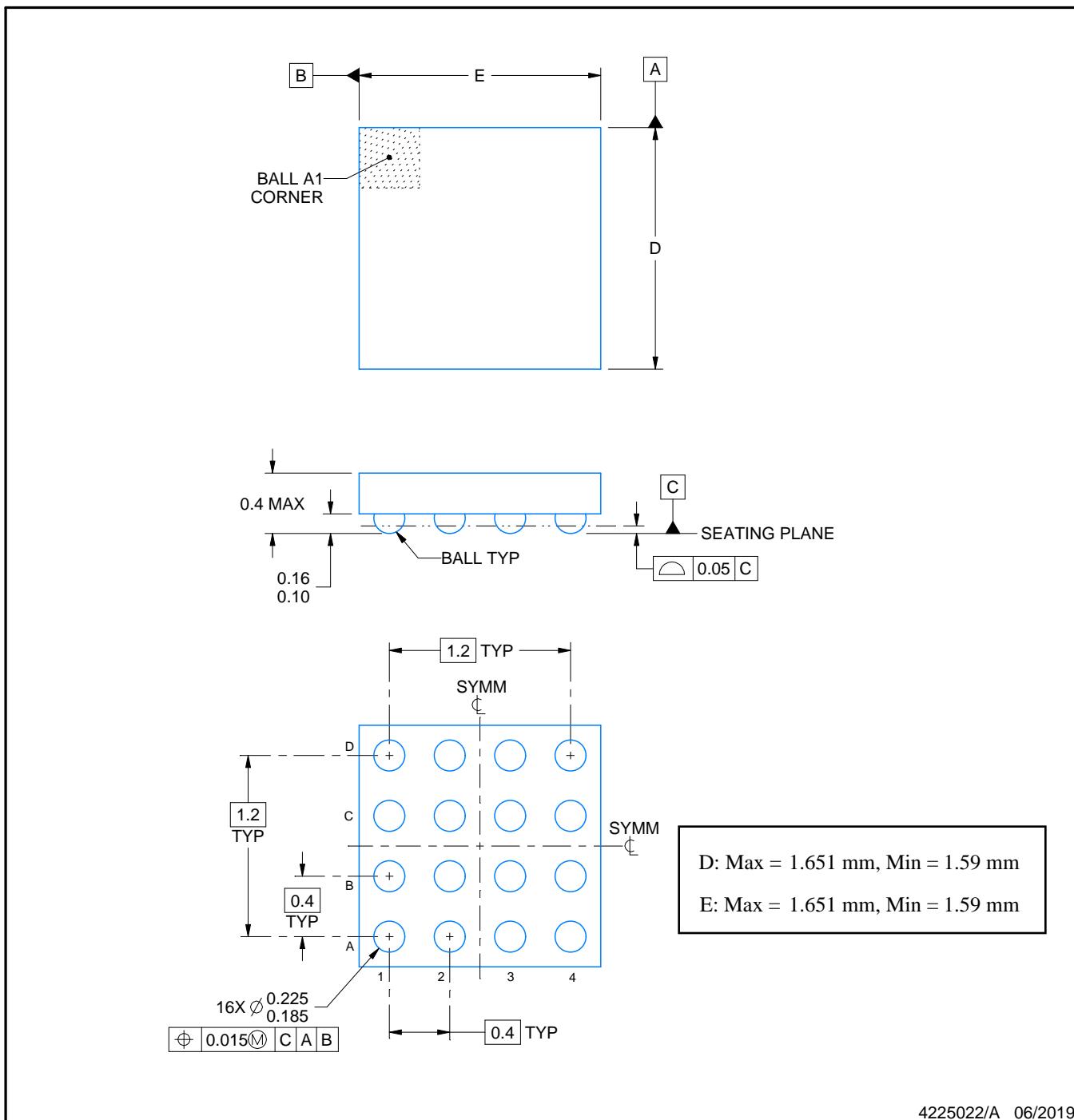

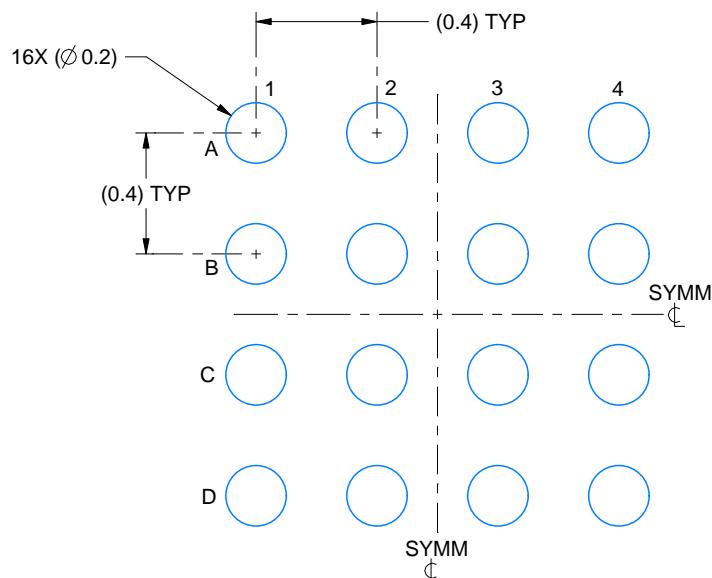

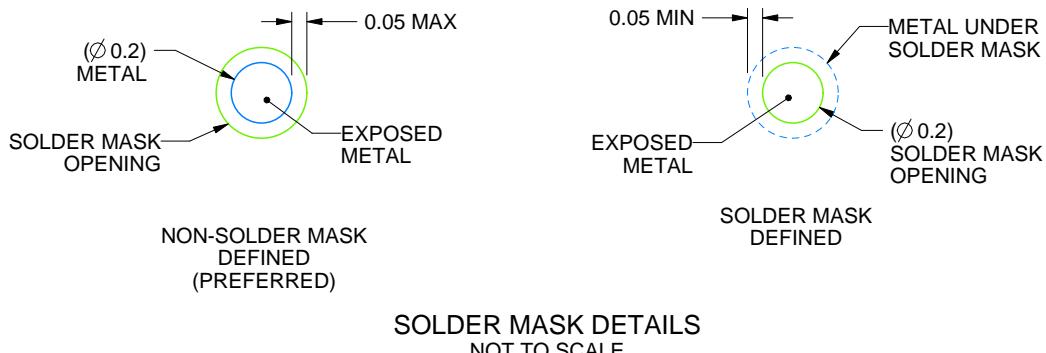

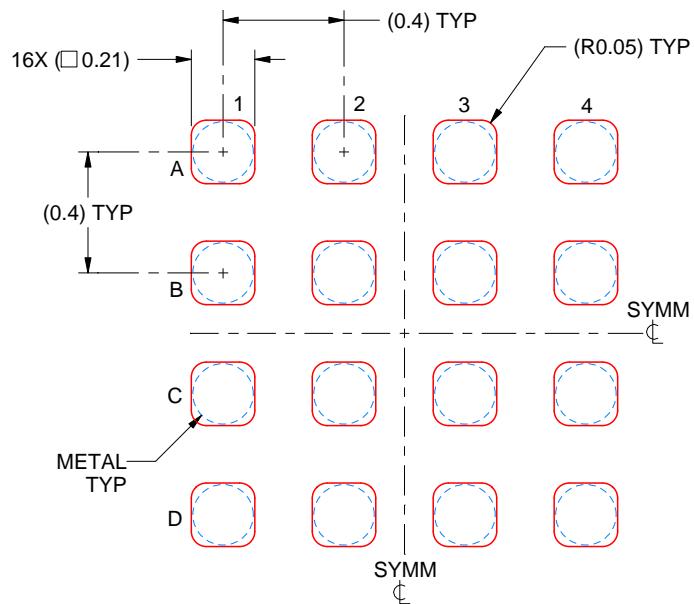

**図 4-2. YBH Package, 16-Pin DSBGA

(Top View)**

**表 4-2. Pin Functions: YBH Package**

| PIN |            | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                 |

|-----|------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| YBH | NAME       |                     |                                                                                                                                             |

| A1  | AIN5/GPIO5 | AI, DI, DO          | Channel 5; configurable as either an analog input (default) or GPIO.                                                                        |

| A2  | DVDD       | P                   | Digital I/O supply voltage. Connect a 1 $\mu$ F capacitor to GND.                                                                           |

| A3  | AVDD       | P                   | Analog supply voltage. Connect a 1 $\mu$ F capacitor to GND.                                                                                |

| A4  | REF        | P                   | Internal reference buffer output; external reference input. Connect a 1 $\mu$ F capacitor to GND.                                           |

| B1  | AIN4/GPIO4 | AI, DI, DO          | Channel 4; configurable as either an analog input (default) or GPIO.                                                                        |

| B2  | AIN6/GPIO6 | AI, DI, DO          | Channel 6; configurable as either an analog input (default) or GPIO.                                                                        |

| B3  | AIN7/GPIO7 | AI, DI, DO          | Channel 7; configurable as either an analog input (default) or GPIO.                                                                        |

| B4  | GND        | P                   | Ground for power supply, all analog and digital signals are referred to this pin.                                                           |

| C1  | AIN3/GPIO3 | AI, DI, DO          | Channel 3; configurable as either an analog input (default) or GPIO.                                                                        |

| C2  | AIN1/GPIO1 | AI, DI, DO          | Channel 1; configurable as either an analog input (default) or GPIO.                                                                        |

| C3  | AIN0/GPIO0 | AI, DI, DO          | Channel 0; configurable as either an analog input (default) or general-purpose input/output (GPIO).                                         |

| C4  | CS         | DI                  | Chip-select input pin; active low.<br>The device takes control of the data bus when CS is low.<br>The SDO pin goes to Hi-Z when CS is high. |

| D1  | AIN2/GPIO2 | AI, DI, DO          | Channel 2; configurable as either an analog input (default) or GPIO.                                                                        |

| D2  | SDI        | DI                  | Serial data input pin for SPI interface.                                                                                                    |

| D3  | SDO        | DO                  | Serial data output pin for SPI interface.                                                                                                   |

| D4  | SCLK       | DI                  | Clock input pin for the SPI interface.                                                                                                      |

(1) AI = analog input, DI = digital input, DO = digital output, P = power supply.

## 5 Specifications

### 5.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                            |  | MIN       | MAX        | UNIT |

|------------------------------------------------------------|--|-----------|------------|------|

| DVDD to GND                                                |  | –0.3      | 5.5        | V    |

| AVDD to GND                                                |  | –0.3      | 5.5        | V    |

| AINx/GPIO <sup>(2)</sup> to GND                            |  | GND – 0.3 | AVDD + 0.3 | V    |

| REF to GND                                                 |  | GND – 0.3 | AVDD + 0.3 | V    |

| Digital inputs (CS, SDI, SCLK) to GND                      |  | GND – 0.3 | 5.5        | V    |

| Input current to any pin except supply pins <sup>(3)</sup> |  | –10       | 10         | mA   |

| Junction temperature, $T_J$                                |  | –40       | 150        | °C   |

| Storage temperature, $T_{stg}$                             |  | –60       | 150        | °C   |

(1) Operation outside the *Absolute Maximum Ratings* may cause permanent device damage. *Absolute Maximum Ratings* do not imply functional operation of the device at these or any other conditions beyond those listed under *Recommended Operating Conditions*. If used outside the *Recommended Operating Conditions* but within the *Absolute Maximum Ratings*, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) AINx/GPIOx refers to AIN0/GPIO0, AIN1/GPIO1, AIN2/GPIO2, AIN3/GPIO3, AIN4/GPIO4, AIN5/GPIO5, AIN6/GPIO6, and AIN7/GPIO7 pins.

(3) Pin current must be limited to 10 mA or less.

### 5.2 ESD Ratings

|             |                         |                                                                                 | VALUE | UNIT |

|-------------|-------------------------|---------------------------------------------------------------------------------|-------|------|

| $V_{(ESD)}$ | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | V    |

|             |                         | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±500  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                | TEST CONDITIONS              |                            | MIN  | TYP           | MAX  | UNIT |

|--------------------------|------------------------------|----------------------------|------|---------------|------|------|

| <b>POWER SUPPLY</b>      |                              |                            |      |               |      |      |

| AVDD                     | Analog power supply          | AVDD to GND                | 3    | 3.3           | 5.5  | V    |

| DVDD                     | Digital power supply         | DVDD to GND                | 1.65 | 3.3           | 5.5  | V    |

| <b>REFERENCE VOLTAGE</b> |                              |                            |      |               |      |      |

| $V_{REF}$                | Reference voltage to the ADC | Internal reference         |      | 2.5           |      | V    |

|                          |                              | External reference         | 2.4  |               | AVDD |      |

| <b>ANALOG INPUTS</b>     |                              |                            |      |               |      |      |

| FSR                      | Full-scale input range       | RANGE = 0b                 | 0    | $V_{REF}$     |      | V    |

|                          |                              | RANGE = 1b                 | 0    | 2 x $V_{REF}$ |      |      |

| $V_{IN}$                 | Absolute input voltage       | AINx <sup>(1)</sup> to GND | –0.1 | AVDD + 0.1    |      | V    |

| <b>TEMPERATURE RANGE</b> |                              |                            |      |               |      |      |

| $T_A$                    | Ambient temperature          |                            | –40  | 25            | 125  | °C   |

(1) AINx refers to analog inputs AIN0, AIN1, AIN2, AIN3, AIN4, AIN5, AIN6, and AIN7.

## 5.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | ADS7067     |            | UNIT |

|-------------------------------|----------------------------------------------|-------------|------------|------|

|                               |                                              | YBH (DSBGA) | RTE (WQFN) |      |

|                               |                                              | 16 PINS     | 16 PINS    |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 80.2        | 46.4       | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 0.4         | 47.2       | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 18.8        | 21.2       | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.2         | 0.8        | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 18.8        | 21.2       | °C/W |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | NA          | 6.5        | °C/W |

- (1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics application report](#).

## 5.5 Electrical Characteristics

at AVDD = 3V to 5.5V, DVDD = 1.65V to 5.5V, V<sub>REF</sub> = 2.5V (internal), and maximum throughput (unless otherwise noted); minimum and maximum values at T<sub>A</sub> = -40°C to +125°C; typical values at T<sub>A</sub> = 25°C

| PARAMETER              |                                                  | TEST CONDITIONS                                                           | MIN    | TYP    | MAX   | UNIT   |

|------------------------|--------------------------------------------------|---------------------------------------------------------------------------|--------|--------|-------|--------|

| <b>ANALOG INPUTS</b>   |                                                  |                                                                           |        |        |       |        |

| C <sub>IN</sub>        | Input capacitance                                | ADC and MUX capacitance                                                   |        | 30     |       | pF     |

| <b>DC PERFORMANCE</b>  |                                                  |                                                                           |        |        |       |        |

|                        | Resolution                                       | No missing codes                                                          |        | 16     |       | Bits   |

| DNL                    | Differential nonlinearity                        |                                                                           | -0.75  | ±0.4   | 0.75  | LSB    |

| INL                    | Integral nonlinearity                            |                                                                           | -4     | ±1     | 4     | LSB    |

| V <sub>(OS)</sub>      | Input offset error                               | Post offset calibration, OSR[2:0] = 7                                     | -9     | ±0.5   | 9     | LSB    |

| dV <sub>OS</sub> /dT   | Input offset thermal drift                       | Post offset calibration, OSR[2:0] = 7                                     |        | ±0.6   |       | ppm/°C |

|                        | Offset error match                               | OSR[2:0] = 7                                                              | -2.75  | 0.5    | 2.75  | LSB    |

| G <sub>E</sub>         | Gain error <sup>(1)</sup>                        | External V <sub>REF</sub> = 2.5 V, OSR[2:0] = 7                           | -0.06  | ±0.01  | 0.06  | %FSR   |

| dG <sub>E</sub> /dT    | Gain error thermal drift                         | External V <sub>REF</sub> = 2.5 V, OSR[2:0] = 7                           |        | ±0.5   |       | ppm/°C |

|                        | Gain error match                                 | OSR[2:0] = 7                                                              | -0.005 | ±0.001 | 0.005 | %FSR   |

| <b>AC PERFORMANCE</b>  |                                                  |                                                                           |        |        |       |        |

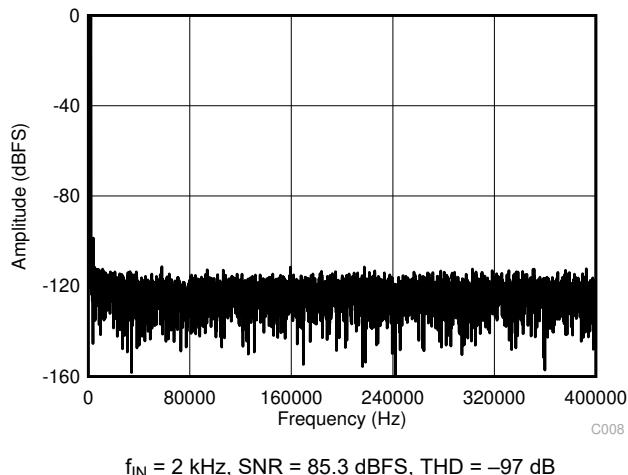

| SINAD                  | Signal-to-noise + distortion ratio               | f <sub>IN</sub> = 2kHz, V <sub>REF</sub> = 2.5V (internal)                | 82.3   | 85.1   |       | dB     |

|                        |                                                  | f <sub>IN</sub> = 2kHz, V <sub>REF</sub> = 5V, AVDD = 5V                  | 86.7   | 89.3   |       |        |

| SNR                    | Signal-to-noise ratio                            | f <sub>IN</sub> = 2kHz, V <sub>REF</sub> = 2.5V (internal)                | 82.4   | 85.3   |       | dB     |

|                        |                                                  | f <sub>IN</sub> = 2kHz, V <sub>REF</sub> = 5V, AVDD = 5V                  | 87.7   | 90     |       |        |

| THD                    | Total harmonic distortion                        | f <sub>IN</sub> = 2kHz                                                    |        | -100   |       | dB     |

| SFDR                   | Spurious-free dynamic range                      | f <sub>IN</sub> = 2kHz                                                    |        | 101    |       | dB     |

|                        | Isolation crosstalk                              | f <sub>IN</sub> = 10kHz                                                   |        | -110   |       | dB     |

| <b>REFERENCE</b>       |                                                  |                                                                           |        |        |       |        |

| V <sub>REF</sub>       | Internal reference output voltage <sup>(3)</sup> | At T <sub>A</sub> = 25°C                                                  | 2.497  | 2.5    | 2.503 | V      |

| dV <sub>REF</sub> /dT  | Internal reference voltage temperature drift     |                                                                           |        | 6      | 19    | ppm/°C |

| C <sub>REF</sub>       | Decoupling capacitor at REF pin                  |                                                                           | 1      |        | 10    | μF     |

| <b>DIGITAL INPUTS</b>  |                                                  |                                                                           |        |        |       |        |

| V <sub>IL</sub>        | Input low logic level                            | For CS, SCLK, and SDI pins                                                | -0.3   | 0.3    | DVDD  | V      |

|                        |                                                  | For GPIO <sub>X</sub> <sup>(2)</sup> pins                                 | -0.3   | 0.3    | AVDD  |        |

| V <sub>IH</sub>        | Input high logic level                           | For CS, SCLK, and SDI pins                                                | 0.7    | DVDD   |       | V      |

|                        |                                                  | For GPIO <sub>X</sub> pins                                                | 0.7    | AVDD   |       |        |

| <b>DIGITAL OUTPUTS</b> |                                                  |                                                                           |        |        |       |        |

| V <sub>OL</sub>        | Output low logic level                           | For SDO pin, I <sub>OL</sub> = 500μA sink                                 | 0      | 0.2    | DVDD  | V      |

|                        |                                                  | For GPIO <sub>X</sub> <sup>(2)</sup> pins, I <sub>OL</sub> = 500μA sink   | 0      | 0.2    | AVDD  |        |

| V <sub>OH</sub>        | Output high logic level                          | For SDO pin, I <sub>OH</sub> = 500μA source                               | 0.8    | DVDD   |       | V      |

|                        |                                                  | For GPIO <sub>X</sub> <sup>(2)</sup> pins, I <sub>OH</sub> = 500μA source | 0.8    | AVDD   |       |        |

| <b>POWER SUPPLY</b>    |                                                  |                                                                           |        |        |       |        |

| I <sub>AVDD</sub>      | Analog supply current                            | AVDD = 3.3V, external reference                                           | 1      | 2      |       | mA     |

|                        |                                                  | AVDD = 3.3V, internal reference                                           | 1.5    | 2.8    |       |        |

|                        |                                                  | No conversion, external reference                                         | 250    |        |       | μA     |

|                        |                                                  | No conversion, internal reference                                         | 800    |        |       |        |

| I <sub>DVDD</sub>      | Digital supply current                           | At full-speed                                                             | 720    |        |       | μA     |

|                        |                                                  | No conversion                                                             | 32     |        |       |        |

(1) These specifications include full temperature range variation but not the error contribution from internal reference.

(2) GPIO<sub>X</sub> refers to GPIO0, GPIO1, GPIO2, GPIO3, GPIO4, GPIO5, GPIO6, and GPIO7 pins.

(3) Does not include the variation in voltage resulting from solder shift effects.

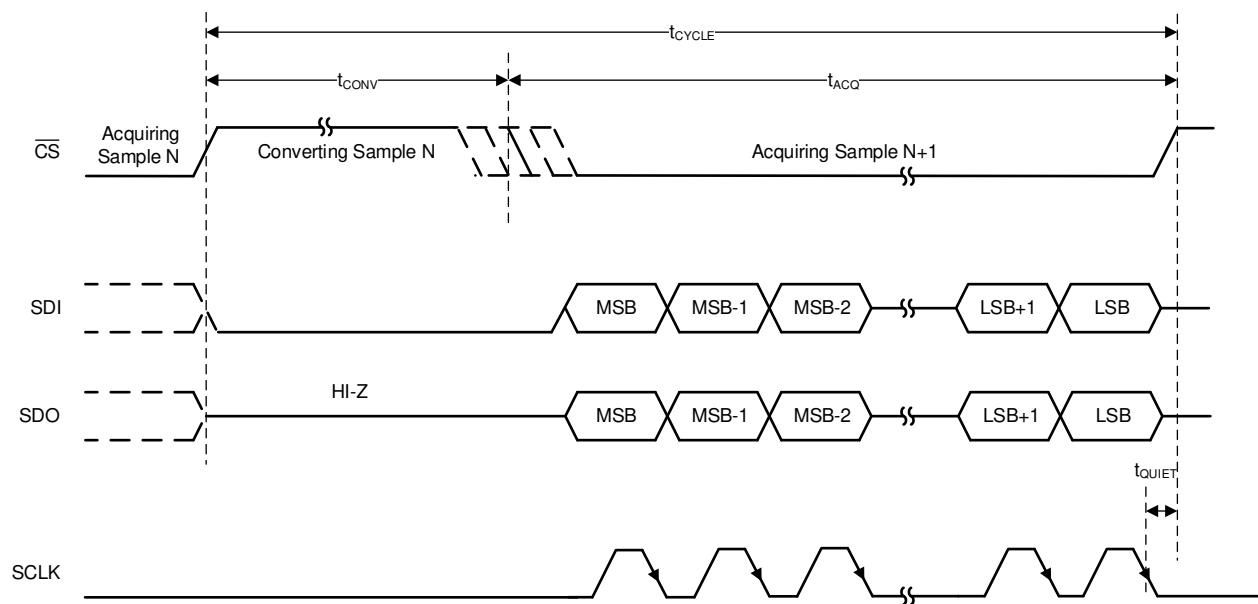

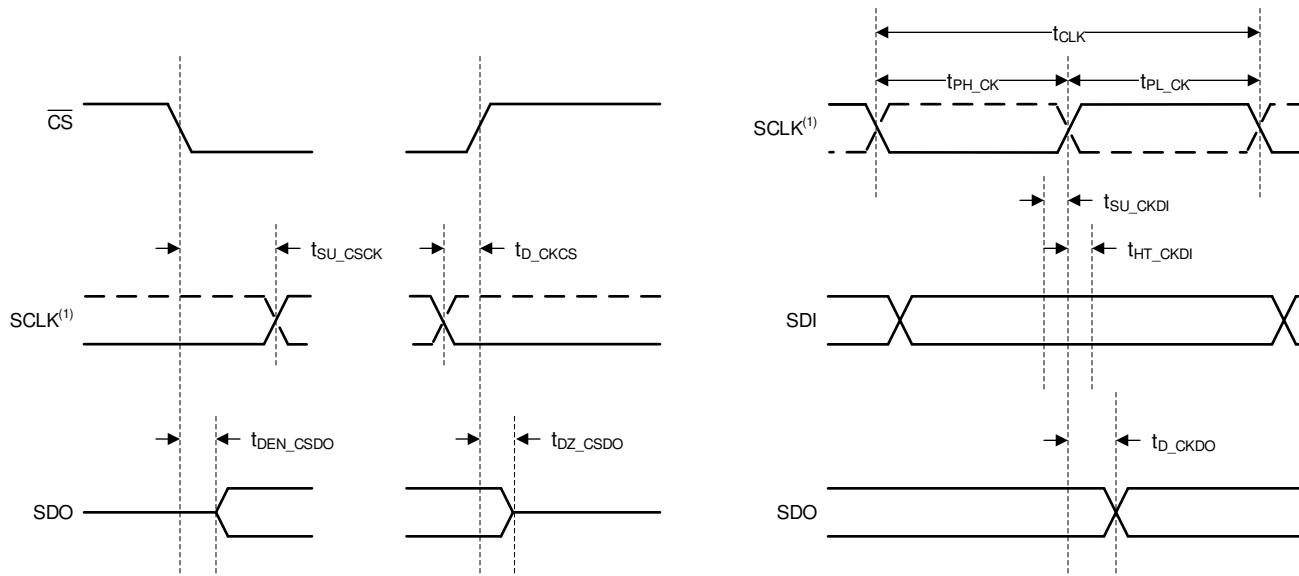

## 5.6 Timing Requirements

at AVDD = 3 V to 5 V, DVDD = 1.65 V to 5.5 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ ; typical values at  $T_A = 25^\circ\text{C}$ .

|                              |                                                       | MIN                   | MAX   | UNIT                  |

|------------------------------|-------------------------------------------------------|-----------------------|-------|-----------------------|

| <b>CONVERSION CYCLE</b>      |                                                       |                       |       |                       |

| $f_{\text{CYCLE}}$           | Sampling frequency                                    |                       | 800   | kSPS                  |

| $t_{\text{CYCLE}}$           | ADC cycle-time period                                 | 1/ $f_{\text{CYCLE}}$ |       | s                     |

| $t_{\text{QUIET}}$           | Quiet acquisition time                                |                       | 20    | ns                    |

| $t_{\text{ACQ}}$             | Acquisition time                                      |                       | 300   | ns                    |

| $t_{\text{WH\_CSZ}}$         | Pulse duration: CS high                               |                       | 220   | ns                    |

| $t_{\text{WL\_CSZ}}$         | Pulse duration: CS low                                |                       | 210   | ns                    |

| <b>SPI INTERFACE TIMINGS</b> |                                                       |                       |       |                       |

| $f_{\text{CLK}}$             | Maximum SCLK frequency                                |                       | 60    | MHz                   |

| $t_{\text{CLK}}$             | Minimum SCLK time period                              |                       | 16.67 | ns                    |

| $t_{\text{PH\_CK}}$          | SCLK high time                                        |                       | 0.45  | 0.55 $t_{\text{CLK}}$ |

| $t_{\text{PL\_CK}}$          | SCLK low time                                         |                       | 0.45  | 0.55 $t_{\text{CLK}}$ |

| $t_{\text{SU\_CSCK}}$        | Setup time: CS falling to the first SCLK capture edge |                       | 15    | ns                    |

| $t_{\text{SU\_CKDI}}$        | Setup time: SDI data valid to the SCLK capture edge   |                       | 6.4   | ns                    |

| $t_{\text{HT\_CKDI}}$        | Hold time: SCLK capture edge to data valid on SDI     |                       | 4     | ns                    |

| $t_{\text{D\_CKCS}}$         | Delay time: last SCLK falling to CS rising            |                       | 0.8   | ns                    |

## 5.7 Switching Characteristics

at AVDD = 3 V to 5.5 V, DVDD = 1.65 V to 5.5 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ ; typical values at  $T_A = 25^\circ\text{C}$ .

| PARAMETER                    | TEST CONDITIONS                                                  | MIN             | MAX | UNIT |

|------------------------------|------------------------------------------------------------------|-----------------|-----|------|

| <b>CONVERSION CYCLE</b>      |                                                                  |                 |     |      |

| $t_{\text{CONV}}$            | ADC conversion time                                              |                 | 950 | ns   |

| <b>RESET</b>                 |                                                                  |                 |     |      |

| $t_{\text{PU}}$              | Power-up time for device                                         | AVDD $\geq$ 3 V |     | 5 ms |

| $t_{\text{RST}}$             | Delay time; RST bit = 1b to device reset complete <sup>(1)</sup> |                 |     | 5 ms |

| <b>SPI INTERFACE TIMINGS</b> |                                                                  |                 |     |      |

| $t_{\text{DEN\_CSDO}}$       | Delay time: CS falling to data enable                            |                 | 22  | ns   |

| $t_{\text{DZ\_CSDO}}$        | Delay time: CS rising to SDO going Hi-Z                          |                 | 50  | ns   |

| $t_{\text{D\_CKDO}}$         | Delay time: SCLK launch edge to (next) data valid on SDO         |                 | 16  | ns   |

(1) RST bit is automatically reset to 0b after  $t_{\text{RST}}$ .

## 5.8 Timing Diagrams

図 5-1. Conversion Cycle Timing

図 5-2. SPI Interface Timing

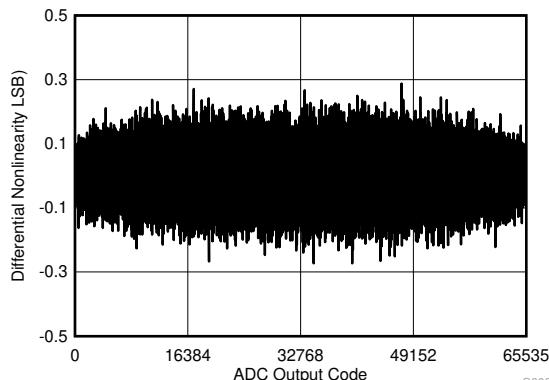

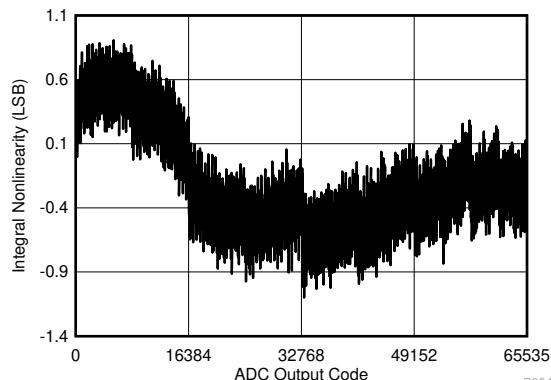

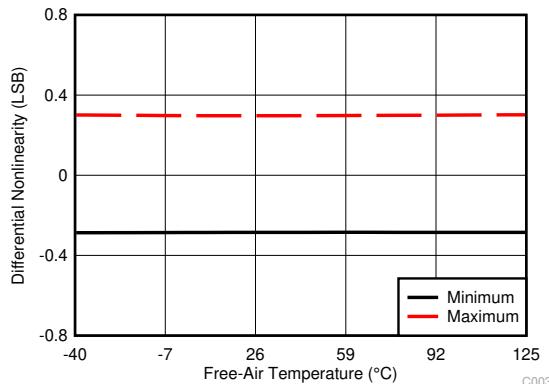

## 5.9 Typical Characteristics

at  $T_A = 25^\circ\text{C}$ ,  $\text{AVDD} = 5\text{ V}$ ,  $\text{DVDD} = 1.65\text{ V}$  to  $5.5\text{ V}$ , and maximum throughput (unless otherwise noted)

図 5-3. Typical DNL

図 5-4. Typical INL

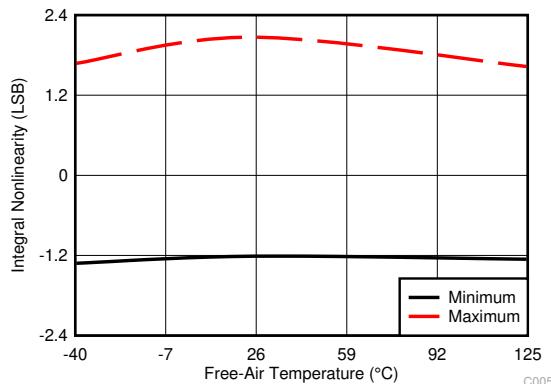

図 5-5. DNL vs Temperature

図 5-6. INL vs Temperature

図 5-7. DNL vs External Reference Voltage

図 5-8. INL vs External Reference Voltage

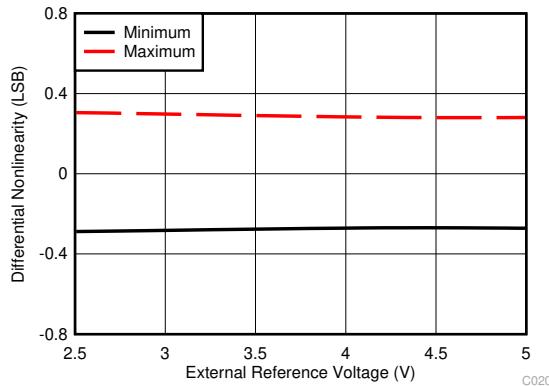

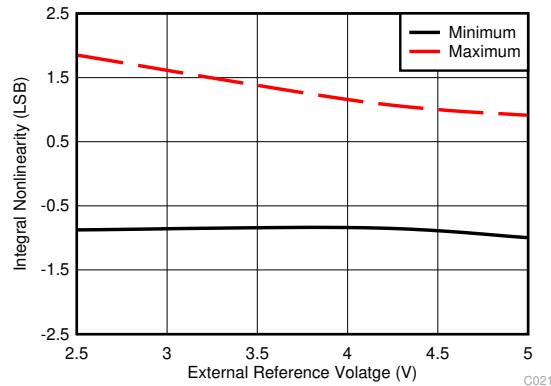

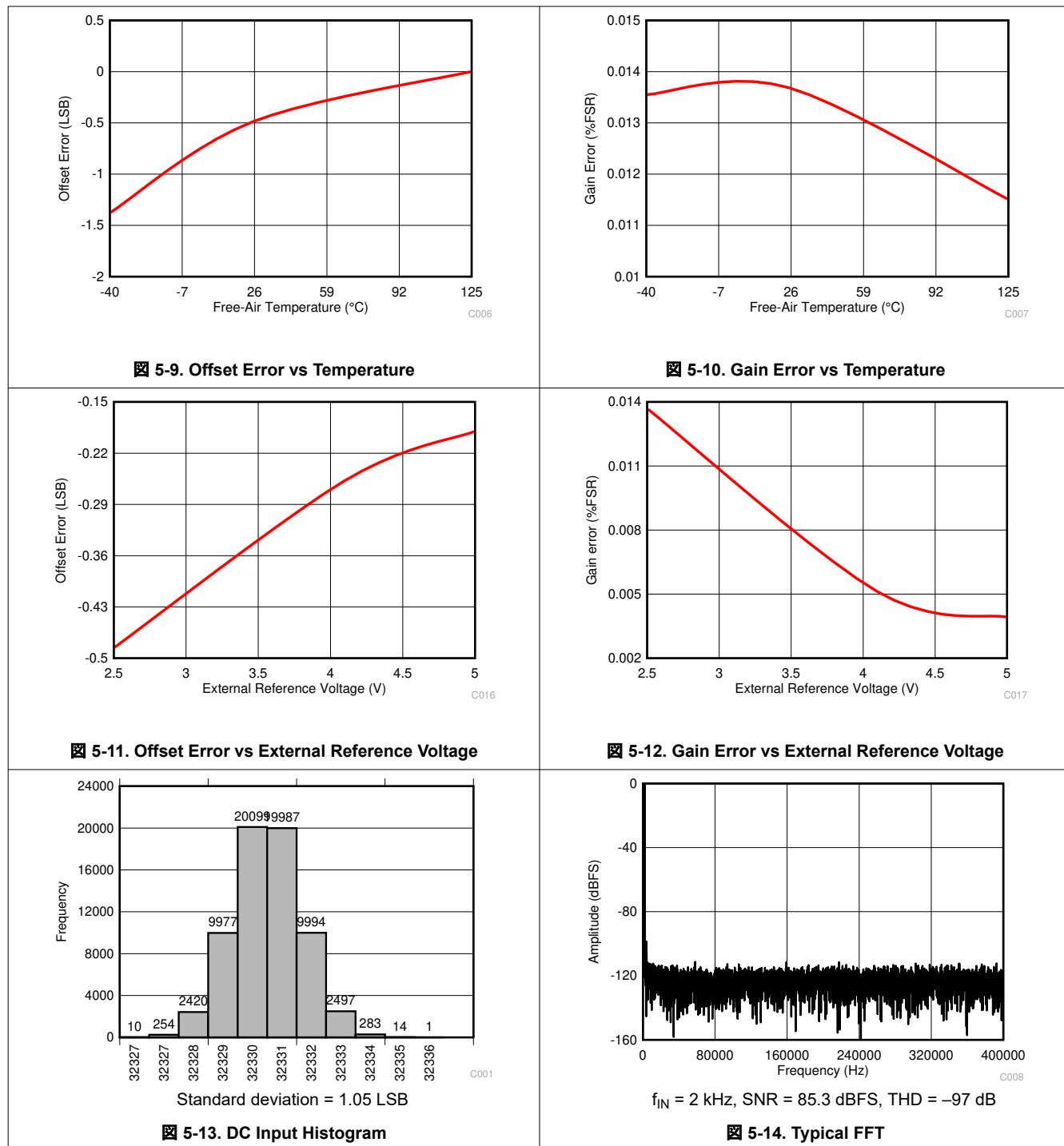

## 5.9 Typical Characteristics (continued)

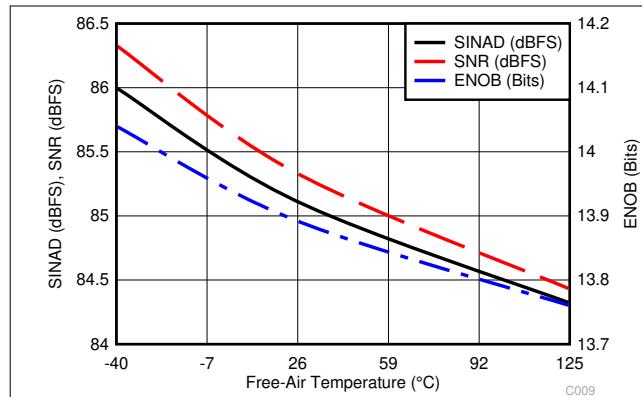

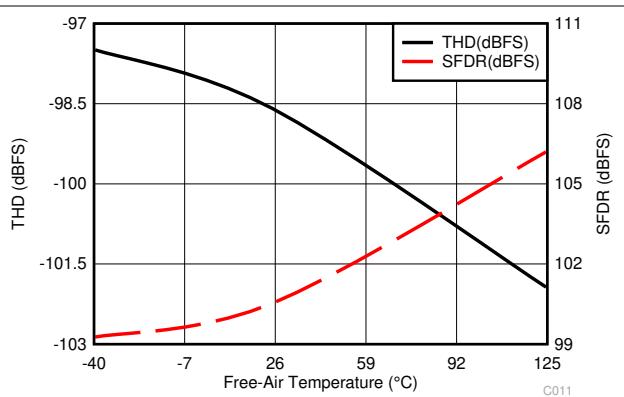

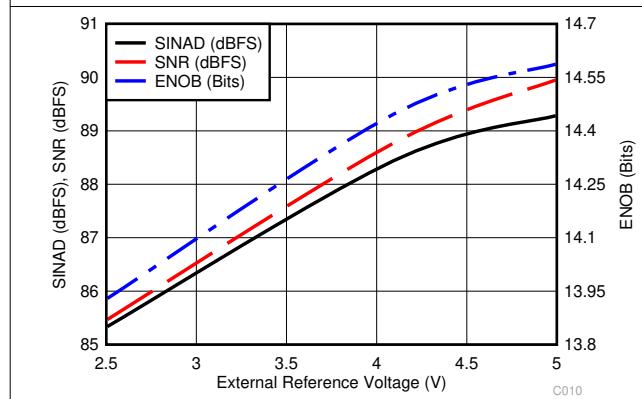

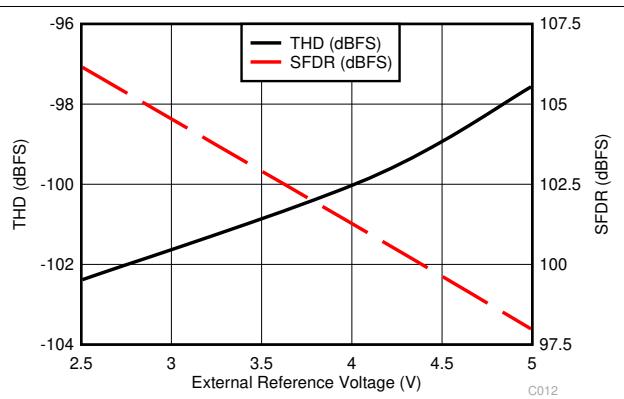

at  $T_A = 25^\circ\text{C}$ ,  $\text{AVDD} = 5\text{ V}$ ,  $\text{DVDD} = 1.65\text{ V}$  to  $5.5\text{ V}$ , and maximum throughput (unless otherwise noted)

## 5.9 Typical Characteristics (continued)

at  $T_A = 25^\circ\text{C}$ ,  $\text{AVDD} = 5\text{ V}$ ,  $\text{DVDD} = 1.65\text{ V}$  to  $5.5\text{ V}$ , and maximum throughput (unless otherwise noted)

图 5-15. Noise Performance vs Temperature

图 5-16. Distortion Performance vs Temperature

图 5-17. Noise Performance vs External Reference Voltage

图 5-18. Distortion Performance vs External Reference Voltage

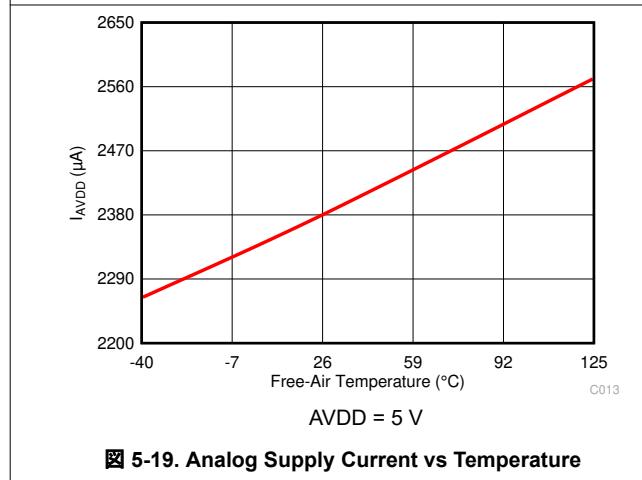

图 5-19. Analog Supply Current vs Temperature

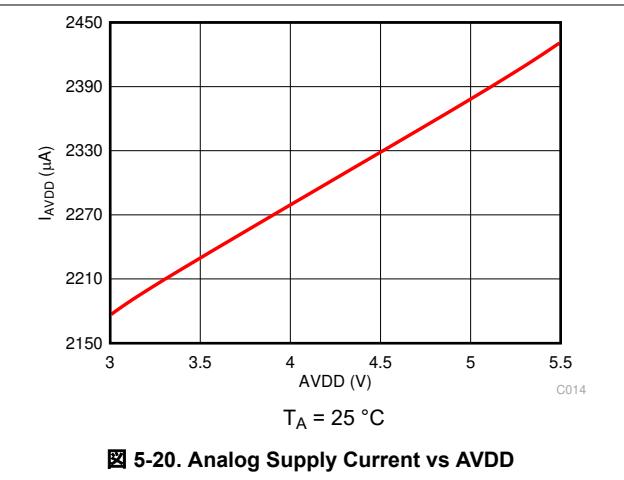

图 5-20. Analog Supply Current vs AVDD

## 5.9 Typical Characteristics (continued)

at  $T_A = 25^\circ\text{C}$ ,  $\text{AVDD} = 5\text{ V}$ ,  $\text{DVDD} = 1.65\text{ V}$  to  $5.5\text{ V}$ , and maximum throughput (unless otherwise noted)

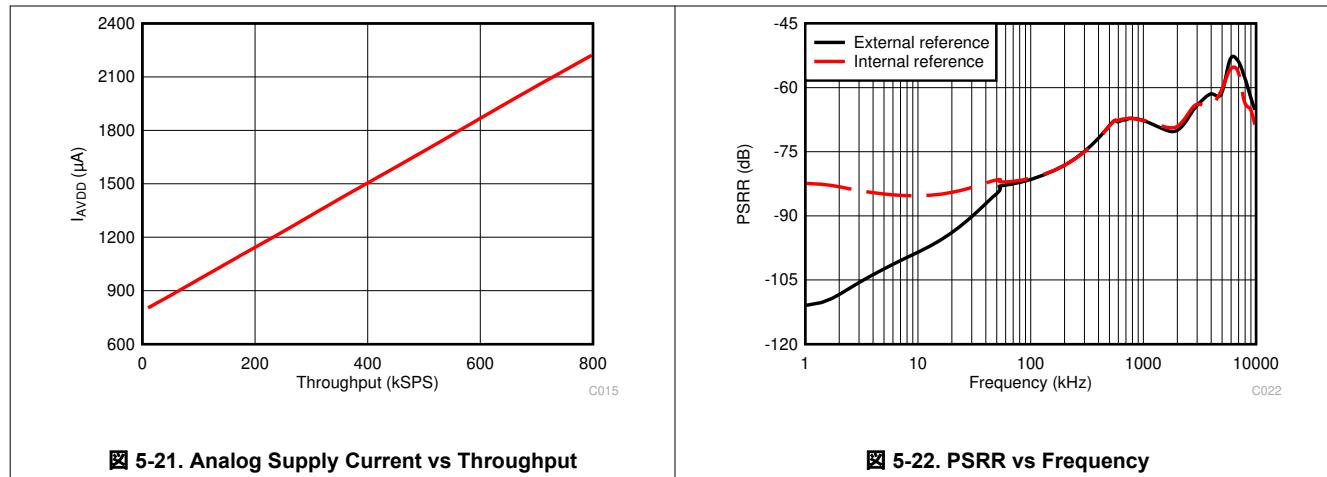

図 5-21. Analog Supply Current vs Throughput

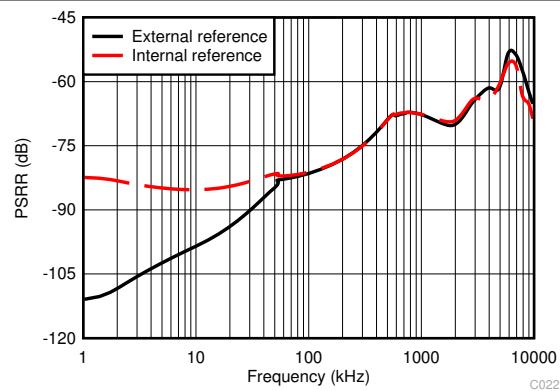

図 5-22. PSRR vs Frequency

## 6 Detailed Description

### 6.1 Overview

The ADS7067 is a 16-bit, successive approximation register (SAR) analog-to-digital converter (ADC) with an analog multiplexer. This device integrates a reference, reference buffer, low-dropout regulator (LDO), and features high performance at full throughput and low-power consumption.

The ADS7067 supports unipolar, single-ended analog input signals. The internal reference generates a low-drift, buffered, 2.5-V reference output. The device uses an internal clock to perform conversions. At the end of the conversion process, the device enters an acquisition phase.

### 6.2 Functional Block Diagram

## 6.3 Feature Description

### 6.3.1 Analog Input and Multiplexer

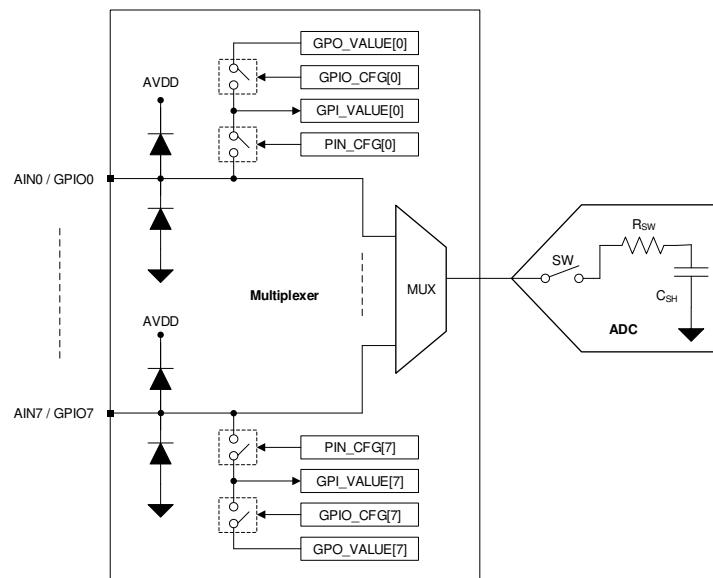

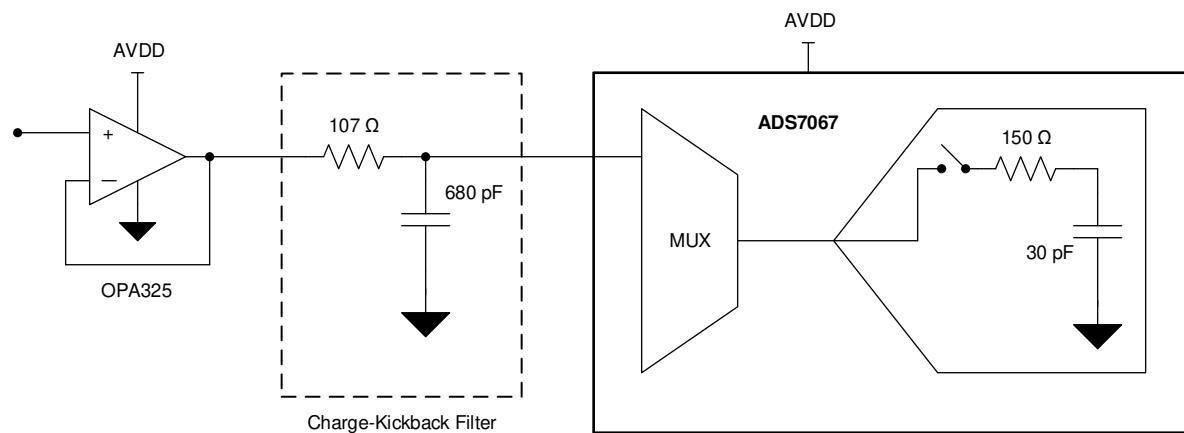

The eight channels of the multiplexer can be independently configured as ADC inputs or general-purpose inputs/outputs (GPIOs). As shown in [图 6-1](#), each input pin has ESD protection diodes to AVDD and GND. On power-up or after device reset, all eight channels of the multiplexer are configured as analog inputs.

**图 6-1. Analog Inputs, GPIOs, and ADC Connections**

[图 6-1](#) shows an equivalent circuit for the pins configured as analog inputs. The ADC sampling switch is represented by an ideal switch (SW) in series with a resistor ( $R_{SW}$ , typically  $150\ \Omega$ ) and a sampling capacitor ( $C_{SH}$ , typically  $30\ pF$ ). During acquisition, the SW switch is closed to allow the signal on the selected analog input channel to charge the internal sampling capacitor. During conversion, the SW switch is opened to disconnect the analog input channel from the sampling capacitor.

The multiplexer channels can be configured as GPIOs in the PIN\_CFG register. On power-up, all channels of the multiplexer are configured as analog inputs. The direction of a GPIO, input or output, can be set in the GPIO\_CFG register. The logic level of channels configured as digital inputs can be read from the GPI\_VALUE register. The digital outputs can be accessed by writing to the GPO\_VALUE register. The digital outputs can be configured as open-drain or push-pull in the GPO\_DRIVE\_CFG register.

### 6.3.2 Reference

The ADS7067 has a precision, low-drift voltage reference internal to the device.

#### 6.3.2.1 External Reference

External reference is the default configuration on power-up or after device reset. An external reference voltage source can be connected to the REF pin with an appropriate decoupling capacitor placed between the REF and GND pins. Best SNR is achieved with a 5-V external reference because the internal reference is limited to 2.5 V. For improved thermal drift performance, a reference from the REF60xx family ([REF6025](#), [REF6030](#), [REF6033](#), [REF6041](#), [REF6045](#), or [REF6050](#)) is recommended.

#### 6.3.2.2 Internal Reference

The device features an internal reference source with a nominal output value of 2.5 V. On power-up, the internal reference is disabled by default. To enable the internal reference, set EN\_REF = 1b in the GENERAL\_CFG register. A minimum 1- $\mu$ F decoupling capacitor is recommended to be placed between the REF and GND pins.

The capacitor must be placed as close to the REF pin as possible. The REF pin has ESD protection diodes connected to the AVDD and GND pins.

### 6.3.3 ADC Transfer Function

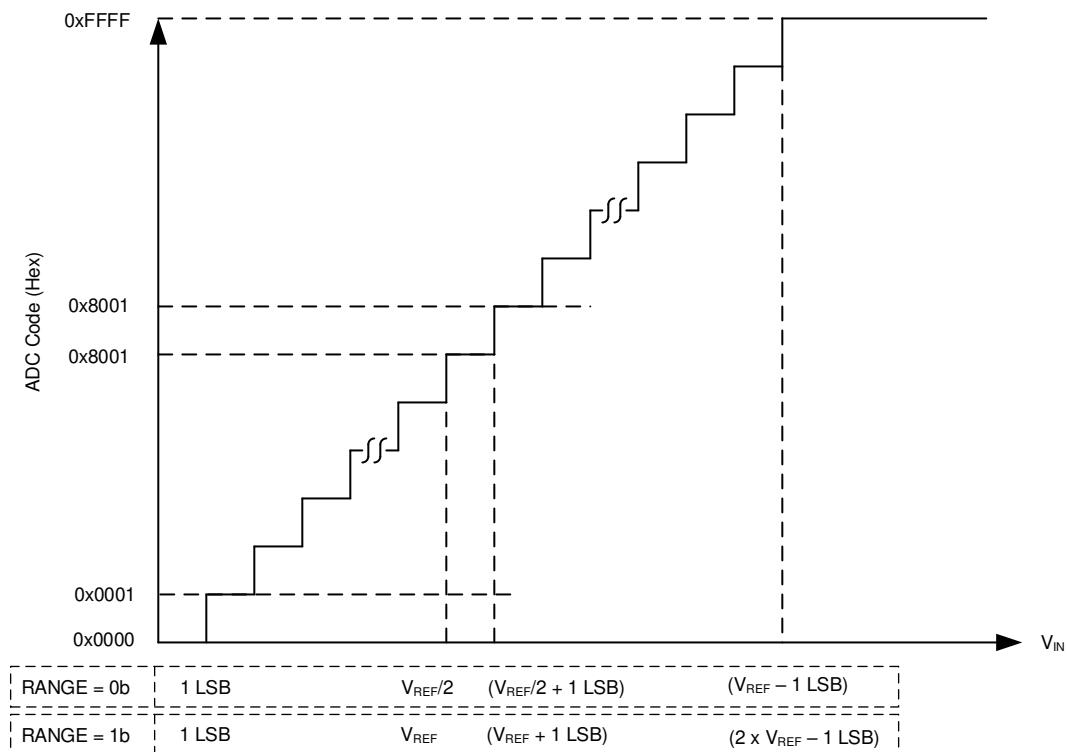

The ADC output is in straight binary format. The full-scale input range (FSR) of the ADC is determined by the RANGE bit. On power-up, the FSR is 0 V to  $V_{REF}$ . When using the  $2 \times V_{REF}$  mode (RANGE = 1b), the ADC can measure analog inputs up to two times the voltage reference. 式 1 can be used to compute the ADC resolution:

$$1 \text{ LSB} = \text{FSR} / 2^N \quad (1)$$

where:

- FSR = Full-scale input range of the ADC

- N = 16

図 6-2 and 表 6-1 show the ideal transfer characteristics for this device.

図 6-2. Ideal Transfer Characteristics

表 6-1. Transfer Characteristics

| INPUT VOLTAGE                                                       |                                                         | CODE               | IDEAL OUTPUT CODE |

|---------------------------------------------------------------------|---------------------------------------------------------|--------------------|-------------------|

| RANGE = 0b                                                          | RANGE = 1b                                              |                    |                   |

| ≤ 1 LSB                                                             | ≤ 1 LSB                                                 | Zero               | 0000              |

| 1 LSB to 2 LSBs                                                     | 1 LSB to 2 LSBs                                         | Zero + 1           | 0001              |

| $(V_{REF} / 2)$ to $(V_{REF} / 2) + 1 \text{ LSB}$                  | $V_{REF}$ to $V_{REF} + 1 \text{ LSB}$                  | Mid-scale code     | 8000              |

| $(V_{REF} / 2) + 1 \text{ LSB}$ to $(V_{REF} / 2) + 2 \text{ LSBs}$ | $V_{REF} + 1 \text{ LSB}$ to $V_{REF} + 2 \text{ LSBs}$ | Mid-scale code + 1 | 8001              |

| ≥ $V_{REF} - 1 \text{ LSB}$                                         | ≥ $2 \times V_{REF} - 1 \text{ LSB}$                    | Full-scale code    | FFFF              |

### 6.3.4 ADC Offset Calibration

The variation in ADC offset error resulting from changes in temperature or reference voltage can be calibrated by setting the CAL bit in the GENERAL\_CFG register. The CAL bit is reset to 0 after calibration. The host can poll the CAL bit to check the ADC offset calibration completion status.

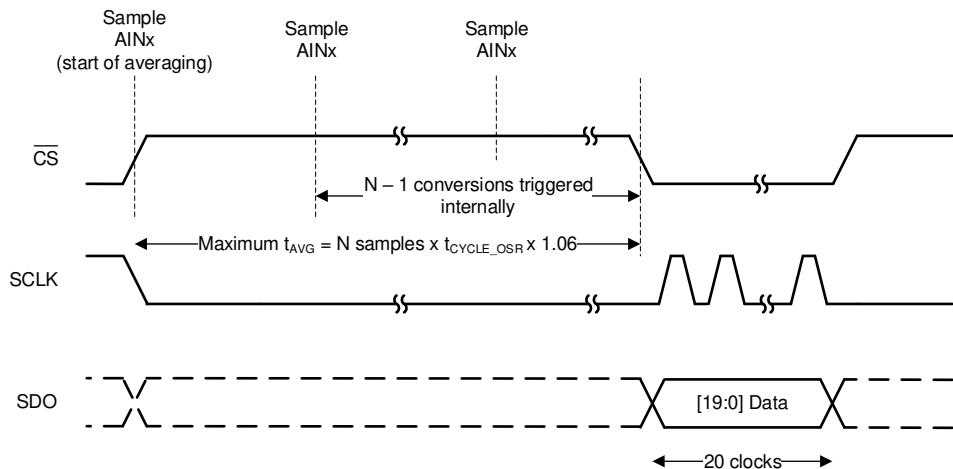

### 6.3.5 Programmable Averaging Filters

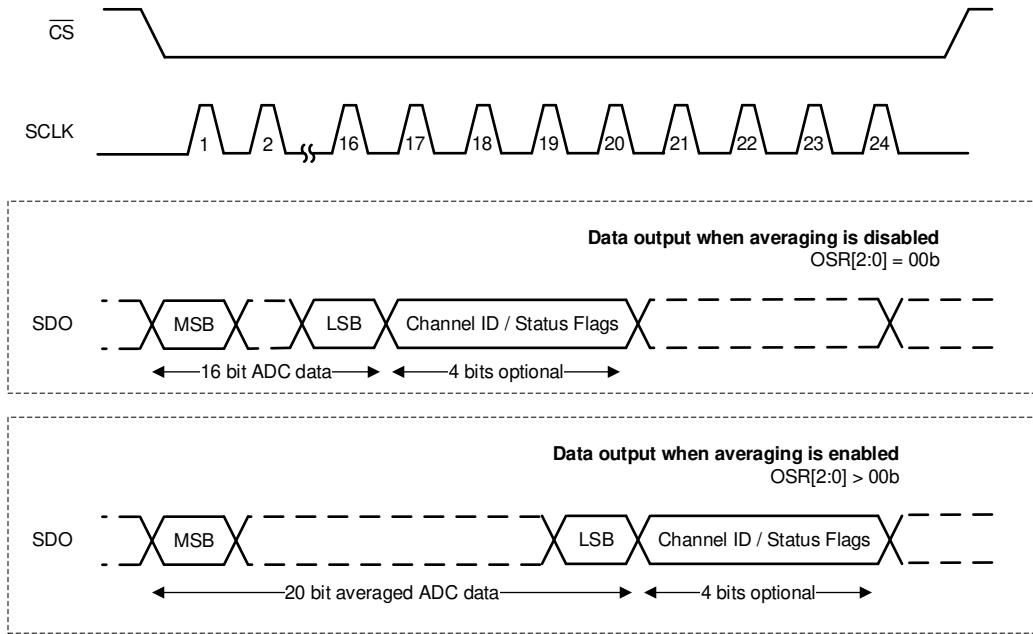

The ADS7067 features a programmable averaging filter that can be used to average analog input samples to output a higher resolution measurement. The averaging filter can be enabled by programming the OSR[2:0] bits in the OSR\_CFG register to the averaging factor desired. The averaging configuration is common to all analog input channels. As shown in [图 6-3](#), the output of the averaging filter is 20 bits long. In manual mode and auto-sequence mode of conversion, only the first conversion for the selected analog input channel must be initiated by the host, as shown in [图 6-3](#); any remaining conversions are generated internally. The time ( $t_{AVG}$ ) required to complete the averaging operation is determined by the sampling speed and number of samples to be averaged; see the [Oscillator and Timing Control](#) section for more details. After completion, the averaged 20-bit result, as shown in [图 6-3](#), can be read-out. For information on the programmable averaging filters and performance results see the [Resolution-Boosting ADS7066 Using Programmable Averaging Filter](#) application report.

In autonomous mode of operation, samples from analog input channels that are enabled in the AUTO\_SEQ\_CH\_SEL register are averaged sequentially.

**图 6-3. Averaged Output Data**

### 6.3.6 CRC on Data Interface

The cyclic redundancy check (CRC) is an error checking code that detects communication errors to and from the host. CRC is the division remainder of the data payload bytes by a fixed polynomial. The data payload is two or three bytes, depending on the output data format; see the [Output Data Format](#) section for details on output data format. The CRC mode is optional and is enabled by the CRC\_EN bit in the GENERAL\_CFG register.

The CRC data byte is the 8-bit remainder of the bitwise exclusive-OR (XOR) operation of the argument by a CRC polynomial. The CRC polynomial is based on the CRC-8-CCITT:  $X^8 + X^2 + X^1 + 1$ . The nine binary polynomial coefficients are: 100000111. The CRC calculation is preset with 1 data values. For more details about the CRC implementation and for a software example, see the [Implementation of CRC for ADS7066](#) application report.

The host must compute and append the appropriate CRC to the command string in the same SPI frame (see the [Register Read/Write Operation](#) section). The ADC also computes the expected CRC corresponding to the payload received from the host and compares the calculated CRC code to the CRC received from the host. The CRC received from the host and the CRC calculated by the ADC over the received payload are compared to check for an exact match.

- If the calculated CRC and received CRC match then the data payload received from the host is valid.

- If the calculated CRC and received CRC do not match then the data payload received from the host is not valid and the command does not execute. The CRCERR\_IN flag is set to 1b. ADC conversion data read and register read processes, with a valid CRC from the host, are still supported. The error condition can be detected, as listed in [表 6-2](#), by either status flags or by a register read. Further register writes to the device are blocked until the CRCERR\_IN flag is cleared to 0b. Register write operations, with a valid CRC from the host, to the SYSTEM\_STATUS (address = 0x00) and GENERAL\_CFG (address = 0x01) registers are still supported.

**表 6-2. Configuring Notifications When a CRC Error is Detected**

| CRC ERROR NOTIFICATION | CONFIGURATION       | DESCRIPTION                                                                                                                                |

|------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Status flags           | APPEND_STATUS = 10b | 4-bit status flags, containing the CRCERR_IN bit appended to the ADC data; see the <a href="#">Output Data Format</a> section for details. |

| Register read          | —                   | Read the CRCERR_IN bit to check if a CRC error was detected.                                                                               |

For a conversion data read or register data read, the ADC responds with a CRC that is computed over the requested data payload bytes. The response data payload is one, two, or three bytes depending on the data operation (see the [Output CRC \(Device to Host\)](#) section).

### 6.3.7 Oscillator and Timing Control

The device uses an internal oscillator for conversion. When using the averaging module, the host initiates the first conversion and subsequent conversions are generated internally by the device. When the device generates the start of a conversion, the sampling rate can be controlled as described in [表 6-3](#) by the OSC\_SEL and CLK\_DIV[3:0] register fields.

The conversion time of the device, given by  $t_{CONV}$  in the *Switching Characteristics* table in the [Specifications](#) section, is independent of the OSC\_SEL and CLK\_DIV[3:0] configuration.

**表 6-3. Configuring the Sampling Rate for Internal Conversion Start Control**

| CLK_DIV[3:0] | OSC_SEL = 0                                 |                                   | OSC_SEL = 1                                 |                                   |

|--------------|---------------------------------------------|-----------------------------------|---------------------------------------------|-----------------------------------|

|              | SAMPLING FREQUENCY, $f_{CYCLE\_OSR}$ (kSPS) | CYCLE TIME, $t_{CYCLE\_OSR}$ (μs) | SAMPLING FREQUENCY, $f_{CYCLE\_OSR}$ (kSPS) | CYCLE TIME, $t_{CYCLE\_OSR}$ (μs) |

| 0000b        | Reserved. Do not use.                       | Reserved. Do not use.             | 31.25                                       | 32                                |

| 0001b        | 666.67                                      | 1.5                               | 20.83                                       | 48                                |

| 0010b        | 500                                         | 2                                 | 15.63                                       | 64                                |

| 0011b        | 333.33                                      | 3                                 | 10.42                                       | 96                                |

| 0100b        | 250                                         | 4                                 | 7.81                                        | 128                               |

| 0101b        | 166.7                                       | 6                                 | 5.21                                        | 192                               |

| 0110b        | 125                                         | 8                                 | 3.91                                        | 256                               |

| 0111b        | 83                                          | 12                                | 2.60                                        | 384                               |

| 1000b        | 62.5                                        | 16                                | 1.95                                        | 512                               |

| 1001b        | 41.7                                        | 24                                | 1.3                                         | 768                               |

| 1010b        | 31.3                                        | 32                                | 0.98                                        | 1024                              |

| 1011b        | 20.8                                        | 48                                | 0.65                                        | 1536                              |

| 1100b        | 15.6                                        | 64                                | 0.49                                        | 2048                              |

| 1101b        | 10.4                                        | 96                                | 0.33                                        | 3072                              |

### 6.3.8 Diagnostic Modes

The ADS7067 features a programmable test voltage generation circuit that can be used for ADC diagnostics.

#### 6.3.8.1 Bit-Walk Test Mode

To enable write access to the configuration registers for diagnostics, write 0x96 in the DIAGNOSTICS\_KEY register. To enable bit-walk test mode, configure BITWALK\_EN = 1b. In the bit-walk test mode (see [図 6-1](#)), the sampling switch (SW) remains open and the test voltage is applied on the sampling capacitor ( $C_{SH}$ ) during the acquisition phase of the ADC. In diagnostic mode, the conversion process of the ADC remains the same as normal device operation. The ADC starts the conversion phase on the rising edge of  $\overline{CS}$  and outputs the code corresponding to the sampled test voltage. The output code of the ADC is expected to be proportional to the test voltage, as shown in [式 2](#), after adjusting for DC errors (such as INL, gain error, offset error, and thermal drift of offset and gain errors).

$$\text{Output code} = \left( \frac{\text{Test voltage}}{V_{REF}} \times 2^{16} \right) \pm \text{TUE} \quad (2)$$

where

- TUE = Total unadjusted error, given by the root sum square of the offset error, gain error, and INL

The test voltage is generated by a DAC configured by the BIT\_SAMPLE\_MSB and BIT\_SAMPLE\_LSB registers. Because the test voltage is derived from the ADC reference, as given by [式 3](#), this diagnostic mode is not sensitive to variations in reference voltage.

$$\text{Test voltage} = \frac{V_{REF}}{\text{BIT\_SAMPLE}[15:0]} \pm \text{TUE} \quad (3)$$

To resume conversion of the ADC input signal, configure BITWALK\_EN = 0b.

#### 6.3.8.2 Fixed Voltage Test Mode

For diagnostics, the ADS7067 features a fixed 1.8 V (typical) test voltage which can be internally connected to AIN6. To connect AIN6 to the internal test voltage, set VTEST\_EN = 1b. When using the fixed voltage test mode, AIN6 pin must be left floating and should not be connected to any external circuit.

If bit-walk test mode is enabled (that is, BITWALK\_EN = 1b), enabling the fixed voltage test mode will connect AIN6 to the test voltage but the conversion result would be according to bit-walk test mode configuration.

### 6.3.9 Output Data Format

[図 6-4](#) illustrates that the output data payload consists of a combination of the conversion result, data bits from averaging filters, status flags, and channel ID. The conversion result is MSB aligned. If averaging is enabled, the output data from the ADC are 20 bits long, otherwise the data are 16 bits long. Optionally, the 4-bit channel ID or status flags can be appended at the end of the output data by configuring the APPEND\_STATUS[1:0] fields.

图 6-4. SPI Frames for Reading Data

#### 6.3.9.1 Status Flags

Status flags can be appended to the ADC output by setting APPEND\_STATUS = 10b. The status flag is appended only to frames where ADC data are being read. Status flags are not appended to data corresponding to a register read operation or when FIX\_PAT = 1b. The 4-bit status flag field is constructed as follows:

Status flag[3:0] = { 1, VTEST\_MODE, CRCERR\_IN, DIAG\_MODE }

where:

- VTEST\_MODE: This flag is set if the current data frame corresponds to fixed voltage test mode (see the [Fixed Voltage Test Mode](#) section).

- CRCERR\_IN: This flag indicates the status of the CRC verification of data received from the digital interface. This flag is the same as the CRCERR\_IN bit in the SYSTEM\_STATUS register.

- DIAG\_MODE: This flag is set if the current data frame corresponds to the bit-walk test mode (see the [Bit-Walk Test Mode](#) section).

#### 6.3.9.2 Output CRC (Device to Host)

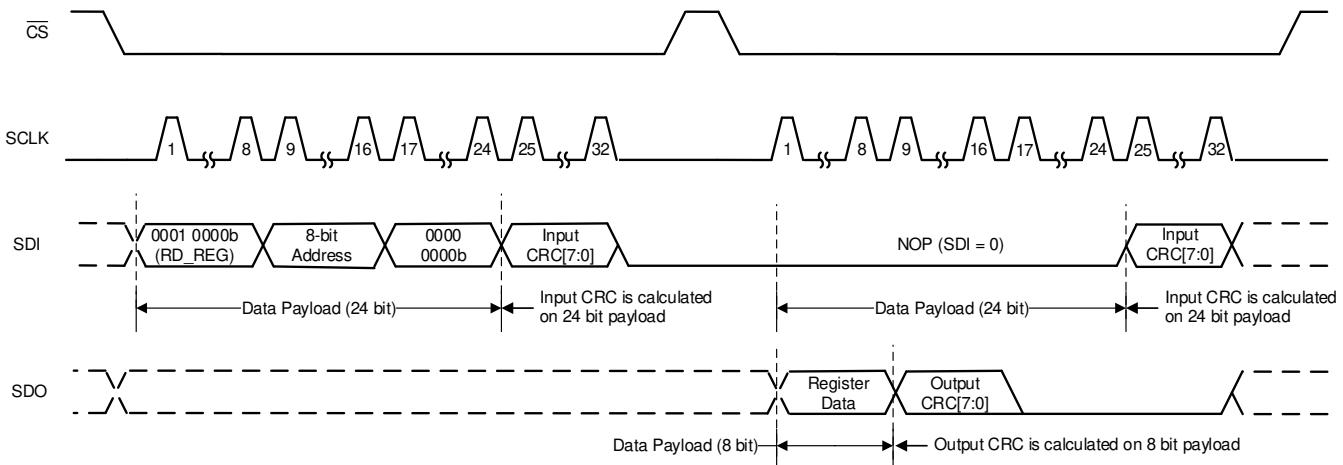

A CRC byte can be appended to the output data by configuring CRC\_EN to 1b. When the CRC module is enabled, the host must use 32-bit frames for SPI communication. The device outputs the data payload followed by the CRC byte computed over the data payload. Additional 0s can be appended by the ADC after the CRC byte to complete the 32-bit SPI frame (see [表 6-4](#)). The host must compute and compare the CRC corresponding to the data payload with the CRC received from the ADC. The additional 0s appended by the device after the CRC byte must be excluded by the host for computing the CRC.

#### 6.3.9.3 Input CRC (Host to Device)

When the CRC module is enabled, the host must always communicate with the ADC using 32-bit SPI frames comprised of a 24-bit data payload and an 8-bit CRC byte. The host must calculate the CRC byte to be appended based on a 24-bit payload. The ADC computes a CRC over the 24-bit data payload and compares the result with the CRC received from the host. [表 6-4](#) lists the output data frames for the CRC\_EN bit.

表 6-4. Output Data Frames

| CRC_EN                           | OSR[2:0]          | APPEND_STATUS[1:0]    | OUTPUT DATA FRAME                                             |

|----------------------------------|-------------------|-----------------------|---------------------------------------------------------------|

| CRC module disabled (CRC_EN = 0) | No averaging      | No flags (00b or 11b) | {Conversion result [15:0], 8'b0}                              |

|                                  |                   | Channel ID (01b)      | {Conversion result [15:0], CHID[3:0], 4'b0}                   |

|                                  |                   | Status flags (10b)    | {Conversion result [15:0], status flags[3:0], 4'b0}           |

|                                  | Averaging enabled | No flags (00b or 11b) | {Conversion result [19:0], 4'b0}                              |

|                                  |                   | Channel ID (01b)      | {Conversion result [19:0], CHID[3:0]}                         |

|                                  |                   | Status flags (10b)    | {Conversion result [19:0], status flags[3:0]}                 |

| CRC module enabled (CRC_EN = 1)  | No averaging      | No flags (00b or 11b) | {Conversion result [15:0], CRC[7:0], 8'b0}                    |

|                                  |                   | Channel ID (01b)      | {Conversion result [15:0], CHID[3:0], 4'b0, CRC[7:0]}         |

|                                  |                   | Status flags (10b)    | {Conversion result [15:0], status flags[3:0], 4'b0, CRC[7:0]} |

|                                  | Averaging enabled | No flags (00b or 11b) | {Conversion result [19:0], 4'b0, CRC[7:0]}                    |

|                                  |                   | Channel ID (01b)      | {Conversion result [19:0], CHID[3:0], CRC[7:0]}               |

|                                  |                   | Status flags (10b)    | {Conversion result [19:0], status flags[3:0], CRC[7:0]}       |

### 6.3.10 Device Programming

#### 6.3.10.1 Enhanced-SPI Interface

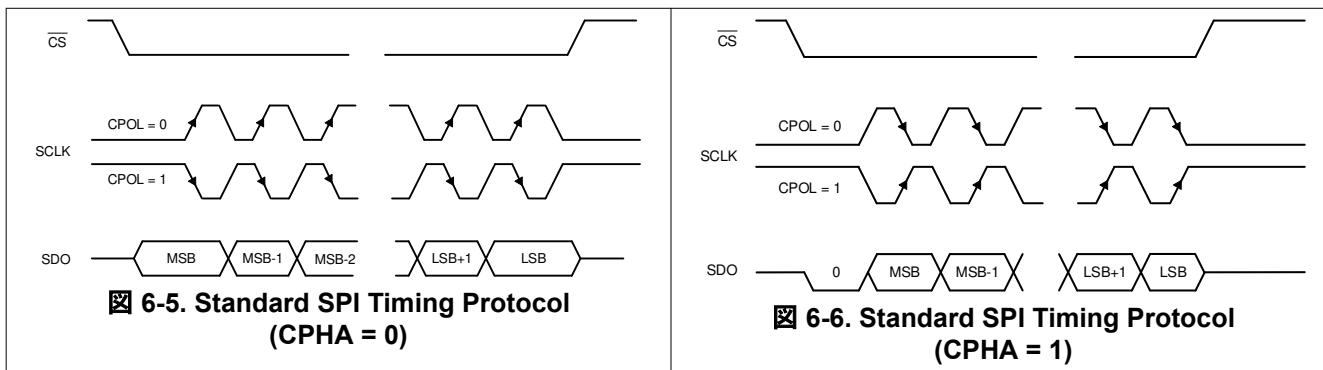

The device features an enhanced-SPI interface that allows the host controller to operate at slower SCLK speeds and still achieve full throughput. As described in 表 6-5, the host controller can use any of the four SPI-compatible protocols (SPI-00, SPI-01, SPI-10, or SPI-11) to access the device.

表 6-5. SPI Protocols for Configuring the Device

| PROTOCOL | SCLK POLARITY (At the CS Falling Edge) | SCLK PHASE (Capture Edge) | CPOL_CPHA[1:0] | DIAGRAM               |

|----------|----------------------------------------|---------------------------|----------------|-----------------------|

| SPI-00   | Low                                    | Rising                    | 00b            | <a href="#">図 6-5</a> |

| SPI-01   | Low                                    | Falling                   | 01b            | <a href="#">図 6-6</a> |

| SPI-10   | High                                   | Falling                   | 10b            | <a href="#">図 6-5</a> |

| SPI-11   | High                                   | Rising                    | 11b            | <a href="#">図 6-6</a> |

On power-up, the device defaults to the SPI-00 protocol for data read and data write operations. To select a different SPI-compatible protocol, program the CPOL\_CPHA[1:0] field. This first write operation must adhere to the SPI-00 protocol. Any subsequent data transfer frames must adhere to the newly-selected protocol.

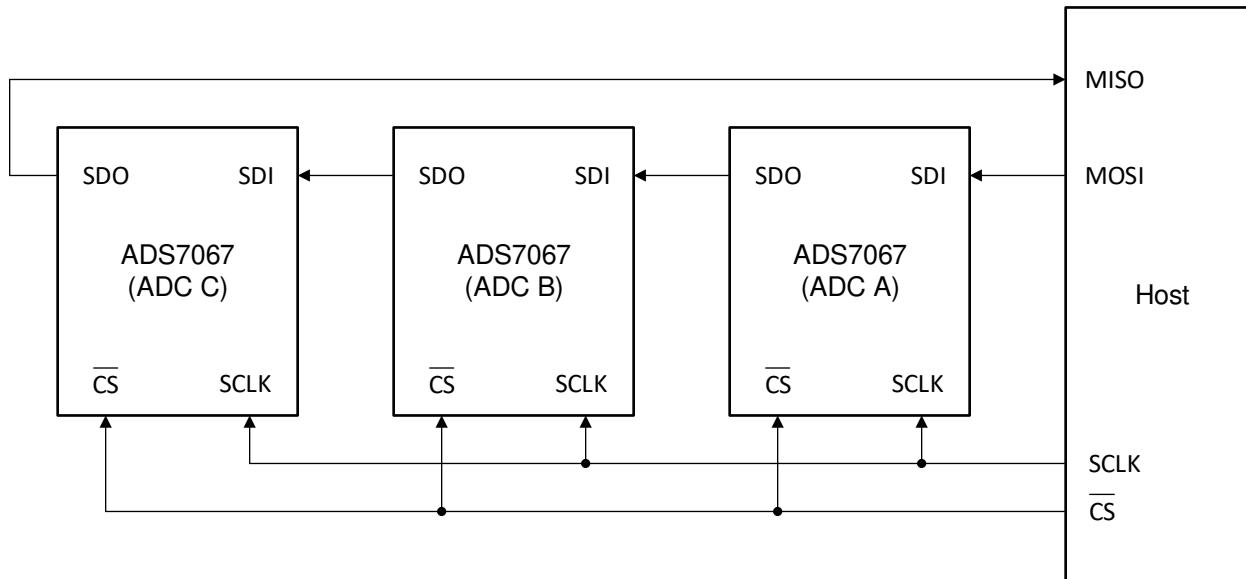

### 6.3.10.2 Daisy-Chain Mode

The ADS7067 can operate as a single converter or in a system with multiple converters. System designers can take advantage of the simple, high-speed, enhanced-SPI serial interface by cascading converters in a daisy-chain configuration when multiple converters are used. No register configuration is required to enable daisy-chain mode. [図 6-7](#) shows a typical connection of three converters in daisy-chain mode.

**図 6-7. Multiple Converters Connected Using Daisy-Chain Mode**

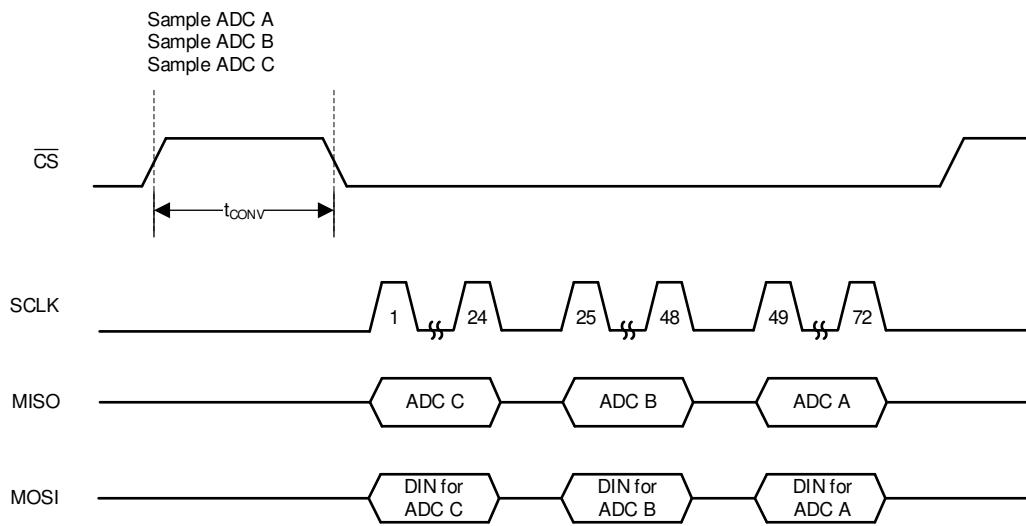

When the ADS7067 is connected in daisy-chain mode, the serial input data passes through the ADS7067 with a 24-SCLK delay, as long as  $\overline{CS}$  is active. [図 6-8](#) shows a detailed timing diagram of this mode. In [図 6-8](#), the conversion in each converter is performed simultaneously.

**図 6-8. Simplified Daisy-Chain Mode Timing**

The ADS7067 supports daisy-chain mode for output data payloads up to 24 bits long; see the [Output Data Format](#) section for more details. If either the status flags or channel ID are appended (APPEND\_STATUS ≠ 00b) and the CRC module is enabled (CRC\_EN = 1b), then the serial input data does not pass through the ADS7067 and daisy-chain mode is disabled.

### 6.3.10.3 Register Read/Write Operation

The device supports the commands listed in [表 6-6](#) to access the internal configuration registers

**表 6-6. Opcodes for Commands**

| OPCODE     | COMMAND DESCRIPTION   |

|------------|-----------------------|

| 0000 0000b | No operation          |

| 0001 0000b | Single register read  |

| 0000 1000b | Single register write |

| 0001 1000b | Set bit               |

| 0010 0000b | Clear bit             |

The clear bit command clears the specified bits (identified by 1) at the 8-bit address (without affecting the other bits), and the set bit command sets the specified bits (identified by 1) at the 8-bit address (without affecting the other bits).

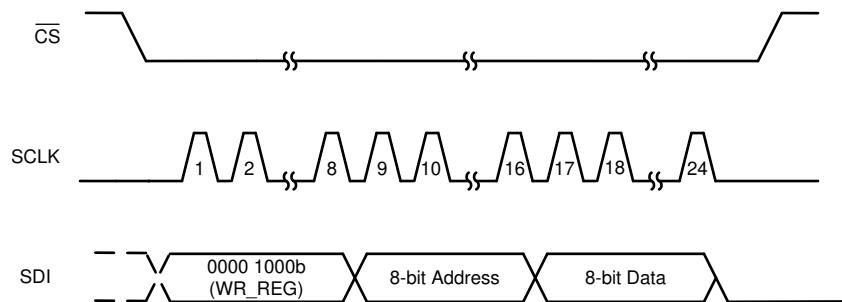

#### 6.3.10.3.1 Register Write

A 24-bit SPI frame is required to write data to configuration registers. The 24-bit data on SDI, as shown in [図 6-9](#), consists of an 8-bit write command (0000 1000b), an 8-bit register address, and 8-bit data. The write command is decoded on the  $\overline{CS}$  rising edge and the specified register is updated with the 8-bit data specified in the register write operation.

**図 6-9. Register Write Operation**

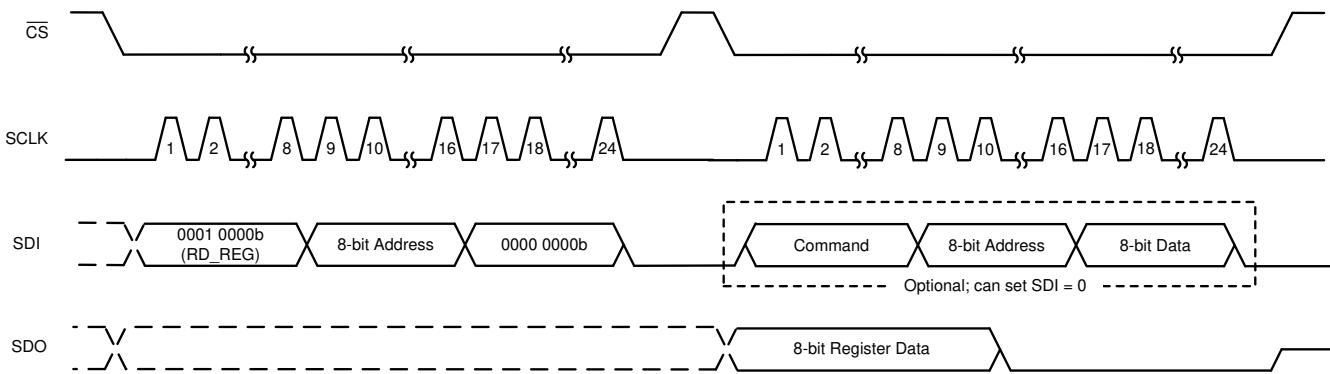

### 6.3.10.3.2 Register Read

A register read operation consists of two SPI frames: the first SPI frame initiates a register read and the second SPI frame reads data from the register address provided in the first frame. As shown in [図 6-10](#), the read command (0001 0000b), the 8-bit register address, and the 8-bit dummy data are sent over the SDI pin during the first 24-bit frame. On the rising edge of  $\overline{CS}$ , the read command is decoded and the requested register data are available for reading during the next frame. During the second frame, the first eight bits on SDO correspond to the requested register read. SDI can be used to initiate another operation or can be set to 0.

**図 6-10. Register Read Operation**

#### 6.3.10.3.2.1 Register Read With CRC

A register read consists of two SPI frames, as described in the [Register Read](#) section. When the CRC module is enabled during a register read, as shown in [図 6-11](#), the device appends an 8-bit output CRC byte along with 8-bit register data. The output CRC is computed by the device on the 8-bit register data.

**図 6-11. Register Read With CRC**

## 6.4 Device Functional Modes

表 6-7 lists the functional modes supported by the ADS7067.

**表 6-7. Functional Modes**

| FUNCTIONAL MODE | CONVERSION CONTROL     | MUX CONTROL                        | SEQ_MODE[1:0] |

|-----------------|------------------------|------------------------------------|---------------|

| Manual          | CS rising edge         | Register write to MANUAL_CHID      | 00b           |

| On-the-fly      | CS rising edge         | First 5 bits after CS falling edge | 10b           |

| Auto-sequence   | CS rising edge         | Channel sequencer                  | 01b           |

| Autonomous      | Internal to the device | Channel sequencer                  | 01b           |

The device powers up in manual mode and can be configured into either of these modes by writing the configuration registers for the desired mode.

### 6.4.1 Device Power-Up and Reset

On power up, the BOR bit is set indicating a power-cycle or reset event. The device can be reset by setting the RST bit or by recycling the power on the AVDD pin.

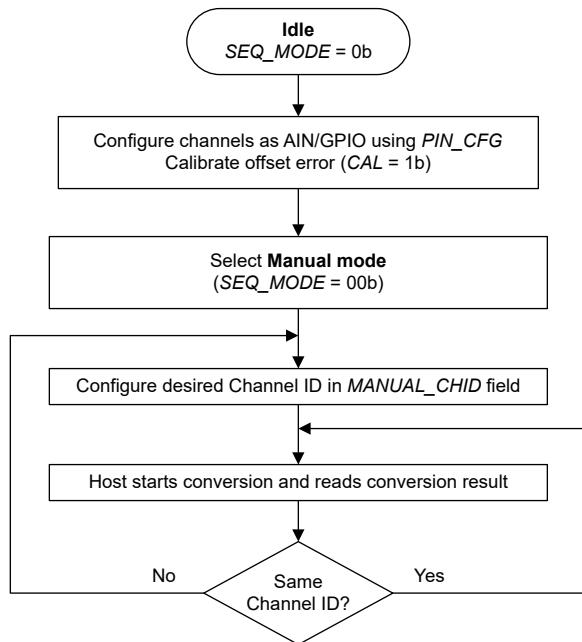

### 6.4.2 Manual Mode

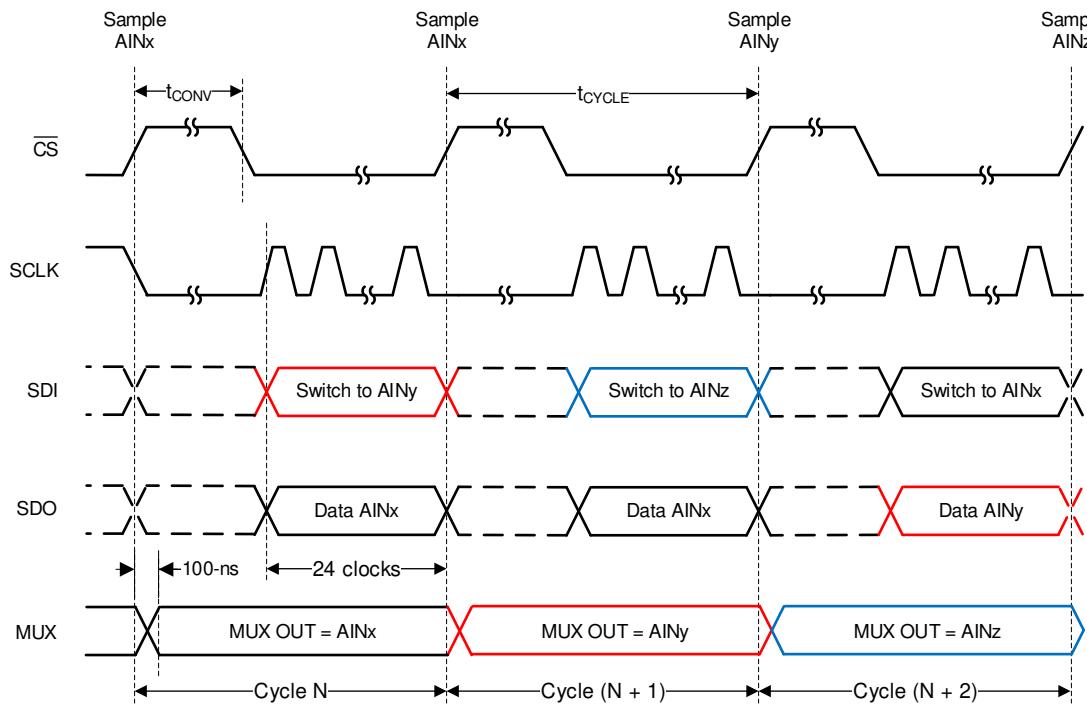

Manual mode allows the external host processor to directly select the analog input channel. 図 6-12 shows steps for operating the device in manual mode.

**図 6-12. Device Operation in Manual Mode**

In manual mode, the command to switch to a new channel, cycle N in 図 6-13, is decoded by the device on the CS rising edge. The CS rising edge is also the start of the conversion cycle, and thus the device samples the previously selected MUX channel in cycle N+1. The newly selected analog input channel data are available in cycle N+2. For switching the analog input channel, a register write to the MANUAL\_CHID field requires 24 clocks; see the [Register Write](#) section for more details. After a channel is selected, the number of clocks required for reading the output data depends on the device output data frame size; see the [Output Data Format](#) section for more details.

図 6-13. Starting a Conversion and Reading Data in Manual Mode

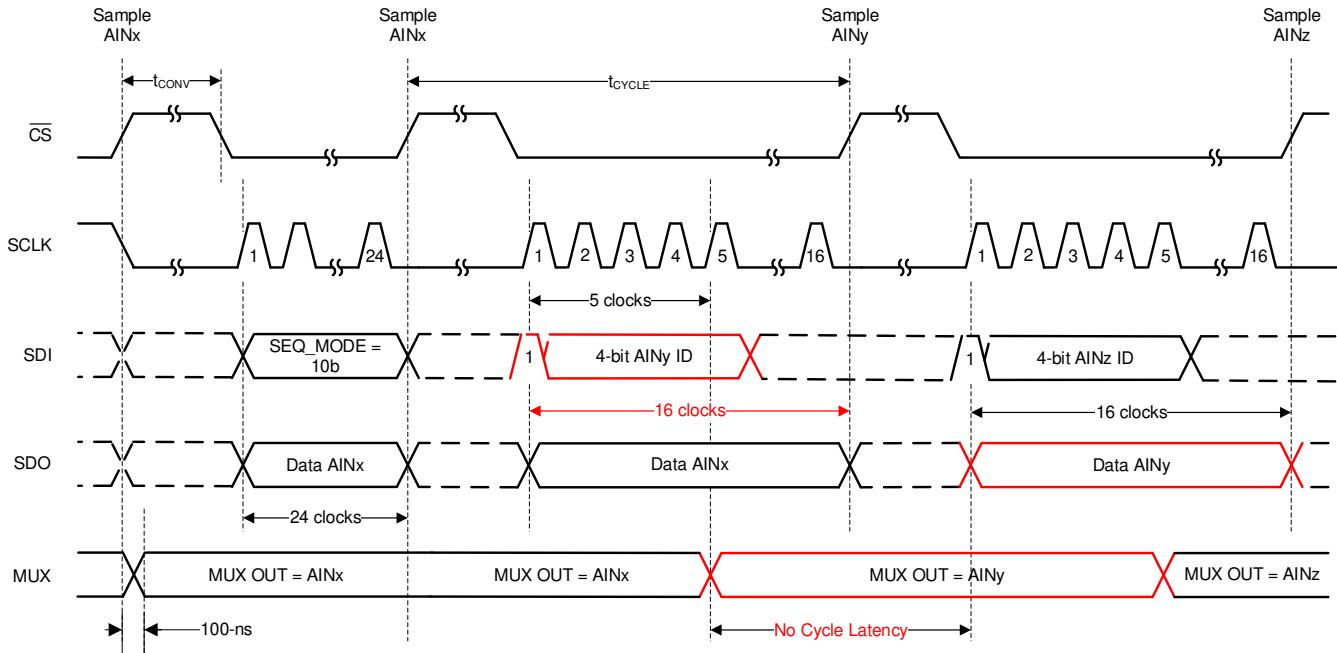

#### 6.4.3 On-the-Fly Mode

In the on-the-fly mode of operation, as shown in 図 6-14, the analog input channel is selected using the first five bits on SDI without waiting for the CS rising edge. Thus, the ADC samples the newly selected channel on the CS rising edge and there is no latency between the channel selection and the ADC output data. 表 6-8 lists the channel selection commands for this mode.

図 6-14. Starting a Conversion and Reading data in On-the-Fly Mode

**表 6-8. On-the-Fly Mode Channel Selection Commands**

| SDI BITS[15:11]  | SDI BITS [10:0] | DESCRIPTION           |

|------------------|-----------------|-----------------------|

| 1 0000           | Don't care      | Select analog input 0 |

| 1 0001           | Don't care      | Select analog input 1 |

| 1 0010           | Don't care      | Select analog input 2 |

| 1 0011           | Don't care      | Select analog input 3 |

| 1 0100           | Don't care      | Select analog input 4 |

| 1 0101           | Don't care      | Select analog input 5 |

| 1 0110           | Don't care      | Select analog input 6 |

| 1 0111           | Don't care      | Select analog input 7 |

| 1 1000 to 1 1111 | Don't care      | Reserved              |

The number of clocks required for reading the output data depends on the device output data frame size; see the [Output Data Format](#) section for more details.

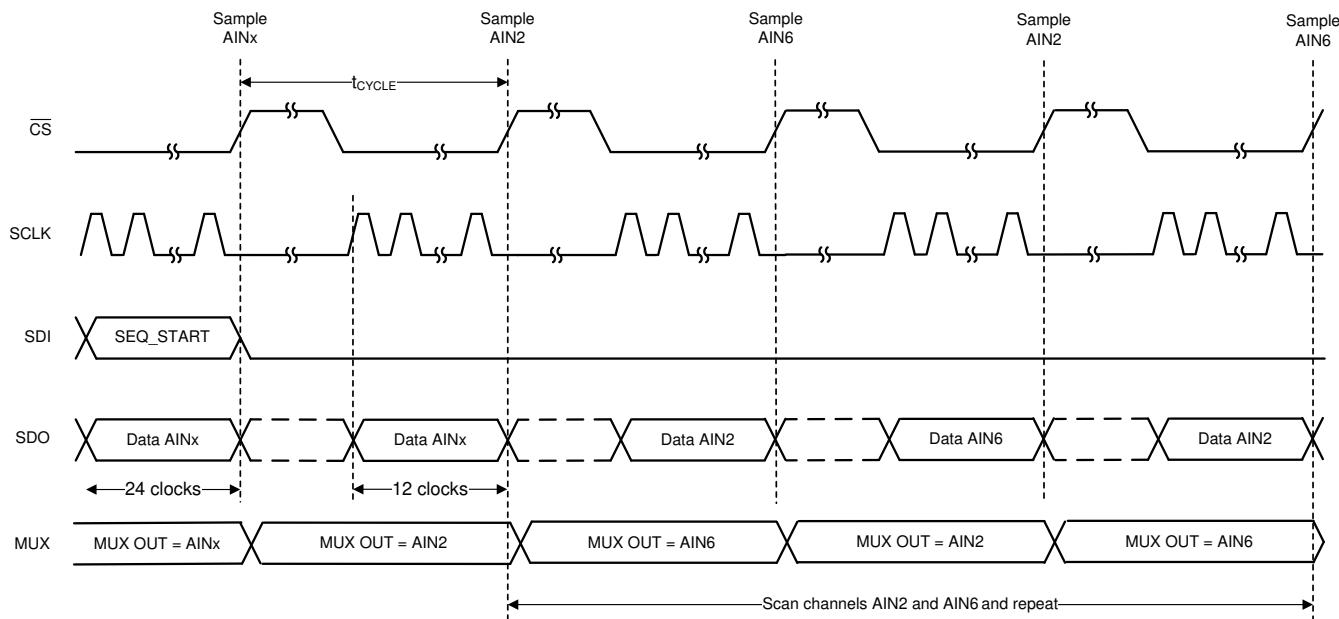

#### 6.4.4 Auto-Sequence Mode

In auto-sequence mode, the internal channel sequencer switches the multiplexer to the next analog input channel after every conversion. The desired analog input channels can be configured for sequencing in the AUTO\_SEQ\_CHSEL register. To enable the channel sequencer, set SEQ\_START = 1b. After every conversion, the channel sequencer switches the multiplexer to the next analog input in ascending order. To stop the channel sequencer from selecting channels, set SEQ\_START = 0b.

In the example shown in [图 6-15](#), AIN2 and AIN6 are enabled for sequencing in the AUTO\_SEQ\_CHSEL register. The channel sequencer loops through AIN2 and AIN6 and repeats until SEQ\_START is set to 0b. The number of clocks required for reading the output data depends on the device output data frame size; see the [Output Data Format](#) section for more details.

**图 6-15. Starting Conversion and Reading Data in Auto-Sequence Mode**

## 6.5 ADS7067 Registers

表 6-9 lists the ADS7067 registers. All register offset addresses not listed in 表 6-9 should be considered as reserved locations and the register contents should not be modified.

**表 6-9. ADS7067 Registers**

| Address | Acronym          | Register Name                                           | Section |

|---------|------------------|---------------------------------------------------------|---------|

| 0x0     | SYSTEM_STATUS    | SYSTEM_STATUS Register (Address = 0x0) [reset = 0x81]   |         |

| 0x1     | GENERAL_CFG      | GENERAL_CFG Register (Address = 0x1) [reset = 0x0]      |         |

| 0x2     | DATA_CFG         | DATA_CFG Register (Address = 0x2) [reset = 0x0]         |         |

| 0x3     | OSR_CFG          | OSR_CFG Register (Address = 0x3) [reset = 0x0]          |         |

| 0x4     | OPMODE_CFG       | OPMODE_CFG Register (Address = 0x4) [reset = 0x1]       |         |

| 0x5     | PIN_CFG          | PIN_CFG Register (Address = 0x5) [reset = 0x0]          |         |

| 0x7     | GPIO_CFG         | GPIO_CFG Register (Address = 0x7) [reset = 0x0]         |         |

| 0x9     | GPO_DRIVE_CFG    | GPO_DRIVE_CFG Register (Address = 0x9) [reset = 0x0]    |         |

| 0xB     | GPO_OUTPUT_VALUE | GPO_OUTPUT_VALUE Register (Address = 0xB) [reset = 0x0] |         |

| 0xD     | GPI_VALUE        | GPI_VALUE Register (Address = 0xD) [reset = 0x0]        |         |

| 0x10    | SEQUENCE_CFG     | SEQUENCE_CFG Register (Address = 0x10) [reset = 0x0]    |         |

| 0x11    | CHANNEL_SEL      | CHANNEL_SEL Register (Address = 0x11) [reset = 0x0]     |         |

| 0x12    | AUTO_SEQ_CH_SEL  | AUTO_SEQ_CH_SEL Register (Address = 0x12) [reset = 0x0] |         |

| 0xBF    | DIAGNOSTICS_KEY  | DIAGNOSTICS_KEY Register (Address = 0xBF) [reset = 0x0] |         |

| 0xC0    | DIAGNOSTICS_EN   | DIAGNOSTICS_EN Register (Address = 0xC0) [reset = 0x0]  |         |

| 0xC1    | BIT_SAMPLE_LSB   | BIT_SAMPLE_LSB Register (Address = 0xC1) [reset = 0x0]  |         |

| 0xC2    | BIT_SAMPLE_MSB   | BIT_SAMPLE_MSB Register (Address = 0xC2) [reset = 0x0]  |         |

Complex bit access types are encoded to fit into small table cells. 表 6-10 shows the codes that are used for access types in this section.

**表 6-10. ADS7067 Access Type Codes**

| Access Type              | Code | Description                                                                                                                                                                                                                                                                          |

|--------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read Type                |      |                                                                                                                                                                                                                                                                                      |

| R                        | R    | Read                                                                                                                                                                                                                                                                                 |

| Write Type               |      |                                                                                                                                                                                                                                                                                      |

| W                        | W    | Write                                                                                                                                                                                                                                                                                |

| Reset or Default Value   |      |                                                                                                                                                                                                                                                                                      |

| - n                      |      | Value after reset or the default value                                                                                                                                                                                                                                               |

| Register Array Variables |      |                                                                                                                                                                                                                                                                                      |

| i,j,k,l,m,n              |      | When these variables are used in a register name, an offset, or an address, they refer to the value of a register array where the register is part of a group of repeating registers. The register groups form a hierarchical structure and the array is represented with a formula. |

| y                        |      | When this variable is used in a register name, an offset, or an address it refers to the value of a register array.                                                                                                                                                                  |

### 6.5.1 SYSTEM\_STATUS Register (Address = 0x0) [reset = 0x81]

SYSTEM\_STATUS is shown in [図 6-16](#) and described in [表 6-11](#).

Return to the [Summary Table](#).

**図 6-16. SYSTEM\_STATUS Register**

| 7    | 6          | 5        | 4 | 3           | 2         | 1      | 0   |

|------|------------|----------|---|-------------|-----------|--------|-----|

| RSVD | SEQ_STATUS | RESERVED |   | CRCERR_FUSE | CRCERR_IN |        | BOR |

| R-1b | R-0b       | R-0b     |   | R-0b        | R/W-0b    | R/W-1b |     |

**表 6-11. SYSTEM\_STATUS Register Field Descriptions**

| Bit | Field       | Type | Reset | Description                                                                                                                                                                                                                                                         |

|-----|-------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RSVD        | R    | 1b    | Reads return 1b.                                                                                                                                                                                                                                                    |

| 6   | SEQ_STATUS  | R    | 0b    | Status of the channel sequencer.<br>0b = Sequence stopped<br>1b = Sequence in progress                                                                                                                                                                              |

| 5-3 | RESERVED    | R    | 0b    | Reserved Bit                                                                                                                                                                                                                                                        |

| 2   | CRCERR_FUSE | R    | 0b    | Device power-up configuration CRC check status. To re-evaluate this bit, software reset the device or power cycle AVDD.<br>0b = No problems detected in power-up configuration.<br>1b = Device configuration not loaded correctly.                                  |

| 1   | CRCERR_IN   | R/W  | 0b    | Status of CRC check on incoming data. Write 1b to clear this error flag.<br>0b = No CRC error.<br>1b = CRC error detected. All register writes, except to addresses 0x00 and 0x01, are blocked.                                                                     |

| 0   | BOR         | R/W  | 1b    | Brown out reset indicator. This bit is set if brown out condition occurs or device is power cycled. Write 1b to this bit to clear the flag.<br>0b = No brown out since last time this bit was cleared.<br>1b = Brown out condition detected or device power cycled. |

### 6.5.2 GENERAL\_CFG Register (Address = 0x1) [reset = 0x0]

GENERAL\_CFG is shown in [図 6-17](#) and described in [表 6-12](#).

Return to the [Summary Table](#).

**図 6-17. GENERAL\_CFG Register**

| 7      | 6      | 5        | 4 | 3      | 2      | 1      | 0    |

|--------|--------|----------|---|--------|--------|--------|------|

| REF_EN | CRC_EN | RESERVED |   | RANGE  | CH_RST | CAL    | RST  |

| R/W-0b | R/W-0b | R-0b     |   | R/W-0b | R/W-0b | R/W-0b | W-0b |

**表 6-12. GENERAL\_CFG Register Field Descriptions**

| Bit | Field    | Type | Reset | Description                                                                                                                                             |

|-----|----------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | REF_EN   | R/W  | 0b    | Enable or disable the internal reference.<br>0b = Internal reference is powered down.<br>1b = Internal reference is enabled.                            |

| 6   | CRC_EN   | R/W  | 0b    | Enable or disable the CRC on device interface.<br>0b = CRC module disabled.<br>1b = CRC appended to data output. CRC check is enabled on incoming data. |

| 5-4 | RESERVED | R    | 0b    | Reserved Bit                                                                                                                                            |

| 3   | RANGE    | R/W  | 0b    | Select the input range of the ADC.<br>0b = Input range of the ADC is 1x VREF<br>1b = Input range of the ADC is 2x VREF                                  |

**表 6-12. GENERAL\_CFG Register Field Descriptions (続き)**

| Bit | Field  | Type | Reset | Description                                                                                                                                                                 |

|-----|--------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | CH_RST | R/W  | 0b    | Force all channels to be analog inputs.<br>0b = Normal operation<br>1b = All channels will be set as analog inputs irrespective of configuration in other registers         |

| 1   | CAL    | R/W  | 0b    | Calibrate ADC offset.<br>0b = Normal operation.<br>1b = ADC offset is calibrated. After calibration is complete, this bit is set to 0b.                                     |

| 0   | RST    | W    | 0b    | Software reset all registers to default values.<br>0b = Normal operation.<br>1b = Device is reset. After reset is complete, this bit is set to 0b and BOR bit is set to 1b. |

**6.5.3 DATA\_CFG Register (Address = 0x2) [reset = 0x0]**DATA\_CFG is shown in [図 6-18](#) and described in [表 6-13](#).Return to the [Summary Table](#).**図 6-18. DATA\_CFG Register**

| 7       | 6        | 5                  | 4 | 3        | 2 | 1              | 0 |

|---------|----------|--------------------|---|----------|---|----------------|---|

| FIX_PAT | RESERVED | APPEND_STATUS[1:0] |   | RESERVED |   | CPOL_CPHA[1:0] |   |

| R/W-0b  | R-0b     | R/W-0b             |   | R-0b     |   | R/W-0b         |   |

**表 6-13. DATA\_CFG Register Field Descriptions**

| Bit | Field              | Type | Reset | Description                                                                                                                                                                                                                                          |

|-----|--------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | FIX_PAT            | R/W  | 0b    | Device outputs fixed data bits which can be helpful for debugging communication with the device.<br>0b = Normal operation.<br>1b = Device outputs fixed code 0xA5A5 repetitively when reading ADC data.                                              |

| 6   | RESERVED           | R    | 0b    | Reserved Bit                                                                                                                                                                                                                                         |

| 5-4 | APPEND_STATUS[1:0] | R/W  | 0b    | Append 4-bit channel ID or status flags to output data.<br>0b = Channel ID and status flags are not appended to ADC data.<br>1b = 4-bit channel ID is appended to ADC data.<br>10b = 4-bit status flags are appended to ADC data.<br>11b = Reserved. |

| 3-2 | RESERVED           | R    | 0b    | Reserved Bit                                                                                                                                                                                                                                         |

| 1-0 | CPOL_CPHA[1:0]     | R/W  | 0b    | This field sets the polarity and phase of SPI communication.<br>0b = CPOL = 0, CPHA = 0.<br>1b = CPOL = 0, CPHA = 1.<br>10b = CPOL = 1, CPHA = 0.<br>11b = CPOL = 1, CPHA = 1.                                                                       |

**6.5.4 OSR\_CFG Register (Address = 0x3) [reset = 0x0]**OSR\_CFG is shown in [図 6-19](#) and described in [表 6-14](#).Return to the [Summary Table](#).**図 6-19. OSR\_CFG Register**

| 7        | 6 | 5 | 4 | 3 | 2 | 1        | 0 |

|----------|---|---|---|---|---|----------|---|

| RESERVED |   |   |   |   |   | OSR[2:0] |   |

| R-0b     |   |   |   |   |   | R/W-0b   |   |

**図 6-19. OSR\_CFG Register (続き)**

**表 6-14. OSR\_CFG Register Field Descriptions**

| Bit | Field    | Type | Reset | Description                                                                                                                                                                                                                 |