# 16ビット、250KSPS サンプリング CMOS ADコンバータ

## 特 長

- 工業標準入力範囲： $\pm 10V$

- SNR：90dB (20kHz入力時 (Min))

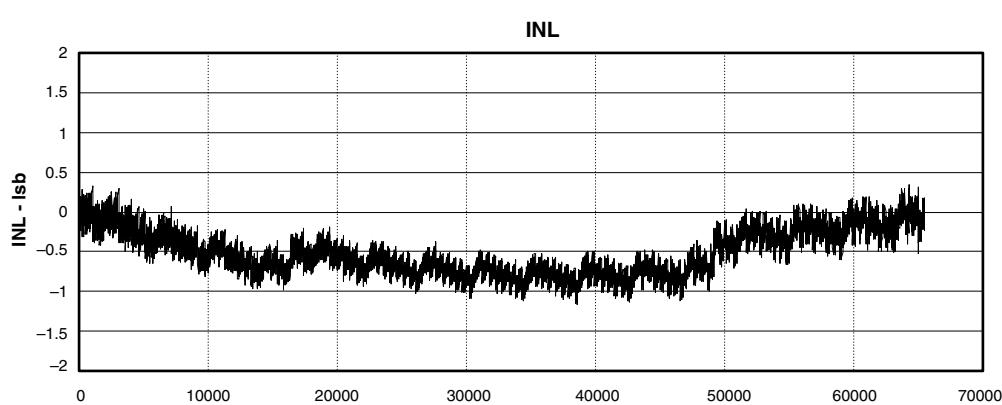

- INL： $\pm 2.0\text{ LSB}$  (Max)

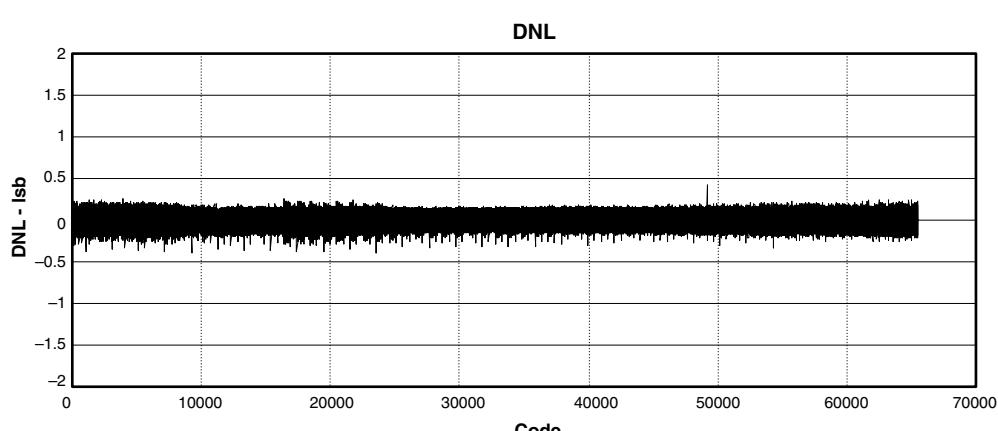

- DNL： $\pm 1\text{ LSB}$  (Max)

- 16ビットノーミッシング・コード

- アナログ電源 ( $V_{ANA}$ )：4.75V～5.25V

- I/O電源電圧 ( $V_{DIG}$ )：1.65V～5.25V

- ADS7805/10 (低速)、ADS7804/8504とピン配列互換性

- 内部または、外部リファレンスを使用可能

- パラレル・データ出力

- 消費電力：100mW (250KSPS時 (Typ))

- 28ピンSSOPパッケージ

## アプリケーション

- 産業用プロセス制御

- データ・アクイジション・システム

- デジタル信号処理

- 医療用機器

- 計装機器

## 概 要

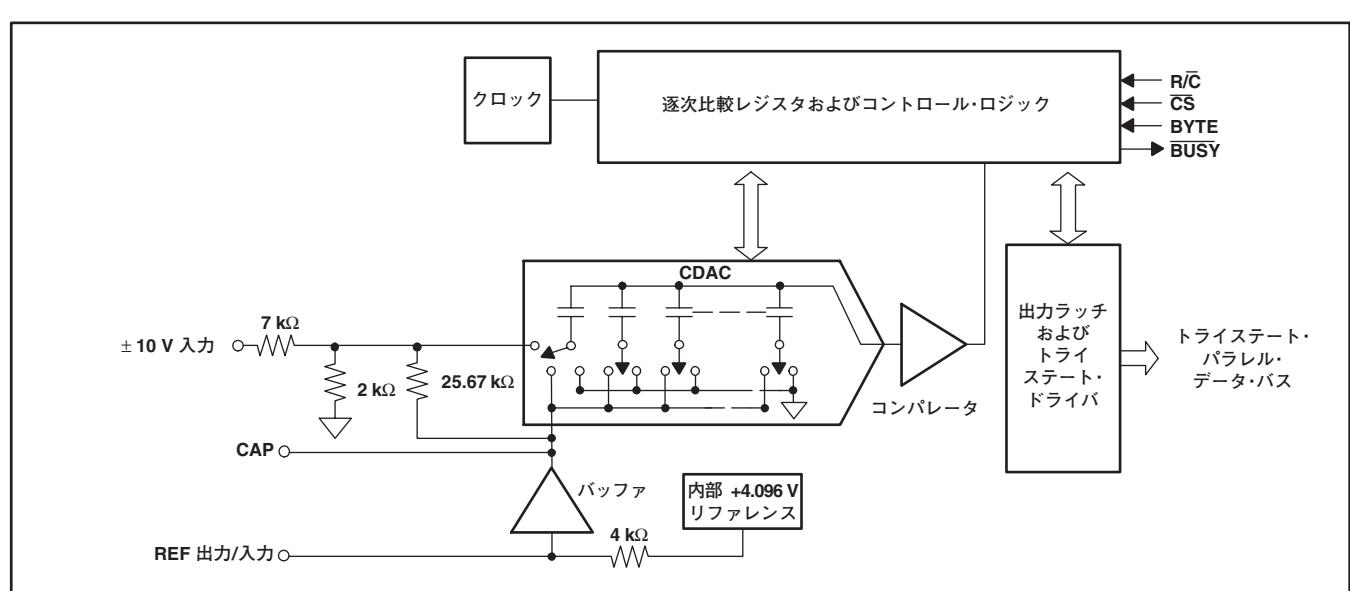

ADS8515は、最新のCMOS構造を採用した16ビット・サンプリングADコンバータ(ADC)です。またADS8515は、16ビット、電荷再分配方式の逐次比較型(SAR)ADコンバータであり、サンプル・ホールド、リファレンス、クロック回路、マイクロプロセッサ用のインターフェイス、およびトライ・スタート出力ドライバ、全てを備えています。

ADS8515は、-40°C～+85°Cの範囲で250kHzのサンプリング・レートが規定されています。斬新な設計により、+5V単電源で動作しながら高精度の抵抗で工業標準の $\pm 10V$ 入力範囲を実現し、消費電力は100mWを下回ります。

ADS8515は28ピンSSOPパッケージで供給され、産業用の-40°C～+85°Cの温度範囲で動作が規定されています。

すべての商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを伝導性のフォームに入れる必要があります。

### 製品情報<sup>(1)</sup>

| 製品名       | 最小 INL<br>(LSB) | ノーミッキング・コード | 最小 SINAD<br>(dB) | 仕様 温度範囲                                       | パッケージ・リード | パッケージ・コード | 製品型番         | 出荷形態,<br>数量  |

|-----------|-----------------|-------------|------------------|-----------------------------------------------|-----------|-----------|--------------|--------------|

| ADS8515IB | $\pm 2$         | 16          | 89               | $-40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ | SSOP-28   | DB        | ADS8515IBDB  | チューブ、50      |

|           |                 |             |                  |                                               |           |           | ADS8515IBDBR | テープ・リール、2000 |

| ADS8515I  | $\pm 3$         | 16          | 87               | $-40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ | SSOP-28   | DB        | ADS8515IDB   | チューブ、50      |

|           |                 |             |                  |                                               |           |           | ADS8515IDBR  | テープ・リール、2000 |

(1) 最新のパッケージ情報と発注情報については、このデータシートの末尾にある、追捕：「パッケージ・オプション」を参照するか、またはwww.tij.co.jpにあるTIのWebサイトを参照してください。

### 絶対最大定格<sup>(1)</sup>

|                 |                                      | ADS8515                                                           |

|-----------------|--------------------------------------|-------------------------------------------------------------------|

| アナログ入力          | $V_{\text{IN}}$                      | $\pm 25\text{V}$                                                  |

|                 | CAP                                  | $\text{AGND2} - 0.3\text{ V} \sim +V_{\text{ANA}} + 0.3\text{ V}$ |

|                 | REF                                  | $\text{AGND2} \sim \text{永久接続}, V_{\text{ANA}} \sim \text{瞬時短絡}$  |

| グランド間の電位差       | DGND, AGND1, AGND2                   | $\pm 0.3\text{ V}$                                                |

|                 | $V_{\text{ANA}}$                     | 6 V                                                               |

|                 | $V_{\text{DIG}} \sim V_{\text{ANA}}$ | 0.3 V                                                             |

|                 | $V_{\text{DIG}}$                     | 6 V                                                               |

| デジタル入力          |                                      | $-0.3\text{ V} \sim +V_{\text{DIG}} + 0.3\text{ V}$               |

| 最大接合温度          |                                      | 165°C                                                             |

| 消費電力            |                                      | 825 mW                                                            |

| リード温度 (半田付け10秒) |                                      | 300°C                                                             |

(1) 絶対最大定格を超えるストレスは、デバイスに永久的な損傷を与えます。絶対最大定格の状態で長時間動作させると、デバイスの信頼性が低下します。これはストレスの定格のみについて示してあり、本製品の仕様を越える状態での機能動作を意味するものではありません。

(2) 電圧値はすべてネットワーク・グランド端子を基準としています。

### 電気的特性

$T_A = -40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ 、 $f_s = 250\text{kHz}$ 、 $V_{\text{DIG}} = V_{\text{ANA}} = 5\text{V}$ 、内部リファレンス使用(特に記述のない限り)

| パラメータ                      | テスト条件               | ADS8515I |       |     | ADS8515IB |       |     | 単位                 |

|----------------------------|---------------------|----------|-------|-----|-----------|-------|-----|--------------------|

|                            |                     | MIN      | TYP   | MAX | MIN       | TYP   | MAX |                    |

| 分解能                        |                     |          |       |     |           |       |     |                    |

| アナログ入力                     |                     |          |       | 16  |           |       | 16  | Bits               |

| 電圧範囲                       |                     |          |       |     |           |       |     |                    |

| インピーダンス                    |                     |          | 8.885 |     |           | 8.885 |     | kΩ                 |

| 入力容量                       |                     |          | 75    |     |           | 75    |     | pF                 |

| スループット速度                   |                     |          |       |     |           |       |     |                    |

| 変換サイクル時間                   | Acquire and convert |          |       | 4   |           | 4     |     | μs                 |

| スループット・レート                 |                     | 250      |       |     | 250       |       |     | kHz                |

| DC精度                       |                     |          |       |     |           |       |     |                    |

| INL 構成直線性誤差                |                     | -3       |       | 3   | -2        |       | 2   | LSB <sup>(1)</sup> |

| DNL 微構成直線性誤差               |                     | -1       |       | 2   | -1        |       | 1   | LSB <sup>(1)</sup> |

| ノーミッキング・コード                |                     | 16       |       |     | 16        |       |     | Bits               |

| トランジション・ノイズ <sup>(2)</sup> |                     | 0.67     |       |     | 0.67      |       |     | LSB                |

(1) LSBは「least significant bit」の略で、最下位ビットを表します。16bit、 $\pm 10\text{V}$ 入力のとき、ADS8515では、1 LSBは $305\mu\text{V}$ です。

(2) ノイズの実効値(Typ)は、トランジションと温度がワースト・ケースの値です。

## 電気的特性

$T_A = -40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ 、 $f_s = 250\text{kHz}$ 、 $V_{\text{DIG}} = V_{\text{ANA}} = 5\text{V}$ 、内部リファレンス使用(特に記述のない限り)

| パラメータ                                           | テスト条件                                                     | ADS8515I                                            |                             |                                 | ADS8515IB                    |                                 |       | 単位     |

|-------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------|-----------------------------|---------------------------------|------------------------------|---------------------------------|-------|--------|

|                                                 |                                                           | MIN                                                 | TYP                         | MAX                             | MIN                          | TYP                             | MAX   |        |

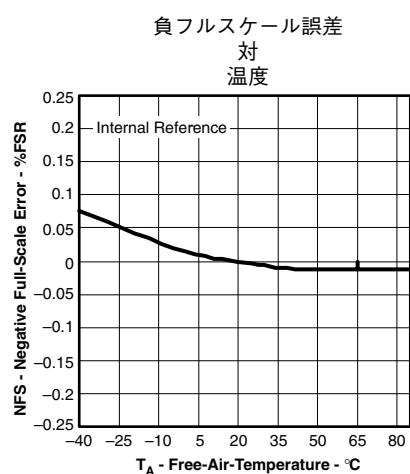

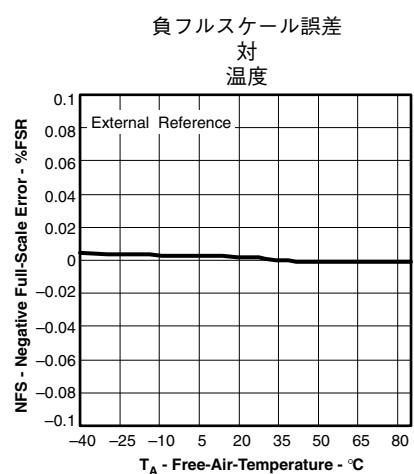

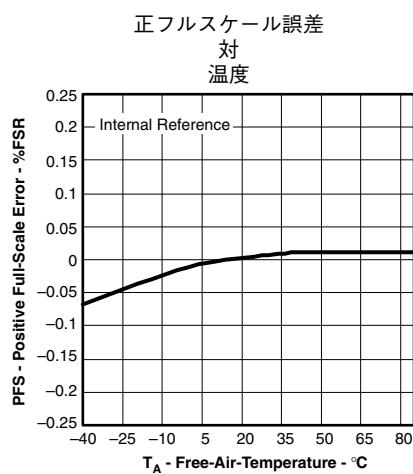

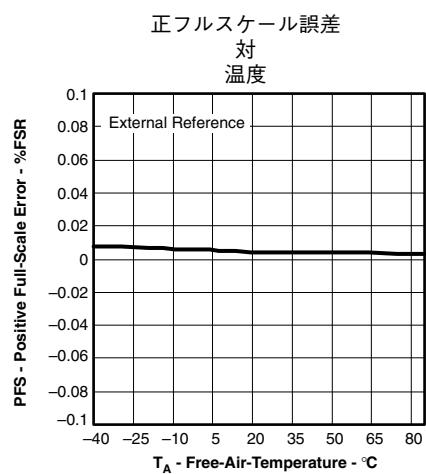

| フルスケール誤差 <sup>(3)(4)</sup>                      | 内部リファレンス                                                  | -0.5                                                |                             | 0.5                             | -0.25                        |                                 | 0.25  | %FSR   |

| フルスケール誤差ドリフト                                    | 内部リファレンス                                                  |                                                     | ±7                          |                                 |                              | ±7                              |       | ppm/°C |

| フルスケール誤差 <sup>(3)(4)</sup>                      | 外部4.096Vリファレンス                                            | -0.25                                               |                             | 0.25                            | -0.1                         |                                 | 0.1   | %FSR   |

| フルスケール誤差ドリフト                                    | 外部4.096Vリファレンス                                            |                                                     | ±2                          |                                 |                              | ±2                              |       | ppm/°C |

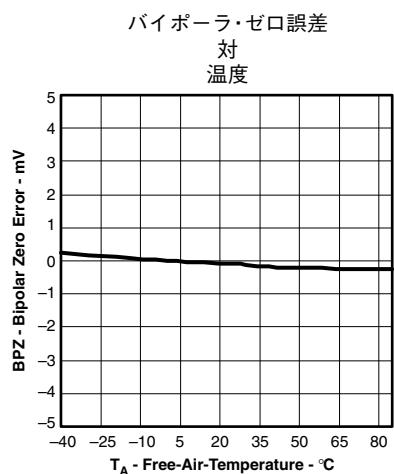

| バイポーラ・ゼロ誤差 <sup>(3)</sup>                       |                                                           | -4                                                  |                             | 4                               | -2                           |                                 | 2     | mV     |

| バイポーラ・ゼロ誤差ドリフト                                  |                                                           |                                                     | ±2                          |                                 |                              | ±2                              |       | ppm/°C |

| 電源感度( $V_{\text{DIG}} = V_{\text{ANA}} = V_D$ ) | +4.75 V < $V_D$ < +5.25 V                                 | -8                                                  |                             | 8                               | -8                           |                                 | 8     | LSB    |

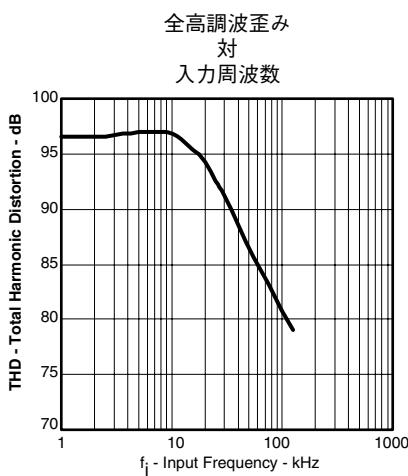

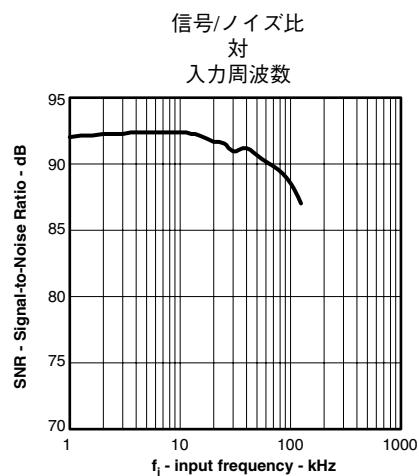

| AC精度                                            |                                                           |                                                     |                             |                                 |                              |                                 |       |        |

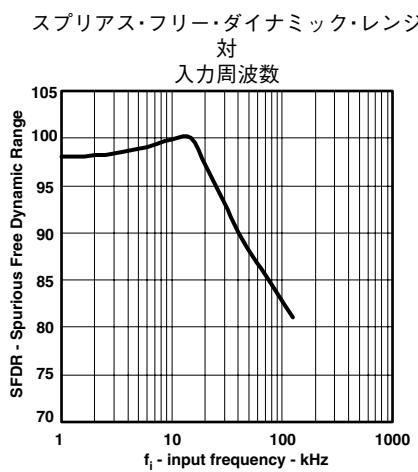

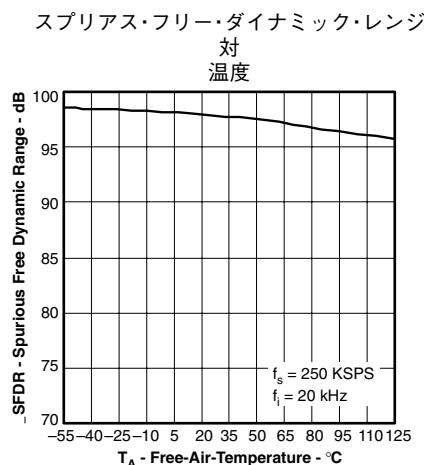

| SFDR                                            | スプリアス・フリー・ダイナミック・レンジ                                      | $f_i = 20\text{ kHz}$                               |                             | 95                              | 102                          |                                 | 97    | 102    |

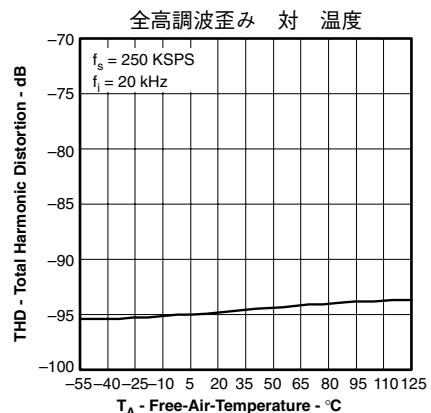

| THD                                             | 全高調波歪み                                                    | $f_i = 20\text{ kHz}$                               |                             | -100                            | -94                          |                                 | -100  | -96    |

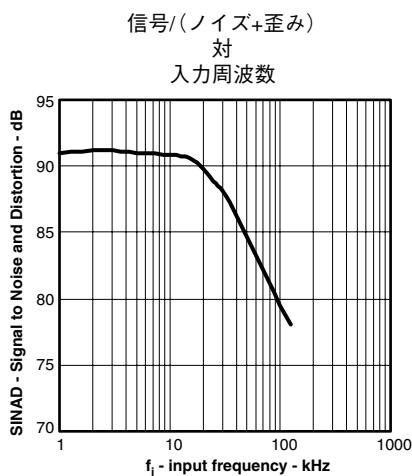

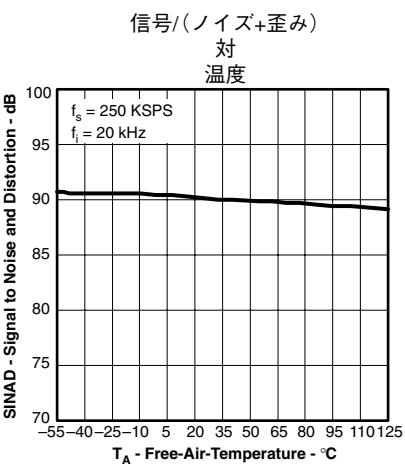

| SINAD                                           | 信号対(ノイズ+歪み)                                               | $f_i = 20\text{ kHz}$                               | 87                          | 91                              |                              | 89                              | 91    | dB     |

|                                                 | -60-dB Input                                              |                                                     |                             | 30                              |                              |                                 | 32    | dB     |

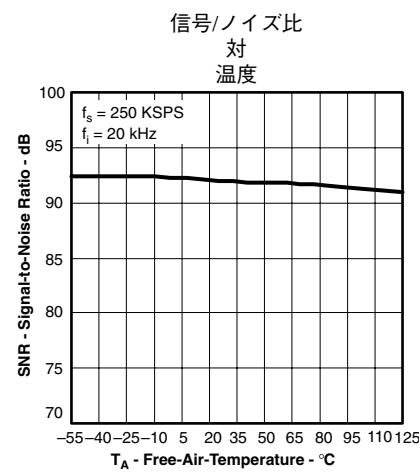

| SNR                                             | 信号対ノイズ比                                                   | $f_i = 20\text{ kHz}$                               | 88                          | 92                              |                              | 90                              | 92    | dB     |

|                                                 | フルパワー帯域幅 <sup>(6)</sup>                                   |                                                     |                             | 500                             |                              |                                 | 500   | kHz    |

| サンプリング・ダイナミック                                   |                                                           |                                                     |                             |                                 |                              |                                 |       |        |

| アバーチャ遅延                                         |                                                           |                                                     |                             | 5                               |                              |                                 | 5     | ns     |

| トランジエント応答                                       | フルスケール・ステップ                                               |                                                     |                             |                                 | 2                            |                                 |       | 2 μs   |

| 過電圧復帰 <sup>(7)</sup>                            |                                                           |                                                     |                             | 150                             |                              |                                 | 150   | ns     |

| リファレンス電圧                                        |                                                           |                                                     |                             |                                 |                              |                                 |       |        |

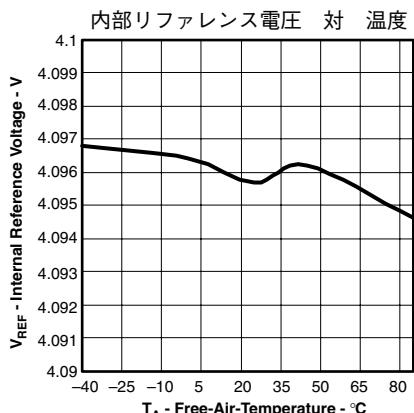

| 内部リファレンス電圧                                      |                                                           |                                                     | 4.076                       | 4.096                           | 4.116                        |                                 | 4.076 | 4.096  |

| 内部リファレンス出力電流<br>(外部バッファ使用のこと)                   |                                                           |                                                     |                             | 1                               |                              |                                 | 1     | μA     |

| 内部リファレンスドリフト                                    |                                                           |                                                     |                             | 8                               |                              |                                 | 8     | ppm/°C |

| 直線性仕様を満たす外部<br>リファレンス電圧範囲                       |                                                           | 3.9                                                 | 4.096                       | 4.2                             |                              | 3.9                             | 4.096 | 4.2    |

| 外部リファレンスからの流入電流                                 | 外部4.096Vリファレンス                                            |                                                     |                             | 100                             |                              |                                 | 100   | μA     |

| デジタル入力                                          |                                                           |                                                     |                             |                                 |                              |                                 |       |        |

| ロジック・レベル                                        |                                                           |                                                     |                             |                                 |                              |                                 |       |        |

| $V_{IL}$                                        | “L” レベル入力電圧                                               | $V_{\text{DIG}} = 1.65\text{ V} \sim 5.25\text{ V}$ | -0.3                        | 0.8                             | -0.3                         | $0.35 \times V_{\text{DIG}}$    |       | V      |

| $V_{IH}$                                        | “H” レベル入力電圧                                               | $V_{\text{DIG}} = 1.65\text{ V} \sim 5.25\text{ V}$ | 2.0                         | $V_{\text{DIG}} + 0.3\text{ V}$ | $0.65 \times V_{\text{DIG}}$ | $V_{\text{DIG}} + 0.3\text{ V}$ |       | V      |

| $I_{IL}$                                        | “L” レベル入力電流                                               | $V_{IL} = 0\text{ V}$                               |                             | ±10                             |                              |                                 | ±10   | μA     |

| $I_{IH}$                                        | “H” レベル入力電流                                               | $V_{IH} = 5\text{ V}$                               |                             | ±10                             |                              |                                 | ±10   | μA     |

| デジタル出力                                          |                                                           |                                                     |                             |                                 |                              |                                 |       |        |

| データ・フォーマット(パラレル16ビット)                           |                                                           |                                                     |                             |                                 |                              |                                 |       |        |

| データ・コード(2の補数バイナリ)                               |                                                           |                                                     |                             |                                 |                              |                                 |       |        |

| $V_{OL}$                                        | “L” レベル出力電圧                                               | $I_{\text{SINK}} = 1.6\text{ mA}$                   |                             | 0.4                             |                              |                                 | 0.4   | V      |

| $V_{OH}$                                        | “H” レベル出力電圧                                               | $I_{\text{SOURCE}} = 500\text{ μA}$                 | $0.8 \times V_{\text{DIG}}$ |                                 | $0.8 \times V_{\text{DIG}}$  |                                 |       | V      |

| リード電流                                           | ハイ・インピーダンス時<br>$V_{OUT} = 0\text{ V} \sim V_{\text{DIG}}$ |                                                     |                             | ±5                              |                              |                                 | ±5    | μA     |

| 出力容量                                            | ハイ・インピーダンス時                                               |                                                     |                             | 15                              |                              |                                 | 15    | pF     |

| デジタル・タイミング                                      |                                                           |                                                     |                             |                                 |                              |                                 |       |        |

| バス・アクセス・タイミング                                   |                                                           |                                                     |                             | 83                              |                              |                                 | 83    | ns     |

| バス解放タイミング                                       |                                                           |                                                     |                             | 83                              |                              |                                 | 83    | ns     |

(3) 図25(a)に示す抵抗値で測定。外部ボテンショ・メータによりゼロに調整。

(4) フルスケール誤差は、入力が最小値コードから最大値コードに変化したときの-フルスケール、または+フルスケールの理論値に対する偏差のワースト・ケースであり、変化した電圧(フルスケール・レンジではなく)で除算し、オフセットによる誤差が含まれます。

(5) dB表示は、すべてフルスケールの±10V入力を基準としています。

(6) フルパワー帯域幅は、フルスケール入力において、信号対(ノイズ+歪み)が60dBに低下する時、もしくは精度が10ビットに低下する時の周波数として規定されています。

(7) 2×FSの入力過電圧を印加後、規定の特性に復帰するまでの時間。

## 電気的特性

$T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$ 、 $f_s = 250\text{kHz}$ 、 $V_{\text{DIG}} = V_{\text{ANA}} = 5\text{V}$ 、内部リファレンス使用(特に記述のない限り)

| パラメータ                                | テスト条件                 | ADS8515I                  |      |      | ADS8515IB |      |      | 単位   |

|--------------------------------------|-----------------------|---------------------------|------|------|-----------|------|------|------|

|                                      |                       | MIN                       | TYP  | MAX  | MIN       | TYP  | MAX  |      |

| <b>電源</b>                            |                       |                           |      |      |           |      |      |      |

| $V_{\text{DIG}}$                     | デジタル電源電圧              | $V_{\text{ANA}}$ 以下であること。 | 1.65 | 5.25 | 1.65      | 5.25 | 5.25 | V    |

| $V_{\text{ANA}}$                     | アナログ電源電圧              |                           | 4.75 | 5    | 5.25      | 4.75 | 5    | 5.25 |

| $I_{\text{DIG}}$                     | デジタル電源電流              |                           | 0.1  | 1    | 0.1       | 1    | 1    | mA   |

| $I_{\text{ANA}}$                     | アナログ電源電流              |                           | 20   | 25   | 20        | 25   | 25   | mA   |

| 消費電力                                 | $f_s = 250\text{kHz}$ |                           | 100  | 125  | 100       | 125  | 125  | mW   |

| <b>動作温度範囲</b>                        |                       |                           |      |      |           |      |      |      |

| 規定                                   |                       |                           | -40  | 85   | -40       | 85   | 85   | °C   |

| ディレーティング <sup>(8)</sup>              |                       |                           | -55  | 125  | -55       | 125  | 125  | °C   |

| ストレージ                                |                       |                           | -65  | 150  | -65       | 150  | 150  | °C   |

| <b>熱抵抗(<math>\Theta_{JA}</math>)</b> |                       |                           |      |      |           |      |      |      |

| SSOP                                 |                       |                           | 67   |      | 67        |      | 67   | °C/W |

(8) 内部リファレンスは産業用温度範囲(-40°C~+85°C)外では動作を開始しないことがあります。その場合、外部リファレンスを使用することを推奨します。

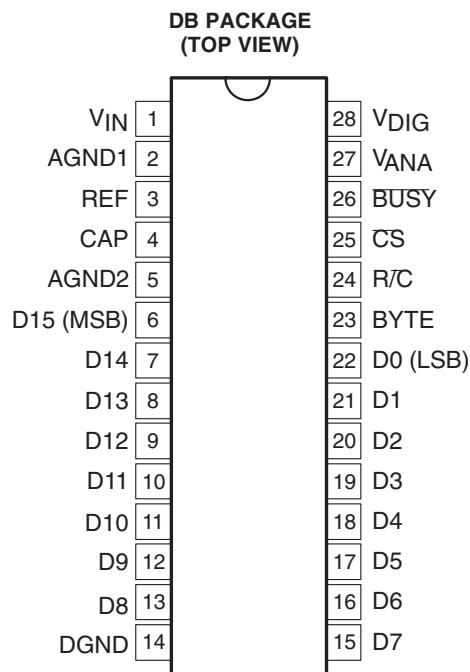

## ピン配置

## ピン構成

| 端子        |          | デジタル<br>入出力 | 説明                                                                 |

|-----------|----------|-------------|--------------------------------------------------------------------|

| 名称        | ピン<br>番号 |             |                                                                    |

| AGND1     | 2        |             | アナログ・グランド。内部のグランド基準点として使用します。                                      |

| AGND2     | 5        |             | アナログ・グランド。                                                         |

| BUSY      | 26       | O           | BUSYは変換の開始で“Low”になり、変換が完了してデジタル出力が更新されるまで“Low”的ままでです。              |

| BYTE      | 23       | I           | 上位8ビット(low)あるいは下位8ビット(high)を選択します。                                 |

| CAP       | 4        |             | リファレンス・バッファ用コンデンサ。グランドへ2.2μFのタンタル・コンデンサを接続します。                     |

| CS        | 25       | I           | R/Cと内部でOR接続。R/Cが“Low”的場合、CSの立ち下がりエッジで新規の変換を開始します。                  |

| DGND      | 14       |             | デジタル・グランド                                                          |

| D15 (MSB) | 6        | O           | データ・ビット15. 変換結果の最上位ビット(MSB)。CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。 |

| D14       | 7        | O           | データ・ビット14. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                  |

| D13       | 8        | O           | データ・ビット13. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                  |

| D12       | 9        | O           | データ・ビット12. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                  |

| D11       | 10       | O           | データ・ビット11. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                  |

| D10       | 11       | O           | データ・ビット10. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                  |

| D9        | 12       | O           | データ・ビット9. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                   |

| D8        | 13       | O           | データ・ビット8. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                   |

| D7        | 15       | O           | データ・ビット7. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                   |

| D6        | 16       | O           | データ・ビット6. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                   |

| D5        | 17       | O           | データ・ビット5. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                   |

| D4        | 18       | O           | データ・ビット4. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                   |

| D3        | 19       | O           | データ・ビット3. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                   |

| D2        | 20       | O           | データ・ビット2. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                   |

| D1        | 21       | O           | データ・ビット1. CSが“High”またはR/Cが“Low”的とき、ハイ・インピーダンスです。                   |

## ピン構成

|                   |    |   |                                                                                                                                                                       |

|-------------------|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0 (LSB)          | 22 | O | データ・ビット0。変換結果の最下位ビット(LSB)。 $\overline{CS}$ が“High”またはR/ $\overline{C}$ が“Low”的とき、ハイ・インピーダンスです。                                                                        |

| R/ $\overline{C}$ | 24 | I | $\overline{CS}$ が“Low”かつ $\overline{BUSY}$ が“High”的とき、R/ $\overline{C}$ の立ち下がりエッジで新規の変換を開始します。 $\overline{CS}$ が“Low”的とき、R/ $\overline{C}$ の立ち上がりエッジでパラレル出力をイネーブルします。 |

| REF               | 3  |   | リファレンス入力/出力。グランドへ2.2 $\mu$ Fのタンタル・コンデンサを接続します。                                                                                                                        |

| V <sub>ANA</sub>  | 27 |   | アナログ電源入力。公称値+5V。0.1 $\mu$ Fのセラミックと10 $\mu$ Fのタンタル・コンデンサでグランドへデカップリングします。                                                                                              |

| V <sub>DIG</sub>  | 28 |   | デジタル電源入力。公称値+5V。27ピンに直に接続します。V <sub>ANA</sub> 以下であること。                                                                                                                |

| V <sub>IN</sub>   | 1  |   | アナログ入力。図24参照。                                                                                                                                                         |

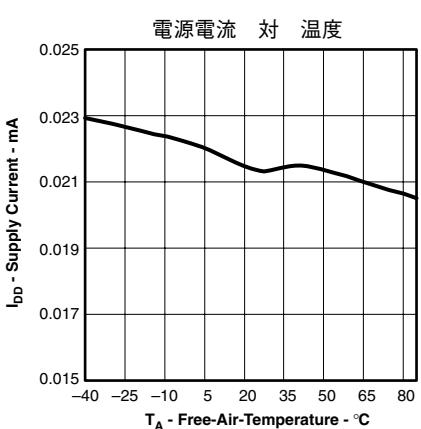

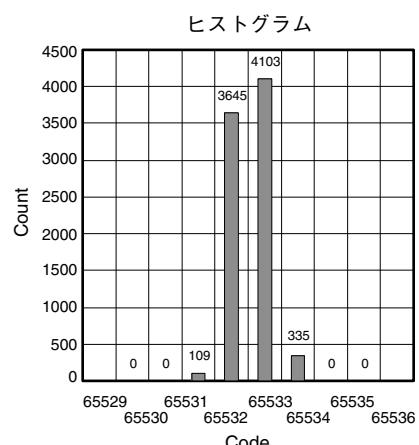

## 代表的特性

図 1

図 2

図 3

図 4

図 5

図 6

## 代表的特性

図 7

図 8

図 9

図 10

図 11

図 12

図 13

図 14

図 15

## 代表的特性

図 16

図 17

図 18

## 基本動作

図19にADS8515がパラレル・データ出力動作をする基本回路を示します。R/C(24ピン)を40ns以上“Low”にすると、変換を開始します。そしてBUSY(26ピン)が“Low”になり、変換が完了し出力レジスタを更新するまでBUSYを“Low”に保持します。データは2の補数バイナリ・フォーマットで出力し、6ピンがMSBです。BUSYの立ち上がりエッジを、データのラッチに使用する事ができます。

ADS8515は変換終了時に入力信号のトラッキングを始めます。変換コマンドの間隔を4μs確保すると、信号を正確にアクイジションすることができます。

## 変換の開始

$\overline{CS}$ (25ピン)とR/C(24ピン)の両方を最低40nsの間“Low”にすると、直ちにADS8515のサンプル/ホールドがホールド状態になり、変換“n”を開始します。BUSY(26ピン)が“Low”になり、変換“n”が完了して内部の出力レジスタが更新されるまでBUSYの“Low”が保持されます。

ADS8515は変換の終わりに入力信号のトラッキングを始めるので、変換コマンドの間隔を4μs確保すると、信号の変化に正確に追従したアクイジションとすることができます。 $\overline{CS}$ , R/CおよびBUSYの各状態については表1を、タイミング図は図21、図22、および図23を参照してください。

$\overline{CS}$ とR/Cは内部でOR接続されておりレベル・トリガーとなっていますので、変換を開始する際、どちらの入力が先に“Low”になるかという条件はありません。しかし、 $\overline{CS}$ あるいはR/Cにより変換“n”が開始しようとする時、タイミングの重要な違いでない入力を開始タイミングを決める入力よりも少なくとも10ns先行させることが必要です。

制御端子の数を少なくするには、 $\overline{CS}$ を“Low”に固定し、R/Cをリードおよび変換モードの制御に使用することができます。R/Cが“High”になると、パラレル出力は常にアクティブになります。以上については、「データの読み取り」項を参照してください。

| $\overline{CS}$ | R/C | BUSY | 動作                                                                                      |

|-----------------|-----|------|-----------------------------------------------------------------------------------------|

| 1               | X   | X    | なし。データ・バスはハイ・インピーダンス状態。                                                                 |

| ↓               | 0   | 1    | 変換“n”的開始。データ・バスはハイ・インピーダンス状態のまま。                                                        |

| 0               | ↓   | 1    | 変換“n”的開始。データ・バスはハイ・インピーダンス状態に入る。                                                        |

| 0               | 1   | ↑    | 変換“n”的終了。変換“n”的有効データがデータ・バス上にある。                                                        |

| ↓               | 1   | 1    | 変換“n”的有効データがあり、データ・バスをイネーブルにする。                                                         |

| ↓               | 1   | 0    | 変換“n-1” <sup>(1)</sup> の有効データがあり、データ・バスをイネーブルにする。変換“n”は進行中。                             |

| 0               | ↑   | 0    | 変換“n-1” <sup>(1)</sup> の有効データがあり、データ・バスをイネーブルにする。変換“n”は進行中。                             |

| 0               | 0   | ↑    | 新信号を収集せずに新しい変換を開始。データは無効。BUSYが“High”になるとき、 $\overline{CS}$ およびR/Cの両方あるいは一方が“High”であること。 |

| X               | X   | 0    | 変換“n”が進行中。                                                                              |

表1. リードおよび変換に関する制御ライン機能

(1) 変換“n-1”からの有効データに関する制約については、図21および図22を参照。

図19. 基本動作

| 解説               | アナログ入力                   | デジタル出力は、2の補数バイナリ    |         |

|------------------|--------------------------|---------------------|---------|

|                  |                          | バイナリ・コード            | ヘキサ・コード |

| フルスケール範囲         | $\pm 10\text{ V}$        |                     |         |

| 最下位ビット( LSB)     | $305\text{ }\mu\text{V}$ |                     |         |

| フルスケール(10V-1LSB) | $9.999695\text{ V}$      | 0111 1111 1111 1111 | 7FFF    |

| ミッドスケール          | 0 V                      | 0000 0000 0000 0000 | 0000    |

| ミッドスケールの1LSB下    | $-305\mu\text{V}$        | 1111 1111 1111 1111 | FFFF    |

| -フルスケール          | -10V                     | 1000 0000 0000 0000 | 8000    |

表2. 理想入力電圧と出力コード

## データの読み取り

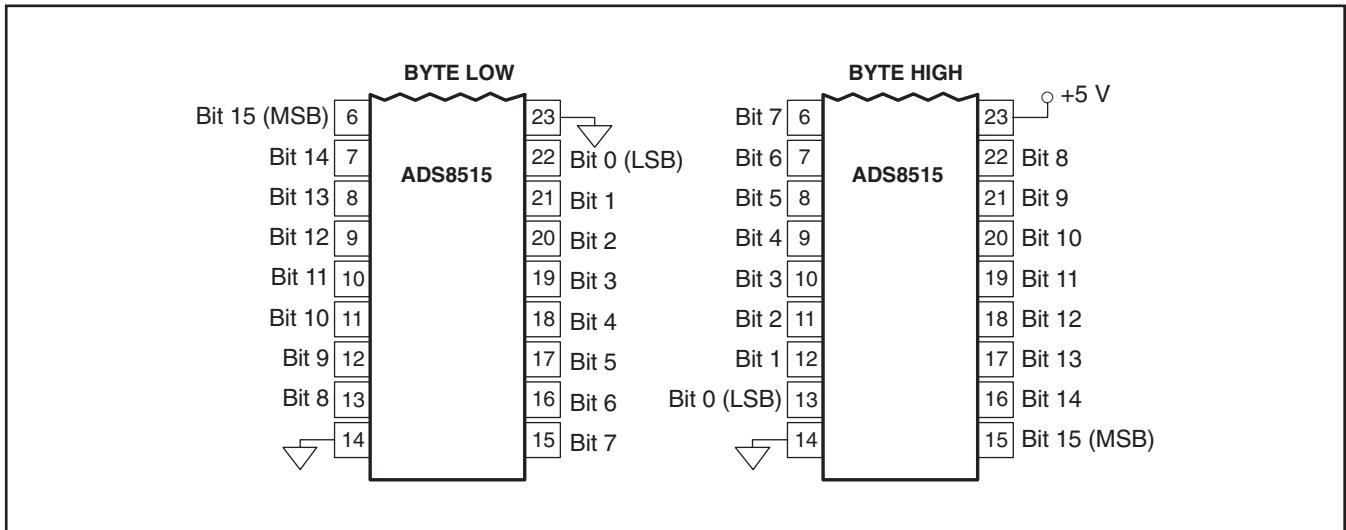

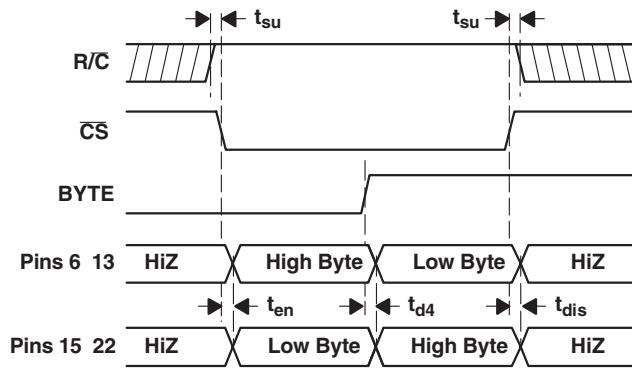

ADS8515は、2の補数バイナリのデータ出力フォーマットで、フルあるいはバイト単位読み取りのパラレル・データを出力します。パラレル・データ出力は、R/C(24ピン)が“High”かつCS(25ピン)が“Low”的ときにアクティブです。CSとR/Cの他の組み合わせでは、すべてパラレル出力はトライ・ステートになります。有効な変換データは、フル・パラレルの16ビット・ワードまたは2個の8ビット・バイトで、6~13ピンおよび15~22ピンにて読み取ることができます。また、BYTE(23ピン)をトグルすると、1変換サイクル内で2バイトを読み取ることができます。理想的な出力コードについては表2を、BYTEの状態によるビット・ロケーションについては図20を参照してください。

## パラレル出力(変換後)

変換“n”が完了して出力レジスタが更新された後、BUSY(26ピン)が“High”になります。このとき、変換“n”的有効データは、D15~D0(6~13および15~22ピン)で得られます。BUSYの“High”になるのを利用してデータをラッチすることができます。以上のタイミング仕様については、表3と図21、図22、および図23を参照してください。

## パラレル出力(変換中)

変換“n”が開始された後、変換“n-1”的有効なデータを読み取ることができます。このデータは変換“n”的開始から最大t<sub>v</sub>まで有効です。変換“n”的開始のt<sub>v</sub>後からBUSY(26ピン)が“High”になるまでの間、データの読み取りを行なってはいけません。これは、無効データを読み取ることになります。以上のタイミング仕様については、表3と図21、図22、および図23を参照してください。

注意：最高の性能を得るには、変換中にデータを読み取らないで下さい。非同期データ伝送のスイッチング・ノイズによりデジタル・フィードスルーが生じ、コンバータの性能が低下します。

CSを“Low”に接続しながら、R/Cの立ち下がりエッジを変換開始に使用し、R/Cの立ち上がりをコンバータの出力モードのイネーブルに使用すると、制御ラインの数を低減することができます。これについては図21をご覧ください。

| 記号                                   | 説明                               | MIN | TYP | MAX | 単位 |

|--------------------------------------|----------------------------------|-----|-----|-----|----|

| t <sub>w1</sub>                      | 変換開始パルス幅                         | 40  |     |     | ns |

| t <sub>a</sub>                       | R/C “Low” 後の有効データアクセス時間          |     | 0.8 | 1.2 | μs |

| t <sub>pd</sub>                      | R/C “Low” からBUSY “Low” までの伝播遅延時間 |     | 6   | 20  | ns |

| t <sub>w2</sub>                      | BUSY “Low” パルス幅                  |     |     | 2   | μs |

| t <sub>d1</sub>                      | 変換終了からBUSYの立ち上がりまでの遅延時間          |     | 5   |     | ns |

| t <sub>d2</sub>                      | アバーチャ遅延時間                        |     | 5   |     | ns |

| t <sub>conv</sub>                    | 変換時間                             |     |     | 2   | μs |

| t <sub>acq</sub>                     | アクイジョン時間                         | 2   |     |     | μs |

| t <sub>dis</sub>                     | バス・ディスエーブル時間                     | 10  | 15  | 83  | ns |

| t <sub>d3</sub>                      | データ有効からBUSYの立ち上がりまでの遅延時間         | 35  | 50  |     | ns |

| t <sub>v</sub>                       | R/C “Low” 後に先のデータが有効である時間        | 1.5 | 2   |     | μs |

| t <sub>conv</sub> + t <sub>acq</sub> | スループット時間                         |     |     | 4   | μs |

| t <sub>su</sub>                      | セットアップ時間、R/CとCSの関係               | 10  |     |     | ns |

| t <sub>c</sub>                       | コンバージョン・サイクル・タイム                 |     | 4   |     | μs |

| t <sub>en</sub>                      | バス・イネーブル時間                       | 10  | 15  | 30  | ns |

| t <sub>d4</sub>                      | BYTE遅延時間                         | 10  | 15  | 30  | ns |

表3. 変換タイミング

図 20. BYTE(23ピン)の状態に対するビット・ロケーション

図 21. 変換後の出力イネーブルの変換タイミング( $\overline{CS}$ を“Low”に固定)

図 22.  $\overline{CS}$ を使用する場合の変換およびリード制御のタイミング

図 23. データ・バスの制御にCSとBYTEを使用

## ADCリセット

ADS8515のADCリセット機能を使用して、現行の変換サイクルを終了することができます。BUSYが“Low”の間にR/Cを最低40nsの間“Low”になると、ADCのリセットが開始されます。新しく変換を開始するにはR/Cが“High”状態に戻し、次の変換を開始するために“Low”にする前に、新しいデータを収集するのに十分な時間(表3のt<sub>c</sub>を参照)、R/Cは“High”を保持する必要があります。BUSY信号を監視しないアプリケーションでは、システムの初期化シーケンスの一部としてADCリセット機能を実装することを推奨します。

## 入力範囲

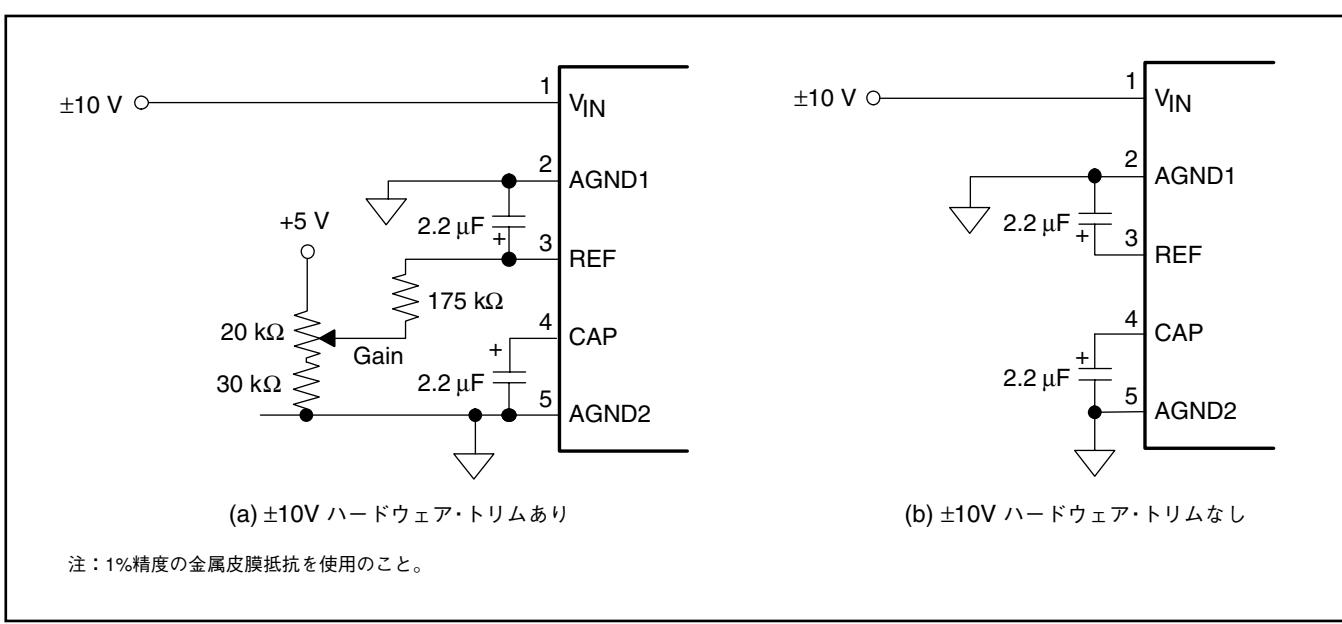

ADS8515は標準の±10V入力範囲を備えています。図25に、外部トリムが有る場合と無い場合のADS8515に必要な回路接続を示します。ADS8515のオフセットおよびフルスケール誤差の仕様は、図25(b)に示す回路で試験および規定されています。フルスケール誤差には、+FSと-FSの両方で測定されたオフセットおよびゲイン誤差が含まれています。オフセットとゲインの調整については、本データシートの「キャリブレーション」節で解説しております。

オフセットとゲインは、単電源の外部トリムが可能であるようにデバイス内部で調整されています。外付け抵抗はこの調整分を補償します。また、オフセットとゲインがソフトウェアで修正される場合、この抵抗は外すことができます(「キャリブレーション」節を参照)。

入力インピーダンスの公称値6.35kΩは、本製品データシートの始めのページで示す内部抵抗網の組み合わせから得られています。この入力抵抗分圧網により、最小±25Vの過電圧保護が達成されています。外付け回路で1%精度の抵抗を使用すると、コンバータの精度およびドリフト特性が悪化しません。1%精度の抵抗は内部抵抗に対してほとんど影響せず、それ以上の精度は必要ありません。

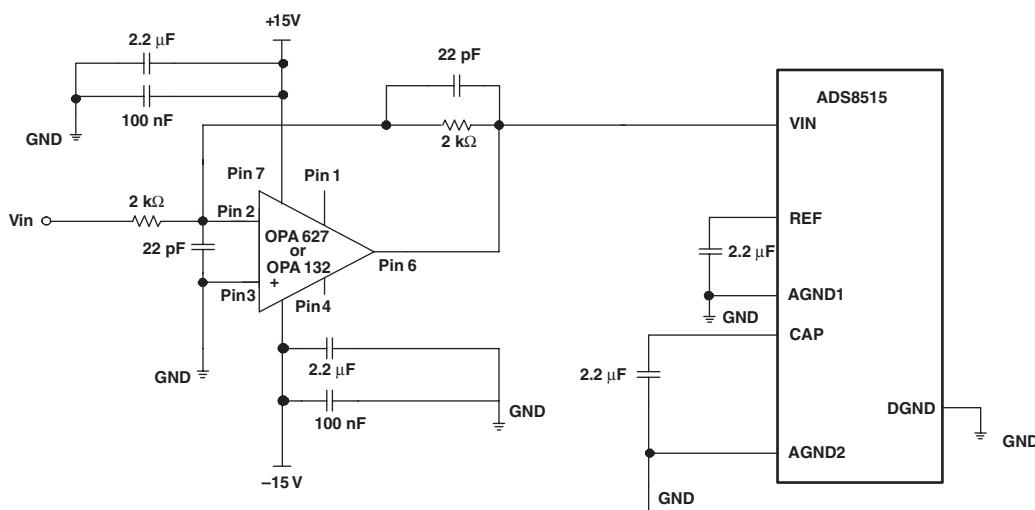

入力信号はAGND1を基準とする必要があります。それによって、アナログ設計にありがちなグランド・ループ問題が最小限に抑えられます。アナログ信号は低インピーダンス信号源によってドライブします。OPA627やOPA132を使用した標準的なドライブ回路を図24に示します。

図 24. 標準的なドライブ回路(±10V, 外部トリムなし)

## アプリケーション情報 キャリブレーション

ADS8515のゲインは、ソフトウェアでトリムすることができます。最適な特性を実現するには、数回の反復調整が必要になります。

### ハードウェア・キャリブレーション

ADS8515のゲインをトリムするため図25(a)に示す抵抗と可変抵抗から成る回路を実装します。ADS8515のゲインの調整範囲はおよそ $\pm 100\text{mV}$ になります。

### ソフトウェア・キャリブレーション

ADS8515のオフセットとゲインはソフトウェアで校正することができます。その回路接続は図25(b)をご覧ください。

### 基準電圧

ADS8515は、内部の4.096Vリファレンスあるいは外部リファレンスで動作できます。外部リファレンスを5ピンに供給すると、内部リファレンスはバイパスされます。REF端子におけるリファレンスは内部でバッファされ、CAP端子(4ピン)に出力されます。

内部リファレンスには8ppm/ $^{\circ}\text{C}$  (Typ) のドリフトがあり、フルスケール誤差(低グレード版でFSE =  $\pm 0.5\%$ 、高グレード版でFSE =  $\pm 0.25\%$ )のおよそ20%を占めています。

### REF端子

REF端子(3ピン)は外部リファレンスには入力であり、内部4.096V基準電圧には出力になります。REF端子には、 $2.2\mu\text{F}$ のコンデンサをできるだけ近くに接続します。このコンデンサとREFの出力抵抗によりローパス・フィルタが形成され、リファレンスのノイズ帯域を制限します。より小さい値のコンデンサを使用した場合、より多くのノイズがリファレンスに乗り、SNRおよびSINADが低下します。REF端子は、外部のACあるいはDC負荷のドライブに使用してはなりません。

コンデンサをできるだけ近くに接続します。このコンデンサとREFの出力抵抗によりローパス・フィルタが形成され、リファレンスのノイズ帯域を制限します。より小さい値のコンデンサを使用した場合、より多くのノイズがリファレンスに乗り、SNRおよびSINADが低下します。REF端子は、外部のACあるいはDC負荷のドライブに使用してはなりません。

外部リファレンスの範囲は3.9Vから4.2Vであり、これによって実際の LSB サイズが定まります。リファレンス電圧を高くすると、コンバータのフルスケール範囲およびLSBサイズが大きくなり、SNRを改善することができます。

### CAP端子

CAP端子(4ピン)は内部リファレンス・バッファの出力です。CAP端子には $2.2\mu\text{F}$ のコンデンサをできるだけ近くに接続して、変換サイクルの間CDACに最適なスイッチング電流を供給し、また、内部バッファ出力の補償を行います。 $1\mu\text{F}$ より小さいコンデンサを使用すると、出力バッファに発振が生じ、さらにCDACへの充電電荷が不足します。 $2.2\mu\text{F}$ より大きな値のコンデンサは、特性の改善にほとんど寄与しません。これら補償用コンデンサのESR(等価直列抵抗)も重要です。全体のESRは $3\Omega$ より低くしてください。

バッファの出力は、最大2mAの電流をDC負荷にドライブする能力があります。しかし、CAP端子におけるあらゆる外部負荷によりADS8515の直線性は劣化します。外部バッファを使用すると、内部リファレンスはより大きなDC負荷およびAC負荷に使用することができます。CAP端子の出力電圧でAC負荷を直接ドライブしてはなりません。これを行うと、コンバータの性能低下が生じます。

図 25. ソフトウェア・トリミング用の回路図

## レイアウト

### 電源

最適特性を実現するため、アナログおよびデジタルの電源端子は同一の+5V電源に接続し、アナログおよびデジタルのグランドは相互に接続します。電気的仕様で述べたように、ADS8515はその電力の90%をアナログ回路で消費します。したがって、ADS8515はアナログ部品として見なすべきです。

ADコンバータ用の+5V電源は、システムのデジタル・ロジックに使用される+5V電源から分離します。 $V_{DIG}$  (28ピン) を直接にデジタル用電源に接続すると、デジタル・ロジックからのスイッチング・ノイズによりコンバータの性能が低下します。最高の性能を得るには、アナログ・シグナル・コンディショニング以外に使用されているアナログ電源から+5V電源を作ります。 $+12V$ や $+15V$ 電源がある場合は、単純な+5Vレギュレータが使用できます。勧められることではありませんが、デジタル電源からコンバータに電力を供給しなければならない場合は、その電源を適切にフィルタリングします。フィルタリングしたデジタル電源であれ、レギュレーションしたアナログ電源であれ、それを使用するときは $V_{DIG}$ および $V_{ANA}$ を同一の+5V電源に接続します。

### グランドの取り方

3本のグランド端子がADS8515にあります。 $DGND$ はデジタル電源用のグランドです。 $AGND2$ はアナログ電源用グランドです。 $AGND1$ は、AD内部へのすべてのアナログ信号の基準となるグランドです。 $AGND1$ は電流誘起による電圧降下に対してより敏感であり、電源への最小抵抗の帰路がなければなりません。

ADのグランド端子は、すべてアナログ・グランドのプレーンに接続し、システムのデジタル・ロジック・グランドから分離して最適な性能を実現します。アナログおよびデジタル・グランドのプレーンは、ともに電源にできるだけ近い所でシステム・グランドに接続します。このように接続すると、電源グランドへの共通インピーダンスを経由して、デジタル・グランドのダイナミック電流がアナログ・グランドを変調するのを防止します。

### シグナル・コンディショニング

多くのCMOS ADコンバータのサンプル・ホールド回路で使用されるFETスイッチは、オペアンプを発振に至らしめる非常に大量のチャージ・インジェクションを生じさせることができます。ADS8515のFETスイッチは、他のCMOS ADコンバータのFETスイッチに比べ、電荷注入量は5%から10%に過ぎません。また、抵抗性のフロントエンド回路があり、注入されたあらゆる電荷が減衰されます。その結果、フロントエンドにおけるアンチ・エイリアシング・フィルタの要求条件が最小限度に緩和されます。アプリケーションにおいて信号を十分ドライブできるオペアンプならば、ADS8515をも十分にドライブできます。

また、ADS8515は抵抗によるフロントエンド回路により、 $\pm 25V$ の過電圧から保護されます。ほとんどの場合、このフロントエンドによって外部の入力保護回路が不要になります。

### 中間ラッチ

ADS8515のパラレル・ポートはトライ・ステート出力ですが、変換中にもバスがアクティブであることが必要な場合は、中間ラッチを使用します。バスが変換中にアクティブでない場合、トライ・ステート出力を使用してADを同一バスの他の周辺装置から分離することができます。また、ADがデータ・バスの唯一の周辺装置である場合も、トライ・ステート出力が使用できます。

中間ラッチは、あらゆるモノリシックADコンバータに役立ちます。ADS8515の内部では、1 LSB当り $38\mu V$ です。パラレル・ポートの高速スイッチング信号によるトランジメントは、AD出力がトライ・ステートの場合でもサブストレートを経由してアナログ回路と結合し、コンバータの性能劣化の原因になります。

**PACKAGING INFORMATION**

| Orderable part number        | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|------------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">ADS8515IBDB</a>  | Active        | Production           | SSOP (DB)   28 | 50   TUBE             | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 85    | ADS8515I<br>B       |

| ADS8515IBDB.A                | Active        | Production           | SSOP (DB)   28 | 50   TUBE             | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 85    | ADS8515I<br>B       |

| <a href="#">ADS8515IBDBR</a> | Active        | Production           | SSOP (DB)   28 | 2000   LARGE T&R      | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 85    | ADS8515I<br>B       |

| ADS8515IBDBR.A               | Active        | Production           | SSOP (DB)   28 | 2000   LARGE T&R      | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 85    | ADS8515I<br>B       |

| <a href="#">ADS8515IDB</a>   | Active        | Production           | SSOP (DB)   28 | 50   TUBE             | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 85    | ADS8515I            |

| ADS8515IDB.A                 | Active        | Production           | SSOP (DB)   28 | 50   TUBE             | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 85    | ADS8515I            |

| <a href="#">ADS8515IDBR</a>  | Active        | Production           | SSOP (DB)   28 | 2000   LARGE T&R      | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 85    | ADS8515I            |

| ADS8515IDBR.A                | Active        | Production           | SSOP (DB)   28 | 2000   LARGE T&R      | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 85    | ADS8515I            |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

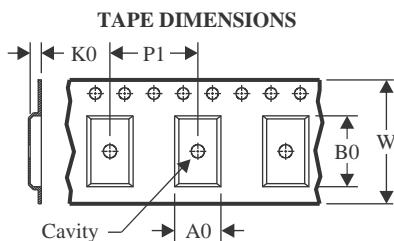

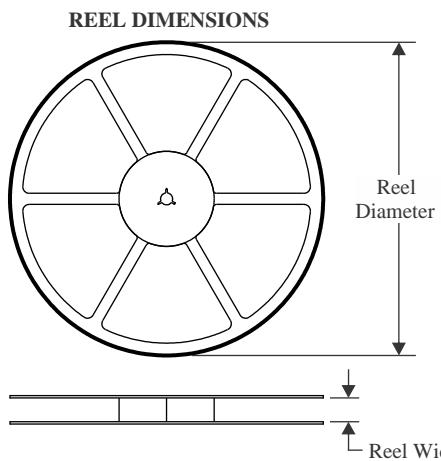

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

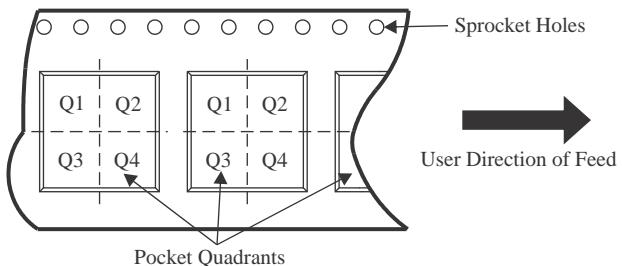

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| ADS8515IBDBR | SSOP         | DB              | 28   | 2000 | 330.0              | 16.4               | 8.1     | 10.4    | 2.5     | 12.0    | 16.0   | Q1            |

| ADS8515IDBR  | SSOP         | DB              | 28   | 2000 | 330.0              | 16.4               | 8.1     | 10.4    | 2.5     | 12.0    | 16.0   | Q1            |

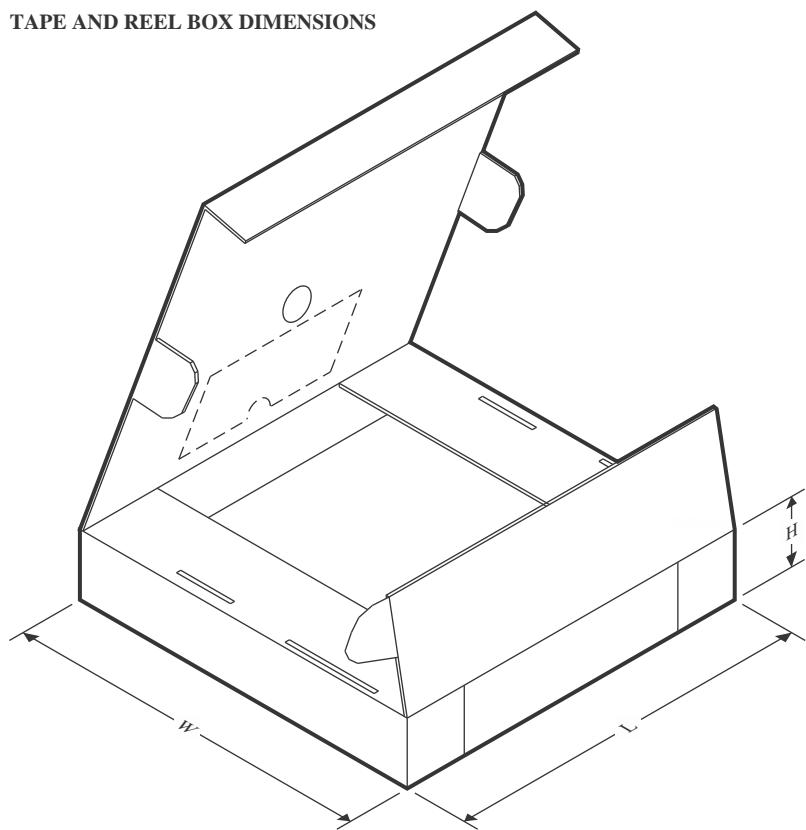

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ADS8515IBDBR | SSOP         | DB              | 28   | 2000 | 350.0       | 350.0      | 43.0        |

| ADS8515IDBR  | SSOP         | DB              | 28   | 2000 | 350.0       | 350.0      | 43.0        |

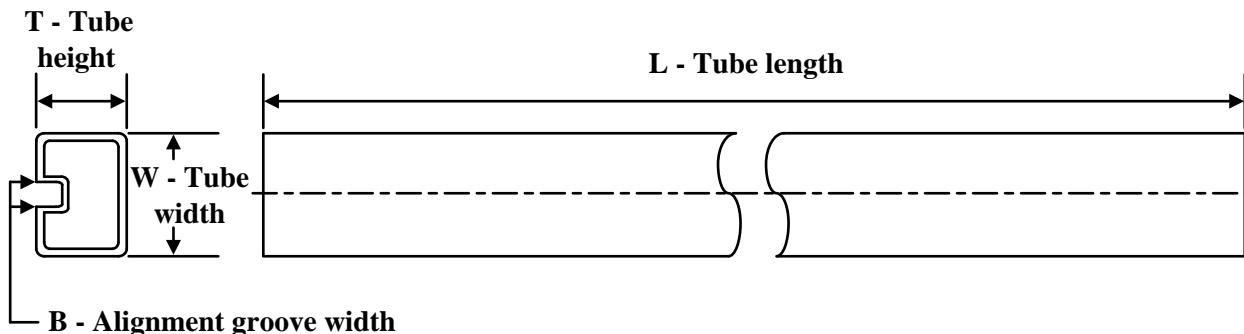

**TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| ADS8515IBDB   | DB           | SSOP         | 28   | 50  | 530    | 10.5   | 4000         | 4.1    |

| ADS8515IBDB.A | DB           | SSOP         | 28   | 50  | 530    | 10.5   | 4000         | 4.1    |

| ADS8515IDB    | DB           | SSOP         | 28   | 50  | 530    | 10.5   | 4000         | 4.1    |

| ADS8515IDB.A  | DB           | SSOP         | 28   | 50  | 530    | 10.5   | 4000         | 4.1    |

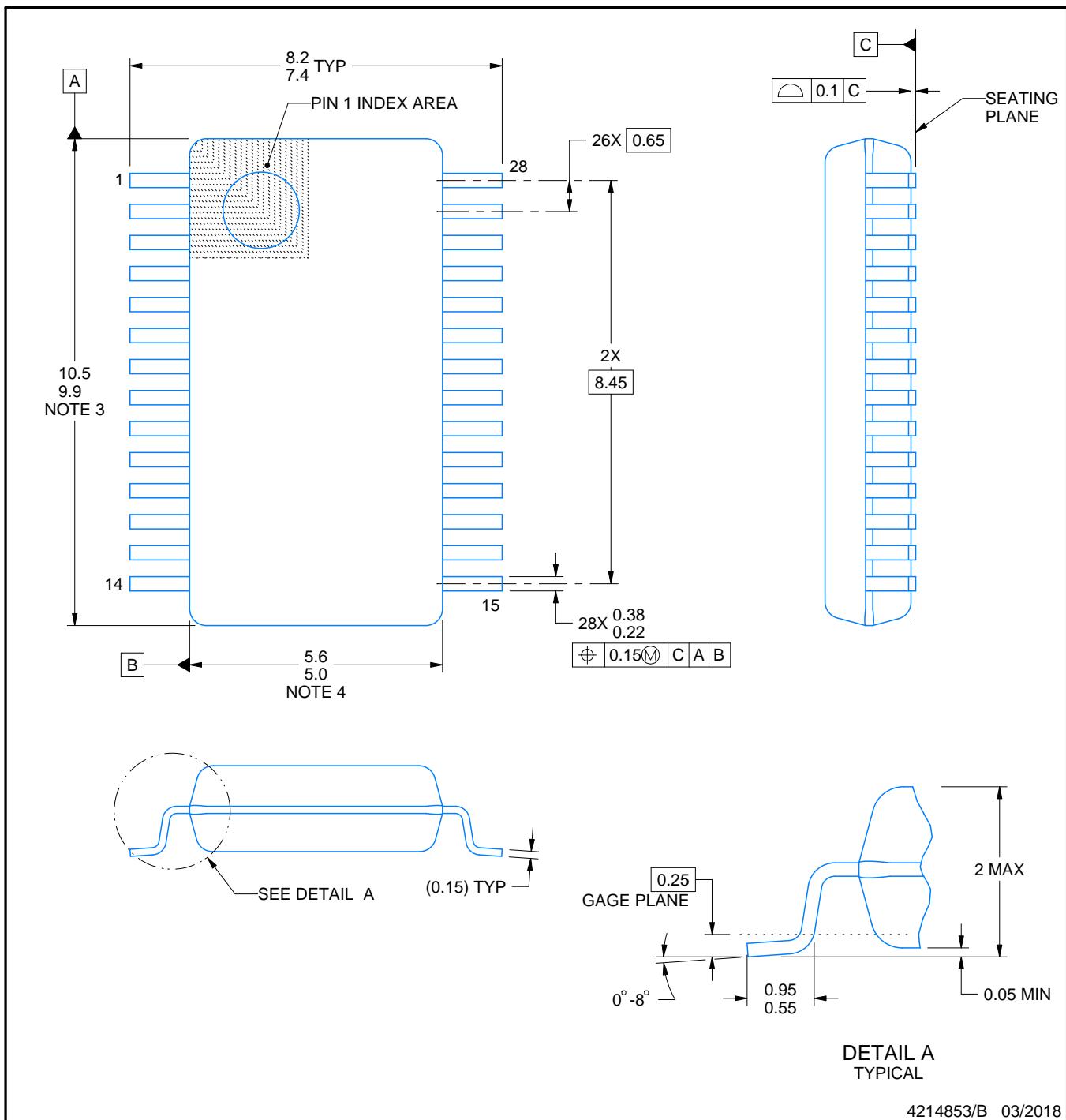

# PACKAGE OUTLINE

## SSOP - 2 mm max height

SMALL OUTLINE PACKAGE

### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- Reference JEDEC registration MO-150.

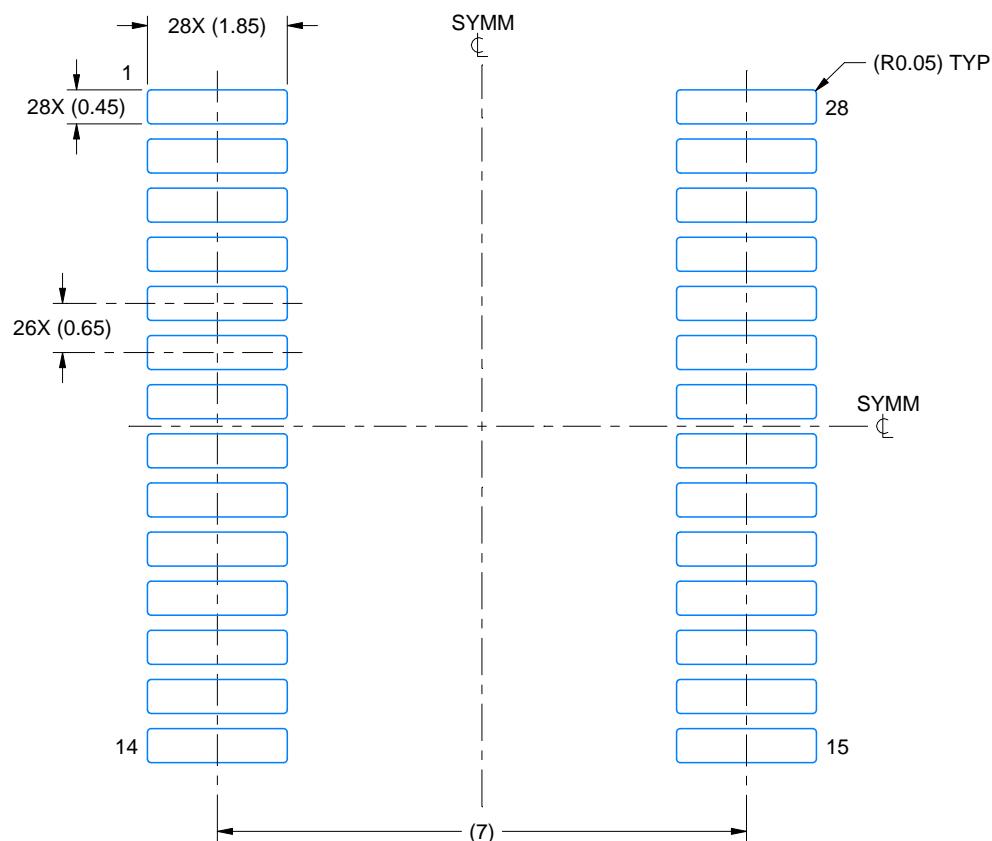

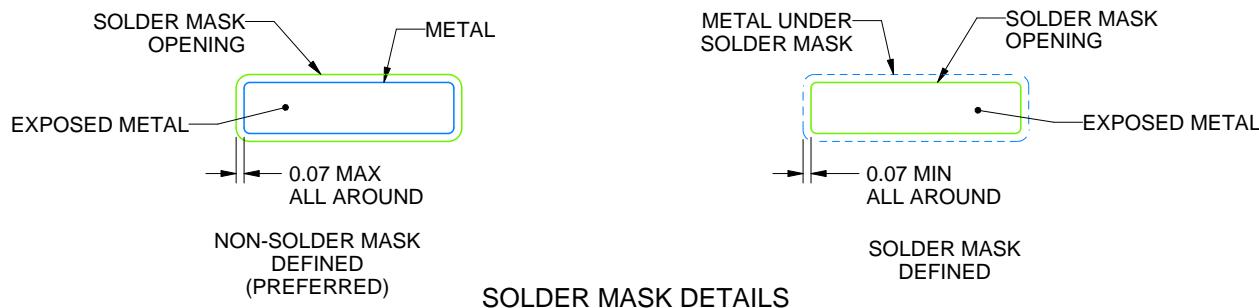

# EXAMPLE BOARD LAYOUT

DB0028A

SSOP - 2 mm max height

SMALL OUTLINE PACKAGE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 10X

4214853/B 03/2018

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

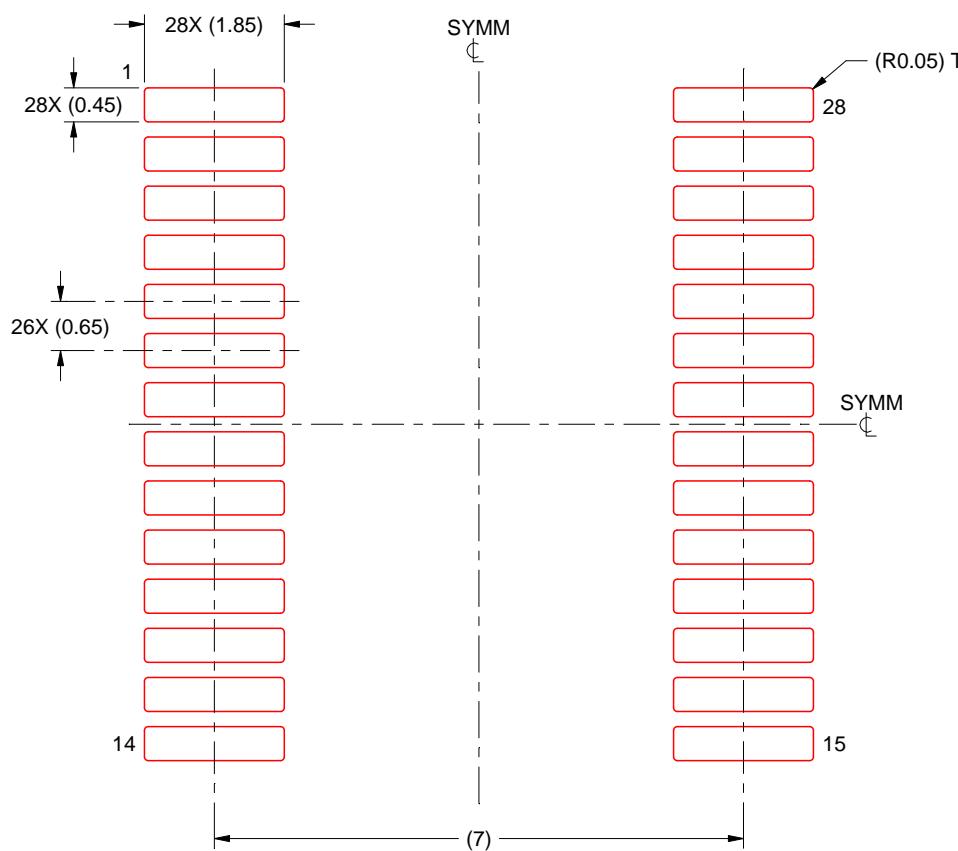

# EXAMPLE STENCIL DESIGN

DB0028A

SSOP - 2 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 10X

4214853/B 03/2018

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月