# ADS868xW 16 ビット、500kSPS、4 および 8 チャネル、単一電源、SAR ADC、バイポーラ入力範囲に対応

## 1 特長

- アナログ フロント エンド内蔵の 16 ビット ADC

- 自動/手動スキャン機能搭載 4-、8 チャネル マルチプレクサ

- チャネルを独立してプログラム可能な入力:

- $\pm 12.288V$ 、 $\pm 6.144V$ 、 $\pm 3.072V$

- $12.288V \sim 0V$  および  $6.144V \sim 0V$

- 5V アナログ電源:  $1.65V \sim 5V$  の I/O 電源

- 一定の抵抗性入力インピーダンス:  $1.2M\Omega$

- 入力過電圧保護: 最大  $\pm 20V$

- オンチップの低ドリフト  $4.096V$  リファレンス

- 優れた性能:

- 500kSPS 集約スループット

- DNL:  $\pm 0.6LSB$ 、INL:  $\pm 0.8LSB$

- ゲイン誤差とオフセットの低ドリフト

- 信号対雑音比:  $91.5dB$ 、THD:  $-102dB$

- 低消費電力:  $65mW$

- AUX 入力 → ADC 入力への直接接続

- ALARM → チャネルあたりの High および Low スレッショルド

- デイジーチェーン接続に対応した SPI™ 互換インターフェイス

- 産業用温度範囲:  $-40^\circ C \sim 125^\circ C$

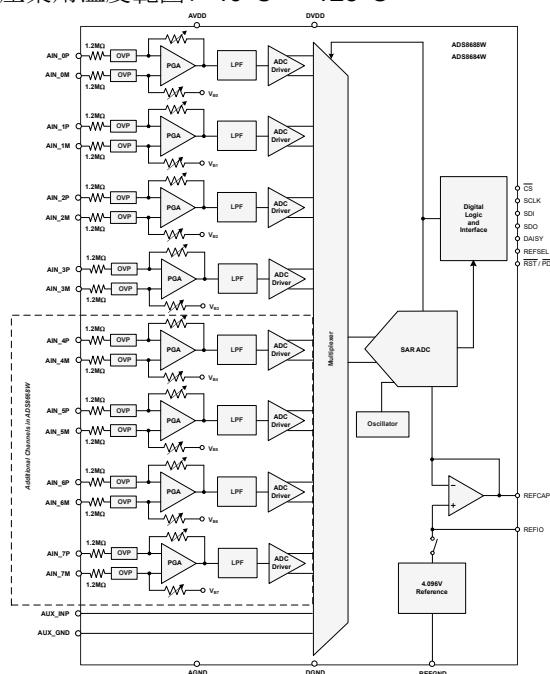

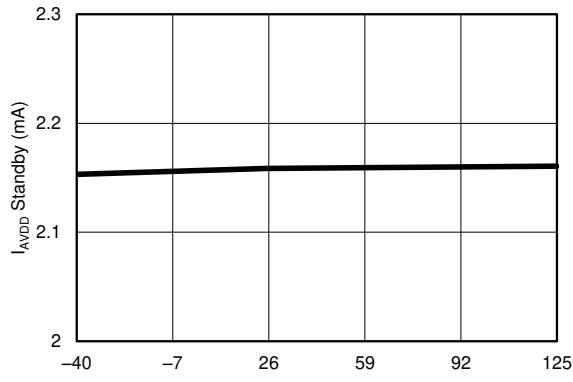

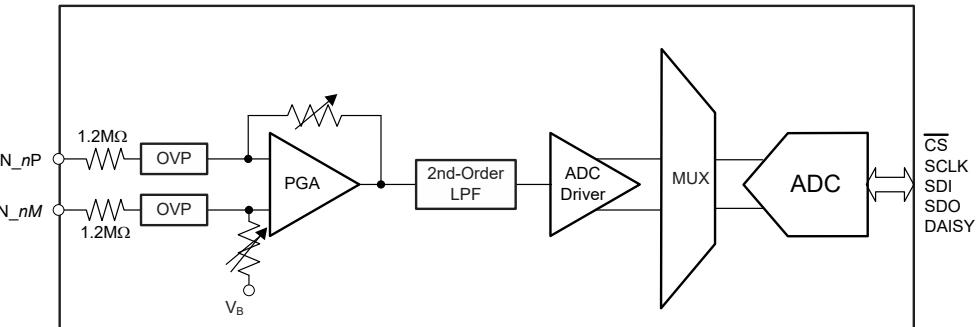

ブロック図

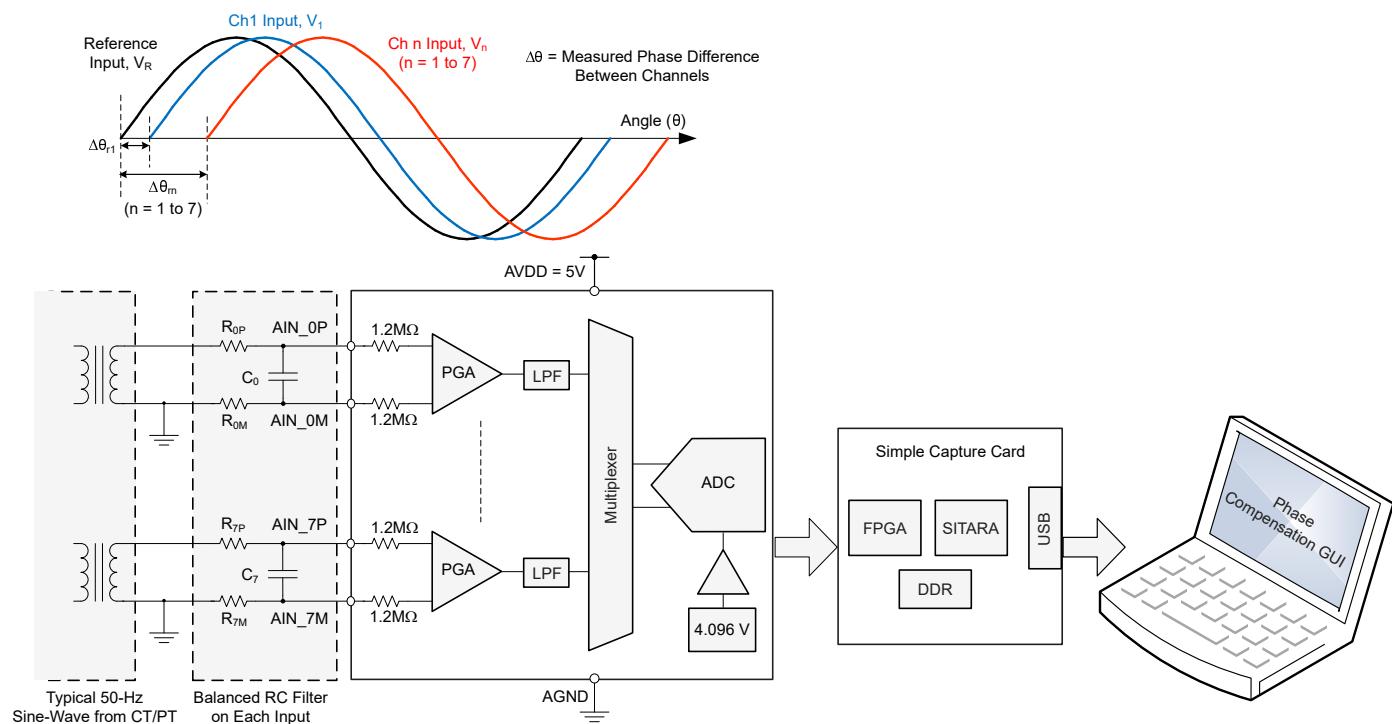

## 2 アプリケーション

- アナログ入力モジュール

- AC 伝送リレー

## 3 説明

ADS8684W および ADS8688W は、16 ビット逐次比較型 (SAR) A/D コンバータ (ADC) をベースとした 4 チャネルおよび 8 チャネルの統合型データ収集システムで、500kSPS のスループットで動作します。デバイスには、各入力チャネルに最大  $\pm 20V$  の過電圧保護を備えたアナログ フロント エンド回路、自動および手動スキャン モードを備えた 4 チャネルまたは 8 チャネルのマルチプレクサ、そして低温度ドリフト係数の低いオンチップ  $4.096V$  リファレンス電圧が内蔵されています。5V 単一アナログ電源で動作し、デバイスの各入力チャネルは  $\pm 12.288V$ 、 $\pm 6.144V$ 、 $\pm 3.072V$  のバイポーラ入力範囲と、 $12.288V \sim 0V$  および  $6.144V \sim 0V$  のユニポーラ入力範囲に対応できます。

ADS8684W および ADS8688W には、デジタル ホストと接続するための単純な SPI 互換のシリアル インターフェイスがあり、複数のデバイスをデイジーチェーン接続できます。デジタル電源は  $1.65V \sim 5.25V$  で動作し、広範なホストコントローラと直接接続できます。

## パッケージ情報

| 部品番号                  | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|-----------------------|----------------------|-------------------------|

| ADS8684W、<br>ADS8688W | DBT (TSSOP、38)       | 9.70mm × 6.40mm         |

(1) 詳細については、[セクション 12](#) を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はビンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|              |    |                         |    |

|--------------|----|-------------------------|----|

| 1 特長         | 1  | 7.4 デバイスの機能モード          | 37 |

| 2 アプリケーション   | 1  | 8 レジスタ マップ              | 52 |

| 3 説明         | 1  | 8.1 コマンド レジスタの説明        | 52 |

| 4 デバイス比較表    | 3  | 8.2 プログラム レジスタの説明       | 53 |

| 5 ピン構成および機能  | 3  | 9 アプリケーションと実装           | 71 |

| 6 仕様         | 5  | 9.1 アプリケーション情報          | 71 |

| 6.1 絶対最大定格   | 5  | 9.2 代表的なアプリケーション        | 71 |

| 6.2 ESD 定格   | 5  | 9.3 電源に関する推奨事項          | 72 |

| 6.3 推奨動作条件   | 6  | 9.4 レイアウト               | 73 |

| 6.4 熱に関する情報  | 6  | 10 デバイスおよびドキュメントのサポート   | 75 |

| 6.5 電気的特性    | 7  | 10.1 ドキュメントのサポート        | 75 |

| 6.6 タイミング要件  | 10 | 10.2 ドキュメントの更新通知を受け取る方法 | 75 |

| 6.7 スイッチング特性 | 11 | 10.3 サポート・リソース          | 75 |

| 6.8 タイミング図   | 12 | 10.4 商標                 | 75 |

| 6.9 代表的特性    | 13 | 10.5 静電気放電に関する注意事項      | 75 |

| 7 詳細説明       | 21 | 10.6 用語集                | 75 |

| 7.1 概要       | 21 | 11 改訂履歴                 | 75 |

| 7.2 機能ブロック図  | 22 | 12 メカニカル、パッケージ、および注文情報  | 76 |

| 7.3 機能説明     | 22 |                         |    |

## 4 デバイス比較表

| 製品名     | 分解能 (ビット数) | チャネル      | サンプル レート (kSPS) |

|---------|------------|-----------|-----------------|

| ADS8674 | 14         | 4、シングルエンド | 500             |

| ADS8678 | 14         | 8、シングルエンド | 500             |

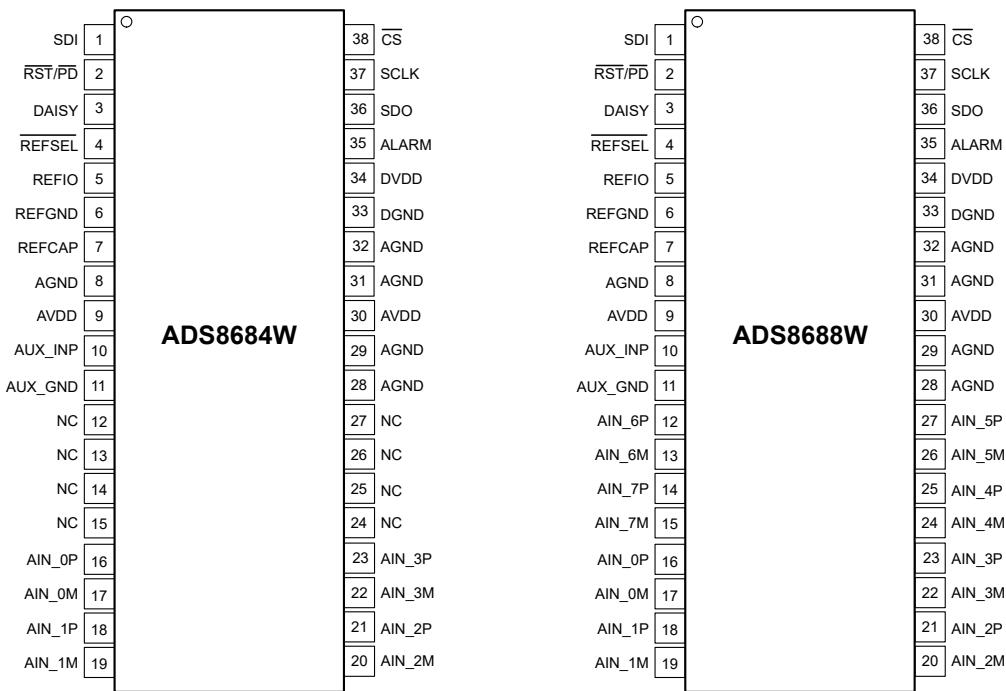

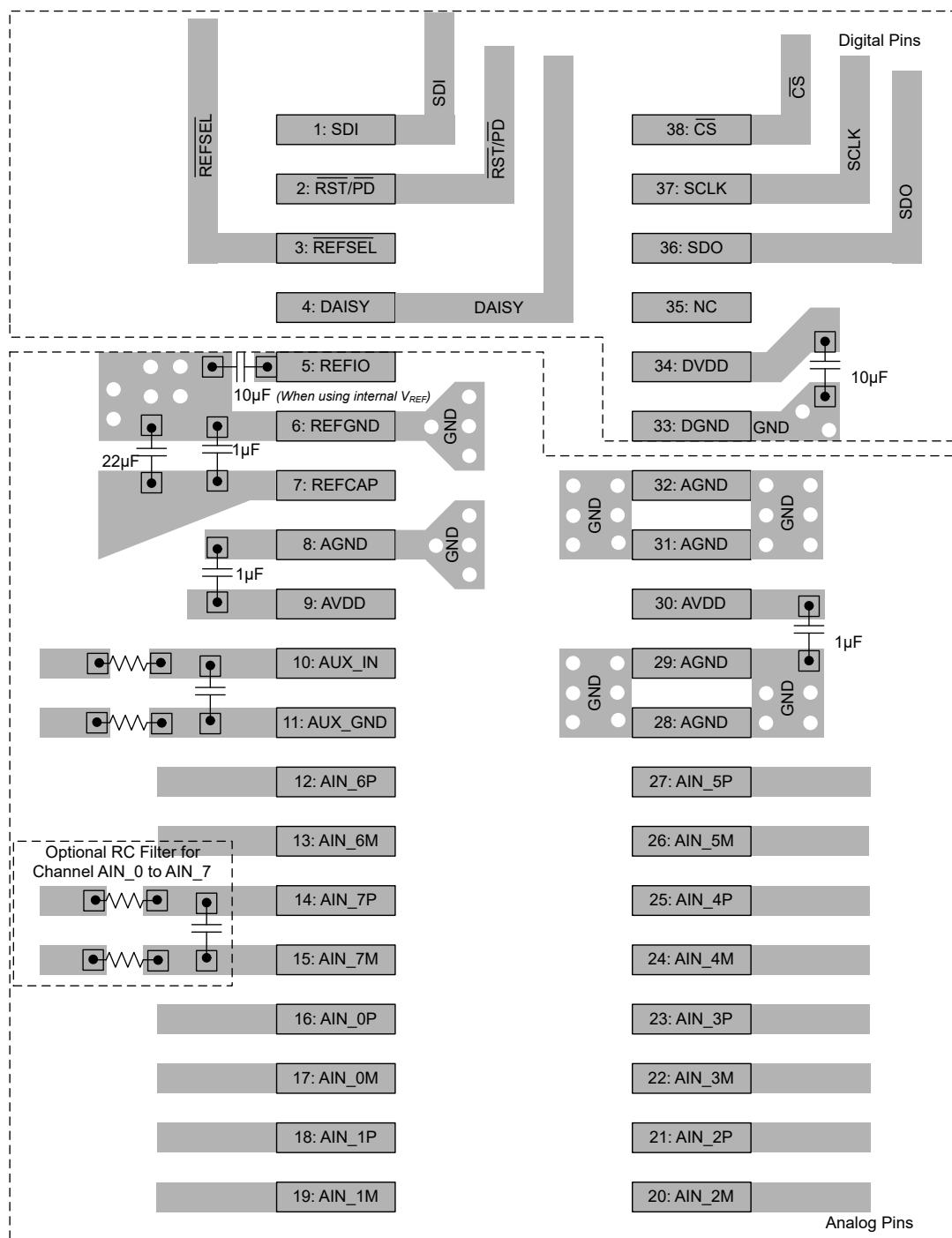

## 5 ピン構成および機能

図 5-1. DBT パッケージ、38 ピン TSSOP 上面図 (原寸に比例していない)

表 5-1. ピンの機能

| 番号 | ピン       |           | タイプ    | 説明                                                                                                                                                                    |  |  |

|----|----------|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    | 名称       |           |        |                                                                                                                                                                       |  |  |

|    | ADS8684W | ADS8688W  |        |                                                                                                                                                                       |  |  |

| 1  | SDI      |           | デジタル入力 | シリアル通信用データ入力。                                                                                                                                                         |  |  |

| 2  | RST/PD   |           | デジタル入力 | アクティブ low のロジック入力。<br>デバイスをリセットまたはパワーダウンするデュアル機能。                                                                                                                     |  |  |

| 3  | DAISY    |           | デジタル入力 | デイジーチェーン モードでのシリアル通信中のチェーン データ入力。                                                                                                                                     |  |  |

| 4  | REFSEL   |           | デジタル入力 | 内部リファレンス電圧を有効するためのアクティブ Low ロジック入力。<br>Low になると、内部リファレンスが有効化。<br>REFIO は $V_{REF}$ 電圧を含む出力となります。<br>High になると、内部リファレンスが無効化。<br>REFIO は外部 $V_{REF}$ 電圧を印加するための入力になります。 |  |  |

| 5  | REFIO    | アナログ入力、出力 |        | 内部リファレンス出力と外部リファレンス入力ピン。ピン 6 の REFGND でデカップリング。                                                                                                                       |  |  |

| 6  | REFGND   | 電源        |        | リファレンス GND ピン。アナログ GND プレーンに短絡。<br>ピン 5 の REFIO、ピン 7 の REFCAP でデカップリング。                                                                                               |  |  |

| 7  | REFCAP   | アナログ出力    |        | ADC リファレンス デカップリング コンデンサ ピン。ピン 6 の REFGND でデカップリング。                                                                                                                   |  |  |

| 8  | AGND     | 電源        |        | アナログ グラウンド ピン。ピン 9 の AVDD でデカップリング。                                                                                                                                   |  |  |

| 9  | AVDD     | 電源        |        | アナログ電源ピン。ピン 8 の AGND でデカップリング。                                                                                                                                        |  |  |

| 10 | AUX_INP  | アナログ入力    |        | 補助入力チャネル: 正入力。ピン 11 の AUX_GND でデカップリング。                                                                                                                               |  |  |

| 11 | AUX_GND  | アナログ入力    |        | 補助入力チャネル: 負入力。ピン 10 の AUX_INP でデカップリング。                                                                                                                               |  |  |

表 5-1. ピンの機能 (続き)

| 番号 | ピン       |          | タイプ    | 説明                                                                                                      |  |  |

|----|----------|----------|--------|---------------------------------------------------------------------------------------------------------|--|--|

|    | 名称       |          |        |                                                                                                         |  |  |

|    | ADS8684W | ADS8688W |        |                                                                                                         |  |  |

| 12 | NC       | AIN_6P   | アナログ入力 | アナログ入力チャネル 6、正入力。ピン 13 の AIN_6M でデカップリング。<br>ADS8684W はノー コネクション。このピンは接続せずにフローティング状態にしておくか、AGND に接続します。 |  |  |

| 13 | NC       | AIN_6M   | アナログ入力 | アナログ入力チャネル 6、負入力。ピン 12 の AIN_6P でデカップリング。<br>ADS8684W はノー コネクション。このピンは接続せずにフローティング状態にしておくか、AGND に接続します。 |  |  |

| 14 | NC       | AIN_7P   | アナログ入力 | アナログ入力チャネル 7、正入力。ピン 15 の AIN_7M でデカップリング。<br>ADS8684W はノー コネクション。このピンは接続せずにフローティング状態にしておくか、AGND に接続します。 |  |  |

| 15 | NC       | AIN_7M   | アナログ入力 | アナログ入力チャネル 7、負入力。ピン 14 の AIN_7P でデカップリング。<br>ADS8684W はノー コネクション。このピンは接続せずにフローティング状態にしておくか、AGND に接続します。 |  |  |

| 16 | AIN_0P   |          | アナログ入力 | アナログ入力チャネル 0、正入力。ピン 17 の AIN_0M でデカップリング。                                                               |  |  |

| 17 | AIN_0M   |          | アナログ入力 | アナログ入力チャネル 0、負入力。ピン 16 の AIN_0P でデカップリング。                                                               |  |  |

| 18 | AIN_1P   |          | アナログ入力 | アナログ入力チャネル 1、正入力。ピン 19 の AIN_1M でデカップリング。                                                               |  |  |

| 19 | AIN_1M   |          | アナログ入力 | アナログ入力チャネル 1、負入力。ピン 18 の AIN_1P でデカップリング。                                                               |  |  |

| 20 | AIN_2M   |          | アナログ入力 | アナログ入力チャネル 2、負入力。ピン 21 の AIN_2P でデカップリング。                                                               |  |  |

| 21 | AIN_2P   |          | アナログ入力 | アナログ入力チャネル 2、正入力。ピン 20 の AIN_2M でデカップリング。                                                               |  |  |

| 22 | AIN_3M   |          | アナログ入力 | アナログ入力チャネル 3、負入力。ピン 23 の AIN_3P でデカップリング。                                                               |  |  |

| 23 | AIN_3P   |          | アナログ入力 | アナログ入力チャネル 3、正入力。ピン 22 の AIN_3M でデカップリング。                                                               |  |  |

| 24 | NC       | AIN_4M   | アナログ入力 | アナログ入力チャネル 4、負入力。ピン 25 の AIN_4P でデカップリング。<br>ADS8684W はノー コネクション。このピンは接続せずにフローティング状態にしておくか、AGND に接続します。 |  |  |

| 25 | NC       | AIN_4P   | アナログ入力 | アナログ入力チャネル 4、正入力。ピン 24 の AIN_4M でデカップリング。<br>ADS8684W はノー コネクション。このピンは接続せずにフローティング状態にしておくか、AGND に接続します。 |  |  |

| 26 | NC       | AIN_5M   | アナログ入力 | アナログ入力チャネル 5、負入力。ピン 27 の AIN_5P でデカップリング。<br>ADS8684W はノー コネクション。このピンは接続せずにフローティング状態にしておくか、AGND に接続します。 |  |  |

| 27 | NC       | AIN_5P   | アナログ入力 | アナログ入力チャネル 5、正入力。ピン 26 の AIN_5M でデカップリング。<br>ADS8684W はノー コネクション。このピンは接続せずにフローティング状態にしておくか、AGND に接続します。 |  |  |

| 28 | AGND     |          | 電源     | アナログ グランドピン                                                                                             |  |  |

| 29 | AGND     |          | 電源     | アナログ グランドピン                                                                                             |  |  |

| 30 | AVDD     |          | 電源     | アナログ電源ピン。ピン 31 の AGND でデカップリング。                                                                         |  |  |

| 31 | AGND     |          | 電源     | アナログ グランドピン。ピン 30 の AVDD でデカップリング。                                                                      |  |  |

| 32 | AGND     |          | 電源     | アナログ グランドピン。                                                                                            |  |  |

| 33 | DGND     |          | 電源     | デジタル グランドピン。ピン 34 の DVDD でデカップリング。                                                                      |  |  |

| 34 | DVDD     |          | 電源     | デジタル電源ピン。ピン 33 の DGND でデカップリング。                                                                         |  |  |

| 35 | ALARM    |          | デジタル出力 | アクティブ High アラーム出力。                                                                                      |  |  |

| 36 | SDO      |          | デジタル出力 | シリアル通信用データ出力。                                                                                           |  |  |

| 37 | SCLK     |          | デジタル入力 | シリアル通信用クロック入力。100Ω 抵抗を SCLK ピンの近くに直列に接続します。                                                             |  |  |

| 38 | CS       |          | デジタル入力 | アクティブ Low ロジック入力。チップ セレクト信号。                                                                            |  |  |

## 6 仕様

### 6.1 絶対最大定格

動作周囲温度範囲の全体にわたって (特に記述のない限り)<sup>(1)</sup>

|                                      |                            | 最小値  | 最大値        | 単位 |

|--------------------------------------|----------------------------|------|------------|----|

| AIN_nP, AIN_nM から AGND へ             | AVDD = 5V <sup>(2)</sup>   | -20  | 20         | V  |

|                                      | AVDD = 電源オフ <sup>(3)</sup> | -15  | 15         |    |

| AUX_INP および AUX_GND から AGND へ        |                            | -0.3 | AVDD + 0.3 | V  |

| AVDD から AGND または DVDD から DGND へ      |                            | -0.3 | 7          | V  |

| REFCAP から REFGND または REFIO から REFGND |                            | -0.3 | 5.7        | V  |

| AGND から REFGND へ                     |                            | -0.3 | 0.3        | V  |

| AGND から DGND へ                       |                            | -0.3 | 0.3        | V  |

| デジタル入力ピンから DGND                      |                            | -0.3 | DVDD + 0.3 | V  |

| デジタル出力ピンから DGND                      |                            | -0.3 | DVDD + 0.3 | V  |

| 電源ピンを除く任意のピンへの入力電流                   |                            | -10  | 10         | mA |

| 接合部温度、 $T_J$                         |                            | -40  | 150        | °C |

| 保管温度、 $T_{stg}$                      |                            | -60  | 150        | °C |

- (1) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) AVDD = 5V またはは、ソースインピーダンス 30kΩ 以下を提供します。

- (3) AVDD = ソースインピーダンス 30kΩ 以上でフローティングです。

### 6.2 ESD 定格

|             |      |                                                                                | 値     | 単位 |

|-------------|------|--------------------------------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠、アナログ入力ピン (AIN_nP, AIN_nM) <sup>(1)</sup> | ±6000 | V  |

|             |      | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、他すべてのピン <sup>(1)</sup>                  | ±2000 |    |

|             |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup>               | ±500  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ            |                               | テスト条件                            | 最小値     | 標準値    | 最大値   | 単位 |

|------------------|-------------------------------|----------------------------------|---------|--------|-------|----|

| <b>電源</b>        |                               |                                  |         |        |       |    |

| AVDD             | アナログ電源                        | AVDD から AGND へ                   | 4.75    | 5      | 5.25  | V  |

| DVDD             | デジタル インターフェイス電源               | DVDD から DGND へ                   | 1.65    | 3.3    | AVDD  | V  |

| <b>基準電圧</b>      |                               |                                  |         |        |       |    |

| $V_{REFIO\_EXT}$ | REFIO での外部リファレンス電圧            | REFIO ピンは入力として構成                 | 4.046   | 4.096  | 4.146 | V  |

| <b>アナログ入力</b>    |                               |                                  |         |        |       |    |

| AIN_x            | フルスケール入力スパン (AIN_nP ~ AIN_nM) | 入力範囲 = $\pm 3 \times V_{REF}$    | -12.288 | 12.288 | V     |    |

|                  |                               | 入力範囲 = $\pm 1.5 \times V_{REF}$  | -6.144  | 6.144  |       |    |

|                  |                               | 入力範囲 = $\pm 0.75 \times V_{REF}$ | -2.56   | 2.56   |       |    |

|                  |                               | 入力範囲 = $2.5 \times V_{REF}$      | 0       | 10.24  |       |    |

|                  |                               | 入力範囲 = $1.5 \times V_{REF}$      | 0       | 6.144  |       |    |

| <b>温度範囲</b>      |                               |                                  |         |        |       |    |

| $T_A$            | 周囲温度                          |                                  | -40     | 25     | 125   | °C |

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | ADS868xW    | 単位   |

|----------------------|---------------------|-------------|------|

|                      |                     | DBT (TSSOP) |      |

|                      |                     | 38 ピン       |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 68.8        | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 19.9        | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 30.4        | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 1.3         | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 29.8        | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 該当なし        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

すべての最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、標準仕様は  $T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3.3V、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

| パラメータ               |                   | テスト条件                                                                                                                                         | 最小値                                     | 標準値        | 最大値  | 単位                    |  |

|---------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------|------|-----------------------|--|

| <b>アナログ入力</b>       |                   |                                                                                                                                               |                                         |            |      |                       |  |

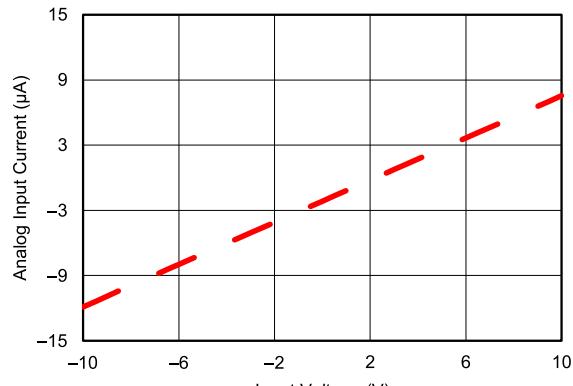

| $R_{\text{IN}}$     | 入力インピーダンス         | $\text{AIN}_{-n\text{P}} \text{ピン} = V_{\text{IN}}$ および $\text{AIN}_{-n\text{M}} = \text{GND}$ でのすべての入力範囲                                     | 1.02                                    | 1.2        |      | $\text{M}\Omega$      |  |

| $I_{\text{IN}}$     | 入力電流              | 入力範囲 = $\pm 3 \times V_{\text{REF}}$ 、 $\text{AIN}_{-n\text{P}} \text{ピン} = V_{\text{IN}}$ および $\text{AIN}_{-n\text{M}} = \text{GND}$ での電圧    | $(V_{\text{IN}} - 2.5) / R_{\text{IN}}$ |            |      | $\mu\text{A}$         |  |

|                     |                   | 入力範囲 = $\pm 1.5 \times V_{\text{REF}}$ 、 $\text{AIN}_{-n\text{P}} \text{ピン} = V_{\text{IN}}$ および $\text{AIN}_{-n\text{M}} = \text{GND}$ での電圧  | $(V_{\text{IN}} - 2.0) / R_{\text{IN}}$ |            |      |                       |  |

|                     |                   | 入力範囲 = $\pm 0.75 \times V_{\text{REF}}$ 、 $\text{AIN}_{-n\text{P}} \text{ピン} = V_{\text{IN}}$ および $\text{AIN}_{-n\text{M}} = \text{GND}$ での電圧 | $(V_{\text{IN}} - 1.6) / R_{\text{IN}}$ |            |      |                       |  |

|                     |                   | 入力範囲 = $3 \times V_{\text{REF}}$ 、 $\text{AIN}_{-n\text{P}} \text{ピン} = V_{\text{IN}}$ および $\text{AIN}_{-n\text{M}} = \text{GND}$ での電圧        | $(V_{\text{IN}} - 2.6) / R_{\text{IN}}$ |            |      |                       |  |

|                     |                   | 入力範囲 = $1.5 \times V_{\text{REF}}$ 、 $\text{AIN}_{-n\text{P}} \text{ピン} = V_{\text{IN}}$ および $\text{AIN}_{-n\text{M}} = \text{GND}$ での電圧      | $(V_{\text{IN}} - 2.7) / R_{\text{IN}}$ |            |      |                       |  |

| <b>入力過電圧保護回路</b>    |                   |                                                                                                                                               |                                         |            |      |                       |  |

| $V_{\text{OVP}}$    | すべての入力範囲          | AVDD = 5V、すべての入力範囲                                                                                                                            | -20                                     | 20         |      | V                     |  |

|                     |                   | AVDD = フローティング、すべての入力範囲                                                                                                                       | -15                                     | 15         |      |                       |  |

| <b>入力帯域幅</b>        |                   |                                                                                                                                               |                                         |            |      |                       |  |

| $f_{-3\text{dB}}$   | 小信号入力帯域幅、-3dB     | $T_A = 25^\circ\text{C}$ でのすべての入力範囲                                                                                                           | 15                                      |            |      | kHz                   |  |

| $f_{-0.1\text{dB}}$ | 小信号入力帯域幅、-0.1dB   | $T_A = 25^\circ\text{C}$ でのすべての入力範囲                                                                                                           | 2.5                                     |            |      | kHz                   |  |

| <b>DC 特性</b>        |                   |                                                                                                                                               |                                         |            |      |                       |  |

|                     | 分解能               |                                                                                                                                               | 16                                      |            |      | ビット                   |  |

| NMC                 | ミッシング コードなし       |                                                                                                                                               | 16                                      |            |      | ビット                   |  |

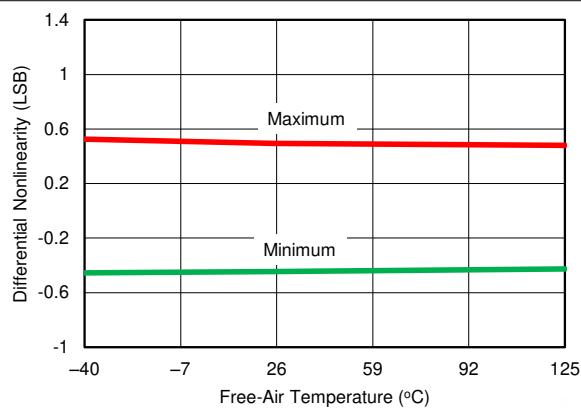

| DNL                 | 微分非直線性            | すべての入力範囲                                                                                                                                      | -0.9                                    | $\pm 0.6$  | 0.9  | LSB                   |  |

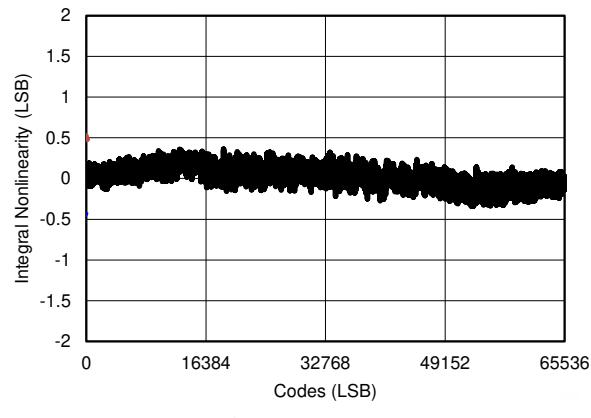

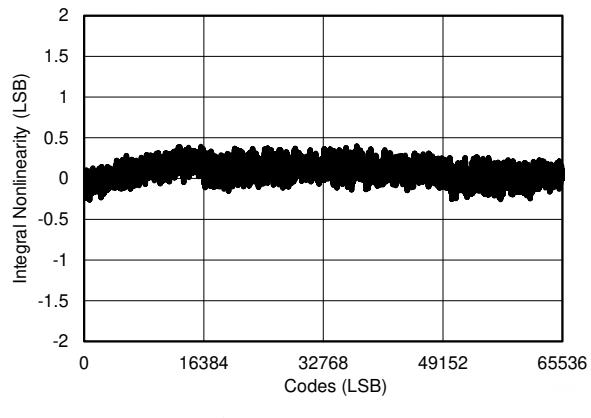

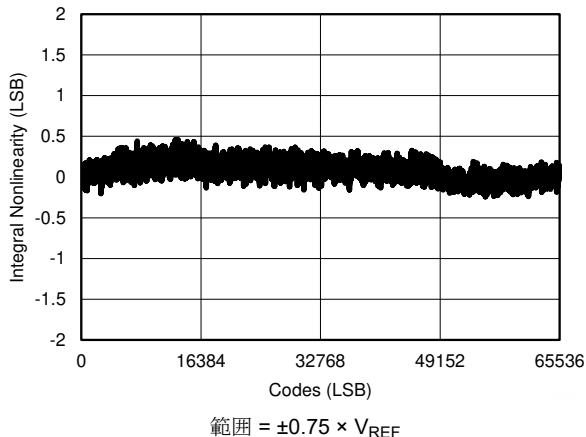

| INL                 | 積分非直線性            | すべての入力バイポーラレンジ                                                                                                                                | -2                                      | $\pm 0.8$  | 2    | LSB                   |  |

|                     |                   | すべてのユニポーラレンジ                                                                                                                                  | -2                                      | $\pm 0.6$  | 2    |                       |  |

| $E_O$               | オフセット誤差           | バイポーラレンジ = $\pm 3 \times V_{\text{REF}}$ および $\pm 1.5 \times V_{\text{REF}}$ 、 $T_A = 25^\circ\text{C}$                                       | -1.8                                    | $\pm 0.2$  | 1.8  | mV                    |  |

| $E_O$               |                   | バイポーラレンジ = $\pm 0.75 \times V_{\text{REF}}$ 、 $T_A = 25^\circ\text{C}$                                                                        | -4.5                                    | $\pm 0.2$  | 4.5  | mV                    |  |

|                     |                   | ユニポーラレンジ = $3 \times V_{\text{REF}}$ および $1.5 \times V_{\text{REF}}$ 、 $T_A = 25^\circ\text{C}$                                               | -2.4                                    | $\pm 0.2$  | 2.4  |                       |  |

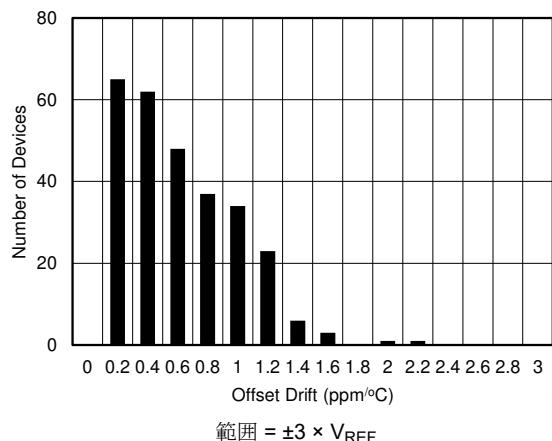

|                     | 温度によるオフセット誤差のドリフト | すべての入力範囲                                                                                                                                      | -4.5                                    | $\pm 0.75$ | 4.5  | ppm/ $^\circ\text{C}$ |  |

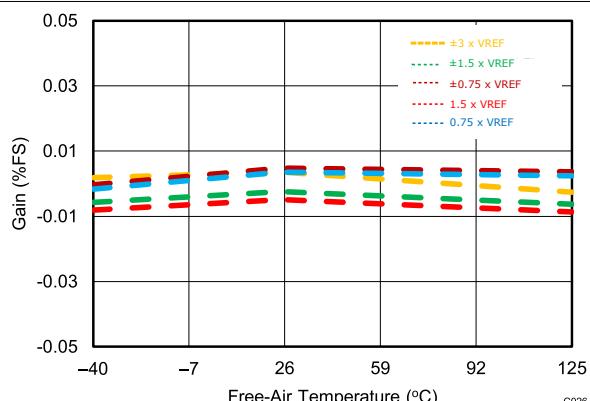

| $E_G$               | ゲイン誤差             | $T_A = 25^\circ\text{C}$ でのすべての入力範囲                                                                                                           | -0.05                                   | $\pm 0.01$ | 0.05 | %FSR                  |  |

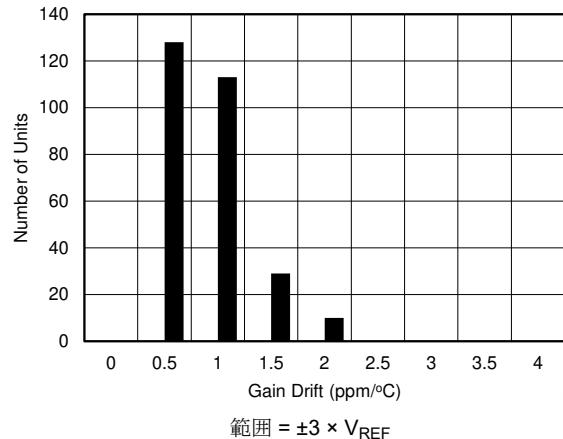

|                     | 温度によるゲイン誤差のドリフト   | すべての入力範囲                                                                                                                                      | -5                                      | $\pm 1$    | 5    | ppm/ $^\circ\text{C}$ |  |

| <b>AC 特性</b>        |                   |                                                                                                                                               |                                         |            |      |                       |  |

| SNR                 | 信号対雑音比            | 入力範囲 = $\pm 3 \times V_{\text{REF}}$                                                                                                          | 89.5                                    | 91.5       |      | dB                    |  |

|                     |                   | 入力範囲 = $\pm 1.5 \times V_{\text{REF}}$                                                                                                        | 88.5                                    | 90.5       |      |                       |  |

|                     |                   | 入力範囲 = $\pm 0.75 \times V_{\text{REF}}$                                                                                                       | 85.5                                    | 87.8       |      |                       |  |

|                     |                   | 入力範囲 = $3 \times V_{\text{REF}}$                                                                                                              | 87.9                                    | 90         |      |                       |  |

|                     |                   | 入力範囲 = $1.5 \times V_{\text{REF}}$                                                                                                            | 85.5                                    | 87.8       |      |                       |  |

| THD                 | 全高調波歪             | すべての入力範囲                                                                                                                                      | -102                                    |            |      | dB                    |  |

すべての最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、標準仕様は  $T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3.3V、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

| パラメータ                    |                              | テスト条件                                                                              | 最小値        | 標準値              | 最大値       | 単位     |

|--------------------------|------------------------------|------------------------------------------------------------------------------------|------------|------------------|-----------|--------|

| SINAD                    | 信号対雑音 + 歪み                   | 入力範囲 = $\pm 3 \times V_{\text{REF}}$                                               | 87.2       | 91               |           | dB     |

|                          |                              | 入力範囲 = $\pm 1.5 \times V_{\text{REF}}$                                             | 86.8       | 90               |           |        |

|                          |                              | 入力範囲 = $\pm 0.75 \times V_{\text{REF}}$                                            | 83.5       | 86.5             |           |        |

|                          |                              | 入力範囲 = $3 \times V_{\text{REF}}$                                                   | 85.7       | 89.5             |           |        |

|                          |                              | 入力範囲 = $1.5 \times V_{\text{REF}}$                                                 | 83.3       | 86.4             |           |        |

| SFDR                     | スプリアスフリー ダイナミックレンジ           | すべての入力範囲                                                                           |            | 103              |           | dB     |

|                          | クロストーク絶縁 <sup>(1)</sup>      | アグレッサ チャネル入力は、2倍の最大入力電圧にオーバードライブされます                                               |            | 110              |           | dB     |

|                          | クロストーク メモリ <sup>(2)</sup>    | アグレッサ チャネル入力は、2倍の最大入力電圧にオーバードライブされます                                               |            | 90               |           | dB     |

| 補助チャネル                   |                              |                                                                                    |            |                  |           |        |

|                          | 分解能                          |                                                                                    | 16         |                  |           | ビット    |

| $V_{\text{AUX\_IN}}$     | AUX_IN 電圧範囲                  | ( $AUX_{\text{INP}} - AUX_{\text{GND}}$ )                                          | 0          | $V_{\text{REF}}$ |           | V      |

|                          | 動作入力範囲                       | $AUX_{\text{INP}}$                                                                 | 0          | $V_{\text{REF}}$ |           | V      |

|                          |                              | $AUX_{\text{GND}}$                                                                 |            | 0                |           |        |

|                          | 入力容量                         | サンプリング中                                                                            | 75         |                  |           | pF     |

|                          |                              | 変換中                                                                                | 5          |                  |           |        |

|                          | 入力リーク電流                      |                                                                                    | 100        |                  |           | nA     |

|                          | 微分非直線性                       |                                                                                    | -0.99      | 1.5              |           | LSB    |

|                          | 積分非直線性                       |                                                                                    | -4         | 4                |           | LSB    |

|                          | ゲイン誤差                        | $T_A = 25^\circ\text{C}$ 時                                                         |            |                  | $\pm 0.2$ | %FSR   |

|                          | オフセット誤差                      | $T_A = 25^\circ\text{C}$ 時                                                         | -10        | 10               |           | mV     |

|                          | 信号対雑音比                       | $V_{\text{AUX\_IN}} = -0.5\text{dBFS}$ (1kHz 時)                                    | 87         | 89               |           | dB     |

|                          | 全高調波歪                        | $V_{\text{AUX\_IN}} = -0.5\text{dBFS}$ (1kHz 時)                                    |            | -102             |           | dB     |

|                          | 信号対雑音 + 歪み                   | $V_{\text{AUX\_IN}} = -0.5\text{dBFS}$ (1kHz 時)                                    | 86         | 88.5             |           | dB     |

|                          | スプリアスフリー ダイナミックレンジ           | $V_{\text{AUX\_IN}} = -0.5\text{dBFS}$ (1kHz 時)                                    |            | 103              |           | dB     |

| 内部リファレンス出力               |                              |                                                                                    |            |                  |           |        |

| $V_{\text{REFIO}}$       | REFIO ピン (出力として構成)           | $T_A = 25^\circ\text{C}$                                                           | 4.092      | 4.096            | 4.1       | V      |

| $dV_{\text{REFIO}}/dT_A$ | 内部リファレンス温度ドリフト               |                                                                                    |            | 5                |           | ppm/°C |

| $C_{\text{OUT\_REFIO}}$  | REFIO ピンのデカップリングコンデンサ        |                                                                                    | 4.7        |                  |           | μF     |

| $V_{\text{REFCAP}}$      | ADC へのリファレンス電圧 (REFCAP ピン経由) |                                                                                    | 4.092      | 4.096            | 4.1       | V      |

|                          | リファレンス バッファ出力インピーダンス         |                                                                                    |            | 0.5              | 1         | Ω      |

|                          | リファレンス バッファ温度ドリフト            |                                                                                    |            | 0.5              | 1.5       | ppm/°C |

| $C_{\text{OUT\_REFCAP}}$ | REFCAP ピンのデカップリングコンデンサ       |                                                                                    | 10         | 22               |           | μF     |

|                          | ターンオン時間                      | $C_{\text{OUT\_REFCAP}} = 10\mu\text{F}$ 、 $C_{\text{OUT\_REFIO}} = 10\mu\text{F}$ |            | 20               |           | ms     |

| デジタル入力                   |                              |                                                                                    |            |                  |           |        |

| $V_{\text{IH}}$          | デジタル高入力電圧ロジックレベル             | $DVDD > 2.1\text{V}$                                                               | 0.7 × DVDD | 0.3              |           | V      |

|                          |                              | $DVDD \leq 2.1\text{V}$                                                            | 0.8 × DVDD | 0.3              |           |        |

すべての最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、標準仕様は  $T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3.3V、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

| パラメータ                          |                                           | テスト条件                      | 最小値        | 標準値        | 最大値        | 単位 |

|--------------------------------|-------------------------------------------|----------------------------|------------|------------|------------|----|

| $V_{\text{IL}}$                | デジタル低入力電圧ロジック レベル                         | DVDD > 2.1V                | -0.3       | 0.3 x DVDD | 0.2 x DVDD | V  |

|                                |                                           | DVDD ≤ 2.1V                | -0.3       | 0.2 x DVDD |            |    |

|                                | 入力リーク電流                                   |                            | 100        |            | nA         |    |

|                                | 入力ピン容量                                    |                            | 5          |            | pF         |    |

| <b>デジタル出力</b>                  |                                           |                            |            |            |            |    |

| $V_{\text{OH}}$                | デジタル高出力電圧ロジック レベル                         | $I_O = 500\mu\text{A}$ ソース | 0.8 x DVDD | DVDD       | V          |    |

| $V_{\text{OL}}$                | デジタル低出力電圧ロジック レベル                         | $I_O = 500\mu\text{A}$ シンク | 0          | 0.2 x DVDD | V          |    |

|                                | フローティング状態のリーク電流                           | SDO のみ                     | 1          |            | μA         |    |

|                                | 内部ピン容量                                    |                            | 5          |            | pF         |    |

| <b>電源要件</b>                    |                                           |                            |            |            |            |    |

| $I_{\text{AVDD\_DY}}$<br>$N$   | アナログ電源電流、デバイスは内部リファレンスを使用して最大スループットで変換します | ADS8688W                   | 13         | 16         | mA         |    |

|                                |                                           | ADS8684W                   | 8.5        | 11.5       |            |    |

| $I_{\text{AVDD\_STC}}$         | アナログ電源電流、デバイスは内部リファレンスを使用して変換しません         | ADS8688W                   | 10         | 12         | mA         |    |

|                                |                                           | ADS8684W                   | 5.5        | 8.5        |            |    |

| $I_{\text{AVDD\_STD}}$<br>$BY$ | アナログ電源電流、デバイスは STANDBY モード                | デバイスは STDBY モードと内部リファレンス電圧 | 3          | 4.5        | mA         |    |

| $I_{\text{AVDD\_PD}}$          | アナログ電源電流、デバイスは PD モード                     | デバイスは PWR_DN モード           | 3          | 20         | μA         |    |

| $I_{\text{DVDD\_DY}}$<br>$N$   | デジタル電源電流、最大スループット                         | DVDD = 3.3V の場合、出力 = 0000h | 0.5        |            | mA         |    |

- (1) 絶縁クロストークは、マルチブレクシング シーケンスで選択されていないチャネルに最大 10kHz までのフルスケール正弦波信号を印加し、選択されているいずれかのチャネルの出力に与える影響を測定することで測定されます。

- (2) メモリクロストークは、マルチブレクシング シーケンスで選択されているチャネルに最大 10kHz のフルスケール正弦波信号を印加し、入力チャネルのすべての組み合わせについて、次に選択されたチャネルの出力に与える影響を測定することで測定されます。

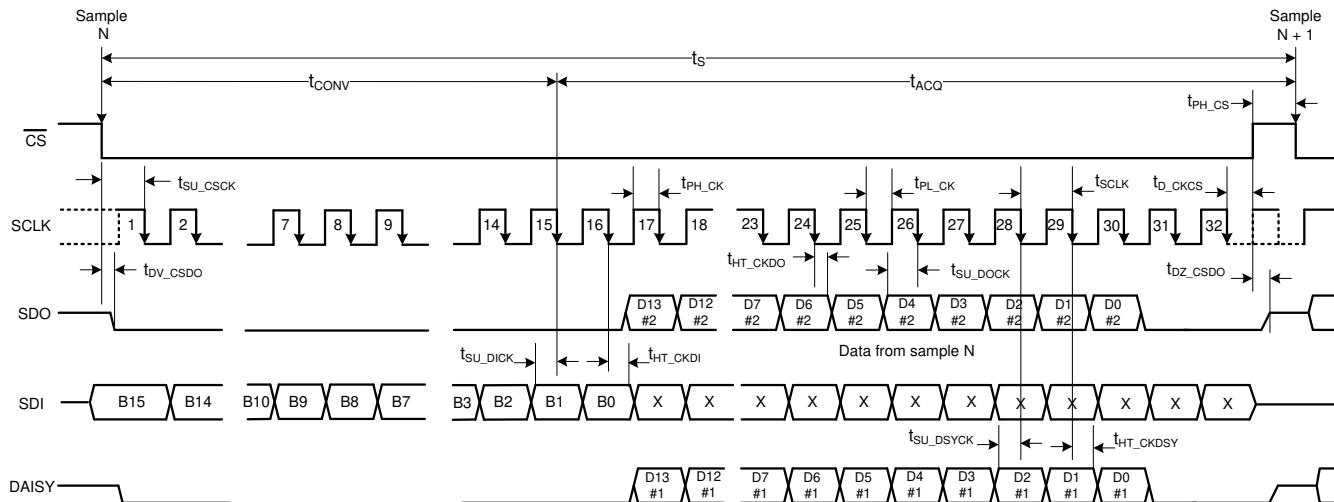

## 6.6 タイミング要件

すべての最小値および最大値の仕様は  $T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ 、標準仕様は  $T_A = 25^{\circ}\text{C}$ 、AVDD = 5V、DVDD = 3.3V、VREF = 4.096V (内部)、および最大スループット (特に記述のない限り)

|                            |                                                          | 最小値                 | 標準値 | 最大値 | 単位               |

|----------------------------|----------------------------------------------------------|---------------------|-----|-----|------------------|

| <b>変換サイクル</b>              |                                                          |                     |     |     |                  |

| $f_{\text{cycle}}$         | サンプリング周波数                                                |                     |     | 500 | kSPS             |

| $t_{\text{cycle}}$         | ADC サイクル時間周期                                             | 2                   |     |     | $\mu\text{s}$    |

| $t_{\text{acq}}$           | アクイジョン時間                                                 | 1150                |     |     | ns               |

| <b>非同期リセット</b>             |                                                          |                     |     |     |                  |

| $t_{\text{WL\_RST}}$       | パルス幅 $\overline{\text{RST}}$ が Low                       | 100                 |     |     | ns               |

| <b>SPI 互換シリアル インターフェイス</b> |                                                          |                     |     |     |                  |

| $f_{\text{SCLK}}$          | シリアル クロック周波数                                             |                     |     | 17  | MHz              |

| $t_{\text{SCLK}}$          | シリアル クロック期間                                              | $1/f_{\text{SCLK}}$ |     |     |                  |

| $t_{\text{PH\_CK}}$        | SCLK High 時間                                             | 0.4                 |     | 0.6 | $t_{\text{CLK}}$ |

| $t_{\text{PL\_CK}}$        | SCLK Low 時間                                              | 0.4                 |     | 0.6 | $t_{\text{CLK}}$ |

| $t_{\text{SU\_CSCK}}$      | セットアップ時間: $\overline{\text{CS}}$ 立ち下がりから最初の SCLK 立ち下がりまで | 30                  |     |     | ns               |

| $t_{\text{SU\_CKDI}}$      | セットアップ時間: SDI データ有効から SCLK 立ち下がりまで                       | 5                   |     |     | ns               |

| $t_{\text{HT\_CKDI}}$      | ホールド時間: SCLK 立ち下がりから (前の) データが SDI で有効になるまで              | 5                   |     |     | ns               |

| $t_{\text{SU\_CKDSY}}$     | セットアップ時間: DAISY データ有効から SCLK 立ち下がりまで                     | 5                   |     |     |                  |

| $t_{\text{HT\_CKDSY}}$     | ホールド時間: SCLK 立ち下がりから (前の) データが DAISY で有効になるまで            | 5                   |     |     |                  |

## 6.7 スイッチング特性

すべての最小値および最大値の仕様は  $T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ 、標準仕様は  $T_A = 25^{\circ}\text{C}$ 、AVDD = 5V、DVDD = 3.3V、VREF = 4.096V (内部)、および最大スループット (特に記述のない限り)

|                            |                                                           | 最小値 | 標準値 | 最大値 | 単位 |

|----------------------------|-----------------------------------------------------------|-----|-----|-----|----|

| <b>非同期リセット</b>             |                                                           |     |     |     |    |

| $t_{\text{conv}}$          | 変換時間                                                      |     |     | 850 | ns |

|                            | ターンオン時間                                                   |     |     | 15  | ms |

| <b>SPI 互換シリアル インターフェイス</b> |                                                           |     |     |     |    |

| $t_{\text{HT\_CKCS}}$      | 遅延時間:最後の SCLK 立ち下がりエッジから $\overline{\text{CS}}$ 立ち上がりまで   |     | 10  |     | ns |

| $t_{\text{DEN\_CSDO}}$     | 遅延時間: $\overline{\text{CS}}$ 立ち下がりエッジからデータイネーブルまで         |     |     | 10  | ns |

| $t_{\text{DZ\_CSDO}}$      | 遅延時間: $\overline{\text{CS}}$ 立ち上がりから SDO の 3-state への移行まで |     | 10  |     | ns |

| $t_{\text{D\_CKDO}}$       | 遅延時間:SCLK の立ち下がりエッジから(次の)データが SDO で有効になるまでの時間             |     |     | 25  | ns |

| $t_{\text{HT\_CKDO}}$      | 遅延時間:SCLK の立ち下がりエッジから(前の)データが SDO で有効になるまでの時間             | 5   |     |     | ns |

**図 6-1. シリアルインターフェイスタイミング図**

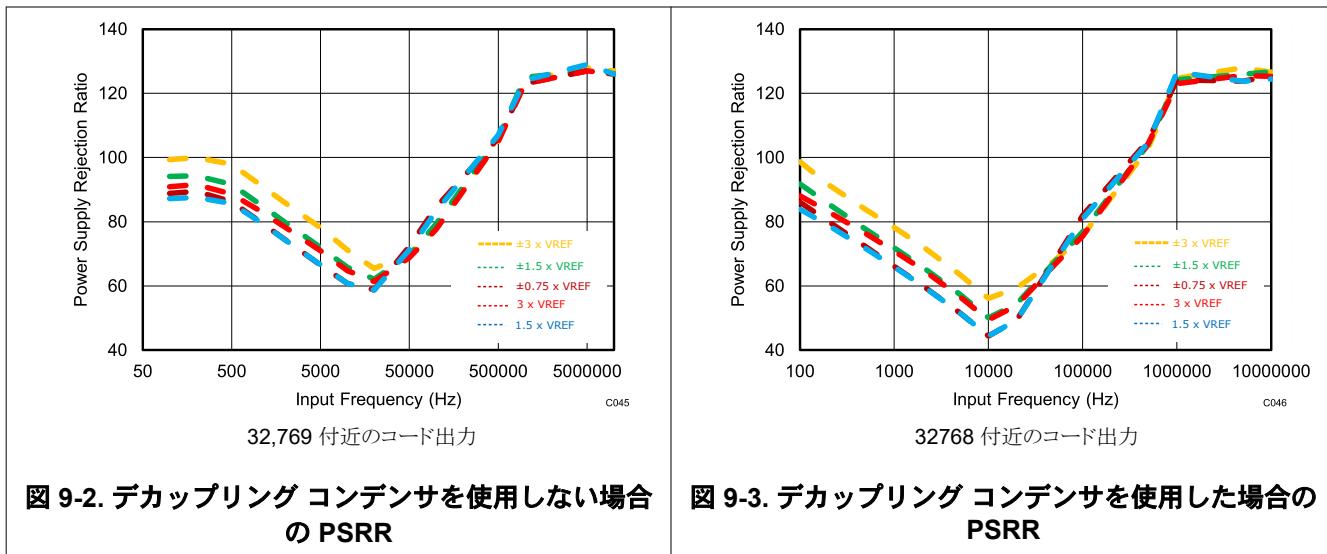

## 6.9 代表的特性

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 5\text{V}$ 、 $\text{DVDD} = 3\text{V}$ 、内部リファレンス  $V_{\text{REF}} = 4.096\text{V}$ 、 $f_{\text{SAMPLE}} = 500\text{kSPS}$  (特に記述のない限り)。

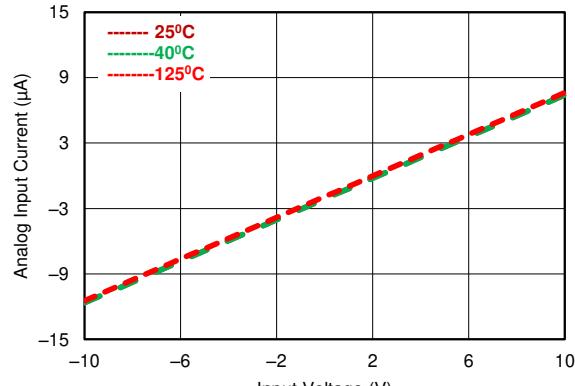

図 6-2. 入力 I-V 特性

図 6-3. 入力電流と温度との関係

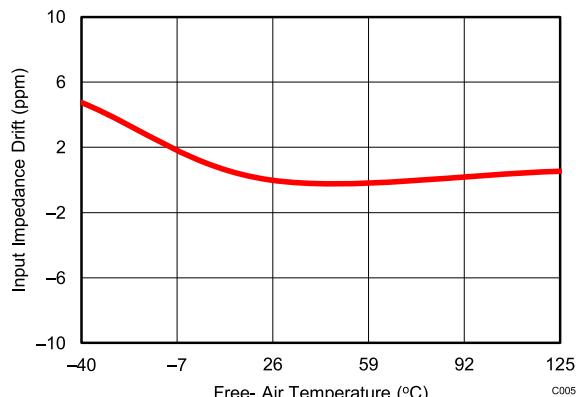

図 6-4. 入力インピーダンスの変動と温度との関係

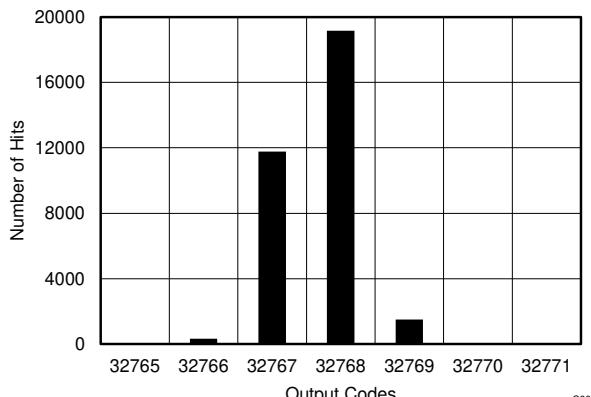

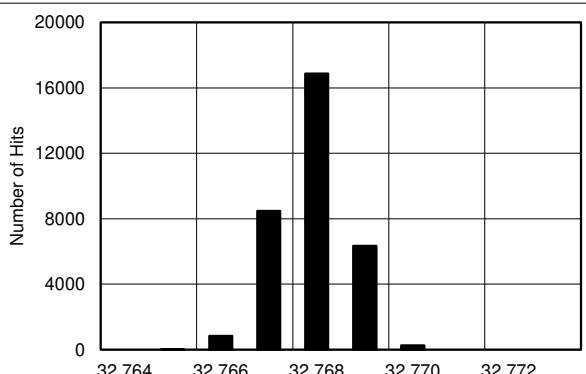

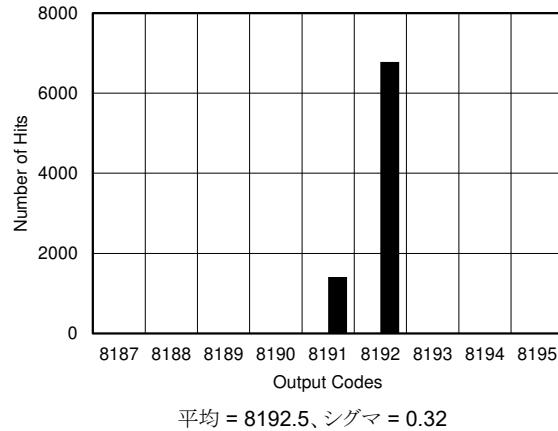

図 6-5. ミッドスケール入力の DC ヒストグラム ( $\pm 3 \times V_{\text{REF}}$ )

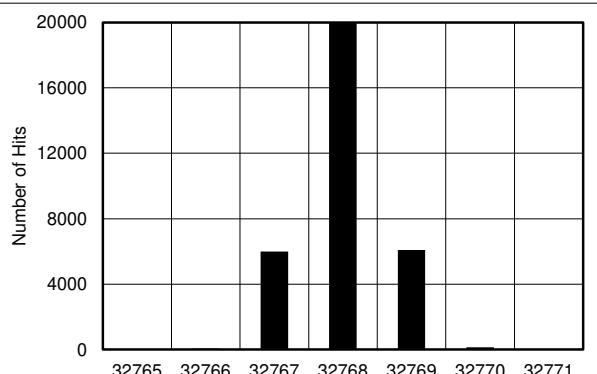

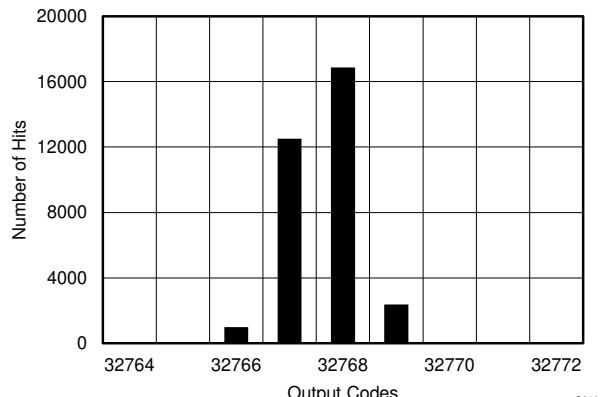

平均 = 32768.60、シグマ = 0.63、入力 = 0V、範囲 =  $\pm 1.5 \times V_{\text{REF}}$

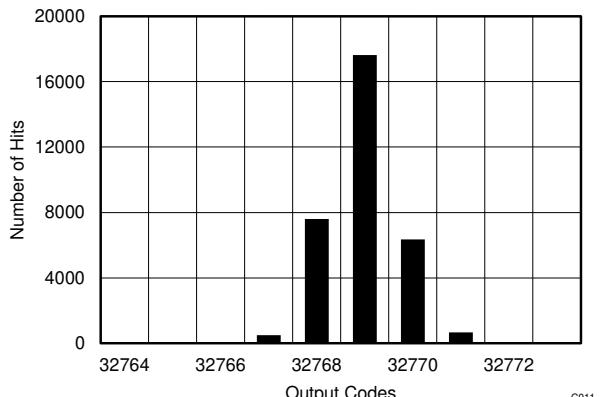

平均 = 32768.8、シグマ = 0.76、入力 = 0V、範囲 =  $\pm 0.75 \times V_{\text{REF}}$

図 6-6. ミッドスケール入力の DC ヒストグラム ( $\pm 1.5 \times V_{\text{REF}}$ )

図 6-7. ミッドスケール入力の DC ヒストグラム ( $\pm 0.75 \times V_{\text{REF}}$ )

## 6.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 5\text{V}$ 、 $\text{DVDD} = 3\text{V}$ 、内部リファレンス  $V_{\text{REF}} = 4.096\text{V}$ 、 $f_{\text{SAMPLE}} = 500\text{kSPS}$  (特に記述のない限り)。

平均 = 32767.75、シグマ = 0.65、入力 =  $1.5 \times V_{\text{REF}}$ 、範囲 =  $3 \times V_{\text{REF}}$

図 6-8. ミッドスケール入力の DC ヒストグラム ( $3 \times V_{\text{REF}}$ )

平均 = 32768.2、シグマ = 0.75、入力 =  $0.625 \times V_{\text{REF}}$ 、範囲 =  $1.5 \times V_{\text{REF}}$

図 6-9. ミッドスケール入力の DC ヒストグラム ( $1.5 \times V_{\text{REF}}$ )

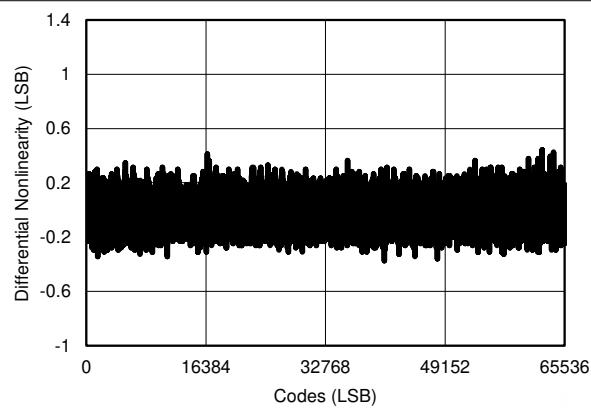

すべての入力範囲

図 6-10. すべてのコードの標準 DNL

すべての入力範囲

図 6-11. DNL と温度との関係

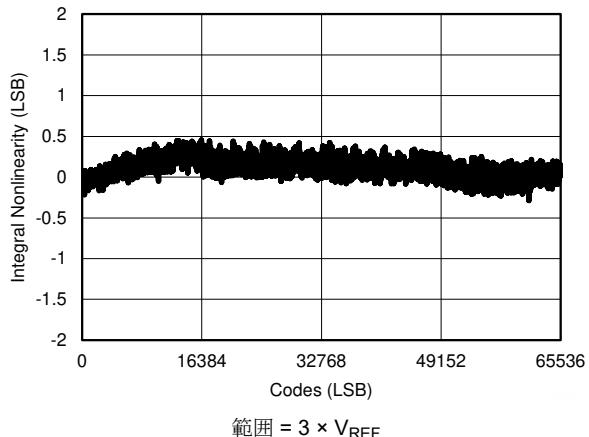

範囲 =  $\pm 3 \times V_{\text{REF}}$

図 6-12. すべてのコードの標準 INL

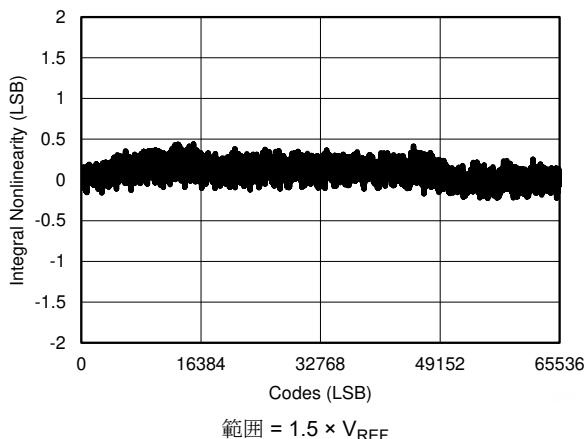

範囲 =  $\pm 1.5 \times V_{\text{REF}}$

図 6-13. すべてのコードの標準 INL

## 6.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 5\text{V}$ 、 $\text{DVDD} = 3\text{V}$ 、内部リファレンス  $V_{\text{REF}} = 4.096\text{V}$ 、 $f_{\text{SAMPLE}} = 500\text{kSPS}$  (特に記述のない限り)。

図 6-14. すべてのコードの標準 INL

図 6-15. すべてのコードの標準 INL

図 6-16. すべてのコードの標準 INL

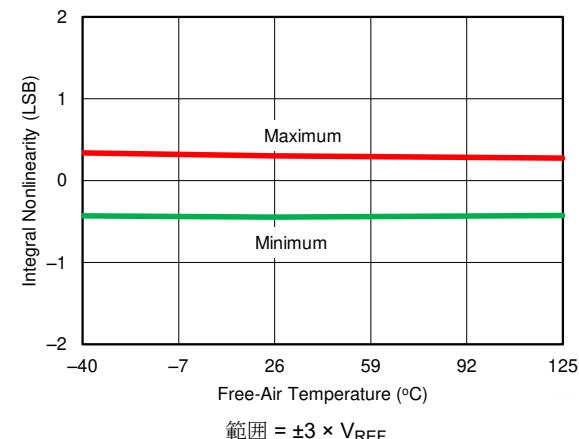

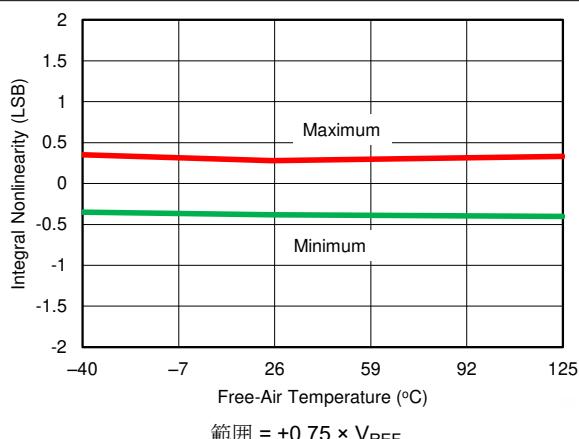

図 6-17. INL と温度との関係 ( $\pm 3 \times V_{\text{REF}}$ )

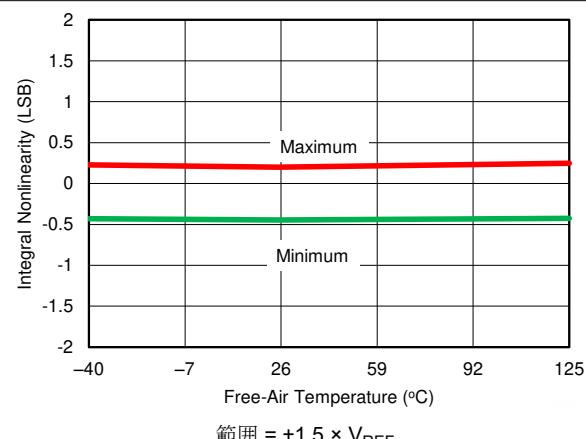

図 6-18. INL と温度との関係 ( $\pm 1.5 \times V_{\text{REF}}$ )

図 6-19. INL と温度との関係 ( $\pm 0.75 \times V_{\text{REF}}$ )

## 6.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3V、内部リファレンス  $V_{\text{REF}} = 4.096\text{V}$ 、 $f_{\text{SAMPLE}} = 500\text{kSPS}$  (特に記述のない限り)。

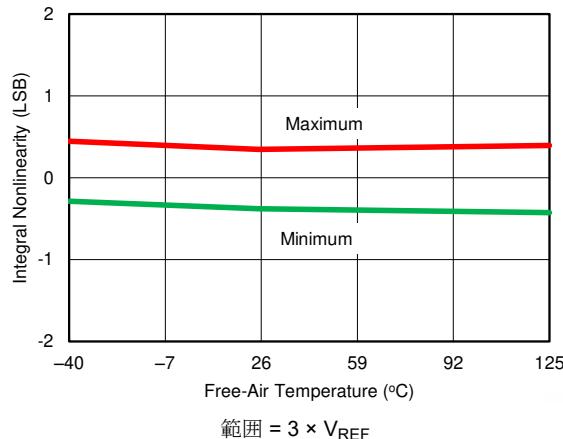

図 6-20. INL と温度との関係 ( $3 \times V_{\text{REF}}$ )

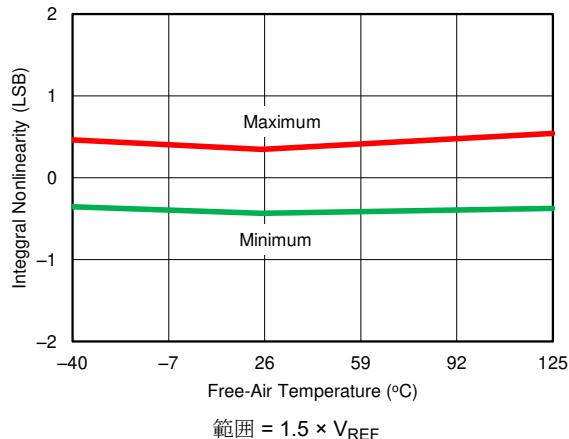

図 6-21. INL と温度との関係 ( $1.5 \times V_{\text{REF}}$ )

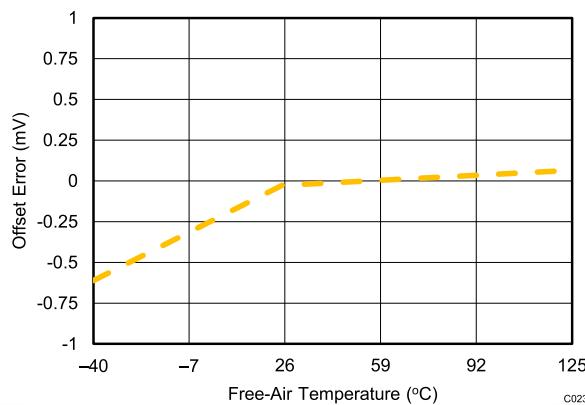

図 6-22. すべての入力範囲のオフセット誤差と温度との関係

図 6-23. オフセット ドリフトの標準的なヒストグラム

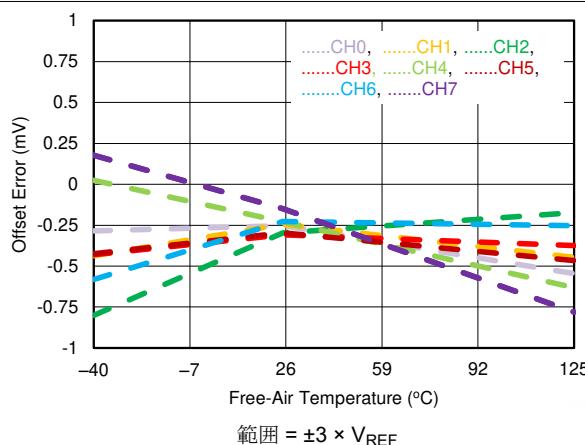

図 6-24. すべてのチャネルにわたるオフセット誤差と温度との関係

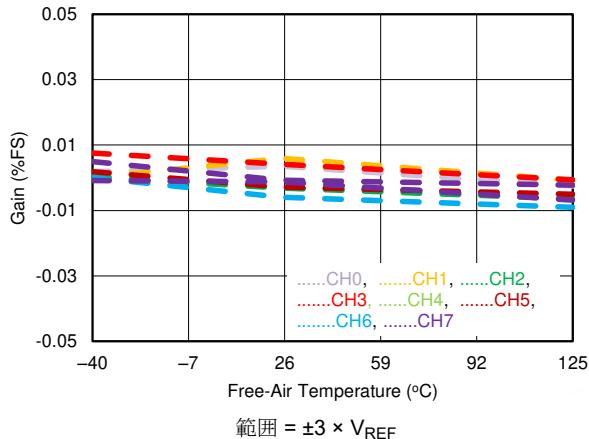

図 6-25. すべての入力範囲にわたるゲイン誤差と温度との関係

## 6.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3V、内部リファレンス  $V_{\text{REF}} = 4.096\text{V}$ 、 $f_{\text{SAMPLE}} = 500\text{kSPS}$  (特に記述のない限り)。

図 6-26. ゲイン誤差ドリフトの標準的なヒストグラム

図 6-27. すべてのチャネルにわたるゲイン誤差と温度との関係

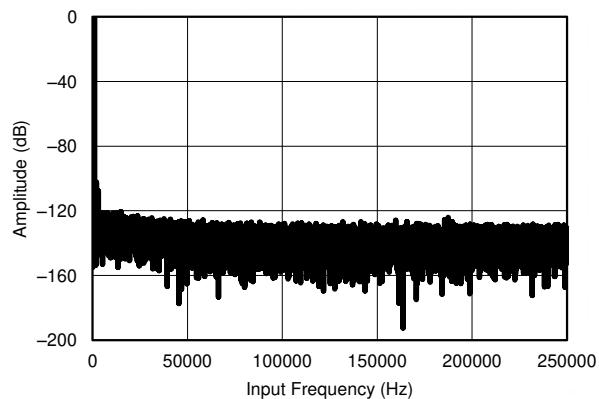

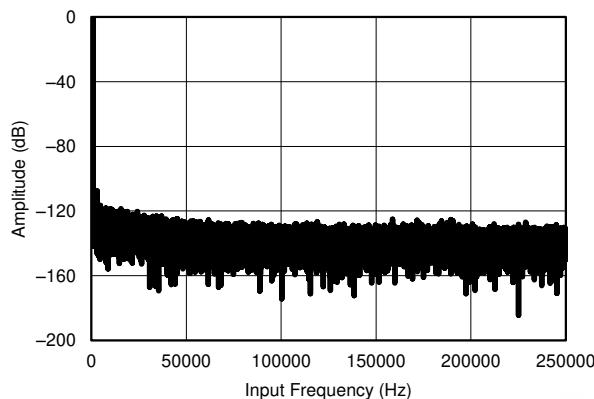

ポイント数 = 64k、 $f_{\text{IN}} = 1\text{kHz}$ 、SNR = 92.3dB、SINAD = 85.35 91.9dB、THD = -104.68dB 101dB、SFDR = 105dB 104dB

図 6-28. 標準的な FFT プロット ( $\pm 3 \times V_{\text{REF}}$ )

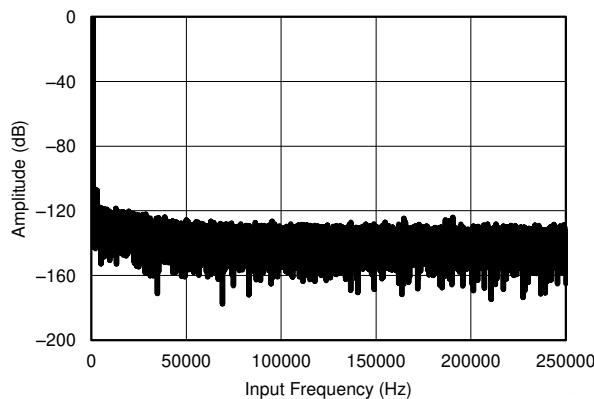

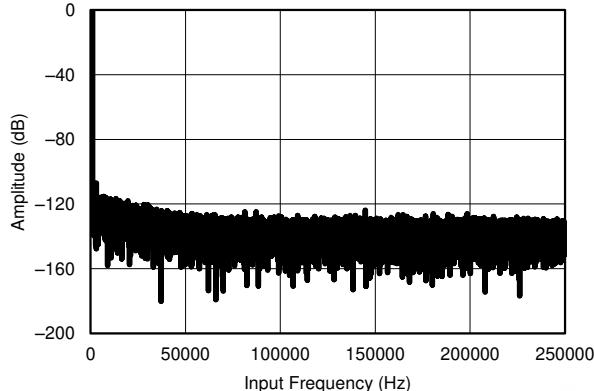

ポイント数 = 64k、 $f_{\text{IN}} = 1\text{kHz}$ 、SNR = 91.4dB、SINAD = 91.2dB、THD = 105dB、SFDR = 107dB

図 6-29. 標準的な FFT プロット ( $\pm 1.5 \times V_{\text{REF}}$ )

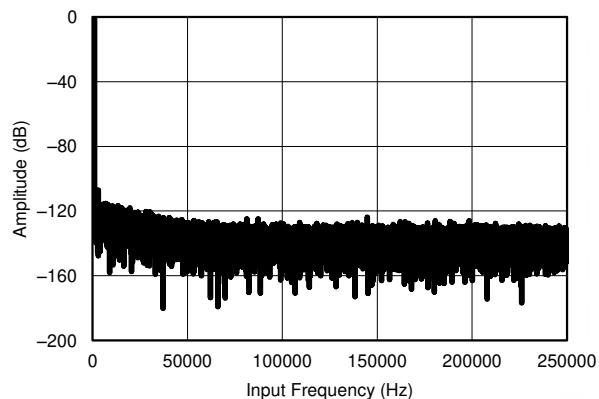

ポイント数 = 64k、 $f_{\text{IN}} = 1\text{kHz}$ 、SNR = 89.6dB、SINAD = 89.5dB、THD = 106dB、SFDR = 107dB

図 6-30. 標準的な FFT プロット ( $\pm 0.75 \times V_{\text{REF}}$ )

ポイント数 = 64k、 $f_{\text{IN}} = 1\text{kHz}$ 、SNR = 90.93dB、SINAD = 90.48dB、THD = 100dB、SFDR = 102dB

図 6-31. 標準的な FFT プロット ( $3 \times V_{\text{REF}}$ )

## 6.9 代表的特性 (続き)

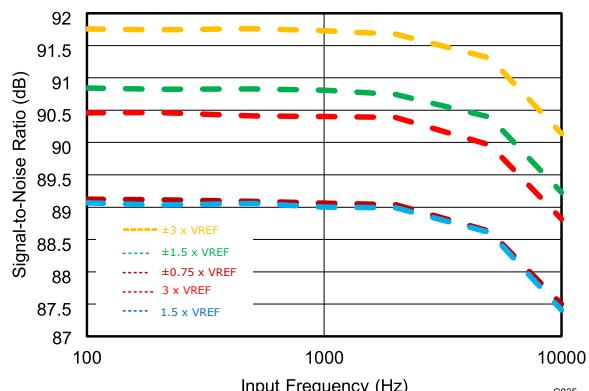

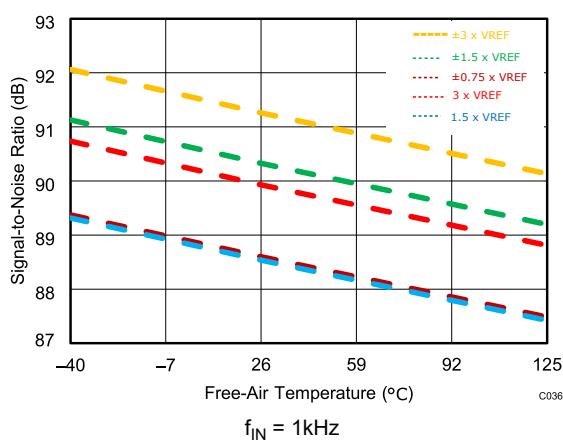

$T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3V、内部リファレンス  $V_{\text{REF}} = 4.096\text{V}$ 、 $f_{\text{SAMPLE}} = 500\text{kSPS}$  (特に記述のない限り)。

図 6-32. 標準的な FFT プロット (1.5 ×  $V_{\text{REF}}$ )

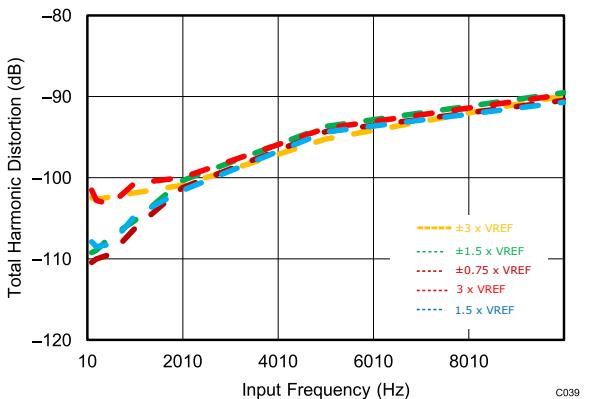

図 6-33. SNR と入力周波数との関係

図 6-34. SNR と温度との関係

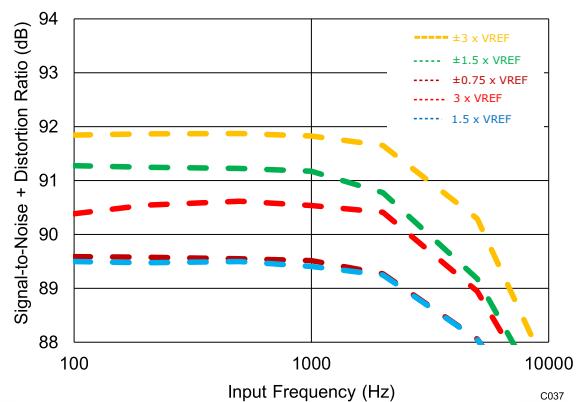

図 6-35. SINAD と入力周波数との関係

図 6-36. SINAD と温度との関係

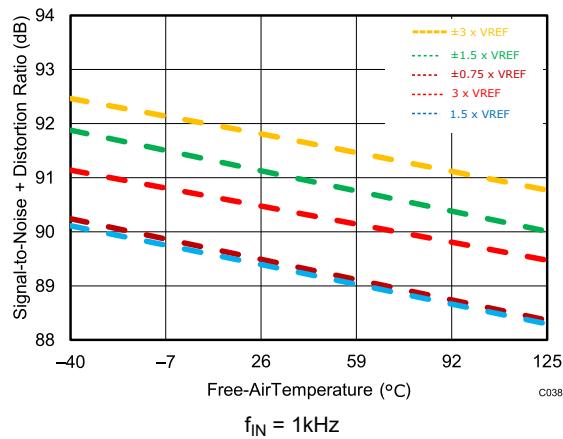

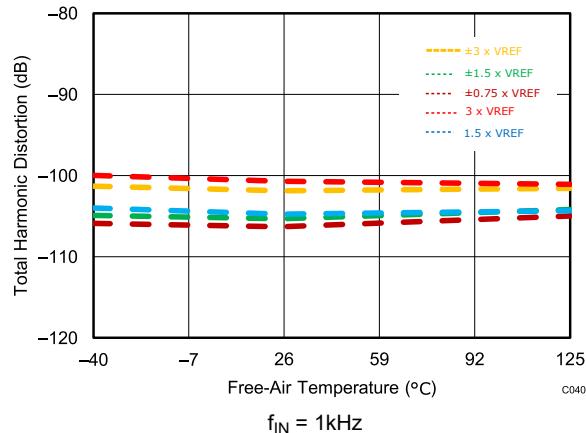

図 6-37. THD と入力周波数との関係

## 6.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 5\text{V}$ 、 $\text{DVDD} = 3\text{V}$ 、内部リファレンス  $V_{\text{REF}} = 4.096\text{V}$ 、 $f_{\text{SAMPLE}} = 500\text{kSPS}$  (特に記述のない限り)。

図 6-38. THD と温度との関係

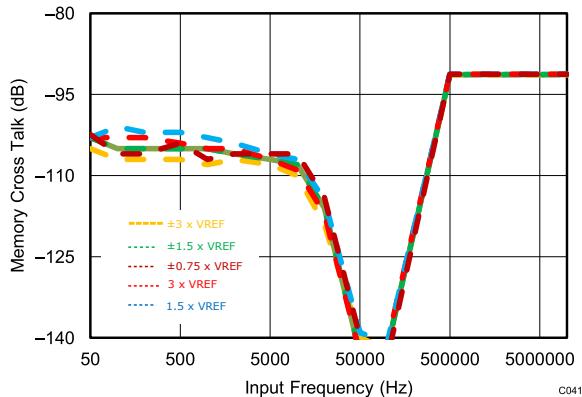

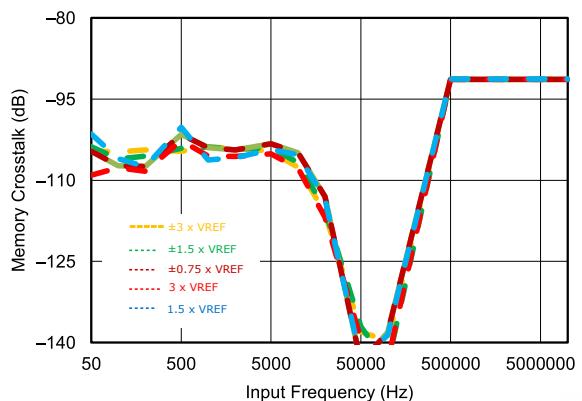

図 6-39. メモリ クロストークと周波数との関係

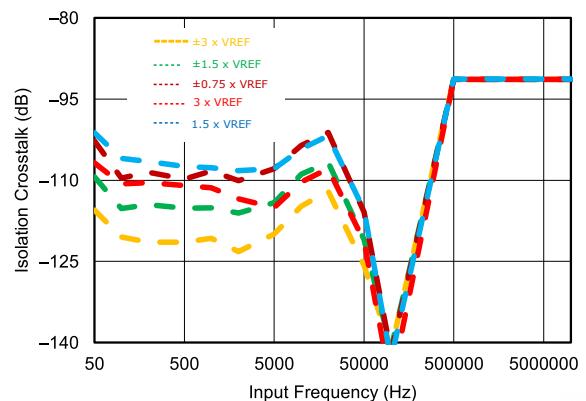

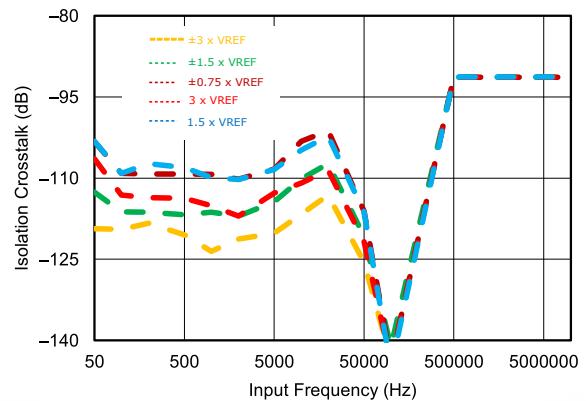

図 6-40. 絶縁クロストークと周波数との関係

入力 = 2 × 最大入力電圧

図 6-41. 過電圧入力におけるメモリ クロストークと周波数との関係

入力 = 2 × 最大入力電圧

図 6-42. 過電圧入力における絶縁クロストークと周波数との関係

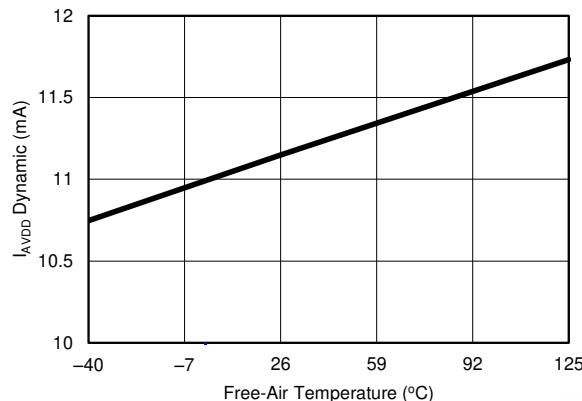

図 6-43. ADS8688W の AVDD 電流と温度との関係 ( $f_s = 500\text{kSPS}$ )

## 6.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3V、内部リファレンス  $V_{\text{REF}} = 4.096\text{V}$ 、 $f_{\text{SAMPLE}} = 500\text{kSPS}$  (特に記述のない限り)。

図 6-44. AVDD 電流と温度との関係 (STANDBY)

図 6-45. AVDD 電流と温度との関係 (パワーダウン)

## 7 詳細説明

### 7.1 概要

ADS8688W は、8 チャネルのアナログ入力を備えた 16 ビットのデータ アクイジション システムです。各アナログ入力チャネルは、過電圧保護回路、プログラマブル ゲイン アンプ (PGA)、2 次アンチエイリアス フィルタで構成されており、入力信号を 8 チャネルのアナログ マルチプレクサ (MUX) に供給する前に調整します。マルチプレクサの出力は、逐次比較型レジスタ (SAR) アーキテクチャに基づき、16 ビットの A/D コンバータ (ADC) を使用してデジタル化されます。このシステム全体で、すべてのチャネルを合計すると、最大 500kSPS のスループットを実現できます。デバイスは、高速セトリング バッファを備えた 4.096V の内部リファレンスと、デイジーチェーン (DAISY) 機能および ALARM 機能を備えたシンプルな SPI 互換シリアル インターフェイスを特長としています。

デバイスは 5V 単一アナログ電源で動作し、最大

$\pm 3 \times V_{REF}$  の真のバイポーラ入力信号に対応できます。このデバイスは、サンプリング周波数や選択された入力レンジに関係なく、一定の  $1.2M\Omega$  の抵抗性入力インピーダンスを提供します。高入力インピーダンスのマルチチャネル高精度アナログ フロント エンド回路を統合し、5V 単一電源で動作する高精度 ADC を備えているため、外部の高電圧バイポーラ電源や複雑なドライバ回路を必要とせずに、簡素化したエンドソリューションが実現します。

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 アナログ入力

ADS8688W は、シングルエンド入力と差動入力の両方をサポートする 8 つのアナログ入力チャネルを備えています。図 7-1 に、各アナログ入力チャネルの概略回路図を示します。これには、入力過電圧保護回路、PGA、ローパス フィルタ (LPF)、高速 ADC ドライバ、アナログ マルチプレクサが含まれています。

図 7-1. 各アナログ入力チャネルのフロント エンド回路図

デバイスは、プログラム レジスタ構成に基づいて、複数のユニポーラまたはバイポーラ、シングルエンドおよび差動入力電圧範囲をサポートしています。「[範囲選択レジスタ](#)」セクションに説明されているように、各アナログ チャネルの入力電圧範囲は、 $\pm 12.288V$ 、 $\pm 6.144V$ 、 $\pm 3.072V$  のバイポーラ レンジ、または  $0V \sim 12.288V$  および  $0V \sim 6.144V$  のユニポーラ レンジに構成できます。これらの入力範囲のいずれかを、デバイスの任意のアナログ入力チャネルに割り当てることができます。たとえば、 $\pm 12.288V$  の範囲は AIN\_1P に、 $\pm 6.144V$  の範囲は AIN\_2P に、 $0V \sim 12.288V$  の範囲は AIN\_3P に割り当てることができます。

デバイスは、選択されたアナログ入力チャネル間の電圧差 ( $AIN_{nP} - AIN_{nM}$ ) をサンプリングします。デバイスに対するアナログ入力ピン ( $AIN_{nP}$ ) がフローティングのままになっている場合、ADC の出力は内部バイアス電圧に対応します。入力ピンがフローティング状態になっている場合、ADC からの出力は無効とみなす必要があります。この条件によってデバイスが損傷することはありません、ピンに有効な入力電圧が印加されると、完全に機能します。

### 7.3.2 アナログ入力インピーダンス

デバイスの各アナログ入力チャネルは、 $1.2M\Omega$  の一定の抵抗性インピーダンスを示します。入力インピーダンスは、ADC サンプリング周波数や入力信号の周波数または範囲に依存しません。このような高インピーダンス入力の主な利点は、出力インピーダンスの低いアンプを駆動する必要がなく、ADC 入力を簡単に駆動できることです。この ADC は高電圧のフロント エンド ドライバを必要としないため、システムではバイポーラの高電圧電源は必要ありません。ほとんどのアプリケーションでは、信号源またはセンサ出力が ADC 入力に直接接続されるため、シグナル チェーンの設計を大幅に簡素化できます。

システムの **dc** 精度を維持するために、 $AIN_{nP}$  入力ピンの外部ソース インピーダンスを、 $AIN_{nM}$  ピンの等価抵抗と一致させることを推奨します。一致させることで、外部抵抗に起因する追加のオフセット誤差を打ち消すのに役立ちます。

### 7.3.3 入力過電圧保護回路

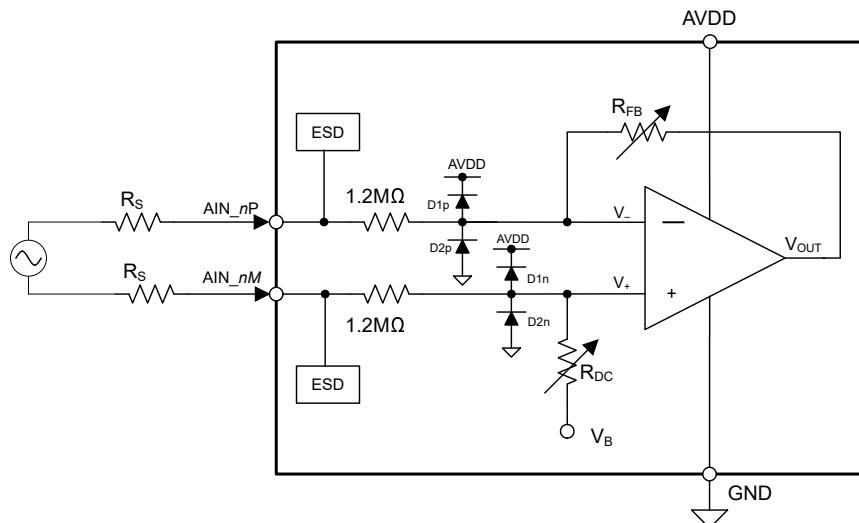

ADS8688W は、アナログ入力チャネルそれぞれに内部過電圧保護回路を備えています。これらの保護回路は、デバイスを保護する 2 次保護方式として使用してください。サージ、静電気放電 (ESD)、電気的高速過渡 (EFT) の各条件に対して、外部保護デバイスを使用することを強く推奨します。図 7-2 に、内部過電圧保護 (OVP) 回路の概念ブロック図を示します。

図 7-2. 入力過電圧保護回路の回路図

図 7-2 に示されているように、 $1.2\text{M}\Omega$  の入力抵抗と PGA のゲイン設定抵抗 ( $R_{FB}$  および  $R_{DC}$ ) を組み合わせることで、入力ピンに流れ込む電流が制限されます。逆並列ダイオード (D1 および D2) の組み合わせを各入力ピンに追加して、内部回路を保護し、過電圧保護制限を設定します。

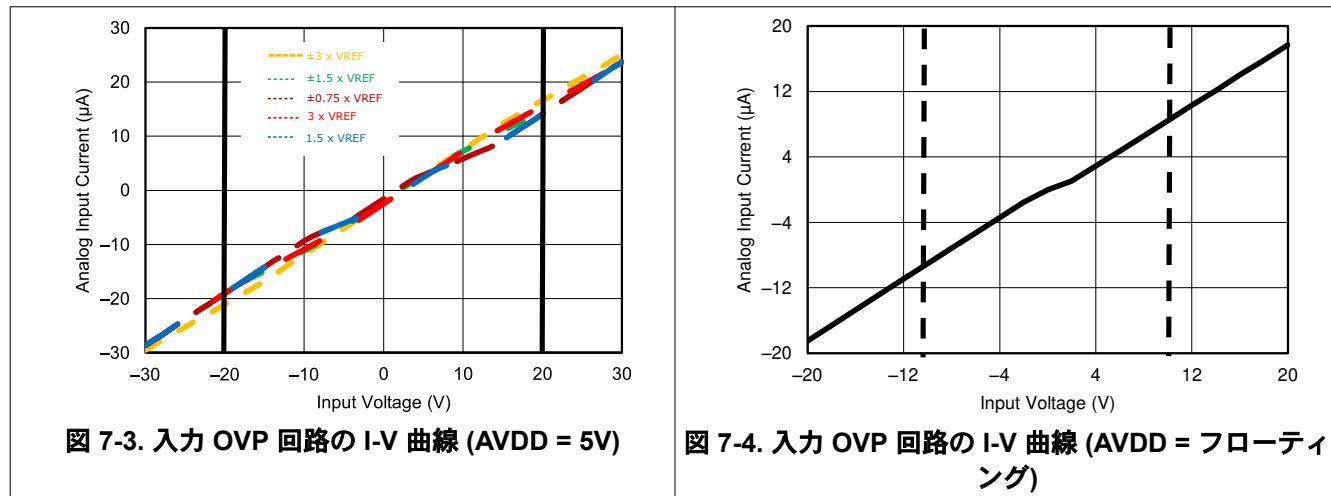

表 7-1 に、デバイスの電源オン時におけるデバイスのさまざまな動作条件を示します。表 7-1 は、デバイスの AVDD ピンが適切な電源電圧 (AVDD = 5V) に接続されている場合、または  $30\text{k}\Omega$  未満の低インピーダンスを実現している場合、内部過電圧保護回路はアナログ入力ピンで最大  $\pm 20\text{V}$  まで耐えられることを示しています。

表 7-1. AVDD = 5V または低インピーダンス (30kΩ 未満) のときの入力過電圧保護制限 (1)

| 入力条件<br>( $V_{OVP} = \pm 20V$ )      | テスト条件             | ADC 出力   | 備考                                                                    |

|--------------------------------------|-------------------|----------|-----------------------------------------------------------------------|

| $ V_{IN}  <  V_{RANGE} $             | 動作範囲内             | すべての入力範囲 | 有効<br>デバイスは、データシートの仕様に従って機能します                                        |

| $ V_{RANGE}  <  V_{IN}  <  V_{OVP} $ | 動作範囲を超えているが過電圧範囲内 | すべての入力範囲 | 飽和状態<br>ADC 出力は飽和していますが、デバイスは内部的に保護されています (これは長時間にわたって使用することは推奨されません) |

| $ V_{IN}  >  V_{OVP} $               | 過電圧範囲外            | すべての入力範囲 | 飽和状態<br>この使用状態により、デバイスに回復できない損傷が発生する可能性があります                          |

(1)  $GND = 0$ 、 $AIN\_nM = 0V$ 、 $|V_{RANGE}|$  は、選択されたすべての入力範囲の最大入力電圧です。 $|V_{OVP}|$  は、内部 OVP 回路のブレーカダウン電圧です。 $R_C$  が約 0 であると仮定します。

表 7-1 に示されている結果は、アナログ入力ピンが非常に低いインピーダンスソースによって駆動されるという前提に基づいています ( $R_S$  は約 0)。しかし、入力を駆動するソースのインピーダンスがより高い場合、保護ダイオードを流れる電流がさらに減少し、OVP 電圧範囲が拡大します。ソースインピーダンスが高いと、ゲイン誤差が生じ、システム全体のノイズ性能にも影響を与えることに注意してください。

図 7-3 に、デバイスのパワーアップ時の内部過電圧保護回路の電圧と電流応答の関係を示します。この I-V (電流から電圧へ) 応答によると、デバイスの入力ピンに流れる電流は  $1.2\text{M}\Omega$  入力インピーダンスによって制限されます。しかし、 $\pm 20\text{V}$  を超える電圧の場合、内部ノード電圧が内部トランジスタのブレークダウン電圧を上回るため、入力ピンの過電圧保護の制限が設定されます。

同じ過電圧保護回路によって、デバイスの電源がオンになっていない場合やインピーダンス  $30\text{k}\Omega$  以上で AVDD がフローティングになっている場合に、デバイスが保護されます。この状態は、ADC の電源が完全にオンになる前に入力信号が印加された場合に発生する可能性があります。表 7-2 に、この条件の過電圧保護制限を示します。

表 7-2. AVDD = インピーダンス  $30\text{k}\Omega$  以上のフローティング時の入力過電圧保護の限界 <sup>(1)</sup>

| 入力条件<br>( $V_{OVP} = \pm 11\text{V}$ ) | テスト条件    | ADC 出力 | 備考                                    |

|----------------------------------------|----------|--------|---------------------------------------|

| $ V_{IN}  <  V_{OVP} $ 過電圧範囲内          | すべての入力範囲 | 無効     | デバイスは機能しませんが、OVP 回路によって内部で保護されています。   |

| $ V_{IN}  >  V_{OVP} $ 過電圧範囲外          | すべての入力範囲 | 無効     | この使用状態により、デバイスに回復できない損傷が発生する可能性があります。 |

(1) AVDD = フローティング、GND = 0、AIN\_nM = 0V、 $|V_{RANGE}|$  は、選択されたすべての入力範囲の最大入力電圧です。 $|V_{OVP}|$  は、内部 OVP 回路のブレークダウン電圧です。 $R_S$  が約 0 であると仮定します。

図 7-4 に、デバイスのパワーダウン時の内部過電圧保護回路の電圧と電流応答の関係を示します。この I-V 応答によると、デバイスの入力ピンに流れる電流は  $1.2\text{M}\Omega$  入力インピーダンスによって制限されます。しかし、 $\pm 11\text{V}$  を超える電圧の場合、内部ノード電圧が内部トランジスタのブレークダウン電圧を上回るため、入力ピンの過電圧保護の制限が設定されます。

### 7.3.4 プログラマブル ゲイン アンプ (PGA)

デバイスには、個別のアナログ入力チャネルごとにプログラマブル ゲイン アンプ (PGA) が搭載されており、元のシングルエンド入力信号を完全差動信号に変換して、内蔵 16 ビット ADC を駆動します。また、PGA は、入力信号の同相モードレベルを ADC に供給する前に調整して、ADC 入力ダイナミック レンジを最大限に活用できます。入力信号の範囲に応じて、プログラム レジスタの Range\_CHn[3:0] ビットを設定することで、PGA のゲインを適切に調整できます。Range\_CHn[3:0] ビットのデフォルトまたはパワー オン 状態は 0000 であり、 $\pm 3 \times V_{REF}$  の入力信号範囲に対応します。表 7-3 に、さまざまなアナログ入力電圧範囲に対する Range\_CHn[3:0] ビットのさまざまな設定を示します。

PGA は、複数のゲイン構成に対応するために、非常に精度の高い抵抗ネットワークを使用します。すべてのチャネルにわたってこれらの抵抗とアンプの間のマッチングが正確に調整され、すべてのチャネルおよび入力範囲にわたって総合的なゲイン誤差が低く維持されます。

表 7-3. 入力レンジ選択ビット構成

| アナログ入力電圧範囲                     | Range_CHn[3:0] |       |       |       |

|--------------------------------|----------------|-------|-------|-------|

|                                | ビット 3          | ビット 2 | ビット 1 | ビット 0 |

| $\pm 3 \times V_{REF}$         | 0              | 0     | 0     | 0     |

| $\pm 1.5 \times V_{REF}$       | 0              | 0     | 0     | 1     |

| $\pm 0.75 \times V_{REF}$      | 0              | 0     | 1     | 0     |

| $\pm 0.3125 \times V_{REF}$    | 0              | 0     | 1     | 1     |

| $\pm 0.15625 \times V_{REF}$   | 1              | 0     | 1     | 1     |

| $0 \sim 3 \times V_{REF}$      | 0              | 1     | 0     | 1     |

| $0 \sim 1.5 \times V_{REF}$    | 0              | 1     | 1     | 0     |

| $0 \sim 0.625 \times V_{REF}$  | 0              | 1     | 1     | 1     |

| $0 \sim 0.3125 \times V_{REF}$ | 1              | 1     | 1     | 1     |

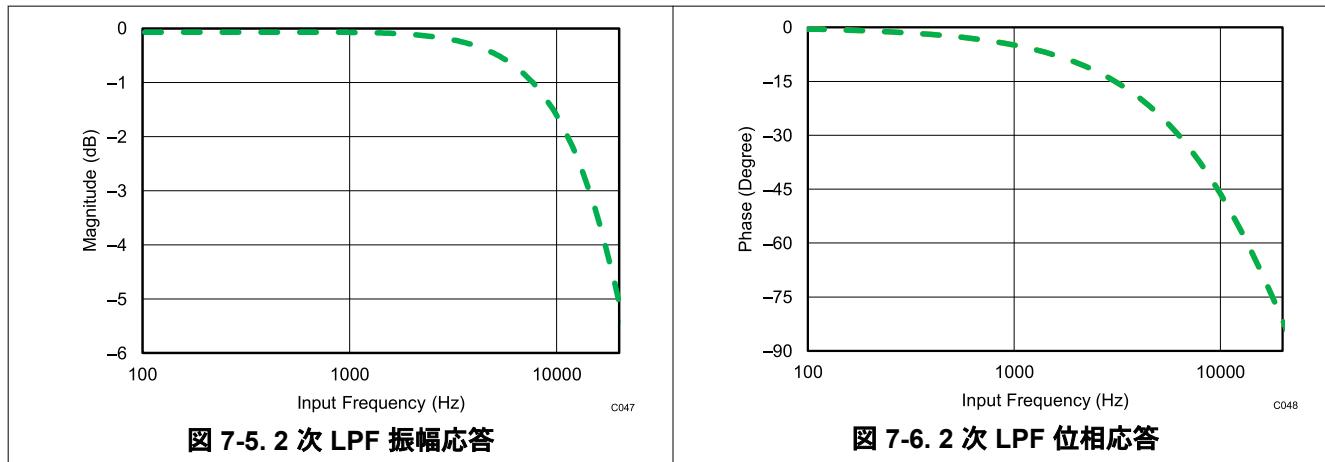

### 7.3.5.2 次ローパス フィルタ (LPF)

フロントエンド アンプと PGA のゲイン抵抗によるノイズを低減するため、ADS8688W の各アナログ入力チャネルには、PGA の出力での 2 次アンチ エイリアス LPF が搭載されています。アナログ アンチエイリアス フィルタの振幅応答と位相応答をそれぞれ 図 7-5 と 図 7-6 に示します。最大限の性能を得るために、アンチエイリアス フィルタの -3dB カットオフ周波数は、通常 15kHz に設定します。フィルタの性能は、ADC でサポートされるすべての入力範囲にわたって一貫しています。

図 7-5. 2 次 LPF 振幅応答

図 7-6. 2 次 LPF 位相応答

### 7.3.6 ADC ドライバ

16 ビット SAR ADC の最大サンプリング レート (500kSPS) での性能を満たすためには、ADC 入力部のサンプル & ホールド コンデンサが、サンプリング時間内に適切に充電および放電される必要があります。ADC の入力時この駆動要件を満たすには、高帯域幅かつ低ノイズで安定したアンプ バッファを使用する必要があります。このような入力ドライバは、このデバイスの各アナログ入力チャネルのフロント エンド信号路に組み込まれています。マルチプレクサの 1 つのチャネルから別のチャネルへの遷移中に、高速な内蔵ドライバにより、各チャネルの入力レベルに関係なく、ADC のアクイジョン時間内にマルチプレクサ出力が 16 ビット精度で安定していることが検証されます。

### 7.3.7 マルチプレクサ (MUX)

ADS8688W は、内蔵アナログ マルチプレクサを搭載しています。各アナログ入力チャネルについて、正のアナログ入力  $AIN_{NP}$  と負のグランド入力  $AIN_{nM}$  との間の電圧差は、マルチプレクサに供給される前にアナログ フロント エンド回路によって調整されます。マルチプレクサの出力は、ADC によって直接サンプリングされます。「[チャネル シーケンシング モード](#)」セクションの説明のように、デバイスのマルチプレクサは、手動モードまたは自動スキャン モードでこれらのアナログ入力をスキャンできます。手動モード ( $MAN_{Ch\_n}$ ) では、レジスタ書き込みにより、サンプルごとにチャネルが選択されます。自動スキャン モード ( $AUTO\_RST$ ) では、現在のチャネルがサンプリングされた後、 $\overline{CS}$  立ち下がりエッジごとにチャネル番号が自動的にインクリメントします。アナログ入力は、レジスタ設定による自動スキャン用に選択できます（「[自動スキャン シーケンシング制御レジスタ](#)」セクションを参照）。デバイスは、選択したアナログ入力のみを昇順に自動的にスキャンします。

全体的な ADS8688W の最大スループットは、すべてのチャネルで 500kSPS で規定されています。チャネルあたりのスループットは、マルチプレクサ スキャン シーケンスで選択されたチャネル数に依存します。たとえば、2 つのチャネルのみを選択した場合は、チャネルあたりのスループットは 250kSPS に等しくなり、4 つのチャネルを選択した場合は、チャネルあたり 125kSPS に等しくなります（以下同様）。

個別のアナログ チャネルに対して自動スキャン モードと手動スキャン モードを切り替えるコマンドレジスタの設定については、[表 8-1](#) を参照してください。

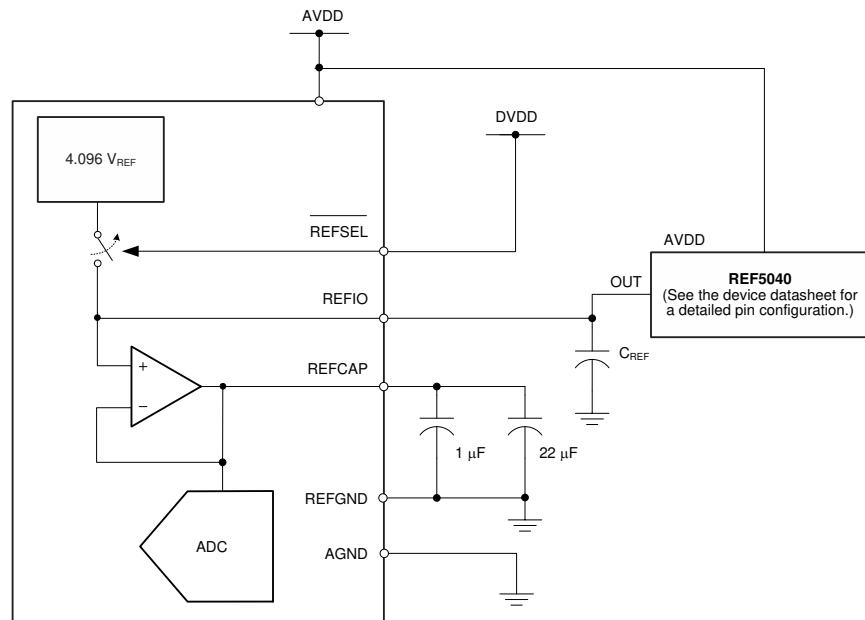

### 7.3.8 リファレンス

ADS8688W は、内蔵電圧リファレンスまたは内蔵バッファを使用した外部電圧リファレンスのいずれかを使用して動作させることができます。内部または外部のリファレンス電圧の選択は、外部  $REFSEL$  ピンによって決定されます。このデバイスは、内部 ADC コアの実際のリファレンス入力を駆動し、性能を最大限に高めるバッファ アンプを内蔵しています。

### 7.3.8.1 内部リファレンス

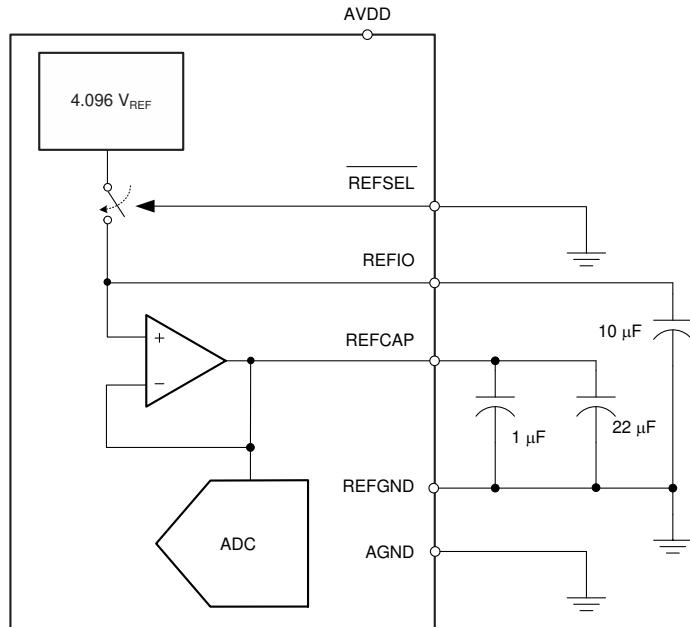

デバイスには、4.096V (公称値) のリファレンスが内蔵されています。内部リファレンスを選択するには、REFSEL ピンを Low に接続するか、AGND に接続する必要があります。内部リファレンスを使用すると、REFIO (ピン 5) は内部リファレンス値での出力になります。図 7-7 に示されているように、REFIO ピンと REFGND (ピン 6) の間に  $10\mu\text{F}$  (最小値) のデカップリングコンデンサを配置することを推奨します。コンデンサは、REFIO ピンのできるだけ近くに配置する必要があります。内部バンドギャップ回路の出力インピーダンスによって、このコンデンサと一緒にローパス フィルタが形成され、リファレンスのノイズを帯域制限します。コンデンサの値を小さくすると、システム内のリファレンスノイズが増加するため、SNR と SINAD の性能が低下します。REFIO の電流出力能力は制限されているため、REFIO ピンを使用して外部 ac または dc 負荷を駆動しないでください。REFIO ピンは、適切なオペアンプ バッファ (OPA320 など) を接続すれば、ソースとして使用できます。

図 7-7. 4.096V 内部リファレンスを使用したデバイス接続

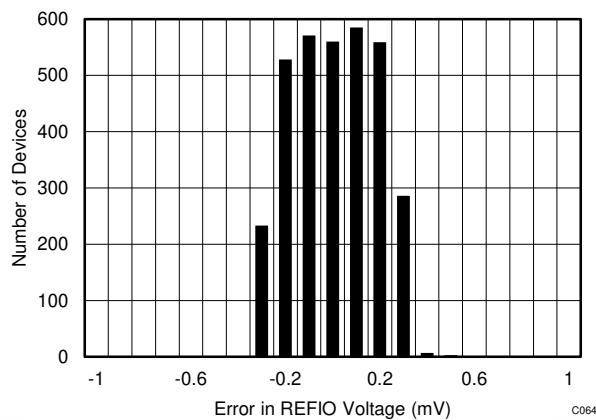

このデバイスの内部リファレンス電圧は、最大初期精度  $\pm 1\text{mV}$  になるように調整されています。図 7-8 のヒストグラムに、3300 を超える量産デバイスから取得した内部電圧リファレンス出力の分布を示します。

図 7-8. 室温での内部リファレンス精度のヒストグラム

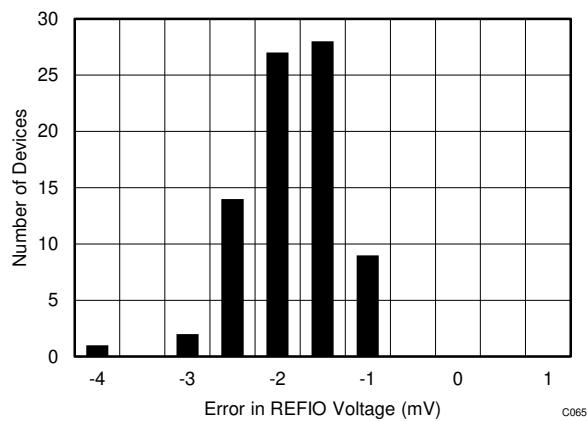

ダイが機械的ストレスまたは熱ストレスにさらされると、内部リファレンスの初期精度の仕様が低下する可能性があります。PCB に半田付けする際、およびその後のリフロー半田付け時にデバイスが加熱されることが、 $V_{REF}$  値変動の主要原因です。熱ヒステリシスの主な原因是、ダイにかかる応力の変化です。そのため、これはパッケージ、ダイ接着材料、モールド化合物、デバイスレイアウトによって左右されます。

この影響を確認するため、『AN-2029 取り扱いおよびプロセスの推奨事項』アプリケーション ノートに記載されているように、80 個のデバイスを鉛フリーの半田ペーストを使用して、メーカーが推奨するリフロー プロファイルに従って半田付けします。内部電圧リファレンスの出力は、リフロー プロセスの前後に測定します。図 7-9 に、値の標準的なシフトを示します。テストしたユニットすべてで、出力電圧に正のシフトが示されました。負のシフトも可能です。図 7-9 のヒストグラムは、単一のリフロー条件にさらされた際の典型的なシフトを示していることに注意してください。両面に表面実装部品があるプリント基板では、複数回のリフローにさらされることが一般的であり、これが出力電圧にさらなるシフトを引き起こします。PCB にリフローが何回も行われる場合は、ADS8688W を 2 回目のパスで半田付けすることで、デバイスへの熱ストレスを最小限に抑えることができます。

図 7-9. 半田付けの熱によるシフトの分布ヒストグラム

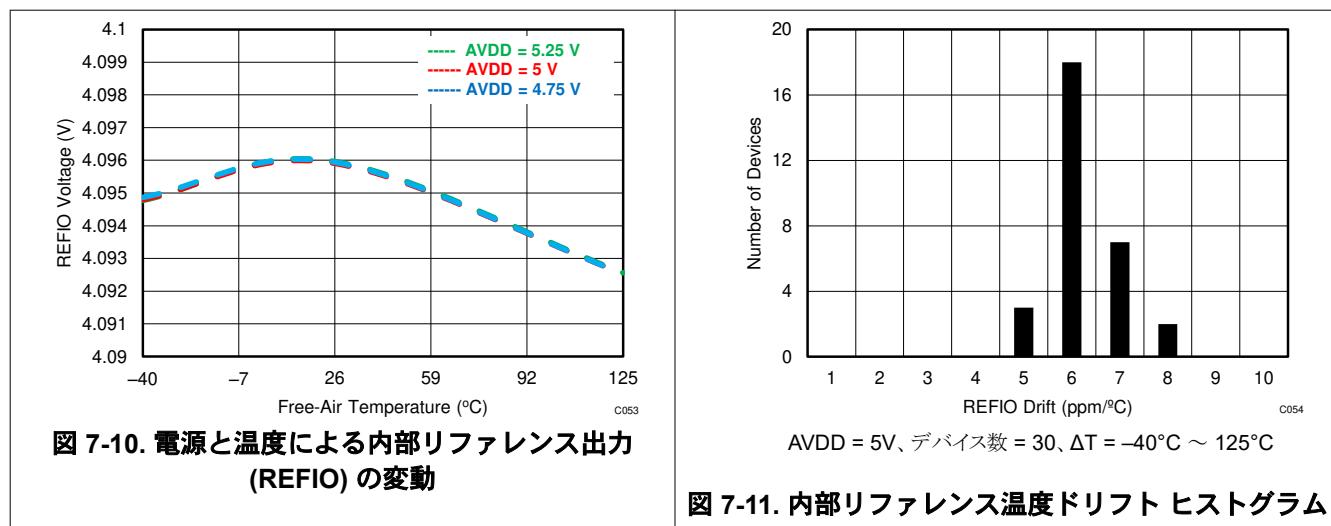

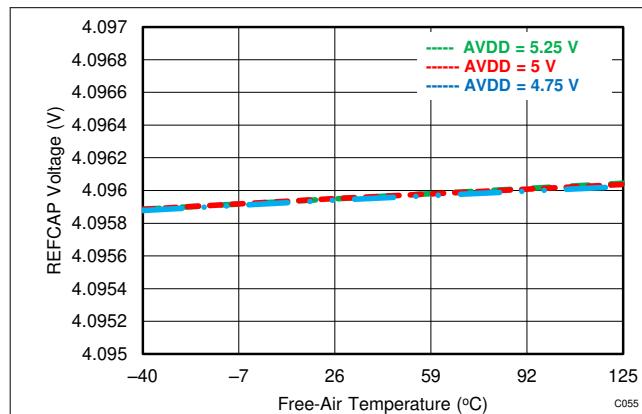

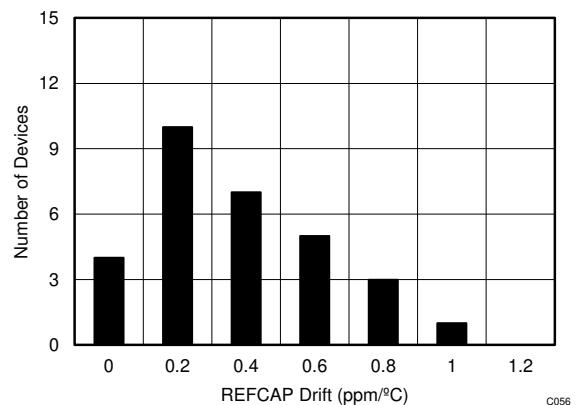

内部リファレンスも温度補償されており、 $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$  の拡張産業用温度範囲にわたって優れた温度ドリフトを提供します。図 7-10 に、AVDD 電源電圧の異なる値に対する温度全体の内部リファレンス電圧の変動を示します。温度範囲全体にわたるリファレンス電圧ドリフトの規定の標準値は 8ppm/ $^{\circ}\text{C}$  (図 7-11) と等しくなります。規定の最大温度ドリフトは 20ppm/ $^{\circ}\text{C}$  です。

図 7-10. 電源と温度による内部リファレンス出力 (REFIO) の変動

図 7-11. 内部リファレンス温度ドリフト ヒストグラム

### 7.3.8.2 外部リファレンス

複数のデバイスのためにより優れたリファレンス電圧や一般的なリファレンス電圧を必要とするアプリケーションのために、ADS8688W は外部リファレンスとともに、ADC リファレンスピンを駆動するための内部バッファを備えています。外部リファレンスモードを選択するには、REFSEL ピンを High に接続するか、このピンを DVDD 電源に接続します。このモードでは、入力ピンとなる REFIO (ピン 5) に外部 4.096V リファレンス電圧を印加する必要があります。このモードでは、内部バッファが ADC リファレンス入力に内部接続されている REF CAP ピンの動的負荷を処理するように最適に設計されているため、ローパワー、低ドリフト、小型サイズの外部リファレンスを使用できます。リファレンスノイズがシステム性能に及ぼす影響を最小限に抑えるために、外部リファレンスの出力は適切にフィルタリングする必要があります。図 7-12 に、このモードの代表的なピン配置を示します。

図 7-12. 4.096V 外部リファレンスを使用したデバイス接続

内部リファレンスバッファの出力は、REFCAP ピンに現われます。REFCAP (ピン 7) と REFGND (ピン 6) の間に  $10\mu\text{F}$  の最小容量を配置する必要があります。高周波信号のデカッピングのために、 $1\mu\text{F}$  コンデンサを REFCAP ピンのできるだけ近くに配置します。このバッファの電流出力能力は制限されているため、内部バッファを使用して外部 AC 負荷または DC 負荷を駆動しないでください。

内部バッファ出力の性能は、 $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$  の動作温度範囲全体で非常に安定します。図 7-13 に、AVDD 電源電圧の異なる値について、温度範囲全体にわたる REFCAP 出力の変動を示します。温度範囲全体でのリファレンスバッファドリフトの規定の標準値は  $1\text{ppm}/^{\circ}\text{C}$  (図 7-14) です。規定の最大温度ドリフトは  $1.5\text{ppm}/^{\circ}\text{C}$  です。

図 7-13. リファレンスバッファ出力 (REFCAP) の変動と電源 & 温度との関係

図 7-14. リファレンスバッファの温度ドリフトヒストグラム

### 7.3.9 拡助チャネル

このデバイスには、シングルエンド補助入力チャネル (AUX\_IN および AUX\_GND) が搭載されています。AUX チャネルは、マルチプレクサ経由で内部の高精度 16 ビット ADC と直接接続できます。これは、このチャネルには、他のアナログ入力チャネルが持つフロントエンドアナログシグナルコンディショニングが含まれていないためです。AUX チャネルは、フロントエンド PGA がないため、 $0\text{V} \sim V_{\text{REF}}$  の單一ユニポーラ入力範囲をサポートします。AUX\_IN ピンの入力信号は  $0\text{V}$  から  $V_{\text{REF}}$  まで変動する可能性があり、AUX\_GND ピンは GND に接続する必要があります。

変換が開始されると、これらのピン間の電圧は内部サンプリングコンデンサ ( $75\text{pF}$ 、標準値) で直接サンプリングされます。サンプリングコンデンサの充電に必要な入力電流は、サンプリングレート、入力周波数、ソースインピーダンスなど、いくつかの要因によって決定されます。低インピーダンスソースを使用する低速アプリケーションでは、AUX チャネルの入力を直接駆動できます。スループット、入力周波数、またはソースインピーダンスが増加した場合、AUX チャネルから優れた ac 性能を実現するために、駆動アンプを入力に使用する必要があります。駆動アンプのいくつかの主要な要件については、「[AUX チャネルの入力ドライバ](#)」セクションに説明が記載されています。

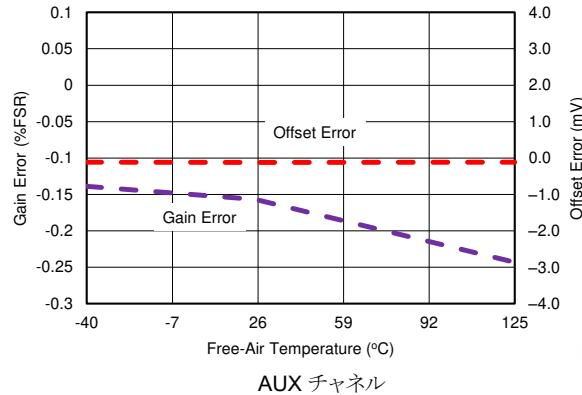

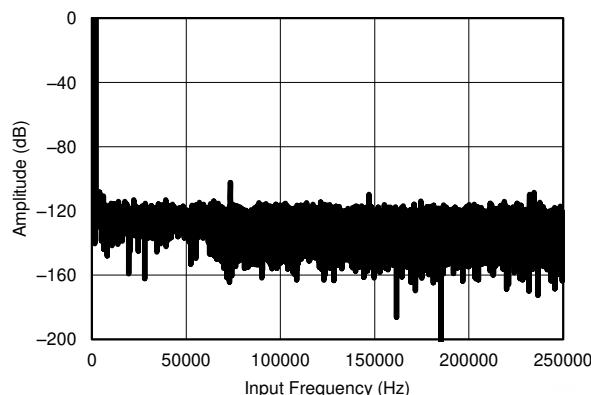

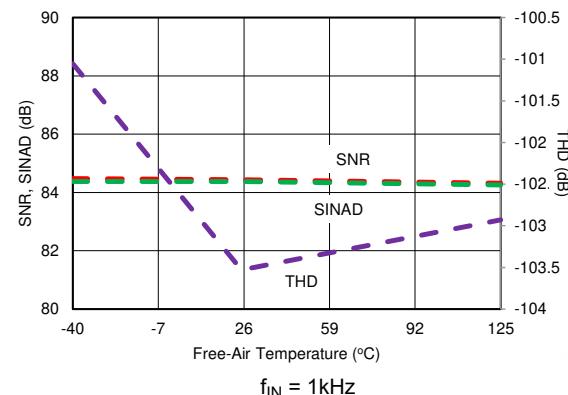

ADS8688W の AUX チャネルは、ノーミッキング コードで、真の 16 ビット性能を実現します。図 7-15 ~ 図 7-18 に、AUX チャネルの代表的性能特性を示します。

図 7-15. ミッドスケール入力の DC ヒストグラム

(AUX チャネル)

図 7-16. オフセットおよびゲインと温度との関係

(AUX チャネル)

図 7-17. 標準的な FFT プロット (AUX チャネル)

図 7-18. SNR、SINAD、THD と温度との関係 (AUX チャネル)

### 7.3.9.1 AUX チャネルの入力ドライバ

AUX 入力チャネルを高スループットおよび高入力周波数で使用するアプリケーションでは、内蔵の 14 ビット ADC の ac 性能を満たすには、出力インピーダンスの低い駆動アンプが必要です。入力駆動アンプの主な仕様を以下に示します。

- **小信号帯域幅。**アンプの帯域幅制限によって入力信号の減衰が発生しないことを確認するため、入力駆動アンプの小信号帯域幅は AUX 入力の帯域幅よりもはるかに高くする必要があります。代表的なデータアクイジションシステムでは、低いカットオフ周波数で、高分解能 ADC の入力にアンチエイリアスフィルタが使用されます。アンチエイリアスフィルタを駆動するアンプは、安定性のために閉ループ出力インピーダンスを小さくする必要があるため、アンプのゲイン帯域幅が広くなります。小信号帯域幅が高いと、高い入力周波数での高調波歪みも最小化されます。一般的に、アンプの帯域幅要件は、式 1 をベースとして計算できます。

$$GBW \geq 4 \times f_{-3\text{dB}} \quad (1)$$

ここで

- $f_{-3\text{dB}}$  は RC フィルタの 3dB 帯域幅です。

- **歪み。**式 2 に示されているように、AUX チャネルの歪み性能を達成するには、入力ドライバの歪みを、内部 ADC の仕様歪みよりも少なくとも 10dB 低くする必要があります。

$$THD_{\text{AMP}} \leq THD_{\text{ADC}} - 10 \text{ (dB)} \quad (2)$$

- **ノイズ。**システムの SNR の性能低下を防止するため、低ノイズのフロントエンドアンプを選択する場合は慎重に検討する必要があります。一般的に、データアクイジションシステムのノイズ性能がフロントエンド回路によって制限されないことを確認するには、フロントエンド回路からのノイズの寄与の合計を ADC の入力換算ノイズの 20% 未満に維持します。式 3 で説明されているように、入力ドライバ回路からのノイズは、入力アンチエイリアスフィルタの低いカットオフ周波数によって帯域制限されます。

$$N_G \times \sqrt{\left( \frac{V_{1/f\_AMP\_PP}}{6.6} \right)^2 + e_{n\_RMS}^2 \times \frac{\pi}{2} \times f_{-3\text{dB}}} \leq \frac{1}{5} \times \frac{V_{\text{FSR}}}{2\sqrt{2}} \times 10^{-\frac{\text{SNR(dB)}}{20}} \quad (3)$$

ここで

- $V_{1/f\_AMP\_PP}$  はピークツーピークのフリッカーノイズです。

- $e_{n\_RMS}$  はアンプの広帯域ノイズ密度 ( $\text{nV}/\sqrt{\text{Hz}}$ ) です。

- $N_G$  はフロントエンド回路のノイズゲインで、バッファ構成では 1 に等しくなります。

### 7.3.10 ADC の伝達関数

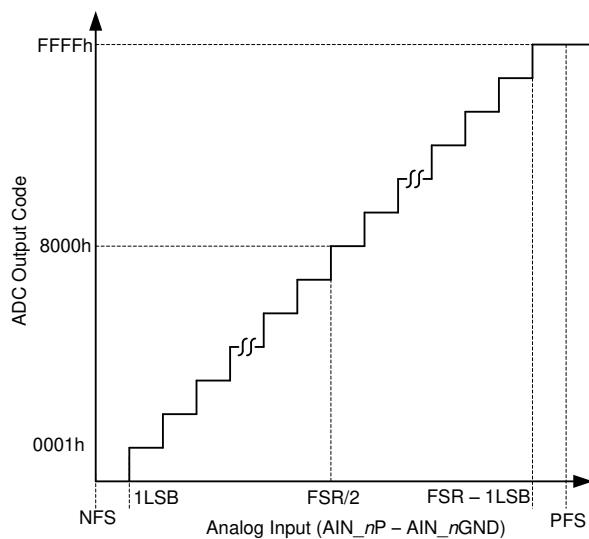

ADS8688W の出力は、バイポーラとユニポーラの両方の入力範囲に対して、ストレート バイナリ形式です。出力コードの形式は、すべてのアナログ チャンネルで同じです。

図 7-19 に、すべての入力範囲について、各 ADC チャンネルの理想的な伝達特性を示します。各入力信号のフルスケール範囲 (FSR) は、正のフルスケール (PFS) 入力電圧と負のフルスケール (NFS) の入力電圧の差に等しくなります。 LSB サイズは  $FSR/2^{16} = FSR/65536$  と等しくなります。これは、ADC の分解能が 16 ビットであるためです。リファレンス電圧  $V_{REF} = 4.096V$  については、表 7-4 にそれぞれの異なる入力範囲に対応する LSB の値を示します。

図 7-19. 16 ビット ADC 伝達関数 (ストレート バイナリ形式)

表 7-4. 異なる入力範囲の ADC LSB 値 ( $V_{REF} = 4.096V$ )

| 入力範囲                           | 正のフルスケール | 負のフルスケール | フルスケール レンジ | LSB ( $\mu V$ ) |

|--------------------------------|----------|----------|------------|-----------------|

| $\pm 3 \times V_{REF}$         | 12.288V  | -12.288V | 24.576V    | 312.50          |

| $\pm 1.5 \times V_{REF}$       | 6.144V   | -6.144V  | 12.288V    | 156.25          |

| $\pm 0.75 \times V_{REF}$      | 3.072V   | -3.072V  | 6.144V     | 78.125          |

| $\pm 0.3125 \times V_{REF}$    | 1.28V    | -1.28V   | 2.56V      | 156.25          |

| $\pm 0.15625 \times V_{REF}$   | 0.64V    | -0.64V   | 1.28V      | 78.125          |

| $0 \sim 3 \times V_{REF}$      | 12.288V  | 0V       | 12.288V    | 156.25          |

| $0 \sim 1.5 \times V_{REF}$    | 6.144V   | 0V       | 6.144V     | 78.125          |

| $0 \sim 0.625 \times V_{REF}$  | 2.56V    | 0V       | 2.56V      | 156.25          |

| $0 \sim 0.3125 \times V_{REF}$ | 1.28V    | 0V       | 1.28V      | 78.125          |

### 7.3.11 アラーム機能

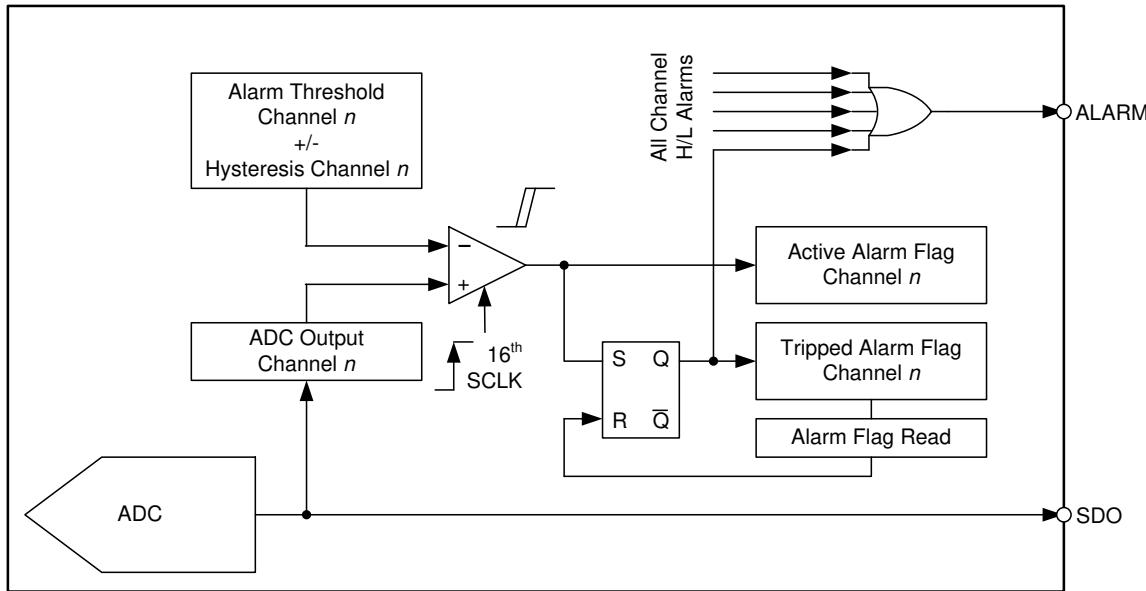

このデバイスは、ピン 35 にアクティブ high の ALARM 出力を備えています。ALARM 信号は同期的で、SCLK 信号の 16 番目の立ち下がりエッジで状態が変化します。ALARM が high レベルの場合、デバイスの 1 つまたは複数のチャネルでアラーム フラグがトリップしたことを示します。このピンを配線して、ホスト入力を割り込みさせることができます。ALARM 割り込みを受信すると、アラーム フラグ レジスタが読み出され、どのチャネルにアラームがあるかを決定します。デバイスは、チャネルごとに独立したプログラマブルアラーム機能を備えています。チャネルごとに 2 つのアラーム (low アラームと high アラーム) があり、各アラーム スレッショルドには個別のヒステリシス設定があります。

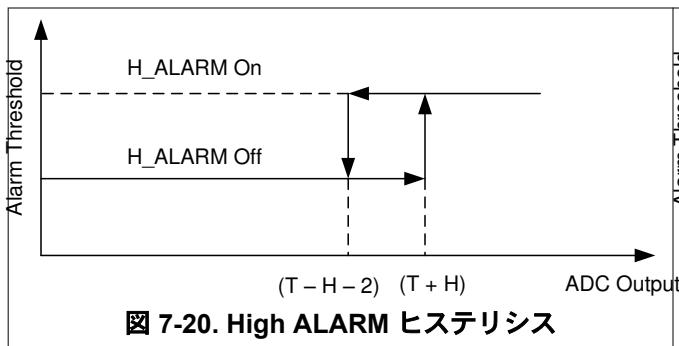

ADS8688W は、特定チャネルのデジタル出力が high アラーム上限値 [high アラームスレッショルド (T) + ヒステリシス (H)] を超えた場合に、high アラームを発します。チャネルのデジタル出力が high アラーム下限値 (high アラーム  $T - H - 2$ ) を下回ると、アラームはリセットされます。図 7-20 に、この関数を示します。

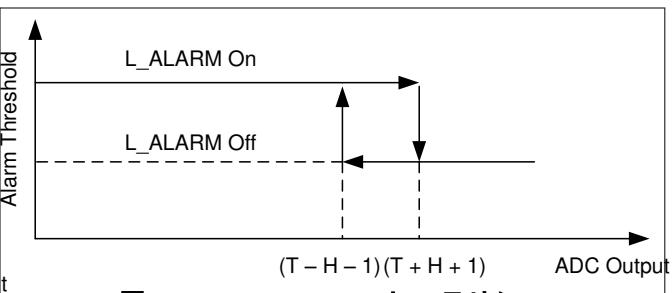

同様に、特定チャネルのデジタル出力が low アラーム下限値 (low アラームスレッショルド  $T - H - 1$ ) を下回ると、low アラームがトリガされます。デジタル出力が low アラーム上限値 (low アラーム  $T + H + 1$ ) を上回ると、アラームはリセットされます。図 7-21 に、この関数を示します。

図 7-22 に、シングルチャネルアラームの機能ブロック図を示します。high アラームと low アラームには、アクティブアラーム フラグとトリップアラーム フラグの 2 つのフラグがあります。詳細については、「アラーム フラグ レジスタ (読み取り専用)」セクションを参照してください。アクティブアラーム フラグは、特定のチャネルでアラーム状態が発生したときにトリガされます。アクティブアラーム フラグは、アラームがオフになったときにリセットされます。トリップアラーム フラグは、アクティブアラーム フラグと同じ方法でアラーム状態を設定します。しかし、トリップアラーム フラグはラッチされたままになり、適切なアラーム フラグ レジスタが読み出されたときにのみリセットされます。

図 7-22. アラーム機能の回路図

## 7.4 デバイスの機能モード

### 7.4.1 デバイスインターフェイス

#### 7.4.1.1 デジタル ピンの説明

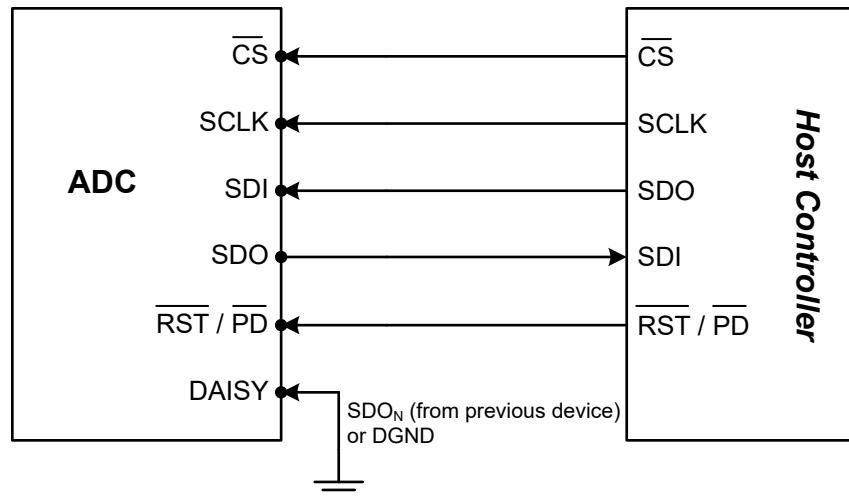

図 7-23 に、ADS8688W のデジタル データ インターフェイスを示します。

図 7-23. デジタル インターフェイスのピン構成

図 7-23 に示されている信号は、以下のように分類されます。

#### 7.4.1.1.1 $\overline{CS}$ (入力)

$\overline{CS}$  はアクティブ Low のチップ セレクト信号を示します。 $\overline{CS}$  は、立ち下がりエッジで変換をトリガする制御信号としても使用されます。各データ フレームは、 $\overline{CS}$  信号の立ち下がりエッジで開始します。特定のフレーム中に変換されるアナログ入力チャネルは、前のフレームで選択されます。 $\overline{CS}$  立ち下がりエッジで、デバイスは選択したチャネルから入力信号をサンプリングし、内部クロックを使用して変換が開始されます。次のデータ フレームのデバイス設定は、この変換プロセス中に入力できます。 $\overline{CS}$  信号が High のとき、ADC はアイドル状態とみなされます。

#### 7.4.1.1.2 SCLK (入力)

このピンは、データ インターフェイスの外部クロック入力を示します。デバイスへのすべての同期アクセスは、SCLK 信号の立ち下がりエッジを基準にしてタイミングが設定されます。

#### 7.4.1.1.3 SDI (入力)

SDI は、シリアル データ入力ラインです。SDI は、ホスト プロセッサによって、デバイス構成用の内部デバイス レジスタをプログラムするために使用されます。各データ フレームの開始時に、 $\overline{CS}$  信号が low になり、SDI ラインのデータは次の 16 SCLK サイクルにわたって、SCLK 信号の立ち下がりエッジごとにデバイスによって読み取られます。特定のデータ フレームでデバイス構成に加えられた変更は、 $\overline{CS}$  信号の以後の立ち下がりエッジでデバイスに適用されます。

#### 7.4.1.1.4 SDO (出力)

SDO は、シリアル データ出力ラインです。SDO は、デバイスが変換データを出力するために使用されます。データ出力フレームのサイズは、SDO フォーマットのレジスタ設定によって異なります。[表 8-18](#) を参照してください。 $\overline{CS}$  が low レベルになると、SDO ピンはハイ インピーダンス状態から解放されます。SDO は、最初の 15 SCLK 立ち下がりエッジ間、low に維持されます。出力データストリームの MSB は、SCLK の 16 番目の立ち下がりエッジで SDO でクロック アウトされ、後に続く立ち下がりエッジごとにそれ以降のデータビットが続きます。SDO ラインは、データ フレーム全体が出力されると low になり、 $\overline{CS}$  が high になるとハイ インピーダンス状態になります。

#### 7.4.1.1.5 DAISY (入力)

DAISY はシリアル入力ピンです。図 7-26 に示されているように、複数のデバイスをデイジーチェーン モードで接続する場合、チェーン内の最初のデバイスの DAISY ピンが GND に接続されます。以後のすべてのデバイスの DAISY ピンは前のデバイスの SDO 出力ピンに接続され、チェーン内の最後のデバイスの SDO 出力はホスト プロセッサの SDI に接続されます。アプリケーションでスタンドアローン デバイスを使用する場合、DAISY ピンを GND に接続します。

#### 7.4.1.1.6 $\overline{\text{RST}}/\overline{\text{PD}}$ (入力)

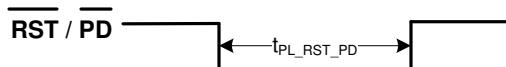

$\overline{\text{RST}}/\overline{\text{PD}}$  はデュアル機能ピンです。図 7-24 に、このピンのタイミングを示します。表 7-5 で、このピンの使用方法について説明します。

図 7-24.  $\overline{\text{RST}}/\overline{\text{PD}}$  ピンのタイミング

表 7-5.  $\overline{\text{RST}}/\overline{\text{PD}}$  ピンの機能

| 条件                                                | デバイス モード                                                              |

|---------------------------------------------------|-----------------------------------------------------------------------|

| $40\text{ns} < t_{PL\_RST\_PD} \leq 100\text{ns}$ | デバイスは RST モードで、PWR_DN モードには移行しません。                                    |

| $100\text{ns} < t_{PL\_RST\_PD} < 400\text{ns}$   | デバイスは RST モードで、PWR_DN モードに移行する場合と移行しない場合があります。<br>注記: この設定は推奨されていません。 |

| $t_{PL\_RST\_PD} \geq 400\text{ns}$               | デバイスは PWR_DN モードに移行し、プログラム レジスタはデフォルト値にリセットされます。                      |

$\overline{\text{RST}}/\overline{\text{PD}}$  ピンをロジック low 状態に 400ns 以上プルダウンすることで、パワーダウン (PWR\_DN) モードに移行できます。 $\overline{\text{RST}}/\overline{\text{PD}}$  ピンはクロックとは非同期であるため、 $\overline{\text{RST}}/\overline{\text{PD}}$  は他のピン (アナログ入力チャネルを含む) の状態に関係なく、いつでもトリガすることができます。デバイスがパワーダウン モードのときは、デジタル入力ピンのアクティビティ ( $\overline{\text{RST}}/\overline{\text{PD}}$  ピンを除く) は無視されます。

デバイスのプログラム レジスタは、 $\overline{\text{RST}}/\overline{\text{PD}}$  ピンを 100ns 以内の間ロジック Low 状態にすることで、デフォルト値 (RST) にリセットできます。この入力は、クロックに非同期です。 $\overline{\text{RST}}/\overline{\text{PD}}$  がロジック High 状態に戻ると、デバイスは通常モードになります。デバイスを構成するためのプログラム レジスタで有効な書き込み動作を 1 回実行した後、変換を開始するための適切なコマンド (AUTO\_RST または MAN) を送信する必要があります。

$\overline{\text{RST}}/\overline{\text{PD}}$  ピンがロジック high レベルに戻ると、デバイスはデフォルト状態でウェークアップし、プログラム レジスタはデフォルト値にリセットされます。

#### 7.4.1.2 データ アクイジョンの例

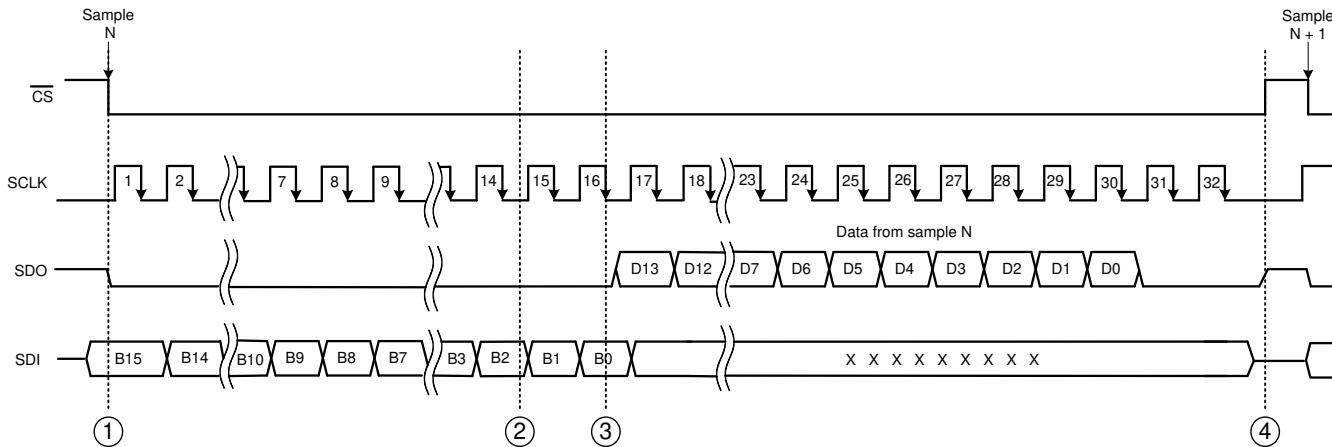

このセクションでは、ホスト プロセッサがデバイス インターフェイスを使用してデバイスの内部レジスタを構成し、特定の入力チャネル サンプリング用のデータの変換および取得を行う方法の例を示します。詳細については、図 7-25 に示されているタイミング図を参照してください。

図 7-25. シリアル インターフェイスを使用したデバイス動作のタイミング図

図 7-25 には、4 つのイベントが示されています。これらのイベントについて以下に説明します。

- **イベント 1:** ホストは、 $\overline{CS}$  信号の立ち下がりエッジによってデータ変換フレームを開始します。 $\overline{CS}$  立ち下がりエッジ時のアナログ入力信号は ADC によってサンプリングされ、内部発振器クロックを使用して変換が実行されます。このフレーム中に変換されたアナログ入力チャネルは、前のデータフレームで選択されます。このデータフレーム中に SDI および SCLK 入力を使用して、次の変換用のデバイスの内部レジスタ設定を入力できます。この瞬間に SCLK を開始し、次の 16 SCLK サイクルにわたって、SCLK 立ち下がりエッジごとに SDI ラインのデータをデバイスにラッピします。この時点で、最初の 16 SCLK サイクルの間、デバイスは SDO ラインに内部変換データを出力しないため、SDO は Low になります。

- **イベント 2:** 最初の 16 SCLK サイクルの間に、デバイスは内部変換プロセスを完了し、これでコンバータ内でデータの準備が整います。しかし、SCLK 入力に 16 番目の立ち下がりエッジが発生するまで、デバイスは SDO にデータビットを出力しません。ADC 変換時間は固定されているため (最大値は [電気的特性](#) 表を参照)、内部変換が終了した後、16 番目の SCLK 立ち下がりエッジが発生する必要があります。そうしないと、デバイスからのデータ出力が不正確になります。したがって、SCLK 周波数は、「[タイミング要件:シリアル インターフェイス](#)」表に規定されている最大値を超えることはできません。

- **イベント 3:** SCLK 信号の 16 番目の立ち下がりエッジで、デバイスは SDI ラインの入力ワードの LSB を読み取ります。残りのデータフレームについては、デバイスは SDI ラインから何も読み出しません。同じエッジにおいて、変換データの MSB が SDO ラインに出力され、ホスト プロセッサは SCLK 信号の以降の立ち下がりエッジでそれを読み取ることができます。出力データが 14 ビットについては、30 番目の SCLK 立ち下がりエッジで LSB を読み取ることができます。SDO は、以後の変換が開始されるまで、次の SCLK 立ち下がりエッジで 0 を出力します。

- **イベント 4:** デバイスから内部データを受信すると、ホストは CS 信号を high にすることでデータフレームを終了させます。イベント 1 で説明されているように、SDO 出力は、次のデータフレームが開始されるまでハイインピーダンス状態になります。

#### 7.4.1.3 ホスト / デバイス間の接続トポロジ

ADS8688W のデジタル インターフェイスは、ホスト コントローラがデバイスとデータやコマンドを交換する方法において、非常に高い柔軟性を提供します。図 7-23 に、ホスト コントローラとスタンドアローン デバイス間の代表的な接続を示します。複数の ADC を必要とするアプリケーションもありますが、ホスト コントローラではインターフェイス機能に制限があります。このセクションでは、このようなアプリケーションの要件に対応するために使用できる 2 つの接続トポロジについて説明します。

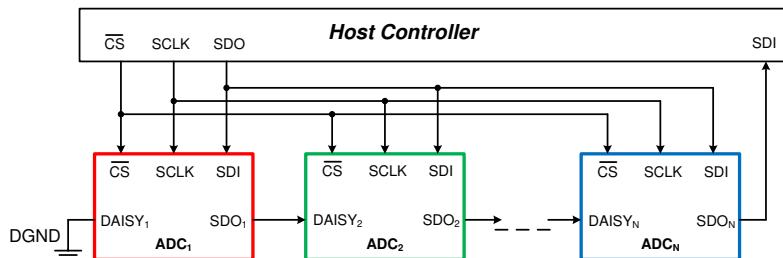

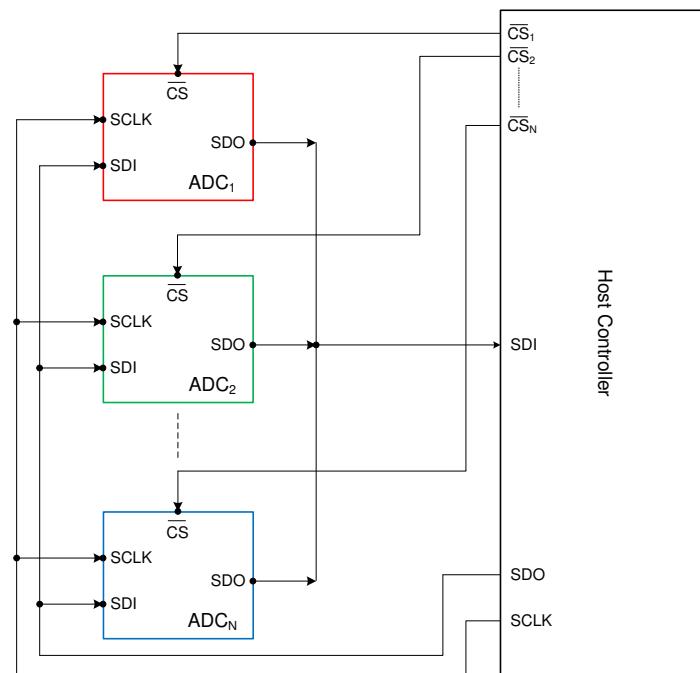

#### 7.4.1.3.1 デイジーチェーン接続

図 7-26 に、デイジーチェーン モードの複数のデバイスを扱う代表的な接続図を示します。すべてのデバイスの  $\overline{CS}$ 、SCLK、SDI 入力は相互に接続され、それぞれホスト コントローラの单一の  $\overline{CS}$ 、SCLK、SDI ピンによって制御されます。チェーン内の最初の ADC の DAISY<sub>1</sub> 入力ピンは DGND に接続され、SDO<sub>1</sub> 出力ピンは ADC<sub>2</sub> の DAISY<sub>2</sub> 入力に接続されます (以下同様)。チェーン内の N 番目の ADC の SDO<sub>N</sub> ピンは、ホスト コントローラの SDI ピンに接続されます。デバイスがデイジーチェーン モードに移行するのに特別なハードウェアやソフトウェア構成は必要ありません。

図 7-26. デイジーチェーン接続の回路図

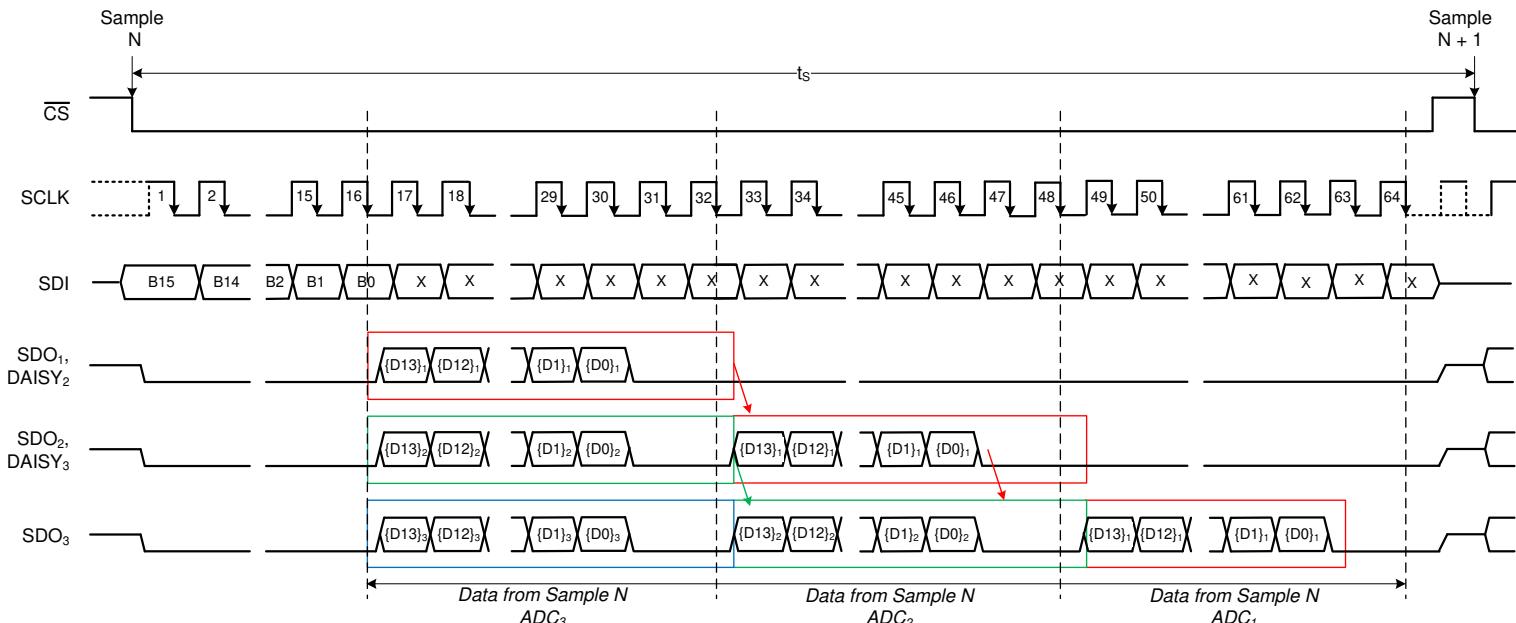

図 7-27 に、デイジーチェーン モードで接続された 3 つのデバイスの代表的なタイミング図を示します。

図 7-27. デイジーチェーン モードで接続された 3 つのデバイスのタイミング図

$\overline{CS}$  信号の立ち下がりエッジで、すべてのデバイスは選択されたチャネルで入力信号をサンプリングし、変換フェーズに移行します。最初の 16 SCLK サイクルでは、チェーン内のすべてのデバイスに共通の SDI ラインを使用して、次の変換のための内部レジスタ設定に移行できます。この期間中、すべてのデバイスの SDO 出力は Low に維持されます。変換が終了すると、チェーン内のすべての ADC によって、内部の 16 ビットシフトレジスタに独自の変換結果がロードされます。14 ビットデバイスの場合、内部シフトレジスタには 14 ビットの出力データに続いて LSB に 00 がロードされます。16 番目の SCLK 立ち下がりエッジで、チェーンのすべての ADC が独自の SDO 出力ピンに MSB ビットを出力します。以後の SCLK 立ち下がりエッジごとに、各 ADC の内部シフトレジスタは DAISY ピンで利用可能なデータをラッチし、SDO ピンの次のデータビットをシフトアウトします。したがって、デジタル ホストは ADC<sub>N</sub> のデータを受信し、それに続いて ADC<sub>N-1</sub> のデータ (MSB ファースト方式) を受信します。チェーン内のすべての N デバイスの出力を取得するには、合計で最低でも  $16 \times N$  SCLK 立ち下がりエッジが必要です。この例では、3 つのデバイスをデイジーチェーン接続で使用しているため、チェーン内のすべてのデバイスの出力を取得するには、 $3 \times 16 = 48$  SCLK サイクルが必要となり、さらに次

の変換のためのレジスタ設定を入力するために 16 SCLK サイクルが必要となるため、データフレーム全体で合計 64 SCLK サイクルが必要になります。システム全体のスループットは、デイジーチェーン構成で接続されるデバイスの数に比例して減少することに注意してください。

図 7-26 に示されているデイジーチェーン構成については、以下の点に注意する必要があります。

- すべてのデバイスの SDI ピンは互いに接続されているため、各デバイスは同じ内部構成で動作します。この制限は、独自の構成を持つデバイスの  $\overline{CS}$  または SDI 入力を制御するために追加のホストコントローラリソースを使用することで克服できます。

- デイジーチェーン接続されたデバイスの数が 4 つを超える場合、ホストコントローラからの共有出力ライン ( $\overline{CS}$ 、SDO、SCLK) の負荷が増加します。負荷が増加すると、デジタルタイミング誤差につながる可能性があります。この制限は、共有デジタルラインを追加のデバイスに供給する前に、ホストコントローラから共有出力のデジタルバッファを使用することで克服できます。

#### 7.4.1.3.2 スタートポロジ

図 7-28 に、スタートポロジで複数のデバイスを扱う代表的な接続図を示します。すべてのデバイスの SDI および SCLK 入力は相互に接続され、それぞれホストコントローラの单一の SDO および SCLK ピンによって制御されます。同様に、すべてのデバイスの SDO 出力は互いに接続され、ホストコントローラの SDI 入力ピンに接続されます。各デバイスの  $\overline{CS}$  入力ピンは、ホストコントローラからの個別の  $\overline{CS}$  制御ラインによって個別に制御されます。

図 7-28. スタートポロジ接続回路図

図 7-25 に示されているように、スタートポロジにおける代表的なデータフレームのタイミング図はスタンドアローンデバイスの動作時の場合と同じです。特定のデバイスのデータフレームは、 $\overline{CS}$  信号の立ち下がりエッジで開始し、 $\overline{CS}$  信号が High になると終了します。ホストコントローラは、このトポロジでは各デバイスに対して個別の  $\overline{CS}$  制御信号を提供するため、ユーザーは任意の順序でデバイスを選択し、特定のデバイスの  $\overline{CS}$  信号を下げることで変換を開始できます。図 7-25 の説明のように、各データフレームの終わりで  $\overline{CS}$  が high になると、デバイスの SDO 出力がハイインピーダンス状態になります。したがって、スタートポロジの共有 SDO ラインは、アクティブデータフレーム ( $\overline{CS}$  が low) を備えたデバイスによってのみ制御されます。SDO ラインを同時に駆動する複数のデバイスに関連する競合を避けるため、ホストコントローラが特定の時点での  $\overline{CS}$  信号のみをプルダウンすることを確認してください。

TI は、スタートポロジでは最大 4 つのデバイスを接続することを推奨します。それを超えると、ホストコントローラ (SDO および SCLK) からの共有出力ラインの負荷が増加する可能性があります。この負荷は、デジタルタイミング誤差につながる可能性があります。この制限は、ホストコントローラからの共有出力のデジタルバッファを使用してから、追加のデバイスに供給することで克服できます。

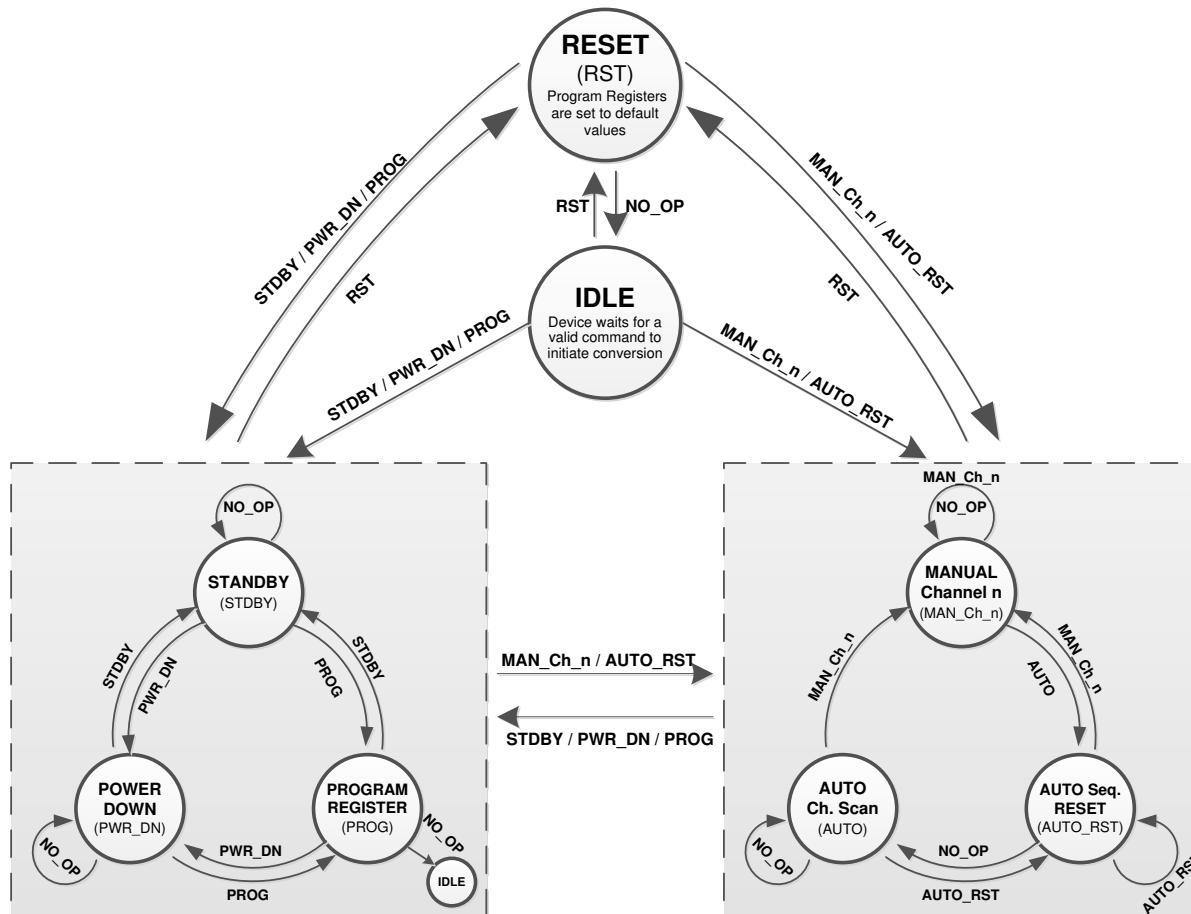

#### 7.4.2 デバイスモード

ADS8688W は、ソフトウェアでプログラム可能な複数の動作モードをサポートしています。パワーアップ後、デバイスはアイドルモードになり、ユーザーからコマンドを受信するまでは機能を実行しません。表 8-1 に、デバイスの各種モードに移行するためのすべてのコマンドを示します。パワーアップ後、プログラムレジスタはデフォルト値でウェークアップします。変換を実行する前に、適切な構成設定が必要です。図 7-29 の図に、デバイスのある動作モードから別の動作モードに切り替える方法の説明を示します。

図 7-29. 状態遷移図

##### 7.4.2.1 選択されたモードでの継続動作 (NO\_OP)

デバイス動作中に SDI ラインを継続的に Low に維持 (16 ビットすべてに 0 を書き込むのと同等) すると、デバイスは最後に選択されたモード (STDBY、PWR\_DN、AUTO\_RST、MAN\_Ch\_n のいずれか) で動作を続行します。このモードでは、デバイスはプログラムレジスタにすでに設定されているのと同じ設定に従います。

デバイスがプログラムレジスタ (PROG モード) で読み取りまたは書き込み動作を実行しているときに NO\_OP 状態が発生した場合、デバイスはプログラムレジスタの現在の設定を保持します。デバイスは IDLE モードに戻り、ユーザーがプログラムレジスタの読み取りまたは書き込み構成を実行するための適切なコマンドを入力するまで待機します。

#### 7.4.2.2 フレーム中止条件 (FRAME\_ABORT)

「データ アクイジョンの例」セクションに説明されているように、デバイスのデジタル インターフェイスは、各データ フレームが  $\overline{CS}$  信号の立ち下がりエッジで開始するように設計されています。最初の 16 SCLK サイクルの間、デバイスは SDI ラインで 16 ビットのコマンド ワードを読み出します。デバイスは、コマンドの実行を待機している間、コマンドの最後のビットを受信します。このビットは、16 番目の SCLK 立ち下がりエッジでラッチされます。この動作中は、 $\overline{CS}$  信号を Low に維持する必要があります。データ転送が完了する前に、何らかの理由で  $\overline{CS}$  信号が High になると、デバイスは INVALID 状態に移行し、適切なコマンドが書き込まれるまで待機します。この条件を FRAME\_ABORT 条件と呼びます。デバイスがこの INVALID モードで動作しているとき、デバイスでの読み出し動作はすべて SDO ラインに無効なデータを返します。ALARM ピンの出力は、前に選択されたチャネルの入力信号のステータスを反映し続けます。

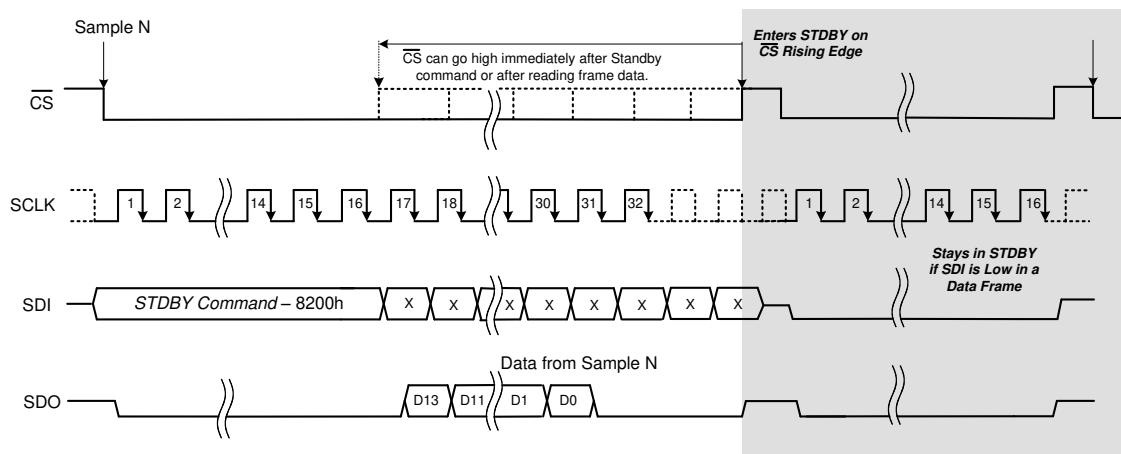

#### 7.4.2.3 スタンバイ モード (STDBY)

このデバイスは、回路の一部のみがパワーダウンする低消費電力のスタンバイ モード (STDBY) をサポートしています。内部リファレンスとバッファはパワーダウンしないため、デバイスは 20 $\mu$ s で迅速にパワーアップして STDBY モードを終了できます。デバイスが STDBY モードから復帰しても、プログラム レジスタはデフォルト値にリセットされません。

図 7-30 に示されているように、STDBY モードに移行するには、STDBY コマンド 8200h でコマンド レジスタへの有効な書き込み動作を実行します。このコマンドが実行されると、この書き込み動作に続く次の  $\overline{CS}$  信号の立ち上がりエッジで、デバイスは STDBY モードに移行します。以後のデータ フレーム中に、有効な変換コマンド (AUTO\_RST または MAN\_Ch\_n) が実行されず、SDI が low に維持されている場合、デバイスは STDBY モードのままになります (「選択されたモードでの継続動作」セクションを参照)。デバイスが STDBY モードで動作している場合、16 SCLK サイクルを使用してプログラム レジスタの設定を更新できます (「プログラム レジスタの読み取り書き込み動作」セクションの説明を参照)。しかし、32 の完全な SCLK サイクルが供給される場合、STDBY モードでの変換処理がないため、デバイスは SDO ラインに無効なデータを返します。このモード中は、プログラム レジスタの読み取り動作を通常に行うことができます。

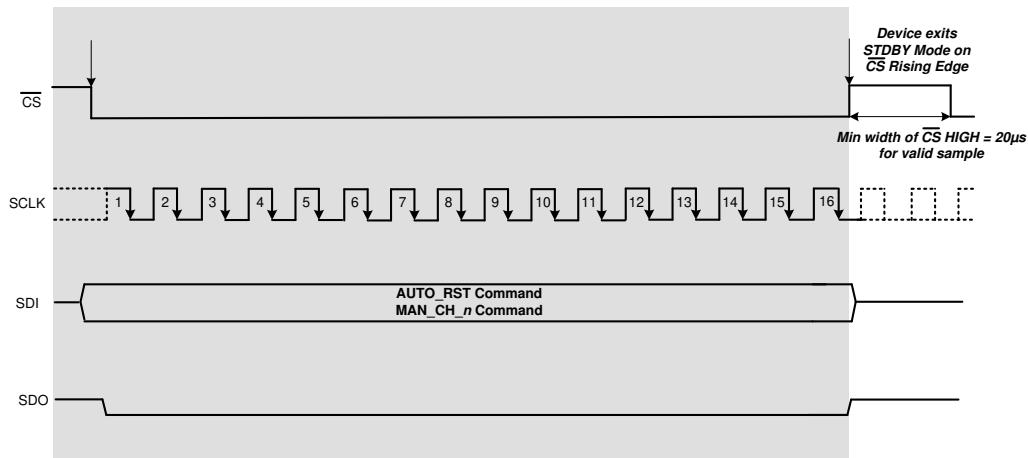

図 7-30. STDBY モードへの移行と維持のタイミング図

図 7-31 に示されているように、STDBY モードを終了するには、自動 (AUTO\_RST) または手動 (MAN\_CH\_n) スキャンモードに移行するために、有効な 16 ビット書き込みコマンドを実行する必要があります。デバイスは、次の  $\overline{\text{CS}}$  立ち上がりエッジで STDBY モードの終了を開始します。次の  $\overline{\text{CS}}$  信号の立ち下がりエッジで、デバイスは  $\text{MAN\_CH}_n$  コマンドで選択されたチャネル、または AUTO\_RST モードシーケンスの最初のチャネルのアナログ入力をサンプリングします。入力信号が正しくサンプリングされていることを確認するため、STDBY モードを終了した後は、 $\overline{\text{CS}}$  信号の最小幅を  $20\mu\text{s}$  に維持します。これにより、サンプリングを行う前に、デバイスの内部回路が完全にパワーアップし、バイアスされるようになります。図 7-25 の説明のように、選択されたチャネルのデータ出力は同じデータフレーム中に読み取ることができます。

図 7-31. STDBY モード終了のタイミング図

#### 7.4.2.4 パワーダウン モード (PWR\_DN)

デバイスは、ハードウェアおよびソフトウェアのパワーダウン モード (PWR\_DN) をサポートしており、内部リファレンス回路やバッファを含むすべての内部回路の電源がオフになります。デバイスが内部リファレンス モード ( $\overline{\text{REFSEL}} = 0$ ) で動作している場合、デバイスがパワーアップして、選択されたアナログ入力チャネルを PWR\_DN モードを終了後に変換するまでに 15ms 以上が必要です。デバイスのハードウェア電源モードについては、「[RST/PD \(入力\)](#)」セクションに説明が記載されています。ハードウェア パワーダウン モードとソフトウェア パワーダウン モードの主な違いは、ハードウェア パワーダウン モードからデバイスがウェークアップする際にはプログラム レジスタがデフォルト値にリセットされるのに対し、ソフトウェア パワーダウン モードからウェークアップする際にはプログラム レジスタの以前の設定が保持される点です。

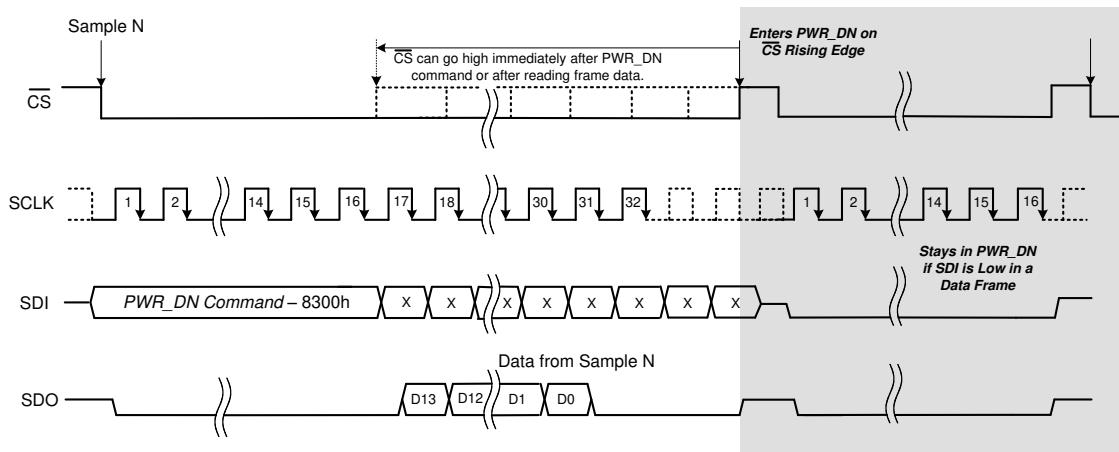

図 7-32 に示されているように、ソフトウェアを使用して PWR\_DN モードに移行するには、ソフトウェア PWR\_DN コマンド 8300h で、コマンド レジスタで有効な書き込み動作を実行します。このコマンドが実行されると、この書き込み動作に続く次の  $\overline{\text{CS}}$  信号の立ち上がりエッジで、デバイスは PWR\_DN モードに移行します。以後のデータ フレーム中に、有効な変換コマンド (AUTO\_RST または MAN\_Ch\_n) が実行されず、SDI が Low に維持されている場合、デバイスは PWR\_DN モードのままになります（「[選択されたモードでの継続動作](#)」セクションを参照）。デバイスが PWR\_DN モードで動作している場合、16 SCLK サイクルを使用してプログラム レジスタの設定を更新できます（「[プログラム レジスタの読み取り書き込み動作](#)」セクションの説明を参照）。しかし、32 の完全な SCLK サイクルが供給される場合、PWR\_DN モードでの変換処理がないため、デバイスは SDO ラインに無効なデータを返します。このモード中は、プログラム レジスタの読み取り動作を通常に行うことができます。

図 7-32. PWR\_DN モードへの移行と維持のタイミング図

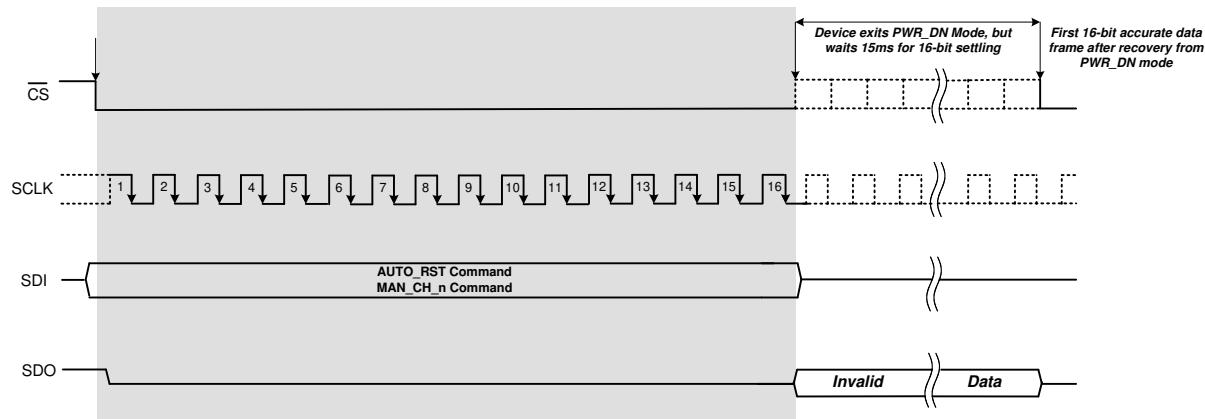

図 7-33 に示されているように、PWR\_DN モードを終了するには、有効な 16 ビット書き込みコマンドを実行する必要があります。デバイスは、次の  $\overline{\text{CS}}$  立ち上がりエッジで PWR\_DN モードから復帰します。内部リファレンス モード ( $\overline{\text{REFSEL}} = 0$ ) で動作している場合、デバイスがリファレンス回路や他の内部回路をパワーアップして、選択された入力チャネルの有効な変換データが出力される前に必要な精度で安定するまでに 15ms が必要です。

図 7-33. PWR\_DN モード終了のタイミング図

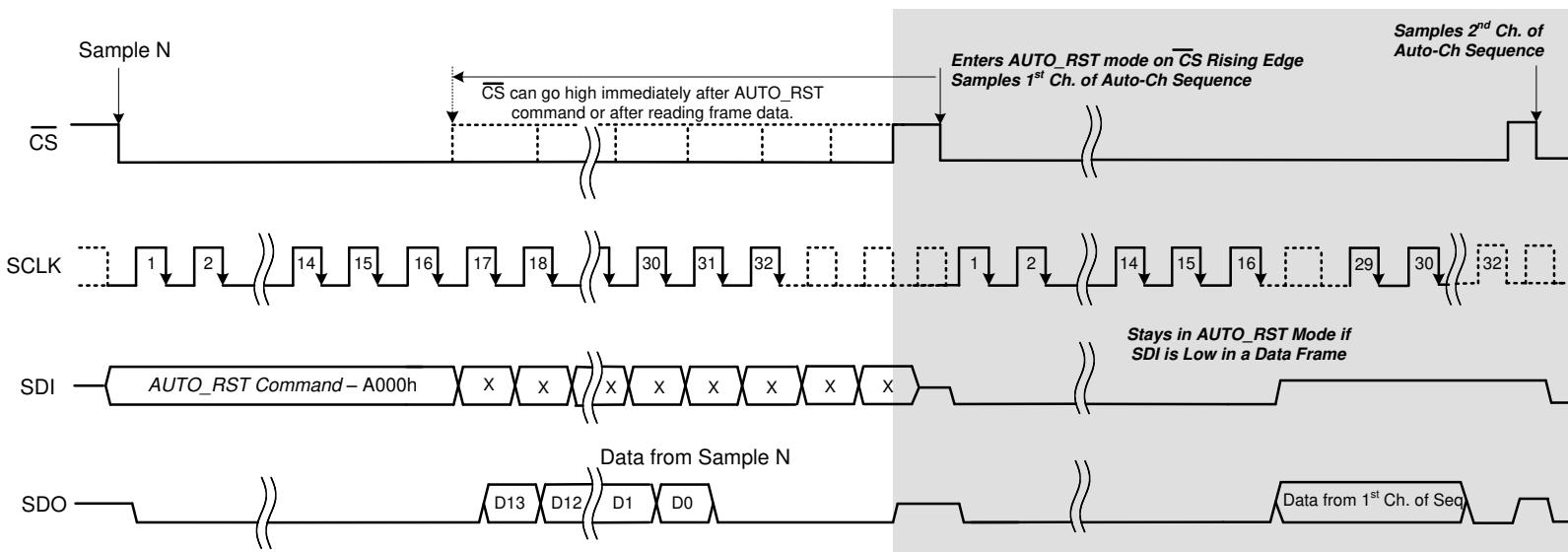

#### 7.4.2.5 リセットによる自動チャネル イネーブル (AUTO\_RST)

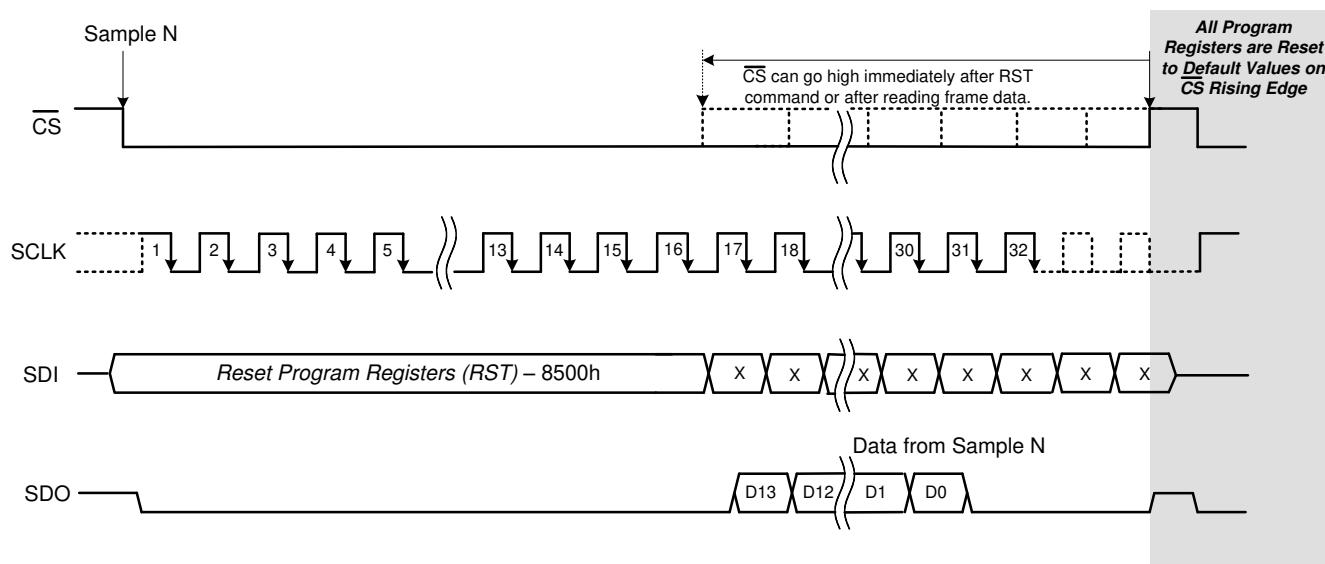

図 7-34 に説明されているように、デバイスは、コマンド レジスタにリセット (AUTO\_RST, A000h) コマンドを含む有効な自動チャネル シーケンスを書き込むことで、すべてのアナログ チャネルの入力信号を自動的にスキャンするようにプログラムできます。図 7-34 に示されているように、AUTO\_RST コマンドの後、またはフレームの出力データを読み取った後で、 $\overline{CS}$  信号は直ちに High にできます。しかし、次のデータ フレームの最初に選択されたチャネルで入力信号を正確に収集および変換するには、コマンド フレームに 32 SCLK サイクルの完全なフレームが必要です。

自動スキャンのチャネル シーケンスは、プログラム レジスタの AUTO SCAN シーケンシング制御レジスタ (01h ~ 02h) を使用して設定できます。「プログラム レジスタ マップ」セクションを参照してください。このモードでは、デバイスは選択されたチャネルを最も低いチャネルから順番に、昇順で連続的に切り替えながら、プログラム レジスタで選択されたすべてのチャネルを変換します。シーケンスが完了すると、デバイスはプログラム レジスタの最も低いカウント チャネルに戻り、シーケンスを繰り返します。自動スキャン シーケンスの各チャネルの入力電圧範囲は、プログラム レジスタの「範囲選択レジスタ」を設定することで設定できます。

図 7-34. AUTO\_RST モードへの移行のタイミング図

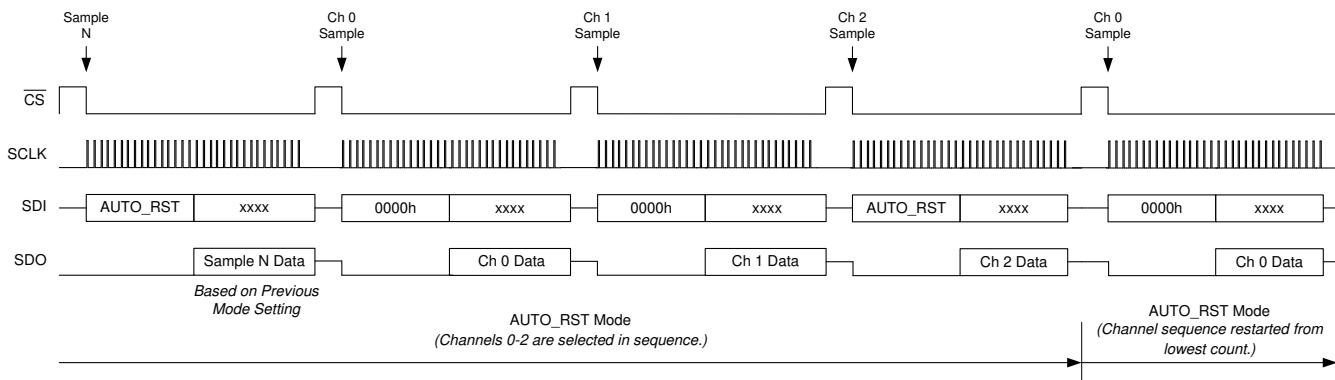

以後のデータ フレーム中に、他の有効なコマンドが実行されず、SDI が Low に維持されている場合、デバイスは AUTO\_RST モードのままになります (「選択されたモードでの継続動作 (NO\_OP)」セクションを参照)。この動作モード中の任意の時点での AUTO\_RST コマンドが再度実行されると、スキャンされたチャネルのシーケンスはリセットされます。デバイスはプログラム レジスタの自動スキャン シーケンスの最も低いカウント チャネルに戻り、このシーケンスを繰り返します。図 7-35 のタイミング図は、チャネル 0 ~ 2 が自動 シーケンスで選択される場合の例を用いて、この動作を示しています。AUTO\_RST モードと MAN\_Ch\_n モードを切り替える方法については、「チャネル シーケンシング モード」セクションを参照してください。

図 7-35. AUTO\_RST モードでのデバイス動作例

#### 7.4.2.6 手動チャネル $n$ 選択 (MAN\_Ch\_n)

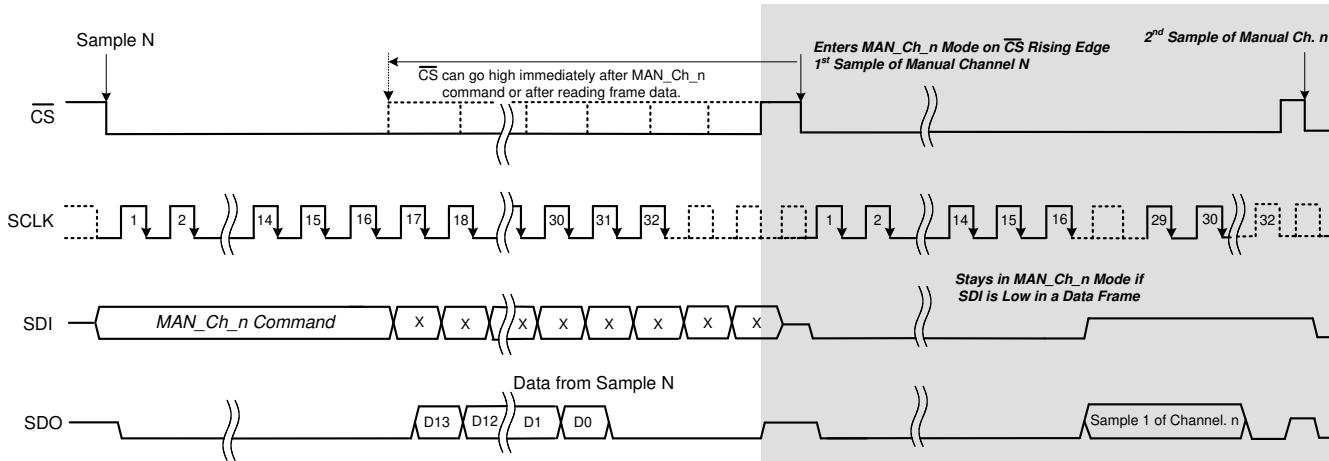

デバイスは、手動チャネル  $n$  スキャン モード (MAN\_Ch\_n) で動作させることで、特定のアナログ入力チャネルを変換するようにプログラムできます。図 7-36 に示されているように、このプログラミングは、コマンド レジスタに有効な手動チャネル  $n$  選択コマンド (MAN\_Ch\_n) を書き込むことで行われます。図 7-36 に示されているように、 $\overline{CS}$  信号は、MAN\_Ch\_n コマンドの直後、またはフレームの出力データを読み取った後で、直ちに High にできます。しかし、次のチャネルの入力信号を正確に取得して変換するには、コマンド フレームは 32 SCLK サイクルからなる完全なフレームである必要があります。MAN\_Ch\_n モードで個々のチャネルを選択するコマンドのリストについては、表 8-1 を参照してください。

図 7-36. MAN\_Ch\_n スキャン モードへの移行のタイミング図

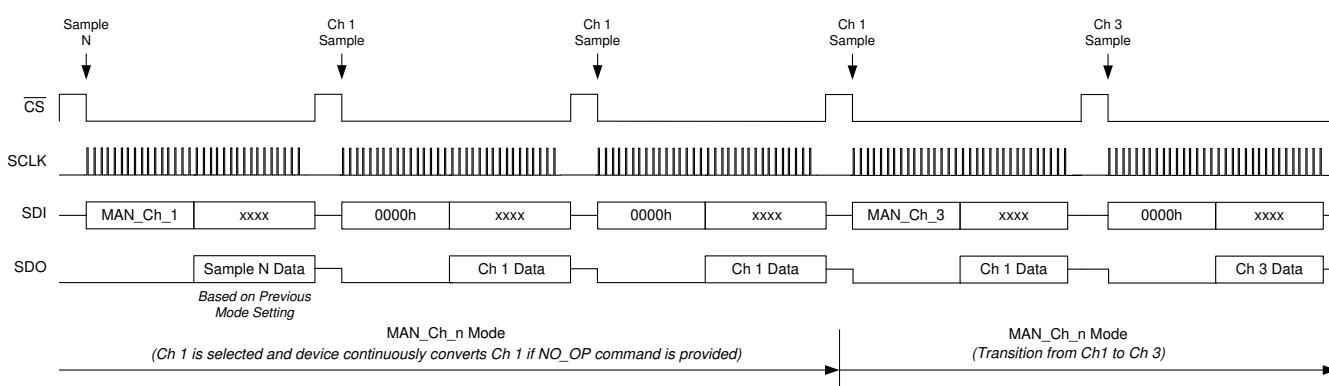

手動チャネル  $n$  選択コマンド (MAN\_Ch\_n) が実行され、デバイスはこの書き込み動作後の次のデータフレームの  $\overline{CS}$  立ち下がりエッジで、選択されたチャネルのアナログ入力をサンプリングします。MAN\_Ch\_n モードでの各チャネルの入力電圧範囲は、プログラム レジスタの「[範囲選択レジスタ](#)」を設定することで設定できます。以後のデータフレーム中に、他の有効なコマンドが実行されず、SDI が Low に維持されている場合、デバイスは同じチャネルでアナログ入力のサンプリングを続けます（「[選択されたモードでの継続動作 \(NO\\_OP\)](#)」のセクションを参照）。図 7-37 のタイミング図に、手動シーケンシング モードでチャネル 1 が選択される場合の例を用いて、この動作を示します。MAN\_Ch\_n モードと AUTO\_RST モードを切り替える方法については、「[チャネルシーケンシング モード](#)」セクションを参照してください。

図 7-37. MAN\_Ch\_n Mode モードでのデバイス動作

#### 7.4.2.7 チャネル シーケンシング モード

デバイスには、2つのチャネル シーケンス モードがあります。AUTO\_RST および MAN\_Ch\_n。

AUTO\_RST モードでは、以後のフレームごとにチャネル番号が自動的にインクリメントします。「[自動スキャン シーケンシング制御レジスタ](#)」セクションに説明されているように、レジスタ設定でアナログ入力を自動スキャンに選択できます。デバイスは、選択されたアナログ入力のみを昇順で自動的にスキャンします。この動作モードでは、選択されていないアナログ入力チャネルをパワーダウンすることもできるため、消費電力を最適化できます。自動モード シーケンスは、自動スキャン中 いつでもリセットできます (AUTO\_RST コマンドを使用)。リセットコマンドを受信すると、進行中の自動モード シーケンスはリセットされ、シーケンスで選択された最も低いチャネルから再開されます。

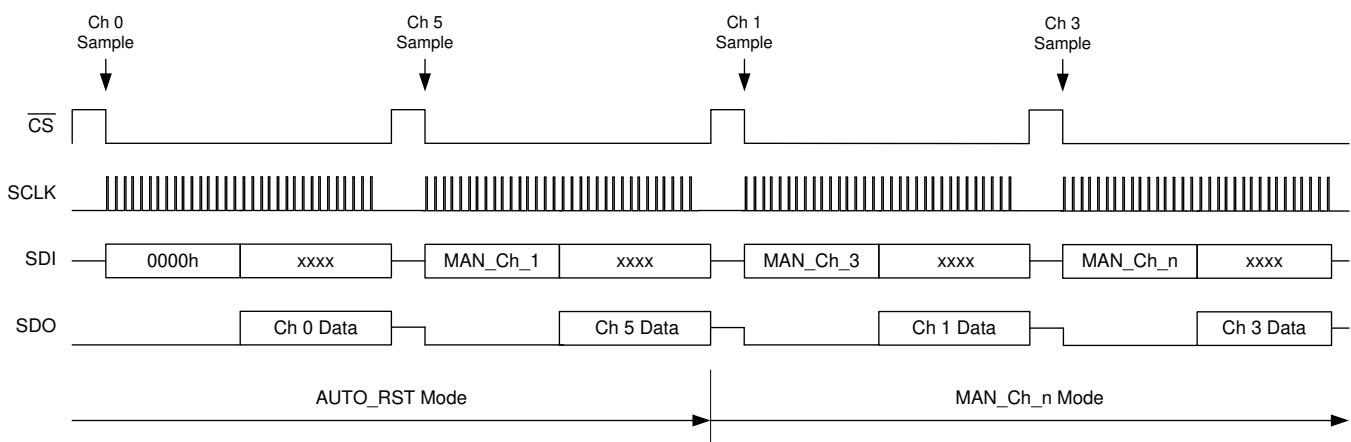

MAN\_Ch\_n モードでは、データ変換フレームごとに同じ入力チャネルが選択されます。表 8-1 に、MAN\_Ch\_n モードで個々のアナログ チャネルを選択するための入力コマンド ワードを示します。データフレーム中に特定の入力チャネルが選択された場合、次のデータフレームでは同じチャネルのアナログ入力がサンプリングされます。図 7-38 に、AUTO\_RST から MAN\_Ch\_n モードへの遷移の SDI コマンド シーケンスを示します。

図 7-38. AUTO\_RST から MAN\_Ch\_n Mode モードへの遷移 (チャネル 0 および 5 が自動シーケンスに選択されている)

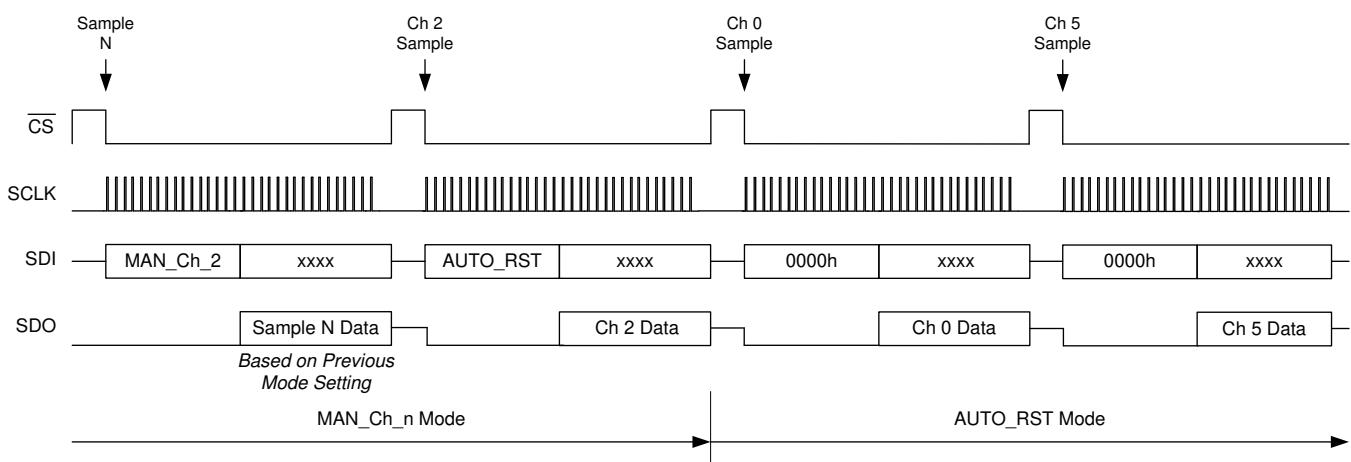

図 7-39 に、MAN\_Ch\_n から AUTO\_RST モードへの遷移の SDI コマンド シーケンスを示します。各 SDI コマンドは、次の CS 立ち下がりエッジで実行されることに注意してください。RST コマンドは、いずれのチャネル シーケンシング モード中にいつでも発行できます。その後、デバイスは次のデータフレームでデフォルトのパワーアップ状態になります。

図 7-39. MAN\_Ch\_n から AUTO\_RST モードへの遷移 (チャネル 0 および 5 が自動シーケンスに選択されている)

#### 7.4.2.8 リセットプログラム レジスタ (RST)

デバイスは、ハードウェアおよびソフトウェアリセット (RST) モードをサポートしており、このモードでは、すべてのプログラム レジスタがデフォルト値にリセットされます。「[RST/PD \(入力\)](#)」セクションの説明のように、ハードウェア ピンを使用してデバイスを RST モードに設定できます。

図 7-40 に示されているように、デバイスのプログラム レジスタは、任意のデータフレーム中、RST コマンド 8500h でコマンド レジスタで有効な書き込み動作を実行することにより、デフォルト値にリセットできます。以後のデータフレーム中に、有効な変換コマンド (AUTO\_RST または MAN\_Ch\_n) が実行されず、SDI が low に維持されている場合、デバイスは RST モードのままになります (「[選択されたモードでの継続動作 \(NO\\_OP\)](#)」セクションを参照)。デバイスが RST モードで動作している場合、16 SCLK サイクルを使用してプログラム レジスタの設定を更新できます (「[プログラム レジスタの読み取り書き込み動作](#)」セクションの説明を参照)。しかし、32 の完全な SCLK サイクルが供給される場合、RST モードでの変換処理がないため、デバイスは SDO ラインに無効なデータを返します。このモード中は、プログラム レジスタの読み取り動作を通常に行うことができます。特定のアナログ チャネルで変換を開始するには、デフォルトのプログラム レジスタ設定を使用して、有効な AUTO\_RST または MAN\_CH\_n のチャネル選択コマンドを実行する必要があります。

図 7-40. リセットプログラム レジスタ (RST) のタイミング図

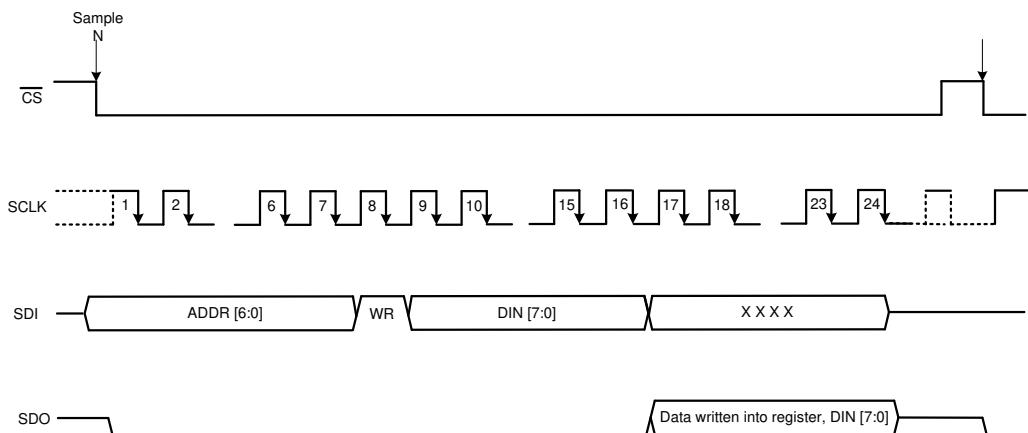

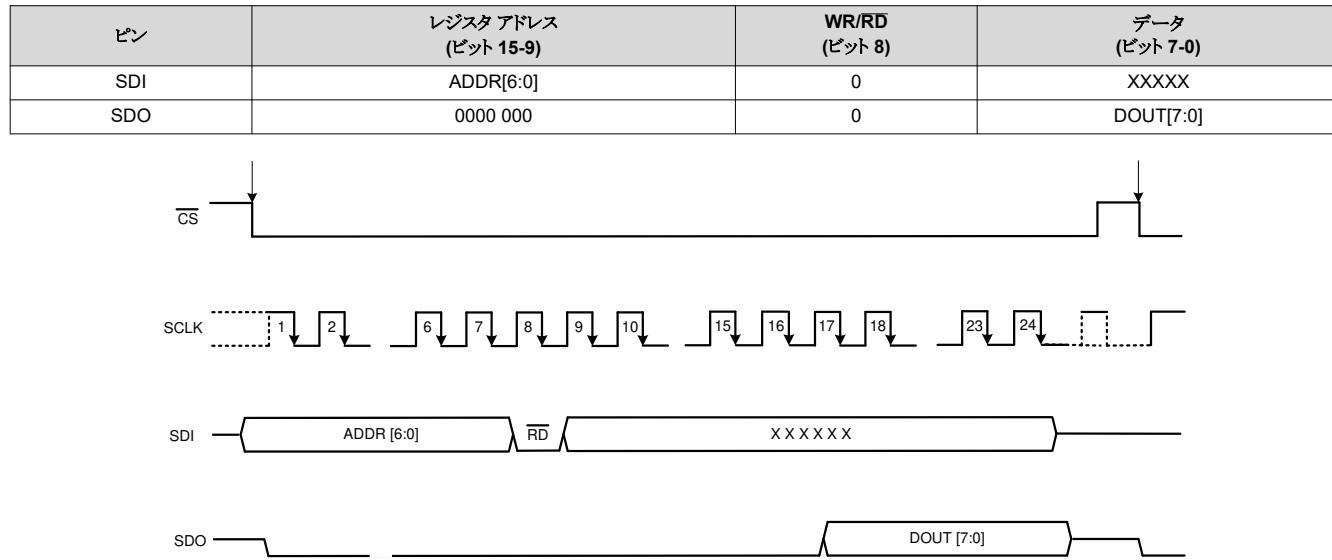

## 8 レジスタ マップ

内部レジスタは、コマンド レジスタとプログラム レジスタの 2 つのカテゴリに分類されます。