# ADS922x デュアル、同時サンプリング、16 ビット、20MSPS、完全差動 ADC 入力ドライバ搭載、SAR 型 A/D コンバータ

## 1 特長

- 高速サンプリング レート: 20MSPS/チャネル

- ADS9229: 20MSPS/チャネル、230mW/チャネル

- ADS9228: 10MSPS/チャネル、146mW/チャネル

- ADS9227: 5MSPS/チャネル、95mW/チャネル

- 2 チャネル、同時サンプリング

- 内蔵機能:

- ADC ドライバ

- 高精度基準電圧

- 同相電圧出力バッファ

- 高性能:

- 16 ビット、ミッシング コードなし

- INL:  $\pm 0.3$ LSB、DNL:  $\pm 0.3$ LSB

- 信号対雑音比: 93.9dB

- 広い入力帯域幅 (-3dB):

- ADS9229 および ADS9228: 90MHz

- ADS9227: 45MHz

- シリアル LVDS インターフェイス:

- SDR および DDR 出力モード

- 同期クロックおよびデータ出力

- 拡張動作範囲: -40°C ~ +125°C

## 2 アプリケーション

- 電力分析

- ソース メジャー ユニット (SMU)

- 海洋機器

- サーボ ドライブ位置フィードバック

- DC/AC 電源、電子負荷

## 3 概要

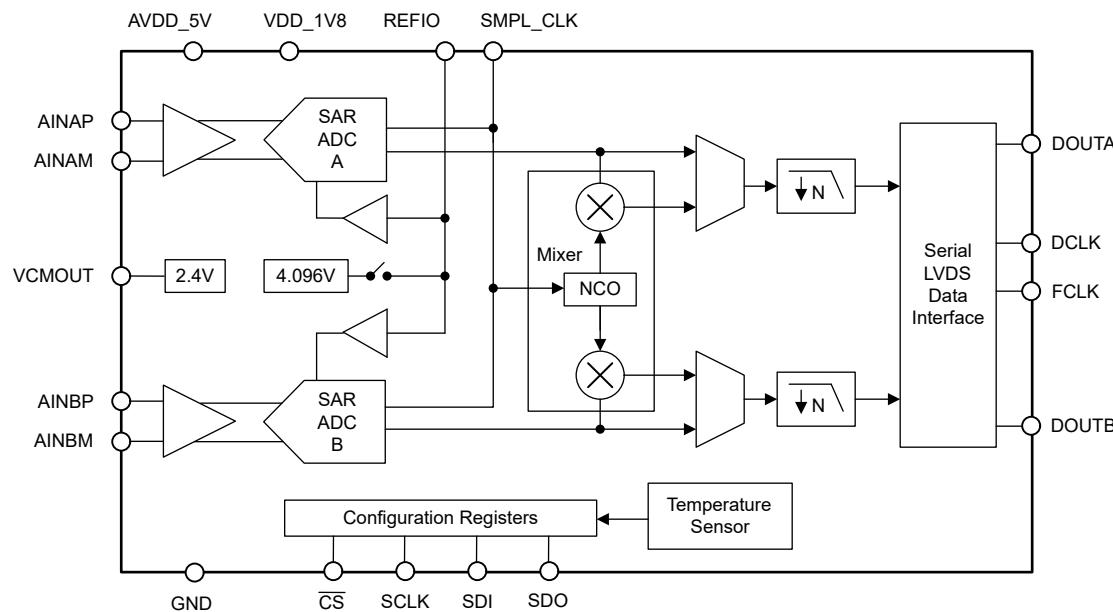

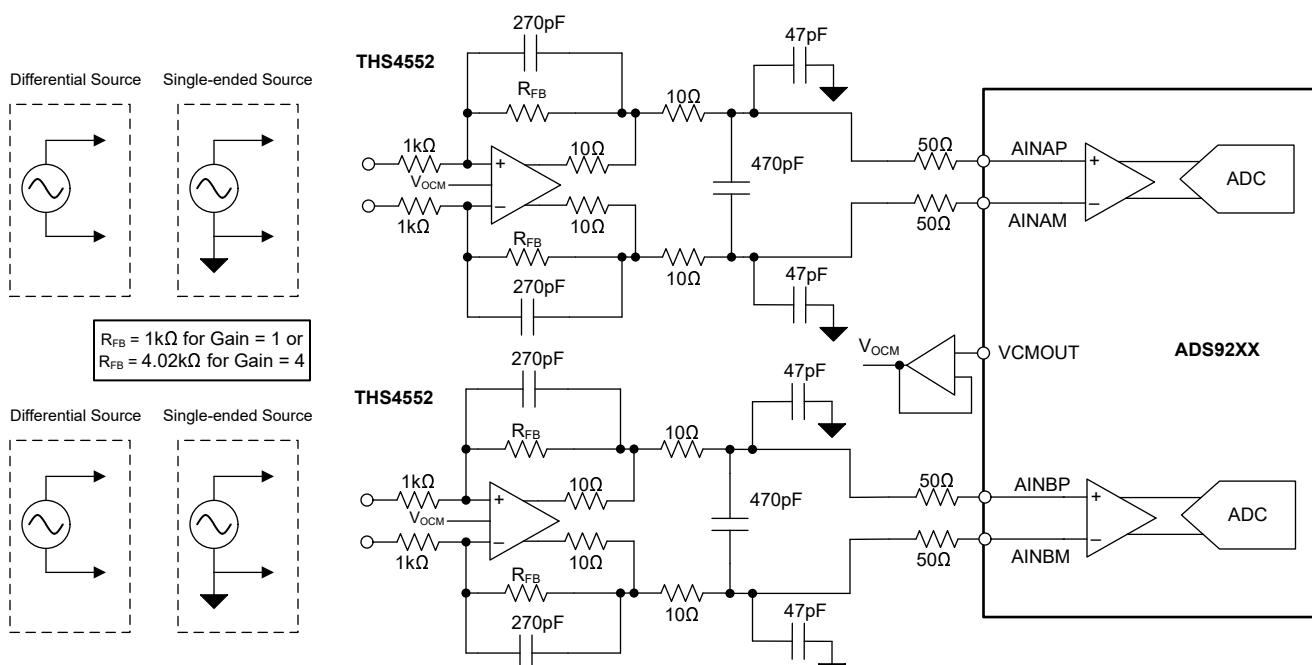

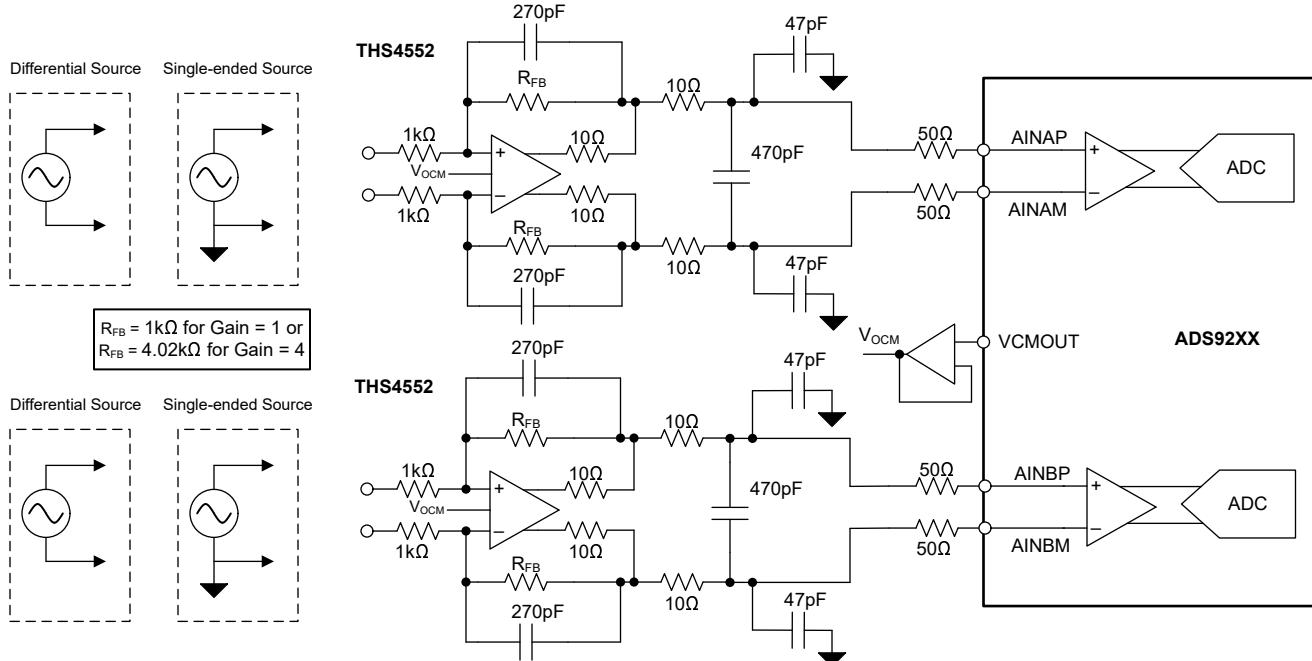

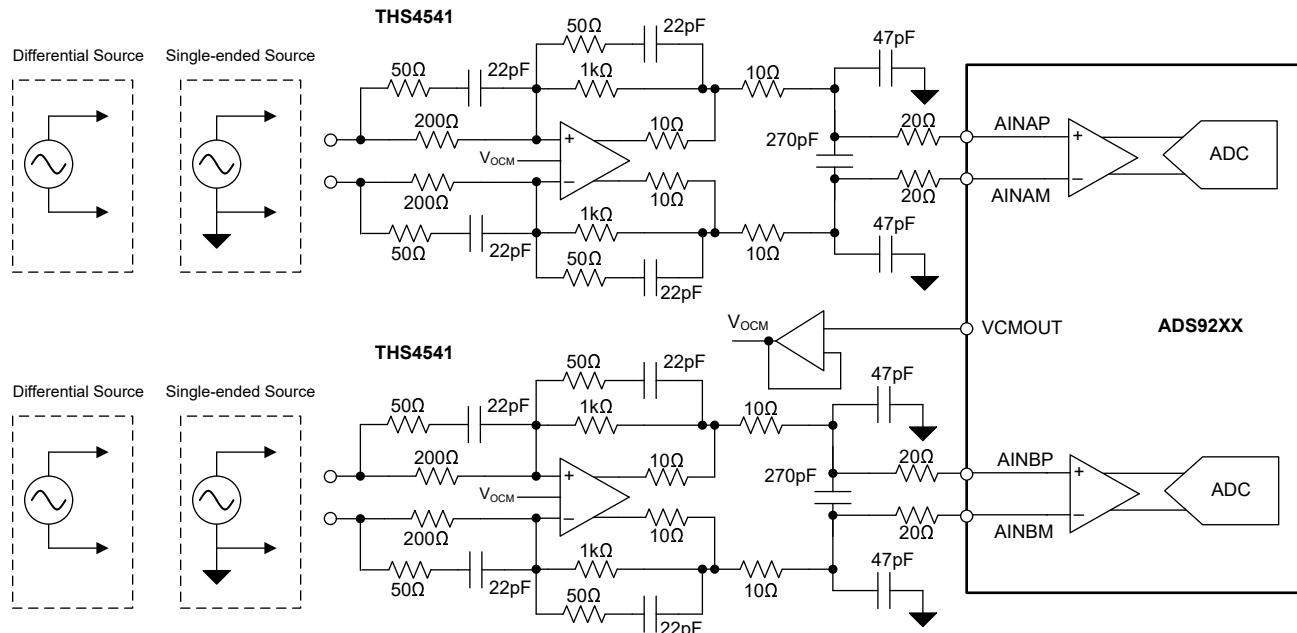

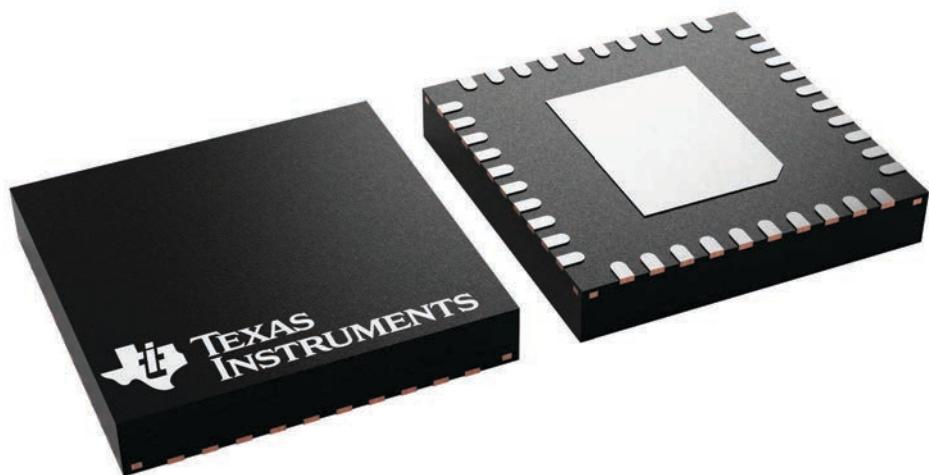

ADS922x は 16 ビット高速デュアルチャネル、同時サンプリングの A/D コンバータ (ADC) で、ADC 入力用のドライバが内蔵されています。ADC ドライバを内蔵しているため、信号チェーンの簡素化、高精度アプリケーションでの消費電力の低減、1MHz を上回る高周波信号のサポートが可能です。外付けデカッピング コンデンサを必要としない内蔵 ADC リファレンス バッファは、広帯域幅アプリケーション向けに最適化されています。

ADS922x は、シリアル LVDS (SLVDS) データ インターフェイスを使用して、デジタル スイッチング ノイズを最小化しながら高速デジタル インターフェイスを実現します。ADC チャネルごとに別々の SLVDS 出力、または両方の ADC チャネルに 1 つの SLVDS 出力を使用して、デュアル チャネル ADC データを読み取ります。

### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| ADS9227 |                      |                          |

| ADS9228 | RHA (VQFN, 40)       | 6mm × 6mm                |

| ADS9229 |                      |                          |

(1) 詳細については、「[メカニカル、パッケージ、および注文情報](#)」を参照してください。

(2) パッケージサイズ (長さ×幅) は公称値であり、ピンを含む場合もあります。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

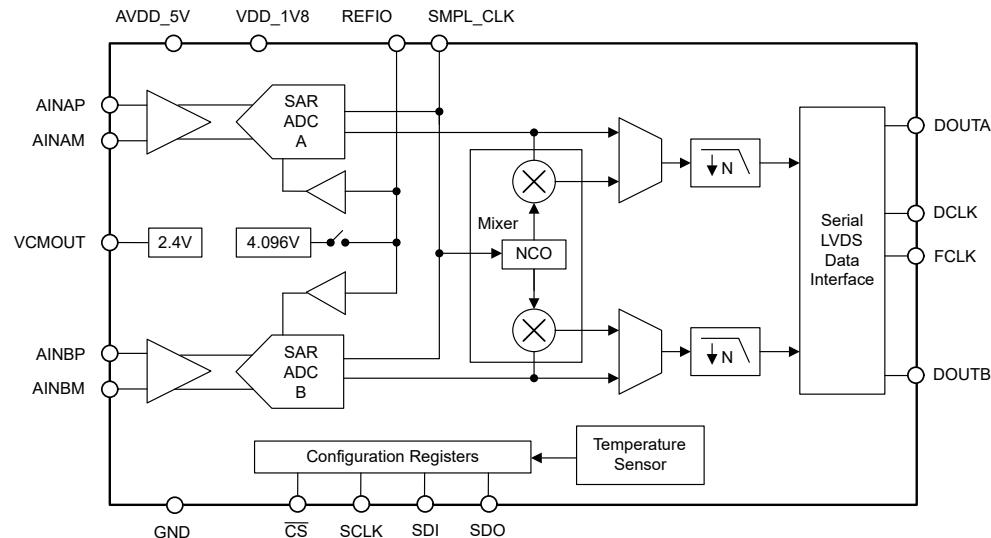

デバイスのブロック図

## 目次

|                    |    |                         |    |

|--------------------|----|-------------------------|----|

| 1 特長               | 1  | 7.3 機能説明                | 22 |

| 2 アプリケーション         | 1  | 7.4 デバイスの機能モード          | 32 |

| 3 概要               | 1  | 7.5 プログラミング             | 33 |

| 4 デバイス比較表          | 4  | 8 レジスタ マップ              | 37 |

| 5 ピン構成および機能        | 5  | 8.1 レジスタ バンク 0          | 37 |

| 6 仕様               | 7  | 8.2 レジスタ バンク 1          | 40 |

| 6.1 絶対最大定格         | 7  | 8.3 レジスタ バンク 2          | 55 |

| 6.2 ESD 定格         | 7  | 9 アプリケーションと実装           | 56 |

| 6.3 熱に関する情報        | 7  | 9.1 アプリケーション情報          | 56 |

| 6.4 推奨動作条件         | 8  | 9.2 代表的なアプリケーション        | 56 |

| 6.5 電気的特性          | 9  | 9.3 電源に関する推奨事項          | 61 |

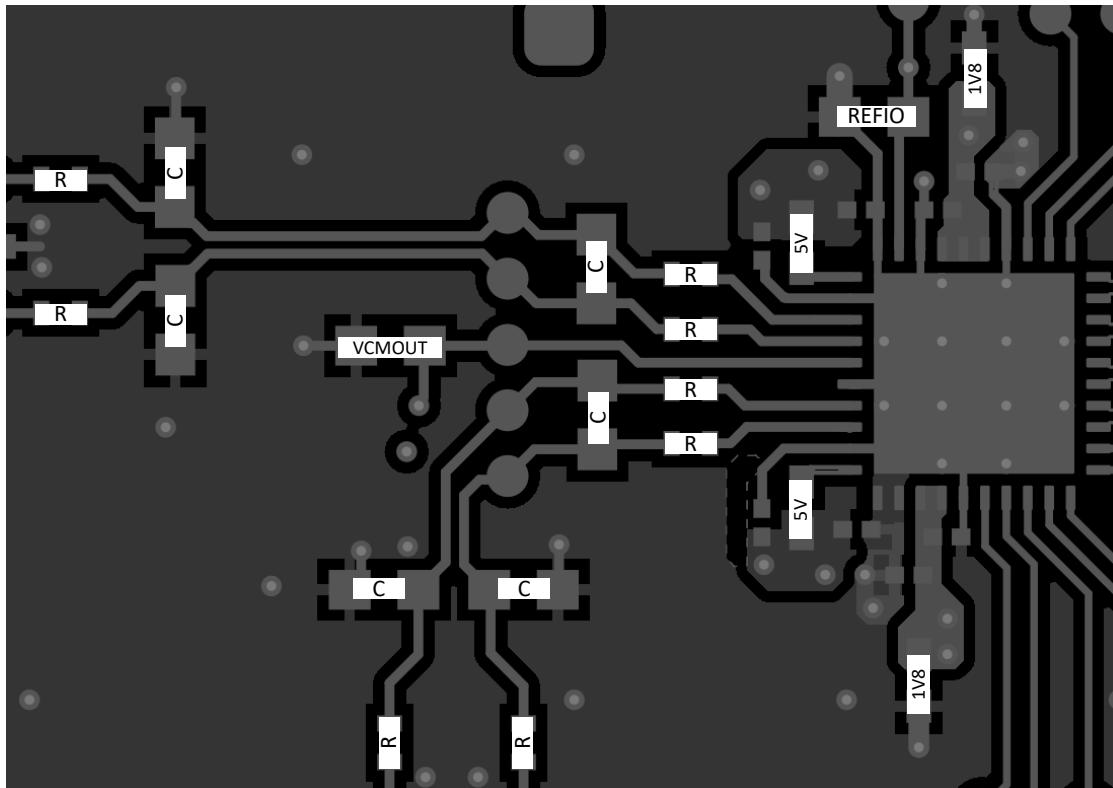

| 6.6 タイミング要件        | 11 | 9.4 レイアウト               | 62 |

| 6.7 スイッチング特性       | 12 | 10 デバイスおよびドキュメントのサポート   | 63 |

| 6.8 タイミング図         | 13 | 10.1 ドキュメントのサポート        | 63 |

| 6.9 代表的特性:すべてのデバイス | 16 | 10.2 ドキュメントの更新通知を受け取る方法 | 63 |

| 6.10 代表的特性:ADS9229 | 18 | 10.3 サポート・リソース          | 63 |

| 6.11 代表的特性:ADS9228 | 19 | 10.4 商標                 | 63 |

| 6.12 代表的特性:ADS9227 | 20 | 10.5 静電気放電に関する注意事項      | 63 |

| 7 詳細説明             | 21 | 10.6 用語集                | 63 |

| 7.1 概要             | 21 | 11 改訂履歴                 | 64 |

| 7.2 機能ブロック図        | 21 | 12 メカニカル、パッケージ、および注文情報  | 64 |

## 4 デバイス比較表

| 部品番号    | チャネル | 分解能 | SPEED  |

|---------|------|-----|--------|

| ADS9219 | 2    | 18  | 20MSPS |

| ADS9218 |      |     | 10MSPS |

| ADS9217 |      |     | 5MSPS  |

| ADS9229 |      | 16  | 20MSPS |

| ADS9228 |      |     | 10MSPS |

| ADS9227 |      |     | 5MSPS  |

| ADS9119 | 1    | 18  | 20MSPS |

| ADS9118 |      |     | 10MSPS |

| ADS9117 |      |     | 5MSPS  |

| ADS9129 |      | 16  | 20MSPS |

| ADS9128 |      |     | 10MSPS |

| ADS9127 |      |     | 5MSPS  |

## 5 ピン構成および機能

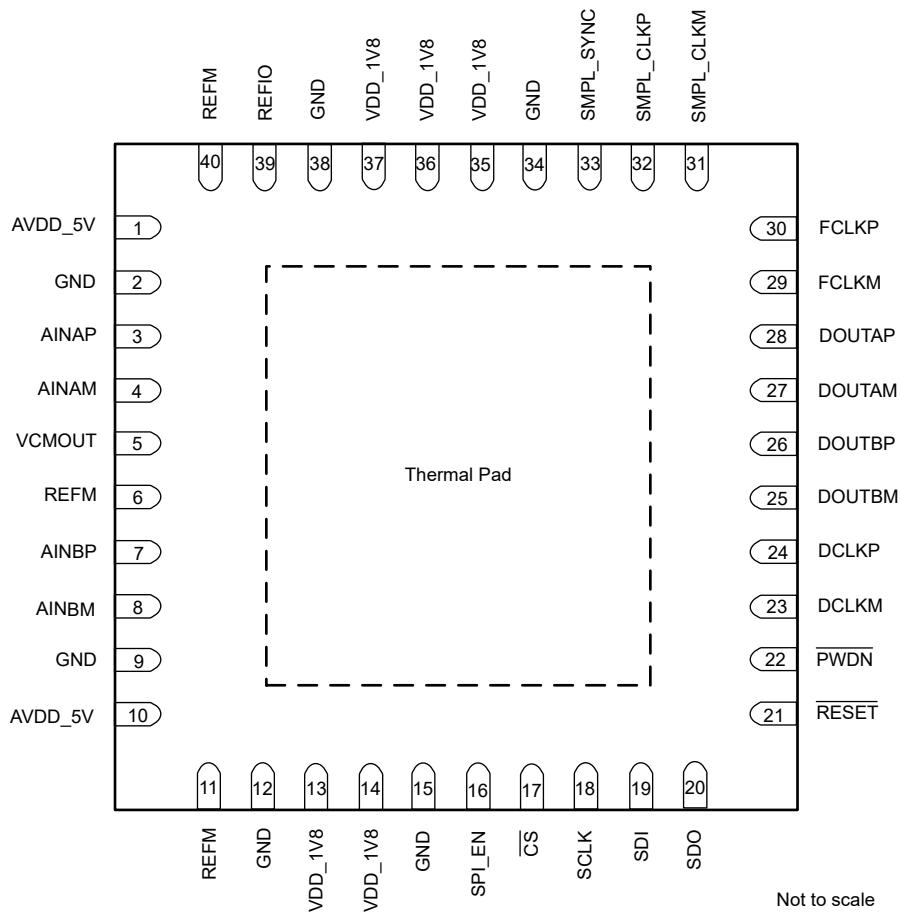

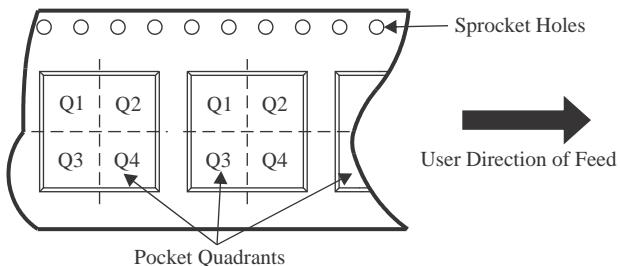

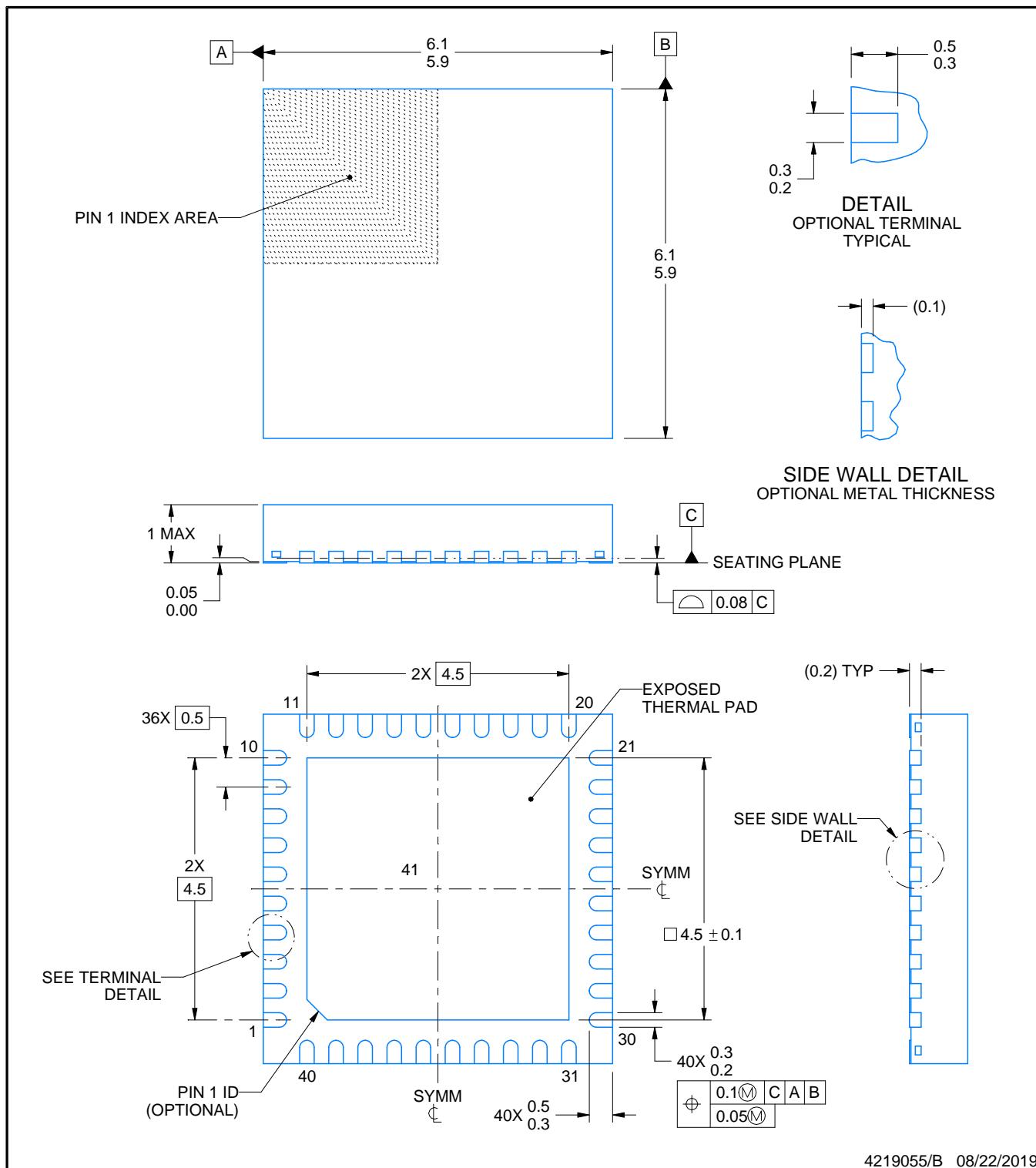

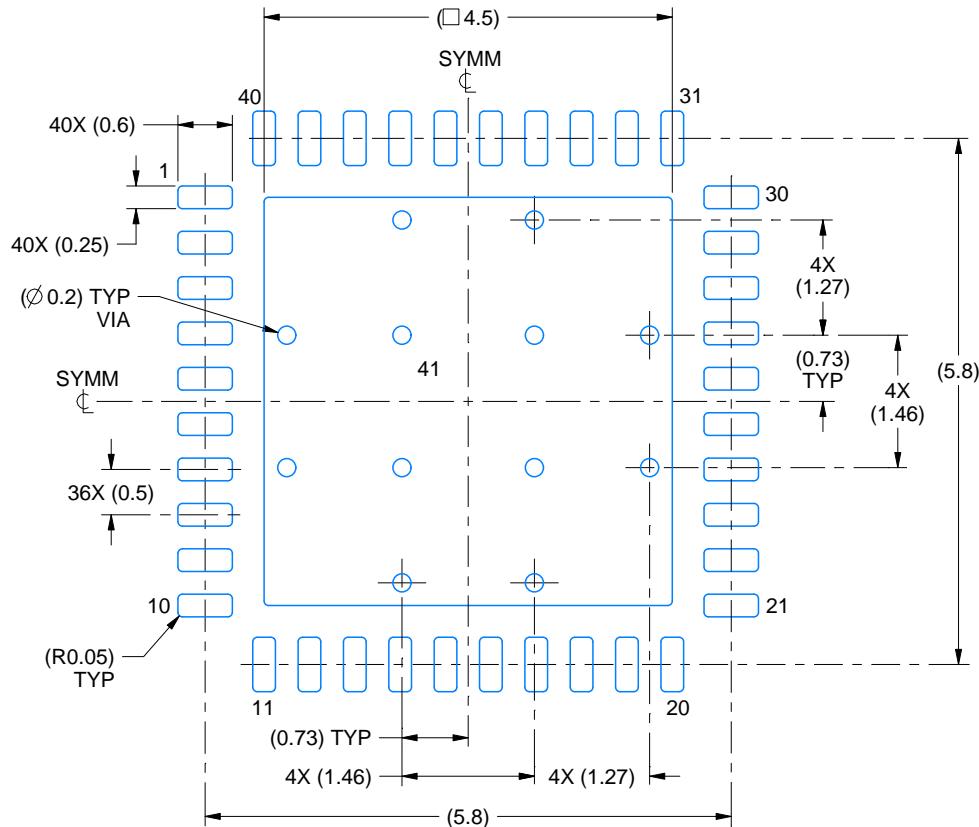

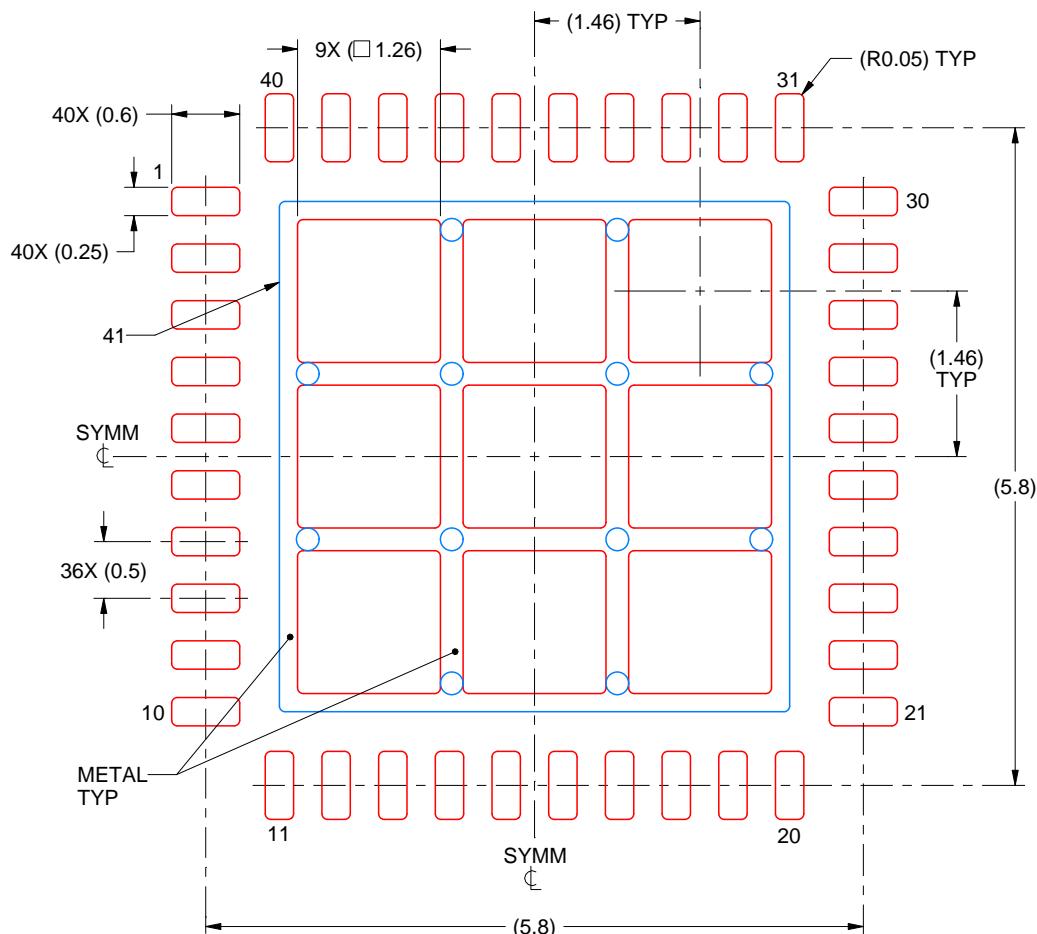

図 5-1. RHA パッケージ、6mm × 6mm、40 ピン VQFN (上面図)

### ピンの機能

| ピン      |       | 種類 (1) | 説明                                                                                                                            |

|---------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 番号    |        |                                                                                                                               |

| AINAM   | 4     | I      | ADC A の負アナログ入力                                                                                                                |

| AINAP   | 3     | I      | ADC A の正アナログ入力                                                                                                                |

| AINBM   | 8     | I      | ADC B の負アナログ入力                                                                                                                |

| AINBP   | 7     | I      | ADC B の正アナログ入力                                                                                                                |

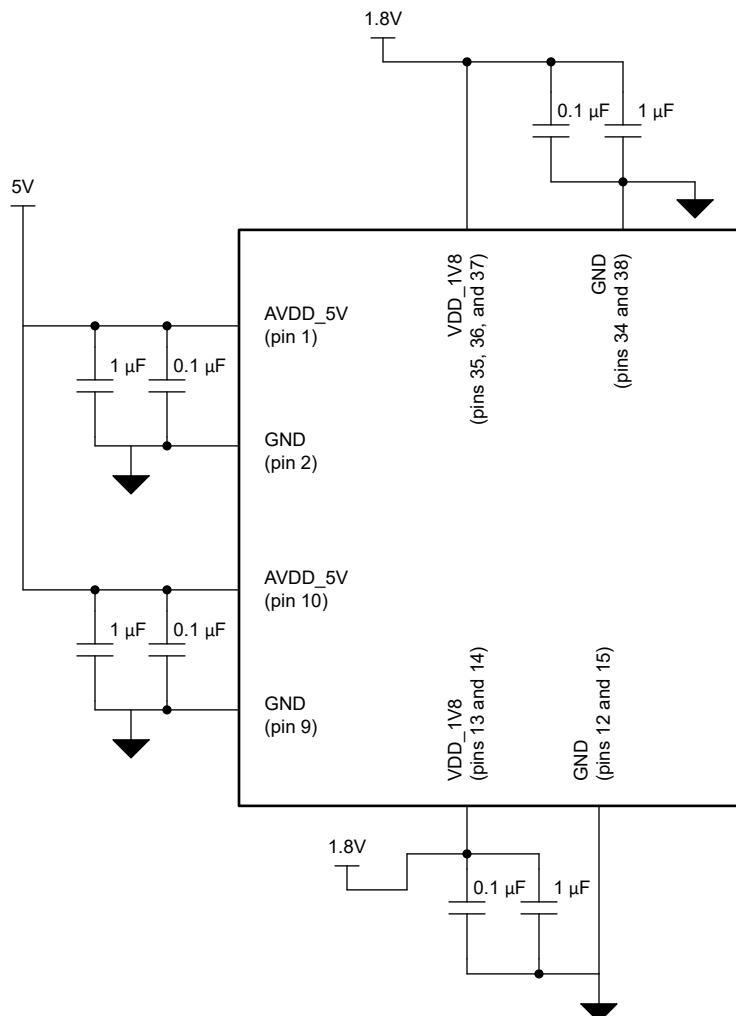

| AVDD_5V | 1, 10 | P      | 5V アナログ電源ピン。                                                                                                                  |

| CS      | 17    | I      | 構成インターフェイスのチップ セレクト入力ピン、アクティブ Low。                                                                                            |

| DCLKM   | 23    | O      | 負の差動データクロック出力。DCLKP と DCLKM の間に 100Ω の抵抗を、レシーバに近づけて接続します。                                                                     |

| DCLKP   | 24    | O      | 正の差動データクロック出力。DCLKP と DCLKM の間に 100Ω の抵抗を、レシーバに近づけて接続します。                                                                     |

| DOUTAM  | 27    | O      | 負の差動データ出力。DOUTAP と DOUTAM の間に 100Ω の抵抗を、レシーバに近づけて接続します。<br>ADC A データを 2 レーン モードで送信します。<br>ADC A と ADC B データを 1 レーン モードで送信します。 |

### ピンの機能 (続き)

| ピン           |                         | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                            |

|--------------|-------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称           | 番号                      |                   |                                                                                                                                                                                                                                                               |

| DOUTAP       | 28                      | O                 | ADC A に対応する正の差動データ出力。DOUTAP と DOUTAM の間に $100\Omega$ の抵抗を、レシーバに近づけて接続します。<br>ADC A データを 2 レーン モードで送信します。<br>ADC A と ADC B データを 1 レーン モードで送信します。                                                                                                               |

| DOUTBM       | 25                      | O                 | 2 レーン モードの ADC B に対応する負の差動データ出力。DOUTBP と DOUTBM の間に $100\Omega$ の抵抗を、レシーバに近づけて接続します。1 レーン モードでは使用されません。                                                                                                                                                       |

| DOUTBP       | 26                      | O                 | 2 レーン モードの ADC B に対応する正の差動データ出力。DOUTBP と DOUTBM の間に $100\Omega$ の抵抗を、レシーバに近づけて接続します。1 レーン モードでは使用されません。                                                                                                                                                       |

| FCLKM        | 29                      | O                 | 負の差動データフレームクロック出力。FCLKP と FCLKM の間に $100\Omega$ の抵抗を、レシーバに近づけて接続します。                                                                                                                                                                                          |

| FCLKP        | 30                      | O                 | 正の差動データフレームクロック出力。FCLKP と FCLKM の間に $100\Omega$ の抵抗を、レシーバに近づけて接続します。                                                                                                                                                                                          |

| GND          | 2, 9, 12, 15, 34、<br>38 | P                 | グランド。                                                                                                                                                                                                                                                         |

| PWDN         | 22                      | I                 | パワーダウン制御、アクティブ Low。使用しない場合は VDD_1V8 に接続します。                                                                                                                                                                                                                   |

| REFIO        | 39                      | I/O               | 内部リファレンス電圧出力。外部リファレンス電圧入力。 $10\mu\text{F}$ のデカップリングコンデンサを REFM に接続します。                                                                                                                                                                                        |

| REFM         | 6, 11, 40               | P                 | 基準グランド。GND に接続。                                                                                                                                                                                                                                               |

| RESET        | 21                      | I                 | リセット入力 (アクティブ Low) 使用しない場合は VDD_1V8 に接続します。                                                                                                                                                                                                                   |

| SCLK         | 18                      | I                 | 構成インターフェイスのシリアルクロック入力。                                                                                                                                                                                                                                        |

| SDI / EXTREF | 19                      | I                 | SDI は、マルチファンクションロジック入力です。ピンの機能は SPI_EN ピンで決定されます。SDI には、GND への $100\text{k}\Omega$ 内部ブルダウン抵抗があります。SPI_EN = 0b: SDI は、内部リファレンスと外部リファレンスのいずれかを選択するためのロジック入力です。外部リファレンスの場合は、SDI を GND に接続します。内部リファレンスの場合は、SDI を VDD_1V8 に接続します。SPI_EN = 1b: 構成インターフェイスのシリアルデータ入力 |

| SDO          | 20                      | O                 | 構成インターフェイスのシリアルデータ出力。                                                                                                                                                                                                                                         |

| SMPL_CLKM    | 31                      | I                 | ADC サンプリングクロック入力。LVDS サンプリングクロックの負の差動入力。CMOS サンプリングクロックの場合は、このピンを GND に接続します。                                                                                                                                                                                 |

| SMPL_CLKP    | 32                      | I                 | ADC サンプリングクロック入力。LVDS サンプリングクロックの正の差動入力。CMOS サンプリングクロックのクロック入力。                                                                                                                                                                                               |

| SMPL_SYNC    | 33                      | I                 | 内部の平均化フィルタの同期入力。<br>未使用時は GND に接続します。SMPL_SYNC ピンの使用方法については、 <a href="#">複数の ADC の同期</a> セクションを参照してください。                                                                                                                                                      |

| SPI_EN       | 16                      | I                 | SPIインターフェイスの構成を有効にする制御、アクティブ High。<br>構成インターフェイスを有効のままにするため、VDD_1V8 にブルアップ抵抗を接続します。SPI構成が未使用の場合は GND に接続します。SPI_EN = 0 の場合、SDI/EXTREF ピンでリファレンス電圧を選択します。                                                                                                      |

| サーマルパッド      | —                       | P                 | 露出したサーマルパッド。GND に接続。                                                                                                                                                                                                                                          |

| VCMOUT       | 5                       | O                 | 同相電圧出力。VCMOUT を使用して、ADC 入力の同相電圧を設定します。 $1\mu\text{F}$ のデカップリングコンデンサを GND に接続します。                                                                                                                                                                              |

| VDD_1V8      | 13, 14, 35, 36, 37      | P                 | 1.8V 電源。 $1\mu\text{F}$ と $0.1\mu\text{F}$ のデカップリングコンデンサを GND に接続します。                                                                                                                                                                                         |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 6 仕様

### 6.1 絶対最大定格

動作時周囲温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                                   | 最小値        | 最大値           | 単位 |

|-----------------------------------|------------|---------------|----|

| VDD_1V8 から GND へ                  | -0.3       | 2.1           | V  |

| AVDD_5V から GND へ                  | -0.3       | 5.5           | V  |

| AINAP、AINAM、AINBP、AINBM から GND へ  | GND - 0.3  | AVDD_5V + 0.3 | V  |

| REFIO から REFM へ                   | REFM - 0.3 | AVDD_5V + 0.3 | V  |

| デジタル入力から GND へ                    | GND - 0.3  | VDD_1V8 + 0.3 | V  |

| REFM から GND へ                     | -0.3       | 0.3           | V  |

| 電源ピンを除く任意のピンへの入力電流 <sup>(2)</sup> | -10        | 10            | mA |

| 接合部温度、T <sub>J</sub>              | -40        | 150           | °C |

| 保管温度、T <sub>stg</sub>             | -60        | 150           | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) ピン電流は 10 mA 以下に制限する必要があります。

### 6.2 ESD 定格

|                    |      | 値                                                                                     | 単位    |

|--------------------|------|---------------------------------------------------------------------------------------|-------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠、アナログ入力ピン AINAP、AINAM、AINBP、AINBM <sup>(1)</sup> | ±2000 |

|                    |      | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、他すべてのピン <sup>(1)</sup>                         | ±1000 |

|                    |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup>                      | ±500  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | ADS922x    |      |

|-----------------------|---------------------|------------|------|

|                       |                     | RHA (VQFN) |      |

|                       |                     | 40 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 25.8       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 13.3       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 7.5        | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.1        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 7.4        | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 1.1        | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 6.4 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ            | テスト条件                      | 最小値                                         | 標準値                       | 最大値                       | 単位     |

|------------------|----------------------------|---------------------------------------------|---------------------------|---------------------------|--------|

| <b>電源</b>        |                            |                                             |                           |                           |        |

| AVDD_5V          | アナログ電源<br>AVDD_5V から GND へ | ADS9227                                     | 4.5                       | 5                         | 5.5    |

|                  |                            | ADS9228、ADS9229                             | 4.75                      | 5                         | 5.25   |

| VDD_1V8          | 電源                         | VDD_1V8 から GND へ                            | 1.75                      | 1.8                       | 1.85   |

| <b>基準電圧</b>      |                            |                                             |                           |                           |        |

| V <sub>REF</sub> | ADC へのリファレンス電圧             | 外部リファレンス                                    | 4.076                     | 4.096                     | 4.116  |

| <b>アナログ入力</b>    |                            |                                             |                           |                           |        |

| V <sub>IN</sub>  | 絶対入力電圧                     | AINx <sup>(1)</sup> から GND へ                | V <sub>CM</sub> – 1.6     | V <sub>CM</sub> + 1.6     | V      |

| FSR              | フルスケール入力レンジ                | (AINAP – AINAM) および (AINBP – AINBM)         | -3.2                      | 3.2                       | V      |

| V <sub>CM</sub>  | 同相入力範囲 <sup>(2)</sup>      | (AINAP + AINAM) / 2 および (AINBP + AINBM) / 2 | V <sub>CMOUT</sub> – 0.07 | V <sub>CMOUT</sub> + 0.07 | V      |

| <b>温度範囲</b>      |                            |                                             |                           |                           |        |

| T <sub>A</sub>   | 周囲温度                       |                                             | -40                       | 25                        | 125 °C |

(1) AINx とは、アナログ入力の AINAP、AINAM、AINBP、AINBM を指します。

(2) 入力同相電圧が仕様を超えると、ADC チャネルがパワーダウンします。

## 6.5 電気的特性

ADS9229 および ADS9228 の場合は AVDD\_5V = 4.75V ~ 5.25V、ADS9227 の場合は AVDD\_5V = 4.5V ~ 5.5V、VDD\_1V8 = 1.75V ~ 1.85V、内部 V<sub>REF</sub> = 4.096V、最大スループット (特に記述のない限り)、T<sub>A</sub> = -40°C ~ +125°C での最小値および最大値、T<sub>A</sub> = 25°C での標準値

| パラメータ                           | テスト条件                          | 最小値                                       | 標準値   | 最大値   | 単位                |  |

|---------------------------------|--------------------------------|-------------------------------------------|-------|-------|-------------------|--|

| <b>アナログ入力</b>                   |                                |                                           |       |       |                   |  |

| I <sub>B</sub>                  | 入力バイアス電流                       |                                           | 0.1   |       | nA                |  |

| 入力バイアス電流の熱ドリフト                  | T <sub>A</sub> = 0°C ~ 70°C    |                                           | 0.02  |       | nA/°C             |  |

|                                 | T <sub>A</sub> = -40°C ~ 125°C |                                           | 0.1   |       |                   |  |

| <b>DC 特性</b>                    |                                |                                           |       |       |                   |  |

|                                 | 分解能                            | ミッシング コードなし                               | 16    |       | ビット               |  |

| DNL                             | 微分非直線性                         |                                           | -0.9  | ±0.3  | 0.9               |  |

| INL                             | 積分非直線性                         | T <sub>A</sub> = °C ~ 70°C、すべてのデバイス       | -0.4  | ±0.3  | 0.4               |  |

|                                 |                                | ADS9228、ADS9227                           | -0.75 | ±0.3  | 0.75              |  |

|                                 |                                | ADS9229                                   | -1    | ±0.3  | 1                 |  |

| V <sub>(OS)</sub>               | 入力オフセット誤差                      |                                           | ±10   |       | LSB               |  |

| dV <sub>OS</sub> /dT            | 入力オフセット誤差の熱ドリフト                |                                           | 0.25  | 1     | ppm/°C            |  |

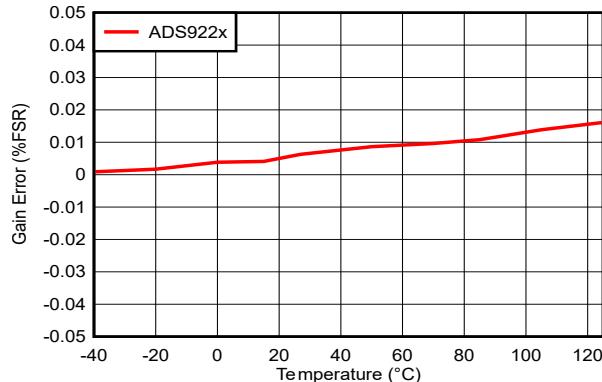

| G <sub>E</sub>                  | ゲイン誤差 <sup>(1)</sup>           |                                           | -0.05 | ±0.01 | 0.05              |  |

| dG <sub>E</sub> /dT             | ゲイン誤差の温度係数 <sup>(1)</sup>      |                                           | 0.5   | 2     | ppm/°C            |  |

| <b>AC 特性</b>                    |                                |                                           |       |       |                   |  |

| SINAD                           | 信号対雑音比 + 歪み比                   | f <sub>IN</sub> = 2kHz                    | 92    | 93.8  | dB                |  |

|                                 |                                | f <sub>IN</sub> = 1MHz                    |       | 92.9  |                   |  |

| SNR                             | 信号対雑音比                         | f <sub>IN</sub> = 2kHz                    | 92.3  | 93.9  | dBFS              |  |

|                                 |                                | f <sub>IN</sub> = 1MHz                    |       | 93.3  |                   |  |

| THD                             | 全高調波歪                          | f <sub>IN</sub> = 2kHz                    |       | -120  | dB                |  |

|                                 |                                | f <sub>IN</sub> = 1MHz                    |       | -104  |                   |  |

| SFDR                            | スプリアスフリー ダイナミックレンジ             | f <sub>IN</sub> = 2kHz                    |       | 120   | dB                |  |

|                                 |                                | f <sub>IN</sub> = 1MHz                    |       | 104   |                   |  |

| 絶縁クロストーク                        |                                | f <sub>IN</sub> = 2kHz                    |       | 120   | dB                |  |

| <b>サンプリングのダイナミック特性</b>          |                                |                                           |       |       |                   |  |

|                                 | アパー チャ ジッタ                     | SMPL_CLKP の シングルエンド CMOS クロック             |       | 0.3   | ps <sub>RMS</sub> |  |

|                                 |                                | 差動 LVDS サンプリング クロック                       |       | 0.8   |                   |  |

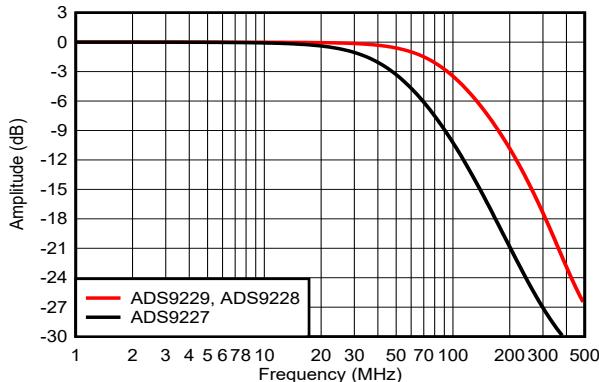

| BW                              | 入力帯域幅                          | ADS9229、ADS9228                           |       | 90    | MHz               |  |

|                                 |                                | ADS9227                                   |       | 45    |                   |  |

| <b>内部リファレンス</b>                 |                                |                                           |       |       |                   |  |

| V <sub>REF</sub> <sup>(2)</sup> | REFIO ピンの電圧<br>(出力として構成)       | REFIO ピンの 1μF コンデンサ、T <sub>A</sub> = 25°C | 4.092 | 4.096 | 4.1               |  |

|                                 | 基準温度ドリフト                       |                                           |       | 6     | 20 ppm/°C         |  |

| <b>同相モード出力パッファ</b>              |                                |                                           |       |       |                   |  |

| V <sub>CMOUT</sub>              | 同相出力電圧                         | ADS9229                                   | 2.2   | 2.460 | 2.65              |  |

|                                 |                                | ADS9228                                   | 2.2   | 2.410 | 2.65              |  |

|                                 |                                | ADS9227                                   | 2.2   | 2.385 | 2.65              |  |

| 出力電流駆動                          |                                |                                           | 0     | 5     | μA                |  |

| <b>LVDS レシーバ (SMPL_CLK)</b>     |                                |                                           |       |       |                   |  |

## 6.5 電気的特性 (続き)

ADS9229 および ADS9228 の場合は AVDD\_5V = 4.75V ~ 5.25V、ADS9227 の場合は AVDD\_5V = 4.5V ~ 5.5V、VDD\_1V8 = 1.75V ~ 1.85V、内部 V<sub>REF</sub> = 4.096V、最大スループット (特に記述のない限り)、T<sub>A</sub> = -40°C ~ +125°C での最小値および最大値、T<sub>A</sub> = 25°C での標準値

| パラメータ            |                      | テスト条件 | 最小値 | 標準値  | 最大値 | 単位 |

|------------------|----------------------|-------|-----|------|-----|----|

| V <sub>TH</sub>  | High レベル入力電圧 (P – M) | AC 結合 | 100 |      |     | mV |

|                  |                      | DC 結合 | 300 |      |     |    |

| V <sub>TL</sub>  | Low レベル入力電圧 (P – M)  | AC 結合 |     | -100 |     | mV |

|                  |                      | DC 結合 |     | -300 |     |    |

| V <sub>ICM</sub> | 入力同相電圧               |       | 0.5 | 1.2  | 1.4 | V  |

### LVDS 出力 (CLKOUT, DOUTA, DOUTB)

|                    |        |                       |      |     |      |    |

|--------------------|--------|-----------------------|------|-----|------|----|

| V <sub>ODIFF</sub> | 差動出力電圧 | R <sub>L</sub> = 100Ω | 200  | 350 | 500  | mV |

| V <sub>OCM</sub>   | 出力同相電圧 | R <sub>L</sub> = 100Ω | 0.88 | 1.1 | 1.32 | V  |

### CMOS 入力 (CS, SCLK, SDI)

|                 |                  |  |      |         |   |

|-----------------|------------------|--|------|---------|---|

| V <sub>IL</sub> | 入力 Low ロジック レベル  |  | -0.1 | 0.5     | V |

| V <sub>IH</sub> | 入力 High ロジック レベル |  | 1.3  | VDD_1V8 | V |

### CMOS 出力 (SDO)

|                 |                  |                              |     |         |   |

|-----------------|------------------|------------------------------|-----|---------|---|

| V <sub>OL</sub> | 出力 Low ロジック レベル  | I <sub>OL</sub> = 200 μA シンク | 0   | 0.4     | V |

| V <sub>OH</sub> | 出力 High ロジック レベル | I <sub>OH</sub> = 200 μA ソース | 1.4 | VDD_1V8 | V |

### 電源

|                      |                 |                           |      |     |    |

|----------------------|-----------------|---------------------------|------|-----|----|

| I <sub>AVDD_5V</sub> | AVDD_5V からの電源電流 | 20MSPS のスループット時 (ADS9229) | 55   | 59  | mA |

|                      |                 | 10MSPS のスループット時 (ADS9228) | 33   | 40  |    |

|                      |                 | 5MSPS のスループット時 (ADS9227)  | 20   | 24  |    |

|                      |                 | パワーダウン                    |      | 2   |    |

| I <sub>VDD_1V8</sub> | VDD_1V8 からの電源電流 | 20MSPS のスループット時 (ADS9229) | 103  | 110 | mA |

| I <sub>VDD_1V8</sub> | VDD_1V8 からの電源電流 | 10MSPS のスループット時 (ADS9228) | 70.5 | 89  |    |

|                      |                 | 5MSPS のスループット時 (ADS9227)  | 50   | 66  |    |

|                      |                 | パワーダウン                    |      | 2   |    |

(1) これらの仕様は全動作温度範囲での変動を想定していますが、誤差が内部リファレンスから寄与するものではありません。

(2) 半田シフトの影響による電圧の変動は含まれていません。

## 6.6 タイミング要件

ADS9229 および ADS9228 の場合は AVDD\_5V = 4.75V ~ 5.25V、ADS9227 の場合は AVDD\_5V = 4.5V ~ 5.5V、VDD\_1V8 = 1.75V ~ 1.85V、内部 V<sub>REF</sub> = 4.096V、最大スループット (特に記述のない限り)、T<sub>A</sub> = -40°C ~ +125°C での最小値および最大値、T<sub>A</sub> = 25°C での標準値

|                        |                                           | 最小値                    | 最大値  | 単位                 |

|------------------------|-------------------------------------------|------------------------|------|--------------------|

| <b>変換サイクル</b>          |                                           |                        |      |                    |

| f <sub>CYCLE</sub>     | サンプリング周波数                                 | ADS9229                | 7    | 20                 |

|                        |                                           | ADS9228                | 3.9  | 10                 |

|                        |                                           | ADS9227                | 3.9  | 5                  |

| t <sub>CYCLE</sub>     | ADC サイクル時間周期                              | 1 / f <sub>CYCLE</sub> |      | s                  |

| t <sub>PL_SMPCLK</sub> | サンプル クロック Low 時間                          | 0.4                    | 0.6  | t <sub>CYCLE</sub> |

| t <sub>PH_SMPCLK</sub> | サンプル クロック High 時間                         | 0.4                    | 0.6  | t <sub>CYCLE</sub> |

| f <sub>CLK</sub>       | SCLK の最大周波数                               | 10                     |      | MHz                |

| t <sub>CLK</sub>       | 最小 SCLK 時間周期                              | 100                    |      | ns                 |

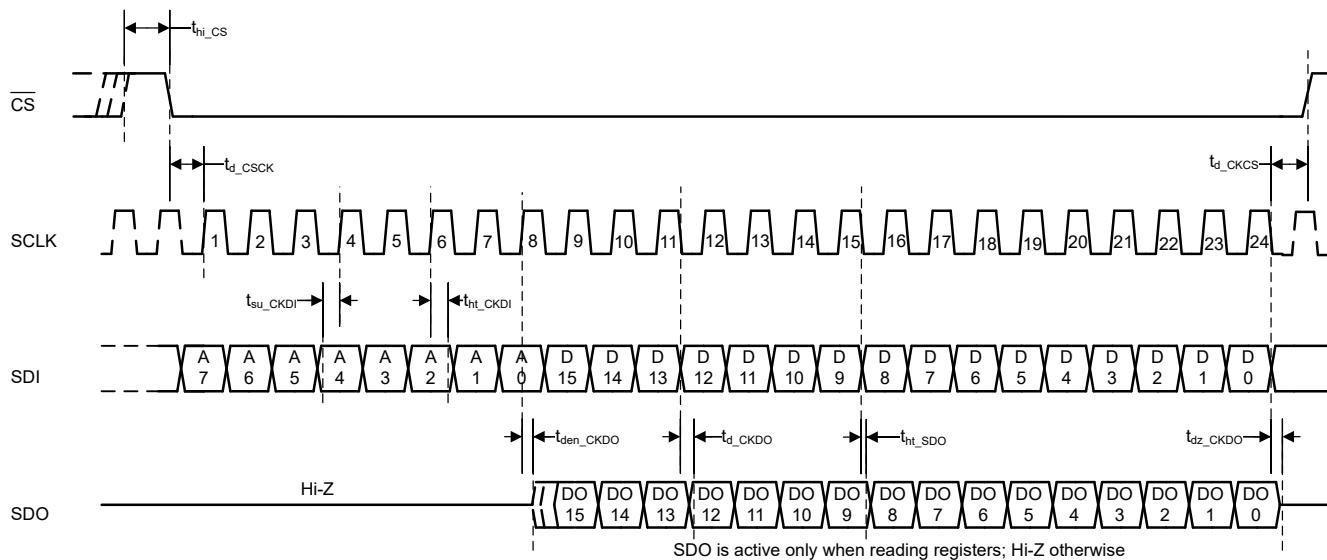

| <b>SPI タイミング</b>       |                                           |                        |      |                    |

| t <sub>hi_CSZ</sub>    | パルス幅 CS High                              | 220                    |      | ns                 |

| t <sub>PH_CK</sub>     | SCLK High 時間                              | 0.48                   | 0.52 | t <sub>CLK</sub>   |

| t <sub>PL_CK</sub>     | SCLK Low 時間                               | 0.48                   | 0.52 | t <sub>CLK</sub>   |

| t <sub>d_CSCK</sub>    | セットアップ時間: CS 立ち下がりから最初の SCLK の立ち上がりエッジまで  | 20                     |      | ns                 |

| t <sub>su_CKDI</sub>   | セットアップ時間: SDI データ有効から対応する SCLK 立ち上がりエッジまで | 10                     |      | ns                 |

| t <sub>ht_CKDI</sub>   | ホールド時間: SCLK 立ち上がりエッジから SDI での対応するデータ有効まで | 5                      |      | ns                 |

| t <sub>d_ckcs</sub>    | 遅延時間: 最後の SCLK 立ち下がりエッジから CS 立ち上がりまで      | 5                      |      | ns                 |

## 6.7 スイッチング特性

ADS9229 および ADS9228 の場合は AVDD\_5V = 4.75V ~ 5.25V、ADS9227 の場合は AVDD\_5V = 4.5V ~ 5.5V、VDD\_1V8 = 1.75V ~ 1.85V、内部 V<sub>REF</sub> = 4.096V、最大スループット (特に記述のない限り)、T<sub>A</sub> = -40°C ~ +125°C での最小値および最大値、T<sub>A</sub> = 25°C での標準値

| パラメータ                     |                                                 | テスト条件                                                           | 最小値                          | 最大値                          | 単位 |

|---------------------------|-------------------------------------------------|-----------------------------------------------------------------|------------------------------|------------------------------|----|

| <b>リセット</b>               |                                                 |                                                                 |                              |                              |    |

| t <sub>PU</sub>           | デバイスのパワーアップ時間                                   |                                                                 |                              | 25                           | ms |

| <b>LVDS データ インターフェイス</b>  |                                                 |                                                                 |                              |                              |    |

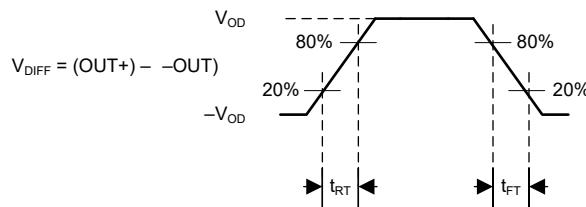

| t <sub>RT</sub>           | 立ち上がり時間                                         | 50Ω 伝送ライン長 = 20mm、差動 R <sub>L</sub> = 100Ω、C <sub>L</sub> = 1pF |                              | 600                          | ps |

| t <sub>FT</sub>           | 立ち下がり時間                                         |                                                                 |                              | 600                          | ps |

| t <sub>CYCLE</sub>        | サンプリング クロック周期                                   | ADS9229                                                         | 50                           |                              | ns |

|                           |                                                 | ADS9228                                                         | 100                          |                              |    |

|                           |                                                 | ADS9227                                                         | 200                          |                              |    |

| t <sub>DCLK</sub>         | クロック出力                                          |                                                                 | 4.167                        |                              | ns |

|                           | クロック デューティ サイクル                                 |                                                                 | 45                           | 55                           | %  |

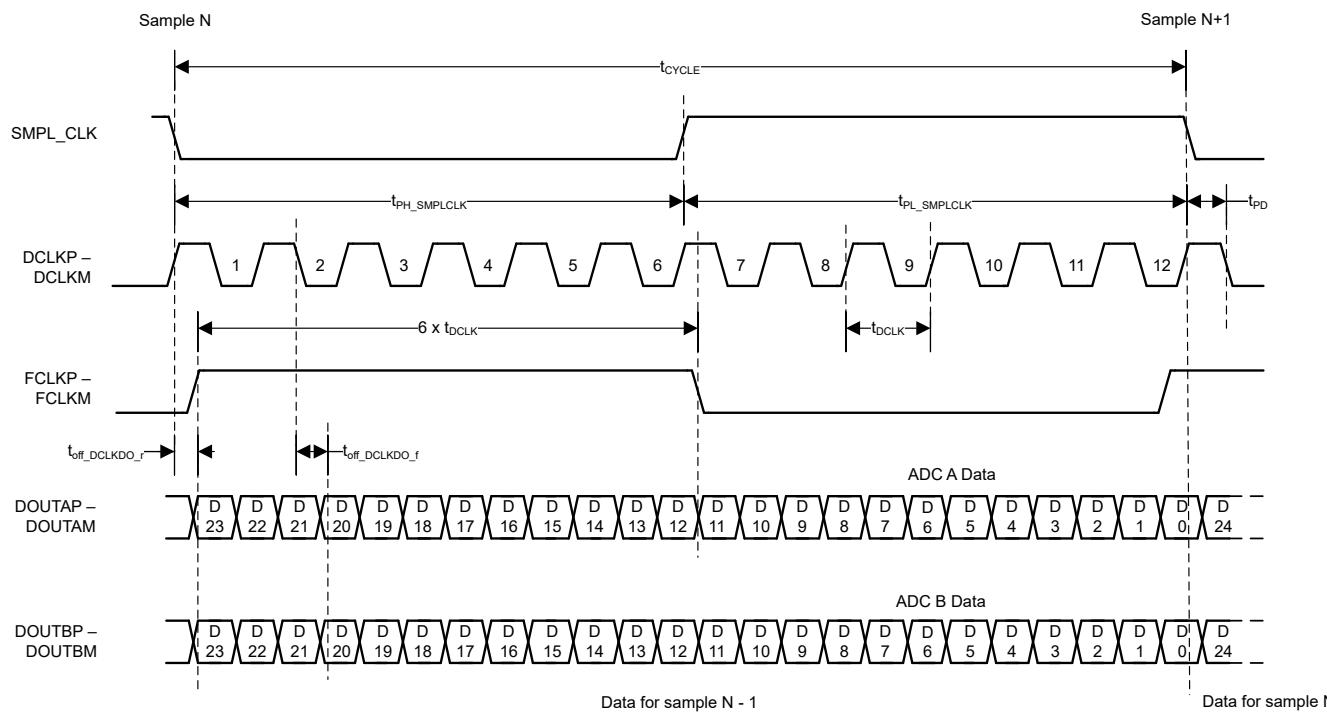

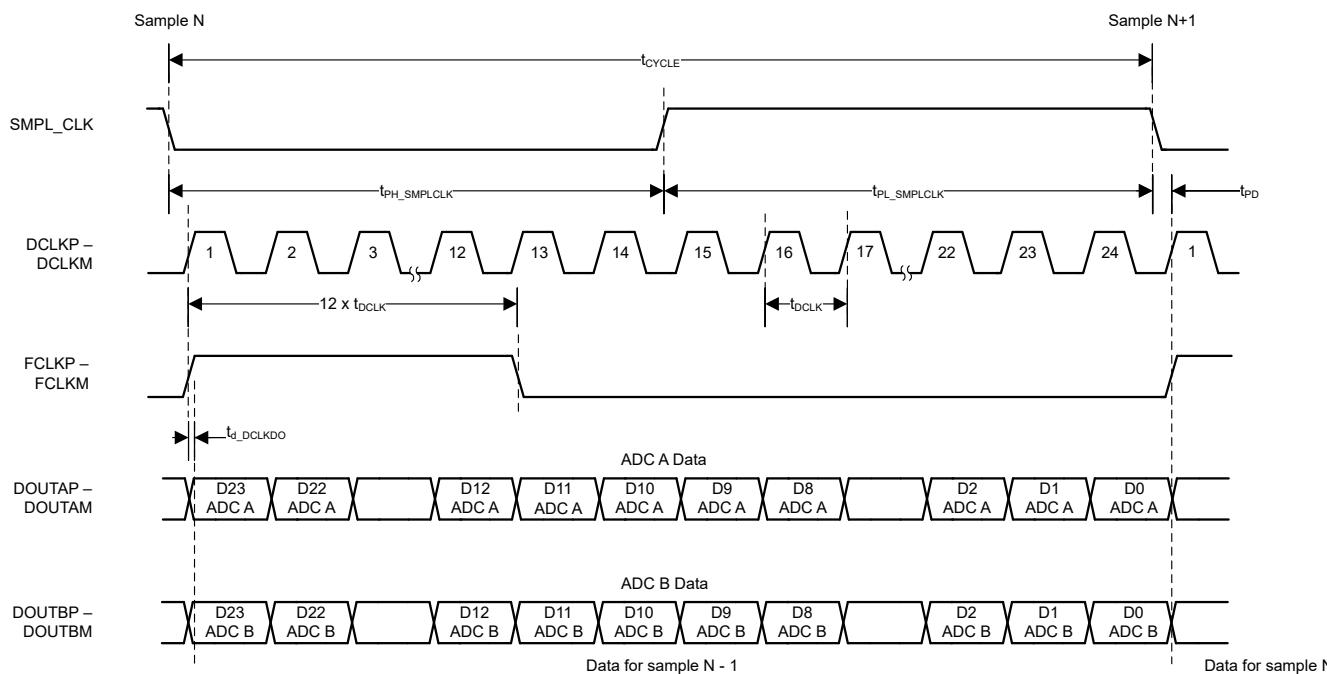

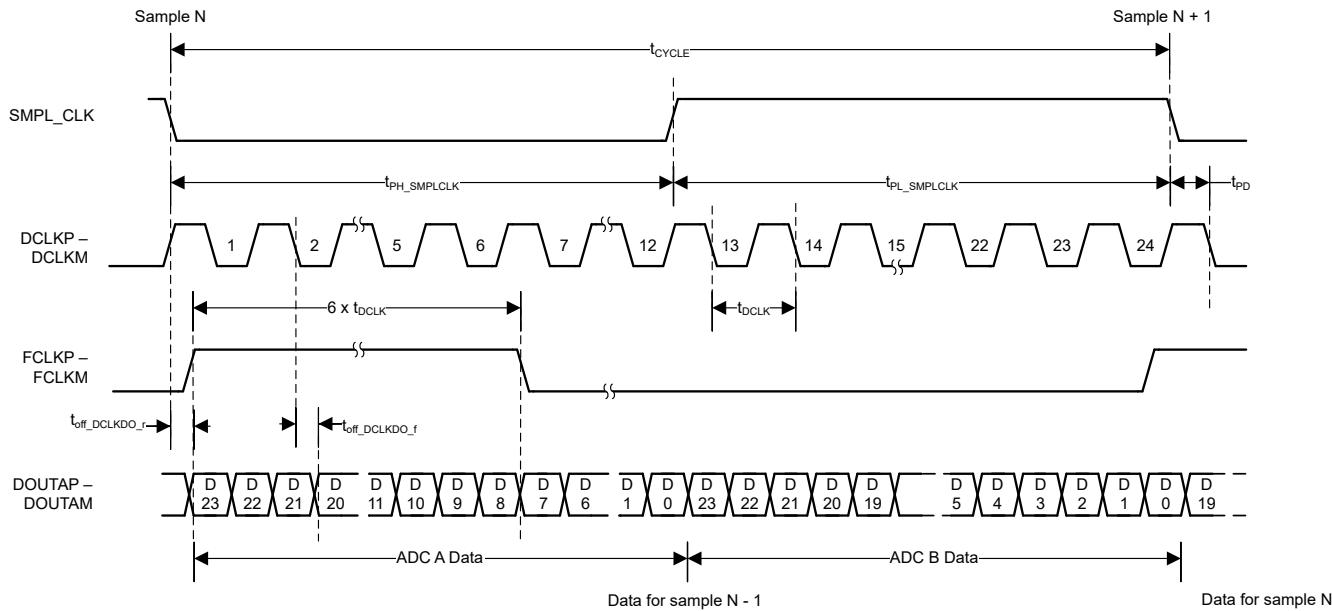

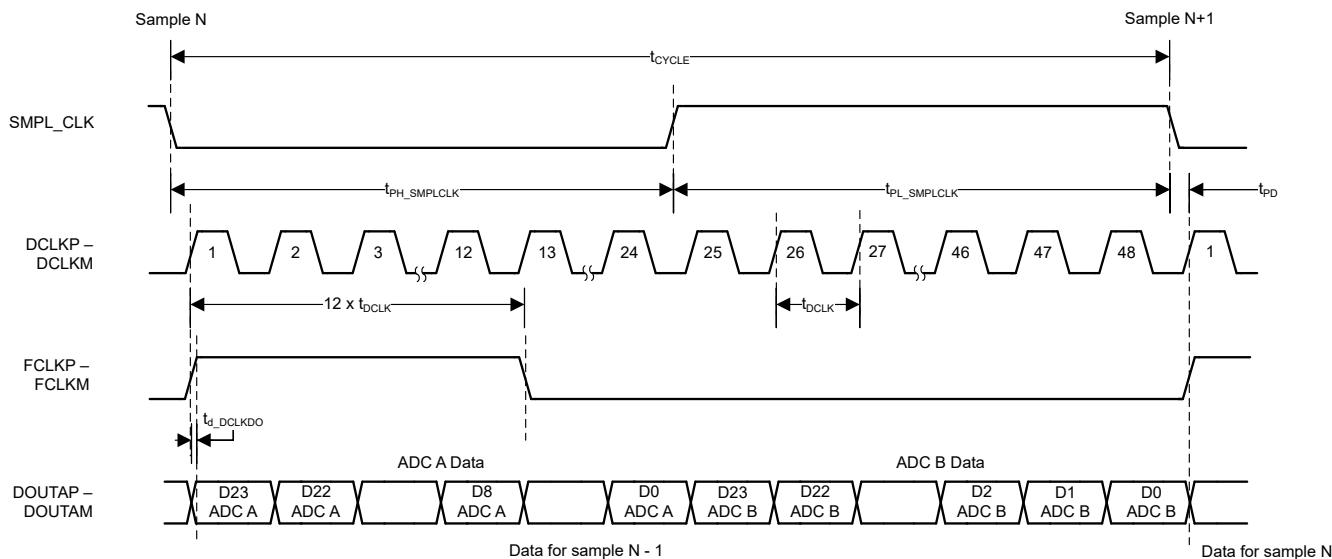

| t <sub>d_DCLKDO</sub>     | 時間遅延:DCLKP 立ち上がりから対応するデータ有効まで                   | SDR モード                                                         | -0.35                        | 0.35                         | ns |

| t <sub>off_DCLKDO_r</sub> | 時間オフセット:DCLKP 立ち上がりから対応するデータ有効まで                | DDR モード                                                         | t <sub>DCLK</sub> / 4 - 0.35 | t <sub>DCLK</sub> / 4 + 0.35 | ns |

| t <sub>off_DCLKDO_f</sub> | 時間オフセット:DCLKP 立ち下がりから対応するデータ有効まで                | DDR モード                                                         | t <sub>DCLK</sub> / 4 - 0.35 | t <sub>DCLK</sub> / 4 + 0.35 | ns |

| t <sub>PD</sub>           | 時間遅延:SmPL_CLK 立ち下がりから DCLKP 立ち上がりまで             |                                                                 |                              | t <sub>DCLK</sub>            | ns |

| t <sub>PU_SMPL_CLK</sub>  | 時間遅延:SmPL_CLK に接続されたフリーランニング クロックから ADC データ有効まで |                                                                 |                              | 100                          | μs |

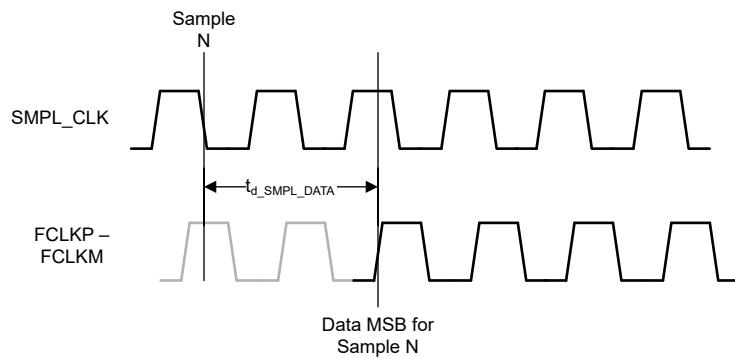

| t <sub>d_SMPL_DATA</sub>  | 時間遅延:SmPL_CLK 立ち下がりから FCLKP 立ち上がりまで             | ADS9229                                                         | 370                          | 378                          | ns |

|                           |                                                 | ADS9228                                                         | 186                          | 196                          |    |

|                           |                                                 | ADS9227                                                         | 103                          | 112                          |    |

| <b>SPI タイミング</b>          |                                                 |                                                                 |                              |                              |    |

| t <sub>den_CKDO</sub>     | 時間遅延:8 回目の SCLK 立ち上がりエッジから SDO 有効化まで            |                                                                 |                              | 30                           | ns |

| t <sub>dz_CKDO</sub>      | 時間遅延:24 回目の SCLK 立ち上がりエッジから SDO がハイインピーダンスになるまで |                                                                 |                              | 30                           | ns |

| t <sub>d_CKDO</sub>       | 時間遅延:SCLK 起動エッジから SDO での対応するデータ有効まで             |                                                                 |                              | 30                           | ns |

| t <sub>ht_CKDO</sub>      | ホールド時間:SCLK 起動エッジから SDO での前のデータ有効まで             |                                                                 | 2                            |                              | ns |

## 6.8 タイミング図

図 6-1. LVDS データ インターフェイス : 2 レーン DDR

図 6-2. LVDS データ インターフェイス : 2 レーン SDR

図 6-3. LVDS データ インターフェイス : 1 レーン DDR

図 6-4. LVDS データ インターフェイス : 1 レーン SDR

図 6-5. LVDS 出力遷移時間

図 6-6. 構成 SPI

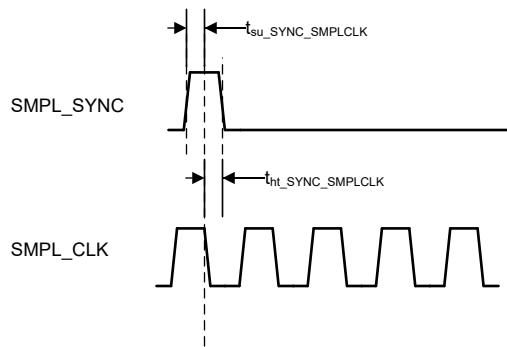

図 6-7. SMPL\_SYNC タイミング

図 6-8. サンプリング エッジから対応するデータ MSB 出力タイミングまで

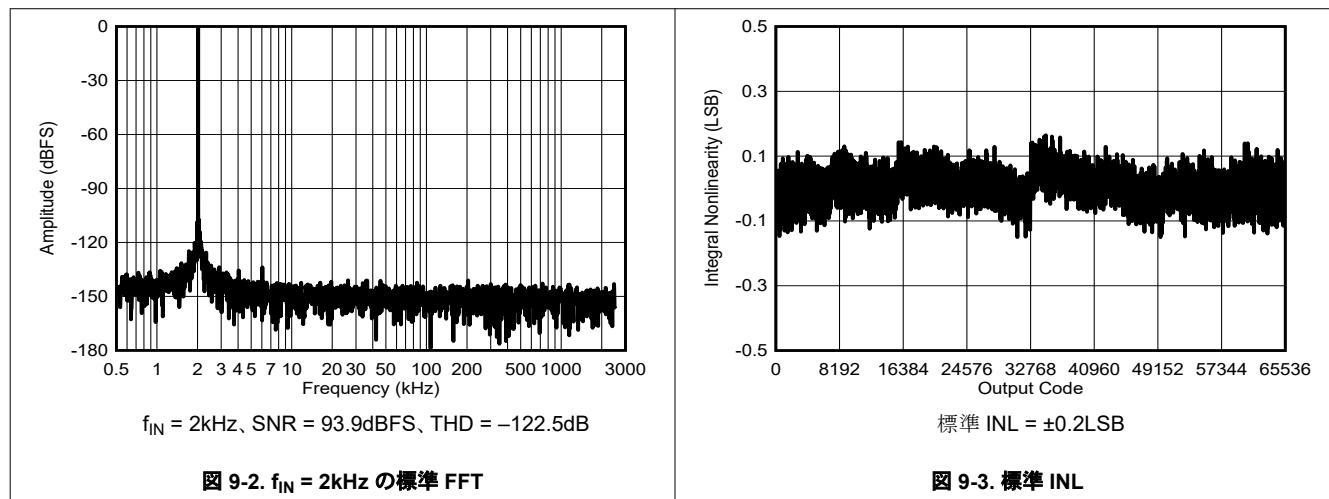

## 6.9 代表的特性：すべてのデバイス

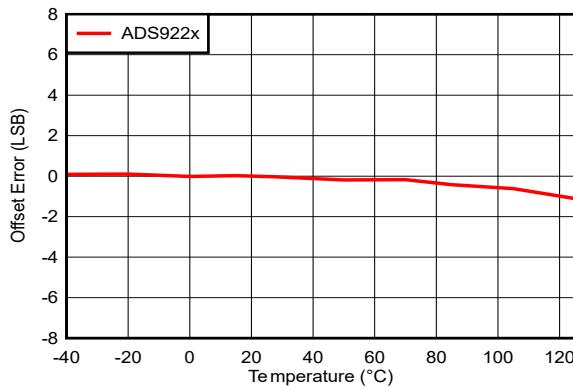

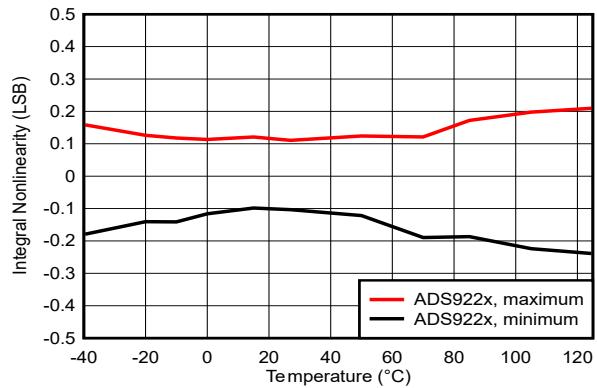

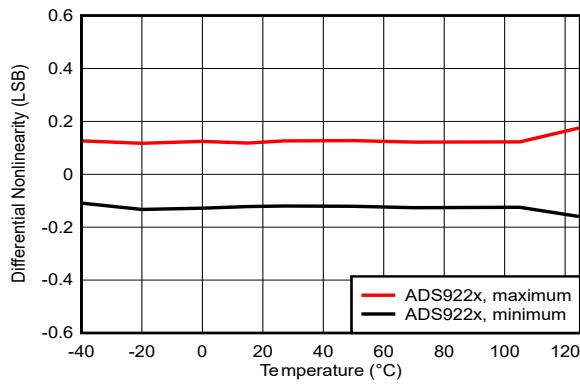

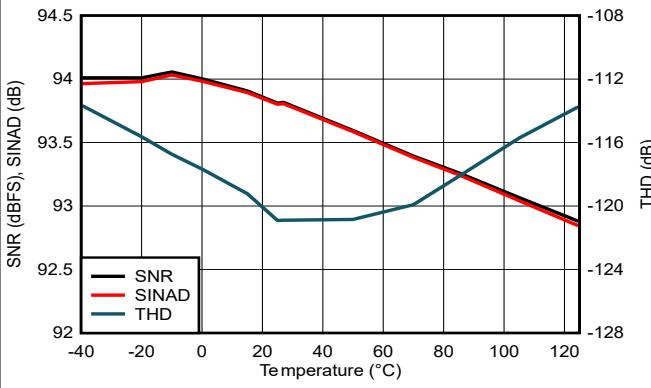

$T_A = 25^\circ\text{C}$ 、AVDD\_5V = 5V、VDD\_1V8 = 1.8V、外部  $V_{\text{REF}} = 4.096\text{V}$ 、最大スループット（特に記述のない限り）

図 6-9. 代表的なアナログ入力帯域幅

図 6-10. ゲイン誤差と温度との関係

図 6-11. オフセット誤差と温度との関係

図 6-12. INL と温度との関係

図 6-13. DNL と温度との関係

図 6-14. 信号対雑音比、SINAD、THD と温度との関係

## 6.9 代表的特性：すべてのデバイス (続き)

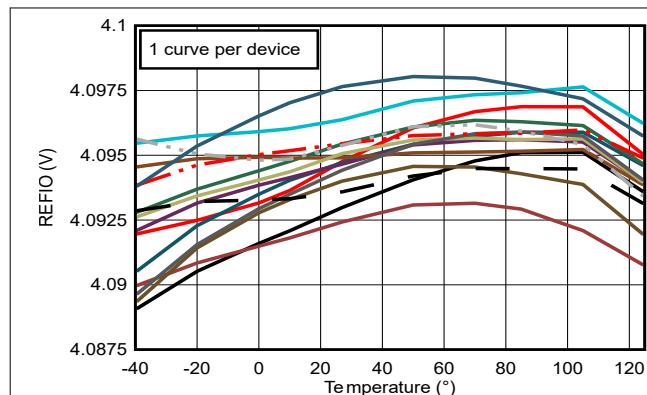

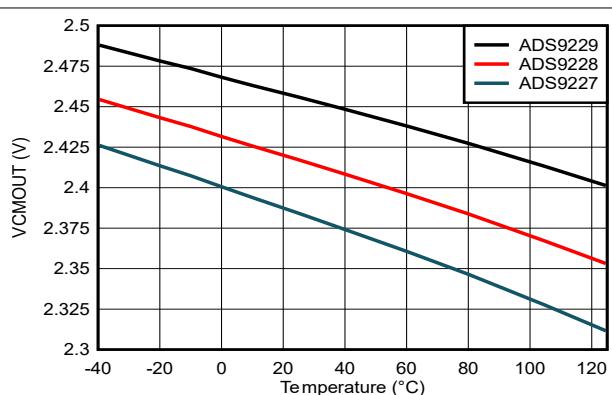

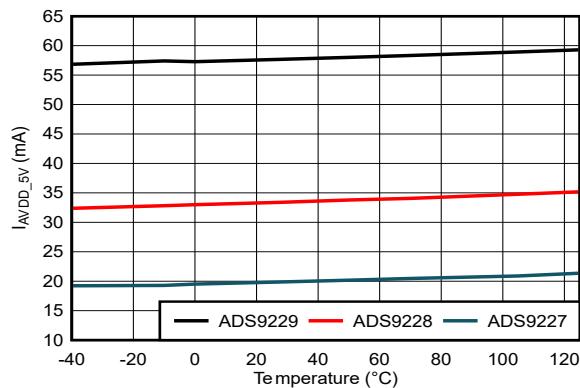

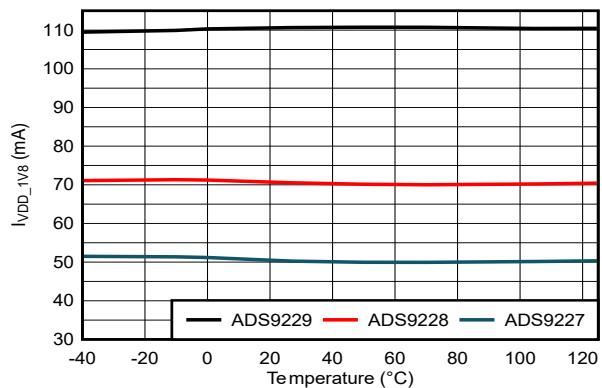

$T_A = 25^\circ\text{C}$ 、AVDD\_5V = 5V、VDD\_1V8 = 1.8V、外部  $V_{\text{REF}} = 4.096\text{V}$ 、最大スループット (特に記述のない限り)

図 6-15. REFIO 電圧と温度との関係

図 6-16. VCMOUT 電圧と温度との関係

図 6-17. AVDD\_5V 電流と温度との関係

図 6-18. VDD\_1V8 電流と温度との関係

## 6.10 代表的特性：ADS9229

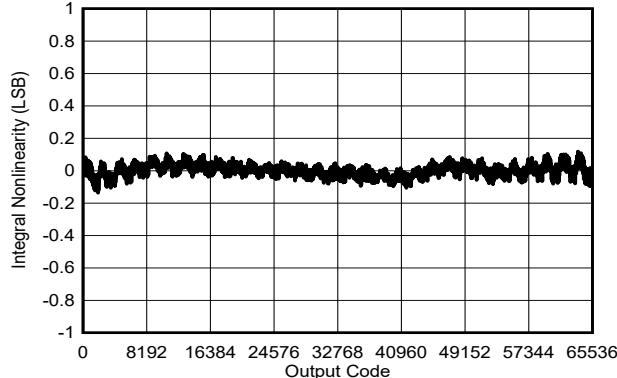

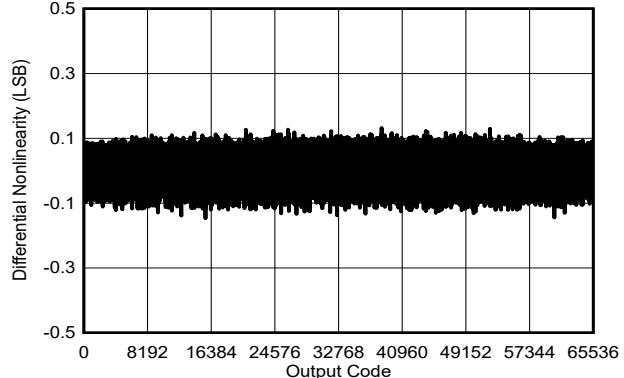

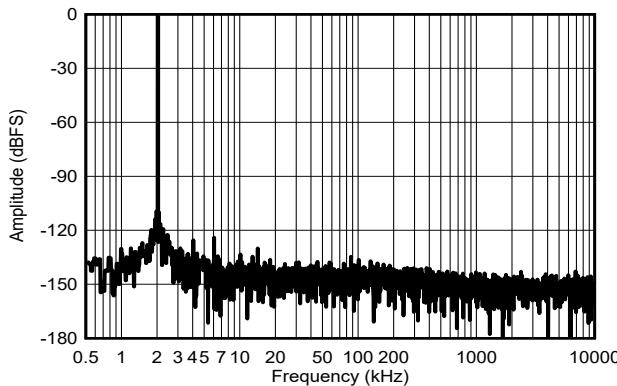

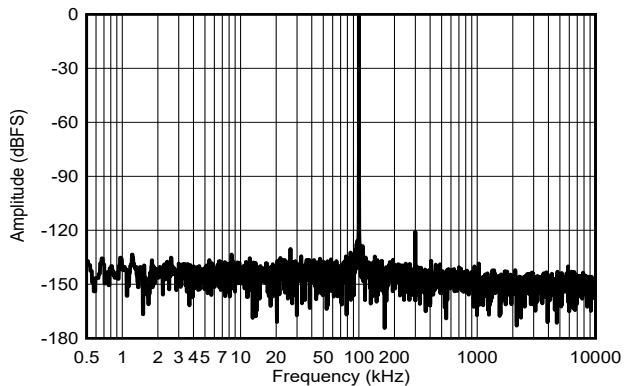

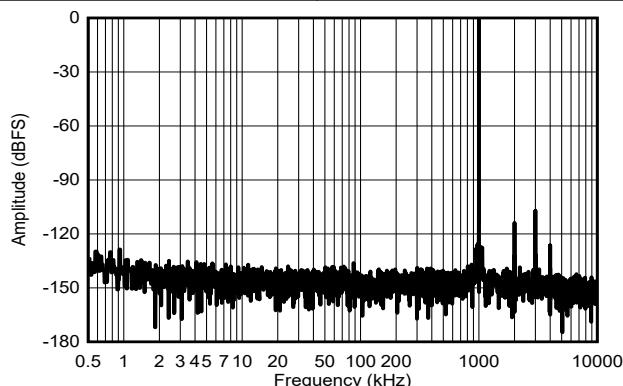

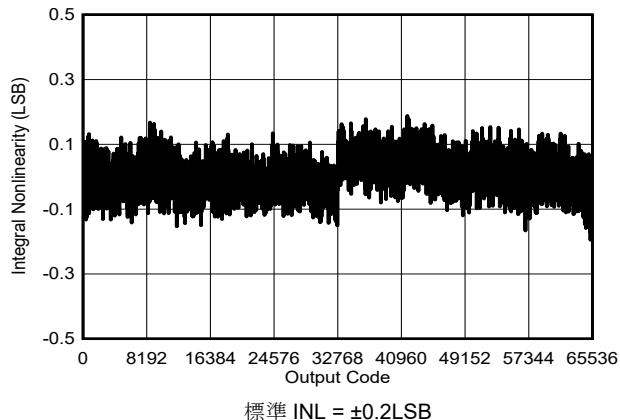

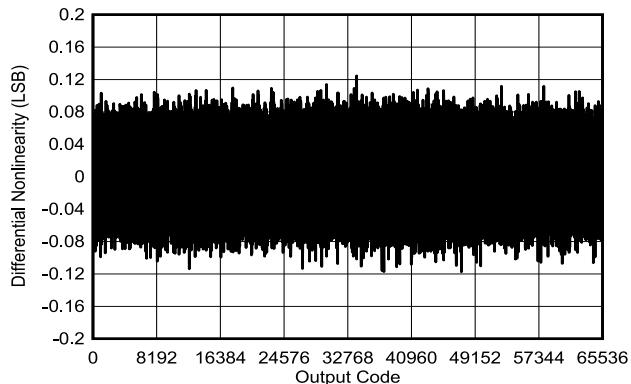

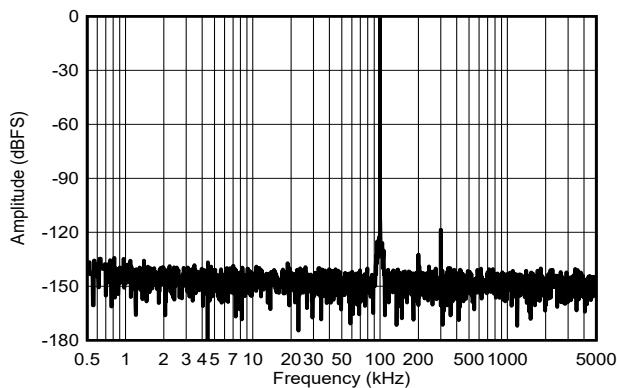

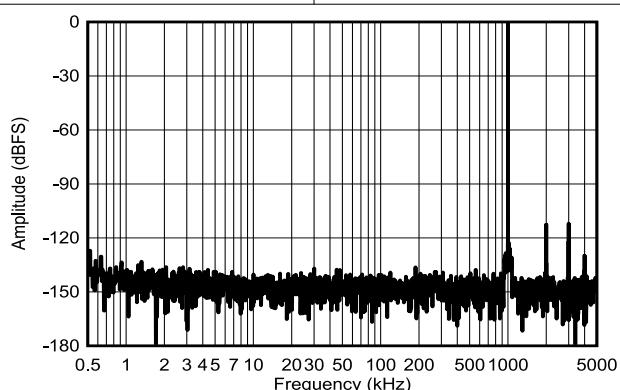

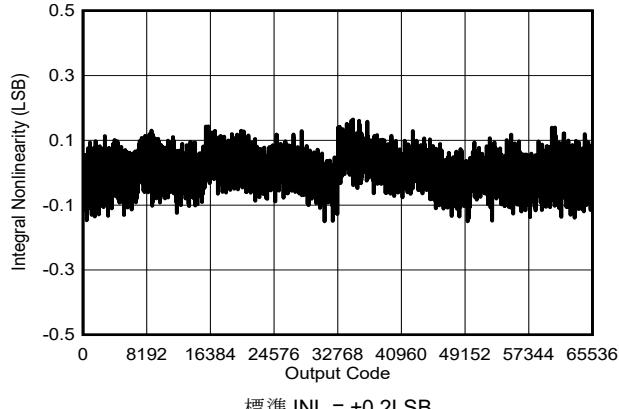

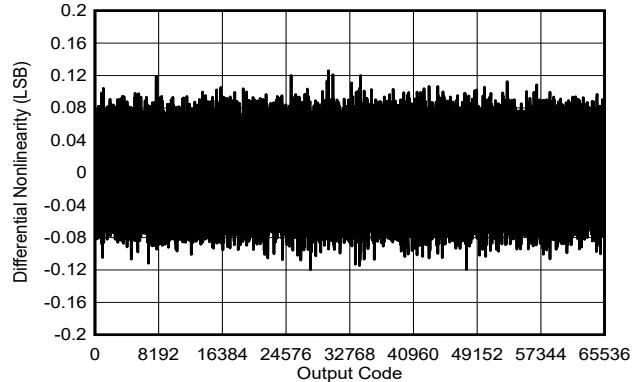

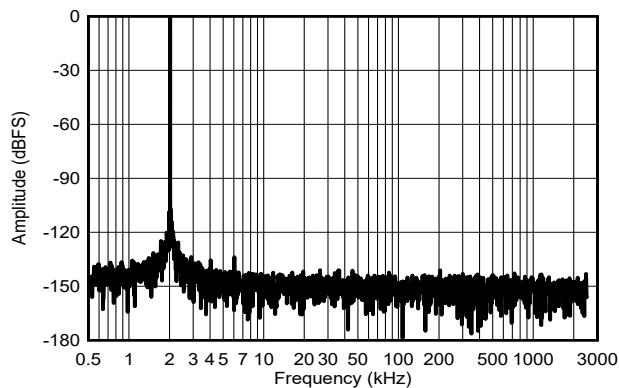

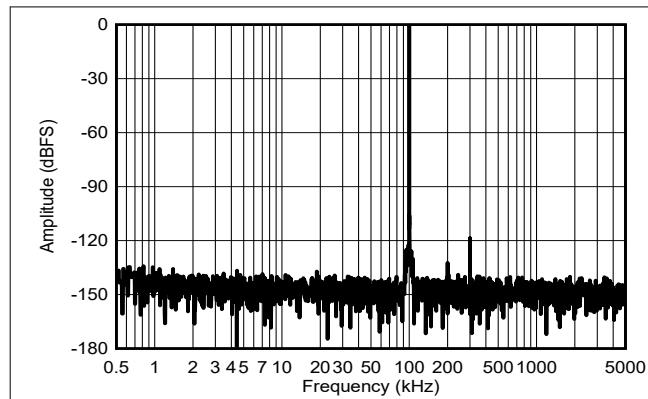

$T_A = 25^\circ\text{C}$ 、AVDD\_5V = 5V、VDD\_1V8 = 1.8V、外部  $V_{\text{REF}} = 4.096\text{V}$ 、最大スループット（特に記述のない限り）

図 6-19. 標準 INL

図 6-20. 標準 DNL : ADS9229

図 6-21.  $f_{\text{IN}} = 2\text{kHz}$  の標準 FFT

図 6-22.  $f_{\text{IN}} = 100\text{kHz}$  の標準 FFT

図 6-23.  $f_{\text{IN}} = 1\text{MHz}$  の標準 FFT

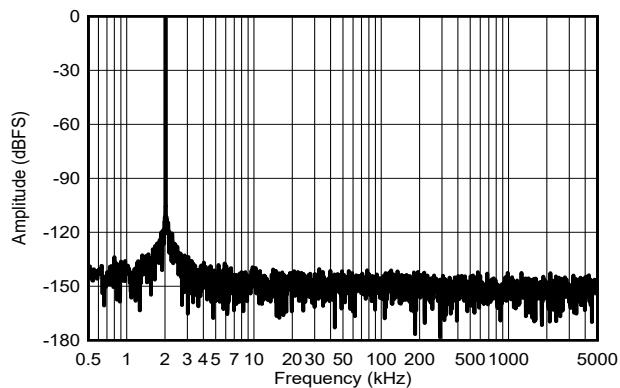

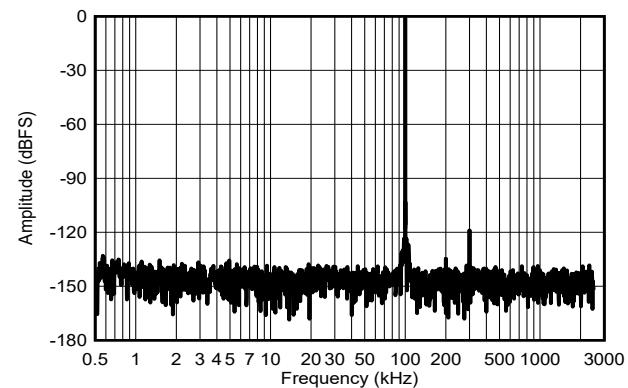

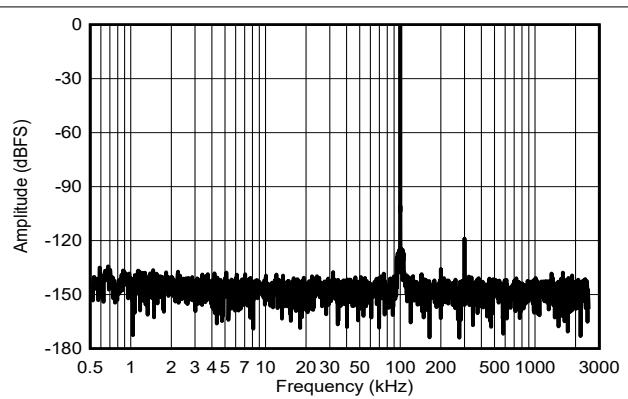

## 6.11 代表的特性：ADS9228

$T_A = 25^\circ\text{C}$ 、AVDD\_5V = 5V、VDD\_1V8 = 1.8V、内部  $V_{\text{REF}} = 4.096\text{V}$ 、最大スループット（特に記述のない限り）

図 6-24. 標準 INL

図 6-25. 標準 DNL

図 6-26.  $f_{\text{IN}} = 2\text{kHz}$  の標準 FFT

図 6-27.  $f_{\text{IN}} = 100\text{kHz}$  の標準 FFT

図 6-28.  $f_{\text{IN}} = 1\text{MHz}$  の標準 FFT

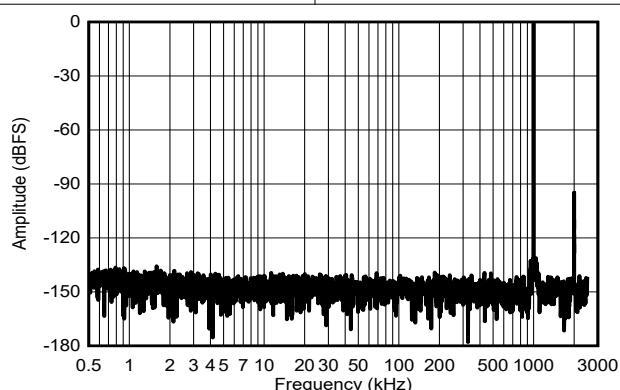

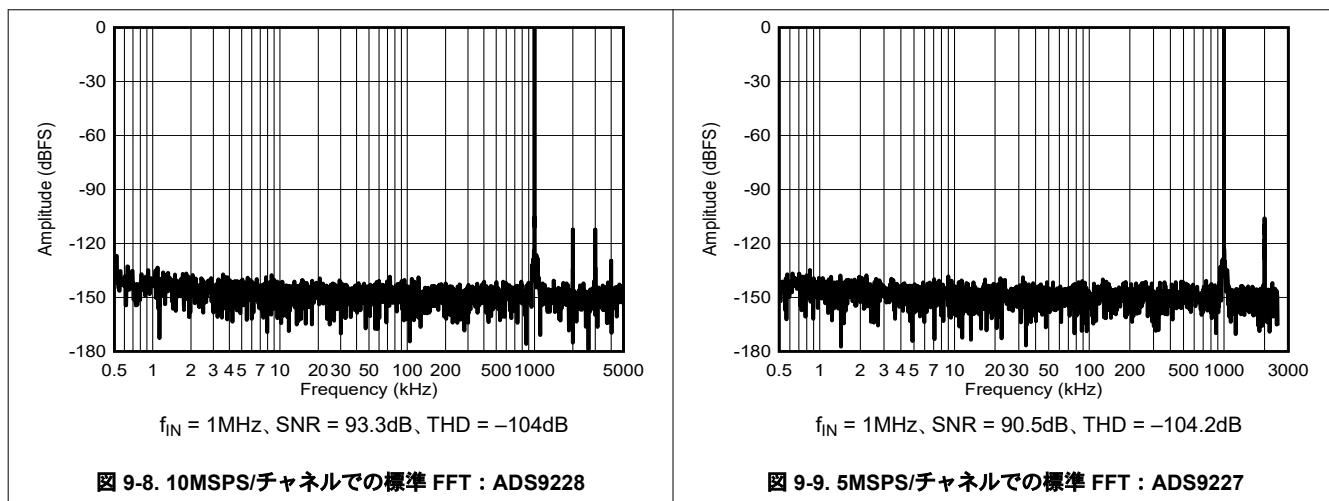

## 6.12 代表的特性：ADS9227

$T_A = 25^\circ\text{C}$ 、AVDD\_5V = 5V、VDD\_1V8 = 1.8V、内部  $V_{\text{REF}} = 4.096\text{V}$ 、最大スループット（特に記述のない限り）

図 6-29. 標準 INL

図 6-30. 標準 DNL

図 6-31.  $f_{\text{IN}} = 2\text{kHz}$  の標準 FFT

図 6-32.  $f_{\text{IN}} = 100\text{kHz}$  の標準 FFT

図 6-33.  $f_{\text{IN}} = 1\text{MHz}$  の標準 FFT

## 7 詳細説明

### 7.1 概要

ADS922x は、16 ビット、20MSPS/チャネル、デュアル チャネル、同時サンプリングの A/D コンバータ (ADC) です。ADS922x は、ADC 入力に高インピーダンス バッファ、電圧リファレンス、リファレンス バッファ、同相電圧出力バッファを内蔵しています。ADS9229 は、ユニポーラ差動アナログ入力信号をサポートします。ADC 入力のバッファは、低歪みでローパワー動作に最適化されています。

アナログ入力信号の DC レベルシフトのために、このデバイスは同相電圧出力バッファを備えています。同相電圧は、内蔵リファレンス バッファの出力から生成されます。変換が開始されると、(AINAP–AINAM) ピンと (AINBP–AINBM) ピンの間の差動入力がサンプリングされます。ADS922x は、SMPL\_CLKP ピンのクロック入力を使用して変換を開始します。

20MSPS/チャネル での動作時、ADS922x の消費電力はわずか 230mW/チャネル です。これには、ADC 入力におけるバッファ消費電力が含まれます。シリアル LVDS (SLVDS) デジタルインターフェイスにより、基板レイアウト、タイミング、ファームウェアを簡素化し、低いクロック速度でフルスループットをサポートします。

### 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 アナログ入力

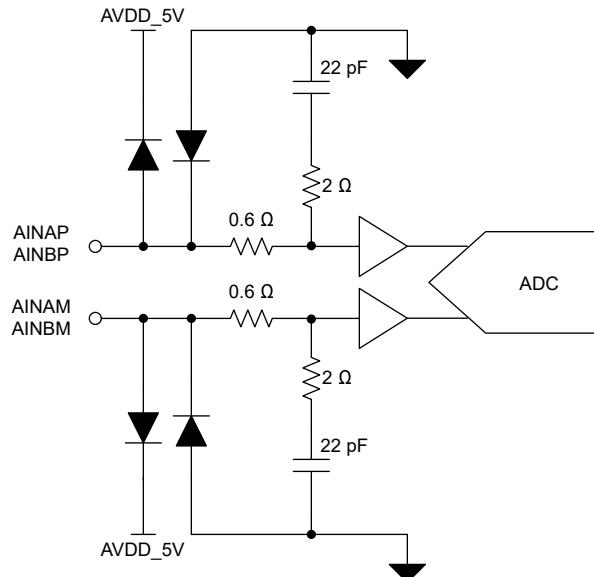

ADS922x は、AC 結合と DC 結合の両方の差動アナログ入力をサポートしています。アナログ入力の入力同相電圧が VCMOUT ピンの電圧レベルと一致することを確認します。図 7-1 に、デバイスの等価入力ネットワーク図が示されています。

図 7-1. 等価入力ネットワーク

### 7.3.2 アナログ入力帯域幅

図 6-9 に、ADS922x デバイス ファミリのアナログ最大出力入力帯域幅が示されています。3dB の帯域幅は、ADS9229 と ADS9228 では 90MHz、ADS9227 では 45MHz です。

### 7.3.3 ADC の伝達関数

ADS922x は、 $\pm 3.2V$  の差動入力範囲をサポートします。16 ビット の変換データは、ストレート バイナリまたはバイナリ 2 の補数形式で出力されます。表 7-1 に示されているように、出力コードの形式はすべてのアナログ チャネルで同じです。レジスタ アドレス 0x0D の DATA\_FORMAT フィールドを使用して、出力コードのフォーマットを構成します。ADC の最下位ビット (LSB) は、 $1\text{ LSB} = 6.4V / 2^{16}$  で提供されます。

表 7-1. 伝達特性

| 入力電圧                        | 説明           | 2 の補数形式の ADC 出力 | ストレート バイナリ形式の ADC 出力 |

|-----------------------------|--------------|-----------------|----------------------|

| $\leq -3.2V + 1\text{ LSB}$ | 負のフルスケール コード | 0x8000          | 0x0000               |

| $0V + 1\text{ LSB}$         | ミッドコード       | 0x0000          | 0x7FFF               |

| $\geq 3.2V - 1\text{ LSB}$  | 正のフルスケール コード | 0x7FFF          | 0xFFFF               |

### 7.3.4 リファレンス

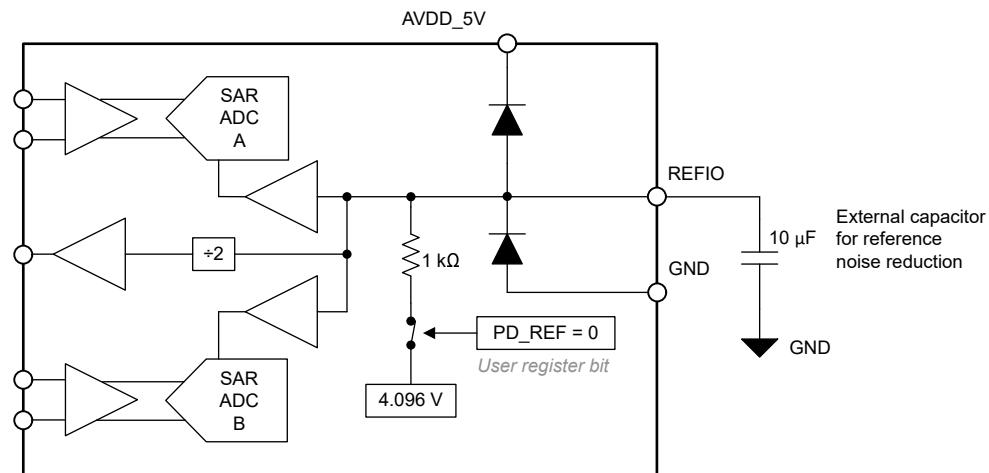

ADS922x は、高精度で低ドリフトの電圧リファレンスをデバイスに内蔵しています。最高の性能を得るために、 $10\mu\text{F}$  セラミック バイパス コンデンサを REFIO ピンに接続して、内部リファレンス ノイズをフィルタします。レジスタ アドレス 0xC1 の PD\_REF フィールドに書き込むことで、内部リファレンス電圧を無効化した状態で REFIO ピンに外部リファレンスを接続します。

### 7.3.4.1 内部リファレンス電圧

ADS922x には、公称出力電圧 4.096V の内部リファレンス電圧が備わっています。パワーアップ時に、内部リファレンスはデフォルトで有効化されます。REFIO ピンと REFM ピンの間に、最小 10 $\mu$ F デカップリングコンデンサを配置します。図 7-2 に、内部リファレンス電圧のブロック図が示されています。

図 7-2. 内部リファレンス電圧

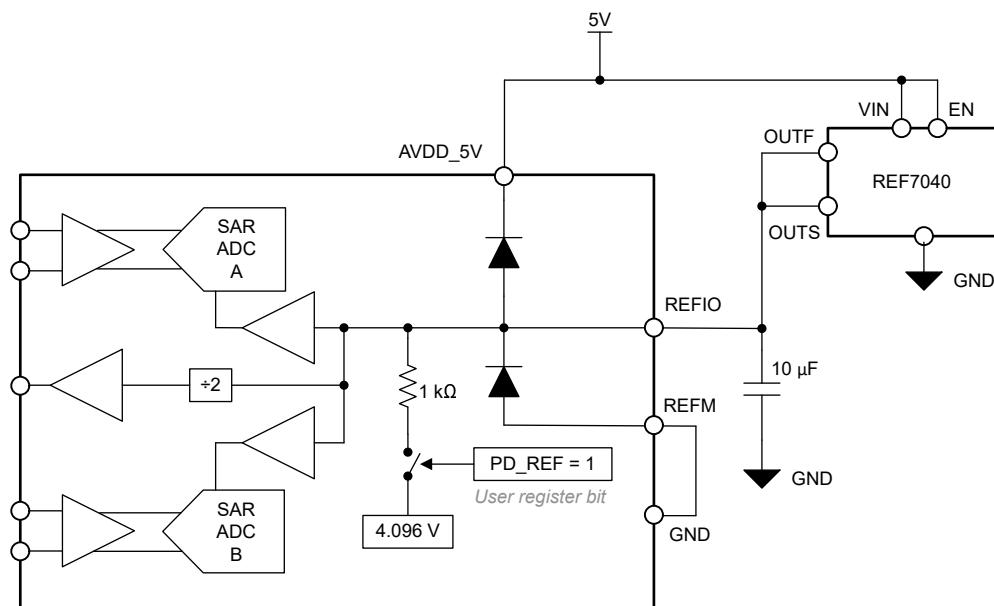

### 7.3.4.2 外部基準電圧

4.096V の外部リファレンス電圧を REFIO ピンに接続します。REFIO ピンと REFM ピンの間に適切なデカップリングコンデンサを配置します。熱ドリフト性能を向上させるために、REF7040 が推奨されます。内部リファレンスを無効にするには、レジスタ バンク 1 のアドレス 0xC1 で PD\_REF = 1b に設定します。REFIO ピンには静電放電 (ESD) 保護ダイオードがあり、AVDD\_5V ピンと REFM ピンに接続されています。図 7-3 に、外部リファレンス回路図が示されています。

図 7-3. 外部基準電圧

### 7.3.5 温度センサ

ADS922x には、デバイス内部の温度を測定するための 10 ビットの温度センサが搭載されています。表 7-2 に示されているシーケンスに従って、SPI で温度センサの出力を読み出します。ADC データインターフェイスに依存せず、いつでも温度センサのデータを読み出すことができます。

温度センサの伝達関数は、式 1 で計算されます。

$$\text{Temperature} = -85.0172 + (10 \text{ bit output} \times 0.24918) ^\circ\text{C} \quad (1)$$

表 7-2. 温度センサ出力を読み出すシーケンス

| レジスタ アドレス | レジスタ バンク | 値                | 備考                                  |

|-----------|----------|------------------|-------------------------------------|

| 0x90      | 1        | 0x4000           | レジスタを書き込み、アドレス 0x91 の温度センサ出力をロードします |

| 0x91      | 1        | 10 ビットの温度センサ データ | 温度センサ出力のレジスタを読み出します                 |

| 0x90      | 1        | 0x0000           | 書き込みレジスタ                            |

### 7.3.6 データの平均化

ADS922x は、ADC からの変換結果の平均化を行うデシメーション フィルタを内蔵しています。データの平均化が進むと、出力データ レートが低下します。表 7-3 は、ADC 出力速度を信号対雑音比および OSR と比較したものです。表 7-4 の平均化による信号対雑音比の向上は、オーバーサンプリング レートに対応するレジスタ設定を示しています。

表 7-3. 信号対雑音比と OSR との関係

| OSR | 信号対雑音比 (dBFS) | ADC 出力速度                |

|-----|---------------|-------------------------|

| 1   | 93.8          | f <sub>CYCLE</sub>      |

| 2   | 94.9          | f <sub>CYCLE</sub> / 2  |

| 4   | 95.9          | f <sub>CYCLE</sub> / 4  |

| 8   | 96.6          | f <sub>CYCLE</sub> / 8  |

| 16  | 97.0          | f <sub>CYCLE</sub> / 16 |

表 7-4. OSR のレジスタ マップ設定

| デシメーション | レジスタ                    | インターフェイス モード <sup>(1)</sup>                              |                                       |

|---------|-------------------------|----------------------------------------------------------|---------------------------------------|

|         |                         | 2 レーン SDR および DDR <sup>(2)</sup>                         | 1 レーン SDR および DDR <sup>(3)</sup>      |

| OSR 初期化 | CLK3 (0xC5[9])          | 1                                                        | OSR = 2 の場合:0<br>OSR = 4, 8, 16 の場合:1 |

|         | OSR_INIT1 (0xC0[11:10]) | DATA_LANES = 5 または 7 の場合:0<br>DATA_LANES = 0 または 2 の場合:1 |                                       |

|         | OSR_INIT2 (0xC4[5:4])   | 2                                                        | OSR = 2 の場合:0<br>OSR = 4, 8, 16 の場合:2 |

|         | OSR_INIT3 (0xC4[1])     | 1                                                        | OSR = 2 の場合:0<br>OSR = 4, 8, 16 の場合:1 |

|         | OSR_EN (0xD[6])         | 1                                                        | 1                                     |

|         | OSR_RD (0xC5[6:5])      | 1                                                        | OSR = 2 の場合:0<br>OSR = 4, 8, 16 の場合:1 |

| 2       | OSR (0xD[5:2])          | 0                                                        | 0                                     |

|         | OSR_CLK (0xC0[9:7])     | 0                                                        | 0                                     |

| 4       | OSR (0xD[5:2])          | 1                                                        | 1                                     |

|         | OSR_CLK (0xC0[9:7])     | 4                                                        | 0                                     |

| 8       | OSR (0xD[5:2])          | 2                                                        | 2                                     |

|         | OSR_CLK (0xC0[9:7])     | 5                                                        | 4                                     |

表 7-4. OSR のレジスタ マップ設定 (続き)

| デシメーション | レジスタ                | インターフェイス モード <sup>(1)</sup>      |                                  |

|---------|---------------------|----------------------------------|----------------------------------|

|         |                     | 2 レーン SDR および DDR <sup>(2)</sup> | 1 レーン SDR および DDR <sup>(3)</sup> |

| 16      | OSR (0x0D[5:2])     | 3                                | 3                                |

|         | OSR_CLK (0xC0[9:7]) | 6                                | 5                                |

(1) DATA\_LANES の構成については、表 7-7 および 表 7-8 を参照してください。

(2) ADS9227 は、すべてのデータインターフェイス モードを備えています。

(3) ADS9227 には適用されません。

図 7-4 に示されているように、SMPL\_SYNC ピンのパルスにより、デシメーション フィルタがリセットされます。SMPL\_SYNC のパルスは、デシメーション フィルタを使用する場合、複数の ADS922x デバイスを同期します。

図 7-4. デシメーションによるデータ出力

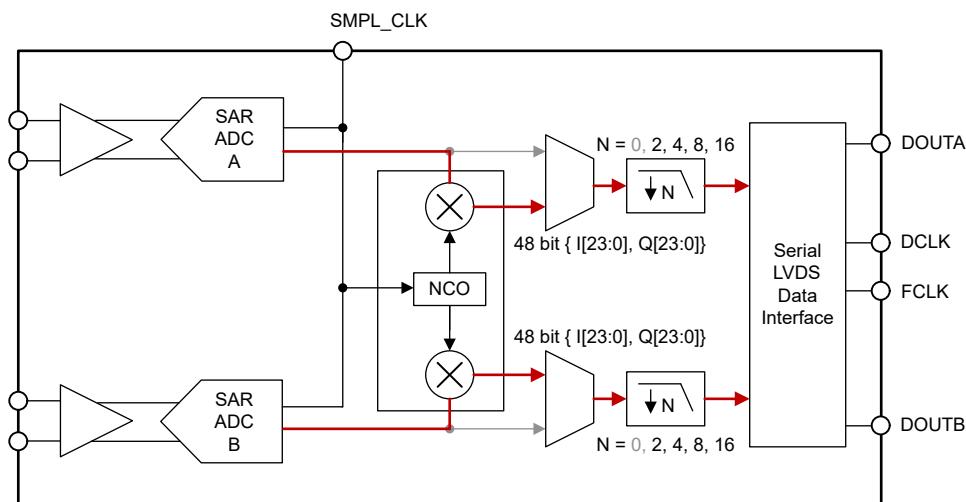

### 7.3.7 デジタルダウンコンバータ

ADS922x には、レジスタ アドレス Fbh ~ Feh によって構成されるオプションのオンチップのデジタル ダウン変換 (DDC) が含まれています。図 7-5 に示されているように、DDC にはデジタル ミキサと 24 ビットの数値制御発振器 (NCO) が内蔵されています。デジタル ミキサは、ADC 出力データと NCO 出力周波数の複雑な混合を表現する 24 ビットの I および Q 出力を生成します。ADC の各チャネルは、デジタル ミキサからそれぞれ 24 ビットの I および Q 出力に対応する 48 ビット出力を生成します。

図 7-5. デジタルダウンコンバータを使用するときのデータバス

NCO は ADC A と ADC B の両方で共通です。式 2 で得られる NCO の出力周波数は、NCO\_FREQUENCY レジスタ (アドレス 0xFD および 0xFE) を使用して構成します。

$$f_{NCO} = \frac{f_{SMPL\_CLK}}{2^{24}} \times (NCO\_FREQUENCY[23:0] \& 0xFFFFF0) \text{ Hz} \quad (2)$$

NCO の出力位相は、SMPL\_SYNC ピンにパルスを印加することでリセットされます (図 6-7 を参照)。式 3 および 表 7-5 に示されているように、NCO 出力の初期位相は、NCO\_PHASE レジスタ (アドレス 0xFC および 0xFD) を使用して構成されます。

$$NCO\_PHASE[23:0] = \left( \frac{\text{Initial phase}}{2\pi} \times 2^{24} \right) \& 0xFFFFF0 \quad (3)$$

**表 7-5. NCO の初期位相**

| NCO_PHASE[23:0] | 初期位相   |

|-----------------|--------|

| 0x000000        | 0      |

| 0x7FFFF0        | $\pi$  |

| 0xFFFFF0        | $2\pi$ |

DDC では、デシメーション係数 2、4、8、または 16 を使用します。表 7-6 に、DDC 出力をデシメーションするレジスタの構成が示されています。

**表 7-6. DDC のデシメーション設定**

| デシメーション                | レジスタ                    | 値 |

|------------------------|-------------------------|---|

| 2                      | OSR_EN (0x0D[6])        | 1 |

|                        | OSR (0x0D[5:2])         | 0 |

|                        | OSR_CLK (0xC0[9:7])     | 0 |

| デシメーション係数 4、8、16 の共通設定 | CLK3 (0xC5[9])          | 1 |

|                        | OSR_INIT1 (0xC0[11:10]) | 1 |

|                        | OSR_INIT2 (0xC4[5:4])   | 2 |

|                        | OSR_INIT3 (0xC4[1])     | 1 |

|                        | OSR_EN (0x0D[6])        | 1 |

|                        | OSR_RD (0xC5[6:5])      | 1 |

| 4                      | OSR (0x0D[5:2])         | 1 |

|                        | OSR_CLK (0xC0[9:7])     | 0 |

| 8                      | OSR (0x0D[5:2])         | 2 |

|                        | OSR_CLK (0xC0[9:7])     | 4 |

| 16                     | OSR (0x0D[5:2])         | 3 |

|                        | OSR_CLK (0xC0[9:7])     | 5 |

### 7.3.8 データインターフェイス

ADS922x は高速なシリアル LVDS データインターフェイスを備えており、2 レーンと 1 レーンのデータ出力オプションがあります。ホストは、出力データフレーム幅を、20 ビットまたは 24 ビット、シングルデータレート (SDR) およびダブルデータレート (DDR) モードで構成します。[表 7-7](#) および [表 7-8](#) の構成。

[表 7-7](#) および [表 7-8](#) に説明されているように、他のレジスタフィールドに書き込む前に INIT\_1 レジスタフィールドを構成します。

**表 7-7. ADS9227 の出力データインターフェイスのレジスタマップ設定**

| データフレーム幅 (ビット) | データレート | 出力レーン | INIT_1<br>0x04[3:0] | DATA_LA_NES<br>0x12[2:0] | DATA_RA_TE<br>0xC1[8] | CLK1<br>0xC0[12] | CLK2<br>0xC1[0] | CLK3<br>0xC5[9] | CLK4<br>0xC5[3:2] | CLK5<br>0xFB[1] | CLK6<br>0x1C[7:6] |

|----------------|--------|-------|---------------------|--------------------------|-----------------------|------------------|-----------------|-----------------|-------------------|-----------------|-------------------|

| 20             | SDR    | 1     | 0x000B              | 5                        | 1                     | 1                | 1               | 1               | 3                 | 0               | 3                 |

| 20             | SDR    | 2     | 0x000B              | 0                        | 1                     | 0                | 1               | 0               | 3                 | 0               | 3                 |

| 20             | DDR    | 1     | 0x000B              | 5                        | 0                     | 1                | 1               | 1               | 3                 | 0               | 3                 |

| 20             | DDR    | 2     | 0x000B              | 0                        | 0                     | 0                | 1               | 0               | 3                 | 0               | 3                 |

| 24             | SDR    | 1     | 0x000B              | 7                        | 1                     | 1                | 0               | 1               | 3                 | 0               | 3                 |

| 24             | SDR    | 2     | 0x0000              | 2                        | 1                     | 0                | 0               | 0               | 0                 | 0               | 0                 |

| 24             | DDR    | 1     | 0x000B              | 7                        | 0                     | 1                | 0               | 1               | 3                 | 0               | 3                 |

| 24             | DDR    | 2     | 0x0000              | 2                        | 0                     | 0                | 0               | 0               | 0                 | 0               | 0                 |

**表 7-8. ADS9229 と ADS9228 の出力データインターフェイスのレジスタマップ設定**

| データフレーム幅 (ビット) | データレート | 出力レーン | INIT_1<br>0x04[3:0] | DATA_LA_NES<br>0x12[2:0] | DATA_RA_TE<br>0xC1[8] | CLK1<br>0xC0[12] | CLK2<br>0xC1[0] | CLK3<br>0xC5[9] | CLK4<br>0xC5[3:2] | CLK5<br>0xFB[1] | CLK6<br>0x1C[7:6] |

|----------------|--------|-------|---------------------|--------------------------|-----------------------|------------------|-----------------|-----------------|-------------------|-----------------|-------------------|

| 20             | SDR    | 1     | -                   |                          |                       |                  |                 |                 |                   |                 | 非対応               |

| 20             | SDR    | 2     | -                   |                          |                       |                  |                 |                 |                   |                 | 非対応               |

| 20             | DDR    | 1     | -                   |                          |                       |                  |                 |                 |                   |                 | 非対応               |

| 20             | DDR    | 2     | -                   |                          |                       |                  |                 |                 |                   |                 | 非対応               |

| 24             | SDR    | 1     | -                   | 2                        | 1                     | 0                | 0               | 0               | 0                 | 1               | 0                 |

| 24             | SDR    | 2     | -                   | 2                        | 1                     | 0                | 0               | 0               | 0                 | 0               | 0                 |

| 24             | DDR    | 1     | -                   | 2                        | 0                     | 0                | 0               | 0               | 0                 | 1               | 0                 |

| 24             | DDR    | 2     | -                   | 2                        | 0                     | 0                | 0               | 0               | 0                 | 0               | 0                 |

ADS922x は、ADC サンプリングクロック SMPL\_CLK の倍数であるデータクロック DCLK を生成します。データクロック周波数は、データ出力レーン数 (1 または 2)、データフレーム幅、データレートによって異なります。データフレーム幅は 20 ビットまたは 24 ビットで、データレートは SDR または DDR です。[式 4](#) で、DCLK の速度を計算します。[表 7-9](#) に、出力データクロック周波数の可能な値が示されています。

$$\text{DCLK speed} = \frac{2 \text{ ADC channels} \times \text{Data Frame Width (24 bit or 20 bit)}}{\text{Data Lanes (1 or 2)} \times \text{Data Rate (SDR = 1, DDR = 2)}} \times \text{SMPL_CLK} \quad (4)$$

**表 7-9. データ クロック (DCLK) 速度**

| ADC チャネル | データ フレーム幅 (ビット) | データ レート (1 = SDR、2 = DDR) | 出力レーン <sup>(1)</sup> | SMPL_CLK 乗算器 | DCLK (SMPL_CLK = 5MHz) | DCLK (SMPL_CLK = 10MHz) | DCLK (SMPL_CLK = 20MHz) |

|----------|-----------------|---------------------------|----------------------|--------------|------------------------|-------------------------|-------------------------|

| 2        | 24              | 1                         | 1                    | 48           | 240MHz                 | —                       | —                       |

|          |                 |                           | 2                    | 24           | 120MHz                 | — <sup>(2)</sup>        | — <sup>(2)</sup>        |

|          |                 | 2                         | 1                    | 24           | 120MHz                 | 240MHz                  | 480MHz                  |

|          |                 |                           | 2                    | 12           | 60MHz                  | 120MHz                  | 240MHz                  |

|          | 20              | 1                         | 1                    | 40           | 200MHz                 | — <sup>(3)</sup>        | — <sup>(3)</sup>        |

|          |                 |                           | 2                    | 20           | 100MHz                 | — <sup>(3)</sup>        | — <sup>(3)</sup>        |

|          |                 | 2                         | 1                    | 20           | 100MHz                 | — <sup>(3)</sup>        | — <sup>(3)</sup>        |

|          |                 |                           | 2                    | 10           | 50MHz                  | — <sup>(3)</sup>        | — <sup>(3)</sup>        |

(1) LVDS 出力データとクロックは、600MHz までの動作が規定されています。より高速な速度はサポートされていません。

(2) ADS9229 および ADS9228 の場合、1 レーンのデータ出力は、データ平均化が有効な場合のみサポートされます。[データの平均化](#) セクションを参照してください。

(3) ADS9229 または ADS9228 では、20 ビットのデータフレーム幅はサポートされていません。

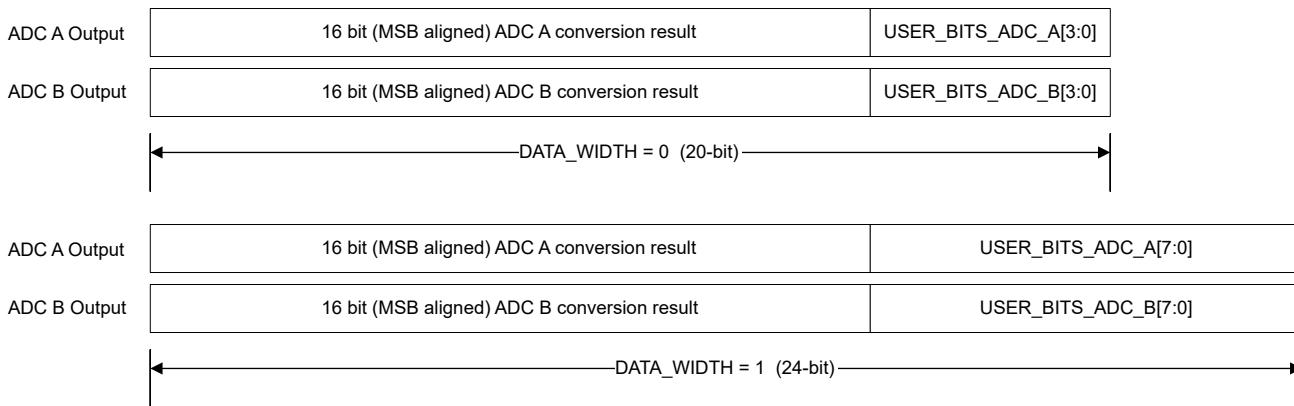

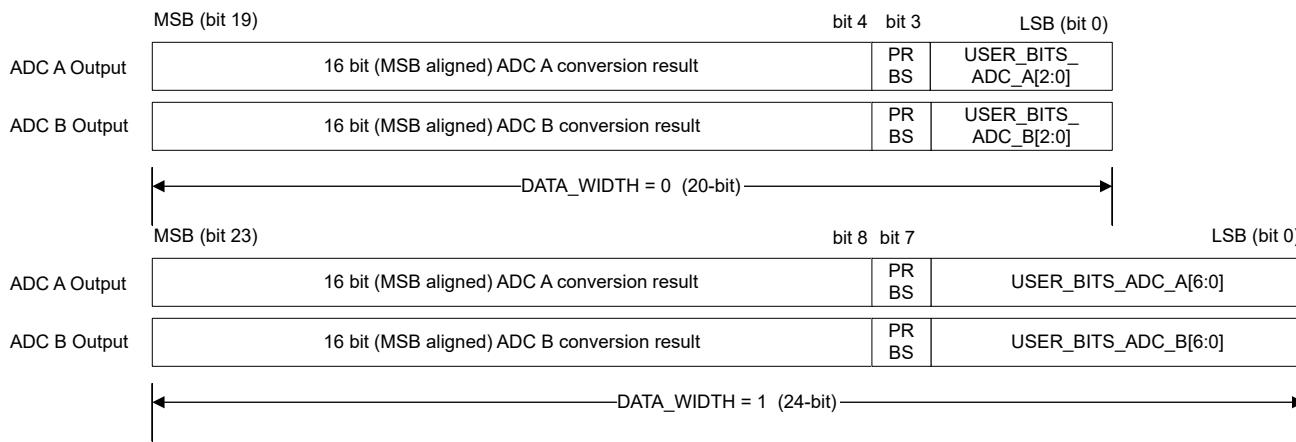

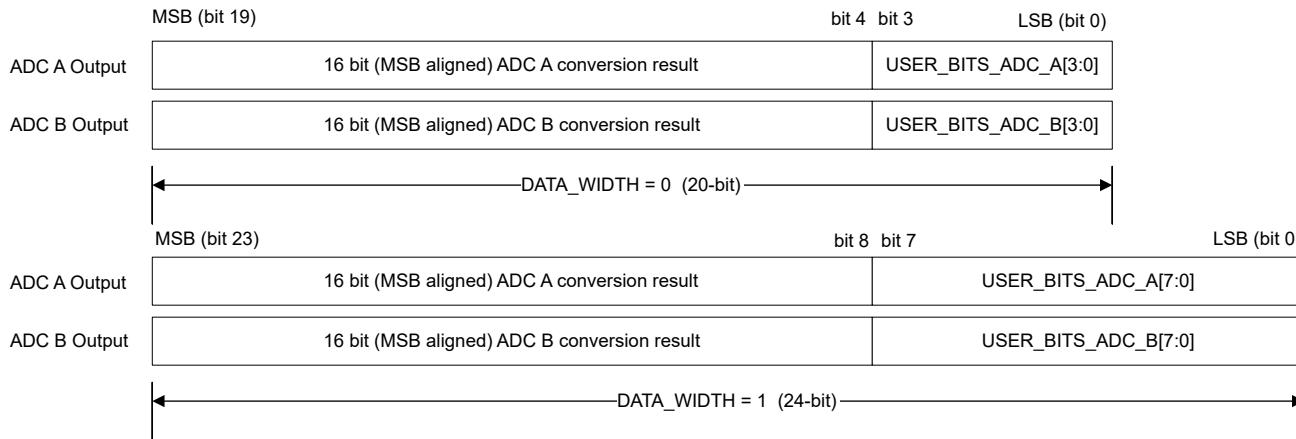

### 7.3.8.1 データ フレーム幅

図 7-6 に示されているように、ADS922x は 24 ビットおよび 20 ビットのデータフレーム幅オプションをサポートしています。データフレーム幅を選択するには、アドレス 0x12 の DATA\_WIDTH フィールドを構成します。デフォルトの出力データフレーム幅は 24 ビットです。ADC の分解能は 16 ビットで、20 ビットで表されます。

**図 7-6. データフレーム幅の構成**

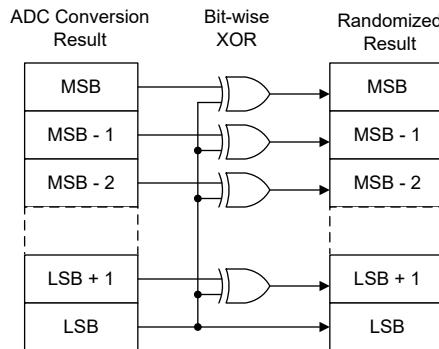

### 7.3.8.2 ADC 出力データ ランダマイザー

ADS922x には、データ出力ランダマイザーがあります。有効になっている場合、ADC 変換結果はビット単位の排他論理和 (XOR) となります。図 7-7 に、このような XOR 動作の図が示されています。変換結果 (図 7-9) の LSB または XOR\_PRBS ビット (デフォルト) のいずれかが ADC データ出力 (図 7-8) に追加されます。ADC 変換結果の LSB と XOR\_PRBS は、1 または 0 の確率が同じです。XOR 動作の結果、ADS922x からのデータ出力はランダム化されます。データインターフェイス上でランダム化された結果を送信することにより発生するグランド バウンスは、アナログ入力電圧とは相関していません。この無相関転送により、PCB レイアウトでグランド バウンスが最小限に抑えられないときに、データ転送と ADC のアナログ性能との間の干渉を最小限に抑えることができます。

図 7-7. ピット単位の XOR 動作

図 7-8. PRBS XOR が有効な場合のデータフレーム幅の構成

図 7-9. LSB XOR が有効な場合のデータフレーム幅の構成

### 7.3.8.3 複数の ADC の同期

対応する ADS922x デバイスの **SMPL\_CLK** ピンを共通サンプリング クロックで駆動します。各 ADC の **SMPL\_CLK** の同じ PCB パターン長を使用して、ADC 外部のクロック パスのタイミング遅延を一致させます。

内部デシメーション フィルタを使用する際に、**SMPL\_SYNC** ピンを使用して複数の ADC を同期します。**SMPL\_SYNC** ピンは、サンプリング クロックの立ち下がりエッジによってラッチされます。**SMPL\_SYNC** のパルスは、内部デシメーション フィルタをリセットします。

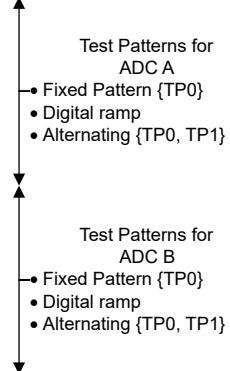

### 7.3.9 データインターフェイスのテストパターン

ADS922x は、データインターフェイスのデバッグと検証のためにホストで使用されるテストパターン(図 7-10)を備えています。テストパターンは、ADC 出力データを事前定義済みデジタルデータに置き換えます。バンク 1 の対応するレジスタアドレス 0x13 ~ 0x1B を構成することで、テストパターンを有効にします。

表 7-10 に、ADS922x でサポートされているテストパターンが示されています。

| Register Address | Bit 15                              | Bit 8 | Bit 7 | Bit 0 |

|------------------|-------------------------------------|-------|-------|-------|

| 0x13             | ADC A Test Pattern Control Register |       |       |       |

| 0x14             | TP0_A                               |       |       |       |

| 0x15             | TP1_A                               | LSB   | MSB   | TP0_A |

| 0x16             | TP1_A                               |       |       |       |

| 0x18             | ADC B Test Pattern Control Register |       |       |       |

| 0x19             | TP0_B                               |       |       |       |

| 0x1A             | TP1_B                               | LSB   | MSB   | TP0_B |

| 0x1B             | TP1_B                               |       |       |       |

図 7-10. テストパターンのレジスタバンク

表 7-10. テストパターン構成

| ADC 出力       | TP_EN_CHA<br>TP_EN_CHB | TP_MODE_CHA<br>TP_MODE_CHB | セクション     | 結果 1                                         |

|--------------|------------------------|----------------------------|-----------|----------------------------------------------|

| ADC 変換結果     | 0                      | —                          | —         | —                                            |

| 固定パターン       | 1                      | 0 または 1                    | 固定パターン    | ADC A = TP0_A<br>ADC B = TP0_B               |

| デジタルランプ      | 1                      | 2                          | デジタルランプ   | ADC A = デジタルランプ<br>ADC B = デジタルランプ           |

| テストパターンの交互配置 | 1                      | 3                          | 交互テストパターン | ADC A = TP0_A, TP1_A<br>ADC B = TP0_B, TP1_B |

#### 注

- 2つの独立したチャネルグループ ADC A と ADC B のテストパターンを構成します。

#### 7.3.9.1 固定パターン

ADC は、それぞれ ADC A および ADC B データの代わりに、TP0\_A および TP0\_B レジスタに定義された固定パターンを出力します。

- TP0\_A と TP0\_B のテストパターンを構成します

- TP\_EN\_A = 1, TP\_MODE\_A = 0 (アドレス = 0x13)、TP\_EN\_B = 1, TP\_MODE\_B = 0 (アドレス = 0x18) に設定します

#### 7.3.9.2 デジタルランプ

ADC は、ADC A および ADC B データの代わりに、デジタルランプ値をそれぞれ RAMP\_INC\_A および RAMP\_INC\_B レジスタで指定されたインクリメントだけで出力します。

- RAMP\_INC\_A (アドレス = 0x13) および RAMP\_INC\_B (アドレス = 0x18) レジスタのデジタルランプの 2 つの連続する手順間のインクリメント値をそれぞれ構成します。デジタルランプは N+1 だけインクリメントします。ここで、N はこれらのレジスタで構成された値です。

- TP\_EN\_A = 1, TP\_MODE\_A = 2 (アドレス = 0x13)、TP\_EN\_B = 1, TP\_MODE\_B = 2 (アドレス = 0x18) に設定します

### 7.3.9.3 交互テストパターン

ADC は、それぞれ ADC A と ADC B データの代わりに、TP0\_A, TP1\_A および TP0\_B, TP1\_B レジスタで定義された交互テストパターンを出力します。

- TP0\_A, TP1\_A, TP0\_B, TP1\_B のテストパターンを構成します

- TP\_EN\_A = 1, TP\_MODE\_A = 3 (アドレス = 0x13), TP\_EN\_B = 1, TP\_MODE\_B = 3 (アドレス = 0x18) に設定します

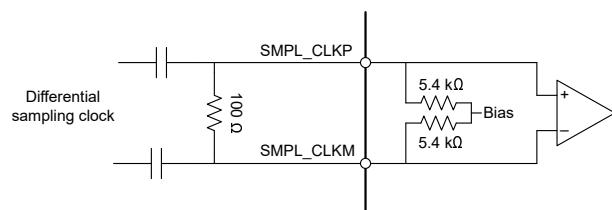

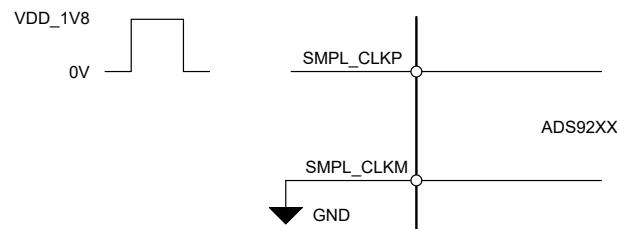

### 7.3.10 ADC サンプリングクロック入力

信号対雑音比の性能を最大限に高めるには、スルーレートの高い低ジッタの外部クロックを使用します。差動またはシングルエンドのクロック入力で ADS922x を動作させます。クロック振幅は ADC のアペーチャジッタに影響し、結果として信号対雑音比にも影響を与えます。最大限の信号対雑音比の性能を得るために、VDD\_1V8 レベルと GND レベル間のスイングを最大化する高速スルーレートのクロック信号を提供します。

サンプリングクロックがフリーランニングの連続クロックであることを確認します。[スイッチング特性](#) に示されているように、ADC はフリーランニングサンプリングクロックが印加された後で、有効な出力データ、データクロック、フレームクロック t<sub>PU\_SMPL\_CLK</sub> 生成します。サンプリングクロックが停止すると、ADC はパワーダウン状態になり、出力データ、データクロック、フレームクロックは無効になります。

図 7-11 に、差動サンプリングクロック入力の図が示されています。この構成では、差動サンプリングクロック入力を SMPL\_CLKP ピンおよび SMPL\_CLKM ピンに接続します。図 7-12 に、シングルエンドサンプリングクロック入力の図が示されています。この構成では、シングルエンドサンプリングクロックを SMPL\_CLKP に接続し、SMPL\_CLKM を接地します。

図 7-11. AC 結合差動サンプリングクロック

図 7-12. シングルエンドサンプリングクロック

## 7.4 デバイスの機能モード

### 7.4.1 リセット

**RESET** ピンのロジック 0 を使用して ADS922x をパワーダウンするか、RESET フィールド (アドレス 0x00、レジスタ バンク 0) に 1b を書き込みます。デバイス レジスタは、リセット後にデフォルト値に初期化されます。ADS9228 を初期化するためにレジスタ書き込み動作は必要ありません。

### 7.4.2 パワーダウン オプション

**PWDN** ピンのロジック 0 を使用して ADS922x をパワーダウンするか、PD\_CH フィールド (アドレス 0xC0、レジスタ バンク 1) に 11b を書き込みます。デバイス レジスタは、パワーアップ後にデフォルト値に初期化されます。ADS9228 を初期化するためにレジスタ書き込み動作は必要ありません。

### 7.4.3 通常動作

通常動作モードでは、ADS922x がパワーアップし、サンプリング クロックの立ち下がりエッジでアナログ入力がデジタル化されます。ADC は、データ クロック、フレーム クロック、MSB アラインで 16 ビットの変換結果を出力します。

### 7.4.4 初期化シーケンス

ADS922x レジスタ マップは、パワーアップ時にデフォルト値で初期化されます。表 7-11 に、ゲイン誤差較正を有効にし(推奨)、出力データ インターフェイスを変更する手順が示されています。ADS9229 の場合のみ、表 7-12 の初期化手順に従います。

表 7-11. ADS9229、ADS9228、ADS9227 のユーザー定義構成

| 手順番号 | レジスタ |      |                                                                                 | 備考                                  |

|------|------|------|---------------------------------------------------------------------------------|-------------------------------------|

|      | バンク  | アドレス | VALUE[15:0]                                                                     |                                     |

| 1    | 1    | 0x0D | ユーザー定義                                                                          | ゲイン誤差の較正を有効にし、ADC 出力データフォーマットを選択します |

| 2    | 1    | 0x33 | 0x2040                                                                          | ゲイン誤差の較正を有効にします                     |

| 3    | 0    | 0x04 | データフレーム幅 = 24 ビットおよび出力レーン = 2 の場合は 0x0000<br>データフレーム幅と出力レーンの他の組み合わせの場合 = 0x000B |                                     |

表 7-12. ADS9229 のみの初期化構成

| 手順番号 | レジスタ |            |             |

|------|------|------------|-------------|

|      | バンク  | アドレス       | VALUE[15:0] |

| 1    | 1    | 0x0D [9:8] | 0x3         |

| 2    | 1    | 0x34 [1]   | 0x1         |

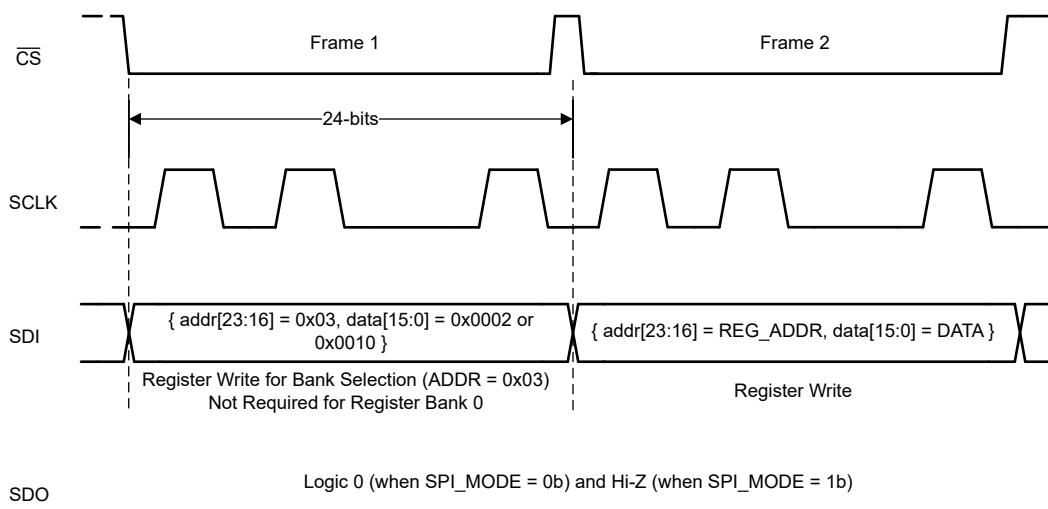

## 7.5 プログラミング

### 7.5.1 レジスタ書き込み

レジスタ書き込みアクセスは、**SPI\_RD\_EN = 0b** を設定することで有効化されます。16 ビットの構成レジスタは 3 つのレジスタ バンクにグループ化されており、8 ビットのレジスタ アドレスでアドレス指定されます。**REG\_BANK\_SEL** ビットを構成することで、レジスタ バンク 1 とレジスタ バンク 2 が読み出しありまたは書き込み動作のために選択されます。バンク 0 のレジスタは、**REG\_BANK\_SEL** ビットに関係なく、常にアクセスできます。バンク 0 のレジスタ アドレスは固有であり、レジスタ バンク 1 および 2 では使用されません。

図 7-13 に示されているように、レジスタに書き込む手順は以下の通りです。

- フレーム 1:次のレジスタ書き込みのためにレジスタ バンク 1 または バンク 2 を選択するには、レジスタ バンク 0 のレジスタ アドレス **0x03** に書き込みます。バンク 0 のレジスタに書き込む場合、このフレームは影響を与えません。

- フレーム 2:フレーム 1 で選択されたバンクのレジスタに書き込みます。同じレジスタ バンク内に複数のレジスタに書き込む場合は、この手順を繰り返します。

図 7-13. レジスタ書き込み

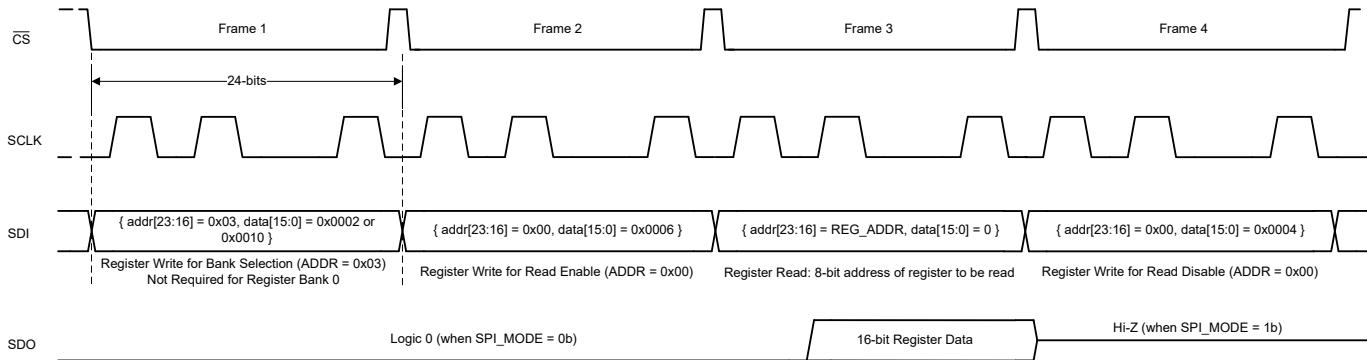

### 7.5.2 レジスタ読み出し

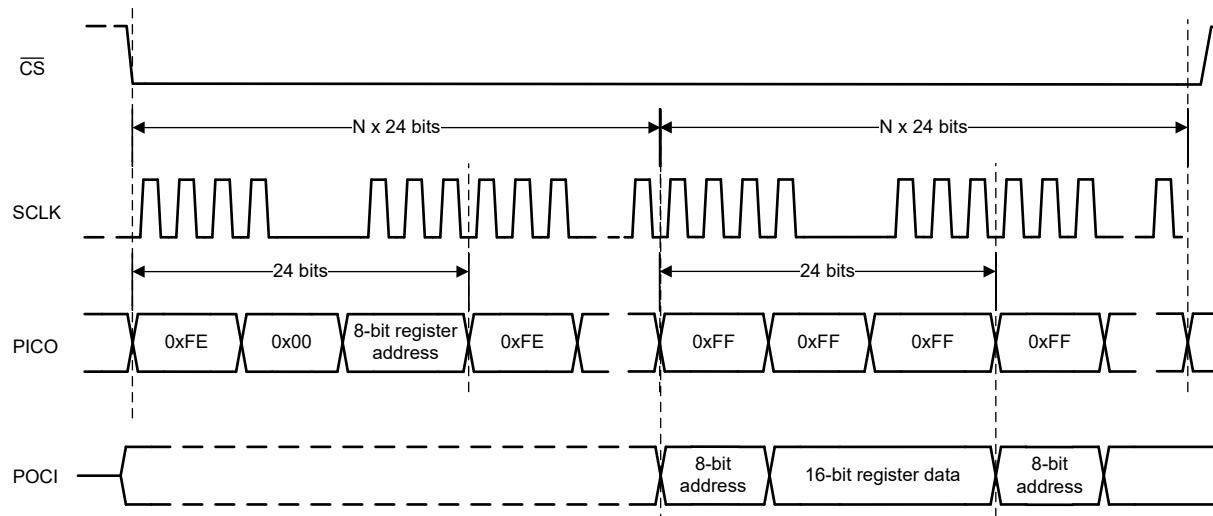

レジスタ バンク 0 のレジスタ アドレス **0x03** に書き込み、目的のレジスタ バンクを選択します。レジスタ読み出しアクセスは、レジスタ バンク 0 で **SPI\_RD\_EN = 1b** および **SPI\_MODE = 1b** を設定することで有効化されます。図 7-14 に示されているように、**SPI\_RD\_EN** および **SPI\_MODE** が設定された後、2 つの 24 ビット SPI フレームを使ってレジスタを読み出すことができます。最初の SPI フレームでレジスタ バンクが選択されます。ADC は、8 ビットのレジスタ アドレスに対応する 2 番目の SPI フレームで 16 ビットのレジスタ値を返します。

図 7-14 に示されているように、レジスタを読み出す手順は以下の通りです。

- フレーム 1:**SPI\_RD\_EN = 0b** の場合、レジスタ バンク 0 のレジスタ アドレス **0x03** に書き込み、読み出し対象のレジスタ バンクを選択します。

- フレーム 2:レジスタ バンク 0 のレジスタ アドレス **0x00** で **SPI\_RD\_EN = 1b**、**SPI\_MODE = 1b** に設定します。

- フレーム 3:目的のレジスタ アドレスを含む 24 ビットの SPI フレームを使用して、選択されたバンクのいずれかのレジスタを読み出します。選択したバンクのいずれかのレジスタのアドレスで、対応するレジスタを読み出し、この手順を繰り返します。

- フレーム 4:**SPI\_RD\_EN** を **0** に設定すると、レジスタ読み出しが無効になり、レジスタ書き込みが再度有効になります。

- 手順 1 ~ 4 を繰り返して、別のバンクのレジスタを読み出します。

図 7-14. レジスタ読み出し

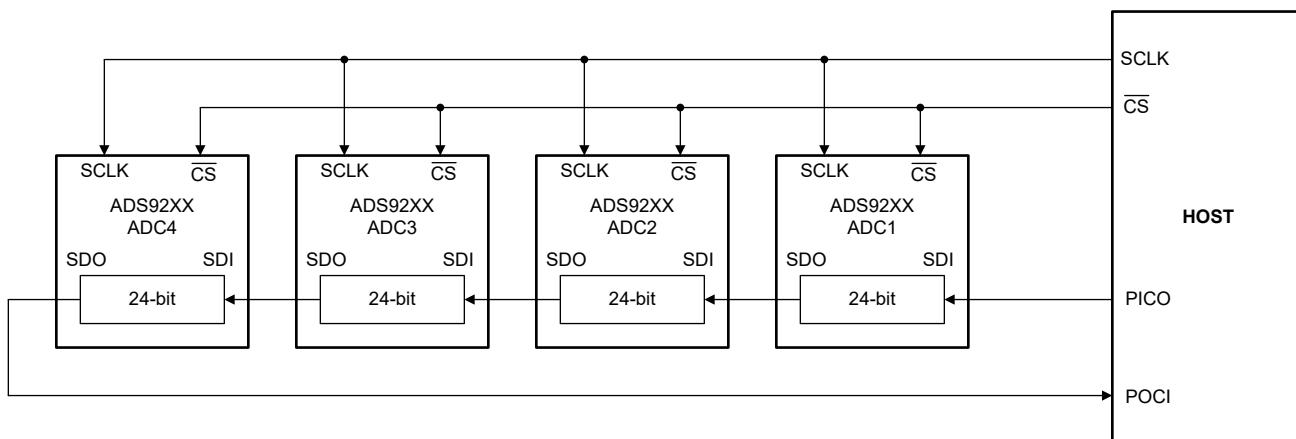

### 7.5.3 複数のデバイス : SPI 構成のデイジーチェーントポロジ

図 7-15 に、デイジーチェーントポロジで複数のデバイスを使用した一般的な接続図が示されています。

図 7-15. SPI 構成のデイジーチェーン接続

すべての ADC の  $\overline{CS}$  および SCLK 入力は互いに接続され、それぞれコントローラの単一の  $\overline{CS}$  および SCLK ピンによって制御されます。チェーンの最初の ADC (ADC1) の SDI 入力ピンは、コントローラのペリフェラル入力コントローラ出力 (POCO) ピンに接続されています。ADC1 の SDO 出力ピンは、ADC2 の SDI 入力ピンに接続され、以下同様に接続されます。チェーン内の最後の ADC の SDO 出力ピン (ADC4) は、コントローラのペリフェラル出力コントローラ入力 (POCI) ピンに接続されます。POCO ピンのデータは、 $\overline{CS}$  がアクティブである限り、24 SCLK の遅延で ADC1 を通過します。

パワーアップ後またはデバイスのリセット後に、デイジーチェーン モードを有効にします。デイジーチェーン モードを有効にするには、DAISY\_CHAIN\_LEN レジスタのデイジーチェーンの長さを設定します。デイジーチェーンの長さは、ADC1 を除くチェーン内の ADC の数です。図 7-15 では、DAISE\_CHAIN\_LEN は 3 です。

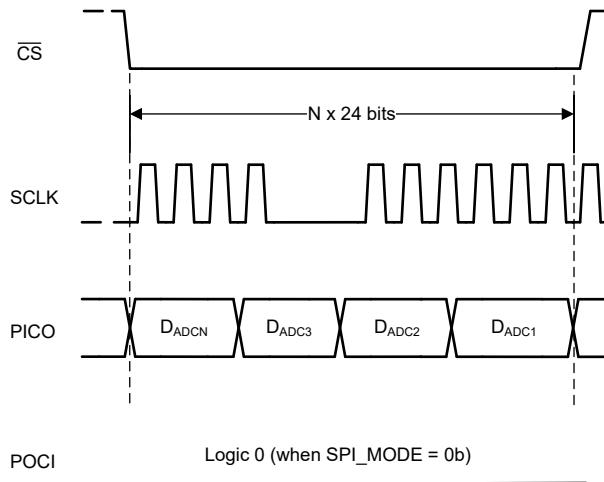

#### 7.5.3.1 デイジーチェーンでのレジスタ書き込み

デイジーチェーン構成でレジスタに書き込むには、1 つの SPI フレームで  $N \times 24$  SCLK が必要です。図 7-15 に示されているように、4 つの ADC を含むデイジーチェーン構成でのレジスタ書き込みには 96 の SCLK が必要です。

デイジーチェーン モードは、パワーアップ時またはデバイスのリセット後に有効になります。DAISY\_CHAIN\_LEN フィールドを構成して、デイジーチェーン モードを有効にします。図 7-16 に示されている波形を N 回繰り返します。ここで、N はデイジーチェーン内の ADC の数です。図 7-17 に、N ADC のデイジーチェーン モードを有効にするための N SPI フレームを含む SPI 波形が示されています。

図 7-16. デイジーチェーンでのレジスタ書き込み

図 7-17. デイジーチェーンの長さを構成するためのレジスタ書き込み

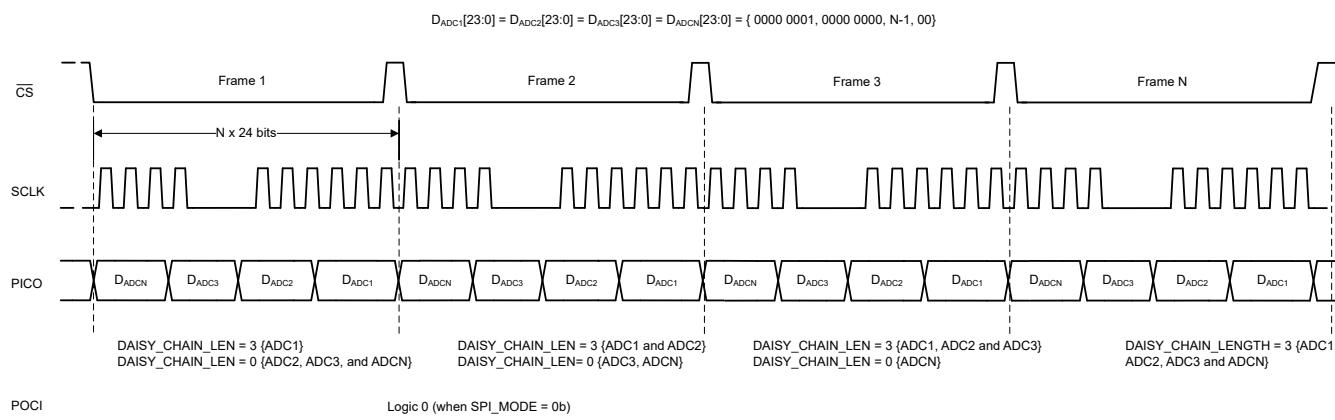

### 7.5.3.2 デイジーチェーンでのレジスタ読み出し

図 7-18 に、デイジーチェーン構成のレジスタを読み出すための SPI 波形が示されています。デイジーチェーン接続された N 個の ADC からレジスタを読み出す手順は以下の通りです。

1. レジスタ読み出しは、次のレジスタに書き込むことで有効になります。

- a. REG\_BANK\_SEL に書き込み、目的のレジスタ バンクを選択します

- b. SPI\_RD\_EN = 0b を書き込み、レジスタ読み出しを有効にします（パワーアップ時のデフォルト）

2. レジスタ バンクが選択されている状態で、SPI\_RD\_EN = 0b のとき、コントローラは以下の方法でレジスタデータを読み出します。

- a. 読み出し対象の 8 ビットレジスタ アドレスを含む N×24 ビット SPI フレーム:N 時間 (0xFE, 0x00, 8 ビットのレジスタ アドレス)

- b. レジスタデータを読み出すための N×24 ビット SPI フレーム:N 回 (0xFF, 0xFF, 0xFF)

手順 2a の 0xFE は、指定された 8 ビットアドレスからのレジスタ読み出しのための ADC を構成します。手順 2a が終了すると、ADC の出力シフトレジスタにレジスタのデータがロードされます。ADC は、8 ビットのレジスタアドレス、およびそれに対応する 16 ビットのレジスタデータを手順 2b で返します。

図 7-18. デイジーチェーン構成でのレジスタ読み出し

## 8 レジスタ マップ

### 8.1 レジスタ バンク 0

図 8-1. レジスタ バンク 0 マップ

| 追加  | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2               | D1            | D0   |

|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|------------------|---------------|------|

| 00h |     |     |     |     |     |     |    |    |    |    |    |    |    | SPI_MO<br>DE     | SPI_RD<br>_EN | リセット |

| 01h |     |     |     |     |     |     |    |    |    |    |    |    |    | DAISY_CHAIN_LEN  |               | 予約済み |

| 03h |     |     |     |     |     |     |    |    |    |    |    |    |    | REG_BANK_SEL     |               |      |

| 04h |     |     |     |     |     |     |    |    |    |    |    |    |    |                  | INIT_1        |      |

| 06h |     |     |     |     |     |     |    |    |    |    |    |    |    | REG_00H_READBACK |               |      |

表 8-1. レジスタ セクション / ブロック アクセス タイプ コード

| アクセス タイプ      | 表記  | 概要               |

|---------------|-----|------------------|

| R             | R   | 読み出し             |

| W             | W   | 書き込み             |

| R/W           | R/W | 読み出しありまたは書き込み    |

| リセットまたはデフォルト値 |     |                  |

| -n            |     | リセット後の値またはデフォルト値 |

#### 8.1.2 レジスタ 00h (オフセット = 0h) [リセット = 0h]

図 8-2. レジスタ 00h

|      |    |    |    |    |          |           |      |

|------|----|----|----|----|----------|-----------|------|

| 15   | 14 | 13 | 12 | 11 | 10       | 9         | 8    |

| 予約済み |    |    |    |    |          |           |      |

| W-0h |    |    |    |    |          |           |      |

| 7    | 6  | 5  | 4  | 3  | 2        | 1         | 0    |

| 予約済み |    |    |    |    | SPI_MODE | SPI_RD_EN | リセット |

| W-0h |    |    |    |    | W-0h     | W-0h      | W-0h |

図 8-3. レジスタ 00h のフィールドの説明

| ピット  | フィールド     | タイプ | リセット | 概要                                                                                                         |

|------|-----------|-----|------|------------------------------------------------------------------------------------------------------------|

| 15-3 | 予約済み      | W   | 0h   | 予約済み。デフォルトのリセット値から変更しないでください。                                                                              |

| 2    | SPI_MODE  | W   | 0h   | レジスタ アクセスの構成インターフェイスとして、従来の SPI モードとデイジーチェーン SPI モードのどちらかを選択します。<br>0: デイジーチェーン SPI モード<br>1: レガシー SPI モード |

| 1    | SPI_RD_EN | W   | 0h   | レガシー SPI モードでレジスタ読み出しアクセスを有効にします。このビットは、デイジーチェーン SPI モードでは無効です。<br>0: レジスタ読み出しは無効化<br>1: レジスタ読み出しは有効化      |

| 0    | リセット      | W   | 0h   | ADC リセット制御。<br>0: 通常のデバイス動作<br>1: すべてのレジスタをリセット                                                            |

### 8.1.3 レジスタ 01h (オフセット = 1h) [リセット = 0h]

図 8-4. レジスタ 01h

|                 |    |    |    |    |    |   |   |

|-----------------|----|----|----|----|----|---|---|

| 15              | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| 予約済み            |    |    |    |    |    |   |   |

| R/W-0h          |    |    |    |    |    |   |   |

| 7               | 6  | 5  | 4  | 3  | 2  | 1 | 0 |

| DAISY_CHAIN_LEN |    |    |    |    |    |   |   |

| R/W-0h          |    |    |    |    |    |   |   |

図 8-5. レジスタ 01h のフィールドの説明

| ビット  | フィールド               | タイプ | リセット | 概要                                                                        |

|------|---------------------|-----|------|---------------------------------------------------------------------------|

| 15-7 | 予約済み                | R/W | 0h   | 予約済み。デフォルトのリセット値から変更しないでください。                                             |

| 6-2  | DAISY_CHAIN_L<br>EN | R/W | 0h   | SPI 構成のために、デイジーチェーン接続された ADC の数を構成します。<br>0:1 ADC<br>1:2 ADC<br>31:32 ADC |

| 1-0  | 予約済み                | R/W | 0h   | 予約済み。デフォルトのリセット値から変更しないでください。                                             |

### 8.1.4 レジスタ 03h (オフセット = 3h) [リセット = 2h]

図 8-6. レジスタ 03h

|              |    |    |    |    |    |   |   |

|--------------|----|----|----|----|----|---|---|

| 15           | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| 予約済み         |    |    |    |    |    |   |   |

| R/W-0h       |    |    |    |    |    |   |   |

| 7            | 6  | 5  | 4  | 3  | 2  | 1 | 0 |

| REG_BANK_SEL |    |    |    |    |    |   |   |

| R/W-2h       |    |    |    |    |    |   |   |

図 8-7. レジスタ 03h のフィールドの説明

| ビット  | フィールド        | タイプ | リセット | 概要                                                                                      |

|------|--------------|-----|------|-----------------------------------------------------------------------------------------|

| 15-8 | 予約済み         | R/W | 0h   | 予約済み。デフォルトのリセット値から変更しないでください。                                                           |

| 7-0  | REG_BANK_SEL | R/W | 2h   | 読み出しおよび書き込み動作のレジスタ バンクの選択。<br>0:レジスタ バンク 0 を選択<br>2:レジスタ バンク 1 を選択<br>16:レジスタ バンク 2 を選択 |

### 8.1.5 レジスタ 04h (オフセット = 4h) [リセット = 0h]

図 8-8. レジスタ 04h

|        |    |    |    |        |    |   |   |

|--------|----|----|----|--------|----|---|---|

| 15     | 14 | 13 | 12 | 11     | 10 | 9 | 8 |

| 予約済み   |    |    |    |        |    |   |   |

| R-0h   |    |    |    |        |    |   |   |

| 7      | 6  | 5  | 4  | 3      | 2  | 1 | 0 |

| 予約済み   |    |    |    | INIT_1 |    |   |   |

| R/W-0h |    |    |    |        |    |   |   |

図 8-9. レジスタ 04h のフィールドの説明

| ビット | フィールド  | タイプ | リセット | 概要                                                                      |

|-----|--------|-----|------|-------------------------------------------------------------------------|

| 3-0 | INIT_1 | R/W | 0h   | デバイス初期化の INIT_1 フィールド。初期化シーケンスの間に 1011b を書き込みます。通常動作の場合は 0000b を書き込みます。 |

### 8.1.6 レジスタ 06h (オフセット = 6h) [リセット = 2h]

図 8-10. レジスタ 06h

|                  |    |    |    |    |    |   |   |

|------------------|----|----|----|----|----|---|---|

| 15               | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| REG_00H_READBACK |    |    |    |    |    |   |   |

| R-0h             |    |    |    |    |    |   |   |

| 7                | 6  | 5  | 4  | 3  | 2  | 1 | 0 |

| REG_00H_READBACK |    |    |    |    |    |   |   |

| R-5h             |    |    |    |    |    |   |   |

図 8-11. レジスタ 06h のフィールドの説明

| ビット  | フィールド            | タイプ | リセット | 概要                                                                                                                                    |

|------|------------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------|

| 15-0 | REG_00H_READBACK | R   | 2h   | このレジスタは、読み戻しのためのレジスタ アドレス 0x00 のコピーです。レジスタ アドレス 0x00 は書き込み専用です。レジスタ 読み出しには、アドレス 0x00 の SPI_RD_EN を 1 に設定する必要があるため、デフォルトの読み戻し値は 2h です。 |

## 8.2 レジスタ バンク 1

図 8-12. レジスタ バンク 1 マップ

| 追加  | D15  | D14         | D13    | D12                | D11  | D10                   | D9         | D8         | D7        | D6                     | D5          | D4        | D3       | D2   | D1   | D0     |

|-----|------|-------------|--------|--------------------|------|-----------------------|------------|------------|-----------|------------------------|-------------|-----------|----------|------|------|--------|

| 0Dh | 予約済み | DATA_FORMAT |        | 予約済み               |      | LAT_INC               | GE_CAL_EN1 | OSR_EN     |           |                        | OSR         |           |          |      | 予約済み |        |

| 10h |      |             |        | 予約済み               |      |                       |            |            |           |                        |             |           |          |      |      | HIFREQ |

| 12h |      |             |        | 予約済み               |      |                       |            |            | XOR_EN    |                        | DATA_LANES  |           |          |      |      |        |

| 13h |      |             |        | 予約済み               |      |                       |            | RAMP_INC_A |           |                        | TP_MODE_CHA | TP_EN_CHA |          | 予約済み |      |        |

| 14h |      |             |        |                    |      | TP0_A                 |            |            |           |                        |             |           |          |      |      |        |

| 15h |      |             |        | TP1_A              |      |                       |            |            |           | TP0_A                  |             |           |          |      |      |        |

| 16h |      |             |        |                    |      | TP1_A                 |            |            |           |                        |             |           |          |      |      |        |

| 18h |      |             |        | 予約済み               |      |                       |            | RAMP_INC_B |           |                        | TP_MODE_CHB | TP_EN_CHB |          | 予約済み |      |        |

| 19h |      |             |        |                    |      | TP0_B                 |            |            |           |                        |             |           |          |      |      |        |

| 1Ah |      |             |        | TP1_B              |      |                       |            |            |           | TP0_B                  |             |           |          |      |      |        |

| 1Bh |      |             |        |                    |      | TP1_B                 |            |            |           |                        |             |           |          |      |      |        |

| 1Ch |      |             |        | USER_BITS_ADC_B    |      |                       |            |            |           | USER_BITS_ADC_A        |             |           |          |      |      |        |

| 33h | 予約済み | GE_CAL_EN3  |        | 予約済み               |      |                       | GE_CAL_EN2 |            |           | 予約済み                   |             |           |          |      |      |        |

| 34h |      |             |        | 予約済み               |      |                       |            | LAT_EN     |           | 予約済み                   |             |           |          |      |      |        |

| 90h | 予約済み | TS_LD       |        |                    |      |                       | 予約済み       |            |           |                        |             |           |          |      |      |        |

| 91h |      |             |        | 予約済み               |      |                       |            |            |           | TEMPERATURE_SENSOR     |             |           |          |      |      |        |

| C0h | 予約済み |             | CLK1   | OSR_INIT1          |      |                       | OSR_CLK    |            |           | 予約済み                   |             |           | PD_CH    |      |      |        |

| C1h | 予約済み |             | PD_REF |                    | 予約済み | DATA_RATE             |            |            |           | 予約済み                   |             |           |          | CLK2 |      |        |

| C4h |      |             |        | 予約済み               |      |                       |            |            | OSR_INIT2 |                        | 予約済み        | OSR_INIT3 | PD_CHI_P |      |      |        |

| C5h | 予約済み | HIFREQ_EN   |        | 予約済み               | CLK3 |                       | 予約済み       |            | RD_CLK    | 予約済み                   | CLK4        |           | 予約済み     |      |      |        |

| FBh |      |             |        | 予約済み               |      |                       |            |            |           | NCO_SY_SREF            | XOR_MODE    | CLK5      | MIXER_EN |      |      |        |

| FCh |      |             |        |                    |      | NCO_PHASE_COUNT[15:0] |            |            |           |                        |             |           |          |      |      |        |

| FDh |      |             |        | NCO_FREQUENCY[7:0] |      |                       |            |            |           | NCO_PHASE_COUNT[23:16] |             |           |          |      |      |        |

| FEh |      |             |        |                    |      | NCO_FREQUENCY[23:8]   |            |            |           |                        |             |           |          |      |      |        |

表 8-2. レジスタ セクション / ブロック アクセス タイプ コード

| アクセス タイプ      | 表記  | 概要               |

|---------------|-----|------------------|

| R             | R   | 読み出し             |

| W             | W   | 書き込み             |

| R/W           | R/W | 読み出しましたは書き込み     |

| リセットまたはデフォルト値 |     |                  |

| -n            |     | リセット後の値またはデフォルト値 |

### 8.2.1 レジスタ 0Dh (オフセット = Dh) [リセット = 2002h]

図 8-13. レジスタ 0Dh

|            |             |        |    |    |         |   |   |

|------------|-------------|--------|----|----|---------|---|---|

| 15         | 14          | 13     | 12 | 11 | 10      | 9 | 8 |

| 予約済み       | DATA_FORMAT | 予約済み   |    |    | LAT_INC |   |   |

| R/W-0h     | R/W-1h      | R/W-0h |    |    | R/W-0h  |   |   |

| 7          | 6           | 5      | 4  | 3  | 2       | 1 | 0 |

| GE_CAL_EN1 | OSR_EN      | OSR    |    |    | 予約済み    |   |   |

| R/W-0h     | R/W-0h      | R/W-0h |    |    | R/W-2h  |   |   |

図 8-14. レジスタ 0Dh のフィールドの説明

| ビット   | フィールド       | タイプ | リセット | 概要                                                                                  |