# AWR2944P/AWR2E44P/AWR2944-ECO/AWR2E44-ECO/AWR2944LC/AWR2E44LC シン グルチップ 76~81GHz FMCW 車載レーダー センサ

## 1 特長

- FMCW レーダー

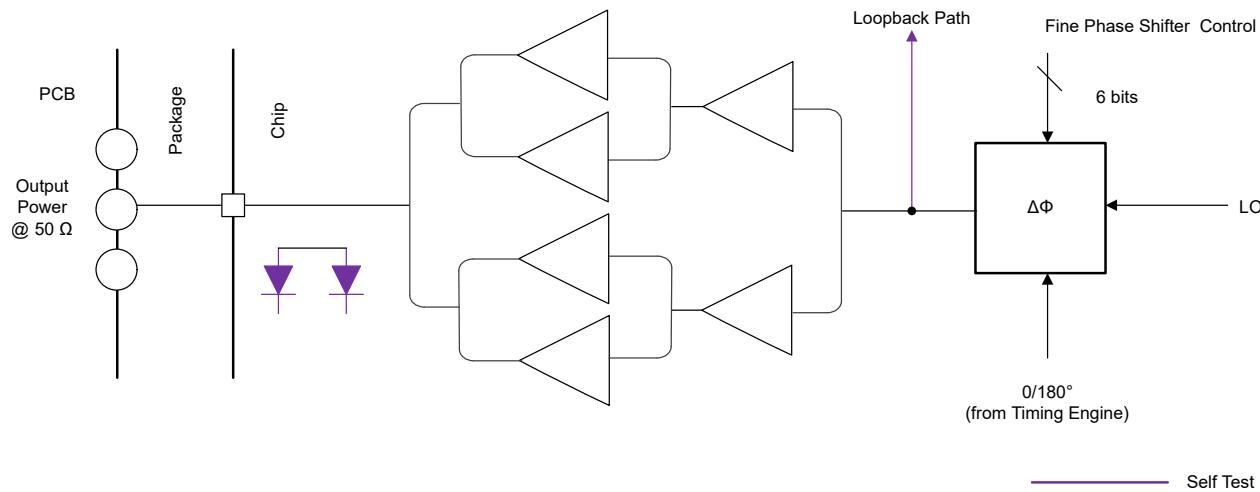

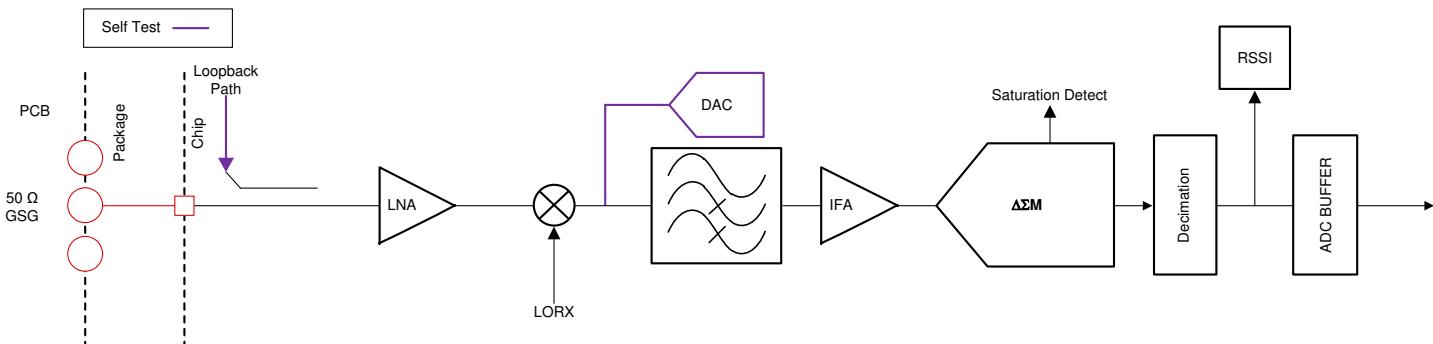

- PLL、トランシミッタ、レシーバ、ベースバンド、ADC を内蔵

- 76GHz ~ 81GHz の周波数帯をカバーし、5GHz の有効 BW を備えた 4 個の送信チャネルと 4 個の受信チャネルを提供

- AWR2944P/AWR2944-ECO/AWR2944LC: アンテナへの PCB インターフェイス

- AWR2E44P/AWR2E44-ECO/AWR2E44LC: アンテナに対するローンチ オン パッケージ (LOP) インターフェイス

- 送信用位相シフタ

- フラクショナル-N PLL による超高精度チャーブ エンジン

- TX 出力

- AWR2944P: 14dBm

- AWR2944-ECO/AWR2944LC: 13.5dBm

- AWR2E44P: 13.5dBm

- AWR2E44-ECO/AWR2E44LC: 12.5dBm

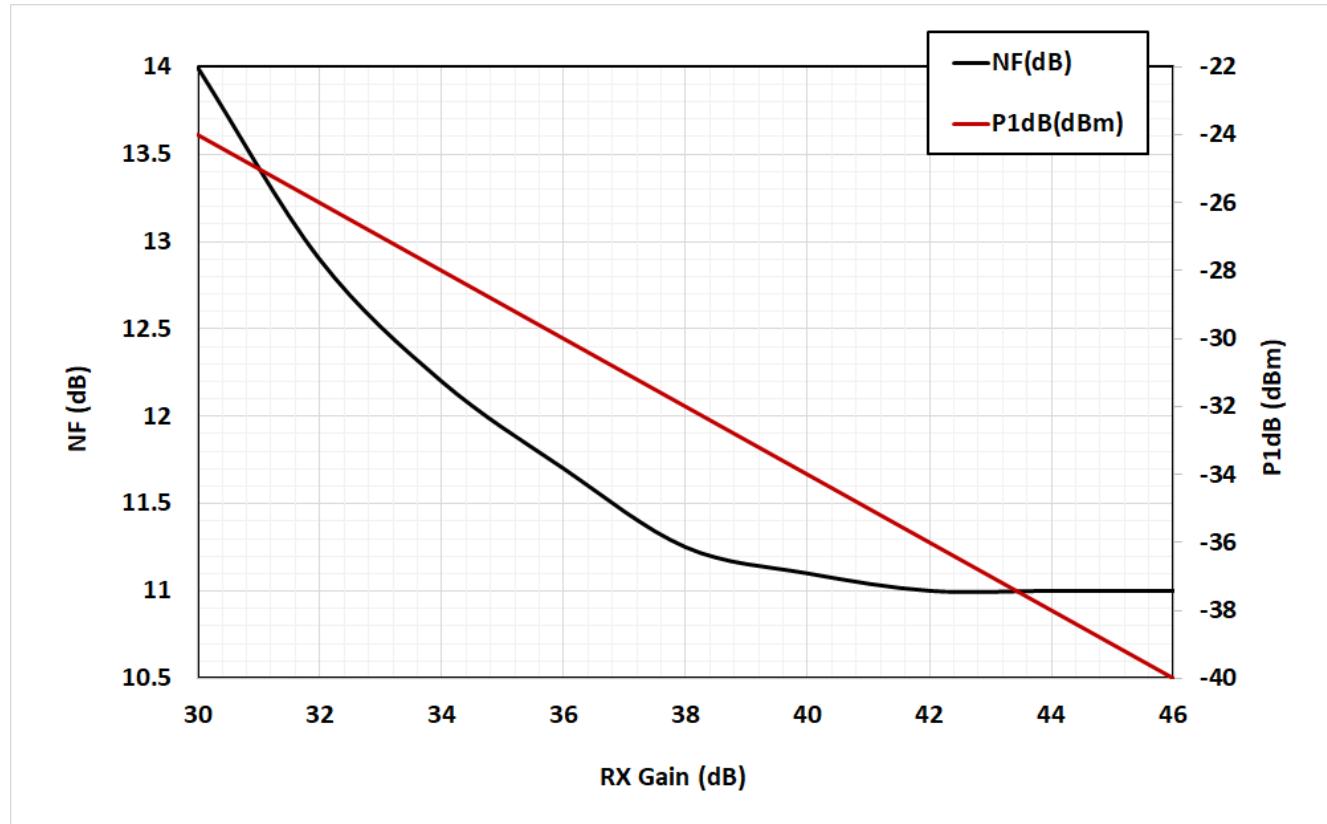

- RX ノイズ指数

- AWR2944P: 10.5dB

- AWR2944-ECO/AWR2944LC: 12dB

- AWR2E44P: 11dB

- AWR2E44-ECO/AWR2E44LC: 12.5dB

- 1MHz での位相ノイズ

- VCO1: -96dBc/Hz (76~77GHz)

- VCO2: -95dBc/Hz (76~81GHz)

- 処理部品

- 400MHz で動作する Arm® Cortex-R5F® コア (ロック ステップ動作をサポート)

- 450MHz で動作する、テキサス・インスツルメンツのデジタル信号プロセッサ C66x

2944LC および AWR2E44LC には該当しません

- FFT、対数振幅、メモリ圧縮などの動作向け、TI のレーダー ハードウェア アクセラレータ (HWA2.1)

- データ移動用の複数の EDMA インスタンス

- Arm® Cortex-M4 を使用した、プログラマブルな組み込みハードウェア セキュリティ モジュール (HSM)

- DSS (DSP サブシステム) 内の 2 番目の Arm® Cortex M4 コアが、HWA2.1 の制御および構成を担当

- 機能安全準拠製品向け

- 機能安全アプリケーション向けに開発

- ISO 26262 機能安全システム設計を支援するドキュメントを準備中

- ASIL B までを対象とするハードウェア インテグリティ

- ユーザー アプリケーションで利用可能なその他のインターフェイス (特定の品番に限る)

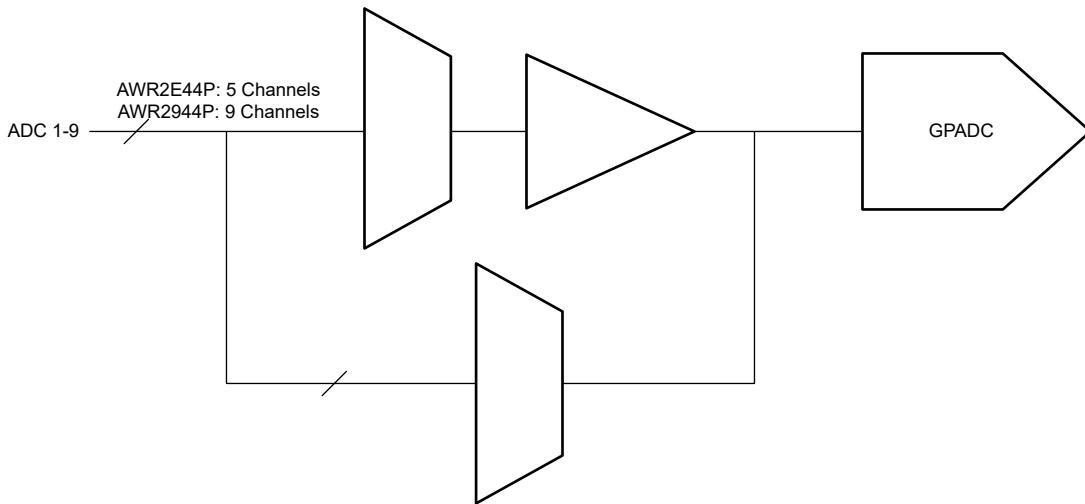

- デバイスバリエントに基づいて最大 9 つの ADC チャネル

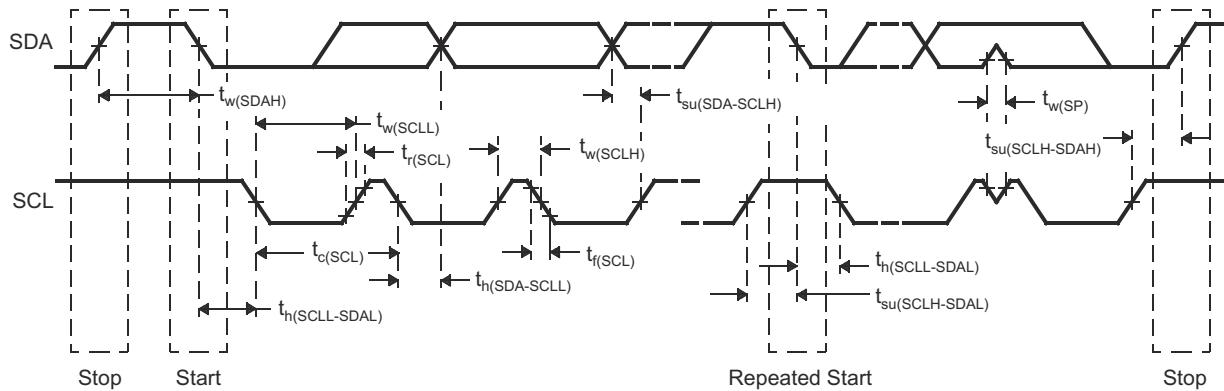

- 2 つの SPI | 4 つの UART | I<sup>2</sup>C | GPIO | 3 つの EPWM

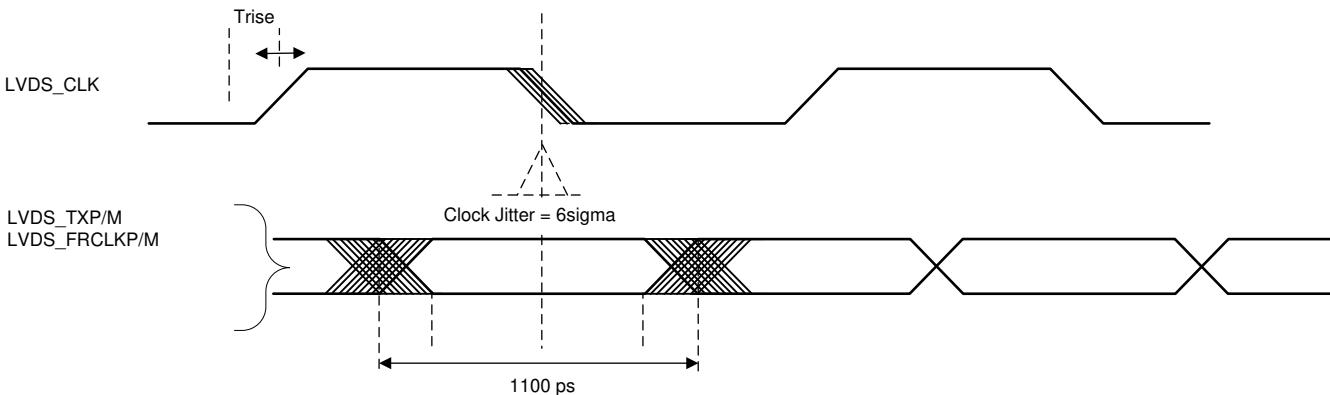

- 未加工 ADC データおよびデバッグ計測機器向け 4 レーン Aurora LVDS インターフェイス

- 2 レーンの CSI2 Rx でキャプチャされたデータの再生が可能

- オンチップ RAM (DSP、MCU、および共有 L3 に分割)

- 3MB ~ 4.5MB のオンチップ RAM (AWR2944P/AWR2E44P: 4.5MB, AWR2944-ECO/AWR2E44-ECO: 4MB, AWR2944LC//AWR2E44LC: 3MB)

- ホストインターフェイス

- 2 個の CAN-FD

- 10/100/1000Mbps イーサネット

- AWR2944-ECO/AWR2E44-ECO 向けの 10/100Mbps

- AWR2944LC/AWR2E44LC には適用されません

- シリアル フラッシュ メモリ インターフェイスをサポート (QSPI フラッシュ メモリからのユーザー アプリケーションのロード)

- デバイスのセキュリティ (一部の型番のみ)

- セキュア認証および暗号化ポートのサポート

- 顧客がプログラム可能なルートキー、対称キー (256 ビット)、非対称キー (RSA-4K または ECC-512 まで)、キー失効機能付き

- 暗号化ハードウェア アクセラレータ: ECC 付き PKA、AES (最大 256 ビット)、SHA (最大 512 ビット)、TRNG/DRBG、および SM2、SM3、SM4 (中国語暗号化アルゴリズム)

- 内蔵ファームウェア (ROM) およびプロセスと温度全体のセルフ キャリブレーション システム

- AEC-Q100 認定済み

- 高度な機能

- 外部プロセッサの関与を必要としない自己監視機能を内蔵

- 干渉検出機能を内蔵

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

- パワー マネージメント

- オンダイ LDO ネットワークにより PSRR の向上を実現

- LVC MOS IO は 3.3V、1.8V のデュアル電圧に対応

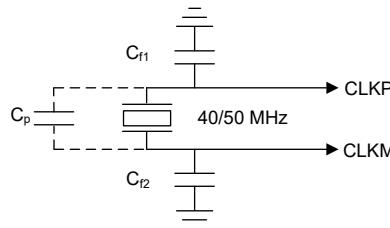

- クロック ソース

- 50/40MHz の水晶振動子と内部発振器

- 50/40MHz の外部駆動発振器またはクロック (方形波 / 正弦波) をサポート

- 50MHz クロックを使用する場合、イーサネット PHY 用の外部水晶発振器を不要にするための 25MHz 外部クロック。

- 最適なパワー マネージメント ソリューション

- 推奨される [LP87745-Q1 パワー マネージメント IC \(PMIC\)](#)

- デバイスの電源要件を満たすように特別に設計されたコンパニオン PMIC

- さまざまな使用事例をサポートするためのフレキシブルなマッピングと工場出荷時にプログラムされた構成

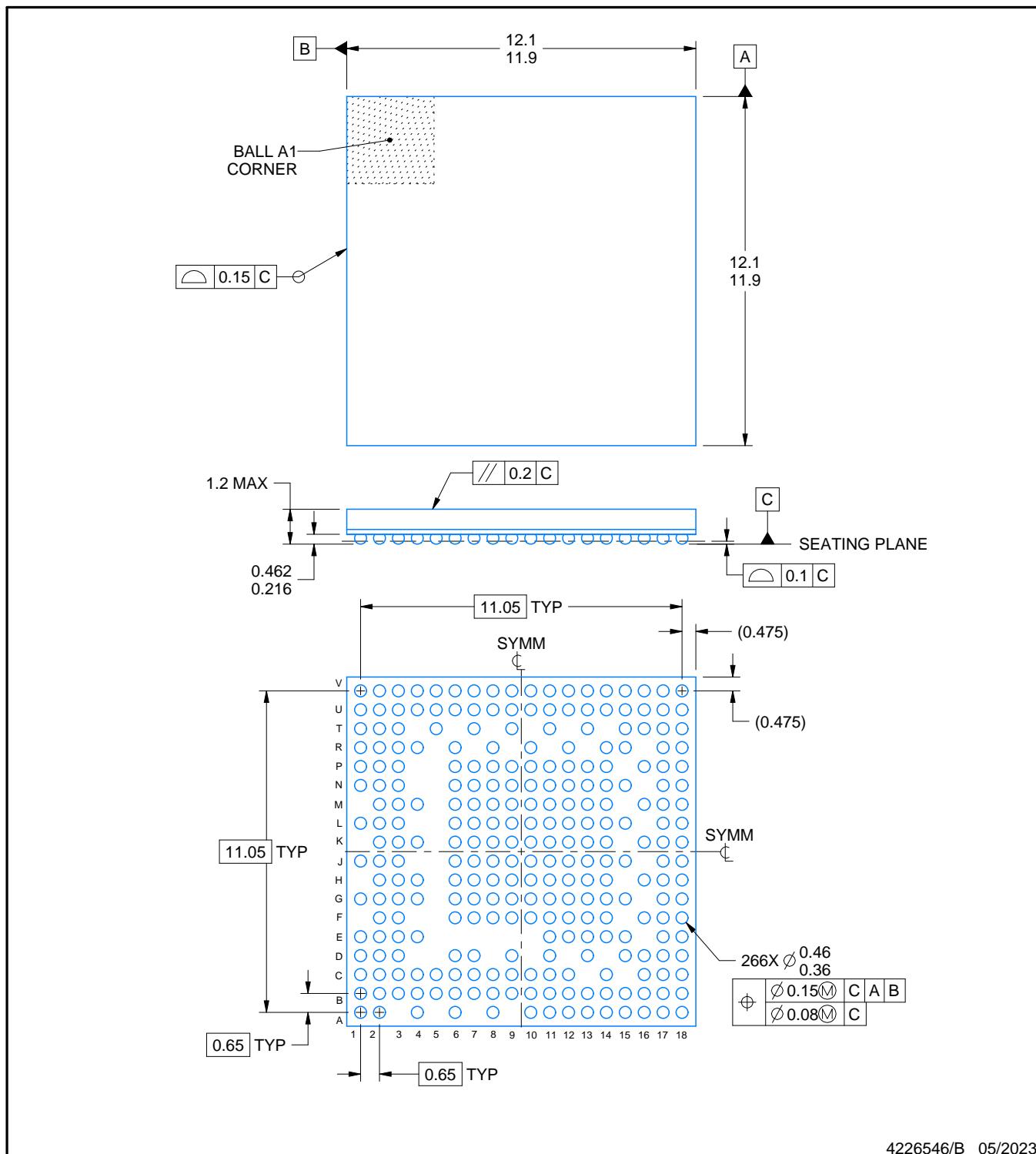

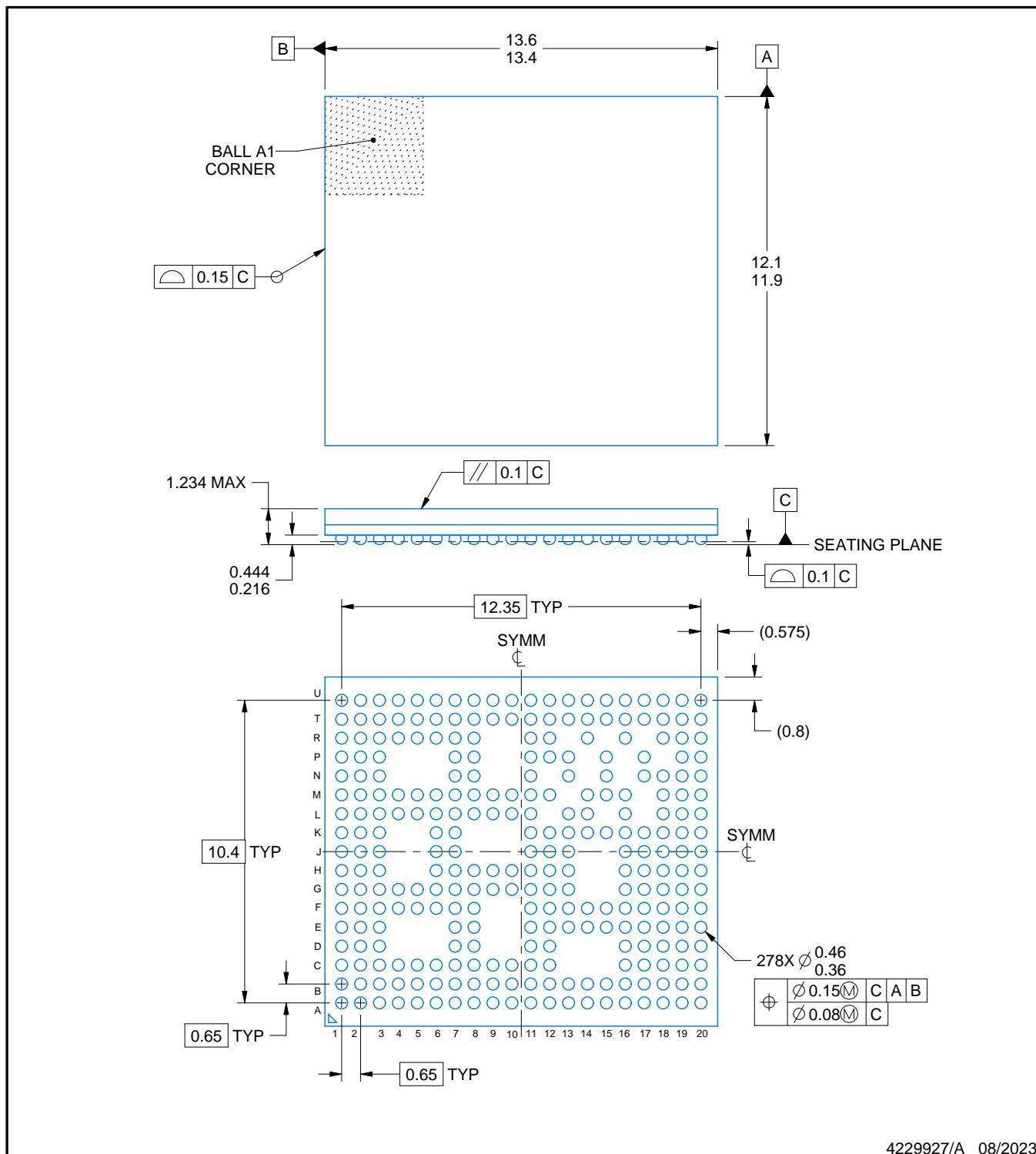

- 0.65mm ピッチの FCCSP パッケージを使用した、低コストのハードウェア設計

- AWR2944P/AWR2944-ECO/AWR2944LC: 12mm × 12mm

- AWR2E44P/AWR2E44-ECO/AWR2E44LC: 13.5mm × 12mm

- 車載接合部温度の動作範囲 -40°C~140°C をサポート

## 2 アプリケーション

- コーナーレーダー

- 前方および後方カメラ

- 車線変更支援

- 死角検出

- 自動緊急ブレーキ

- アダプティブ クルーズ コントロール

- クロストラフィック アラート

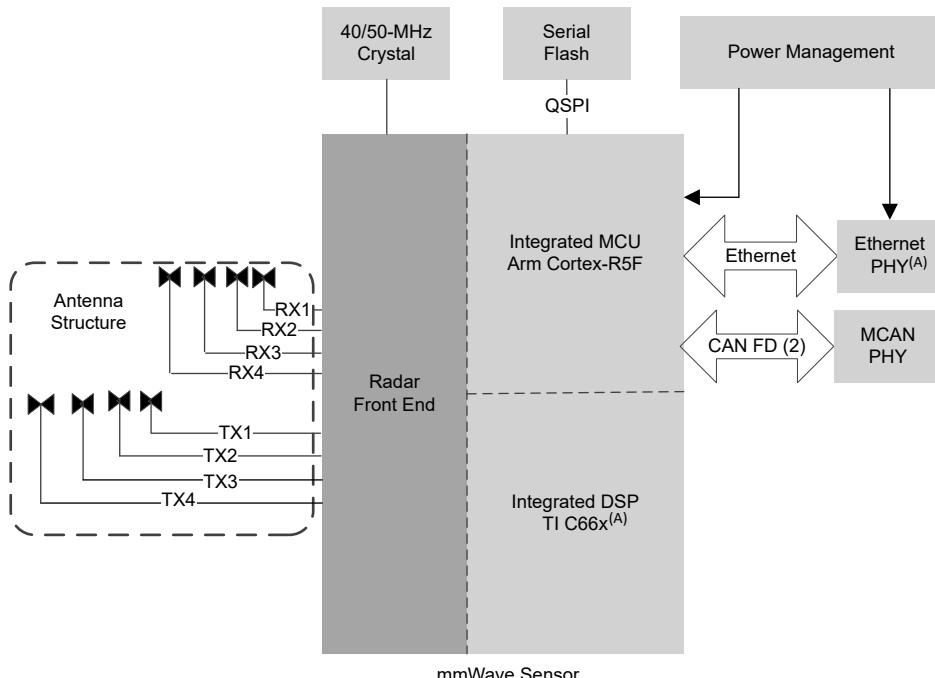

図 2-1. 車載アプリケーション用の自律レーダー センサ

### 注

A. DSP とイーサネットは、一部の型番で利用可能です。詳細については、[セクション 4](#) を参照してください

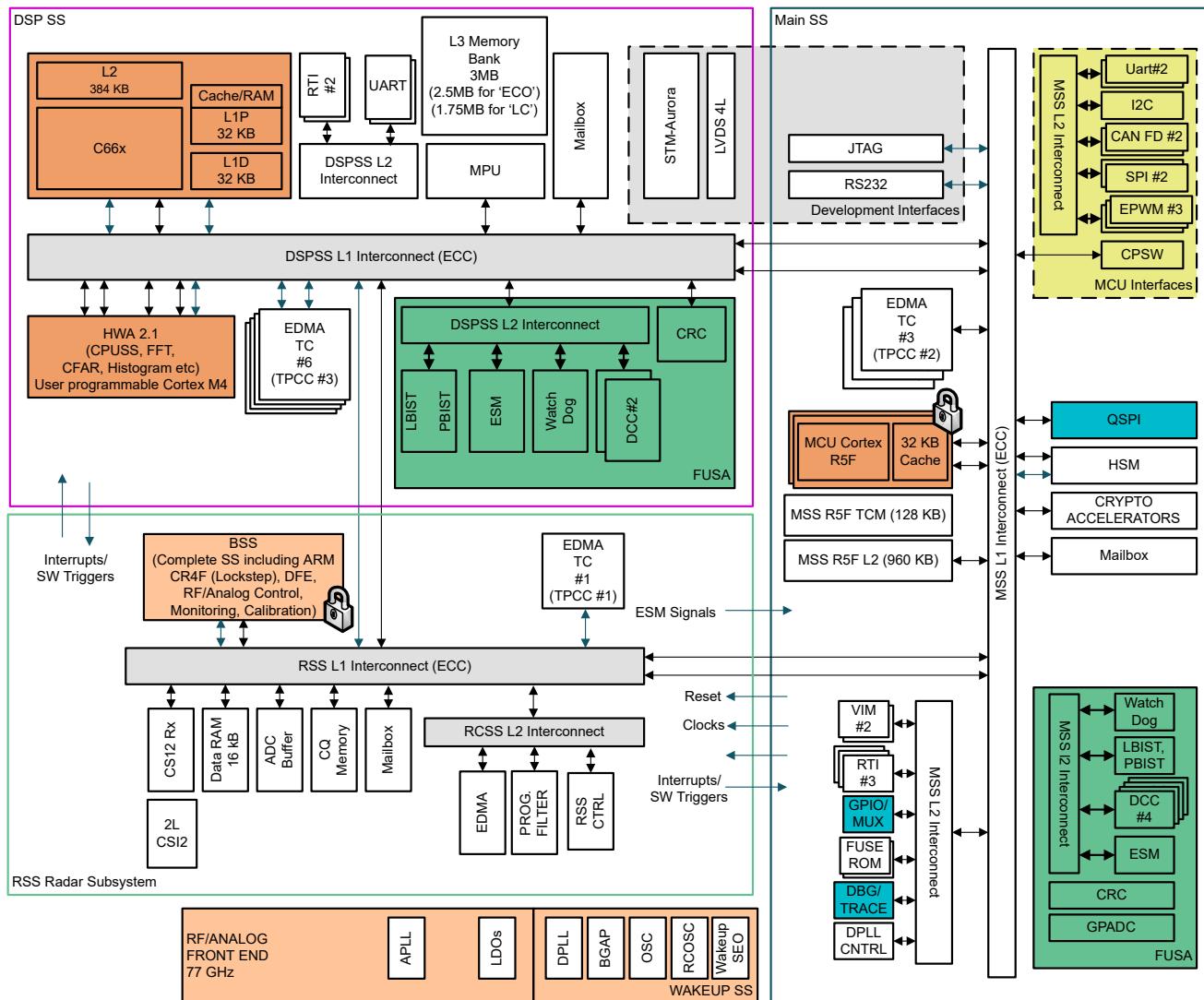

### 3 説明

AWR2944P/AWR2E44P は **AWR2944** 製品ラインアップの高性能版で、強化された RF とコンピューティング性能で NCAP と自動運転の要件を満たします。AWR2944-ECO/AWR2E44-ECO と AWR2944LC/AWR2E44LC は、それぞれメインストリーム品と機能最適化品であり、同一ファミリ内で P、ECO、LC デバイス間のスケーラブルな製品展開を可能にします。AWR2944P、AWR2E44P、AWR2944-ECO、AWR2E44-ECO、AWR2944LC、AWR2E44LC は、76～81GHz 帯で動作可能な FMCW トランシーバ、レーダー データ処理要素、および車載ネットワーク用のペリフェラル機能を統合した單一チップのミリ波センサーです。このレーダー センサーは、TI の低消費電力 45nm RFCMOS プロセスで製造されており、RF および演算性能を強化する設計により、小型フォームファクタと最小限の BOM で、これまでにない統合レベルを実現しています。**AWR2944P/AWR2E44P/AWR2944-ECO/AWR2E44-ECO/AWR2944LC/AWR2E44LC** デバイスは、自動車分野における低消費電力、自己監視型、超高精度レーダー システム向けに設計されています。

AWR2E44P、AWR2E44-ECO、および AWR2E44LC バリアントは、アンテナをパッケージ上に直接実装可能とする優れたローンチ オン パッケージ (LOP) アンテナ機能を備えており、顧客に対して高い実装柔軟性を提供します。LOP テクノロジーを使用すると、PCB の穴を経由して AWR2E44P/AWR2E44-ECO/AWR2E44LC チップの底面から発する信号をアンテナに損失なく送信することができます。チップとアンテナは PCB に直接半田付けされているため、高価な高周波材料の代わりに、低コストの PCB 材料を使用できます。

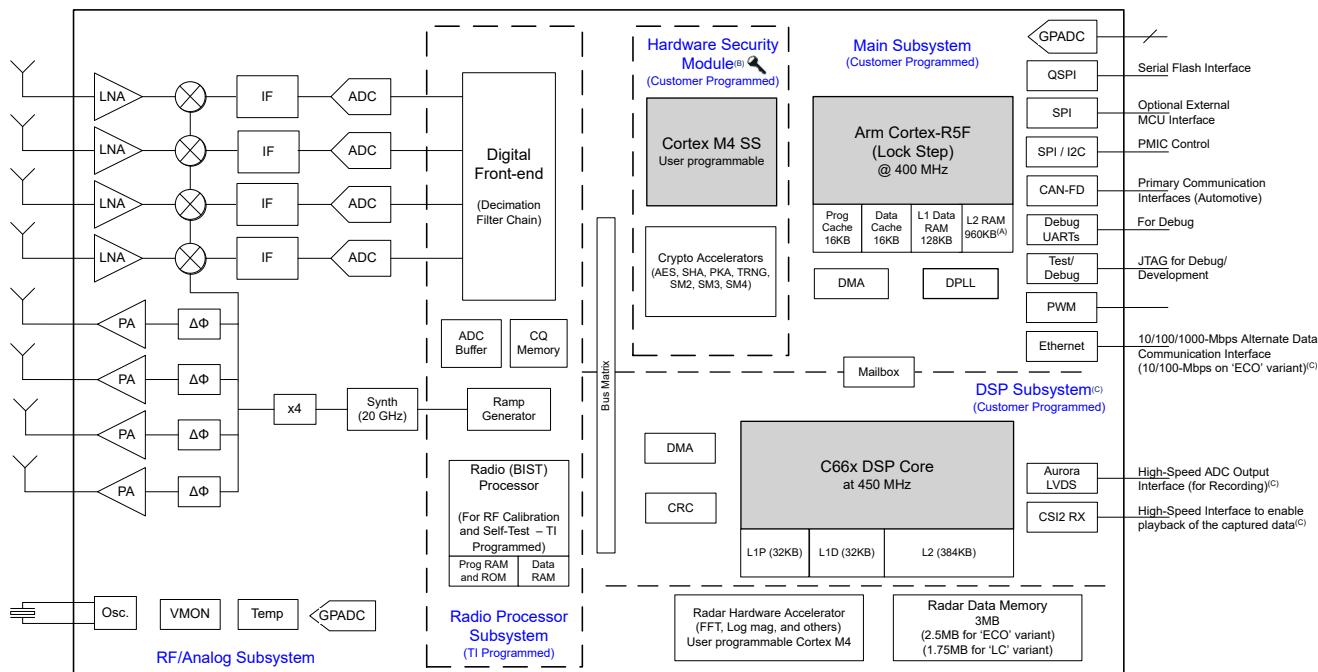

テキサス・インスツルメンツの低消費電力 45nm RFCMOS プロセスにより、PLL、VCO、ミキサ、ベースバンド ADC を内蔵し、4 個の TX、4 個の RX を備えたシステムのモノリシック実装が可能になります。DSP サブシステム (DSS) には、テキサス・インスツルメンツのレーダー信号処理用高性能 C66x DSP が組み込まれています。このデバイスは、レーダー フロントエンドの構成、制御、較正を行う、無線プロセッサ サブシステムも備えています。メイン サブシステム (MSS) 内には、ユーザーによるプログラムが可能な Arm Cortex-R5F プロセッサが実装されており、カスタム制御アプリケーションや車載用インターフェイス アプリケーションに使用できます。ハードウェア アクセラレータ ブロック (HWA 2.1) は、FFT、CFAR (Constant False Alarm Rate、一定誤警報率)、スケーリング、圧縮などの一般的なレーダー処理を負荷分担して、DSS と MSS を補完します。これにより DSS と MSS の MIPS が軽減され、カスタム アプリケーションや高度なアルゴリズムのためにリソースが使えるようになります。

ハードウェア セキュリティ モジュール (HSM) もこのデバイスに用意されています (セキュア部品バリアントのみで使用可能)。HSM は、プログラム可能な Arm Cortex-M4 コアと、デバイス内でセキュアな動作ゾーンを実現するために必要なインフラで構成されます。

AWR2944P/AWR2E44P/AWR2944-ECO/AWR2E44-ECO/AWR2944LC/AWR2E44LC は、ハードウェア アクセラレータ モジュール (HWA 2.1) の設定および制御を行うための Cortex-M4 プロセッサも搭載しています。

プログラミング モデルを変更するだけで、さまざまなセンサ (短距離、中距離、長距離) を実装でき、マルチモード センサの実装においては動的再構成にも対応します。

また、**AWR2944P/AWR2E44P/AWR2944-ECO/AWR2E44-ECO/AWR2944LC/AWR2E44LC** は、TI のハードウェア およびソフトウェアのリファレンス デザイン、ソフトウェア ドライバ、構成例、API ガイド、ユーザー マニュアルを含む完全なプラットフォーム デバイスとして提供しています。

#### 製品情報

| 部品番号             | パッケージ <sup>(1)</sup> | パッケージ サイズ (公称) <sup>(2)</sup> | バリアント          |

|------------------|----------------------|-------------------------------|----------------|

| AWR2944PBGALTRQ1 | ALT (FCCSP、266)      | 12mm × 12 mm                  | AWR2944P       |

| AWR2944PBSALTRQ1 | ALT (FCCSP、266)      | 12mm × 12 mm                  | AWR2944P HS    |

| AWR2944EBGALTRQ1 | ALT (FCCSP、266)      | 12mm × 12 mm                  | AWR2944-ECO    |

| AWR2944EBSALTRQ1 | ALT (FCCSP、266)      | 12mm × 12 mm                  | AWR2944-ECO HS |

| AWR2E44PBGAMXRQ1 | AMX (FCCSP、278)      | 13.5 mm × 12mm                | AWR2E44P       |

| AWR2E44PBSAMXRQ1 | AMX (FCCSP、278)      | 13.5 mm × 12mm                | AWR2E44P HS    |

製品情報 (続き)

| 部品番号             | パッケージ <sup>(1)</sup> | パッケージ サイズ (公称) <sup>(2)</sup> | バリアント          |

|------------------|----------------------|-------------------------------|----------------|

| AWR2E44EBGAMXRQ1 | AMX (FCCSP, 278)     | 13.5 mm × 12mm                | AWR2E44-ECO    |

| AWR2E44EBSAMXRQ1 | AMX (FCCSP, 278)     | 13.5 mm × 12mm                | AWR2E44-ECO HS |

| AWR2944LBGALTRQ1 | ALT (FCCSP, 266)     | 12mm × 12 mm                  | AWR2944LC      |

| AWR2944LBSALTRQ1 | ALT (FCCSP, 266)     | 12mm × 12 mm                  | AWR2944LC HS   |

| AWR2E44LBGAMXRQ1 | AMX (FCCSP, 278)     | 13.5 mm × 12mm                | AWR2E44LC      |

| AWR2E44LBSAMXRQ1 | AMX (FCCSP, 278)     | 13.5 mm × 12mm                | AWR2E44LC HS   |

(1) 詳細については、[セクション 13](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

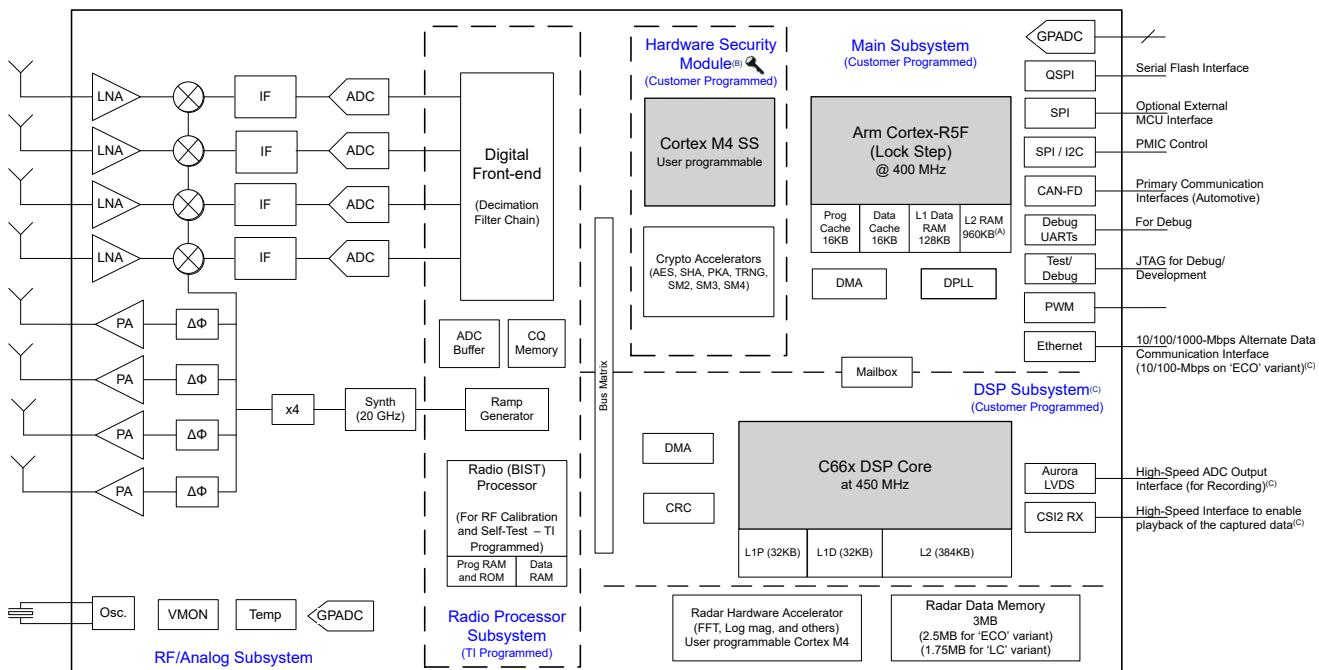

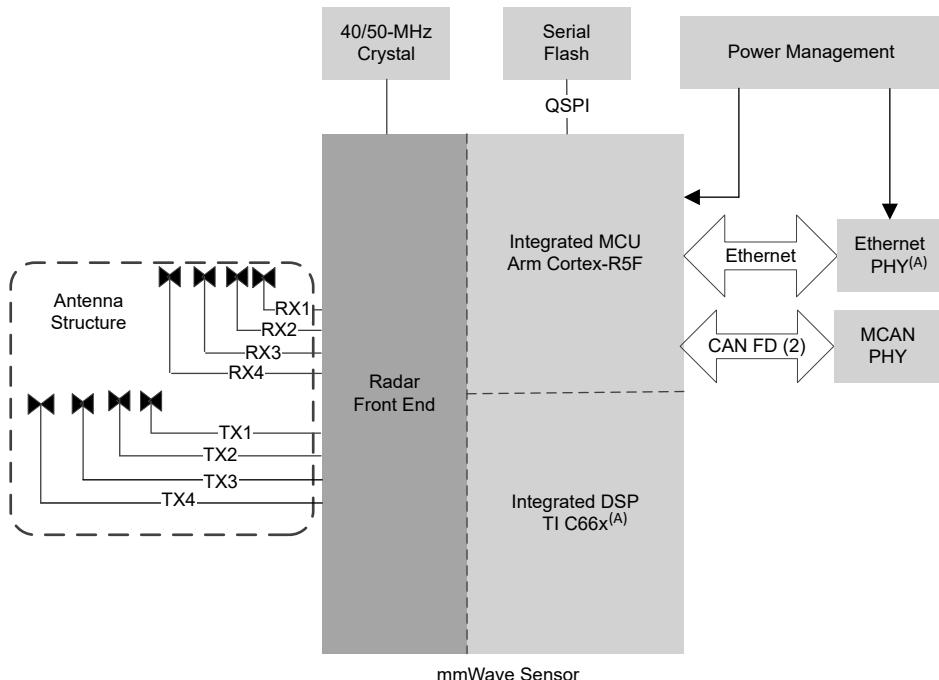

### 3.1 機能ブロック図

図 3-1 は、デバイスの機能ブロック図です。

図 3-1. 機能ブロック図

- A. アプリケーションの使用用途に応じて、構成可能なメモリはレーダー データ用メモリからメイン Cortex-R5F のプログラムおよびデータ RAM に切り替えることができます。

- B. この機能は、セクション 3「製品情報」表の「デバイス タイプ」識別子で示されているように、一部の部品バリエーションでのみ使用できます。

- C. この機能は、AWR2944LC および AWR2E44LC のバリエーションでは利用できません。

## 目次

|                                                |    |                          |    |

|------------------------------------------------|----|--------------------------|----|

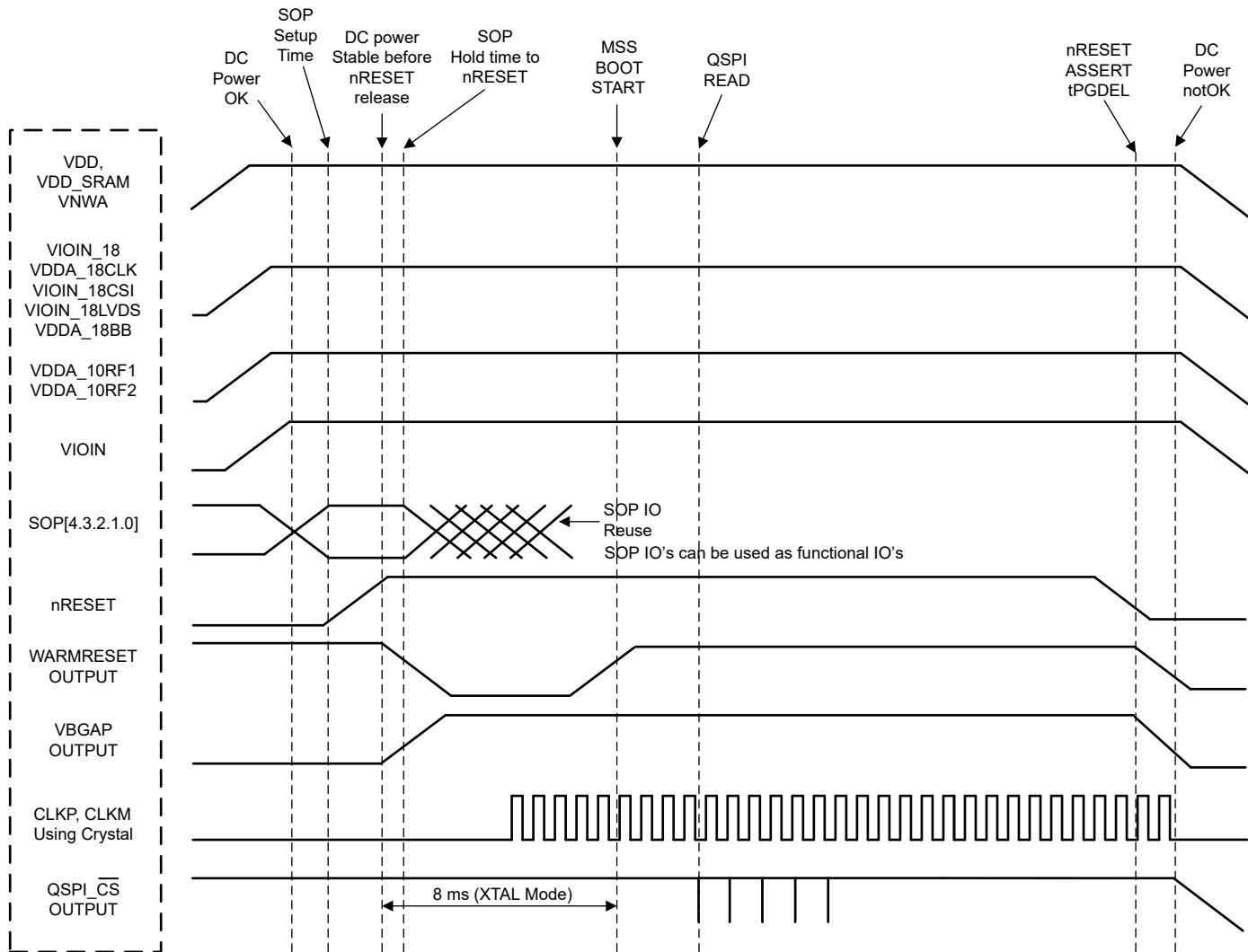

| 1 特長                                           | 1  | 7.10 電源シーケンスおよびリセットタイミング | 46 |

| 2 アプリケーション                                     | 2  | 7.11 入力クロックおよび発振器        | 47 |

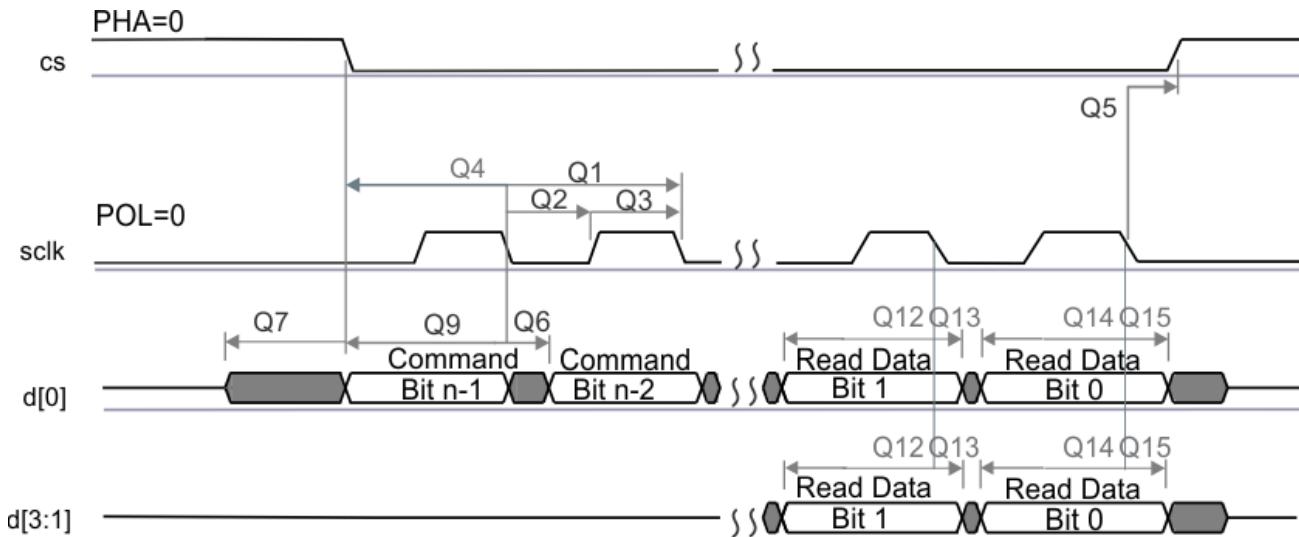

| 3 説明                                           | 3  | 7.12 ペリフェラル情報            | 48 |

| 3.1 機能ブロック図                                    | 5  | 7.13 エミュレーションおよびデバッグ     | 71 |

| 4 デバイスの比較                                      | 7  | 8 詳細説明                   | 74 |

| 5 関連製品                                         | 9  | 8.1 概要                   | 74 |

| 6 ピン構成および機能                                    | 10 | 8.2 機能ブロック図              | 74 |

| 6.1 ピン配置図 - AWR2944P/AWR2944-ECO/<br>AWR2944LC | 10 | 8.3 サブシステム               | 75 |

| 6.2 ピン配置図 - AWR2E44P/AWR2E44-ECO/<br>AWR2E44LC | 11 | 8.4 その他のサブシステム           | 79 |

| 6.3 ピン属性                                       | 12 | 9 監視と診断                  | 81 |

| 6.4 信号の説明 - デジタル                               | 25 | 9.1 監視と診断のメカニズム          | 81 |

| 6.5 信号の説明 - アナログ                               | 34 | 10 アプリケーション、実装、およびレイアウト  | 84 |

| 7 仕様                                           | 38 | 10.1 アプリケーション情報          | 84 |

| 7.1 絶対最大定格                                     | 38 | 10.2 短距離、中距離、長距離のレーダー    | 84 |

| 7.2 ESD 定格                                     | 38 | 10.3 リファレンス回路図           | 84 |

| 7.3 電源投入時間 (POH)                               | 39 | 11 デバイスおよびドキュメントのサポート    | 85 |

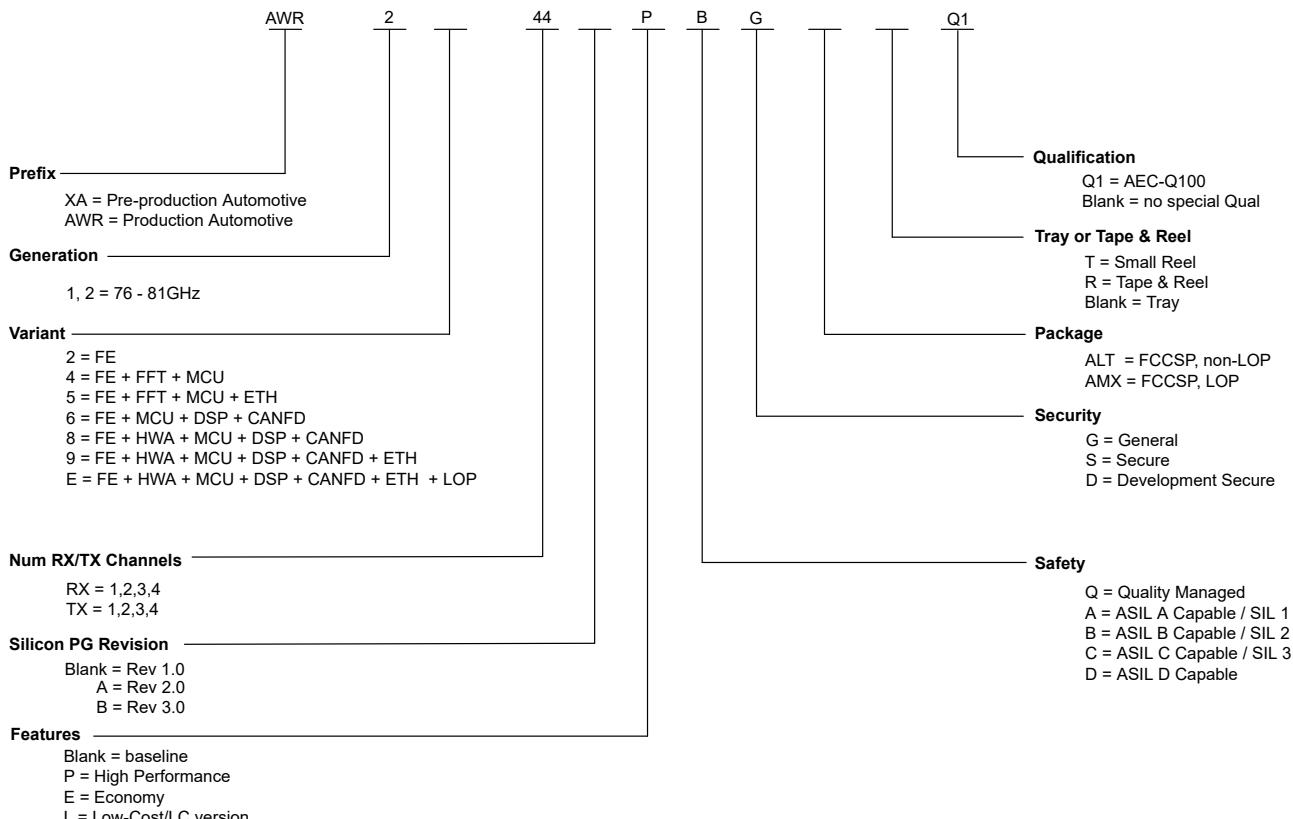

| 7.4 推奨動作条件                                     | 39 | 11.1 デバイスの命名規則           | 86 |

| 7.5 ワンタイムプログラマブル (OTP) eFuse の VPP 仕<br>様      | 40 | 11.2 ツールとソフトウェア          | 87 |

| 7.6 電源仕様                                       | 41 | 11.3 ドキュメントのサポート         | 87 |

| 7.7 消費電力の概略                                    | 42 | 11.4 サポート・リソース           | 87 |

| 7.8 RF の仕様                                     | 43 | 11.5 商標                  | 87 |

| 7.9 熱抵抗特性                                      | 45 | 11.6 静電気放電に関する注意事項       | 88 |

|                                                |    | 11.7 用語集                 | 88 |

|                                                |    | 12 改訂履歴                  | 88 |

|                                                |    | 13 メカニカル、パッケージ、および注文情報   | 89 |

## 4 デバイスの比較

表 4-1. デバイスの機能の比較

| 機能                                                         | AWR2944P              | AWR2E44P              | AWR2944-ECO           | AWR2E44-ECO           | AWR2944LC             | AWR2E44LC             | AWR2544           | AWR2944             |

|------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------|---------------------|

| Launch on Package (LOP) アンテナ                               | —                     | あり                    | —                     | あり                    | —                     | あり                    | あり                | —                   |

| レシーバの数                                                     | 4                     | 4                     | 4                     | 4                     | 4                     | 4                     | 4                 | 4                   |

| トランスマッタの数                                                  | 4                     | 4                     | 4                     | 4                     | 4                     | 4                     | 4                 | 4                   |

| オンチップ メモリ                                                  | 4.5MB                 | 4.5MB                 | 4MB                   | 4MB                   | 3MB                   | 3MB                   | 2MB               | 4MB                 |

| 最大 I/F (中間周波数) (MHz)                                       | 20                    | 20                    | 20                    | 20                    | 20                    | 20                    | 20                | 15                  |

| 最大実数 / 複素数 2x サンプリング レート (MSPS)                            | 45 <sup>(1)</sup>     | 45 <sup>(1)</sup> | 37.5 <sup>(1)</sup> |

| セーフティおよびセキュリティ <sup>(2)</sup>                              |                       |                       |                       |                       |                       |                       |                   |                     |

| デバイスのセキュリティ <sup>(3)</sup>                                 | あり                    | あり                    | あり                    | あり                    | あり                    | あり                    | あり                | あり                  |

| AEC-Q100 認定済み                                              | あり                    | あり                    | あり                    | あり                    | あり                    | あり                    | あり                | あり                  |

| プロセッサ                                                      |                       |                       |                       |                       |                       |                       |                   |                     |

| MCU (RxF)                                                  | あり                    | あり                    | あり                    | あり                    | あり                    | あり                    | あり                | あり                  |

| DSP (C6xx)                                                 | あり <sup>(4)</sup>     | あり <sup>(4)</sup>     | あり <sup>(4)</sup>     | あり <sup>(4)</sup>     | —                     | —                     | —                 | あり <sup>(4)</sup>   |

| ハードウェア アクセラレータ <sup>(6)</sup>                              | HWA2.1 <sup>(5)</sup> | HWA1.5            | HWA2.1              |

| HWA 制御向けの DSS_M4                                           | あり                    | あり                    | あり                    | あり                    | あり                    | あり                    | —                 | —                   |

| ハードウェア セキュリティ モジュール (HSM) <sup>(7)</sup><br><sup>(8)</sup> | あり                    | あり                    | あり                    | あり                    | あり                    | あり                    | あり                | あり                  |

| セキュリティ アクセラレータ <sup>(7)</sup>                              | あり                    | あり                    | あり                    | あり                    | あり                    | あり                    | あり                | あり                  |

| 周辺機器                                                       |                       |                       |                       |                       |                       |                       |                   |                     |

| シリアル ベリフェラル インターフェイス (SPI) ポート                             | 2                     | 2                     | 2                     | 2                     | 2                     | 2                     | 1                 | 2                   |

| クワッドシリアル ベリフェラル インターフェイス (QSPI)                            | あり                    | あり                    | あり                    | あり                    | あり                    | あり                    | あり                | あり                  |

| LVDS / デバッグ                                                | あり                    | あり                    | あり                    | あり                    | あり                    | あり                    | あり                | あり                  |

| Aurora 向け LVDS                                             | あり                    | あり                    | あり                    | あり                    | —                     | —                     | —                 | あり                  |

| イーサネット インターフェイス                                            | あり                    | あり                    | あり                    | あり                    | —                     | —                     | あり                | あり                  |

| イーサネット用のリファレンスクロック                                         | あり                    | あり                    | あり                    | あり                    | —                     | —                     | あり                | —                   |

| I <sup>2</sup> C (Inter-Integrated Circuit) インターフェイス       | 1                     | 1                     | 1                     | 1                     | 1                     | 1                     | 1                 | 1                   |

| CAN FD                                                     | 2                     | 2                     | 2                     | 2                     | 2                     | 2                     | —                 | 2                   |

| トレース                                                       | あり                    | あり                    | あり                    | あり                    | あり                    | あり                    | あり                | あり                  |

表 4-1. デバイスの機能の比較 (続き)

| 機能                              | AWR2944P                                        | AWR2E44P          | AWR2944-ECO       | AWR2E44-ECO       | AWR2944LC         | AWR2E44LC         | AWR2544           | AWR2944           |

|---------------------------------|-------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| ePWM                            | あり                                              | あり                | あり                | あり                | あり                | あり                | あり                | あり                |

| DMM インターフェイス                    | あり                                              | あり                | あり                | あり                | あり                | あり                | —                 | あり                |

| GPADC                           | あり <sup>(9)</sup>                               | あり <sup>(9)</sup> | あり <sup>(9)</sup> | あり <sup>(9)</sup> | あり <sup>(9)</sup> | あり <sup>(9)</sup> | あり <sup>(9)</sup> | あり <sup>(9)</sup> |

| CSI2 TX                         | —                                               | —                 | —                 | —                 | —                 | —                 | あり                | —                 |

| CSI2 RX                         | あり                                              | あり                | あり                | あり                | —                 | —                 | —                 | あり                |

| JTAG                            | あり                                              | あり                | あり                | あり                | あり                | あり                | あり                | あり                |

| チャーブごとに構成可能な Tx 位相シフタ           | あり                                              | あり                | あり                | あり                | あり                | あり                | あり                | あり                |

| 製品<br>ステー<br>タス <sup>(10)</sup> | 製品プレビュー<br>(PP)、<br>事前情報 (AI)、<br>量産データ<br>(PD) | PD                |

- (1) 実数信号専用のレシーバをサポート

- (2) 機能安全アプリケーション向けに開発された AWR2944P/ AWR2E44P/ AWR2944-ECO/ AWR2E44-ECO/ AWR2944LC/ AWR2E44LC は、ハードウェアの整合性において ASIL-B までの対応を想定しています。他のデバイスについては、各製品のデータシートを参照してください。

- (3) セキュア ブートやお客様がプログラム可能なキーなどのデバイス セキュリティ機能は、セクション 3「デバイス情報」表に記載されているデバイス タイプ識別子によって示される、特定の品番バリエントに適用されます。

- (4) DSP プロセッキング コアは、AWR1843 の C67x から C66x にアップグレードされています。

- (5) ユーザーが Arm® Cortex-M4 を使用してプログラム可能です。

- (6) ハードウェア アクセラレータは HWA2.1 にアップグレードされ、AWR1843 に比べて機能が追加されています。

- (7) セキュア部品バリエントにのみ適用できます

- (8) ユーザープログラム可能な Arm® Cortex-M4

- (9) 外部電圧監視用の専用 GPADC を搭載

- (10) 量産データの情報は、公開日の時点で最新のものです。製品は、テキサス・インスツルメンツの標準保証条件に基づく仕様に準拠しています。量産プロセスにすべてのパラメータのテストが含まれているとは限りません。

事前情報は、開発のサンプリングまたは量産開始前フェーズの新製品に関するものです。特性データおよびその他の仕様は、予告なく変更される場合があります。

## 5 関連製品

この製品ファミリまたは関連製品の他のデバイスの詳細については、以下のリンクを参照してください。

**ミリ波センサ** テキサス・インスツルメンツの最もフットプリントが小さい車載アプリケーション向けミリ波センサは、小さい電力で、距離、角度、速度を迅速かつ正確に検出します。

**車載ミリ波センサ** テキサス・インスツルメンツの車載ミリ波センサ製品ラインアップは、超高分解能、小型、低消費電力のシングルチップレーダー ソリューションに高性能レーダー フロントエンドを提供します。テキサス・インスツルメンツのスケーラブルなセンサ製品ラインアップは、すべての自動車の快適性機能から安全性機能に至るまで、あらゆる性能、アプリケーション、センサ構成に対応する ADAS システム ソリューションの設計と開発を可能にします。

## 6 ピン構成および機能

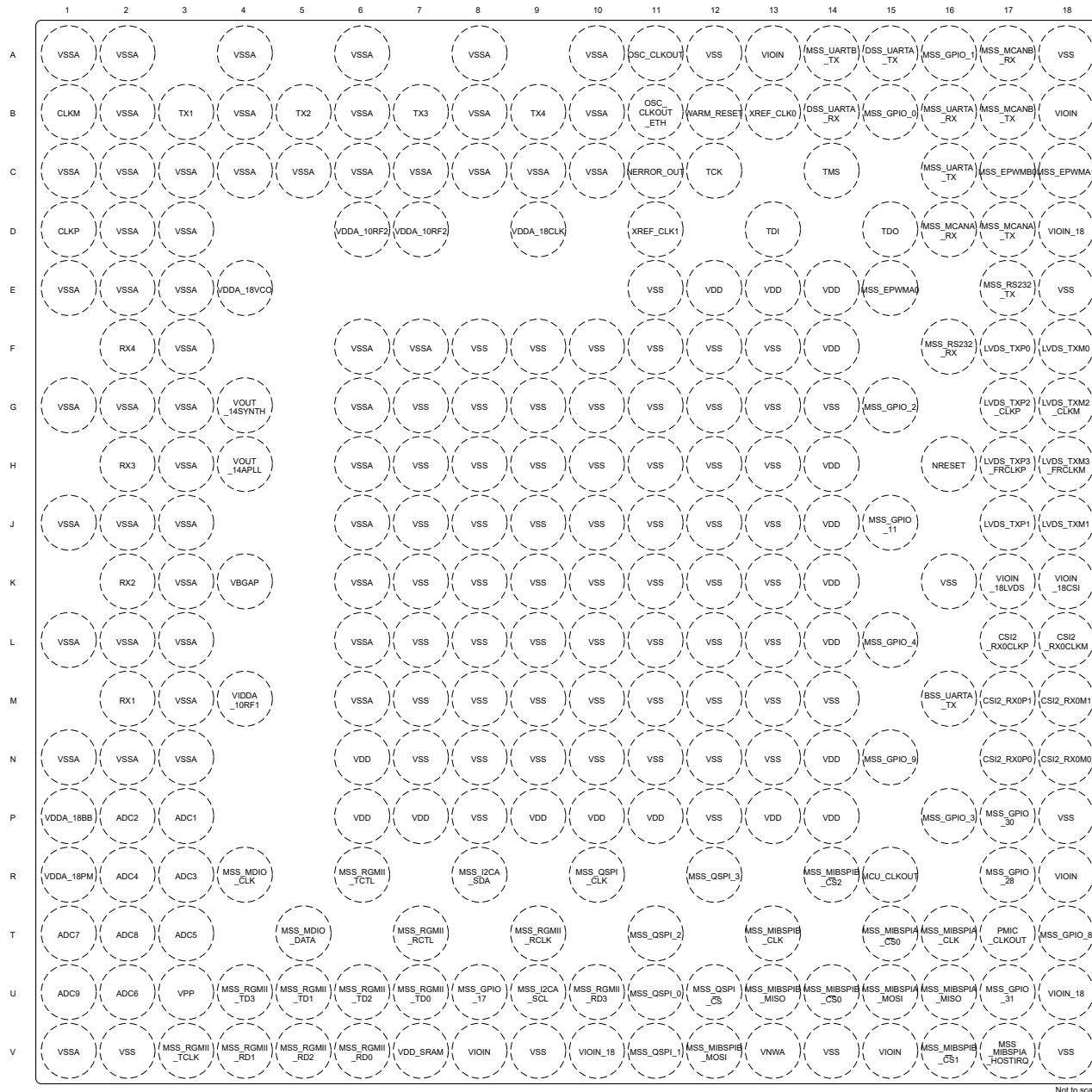

## 6.1 ピン配置図 - AWR2944P/AWR2944-ECO/AWR2944LC

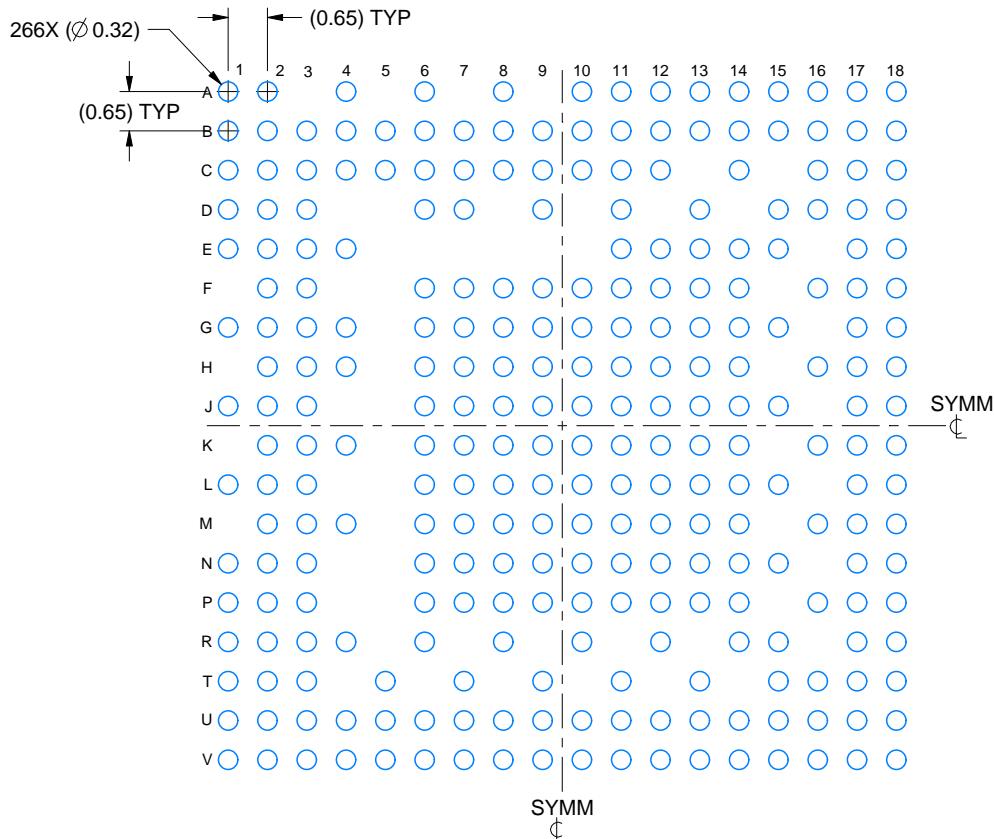

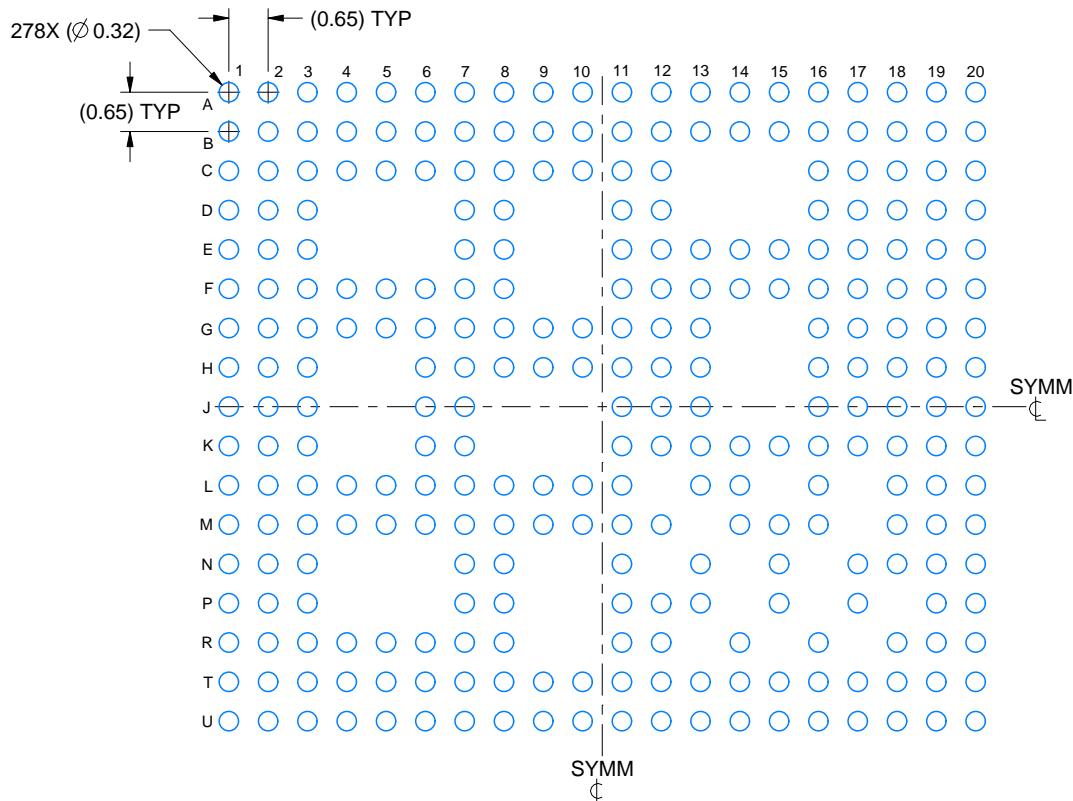

図 6-1 は、AWR2944P/ AWR2944-ECO/ AWR2944LC の 12mm × 12mm FCCSP 非 LOP パッケージにおけるピン配置を示しています。<sup>1</sup>

図 6-1. ピン配置図 - AWR2944P/AWR2944-ECO/AWR2944LC

<sup>1</sup> AWR2944LC では、一部のピンがディセーブルになっています。詳細情報については、[セクション 6.4](#) をご覧ください。

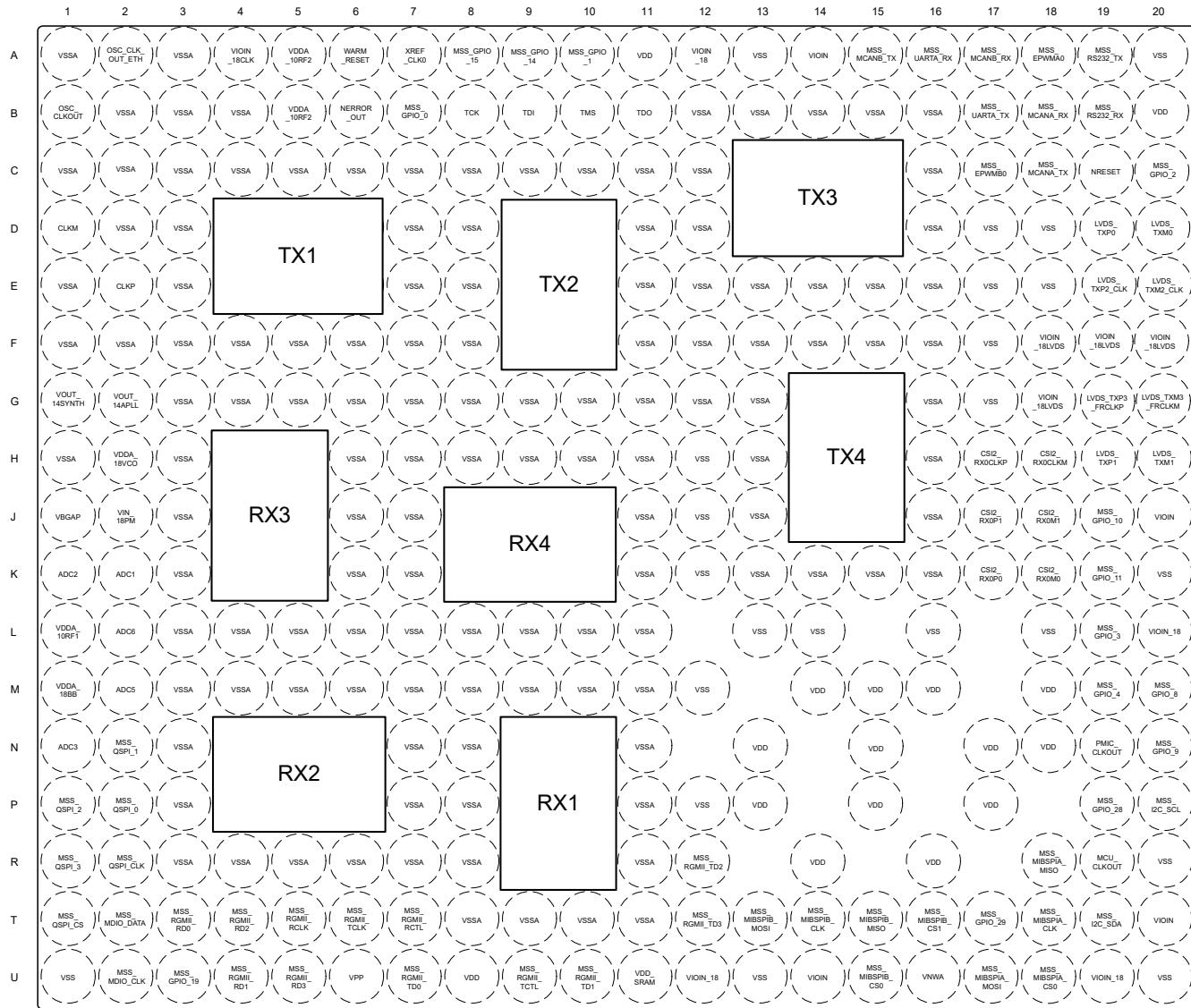

## 6.2 ピン配置図 - AWR2E44P/AWR2E44-ECO/AWR2E44LC

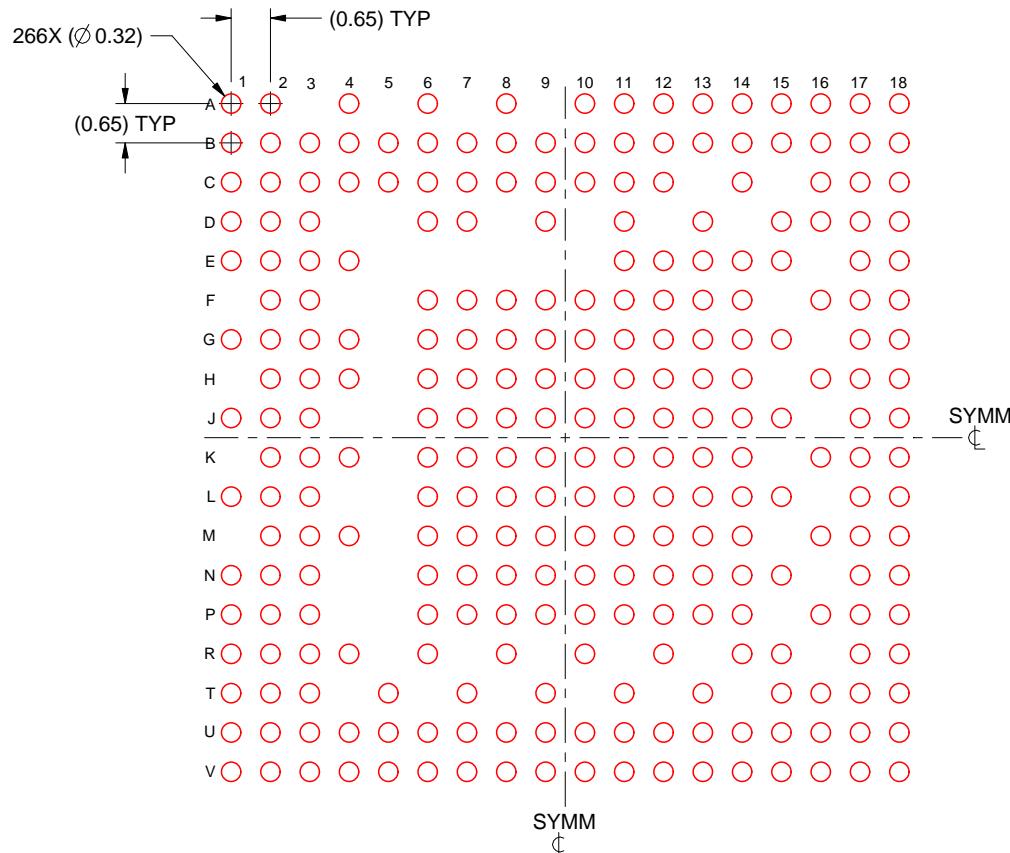

図 6-2 は、AWR2E44P/AWR2E44-ECO/AWR2E44LC の 13.5mm × 12mm FCCSP LOP パッケージのピン配置を示します。<sup>2</sup>

#### ■ 6.2 ピン配置図 AWD3E41R/AWD3E41\_ECO/AWD3E41L\_C

<sup>2</sup> AWR2E44LC では、一部のピンがディセーブルになっています。詳細情報については、セクション 6.4 をご覧ください。

## 6.3 ピン属性

| ポール番号 <sup>1</sup>             |                                | パッド名 <sup>8</sup> | ポール名 <sup>2</sup>    | 信号名 <sup>3</sup>    | モード <sup>4</sup><br>8 | タイプ <sup>5</sup> | ポールリ<br>セット状<br>態 <sup>6</sup> | ブルアップ/ダ<br>ウンタイプ <sup>7</sup> |

|--------------------------------|--------------------------------|-------------------|----------------------|---------------------|-----------------------|------------------|--------------------------------|-------------------------------|

| AWR2944P/AWR2944-ECO/AWR2944LC | AWR2E44P/AWR2E44-ECO/AWR2E44LC |                   |                      |                     |                       |                  |                                |                               |

| V16                            | T16                            | PAD_AA            | MSS_MIBSPI<br>B_CS1  | MSS_GPIO_12         | 0                     | IO               | 出力ディ<br>ゼーブル                   | ブルダウン                         |

|                                |                                |                   |                      | MSS_MIBSPIA_HOSTIRQ | 1                     | O                |                                |                               |

|                                |                                |                   |                      | ADC_VALID           | 2                     | O                |                                |                               |

|                                |                                |                   |                      | MSS_MIBSPIB_CS1     | 6                     | IO               |                                |                               |

| B15                            | C17                            | PAD_AB            | MSS_EPWM<br>B0       | MSS_GPIO_13         | 0                     | IO               | 出力ディ<br>ゼーブル                   | ブルダウン                         |

|                                |                                |                   |                      | MSS_GPIO_0          | 1                     | IO               |                                |                               |

|                                |                                |                   |                      | PMIC_CLKOUT         | 2                     | O                |                                |                               |

|                                |                                |                   |                      | MSS_EPWM_TZ2        | 3                     | I                |                                |                               |

|                                |                                |                   |                      | MSS_EPWMA1          | 10                    | O                |                                |                               |

|                                |                                |                   |                      | MSS_EPWMB0          | 11                    | O                |                                |                               |

| A16                            | A10                            | PAD_AC            | MSS_GPIO_1           | MSS_GPIO_16         | 0                     | IO               | 出力ディ<br>ゼーブル                   | ブルダウン                         |

|                                |                                |                   |                      | MSS_GPIO_1          | 1                     | IO               |                                |                               |

|                                |                                |                   |                      | SYNC_OUT            | 2                     | O                |                                |                               |

|                                |                                |                   |                      | MSS_EPWM_TZ1        | 3                     | I                |                                |                               |

|                                |                                |                   |                      | BSS_UARTA_TX        | 7                     | O                |                                |                               |

|                                |                                |                   |                      | READY_INT           | 8                     | O                |                                |                               |

|                                |                                |                   |                      | LVDS_VALID          | 9                     | O                |                                |                               |

|                                |                                |                   |                      | DMM_MUX_IN          | 12                    | I                |                                |                               |

|                                |                                |                   |                      | MSS_MIBSPIB_CS1     | 13                    | IO               |                                |                               |

|                                |                                |                   |                      | MSS_MIBSPIB_CS2     | 14                    | IO               |                                |                               |

|                                |                                |                   |                      | MSS_EPWMA_SYNC1     | 15                    | I                |                                |                               |

| V12                            | T13                            | PAD_AH            | MSS_MIBSPI<br>B_MOSI | MSS_GPIO_21         | 0                     | IO               | 出力ディ<br>ゼーブル                   | ブルアップ                         |

|                                |                                |                   |                      | MSS_MIBSPIB_MOSI    | 1                     | IO               |                                |                               |

|                                |                                |                   |                      | MSS_I2C_SDA         | 2                     | IO               |                                |                               |

|                                |                                |                   |                      | MSS_EPWMA0          | 3                     | O                |                                |                               |

|                                |                                |                   |                      | MSS_MCANB_RX        | 7                     | I                |                                |                               |

| U13                            | T15                            | PAD_AI            | MSS_MIBSPI<br>B_MISO | MSS_GPIO_22         | 0                     | IO               | 出力ディ<br>ゼーブル                   | ブルアップ                         |

|                                |                                |                   |                      | MSS_MIBSPIB_MISO    | 1                     | IO               |                                |                               |

|                                |                                |                   |                      | MSS_I2C_SCL         | 2                     | IO               |                                |                               |

|                                |                                |                   |                      | MSS_EPWMB0          | 3                     | O                |                                |                               |

|                                |                                |                   |                      | DSS_UARTA_TX        | 6                     | IO               |                                |                               |

|                                |                                |                   |                      | MSS_MCANB_TX        | 7                     | O                |                                |                               |

|                                |                                |                   |                      |                     |                       |                  |                                |                               |

| ポート番号 1                        |                                | ポート名 8 | ポート名 2              | 信号名 3           | モード 4<br>8 | タイプ 5 | ポートリ<br>セット状<br>態 6      | ブルアップ/ダ<br>ウンタイプ 7 |

|--------------------------------|--------------------------------|--------|---------------------|-----------------|------------|-------|--------------------------|--------------------|

| AWR2944P/AWR2944-ECO/AWR2944LC | AWR2E44P/AWR2E44-ECO/AWR2E44LC |        |                     |                 |            |       |                          |                    |

| T13                            | T14                            | PAD_AJ | MSS_MIBSPI<br>B_CLK | MSS_GPIO_5      | 0          | IO    | 出力ディ<br>セーブル             | ブルアップ              |

|                                |                                |        |                     | MSS_MIBSPI_CLK  | 1          | IO    |                          |                    |

|                                |                                |        |                     | MSS_UARTA_RX    | 2          | IO    |                          |                    |

|                                |                                |        |                     | MSS_EPWMCO      | 3          | O     |                          |                    |

|                                |                                |        |                     | MSS_UARTB_TX    | 6          | IO    |                          |                    |

|                                |                                |        |                     | BSS_UARTA_TX    | 7          | O     |                          |                    |

|                                |                                |        |                     | MSS_MCANA_RX    | 8          | I     |                          |                    |

| U14                            | U15                            | PAD_AK | MSS_MIBSPI<br>B_CS0 | MSS_GPIO_4      | 0          | IO    | 出力ディ<br>セーブル             | ブルアップ              |

|                                |                                |        |                     | MSS_MIBSPI_CS0  | 1          | IO    |                          |                    |

|                                |                                |        |                     | MSS_UARTA_TX    | 2          | IO    |                          |                    |

|                                |                                |        |                     | MSS_UARTB_TX    | 6          | IO    |                          |                    |

|                                |                                |        |                     | BSS_UARTA_TX    | 7          | O     |                          |                    |

|                                |                                |        |                     | MSS_MCANA_TX    | 9          | O     |                          |                    |

|                                |                                |        |                     | MSS_GPIO_8      | 0          | IO    |                          |                    |

| U11                            | P2                             | PAD_AL | MSS_QSPI_0          | MSS_QSPI_0      | 1          | IO    | 出力ディ<br>セーブル             | ブルダウン              |

|                                |                                |        |                     | MSS_MIBSPI_MISO | 2          | IO    |                          |                    |

|                                |                                |        |                     | MSS_GPIO_9      | 0          | IO    |                          |                    |

| V11                            | N2                             | PAD_AM | MSS_QSPI_1          | MSS_QSPI_1      | 1          | I     | 出力ディ<br>セーブル             | ブルダウン              |

|                                |                                |        |                     | MSS_MIBSPI_MOSI | 2          | IO    |                          |                    |

|                                |                                |        |                     | MSS_MIBSPI_CS2  | 8          | IO    |                          |                    |

|                                |                                |        |                     | MSS_GPIO_10     | 0          | IO    |                          |                    |

| T11                            | P1                             | PAD_AN | MSS_QSPI_2          | MSS_QSPI_2      | 1          | I     | 出力ディ<br>セーブル             | ブルアップ              |

|                                |                                |        |                     | ADC_VALID       | 2          | O     |                          |                    |

|                                |                                |        |                     | MSS_MCANA_TX    | 8          | O     |                          |                    |

|                                |                                |        |                     | MSS_GPIO_11     | 0          | IO    |                          |                    |

| R12                            | R1                             | PAD_AO | MSS_QSPI_3          | MSS_QSPI_3      | 1          | I     | 出力ディ<br>セーブル             | ブルアップ              |

|                                |                                |        |                     | ADC_VALID       | 2          | O     |                          |                    |

|                                |                                |        |                     | MSS_MCANA_RX    | 8          | I     |                          |                    |

|                                |                                |        |                     | MSS_GPIO_12     | 0          | IO    |                          |                    |

| R10                            | R2                             | PAD_AP | MSS_QSPI_CLK        | MSS_QSPI_CLK    | 1          | IO    | 出力ディ<br>セーブル             | ブルダウン              |

|                                |                                |        |                     | MSS_MIBSPI_CLK  | 2          | IO    |                          |                    |

|                                |                                |        |                     | DSS_UARTA_TX    | 6          | IO    |                          |                    |

|                                |                                |        |                     | MSS_GPIO_13     | 0          | IO    |                          |                    |

| U12                            | T1                             | PAD_AQ | MSS_QSPI_CS         | MSS_QSPI_CS     | 1          | O     | 出力ディ<br>セーブル             | ブルアップ              |

|                                |                                |        |                     | MSS_MIBSPI_CS0  | 2          | IO    |                          |                    |

|                                |                                |        |                     | MSS_GPIO_14     | 0          | IO    |                          |                    |

| B12                            | A6                             | PAD_AS | WARM_RESET          | WARM_RESET      | 0          | IO    | HIZ 入力<br>(オープン<br>ドレイン) |                    |

| ポート番号 1                        |                                | ポート名 8 | ポート名 2     | 信号名 3        | モード 4<br>8  | タイプ 5 | ポートリ<br>セット状<br>態 6 | ブルアップ/ダ<br>ウンタイプ 7 |

|--------------------------------|--------------------------------|--------|------------|--------------|-------------|-------|---------------------|--------------------|

| AWR2944P/AWR2944-ECO/AWR2944LC | AWR2E44P/AWR2E44-ECO/AWR2E44LC |        |            |              |             |       |                     |                    |

| C11                            | B6                             | PAD_AT | NERROR_OUT | NERROR_OUT   | 0           | O     | HiZ (オーブンドレイン)      |                    |

| C12                            | B8                             | PAD_AU | TCK        | MSS_GPIO_17  | 0           | IO    | 出力ディ<br>セーブル        | ブルダウン              |

|                                |                                |        |            | TCK          | 1           | I     |                     |                    |

|                                |                                |        |            | MSS_UARTB_TX | 2           | IO    |                     |                    |

|                                |                                |        |            | BSS_UARTA_RX | 6           | I     |                     |                    |

|                                |                                |        |            | MSS_MCANA_TX | 8           | O     |                     |                    |

| C14                            | B10                            | PAD_AV | TMS        | MSS_GPIO_18  | 0           | IO    | 出力ディ<br>セーブル        | ブルアップ              |

|                                |                                |        |            | TMS          | 1           | IO    |                     |                    |

|                                |                                |        |            | BSS_UARTA_TX | 2           | O     |                     |                    |

|                                |                                |        |            | MSS_MCANA_RX | 6           | I     |                     |                    |

| D13                            | B9                             | PAD_AW | TDI        | MSS_GPIO_23  | 0           | IO    | 出力ディ<br>セーブル        | ブルアップ              |

|                                |                                |        |            | TDI          | 1           | I     |                     |                    |

|                                |                                |        |            | MSS_UARTA_RX | 2           | IO    |                     |                    |

|                                |                                |        |            | DSS_UARTA_RX | 7           | IO    |                     |                    |

| D15                            | B11                            | PAD_AX | TDO        | SOP[0]       | パワーア<br>ップ時 | I     | 出力イネ<br>ーブル         |                    |

|                                |                                |        |            | MSS_GPIO_24  | 0           | IO    |                     |                    |

|                                |                                |        |            | TDO          | 1           | O     |                     |                    |

|                                |                                |        |            | MSS_UARTA_TX | 2           | IO    |                     |                    |

|                                |                                |        |            | MSS_UARTB_TX | 6           | IO    |                     |                    |

|                                |                                |        |            | BSS_UARTA_TX | 7           | O     |                     |                    |

|                                |                                |        |            | NDMM_EN      | 9           | O     |                     |                    |

| R15                            | R19                            | PAD_AY | MCU_CLKOUT | MSS_GPIO_25  | 0           | IO    | 出力ディ<br>セーブル        | ブルダウン              |

|                                |                                |        |            | MCU_CLKOUT   | 1           | O     |                     |                    |

|                                |                                |        |            | TRACE_CLK    | 2           | O     |                     |                    |

|                                |                                |        |            | FRAME_START  | 7           | O     |                     |                    |

|                                |                                |        |            | READY_INT    | 8           | O     |                     |                    |

|                                |                                |        |            | LVDS_VALID   | 9           | O     |                     |                    |

|                                |                                |        |            | BSS_UARTA_RX | 10          | I     |                     |                    |

|                                |                                |        |            | MSS_EPWMA0   | 12          | O     |                     |                    |

|                                |                                |        |            | DMM_CLK      | 14          | I     |                     |                    |

|                                |                                |        |            | OBS_CLKOUT   | 15          | O     |                     |                    |

| ポール番号 1                        |                                | パッド名 8 | ポール名 2      | 信号名 3        | モード 4 8 | タイプ 5 | ポールリセット状態 6 | ブルアップ/ダウンタイプ 7 |

|--------------------------------|--------------------------------|--------|-------------|--------------|---------|-------|-------------|----------------|

| AWR2944P/AWR2944-ECO/AWR2944LC | AWR2E44P/AWR2E44-ECO/AWR2E44LC |        |             |              |         |       |             |                |

| G15                            | C20                            | PAD_AZ | MSS_GPIO_2  | MSS_GPIO_26  | 0       | IO    | 出力ディーセーブル   | ブルダウン          |

|                                |                                |        |             | MSS_GPIO_2   | 1       | IO    |             |                |

|                                |                                |        |             | MSS_UARTB_TX | 7       | IO    |             |                |

|                                |                                |        |             | MSS_GPIO_2   |         | IO    |             |                |

|                                |                                |        |             | SYNC_OUT     | 9       | O     |             |                |

|                                |                                |        |             | PMIC_CLKOUT  | 10      | O     |             |                |

|                                |                                |        |             | CHIRP_START  | 11      | O     |             |                |

|                                |                                |        |             | CHIRP_END    | 12      | O     |             |                |

|                                |                                |        |             | FRAME_START  | 13      | O     |             |                |

|                                |                                |        |             | MSS_EPWM_TZ0 | 14      | I     |             |                |

|                                |                                |        |             | LVDS_VALID   | 15      | O     |             |                |

|                                |                                |        |             | SOP[2]       | パワーアップ時 | I     | 出力ディーセーブル   | ブルなし           |

|                                |                                |        |             | MSS_GPIO_27  |         | IO    |             |                |

| T17                            | N19                            | PAD_BA | PMIC_CLKOUT | PMIC_CLKOUT  | 1       | O     |             |                |

|                                |                                |        |             | OBS_CLKOUT   | 2       | O     |             |                |

|                                |                                |        |             | TRACE_CTL    | 3       | O     |             |                |

|                                |                                |        |             | CHIRP_START  | 6       | O     |             |                |

|                                |                                |        |             | CHIRP_END    | 7       | O     |             |                |

|                                |                                |        |             | FRAME_START  | 8       | O     |             |                |

|                                |                                |        |             | READY_INT    | 9       | O     |             |                |

|                                |                                |        |             | LVDS_VALID   | 10      | O     |             |                |

|                                |                                |        |             | MSS_EPWMA1   | 11      | O     |             |                |

|                                |                                |        |             | MSS_EPWMB0   | 12      | O     |             |                |

|                                |                                |        |             | DMM_SYNC     | 13      | I     |             |                |

| R17                            | P19                            | PAD_BB | MSS_GPIO_28 | MSS_GPIO_28  | 0       | IO    | 出力ディーセーブル   | ブルダウン          |

|                                |                                |        |             | SYNC_IN      | 1       | I     |             |                |

|                                |                                |        |             | ADC_VALID    | 2       | O     |             |                |

|                                |                                |        |             | MSS_UARTB_RX | 6       | IO    |             |                |

|                                |                                |        |             | DMM_MUX_IN   | 7       | I     |             |                |

|                                |                                |        |             | DSS_UARTA_RX | 8       | IO    |             |                |

|                                |                                |        |             | SYNC_OUT     | 9       | O     |             |                |

| ポート番号 1                        |                                | ポート名 8 | ポート名 2       | 信号名 3           | モード 4<br>8      | タイプ 5 | ポートリ<br>セット状<br>態 6 | ブルアップ/ダ<br>ウンタイプ 7 |

|--------------------------------|--------------------------------|--------|--------------|-----------------|-----------------|-------|---------------------|--------------------|

| AWR2944P/AWR2944-ECO/AWR2944LC | AWR2E44P/AWR2E44-ECO/AWR2E44LC |        |              |                 |                 |       |                     |                    |

| R14                            | T17                            | PAD_BC | MSS_GPIO_29  | SOP[1]          | パワー<br>ア<br>ップ時 | I     | 出力デイ<br>セーブル        | ブルアップ              |

|                                |                                |        |              | MSS_GPIO_29     | 0               | IO    |                     |                    |

|                                |                                |        |              | SYNC_OUT        | 1               | O     |                     |                    |

|                                |                                |        |              | RCOSC_CLK       | 2               | O     |                     |                    |

|                                |                                |        |              | READY_INT       | 6               | O     |                     |                    |

|                                |                                |        |              | LVDS_VALID      | 7               | O     |                     |                    |

|                                |                                |        |              | DMM_MUX_IN      | 9               | I     |                     |                    |

|                                |                                |        |              | MSS_MIBSPIB_CS1 | 10              | IO    |                     |                    |

|                                |                                |        |              | MSS_MIBSPIB_CS2 | 11              | IO    |                     |                    |

|                                |                                |        |              | MSS_EPWMB0      | 12              | O     |                     |                    |

| F16                            | B19                            | PAD_BD | MSS_RS232_RX | MSS_GPIO_15     | 0               | IO    | 出力デイ<br>セーブル        | ブルアップ              |

|                                |                                |        |              | MSS_RS232_RX    | 1               | IO    |                     |                    |

|                                |                                |        |              | MSS_UARTA_RX    | 2               | IO    |                     |                    |

|                                |                                |        |              | TRACE_CLK       | 3               | O     |                     |                    |

|                                |                                |        |              | BSS_UARTA_TX    | 6               | O     |                     |                    |

|                                |                                |        |              | MSS_UARTB_RX    | 7               | IO    |                     |                    |

|                                |                                |        |              | MSS_MCANA_RX    | 8               | I     |                     |                    |

|                                |                                |        |              | MSS_I2C_SCL     | 9               | IO    |                     |                    |

|                                |                                |        |              | MSS_EPWMB0      | 10              | O     |                     |                    |

|                                |                                |        |              | MSS_EPWMB1      | 11              | O     |                     |                    |

|                                |                                |        |              | MSS_EPWMC0      | 12              | O     |                     |                    |

| ポート番号 1                        |                                | ポート名 8 | ポート名 2           | 信号名 3           | モード 4<br>8 | タイプ 5 | ポートリ<br>セット状<br>態 6 | ブルアップ/ダ<br>ウンタイプ 7 |

|--------------------------------|--------------------------------|--------|------------------|-----------------|------------|-------|---------------------|--------------------|

| AWR2944P/AWR2944-ECO/AWR2944LC | AWR2E44P/AWR2E44-ECO/AWR2E44LC |        |                  |                 |            |       |                     |                    |

| E17                            | A19                            | PAD_BE | MSS_RS232<br>_TX | MSS_GPIO_14     | 0          | IO    | 出力イネ<br>ーブル         | ブルアップ              |

|                                |                                |        |                  | MSS_RS232_TX    | 1          | IO    |                     |                    |

|                                |                                |        |                  | TRACE_CTL       | 2          | O     |                     |                    |

|                                |                                |        |                  | MSS_UARTA_TX    | 5          | IO    |                     |                    |

|                                |                                |        |                  | MSS_UARTB_TX    | 6          | IO    |                     |                    |

|                                |                                |        |                  | BSS_UARTA_TX    | 7          | O     |                     |                    |

|                                |                                |        |                  | READY_INT       | 8          | O     |                     |                    |

|                                |                                |        |                  | LVDS_VALID      | 9          | O     |                     |                    |

|                                |                                |        |                  | MSS_MCANA_TX    | 10         | O     |                     |                    |

|                                |                                |        |                  | MSS_I2C_SDA     | 11         | IO    |                     |                    |

|                                |                                |        |                  | MSS_EPWMA0      | 12         | O     |                     |                    |

|                                |                                |        |                  | MSS_EPWMA1      | 13         | O     |                     |                    |

|                                |                                |        |                  | NDMM_EN         | 14         | O     |                     |                    |

|                                |                                |        |                  | MSS_EPWMB0      | 15         | O     |                     |                    |

| U17                            | T19                            | PAD_BF | MSS_I2C_SD<br>A  | TRACE_DATA_0    | 0          | O     | 出力ディ<br>ーセーブル       | ブルダウン              |

|                                |                                |        |                  | MSS_GPIO_31     | 1          | IO    |                     |                    |

|                                |                                |        |                  | DMM0            | 2          | I     |                     |                    |

|                                |                                |        |                  | MSS_UARTA_TX    | 4          | IO    |                     |                    |

|                                |                                |        |                  | MSS_GPIO_31     | 6          | IO    |                     |                    |

|                                |                                |        |                  | MSS_I2C_SDA     | 10         | IO    |                     |                    |

| P17                            | P20                            | PAD_BG | MSS_I2C_SC<br>L  | TRACE_DATA_1    | 0          | O     | 出力ディ<br>ーセーブル       | ブルダウン              |

|                                |                                |        |                  | MSS_GPIO_30     | 1          | IO    |                     |                    |

|                                |                                |        |                  | DMM1            | 2          | I     |                     |                    |

|                                |                                |        |                  | MSS_EPWMC_SYNCI | 3          | I     |                     |                    |

|                                |                                |        |                  | MSS_UARTA_RX    | 4          | IO    |                     |                    |

|                                |                                |        |                  | MSS_GPIO_0      | 6          | IO    |                     |                    |

|                                |                                |        |                  | MSS_I2C_SCL     | 10         | IO    |                     |                    |

| T18                            | M20                            | PAD_BH | MSS_GPIO_8       | TRACE_DATA_2    | 0          | O     | 出力ディ<br>ーセーブル       | ブルダウン              |

|                                |                                |        |                  | MSS_GPIO_29     | 1          | IO    |                     |                    |

|                                |                                |        |                  | DMM2            | 2          | I     |                     |                    |

|                                |                                |        |                  | MSS_EPWMB_SYNCI | 3          | I     |                     |                    |

|                                |                                |        |                  | MSS_GPIO_1      | 6          | IO    |                     |                    |

|                                |                                |        |                  | MSS_GPIO_8      | 7          | IO    |                     |                    |

| ポート番号 1                        |                                | ポート名 8 | ポート名 2       | 信号名 3           | モード 4<br>8 | タイプ 5 | ポートリ<br>セット状<br>態 6 | ブルアップ/ダ<br>ウンタイプ 7 |

|--------------------------------|--------------------------------|--------|--------------|-----------------|------------|-------|---------------------|--------------------|

| AWR2944P/AWR2944-ECO/AWR2944LC | AWR2E44P/AWR2E44-ECO/AWR2E44LC |        |              |                 |            |       |                     |                    |

| N15                            | N20                            | PAD_BI | MSS_GPIO_9   | TRACE_DATA_3    | 0          | O     | 出力ディ<br>セーブル        | ブルダウン              |

|                                |                                |        |              | MSS_GPIO_28     | 1          | IO    |                     |                    |

|                                |                                |        |              | DMM3            | 2          | I     |                     |                    |

|                                |                                |        |              | MSS_EPWMC_SYNC0 | 4          | O     |                     |                    |

|                                |                                |        |              | MSS_GPIO_2      | 6          | IO    |                     |                    |

|                                |                                |        |              | MSS_GPIO_9      | 7          | IO    |                     |                    |

| P16                            | L19                            | PAD_BJ | MSS_GPIO_3   | TRACE_DATA_4    | 0          | O     | 出力ディ<br>セーブル        | ブルダウン              |

|                                |                                |        |              | MSS_GPIO_3      | 1          | IO    |                     |                    |

|                                |                                |        |              | DMM4            | 2          | I     |                     |                    |

|                                |                                |        |              | MSS_EPWMB_SYNC0 | 4          | O     |                     |                    |

|                                |                                |        |              | MSS_GPIO_27     | 6          | IO    |                     |                    |

|                                |                                |        |              | TRACE_DATA_5    | 0          | O     |                     |                    |

| L15                            | M19                            | PAD_BK | MSS_GPIO_4   | MSS_GPIO_4      | 1          | IO    | 出力ディ<br>セーブル        | ブルダウン              |

|                                |                                |        |              | DMM5            | 2          | I     |                     |                    |

|                                |                                |        |              | MSS_EPWM_TZ2    | 4          | I     |                     |                    |

|                                |                                |        |              | MSS_UARTB_TX    | 5          | IO    |                     |                    |

|                                |                                |        |              | MSS_GPIO_26     | 6          | IO    |                     |                    |

|                                |                                |        |              | TRACE_DATA_6    | 0          | O     |                     |                    |

| M16                            | J19                            | PAD_BL | BSS_UARTA_TX | MSS_GPIO_5      | 1          | IO    | 出力ディ<br>セーブル        | ブルダウン              |

|                                |                                |        |              | DMM6            | 2          | I     |                     |                    |

|                                |                                |        |              | MSS_EPWM_TZ1    | 4          | I     |                     |                    |

|                                |                                |        |              | BSS_UARTA_TX    | 5          | IO    |                     |                    |

|                                |                                |        |              | MSS_GPIO_25     | 6          | IO    |                     |                    |

|                                |                                |        |              | MSS_GPIO_10     | 7          | IO    |                     |                    |

|                                |                                |        |              | TRACE_DATA_7    | 0          | O     |                     |                    |

| J15                            | K19                            | PAD_BM | MSS_GPIO_11  | MSS_GPIO_6      | 1          | IO    | 出力ディ<br>セーブル        | ブルダウン              |

|                                |                                |        |              | DMM7            | 2          | I     |                     |                    |

|                                |                                |        |              | MSS_EPWM_TZ0    | 4          | I     |                     |                    |

|                                |                                |        |              | DSS_UARTA_TX    | 5          | IO    |                     |                    |

|                                |                                |        |              | MSS_GPIO_24     | 6          | IO    |                     |                    |

|                                |                                |        |              | MSS_GPIO_11     | 7          | IO    |                     |                    |

|                                |                                |        |              |                 |            |       |                     |                    |

| ポール番号 1                                                                                                                                                                             |                                | パッド名 8                       | ポール名 2        | 信号名 3           | モード 4 8 | タイプ 5 | ポールリセット状態 6 | ブルアップ/ダウンタイプ 7 |  |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------|---------------|-----------------|---------|-------|-------------|----------------|--|--|--|--|--|--|--|--|--|--|--|

| AWR2944P/AWR2944-ECO/AWR2944LC                                                                                                                                                      | AWR2E44P/AWR2E44-ECO/AWR2E44LC |                              |               |                 |         |       |             |                |  |  |  |  |  |  |  |  |  |  |  |

| D17                                                                                                                                                                                 | C18                            | PAD_BN                       | MSS_MCAN_A_TX | TRACE_DATA_8    | 0       | O     | 出力ディーセーブル   | ブルダウン          |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_GPIO_7      | 1       | IO    |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | DMM8            | 2       | I     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_MCANA_TX    | 4       | O     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_EPWMA_SYNC1 | 5       | I     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_GPIO_23     | 6       | IO    |             |                |  |  |  |  |  |  |  |  |  |  |  |

| D16                                                                                                                                                                                 | B18                            | PAD_BO                       | MSS_MCAN_A_RX | TRACE_DATA_9    | 0       | O     | 出力ディーセーブル   | ブルダウン          |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_GPIO_8      | 1       | IO    |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | DMM9            | 2       | I     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_MCANA_RX    | 4       | I     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_EPWMA_SYNC0 | 5       | O     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_GPIO_22     | 6       | IO    |             |                |  |  |  |  |  |  |  |  |  |  |  |

| E15                                                                                                                                                                                 | A18                            | PAD_BP                       | MSS_EPWM_A0   | TRACE_DATA_10   | 0       | O     | 出力ディーセーブル   | ブルダウン          |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_GPIO_9      | 1       | IO    |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | DMM10           | 2       | I     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_EPWMA0      | 3       | O     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_EPWMC0      | 4       | O     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_GPIO_21     | 6       | IO    |             |                |  |  |  |  |  |  |  |  |  |  |  |

| C18                                                                                                                                                                                 | —                              | PAD_BQ                       | MSS_EPWM_A1   | TRACE_DATA_11   | 0       | O     | 出力ディーセーブル   | ブルダウン          |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_GPIO_10     | 1       | IO    |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | DMM11           | 2       | I     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_EPWMA1      | 3       | O     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_EPWMC1      | 4       | O     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_GPIO_20     | 6       | IO-   |             |                |  |  |  |  |  |  |  |  |  |  |  |

| B17                                                                                                                                                                                 | A15                            | PAD_BR                       | MSS_MCAN_B_TX | TRACE_DATA_12   | 0       | O     | 出力ディーセーブル   | ブルダウン          |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_GPIO_11     | 1       | IO    |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | DMM12           | 2       | I     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_EPWMB0      | 3       | O     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_EPWMA0      | 4       | O     |             |                |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                     |                                |                              |               | MSS_MCANB_TX    | 5       | O     |             |                |  |  |  |  |  |  |  |  |  |  |  |

| Copyright © 2025 Texas Instruments Incorporated                                                                                                                                     |                                | 資料に関するフィードバック(ご意見やお問い合わせ)を送信 |               |                 |         |       |             |                |  |  |  |  |  |  |  |  |  |  |  |

| Product Folder Links: <a href="#">AWR2944P</a> <a href="#">AWR2E44P</a> <a href="#">AWR2944-ECO</a> <a href="#">AWR2E44-ECO</a> <a href="#">AWR2944LC</a> <a href="#">AWR2E44LC</a> |                                |                              |               |                 |         |       |             |                |  |  |  |  |  |  |  |  |  |  |  |

| English Data Sheet: <a href="#">SWRS318</a>                                                                                                                                         |                                |                              |               |                 |         |       |             |                |  |  |  |  |  |  |  |  |  |  |  |

| ポート番号 1                        |                                | ポート名 8 | ポート名 2         | 信号名 3           | モード 4<br>8 | タイプ 5 | ポートリ<br>セット状<br>態 6 | ブルアップ/ダ<br>ウンタイプ 7 |

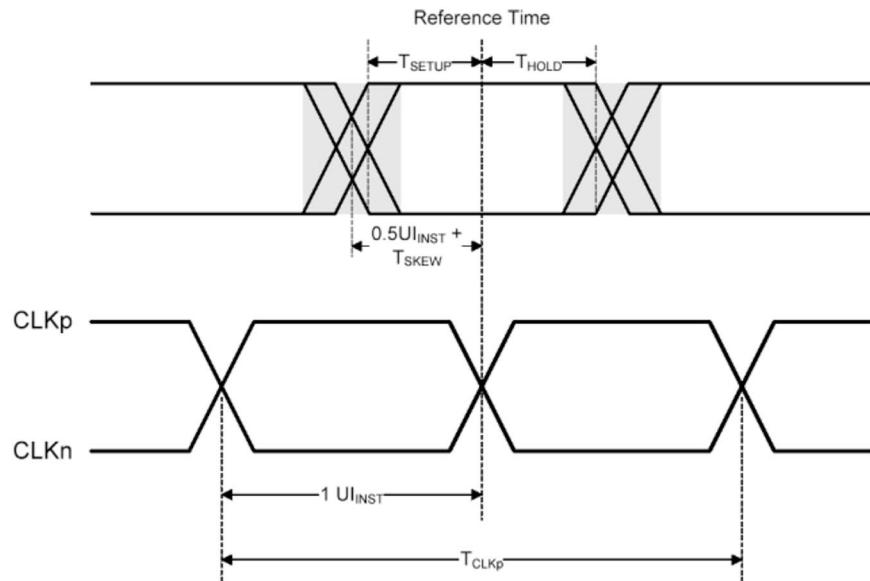

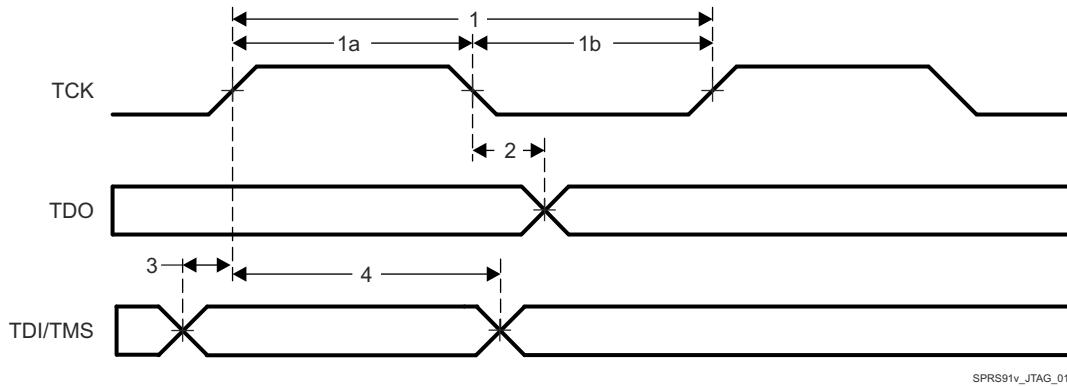

|--------------------------------|--------------------------------|--------|----------------|-----------------|------------|-------|---------------------|--------------------|