# DACx3204-Q1 車載用、12 ビット、10 ビット、クワッド電圧および電流出力スマート DAC、I<sup>2</sup>C、PMBus<sup>TM</sup>、SPI 自動検出機能付き

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

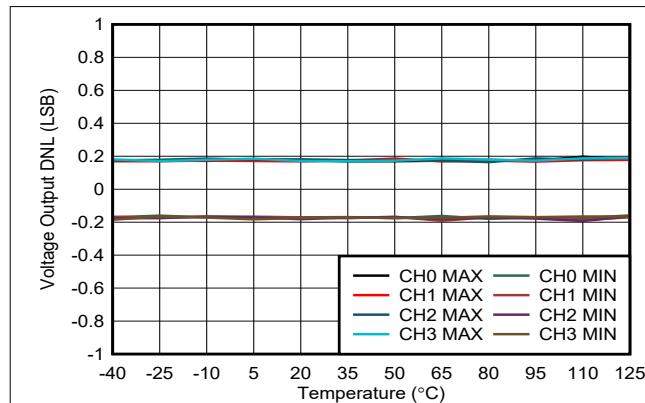

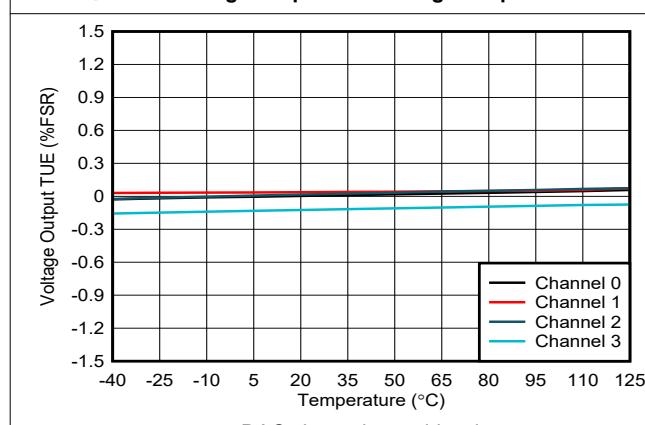

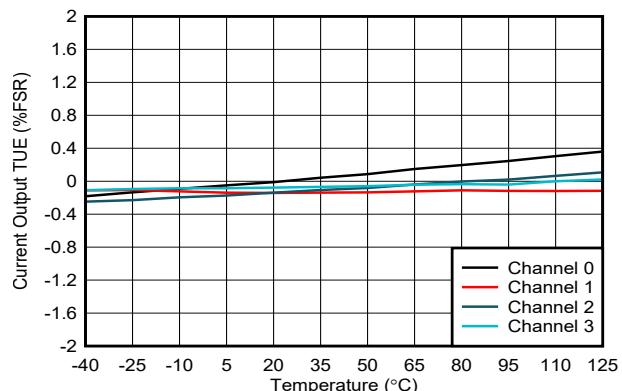

- 温度グレード 1: -40°C ~ +125°C, T<sub>A</sub>

- 柔軟な構成でプログラム可能な電圧または電流出力:

- 電圧出力:

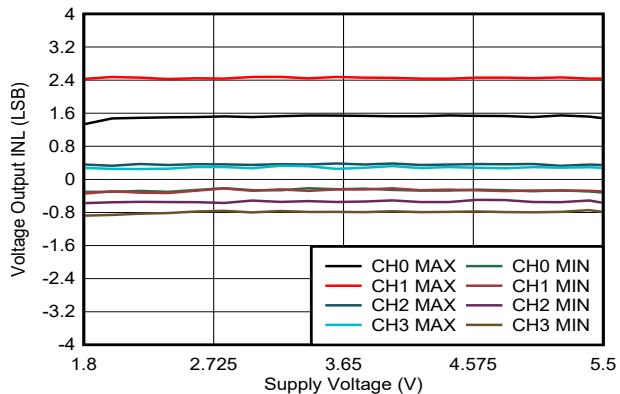

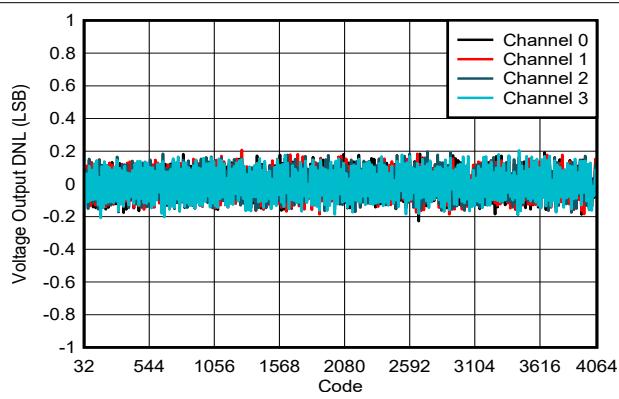

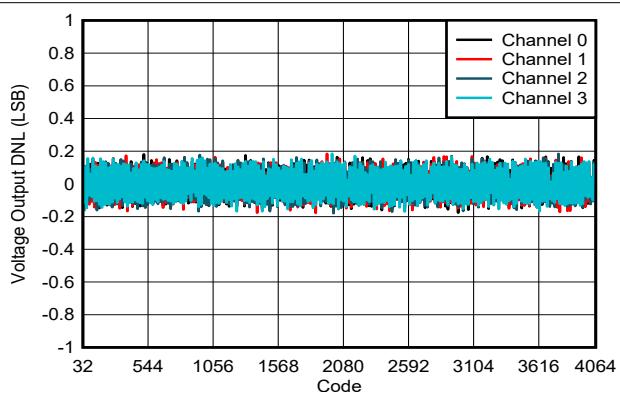

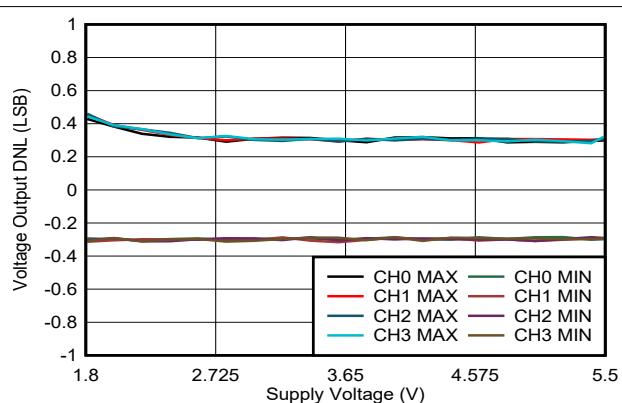

- 1LSB の DNL

- 1×、1.5×、2×、3×、4× のゲイン

- 電流出力:

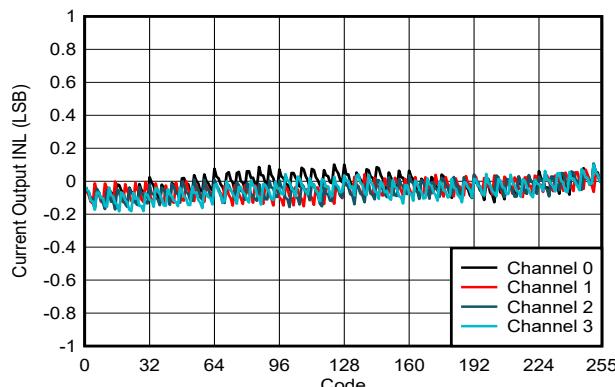

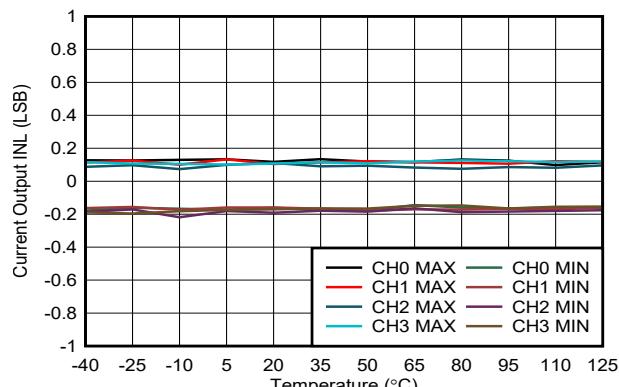

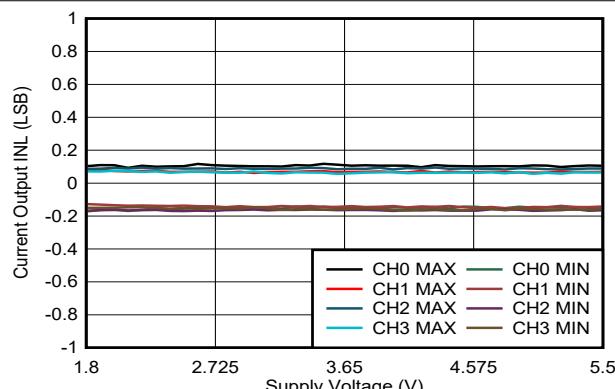

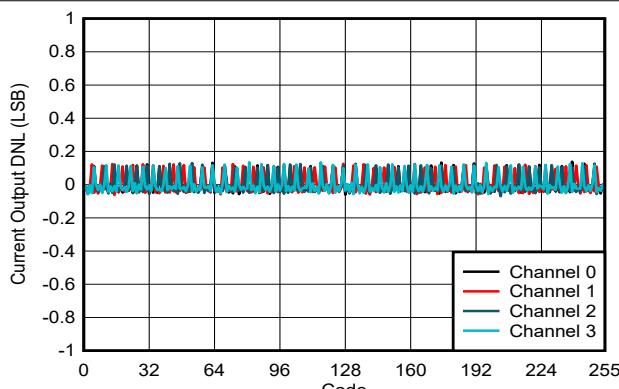

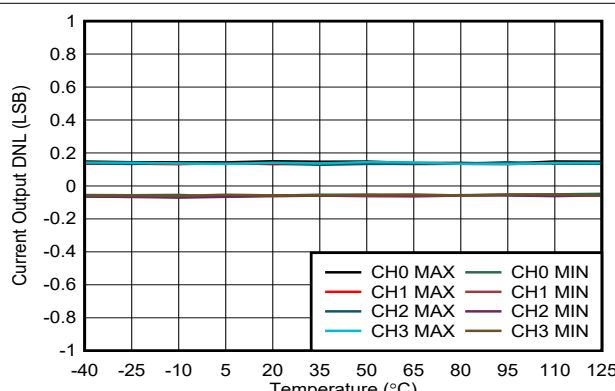

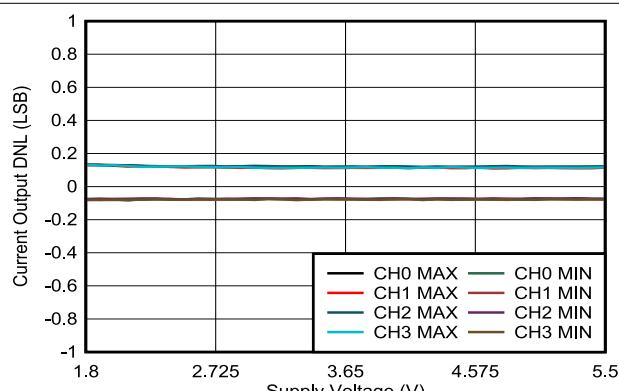

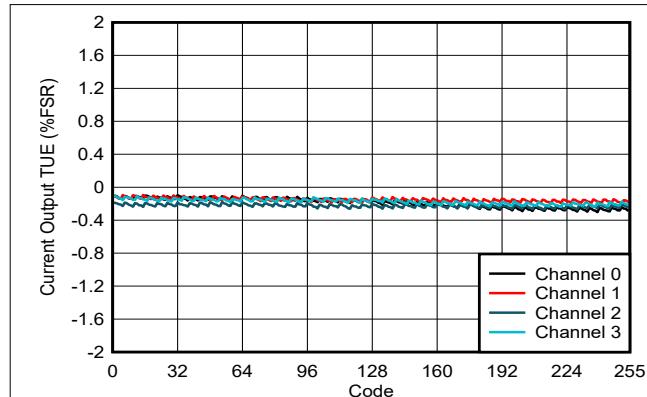

- 1LSB INL および DNL (8 ビット)

- ±25µA、±50µA、±125µA、±250µA の出力範囲を選択可能

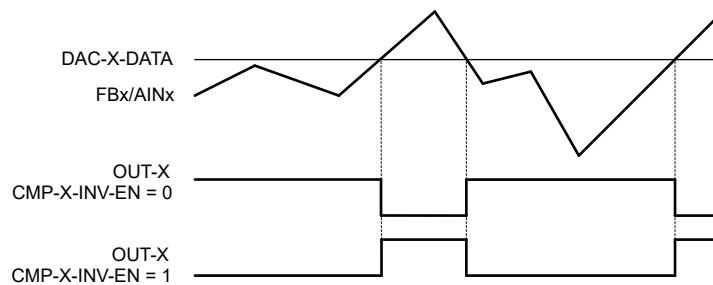

- すべてのチャネルでコンパレータ・モードにプログラム可能

- V<sub>DD</sub> オフ時にハイ・インピーダンス出力

- ハイ・インピーダンスおよび抵抗性プルダウンのパワーダウン・モード

- 50MHz、SPI 互換インターフェイス

- I<sup>2</sup>C、SPI、PMBus<sup>TM</sup> インターフェイスを自動検出

- V<sub>IH</sub>: 1.62V (V<sub>DD</sub> = 5.5V)

- さまざまな機能に構成可能な汎用入出力 (GPIO)

- あらかじめ定義された波形生成: 正弦波、三角波、のこぎり波

- ユーザーがプログラム可能な不揮発性メモリ (NVM)

- 基準電圧として、内部、外部または電源を使用可能

- 広い動作範囲:

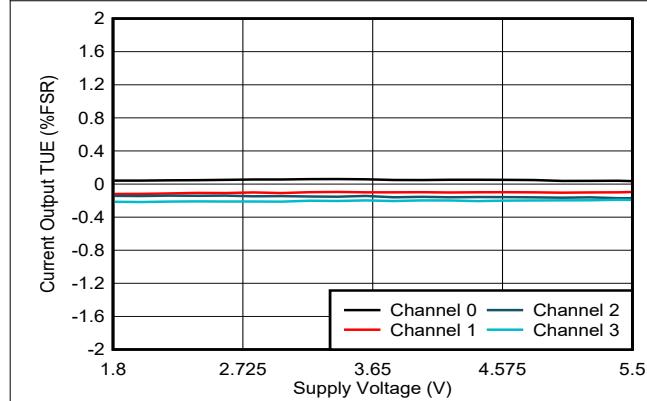

- 電源: 1.8V ~ 5.5V

- 温度範囲: -40°C ~ +125°C

- 超小型パッケージ: 16 ピン WQFN (3mm × 3mm)

## 2 アプリケーション

- 機械式スキャン LIDAR

- パワー・ディストリビューション・ボックス

- 電圧コンディショニング・モジュール

- 車載 USB 充電

- 車載メディア・ハブ

## 3 概要

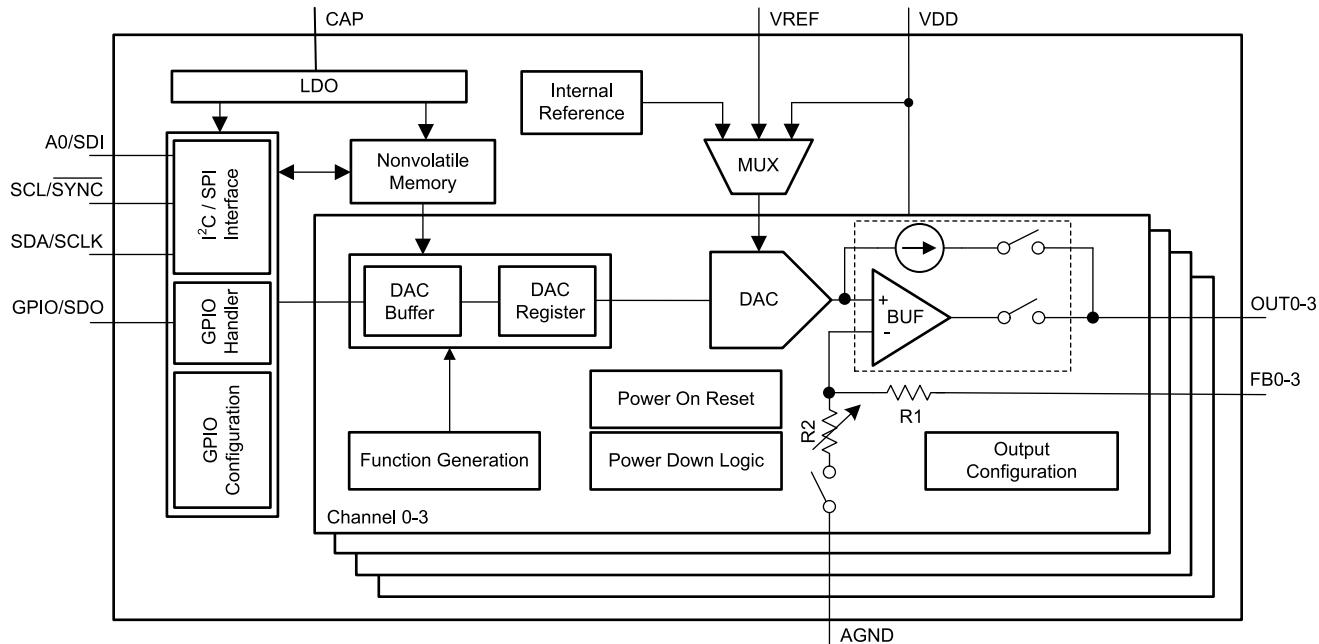

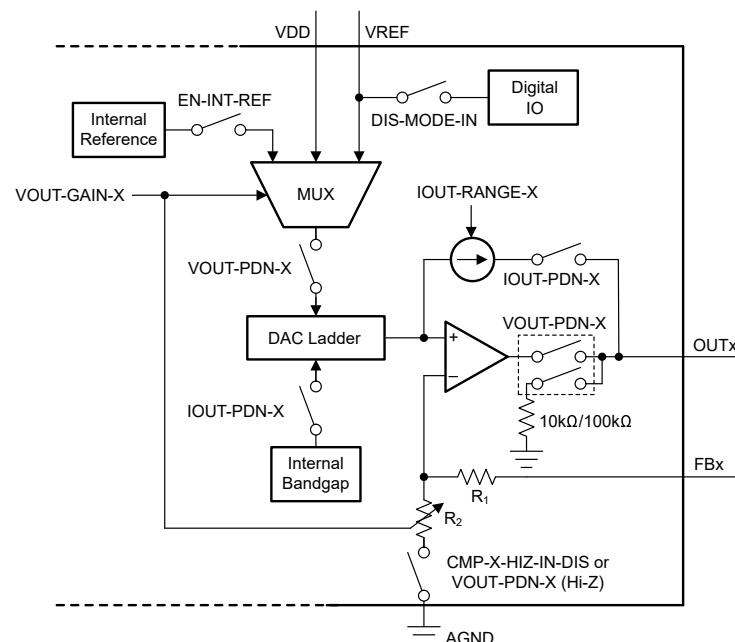

12 ビット DAC63204-Q1 および 10 ビット DAC53204-Q1 (DACx3204-Q1) は、車載用、クワッド・チャネル、バッファ付き、電圧出力および電流出力のスマート D/A コンバータ (DAC) のピン互換ファミリです。DACx3204-Q1 デバイスは、ハイ・インピーダンスのパワーダウン・モードと、電源オフ状態でのハイ・インピーダンス出力をサポートしています。DAC 出力は、プログラマブル・コンパレータおよび電流シンクとして使用するためのフォース・センス・オプションを備えています。このスマート DAC は、多機能 GPIO、関数生成、NVM によって、プロセッサレス・アプリケーションや設計の再利用を実現できます。I<sup>2</sup>C、PMBus、SPI を自動的に検出します。また、内部リファレンスを搭載しています。

この DACx3204-Q1 スマート DAC は、小型パッケージおよび低消費電力という特長を備えており、電圧マージン設定およびスケーリング、バイアスおよびキャリブレーション用の DC セット・ポイント、波形生成などの用途に最適です。

## 製品情報

| 部品番号        | 分解能    | パッケージ <sup>(1)</sup> |

|-------------|--------|----------------------|

| DAC63204-Q1 | 12 ビット | RTE (WQFN、16)        |

| DAC53204-Q1 | 10 ビット | RTE (WQFN、16)        |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、最新版の英語版をご参照ください。

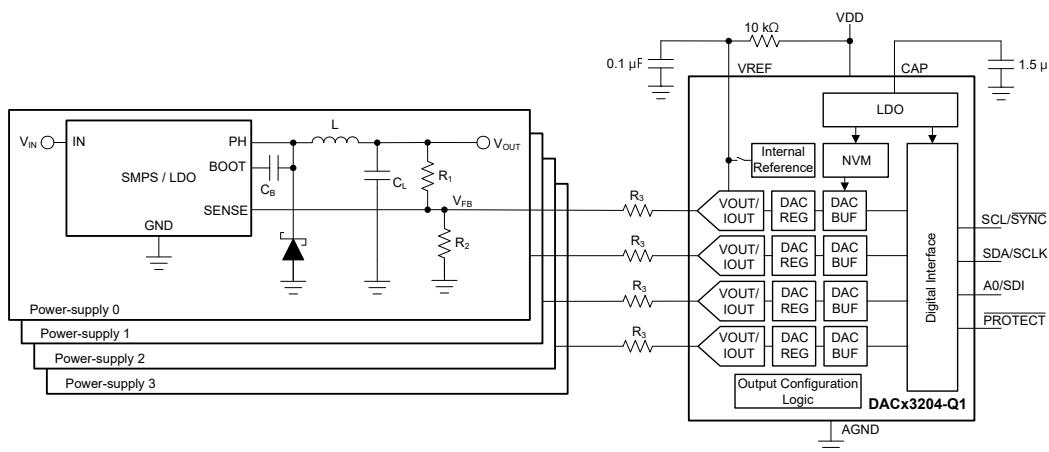

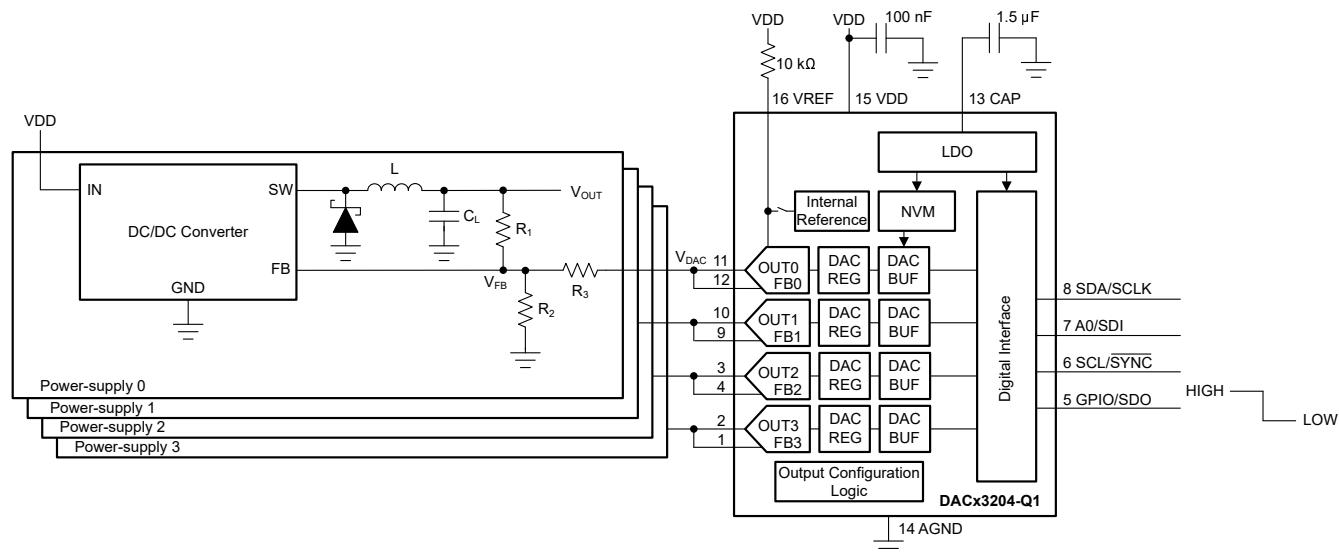

DACx3204-Q1 を使用した電圧マージン設定およびスケーリング

## Table of Contents

|                                                                            |    |                                                                |    |

|----------------------------------------------------------------------------|----|----------------------------------------------------------------|----|

| 1 特長                                                                       | 1  | 6.18 Typical Characteristics: Current Output                   | 20 |

| 2 アプリケーション                                                                 | 1  | 6.19 Typical Characteristics: Comparator                       | 24 |

| 3 概要                                                                       | 1  | 6.20 Typical Characteristics: General                          | 25 |

| 4 Revision History                                                         | 3  | <b>7 Detailed Description</b>                                  | 26 |

| 5 Pin Configuration and Functions                                          | 4  | 7.1 Overview                                                   | 26 |

| 6 Specifications                                                           | 5  | 7.2 Functional Block Diagram                                   | 26 |

| 6.1 Absolute Maximum Ratings                                               | 5  | 7.3 Feature Description                                        | 27 |

| 6.2 ESD Ratings                                                            | 5  | 7.4 Device Functional Modes                                    | 29 |

| 6.3 Recommended Operating Conditions                                       | 5  | 7.5 Programming                                                | 46 |

| 6.4 Thermal Information                                                    | 5  | 7.6 Register Map                                               | 55 |

| 6.5 Electrical Characteristics: Voltage Output                             | 6  | <b>8 Application and Implementation</b>                        | 74 |

| 6.6 Electrical Characteristics: Current Output                             | 8  | 8.1 Application Information                                    | 74 |

| 6.7 Electrical Characteristics: Comparator Mode                            | 9  | 8.2 Typical Application                                        | 74 |

| 6.8 Electrical Characteristics: General                                    | 10 | 8.3 Power Supply Recommendations                               | 77 |

| 6.9 Timing Requirements: I <sup>2</sup> C Standard Mode                    | 11 | 8.4 Layout                                                     | 77 |

| 6.10 Timing Requirements: I <sup>2</sup> C Fast Mode                       | 11 | <b>9 Device and Documentation Support</b>                      | 78 |

| 6.11 Timing Requirements: I <sup>2</sup> C Fast Mode Plus                  | 11 | 9.1 Documentation Support                                      | 78 |

| 6.12 Timing Requirements: SPI Write Operation                              | 12 | 9.2 ドキュメントの更新通知を受け取る方法                                         | 78 |

| 6.13 Timing Requirements: SPI Read and Daisy<br>Chain Operation (FSDO = 0) | 12 | 9.3 サポート・リソース                                                  | 78 |

| 6.14 Timing Requirements: SPI Read and Daisy<br>Chain Operation (FSDO = 1) | 12 | 9.4 Trademarks                                                 | 78 |

| 6.15 Timing Requirements: GPIO                                             | 13 | 9.5 静電気放電に関する注意事項                                              | 78 |

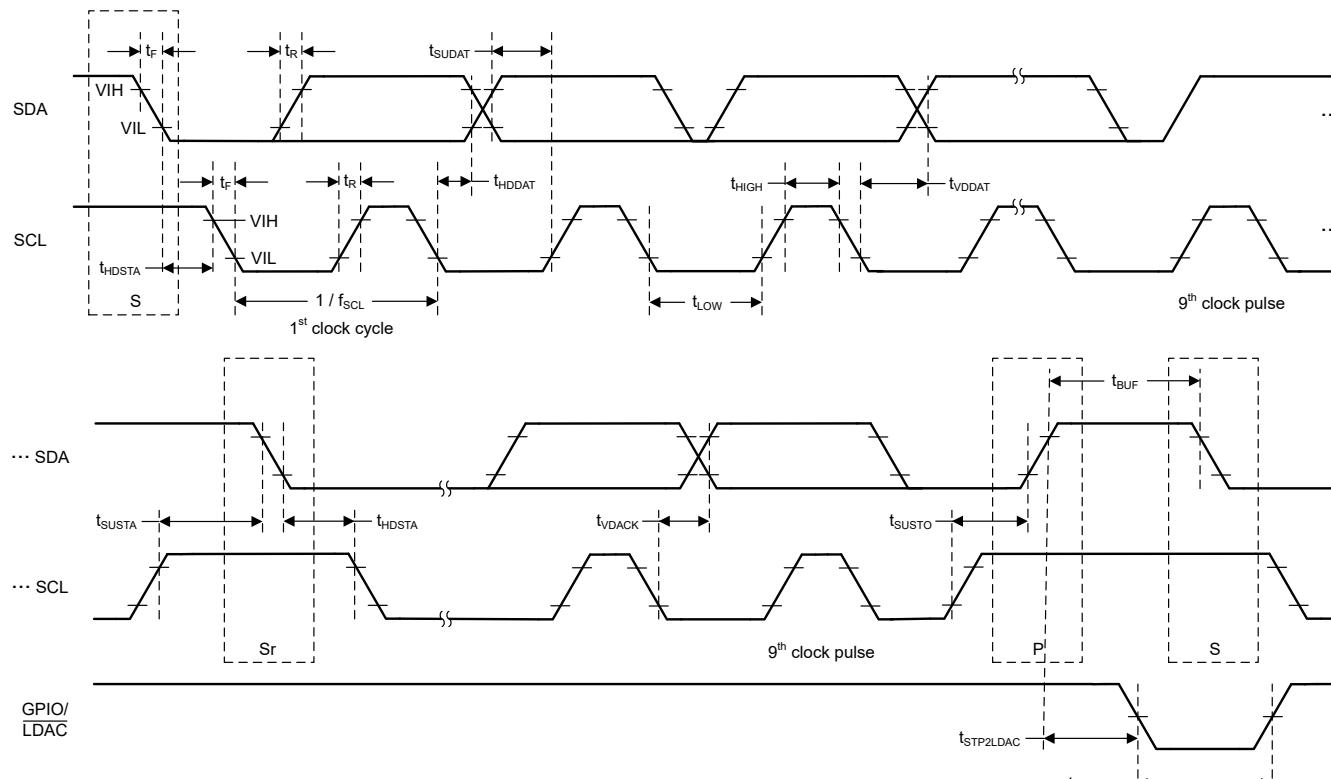

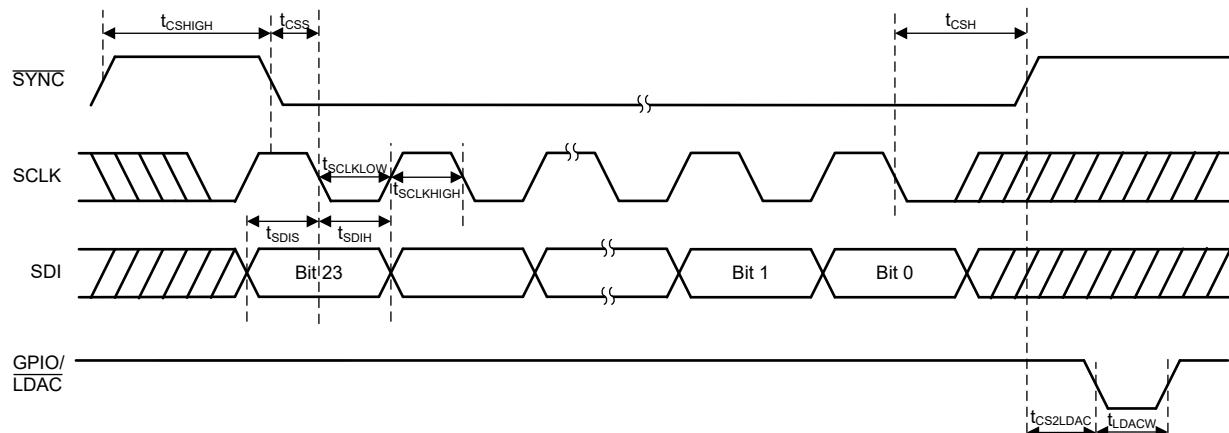

| 6.16 Timing Diagrams                                                       | 13 | 9.6 用語集                                                        | 78 |

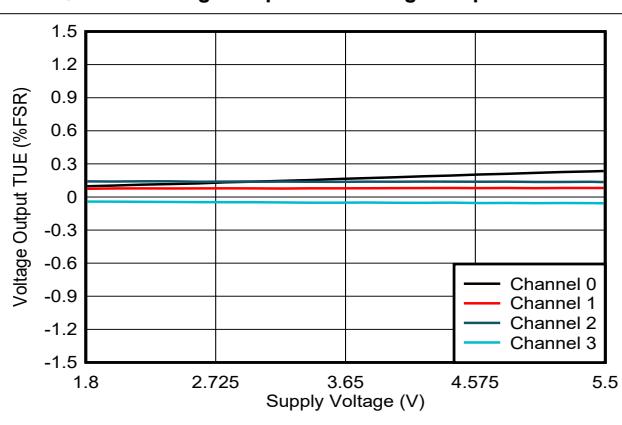

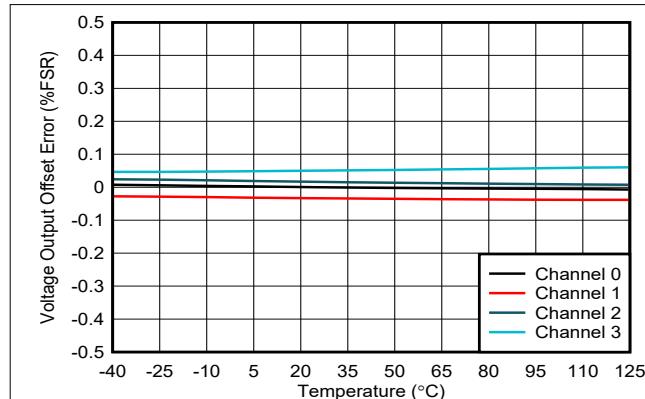

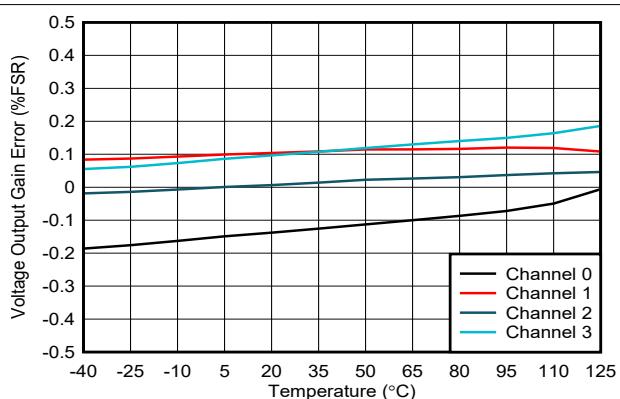

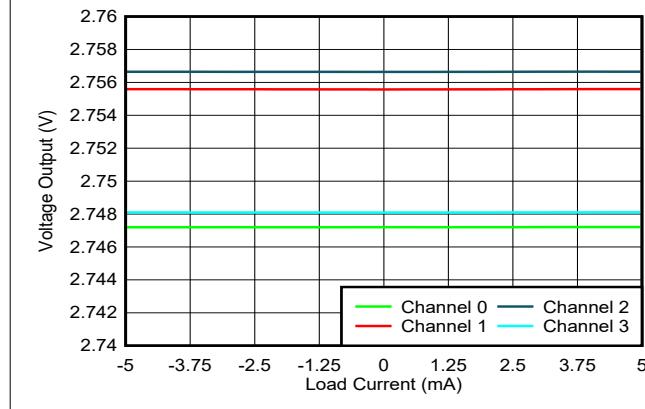

| 6.17 Typical Characteristics: Voltage Output                               | 15 | <b>10 Mechanical, Packaging, and Orderable<br/>Information</b> | 78 |

## 4 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE       | REVISION | NOTES           |

|------------|----------|-----------------|

| April 2023 | *        | Initial Release |

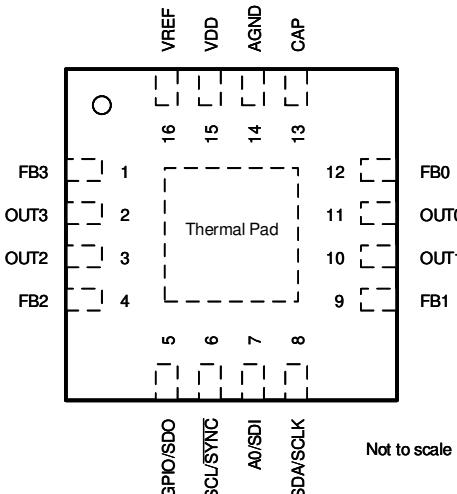

## 5 Pin Configuration and Functions

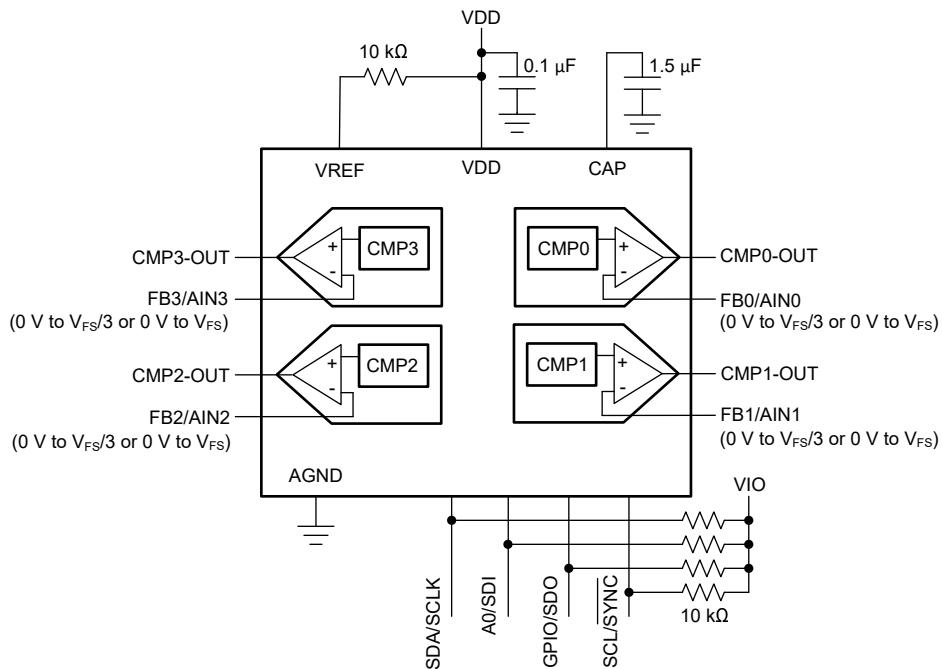

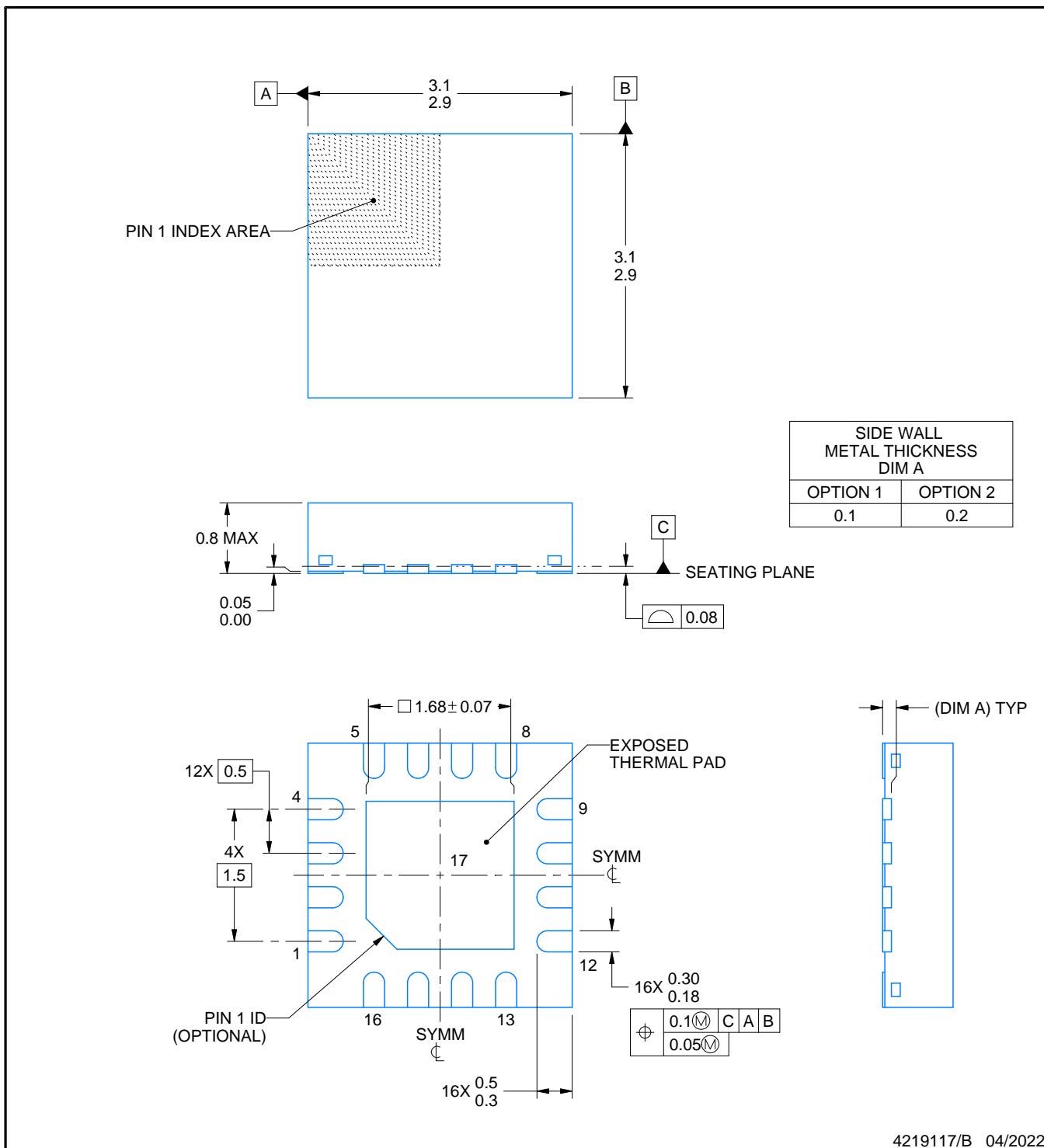

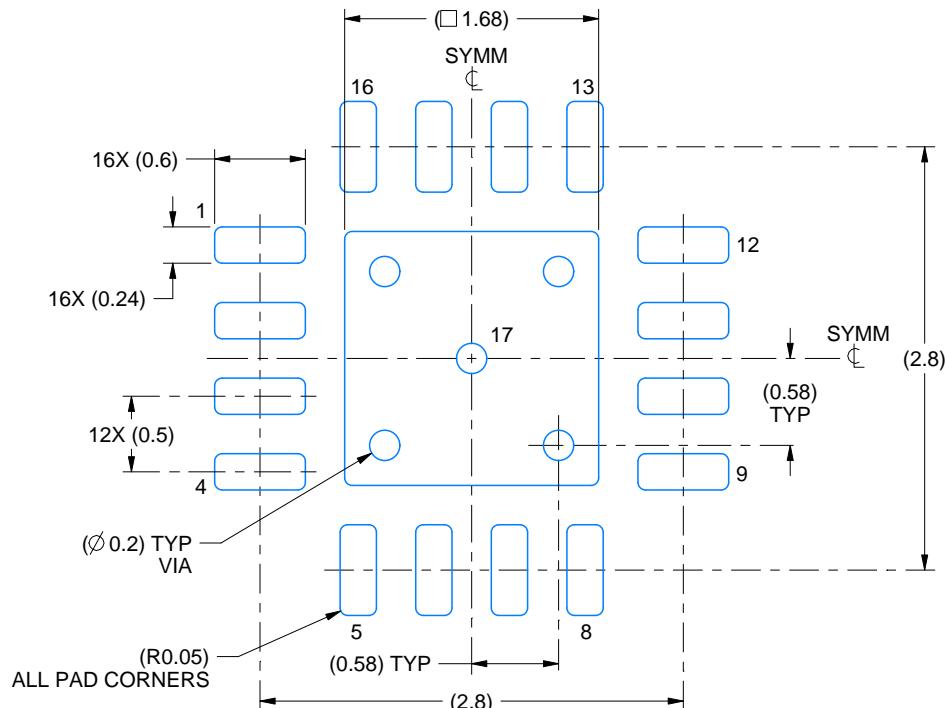

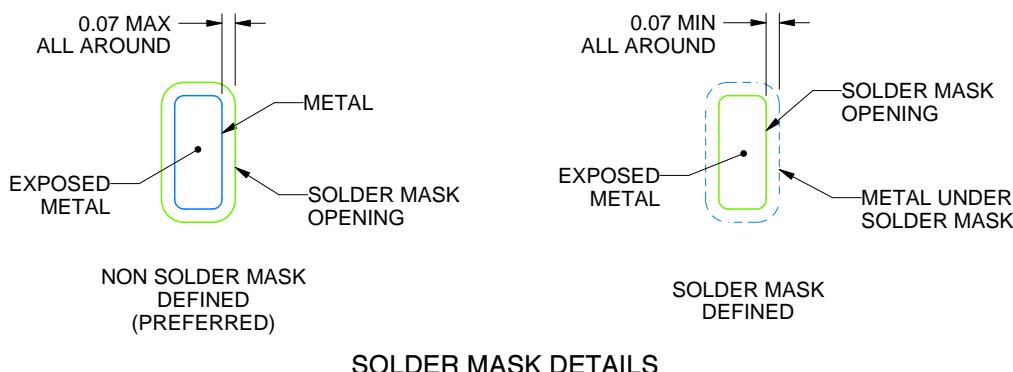

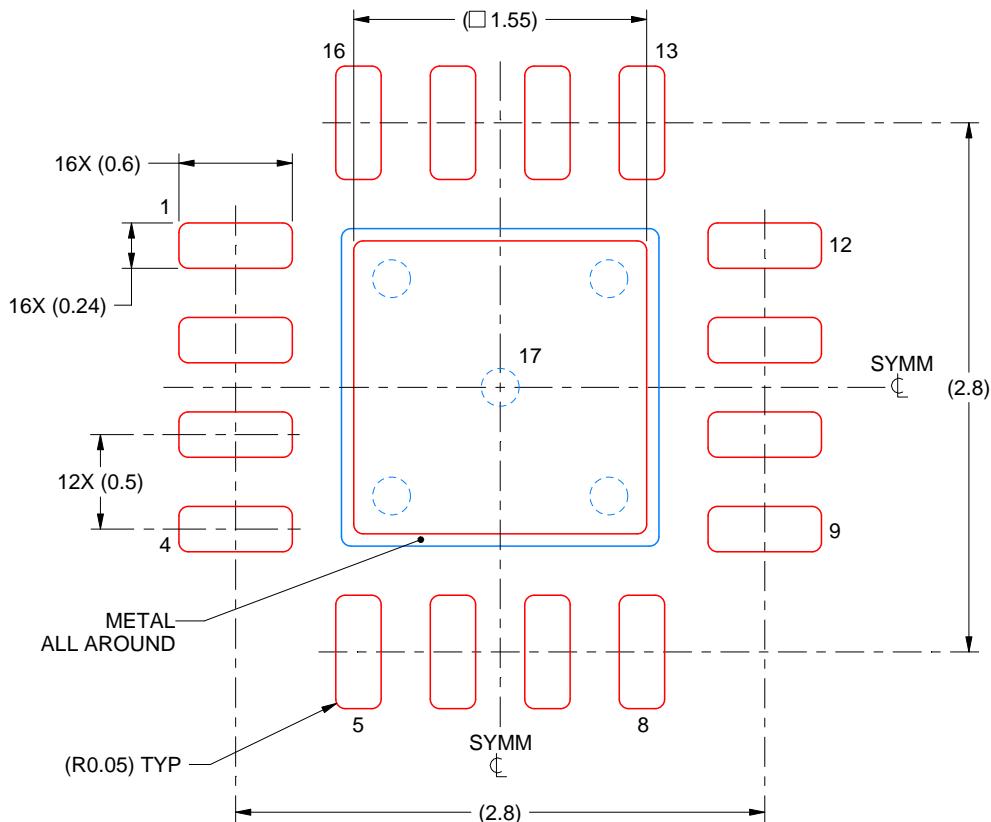

図 5-1. RTE Package, 16-pin WQFN, Top View

表 5-1. Pin Functions

| PIN |             | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                                     |

|-----|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        |              |                                                                                                                                                                                                                                                                                                 |

| 1   | FB3         | Input        | Voltage feedback pin for channel 3. In voltage-output mode, connect to OUT3 for closed-loop amplifier output. In current-output mode, keep the FB3 pin unconnected to minimize leakage current.                                                                                                 |

| 2   | OUT3        | Output       | Analog output voltage from DAC channel 3.                                                                                                                                                                                                                                                       |

| 3   | OUT2        | Output       | Analog output voltage from DAC channel 2.                                                                                                                                                                                                                                                       |

| 4   | FB2         | Input        | Voltage feedback pin for channel 2. In voltage-output mode, connect to OUT2 for closed-loop amplifier output. In current-output mode, keep the FB2 pin unconnected to minimize leakage current.                                                                                                 |

| 5   | GPIO/SDO    | Input/Output | General-purpose input/output configurable as LDAC, PD, PROTECT, RESET, SDO, and STATUS. For STATUS and SDO, connect the pin to the IO voltage with an external pullup resistor. If unused, connect the GPIO pin to VDD or AGND using an external resistor. This pin can ramp up before VDD.     |

| 6   | SCL/SYNC    | Output       | I <sup>2</sup> C serial interface clock or SPI chip select input. This pin must be connected to the IO voltage using an external pullup resistor. This pin can ramp up before VDD.                                                                                                              |

| 7   | A0/SDI      | Input        | Address configuration pin for I <sup>2</sup> C or serial data input for SPI. For A0, connect this pin to VDD, AGND, SDA, or SCL for address configuration (セクション 7.5.2.2.1). For SDI, this pin need not be pulled up or pulled down. This pin can ramp up before VDD.                           |

| 8   | SDA/SCLK    | Input/Output | Bidirectional I <sup>2</sup> C serial data bus or SPI clock input. This pin must be connected to the IO voltage using an external pullup resistor in the I <sup>2</sup> C mode. This pin can ramp up before VDD.                                                                                |

| 9   | FB1         | Input        | Voltage feedback pin for channel 1. In voltage-output mode, connect to OUT1 for closed-loop amplifier output. In current-output mode, keep the FB1 pin unconnected to minimize leakage current.                                                                                                 |

| 10  | OUT1        | Output       | Analog output voltage from DAC channel 1.                                                                                                                                                                                                                                                       |

| 11  | OUT0        | Output       | Analog output voltage from DAC channel 0.                                                                                                                                                                                                                                                       |

| 12  | FB0         | Input        | Voltage feedback pin for channel 0. In voltage-output mode, connect to OUT0 for closed-loop amplifier output. In current-output mode, keep the FB0 pin unconnected to minimize leakage current.                                                                                                 |

| 13  | CAP         | Power        | External bypass capacitor for the internal LDO. Connect a capacitor (approximately 1.5 $\mu$ F) between CAP and AGND.                                                                                                                                                                           |

| 14  | AGND        | Ground       | Ground reference point for all circuitry on the device.                                                                                                                                                                                                                                         |

| 15  | VDD         | Power        | Supply voltage.                                                                                                                                                                                                                                                                                 |

| 16  | VREF        | Power        | External reference input. Connect a capacitor (approximately 0.1 $\mu$ F) between VREF and AGND. Use a pullup resistor to VDD when the external reference is not used. This pin must not ramp up before VDD. In case an external reference is used, make sure the reference ramps up after VDD. |

| —   | Thermal Pad | Ground       | Connect the thermal pad to AGND.                                                                                                                                                                                                                                                                |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|           |                                                          | MIN  | MAX            | UNIT |

|-----------|----------------------------------------------------------|------|----------------|------|

| $V_{DD}$  | Supply voltage, $V_{DD}$ to AGND                         | −0.3 | 6              | V    |

|           | Digital inputs to AGND                                   | −0.3 | $V_{DD} + 0.3$ | V    |

|           | $V_{FBX}$ to AGND                                        | −0.3 | $V_{DD} + 0.3$ | V    |

|           | $V_{OUTX}$ to AGND                                       | −0.3 | $V_{DD} + 0.3$ | V    |

| $V_{REF}$ | External reference, $V_{REF}$ to AGND                    | −0.3 | $V_{DD} + 0.3$ | V    |

|           | Current into any pin except the OUTx, VDD, and AGND pins | −10  | 10             | mA   |

| $T_J$     | Junction temperature                                     | −40  | 150            | °C   |

| $T_{stg}$ | Storage temperature                                      | −65  | 150            | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 6.2 ESD Ratings

|             |                            |                                                                                           | VALUE | UNIT |

|-------------|----------------------------|-------------------------------------------------------------------------------------------|-------|------|

| $V_{(ESD)}$ | Electrostatic<br>discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD classification level 2 | ±2000 | V    |

|             |                            | Charged device model (CDM), per AEC Q100-011<br>CDM ESD classification level C4B          | ±750  |      |

|             |                            | All pins                                                                                  | ±500  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|           |                                                                         | MIN  | NOM | MAX      | UNIT |

|-----------|-------------------------------------------------------------------------|------|-----|----------|------|

| $V_{DD}$  | Positive supply voltage to ground (AGND)                                | 1.7  |     | 5.5      | V    |

| $V_{REF}$ | External reference to ground (AGND)                                     | 1.7  |     | $V_{DD}$ | V    |

| $V_{IH}$  | Digital input high voltage, $1.7 \text{ V} < V_{DD} \leq 5.5 \text{ V}$ | 1.62 |     |          | V    |

| $V_{IL}$  | Digital input low voltage                                               |      |     | 0.4      | V    |

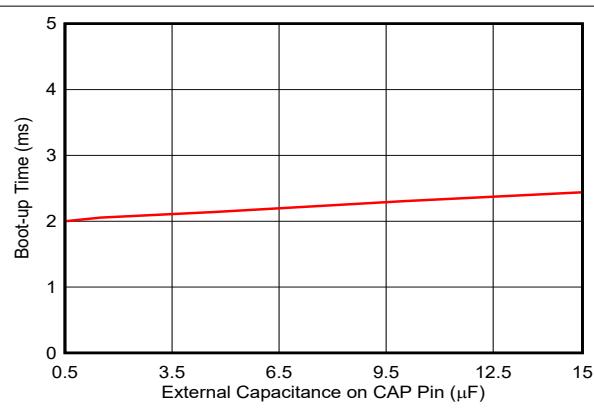

| $C_{CAP}$ | External capacitor on CAP pin                                           | 0.5  |     | 15       | μF   |

| $T_A$     | Ambient temperature                                                     | −40  |     | 125      | °C   |

### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | DACx3204-Q1 | UNIT |

|-------------------------------|----------------------------------------------|-------------|------|

|                               |                                              | RTE (WQFN)  |      |

|                               |                                              | 16 PINS     |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 49          | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 50          | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 24.1        | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 1.1         | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 24.1        | °C/W |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | 8.7         | °C/W |

(1) For information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics application report](#).

## 6.5 Electrical Characteristics: Voltage Output

all minimum and maximum specifications at  $-40^\circ\text{C} \leq T_A \leq +125^\circ\text{C}$ ; typical specifications at  $T_A = 25^\circ\text{C}$ ,  $1.7 \text{ V} \leq V_{DD} \leq 5.5 \text{ V}$ , DAC reference tied to VDD, gain = 1  $\times$ , DAC output pin (OUT) loaded with resistive load ( $R_L = 5 \text{ k}\Omega$  to AGND) and capacitive load ( $C_L = 200 \text{ pF}$  to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

| PARAMETER                                               |                                                                                                                                        | TEST CONDITIONS                                                                                                                                                                                                                                                                          | MIN          | TYP      | MAX  | UNIT                         |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|------|------------------------------|

| <b>STATIC PERFORMANCE</b>                               |                                                                                                                                        |                                                                                                                                                                                                                                                                                          |              |          |      |                              |

| Resolution                                              | DAC63204-Q1                                                                                                                            |                                                                                                                                                                                                                                                                                          | 12           |          |      | Bits                         |

|                                                         | DAC53204-Q1                                                                                                                            |                                                                                                                                                                                                                                                                                          | 10           |          |      |                              |

| INL                                                     | DAC63204-Q1                                                                                                                            |                                                                                                                                                                                                                                                                                          | -5           | 5        |      | LSB                          |

|                                                         | DAC53204-Q1                                                                                                                            |                                                                                                                                                                                                                                                                                          | -1.25        | 1.25     |      |                              |

| DNL                                                     | Differential nonlinearity <sup>(1)</sup>                                                                                               |                                                                                                                                                                                                                                                                                          | -1           | 1        |      | LSB                          |

| Zero-code error <sup>(4)</sup>                          | Code 0d into DAC, external reference, $V_{DD} = 5.5 \text{ V}$                                                                         |                                                                                                                                                                                                                                                                                          | 6            | 12       |      | mV                           |

|                                                         | Code 0d into DAC, internal $V_{REF}$ , gain = 4 $\times$ , $V_{DD} = 5.5 \text{ V}$                                                    |                                                                                                                                                                                                                                                                                          | 6            | 15       |      |                              |

| Zero-code error temperature coefficient <sup>(4)</sup>  | Code 0d into DAC                                                                                                                       |                                                                                                                                                                                                                                                                                          | $\pm 10$     |          |      | $\mu\text{V}/^\circ\text{C}$ |

| Offset error <sup>(4) (6)</sup>                         | 1.7 $\text{V} \leq V_{DD} < 2.7 \text{ V}$ , FBx pin shorted to OUTx, DAC code: 32d for 12-bit resolution, 8d for 10-bit resolution    |                                                                                                                                                                                                                                                                                          | -0.75        | 0.3      | 0.75 | %FSR                         |

|                                                         | 2.7 $\text{V} \leq V_{DD} \leq 5.5 \text{ V}$ , FBx pin shorted to OUTx, DAC code: 32d for 12-bit resolution, 8d for 10-bit resolution |                                                                                                                                                                                                                                                                                          | -0.5         | 0.25     | 0.5  |                              |

| Offset-error temperature coefficient <sup>(4)</sup>     | FBx pin shorted to OUTx, DAC code: 32d for 12-bit resolution, 8d for 10-bit resolution                                                 |                                                                                                                                                                                                                                                                                          | $\pm 0.0003$ |          |      | %FSR/ $^\circ\text{C}$       |

| Gain error <sup>(4)</sup>                               | Between end-point codes: 32d to 4064d for 12-bit resolution, 8d to 1016d for 10-bit resolution                                         |                                                                                                                                                                                                                                                                                          | -0.5         | 0.25     | 0.5  | %FSR                         |

| Gain-error temperature coefficient <sup>(4)</sup>       | Between end-point codes: 32d to 4064d for 12-bit resolution, 8d to 1016d for 10-bit resolution                                         |                                                                                                                                                                                                                                                                                          | $\pm 0.0008$ |          |      | %FSR/ $^\circ\text{C}$       |

| Full-scale error <sup>(4) (6)</sup>                     | 1.7 $\text{V} \leq V_{DD} < 2.7 \text{ V}$ , DAC at full-scale                                                                         |                                                                                                                                                                                                                                                                                          | -1           | 1        |      | %FSR                         |

|                                                         | 2.7 $\text{V} \leq V_{DD} \leq 5.5 \text{ V}$ , DAC at full-scale                                                                      |                                                                                                                                                                                                                                                                                          | -0.6         | 0.6      |      |                              |

| Full-scale-error temperature coefficient <sup>(4)</sup> | DAC at full-scale                                                                                                                      |                                                                                                                                                                                                                                                                                          | $\pm 0.0008$ |          |      | %FSR/ $^\circ\text{C}$       |

| <b>OUTPUT</b>                                           |                                                                                                                                        |                                                                                                                                                                                                                                                                                          |              |          |      |                              |

|                                                         | Output voltage                                                                                                                         | Reference tied to $V_{DD}$                                                                                                                                                                                                                                                               | 0            | $V_{DD}$ |      | V                            |

| $C_L$                                                   | Capacitive load <sup>(2)</sup>                                                                                                         | $R_L = \text{infinite}$ , phase margin = 30°                                                                                                                                                                                                                                             |              | 200      |      | pF                           |

|                                                         |                                                                                                                                        | Phase margin = 30°                                                                                                                                                                                                                                                                       |              | 1000     |      |                              |

| Short-circuit current                                   |                                                                                                                                        | $V_{DD} = 1.7 \text{ V}$ , full-scale output shorted to AGND or zero-scale output shorted to $V_{DD}$                                                                                                                                                                                    |              | 15       |      | mA                           |

|                                                         |                                                                                                                                        | $V_{DD} = 2.7 \text{ V}$ , full-scale output shorted to AGND or zero-scale output shorted to $V_{DD}$                                                                                                                                                                                    |              | 50       |      |                              |

|                                                         |                                                                                                                                        | $V_{DD} = 5.5 \text{ V}$ , full-scale output shorted to AGND or zero-scale output shorted to $V_{DD}$                                                                                                                                                                                    |              | 60       |      |                              |

| Output-voltage headroom <sup>(2)</sup>                  |                                                                                                                                        | To $V_{DD}$ (DAC output unloaded, internal reference = 1.21 V), $V_{DD} \geq 1.21 \text{ V} \times \text{gain} + 0.2 \text{ V}$                                                                                                                                                          |              | 0.2      |      | V                            |

|                                                         |                                                                                                                                        | To $V_{DD}$ and AGND (DAC output unloaded, external reference at $V_{DD}$ , gain = 1 $\times$ , the VREF pin is not shorted to VDD)                                                                                                                                                      |              | 0.8      |      |                              |

|                                                         |                                                                                                                                        | To $V_{DD}$ and AGND ( $I_{LOAD} = 10 \text{ mA}$ at $V_{DD} = 5.5 \text{ V}$ , $I_{LOAD} = 3 \text{ mA}$ at $V_{DD} = 2.7 \text{ V}$ , $I_{LOAD} = 1 \text{ mA}$ at $V_{DD} = 1.8 \text{ V}$ ), external reference at $V_{DD}$ , gain = 1 $\times$ , the VREF pin is not shorted to VDD |              | 10       |      |                              |

## 6.5 Electrical Characteristics: Voltage Output (continued)

all minimum and maximum specifications at  $-40^{\circ}\text{C} \leq T_A \leq +125^{\circ}\text{C}$ ; typical specifications at  $T_A = 25^{\circ}\text{C}$ ,  $1.7 \text{ V} \leq V_{\text{DD}} \leq 5.5 \text{ V}$ , DAC reference tied to VDD, gain =  $1 \times$ , DAC output pin (OUT) loaded with resistive load ( $R_L = 5 \text{ k}\Omega$  to AGND) and capacitive load ( $C_L = 200 \text{ pF}$  to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

| PARAMETER           |                                                    | TEST CONDITIONS                                                                                                                                                               | MIN  | TYP  | MAX | UNIT                           |

|---------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|--------------------------------|

| $Z_O$               | $V_{\text{FB}}$ dc output impedance <sup>(3)</sup> | DAC output enabled, internal reference (gain = $1.5 \times$ or $2 \times$ ) or external reference at $V_{\text{DD}}$ (gain = $1 \times$ ), the VREF pin is not shorted to VDD | 400  | 500  | 600 | $\text{k}\Omega$               |

|                     |                                                    | DAC output enabled, internal $V_{\text{REF}}$ , gain = $3 \times$ or $4 \times$                                                                                               | 325  | 400  | 485 |                                |

|                     | Power-supply rejection ratio (dc)                  | Internal $V_{\text{REF}}$ , gain = $2 \times$ , DAC at midscale, $V_{\text{DD}} = 5 \text{ V} \pm 10\%$                                                                       |      | 0.25 |     | $\text{mV/V}$                  |

| DYNAMIC PERFORMANCE |                                                    |                                                                                                                                                                               |      |      |     |                                |

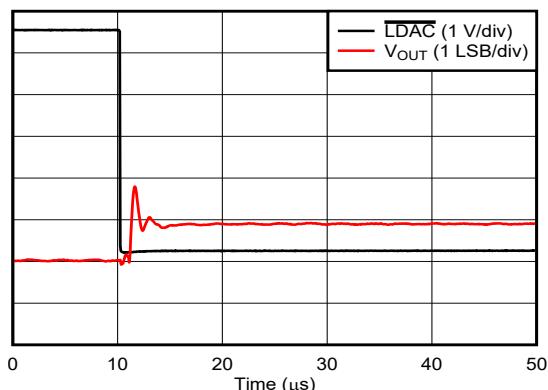

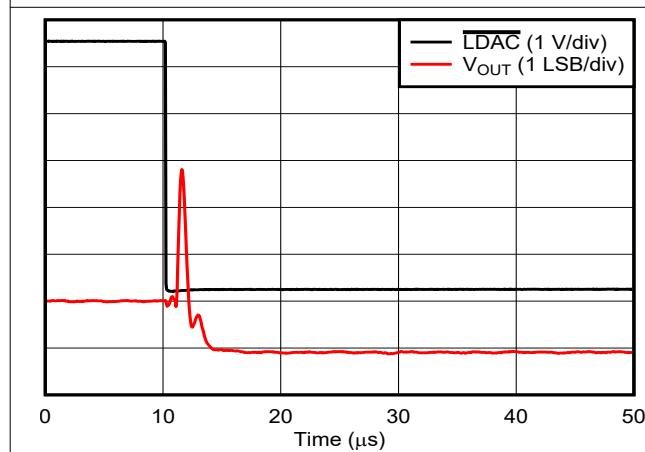

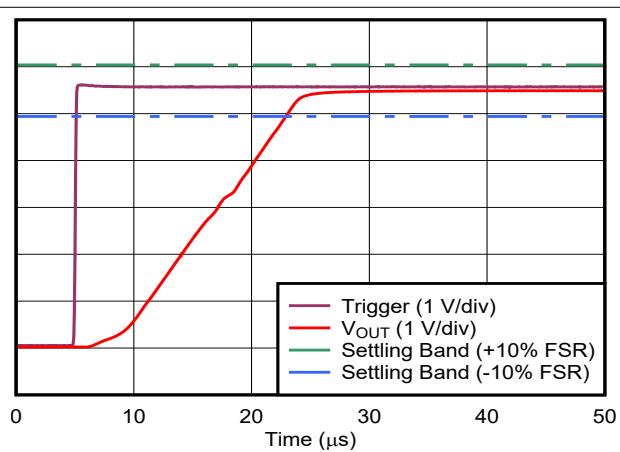

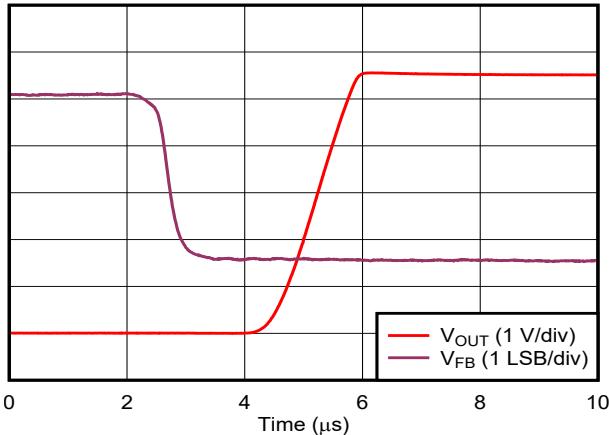

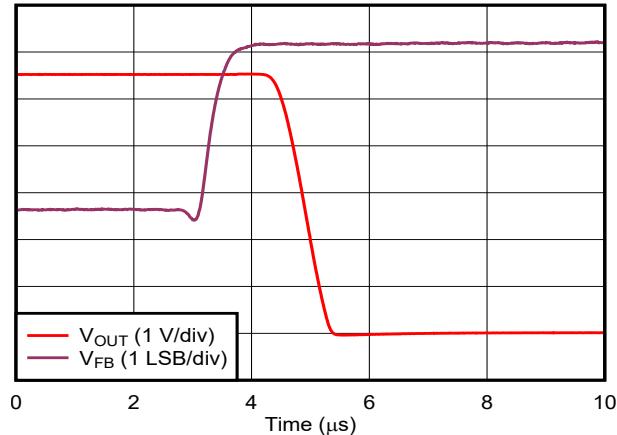

| $t_{\text{sett}}$   | Output voltage settling time                       | 1/4 to 3/4 scale and 3/4 to 1/4 scale settling to 10%FSR, $V_{\text{DD}} = 5.5 \text{ V}$                                                                                     | 20   |      |     | $\mu\text{s}$                  |

|                     |                                                    | 1/4 to 3/4 scale and 3/4 to 1/4 scale settling to 10%FSR, $V_{\text{DD}} = 5.5 \text{ V}$ , internal $V_{\text{REF}}$ , gain = $4 \times$                                     | 25   |      |     |                                |

|                     | Slew rate                                          | $V_{\text{DD}} = 5.5 \text{ V}$                                                                                                                                               | 0.3  |      |     | $\text{V}/\mu\text{s}$         |

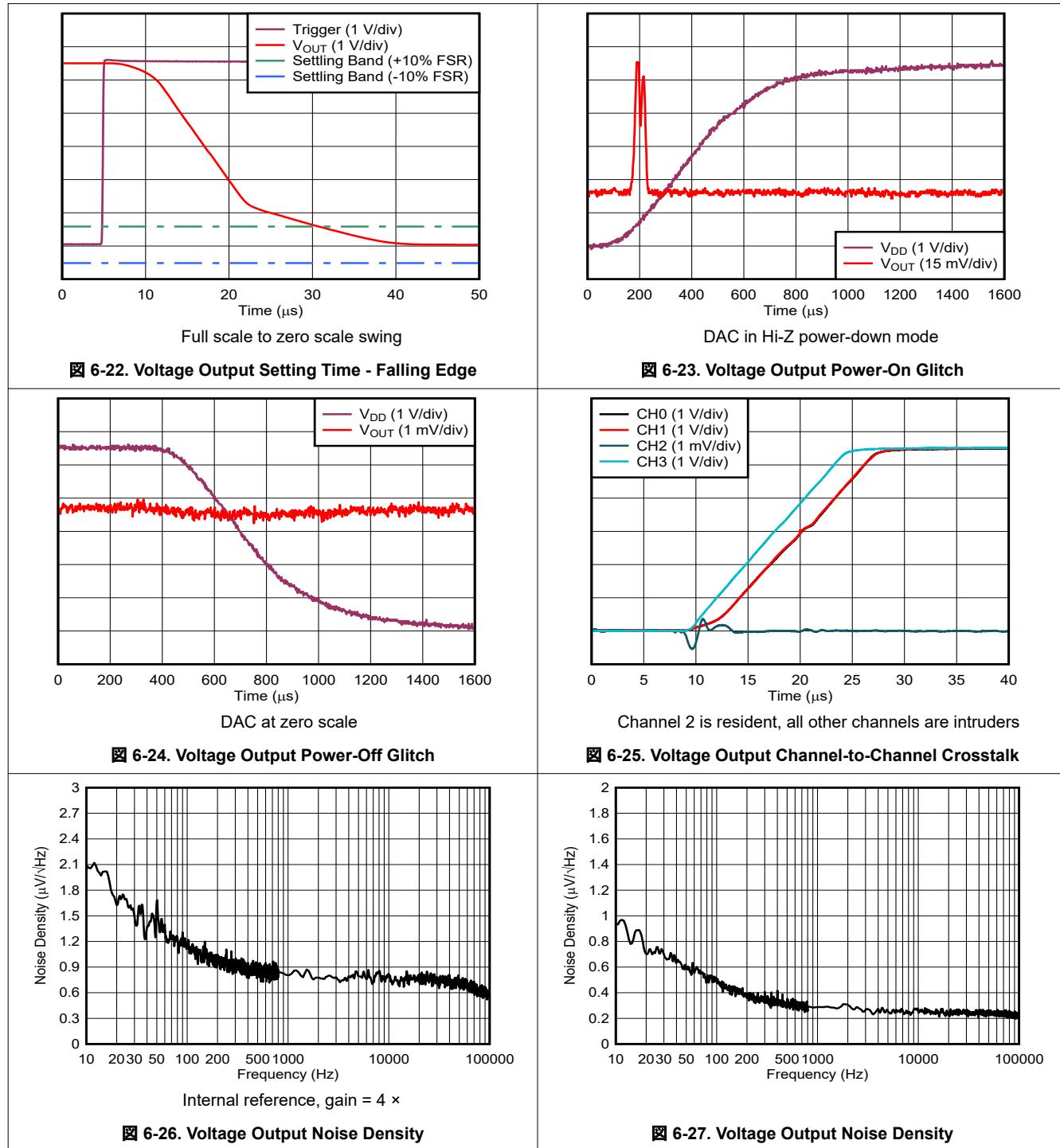

|                     | Power-on glitch magnitude                          | At startup (DAC output disabled)                                                                                                                                              | 75   |      |     | $\text{mV}$                    |

|                     |                                                    | At startup (DAC output disabled), $R_L = 100 \text{ k}\Omega$                                                                                                                 | 200  |      |     |                                |

|                     | Output-enable glitch magnitude                     | DAC output disabled to enabled (DAC registers at zero scale), $R_L = 100 \text{ k}\Omega$                                                                                     | 250  |      |     | $\text{mV}$                    |

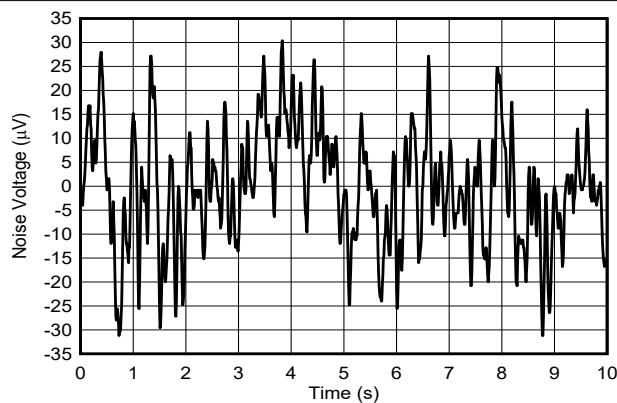

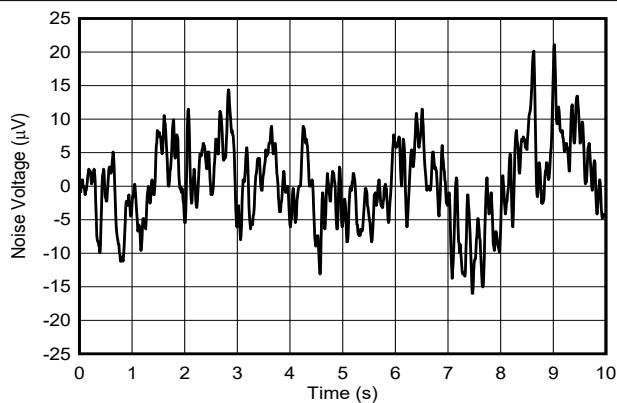

| $V_n$               | Output noise voltage (peak to peak)                | $f = 0.1 \text{ Hz}$ to $10 \text{ Hz}$ , DAC at midscale, $V_{\text{DD}} = 5.5 \text{ V}$                                                                                    | 50   |      |     | $\mu\text{V}_{\text{PP}}$      |

|                     |                                                    | Internal $V_{\text{REF}}$ , gain = $4 \times$ , $f = 0.1 \text{ Hz}$ to $10 \text{ Hz}$ , DAC at midscale, $V_{\text{DD}} = 5.5 \text{ V}$                                    | 90   |      |     |                                |

|                     | Output noise density                               | $f = 1 \text{ kHz}$ , DAC at midscale, $V_{\text{DD}} = 5.5 \text{ V}$                                                                                                        | 0.35 |      |     | $\mu\text{V}/\sqrt{\text{Hz}}$ |

|                     |                                                    | Internal $V_{\text{REF}}$ , gain = $4 \times$ , $f = 1 \text{ kHz}$ , DAC at midscale, $V_{\text{DD}} = 5.5 \text{ V}$                                                        | 0.9  |      |     |                                |

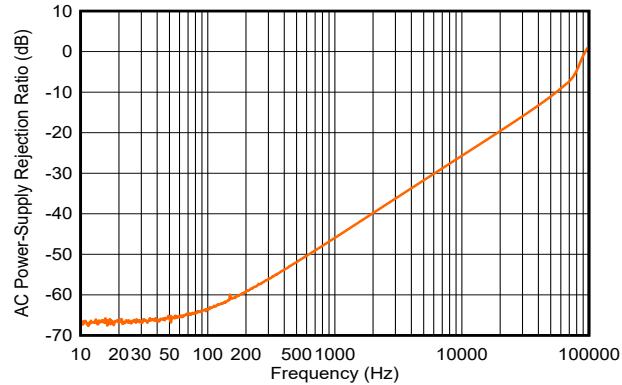

|                     | Power-supply rejection ratio (ac) <sup>(3)</sup>   | Internal $V_{\text{REF}}$ , gain = $4 \times$ , 200-mV 50-Hz or 60-Hz sine wave superimposed on power supply voltage, DAC at midscale                                         | -68  |      |     | $\text{dB}$                    |

|                     | Code change glitch impulse                         | $\pm 1\text{-LSB}$ change around midscale (including feedthrough)                                                                                                             | 10   |      |     | $\text{nV}\cdot\text{s}$       |

|                     | Code change glitch impulse magnitude               | $\pm 1\text{-LSB}$ change around midscale (including feedthrough)                                                                                                             | 15   |      |     | $\text{mV}$                    |

| POWER               |                                                    |                                                                                                                                                                               |      |      |     |                                |

| $I_{\text{DD}}$     | Current flowing into VDD <sup>(4) (5)</sup>        | Normal operation, DACs at full scale, digital pins static, external reference at $V_{\text{DD}}$ but the VREF pin is not shorted to VDD                                       | 150  |      |     | $\mu\text{A}/\text{ch}$        |

- (1) Measured with DAC output unloaded. For external reference and internal reference  $V_{\text{DD}} \geq 1.21 \times \text{gain} + 0.2 \text{ V}$ , between end-point codes: 32d to 4064d for 12-bit resolution, 8d to 1016d for 10-bit resolution.

- (2) Specified by design and characterization, not production tested.

- (3) Specified with 200-mV headroom with respect to reference value when internal reference is used.

- (4) Measured with DAC output unloaded.

- (5) The total power consumption is calculated by  $I_{\text{DD}} \times (\text{total number of channels powered on}) + (\text{sleep-mode current})$ .

- (6) When a DAC channel is configured in IOUT mode for long term and then switched to VOUT mode, the VOUT mode can show parametric drift.

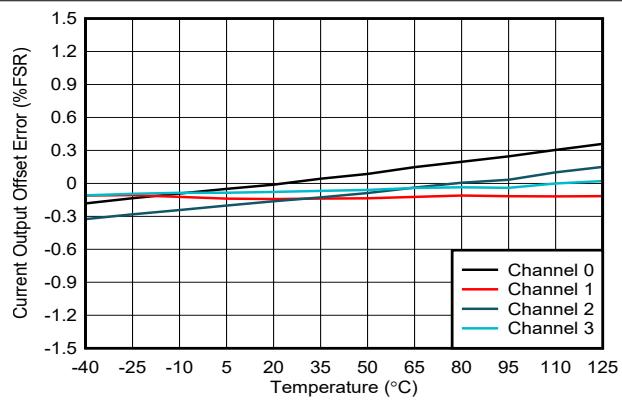

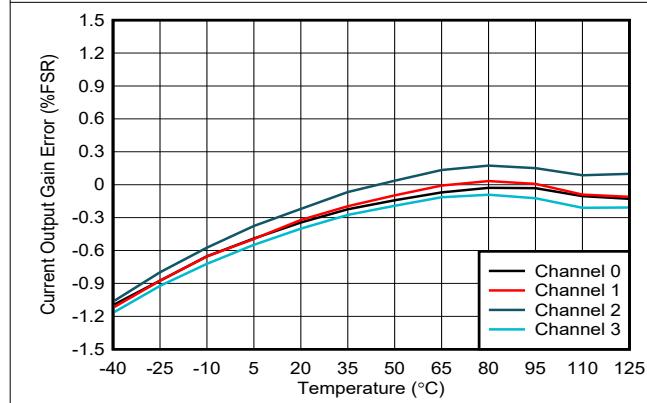

## 6.6 Electrical Characteristics: Current Output

all minimum and maximum specifications at  $-40^{\circ}\text{C} \leq T_A \leq +125^{\circ}\text{C}$ ; typical specifications at  $T_A = 25^{\circ}\text{C}$ ,  $1.7 \text{ V} \leq V_{\text{DD}} \leq 5.5 \text{ V}$ ,  $\pm 250\text{-}\mu\text{A}$  output range, and digital inputs at VDD or AGND (unless otherwise noted)

| PARAMETER                  | TEST CONDITIONS                                         | MIN                                                                                                                                                                 | TYP       | MAX | UNIT                         |

|----------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|------------------------------|

| <b>STATIC PERFORMANCE</b>  |                                                         |                                                                                                                                                                     |           |     |                              |

| Resolution                 |                                                         | 8                                                                                                                                                                   |           |     | Bits                         |

| Offset error               | DAC at midscale                                         |                                                                                                                                                                     | $\pm 1$   |     | %FSR                         |

| Gain error                 | DAC codes between 0d and 255d                           |                                                                                                                                                                     | $\pm 1.3$ |     | %FSR                         |

| <b>OUTPUT</b>              |                                                         |                                                                                                                                                                     |           |     |                              |

|                            | Output compliance voltage <sup>(1)</sup>                | To $V_{\text{DD}}$ and AGND                                                                                                                                         | 400       |     | mV                           |

| $Z_O$                      | $I_{\text{OUT}}$ dc output impedance <sup>(2)</sup>     | DAC at midscale, DAC output kept at $V_{\text{DD}}/2$                                                                                                               | 60        |     | $\text{M}\Omega$             |

|                            | Power-supply rejection ratio (dc)                       | DAC at midscale, all bipolar ranges, $V_{\text{DD}}$ changed from 4.5 V to 5.5 V                                                                                    | 0.23      |     | LSB/V                        |

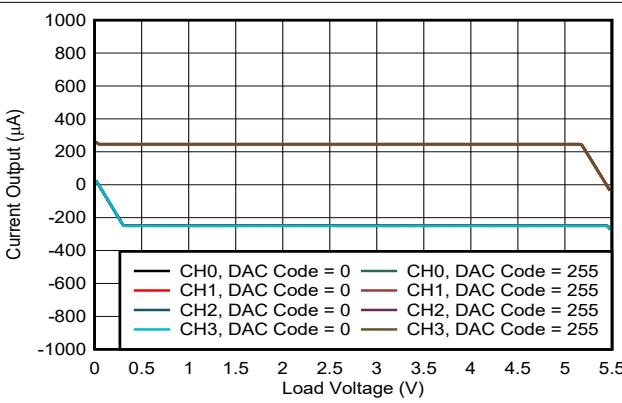

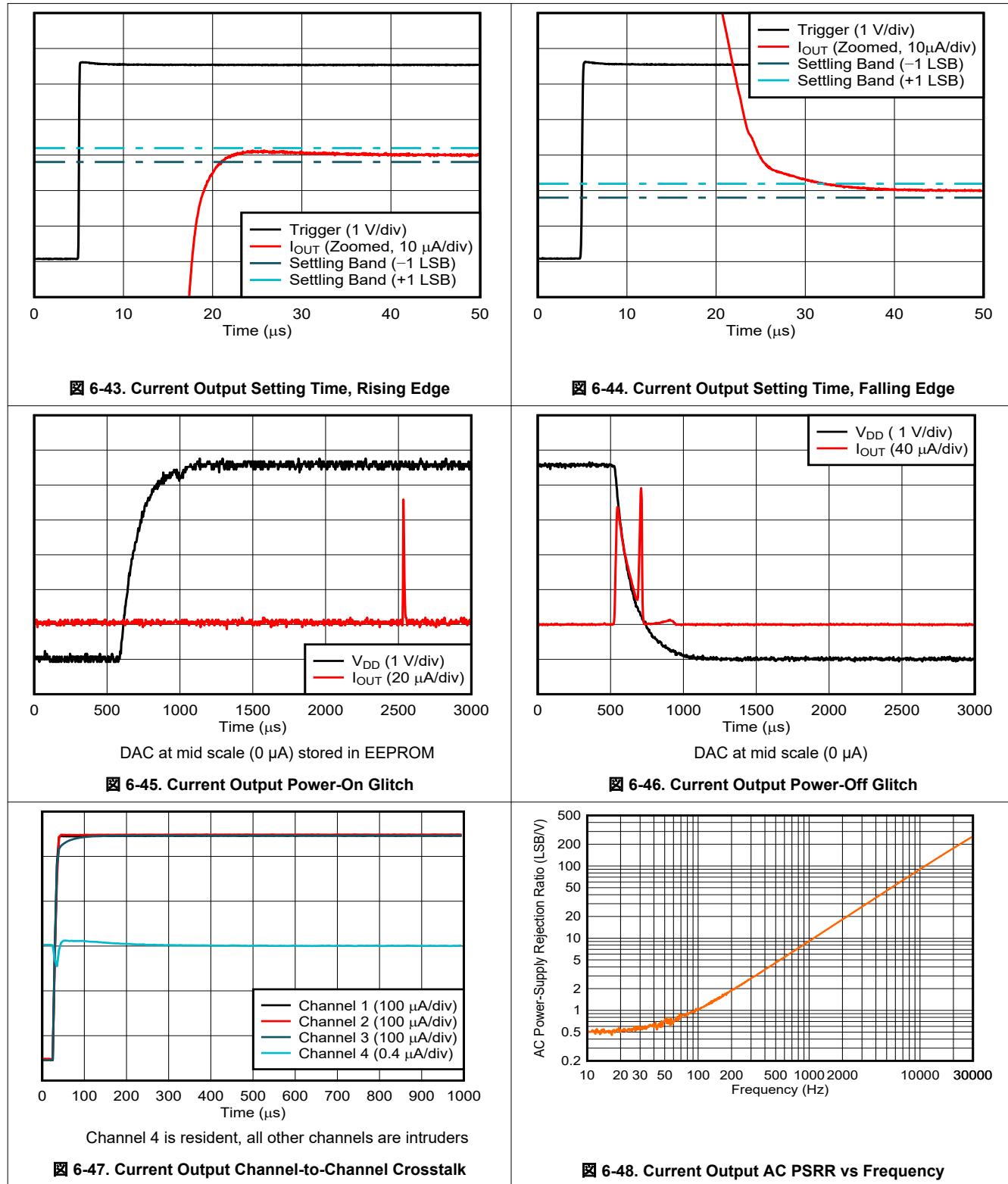

| <b>DYNAMIC PERFORMANCE</b> |                                                         |                                                                                                                                                                     |           |     |                              |

| $t_{\text{sett}}$          | Output current settling time                            | 1/4 to 3/4 scale and 3/4 to 1/4 scale settling to 1 LSB at 8-bit resolution, $V_{\text{DD}} = 5.5 \text{ V}$ , common-mode voltage at OUTx pin is $V_{\text{DD}}/2$ | 60        |     | $\mu\text{s}$                |

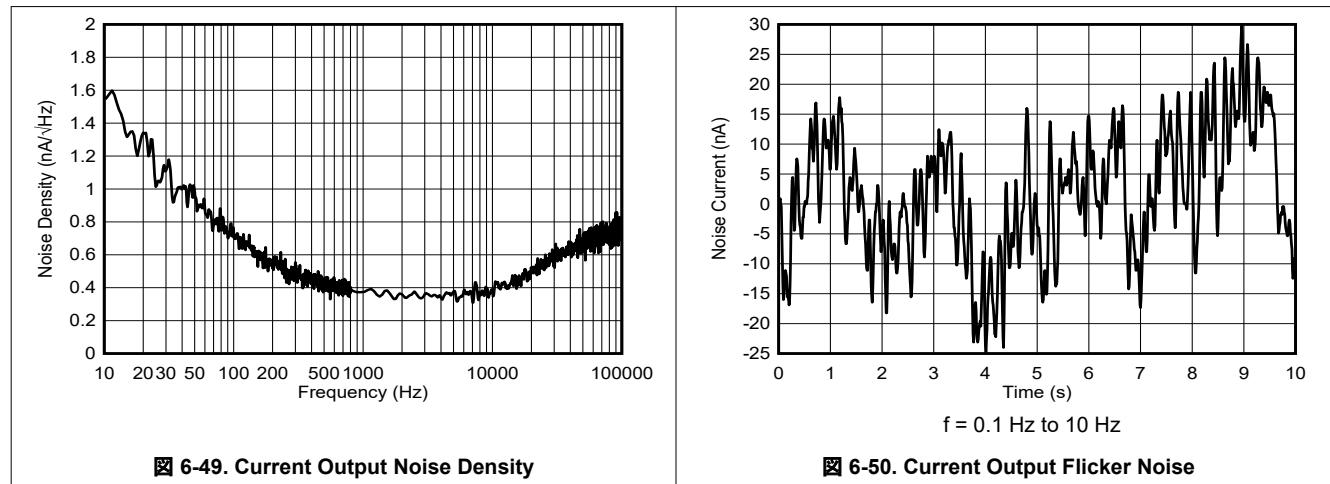

| $V_n$                      | Output noise current (peak to peak)                     | 0.1 Hz to 10 Hz, DAC at midscale, $V_{\text{DD}} = 5.5 \text{ V}$ , $\pm 250\text{-}\mu\text{A}$ output range                                                       | 150       |     | $\text{nA}_{\text{PP}}$      |

|                            | Output noise density                                    | $f = 1 \text{ kHz}$ , DAC at midscale, $V_{\text{DD}} = 5.5 \text{ V}$ , $\pm 250\text{-}\mu\text{A}$ output range                                                  | 1         |     | $\text{nA}/\sqrt{\text{Hz}}$ |

|                            | Power-supply rejection ratio (ac) <sup>(3)</sup>        | $\pm 250\text{-}\mu\text{A}$ output range, 200-mV 50-Hz or 60-Hz sine wave superimposed on power-supply voltage, DAC at midscale                                    | 0.65      |     | LSB/V                        |

| <b>POWER</b>               |                                                         |                                                                                                                                                                     |           |     |                              |

| $I_{\text{DD}}$            | Current flowing into $V_{\text{DD}}$ <sup>(3) (4)</sup> | Normal operation, DACs at full scale, $\pm 25\text{-}\mu\text{A}$ output range, digital pins static                                                                 | 42        | 50  | $\mu\text{A}/\text{ch}$      |

|                            |                                                         | Normal operation, DACs at full scale, $\pm 50\text{-}\mu\text{A}$ output range, digital pins static                                                                 | 56        | 70  |                              |

|                            |                                                         | Normal operation, DACs at full scale, $\pm 125\text{-}\mu\text{A}$ output range, digital pins static                                                                | 98        | 120 |                              |

|                            |                                                         | Normal operation, DACs at full scale, $\pm 250\text{-}\mu\text{A}$ output range, digital pins static                                                                | 167       | 200 |                              |

(1) Measured between DAC codes 0d and 255d.

(2) Specified by design and characterization, not production tested.

(3) The current flowing into  $V_{\text{DD}}$  does not account for the load current sourced or sunked on the OUTx pins. The VREF pin is connected to  $V_{\text{DD}}$ .

(4) The total power consumption is calculated by  $I_{\text{DD}} \times (\text{total number of channels powered on}) + (\text{sleep-mode current})$ .

## 6.7 Electrical Characteristics: Comparator Mode

all minimum and maximum specifications at  $-40^{\circ}\text{C} \leq T_A \leq +125^{\circ}\text{C}$ ; typical specifications at  $T_A = 25^{\circ}\text{C}$ ,  $1.7 \text{ V} \leq V_{\text{DD}} \leq 5.5 \text{ V}$ , DAC reference tied to VDD, gain =  $1 \times$  in voltage output mode, DAC output pin (OUT) loaded with resistive load ( $R_L = 5 \text{ k}\Omega$  to AGND) and capacitive load ( $C_L = 200 \text{ pF}$  to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

| PARAMETER                  | TEST CONDITIONS                                                      | MIN                                                                                                                                                                                                                                                                                                                                                          | TYP  | MAX                           | UNIT          |

|----------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------|---------------|

| <b>STATIC PERFORMANCE</b>  |                                                                      |                                                                                                                                                                                                                                                                                                                                                              |      |                               |               |

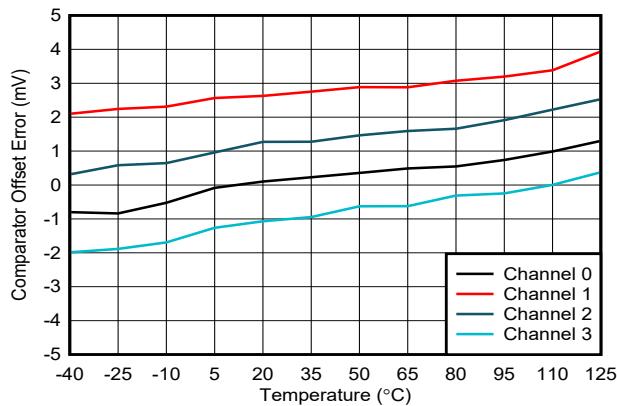

|                            | Offset error <sup>(1) (2)</sup>                                      | 1.7 V $\leq V_{\text{DD}} \leq 5.5 \text{ V}$ , DAC at midscale, comparator input at Hi-Z, and DAC operating with external reference                                                                                                                                                                                                                         | -7.5 | 0                             | 7.5 mV        |

|                            | Offset error time drift <sup>(1)</sup>                               | $V_{\text{DD}} = 5.5 \text{ V}$ , external reference, $T_A = 125^{\circ}\text{C}$ , FBx in Hi-Z mode, DAC at full scale and $V_{\text{FB}}$ at 0 V or DAC at zero scale and $V_{\text{FB}}$ at 1.84 V, drift specified for 10 years of continuous operation                                                                                                  |      | 4                             | mV            |

| <b>OUTPUT</b>              |                                                                      |                                                                                                                                                                                                                                                                                                                                                              |      |                               |               |

| Input voltage              | VREF connected to VDD, FBx resistor network connected to ground      | 0                                                                                                                                                                                                                                                                                                                                                            |      | $V_{\text{DD}}$               | V             |

|                            | VREF connected to VDD, FBx resistor network disconnected from ground | 0                                                                                                                                                                                                                                                                                                                                                            |      | $V_{\text{DD}} (1/3 - 1/100)$ |               |

| $V_{\text{OL}}$            | Logic low output voltage                                             | $I_{\text{LOAD}} = 100 \mu\text{A}$ , output in open-drain mode                                                                                                                                                                                                                                                                                              | 0.1  |                               | V             |

| <b>DYNAMIC PERFORMANCE</b> |                                                                      |                                                                                                                                                                                                                                                                                                                                                              |      |                               |               |

| $t_{\text{resp}}$          | Output response time                                                 | DAC at midscale with 10-bit resolution, FBx input at Hi-Z, and transition step at FBx node is $(V_{\text{DAC}} - 2 \text{ LSB})$ to $(V_{\text{DAC}} + 2 \text{ LSB})$ , transition time measured between 10% and 90% of output, output current of 100 $\mu\text{A}$ , comparator output configured in push-pull mode, load capacitor at DAC output is 25 pF | 10   |                               | $\mu\text{s}$ |

(1) Specified by design and characterization, not production tested.

(2) This specification does not include the total unadjusted error (TUE) of the DAC.

## 6.8 Electrical Characteristics: General

all minimum and maximum specifications at  $-40^{\circ}\text{C} \leq T_A \leq +125^{\circ}\text{C}$ ; typical specifications at  $T_A = 25^{\circ}\text{C}$ ,  $1.7 \text{ V} \leq V_{\text{DD}} \leq 5.5 \text{ V}$ , DAC reference tied to VDD, gain =  $1 \times$  in voltage output mode or  $\pm 250\text{-}\mu\text{A}$  output range in current output mode, DAC output pin (OUT) loaded with resistive load ( $R_L = 5 \text{ k}\Omega$  to AGND) in voltage-output mode and capacitive load ( $C_L = 200 \text{ pF}$  to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

| PARAMETER                                                   | TEST CONDITIONS                                                                                                                                                              | MIN                                                                                                                                                             | TYP     | MAX   | UNIT                       |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|----------------------------|

| <b>INTERNAL REFERENCE</b>                                   |                                                                                                                                                                              |                                                                                                                                                                 |         |       |                            |

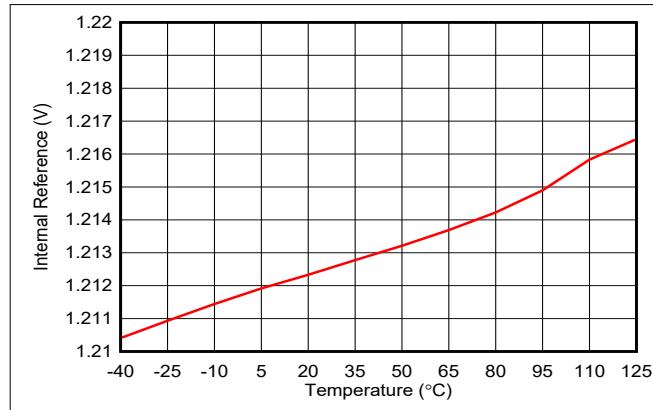

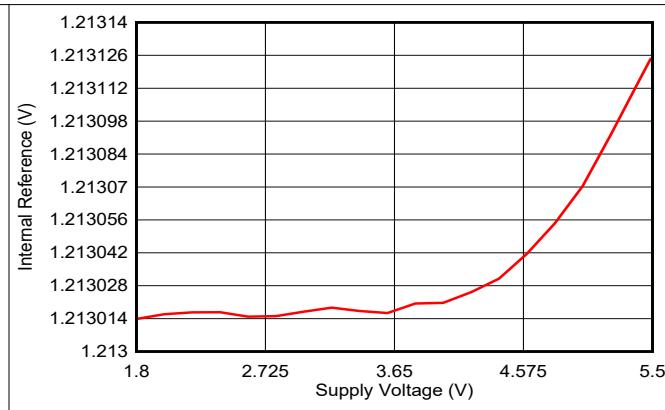

| Initial accuracy                                            | $T_A = 25^{\circ}\text{C}$                                                                                                                                                   | 1.1979                                                                                                                                                          | 1.212   | 1.224 | V                          |

| Reference output temperature coefficient <sup>(1) (2)</sup> |                                                                                                                                                                              |                                                                                                                                                                 | 60      |       | ppm/ $^{\circ}\text{C}$    |

| <b>EXTERNAL REFERENCE</b>                                   |                                                                                                                                                                              |                                                                                                                                                                 |         |       |                            |

| $V_{\text{REF}}$ input impedance <sup>(1) (3)</sup>         |                                                                                                                                                                              |                                                                                                                                                                 | 192     |       | $\text{k}\Omega\text{-ch}$ |

| <b>EEPROM</b>                                               |                                                                                                                                                                              |                                                                                                                                                                 |         |       |                            |

| Endurance <sup>(1)</sup>                                    | $-40^{\circ}\text{C} \leq T_A \leq +85^{\circ}\text{C}$<br>$T_A = 125^{\circ}\text{C}$                                                                                       | 20000                                                                                                                                                           |         |       | Cycles                     |

| Data retention <sup>(1)</sup>                               | $T_A = 25^{\circ}\text{C}$                                                                                                                                                   | 50                                                                                                                                                              |         |       | Years                      |

| EEPROM programming write cycle time <sup>(1)</sup>          |                                                                                                                                                                              | 200                                                                                                                                                             |         |       | ms                         |

| Device boot-up time <sup>(1)</sup>                          | Time taken from power valid ( $V_{\text{DD}} \geq 1.7 \text{ V}$ ) to output valid state (output state as programmed in EEPROM), 0.5- $\mu\text{F}$ capacitor on the CAP pin | 5                                                                                                                                                               |         |       | ms                         |

| <b>DIGITAL INPUTS</b>                                       |                                                                                                                                                                              |                                                                                                                                                                 |         |       |                            |

| Digital feedthrough                                         | Voltage output mode, DAC output static at midscale, fast mode plus, SCL toggling                                                                                             | 20                                                                                                                                                              |         |       | nV-s                       |

| Pin capacitance                                             | Per pin                                                                                                                                                                      | 10                                                                                                                                                              |         |       | pF                         |

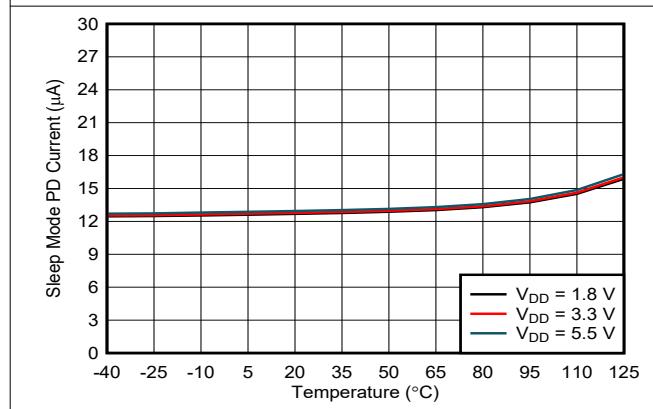

| <b>POWER-DOWN MODE</b>                                      |                                                                                                                                                                              |                                                                                                                                                                 |         |       |                            |

| $I_{\text{DD}}$                                             | Current flowing into VDD <sup>(1)</sup>                                                                                                                                      | DAC in sleep mode, internal reference powered down, external reference at 5.5 V                                                                                 | 28      |       |                            |

|                                                             |                                                                                                                                                                              | DAC in sleep mode, internal reference enabled, additional current through internal reference                                                                    | 10      |       |                            |

|                                                             |                                                                                                                                                                              | DAC channels enabled, internal reference enabled, additional current through internal reference per DAC channel in voltage-output mode                          | 12.5    |       |                            |

| <b>HIGH-IMPEDANCE OUTPUT</b>                                |                                                                                                                                                                              |                                                                                                                                                                 |         |       |                            |

| $I_{\text{LEAK}}$                                           | Current flowing into $V_{\text{OUTX}}$ and $V_{\text{FBX}}$                                                                                                                  | DAC in Hi-Z output mode, $1.7 \text{ V} \leq V_{\text{DD}} \leq 5.5 \text{ V}$                                                                                  | 10      |       |                            |

|                                                             |                                                                                                                                                                              | $V_{\text{DD}} = 0 \text{ V}$ , $V_{\text{OUT}} \leq 1.5 \text{ V}$ , decoupling capacitor between $V_{\text{DD}}$ and AGND = 0.1 $\mu\text{F}$                 | 200     |       |                            |

|                                                             |                                                                                                                                                                              | $V_{\text{DD}} = 0 \text{ V}$ , $1.5 \text{ V} < V_{\text{OUT}} \leq 5.5 \text{ V}$ , decoupling capacitor between $V_{\text{DD}}$ and AGND = 0.1 $\mu\text{F}$ | 500     |       |                            |

|                                                             |                                                                                                                                                                              | 100 $\text{k}\Omega$ between $V_{\text{DD}}$ and AGND, $V_{\text{OUT}} \leq 1.25 \text{ V}$ , series resistance of 10 $\text{k}\Omega$ at OUTx pin              | $\pm 2$ |       | $\mu\text{A}$              |

(1) Specified by design and characterization, not production tested.

(2) Measured at  $-40^{\circ}\text{C}$  and  $+125^{\circ}\text{C}$  and calculated the slope.

(3) Impedances for the DAC channels are connected in parallel.

## 6.9 Timing Requirements: I<sup>2</sup>C Standard Mode

all input signals are timed from V<sub>IL</sub> to 70% of V<sub>pull-up</sub>, 1.7 V ≤ V<sub>DD</sub> ≤ 5.5 V, -40°C ≤ T<sub>A</sub> ≤ +125°C, and 1.7 V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub>

|                    |                                                                                                | MIN | NOM  | MAX  | UNIT |

|--------------------|------------------------------------------------------------------------------------------------|-----|------|------|------|

| f <sub>SCL</sub>   | SCL frequency                                                                                  |     |      | 100  | kHz  |

| t <sub>BUF</sub>   | Bus free time between stop and start conditions                                                |     | 4.7  |      | μs   |

| t <sub>HDSTA</sub> | Hold time after repeated start                                                                 |     | 4    |      | μs   |

| t <sub>SUSTA</sub> | Repeated start setup time                                                                      |     | 4.7  |      | μs   |

| t <sub>SUSTO</sub> | Stop condition setup time                                                                      |     | 4    |      | μs   |

| t <sub>HDDAT</sub> | Data hold time                                                                                 |     | 0    |      | ns   |

| t <sub>SUDAT</sub> | Data setup time                                                                                |     | 250  |      | ns   |

| t <sub>LOW</sub>   | SCL clock low period                                                                           |     | 4700 |      | ns   |

| t <sub>HIGH</sub>  | SCL clock high period                                                                          |     | 4000 |      | ns   |

| t <sub>F</sub>     | Clock and data fall time                                                                       |     |      | 300  | ns   |

| t <sub>R</sub>     | Clock and data rise time                                                                       |     |      | 1000 | ns   |

| t <sub>VDDAT</sub> | Data valid time, R = 360 Ω, C <sub>trace</sub> = 23 pF, C <sub>probe</sub> = 10 pF             |     |      | 3.45 | μs   |

| t <sub>VDACK</sub> | Data valid acknowledge time, R = 360 Ω, C <sub>trace</sub> = 23 pF, C <sub>probe</sub> = 10 pF |     |      | 3.45 | μs   |

## 6.10 Timing Requirements: I<sup>2</sup>C Fast Mode

all input signals are timed from V<sub>IL</sub> to 70% of V<sub>pull-up</sub>, 1.7 V ≤ V<sub>DD</sub> ≤ 5.5 V, -40°C ≤ T<sub>A</sub> ≤ +125°C, and 1.7 V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub>

|                    |                                                                                                | MIN | NOM  | MAX | UNIT |

|--------------------|------------------------------------------------------------------------------------------------|-----|------|-----|------|

| f <sub>SCL</sub>   | SCL frequency                                                                                  |     |      | 400 | kHz  |

| t <sub>BUF</sub>   | Bus free time between stop and start conditions                                                |     | 1.3  |     | μs   |

| t <sub>HDSTA</sub> | Hold time after repeated start                                                                 |     | 0.6  |     | μs   |

| t <sub>SUSTA</sub> | Repeated start setup time                                                                      |     | 0.6  |     | μs   |

| t <sub>SUSTO</sub> | Stop condition setup time                                                                      |     | 0.6  |     | μs   |

| t <sub>HDDAT</sub> | Data hold time                                                                                 |     | 0    |     | ns   |

| t <sub>SUDAT</sub> | Data setup time                                                                                |     | 100  |     | ns   |

| t <sub>LOW</sub>   | SCL clock low period                                                                           |     | 1300 |     | ns   |

| t <sub>HIGH</sub>  | SCL clock high period                                                                          |     | 600  |     | ns   |

| t <sub>F</sub>     | Clock and data fall time                                                                       |     |      | 300 | ns   |

| t <sub>R</sub>     | Clock and data rise time                                                                       |     |      | 300 | ns   |

| t <sub>VDDAT</sub> | Data valid time, R = 360 Ω, C <sub>trace</sub> = 23 pF, C <sub>probe</sub> = 10 pF             |     |      | 0.9 | μs   |

| t <sub>VDACK</sub> | Data valid acknowledge time, R = 360 Ω, C <sub>trace</sub> = 23 pF, C <sub>probe</sub> = 10 pF |     |      | 0.9 | μs   |

## 6.11 Timing Requirements: I<sup>2</sup>C Fast Mode Plus

all input signals are timed from V<sub>IL</sub> to 70% of V<sub>pull-up</sub>, 1.7 V ≤ V<sub>DD</sub> ≤ 5.5 V, -40°C ≤ T<sub>A</sub> ≤ +125°C, and 1.7 V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub>

|                    |                                                                                                | MIN | NOM  | MAX  | UNIT |

|--------------------|------------------------------------------------------------------------------------------------|-----|------|------|------|

| f <sub>SCL</sub>   | SCL frequency                                                                                  |     |      | 1    | MHz  |

| t <sub>BUF</sub>   | Bus free time between stop and start conditions                                                |     | 0.5  |      | μs   |

| t <sub>HDSTA</sub> | Hold time after repeated start                                                                 |     | 0.26 |      | μs   |

| t <sub>SUSTA</sub> | Repeated start setup time                                                                      |     | 0.26 |      | μs   |

| t <sub>SUSTO</sub> | Stop condition setup time                                                                      |     | 0.26 |      | μs   |

| t <sub>HDDAT</sub> | Data hold time                                                                                 |     | 0    |      | ns   |

| t <sub>SUDAT</sub> | Data setup time                                                                                |     | 50   |      | ns   |

| t <sub>LOW</sub>   | SCL clock low period                                                                           |     | 0.5  |      | μs   |

| t <sub>HIGH</sub>  | SCL clock high period                                                                          |     | 0.26 |      | μs   |

| t <sub>F</sub>     | Clock and data fall time                                                                       |     |      | 120  | ns   |

| t <sub>R</sub>     | Clock and data rise time                                                                       |     |      | 120  | ns   |

| t <sub>VDDAT</sub> | Data valid time, R = 360 Ω, C <sub>trace</sub> = 23 pF, C <sub>probe</sub> = 10 pF             |     |      | 0.45 | μs   |

| t <sub>VDACK</sub> | Data valid acknowledge time, R = 360 Ω, C <sub>trace</sub> = 23 pF, C <sub>probe</sub> = 10 pF |     |      | 0.45 | μs   |

## 6.12 Timing Requirements: SPI Write Operation

all input signals are specified with  $t_r = t_f = 1 \text{ V/ns}$  (10% to 90% of  $V_{IO}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH}) / 2$ ,  $1.7 \text{ V} \leq V_{IO} \leq 5.5 \text{ V}$ ,  $1.7 \text{ V} \leq V_{DD} \leq 5.5 \text{ V}$ , and  $-40^\circ\text{C} \leq T_A \leq +125^\circ\text{C}$

|                 |                                                                                               | MIN | NOM | MAX | UNIT          |

|-----------------|-----------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $f_{SCLK}$      | Serial clock frequency                                                                        |     |     | 50  | MHz           |

| $t_{SCLKHIGH}$  | SCLK high time                                                                                | 9   |     |     | ns            |

| $t_{SCLKLOW}$   | SCLK low time                                                                                 | 9   |     |     | ns            |

| $t_{SDIS}$      | SDI setup time                                                                                | 8   |     |     | ns            |

| $t_{SDIH}$      | SDI hold time                                                                                 | 8   |     |     | ns            |

| $t_{CSS}$       | $\bar{CS}$ to SCLK falling edge setup time                                                    | 18  |     |     | ns            |

| $t_{CSH}$       | SCLK falling edge to $\bar{CS}$ rising edge                                                   | 10  |     |     | ns            |

| $t_{CSHIGH}$    | $\bar{CS}$ high time                                                                          | 50  |     |     | ns            |

| $t_{DACPWAIT}$  | Sequential DAC update wait time (time between subsequent LDAC falling edges) for same channel | 2   |     |     | $\mu\text{s}$ |

| $t_{BCASTWAIT}$ | Broadcast DAC update wait time (time between subsequent LDAC falling edges)                   | 2   |     |     | $\mu\text{s}$ |

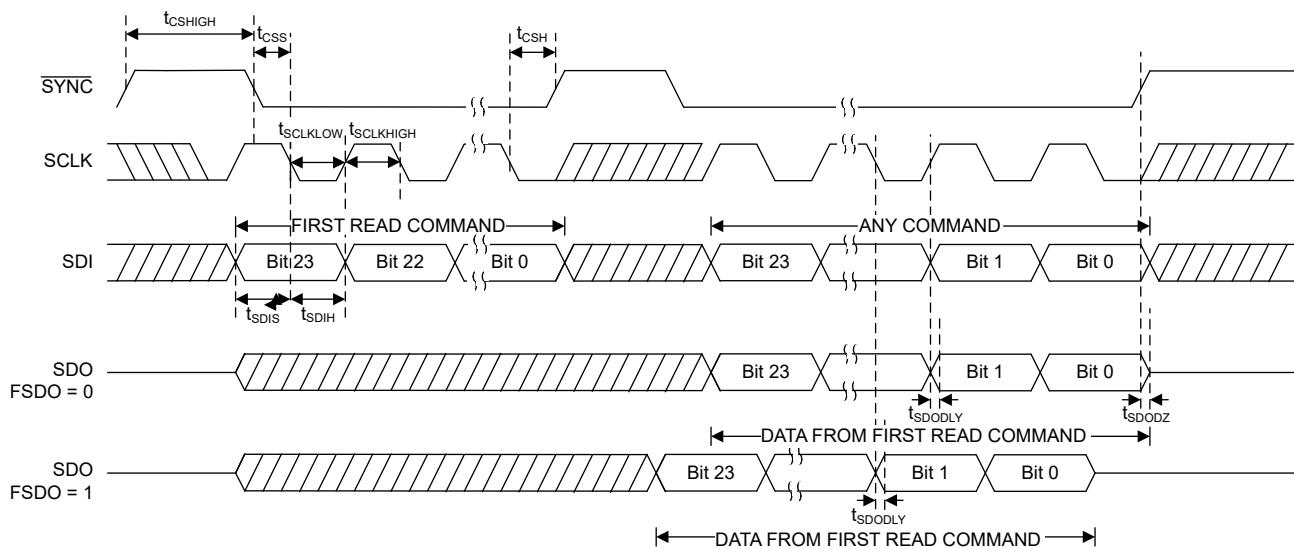

## 6.13 Timing Requirements: SPI Read and Daisy Chain Operation (FSDO = 0)

all input signals are specified with  $t_r = t_f = 1 \text{ V/ns}$  (10% to 90% of  $V_{IO}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH}) / 2$ ,  $1.7 \text{ V} \leq V_{IO} \leq 5.5 \text{ V}$ ,  $1.7 \text{ V} \leq V_{DD} \leq 5.5 \text{ V}$ ,  $-40^\circ\text{C} \leq T_A \leq +125^\circ\text{C}$ , and  $FSDO = 0$

|                |                                                                                            | MIN | NOM | MAX  | UNIT          |

|----------------|--------------------------------------------------------------------------------------------|-----|-----|------|---------------|

| $f_{SCLK}$     | Serial clock frequency                                                                     |     |     | 1.25 | MHz           |

| $t_{SCLKHIGH}$ | SCLK high time                                                                             | 350 |     |      | ns            |

| $t_{SCLKLOW}$  | SCLK low time                                                                              | 350 |     |      | ns            |

| $t_{SDIS}$     | SDI setup time                                                                             | 8   |     |      | ns            |

| $t_{SDIH}$     | SDI hold time                                                                              | 8   |     |      | ns            |

| $t_{CSS}$      | SYNC to SCLK falling edge setup time                                                       | 400 |     |      | ns            |

| $t_{CSH}$      | SCLK falling edge to SYNC rising edge                                                      | 400 |     |      | ns            |

| $t_{CSHIGH}$   | SYNC high time                                                                             | 1   |     |      | $\mu\text{s}$ |

| $t_{SDODLY}$   | SCLK rising edge to SDO falling edge, $I_{OL} \leq 5 \text{ mA}$ , $C_L = 20 \text{ pF}$ . |     | 300 |      | ns            |

## 6.14 Timing Requirements: SPI Read and Daisy Chain Operation (FSDO = 1)

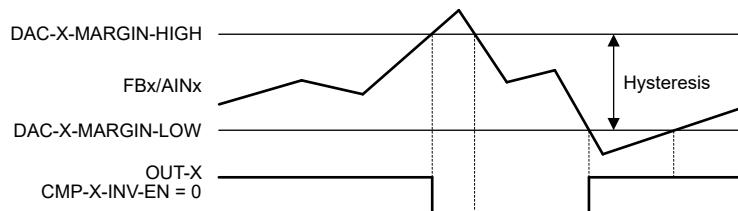

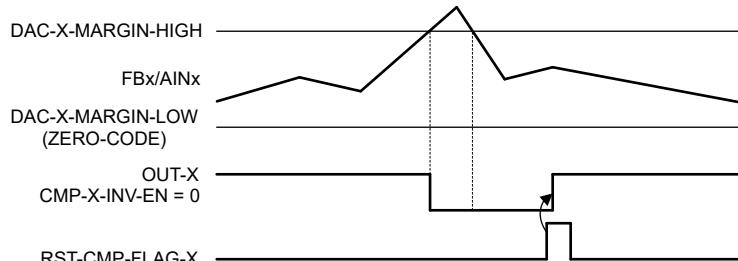

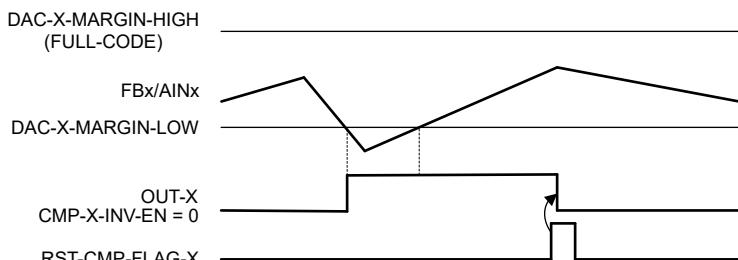

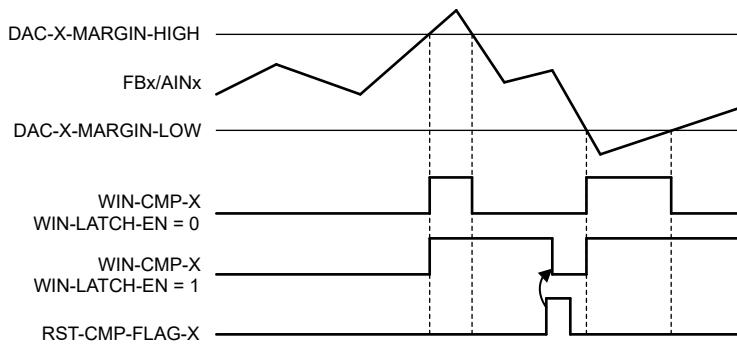

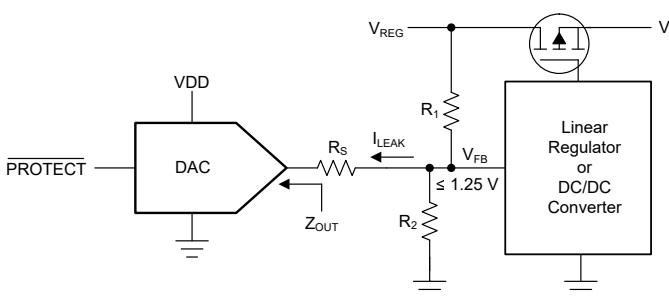

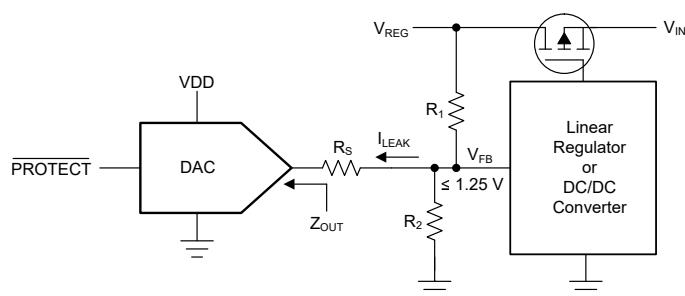

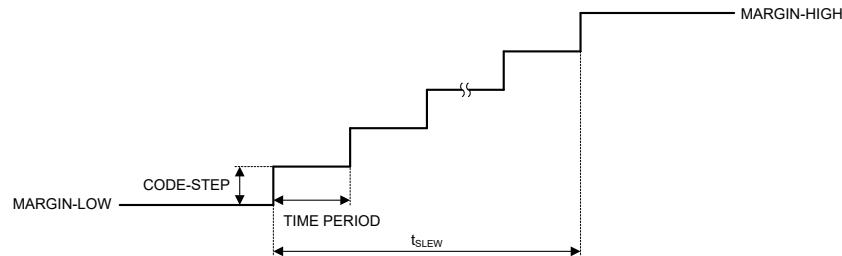

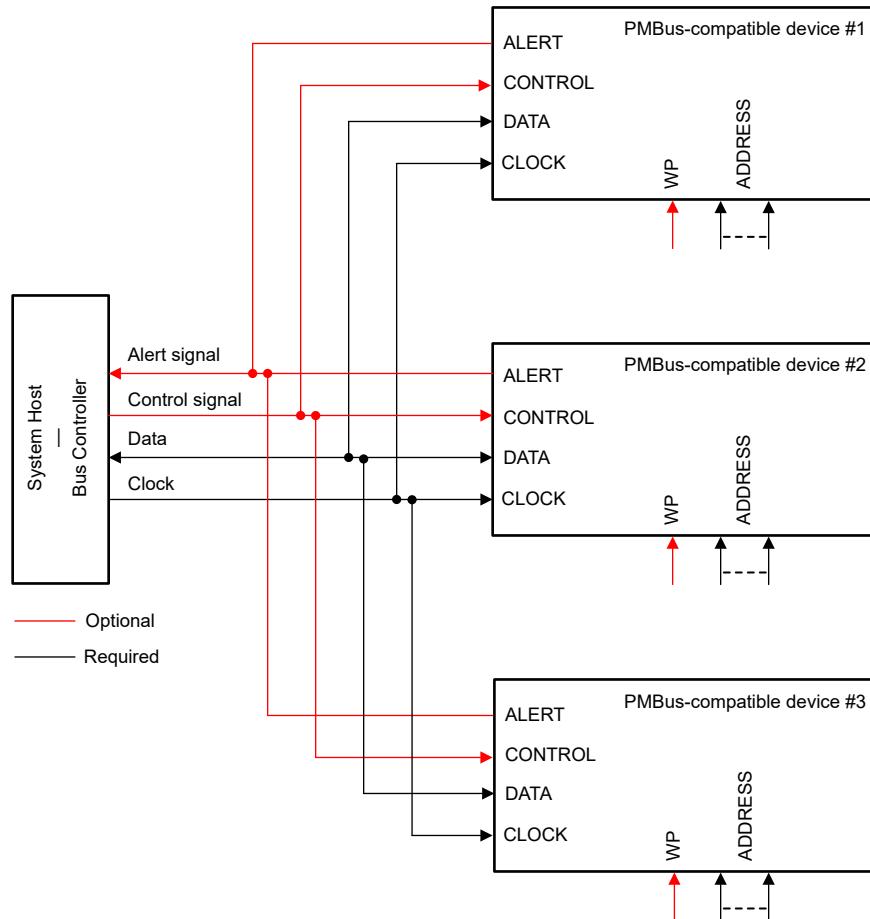

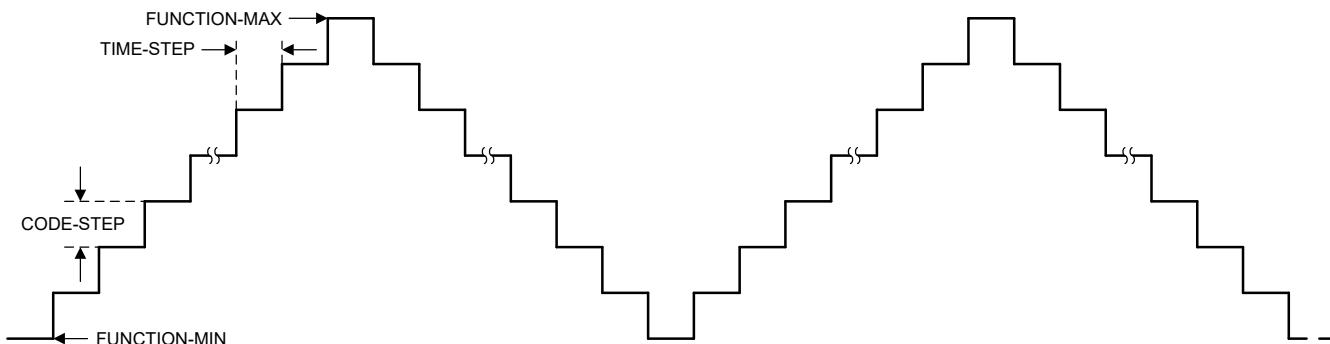

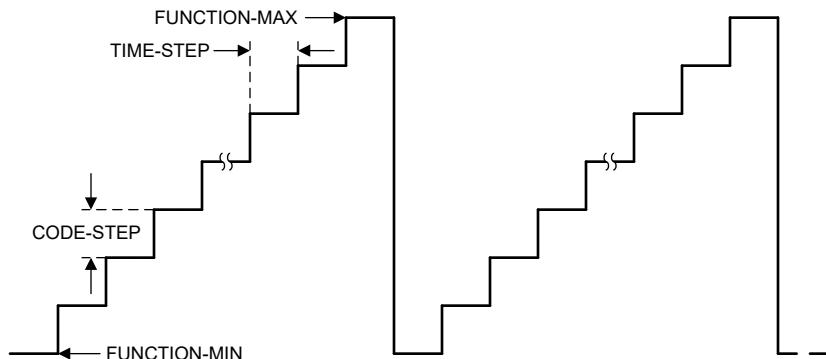

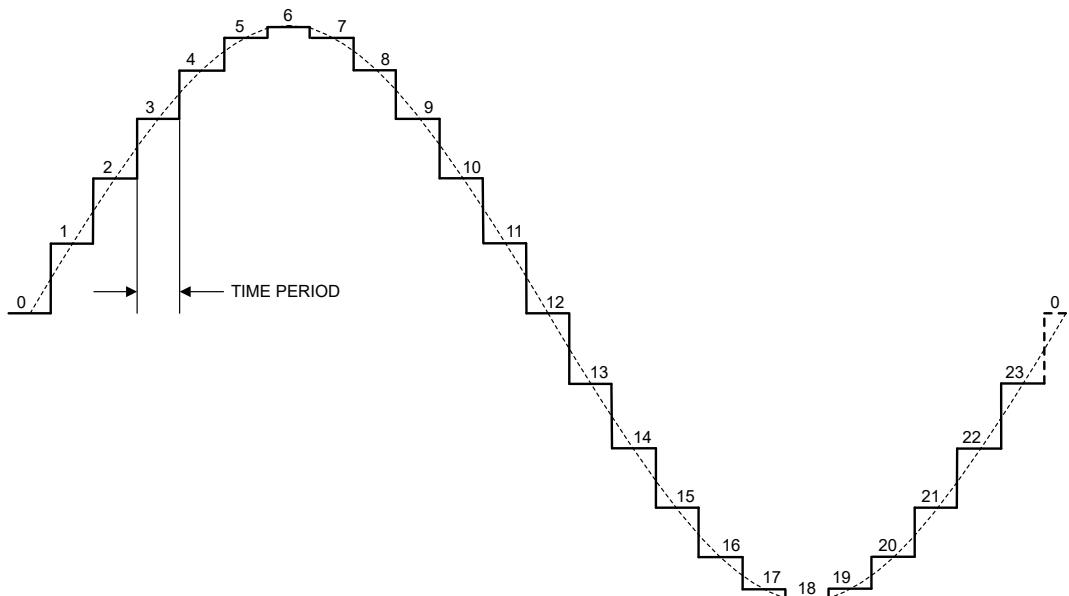

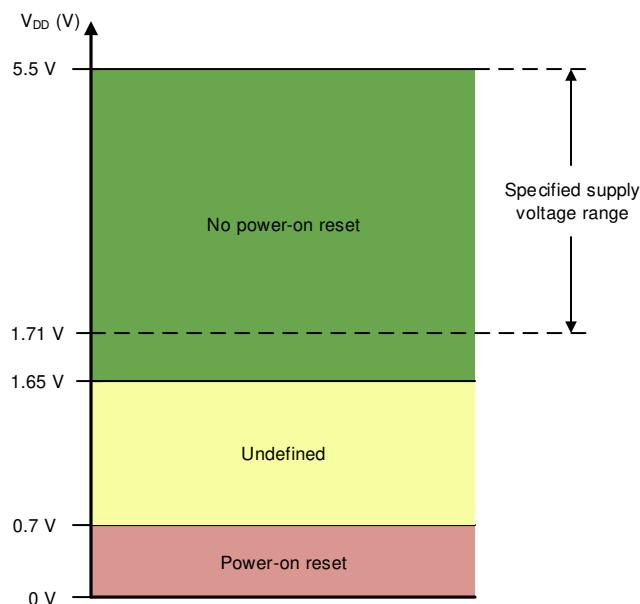

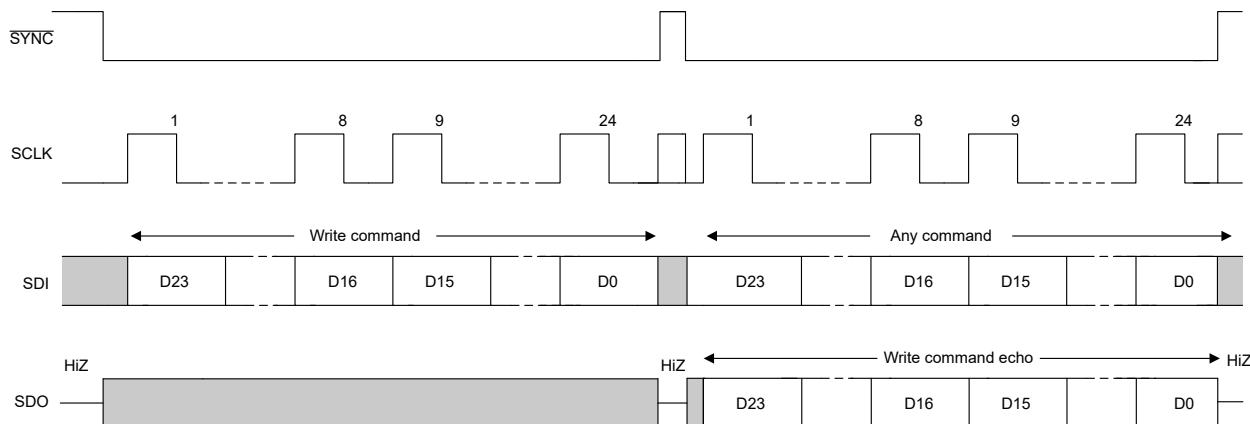

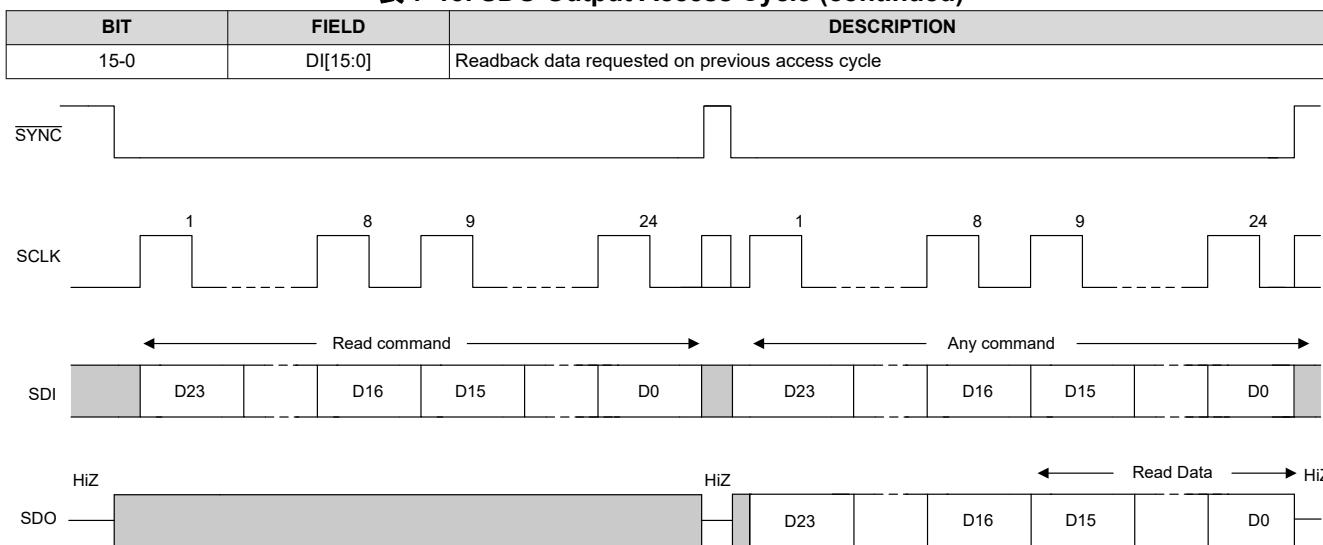

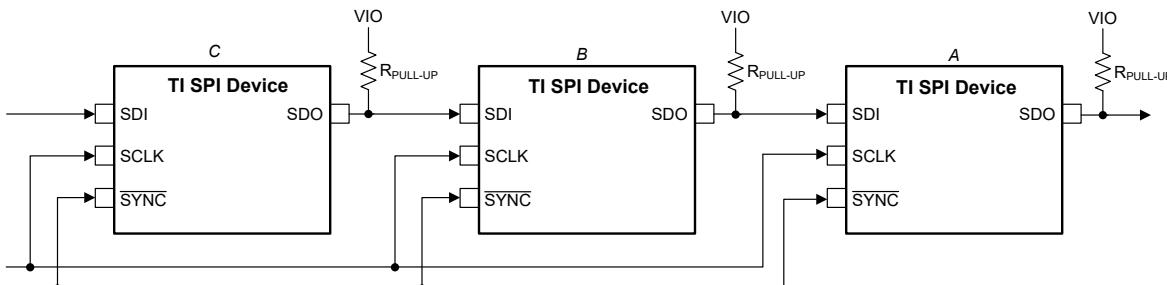

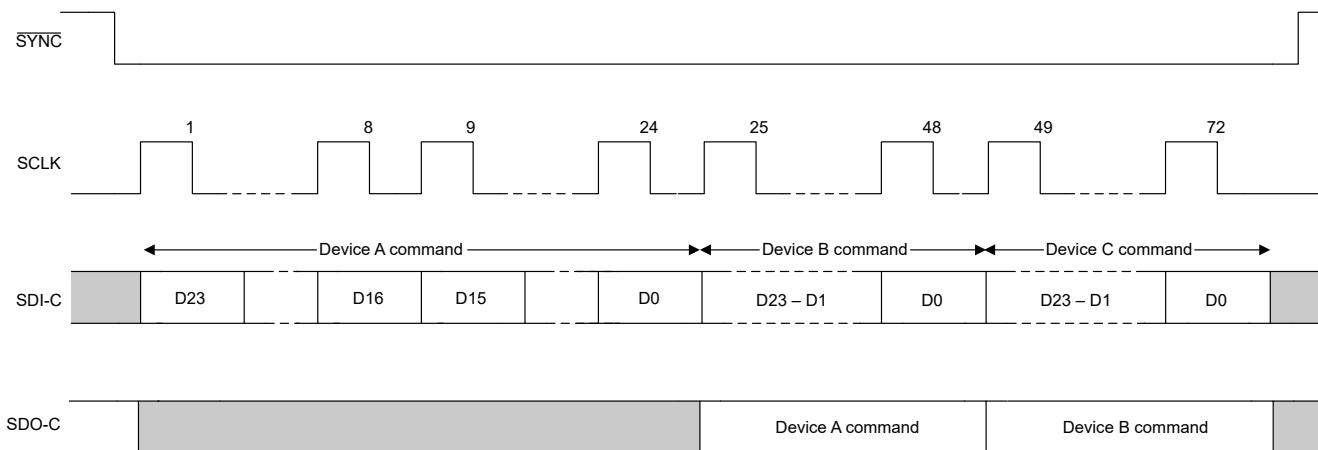

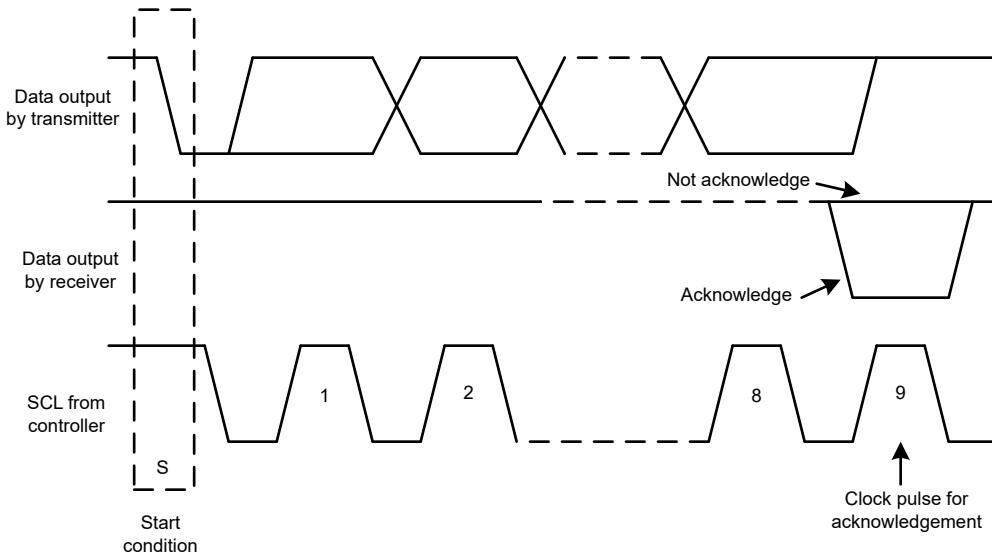

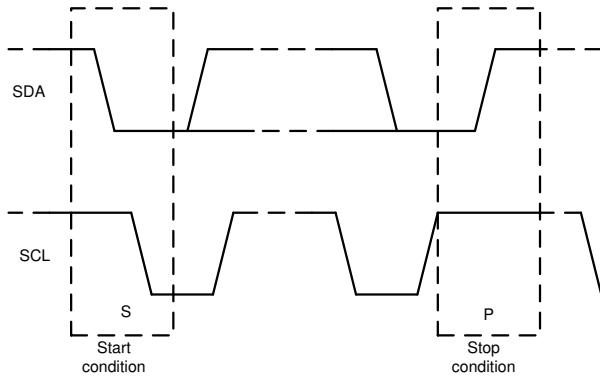

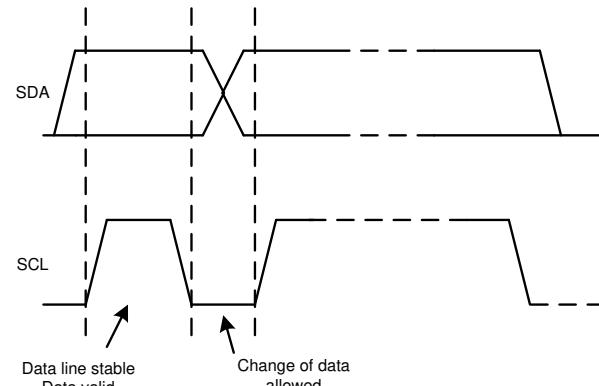

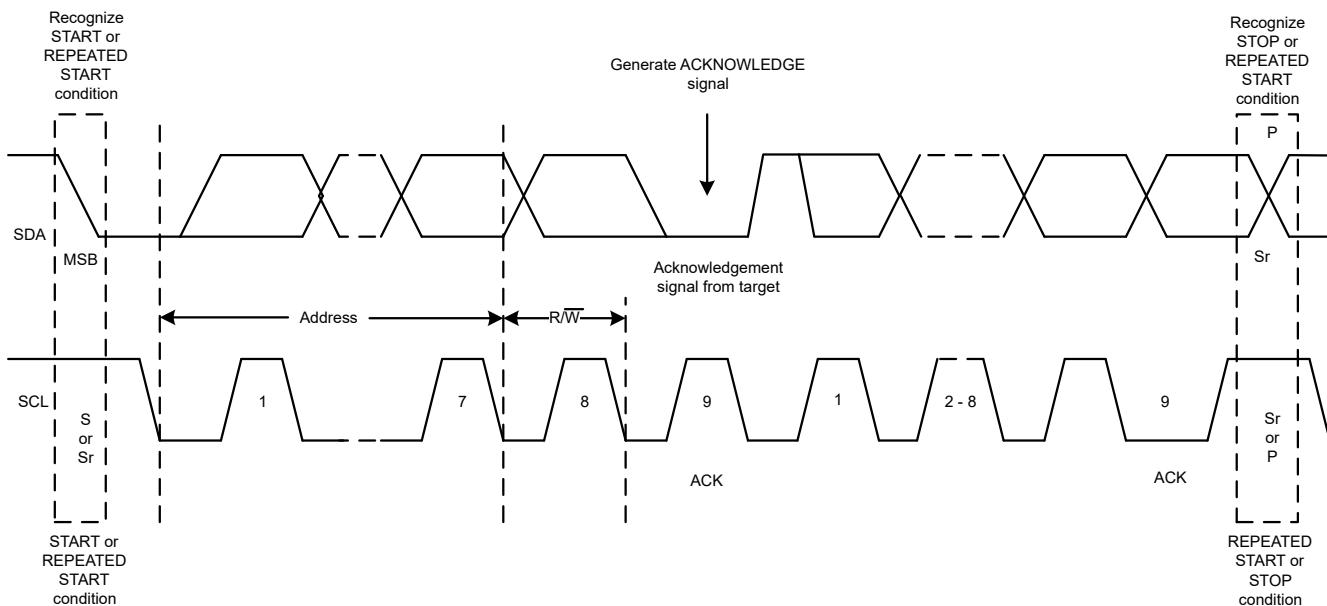

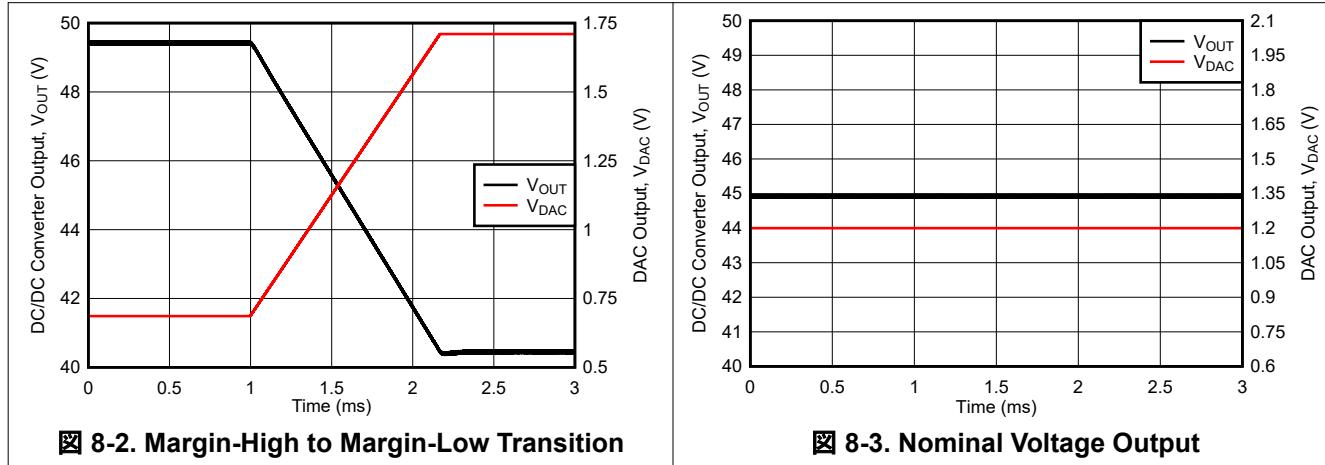

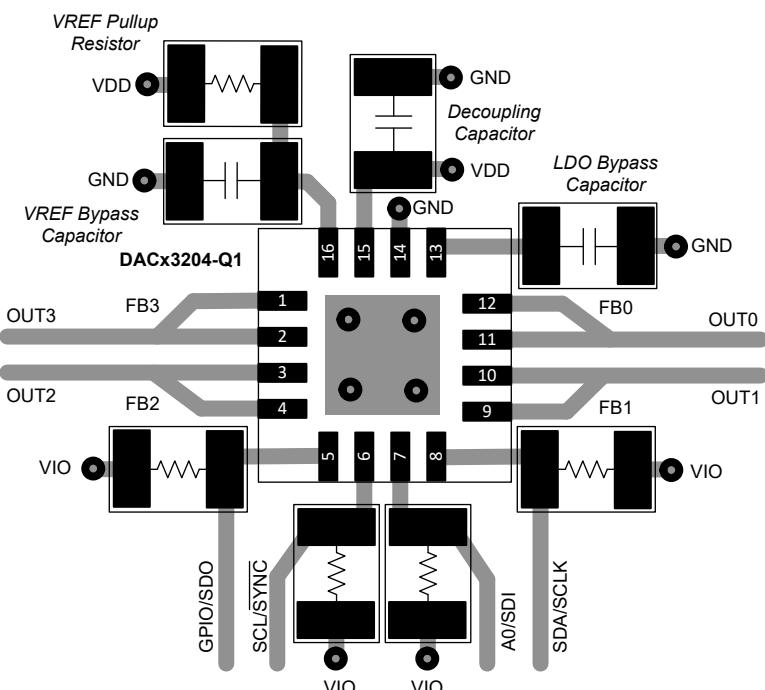

all input signals are specified with  $t_r = t_f = 1 \text{ V/ns}$  (10% to 90% of  $V_{IO}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH}) / 2$ ,  $1.7 \text{ V} \leq V_{IO} \leq 5.5 \text{ V}$ ,  $1.7 \text{ V} \leq V_{DD} \leq 5.5 \text{ V}$ ,  $-40^\circ\text{C} \leq T_A \leq +125^\circ\text{C}$ , and  $FSDO = 1$