# DAC60516W リファレンス内蔵、16 チャネル、12 ビット、電圧出力 DAC

## 1 特長

- 性能:

- INL: 12 ビット分解能で  $\pm 1$ LSB 以下

- TUE (総合未調整誤差): FSR 最大値  $\pm 0.15\%$

- 2.5V の高精度内部リファレンスを搭載

- 初期精度:  $\pm 5$ mV (最大値)

- ドリフト:  $25\text{ppm}/^\circ\text{C}$  標準値、 $40\text{ppm}/^\circ\text{C}$  最大値

- 高い駆動能力: 電源レールからの供給で、0.5V 出力時に 50mA

- 柔軟な構成オプション

- ユーザー選択可能なゲイン:  $2\times$ ,  $1\times$

- ゼロスケールへのリセット

- クリア出力機能

- 広い動作範囲:

- 電源: 2.7V ~ 5.5V

- 温度範囲:  $-40^\circ\text{C} \sim +125^\circ\text{C}$

- SPI および I<sup>2</sup>C インターフェイス: 1.7V ~ 5.5V で動作

- SPI: 4 線式インターフェイス

- I<sup>2</sup>C: 4 つのターゲットアドレス

## 2 アプリケーション

- 光モジュール

- DC 間の相互接続

- アナログ出力モジュール

## 3 説明

DAC60516W は、低消費電力、16 チャネル、バッファ付き、電圧出力の D/A コンバータ (DAC) です。DAC60516W には 2.5V の内部リファレンスが搭載されているため、ほとんどのアプリケーションで外付けの高精度リファレンスを必要としません。ユーザーが選択可能なゲイン構成を使用して、2.5V または 5V のフルスケール出力電圧を供給できます。DAC60516W が動作するには、外部の AV<sub>DD</sub> および V<sub>IO</sub> 電源が必要で、これらの電源を互いに短絡することができます。

DAC60516W との通信は、SPI および I<sup>2</sup>C をサポートするシリアルインターフェイスで行われ、最大 50MHz のクロック速度で動作します (デバイスに対する SPI 書き込み中)。VIO ピンにより、1.7V ~ 5.5V のシリアルインターフェイス動作が可能です。DAC60516W の柔軟なインターフェイスにより、業界標準の広範なマイクロプロセッサやマイクロコントローラとの動作が可能です。

DAC60516W は、 $-40^\circ\text{C} \sim +125^\circ\text{C}$  の温度範囲での動作が規定されており、12 ビットの分解能を備えた小型の W CSP パッケージで供給されます。

### パッケージ情報

| 部品番号      | パッケージ (1)         | パッケージ サイズ(2)    |

|-----------|-------------------|-----------------|

| DAC60516W | YBH (WCSP), 34 ピン | 2.59mm × 2.59mm |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

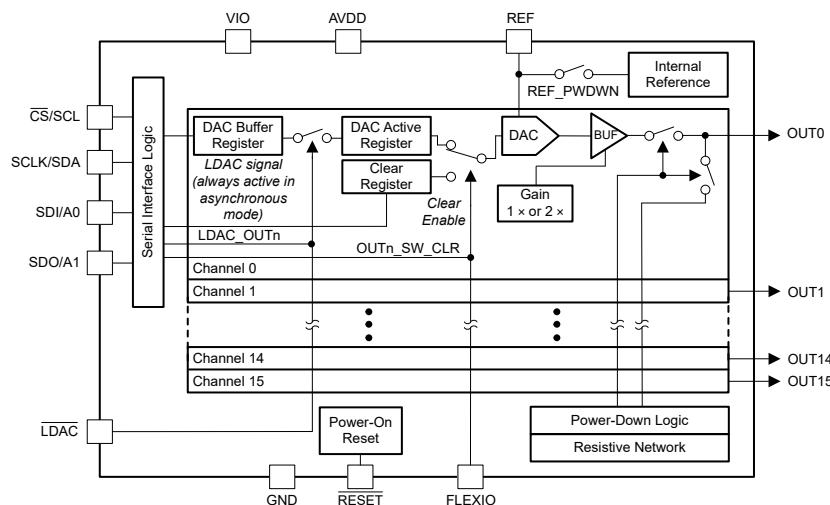

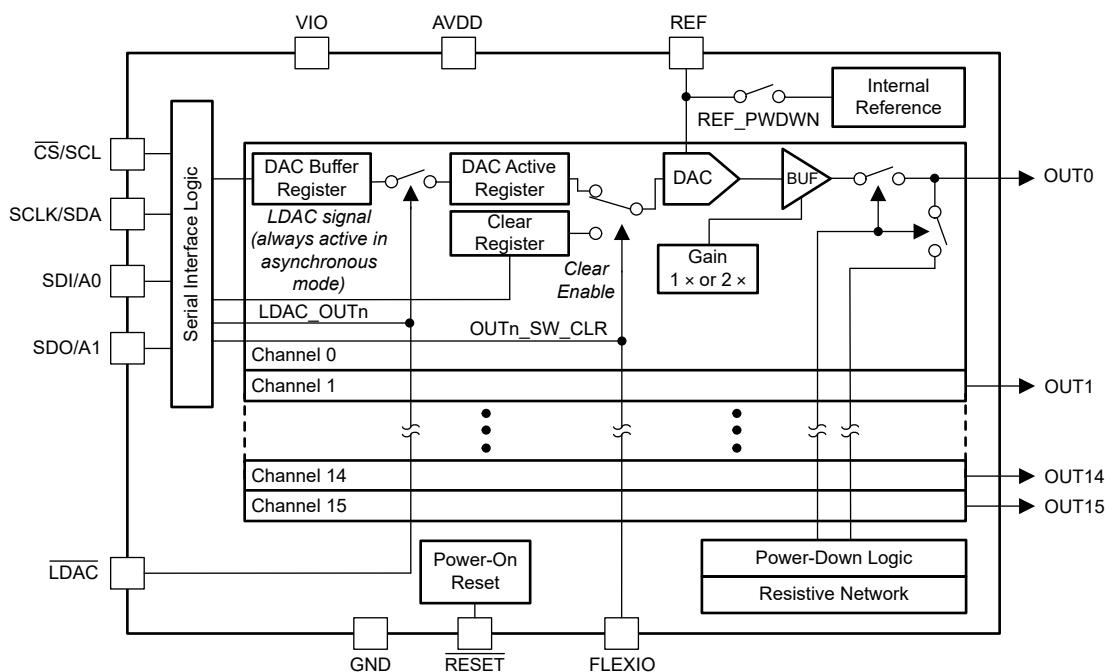

機能ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLASFN4](#)

## 目次

|                                               |    |                             |    |

|-----------------------------------------------|----|-----------------------------|----|

| 1 特長.....                                     | 1  | 6.3 機能説明.....               | 22 |

| 2 アプリケーション.....                               | 1  | 6.4 デバイスの機能モード.....         | 24 |

| 3 説明.....                                     | 1  | 6.5 プログラミング.....            | 25 |

| 4 ピン構成および機能.....                              | 3  | 7 レジスタ マップ.....             | 30 |

| 5 仕様.....                                     | 5  | 7.1 レジスタ.....               | 33 |

| 5.1 絶対最大定格.....                               | 5  | 8 アプリケーションと実装.....          | 55 |

| 5.2 ESD 定格.....                               | 5  | 8.1 アプリケーション情報.....         | 55 |

| 5.3 推奨動作条件.....                               | 5  | 8.2 代表的なアプリケーション.....       | 56 |

| 5.4 熱に関する情報.....                              | 5  | 8.3 初期設定.....               | 57 |

| 5.5 電気的特性.....                                | 6  | 8.4 電源に関する推奨事項.....         | 58 |

| 5.6 タイミング要件 - I <sup>2</sup> C 標準モード.....     | 9  | 8.5 レイアウト.....              | 58 |

| 5.7 タイミング要件 - I <sup>2</sup> C 高速モード.....     | 9  | 9 デバイスおよびドキュメントのサポート.....   | 59 |

| 5.8 タイミング要件 - I <sup>2</sup> C 高速モード プラス..... | 9  | 9.1 ドキュメントのサポート.....        | 59 |

| 5.9 タイミング要件: SPI.....                         | 11 | 9.2 ドキュメントの更新通知を受け取る方法..... | 59 |

| 5.10 スイッチング特性.....                            | 11 | 9.3 サポート・リソース.....          | 59 |

| 5.11 タイミング図.....                              | 12 | 9.4 商標.....                 | 59 |

| 5.12 代表的特性.....                               | 13 | 9.5 静電気放電に関する注意事項.....      | 59 |

| 6 詳細説明.....                                   | 21 | 9.6 用語集.....                | 59 |

| 6.1 概要.....                                   | 21 | 10 改訂履歴.....                | 59 |

| 6.2 機能ブロック図.....                              | 21 | 11 メカニカル、パッケージ、および注文情報..... | 59 |

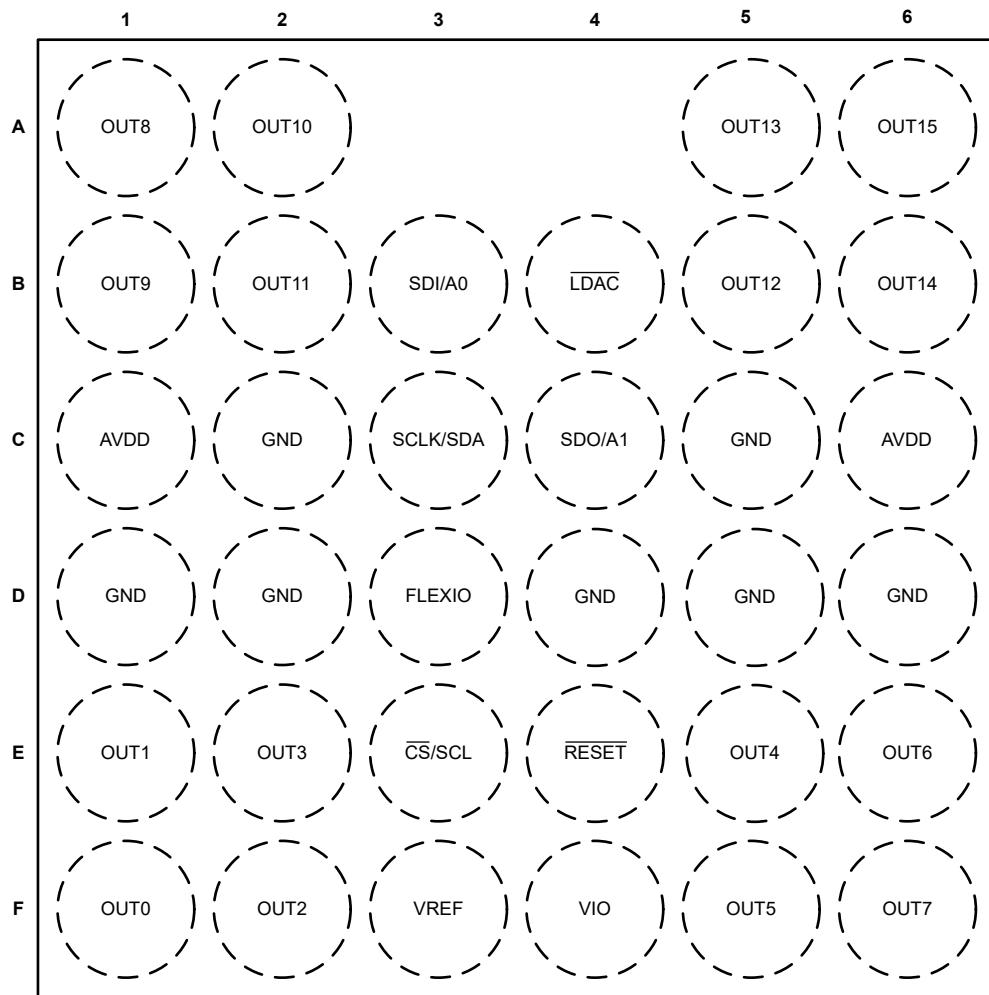

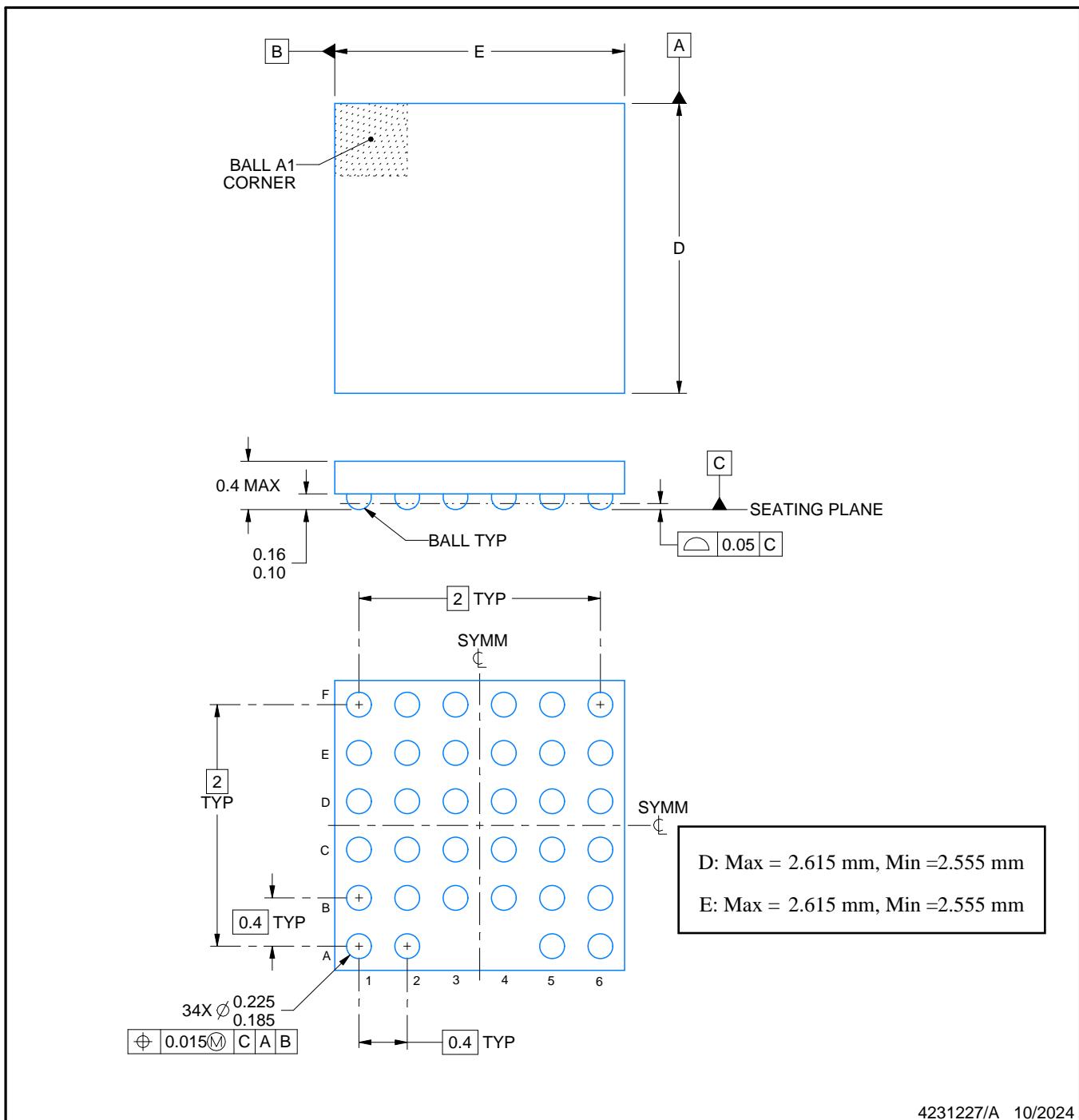

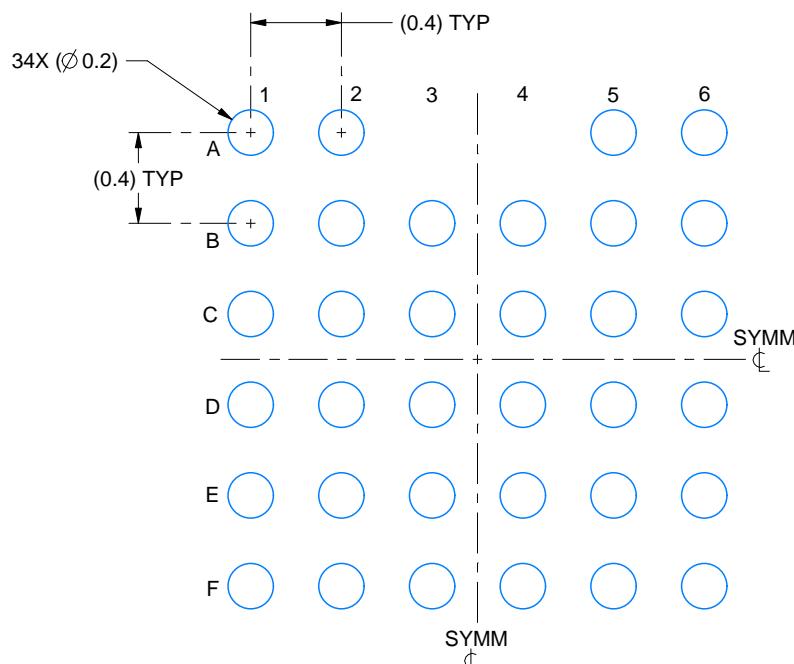

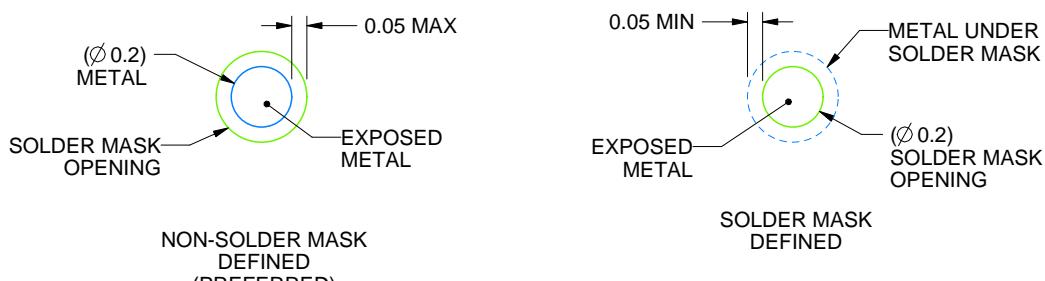

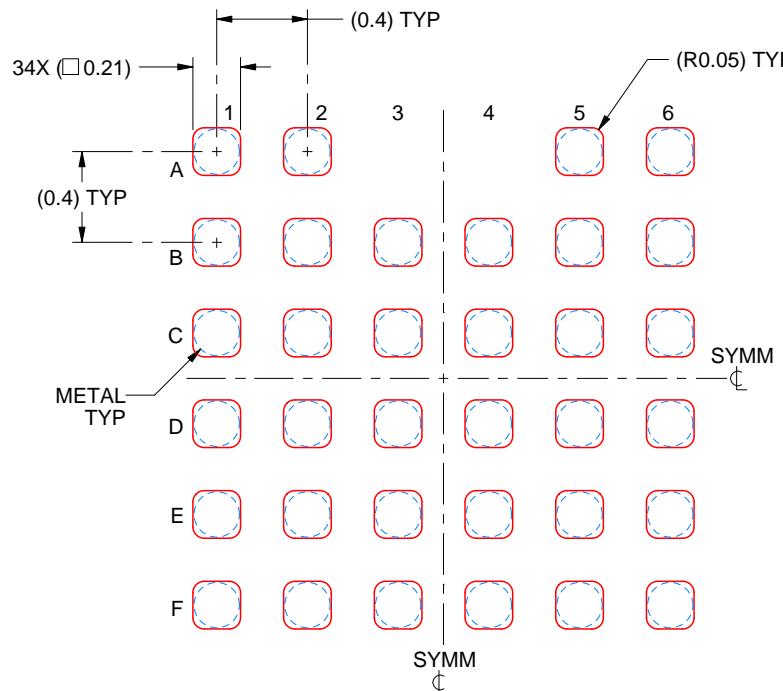

## 4 ピン構成および機能

図 4-1. 34 ピン WCSP (上面図)

表 4-1. ピンの機能

| ピン |        | タイプ | 説明                                                                                         |

|----|--------|-----|--------------------------------------------------------------------------------------------|

| 番号 | 名称     |     |                                                                                            |

| A1 | OUT8   | 出力  | DAC 出力。                                                                                    |

| A2 | OUT10  | 出力  | DAC 出力。                                                                                    |

| A5 | OUT13  | 出力  | DAC 出力。                                                                                    |

| A6 | OUT15  | 出力  | DAC 出力。                                                                                    |

| B1 | OUT9   | 出力  | DAC 出力。                                                                                    |

| B2 | OUT11  | 出力  | DAC 出力。                                                                                    |

| B3 | A0/SDI | 入力  | I <sup>2</sup> C:ターゲット アドレス セレクタ。<br>SPI:データ入力。データは SCLK ピンの各立ち下がりエッジで入力シフト レジスタにクロックされます。 |

| B4 | LDAC   | 入力  | アクティブ Low DAC 同期信号。 <u>LDAC</u> ピンの High から Low への遷移は、同期モードに設定された DAC の出力を同時に更新します。        |

| B5 | OUT12  | 出力  | DAC 出力。                                                                                    |

| B6 | OUT14  | 出力  | DAC 出力。                                                                                    |

| C1 | AVDD   | 電源  | アナログ電源電圧。                                                                                  |

表 4-1. ピンの機能 (続き)

| ピン |          | タイプ     | 説明                                                                                                                                      |

|----|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 番号 | 名称       |         |                                                                                                                                         |

| C2 | GND      | グランド    | デバイスの全回路のグランド基準点。                                                                                                                       |

| C3 | SDA/SCLK | 入力 / 出力 | I <sup>2</sup> C: 双方向データライン。<br>SPI: クロック入力。                                                                                            |

| C4 | A1/SDO   | 入力 / 出力 | I <sup>2</sup> C: ターゲットアドレスセレクタ。<br>SPI: データ出力。データは、FSDO ビットで指定されたとおりに、SCLK ピンの立ち上がりエッジまたは立ち下がりエッジで入力シフトレジスタからクロックアウトされます。              |

| C5 | GND      | グランド    | デバイスの全回路のグランド基準点。                                                                                                                       |

| C6 | AVDD     | 電源      | アナログ電源電圧。                                                                                                                               |

| D1 | GND      | グランド    | デバイスの全回路のグランド基準点。                                                                                                                       |

| D2 | GND      | グランド    | デバイスの全回路のグランド基準点。                                                                                                                       |

| D3 | FLEXIO   | 入力 / 出力 | GPIO および DAC クリアピン機能を含む FLEXIO ピン。                                                                                                      |

| D4 | GND      | グランド    | デバイスの全回路のグランド基準点。                                                                                                                       |

| D5 | GND      | グランド    | デバイスの全回路のグランド基準点。                                                                                                                       |

| D6 | GND      | グランド    | デバイスの全回路のグランド基準点。                                                                                                                       |

| E1 | OUT1     | 出力      | DAC 出力。                                                                                                                                 |

| E2 | OUT3     | 出力      | DAC 出力。                                                                                                                                 |

| E3 | SCL/CS   | 入力      | I <sup>2</sup> C: クロック入力。<br>SPI: アクティブ Low のシリアルデータを有効にします。この入力は、シリアルデータのフレーム同期信号です。この信号が Low になると、このピンはシリアルインターフェイスの入力シフトレジスタを有効にします。 |

| E4 | RESET    | 入力      | アクティブ Low のリセット入力。このピンでロジックが Low になると、リセットイベントが始まります。                                                                                   |

| E5 | OUT4     | 出力      | DAC 出力。                                                                                                                                 |

| E6 | OUT6     | 出力      | DAC 出力。                                                                                                                                 |

| F1 | OUT0     | 出力      | DAC 出力。                                                                                                                                 |

| F2 | OUT2     | 出力      | DAC 出力。                                                                                                                                 |

| F3 | VREF     | 入力 / 出力 | DAC 電圧リファレンス入力/出力。このピンはデフォルトで入力ピン REFIN として機能します (内部リファレンスは無効化されています)。内部リファレンスが有効である場合、このピンは出力ピン REFOUT として機能します。                       |

| F4 | VIO      | 電源      | I/O 電源電圧。このピンは、デバイスの I/O 動作電圧を設定します。                                                                                                    |

| F5 | OUT5     | 出力      | DAC 出力。                                                                                                                                 |

| F6 | OUT7     | 出力      | DAC 出力。                                                                                                                                 |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                  |                                    | 最小値  | 最大値                    | 単位 |

|------------------|------------------------------------|------|------------------------|----|

| AV <sub>DD</sub> | アナログ電源電圧、AV <sub>DD</sub> から GND へ | -0.3 | 6                      | V  |

| V <sub>IO</sub>  | デジタル電源電圧、V <sub>IO</sub> から GND へ  | -0.3 | AV <sub>DD</sub>       | V  |

|                  | アナログ出力(OUT)ピン電圧                    | -0.3 | AV <sub>DD</sub> + 0.3 | V  |

|                  | リファレンスピン電圧                         | -0.3 | AV <sub>DD</sub> + 0.3 | V  |

|                  | シリアルインターフェイスピン電圧                   | -0.3 | V <sub>IO</sub> + 0.3  | V  |

| T <sub>J</sub>   | 動作時接合部温度                           | -40  | 150                    | °C |

| T <sub>stg</sub> | 保存温度                               | -60  | 150                    | °C |

(1) 「絶対最大定格」を超える動作は、デバイスに恒久的な損傷を与える可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の範囲内であっても推奨動作条件の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能性、性能に影響を及ぼし、デバイスの寿命を短縮する可能性があります。

### 5.2 ESD 定格

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | 値     | 単位 |

|--------------------|------|------------------------------------------------------------------|-------|----|

|                    |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | ±1500 |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                  |                                    | 最小値 | 公称値              | 最大値              | 単位 |

|------------------|------------------------------------|-----|------------------|------------------|----|

| AV <sub>DD</sub> | アナログ電源電圧、AV <sub>DD</sub> から GND へ | 2.7 | 5.5              | 6                | V  |

| V <sub>IO</sub>  | IO 電源電圧、V <sub>IO</sub> から GND へ   | 1.7 | AV <sub>DD</sub> | AV <sub>DD</sub> | V  |

|                  | GND へのシリアルインターフェイス入力電圧             | 0   | V <sub>IO</sub>  | V <sub>IO</sub>  | V  |

| T <sub>J</sub>   | 動作時接合部温度                           | -40 | 125              | 150              | °C |

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                   | DAC60516W  | 単位   |

|-----------------------|-------------------|------------|------|

|                       |                   | YBH (WCSP) |      |

|                       |                   | 34 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 57.9       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 0.2        | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 14.1       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 0.1        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 14.1       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

$T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$  で、 $\text{AV}_{\text{DD}} = 2.7\text{V} \sim 5.5\text{V}$ 、 $\text{V}_{\text{IO}} = 1.7\text{V} \sim \text{AV}_{\text{DD}}$ 、 $\text{V}_{\text{REFIN}} = 2.4\text{V} \sim 5.5\text{V}$ 、DAC 出力無負荷、および  $\text{V}_{\text{IO}}$  または GND でのデジタル入力(特に記述のない限り)

| パラメータ                | テスト条件                                                                                                                                                    | 最小値                                         | 標準値                              | 最大値        | 単位                           |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------|------------|------------------------------|

| <b>安定動作 (1)</b>      |                                                                                                                                                          |                                             |                                  |            |                              |

| INL                  | 分解能                                                                                                                                                      | 12                                          |                                  |            | ビット                          |

| INL                  | 積分非直線性                                                                                                                                                   |                                             | $\pm 0.3$                        | $\pm 1$    | LSB                          |

| DNL                  | 微分非直線性                                                                                                                                                   | -1                                          | $\pm 0.3$                        | 1          | LSB                          |

| TUE                  | 総合未調整誤差                                                                                                                                                  | DAC 出力範囲 = 0V ~ 5V                          | $\pm 0.04$                       | $\pm 0.15$ | %FSR                         |

|                      | オフセット誤差                                                                                                                                                  | ゲイン = 1 または 2                               | $\pm 0.75$                       | $\pm 3$    | mV                           |

|                      | ゼロスケール誤差                                                                                                                                                 | すべて 0 がロードされた DAC レジスタ                      | 0                                | 0.5        | 3 mV                         |

|                      | フルスケール誤差                                                                                                                                                 | DAC レジスタはフルスケールコードでロードされ、DAC 出力範囲 = 0V ~ 5V | $\pm 0.04$                       | $\pm 0.15$ | %FSR                         |

|                      | ゲイン誤差                                                                                                                                                    | ゲイン = 1 または 2                               | $\pm 0.04$                       | $\pm 0.15$ | %FSR                         |

|                      | オフセット誤差のドリフト                                                                                                                                             |                                             | $\pm 3$                          |            | $\mu\text{V}/^\circ\text{C}$ |

|                      | ゼロスケール誤差のドリフト                                                                                                                                            |                                             | $\pm 2$                          |            | $\mu\text{V}/^\circ\text{C}$ |

|                      | フルスケール誤差のドリフト                                                                                                                                            |                                             | $\pm 3$                          |            | $\text{ppm}/^\circ\text{C}$  |

|                      | ゲイントリフト                                                                                                                                                  |                                             | $\pm 2$                          |            | $\text{ppm}/^\circ\text{C}$  |

| <b>出力特性</b>          |                                                                                                                                                          |                                             |                                  |            |                              |

| 出力電圧(2)              | ゲイン = 2                                                                                                                                                  | 0                                           | $2 \times \text{V}_{\text{REF}}$ |            | V                            |

|                      | ゲイン = 1                                                                                                                                                  | 0                                           | $\text{V}_{\text{REF}}$          |            |                              |

| 出力電圧ヘッドルーム/フルルーム     | $\text{AV}_{\text{DD}}$ へ、および GND から ( $-50\text{mA} \leq I_{\text{OUT}} \leq 50\text{mA}$ )                                                             | 0.5                                         |                                  |            | V                            |

| 負荷電流                 | 出力電圧ヘッドルーム = 0.5V                                                                                                                                        |                                             | 50                               |            | mA                           |

| 短絡電流(3)              | フルスケール出力を GND に短絡                                                                                                                                        |                                             | 75                               |            | mA                           |

|                      | $\text{V}_{\text{DD}}$ に短絡したゼロスケール出力                                                                                                                     |                                             | 75                               |            |                              |

| 容量性負荷(4)             | $R_{\text{LOAD}} = \text{開}$                                                                                                                             | 0                                           | 2                                |            | nF                           |

| DC 出力インピーダンス         | $\text{AV}_{\text{DD}}/2$ での DAC 出力                                                                                                                      |                                             | 0.08                             |            | $\Omega$                     |

|                      | $\text{AV}_{\text{DD}}$ または GND での DAC 出力                                                                                                                |                                             | 10                               |            |                              |

| <b>ダイナミック性能</b>      |                                                                                                                                                          |                                             |                                  |            |                              |

| 出力電圧セトリング時間          | $1/4$ から $3/4$ のスケール、 $3/4$ から $1/4$ のスケールの設定時間を $\pm 2$ LSB、 $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $\text{V}_{\text{REFIN}} = 2.5\text{V}$ 、ゲイン = 2 に |                                             | 6                                |            | $\mu\text{s}$                |

| スルーレート               | $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $\text{V}_{\text{REFIN}} = 2.5\text{V}$                                                                          |                                             | 1.7                              |            | $\text{V}/\mu\text{s}$       |

| 電源オン時のグリッチ振幅         | DAC コード = ゼロスケール                                                                                                                                         |                                             | 25                               |            | mV                           |

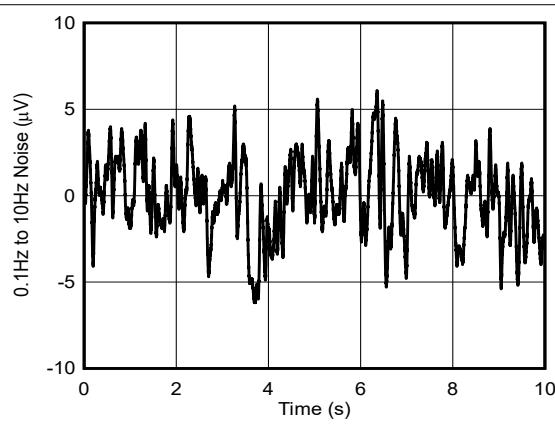

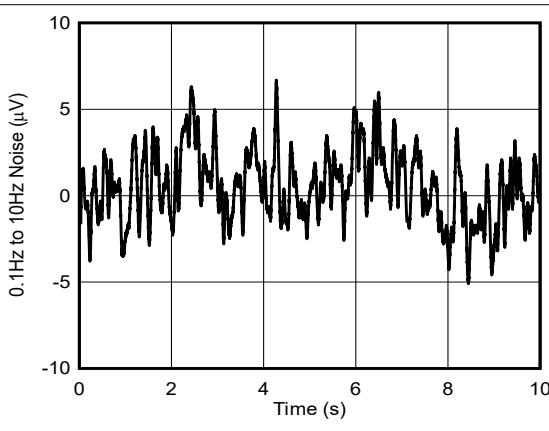

| 出力ノイズ電圧              | $0.1\text{Hz} \sim 10\text{Hz}$ 、DAC コード = ミッドスケール                                                                                                       |                                             | 12                               |            | $\mu\text{Vpp}$              |

| 出力ノイズ 密度             | $1\text{kHz}$ 、DAC コード = ミッドスケール、 $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $\text{V}_{\text{REFIN}} = 2.5\text{V}$                                        |                                             | 65                               |            | $\text{nV}/\text{Hz}$        |

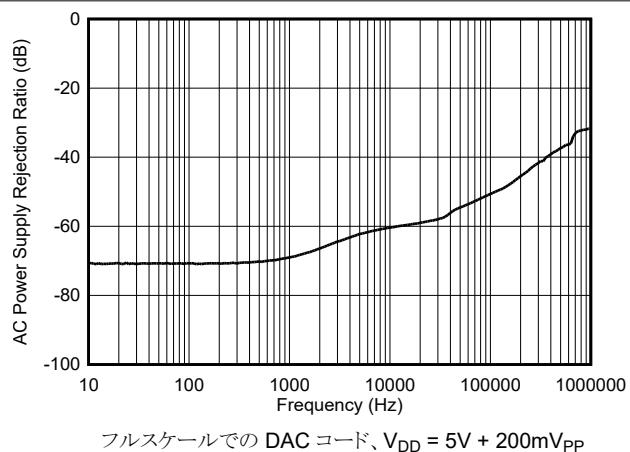

| AC PSRR              | DAC コード = ミッドスケール、周波数 = $60\text{Hz}$ 、振幅 $200\text{mVpp}$ を $\text{AV}_{\text{DD}}$ に重畠                                                                 |                                             | 80                               |            | dB                           |

| DC PSRR              | DAC コード = ミッドスケール、 $\text{AV}_{\text{DD}} = 5\text{V} \pm 0.5\text{V}$                                                                                   |                                             | 0.01                             |            | $\text{mV}/\text{V}$         |

| コード書き換えによるグリッチ インパルス | メジャー・キャリアを中心に 1 LSB 変更                                                                                                                                   |                                             | 1                                |            | $\text{nV}\cdot\text{s}$     |

| チャネル間 AC クロストーク      | DAC コード = ゼロスケール、隣接チャネルでのフルスケールスイング                                                                                                                      |                                             | 1                                |            | $\text{nV}\cdot\text{s}$     |

$T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$  で、 $\text{AV}_{\text{DD}} = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{\text{IO}} = 1.7\text{V} \sim \text{AV}_{\text{DD}}$ 、 $V_{\text{REFIN}} = 2.4\text{V} \sim 5.5\text{V}$ 、DAC 出力無負荷、および  $V_{\text{IO}}$  または GND でのデジタル入力(特に記述のない限り)

| パラメータ                   | テスト条件                                                                                                                  | 最小値                                         | 標準値                        | 最大値                       | 単位                          |

|-------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------|---------------------------|-----------------------------|

| チャネル間 DC クロストーク         | ゼロスケールで測定されたチャネル、フルスケールでの隣接チャネル                                                                                        | 12                                          |                            | 12                        | $\mu\text{V}$               |

|                         | ゼロスケールで測定されたチャネル、他のすべてのチャネルはフルスケールで測定                                                                                  |                                             |                            |                           |                             |

| デジタル フィードスルー            | DAC コード = ミッドスケール、 $f_{\text{SCLK}} = 1\text{MHz}$                                                                     | 0.1                                         |                            |                           | $\text{nV}\cdot\text{s}$    |

| パワーアップ時間 <sup>(5)</sup> | $A_{\text{VDD}}$ が $2.4\text{V}$ 、 $V_{\text{REFIN}} = 2.5\text{V}$ まで上昇した後で、DAC チャネルに電源が投入され、 $0\text{V}$ を出力するまでの時間。 | 120                                         |                            |                           | $\mu\text{s}$               |

| <b>外部リファレンス入力</b>       |                                                                                                                        |                                             |                            |                           |                             |

| $V_{\text{REFIN}}$      | 基準入力電圧範囲                                                                                                               | ゲイン = 1                                     | 1                          | $\text{V}_{\text{DD}}$    | $\text{V}$                  |

|                         |                                                                                                                        | ゲイン = 2                                     | 1                          | $\text{AV}_{\text{DD}/2}$ |                             |

| 基準入力電流                  | $V_{\text{REFIN}} = 2.5\text{V}$                                                                                       |                                             | 85                         |                           | $\mu\text{A}$               |

| リファレンス入力インピーダンス         |                                                                                                                        |                                             | 29                         | 35                        | $\text{k}\Omega$            |

| 基準入力容量                  |                                                                                                                        |                                             | 5                          |                           | $\text{pF}$                 |

| <b>内部リファレンス</b>         |                                                                                                                        |                                             |                            |                           |                             |

| $V_{\text{REFOUT}}$     | 基準出力電圧範囲                                                                                                               | $T_J = 25^\circ\text{C}$                    | 2.495                      | 2.505                     | $\text{V}$                  |

|                         | リファレンス出力のドリフト                                                                                                          |                                             | 25                         | 40                        | $\text{ppm}/^\circ\text{C}$ |

|                         | リファレンス出力インピーダンス                                                                                                        |                                             | 0.2                        |                           | $\Omega$                    |

|                         | リファレンス出力ノイズ                                                                                                            | $0.1\text{Hz} \sim 10\text{Hz}$             | 10                         |                           | $\mu\text{Vpp}$             |

|                         | リファレンス出力ノイズ密度                                                                                                          | $10\text{kHz}$ 、リファレンス負荷 = $10\text{nF}$    | 125                        |                           | $\text{nV}/\text{Hz}$       |

|                         | リファレンス負荷電流                                                                                                             |                                             | -4                         | 10                        | $\text{mA}$                 |

|                         | 基準負荷レギュレーション                                                                                                           | ソースおよびシンク                                   | 175                        |                           | $\mu\text{V}/\text{mA}$     |

|                         | 基準ライン レギュレーション                                                                                                         |                                             | 500                        |                           | $\mu\text{V}/\text{V}$      |

| <b>デジタル入出力</b>          |                                                                                                                        |                                             |                            |                           |                             |

| $V_{\text{IH}}$         | HIGH レベル入力電圧、 $V_{\text{IH}}$                                                                                          |                                             | $0.7 \times V_{\text{IO}}$ |                           | $\text{V}$                  |

| $V_{\text{IL}}$         | LOW レベル入力電圧、 $V_{\text{IL}}$                                                                                           |                                             | $0.3 \times V_{\text{IO}}$ |                           | $\text{V}$                  |

|                         | 入力電流                                                                                                                   |                                             | $\pm 2$                    |                           | $\mu\text{A}$               |

|                         | 入力ピン容量                                                                                                                 |                                             | 8                          |                           | $\text{pF}$                 |

| $V_{\text{OH}}$         | ハイレベル出力電圧、 $V_{\text{OH}}$                                                                                             | $I_{\text{OH}} = 0.2\text{mA}$              | $V_{\text{IO}} - 0.2$      |                           | $\text{V}$                  |

| $V_{\text{OL}}$         | Low レベル出力電圧、 $V_{\text{OL}}$                                                                                           | $I_{\text{OL}} = 0.2\text{mA}$              |                            | 0.4                       | $\text{V}$                  |

|                         | 出力ピンの容量                                                                                                                |                                             | 4                          |                           | $\text{pF}$                 |

| <b>電源要件</b>             |                                                                                                                        |                                             |                            |                           |                             |

| $I_{\text{AVDD}}$       | $\text{AV}_{\text{DD}}$ 電源電流                                                                                           | アクティブモード、内部リファレンス有効、DAC コード = フルスケール、SPI 静的 | 8.5                        | 13                        | $\text{mA}$                 |

|                         |                                                                                                                        | アクティブモード、内部リファレンス無効、DAC コード = フルスケール、SPI 静的 | 8                          | 12.5                      |                             |

|                         | $\text{AV}_{\text{DD}}$ 電源電流                                                                                           | パワーダウン モード                                  | 10                         | 20                        | $\mu\text{A}$               |

| $I_{\text{VIO}}$        | $V_{\text{IO}}$ の電源電流                                                                                                  |                                             | 0.1                        | 1                         | $\mu\text{A}$               |

- (1) エンドポイントはコード 16~4080 の間にあります

- (2) 外部リファレンスを使用する場合、 $V_{\text{REF}} = V_{\text{REFIN}}$  となります。そうでない場合、 $V_{\text{REF}} = 2.5\text{V}$ (内部リファレンス電圧)です。

- (3) 一時的な過負荷状態保護。電流制限中に、接合部温度が超過する可能性があります。規定された最大接合部温度を超える温度での動作は、デバイスの信頼性を損なう可能性があります。

- (4) 設計と特性評価による仕様で、製造テストは未実施。

- (5) デバイスがメモリから内部キャリブレーション係数をロードする間、さらに一定時間(5 ~ 10ms)、デバイスへの SPI または I2C 通信がブロックされます。この時間枠内のデジタル通信はすべて無視されます。

## 5.6 タイミング要件 - I<sup>2</sup>C 標準モード

$T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  で、 $\text{AV}_{\text{DD}} = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{\text{IO}} = 1.7\text{V} \sim \text{AV}_{\text{DD}}$ 、 $V_{\text{REFIN}} = 2.4\text{V} \sim 5.5\text{V}$ 、および  $V_{\text{IO}}$  または  $\text{GND}$  でデジタル入力

|                      |                    | 最小値  | 公称値 | 最大値  | 単位  |

|----------------------|--------------------|------|-----|------|-----|

| $t_{\text{SCL}}$     | SCL 周波数            |      |     | 100  | kHz |

| $t_{\text{BUF}}$     | 停止条件と始動条件の間のバス解放時間 | 4.7  |     |      | μs  |

| $t_{\text{HDSTA}}$   | リピートスタート後のホールド時間   | 4    |     |      | μs  |

| $t_{\text{SUSTA}}$   | 繰り返しスタートのセットアップ時間  | 4.7  |     |      | μs  |

| $t_{\text{SUSTO}}$   | STOP 条件のセットアップ時間   | 4    |     |      | μs  |

| $t_{\text{HDDAT}}$   | データホールド時間          | 0    |     |      | ns  |

| $t_{\text{SUDAT}}$   | データセットアップ時間        | 250  |     |      | ns  |

| $t_{\text{LOW}}$     | SCL クロックの Low 期間   | 4700 |     |      | ns  |

| $t_{\text{HIGH}}$    | SCL クロックの High 期間  | 4000 |     |      | ns  |

| $t_{\text{F}}$       | クロック / データの立ち下がり時間 |      |     | 300  | ns  |

| $t_{\text{R}}$       | クロック / データの立ち上がり時間 |      |     | 1000 | ns  |

| $t_{\text{VD\_DAT}}$ | データ有効時間            |      |     | 3.45 | μs  |

| $t_{\text{VD\_ACK}}$ | データ有効アクノリッジ時間      |      |     | 3.45 | μs  |

## 5.7 タイミング要件 - I<sup>2</sup>C 高速モード

$T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  で、 $\text{AV}_{\text{DD}} = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{\text{IO}} = 1.7\text{V} \sim \text{AV}_{\text{DD}}$ 、 $V_{\text{REFIN}} = 2.4\text{V} \sim 5.5\text{V}$ 、および  $V_{\text{IO}}$  または  $\text{GND}$  でデジタル入力

|                      |                    | 最小値  | 公称値 | 最大値 | 単位  |

|----------------------|--------------------|------|-----|-----|-----|

| $t_{\text{SCL}}$     | SCL 周波数            |      |     | 400 | kHz |

| $t_{\text{BUF}}$     | 停止条件と始動条件の間のバス解放時間 | 1.3  |     |     | μs  |

| $t_{\text{HDSTA}}$   | リピートスタート後のホールド時間   | 0.6  |     |     | μs  |

| $t_{\text{SUSTA}}$   | 繰り返しスタートのセットアップ時間  | 0.6  |     |     | μs  |

| $t_{\text{SUSTO}}$   | STOP 条件のセットアップ時間   | 0.6  |     |     | μs  |

| $t_{\text{HDDAT}}$   | データホールド時間          | 0    |     |     | ns  |

| $t_{\text{SUDAT}}$   | データセットアップ時間        | 100  |     |     | ns  |

| $t_{\text{LOW}}$     | SCL クロックの Low 期間   | 1300 |     |     | ns  |

| $t_{\text{HIGH}}$    | SCL クロックの High 期間  | 600  |     |     | ns  |

| $t_{\text{F}}$       | クロック / データの立ち下がり時間 |      |     | 300 | ns  |

| $t_{\text{R}}$       | クロック / データの立ち上がり時間 |      |     | 300 | ns  |

| $t_{\text{VD\_DAT}}$ | データ有効時間            |      |     | 0.9 | μs  |

| $t_{\text{VD\_ACK}}$ | データ有効アクノリッジ時間      |      |     | 0.9 | μs  |

## 5.8 タイミング要件 - I<sup>2</sup>C 高速モード プラス

$T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  で、 $\text{AV}_{\text{DD}} = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{\text{IO}} = 1.7\text{V} \sim \text{AV}_{\text{DD}}$ 、 $V_{\text{REFIN}} = 2.4\text{V} \sim 5.5\text{V}$ 、および  $V_{\text{IO}}$  または  $\text{GND}$  でデジタル入力

|                    |                    | 最小値  | 公称値 | 最大値 | 単位  |

|--------------------|--------------------|------|-----|-----|-----|

| $t_{\text{SCL}}$   | SCL 周波数            |      |     | 1   | MHz |

| $t_{\text{BUF}}$   | 停止条件と始動条件の間のバス解放時間 | 0.5  |     |     | μs  |

| $t_{\text{HDSTA}}$ | リピートスタート後のホールド時間   | 0.26 |     |     | μs  |

| $t_{\text{SUSTA}}$ | 繰り返しスタートのセットアップ時間  | 0.26 |     |     | μs  |

| $t_{\text{SUSTO}}$ | STOP 条件のセットアップ時間   | 0.26 |     |     | μs  |

| $t_{\text{HDDAT}}$ | データホールド時間          | 0    |     |     | ns  |

| $t_{\text{SUDAT}}$ | データセットアップ時間        | 50   |     |     | ns  |

| $t_{\text{LOW}}$   | SCL クロックの Low 期間   | 0.5  |     |     | μs  |

| $t_{\text{HIGH}}$  | SCL クロックの High 期間  | 0.26 |     |     | μs  |

$T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  で、 $\text{AV}_{\text{DD}} = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{\text{IO}} = 1.7\text{V} \sim \text{AV}_{\text{DD}}$ 、 $V_{\text{REFIN}} = 2.4\text{V} \sim 5.5\text{V}$ 、および  $V_{\text{IO}}$  または GND でデジタル入力

|               |                    | 最小値 | 公称値 | 最大値  | 単位 |

|---------------|--------------------|-----|-----|------|----|

| $t_F$         | クロック / データの立ち下がり時間 |     |     | 120  | ns |

| $t_R$         | クロック / データの立ち上がり時間 |     |     | 120  | ns |

| $t_{VD\_DAT}$ | データ有効時間            |     |     | 0.45 | μs |

| $t_{VD\_ACK}$ | データ有効アクリッジ時間       |     |     | 0.45 | μs |

## 5.9 タイミング要件 : SPI

$T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  で、 $\text{AV}_{\text{DD}} = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{\text{IO}} = 1.7\text{V} \sim \text{AV}_{\text{DD}}$ 、 $V_{\text{REFIN}} = 2.4\text{V} \sim 5.5\text{V}$ 、および  $V_{\text{IO}}$  または  $\text{GND}$  でデジタル入力

|                                          |                                  | 最小値 | 公称値 | 最大値 | 単位  |

|------------------------------------------|----------------------------------|-----|-----|-----|-----|

| <b>SPI TIMING REQUIREMENTS, FSDO = 0</b> |                                  |     |     |     |     |

| $f_{(\text{SCLK})}$                      | SCLK 周波数                         |     |     | 20  | MHz |

| $t_{(\text{SCLKH})}$                     | SCLK High 時間                     |     | 20  |     | ns  |

| $t_{(\text{SCLKL})}$                     | SCLK Low 時間                      |     | 23  |     | ns  |

| $t_{(\text{SDIS})}$                      | SDI のセットアップ時間                    |     | 5   |     | ns  |

| $t_{(\text{SDIH})}$                      | SDI のホールド時間                      |     | 8   |     | ns  |

| $t_{(\text{SDOTOZ})}$                    | SDO アクティブ出力から tri 状態出力までの遅延      | 0   |     | 17  | ns  |

| $t_{(\text{SDOEN})}$                     | SDO tri 状態出力からアクトティブ出力までの遅延      | 0   |     | 21  | ns  |

| $t_{(\text{SDOTOD})}$                    | SDO 出力遅延                         | 2   |     | 23  | ns  |

| $t_{(\text{CSS})}$                       | $\overline{\text{CS}}$ のセットアップ時間 | 15  |     |     | ns  |

| $t_{(\text{CSH})}$                       | $\overline{\text{CS}}$ のホールド時間   | 15  |     |     | ns  |

| $t_{(\text{CSHIGH})}$                    | $\overline{\text{CS}}$ High 時間   | 15  |     |     | ns  |

| <b>SPI TIMING REQUIREMENTS, FSDO = 1</b> |                                  |     |     |     |     |

| $f_{(\text{SCLK})}$                      | SCLK 周波数 <sup>(1)</sup>          |     |     | 30  | MHz |

| $t_{(\text{SCLKH})}$                     | SCLK High 時間                     |     | 14  |     | ns  |

| $t_{(\text{SCLKL})}$                     | SCLK Low 時間                      |     | 16  |     | ns  |

| $t_{(\text{SDIS})}$                      | SDI のセットアップ時間                    |     | 5   |     | ns  |

| $t_{(\text{SDIH})}$                      | SDI のホールド時間                      |     | 8   |     | ns  |

| $t_{(\text{SDOTOZ})}$                    | SDO アクティブ出力から tri 状態出力までの遅延      | 0   |     | 17  | ns  |

| $t_{(\text{SDOEN})}$                     | SDO tri 状態出力からアクトティブ出力までの遅延      | 0   |     | 21  | ns  |

| $t_{(\text{SDOTOD})}$                    | SDO 出力遅延                         | 2.5 |     | 30  | ns  |

| $t_{(\text{CSS})}$                       | $\overline{\text{CS}}$ のセットアップ時間 | 15  |     |     | ns  |

| $t_{(\text{CSH})}$                       | $\overline{\text{CS}}$ のホールド時間   | 15  |     |     | ns  |

| $t_{(\text{CSHIGH})}$                    | $\overline{\text{CS}}$ High 時間   | 15  |     |     | ns  |

(1) デバイスへの書き込みは、50MHz までの周波数で実行できます。

## 5.10 スイッチング特性

$T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  で、 $\text{AV}_{\text{DD}} = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{\text{IO}} = 1.7\text{V} \sim \text{AV}_{\text{DD}}$ 、 $V_{\text{REFIN}} = 2.4\text{V} \sim 5.5\text{V}$ 、DAC 出力アンロード、および  $V_{\text{IO}}$  または  $\text{GND}$  でデジタル入力

| パラメータ                        | テスト条件                          | 最小値                                                  | 標準値 | 最大値 | 単位 |

|------------------------------|--------------------------------|------------------------------------------------------|-----|-----|----|

| <b>RESET CHARACTERISTICS</b> |                                |                                                      |     |     |    |

| $t_{\text{DACRDY}}$          | デバイス準備待ち時間                     | リセットイベントから測定した、シリアルインターフェイスアクセスの有効時間                 |     | 10  | ms |

| $t_{\text{RESET}}$           | RESET パルス幅                     |                                                      | 20  |     | ns |

| <b>DAC の特性</b>               |                                |                                                      |     |     |    |

| $t_{\text{DACCCLR}}$         | DAC クリア応答時間                    | $\overline{\text{CLEAR}}$ トリガ後に DAC がコード変更を開始するまでの時間 | 50  |     | ns |

| $t_{\text{CLRWDTTH}}$        | $\overline{\text{CLEAR}}$ パルス幅 |                                                      | 100 |     | ns |

| $t_{\text{LDACWDTTH}}$       | $\overline{\text{LDAC}}$ パルス幅  |                                                      | 100 |     | ns |

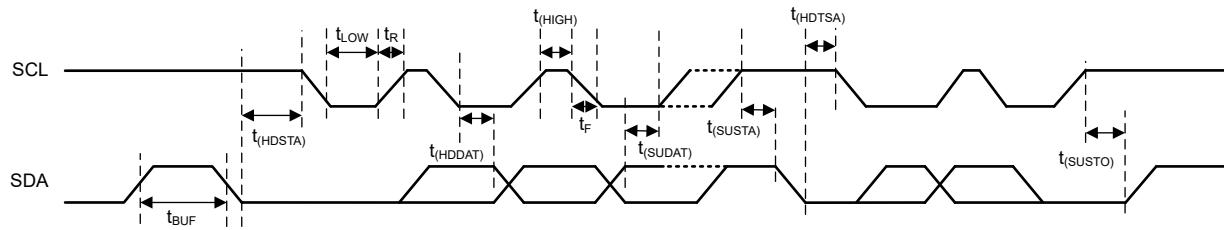

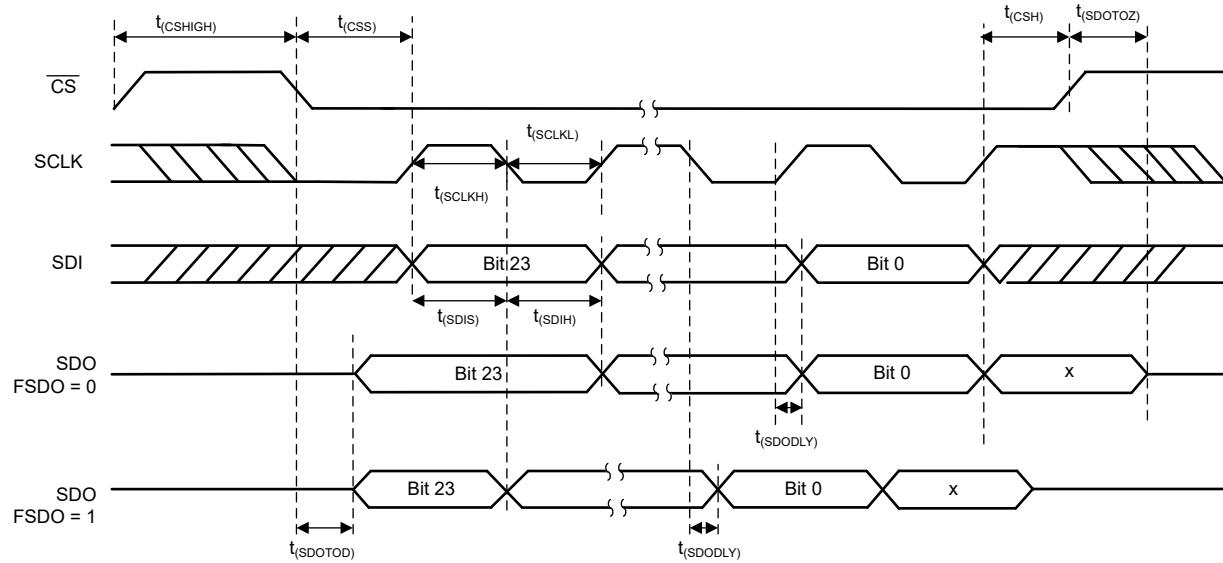

## 5.11 タイミング図

図 5-1. I<sup>2</sup>C のタイミング図

図 5-2. SPI タイミング図

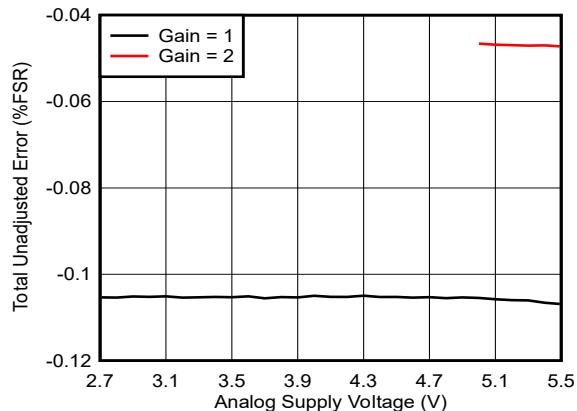

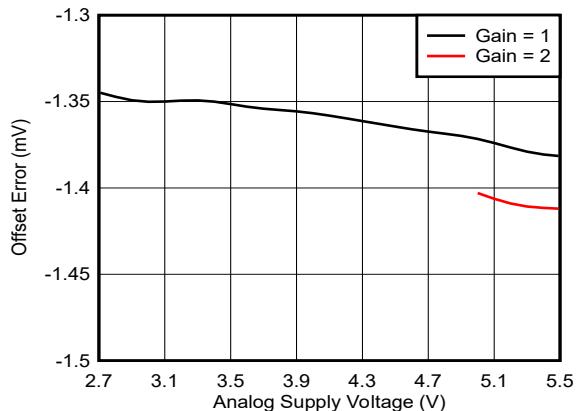

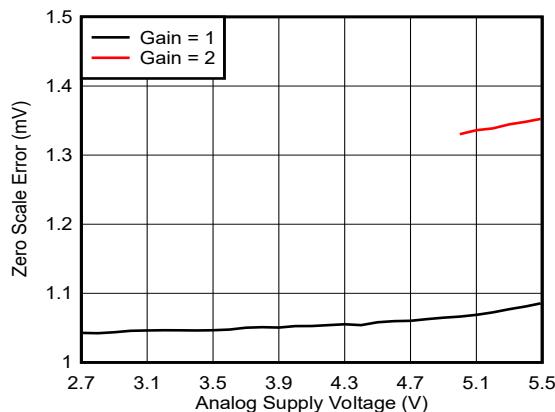

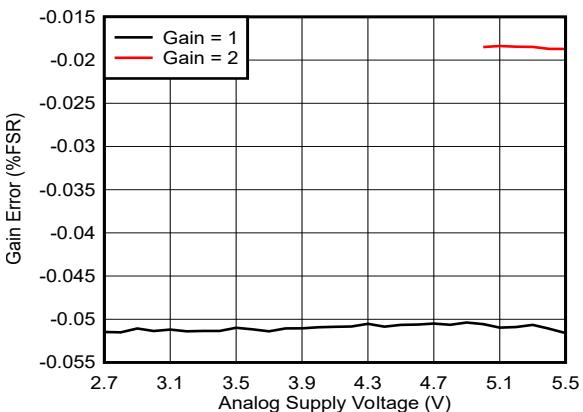

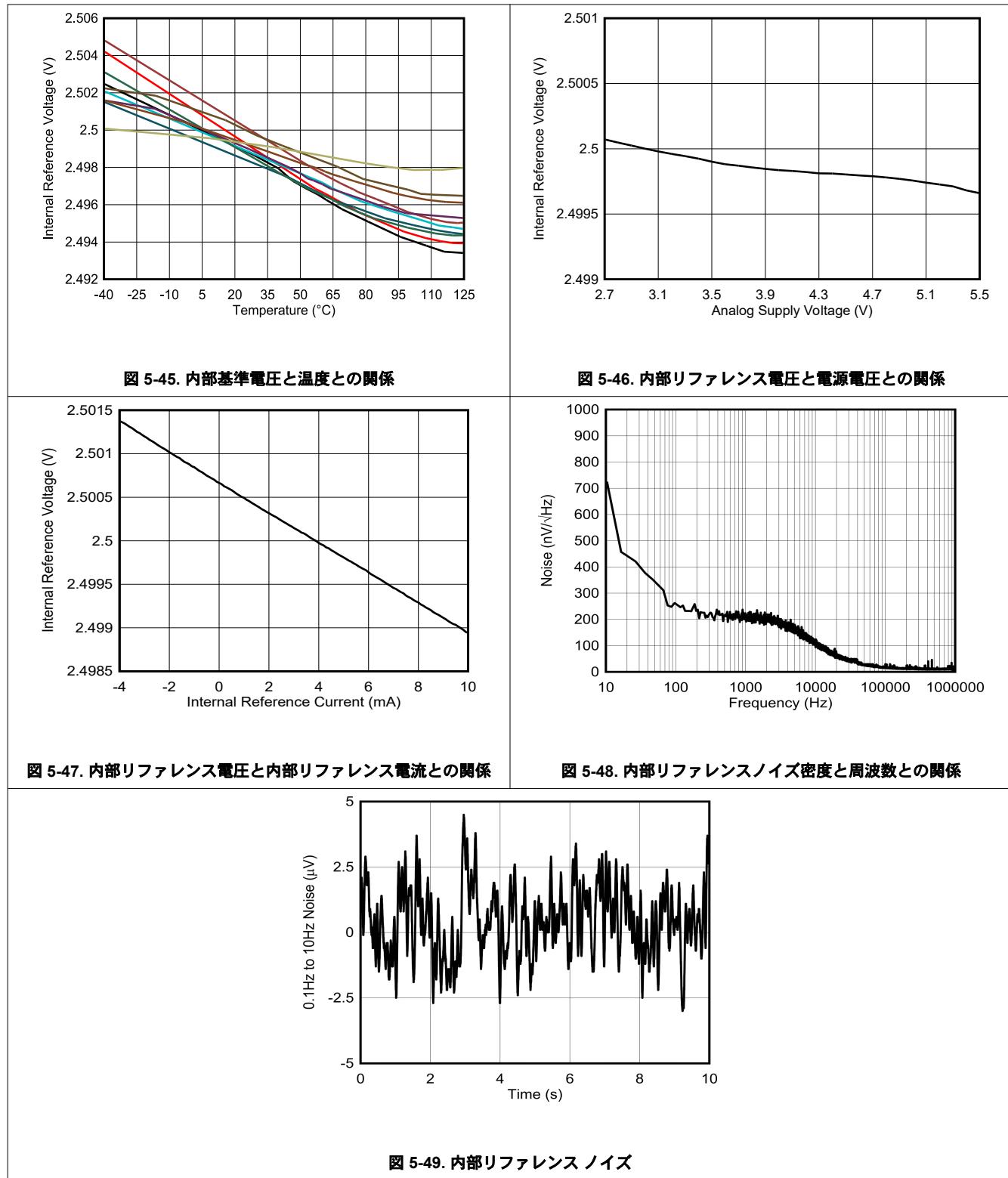

## 5.12 代表的特性

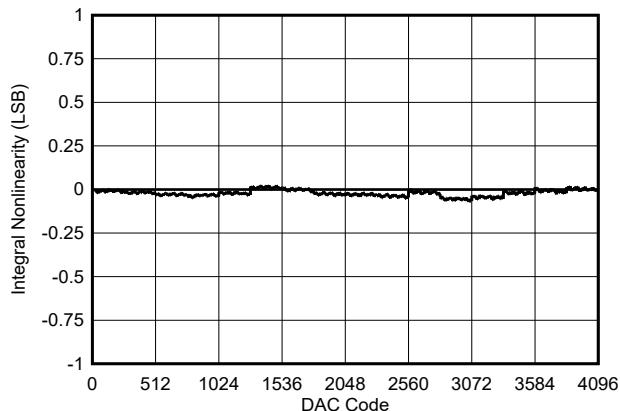

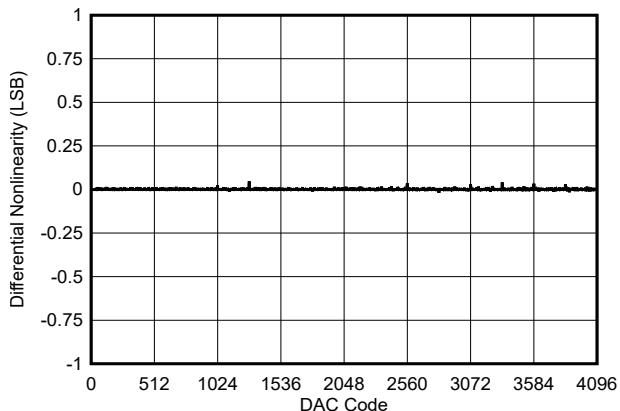

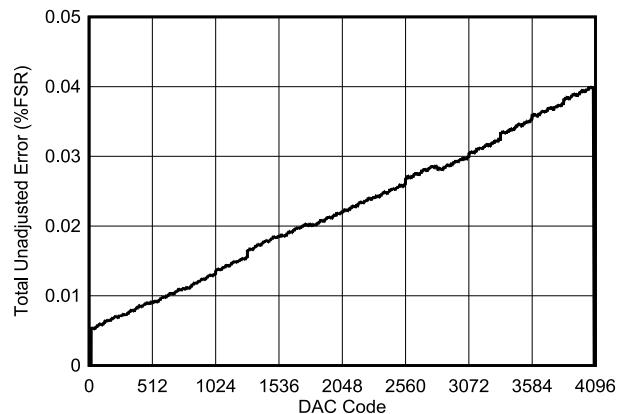

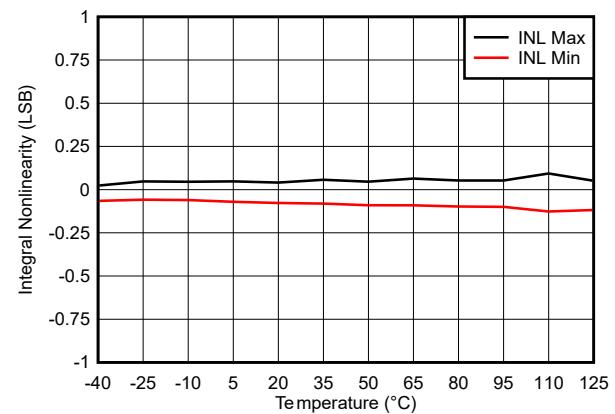

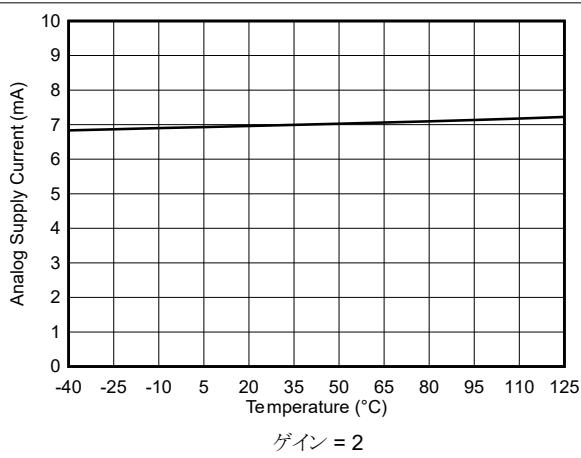

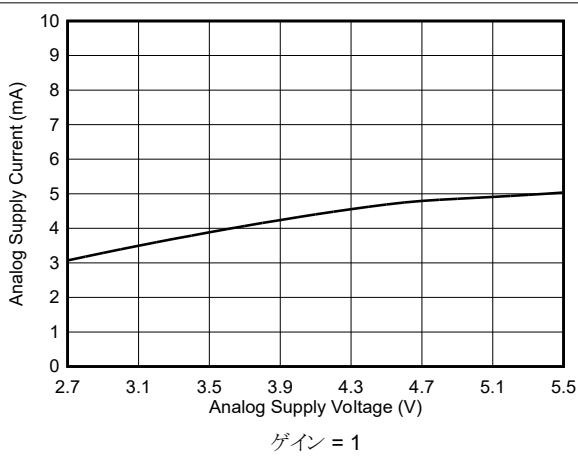

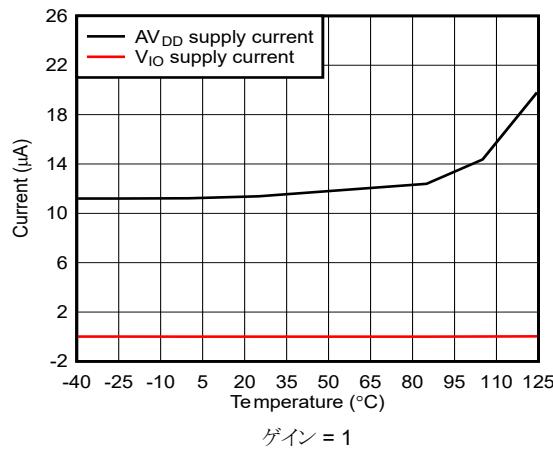

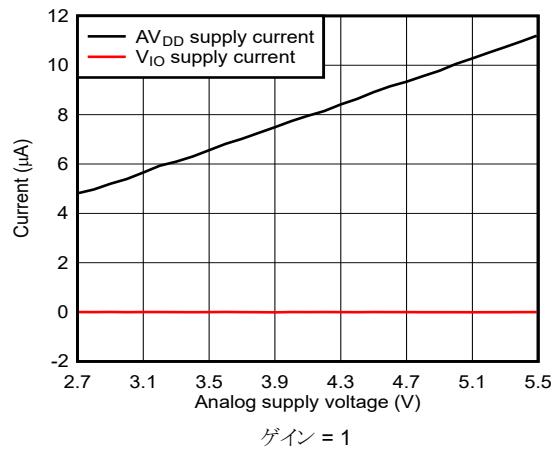

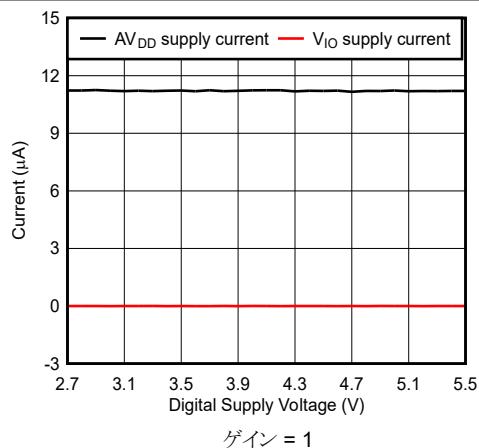

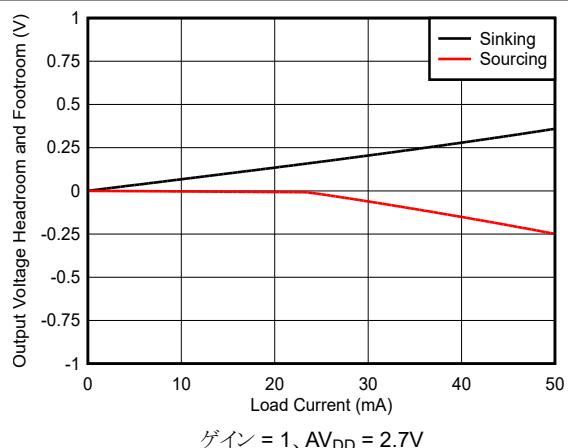

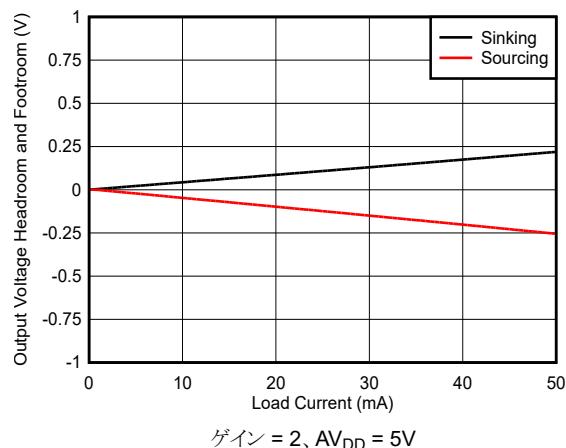

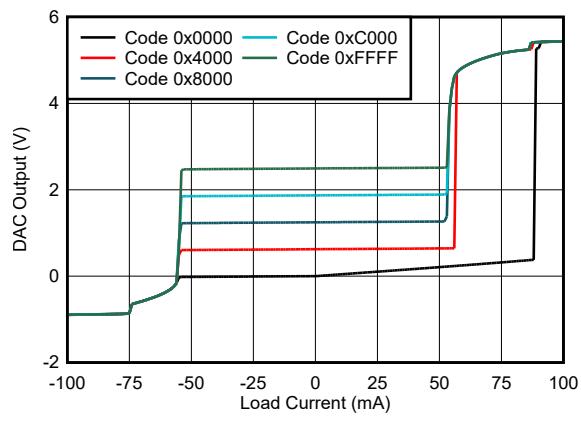

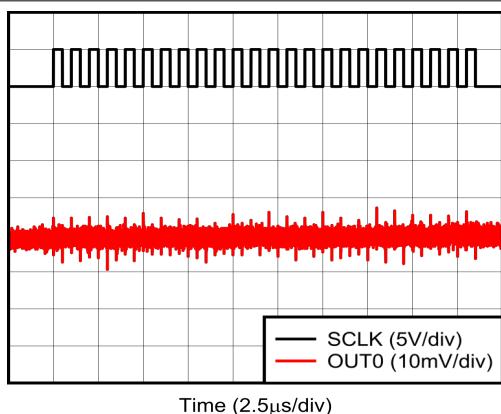

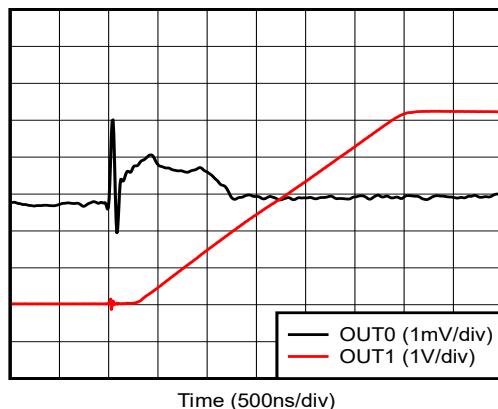

$T_J = 25^\circ\text{C}$  で、 $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $\text{V}_{\text{IO}} = 5.5\text{V}$ 、内部リファレンス = 2.5V、ゲイン = 2、DAC 出力は無負荷(特に記述のない限り)

図 5-3. 積分非直線性とデジタル入力コードとの関係

図 5-4. 微分非直線性とデジタル入力コードとの関係

図 5-5. 総未調整誤差とデジタル入力コードとの関係

図 5-6. 積分非線形性と温度との関係

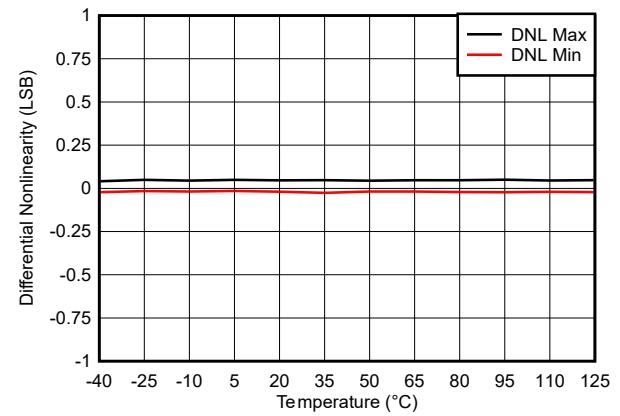

図 5-7. 微分非線形性と温度との関係

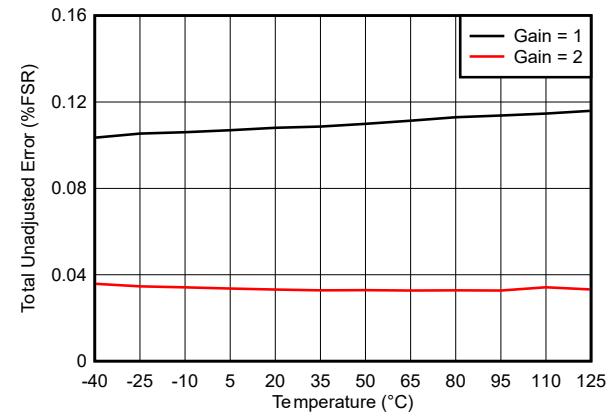

図 5-8. 総未調整誤差と温度との関係

## 5.12 代表的特性 (続き)

$T_J = 25^\circ\text{C}$  で、 $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $\text{V}_{\text{IO}} = 5.5\text{V}$ 、内部リファレンス = 2.5V、ゲイン = 2、DAC 出力は無負荷(特に記述のない限り)

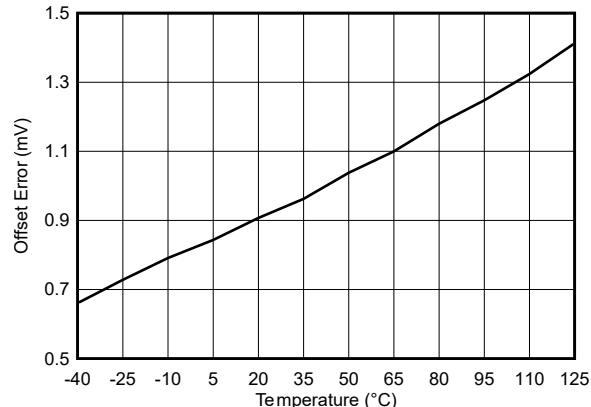

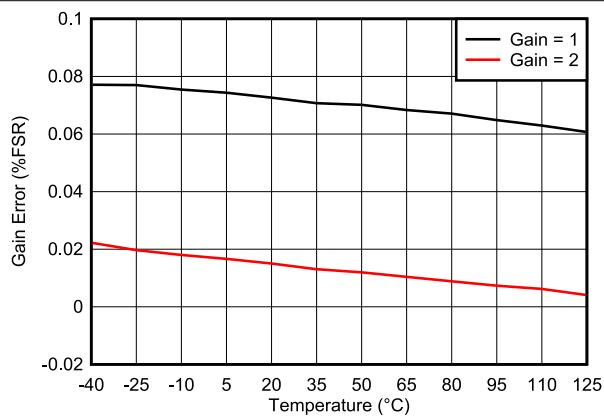

図 5-9. オフセット誤差と温度との関係

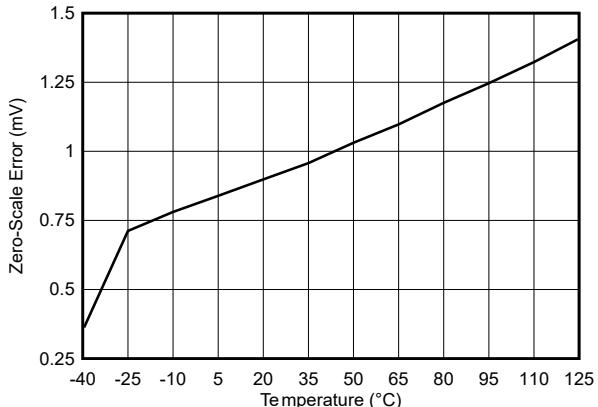

図 5-10. ゼロスケール誤差と温度との関係

図 5-11. ゲイン誤差と温度との関係

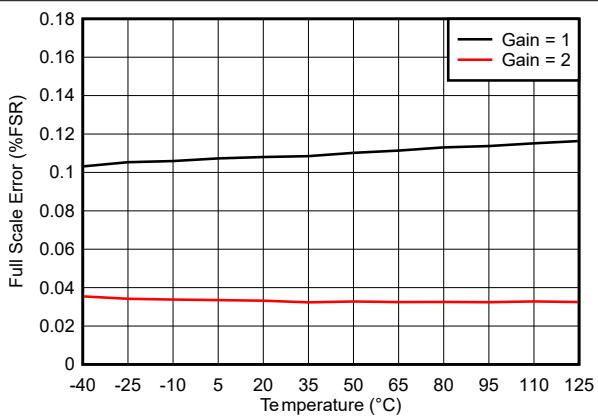

図 5-12. フルスケール誤差と温度との関係

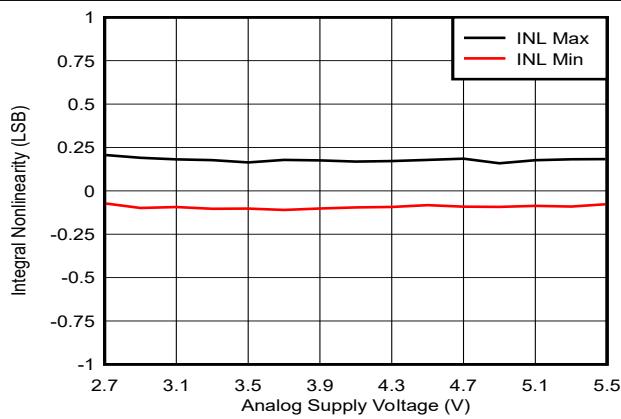

図 5-13. 積分非線形性と電源電圧との関係

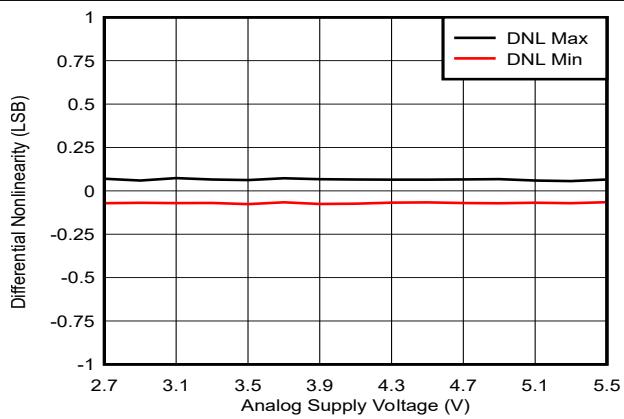

図 5-14. 微分非線形性と電源電圧との関係

## 5.12 代表的特性 (続き)

$T_J = 25^\circ\text{C}$  で、 $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $V_{\text{IO}} = 5.5\text{V}$ 、内部リファレンス = 2.5V、ゲイン = 2、DAC 出力は無負荷(特に記述のない限り)

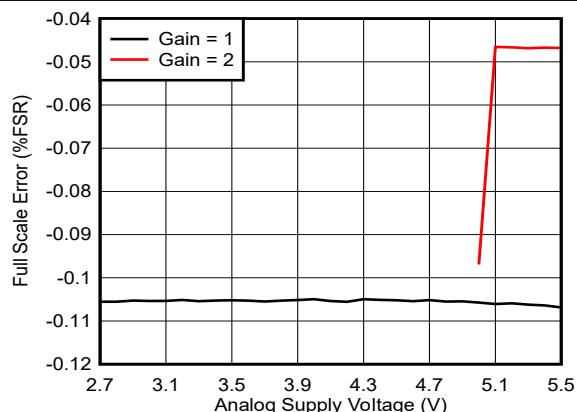

図 5-15. 総未調整誤差と電源電圧との関係

図 5-16. オフセット誤差と電源電圧との関係

図 5-17. ゼロスケール誤差と電源電圧との関係

図 5-18. ゲイン誤差と電源電圧との関係

図 5-19. フルスケール誤差と電源電圧との関係

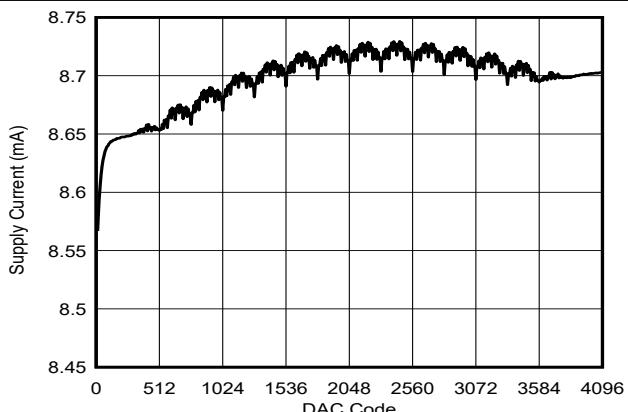

図 5-20. 内部リファレンス供給電流とデジタル入力コードとの関係

## 5.12 代表的特性 (続き)

$T_J = 25^\circ\text{C}$  で、 $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $\text{V}_{\text{IO}} = 5.5\text{V}$ 、内部リファレンス = 2.5V、ゲイン = 2、DAC 出力は無負荷(特に記述のない限り)

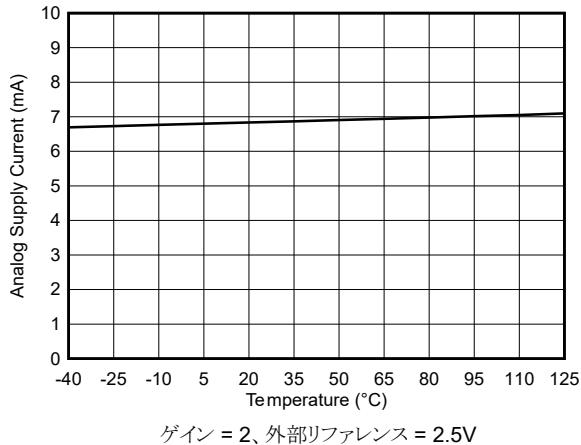

図 5-21. 外部リファレンス供給電流と温度との関係

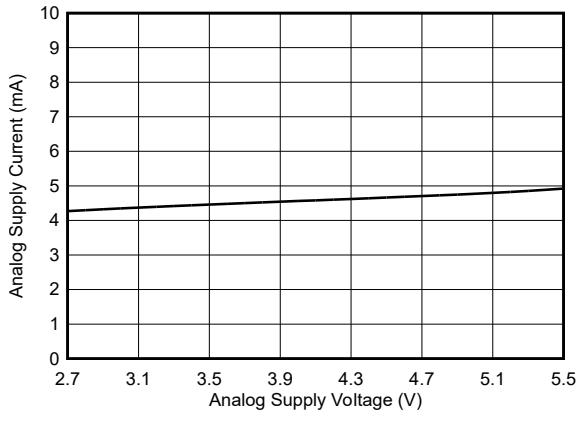

図 5-22. 外部リファレンス供給電流と電源電圧との関係

図 5-23. 内部リファレンス供給電流と温度との関係

図 5-24. 内部リファレンス供給電流と電源電圧との関係

図 5-25. パワーダウン電流と温度との関係

図 5-26. パワーダウン電流と電源電圧との関係

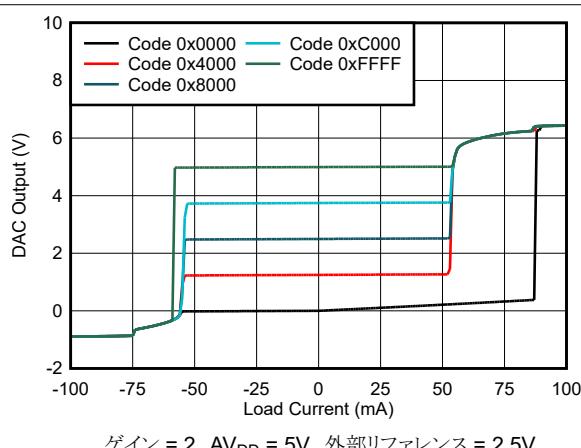

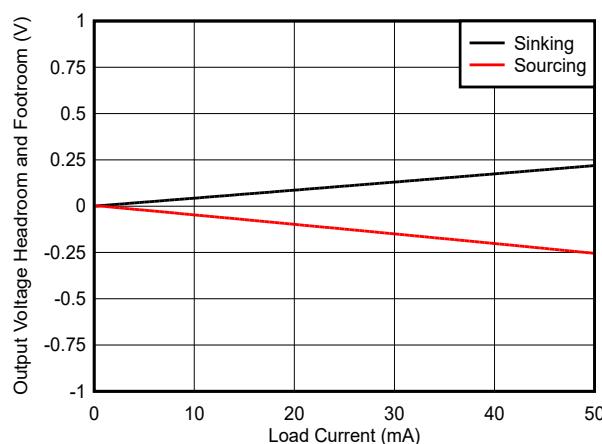

## 5.12 代表的特性 (続き)

$T_J = 25^\circ\text{C}$  で、 $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $\text{V}_{\text{IO}} = 5.5\text{V}$ 、内部リファレンス = 2.5V、ゲイン = 2、DAC 出力は無負荷(特に記述のない限り)

図 5-27. パワーダウン電流と  $\text{V}_{\text{IO}}$  との関係

図 5-28. ヘッドルームおよびフットルームと負荷電流との関係

図 5-29. ヘッドルームおよびフットルームと負荷電流との関係

図 5-30. ソースおよびシンク振幅

図 5-31. ソースおよびシンク振幅

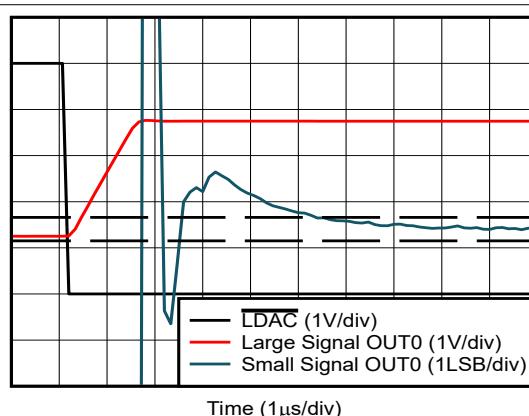

破線は、安定化時間を表します。

図 5-32. フルスケールセッティング時間、立ち上がりエッジ

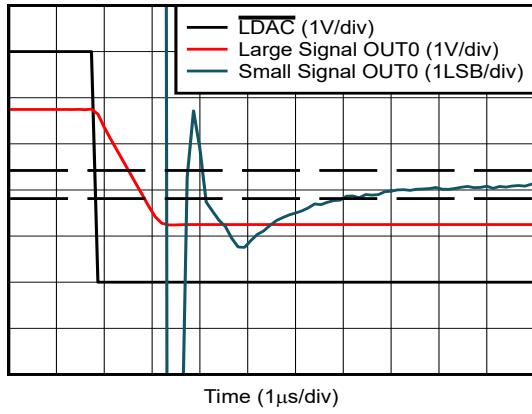

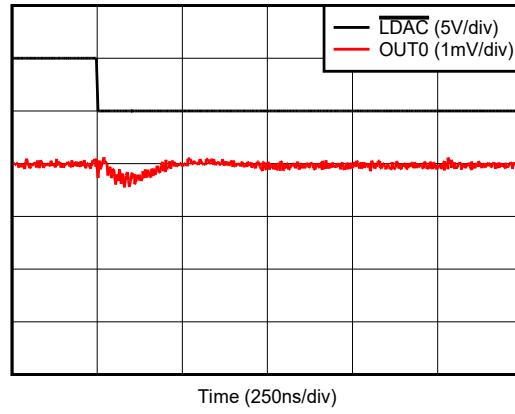

## 5.12 代表的特性 (続き)

$T_J = 25^\circ\text{C}$  で、 $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $V_{\text{IO}} = 5.5\text{V}$ 、内部リファレンス = 2.5V、ゲイン = 2、DAC 出力は無負荷(特に記述のない限り)

図 5-33. フルスケール セトリング時間、立ち下がりエッジ

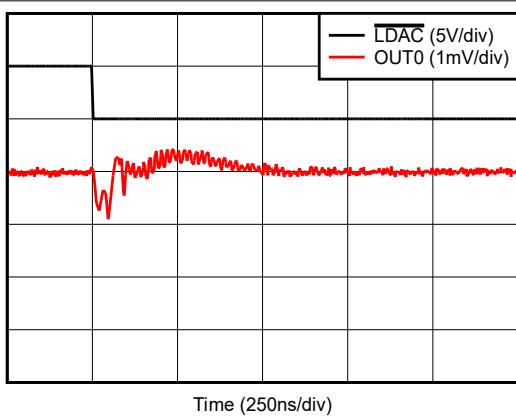

図 5-34. グリッチインパルス、立ち下がりエッジ

1LSB ステップ

図 5-35. グリッチインパルス、立ち上がりエッジ

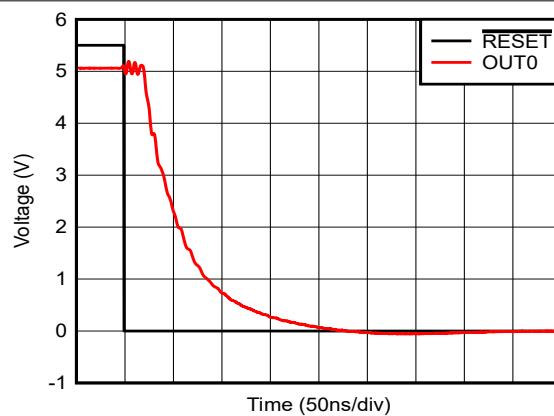

図 5-36. パワーオン、ゼロスケールにリセット

Time (500ns/div)

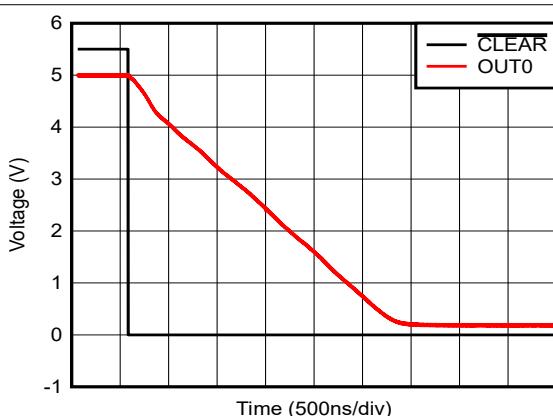

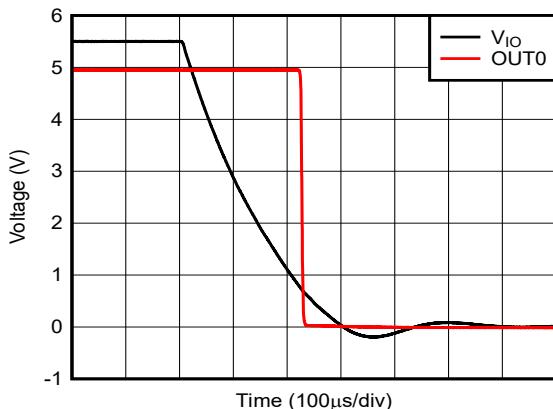

図 5-37. ゼロスケールにクリア

Time (100μs/div)

図 5-38.  $\text{AV}_{\text{DD}}$  パワーダウン応答

## 5.12 代表的特性 (続き)

$T_J = 25^\circ\text{C}$  で、 $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $V_{\text{IO}} = 5.5\text{V}$ 、内部リファレンス = 2.5V、ゲイン = 2、DAC 出力は無負荷(特に記述のない限り)

## 5.12 代表的特性 (続き)

$T_J = 25^\circ\text{C}$  で、 $\text{AV}_{\text{DD}} = 5.5\text{V}$ 、 $V_{\text{IO}} = 5.5\text{V}$ 、内部リファレンス = 2.5V、ゲイン = 2、DAC 出力は無負荷(特に記述のない限り)

## 6 詳細説明

### 6.1 概要

DAC60516W は、低消費電力、16 チャネル、12 ビット分解能、バッファ付き電圧出力の D/A コンバータ(DAC)です。DAC60516W には 2.5V のリファレンスが内蔵されており、ソフトウェアでユーザーが選択できるゲイン設定を提供します。この設定を使って、一度に 4 つの DAC のグループに対するフルスケール出力電圧範囲を設定できます(セクション 6.3.1.1 も参照)。本デバイスは外部の AV<sub>DD</sub> および V<sub>IO</sub> 電源で動作します。AVDD および VIO ピンを单一電源(2.7V ~ 5.5V)に短絡することもできます。DAC60516W との通信は、SPI および I<sup>2</sup>C 通信をサポートするシリアルインターフェースを介して行われます。

DAC60516W にはパワー オンリセット回路が組み込まれており、電源投入後、有効なコードがデバイスに書き込まれるまで DAC 出力をゼロスケールに維持します。

クリアピンにより、複数の DAC チャネルを指定されたクリア値に同時に更新することができます。

### 6.2 機能ブロック図

## 6.3 機能説明

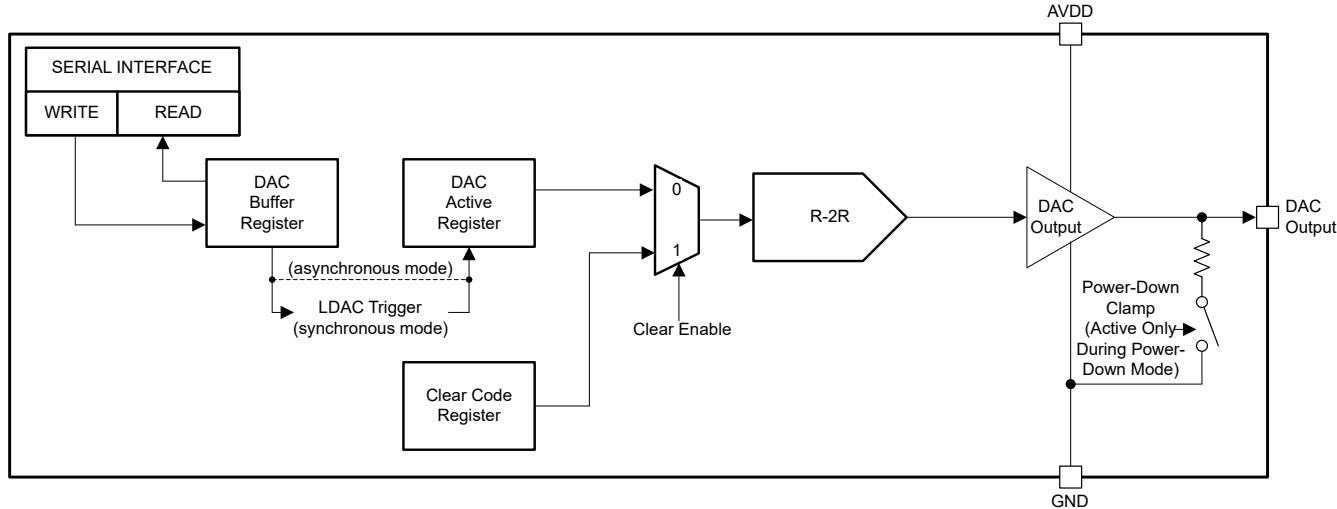

### 6.3.1 デジタル/アナログ コンバータ (DAC) アーキテクチャ

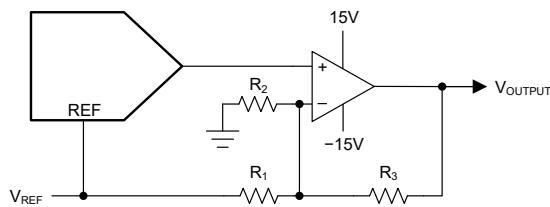

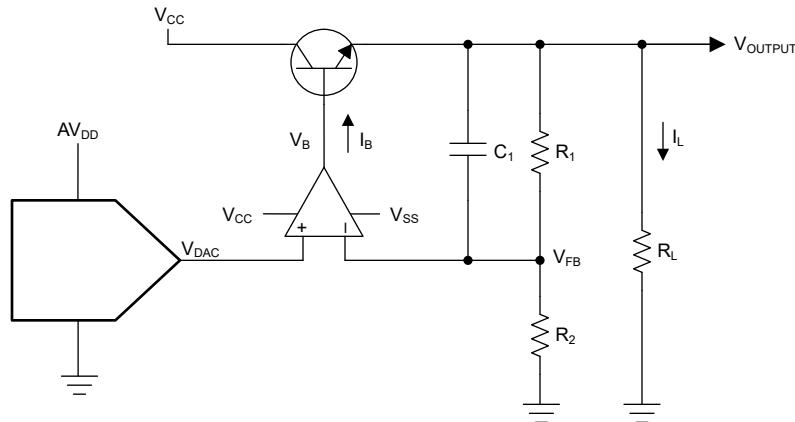

DAC60516W の各出力チャネルは、R-2R ラダーアーキテクチャと、それに続く出力バッファアンプで構成されています。図 6-1 に、DAC アーキテクチャのブロック図を示します。

図 6-1. DAC60516W DAC ブロック図

リセットイベント後、すべての DAC レジスタはゼロコードに設定され、DAC 出力アンプはパワーダウンし、DAC 出力はプルダウンレジスタを介して GND にクランプされます。各 DAC 出力は、PWDWN レジスタの適切なビットに書き込むことで、ソフトウェアで個別に有効化または無効化できます。無効化されている場合は、DAC 出力はプルダウンレジスタを介してグランドにクランプされます。

#### 6.3.1.1 DAC レジスタ構造

DAC は、12 ビットの入力コードに比例した出力電圧を生成します。入力データは、すべての出力レンジに対してストレートバイナリ形式で DAC データレジスタに書き込まれます。DAC\_GAIN レジスタに書き込むことで、最大フルスケール DAC 出力電圧を  $1 \times V_{REF}$  または  $2 \times V_{REF}$  (最大 5V) に設定できます。ここで  $V_{REF}$  は内部または外部のリファレンス入力電圧です。セクション 7.1.5 は、QUAD0 (OUT0 ~ OUT3)、QUAD1 (OUT4 ~ OUT7)、QUAD2 (OUT8 ~ OUT11)、QUAD3 (OUT12 ~ OUT15) のゲイン設定が可能であることを示しています。QUAD グループのすべての DAC チャネルで、同じゲイン設定が共有されます。

DAC データレジスタに書き込まれたデータは、最初に DAC バッファレジスタに格納されます。DAC バッファレジスタから DAC アクティブレジスタへのデータ転送は、即時に行われるよう設定することも(非同期モード)、DAC トリガ信号によって開始することも(同期モード)可能です。DAC アクティブレジスタが更新されると、DAC 出力チャネルは新しい値に変わります。

DAC\_BCAST\_EN レジスタの対応する BCAST\_EN ビットを設定することで、各 DAC をブロードキャストモードで動作するように設定することができます。BCAST\_DAC\_DATA レジスタに値が書き込まれると、この値はブロードキャストモードで動作するすべての DAC のバッファおよびアクティブデータレジスタに自動で保存されます。

さらに、各 DAC には短絡検出回路があります。DAC\_STATUS レジスタは、現在短絡状態の DAC チャネルを示します。グローバルステータスビット (STATUS レジスタ内の GDAC\_SC\_STS) は、すべての DAC\_STATUS ビットの論理 OR であり、短絡状態のチャネルが存在するかどうかを判定するために使用できます。

### 6.3.1.1.1 DAC 同期動作

各 DAC チャネルの更新モードは、各 DAC を SYNC\_EN レジスタに書き込むことで設定される DAC 同期設定によって決定されます。非同期モードでは、DAC バッファデータレジスタへの書き込みにより、CS の立ち上がりエッジで DAC のアクティブレジスタが即座に更新されます。同期モードでは、DAC バッファデータレジスタに書き込んでも DAC アクティブレジスタは自動的に更新されません。代わりに、更新は DAC トリガ信号の生成後にのみ行われます。LDAC ピンを Low にすると、DAC トリガ信号を生成することができます。この場合、同期モードで動作しているすべての DAC 出力チャネルのアクティブレジスタが同時に更新されます。LDAC ピンは、SYNC\_EN レジスタすでに非同期に設定されているチャネルのアクティブレジスタには影響しません。ただし、他のすべてのチャネル(SYNC\_EN レジスタで同期に設定されている)は、LDAC ピンがロジック Low に保持されている限り、非同期モードで動作します。TRIGGER レジスタで適切に LDAC\_OUTn ビットに書き込むことで、ソフトウェアでも DAC トリガを生成できます。ソフトウェアトリガにより、2 つの DAC チャネルのアクティブレジスタが一度に更新されます。TRIGGER レジスタの各ビットは出力チャネルのペアに対応し、ビットを 1 に設定すると、対応する両方のチャネルが同時に更新されます。

### 6.3.1.1.2 DAC バッファ アンプ

DAC 出力バッファアンプは、低ノイズ、低ドリフトの電圧出力を特徴とし、レールツーレールで動作できます。アンプの出力は DAC の出力ピンで利用できます。DAC の最大出力電圧範囲は、AV<sub>DD</sub> 電源によって制限されます。

このデバイスの高出力電流により、大きな容量性負荷でも良好なスルー特性が得られます。大きな容量性負荷に対する正と負のスルーレートを見積もるには、ソースおよびシンクの短絡電流値をコンデンサで割ります。

### 6.3.1.1.3 DAC の伝達関数

DAC 伝達関数は式 1 で与えられます。

$$V_{DAC} = \left( \frac{Dacin}{2^N} \right) \times FSR \quad (1)$$

ここで、

- Dacin = DAC レジスタにロードされるバイナリコードの 10 進数換算値。Dacin 範囲 = 0~2<sup>12</sup>-1。

- 選択した出力範囲に対する FSR = DAC フルスケール出力。FSR は、0V ~ 2.5V の範囲で 2.5V、0V ~ 5V の範囲で 5V です。

- N = DAC デバイスの分解能。DAC60516W の N は 12。

DAC 出力は、表 6-1 に示す電圧範囲にわたります。

表 6-1. DAC データ形式

| DAC データレジスタ    |      | DAC 出力電圧 (V) |           |

|----------------|------|--------------|-----------|

| 2 進数           | 16 進 | 0V ~ 5V      | 0V ~ 2.5V |

| 0000 0000 0000 | 000  | 0            | 0         |

| 0000 0000 0001 | 001  | 0.00122      | 0.00061   |

| 1000 0000 0000 | 800  | 2.5          | 1.25      |

| 1111 1111 1110 | FFE  | 4.99755      | 2.49878   |

| 1111 1111 1111 | FFF  | 5            | 2.5       |

### 6.3.2 内部リファレンス

DAC60516W には、2.5V の高精度バンドギャップ リファレンスが内蔵されています。外部リファレンスで動作させる場合は、GEN\_CONFIG レジスタの REF\_PWDWN ビットに書き込んで、内部リファレンスを無効にします。このビットは、デフォルトで設定されているため、内部リファレンスを有効にするにはクリアする必要があります。内部リファレンスは、REF ピンで外部から入手できます。

ノイズ フィルタリングのため、リファレンス出力と GND の間に 150nF 以上のコンデンサを配置することを推奨します。

### 6.3.3 パワーオン リセット (POR)

DAC60516W には、パワー オンリセット (POR) 機能が備わります。起動後、AV<sub>DD</sub> および V<sub>IO</sub> 電源が確立されると、デバイスが正しく初期化されるように POR が発行されます。DAC60516W では、POR 後にシリアルインターフェイスを初期化するために最大 10ms が必要です。

動作中、次の 3 つの条件によってリセットがトリガされる可能性があります：

1. AV<sub>DD</sub> または V<sub>IO</sub> が、推奨最小動作値(200mV 以上)を下回った

2. TRIGGER レジスタの SOFT\_RST フィールドに 0xA の値が書き込まれます

3. デバイスの **RESET** ピンは、ロジック 0 になります。ピンがロジック 0 に保持されると、デバイスは、ピンがロジック 1 にセットされるまで、電源オフ状態を維持します(その時点で、デバイスはシリアルインターフェイスの初期化を再度実行します)。

## 6.4 デバイスの機能モード

### 6.4.1 クリアモード

各 DAC は、ハードウェアまたはソフトウェアを使用してクリア状態に移行するように設定することができます。DAC がクリア状態に移行すると、DAC に対応する CLEAR\_CODE レジスタに保存されたデータ(デフォルトではコード 0)がロードされ、出力は対応する電圧レベルに設定されます。

DAC がクリア状態に移行しても、DAC バッファおよびアクティブレジスタは変更されません。これにより、DAC はクリアイベントの前に動作ポイントに戻ります。DAC バッファおよびアクティブレジスタは、DAC がクリア状態のときも更新できるため、DAC が通常動作に戻ったときに新しい値を出力できます。クリア状態を終了すると、DAC にアクティブレジスタのデータが即座にロードされ、DAC 出力チャネルは対応するレベルに設定されて復元動作が行われます。

各 DAC は、クリアレジスタの適切なビットに書き込むことで、クリア状態を開始または終了するようにソフトウェアで設定することができます。アクティブ Low CLEAR ピンとして設定されている場合、各 DAC は FLEXIO ピンを使用して強制的にクリア状態にすることもできます。この設定は、GEN\_CONFIG レジスタの FLEXIO\_FUNC ビットを設定することで行われます(デフォルトでは、このビットは 0 で、FLEXIO は汎用入出力ピンとして機能します)。デフォルトでは、CLEAR ピンがロジック低レベルにアサートされている場合、CLEAR\_PIN\_MASK レジスタで適切なビットが設定されない限り、各 DAC 出力は自動でクリアされます。DAC がクリア状態を終了すると、アクティブレジスタのコンテンツが DAC にリロードされ、それに応じて DAC 出力チャネルが更新されます。

また、このデバイスを使用すると、各 DAC に共通のクリアコードを設定することができます。このコードは、BCAST\_CLR\_DATA レジスタに書き込むことで実行できます。このレジスタに保存された値は、ブロードキャストモードで動作するすべての DAC の CLEAR\_CODE レジスタに書き込まれ(BCAST\_EN レジスタの適切なビット設定で決定される)、同じコードで複数の DAC チャネルを同時にクリアするために使用することができます。

何らかの理由で DAC チャネルがパワーダウン状態の場合、そのチャネルがパワーダウン状態を脱するまで、DAC でのクリアコマンドは無視されます。

## 6.5 プログラミング

このデバイスは、I<sup>2</sup>C 互換 2 線式バスまたは SPI 互換バスをサポートするシリアル インターフェースを通じてシステム コントローラと通信します。このデバイスには、SPI 互換または I<sup>2</sup>C 互換コントローラを検出し、それに応じて自動的にインターフェースを設定する堅牢なメカニズムが搭載されています。インターフェース検出メカニズムは起動時に動作するため、通常動作中にプロトコルが変更されることはありません。

レジスタマップアドレスの範囲は 0x00 ~ 0x32 で、各レジスタ内のビットにアクセスできます（詳細は、[セクション 7](#) を参照してください）。

### 6.5.1 I<sup>2</sup>C シリアル インターフェイス

I<sup>2</sup>C モードでは、デバイスは 2 線式バス上でターゲット デバイスとしてのみ動作します。オープンドラインの I/O ラインである SDA および SCL を使用してバスに接続されます。SDA と SCL ピンは、スパイク抑制フィルタとシュミットトリガを内蔵し、入力スパイクとバスノイズの影響を最小限に抑えます。このデバイスは、標準モード、高速モード、高速モードプラスの伝送プロトコルに対応しています。すべてのデータ バイトは、MSB が最初に送信されます。

#### 6.5.1.1 I<sup>2</sup>C バスの概要

I<sup>2</sup>C プロトコルでは、転送を開始するデバイスをコントローラと呼び、コントローラによって制御されるデバイスをターゲットと呼びます。バスは、コントローラ デバイスにより制御されます。コントローラ デバイスはシリアル クロック (SCL) を生成し、バスへのアクセスを制御して、START 条件および STOP 条件を生成します。

特定のデバイスをアドレス指定するには、START 条件が開始されます。START 条件は、SCL が High の間にデータライン (SDA) を High から Low のロジックレベルにプルダウンすることで示されます。バス上のすべてのターゲットは、ターゲット アドレス バイトを受信し、最下位ビットは読み出し動作か書き込み動作かを示します。アドレス指定されたターゲットは、9 番目のクロック パルスのときアクノリッジ ビットを生成し、SDA を Low にすることで、コントローラに応答します。

その後でデータ転送が開始され、8 つのクロック パルスに合わせて送信されてから、アクノリッジ ビットが続きます。データ転送中、SCL が High のとき、SDA ラインは安定状態を維持する必要があります。SCL が High の間に SDA が変化すると、制御信号と解釈されるからです。

すべてのデータが転送された後、コントローラは STOP 条件を生成します。STOP 条件は、SCL が High の間に SDA を Low から High にプルダウンすることで示されます。

### 6.5.1.2 I<sup>2</sup>C バスの定義

デバイスは I<sup>2</sup>C に対応し、バス定義が表 6-2 に示されています。

**表 6-2. I<sup>2</sup>C 記号セット**

| 条件             | 記号 | ソース          | 説明                                                                                                                                                                          |

|----------------|----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START          | S  | コントローラ       | すべてのバストランザクションを開始します。SDA ラインの状態が High から Low に変化することで、SCL ラインが High のとき、START 条件が定義されます。START 条件に従って、各データ転送が開始されます。                                                         |

| ストップ           | P  | コントローラ       | すべてのトランザクションを終了し、バスをリセットします。SCL ラインが High の間に、SDA ラインの状態が Low から High に変化すると、STOP 条件が定義されます。各データ転送は、START 条件または STOP 条件の繰り返しで終了します。                                         |

| IDLE           | I  | コントローラ       | バスアイドル。SDA ラインと SCL ラインが共に High です。                                                                                                                                         |

| ACK (アクリッジ)    | A  | コントローラ/ターゲット | ハンドシェイクビット (low)。受信側の各デバイスは、アドレス指定された場合、アクリッジビットを生成する義務を負います。アクリッジを行うデバイスは、アクリッジクロックパルスが HIGH の間、SDA ラインが安定して LOW を維持するように、SDA ラインをプルダウンする必要があります。セットアップおよびホールド時間を考慮してください。 |

| NACK (アクリッジなし) | Ā  | コントローラ/ターゲット | ハンドシェイクビット (high)。コントローラの受信では、コントローラがターゲットから送信された最後のバイトに対して非アクリッジを生成することで、データ転送の終了を通知できます。                                                                                  |

| 読み取り           | R  | コントローラ       | ターゲットアドレスシーケンスの直後に続くアクティブ上位ビット。コントローラがターゲットからコントローラへのデータ転送を開始していることを示します。 <b>START</b> 条件と <b>STOP</b> 条件の間に転送されるデータのバイト数は制限されおらず、コントローラデバイスで決定されます。レシーバがデータ転送をアクリッジします。    |

| 書き込み           | W  | コントローラ       | ターゲットアドレスシーケンスの直後に続くアクティブ下位ビット。コントローラがコントローラからターゲットへのデータ転送を開始していることを示します。 <b>START</b> 条件と <b>STOP</b> 条件の間に転送されるデータのバイト数は制限されおらず、コントローラデバイスで決定されます。レシーバがデータ転送をアクリッジします。    |

| リピートスタート       | Sr | コントローラ       | コントローラによって生成され、 <b>START</b> 条件と同じ機能を持ちます ( <b>STOP</b> 条件が厳密には不要であることを強調)。                                                                                                 |

| ブロックアクセス       | B  | コントローラ       | アクティブハイのビットは、コントローラがブロックアクセスデータ転送を開始していることを示します。                                                                                                                            |

### 6.5.1.3 I<sup>2</sup>C ターゲットアドレスの選択

I<sup>2</sup>C バスのターゲットアドレスは、A0、A1 ピンを V<sub>IO</sub> または GND レールに接続することで選択することができます。I<sup>2</sup>C バスの START 条件が発生するたびに、A0 ピンと A1 ピンの状態がテストされます。デバイスは、各ピンに対して、V<sub>IO</sub> へのシャント(ロジック 1)と GND へのシャント(ロジック 0)の 2 つの可能なオプションのいずれかを判別し、合計 4 つのターゲットアドレス(図 表 6-3 を参照)を決定します。

**表 6-3. I<sup>2</sup>C ターゲットアドレス空間**

| デバイスピン |    | I <sup>2</sup> C ターゲットアドレス |

|--------|----|----------------------------|

| A1     | A0 | [A6:A0]                    |

| 0      | 0  | 101 0000                   |

| 0      | 1  | 101 0001                   |

| 1      | 0  | 101 0100                   |

| 1      | 1  | 101 0101                   |

### 6.5.1.4 I<sup>2</sup>C 読み取り / 書き込み動作

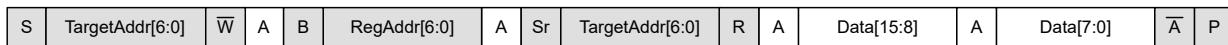

デバイスに書き込む際、アドレスレジスタに対する値は、R/W ビットが Low になったターゲットアドレス バイトの直後に送信される最初のバイトです。図 6-2 に示すように、すべての書き込み動作ごとにアドレスレジスタの値が必要です。

From Controller to Target

From Target to Controller

**図 6-2. I<sup>2</sup>C 書き込みアクセスプロトコル**

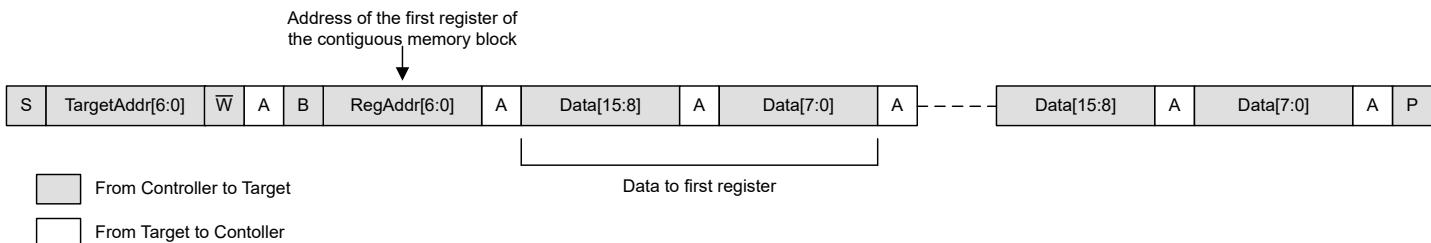

デバイスから読み出す際は、直前の書き込み動作でアドレスレジスタに格納された値が使用され、どのレジスタを読み出すかが決まります。読み取り操作で参照されるレジスタを変更するには、新しい値をアドレスレジスタに書き込む必要があります。このトランザクションは、R/W ビットを Low にしたターゲットアドレス バイトを送信し、その後にアドレスレジスタのバイトを続けることで実行されます。追加のデータは必要ありませんその後、コントローラは START 条件を生成し、R/W ビットを High に設定したターゲットアドレス バイトを送信して、読み取りコマンドを開始できます。

同じレジスタから繰り返し読み出す場合、毎回アドレスレジスタのバイトを送信する必要はありません。なぜなら、デバイスは次の書き込み操作で値が変更されるまで、アドレスレジスタの値を保持し続けるからです。レジスタバイトは、ビッグエンディアンで左揃えです。

読み取り操作を終了するには、最後に読み取るバイトの後に非アクノリッジコマンドを発行してください。図 6-3 で示されているように、コントローラは、ターゲットから読み取られた最後のバイトを確認応答する間、SDA ラインを High のままにしておく必要があります。

From Controller to Target

From Target to Controller

**図 6-3. I<sup>2</sup>C 読み取りアクセスプロトコル**

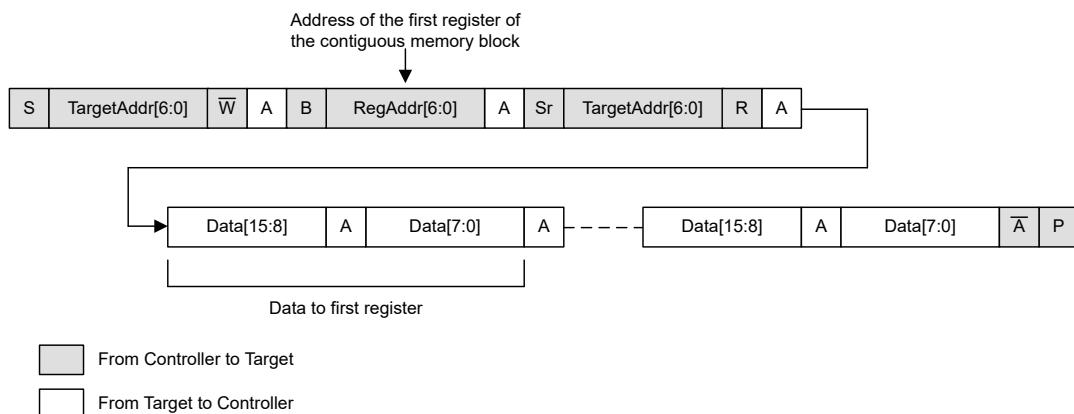

ブロックアクセス機能は、大規模なデータセットの転送オーバーヘッドを最小限に抑えるために提供されます。ブロックアクセスにより、マルチバイトの転送が可能になり、ブロックアクセスピットを **high** に設定して設定します。トランザクションが STOP コンディションによって終了するまで、デバイスは図 [図 6-4](#) および [図 6-5](#) に示すように、後続のメモリ位置の読み取りと書き込みを行います。

図 6-4. I<sup>2</sup>C ブロック書き込みアクセス

図 6-5. I<sup>2</sup>C ブロック読み取りアクセス

### 6.5.1.5 I<sup>2</sup>C ゼネラルコールリセット

デバイスは、2 線式のゼネラルコールアドレス 00h (0000 0000b) によるリセットをサポートしています。このデバイスは、ゼネラルコールアドレスをアクノリッジし、2 バイト目に応答します。2 バイト目が 06h (0000 0110b) の場合、デバイスはソフトウェアリセットを実行します。このソフトウェアリセットにより、リセットイベントが開始されます。デバイスは、2 番目のバイトにある他の値に応答して、何も動作を行いません。

## 6.5.2 シリアル・ペリフェラル・インターフェイス (SPI)

SPI モードでは、多くのマイクロ コントローラや DSP コントローラで使用されている SPI タイプのインターフェースと互換性のある、柔軟な 4 線式シリアル インターフェースを介してデバイスを制御します。このインターフェイスを使用すると、デバイスのレジスタにアクセスできます。

### 6.5.2.1 SPI バスの概要

シリアル インターフェイスのアクセス サイクルは、**CS** ピンを **Low** にすることで開始されます。シリアル クロック **SCLK** は連続クロックでもゲート付きクロックでも使用できます。SDI データは **SCLK** の立ち下がりエッジでクロックされるため、コントローラが **SCLK** の立ち上がりエッジで(またはそれに近接した場所)で更新するようにします。

通常のシリアルインターフェイスのアクセスサイクルは 24 ビット長なので、少なくとも 24 **SCLK** 立ち下がりエッジの間、**CS** ピンは、**Low** で維持する必要があります。**CS** ピンが **High** にデアサークトされると、アクセス サイクルは終了します。アクセス サイクルに最小クロック エッジよりも短い場合、通信は無視されます。アクセス サイクルで最小クロック数を超える場合、デバイスは最後の 24 ビットのみを使用します。**CS** ピンが **High** のとき、**SCLK** および SDI 信号はブロックされ、**SDO** ピンはハイインピーダンス (Hi-Z) 状態になります。

シリアルインターフェイスのアクセスサイクルでは、SDI に入力される最初のバイトが、リクエストが読み取りコマンドか書き込みコマンドかを識別する命令サイクルおよびアクセスする 7 ビットレジスタのアドレスとなります。このサイクルの次のビットは、表 6-4 に示すように、データサイクルを形成します。

**表 6-4. SPI シリアルインターフェイスのアクセスサイクル**

| ビット   | フィールド    | 説明                                                                                                              |

|-------|----------|-----------------------------------------------------------------------------------------------------------------|

| 23    | RW       | アドレス指定されたレジスタに対する読み取りまたは書き込みコマンドとして通信を識別します。<br><b>RW = 0</b> は書き込み動作を設定します。<br><b>RW = 1</b> は読み取り動作を設定します。    |

| 22:16 | A[6:0]   | レジスタ アドレス。読み取りまたは書き込み操作中にアクセスするレジスタを指定します。                                                                      |

| 15:0  | DI[15:0] | データ サイクル ビット。<br>書き込みコマンドの場合、データ サイクルのビットはアドレス A[6:0] のレジスタに書き込まれる値となります。<br>読み取りコマンドの場合、データ サイクルのビットは無効値となります。 |

読み取り操作を行うには、まず **SDO\_EN** ビットを設定して **SDO** ピンを有効化する必要があります。読み取り操作は、読み取りコマンドのアクセス サイクルを発行することで開始されます。読み取りコマンドの後、要求されたデータを取得するために、表 6-5 に示されているようにフォーマットし、2 回目のアクセス サイクルを発行する必要があります。データは、**FSDO** ビットの設定に応じて、**SCLK** の立ち下がりエッジまたは立ち上がりエッジのいずれかの **SDO** ピンでクロック出力されます。

**表 6-5. SDO 出力アクセスサイクル**

| ビット   | フィールド       | 説明                                   |

|-------|-------------|--------------------------------------|

| 23    | RW          | 前回のアクセス サイクルから <b>RW</b> ビットをエコーします。 |

| 22:16 | STATUS[6:0] | STATUS レジスタの下位 7 ビット。                |

| 15:0  | DO[15:0]    | 前のアクセス サイクルで要求されたデータの読み戻し。           |

## 7 レジスタ マップ

表 7-1. レジスタ マップ

| ADDR<br>(HEX) | レジスタ                     | タイプ | リセット<br>時の値<br>(HEX) | ビットの詳細                        |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              |                              |                              |                              |                              |                  |  |  |  |  |  |  |  |  |

|---------------|--------------------------|-----|----------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------|--|--|--|--|--|--|--|--|

|               |                          |     |                      | 15                            | 14                            | 13                            | 12                            | 11                            | 10                            | 9                            | 8                            | 7                            | 6                            | 5                            | 4                            | 3                            | 2                            | 1                            | 0                            |                  |  |  |  |  |  |  |  |  |

| 00            | NOP                      | W   | 0000                 | NOP[15:0]                     |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              |                              |                              |                              |                              |                  |  |  |  |  |  |  |  |  |

| 01            | DEVICE_ID                | R   | 6A16                 | CHIP_ID[15:0]                 |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              |                              |                              |                              |                              |                  |  |  |  |  |  |  |  |  |

| 02            | VERSION_ID               | R   | 0000                 | 予約済み                          |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              | VERSION_ID[2:0]              |                              |                              |                              |                  |  |  |  |  |  |  |  |  |

| 03            | PWDWN                    | R/W | FFFF                 | OUT15_<br>PWDWN               | OUT14_<br>PWDWN               | OUT13_<br>PWDWN               | OUT12_<br>PWDWN               | OUT11_<br>PWDWN               | OUT10_<br>PWDWN               | OUT9_<br>PWDWN               | OUT8_<br>PWDWN               | OUT7_<br>PWDWN               | OUT6_<br>PWDWN               | OUT5_<br>PWDWN               | OUT4_<br>PWDWN               | OUT3_<br>PWDWN               | OUT2_<br>PWDWN               | OUT1_<br>PWDWN               | OUT0_<br>PWDWN               |                  |  |  |  |  |  |  |  |  |

| 04            | DAC_GAIN                 | R/W | 0000                 | 予約済み                          |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              | OUT_QUAD3_<br>GAIN           | OUT_QUAD2_<br>GAIN           | OUT_QUAD1_<br>GAIN           | OUT_QUAD0_<br>GAIN           |                  |  |  |  |  |  |  |  |  |

| 05            | TRIGGER                  | W   | 0000                 | LDAC_<br>OUT15_<br>OUT14      | LDAC_<br>OUT13_<br>OUT12      | LDAC_<br>OUT11_<br>OUT10      | LDAC_<br>OUT9_<br>OUT8        | LDAC_<br>OUT7_<br>OUT6        | LDAC_<br>OUT5_<br>OUT4        | LDAC_<br>OUT3_<br>OUT2       | LDAC_<br>OUT1_<br>OUT0       | 予約済み                         |                              |                              |                              | SOFT_RST[3:0]                |                              |                              |                              |                  |  |  |  |  |  |  |  |  |

| 06            | BCAST_<br>DAC_<br>DATA   | R/W | 0000                 | DATA[11:0]                    |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              | 予約済み                         |                              |                              |                              |                  |  |  |  |  |  |  |  |  |

| 07            | STATUS                   | R   | 4008                 | 予約済み                          |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              |                              |                              |                              |                              | GDAC_SC_STS      |  |  |  |  |  |  |  |  |

| 08            | SDO_EN                   | R/W | 0000                 | 予約済み                          |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              |                              |                              |                              |                              | FSDO SDO_EN      |  |  |  |  |  |  |  |  |

| 09            | GEN_CONFIG               | R/W | 0014                 | 予約済み                          |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              | FLEXIO_OUT_<br>POL           | FLEXIO_OUT_<br>ODE           | 予約済み                         | REF_PWDWN                    | 予約済み FLEXIO_FUNC |  |  |  |  |  |  |  |  |

| 0A            | SYNC_<br>EN              | R/W | 0000                 | OUT15_<br>SYNC_<br>EN         | OUT14_<br>SYNC_<br>EN         | OUT13_<br>SYNC_<br>EN         | OUT12_<br>SYNC_<br>EN         | OUT11_<br>SYNC_<br>EN         | OUT10_<br>SYNC_<br>EN         | OUT9_<br>SYNC_<br>EN         | OUT8_<br>SYNC_<br>EN         | OUT7_<br>SYNC_<br>EN         | OUT6_<br>SYNC_<br>EN         | OUT5_<br>SYNC_<br>EN         | OUT4_<br>SYNC_<br>EN         | OUT3_<br>SYNC_<br>EN         | OUT2_<br>SYNC_<br>EN         | OUT1_<br>SYNC_<br>EN         | OUT0_<br>SYNC_<br>EN         |                  |  |  |  |  |  |  |  |  |

| 0B            | BCAST_<br>EN             | R/W | FFFF                 | OUT15_<br>BCAST_<br>EN        | OUT14_<br>BCAST_<br>EN        | OUT13_<br>BCAST_<br>EN        | OUT12_<br>BCAST_<br>EN        | OUT11_<br>BCAST_<br>EN        | OUT10_<br>BCAST_<br>EN        | OUT9_<br>BCAST_<br>EN        | OUT8_<br>BCAST_<br>EN        | OUT7_<br>BCAST_<br>EN        | OUT6_<br>BCAST_<br>EN        | OUT5_<br>BCAST_<br>EN        | OUT4_<br>BCAST_<br>EN        | OUT3_<br>BCAST_<br>EN        | OUT2_<br>BCAST_<br>EN        | OUT1_<br>BCAST_<br>EN        | OUT0_<br>BCAST_<br>EN        |                  |  |  |  |  |  |  |  |  |

| 0C            | CLEAR                    | R/W | 0000                 | OUT15_<br>SW_<br>CLR          | OUT14_<br>SW_<br>CLR          | OUT13_<br>SW_<br>CLR          | OUT12_<br>SW_<br>CLR          | OUT11_<br>SW_<br>CLR          | OUT10_<br>SW_<br>CLR          | OUT9_<br>SW_<br>CLR          | OUT8_<br>SW_<br>CLR          | OUT7_<br>SW_<br>CLR          | OUT6_<br>SW_<br>CLR          | OUT5_<br>SW_<br>CLR          | OUT4_<br>SW_<br>CLR          | OUT3_<br>SW_<br>CLR          | OUT2_<br>SW_<br>CLR          | OUT1_<br>SW_<br>CLR          | OUT0_<br>SW_<br>CLR          |                  |  |  |  |  |  |  |  |  |

| 0D            | CLEAR_PIN_<br>MASK       | R/W | 0000                 | OUT15_<br>HW_<br>CLR_<br>MASK | OUT14_<br>HW_<br>CLR_<br>MASK | OUT13_<br>HW_<br>CLR_<br>MASK | OUT12_<br>HW_<br>CLR_<br>MASK | OUT11_<br>HW_<br>CLR_<br>MASK | OUT10_<br>HW_<br>CLR_<br>MASK | OUT9_<br>HW_<br>CLR_<br>MASK | OUT8_<br>HW_<br>CLR_<br>MASK | OUT7_<br>HW_<br>CLR_<br>MASK | OUT6_<br>HW_<br>CLR_<br>MASK | OUT5_<br>HW_<br>CLR_<br>MASK | OUT4_<br>HW_<br>CLR_<br>MASK | OUT3_<br>HW_<br>CLR_<br>MASK | OUT2_<br>HW_<br>CLR_<br>MASK | OUT1_<br>HW_<br>CLR_<br>MASK | OUT0_<br>HW_<br>CLR_<br>MASK |                  |  |  |  |  |  |  |  |  |

| 0E            | BCAST_CLR_<br>DATA       | R/W | 0000                 | DATA[11:0]                    |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              | 予約済み                         |                              |                              |                              |                  |  |  |  |  |  |  |  |  |

| 0F            | RESET_<br>FLAGS          | W   | 000F                 | 予約済み                          |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              | VDD_COLLAPSE_<br>FLAG        | RSTPIN_<br>FLAG              | VIO_FLAG                     | PORBASE_<br>FLAG             |                  |  |  |  |  |  |  |  |  |

| 10            | OUT0_<br>BUFFER_<br>CODE | R/W | 0000                 | DATA[11:0]                    |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              | 予約済み                         |                              |                              |                              |                  |  |  |  |  |  |  |  |  |

| 11            | OUT1_<br>BUFFER_<br>CODE | R/W | 0000                 | DATA[11:0]                    |                               |                               |                               |                               |                               |                              |                              |                              |                              |                              |                              | 予約済み                         |                              |                              |                              |                  |  |  |  |  |  |  |  |  |

**表 7-1. レジスタ マップ (続き)**

| ADDR<br>(HEX) | レジスタ              | タイプ | リセット<br>時の値<br>(HEX) | ビットの詳細     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |      |

|---------------|-------------------|-----|----------------------|------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|------|

|               |                   |     |                      | 15         | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |      |

| 12            | OUT2_BUFFER_CODE  | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 13            | OUT3_BUFFER_CODE  | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 14            | OUT4_BUFFER_CODE  | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 15            | OUT5_BUFFER_CODE  | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 16            | OUT6_BUFFER_CODE  | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 17            | OUT7_BUFFER_CODE  | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 18            | OUT8_BUFFER_CODE  | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 19            | OUT9_BUFFER_CODE  | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 1A            | OUT10_BUFFER_CODE | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 1B            | OUT11_BUFFER_CODE | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 1C            | OUT12_BUFFER_CODE | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 1D            | OUT13_BUFFER_CODE | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 1E            | OUT14_BUFFER_CODE | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 1F            | OUT15_BUFFER_CODE | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 20            | OUT0_CLEAR_CODE   | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

| 21            | OUT1_CLEAR_CODE   | R/W | 0000                 | DATA[11:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 予約済み |

表 7-1. レジスタ マップ(続き)

| ADDR<br>(HEX) | レジスタ                     | タイプ | リセット<br>時の値<br>(HEX) | ビットの詳細               |                      |                      |                      |                      |                      |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |      |

|---------------|--------------------------|-----|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|------|

|               |                          |     |                      | 15                   | 14                   | 13                   | 12                   | 11                   | 10                   | 9                   | 8                   | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |      |

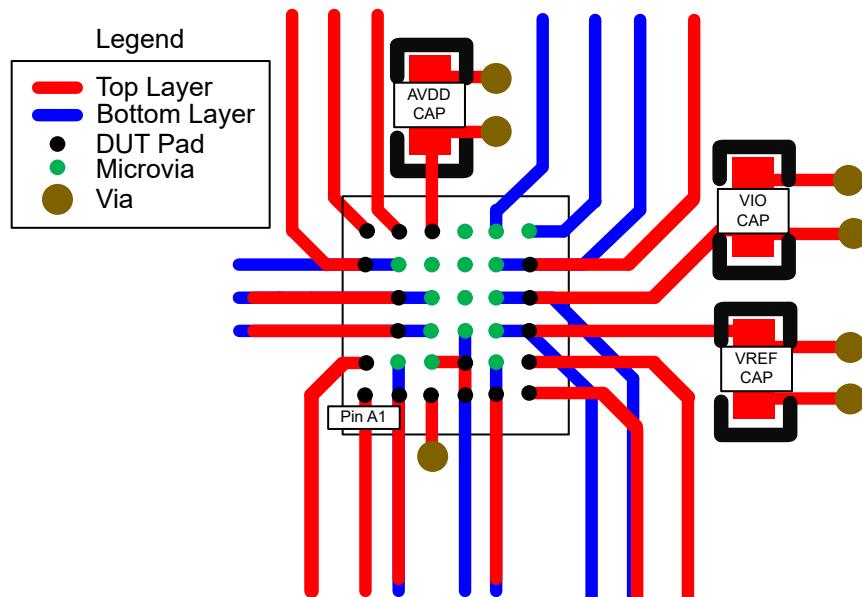

| 22            | OUT2_<br>CLEAR_<br>CODE  | R/W | 0000                 | DATA[11:0]           |                      |                      |                      |                      |                      |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     | 予約済み |