# DLP3944-Q1 0.39 インチ (0.99cm) 4K UHD 車載対応ディスプレイ アプリケーション向け、デジタルマイクロミラー デバイス

## 1 特長

- 車載アプリケーション認定済み –

- DMD アレイの動作温度範囲: -40°C ~ 105°C

- DLP3944-Q1 車載用チップセットには以下のものが含まれます。

- DLP3944-Q1 DMD

- DLPC431: DMD コントローラ

- DLPA3085/DLPA3082 システム管理および照明コントローラ

- 対角 0.39 インチ (0.99cm) のマイクロミラー アレイ

- 4K UHD (3840 × 2160 ディスプレイ解像度 (60Hz)

- 1080p FHD (1920 × 1080) ディスプレイ解像度 (240Hz)

- 4.5µm のマイクロミラーピッチ

- マイクロミラー傾斜角: ±14.5° (平面に対して)

- サイド照明

- LED またはレーザー照明に対応可能

- 最大 720MHz SubLVDS DMD インターフェイスによる低い消費電力と放射妨害

- 上限や下限の温度でも 10kHz の DMD リフレッシュレートを維持

- DMD メモリセルの内蔵セルフテスト (BIST)

## 2 アプリケーション

- 後部座席用エンターテインメント (RSE)

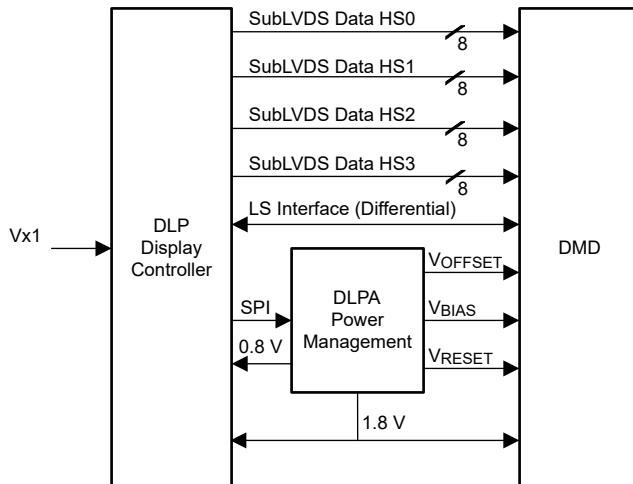

アプリケーション概略図

## 3 説明

DLP3944-Q1 デジタルマイクロミラー デバイス (DMD) は、デジタル制御型の MEMS (micro-electro-mechanical system) 空間光変調器 (SLM) で、色鮮やかな 4K UHD ディスプレイシステムを実現します。TI の DLP® 製品である 0.39 インチ (0.99cm) 4K UHD チップセットは、DMD、DLPC431 ディスプレイ コントローラ、DLPA3085/DLPA3082 PMIC および照明ドライバで構成されています。このコンパクトなチップセットは、小型の 4K UHD ディスプレイを実現する完全なシステムソリューションを提供します。

### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ<br>サイズ     |

|------------|----------------------|------------------|

| DLP3944-Q1 | FSC (154)            | 18.35mm × 9.60mm |

(1) 詳細については、このデータシートの末尾にある付録を参照してください。

## 目次

|                                  |    |                                           |    |

|----------------------------------|----|-------------------------------------------|----|

| <b>1 特長</b>                      | 1  | 6.6 マイクロミラー アレイ温度の計算                      | 24 |

| <b>2 アプリケーション</b>                | 1  | 6.7 マイクロミラーの電力密度の計算                       | 26 |

| <b>3 説明</b>                      | 1  | 6.8 ウィンドウ アパー・チャイルミネーション オーバーフィル計算        | 27 |

| <b>4 ピン構成および機能</b>               | 3  | 6.9 マイクロミラーのランデッド オン / ランデッド オフ デューティサイクル | 28 |

| <b>5 仕様</b>                      | 7  | <b>7 アプリケーションと実装</b>                      | 28 |

| 5.1 絶対最大定格                       | 7  | 7.1 アプリケーション情報                            | 28 |

| 5.2 保存条件                         | 8  | 7.2 代表的なアプリケーション                          | 29 |

| 5.3 ESD 定格                       | 8  | 7.3 温度検出                                  | 31 |

| 5.4 推奨動作条件                       | 9  | <b>8 電源に関する推奨事項</b>                       | 33 |

| 5.5 熱に関する情報                      | 10 | 8.1 DMD 電源のパワーアップ手順                       | 34 |

| 5.6 電気的特性                        | 11 | 8.2 DMD 電源のパワーダウン手順                       | 34 |

| 5.7 スイッチング特性                     | 12 | 8.3 DMD 電源シーケンシング要件                       | 35 |

| 5.8 タイミング要件                      | 12 | <b>9 レイアウト</b>                            | 36 |

| 5.9 システム実装インターフェイスの荷重            | 17 | 9.1 レイアウトのガイドライン                          | 36 |

| 5.10 マイクロミラー アレイの物理特性            | 18 | <b>10 デバイスおよびドキュメントのサポート</b>              | 37 |

| 5.11 マイクロミラー アレイの光学特性            | 19 | 10.1 サード・パーティ製品に関する免責事項                   | 37 |

| 5.12 ウィンドウの特性                    | 19 | 10.2 デバイスサポート                             | 37 |

| 5.13 チップセットコンポーネントの使用方法の仕様       | 20 | 10.3 サポートリソース                             | 38 |

| <b>6 詳細説明</b>                    | 21 | 10.4 商標                                   | 38 |

| 6.1 概要                           | 21 | 10.5 静電気放電に関する注意事項                        | 38 |

| 6.2 機能ブロック図                      | 21 | 10.6 用語集                                  | 38 |

| 6.3 機能説明                         | 22 | <b>11 改訂履歴</b>                            | 38 |

| 6.4 デバイスの機能モード                   | 22 | <b>12 メカニカル、パッケージ、および注文情報</b>             | 39 |

| 6.5 光学インターフェイスおよびシステムの画質に関する検討事項 | 22 |                                           |    |

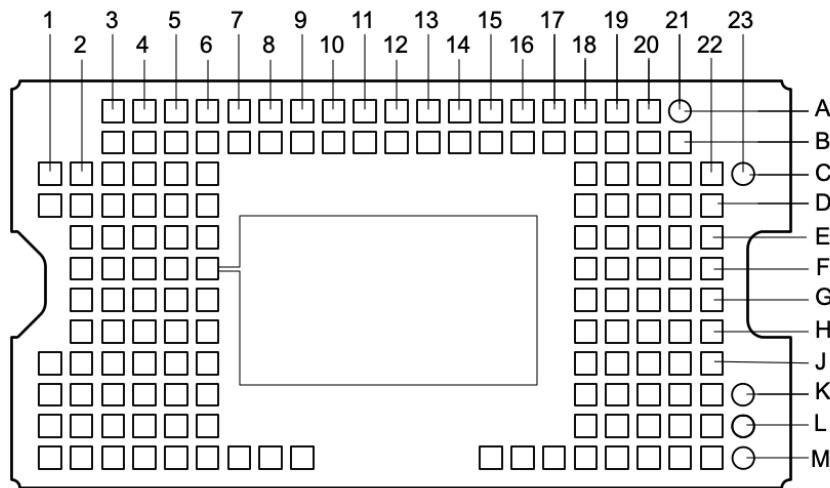

## 4 ピン構成および機能

図 4-1. FSC パッケージ 154 ピン LGA (底面図)

表 4-1. ピンの機能

| ピン       |        | タイプ <sup>(1)</sup> | 説明              | 終端      | パターン長<br>(mm) |

|----------|--------|--------------------|-----------------|---------|---------------|

| 名称       | パッド ID |                    |                 |         |               |

| D_AP (0) | C2     | I                  | 高速差動データペアレーン A0 | 差動 100Ω | 1.123         |

| D_AN (0) | C3     | I                  | 高速差動データペアレーン A0 | 差動 100Ω | 1.414         |

| D_AP (1) | D2     | I                  | 高速差動データペアレーン A1 | 差動 100Ω | 1.212         |

| D_AN (1) | D3     | I                  | 高速差動データペアレーン A1 | 差動 100Ω | 1.626         |

| D_AP (2) | C4     | I                  | 高速差動データペアレーン A2 | 差動 100Ω | 3.011         |

| D_AN (2) | C5     | I                  | 高速差動データペアレーン A2 | 差動 100Ω | 3.388         |

| D_AP (3) | D5     | I                  | 高速差動データペアレーン A3 | 差動 100Ω | 3.682         |

| D_AN (3) | D6     | I                  | 高速差動データペアレーン A3 | 差動 100Ω | 3.912         |

| D_AP (4) | G5     | I                  | 高速差動データペアレーン A4 | 差動 100Ω | 3.542         |

| D_AN (4) | G6     | I                  | 高速差動データペアレーン A4 | 差動 100Ω | 3.662         |

| D_AP (5) | E2     | I                  | 高速差動データペアレーン A5 | 差動 100Ω | 0.972         |

| D_AN (5) | E3     | I                  | 高速差動データペアレーン A5 | 差動 100Ω | 1.335         |

| D_AP (6) | E5     | I                  | 高速差動データペアレーン A6 | 差動 100Ω | 4.520         |

| D_AN (6) | E6     | I                  | 高速差動データペアレーン A6 | 差動 100Ω | 4.634         |

| D_AP (7) | H5     | I                  | 高速差動データペアレーン A7 | 差動 100Ω | 3.200         |

| D_AN (7) | H6     | I                  | 高速差動データペアレーン A7 | 差動 100Ω | 3.515         |

| DCLK_AP  | F4     | I                  | 高速差動クロック A      | 差動 100Ω | 2.610         |

| DCLK_AN  | F5     | I                  | 高速差動クロック A      | 差動 100Ω | 3.068         |

| D_BP (0) | C20    | I                  | 高速差動データペアレーン B0 | 差動 100Ω | 2.563         |

| D_BN (0) | C19    | I                  | 高速差動データペアレーン B0 | 差動 100Ω | 2.636         |

| D_BP (1) | D21    | I                  | 高速差動データペアレーン B1 | 差動 100Ω | 2.329         |

| D_BN (1) | D20    | I                  | 高速差動データペアレーン B1 | 差動 100Ω | 2.487         |

| D_BP (2) | C18    | I                  | 高速差動データペアレーン B2 | 差動 100Ω | 4.300         |

表 4-1. ピンの機能 (続き)

| ピン<br>名称 | パッド ID | タイプ <sup>(1)</sup> | 説明              | 終端      | パターン長<br>(mm) |

|----------|--------|--------------------|-----------------|---------|---------------|

| D_BN (2) | D18    | I                  | 高速差動データペアレーン B2 | 差動 100Ω | 4.569         |

| D_BP (3) | E20    | I                  | 高速差動データペアレーン B3 | 差動 100Ω | 3.112         |

| D_BN (3) | E19    | I                  | 高速差動データペアレーン B3 | 差動 100Ω | 3.485         |

| D_BP (4) | F22    | I                  | 高速差動データペアレーン B4 | 差動 100Ω | 1.073         |

| D_BN (4) | F21    | I                  | 高速差動データペアレーン B4 | 差動 100Ω | 1.239         |

| D_BP (5) | H18    | I                  | 高速差動データペアレーン B5 | 差動 100Ω | 4.146         |

| D_BN (5) | G18    | I                  | 高速差動データペアレーン B5 | 差動 100Ω | 4.330         |

| D_BP (6) | F18    | I                  | 高速差動データペアレーン B6 | 差動 100Ω | 4.241         |

| D_BN (6) | E18    | I                  | 高速差動データペアレーン B6 | 差動 100Ω | 4.494         |

| D_BP (7) | G22    | I                  | 高速差動データペアレーン B7 | 差動 100Ω | 0.663         |

| D_BN (7) | G21    | I                  | 高速差動データペアレーン B7 | 差動 100Ω | 1.054         |

| DCLK_BP  | F20    | I                  | 高速差動クロック B      | 差動 100Ω | 2.404         |

| DCLK_BN  | F19    | I                  | 高速差動クロック B      | 差動 100Ω | 2.610         |

| D_CP (0) | G2     | I                  | 高速差動データペアレーン C0 | 差動 100Ω | 1.052         |

| D_CN (0) | G3     | I                  | 高速差動データペアレーン C0 | 差動 100Ω | 1.112         |

| D_CP (1) | M7     | I                  | 高速差動データペアレーン C1 | 差動 100Ω | 6.519         |

| D_CN (1) | M8     | I                  | 高速差動データペアレーン C1 | 差動 100Ω | 6.611         |

| D_CP (2) | H2     | I                  | 高速差動データペアレーン C2 | 差動 100Ω | 0.921         |

| D_CN (2) | H3     | I                  | 高速差動データペアレーン C2 | 差動 100Ω | 1.376         |

| D_CP (3) | M5     | I                  | 高速差動データペアレーン C3 | 差動 100Ω | 5.196         |

| D_CN (3) | M6     | I                  | 高速差動データペアレーン C3 | 差動 100Ω | 5.318         |

| D_CP (4) | K3     | I                  | 高速差動データペアレーン C4 | 差動 100Ω | 1.579         |

| D_CN (4) | K4     | I                  | 高速差動データペアレーン C4 | 差動 100Ω | 1.648         |

| D_CP (5) | M3     | I                  | 高速差動データペアレーン C5 | 差動 100Ω | 3.414         |

| D_CN (5) | M4     | I                  | 高速差動データペアレーン C5 | 差動 100Ω | 3.857         |

| D_CP (6) | L4     | I                  | 高速差動データペアレーン C6 | 差動 100Ω | 2.460         |

| D_CN (6) | L5     | I                  | 高速差動データペアレーン C6 | 差動 100Ω | 2.566         |

| D_CP (7) | K1     | I                  | 高速差動データペアレーン C7 | 差動 100Ω | 1.114         |

| D_CN (7) | L1     | I                  | 高速差動データペアレーン C7 | 差動 100Ω | 1.707         |

| DCLK_CP  | K5     | I                  | 高速差動クロック C      | 差動 100Ω | 3.744         |

| DCLK_CN  | K6     | I                  | 高速差動クロック C      | 差動 100Ω | 3.883         |

| D_DP (0) | J19    | I                  | 高速差動データペアレーン D0 | 差動 100Ω | 4.189         |

| D_DN (0) | J18    | I                  | 高速差動データペアレーン D0 | 差動 100Ω | 4.435         |

| D_DP (1) | M18    | I                  | 高速差動データペアレーン D1 | 差動 100Ω | 6.588         |

| D_DN (1) | M17    | I                  | 高速差動データペアレーン D1 | 差動 100Ω | 6.867         |

| D_DP (2) | H21    | I                  | 高速差動データペアレーン D2 | 差動 100Ω | 1.754         |

| D_DN (2) | H20    | I                  | 高速差動データペアレーン D2 | 差動 100Ω | 1.936         |

| D_DP (3) | J22    | I                  | 高速差動データペアレーン D3 | 差動 100Ω | 1.339         |

| D_DN (3) | J21    | I                  | 高速差動データペアレーン D3 | 差動 100Ω | 1.634         |

| D_DP (4) | L20    | I                  | 高速差動データペアレーン D4 | 差動 100Ω | 3.329         |

| D_DN (4) | L19    | I                  | 高速差動データペアレーン D4 | 差動 100Ω | 3.436         |

**表 4-1. ピンの機能 (続き)**

| ピン            |                                                                                                                  | タイプ <sup>(1)</sup> | 説明                                    | 終端           | パターン長<br>(mm) |

|---------------|------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------|--------------|---------------|

| 名称            | パッド ID                                                                                                           |                    |                                       |              |               |

| D_DP (5)      | M20                                                                                                              | I                  | 高速差動データペアレーン D5                       | 差動 100Ω      | 3.631         |

| D_DN (5)      | M19                                                                                                              | I                  | 高速差動データペアレーン D5                       | 差動 100Ω      | 3.738         |

| D_DP (6)      | M22                                                                                                              | I                  | 高速差動データペアレーン D6                       | 差動 100Ω      | 2.420         |

| D_DN (6)      | M21                                                                                                              | I                  | 高速差動データペアレーン D6                       | 差動 100Ω      | 2.573         |

| D_DP (7)      | K22                                                                                                              | I                  | 高速差動データペアレーン D7                       | 差動 100Ω      | 1.406         |

| D_DN (7)      | K21                                                                                                              | I                  | 高速差動データペアレーン D7                       | 差動 100Ω      | 1.881         |

| DCLK_DP       | K19                                                                                                              | I                  | 高速差動クロック D                            | 差動 100Ω      | 3.916         |

| DCLK_DN       | K18                                                                                                              | I                  | 高速差動クロック D                            | 差動 100Ω      | 4.022         |

| TEMP_N        | M2                                                                                                               | I                  | 温度ダイオード N                             |              | 1.133         |

| TEMP_P        | M1                                                                                                               | I                  | 温度ダイオード P                             |              | 1.237         |

| LS_RDATA_D    | B5                                                                                                               | O                  | 低速出力                                  |              | 2.396         |

| LS_RDATA_C    | A4                                                                                                               | O                  | 低速出力                                  |              | 2.255         |

| LS_RDATA_B    | A5                                                                                                               | O                  | 低速出力                                  |              | 2.925         |

| LS_RDATA_A    | A3                                                                                                               | O                  | 低速出力                                  |              | 2.045         |

| LS_WDATA_N    | B7                                                                                                               | I                  | 低速差動入力 N                              |              | 5.297         |

| LS_WDATA_P    | A7                                                                                                               | I                  | 低速差動入力 P                              |              | 5.253         |

| LS_CLK_N      | A8                                                                                                               | I                  | 低速差動クロック入力 N                          |              | 7.225         |

| LS_CLK_P      | A9                                                                                                               | I                  | 低速差動クロック入力 P                          |              | 6.962         |

| DMD_DEN_ARSTZ | D1                                                                                                               | I                  | 非同期リセットアクティブ Low。論理 High で DMD はイネーブル | 17.5kΩ プルダウン | 0.735         |

| VDD           | A6、A10、<br>A12、A14、<br>A16、A18、<br>B4、B11、<br>B13、B15、<br>B19、B21、<br>C21、D22、<br>E21、G4、<br>J1、J4、J6、<br>L2、M15 | P                  | デジタル コア電源電圧                           |              | 平面            |

| VBIAS         | A20、B6                                                                                                           | P                  | マイクロミラーのリセット信号用の正のバイアスの供給電圧           |              | 平面            |

| VRESET        | B8、B17                                                                                                           | P                  | マイクロミラーのリセット信号用の負のバイアスの供給電圧           |              | 平面            |

| VOFFSET       | B9、M16                                                                                                           | P                  | HVCMOS ロジックの電源電圧、ロジック レベルを昇圧          |              | 平面            |

| VDDI          | C22、E4、<br>F2、G20、<br>J2、L22                                                                                     | P                  | SubLVDS レシーバの電源電圧                     |              | 平面            |

**表 4-1. ピンの機能 (続き)**

| ピン  |                                                                                                                                                                                                   | タイプ <sup>(1)</sup> | 説明    | 終端 | パターン長<br>(mm) |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|----|---------------|

| 名称  | パッド ID                                                                                                                                                                                            |                    |       |    |               |

| VSS | A11, A13,<br>A15, A17,<br>A19, B3,<br>B10, B12,<br>B14, B16,<br>B18,<br>B20,C1,<br>C6, D4,<br>D19, E22,<br>F3, F6,<br>G19, H4,<br>H19, H22,<br>J3, J5, J20,<br>K2, K20,L3,<br>L6, L18,<br>L21, M9 | G                  | グランド  |    | 平面            |

| N/C | A21、C23、<br>K23、L23、<br>M23                                                                                                                                                                       | NC                 | 未接続ピン |    | 該当なし          |

(1) I = 入力、O = 出力、P = 電源、G = グランド、NC = 未接続

## 5 仕様

### 5.1 絶対最大定格

「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外の場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

|                                         |                                                             | 最小値  | 最大値                    | 単位  |

|-----------------------------------------|-------------------------------------------------------------|------|------------------------|-----|

| <b>電源電圧</b>                             |                                                             |      |                        |     |

| V <sub>DD</sub>                         | LVC MOS コア ロジックおよび低速インターフェイス (LSIF) のための電源電圧 <sup>(1)</sup> | -0.5 | 2.3                    | V   |

| V <sub>DDI</sub>                        | SubLVDS レシーバの電源電圧 <sup>(1)</sup>                            | -0.5 | 2.3                    | V   |

| V <sub>OFFSET</sub>                     | HVC MOS およびマイクロミラー電極の電源電圧 <sup>(1) (2)</sup>                | -0.5 | 11                     | V   |

| V <sub>BIAS</sub>                       | マイクロミラー電極の電源電圧 <sup>(1)</sup>                               | -0.5 | 19                     | V   |

| V <sub>RESET</sub>                      | マイクロミラー電極の電源電圧 <sup>(1)</sup>                               | -15  | 0.5                    | V   |

| V <sub>DDI</sub> - V <sub>DD</sub>      | 電源電圧のデルタ、絶対値 <sup>(3)</sup>                                 |      | 0.3                    | V   |

| V <sub>BIAS</sub> - V <sub>OFFSET</sub> | 電源電圧のデルタ、絶対値 <sup>(4)</sup>                                 |      | 11                     | V   |

| V <sub>BIAS</sub> - V <sub>RESET</sub>  | 電源電圧のデルタ、絶対値 <sup>(5)</sup>                                 |      | 34                     | V   |

| <b>入力電圧</b>                             |                                                             |      |                        |     |

|                                         | その他の入力の入力電圧 -- LSIF および LVC MOS                             | -0.5 | V <sub>DD</sub> + 0.5  | V   |

|                                         | その他の入力の入力電圧 -- SubLVDS <sup>(1) (6)</sup>                   | -0.5 | V <sub>DDI</sub> + 0.5 | V   |

| <b>SUBLVDS インターフェイス</b>                 |                                                             |      |                        |     |

| V <sub>ID</sub>                         | SubLVDS 入力差動電圧 (絶対値) <sup>(6)</sup>                         |      | 810                    | mV  |

| I <sub>ID</sub>                         | SubLVDS 入力差動電流                                              |      | 10                     | mA  |

| <b>クロック周波数</b>                          |                                                             |      |                        |     |

| f <sub>clock</sub>                      | 低速インターフェイス LS_CLK のクロック周波数                                  | 100  | 130                    | MHz |

| <b>温度ダイオード</b>                          |                                                             |      |                        |     |

| I <sub>TEMP_DIODE</sub>                 | 温度ダイオードへの最大電流ソース                                            |      | 120                    | μA  |

| <b>環境<sup>(8)</sup></b>                 |                                                             |      |                        |     |

| T <sub>ARRAY</sub>                      | 温度、動作時 <sup>(7)</sup>                                       | -40  | 105                    | °C  |

| T <sub>ARRAY</sub>                      | 温度、非動作時 <sup>(7)</sup>                                      | -40  | 125                    | °C  |

- (1) すべての電圧値は、グランド端子 (V<sub>SS</sub>) を基準としています。DMD を適切に動作させるには、以下に示す必要な電源を接続する必要があります: V<sub>DD</sub>, V<sub>DDI</sub>, V<sub>OFFSET</sub>, V<sub>BIAS</sub>, V<sub>RESET</sub> すべての V<sub>SS</sub> 接続も必要です。

- (2) V<sub>OFFSET</sub> 電源過渡電圧は、規定電圧内に収まる必要があります。

- (3) V<sub>DDI</sub> と V<sub>DD</sub> との推奨許容絶対電圧差を超えると、過剰な電流が流れ、デバイスに永続的な損傷が発生する恐れがあります。

- (4) V<sub>BIAS</sub> と V<sub>OFFSET</sub> との推奨許容絶対電圧差を超えると、過剰な電流が流れ、デバイスに永続的な損傷が発生する恐れがあります。

- (5) V<sub>BIAS</sub> と V<sub>RESET</sub> との推奨許容絶対電圧差を超えると、過剰な電流が流れ、デバイスに永続的な損傷が発生する恐れがあります。

- (6) この最大入力電圧定格は、差動ペアの各入力電圧が同じ電位のときに適用されます。Sub-LVDS 差動入力は指定された制限を超えてはなりません。超えると内部終端抵抗が損傷する可能性があります。

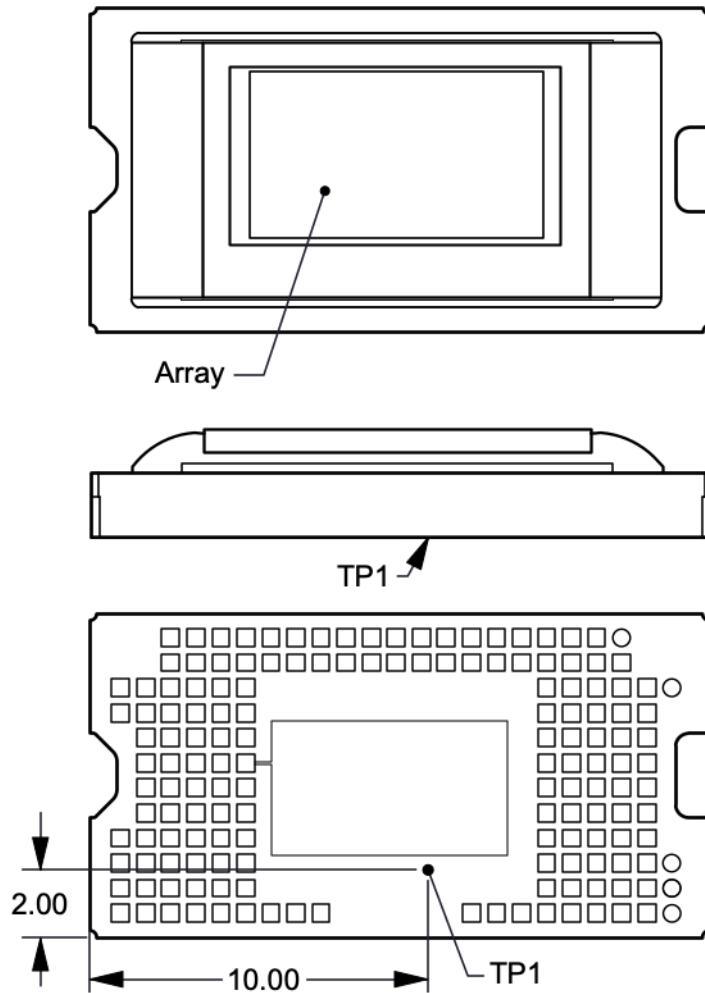

- (7) アレイ温度は直接測定することはできず、図 6-5 に示すテストポイント 1 (TP1) で測定した温度から、マイクロミラー アレイ温度計算を用いて解析的に算出する必要があります。

- (8) 高温で動作させた場合のデジタル マイクロミラー デバイス (DMD) の信頼性データについては、『車載用アプリケーションにおける RDP DMD の信頼性寿命推定値』アプリケーション レポート (DLPA146) を参照してください。

## 5.2 保存条件

部品としての DMD、またはシステムで動作していない DMD に適用できます。

|                  |        | 最小値 | 最大値 | 単位 |

|------------------|--------|-----|-----|----|

| T <sub>DMD</sub> | DMD 温度 | -40 | 125 | °C |

## 5.3 ESD 定格

|                    |       |                                | 値     | 単位 |

|--------------------|-------|--------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM) <sup>(1)</sup>     | ±1000 | V  |

|                    |       | デバイス帶電モデル (CDM) <sup>(2)</sup> | ±250  | V  |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.4 推奨動作条件

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り)

|                                         |                                                    | 最小値                   | 標準値                   | 最大値   | 単位                 |

|-----------------------------------------|----------------------------------------------------|-----------------------|-----------------------|-------|--------------------|

| <b>電源電圧範囲</b>                           |                                                    |                       |                       |       |                    |

| V <sub>DD</sub>                         | LVC MOS コア ロジックの電源電圧 LPSDR 低速インターフェイスの電源電圧 (1) (2) | 1.71                  | 1.8                   | 1.95  | V                  |

| V <sub>DDI</sub>                        | SubLVDS レシーバの電源電圧 (1) (2)                          | 1.71                  | 1.8                   | 1.95  | V                  |

| V <sub>OFFSET</sub>                     | HVC MOS およびマイクロミラー電極の電源電圧 (1) (2) (3)              | 9.5                   | 10                    | 10.5  | V                  |

| V <sub>BIAS</sub>                       | ミラー電極の電源電圧 (1) (2)                                 | 17.5                  | 18                    | 18.5  | V                  |

| V <sub>RESET</sub>                      | マイクロミラー電極の電源電圧 (1) (2)                             | -14.5                 | -14                   | -13.5 | V                  |

| V <sub>DDI</sub> - V <sub>DD</sub>      | 電源電圧差 (絶対値) (1) (2) (4)                            |                       |                       | 0.3   | V                  |

| V <sub>BIAS</sub> - V <sub>OFFSET</sub> | 電源電圧差 (絶対値) (1) (2) (5)                            |                       |                       | 10.5  | V                  |

| V <sub>BIAS</sub> - V <sub>RESET</sub>  | 電源電圧差 (絶対値) (1) (2) (6)                            |                       |                       | 33    | V                  |

| <b>LPSDR インターフェイス</b>                   |                                                    |                       |                       |       |                    |

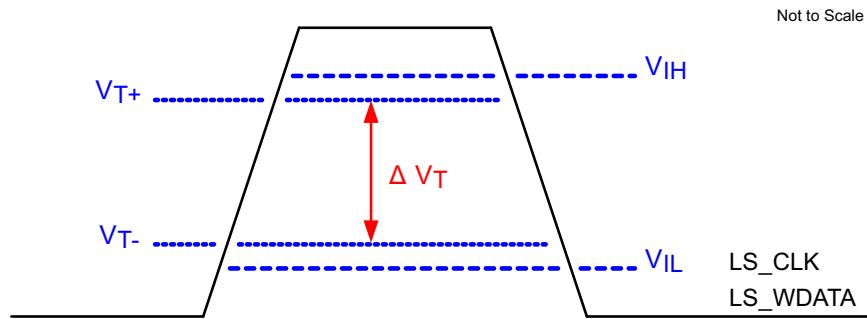

| V <sub>IH</sub>                         | High レベル入力電圧                                       | 0.7 × V <sub>DD</sub> |                       |       | V                  |

| V <sub>IL</sub>                         | Low レベル入力電圧                                        |                       | 0.3 × V <sub>DD</sub> |       | V                  |

| V <sub>IH(AC)</sub>                     | AC 入力高電圧                                           | 0.8 × V <sub>DD</sub> | V <sub>DD</sub> + 0.3 |       | V                  |

| V <sub>IL(AC)</sub>                     | AC 入力低電圧                                           | -0.3                  | 0.2 × V <sub>DD</sub> |       | V                  |

| V <sub>Hyst</sub>                       | 入力ヒステリシス                                           | 0.1 × V <sub>DD</sub> | 0.4 × V <sub>DD</sub> |       | V                  |

| f <sub>max_LS</sub>                     | 低速インターフェイス LS_CLK のクロック周波数 (7)                     | 108                   | 120                   | 130   | MHz                |

| DCD <sub>IN</sub>                       | LSIF デューティ サイクル歪み (LS_CLK) (7)                     | 44                    |                       | 56    | %                  |

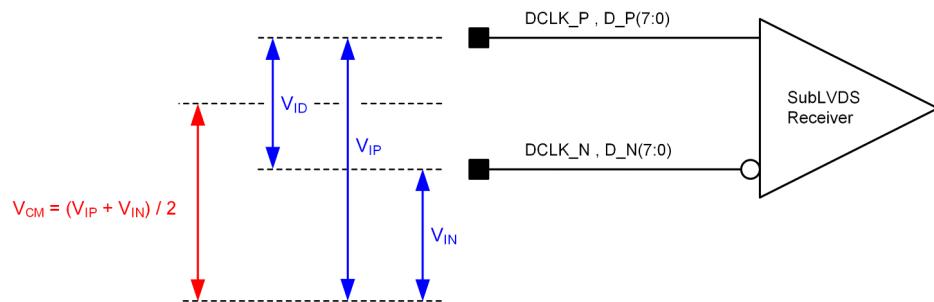

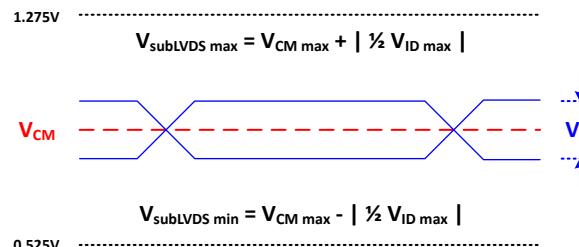

| <b>SubLVDS インターフェイス</b>                 |                                                    |                       |                       |       |                    |

| f <sub>max_HS</sub>                     | 高速インターフェイス DCLK のクロック周波数 (8)                       | 600                   | 720                   |       | MHz                |

| DCD <sub>IN</sub>                       | LVDS デューティ サイクル歪み (DCLK)                           | 48                    | 52                    |       | %                  |

| V <sub>ID</sub>                         | LVDS 差動入力電圧の振幅 (8)                                 | 150                   | 250                   | 350   | mV                 |

| V <sub>CM</sub>                         | 同相電圧 (8)                                           | 700                   | 900                   | 1100  | mV                 |

| V <sub>SUBLVDS</sub>                    | SubLVDS 電圧 (8)                                     | 525                   |                       | 1275  | mV                 |

| Z <sub>IN</sub>                         | 内部差動終端抵抗                                           | 80                    | 100                   | 120   | Ω                  |

| <b>温度ダイオード</b>                          |                                                    |                       |                       |       |                    |

| I <sub>TEMP_DIODE</sub>                 | 温度ダイオードへの最大電流ソース                                   |                       |                       | 120   | μA                 |

| <b>環境</b>                               |                                                    |                       |                       |       |                    |

| T <sub>ARRAY</sub>                      | アレイ温度、長期動作 (9) (10) (11)                           | -40                   | 105                   |       | °C                 |

| Q <sub>AP-ILL</sub>                     | ウインドウ開口部照明オーバーフィル (12) (13) (14)                   |                       |                       | 80    | mW/mm <sup>2</sup> |

| <b>照明</b>                               |                                                    |                       |                       |       |                    |

| ILL <sub>UV</sub>                       | 波長 < 410nm における照明強度 (9) (15)                       |                       |                       | 10    | mW/cm <sup>2</sup> |

- (1) DMD の動作には、以下の電源装置がすべて必要です。V<sub>DD</sub>、V<sub>DDI</sub>、V<sub>OFFSET</sub>、V<sub>BIAS</sub>、V<sub>RESET</sub> すべての V<sub>SS</sub> 接続も必要です。

- (2) すべての電圧値は、グランドピン (V<sub>SS</sub>) を基準としています。

- (3) V<sub>OFFSET</sub> 電源過渡電圧は、規定最大電圧内に収まる必要があります。

- (4) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>DDI</sub> - V<sub>DD</sub>| は、指定限界値よりも小さい必要があります。

- (5) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>BIAS</sub> - V<sub>OFFSET</sub>| は、指定限界値よりも小さい必要があります。

- (6) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>BIAS</sub> - V<sub>RESET</sub>| は、指定限界値よりも小さい必要があります。

- (7) リセット波形コマンドの内部 DMD タイミングを確保するため、指定されたとおりに LS\_CLK を実行する必要があります。

- (8) **タイミング要件**の SubLVDS タイミング要件を参照してください。

- (9) DMD を最大推奨動作条件の温度および UV 照明に同時に曝露すると、デバイスの寿命が短くなります。

- (10) アレイ温度を直接測定することはできず、図 6-5 に示すテストポイント (TP1) で測定された温度と **マイクロミラー アレイ温度計算**を使用したパッケージの熱抵抗から、解析的に計算する必要があります。

- (11) 長期は、デバイスの使用可能寿命と定義されます。

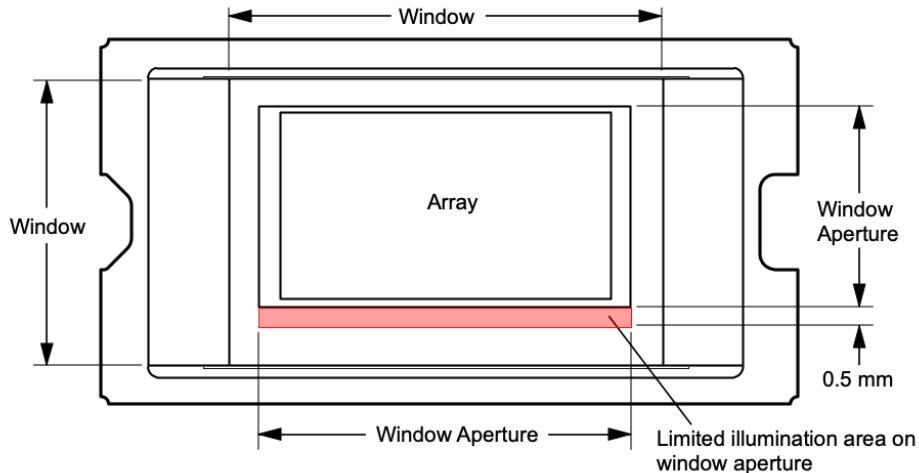

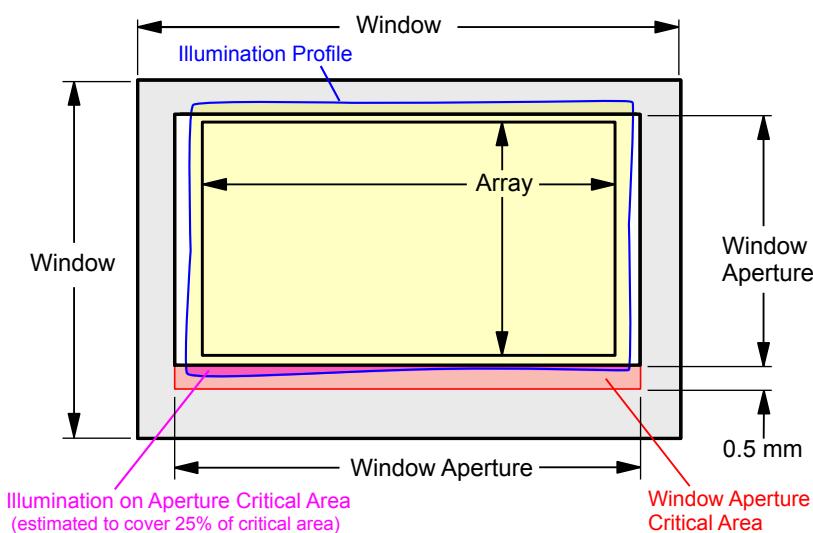

- (12) 図 5-1 で定義されている領域に適用されます。

- (13) DMD のアクティブ領域は、DMD ウィンドウ表面の内部にある開口によって取り囲まれており、DMD デバイスアセンブリの構造を正常な表示のためにマスクします。開口部は、いくつかの光学条件を想定した大きさになっています。アクティブ アレイの外側を照らすオーバーフィル光は散乱し、DMD を使用する最終アプリケーションの性能に悪影響を及ぼす可能性があります。アクティブ アレイの外部に入射する光の光束を最小限に抑えることが、照明光学システムの設計要件となっています。システムの光学アーキテクチャとアセンブリ許容誤差によつては、アクティブ アレイの外側のオーバーフィル光量がシステム性能の劣化を引き起こす可能性があります。

- (14) 計算方法については、「[ウィンドウ開口照度オーバーフィル計算](#)」を参照してください。

- (15) 計算については、「[マイクロミラー電力密度の計算](#)」を参照してください。

図 5-1. イルミネーション オーバーフィル ダイアグラム - クリティカル エリア

## 5.5 热に関する情報

| 熱評価基準 |                                            | DLP3944-Q1 | 単位   |

|-------|--------------------------------------------|------------|------|

| 熱抵抗   | FSC                                        |            |      |

|       | 154 PIN                                    |            |      |

|       | テスト ポイント 1 (TP1) 対するアクティブ領域 <sup>(1)</sup> | 2.6        | °C/W |

|       | アクティブ領域から温度への検出ダイオード <sup>(1)</sup>        | 0.1        | °C/W |

- (1) DMD は、吸収および放散された熱をパッケージの裏面に伝導するよう設計されています。冷却システムは、「[推奨動作条件](#)」に規定されている温度範囲内に DMD を維持できる必要があります。DMD の合計熱負荷は、主にアクティブ領域によって吸収される入射光によって決まりますが、その他の寄与としてウィンドウ開口部によって吸収される光エネルギーやアレイの消費電力があります。光学システムは、ウィンドウの開放口から外れた光エネルギーを最小限に抑えるよう設計する必要があります。これは、この領域に熱負荷が増大すると、デバイスの信頼性が大幅に低下する可能性があるためです。

## 5.6 電気的特性

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ <sup>(6)</sup> |                                              | テスト条件 <sup>(2)</sup>                            | 最小値                   | 標準値    | 最大値 | 単位 |

|----------------------|----------------------------------------------|-------------------------------------------------|-----------------------|--------|-----|----|

| <b>CURRENT</b>       |                                              |                                                 |                       |        |     |    |

| I <sub>DD</sub>      | 消費電流: V <sub>DD</sub> <sup>(3) (4)</sup>     | 標準値                                             |                       | 140    | mA  |    |

| I <sub>DDI</sub>     | 消費電流: V <sub>DDI</sub> <sup>(3) (4)</sup>    | 標準値                                             |                       | 45     | mA  |    |

| I <sub>OFFSET</sub>  | 消費電流: V <sub>OFFSET</sub> <sup>(5)</sup>     | 標準値                                             |                       | 6      | mA  |    |

| I <sub>BIAS</sub>    | 消費電流: V <sub>BIAS</sub> <sup>(5)</sup>       | 標準値                                             |                       | 0.6    | mA  |    |

| I <sub>RESET</sub>   | 消費電流: V <sub>RESET</sub>                     | 標準値                                             |                       | 1.8    | mA  |    |

| <b>電源</b>            |                                              |                                                 |                       |        |     |    |

| P <sub>DD</sub>      | 電源の消費電力: V <sub>DD</sub> <sup>(3) (4)</sup>  | 標準値                                             |                       | 252    | mW  |    |

| P <sub>DDI</sub>     | 電源の消費電力: V <sub>DDI</sub> <sup>(3) (4)</sup> | 標準値                                             |                       | 81     | mW  |    |

| P <sub>OFFSET</sub>  | 電源の消費電力: V <sub>OFFSET</sub> <sup>(5)</sup>  | 標準値                                             |                       | 60     | mW  |    |

| P <sub>BIAS</sub>    | 電源の消費電力: V <sub>BIAS</sub> <sup>(5)</sup>    | 標準値                                             |                       | 1.08   | mW  |    |

| P <sub>RESET</sub>   | 電源の消費電力: V <sub>RESET</sub>                  | 標準値                                             |                       | 25.2   | mW  |    |

| P <sub>TOTAL</sub>   | 電源の合計消費電力                                    | 標準値                                             |                       | 419.28 | mW  |    |

| <b>LPSDR 入力</b>      |                                              |                                                 |                       |        |     |    |

| I <sub>IL</sub>      | Low レベル入力電流                                  | V <sub>DD</sub> = 1.95 V、V <sub>I</sub> = 0V    | -100                  |        | nA  |    |

| I <sub>IH</sub>      | High レベル入力電流                                 | V <sub>DD</sub> = 1.95 V、V <sub>I</sub> = 1.95V | 135                   |        | μA  |    |

| <b>LPSDR 出力</b>      |                                              |                                                 |                       |        |     |    |

| V <sub>OH</sub>      | DC 出力高電圧 <sup>(7) (8) (9)</sup>              | I <sub>OH</sub> = -2mA                          | 0.8 × V <sub>DD</sub> |        | V   |    |

| V <sub>OL</sub>      | DC 出力低電圧 <sup>(7) (8) (9)</sup>              | I <sub>OL</sub> = 2mA                           | 0.2 × V <sub>DD</sub> |        | V   |    |

| <b>容量</b>            |                                              |                                                 |                       |        |     |    |

| C <sub>IN</sub>      | 入力容量 LVC MOS                                 | F = 1MHz                                        |                       | 10     | pF  |    |

| C <sub>IN</sub>      | 入力容量 SubLVDS                                 | F = 1MHz                                        |                       | 20     | pF  |    |

| C <sub>OUT</sub>     | 出力容量                                         | F = 1MHz                                        |                       | 10     | pF  |    |

| C <sub>TEMP</sub>    | 温度センス ダイオード容量                                | F = 1MHz                                        |                       | 20     | pF  |    |

- (1) デバイスの電気的特性は、特に記述のない限りセクション 5.4 以上です。

- (2) すべての電圧値は、グランドピン (V<sub>SS</sub>) を基準としたものです。

- (3) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>DDI</sub> – V<sub>DD</sub>| は、指定限界値よりも小さい必要があります。

- (4) 非圧縮のコマンドとデータに基づく電源消費電力。

- (5) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>BIAS</sub> – V<sub>OFFSET</sub>| は、指定限界値よりも小さい必要があります。

- (6) DMD を動作させるには、すべての電源接続が必要です。VDD、VDDI、VOFFSET、VBIAS、および VRESET。すべての VSS 接続も必要です。

- (7) LPSDR 仕様は、LS\_CLK ピンと LS\_WDATA ピン用です。

- (8) 低速インターフェイスは LPSDR であり、JEDEC 規格 No. 209-2F、低消費電力ダブルデータレート (LPDDR) JESD209-2F の「電気的特性」および「AC/DC 動作条件」表に準拠しています。

- (9) LPSDR 出力仕様は、LS\_RDATA\_A、LS\_RDATA\_B、LS\_RDATA\_C、および LS\_RDATA\_D ピン用です。

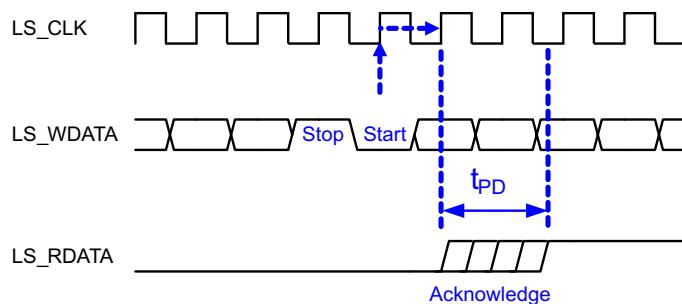

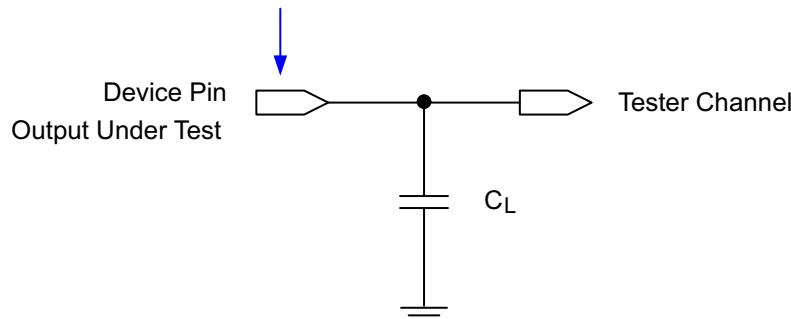

## 5.7 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ    |                                                                     | テスト条件               | 最小値 | 標準値 | 最大値 | 単位   |

|----------|---------------------------------------------------------------------|---------------------|-----|-----|-----|------|

| $t_{PD}$ | 出力伝搬、クロックから Q まで、LS_CLK 入力の立ち上がりエッジから LS_RDATA 出力まで。 <sup>(1)</sup> | $C_L = 15\text{pF}$ |     | 15  |     | ns   |

|          | スルーレート、LS_RDATA                                                     |                     |     | 0.3 |     | V/ns |

|          | 出力デューティ サイクル歪み、LS_RDATA                                             |                     | 40  |     | 60  | %    |

(1) デバイスの電気的特性は、特に記述のない限りセクション 5.4 以上です。

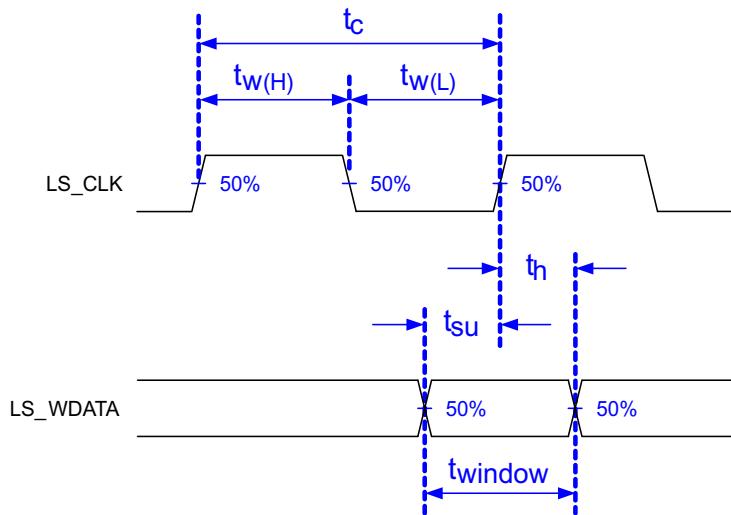

## 5.8 タイミング要件

自由気流での動作温度範囲内 (特に記述のない限り)

|                |                            |                                        | 最小値  | 公称値  | 最大値 | 単位   |

|----------------|----------------------------|----------------------------------------|------|------|-----|------|

| <b>LVC MOS</b> |                            |                                        |      |      |     |      |

| <b>LPSDR</b>   |                            |                                        |      |      |     |      |

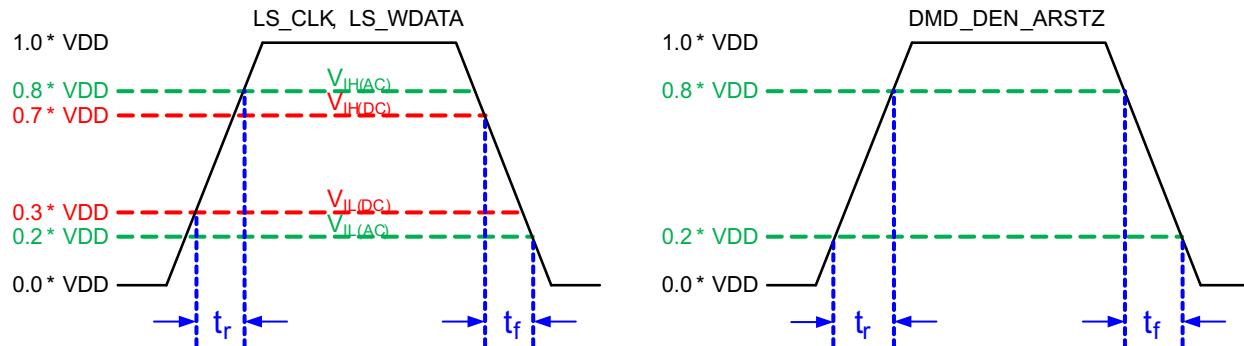

| $t_r$          | 立ち上がりスルーレート <sup>(2)</sup> | $(20\% \sim 80\%) \times VDD^{(6)}$    | 0.25 |      |     | V/ns |

| $t_f$          | 立ち下がりスルーレート <sup>(2)</sup> | $(80\% \sim 20\%) \times VDD^{(6)}$    | 0.25 |      |     | V/ns |

| $t_r$          | 立ち上がりスルーレート <sup>(1)</sup> | $(30\% \sim 80\%) \times VDD^{(6)}$    | 1    |      | 3   | V/ns |

| $t_f$          | 立ち下がりスルーレート <sup>(1)</sup> | $(70\% \sim 20\%) \times VDD^{(6)}$    | 1    |      | 3   | V/ns |

| $t_{W(H)}$     | パルス幅 LS_CLK High           | 50% ~ 50% のリファレンス ポイント <sup>(5)</sup>  | 4.2  |      |     | ns   |

| $t_{W(L)}$     | パルス幅 LS_CLK Low            | 50% ~ 50% のリファレンス ポイント <sup>(5)</sup>  | 4.2  |      |     | ns   |

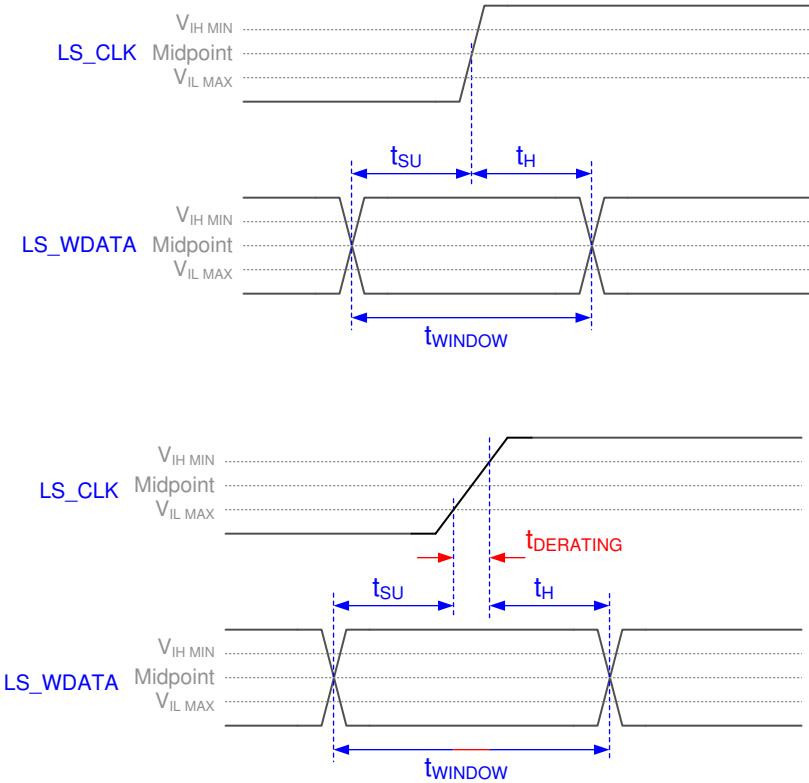

| $t_{su}$       | セットアップ時間                   | LS_WDATA は LS_CLK の前に有効 <sup>(5)</sup> |      | 1.5  |     | ns   |

| $t_h$          | ホールド時間                     | LS_WDATA は LS_CLK の後に有効 <sup>(5)</sup> |      | 1.5  |     | ns   |

| <b>SubLVDS</b> |                            |                                        |      |      |     |      |

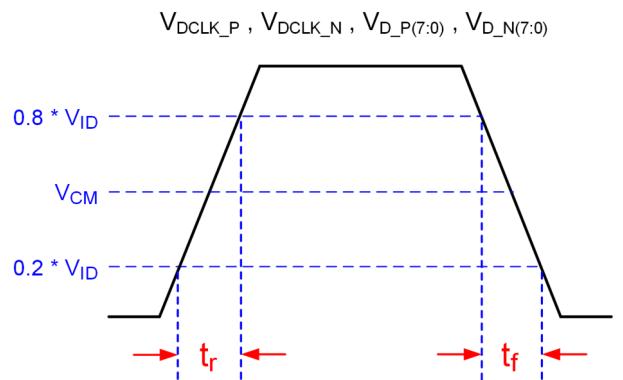

| $t_r$          | 立ち上がりスルーレート                | 20% ~ 80% のリファレンス ポイント <sup>(7)</sup>  | 0.7  | 1    |     | V/ns |

| $t_f$          | 立ち下がりスルーレート                | 80% ~ 20% のリファレンス ポイント <sup>(7)</sup>  | 0.7  | 1    |     | V/ns |

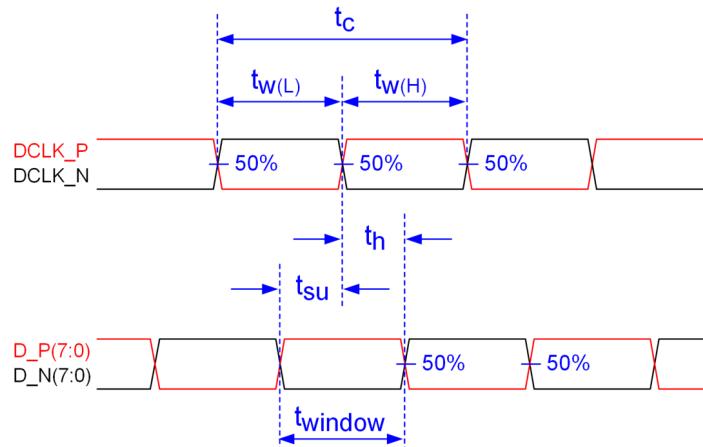

| $t_{W(H)}$     | パルス幅 DCLK High             | 50% ~ 50% のリファレンス ポイント <sup>(8)</sup>  | 0.7  |      |     | ns   |

| $t_{W(L)}$     | パルス幅 DCLK Low              | 50% ~ 50% のリファレンス ポイント <sup>(8)</sup>  | 0.7  |      |     | ns   |

| $t_{WINDOW}$   | ウインドウ時間 <sup>(1) (3)</sup> | セットアップ時間 + ホールド時間 <sup>(5)</sup>       | 0.25 |      |     | ns   |

| $t_{su}$       | セットアップ時間                   | HS_CLK の前に HS_DATA 有効 <sup>(8)</sup>   |      | 0.17 |     | ns   |

| $t_h$          | ホールド時間                     | HS_CLK の後に HS_DATA 有効 <sup>(8)</sup>   |      | 0.17 |     | ns   |

| $t_{POWER}$    | パワーアップ レシーバ <sup>(4)</sup> |                                        |      | 200  |     | ns   |

- (1) 仕様は、DMD\_DEN\_ARSTZ ピンのものです。図 5-3 の LPSDR 入力の立ち上がりおよび立ち下がりスルーレートを参照。

- (2) 仕様は LS\_CLK ピンと LS\_WDATA ピンのものです。図 5-3 の LPSDR 入力の立ち上がりおよび立ち下がりスルーレートを参照。

- (3) ウィンドウ時間のディレーティングの例: 0.5V/ns のスルーレートにより、ウィンドウ時間が 0.7ns 増加し、3ns から 3.7ns になります。図 5-5 を参照。

- (4) この仕様は SubLVDS レシーバ時間のみを対象としており、コマンド送信やコマンド送信後のレイテンシは考慮されていません。

- (5) 図 5-2 を参照。

- (6) 図 5-3 を参照。

- (7) 図 5-4 を参照。

- (8) 図 5-6 を参照。

低速インターフェイスは LPSDR であり、JEDEC 規格 No. 209-2F、低消費電力ダブル データレート(LPDDR) JESD209-2F の「電気的特性」および「AC/DC 動作条件」表に準拠しています。

図 5-2. LPSDR スイッチング パラメータ

図 5-3. LPSDR 入力の立ち上がりおよび立ち下がりスルーレート

Not to Scale

図 5-4. SubLVDS 入力の立ち上がりおよび立ち下がりスルーレート

図 5-5. ウィンドウ時間ディレーティングの概念

Not to Scale

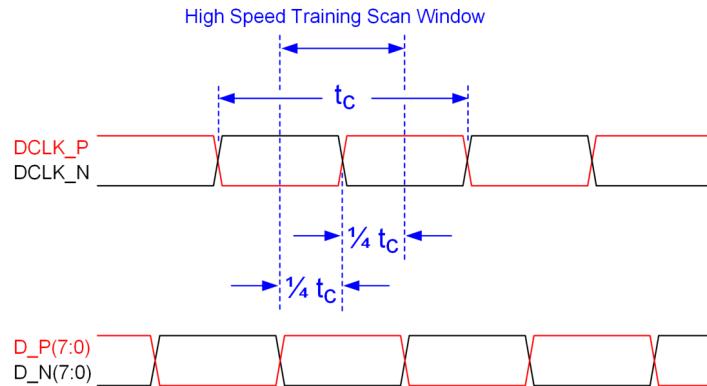

図 5-6. SubLVDS スイッチング パラメータ

注: 詳細については、[セクション 5.8](#) を参照してください。

図 5-7. 高速トレーニング スキャン ウィンドウ

図 5-8. SubLVDS 電圧パラメータ

図 5-9. SubLVDS 波形パラメータ

図 5-10. SubLVDS 等価入力回路

図 5-11. LPSDR 入力ヒステリシス

図 5-12. LPSDR 読み出し

Data Sheet Timing Reference Point

詳細については、[セクション 5.6](#) を参照してください。

図 5-13. 出力伝搬測定用のテスト負荷回路

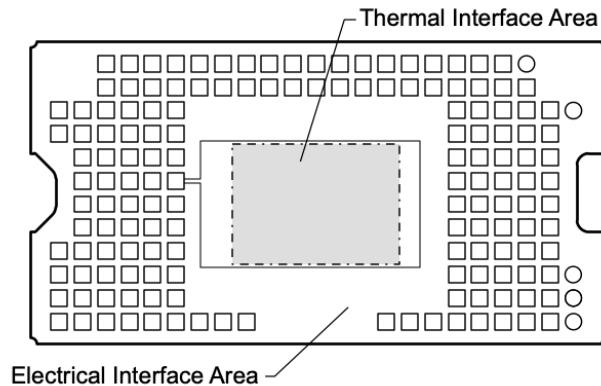

## 5.9 システム実装インターフェイスの荷重

| パラメータ          | 条件                   | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|----------------------|-----|-----|-----|----|

| サーマルインターフェイス領域 | 各領域に均等に分配される最大負荷 (1) |     |     | 50  |    |

| 電気的インターフェイス領域  | 各領域に均等に分配される最大負荷 (1) |     |     | 143 | N  |

(1) [図 5-14](#) をご覧ください。

図 5-14. システム実装インターフェイスの荷重

## 5.10 マイクロミラー アレイの物理特性

| パラメータの説明   |                                     | 値                            | 単位            |

|------------|-------------------------------------|------------------------------|---------------|

| M          | アクティブな列の数 <sup>(1)</sup> (2)        | 1360                         | マイクロミラー       |

| N          | アクティブな行の数 <sup>(1)</sup> (2)        | 1536                         | マイクロミラー       |

| $\epsilon$ | マイクロミラー ピッチ、対角線 <sup>(1)</sup>      | 4.525                        | μm            |

| P          | マイクロミラー ピッチ、垂直、水平 <sup>(1)</sup>    | 6.4                          | μm            |

|            | マイクロミラーのアクティブ アレイの幅 <sup>(1)</sup>  | $(P \times M) + (P / 2)$     | mm            |

|            | マイクロミラーのアクティブ アレイの高さ <sup>(1)</sup> | $(P \times N) / 2 + (P / 2)$ | mm            |

|            | マイクロミラーのアクティブ境界 <sup>(3)</sup>      | マイクロミラーの池 (POM)              | マイクロミラー / サイド |

|            |                                     | 15                           |               |

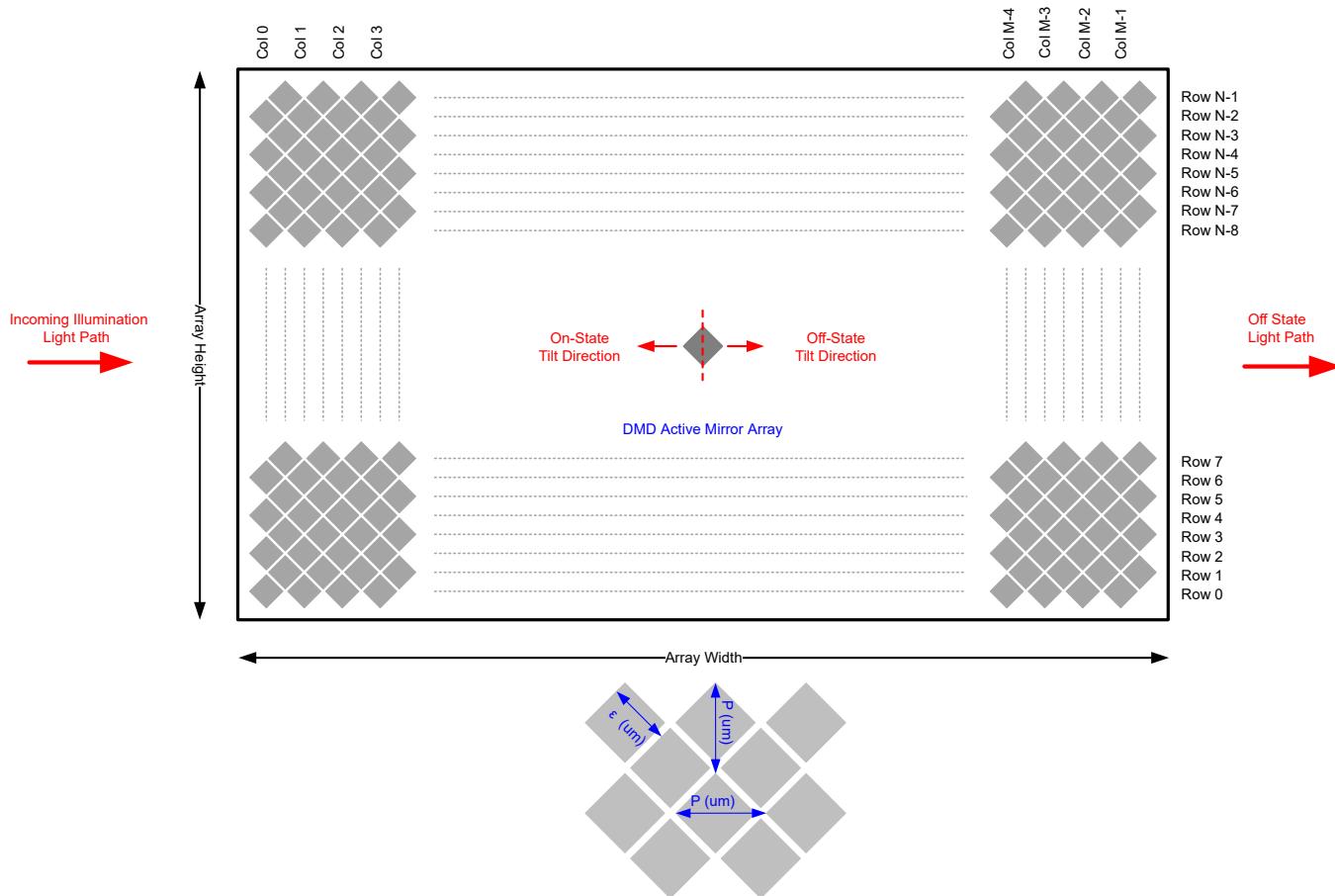

- (1) 図 5-15 を参照。

- (2) DMD マイクロミラーの高速なスイッチング速度と、高度な DLP 画像処理アルゴリズムとの組み合わせにより、各マイクロミラーは各フレーム中に画面上に 4 つの個別のピクセルを表示でき、その結果、 $3840 \times 2160$  ピクセルの画像全体を表示できます。

- (3) アクティブ アレイの周囲にある境界（単数または複数）の構造と品質には、マイクロミラーの池 (POM) と呼ばれる、部分的に機能するマイクロミラーのバンドが含まれています。これらのマイクロミラーは構造的および/または電気的に、明るい状態またはオン状態へ傾けることを防止しますが、オフ状態へ傾けるには電気的バイアスが必要です。

## ADVANCE INFORMATION

図 5-15. マイクロミラー アレイの物理特性

## 5.11 マイクロミラー アレイの光学特性

| パラメータ                | テスト条件                    | 最小値           | 公称値  | 最大値  | 単位      |

|----------------------|--------------------------|---------------|------|------|---------|

| マイクロミラーの傾斜角          | DMD 着陸状態 (1) (2) (3) (4) | 13.5          | 14.5 | 15.5 | 度       |

| マイクロミラーのクロスオーバー時間(5) |                          |               | 1    | 3    | μs      |

| マイクロミラーのスイッチング時間(6)  |                          | 6             |      |      | μs      |

| 画像性能(7)              | アクティブ領域の明るいピクセル(8)       | グレイの 10 画面(9) |      | 0    | マイクロミラー |

|                      | POM 内の明るいピクセル(10)        | グレイの 10 画面(9) |      | 1    |         |

|                      | アクティブ領域の暗いピクセル(11)       | 白い画面          |      | 4    |         |

|                      | 隣接ピクセル(12)               | 任意の画面         |      | 0    |         |

|                      | アクティブ領域で不安定なピクセル(13)     | 任意の画面         |      | 0    |         |

- (1) マイクロミラー アレイ全体から形成されるプレーンを基準として測定されます。

(2) マイクロミラー アレイとパッケージのデータム間には、さらに大きな変動があります。

(3) 同じデバイス上または異なるデバイス上に配置された任意の 2 つの個別マイクロミラー間で発生する可能性のある変動を表しています。

(4) 一部のアプリケーションでは、システム全体の光学設計においてマイクロミラーの傾斜角の変動を考慮することが重要です。一部のシステム光学設計では、デバイス内のマイクロミラーの傾斜角が変動すると、マイクロミラー アレイから反射された光磁界では不均一性が認識される場合があります。一部のシステム光学設計では、デバイス間でマイクロミラーの傾斜角が変動すると、色測定のバラツキ、システム効率のバラツキ、またはシステムコントラストのバラツキが生じる場合があります。

(5) マイクロミラーがある着地状態から反対側の着地状態に公称遷移するために必要な時間。

(6) マイクロミラーの連続する遷移間の最小時間。

(7) 受け入れの条件:すべての DMD 画質に関する返品は、以下の投影画像テスト条件を使用して評価されます。

• テストセットのデガンマは線形である必要があります。

• テストセットの輝度とコントラストは公称値に設定する必要があります。

• 投影画像の対角サイズは、最低 20 インチ (50.8cm) であるものとします。

• 投影スクリーンはユニティ ゲインにするものとします。

• 投影画像は、最小 38 インチ (96.52cm) の距離から検査する必要があります。

• すべての画質テスト中は、画像に焦点を合わせます。

(8) 明るいピクセルの定義:シングル ピクセルまたはミラーがオン位置に固定され、周囲のピクセルよりも目に見えて明るいこと。

(9) グレイの 10 画面の定義:画面のすべての領域には、

赤 = 10/255

緑 = 10/255

青 = 10/255 の設定で色分けされます

(10) POM の定義:アクティブ領域を取り囲むオフ状態ミラーの長方形境界線。

(11) 暗いピクセルの定義:シングル ピクセルまたはミラーがオフ位置に固定され、周囲のピクセルよりも目に見えて暗いこと。

(12) 隣接ピクセルの定義:共通の境界または共通のポイントを共有する 2 つ以上のスタッカピクセル (クラスタとも呼ばれます)。

(13) 不安定なピクセルの定義:パラメータをメモリにロードした順序で動作しないシングル ピクセルまたはミラー。不安定なピクセルは、画像と非同期にちらつきがあるよう見える。

## 5.12 ウィンドウの特性

| パラメータ                   | 最小値         | 公称値              | 最大値    |

|-------------------------|-------------|------------------|--------|

| ウィンドウ材質                 |             | Corning Eagle XG |        |

| ウィンドウ屈折率                | 波長 546.1 nm |                  | 1.5119 |

| ウィンドウ開口部 <sup>(1)</sup> |             |                  |        |

| オーバーフィル照射               |             | セクション 6.5 を参照。   |        |

- (1) ウィンドウ開口部のサイズと位置の詳細については、機械的パッケージの ICD を参照してください。

## 5.13 チップセットコンポーネントの使用方法の仕様

DLP3944-Q1 DMD の信頼性の高い機能と動作を実現するには、テキサス インstrument (TI) の DMD 制御テクノロジーを採用または実装する部品など、該当する DLP チップセットの他の部品と組み合わせて使用する必要があります。TI の DMD 制御テクノロジーは、DLP DMD の動作または制御に使用される TI のテクノロジーとデバイスで構成されています。

### 注

TI は、前述の制限を超える光学システムの動作条件によって発生する画質のアーチファクトまたは DMD の故障については、一切責任を負いません。

## 6 詳細説明

### 6.1 概要

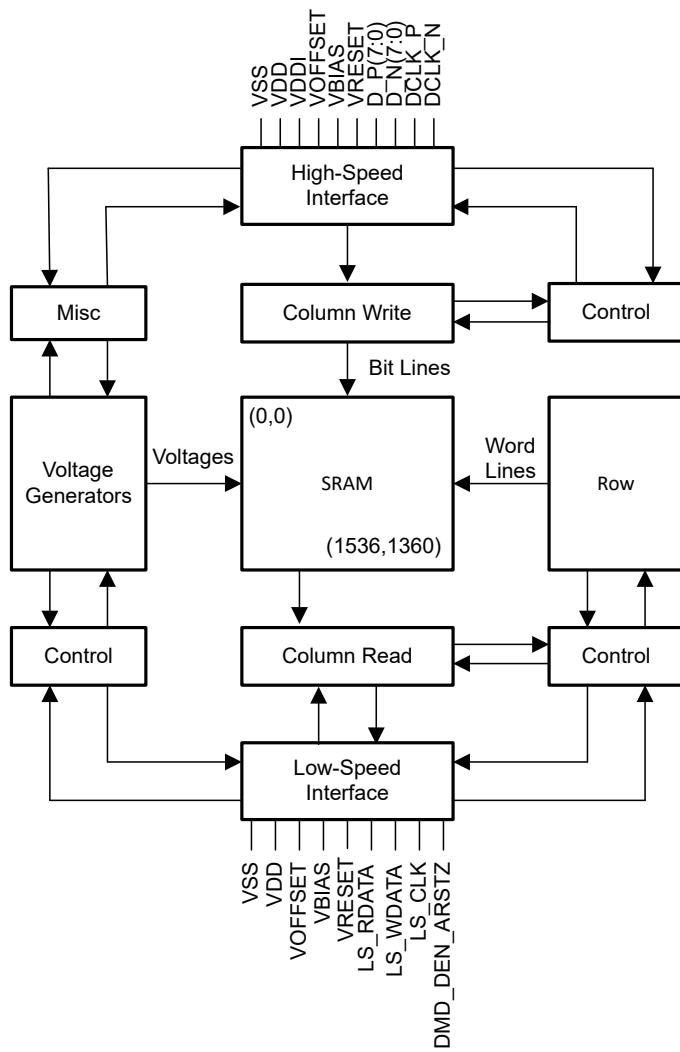

DLP3944-Q1 デジタルマイクロミラー デバイス (DMD) は、対角 0.39 インチ (0.99cm) の空間光変調器で、高反射率のアルミニウム製マイクロミラーのアレイで構成されています。DMD は、電気入力、光出力の光マイクロマシン (MOEMS) です。DMD マイクロミラーの高速なスイッチング速度と、高度な DLP 画像処理アルゴリズムとの組み合わせにより、各マイクロミラーは各フレーム中に画面上に 4 つの個別のピクセルを表示でき、その結果、3840×2160 ピクセルの画像全体を表示できます。電気的インターフェイスは、低電圧差動信号伝送 (LVDS) です。DMD は、1 ビット CMOS メモリセルの 2 次元アレイで構成されます。アレイは、M 個のメモリセル列と N 個のメモリセル行の格子状に編成されます。[セクション 6.2](#) を参照してください。マイクロミラーの偏向 (正または負) は、基礎となる CMOS アドレス指定回路のアドレス電圧とマイクロミラーリセット信号 (MBRST) を変更することによって個別に制御されます。

DLP 0.39 インチ (0.99cm) 4K UHD チップセットは、DLP3944-Q1 DMD、DLPC431 ディスプレイコントローラ、DLPA3085/DLPA3082 PMIC および LED ドライバで構成されています。信頼性の高い動作を保証するため、DLP3944-Q1 DMD は、DLP ディスプレイコントローラおよびチップセットで指定されている PMIC と一緒に使う必要があります。

### 6.2 機能ブロック図

図 6-1. 機能ブロック図

## 6.3 機能説明

DLP3944-Q1 は、DLPC431 から SubLVDS バスで駆動され、DLPA3085/DLPA3082 から電力が供給される 2 次元の 1 ビット CMOS メモリ セルのアレイで構成されます。温度センシング ダイオードは、DMD アレイの温度を継続的に監視するために使用されます。

信頼性の高い動作を保証するために、DLP3944-Q1 は DLPC431 DMD ディスプレイ コントローラおよび DLPA3085/DLPA3082 システム管理および照明コントローラとともに使用する必要があります。

### 6.3.1 SubLVDS データインターフェイス

SubLVDS 信号プロトコルは、非常に高速な DMD データリフレッシュレートを実現すると同時に、低い消費電力と低い放射妨害を維持するように設計されています。高速インターフェイスの目的は、ピクセル データを迅速かつ効率的に転送することであり、高速 DDR 転送および圧縮技術を使用して電力と時間を節約することです。高速インターフェースは、専用クロックを備えた入力用の差動 SubLVDS レシーバで構成されています。

データは、DLPC431 からの SubLVDS インターフェイスを使用して、各マイクロミラーの下の SRAM にロードされます。このインターフェイスは、16 ペアの差動データ信号と、4 つのクロックペアを備えて 4 つの独立したバス A、B、C、D で構成され、SRAM アレイの左半分と右半分をロードします。両方の遷移でデータがラッチされ、DDR (ダブル データ レート) インターフェイスを形成します。SubLVDS インターフェイスは、より堅牢なインターフェイスを実現するため、データおよびクロックタイミングを最適化するため、連続トレーニング アルゴリズムも実装しています。

高速 SubLVDS インターフェイスにより、210 万ピクセルの DMD アレイ全体が 100 $\mu$ s 未満の速度で更新可能です。

### 6.3.2 制御用の低速インターフェイス

低速インターフェイスは、DMD を構成し、リセット動作を制御する命令を処理します。LS\_CLK は低速クロック、LS\_WDATA は低速データ入力です。

低速インターフェイスの目的は、パワーアップ時とパワーダウン時に DMD を構成し、データ ロードと同期しているマイクロミラーのリセット電圧レベルを制御することです。マイクロミラーのリセット電圧は、ミラーが機械的に切り替わる時間を制御します。低速差動インターフェイスには、データとクロックを書き込むための 2 ペアの信号と、出力 (A、B、C、および B) 用の 4 つのシングル エンド信号が含まれています。

### 6.3.3 電源インターフェイス

DMD は次の 4 つの DC 電圧を必要とします。1.8V ソース ( $V_{DD}$  および  $V_{DDI}$ )、 $V_{OFFSET}$ 、 $V_{RESET}$  および  $V_{BIAS}$ 。一般的な LED ベースのシステムでは、1.8V、 $V_{OFFSET}$ 、 $V_{RESET}$ 、および  $V_{BIAS}$  は、DLPA3085/DLPA3082 PMIC および LED ドライバによって管理されます。

### 6.3.4 タイミング

データシートには、デバイス ピンでのタイミングが記載されています。出力タイミング解析では、テスタのピン エレクトロニクスとその伝送ラインの影響を考慮に入れる必要があります。図 5-13 に、テスト対象の出力の等価テスト負荷回路を示します。タイミング基準負荷は、特定のシステム環境を精密に表現したり、製造試験で示される実際の負荷を表現したりすることを意図したものではありません。システム設計者は、IBIS または他のシミュレーション ツールを使用して、タイミング基準負荷をシステム環境に関連付ける必要があります。記載されている負荷容量値は、AC タイミング信号の特性評価と測定のみを目的としています。この負荷容量の値は、デバイスが駆動可能な最大負荷を示しているわけではありません。

## 6.4 デバイスの機能モード

DMD の機能モードは、DLPC431 ディスプレイ コントローラによって制御されます。DLPC431 ディスプレイ コントローラのデータシートを参照するか、TI アプリケーション エンジニアにお問い合わせください。

## 6.5 光学インターフェイスおよびシステムの画質に関する検討事項

TI は、最終製品の光学性能について一切責任を負いません。目的の最終製品の光学性能を実現するには、多数の部品とシステム設計パラメータとの間でトレードオフを決定する必要があります。システムの光学性能と画像品質の最適化は、光学システム設計のパラメータのトレードオフに大きく関係しています。想定可能なすべてのアプリケーションを予測

できるわけではありませんが、プロジェクタの画質と光学性能は、以下のセクションに示す光学システムの動作条件への準拠によって決まります。

### 6.5.1 開口数および迷光制御

TI は、照明光学系の開口数によって定義される光円錐角は、投影光学系の開口数によって定義される光円錐角と同じであることが望ましいことを推奨しています。この角度は、照明および投影瞳孔に適切な開口部を追加して、投影レンズからの平面光および迷光をブロックする場合を除いて、公称デバイスのマイクロミラー傾斜角を超えないようにする必要があります。これは一般に「照明オーバードライブ」と呼ばれます。DLP3944-Q1 の傾き角度は  $14.5^\circ$  で、これは f/2.0 の開口数に対応します。マイクロミラーの傾斜角により、DMD の「オン」光路をその他のライトパスから分離できます。これには、DMD ウィンドウからの望ましくない平面状態の反射、DMD の境界構造、または DMD 付近にあるプリズムやレンズ表面などのその他のシステム表面などが含まれます。照明光学系または投影光学系のアーチャ角の値がマイクロミラーの傾斜角を超えると、コントラストの劣化や、ディスプレイ境界やアクティブ領域に好ましくないアーティファクトが発生する可能性があります。

### 6.5.2 瞳孔一致

光学的品質および画質に関する TI の仕様は、照明用光学素子の射出瞳が公称値として投影光学素子の入射瞳から  $2^\circ$  以内の位置を中心としていると仮定しています。瞳孔のずれは、ディスプレイ境界とアクティブ領域に不快なアーティファクトを発生させる可能性があり、特にシステムの開口数がピクセル チルト角度を超える場合は、制御するために追加のシステム開口部が必要になる場合があります。

### 6.5.3 オーバーフィル照射

デバイスのアクティブ領域は、DMD チップ アセンブリの構造を通常の視界から覆い隠す、DMD ウィンドウ面の内側にある開口部で囲まれ、複数の光学動作条件を想定したサイズとなっています。ウィンドウ開口部を照らすオーバーフィル光は、ウィンドウ開口部の端からアーティファクトが発生したり、その他の表面異常が画面に表示されたりする可能性があります。照明光学システムは、ウィンドウ開口部上の任意の場所に入射する光束が、アクティブ領域の平均光束レベルの約 10% を超えないように設計する必要があります。特定のシステムの光学的アーキテクチャによっては、ウィンドウ開口部上のオーバーフィル光を推奨される 10% 未満にさらに低減して、許容可能な範囲にする必要があります。

## 6.6 マイクロミラー アレイ温度の計算

図 6-2. DMD の温度テスト ポイント

アクティブ アレイの温度は、パッケージ外部の熱測定点、パッケージの熱抵抗、電力消費、および照明による熱負荷から解析的に算出できます。以下の式は、アレイ温度と 図 6-2 の熱試験の基準セラミック温度 (TP1) との関係を示しています。

$$T_{ARRAY} = T_{CERAMIC} + (Q_{ARRAY} \times R_{ARRAY-TO-CERAMIC}) \quad (1)$$

$$Q_{ILLUMINATION} = Q_{INCIDENT} \times \text{DMD Absorption Constant} \quad (2)$$

$$Q_{ARRAY} = Q_{ELECTRICAL} + Q_{ILLUMINATION} \quad (3)$$

ここで、

- $T_{ARRAY}$  = 算出されたアレイ温度 ( $^{\circ}\text{C}$ )

- $T_{CERAMIC}$  = 図 6-2 の TP1 の場所で測定されたセラミック温度 ( $^{\circ}\text{C}$ )

- $R_{ARRAY-TO-CERAMIC}$  = アレイから熱テスト ポイント TP1 までの DMD パッケージの熱抵抗 ( $^{\circ}\text{C}/\text{W}$ )

- $Q_{ARRAY}$  = DMD アレイ (W) 上の 総電力 (電気と吸収)

- DMD による  $Q_{ELECTRICAL}$  = の公称消費電力 (W)

- $Q_{ILLUMINATION}$  = 吸収照明熱負荷 (W)

- $Q_{INCIDENT}$  = DMD での総入射光パワー (W)

DMD 吸収定数は、アクティブ アレイとアレイ境界の照明分布、入射角 (AOI)、システムの  $f$  数、ミラーの動作状態の関数です。吸収定数は、オン状態のときよりもオフ状態のときに高くなります。ミラーのオンとオフの両方の状態について、吸収定数を計算する式が用意されています。式は 29 度の AOI、f/2.0 系を想定しており、アクティブ アレイ、POM、およびアレイ境界上の光の分布を説明します。

$$\text{DMD Absorption Constant (OFF state)} = 1.004 - 0.005235 \times (\% \text{ of light on ActiveArray} + \text{POM}) \quad (4)$$

$$\text{DMD Absorption Constant (ON state)} = 1.004 - 0.007776 \times (\% \text{ of light on ActiveArray} + \text{POM}) \quad (5)$$

DMD の消費電力は変数で、電圧、データ レート、動作周波数に依存します。

以下の計算例では、入射光全体の 10% がアクティブ アレイおよび POM を外れ、ミラーがオフ状態になることを想定しています。

1.  $T_{CERAMIC} = 50^\circ\text{C}$  (測定値)

2.  $Q_{INCIDENT} = 10\text{W}$  (測定値)

3. DMD 吸収定数 =  $1.004 - 0.005235 \times 90 = 0.533$

4.  $Q_{ELECTRICAL} = 0.5\text{W}$

5.  $R_{ARRAY-TO-CERAMIC} = 2.6^\circ\text{C/W}$

6.  $Q_{ARRAY} = 0.5\text{W} + (0.533 \times 10\text{W}) = 5.83\text{W}$

7.  $T_{ARRAY} = 50^\circ\text{C} \times (5.83\text{W} \times 2.6^\circ\text{C/W}) = 65.2^\circ\text{C}$

DMD ヒートシンク ソリューションを設計する場合、アレイから基準セラミック温度までのパッケージ熱抵抗 (熱電対位置 TP1 を使用して、以下の式に従ってパッケージ全体の温度上昇を求めることができます。

$$T_{ARRAY-TO-CERAMIC} = Q_{ARRAY} \times R_{ARRAY-TO-CERAMIC} \quad (6)$$

### 6.6.1 温度センスダイオードを使用したアレイ温度の監視

アクティブアレイの温度は、温度センスダイオード測定値、アレイからダイオードまでの熱抵抗、電力、および照明の熱負荷から解析的に計算できます。アレイの温度と温度センスダイオードの温度との関係は、以下の式で示されます。

$$T_{ARRAY} = T_{DIODE} + (Q_{ARRAY} \times R_{ARRAY-TO-DIODE}) \quad (7)$$

$$Q_{ILLUMINATION} = (Q_{INCIDENT} \times DMD \text{ Absorption Constant}) \quad (8)$$

$$Q_{ARRAY} = Q_{ELECTRICAL} + Q_{ILLUMINATION} \quad (9)$$

ここで、

- $T_{ARRAY}$  = 算出されたアレイ温度 (°C)

- $T_{DIODE}$  = 測定された温度検知ダイオードの温度 (°C)

- $R_{ARRAY-TO-DIODE}$  = アレイからダイオードへのパッケージの熱抵抗 (°C/W)

- $Q_{ARRAY}$  = DMDアレイ (W) 上の総電力 (電気と吸収)

詳細については、[セクション 6.6](#)を参照してください。

- DMDによる $Q_{ELECTRICAL}$  = の公称消費電力 (W)

- $Q_{ILLUMINATION}$  = 吸收照明熱負荷 (W)

- $Q_{INCIDENT}$  = DMDでの総入射光パワー (W)

以下の計算例では、入射光全体の 10% がアクティブアレイおよび POM を外れ、ミラーがオフ状態になることを想定しています。

1.  $T_{DIODE} = 55^{\circ}\text{C}$

2.  $Q_{INCIDENT} = 10\text{W}$  (測定値)

3. DMD 吸收定数 =  $1.004 - 0.005235 \times 90 = 0.533$

4.  $Q_{ELECTRICAL} = 0.5\text{W}$

5.  $R_{ARRAY-TO-DIODE} = 0.1^{\circ}\text{C}/\text{W}$

6.  $Q_{ARRAY} = 0.5\text{W} + (0.533 \times 10\text{W}) = 5.83\text{W}$

7.  $T_{ARRAY} = 55^{\circ}\text{C} + (5.83\text{W} \times 0.1^{\circ}\text{C}/\text{W}) = 55.6^{\circ}\text{C}$

### 6.7 マイクロミラーの電力密度の計算

さまざまな波長帯域で DMD 上の照明の光出力密度を計算するには、DMD で測定された合計光出力、照明のオーバーフィル率、アクティブアレイの面積、目的の波長帯域でのスペクトルの合計光出力に対する比率を使用します。

$$ILL_{UV} = [OP_{UV-RATIO} \times Q_{INCIDENT}] \times 1000\text{mW}/\text{W} \div A_{ILL} (\text{mW}/\text{cm}^2) \quad (10)$$

$$A_{ILL} = A_{ARRAY} \div (1 - OV_{ILL}) (\text{cm}^2) \quad (11)$$

ここで

- $ILL_{UV}$  = DMD での UV 照明の電力密度 ( $\text{mW}/\text{cm}^2$ )

- $A_{ILL}$  = DMD での照明領域 ( $\text{cm}^2$ )

- $Q_{INCIDENT}$  = DMD での総入射光パワー (W) (測定値)

- $A_{ARRAY}$  = アレイの面積 ( $\text{cm}^2$ ) (データシート)

- $OV_{ILL}$  = アレイ外の DMD の総照明パーセント (%) (光学モデル)

- $OP_{UV-RATIO}$  = 照明スペクトルの総光出力に対する、波長が 410nm 未満の場合の光出力比 (スペクトル測定)

照明領域は、照明オーバーフィルによって異なります。DMD 上の総照明領域は、アレイ領域と、アレイの周囲のオーバーフィル領域です。光学モデルを使用して、アレイの外部にある DMD 上の全照明の割合 ( $OV_{ILL}$ ) と、アクティブアレイ上にある全照明の割合を決定します。これらの値から、照明領域 ( $A_{ILL}$ ) が計算されます。照明は、アレイ全体で一様であると仮定します。

測定された照明スペクトルから、総光出力に対する、対象の波長帯域における光出力との比が計算されます。

計算例：

$$Q_{\text{INCIDENT}} = 12.1 \text{ W} \text{ (measured)}$$

$$A_{\text{ARRAY}} = ((8.7072\text{mm} \times 4.9184\text{mm}) \div 100\text{mm}^2/\text{cm}^2) = 0.4283\text{cm}^2 \text{ (data sheet)}$$

$$OV_{\text{ILL}} = 16.3\% \text{ (optical model)}$$

$$OP_{\text{UV-RATIO}} = 0.00021 \text{ (spectral measurement)}$$

$$A_{\text{ILL}} = 0.4283\text{cm}^2 \div (1 - 0.163) = 0.5117\text{cm}^2$$

$$ILL_{\text{UV}} = [0.00021 \times 12.1 \text{ W}] \times 1000\text{mW/W} \div 0.5117\text{cm}^2 = 4.966\text{mW/cm}^2$$

## 6.8 ウィンドウ アーチャイル ミネーション オーバーフィル計算

ウィンドウ開口部のクリティカル領域の光学的オーバーフィルの量は直接測定できません。アレイ上で照射が均一なシステムの場合、この量は、DMD の入射光パワーの合計測定値と、定義された重要領域における DMD の総光パワーの比率を使用して決定されます。この光学モデルを使用して、ウィンドウ開口部臨界面積の光出力の割合を決定し、面積のサイズを推定します。

- $Q_{\text{AP-ILL}} = [Q_{\text{INCIDENT}} \times OP_{\text{AP\_ILL\_RATIO}}] \div A_{\text{AP\_ILL}} \text{ (W/cm}^2)$

ここで

- $Q_{\text{AP-ILL}}$  = ウィンドウ開口部照明オーバーフィル ( $\text{W/cm}^2$ )

- $Q_{\text{INCIDENT}}$  = DMD での総入射光パワー (ワット) (測定値)

- $OP_{\text{AP\_ILL\_RATIO}}$  = ウィンドウ開口部の重要領域の光出力と DMD の合計光出力との比率 (光学モデル)

- $A_{\text{AP-ILL}}$  = ウィンドウ開口部臨界面積 ( $\text{cm}^2$ ) (データシート)

- $OP_{\text{CA\_RATIO}}$  = 入射光パワー(%) (光学モデル) を持つウィンドウ開口重要領域のパーセンテージ

計算例：

図 6-3. ウィンドウ アーチャのオーバーフィルの例

クリティカル アーチャの長さについては、上の図を参照してください。

$$Q_{\text{INCIDENT}} = 12.1 \text{ W} \text{ (measured)}$$

(12)

$$OP_{AP\_ILL\_RATIO} = 0.312\% \text{ (optical model)} \quad (13)$$

$$OV_{CA\_RATIO} = 25\% \text{ (optical model)} \quad (14)$$

Length of the window aperture for critical area = 0.9802cm (data sheet) (15)

Width of critical area = 0.050 cm (data sheet) (16)

$$A_{AP-ILL} = 0.9802\text{cm} \times 0.050 \text{ cm} = 0.04901\text{cm}^2 \quad (17)$$

$$Q_{AP-ILL} = (12.1 \text{ W} \times 0.00312) \div (0.04901\text{cm}^2 \times 0.25) = 3.08\text{W/cm}^2 \text{ (W/cm}^2\text{)} \quad (18)$$

## 6.9 マイクロミラーのランデッド オン / ランデッド オフ デューティ サイクル

### 6.9.1 マイクロミラーのランデッド オン / ランデッド オフ デューティ サイクルの定義

マイクロミラーのランデッド オン / ランデッド オフ デューティ サイクル (ランデッド デューティ サイクル) は、個々のマイクロミラーがオン状態で着地している時間の割合を、同じマイクロミラーがオフ状態で着地している時間に対する割合として示します。

たとえば、90/10 のランデッド デューティ サイクルは、基準のピクセルがオン状態の時間 90% (オフ状態の時間 10%) にあることを示しています。一方、10/90 は、ピクセルがオフ状態の時間 90% にあることを示しています。同様に、50/50 はピクセルがオン状態の時間 50% (オフ状態の時間 50%) になっていることを示します。

なお、ランデッド デューティ サイクルを評価する際、一方の状態 (オンまたはオフ) から他方の状態 (オフまたはオン) に切り替わるのに要する時間は無視できるものと見なされます。

マイクロミラーはどちらか一方の状態 (オンまたはオフ) でしか着地できないため、2 つの数値 (パーセンテージ) の合計は必ず 100 になります。

## 7 アプリケーションと実装

### 注

以下のアプリケーション セクションにある情報は、TI の製品仕様に含まれるものではなく、TI はその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

DMD は空間光変調器であり、照射用光源から受け入れた光を 2 方向のいずれかに反射します。主な方向は、プロジェクションまたは集光光学系です。各アプリケーションは、主にシステムの光学アーキテクチャと、DLPC431 コントローラが受け入れるデータ形式の違いで派生するものです。サイド照度の高い DMD の高傾斜ピクセルにより、輝度性能が向上し、厚さに制約のあるアプリケーション向けにシステムのフットプリントを小型化できます。DLP3944-Q1 を使用した代表的なアプリケーションとして、後部座席用エンターテインメントやフロント ガラス ディスプレイシステムなどの車載用アプリケーションがあります。

DMD のパワーアップ / パワーダウン シーケンシングは、DLPA3085/DLPA3082 によって厳密に制御されます。パワーアップとパワーダウンの仕様については、[セクション 8](#) を参照してください。信頼性の高い動作を保証するために、DLP3944-Q1 DMD は常に、DLPC431 コントローラおよび DLPA3085/DLPA3082 PMIC とともに使用する必要があります。

## 7.2 代表的なアプリケーション

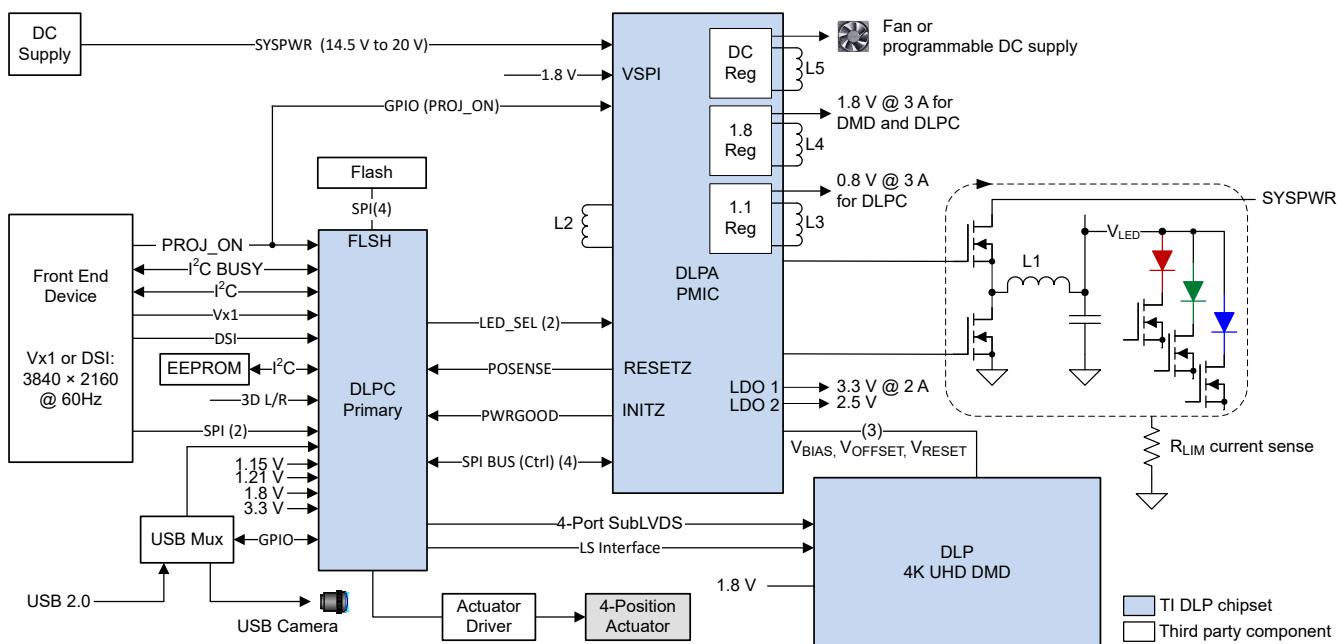

このチップセットは、DLP3944-Q1 車載 DMD、DLPC431、DLPA3085/DLPA3082 の 3 つのコンポーネントで構成されています。DMD は、画像の形成と投射に使用される超小型ミラーで構成された光変調器です。DLPC431 は、DMD のコントローラです。入力ビデオをフォーマットし、入力ビデオを表示するために DMD 照射用光源と DMD のタイミングを制御します。DLPA3085/DLPA3082 は、DMD 用の高性能電圧レギュレータ、光源 (LED またはレーザーなど) 用コントローラ、およびチップセット全体を対象とする管理 IC です。DLPC431 と DLPA3085/DLPA3082 を組み合わせることにより、システム レベルの監視、診断、障害検出機能を実現できます。図 7-1 は、DLP 後部座席用エンターテインメント構成のこれらのデバイスを使ったシステム レベルのブロック図で、各デバイスの主な特長と機能を示しています。

図 7-1. 後部座席用エンターテインメント システム ブロック図

## 7.2.1 アプリケーションの概要

図 7-1 に、DLP モジュールのシステム ブロック図を示します。このシステムは、DLPC431、DLPA3085/DLPA3082 および DLP3944-Q1 車載用 DMD を使用します。DLPC431 と DLPA3085/DLPA3082 を組み合わせることにより、外部 SDRAM と専用のマイクロプロセッサは不要になります。このチップセットは、LED 光源の照明制御、電源シーケンス機能、システム管理機能を管理します。さらに、チップセットは多くのシステム診断機能や内蔵セルフテスト (BIST) 機能もサポートしています。

DLPC431 は、DMD および DLP モジュール内の光源用コントローラです。ホストから入力ビデオを受け取り、DMD と光源のタイミングを同期して、目的のビデオを達成します。DLPC431 は、DMD に表示される入力ビデオ データをフォーマットします。これらのビデオ セグメントを光源タイミングで同期し、グレイスケールのシェーディングと複数の色のビデオを作成します（該当する場合）。

DLPC431 は、車両のホスト プロセッサからの入力を受信します。ホストは、コマンドを提供すると同時に、ビデオ データを入力します。ホスト コマンドは、I<sub>2</sub>C バスまたは SPI バスを使用して送信できます。ホスト コマンドに使用されていないバスは、診断用の読み取り専用バスとして使用できます。入力ビデオは、で送信できます。V-by-One HS インターフェイス。SPI フラッシュ メモリは、DLPC431 の ARM コア用の組込みソフトウェア、キャリブレーション データ、およびデフォルト設定を提供します。

DLPC431 の出力は、DLPA3085/DLPA3082 への構成および監視コマンド、LED またはレーザー ドライバへのタイミング制御、DMD への制御およびデータ信号、ホスト プロセッサへの監視および診断情報です。DMD への制御信号は、SubLVDS インターフェイスを使用して送信されます。

DLPA3085/DLPA3082 の電源シーケンスおよび監視ブロックは、DMD に適切に電源を投入し、高精度の DMD 電圧レール (-14V、10V、18V) を提供して、動作中にシステムの電源レールを監視します。これらの機能を 1 つの IC に統合することにより、設計期間の短縮と複雑さの大幅な低減が可能になります。

DMD は、電気信号を入力（ビデオ データ）として受信し、機械出力（ミラー位置）を生成する微小電子機械システム（MEMS）デバイスです。DMD への電気的インターフェイスは、DLPC431 との SubLVDS インターフェイスです。機械的出力は、DMD アレイ内の 210 万個以上のミラーの状態で、±14.5° に傾けることができます。プロジェクト システムでは、ミラーが画像を表示するためのピクセルとして使用されます。

## 7.2.2 リファレンス デザイン

DLP3944-Q1 DMD、DLPC431 コントローラ、DLPA3085/DLPA3082 を接続する方法の詳細については、DLP3944-Q1 評価基板（EVM）の詳細情報に関する TI アプリケーション チームにお問い合わせください。TI は光学機械関連のリファレンス デザインを提供しています。詳細については、TI E2E™ 設計サポート フォーラムで TI にお問い合わせください。

## 7.2.3 アプリケーション ミッション プロファイルの考慮事項

各アプリケーションでは、異なる温度で異なるミッション プロファイルまたは動作時間数が予想されます。評価を支援するために、将来的にアプリケーション レポートを提供することができます。詳細については、TI E2E™ 設計サポート フォーラムで TI にお問い合わせください。

## 7.2.4 設計要件

ディスプレイ システムのその他の中核部品としては、照射用光源、照明および投影光学系用の光学エンジン、その他の電気部品および機械部品、ソフトウェアがあります。使用する照明の種類と目的の輝度は、システム全体の設計とサイズに大きな影響を及ぼします。

ディスプレイ システムは DLP3944-Q1 をコア画像処理デバイスとして使用し、0.39 インチ (0.99cm) のマイクロミラー アレイを搭載しています。DLPC431 コントローラは、DMD とシステムの他の部分との間のデジタル インターフェイスであり、フロントエンド レシーバからデジタル入力を取得し、高速インターフェイスで DMD を駆動します。DLPA3085/DLPA3082 PMIC は、DMD、コントローラ、LED 照明機能用電圧レギュレータとして機能します。

## 7.2.5 詳細な設計手順

包括的な DLP システムを実現するには、DLP3944-Q1 DMD、関連する照射用光源、光学素子、必要な機械部品を含む光学モジュールまたは光学エンジンが必要です。

信頼性の高い動作を保証するために、DMD は常に DLPC431 ディスプレイコントローラおよび DLPA3085/DLPA3082 PMIC ドライバと一緒に使用する必要があります。

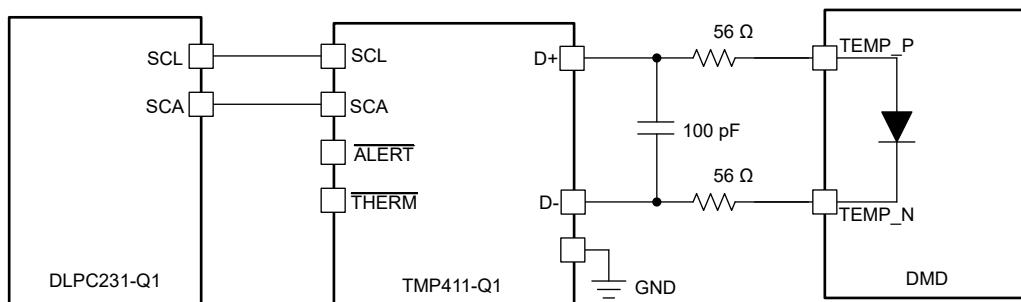

## 7.3 温度検出

このソフトウェア アプリケーションは、DLP3944-Q1 DMD 温度センサ ダイオードを読み取るよう TMP411A-Q1 を構成する機能を備えています。このデータを使用して、照明やファン速度の調整など、システム設計全体に追加機能を組み込むことができます。I<sup>2</sup>C インターフェイスを使用して、TMP411A-Q1 と DLPC431 コントローラ間のすべての通信を完了します。TMP411A-Q1 は、セクション 4 に示すピンを経由して DMD に接続されます。

### 7.3.1 温度センシングダイオード

DMD には、TMP411-Q1 温度監視デバイスと組み合わせて使用するように設計された温度センシングダイオードが含まれています。DLPC431 は、TMP411A-Q1 によって温度センスダイオードを監視します。DMD タイミングの DLPC431 動作は、DMD アレイ温度に基づいて調整できるため、DMD の信頼性の高い動作を確保するためには、この接続が不可欠です。

図 7-2 に、DLPC431、TMP411A-Q1、および DMD の間の代表的な接続を示します。

図 7-2. 温度センスダイオードの代表的な回路構成

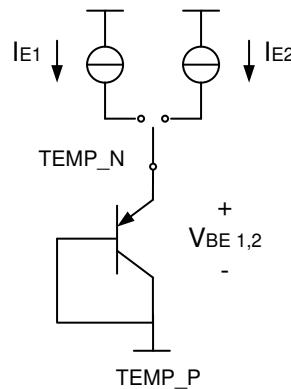

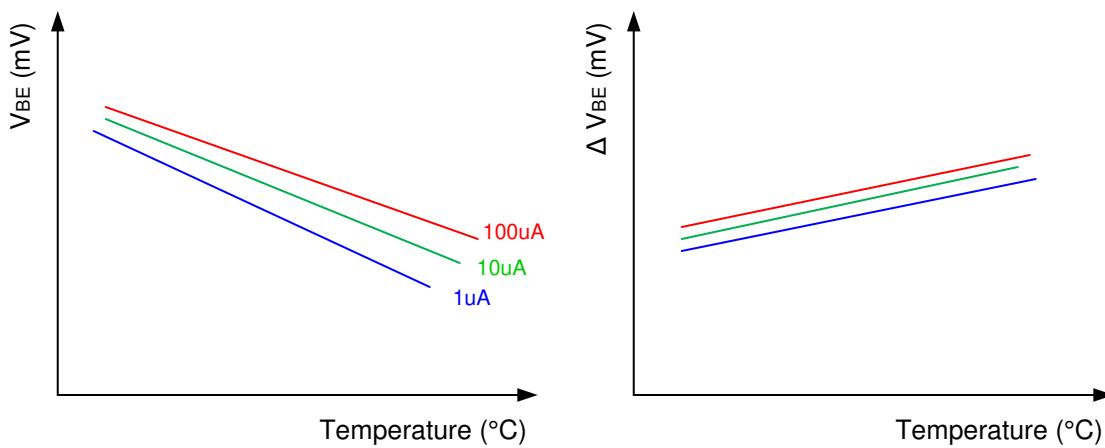

#### 7.3.1.1 温度センスダイオード理論

温度センシングダイオードは、トランジスタの基本的な電流および温度特性に基づいています。ダイオードは、トランジスタベースをコレクタに接続することにより形成されます。ダイオードを流れる 3 種類の電流が既知であり、その結果として得られるダイオード電圧をそれぞれのケースで測定します。ベースエミッタ電圧の差はトランジスタの絶対温度に比例します。

温度ダイオードの理論と測定の詳細については、TMP411A-Q1 のデータシートを参照してください。図 7-3 および図 7-4 に、ダイオードを流れる電流と電圧の関係を示します。

図 7-3. 温度測定理論

図 7-4. デルタ  $V_{BE}$  と温度との関係の例

## 8 電源に関する推奨事項

DMD の動作には、以下の電源装置がすべて必要です。

- $V_{SS}$

- $V_{BIAS}$

- $V_{DD}$

- $V_{DDI}$

- $V_{OFFSET}$

- $V_{RESET}$

DMD のパワーアップ / パワーダウン シーケンシングは、DLP ディスプレイ コントローラによって厳密に制御されます。

### 注意

DMD を確実に動作させるには、以下の電源シーケンシング要件に従う必要があります。規定されたパワーアップおよびパワーダウン要件のいずれかに準拠しない場合、デバイスの信頼性に影響を及ぼす可能性があります。『[DMD の電源要件](#)』の DMD 電源シーケンス要件を参照してください。

$V_{BIAS}$ 、 $V_{DD}$ 、 $V_{DDI}$ 、 $V_{OFFSET}$ 、 $V_{RESET}$  電源をパワーアップおよびパワーダウン動作時に調整する必要があります。以下の各要件のいずれかに適合していない場合、DMD の信頼性と寿命が大幅に低下します。共通のグランド  $V_{SS}$  も接続する必要があります。

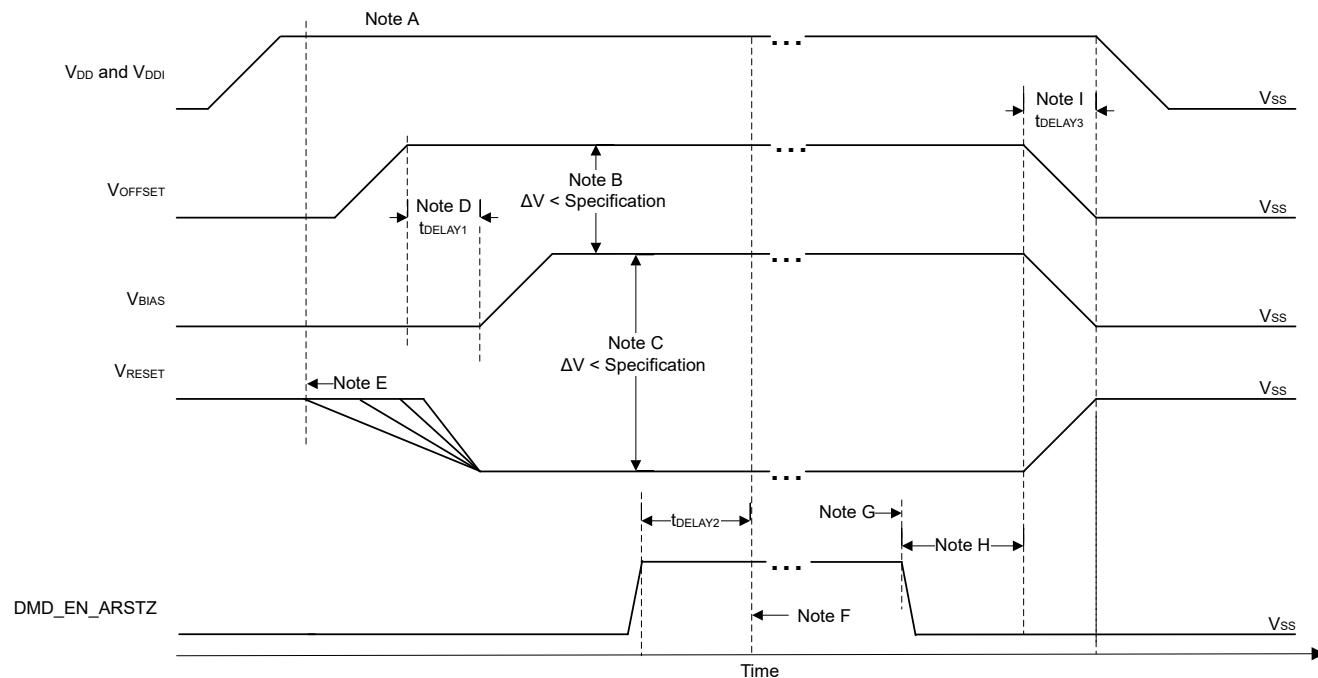

**表 8-1. DMD 電源シーケンシング要件**

| 記号                          | パラメータ       | 説明                                                                                  | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------------------|-------------|-------------------------------------------------------------------------------------|-----|-----|-----|----|

| $t_{DELAY1}$ <sup>(1)</sup> | 電源オン遅延の要件   | $V_{OFFSET}$ が推奨動作電圧で安定してから、 $V_{BIAS}$ および $V_{RESET}$ のパワーアップまで                   | 2   |     |     | ms |

| $t_{DELAY3}$ <sup>(1)</sup> | パワーダウン遅延の要件 | $V_{OFFSET}$ 、 $V_{BIAS}$ 、および $V_{RESET}$ のパワーダウンから遅延 $V_{DD}$ を High に保持する必要があります | 50  |     |     | us |

| $V_{OFFSET}$                | 電源電圧レベル     | パワーアップ シーケンスの遅延の開始時                                                                 | 6   |     |     | V  |

| $V_{BIAS}$                  | 電源電圧レベル     | パワーアップ シーケンスの遅延の終了時                                                                 | 6   |     |     | V  |

(1) [DMD 電源要件](#)を参照してください。

## 8.1 DMD 電源のパワーアップ手順

- パワーアップ時には常に、 $V_{OFFSET}$  に  $t_{DELAY1}$  を加えた電圧、 $V_{BIAS}$ 、および  $V_{RESET}$  電圧が DMD に印加される前に、 $V_{DD}$  および  $V_{DDI}$  が起動および安定する必要があります。

- パワーアップ時には、 $V_{BIAS}$  と  $V_{OFFSET}$  の電圧差が、「推奨動作条件」に示される指定限界内でなければならないという厳しい要件があります。

- パワーアップ中、 $V_{BIAS}$  を基準とした  $V_{RESET}$  の相対タイミングは不要です。

- 過渡電圧レベルが「絶対最大定格」、「推奨動作条件」、および「DMD 電源要件」で指定された要件に従っている限り、パワーアップ時の電源スルーレートは柔軟です。

- パワーアップ時、[推奨動作条件](#)に示す動作電圧で  $V_{DD}$  が安定するまで、LVC MOS 入力ピンを high に駆動しないでください。

## 8.2 DMD 電源のパワーダウン手順

- パワーダウン時には、 $V_{BIAS}$ 、 $V_{RESET}$ 、および  $V_{OFFSET}$  がグランドの指定限界内で放電されるまで、 $V_{DD}$  および  $V_{DDI}$  を供給する必要があります。

- パワーダウン時には、 $V_{BIAS}$  と  $V_{OFFSET}$  の電圧差が、「推奨動作条件」に示される指定限界内でなければならないという厳しい要件があります。

- パワーダウン中、 $V_{BIAS}$  を基準とした  $V_{RESET}$  の相対タイミングは不要です。

- 過渡電圧レベルが「絶対最大定格」、「推奨動作条件」、および「DMD 電源要件」で指定された要件に従っている限り、パワーダウン時の電源スルーレートは柔軟です。

- パワーダウン中、LVC MOS 入力ピンは「[推奨動作条件](#)」で指定された値未満である必要があります。

### 8.3 DMD 電源シーケンシング要件

- A. ピン機能表については、「[ピン構成および機能](#)」を参照してください。

- B. 過剰な電流を防止するため、電源電圧の差  $|V_{OFFSET} - V_{BIAS}|$  は、「[推奨動作条件](#)」の指定限界値よりも小さい必要があります。

- C. 過剰な電流を防止するため、電源差  $|V_{BIAS} - V_{RESET}|$  は、「[推奨動作条件](#)」の指定限界値よりも小さい必要があります。

- D.  $V_{BIAS}$  は、 $V_{OFFSET}$  がパワーアップした後に、t<sub>DELAY1</sub> 仕様に従ってパワーアップする必要があります。

- E. DLP コントローラ ソフトウェアにより、グローバル  $V_{BIAS}$  コマンドが開始されます。

- F. DMD のマイクロミラー パークシーケンスの完了後、DLP コントローラ ソフトウェアはハードウェア パワーダウンを開始し、DMD\_EN\_ARSTZ を有効にして、 $V_{BIAS}$ 、 $V_{RESET}$ 、 $V_{OFFSET}$  を無効化します。

- G. 電力損失条件下で、DLP コントローラのハードウェア DMD\_EN\_ARSTZ によって緊急 DMD マイクロミラー パーク手順が実行されている場合は、low になります。

- H. t<sub>DELAY3</sub> 仕様に準拠して、 $V_{OFFSET}$ 、 $V_{BIAS}$ 、 $V_{RESET}$  が low になるまで、 $V_{DD}$  は high に維持する必要があります。

- I. 過剰な電流を防止するため、電源電圧のデルタ  $|V_{DDI} - V_{DD}|$  は、「[推奨動作条件](#)」の指定限界値よりも小さい必要があります。

図 8-1. DMD 電源要件

## 9 レイアウト

### 9.1 レイアウトのガイドライン

具体的な PCB レイアウトと配線ガイドラインについては、DLPC431 および DLPA3085/DLPA3082 データシートを参照してください。DMD の PCB 固有のガイドラインについては、以下を使用してください。

- LS\_WDATA 信号と LS\_CLK 信号の長さを一致させます。

- HS バス信号のピア、層変更、巻線を最小限に抑えます。

- $V_{BIAS}$  の近くにある最小で 2 つの 220nF (25V) デカップリング コンデンサ。

- $V_{RESET}$  の近くにある最小で 2 つの 220nF (25V) デカップリング コンデンサ。

- $V_{OFFSET}$  の近くにある最小で 3 つの 4.7 $\mu$ F デカップリング コンデンサ。

- $V_{DDI}$  および  $V_{DD}$  の近くにある最小で 4 つの 100nF デカップリング コンデンサ。

- 温度ダイオードピン:DMD には、外部の TI TMP411A-Q1 温度センシング IC と組み合わせて使用することを目的とした内部ダイオード (PN 接合) が搭載されています。DMD の温度ダイオード ピンから TMP411A-Q1 への PCB パターンはノイズの影響を受けやすくなります。具体的な配線推奨事項については、『[TMP411±1°C N 係数および直列抵抗補正付きリモートおよびローカル温度センサ』データシートを参照してください。](#)

## 10 デバイスおよびドキュメントのサポート

### 10.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インストルメンツの出版物は、単独またはテキサス・インストルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 10.2 デバイス サポート

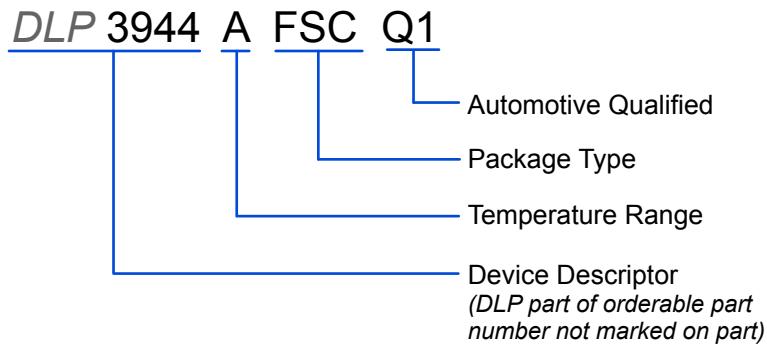

#### 10.2.1 デバイスの命名規則

図 10-1. 部品番号の説明

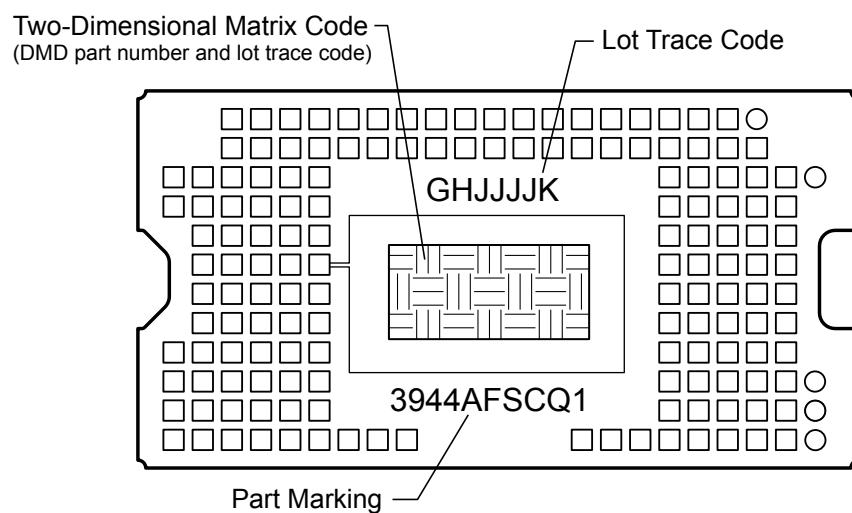

#### 10.2.2 デバイスのマーキング

デバイスのマーキングには、人間が読める情報と2次元マトリクスコードの両方を使用しています。人間が読める情報は図 10-2 に示されており、判読可能な文字列 GHJJJK 3944AFSCQ1 が含まれています。GHJJJK はロットのトレースコードで、3944AFSCQ1 はデバイスのマーキングです。

例: GHJJJK 3944AFSCQ1

図 10-2. DMD のマーキング位置

## 10.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

## 10.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

DLP® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 10.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 10.6 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 11 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付            | 改訂 | 注      |

|---------------|----|--------|

| December 2025 | *  | 初版リリース |

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins   | Package qty   Carrier    | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|------------------|--------------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| XDLP3944AFSCQ1        | Active        | Preproduction        | CLGA (FSC)   154 | 96   JEDEC<br>TRAY (5+1) | -           | Call TI                              | Call TI                           | -40 to 105   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月