# DLP651NE 0.65 インチ 1080p デジタルマイクロミラー デバイス

## 1 特長

- 対角 0.65 インチのマイクロミラー アレイ

- ディスプレイ解像度: 1080p (1920 × 1080)

- 7.6 $\mu\text{m}$  のマイクロミラー ピッチ

- マイクロミラー傾斜角:  $\pm 12^\circ$  (平面に対して)

- コーナー照明

- 高速シリアルインターフェイス (High-Speed Serial Interface、HSSI) 入力データバス

- 最大 240Hz の 1080p (フル HD) をサポート

- DLPC7530** ディスプレイコントローラ、**DLPA100** パワー マネージメント、およびモータドライバ IC によってサポートされたレーザー蛍光 / LED / RGB レーザー / ランプ動作

## 2 アプリケーション

- レーザー TV

- スマートプロジェクトタ

- 企業向けプロジェクトタ

## 3 説明

DLP651NE デジタルマイクロミラー デバイス (DMD) は、デジタル制御型の MEMS (micro-electromechanical system) 空間光変調器 (SLM) で、色鮮やかな 1080p ディスプレイシステムを実現します。DLP® 製品の 0.65 インチ 1080p チップセットは、DMD、または **DLPC7530** ディスプレイコントローラ、**DLPA100** パワーおよびモータドライバで構成されています。このコンパクトなチップセットは、小型の 1080p ディスプレイを実現する完全なシステムソリューションを提供します。

DMD のエコシステムに、設計期間の短縮に役立つ定評あるリソースが用意されています。承認済みの光学モジュール メーカーやサード パーティー プロバイダを探すには、**DLP® Products サード パーティー プロバイダ検索ツール**をご利用ください。

DMD を使用して設計を始める方法の詳細については、『[TI の DLP ディスプレイテクノロジーを使用した設計の開始](#)』をご覧ください。

### 製品情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ<br>サイズ    |

|----------|----------------------|-----------------|

| DLP651NE | FYP(149)             | 32.2mm × 22.3mm |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

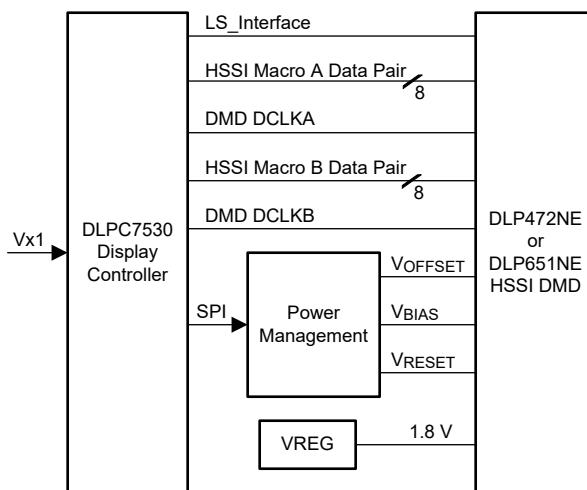

アプリケーション概略図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                   |           |                                            |           |

|-----------------------------------|-----------|--------------------------------------------|-----------|

| <b>1 特長</b>                       | <b>1</b>  | 6.9 マイクロミラーのランデッド オン / ランデッド オフ デューティ サイクル | 27        |

| <b>2 アプリケーション</b>                 | <b>1</b>  | <b>7 アプリケーションと実装</b>                       | <b>30</b> |

| <b>3 説明</b>                       | <b>1</b>  | 7.1 アプリケーション情報                             | 30        |

| <b>4 ピン構成および機能</b>                | <b>3</b>  | 7.2 代表的なアプリケーション                           | 30        |

| <b>5 仕様</b>                       | <b>6</b>  | 7.3 溫度センサ ダイオード                            | 32        |

| 5.1 絶対最大定格                        | 6         | <b>8 電源に関する推奨事項</b>                        | <b>34</b> |

| 5.2 保存条件                          | 6         | 8.1 電源シーケンス要件                              | 34        |

| 5.3 ESD 定格                        | 7         | 8.2 DMD 電源のパワーアップ手順                        | 34        |

| 5.4 推奨動作条件                        | 7         | 8.3 DMD 電源のパワーダウン手順                        | 34        |

| 5.5 熱に関する情報                       | 9         | <b>9 レイアウト</b>                             | <b>36</b> |

| 5.6 電気的特性                         | 10        | 9.1 レイアウトのガイドライン                           | 36        |

| 5.7 スイッチング特性                      | 11        | 9.2 インピーダンス要件                              | 36        |

| 5.8 タイミング要件                       | 11        | 9.3 基板面                                    | 36        |

| 5.9 システム実装インターフェイスの荷重             | 15        | 9.4 パターン幅、間隔                               | 37        |

| 5.10 マイクロミラー アレイの物理特性             | 16        | 9.5 電源                                     | 37        |

| 5.11 マイクロミラー アレイの光学特性             | 18        | 9.6 パターン長のマッピングの推奨                         | 37        |

| 5.12 ウィンドウの特性                     | 19        | <b>10 デバイスおよびドキュメントのサポート</b>               | <b>39</b> |

| 5.13 チップセットコンポーネントの使用方法の仕様        | 19        | 10.1 サード・パーティ製品に関する免責事項                    | 39        |

| <b>6 詳細説明</b>                     | <b>20</b> | 10.2 デバイス サポート                             | 39        |

| 6.1 概要                            | 20        | 10.3 ドキュメントのサポート                           | 39        |

| 6.2 機能ブロック図                       | 21        | 10.4 ドキュメントの更新通知を受け取る方法                    | 40        |

| 6.3 機能説明                          | 22        | 10.5 サポート・リソース                             | 40        |

| 6.4 デバイスの機能モード                    | 22        | 10.6 商標                                    | 40        |

| 6.5 光学インターフェイスおよびシステムの画質に関する検討事項  | 22        | 10.7 静電気放電に関する注意事項                         | 40        |

| 6.6 マイクロミラー アレイ温度の計算              | 23        | 10.8 用語集                                   | 40        |

| 6.7 マイクロミラーの電力密度の計算               | 24        | <b>11 改訂履歴</b>                             | <b>40</b> |

| 6.8 ウィンドウ アパーチャイルミネーション オーバーフィル計算 | 26        | <b>12 メカニカル、パッケージ、および注文情報</b>              | <b>42</b> |

|                                   |           | 12.1 付録:パッケージ オプション                        | 43        |

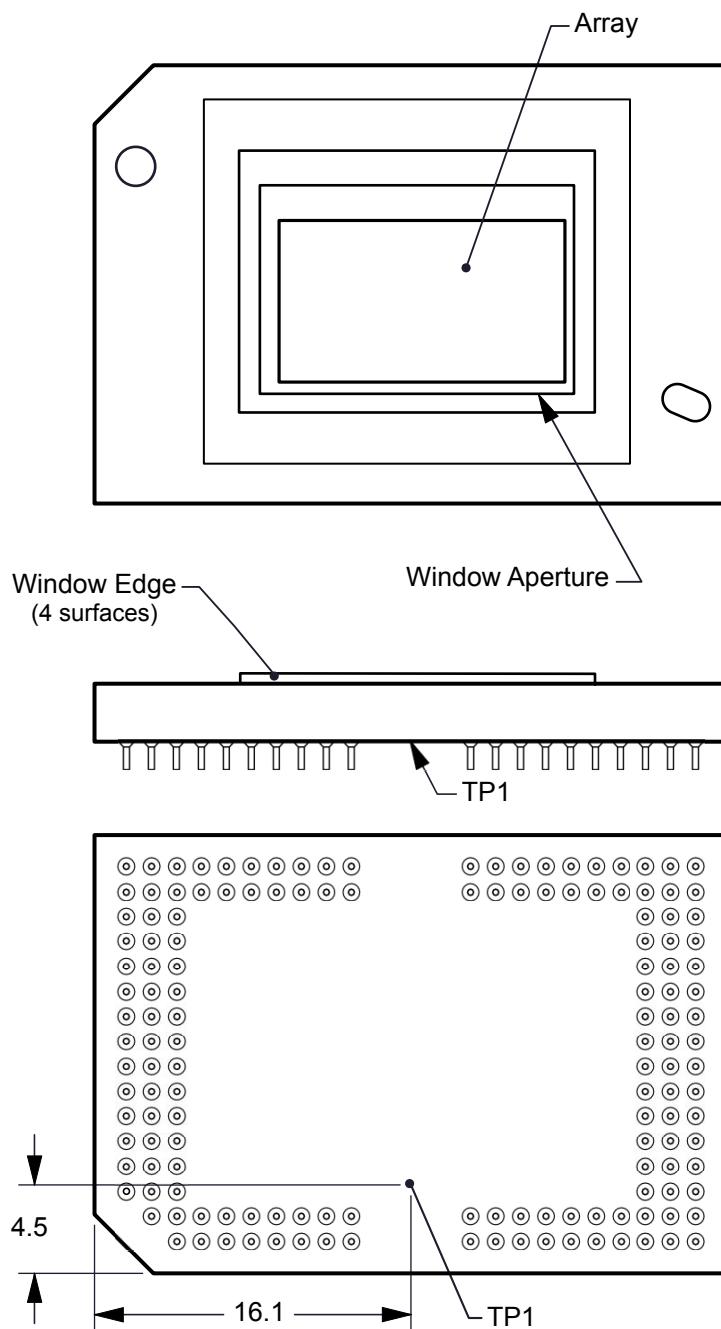

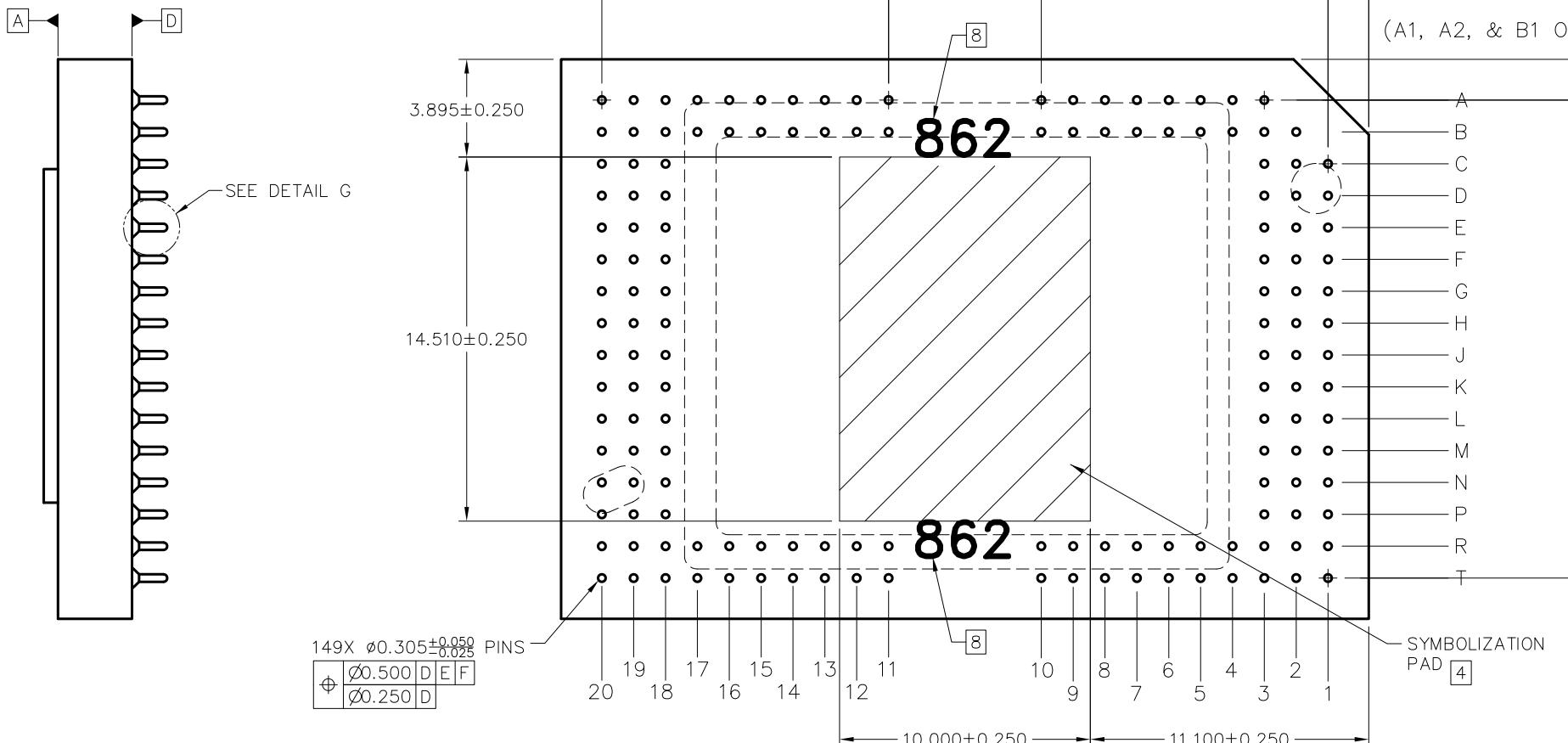

## 4 ピン構成および機能

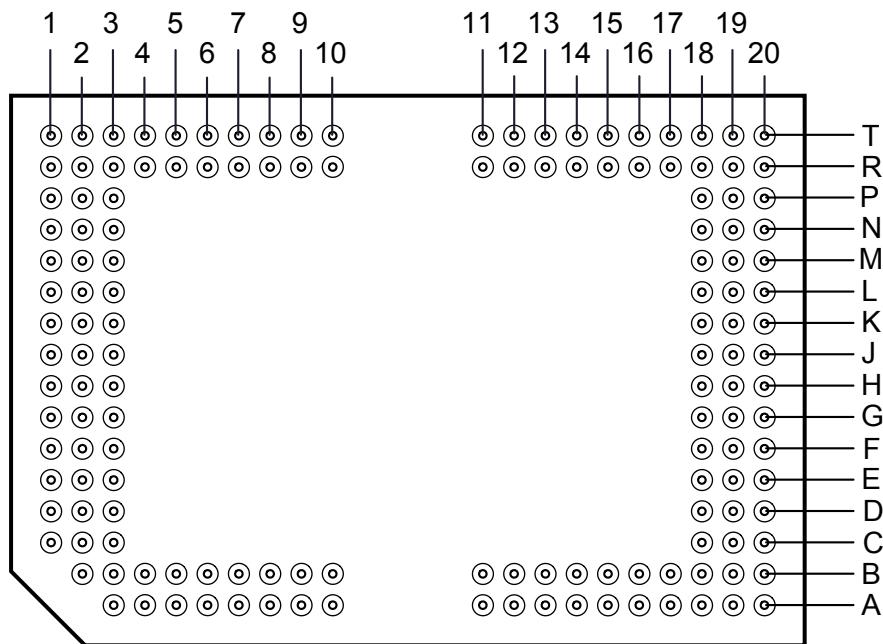

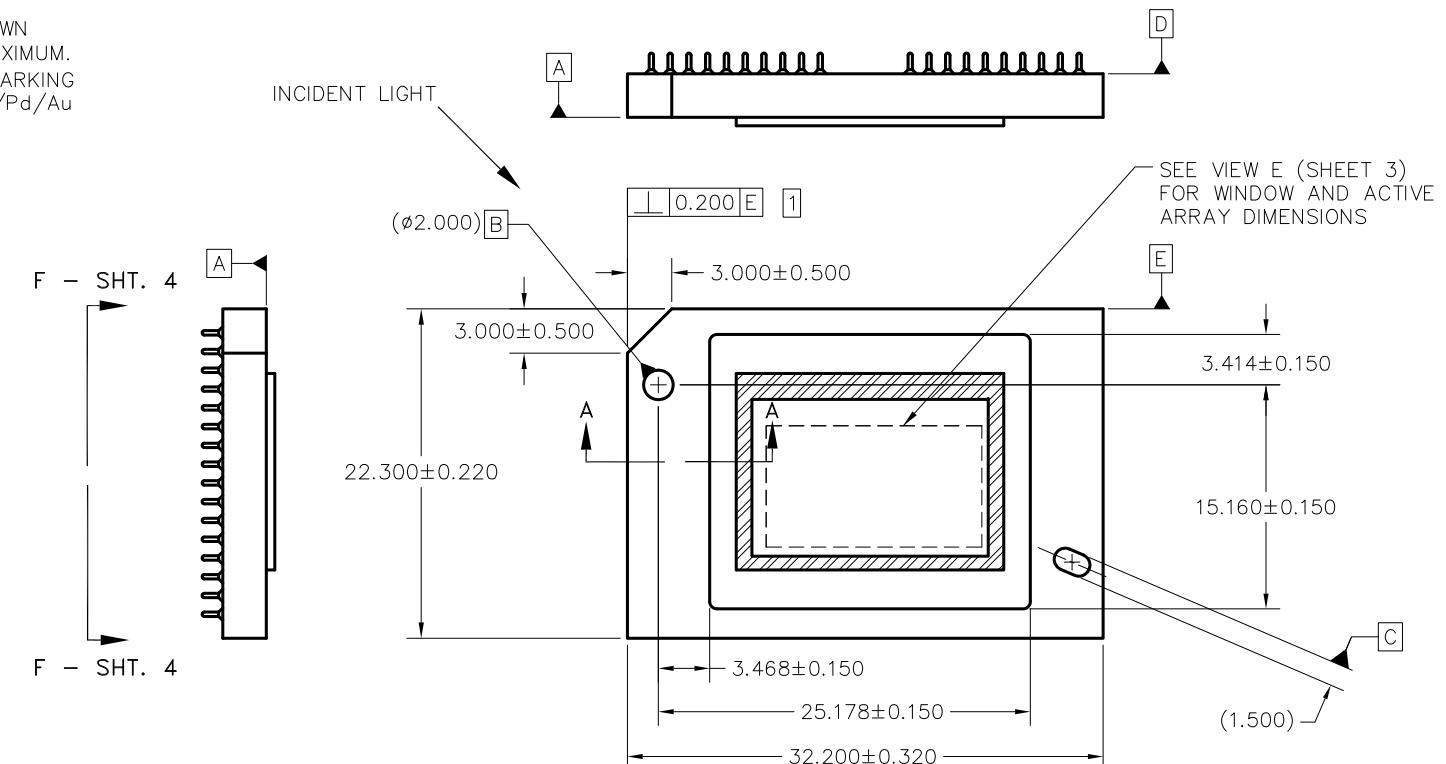

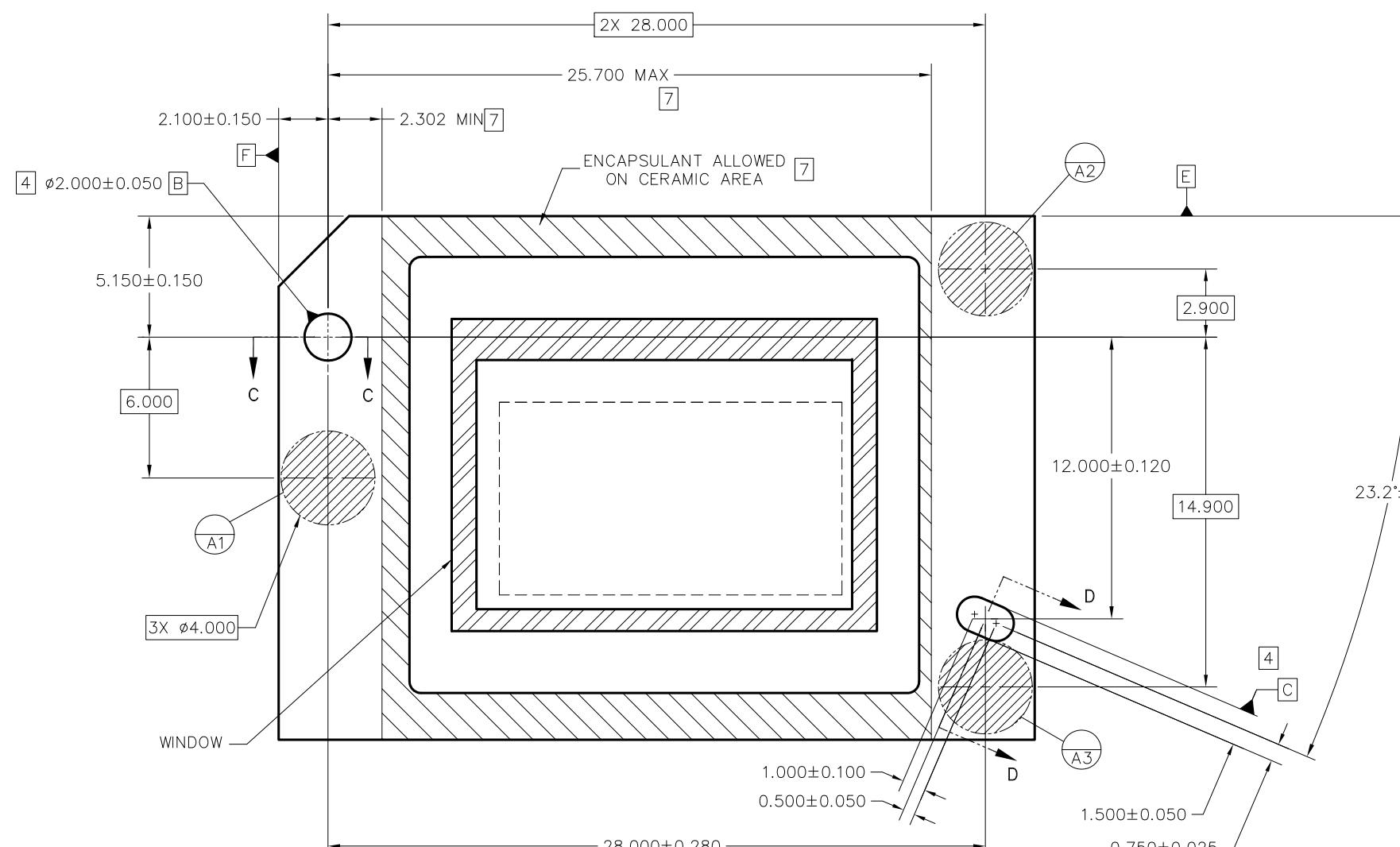

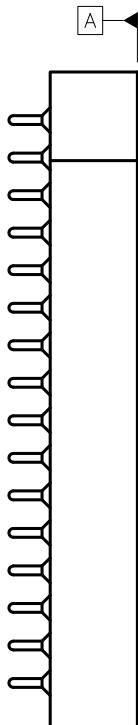

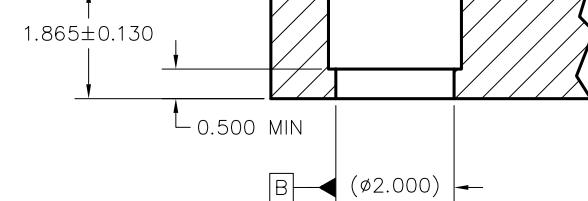

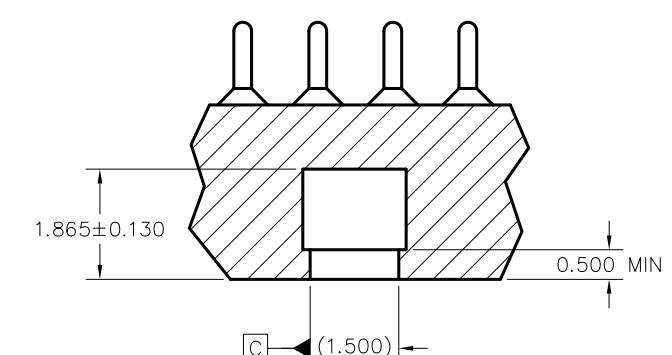

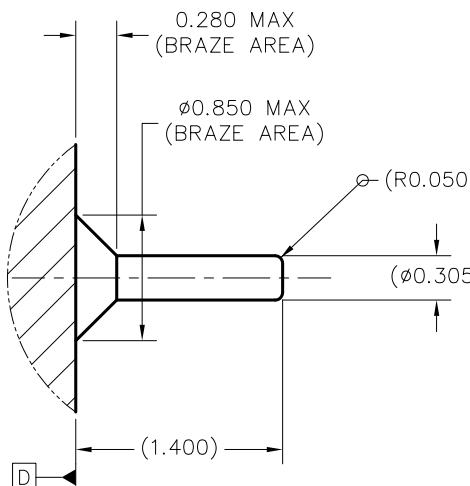

図 4-1. FYP パッケージ 149 ピン CPGA 底面図

表 4-1. ピンの機能

| ピン       |        | タイプ <sup>(1)</sup> | ピンの説明           | パターン長<br>(mm) |

|----------|--------|--------------------|-----------------|---------------|

| 名称       | パッド ID |                    |                 |               |

| D_AP (0) | J1     |                    | 高速差動データペアレーン A0 | 18.09088      |

| D_AN (0) | H1     |                    | 高速差動データペアレーン A0 | 18.0916       |

| D_AP (1) | G1     |                    | 高速差動データペアレーン A1 | 18.11696      |

| D_AN (1) | F1     |                    | 高速差動データペアレーン A1 | 18.11641      |

| D_AP (2) | A3     |                    | 高速差動データペアレーン A2 | 11.11822      |

| D_AN (2) | A4     |                    | 高速差動データペアレーン A2 | 11.11745      |

| D_AP (3) | D2     |                    | 高速差動データペアレーン A3 | 12.04461      |

| D_AN (3) | C2     |                    | 高速差動データペアレーン A3 | 12.04491      |

| D_AP (4) | F2     |                    | 高速差動データペアレーン A4 | 15.1345       |

| D_AN (4) | E2     |                    | 高速差動データペアレーン A4 | 15.13457      |

| D_AP (5) | A5     |                    | 高速差動データペアレーン A5 | 12.80888      |

| D_AN (5) | A6     |                    | 高速差動データペアレーン A5 | 12.80825      |

| D_AP (6) | A7     |                    | 高速差動データペアレーン A6 | 6.34763       |

| D_AN (6) | A8     |                    | 高速差動データペアレーン A6 | 6.34706       |

| D_AP (7) | A9     |                    | 高速差動データペアレーン A7 | 4.45653       |

| D_AN (7) | A10    |                    | 高速差動データペアレーン A7 | 4.45875       |

| DCLK_AP  | C1     |                    | 高速差動クロック A      | 15.08029      |

| DCLK_AN  | D1     |                    | 高速差動クロック A      | 15.07977      |

| D_BP (0) | A11    |                    | 高速差動データペアレーン B0 | 4.06642       |

| D_BN (0) | A12    |                    | 高速差動データペアレーン B0 | 4.06697       |

表 4-1. ピンの機能 (続き)

| ピン               |                                                                                                                     | タイプ <sup>(1)</sup> | ピンの説明                         | パターン長<br>(mm) |

|------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|---------------|

| 名称               | パッド ID                                                                                                              |                    |                               |               |

| D_BP (1)         | A13                                                                                                                 |                    | 高速差動データペアレーン B1               | 6.42676       |

| D_BN (1)         | A14                                                                                                                 |                    | 高速差動データペアレーン B1               | 6.42716       |

| D_BP (2)         | A15                                                                                                                 |                    | 高速差動データペアレーン B2               | 11.90485      |

| D_BN (2)         | A16                                                                                                                 |                    | 高速差動データペアレーン B2               | 11.90509      |

| D_BP (3)         | A18                                                                                                                 |                    | 高速差動データペアレーン B3               | 13.80223      |

| D_BN (3)         | A19                                                                                                                 |                    | 高速差動データペアレーン B3               | 13.80269      |

| D_BP (4)         | D19                                                                                                                 |                    | 高速差動データペアレーン B4               | 12.45294      |

| D_BN (4)         | C19                                                                                                                 |                    | 高速差動データペアレーン B4               | 12.45252      |

| D_BP (5)         | H20                                                                                                                 |                    | 高速差動データペアレーン B5               | 15.7909       |

| D_BN (5)         | J20                                                                                                                 |                    | 高速差動データペアレーン B5               | 15.79026      |

| D_BP (6)         | D20                                                                                                                 |                    | 高速差動データペアレーン B6               | 11.02899      |

| D_BN (6)         | E20                                                                                                                 |                    | 高速差動データペアレーン B6               | 11.02947      |

| D_BP (7)         | F20                                                                                                                 |                    | 高速差動データペアレーン B7               | 14.7517       |

| D_BN (7)         | G20                                                                                                                 |                    | 高速差動データペアレーン B7               | 14.75085      |

| DCLK_BP          | B17                                                                                                                 |                    | 高速差動クロック B                    | 9.17864       |

| DCLK_BN          | B18                                                                                                                 |                    | 高速差動クロック B                    | 9.17821       |

| LS_WDATA_P       | T10                                                                                                                 |                    | LVDS データ                      | 11.27905      |

| LS_WDATA_N       | R11                                                                                                                 |                    | LVDS データ                      | 6.76474       |

| LS_CLK_P         | R9                                                                                                                  |                    | LVDS CLK                      | 13.5461       |

| LS_CLK_N         | R10                                                                                                                 |                    | LVDS CLK                      | 12.56934      |

| LS_RDATA_A_BISTA | T13                                                                                                                 | O                  | LVC MOS 出力                    | 3.12045       |

| BIST_B           | T12                                                                                                                 | O                  | LVC MOS 出力                    | 5.63628       |

| AMUX_OUT         | B20                                                                                                                 | O                  | アナログ テスト マルチプレクサ              | 9.3849        |

| DMUX_OUT         | R14                                                                                                                 | O                  | デジタル テスト マルチプレクサ              | 3.85333       |

| DMD_DEN_ARSTZ    | T11                                                                                                                 |                    | ARSTZ                         | 5.86593       |

| TEMP_N           | R8                                                                                                                  |                    | 温度ダイオード N                     | 14.63792      |

| TEMP_P           | R7                                                                                                                  |                    | 温度ダイオード P                     | 15.93219      |

| VDD              | B7、B13、<br>C18、E3、H3、<br>J2、K3、L2、<br>L19、M1、M2、<br>N3、N19、P2、<br>P18、R3、R5、<br>R12、R17、<br>R19、T2、T4、<br>T6、T8、T18 | P                  | デジタル コア電源電圧                   | 平面            |

| VDDA             | B4、B9、B11、<br>B16、C20、<br>D3、E18、G2、<br>G19                                                                         | P                  | HSSI 電源                       | 平面            |

| VRESET           | B3、R1                                                                                                               | P                  | マイクロミラー リセット信号の負のバイアスに対する電源電圧 | 平面            |

| VBIAS            | E1、P1                                                                                                               | P                  | マイクロミラー リセット信号の正のバイアスに対する電源電圧 | 平面            |

| VOFFSET          | A20、B2、T1、<br>T20                                                                                                   | P                  | HVC MOS ロジックの電源電圧、ロジック レベルを昇圧 | 平面            |

**表 4-1. ピンの機能 (続き)**

| ピン   |                                                                                                                                           | タイプ <sup>(1)</sup> | ピンの説明 | パターン長<br>(mm) |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|---------------|

| 名称   | パッド ID                                                                                                                                    |                    |       |               |

| VSS  | A17、B6、<br>B10、B14、<br>D18、F3、<br>F19、J3、K2、<br>K19、L1、L3、<br>M3、N2、N18、<br>N20、P3、<br>P20、R2、R4、<br>R6、R13、<br>R20、T5、T7、<br>T16、T17、T19 | G                  | グランド  | 平面            |

| VSSA | B5、B8、B12、<br>B15、B19、<br>C3、E19、G3、<br>H2、H19、K1、<br>N1、P19、<br>R18、T3、T9                                                                | G                  | グランド  | 平面            |

| N/C  | R15、T14、<br>T15、R16、<br>H18、J18、<br>G18、J19、<br>F18、K20、<br>K18、M19、<br>L20、M18、<br>L18、M20                                               |                    | 無接続   |               |

(1) I = 入力、O = 出力、P = 電源、G = グランド、NC = 未接続

## 5 仕様

### 5.1 絶対最大定格

「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

| パラメータ名                                  | 説明                                                             | 最小値  | 最大値              | 単位  |

|-----------------------------------------|----------------------------------------------------------------|------|------------------|-----|

| <b>電源電圧</b>                             |                                                                |      |                  |     |

| V <sub>DD</sub>                         | LVC MOS コアロジックと LVC MOS 低速インターフェイス (LSIF) の電源電圧 <sup>(1)</sup> | -0.5 | 2.3              | V   |

| V <sub>DDA</sub>                        | 高速シリアルインターフェイス (HSSI) レシーバの電源電圧 <sup>(1)</sup>                 | -0.3 | 2.2              | V   |

| V <sub>OFFSET</sub>                     | HVC MOS およびマイクロミラー電極の電源電圧 <sup>(1) (2)</sup>                   | -0.5 | 11               | V   |

| V <sub>BIAS</sub>                       | マイクロミラー電極の電源電圧 <sup>(1)</sup>                                  | -0.5 | 17               | V   |

| V <sub>RESET</sub>                      | マイクロミラー電極の電源電圧 <sup>(1)</sup>                                  | -13  | 0.5              | V   |

| V <sub>DDA</sub> – V <sub>DD</sub>      | 電源電圧差 (絶対値) <sup>(3)</sup>                                     |      | 0.3              | V   |

| V <sub>BIAS</sub> – V <sub>OFFSET</sub> | 電源電圧差 (絶対値) <sup>(4)</sup>                                     |      | 11               | V   |

| V <sub>BIAS</sub> – V <sub>RESET</sub>  | 電源電圧差 (絶対値) <sup>(5)</sup>                                     |      | 30               | V   |

| <b>入力電圧</b>                             |                                                                |      |                  |     |

|                                         | その他の入力の入力電圧 - LSIF および LVC MOS <sup>(1)</sup>                  | -0.5 | 2.45             | V   |

|                                         | その他の入力の入力電圧 - HSSI <sup>(1) (6)</sup>                          | -0.2 | V <sub>DDA</sub> | V   |

| <b>低速インターフェイス (LSIF)</b>                |                                                                |      |                  |     |

| f <sub>CLOCK</sub>                      | LSIF クロック周波数 (LS_CLK)                                          |      | 130              | MHz |

| V <sub>ID</sub>                         | LSIF 差動入力電圧の振幅 <sup>(6)</sup>                                  |      | 810              | mV  |

| I <sub>ID</sub>                         | LSIF 差動入力電流 <sup>(7)</sup>                                     |      | 10               | mA  |

| <b>高速シリアルインターフェイス (HSSI)</b>            |                                                                |      |                  |     |

| f <sub>CLOCK</sub>                      | HSSI クロック周波数 (DCLK)                                            |      | 1.65             | GHz |

| V <sub>ID</sub>                         | HSSI 差動入力電圧振幅データレーン <sup>(6)</sup>                             |      | 700              | mV  |

| V <sub>ID</sub>                         | HSSI 差動入力電圧振幅クロックレー <sup>(6)</sup>                             |      | 700              | mV  |

| <b>環境</b>                               |                                                                |      |                  |     |

| T <sub>ARRAY</sub>                      | 温度、動作時 <sup>(8)</sup>                                          | 0    | 90               | °C  |

| T <sub>ARRAY</sub>                      | 温度、非動作時 <sup>(8)</sup>                                         | -40  | 90               | °C  |

| T <sub>DP</sub>                         | 露点温度、動作時および非動作時 (結露なし)                                         |      | 81               | °C  |

- (1) すべての電圧値は、グランド端末 (V<sub>SS</sub>) を基準としたものです。DMD を適切に動作させるには、以下に示す必要な電源を接続する必要があります: V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>OFFSET</sub>, V<sub>BIAS</sub> および V<sub>RESET</sub>。すべての V<sub>SS</sub> 接続も必要です。

- (2) V<sub>OFFSET</sub> 電源過渡電圧は、規定電圧内に収まる必要があります。

- (3) V<sub>DDA</sub> と V<sub>DD</sub> の間の許容される絶対電圧差を超えると、過剰な電流が流れる場合があります。

- (4) V<sub>BIAS</sub> と V<sub>OFFSET</sub> の間の許容される絶対電圧差を超えると、過剰な電流が流れる場合があります。

- (5) V<sub>BIAS</sub> と V<sub>RESET</sub> の間の許容される絶対電圧差を超えると、過剰な電流が流れる場合があります。

- (6) この最大入力電圧定格は、差動ペアの各入力電圧が同じ電位のときに適用されます。LVDS と Sub-HSSI 差動入力は、指定限界値を超えないようにする必要があります。さもなければ、内部終端抵抗が損傷する可能性があります。

- (7) 差動入力は、指定限界値を超えないようにする必要があります。さもなければ、内部終端抵抗が損傷する場合があります。この仕様は、高速シリアルインターフェイス(HSSI)と低速インターフェイス (LSI) の両方に適用されます。

- (8) アレイ温度を直接測定することはできず、テストポイント (TP1) で測定された温度とマイクロミラー アレイ温度計算を使用したパッケージの熱抵抗から、解析的に計算する必要があります。

### 5.2 保存条件

部品としての DMD、またはシステムで動作していない DMD に適用できます。

| 記号               | パラメータ     | 最小値 | 最大値 | 単位 |

|------------------|-----------|-----|-----|----|

| T <sub>DMD</sub> | DMD の保存温度 | -40 | 80  | °C |

## 5.2 保存条件 (続き)

部品としての DMD、またはシステムで動作していない DMD に適用できます。

| 記号           | パラメータ                           | 最小値 | 最大値 | 単位 |

|--------------|---------------------------------|-----|-----|----|

| $T_{DP-AVG}$ | 平均露点温度 (結露なし) <sup>(1)</sup>    |     | 28  | °C |

| $T_{DP-ELR}$ | 高温の露点温度範囲、(結露なし) <sup>(2)</sup> | 28  | 36  | °C |

| $CT_{ELR}$   | 高温の露点温度範囲における累積時間               |     | 24  | 毎月 |

(1) デバイスが「高温の露点温度範囲」にない経時的な平均値 (保存や動作を含む)。

(2) 保存時および動作時の高温範囲で露点温度への曝露は、 $CT_{ELR}$  の合計累積時間未満に制限する必要があります。

## 5.3 ESD 定格

| 記号          | パラメータ | 説明                                                       | 値     | 単位 |

|-------------|-------|----------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電  | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | ±2000 | V  |

| $V_{(ESD)}$ | 静電放電  | 荷電デバイス モデル (CDM), JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup> | ±500  | V  |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.4 推奨動作条件

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ名                        |                                              | 最小値            | 公称値            | 最大値   | 単位  |

|-------------------------------|----------------------------------------------|----------------|----------------|-------|-----|

| <b>電源電圧<sup>(2) (3)</sup></b> |                                              |                |                |       |     |

| $V_{DD}$                      | LVC MOS コア ロジックおよび低速インターフェイス (LSIF) のための電源電圧 | 1.71           | 1.8            | 1.95  | V   |

| $V_{DDA}$                     | 高速シリアル インターフェイス (HSSI) レシーバの電源電圧             | 1.71           | 1.8            | 1.95  | V   |

| $V_{OFFSET}$                  | HVC MOS およびマイクロミラー電極の電源電圧 <sup>(4)</sup>     | 9.5            | 10             | 10.5  | V   |

| $V_{BIAS}$                    | マイクロミラー電極の電源電圧                               | 15.5           | 16             | 16.5  | V   |

| $V_{RESET}$                   | マイクロミラー電極の電源電圧                               | -12.5          | -12            | -11.5 | V   |

| $ V_{DDA} - V_{DD} $          | 電源電圧のデルタ、絶対値 <sup>(5)</sup>                  |                | 0.3            |       | V   |

| $ V_{BIAS} - V_{OFFSET} $     | 電源電圧のデルタ、絶対値 <sup>(6)</sup>                  |                | 10.5           |       | V   |

| $ V_{BIAS} - V_{RESET} $      | 電源電圧のデルタ、絶対値                                 |                | 29             |       | V   |

| <b>LVC MOS 入力</b>             |                                              |                |                |       |     |

| $V_{IH}$                      | 高レベル入力電圧 <sup>(7)</sup>                      | 0.7 × $V_{DD}$ |                |       | V   |

| $V_{IL}$                      | 低レベル入力電圧 <sup>(7)</sup>                      |                | 0.3 × $V_{DD}$ |       | V   |

| <b>低速インターフェイス (LSIF)</b>      |                                              |                |                |       |     |

| $f_{CLOCK}$                   | LSIF クロック周波数 ( $LS\_CLK$ ) <sup>(8)</sup>    | 108            | 120            | 130   | MHz |

| $DCD_{IN}$                    | LSIF デューティ サイクル歪み ( $LS\_CLK$ )              |                | 44%            | 56%   |     |

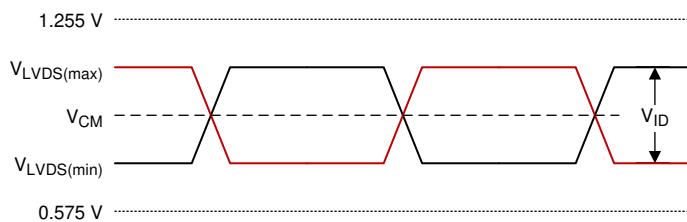

| $ V_{ID} $                    | LSIF 差動入力電圧の振幅 <sup>(8)</sup>                | 150            | 350            | 440   | mV  |

| $V_{LVDS}$                    | LSIF 電圧 <sup>(8)</sup>                       | 575            |                | 1520  | mV  |

| $V_{CM}$                      | 同相電圧 <sup>(8)</sup>                          | 700            | 900            | 1300  | mV  |

| $Z_{LINE}$                    | ライン差動インピーダンス (PWB / パターン)                    | 90             | 100            | 110   | Ω   |

| $Z_{IN}$                      | 内部差動終端抵抗                                     | 80             | 100            | 120   | Ω   |

| <b>高速シリアル インターフェイス (HSSI)</b> |                                              |                |                |       |     |

| $f_{CLOCK}$                   | HSSI クロック周波数 (DCLK) <sup>(9)</sup>           | 1.2            |                | 1.6   | GHz |

| $DCD_{IN}$                    | HSSI デューティ サイクル歪み (DCLK)                     |                | 44%            | 50%   | 56% |

| $ V_{ID}  Data$               | HSSI 差動入力電圧振幅データレーン <sup>(9)</sup>           | 100            |                | 600   | mV  |

## 5.4 推奨動作条件 (続き)

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ名                           |                                                                | 最小値 | 公称値   | 最大値 | 単位                 |

|----------------------------------|----------------------------------------------------------------|-----|-------|-----|--------------------|

| V <sub>ID</sub>   CLK            | HSSI 差動入力電圧振幅クロックレー <sup>(9)</sup>                             | 295 | 600   | 600 | mV                 |

| V <sub>CM<sub>DC</sub></sub> データ | 入力同相電圧 (DC) データレーン <sup>(9)</sup>                              | 200 | 600   | 800 | mV                 |

| V <sub>CM<sub>DC</sub></sub> CLK | 入力同相電圧 (DC) クロックレーン <sup>(9)</sup>                             | 200 | 600   | 800 | mV                 |

| V <sub>CM<sub>ACp-p</sub></sub>  | データレーンおよびクロックレーンの同相モード電圧における AC ピークツーピーク (リップル) <sup>(9)</sup> |     |       | 100 | mV                 |

| Z <sub>LINE</sub>                | ライン差動インピーダンス (PWB / パターン)                                      |     | 100   |     | Ω                  |

| Z <sub>IN</sub>                  | 内部差動終端抵抗 (R <sub>Xterm</sub> )                                 | 80  | 100   | 120 | Ω                  |

| <b>環境</b>                        |                                                                |     |       |     |                    |

| T <sub>ARRAY</sub>               | アレイ温度、長期動作 <sup>(10) (11) (12) (13)</sup>                      | 10  | 40~70 |     | °C                 |

|                                  | アレイ温度、短期動作、最大 500 時間 <sup>(11) (14)</sup>                      | 0   | 10    |     | °C                 |

| T <sub>DP-AVG</sub>              | 平均露点温度 (結露なし) <sup>(15)</sup>                                  |     | 28    |     | °C                 |

| T <sub>DP-ELR</sub>              | 高温の露点温度範囲 (結露なし) <sup>(16)</sup>                               | 28  | 36    |     | °C                 |

| C <sub>T<sub>ELR</sub></sub>     | 高温の露点温度範囲における累積時間                                              |     | 24    |     | 毎月                 |

| Q <sub>AP-ILL</sub>              | ウインドウ開口部照明オーバーフィル <sup>(17) (18)</sup>                         |     | 17    |     | W/cm <sup>2</sup>  |

| <b>ランプ点灯</b>                     |                                                                |     |       |     |                    |

| ILL <sub>UV</sub>                | 照明、波長 395nm 未満 <sup>(10)</sup>                                 |     | 0.68  | 2   | mW/cm <sup>2</sup> |

| ILL <sub>VIS</sub>               | 395nm ~ 800nm の範囲の照明波長                                         |     | 29.3  |     | W/cm <sup>2</sup>  |

| ILL <sub>IR</sub>                | 照明、波長 800nm 超過                                                 |     | 10    |     | mW/cm <sup>2</sup> |

| <b>ソリッドステート点灯</b>                |                                                                |     |       |     |                    |

| ILL <sub>UV</sub>                | 照明、波長 410nm 未満 <sup>(10)</sup>                                 |     | 3     |     | mW/cm <sup>2</sup> |

| ILL <sub>VIS</sub>               | 410nm ~ 800nm の範囲の照明波長                                         |     | 34.7  |     | W/cm <sup>2</sup>  |

| ILL <sub>IR</sub>                | 照明、波長 800nm 超過                                                 |     | 10    |     | mW/cm <sup>2</sup> |

- (1) 「推奨動作条件」は、最終製品に DMD を取り付けた後に適用されます。

- (2) DMD を動作させるには、すべての電源接続が必要です。V<sub>DD</sub>、V<sub>D<sub>DA</sub></sub>、V<sub>O<sub>F<sub>SET</sub></sub></sub>、V<sub>B<sub>I<sub>A<sub>S</sub></sub></sub></sub> および V<sub>R<sub>E<sub>S<sub>E<sub>T</sub></sub></sub></sub>。DMD を動作させるには、すべての V<sub>SS</sub> 接続が必要です。</sub>

- (3) すべての電圧値は、V<sub>SS</sub> グランドピンを基準としたものです。

- (4) V<sub>O<sub>F<sub>SET</sub></sub></sub> 電源過渡電圧は、規定最大電圧内に収まる必要があります。

- (5) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>D<sub>DA</sub></sub> - V<sub>DD</sub>| は、指定限界値よりも小さい必要があります。

- (6) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>B<sub>I<sub>A<sub>S</sub></sub></sub></sub> - V<sub>O<sub>F<sub>SET</sub></sub></sub>| は、指定限界値よりも小さい必要があります。

- (7) LVC MOS 入力ピンは DMD\_DEN\_ARSTZ です。

- (8) タイミング要件の低速インターフェイス (LSIF) のタイミング要件を参照してください。

- (9) タイミング要件の高速シリアルインターフェイス (HSSI) のタイミング要件を参照してください。

- (10) DMD を最大推奨動作条件の温度および UV 照明に同時に曝露すると、デバイスの寿命が短くなります。

- (11) 図 6-1 に示されているように、アレイ温度を直接測定することはできず、テストポイント (TP1) で測定された温度とマイクロミラー アレイ温度計算を使用したパッケージの熱抵抗から、解析的に計算する必要があります。

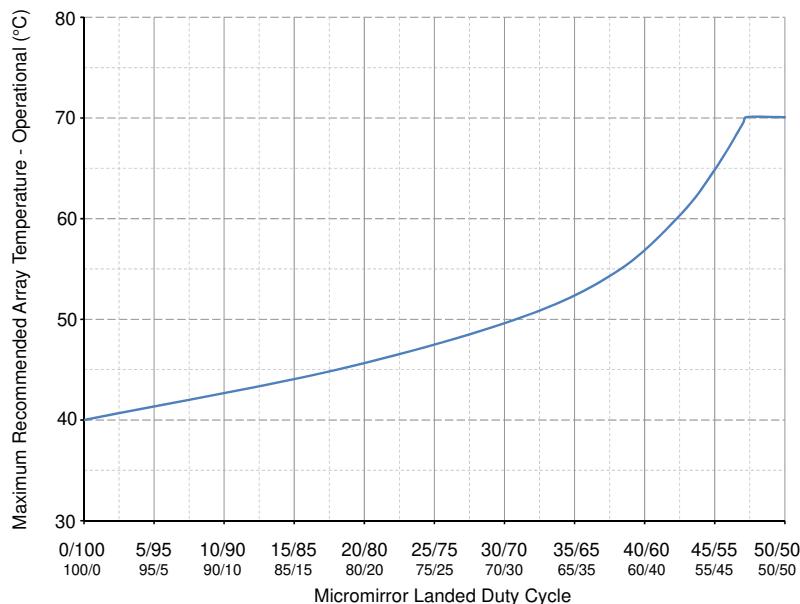

- (12) 図 5-1 に従って、最大動作アレイ温度は、最終アプリケーションにおいて DMD が受けるマイクロミラーの着地デューティサイクルに基づいてディレーティングする必要があります。マイクロミラーのランデッドデューティサイクルの定義については、『マイクロミラーのランデッドデューティサイクル』を参照してください。

- (13) 長期は、デバイスの使用可能寿命と定義されます。

- (14) 短期は、デバイスの有効寿命全体にわたる合計累積時間です。

- (15) デバイスが「高温の露点温度範囲」にない経時的な平均値(保存や動作を含む)。

- (16) 保存時および動作時の高温範囲で露点温度への曝露は、C<sub>T<sub>ELR</sub></sub> の合計累積時間未満に制限する必要があります。

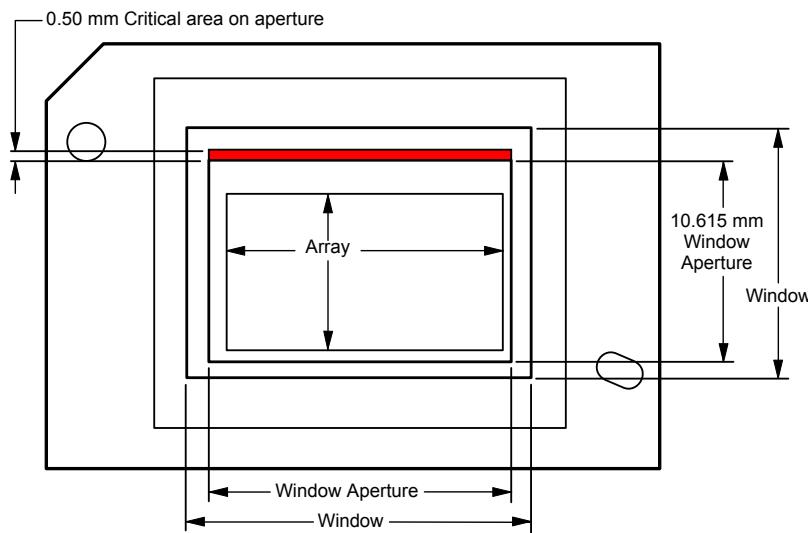

- (17) DMD のアクティブ領域は、DMD デバイスアセンブリの構造を通常の視界から覆い隠す、DMD ウィンドウ面の内側にある開口部で囲まれています。開口部は、いくつかの光学条件を想定した大きさになっています。アクティブ アレイの外側を照らすオーバーフィル光は散乱し、DMD を使用する最終アプリケーションの性能に悪影響を及ぼす可能性があります。照明光学システムは、アクティブ アレイ外での光束の入射を最小限に抑えるように設計する必要があります。システムの光学アーキテクチャとアセンブリ許容誤差によっては、アクティブ アレイの外側のオーバーフィル光量がシステム性能の劣化を引き起こす可能性があります。

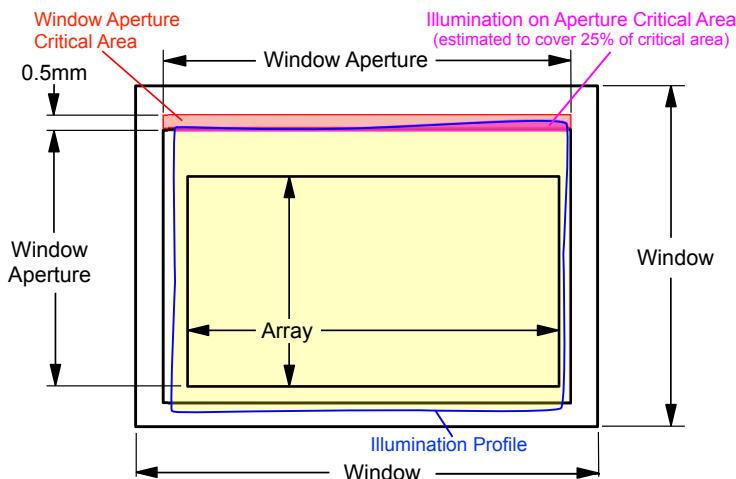

- (18) 図 5-2 の赤色の領域に適用されます。

図 5-1. 推奨最大アレイ温度—ディレーティング曲線

図 5-2. イルミネーション オーバーフィル ダイアグラム - クリティカルエリア

## 5.5 热に関する情報

| 熱評価基準                                           | DLP651NE  |        | 単位 |  |

|-------------------------------------------------|-----------|--------|----|--|

|                                                 | FYP パッケージ | 149 ピン |    |  |

|                                                 | 149 ピン    |        |    |  |

| 熱抵抗、テスト ポイント 1 (TP1) に対するアクティブ領域 <sup>(1)</sup> | 0.60      | °C/W   |    |  |

- (1) DMD は、吸収および放散された熱をパッケージの裏面に伝導するよう設計されています。冷却システムは、「推奨動作条件」に規定されている温度範囲内にパッケージを維持する必要があります。

DMD の合計熱負荷は、主にアクティブ領域によって吸収される入射光によって決まりますが、その他の寄与としてウインドウ開口部によって吸収される光エネルギーとアレイの消費電力があります。

光学システムは、ウインドウの開放口から外れた光エネルギーを最小限に抑えるよう設計する必要があります。これは、この領域に熱負荷が増大すると、デバイスの信頼性が大幅に低下する可能性があるためです。

## 5.6 電気的特性

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り)

| 記号                  | パラメータ <sup>(1) (2)</sup>                            | テスト条件 <sup>(1)</sup>                            | 最小値                   | 標準値                   | 最大値 | 単位 |

|---------------------|-----------------------------------------------------|-------------------------------------------------|-----------------------|-----------------------|-----|----|

| <b>電流 - 代表値</b>     |                                                     |                                                 |                       |                       |     |    |

| I <sub>DD</sub>     | 消費電流 V <sub>DD</sub> <sup>(3)</sup>                 |                                                 | 800                   | 1250                  | mA  |    |

| I <sub>DDA</sub>    | 消費電流 V <sub>DDA</sub> <sup>(3)</sup>                |                                                 | 900                   | 1200                  | mA  |    |

| I <sub>DDA</sub>    | 消費電流 V <sub>DDA</sub> <sup>(3)</sup>                | 单一マクロ モード                                       | 500                   | 600                   | mA  |    |

| I <sub>OFFSET</sub> | 消費電流 V <sub>OFFSET</sub> <sup>(4) (5)</sup>         |                                                 | 23                    | 35                    | mA  |    |

| I <sub>BIAS</sub>   | 消費電流 V <sub>BIAS</sub> <sup>(4) (5)</sup>           |                                                 | 2.4                   | 3.8                   | mA  |    |

| I <sub>RESET</sub>  | 消費電流 V <sub>RESET</sub> <sup>(5)</sup>              |                                                 | -10.5                 | -7.7                  | mA  |    |

| <b>パワー - 標準</b>     |                                                     |                                                 |                       |                       |     |    |

| P <sub>DD</sub>     | 電源消費電力 V <sub>DD</sub> <sup>(3)</sup>               |                                                 | 1440                  | 2437.5                | mW  |    |

| P <sub>DDA</sub>    | 電源消費電力 V <sub>DDA</sub> <sup>(3)</sup>              |                                                 | 1620                  | 2340                  | mW  |    |

| P <sub>DDA</sub>    | 電源消費電力 V <sub>DDA</sub> <sup>(3)</sup>              | 单一マクロ モード                                       | 900                   | 1170                  | mW  |    |

| P <sub>OFFSET</sub> | 電源消費電力 V <sub>OFFSET</sub> <sup>(4) (5)</sup>       |                                                 | 230                   | 367.5                 | mW  |    |

| P <sub>BIAS</sub>   | 電源消費電力 V <sub>BIAS</sub> <sup>(4) (5)</sup>         |                                                 | 38.4                  | 62.7                  | mW  |    |

| P <sub>RESET</sub>  | 電源消費電力 V <sub>RESET</sub> <sup>(5)</sup>            |                                                 | 92.4                  | 131.25                | mW  |    |

| P <sub>TOTAL</sub>  | 電源の合計消費電力                                           |                                                 | 3420.8                | 5338.95               | mW  |    |

| <b>LVC MOS 入力</b>   |                                                     |                                                 |                       |                       |     |    |

| I <sub>IL</sub>     | 低レベル入力電流 <sup>(6)</sup>                             | V <sub>DD</sub> = 1.95V, V <sub>I</sub> = 0V    | -100                  |                       | nA  |    |

| I <sub>IH</sub>     | 高レベル入力電流 <sup>(6)</sup>                             | V <sub>DD</sub> = 1.95V, V <sub>I</sub> = 1.95V |                       | 135                   | μA  |    |

| <b>LVC MOS 出力</b>   |                                                     |                                                 |                       |                       |     |    |

| V <sub>OH</sub>     | DC 出力高電圧 <sup>(7)</sup>                             | I <sub>OH</sub> = -2mA                          | 0.8 × V <sub>DD</sub> |                       | V   |    |

| V <sub>OL</sub>     | DC 出力低電圧 <sup>(7)</sup>                             | I <sub>OL</sub> = 2mA                           |                       | 0.2 × V <sub>DD</sub> | V   |    |

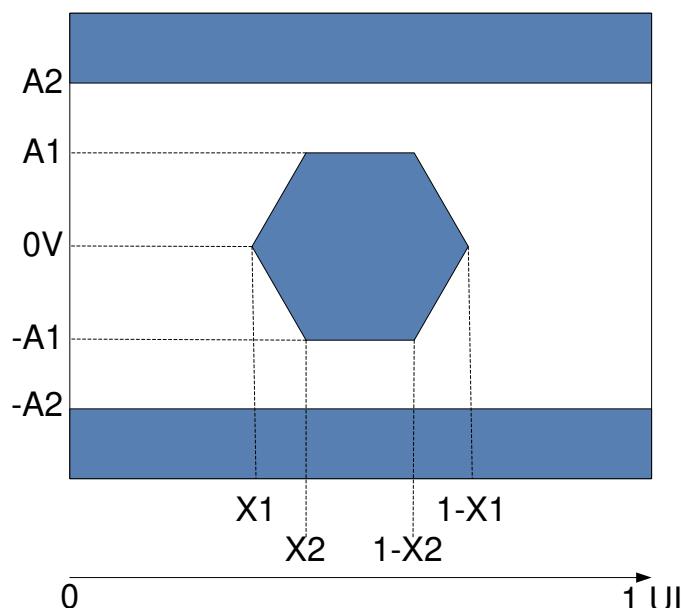

| <b>レシーバのアイ特性</b>    |                                                     |                                                 |                       |                       |     |    |

| A1                  | 最小データアイ開口 <sup>(8)</sup>                            |                                                 | 100                   | 600                   | mV  |    |

| A1                  | 最小クロックアイ開口 <sup>(8)</sup>                           |                                                 | 295                   | 600                   | mV  |    |

| A2                  | 最大信号スイング <sup>(8) (9)</sup>                         |                                                 |                       | 600                   | mV  |    |

| X1                  | 最大アイクロージャ <sup>(8)</sup>                            |                                                 |                       | 0.275                 | UI  |    |

| X2                  | 最大アイクロージャ <sup>(8)</sup>                            |                                                 |                       | 0.4                   | UI  |    |

| t <sub>DRIFT</sub>  | トレーニングパターン間のクロックとデータのドリフト                           |                                                 |                       | 20                    | ps  |    |

| <b>容量</b>           |                                                     |                                                 |                       |                       |     |    |

| C <sub>IN</sub>     | 入力容量 LVC MOS                                        | f = 1MHz                                        |                       | 10                    | pF  |    |

| C <sub>IN</sub>     | 入力容量 LSIF (低速インターフェイス)                              | f = 1MHz                                        |                       | 20                    | pF  |    |

| C <sub>IN</sub>     | 入力キヤパシタンス HSSI (高速シリアル インターフェイス)- 差動 - クロックピンとデータピン | f = 1MHz                                        |                       | 5                     | pF  |    |

| C <sub>OUT</sub>    | 出力容量                                                | f = 1MHz                                        |                       | 10                    | pF  |    |

- (1) DMD を動作させるには、すべての電源接続が必要です。V<sub>DD</sub>、V<sub>DDA</sub>、V<sub>OFFSET</sub>、V<sub>BIAS</sub> および V<sub>RESET</sub>。DMD を動作させるには、すべての V<sub>SS</sub> 接続が必要です。

- (2) すべての電圧値は、グラントピン (V<sub>SS</sub>) を基準としたものです。

- (3) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>DDA</sub> – V<sub>DD</sub>| は、指定限界値よりも小さい必要があります。

- (4) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>BIAS</sub> – V<sub>OFFSET</sub>| は、指定限界値よりも小さい必要があります。

- (5) 200μs の 3 つのグローバルリセットに基づく電源消費電力。

- (6) LVC MOS 入力仕様は、ピン DMD\_DEN\_ARSTZ に対するものです。

- (7) LVC MOS 出力仕様は、ピン LS\_RDATA\_A および LS\_RDATA\_B に対するものです。

- (8) 図 5-12 (1e-12 BER) を参照してください。

- (9) 「推奨動作条件」で定義

## 5.7 スイッチング特性

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り)

| 記号       | パラメータ                                                             | テスト条件                                                           | 最小値  | 標準値  | 最大値 | 単位   |

|----------|-------------------------------------------------------------------|-----------------------------------------------------------------|------|------|-----|------|

| $t_{pd}$ | 出力伝搬、クロックから Q まで、LS_CLK (差動クロック信号)<br>入力の立ち上がりエッジから LS_RDATA 出力まで | $C_L = 5\text{pF}$                                              |      | 11.1 |     | ns   |

| $t_{pd}$ | 出力伝搬、クロックから Q まで、LS_CLK (差動クロック信号)<br>入力の立ち上がりエッジから LS_RDATA 出力まで | $C_L = 10\text{pF}$                                             |      | 11.3 |     | ns   |

|          | スルーレート、LS_RDATA                                                   | 20% ~ 80%, $C_L < 40\text{pF}$                                  | 0.35 |      |     | V/ns |

|          | 出力デューティサイクル歪み、LS_RDATA_A および<br>LS_RDATA_B                        | $50 - (C2Q_{rise} - C2Q_{fall}) \times 130\text{e}6 \times 100$ | 40%  | 60%  |     |      |

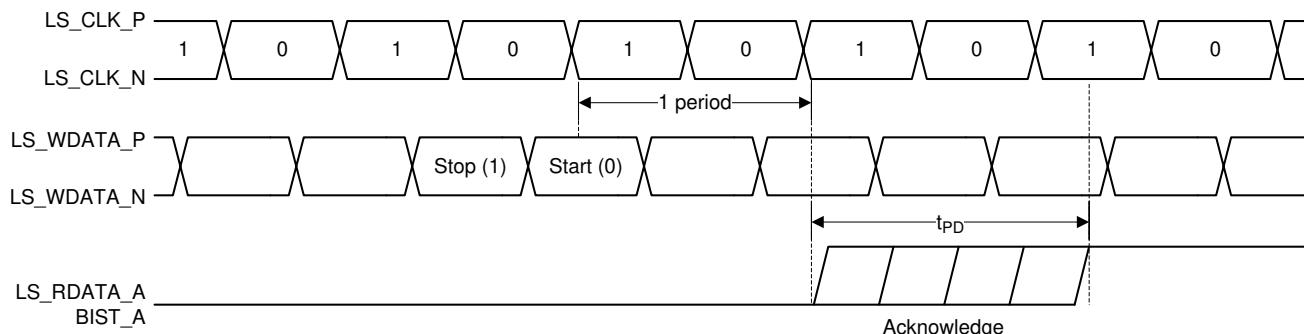

図 5-3. スイッチング特性

## 5.8 タイミング要件

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り)

| 記号                           | パラメータ           | テスト条件                                      | 最小値 | 標準値 | 最大値 | 単位 |

|------------------------------|-----------------|--------------------------------------------|-----|-----|-----|----|

| <b>LVC MOS</b>               |                 |                                            |     |     |     |    |

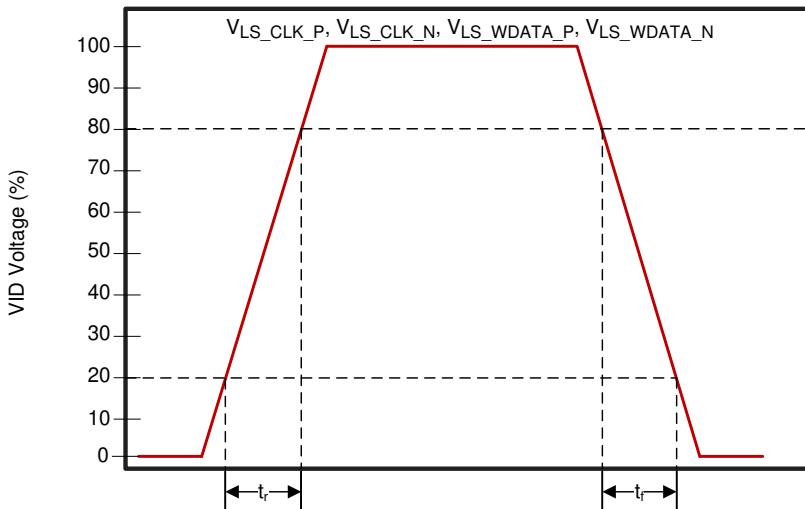

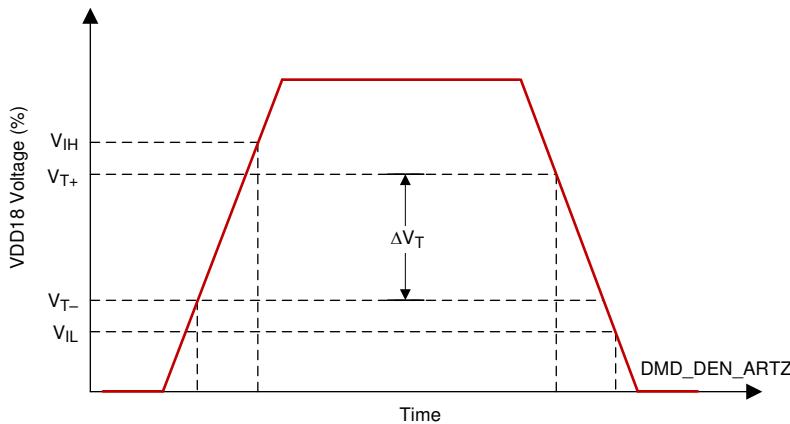

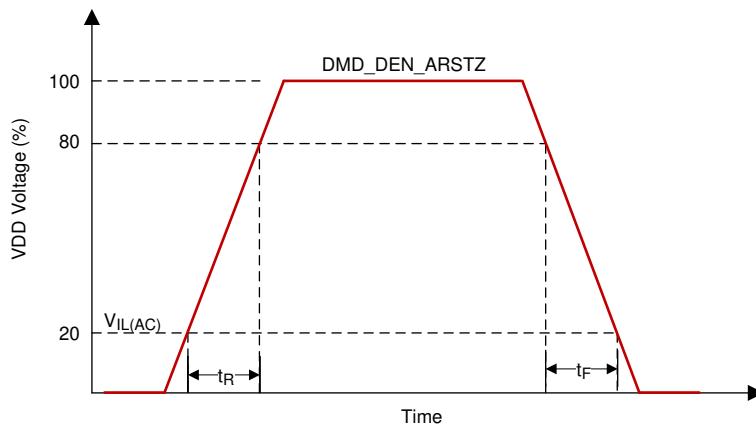

| $t_r$                        | 立ち上がり時間 (1)     | 20% ~ 80%のリファレンス ポイント                      |     | 25  |     | ns |

| $t_f$                        | 立ち下がり時間 (1)     | 80% ~ 20%のリファレンス ポイント                      |     | 25  |     | ns |

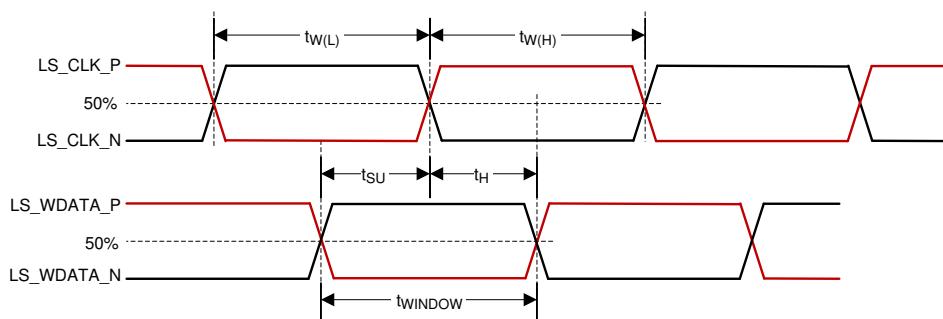

| <b>低速インターフェイス (LSIF)</b>     |                 |                                            |     |     |     |    |

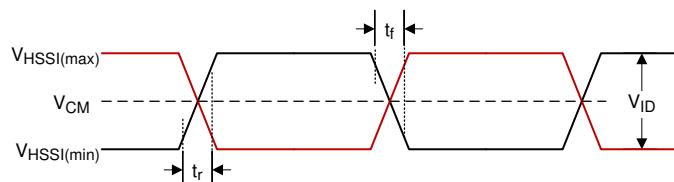

| $t_r$                        | 立ち上がり時間 (2)     | 20% ~ 80%のリファレンス ポイント                      |     | 450 |     | ps |

| $t_f$                        | 立ち下がり時間 (2)     | 80% ~ 20%のリファレンス ポイント                      |     | 450 |     | ps |

| $t_{W(H)}$                   | パルス幅、high (3)   | LS_CLK 50% ~ 50%のリファレンス ポイント               | 3.1 |     |     | ns |

| $t_{W(L)}$                   | パルス幅、low (3)    | LS_CLK 50% ~ 50%のリファレンス ポイント               | 3.1 |     |     | ns |

| $t_{su}$                     | セットアップ時間 (4)    | LS_WDATA が有効になってから LS_CLK の立ち上がりエッジまで (差分) | 1.5 |     |     | ns |

| $t_h$                        | ホールド時間 (4)      | LS_CLK の立ち上がりエッジの後に LS_WDATA 有効            | 1.5 |     |     | ns |

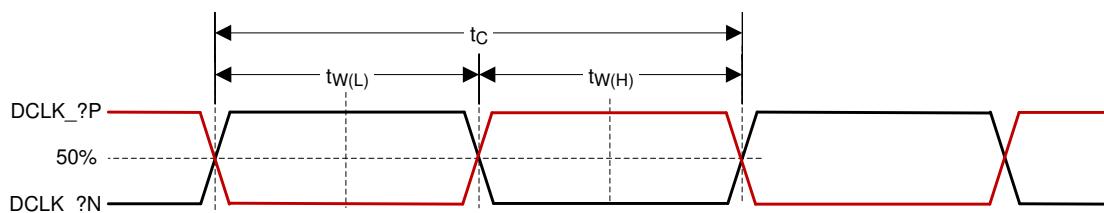

| <b>高速シリアルインターフェイス (HSSI)</b> |                 |                                            |     |     |     |    |

| $t_r$                        | 立ち上がり時間(5)、データ  | -A1 から A1 までの最小アイドリス                       | 50  | 115 |     | ps |

| $t_r$                        | 立ち上がり時間(5)、クロック | -A1 から A1 までの最小アイドリス                       | 50  | 135 |     | ps |

| $t_f$                        | 立ち下がり時間(5)、データ  | A1 から -A1 までの最小アイドリス                       | 50  | 115 |     | ps |

## 5.8 タイミング要件 (続き)

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り)

| 記号         | パラメータ                        | テスト条件                      | 最小値   | 標準値   | 最大値 | 単位 |

|------------|------------------------------|----------------------------|-------|-------|-----|----|

| $t_f$      | 立ち下がり時間 <sup>(5)</sup> 、クロック | A1 から -A1 までの最小アイ高仕様       | 50    | 135   | ps  |    |

| $t_{W(H)}$ | パルス幅、high <sup>(6)</sup>     | DCLK。50% ~ 50%のリファレンス ポイント | 0.275 |       | ns  |    |

| $t_{W(L)}$ | パルス幅、low <sup>(6)</sup>      | DCLK。50% ~ 50%のリファレンス ポイント | 0.275 |       | ns  |    |

| $t_c$      | サイクル時間 <sup>(6)</sup>        | DCLK                       | 0.625 | 0.833 | ns  |    |

- (1) 「LVCMOS の立ち上がり、立ち下がり時間のスルーレート」の図を参照してください。仕様は、DMD\_DEN\_ARSTZ ピン (LVCMOS) のものです。

- (2) LSIF の立ち上がり時間と立ち下がり時間については、図を参照してください。

- (3) LSIF のパルス幅の high 時間および low 時間にについては、図を参照してください。

- (4) LSIF のセットアップ時間およびホールド時間については、図を参照してください。

- (5) HSSI の立ち上がり時間/立ち下がり時間については、図を参照してください。

- (6) HSSI のパルス幅の high 時間と low 時間およびサイクル時間については、図を参照してください。

A. 式 1 および を参照してください。

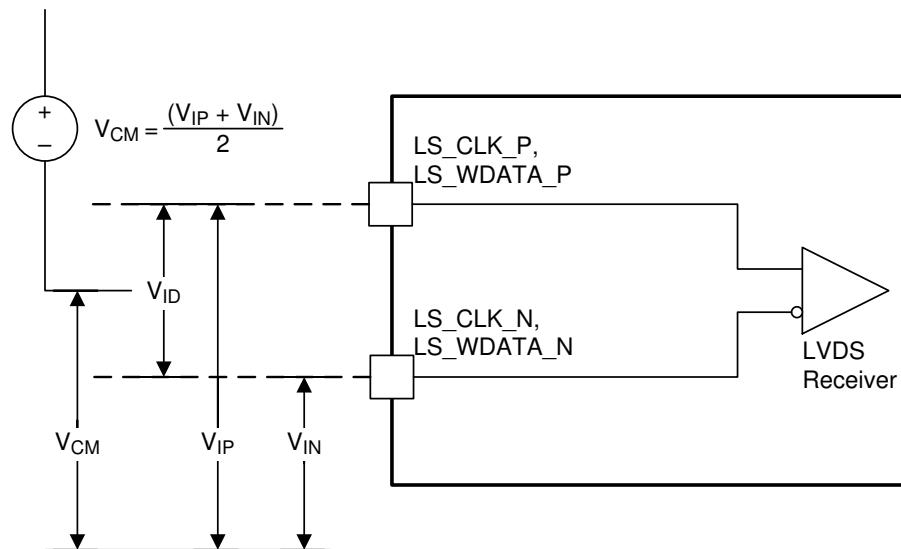

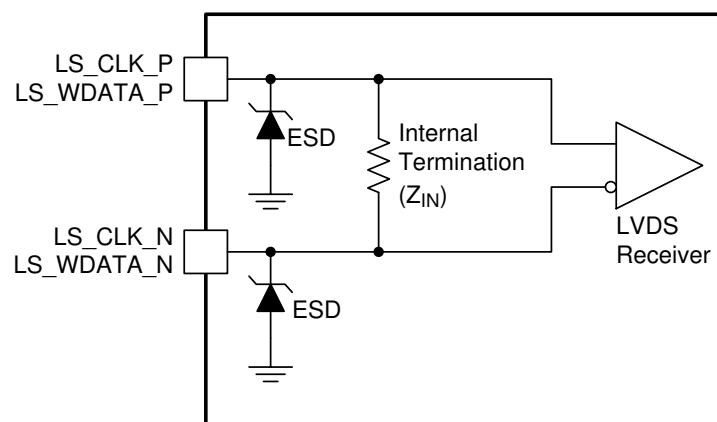

図 5-4. LSIF 波形要件

$$V_{LVDS(\max)} = V_{CM(\max)} + \left| \frac{1}{2} \times V_{ID(\max)} \right| \quad (1)$$

$$V_{LVDS(\min)} = V_{CM(\min)} - \left| \frac{1}{2} \times V_{ID(\max)} \right| \quad (2)$$

図 5-5. LSIF のタイミング要件

図 5-6. LSIF の立ち上がり/立ち下がり時間のスルーレート

図 5-7. LSIF 電圧要件

図 5-8. LSIF 等価入力

図 5-9. LVC MOS 入力ヒステリシス

図 5-10. LVC MOS の立ち上がり/立ち下がり時間のスルーレート

A. 式 3 および 式 4 を参照してください

◦

図 5-11. HSSI 波形要件

$$V_{HSSI(max)} = V_{CM(max)} + \left| \frac{1}{2} \times V_{ID(max)} \right| \quad (3)$$

$$V_{HSSI(min)} = V_{CM(min)} - \left| \frac{1}{2} \times V_{ID(max)} \right| \quad (4)$$

図 5-12. HSSI アイ特性

図 5-13. HSSI の CLK 特性

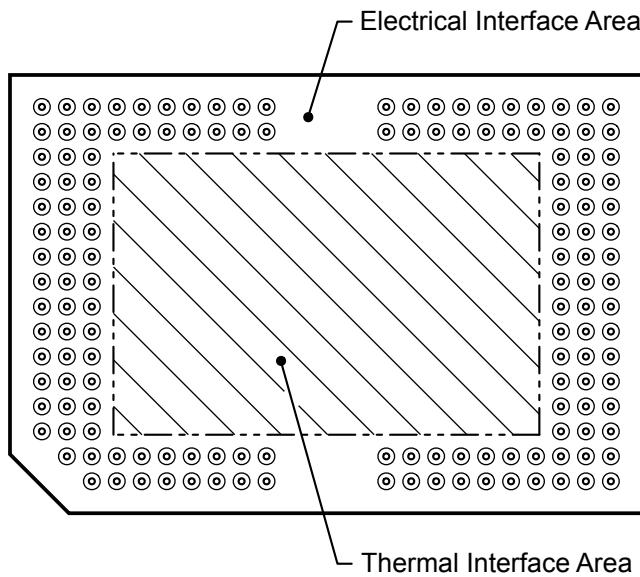

## 5.9 システム実装インターフェイスの荷重

| パラメータ                                   | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------------------------------|-----|-----|-----|----|

| 電気およびサーマルインターフェイス領域の両方に荷重がかかる場合         |     |     |     |    |

| 電気インターフェイス領域に適用される最大荷重 <sup>(1)</sup>   |     |     | 111 | N  |

| サーマルインターフェイス領域に適用される最大荷重 <sup>(1)</sup> |     |     | 111 | N  |

| 電気インターフェイス領域のみに荷重がかかる場合                 |     |     |     |    |

| 電気インターフェイス領域に適用される最大荷重 <sup>(1)</sup>   |     |     | 222 | N  |

| サーマルインターフェイス領域に適用される最大荷重 <sup>(1)</sup> |     |     | 0   | N  |

(1) 荷重は、図 5-14 に示されている対応領域に均一に適用する必要があります。

図 5-14. システム実装インターフェイスの荷重

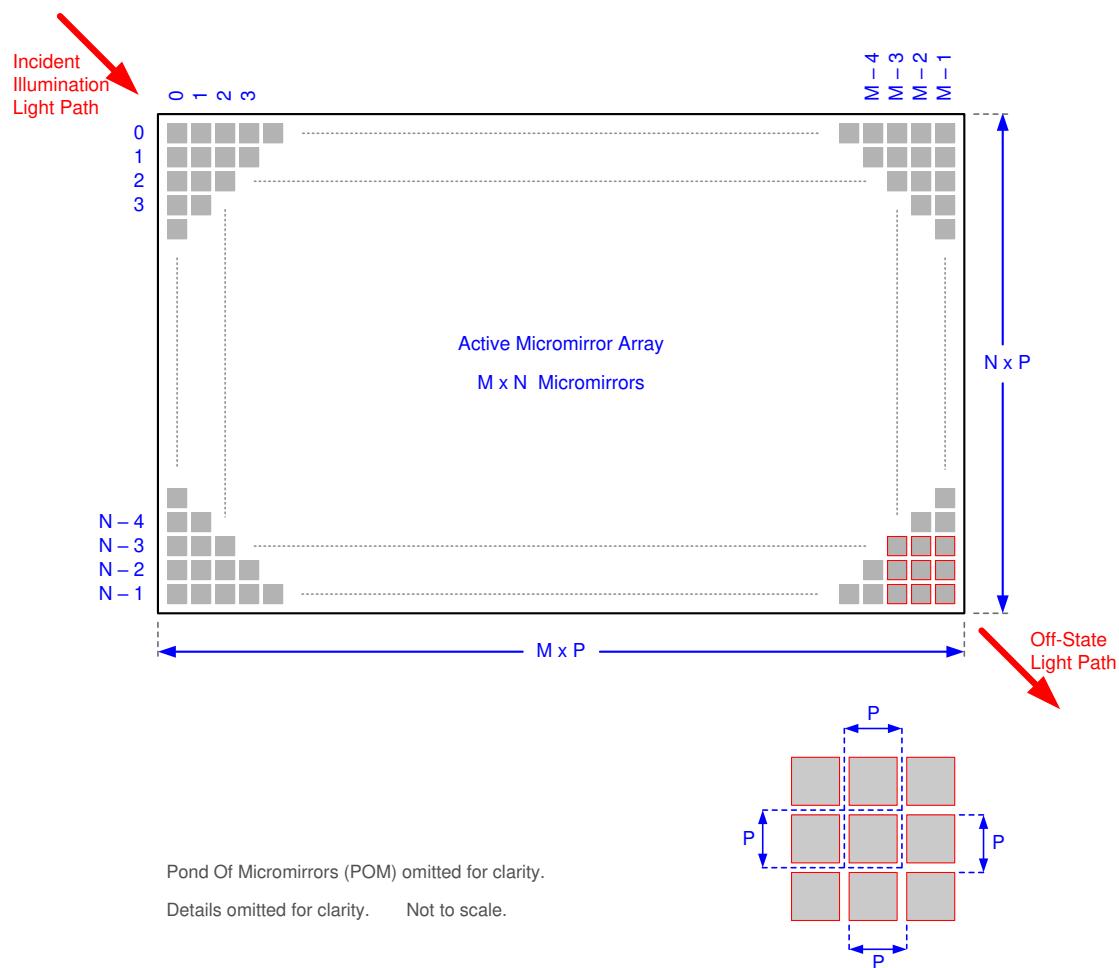

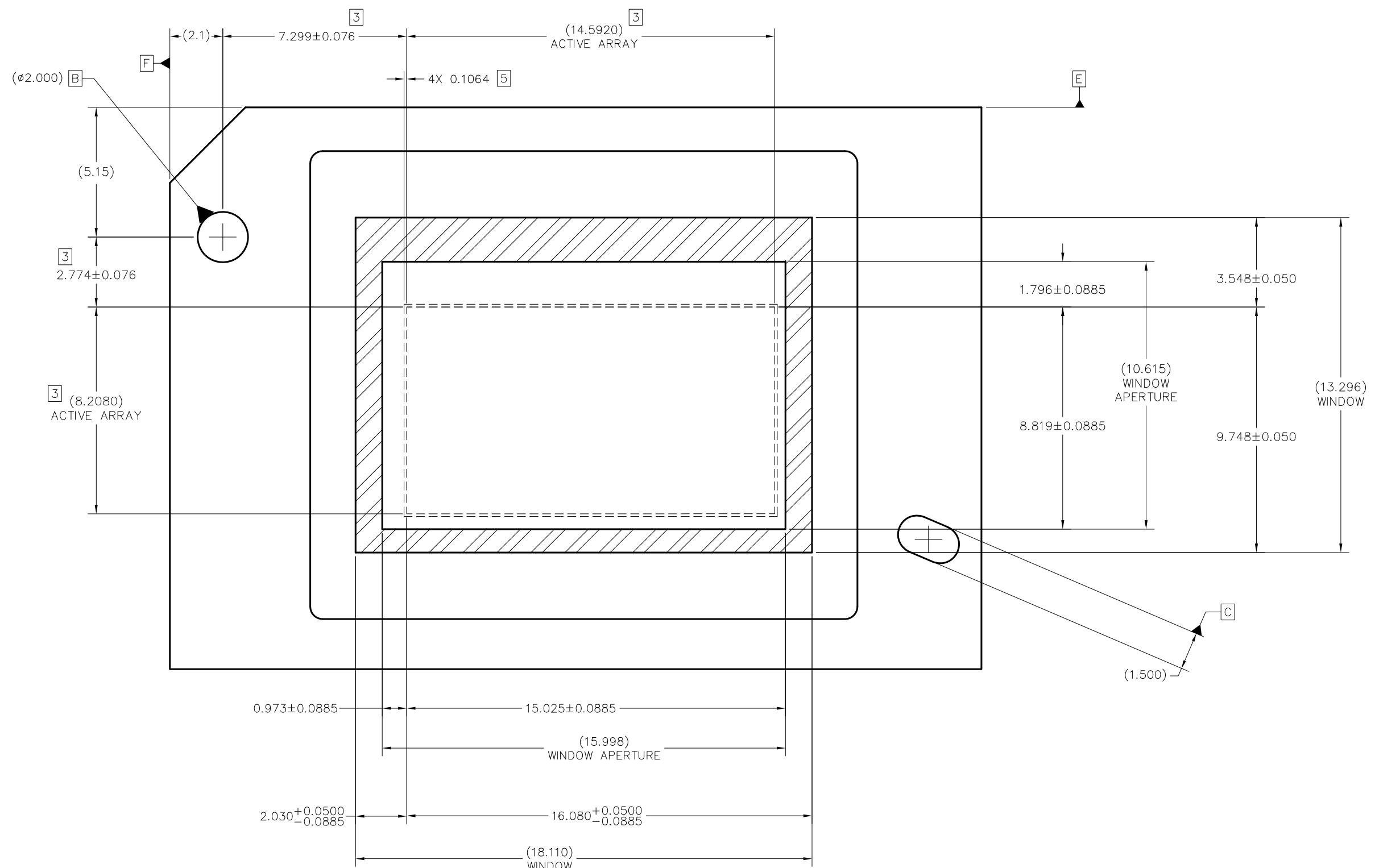

## 5.10 マイクロミラー アレイの物理特性

| 記号 | パラメータ                               | 説明                         | 最小値    | 標準値 | 最大値 | 単位            |

|----|-------------------------------------|----------------------------|--------|-----|-----|---------------|

| M  | アクティブ列の数 <sup>(1)</sup>             |                            | 1920   |     |     | マイクロミラー       |

| N  | アクティブ行の数 <sup>(1)</sup>             |                            | 1080   |     |     | マイクロミラー       |

| P  | マイクロミラー (ピクセル) ピッチ <sup>(1)</sup>   |                            | 7.6    |     |     | μm            |

|    | マイクロミラーのアクティブ アレイの幅 <sup>(1)</sup>  | (マイクロミラーのピッチ) × (アクティブ列の数) | 14.592 |     |     | mm            |

|    | マイクロミラーのアクティブ アレイの高さ <sup>(1)</sup> | (マイクロミラーのピッチ) × (アクティブ行の数) | 8.208  |     |     | mm            |

|    | マイクロミラーのアクティブ境界 <sup>(2)</sup>      | マイクロミラーの池 (POM)            | 14     |     |     | マイクロミラー / サイド |

(1) 図 6-15 を参照。

(2) アクティブ アレイの周囲の構造と特性には、部分的に機能するマイクロミラーで POM と呼ばれる帯状の領域が含まれています。これらのマイクロミラーは構造的および / または電気的に、明るい状態またはオン状態へ傾けることを防止しますが、オフ状態へ傾けるには電気的バイアスが必要です。

図 5-15. マイクロミラー アレイの物理特性

## 5.11 マイクロミラー アレイの光学特性

| パラメータ                                 | テスト条件                | 最小値            | 公称値 | 最大値 | 単位      |

|---------------------------------------|----------------------|----------------|-----|-----|---------|

| マイクロミラーの傾斜角、デバイスごとに変化 (2) (3) (4) (5) | 着地状態(1)              | 11             | 12  | 13  | 度       |

| 画像性能(6)                               | アクティブ領域の明るいピクセル(7)   | グレイの 10 画面(10) |     | 0   | マイクロミラー |

|                                       | POM 内の明るいピクセル(7) (9) | グレイの 10 画面(10) |     | 1   |         |

|                                       | アクティブ領域の暗いピクセル(8)    | 白色画面(11)       |     | 4   |         |

|                                       | 隣接ピクセル(12)           | 任意の画面          |     | 0   |         |

|                                       | アクティブ領域で不安定なピクセル(13) | 任意の画面          |     | 0   |         |

- (1) マイクロミラー アレイ全体から形成されるプレーンを基準として測定されます。

- (2) マイクロミラー アレイとパッケージのデータム間には、さらに大きな変動があります。

- (3) これは、同じデバイス上または異なるデバイス上に配置された任意の 2 つの個別マイクロミラー間で発生する可能性のある変動を表しています。

- (4) 一部のアプリケーションでは、システム全体の光学設計においてマイクロミラーの傾斜角の変動を考慮することが重要です。一部のシステム光学設計では、デバイス内のマイクロミラーの傾斜角が変動すると、マイクロミラー アレイから反射された光磁界では不均一性が認識される場合があります。一部のシステム光学設計では、デバイス間でマイクロミラーの傾斜角が変動すると、色測定のバラツキ、システム効率のバラツキ、またはシステムコントラストのバラツキが生じる場合があります。

- (5) [図 5-16](#) を参照してください。

- (6) 受け入れの条件。すべての DMD 画像性能リターンは、以下の投影画像試験条件を用いて評価されます。

- 試験セットのデガンマは線形である必要があります。

- テストセットの輝度とコントラストは公称値に設定する必要があります。

- 投影画像の対角サイズは、最低 60 インチであるものとします。

- 投影スクリーンは 1 ゲインにする必要があります。

- 投影画像は、最小 8 フィートの距離から検査する必要があります。

- すべての画像性能試験において、画像はフォーカスされている必要があります。

- (7) 明るいピクセルの定義: シングルピクセルまたはミラーがオフ位置に固定され、周囲のピクセルよりも目に見えて明ること。

- (8) 暗いピクセルの定義: シングルピクセルまたはミラーがオフ位置に固定され、周囲のピクセルよりも目に見えて暗いこと。

- (9) POM の定義: アクティブ領域を取り囲むオフ状態ミラーの長方形境界線。

- (10) グレイの 10 画面の定義: RGB 値を R=10/255, G=10/255, B=10/255 に設定したフルスクリーン。

- (11) 白色画面の定義: RGB 値を R = 255/255, G = 255/255, B = 255/255 に設定したフルスクリーン。

- (12) 隣接ピクセルの定義: 共通の境界または共通のポイントを共有する 2 つ以上のスタッカビクセル。クラスタとも呼ばれます。

- (13) 不安定なピクセルの定義: パラメータをメモリにロードした順序で動作しないシングルピクセルまたはミラー。不安定なピクセルは、画像と非同期にちらつきがあるように見える。

- A. マイクロミラーの池 (POM) は明確にするため省略。

- B. M、N、P の仕様については、「マイクロミラー アレイの物理特性」表を参照してください。

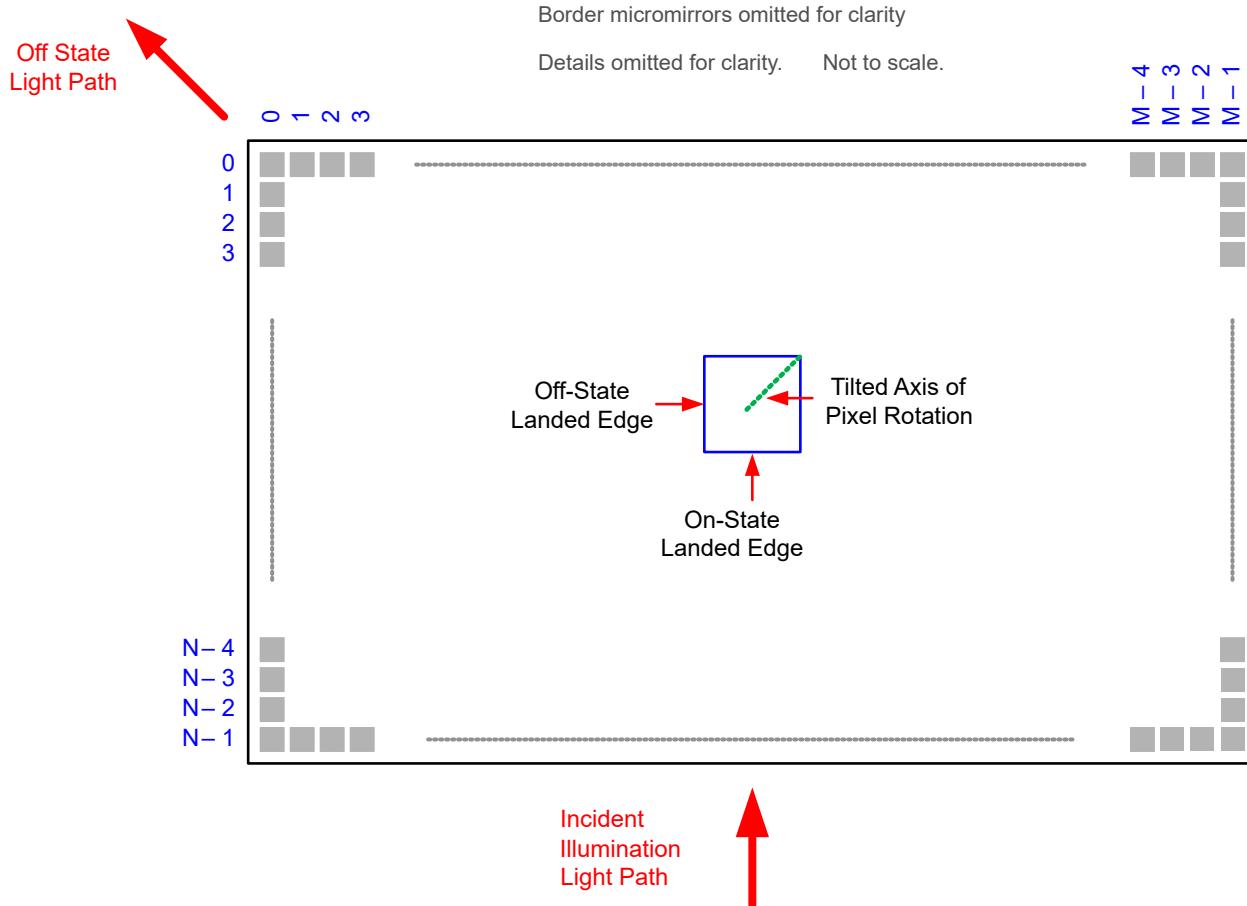

図 5-16. マイクロミラーの着地方向と傾き

## 5.12 ウィンドウの特性

| パラメータ     | テスト条件          | 最小値 | 標準値              | 最大値 | 単位 |

|-----------|----------------|-----|------------------|-----|----|

| ウィンドウ材料名称 | WLP            |     | コーニング<br>EagleXG |     |    |

| ウィンドウ屈折率  | 波長 546.1nm の場合 |     | 1.5119           |     |    |

## 5.13 チップセット コンポーネントの使用方法の仕様

DLP651NE DMD の信頼性の高い機能と動作を実現するには、TI の DMD 制御テクノロジーを採用または実装する部品など、該当する DLP チップセットの他の部品と組み合わせて使用する必要があります。TI の DMD 制御テクノロジーは、DLP DMD の動作または制御に使用される TI のテクノロジーとデバイスで構成されています。

### 注

TI は、前述の制限を超える光学システムの動作条件によって発生する画質のアーチファクトまたは DMD の故障については、一切責任を負いません。

## 6 詳細説明

### 6.1 概要

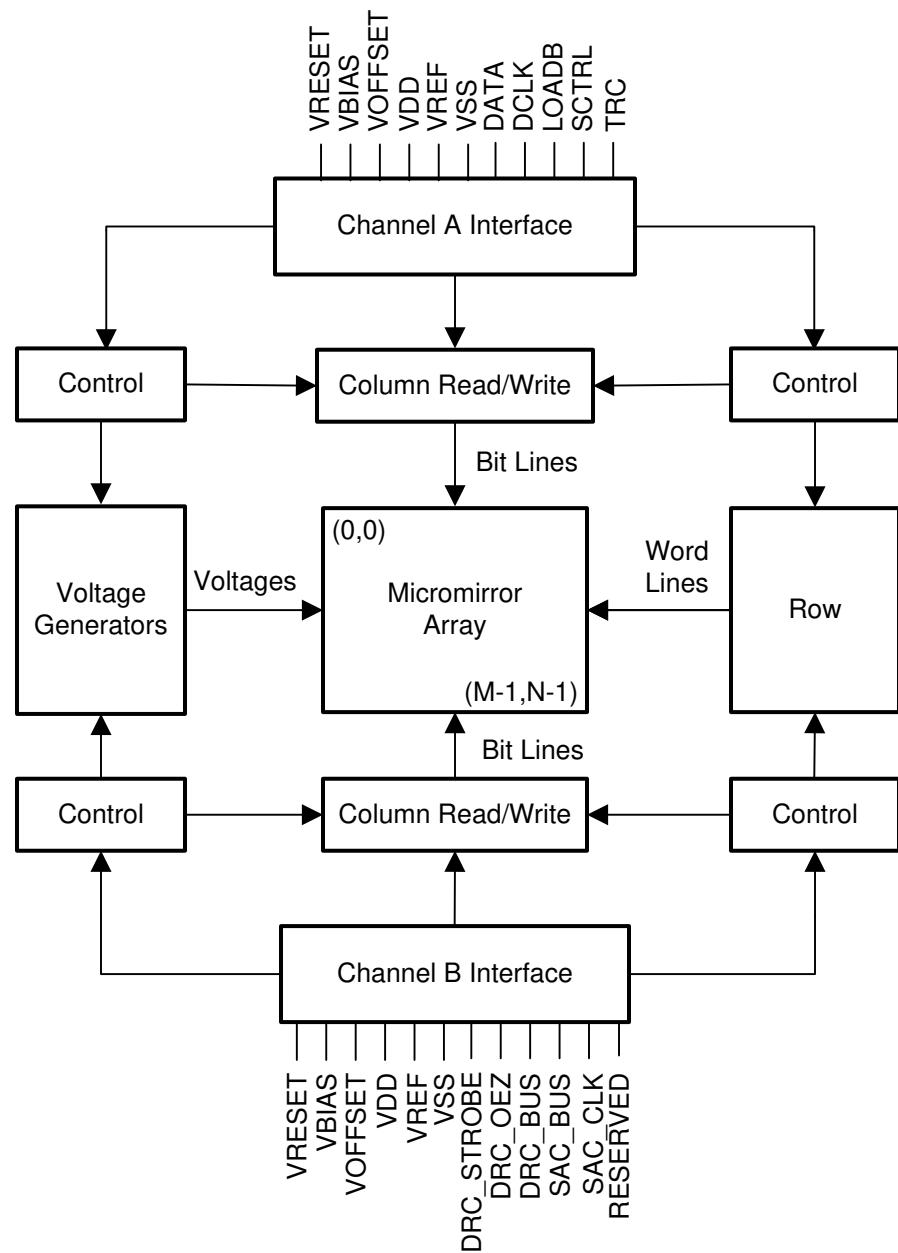

DMD は、対角 0.65 インチの空間光変調器で、反射率の高いアルミニウム製マイクロミラー アレイを内蔵しています。DMD は、電気入力、光出力の光マイクロマシン (MOEMS) です。DMD マイクロミラーの高速な切り替え速度と、先進的な DLP 画像処理アルゴリズムを組み合わせることで、最大 240Hz のフレーム レートで表示することが可能になります。電気的インターフェイスは、低電圧差動信号伝送 (LVDS) です。DMD は、1 ビット CMOS メモリ セルの 2 次元アレイで構成されます。アレイは、M 個のメモリ セル列と N 個のメモリ セル行の格子状に編成されます。[セクション 6.2](#) を参照してください。マイクロミラーの正または負の偏向角度は、基盤となる CMOS アドレッシング回路とマイクロミラー リセット信号 (MBRST) のアドレス電圧を変更することで、個別に制御可能です。

DLP 0.65 インチ 1080p チップセットは、DLP651NE DMD、[DLPC7530](#) ディスプレイ コントローラ、[DLPA100](#) 電源管理およびモータードライバで構成されています。信頼性の高い動作を確保するために、DLP651NE DMD は、常に指定されたチップセットに含まれる DLP ディスプレイ コントローラおよび電源管理、モータードライバと一緒に使用する必要があります。

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 電源インターフェイス

DMD は次の 4 つの DC 電圧を必要とします。1.8V ソース、 $V_{OFFSET}$ 、 $V_{RESET}$ 、 $V_{BIAS}$  標準的な構成では、[DLPA100](#) 電源管理およびモータードライバによって 3.3V が生成され、DMD ボードで使用されて 1.8V を生成します。TI の電圧レギュレータ [TPS65145](#) は 3.3V を取り込み、 $V_{OFFSET}$ 、 $V_{RESET}$ 、 $V_{BIAS}$  を出力します。

### 6.3.2 タイミング

データシートには、デバイスピンでのタイミングが記載されています。出力タイミング解析では、テスタのピンエレクトロニクスとその伝送ラインの影響を考慮に入れる必要があります。タイミング基準負荷は、特定のシステム環境を精密に表現したり、製造試験で示される実際の負荷を表現したりすることを意図したものではありません。TI はシステム設計者が IBIS または他のシミュレーションツールを使用して、タイミング基準負荷をシステム環境に関連付けることを推奨しております。AC タイミング信号の特性評価および測定には、指定の負荷容量値のみを使用してください。この負荷容量の値は、デバイスが駆動可能な最大負荷を示しているわけではありません。

## 6.4 デバイスの機能モード

DMD の機能モードは、[DLPC7530 ディスプレイコントローラのデータシート](#) を参照するか、TI アプリケーションエンジニアにお問い合わせください。

## 6.5 光学インターフェイスおよびシステムの画質に関する検討事項

TI は、最終製品の光学性能について一切責任を負いません。目的の最終製品の光学性能を実現するには、多数の部品とシステム設計パラメータとの間でトレードオフを決定する必要があります。システムの光学性能と画像品質の最適化は、光学システム設計のパラメータのトレードオフに大きく関係しています。想定可能なすべてのアプリケーションを予測できるわけではありませんが、プロジェクトの画質と光学性能は、以下のセクションに示す光学システムの動作条件への準拠によって決まります。

### 6.5.1 開口数および迷光制御

テキサス・インスルメンツは、照明光学系の開口数によって定義される光円錐角は、投影光学系の開口数によって定義される光円錐角と同じであることが望ましいことを推奨しています。この角度は、照明および投影瞳孔に適切な開口部を追加して、投影レンズからの平面光および迷光をブロックする場合を除いて、公称デバイスのマイクロミラー傾斜角を超えないようにする必要があります。マイクロミラーの傾斜角により、DMD の「オン」光路をその他のライトパスから分離できます。これには、DMD ウィンドウからの望ましくない平面状態の反射、DMD の境界構造、または DMD 付近にあるプリズムやレンズ表面などの他のシステム表面などが含まれます。開口数がマイクロミラーの傾斜角を超える場合、または投影開口数角度が照明開口数角度より 2 度以上大きい場合（その逆も同様）、コントラストが低下し、表示境界やアクティブ領域に望ましくないアーチファクトが発生する可能性があります。

### 6.5.2 瞳孔一致

光学的品質および画質に関する TI の仕様は、照明用光学素子の射出瞳が公称値として投影光学素子の入射瞳から 2° 以内の位置を中心としていることを仮定しています。瞳孔のずれは、ディスプレイ境界とアクティブ領域に不快なアーチファクトを発生させる可能性があり、特にシステムの開口数がピクセルチルト角度を超える場合は、制御するために追加のシステム開口部が必要になる場合があります。

### 6.5.3 オーバーフィル照射

デバイスのアクティブ領域は、DMD チップアセンブリの構造を通常の視界から覆い隠す、DMD ウィンドウ面の内側にある開口部で囲まれ、複数の光学動作条件を想定したサイズとなっています。ウィンドウ開口部を照らすオーバーフィル光は、ウィンドウ開口部の端からアーチファクトが発生したり、他の表面異常が画面に表示されたりする可能性があります。照明光学システムは、ウィンドウ開口部上の任意の場所に入射する光束が、アクティブ領域の平均光束レベルの約 10% を超えないように設計する必要があります。特定のシステムの光学的アーキテクチャによっては、オーバーフィル光を推奨される 10% 未満にさらに低減して、許容可能な範囲にする必要があります。

## 6.6 マイクロミラー アレイ温度の計算

図 6-1. DMD の温度テスト ポイント

マイクロミラー アレイの温度は直接測定できないため、パッケージ外部の測定ポイント、パッケージの熱抵抗、電力、照明の熱負荷から、解析的に計算する必要があります。アレイ温度と基準セラミック温度(熱テスト TP1)の関係は、以下の式で計算します。

$$T_{ARRAY} = T_{CERAMIC} + (Q_{ARRAY} \times R_{ARRAY-TO-CERAMIC}) \quad (5)$$

$$Q_{ARRAY} = Q_{ELECTRICAL} + Q_{ILLUMINATION} \quad (6)$$

ここで、

- $T_{ARRAY}$  = 算出されたアレイ温度 (°C)

- $T_{CERAMIC}$  = 測定されたアレイ温度 (°C) (TP1 の場所)

- $R_{ARRAY-TO-CERAMIC}$  = アレイからセラミック TP1 までの [熱に関する情報](#) で規定するパッケージの熱抵抗 (°C/ワット)

- $Q_{ARRAY}$  = アレイ上の DMD 全体の消費電力 (W) (電力 + 吸收光)

- $Q_{ELECTRICAL}$  = 公称電力(W)

- $Q_{INCIDENT}$  = インシデント照明光出力 (W)

- $Q_{ILLUMINATION} = (DMD \text{ 平均熱吸収率} \times Q_{INCIDENT}) (W)$

- DMD の平均熱吸収率 = 0.45

DMD の消費電力は変数で、電圧、データレート、動作周波数に依存します。アレイ温度の計算時に使用する公称消費電力量は 3.0W です。照射用光源から吸収される電力は変数で、マイクロミラーの動作状態と光源の強度に依存します。上記の式は、シングル チップまたはマルチ チップの DMD システムに有効です。この想定では、アクティブ アレイで 83.7%、アレイ境界で 16.3% の照度分布を想定しています。

標準的な投影アプリケーションの計算例は次のとおりです。

$$Q_{INCIDENT} = 48W \text{ (measured)} \quad (7)$$

$$T_{CERAMIC} = 55.0^{\circ}\text{C} \text{ (measured)} \quad (8)$$

$$Q_{ELECTRICAL} = 3.0W \quad (9)$$

$$Q_{ARRAY} = 3.0W + (0.45 \times 48W) = 24.6W \quad (10)$$

$$T_{ARRAY} = 55.0^{\circ}\text{C} + (24.6W \times 0.6^{\circ}\text{C}/W) = 69.8^{\circ}\text{C} \quad (11)$$

## 6.7 マイクロミラーの電力密度の計算

さまざまな波長帯域で DMD 上の照明の光出力密度を計算するには、DMD で測定された合計光出力、照明のオーバーフィル率、アクティブ アレイの面積、目的の波長帯域でのスペクトルの合計光出力に対する比率を使用します。

- $ILL_{UV} = [OP_{UV-RATIO} \times Q_{INCIDENT}] \times 1000\text{mW/W} \div A_{ILL} (\text{mW/cm}^2)$

- $ILL_{VIS} = [OP_{VIS-RATIO} \times Q_{INCIDENT}] \div A_{ILL} (\text{W/cm}^2)$

- $ILL_{IR} = [OP_{IR-RATIO} \times Q_{INCIDENT}] \times 1000\text{mW/W} \div A_{ILL} (\text{mW/cm}^2)$

- $ILL_{BLU} = [OP_{BLU-RATIO} \times Q_{INCIDENT}] \div A_{ILL} (\text{W/cm}^2)$

- $ILL_{BLU1} = [OP_{BLU1-RATIO} \times Q_{INCIDENT}] \div A_{ILL} (\text{W/cm}^2)$

- $A_{ILL} = A_{ARRAY} \div (1 - OV_{ILL}) (\text{cm}^2)$

ここで

- $ILL_{UV}$  = DMD での UV 照明の電力密度 ( $\text{mW/cm}^2$ )

- $ILL_{VIS} = DMD$  での VIS 照明の電力密度 ( $W/cm^2$ )

- $ILL_{IR} = DMD$  での IR 照明の電力密度 ( $mW/cm^2$ )

- $ILL_{BLU} = DMD$  での BLU 照明の電力密度 ( $W/cm^2$ )

- $ILL_{BLU1} = DMD$  での BLU1 照明の電力密度 ( $W/cm^2$ )

- $A_{ILL} = DMD$  での照明領域 ( $cm^2$ )

- $Q_{INCIDENT} = DMD$  での総入射光パワー ( $W$ ) (測定値)

- $A_{ARRAY} =$ アレイの面積 ( $cm^2$ ) (データシート)

- $OV_{ILL} =$ アレイ外の DMD の総照明パーセント (%) (光学モデル)

- $OP_{UV-RATIO} =$ 照明スペクトルの総光出力に対する、波長が 410nm 未満の場合の光出力比 (スペクトル測定)

- $OP_{VIS-RATIO} =$ 照明スペクトルの総光出力に対する、波長が 410nm 以上 800nm 以下の場合の光出力比 (スペクトル測定)

- $OP_{IR-RATIO} =$ 照明スペクトルの総光出力に対する、波長が 800nm 超の場合の光出力比 (スペクトル測定)

- $OP_{BLU-RATIO} =$ 照明スペクトルの総光出力に対する、波長が 410nm 以上 475nm 以下の場合の光出力比 (スペクトル測定)

- $OP_{BLU1-RATIO} =$ 照明スペクトルの総光出力に対する、波長が 410nm 以上 440nm 以下の場合の光出力比 (スペクトル測定)

照明領域は、照明オーバーフィルによって異なります。DMD 上の総照明領域は、アレイ領域と、アレイの周囲のオーバーフィル領域です。光学モデルを使用して、アレイの外部にある DMD 上の全照明の割合 ( $OV_{ILL}$ ) と、アクティブ アレイ上にある全照明の割合を決定します。これらの値から、照明領域 ( $A_{ILL}$ ) が計算されます。照明は、アレイ全体で一様であると仮定します。

測定された照明スペクトルから、総光出力に対する、対象の波長帯域における光出力との比が計算されます。

計算例：

$$Q_{INCIDENT} = 48W \text{ (measured)}$$

$$A_{ARRAY} = (14.5920mm \times 8.2080mm) \div 100mm^2/cm^2 = 1.1977cm^2 \text{ (data sheet)}$$

$$OV_{ILL} = 16.3\% \text{ (optical model)}$$

$$OP_{UV-RATIO} = 0.00017 \text{ (spectral measurement)}$$

$$OP_{VIS-RATIO} = 0.99977 \text{ (spectral measurement)}$$

$$OP_{IR-RATIO} = 0.00006 \text{ (spectral measurement)}$$

$$OP_{BLU-RATIO} = 0.28100 \text{ (spectral measurement)}$$

$$OP_{BLU1-RATIO} = 0.03200 \text{ (spectral measurement)}$$

$$A_{ILL} = 1.1977cm^2 \div (1 - 0.163) = 1.4310cm^2$$

$$ILL_{UV} = [0.00017 \times 48W] \times 1000mW/W \div 1.4310cm^2 = 5.702mW/cm^2$$

$$ILL_{VIS} = [0.99977 \times 48W] \div 1.4310cm^2 = 33.54W/cm^2$$

$$ILL_{IR} = [0.00006 \times 48W] \times 1000mW/W \div 1.4310cm^2 = 2.013mW/cm^2$$

$$ILL_{BLU} = [0.28100 \times 48W] \div 1.4310\text{cm}^2 = 9.43\text{W/cm}^2$$

$$ILL_{BLU1} = [0.03200 \times 48W] \div 1.4310\text{cm}^2 = 1.07\text{W/cm}^2$$

## 6.8 ウィンドウ アーチャイルミネーションオーバーフィル計算

ウィンドウ開口部のクリティカル領域の光学的オーバーフィルの量は直接測定できません。アレイ上で照射が均一なシステムの場合、この量は、DMD の入射光パワーの合計測定値と、定義された重要領域における DMD の総光パワーの比率を使用して決定されます。この光学モデルを使用して、ウィンドウ開口部臨界面積の光出力の割合を決定し、面積のサイズを推定します。

- $Q_{AP-ILL} = [Q_{INCIDENT} \times OP_{AP\_ILL\_RATIO}] + A_{AP\_ILL} (\text{W/cm}^2)$

ここで

- $Q_{AP-ILL}$  = ウィンドウ開口部照明オーバーフィル ( $\text{W/cm}^2$ )

- $Q_{INCIDENT}$  = DMD での総入射光パワー (ワット) (測定値)

- $OP_{AP\_ILL\_RATIO}$  = ウィンドウ開口部の重要領域の光出力と DMD の合計光出力との比率 (光学モデル)

- $A_{AP\_ILL}$  = ウィンドウ開口部臨界面積 ( $\text{cm}^2$ ) (データシート)

- $OP_{CA\_RATIO}$  = 入射光パワー (%) (光学モデル) を持つウィンドウ開口重要領域のパーセンテージ

図 6-2. イルミネーションオーバーフィルダイアグラム - クリティカルエリア

$Q_{INCIDENT}=48\text{W}$  (measured)

$OP_{AP\_ILL\_RATIO}=0.312\%$  (optical model)

$OP_{CA\_RATIO}=25\%$  (optical model)

Length of the window aperture for critical area =  $1.5998\text{cm}$  (data sheet mechanical icd)

Width of critical area =  $0.050\text{cm}$  (data sheet)

$$A_{AP\_ILL}=1.5998\text{cm} \times 0.050\text{cm}=0.079990\text{cm}^2$$

$$Q_{AP-ILL}=(48\text{W} \times 0.00312)+(0.079990\text{cm}^2 \times 0.25)=7.5\text{W/cm}^2$$

## 6.9 マイクロミラーのランデッド オン / ランデッド オフ デューティ サイクル

### 6.9.1 マイクロミラーのランデッド オン / ランデッド オフ デューティ サイクルの定義

マイクロミラーのランデッド オン / ランデッド オフ デューティ サイクル (ランデッド デューティ サイクル) は、個々のマイクロミラーがオン状態で着地している時間の割合を、同じマイクロミラーがオフ状態で着地している時間に対する割合として示します。

たとえば、100/0 のランデッド デューティ サイクルは、基準のピクセルがオン状態の時間 100% (オフ状態の時間 0%) にあることを示しています。一方、0/100 は、ピクセルがオフ状態の時間 100% にあることを示しています。同様に、50/50 はピクセルがオン状態の時間 50% (オフ状態の時間 50%) になっていることを示します。

なお、ランデッド デューティ サイクルを評価する際、一方の状態 (オンまたはオフ) から他方の状態 (オフまたはオン) に切り替わるのに要する時間は無視できるものと見なされます。

マイクロミラーはどちらか一方の状態 (オンまたはオフ) でしか着地できないため、2 つの数値 (パーセンテージ) の合計は必ず 100 になります。

### 6.9.2 DMD のランデッド デューティ サイクルと有効寿命

(最終製品またはアプリケーションの) 長期平均ランデッド デューティ サイクルを把握することが重要です。DMD マイクロミラー アレイ (アクティブ アレイとも呼ばれます) のすべて (または一部) を非対称ランデッド デューティ サイクルに長時間適用すると、DMD の有効寿命が短くなるためです。

ランデッド デューティ サイクルの対称性 / 非対称性が関連することに注意してください。ランデッド デューティ サイクルの対称性は、2 つの数値 (パーセンテージ) がどれだけ等しいかによって決まります。たとえば、50/50 のランデッド デューティ サイクルは完全に対称ですが、100/0 または 0/100 のランデッド デューティ サイクルは完全に非対称です。

### 6.9.3 ランデッド デューティ サイクルと動作時の DMD 温度

DMD の動作温度とランデッド デューティ サイクルは DMD の耐用年数に影響を及ぼします。この相互作用を利用すると、非対称ランデッド デューティ サイクルが DMD の耐用年数に及ぼす影響を低減できます。これは、「最大推奨アレイ温度低下曲線」に示すディレーティング曲線で定量化されます。この曲線の重要性は次のとおりです。

- この曲線に沿ったすべてのポイントは、同じ耐用年数を表します。

- この曲線より上のすべてのポイントは、より短い耐用年数を表します (そして、曲線から離れているほど、耐用年数は短くなります)。

- この曲線より下のすべてのポイントは、より長い耐用年数を表します (そして、曲線から離れているほど、耐用年数は長くなります)。

実際には、この曲線は、所定の長期平均ランディング デューティ サイクルにおける DMD の最大動作温度を指定します。

### 6.9.4 製品またはアプリケーションの長期平均ランデッド デューティ サイクルの推定

所定の期間中、特定のピクセルのランデッド デューティ サイクルは、そのピクセルによって表示される画像内容から追従します。

たとえば、最も単純なケースでは、ある一定の期間、あるピクセルに純粋な白を表示する場合、そのピクセルはその期間中に 100/0 ランデッド デューティ サイクル下で動作します。同様に、純粋な黒を表示する場合、ピクセルは 0/100 ランデッド デューティ サイクル下で動作します。

この 2 つの極端な値の間 (入力画像に適用される色と画像処理をとりあえず無視します)、ランデッド デューティ サイクルは、表 6-1 に示すように、グレイスケール値で 1 対 1 を追跡します。

**表 6-1. グレイスケール値とランデッド デューティ サイクル**

| グレイスケール値 | ランデッド デューティ サイクル |

|----------|------------------|

| 0%       | 0/100            |

| 10%      | 10/90            |

| 20%      | 20/80            |

**表 6-1. グレイスケール値とランデッド デューティ サイクル (続き)**

| グレイスケール値 | ランデッド デューティ サイクル |

|----------|------------------|

| 30%      | 30/70            |

| 40%      | 40/60            |

| 50%      | 50/50            |

| 60%      | 60/40            |

| 70%      | 70/30            |

| 80%      | 80/20            |

| 90%      | 90/10            |

| 100%     | 100/0            |

演色を考慮(ただしこれでも画像処理を無視します)するには、特定のピクセルの各構成原色(赤、緑、青)のカラー強度(0%から100%)と、各原色のカラー サイクル時間(「カラー サイクル時間」は、目的のホワイト ポイントを達成するために特定の原色が表示されるフレーム時間の合計割合)の両方を知る必要があります。

特定の期間内に、特定のピクセルのランデッド デューティ サイクルを計算するにはこの式を使用します。

Landed Duty Cycle =

$$\begin{aligned}

& (\text{Red_Cycle\_ \%} \times \text{Red_Scale_Value}) + \\

& (\text{Green_Cycle\_ \%} \times \text{Green_Scale_Value}) + \\

& (\text{Blue_Cycle\_ \%} \times \text{Blue_Scale_Value})

\end{aligned}$$

ここで、

- Red\_Cycle\_% は、目的のホワイト ポイントを達成するために赤で表示されるフレーム時間の割合を表します

- Green\_Cycle\_% は、目的のホワイト ポイントを達成するために緑で表示されるフレーム時間の割合を表します

- Blue\_Cycle\_% は、目的のホワイト ポイントを達成するために青で表示されるフレーム時間の割合を表します

たとえば、赤、緑、青のカラー サイクル時間がそれぞれ 30%、50%、20% であると仮定し、(目的のホワイト ポイントを達成するため) 赤、緑、青の強度のさまざまな組み合わせに対するランデッド デューティ サイクルは、表 6-2 と表 6-3 に示すようになります。

**表 6-2. フルカラー、カラー パーセンテージに対するランデッド デューティ サイクルの例**

| サイクル パーセンテージ |     |     |

|--------------|-----|-----|

| 赤色           | 緑色  | 青色  |

| 30%          | 50% | 20% |

**表 6-3. フルカラーのランデッド デューティ サイクルの例**

| 赤色   | 緑色   | 青色   | スケール値 | ランデッド デューティ サイクル |

|------|------|------|-------|------------------|

|      |      |      |       |                  |

| 0%   | 0%   | 0%   | 0/100 |                  |

| 100% | 0%   | 0%   | 30/70 |                  |

| 0%   | 100% | 0%   | 50/50 |                  |

| 0%   | 0%   | 100% | 20/80 |                  |

| 0%   | 12%  | 0%   | 6/94  |                  |

| 0%   | 0%   | 35%  | 7/93  |                  |

| 60%  | 0%   | 0%   | 18/82 |                  |

| 0%   | 100% | 100% | 70/30 |                  |

| 100% | 0%   | 100% | 50/50 |                  |

**表 6-3. フルカラーのランデッド デューティ サイクルの

例 (続き)**

| スケール値 |      |      | ランデッド デューティ サイクル |

|-------|------|------|------------------|

| 赤色    | 緑色   | 青色   |                  |

| 100%  | 100% | 0%   | 80/20            |

| 0%    | 12%  | 35%  | 13/87            |

| 60%   | 0%   | 35%  | 25/75            |

| 60%   | 12%  | 0%   | 24/76            |

| 100%  | 100% | 100% | 100/0            |

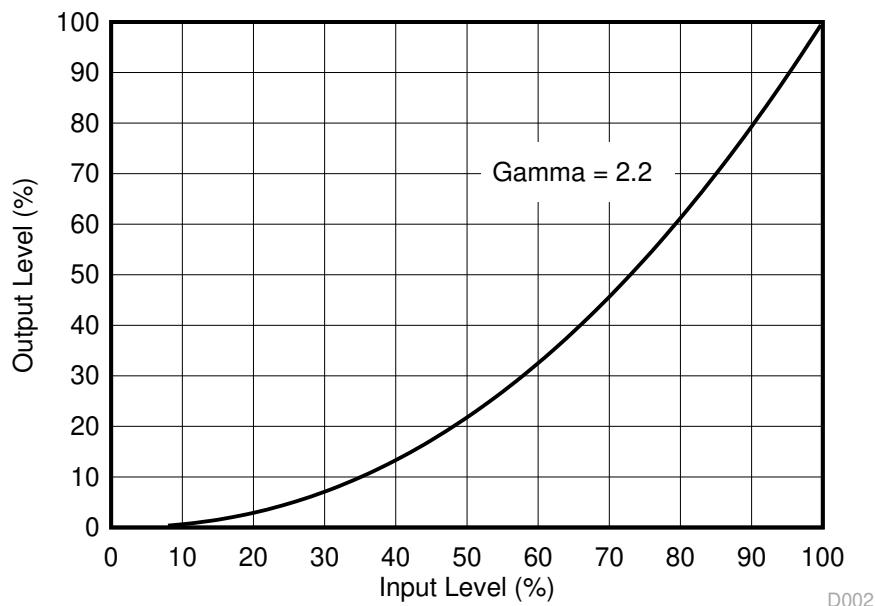

ランデッド デューティ サイクルを推定する際に考慮すべき最後の要因は、適用されている画像処理です。DLP7530 コントローラ内では、ガンマ機能はランデッド デューティ サイクルに影響を与えます。

ガンマは、 $\text{Output\_Level} = A \times \text{Input\_Level}^{\text{Gamma}}$  という形式の電力関数です。ここで、A は通常 1 に設定されるスケーリング係数です。

DLP7530 コントローラでは、ピクセル単位で入力画像データにガンマが適用されます。一般的なガンマ係数は 2.2 で、図 6-3 に示すように入力データが変換されます。

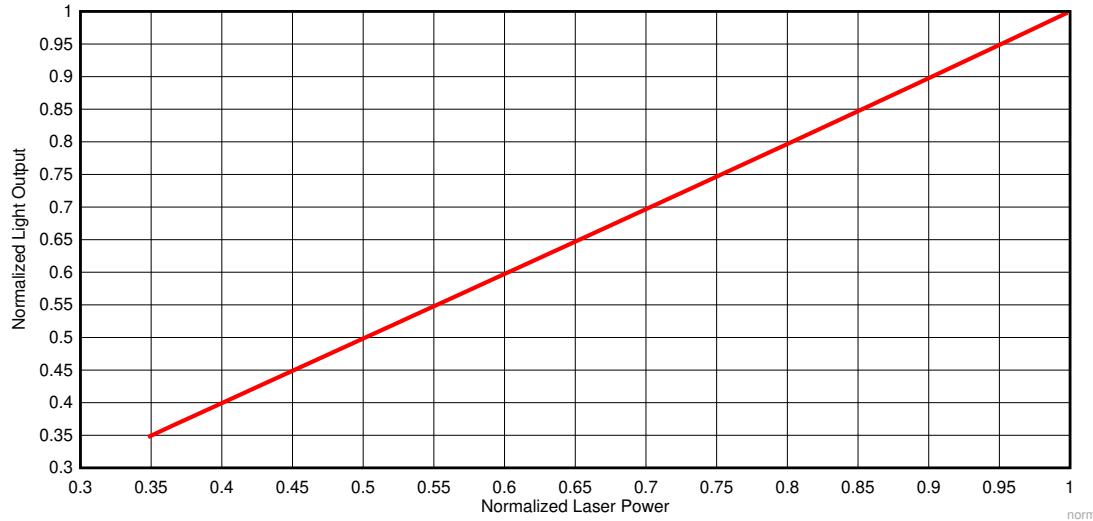

**図 6-3. ガンマ= 2.2 の例**

図 6-3 から、指定された入力ピクセルのグレイスケール値が 40% の場合 (ガンマが適用される前)、ガンマが適用された後でグレイスケール値は 13% になります。したがって、ガンマは表示されるピクセルのグレイスケール レベルに直接影響するため、ピクセルのランデッド デューティ サイクルにも直接的な影響を与えることがわかります。

DLP7530 コントローラの前に発生する画像処理についても考慮する必要があります。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

DMD は空間光変調器であり、照射用光源から受け入れた光を 2 方向のいずれかに反射します。主な方向は、プロジェクションまたは集光光学系です。各アプリケーションは、主にシステムの光学アーキテクチャと、DLPC7530 コントローラが受け入れるデータ形式の違いで派生するものです。DLP651NE DMD を使用する代表的なアプリケーションには、レーザー テレビ、スマート プロジェクター、エンターブライズ プロジェクターなどがあります。

DMD のパワーアップおよびパワーダウン シーケンスは、TPS65145 PMIC を通じて DLPC7530 によって厳密に制御されています。パワーアップとパワーダウンの仕様については、[セクション 8](#) を参照してください。信頼性の高い動作を保証するために、DLP651NE DMD は常に、DLPC7530 コントローラ、DLPA100 PMIC/ モーター ドライバ、および TPS65145 PMIC とともに使用する必要があります。

### 7.2 代表的なアプリケーション

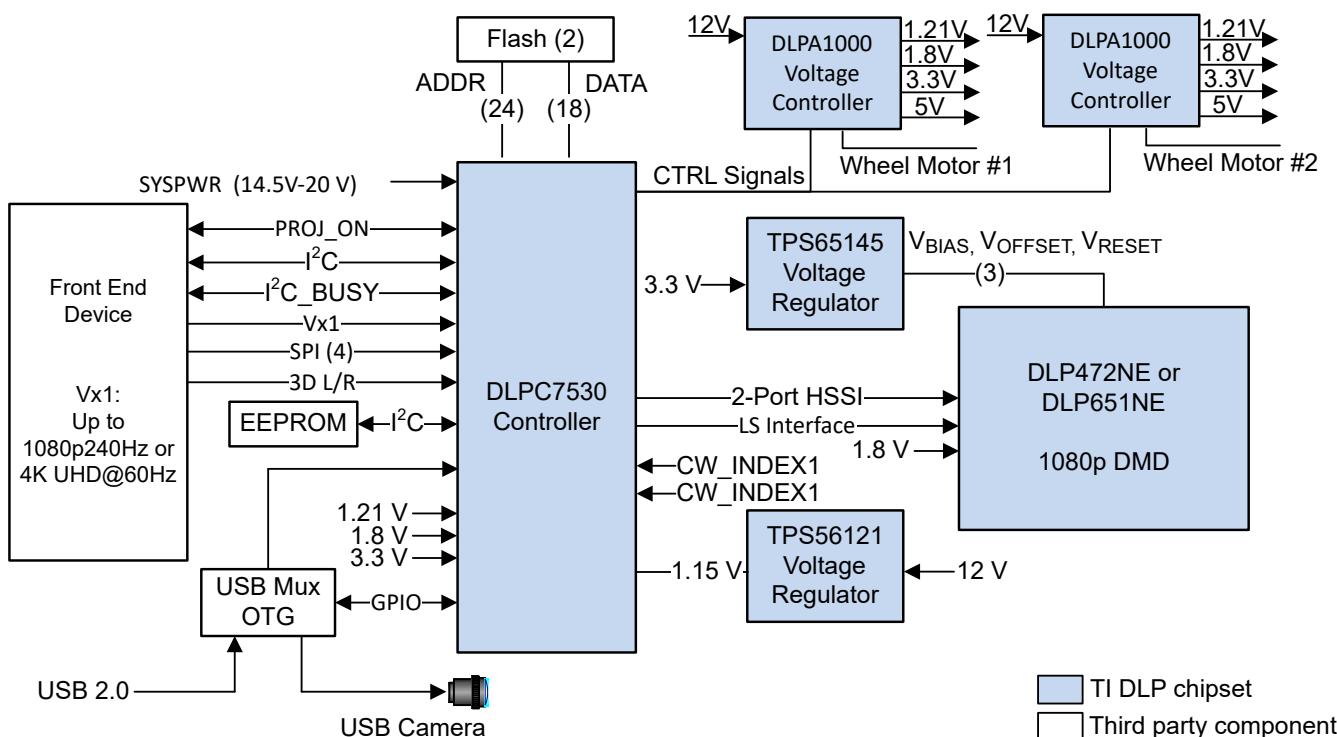

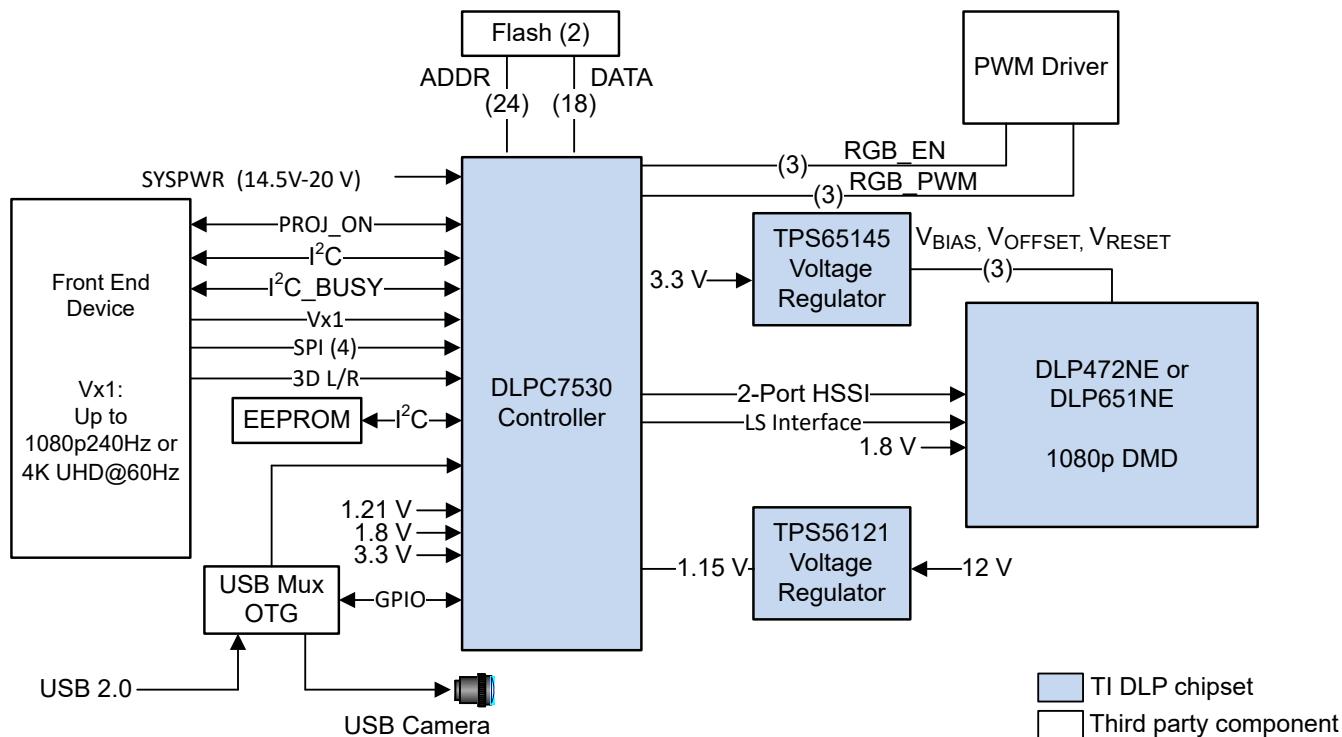

DLP651NE DMD は、DLPC7530 デジタル コントローラやパワー マネージメント デバイスと組み合わせることにより、高輝度で色鮮やかなディスプレイ用途に最適なフル 1080p 解像度を実現します。レーザー蛍光照明を使用する代表的なディスプレイシステムでは、DLP651NE DMD、DLPC7530 ディスプレイ コントローラ、TPS65145 電圧レギュレータおよび DLPA100 PMIC およびモータードライバを組み合わせています。下図に、DLP 0.65 インチ 1080p チップセットのレーザー蛍光構成のシステム ブロック図を示します。[図 7-2](#) に、DLP 0.65 インチ 1080p チップセットの LED 構成のシステム ブロック図を示します。部品には、DLP651NE DMD、DLPC7530 ディスプレイ コントローラ、DLPA100 PMIC およびモータードライバ、TPS65145 PMIC が含まれます。

図 7-1. フル HD レーザー蛍光の代表的なアプリケーション図

図 7-2. フル HD LED の代表的なアプリケーション図

### 7.2.1 設計要件

ディスプレイシステムのその他の中核部品としては、照射用光源、照明および投影光学系用の光学エンジン、その他の電気部品および機械部品、ソフトウェアがあります。使用する照明の種類と目的の輝度は、システム全体の設計とサイズに大きな影響を及ぼします。

ディスプレイシステムは DLP651NE DMD をコア画像処理デバイスとして使用し、0.65 インチのマイクロミラー アレイを搭載しています。DLPC7530 コントローラは、DMD とシステムの他の部分との間のデジタルインターフェイスであり、フロントエンドレシーバからデジタル入力を取得し、高速インターフェイスで DMD を駆動します。DLPA100 PMIC はコントローラ用の電圧レギュレータとして機能し、カラーフィルタホイールと蛍光体ホイールモーターの制御を行います。TPS65145 は、DMD リセット、オフセット、バイアス電圧を供給します。LMR33630C は、DLP651NE DMD に 1.8V 電源を供給します。

### 7.2.2 詳細な設計手順

包括的な DLP システムを実現するには、DLP651NE DMD、関連する照射用光源、光学素子、必要な機械部品を含む光学モジュールまたは光学エンジンが必要です。

信頼性の高い動作を保証するために、DMD は常に DLPC7530 ディスプレイコントローラおよび TPS65145 PMIC および DLPA100 とともに使用する必要があります。レイアウトと設計の推奨事項については、DMD 基板のリファレンス デザインおよび DLPC7530 のリファレンス デザインを参照してください。

### 7.2.3 アプリケーション曲線

一般的なプロジェクター アプリケーションでは、DMD からスクリーン上の光束はプロジェクターの光学設計によって異なります。照明光学系と投影光学系の効率および総電力によって、プロジェクターの全体的な光出力が決まります。DMD は本質的に線形空間光変調器であるため、その効率は光出力に比例します。図 7-3 は、蛍光体が熱消光限界に達していないレーザー蛍光体照明システムにおける、レーザー入力光出力と光出力の関係を表します。

図 7-3. レーザー蛍光照明での標準化光出力と標準化レーザー電力との関係

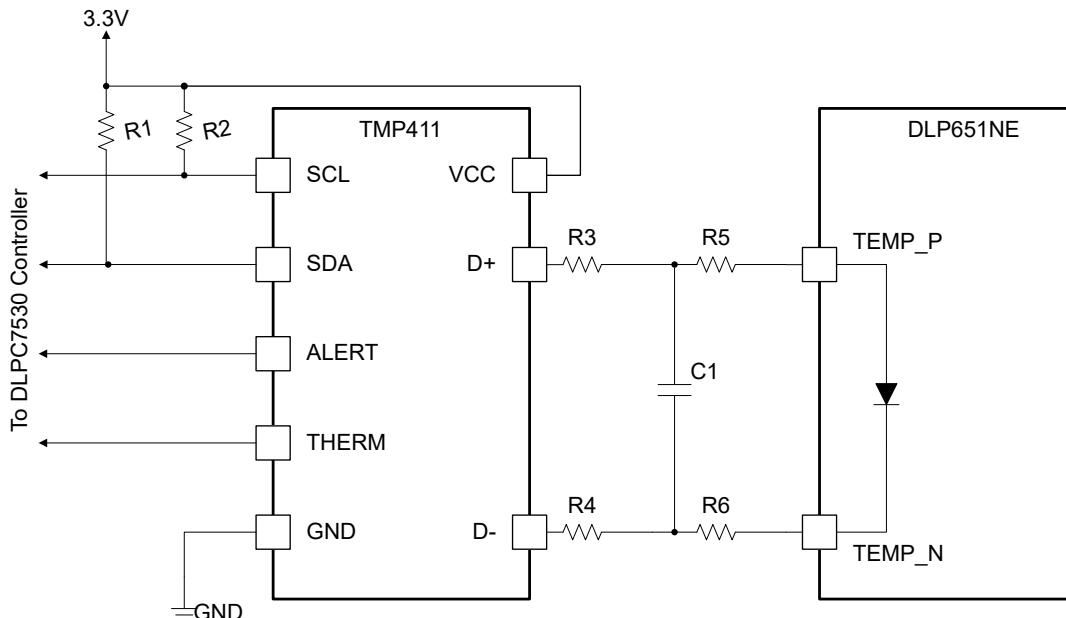

### 7.3 温度センサ ダイオード

DMD には、マイクロミラー アレイの外側にあるダイの一角落温を測定するための内蔵サーマル ダイオードが搭載されています。サンプル回路図に示されているように、サーマルダイオードは TMP411 温度センサと接続できます。このソフトウェア アプリケーションは、DLP651NE DMD 温度センサ ダイオードを読み取る様に TMP411 を構成する機能が含まれています。このデータは、照明の調整やファンの速度制御など、全体のシステム設計に追加機能を組み込むために活用できます。I<sup>2</sup>C インターフェイスを使用して、TMP411 と DLPC7530 コントローラ間のすべての通信を完了します。TMP411 は、「ピンの機能」に示すピンを経由して DMD に接続されます。

温度センサを使用しない場合、TEMP\_N ピンおよび TEMP\_P ピンは未接続 (NC) のままになります。

- A. わかりやすくするため、詳細は省略しています。

- B. システム基板のレイアウトに関する推奨事項については、[TMP411 データシート](#)を参照してください。

- C. R1、R2、R3、R4、C1 の推奨部品値については、[TMP411 データシート](#)を参照してください。

D.  $R5 = 0\Omega$ . $R6 = 0\Omega$ . $0\Omega$  の抵抗を DMD パッケージピンの近くに配置します。

図 7-4. TMP411 のサンプル回路図

## 8 電源に関する推奨事項

DMD の動作には、以下の電源装置がすべて必要です。

- $V_{SS}$

- $V_{BIAS}$

- $V_{DD}$

- $V_{OFFSET}$

- $V_{RESET}$

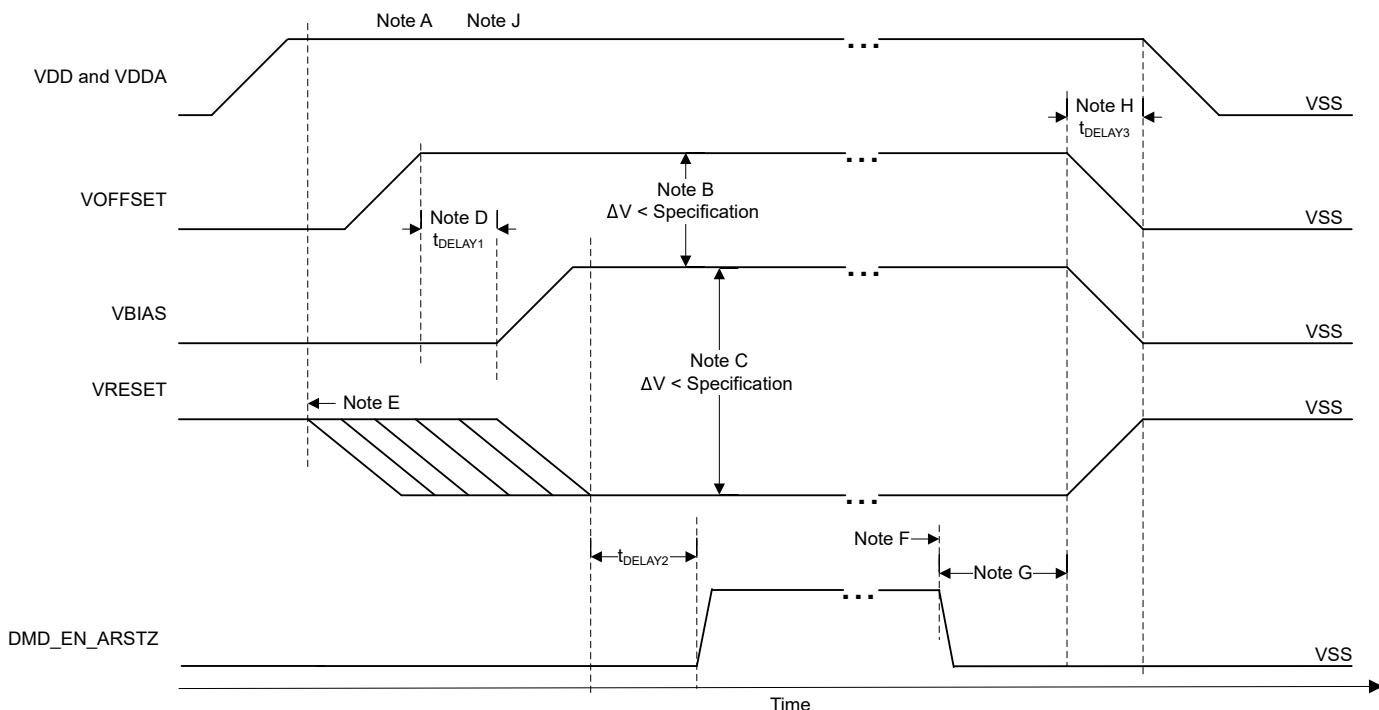

DMD のパワーアップ / パワーダウン シーケンシングは、DLP ディスプレイコントローラによって厳密に制御されます。

### 注意

DMD を確実に動作させるには、以下の電源シーケンシング要件に従う必要があります。規定されたパワーアップおよびパワーダウン要件のいずれかに準拠しない場合、デバイスの信頼性に影響を及ぼす可能性があります。[図 8-1](#) の DMD 電源シーケンシング要件を参照してください。

$V_{BIAS}$ 、 $V_{DD}$ 、 $V_{OFFSET}$ 、 $V_{RESET}$  電源をパワーアップおよびパワーダウン動作時に調整する必要があります。以下の各要件のいずれかに適合していない場合、DMD の信頼性と寿命が大幅に低下します。共通のグランド  $V_{SS}$  も接続する必要があります。

### 8.1 電源シーケンス要件

| 記号           | パラメータ | 説明                                                                                        | 最小値 | 標準値 | 最大値 | 単位 |

|--------------|-------|-------------------------------------------------------------------------------------------|-----|-----|-----|----|

| $t_{DELAY1}$ | 遅延要件  | $V_{OFFSET}$ パワーアップから $V_{BIAS}$ パワーアップまで                                                 | 1   | 2   |     | ms |

| $t_{DELAY2}$ | 遅延要件  | $V_{BIAS}$ および $V_{RESET}$ の電源がオンになり、 $DMD\_EN\_ARSTZ$ が high になり安定するまで                   |     | 20  |     | μs |

| $t_{DELAY3}$ | 遅延要件  | $V_{OFFSET}$ 、 $V_{BIAS}$ 、 $V_{RESET}$ のパワーダウンから、 $V_{DD}$ および $V_{DDA}$ のパワーダウンが可能な時点まで |     | 50  |     | μs |

### 8.2 DMD 電源のパワーアップ手順

- パワーアップ時には常に、 $V_{OFFSET}$  に「電源シーケンス要件」で指定された  $t_{DELAY1}$  を加えた電圧、 $V_{BIAS}$ 、および  $V_{RESET}$  電圧が DMD に印加される前に、 $V_{DD}$  が起動および安定する必要があります。

- パワーアップ時には、 $V_{BIAS}$  と  $V_{OFFSET}$  の電圧差が、「推奨動作条件」に示される指定限界内でなければならないという厳しい要件があります。

- パワーアップ中、 $V_{BIAS}$  を基準とした  $V_{RESET}$  の相対タイミングは不要です。

- 過渡電圧レベルが「絶対最大定格」、「推奨動作条件」、および「DMD 電源要件」で指定された要件に従っている限り、パワーアップ時の電源スルーレートは柔軟です。

- パワーアップ時、「推奨動作条件」に示す動作電圧で  $V_{DD}$  が安定するまで、LVCMOS 入力ピンを high に駆動しないでください。

### 8.3 DMD 電源のパワーダウン手順

- パワーダウン時には、 $V_{BIAS}$ 、 $V_{RESET}$ 、および  $V_{OFFSET}$  がグランドの指定限界内で放電されるまで、 $V_{DD}$  を供給する必要があります。「電源シーケンシング要件」を参照してください。

- パワーダウン時には、 $V_{BIAS}$  と  $V_{OFFSET}$  の電圧差が、「推奨動作条件」に示される指定限界内でなければならないという厳しい要件があります。

- パワーダウン中、 $V_{BIAS}$  を基準とした  $V_{RESET}$  の相対タイミングは不要です。

- 過渡電圧レベルが「絶対最大定格」、「推奨動作条件」、および「DMD 電源要件」で指定された要件に従っている限り、パワーダウン時の電源スルーレートは柔軟です。

- パワーダウン中、LVCMOS 入力ピンは「推奨動作条件」で指定された値未満である必要があります。

- 「ピンの機能」表を参照してください。

- 過剰な電流を防止するため、電源電圧の差  $|V_{BIAS} - V_{OFFSET}|$  は、「推奨動作条件」の指定限界値よりも小さい必要があります。

- 過剰な電流を防止するため、電源差  $|V_{BIAS} - V_{RESET}|$  は、「推奨動作条件」の指定限界値よりも小さい必要があります。

- $V_{BIAS}$  は、 $V_{OFFSET}$  がパワーアップした後に、「電源シーケンス要件」の  $t_{DELAY1}$  仕様に従ってパワーアップする必要があります。

- $V_{RESET}$ 、 $V_{OFFSET}$ 、および  $V_{BIAS}$  ランプは、 $VDD$  および  $VDDA$  が起動して安定した後に開始する必要があります。

- DMD のマイクロミラー パーク シーケンスの完了後、DLP コントローラ ソフトウェアはハードウェア パワーダウンを開始し、**DMD\_EN\_ARSTZ** を有効にして、 $V_{BIAS}$ 、 $V_{RESET}$ 、 $V_{OFFSET}$  を無効化します。

- 電力損失条件下で、DLP コントローラのハードウェア **DMD\_EN\_ARSTZ** によって緊急 DMD マイクロミラー パーク手順が実行されている場合は、**low** になります。

- 「電源シーケンス要件」の  $t_{DELAY3}$  仕様に従って、 $V_{OFFSET}$ 、 $V_{BIAS}$ 、および  $V_{RESET}$  の電源がオフになるまで、 $V_{DD}$  は電源オンのままで安定した状態を維持する必要があります。

- 過剰な電流を防止するため、電源電圧差  $|V_{DDA} - V_{DD}|$  は、「推奨動作条件」の指定限界値よりも小さい必要があります。

- スケールしていません。わかりやすくするために、詳細は省略しています。

図 8-1. DMD 電源要件

## 9 レイアウト

### 9.1 レイアウトのガイドライン

DLP651NE DMD は、[DLPC7530](#) ディスプレイ コントローラによって制御されるチップセットの一部であり、[TPS65145](#) PMIC および [DLPA100](#) 電源およびモーター コントローラと連携して動作します。これらのガイドラインは、DLP651NE DMD を使用した PCB 基板の設計を対象としています。DMD ボードは、高速デジタル ロジックを主とした高速多層 PCB であり、DMD には 3.2Gbps のダブル データ レート信号や 250Mbps の差動データ バスが接続されています。TI は、 $V_{OFFSET}$ 、 $V_{RESET}$ 、および  $V_{BIAS}$  には、フル電源プレーンまたはミニ電源プレーンを使用することを推奨しています。グランド ( $V_{SS}$ ) にはソリッド プレーンが必要です。PCB の目標インピーダンスは  $50\Omega \pm 10\%$  です（表 9-1 に示す例外を除きます）。TI は、表 9-2 に示すように、10 層の積層を推奨します。TI では、高品質の FR-4 材料を使用して PCB を製造することを推奨します。

### 9.2 インピーダンス要件

TI は、すべての信号に対して PCB のターゲットインピーダンスを  $50\Omega \pm 10\%$  にすることを推奨しています。例外が 表 9-1 に一覧表示されています。

**表 9-1. 特別なインピーダンス要件**

| 信号のタイプ           | 信号名                                                                                                                                                                         | インピーダンス ( $\Omega$ )                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| DMD 高速データ信号      | DMD_HSSI0_N_(0...7)、<br>DMD_HSSI0_P_(0...7)、<br>DMD_HSSI1_N_(0...7)、<br>DMD_HSSI1_P_(0...7)、<br>DMD_HSSI0_CLK_N、<br>DMD_HSSI0_CLK_P、<br>DMD_HSSI1_CLK_N、<br>DMD_HSSI1_CLK_P | 100 $\Omega$ 差動 (50 $\Omega$ シングル エンド) |

| DMD 低速インターフェイス信号 | DMD_LS0_WDATA_N、<br>DMD_LS0_WDATA_P、<br>DMD_LS0_CLK_N、<br>DMD_LS0_CLK_P                                                                                                     | 100 $\Omega$ 差動 (50 $\Omega$ シングル エンド) |

### 9.3 基板面

表 9-2 に、各層の層の積層と銅重量を示します。

**表 9-2. 層のスタックアップ**

| 層の番号 | レイヤ名                      | 銅重量(オンス)       | 備考                                                                                                   |

|------|---------------------------|----------------|------------------------------------------------------------------------------------------------------|

| 1    | サイド A — DMD、主要部品、電源ミニプレーン | 0.5 オンス (メッキ前) | DMD とエスケープ 2 個のデータ入力コネクタ。電源回路や 2 個のデータ入力コネクタを含む上面のコンポーネント。低周波信号の配線取り回し。銅箔 (GND) の厚さを最大 1 オンスにメッキします。 |

| 2    | グランド                      | 0.5            | 信号層 #1、#3 のソリッド グランド プレーン (ネット GND) リファレンス                                                           |

| 3    | 信号 (高周波)                  | 0.5            | 高速信号層。入力コネクタから DMD への高速差動データ バス                                                                      |

| 4    | グランド                      | 0.5            | 信号層 #3、#5 のソリッド グランド プレーン (ネット GND) リファレンス                                                           |

| 5    | 電源                        | 0.5            | 1.8V、3.3V、10V、-14V、18V 用の 1 次側分割電源プレーン                                                               |

| 6    | 電源                        | 0.5            | 1.8V、3.3V、10V、-14V、18V 用の 1 次側分割電源プレーン                                                               |

| 7    | グランド                      | 0.5            | 信号層 #8 のソリッド グランド プレーン (ネット GND) のリファレンス                                                             |

| 8    | 信号 (高周波)                  | 0.5            | 高速信号層。入力コネクタから DMD への高速差動データ バス                                                                      |

| 9    | グランド                      | 0.5            | 信号層 #8、#10 のソリッド グランド プレーン (ネット GND) リファレンス                                                          |

| 10   | サイド B — 2 次側部品、パワー ミニプレーン | 0.5 オンス (メッキ前) | 必要に応じて個別部品を使用。低周波信号の配線取り回し。銅箔の厚さを最大 1 オンスにメッキします。                                                    |

## 9.4 パターン幅、間隔

特に記述のない限り、TI はすべての信号が 0.005 インチ/0.015 インチ (トレース幅/スペーシング) の設計ルールに従うことを推奨しています。インピーダンスおよびスタックアップ要件の分析を使用して、実際のトレース幅を決定し、計算します。

スペースが許す限り、すべての電圧信号の幅を最大化します。[表 9-3](#) に記載されている幅と間隔の要件に従ってください。

**表 9-3. 特殊なパターン幅、間隔の要件**

| 信号名                 | 最小パターン幅 (MIL) | 最小パターン間隔 (MIL) | レイアウト要件                                                                     |

|---------------------|---------------|----------------|-----------------------------------------------------------------------------|

| GND                 | 最大値           | 5              | 接続ピンへのパターン幅を最大化します。                                                         |

| P3P3V               | 40            | 15             | 必要に応じて、レイヤ 1 とレイヤ 10 にミニプレーンを作成します。必要に応じて、複数のビアを使用してレイヤ 1 と 10 のデバイスに接続します。 |

| P1P8V               | 40            | 15             | 必要に応じて、レイヤ 1 とレイヤ 10 にミニプレーンを作成します。必要に応じて、複数のビアを使用してレイヤ 1 と 10 のデバイスに接続します。 |

| V <sub>OFFSET</sub> | 40            | 15             | 必要に応じて、レイヤ 1 とレイヤ 10 にミニプレーンを作成します。必要に応じてレイヤ 1 とレイヤ 10 のデバイスに接続します。         |

| V <sub>RESET</sub>  | 40            | 15             | 必要に応じて、レイヤ 1 とレイヤ 10 にミニプレーンを作成します。必要に応じてレイヤ 1 とレイヤ 10 のデバイスに接続します。         |

| V <sub>BIAIS</sub>  | 40            | 15             | 必要に応じて、レイヤ 1 とレイヤ 10 にミニプレーンを作成します。必要に応じてレイヤ 1 とレイヤ 10 のデバイスに接続します。         |

## 9.5 電源

TI は、電源プレーンや電源プレーンに隣接するプレーン上での信号配線を強く避けるよう推奨しています。信号が電源プレーンに隣接するレイヤで配線される必要がある場合、EMI を防止し、信号の整合性を保つために、信号は電源プレーンの分割部分を越えてはなりません。

すべての内部デジタル グランド (GND) プレーンは、可能な限り多くの場所に接続します。すべての内部グランド プレーンは、接続間の最小距離が 0.5 インチになるように接続してください。デバイスの通常のグランド接続により十分なグラウンド ビアがある場合、追加のビアは必要ないかもしれません。

各部品の電源ピンおよびグランド ピンは、少なくとも 1 つのビアを使用して電源プレーンおよびグランド プレーンに接続します。部品の電源ピンおよびグランド ピンのトレース長は最小限に抑えます。(理想的には、0.100 インチ未満)。

グラウンド プレーン スロットは推奨しません。

## 9.6 パターン長のマッチングの推奨

[表 9-4](#) および [表 9-5](#) に、信号パターン長のマッチングの推奨要件を示します。次のガイドラインに従って、PCB 上の広い領域にわたって長い配線を引くのを避けてください:

- 長い信号が蛇行パターンで配線されるように、パターン長を一致させます

- 回転の数は可能な限り少なくします。

- 回転角度が 45 度以下でないことを確認します。

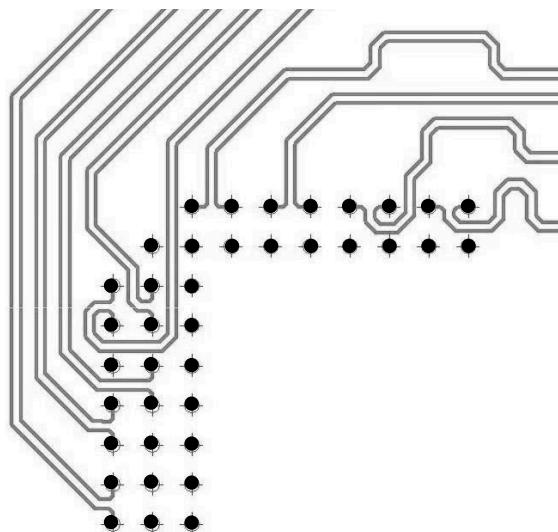

[図 9-1](#) に、HSSI 信号ペアの配線例を示します。

[表 9-4](#) に示す信号は、最大 3.2Gbps のデータレートで動作するように規定されています。これらの信号については、レイヤの変更を最小限に抑えます。ビアの数は可能な限り少なくします。長さを最小限に抑えつつ、急な曲がりやレイヤの切り替えは避けます。レイヤの切り替えが必要な場合は、信号ビアの周囲に GND ビアを配置して、信号の帰路を確保します。差動信号ペアから別のペアへの距離は、ペア内の距離の少なくとも 2 倍にする必要があります。

**表 9-4. HSSI 高速 DMD データ信号**

| 信号名                                       | リファレンス信号                           | ルーティング仕様 | 単位  |

|-------------------------------------------|------------------------------------|----------|-----|

| DMD_HSSI0_N(0...7),<br>DMD_HSSI0_P(0...7) | DMD_HSSI0_CLK_N,<br>DMD_HSSI_CLK_P | ±0.25    | インチ |

| DMD_HSSI1_N(0...7),<br>DMD_HSSI1_P(0...7) | DMD_HSSI0_CLK_N,<br>DMD_HSSI_CLK_P | ±0.25    | インチ |

| DMD_HSSI0_CLK_P                           | DMD_HSSI1_CLK_P                    | ±0.05    | インチ |

| Intra-pair P                              | Intra-pair N                       | ±0.01    | インチ |

**表 9-5. その他のタイミング クリティカルな信号**

| 信号名                                                           | 制約                                                        | ルーティング レイヤ |

|---------------------------------------------------------------|-----------------------------------------------------------|------------|

| LS_CLK_P, LS_CLK_N<br>LS_WDATA_P,<br>LS_WDATA_N<br>LS_RDATA_A | ペア内 (P から N)<br>0.01 インチ単位で一致<br>信号間<br>+/- 0.25 インチ単位で一致 | レイヤ 3, 8   |

**図 9-1. HSSI PCB 配線の例**

## 10 デバイスおよびドキュメントのサポート

### 10.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インストルメンツの出版物は、単独またはテキサス・インストルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 10.2 デバイス サポート

#### 10.2.1 デバイスの命名規則

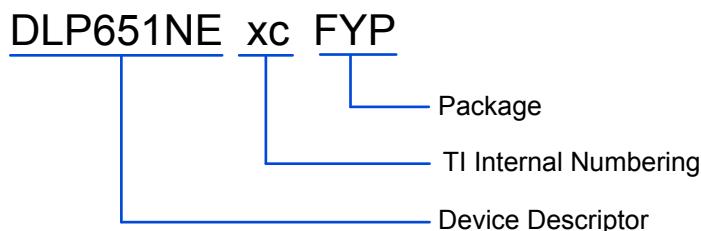

図 10-1. 部品番号の説明

#### 10.2.2 デバイスのマーキング

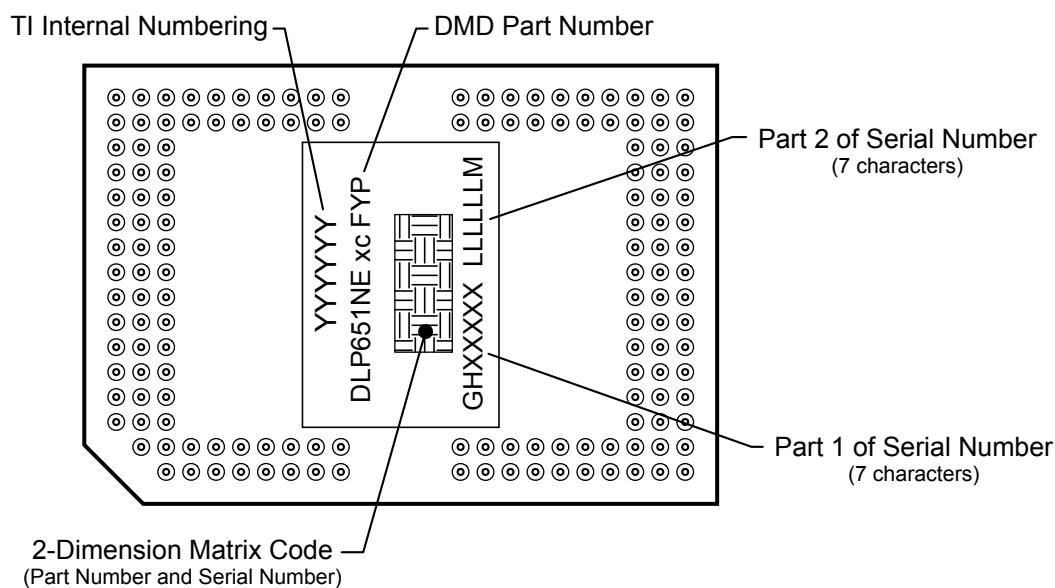

デバイスのマーキングには、人間が読める情報と2次元マトリクスコードの両方を使用しています。図 10-2 に、人間可読形式の情報を示します。2次元マトリクスコードは、DMD 型番、シリアル番号のパート 1 およびパート 2 を含む英数字の文字列です。

例:

図 10-2. DMD のマーキング位置

### 10.3 ドキュメントのサポート

#### 10.3.1 関連資料

次のドキュメントには、DMD とともに使用されるチップセットコンポーネントについての追加情報が掲載されています。

- [DLPC7530 ディスプレイコントローラデータシート](#)

- [TPS65145 データシート](#)

- [『DLPA100 パワー/モータードライバ』データシート](#)

## 10.4 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

## 10.5 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

## 10.6 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

DLP® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 10.7 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 10.8 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 11 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision B (January 2025) to Revision C (September 2025)</b> | <b>Page</b> |

|------------------------------------------------------------------------------|-------------|

| • 「推奨動作条件」を更新.....                                                           | 7           |

| • 「熱に関する情報」のデバイスの誤字を修正.....                                                  | 9           |

| • 行 $Q_{ARRAY}=3.0W + (0.45 \times 48W)=24.6W$ の誤字を訂正.....                   | 23          |

| <b>Changes from Revision A (May 2022) to Revision B (January 2025)</b>            | <b>Page</b> |

|-----------------------------------------------------------------------------------|-------------|

| • ドキュメント全体のコントローラを DLPC7530 に更新.....                                              | 1           |

| • DLP 製品のサードパーティ検索ツールおよび『テキサス・インスツルメンツの DLP ディスプレイテクノロジーを使用した設計の開始』へのリンクを追加。..... | 1           |

| • マイクロミラー アレイの光学特性表を更新.....                                                       | 18          |

| • マイクロミラー アレイ温度の計算を更新.....                                                        | 23          |

| • マイクロミラーの電力密度の計算セクションを追加.....                                                    | 24          |

| • ウィンドウ開口部照明オーバーフィルの計算を追加.....                                                    | 26          |

---

|                                            |    |

|--------------------------------------------|----|

| • ランデッド デューティ サイクルの計算式を更新.....             | 27 |

| • 代表的なアプリケーションに関する変更:レーザー蛍光構成と LED 構成..... | 30 |

---

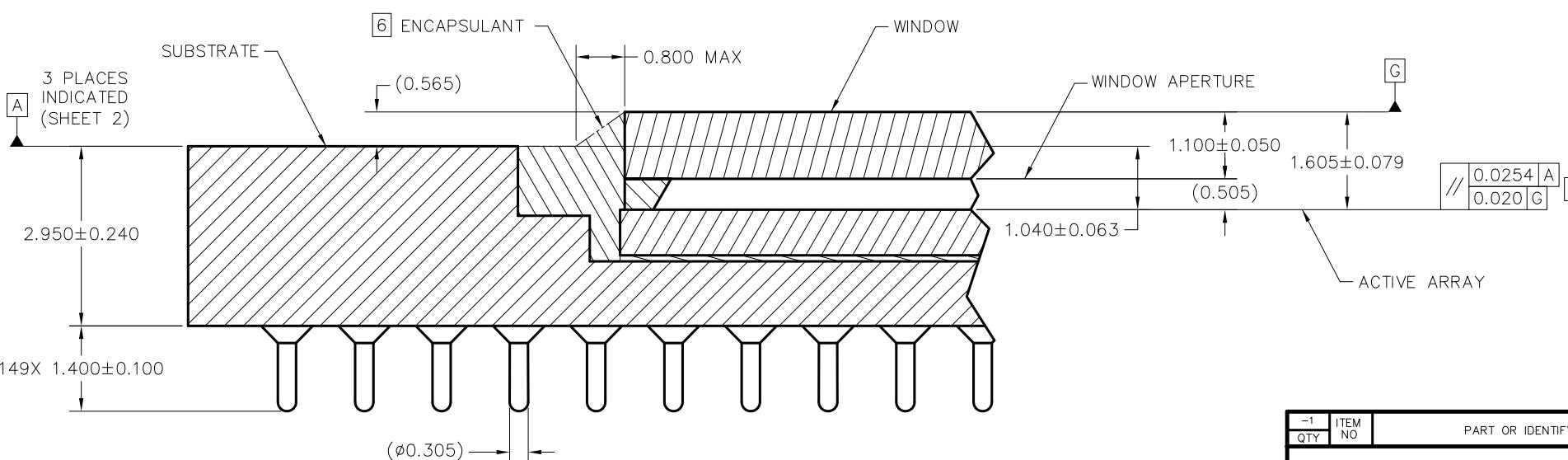

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 12.1 付録：パッケージオプション

### 12.1.1 パッケージ情報

| 発注可能なデバイス     | ステータス <sup>(1)</sup> | パッケージタイプ | パッケージ図 | ピン  | パッケージの数量 | エコプラン <sup>(2)</sup> | リード / ボール仕上げ <sup>(4)</sup> | MSL ピーク温度 <sup>(3)</sup> | 動作温度 (°C) | デバイスマーキング <sup>(5) (6)</sup> |

|---------------|----------------------|----------|--------|-----|----------|----------------------|-----------------------------|--------------------------|-----------|------------------------------|