# DP83TC815-Q1 100Base-T1 車載用イーサネット PHY トランシーバ、 IEEE802.1AS および TC10 スリープ・ウェーク付

## 1 特長

- IEEE802.3bw 準拠 100BASE-T1 PHY

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1:-40°C ~ +125°C, TA

- IEEE 802.1AS 時間同期

- 高精度 1pps 信号

- 同期ジッタ:< ±15ns 未満 (オプションで ±1ns まで低減)

- 同期オフセット:< ±30ns

- イベントのキャプチャとトリガに対応する複数の IO

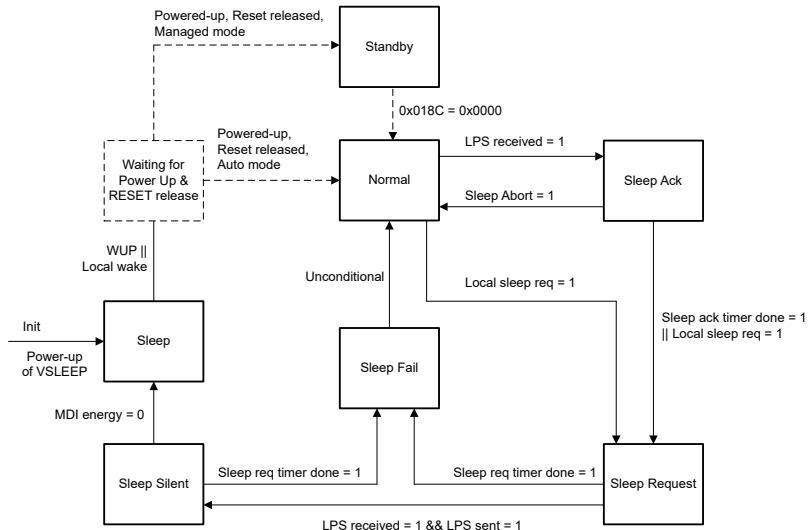

- OA TC-10 準拠のスリープ機能を備え、

- 堅牢な EMC 性能

- IEC62228-5、OA EMC 準拠

- IEC61000-4-2 ESD レベル 4 MDI:±8kV CD

- SAE J2962-3 EMC 準拠

- ±5% の非対称性で 39dBm の DPI 耐性

- GPS および Glonass 帯域の放射エミッションは 4dBμV 未満です

- ストリップライン放射:クラス II 準拠

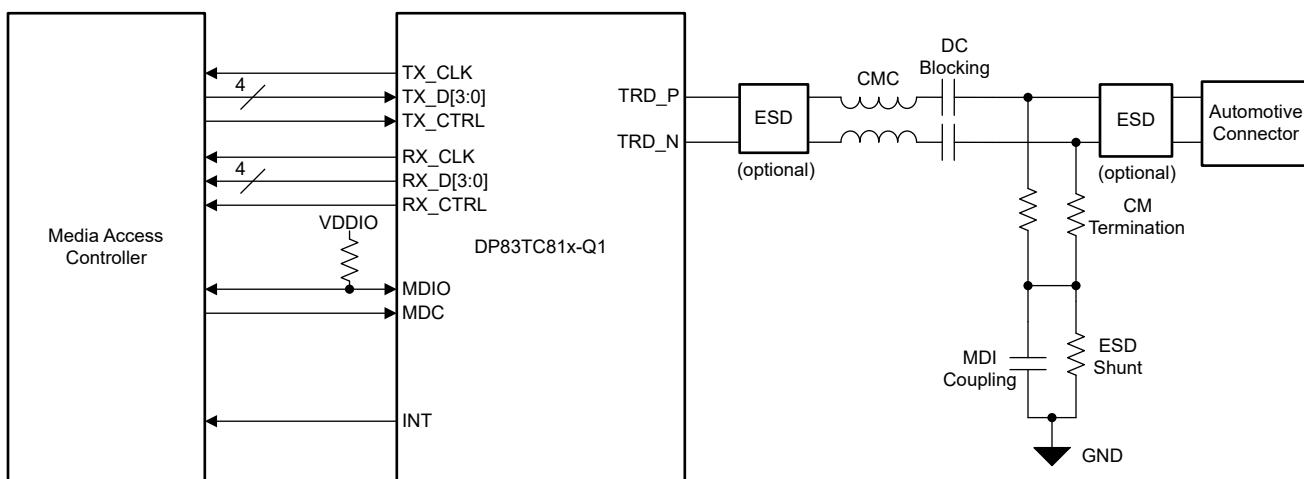

- MAC インターフェイス:MII、RMII、RGMII、SGMII

- TI の 100BASE-T1 および 1000BASE-T1 PHY とネットプリント互換 (BOM オプションあり)

- 48V 準備完了:MDI への VBAT 過渡電圧は最大 ±70V まで対応

- 診断ツール キット

- 信号品質インジケータ (SQI) および時間領域反射測定 (TDR)

- 電圧、温度および ESD センサ

- PPM モニタ:外部クロックの ppm ドリフトを監視 (最大 ±100ppb の精度)

- 単一の 3.3V 電源で動作可能

## 2 アプリケーション

- 先進運転支援システム (ADAS)

- レーダ同期

- ボディ エレクトロニクスおよび照明

- ボディコントロール モジュール

- ゾーン制御モジュール

- テレマティクス

## 3 説明

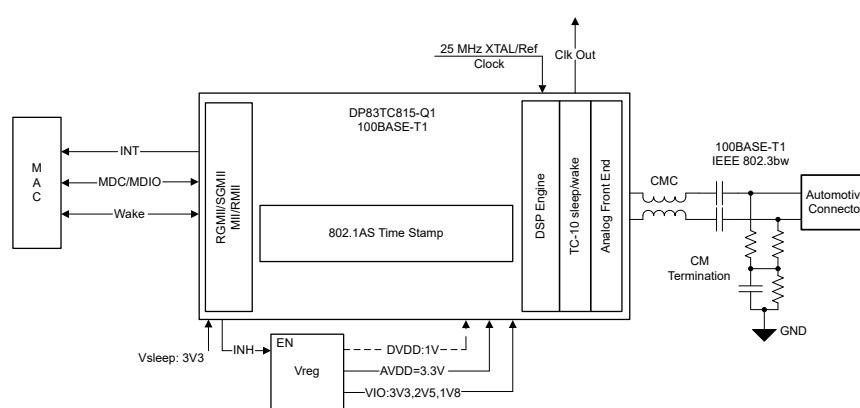

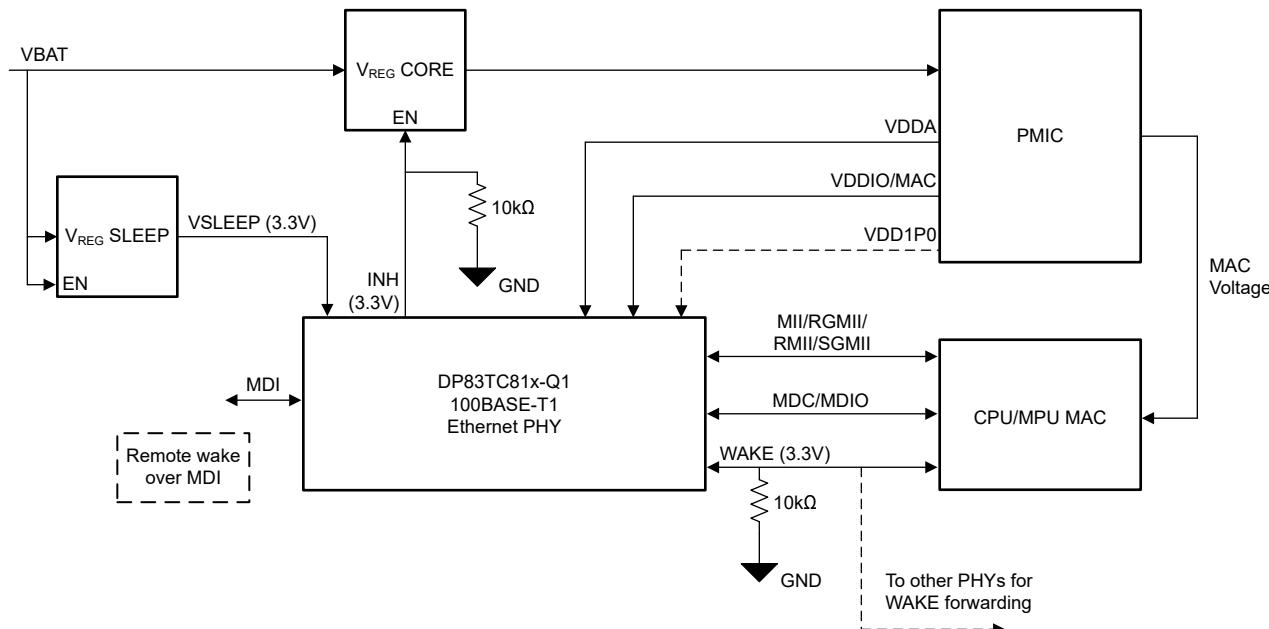

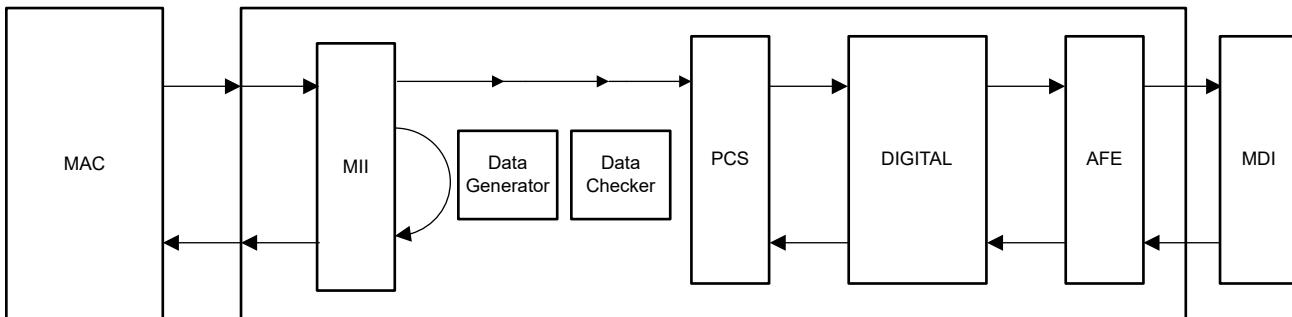

DP83TC815-Q1 デバイスは、IEEE 802.3bw と Open Alliance (OA) に準拠した車載認定済み 100Base-T1 イーサネット物理層トランシーバです。このデバイスは、シールドあり、なしの単一ツイストペア ケーブル上でデータを送受信するために必要なすべての物理層機能を、xMII インターフェイスの柔軟性で提供します。

DP83TC815-Q1 は IEEE802.1AS および IEEE1588v2 を統合しており、時間に敏感なリアルタイム制御アプリケーション向けに、高精度な時刻同期およびハードウェア タイムスタンピングを実現します。

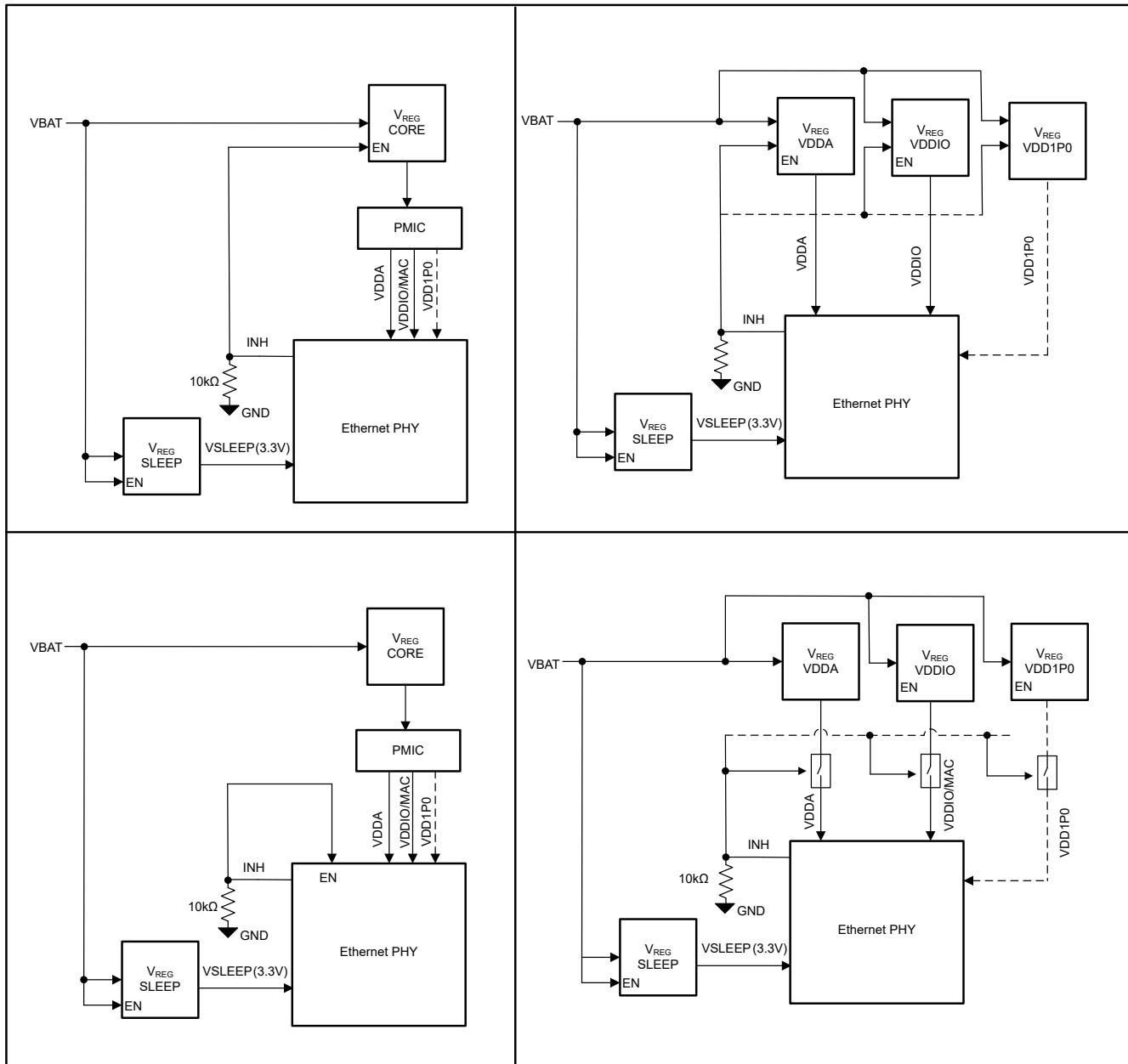

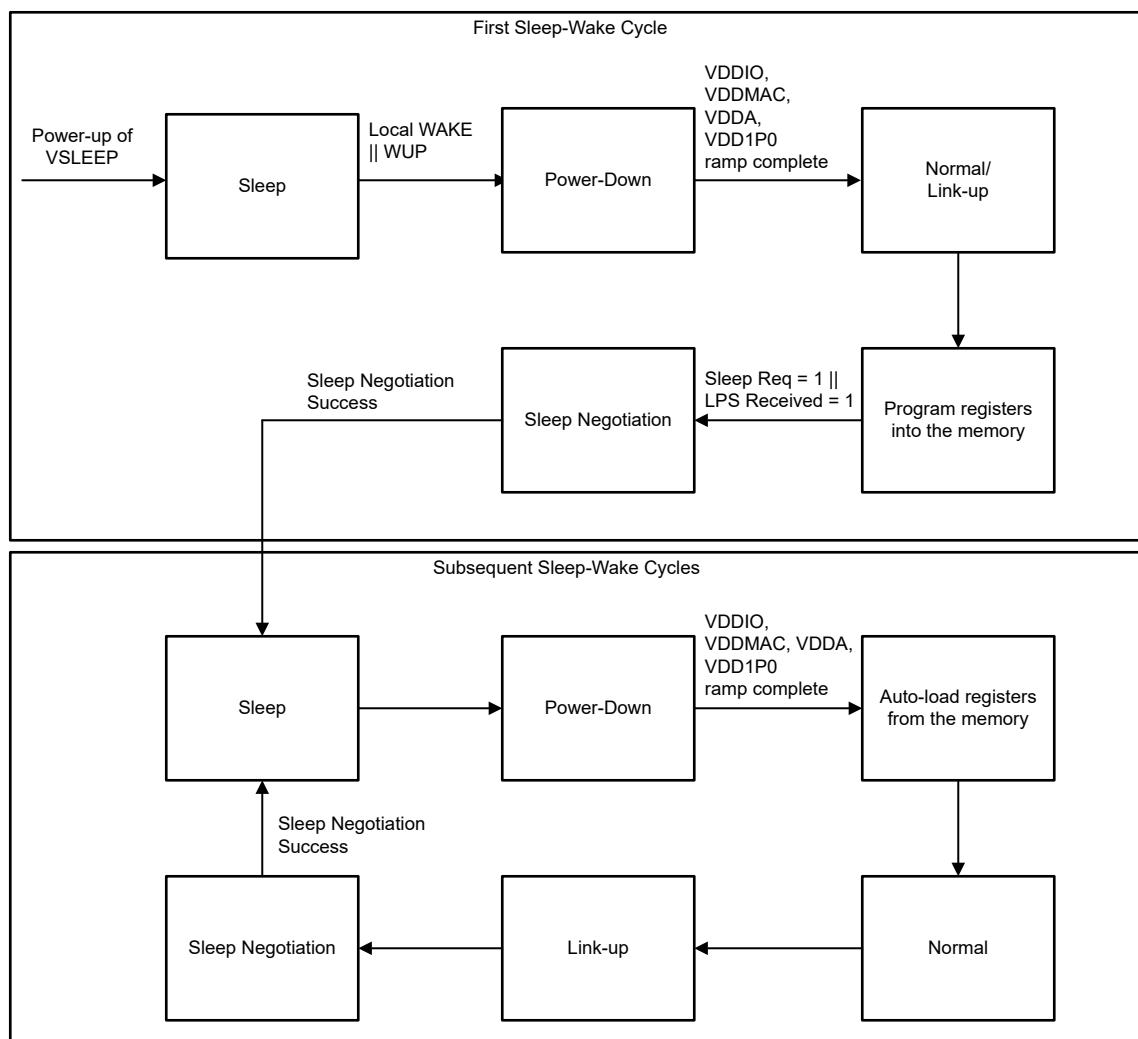

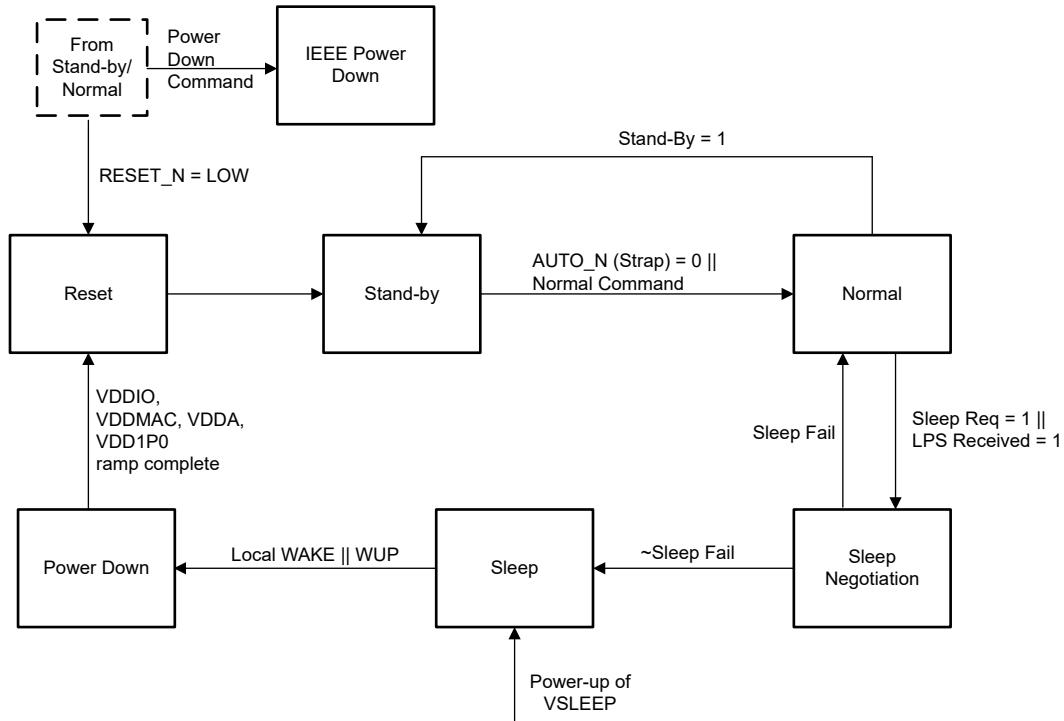

DP83TC815-Q1 は、通信が不要なときにシステムの消費電力を低減するためのウェークアップ転送機能を備えた OA TC-10 低消費電力スリープ機能をサポートしています。

### パッケージ情報

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|--------------|----------------------|--------------------------|

| DP83TC815-Q1 | RHA (VQFN, 36)       | 6.00mm × 6.00mm          |

(1) 詳細については、セクション 12 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はビンも含まれます。

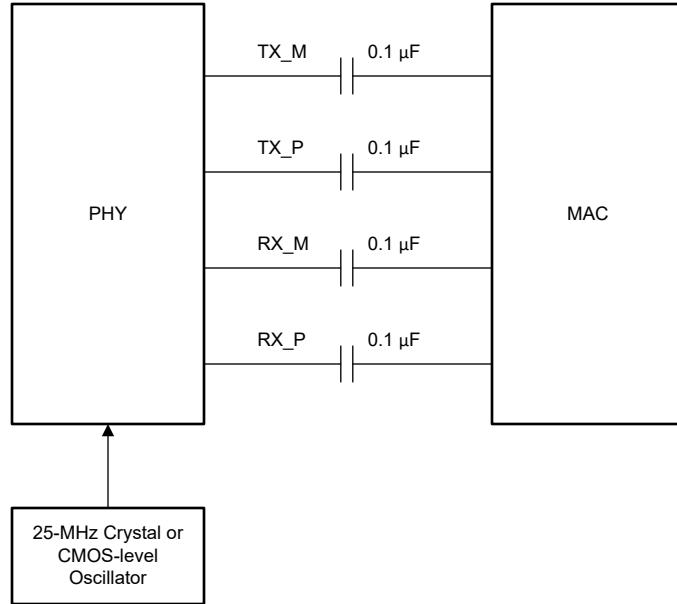

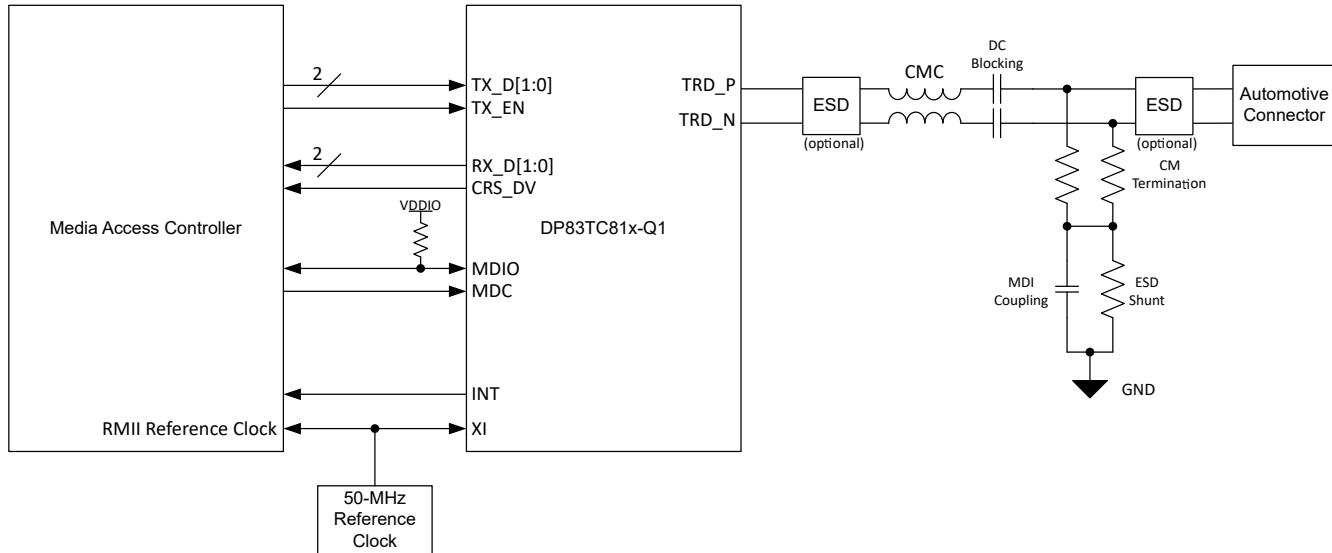

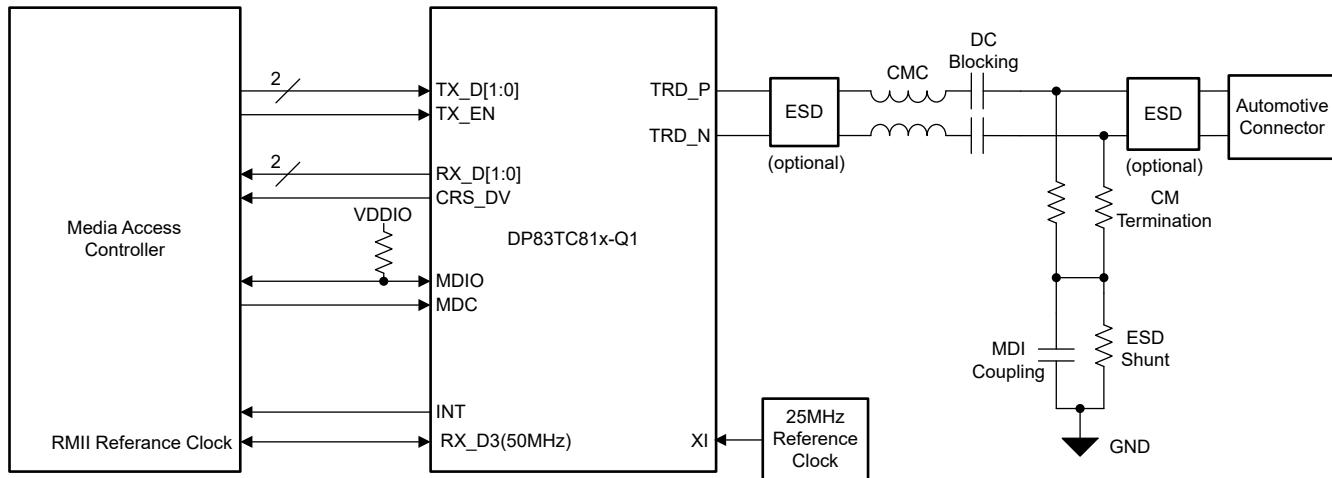

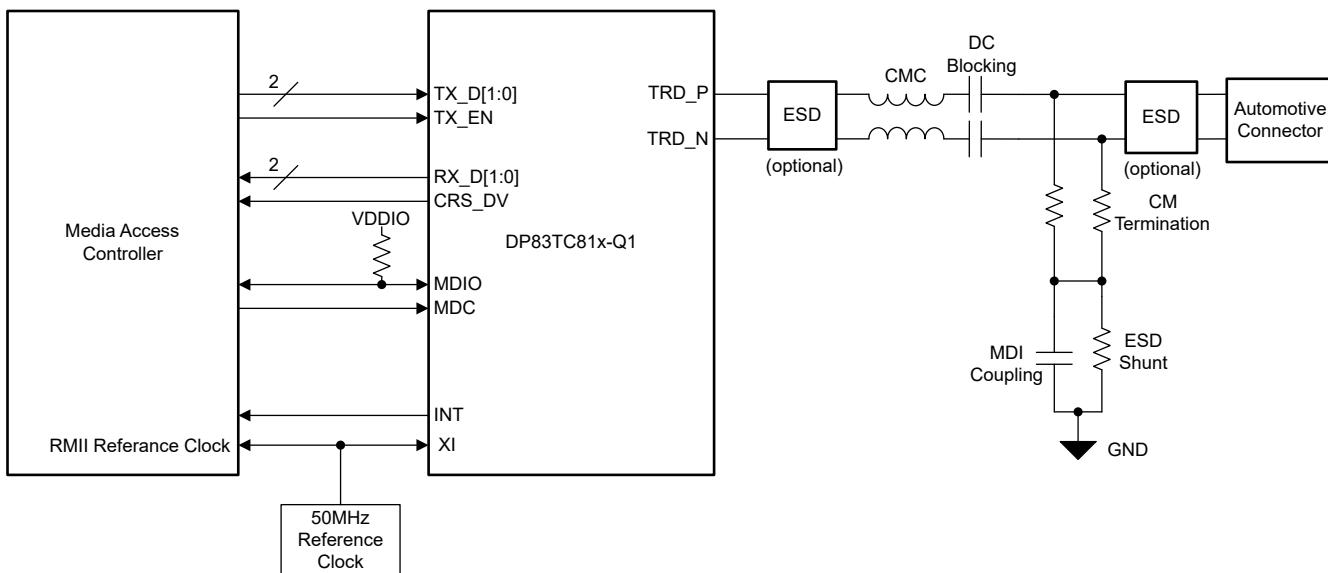

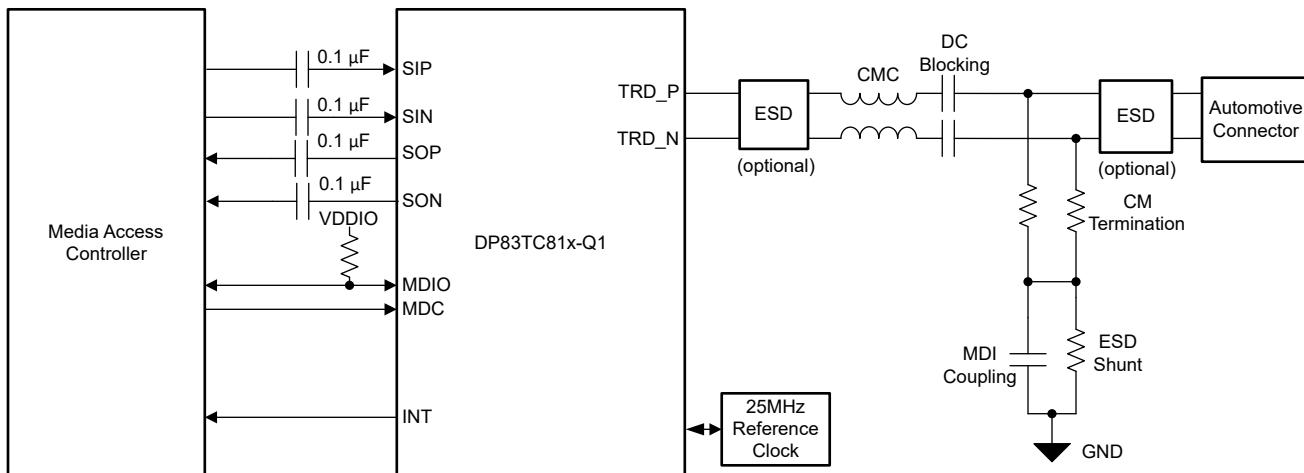

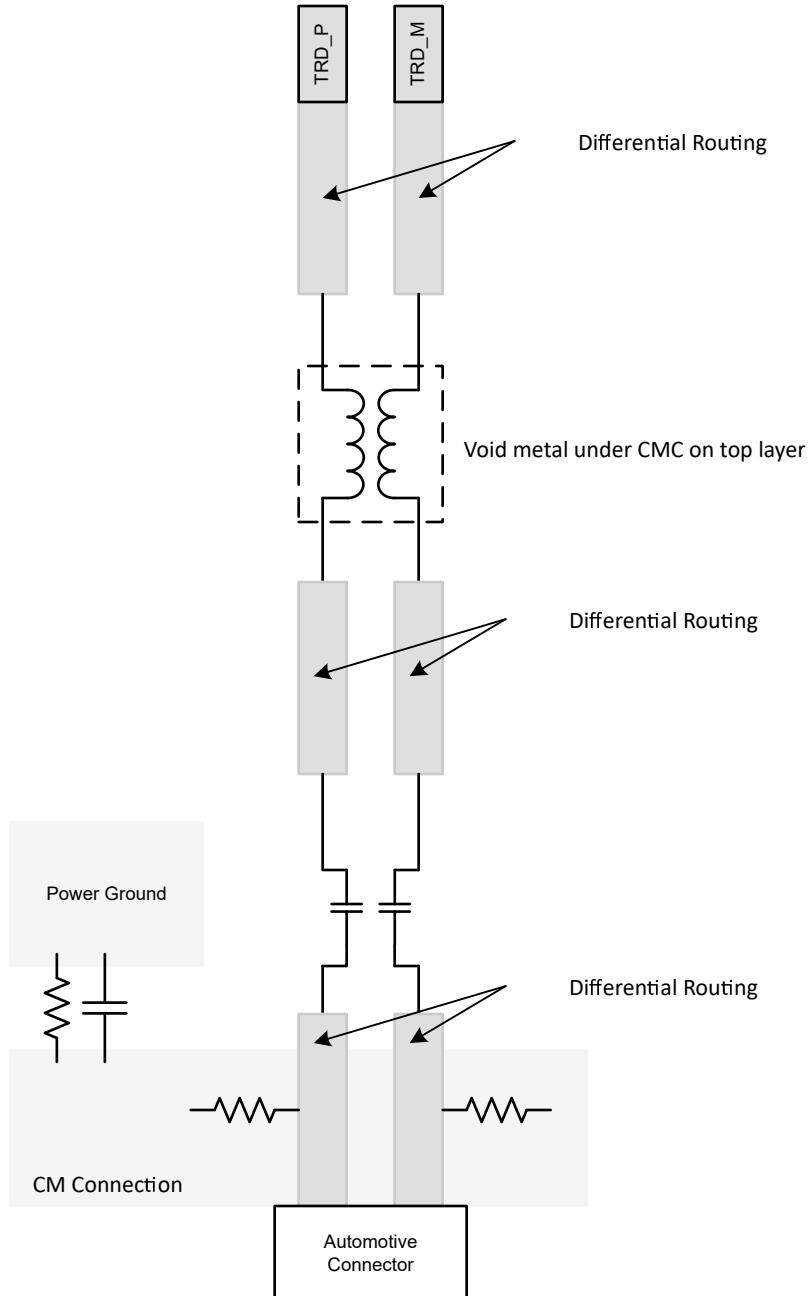

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|               |    |                         |     |

|---------------|----|-------------------------|-----|

| 1 特長          | 1  | 7.3 機能説明                | 34  |

| 2 アプリケーション    | 1  | 7.4 デバイスの機能モード          | 68  |

| 3 説明          | 1  | 7.5 プログラミング             | 80  |

| 4 デバイス比較表     | 3  | 8 レジスタ マップ              | 84  |

| 5 ピン構成および機能   | 4  | 8.1 レジスタ アクセスの概要        | 84  |

| 5.1 ピンの電源ドメイン | 8  | 8.2 DP83TC815 のレジスタ     | 85  |

| 5.2 ピンの状態     | 9  | 9 アプリケーションと実装           | 163 |

| 5.3 ピン多重化     | 14 | 9.1 アプリケーション情報          | 163 |

| 6 仕様          | 15 | 9.2 代表的なアプリケーション        | 163 |

| 6.1 絶対最大定格    | 15 | 9.3 電源に関する推奨事項          | 168 |

| 6.2 ESD 定格    | 15 | 9.4 レイアウト               | 171 |

| 6.3 推奨動作条件    | 15 | 10 デバイスおよびドキュメントのサポート   | 175 |

| 6.4 熱に関する情報   | 16 | 10.1 デバイス サポート          | 175 |

| 6.5 電気的特性     | 16 | 10.2 ドキュメントの更新通知を受け取る方法 | 175 |

| 6.6 タイミング要件   | 20 | 10.3 サポート・リソース          | 175 |

| 6.7 タイミング図    | 24 | 10.4 商標                 | 175 |

| 6.8 代表的特性     | 31 | 10.5 静電気放電に関する注意事項      | 175 |

| 7 詳細説明        | 32 | 10.6 用語集                | 175 |

| 7.1 概要        | 32 | 11 改訂履歴                 | 175 |

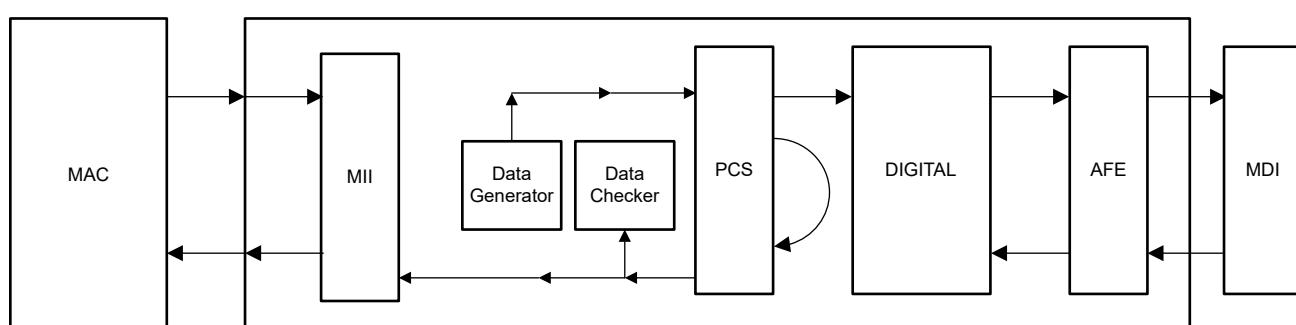

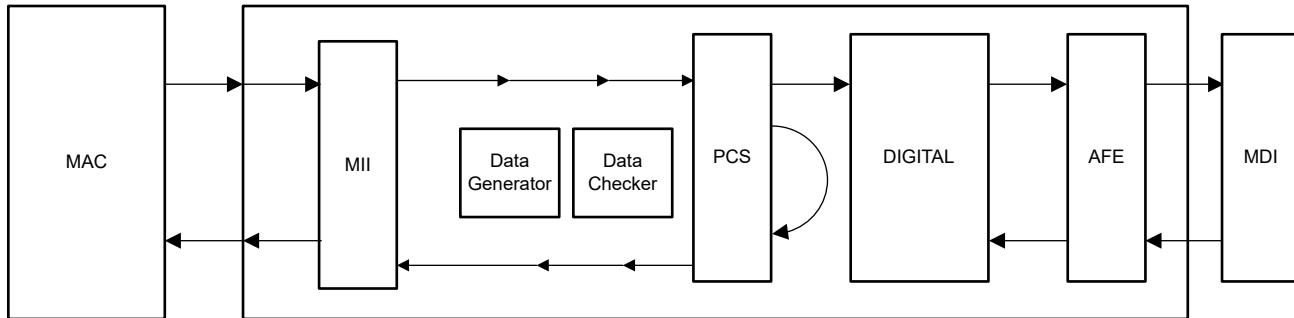

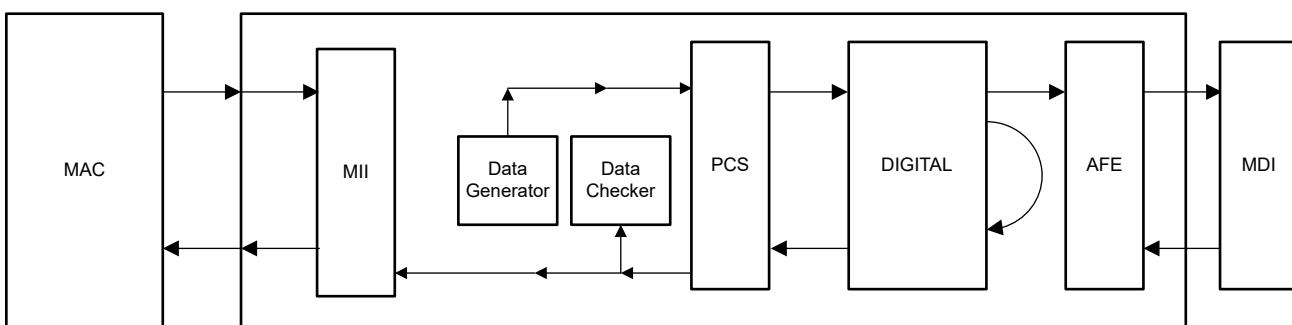

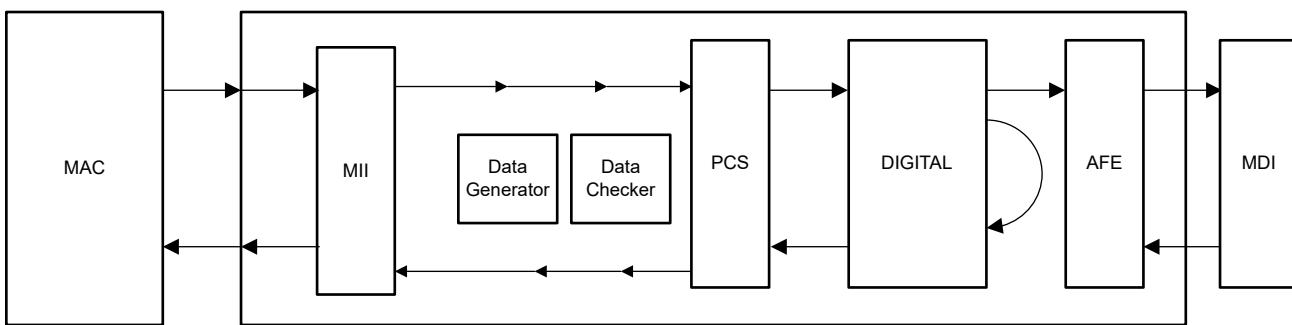

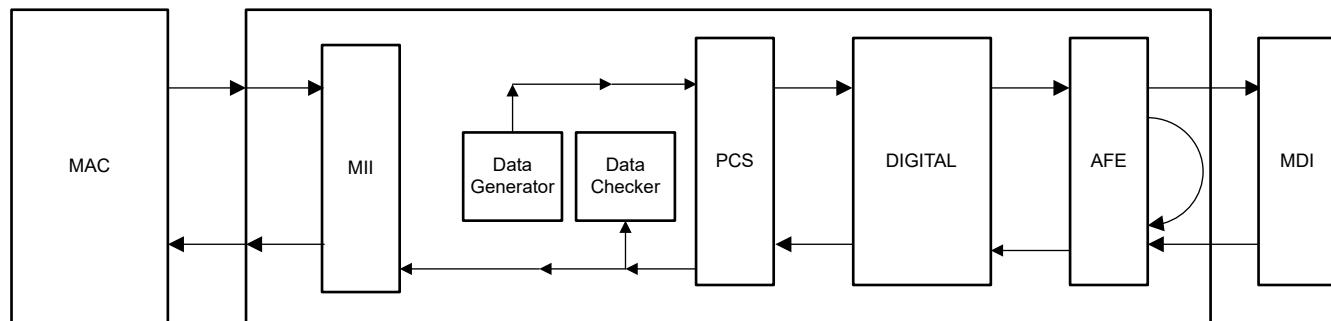

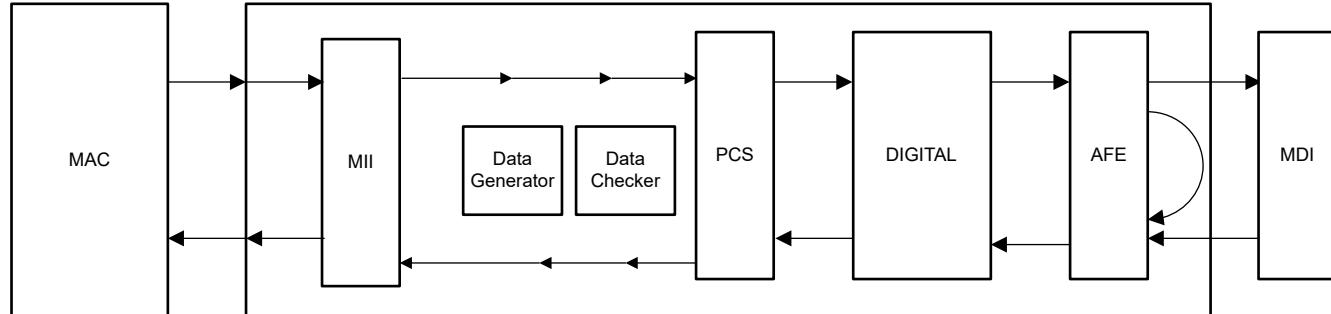

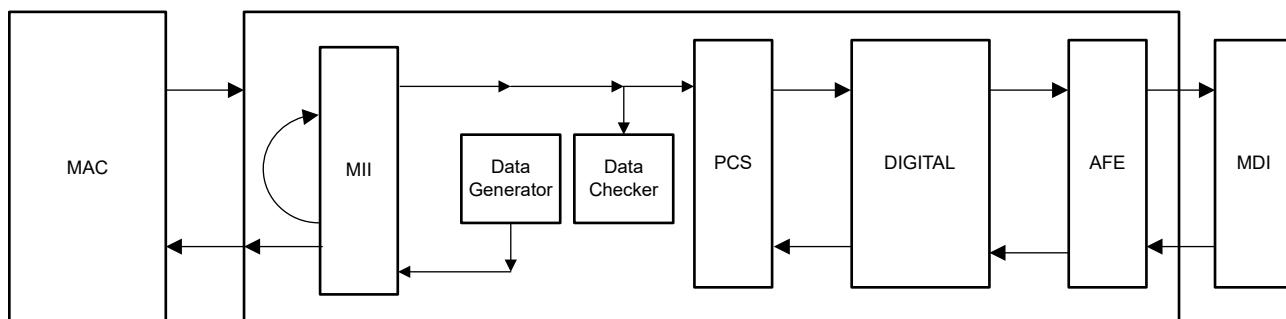

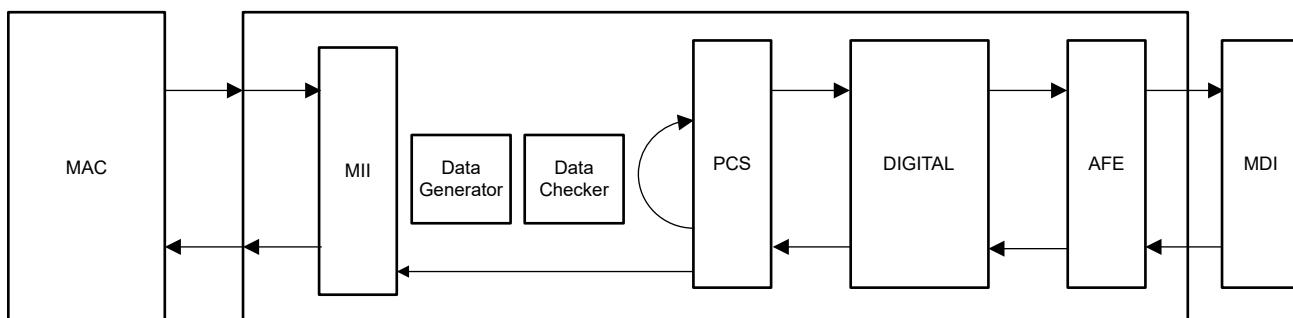

| 7.2 機能ブロック図   | 33 | 12 メカニカル、パッケージ、および注文情報  | 176 |

## 4 デバイス比較表

| 部品番号          | TC10? | MACsec? | 802.1AS? | AVB クロック? | フットプリント互換? |

|---------------|-------|---------|----------|-----------|------------|

| DP83TC812x-Q1 | あり    | なし      | なし       | なし        | あり         |

| DP83TC814x-Q1 | なし    | なし      | なし       | なし        | あり         |

| DP83TC815-Q1  | あり    | なし      | あり       | なし        | あり         |

| DP83TC816-Q1  | あり    | なし      | あり       | あり        | あり         |

| DP83TC817S-Q1 | あり    | あり      | あり       | なし        | あり         |

| DP83TC818S-Q1 | あり    | あり      | あり       | あり        | あり         |

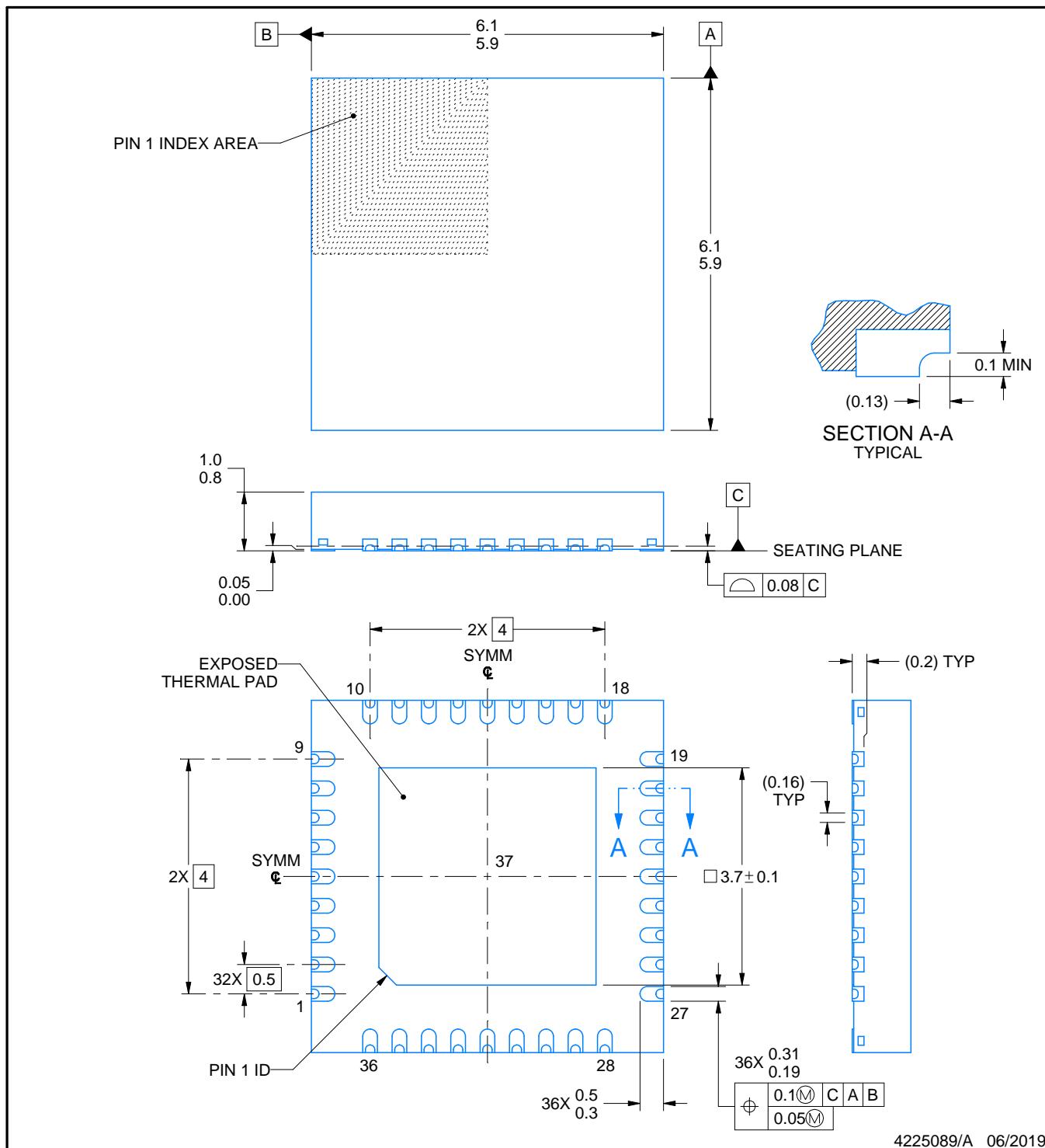

## 5 ピン構成および機能

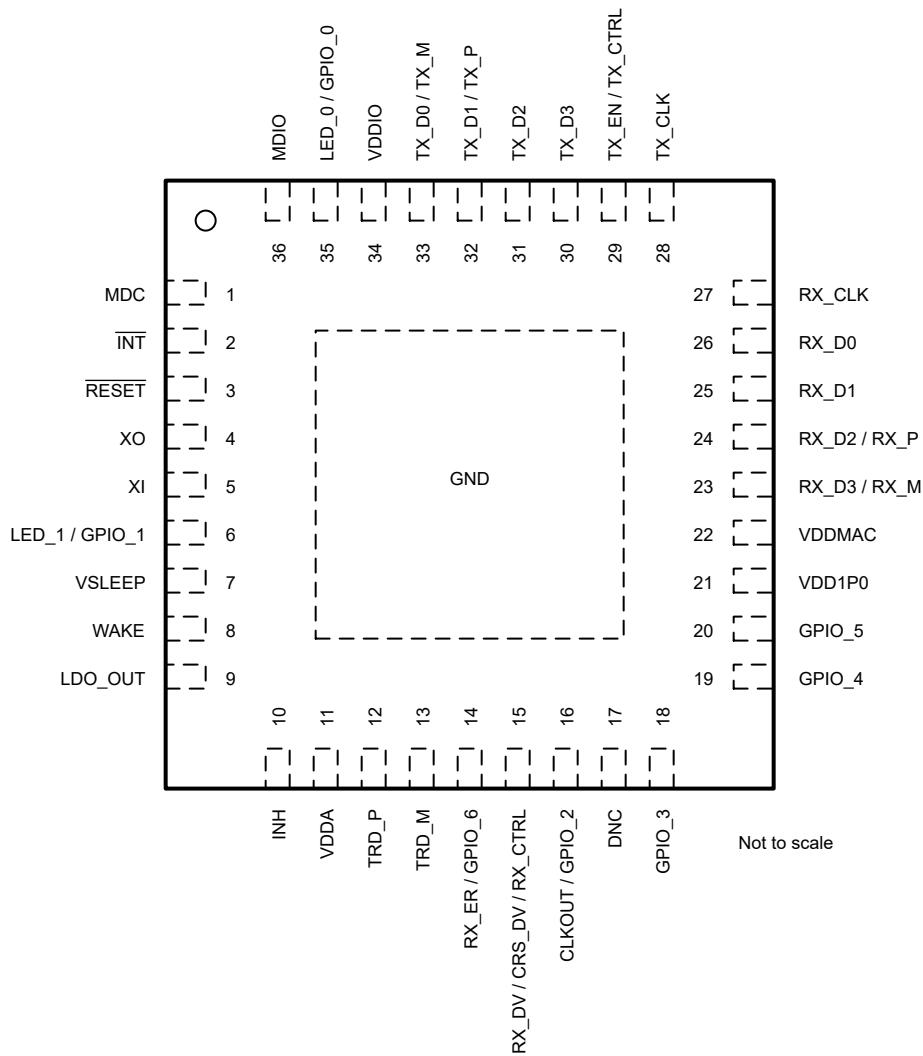

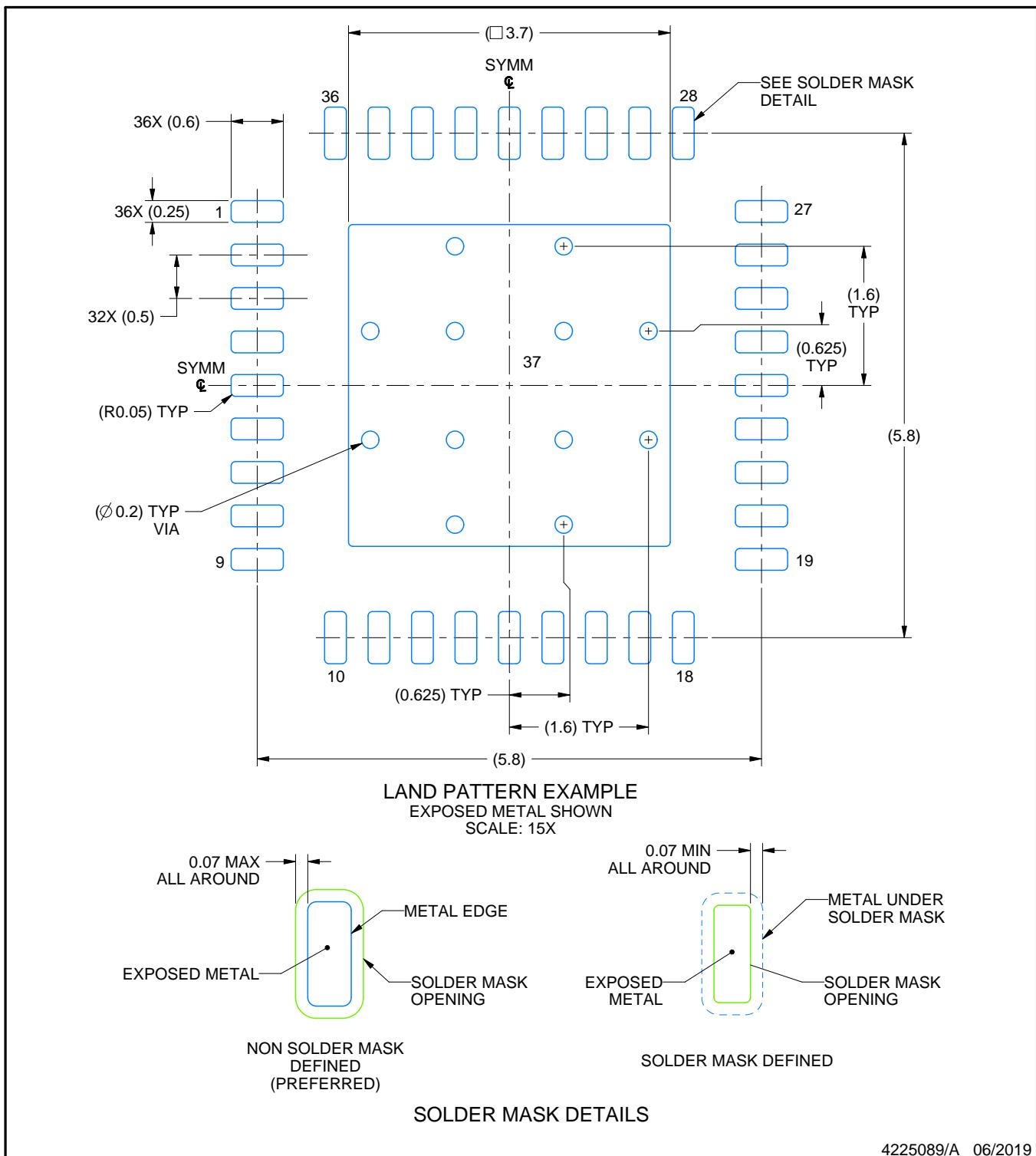

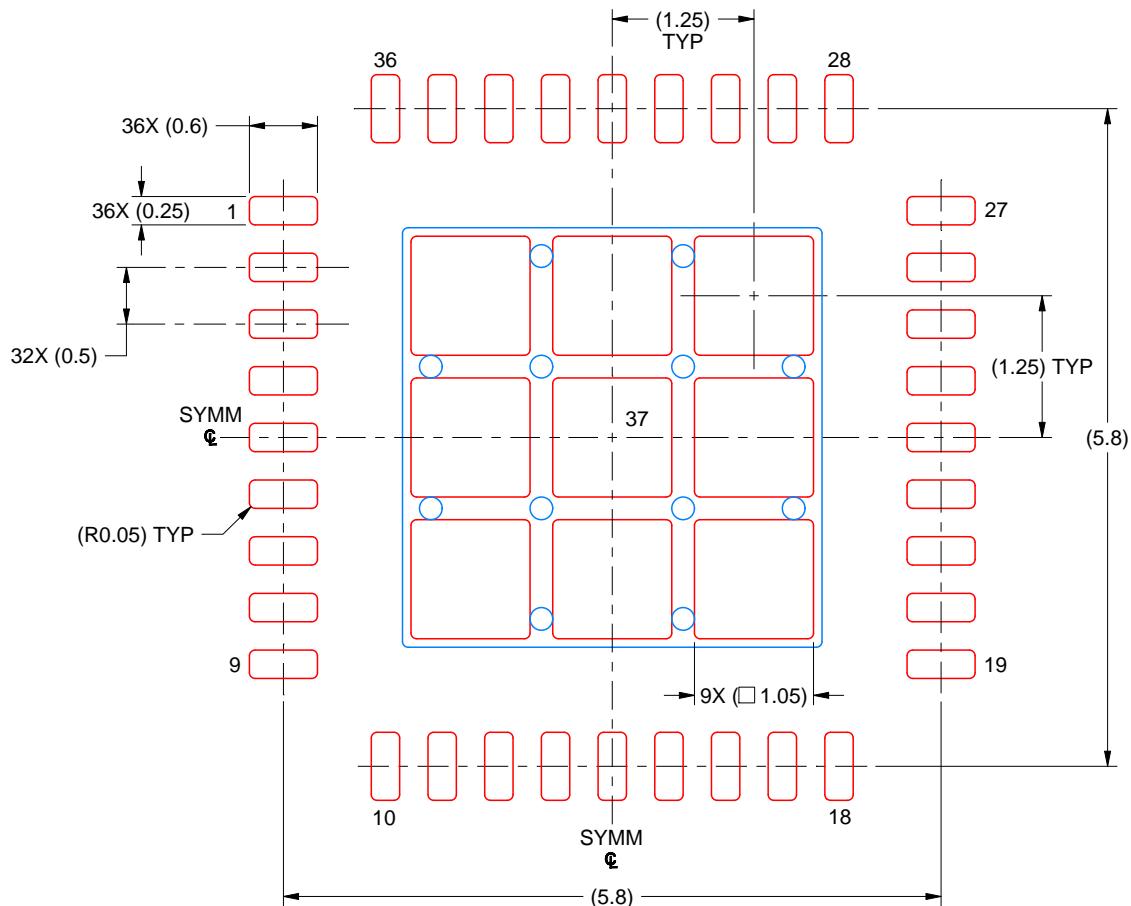

図 5-1. DP83TC815-Q1 RHA パッケージ 36 ピン VQFN 上面図

**表 5-1. ピンの機能**

| ピン                           |    | 状態 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------|----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2)</sup>            | 番号 |                   |                                                                                                                                                                                                                                                                                                                                                     |

| <b>MAC インターフェイス</b>          |    |                   |                                                                                                                                                                                                                                                                                                                                                     |

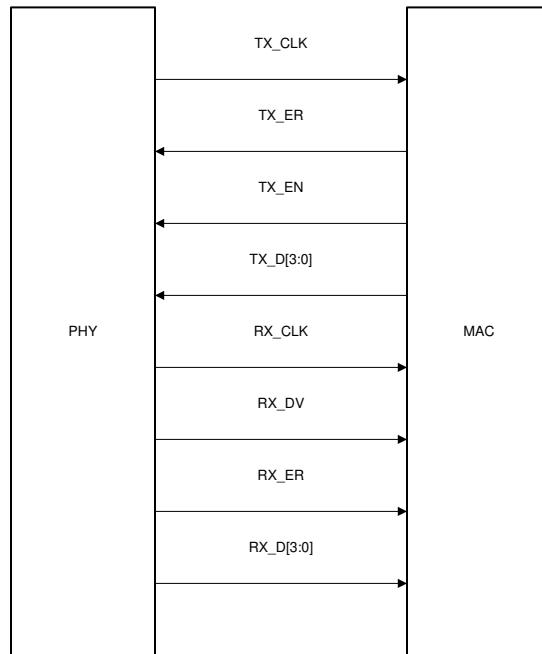

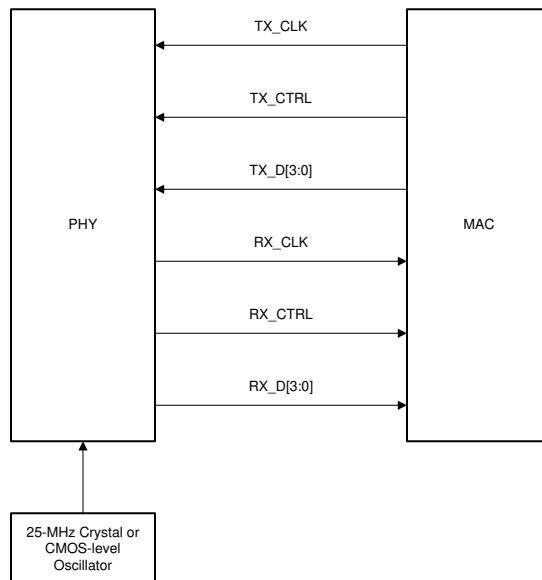

| RX_CLK                       | 27 | S, PD, O          | <b>受信クロック:</b> MII および RGMII モードでは、受信クロックから 25MHz 基準クロックが供給されます。<br><b>RMII および SGMII モードでは未使用</b>                                                                                                                                                                                                                                                  |

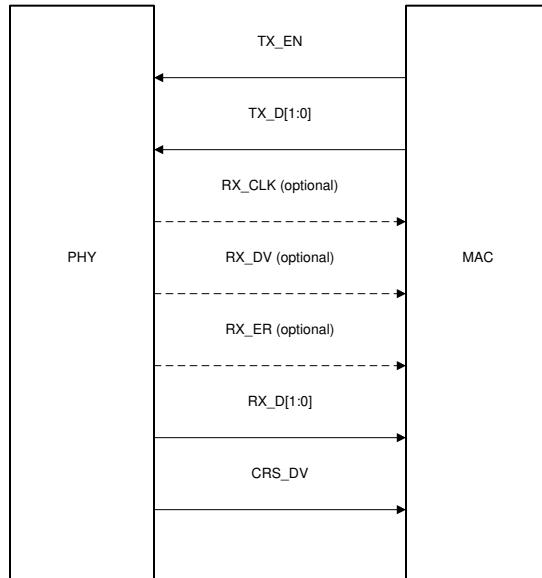

| RX_D0                        | 26 | S, PD, O          | <b>受信データ:</b> ケーブルで受信されたシンボルはデコードされ、RX_CLK の立ち上がりエッジに同期してこれらのピンから送信されます。RX_DV がアサートされている間のみ有効なデータを含みます。MII および RGMII モードでは、データニブル RX_D[3:0] を出力します。RMII モードでは 2 ビット RX_D[1:0] を出力します。                                                                                                                                                               |

| RX_D1                        | 25 |                   | PHY が RMII リーダー モードにブートストラップされている場合、50MHz クロック基準が RX_D3 に自動的に出力されます。このクロックは MAC に入力する必要があります。                                                                                                                                                                                                                                                       |

| RX_D2/<br>RX_P               | 24 |                   | <b>RX_M/RX_P:</b> 差動 SGMII データ出力。これらのピンは PHY から MAC にデータを送信します。                                                                                                                                                                                                                                                                                     |

| RX_D3/<br>RX_M               | 23 |                   |                                                                                                                                                                                                                                                                                                                                                     |

| RX_DV/<br>CRS_DV/<br>RX_CTRL | 15 | S, PD, O          | <b>受信データ有効:</b> MII モードでは、このピンは RX_D[3:0] 上に有効なデータが出力されていることを示します。<br><b>キャリア センス データ有効:</b> このピンは、キャリア検出とデータ有効を 1 本の非同期信号にまとめて示します。RMII モードでは、CRS_DV がアサートされているときに RX_D[1:0] にデータが出力されます。<br><b>RGMII 受信制御:</b> 受信制御は、受信データ有効表示と受信エラー表示を 1 つの信号に統合したものです。RX_DV は RX_CLK の立ち上がりエッジに示され、RX_ER は RX_CLK の立ち下りエッジに示されます。<br><b>SGMII モードでは未使用</b>      |

| RX_ER/<br>GPIO_6             | 14 | S, PD, O          | <b>受信エラー:</b> MII および RMII モードでは、このピンは受信パケット内で受信エラー シンボルが検出されたことを示します。MII モードでは、RX_CLK の立ち上がりエッジに同期して、RX_ER が High にアサートされます。RMII モードでは、基準クロックの立ち上がりエッジに同期して、RX_ER が High にアサートされます。PHY は受信エラーの際にデータを自動的に破損するため、MII または RMII ではこのピンはオプションです。<br><b>RGMII および SGMII モードでは未使用</b><br>このピンは GPIO_6 として使用することもできます。                                     |

| TX_CLK                       | 28 | PD, I, O          | <b>送信クロック:</b> MII モードでは、送信クロックとして 25MHz の出力 (50Ω ドライバ) を供給します。RGMII モードでは、このクロックが MAC 層から PHY へ入力されます。 <b>タイミング要件</b> に示す RGMII タイミング要件を満たすには、RGMII モードで 25MHz クロックを供給する必要があります。<br><b>RMII および SGMII モードでは未使用</b>                                                                                                                                 |

| TX_D0/<br>TX_M               | 33 | PD, I             | <b>送信データ:</b> MII および RGMII モードでは、送信データニブル TX_D[3:0] を、TX_CLK の立ち上がりエッジより前に MAC から受信します。RMII モードでは、TX_D[1:0] を基準クロックの立ち上がりエッジより前に MAC から受信します。RMII モードでは TX_D[3:2] は使用しません。<br><b>TX_M/TX_P:</b> 差動 SGMII データ入力。これらのピンは、MAC から PHY に送信されたデータを受信します。                                                                                                 |

| TX_D1/TX_P                   | 32 |                   |                                                                                                                                                                                                                                                                                                                                                     |

| TX_D2                        | 31 |                   |                                                                                                                                                                                                                                                                                                                                                     |

| TX_D3                        | 33 |                   |                                                                                                                                                                                                                                                                                                                                                     |

| TX_EN/<br>TX_CTRL            | 29 | PD, I             | <b>送信イネーブル:</b> MII モードでは、送信イネーブルは送信クロックの立ち上がりエッジより前に提示されます。TX_EN は、TX_D[3:0] に有効なデータ入力が存在することを示します。RMII リーダー モードでは、RX_D3 の立ち上がりエッジの前に送信の有効化が提示されます。TX_EN は、TX_D[1:0] に有効なデータ入力が存在することを示します。<br><b>RGMII 送信制御:</b> 送信制御は、送信イネーブルと送信エラー表示を 1 つの信号に統合したものです。TX_EN は TX_CLK の立ち上がりエッジの前に示され、TX_ER は TX_CLK の立ち下りエッジより前に示されます。<br><b>SGMII モードでは未使用</b> |

| <b>シリアル マネージメント インターフェイス</b> |    |                   |                                                                                                                                                                                                                                                                                                                                                     |

| MDC                          | 1  | I                 | <b>管理データ クロック:</b> MDIO シリアル マネージメント入力および出力データに同期したクロック。このクロックは、MAC の送信クロックおよび受信クロックと非同期にすることができます。最大クロック レートは 20MHz です。最小クロック レートはありません。                                                                                                                                                                                                           |

| MDIO                         | 36 | OD, IO            | <b>管理データ入出力 (Management Data Input/Output):</b> 管理ステーションまたは PHY から出力される可能性がある双方向管理データ信号。このピンはブルアップ抵抗を必要とします。同一の MDIO-MDC パスを複数の PHY で共有するシステムでは、MDIO ラインに 1 本だけブルアップ抵抗を使用する必要があります。<br>2.2kΩ と 9kΩ の間に抵抗を使用することを推奨します。<br>Open Alliance 準拠に合格するには MDIO/MDC へのアクセスが必要です。 <a href="#">セクション 7.3.8</a> を参照してください。                                      |

表 5-1. ピンの機能 (続き)

| ピン                       |    | 状態 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2)</sup>        | 番号 |                   |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>制御インターフェイス</b>        |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                       |

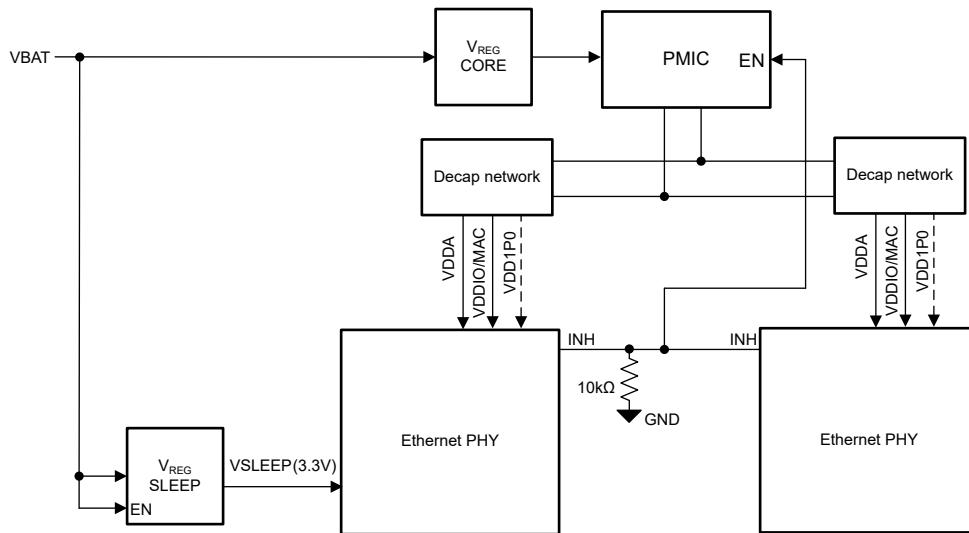

| INH                      | 10 | O, OD             | <b>INH:</b> アクティブ HIGH 出力です。PHY が TC-10 スリープのとき、このピンは ハイインピーダンスになります。このピンは、その他のすべての PHY 状態では HIGH になります。TC-10 回路を実装する場合は、2kΩ ~ 10kΩ の外付けプルダウン抵抗を使用する必要があります。複数のデバイスが INH ピンを共有している場合は、プルダウン抵抗を 1 本だけ使用します。                                                                                                                                                                                                            |

| INT                      | 2  | PU, OD, IO        | <b>割り込み:</b> アクティブ Low 出力で、割り込み条件が発生すると、Low にアサートされます。このピンは弱いプルアップを内蔵しています。各種割り込みトリガを有効化するには、レジスタ アクセスが必要です。割り込みイベントフラグが一度セットされると、その割り込みイベントをクリアするためにもレジスタ アクセスが必要になります。このピンは、レジスタ 0x0011 を用いてアクティブ HIGH 出力として構成することもできます。<br>レジスタ 12 ~ 13 の割り込みステータスは、INT_N が LOW のときにのみ読み取ることを推奨します。また、このピンをパワーダウン制御ピンとして動作させることもでき、その場合は本ピンを low にアサートすると PHY をパワーダウン モードにし、high にアサートすると通常モードに戻します。この機能は、レジスタ 0x0011 によって有効化できます。 |

| RESET                    | 3  | PU, I             | <b>リセット:</b> アクティブ Low 入力で、PHY を初期化または再初期化します。このピンを 1μs 以上 Low にアサートすると、リセットプロセスが強制的に開始されます。すべての内部レジスタは、「レジスタ マップ」セクションで各ビットに対して指定されたデフォルト状態に再初期化されます。リセットのデアサート時に、すべてのブートストラップ ピンが再サンプリングされます。                                                                                                                                                                                                                       |

| WAKE                     | 8  | PD, I/O           | <b>WAKE:</b> デフォルトではアクティブ HIGH の入出力ピンとして動作します。このピンは入力として、TC-10 スリープから PHY をウェークアップします。電源投入時にこのピンを HIGH にアサートすると、PHY をスリープ状態から復帰させます。TC-10 回路を実装する場合は、誤ってウェークアップしてしまうことを防ぐため、10kΩ の外付けプルダウン抵抗を使用できます。このピンは、デバイスをウェークアップするために VSLEEP に直接接続するか、抵抗を介して VSLEEP にプルアップすることもできます。<br>このピンは、PHY によって生成された WAKE ブラッシュを使用して、同じシステム内の他の PHY をウェークアップするウェークアップ転送機能もサポートしています。                                                     |

| <b>クロックインターフェイス</b>      |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XI                       | 5  | I                 | <b>基準クロック入力 (RMII):</b> RMII リーダー モードは、25MHz の水晶または発振器を基準クロックとして入力します。<br><b>基準クロック入力 (その他の MAC インターフェイス):</b> 25MHz の水晶または発振器を基準クロック入力として使用します。本デバイスは、外付け水晶振動子 (ピン XI とピン XO の間に接続) と外付け CMOS レベル発振器 (ピン XI のみに接続、XO は浮動) のどちらにも対応しています。このピンは、イーサネット MAC や別のイーサネット PHY など、他のデバイスからのクロック入力も受け付け、デイジーチェーン構成で使用することができます。<br>水晶を使用する場合は、XI ピンに 100Ω の直列抵抗を接続してください                                                      |

| XO                       | 4  | O                 | <b>基準クロック出力:</b> XO ピンは水晶振動子の場合にのみ使用されます。CMOS レベル発振器を XI に接続する場合、このピンを浮動にする必要があります。                                                                                                                                                                                                                                                                                                                                   |

| <b>LED/GPIO インターフェイス</b> |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CLKOUT/<br>GPIO_2        | 16 | IO                | <b>クロック出力:</b> 25MHz の基準クロックを出力します。このピンは、ストラップ設定またはレジスタ設定により、LED ピンまたは GPIO ピンとして使用することもできます。clkout ピンでのスイッチングを無効にするには、レジスタ <0x045F> に 0x000F を、レジスタ <0x0453> に 0x0003 を設定します                                                                                                                                                                                                                                         |

| GPIO_3 <sup>(3)</sup>    | 18 | PD, IO            | <b>汎用 IO ピン</b>                                                                                                                                                                                                                                                                                                                                                                                                       |

| GPIO_4                   | 19 | S, PD, IO         |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GPIO_5                   | 20 | PD, IO            |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LED_0 /<br>GPIO_0        | 35 | S, PD, IO         | <b>LED_0:</b> リンク ステータス LED です。このピンは、レジスタ設定により LED またはクロック出力ピンとしても使用できます。                                                                                                                                                                                                                                                                                                                                             |

| LED_1 /<br>GPIO_1        | 6  | S, PD, IO         | <b>LED_1:</b> リンクステータスの表示と、TX/RX (送受信) アクティビティ時の BLINK (点滅) に使用します。このピンは、ストラップ設定またはレジスタ設定により、LED ピンまたは クロック出力ピンとしても使用できます。                                                                                                                                                                                                                                                                                            |

| <b>メディア依存インターフェイス</b>    |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TRD_M                    | 13 | IO                | <b>差動送信および受信:</b> 100BASE-T1 動作用に構成された双方向差動信号。IEEE 802.3bw 準拠。                                                                                                                                                                                                                                                                                                                                                        |

| TRD_P                    | 12 |                   |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>電源接続</b>              |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                       |

**表 5-1. ピンの機能 (続き)**

| ピン                |     | 状態 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2)</sup> | 番号  |                   |                                                                                                                                                                                                                                                                                                                                                                                          |

| GND               | GND | グランド              | グランド:これは、常に電源グランドに接続する必要があります。                                                                                                                                                                                                                                                                                                                                                           |

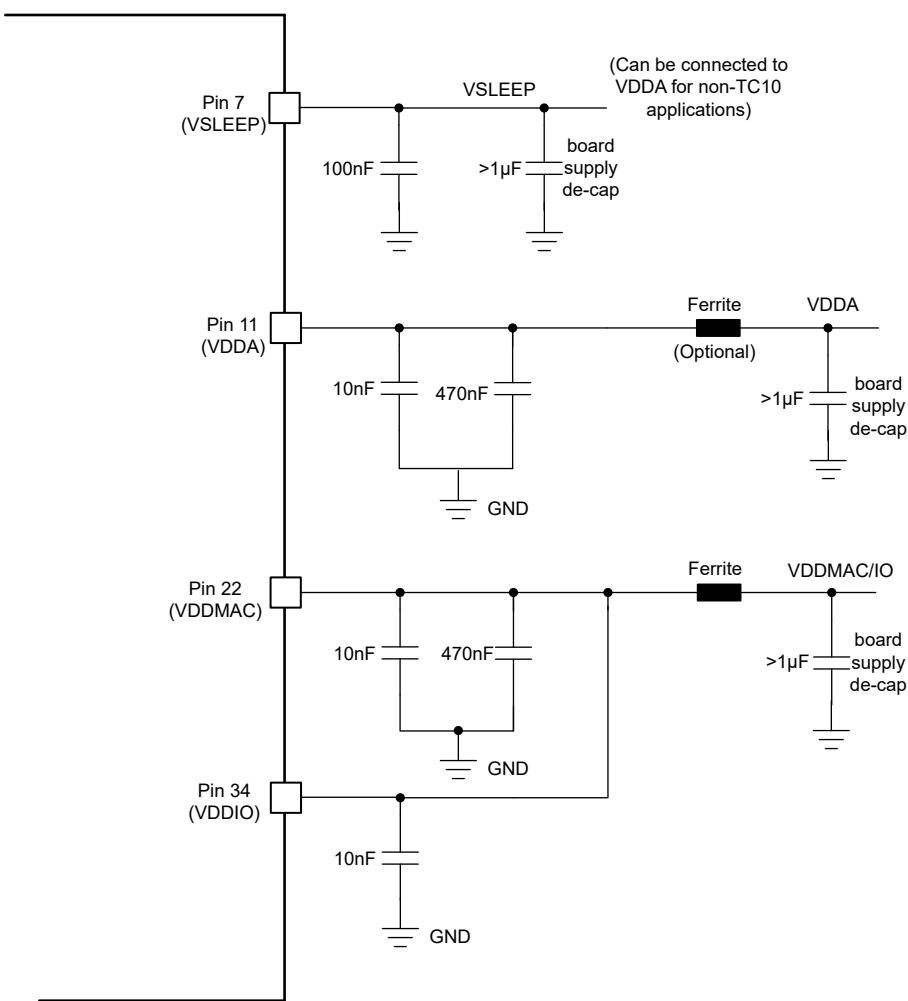

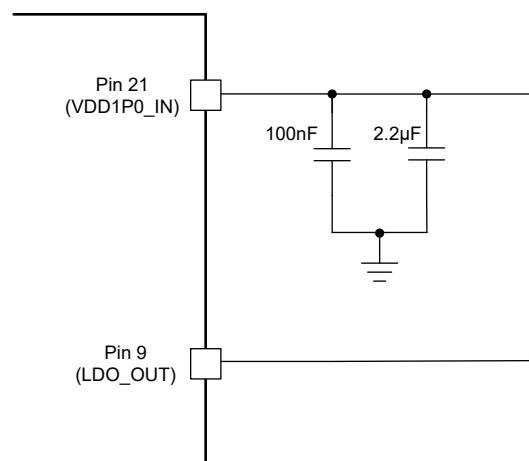

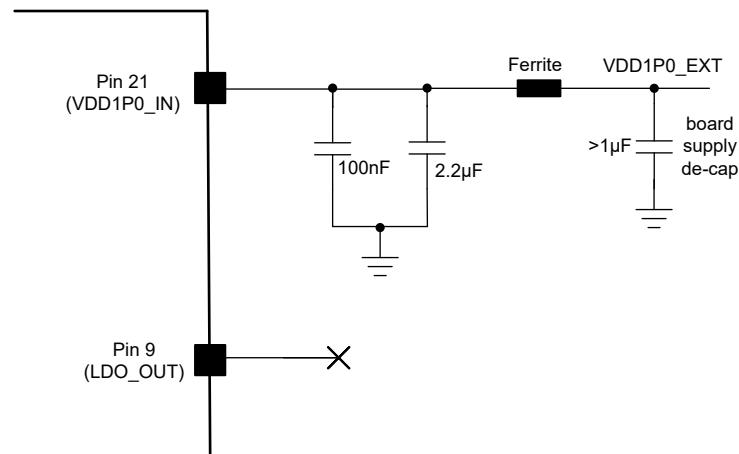

| LDO_OUT           | 9   | 電源                | <b>1.0V LDO 出力:</b> 1.0V 内部 LDO レギュレータ出力<br>1.0V は 3.3V の VDDA コア電源から内部的に生成します。<br>単一電源モードでは、VDD1P0 (ピン 21) に接続します。<br>デュアル電源モードの場合はフローティングのままにしておきます                                                                                                                                                                                                                                    |

| VDD1P0            | 21  | 電源                | <b>VDD1P0 電源:</b> 1.0V<br>単一電源モードの場合は LDO_OUT (ピン 9) に接続します。<br>デュアル電源モードでは外部レギュレータに接続します。<br>デュアル電源モードでは、フェライトビーズと 2.2μF および 0.1μF セラミック デカップリング コンデンサの使用を推奨します。                                                                                                                                                                                                                        |

| VDDA              | 11  | 電源                | <b>コア電源:</b> 3.3V<br>0.47μF および 0.01μF セラミック デカップリング コンデンサの使用を推奨します。オプションとしてフェライトビーズを使用できます。                                                                                                                                                                                                                                                                                             |

| VDDIO             | 34  | 電源                | <b>IO 電源:</b> 1.8V、2.5V、または 3.3V<br>フェライトビーズ、0.47μF および 0.01μF セラミック デカップリング コンデンサの使用を推奨します。                                                                                                                                                                                                                                                                                             |

| VDDMAC            | 22  | 電源                | オプションの <b>MAC インターフェイス電源:</b> 1.8V、2.5V、または 3.3V<br>MAC インターフェイスピン向けのオプションの独立電源です。このピンは MAC インターフェイスピンに電源を供給し、他の IO ピンとは異なる電圧レベルに設定できます。0.47μF および 0.01μF セラミック デカップリング コンデンサ、フェライトビーズの使用を推奨します。システムで個別の VDDMAC を必要としない場合は、VDDIO に接続しなければなりません。VDDIO に接続する場合、VDDIO 側の 0.47μF コンデンサは取り外すことができます。0.47μF コンデンサは VDDMAC 近傍には引き続き接続しておく必要があります。この場合、VDDIO と VDDMAC の間に共通のフェライトビーズを 1 つ使用できます。 |

| VSLEEP            | 7   | 電源                | <b>VSLEEP 電源:</b> 3.3V<br>0.1μF セラミック デカップリング コンデンサの使用を推奨します。                                                                                                                                                                                                                                                                                                                            |

| <b>接続禁止</b>       |     |                   |                                                                                                                                                                                                                                                                                                                                                                                          |

| DNC               | 17  | -                 | <b>DNC:</b> 接続せず、フローティングのままにします                                                                                                                                                                                                                                                                                                                                                          |

(1) ピンの種類:

I = 入力

O = 出力

IO = 入出力

OD = オープンドレイン

PD = 内部プルダウン

PU = 内部プルアップ

S = ブートストラップ構成ピン (すべての設定ピンには弱い内部プルアップまたはプルダウンが入っています)

- (2) ピンを使用しない場合は、上記の表に示す推奨接続要件に従ってください。必要な終端がないピンは、フローティングのままでかまいません。

(3) GPIO\_3 を電源投入前に HIGH に駆動しないでください。

## 5.1 ピンの電源ドメイン

表 5-2. ピン ドメイン

| ピン番号 | ピン名                  | 電圧ドメイン |

|------|----------------------|--------|

| 1    | MDC                  | VDDIO  |

| 2    | INT_N                | VDDIO  |

| 3    | RESET_N              | VDDIO  |

| 4    | XO                   | VDDIO  |

| 5    | XI                   | VDDIO  |

| 6    | LED_1/GPIO_1         | VDDIO  |

| 8    | WAKE                 | VSLEEP |

| 10   | INH                  | VSLEEP |

| 12   | TRD_P                | VDDA   |

| 13   | TRD_M                | VDDA   |

| 14   | RX_ER/GPIO_6         | VDDMAC |

| 15   | RX_DV/CRS_DV/RX_CTRL | VDDMAC |

| 16   | CLKOUT/GPIO_2        | VDDMAC |

| 18   | GPIO_3               | VDDMAC |

| 19   | GPIO_4               | VDDMAC |

| 20   | GPIO_5               | VDDMAC |

| 23   | RX_D3/RX_M           | VDDMAC |

| 24   | RX_D2/RX_P           | VDDMAC |

| 25   | RX_D1                | VDDMAC |

| 26   | RX_D0                | VDDMAC |

| 27   | RX_CLK               | VDDMAC |

| 28   | TX_CLK               | VDDMAC |

| 29   | TX_EN/TX_CTRL        | VDDMAC |

| 30   | TX_D3                | VDDMAC |

| 31   | TX_D2                | VDDMAC |

| 32   | TX_D1/TX_P           | VDDMAC |

| 33   | TX_D0/TX_M           | VDDMAC |

| 35   | LED_0/GPIO_0         | VDDIO  |

| 36   | MDIO                 | VDDIO  |

## 5.2 ピンの状態

表 5-3. ピンの状態 - 電源投入 / リセット

| ピン番号 | ピン名     | 起動 / リセット |       |          |

|------|---------|-----------|-------|----------|

|      |         | ピンの状態 (1) | プルタイプ | プル値 (kΩ) |

| 1    | MDC     | I         | なし    | なし       |

| 2    | INT     | OD, O     | PU    | 9        |

| 3    | RESET   | I         | PU    | 9        |

| 4    | XO      | O         | なし    | なし       |

| 5    | XI      | I         | なし    | なし       |

| 6    | LED_1   | I         | PD    | 9        |

| 7    | VSLEEP  | 電源        | なし    | なし       |

| 8    | WAKE    | I/O       | PD    | 455      |

| 9    | LDO_OUT | O         | なし    | なし       |

| 10   | INH     | OD, O     | なし    | なし       |

| 11   | VDDA    | 電源        | なし    | なし       |

| 12   | TRD_P   | IO        | なし    | なし       |

| 13   | TRD_M   | IO        | なし    | なし       |

| 14   | RX_ER   | I         | PD    | 6        |

| 15   | RX_DV   | I         | PD    | 6        |

| 16   | CLKOUT  | O         | なし    | なし       |

| 17   | DNC     | フローティング   | なし    | なし       |

| 18   | GPIO_3  | I         | PD    | 9        |

| 19   | GPIO_4  | I         | PD    | 9        |

| 20   | GPIO_5  | I         | PD    | 9        |

| 21   | VDD1P0  | 電源        | なし    | なし       |

| 22   | VDDMAC  | 電源        | なし    | なし       |

| 23   | RX_D3   | I         | PD    | 9        |

| 24   | RX_D2   | I         | PD    | 9        |

| 25   | RX_D1   | I         | PD    | 9        |

| 26   | RX_D0   | I         | PD    | 9        |

| 27   | RX_CLK  | I         | PD    | 9        |

| 28   | TX_CLK  | I         | なし    | なし       |

| 29   | TX_EN   | I         | なし    | なし       |

| 30   | TX_D3   | I         | なし    | なし       |

| 31   | TX_D2   | I         | なし    | なし       |

| 32   | TX_D1   | I         | なし    | なし       |

| 33   | TX_D0   | I         | なし    | なし       |

| 34   | VDDIO   | 電源        | なし    | なし       |

| 35   | LED_0   | I         | PD    | 9        |

| 36   | MDIO    | OD, IO    | なし    | なし       |

表 5-4. ピンの状態 - TC10 スリープ

| ピン番号 | ピン名                   | TC10 スリープ (すべての電源がオン) |       |          |

|------|-----------------------|-----------------------|-------|----------|

|      |                       | ピンの状態 <sup>(1)</sup>  | プルタイプ | プル値 (kΩ) |

| 1    | MDC                   | I                     | なし    | なし       |

| 2    | INT                   | OD、O                  | PU    | 9        |

| 3    | RESET                 | I                     | PU    | 9        |

| 4    | XO                    | O                     | なし    | なし       |

| 5    | XI                    | I                     | なし    | なし       |

| 6    | LED_1 <sup>(1)</sup>  | I                     | PD    | 9        |

| 7    | VSLEEP                | 電源                    | なし    | なし       |

| 8    | WAKE                  | I/O                   | PD    | 455      |

| 9    | LDO_OUT               | O                     | なし    | なし       |

| 10   | INH                   | OD、O                  | なし    | なし       |

| 11   | VDDA                  | 電源                    | なし    | なし       |

| 12   | TRD_P                 | IO                    | なし    | なし       |

| 13   | TRD_M                 | IO                    | なし    | なし       |

| 14   | RX_ER                 | I                     | PD    | 6        |

| 15   | RX_DV                 | I                     | PD    | 6        |

| 16   | CLKOUT <sup>(2)</sup> | O                     | なし    | なし       |

| 17   | DNC                   | フローティング               | なし    | なし       |

| 18   | GPIO_3                | I                     | PD    | 9        |

| 19   | GPIO_4                | I                     | PD    | 9        |

| 20   | GPIO_5                | I                     | PD    | 9        |

| 21   | VDD1P0                | 電源                    | なし    | なし       |

| 22   | VDDMAC                | 電源                    | なし    | なし       |

| 23   | RX_D3                 | I                     | PD    | 9        |

| 24   | RX_D2                 | I                     | PD    | 9        |

| 25   | RX_D1                 | I                     | PD    | 9        |

| 26   | RX_D0                 | I                     | PD    | 9        |

| 27   | RX_CLK                | I                     | PD    | 9        |

| 28   | TX_CLK                | I                     | なし    | なし       |

| 29   | TX_EN                 | I                     | なし    | なし       |

| 30   | TX_D3                 | I                     | なし    | なし       |

| 31   | TX_D2                 | I                     | なし    | なし       |

| 32   | TX_D1                 | I                     | なし    | なし       |

| 33   | TX_D0                 | I                     | なし    | なし       |

| 34   | VDDIO                 | 電源                    | なし    | なし       |

| 35   | LED_0                 | I                     | PD    | 9        |

| 36   | MDIO                  | OD、IO                 | なし    | なし       |

(1) LED\_1 が CLKOUT として構成されている場合、TC10 のスリープ IO 状態は次のようになります: 出力にプル抵抗を使用しない場合

(2) CLKOUT が LED\_1 に構成されている場合、TC10 のスリープ IO 状態は次のようになります: 入力、9kΩ プルダウン

**表 5-5. ピンの状態 - MAC 分離および IEEE PWDN**

| ピン番号 | ピン名     | MAC 分離    |       |          | IEEE PWDN |       |          |

|------|---------|-----------|-------|----------|-----------|-------|----------|

|      |         | ピンの状態 (1) | プルタイプ | プル値 (kΩ) | ピンの状態 (1) | プルタイプ | プル値 (kΩ) |

| 1    | MDC     | I         | なし    | なし       | I         | なし    | なし       |

| 2    | INT     | OD, O     | PU    | 9        | OD, O     | PU    | 9        |

| 3    | RESET   | I         | PU    | 9        | I         | PU    | 9        |

| 4    | XO      | O         | なし    | なし       | O         | なし    | なし       |

| 5    | XI      | I         | なし    | なし       | I         | なし    | なし       |

| 6    | LED_1   | O         | なし    | なし       | O         | なし    | なし       |

| 7    | VSLEEP  | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 8    | WAKE    | IO        | PD    | 455      | IO        | PD    | 455      |

| 9    | LDO_OUT | O         | なし    | なし       | O         | なし    | なし       |

| 10   | INH     | OD, O     | なし    | なし       | OD, O     | なし    | なし       |

| 11   | VDDA    | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 12   | TRD_P   | IO        | なし    | なし       | IO        | なし    | なし       |

| 13   | TRD_M   | IO        | なし    | なし       | IO        | なし    | なし       |

| 14   | RX_ER   | I         | PD    | 6        | I         | PD    | 6        |

| 15   | RX_DV   | I         | PD    | 6        | O         | なし    | なし       |

| 16   | CLKOUT  | O         | なし    | なし       | O         | なし    | なし       |

| 17   | DNC     | フローティング   | なし    | なし       | フローティング   | なし    | なし       |

| 18   | GPIO_3  | I         | PD    | 9        | I         | PD    | 9        |

| 19   | GPIO_4  | I         | PD    | 9        | I         | PD    | 9        |

| 20   | GPIO_5  | I         | PD    | 9        | I         | PD    | 9        |

| 21   | VDD1P0  | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 22   | VDDMAC  | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 23   | RX_D3   | I         | PD    | 9        | O         | なし    | なし       |

| 24   | RX_D2   | I         | PD    | 9        | O         | なし    | なし       |

| 25   | RX_D1   | I         | PD    | 9        | O         | なし    | なし       |

| 26   | RX_D0   | I         | PD    | 9        | O         | なし    | なし       |

| 27   | RX_CLK  | I         | PD    | 9        | O         | なし    | なし       |

| 28   | TX_CLK  | I         | PD    | 9        | I         | なし    | なし       |

| 29   | TX_EN   | I         | PD    | 9        | I         | なし    | なし       |

| 30   | TX_D3   | I         | PD    | 9        | I         | なし    | なし       |

| 31   | TX_D2   | I         | PD    | 9        | I         | なし    | なし       |

| 32   | TX_D1   | I         | PD    | 9        | I         | なし    | なし       |

| 33   | TX_D0   | I         | PD    | 9        | I         | なし    | なし       |

| 34   | VDDIO   | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 35   | LED_0   | O         | なし    | なし       | O         | なし    | なし       |

| 36   | MDIO    | OD, IO    | なし    | なし       | OD, IO    | なし    | なし       |

表 5-6. ピンの状態 - MII および RGMII

| ピン番号 | ピン名     | MII       |       |          | RGMII     |       |          |

|------|---------|-----------|-------|----------|-----------|-------|----------|

|      |         | ピンの状態 (1) | プルタイプ | プル値 (kΩ) | ピンの状態 (1) | プルタイプ | プル値 (kΩ) |

| 1    | MDC     | I         | なし    | なし       | I         | なし    | なし       |

| 2    | INT     | OD, O     | PU    | 9        | OD, O     | PU    | 9        |

| 3    | RESET   | I         | PU    | 9        | I         | PU    | 9        |

| 4    | XO      | O         | なし    | なし       | O         | なし    | なし       |

| 5    | XI      | I         | なし    | なし       | I         | なし    | なし       |

| 6    | LED_1   | O         | なし    | なし       | O         | なし    | なし       |

| 7    | VSLEEP  | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 8    | WAKE    | IO        | PD    | 455      | IO        | PD    | 455      |

| 9    | LDO_OUT | O         | なし    | なし       | O         | なし    | なし       |

| 10   | INH     | OD, O     | なし    | なし       | OD, O     | なし    | なし       |

| 11   | VDDA    | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 12   | TRD_P   | IO        | なし    | なし       | IO        | なし    | なし       |

| 13   | TRD_M   | IO        | なし    | なし       | IO        | なし    | なし       |

| 14   | RX_ER   | O         | なし    | なし       | I         | PD    | 6        |

| 15   | RX_DV   | O         | なし    | なし       | O         | なし    | なし       |

| 16   | CLKOUT  | O         | なし    | なし       | O         | なし    | なし       |

| 17   | DNC     | フローティング   | なし    | なし       | フローティング   | なし    | なし       |

| 18   | GPIO_3  | I         | PD    | 9        | I         | PD    | 9        |

| 19   | GPIO_4  | I         | PD    | 9        | I         | PD    | 9        |

| 20   | GPIO_5  | I         | PD    | 9        | I         | PD    | 9        |

| 21   | VDD1P0  | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 22   | VDDMAC  | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 23   | RX_D3   | O         | なし    | なし       | O         | なし    | なし       |

| 24   | RX_D2   | O         | なし    | なし       | O         | なし    | なし       |

| 25   | RX_D1   | O         | なし    | なし       | O         | なし    | なし       |

| 26   | RX_D0   | O         | なし    | なし       | O         | なし    | なし       |

| 27   | RX_CLK  | O         | なし    | なし       | O         | なし    | なし       |

| 28   | TX_CLK  | O         | なし    | なし       | I         | なし    | なし       |

| 29   | TX_EN   | I         | なし    | なし       | I         | なし    | なし       |

| 30   | TX_D3   | I         | なし    | なし       | I         | なし    | なし       |

| 31   | TX_D2   | I         | なし    | なし       | I         | なし    | なし       |

| 32   | TX_D1   | I         | なし    | なし       | I         | なし    | なし       |

| 33   | TX_D0   | I         | なし    | なし       | I         | なし    | なし       |

| 34   | VDDIO   | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 35   | LED_0   | O         | なし    | なし       | O         | なし    | なし       |

| 36   | MDIO    | OD, IO    | なし    | なし       | OD, IO    | なし    | なし       |

**表 5-7. ピンの状態 - SGMII**

| ピン番号 | ピン名     | SGMII     |       |          |

|------|---------|-----------|-------|----------|

|      |         | ピンの状態 (1) | プルタイプ | プル値 (kΩ) |

| 1    | MDC     | I         | なし    | なし       |

| 2    | INT     | OD, O     | PU    | 9        |

| 3    | RESET   | I         | PU    | 9        |

| 4    | XO      | O         | なし    | なし       |

| 5    | XI      | I         | なし    | なし       |

| 6    | LED_1   | O         | なし    | なし       |

| 7    | VSLEEP  | 電源        | なし    | なし       |

| 8    | WAKE    | IO        | PD    | 455      |

| 9    | LDO_OUT | O         | なし    | なし       |

| 10   | INH     | OD, O     | なし    | なし       |

| 11   | VDDA    | 電源        | なし    | なし       |

| 12   | TRD_P   | IO        | なし    | なし       |

| 13   | TRD_M   | IO        | なし    | なし       |

| 14   | RX_ER   | I         | PD    | 6        |

| 15   | RX_DV   | I         | PD    | 6        |

| 16   | CLKOUT  | O         | なし    | なし       |

| 17   | DNC     | フローティング   | なし    | なし       |

| 18   | GPIO_3  | I         | PD    | 9        |

| 19   | GPIO_4  | I         | PD    | 9        |

| 20   | GPIO_5  | I         | PD    | 9        |

| 21   | VDD1P0  | 電源        | なし    | なし       |

| 22   | VDDMAC  | 電源        | なし    | なし       |

| 23   | RX_D3   | O         | なし    | なし       |

| 24   | RX_D2   | O         | なし    | なし       |

| 25   | RX_D1   | I         | PD    | 9        |

| 26   | RX_D0   | I         | PD    | 9        |

| 27   | RX_CLK  | I         | PD    | 9        |

| 28   | TX_CLK  | I         | なし    | なし       |

| 29   | TX_EN   | I         | なし    | なし       |

| 30   | TX_D3   | I         | なし    | なし       |

| 31   | TX_D2   | I         | なし    | なし       |

| 32   | TX_D1   | I         | なし    | なし       |

| 33   | TX_D0   | I         | なし    | なし       |

| 34   | VDDIO   | 電源        | なし    | なし       |

| 35   | LED_0   | O         | なし    | なし       |

| 36   | MDIO    | OD, IO    | なし    | なし       |

- (1) 種類:I = 入力

O = 出力

IO = 入出力

OD = オープンドレイン

PD = 内部ブルダウン

PU = 内部ブルアップ

### 5.3 ピン多重化

次の表に、GPIO ピンで利用可能な各種機能の詳細を示します。

|                         |                                                      |

|-------------------------|------------------------------------------------------|

| <b>LED:</b>             | LED 表示として構成されたピン。                                    |

| <b>CLKOUT:</b>          | クロック出力信号として構成されたピン                                   |

| <b>イベントトリガ / キャプチャ:</b> | 802.1AS タイムスタンプによって生成されたイベントをキャプチャおよびトリガするように構成されたピン |

| <b>PTP 割り込み:</b>        | 802.1AS/PTP 固有の割り込みを出力するように構成されたピン                   |

| <b>50/25MHz PTP 入力:</b> | PTP 用の 50/ 25MHz 基準クロック                              |

| <b>同期クロック:</b>          | PTP ウォールクロックに同期する、プログラマブル周波数クロック                     |

| <b>PPM モニタ:</b>         | 内部クロックに関して PPM を監視するために外部クロック入力用に構成されたピン             |

**表 5-8. ピン多重化**

| フィールド          | ピン | デフォルト  | LED | CLKOUT 25MHz | イベントトリガ / キャプチャ |

|----------------|----|--------|-----|--------------|-----------------|

| LED_0 / GPIO_0 | 35 | LED_0  | あり  |              | あり              |

| LED_1 / GPIO_1 | 6  | LED_1  | あり  | あり           | あり              |

| CLKOUT/GPIO_2  | 16 | CLKOUT | あり  | あり           | あり              |

| GPIO_3         | 18 | GPIO_3 |     |              | あり              |

| GPIO_4         | 19 | GPIO_4 |     |              | あり              |

| GPIO_5         | 20 | GPIO_5 |     |              | あり              |

| RX_ER(GPIO_6)  | 14 | RX_ER  |     |              | あり              |

**表 5-9. ピン多重化 - PTP、割り込み**

| フィールド          | ピン | 50 / 25MHz PTP 入力 | PTP 同期クロック | PTP 割り込み |

|----------------|----|-------------------|------------|----------|

| LED_0 / GPIO_0 | 35 | あり                |            | あり       |

| LED_1 / GPIO_1 | 6  |                   |            | あり       |

| CLKOUT/GPIO_2  | 16 |                   | あり         | あり       |

| GPIO_3         | 18 |                   | あり         | あり       |

| GPIO_4         | 19 |                   | あり         | あり       |

| GPIO_5         | 20 | あり                |            | あり       |

| RX_ER(GPIO_6)  | 14 |                   |            | あり       |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                  |                                                                                                         | 最小値  | 標準値          | 最大値 | 単位 |

|------------------|---------------------------------------------------------------------------------------------------------|------|--------------|-----|----|

| 入力電圧             | VDDA                                                                                                    | -0.3 |              | 4   | V  |

| 入力電圧             | VDD1P0                                                                                                  | -0.3 |              | 1.4 | V  |

| 入力電圧             | VDDIO (3.3V)                                                                                            | -0.3 |              | 4   | V  |

| 入力電圧             | VDDIO (2.5V)                                                                                            | -0.3 |              | 4   | V  |

| 入力電圧             | VDDIO (1.8V)                                                                                            | -0.3 |              | 4   | V  |

| 入力電圧             | VSLEEP                                                                                                  | -0.3 |              | 4   | V  |

| ピン               | MDI (TRD_M, TRD_P)                                                                                      | -0.3 |              | 4   | V  |

| 入力電圧             | MDC, RESET, XI, LED_1, RX_ER, RX_CTRL, CLKOUT, RX_D[3:0], TX_CLK, TX_CTRL, TX_D[3:0], LED_0, MDIO, GPIO | -0.3 | VDDIO + 0.3  |     | V  |

| ピン               | MDIO, MDC, GPIO, XI, XO, INT, RESET, CLKOUT                                                             | -0.3 | VDDIO + 0.3  |     | V  |

| 出力電圧             | INH                                                                                                     | -0.3 | VSLEEP + 0.3 |     | V  |

| 入力電圧             | WAKE                                                                                                    | -0.3 | VSLEEP + 0.3 |     | V  |

| 出力電圧             | INT, LED_1, RX_CTRL, CLKOUT, RX_D[3:0], RX_CLK, LED_0, MDIO, GPIO                                       | -0.3 |              | 4   | V  |

| T <sub>J</sub>   | 接合部温度                                                                                                   | -40  |              | 150 | °C |

| T <sub>stg</sub> | 保存温度                                                                                                    | -65  |              | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。

「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しなくなる可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|                    |      |                                             | 値               | 単位    |

|--------------------|------|---------------------------------------------|-----------------|-------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 に準拠 <sup>(1)</sup> | すべてのピン          | ±2000 |

|                    |      | TRD_N, TRD_P ピン                             | ±8000           | V     |

|                    |      | 荷電デバイス モデル (CDM)、AEC Q100-011 準拠            | すべてのピン          |       |

|                    |      | IEC 61000-4-2 接触放電                          | TRD_N, TRD_P ピン | ±500  |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                |                 | 最小値    | 公称値 | 最大値    | 単位 |

|----------------|-----------------|--------|-----|--------|----|

| VDDIO / VDDMAC | IO 電源電圧、1.8V 動作 | 1.665  | 1.8 | 1.935  | V  |

|                | IO 電源電圧、2.5V 動作 | 2.3125 | 2.5 | 2.6875 |    |

|                | IO 電源電圧、3.3V 動作 | 3.0525 | 3.3 | 3.5475 |    |

| VDDA           | コア電源電圧、3.3V     | 2.97   | 3.3 | 3.63   | V  |

| VDD1P0         | コア デジタル外部電源 1V  | 0.95   | 1.0 | 1.1    | V  |

| VSLEEP         | スリープ電源電圧、3.3V   | 2.97   | 3.3 | 3.63   | V  |

| T <sub>A</sub> | 周囲温度            | -40    |     | 125    | °C |

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup>        |                   | RHA (VQFN) | 単位   |

|-----------------------------|-------------------|------------|------|

|                             |                   | 36 ピン      |      |

| $R_{\theta JA}$             | 接合部から周囲への热抵抗      | 30.7       | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への热抵抗 | 21.6       | °C/W |

| $R_{\theta JB}$             | 接合部から基板への热抵抗      | 13.1       | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 0.3        | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 11.9       | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース(底面)への热抵抗 | 2.8        | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体および IC パッケージの热評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

自由気流での動作温度範囲内(特に記述のない限り)

| パラメータ                        | テスト条件                                   | 最小値                                  | 標準値                 | 最大値                 | 単位       |

|------------------------------|-----------------------------------------|--------------------------------------|---------------------|---------------------|----------|

| <b>100BASE-T1 PMA 準拠</b>     |                                         |                                      |                     |                     |          |

| $V_{OD-MDI}$                 | 出力差動電圧 $R_{L(\text{diff})} = 100\Omega$ |                                      | 2.2                 |                     | V        |

| $R_{MDI-Diff}$               | 内蔵差動出力終端 TRD_P および TRD_M                |                                      | 100                 |                     | $\Omega$ |

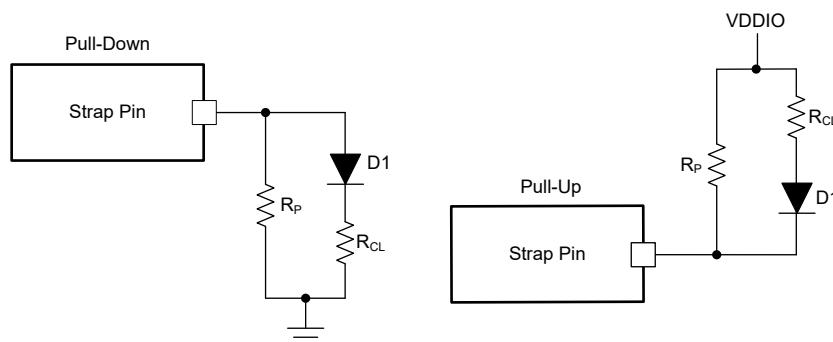

| <b>ポートストラップ DC 特性(2 レベル)</b> |                                         |                                      |                     |                     |          |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 3.3V \pm 7.5\%$ 、2 レベルストラップ | 0                   | 0.8                 | V        |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 3.3V \pm 7.5\%$ 、2 レベルストラップ | 2                   | $VDDIO$             | V        |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 2.5V \pm 7.5\%$ 、2 レベルストラップ | 0                   | 0.7                 | V        |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 2.5V \pm 7.5\%$ 、2 レベルストラップ | 1.7                 | $VDDIO$             | V        |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 1.8V \pm 7.5\%$ 、2 レベルストラップ | 0                   | $0.35 \times VDDIO$ | V        |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 1.8V \pm 7.5\%$ 、2 レベルストラップ | $0.65 \times VDDIO$ | $VDDIO$             | V        |

| <b>ポートストラップ DC 特性(3 レベル)</b> |                                         |                                      |                     |                     |          |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 3.3V \pm 7.5\%$ 、3 レベルストラップ | 0                   | $0.18 \times VDDIO$ | V        |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 3.3V \pm 7.5\%$ 、3 レベルストラップ | $0.22 \times VDDIO$ | $0.42 \times VDDIO$ | V        |

| $V_{MODE3}$                  | モード 3 ストラップ電圧範囲                         | $VDDIO = 3.3V \pm 7.5\%$ 、3 レベルストラップ | $0.46 \times VDDIO$ | $VDDIO$             | V        |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 2.5V \pm 7.5\%$ 、3 レベルストラップ | 0                   | $0.25 \times VDDIO$ | V        |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 2.5V \pm 7.5\%$ 、3 レベルストラップ | $0.29 \times VDDIO$ | $0.56 \times VDDIO$ | V        |

| $V_{MODE3}$                  | モード 3 ストラップ電圧範囲                         | $VDDIO = 2.5V \pm 7.5\%$ 、3 レベルストラップ | $0.65 \times VDDIO$ | $VDDIO$             | V        |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 1.8V \pm 7.5\%$ 、3 レベルストラップ | 0                   | $0.35 \times VDDIO$ | V        |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 1.8V \pm 7.5\%$ 、3 レベルストラップ | $0.40 \times VDDIO$ | $0.75 \times VDDIO$ | V        |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ               |                             | テスト条件                                     | 最小値            | 標準値            | 最大値   | 単位 |

|---------------------|-----------------------------|-------------------------------------------|----------------|----------------|-------|----|

| V <sub>MODE3</sub>  | モード3 ストラップ電圧範囲              | VDDIO = 1.8V ±7.5%、3 レベルストラップ             |                | 0.84 × VDDIO   | VDDIO | V  |

| <b>IO 特性</b>        |                             |                                           |                |                |       |    |

| V <sub>IH</sub>     | High レベル入力電圧                | VDDIO = 3.3V ±7.5%                        | 2              |                |       | V  |

| V <sub>IL</sub>     | Low レベル入力電圧                 | VDDIO = 3.3V ±7.5%                        |                | 0.8            | V     |    |

| V <sub>OH</sub>     | High レベル出力電圧                | I <sub>OH</sub> = -2mA、VDDIO = 3.3V ±7.5% | 2.4            |                |       | V  |

| V <sub>OL</sub>     | Low レベル出力電圧                 | I <sub>OH</sub> = -2mA、VDDIO = 3.3V ±7.5% |                | 0.4            | V     |    |

| V <sub>IH</sub>     | High レベル入力電圧                | VDDIO = 2.5V ±7.5%                        | 1.7            |                |       | V  |

| V <sub>IL</sub>     | Low レベル入力電圧                 | VDDIO = 2.5V ±7.5%                        |                | 0.7            | V     |    |

| V <sub>OH</sub>     | High レベル出力電圧                | I <sub>OH</sub> = -2mA、VDDIO = 2.5V ±7.5% | 2              |                |       | V  |

| V <sub>OL</sub>     | Low レベル出力電圧                 | I <sub>OH</sub> = -2mA、VDDIO = 2.5V ±7.5% |                | 0.4            | V     |    |

| V <sub>IH</sub>     | High レベル入力電圧                | VDDIO = 1.8V ±7.5%                        | 0.65*VDDI<br>O |                |       | V  |

| V <sub>IL</sub>     | Low レベル入力電圧                 | VDDIO = 1.8V ±7.5%                        |                | 0.35*VDDI<br>O | V     |    |

| V <sub>OH</sub>     | High レベル出力電圧                | I <sub>OH</sub> = -2mA、VDDIO = 1.8V ±7.5% | VDDIO-0.<br>45 |                |       | V  |

| V <sub>OL</sub>     | Low レベル出力電圧                 | I <sub>OH</sub> = -2mA、VDDIO = 1.8V ±7.5% |                | 0.45           | V     |    |

| I <sub>IH</sub>     | 入力 High 電流 <sup>(1)</sup>   | VIN = VDDIO、XI および WAKE 以外のすべてのピン         | -10            | 10             | μA    |    |

| I <sub>IH-XI</sub>  | 入力 High 電流 <sup>(1)</sup>   | VIN = VDDIO、XI ピン                         | -15            | 15             | μA    |    |

| I <sub>IL-XI</sub>  | 入力 Low 電流 <sup>(1)</sup>    | VIN = GND、XI ピン                           | -15            | 15             | μA    |    |

| I <sub>IL</sub>     | 入力 Low 電流 <sup>(1)</sup>    | VIN = GND、XI を除くすべてのピン、RESET_N ピン         | -10            | 10             | μA    |    |

| I <sub>IL-RST</sub> | 入力 Low 電流                   | VIN = GND、RESET ピン                        | -500           | 0              | μA    |    |

| I <sub>OZH</sub>    | トライステート出力高電流 <sup>(2)</sup> | VIN = VDDIO、RX_CTRL および RX_ER を除くすべてのピン   | -10            | 10             | μA    |    |

| I <sub>OZH</sub>    | トライステート出力高電流 <sup>(2)</sup> | VIN = VDDIO、RX_CTRL、RX_ER                 | -52            | 52             | μA    |    |

| I <sub>OZL</sub>    | トライステート出力低電流 <sup>(2)</sup> | VOUT = GND                                | -10            | 10             | μA    |    |

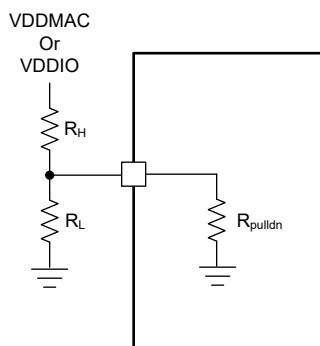

| R <sub>pulldn</sub> | 内蔵プルダウン抵抗                   | RX_D[3:0]、RX_CLK、LED_0、LED_1、TX_CTRL      | 6.2            | 8.4            | 10.7  | kΩ |

| R <sub>pulldn</sub> | 内蔵プルダウン抵抗                   | RX_CTRL、RX_ER                             | 4.725          | 5.8            | 7.2   | kΩ |

| R <sub>pulldn</sub> | 内蔵プルダウン抵抗                   | WAKE                                      | 320            | 455            | 590   | kΩ |

| R <sub>pullup</sub> | 内蔵プルアップ抵抗                   | INT、RESET                                 | 6.3            | 9              | 11.2  | kΩ |

| XI V <sub>IH</sub>  | High レベル入力電圧                |                                           | 1.3            | VDDIO          | V     |    |

| XI V <sub>IL</sub>  | Low レベル入力電圧                 |                                           |                | 0.5            | V     |    |

| C <sub>IN</sub>     | XI の入力容量                    |                                           | 1              |                | pF    |    |

| C <sub>IN</sub>     | 入力ピンの入力容量                   |                                           | 5              |                | pF    |    |

| C <sub>OUT</sub>    | XO の出力容量                    |                                           | 1              |                | pF    |    |

| C <sub>OUT</sub>    | 出力ピンの出力容量                   |                                           | 5              |                | pF    |    |

| R <sub>series</sub> | 内蔵 MAC 直列終端抵抗               | RX_D[3:0]、RX_ER、RX_DV、RX_CLK              | 35             | 50             | 65    | Ω  |

| <b>消費電力 VDDIO</b>   |                             |                                           |                |                |       |    |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                       |       | テスト条件        | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------------------|-------|--------------|-----|-----|-----|----|

| I(VDDIO=3.3V)               | MII   |              | 20  | 25  | mA  |    |

|                             | RMII  |              | 19  | 25  | mA  |    |

|                             | RGMII |              | 17  | 23  | mA  |    |

|                             | SGMII |              | 10  | 14  | mA  |    |

| I(VDDIO=2.5V)               | MII   |              | 14  | 18  | mA  |    |

|                             | RMII  |              | 13  | 18  | mA  |    |

|                             | RGMII |              | 12  | 16  | mA  |    |

|                             | SGMII |              | 6   | 9   | mA  |    |

| I(VDDIO=1.8V)               | MII   |              | 10  | 13  | mA  |    |

|                             | RMII  |              | 9   | 13  | mA  |    |

|                             | RGMII |              | 8   | 12  | mA  |    |

|                             | SGMII |              | 4   | 6   | mA  |    |

| I(VDDIO=3.3V)               | MII   |              | 22  | 28  | mA  |    |

|                             | RMII  |              | 23  | 28  | mA  |    |

|                             | RGMII |              | 20  | 28  | mA  |    |

|                             | SGMII |              | 13  | 22  | mA  |    |

| I(VDDIO=2.5V)               | MII   | 802.1AS 有効   | 16  | 22  | mA  |    |

|                             | RMII  |              | 15  | 21  | mA  |    |

|                             | RGMII |              | 14  | 19  | mA  |    |

|                             | SGMII |              | 8   | 15  | mA  |    |

| I(VDDIO=1.8V)               | MII   |              | 11  | 17  | mA  |    |

|                             | RMII  |              | 11  | 17  | mA  |    |

|                             | RGMII |              | 8   | 17  | mA  |    |

|                             | SGMII |              | 6   | 12  | mA  |    |

| <b>消費電力:コア電源</b>            |       |              |     |     |     |    |

| 単電源:I(3V3)                  | xMII  |              | 71  | 172 | mA  |    |

|                             | SGMII |              | 91  | 193 | mA  |    |

| デュアル外部電源:I(3V3)             | xMII  |              | 48  | 70  | mA  |    |

|                             | SGMII |              | 68  | 91  | mA  |    |

| デュアル外部電源:I(1V0)             | xMII  |              | 23  | 102 | mA  |    |

|                             | SGMII |              | 23  | 102 | mA  |    |

| <b>消費電力:コア電源、802.1AS 有効</b> |       |              |     |     |     |    |

| 単電源:I(3V3)                  | xMII  |              | 87  | 194 | mA  |    |

|                             | SGMII |              | 107 | 215 | mA  |    |

| デュアル外部電源:I(3V3)             | xMII  |              | 60  | 83  | mA  |    |

|                             |       |              | 27  | 111 | mA  |    |

| デュアル外部電源:I(1V0)             | xMII  | 同期間隔 = 125ms | 80  | 104 | mA  |    |

|                             | SGMII |              | 27  | 111 | mA  |    |

| デュアル外部電源:I(3V3)             | SGMII |              |     |     |     |    |

|                             |       |              |     |     |     |    |

| デュアル外部電源:I(1V0)             | SGMII |              |     |     |     |    |

|                             |       |              |     |     |     |    |

| <b>消費電力:低消費電力モード</b>        |       |              |     |     |     |    |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                |                    | テスト条件                               | 最小値  | 標準値 | 最大値 | 単位 |

|----------------------|--------------------|-------------------------------------|------|-----|-----|----|

| I(VDDA3V3)           | リセット               | 単一電源                                | 17   | 103 | mA  |    |

| I(VDDA3V3)           |                    | デュアル電源                              | 9    | 21  | mA  |    |

| I(DVDD1P0)           |                    | デュアル電源                              | 8    | 82  | mA  |    |

| I(VDDIO=3.3V)        |                    | VDDIO = VDDMAC                      | 12   | 18  | mA  |    |

| I(VDDIO=2.5V)        |                    |                                     | 8.5  | 14  | mA  |    |

| I(VDDIO=1.8V)        |                    |                                     | 6    | 10  | mA  |    |

| I(VDDA3V3)           | IEEE パワーダウン        | 単一電源                                | 15   | 98  | mA  |    |

| I(VDDA3V3)           |                    | デュアル電源                              | 10   | 21  | mA  |    |

| I(VDDD1P0)           |                    | デュアル電源                              | 5    | 77  | mA  |    |

| I(VDDIO=3.3V)        |                    | VDDIO = VDDMAC                      | 12   | 18  | mA  |    |

| I(VDDIO=1.8V)        |                    |                                     | 8    | 11  | mA  |    |

| I(VDDIO=2.5V)        |                    |                                     | 8    | 14  | mA  |    |

| I(VDDA3V3)           | スタンバイ              | 単一電源                                | 31   | 119 | mA  |    |

| I(VDDA3V3)           |                    | デュアル電源                              | 22   | 37  | mA  |    |

| I(DVDD1P0)           |                    | デュアル電源                              | 9    | 82  | mA  |    |

| I(VDDIO=3.3V)        |                    | xMII、VDDIO = VDDMAC                 | 15   | 22  | mA  |    |

|                      |                    | SGMII、VDDIO = VDDMAC                | 12   | 15  | mA  |    |

| I(VDDIO=2.5V)        |                    | xMII、VDDIO = VDDMAC                 | 11   | 16  | mA  |    |

| I(VDDIO=1.8V)        |                    | SGMII、VDDIO = VDDMAC                | 8    | 13  | mA  |    |

|                      | TC-10 スリープ         | xMII、VDDIO = VDDMAC                 | 8    | 13  | mA  |    |

| I(VSLEEP)            |                    | SGMII、VDDIO = VDDMAC                | 6    | 8   | mA  |    |

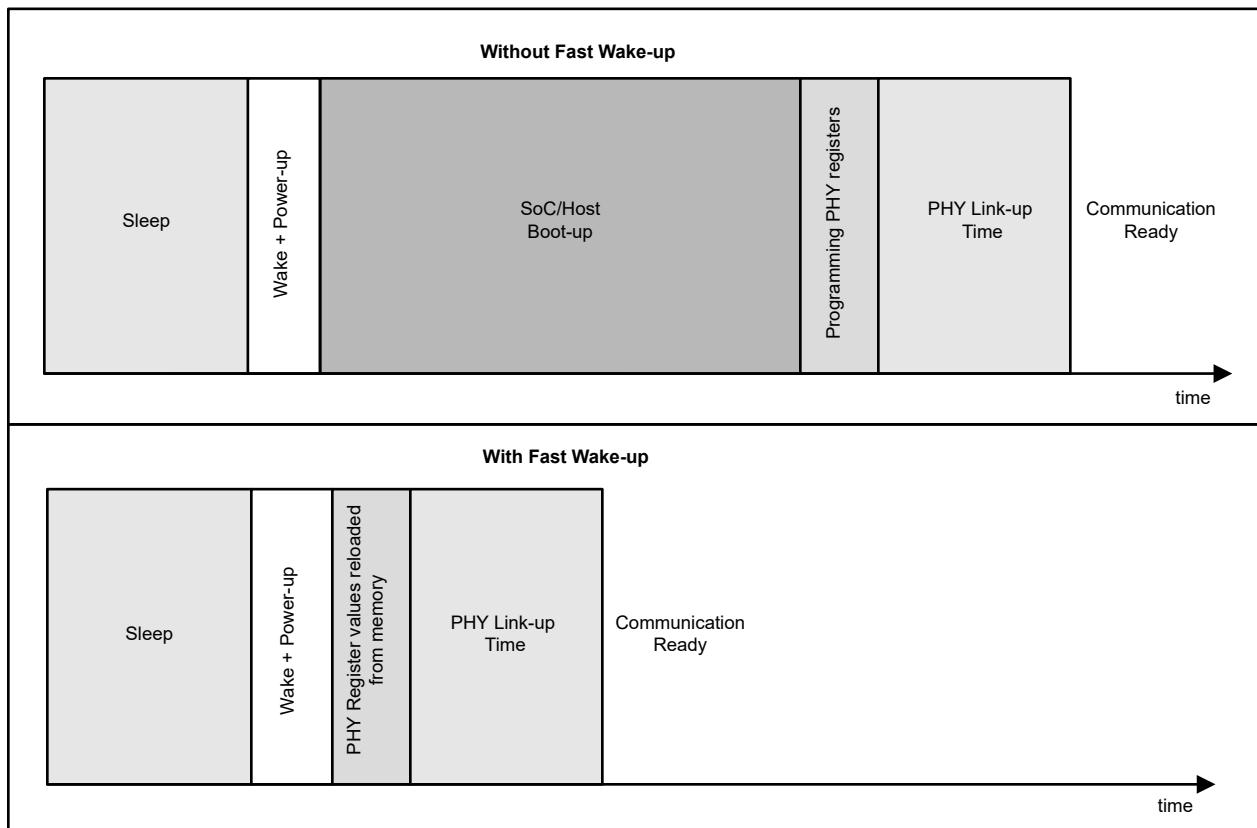

|                      | TC-10 Sleep、電源オン   | 他のすべての電源オフ                          | 7    | 18  | μA  |    |

| I(VSLEEP)            |                    | 他のすべての電源オフ、高速ウェークアップ モード有効          | 25   | 50  | μA  |    |

| I(VDDIO=3.3V)        |                    | VDDIO = VDDMAC                      | 12   | 16  | mA  |    |

| I(VDDIO=2.5V)        |                    |                                     | 8.5  | 12  | mA  |    |

| I(VDDIO=1.8V)        |                    |                                     | 6    | 9   | mA  |    |

| I(VDDA3V3)           |                    | 単一電源                                | 35   | 132 | mA  |    |

| I(VDDA3V3)           |                    | デュアル電源                              | 28   | 50  | mA  |    |

| I(VDDD1P0)           |                    | デュアル電源                              | 7    | 82  | mA  |    |

| <b>SGMII 入力</b>      |                    |                                     |      |     |     |    |

| V <sub>IDTH</sub>    | 入力差動電圧許容値          | SI_P および SI_N、AC 結合                 | 0.1  |     |     | V  |

| R <sub>IN-DIFF</sub> | 受信差動入力インピーダンス (DC) |                                     | 80   | 120 |     | Ω  |

| <b>SGMII 出力</b>      |                    |                                     |      |     |     |    |

|                      | クロック信号デューティサイクル    | SO_P および SO_N、AC 結合、0101010101 パターン | 48   | 52  |     | %  |

|                      | 出力差動電圧             | SO_P および SO_N、AC 結合                 | 150  | 400 |     | mV |

| <b>電圧センサ</b>         |                    |                                     |      |     |     |    |

| VDDA                 | VDDA センサの範囲        |                                     | 2.7  | 3.3 | 4   | V  |

|                      | VDDA センサの分解能 (LSB) |                                     |      | 8.8 |     | mV |

|                      | VDDA センサの精度        | シングル部品における電圧および温度変動                 | -150 | 150 |     | mV |

|                      | VDDA センサの精度        | 部品間のバラツキ                            | -100 | 100 |     | mV |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ        |                            | テスト条件               | 最小値  | 標準値 | 最大値 | 単位 |

|--------------|----------------------------|---------------------|------|-----|-----|----|

| VDDIO/VDDMAC | VDDIO/VDDMAC センサの範囲        |                     | 1.44 |     | 3.9 | V  |

|              | VDDIO/VDDMAC センサの分解能 (LSB) |                     |      | 16  |     | mV |

|              | VDDIO/VDDMAC センサの精度        | シングル部品における電圧および温度変動 | -200 |     | 200 | mV |

|              | VDDIO/VDDMAC センサの精度        | 部品間のバラツキ            | -100 |     | 100 | mV |

| VSLEEP       | VSLEEP センサの範囲              | 部品および VT の変動        | 2.7  | 3.3 | 4   | V  |

|              | VSLEEP センサの分解能 (LSB)       |                     |      | 8.8 |     | mV |

|              | VSLEEP センサの精度              | シングル部品における電圧および温度変動 | -150 |     | 150 | mV |

|              | VSLEEP センサの精度              | 部品間のバラツキ            | -100 |     | 100 | mV |

| VDD1P0       | VDD1P0 センサの範囲              |                     | 0.9  | 1   | 1.2 | V  |

|              | VDD1P0 センサの分解能 (LSB)       |                     |      | 2.7 |     | mV |

|              | VDD1P0 センサの精度              | 各部品で室温オフセット校正を実施    | -60  |     | 60  | mV |

|              | VDD1P0 センサの精度              | 部品間                 | -40  |     | 40  | mV |

| <b>温度センサ</b> |                            |                     |      |     |     |    |

| 温度           | 温度センサの範囲                   |                     | -40  |     | 150 | °C |

| 温度           | 温度センサの分解能 (LSB)            |                     |      | 1.1 |     | °C |

- (1) 対象ピン:MDC、TX\_CLK、TX\_CTRL、TX\_D[3:0]、RESET\_N

(2) 対象ピン:RX\_D[3:0]、RX\_CLK、RX\_CTRL、MDIO、INT\_N、XO。

## 6.6 タイミング要件

| パラメータ                  |                                                     | テスト条件 | 最小値 | 公称値 | 最大値 | 単位 |

|------------------------|-----------------------------------------------------|-------|-----|-----|-----|----|

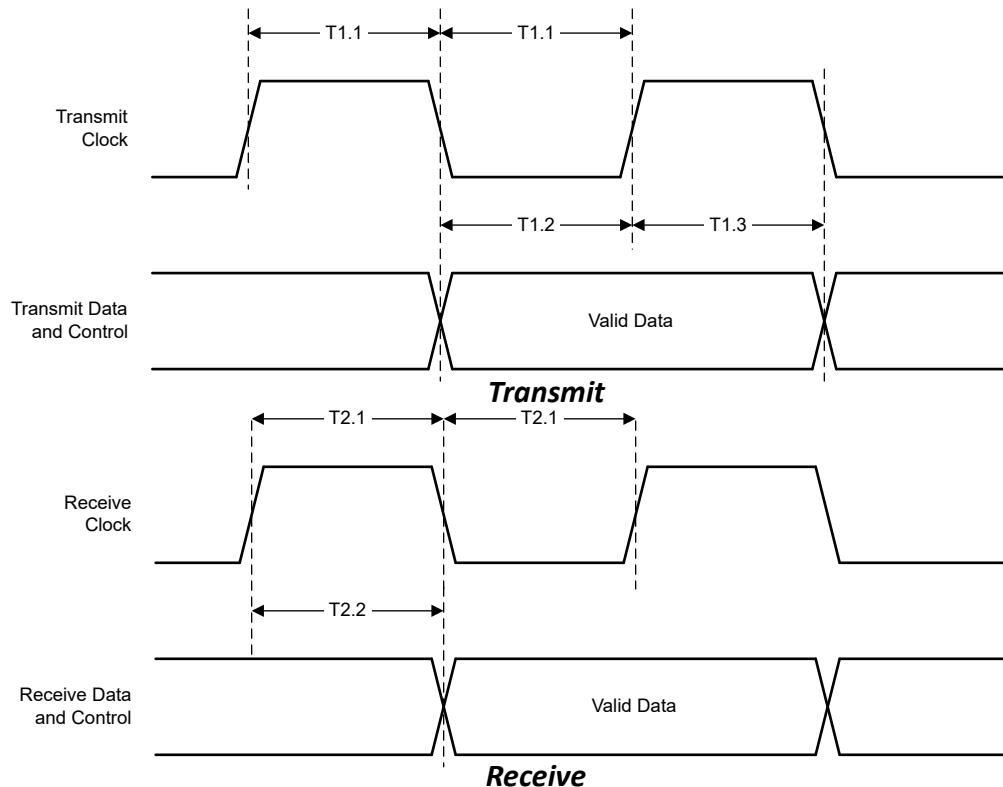

| <b>MII タイミング</b>       |                                                     |       |     |     |     |    |

| T1.1                   | TX_CLK High / Low 時間                                |       | 16  | 20  | 24  | ns |

| T1.2                   | TX_CLK までの TX_D[3:0]、TX_ER、TX_EN のセットアップ            |       | 10  |     |     | ns |

| T1.3                   | TX_CLK からの TX_D[3:0]、TX_ER、TX_EN のホールド              |       | 0   |     |     | ns |

| T2.1                   | RX_CLK High / Low 時間                                |       | 16  | 20  | 24  | ns |

| T2.2                   | RX_CLK 立ち上がりからの RX_D[3:0]、RX_ER、RX_DV の遅延           |       | 10  |     | 30  | ns |

| <b>RMII リーダー タイミング</b> |                                                     |       |     |     |     |    |

| T3.1                   | RMII リーダー クロック周期                                    |       |     | 20  |     | ns |

|                        | RMII リーダー クロック デューティ サイクル                           |       | 35  |     | 65  | %  |

| T3.2                   | TX_D[1:0]、TX_ER、TX_EN の RMII リーダ クロックに対するセットアップ     |       | 4   |     |     | ns |

| T3.3                   | TX_D[1:0]、TX_ER、TX_EN の RMII リーダ クロックからのホールド        |       | 2   |     |     | ns |

| T3.4                   | RX_D[1:0]、RX_ER、CRS_DV の RMII リーダ クロック立ち上がりエッジからの遅延 |       | 4   | 10  | 14  | ns |

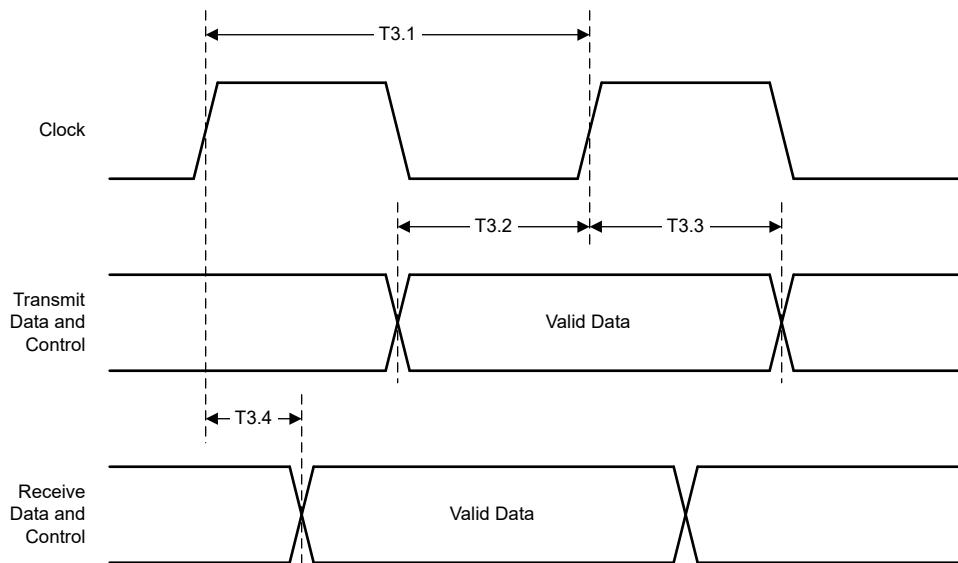

| <b>RMII フォロワ タイミング</b> |                                                     |       |     |     |     |    |

| T3.1                   | 入力基準クロック周期                                          |       |     | 20  |     | ns |

|                        | 入力クロック デューティ サイクル                                   |       | 35  |     | 65  | %  |

## 6.6 タイミング要件 (続き)

| パラメータ                      |                                                                      | テスト条件      | 最小値  | 公称値 | 最大値  | 単位  |

|----------------------------|----------------------------------------------------------------------|------------|------|-----|------|-----|

| T3.2                       | XI クロックの立ち上がりまでの TX_D[1:0]、TX_ER、TX_EN のセットアップ                       |            | 4    |     |      | ns  |

| T3.3                       | XI クロックの立ち上がりからの TX_D[1:0]、TX_ER、TX_EN のホールド                         |            | 2    |     |      | ns  |

| T3.4                       | XI クロックの立ち上がりからの RX_D[1:0]、RX_ER、CRS_DV の遅延                          |            | 4    | 14  |      | ns  |

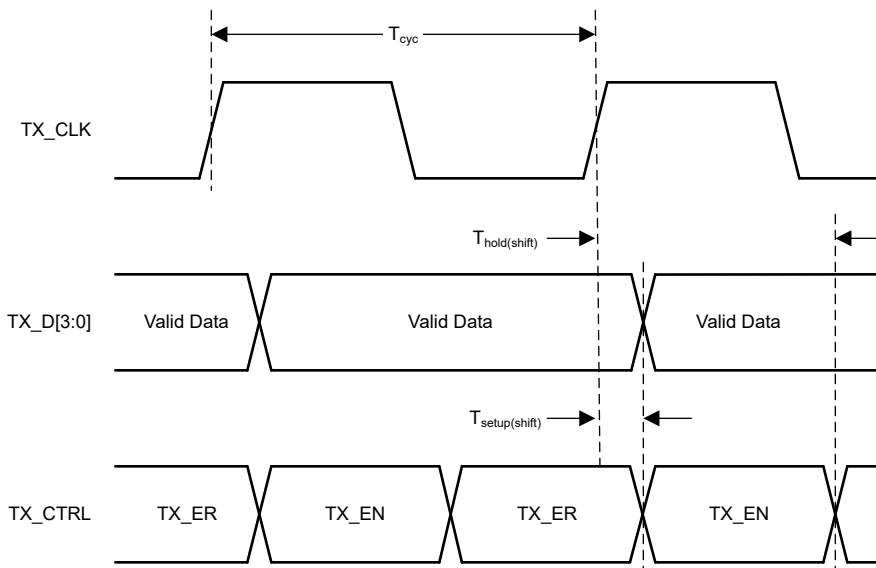

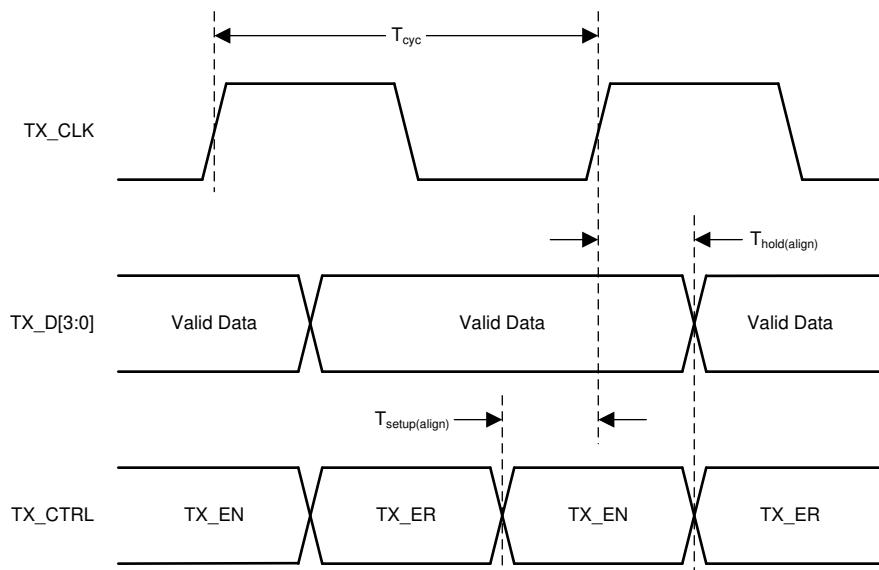

| <b>RGMII 入力タイミング</b>       |                                                                      |            |      |     |      |     |

| T <sub>cyc</sub>           | クロック周期                                                               | TX_CLK     | 36   | 40  | 44   | ns  |

| T <sub>setup(align)</sub>  | TX_D[3:0]、TX_CLK までの TX_CTRL のセットアップ時間 (整列モード)                       |            | 1    | 2   |      | ns  |

| T <sub>hold(align)</sub>   | TX_D[3:0]、TX_CLK からの TX_CTRL のホールド時間 (整列モード)                         |            | 1    | 2   |      | ns  |

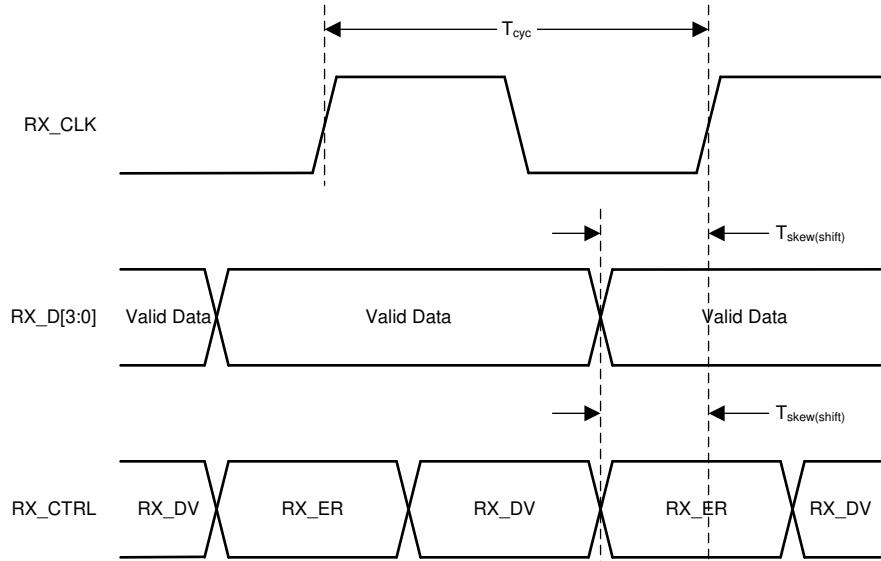

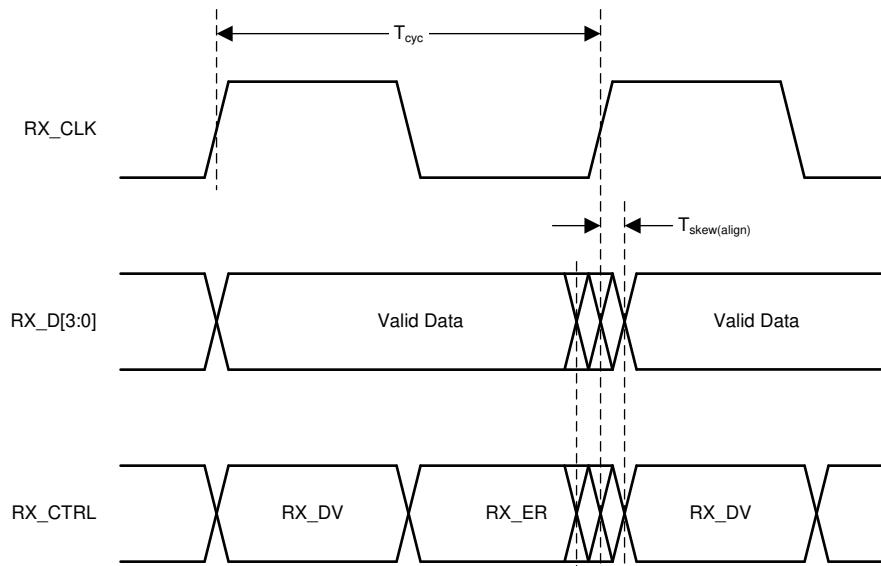

| <b>RGMII 出力タイミング</b>       |                                                                      |            |      |     |      |     |

| T <sub>skew(align)</sub>   | RX_D[3:0]、RX_CLK からの RX_CTRL の遅延時間 (整列モード有効)                         | PHY ピン上    | -1.2 | 1.2 |      | ns  |

| T <sub>setup(shift)</sub>  | RX_D[3:0]、RX_CLK からの RX_CTRL の遅延時間 (シフトモード有効デフォルト)                   | PHY ピン上    | 2    |     |      | ns  |

| T <sub>cyc</sub>           | クロック周期                                                               | RX_CLK     | 36   | 40  | 44   | ns  |

| Duty_G                     | デューティサイクル                                                            | RX_CLK     | 45   | 50  | 55   | %   |

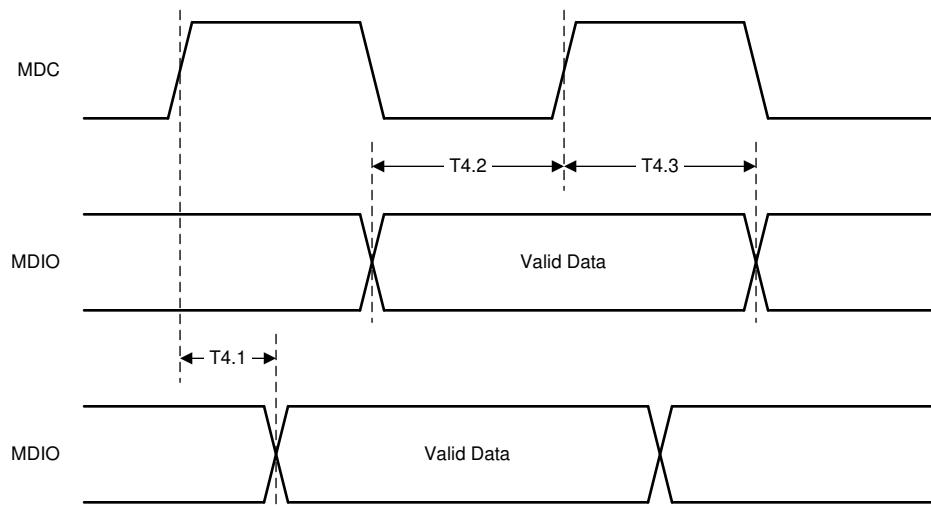

| <b>SMI タイミング</b>           |                                                                      |            |      |     |      |     |

| T4.1                       | MDC から MDIO (出力) までの遅延時間                                             | 25pF の負荷容量 | 0    | 40  |      | ns  |

| T4.2                       | MDC に対する MDIO (入力) のセットアップ時間                                         |            | 10   |     |      | ns  |

| T4.3                       | MDC に対する MDIO (入力) のホールド時間                                           |            | 10   |     |      | ns  |

|                            | MDC 周波数                                                              |            |      | 2.5 | 20   | MHz |

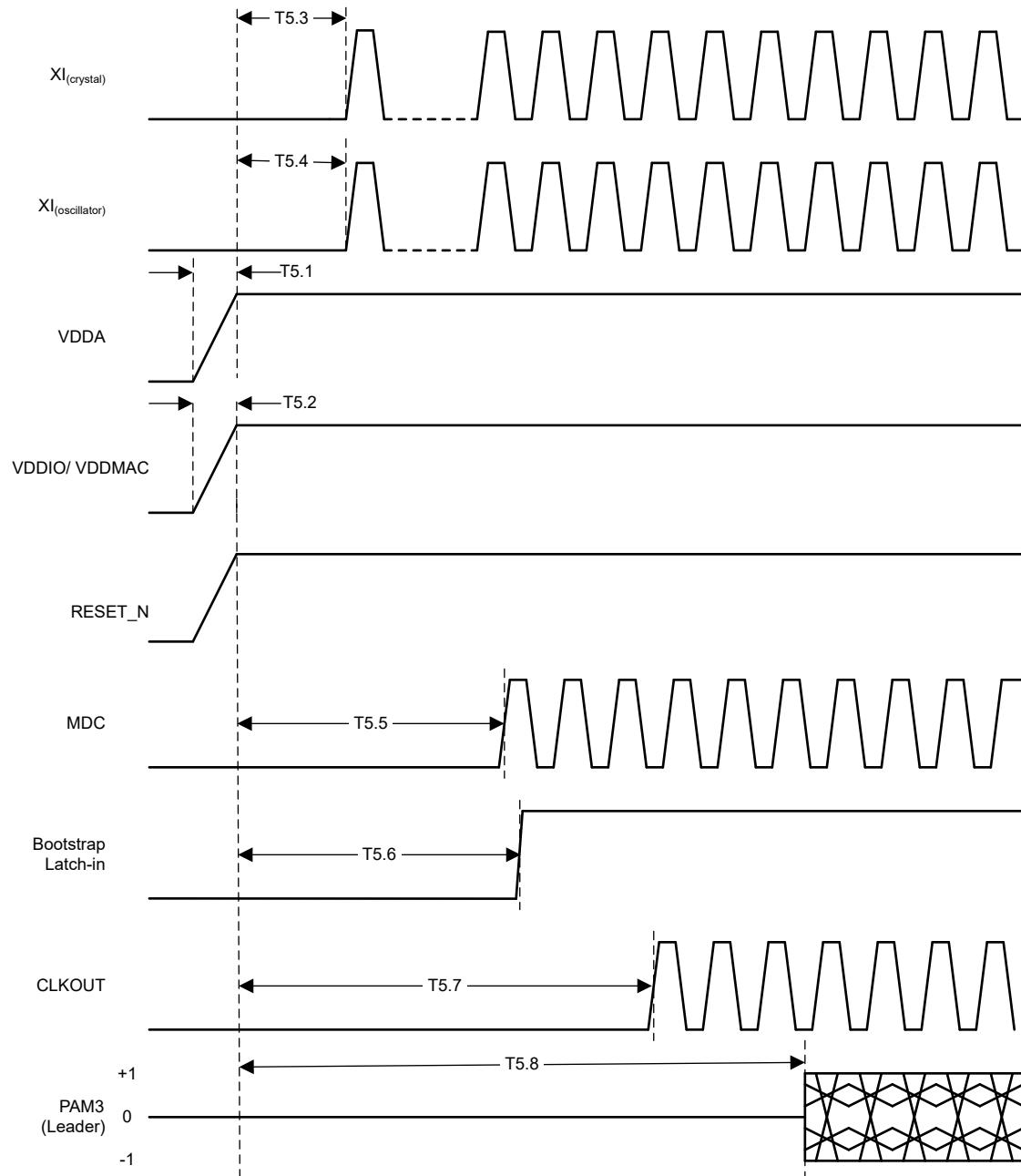

| <b>電源投入のタイミング</b>          |                                                                      |            |      |     |      |     |

| T5.1                       | 電源ランプ時間: AVDD、DVDD、VDDIO <sup>(1)</sup>                              |            | 0.2  | 8   |      | ms  |

| T5.1                       | 電源ランプ時間: Vsleep <sup>(1)</sup>                                       |            | 0.4  | 8   |      | ms  |

| T5.2                       | 電源ランプ遅延オフセット: すべての電源                                                 |            |      |     | 10   | ms  |

| T5.3                       | XTAL の起動 / セトリング: 電源投入から XI 正常 / 安定化まで                               |            |      |     | 1.5  | ms  |

| T5.4                       | 電源投入からの発振器の安定化時間                                                     |            |      |     | 10   | ms  |

|                            | 最終電源立ち上げ後、クロック安定からリセット解除まで                                           |            |      |     | 10   | ms  |

| T5.5                       | 電源投入後、SMI 準備完了まで: 電源投入後、レジスタアクセスのために MDC プリアンブルを送信できるようになるまでに必要な待ち時間 |            |      | 10  |      | ms  |

| T5.6                       | 電源オンからストラップラッチインまで                                                   |            |      |     | 10   | ms  |

| T5.7                       | CLKOUT の起動 / セトリング: 電源投入から CLKOUT 正常 / 安定化まで                         |            |      |     | 10   | ms  |

| T5.8                       | 電源投入からアイドルストリーム出力まで                                                  |            |      |     | 10   | ms  |

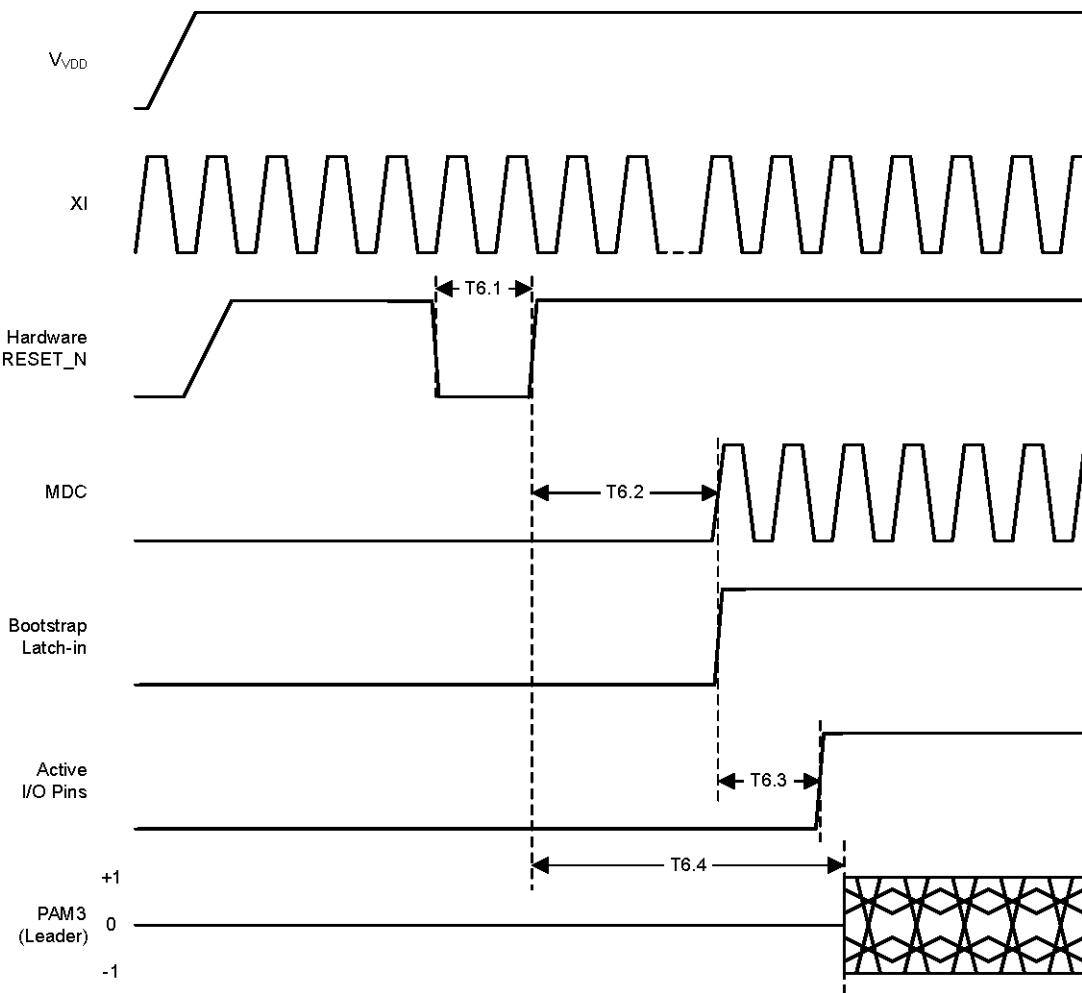

| <b>リセットタイミング (RESET_N)</b> |                                                                      |            |      |     |      |     |

| T6.1                       | リセットパルス幅: リセット可能な最小リセットパルス幅                                          |            | 100  |     |      | μs  |

| T6.2                       | リセットから SMI レディまで: リセット後、レジスタアクセスのために MDC プリアンブルを送信できるようになるまでに必要な待ち時間 |            | 1    |     |      | ms  |

| T6.3                       | リセットからストラップラッチインまで: ハードウェア構成のピンの遷移から出力ドライバまで                         |            |      | 80  |      | μs  |

| T6.4                       | リセットからアイドルストリーム出力まで                                                  |            |      |     | 1800 | μs  |

## 6.6 タイミング要件 (続き)

| パラメータ                                                           | テスト条件   | 最小値  | 公称値  | 最大値 | 単位  |

|-----------------------------------------------------------------|---------|------|------|-----|-----|

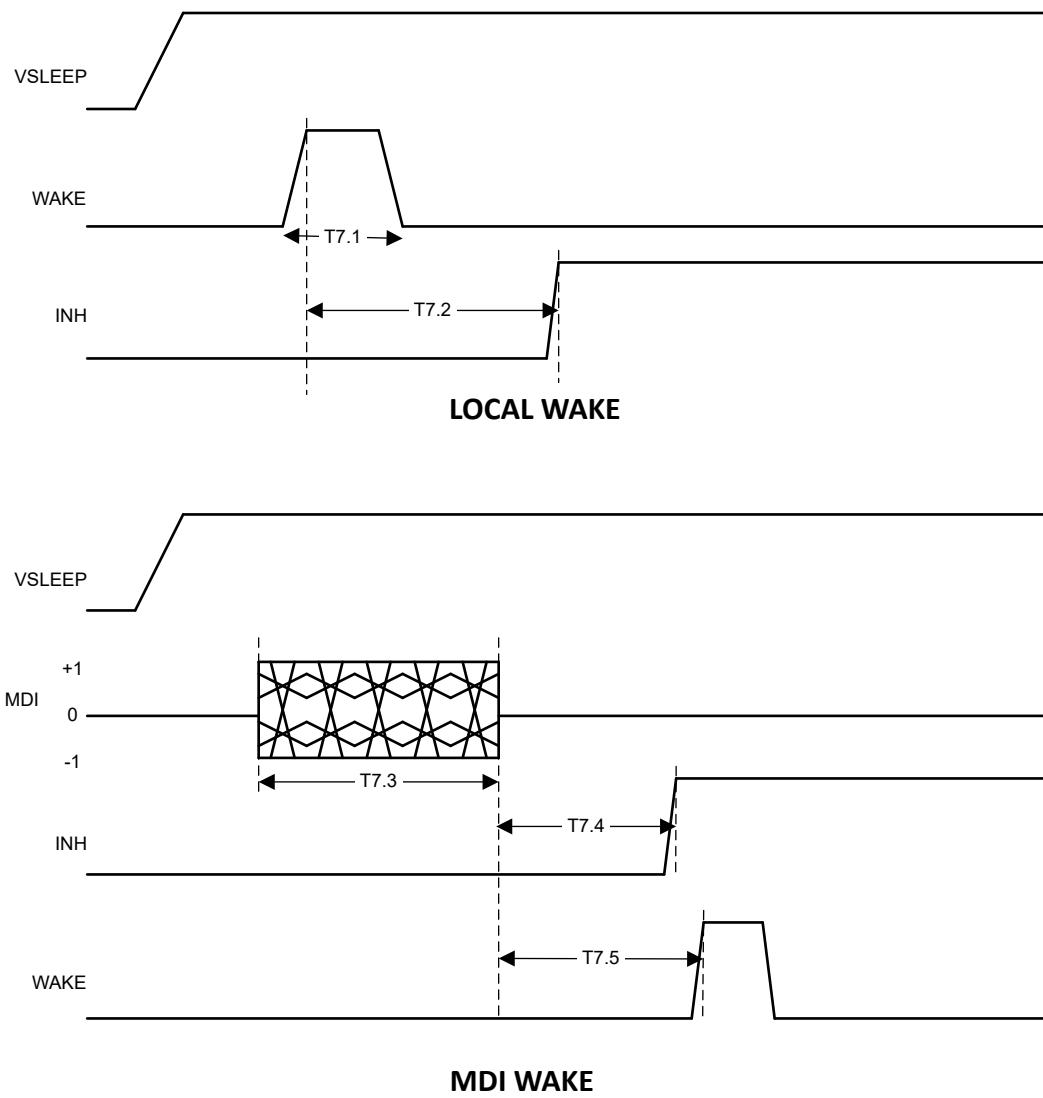

| <b>ウェーク要求とウェーク パルスのタイミング</b>                                    |         |      |      |     |     |

| T7.1 ローカル ウェークアップ パルス幅                                          |         | 40   |      |     | μs  |

| T7.2 ローカル ウェークアップから INH 遷移まで                                    |         |      | 40   |     | μs  |

| T7.3 エナジー検出に基づくウェークアップ パルス幅                                     |         |      | 0.7  |     | ms  |

| T7.4 エナジー検出に基づくウェークアップから INH 遷移まで                               |         |      | 0.7  |     | ms  |

| T7.5 エナジー検出に基づくウェークアップから WAKE 転送パルスまで                           |         |      | 1.4  |     | ms  |

| <b>送信レイテンシ タイミング</b>                                            |         |      |      |     |     |

| MII の TX_CLK の立ち上がりエッジ (TX_EN アサート時) から MD の SSD シンボルまで         |         | 190  | 275  |     | ns  |

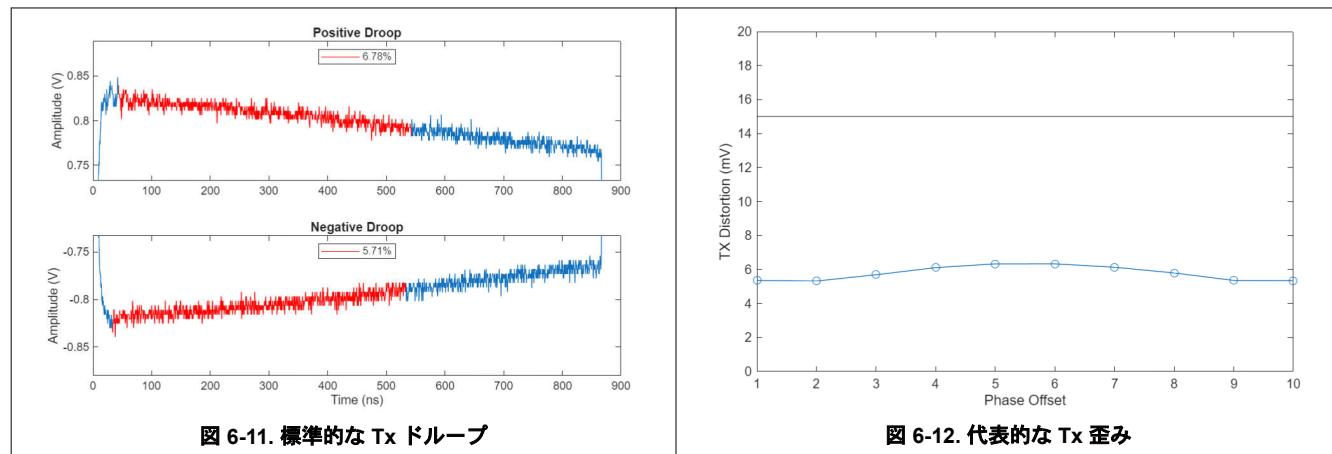

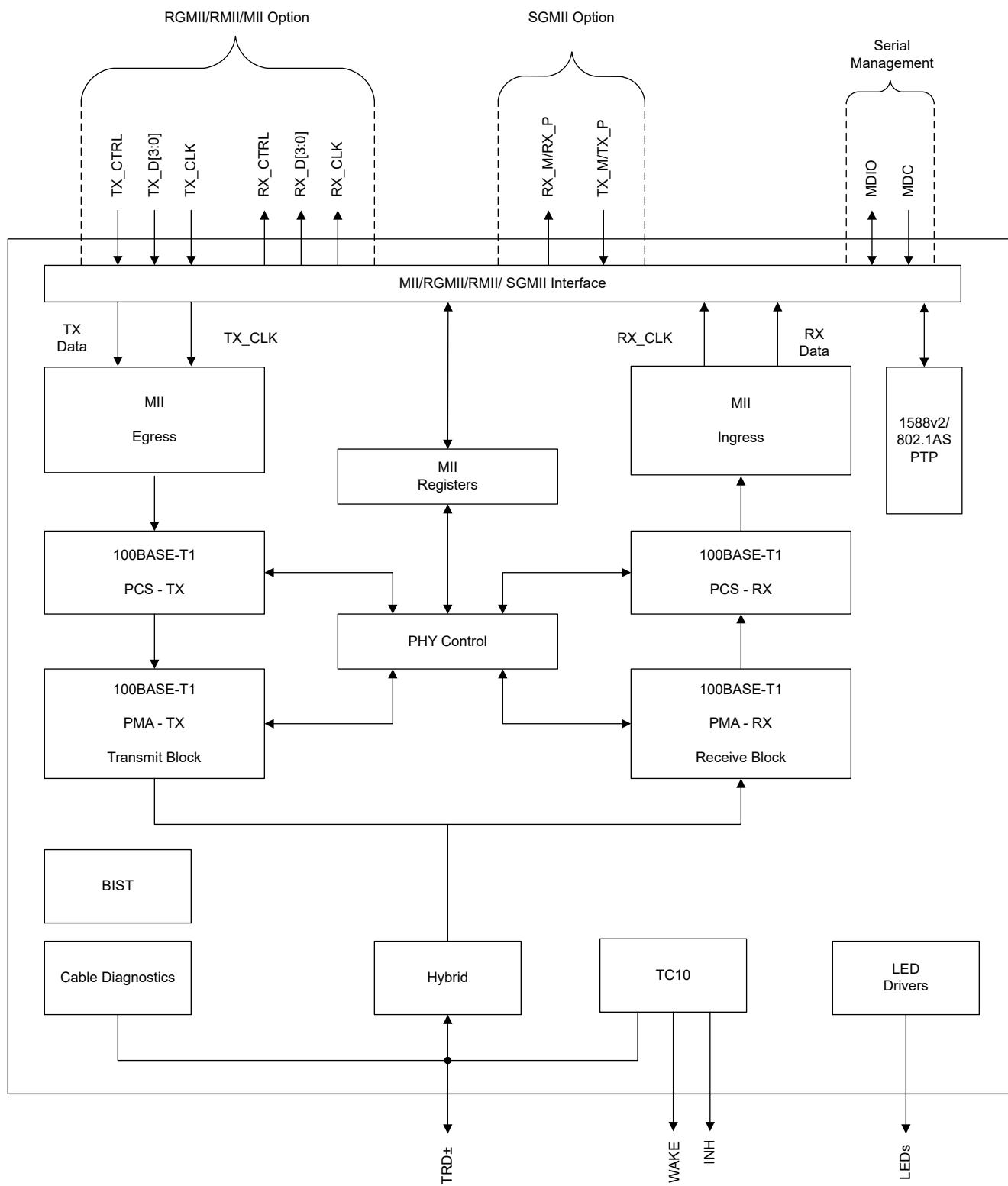

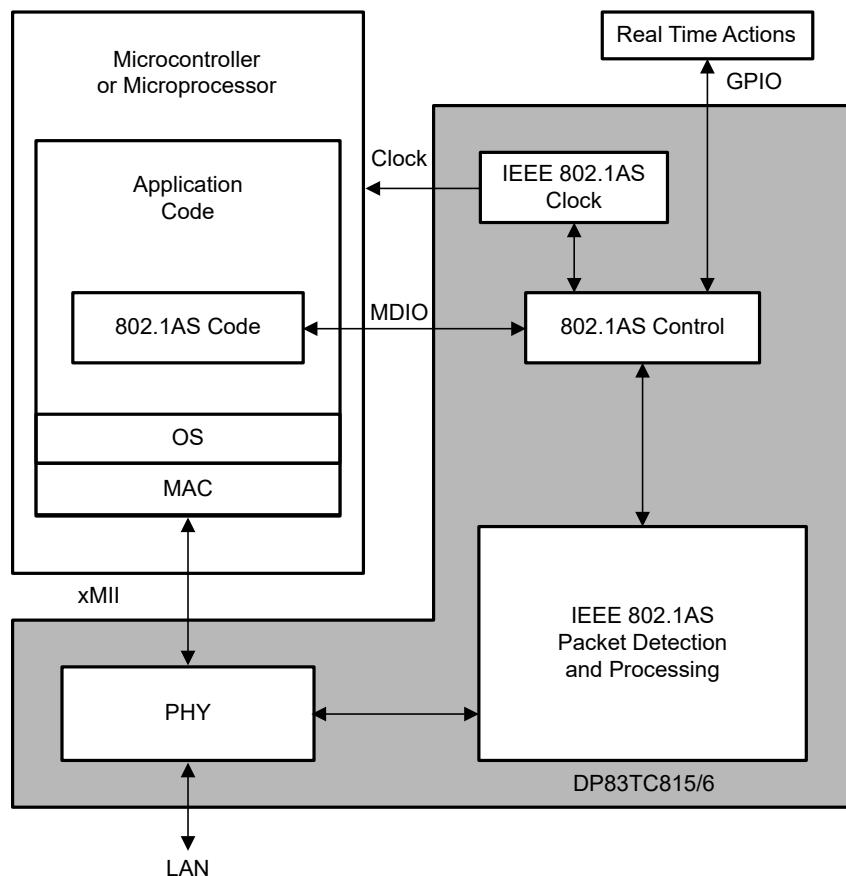

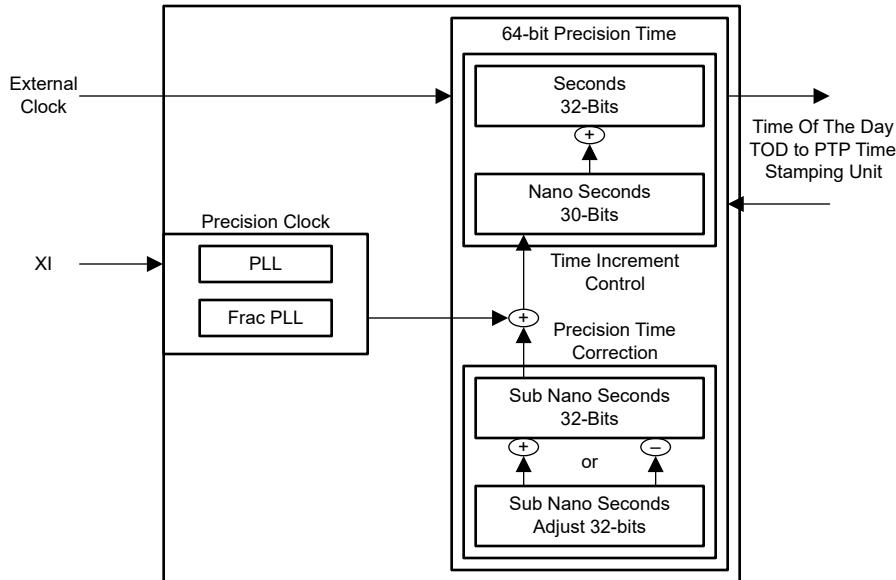

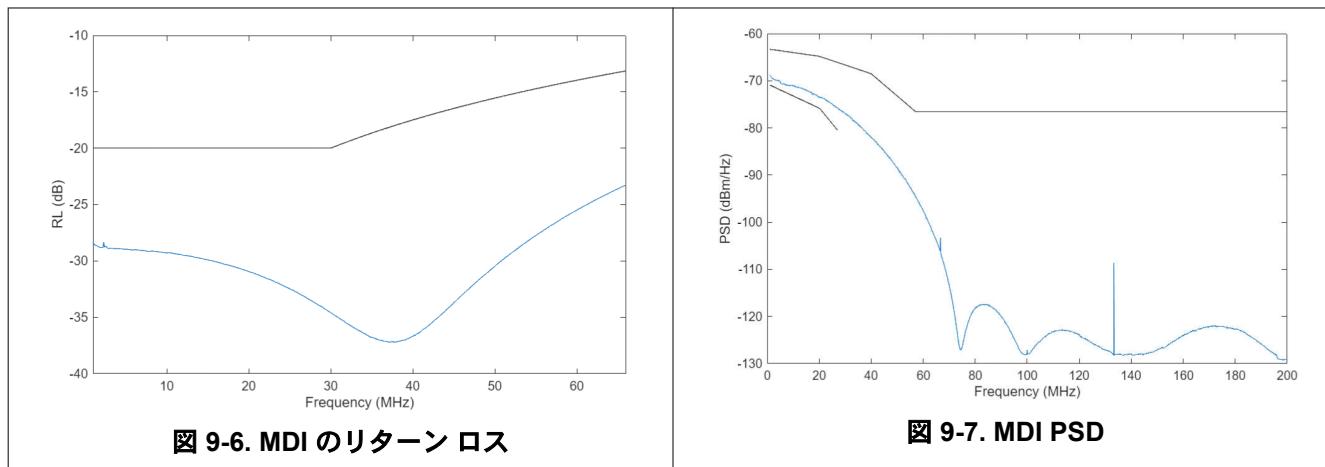

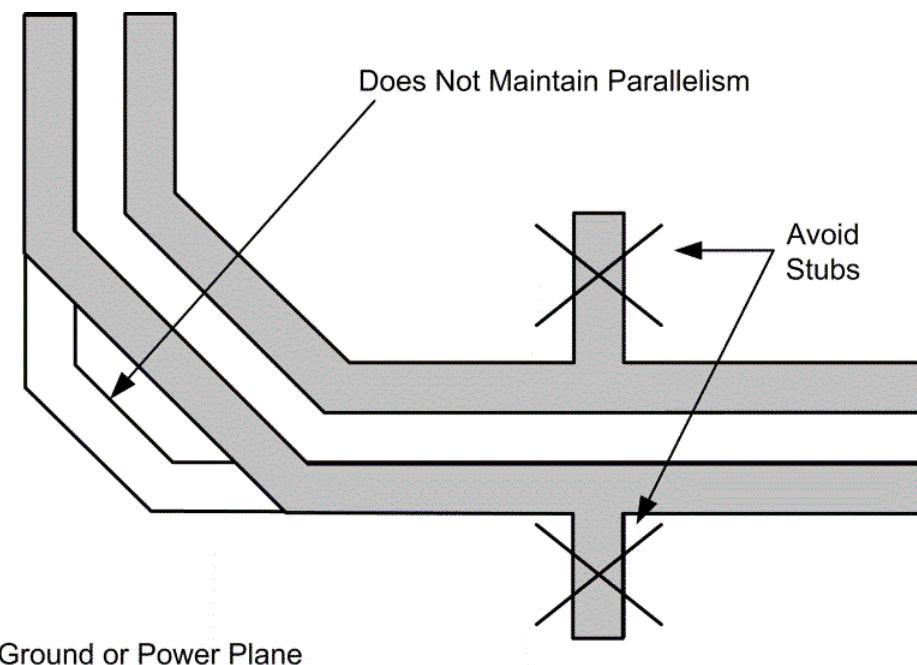

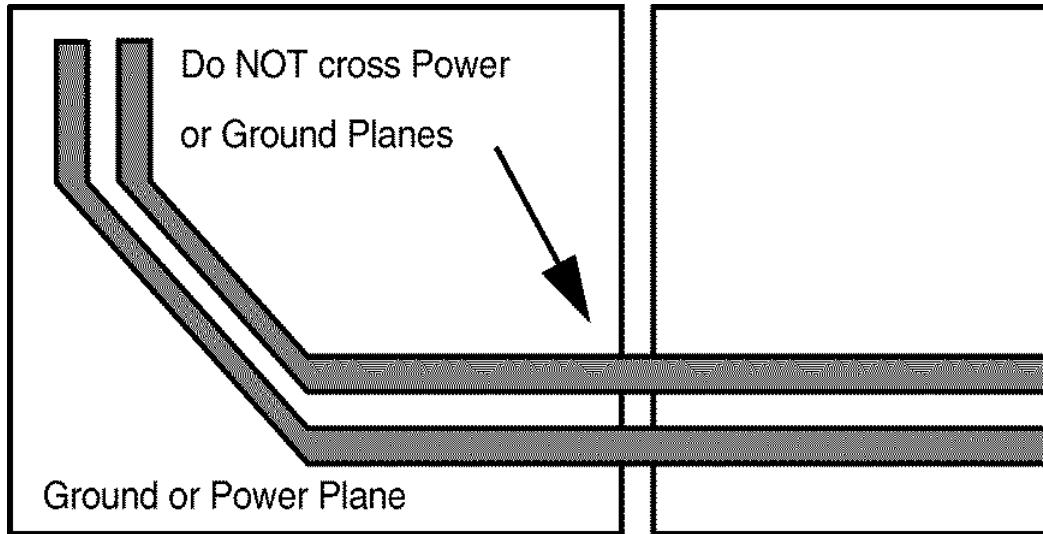

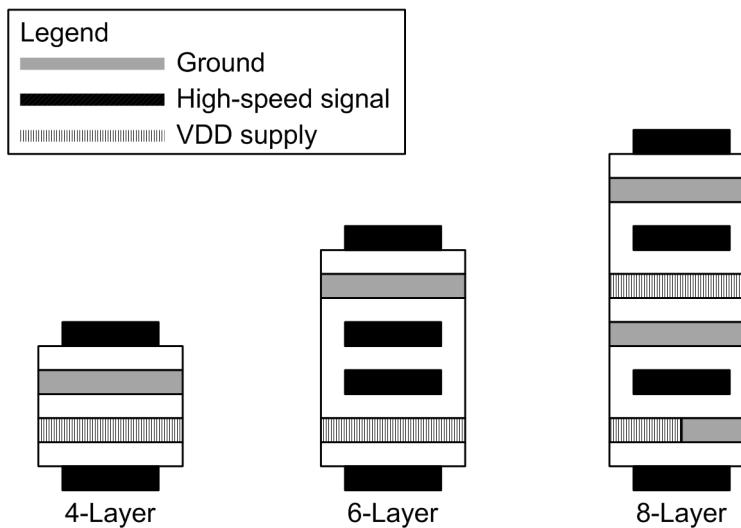

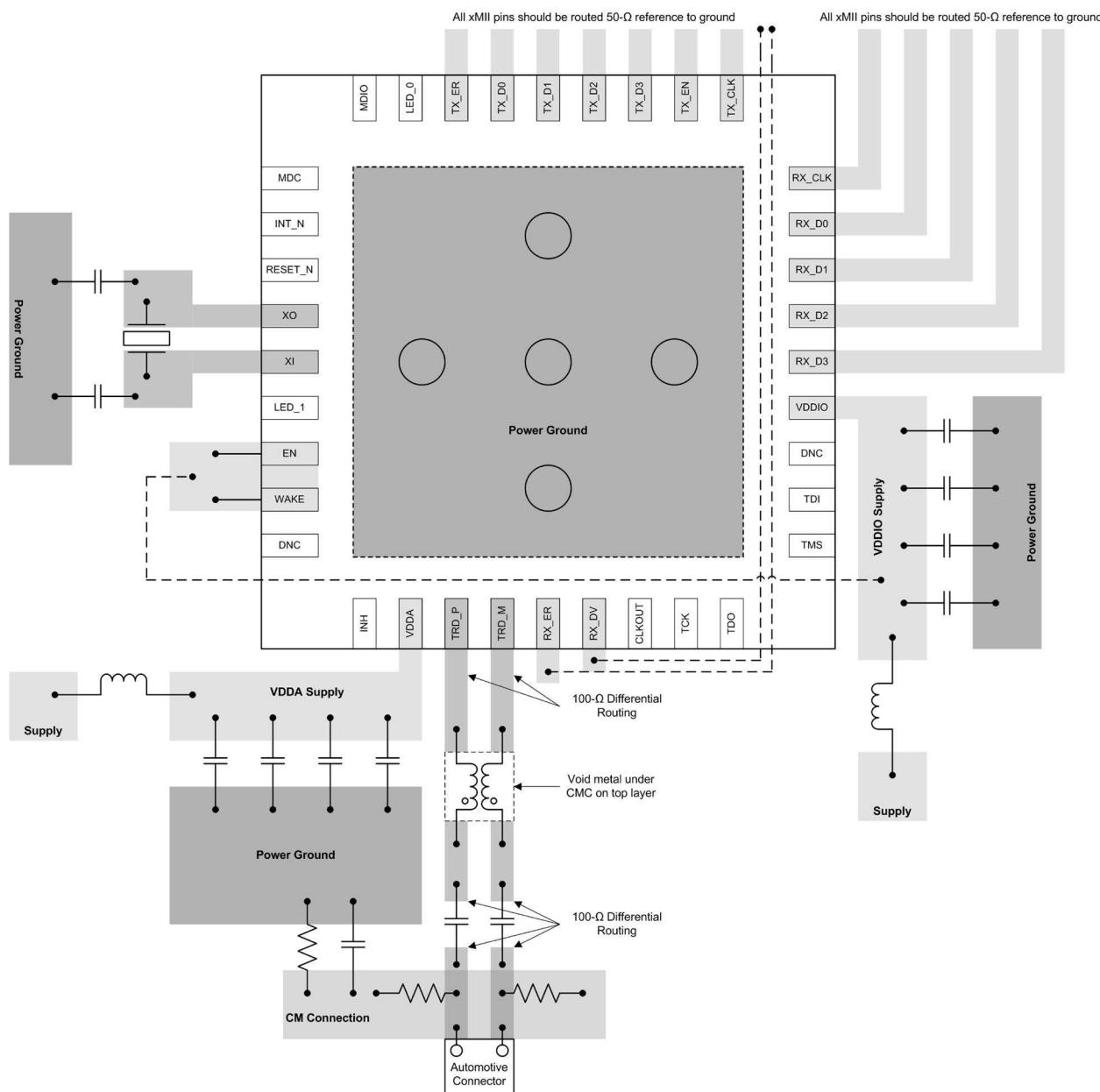

| MII の TX_CLK の立ち上がりエッジ (TX_EN アサート時) から MD の SSD シンボルまで         | PTP 有効時 | 170  | 275  |     | ns  |