# DRV81646 : 65V 4 チャネル ローサイド ドライバ、ハードウェア、SPI、構成可能なスルーレート、カットオフ期間を実装

## 1 特長

- 4 チャネル内蔵ローサイド スイッチ

- 25°C で **140mΩ R<sub>DS(ON)</sub>**

- 動作電源電圧範囲: **4.5V ~ 65V (絶対最大定格 70V)**

- チャネルごとに **0.5A ~ 4A** の電流制限を選択可能

- 最大 **500kHz** の高速 PWM スイッチング

- 柔軟なインターフェイス オプション:

- 独立したチャネル PWM 入力を備えたハードウェアインターフェイス

- SPI** により、チャネル数の多い設計における GPIO と絶縁オーバーヘッドの削減が可能

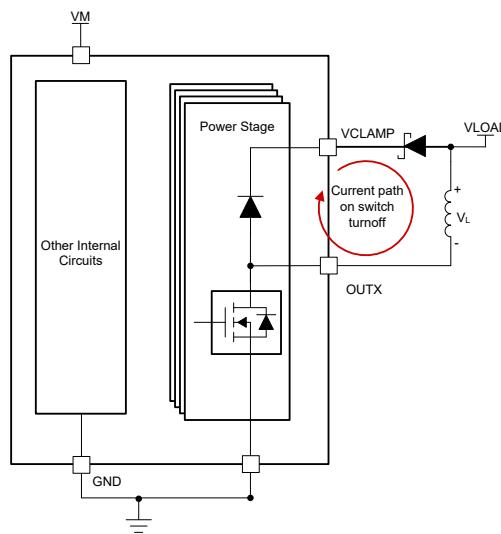

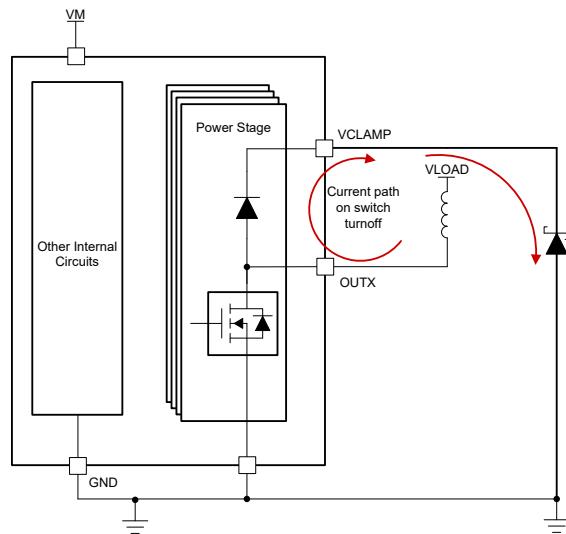

- 柔軟な減衰モードを実現する内蔵キャッチ ダイオードと、スイッチのターンオフ時の代替電流パスとして使用できるオプションの外部 TVS/ツェナーダイオード

- スルーレートを構成可能 (100ns ~ 1500ns) で、低速 / 高速の両方のスイッチング アプリケーションに対応

- 診断フィードバック

- MCU フォルト割り込み信号 (**nFAULT**)

- チャネルごとの異常検出出力を SPI 経由で使用可能

- 保護機能

- ユーザー設定可能な電流制限

- 各チャネルに対して独立した過熱および過電流保護

- 構成可能な過電流カットオフ遅延 (COD) 0.5ms ~ 2ms

## 2 アプリケーション

- PLC

- 分散 I/O

- フィールド デバイス

- 汎用リレーおよびソレノイド ドライブ

- 繊維機械

## 3 説明

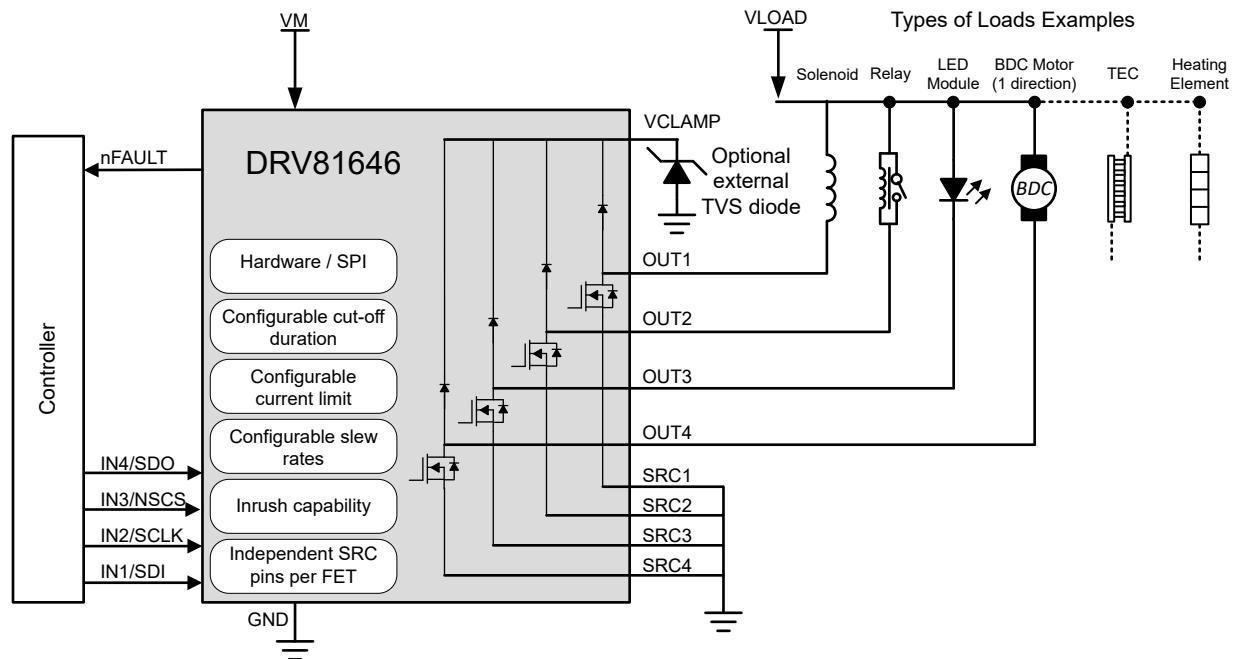

DRV81646 は、4.5V ~ 65V で動作し、広範囲の負荷電流をサポートする 4 チャネル ローサイド スイッチ ドライバです。このデバイスには 140mΩ の R<sub>DS(ON)</sub> を持つ 4 つのローサイド スイッチが内蔵されており、それぞれに VCLAMP ピンへのフリーホイール ダイオードが付属しています。この機能により、再循環電流を行うか、誘導性負荷をオフにするために外部 TVS を接続することができます。

このデバイスは、ハードウェア GPIO インターフェイスまたは標準の 4 線式 SPI で制御できます。各チャネルは個別の過熱保護機能を備えており、ILIM ピンの外部抵抗でアナログ電流制限を設定できます。オプションのカットオフ遅延 (COD) 構成があり、それぞれのチャネルについて電流制限状態の持続時間を制限することで、デバイスまたは負荷の損傷を防止できます。出力スルーレートは、RSLEW/CNTL ピンに抵抗を設定することで構成できるため、出力スイッチをより柔軟に制御できます。このデバイスは、容量性負荷の電流制限スレッショルドを昇圧する INRUSH モードを備えています。

DRV81646 はフォルト状態を通知するためのフォルト出力ピン (**nFAULT**) を備えており、SPI モードでチャネルごとのフォルト状態を監視できます。この機能により、ユーザーはフォルトが発生した場合にすばやく識別し、対応できます。

### パッケージ情報

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|--------------|----------------------|--------------------------|

| DRV81646PWPR | PWP (HTSSOP、20)      | 6.50mm × 6.40mm          |

| DRV81646DGQR | DGQ (HVSSOP、24)      | 7.10mm × 4.90mm          |

(1) 詳細については、[セクション 10](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピッチも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

概略回路図

## 目次

|             |    |                        |    |

|-------------|----|------------------------|----|

| 1 特長        | 1  | 6.4 デバイスの機能モード         | 22 |

| 2 アプリケーション  | 1  | 7 アプリケーションと実装          | 27 |

| 3 説明        | 1  | 7.1 アプリケーション情報         | 27 |

| 4 ピン構成および機能 | 4  | 7.2 代表的なアプリケーション       | 27 |

| 5 仕様        | 6  | 7.3 電源に関する推奨事項         | 31 |

| 5.1 絶対最大定格  | 6  | 7.4 レイアウト              | 32 |

| 5.2 ESD 定格  | 6  | 8 デバイスおよびドキュメントのサポート   | 33 |

| 5.3 推奨動作条件  | 6  | 8.1 ドキュメントのサポート        | 33 |

| 5.4 熱に関する情報 | 7  | 8.2 ドキュメントの更新通知を受け取る方法 | 33 |

| 5.5 電気的特性   | 7  | 8.3 サポート・リソース          | 33 |

| 5.6 タイミング要件 | 10 | 8.4 商標                 | 33 |

| 5.7 代表的特性   | 11 | 8.5 静電気放電に関する注意事項      | 33 |

| 6 詳細説明      | 12 | 8.6 用語集                | 33 |

| 6.1 概要      | 12 | 9 改訂履歴                 | 33 |

| 6.2 機能ブロック図 | 12 | 10 メカニカル、パッケージ、および注文情報 | 33 |

| 6.3 機能説明    | 13 |                        |    |

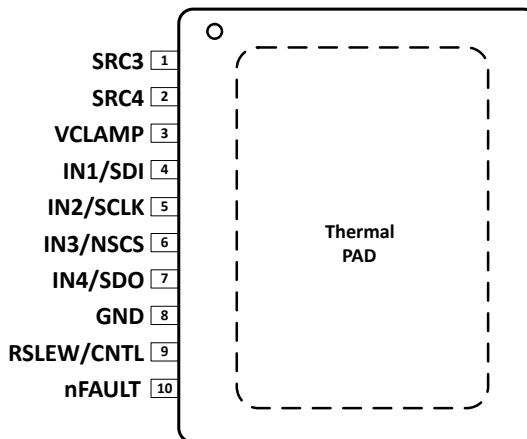

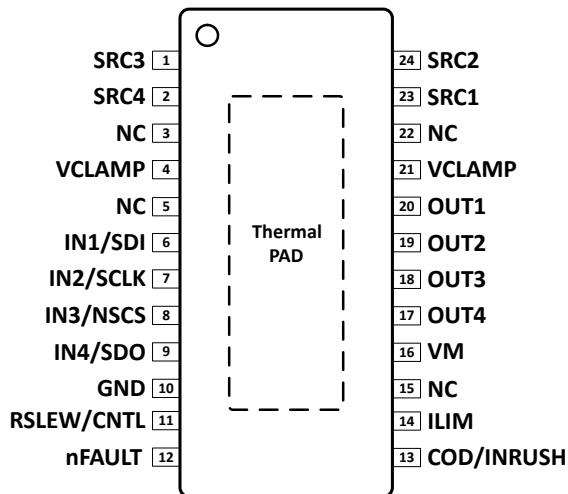

## 4 ピン構成および機能

図 4-1. 20 ピン PWP パッケージ、HTSSOP (上面図)

図 4-2. 24 ピン DGQ パッケージ、HVSSOP (上面図)

表 4-1. ピンの機能

| ピン               |          | タイプ <sup>(1)</sup> | 説明       |                                                                                                                                     |

|------------------|----------|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| 名称               | PWP (20) |                    | DGQ (24) |                                                                                                                                     |

| <b>電源およびグランド</b> |          |                    |          |                                                                                                                                     |

| VM               | 13       | 16                 | PWR      | 電源。<br>このピンは、0.1 $\mu$ F セラミック コンデンサと、VM 定格の十分なバーケ容量を使用して GND ピンにバイパスします。                                                           |

| VCLAMP           | 3, 18    | 4, 21              | PWR      | VM 電源に直接接続するか、ツエナー ダイオードを VM 電源または GND に接続します。このピンを未接続のままにしないでください。                                                                 |

| GND              | 8        | 10                 | GND      | デバイスのグランド。システム グランドに接続。                                                                                                             |

| SRC1             | 19       | 23                 | GND      | チャネル 1 ローサイド FET のソース端子。外部電流センスのために、システム グランドまたはオプションのセンス抵抗をシステム グランドに接続します                                                         |

| SRC2             | 20       | 24                 | GND      | チャネル 2 ローサイド FET のソース端子。外部電流センスのために、システム グランドまたはオプションのセンス抵抗をシステム グランドに接続します                                                         |

| SRC3             | 1        | 1                  | GND      | チャネル 3 ローサイド FET のソース端子。外部電流センスのために、システム グランドまたはオプションのセンス抵抗をシステム グランドに接続します                                                         |

| SRC4             | 2        | 2                  | GND      | チャネル 4 ローサイド FET のソース端子。外部電流センスのために、システム グランドまたはオプションのセンス抵抗をシステム グランドに接続します                                                         |

| サーマル パッド         | —        | —                  | —        | サーマル パッド。システム グランドに接続。<br>最高の放熱特性を得るため、直接結合ビアを使用して、連続的なグランドプレーン銅プレーンに接続します。                                                         |

| NC               | —        | 3, 5, 15, 22       | —        |                                                                                                                                     |

| <b>制御</b>        |          |                    |          |                                                                                                                                     |

| ILIM             | 12       | 14                 | I        | 電流制限入力。<br>電流制限スレッショルドを設定するため、ILIM と GND 間に抵抗を接続します。詳細は、セクション 6.3.4.1 を参照してください。<br>このピンを未接続のままにしないでください。最大電流制限設定の場合は、GND に直接接続します。 |

**表 4-1. ピンの機能 (続き)**

| ピン         |          |          | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                        |

|------------|----------|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称         | PWP (20) | DGQ (24) |                    |                                                                                                                                                                                                                                           |

| RSLEW/CNTL | 9        | 11       | I                  | スルーレートと制御インターフェイスの選択入力。<br>目的のスルーレートと制御インターフェイス設定の組み合わせのために、GND に抵抗を接続します。詳細については、 <a href="#">セクション 6.3.1</a> を参照してください。                                                                                                                 |

| COD/INRUSH | 11       | 13       | I                  | カットオフ遅延または突入モードのデバイス構成ピン。適切な抵抗を GND に接続して、対応するカットオフ遅延時間を設定します。この機能を無効化するには、GND に接続します。<br>INRUSH モードの場合は未接続 (ハイインピーダンス) のままにします                                                                                                           |

| IN1/SDI    | 4        | 6        | I                  | ハードウェア モードでは、このピンはチャネル 1 の出力を制御します。このチャネルを使用しない場合は、このピンを GND に直接接続するか、10kΩ を使用して接続します<br>SPI モードでは、このピンはシリアル データ入力です。<br>ピンは内部プルダウン抵抗を備えています。                                                                                             |

| IN2/SCLK   | 5        | 7        | I                  | ハードウェア モードでは、このピンはチャネル 2 の出力を制御します。このチャネルを使用しない場合は、このピンを GND に直接接続するか、10kΩ を使用して接続します<br>SPI モードでは、このピンはシリアル クロック入力です。シリアル データはこのピンの立ち上がりエッジでシフトアウトされ、このピンの立ち下がりエッジでキャプチャされます。<br>ピンは内部プルダウン抵抗を備えています。                                    |

| IN3/NSCS   | 6        | 8        | I                  | ハードウェア モードでは、このピンはチャネル 3 の出力を制御します。このチャネルを使用しない場合は、このピンを GND に直接接続するか、10kΩ を使用して接続します<br>SPI モードでは、このピンはシリアル チップ セレクトです。このピンを Low にするとシリアルインターフェイス通信が有効になります。<br>ピンは内部プルダウン抵抗を備えています。                                                     |

| IN4/SDO    | 7        | 9        | I/O                | ハードウェア モードでは、このピンはチャネル 4 の出力を制御します。このチャネルを使用しない場合は、このピンを GND に直接接続するか、10kΩ を使用して接続します。<br>ハードウェア モードでは、このピンには内部プルダウン抵抗があります。<br>SPI モードでは、このピンはシリアル データ出力です。データは、SCLK ピンの立ち上がりエッジでシフト アウトされます。SPI モードでは、このピンはオープン ドレイン出力で、外部プルアップ抵抗が必要です。 |

| nFAULT     | 10       | 12       | O                  | オープン ドレイン出力。プルアップ抵抗を外部ロジック電源に接続します。フォルト状態時はロジック Low です。                                                                                                                                                                                   |

| <b>出力</b>  |          |          |                    |                                                                                                                                                                                                                                           |

| OUT1       | 17       | 20       | O                  | 負荷 1 に接続                                                                                                                                                                                                                                  |

| OUT2       | 16       | 19       | O                  | 負荷 2 に接続                                                                                                                                                                                                                                  |

| OUT3       | 15       | 18       | O                  | 負荷 3 に接続                                                                                                                                                                                                                                  |

| OUT4       | 14       | 17       | O                  | 負荷 4 に接続                                                                                                                                                                                                                                  |

(1) I = 入力、O = 出力、PWR = 電源、GND = グラウンド

## 5 仕様

### 5.1 絶対最大定格

動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                     | ピン                                | 最小値  | 最大値        | 単位 |

|-------------------------------------|-----------------------------------|------|------------|----|

| 電源電圧                                | VM                                | -0.3 | 70         | V  |

| 出力電圧                                | OUTx                              | -0.3 | VCLAMP+0.3 | V  |

| ピーク出力電流                             | OUTx                              |      | 内部的に制限     | A  |

| クランプ電圧                              | VCLAMP                            | -0.3 | 70         | V  |

| GND を基準とする FET ソース端子電圧 (定常状態)       | SRCx                              | -0.6 | 0.6        | V  |

| VCLAMP の連続 RMS 電流 (ピン 3、18 を互いに接続)  | VCLAMP                            |      | 8          | A  |

| VCLAMP の過渡電流 < 1ms (ピン 3、18 を互いに接続) | VCLAMP                            |      | 20         | A  |

| SRCx と基板 GND の間のセンス抵抗               | SRCx                              |      | 300        | mΩ |

| OUTx FET 還流ダイオード電流 RMS または連続        | OUTx FET ボディダイオード                 |      | 5          | A  |

| デジタル入力ピン電圧                          | ILIM, RSLEW/CNTL, COD/INRUSH, INx | -0.5 | 5.5        | V  |

| デジタル出力電流                            | nFAULT, SDO                       |      | 10         | mA |

| デジタル出力ピン電圧                          | nFAULT, SDO                       | -0.5 | 7          | V  |

| 動作仮想接合部温度、T <sub>J</sub>            |                                   | -40  | 150        | °C |

| 保管温度、T <sub>stg</sub>               |                                   | -60  | 150        | °C |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                    |      |                                                         | 値     | 単位 |

|--------------------|------|---------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | ±3000 | V  |

|                    |      | 荷電デバイス モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup> | ±1000 |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|                    |                |                                                | 最小値       | 公称値 | 最大値 | 単位 |

|--------------------|----------------|------------------------------------------------|-----------|-----|-----|----|

| V <sub>M</sub>     | 電源電圧           |                                                | 4.5       | 65  | 70  | V  |

| V <sub>CLAMP</sub> | 出力クランプ電圧       |                                                |           | 65  | 70  | V  |

| I <sub>OUT</sub>   | 連続出力電流 (各チャネル) | PWP パッケージ、T <sub>A</sub> = 25°C <sup>(1)</sup> | 1 チャネル オン |     | 3.7 | A  |

|                    |                |                                                | 4 チャネル オン |     | 2.7 | A  |

|                    |                | DGQ パッケージ、T <sub>A</sub> = 25°C <sup>(1)</sup> | 1 チャネル オン |     | 3.4 | A  |

|                    |                |                                                | 4 チャネル オン |     | 2.5 | A  |

| T <sub>AMB</sub>   | 動作時周囲温度        |                                                | -40       | 125 | 150 | °C |

| T <sub>J</sub>     | 動作時接合部温度       |                                                | -40       | 150 | 150 | °C |

- (1) 温度範囲全体の定格については、「[連続電流能力](#)」を参照してください

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup>        |                   | DRV81646     |              | 単位   |

|-----------------------------|-------------------|--------------|--------------|------|

|                             |                   | PWP (HTSSOP) | DGQ (HVSSOP) |      |

|                             |                   | 20 ピン        | 24 ピン        |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗      | 30.6         | 32.1         | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 | 26.5         | 33.6         | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗      | 10.6         | 8.9          | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 0.8          | 1.0          | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 10.5         | 8.9          | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース(底面)への熱抵抗 | 2.7          | 1.6          | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーションノートを参照してください。

## 5.5 電気的特性

$4.5V \leq V_{VM} \leq 65V$ 、 $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$  (特に記述のない限り)、24V、25°C での標準値

| パラメータ                                   | テスト条件                                               | 最小値                                | 標準値  | 最大値  | 単位            |

|-----------------------------------------|-----------------------------------------------------|------------------------------------|------|------|---------------|

| <b>電源</b>                               |                                                     |                                    |      |      |               |

| $I_{VM}$                                | VM 動作電源電流                                           | $V_M = 24V$ 、スイッチングなし              |      | 3    | mA            |

|                                         |                                                     | $V_M = 24V$ 、200kHz で出力スイッチング      |      | 5    | mA            |

| $V_{UVLO}$                              | VM 低電圧誤動作防止電圧                                       | $V_M$ 立ち上がり                        | 4.1  | 4.25 | $V$           |

|                                         |                                                     | $V_M$ 立ち下がり                        | 4.0  | 4.15 | $V$           |

| $V_{UVLO\_HYS}$                         | VM 低電圧誤動作防止ヒステリス                                    |                                    | 100  |      | mV            |

| $t_{UVLO}$                              | VM 低電圧グリッチ除去                                        |                                    | 10   |      | $\mu\text{s}$ |

| <b>ロジックレベル入力 (INx, nSCS, SCLK, SDI)</b> |                                                     |                                    |      |      |               |

| $V_{IL}$                                | 入力 Low 電圧                                           |                                    |      | 0.8  | $V$           |

| $V_{IH}$                                | 入力 High 電圧                                          |                                    | 2    |      | $V$           |

| $V_{HYS}$                               | 入力ヒステリシス                                            |                                    | 0.4  |      | $V$           |

| $I_{IL}$                                | 入力 Low 電流                                           | $V_{IN} = 0$                       | -5   | 5    | $\mu\text{A}$ |

| $I_{IH}$                                | 高入力電流                                               | $V_{IN} = 3.3V$                    | 50   | 100  | $\mu\text{A}$ |

| <b>オーブンドレイン出力 (nFAULT, SDO)</b>         |                                                     |                                    |      |      |               |

| $V_{OL}$                                | nFAULT の出力 Low 電圧、SDO                               | $I_O = 5\text{mA}$                 |      | 0.1  | $V$           |

| $I_{OH}$                                | nFAULT の出力高リーケ電流、SDO                                | 5V へのプルアップ抵抗                       |      | 1    | $\mu\text{A}$ |

| $t_{nFAULT\_VALID}$                     | $V_{VM} > V_{UVLO}$ (立ち上がり) 後、nFAULT 信号が有効になるまでの時間。 |                                    |      | 30   | $\mu\text{s}$ |

| <b>7 レベル入力 (RSLEW/CNTL)</b>             |                                                     |                                    |      |      |               |

| $V_{LVL1}$                              | 7 段階の レベル 1                                         | GND に接続                            | 0    | 0.1  | $V$           |

| $V_{LVL2}$                              | 7 段階の レベル 2                                         | 14.7k $\Omega$ $\pm 5\%$ を GND へ   | 0.2  | 0.35 | $V$           |

| $V_{LVL3}$                              | 7 段階の レベル 3                                         | 44.2k $\Omega$ $\pm 5\%$ を GND に接続 | 0.55 | 0.8  | $V$           |

| $V_{LVL4}$                              | 7 段階の レベル 4                                         | 100k $\Omega$ $\pm 5\%$ を GND に接続  | 1    | 1.25 | $V$           |

| $V_{LVL5}$                              | 7 段階の レベル 5                                         | 249k $\Omega$ $\pm 5\%$ を GND に接続  | 1.5  | 1.75 | $V$           |

| $V_{LVL6}$                              | 7 段階の レベル 6                                         | ハイインピーダンス                          | 2.1  | 2.4  | $V$           |

| $V_{LVL7}$                              | 7 段階の レベル 7                                         | DVDD (ロジック電圧) に接続                  | 3    | 5    | $V$           |

| $I_{RSLEW/CNTL}$                        | 入力電流                                                |                                    | 22.5 |      | $\mu\text{A}$ |

| <b>スイッチング</b>                           |                                                     |                                    |      |      |               |

## 5.5 電気的特性 (続き)

4.5V  $\leq V_{VM} \leq 65V$ ,  $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  (特に記述のない限り), 24V, 25°C での標準値

| パラメータ                  |                                                                                                                                                                | テスト条件                                             | 最小値 | 標準値  | 最大値  | 単位  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|------|------|-----|

| $t_R$                  | 立ち上がり時間<br>10% ~ 90% の OUTx 立ち上がり<br>$V_M = 24V$ , $R_L = 48\Omega$ , $C_L = 0.1nF$                                                                            | RSLEW/CNTL の $V_{LVL1}$                           |     | 100  | 150  | ns  |

|                        |                                                                                                                                                                | RSLEW/CNTL の $V_{LVL6}$ または $V_{LVL7}$            |     | 300  | 450  | ns  |

|                        |                                                                                                                                                                | RSLEW/CNTL の $V_{LVL4}$ または $V_{LVL5}$            |     | 700  | 1000 | ns  |

|                        |                                                                                                                                                                | RSLEW/CNTL の $V_{LVL2}$ または $V_{LVL3}$            |     | 1500 | 2300 | ns  |

| $t_F$                  | 立ち下がり時間<br>90% ~ 10% の OUTx 立ち下がり<br>$V_M = 24V$ , $R_L = 48\Omega$ , $C_L = 0.1nF$                                                                            | RSLEW/CNTL の $V_{LVL1}$                           |     | 100  | 150  | ns  |

|                        |                                                                                                                                                                | RSLEW/CNTL の $V_{LVL6}$ または $V_{LVL7}$            |     | 300  | 450  | ns  |

|                        |                                                                                                                                                                | RSLEW/CNTL の $V_{LVL4}$ または $V_{LVL5}$            |     | 700  | 1000 | ns  |

|                        |                                                                                                                                                                | RSLEW/CNTL の $V_{LVL2}$ または $V_{LVL3}$            |     | 1500 | 2300 | ns  |

| $t_{PD}$               | 入力から出力までの伝搬遅延<br>$V_{IH}$ 以上への INx 立ち上がりから 90% への OUTx 立ち下がり、または $V_{IL}$ 以下への INx 立ち下がりから 10% への OUTx 立ち上がり<br>$V_M = 24V$ , $R_L = 48\Omega$ , $C_L = 0.1nF$ | RSLEW/CNTL の $V_{LVL1}$                           |     | 100  | 150  | ns  |

|                        |                                                                                                                                                                | RSLEW/CNTL の $V_{LVL6}$ または $V_{LVL7}$            |     | 250  | 370  | ns  |

|                        |                                                                                                                                                                | RSLEW/CNTL の $V_{LVL4}$ または $V_{LVL5}$            |     | 400  | 600  | ns  |

|                        |                                                                                                                                                                | RSLEW/CNTL の $V_{LVL2}$ または $V_{LVL3}$            |     | 700  | 1000 | ns  |

| ドライバ出力 (OUTx)          |                                                                                                                                                                |                                                   |     |      |      |     |

| $R_{DS(ON)}$           | FET オン抵抗                                                                                                                                                       | $V_M < 24V$ , $I_O = 500mA$ , $T_J = 25^{\circ}C$ |     | 140  |      | mΩ  |

|                        |                                                                                                                                                                | $V_M < 24V$ , $I_O = 500mA$ , $T_J = 85^{\circ}C$ |     |      | 225  | mΩ  |

| $I_{OFF}$              | オフ状態のリーキ電流                                                                                                                                                     | $V_{OUT} = V_M = 24V$                             |     | 0.5  |      | μA  |

| $I_{OFF}$              | オフ状態のリーキ電流                                                                                                                                                     | $V_{OUT} = V_M = 65V$                             |     |      | 10   | μA  |

| $V_F$                  | 還流ダイオード順方向電圧                                                                                                                                                   | $V_{OUT} = 24V$ , $I_O = 500mA$                   |     |      | 1.2  | V   |

| $I_{OFF}$              | 還流ダイオード逆リーキ電流                                                                                                                                                  | $V_{OUT} = 0V$ , $V_{CLAMP} = 65V$                |     |      | 10   | μA  |

| 保護回路                   |                                                                                                                                                                |                                                   |     |      |      |     |

| $I_{LIM}$              | 電流制限値<br>$30k\Omega \leq R_{ILIM} \leq 120k\Omega$ の場合、 $60/R_{ILIM}[k\Omega]$ に従う                                                                             | $R_{ILIM}$ は GND へ短絡または $R_{ILIM} < 20k\Omega$    |     | 3    |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 30k\Omega$                            |     | 1.4  | 2    | 2.6 |

|                        |                                                                                                                                                                | $R_{ILIM} = 60k\Omega$                            |     | 0.7  | 1    | 1.3 |

|                        |                                                                                                                                                                | $R_{ILIM} = 90k\Omega$                            |     | 0.4  | 0.66 | 0.9 |

|                        |                                                                                                                                                                | $R_{ILIM} = 120k\Omega$                           |     | 0.3  | 0.5  | 0.7 |

| $I_{LIM\_ACTIVATE}$    | 電流制限のアクティピ化スレッショルド<br>$I_{LIM}+50\%$ に従う                                                                                                                       | $R_{ILIM} = GND$ への短絡                             |     | 4.7  |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 30k\Omega$                            |     | 3    |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 60k\Omega$                            |     | 1.5  |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 90k\Omega$                            |     | 1    |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 120k\Omega$                           |     | 0.75 |      | A   |

| $I_{INRUSH}$           | $t_{INRUSH}$ 中の電流制限値<br>$R_{ILIM} \geq 40k\Omega$ の場合、 $2*I_{LIM}[k\Omega]$ に従う                                                                                | $R_{ILIM} = GND$ への短絡                             |     | 4    |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 30k\Omega$                            |     | 4    |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 60k\Omega$                            |     | 1.4  | 2    | 2.6 |

|                        |                                                                                                                                                                | $R_{ILIM} = 90k\Omega$                            |     | 0.8  | 1.2  | 1.6 |

|                        |                                                                                                                                                                | $R_{ILIM} = 120k\Omega$                           |     | 0.6  | 1    | 1.4 |

| $I_{INRUSH\_ACTIVATE}$ | INRUSH 中の電流制限のアクティピ化スレッショルド<br>$I_{INRUSH}+50\%$ に従う                                                                                                           | $R_{ILIM} = GND$ への短絡                             |     | 6.5  |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 30k\Omega$                            |     | 6    |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 60k\Omega$                            |     | 3    |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 90k\Omega$                            |     | 2    |      | A   |

|                        |                                                                                                                                                                | $R_{ILIM} = 120k\Omega$                           |     | 1.5  |      | A   |

## 5.5 電気的特性 (続き)

4.5V  $\leq V_{VM} \leq 65V$ ,  $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  (特に記述のない限り), 24V, 25°C での標準値

| パラメータ          |                                                                                                                              | テスト条件                                      | 最小値 | 標準値  | 最大値 | 単位 |

|----------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----|------|-----|----|

| $R_{HIZ}$      | 突入モードの選択。                                                                                                                    | COD/突入ピンのプルダウン抵抗。それを上回ると突入モードが選択される外部抵抗の値。 | 1   |      |     | MΩ |

| $t_{COD\_DIS}$ | カットオフ遅延ディスエーブル スレッショルド                                                                                                       | それを下回るとカットオフ機能が無効化される外部抵抗の値。               |     | 20   |     | kΩ |

| $t_{COD}$      | カットオフ遅延<br>外部抵抗 $R_{COD}$ から GND で調整<br>$60k\Omega \leq R_{COD} \leq 240k\Omega$ の場合、<br>$R_{COD}[k\Omega]/120 \pm 15\%$ に従う | $R_{COD} = 60k\Omega$                      | 0.4 | 0.5  | 0.6 | ms |

|                |                                                                                                                              | $R_{COD} = 120k\Omega$                     | 0.8 | 1    | 1.2 | ms |

|                |                                                                                                                              | $R_{COD} = 180k\Omega$                     | 1.2 | 1.5  | 1.8 | ms |

|                |                                                                                                                              | $R_{COD} = 240k\Omega$                     | 1.6 | 2    | 2.4 | ms |

| $t_{INRUSH}$   | 突入モードの持続時間                                                                                                                   | COD/INRUSH ピン未接続                           |     | 10   |     | ms |

| $t_{RETRY}$    | 過電流保護再試行時間<br>外部抵抗 $R_{COD}$ から GND で調整<br>$60k\Omega \leq R_{COD} \leq 240k\Omega$ の場合、 $32 \cdot t_{COD} \pm 15\%$ に従う     | $R_{COD} = 60k\Omega$                      |     | 15.5 |     | ms |

|                |                                                                                                                              | $R_{COD} = 120k\Omega$                     |     | 31   |     | ms |

|                |                                                                                                                              | $R_{COD} = 180k\Omega$                     |     | 46.5 |     | ms |

|                |                                                                                                                              | $R_{COD} = 240k\Omega$                     |     | 62   |     | ms |

| $T_{TSD}$      | サーマル シャットダウン温度                                                                                                               | ダイ温度                                       | 150 | 170  | 190 | °C |

| $T_{TSD\_HYS}$ | サーマル シャットダウン温度ヒステリシス                                                                                                         |                                            |     | 40   |     | °C |

| $t_{TSD\_DG}$  | サーマル シャットダウン グリッチ除去                                                                                                          |                                            |     | 20   |     | μs |

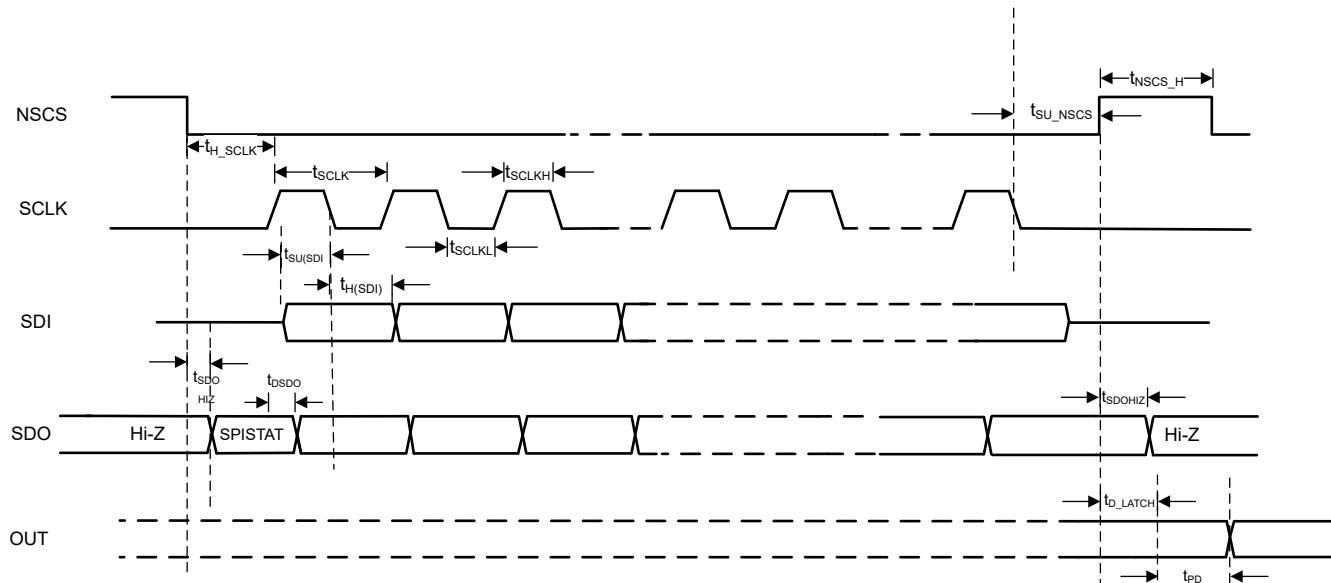

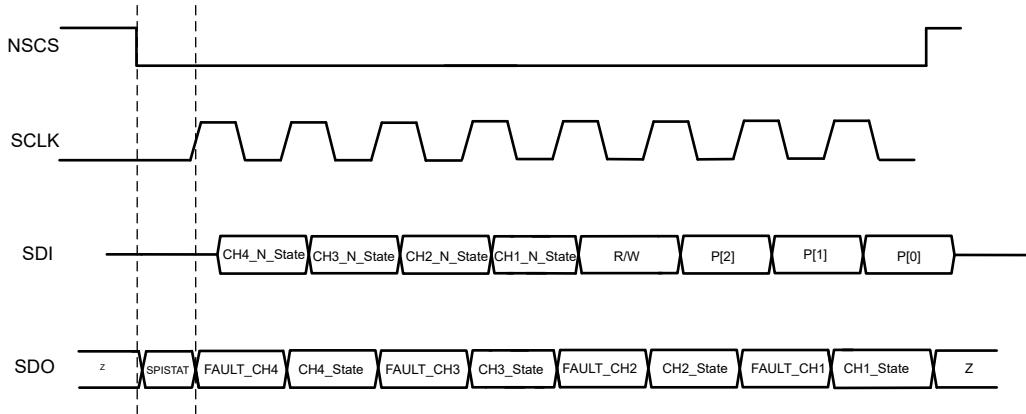

## 5.6 タイミング要件

|                |                                                            | 最小値  | 公称値 | 最大値  | 単位 |

|----------------|------------------------------------------------------------|------|-----|------|----|

| $t_{SCLK}$     | SCLK サイクル時間                                                | 500  |     |      | ns |

| $t_{SCLKH}$    | SCLK High 時間                                               | 170  |     |      | ns |

| $t_{SCLKL}$    | SCLK Low 時間                                                | 170  |     |      | ns |

| $t_{H\_SCLK}$  | ホールド時間、nSCS 立ち下がりから SCLK 立ち上がりエッジまで                        | 1000 |     |      | ns |

| $t_{SU(SDI)}$  | セットアップ時間、SDI 有効から SCLK 立ち下がりエッジまで                          | 30   |     |      | ns |

| $t_{H(SDI)}$   | ホールド時間、SCLK 立ち上がりエッジから SDI 無効まで                            | 30   |     |      | ns |

| $t_{D(SDO)}$   | 遅延時間、SCLK 立ち上がりエッジから SDO 有効まで ( $C_{LOAD} < 20\text{pF}$ ) |      |     | 100  | ns |

| $t_{SU\_NSCS}$ | 最終 SCLK 立ち下がりエッジから nSCS 立ち上がりエッジまでの遅延                      | 200  |     |      | ns |

| $t_{SDOHIZ}$   | NSCS 立ち上がりエッジから SDO HiZ までの遅延                              |      |     | 100  | ns |

| $t_{NSCS\_H}$  | nSCS のパルス幅                                                 | 1000 |     |      | ns |

| $t_{D\_LATCH}$ | nSCS 立ち上がりエッジからデバイスで入力データがラッチされるまで                         |      |     | 2000 | ns |

図 5-1. SPI タイミング パラメータ

## 5.7 代表的特性

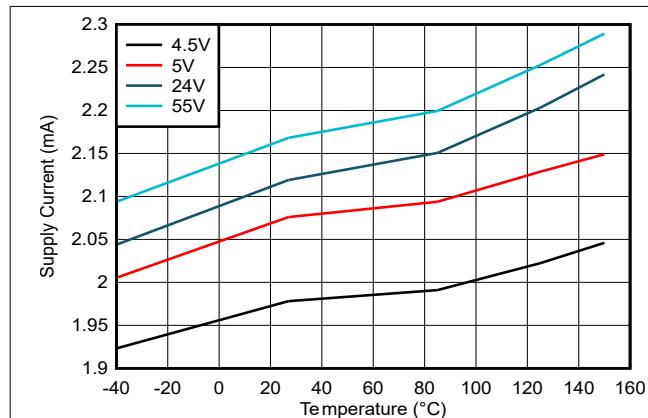

図 5-2. 電源電流と温度との関係

図 5-3. 電源電流と  $V_M$  との関係

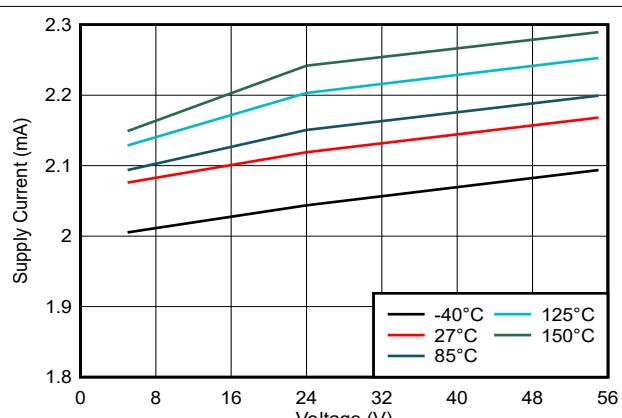

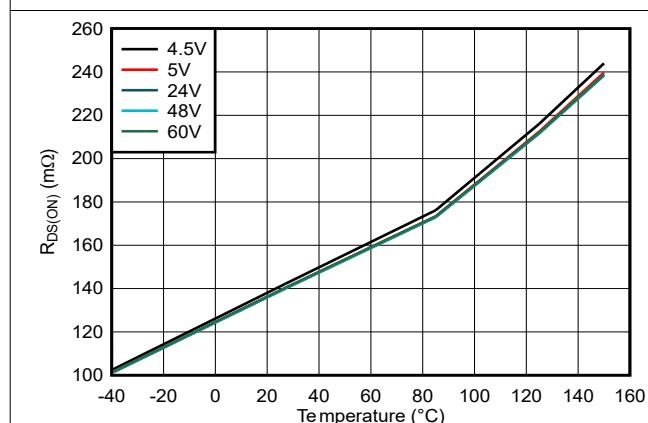

図 5-4.  $R_{DS(on)}$  と温度との関係

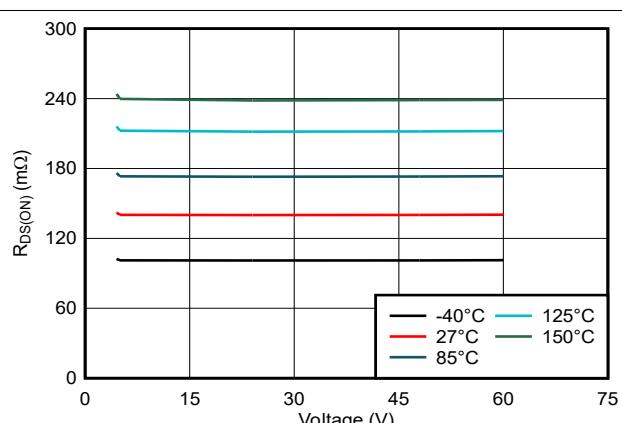

図 5-5.  $R_{DS(on)}$  と  $V_M$  との関係

## 6 詳細説明

### 6.1 概要

DRV81646 は、4.5V ~ 65V の広い電圧範囲で動作し、幅広い負荷電流要件に対応する多用途の 4 チャネル ローサイド スイッチング ドライバです。このデバイスには 4 つのローサイド スイッチを内蔵しています。各スイッチは  $140\text{m}\Omega$  の低いオン抵抗を実装し、VCLAMP ピンに接続されたフリー ホイール ダイオードを搭載しています。この構成により、電流を再循環させるか、外部過渡電圧サプレッサ (TVS) を接続することで、誘導性負荷がターンオフした安全な状態を管理できます。

このデバイスは、ハードウェア GPIO や標準的な 4 線式 SPI 通信など、複数のインターフェイス オプションで柔軟な制御を実現します。各チャネルには専用の過熱保護機能と調節可能な電流制限機能が搭載されており、ILIM ピンの外付け抵抗を使用して構成できます。オプションのカットオフ遅延 (COD) 構成があり、それぞれのチャネルの電流制限状態の持続時間を制限することで、デバイスまたは接続した負荷の損傷を防止できます。出力スイッチング レートは、RSLEW/CNTL ピンの抵抗構成でカスタマイズできます。これにより、出力スイッチを柔軟に制御できます。さらに、このデバイスは、容量性負荷アプリケーションに対応するために、電流制限スレッショルドを一時的に上昇させる INRUSH モードを搭載しています。

DRV81646 はエラー状態を通知するための専用のフォルト出力ピン (nFAULT) を備えており、SPI モードで動作しているときにチャネルごとのフォルト状態を監視できます。この機能により、発生した障害条件を迅速に識別、応答することができ、効率的で信頼性の高いシステム動作をサポートします。

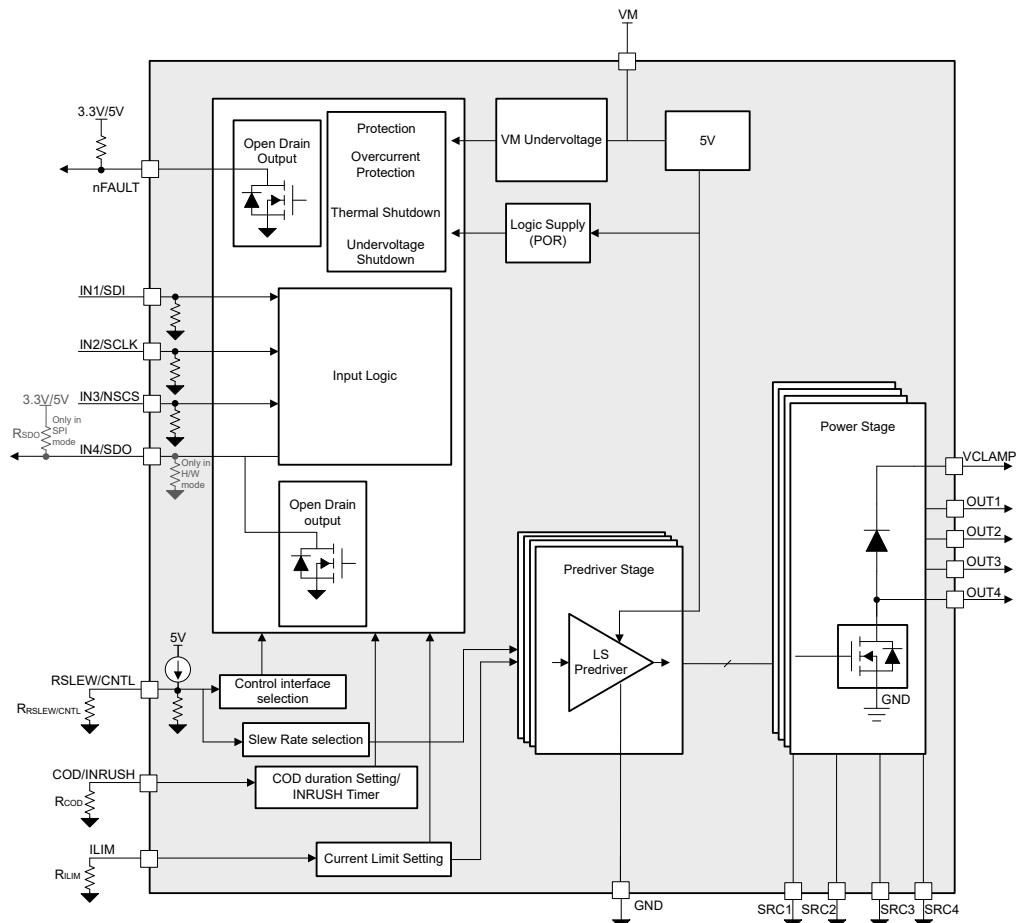

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 制御インターフェイスおよびスルーレート (RSLEW/CNTL)

RSLEW/CNTL ピンにより、出力スルーレートおよび制御インターフェイスを設定します。このピンは外部抵抗で設定することも、マイコン DAC によって直接制御することもできます。スルーレートおよび制御インターフェイスは、VM が  $V_{UVLO}$  を上回ると、デバイスの起動時にラッピングされ、動作中に変更することはできません。[表 6-1](#) に、ハードウェア モードで使用可能な立ち上がり/立ち下がり時間とスルーレートを示します。[表 6-2](#) に、SPI モードで使用可能な立ち上がり/立ち下がり時間とスルーレートを示します。

スルーレートは、VM および VLOAD 電圧全体にわたってほぼ一定に保たれます。立ち上がり時間は電圧に基づいて変化します。たとえば、同じスルーレートの場合、 $V_{VM} = 12V$  の立ち上がり時間は  $V_{VM} = 24V$  と約半分になります。

**表 6-1. ハードウェア モードのスルーレート選択**

| 制御インターフェイス    | 立ち上がり時間または立ち下がり時間 (標準値: $V_{VM} = 24V$ ) | $V_{VM} = 24V$ のスルーレート | RSLEW/CNTL ピン電圧                |

|---------------|------------------------------------------|------------------------|--------------------------------|

| ハードウェア (GPIO) | 100ns                                    | 192V/μs                | $V_{LVL1}$ (GND に接続)           |

|               | 300ns                                    | 64V/μs                 | $V_{LVL6}$ (ハイインピーダンス/フローティング) |

|               | 700ns                                    | 27.4V/μs               | $V_{LVL4}$ (100kΩ から GND へ)    |

|               | 1500ns                                   | 12.8V/μs               | $V_{LVL3}$ (44.2kΩ から GND へ)   |

**表 6-2. SPI モードのスルーレート選択**

| 制御インターフェイス | 立ち上がり時間または立ち下がり時間 (標準値: $V_{VM} = 24V$ ) | $V_{VM} = 24V$ のスルーレート | RSLEW/CNTL ピン電圧              |

|------------|------------------------------------------|------------------------|------------------------------|

| SPI        | 300ns                                    | 64V/μs                 | $V_{LVL7}$ (ロジック電圧に接続)       |

|            | 700ns                                    | 27.4V/μs               | $V_{LVL5}$ (249kΩ から GND へ)  |

|            | 1500ns                                   | 12.8V/μs               | $V_{LVL2}$ (14.7kΩ から GND へ) |

### 6.3.2 FET ソース端子による電流検出

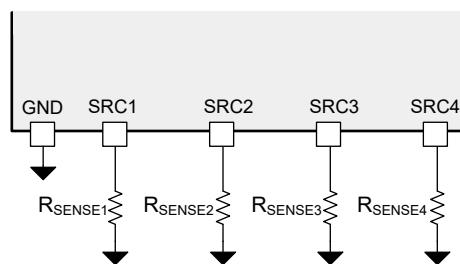

各 MOSFET のソース端子は、SRCx ピンに露出しています。[図 6-1](#) に示されているように、SRC ピンと GND の間に外部センス抵抗を接続して、そのチャネルの電流を測定できます。

**図 6-1. 各 SRC ピンのセンス抵抗**

外部電流検出を使用しない場合は、SRC ピンを GND に直接接続する必要があります。

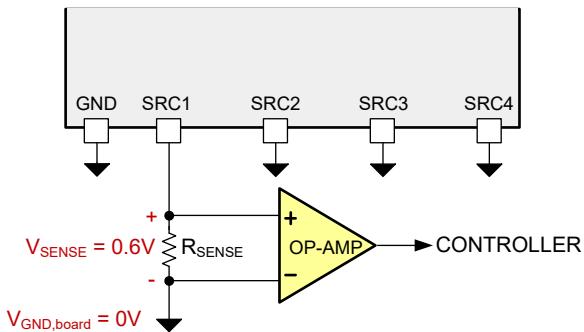

SRCx ピンの絶対最大定格では、シャント抵抗の最大電圧が 0.6V に設定されます。最大負荷電流時にセンス抵抗の両端の電圧が 0.6V を超えないように、シャント抵抗のサイズを設定する必要があります。

図 6-2. 電流センス抵抗を使用した基板グランドを基準とする SRCx 電圧

例では、最大  $V_{SENSE}$  として 250mV を使用します。これは 0.6V 未満で、安全や誤差の余裕があります。例として、 $I_{LIM} = 2A$  および  $I_{LIM\_ACTIVATE} = 3A$  の場合に  $I_{LIM}$  を 30k $\Omega$  に設定するように、負荷の最大  $I_{PEAK}$  電流を 4A とします。

$$R_{SENSE} = \frac{V_{SENSE}}{I_{PEAK}} = \frac{0.250V}{4A} = 0.0625\Omega = 62.5m\Omega \quad (1)$$

この例の負荷の 4A ピーク電流では、 $V_{SENSE}$  を 250mV 未満に維持するために、電流センス抵抗は 62.5m $\Omega$  以下にする必要があります。また、センス抵抗のサイズは、消費電力に適したものとする必要があります。この例では、62.5m $\Omega$  抵抗の両端に 4A を供給する場合、消費電力は：

$$D = I^2R = 4A^2 \times 0.0625\Omega = 1.0W \quad (2)$$

したがって、この例では 1W 以上の抵抗を推奨します。

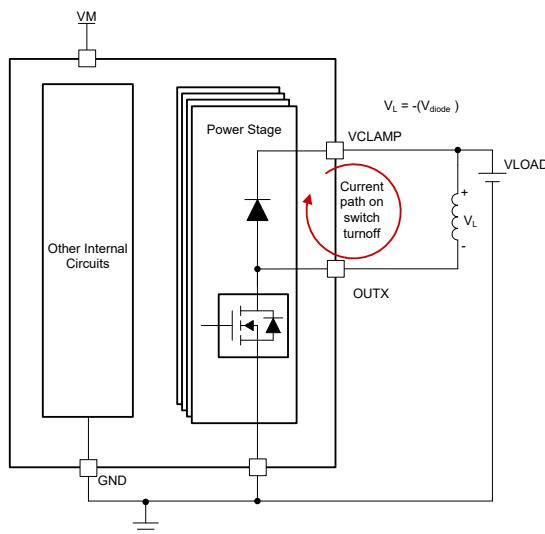

### 6.3.3 内蔵クランプダイオード、VCLAMP

DRV81646 には、保護された 4 つのローサイド ドライバが搭載されています。各出力には、共通のピン VCLAMP に接続されたクランプ ダイオードが内蔵されています。

VCLAMP は、ツェナーまたは TVS ダイオードから VM または GND に接続できます。これにより、スイッチ電圧がメイン電源電圧 VM を超えることができます。この接続は、非常に高速な電流減衰が必要な負荷を駆動する場合に有益です。各出力には VCLAMP ピンへのダイオードがあるため、4 つのチャネルすべてで 1 つの外部 TVS ダイオードを共有できます。または、VCLAMP をメイン電源電圧 (VM) に直接接続することもできます。

いずれの場合も、出力の電圧が DRV81646 の最大出力電圧仕様を超えないようにする必要があります。DRV81646 がサポートしている構成を以下に示します。

図 6-3. 低速減衰 (VCLAMP を VLOAD に接続)

図 6-4. 最高速の減衰 (TVS/ツェナー VCLAMP から VLOAD へ)

図 6-5. 高速減衰 (TVS/ツェナー CLAMP から GND へ)

表 6-3. VCLAMP 減衰モード

| VCLAMP 接続             | デイケイ モード | 使用に適した状況                                                                                         | V <sub>L</sub> 電圧                                                                |

|-----------------------|----------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| VLOAD に直接接続           | スロー デイケイ | 高速減衰が必要ない負荷。VM の全動作範囲において安全です。                                                                   | V <sub>L</sub> = -V <sub>diode</sub>                                             |

| TVS またはツェナーから VLOAD へ | 高速減衰     | 最高速の電流減衰。OUTx 最大電圧を超える可能性があるため、VM または VLOAD > 28V の場合は推奨しません。                                    | V <sub>L</sub> = -[V <sub>diode</sub> + V <sub>zener</sub> ]                     |

| TVS またはツェナーから GND へ   | 高速減衰     | TVS から VLOAD までのクランプ電圧は低いけれども、高速電流減衰はわずかに遅くなります。TVS は、リード電流を防止するために、VLOAD よりも高いブレーカダウン電圧を必要とします。 | V <sub>L</sub> = -[V <sub>diode</sub> + V <sub>zener</sub> - V <sub>LOAD</sub> ] |

### 6.3.4 保護回路

DRV81646 は、VM 低電圧、チャネルごとの過熱、ダイ過熱、過電流イベントから保護されています。

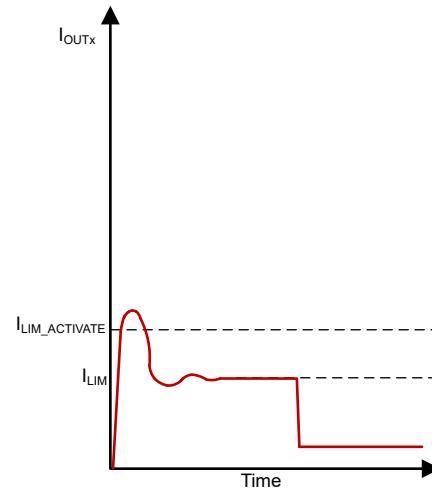

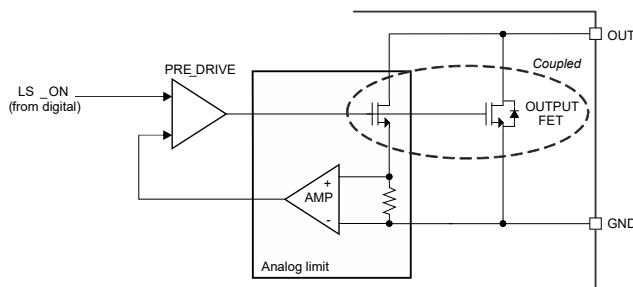

#### 6.3.4.1 ILIM アナログ電流制限

DRV81646 は、短絡や大きな突入電流の容量性負荷に対する保護のために、各出力にアナログ電流制限を実装しています。出力段で高電流の状態  $I > I_{LIM\_ACTIVATE}$  が検出されると、FET のゲート駆動電圧が低下し、出力電流を  $I_{LIM}$  レベルでレギュレートします。このゲート駆動調整により、FET がリニア領域で動作するため、 $R_{DS(ON)}$  がはるかに高くなり、大きな電力が消費されます。この電流制限機能 (ILIM) は過電流保護に似たように設計されていますが、過電流イベント中に FET を完全にオフにするのではなく、デバイスが過熱するまで電流は安全なレベルに制限されます。

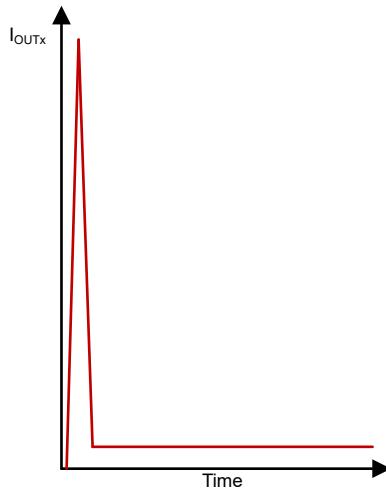

図 6-6 と図 6-7 に、容量性負荷の場合など、定常状態の連続電流より前の突入電流を安全なレベルまで低減する ILIM を示します。この機能により、PCB のパターン幅を減らし、システムの電源能力の要件を低減できるというシステムレベルの利点が得られます。

図 6-6. 電流制限保護がない場合の大きなスタートアップ電流

図 6-7. ILIM 電流制限保護を行った場合の制御されたスタートアップ電流

表 6-4 に示されているように、アナログ電流制限レベル  $I_{LIM}$  は、ILIM ピンと GND との間にプルダウン抵抗を接続することで構成できます。 $I_{LIM}$  は、 $R_{ILIM}$  に基づいて 4 つのチャネルすべてに対して同じ値が設定されます。チップ全体の過熱などのイベントが発生しない限り、1 つのチャネルの電流制限状態は他のチャネルには影響を与えません。

表 6-4. ILIM 抵抗に応じたアナログ電流制限レベル

| ILIM PIN と GND 間の $R_{ILIM}$ 抵抗                        | 電流制限レベル、 $I_{LIM}$                                            |

|--------------------------------------------------------|---------------------------------------------------------------|

| $0 \leq R_{LIM} < 20\text{k}\Omega$                    | 3A                                                            |

| $30\text{k}\Omega \leq R_{LIM} \leq 120\text{k}\Omega$ | $I_{LIM}[\text{A}] = 60/R_{LIM}[\text{k}\Omega]$              |

| $R_{LIM} \geq 120\text{k}\Omega$                       | $I_{LIM}[\text{A}] = 60/R_{LIM}[\text{k}\Omega]$ 、非線形にすることが可能 |

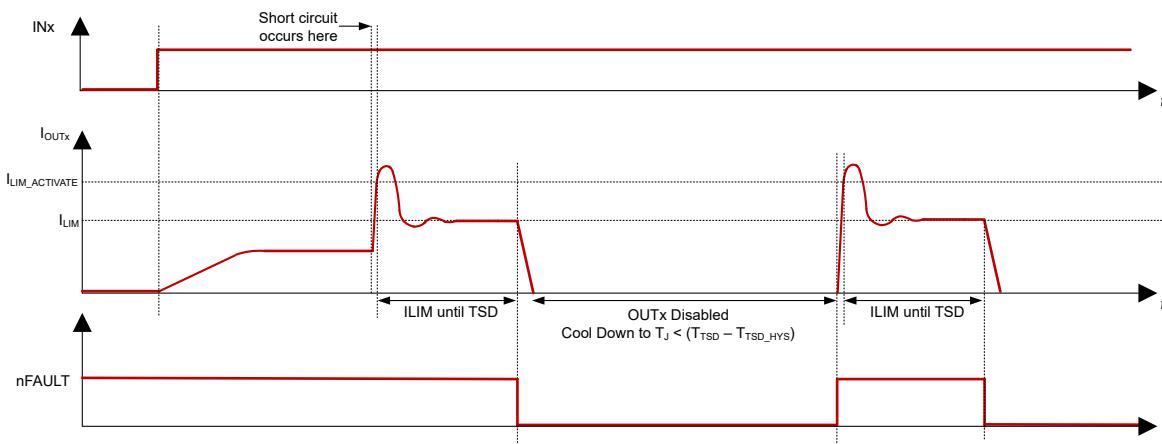

図 6-8 に、カットオフ遅延が無効化された短絡条件での  $t_{TIME\_TO\_TSD}$  間のアクティブ電流制限を示しています ( $0\text{k}\Omega \leq R_{COD} < 20\text{k}\Omega$ )。セクション 6.3.4.2 に、カットオフ遅延機能の詳細が記載されています。チャネルがオフになってから、チャネル温度が安全なレベル ( $t_{TSD} - t_{TSD\_HYS}$ ) に戻った後のみ、チャネルは再試行を行います。 $I_{LIM}$  条件中にチャネル  $IN_x$  の状態が変化した場合、コントローラは出力をオフにするなど、入力状態の変化に応答します。TSD によってデバイスがオフになり、温度が依然として安全なレベルを超えている場合、デバイスは入力状態の変化に応答しません。つまり、 $IN_x$  がトグルされても、デバイスがまだ高温であれば、デバイスは出力をオンに戻しません。

図 6-8. サーマルシャットダウンベースの再試行による短絡への電流制限応答 (カットオフ遅延ディスエーブル)

図 6-9 に、各ローサイド FET のアナログ電流制限回路の概略回路図を示します。

図 6-9. アナログ電流制限および検出図

#### 6.3.4.1.1 TSD 前の消費電力に対する負荷抵抗の影響

サーマルシャットダウンに達するまでのリニア領域でチャネルが動作する時間に、負荷の抵抗が影響を及ぼします。この抵抗はリニアドロップアウトレギュレータ (LDO) と同様に機能し、電圧降下が高い場合、デバイスはより多くの電力を消費する必要があります。

例として、 $5\Omega$  負荷と  $11\Omega$  負荷の場合の  $1\text{A}$   $I_{LIM}$  設定の  $24\text{V}$  システムを取り上げます。電流制限なしでは、これらの消費電流はそれぞれ  $4.8\text{A}$  と  $2.2\text{A}$  ですが、 $I_{LIM}$  機能を使用すると、これらは  $1\text{A}$  にレギュレートされます。式 3 を使用して FET のリニア領域抵抗を計算し、この  $1\text{A}$  の電流制限を実現します：

$$I = \frac{V}{R} \quad (3)$$

$$I_{LIM} = \frac{V_{VM}}{[R_{LOAD} + R_{DS(ON)}]} \quad (4)$$

式 4 を並べ替えて  $R_{DS(ON)}$  を求め、次に負荷が  $5\Omega$  と  $11\Omega$  の場合のシステム値を代入します：

$$R_{DS(ON)} = \left[ \frac{V_{VM}}{I_{LIM}} \right] - R_{LOAD} \quad (5)$$

$$R_{DS(ON)} \text{ } 5\Omega = \left( \frac{24V}{1A} \right) - 5\Omega \rightarrow R_{DS(ON)} \text{ } 5\Omega = 19\Omega \quad (6)$$

$$R_{DS(ON)} \text{ } 11\Omega = \left( \frac{24V}{1A} \right) - 11\Omega \rightarrow R_{DS(ON)} \text{ } 11\Omega = 13\Omega \quad (7)$$

この抵抗を使って、DRV81646 FET 内で消費される電力を計算します。

$$P_{FET \text{ } 5\Omega} = I^2 \times R = 1A^2 \times 19\Omega = 19W \quad (8)$$

$$P_{FET \text{ } 11\Omega} = I^2 \times R = 1A^2 \times 13\Omega = 13W \quad (9)$$

式 8 および式 9 から分かるように、両方の負荷が  $1A$  に制限されても、DRV81646 は  $11\Omega$  負荷より  $5\Omega$  負荷の場合に、より多くの電力を消費します。この消費電力は、時間経過による FET の温度上昇に直接関係します。消費電力が大きいほど、チャネルがサーマル シャットダウンに至るまでの時間が短くなります。

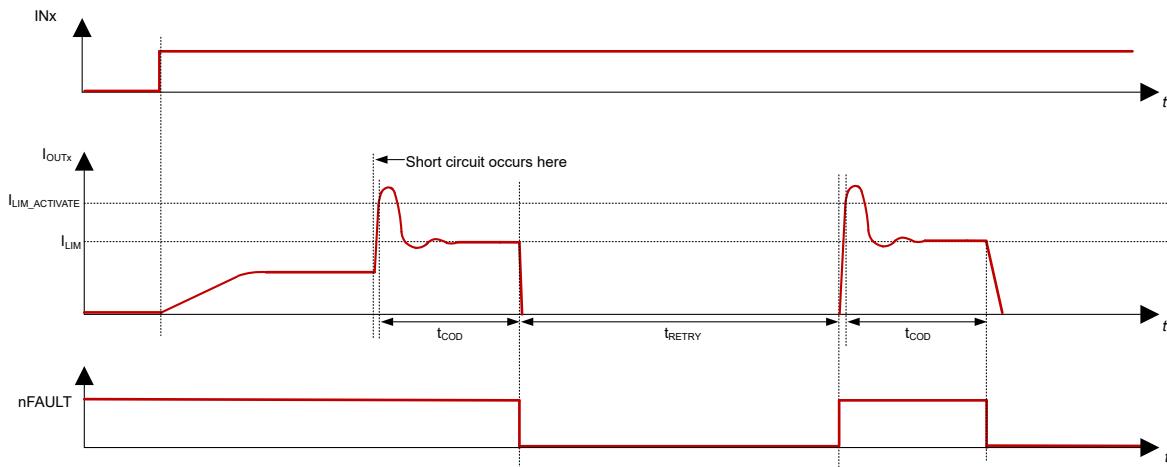

#### 6.3.4.2 カットオフ遅延 (COD)

アナログ電流制限条件により消費電力が非常に大きくなるため、DRV81646 にはカットオフ遅延機能があり、 $I_{LIM}$  または過電流状態の最大長を制御します。これにより、表 6-5 に示されているように、COD/INRUSH ピンのプルダウン抵抗によって  $t_{COD}$  を調整できます。

表 6-5. カットオフ遅延 (COD) 設定

| COD/突入電流と GND の間の $R_{COD}$ 抵抗            | 関数の動作                                                                  | nFAULT ピン                                                    | FAULT ピット (SPI)                                                                            |

|-------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| $0 \leq R_{COD} < 20k\Omega$              | カットオフ遅延機能は無効化され、出力段と IC はサーマル シャットダウンによってのみ保護されます                      | チャネルがサーマル シャットダウンに達すると Low にプルされます。チャネル温度が安全なレベルに戻ると解放されます   | チャネルがサーマル シャットダウンに達すると、対応するチャネルの FAULT ピットが設定されます。このピットは、有効な SPI トランザクションが終了すると自動的にクリアされます |

| $60k\Omega \leq R_{COD} \leq 240k\Omega$  | 電力段がオフになる前に、電流制限は $t_{COD} = R_{COD}(k\Omega)/120ms$ (標準値) 間の持続が許可されます | $t_{COD}$ が経過すると Low になります。<br>$t_{RETRY}$ が経過すると解除されます。     | $t_{COD}$ が経過すると、対応するチャネルの FAULT ピットが設定されます。このピットは、有効な SPI トランザクションが終了すると自動的にクリアされます       |

| $240k\Omega \leq R_{COD} \leq 470k\Omega$ | $COD = R_{COD}(k\Omega)/120ms$ ですが、直線性は規定されていません。                      |                                                              |                                                                                            |

| $R_{COD} \geq 1M\Omega$                   | INRUSH モード イネーブル。 $t_{INRUSH} = 10ms$ (標準値)。                           | 突入電流期間 $t_{INRUSH}$ 中にマスクされ、電力段がサーマル シャットダウンに達すると Low になります。 | 対応するチャネルの FAULT ピットは突入期間 $t_{INRUSH}$ 中にマスクされ、電力段がサーマル シャットダウンに達すると Low になります。             |

$60k\Omega \leq R_{COD} \leq 240k\Omega$  の場合、デバイスは  $t_{COD} = R_{COD}(k\Omega)/120 ms$  の間、電流制限条件で安定します。チャネルがオフになった後、チャネルは  $t_{RETRY} = (t_{COD} \times 32) ms$  (標準値) が経過した後にのみ再試行を行います。電流制限条件中にチャネル状態を変更した場合、コントローラは入力状態の変化に応答します。しかし、 $t_{RETRY}$  中は、コントローラは入力状態の変化に応答しません。

$R_{COD} \geq 240\text{k}\Omega$  の場合、同じ式  $t_{COD} (\text{ms}) = R_{COD}(\text{k}\Omega)/120$  が成り立ちますが、直線性は規定されません。

COD 期間中にサーマル シャットダウンが発生すると、チャネルはオフになり、温度が安全なレベルに達すると再試行されます。サーマル シャットダウンにより出力がオフになる間、COD タイマは一時停止します。

図 6-10. COD イネーブルの場合の短絡に対する電流制限回路の応答

$t_{COD}$  および  $t_{RETRY}$  機能のカットオフ遅延に基づくタイミングにより、サーマル シャットダウンに基づく再試行に比べて平均消費電力が低減されます。COD を使用しない場合、デバイスは 1 チャネルがオンのときに室温で  $1 \sim 5\text{ms}$  でサーマル シャットダウンから回復します。COD を使用すると、デバイスは  $t_{RETRY}$  全期間を待機してから、出力を再度有効にします。例として、 $R_{ILIM}=100\text{k}\Omega$ 、 $V_{VM} = V_{LOAD} = 24\text{V}$ 、 $R_{LOAD} = 1\Omega$  の条件で、COD を使用した場合と使用しない場合のサイクルあたりの平均消費電力を計算します

$$I_{ILIM} = \frac{60}{R_{ILIM}} = \frac{60}{100} = 0.6\text{A} \quad (10)$$

$$\begin{aligned} P_{OUTx\_ILIM} &= V_{OUTx} \times I_{ILIM} = [V_{LOAD} - I_{ILIM} \times R_{LOAD}] \times I_{ILIM} \\ &= [24\text{V} - 1\Omega \times 0.6\text{A}] = 0.6\text{A} = 14.0\text{W} \end{aligned} \quad (11)$$

カットオフ遅延が有効な場合 ( $60\text{k}\Omega \leq R_{COD} \leq 240\text{k}\Omega$ )、平均電流は  $t_{COD}$  および  $t_{RETRY} = t_{COD} \times 32\text{ms}$  に依存します。

$R_{COD} = 120\text{k}\Omega$  の場合

$$t_{COD} = \frac{R_{COD}[\text{k}\Omega]}{120} = \frac{120}{120} = 1\text{ms} \quad (12)$$

$$t_{RETRY} = t_{COD} \times 32 = 1\text{ms} \times 32 = 32\text{ms} \quad (13)$$

$$P_{COD\_AVERAGE} = \frac{[P_{OUTx\_ILIM} \times t_{COD}]}{t_{COD} + t_{RETRY}} = \frac{[14.0\text{W} \times 1\text{ms}]}{1\text{ms} + 32\text{ms}} = 0.43\text{W} \quad (14)$$

カットオフ遅延 (COD ピンが GND に接続されている、または  $R_{COD} < 20\text{k}\Omega$ ) なしで、デバイスは熱ヒステリシス ( $T_J < (t_{TSD} - t_{TSD\_HYS})$  後に自動的に再試行します。再試行時間  $t_{TSD\_HYS\_RETRY} = 2.5\text{ms}$  と、 $t_{TSD} = 1\text{ms}$  後にデバイスがサーマル シャットダウンした場合と同じ  $1\text{ms}$  のオン時間を使用して、平均消費電力を計算します。

$$P_{ILIM\_AVERAGE} = \frac{[P_{OUTx\_ILIM} \times t_{TSD}]}{[t_{TSD} + t_{TSD\_HYS\_RETRY}]} = \frac{[14.0\text{W} \times 1\text{ms}]}{[1\text{ms} + 2.5\text{ms}]} = 4\text{W} \quad (15)$$

カットオフ遅延により、サーマル シャットダウンに基づく保護 (この例では  $4\text{W}$ ) よりも、平均消費電力が大幅に低減されます (この例では  $0.43\text{W}$ )。その結果、システム全体の発熱が低減し、隣接デバイス チャネルの性能が向上します。

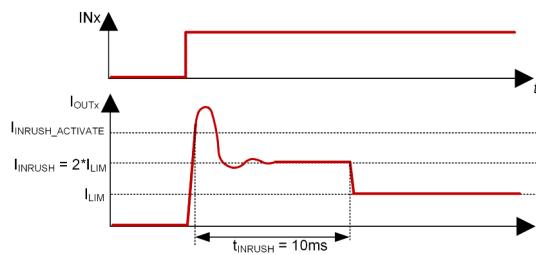

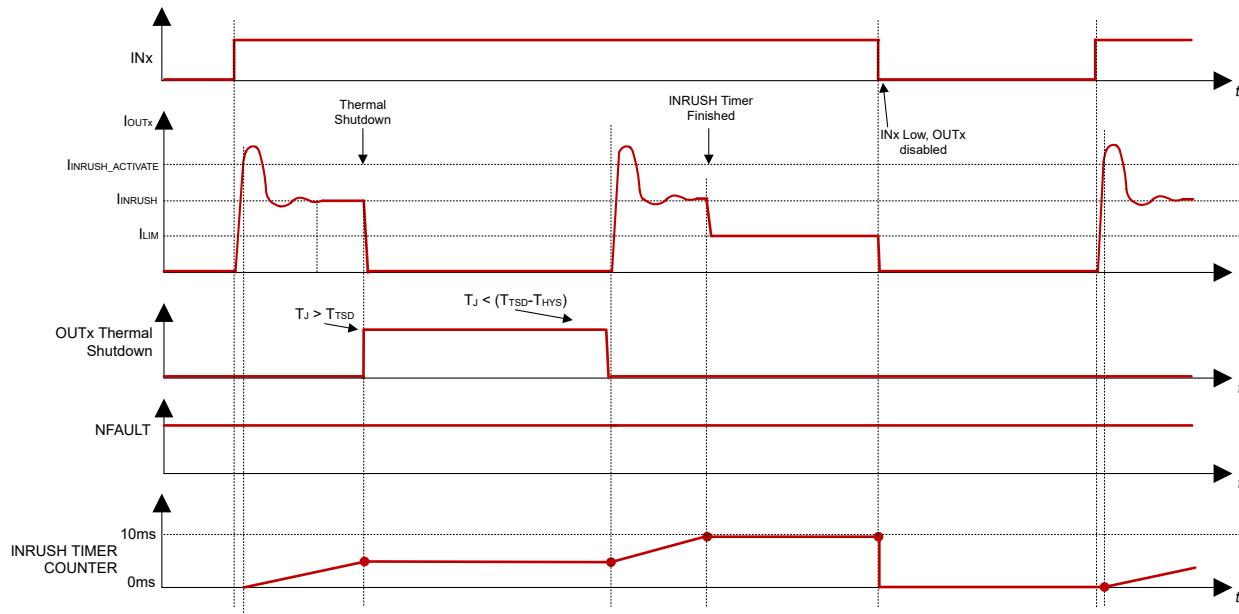

### 6.3.4.3 INRUSH モード

DRV81646 は INRUSH モードを備えており、ターンオン時に大きな電流を必要とするランプなどの容量性負荷に対応でき、電流制限を 10ms 間隔 ( $t_{INRUSH}$ ) に昇圧します。INRUSH モードを有効にするには、COD/INRUSH ピンを未接続のままにするか、ピンに  $1M\Omega$  以上のプルダウン抵抗を配置します。

$t_{INRUSH}$  中の電流制限値は、 $R_{ILIM} \geq 40k\Omega$  の場合、 $I_{INRUSH} = 120/R_{ILIM}[k\Omega]$  となります。これは、 $I_{LIM}$  電流制限値の 2 倍に等しくなります。 $I_{INRUSH\_ACTIVATE} = I_{INRUSH} + 50\%$ 、または

$$I_{INRUSH}[A] = 120 \times R_{ILIM}[k\Omega] \quad (16)$$

$$I_{INRUSH\_ACTIVATE}[A] = I_{INRUSH} \times 1.50 \quad (17)$$

たとえば、 $I_{LIM}$  ピンに  $60k\Omega$  抵抗を接続すると、 $I_{INRUSH} = 120 \div 60 = 2.0A$  となります。突入電流レギュレーションは、電流が  $I_{INRUSH\_ACTIVATE} = 2.0A \times 1.5 = 3.0A$  を超えた後にのみ有効になります。10ms 後、電流は  $I_{LIM}$  レベルでレギュレートされます。図 6-11 に、突入動作の後、サーマル シャットダウンが行われるまで、または電流が  $I_{LIM}$  レベルを下回るまでの通常の  $I_{LIM}$  電流レギュレーションを示します。

図 6-11. INRUSH 中の電流制限値

サーマル シャットダウンにより  $t_{INRUSH}$  中にチャネルがオフになると、チャネル温度が  $T_{TSD}-T_{TSD\_HYS}$  未満の安全なレベルに低下するまで、突入タイマは一時停止されます。その後、タイマは昇圧された電流制限  $I_{INRUSH}$  の状態で動作を継続します。対応する INx が Low にプルされると、突入タイマ数はリセットされます。INx が High になると、突入カウンタが再起動します。図 6-12 に、 $t_{INRUSH}$  中にサーマル シャットダウンを発生させる負荷でのこのタイマ機能を示します。 $t > t_{INRUSH}$  後に電流レギュレーションが  $I_{LIM}$  設定まで低下します。

$t_{INRUSH}$  中、そのチャネルに nFAULT ピンと nFAULT SPI ビットがマスクされ、最初の突入期間中の不要なフォルトトリガを防止します。nFAULT ピンとビットは引き続き「別の」チャネルでフォルトを通知します。たとえば、チャネル 1 が  $t_{INRUSH}$  内で、チャネル 3 がサーマル シャットダウンの場合、nFAULT ピンとビットはフォルトを通知します。

表 6-6. INRUSH モードの異常検出出力

| デバイスの状態          | 電流制限         | nFAULT ピン                                           | FAULT ビット (SPI)                                                                             |

|------------------|--------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------|

| $t < t_{INRUSH}$ | $I_{INRUSH}$ | 突入期間 $t_{INRUSH}$ 中にマスクされま                          | 対応するチャネルの FAULT ビットは、突入期間 $t_{INRUSH}$ 中にマスクされます。                                           |

| $t > t_{INRUSH}$ | $I_{LIM}$    | 電力段がサーマル シャットダウンに達すると、Low にプルされます。チャネル温度が安全なレベルに戻ると | チャネルがサーマル シャットダウンに達すると、対応するチャネルの FAULT ビットが設定されます。このビットは、有効な SPI トランザクションが終了すると自動的にクリアされます。 |

図 6-12.  $t_{INRUSH}$  中のチャネル サーマル シャットダウンによる INRUSH タイマの例

#### 6.3.4.4 サーマル シャットダウン (TSD)

各パワー FET の近くに専用のサーマル センサを配置します。チャネルが過熱状態になると、対応するパワー FET が無効化され、NFAULT ピンが Low にアサートされます。4 つの出力電力段の過熱保護は独立しています。

SPI モードでは、チャネルがサーマル シャットダウンに達すると、対応するチャネル FAULT ビットが設定されます。入力状態の変化が検出されると、このビットは自動的にクリアされます。

ダイ温度が安全限界を超えると、すべての出力 FET は無効になり、nFAULT ピンは Low レベルに駆動されます。ダイ温度が安全なレベルまで下がった後、動作が自動的に再開されます。SPI モードでは、ダイレベルの過熱イベントが完全に発生した場合に、すべてのチャネルの FAULT ビットが設定されます。

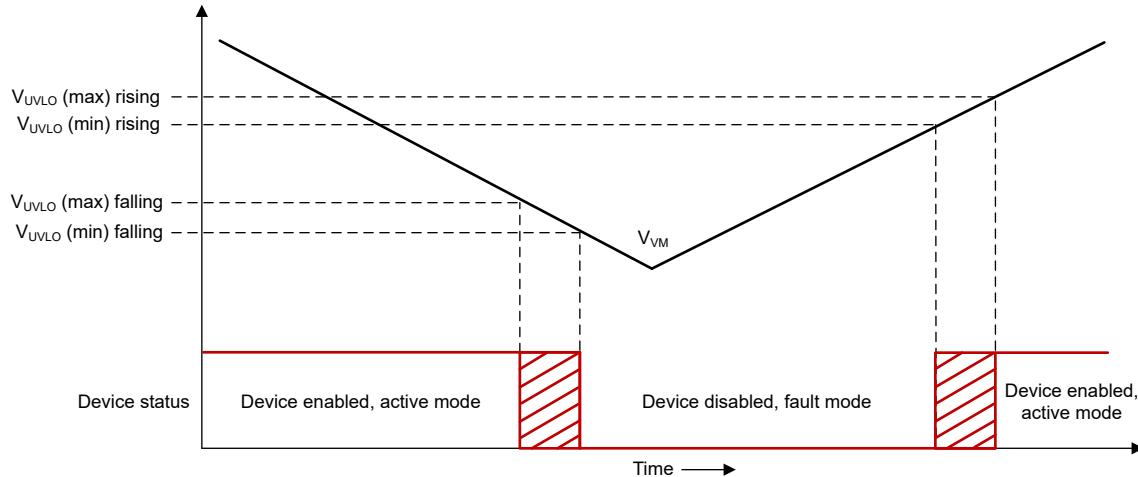

#### 6.3.4.5 低電圧誤動作防止 (UVLO)

VM ピンの電圧が UVLO の立ち下がりスレッショルド電圧  $V_{UVLO}$  を下回ると、デバイスのすべての回路がディセーブルされ、出力 FETS がディセーブルされて、すべての内部ロジックがリセットされます。図 6-13 に示されているように、 $V_{VM}$  電圧が UVLO の立ち上がりスレッショルドを上回ると、動作が再開されます

図 6-13. VM UVLO の動作

### 6.3.5 フォルト条件のまとめ

表 6-7 は、フォルト条件と、各条件から回復する方法の要約です。また、本デバイスが最初にウェークアップする ( $VM > V_{UVLO(rising)}$ ) とき、nFAULT ピンは瞬間に Low にプルされます。 $t_{nFAULT\_VALID}$  時間が経過すると、nFAULT ピンはフォルト状態を正確に通知しますが、 $t_{nFAULT\_VALID}$  時間の間、マイコンはすべての nFAULT Low 信号を無視できます。

表 6-7. フォルト条件のまとめ

| フォルト                                        |                      | SPI FAULT [X] – チャネル X のフォルトビット | INRUSH カウント | nFAULT ピン   | SDO IN $T_{H\_SCLK}$ 間隔 | 復帰                               |

|---------------------------------------------|----------------------|---------------------------------|-------------|-------------|-------------------------|----------------------------------|

| チャネル過熱、 $T_{J\_CHx} > T_{TSD}$              | $0 < t < t_{INRUSH}$ | 設定なし                            | 一時停止済み      | High        | SDI                     | $T_J < (T_{TSD} - T_{TSD\_HYS})$ |

|                                             | $t > t_{INRUSH}$     | 影響を受けるチャネルにのみ設定                 | -           | Low にプル     | SDI                     |                                  |

| グローバル (ダイ) 過熱、 $T_J > T_{TSD}$              | $0 < t < t_{INRUSH}$ | すべてのチャネルに設定                     | 一時停止済み      | Low にプル     | SDI                     | $T_J < (T_{TSD} - T_{TSD\_HYS})$ |

|                                             | $t > t_{INRUSH}$     |                                 | -           |             |                         |                                  |

| COD 時間の満了 (COD イネーブルの場合)                    |                      | 影響を受けるチャネルにのみ設定                 | -           | Low にプル     | SDI                     | $t_{RETRY}$ 経過                   |

| SPI 誤差                                      |                      | 設定なし                            | -           | High        | Low                     | 次の有効な SPI フレーム                   |

| VM 低電圧 (UVLO)、 $V_{VM} < V_{UVLO}$ VM 立ち下がり |                      | SPI 利用不可                        | -           | 内部回路ディスエーブル | SPI 利用不可                | $V_{VM} > V_{UVLO}$ VM 立ち上がり     |

## 6.4 デバイスの機能モード

### 6.4.1 ハードウェアインターフェイス動作

DRV81646 は、IN<sub>x</sub> が OUT<sub>x</sub> の状態を決定するシンプルなハードウェアインターフェイスを介して制御できます。IN<sub>x</sub> ピンを High に駆動すると、対応する出力 FET が内部ロジックスイッチでオンになります。IN<sub>x</sub> を Low に設定すると、対応する OUT<sub>x</sub> FET がオフになります。表 6-8 に、この制御方式を示します。

表 6-8. チャネル x のハードウェア制御モード

| IN <sub>x</sub> | OUT <sub>x</sub> | 説明                                   |

|-----------------|------------------|--------------------------------------|

| 0               | ハイインピーダンス        | OUT <sub>x</sub> ディスエーブル (ハイインピーダンス) |

| 1               | L                | OUT <sub>x</sub> FET オン              |

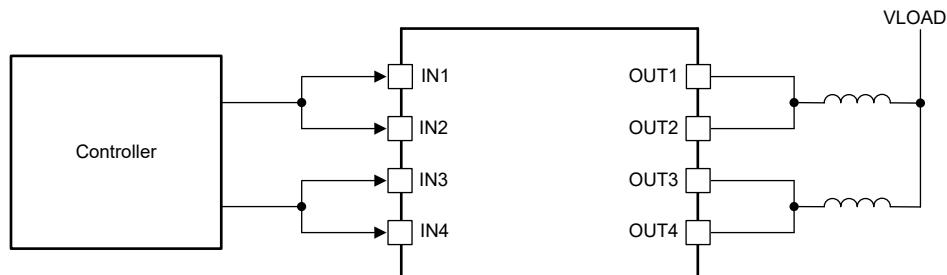

#### 6.4.2 パラレル出力

2つの出力を並列に接続することで、より大きな電流を供給できます。図 6-14 に、2つのソレノイド負荷を駆動する DRV81646 の回路図を示します。このデバイスは、4つのチャネルすべての並列接続もサポートしています。

図 6-14. より大きな電流で 2 つのソレノイドを駆動

VCLAMP ピンにおける還流電流が、連続 RMS 電流または過渡電流  $<1\text{ms}$  の絶対最大定格を超えないように注意してください。誘導性負荷の大きい PWM は、VCLAMP に高電流を発生させる可能性があります。

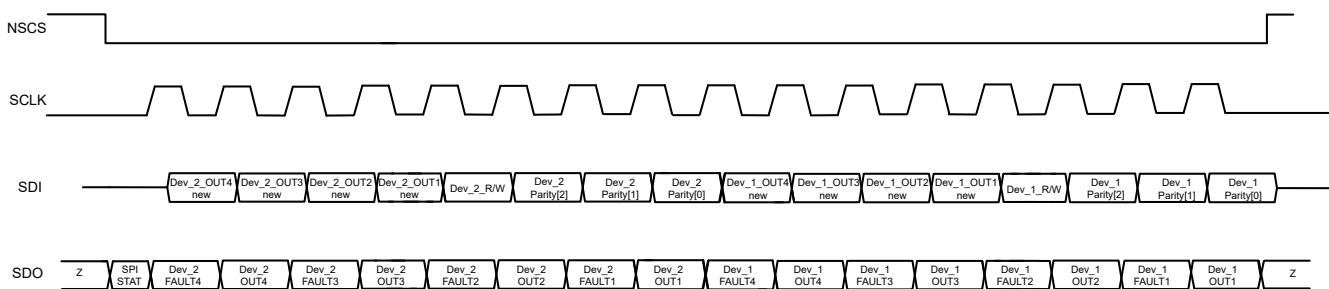

### 6.4.3 SPI フーム

DRV81646 は 4 線式のシリアル ペリフェラル インターフェイス (SPI) を備えており、ユーザーはチャネル状態をプログラムすること、および各チャネルのフルト情報を読み戻すことができます。図 6-15 に示されているように、シリアル データは 8 ビット形式である必要があります。

図 6-15. SPI データ - SPISTAT による標準「8 ビット」フレーム

#### 6.4.3.1 パリティ ビット計算

P[2:0] は 3 つのパリティビットのセットで、受信データワードの正確性をチェックするために使用されます。パリティチェックに失敗した場合、出力状態は更新されません。パリティビットは以下のように計算されます。ここで、 $\oplus$  は XOR です：

- P[2]: B7  $\oplus$  B6  $\oplus$  B5

- P[1]: B6  $\oplus$  B5  $\oplus$  B4

- P[0]: B5  $\oplus$  B4  $\oplus$  B3

例えば、チャネルを OUT4=1、OUT3=0、OUT2=0、OUT1=1 に設定 (R/W=1) する場合、パリティ計算とフレーム構成は以下のようになります。

- P[2] = (1  $\oplus$  0  $\oplus$  0) = 1

- P[1] = (0  $\oplus$  1  $\oplus$  1) = 0

- P[0] = (0  $\oplus$  1  $\oplus$  1) = 0

- したがって、P[2:0] = 0b100

- フル フレーム = 0b1001 1100 = 0x9C

以下に、パリティビット計算を実装した評価基板ファームウェアからの疑似コードを示します。

```

bool B7 = startout4;

bool B6 = startout3;

bool B5 = startout2;

bool B4 = startout1;

bool B3 = rw_bit;

bool P2 = B7 ^ B6 ^ B5;

bool P1 = B6 ^ B5 ^ B4;

bool P0 = B5 ^ B4 ^ B3;

uint8_t CMD = (B7 << 7) | (B6 << 6) | (B5 << 5) | (B4 << 4) | (B3 << 3) | (P2 << 2) | (P1 << 1) | (P0 << 0);

```

#### 6.4.3.2 SPI 入力パケット

表 6-9. SPI 入力パケット

| ビット 7       | ビット 6       | ビット 5       | ビット 4       | ビット 3 | ビット 2 | ビット 1  | ビット 0 |

|-------------|-------------|-------------|-------------|-------|-------|--------|-------|

| CH4_N_State | CH3_N_State | CH2_N_State | CH1_N_State | R/W   |       | P[2:0] |       |

**CHx\_N\_State** ビットが 1 にセットされると、内部ロジックにより、対応するローサイド出力のチャネル N-FET がオンに切り替わります。**CHx\_N\_State** を 0 にセットすると、対応する OUTx がオフになります。

R/W (読み取り/書き込み) ビットは、**CHx\_N\_state** ビットを出力に伝搬するかどうかを決定します。R/W を 1 にセットすると書き込み動作を実行します。R/W を 0 にセットすると、既存の出力状態と故障情報を読み取りますが、現在の出力状態は変更されません。出力に故障が発生すると出力がオフに切り替わり、状態は 0 を返します。

#### 6.4.3.3 SPI 応答パケット

**表 6-10. SPI 応答パケット**

| ビット 7     | ビット 6     | ビット 5     | ビット 4     | ビット 3     | ビット 2     | ビット 1     | ビット 0     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| FAULT_CH4 | CH4_State | FAULT_CH3 | CH3_State | FAULT_CH2 | CH2_State | FAULT_CH1 | CH1_State |

各チャネルの現在のチャネル状態は、nSCS ピンの立ち下がりエッジ (SPI トランザクションの開始時) でラッチされます。ラッチ故障は nSCS ピンの立ち上がりエッジでクリアされます。

**表 6-11. FAULT\_CHx ビットの説明**

| FAULT_CHx | 説明                                                                                                                                             |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | 最後の SPI トランザクション以降、チャネルが正常に動作しています。                                                                                                            |

| 1         | チャネル X で故障が発生しました。最後の SPI トランザクション以降にチャネル X で故障が発生した場合、このビットがセットされます。有効な SPI トランザクション (パリティチェック成功) の終了時に NSCS が High にプルバックされると、このビットはクリアされます。 |

#### 6.4.3.4 SPI エラー報告

SPI エラーが発生するのは、次の場所です。

- 受信データビットのパリティチェックが、受信パリティビットと一致していない場合

- NSCS が Low のときに受信される SCLK パルスの数が 8 の倍数でない場合

DRV81646 が  $t_{H\_SCLK}$  間隔中に SDO を Low/High にすると、現在のトランザクションにおける SPI エラーが次のトランザクションで通知されます。SDO 状態は SPISTAT = (SDI) and NOT(SPI\_ERROR) に設定されます。最も簡単な SPISTAT 値の読み取り方法は、 $t_{H\_SCLK}$  間隔の間に SDI = 1 に保持し、 $t_{SDOHIZ}$  後に SPISTAT を読み取ることです。これにより、SPI エラーが発生すると SPISTAT = 0 になり、それ以外の場合は SPISTAT = 1 になります。

SPI エラーは nFAULT ピンで通知されません。

**表 6-12. SPISTAT SPI エラー報告**

| SPI エラー? | NOT(SPI_ERROR) | SDI | SPISTAT |

|----------|----------------|-----|---------|

| なし       | 1              | 0   | 0       |

| なし       | 1              | 1   | 1       |

| あり       | 0              | 0   | 0       |

| あり       | 0              | 1   | 0       |

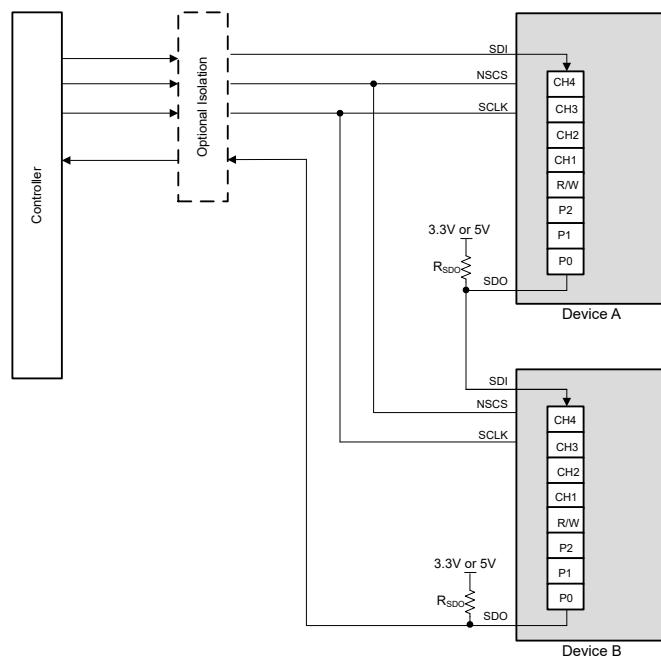

#### 6.4.3.5 SPI デイジーチェーン

複数のデバイスをコントローラに接続するには、デイジーチェーンを使う方法と、使わない方法があります。デイジーチェーンを使用せずに「n」台のデバイスをコントローラに接続する場合は、個々の NSCS ピンがコントローラからの GPIO リソースを「n」個利用できるようにする必要があります。これに対して、デイジーチェーン構成を使用すると、単一の NSCS ラインを使って複数のデバイスを接続できます。

図 6-16 に、2 つの DRV81646 デバイスをデイジーチェーン接続して GPIO または絶縁ピンの節約を活用する方法を示します。1 つのデバイスの SDO ピンは、チェーンの次のデバイスの SDI ピンに供給されます。このピンはオープンドレインであるため、各 SDO ピンにプルアップ抵抗を接続する必要があることに注意してください。

図 6-16. デイジーチェーン接続された 2 つの DRV81646 デバイス

図 6-17 に示されているように、2 つのデバイスに書き込むには、16 ビットのデータを書き込む必要があります。SDO は SCLK の正のエッジで送信されることに注意してください。SDO は、SCLK の次の負のエッジでサンプリングする準備ができます。SDI ピンの値は、SCLK の負のエッジでもサンプリングされます。

図 6-17. 2 つのデイジーチェーン接続されたデバイスでの通信の 16 ビットデータパケット

コマンドワードデコードは、NSCS 立ち下がりエッジと立ち上がりエッジの間に検出された SCLK サイクル数が 8 の倍数の場合にのみ、NSCS の立ち上がりエッジで実行されます。SPI 通信で検出されたエラーは、SPI\_STAT ビット (NSCS 立ち下がりエッジと最初の SCLK 立ち上がりエッジの間の SDO 状態) で通知され、次の SPI トランザクションで読み戻すことができます。NFAULT ピンでは通知されません。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の部品仕様に含まれるものではなく、TI はその正確性も完全性も保証しません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

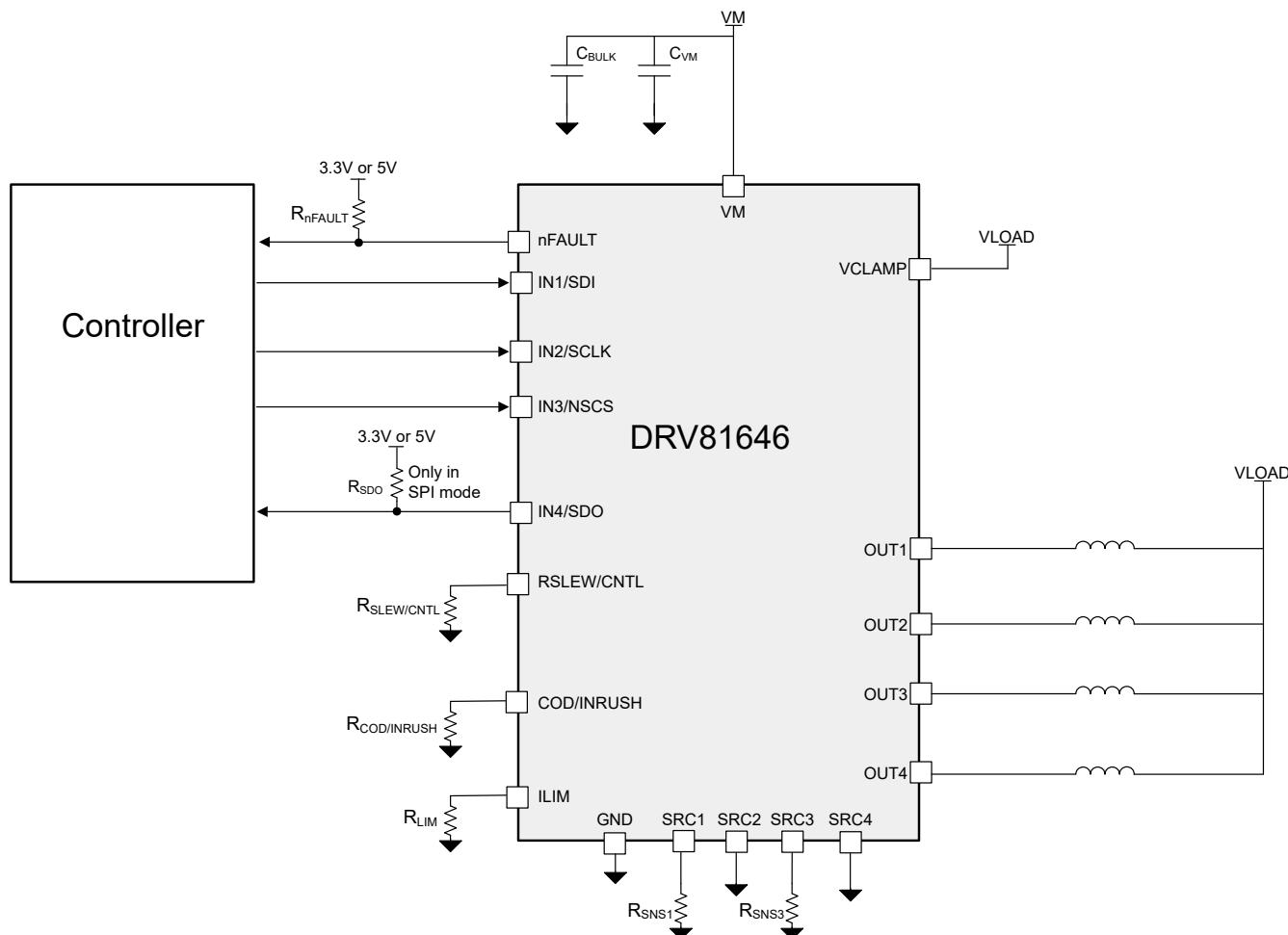

DRV81646 はクワッド チャネルのローサイドであり、電球、コイル、ユニポーラ BDC モーター、LED モジュールなどの容量性負荷など、グランドへの負荷を駆動するために使用できます。チャネルを並列に接続すると、より大きな電流を駆動できます。PWM タイプの制御を必要とする誘導性負荷の場合、DRV81646 には OUT から VCLAMP へのキャッチ ダイオードも内蔵されており、低速減衰のために電流を再循環するために使用できます。高速ターンオフのため、誘導性負荷の電流を高速減衰させるために VCLAMP ピンにブレーキダ운 ツエナーを接続できます。

### 7.2 代表的なアプリケーション

図 7-1. 代表的なアプリケーション回路図

図 7-1 に、DRV81646 のアプリケーション回路図を示します。この例の図は、これらのチャネルの外部電流検出の SRC1 および SRC3 にオプションのセンス抵抗を示しています。VLOAD と VM は互いに接続できます。または、電圧がピンの絶対最大定格を超えない限り異なる電圧にできます。

## 7.2.1 外付け部品

表 7-1 に DRV81646 の推奨外付け部品を、表 7-2 には性能向上や電気的絶縁の追加に使用できる追加部品を示します。

**表 7-1. 必要な外付け部品**

| 記号                | 説明                                                | 値            | 目的                                        |

|-------------------|---------------------------------------------------|--------------|-------------------------------------------|

| $C_{VM}$          | VM のコンデンサ                                         | 1uF          | 電源電圧フィルタリング                               |

| $C_{BULK}$        | VM のバルク キャパシタ                                     | 47uF ~ 100uF | 電源電圧の突入およびリップルの平滑化                        |

| $R_{COD\_INRUSH}$ | COD_INRUSH ピンのプルダウン抵抗                             |              | 目的のカットオフ遅延と INRUSH モードに基づいて抵抗を設定          |

| $R_{SLEW\_CNTL}$  | RSLEW/CNTL ピンのプルダウン抵抗                             |              | 目的のスルーレート設定と制御インターフェイスに基づいてプルダウン抵抗を設定     |

| $R_{ILIM}$        | ILIM ピンのプルダウン抵抗                                   |              | 目的の電流制限に基づいて抵抗を設定                         |

| $R_{SDO}$         | SPI モードの場合におけるオープンドレイン IN4/SDO ピンのロジック電圧へのプルアップ抵抗 | 10kΩ         | ピンが Low にプルされないとき、SDO 電圧をロジック High まで上昇   |

| $R_{nFAULT}$      | オープンドレイン nFAULT ピンのロジック電圧へのプルアップ抵抗                | 10kΩ         | ピンが Low にプルされていないとき、nFAULT 電圧を High にバイアス |

**表 7-2. オプションの外付け部品**

| 記号                   | 説明                                   | 値                               | 目的                            |

|----------------------|--------------------------------------|---------------------------------|-------------------------------|

| $C_{OUT}$            | 各 OUTx から GND へのコンデンサ                | 10nF                            | システム レベル ESD のフィルタリング         |

| TVS <sub>SURGE</sub> | VCLAMP ピンのサージ ダイオード                  | SMAJ33CA または TVS3300            | システム レベルの電圧サージおよび誘導性消磁に対する保護  |

| $R_{SNS}$            | SRC ピンから GND への電流センス抵抗               | < 200mΩ                         | 負荷電流検出の SRC ピンでのオプションの抵抗      |

| $U_{ISOLATION}$      | INx または SPI 信号のクワッド チャネル デジタル アイソレータ | INx 制御: ISO6440<br>SPI: ISO6441 | 回路の残りの部分と DRV81646 間に電気的絶縁を提供 |

## 7.2.2 連続電流能力

以下の表 7-3 と表 7-4 は、さまざまなチャネル数と周囲温度について、各チャネルの連続電流能力の推定値を示しています。「1 チャネルがオン」の行は、1 つの OUT がオンで、他の 3 つの出力がオフの場合の連続電流能力を示しています。「2 チャネルがオン」の行は、2 つのチャネルが同じ負荷でオン、他の 2 つの出力がオフの場合を示しています。「4 チャネルがオン」の行は、4 つのチャネルすべてが同時にオンで、それぞれに同じ負荷がかかる場合を示しています。たとえば、各「4 チャネルがオン」のとき、各チャネルは 2.7A (PWP パッケージ) を出力でき、デバイスを流れる合計電流は 10.8A です。

このデータは、消費電力に最適化されたレイアウトを持つ大きな PCB 上のベンチ テストによるもので、連続電流能力はシステムと PCB の設計によって異なります。

**表 7-3. OUTx ごとの FET DC 電流能力 - PWP パッケージ**

| 構成        | 25°C | 55°C | 85°C | 125°C |

|-----------|------|------|------|-------|

| 1 チャネルがオン | 3.7A | 3.4A | 3.2A | 2.5A  |

| 2 チャネルがオン | 3.5A | 3.0A | 2.7A | 2.1A  |

| 4 チャネルがオン | 2.7A | 2.4A | 2.0A | 1.5A  |

**表 7-4. OUTx ごとの FET DC 電流能力 - DGQ パッケージ**

| 構成        | 25°C | 55°C | 85°C | 125°C |

|-----------|------|------|------|-------|

| 1 チャネルがオン | 3.4A | 3.1A | 2.9A | 2.4A  |

| 2 チャネルがオン | 3.1A | 2.7A | 2.4A | 1.8A  |

表 7-4. OUTx ごとの FET DC 電流能力 - DGQ パッケージ (続き)

| 構成        | 25°C | 55°C | 85°C | 125°C |

|-----------|------|------|------|-------|

| 4 チャネルがオン | 2.5A | 2.2A | 1.7A | 1.3A  |

これは、連続的にオンの負荷にのみ適用され、PWM には適用されないことに注意してください。PWM で出力をスイッチングするとスイッチング損失が発生し、デバイスの発熱がさらに増大して、平均電流能力が大幅に低下します。

### 7.2.3 消費電力

DRV81646 デバイスでの電力消費は、主に出力 FET 抵抗、つまり  $R_{DS(on)}$  で消費される電力によって大きく左右されます。静的負荷をかけた状態で各 FET が消費する平均電力は、式 18 で概算できます。

$$P = R_{DS(ON)} \times [I_{OUT}]^2 \quad (18)$$

ここで、

- $P$  は 1 つの FET の電力損失です。

- $R_{DS(ON)}$  は各 FET の抵抗です。

- $I_{OUT}$  は、負荷により流れる平均電流と等しくなります。

起動時およびフォルト状態では、この電流は通常動作電流よりもはるかに高くなります。これらのピーク電流とその持続時間を考慮する必要があります。複数の負荷を同時に駆動する場合は、すべてのアクティブな出力段の電力を加算する必要があります。

デバイスが放散できる電力の最大値は、周囲温度とヒートシンクに依存します。

$R_{DS(on)}$  は温度とともに上昇するので、デバイスが発熱すると消費電力が増大することに注意してください。ヒートシンクのサイズを決定する際には、この点を考慮に入れてください。

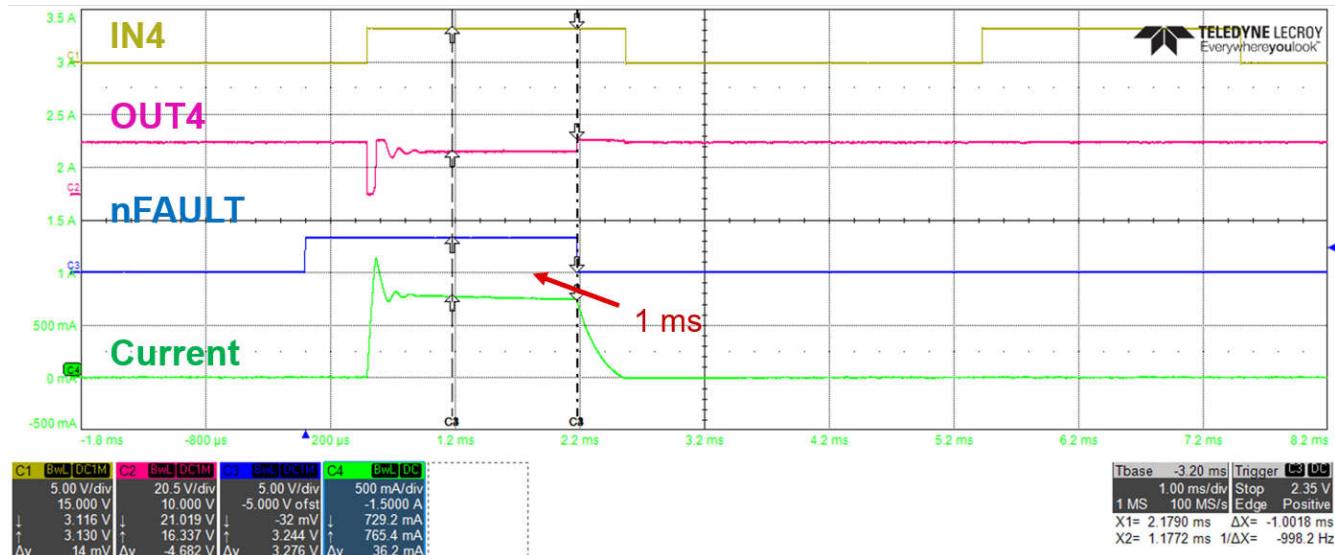

### 7.2.4 アプリケーション曲線

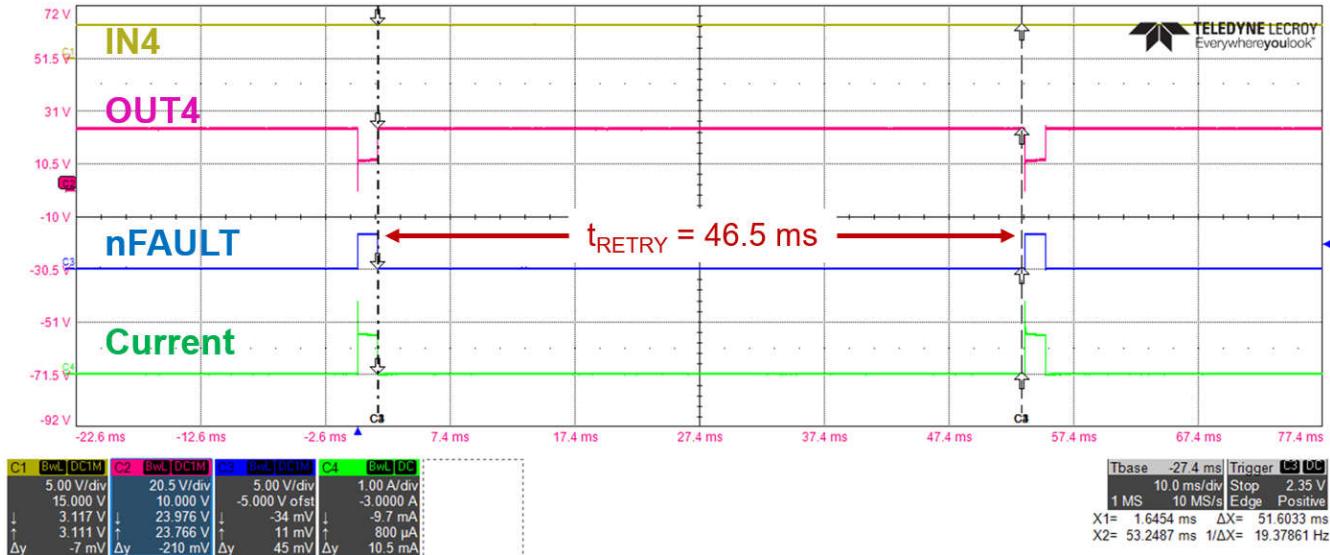

図 7-2.  $R_{COD} = 120\text{k}\Omega$  での  $t_{COD} = 1\text{ms}$ 、12V、12Ω 負荷、VCLAMP を VM に短絡

図 7-3. カットオフ遅延 (COD) イネーブルでの  $t_{RETRY} = 46.5\text{ms}$ 、 $R_{COD} = 180\text{k}\Omega$ 、12V、12 $\Omega$  1mH 負荷、VCLAMP を VM に短絡

## 7.3 電源に関する推奨事項

### 7.3.1 バulk コンデンサ

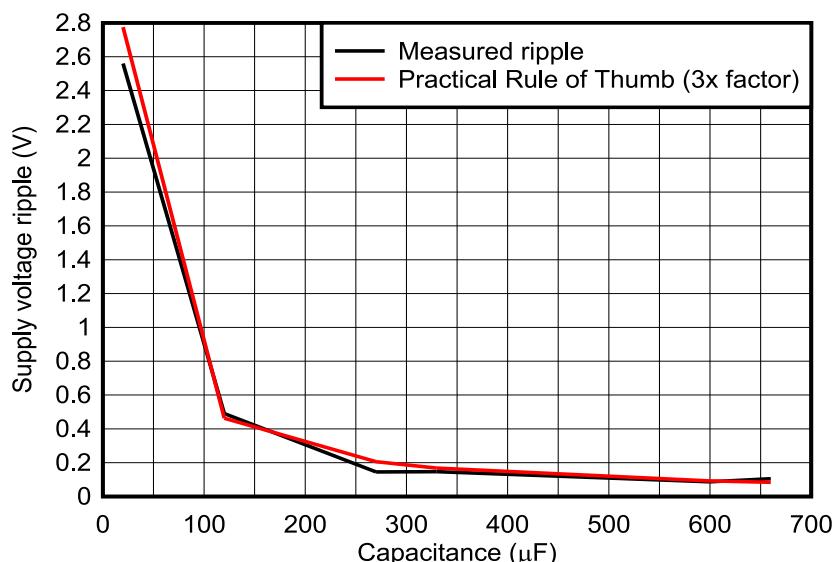

適切なローカル バulk容量の確保は、モーター駆動システムの設計において重要な要素です。一般的に、バulk容量が大きいことは有益ですが、コストと物理的なサイズが大きくなるというデメリットもあります。モーター ドライバの近くにあるバulkコンデンサは、モーターの電流変動を平滑化するための局所的な電荷貯蔵庫として機能します。

経験豊富なエンジニアは多くの場合、バulk容量に関する一般的なガイドラインを使用してコンデンサの値を選択します。そのようなガイドラインの 1 つでは、負荷電力 1 ワットごとに少なくとも  $1\mu\text{F} \sim 4\mu\text{F}$  の静電容量を使用するように指示されています。たとえば、24V 電源から 4 アンペアを引き出すソレノイドは 96 ワットの電力を持ち、この一般的なガイドラインに従うと、バulk静電容量は  $96\mu\text{F} \sim 384\mu\text{F}$  になります。

モータが電源にエネルギーを伝達する場合のマージンを確保するため、バulk コンデンサの定格電圧は動作電圧より高くする必要があります。

ソレノイドの起動、負荷トルクの変化、PWM 動作などの電流遷移時に一定の VM 電源電圧を供給するには、大きなバulk容量が求められます。安定した電源供給に必要な容量の概算は、基板電子回路の複雑さ、コスト、およびサイズを抑えるために不可欠です。予想される負荷電流の変動と許容されるモーター電源電圧の変動に基づいて適切なコンデンサのサイズを見つけるには、一般的なガイドラインの方法が使えます。

$$C_{BULK} > k \times \Delta I_{MOTOR} \times t_{PWM} \div \Delta V_{SUPPLY} \quad (19)$$

ここで：

$C_{BULK}$  は、バulk容量です。

$k$  は、この種のアプリケーションで一般的なコンデンサの ESR を表す係数で、このような場合は  $k \approx 3$  が実用的です。

$\Delta I_{MOTOR}$  はモータ電流の予想される変化、 $i_{max} - i_{min}$  です

$t_{PWM}$  は、PWM 周波数の逆数で、PWM サイクルです

$\Delta V_{SUPPLY}$  は、モーターの電源電圧の許容変動幅です。

図 7-4 は複数のデータ ポイントをプロットしたもので、この一般的なガイドラインを適用しています。比較的良好な一致を示しています。

図 7-4. 測定結果と 3 x 一般的なガイドライン、電解コンデンサの実際にはゼロではない ESR 値を考慮

『DC モーター駆動アプリケーションのバルク キャパシタのサイズ設定』アプリケーション ノートも参照してください。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

- バルク キャパシタは、モーター ドライバ デバイスを通る高電流パスの距離ができるだけ短くなるように配置します。接続用の金属パターンはできる限り幅を広くし、PCB 層を接続する際には多数のビアを使用します。これらの手法により、インダクタンスが最小限に抑えられ、バルクコンデンサが大電流を供給できるようになります。

- 高電流デバイス出力には幅の広い金属パターンを使用します。

- VM ピンは、VM に対応した定格を備えた低 ESR セラミックバイパスコンデンサを用いて GND ピンにバイパスされます。これらのコンデンサは VM ピンのできるだけ近くに配置し、太いパターンまたはグラウンドプレーンを介してデバイスの VNEG ピンへ接続することが推奨されます。

- 一般に、電源ピンとデカップリングコンデンサの間のインダクタンスを防ぐ必要があります。

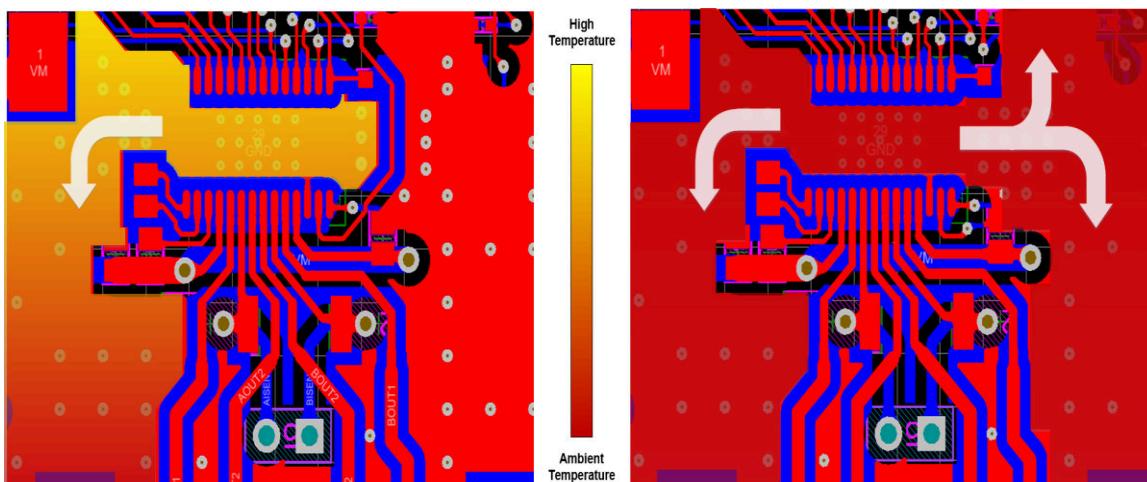

- サーマル パッドは、システム グランドに接続する必要があります。

- システム/基板全体に対して、大きく途切れのない単一のグラウンドプレーンを使用するようにしてください。グランドプレーンは PCB の下層に作成できます。図 7-5 に、ドライバの下のグラウンドプレーンが連続的である場合に対して、グラウンドプレーンがくびれている場合に温度が上昇する例を示します。

- インピーダンスとインダクタンスを最小化するには、ビアを経由して下層のグラウンドプレーンに接続する前に、グランドピンからのパターンをできる限り短く、幅広くする必要があります。

- インピーダンスを小さくするために、複数のビアを使用します。

- 熱の拡散を改善するために、デバイスの周囲のスペースをできるだけ大きく、特に PCB の下層に確保してください。

- サーマル PAD に接続された内部グラウンドプレーン(単一または複数)を利用して放熱性を高め、熱抵抗を低減可能。

- レイアウトガイドラインおよびベスト プラクティスの詳細については、『モーター ドライバーの基板レイアウトのベスト プラクティス』アプリケーション ノートを参照してください。

図 7-5. くびれたグラウンドプレーンと連続的なグラウンドプレーンの温度分布の比較

### 7.4.2 レイアウト例

レイアウト例については、評価基板 (EVM) を参照してください。DRV81646EVM または DRV81646DGQEVM 製品フォルダから Altium 設計ファイルをダウンロード可能です。

## 8 デバイスおよびドキュメントのサポート

### 8.1 ドキュメントのサポート

#### 8.1.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『モータードライバの基板レイアウトのベストプラクティス』アプリケーションノート

- テキサス・インスツルメンツ、『DCモーター駆動アプリケーションのバルクキャパシタのサイズ設定』アプリケーションノート

- テキサス・インスツルメンツ、『PowerPAD™ 入門』アプリケーションノート

- テキサス・インスツルメンツ、『熱特性強化型パッケージ PowerPAD™』アプリケーションノート

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 8.4 商標

PowerPAD™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (September 2025) to Revision A (December 2025) | Page |

|------------------------------------------------------------------------|------|

| ドキュメントのステータスを「事前情報」から「量産データ」に変更.....                                   | 1    |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| DRV81646DGQR          | Active        | Production           | HVSSOP (DGQ)   24 | 3000   LARGE T&R      | -           | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 81646               |

| DRV81646PWPR          | Active        | Production           | HTSSOP (PWP)   20 | 3000   LARGE T&R      | -           | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | DRV81646            |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

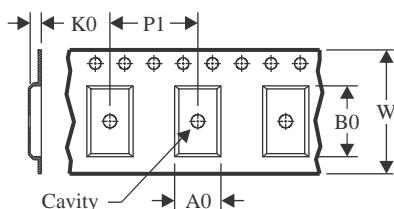

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

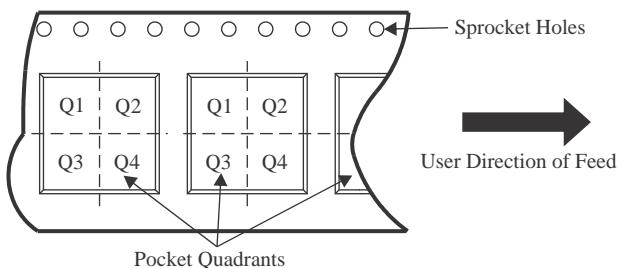

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| DRV81646DGQR | HVSSOP       | DGQ             | 24   | 3000 | 330.0              | 16.4               | 5.44    | 6.4     | 1.45    | 8.0     | 16.0   | Q1            |

| DRV81646PWPR | HTSSOP       | PWP             | 20   | 3000 | 330.0              | 16.4               | 6.95    | 7.0     | 1.4     | 8.0     | 16.0   | Q1            |

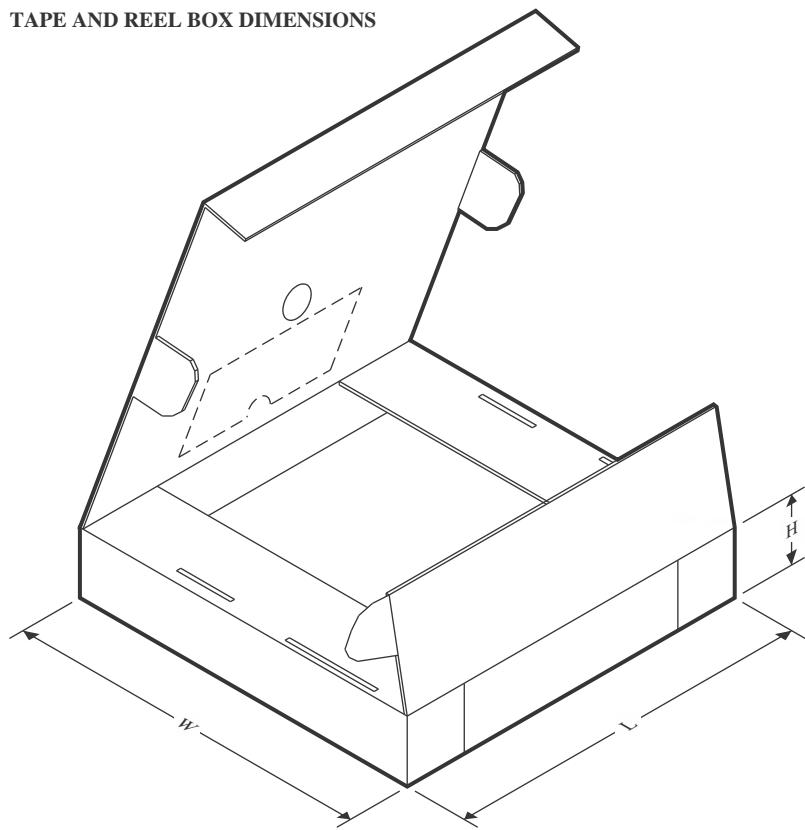

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV81646DGQR | HVSSOP       | DGQ             | 24   | 3000 | 353.0       | 353.0      | 32.0        |

| DRV81646PWPR | HTSSOP       | PWP             | 20   | 3000 | 353.0       | 353.0      | 32.0        |

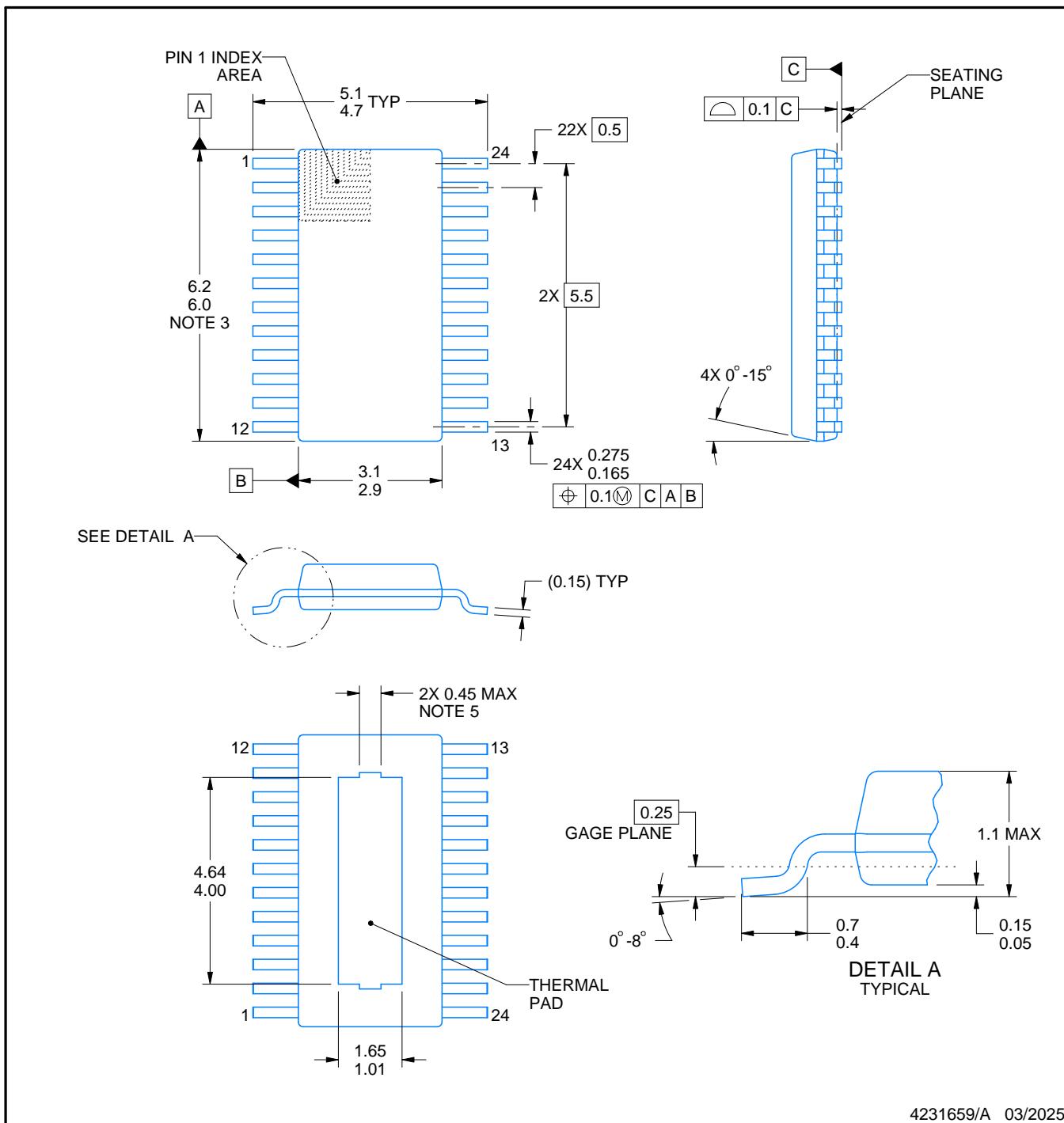

# PACKAGE OUTLINE

DGQ0024A

PowerPAD™ VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. No JEDEC registration as of September 2020.

5. Features may differ or may not be present.

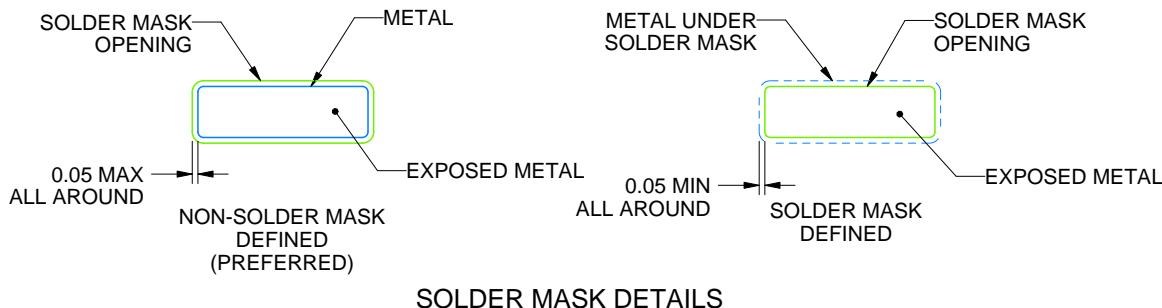

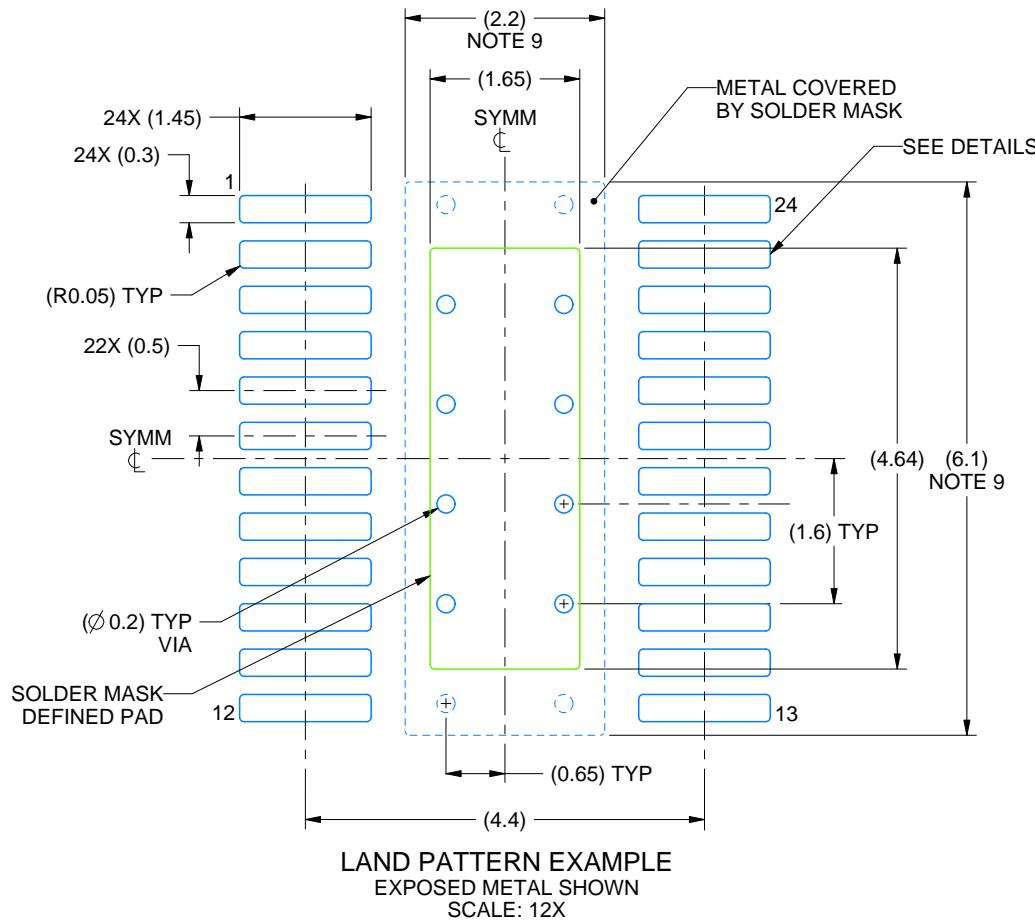

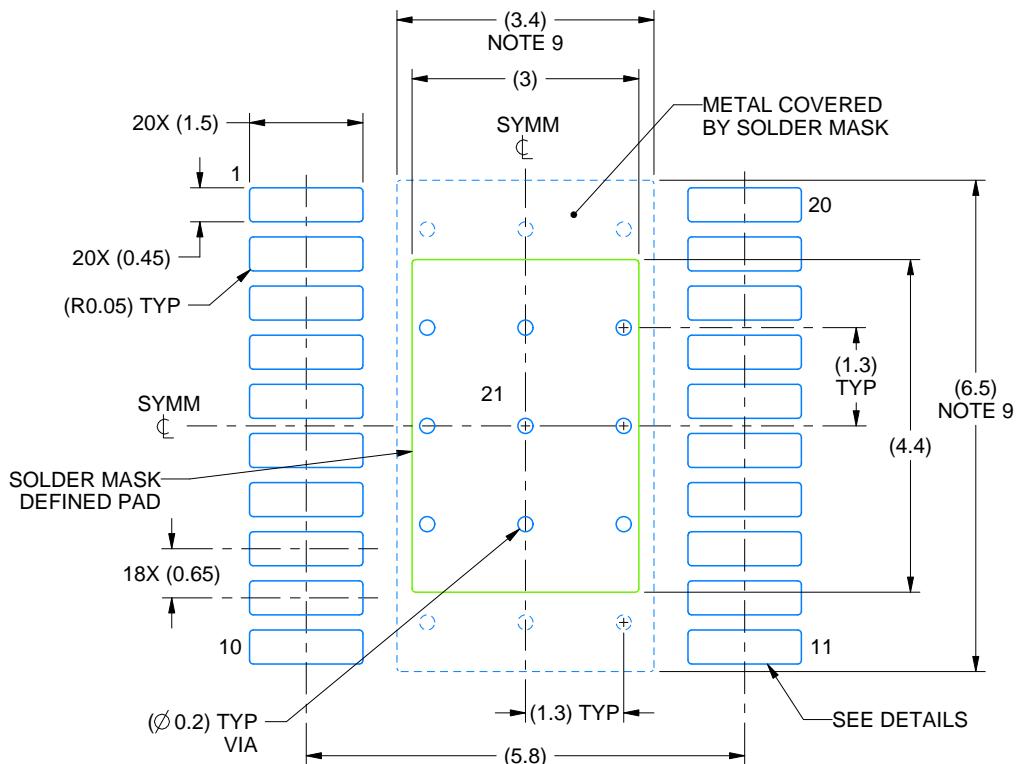

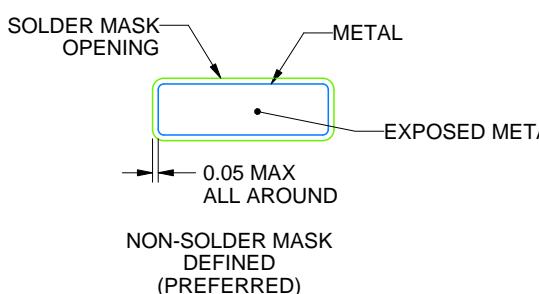

# EXAMPLE BOARD LAYOUT

DGQ0024A

PowerPAD™ VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

4231659/A 03/2025

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

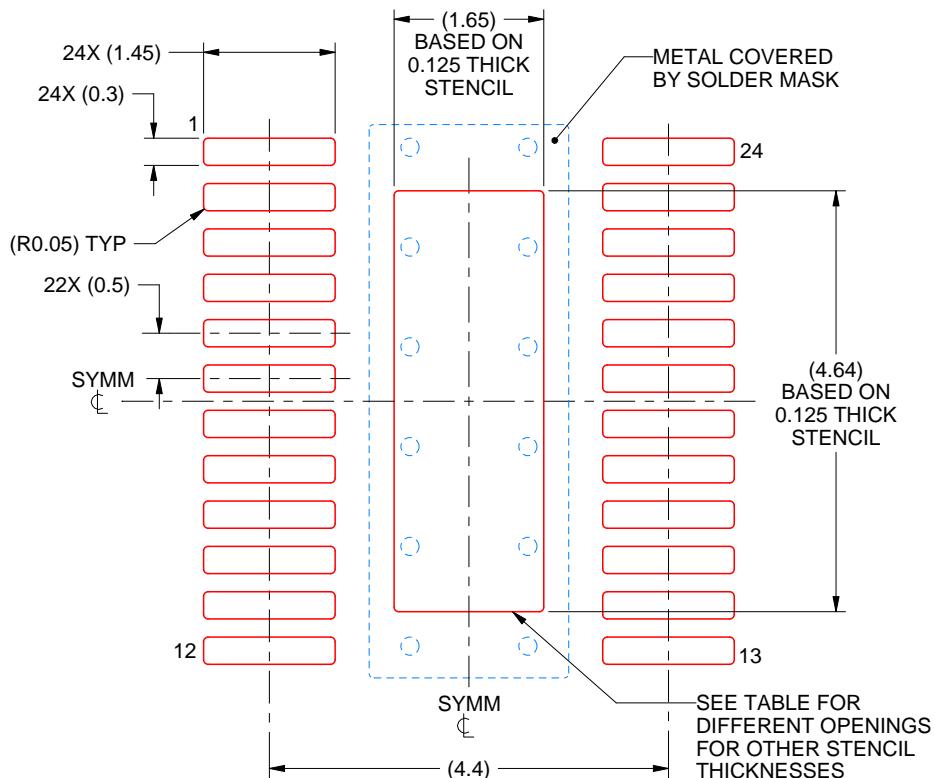

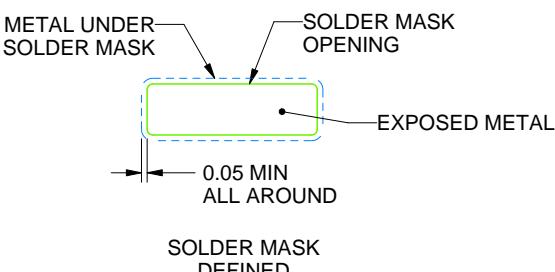

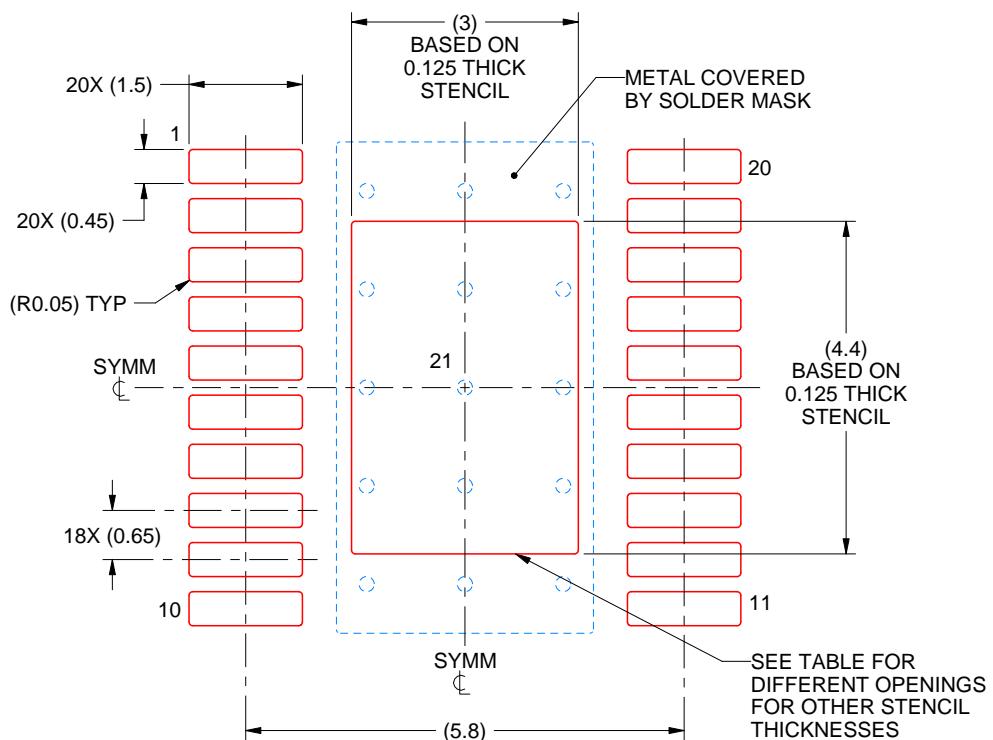

# EXAMPLE STENCIL DESIGN

DGQ0024A

PowerPAD™ VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 12X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 1.84 X 5.19            |

| 0.125             | 1.65 X 4.64 (SHOWN)    |

| 0.15              | 1.51 X 4.24            |

| 0.175             | 1.39 X 3.92            |

4231659/A 03/2025

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

## GENERIC PACKAGE VIEW

### PWP 20

6.5 x 4.4, 0.65 mm pitch

HTSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4224669/A

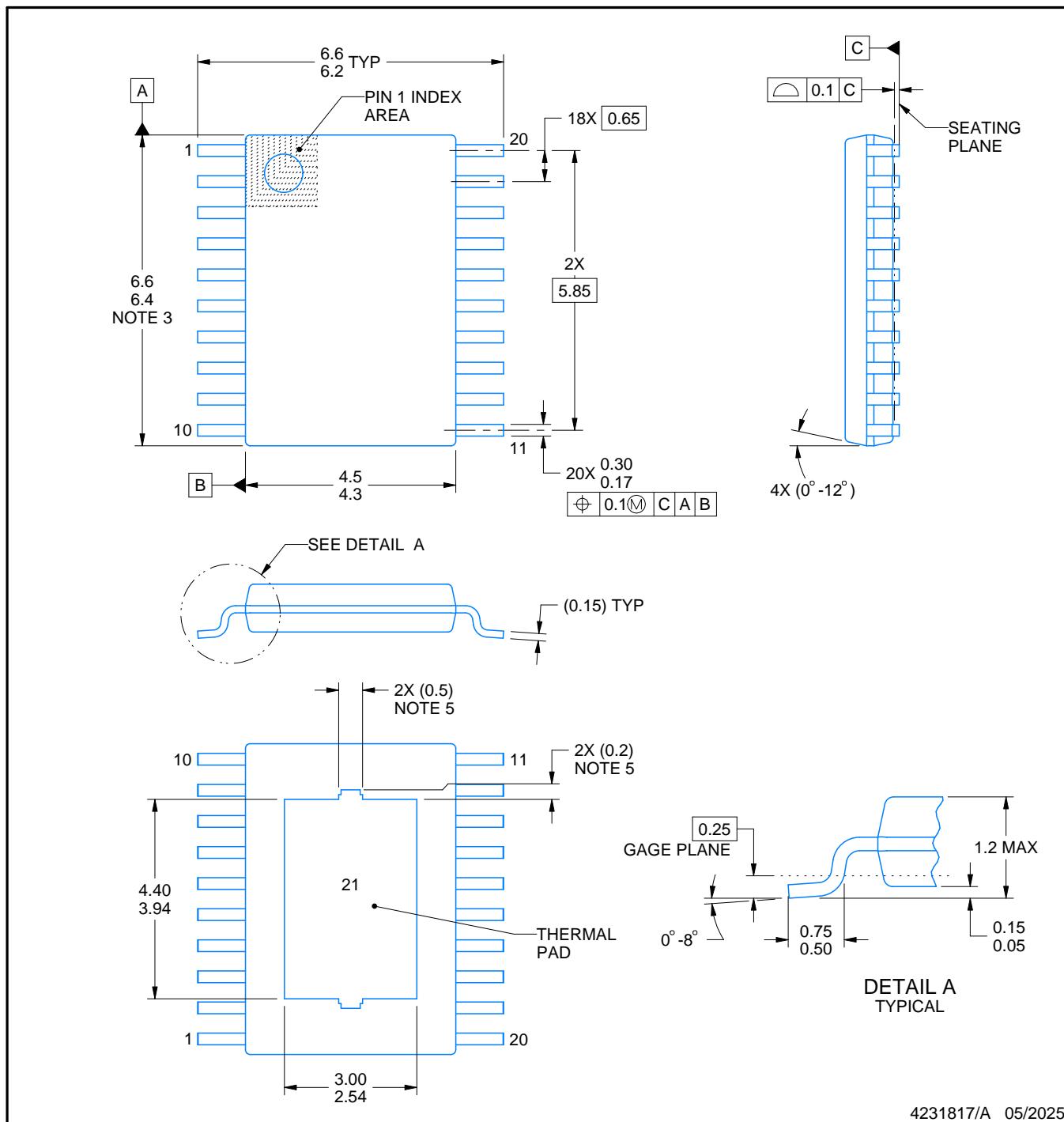

## PACKAGE OUTLINE

**PWP0020AC**

## PowerPAD™ TSSOP - 1.2 mm max height

## SMALL OUTLINE PACKAGE

## NOTES:

PowerPAD is a trademark of Texas Instruments.