DRV8316C-Q1 JAJSPW6 - FEBRUARY 2023

## DRV8316C-Q1 車載 3 相統合 FET モーター・ドライバ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証を取得

- 温度グレード 1:-40°C ≤ TA ≤ 125°C

- 三相 BLDC モーター・ドライバ

- サイクル単位の電流制限により位相電流を制限

- 最大 200kHz の PWM 周波数をサポート

- アクティブ消磁により電力損失を低減

- 動作電圧:4.5V~35V (絶対最大定格 40V)

- 高い出力電流能力:ピーク8A

- 低い MOSFET ON 抵抗

- T<sub>A</sub> = 25°C で 95mΩ(標準値) の R<sub>DS(ON)</sub> (HS + LS)

- 低消費電力スリープ・モード

- V<sub>VM</sub> = 13.5V、T<sub>A</sub> = 25℃ で 2.5µA (最大値)

- 複数の制御インターフェイス・オプション

- 6x PWM 制御インターフェイス

- 3x PWM 制御インターフェイス

- サイクルごとの電流制限付き 6x PWM 制御インタ

- サイクルごとの電流制限付き 3x PWM 制御インタ ーフェイス

- 電流センス機能内蔵、外付け電流センス抵抗不要

- 柔軟なデバイス構成オプション

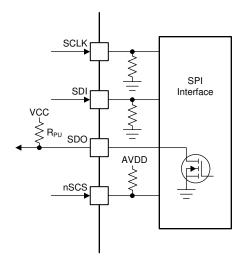

- DRV8316CR-Q1:デバイスの構成とフォルト・ステ ータスのための 5MHz、16 ビット SPI インターフェ イス

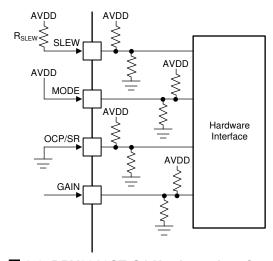

- DRV8316CT-Q1:ハードウェア・ピンを使った構成

- 1.8V、3.3V、5V のロジック入力電圧に対応

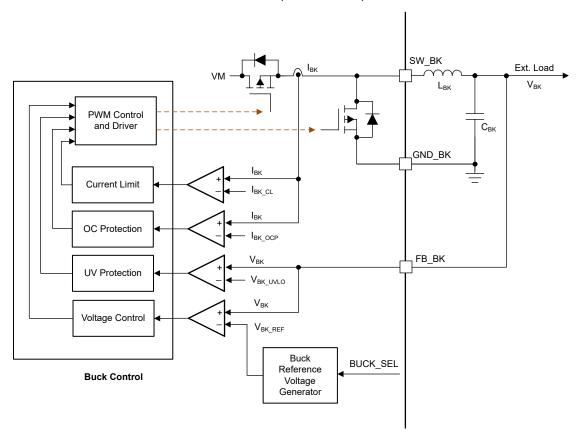

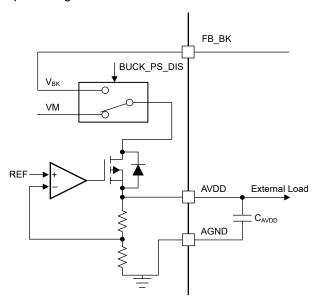

- 3.3V/5V、200mA の降圧レギュレータを内蔵

- 3.3V、30mA の LDO レギュレータを内蔵

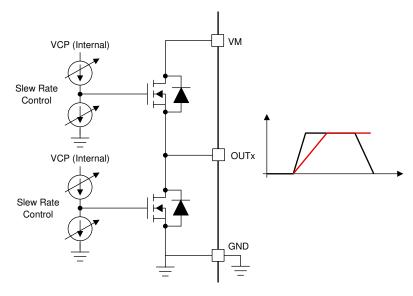

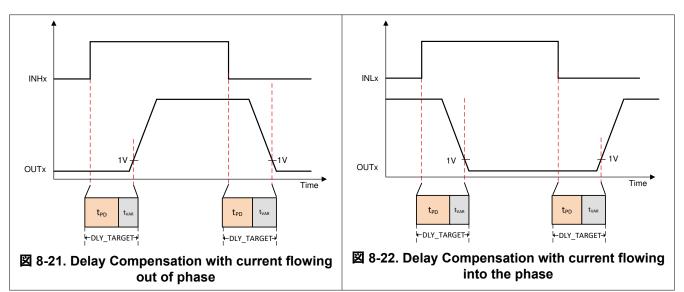

- 遅延補償によりデューティ・サイクルの歪みを低減

- 各種保護機能を内蔵

- 電源低電圧誤動作防止 (UVLO)

- チャージ・ポンプ低電圧 (CPUV)

- 過電流保護 (OCP)

- 熱警告およびシャットダウン (OTW/OTSD)

- フォルト状態通知ピン (nFAULT)

- SPI インターフェイスによるフォルト診断 (オプショ ン)

## 2 アプリケーション

- ブラシレス DC (BLDC) モーター・モジュール

- 車載用 LIDAR

- 小型の車載用ファンおよびポンプ

- 車載用アクチュエータ

## 3 概要

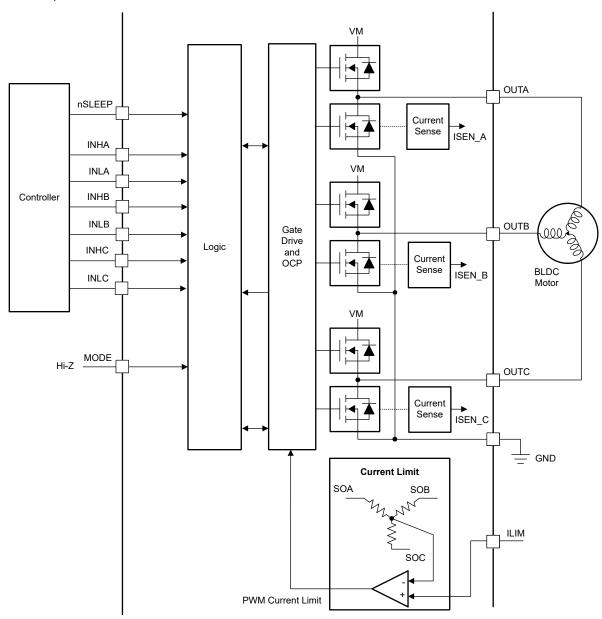

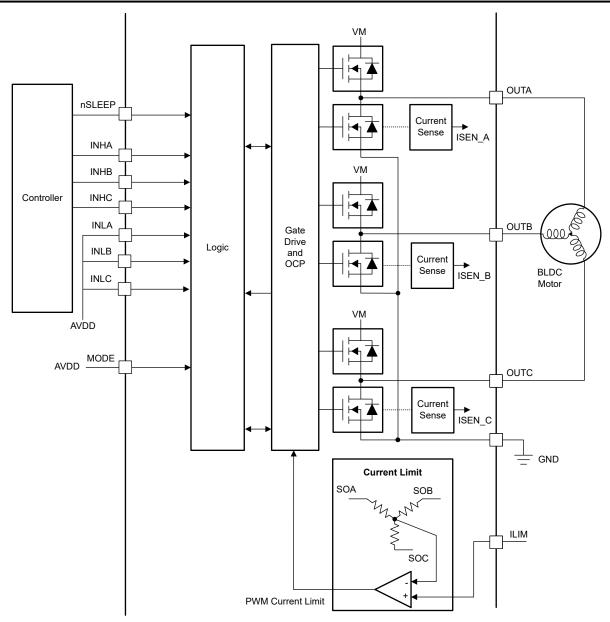

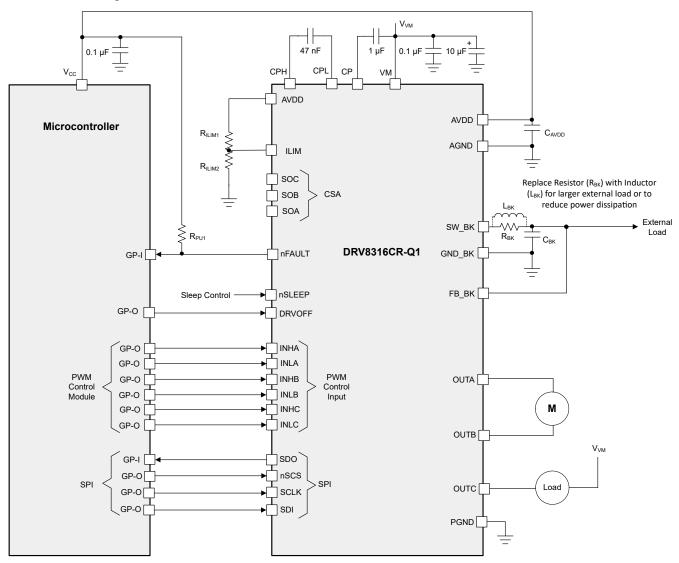

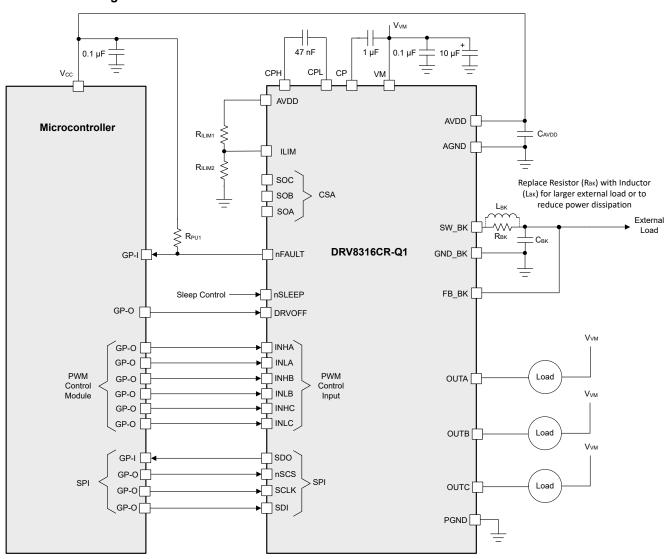

DRV8316C-Q1 は、3 つの H ブリッジを内蔵し、40V の 絶対最大定格、95mΩ (ハイサイド + ローサイド) という非 常に低い R<sub>DS(ON)</sub> を備えており、12V の車載ブラシレス DC モーターで高い電力駆動能力を実現できます。 DRV8316C-Q1 には電流検出機能が組み込まれている ので、外付けの検出抵抗は不要です。 **DRV8316C-Q1** に は、電圧調整可能な降圧レギュレータ (3.3V/5V、200mA) および LDO (3.3V/30mA) を含む電源管理回路が内蔵さ れており、外部回路への電力供給に使用できます。

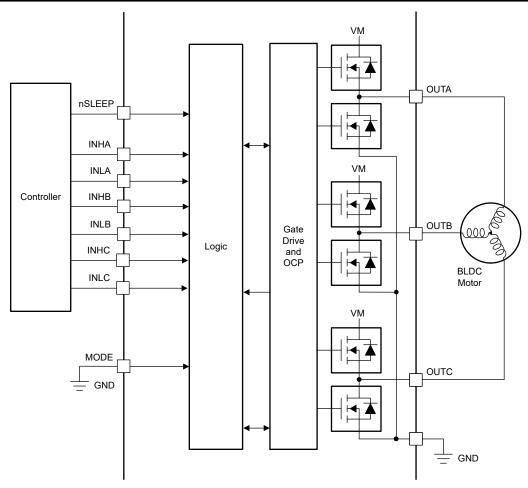

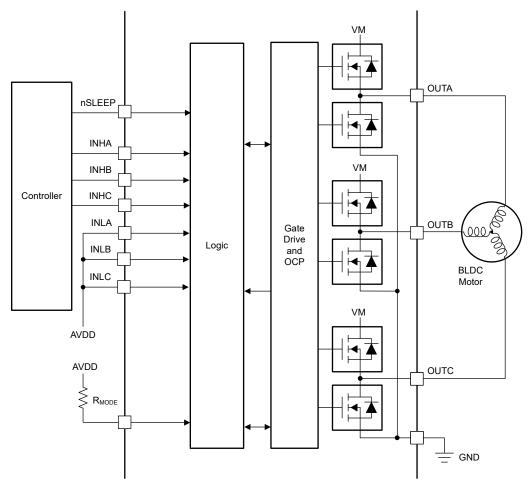

DRV8316C-Q1 には構成可能な 6x または 3x PWM 制 御方式が実装されており、外付けマイコンを使って、セン サ付きまたはセンサレスの磁界方向制御 (FOC)、正弦波 制御、または台形制御を実現できます。DRV8316C-Q1 は、最大 200kHz の PWM 周波数を駆動できます。 DRV8316C-Q1 は、SPI (DRV8316CR-Q1) またはピン (DRV8316CT-Q1) のいずれかを使用して高度に構成で きます。PWM モード、スルーレート、OCP レベル、電流 センス・ゲインは、構成可能な機能の一部です。

DRV8316C-Q1 には、電源低電圧ロックアウト (UVLO)、 過電圧保護 (OVP)、チャージ・ポンプ低電圧 (CPUV)、過 電流保護 (OCP)、過熱警告 (OTW)、過熱シャットダウン (OTSD) などの多くの保護機能が内蔵されており、デバイ ス、モーター、システムをフォルト・イベントから保護しま す。フォルト状態は、nFAULT ピンで通知されます。

設計上の考慮事項とデバイス使用上の推奨事項について は、Application Information を参照してください。

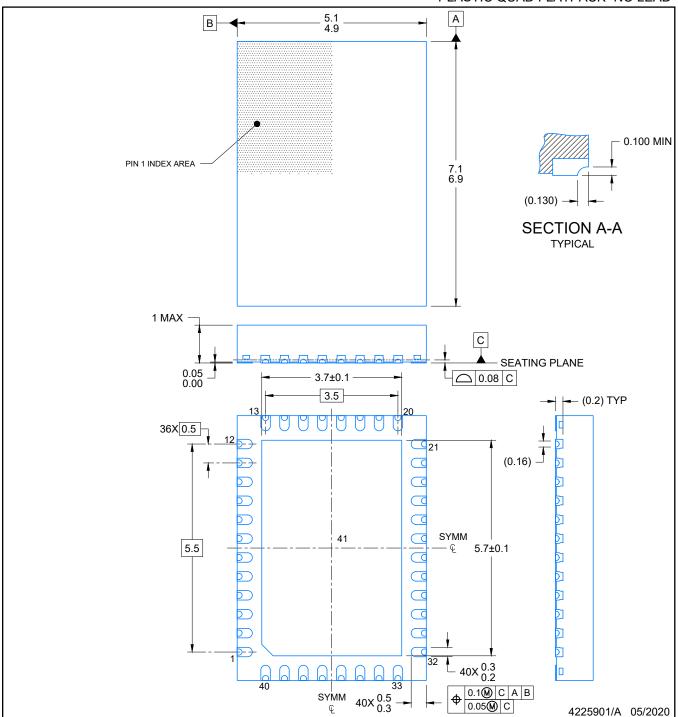

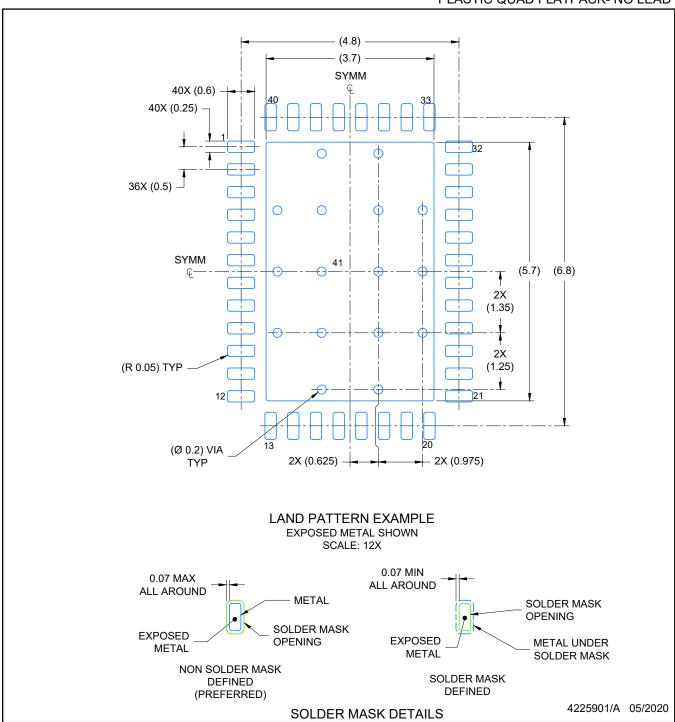

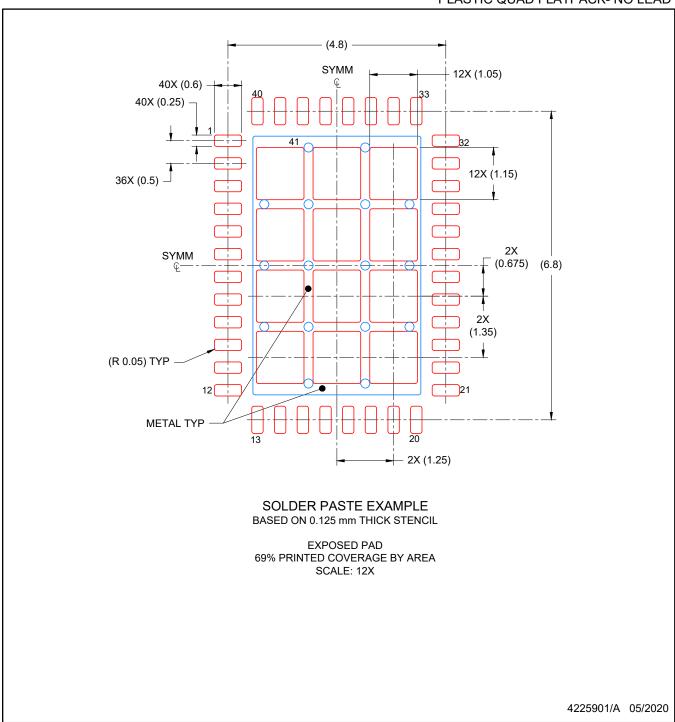

### デバイス情報<sup>(1)</sup>

| 部品番号         | パッケージ 本体サイズ (公称) |                 |

|--------------|------------------|-----------------|

| DRV8316CR-Q1 | VQFN (40)        | 7.00mm × 5.00mm |

| DRV8316CT-Q1 | VQFN (40)        | 7.00mm × 5.00mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

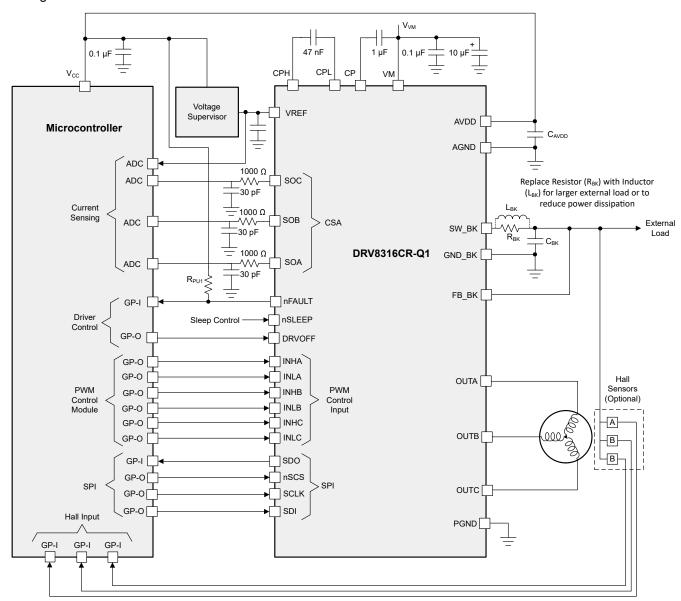

簡略回路図

## **Table of Contents**

| 1 特長                                 | 1  | 8.5 SPI Communication                   | 54              |

|--------------------------------------|----|-----------------------------------------|-----------------|

| 2 アプリケーション                           |    | 8.6 Register Map                        | 57              |

| 3 概要                                 |    | 9 Application and Implementation        | <mark>69</mark> |

| 4 Revision History                   |    | 9.1 Application Information             | 69              |

| 5 Device Comparison Table            |    | 9.2 Typical Applications                | 70              |

| 6 Pin Configuration and Functions    |    | 10 Power Supply Recommendations         | 82              |

| 7 Specifications                     |    | 10.1 Bulk Capacitance                   | 82              |

| 7.1 Absolute Maximum Ratings         |    | 11 Layout                               | <mark>83</mark> |

| 7.2 ESD Ratings Auto                 |    | 11.1 Layout Guidelines                  | 83              |

| 7.3 Recommended Operating Conditions |    | 11.2 Layout Example                     | 84              |

| 7.4 Thermal Information              |    | 11.3 Thermal Considerations             | 85              |

| 7.5 Electrical Characteristics       |    | 12 Device and Documentation Support     | 86              |

| 7.6 SPI Timing Requirements          |    | 12.1 Documentation Support              | 86              |

| 7.7 SPI Slave Mode Timings           |    | <b>12.2</b> サポート・リソース                   | 8 <del>6</del>  |

| 7.8 Typical Characteristics          |    | 12.3 Trademarks                         | <mark>86</mark> |

| 8 Detailed Description               |    | 12.4 静電気放電に関する注意事項                      | 86              |

| 8.1 Overview                         |    | 12.5 用語集                                | 86              |

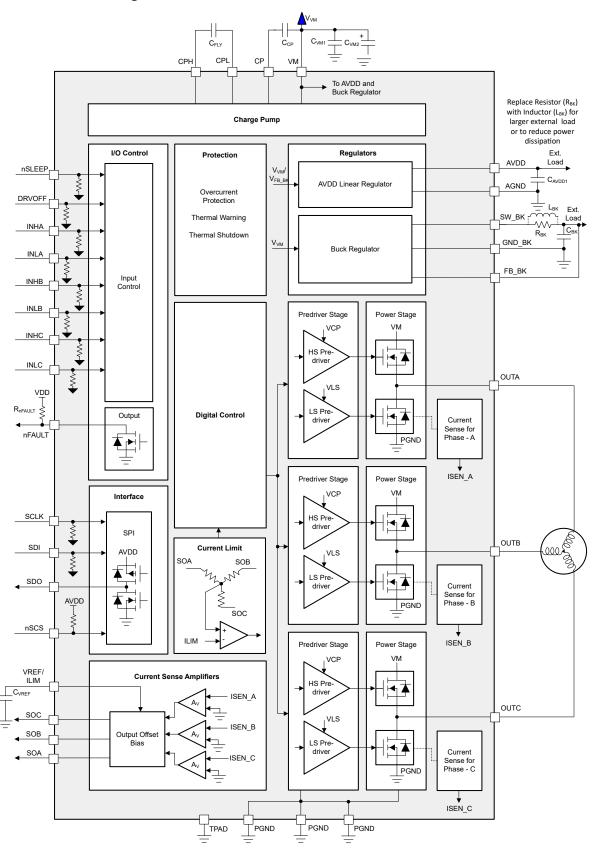

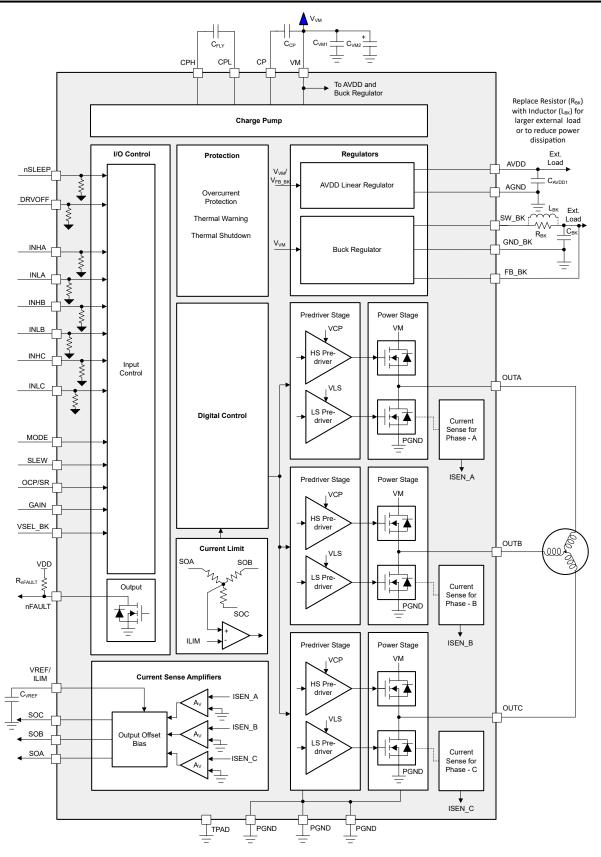

| 8.2 Functional Block Diagram         | 17 | 13 Mechanical, Packaging, and Orderable |                 |

| 8.3 Feature Description              |    | Information                             | 86              |

| 8.4 Device Functional Modes          |    |                                         |                 |

|                                      |    |                                         |                 |

# **4 Revision History**

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| February 2023 | *        | Initial release. |

## **5 Device Comparison Table**

| DEVICE       | PACKAGES                 | INTERFACE      | BUCK REGULATOR |

|--------------|--------------------------|----------------|----------------|

| DRV8316CR-Q1 | 40-pin VQFN (7x5 mm)     | SPI            | Yes            |

| DRV8316CT-Q1 | 40-piii vQFN (7X3 IIIII) | Hardware (Pin) | 165            |

## 表 5-1. DRV8316CR-Q1 (SPI variant) vs. DRV8316CT-Q1 (Hardware variant) configuration comparison

| Parameters                   | DRV8316CR-Q1 (SPI variant) | DRV8316CT-Q1 (Hardware variant)     |

|------------------------------|----------------------------|-------------------------------------|

| PWM mode                     | PWM_MODE (4 settings)      | MODE pin (4 settings)               |

| Slew rate                    | SLEW (4 settings)          | SLEW pin (4 settings)               |

| CSA gain                     | CSA_GAIN (4 settings)      | GAIN pin (4 settings)               |

| SDO pin configuration        | SDO_MODE (2 settings)      | N/A                                 |

| DRVOFF pin configuration     | DRV_OFF (2 settings)       | Enabled                             |

| OCP level                    | OCP_LVL (2 settings)       | OCP/SR pin (2 settings)             |

| OCP mode                     | OCP_MODE (4 settings)      | Latched fault                       |

| OCP retry time               | OCP_RETRY (2 settings)     | N/A since OCP mode is latched fault |

| Overvoltage protection (OVP) | OVP_EN (2 settings)        | Enabled                             |

| OVP threshold                | OVP_SEL (2 settings)       | 34-V                                |

## **6 Pin Configuration and Functions**

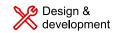

図 6-1. DRV8316CR-Q1 40-Pin VQFN With Exposed Thermal Pad Top View

図 6-2. DRV8316CT-Q1 40-Pin VQFN With Exposed Thermal Pad Top View

表 6-1. Pin Functions

| PIN    | 40-pin F         | Package      |                     |                                                                                                                                                                               |  |

|--------|------------------|--------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME   | DRV8316CR-<br>Q1 | DRV8316CT-Q1 | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                   |  |

| AGND   | 2, 26            | 2, 26        | GND                 | Device analog ground. Refer セクション 11.1 for connections recommendation.                                                                                                        |  |

| AVDD   | 25               | 25           | PWR O               | 3.3-V internal regulator output. Connect an X5R or X7R, 1- $\mu$ F, 6.3-V ceramic capacitor between the AVDD and AGND pins. This regulator can source up to 30 mA externally. |  |

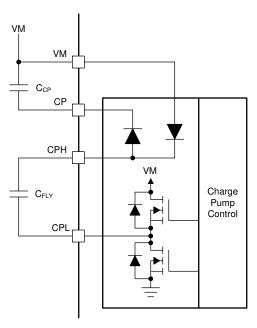

| СР     | 8                | 8            | PWR O               | Charge pump output. Connect a X5R or X7R, 1-µF, 16-V ceramic capacitor between the CP and VM pins.                                                                            |  |

| СРН    | 7                | 7            | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, ceramic                                                                                                              |  |

| CPL    | 6                | 6            | PWR                 | capacitor between the CPH and CPL pins. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the device.                                   |  |

| DRVOFF | 21               | 21           | I                   | When this pin is pulled high the six MOSFETs in the power stage are turned OFF making all outputs Hi-Z.                                                                       |  |

| FB_BK  | 3                | 3            | PWR I               | Feedback for buck regulator. Connect to buck regulator output after the inductor/resistor.                                                                                    |  |

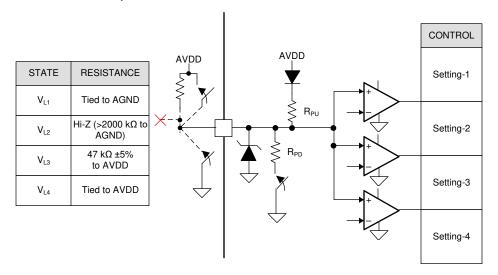

| GAIN   | _                | 36           | I                   | Amplifier gain setting. The pin is a 4-level input pin set by an external resistor.                                                                                           |  |

| GND_BK | 4                | 4            | GND                 | Buck regulator ground. Refer セクション 11.1 for connections recommendation.                                                                                                       |  |

| INHA   | 27               | 27           | I                   | High-side driver control input for OUTA. This pin controls the output of the high-side MOSFET.                                                                                |  |

| INHB   | 29               | 29           | I                   | High-side driver control input for OUTB. This pin controls the output of the high-side MOSFET.                                                                                |  |

| INHC   | 31               | 31           | I                   | High-side driver control input for OUTC. This pin controls the output of the high-side MOSFET.                                                                                |  |

| INLA   | 28               | 28           | ı                   | Low-side driver control input for OUTA. This pin controls the output of the low-side MOSFET.                                                                                  |  |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## 表 6-1. Pin Functions (continued)

|             |                  |              | <b>3</b> C 1        |                                                                                                                                                                                                                                                                                           |  |  |

|-------------|------------------|--------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN         | 40-pin           | Package      |                     |                                                                                                                                                                                                                                                                                           |  |  |

| NAME        | DRV8316CR-<br>Q1 | DRV8316CT-Q1 | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                               |  |  |

| INLB        | 30               | 30           | I                   | Low-side driver control input for OUTB. This pin controls the output of the low-side MOSFET.                                                                                                                                                                                              |  |  |

| INLC        | 32               | 32           | I                   | Low-side driver control input for OUTC. This pin controls the output of the low-side MOSFET.                                                                                                                                                                                              |  |  |

| MODE        | _                | 33           | I                   | PWM input mode setting. This pin is a 4-level input pin set by an external resistor.                                                                                                                                                                                                      |  |  |

| NC          | 1, 24            | 1            | _                   | No connection, open                                                                                                                                                                                                                                                                       |  |  |

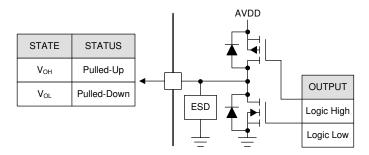

| nFAULT      | 22               | 22           | 0                   | Fault indicator. Pulled logic-low with fault condition; Open-drain output requir an external pull-up resistor to 1.8 V to 5.0 V. If external supply is used to pull up nFAULT, ensure that it is pulled to >2.2 V on power up or the device will enter test mode                          |  |  |

| nSCS        | 36               | _            | I                   | Serial chip select. A logic low on this pin enables serial interface communication.                                                                                                                                                                                                       |  |  |

| nSLEEP      | 23               | 23           | I                   | Driver nSLEEP. When this pin is logic low, the device goes into a low-power sleep mode. A 20 to 40-µs low pulse can be used to reset fault conditions without entering sleep mode.                                                                                                        |  |  |

| OCP/SR      | _                | 35           | I                   | OCP level and Synchronous Rectification (Active Demagnetization) setting. This pin is a 4-level input pin set by an external resistor.                                                                                                                                                    |  |  |

| OUTA        | 13, 14           | 13, 14       | PWR O               | Half bridge output A                                                                                                                                                                                                                                                                      |  |  |

| OUTB        | 16, 17           | 16, 17       | PWR O               | Half bridge output B                                                                                                                                                                                                                                                                      |  |  |

| OUTC        | 19, 20           | 19, 20       | PWR O               | Half bridge output C                                                                                                                                                                                                                                                                      |  |  |

| PGND        | 12, 15, 18       | 12, 15, 18   | GND                 | Device power ground. Refer セクション 11.1 for connections recommendation.                                                                                                                                                                                                                     |  |  |

| SCLK        | 35               | _            | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin (SPI devices).                                                                                                                                                       |  |  |

| SDI         | 34               | _            | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin (SPI devices).                                                                                                                                                                                                    |  |  |

| SDO         | 33               | _            | 0                   | Serial data output. Data is shifted out on the rising edge of the SCLK pin. This pin requires an external pullup resistor (SPI devices).                                                                                                                                                  |  |  |

| SLEW        | _                | 34           | I                   | Slew rate control setting. This pin is a 4-level input pin set by an external resistor.                                                                                                                                                                                                   |  |  |

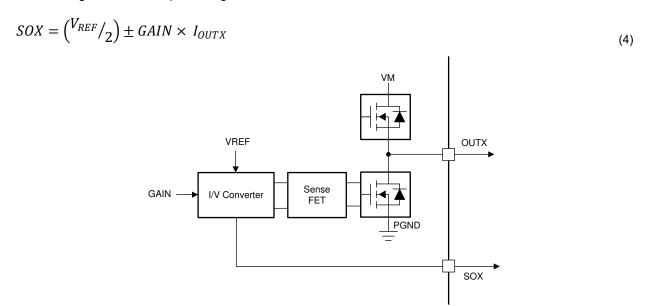

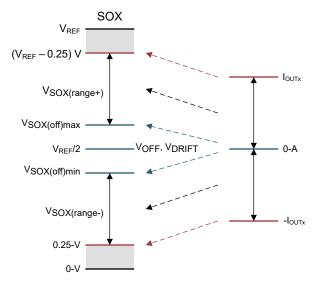

| SOA         | 40               | 40           | 0                   | Current sense amplifier output. Supports capacitive load or low pass filter (resistor in series and capacitor to GND)                                                                                                                                                                     |  |  |

| SOB         | 39               | 39           | 0                   | Current sense amplifier output. Supports capacitive load or low pass filter (resistor in series and capacitor to GND)                                                                                                                                                                     |  |  |

| soc         | 38               | 38           | 0                   | Current sense amplifier output. Supports capacitive load or low pass filter (resistor in series and capacitor to GND)                                                                                                                                                                     |  |  |

| SW_BK       | 5                | 5            | PWR O               | Buck switch node. Connect this pin to an inductor or resistor.                                                                                                                                                                                                                            |  |  |

| VM          | 9, 10, 11        | 9, 10, 11    | PWR I               | Power supply. Connect to motor supply voltage; bypass to PGND with two 0.1- $\mu\text{F}$ capacitors (for each pin) plus one bulk capacitor rated for VM. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the device.                             |  |  |

| VSEL_BK     | _                | 24           | I                   | Buck output voltage setting. This pin is a 4-level input pin set by an external resistor.                                                                                                                                                                                                 |  |  |

| VREF/ILIM   | 37               | 37           | PWR/I               | VREF in PWM Mode 1 and Mode 3: Current sense amplifier power supply input and reference. Connect a X5R or X7R, 0.1-µF, 6.3-V ceramic capacitor between the VREF and AGND pins.  ILIM in PWM Mode 2 and Mode 4: Sets the threshold for phase current used in cycle by cycle current limit. |  |  |

| Thermal pad |                  |              | GND                 | Must be connected to analog ground.                                                                                                                                                                                                                                                       |  |  |

|             |                  | 1            | I.                  | 1                                                                                                                                                                                                                                                                                         |  |  |

<sup>(1)</sup> I = input, O = output, GND = ground pin, PWR = power, NC = no connect

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)(1)

|                                                                       | MIN  | MAX                  | UNIT |

|-----------------------------------------------------------------------|------|----------------------|------|

| Power supply pin voltage (VM)                                         | -0.3 | 40                   | V    |

| Power supply voltage ramp (VM)                                        |      | 4                    | V/µs |

| Voltage difference between ground pins (GND_BK, PGND, AGND)           | -0.3 | 0.3                  | V    |

| Charge pump voltage (CPH, CP)                                         | -0.3 | V <sub>M</sub> + 6   | V    |

| Charge pump negative switching pin voltage (CPL)                      | -0.3 | V <sub>M</sub> + 0.3 | V    |

| Switching regulator pin voltage (FB_BK)                               | -0.3 | 6                    | V    |

| Switching node pin voltage (SW_BK)                                    | -0.3 | V <sub>M</sub> + 0.3 | V    |

| Analog regulator pin voltage (AVDD)                                   | -0.3 | 4                    | V    |

| Logic pin input voltage (DRVOFF, INHx, INLx, nSCS, nSLEEP, SCLK, SDI) | -0.3 | 5.75                 | V    |

| Logic pin output voltage (nFAULT, SDO)                                | -0.3 | 5.75                 | V    |

| Output pin voltage (OUTA, OUTB, OUTC)                                 | -1   | V <sub>M</sub> + 1   | V    |

| Ambient temperature, T <sub>A</sub>                                   | -40  | 125                  | °C   |

| Junction temperature, T <sub>J</sub>                                  | -40  | 150                  | °C   |

| Storage tempertaure, T <sub>stg</sub>                                 | -65  | 150                  | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 7.2 ESD Ratings Auto

|                    |                                                              |                                                                                           |            | VALUE | UNIT |

|--------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------|-------|------|

|                    | Electrostatic                                                | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD Classification Level 2 |            | ±2000 |      |

| V <sub>(ESD)</sub> | (ESD) discharge Charged device model (CDM), per AEC Q100-011 | Corner pins                                                                               | ±750       | V     |      |

|                    |                                                              | CDM ESD Classification Level C4B                                                          | Other pins | ±750  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                      |                                |                                             | MIN  | NOM | MAX  | UNIT |

|----------------------|--------------------------------|---------------------------------------------|------|-----|------|------|

| $V_{VM}$             | Power supply voltage           | V <sub>VM</sub>                             | 4.5  | 24  | 35   | V    |

| f <sub>PWM</sub>     | Output PWM frequency           | OUTA, OUTB, OUTC                            |      |     | 200  | kHz  |

| I <sub>OUT</sub> (1) | Peak output winding current    | OUTA, OUTB, OUTC                            |      |     | 8    | Α    |

| V <sub>IN</sub>      | Logic input voltage            | DRVOFF, INHx, INLx, nSCS, nSLEEP, SCLK, SDI | -0.1 |     | 5.5  | V    |

| V <sub>OD</sub>      | Open drain pullup voltage      | nFAULT, SDO                                 | -0.1 |     | 5.5  | V    |

| V <sub>SDO</sub>     | Push-pull voltage              | SDO                                         | 2.2  |     | 5.5  | V    |

| I <sub>OD</sub>      | Open drain output current      | nFAULT, SDO                                 |      |     | 5    | mA   |

| V <sub>VREF</sub>    | Voltage reference pin voltage  | VREF                                        | 2.8  |     | AVDD | V    |

| T <sub>A</sub>       | Operating ambient temperature  |                                             | -40  |     | 125  | °C   |

| TJ                   | Operating Junction temperature |                                             | -40  |     | 150  | °C   |

(1) Power dissipation and thermal limits must be observed

## 7.4 Thermal Information

|                       |                                              | DRV8316CR-Q1,<br>DRV8316CT-Q1 |      |

|-----------------------|----------------------------------------------|-------------------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | VQFN (RGF)                    | UNIT |

|                       |                                              | 40 Pins                       |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 25.7                          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 15.2                          | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 7.3                           | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2                           | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 7.2                           | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.0                           | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

|                   | PARAMETER                                            | TEST CONDITIONS                                                                                                             | MIN | TYP | MAX   | UNIT |

|-------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------|

| POWER             | SUPPLIES                                             |                                                                                                                             |     |     |       |      |

|                   | VM along woods assument                              | V <sub>VM</sub> > 6 V, nSLEEP = 0, T <sub>A</sub> = 25 °C                                                                   |     | 1.5 | 2.5   | μA   |

| $I_{VMQ}$         | VM sleep mode current                                | nSLEEP = 0                                                                                                                  |     | 2.5 | 5     | μΑ   |

|                   | VM standby made surrent                              | nSLEEP = 1, INHx = INLx = 0, SPI = 'OFF', BUCK_DIS = 1;                                                                     |     | 4   | 10    | mA   |

| I <sub>VMS</sub>  | VM standby mode current<br>(Buck regulator disabled) | V <sub>VM</sub> > 6 V, nSLEEP = 1, INHx = INLx = 0, SPI = 'OFF', T <sub>A</sub> = 25 °C, BUCK_DIS = 1;                      |     | 4   | 5     | mA   |

| I <sub>VMS</sub>  | VM standby mode current                              | V <sub>VM</sub> > 6 V, nSLEEP = 1, INHx = INLx = 0, SPI = 'OFF', I <sub>BK</sub> = 0, T <sub>A</sub> = 25 °C, BUCK_DIS = 0; |     | 5   | 6     | mA   |

|                   | (Buck regulator enabled)                             | nSLEEP = 1, INHx = INLx = 0, SPI = 'OFF', I <sub>BK</sub> = 0, BUCK_DIS = 0;                                                |     | 6   | 10    | mA   |

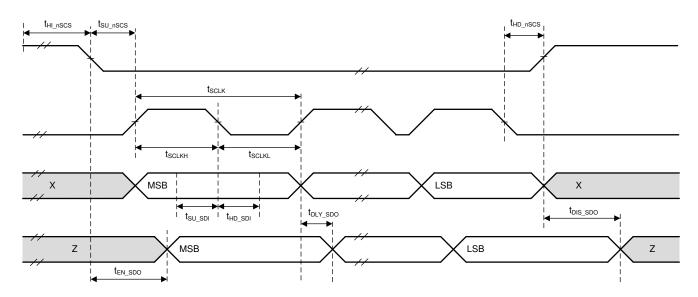

|                   | VM operating mode current (Buck regulator disabled)  | V <sub>VM</sub> > 6 V, nSLEEP = 1, f <sub>PWM</sub> = 25 kHz,<br>T <sub>A</sub> = 25 °C, BUCK_DIS = 1                       |     | 10  | 13    | mA   |

|                   |                                                      | V <sub>VM</sub> > 6 V, nSLEEP = 1, f <sub>PWM</sub> = 200 kHz,<br>T <sub>A</sub> = 25 °C, BUCK_DIS = 1                      |     | 18  | 21    | mA   |

| I <sub>VM</sub>   |                                                      | nSLEEP =1, f <sub>PWM</sub> = 25 kHz, BUCK_DIS<br>= 1                                                                       |     | 11  | 16    | mA   |

|                   |                                                      | nSLEEP =1, f <sub>PWM</sub> = 200 kHz,<br>BUCK_DIS = 1                                                                      |     | 17  | 25    | mA   |

|                   |                                                      | $V_{VM} > 6$ V, $nSLEEP = 1$ , $f_{PWM} = 25$ kHz,<br>$T_A = 25$ °C, $BUCK\_DIS = 0$ ; $BUCK\_PS\_DIS = 0$                  |     | 11  | 13    | mA   |

| $I_{VM}$          | VM operating mode current (Buck regulator enabled)   | $V_{VM} > 6$ V, $nSLEEP = 1$ , $f_{PWM} = 200$ kHz, $T_A = 25$ °C, $BUCK\_DIS = 0$ ; $BUCK\_PS\_DIS = 0$                    |     | 19  | 22    | mA   |

|                   |                                                      | nSLEEP =1, f <sub>PWM</sub> = 25 kHz, BUCK_DIS<br>= 0; BUCK_PS_DIS = 0                                                      |     | 12  | 17    | mA   |

|                   |                                                      | nSLEEP =1, f <sub>PWM</sub> = 200 kHz,<br>BUCK_DIS = 0; BUCK_PS_DIS = 0                                                     |     | 18  | 27    | mA   |

| V <sub>AVDD</sub> | Analog regulator voltage                             | 0 mA $\leq$ I <sub>AVDD</sub> $\leq$ 30 mA; BUCK_PS_DIS = 0                                                                 | 3.1 | 3.3 | 3.465 | ٧    |

| I <sub>AVDD</sub> | External analog regulator load                       |                                                                                                                             |     |     | 30    | mA   |

| V <sub>VCP</sub>  | Charge pump regulator voltage                        | VCP with respect to VM                                                                                                      | 3.6 | 4.7 | 5.25  | V    |

|                    | PARAMETER                                                                                     | TEST CONDITIONS                                                                                                                              | MIN             | TYP                                                             | MAX | UNIT |

|--------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------|-----|------|

| t <sub>WAKE</sub>  | Wakeup time                                                                                   | V <sub>VM</sub> > V <sub>UVLO</sub> , nSLEEP = 1 to outputs ready and nFAULT released                                                        |                 |                                                                 | 1   | ms   |

| t <sub>SLEEP</sub> | Sleep Pulse time                                                                              | nSLEEP = 0 period to enter sleep mode                                                                                                        | 120             |                                                                 |     | μs   |

| t <sub>RST</sub>   | Reset Pulse time                                                                              | nSLEEP = 0 period to reset faults                                                                                                            | 20              |                                                                 | 40  | μs   |

| BUCK RE            | GULATOR                                                                                       |                                                                                                                                              |                 |                                                                 |     |      |

|                    |                                                                                               | $V_{VM} > 6 \text{ V, 0 mA} \le I_{BK} \le 200 \text{ mA,}$<br>BUCK_SEL = 00b                                                                | 3.1             | 3.3                                                             | 3.5 | V    |

|                    |                                                                                               | $V_{VM} > 6 \text{ V, 0 mA} \le I_{BK} \le 200 \text{ mA,}$<br>BUCK_SEL = 01b                                                                | 4.6             | 5.0                                                             | 5.4 | V    |

| $V_{BK}$           | Buck regulator average voltage ( $L_{BK}$ = 47 $\mu$ H, $C_{BK}$ = 22 $\mu$ F)                | $V_{VM} > 6 \text{ V}, 0 \text{ mA} \le I_{BK} \le 200 \text{ mA},$<br>BUCK_SEL = 10b                                                        | 3.7             | 4.0                                                             | 4.3 | V    |

|                    | (SPI Device)                                                                                  | $V_{VM} > 6.7 \text{ V}, 0 \text{ mA} \le I_{BK} \le 200 \text{ mA},$<br>BUCK_SEL = 11b                                                      | 5.2             | 5.7                                                             | 5.8 | V    |

|                    |                                                                                               | $V_{VM} < 6.0 \text{ V (BUCK\_SEL} = 00b, 01b, 10b) or V_{VM} < 6.0 \text{ V (BUCK\_SEL} = 11b), 0 \text{ mA} \le I_{BK} \le 200 \text{ mA}$ | Ι <sub>Β</sub>  | V <sub>VM</sub> -<br>K*(R <sub>LBK</sub> +<br>2) <sup>(1)</sup> |     | V    |

| V <sub>BK</sub>    |                                                                                               | $V_{VM} > 6 \text{ V}, 0 \text{ mA} \le I_{BK} \le 50 \text{ mA},$<br>BUCK_SEL = 00b                                                         | 3.1             | 3.3                                                             | 3.5 | V    |

|                    | Buck regulator average voltage ( $L_{BK}$ = 22 $\mu$ H, $C_{BK}$ = 22 $\mu$ F) (SPI Device)   | $V_{VM} > 6 \text{ V, 0 mA} \le I_{BK} \le 50 \text{ mA},$<br>BUCK_SEL = 01b                                                                 | 4.6             | 5.0                                                             | 5.4 | V    |

|                    |                                                                                               | $V_{VM} > 6 \text{ V}, 0 \text{ mA} \le I_{BK} \le 50 \text{ mA},$<br>BUCK_SEL = 10b                                                         | 3.7             | 4.0                                                             | 4.3 | V    |

|                    |                                                                                               | $V_{VM} > 6.7 \text{ V}, 0 \text{ mA} \le I_{BK} \le 50 \text{ mA}, \\ BUCK\_SEL = 11b$                                                      | 5.2             | 5.7                                                             | 5.8 | V    |

|                    |                                                                                               | $V_{VM}$ < 6.0 V (BUCK_SEL = 00b, 01b, 10b) or $V_{VM}$ < 6.0 V (BUCK_SEL = 11b), 0 mA $\leq$ I <sub>BK</sub> $\leq$ 50 mA                   | Ι <sub>Β</sub>  | V <sub>VM</sub> -<br>K*(R <sub>LBK</sub> +<br>2) (1)            |     | V    |

|                    |                                                                                               | $V_{VM} > 6 \text{ V}, 0 \text{ mA} \le I_{BK} \le 40 \text{ mA},$<br>BUCK_SEL = 00b                                                         | 3.1             | 3.3                                                             | 3.5 | V    |

|                    |                                                                                               | $V_{VM} > 6 \text{ V}, 0 \text{ mA} \le I_{BK} \le 40 \text{ mA},$<br>BUCK_SEL = 01b                                                         | 4.6             | 5.0                                                             | 5.4 | V    |

| $V_{BK}$           | Buck regulator average voltage ( $R_{BK}$ = 22 $\Omega$ , $C_{BK}$ = 22 $\mu$ F)              | $V_{VM} > 6 \text{ V}, 0 \text{ mA} \le I_{BK} \le 40 \text{ mA},$<br>BUCK_SEL = 10b                                                         | 3.7             | 4.0                                                             | 4.3 | V    |

|                    | (SPI Device)                                                                                  | $V_{VM} > 6.7 \text{ V}, 0 \text{ mA} \le I_{BK} \le 40 \text{ mA},$<br>BUCK_SEL = 11b                                                       | 5.2             | 5.7                                                             | 5.8 | V    |

|                    |                                                                                               | $V_{VM}$ < 6.0 V (BUCK_SEL = 00b, 01b, 10b) or $V_{VM}$ < 6.0 V (BUCK_SEL = 11b), 0 mA $\leq$ I <sub>BK</sub> $\leq$ 40 mA                   | I <sub>BI</sub> | V <sub>VM</sub> -<br><*(R <sub>BK</sub> +2                      |     | V    |

|                    |                                                                                               | V <sub>VM</sub> > 6 V, 0 mA ≤ I <sub>BK</sub> ≤ 200 mA,<br>VSEL_BK pin tied to AGND                                                          | 3.1             | 3.3                                                             | 3.5 | V    |

|                    |                                                                                               | $V_{VM} > 6 \text{ V}, 0 \text{ mA} \le I_{BK} \le 200 \text{ mA}, VSEL_BK pin to Hi-Z}$                                                     | 4.6             | 5.0                                                             | 5.4 | V    |

| $V_{BK}$           | Buck regulator average voltage (L <sub>BK</sub> = 47 μH, C <sub>BK</sub> = 22 μF) (HW Device) | $V_{VM}$ > 6 V, 0 mA ≤ $I_{BK}$ ≤ 200 mA, VSEL_BK pin to 47 kΩ +/- 5% tied to AVDD                                                           | 3.7             | 4.0                                                             | 4.3 | V    |

|                    | ,                                                                                             | $V_{VM} > 6.7 \text{ V}, 0 \text{ mA} \le I_{BK} \le 200 \text{ mA},$<br>VSEL_BK pin tied to AVDD                                            | 5.2             | 5.7                                                             | 5.8 | V    |

|                    |                                                                                               | V <sub>VM</sub> < 6.0 V, 0 mA ≤ I <sub>BK</sub> ≤ 200 mA                                                                                     | Ι <sub>Β</sub>  | V <sub>VM</sub> -<br>K*(R <sub>LBK</sub> +<br>2) <sup>(1)</sup> |     | V    |

|                     | PARAMETER                                                                                     | TEST CONDITIONS                                                                                                                                | MIN  | TYP                                            | MAX                        | UNIT |

|---------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------|----------------------------|------|

|                     |                                                                                               | V <sub>VM</sub> > 6 V, 0 mA ≤ I <sub>BK</sub> ≤ 50 mA,<br>VSEL_BK pin tied to AGND                                                             | 3.1  | 3.3                                            | 3.5                        | V    |

|                     |                                                                                               | $V_{VM} > 6 \text{ V}, 0 \text{ mA} \le I_{BK} \le 50$<br>mA, VSEL_BK pin to Hi-Z                                                              | 4.6  | 5.0                                            | 5.4                        | V    |

| √ <sub>BK</sub>     | Buck regulator average voltage (L <sub>BK</sub> = 22 μH, C <sub>BK</sub> = 22 μF) (HW Device) | $V_{VM}$ > 6 V, 0 mA $\leq$ I <sub>BK</sub> $\leq$ 50 mA, VSEL_BK pin to 47 k $\Omega$ +/- 5% tied to AVDD                                     | 3.7  | 4.0                                            | 4.3                        | V    |

|                     | (in Dense)                                                                                    | $V_{VM}$ > 6.7 V, 0 mA $\leq$ I <sub>BK</sub> $\leq$ 50 mA, VSEL_BK pin tied to AVDD                                                           | 5.2  | 5.7                                            | 5.8                        | V    |

|                     |                                                                                               | V <sub>VM</sub> < 6.0 V, 0 mA ≤ I <sub>BK</sub> ≤ 50 mA                                                                                        |      | $V_{VM}^{-}$ $I_{BK}^{*}(R_{LBK}^{+}+2)^{(1)}$ |                            | V    |

|                     |                                                                                               | V <sub>VM</sub> > 6 V, 0 mA ≤ I <sub>BK</sub> ≤ 40 mA,<br>VSEL_BK pin tied to AGND                                                             | 3.1  | 3.3                                            | 3.5                        | V    |

|                     |                                                                                               | $V_{VM} > 6 \text{ V}, 0 \text{ mA} \le I_{BK} \le 40$<br>mA, VSEL_BK pin to Hi-Z                                                              | 4.6  | 5.0                                            | 5.4                        | V    |

| V <sub>BK</sub>     | Buck regulator average voltage ( $R_{BK}$ = 22 $\Omega$ , $C_{BK}$ = 22 $\mu$ F) (HW Device)  | $V_{VM}$ > 6 V, 0 mA $\leq$ I <sub>BK</sub> $\leq$ 40 mA, VSEL_BK pin to 47 k $\Omega$ +/- 5% tied to AVDD                                     | 3.7  | 4.0                                            | 4.3                        | V    |

|                     |                                                                                               | $V_{VM} > 6.7 \text{ V}, 0 \text{ mA} \le I_{BK} \le 40 \text{ mA},$ VSEL_BK pin tied to AVDD                                                  | 5.2  | 5.7                                            | 5.8                        | V    |

|                     |                                                                                               | V <sub>VM</sub> < 6.0 V, 0 mA ≤ I <sub>BK</sub> ≤ 40 mA                                                                                        |      | $V_{VM}-I_{BK}^*(R_{BK}+2)$                    |                            | V    |

|                     | Buck regulator ripple voltage                                                                 | $V_{VM}$ > 6 V, 0 mA $\leq$ I <sub>BK</sub> $\leq$ 200 mA, Buck regulator with inductor, L <sub>BK</sub> = 47 uH, C <sub>BK</sub> = 22 $\mu$ F | -100 |                                                | 100                        | mV   |

| V <sub>BK_RIP</sub> |                                                                                               | $V_{VM}$ > 6 V, 0 mA $\leq$ I <sub>BK</sub> $\leq$ 50 mA, Buck regulator with inductor, L <sub>BK</sub> = 22 uH, C <sub>BK</sub> = 22 $\mu$ F  | -100 |                                                | 100                        | mV   |

|                     |                                                                                               | $V_{VM}$ > 6 V, 0 mA ≤ $I_{BK}$ ≤ 50 mA, Buck regulator with resistor; $R_{BK}$ = 22 $\Omega$ , $C_{BK}$ = 22 $\mu$ F                          | -100 |                                                | 100                        | mV   |

|                     |                                                                                               | L <sub>BK</sub> = 47 uH, C <sub>BK</sub> = 22 μF,<br>BUCK_PS_DIS = 1b                                                                          |      |                                                | 200                        | mA   |

|                     |                                                                                               | L <sub>BK</sub> = 47 uH, C <sub>BK</sub> = 22 μF,<br>BUCK_PS_DIS = 0b                                                                          |      |                                                | 200 –<br>I <sub>AVDD</sub> | mA   |

| L                   | External buck regulator load                                                                  | L <sub>BK</sub> = 22 uH, C <sub>BK</sub> = 22 μF, BUCK_PS_DIS = 1b                                                                             |      |                                                | 50                         | mA   |

| Івк                 | External puck regulator load                                                                  | L <sub>BK</sub> = 22 μH, C <sub>BK</sub> = 22 μF,<br>BUCK_PS_DIS = 0b                                                                          |      |                                                | 50 –<br>I <sub>AVDD</sub>  | mA   |

|                     |                                                                                               | $R_{BK}$ = 22 $\Omega$ , $C_{BK}$ = 22 $\mu$ F, BUCK_PS_DIS = 1b                                                                               |      |                                                | 40                         | mA   |

|                     |                                                                                               | $R_{BK}$ = 22 $\Omega$ , $C_{BK}$ = 22 $\mu$ F, BUCK_PS_DIS = 0b                                                                               |      |                                                | 40 –<br>I <sub>AVDD</sub>  | mA   |

| FOW D'              | Buck regulator switching frequency                                                            | Regulation Mode                                                                                                                                | 20   |                                                | 535                        | kHz  |

| f <sub>SW_BK</sub>  | 2 2 3 K Togalator Switching Hoquelley                                                         | Linear Mode                                                                                                                                    | 20   |                                                | 535                        | kHz  |

| , ,, ,                 | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | otherwise noted). Typical limits apply for TEST CONDITIONS            | MIN | TYP | MAX  | UNIT |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|-----|------|------|

|                        | TAKAMETEK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>BK</sub> rising, BUCK_SEL = 00b                                | 2.7 | 2.8 | 2.9  | V    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>BK</sub> falling, BUCK_SEL = 00b                               | 2.7 | 2.6 | 2.9  | V    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                       |     |     |      |      |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>BK</sub> rising, BUCK_SEL = 01b                                | 4.2 | 4.4 | 4.55 | V    |

| V <sub>BK_UV</sub>     | Buck regulator undervoltage lockout (SPI Device)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>BK</sub> falling, BUCK_SEL = 01b                               | 4.0 | 4.2 | 4.35 | V    |

|                        | (SFI Device)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>BK</sub> rising, BUCK_SEL = 10b                                | 2.7 | 2.8 | 2.9  | V    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>BK</sub> falling, BUCK_SEL = 10b                               | 2.5 | 2.6 | 2.7  | V    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>BK</sub> rising, BUCK_SEL = 11b                                | 4.2 | 4.4 | 4.55 | V    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>BK</sub> falling, BUCK_SEL = 11b                               | 4   | 4.2 | 4.35 | V    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>BK</sub> rising, VSEL_BK pin tied to AGND                      | 2.7 | 2.8 | 2.9  | V    |

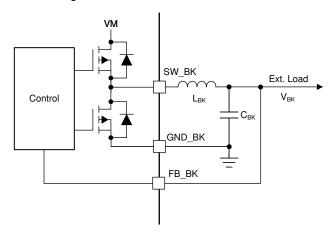

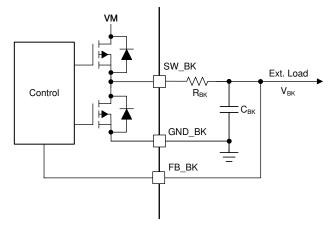

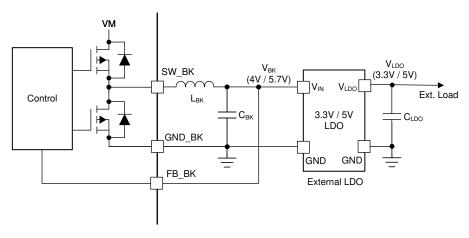

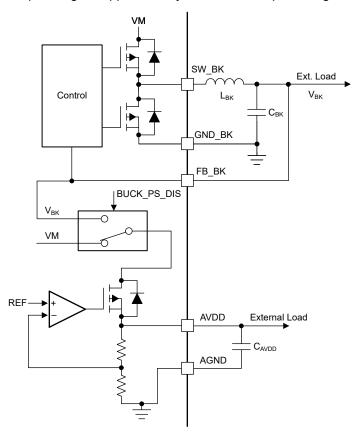

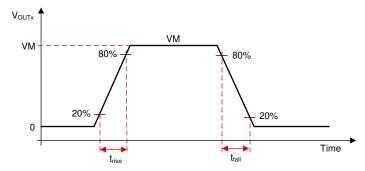

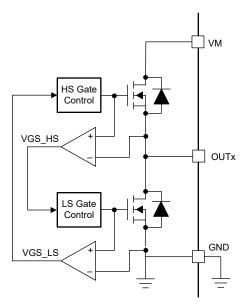

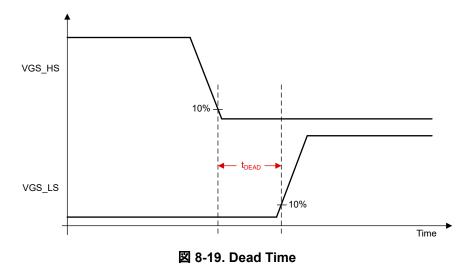

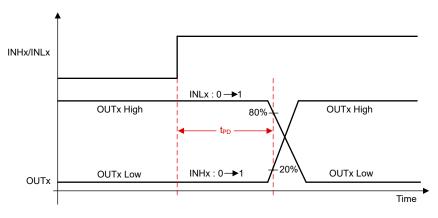

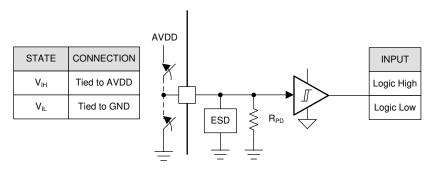

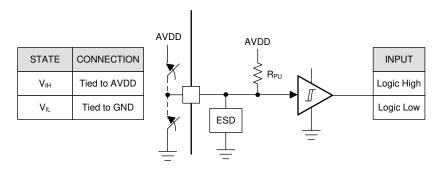

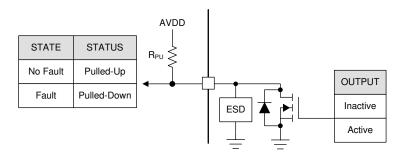

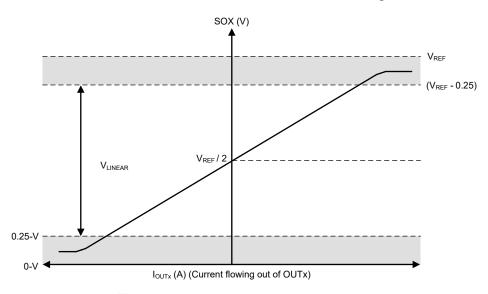

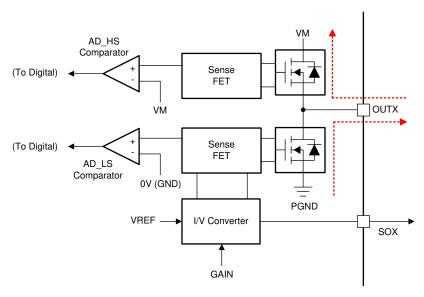

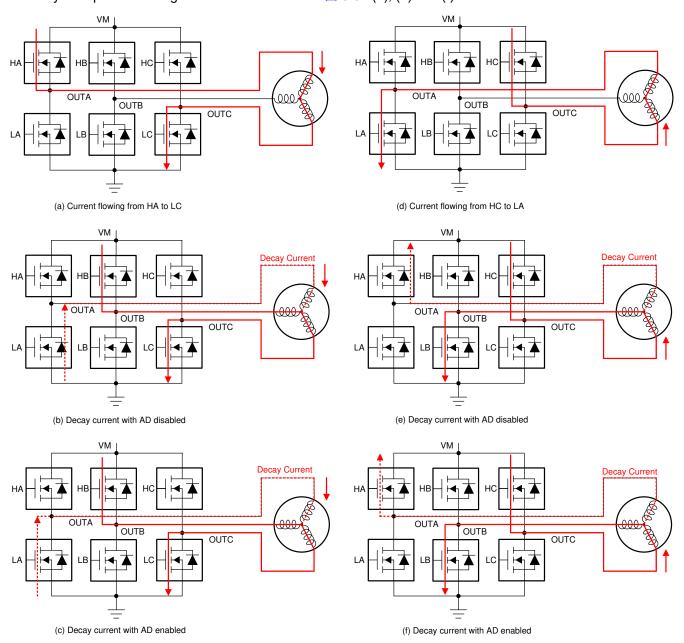

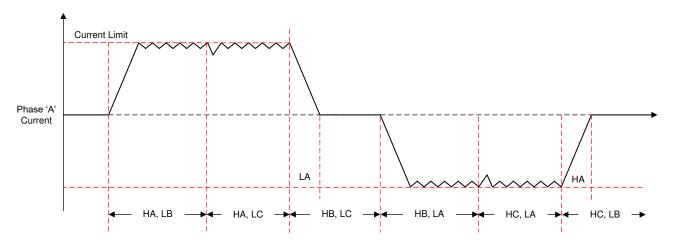

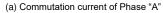

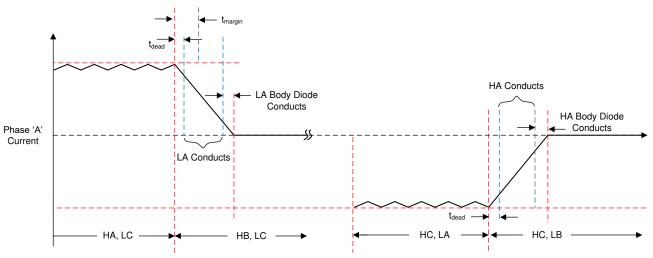

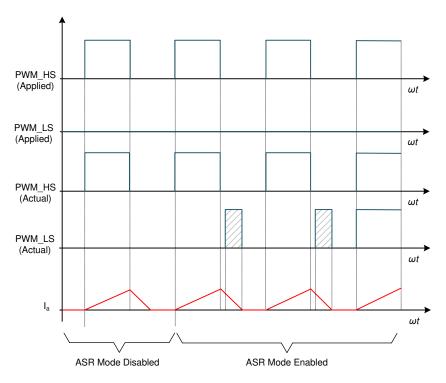

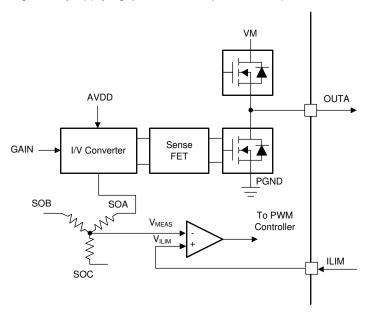

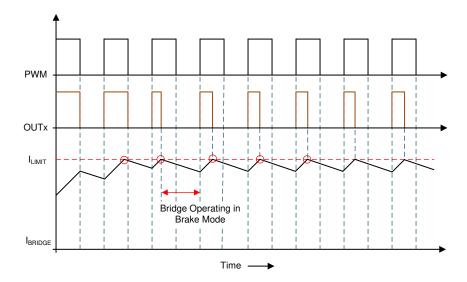

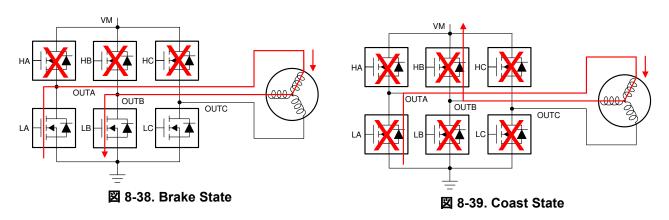

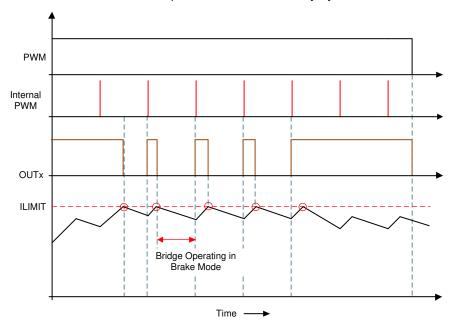

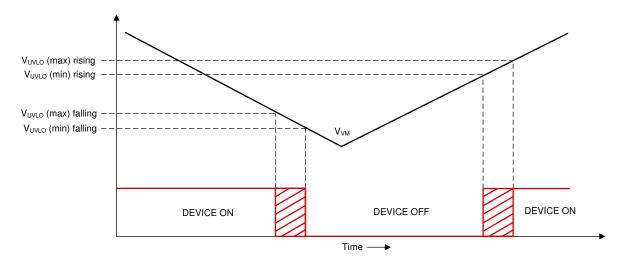

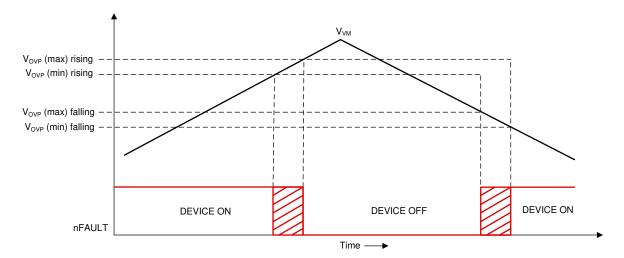

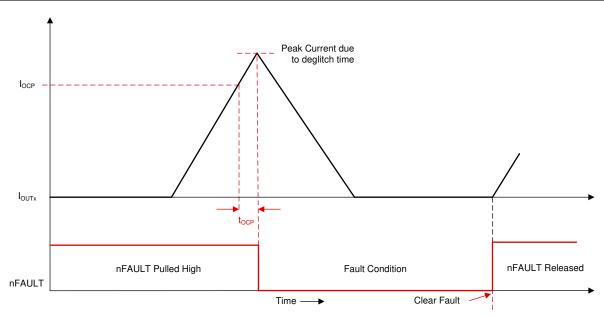

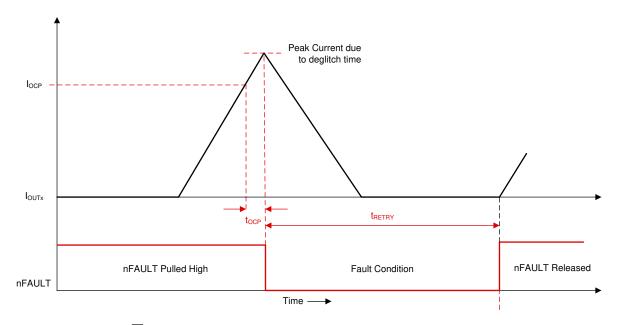

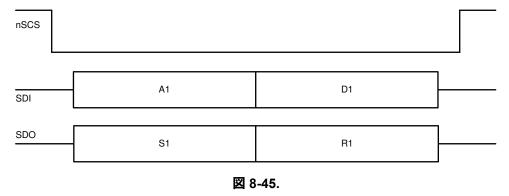

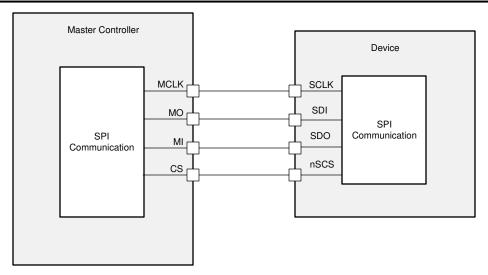

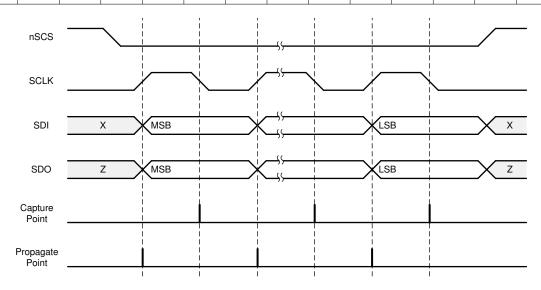

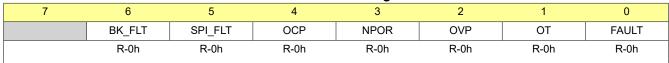

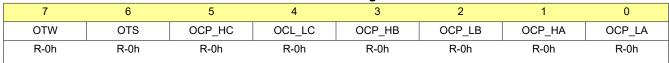

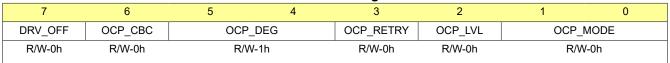

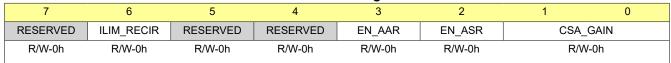

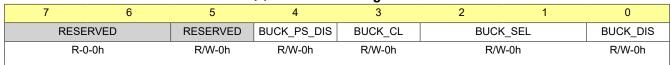

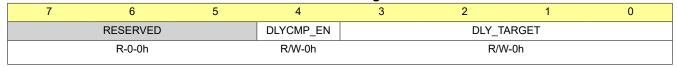

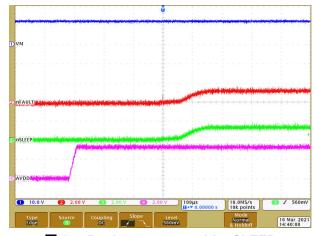

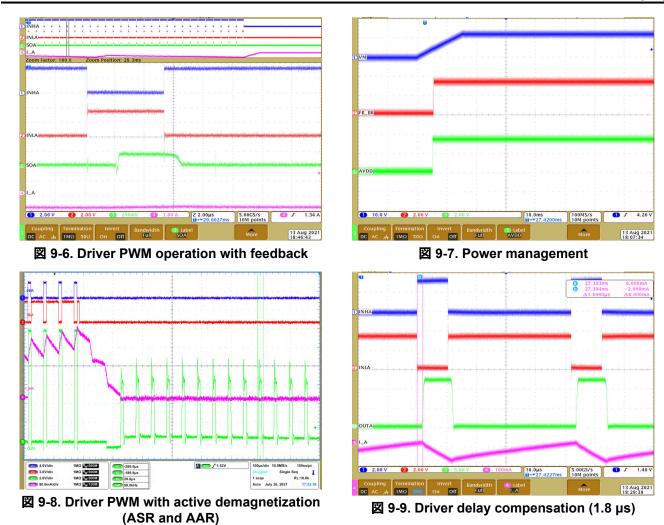

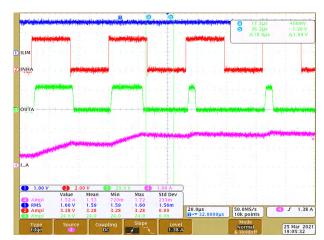

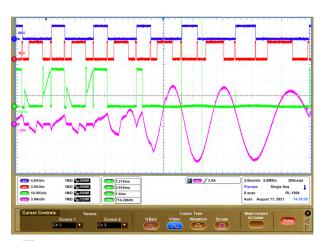

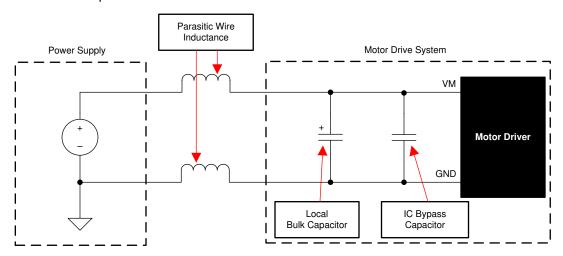

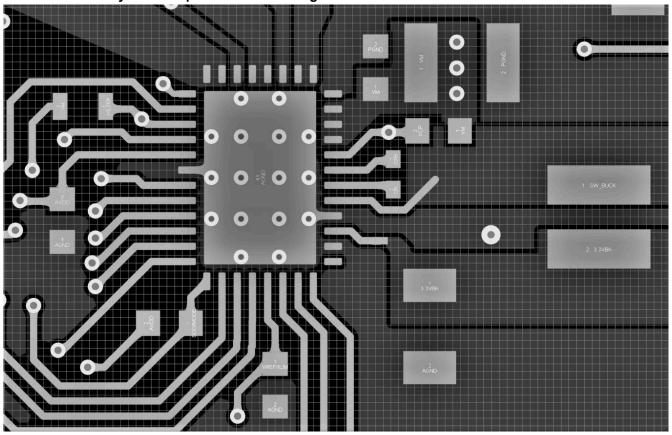

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>BK</sub> falling, VSEL_BK pin tied to AGND                     | 2.5 | 2.6 | 2.7  | V    |