# DRV8363-Q1 48V バッテリ、3相スマートゲートドライバ、高精度電流センシング機能および高度監視機能を搭載

## 1 特長

- 車載アプリケーション向けの AEC-Q100 テスト ガイダンス

- デバイスの周囲温度:  $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$

- 3相ハーフブリッジ ゲートドライバ

- 6個のNチャネル MOSFET (NMOS) を駆動

- 8 ~ 85V の広い動作電圧範囲

- ハイサイド ゲートドライバのブートストラップ アーキテクチャ

- 400nC の MOSFET を 20kHz で駆動可能な 50mA の平均ゲートスイッチング電流をサポート

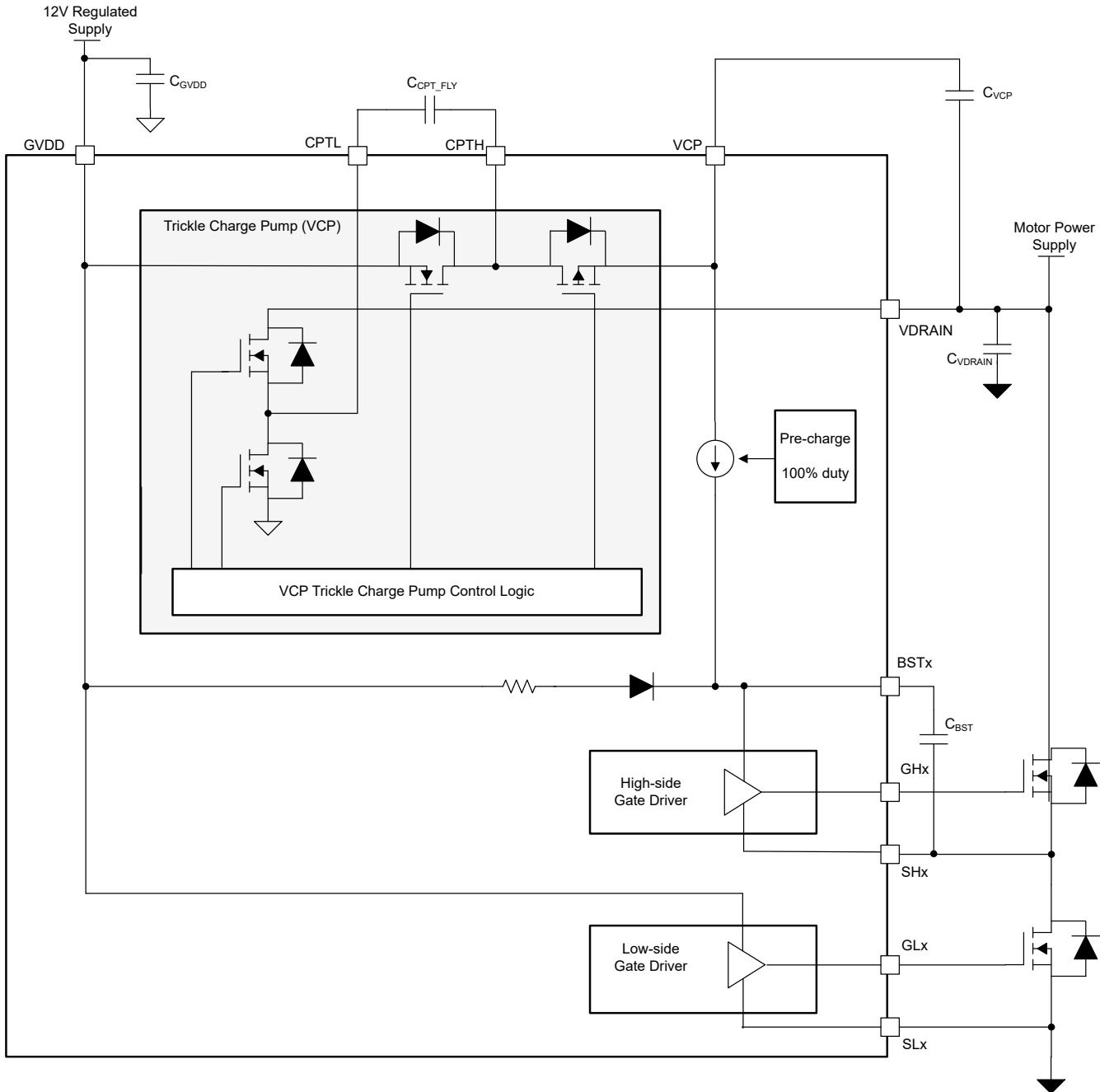

- トリクル チャージ ポンプにより 100% の PWM デューティサイクルをサポートし、外付けの遮断 / 逆極性保護回路を駆動するためのオーバードライブ電源を生成

- スマートゲートドライブ アーキテクチャ

- 15 レベルで構成可能な最大 1000 / 2000mA (ソース / シンク) のピーク ゲートドライブ電流

- ゲートソース電圧監視に基づく閉ループの自動デッドタイム挿入

- 構成可能なソフトシャットダウンにより、過電流シャットダウン時の誘導性電圧スパイクを最小化

- ローサイド電流検出アンプ

- 全温度範囲にわたって 1mV の低入力オフセット

- 4 レベルの可変ゲイン

- 単方向または双方向のセンシングをサポートする調整可能な出力バイアス

- SPI ベースの詳細な構成と診断

- ドライバを個別にディセーブルする DRVOFF ピン

- 高電圧ウェークアップ ピン (nSLEEP)

- モーター ブレーキを制御するための専用 ASCIN ピン (アクティブ短絡回路)

- 6x, 3x, 1x、および独立 PWM モード

- 3.3V および 5V のロジック入力をサポート

- 統合保護機能

- バッテリおよび電源電圧モニタ

- MOSFET  $V_{DS}$  および  $R_{sense}$  過電流監視

- MOSFET  $V_{GS}$  ゲート フォルト監視

- デバイス熱警告とシャットダウン

- フォルト状態インジケータ ピン

## 2 アプリケーション

- 48V の車載用モータ制御アプリケーション

- 燃料、水、油のポンプ

- 車載用のファンとブロワー

- 車載各種ボディ用モーター

- トランスマッジョン アクチュエータ

- 車載用 BLDC および PMSM モーター

- E モビリティ、電動アシスト自転車、電動スクーター

## 3 説明

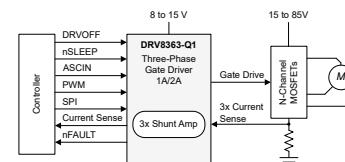

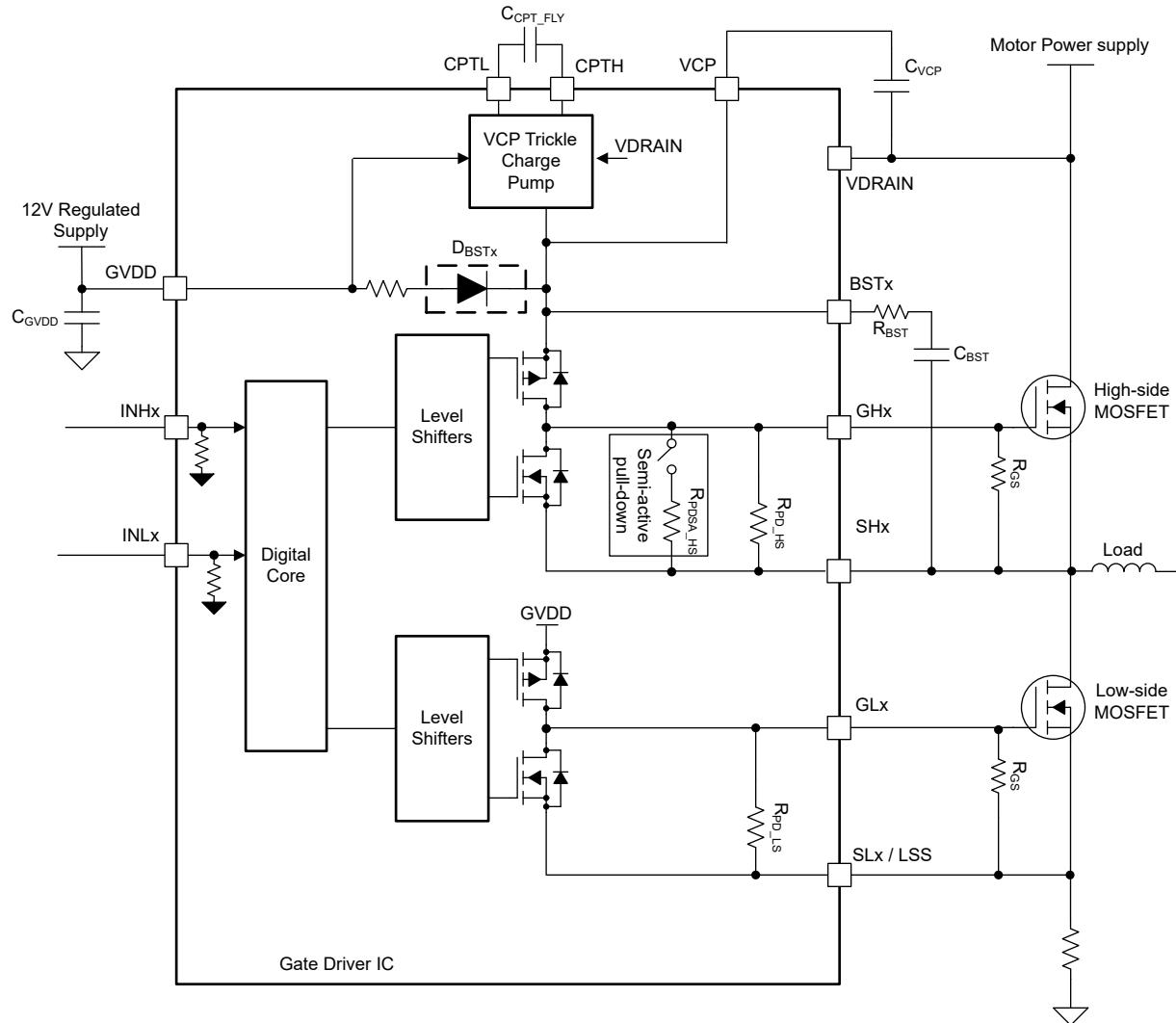

DRV8363-Q1 は、48V の車載用 3相 BLDC アプリケーション向けの統合スマートゲートドライバです。このデバイスには、3つのハーフブリッジ ゲートドライバがあり、それぞれがハイサイドとローサイドの Nチャネル パワー MOSFET を駆動できます。DRV8363-Q1 は、外付け 12V 電源と統合ブートストラップダイオードを使ってハイサイド MOSFET のために適切なゲート駆動電圧を生成します。スマートゲートドライブのアーキテクチャは、16mA から最大でソース 1A、シンク 2A までの構成可能なピークゲート駆動電流をサポートします。DRV8363-Q1 は、モーター接続時に 8V ~ 85V と広い電源電圧範囲で動作します。トリクルチャージポンプにより、ゲートドライバは 100% の PWM デューティサイクル制御をサポートし、外部スイッチのオーバードライブゲート駆動電圧を供給します。

DRV8363-Q1 は、抵抗によるローサイド電流検出をサポートする、ローサイド電流検出アンプを備えています。アンプのオフセットが低いため、システムは正確なモーター電流測定を行うことができます。

DRV8363-Q1 に内蔵されている広範な診断機能と保護機能により、堅牢なモーター駆動システムの設計が可能になります。外部コンポーネントの必要性がなくなります。高度に構成可能なデバイス応答により、このデバイスは、さまざまなシステム設計にシームレスに組み込むことができます。

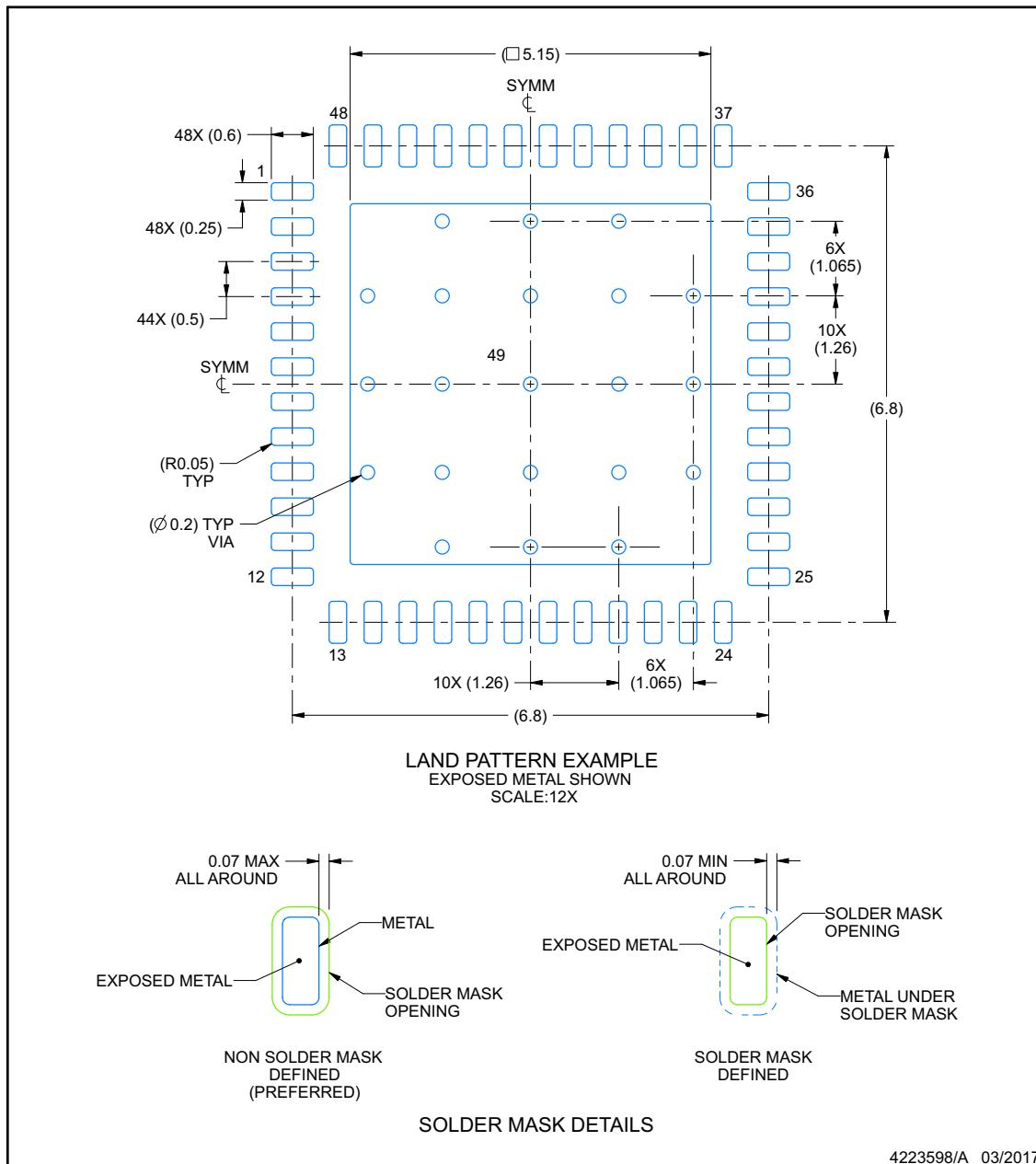

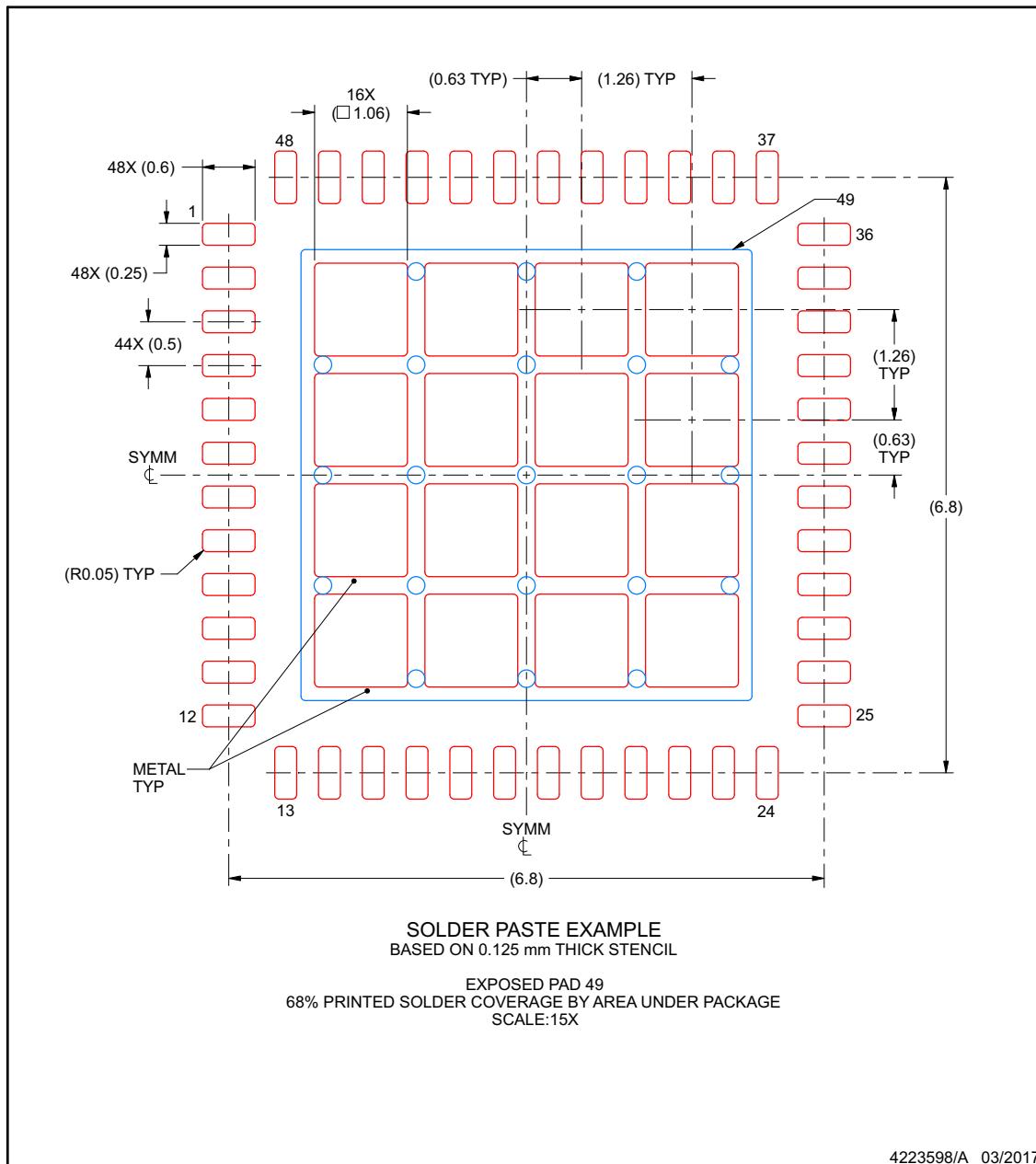

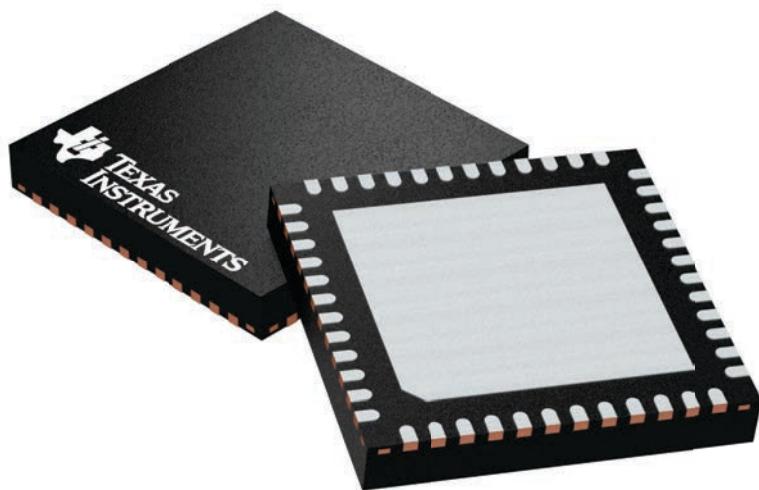

### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ(公称) <sup>(2)</sup> |

|------------|----------------------|------------------------------|

| DRV8363-Q1 | QFN (48)             | 7mm × 7mm                    |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ(長さ × 幅)は公称値であり、該当する場合はピンを含みます。

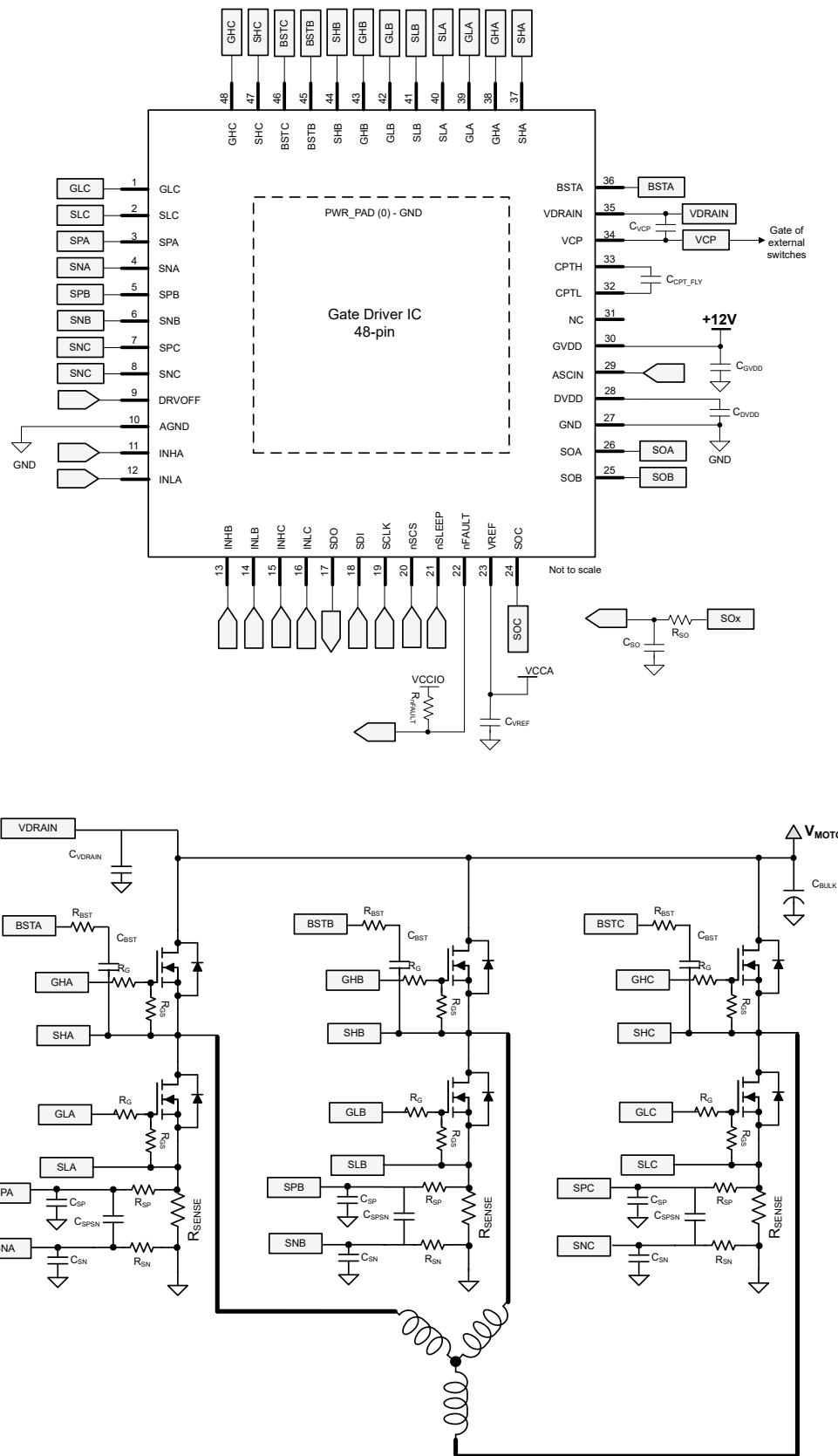

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                |           |                               |           |

|--------------------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>                    | <b>1</b>  | 6.6 プログラミング                   | <b>50</b> |

| <b>2 アプリケーション</b>              | <b>1</b>  | 6.7 レジスタ マップ                  | <b>52</b> |

| <b>3 説明</b>                    | <b>1</b>  | <b>7 アプリケーションと実装</b>          | <b>84</b> |

| <b>4 ピン機能 48 ピン DRV8363-Q1</b> | <b>3</b>  | 7.1 アプリケーション情報                | <b>84</b> |

| <b>5 仕様</b>                    | <b>6</b>  | 7.2 代表的なアプリケーション              | <b>84</b> |

| 5.1 絶対最大定格                     | 6         | 7.3 レイアウト                     | <b>87</b> |

| 5.2 推奨動作条件                     | 7         | <b>8 デバイスおよびドキュメントのサポート</b>   | <b>89</b> |

| 5.3 熱に関する情報 (1pkg)             | 7         | 8.1 ドキュメントのサポート               | <b>89</b> |

| 5.4 電気的特性                      | 8         | 8.2 ドキュメントの更新通知を受け取る方法        | <b>89</b> |

| 5.5 SPI のタイミング要件               | 20        | 8.3 サポートリソース                  | <b>89</b> |

| 5.6 SPI のタイミング図                | 20        | 8.4 商標                        | <b>89</b> |

| <b>6 詳細説明</b>                  | <b>21</b> | 8.5 静電気放電に関する注意事項             | <b>89</b> |

| 6.1 概要                         | 21        | 8.6 用語集                       | <b>89</b> |

| 6.2 機能ブロック図                    | 22        | <b>9 改訂履歴</b>                 | <b>89</b> |

| 6.3 機能説明                       | 23        | <b>10 メカニカル、パッケージ、および注文情報</b> | <b>90</b> |

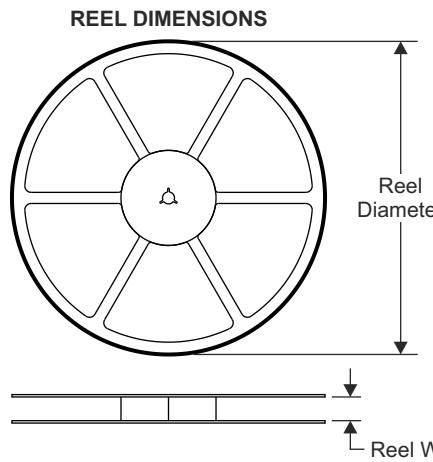

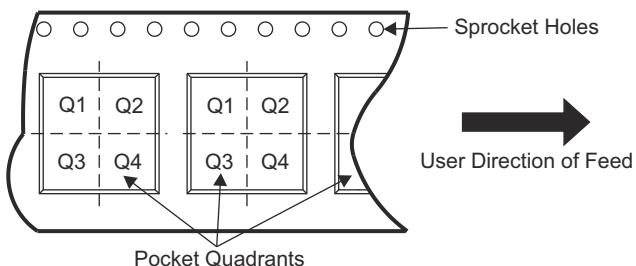

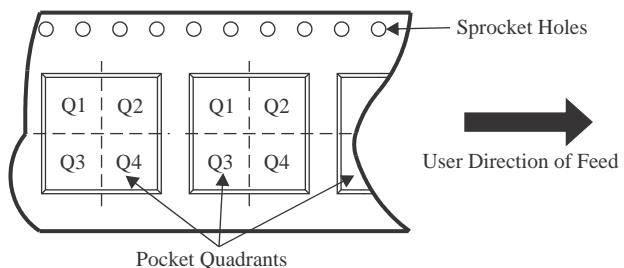

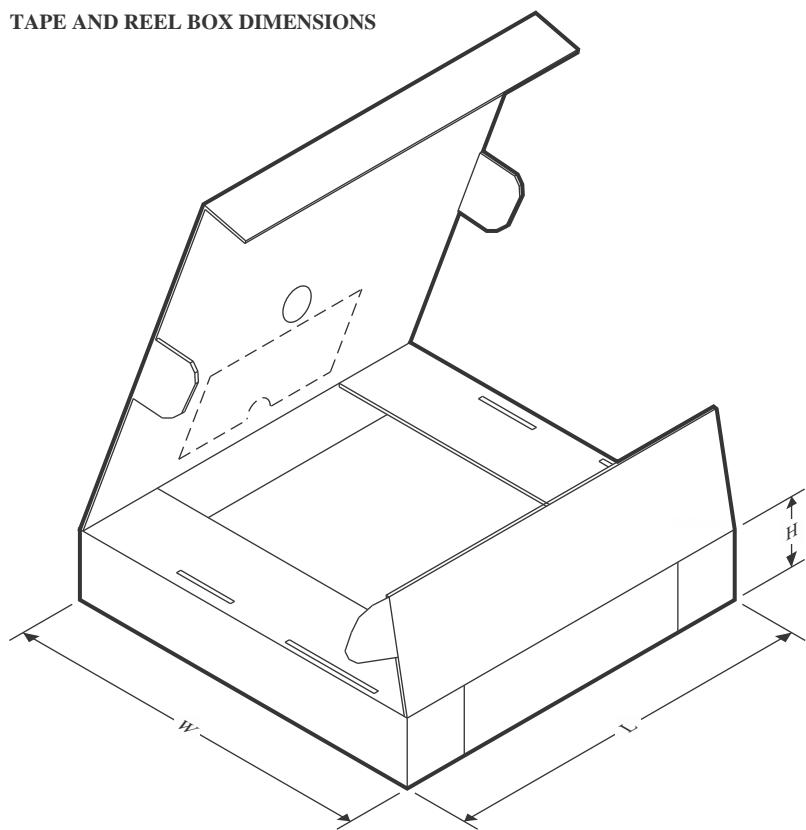

| 6.4 障害検出と応答の概略表 (障害表)          | 42        | 10.1 テープおよびリール情報              | <b>92</b> |

| 6.5 デバイスの機能モード                 | 49        |                               |           |

## 4 ピン機能 48 ピン DRV8363-Q1

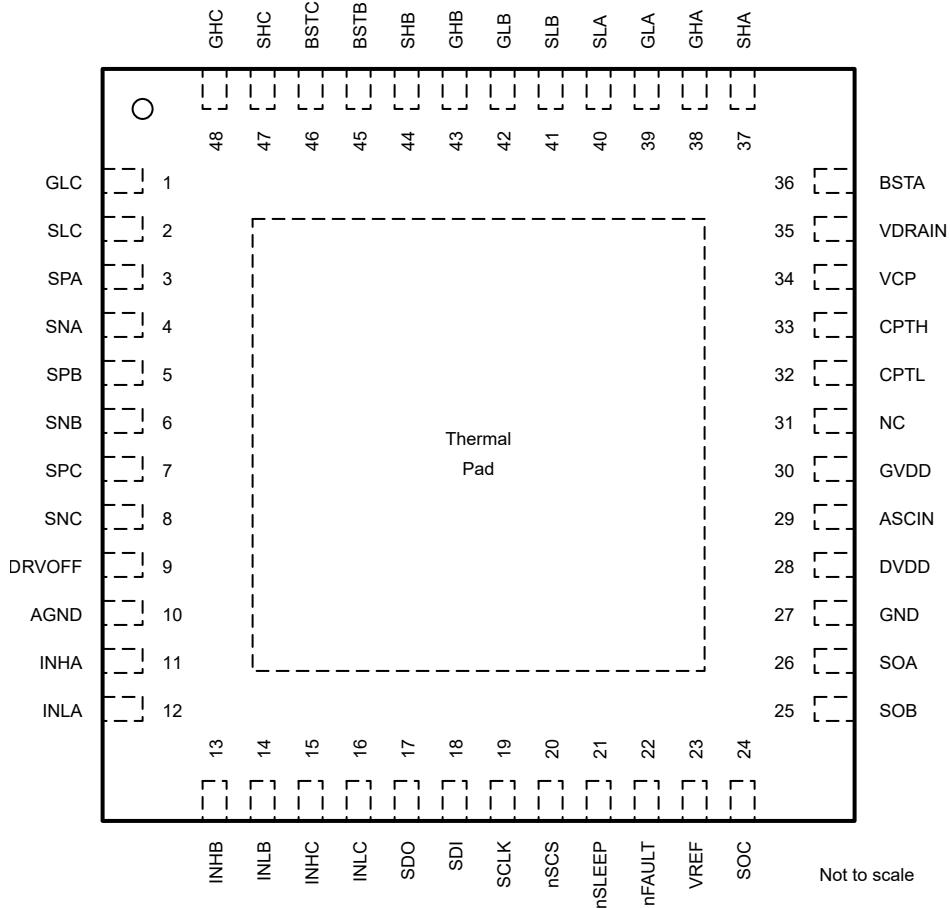

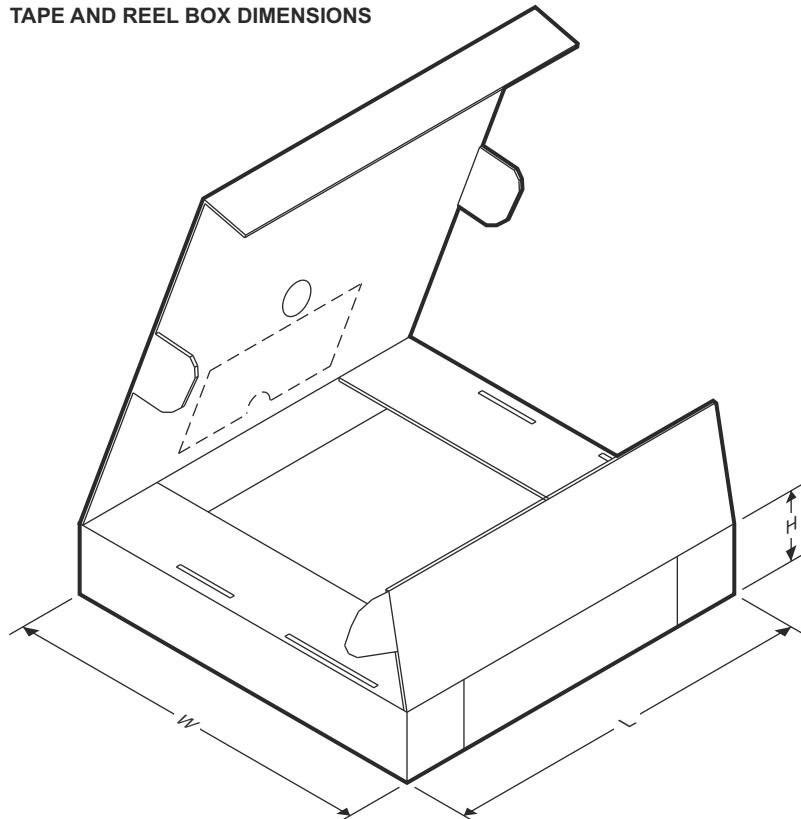

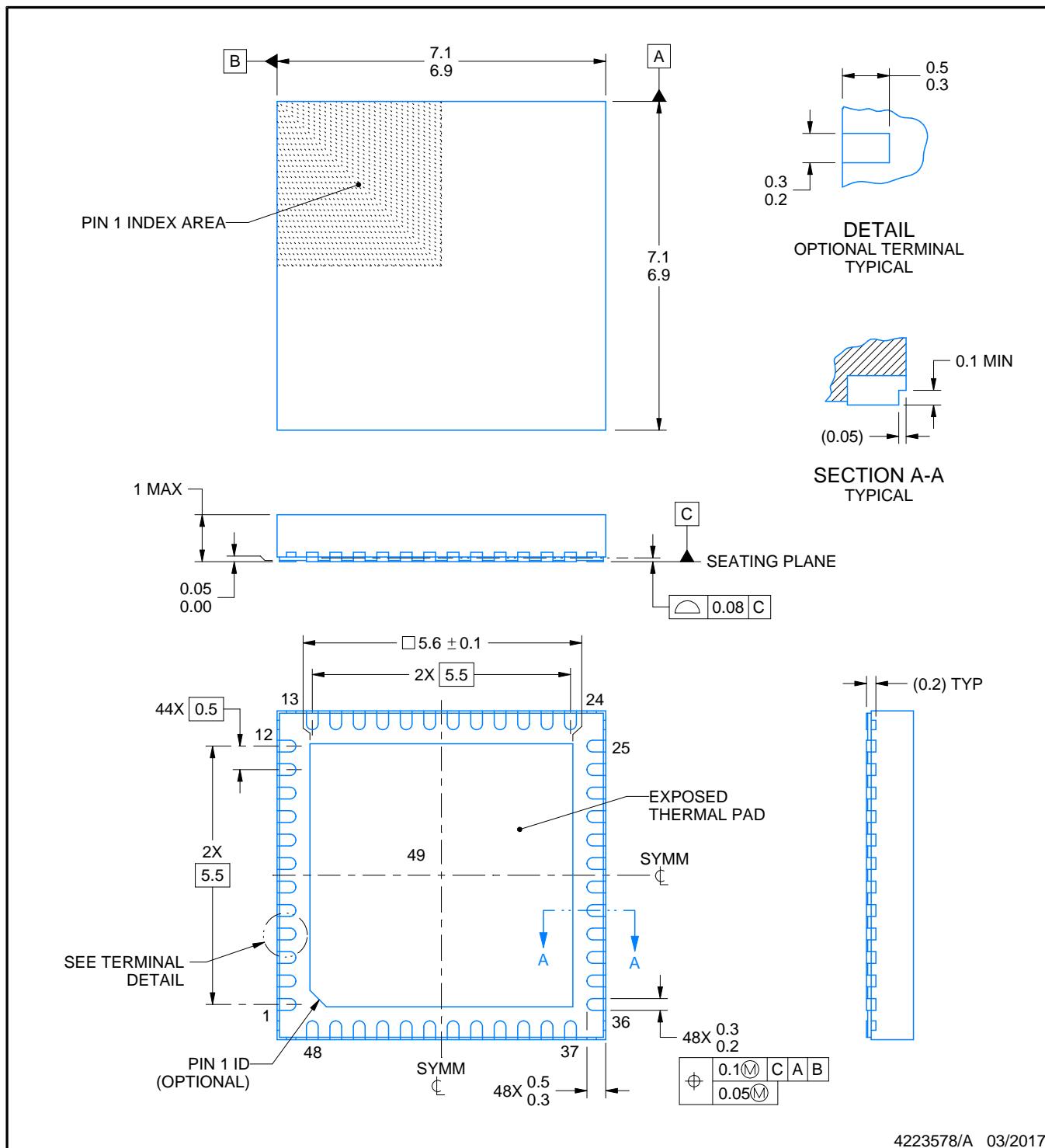

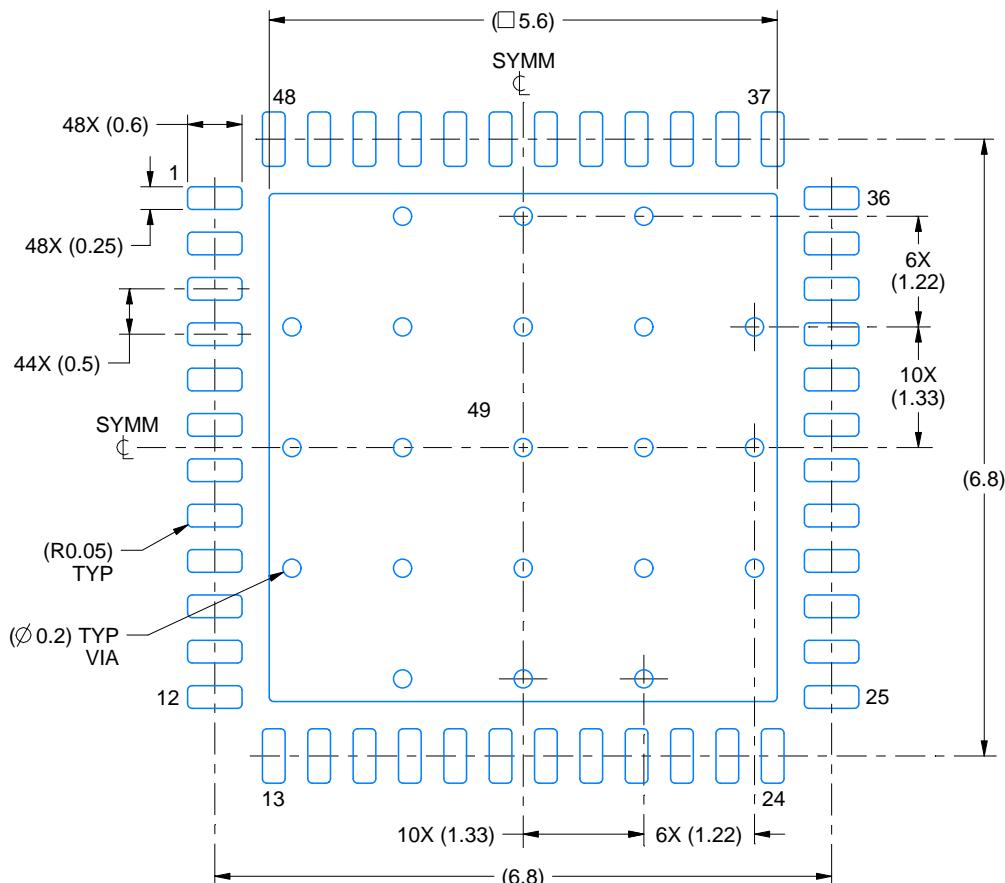

図 4-1. DRV8363-Q1 パッケージ、48 ピン、QFN (露出サーマル パッド付き) 上面図

表 4-1. ピン機能 (48-QFN)

| ピン     |    | I/O <sup>(1)</sup> | 説明                                                          |

|--------|----|--------------------|-------------------------------------------------------------|

| 名称     | 番号 |                    |                                                             |

| GLC    | 1  | O                  | ローサイド ゲートドライバ出力。ローサイド パワー MOSFET のゲートに接続します。                |

| SLC    | 2  | I                  | ローサイド ソース検出入力。ローサイド パワー MOSFET のソースに接続します。                  |

| SPA    | 3  | I                  | ローサイド電流シャントアンプ入力。ローサイド パワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。 |

| SNA    | 4  | I                  | 電流検出アンプ入力。電流シャント抵抗の低電位側に接続します。                              |

| SPB    | 5  | I                  | ローサイド電流シャントアンプ入力。ローサイド パワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。 |

| SNB    | 6  | I                  | 電流検出アンプ入力。電流シャント抵抗の低電位側に接続します。                              |

| SPC    | 7  | I                  | ローサイド電流シャントアンプ入力。ローサイド パワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。 |

| SNC    | 8  | I                  | 電流検出アンプ入力。電流シャント抵抗の低電位側に接続します。                              |

| DRVOFF | 9  | I                  | ゲートドライバ出力 GHx および GLx へのアクティブ High シャットダウン入力。               |

| AGND   | 10 | PWR                | デバイスのグランド。                                                  |

| INHA   | 11 | I                  | ハイサイド ゲートドライバの制御入力。このピンはハイサイド ゲートドライバの出力を制御します。             |

表 4-1. ピン機能 (48-QFN) (続き)

| ピン     |    | I/O <sup>(1)</sup> | 説明                                                                                  |

|--------|----|--------------------|-------------------------------------------------------------------------------------|

| 名称     | 番号 |                    |                                                                                     |

| INLA   | 12 | I                  | ローサイド ゲートドライバの制御入力。このピンはローサイド ゲートドライバの出力を制御します。                                     |

| INHB   | 13 | I                  | ハイサイド ゲートドライバの制御入力。このピンはハイサイド ゲートドライバの出力を制御します。                                     |

| INLB   | 14 | I                  | ローサイド ゲートドライバの制御入力。このピンはローサイド ゲートドライバの出力を制御します。                                     |

| INHC   | 15 | I                  | ハイサイド ゲートドライバの制御入力。このピンはハイサイド ゲートドライバの出力を制御します。                                     |

| INLC   | 16 | I                  | ローサイド ゲートドライバの制御入力。このピンはローサイド ゲートドライバの出力を制御します。                                     |

| SDO    | 17 | O                  | シリアル データ出力。                                                                         |

| SDI    | 18 | I                  | シリアル データ入力。                                                                         |

| SCLK   | 19 | I                  | シリアル クロック入力。                                                                        |

| nSCS   | 20 | I                  | シリアル チップ選択。                                                                         |

| nSLEEP | 21 | I                  | ゲートドライバ nSLEEP。このピンを論理 Low になると、本デバイスは低消費電力のスリープ モードに移行します。                         |

| nFAULT | 22 | OD                 | フォルト通知出力。このピンはフォルト条件中論理 Low にプルされ、外付けプルアップ抵抗を必要とします。                                |

| VREF   | 23 | PWR                | 電流センス アンプ用外部電圧レファレンス。                                                               |

| SOC    | 24 | O                  | 電流センスアンプの出力。                                                                        |

| SOB    | 25 | O                  | 電流センスアンプの出力。                                                                        |

| SOA    | 26 | O                  | 電流センスアンプの出力。                                                                        |

| GND    | 27 | PWR                | デバイスのグランド                                                                           |

| DVDD   | 28 | PWR                | 3.3V/5V LDO 出力。10V を超える定格のセラミックコンデンサを使用して隣接する GND に接続します。                           |

| ASCIN  | 29 | I                  | ASC 外部トリガピン。このピンがロジック High のとき、デバイスは 3 つのローサイドゲートまたはハイサイドゲートのすべてをオンにします。            |

| GVDD   | 30 | PWR                | ゲートドライバの電源入力。GVDD 定格セラミックを使用して、外部からレギュレートされた 8V ~ 15V の電源を GVDD ピンと GND ピンの間に接続します。 |

| NC     | 31 | NC                 | 接続なし。ピンはフローティングのままにしてください。                                                          |

| CPTL   | 32 | PWR                | トリクル チャージ ポンプ スイッチング ノード。チャージ ポンプ フライング コンデンサを CPTL ピンと CPTH ピンの間に接続します。            |

| CPTH   | 33 | PWR                | トリクル チャージ ポンプ スイッチング ノード。チャージ ポンプ フライング コンデンサを CPTL ピンと CPTH ピンの間に接続します。            |

| VCP    | 34 | PWR                | トリクル チャージ ポンプ ストレージ 容量。VCP ピンと VDRAIN ピンの間にセラミック コンデンサを接続します。                       |

| VDRAIN | 35 | PWR                | ハイサイド ドレイン検出およびチャージ ポンプ 電源入力。                                                       |

| BSTA   | 36 | O                  | ブートストラップ出力ピン。BSTA と SHA の間にブートストラップ コンデンサを接続します。                                    |

| SHA    | 37 | I                  | ハイサイド ソース センス入力。ハイサイド パワー MOSFET ソースに接続します。                                         |

| GHA    | 38 | O                  | ハイサイド ゲートドライバ出力。ハイサイド パワー MOSFET のゲートに接続します。                                        |

| GLA    | 39 | O                  | ローサイド ゲートドライバ出力。ローサイド パワー MOSFET のゲートに接続します。                                        |

| SLA    | 40 | I                  | ローサイド ソース検出入力。ローサイド パワー MOSFET のソースに接続します。                                          |

| SLB    | 41 | I                  | ローサイド ソース検出入力。ローサイド パワー MOSFET のソースに接続します。                                          |

| GLB    | 42 | O                  | ローサイド ゲートドライバ出力。ローサイド パワー MOSFET のゲートに接続します。                                        |

| GHB    | 43 | O                  | ハイサイド ゲートドライバ出力。ハイサイド パワー MOSFET のゲートに接続します。                                        |

| SHB    | 44 | I                  | ハイサイド ソース センス入力。ハイサイド パワー MOSFET ソースに接続します。                                         |

| BSTB   | 45 | O                  | ブートストラップ出力ピン。BSTB と SHB の間にブートストラップ コンデンサを接続します。                                    |

| BSTC   | 46 | O                  | ブートストラップ出力ピン。BSTC と SHC の間にブートストラップ コンデンサを接続します。                                    |

| SHC    | 47 | I                  | ハイサイド ソース センス入力。ハイサイド パワー MOSFET ソースに接続します。                                         |

**表 4-1. ピン機能 (48-QFN) (続き)**

| ピン  |    | I/O <sup>(1)</sup> | 説明                                           |

|-----|----|--------------------|----------------------------------------------|

| 名称  | 番号 |                    |                                              |

| GHC | 48 | O                  | ハイサイド ゲートドライバ出力。ハイサイド パワー MOSFET のゲートに接続します。 |

(1) 信号タイプ:I = 入力、O = 出力、I/O = 入力または出力、PWR = 電源

## 5 仕様

### 5.1 絶対最大定格

推奨動作条件範囲内 (特に記述のない限り)<sup>(1)</sup>

|                          |                         | 最小値  | 最大値              | 単位   |

|--------------------------|-------------------------|------|------------------|------|

| ゲートドライバ レギュレータ ピン電圧      | GVDD                    | -0.3 | 20               | V    |

| ハイサイド ドレイン ピン電圧          | VDRAIN                  | -0.3 | 85               | V    |

| ブートストラップ ピン電圧            | BSTx                    | -0.3 | 105              | V    |

| ブートストラップ ピン電圧            | SH を基準とした BST           | -0.3 | 20               | V    |

| ロジック ピン電圧                | nSLEEP、DRVOFF、ASCIN     | -0.3 | 35               | V    |

| ロジック ピン電圧                | nFAULT                  | -0.3 | 6                | V    |

|                          | INHx、INLx               | -0.3 | 35               |      |

|                          | SCLK、nSCS、SDI、SDO       | -0.3 | 6                |      |

| トリクル チャージ ポンプ出力ピン電圧      | VCP                     | -0.3 | 100              | V    |

| トリクル チャージ ポンプ ハイサイド ピン電圧 | CPTH                    | -0.3 | VCP + 0.3        | V    |

| トリクル チャージ ポンプ ローサイド ピン電圧 | CPTL                    | -0.3 | VDRAIN + 0.3     | V    |

| ハイサイド ゲートドライブ ピン電圧       | GH                      | -5   | 105              | V    |

| 過度ハイサイド ゲートドライブ ピンマイナス電圧 | GH、1 μs                 | -20  |                  | V    |

| ハイサイド ゲートドライブ ピン電圧       | SH を基準とした GH            | -0.3 | 20               | V    |

| ハイサイド ソース ピン電圧           | SH、DC                   | -5   | 105              | V    |

| 過度ハイサイド ソース ピンマイナス電圧     | SH、1 μs                 | -20  |                  | V    |

| ハイサイドソースピンのスルーレート        | SH、 $V_{BST-SH} > 4.3V$ |      | 20               | V/ns |

| ローサイド ゲートドライブ ピン電圧       | SL を基準とした GL            | -0.3 | 20               | V    |

| ローサイド ソース検出ピン電圧          | SL                      | -5   | $V_{GVDD} + 0.3$ | V    |

| 過度ローサイド ソースセンスピンマイナス電圧   | SL、1 μs                 | -16  |                  | V    |

| 電流検出アンプ リファレンス入力ピン電圧     | VREF                    | -0.3 | 5.5              | V    |

| シャントアンプ入力ピン電圧            | SN、SP                   | -1   | 1                | V    |

| 過渡 500ns シャントアンプ入力ピン電圧   | SN、SP、500ns             | -16  | 20               | V    |

| シャントアンプ出力ピン電圧            | SO                      | -0.3 | $V_{VREF} + 0.3$ | V    |

| 接合部温度、 $T_J$             |                         | -40  | 150              | °C   |

| 保管温度、 $T_{stg}$          |                         | -65  | 150              | °C   |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限りません。またその結果、本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります

## 5.2 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|                          |                        |                                                                                                                                         | 最小値 | 公称値 | 最大値 | 単位  |

|--------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|

| $V_{GVDD}$               | 電源電圧                   | $GVDD$                                                                                                                                  | 8   | 15  |     | V   |

| $V_{VDRAIN}$             | ハイサイドドレインピン電圧          | VDRAIN、ローサイドゲート駆動、ハイサイドゲート駆動スイッチング(ブートストラップ付き)                                                                                          | 0   | 85  |     | V   |

|                          | ハイサイドドレインピン電圧          | VDRAIN、トリクルチャージポンプ機能をサポートするため $V_{TCP}$ 最小 > $V_{BST\_UV}$ 最大 (立ち下がり)、ハイサイドゲート駆動 100%、 $BST\_UV$ 検出なし。<br>VDRAIN> $GVDD+4V$ 、 $GVDD>9V$ | 13  | 85  |     | V   |

| $V_{BST-SH}$             | SH を基準とするブートストラップピンの電圧 | $BST(V_{BST} - V_{SH})$ 、ハイサイドゲート駆動スイッチング、 $BST\_UV$ 検出なし、 $V_{BST-SH}$ min > $V_{BST\_UV}$ max (r 立ち上がり)、                              | 6.1 | 20  |     | V   |

| $V_{BST}$                | ブートストラップピン電圧           | $BST$                                                                                                                                   | 0   | 105 |     | V   |

| $V_{SH}$                 | ハイサイドソースピン電圧           | SH                                                                                                                                      | -2  | 85  |     | V   |

| $I_{TRICKLE}$            | トリクルチャージポンプの外部負荷電流     | 相負荷と VCP 外部負荷の合計値                                                                                                                       |     | 4   |     | mA  |

| $V_I$                    | 入力電圧                   | INH, INL, SDI, SCLK, nSCS                                                                                                               | 0   | 5.5 |     | V   |

| $f_{PWM}$ <sup>(1)</sup> | PWM 周波数                |                                                                                                                                         | 0   | 200 |     | kHz |

| $V_{OD}$                 | オープンドレイン プルアップ電圧       | nFAULT                                                                                                                                  |     | 5.5 |     | V   |

| $I_{OD}$                 | オープンドレイン出力電流           | nFAULT                                                                                                                                  |     | -5  |     | mA  |

| $V_{VREF}$               | 電流センスアンプリファレンス電圧       | VREF                                                                                                                                    | 3.0 | 5.5 |     | V   |

| $T_A$                    | 動作時周囲温度                |                                                                                                                                         | -40 | 125 |     | °C  |

| $T_J$                    | 動作時接合部温度               |                                                                                                                                         | -40 | 150 |     | °C  |

(1) 消費電力および温度の制限に従う必要があります。

## 5.3 熱に関する情報 (1pkg)

| 熱評価基準 <sup>(1)</sup> |                   | DRV8363   | 単位   |

|----------------------|-------------------|-----------|------|

|                      |                   | RGZ (QFN) |      |

|                      |                   | 48        |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗      | 24.1      | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への熱抵抗 | 12.9      | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗      | 7.6       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 0.2       | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 7.3       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗 | 2.0       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーションレポートを参照してください。

## 5.4 電気的特性

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ                          | テスト条件                             | 最小値                                                                                                                                                                                  | 標準値  | 最大値  | 単位   |    |

|--------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|

| <b>電源 (GVDD, VDRAIN, DVDD)</b> |                                   |                                                                                                                                                                                      |      |      |      |    |

| $I_{VDRAIN\_UNPWR}$            | GVDD 電源が供給されていないときの VDRAIN スリーブ電流 | GVDD = 0V、VDRAIN = 48V、 $V_{BST-SH} = 0V$ 、 $nSLEEP=0V$ 、 $T_J = 25^{\circ}C$ 。SH=VDRAIN および 0V<br>SH=0V 時の VDRAIN のリーク電流。<br>SH=VDRAIN 時の VDRAIN+SH のリーク電流 [すべての 3 つのプリドライバ位相をまとめる] | 2    | 4.5  | 13.5 | μA |

| $I_{GVDD}$                     | GVDD スタンバイ モード電流                  | GVDD = 12V、VDRAIN = 48V、INH = INL = 0。DRVOFF = Low, SHx=0V。TCP = ON, VCP の外部負荷なし。 [TCP スイッチが切り替わります]                                                                                 | 9.5  | 13.4 | 17.5 | mA |

| $I_{GVDD}$                     | GVDD スタンバイ モード電流                  | GVDD = 12V、VDRAIN = 48V、INH = INL = 0。DRVOFF = High, SHx=VDRAIN、TCP = ON, VCP の外部負荷なし。 [TCP スイッチがオンになります]                                                                            | 9.7  | 11.7 | 17.1 | mA |

| $I_{VDRAIN}$                   | VDRAIN アクティブ モード電流                | GVDD = 12V、VDRAIN = 48V、INH = INL = 20kHz でスイッチング。INL=1 時に SH=0、INH=1 時に SH=VDRAIN。<br>INH=INL=0 時に SH は電圧を保持。FET の接続なし。TCP がオン、TCP スイッチが切り替わります                                     | 4.3  | 5.2  | 6.9  | mA |

| $I_{GVDD}$                     | GVDD アクティブ モード電流                  | GVDD = 12V、VDRAIN = 48V、INH = INL = 20kHz でスイッチング。INL=1 時に SH=0、INH=1 時に SH=VDRAIN。<br>INH=INL=0 時に SH は電圧を保持。FET の接続なし。TCP がオン、TCP スイッチが切り替わります                                     | 9.8  | 13.1 | 20   | mA |

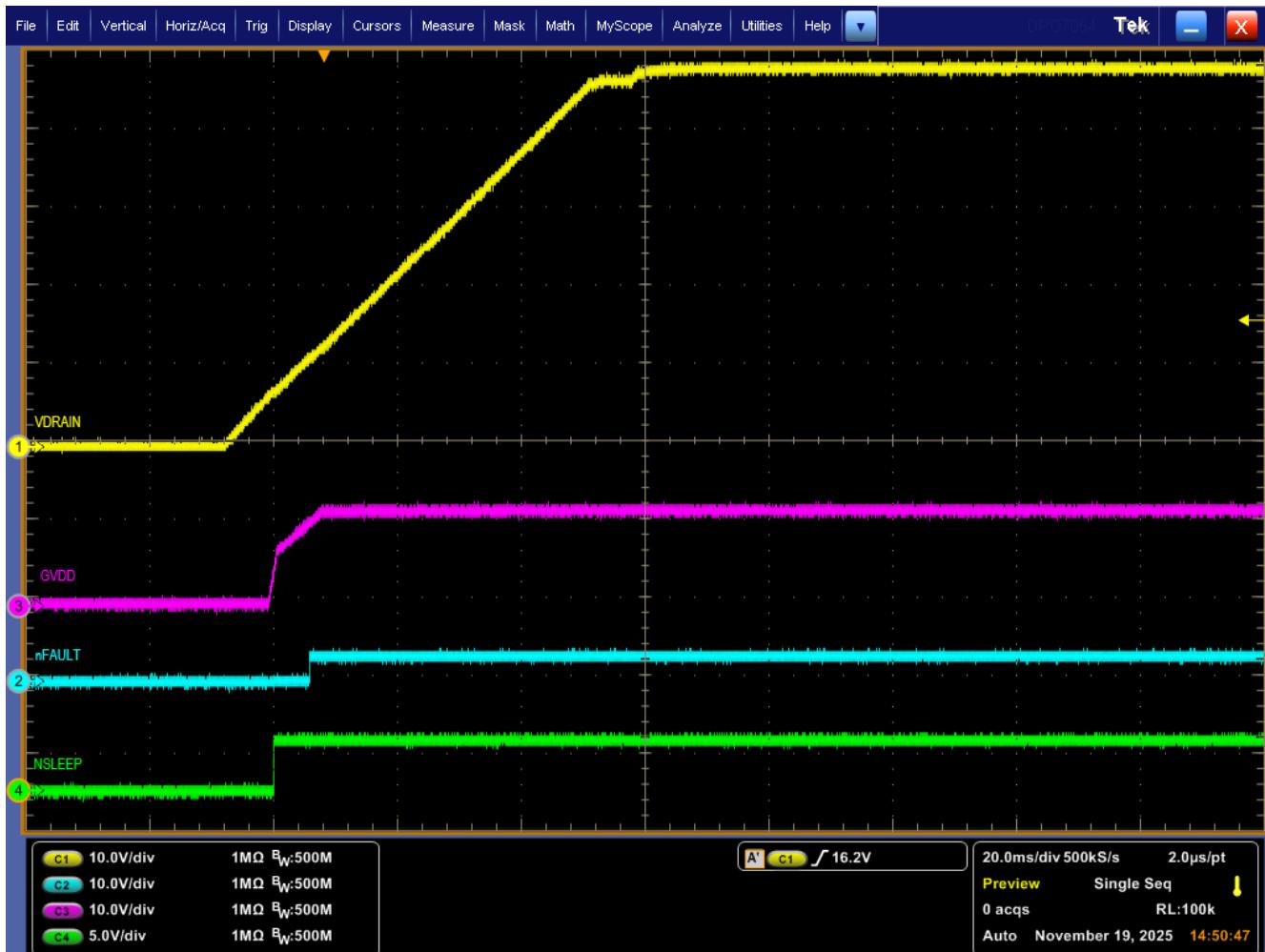

| $t_{WAKE}$                     | ターンオン時間                           | GVDD = 12V<br>$nSLEEP = High$ からアクティブモード (出力準備完了) ( $nFAULT = High$ )                                                                                                                |      |      | 10   | ms |

| $I_{L_{BS\_HSPU}}$             | ハイサイドブートアップ中のブートストラップピンのリーク電流     | INH = High、SH = VDRAIN = 85V。TCP スイッチオフ。TDRIVE=0. $V_{BST-SH} = 12V$ 。                                                                                                               | 200  | 340  | 450  | μA |

| $V_{DVDD\_RT}$                 | DVDD デジタルレギュレータ電圧 (室温)            | $V_{GVDD} \geq GVDD\_UVH$ 、 $0mA \leq I_{DVDD} \leq 30mA$ 外部負荷 + $0mA \sim 5mA$ 内部デジタル負荷、 $T_J = 25^{\circ}C$ 、 $DVDD\_LVL = 0$                                                      | 3.23 | 3.3  | 3.37 | V  |

| $V_{DVDD\_RT}$                 | DVDD デジタルレギュレータ電圧 (室温)            | $V_{GVDD} \geq GVDD\_UVH$ 、 $30mA \leq I_{DVDD} \leq 100mA$ 外部負荷 + $0mA \sim 5mA$ 内部デジタル負荷、 $T_J = 25^{\circ}C$ 、 $DVDD\_LVL = 0$                                                    | 3.23 | 3.3  | 3.37 | V  |

| $V_{DVDD}$                     | DVDD デジタルレギュレータ電圧                 | $V_{GVDD} \geq GVDD\_UVH$ 、 $0mA \leq I_{DVDD} \leq 30mA$ 外部負荷 + $0mA \sim 5mA$ 内部デジタル負荷、 $DVDD\_LVL = 0$                                                                            | 3.21 | 3.3  | 3.39 | V  |

| $V_{DVDD}$                     | DVDD デジタルレギュレータ電圧                 | $V_{GVDD} \geq GVDD\_UVH$ 、 $30mA \leq I_{DVDD} \leq 100mA$ 外部負荷 + $0mA \sim 5mA$ 内部デジタル負荷、 $DVDD\_LVL = 0$                                                                          | 3.21 | 3.3  | 3.39 | V  |

| $V_{DVDD\_RT}$                 | DVDD デジタルレギュレータ電圧 (室温)            | $V_{GVDD} \geq 6.5V$ 、 $0mA \leq I_{DVDD} \leq 30mA$ 外部負荷 + $0mA \sim 5mA$ 内部デジタル負荷、 $T_J = 25^{\circ}C$ 、 $DVDD\_LVL = 1$                                                           | 4.9  | 5    | 5.1  | V  |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ                                    |                                                        | テスト条件                                                                                                               | 最小値  | 標準値 | 最大値  | 単位 |

|------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|-----|------|----|

| $V_{DVDD\_RT}$                           | DVDD デジタルレギュレータ電圧 (室温)                                 | $V_{GVDD} \geq 6.5V, 30mA \leq I_{DVDD} \leq 100mA$<br>外部負荷 + 0mA ~ 5mA 内部デジタル負荷, $T_J = 25^\circ C$ , DVDD_LVL = 1 | 4.9  | 5   | 5.1  | V  |

| $V_{DVDD}$                               | DVDD デジタルレギュレータ電圧                                      | $V_{GVDD} \geq 6.5V, 0mA \leq I_{DVDD} \leq 30mA$ 外部負荷 + 0mA ~ 5mA 内部デジタル負荷, DVDD_LVL = 1                           | 4.85 | 5   | 5.15 | V  |

| $V_{DVDD}$                               | DVDD デジタルレギュレータ電圧                                      | $V_{GVDD} \geq 6.5V, 30mA \leq I_{DVDD} \leq 100mA$<br>外部負荷 + 0mA ~ 5mA 内部デジタル負荷, DVDD_LVL = 1                      | 4.85 | 5   | 5.15 | V  |

| <b>ロジックレベル入力 (INHx, INLx, nSLEEP など)</b> |                                                        |                                                                                                                     |      |     |      |    |

| $V_{IL}$                                 | 入力ロジック Low 電圧                                          | NSLEEP ピン, $GVDD > 6V$                                                                                              |      |     | 0.8  | V  |

| $V_{IL}$                                 | 入力ロジック Low 電圧                                          | DRVOFF ピン, $GVDD > 6V$                                                                                              |      |     | 0.8  | V  |

| $V_{IL}$                                 | 入力ロジック Low 電圧                                          | INLx, INHx, ASCIN, SDI, SCLK, nSCS, $GVDD > 6V$                                                                     |      |     | 0.8  | V  |

| $V_{IH}$                                 | 入力ロジック High 電圧                                         | NSLEEP ピン, $GVDD > 6V$                                                                                              | 2.2  |     |      | V  |

| $V_{IH}$                                 | 入力ロジック High 電圧                                         | DRVOFF ピン, $GVDD > 6V$                                                                                              | 2.2  |     |      | V  |

| $V_{IH}$                                 | 入力ロジック High 電圧                                         | INLx, INHx, DRVOFF, ASCIN, SDI, SCLK, nSCS, $GVDD > 6V$ , $DVDD < 4V$                                               | 2.2  |     |      | V  |

| $V_{IH}$                                 | 入力ロジック High 電圧                                         | INLx, INHx, DRVOFF, ASCIN, SDI, SCLK, nSCS, $GVDD > 6V$ , $DVDD < 5.25V$                                            | 2.6  |     |      | V  |

| $V_{IH}$                                 | 入力ロジック High 電圧                                         | INLx, INHx, DRVOFF, ASCIN, SDI, SCLK, nSCS, $GVDD > 6V$ , $DVDD < 6V$                                               | 2.9  |     |      | V  |

| $V_{OH}$                                 | SDO Voh                                                | $DVDD > 2.5V, ILOAD = 5mA, SDO = H$                                                                                 |      |     | 500  | mV |

| $V_{OL}$                                 | SDO Vol                                                | $DVDD > 2.5V, ILOAD = 5mA, SDO = L$                                                                                 |      |     | 500  | mV |

| $V_{HYS}$                                | 入力ヒステリシス                                               | NSLEEP                                                                                                              | 100  | 250 | 500  | mV |

| $V_{HYS}$                                | 入力ヒステリシス                                               | DRVOFF                                                                                                              | 50   | 200 | 400  | mV |

| $V_{HYS}$                                | 入力ヒステリシス                                               | INLx, INHx, DRVOFF, ASCIN, SDI, SCLK, nSCS                                                                          | 50   | 200 | 400  | mV |

| $I_{IL}$                                 | 入力ロジック Low 電流                                          | INLx, INHx, DRVOFF, ASCIN, SDI, SCLK = 0V                                                                           | -1   | 0   | 1    | μA |

| $R_{PU}$                                 | 入力プルアップ抵抗                                              | nSCS から DVDD ピン                                                                                                     | 50   | 100 | 200  | kΩ |

| $R_{PD}$                                 | 入力プルダウン抵抗                                              | SDI, SCLK から GND                                                                                                    | 50   | 100 | 200  | kΩ |

| $R_{PD}$                                 | 入力プルダウン抵抗                                              | INLx, INHx, DRVOFF, ASCIN, NSLEEP から GND                                                                            | 150  | 250 | 350  | kΩ |

| $t_{NSLEEP\_DG}$                         | NSLEEP 入力のグリッヂ除去時間                                     |                                                                                                                     | 1    | 2   | 4    | μs |

| $t_{DRVOFF\_DG}$                         | DRVOFF 入力のグリッヂ除去時間                                     |                                                                                                                     | 1    | 2   | 4    | μs |

| <b>オーブンドレイン出力 (nFAULT)</b>               |                                                        |                                                                                                                     |      |     |      |    |

| $V_{OL}$                                 | 出力ロジック Low 電圧                                          | $I_{OD} = 5mA, GVDD > 4V$                                                                                           |      |     | 0.4  | V  |

| $I_{OZ}$                                 | 出力ロジック High 電流                                         | $V_{OD} = 5V$                                                                                                       | -1   | 1   |      | μA |

| <b>ポートストラップダイオード (BST)</b>               |                                                        |                                                                                                                     |      |     |      |    |

| $V_{BOOTD}$                              | ポートストラップ ダイオードの順方向電圧                                   | $I_{BOOT} = 100 \mu A$                                                                                              |      |     | 0.82 | V  |

| $V_{BOOTD}$                              | ポートストラップ ダイオードの順方向電圧                                   | $I_{BOOT} = 10 mA$                                                                                                  |      |     | 1    | V  |

| $V_{BOOTD}$                              | ポートストラップ ダイオードの順方向電圧                                   | $I_{BOOT} = 100 mA$                                                                                                 |      |     | 1.6  | V  |

| $R_{BOOTD}$                              | ポートストラップの動的抵抗 ( $\Delta V_{BOOTD} / \Delta I_{BOOT}$ ) | $I_{BOOT} = 100mA$ および $50mA$                                                                                       | 3.9  | 4.8 | 9    | Ω  |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ                           | テスト条件                                                                                                    | 最小値                                                                                                                                          | 標準値  | 最大値   | 単位   |    |

|---------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|----|

| <b>トリクルチャージポンプ (VCP)</b>        |                                                                                                          |                                                                                                                                              |      |       |      |    |

| $V_{TCP}$                       | $V_{VCP-VDRAIN}$ 、 $V_{DRAIN} > 15V$ 、 $GVDD > 11V$ 、 $V_{DRAIN} > GVDD + 4V$ 。外部負荷 $I_{VCP} < 4mA$      | 10.3                                                                                                                                         | 10.7 | 10.9  | V    |    |

| $V_{TCP}$                       | $V_{VCP-VDRAIN}$ 、 $V_{DRAIN} > 15V$ 、 $8V < GVDD < 11V$ 、 $V_{DRAIN} > GVDD + 4V$ 。外部負荷 $I_{VCP} < 2mA$ | 7.5                                                                                                                                          | 7.8  | 8.0   | V    |    |

|                                 | $V_{VCP-VDRAIN}$ 、 $V_{DRAIN} = GVDD$ 、 $8V < GVDD < 11V$ 、外部負荷 $I_{VCP} < 2mA$                          | 4.0                                                                                                                                          | 5.4  | 6.7   | V    |    |

| $V_{BST\_TCPOFF}$               | $V_{VCP}$ の BST 監視電圧により、BST コンデンサの充電を停止 (立ち上がり電圧)                                                        | $INL_x = 0$ 。 $SH_x = 0$ 、 $V_{DRAIN}$ 、 $V_{DRAIN} = 48V$ 、 $85V$                                                                           | 12.0 | 13.2  | 14.6 | V  |

| $T_{PRECHARGE}$                 | ブートストラッププリチャージの起動時間                                                                                      | $INH = INL = 0$ 。 $BST\_UVLO$ = 最高レベル。<br>$TCP\_SWITCH = PRECHARGE$ モード (5mA)。 $GVDD > 11V$ 、 $V_{DRAIN} > GVDD + 4V$ 。 $SH_x = V_{DRAIN}$ 。 |      | 1.5   | 3    | ms |

| $I_{TCP\_NRM}$                  | $V_{VCP}$ から BST へのスイッチ電流。通常モード                                                                          | $BST = SH = 0$ 。 $V_{VCP} > 15V$ 。<br>$TCP\_HD\_DIS = 1$ 。 $TCP\_SW\_CURLIM = 0$ 。                                                           |      | 1.25  |      | mA |

| $I_{TCP\_NRM}$                  | $V_{VCP}$ から BST へのスイッチ電流。通常モード                                                                          | $BST = SH = 0$ 。 $V_{VCP} > 15V$ 。<br>$TCP\_HD\_DIS = 1$ 。 $TCP\_SW\_CURLIM = 1$ 。                                                           |      | 2.3   |      | mA |

| $I_{TCP\_PCHG}$                 | $V_{VCP}$ から BST へのスイッチ電流。プリチャージモード                                                                      | $BST = SH = 0$ 。 $V_{VCP} > 15V$ 。                                                                                                           |      | 5.2   |      | mA |

| $I_{TCP\_HD}$                   | $V_{VCP}$ から BST へのスイッチ電流。<br>$TCP\_SW\_HD\_CURLIM = 0b00$ の High デューティサイクルモード                           | $BST = SH = 0$ 。 $V_{VCP} > 15V$ 。<br>$TCP\_HD\_DIS = 0b$ 。<br>$TCP\_SW\_HD\_CURLIM = 0b00$ 。                                                |      | 7.7   |      | mA |

| $I_{TCP\_HD}$                   | $V_{VCP}$ から BST へのスイッチ電流。<br>$TCP\_SW\_HD\_CURLIM = 0b01$ の High デューティサイクルモード                           | $BST = SH = 0$ 。 $V_{VCP} > 15V$ 。<br>$TCP\_HD\_DIS = 0b$ 。<br>$TCP\_SW\_HD\_CURLIM = 0b01$ 。                                                |      | 6.4   |      | mA |

| $I_{TCP\_HD}$                   | $V_{VCP}$ から BST へのスイッチ電流。<br>$TCP\_SW\_HD\_CURLIM = 0b10$ の High デューティサイクルモード                           | $BST = SH = 0$ 。 $V_{VCP} > 15V$ 。<br>$TCP\_HD\_DIS = 0b$ 。<br>$TCP\_SW\_HD\_CURLIM = 0b10$ 。                                                |      | 10.5  |      | mA |

| $I_{TCP\_HD}$                   | $V_{VCP}$ から BST へのスイッチ電流。<br>$TCP\_SW\_HD\_CURLIM = 0b11$ の High デューティサイクルモード                           | $BST = SH = 0$ 。 $V_{VCP} > 15V$ 。<br>$TCP\_HD\_DIS = 0b$ 。<br>$TCP\_SW\_HD\_CURLIM = 0b11$ 。                                                |      | 9.2   |      | mA |

| <b>ゲートドライバ (GH, GL, SH, SL)</b> |                                                                                                          |                                                                                                                                              |      |       |      |    |

| $V_{GSHx\_LO}$                  | ハイサイドゲート駆動の low レベル電圧 ( $V_{GH} - V_{SH}$ )                                                              | $I_{GHx} = -10mA$ 、 $V_{GVDD} = 12V$ 、 $IDRIVE = 1000mA$ 、FET は接続されていない                                                                      | 0    | 0.022 | 0.2  | V  |

| $V_{GSHx\_HI}$                  | ハイサイドゲート駆動の High レベル電圧 ( $V_{GH} - V_{SH}$ )                                                             | $I_{GHx} = 10mA$ 、 $V_{GVDD} = 12V$ 、 $IDRIVE = 500mA$ 、FET は接続されていない                                                                        | 0    | 0.09  | 0.2  | V  |

| $V_{GSLx\_LO}$                  | ローサイドゲート駆動の low レベル電圧 ( $V_{GL} - V_{SL}$ )                                                              | $I_{GLx} = -10mA$ 、 $V_{GVDD} = 12V$ 、 $IDRIVE = 1000mA$ 、FET は接続されていない                                                                      | 0    | 0.022 | 0.2  | V  |

| $V_{GSLx\_HI}$                  | ローサイドゲート駆動の High レベル電圧 ( $V_{GVDD} - V_{GL}$ )                                                           | $I_{GLx} = 10mA$ 、 $V_{GVDD} = 12V$ 、 $IDRIVE = 500mA$ 、FET は接続されていない                                                                        | 0    | 0.09  | 0.2  | V  |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ          | テスト条件                                               | 最小値 | 標準値  | 最大値  | 単位 |

|----------------|-----------------------------------------------------|-----|------|------|----|

| $I_{DRIVEP0}$  | $V_{BST}-V_{SH} = V_{GVDD} = 12V, IDRVP_{xx} = 0x0$ | 9   | 16   | 26   | mA |

| $I_{DRIVEP1}$  |                                                     | 19  | 32   | 52   | mA |

| $I_{DRIVEP2}$  |                                                     | 38  | 64   | 103  | mA |

| $I_{DRIVEP3}$  |                                                     | 57  | 96   | 154  | mA |

| $I_{DRIVEP4}$  |                                                     | 76  | 128  | 205  | mA |

| $I_{DRIVEP5}$  |                                                     | 96  | 160  | 256  | mA |

| $I_{DRIVEP6}$  |                                                     | 115 | 192  | 308  | mA |

| $I_{DRIVEP7}$  |                                                     | 134 | 224  | 359  | mA |

| $I_{DRIVEP8}$  |                                                     | 153 | 256  | 410  | mA |

| $I_{DRIVEP9}$  |                                                     | 172 | 288  | 461  | mA |

| $I_{DRIVEP10}$ |                                                     | 192 | 320  | 512  | mA |

| $I_{DRIVEP11}$ |                                                     | 230 | 384  | 615  | mA |

| $I_{DRIVEP12}$ |                                                     | 307 | 512  | 820  | mA |

| $I_{DRIVEP13}$ |                                                     | 460 | 768  | 1229 | mA |

| $I_{DRIVEP14}$ |                                                     | 614 | 1024 | 1639 | mA |

| $I_{DRIVEP15}$ |                                                     | 614 | 1024 | 1639 | mA |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ                                  | テスト条件                                               | 最小値                                                   | 標準値  | 最大値  | 単位   |            |

|----------------------------------------|-----------------------------------------------------|-------------------------------------------------------|------|------|------|------------|

| $I_{DRIVEN0}$                          | $V_{BST}-V_{SH} = V_{GVDD} = 12V, IDRVN_{xx} = 0x0$ | 19                                                    | 32   | 52   | mA   |            |

| $I_{DRIVEN1}$                          |                                                     | 38                                                    | 64   | 103  | mA   |            |

| $I_{DRIVEN2}$                          |                                                     | 76                                                    | 128  | 205  | mA   |            |

| $I_{DRIVEN3}$                          |                                                     | 115                                                   | 192  | 308  | mA   |            |

| $I_{DRIVEN4}$                          |                                                     | 153                                                   | 256  | 410  | mA   |            |

| $I_{DRIVEN5}$                          |                                                     | 192                                                   | 320  | 512  | mA   |            |

| $I_{DRIVEN6}$                          |                                                     | 230                                                   | 384  | 615  | mA   |            |

| $I_{DRIVEN7}$                          |                                                     | 268                                                   | 448  | 717  | mA   |            |

| $I_{DRIVEN8}$                          |                                                     | 307                                                   | 512  | 820  | mA   |            |

| $I_{DRIVEN9}$                          |                                                     | 345                                                   | 576  | 922  | mA   |            |

| $I_{DRIVEN10}$                         |                                                     | 384                                                   | 640  | 1024 | mA   |            |

| $I_{DRIVEN11}$                         |                                                     | 460                                                   | 768  | 1229 | mA   |            |

| $I_{DRIVEN12}$                         |                                                     | 614                                                   | 1024 | 1639 | mA   |            |

| $I_{DRIVEN13}$                         |                                                     | 921                                                   | 1536 | 2458 | mA   |            |

| $I_{DRIVEN14}$                         |                                                     | 1228                                                  | 2048 | 3277 | mA   |            |

| $I_{DRIVEN15}$                         |                                                     | 1228                                                  | 2048 | 3277 | mA   |            |

| $R_{PD\_LS}$                           | ローサイド パッシブ プルダウン                                    | GL から SL, $V_{GL} - V_{SL} = 2V$                      | 60   | 85   | 120  | k $\Omega$ |

| $R_{PDSA\_HS}$                         | ハイサイド セミアクティブ プルダウン                                 | $GVDD\_UV = 1$<br>GH から SH, $V_{GH} - V_{SH} = 2V$    | 2    | 4    | 8    | k $\Omega$ |

| $I_{PUHOLD\_L}$                        | ハイサイド プルアップホールド Low 電流                              | $I_{HOLD\_SEL} = 0$                                   | 614  | 1024 | 1639 | mA         |

| $I_{PUHOLD\_H}$                        | ハイサイド プルアップホールド High 電流                             | $I_{HOLD\_SEL} = 1$                                   | 153  | 256  | 410  | mA         |

| $I_{PDSTRONG\_L}$<br>$I_{PDSTRONG\_S}$ | ローサイド・プルダウン強電流                                      |                                                       | 1228 | 2048 | 3277 | mA         |

| $I_{PDSTRONG\_H}$<br>$I_{PDSTRONG\_S}$ | ハイサイド プルダウン強電流                                      |                                                       | 1228 | 2048 | 3277 | mA         |

| <b>ゲートドライバのタイミング</b>                   |                                                     |                                                       |      |      |      |            |

| $t_{PDR\_LS}$                          | ローサイド立ち上がり伝搬遅延                                      | INL から GL 立ち上がりまで, $V_{GVDD} > 8V$                    | 45   | 63   | 90   | ns         |

| $t_{PDF\_LS}$                          | ローサイド立ち下がり伝搬遅延                                      | INL から GL 立ち下がりまで, $V_{GVDD} > 8V$                    | 45   | 64   | 90   | ns         |

| $t_{PDR\_HS}$                          | ハイサイド立ち上がり伝搬遅延                                      | INH から GH 立ち上がりまで, $V_{GVDD} = V_{BST} - V_{SH} > 8V$ | 45   | 62   | 90   | ns         |

| $t_{PDF\_HS}$                          | ハイサイド立ち下がり伝搬遅延                                      | INH から GH 立ち下がりまで, $V_{GVDD} = V_{BST} - V_{SH} > 8V$ | 45   | 65   | 90   | ns         |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ               |                      | テスト条件                                                                                                                                                                    | 最小値  | 標準値     | 最大値 | 単位 |

|---------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-----|----|

| $t_{PD\_MATCH}$     | ローサイドゲートドライバの伝搬遅延の一致 | GL ターンオンから GL ターンオフまで、 $V_{GL-SL} = 1V$ から $V_{GL-SL} = V_{GVDD} - 1V$ 、 $V_{GVDD} = V_{BST} - V_{SH} > 8V$ 、 $V_{SH} = 0V \sim 90V$ 、GH と GL は無負荷                       | -8   | $\pm 4$ | 8   | ns |

|                     | ハイサイドゲートドライバの伝搬遅延の一致 | GH ターンオンから GH ターンオフまで、 $V_{GH-SH} = 1V$ から $V_{GH-SH} = V_{BST-SH} - 1V$ 、 $V_{GVDD} = V_{BST} - V_{SH} > 8V$ 、 $V_{SH} = 0V \sim 90V$ 、GH と GL は無負荷                     | -10  | $\pm 4$ | 10  | ns |

| $t_{PD\_MATCH\_PH}$ | 位相ごとの伝搬遅延のマッチング      | デッドタイムの無効化。GL ターンオフから GH ターンオンまで、 $V_{GL-SL} = V_{GVDD} - 1V$ から $V_{GH-SH} = 1V$ 、 $V_{GVDD} = V_{BST} - V_{SH} > 8V$ 、 $V_{SH} = 0V \sim 90V$ 、GH と GL は無負荷、デッドタイムは無効化 | -12  | $\pm 4$ | 12  | ns |

|                     |                      | デッドタイムの無効化。GH ターンオフから GL ターンオンまで、 $V_{GH-SH} = V_{BST-SH} - 1V$ から $V_{GL-SL} = 1V$ 、 $V_{GVDD} = V_{BST} - V_{SH} > 8V$ 、 $V_{SH} = 0V \sim 90V$ 、GH と GL は無負荷          | -11  | $\pm 4$ | 11  | ns |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 0000b = 0h                                                                                                                                                       | 70   |         |     | ns |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 0001b = 1h                                                                                                                                                       | 120  |         |     | ns |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 0010b = 2h                                                                                                                                                       | 180  |         |     | ns |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 0011b = 3h                                                                                                                                                       | 300  |         |     | ns |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 0100b = 4h                                                                                                                                                       | 400  |         |     | ns |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 0101b = 5h                                                                                                                                                       | 500  |         |     | ns |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 0110b = 6h                                                                                                                                                       | 600  |         |     | ns |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 0111b = 7h                                                                                                                                                       | 750  |         |     | ns |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 1000b = 8h                                                                                                                                                       | 1000 |         |     | ns |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 1001b = 9h                                                                                                                                                       | 1.5  |         |     | us |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 1010b = Ah                                                                                                                                                       | 2    |         |     | us |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 1011b = Bh                                                                                                                                                       | 2.5  |         |     | us |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 1100b = Ch                                                                                                                                                       | 3    |         |     | us |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 1101b = Dh                                                                                                                                                       | 3.5  |         |     | us |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 1110b = Eh                                                                                                                                                       | 5    |         |     | us |

| $t_{DEAD}$          | デジタルゲート駆動デッドタイム      | DEADT = 1111b = Fh                                                                                                                                                       | 10   |         |     | us |

| $t_{DEAD}$          | アナログ伝搬遅延デッドタイムの変動    | デジタルデッドタイムの一番上に挿入                                                                                                                                                        | -12  | 4       | 12  | ns |

**電流シャントアンプ (SNx, SOx, SPx, VREF)**

|                       |                    |               |      |      |        |

|-----------------------|--------------------|---------------|------|------|--------|

| $A_{CSA}$             | 検出アンプのゲイン          | CSAGAIN = 00b | 5    |      | V/V    |

|                       |                    | CSAGAIN = 01b | 10   |      | V/V    |

|                       |                    | CSAGAIN = 10b | 20   |      | V/V    |

|                       |                    | CSAGAIN = 11b | 40   |      | V/V    |

| $A_{CSA}$             | 検出アンプのゲイン          | CSAGAIN = 00b | 4.9  | 5    | 5.08   |

|                       |                    | CSAGAIN = 01b | 9.85 | 10   | 10.15  |

|                       |                    | CSAGAIN = 10b | 19.7 | 20   | 20.3   |

|                       |                    | CSAGAIN = 11b | 39.4 | 40   | 40.8   |

| $A_{CSA\_ERR\_DRIFT}$ | 検出アンプのゲイン誤差の温度ドリフト |               | -30  | 30   | ppm/°C |

| NL                    | 非直線性誤差             |               | 0.01 | 0.05 | %      |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ       |                        | テスト条件                                                                                                              | 最小値   | 標準値               | 最大値 | 単位        |

|-------------|------------------------|--------------------------------------------------------------------------------------------------------------------|-------|-------------------|-----|-----------|

| $t_{SET}$   | $\pm 1\%$ までのセトリング タイム | $V_{STEP} = 1.6V, A_{CSA} = 5V/V, C_{SO} = 500pF, VREF = 4.5V \sim 5.5V, k = 1/2, C_{boardroute} = 0pF \sim 60pF$  |       | 0.6               | 1.6 | $\mu s$   |

|             |                        | $V_{STEP} = 1.6V, A_{CSA} = 10V/V, C_{SO} = 500pF, VREF = 4.5V \sim 5.5V, k = 1/2, C_{boardroute} = 0pF \sim 60pF$ |       | 0.65              | 1.6 | $\mu s$   |

|             |                        | $V_{STEP} = 1.6V, A_{CSA} = 20V/V, C_{SO} = 500pF, VREF = 4.5V \sim 5.5V, k = 1/2, C_{boardroute} = 0pF \sim 60pF$ |       | 0.7               | 1.6 | $\mu s$   |

|             |                        | $V_{STEP} = 1.6V, A_{CSA} = 40V/V, C_{SO} = 500pF, VREF = 4.5V \sim 5.5V, k = 1/2, C_{boardroute} = 0pF \sim 60pF$ |       | 1.25              | 2.1 | $\mu s$   |

| $t_{SET}$   | $\pm 1\%$ までのセトリング タイム | $V_{STEP} = 1.6V, A_{CSA} = 5V/V, C_{SO} = 60pF, VREF = 4.5V \sim 5.5V, k = 1/2, C_{boardroute} = 0pF \sim 60pF$   |       | 0.3               | 0.6 | $\mu s$   |

|             |                        | $V_{STEP} = 1.6V, A_{CSA} = 10V/V, C_{SO} = 60pF, VREF = 4.5V \sim 5.5V, k = 1/2, C_{boardroute} = 0pF \sim 60pF$  |       | 0.35              | 0.6 | $\mu s$   |

|             |                        | $V_{STEP} = 1.6V, A_{CSA} = 20V/V, C_{SO} = 60pF, VREF = 4.5V \sim 5.5V, k = 1/2, C_{boardroute} = 0pF \sim 60pF$  |       | 0.35              | 0.7 | $\mu s$   |

|             |                        | $V_{STEP} = 1.6V, A_{CSA} = 40V/V, C_{SO} = 60pF, VREF = 4.5V \sim 5.5V, k = 1/2, C_{boardroute} = 0pF \sim 60pF$  |       | 0.6               | 0.9 | $\mu s$   |

| $BW$        | 帯域幅                    | $A_{CSA} = 5V/V, C_{LOAD} = 60pF$ 、小信号-3dB                                                                         | 3     | 5                 | 7   | MHz       |

|             |                        | $A_{CSA} = 10V/V, C_{LOAD} = 60pF$ 、小信号-3dB                                                                        | 2.5   | 4.8               | 6.6 | MHz       |

|             |                        | $A_{CSA} = 20V/V, C_{LOAD} = 60pF$ 、小信号-3dB                                                                        | 2     | 4                 | 5.4 | MHz       |

|             |                        | $A_{CSA} = 40V/V, C_{LOAD} = 60pF$ 、小信号-3dB                                                                        | 1.75  | 3                 | 4.2 | MHz       |

| $t_{SR}$    | 出力スルーレート               | $V_{STEP} = 1.6V, A_{CSA} = 5V/V, C_{LOAD} = 60pF$ 、Low から High に遷移                                                |       | 14                |     | $V/\mu s$ |

|             |                        | $V_{STEP} = 1.6V, A_{CSA} = 10V/V, C_{LOAD} = 60pF$ 、Low から High に遷移                                               |       | 13                |     | $V/\mu s$ |

|             |                        | $V_{STEP} = 1.6V, A_{CSA} = 20V/V, C_{LOAD} = 60pF$ 、Low から High に遷移                                               |       | 13                |     | $V/\mu s$ |

|             |                        | $V_{STEP} = 1.6V, A_{CSA} = 40V/V, C_{LOAD} = 60pF$ 、Low から High に遷移                                               |       | 6                 |     | $V/\mu s$ |

| $V_{SWING}$ | 出力電圧範囲                 | $V_{VREF} = 3$                                                                                                     | 0.25  | 2.75              |     | V         |

| $V_{SWING}$ | 出力電圧範囲                 | $V_{VREF} = 5.5$                                                                                                   | 0.25  | 5.25              |     | V         |

| $V_{SWING}$ | 出力電圧範囲                 | $V_{VREF} = 3 \sim 5.5V$                                                                                           | 0.25  | $V_{VREF - 0.25}$ |     | V         |

| $V_{COM}$   | 同相入力範囲                 |                                                                                                                    | -0.15 | 0.15              |     | V         |

| $V_{DIFF}$  | 差動モード入力範囲              | ゲイン $A_{CSA} = 5V/V$                                                                                               | -0.3  | 0.3               |     | V         |

| $V_{OFF}$   | 入力オフセット電圧              | $V_{SP} = V_{SN} = GND$ 。 $T_J = -40^\circ C$ , $G=5V/V$                                                           | -2.65 | 2.65              |     | mV        |

| $V_{OFF}$   | 入力オフセット電圧              | $V_{SP} = V_{SN} = GND$ 。 $T_J = -40^\circ C$ , $G = 10, 20, 40V/V$                                                | -1.5  | 1.5               |     | mV        |

| $V_{OFF}$   | 入力オフセット電圧              | $V_{SP} = V_{SN} = GND$ 。 $T_J = 25^\circ C$ , $G=5V/V$                                                            | -2.65 | 2.65              |     | mV        |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ            |                          | テスト条件                                                                      | 最小値   | 標準値 | 最大値  | 単位               |

|------------------|--------------------------|----------------------------------------------------------------------------|-------|-----|------|------------------|

| $V_{OFF}$        | 入力オフセット電圧                | $V_{SP} = V_{SN} = GND$ 。 $T_J = 25^\circ C$ 、 $G = 10$ 、<br>20、40V/V      | -1.5  |     | 1.5  | mV               |

| $V_{OFF}$        | 入力オフセット電圧                | $V_{SP} = V_{SN} = GND$ 。 $T_J = 150^\circ C$ 、 $G=5V/V$                   | -2.65 |     | 2.65 | mV               |

| $V_{OFF}$        | 入力オフセット電圧                | $V_{SP} = V_{SN} = GND$ 。 $T_J = 150^\circ C$ 、 $G = 10$ 、<br>20、405V/V    | -1.5  |     | 1.5  | mV               |

| $V_{OFF}$        | 入力オフセット電圧                | $V_{SP} = V_{SN} = GND$ 。 $G=5V/V$                                         | -2.6  |     | 2.6  | mV               |

| $V_{OFF\_DRIFT}$ | 入力オフセット電圧ドリフト            | $V_{SP} = V_{SN} = GND$                                                    | -10   | 0   | 10   | $\mu V/^\circ C$ |

| $V_{BIAS}$       | 出力電圧バイアス比                | $V_{SP} = V_{SN} = GND$                                                    |       | 0.5 |      |                  |

| $V_{BIAS\_ACC}$  | 出力電圧バイアス比の精度             |                                                                            | -1.2  |     | 1.8  | %                |

| $I_{BIAS}$       | 入力バイアス電流                 | $V_{SP} = V_{SN} = GND$ 、 $V_{VREF} = 3V \sim 5.5V$                        |       |     | 100  | $\mu A$          |

| $I_{BIAS\_OFF}$  | 入力バイアス電流オフセット            | $I_{SP} - I_{SN}$                                                          | -2.5  |     | 2.5  | $\mu A$          |

| $CMRR$           | 同相除去比                    | DC                                                                         |       | 80  |      | dB               |

|                  |                          | 20kHz                                                                      |       | 60  |      | dB               |

| $PSRR$           | 電源除去比                    | GVDD ~ SOx, DC                                                             |       | 100 |      | dB               |

| $PSRR$           | 電源除去比                    | GVDD ~ SOx, 20kHz                                                          |       | 63  |      | dB               |

| $PSRR$           | 電源除去比 (VREF)             | VREF から SOx, DC、差動                                                         |       | 85  |      | dB               |

|                  |                          | VREF から SOx, 20kHz、差動                                                      |       | 90  |      | dB               |

| $PSRR$           | 電源除去比 (VREF)             | VREF から SOx, 20kHz、シングルエンド                                                 |       | 40  |      | dB               |

| $I_{CSA\_SUP}$   | GVDD 電源オフ時の CSA の電源リーク電流 | $V_{REF}, V_{VREF} = 3V \sim 5.5V$ , GVDD = 0V, VDRAIN = 48V / 0V          |       |     | 1000 | nA               |

| $I_{CSA\_SUP}$   | CSA の消費電流                | $V_{REF}, V_{VREF} = 3V \sim 5.5V$                                         |       | 4.5 | 6.5  | mA               |

| $T_{CMREC}$      | 同相復帰時間                   |                                                                            |       | 2   | 2.5  | us               |

| リップル             | SOx 出力リップル電圧             | ピーク ツー ピーク、 $V_{REF} = 3 \sim 5.5V$ 、<br>SOx 容量 = 500pF、入力換算、SOx / ゲイ<br>ン |       | 850 | 1100 | $\mu V$          |

| $C_{LOAD}$       | 最大負荷容量                   |                                                                            |       | 10  |      | nF               |

**保護回路**

|                       |                          |                           |       |       |       |         |

|-----------------------|--------------------------|---------------------------|-------|-------|-------|---------|

| $V_{GVDD\_UV\_B\_ST}$ | GVDD 低電圧警告スレッショルド立ち上がり   | $GVDD\_UV\_BST\_LV = 1b$  | 9.25  | 9.6   | 9.95  | V       |

| $V_{GVDD\_UV\_B\_ST}$ | GVDD 低電圧警告スレッショルド立ち下がり   | $GVDD\_UV\_BST\_LVL = 1b$ | 9.1   | 9.45  | 9.8   | V       |

| $V_{GVDD\_UV\_B\_ST}$ | GVDD 低電圧警告スレッショルド立ち上がり   | $GVDD\_UV\_BST\_LVL = 0b$ | 10.25 | 10.65 | 10.95 | V       |

| $V_{GVDD\_UV\_B\_ST}$ | GVDD 低電圧警告スレッショルド立ち下がり   | $GVDD\_UV\_BST\_LVL = 0b$ | 10.1  | 10.45 | 10.8  | V       |

| $V_{GVDD\_UVH}$       | GVDD 低電圧障害スレッショルド立ち上がり   |                           | 7.2   | 7.55  | 7.9   | V       |

| $V_{GVDD\_UVH}$       | GVDD 低電圧障害スレッショルド立ち下がり   |                           | 7     | 7.35  | 7.7   | V       |

| $V_{GVDD\_UVLO}$      | GVDD 低電圧誤動作防止スレッショルド     |                           | 5.35  | 5.65  | 5.95  | V       |

| $V_{GVDD\_UVLO}$      | GVDD 低電圧誤動作防止スレッショルド     |                           | 5.25  | 5.55  | 5.85  | V       |

| $V_{GVDD\_OV}$        | GVDD 過電圧スレッショルド立ち上がり     |                           | 16.9  | 17.65 | 18.4  | V       |

| $V_{GVDD\_OV}$        | GVDD 過電圧スレッショルド立ち下がり     |                           | 16.5  | 17.25 | 18    | V       |

| $t_{GVDD\_UVOV\_DEG}$ | GVDD 低電圧／過電圧デグリッチ        |                           | 12    |       |       | $\mu s$ |

| $V_{VDRAIN\_UVH}$     | VDRAIN 低電圧障害スレッショルド立ち上がり | $VDRAIN\_UVH\_LVL = 0b$   | 18    | 19    | 20    | V       |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ                 |                                  | テスト条件                                       | 最小値  | 標準値  | 最大値  | 単位      |

|-----------------------|----------------------------------|---------------------------------------------|------|------|------|---------|

| $V_{VDRINK\_UVH}$     | VDRAIN 低電圧障害スレッショルド立ち上がり         | $VDRINK\_UVH\_LVL = 0b$                     | 17   | 18   | 19   | V       |

| $V_{VDRINK\_UVH}$     | VDRAIN 低電圧障害スレッショルド立ち上がり         | $VDRINK\_UVH\_LVL = 01b$                    | 20   | 21   | 22   | V       |

| $V_{VDRINK\_UVH}$     | VDRAIN 低電圧障害スレッショルド立ち上がり         | $VDRINK\_UVH\_LVL = 01b$                    | 19   | 20   | 21   | V       |

| $V_{VDRINK\_UVH}$     | VDRAIN 低電圧障害スレッショルド立ち上がり         | $VDRINK\_UVH\_LVL = 10b$                    | 22   | 23   | 24   | V       |

| $V_{VDRINK\_UVH}$     | VDRAIN 低電圧障害スレッショルド立ち上がり         | $VDRINK\_UVH\_LVL = 10b$                    | 21   | 22   | 23   | V       |

| $V_{VDRINK\_UVH}$     | VDRAIN 低電圧障害スレッショルド立ち上がり         | $VDRINK\_UVH\_LVL = 11b$                    | 24   | 25   | 26   | V       |

| $V_{VDRINK\_UVH}$     | VDRAIN 低電圧障害スレッショルド立ち上がり         | $VDRINK\_UVH\_LVL = 11b$                    | 23   | 24   | 25   | V       |

| $V_{VDRINK\_UVL}$     | TCP立ち上がりを無効にする VDRINK 低電圧スレッショルド | $VDRINK\_UVL\_LVL = 0b$                     | 10.2 | 10.7 | 11.2 |         |

| $V_{VDRINK\_UVL}$     | TCP立ち上がりを無効にする VDRINK 低電圧スレッショルド | $VDRINK\_UVL\_LVL = 0b$                     | 10   | 10.5 | 11   | V       |

| $V_{VDRINK\_UVL}$     | TCP立ち上がりを無効にする VDRINK 低電圧スレッショルド | $VDRINK\_UVL\_LVL = 1b$                     | 5.15 | 5.65 | 5.95 | V       |

| $V_{VDRINK\_UVL}$     | TCP立ち上がりを無効にする VDRINK 低電圧スレッショルド | $VDRINK\_UVL\_LVL = 1b$                     | 5.05 | 5.55 | 5.85 | V       |

| $t_{VDRINK\_UV\_DEG}$ | VDRAIN 低電圧グリッチ除去                 |                                             |      | 12   |      | $\mu s$ |

| $V_{VDRINK\_OV}$      | VDRAIN 過電圧障害スレッショルド立ち上がり         | $VDRINK\_OV\_LVL = 0b$                      | 55.5 | 58   | 60.5 | V       |

| $V_{VDRINK\_OV}$      | VDRAIN 過電圧障害スレッショルド立ち下がり         | $VDRINK\_OV\_LVL = 0b$                      | 53.5 | 56   | 58.5 | V       |

| $V_{VDRINK\_OV}$      | VDRAIN 過電圧障害スレッショルド立ち上がり         | $VDRINK\_OV\_LVL = 1b$                      | 57.5 | 60   | 62.5 | V       |

| $V_{VDRINK\_OV}$      | VDRAIN 過電圧障害スレッショルド立ち下がり         | $VDRINK\_OV\_LVL = 1b$                      | 55.5 | 58   | 60.5 | V       |

| $V_{VDRINK\_OV}$      | VDRAIN 過電圧障害スレッショルド立ち上がり         | $VDRINK\_OV\_LVL = 10b$                     | 59.5 | 62   | 64.5 | V       |

| $V_{VDRINK\_OV}$      | VDRAIN 過電圧障害スレッショルド立ち下がり         | $VDRINK\_OV\_LVL = 10b$                     | 57.5 | 60   | 62.5 | V       |

| $V_{VDRINK\_OV}$      | VDRAIN 過電圧障害スレッショルド立ち上がり         | $VDRINK\_OV\_LVL = 11b$                     | 78   | 81.5 | 84   | V       |

| $V_{VDRINK\_OV}$      | VDRAIN 過電圧障害スレッショルド立ち下がり         | $VDRINK\_OV\_LVL = 11b$                     | 76   | 79.5 | 82   | V       |

| $t_{VDRINK\_OV\_DEG}$ | VDRAIN 過電圧デグリッチ                  |                                             |      | 6.5  |      | $\mu s$ |

| $V_{VCP\_UV}$         | VCP 低電圧障害スレッショルド立ち上がり            |                                             | 6.7  | 7.6  | 8.4  | V       |

| $V_{VCP\_UV}$         | VCP 低電圧障害スレッショルド立ち下がり            |                                             | 6.5  | 7.4  | 8.2  | V       |

| $t_{VCP\_UV\_DEG}$    | VCP 低電圧グリッチ除去                    |                                             |      | 12   |      | $\mu s$ |

| $V_{BST\_UV\_HI}$     | ブートストラップ低電圧レベル (High) 立ち上がり      | $8V < GVDD < 9V$ 。<br>$PREDRV\_BST\_UVLO=1$ | 4.5  | 5.15 | 5.8  | V       |

| $V_{BST\_UV\_HI}$     | ブートストラップ低電圧レベル (High) 立ち下がり      | $8V < GVDD < 9V$ 。<br>$PREDRV\_BST\_UVLO=1$ | 4.4  | 5.05 | 5.7  | V       |

| $V_{BST\_UV\_LO}$     | ブートストラップ低電圧レベル (Low) 立ち上がり       | $GVDD > 9V$ 。<br>$PREDRV\_BST\_UVLO=0$      | 5.45 | 6.1  | 6.8  | V       |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ               | テスト条件                      | 最小値                                 | 標準値   | 最大値  | 単位      |

|---------------------|----------------------------|-------------------------------------|-------|------|---------|

| $V_{BST\_UV\_LO}$   | ブートストラップ低電圧レベル (Low) 立ち下がり | $GVDD > 9V$ 。 $PREDRV\_BST\_UVLO=0$ | 5.35  | 6    | 6.65    |

| $t_{BST\_UV\_DEG}$  | ブートストラップ低電圧デグリッチ           |                                     |       | 6    | $\mu s$ |

| $V_{DVDD\_UV}$      | DVDD 低電圧障害スレッショルド立ち上がり     |                                     | 2.6   | 2.75 | 2.9     |

| $V_{DVDD\_UV}$      | DVDD 低電圧障害スレッショルド立ち下がり     |                                     | 2.5   | 2.65 | 2.8     |

| $V_{DVDD\_OV}$      | DVDD 過電圧障害スレッショルド立ち上がり     | $DVDD\_LDO\_SEL = 0b$ (3.3V)        | 3.7   | 3.85 | 4.0     |

| $V_{DVDD\_OV}$      | DVDD 過電圧障害スレッショルド立ち下がり     | $DVDD\_LDO\_SEL = 0b$ (3.3V)        | 3.65  | 3.8  | 3.95    |

| $V_{DVDD\_OV}$      | DVDD 過電圧障害スレッショルド立ち上がり     | $DVDD\_LDO\_SEL = 1b$ (5V)          | 5.55  | 5.75 | 5.95    |

| $V_{DVDD\_OV}$      | DVDD 過電圧障害スレッショルド立ち下がり     | $DVDD\_LDO\_SEL = 1b$ (5V)          | 5.5   | 5.7  | 5.9     |

| $t_{DVDD\_OV\_DEG}$ | DVDD 過電圧デグリッチ              |                                     |       | 18   | $\mu s$ |

| $V_{VREF\_UV}$      | VREF 低電圧障害スレッショルド立ち上がり     | VREF 立ち上がり                          | 2.05  | 2.2  | 2.35    |

| $V_{VREF\_UV}$      | VREF 低電圧障害スレッショルド立ち下がり     | VREF 立ち下がり                          | 1.85  | 2    | 2.15    |

| $t_{VREF\_UV\_DEG}$ | VREF 低電圧グリッチ除去             |                                     |       | 12   | $\mu s$ |

| TOTW                | 過熱警告スレッショルド立ち上がり           |                                     | 127   | 142  | 157     |

| TOTW                | 過熱警告スレッショルド立ち下がり           |                                     | 121   | 136  | 151     |

| TOTSD               | 過熱シャットダウンスレッショルド立ち上がり      |                                     | 161   | 176  | 191     |

| TOTSD               | 過熱シャットダウンスレッショルド立ち下がり      |                                     | 155   | 170  | 185     |

| VVDS_LVL0           | VDS 過電流障害レベル               | $VDS\_LVL\_x = 0000b$               | 0.075 | 0.1  | 0.120   |

| VVDS_LVL1           | VDS 過電流障害レベル               | $VDS\_LVL\_x = 0001b$               | 0.125 | 0.15 | 0.170   |

| VVDS_LVL2           | VDS 過電流障害レベル               | $VDS\_LVL\_x = 0010b$               | 0.175 | 0.2  | 0.220   |

| VVDS_LVL3           | VDS 過電流障害レベル               | $VDS\_LVL\_x = 0011b$               | 0.27  | 0.3  | 0.33    |

| VVDS_LVL4           | VDS 過電流障害レベル               | $VDS\_LVL\_x = 0100b$               | 0.38  | 0.4  | 0.42    |

| VVDS_LVL5           | VDS 過電流障害レベル               | $VDS\_LVL\_x = 0101b$               | 0.475 | 0.5  | 0.525   |

| VVDS_LVL6           | VDS 過電流障害レベル               | $VDS\_LVL\_x = 0110b$               | 0.57  | 0.6  | 0.63    |

| VVDS_LVL7           | VDS 過電流障害レベル               | $VDS\_LVL\_x = 0111b$               | 0.67  | 0.7  | 0.73    |

| VVDS_LVL8           | VDS 過電流障害レベル               | $VDS\_LVL\_x = 1000b$               | 0.76  | 0.8  | 0.84    |

| VVDS_LVL9           | VDS 過電流障害レベル               | $VDS\_LVL\_x = 1001b$               | 0.86  | 0.9  | 0.94    |

| VVDS_LVL10          | VDS 過電流障害レベル               | $VDS\_LVL\_x = 1010b$               | 0.95  | 1.0  | 1.05    |

| VVDS_LVL11          | VDS 過電流障害レベル               | $VDS\_LVL\_x = 1011b$               | 1.43  | 1.5  | 1.57    |

| VVDS_LVL12          | VDS 過電流障害レベル               | $VDS\_LVL\_x = 1100b$               | 1.9   | 2.0  | 2.1     |

| VVGS_FLT            | VGS 障害スレッショルド立ち上がり         | 障害 VGS モニタモード。VGS 立ち上がり             | 0.6   | 1.2  | 1.7     |

| VVGS_FLT            | VGS 障害スレッショルド立ち下がり         | 障害 VGS モニタモード。VGS 立ち下がり             | 0.5   | 1.1  | 1.6     |

| $t_{VGS\_DG0}$      | VGS 障害プログラマブルグリッチ除去        | $VGS\_DEG = 00b$                    |       | 0.5  | $\mu s$ |

| $t_{VGS\_DG1}$      | VGS 障害プログラマブルグリッチ除去        | $VGS\_DEG = 01b$                    |       | 1.0  | $\mu s$ |

| $t_{VGS\_DG2}$      | VGS 障害プログラマブルグリッチ除去        | $VGS\_DEG = 10b$                    |       | 1.5  | $\mu s$ |

| $t_{VGS\_DG3}$      | VGS 障害プログラマブルグリッチ除去        | $VGS\_DEG = 11b$                    |       | 2.0  | $\mu s$ |

| $t_{BLNK0}$         | VDS/VGS 監視プログラマブルブランкиング期間 | $VDS\_VGS\_BLK = 000b$              |       | 0    | $\mu s$ |

| $t_{BLNK1}$         | VDS/VGS 監視プログラマブルブランкиング期間 | $VDS\_VGS\_BLK = 001b$              |       | 0.5  | $\mu s$ |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ                    |                              | テスト条件                | 最小値 | 標準値  | 最大値 | 単位 |

|--------------------------|------------------------------|----------------------|-----|------|-----|----|

| tBLNK2                   | VDS/VGS 監視プログラマブルブランкиング期間   | VDS_VGS_BLK = 010b   |     | 1.0  |     | μs |

| tBLNK3                   | VDS/VGS 監視プログラマブルブランкиング期間   | VDS_VGS_BLK = 011b   |     | 2.0  |     | μs |

| tBLNK4                   | VDS/VGS 監視プログラマブルブランкиング期間   | VDS_VGS_BLK = 100b   |     | 6.0  |     | μs |

| tBLNK5                   | VDS/VGS 監視プログラマブルブランкиング期間   | VDS_VGS_BLK = 101b   |     | 8.0  |     | μs |

| tBLNK6                   | VDS/VGS 監視プログラマブルブランкиング期間   | VDS_VGS_BLK = 110b   |     | 10.0 |     | μs |

| tBLNK7                   | VDS/VGS 監視プログラマブルブランкиング期間   | VDS_VGS_BLK = 111b   |     | 12.0 |     | μs |

| t <sub>VDS_DG0</sub>     | V <sub>DS</sub> 保護グリッチ除去時間   | VDS_DEG = 000b       |     | 0.5  |     | μs |

| t <sub>VDS_DG1</sub>     | V <sub>DS</sub> 保護グリッチ除去時間   | VDS_DEG = 001b       |     | 1.0  |     | μs |

| t <sub>VDS_DG2</sub>     | V <sub>DS</sub> 保護グリッチ除去時間   | VDS_DEG = 010b       |     | 1.5  |     | μs |

| t <sub>VDS_DG3</sub>     | V <sub>DS</sub> 保護グリッチ除去時間   | VDS_DEG = 011b       |     | 2.0  |     | μs |

| t <sub>VDS_DG4</sub>     | V <sub>DS</sub> 保護グリッチ除去時間   | VDS_DEG = 100b       |     | 4.0  |     | μs |

| t <sub>VDS_DG5</sub>     | V <sub>DS</sub> 保護グリッチ除去時間   | VDS_DEG = 101b       |     | 6.0  |     | μs |

| t <sub>VDS_DG6</sub>     | V <sub>DS</sub> 保護グリッチ除去時間   | VDS_DEG = 110b, 111b |     | 8.0  |     | μs |

| トリップ ドリフト                | LS および HS VDS スレッショルドの経時ドリフト |                      | -2  | 0    | 2   | mV |

| I <sub>OPENLOAD_PU</sub> | SH ピンの開放負荷プルアップ電流            |                      | 2.4 | 3.5  | 6   | mA |

| I <sub>OPENLOAD_PD</sub> | SH ピンの開放負荷プルダウン電流            |                      | 2.4 | 4.2  | 6   | mA |

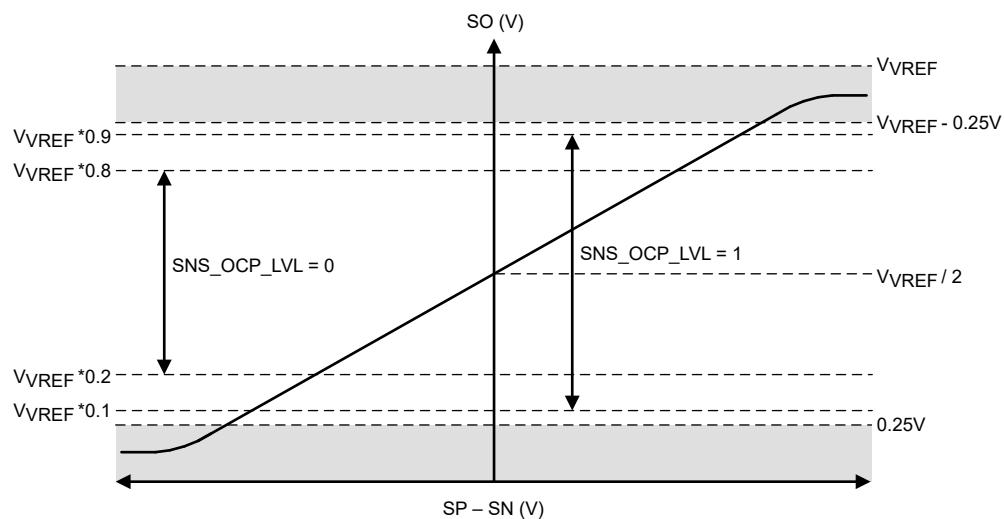

#### RSHUNT\_OCP

|                          |                  |                                                    |           |           |    |

|--------------------------|------------------|----------------------------------------------------|-----------|-----------|----|

| V <sub>RSHUNT_OC_P</sub> | SNS_OCP しきい値     | RSHUNT_OCP_LVL=0                                   | VREF*0.20 | VREF*0.80 |    |

| V <sub>RSHUNT_OC_P</sub> | SNS_OCP しきい値     | RSHUNT_OCP_LVL=1                                   | VREF*0.10 | VREF*0.90 |    |

| RSHUNT_OCP_VAR           | SNS_OCP しきい値ばらつき | RSHUNT_OCP_LVL=0, 1, k=1/2, SN/SP コモンモード = 0V      | -3.2      | 3.2       | %  |

| RSHUNT_OCP_VAR           | SNS_OCP しきい値ばらつき | RSHUNT_OCP_LVL=0, 1, k=1/2, SN/SP コモンモード = -0.175V | -3.5      | 3.5       | %  |

| RSHUNT_OCP_VAR           | SNS_OCP しきい値ばらつき | RSHUNT_OCP_LVL=0, 1, k=1/2, SN/SP コモンモード = 0.7V    | -3.8      | 3.8       | %  |

| RSHUNT_OCP_VAR           | SNS_OCP しきい値ばらつき | RSHUNT_OCP_LVL=0, 1, k=1/8, SN/SP コモンモード = 0V      | -2        | 2         | %  |

| RSHUNT_OCP_VAR           | SNS_OCP しきい値ばらつき | RSHUNT_OCP_LVL=0, 1, k=1/8, SN/SP コモンモード = -0.175V | -2        | 2         | %  |

| RSHUNT_OCP_VAR           | SNS_OCP しきい値ばらつき | RSHUNT_OCP_LVL=0, 1, k=1/8, SN/SP コモンモード = 0.7V    | -2        | 2         | %  |

| t <sub>SNS_OCP_DEG</sub> | SNS_OCP デグリッチ    | SNS_OCP_DEG = 00b                                  |           | 3         | μs |

| t <sub>SNS_OCP_DEG</sub> | SNS_OCP デグリッチ    | SNS_OCP_DEG = 01b                                  |           | 6         | μs |

| t <sub>SNS_OCP_DEG</sub> | SNS_OCP デグリッチ    | SNS_OCP_DEG = 10b                                  |           | 9         | μs |

動作時接合部温度範囲および推奨動作条件下で、(特に記述のない限り)

| パラメータ               | テスト条件         | 最小値 | 標準値               | 最大値 | 単位 |

|---------------------|---------------|-----|-------------------|-----|----|

| $t_{SNS\_OCP\_DEG}$ | SNS_OCP デグリッチ |     | SNS_OCP_DEG = 11b | 12  | μs |

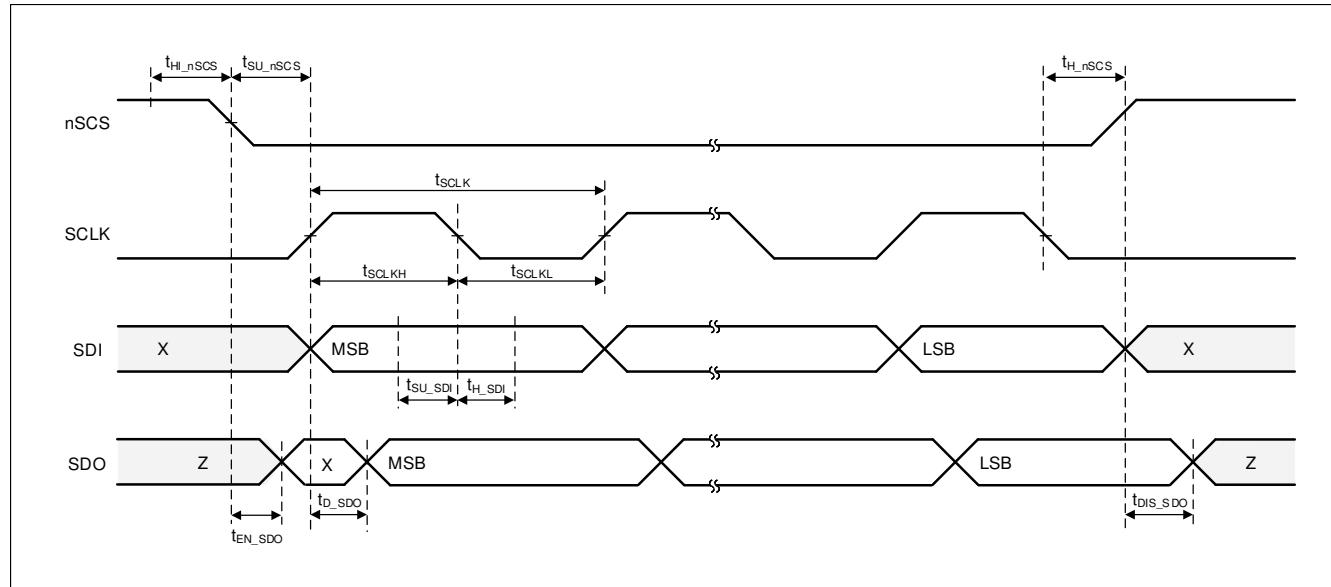

## 5.5 SPI のタイミング要件

$V_{GVDD} = 8 \sim 15 \text{ V}$ 、動作時周囲温度範囲全体 (特に記述のない限り)

|                 |                                   | 最小値 | 公称値 | 最大値 | 単位                                         |

|-----------------|-----------------------------------|-----|-----|-----|--------------------------------------------|

| $t_{CLK}$       | SCLK の最小期間                        | 100 |     |     | ns                                         |

| $t_{CLKH}$      | SCLK 最小 High 時間                   | 50  |     |     | ns                                         |

| $t_{CLKL}$      | SCLK の最小 Low 時間                   | 50  |     |     | ns                                         |

| $t_{SU\_SDI}$   | SDI 入力データ セットアップ時間                | 15  |     |     | ns                                         |

| $t_{H\_SDI}$    | SDI 入力データ ホールド時間                  | 25  |     |     | ns                                         |

| $t_{D\_SDO}$    | SDO 出力データ遅延時間、 $CL = 20\text{pF}$ | 0   | 50  | ns  | SCLK High から SDO 有効まで、 $C_L = 20\text{pF}$ |

| $t_{SU\_nSCS}$  | nSCS 入力セットアップ時間                   | 25  |     |     | ns                                         |

| $t_{H\_nSCS}$   | nSCS 入力ホールド時間                     | 25  |     |     | ns                                         |

| $t_{HI\_nSCS}$  | nSCS のアクティブ Low の前の最小 High 時間     | 450 |     |     | ns                                         |

| $t_{ACC\_nSCS}$ | nSCS アクセス時間                       |     | 50  |     | ns                                         |

| $t_{DIS\_nSCS}$ | nSCS ディスエーブル時間                    |     | 50  |     | ns                                         |

## 5.6 SPI のタイミング図

図 5-1. SPI ペリフェラルモードのタイミング図

## 6 詳細説明

### 6.1 概要

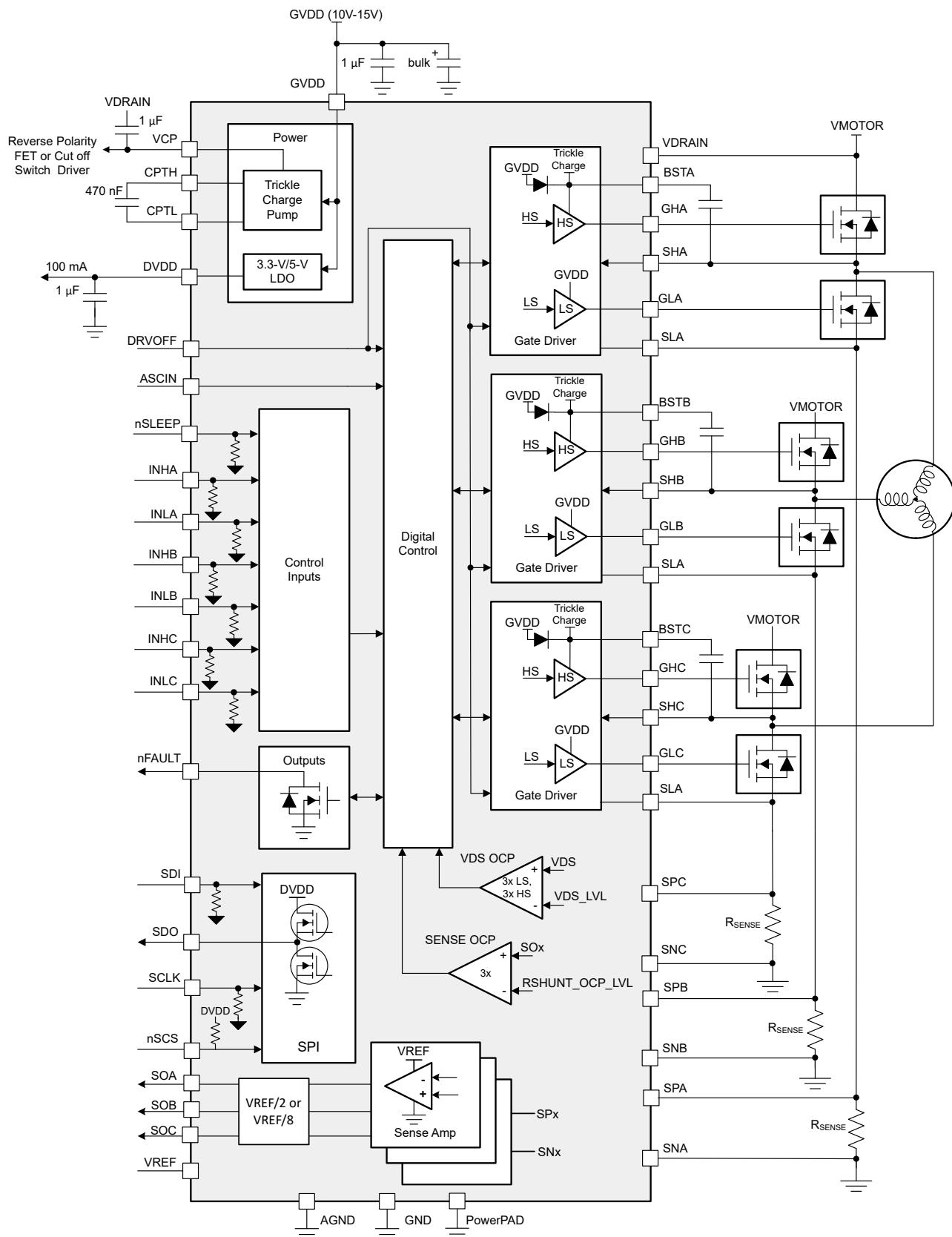

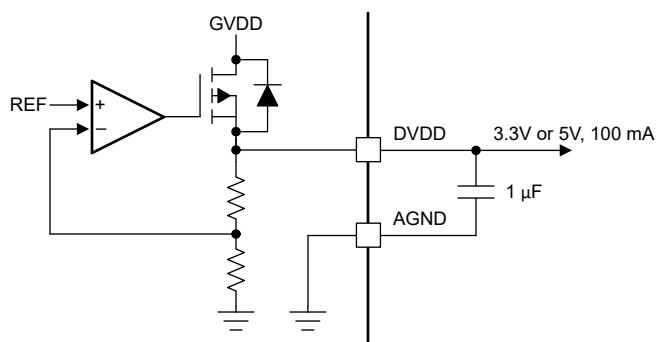

DRV8363-Q1 は、3 位相モーター駆動アプリケーション用の統合型 8V ~ 85V ゲートドライバです。これらのデバイスでは、3 つの独立したハーフブリッジゲートドライバ、トリクルチャージポンプ、低出力マイコンの電源用リニアレギュレータを統合することにより、システムのコンポーネント数、コスト、複雑性を低減しています。このデバイスは、最大 3 つの電流シャント（または電流センス）アンプも内蔵しています。標準のシリアル ペリフェラル インターフェイス (SPI) を使うと、デバイスの各種設定とフォルト診断情報の読み出しを外部コントローラから簡単にすることができます。

本ゲートドライバは外付け N チャネルハイサイド/ローサイドパワー MOSFET をサポートしており、最大 1A ソースおよび 2A シンクのピーク電流を駆動することができます。ハイサイド ゲート駆動の電源電圧は、ブートストラップ コンデンサから生成されます。ローサイドゲートドライバの電源電圧は、公称 12V で外部から供給されます。

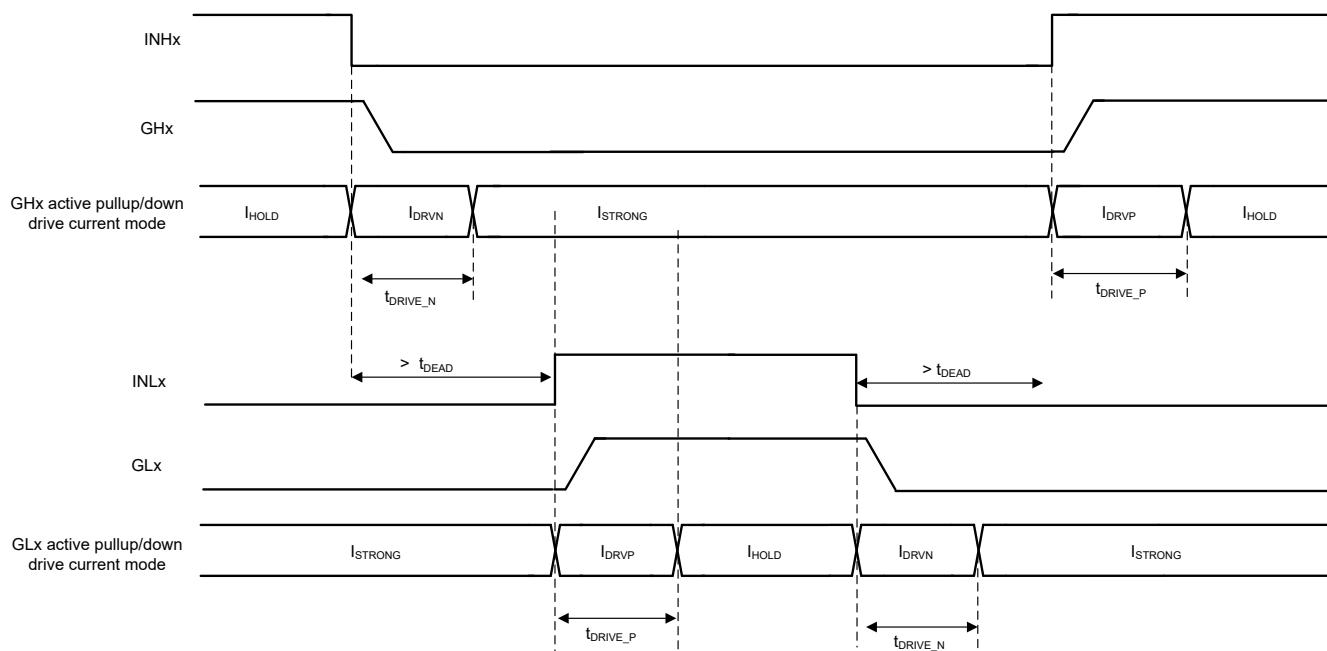

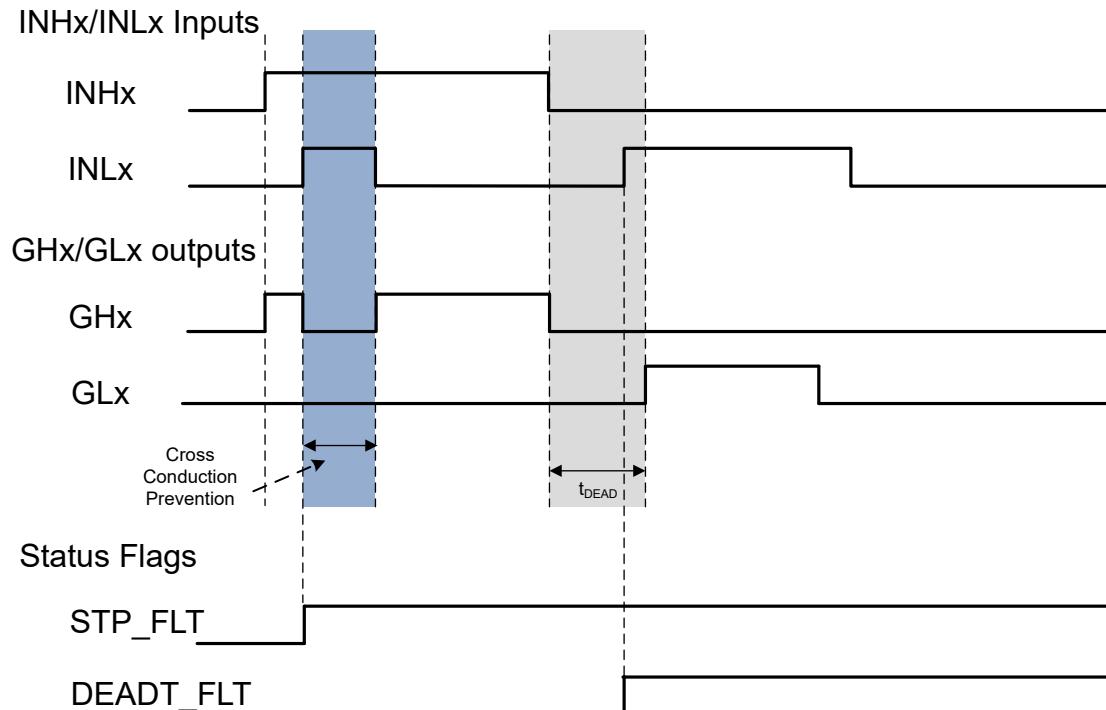

スマート ゲートドライブ アーキテクチャはゲート駆動出力電流の強度を動的に調整する機能を備えています。これにより、ゲートドライバはパワー MOSFET の VDS スイッチング速度を制御できます。この機能により、外部のゲート駆動抵抗およびダイオードが不要になるので、部品表 (BOM) の部品点数や、コスト、プリント基板 (PCB) 上に占める面積が低減します。このアーキテクチャでは、ゲートドライバで発生する短絡からの保護、ハーフブリッジのデッド タイムの制御、外部パワー MOSFET の  $dV/dt$  寄生ターンオンからの保護のために、内部ステートマシンも使用します。

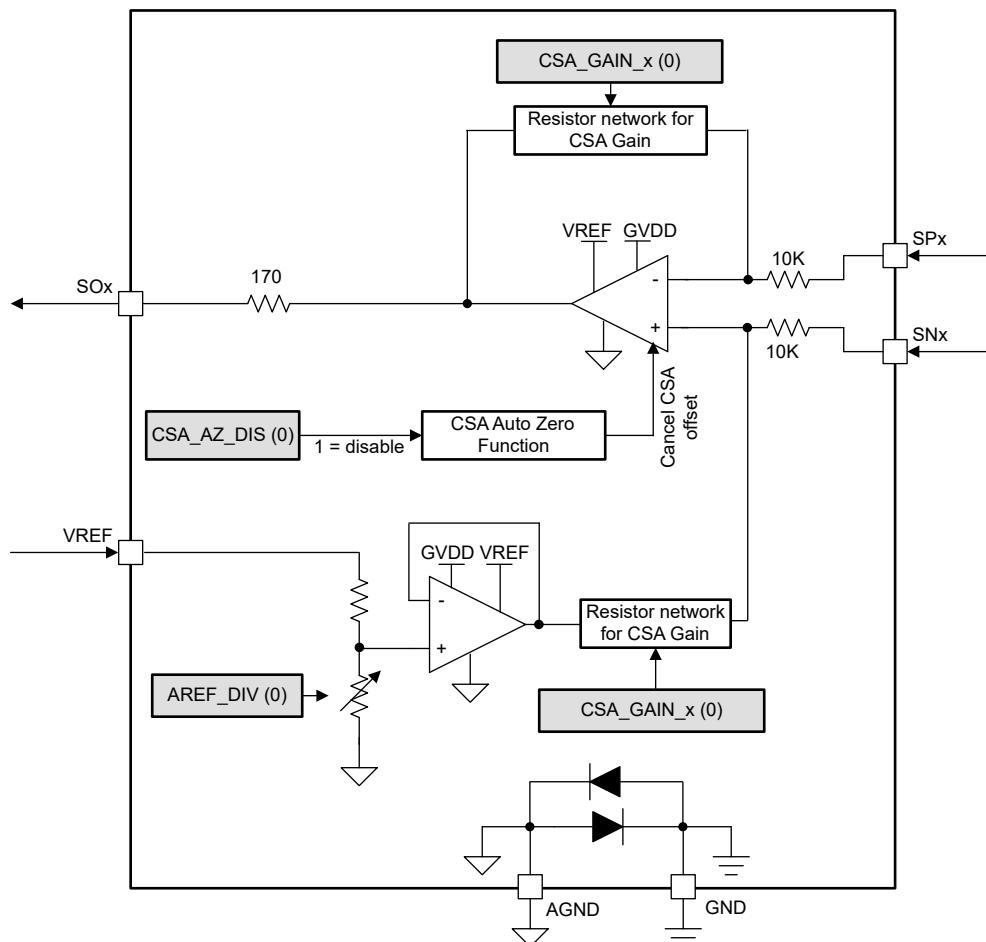

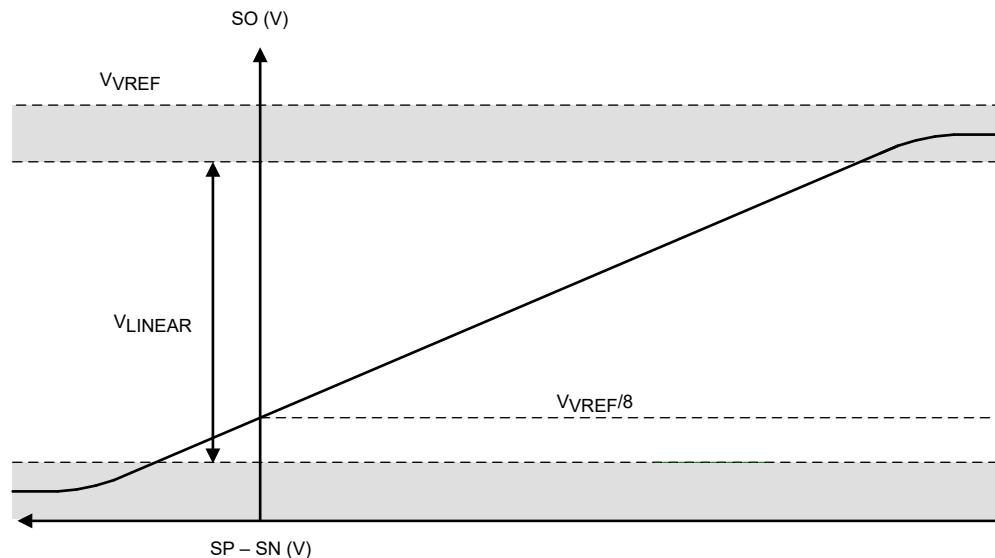

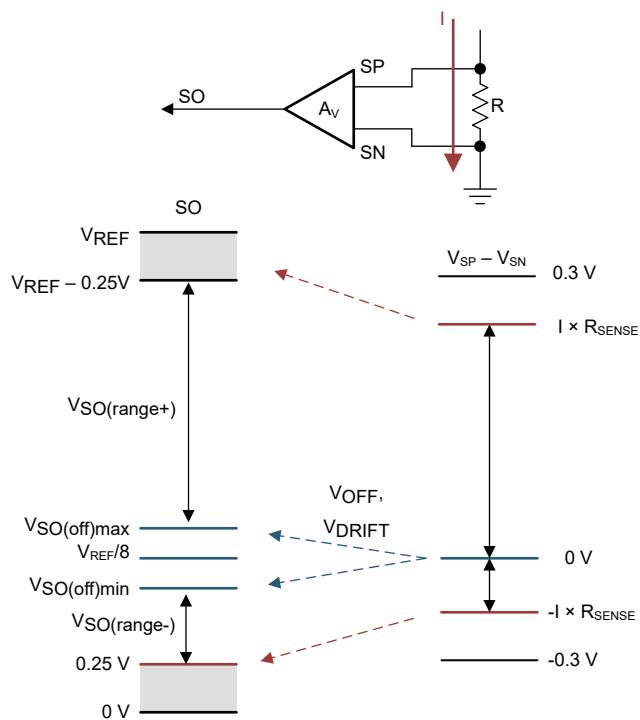

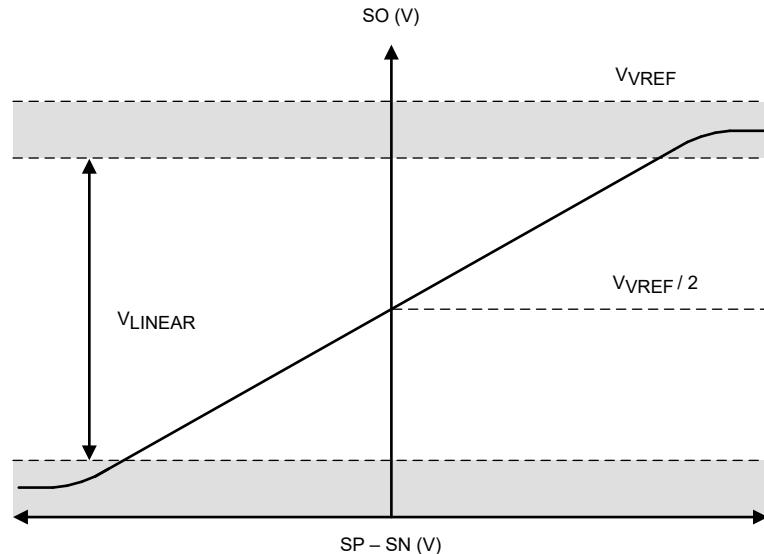

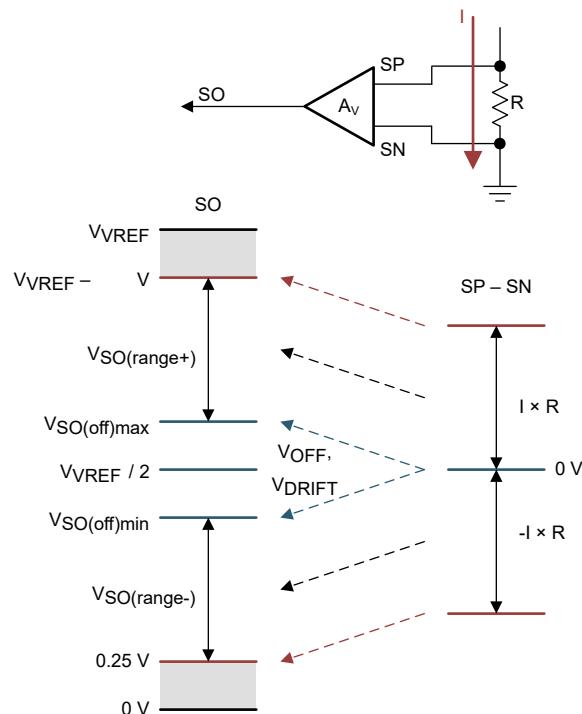

DRV8363-Q1 は、ローサイド シャント抵抗を使用してすべての外部ハーフブリッジを流れる電流のレベルを監視するために、電流センスアンプが内蔵されています。電流センスアンプのゲイン設定は、SPI コマンドを介して調整できます。

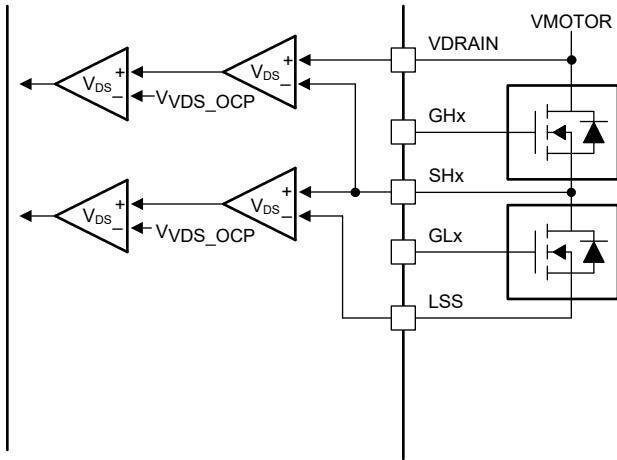

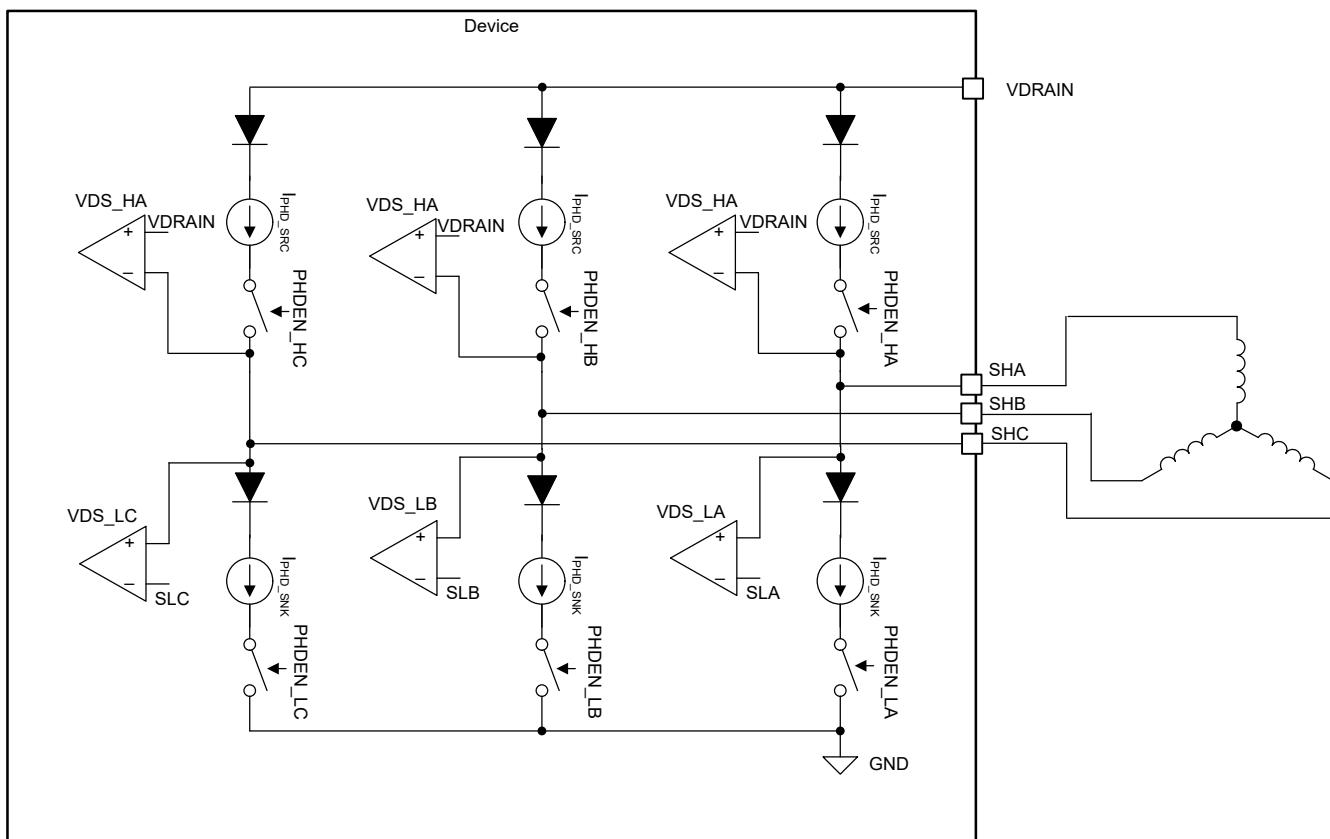

高いレベルでデバイスが統合されていることに加え、DRV8363-Q1 には、広範な保護機能も組み込まれています。主な機能には、電源の低電圧/過電圧監視 (GVDD UV/OV)、ドレイン電源の低電圧/過電圧監視 (VDRAIN UV/OV)、VDS 過電流監視、 $R_{SENSE}$  過電流監視 (SNS\_OCP)、過熱監視/シャットダウン (OTW および OTSD) が含まれます。故障イベントは、nFAULT ピンで通知されます。

## 6.2 機能ブロック図

## 6.3 機能説明

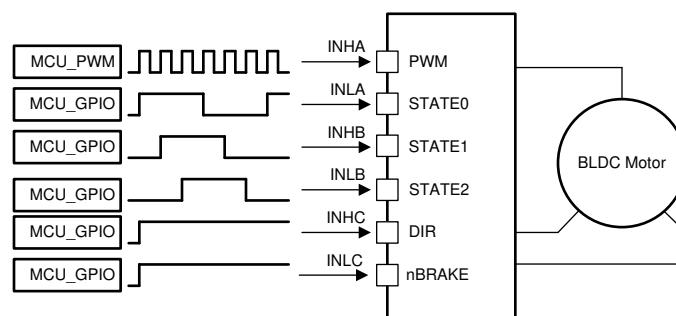

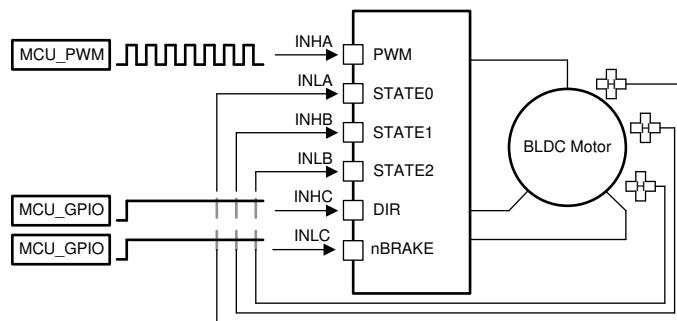

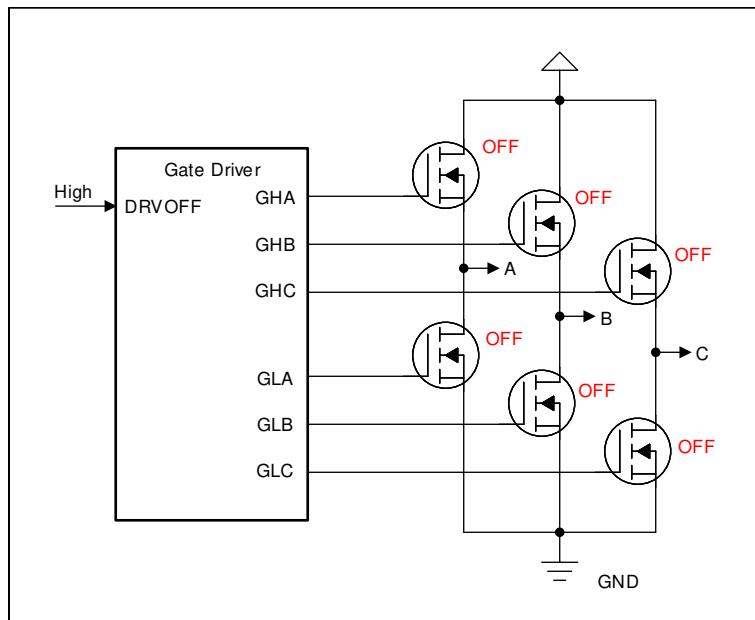

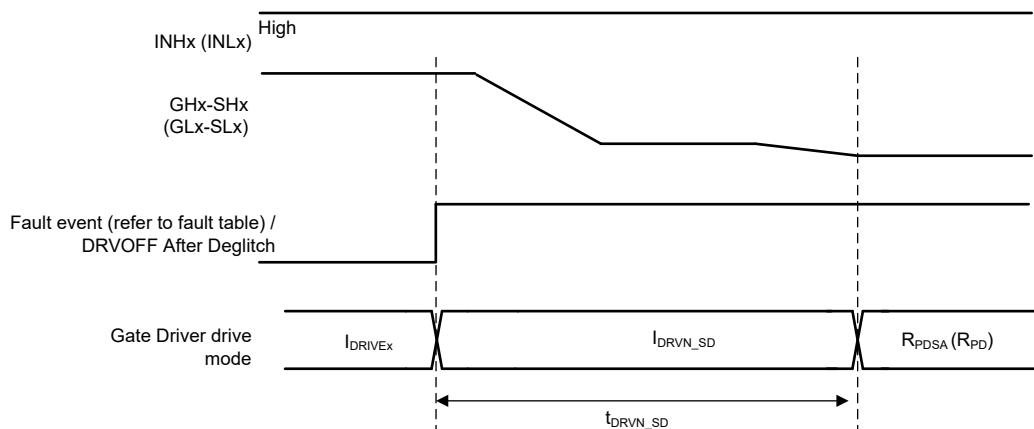

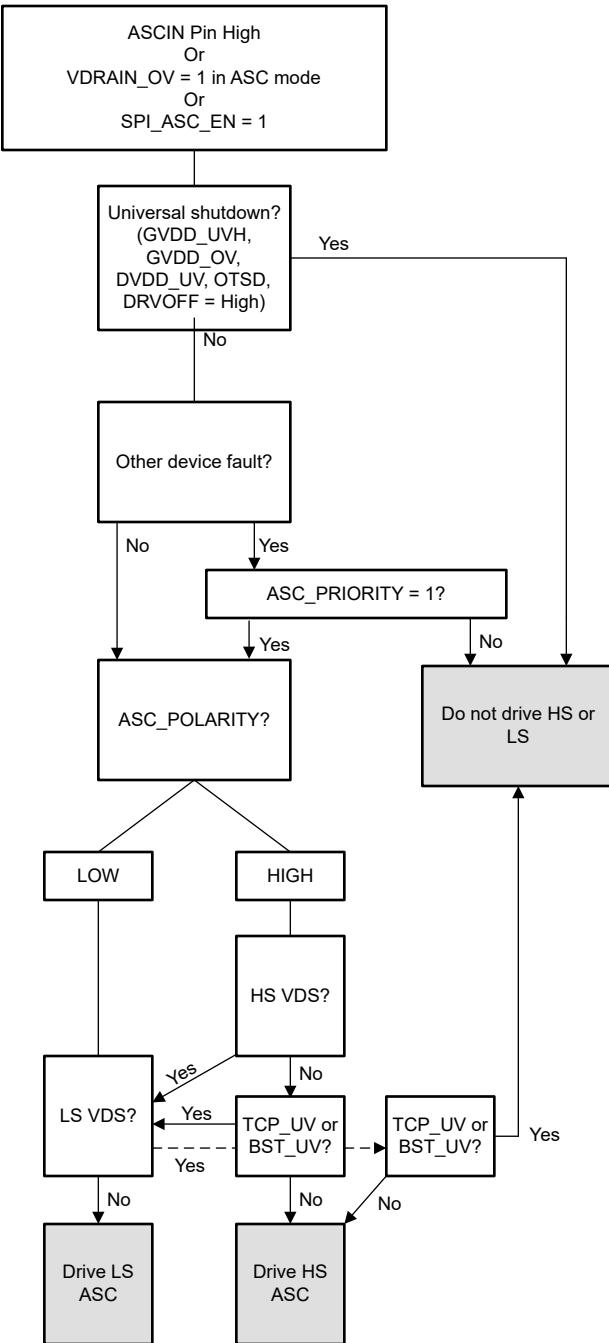

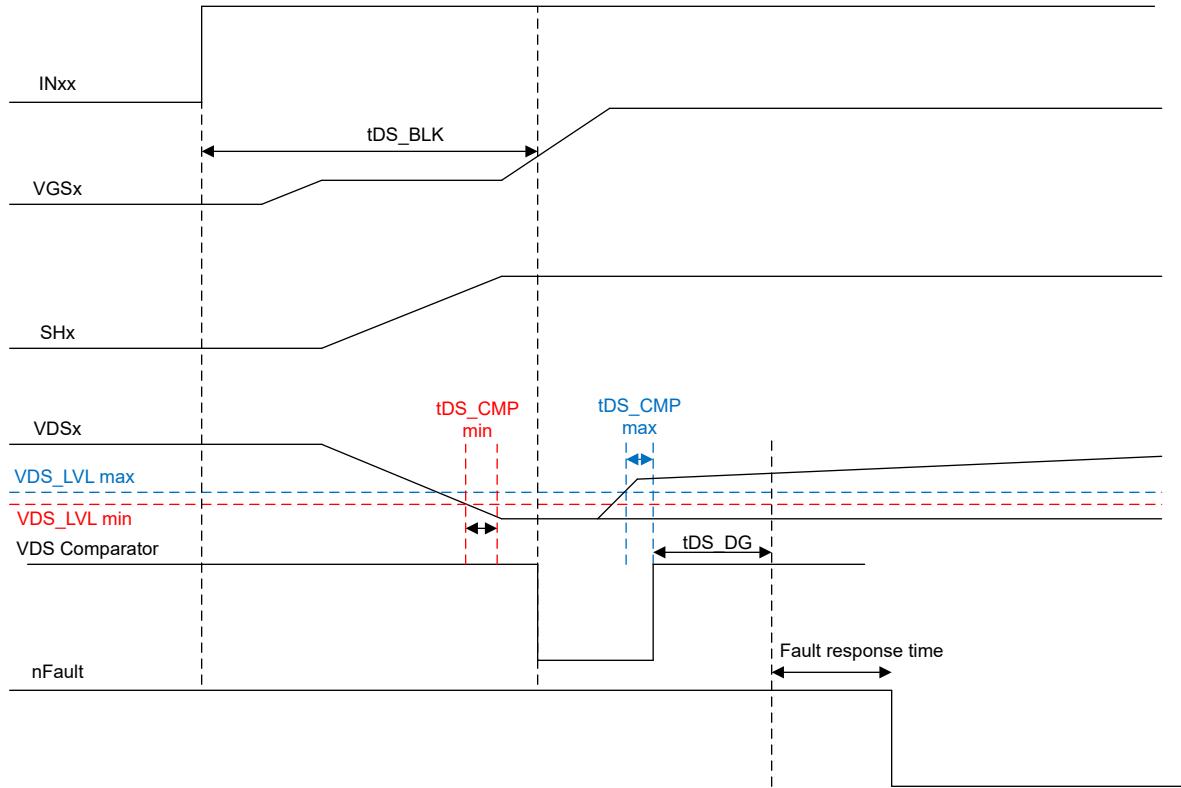

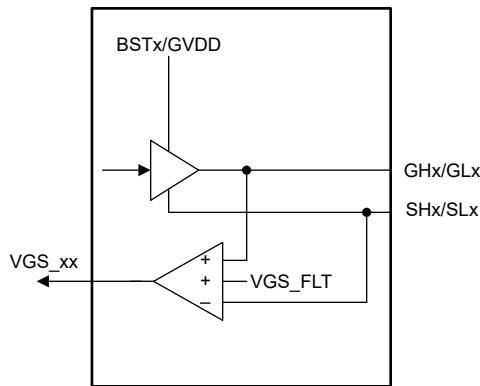

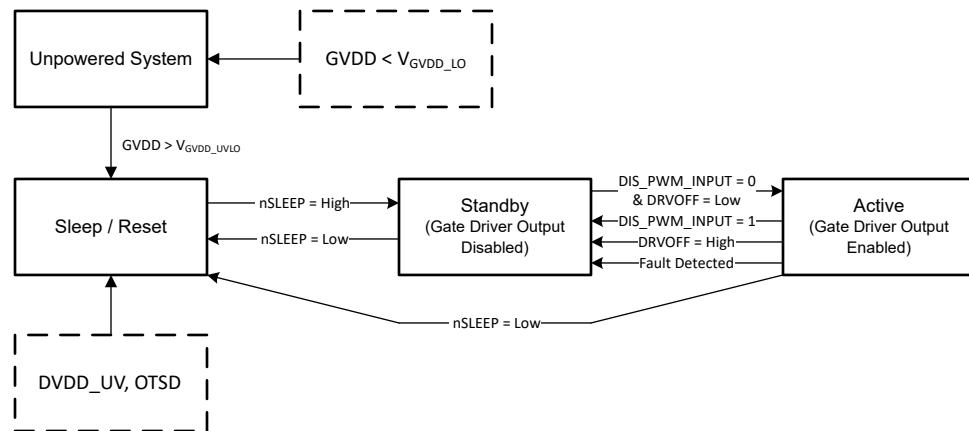

### 6.3.1 3 つの BLDC ゲート ドライバ