**DRV8818**

# DRV8818 ステッピング モーター コントローラ IC

## 1 特長

- パルス幅変調(PWM)マイクロステッピング モータドラ イバ

- マイクロステッピング インデクサ内蔵

- 最大8つのマイクロステップ/ステップ

- ステップ/ディレクティブ制御

- プログラマブルなミクストディケイ、ブランキング、お よびオフ時間

- 巻線あたり最大 2.5A の電流

- 低 0.37 Ω(HS + LS) MOSFET(金属酸化膜半導体 型電界効果トランジスタ) R<sub>DS(ON)</sub>(25°C)

- 8V ~ 35V の動作電源電圧範囲

- 低 R<sub>DS</sub>(ON)の DRV8811 用ピン互換アップグレード

- 熱特性強化型の表面実装パッケージ

- 保護機能

- VM 低電圧誤動作防止 (UVLO)

- 過電流保護 (OCP)

- サーマル シャットダウン (TSD)

## 2 アプリケーション

- プリンタ

- 繊維機械

- ポジショニング/トラッキング

- ファクトリオートメーション

- ロボティクス

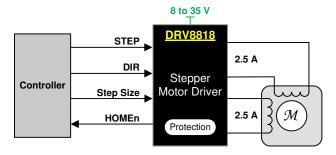

## 3 概要

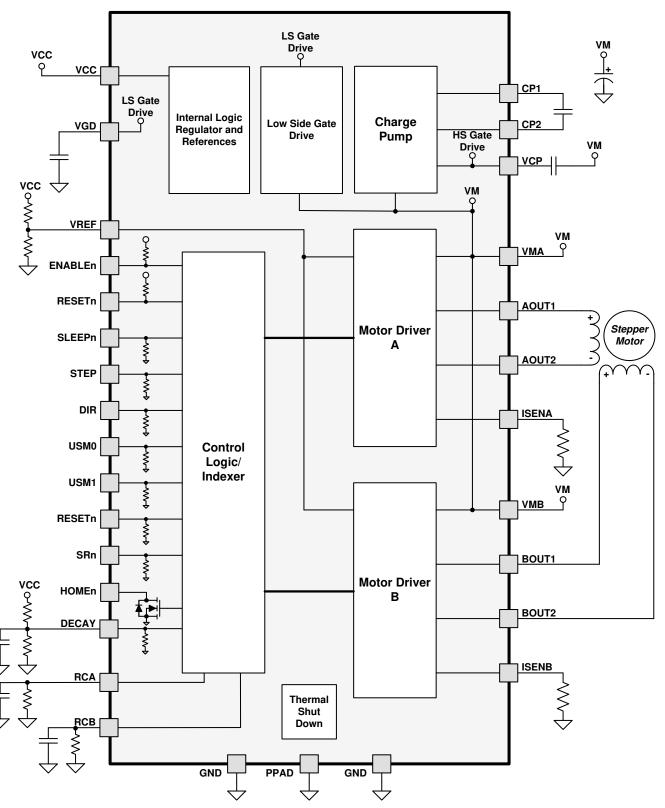

DRV8818 は、プリンタ、スキャナなど、自動化機器アプリ ケーション向けの統合型ステッピングモータドライバを提 供します。このデバイスには、2 つの H ブリッジ ドライバ と、ステッピングモータを制御するマイクロステッピング・イ ンデクサ・ロジックが搭載されています。

各出力ドライバ ブロックには、モータ巻線を駆動するフル H ブリッジとして構成された N チャネル パワー MOSFET が搭載されています。

単純なステップ/ディレクションインターフェースにより、制 御回路に簡単に接続できます。モードピンにより、モータ をフルステップ、ハーフステップ、クォーターステップ、また はエイスステッーモードに設定することが可能になります。 ディケイ(電流減衰) モードおよび PWM(パルス幅変調) オフ時間はプログラマブル。

過電流保護、短絡保護、低電圧誤動作防止、および過熱 保護のために、内部シャットダウン機能が搭載されていま

DRV8818 は PowerPAD™ 付き 28 ピン HTSSOP (Shrink Small-Outline Package) パッケージに封止され ています。

## デバイス情報(1)

| 部品番号    | パッケージ       | パッケージ サイズ <sup>(2)</sup> |

|---------|-------------|--------------------------|

| DRV8818 | HTSSOP (28) | 9.70 mm × 6.40mm         |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

概略回路図

## **Table of Contents**

| 1 特長                                              | 1 | 6.2 Functional Block Diagrar |

|---------------------------------------------------|---|------------------------------|

| 2 アプリケーション                                        |   | 6.3 Feature Description      |

| 3 概要                                              |   | 6.4 Device Functional Mode   |

| 4 Pin Configuration and Functions                 |   | 7 Application and Implement  |

| Pin Functions                                     |   | 7.1 Application Information  |

| 5 Specifications                                  |   | 7.2 Typical Application      |

| 5.1 Absolute Maximum Ratings                      |   | 7.3 Power Supply Recomme     |

| 5.2 ESD Ratings                                   |   | 7.4 Layout                   |

| 5.3 Recommended Operating Conditions              |   | 8 Device and Documentation   |

| 5.4 Thermal Information                           |   | 8.1 Documentation Support.   |

| 5.5 Electrical Characteristics                    |   | 8.2 Community Resources      |

| 5.6 Timing Requirements                           |   | 8.3 Trademarks               |

| 5.7 Motor Driver Timing Switching Characteristics |   | 9 Revision History           |

| 5.8 Typical Characteristics                       |   | 10 Mechanical, Packaging, a  |

| 6 Detailed Description                            |   | Information                  |

| 6.1 Overview                                      |   |                              |

|     | 6.2 Functional Block Diagram         | . IL |

|-----|--------------------------------------|------|

|     | 6.3 Feature Description              | .11  |

|     | 6.4 Device Functional Modes          | .16  |

| 7 / | Application and Implementation       | . 17 |

|     | 7.1 Application Information          |      |

|     | 7.2 Typical Application              |      |

|     | 7.3 Power Supply Recommendations     |      |

|     | 7.4 Layout                           | 20   |

| 8 I | Device and Documentation Support     | .23  |

|     | 8.1 Documentation Support            |      |

|     | 8.2 Community Resources              |      |

|     | 8.3 Trademarks                       | 23   |

| 9 I | Revision History                     | 23   |

|     | Mechanical, Packaging, and Orderable |      |

|     | Information                          | 24   |

|     |                                      |      |

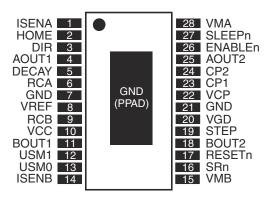

# **4 Pin Configuration and Functions**

図 4-1. PWP Package 28-Pin HTSSOP Top View

#### **Pin Functions**

| PIN       |        | <b>-</b> (1)        |                                       |                                                                                                                                                   |  |  |  |

|-----------|--------|---------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME      | NO.    | TYPE <sup>(1)</sup> | DESCRIPTION                           |                                                                                                                                                   |  |  |  |

| POWER AND | GROUNE | <b>)</b>            | 1                                     |                                                                                                                                                   |  |  |  |

| CP1       | 23     | Ю                   | Charge pump flying capacitor          | Connect a 0.22µF capacitor between CP1 and CP2.                                                                                                   |  |  |  |

| CP2       | 24     | Ю                   | Charge pump flying capacitor          | Connect a 0.22µF capacitor between CP1 and CP2.                                                                                                   |  |  |  |

| GND       | 7, 21  | _                   | Device ground                         |                                                                                                                                                   |  |  |  |

| VCC       | 10     | _                   | Logic supply voltage                  | Connect to 3V to 5V logic supply. Bypass to GND with a 0.1µF ceramic capacitor.                                                                   |  |  |  |

| VCP       | 22     | Ю                   | High-side gate drive voltage          | Connect a 0.22µF ceramic capacitor to V <sub>M</sub> .                                                                                            |  |  |  |

| VGD       | 20     | Ю                   | Low-side gate drive voltage           | Bypass to GND with a 0.22µF ceramic capacitor.                                                                                                    |  |  |  |

| VMA       | 28     | _                   | Bridge A power supply                 | Connect to motor supply (8V to 35V). Both VMA and VMB must be connected to                                                                        |  |  |  |

| VMB       | 15     | _                   | Bridge B power supply                 | same supply.                                                                                                                                      |  |  |  |

| CONTROL   | '      |                     |                                       |                                                                                                                                                   |  |  |  |

| DECAY     | 5      | I                   | Decay mode select                     | Voltage applied sets decay mode - see motor driver description for details. Bypass to GND with a 0.1µF ceramic capacitor. Weak internal pulldown. |  |  |  |

| DIR       | 3      | ı                   | Direction input                       | Level sets the direction of stepping. Weak internal pulldown.                                                                                     |  |  |  |

| ENABLEn   | 26     | I                   | Enable input                          | Logic high to disable device outputs, logic low to enable outputs. Weak internal pullup to VCC.                                                   |  |  |  |

| ISENA     | 1      | _                   | Bridge A ground / Isense              | Connect to current sense resistor for bridge A                                                                                                    |  |  |  |

| ISENB     | 14     | _                   | Bridge B ground / Isense              | Connect to current sense resistor for bridge B                                                                                                    |  |  |  |

| RCA       | 6      | I                   | Bridge A blanking and off time adjust | Connect a parallel resistor and capacitor to GND - see motor driver description for details.                                                      |  |  |  |

| RCB       | 9      | I                   | Bridge B blanking and off time adjust | Connect a parallel resistor and capacitor to GND - see motor driver description for details.                                                      |  |  |  |

| RESETn    | 17     | I                   | Reset input                           | Active-low reset input initializes the indexer logic and disables the H-bridge outputs. Weak internal pullup to VCC.                              |  |  |  |

| SLEEPn    | 27     | I                   | Sleep mode input                      | Logic high to enable device, logic low to enter low-power sleep mode. Weak internal pulldown.                                                     |  |  |  |

| SRn       | 16     | I                   | Sync. Rect. enable input              | Active-low. When low, synchronous rectification is enabled. Weak internal pulldown.                                                               |  |  |  |

| STEP      | 19     | I                   | Step input                            | Rising edge causes the indexer to move one step. Weak internal pulldown.                                                                          |  |  |  |

| USM0      | 13     | I                   | Microstep mode 0                      | USM0 and USM1 set the step mode - full step, half step, quarter step, or eight microsteps/step. Weak internal pulldown.                           |  |  |  |

| USM1      | 12     | I                   | Microstep mode 1                      | USM0 and USM1 set the step mode - full step, half step, quarter step, or eight microsteps/step. Weak internal pulldown.                           |  |  |  |

| VREF      | 8      | I                   | Current set reference input           | Reference voltage for winding current set                                                                                                         |  |  |  |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

3

| PIN     |     | TYPE <sup>(1)</sup> | DESCRIPTION                                               |                                                                        |  |  |  |  |  |

|---------|-----|---------------------|-----------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|

| NAME    | NO. | 11667               |                                                           | DECORNI NON                                                            |  |  |  |  |  |

| OUTPUTS |     |                     |                                                           |                                                                        |  |  |  |  |  |

| AOUT1   | 4   | 0                   | ridge A output 1 Connect to bipolar stepper motor winding |                                                                        |  |  |  |  |  |

| AOUT2   | 25  | 0                   | Bridge A output 2                                         | ridge A output 2 Positive current is AOUT1 → AOUT2                     |  |  |  |  |  |

| BOUT1   | 11  | 0                   | Bridge B output 1                                         | Connect to bipolar stepper motor winding                               |  |  |  |  |  |

| BOUT2   | 18  | 0                   | Bridge B output 2                                         | idge B output 2 Positive current is BOUT1 → BOUT2                      |  |  |  |  |  |

| HOMEn   | 2   | 0                   | Home position                                             | Logic low when at home state of step table, logic high at other states |  |  |  |  |  |

(1) Directions: I = input, O = output, OZ = 3-state output, OD = open-drain output, IO = input/output

Copyright © 2025 Texas Instruments Incorporated

English Data Sheet: SLVSAX9

4

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1) (2) (3)

|                        |                                    | MIN        | MAX             | UNIT |

|------------------------|------------------------------------|------------|-----------------|------|

| V <sub>MX</sub>        | Power supply voltage               | -0.3       | 35              | V    |

| V <sub>CC</sub>        | Power supply voltage               | -0.3       | 7               | V    |

|                        | Digital pin voltage                | -0.5       | 7               | V    |

| V <sub>REF</sub>       | Input voltage                      | 0          | V <sub>CC</sub> | V    |

| ISENSEx <sup>(4)</sup> | Pin voltage                        | -0.875     | 0.875           | V    |

| I <sub>O(peak)</sub>   | Peak motor drive output current    | Internally | / limited       |      |

| P <sub>D</sub>         | Continuous total power dissipation | See セク:    | ション 5.4         |      |

| T <sub>J</sub>         | Operating junction temperature     | -40        | 150             | °C   |

| T <sub>stg</sub>       | Storage temperature                | -60        | 150             | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods can affect device reliability.

- (2) All voltage values are with respect to network ground terminal.

- (3) Power dissipation and thermal limits must be observed.

- (4) Transients of ±1V for less than 25ns are acceptable.

## 5.2 ESD Ratings

|                                       |                           |                                                                                          | VALUE | UNIT |

|---------------------------------------|---------------------------|------------------------------------------------------------------------------------------|-------|------|

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Licotiootatio             | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±4000 | V    |

| (                                     | <sup>ESD)</sup> discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1000 | V    |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

#### 5.3 Recommended Operating Conditions

T<sub>A</sub> = 25°C (unless otherwise noted)

|                  |                                           | MIN  | NOM | MAX             | UNIT |

|------------------|-------------------------------------------|------|-----|-----------------|------|

| V <sub>M</sub>   | Motor power supply voltage <sup>(1)</sup> | 8    |     | 35              | V    |

| V <sub>CC</sub>  | Logic power supply voltage                | 3    |     | 5.5             | V    |

| V <sub>REF</sub> | VREF input voltage                        | 0.05 |     | V <sub>CC</sub> | V    |

| R <sub>X</sub>   | R <sub>X</sub> resistance value           | 12   | 56  | 100             | kΩ   |

| C <sub>X</sub>   | C <sub>X</sub> capacitance value          | 470  | 680 | 1500            | pF   |

<sup>(1)</sup> All  $V_M$  pins must be connected to the same supply voltage.

#### 5.4 Thermal Information

|                       |                                              | DRV8818      |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | UNIT |

|                       |                                              | 28 PINS      |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 32.2         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 16.3         | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 14           | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.5          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 13.8         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.1          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: DRV8818

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

5

## **5.5 Electrical Characteristics**

T<sub>A</sub> = 25°C (unless otherwise noted)

|                     | PARAMETER                                        | TEST CONDITIONS                                                    | MIN                   | TYP        | MAX                   | UNIT |

|---------------------|--------------------------------------------------|--------------------------------------------------------------------|-----------------------|------------|-----------------------|------|

| POWER               | R SUPPLIES                                       |                                                                    |                       |            |                       |      |

| I <sub>VM</sub>     | V <sub>M</sub> operating supply current          | V <sub>M</sub> = 35V, f <sub>PWM</sub> < 50kHz                     |                       | 7          | 10                    | mA   |

| I <sub>VCC</sub>    | V <sub>CC</sub> operating supply current         | f <sub>PWM</sub> < 50kHz                                           |                       | 0.4        | 4                     | mA   |

| I <sub>VMQ</sub>    | V <sub>M</sub> sleep mode supply current         | V <sub>M</sub> = 35V                                               |                       | 3          | 20                    | μA   |

| I <sub>VCCQ</sub>   | V <sub>CC</sub> sleep mode supply current        |                                                                    |                       | 0.5        | 20                    | μΑ   |

| V                   | V <sub>M</sub> undervoltage lockout voltage      | V <sub>M</sub> rising                                              |                       | 6.7        | 7.5                   | V    |

| V <sub>UVLO</sub>   | V <sub>CC</sub> undervoltage lockout voltage     | V <sub>CC</sub> rising                                             |                       | 2.75       | 2.95                  | V    |

| VREF II             | NPUT/CURRENT CONTROL ACCURA                      | CY                                                                 |                       |            |                       |      |

| I <sub>REF</sub>    | VREF input current                               | VREF = 3.3V                                                        | -3                    |            | 3                     | μΑ   |

| ۸۱                  | Chapping current accuracy                        | VREF = 2.0V, 70% to 100% current                                   | -5%                   |            | 5%                    |      |

| ΔI <sub>CHOP</sub>  | Chopping current accuracy                        | VREF = 2.0V, 20% to 56% current                                    | -10%                  |            | 10%                   |      |

| LOGIC-              | LEVEL INPUTS                                     |                                                                    |                       |            |                       |      |

| V <sub>IL</sub>     | Input low voltage                                |                                                                    |                       |            | 0.3 × V <sub>CC</sub> | V    |

| V <sub>IH</sub>     | Input high voltage                               |                                                                    | 0.7 × V <sub>CC</sub> |            |                       | V    |

| V <sub>HYS</sub>    | Input hysteresis                                 |                                                                    |                       | 300        |                       | mV   |

| I <sub>IL</sub>     | Input low current                                | VIN = 0.3 × V <sub>CC</sub>                                        | -20                   |            | 20                    | μΑ   |

| I <sub>IH</sub>     | Input high current                               | VIN = 0.3 × V <sub>CC</sub>                                        | -20                   |            | 20                    | μΑ   |

| R <sub>PU</sub>     | Pullup resistance                                | ENABLEn, RESETn                                                    |                       | 1          |                       | МΩ   |

| R <sub>PD</sub>     | Pulldown resistance                              | DIR, STEP, SLEEPn, USM1, USM0, SRn                                 |                       | 1          |                       | МΩ   |

| HOMEr               | OUTPUT                                           | 1                                                                  |                       |            |                       |      |

| V <sub>OL</sub>     | Output low voltage                               | I <sub>O</sub> = 200μA                                             |                       |            | 0.3 × VCC             | V    |

| V <sub>OH</sub>     | Output high voltage                              | I <sub>O</sub> = -200 μA                                           | 0.7 × VCC             |            |                       | V    |

| DECAY               | INPUT                                            |                                                                    |                       |            |                       |      |

| V <sub>IL</sub>     | Input low threshold voltage                      | For fast decay mode                                                |                       | 0.21 × VCC |                       | V    |

| V <sub>IH</sub>     | Input high threshold voltage                     | For slow decay mode                                                |                       | 0.6 × VCC  |                       | V    |

| H-BRID              | GE FETS                                          |                                                                    |                       |            | '                     |      |

| R <sub>ds(on)</sub> | HS FET on resistance                             | V <sub>M</sub> = 24V, I <sub>O</sub> = 2.5A, T <sub>J</sub> = 25°C |                       | 0.22       | 0.30                  | Ω    |

| R <sub>ds(on)</sub> | LS FET on resistance                             | V <sub>M</sub> = 24V, I <sub>O</sub> = 2.5A, T <sub>J</sub> = 25°C |                       | 0.15       | 0.24                  | Ω    |

| I <sub>LEAK</sub>   | Output leakage current to ground in disable mode | H-bridges are Hi-Z, V <sub>VM</sub> = 35V                          |                       |            | 4400                  | μΑ   |

| PROTE               | CTION CIRCUITS                                   |                                                                    |                       |            |                       |      |

| T <sub>TSD</sub>    | Thermal shutdown temperature                     | Die temperature                                                    | 150                   | 160        | 180                   | °C   |

| I <sub>OCP</sub>    | Overcurrent protection level                     |                                                                    | 3.5                   |            |                       | Α    |

| t <sub>OCP</sub>    | OCP deglitch time                                |                                                                    |                       | 1.5        |                       | μs   |

| t <sub>RET</sub>    | OCP retry time                                   |                                                                    |                       | 800        |                       | μs   |

|                     |                                                  | 1                                                                  | I                     |            |                       |      |

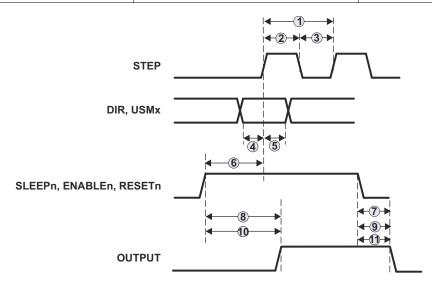

# **5.6 Timing Requirements**

T<sub>A</sub> = 25°C (unless otherwise noted)

|   |                       |                                        | MIN | NOM | MAX | UNIT |

|---|-----------------------|----------------------------------------|-----|-----|-----|------|

| 1 | f <sub>STEP</sub>     | Step frequency                         |     |     | 500 | kHz  |

| 2 | t <sub>WH(STEP)</sub> | Pulse duration, STEP high              | 1   |     |     | μs   |

| 3 | t <sub>WL(STEP)</sub> | Pulse duration, STEP low               | 1   |     |     | μs   |

| 4 | t <sub>SU(STEP)</sub> | Setup time, command before STEP rising | 200 |     |     | ns   |

| 5 | t <sub>H(STEP)</sub>  | Hold time, command after STEP rising   | 264 |     |     | ns   |

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2025 Texas Instruments Incorporated

## $T_A = 25$ °C (unless otherwise noted)

|    |                      |                                                             | MIN | NOM | MAX | UNIT |

|----|----------------------|-------------------------------------------------------------|-----|-----|-----|------|

| 6  | t <sub>WAKE</sub>    | Wakeup time, SLEEPn inactive high to STEP input accepted    |     |     | 1   | ms   |

| 7  | t <sub>SLEEP</sub>   | Sleep time, SLEEPn active low to outputs disabled           |     |     | 5   | μs   |

| 8  | t <sub>ENABLE</sub>  | Enable time, ENABLEn logic low to outputs active            |     |     | 20  | μs   |

| 9  | t <sub>DISABLE</sub> | Disable time, ENABLEn logic high to outputs disabled (Hi-Z) |     |     | 20  | μs   |

| 10 | t <sub>RESETR</sub>  | Reset release time, RESETn inactive high to outputs enabled |     |     | 80  | μs   |

| 11 | t <sub>RESET</sub>   | Reset time, RESETn active low to outputs disabled           |     |     | 7   | μs   |

# **5.7 Motor Driver Timing Switching Characteristics**

T<sub>A</sub> = 25°C (unless otherwise noted)

| 1A - 20 C          | (driicos otrici wisc rioted) |                                 |     |      |      |      |

|--------------------|------------------------------|---------------------------------|-----|------|------|------|

|                    | PARAMETER                    | TEST CONDITIONS                 | MIN | TYP  | MAX  | UNIT |

| t <sub>OFF</sub>   | Off time                     | $Rx = 56k\Omega$ , $Cx = 680pF$ | 35  | 44   | 53   | μs   |

| t <sub>BLANK</sub> | Current sense blanking time  | Rx = 56kΩ, Cx = 680pF           | 900 | 1250 | 1500 | ns   |

| t <sub>DT</sub>    | Dead time                    | SRn = 0                         | 100 | 475  | 800  | ns   |

| t <sub>R</sub>     | Rise time                    |                                 | 10  |      | 80   | ns   |

| t <sub>F</sub>     | Fall time                    |                                 | 10  |      | 80   | ns   |

図 5-1. Timing Diagram

7

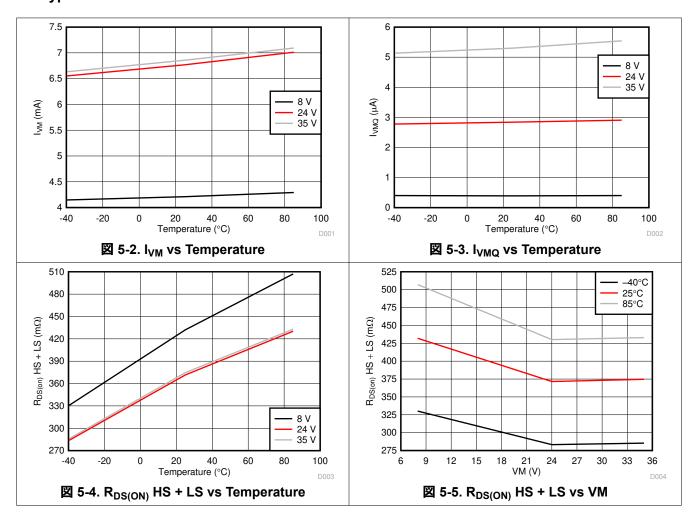

## **5.8 Typical Characteristics**

## **6 Detailed Description**

#### 6.1 Overview

The DRV8818 is a highly configurable, integrated motor driver for bipolar stepper motors. The device integrates two H-bridges, current sense and regulation circuitry, and a microstepping indexer. The DRV8818 can be powered with a supply voltage between 8V and 35V and is capable of providing an output current up to 2.5A full-scale.

A simple STEP/DIR interface allows for easy interfacing to the controller. The internal indexer is able to execute high-accuracy microstepping without requiring the controller to manage the current regulation loop.

The current regulation is highly configurable, with three decay modes of operation that can be selected depending on the application requirements: Fast Decay, Slow Decay, and Mixed Decay. The DRV8818 also provides configurable mixed decay, blanking time, and off time to adjust to a wide range of motors.

A low-power sleep mode is incorporated which allows for minimal power consumption when the system is idle.

9

## **6.2 Functional Block Diagram**

## **6.3 Feature Description**

## 6.3.1 PWM H-Bridge Drivers

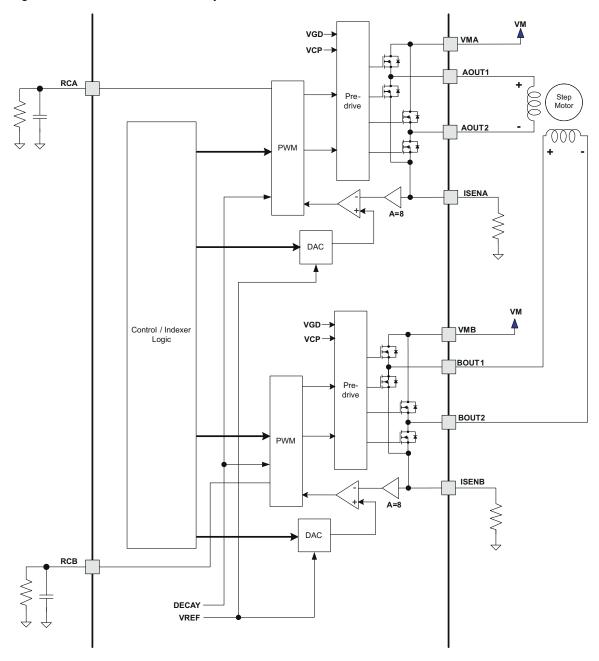

DRV8818 contains two H-bridge motor drivers with current-control PWM circuitry, and a microstepping indexer. A block diagram of the motor control circuitry is shown below.

図 6-1. Motor Control Circuitry

11

#### 6.3.2 Current Regulation

The PWM chopping current is set by a comparator, which compares the voltage across a current sense resistor, multiplied by a factor of 8, with a reference voltage. The reference voltage is input from the VREF pin. The full-scale (100%) chopping current is calculated as follows:

$$I_{CHOP} (A) = \frac{V_{VREF} (V)}{8 \times R_{SENSE} (\Omega)}$$

(1)

#### Example:

If a  $0.22\Omega$  sense resistor is used and the VREFx pin is 3.3V, the full-scale (100%) chopping current is  $3.3V / (8 \times 0.22\Omega) = 1.875A$ .

The reference voltage is also scaled by an internal DAC that allows torque control for fractional stepping of a bipolar stepper motor, as described in the セクション 6.3.4 section.

When a winding is activated, the current through the winding rises until the chopping current threshold described above is reached, then the current is switched off for a fixed off time. The off time is determined by the values of a resistor and capacitor connected to the RCA (for bridge A) and RCB (for bridge B) pins. The off time is approximated by:

$$t_{OFF} (\mu s) = R (\Omega) \times C (nF)$$

(2)

To avoid falsely tripping on transient currents when the winding is first activated, a blanking period is used immediately after turning on the FETs, during which the state of the current sense comparator is ignored. The blanking time is determined by the value of the capacitor connected to the RCx pin and is approximated by:

$$t_{BLANK} (ns) = 1400 (\Omega) \times C (nF)$$

(3)

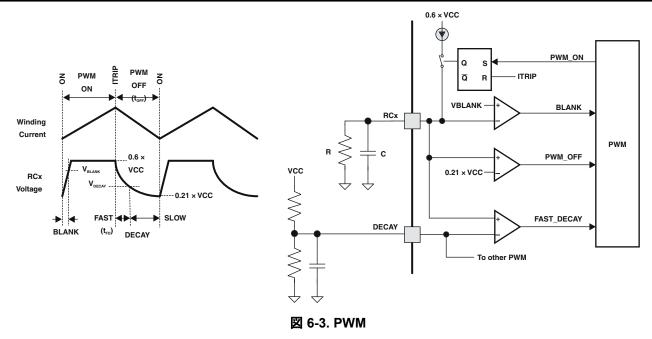

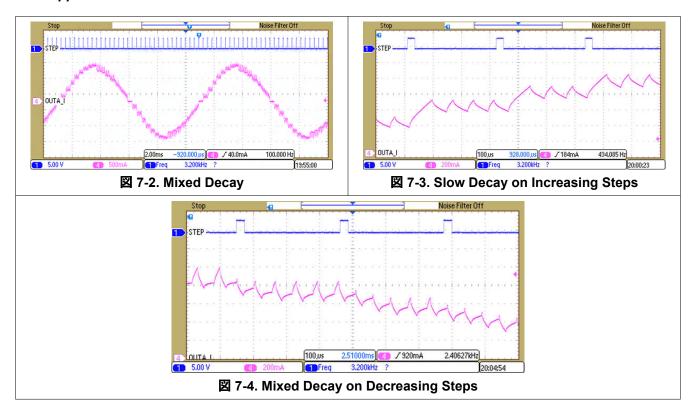

#### 6.3.3 Decay Mode

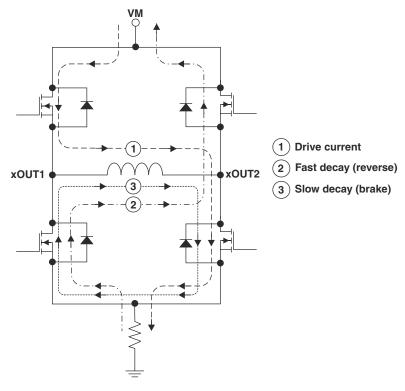

During PWM current chopping, the H-bridge is enabled to drive through the motor winding until the PWM current chopping threshold is reached. This is shown in  $\boxtimes$  6-2, Item 1. The current flow direction shown indicates positive current flow in the step table below.

Once the chopping current threshold is reached, the H-bridge can operate in two different states, fast decay or slow decay.

In fast decay mode, once the PWM chopping current level has been reached, the H-bridge reverses state to allow winding current to flow in a reverse direction. If synchronous rectification is enabled (SRn pin logic low), the opposite FETs are turned on; as the winding current approaches zero, the bridge is disabled to prevent any reverse current flow. If SRn is high, current is recirculated through the body diodes, or through external Schottky diodes. Fast-decay mode is shown in  $\boxtimes$  6-2, Item 2.

In slow-decay mode, winding current is re-circulated by enabling both of the low-side FETs in the bridge. This is shown in  $\boxtimes$  6-2, Item 3.

If SRn is high, current is recirculated only through the body diodes, or through external Schottky diodes. In this case fast decay is always used.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

図 6-2. Decay Mode

The DRV8818 also supports a mixed decay mode. Mixed decay mode begins as fast decay, but after a period of time switches to slow decay mode for the remainder of the fixed off time.

Fast and mixed decay modes are only active if the current through the winding is decreasing; if the current is increasing, then slow decay is always used.

Which decay mode is used is selected by the voltage on the DECAY pin. If the voltage is greater than  $0.6 \times V_{CC}$ , slow decay mode is always used. If DECAY is less than  $0.21 \times V_{CC}$ , the device operates in fast decay mode when the current through the winding is decreasing. If the voltage is between these levels, mixed decay mode is enabled.

In mixed decay mode, the voltage on the DECAY pin sets the point in the cycle that the change to slow decay mode occurs. This time can be approximated by:

$$t_{FD} (\mu s) = R (\Omega) \times C (nF) \times ln \left( \frac{0.6 \times V_{CC} (V)}{V_{DECAY} (V)} \right)$$

(4)

Mixed decay mode is only used while the current though the winding is decreasing; slow decay is used while the current is increasing.

Operation of the blanking, fixed off time, and mixed decay mode is illustrated in 🗵 6-3.

English Data Sheet: SLVSAX9

## 6.3.4 Microstepping Indexer

Built-in indexer logic in the DRV8818 allows a number of different stepping configurations. The USM1 and USM0 pins are used to configure the stepping format as shown in  $\frac{1}{2}$  6-1:

表 6-1. Microstepping Selection Bits

| USM1 | USM0 | STEP MODE                        |  |  |  |  |

|------|------|----------------------------------|--|--|--|--|

| 0    | 0    | Full step (2-phase excitation)   |  |  |  |  |

| 0    | 1    | 1/2 step (1-2 phase excitation)  |  |  |  |  |

| 1    | 0    | 1/4 step (W1-2 phase excitation) |  |  |  |  |

| 1    | 1    | Eight microsteps/step            |  |  |  |  |

表 6-2 shows the relative current and step directions for different settings of USM1 and USM0. At each rising edge of the STEP input, the indexer travels to the next state in the table. The direction is shown with the DIR pin high; if the DIR pin is low the sequence is reversed. Positive current is defined as xOUT1 = positive with respect to xOUT2.

Note that the home state is 45°. This state is entered at power-up or device reset. The HOMEn output pin is driven low in this state. In all other states the HOMEn pin is driven logic high.

English Data Sheet: SLVSAX9

表 6-2. Microstepping Indexer

|                       | 1                    | 衣 0-2.               | wiicrostepping       |                                    |                                    |                   |

|-----------------------|----------------------|----------------------|----------------------|------------------------------------|------------------------------------|-------------------|

| FULL STEP<br>USM = 00 | 1/2 STEP<br>USM = 01 | 1/4 STEP<br>USM = 10 | 1/8 STEP<br>USM = 11 | AOUTx<br>CURRENT<br>(% FULL-SCALE) | BOUTX<br>CURRENT<br>(% FULL-SCALE) | STEP ANGLE<br>(°) |

|                       | 1                    | 1                    | 1                    | 100                                | 0                                  | 0                 |

|                       |                      |                      | 2                    | 98                                 | 20                                 | 11.325            |

|                       |                      | 2                    | 3                    | 92                                 | 38                                 | 22.5              |

|                       |                      |                      | 4                    | 83                                 | 56                                 | 33.75             |

| 1                     | 2                    | 3                    | 5                    | 71                                 | 71                                 | 45 (home state)   |

|                       |                      |                      | 6                    | 56                                 | 83                                 | 56.25             |

|                       |                      | 4                    | 7                    | 38                                 | 92                                 | 67.5              |

|                       |                      |                      | 8                    | 20                                 | 98                                 | 78.75             |

|                       | 3                    | 5                    | 9                    | 0                                  | 100                                | 90                |

|                       |                      |                      | 10                   | -20                                | 98                                 | 101.25            |

|                       |                      | 6                    | 11                   | -38                                | 92                                 | 112.5             |

|                       |                      |                      | 12                   | -56                                | 83                                 | 123.75            |

| 2                     | 4                    | 7                    | 13                   | -71                                | 71                                 | 135               |

|                       |                      |                      | 14                   | -83                                | 56                                 | 146.25            |

|                       |                      | 8                    | 15                   | -92                                | 38                                 | 157.5             |

|                       |                      |                      | 16                   | -98                                | 20                                 | 168.75            |

|                       | 5                    | 9                    | 17                   | -100                               | 0                                  | 180               |

|                       |                      |                      | 18                   | -98                                | -20                                | 191.25            |

|                       |                      | 10                   | 19                   | -92                                | -38                                | 202.5             |

|                       |                      |                      | 20                   | -83                                | -56                                | 213.75            |

| 3                     | 6                    | 11                   | 21                   | -71                                | <b>-71</b>                         | 225               |

|                       |                      |                      | 22                   | -56                                | -83                                | 236.25            |

|                       |                      | 12                   | 23                   | -38                                | -92                                | 247.5             |

|                       |                      |                      | 24                   | -20                                | -98                                | 258.75            |

|                       | 7                    | 13                   | 25                   | 0                                  | -100                               | 270               |

|                       |                      |                      | 26                   | 20                                 | -98                                | 281.25            |

|                       |                      | 14                   | 27                   | 38                                 | -92                                | 292.5             |

|                       |                      |                      | 28                   | 56                                 | -83                                | 303.75            |

| 4                     | 8                    | 15                   | 29                   | 71                                 | <b>-71</b>                         | 315               |

|                       |                      |                      | 30                   | 83                                 | -56                                | 326.25            |

|                       |                      | 16                   | 31                   | 92                                 | -38                                | 337.5             |

|                       |                      |                      | 32                   | 98                                 | -20                                | 348.75            |

|                       |                      |                      | I .                  | 1                                  |                                    |                   |

#### 6.3.5 Protection Circuits

#### **6.3.5.1 Overcurrent Protection (OCP)**

If the current through any FET exceeds the preset overcurrent threshold, all FETs in the H-bridge are disabled for a period of approximately 800µs, or until the ENABLEn pin has been brought inactive high and then back low, or power is removed and reapplied. Overcurrent conditions are sensed in both directions; that is, a short to ground, supply, or across the motor winding all result in an overcurrent shutdown.

Note that overcurrent protection does not use the current sense circuitry used for PWM current control and is independent of the Isense resistor value or VREF voltage. Additionally, in the case of an overcurrent event, the microstepping indexer is reset to the home state.

#### 6.3.5.2 Thermal Shutdown (TSD)

If the die temperature exceeds safe limits, all drivers in the device are shut down and the indexer is reset to the home state. Once the die temperature has fallen to a safe level operation resumes.

#### 6.3.5.3 Undervoltage Lockout (UVLO)

If at any time the voltage on the VM or VCC pins falls below the VM or VCC undervoltage lockout threshold voltage, all circuitry in the device is disabled, and the indexer is reset to the home state. Operation resumes when VM and VCC both rise above each UVLO threshold.

#### **6.4 Device Functional Modes**

#### 6.4.1 Sleep Mode

When the SLEEPn pin is low, the device enters a low-power sleep mode. In sleep mode all the internal MOSFETs are disabled (Hi-Z) and the internal logic regulator, charge pump, and internal clocks are all disabled. The  $t_{\text{SLEEP}}$  time must elapse after a falling edge on the SLEEPn pin before the device enters sleep mode. The device is brought out of sleep automatically if the SLEEPn pin is brought high. The  $t_{\text{WAKE}}$  time must elapse before the device is ready for inputs.

#### 6.4.2 Disable Mode

The ENABLEn pin is used to control the outputs of the device. When ENABLEn is low, the output H-bridges are enabled. When ENABLEn is high, the H-bridges are disabled and the outputs are in a high-impedance state.

Note that when ENABLEn is high, the input pins and control logic, including the indexer (STEP and DIR pins) are still functional.

|   | 衣 6-3. ( | conditions to Enable | or Disable Output |

|---|----------|----------------------|-------------------|

|   |          | Drivers              |                   |

| ſ |          |                      |                   |

| SLEEPn | ENABLEn     | H-BRIDGE |  |  |  |

|--------|-------------|----------|--|--|--|

| 0      | 0 X Disable |          |  |  |  |

| 1      | 1           | Disabled |  |  |  |

| 1      | 0           | Enabled  |  |  |  |

#### 6.4.3 Active Mode

After the supply voltage on the VM pin has crossed the undervoltage threshold  $V_{\text{UVLO}}$ , the SLEEPn pin is logic high, and  $t_{\text{WAKE}}$  has elapsed, the device enters active operating mode. In this mode, the H-Bridge, charge pump, and internal logic are active and the device is ready to receive inputs.

This mode is enabled when -

- · SLEEPn pin is logic high

- ENABLEn pin is logic low

- · RESETn pin is logic high

- $V_M > V_{UVIO}$  for  $V_M$

- $V_{CC} > V_{UVLO}$  for  $V_{CC}$

The t<sub>WAKF</sub> time must elapse before the device is ready for inputs.

#### 6.4.4 Decay Modes

The DRV8818 supports three different decay modes: slow decay, fast decay, and mixed decay. The current through the motor windings is regulated using a fixed off time scheme.

This means that the current will increase until it reaches the current chopping threshold ( $I_{TRIP}$ ), after which it will enter the set decay mode for a fixed period of time. The cycle will then repeat after the decay period expires.

The blanking time  $t_{BLANK}$  defines the minimum drive time for the current chopping.  $I_{TRIP}$  is ignored during  $t_{BLANK}$ , so the winding current may overshoot the trip level.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

## 7 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant the accuracy or completeness of this information. Customers are responsible for determining the appropriateness of components for the intended purposes, as well as validating and testing the design implementation to confirm system functionality

## 7.1 Application Information

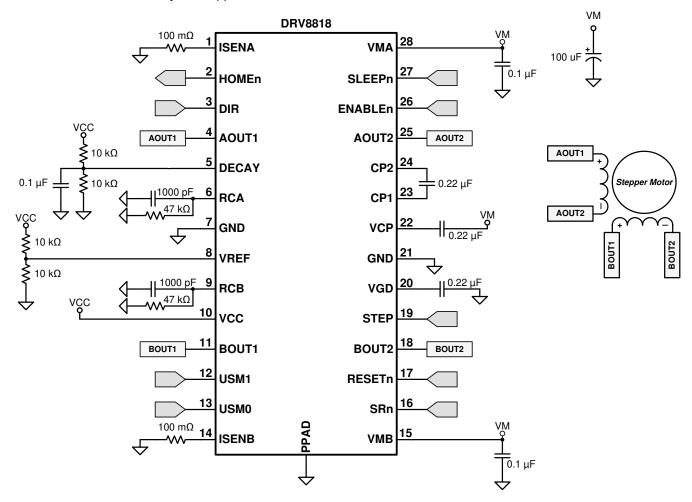

The DRV8818 is used for bipolar stepper motor control. The microstepping motor driver provides precise regulation of the coil current and maintains a smooth rotation from the stepper motor.

## 7.2 Typical Application

図 7-1. Typical Application Schematic

17

## 7.2.1 Design Requirements

See 表 7-1 for the design parameters.

表 7-1. Design Parameters

| DESIGN PARAMETER           | REFERENCE       | EXAMPLE VALUE     |

|----------------------------|-----------------|-------------------|

| Supply Voltage             | VM              | 24V               |

| Motor Winding Resistance   | R <sub>L</sub>  | 4.0Ω              |

| Motor Winding Inductance   | Ι <sub>L</sub>  | 3.7mH             |

| Motor Full Step Angle      | $\theta_{step}$ | 1.8°/step         |

| Target Microstepping Level | n <sub>m</sub>  | 8 µsteps per step |

| Target Motor Speed         | V               | 120 RPM           |

| Target Full-Scale Current  | I <sub>FS</sub> | 1.25A             |

#### 7.2.2 Detailed Design Procedure

#### 7.2.2.1 Stepper Motor Speed

The first step in configuring the DRV8818 requires the desired motor speed and microstepping level. If the target application requires a constant speed, then a square wave with frequency  $f_{\text{step}}$  must be applied to the STEP pin.

A high target motor start-up speed causes the motor to fail to spin. Make sure that the motor can support the target speed or implement an acceleration profile to bring the motor up to speed.

For a desired motor speed (v), microstepping level ( $n_m$ ), and motor full step angle ( $\theta_{step}$ ),

$$f_{step}\left(\mu steps / second\right) = \frac{v\left(\frac{rotations}{minute}\right) \times 360\left(\frac{\circ}{rotation}\right) \times n_{m}\left(\frac{\mu steps}{step}\right)}{60\left(\frac{seconds}{minute}\right) \times \theta_{step}\left(\frac{\circ}{step}\right)}$$

(5)

$$f_{step}\left(\mu steps / second\right) = \frac{120\left(\frac{rotations}{minute}\right) \times 360\left(\frac{\circ}{rotation}\right) \times 8\left(\frac{\mu steps}{step}\right)}{60\left(\frac{seconds}{minute}\right) \times 1.8\left(\frac{\circ}{step}\right)}$$

(6)

$\theta_{\text{step}}$  can be found in the stepper motor data sheet or written on the motor body.

For the DRV8818, the microstepping level is set by the USMx pins. Higher microstepping results in smoother motor motion and less audible noise, but increasing switching losses and requires a higher  $f_{\text{step}}$  to achieve the same motor speed.

#### 7.2.2.2 Current Regulation

In a stepper motor, the set full-scale current ( $I_{FS}$ ) is the maximum current driven through either winding. This quantity depends on the VREF analog voltage and the sense resistor value ( $R_{SENSE}$ ). During stepping,  $I_{FS}$  defines the current chopping threshold (ITRIP) for the maximum current step. The gain of DRV8818 is set for 8V/V.

$$I_{FS}(A) = \frac{VREF(V)}{A_V \times R_{SENSE}(\Omega)} = \frac{VREF(V)}{8 \times R_{SENSE}(\Omega)}$$

(7)

To achieve  $I_{FS}$  = 1.25A with  $R_{SENSE}$  of 0.1 $\Omega$ , set VREF to 1.56V.

#### 7.2.3 Application Curves

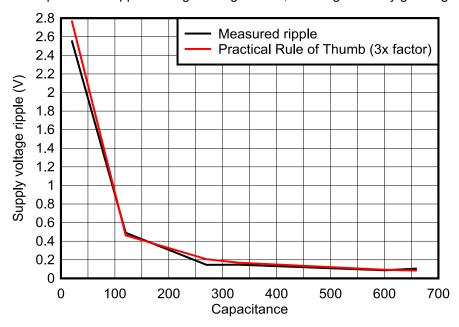

#### 7.3 Power Supply Recommendations

## 7.3.1 Bulk Capacitance

Appropriate local bulk capacitance is an important factor in motor drive system design. Having more bulk capacitance is generally beneficial, although the disadvantages include increased cost and physical size. Bulk capacitors near the motor driver act as a local reservoir of electrical charge to smooth out the motor current variation.

Experienced engineers often use general guidelines about bulk capacitance to select the capacitor values. One such guideline says to use at least 1 to  $4\mu F$  of capacitance for each Watt of motor power. For example, a motor which draws 10 Amps from a 12V supply has a power of 120 Watts, leading to bulk capacitance of 120 to  $480\mu F$ , using this general guideline.

The voltage rating for bulk capacitors must be higher than the operating voltage, to provide margin for cases when the motor transfers energy to the supply.

A large value of bulk capacitance is desired to provide a constant motor supply voltage during current transitions, such as motor start-up, changes in load torque, or PWM operation. A working estimate of the required capacitance for consistent supply is essential to reduce complexity, cost and size of board electronics. We can use a general guideline method to find an appropriate capacitor size based on the expected load current variation and allowable motor supply voltage variation:

$$C_{BULK} > k \times \Delta I_{MOTOR} \times T_{PWM} / \Delta V_{SUPPLY}$$

(8)

Where:

C BULK is the bulk capacitance

English Data Sheet: SLVSAX9

k is a scale factor to account for the ESR for typical capacitors in this type of application; based on the lab measurements with DRV8718-Q1EVM,  $k \approx 3$  is practical for these cases.

$\Delta I_{MOTOR}$  is the expected variation in motor current, i  $_{max}$  – i  $_{min}$

T PWM is the PWM period which is the reciprocal of the PWM frequency

ΔV SUPPLY is the allowable variation in the motor supply voltage

☑ 7-5 plots several data points and applies this general guideline, showing relatively good agreement.

図 7-5. Measured Results and 3x General Guideline, Accounting for Real-World Non-Zero ESR Values of Electrolytic Capacitors

For more information please see the Application Note Bulk Capacitor Sizing for DC Motor Drive Applications .

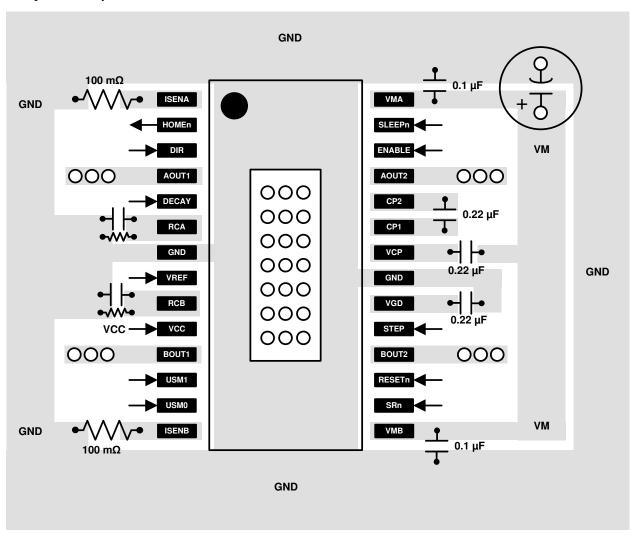

#### 7.4 Layout

#### 7.4.1 Layout Guidelines

Bypass the VMA and VMB pins to GND using low-ESR ceramic bypass capacitors with a recommended value of  $0.1\mu F$  rated for VM. Place this capacitor as close to the VMA and VMB pins as possible with a thick trace or ground plane connection to the device GND pin.

Bypass the VMA and VMB pins to GND using an appropriate bulk capacitor. This component is often an electrolytic and is best located close to the DRV8818.

A low-ESR ceramic capacitor must be placed in between the CP1 and CP2 pins. TI recommends a value of 0.22µF rated for VM. Place this component as close to the pins as possible.

A low-ESR ceramic capacitor must be placed in between the VM and VCP pins. TI recommends a value of 0.22µF rated for 16V. Place this component as close to the pins as possible.

The PowerPAD must be securely connected to a copper plane that is connected to system GND. For best performance, use a copper place with a large area to allow for thermal dissipation from the DRV8818A. See Application Note - Best Practices for Board Layout of Motor Drivers for more information on thermal management, routing techniques, capacitor placement, and grounding optimization for motor drivers.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

#### 7.4.1.1 Heatsinking

The PowerPAD™ package uses an exposed pad to remove heat from the device. For proper operation, this pad must be thermally connected to copper on the PCB to dissipate heat. On a multi-layer PCB with a ground plane, this can be accomplished by adding a number of vias to connect the thermal pad to the ground plane. On PCBs without internal planes, copper area can be added on either side of the PCB to dissipate heat. If the copper area is on the opposite side of the PCB from the device, thermal vias are used to transfer the heat between top and bottom layers.

For details about how to design the PCB, refer to TI Application Report SLMA002, *PowerPAD™ Thermally Enhanced Package* and TI Application Brief SLMA004, *PowerPAD™ Made Easy*, available at www.ti.com.

In general, the more copper area that can be provided, the more power can be dissipated.

#### 7.4.2 Layout Example

図 7-6. Layout Example Schematic

#### 7.4.3 Thermal Considerations

The DRV8818 has thermal shutdown (TSD) as described previously. If the die temperature exceeds approximately 150°C, the device is disabled until the temperature drops to a safe level.

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

21

Any tendency of the device to enter thermal shutdown is an indication of either excessive power dissipation, insufficient heatsinking, or too high ambient temperature.

#### 7.4.3.1 Power Dissipation

Power dissipation in the DRV8818 is dominated by the power dissipated in the output FET resistance, or  $R_{DS(ON)}$ . Average power dissipation when running a stepper motor can be roughly estimated by:

$$P_{TOT} = 4 \times r_{DS(on)} \times (I_{OUT(RMS)})^{2}$$

(9)

#### where

- P<sub>TOT</sub> is the total power dissipation.

- R<sub>DS(ON)</sub> is the resistance of each FET.

- I<sub>OUT(RMS)</sub> is the RMS output current being applied to each winding.

$I_{OUT(RMS)}$  is equal to the approximately 0.7x the full-scale output current setting. The factor of 4 comes from the fact that there are two motor windings, and at any instant two FETs are conducting winding current for each winding (one high-side and one low-side).

The maximum amount of power that can be dissipated in the DRV8818 is dependent on ambient temperature and heatsinking. The thermal dissipation ratings table in the data sheet can be used to estimate the temperature rise for typical PCB constructions.

Note that  $R_{DS(ON)}$  increases with temperature, so as the device heats, the power dissipation increases. This must be taken into consideration when sizing the heatsink.

Product Folder Links: DRV8818

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

## 8 Device and Documentation Support

## 8.1 Documentation Support

#### 8.1.1 Related Documentation

- 1. PowerPAD™ Thermally Enhanced Package, SLMA002

- 2. PowerPAD™ Made Easy, SLMA004

- 3. Current Recirculation and Decay Modes, SLVA321

- 4. Calculating Motor Driver Power Dissipation, SLVA504

- 5. Understanding Motor Driver Current Ratings, SLVA505

## 8.2 Community Resources

#### 8.3 Trademarks

PowerPAD<sup>™</sup> is a trademark of Texas Instruments. is a trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

## 9 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision E (January 2016) to Revision F (February 2025)                         | Page             |

|----------------------------------------------------------------------------------------------|------------------|

| Changed V <sub>RFF</sub> minimum voltage from 0V to 0.05V                                    | 5                |

| Renamed I <sub>OFF</sub> to I <sub>LEAK</sub> , updated description and limits               |                  |

| Changed <i>Timing Requirements</i> enable time and disable time descriptions. Updated hold t |                  |

| time, and reset time limits                                                                  |                  |

| Added Sleep Mode section, Disable Mode section, and Active Mode section within Device        | Functional Modes |

| section  • Updated bulk capacitance description                                              | 16               |

| • Opdated bulk capacitance description                                                       | 19               |

| Changes from Revision D (January 2015) to Revision E (January 2016)                          | Page             |

| • 「特長」から "nFAULT" を削除                                                                        | 1                |

| Changed the minimum value for V <sub>REF</sub> input voltage                                 |                  |

| Moved the motor driver timing to the Switching Characteristics table                         | 7                |

| • Added セクション 8.2                                                                            |                  |

| Changes from Revision C (November 2013) to Revision D (July 2014)                            | Page             |

| Added ESD Rating table, Feature Description section, Device Functional Modes, Application    | ion and          |

| Implementation section, Power Supply Recommendations section, Layout section, Device         |                  |

| Documentation Support section, and Mechanical, Packaging, and Orderable Information          |                  |

|                                                                                              |                  |

| Changes from Revision B (October 2012) to Revision C (November 2013)                         | Page             |

| <ul><li>「特長」セクションを変更</li></ul>                                                               |                  |

| Changed Logic-Level Inputs test conditions in the Electrical Characteristics table           |                  |

| Changed Timing Requirements                                                                  | 6                |

|                                                                                              |                  |

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

23

## 10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Product Folder Links: DRV8818

Copyright © 2025 Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated www.ti.com 11-Feb-2025

#### PACKAGING INFORMATION

| Orderable Device | Status  | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|---------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

| DRV8818PWP       | LIFEBUY | HTSSOP       | PWP                | 28   | 50             | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | DRV8818              |         |

| DRV8818PWPR      | ACTIVE  | HTSSOP       | PWP                | 28   | 2000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | DRV8818              | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

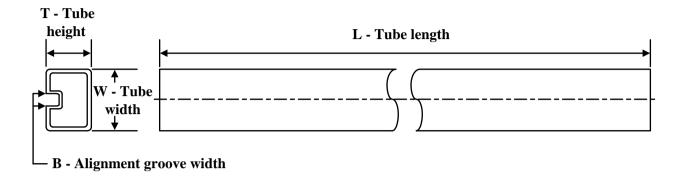

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 11-Feb-2025

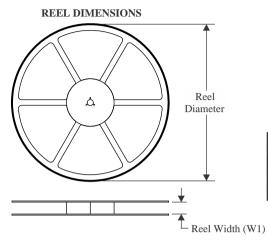

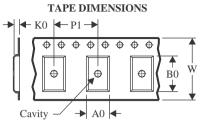

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV8818PWPR | HTSSOP          | PWP                | 28 | 2000 | 330.0                    | 16.4                     | 6.9        | 10.2       | 1.8        | 12.0       | 16.0      | Q1               |

www.ti.com 11-Feb-2025

## \*All dimensions are nominal

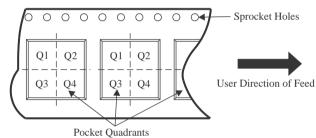

| Device      | Device Package Type |     | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|-------------|---------------------|-----|------|------|-------------|------------|-------------|--|

| DRV8818PWPR | HTSSOP              | PWP | 28   | 2000 | 350.0       | 350.0      | 43.0        |  |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 11-Feb-2025

## **TUBE**

#### \*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| DRV8818PWP | PWP          | HTSSOP       | 28   | 50  | 530    | 10.2   | 3600   | 3.5    |

4.4 x 9.7, 0.65 mm pitch

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PWP (R-PDSO-G28)

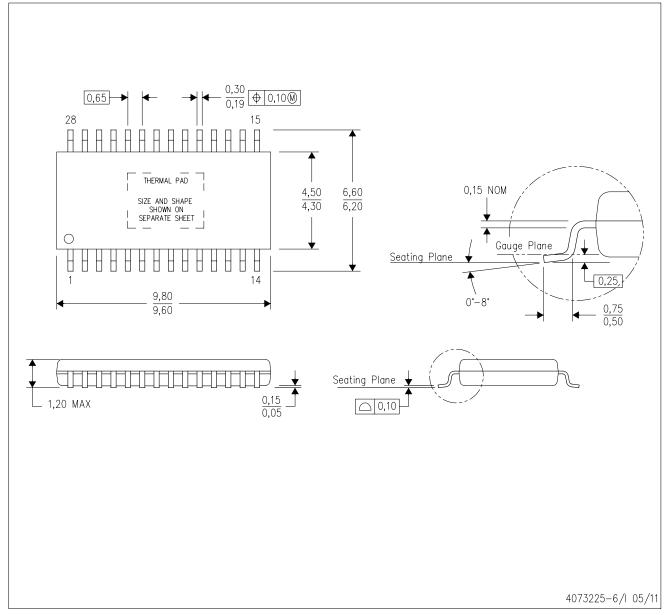

# PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

4206332-34/AO 01/16

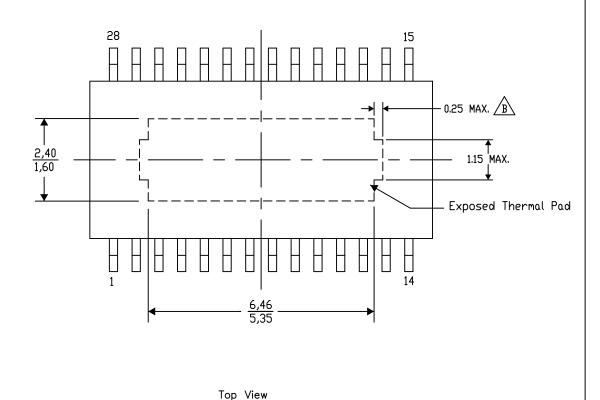

# PWP (R-PDSO-G28) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

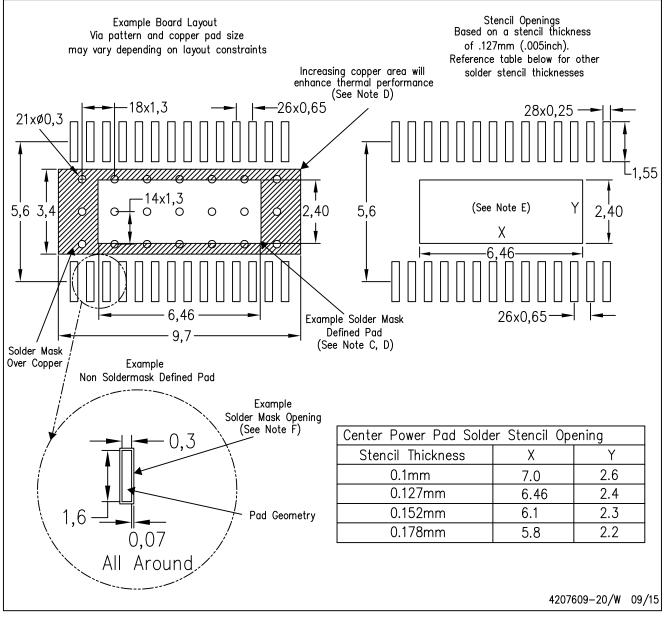

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: A. All linear dimensions are in millimeters

B. Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

Exposed Thermal Pad Dimensions

# PWP (R-PDSO-G28)

# PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated