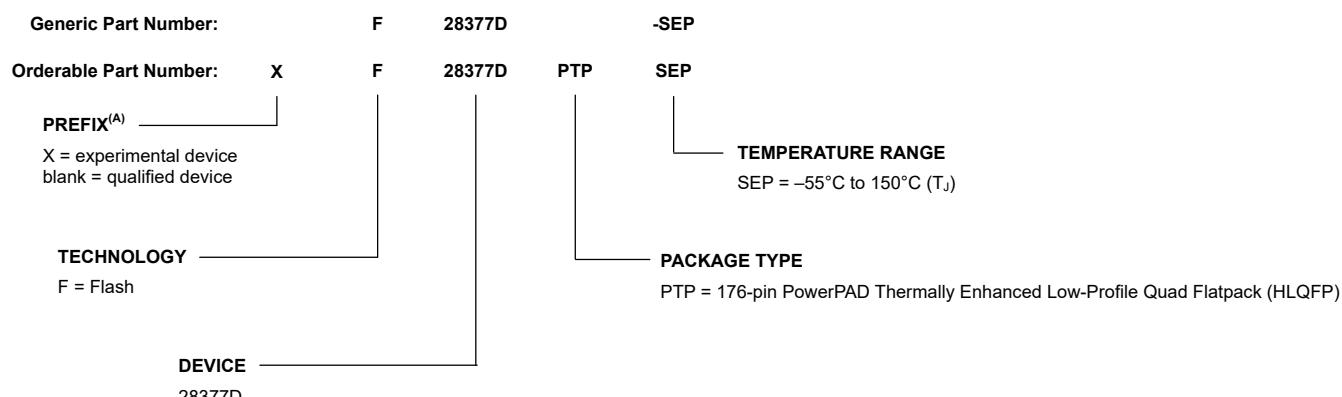

## F28377D-SEP デュアルコアリアルタイムマイクロコントローラ

### 1 特長

- VID - V62/25638

- 放射線耐性を強化

- 単一イベントラッチアップ (SEL) 耐性: 125°Cで 45MeV·cm<sup>2</sup>/mg まで

- すべてのウェハー ロットについて、30krad (Si) までの吸収線量 (TID) RLAT

- 宇宙向け強化プラスチック

- 管理されたベースライン

- 金 (Au) ワイヤ

- 単一のアセンブリ / テスト施設

- 単一の製造施設

- 拡張温度範囲 (-55°C ~ 125°C) で利用可能

- 長期にわたる製品ライフ サイクル

- 長期にわたる製品変更通知

- 製品のトレーサビリティ

- モールド コンパウンドの改良による低いガス放出

- デュアルコア アーキテクチャ

- 2 つの TMS320C28x 32 ビット CPU

- 200MHz

- IEEE 754 単精度浮動小数点ユニット (FPU)

- 三角関数演算ユニット (TMU)

- ビタビ / 複素演算ユニット (VCU-II)

- 2 つのプログラム可能な制御補償器アクセラレータ (CLA)

- 200MHz

- IEEE 754 単精度浮動小数点命令

- メイン CPU と独立にコードを実行

- オンチップ メモリ

- 512KB (256KW) または 1MB (512KW) のフラッシュ (ECC 保護)

- 172KB (86KW) または 204KB (102KW) の RAM (ECC 保護またはパリティ保護)

- デュアルゾーンのセキュリティでサードパーティー の開発をサポート

- 固有の識別番号

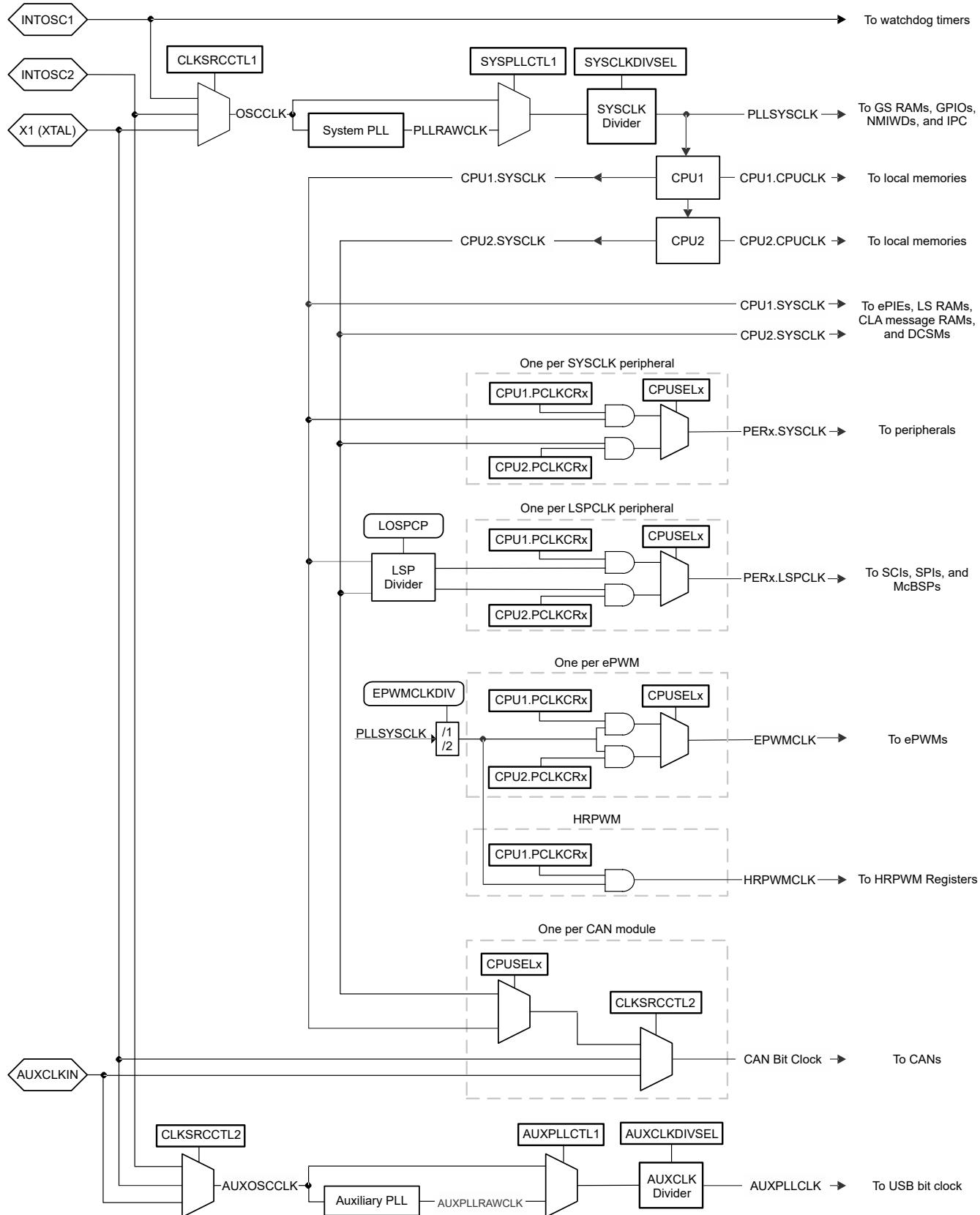

- クロックおよびシステム制御

- 2 つの内部ゼロピン 10MHz 発振器

- オンチップの水晶発振器

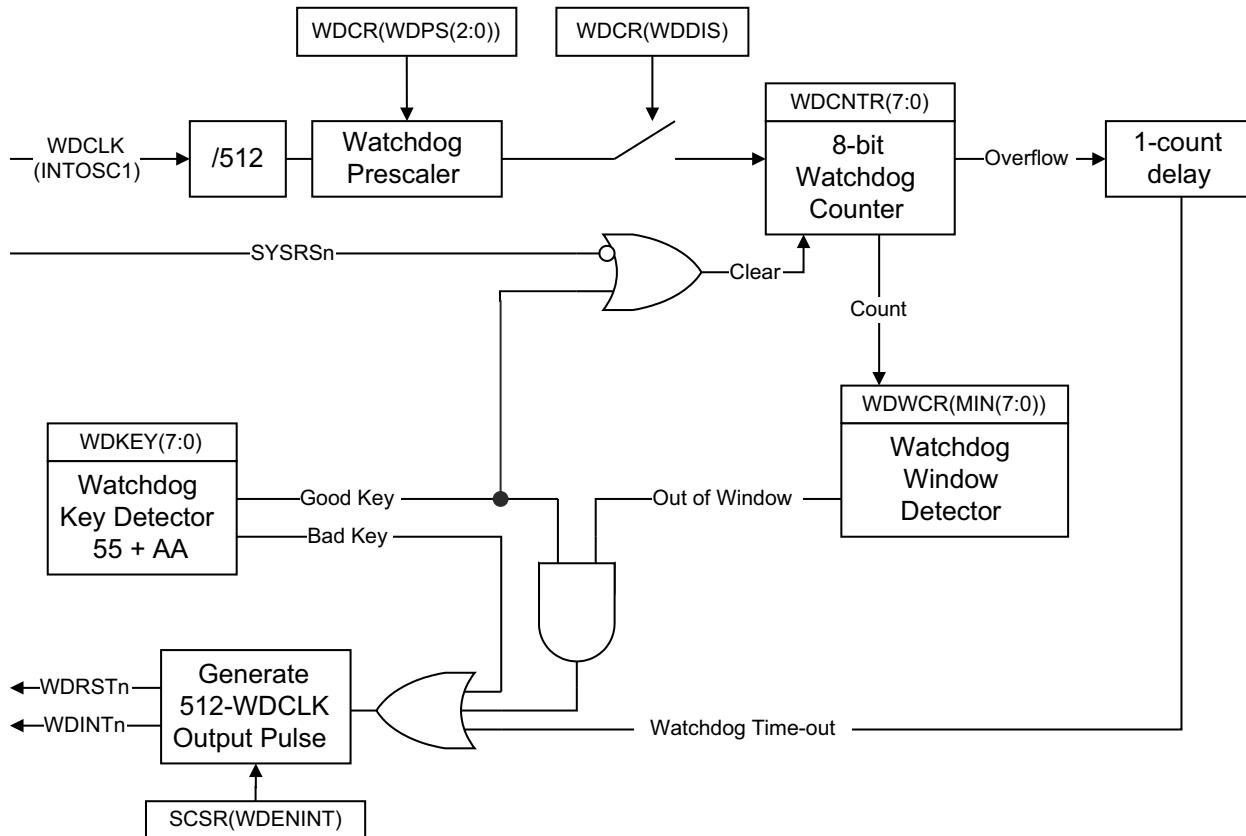

- ウィンドウ付きウォッチドッグ タイマ モジュール

- クロック消失検出回路

- コア 1.2V、I/O 3.3V の設計

- システム ペリフェラル

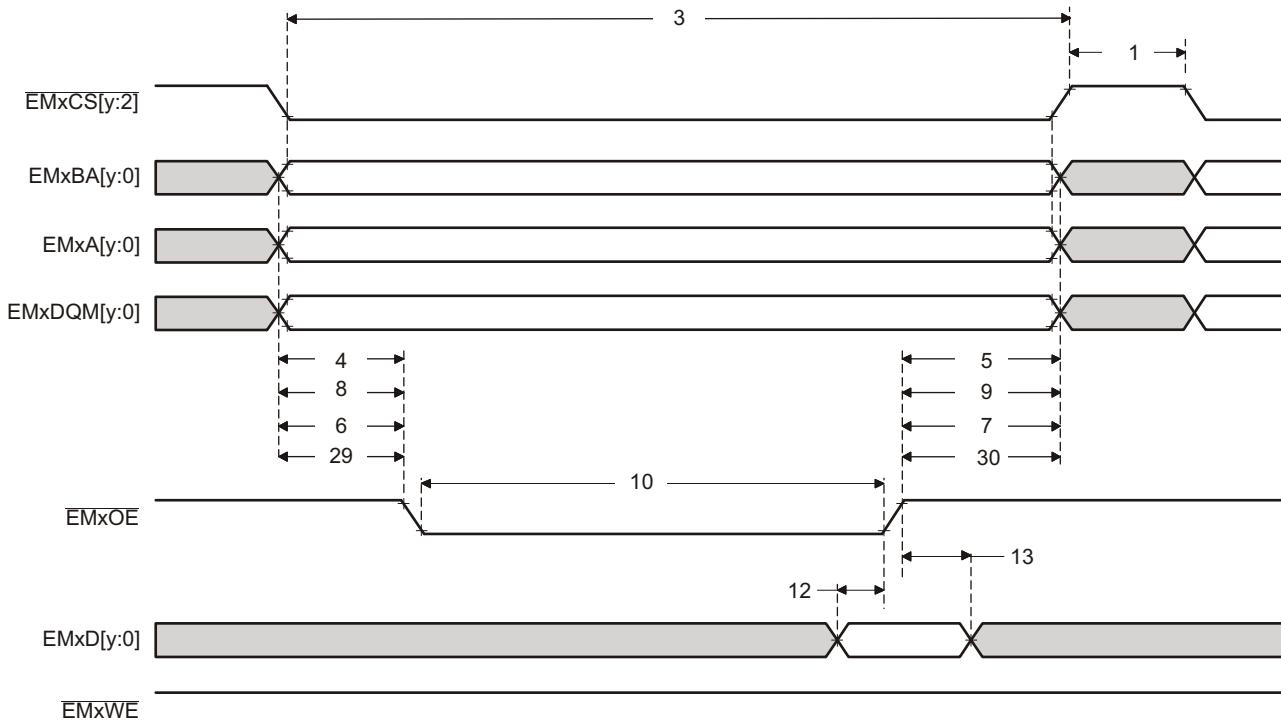

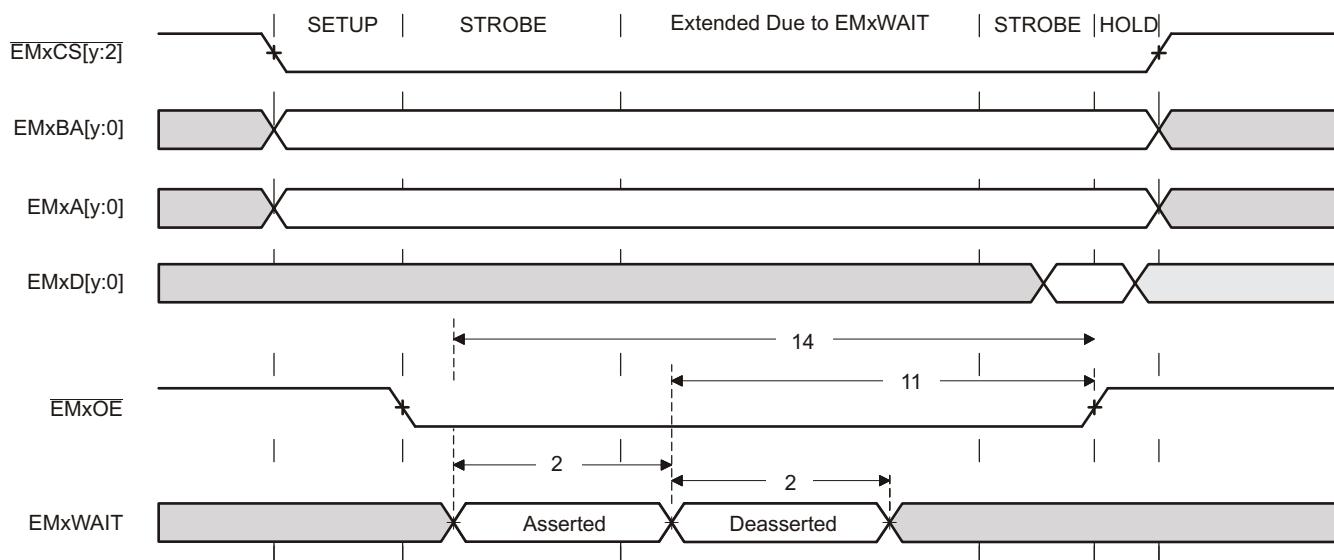

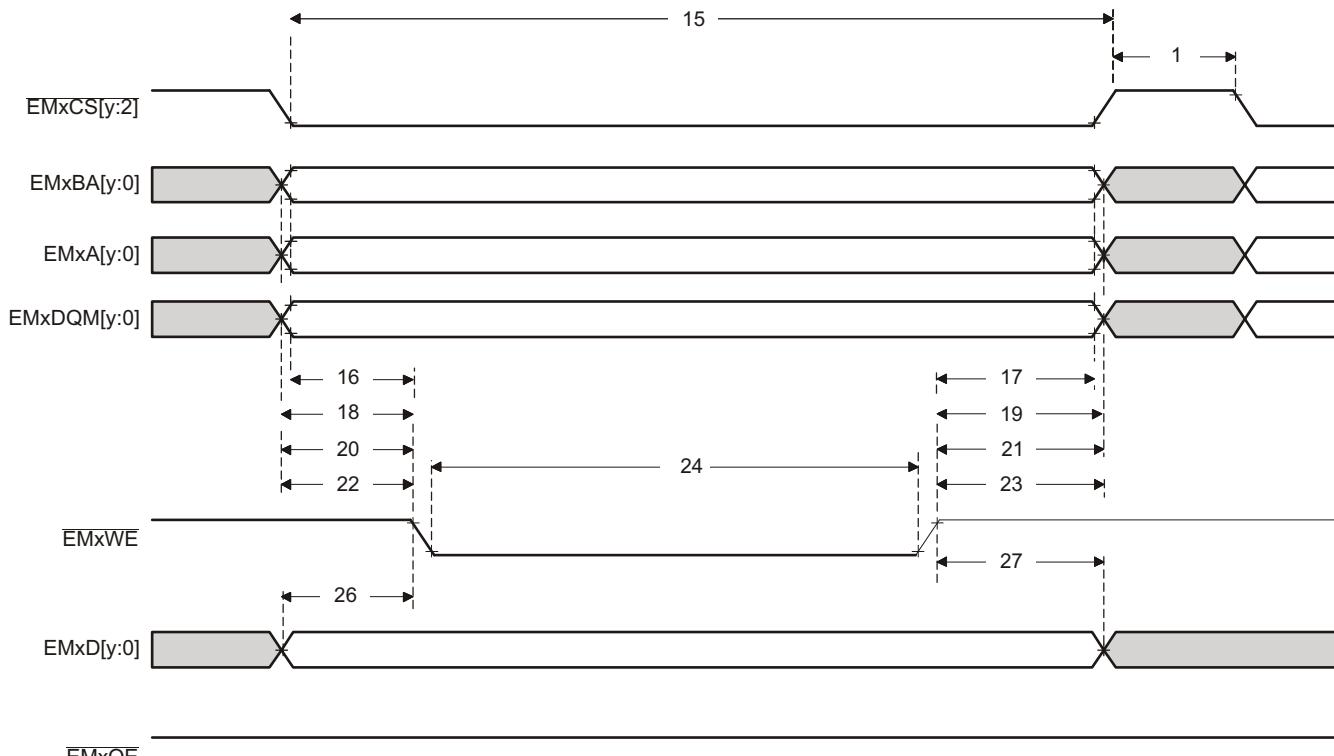

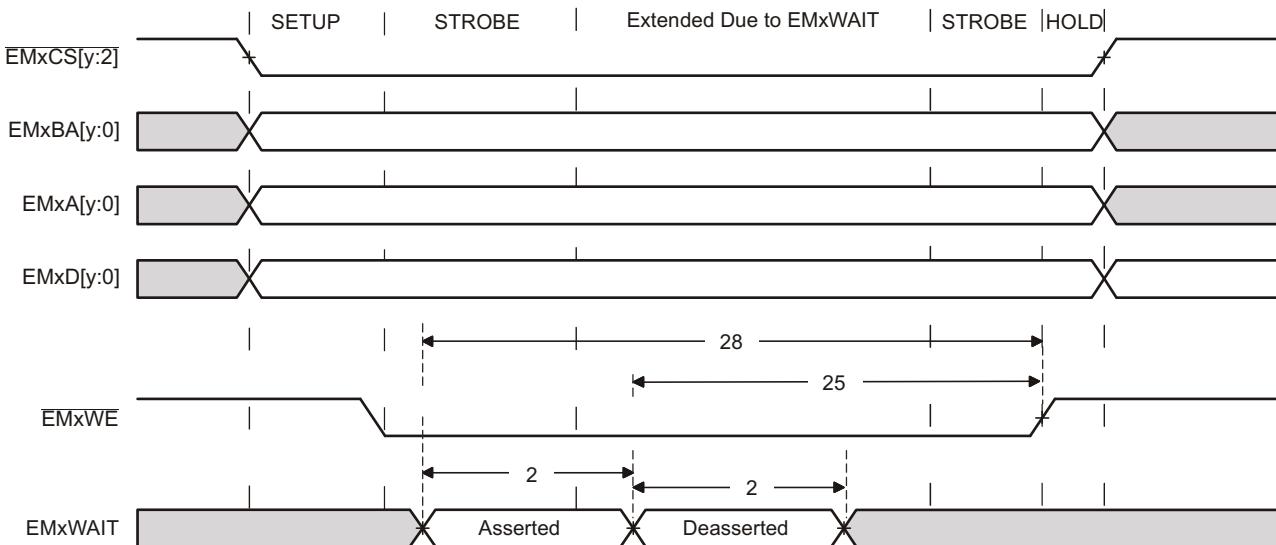

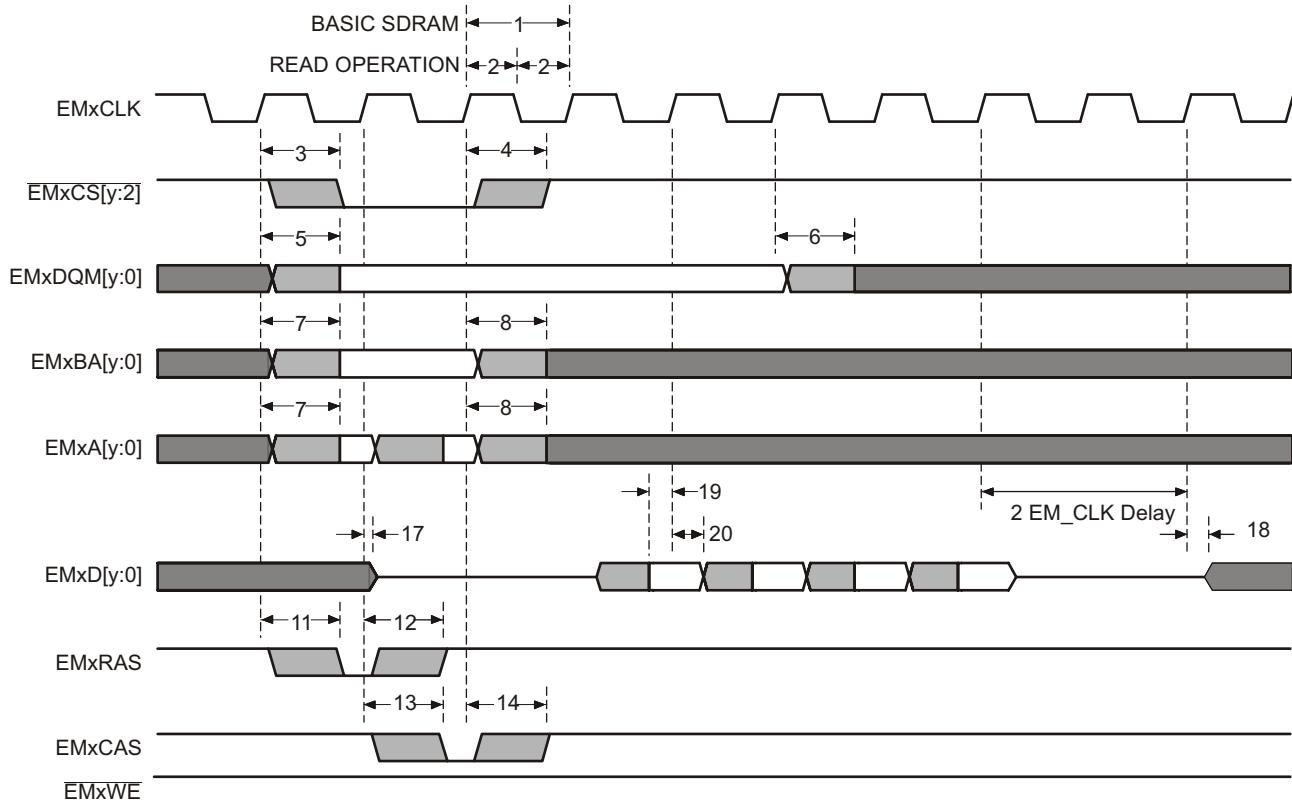

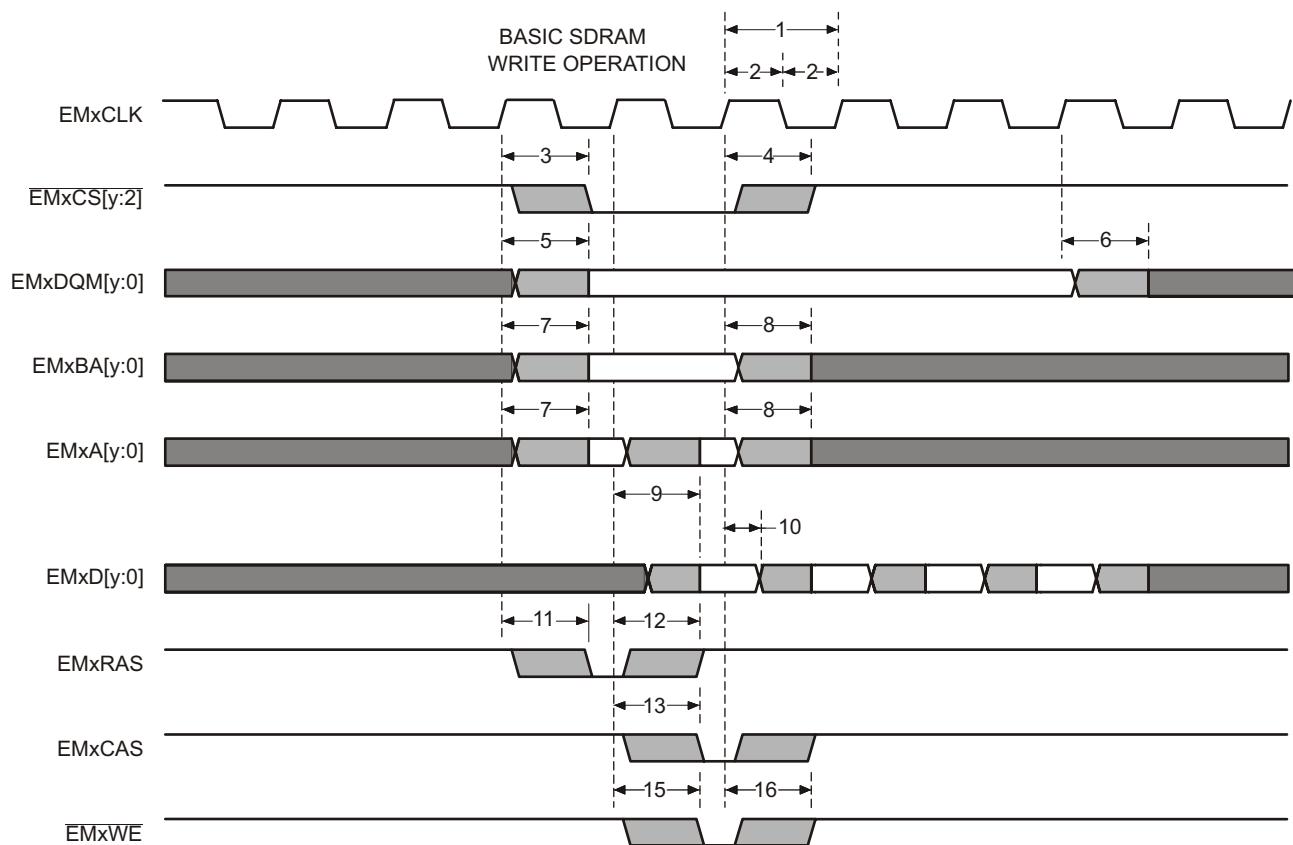

- ASRAM および SDRAM をサポートする 2 つの外部メモリ インターフェイス (EMIF)

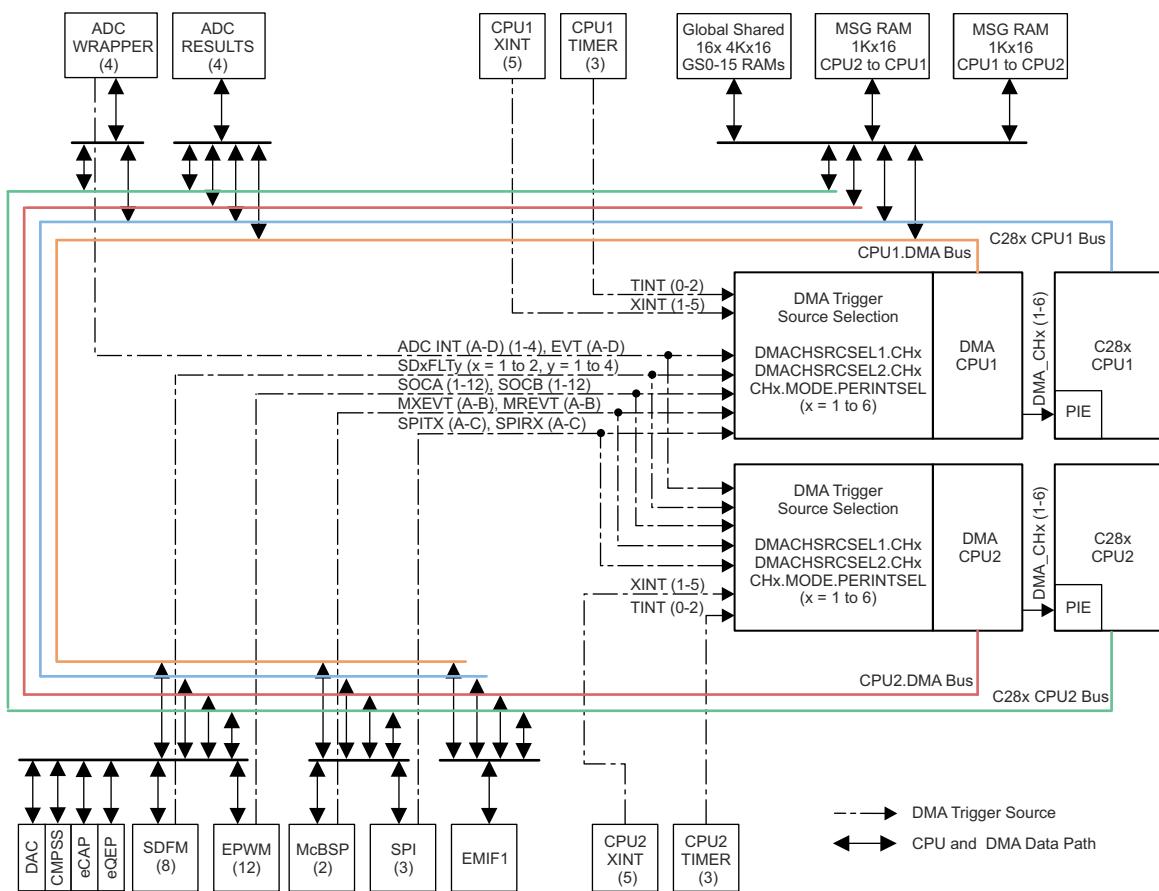

- デュアル 6 チャネルの DMA (Direct Memory Access) コントローラ

- 個別にプログラム可能な最大 169 の多重化された汎用入出力 (GPIO) ピン (入力フィルタ付き)

- 拡張ペリフェラル割り込みコントローラ (ePIE)

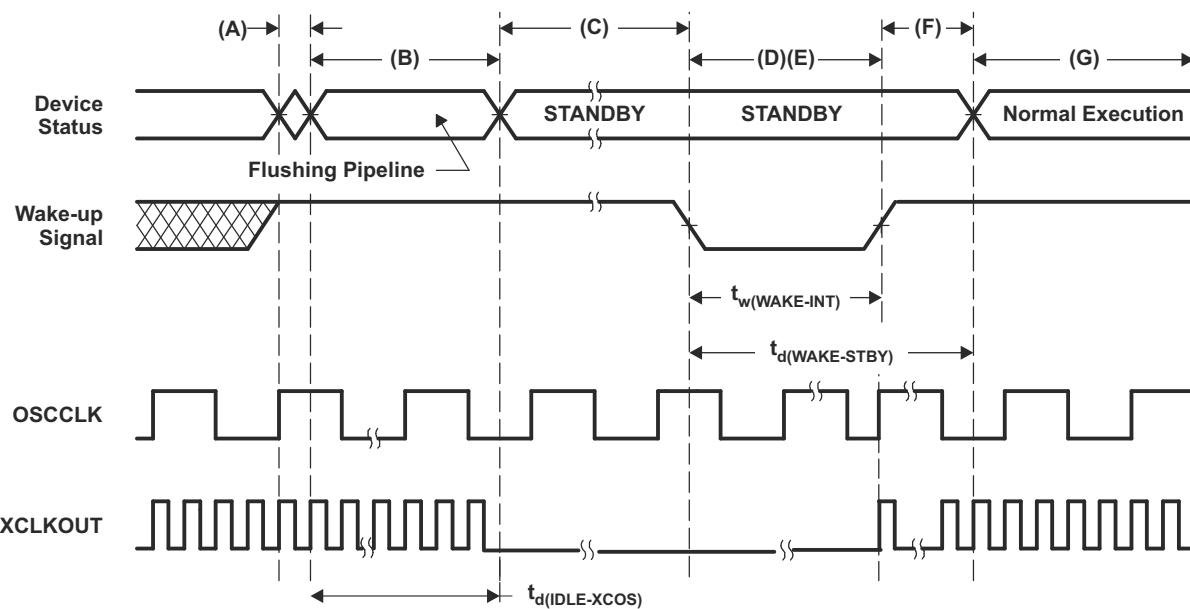

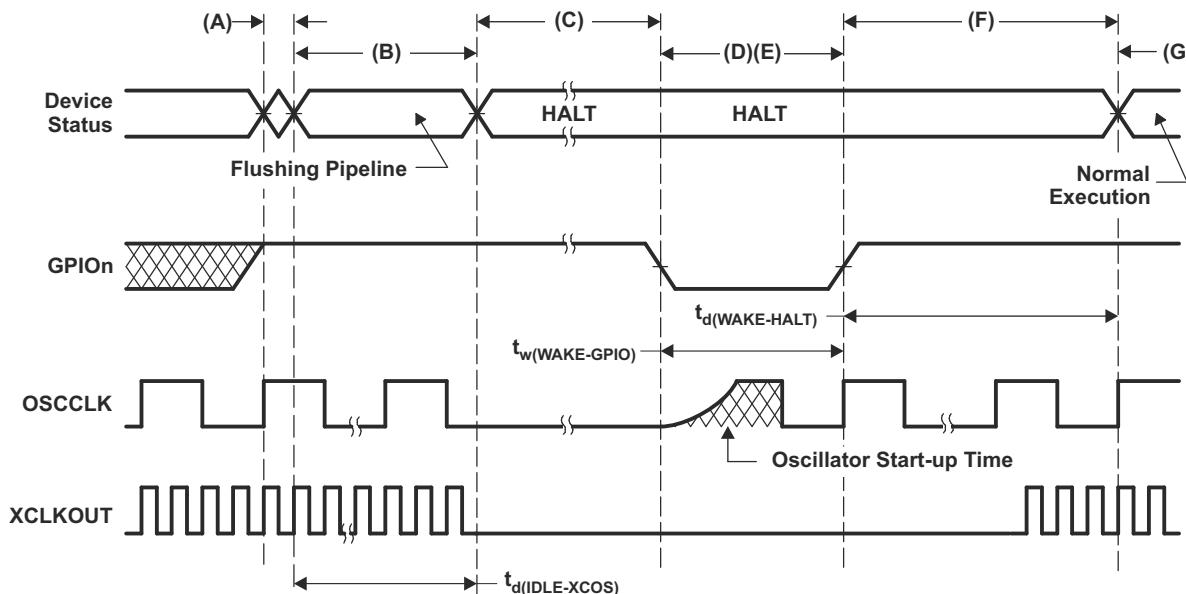

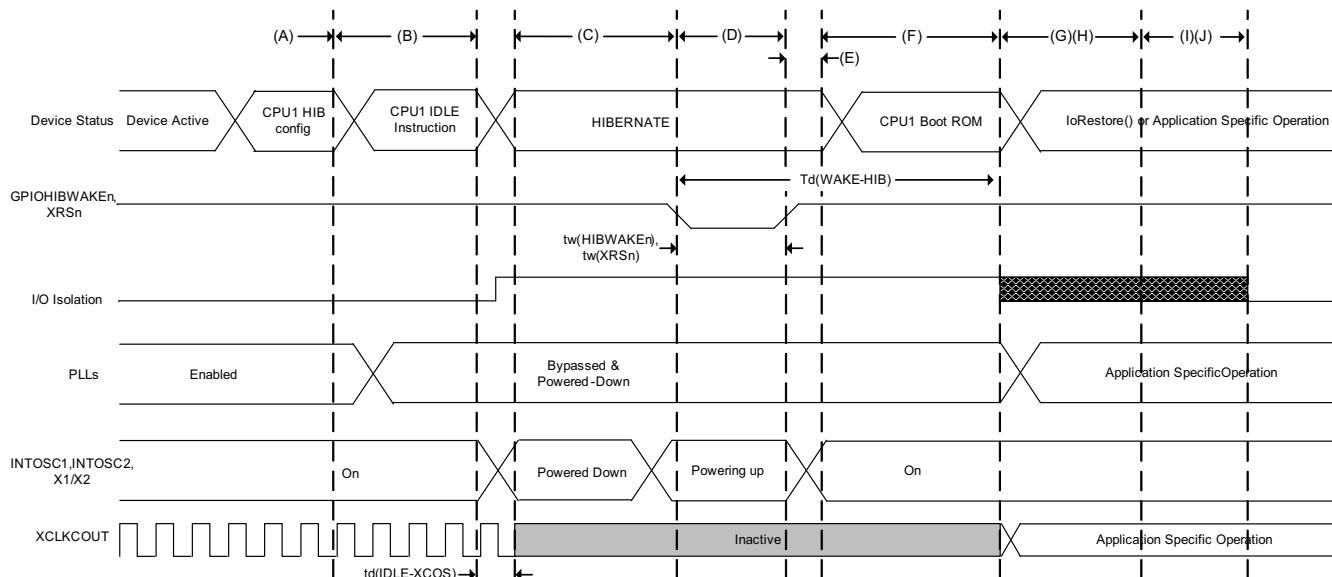

- 外部ウェーイクアップに対応した複数の低消費電力モード (LPM) をサポート

- 通信ペリフェラル

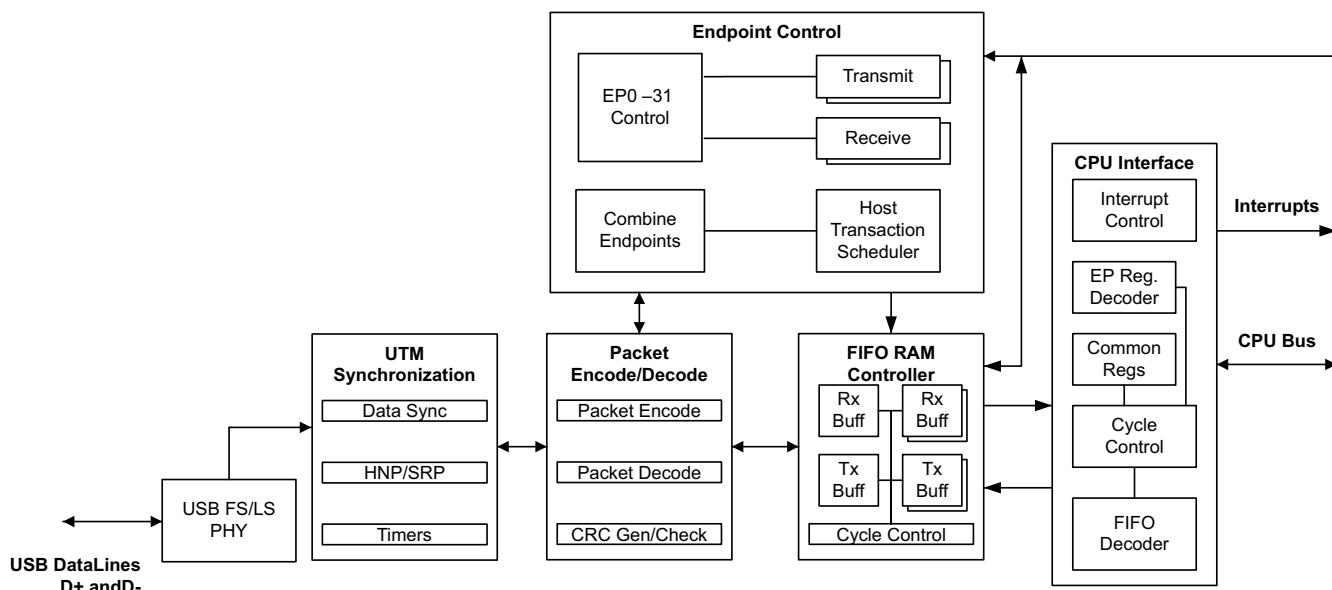

- USB 2.0 (MAC + PHY)

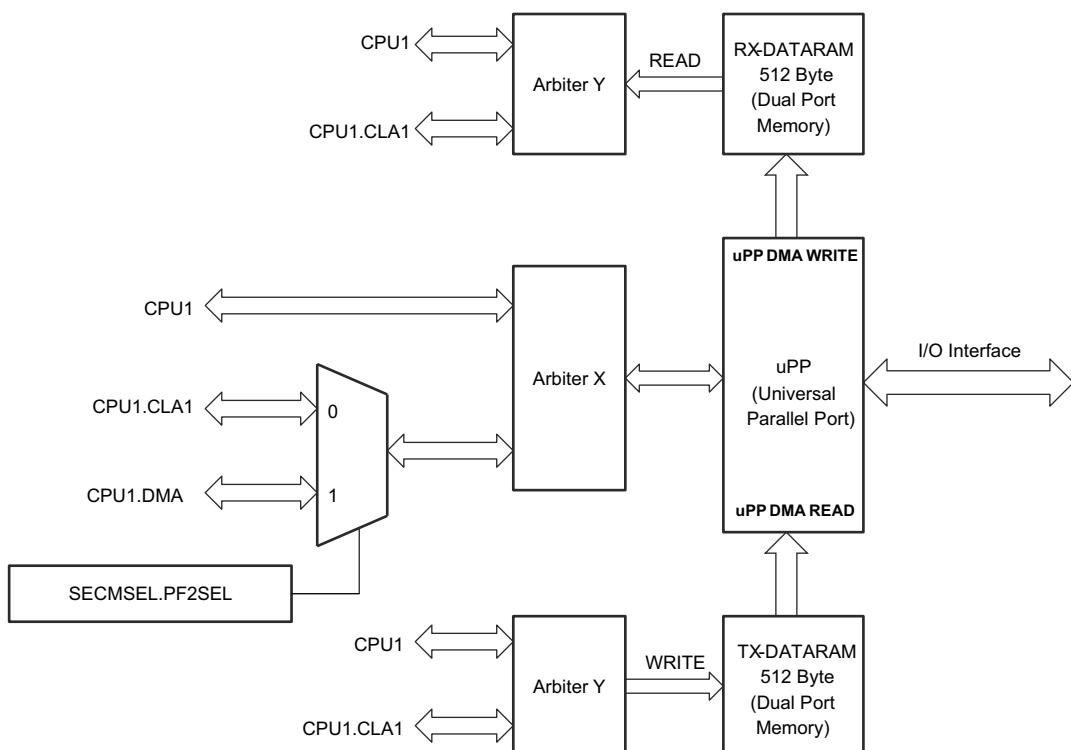

- 12 ピンの 3.3V 互換ユニバーサル パラレル ポート (uPP) インターフェイスをサポート

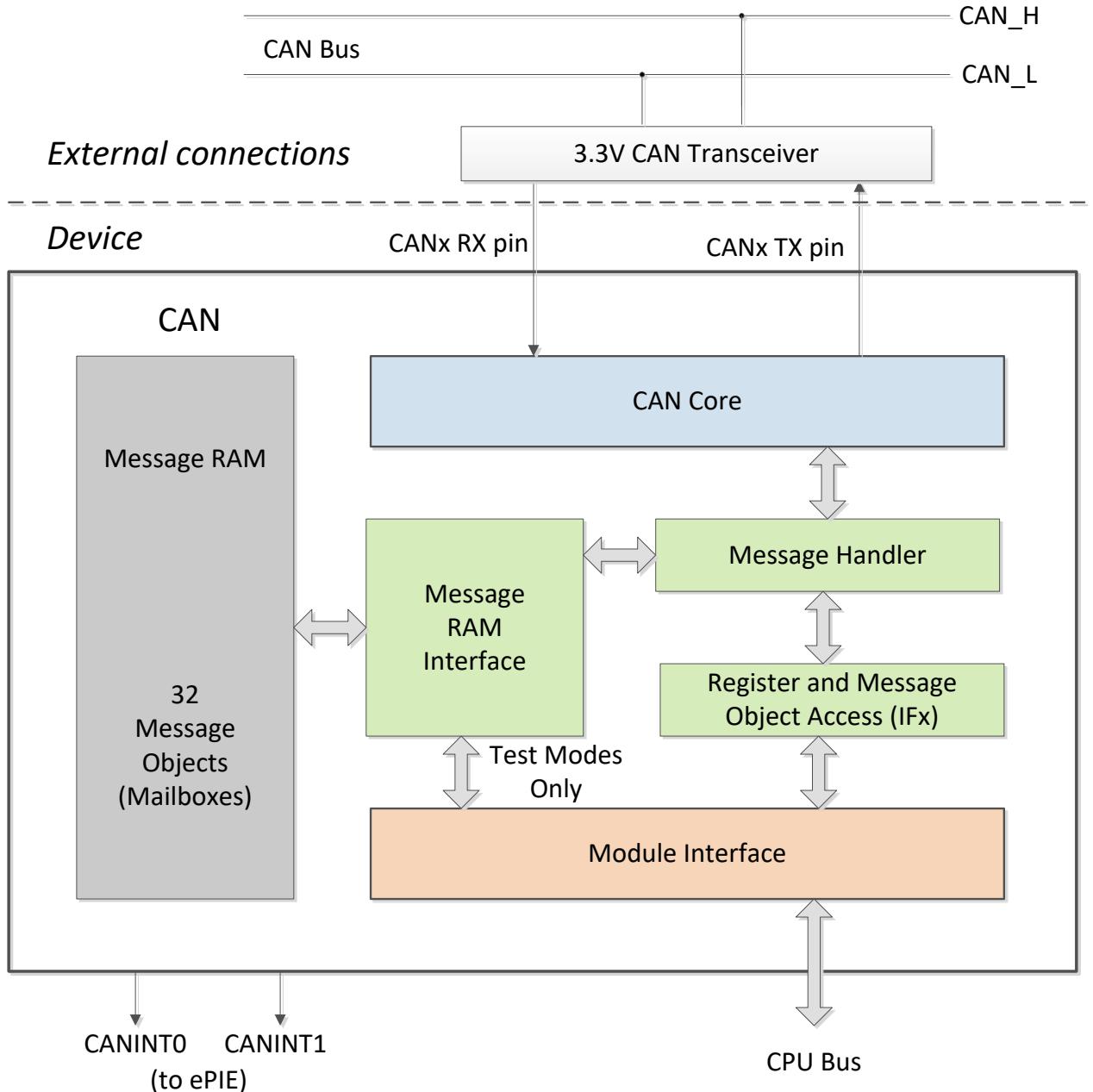

- 2 つの CAN (Controller Area Network) モジュール (ピンでブート可能)

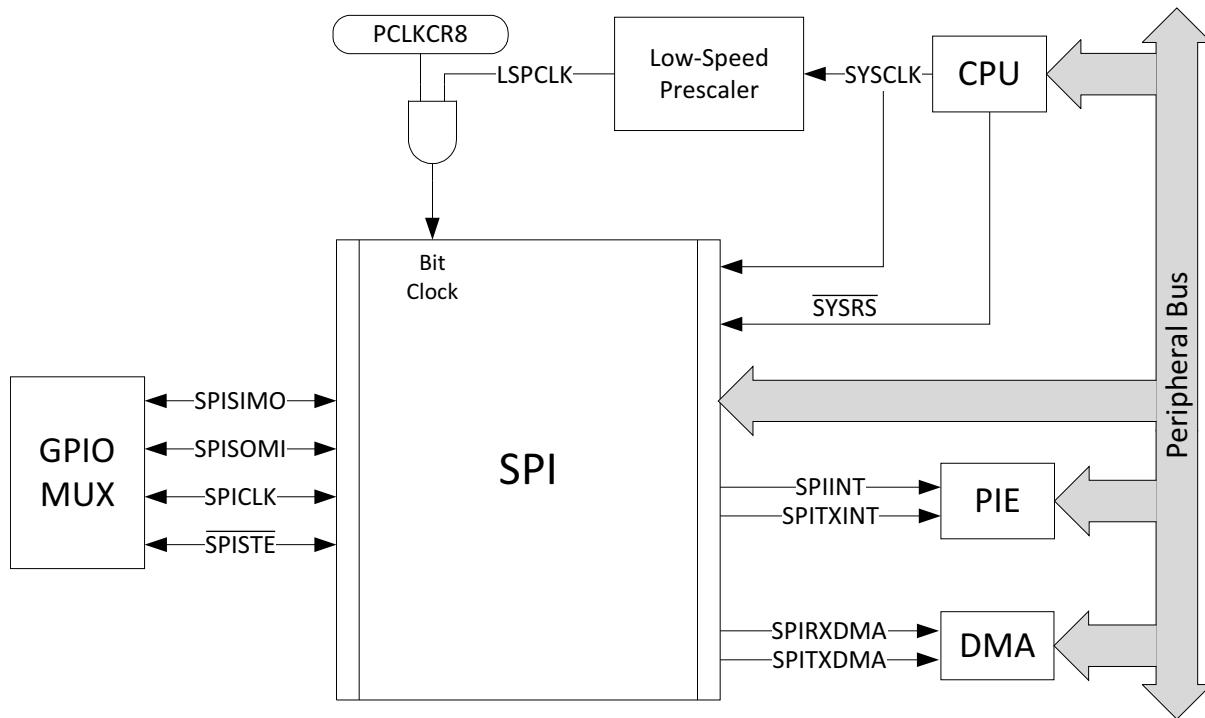

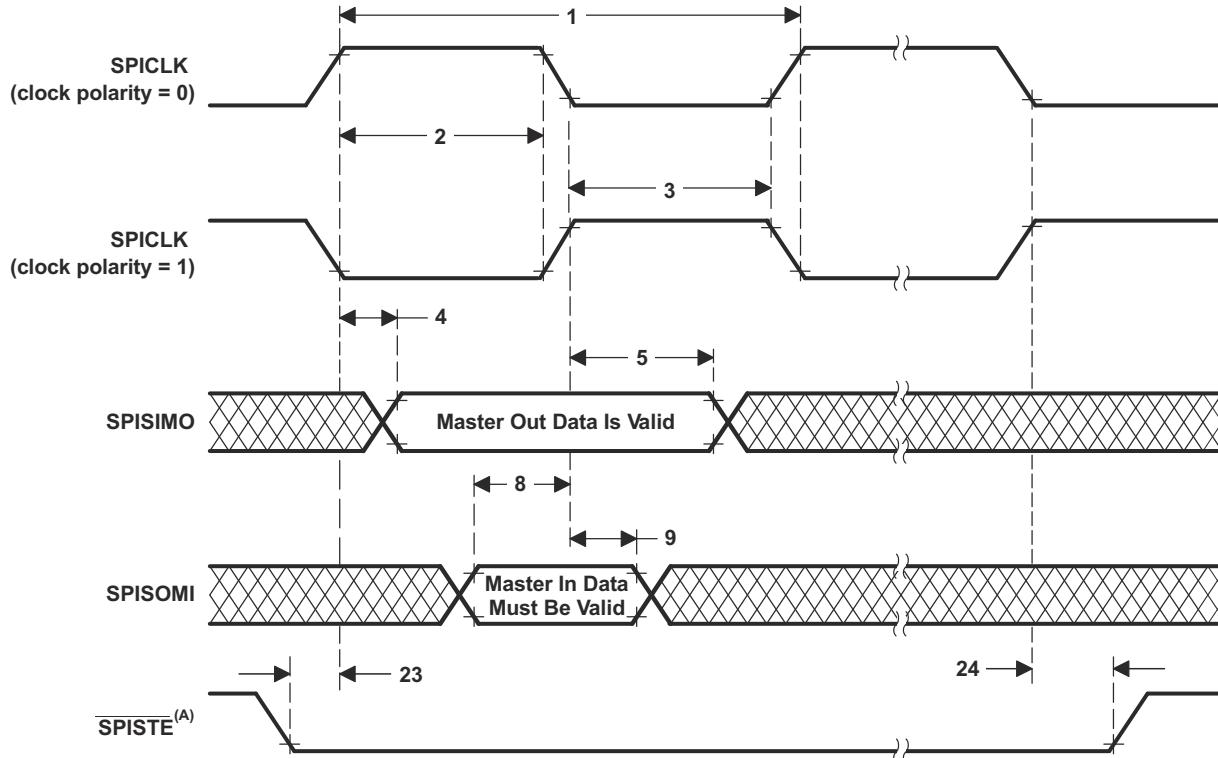

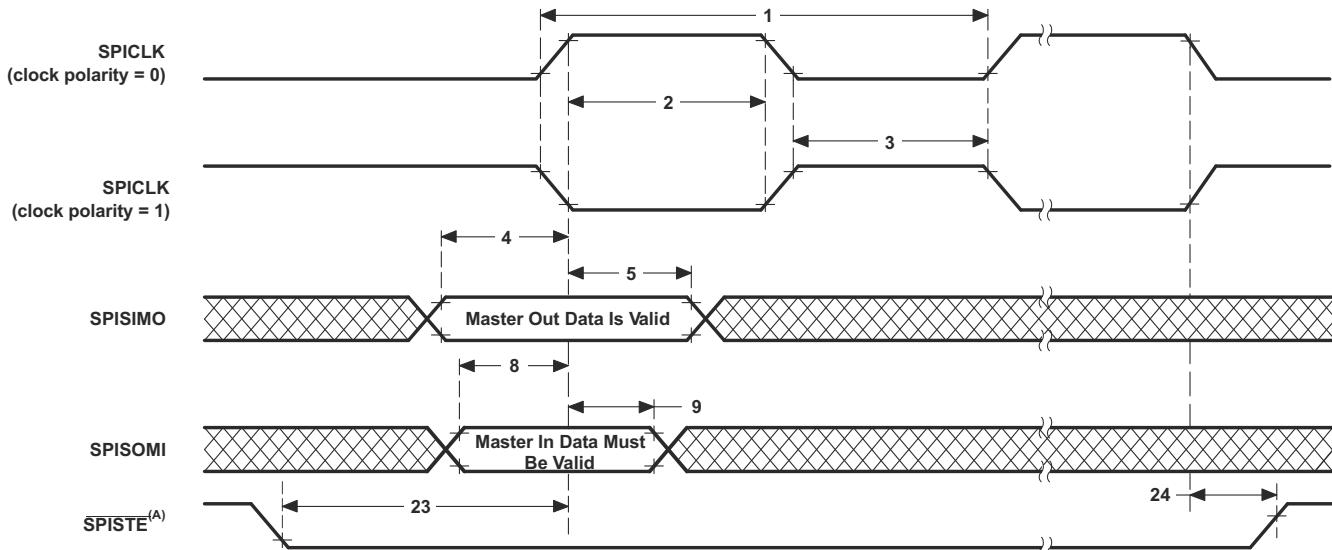

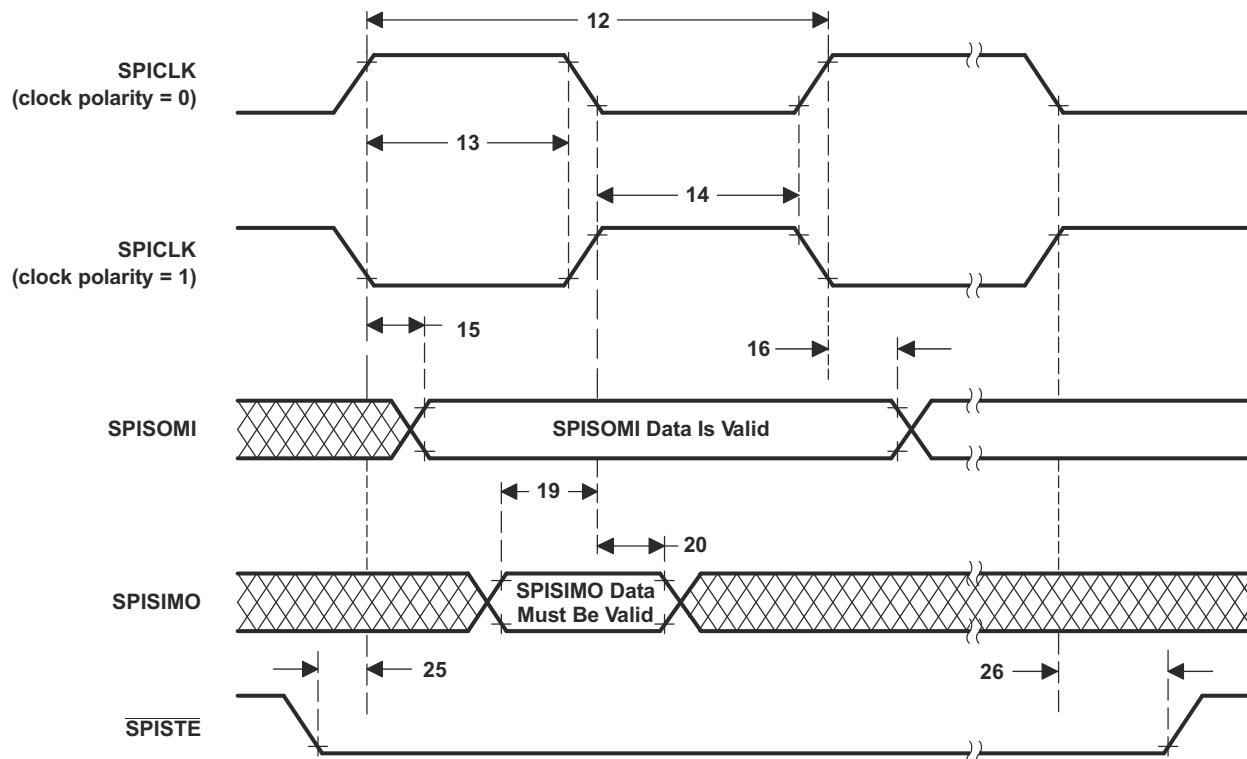

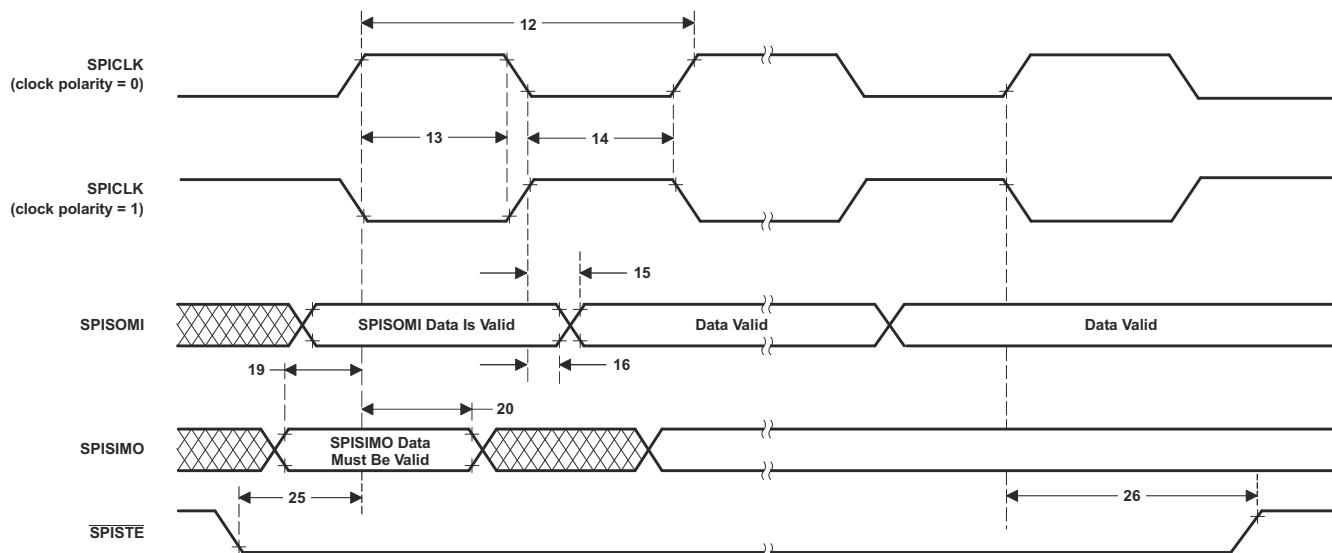

- 3 つの高速 (最高 50MHz) SPI ポート (ピンでブート可能)

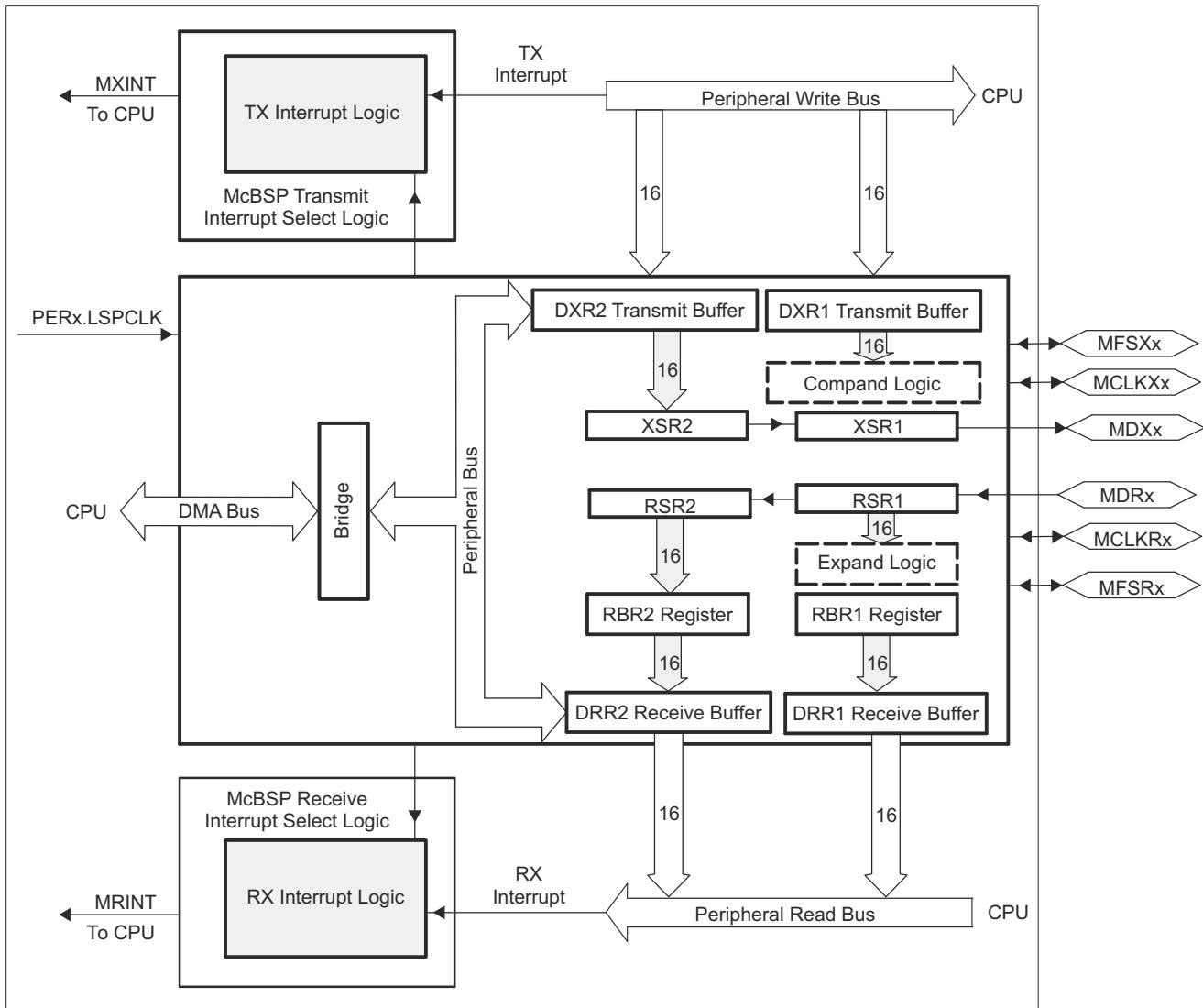

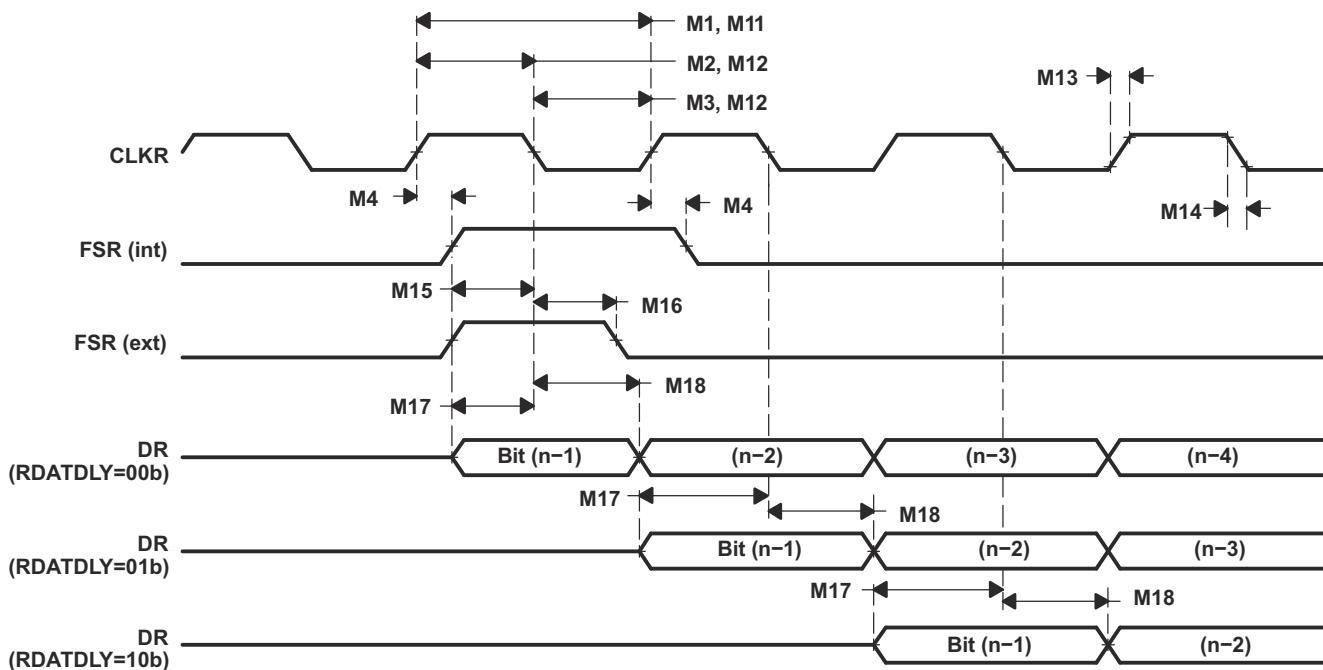

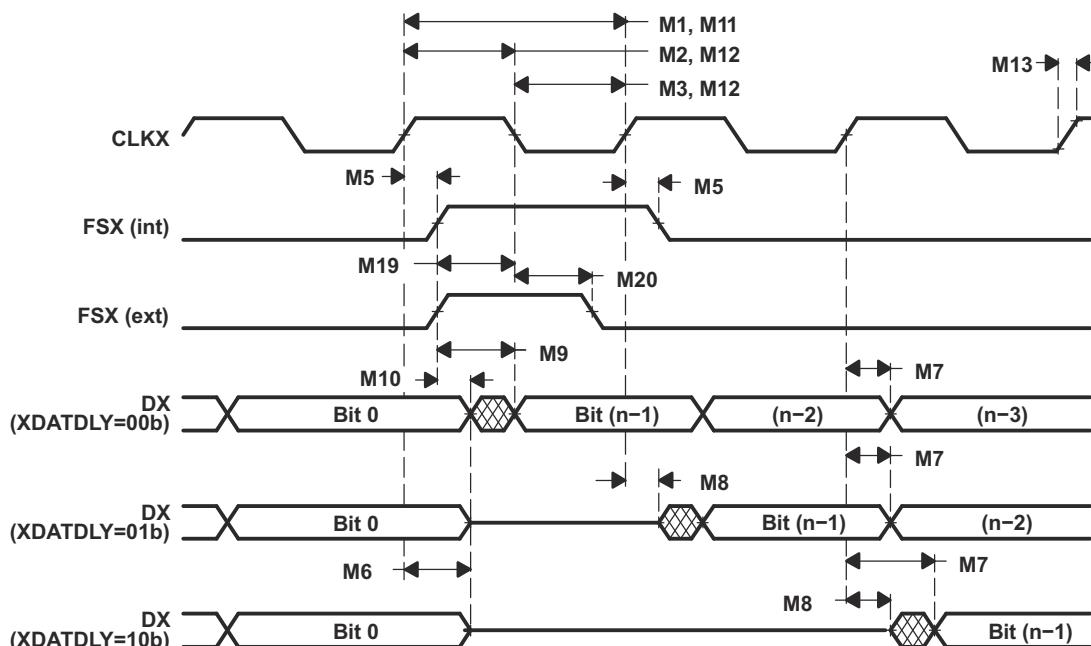

- 2 つのマルチチャネル バッファ付きシリアル ポート (McBSP)

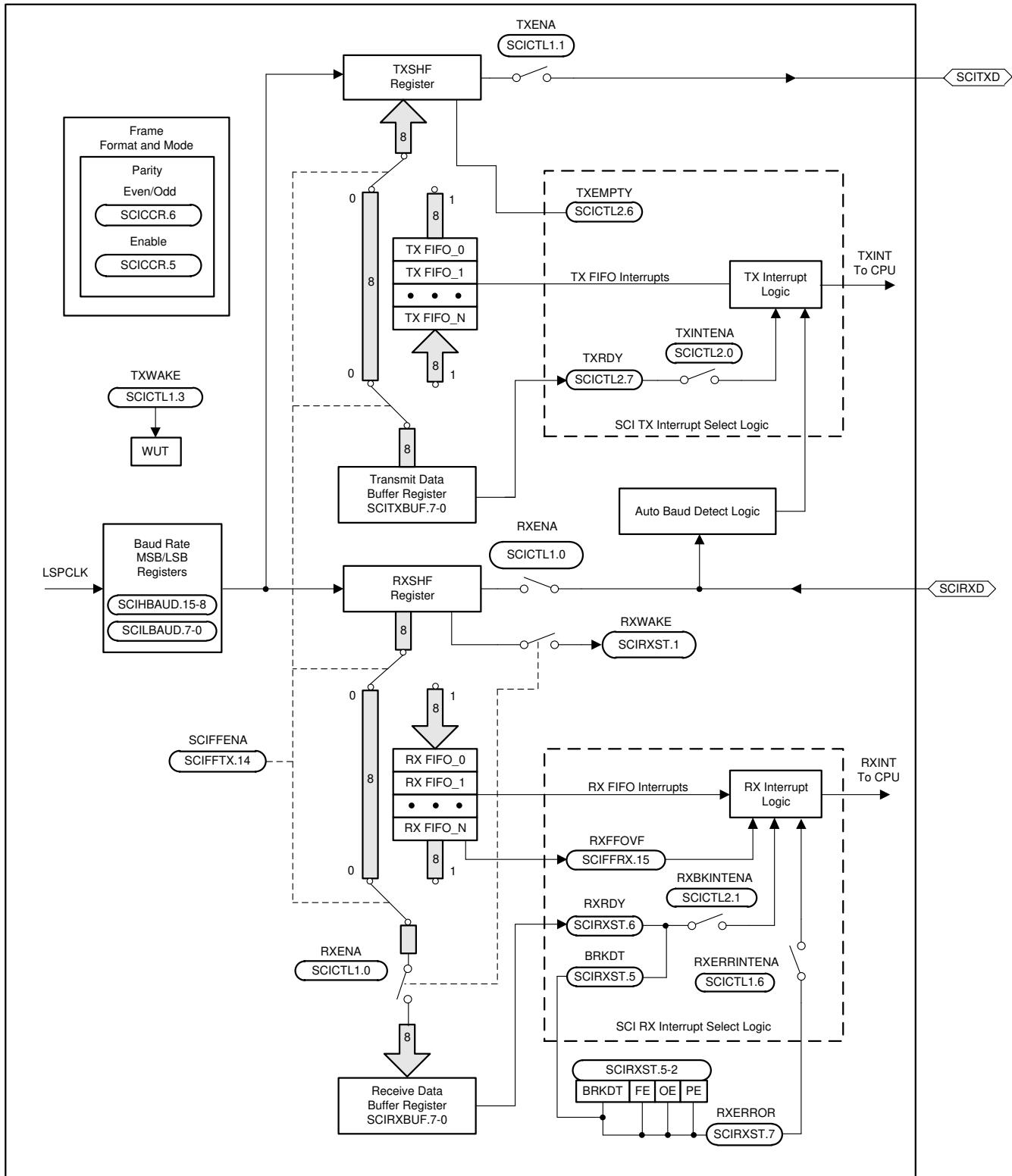

- 4 つのシリアル通信インターフェイス (SCI/UART) (ピンでブート可能)

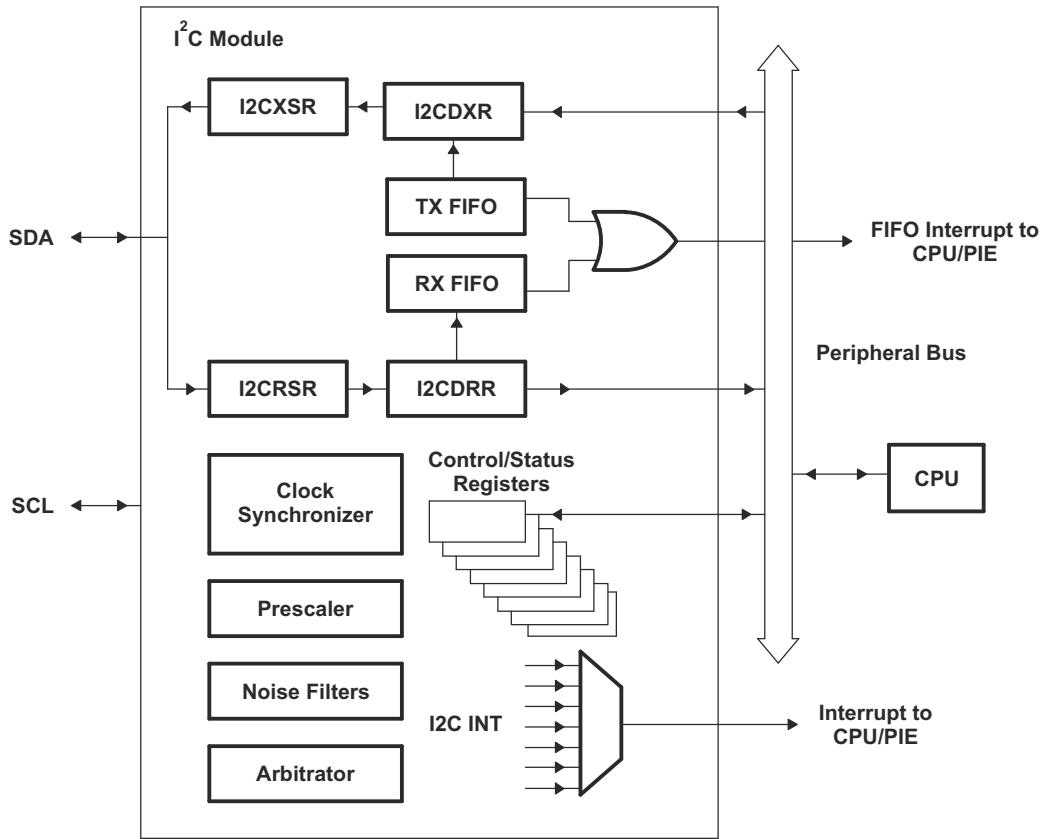

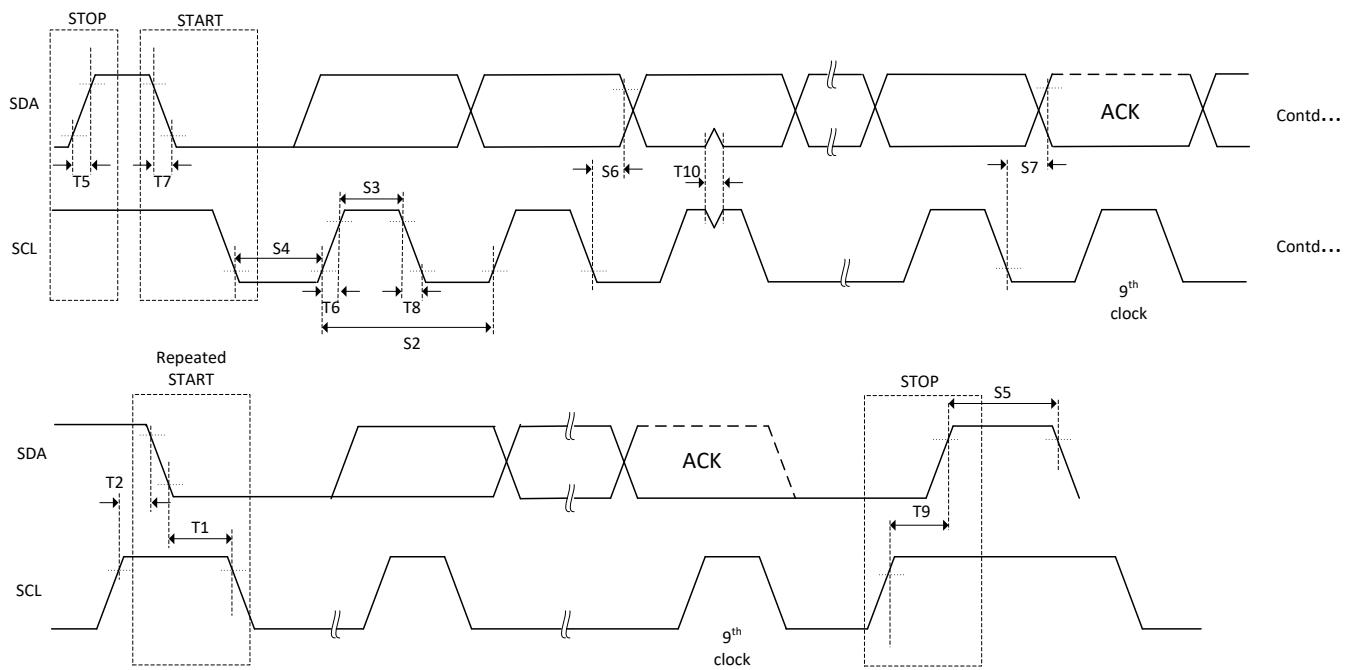

- 2 つの I2C インターフェイス (ピンでブート可能)

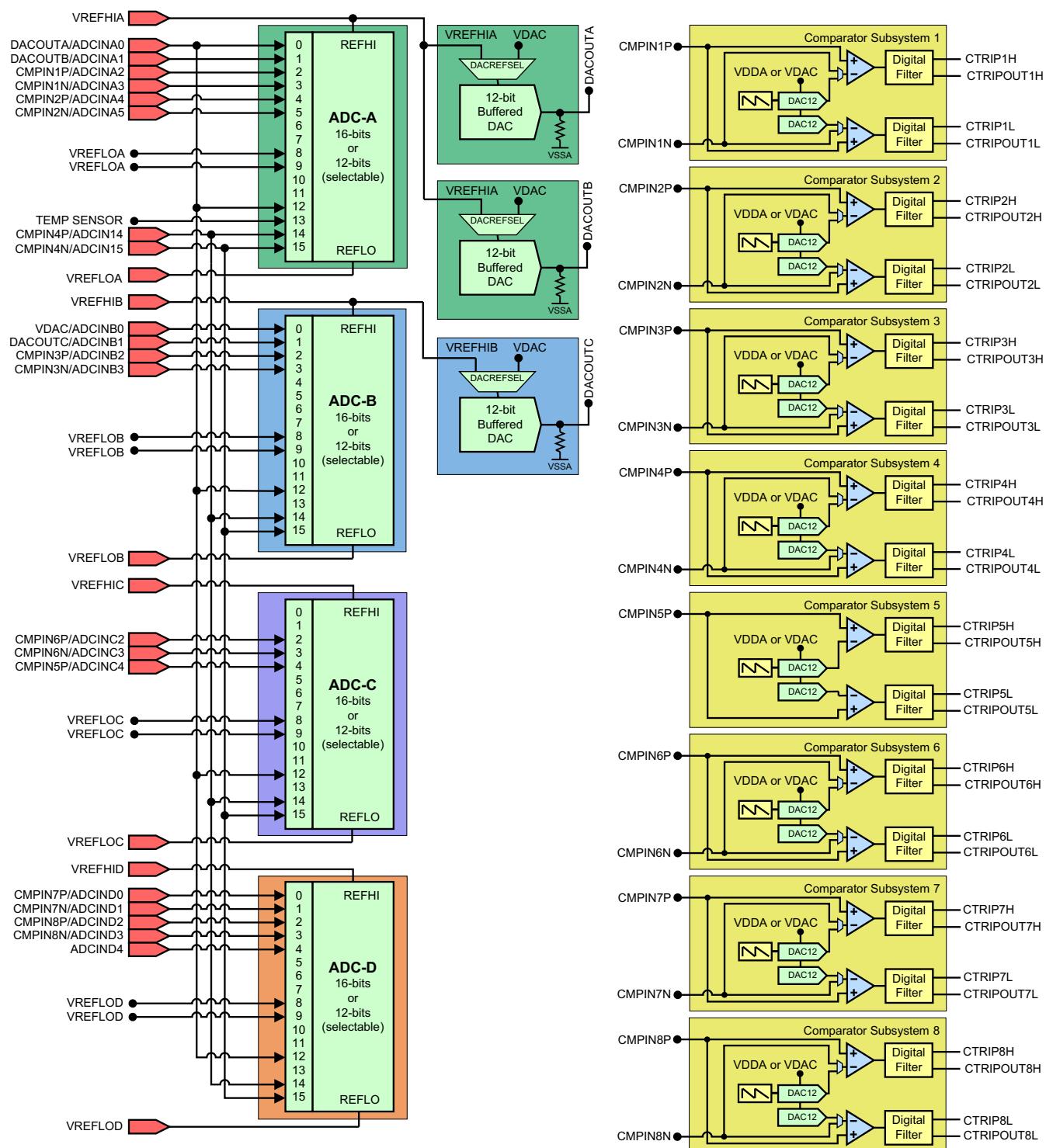

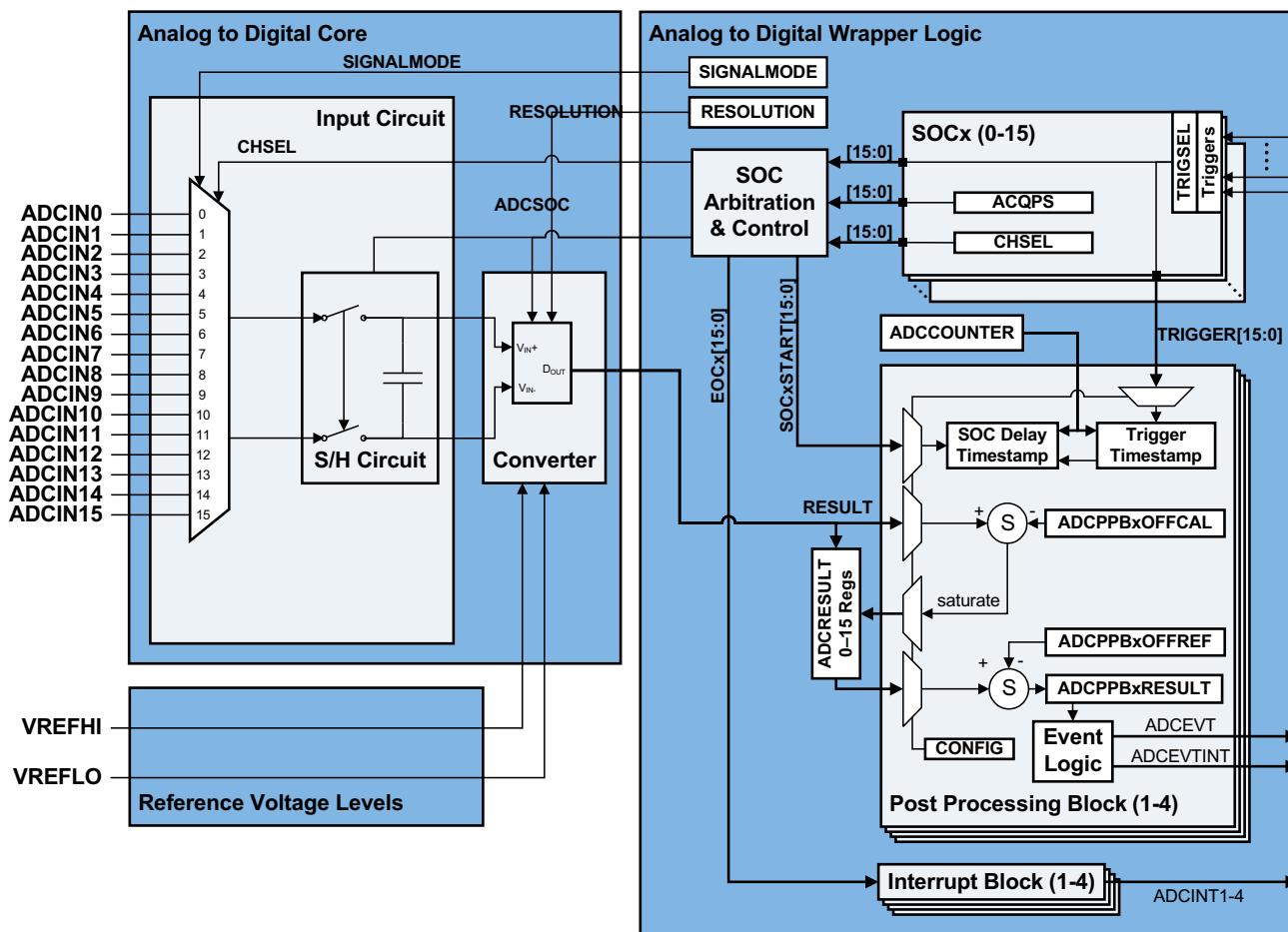

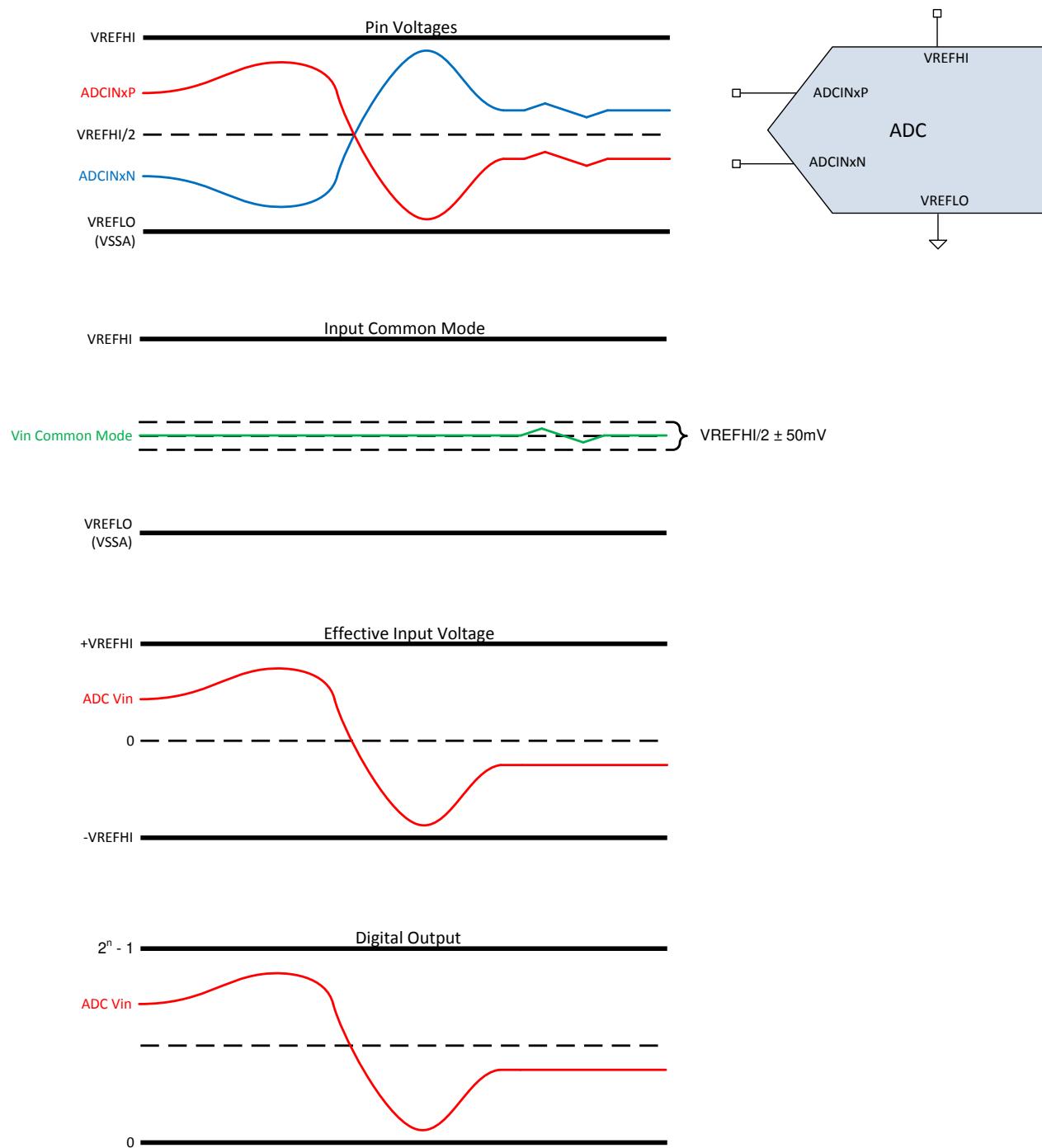

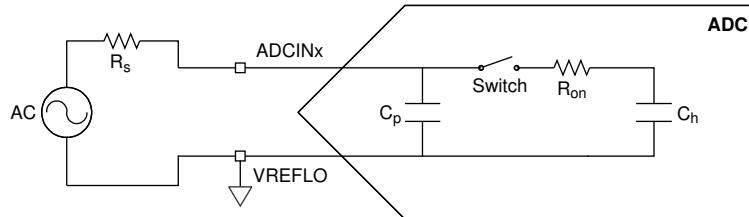

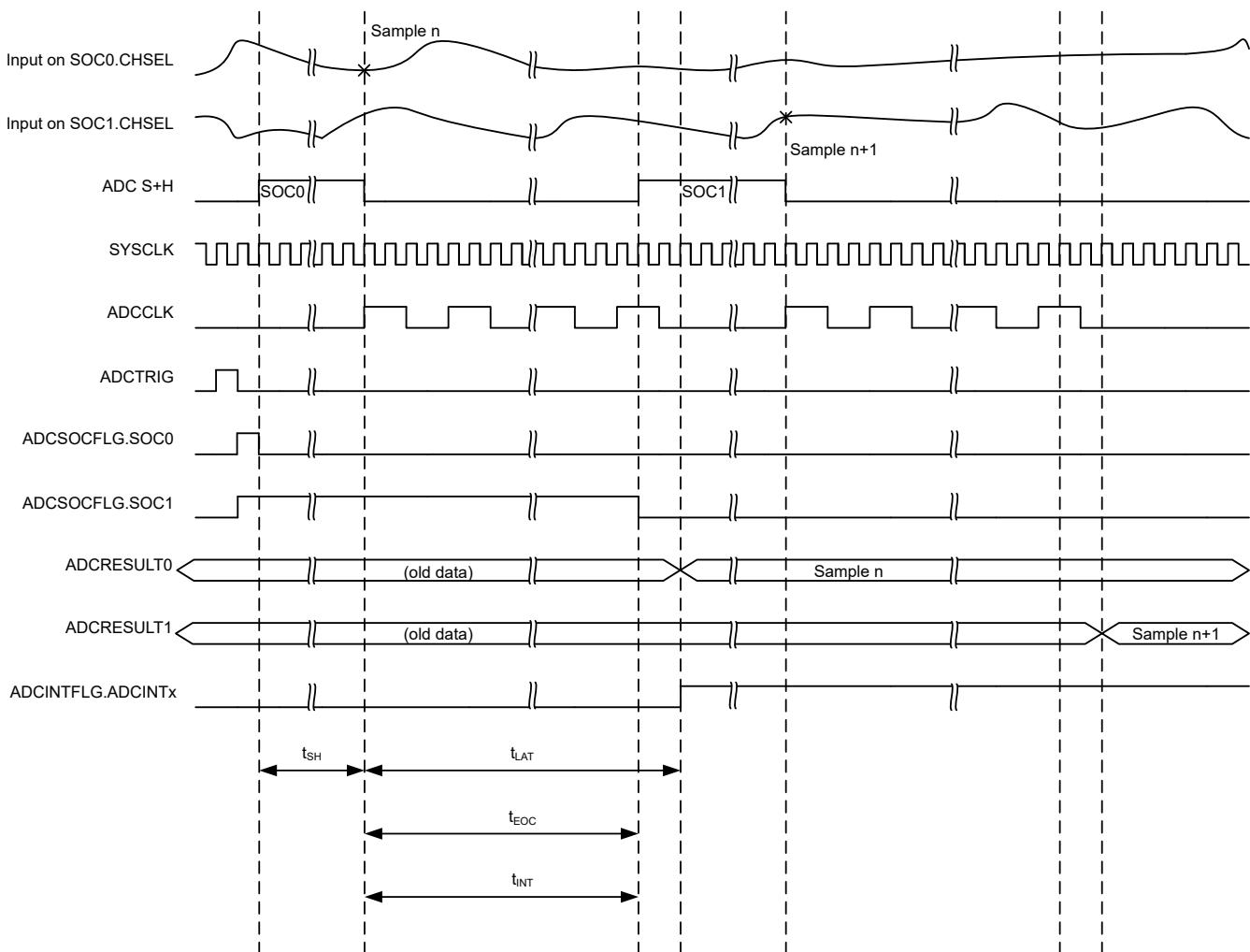

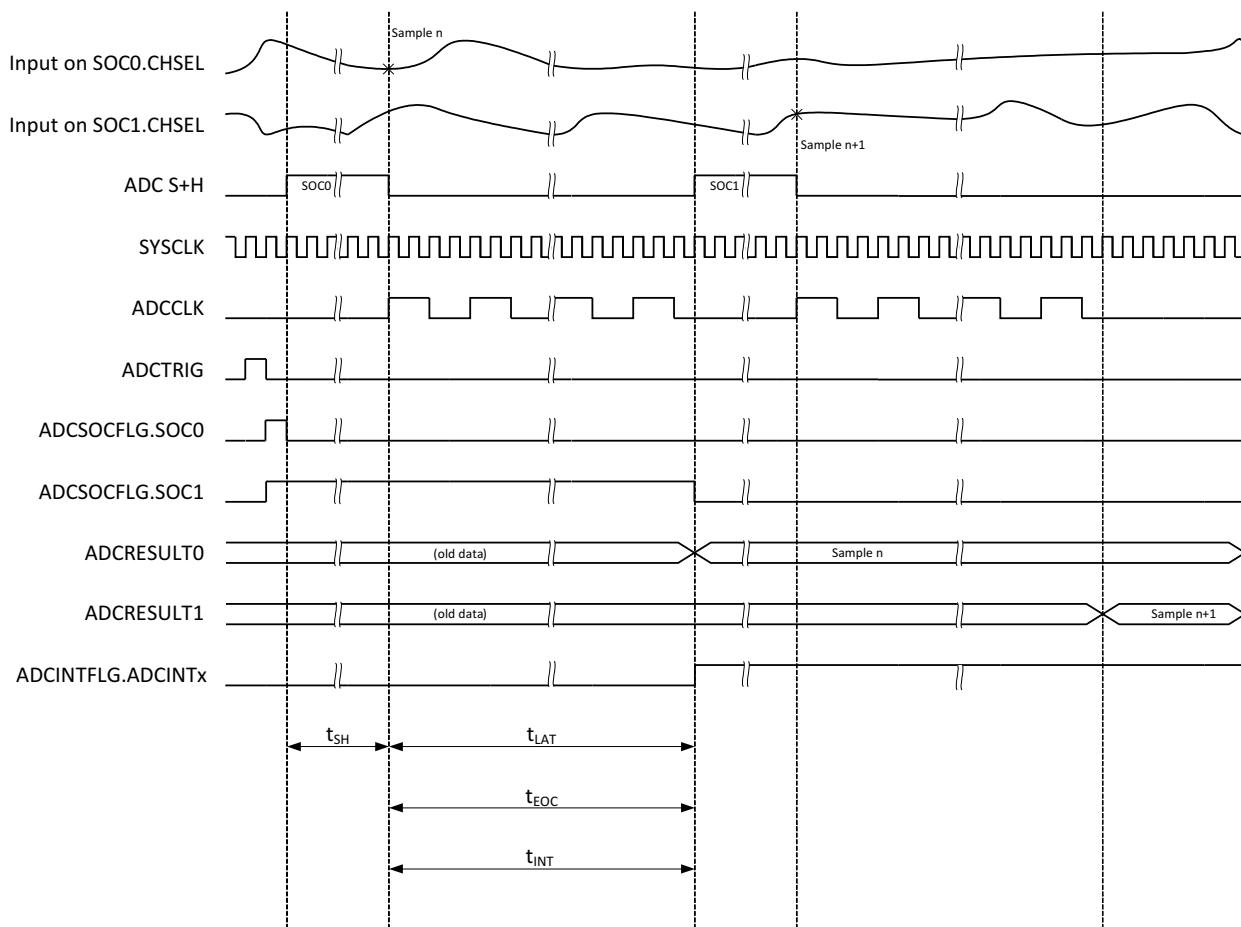

- アナログ サブシステム

- 最大 4 つのアナログ / デジタル コンバータ (ADC)

- 16 ビット モード

- 各 1.1MSPS (最大 4.4MSPS のシステム スループット)

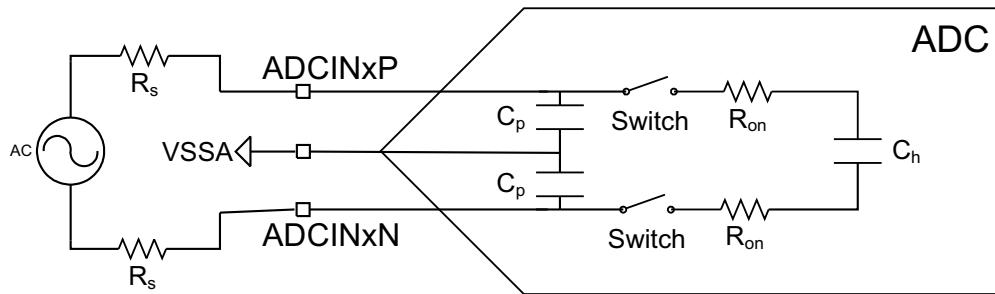

- 差動入力

- 最大 12 の外部チャネル

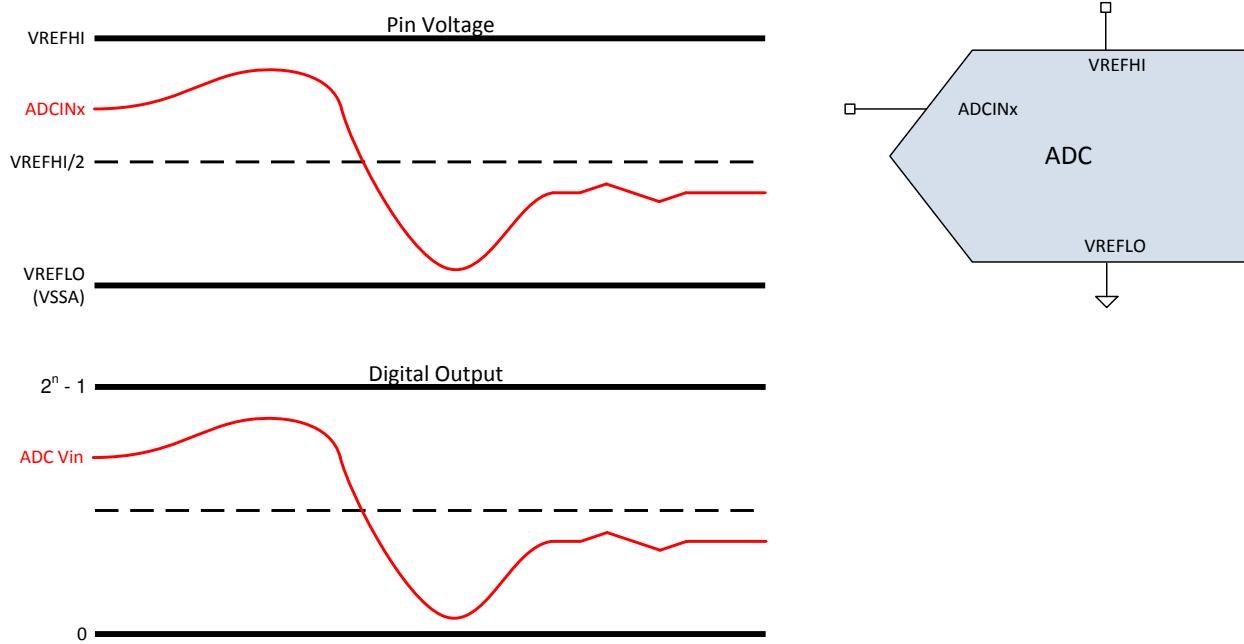

- 12 ビット モード

- 各 3.5MSPS (最大 14MSPS のシステム スループット)

- シングルエンド入力

- 最大 24 の外部チャネル

- 各 ADC に 1 つのサンプル アンド ホールド (S/H)

- ADC 変換の後処理をハードウェアに内蔵

- 飽和オフセット較正

- 設定点からの誤差の計算

- 高、低、およびゼロクロス比較、割り込み機能付き

- トリガからサンプルまでの遅延キャプチャ

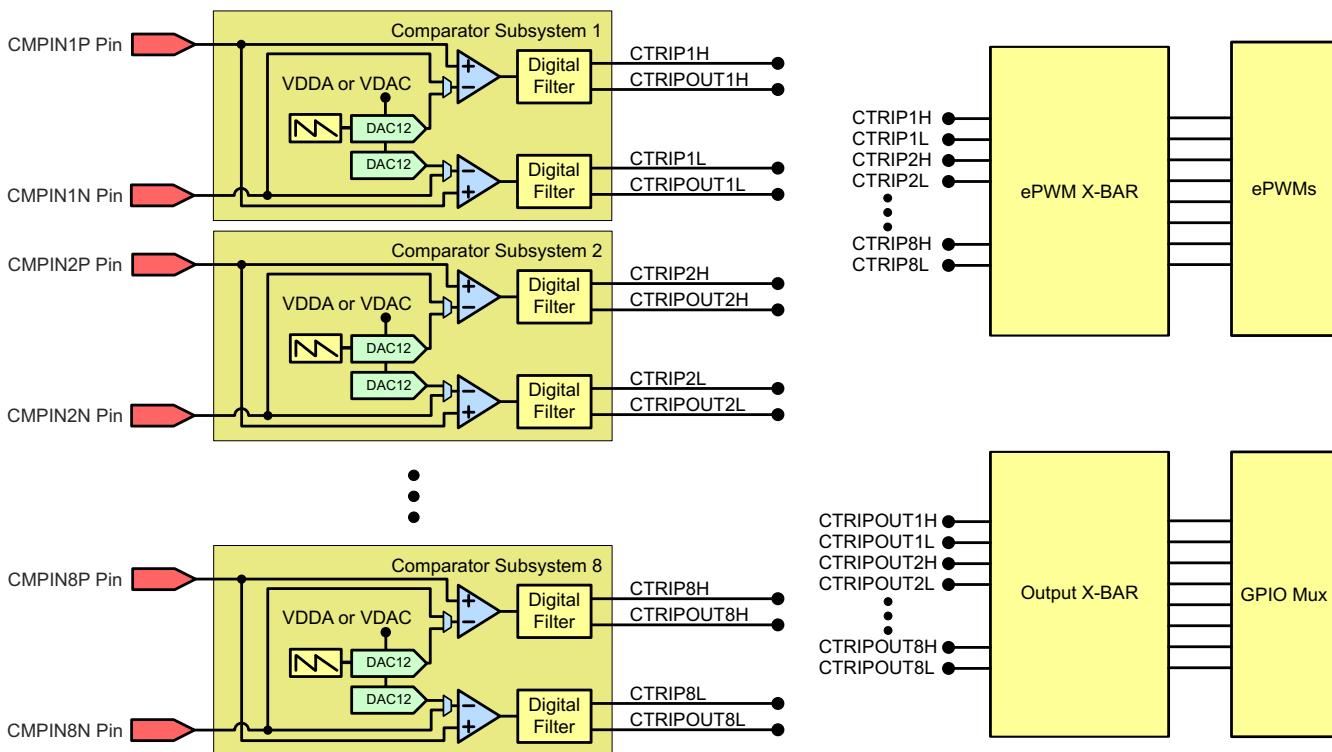

- 8 つのウインドウ付きコンパレータ、12 ビットのデジタル/アナログ コンバータ (DAC) リファレンス付き

- 3 つのバッファ付き 12 ビット DAC 出力

- 拡張制御ペリフェラル

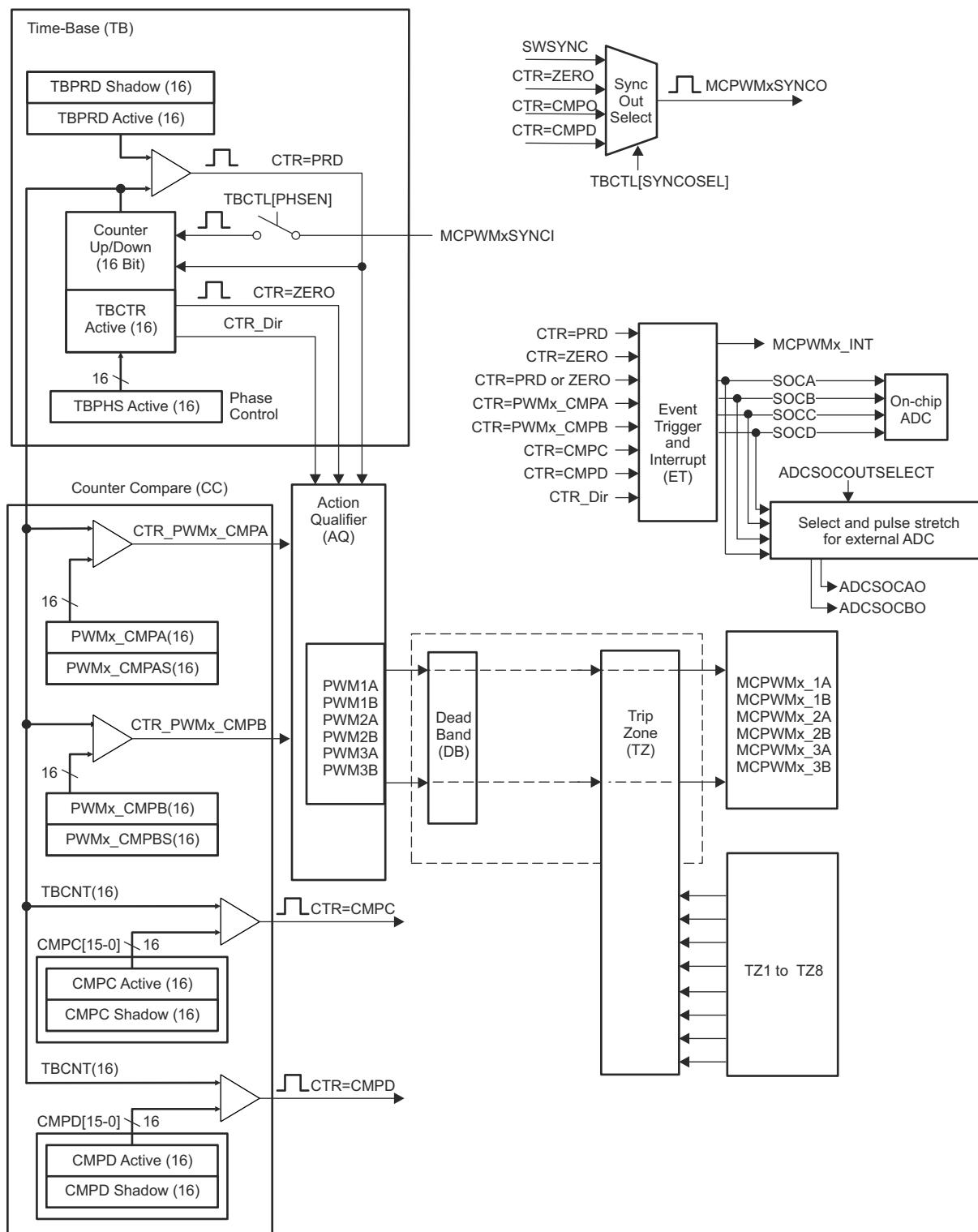

- 拡張機能付きの 24 のパルス幅変調器 (PWM) チャネル

- 16 の高分解能パルス幅変調器 (HRPWM) チャネル

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

- 8つのPWMモジュールのAチャネルとBチャネルの両方が高分解能

- デッドバンドのサポート(標準と高分解能の両方)

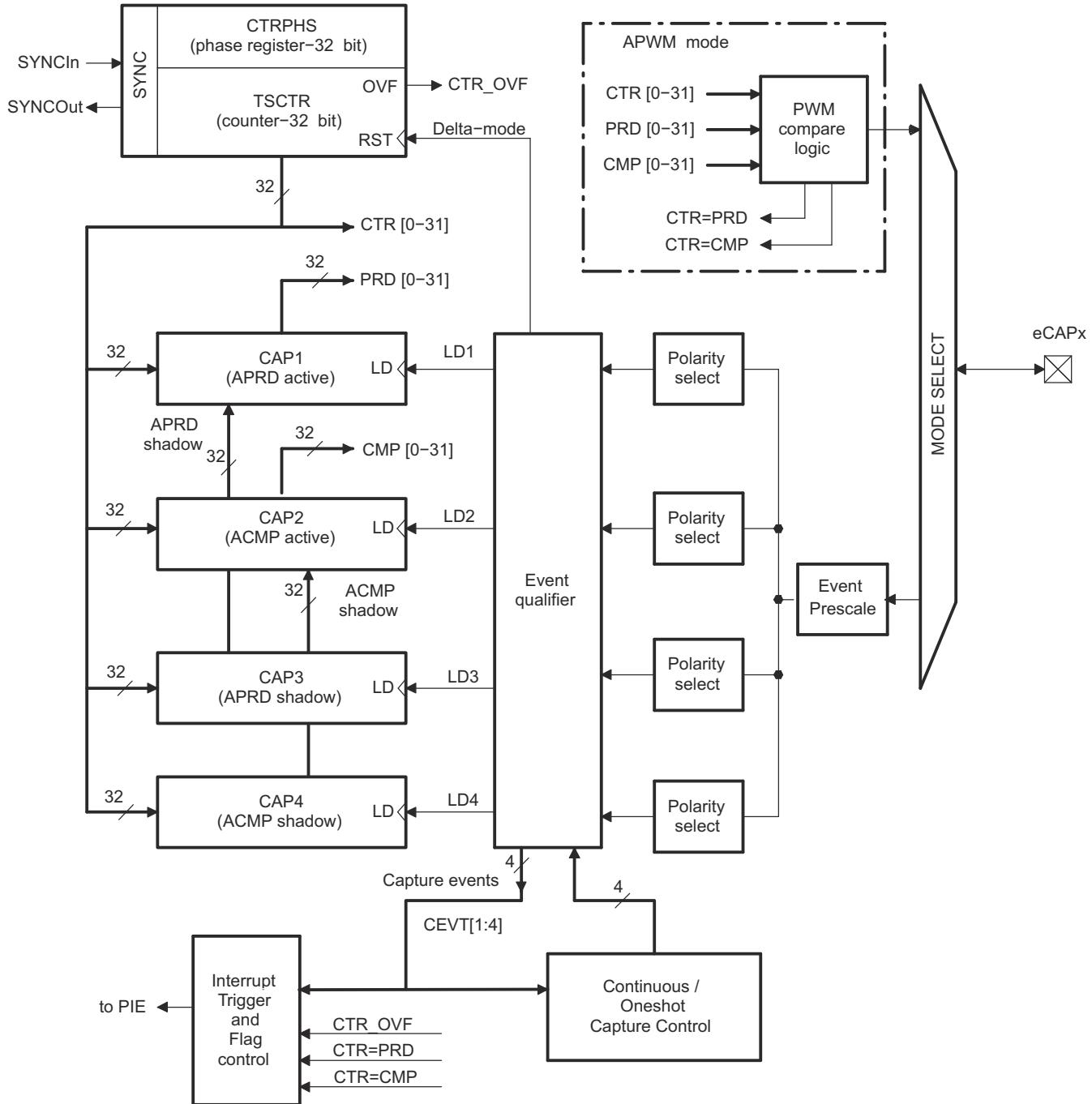

- 6つの拡張キャプチャ(eCAP)モジュール

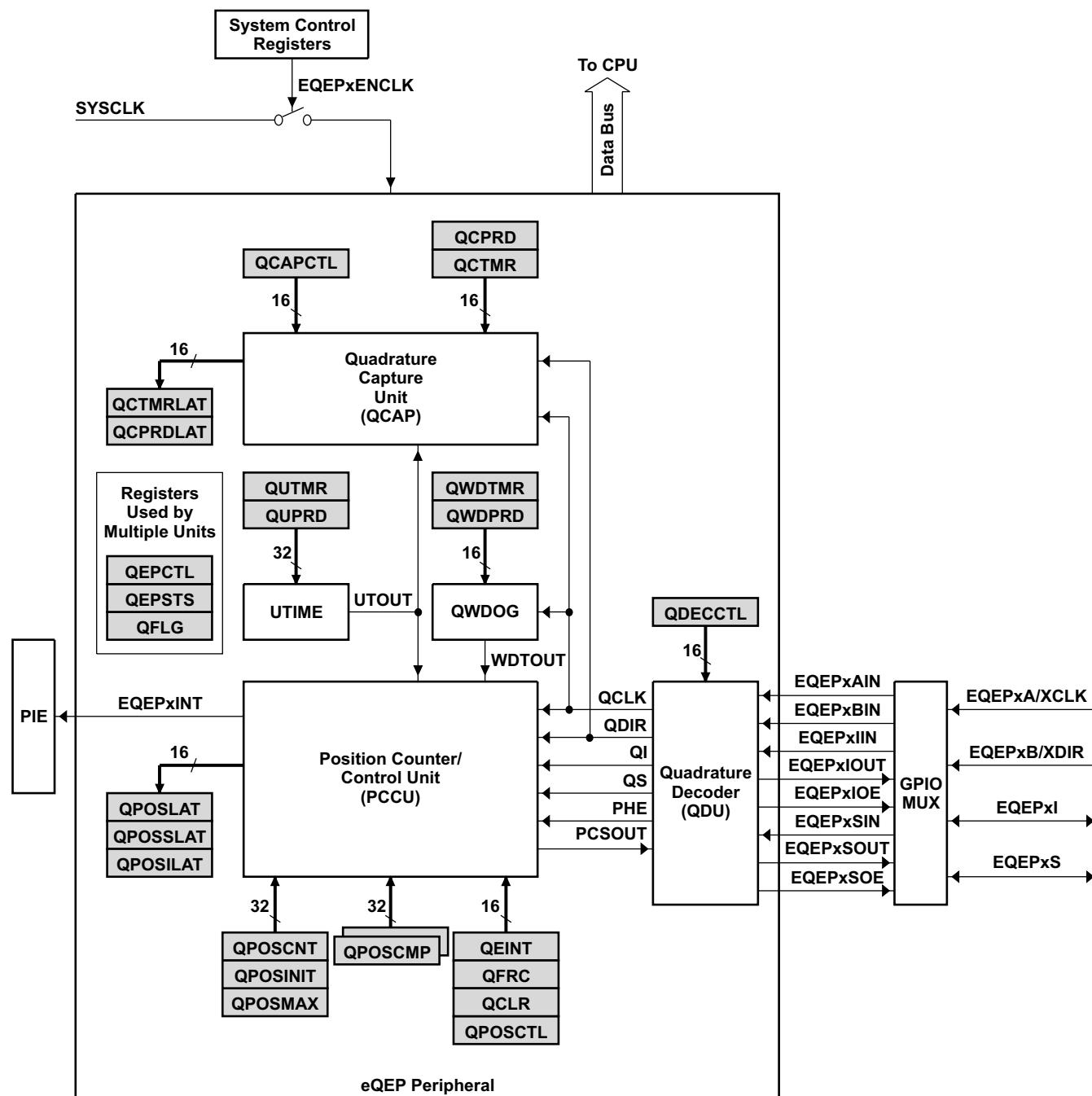

- 3つの拡張直交エンコーダパルス(eQEP)モジュール

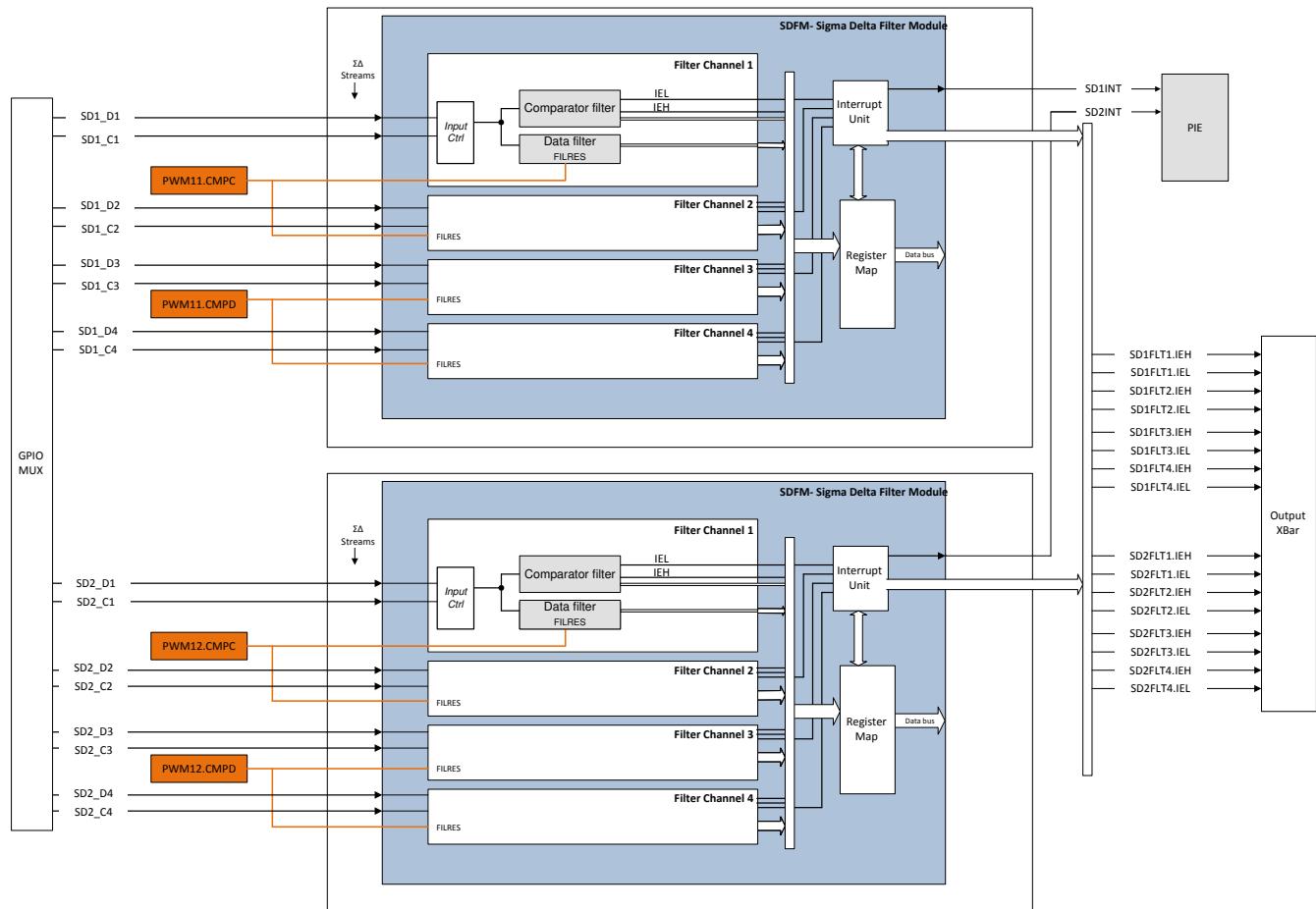

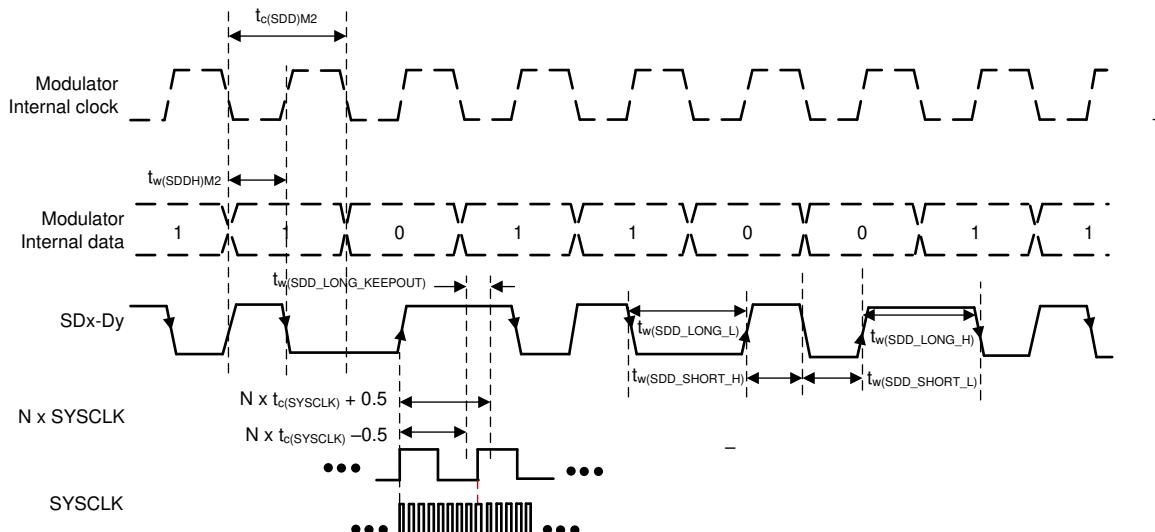

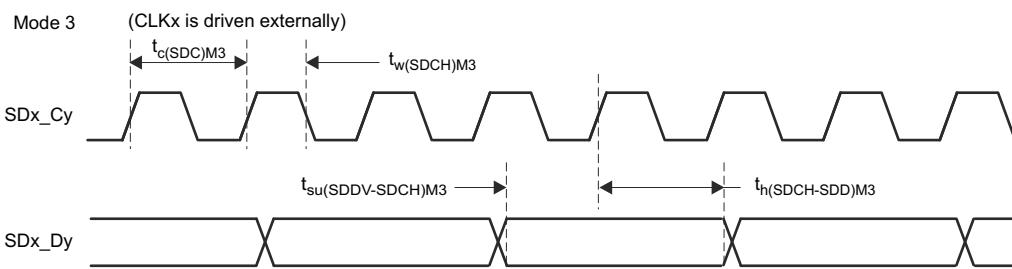

- 8つのシグマ-デルタフィルタモジュール(SDFM)入力チャネル(チャネルごとに2つのパラレルフィルタ)

- 標準SDFMデータフィルタリング

- コンパレータフィルタによる範囲外に対する迅速なアクション

- 防衛および航空宇宙アプリケーションをサポート

- 管理されたベースライン

- 単一のアセンブリ/テスト施設

- 単一の製造施設

- 長期にわたる製品ライフサイクル

- 製品のトレーサビリティ

- ASTM E595に準拠した気体排出試験実施済み

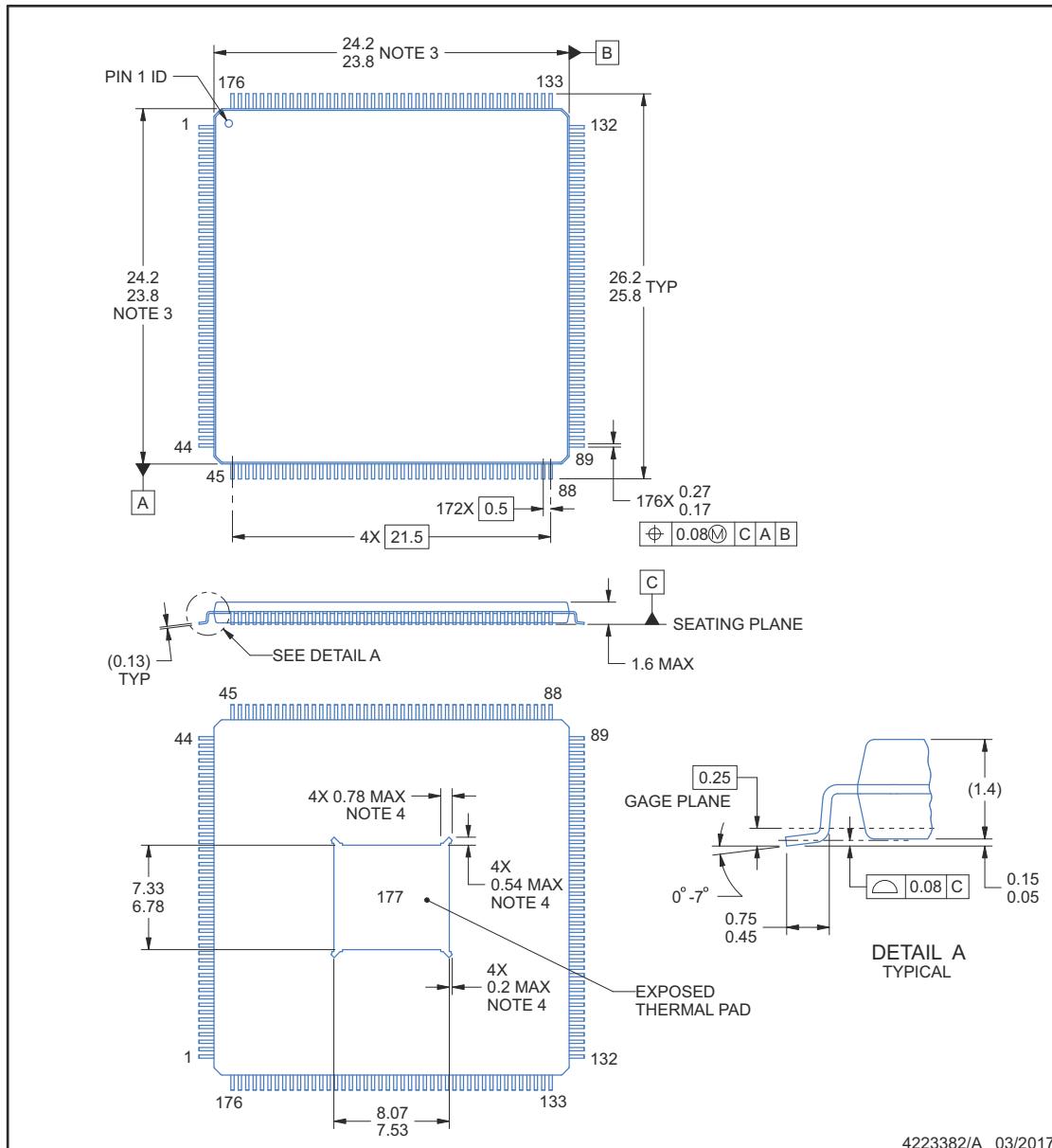

- パッケージ:

- 176ピンPowerPAD™熱的に強化された薄型クリップフラットパック(HLQFP)[接尾辞PTP]

- ハードウェア組み込み自己テスト(HWBIST)

- 温度:

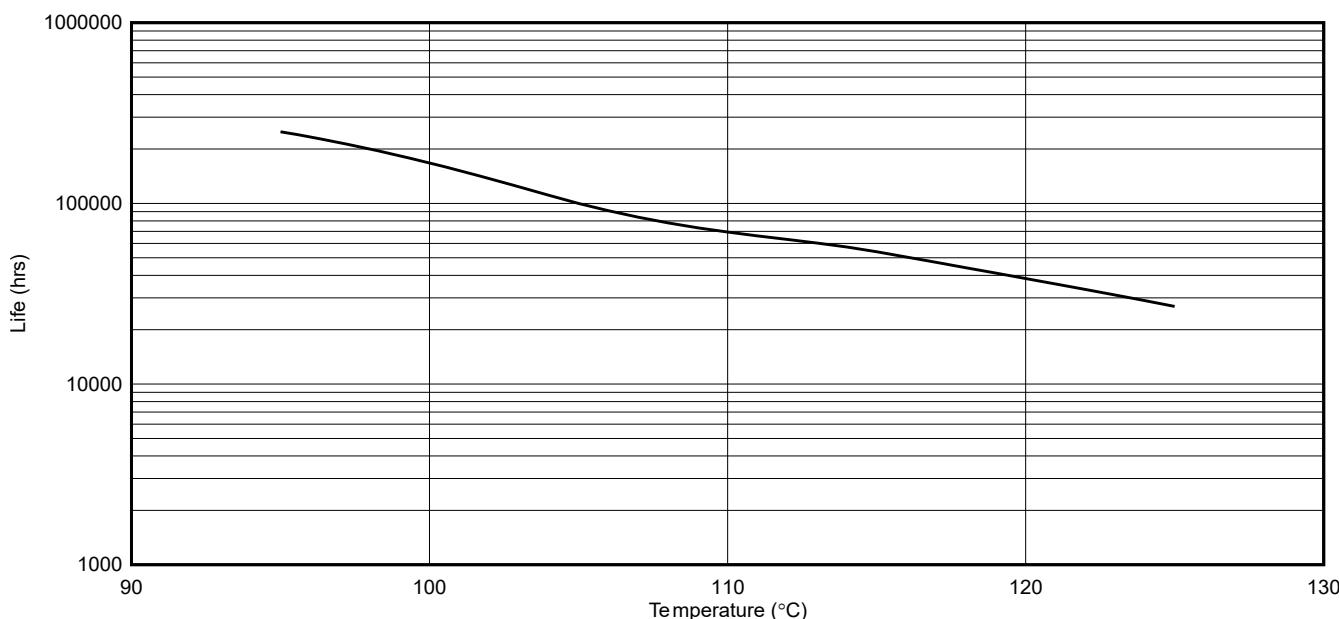

- -55°C~150°Cの接合部温度

### 3 説明

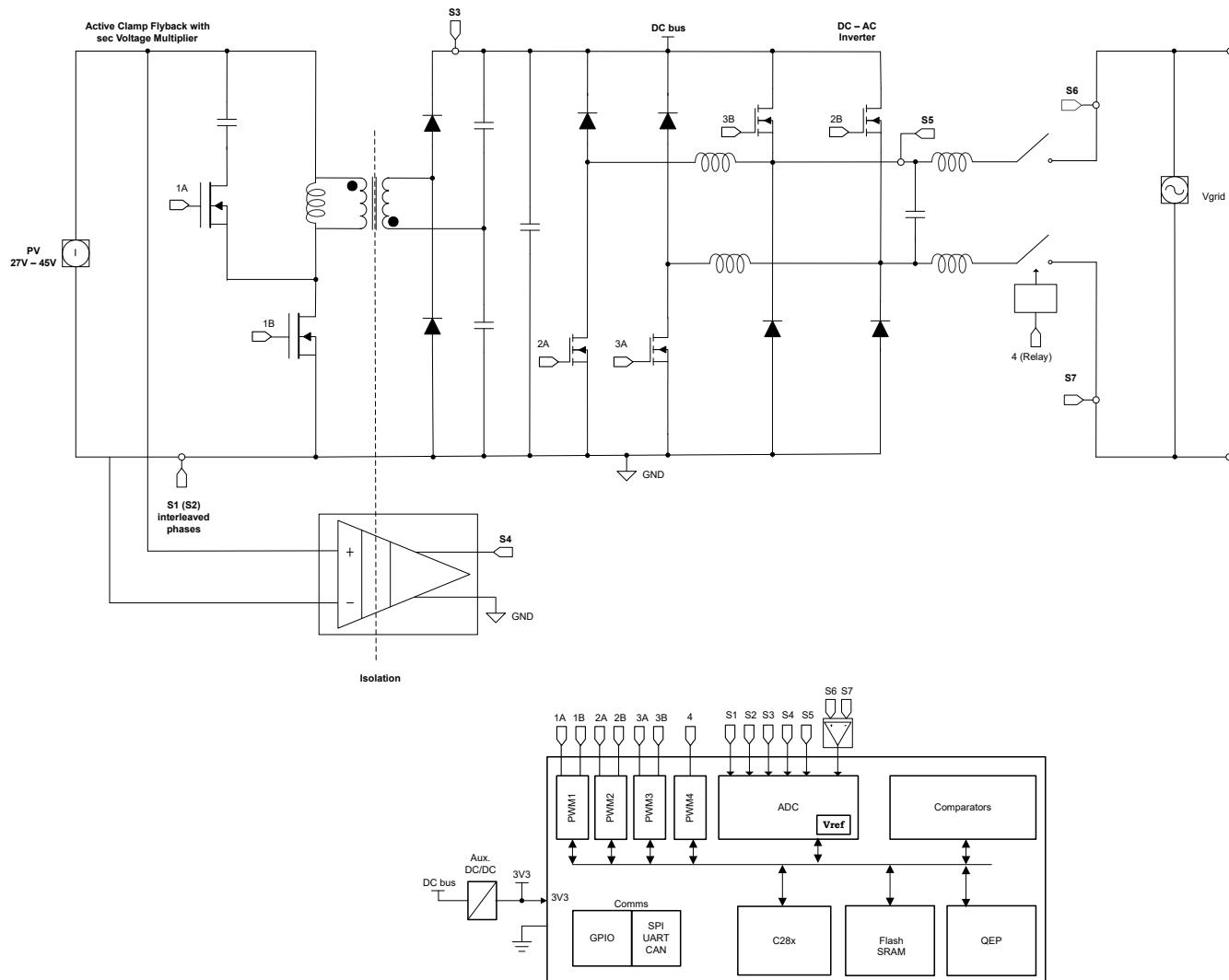

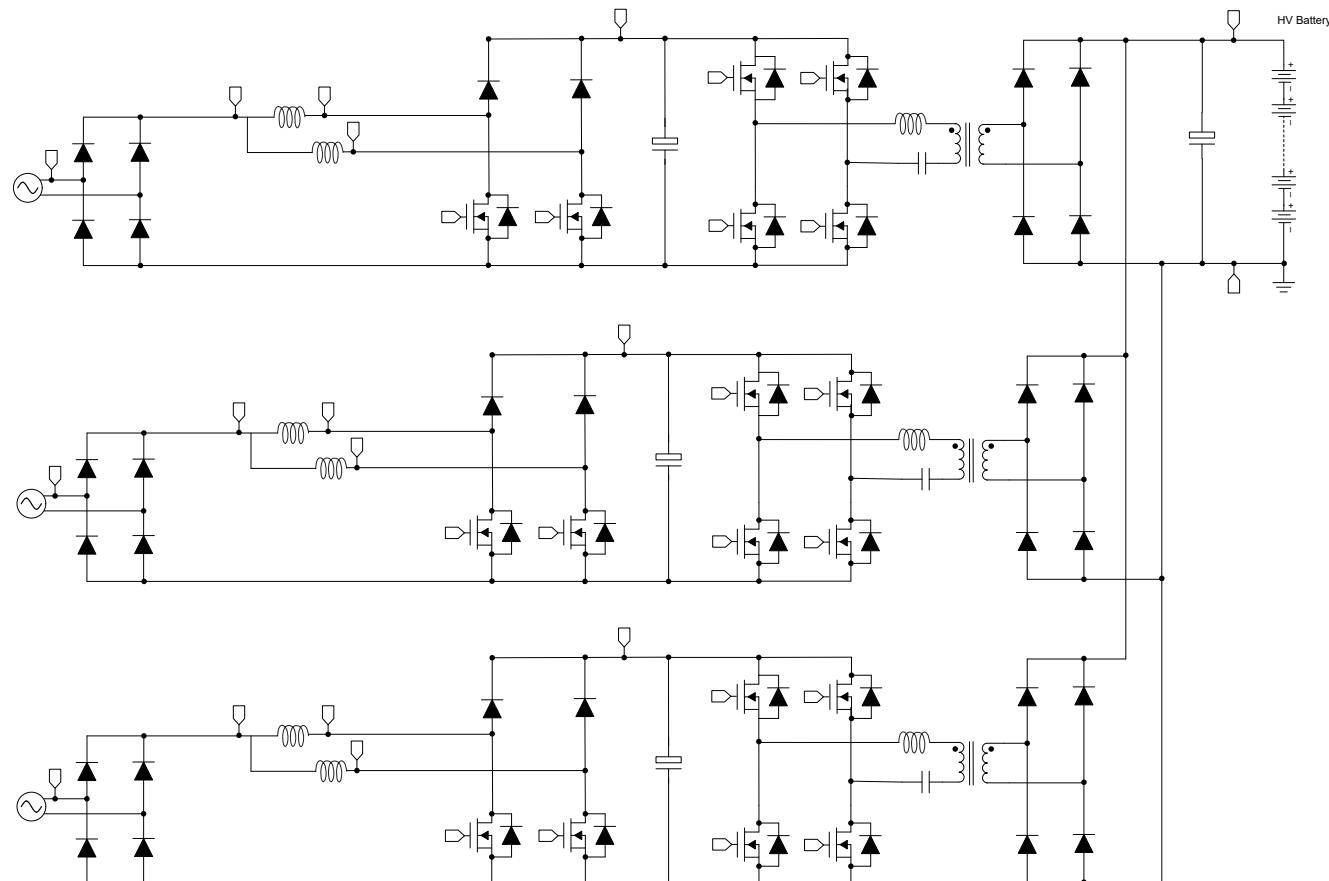

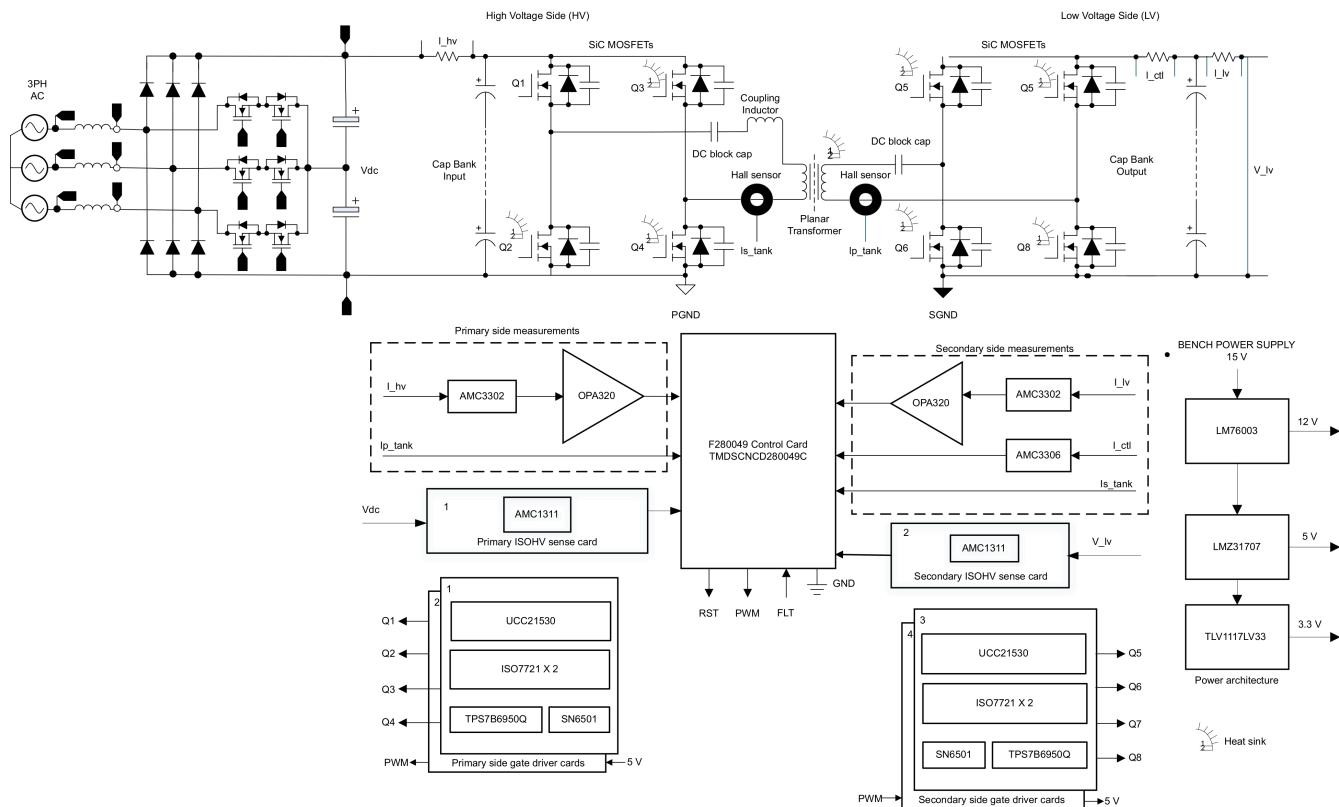

C2000™ 32ビットマイクロコントローラは、処理、センシング、アクチュエーションに最適化されており、リアルタイム制御アプリケーション、たとえば産業用モータードライブ、ソーラーインバータおよびデジタル電源、電気自動車および輸送、モーター制御、センシングおよび信号処理などにおける閉ループ性能が向上しています。C2000ラインには最高性能のMCUとエントリ性能のMCUがあります。

TMS320F2837xDは、産業用モータードライブ、ソーラーインバータおよびデジタル電源、電気自動車および輸送、センシングおよび信号処理などの高度な閉ループ制御アプリケーション用に設計された強力な32ビット浮動小数点マイクロコントローラユニット(MCU)です。アプリケーションを短期間で開発できるように、C2000 MCU向けデジタル電源ソフトウェア開発キット(SDK)とC2000™ MCU向けモーター制御ソフトウェア開発キット(SDK)を提供しています。F2837xDは、システム性能を大幅に向上させる新しいデュアルコアC28xアーキテクチャをサポートしています。また、内蔵のアナログおよび制御ペリフェラルにより、設計者は制御アーキテクチャを統合し、ハイエンドシステムでマルチプロセッサを必要にできます。

デュアルリアルタイム制御サブシステムは、テキサス・インスツルメンツの32ビットC28x浮動小数点CPUを基礎としており、コアごとに200MHzの信号処理能力があります。C28x CPUは、新しいTMUアクセラレータによってさらに高速化され、変換やトルクループ計算で一般的な三角法演算を含むアルゴリズムを高速に実行できます。また、VCUアクセラレータにより、エンコードアプリケーションで一般的な複素数演算の時間が短縮されます。

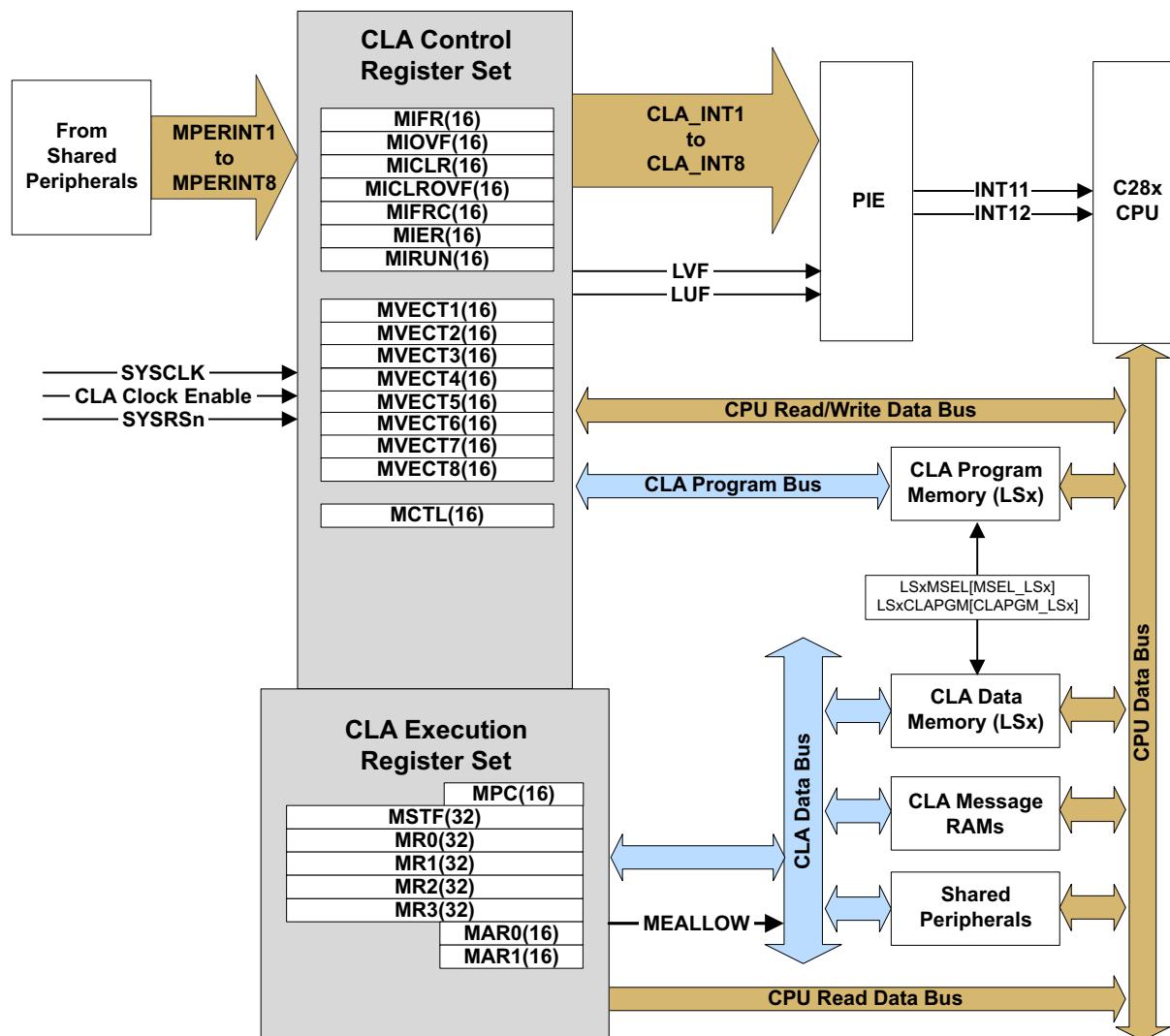

F2837xDマイクロコントローラファミリには、2つのCLAリアルタイム制御コプロセッサが搭載されています。このCLAは独立した32ビットの浮動小数点プロセッサであり、メインCPUと同じ速度で動作します。このCLAは、ペリフェラルのトリガに応答し、メインのC28x CPUと同時にコードを実行します。この並列処理能力により、リアルタイム制御システムの計算能力が実質的に2倍になります。CLAを使って時間に制約のある機能へのサービスを行うことで、メインのC28x CPUは、他のタスク、たとえば通信や診断を自由に実行できます。デュアルのC28x+CLAアーキテクチャにより、各種のシス

## 2 アプリケーション

- 宇宙および航空

- 低軌道衛星用途のサポート

- モーターとアクチュエータ

- 姿勢と軌道の制御システム

- リアクションホイールアセンブリ

- 制御モーメントジャイロスコープ(モーメンタムホイール)

- スラスター ジンバル機構

- 光通信

- ビームステアリングジンバル

- 高速ステアリングミラー

- アンテナポインティング機構

- 極低温冷凍機用コンプレッサー

- デジタル電源

- 宇宙船電力システム

- 電力制御と配電制限

- 宇宙グレードDC/DCコンバータモジュール(共振トポロジを含む)

- 衛星用電源システム

- 慣性測定ユニット(IMU)

テム タスクをインテリジェントに分割できます。たとえば、1 つの C28x+CLA コアを速度と位置の追跡に使用し、もう 1 つの C28x+CLA コアはトルクと電流ループの制御に使用できます。

TMS320F2837xD は、ECC (Error Correction Code)付きの最大 1MB (512KW)のオンボード フラッシュ メモリと、最大 204KB (102KW)の SRAM をサポートしています。各 CPU では、コード保護のため、2 つの 128 ビットのセキュア ゾーンも使用できます。

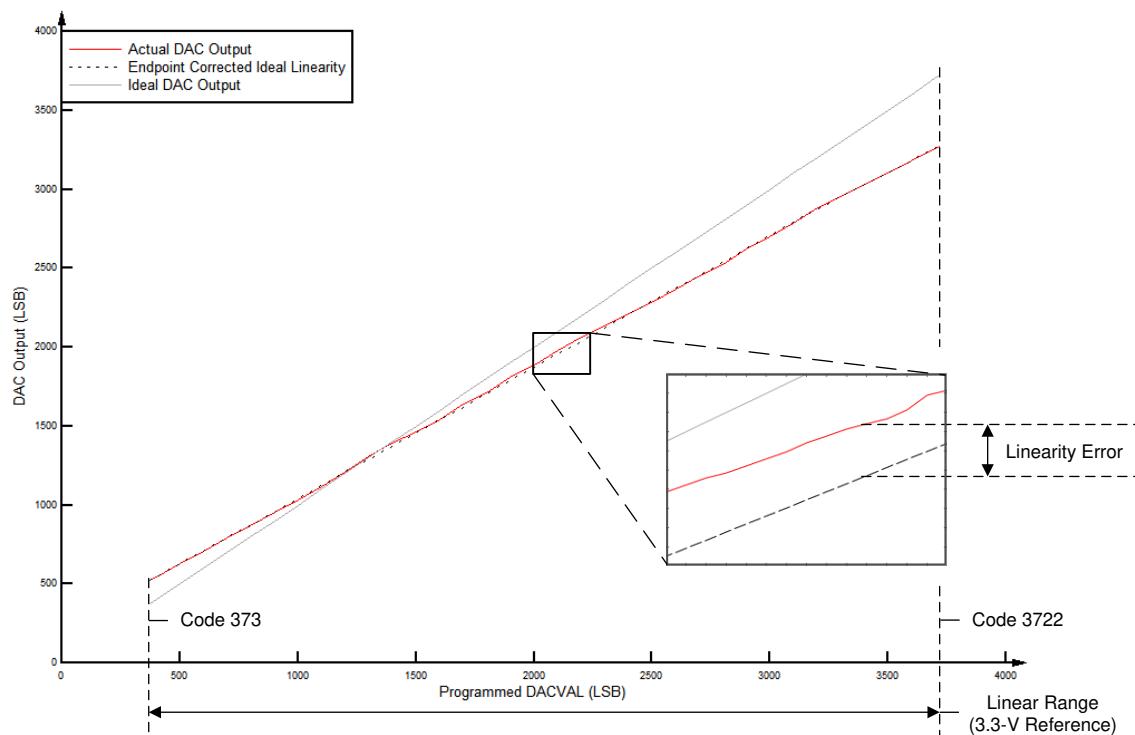

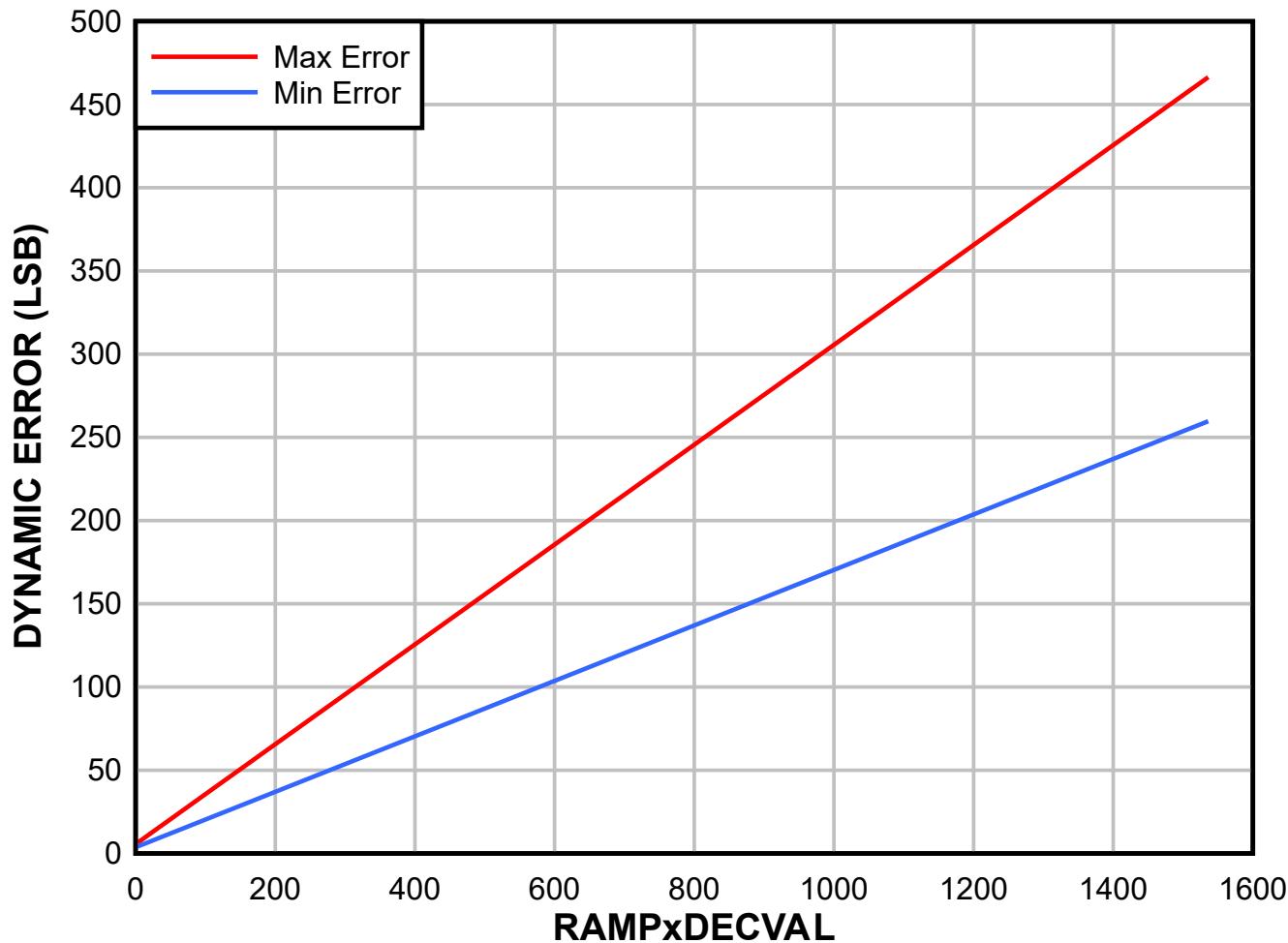

高性能のアナログおよび制御ペリフェラルも F2837xD MCU に内蔵されており、さらにシステムの統合が可能になります。4 つの独立した 16 ビット ADC により、複数のアナログ信号を正確かつ効率的に管理でき、最終的にシステムのスループットが向上します。新しいシグマ-デルタ フィルタ モジュール(SDFM)は、シグマ-デルタ変調器との組み合わせで動作し、絶縁電流シャント測定を可能にします。ウインドウ コンパレータ付きのコンパレータ サブシステム(CMPSS)により、電流制限条件を超過した、または条件が満たされていない場合に、電源段を保護できます。これ以外のアナログおよび制御ペリフェラルとして、DAC、PWM、eCAP、eQEP、その他のペリフェラルがあります。

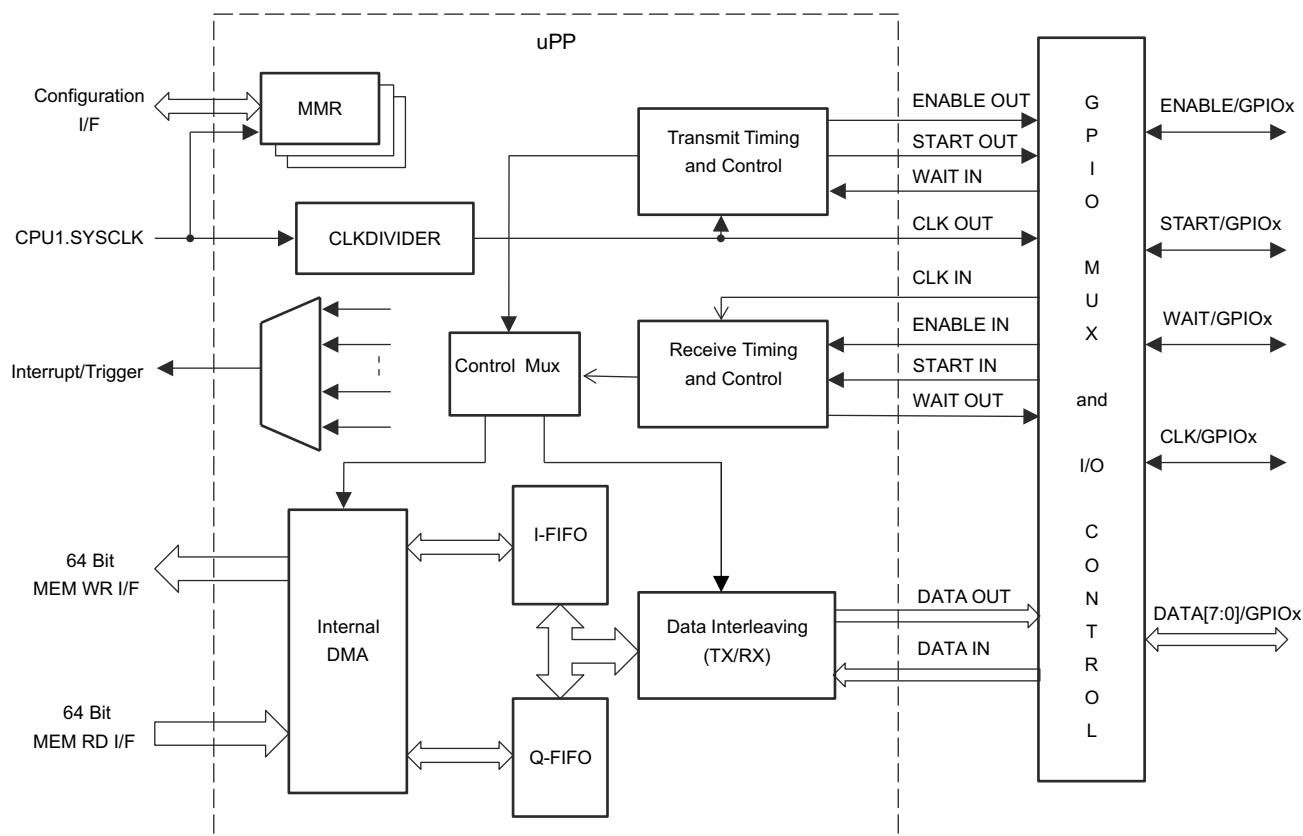

EMIF、CAN モジュール (ISO 11898-1/CAN 2.0B 準拠)、新しい uPP インターフェイスなどのペリフェラルにより、F2837xD の接続性が拡大されます。uPP インターフェイスは、C2000™ MCU の新機能で、FPGA または類似の uPP インターフェイスを持つ他のプロセッサへの高速並列接続をサポートしています。最後に、MAC および PHY 付きの USB 2.0 ポートにより、ユーザーはアプリケーションに USB (Universal Serial Bus) 接続を簡単に追加できます。

C2000 MCU をお客様のリアルタイム制御システムに適した選択肢にしている機能について詳しく知るには、『[C2000™ リアルタイム マイクロコントローラを使った開発のための基本ガイド](#)』をご覧いただくとともに、[C2000™ リアルタイム マイコン](#)のページにアクセスしてください。

『[C2000™ リアルタイム制御マイコン \(MCU\) を使用した設計の開始』入門ガイド』は、C2000 デバイスを使用する開発について、ハードウェアからサポートリソースまで、あらゆる側面をカバーしています。主要な参考資料に加えて、各セクションには関連するリンクとリソースが掲載されており、さらに詳細な情報を知ることができます。](#)

設計を開始する際は、以下の資料をご確認ください。[TMDSCNCD28379D](#) または [LAUNCHXL-F28379D](#) 評価ボードをご覧いただき、[C2000Ware](#) をダウンロードしてください。

C2000 MCU の詳細については、[www.tij.co.jp/c2000](#) で C2000 の概要を参照してください。

#### パッケージ情報

| 部品番号          | グレード <sup>(1)</sup> | パッケージ <sup>(2)</sup> | パッケージ サイズ <sup>(3)</sup> | 本体サイズ <sup>(4)</sup>      |

|---------------|---------------------|----------------------|--------------------------|---------------------------|

| F28377DPTPSEP | 30krad (Si) RLAT    | PTP (HLQFP、176)      | 26mm × 26mm              | 24mm × 24mm<br>質量 = 2.15g |

- (1) 部品のグレードについての詳細は、[部品のグレード](#)をご覧下さい。

- (2) 詳細については、「[メカニカル、パッケージ、および注文情報](#)」を参照してください。

- (3) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

- (4) 質量は公称値であり、本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

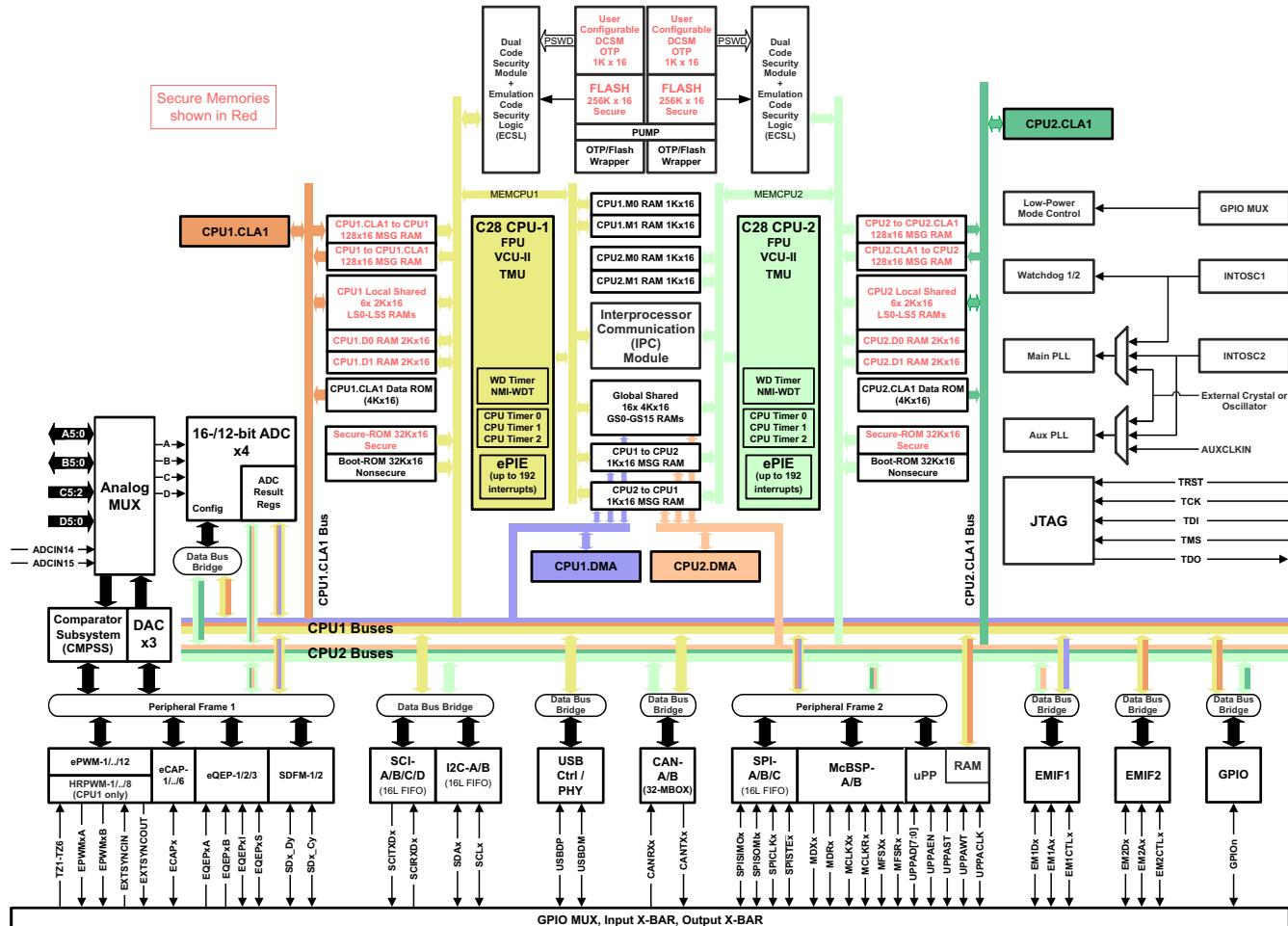

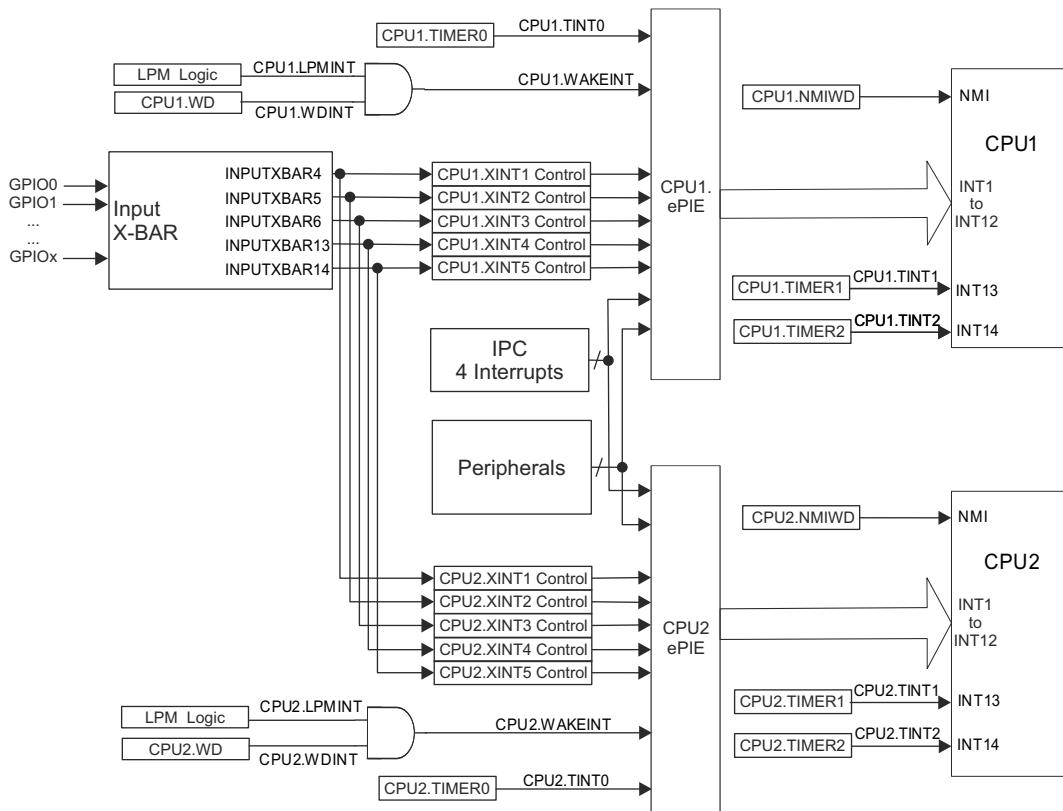

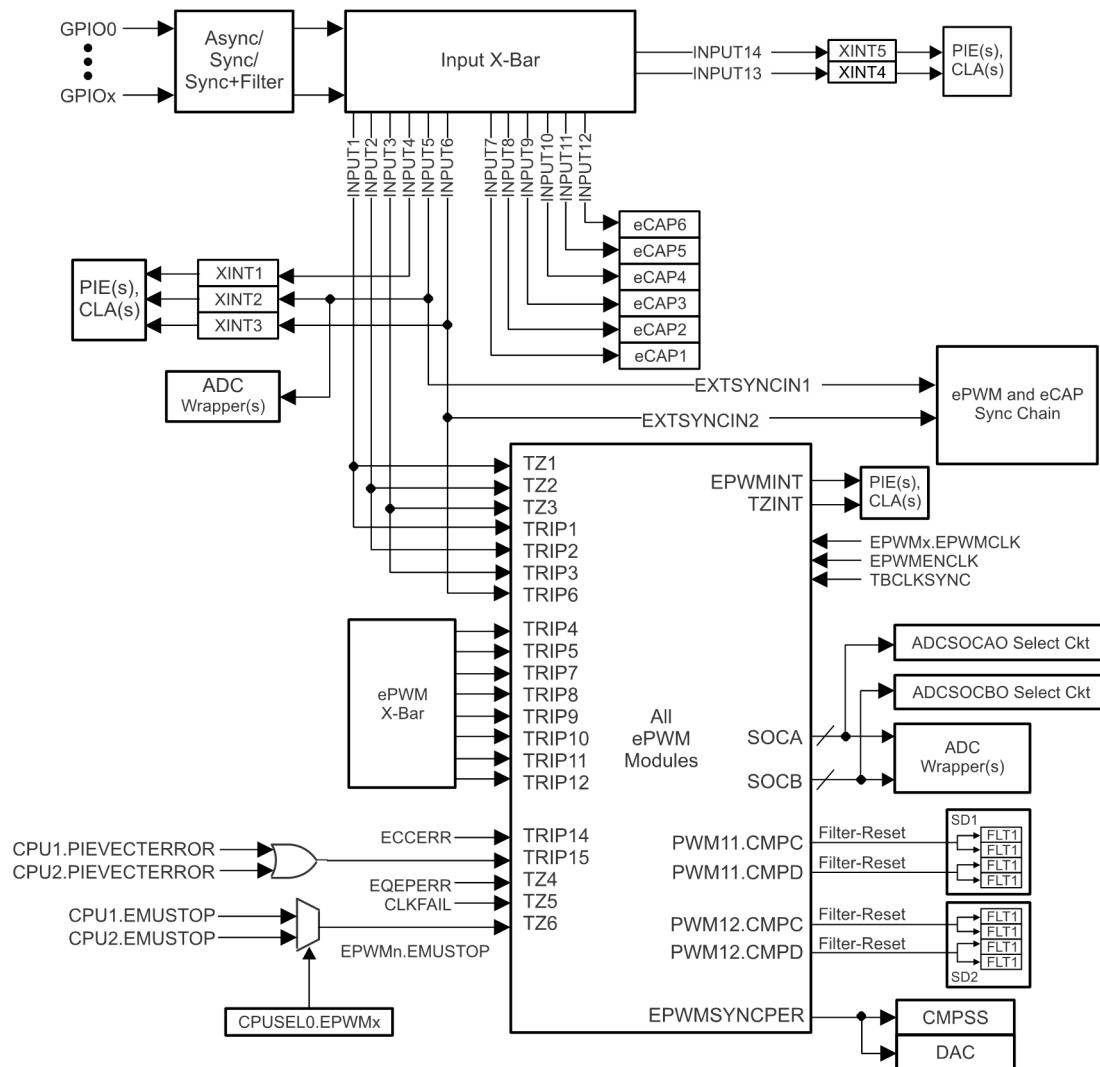

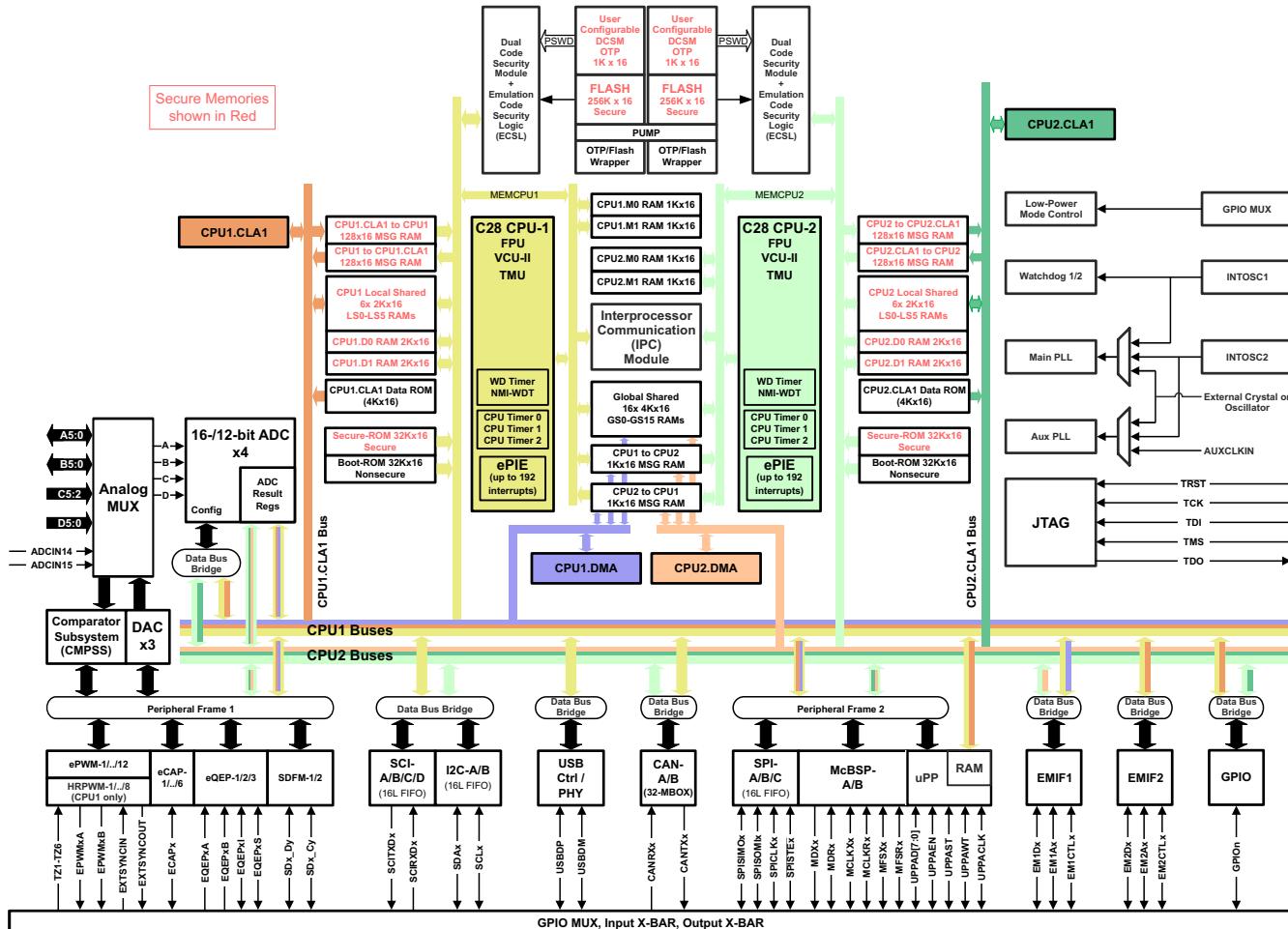

### 3.1 機能ブロック図

「機能ブロック図」に、F2837xD デバイスの CPU システムおよび関連ペリフェラルを示します。F28377D-SEP デバイスで利用可能な機能とペリフェラルについては、表 4-1 を参照してください。

図 3-1. F2837xD の機能ブロック図

## 目次

|                          |     |                                          |     |

|--------------------------|-----|------------------------------------------|-----|

| <b>1 特長</b>              | 1   | 7.5 バス アーキテクチャ – ペリフェラル コネクティビティ         | 197 |

| <b>2 アプリケーション</b>        | 2   | 7.6 C28x プロセッサ                           | 198 |

| <b>3 説明</b>              | 2   | 7.7 制御補償器アクセラレータ (CLA)                   | 201 |

| 3.1 機能ブロック図              | 4   | 7.8 ダイレクトメモリアクセス                         | 202 |

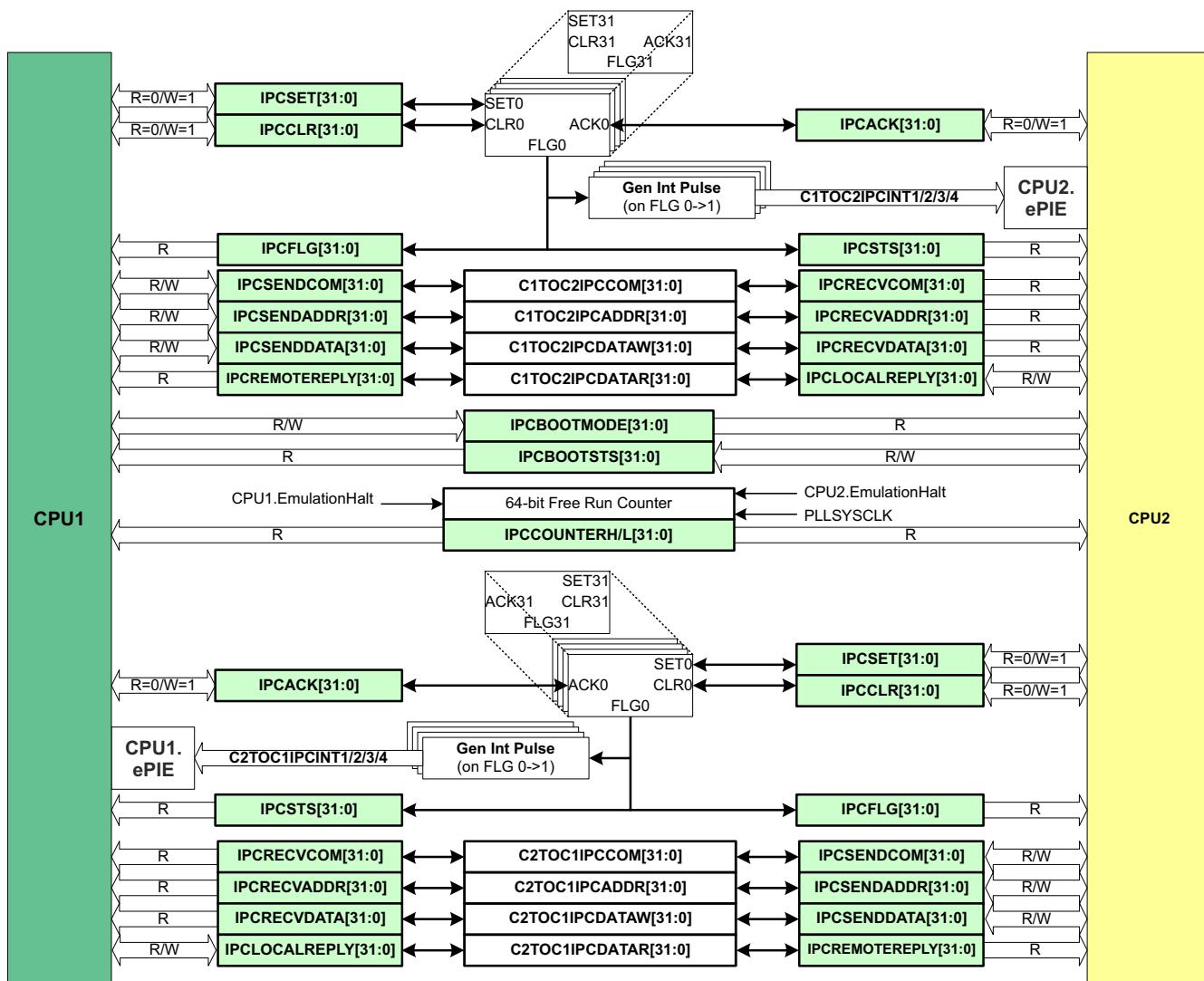

| <b>4 デバイスの比較</b>         | 6   | 7.9 プロセッサ間通信モジュール                        | 204 |

| 4.1 関連製品                 | 7   | 7.10 ブート ROM およびペリフェラル ブート               | 205 |

| <b>5 ピン構成および機能</b>       | 9   | 7.11 デュアル・コード・セキュリティ・モジュール               | 208 |

| 5.1 ピン配置図                | 9   | 7.12 タイマ                                 | 209 |

| 5.2 信号の説明                | 11  | 7.13 ウオッチドッグ タイマ付きノンマスカブル割り込み<br>(NMIWD) | 209 |

| 5.3 内部プルアップおよびプルダウン付きのピン | 35  | 7.14 ウオッチドッグ                             | 210 |

| 5.4 ピン多重化                | 36  |                                          |     |

| 5.5 未使用ピンの接続             | 43  |                                          |     |

| <b>6 仕様</b>              | 44  |                                          |     |

| 6.1 絶対最大定格               | 44  |                                          |     |

| 6.2 ESD 定格               | 44  |                                          |     |

| 6.3 推奨動作条件               | 45  |                                          |     |

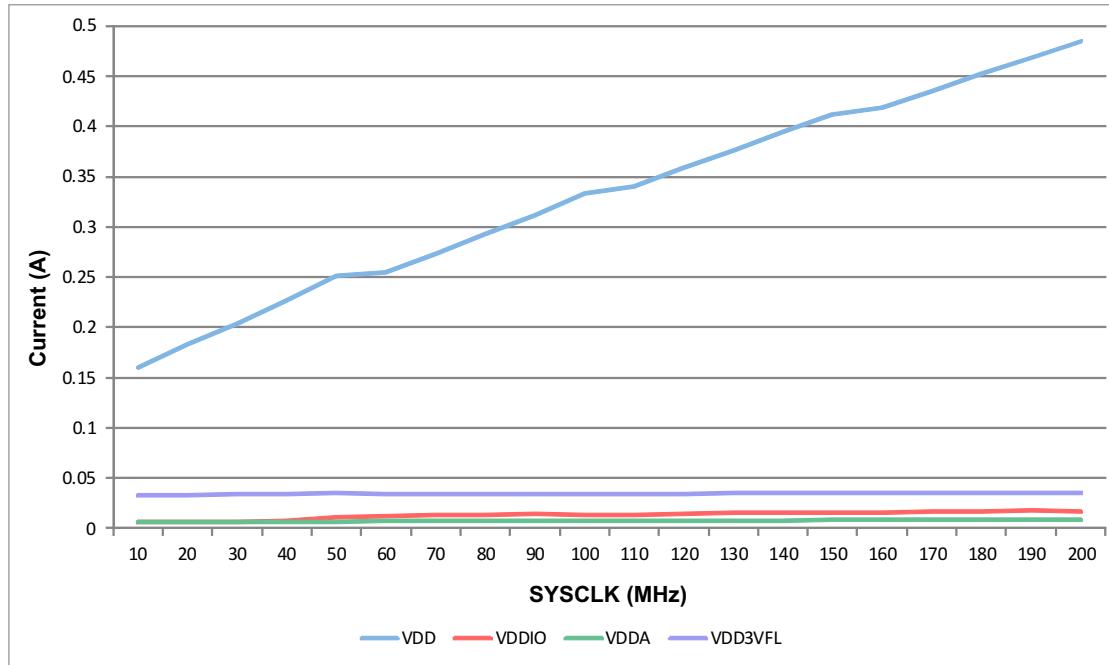

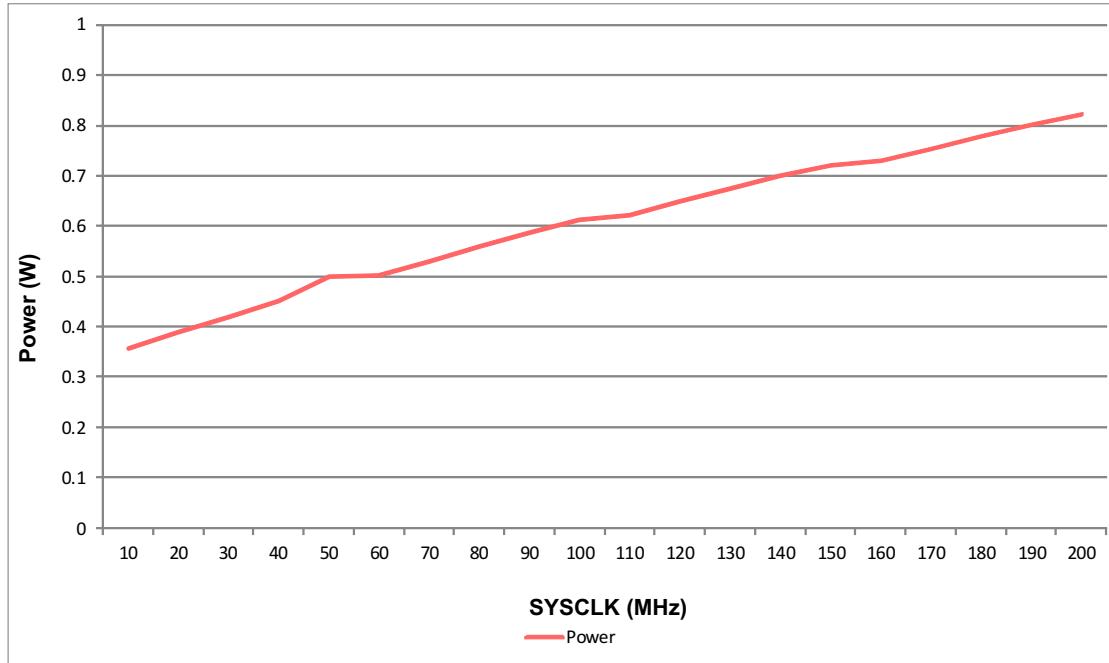

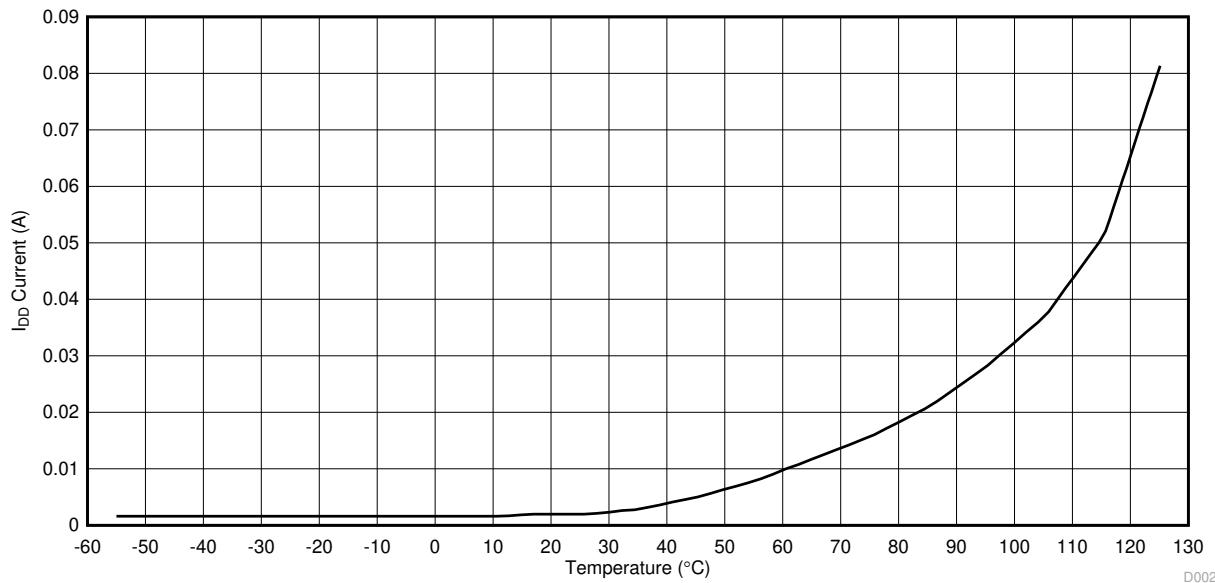

| 6.4 消費電力の概略              | 46  |                                          |     |

| 6.5 電気的特性                | 51  |                                          |     |

| 6.6 熱抵抗特性                | 52  |                                          |     |

| 6.7 热設計の検討事項             | 52  |                                          |     |

| 6.8 システム                 | 53  |                                          |     |

| 6.9 アナログ ペリフェラル          | 100 |                                          |     |

| 6.10 制御ペリフェラル            | 129 |                                          |     |

| 6.11 通信ペリフェラル            | 149 |                                          |     |

| <b>7 詳細説明</b>            | 185 |                                          |     |

| 7.1 概要                   | 185 |                                          |     |

| 7.2 機能ブロック図              | 186 |                                          |     |

| 7.3 メモリ                  | 187 |                                          |     |

| 7.4 識別                   | 196 |                                          |     |

|                          |     | 9.1 デバイスおよび開発ツールの命名規則                    | 219 |

|                          |     | 9.2 マーキング                                | 220 |

|                          |     | 9.3 ツールとソフトウェア                           | 221 |

|                          |     | 9.4 ドキュメントのサポート                          | 224 |

|                          |     | 9.5 サポート・リソース                            | 226 |

|                          |     | 9.6 商標                                   | 226 |

|                          |     | 9.7 静電気放電に関する注意事項                        | 226 |

|                          |     | 9.8 輸出管理に関する注意事項                         | 226 |

|                          |     | 9.9 用語集                                  | 226 |

|                          |     | <b>10 改訂履歴</b>                           | 226 |

|                          |     | <b>11 メカニカル、パッケージ、および注文情報</b>            | 227 |

|                          |     | 11.1 パッケージ情報                             | 227 |

## 4 デバイスの比較

表 4-1 に、F28377D-SEP デバイスの機能を示します。

**表 4-1. デバイスの比較**

| 機能 <sup>(1)</sup>                   |                          | F28377D-SEP                            |

|-------------------------------------|--------------------------|----------------------------------------|

| パッケージ タイプ<br>(PTP は HLQFP パッケージです。) |                          | 176 ピン PTP                             |

| プロセッサおよびアクセラレータ                     |                          |                                        |

| C28x                                | 個数                       | 2                                      |

|                                     | 周波数 (MHz)                | 200                                    |

|                                     | 浮動小数点演算ユニット (FPU)        | あり                                     |

|                                     | VCU-II                   | あり                                     |

| CLA - タイプ 1                         | TMU - タイプ 0              | あり                                     |

|                                     | 個数                       | 2                                      |

| 6 チャネル DMA - タイプ 0                  | 周波数 (MHz)                | 200                                    |

|                                     |                          | 2                                      |

| メモリ                                 |                          |                                        |

| フラッシュ(16 ビット ワード)                   |                          | 1MB (512KW)<br>[CPU ごとに 512KB (256KW)] |

| RAM (16 ビット ワード)                    | 専用およびローカル共有 RAM          | 72KB (36KW)<br>[CPU ごとに 36KB (18KW)]   |

|                                     | グローバル共有 RAM              | 128KB (64KW)                           |

|                                     | メッセージ RAM                | 4KB (2KW)<br>[CPU ごとに 2KB (1KW)]       |

|                                     | <b>RAM 合計</b>            | <b>204KB (102KW)</b>                   |

| オンチップ フラッシュ、RAM、OTP ブロックのコード セキュリティ |                          | あり                                     |

| ブート ROM                             |                          | あり                                     |

| システム                                |                          |                                        |

| 構成可能ロジック ブロック (CLB)                 |                          | なし                                     |

| 32 ビット CPU タイマ                      |                          | 6 (CPU ごとに 3 個)                        |

| ウォッチドッグ タイマ                         |                          | 2 (CPU ごとに 1 個)                        |

| ノンマスカブル割り込みウォッチドッグ (NMIWD) タイマ      |                          | 2 (CPU ごとに 1 個)                        |

| 水晶発振器 / 外部クロック入力                    |                          | 1                                      |

| 0 ピン内部発振器                           |                          | 2                                      |

| I/O ピン (共有)                         | GPIO                     | 97                                     |

| 外部割り込み                              |                          | 5                                      |

| EMIF                                | EMIF1 (16 または 32 ビット)    | 1                                      |

|                                     | EMIF2 (16 ビット)           | –                                      |

| アナログ ペリフェラル                         |                          |                                        |

| ADC 16 ビット モード                      | MSPS                     | 1.1                                    |

|                                     | 変換時間 (ns) <sup>(2)</sup> | 915                                    |

|                                     | 入力ピン                     | 20                                     |

|                                     | チャネル数 (差動)               | 9                                      |

**表 4-1. デバイスの比較 (続き)**

| 機能 <sup>(1)</sup>                               |                          | F28377D-SEP       |

|-------------------------------------------------|--------------------------|-------------------|

| パッケージタイプ<br>(PTP は HLQFP パッケージです。)              |                          | <b>176 ピン PTP</b> |

| ADC 12 ビット モード                                  | MSPS                     | 3.5               |

|                                                 | 変換時間 (ns) <sup>(2)</sup> | 280               |

|                                                 | 入力ピン                     | 20                |

|                                                 | チャネル数 (シングルエンド)          | 20                |

| 16 ビットまたは 12 ビット ADC の数                         |                          | 4                 |

| 12 ビットのみの ADC の数                                |                          | –                 |

| 温度センサ                                           |                          | 1                 |

| CMPSS (各 CMPSS には 2 つのコンパレータと 2 つの内部 DAC があります) |                          | 8                 |

| バッファ付き DAC                                      |                          | 3                 |

| 制御ペリフェラル                                        |                          |                   |

| ECAP 入力 - タイプ 0                                 |                          | 6                 |

| 拡張パルス幅変調器 (ePWM) チャネル - タイプ 4                   |                          | 24                |

| eQEP モジュール - タイプ 0                              |                          | 3                 |

| 高分解能 ePWM チャネル - タイプ 4                          |                          | 16                |

| SDFM チャネル - タイプ 0                               |                          | 8                 |

| 通信ペリフェラル                                        |                          |                   |

| コントローラ エリア ネットワーク(CAN) - タイプ 0 <sup>(3)</sup>   |                          | 2                 |

| I2C (Inter-Integrated Circuit) - タイプ 0          |                          | 2                 |

| マルチチャネル バッファ付きシリアル ポート (McBSP) - タイプ 1          |                          | 2                 |

| シリアル通信インターフェイス (SCI) - タイプ 0 (UART 互換)          |                          | 4                 |

| シリアル ペリフェラル インターフェイス (SPI) - タイプ 2              |                          | 3                 |

| USB - タイプ 0                                     |                          | 1                 |

| UPP - タイプ 0                                     |                          | 1                 |

| 温度および認定                                         |                          |                   |

| 接合部温度 (T <sub>J</sub> )                         | -55°C ~ 150°C            | あり                |

(1) タイプの違いは、ペリフェラル モジュールの機能上の主要な相違を表します。同じペリフェラル タイプのデバイス間でも、モジュールの基本的な機能には影響しないわずかな違いがあることがあります。詳細については、『[C2000 リアルタイム マイコン ペリフェラル リファレンス ガイド](#)』を参照してください。

(2) サンプル アンド ホールド ウィンドウの開始から、次の変換のサンプル アンド ホールド ウィンドウの開始までの時間。

(3) CAN モジュールは、*D\_CAN* と呼ばれる IP を使用します。このドキュメントでは、このペリフェラルに言及するとき、CAN および *D\_CAN* という呼称を同じように使っています。

## 4.1 関連製品

類似製品の詳細については、以下のリンクを参照してください。

### TMS320F2837xD マイクロコントローラ

F2837xD シリーズは、デュアル サブシステムの性能に関する新しい標準を確立します。各サブシステムは、C28x CPU および並列制御補償器アクセラレータ (CLA) で構成され、それぞれが 200MHz で動作します。性能を強化するものとして、TMU および VCU アクセラレータがあります。新しい機能としては、複数の 16 ビット / 12 ビット モード ADC、DAC、デルタシグマ フィルタ、USB、コンフィギュラブル ロジック ブロック (CLB)、オンチップ 発振器、すべてのペリフェラルの拡張バージョンがあります。F2837xD は、最大 1MB のフラッシュを搭載しています。176 ピン QFP または 337 ピン BGA パッケージで供給されます。

### TMS320F2837xS マイクロコントローラ

F2837xS シリーズは、F2837xD のピン互換バージョンですが、C28x-CPU-CLA サブシステムが 1 つのみ有効です。また、[TMS320F2807x](#) シリーズとの互換性を確保するために、100 ピン QFP も用意されています。

## 5 ピン構成および機能

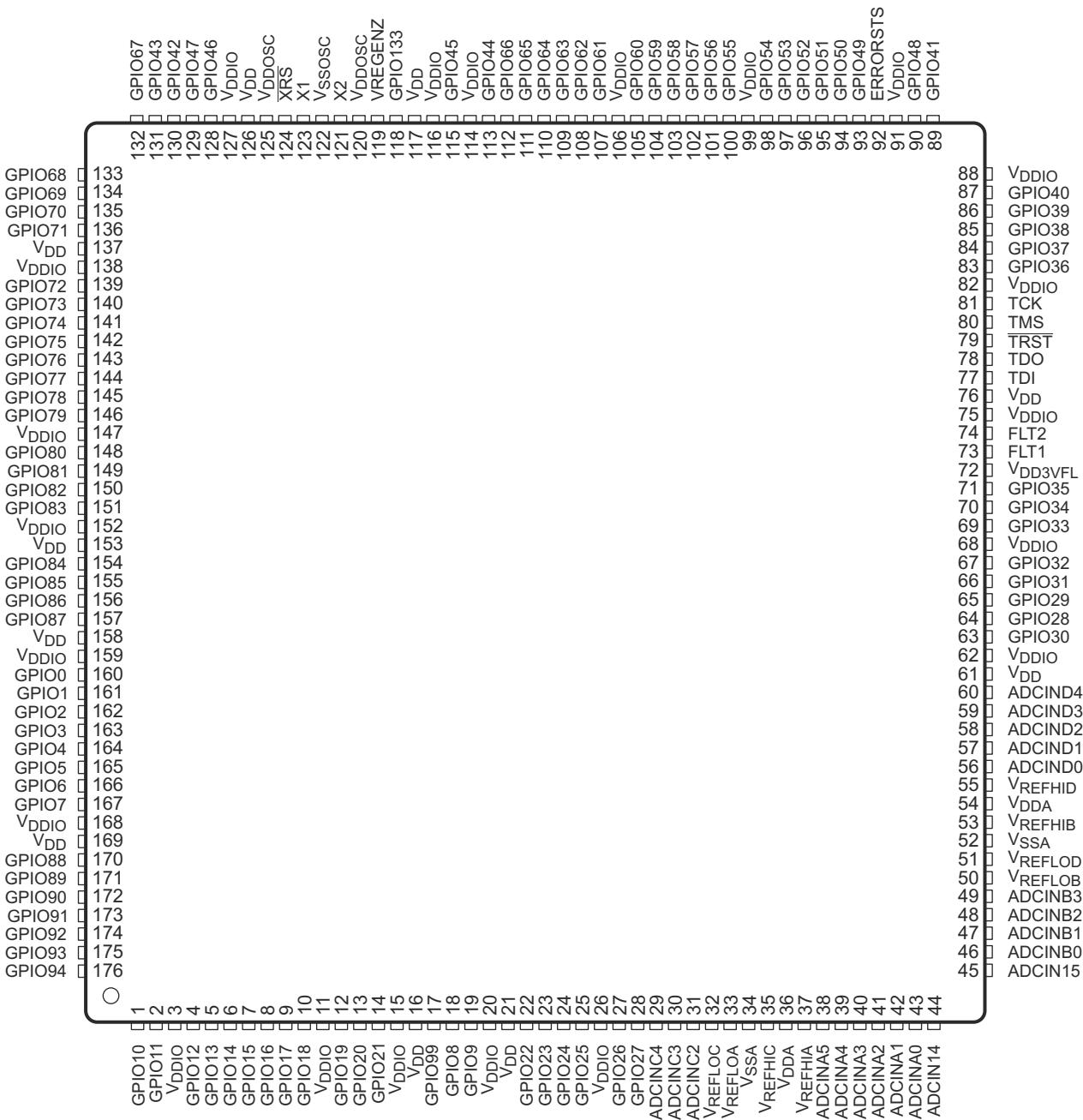

### 5.1 ピン配置図

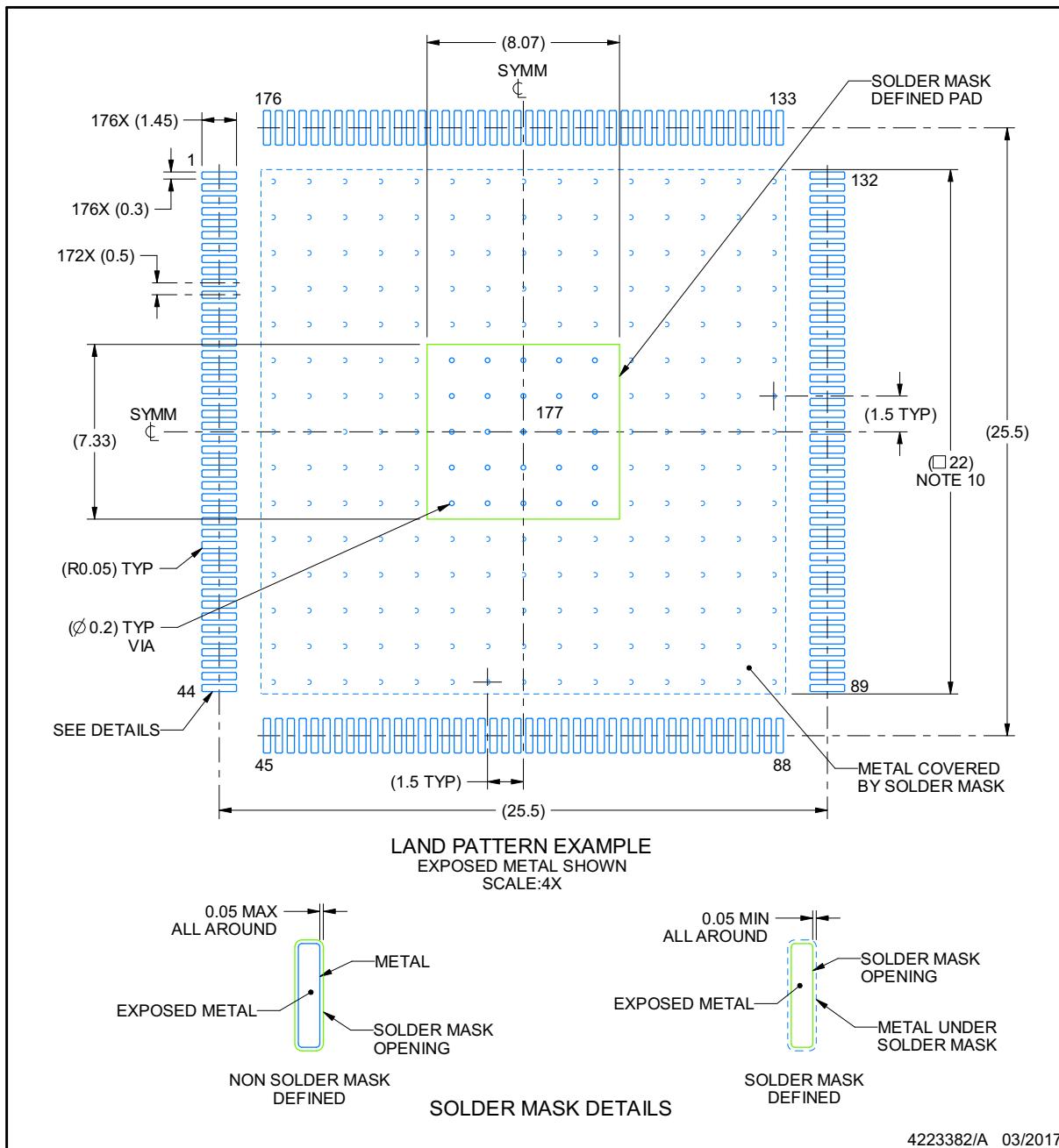

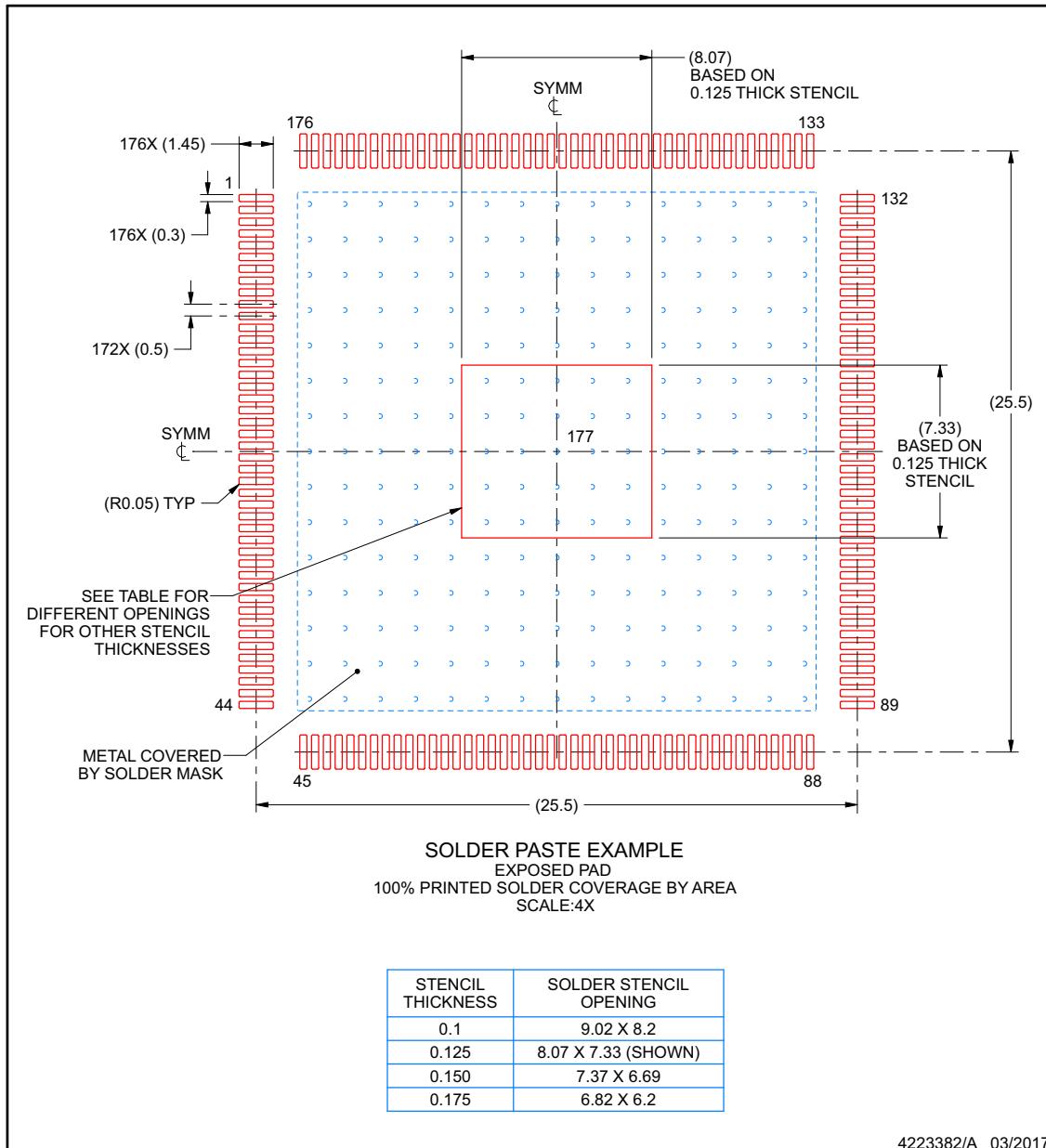

図 5-1 に、176 ピン PTP PowerPAD 热的に強化された薄型クワッド フラットパックのピン配置を示します。

A. GPIO ピンには GPIO 機能のみを表示しています。完全な多重化された信号名については、「信号の説明」セクションを参照してください。

図 5-1. 176 ピン PTP PowerPAD 热的に強化された薄型クワッド フラットパック (上面図)

---

### 注

PowerPAD™ パッケージの露出したリード フレーム ダイ パッドは、ダイからの熱を除去するとともに、デジタル グランドへのグランド パスを提供するという 2 つの機能を備えています (アナログ グランドは専用ピンを介して供給されます)。したがって、PowerPAD は PCB のグランド (GND) プレーンに半田付けする必要があります。これは、デジタル グランド パスと良好な熱伝導パスの両方を提供するからです。PowerPAD パッケージで設計された熱効率を最適に利用するには、このテクノロジーを考慮して PCB を設計する必要があります。PowerPAD 本体直下の PCB 表面に、サーマル ランドが必要です。このサーマル ランドは、PowerPAD パッケージの露出したリード フレーム ダイ パッドに半田付けする必要があります。熱を放散するために、必要に応じて熱ランドを大きくする必要があります。サーマル パッドを基板の内層 GND プレーンに接続するには、複数のサーマル ビアを使用する必要があります。PowerPAD パッケージの使用方法の詳細については、『[PowerPAD™ 热的に強化されたパッケージ](#)』を参照してください。

---

### 注

PCB フットプリントおよび回路図記号はどちらも、ベンダに依存しないフォーマットでダウンロードできます。これは、主要な EDA CAD/CAE 設計ツールにエクスポートすることができます。各デバイスの製品フォルダの「パッケージ」セクションにある「CAD/CAE シンボル」セクションを参照してください。これらのフットプリントおよび記号は、<https://webench.ti.com/cad/> で検索することもできます。

---

## 5.2 信号の説明

**セクション 5.2.1** では、信号について説明します。特に記述のない限り、GPIO 機能がリセット時のデフォルトです。その下に表示されているペリフェラル信号は、代替機能です。一部のペリフェラル機能は、すべてのデバイスで利用できるわけではありません。詳しくは、[表 4-1](#) を参照してください。すべての GPIO ピンは I/O であり、内部プルアップを備えており、ピンごとにイネーブルまたはディセーブルを選択できます。この機能は、GPIO ピンにのみ適用されます。プルアップは、リセット時にはイネーブルされていません。

### 5.2.1 信号の説明

**表 5-1. 信号の説明**

| 端子                       |       |    | PTP<br>ピン<br>番号 | I/O/Z <sup>(1)</sup> | 説明                                                                                                                                                                                                                                               |

|--------------------------|-------|----|-----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                       | 多重化位置 |    |                 |                      |                                                                                                                                                                                                                                                  |

| <b>ADC、DAC、コンパレータの信号</b> |       |    |                 |                      |                                                                                                                                                                                                                                                  |

| V <sub>REFHIA</sub>      |       | 37 | I               |                      | ADC-A の高い基準電圧。この電圧は、ピンに対して外部回路から駆動する必要があります。このピンには、12 ビットモードの場合 1 $\mu$ F 以上、16 ビットモードの場合 22 $\mu$ F 以上のコンデンサを配置します。このコンデンサは、V <sub>REFHIA</sub> ピンと V <sub>REFLOA</sub> ピンの間で、できるだけデバイスに近い場所に配置する必要があります。<br><b>注:</b> このピンには、外部に負荷を接続しないでください。 |

| V <sub>REFHIB</sub>      |       | 53 | I               |                      | ADC-B の高い基準電圧。この電圧は、ピンに対して外部回路から駆動する必要があります。このピンには、12 ビットモードの場合 1 $\mu$ F 以上、16 ビットモードの場合 22 $\mu$ F 以上のコンデンサを配置します。このコンデンサは、V <sub>REFHIB</sub> ピンと V <sub>REFLOB</sub> ピンの間で、できるだけデバイスに近い場所に配置する必要があります。<br><b>注:</b> このピンには、外部に負荷を接続しないでください。 |

| V <sub>REFHIC</sub>      |       | 35 | I               |                      | ADC-C の高い基準電圧。この電圧は、ピンに対して外部回路から駆動する必要があります。このピンには、12 ビットモードの場合 1 $\mu$ F 以上、16 ビットモードの場合 22 $\mu$ F 以上のコンデンサを配置します。このコンデンサは、V <sub>REFHIC</sub> ピンと V <sub>REFLOC</sub> ピンの間で、できるだけデバイスに近い場所に配置する必要があります。<br><b>注:</b> このピンには、外部に負荷を接続しないでください。 |

| V <sub>REFHID</sub>      |       | 55 | I               |                      | ADC-D の高い基準電圧。この電圧は、ピンに対して外部回路から駆動する必要があります。このピンには、12 ビットモードの場合 1 $\mu$ F 以上、16 ビットモードの場合 22 $\mu$ F 以上のコンデンサを配置します。このコンデンサは、V <sub>REFHID</sub> ピンと V <sub>REFLOD</sub> ピンの間で、できるだけデバイスに近い場所に配置する必要があります。<br><b>注:</b> このピンには、外部に負荷を接続しないでください。 |

| V <sub>REFLOA</sub>      |       | 33 | I               |                      | ADC-A の低い基準電圧                                                                                                                                                                                                                                    |

| V <sub>REFLOB</sub>      |       | 50 | I               |                      | ADC-B の低い基準電圧                                                                                                                                                                                                                                    |

| V <sub>REFLOC</sub>      |       | 32 | I               |                      | ADC-C の低い基準電圧                                                                                                                                                                                                                                    |

| V <sub>REFLOD</sub>      |       | 51 | I               |                      | ADC-D の低い基準電圧                                                                                                                                                                                                                                    |

| ADCIN14                  |       |    | I               |                      | すべての ADC への入力 14。このピンは、汎用 ADCIN ピンとして使用できます。また、外部基準電圧からすべての ADC を (シングルエンドまたは差動) 一緒に較正するために使用することもできます。                                                                                                                                          |

| CMPIN4P                  |       | 44 | I               |                      | コンパレータ 4 正入力                                                                                                                                                                                                                                     |

| ADCIN15                  |       |    | I               |                      | すべての ADC への入力 15。このピンは、汎用 ADCIN ピンとして使用できます。また、外部基準電圧からすべての ADC を (シングルエンドまたは差動) 一緒に較正するために使用することもできます。                                                                                                                                          |

| CMPIN4N                  |       | 45 | I               |                      | コンパレータ 4 負入力                                                                                                                                                                                                                                     |

| ADCINA0                  |       |    | I               |                      | ADC-A 入力 0。このピンには、ADC 入力または DAC 出力モードの両方で 50k $\Omega$ の内部プルダウンが付いており、ディセーブルできません。                                                                                                                                                               |

| DACOUTA                  |       | 43 | O               |                      | DAC-A 出力                                                                                                                                                                                                                                         |

表 5-1. 信号の説明 (続き)

| 端子      |       |                 | I/O/Z <sup>(1)</sup> | 説明                                                                                                                                                                                                    |

|---------|-------|-----------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 多重化位置 | PTP<br>ピン<br>番号 |                      |                                                                                                                                                                                                       |

| ADCINA1 |       | 42              | I                    | ADC-A 入力 1。このピンには、ADC 入力または DAC 出力モードの両方で $50\text{k}\Omega$ の内部プルダウンが付いており、ディセーブルできません。                                                                                                              |

| DACOUTB |       |                 | O                    | DAC-B 出力                                                                                                                                                                                              |

| ADCINA2 |       | 41              | I                    | ADC-A 入力 2                                                                                                                                                                                            |

| CMPIN1P |       |                 | I                    | コンパレータ 1 正入力                                                                                                                                                                                          |

| ADCINA3 |       | 40              | I                    | ADC-A 入力 3                                                                                                                                                                                            |

| CMPIN1N |       |                 | I                    | コンパレータ 1 負入力                                                                                                                                                                                          |

| ADCINA4 |       | 39              | I                    | ADC-A 入力 4                                                                                                                                                                                            |

| CMPIN2P |       |                 | I                    | コンパレータ 2 正入力                                                                                                                                                                                          |

| ADCINA5 |       | 38              | I                    | ADC-A 入力 5                                                                                                                                                                                            |

| CMPIN2N |       |                 | I                    | コンパレータ 2 負入力                                                                                                                                                                                          |

| ADCINB0 |       |                 | I                    | ADC-B 入力 0。このピンには、ADC 入力または DAC 基準電圧モードの両方で $V_{SSA}$ に対して $100\text{pF}$ のコンデンサが付いており、ディセーブルすることはできません。このピンをオンチップ DAC のリファレンス電圧として使用する場合は、このピンに少なくとも $1\mu\text{F}$ のコンデンサを配置します。                    |

| VDAC    |       | 46              | I                    | オンチップ DAC の外部リファレンス電圧 (オプション)。このピンには、ADC 入力または DAC 基準電圧モードの両方で $V_{SSA}$ に対して $100\text{pF}$ のコンデンサが付いており、ディセーブルすることはできません。このピンをオンチップ DAC のリファレンス電圧として使用する場合は、このピンに少なくとも $1\mu\text{F}$ のコンデンサを配置します。 |

| ADCINB1 |       | 47              | I                    | ADC-B 入力 1。このピンには、ADC 入力または DAC 出力モードの両方で $50\text{k}\Omega$ の内部プルダウンが付いており、ディセーブルできません。                                                                                                              |

| DACOUTC |       |                 | O                    | DAC-C 出力                                                                                                                                                                                              |

| ADCINB2 |       | 48              | I                    | ADC-B 入力 2                                                                                                                                                                                            |

| CMPIN3P |       |                 | I                    | コンパレータ 3 正入力                                                                                                                                                                                          |

| ADCINB3 |       | 49              | I                    | ADC-B 入力 3                                                                                                                                                                                            |

| CMPIN3N |       |                 | I                    | コンパレータ 3 負入力                                                                                                                                                                                          |

| ADCINB4 |       | –               | I                    | ADC-B 入力 4                                                                                                                                                                                            |

| ADCINB5 |       | –               | I                    | ADC-B 入力 5                                                                                                                                                                                            |

| ADCINC2 |       | 31              | I                    | ADC-C 入力 2                                                                                                                                                                                            |

| CMPIN6P |       |                 | I                    | コンパレータ 6 正入力                                                                                                                                                                                          |

| ADCINC3 |       | 30              | I                    | ADC-C 入力 3                                                                                                                                                                                            |

| CMPIN6N |       |                 | I                    | コンパレータ 6 負入力                                                                                                                                                                                          |

| ADCINC4 |       | 29              | I                    | ADC-C 入力 4                                                                                                                                                                                            |

| CMPIN5P |       |                 | I                    | コンパレータ 5 正入力                                                                                                                                                                                          |

| ADCINC5 |       | –               | I                    | ADC-C 入力 5                                                                                                                                                                                            |

| CMPIN5N |       |                 | I                    | コンパレータ 5 負入力                                                                                                                                                                                          |

| ADCIND0 |       | 56              | I                    | ADC-D 入力 0                                                                                                                                                                                            |

| CMPIN7P |       |                 | I                    | コンパレータ 7 正入力                                                                                                                                                                                          |

| ADCIND1 |       | 57              | I                    | ADC-D 入力 1                                                                                                                                                                                            |

| CMPIN7N |       |                 | I                    | コンパレータ 7 負入力                                                                                                                                                                                          |

**表 5-1. 信号の説明 (続き)**

| 端子      |       |                 | I/O/Z <sup>(1)</sup> | 説明                         |

|---------|-------|-----------------|----------------------|----------------------------|

| 名称      | 多重化位置 | PTP<br>ピン<br>番号 |                      |                            |

| ADCIND2 |       | 58              | I                    | ADC-D 入力 2<br>コンバレータ 8 正入力 |

| CMPIN8P |       |                 | I                    |                            |

| ADCIND3 |       | 59              | I                    | ADC-D 入力 3<br>コンバレータ 8 負入力 |

| CMPIN8N |       |                 | I                    |                            |

表 5-1. 信号の説明 (続き)

| 端子                      |             |                 | I/O/Z <sup>(1)</sup> | 説明                        |

|-------------------------|-------------|-----------------|----------------------|---------------------------|

| 名称                      | 多重化位置       | PTP<br>ピン<br>番号 |                      |                           |

| ADCIND4                 |             | 60              | I                    | ADC-D 入力 4                |

| ADCIND5                 |             | -               | I                    | ADC-D 入力 5                |

| <b>GPIO およびペリフェラル信号</b> |             |                 |                      |                           |

| GPIO0                   | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 0                   |

| EPWM1A                  | 1           | 160             | O                    | 拡張 PWM1 出力 A (HRPWM 対応)   |

| SDAA                    | 6           |                 | I/OD                 | I2C-A データ オープンドレイン双方向ポート  |

| GPIO1                   | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 1                   |

| EPWM1B                  | 1           | 161             | O                    | 拡張 PWM1 出力 B (HRPWM 対応)   |

| MFSRB                   | 3           |                 | I/O                  | McBSP-B 受信フレーム同期          |

| SCLA                    | 6           |                 | I/OD                 | I2C-A クロック オープンドレイン双方向ポート |

| GPIO2                   | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 2                   |

| EPWM2A                  | 1           | 162             | O                    | 拡張 PWM2 出力 A (HRPWM 対応)   |

| OUTPUTXBAR1             | 5           |                 | O                    | 出力クロスバーの出力 1              |

| SDAB                    | 6           |                 | I/OD                 | I2C-B データ オープンドレイン双方向ポート  |

| GPIO3                   | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 3                   |

| EPWM2B                  | 1           |                 | O                    | 拡張 PWM2 出力 B (HRPWM 対応)   |

| OUTPUTXBAR2             | 2           | 163             | O                    | 出力クロスバーの出力 2              |

| MCLKRB                  | 3           |                 | I/O                  | McBSP-B 受信クロック            |

| OUTPUTXBAR2             | 5           |                 | O                    | 出力クロスバーの出力 2              |

| SCLB                    | 6           |                 | I/OD                 | I2C-B クロック オープンドレイン双方向ポート |

| GPIO4                   | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 4                   |

| EPWM3A                  | 1           | 164             | O                    | 拡張 PWM3 出力 A (HRPWM 対応)   |

| OUTPUTXBAR3             | 5           |                 | O                    | 出力クロスバーの出力 3              |

| CANTXA                  | 6           |                 | O                    | CAN-A 送信                  |

| GPIO5                   | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 5                   |

| EPWM3B                  | 1           |                 | O                    | 拡張 PWM3 出力 B (HRPWM 対応)   |

| MFSRA                   | 2           | 165             | I/O                  | McBSP-A 受信フレーム同期          |

| OUTPUTXBAR3             | 3           |                 | O                    | 出力クロスバーの出力 3              |

| CANRXA                  | 6           |                 | I                    | CAN-A 受信                  |

| GPIO6                   | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 6                   |

| EPWM4A                  | 1           |                 | O                    | 拡張 PWM4 出力 A (HRPWM 対応)   |

| OUTPUTXBAR4             | 2           | 166             | O                    | 出力クロスバーの出力 4              |

| EXTSYNCOUT              | 3           |                 | O                    | 外部 ePWM 同期パルス出力           |

| EQEP3A                  | 5           |                 | I                    | 拡張 QEP3 入力 A              |

| CANTXB                  | 6           |                 | O                    | CAN-B 送信                  |

| GPIO7                   | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 7                   |

| EPWM4B                  | 1           |                 | O                    | 拡張 PWM4 出力 B (HRPWM 対応)   |

| MCLKRA                  | 2           | 167             | I/O                  | McBSP-A 受信クロック            |

| OUTPUTXBAR5             | 3           |                 | O                    | 出力クロスバーの出力 5              |

| EQEP3B                  | 5           |                 | I                    | 拡張 QEP3 入力 B              |

| CANRXB                  | 6           |                 | I                    | CAN-B 受信                  |

**表 5-1. 信号の説明 (続き)**

| 端子          |             |                 | I/O/Z <sup>(1)</sup> | 説明                                                       |

|-------------|-------------|-----------------|----------------------|----------------------------------------------------------|

| 名称          | 多重化位置       | PTP<br>ピン<br>番号 |                      |                                                          |

| GPIO8       | 0, 4, 8, 12 | 18              | I/O                  | 汎用入出力 8                                                  |

| EPWM5A      | 1           |                 | O                    | 拡張 PWM5 出力 A (HRPWM 対応)                                  |

| CANTXB      | 2           |                 | O                    | CAN-B 送信                                                 |

| ADCSOCDAO   | 3           |                 | O                    | 外部 ADC 用の ADC 変換開始 A 出力                                  |

| EQEP3S      | 5           |                 | I/O                  | 拡張 QEP3 ストローブ                                            |

| SCITXDA     | 6           |                 | O                    | SCI-A 送信データ                                              |

| GPIO9       | 0, 4, 8, 12 | 19              | I/O                  | 汎用入出力 9                                                  |

| EPWM5B      | 1           |                 | O                    | 拡張 PWM5 出力 B (HRPWM 対応)                                  |

| SCITXDB     | 2           |                 | O                    | SCI-B 送信データ                                              |

| OUTPUTXBAR6 | 3           |                 | O                    | 出力クロスバーの出力 6                                             |

| EQEP3I      | 5           |                 | I/O                  | 拡張 QEP3 インデックス                                           |

| SCIRXDA     | 6           |                 | I                    | SCI-A 受信データ                                              |

| GPIO10      | 0, 4, 8, 12 | 1               | I/O                  | 汎用入出力 10                                                 |

| EPWM6A      | 1           |                 | O                    | 拡張 PWM6 出力 A (HRPWM 対応)                                  |

| CANRXB      | 2           |                 | I                    | CAN-B 受信                                                 |

| ADCSOCBO    | 3           |                 | O                    | 外部 ADC 用の ADC 変換開始 B 出力                                  |

| EQEP1A      | 5           |                 | I                    | 拡張 QEP1 入力 A                                             |

| SCITXDB     | 6           |                 | O                    | SCI-B 送信データ                                              |

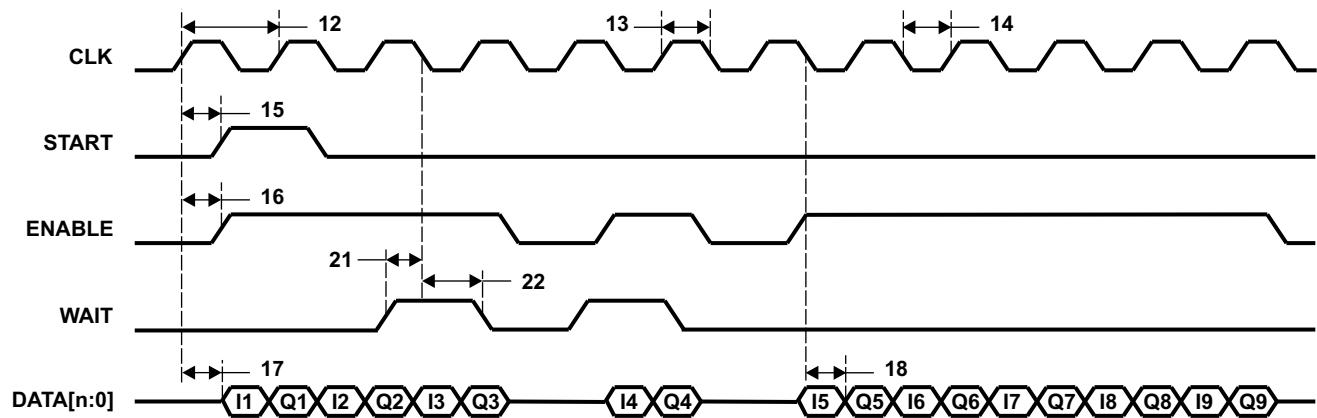

| UPP-WAIT    | 15          |                 | I/O                  | ユニバーサル パラレル ポートウェイト。転送中に、レシーバが一時停止を要求するためにアサートします。       |

| GPIO11      | 0, 4, 8, 12 | 2               | I/O                  | 汎用入出力 11                                                 |

| EPWM6B      | 1           |                 | O                    | 拡張 PWM6 出力 B (HRPWM 対応)                                  |

| SCIRXDB     | 2, 6        |                 | I                    | SCI-B 受信データ                                              |

| OUTPUTXBAR7 | 3           |                 | O                    | 出力クロスバーの出力 7                                             |

| EQEP1B      | 5           |                 | I                    | 拡張 QEP1 入力 B                                             |

| UPP-START   | 15          |                 | I/O                  | ユニバーサル パラレル ポートスタート。DMA ラインの開始時に、トランスマッタがアサートします。        |

| GPIO12      | 0, 4, 8, 12 | 4               | I/O                  | 汎用入出力 12                                                 |

| EPWM7A      | 1           |                 | O                    | 拡張 PWM7 出力 A (HRPWM 対応)                                  |

| CANTXB      | 2           |                 | O                    | CAN-B 送信                                                 |

| MDXB        | 3           |                 | O                    | McBSP-B 送信シリアル データ                                       |

| EQEP1S      | 5           |                 | I/O                  | 拡張 QEP1 ストローブ                                            |

| SCITXDC     | 6           |                 | O                    | SCI-C 送信データ                                              |

| UPP-ENA     | 15          |                 | I/O                  | ユニバーサル パラレル ポートイネーブル。データバスがアクティブになっている間、トランスマッタがアサートします。 |

| GPIO13      | 0, 4, 8, 12 | 5               | I/O                  | 汎用入出力 13                                                 |

| EPWM7B      | 1           |                 | O                    | 拡張 PWM7 出力 B (HRPWM 対応)                                  |

| CANRXB      | 2           |                 | I                    | CAN-B 受信                                                 |

| MDRB        | 3           |                 | I                    | McBSP-B 受信シリアル データ                                       |

| EQEP1I      | 5           |                 | I/O                  | 拡張 QEP1 インデックス                                           |

| SCIRXDC     | 6           |                 | I                    | SCI-C 受信データ                                              |

| UPP-D7      | 15          |                 | I/O                  | ユニバーサル パラレル ポートデータライン 7                                  |

表 5-1. 信号の説明 (続き)

| 端子          |             |                 | I/O/Z <sup>(1)</sup> | 説明                      |

|-------------|-------------|-----------------|----------------------|-------------------------|

| 名称          | 多重化位置       | PTP<br>ピン<br>番号 |                      |                         |

| GPIO14      | 0, 4, 8, 12 | 6               | I/O                  | 汎用入出力 14                |

| EPWM8A      | 1           |                 | O                    | 拡張 PWM8 出力 A (HRPWM 対応) |

| SCITXDB     | 2           |                 | O                    | SCI-B 送信データ             |

| MCLKXB      | 3           |                 | I/O                  | McBSP-B 送信クロック          |

| OUTPUTXBAR3 | 6           |                 | O                    | 出力クロスバーの出力 3            |

| UPP-D6      | 15          |                 | I/O                  | ユニバーサル パラレル ポートデータライン 6 |

| GPIO15      | 0, 4, 8, 12 | 7               | I/O                  | 汎用入出力 15                |

| EPWM8B      | 1           |                 | O                    | 拡張 PWM8 出力 B (HRPWM 対応) |

| SCIRXDB     | 2           |                 | I                    | SCI-B 受信データ             |

| MFSXB       | 3           |                 | I/O                  | McBSP-B 送信フレーム同期        |

| OUTPUTXBAR4 | 6           |                 | O                    | 出力クロスバーの出力 4            |

| UPP-D5      | 15          |                 | I/O                  | ユニバーサル パラレル ポートデータライン 5 |

| GPIO16      | 0, 4, 8, 12 | 8               | I/O                  | 汎用入出力 16                |

| SPISIMOA    | 1           |                 | I/O                  | SPI-A スレーブ入力、マスタ出力      |

| CANTXB      | 2           |                 | O                    | CAN-B 送信                |

| OUTPUTXBAR7 | 3           |                 | O                    | 出力クロスバーの出力 7            |

| EPWM9A      | 5           |                 | O                    | 拡張 PWM9 出力 A            |

| SD1_D1      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 1 データ入力  |

| UPP-D4      | 15          |                 | I/O                  | ユニバーサル パラレル ポートデータライン 4 |

| GPIO17      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 17                |

| SPISOMIA    | 1           | 9               | I/O                  | SPI-A スレーブ出力、マスタ入力      |

| CANRXB      | 2           |                 | I                    | CAN-B 受信                |

| OUTPUTXBAR8 | 3           |                 | O                    | 出力クロスバーの出力 8            |

| EPWM9B      | 5           |                 | O                    | 拡張 PWM9 出力 B            |

| SD1_C1      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 1 クロック入力 |

| UPP-D3      | 15          |                 | I/O                  | ユニバーサル パラレル ポートデータライン 3 |

| GPIO18      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 18                |

| SPICLKA     | 1           | 10              | I/O                  | SPI-A クロック              |

| SCITXDB     | 2           |                 | O                    | SCI-B 送信データ             |

| CANRXA      | 3           |                 | I                    | CAN-A 受信                |

| EPWM10A     | 5           |                 | O                    | 拡張 PWM10 出力 A           |

| SD1_D2      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 2 データ入力  |

| UPP-D2      | 15          |                 | I/O                  | ユニバーサル パラレル ポートデータライン 2 |

| GPIO19      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 19                |

| SPISTEA     | 1           | 12              | I/O                  | SPI-A スレーブ送信イネーブル       |

| SCIRXDB     | 2           |                 | I                    | SCI-B 受信データ             |

| CANTXA      | 3           |                 | O                    | CAN-A 送信                |

| EPWM10B     | 5           |                 | O                    | 拡張 PWM 10 出力 B          |

| SD1_C2      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 2 クロック入力 |

| UPP-D1      | 15          |                 | I/O                  | ユニバーサル パラレル ポートデータライン 1 |

**表 5-1. 信号の説明 (続き)**

| 端子          |             |                 | I/O/Z <sup>(1)</sup> | 説明                      |

|-------------|-------------|-----------------|----------------------|-------------------------|

| 名称          | 多重化位置       | PTP<br>ピン<br>番号 |                      |                         |

| GPIO20      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 20                |

| EQEP1A      | 1           |                 | I                    | 拡張 QEP1 入力 A            |

| MDXA        | 2           |                 | O                    | McBSP-A 送信シリアル データ      |

| CANTXB      | 3           | 13              | O                    | CAN-B 送信                |

| EPWM11A     | 5           |                 | O                    | 拡張 PWM11 出力 A           |

| SD1_D3      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 3 データ入力  |

| UPP-D0      | 15          |                 | I/O                  | ユニバーサル パラレル ポートデータライン 0 |

| GPIO21      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 21                |

| EQEP1B      | 1           |                 | I                    | 拡張 QEP1 入力 B            |

| MDRA        | 2           |                 | I                    | McBSP-A 受信シリアル データ      |

| CANRXB      | 3           | 14              | I                    | CAN-B 受信                |

| EPWM11B     | 5           |                 | O                    | 拡張 PWM11 出力 B           |

| SD1_C3      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 3 クロック入力 |

| UPP-CLK     | 15          |                 | I/O                  | ユニバーサル パラレル ポート送信クロック   |

| GPIO22      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 22                |

| EQEP1S      | 1           |                 | I/O                  | 拡張 QEP1 ストローブ           |

| MCLKXA      | 2           |                 | I/O                  | McBSP-A 送信クロック          |

| SCITXDB     | 3           | 22              | O                    | SCI-B 送信データ             |

| EPWM12A     | 5           |                 | O                    | 拡張 PWM12 出力 A           |

| SPICLKB     | 6           |                 | I/O                  | SPI-B クロック              |

| SD1_D4      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 4 データ入力  |

| GPIO23      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 23                |

| EQEP1I      | 1           |                 | I/O                  | 拡張 QEP1 インデックス          |

| MFSXA       | 2           |                 | I/O                  | McBSP-A 送信フレーム同期        |

| SCIRXDB     | 3           | 23              | I                    | SCI-B 受信データ             |

| EPWM12B     | 5           |                 | O                    | 拡張 PWM12 出力 B           |

| SPISTEB     | 6           |                 | I/O                  | SPI-B スレーブ送信イネーブル       |

| SD1_C4      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 4 クロック入力 |

| GPIO24      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 24                |

| OUTPUTXBAR1 | 1           |                 | O                    | 出力クロスバーの出力 1            |

| EQEP2A      | 2           |                 | I                    | 拡張 QEP2 入力 A            |

| MDXB        | 3           | 24              | O                    | McBSP-B 送信シリアル データ      |

| SPISIMOB    | 6           |                 | I/O                  | SPI-B スレーブ入力、マスタ出力      |

| SD2_D1      | 7           |                 | I                    | シグマ-デルタ 2 チャネル 1 データ入力  |

| GPIO25      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 25                |

| OUTPUTXBAR2 | 1           |                 | O                    | 出力クロスバーの出力 2            |

| EQEP2B      | 2           | 25              | I                    | 拡張 QEP2 入力 B            |

| MDRB        | 3           |                 | I                    | McBSP-B 受信シリアル データ      |

| SPISOMIB    | 6           |                 | I/O                  | SPI-B スレーブ出力、マスタ入力      |

| SD2_C1      | 7           |                 | I                    | シグマ-デルタ 2 チャネル 1 クロック入力 |

表 5-1. 信号の説明 (続き)

| 端子          |             |                 | I/O/Z <sup>(1)</sup> | 説明                               |

|-------------|-------------|-----------------|----------------------|----------------------------------|

| 名称          | 多重化位置       | PTP<br>ピン<br>番号 |                      |                                  |

| GPIO26      | 0, 4, 8, 12 | 27              | I/O                  | 汎用入出力 26                         |

| OUTPUTXBAR3 | 1           |                 | O                    | 出力クロスバーの出力 3                     |

| EQEP2I      | 2           |                 | I/O                  | 拡張 QEP2 インデックス                   |

| MCLKXB      | 3           |                 | I/O                  | McBSP-B 送信クロック                   |

| OUTPUTXBAR3 | 5           |                 | O                    | 出力クロスバーの出力 3                     |

| SPICLKB     | 6           |                 | I/O                  | SPI-B クロック                       |

| SD2_D2      | 7           |                 | I                    | シグマ-デルタ 2 チャネル 2 データ入力           |

| GPIO27      | 0, 4, 8, 12 | 28              | I/O                  | 汎用入出力 27                         |

| OUTPUTXBAR4 | 1           |                 | O                    | 出力クロスバーの出力 4                     |

| EQEP2S      | 2           |                 | I/O                  | 拡張 QEP2 スローブ                     |

| MFSXB       | 3           |                 | I/O                  | McBSP-B 送信フレーム同期                 |

| OUTPUTXBAR4 | 5           |                 | O                    | 出力クロスバーの出力 4                     |

| SPISTEB     | 6           |                 | I/O                  | SPI-B スレーブ送信イネーブル                |

| SD2_C2      | 7           |                 | I                    | シグマ-デルタ 2 チャネル 2 クロック入力          |

| GPIO28      | 0, 4, 8, 12 | 64              | I/O                  | 汎用入出力 28                         |

| SCIRXDA     | 1           |                 | I                    | SCI-A 受信データ                      |

| EM1CS4      | 2           |                 | O                    | 外部メモリインターフェイス 1 チップ セレクト 4       |

| OUTPUTXBAR5 | 5           |                 | O                    | 出力クロスバーの出力 5                     |

| EQEP3A      | 6           |                 | I                    | 拡張 QEP3 入力 A                     |

| SD2_D3      | 7           |                 | I                    | シグマ-デルタ 2 チャネル 3 データ入力           |

| GPIO29      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 29                         |

| SCITXDA     | 1           | 65              | O                    | SCI-A 送信データ                      |

| EM1SDCKE    | 2           |                 | O                    | 外部メモリインターフェイス 1 SDRAM クロック イネーブル |

| OUTPUTXBAR6 | 5           |                 | O                    | 出力クロスバーの出力 6                     |

| EQEP3B      | 6           |                 | I                    | 拡張 QEP3 入力 B                     |

| SD2_C3      | 7           |                 | I                    | シグマ-デルタ 2 チャネル 3 クロック入力          |

| GPIO30      | 0, 4, 8, 12 | 63              | I/O                  | 汎用入出力 30                         |

| CANRXA      | 1           |                 | I                    | CAN-A 受信                         |

| EM1CLK      | 2           |                 | O                    | 外部メモリインターフェイス 1 クロック             |

| OUTPUTXBAR7 | 5           |                 | O                    | 出力クロスバーの出力 7                     |

| EQEP3S      | 6           |                 | I/O                  | 拡張 QEP3 スローブ                     |

| SD2_D4      | 7           |                 | I                    | シグマ-デルタ 2 チャネル 4 データ入力           |

| GPIO31      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 31                         |

| CANTXA      | 1           | 66              | O                    | CAN-A 送信                         |

| EM1WE       | 2           |                 | O                    | 外部メモリインターフェイス 1 書き込みイネーブル        |

| OUTPUTXBAR8 | 5           |                 | O                    | 出力クロスバーの出力 8                     |

| EQEP3I      | 6           |                 | I/O                  | 拡張 QEP3 インデックス                   |

| SD2_C4      | 7           |                 | I                    | シグマ-デルタ 2 チャネル 4 クロック入力          |

| GPIO32      | 0, 4, 8, 12 | 67              | I/O                  | 汎用入出力 32                         |

| SDAA        | 1           |                 | I/OD                 | I2C-A データオーブンドレイン双方向ポート          |

| EM1CS0      | 2           |                 | O                    | 外部メモリインターフェイス 1 チップ セレクト 0       |

**表 5-1. 信号の説明 (続き)**

| 端子          |             |                 | I/O/Z <sup>(1)</sup> | 説明                                                                                                                                                                          |

|-------------|-------------|-----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称          | 多重化位置       | PTP<br>ピン<br>番号 |                      |                                                                                                                                                                             |

| GPIO33      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 33                                                                                                                                                                    |

| SCLA        | 1           | 69              | I/OD                 | I2C-A クロック オープンドレイン双方向ポート                                                                                                                                                   |

| EM1RNW      | 2           |                 | O                    | 外部メモリインターフェイス 1 読み取り、非書き込み                                                                                                                                                  |

| GPIO34      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 34                                                                                                                                                                    |

| OUTPUTXBAR1 | 1           |                 | O                    | 出力クロスバーの出力 1                                                                                                                                                                |

| EM1CS2      | 2           | 70              | O                    | 外部メモリインターフェイス 1 チップセレクト 2                                                                                                                                                   |

| SDAB        | 6           |                 | I/OD                 | I2C-B データ オープンドレイン双方向ポート                                                                                                                                                    |

| GPIO35      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 35                                                                                                                                                                    |

| SCIRXDA     | 1           |                 | I                    | SCI-A 受信データ                                                                                                                                                                 |

| EM1CS3      | 2           | 71              | O                    | 外部メモリインターフェイス 1 チップセレクト 3                                                                                                                                                   |

| SCLB        | 6           |                 | I/OD                 | I2C-B クロック オープンドレイン双方向ポート                                                                                                                                                   |

| GPIO36      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 36                                                                                                                                                                    |

| SCITXDA     | 1           |                 | O                    | SCI-A 送信データ                                                                                                                                                                 |

| EM1WAIT     | 2           | 83              | I                    | 外部メモリインターフェイス 1 非同期 SRAM ウェイト                                                                                                                                               |

| CANRXA      | 6           |                 | I                    | CAN-A 受信                                                                                                                                                                    |

| GPIO37      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 37                                                                                                                                                                    |

| OUTPUTXBAR2 | 1           |                 | O                    | 出力クロスバーの出力 2                                                                                                                                                                |

| EM1OE       | 2           | 84              | O                    | 外部メモリインターフェイス 1 出力イネーブル                                                                                                                                                     |

| CANTXA      | 6           |                 | O                    | CAN-A 送信                                                                                                                                                                    |

| GPIO38      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 38                                                                                                                                                                    |

| EM1A0       | 2           |                 | O                    | 外部メモリインターフェイス 1 アドレスライン 0                                                                                                                                                   |

| SCITXDC     | 5           | 85              | O                    | SCI-C 送信データ                                                                                                                                                                 |

| CANTXB      | 6           |                 | O                    | CAN-B 送信                                                                                                                                                                    |

| GPIO39      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 39                                                                                                                                                                    |

| EM1A1       | 2           |                 | O                    | 外部メモリインターフェイス 1 アドレスライン 1                                                                                                                                                   |

| SCIRXDC     | 5           | 86              | I                    | SCI-C 受信データ                                                                                                                                                                 |

| CANRXB      | 6           |                 | I                    | CAN-B 受信                                                                                                                                                                    |

| GPIO40      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 40                                                                                                                                                                    |

| EM1A2       | 2           | 87              | O                    | 外部メモリインターフェイス 1 アドレスライン 2                                                                                                                                                   |

| SDAB        | 6           |                 | I/OD                 | I2C-B データ オープンドレイン双方向ポート                                                                                                                                                    |

| GPIO41      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 41 ハイバネーション低消費電力モードを使用するアプリケーションでは、このピンは、GPIOHIBWAKE 信号として機能します。詳細については、『TMS320F2837xD デュアルコアリアルタイムマイクロコントローラテクニカルリファレンスマニュアル』の「システム制御」の章にある「低消費電力モード」セクションを参照してください。 |

| EM1A3       | 2           | 89              | O                    | 外部メモリインターフェイス 1 アドレスライン 3                                                                                                                                                   |

| SCLB        | 6           |                 | I/OD                 | I2C-B クロック オープンドレイン双方向ポート                                                                                                                                                   |

| GPIO42      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 42                                                                                                                                                                    |

| SDAA        | 6           |                 | I/OD                 | I2C-A データ オープンドレイン双方向ポート                                                                                                                                                    |

| SCITXDA     | 15          | 130             | O                    | SCI-A 送信データ                                                                                                                                                                 |

| USB0DM      | アナログ        |                 | I/O                  | USB PHY 差動データ                                                                                                                                                               |

表 5-1. 信号の説明 (続き)

| 端子          |             |                 | I/O/Z <sup>(1)</sup> | 説明                         |

|-------------|-------------|-----------------|----------------------|----------------------------|

| 名称          | 多重化位置       | PTP<br>ピン<br>番号 |                      |                            |

| GPIO43      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 43                   |

| SCLA        | 6           | 131             | I/OD                 | I2C-A クロック オープンドレイン双方向ポート  |

| SCIRXDA     | 15          |                 | I                    | SCI-A 受信データ                |

| USB0DP      | アナログ        |                 | I/O                  | USB PHY 差動データ              |

| GPIO44      | 0, 4, 8, 12 | 113             | I/O                  | 汎用入出力 44                   |

| EM1A4       | 2           |                 | O                    | 外部メモリインターフェイス 1 アドレスライン 4  |

| GPIO45      | 0, 4, 8, 12 | 115             | I/O                  | 汎用入出力 45                   |

| EM1A5       | 2           |                 | O                    | 外部メモリインターフェイス 1 アドレスライン 5  |

| GPIO46      | 0, 4, 8, 12 | 128             | I/O                  | 汎用入出力 46                   |

| EM1A6       | 2           |                 | O                    | 外部メモリインターフェイス 1 アドレスライン 6  |

| SCIRXDD     | 6           |                 | I                    | SCI-D 受信データ                |

| GPIO47      | 0, 4, 8, 12 | 129             | I/O                  | 汎用入出力 47                   |

| EM1A7       | 2           |                 | O                    | 外部メモリインターフェイス 1 アドレスライン 7  |

| SCITXDD     | 6           |                 | O                    | SCI-D 送信データ                |

| GPIO48      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 48                   |

| OUTPUTXBAR3 | 1           |                 | O                    | 出力クロスバーの出力 3               |

| EM1A8       | 2           | 90              | O                    | 外部メモリインターフェイス 1 アドレスライン 8  |

| SCITXDA     | 6           |                 | O                    | SCI-A 送信データ                |

| SD1_D1      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 1 データ入力     |

| GPIO49      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 49                   |

| OUTPUTXBAR4 | 1           |                 | O                    | 出力クロスバーの出力 4               |

| EM1A9       | 2           | 93              | O                    | 外部メモリインターフェイス 1 アドレスライン 9  |

| SCIRXDA     | 6           |                 | I                    | SCI-A 受信データ                |

| SD1_C1      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 1 クロック入力    |

| GPIO50      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 50                   |

| EQEP1A      | 1           |                 | I                    | 拡張 QEP1 入力 A               |

| EM1A10      | 2           | 94              | O                    | 外部メモリインターフェイス 1 アドレスライン 10 |

| SPISIMOC    | 6           |                 | I/O                  | SPI-C スレーブ入力、マスタ出力         |

| SD1_D2      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 2 データ入力     |

| GPIO51      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 51                   |

| EQEP1B      | 1           |                 | I                    | 拡張 QEP1 入力 B               |

| EM1A11      | 2           | 95              | O                    | 外部メモリインターフェイス 1 アドレスライン 11 |

| SPISOMIC    | 6           |                 | I/O                  | SPI-C スレーブ出力、マスタ入力         |

| SD1_C2      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 2 クロック入力    |

| GPIO52      | 0, 4, 8, 12 |                 | I/O                  | 汎用入出力 52                   |

| EQEP1S      | 1           |                 | I/O                  | 拡張 QEP1 ストローブ              |

| EM1A12      | 2           | 96              | O                    | 外部メモリインターフェイス 1 アドレスライン 12 |

| SPICLK      | 6           |                 | I/O                  | SPI-C クロック                 |

| SD1_D3      | 7           |                 | I                    | シグマ-デルタ 1 チャネル 3 データ入力     |

**表 5-1. 信号の説明 (続き)**

| 端子       |             |                 | I/O/Z <sup>(1)</sup> | 説明                        |

|----------|-------------|-----------------|----------------------|---------------------------|

| 名称       | 多重化位置       | PTP<br>ピン<br>番号 |                      |                           |

| GPIO53   | 0, 4, 8, 12 | 97              | I/O                  | 汎用入出力 53                  |

| EQEP11   | 1           |                 | I/O                  | 拡張 QEP1 インデックス            |

| EM1D31   | 2           |                 | I/O                  | 外部メモリインターフェイス 1 データライン 31 |

| EM2D15   | 3           |                 | I/O                  | 外部メモリインターフェイス 2 データライン 15 |

| SPISTEC  | 6           |                 | I/O                  | SPI-C スレーブ送信イネーブル         |

| SD1_C3   | 7           |                 | I                    | シグマ-デルタ 1 チャネル 3 クロック入力   |

| GPIO54   | 0, 4, 8, 12 | 98              | I/O                  | 汎用入出力 54                  |

| SPISIMOA | 1           |                 | I/O                  | SPI-A スレーブ入力、マスタ出力        |

| EM1D30   | 2           |                 | I/O                  | 外部メモリインターフェイス 1 データライン 30 |

| EM2D14   | 3           |                 | I/O                  | 外部メモリインターフェイス 2 データライン 14 |

| EQEP2A   | 5           |                 | I                    | 拡張 QEP2 入力 A              |

| SCITXDB  | 6           |                 | O                    | SCI-B 送信データ               |

| SD1_D4   | 7           |                 | I                    | シグマ-デルタ 1 チャネル 4 データ入力    |

| GPIO55   | 0, 4, 8, 12 | 100             | I/O                  | 汎用入出力 55                  |

| SPISOMIA | 1           |                 | I/O                  | SPI-A スレーブ出力、マスタ入力        |

| EM1D29   | 2           |                 | I/O                  | 外部メモリインターフェイス 1 データライン 29 |

| EM2D13   | 3           |                 | I/O                  | 外部メモリインターフェイス 2 データライン 13 |

| EQEP2B   | 5           |                 | I                    | 拡張 QEP2 入力 B              |

| SCIRXDB  | 6           |                 | I                    | SCI-B 受信データ               |

| SD1_C4   | 7           |                 | I                    | シグマ-デルタ 1 チャネル 4 クロック入力   |

| GPIO56   | 0, 4, 8, 12 | 101             | I/O                  | 汎用入出力 56                  |

| SPICLKA  | 1           |                 | I/O                  | SPI-A クロック                |

| EM1D28   | 2           |                 | I/O                  | 外部メモリインターフェイス 1 データライン 28 |

| EM2D12   | 3           |                 | I/O                  | 外部メモリインターフェイス 2 データライン 12 |

| EQEP2S   | 5           |                 | I/O                  | 拡張 QEP2 ストローブ             |

| SCITXDC  | 6           |                 | O                    | SCI-C 送信データ               |

| SD2_D1   | 7           |                 | I                    | シグマ-デルタ 2 チャネル 1 データ入力    |

| GPIO57   | 0, 4, 8, 12 | 102             | I/O                  | 汎用入出力 57                  |

| SPISTEĀ  | 1           |                 | I/O                  | SPI-A スレーブ送信イネーブル         |

| EM1D27   | 2           |                 | I/O                  | 外部メモリインターフェイス 1 データライン 27 |

| EM2D11   | 3           |                 | I/O                  | 外部メモリインターフェイス 2 データライン 11 |

| EQEP2I   | 5           |                 | I/O                  | 拡張 QEP2 インデックス            |

| SCIRXDC  | 6           |                 | I                    | SCI-C 受信データ               |

| SD2_C1   | 7           |                 | I                    | シグマ-デルタ 2 チャネル 1 クロック入力   |

表 5-1. 信号の説明(続き)

| 端子          |             |                 | I/O/Z <sup>(1)</sup> | 説明                                |

|-------------|-------------|-----------------|----------------------|-----------------------------------|

| 名称          | 多重化位置       | PTP<br>ピン<br>番号 |                      |                                   |

| GPIO58      | 0, 4, 8, 12 | 103             | I/O                  | 汎用入出力 58                          |

| MCLKRA      | 1           |                 | I/O                  | McBSP-A 受信クロック                    |

| EM1D26      | 2           |                 | I/O                  | 外部メモリインターフェイス 1 データライン 26         |

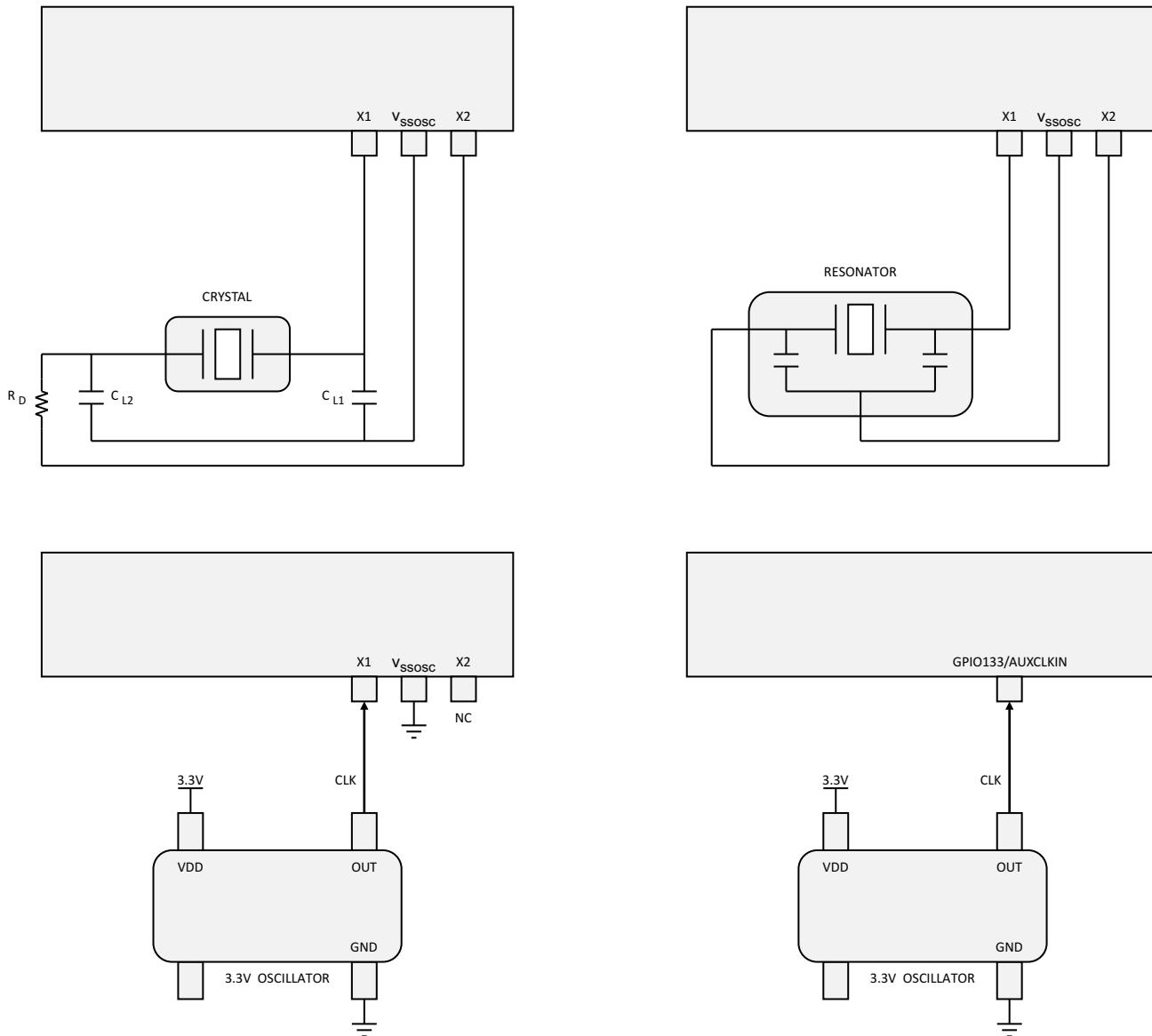

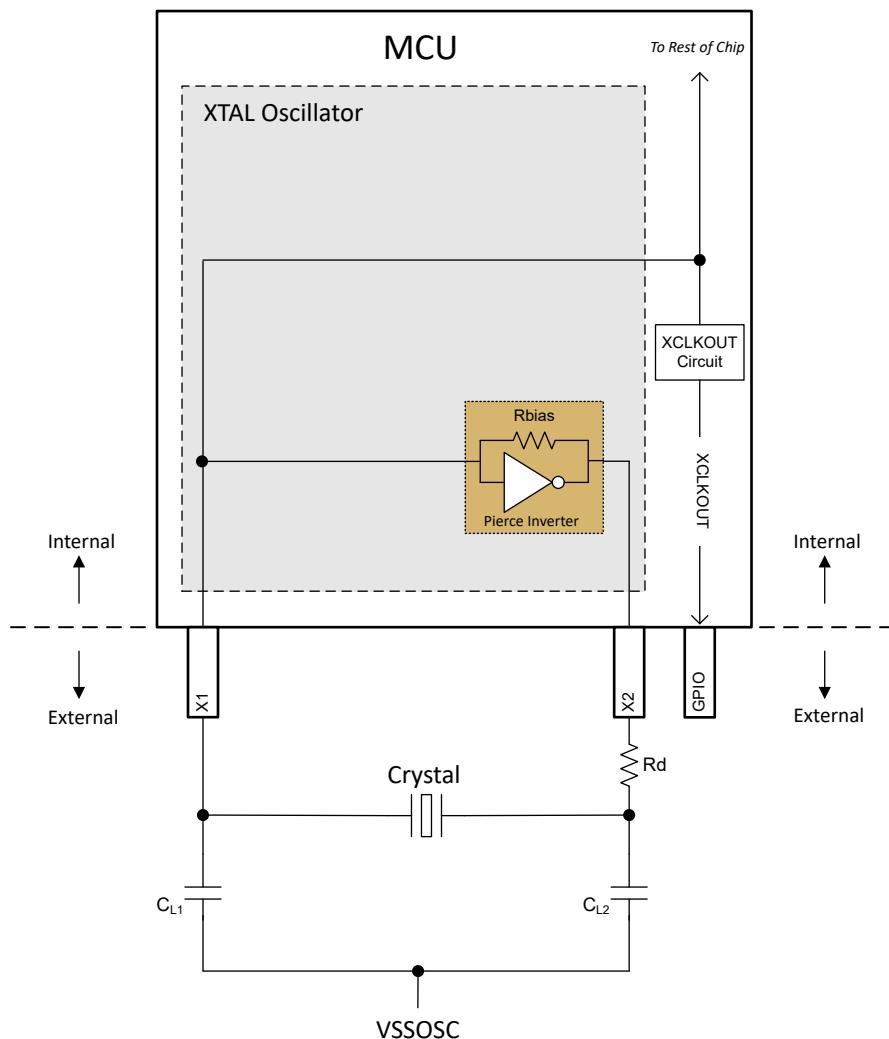

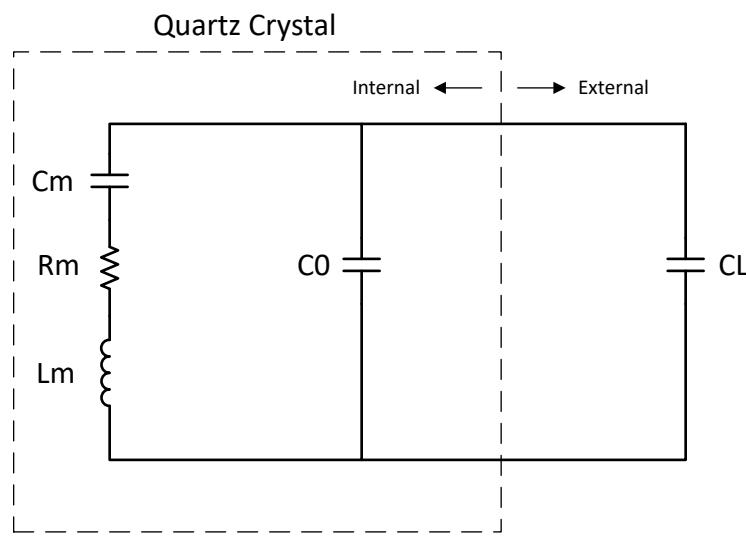

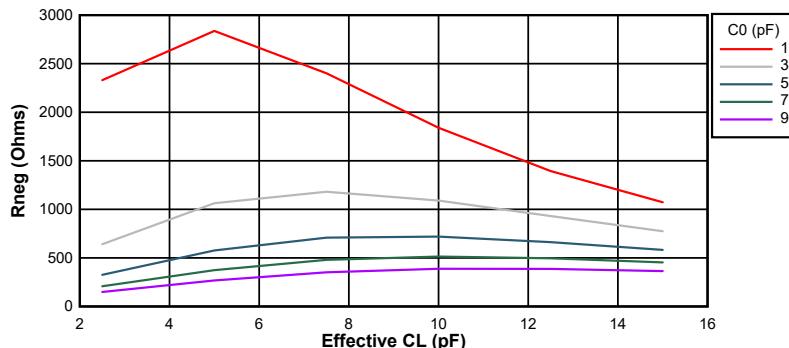

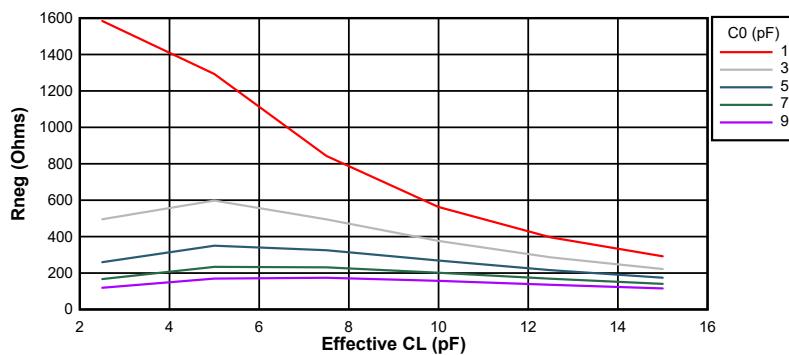

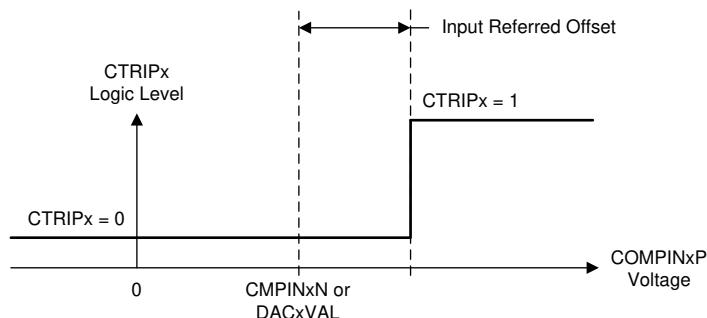

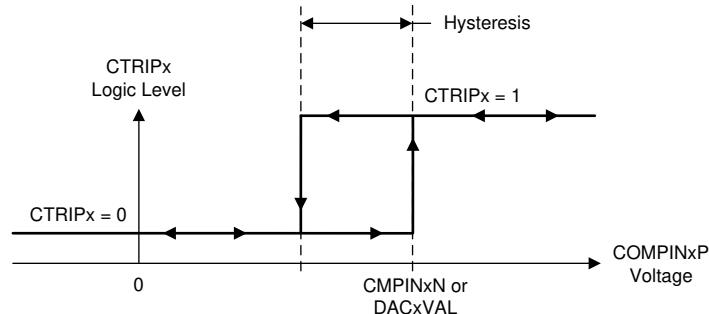

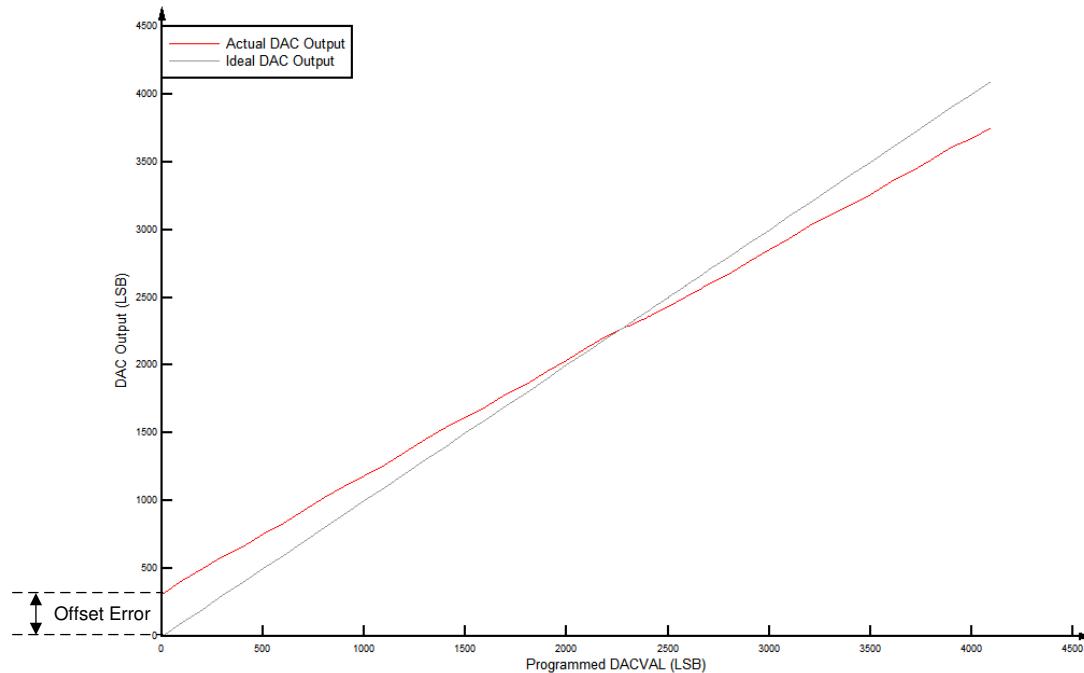

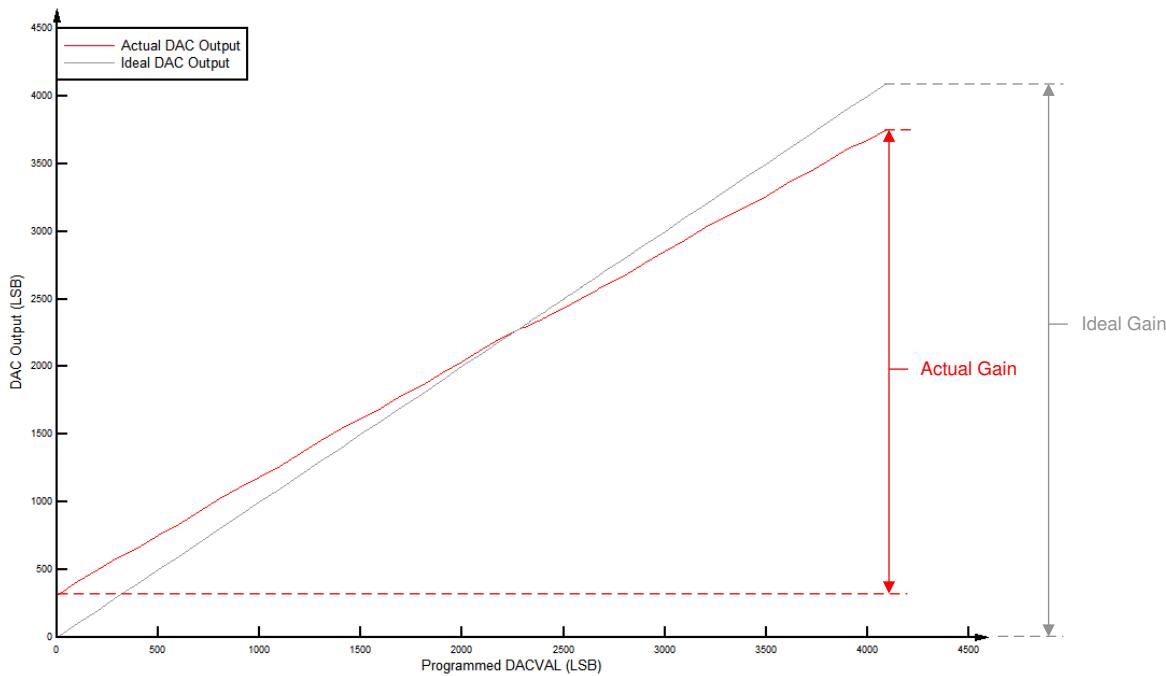

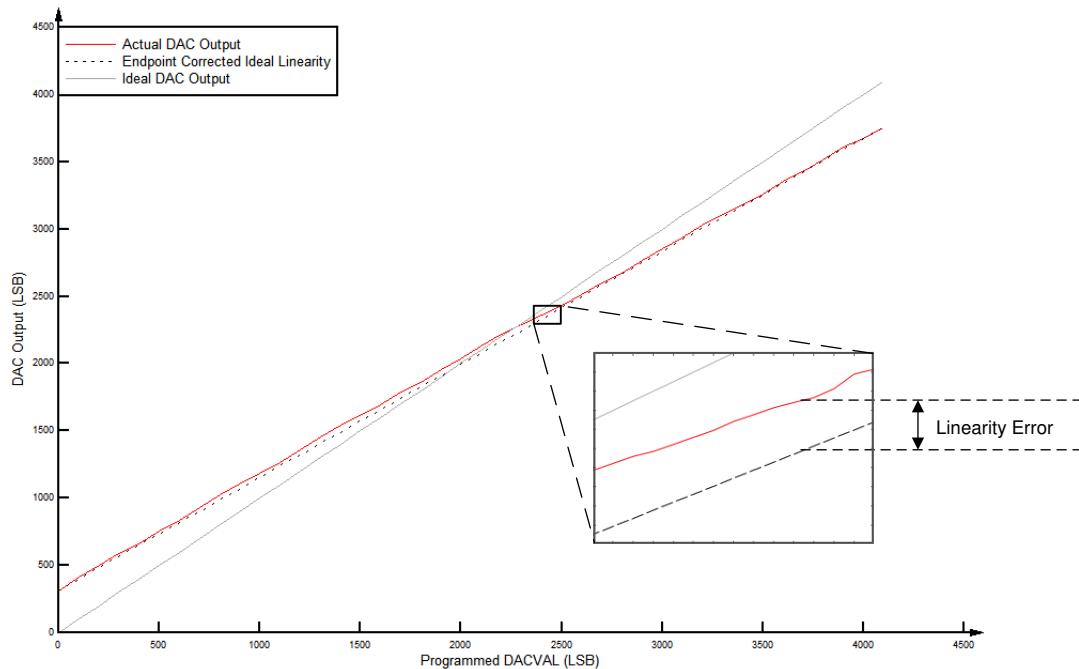

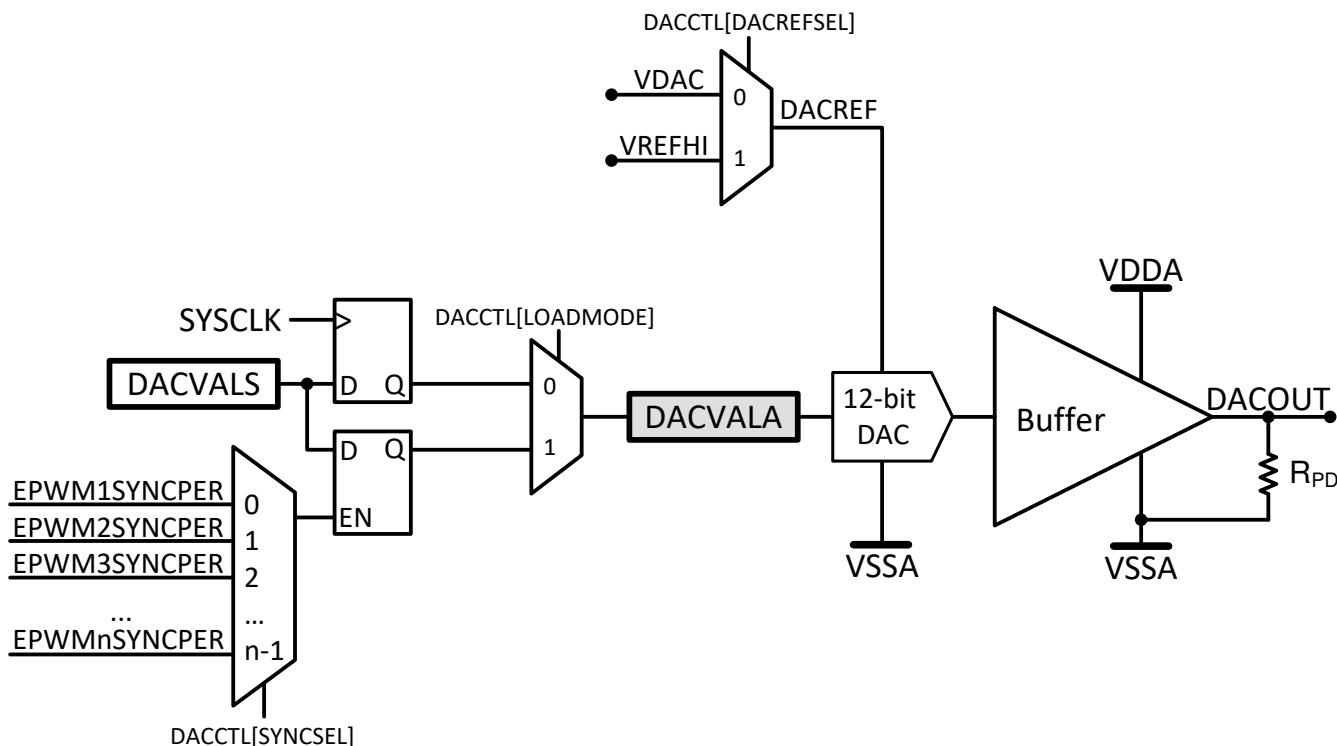

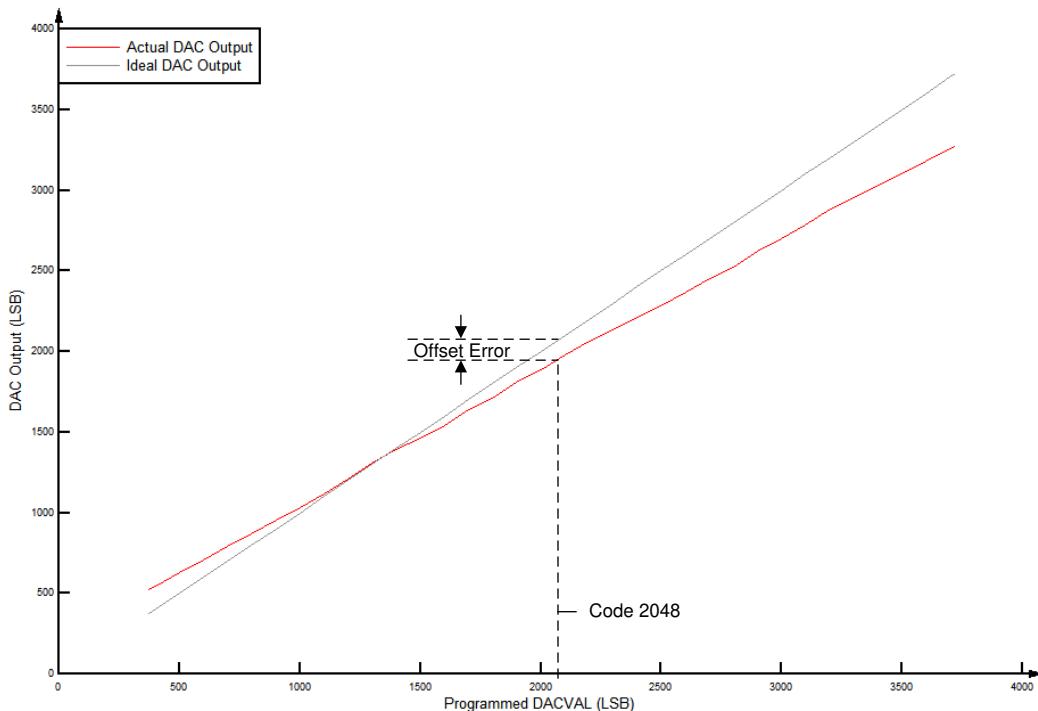

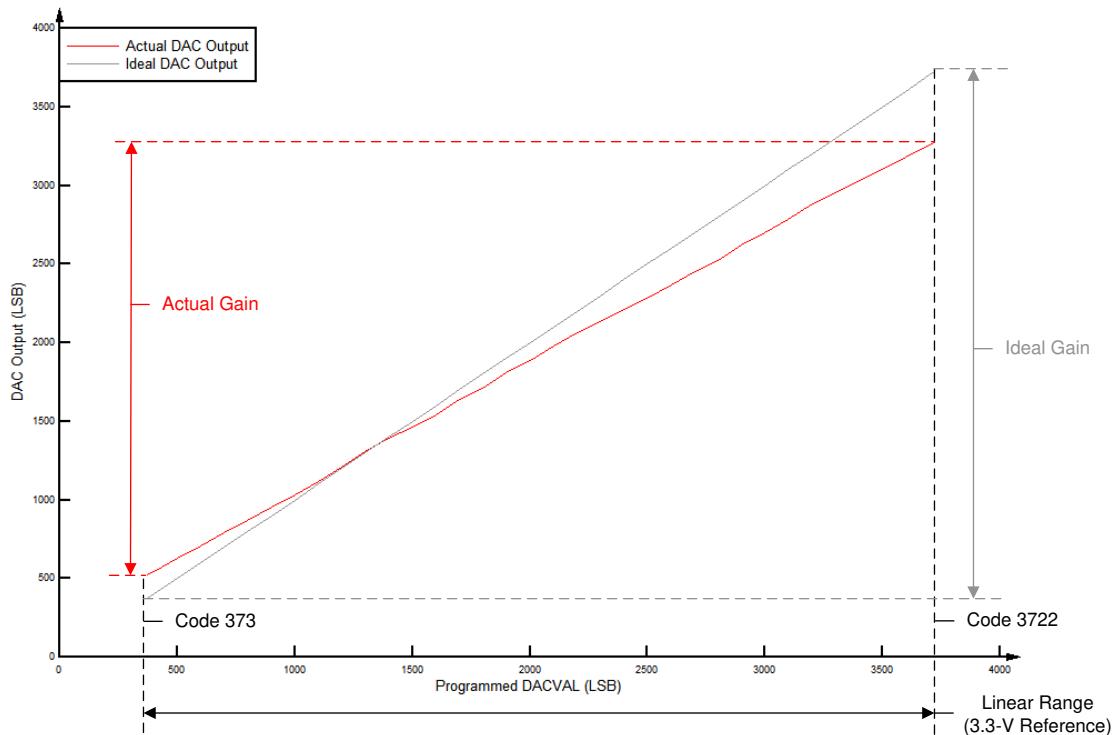

| EM2D10      | 3           |                 | I/O                  | 外部メモリインターフェイス 2 データライン 10         |