# LM251374V ~ 42V、100% デューティ サイクル対応、デュアルチャネル同期整流降圧 DC/DC コントローラ

## 1 特長

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可能

- 機能安全準拠オプション – SIL 2 および SIL 3 – リクエストにより入手可能 (LM25137F)

- デュアルチャネル、同期整流降圧 DC/DC コントローラ

- 4V~42V の広い入力電圧範囲

- 精度 1% の固定 3.3V、5V、12V 出力または可変出力 (0.8V~36V)

- 接合部温度: 150°C (最大値)

- 100% デューティ サイクルに対応するチャージポンプ ゲートドライバ

- 無負荷スリープ電流: 9µA (標準値)

- 2 つのインターリーブ同期整流降圧チャネル

- 2 チャネルまたは単一出力多相

- 最大 4 相にスタック可能

- SYNC In および SYNC Out 機能

- 軽負荷 PFM または FPWM を選択可能

- 堅牢な設計用の本質的な保護機能

- ヒップアップ モードによる過電流の内部保護

- 独立した ENABLE および PGOOD 機能

- 可変出力電圧ソフト スタート

- VCC とゲート駆動の UVLO 保護

- シヤントまたはインダクタ DCR 電流検出

- ヒステリシス付きのサーマル シヤットダウン保護

- 超低 EMI 要件向けの設計

- デュアルランダム スペクトラム拡散機能 (DRSS)

- スイッチング周波数: 100kHz~2.64MHz

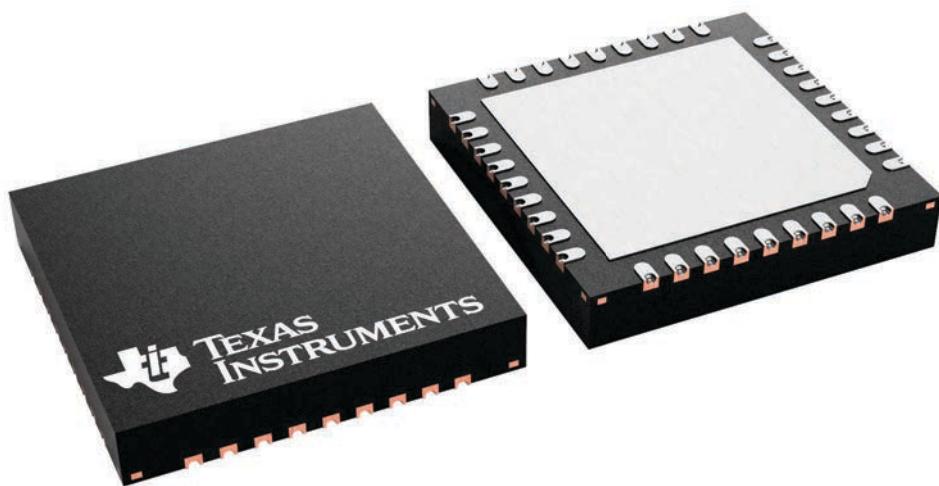

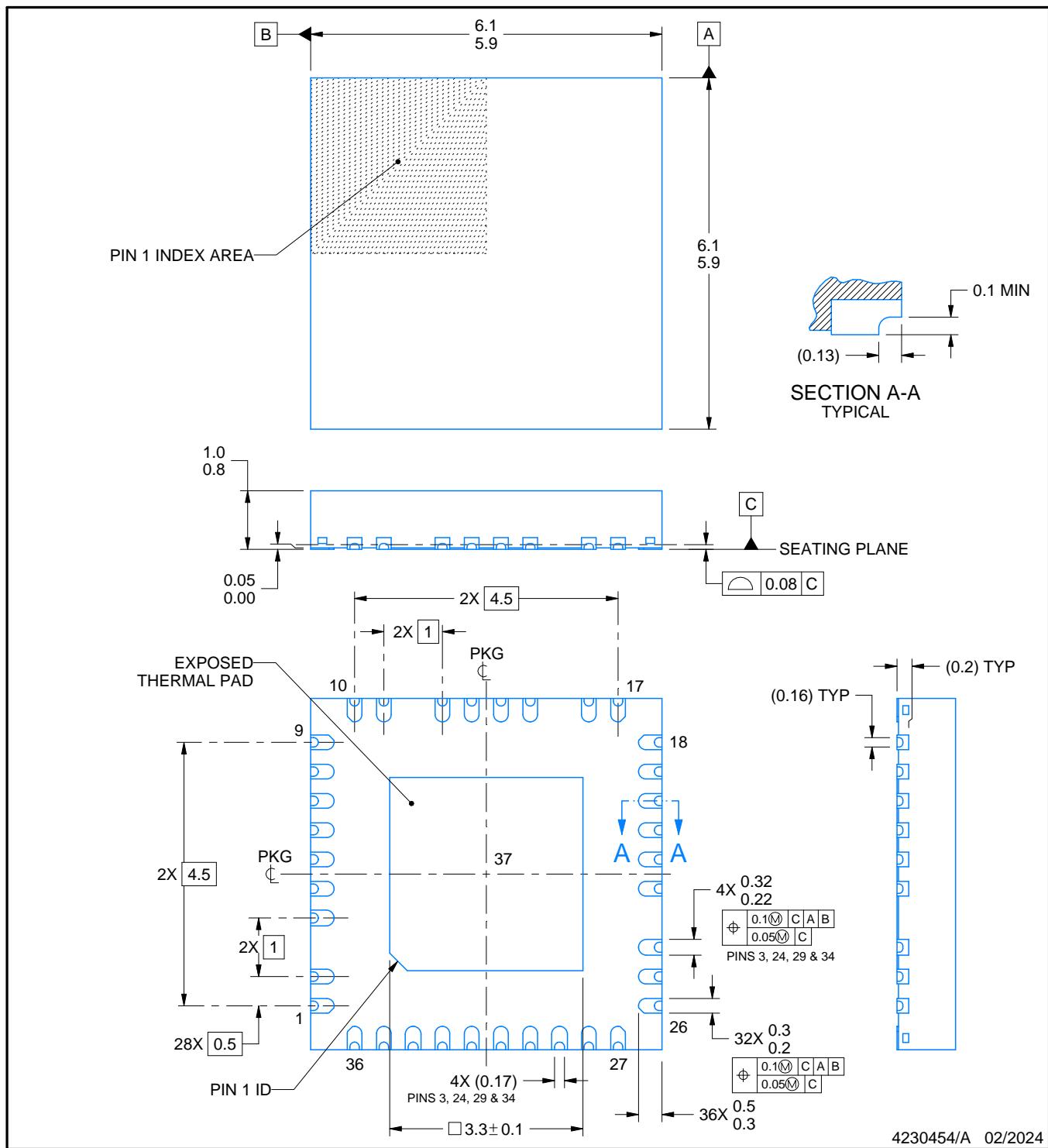

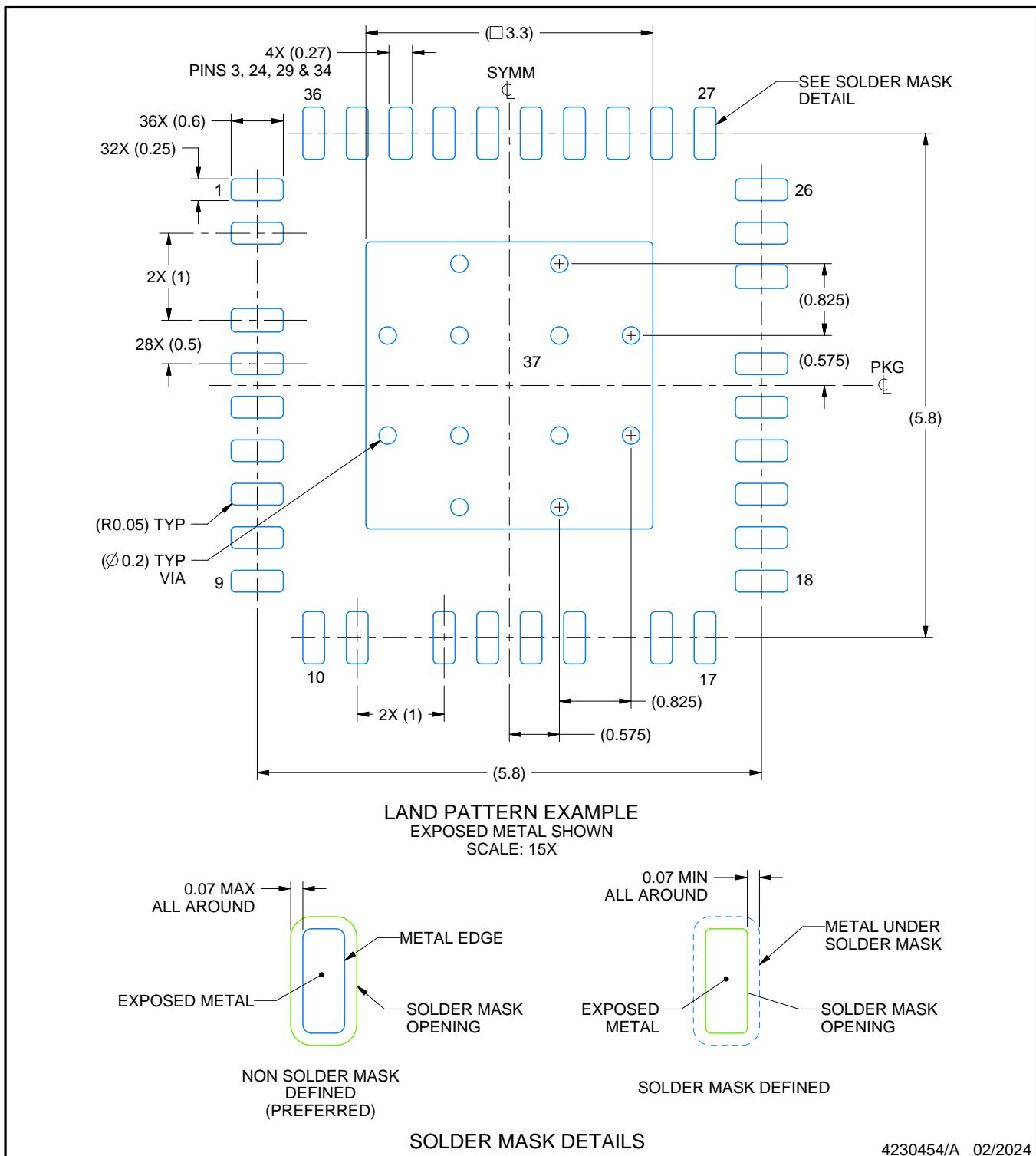

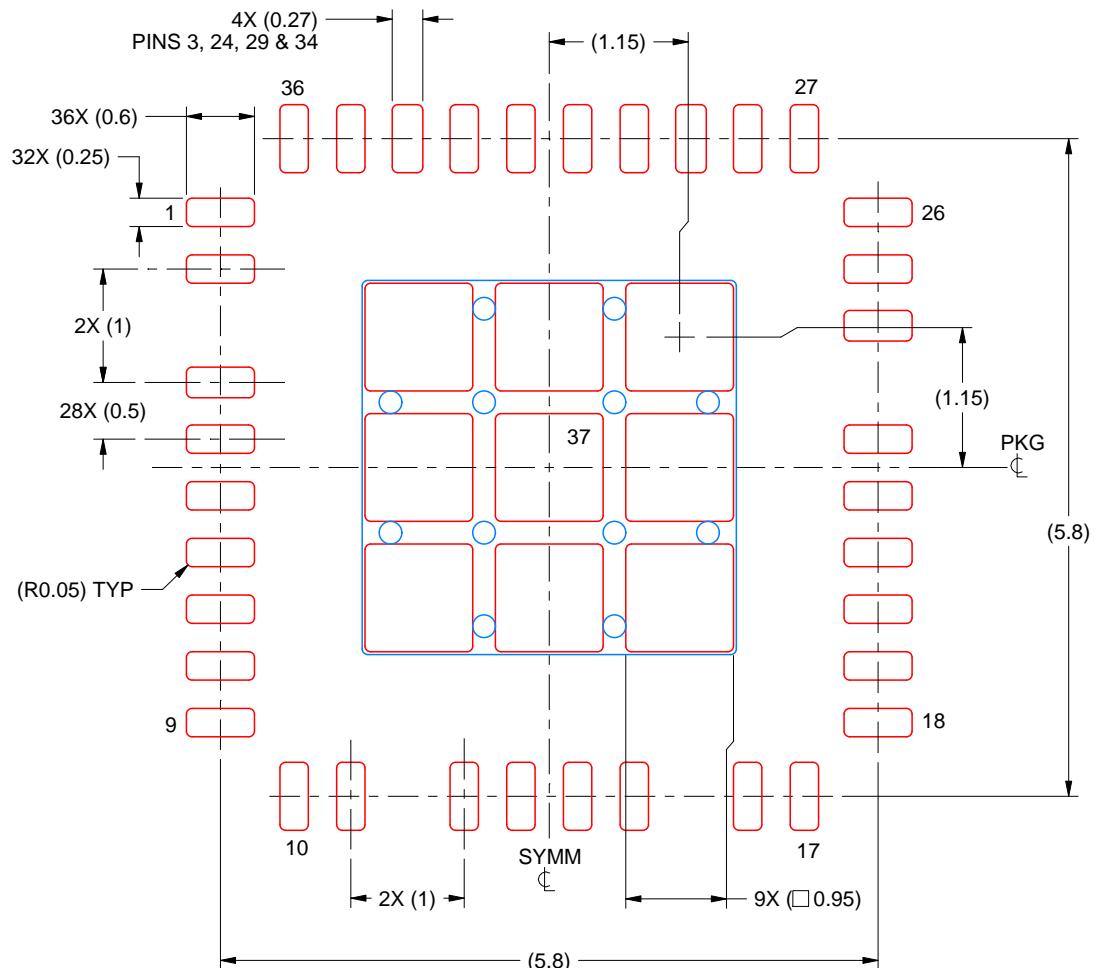

- ウェッタブル フランク付き VQFN-36 パッケージ

- WEBENCH® Power Designer により、LM25137 を使用するカスタム設計を作成

## 2 アプリケーション

- パーソナル エレクトロニクス: コンピュータ ペリフェラル

- 産業用: 24V バスシステム、電力供給

- エンターテイメント システム: 高性能コンピューティング

## 3 説明

LM25137 は、42V の同期整流降圧 DC/DC コントローラ ファミリであり、機能安全を実現するための次の 3 つのオプションが用意されています。SIL 2、SIL 3 対応。インターリーブ方式のスタック可能なピーク電流モード アーキテクチャにより、容易なループ補償、高速な過渡応答、優れた負荷 / ライン制御、並列化した相での正確なカレントシェア (電流共有) を実現し、より大きな出力電流に対応します。

最小オン時間 22ns のハイサイドスイッチは大きい降圧率に対応できるため、12V および 24V の入力から低電圧レールへの直接変換が可能になり、システムの設計コストと複雑性を下げることができます。LM25137 は、最低 4V の入力電圧アップ時にも動作を継続でき、必要に応じて 100% のデューティ サイクルでも動作できます。スリープ時静止電流 (出力電圧をレギュレートした状態) は 1.5µA であるため、バッテリ駆動のシステムの動作時間を延長できます。

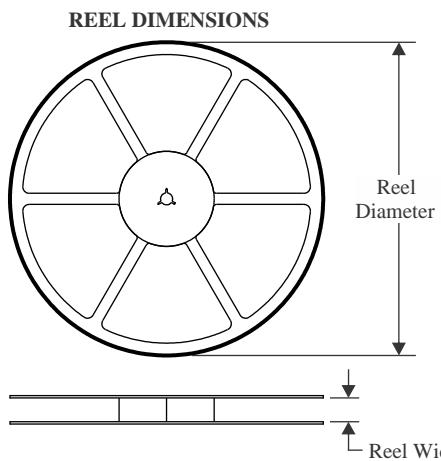

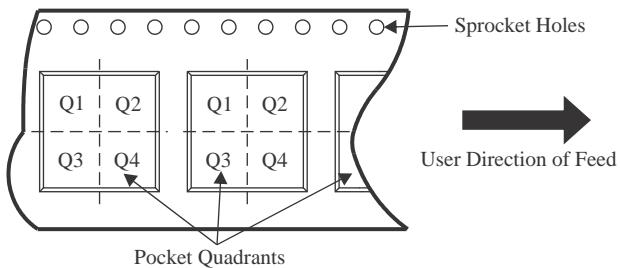

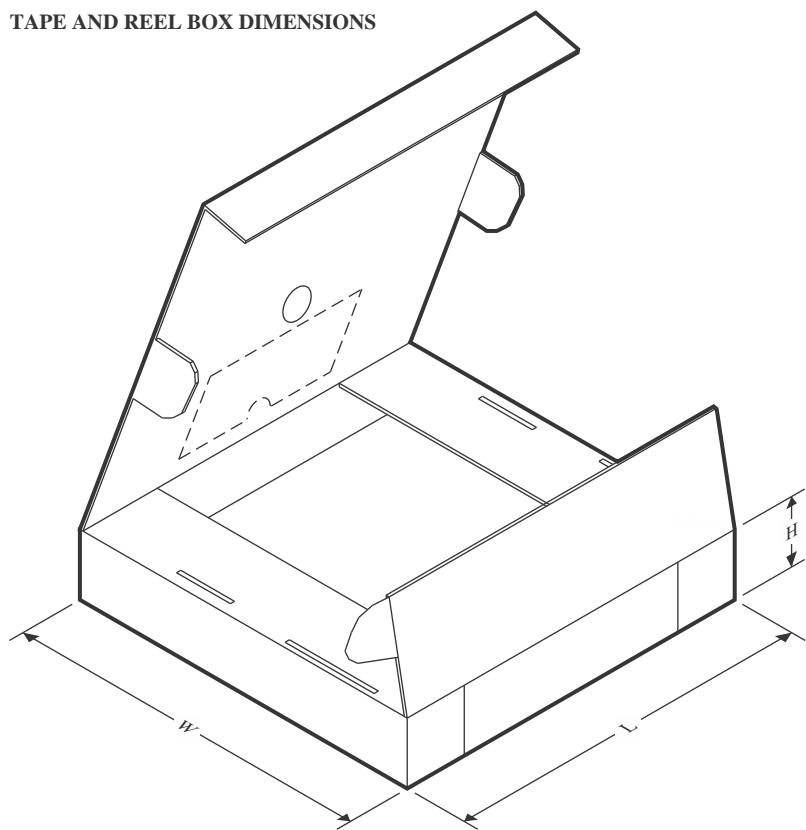

### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| LM25137 | RHA (VQFN、36)        | 6.0mm × 6.0mm            |

(1) 詳細については、セクション 11 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SNVSCU4

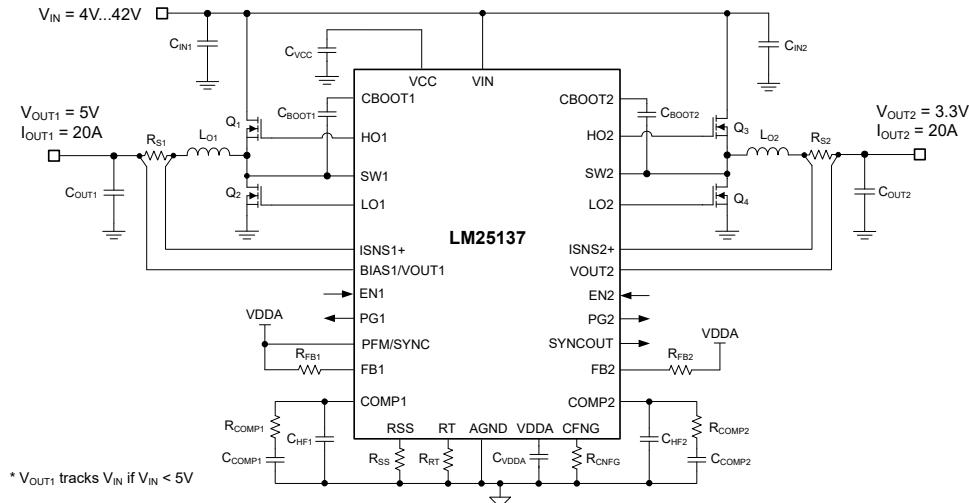

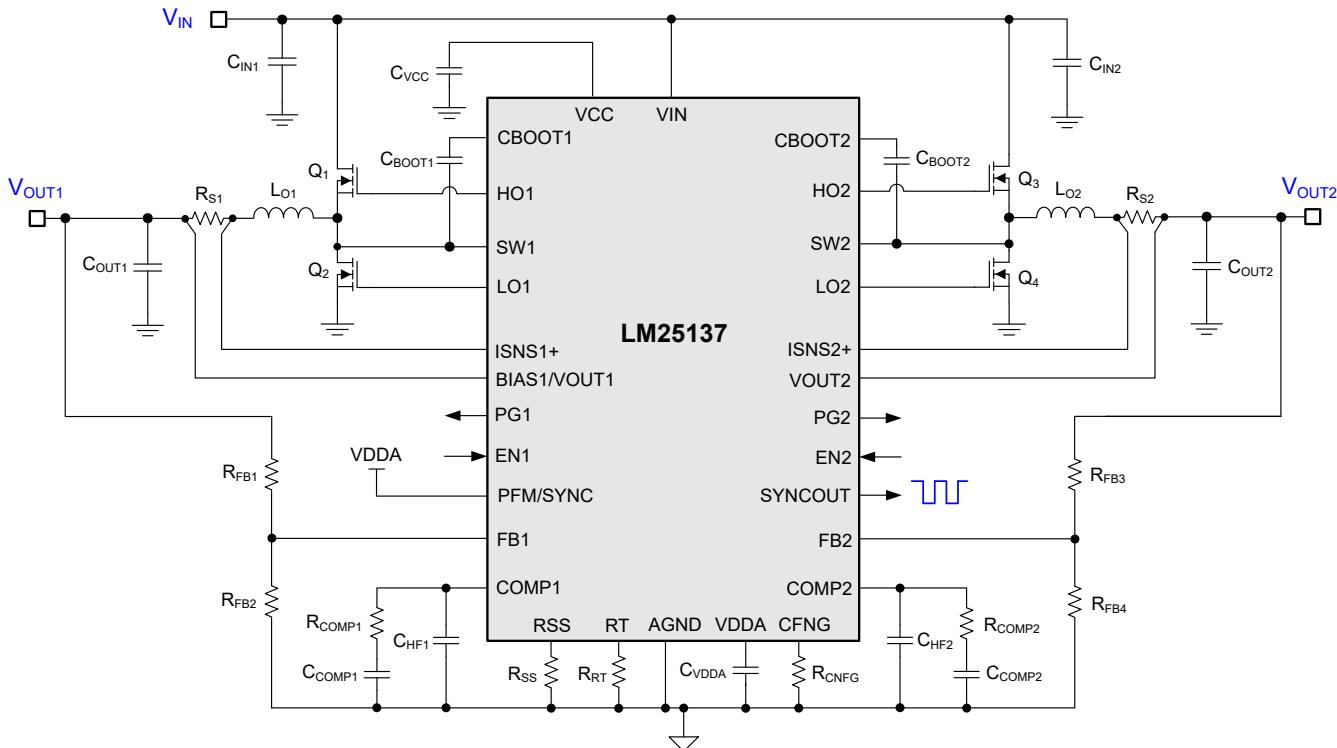

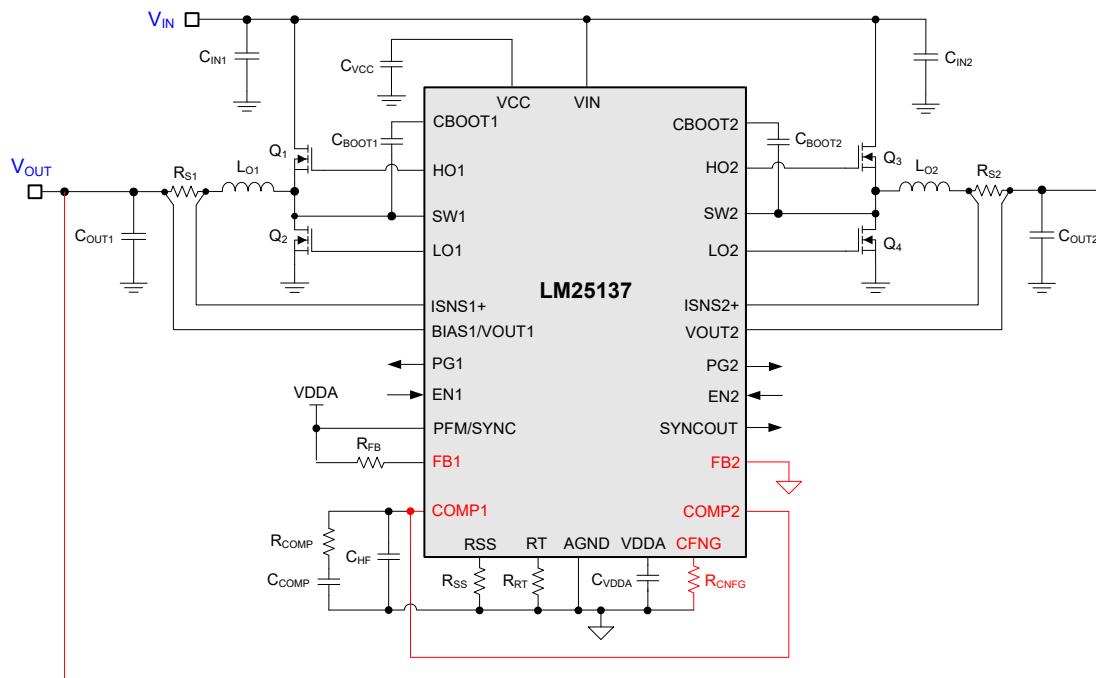

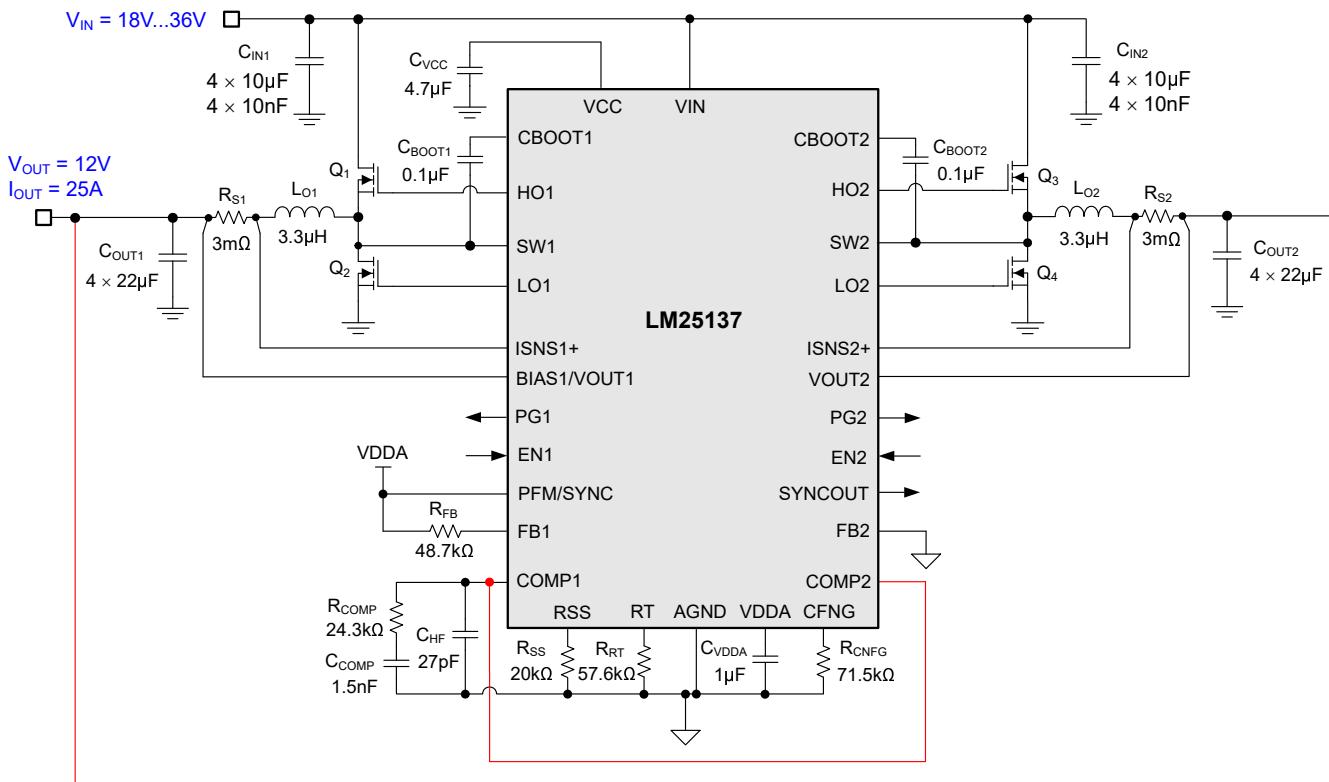

LM25137 デュアル出力降圧スイッチング レギュレータ - 概略回路図

CISPR 11 および CISPR 32 EMI 要件への準拠を容易にする複数の機能が搭載されています。大電流 MOSFET ゲートドライバは、適応的にタイミングを制御し、スイッチング遷移時のボディダイオードの導通を最小限にとどめて、スイッチング損失を低減するとともに、高入力電圧および高スイッチング周波数時の熱および EMI 性能を高めます。入力コンデンサのリップル電流を小さくし、EMI フィルタを小型化するために、2 つの出力の  $180^\circ$  インターリーブ動作もサポートしています。 $90^\circ$  位相差のあるクロック出力は、カスケード、マルチチャネル、またはマルチフェーズ電力段に最適です。スイッチング周波数は、抵抗により最大 2.2MHz まで設定可能で、最大 2.64MHz の外部クロックソースと同期できるため、ノイズに敏感な用途でビート周波数を除去できます。

LM25137 のその他の機能として、最大  $150^\circ\text{C}$  の接合部温度での動作、ユーザー選択可能な PFM モードによる軽負荷時消費電流の低減、設定可能なソフトスタート機能、オープンドレインの PG フラグによるフォルト報告と出力監視、独立したイネーブル入力、プリバイアスされた負荷への単調なスタートアップ、内蔵 VCC バイアス電源レギュレータ (VIN または VOUT1 から電源を供給)、ヒップアップモード過負荷保護、自動回復機能付きサーマルシャットダウン保護があります。電流検出では、インダクタの DCR を使用して最高水準の効率を実現できます。また、オプションのシャント抵抗を使用すれば、高精度を実現できます。

LM25137 コントローラ、 $6\text{mm} \times 6\text{mm}$  の熱特性強化された 36 ピンの VQFN パッケージに搭載されています。また、信頼性向上のための追加ピンクリアランスとウェッタブルフランクピン付きで、製造中の光学検査が容易になります。広い入力電圧範囲、低い静止電流消費、高温での動作、サイクルごとの電流制限、低い EMI シグネチャ、小型設計サイズにより、堅牢性と耐久性の向上が求められるアプリケーションに最適なポイントオブロードレギュレータを選択できます。

## 目次

|                 |    |                        |    |

|-----------------|----|------------------------|----|

| 1 特長            | 1  | 7.4 デバイスの機能モード         | 30 |

| 2 アプリケーション      | 1  | 8 アプリケーションと実装          | 32 |

| 3 説明            | 1  | 8.1 アプリケーション情報         | 32 |

| 4 関連製品          | 4  | 8.2 代表的なアプリケーション       | 40 |

| 5 ピン構成および機能     | 5  | 8.3 電源に関する推奨事項         | 55 |

| 5.1 ウエッタブル フランク | 7  | 8.4 レイアウト              | 56 |

| 6 仕様            | 8  | 9 デバイスおよびドキュメントのサポート   | 62 |

| 6.1 絶対最大定格      | 8  | 9.1 デバイス サポート          | 62 |

| 6.2 ESD 定格      | 8  | 9.2 ドキュメントのサポート        | 63 |

| 6.3 推奨動作条件      | 9  | 9.3 ドキュメントの更新通知を受け取る方法 | 64 |

| 6.4 熱に関する情報     | 9  | 9.4 サポート・リソース          | 64 |

| 6.5 電気的特性       | 9  | 9.5 商標                 | 64 |

| 6.6 代表的特性       | 13 | 9.6 静電気放電に関する注意事項      | 64 |

| 7 詳細説明          | 18 | 9.7 用語集                | 65 |

| 7.1 概要          | 18 | 10 改訂履歴                | 65 |

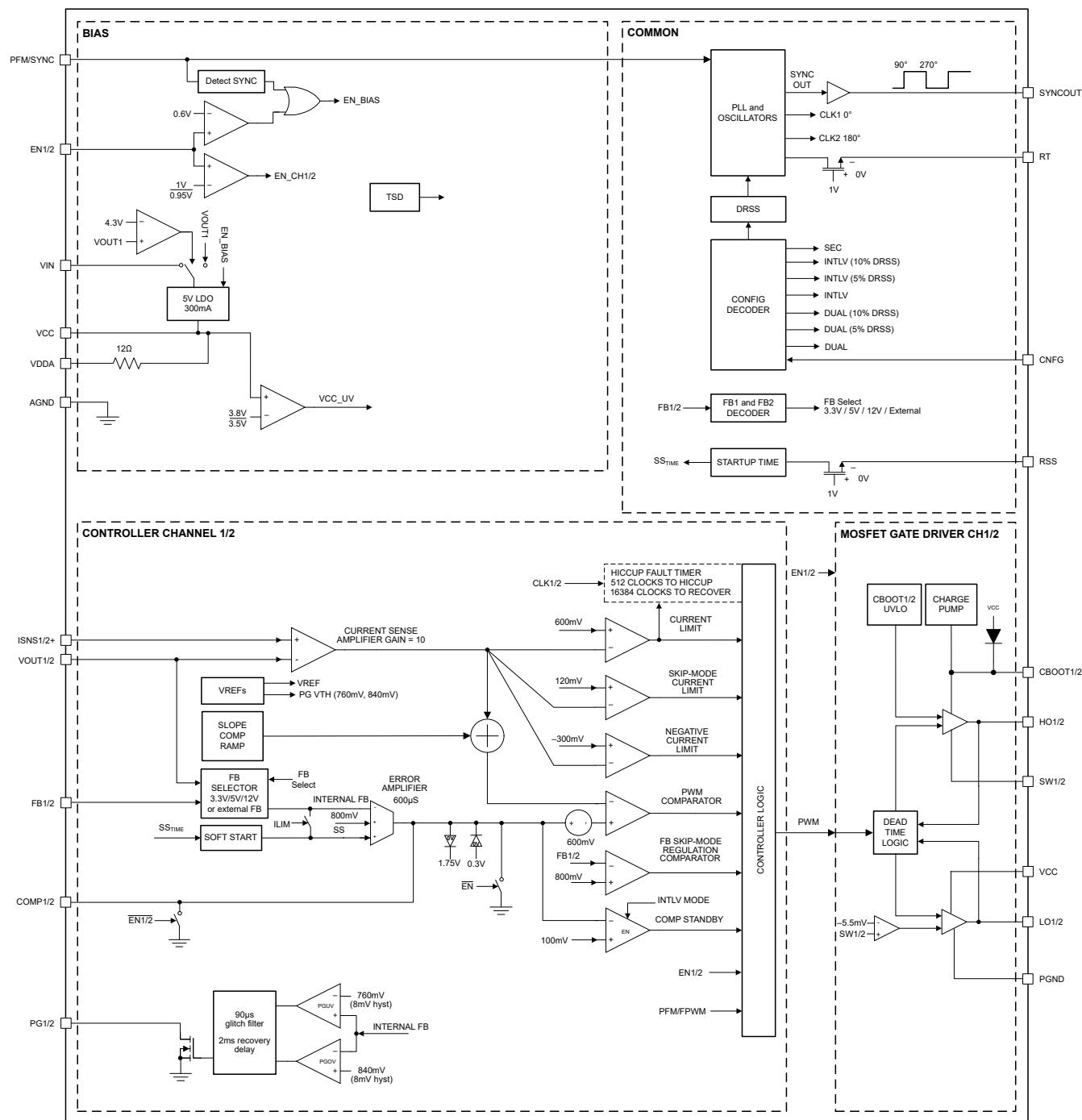

| 7.2 機能ブロック図     | 19 | 11 メカニカル、パッケージ、および注文情報 | 65 |

| 7.3 機能説明        | 20 |                        |    |

## 4 関連製品

表 4-1. 発注型番

| ジェネリック型番                | 発注用製品型番       | TI の機能安全の分類 <sup>(1)</sup> | 製品データシート                        |

|-------------------------|---------------|----------------------------|---------------------------------|

| LM25137                 | LM25137RHAR   | 機能安全対応                     | このデータシート                        |

| LM25137F <sup>(2)</sup> | LM25137F2RHAR | SIL 2 機能安全準拠               | <a href="#">開発中製品のリクエストはこちら</a> |

|                         | LM25137F3RHAR | SIL 3 機能安全準拠               |                                 |

(1) TI の機能安全分類 (開発プロセス、分析レポート、診断の説明) については、[機能安全ホームページ](#)をご覧ください。

(2) 開発中製品情報 (量産データではありません)。

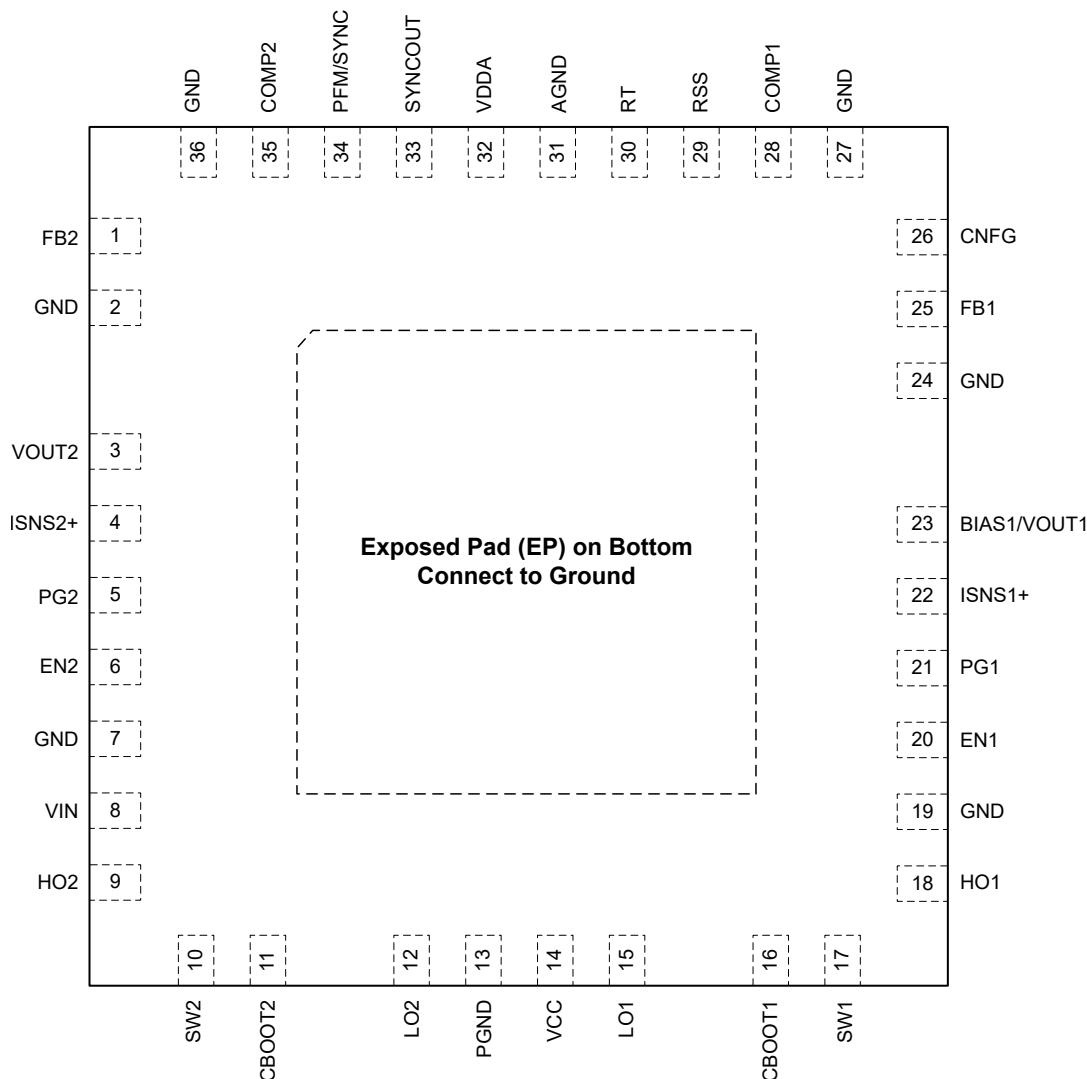

## 5 ピン構成および機能

底面の露出したパッドを PCB 上の AGND と PGND に接続します。

図 5-1. RHA パッケージ、ウェッタブル フランク付き 36 ピン VQFN (上面図)

表 5-1. ピンの機能

| ピン              |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                             |

|-----------------|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称              | 番号 |                    |                                                                                                                                                                                |

| FB2             | 1  | I                  | 7.5kΩ、24.9kΩ、48.7kΩ のいずれかの抵抗を介して FB2 を VDDA に接続し、出力電圧をそれぞれ 3.3V、5V、12V に設定します。または、VOUT2 と FB2 の間に抵抗分圧器を使用して、チャネル 2 の出力電圧設定ポイントを 0.8V ~ 60V の範囲に設定します。FB2 のレギュレーション電圧は 0.8V です。 |

| VOUT2           | 3  | I                  | チャネル 2 の出力電圧センスと電流センスアンプ入力。チャネル 2 の電流センス抵抗の出力側（またはインダクタ DCR 電流センシングが使用されている場合は関連するセンスコンデンサ端子）に VOUT2 を接続します。                                                                   |

| ISNS2+          | 4  | I                  | チャネル 2 電流センスアンプ入力。低電流ケルビン接続を使用して、外部電流センス抵抗のインダクタ側（またはインダクタ DCR 電流センシングが使用されている場合は関連するセンスコンデンサ端子）に ISNS2+ を接続します。                                                               |

| PG2             | 5  | O                  | VOUT2 が指定されたレギュレーションウインドウの範囲外である場合に Low になるオープンドレイン出力                                                                                                                          |

| EN2             | 6  | I                  | アクティブ High 入力 ( $V_{EN2} > 1V$ 標準値) により、チャネル 2 はイネーブルになります。 $V_{EN2} < 0.5V$ の場合、チャネル 2 はディスエーブルになり、PFC/SYNC に SYNC 信号が現れるまでシャットダウンモードで動作します。EN2 はオープン状態のままにしないでください。          |

| VIN             | 8  | P                  | VCC レギュレータの電源電圧入力ソース                                                                                                                                                           |

| HO2             | 9  | P                  | チャネル 2 ハイサイドゲートドライバの出力                                                                                                                                                         |

| SW2             | 10 | P                  | チャネル 2 降圧レギュレータのスイッチングノード。ブートストラップコンデンサ、ハイサイド MOSFET のソース端子、ローサイド MOSFET のドレイン端子に接続します。                                                                                        |

| CBOOT2          | 11 | P                  | ブートストラップゲート駆動用のチャネル 2 ハイサイドドライバ電源                                                                                                                                              |

| LO2             | 12 | P                  | チャネル 2 ローサイドゲートドライバの出力                                                                                                                                                         |

| PGND            | 13 | G                  | ローサイド MOSFET ゲートドライバの電源グランド接続ピン                                                                                                                                                |

| VCC             | 14 | P                  | VCC バイアス電源ピン。VCC と PGND の間にセラミックコンデンサを接続します。                                                                                                                                   |

| LO1             | 15 | P                  | チャネル 1 ローサイドゲートドライバの出力                                                                                                                                                         |

| CBOOT1          | 16 | P                  | ブートストラップゲート駆動用のチャネル 1 ハイサイドドライバ電源                                                                                                                                              |

| SW1             | 17 | P                  | チャネル 1 降圧レギュレータのスイッチングノード。ブートストラップコンデンサ、ハイサイド MOSFET のソース端子、ローサイド MOSFET のドレイン端子に接続します。                                                                                        |

| HO1             | 18 | P                  | チャネル 1 ハイサイドゲートドライバの出力                                                                                                                                                         |

| EN1             | 20 | I                  | アクティブ High 入力 ( $V_{EN1} > 1V$ 標準値) により、チャネル 1 はイネーブルになります。 $V_{EN1} < 0.5V$ の場合、チャネル 1 はディスエーブルになり、PFC/SYNC に SYNC 信号が現れるまでシャットダウンモードで動作します。EN1 はオープン状態のままにしないでください。          |

| PG1             | 21 | O                  | VOUT1 が指定されたレギュレーションウインドウの範囲外である場合に Low になるオープンコレクタ出力。                                                                                                                         |

| ISNS1+          | 22 | I                  | チャネル 1 電流センスアンプ入力。低電流ケルビン接続を使用して、外部電流センス抵抗のインダクタ側（またはインダクタ DCR 電流センシングが使用されている場合は関連するセンスコンデンサ端子）に ISNS1+ を接続します。                                                               |

| BIAS1/<br>VOUT1 | 23 | I                  | $V_{BIAS1} > 4.3V$ の場合、BIAS1 は内部 VCC レギュレータへの電源電圧になります。BIAS1 は、1 次側 VOUT1 センシングおよびチャネル 1 の電流センスアンプ入力としても機能します。BIAS/VOUT1 をチャネル 1 の電流センス抵抗の出力側に接続します。                           |

| CNFG            | 26 | I                  | CNFG と GND の間に抵抗を接続して出力構成を設定し、2 つの変調周波数のいずれかで DRSS を有効化（または無効化）します。表 7-1 も参照してください。                                                                                            |

| FB1             | 25 | I                  | 7.5kΩ、24.9kΩ、48.7kΩ のいずれかの抵抗を介して FB1 を VDDA に接続し、出力電圧をそれぞれ 3.3V、5V、12V に設定します。または、VOUT1 と FB1 の間に抵抗分圧器を使用して、チャネル 1 の出力電圧設定ポイントを 0.8V ~ 60V の範囲に設定します。FB1 のレギュレーション電圧は 0.8V です。 |

| COMP1           | 28 | O                  | チャネル 1 相互コンダクタンス エラー アンプの出力。COMP1 はインターリープモードまたは 2 次モードでハイインピーダンスです。インターリープモードで COMP1 が 100mV 未満にブレると、HO1 および LO1 ゲートドライバ出力は無効化されます。                                           |

| RSS             | 29 | I                  | RSS と GND の間に抵抗を接続して、ソフトスタート時間を 1.5ms ~ 20ms に設定します                                                                                                                            |

| RT              | 30 | O                  | 周波数プログラミングピン。RT と AGND の間に抵抗を配置することにより、発振器の周波数は 100kHz ~ 2.2MHz の範囲に設定されます。                                                                                                    |

| AGND            | 31 | G                  | アナロググランド接続。内部電圧リファレンスとアナログ回路のグランドの帰線。                                                                                                                                          |

**表 5-1. ピンの機能 (続き)**

| ピン       |                         | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                |

|----------|-------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号                      |                    |                                                                                                                                                                                                   |

| VDDA     | 32                      | P                  | 内部アナログバイアスレギュレータ出力。VDDA と AGND の間に $1\mu\text{F}$ のセラミックデカップリングコンデンサを接続します。                                                                                                                       |

| SYNCOUT  | 33                      | O                  | SYNCOUT は、HO1 に約 $90^\circ$ 遅延する (または HO2 に $90^\circ$ 先行する) 立ち上がりエッジを持つロジックレベル信号です。SYNCOUT を使用して 2 つ目の LM25137 コントローラを同期する場合、必要に応じて位相 $0^\circ$ 、 $90^\circ$ 、 $180^\circ$ 、 $270^\circ$ で動作します。 |

| PFM/SYNC | 34                      | I                  | LM25137 を PFM モードで動作させるには、PFM/SYNC を VDDA に接続します。PFM/SYNC を GND に接続すると、軽負荷時に連続導通して強制 PWM (FPWM) モードが有効になります。PFM/SYNC ピンを同期入力として使用して、内部発振器を外部クロックに同期します。                                           |

| COMP2    | 35                      | O                  | チャネル 2 相互コンダクタンス エラー アンプの出力。COMP2 は、单一出力インターリープモードではハイインピーダンスです。インターリープモードで COMP2 が $100\text{mV}$ 未満にプルされると、HO2 および LO2 ゲートドライバ出力は無効化されます。                                                       |

| GND      | 2、7、19、<br>24、27、<br>36 | G                  | 未使用ピン – PCB 上の露出したパッドに接続します。                                                                                                                                                                      |

(1) P = 電源、G = グランド、I = 入力、O = 出力

## 5.1 ウェッタブル フランク

高い信頼性と堅牢性の要件を満たすには、通常は組み立て後に 100% の自動外観検査 (AVI) を行う必要があります。標準的なクワッド フラットのリードなし (QFN) パッケージでは、はんだ付け可能な部分や露出したピンと端子は外側から容易に視認できません。そのため、パッケージとプリント回路基板 (PCB) が確実にはんだ付けされているかどうかを視覚的に確認することは困難です。ウェッタブル フランク プロセスは、鉛フリーなパッケージにおける片面ウェットの問題を解決するために開発されました。LM25137 は、ウェッタブルフランク付きの 36 ピン VQFN パッケージを使用して組み立てられており、はんだ付け可能かどうかを視覚的に示すことができます。これにより、検査時間と製造コストを削減することができます。

## 6 仕様

### 6.1 絶対最大定格

接合部の動作時推奨温度である -40°C ~ 150°Cにおいて (特に記述のない限り)。<sup>(1)</sup>

|                  |                                       | 最小値  | 最大値                  | 単位 |

|------------------|---------------------------------------|------|----------------------|----|

| 入力電圧             | VIN から PGND へ                         | -0.3 | 47                   | V  |

|                  | SW1、SW2 から PGND へ                     | -0.3 | 47                   | V  |

|                  | SW1、SW2 から PGND、過渡 < 20ns             | -5   |                      | V  |

|                  | BIAS1/VOUT1、VOUT2 ~ AGND              | -0.3 | 47                   | V  |

|                  | FB1、FB2 から AGND                       | -0.3 | 20                   | V  |

|                  | PFM/SYNC、RT、CNFG、RSS から AGND          | -0.3 | 6.5                  | V  |

|                  | CNFG から AGND                          | -0.3 | 5.5                  | V  |

|                  | AGND~PGND                             | -0.3 | 0.3                  | V  |

|                  | ISNS1+、ISNS2+ から AGND                 | -0.3 | 47                   | V  |

|                  | EN1、EN2 から PGND へ                     | -0.3 | $V_{IN} + 5$         | V  |

| 出力電圧             | PG1、PG2 から AGND                       | -0.3 | $V_{IN} + 5$         | V  |

|                  | CBOOT1 から SW1 へ、CBOOT2 から SW2 へ       | -0.3 | 6.5                  | V  |

|                  | CBOOT1 から SW1、CBOOT2 から SW2、過渡 < 20ns | -0.3 | 6.5                  | V  |

|                  | HO1 から SW1 へ、HO2 から SW2 へ             | -0.3 | $V_{CBOOT1/2} + 0.3$ | V  |

|                  | HO1 から SW1、HO2 から SW2、過渡 < 20ns       | -0.5 |                      | V  |

|                  | LO1、LO2 から PGND へ                     | -0.3 | $V_{VCC} + 0.3$      | V  |

|                  | LO1、LO2 から PGND、過渡 < 20ns             | -5   |                      | V  |

|                  | VCC、VDDA、SYNCOUT から AGND              | -0.3 | 6.5                  | V  |

| 動作時の接合部温度、 $T_J$ |                                       | -40  | 150                  | °C |

| 保管温度、 $T_{stg}$  |                                       | -55  | 150                  | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または「[推奨動作条件](#)」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「[推奨動作条件](#)」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|             |      |                                                                                                                  | 値             | 単位 |

|-------------|------|------------------------------------------------------------------------------------------------------------------|---------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup><br>デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±2000<br>±750 | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.3 推奨動作条件

接合部の動作時温度範囲  $-40^{\circ}\text{C} \sim 150^{\circ}\text{C}$  (特に記載がない場合)。<sup>(1)</sup>

|                      |                                         | 最小値  | 公称値 | 最大値                         | 単位                 |

|----------------------|-----------------------------------------|------|-----|-----------------------------|--------------------|

| $V_{\text{IN}}$      | 入力電源電圧範囲                                | 4    |     | 42                          | V                  |

| $V_{\text{OUT}}$     | 出力電圧範囲                                  | 0.8  |     | 36                          | V                  |

|                      | SW1、SW2 から PGND へ                       | -0.3 |     | 42                          | V                  |

|                      | HO1 から SW1 へ、HO2 から SW2 へ               | -0.3 |     | $V_{\text{CBOOT1/2}} + 0.3$ | V                  |

|                      | CBOOT1 から SW1 へ、CBOOT2 から SW2 へ         | -0.3 | 5   | 5.3                         | V                  |

|                      | FB1、FB2 から AGND                         | -0.3 |     | 15                          | V                  |

|                      | EN1、EN2、PG1、PG2 から AGND                 | -0.3 |     | $V_{\text{IN}}$             | V                  |

|                      | ISNS1+、ISNS2+、BIAS1/VOUT1、VOUT2 から AGND | -0.3 |     | 42                          | V                  |

|                      | VCC、VDDA、RSS から PGND                    | -0.3 | 5   | 5.3                         | V                  |

| $I_{\text{SYNCOUT}}$ | SYNCOUT 電流                              |      |     | 2                           | mA                 |

|                      | PGND から AGND へ                          | -0.3 |     | 0.3                         | V                  |

| $T_J$                | 動作時接合部温度                                | -40  |     | 150                         | $^{\circ}\text{C}$ |

(1) 推奨動作条件は、デバイスが機能すると想定されている条件です。仕様およびテスト条件については、「電気的特性」を参照してください。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                   | LM25137    | 単位                   |

|-----------------------------|-------------------|------------|----------------------|

|                             |                   | RHA (VQFN) |                      |

|                             |                   | 36 ピン      |                      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗      | 33.2       | $^{\circ}\text{C/W}$ |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 | 24.2       | $^{\circ}\text{C/W}$ |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗      | 14.1       | $^{\circ}\text{C/W}$ |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 0.4        | $^{\circ}\text{C/W}$ |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 14         | $^{\circ}\text{C/W}$ |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース(底面)への熱抵抗 | 3.6        | $^{\circ}\text{C/W}$ |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションノートを参照してください。

## 6.5 電気的特性

標準値は  $T_J = 25^{\circ}\text{C}$  における値です。最小値および最大値は  $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$  で適用されます。特に記載がない限り、 $V_{\text{IN}} = 12\text{V}$  です。

| パラメータ                                    | テスト条件                                                                                     | 最小値                                                                                                                                                                                     | 標準値 | 最大値 | 単位            |

|------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|

| <b>入力電源 (<math>V_{\text{IN}}</math>)</b> |                                                                                           |                                                                                                                                                                                         |     |     |               |

| $I_{\text{Q-SHDN}}$                      | $V_{\text{IN}}$ シャットダウン電流                                                                 | $V_{\text{EN1}} = V_{\text{EN2}} = 0\text{V}$                                                                                                                                           |     | 3.6 | $\mu\text{A}$ |

| $I_{\text{Q-STBY}}$                      | $V_{\text{IN}}$ スタンバイ電流                                                                   | $0.6\text{V} < V_{\text{EN1/2}} < 1\text{V}$                                                                                                                                            |     | 260 | $\mu\text{A}$ |

| $I_{\text{Q-SLEEP}}$                     | $V_{\text{IN}}$ スリープ電流、 $V_{\text{VOUT1}} = 5\text{V}$ 、 $V_{\text{VOUT2}} = 3.3\text{V}$ | $1.05\text{V} \leq V_{\text{EN1/2}} \leq V_{\text{IN}}$ 、 $V_{\text{VOUT1}} = 5\text{V}$ 、 $V_{\text{VOUT2}} = 3.3\text{V}$ 、レギュレーション中に負荷なし、スイッチングなし、 $V_{\text{PFM/SYNC}} = 5\text{V}$ |     | 1.5 | $\mu\text{A}$ |

| <b>内部 LDO (VCC)</b>                      |                                                                                           |                                                                                                                                                                                         |     |     |               |

| $V_{\text{VCC-REG}}$                     | VCC のレギュレーション電圧                                                                           | $I_{\text{VCC}} = 0\text{mA}$                                                                                                                                                           | 4.8 | 5.0 | 5.2           |

| $V_{\text{VCC-UVLO}}$                    | VCC UVLO 立ち上がりスレッショルド                                                                     |                                                                                                                                                                                         | 3.7 | 3.8 | 3.9           |

| $V_{\text{VCC-UVLO-HYST}}$               | VCC UVLO ヒステリシス                                                                           |                                                                                                                                                                                         |     | 300 | $\text{mV}$   |

| $I_{\text{VCC-REG}}$                     | VCC 短絡電流制限                                                                                |                                                                                                                                                                                         | 175 | 300 | $\text{mA}$   |

| <b>内部 LDO (VDDA)</b>                     |                                                                                           |                                                                                                                                                                                         |     |     |               |

| $V_{\text{VDDA-REG}}$                    | VDDA のレギュレーション電圧                                                                          |                                                                                                                                                                                         |     | 5   | V             |

| $R_{\text{VDDA}}$                        | VCC に対する VDDA 抵抗                                                                          |                                                                                                                                                                                         |     | 12  | $\Omega$      |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  における値です。最小値および最大値は  $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  で適用されます。特に記載がない限り、 $V_{IN} = 12\text{V}$  です。

| パラメータ                           | テスト条件                                  | 最小値                                                                                         | 標準値   | 最大値  | 単位    |                         |               |

|---------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------|-------|------|-------|-------------------------|---------------|

| <b>外部バイアス (BIAS1)</b>           |                                        |                                                                                             |       |      |       |                         |               |

| $V_{BIAS-ON}$                   | $V_{BIAS1}/V_{OUT1}$ 立ち上がり             | 4.1                                                                                         | 4.3   | 4.5  | V     |                         |               |

| $V_{BIAS-HYST}$                 | バイアスヒステリシス電圧                           |                                                                                             | 130   |      | mV    |                         |               |

| <b>リファレンス電圧 (FB1、FB2)</b>       |                                        |                                                                                             |       |      |       |                         |               |

| $V_{REF1}$                      | レギュレーション済み FB 電圧                       | 792                                                                                         | 800   | 808  | mV    |                         |               |

| <b>高精度イネーブル (EN1、EN2)</b>       |                                        |                                                                                             |       |      |       |                         |               |

| $V_{SDN1/2}$                    | シャットダウンからスタンバイへのスレッショルド                | $V_{EN1/2}$ 立ち上がり                                                                           | 0.6   |      | V     |                         |               |

| $V_{EN1/2-HIGH}$                | イネーブル電圧立ち上がりリセット                       | $V_{EN1/2}$ 立ち上がり、スイッチングが有効                                                                 | 0.95  | 1.0  | 1.05  | V                       |               |

| $V_{EN1/2-HYS}$                 | イネーブルヒステリシス電圧                          |                                                                                             | 50    |      | mV    |                         |               |

| $I_{EN1/2-HYS}$                 | ヒステリシス電流を有効にする                         | $V_{EN1/2} = 1.1\text{V}$                                                                   | -12   | -10  | -8    | $\mu\text{A}$           |               |

| <b>出力電圧 (VOUT1/BIAS1、VOUT2)</b> |                                        |                                                                                             |       |      |       |                         |               |

| $V_{OUT1/2-3.3V}$               | 3.3V 固定出力設定ポイント                        | $R_{FB1/2} = 7.5\text{k}\Omega$ , $4\text{V} \leq V_{VIN} \leq 42\text{V}$                  | 3.267 | 3.3  | 3.33  | V                       |               |

| $V_{OUT1/2-5V}$                 | 5V 固定出力設定ポイント                          | $R_{FB1/2} = 24.9\text{k}\Omega$                                                            | 4.95  | 5    | 5.05  | V                       |               |

| $V_{OUT1/2-12V}$                | 12V 固定出力設定ポイント                         | $R_{FB1/2} = 48.7\text{k}\Omega$ , $13\text{V} \leq V_{VIN} \leq 42\text{V}$                | 11.82 | 12   | 12.18 | V                       |               |

| <b>エラー アンプ (COMP1、COMP2)</b>    |                                        |                                                                                             |       |      |       |                         |               |

| $g_{m1/2}$                      | EA 相互コンダクタンス                           | $\Delta V_{FB1/2} \pm 50\text{mV}$                                                          | 400   | 600  |       | $\mu\text{s}$           |               |

| $V_{COMP1/2-CLAMP}$             | COMP クランプ電圧                            | $V_{FB1/2} = 0\text{V}$                                                                     |       | 1.75 |       | V                       |               |

| $I_{COMP1/2-SRC}$               | EA ソース電流                               | $V_{COMP1/2} = 1\text{V}$ , $V_{FB1/2} = 0.6\text{V}$                                       |       | 120  |       | $\mu\text{A}$           |               |

| $I_{COMP1/2-SINK}$              | EA シンク電流                               | $V_{COMP1/2} = 1\text{V}$ , $V_{FB1/2} = 1\text{V}$                                         |       | 120  |       | $\mu\text{A}$           |               |

| $V_{DRIVER1/2-DISABLE}$         | それを下回るとドライバが無効化される COMP スレッショルド電圧      |                                                                                             |       | 100  |       | mV                      |               |

| <b>パワーグッド (PG1、PG2)</b>         |                                        |                                                                                             |       |      |       |                         |               |

| $V_{PG1/2-OV}$                  | PG1/2 過電圧                              | 立ち上がりスレッショルド                                                                                | 103   | 105  | 107   | %                       |               |

| $V_{PG1/2-OV-HYST}$             | PG1/2 OV ヒステリシス                        |                                                                                             |       | 1    |       | %                       |               |

| $V_{PG1/2-UV}$                  | PG1/2 低電圧                              | 立ち下がりスレッショルド                                                                                | 93    | 95   | 97    | %                       |               |

| $V_{PG1-UV-HYST}$               | PG1/2 UV ヒステリシス                        |                                                                                             |       | 1    |       | %                       |               |

| $t_{PG1/2-DEGLITCH(R)}$         | PG1/2 グリッチ除去立ち上がり                      |                                                                                             |       | 1.4  | 2     | 2.6                     | ms            |

| $t_{PG1/2-DEGLITCH(F)}$         | PG1/2 グリッチ除去立ち下がり                      |                                                                                             |       | 60   | 90    | 120                     | $\mu\text{s}$ |

| $R_{PG1/2(on)}$                 | PG1/2 オン抵抗                             | オープンドレイン、 $I_{PG1/2} = 250\mu\text{A}$                                                      |       | 100  | 250   | $\Omega$                |               |

| <b>スイッチング周波数 (RT)</b>           |                                        |                                                                                             |       |      |       |                         |               |

| $F_{SW1}$                       | スイッチング周波数 1                            | $R_{RT} = 100\text{k}\Omega$ から AGND                                                        |       | 230  |       | kHz                     |               |

| $F_{SW2}$                       | スイッチング周波数 2                            | $R_{RT} = 10\text{k}\Omega$ から AGND                                                         |       | 1.98 | 2.2   | 2.42                    | MHz           |

| $F_{SW3}$                       | スイッチング周波数 3                            | $R_{RT} = 230\text{k}\Omega$ から AGND                                                        |       | 100  |       | kHz                     |               |

| $SLOPE_1$                       | 内部スロープ補償 1                             | $R_{RT} = 10\text{k}\Omega$ から AGND                                                         |       | 500  |       | $\text{mV}/\mu\text{s}$ |               |

| $SLOPE_2$                       | 内部スロープ補償 2                             | $R_{RT} = 100\text{k}\Omega$ から AGND                                                        |       | 42   |       | $\text{mV}/\mu\text{s}$ |               |

| $t_{ON(min)}$                   | PWM 最小オン時間                             |                                                                                             |       | 22   | 35    | ns                      |               |

| $t_{OFF(min)}$                  | PWM 最小オフ時間                             | 100% のデューティサイクルを達成するため、周波数がフォールドバックする前に、公称周波数で測定                                            |       | 45   |       | ns                      |               |

| $D_{MAX}$                       | 最大デューティサイクル                            |                                                                                             |       | 100  |       | %                       |               |

| <b>同期出力 (SYNCOUT)</b>           |                                        |                                                                                             |       |      |       |                         |               |

| $V_{SYNCOUT-HO}$                | SYNCOUT の High 状態電圧                    | $I_{SYNCOUT} = -4\text{mA}$                                                                 | 2     |      | V     |                         |               |

| $V_{SYNCOUT-LO}$                | SYNCOUT の Low 状態電圧                     | $I_{SYNCOUT} = 4\text{mA}$                                                                  |       | 0.8  | V     |                         |               |

| $t_{SYNCOUT1}$                  | HO1 の立ち上がりエッジから SYNCOUT の立ち上がりエッジまでの遅延 | $V_{PFM/SYNC} = 0\text{V}$ , $T_s = 1/F_{SW}$ , $F_{SW}$ は $R_{RT} = 230\text{k}\Omega$ で設定 |       | 2.5  |       | $\mu\text{s}$           |               |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  における値です。最小値および最大値は  $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  で適用されます。特に記載がない限り、 $V_{IN} = 12\text{V}$  です。

| パラメータ                             |                                         | テスト条件                                                                                       | 最小値  | 標準値  | 最大値           | 単位           |

|-----------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------|------|------|---------------|--------------|

| $t_{SYNCOUT2}$                    | HO1 の立ち上がりエッジから SYNCOUT の立ち下がりエッジまでの遅延  | $V_{PFM/SYNC} = 0\text{V}$ , $T_S = 1/F_{SW}$ , $F_{SW}$ は $R_{RT} = 230\text{k}\Omega$ で設定 | 7.5  |      | $\mu\text{s}$ |              |

| <b>パルス周波数変調および同期入力 (PFM/SYNC)</b> |                                         |                                                                                             |      |      |               |              |

| $V_{PFM-LO}$                      | PFM 検出スレッショルド Low                       |                                                                                             | 0.8  |      | $\text{V}$    |              |

| $V_{PFM-HI}$                      | PFM 検出スレッショルド High                      |                                                                                             | 1.2  |      | $\text{V}$    |              |

| $V_{ZC-SW}$                       | ゼロクロス検出スレッショルド                          |                                                                                             | -5.5 |      | $\text{mV}$   |              |

| $F_{SYNCIN}$                      | 周波数同期範囲                                 | $R_{RT} = 10\text{k}\Omega$ 、公称発信器周波数の $\pm 20\%$                                           | 1760 | 2640 | $\text{kHz}$  |              |

| $t_{SYNC-MIN}$                    | 外部同期の最小パルス幅                             |                                                                                             | 20   |      | $\text{ns}$   |              |

| $t_{SYNCIN-HO}$                   | PFM/SYNC の立ち上がりエッジから HO1 の立ち上がりエッジまでの遅延 |                                                                                             | 90   |      | $\text{ns}$   |              |

| $t_{PFM-FILTER}$                  | SYNCIN から PFM モード                       |                                                                                             | 14   | 70   | $\mu\text{s}$ |              |

| <b>ブートストラップ回路 (CBOOT1、CBOOT2)</b> |                                         |                                                                                             |      |      |               |              |

| $V_{BOOT1/2-DROP}$                | 内部ダイオードの順方向電圧降下                         | $I_{CBOOT1/2} = 20\text{mA}$ 、VCC から CBOOT1/2                                               | 0.8  |      | $\text{V}$    |              |

| $I_{BOOT1/2}$                     | CBOOT から SW への静止電流、スイッチングなし             | $V_{EN1/2} = 5\text{V}$ , $V_{CBOOT1/2} - V_{SW1/2} = 5\text{V}$                            | 2    |      | $\mu\text{A}$ |              |

| $V_{BOOT1/2-SW-UV-R}$             | CBOOT から SW UVLO 立ち上がりスレッショルド           | $V_{CBOOT1/2} - V_{SW1/2}$ 立ち上がり                                                            | 2.7  |      | $\text{V}$    |              |

| $V_{BOOT1/2-SW-UV-F}$             | CBOOT から SW UVLO 立ち下がりスレッショルド           | $V_{CBOOT1/2} - V_{SW1/2}$ 立ち下がり                                                            | 2.47 |      | $\text{V}$    |              |

| $V_{CHARGE-PUMP1/2-UNLOADED}$     | チャージポンプ出力電圧                             | $I_{CBOOT1/2} = 0\mu\text{A}$                                                               | 4.8  |      | $\text{V}$    |              |

| $I_{CHARGE-PUMP1/2}$              | チャージポンプ出力電流                             | $V_{CBOOT1/2} = 3.5\text{V}$                                                                | 20   |      | $\mu\text{A}$ |              |

| <b>ハイサイドゲートドライバ (HO1、HO2)</b>     |                                         |                                                                                             |      |      |               |              |

| $V_{HO1/2-HIGH}$                  | HO1/2 High 状態出力電圧                       | $I_{HO1/2} = -100\text{mA}$                                                                 | 95   |      | $\text{mV}$   |              |

| $V_{HO1/2-LOW}$                   | HO1/2 Low 状態出力電圧                        | $I_{HO1/2} = 100\text{mA}$                                                                  | 43   |      | $\text{mV}$   |              |

| $I_{HO1/2-SRC}$                   | HO1/2 ピークソース電流                          | $V_{HO1/2} = V_{SW1/2} = 0\text{V}$                                                         | 2    |      | $\text{A}$    |              |

| $I_{HO1/2-SINK}$                  | HO1/2 ピークシンク電流                          | $V_{CBOOT1/2} - V_{SW1/2} = 5\text{V}$                                                      | 3    |      | $\text{A}$    |              |

| <b>ローサイドゲートドライバ (LO1、LO2)</b>     |                                         |                                                                                             |      |      |               |              |

| $V_{LO1/2-HIGH}$                  | LO1/2 High 状態出力電圧                       | $I_{LO1/2} = -100\text{mA}$                                                                 | 100  |      | $\text{mV}$   |              |

| $V_{LO1/2-LOW}$                   | LO1/2 Low 状態出力電圧                        | $I_{LO1/2} = 100\text{mA}$                                                                  | 58   |      | $\text{mV}$   |              |

| $I_{LO1/2-SRC}$                   | LO1/2 ピークソース電流                          | $V_{LO1/2} = 0\text{V}$                                                                     | 2    |      | $\text{A}$    |              |

| $I_{LO1/2-SINK}$                  | LO1/2 ピークシンク電流                          | $V_{VCC} = 5\text{V}$                                                                       | 3    |      | $\text{A}$    |              |

| <b>アダプティブ デッドタイム制御</b>            |                                         |                                                                                             |      |      |               |              |

| $t_{DEAD1}$                       | HO1/2 オフから LO1/2 のデッドタイム                |                                                                                             | 20   |      | $\text{ns}$   |              |

| $t_{DEAD2}$                       | LO1/2 オフから HO1/2 オンまでのデッドタイム            |                                                                                             | 20   |      | $\text{ns}$   |              |

| <b>スタートアップ (RSS)</b>              |                                         |                                                                                             |      |      |               |              |

| $R_{SS1}$                         | 1.5ms ソフトスタート時間                         | $R_{SS1} = 0\Omega$                                                                         | 1.5  |      | $\text{ms}$   |              |

| $R_{SS2}$                         | 2ms ソフトスタート時間                           | $R_{SS2} = 8.06\text{k}\Omega$                                                              | 2    |      | $\text{ms}$   |              |

| $R_{SS3}$                         | 20ms ソフトスタート時間                          | $R_{SS3} = 95.3\text{k}\Omega$                                                              | 20   |      | $\text{ms}$   |              |

| <b>デュアルランダム拡散スペクトラム (DRSS)</b>    |                                         |                                                                                             |      |      |               |              |

| $f_m$                             | 変調周波数                                   |                                                                                             | 7.2  | 12   | 16.8          | $\text{kHz}$ |

| $\Delta f_{SS1/2-LF}$             | 低周波数の三角波スペクトラム拡散変調範囲 1 最大               | $R_{CNFG} = 19.1\text{k}\Omega$ または $54.9\text{k}\Omega$                                    | -5   | 5    | $\%$          |              |

| $\Delta f_{SS2-LF}$               | 低周波数の三角波スペクトラム拡散変調範囲 2 最大               | $R_{CNFG} = 29.4\text{k}\Omega$ または $71.5\text{k}\Omega$                                    | -10  | 10   | $\%$          |              |

| <b>過電流保護 (ISNS1+、ISNS2+)</b>      |                                         |                                                                                             |      |      |               |              |

| $V_{CS1/2-TH}$                    | Current limit threshold                 | ISNS1/2+ から VOUT1/2 まで測定                                                                    | 54   | 60   | 66            | $\text{mV}$  |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  における値です。最小値および最大値は  $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  で適用されます。特に記載がない限り、 $V_{IN} = 12\text{V}$  です。

| パラメータ                |                      | テスト条件                                      | 最小値                         | 標準値 | 最大値  | 単位   |

|----------------------|----------------------|--------------------------------------------|-----------------------------|-----|------|------|

| $t_{DELAY1/2-ISNS+}$ |                      | $V_{CS\_TH}$ から HO オフまでの ISNS+ 遅延          | 48                          |     | ns   |      |

| $G_{CS1/2}$          |                      | CS アンプゲイン                                  | 9.5                         |     | 10   | 10.5 |

| $V_{CS-SHARE}$       |                      | COMP から電流の精度                               | $V_{COMP1/2} = 1.2\text{V}$ | 54  | 60   | 66   |

| 内部ヒップモード             |                      |                                            |                             |     |      |      |

| $HIC_{DLY}$          | ヒップモードの起動遅延          | $V_{ISNS1/2+} - V_{VOUT1/2} > 60\text{mV}$ | 512                         |     | サイクル |      |

| $HIC_{TIME}$         | ヒップモードの持続時間          | $V_{ISNS1/2+} - V_{VOUT1/2} > 60\text{mV}$ | 16384                       |     | サイクル |      |

| サーマル シャットダウン         |                      |                                            |                             |     |      |      |

| $T_{SHD}$            | サーマル シャットダウンのスレッショルド | 温度上昇                                       | 175                         |     | °C   |      |

| $T_{SHD-HYS}$        | サーマル シャットダウン ヒステリシス  |                                            | 15                          |     | °C   |      |

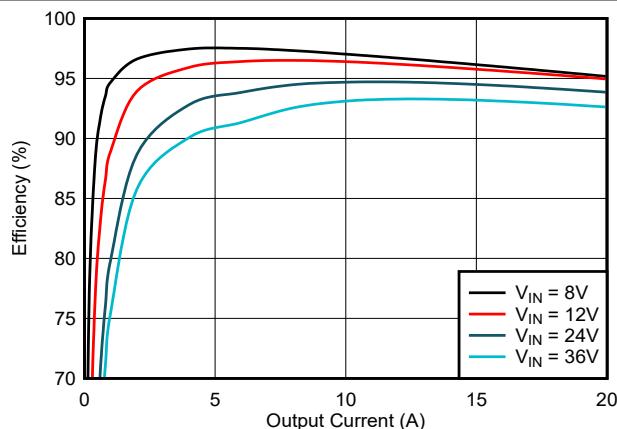

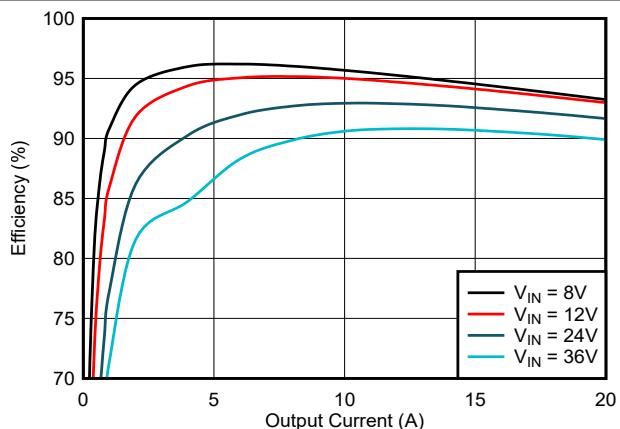

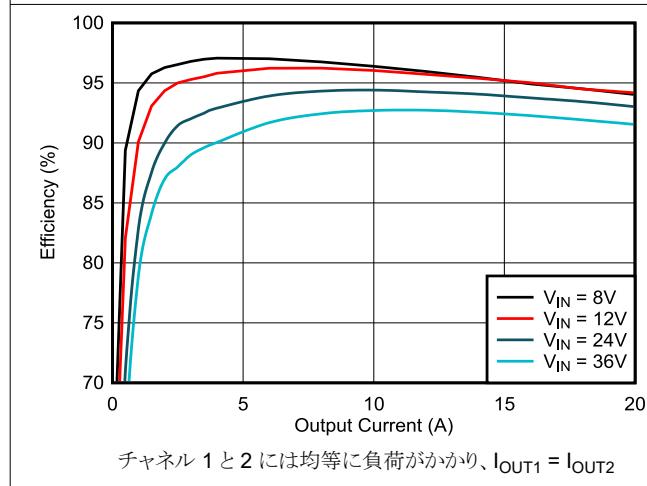

## 6.6 代表的特性

$V_{IN} = 12V$ ,  $T_J = 25^{\circ}C$ 、特に記述のない限り。

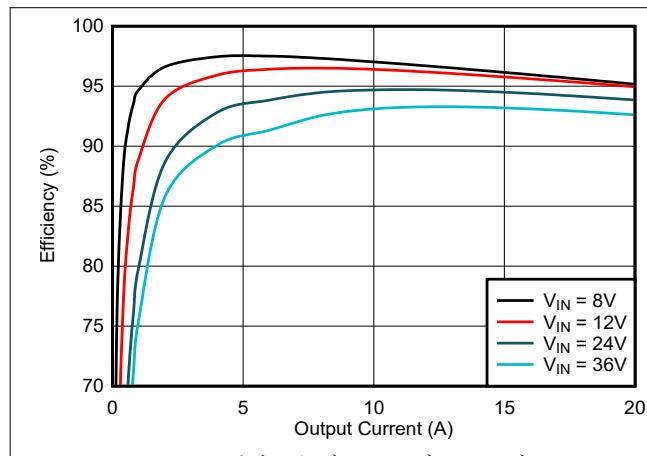

図 8-4 を参照

$V_{EN2} = 0V$        $F_{SW} = 440kHz$

図 6-1. 効率と負荷との関係、5V 出力

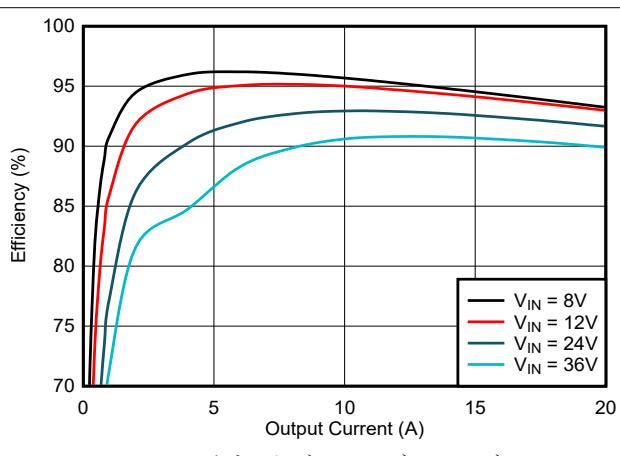

図 8-4 を参照

$V_{EN1} = 0V$        $F_{SW} = 440kHz$

図 6-2. 効率と負荷との関係、3.3V 出力

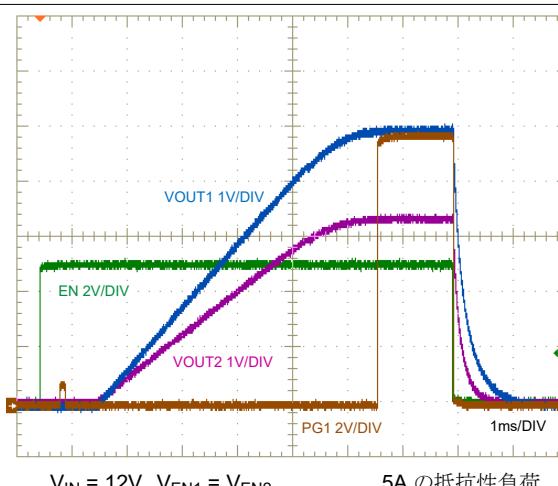

図 8-4 を参照

5A の抵抗性負荷

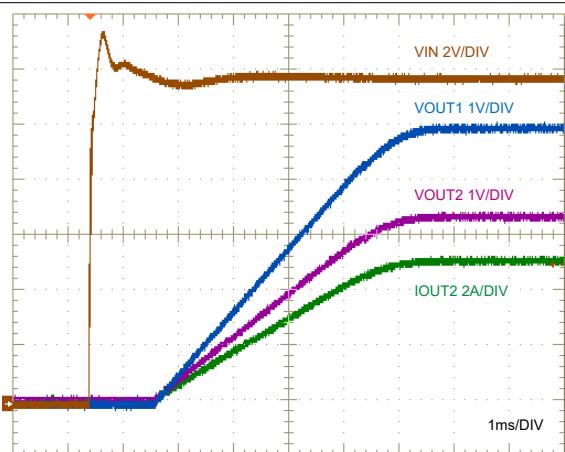

図 6-3. スタートアップ特性

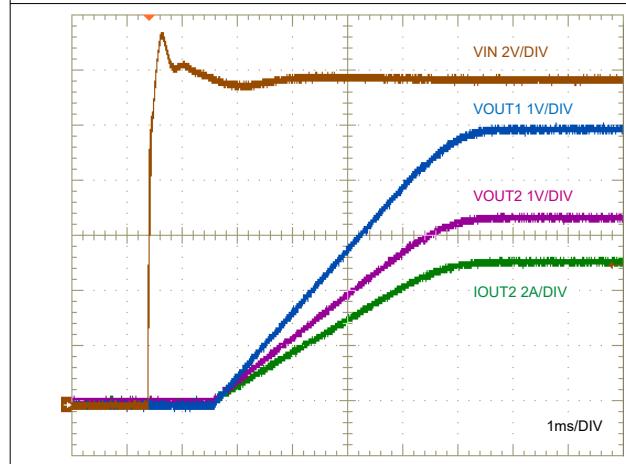

図 8-4 を参照

5A の抵抗性負荷

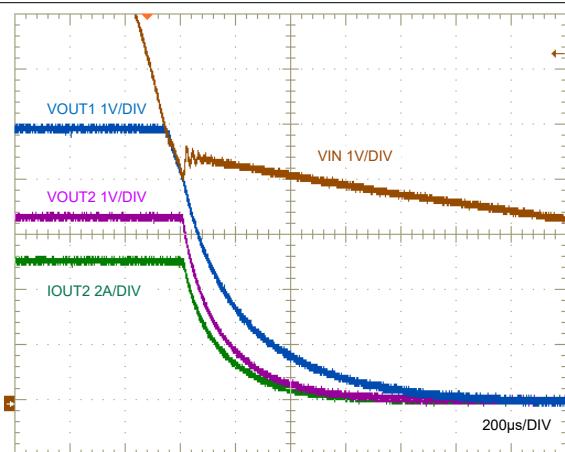

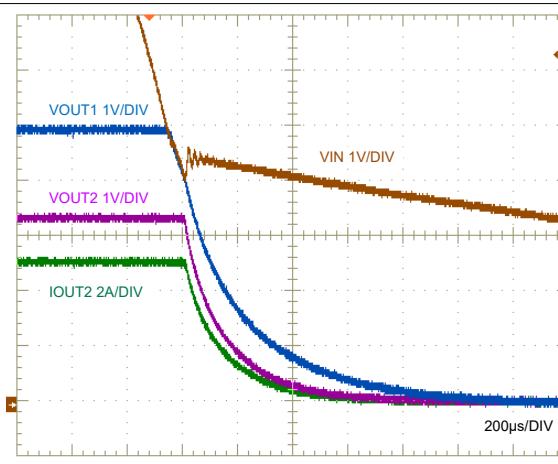

図 6-4. シャットダウン特性

## 6.6 代表的特性 (続き)

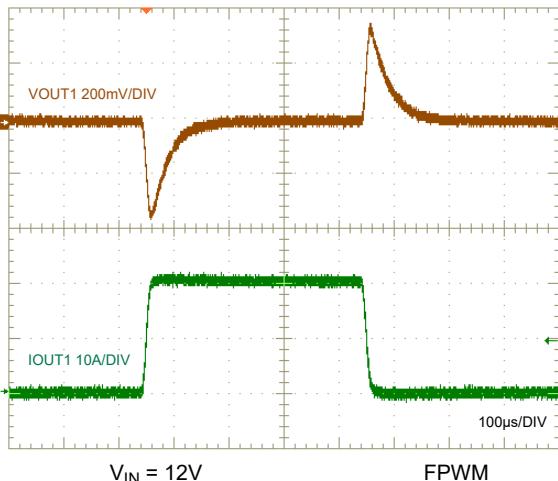

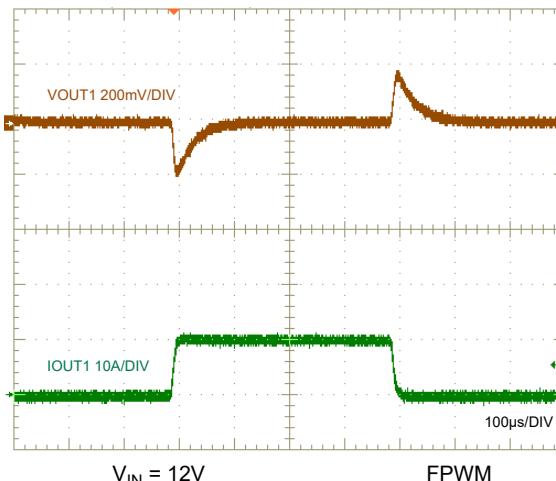

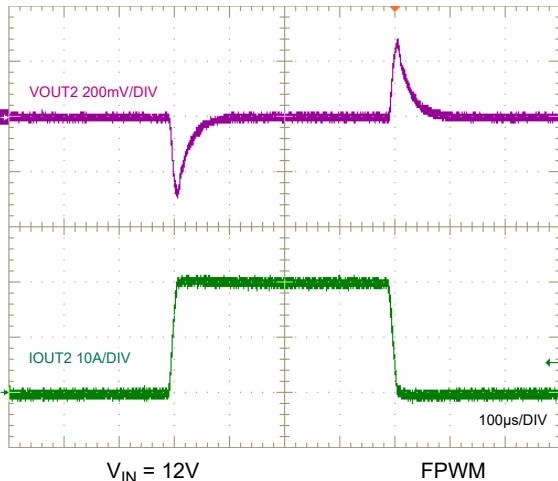

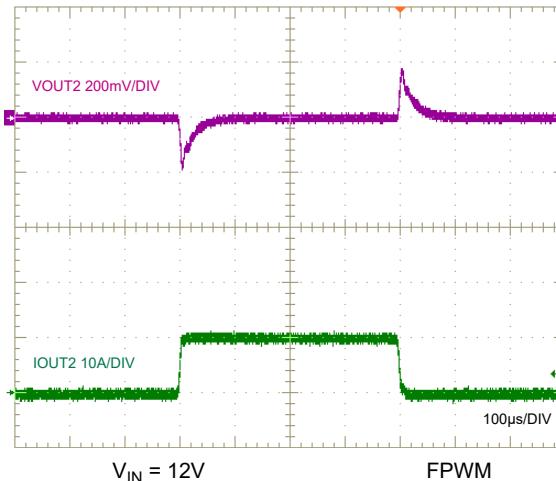

$V_{IN} = 12V$ 、 $T_J = 25^{\circ}\text{C}$ 、特に記述のない限り。

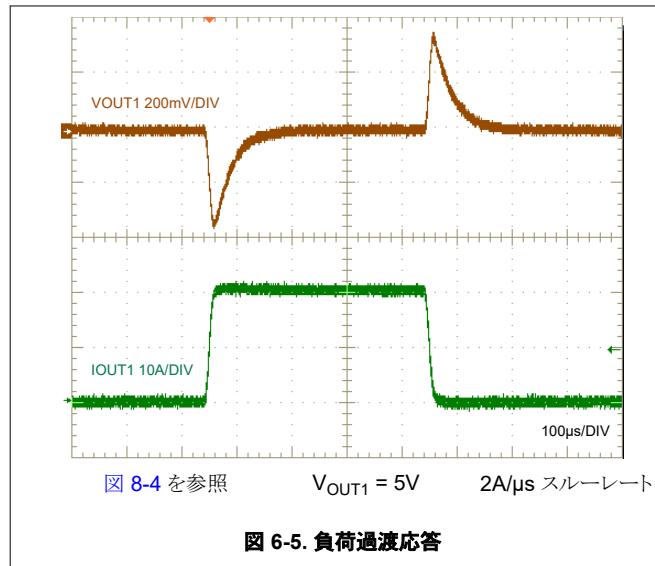

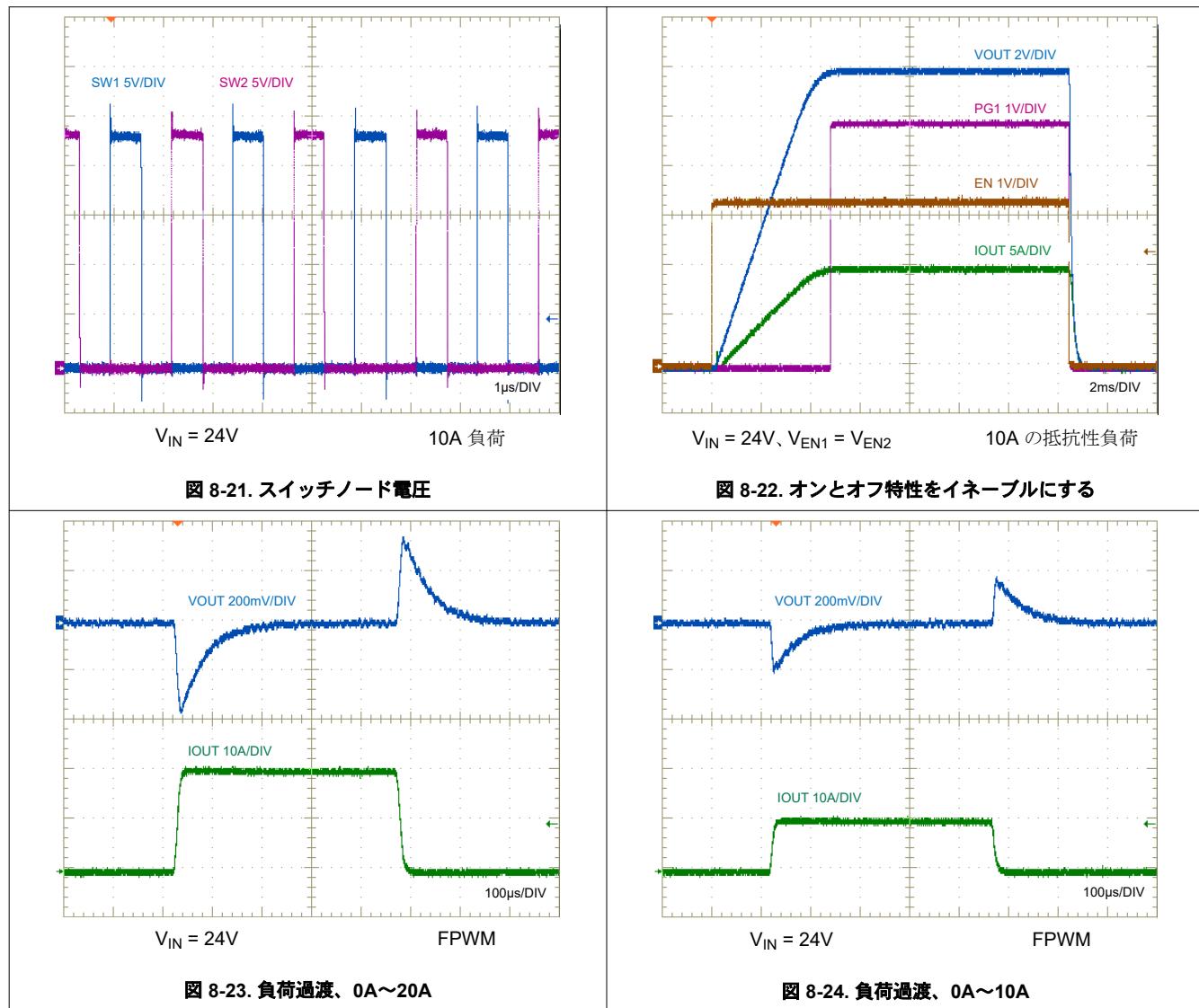

図 6-5. 負荷過渡応答

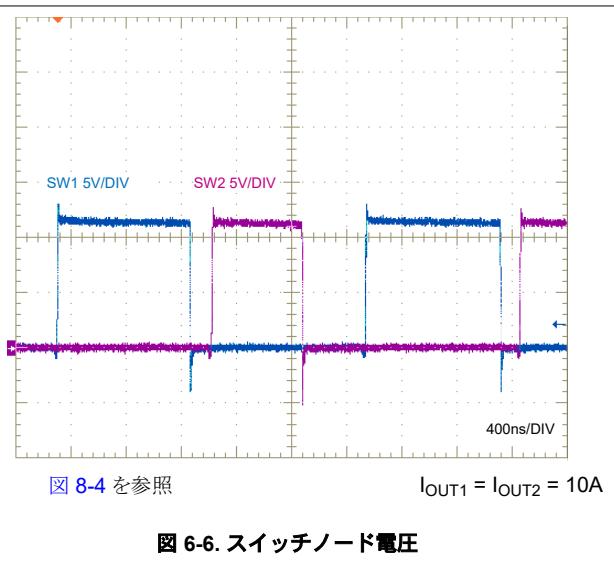

図 6-6. スイッチノード電圧

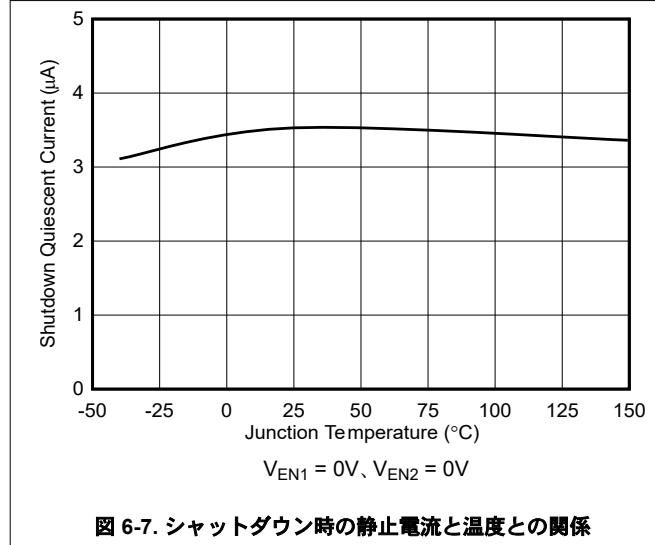

図 6-7. シャットダウン時の静止電流と温度との関係

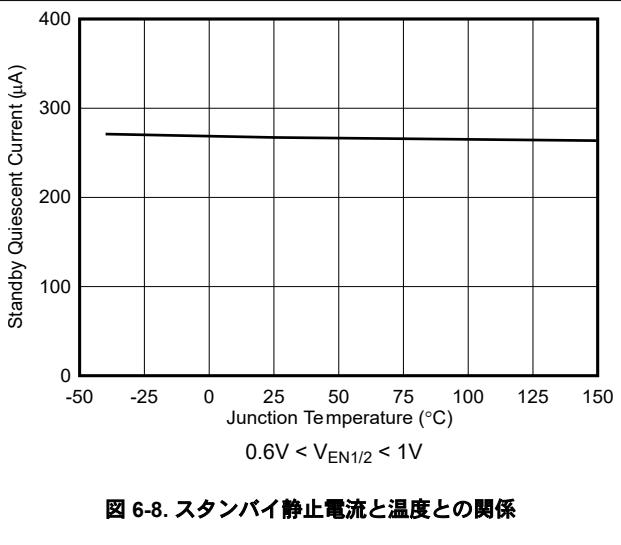

図 6-8. スタンバイ静止電流と温度との関係

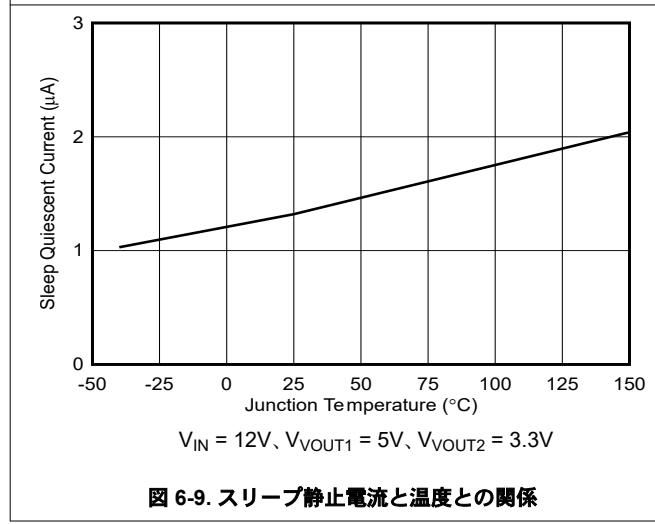

図 6-9. スリープ静止電流と温度との関係

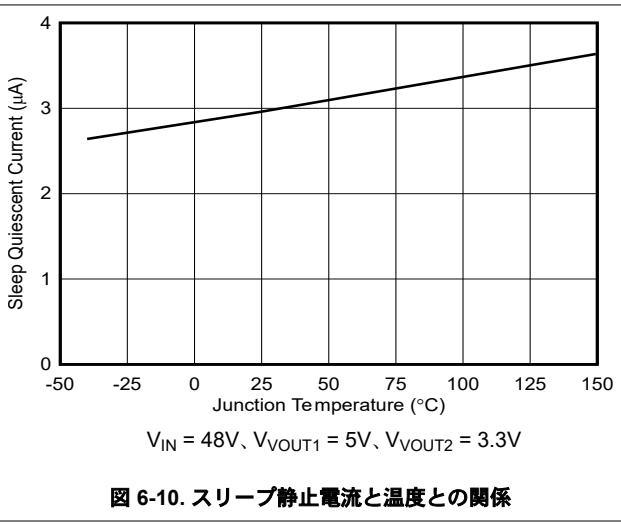

図 6-10. スリープ静止電流と温度との関係

## 6.6 代表的特性 (続き)

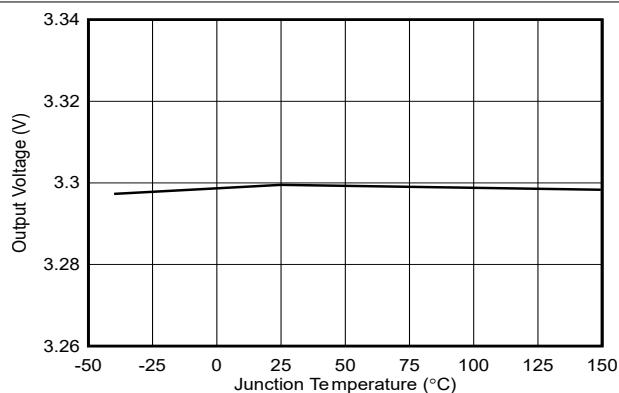

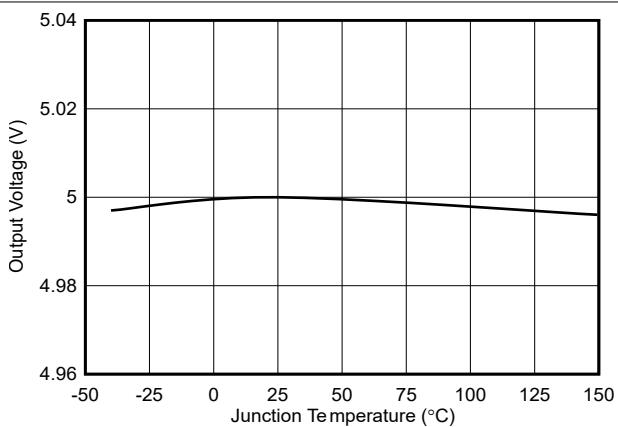

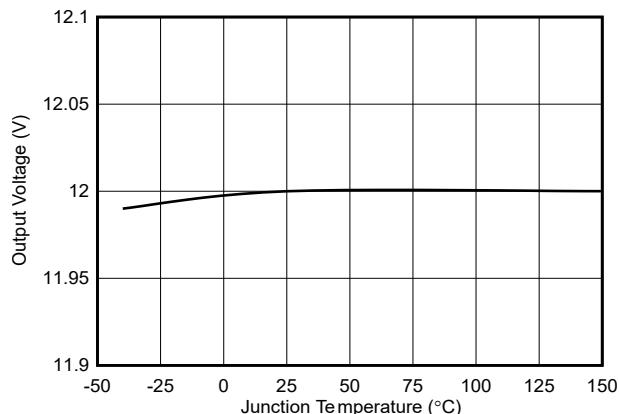

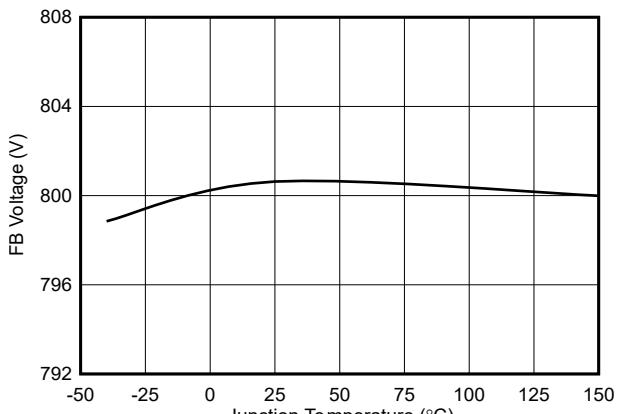

$V_{IN} = 12V$ 、 $T_J = 25^\circ C$ 、特に記述のない限り。

図 6-11. 固定 3.3V 出力電圧と温度との関係

図 6-12. 固定 5V 出力電圧と温度との関係

図 6-13. 固定 12V 出力電圧と温度との関係

図 6-14. 帰還電圧と温度との関係

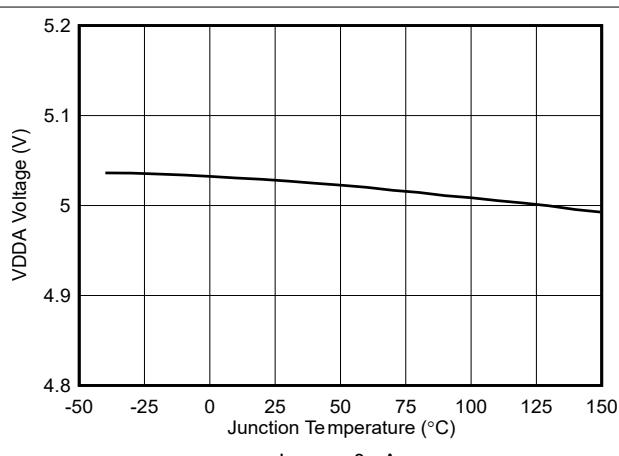

$I_{VDDA} = 0mA$

図 6-15. VDDA レギュレーション電圧と温度との関係

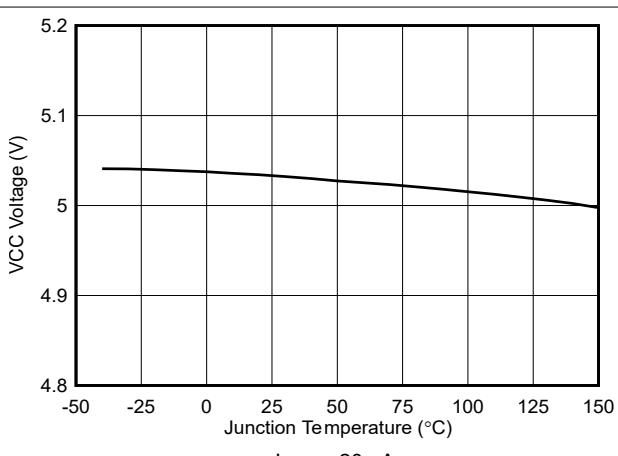

$I_{VCC} = 20mA$

図 6-16. VCC レギュレーション電圧と温度との関係

## 6.6 代表的特性 (続き)

$V_{IN} = 12V$ ,  $T_J = 25^\circ C$ 、特に記述のない限り。

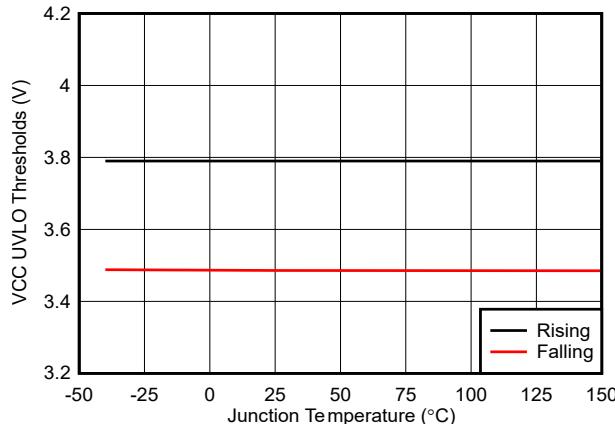

図 6-17. VCC UVLO スレッショルドと温度との関係

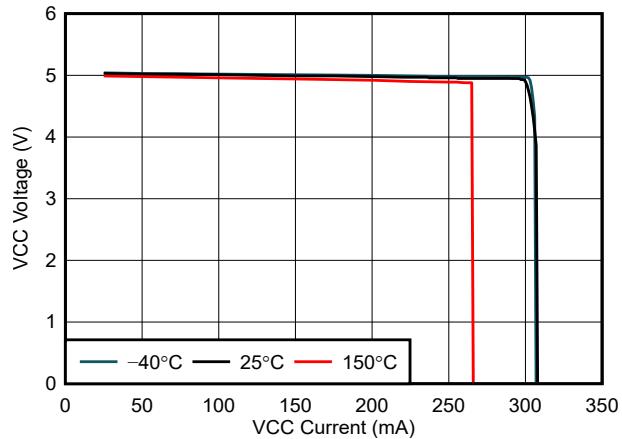

図 6-18. VCC 電流制限と温度との関係

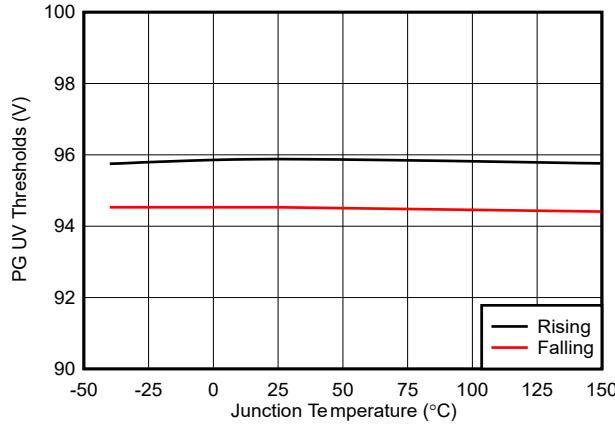

図 6-19. PG UV スレッショルドと温度との関係

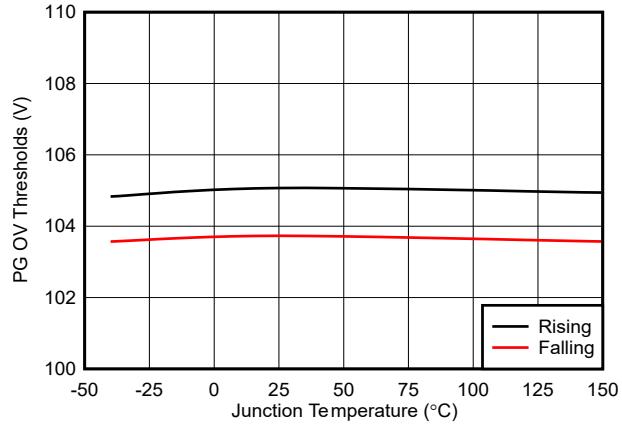

図 6-20. PG OV スレッショルドと温度との関係

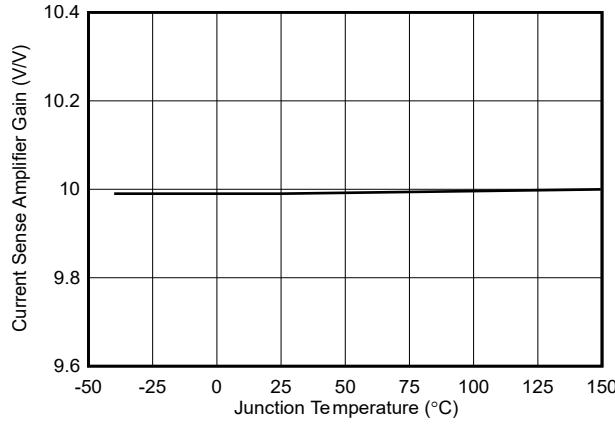

図 6-21. 電流センスアンプゲインと温度との関係

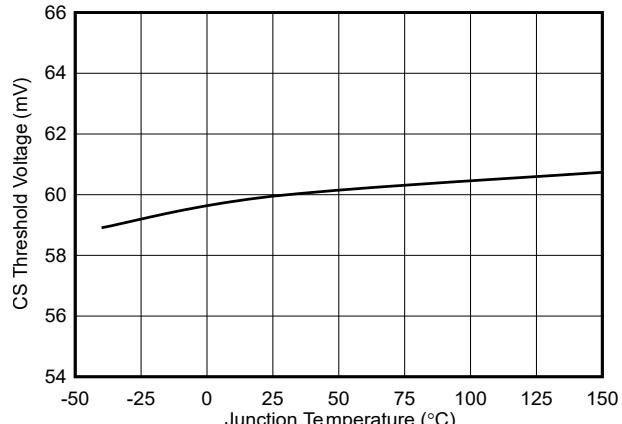

図 6-22. 電流センススレッショルドと温度との関係

## 6.6 代表的特性 (続き)

$V_{IN} = 12V$ 、 $T_J = 25^\circ C$ 、特に記述のない限り。

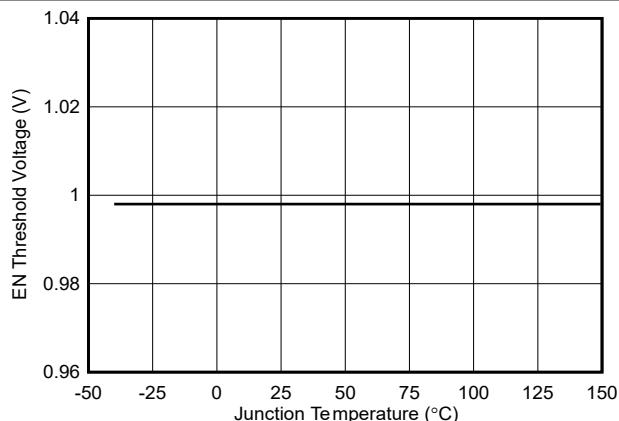

図 6-23. EN 立ち上がりリセット電圧と温度との関係

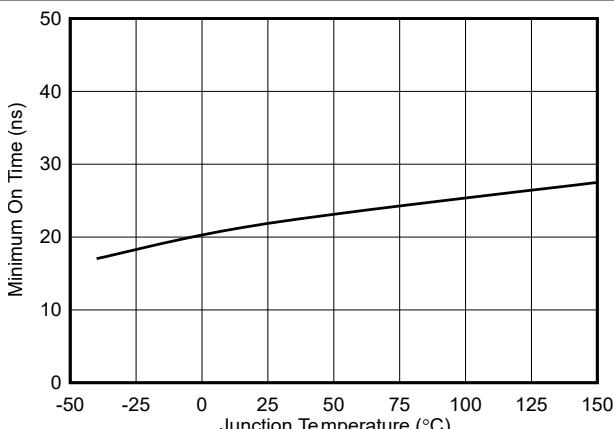

図 6-24. 最小オン時間と温度との関係

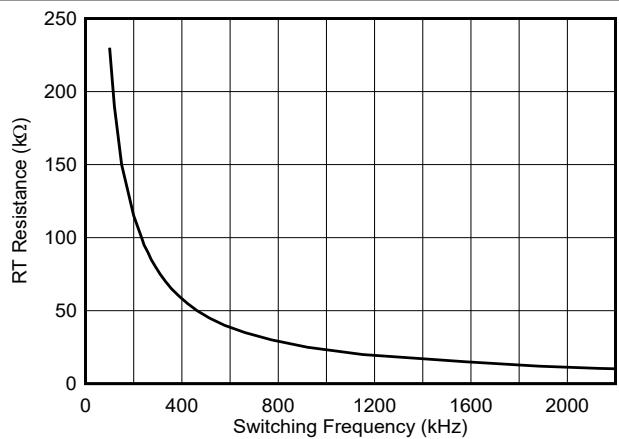

図 6-25. RT 抵抗とスイッチング周波数との関係

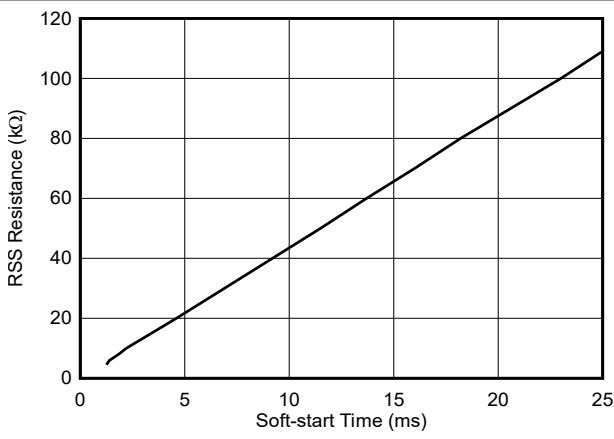

図 6-26. RSS 抵抗とソフトスタート時間との関係

## 7 詳細説明

### 7.1 概要

LM25137 は、高効率の同期整流降圧レギュレータを実装するために必要なすべての機能を備えた、デュアルチャネルスイッチング DC/DC コントローラです。このデバイスはコントローラファミリとして供給され、3 つの機能安全アプリケーションのオプションがあります：SIL 2 または SIL 3 対応。後者の 2 つのオプションには部品番号の接尾辞「F」が付いています。

LM25137 は 4V ~ 42V の広い入力電圧範囲で動作し、3.3V、5V、または 12V の固定出力または 0.8V ~ 36V の可変出力を供給するよう構成されています。この使いやすいコントローラはハイサイドとローサイドの MOSFET ゲートドライバを内蔵しており、それぞれが 2A を供給し、3A のピーク電流をシンクできます。アダプティブ デッドタイム制御は、スイッチング遷移中のボディダイオードの導通を最小限に抑えるように設計されています。

シャント抵抗またはインダクタ DCR 電流センシングを使用するピーク電流モード制御により、固有ラインのフィードフォワード、サイクル単位のピーク電流制限、簡単なループ補償を実現します。また、電流モード制御は、高入力電圧と低ドロップアウトアプリケーションの場合だけでなく、高電圧変換比（たとえば、10 対 1）が必要な場合に、幅広いデューティサイクル範囲をサポートします。発振器の周波数は 100kHz ~ 2.2MHz の間でユーザーがプログラム可能であり、外部クロックを PFM/SYNC に適用することにより、最大 2.5MHz の周波数を同期することができます。ユーザーが選択可能な PFM モード機能により、不連続導通モード (DCM) 動作をイネーブルにして、軽負荷条件時の効率をさらに向上させ、消費電力を低減することができます。

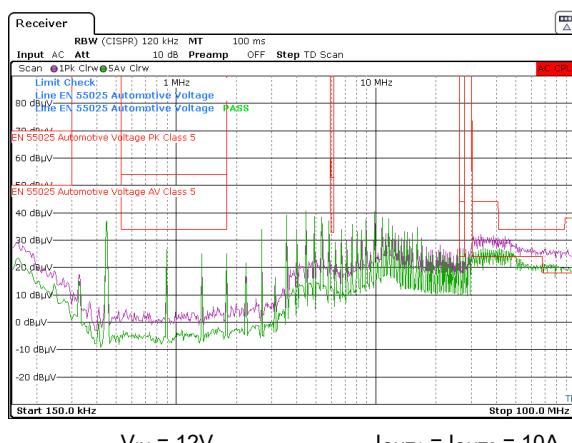

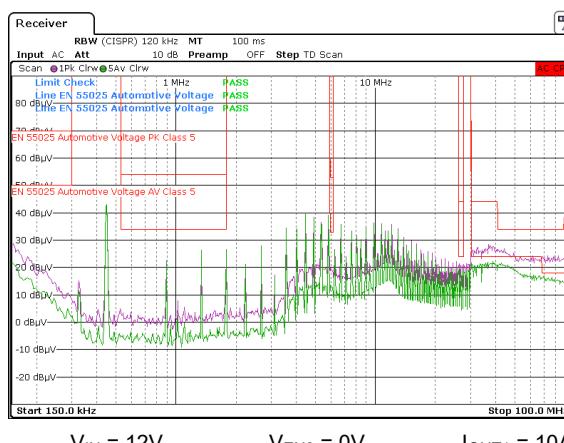

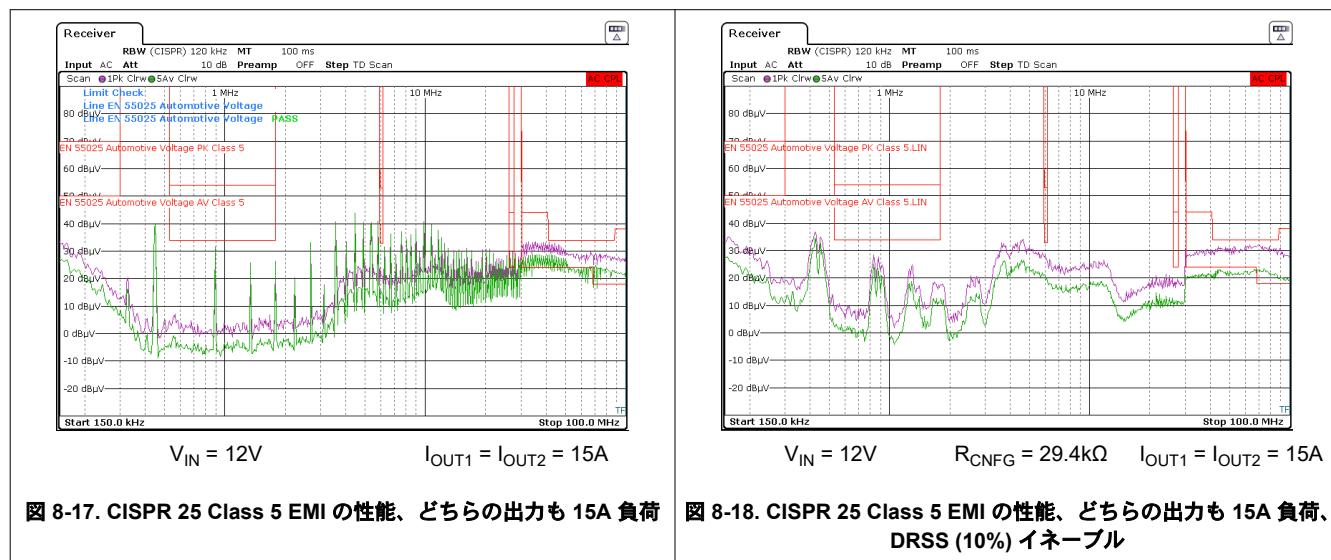

LM25137 には、車載 EMI 要件 (CISPR 25) への準拠を簡易化する機能が搭載されています。オプションのスペクトラム拡散周波数変調 (DRSS) 技術によりピーク EMI シグネチャを低減しながら、同時にアダプティブゲートドライバで高周波放射を最小限に抑えます。最後に、2 つのコントローラ チャネルのインターリーブ動作の位相が 180° ずれていることにより、入力フィルタリングとコンデンサの要件が低減されます。

LM25137 は、放熱に役立つウェッタブルフランクピン配置と露出パッド付きの 36 ピン VQFN パッケージで供給されます。

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 入力電圧範囲 (VIN)

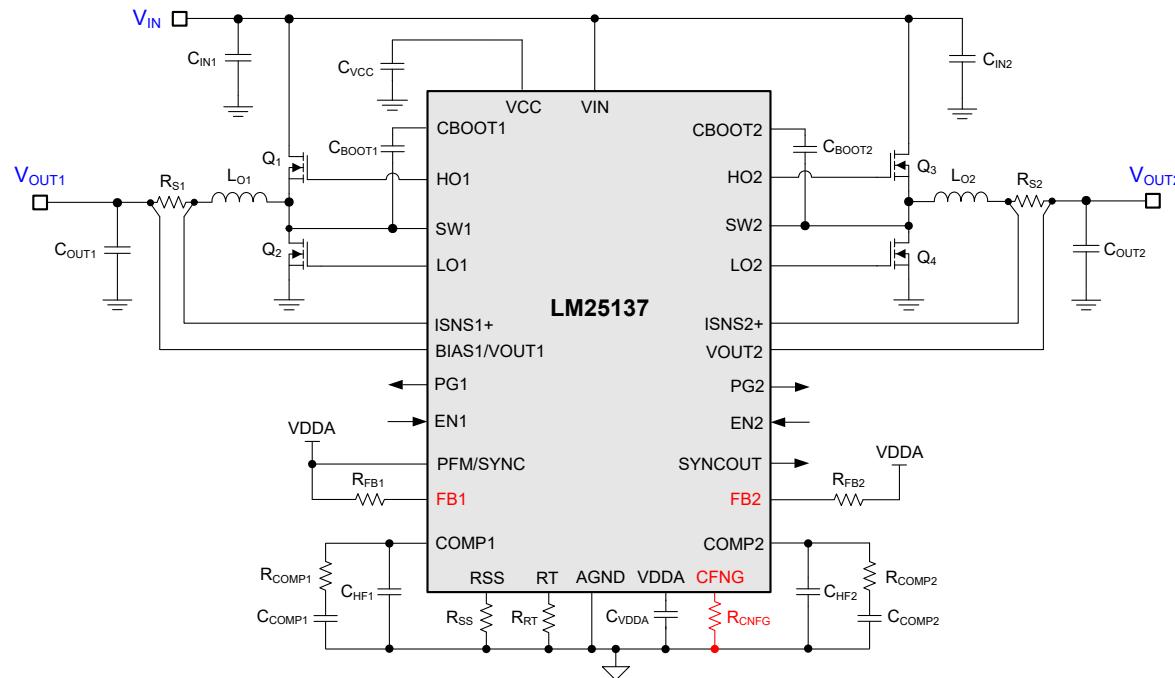

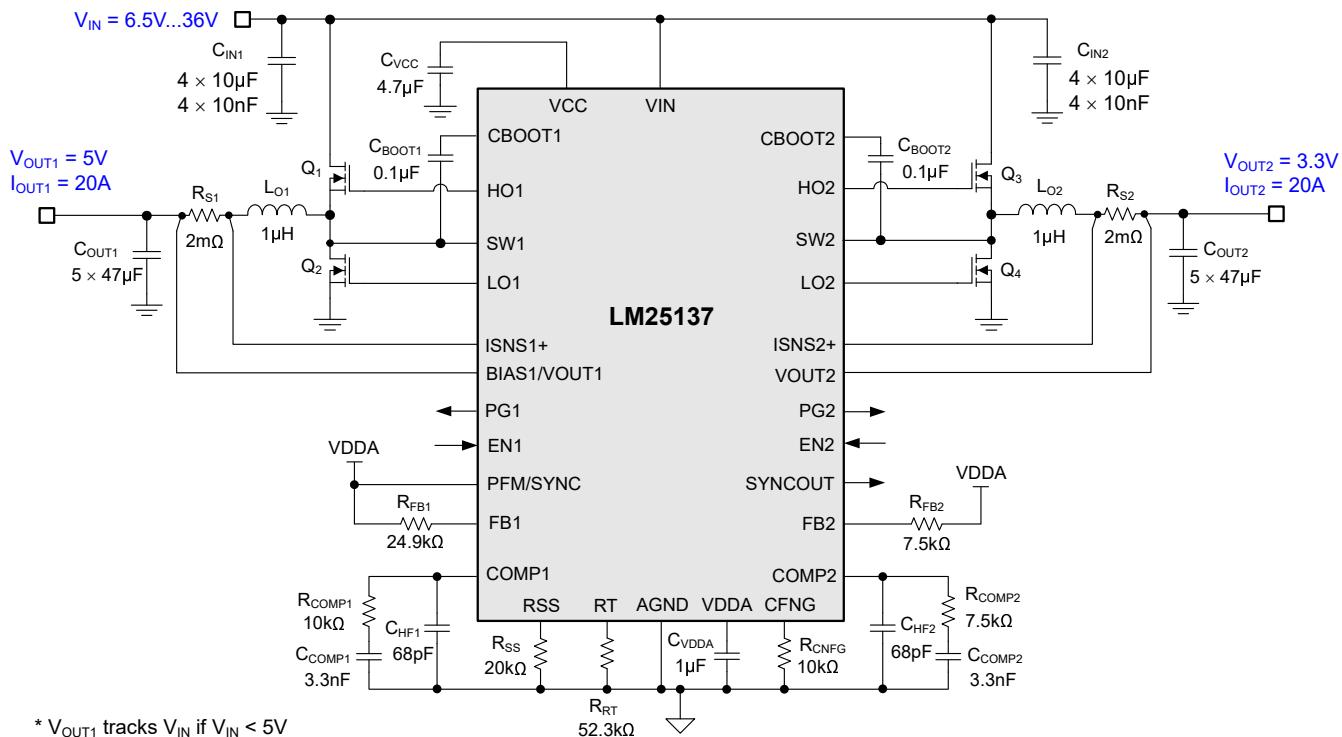

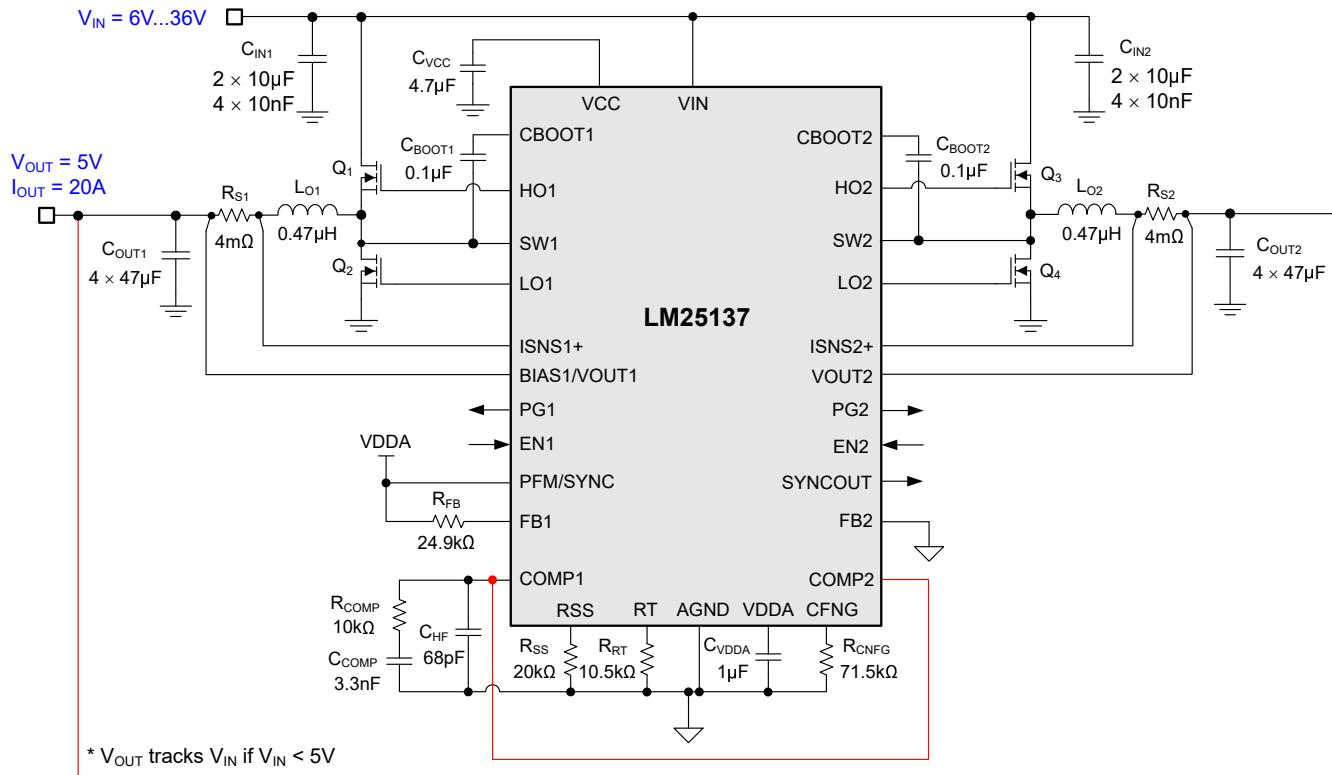

LM25137 の入力電圧動作範囲は 4V ~ 42V です。このデバイスは、12V および 24V の車載電源レールからの降圧変換を目的としています。図 7-1 の回路に、单一入力電源を使用した LM25137 ベースの幅広い  $V_{IN}$  のデュアル出力降圧レギュレータを実装するために必要なすべての部品を示します。

LM25137 は内蔵の LDO サブレギュレータを使用して、ゲート駆動および制御回路用の 5V VCC バイアスレールを供給します（入力電圧は 5V と必要とされるサブレギュレータのドロップアウト仕様を加算した値より大きいと仮定）。また、内蔵 20 $\mu$ A チャージポンプは LM25137 で常にアクティブです。 $V_{IN}$  が  $V_{OUT}$  設定点に近づくと、20 $\mu$ A チャージポンプが  $C_{BOOT}$  を充電し、ハイサイド MOSFET をオンのままにすることで、真の 100% デューティサイクルを実現します。この動作により、入力から出力まで可能な限り低いドロップアウト電圧を実現できます。

図 7-1. LM25137 デュアル出力レギュレータの回路図

高入力電圧のアプリケーションでは、ラインまたは負荷遷移イベント中は、VIN、SW1、SW2 の各ピンが 47V の絶対最大電圧定格を超えないように注意してください。絶対最大定格を超えて電圧が逸脱すると、IC が損傷する可能性があります。スイッチ電圧のオーバーシュートとリンギングを最小限に抑えるには、PCB 基板レイアウト中は注意深く作業を行い、高品質な入力バイパスコンデンサを使用してください。

### 7.3.2 バイアス電源レギュレータ (VCC, BIAS1/VOUT1, VDDA)

LM25137 には、高電圧 VCC バイアスレギュレータが内蔵されており、PWM コントローラ用バイアス電源と、外部 MOSFET 用ゲートドライバを供給します。入力電圧ピン (VIN) は、最大 42V 入力電圧源に直接接続します。入力電圧が VCC 設定点の 5V を下回っている場合、VCC 電圧は VIN からわずかな電圧降下を引いた値となります。

VCC レギュレータの電流制限は 175mA (最小値) です。電源オン時に、レギュレータは VCC コンデンサに電流を供給します。VCC 電圧が 3.8V (標準値) を超えると、出力チャネルは両方ともイネーブルになり (EN1 と EN2 が 1V 以上の場合)、ソフトスタートシーケンスが開始されます。VCC 電圧が VCC 電圧が立ち下がり UVLO スレッショルド 3.5V (標準

値) を下回るまで降下するか、または EN が Low 状態に切り替わるまで、両方のチャネルはアクティブ状態を維持します。 $2.2\mu\text{F} \sim 10\mu\text{F}$  のセラミックコンデンサを VCC と PGND との間に接続します。

$12\Omega$  の内部抵抗により VDDA が VCC に接続されます。低ノイズの内部バイアスレールを実現するには、VDDA と AGND を  $1\mu\text{F}$  のセラミックコンデンサでバイパスします。

BIAS1/VOUT1 電圧が  $4.3\text{V}$  を上回っている場合、BIAS1/VOUT1 は内部で VCC レギュレータの 2 番目の入力に接続されます。この動作により、バイアス電流が VIN ではなく VOUT1 から供給されるため、LM25137 の内部消費電力を低減できます。BIAS1/VOUT1 または VOUT2 は  $36\text{V}$  を超える電圧、または  $-0.3\text{V}$  未満の電圧に接続しないでください。

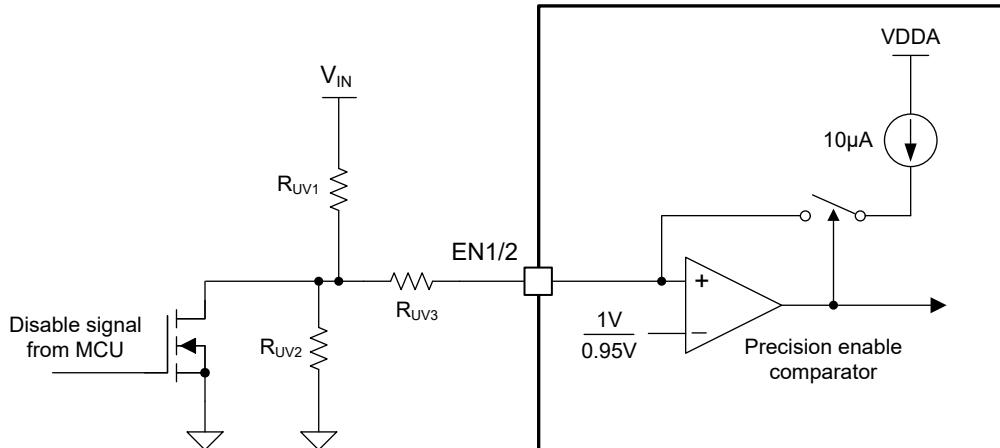

### 7.3.3 高精度イネーブル (EN1、EN2)

LM25137 は、各 EN 入力に高精度イネーブル回路を備えています。EN1 または EN2 電圧が  $1\text{V}$  を超えると、それぞれのチャネルでスイッチングがイネーブルになります。EN1 と EN2 を  $0.5\text{V}$  未満にプルすると、LM25137 はシャットダウン状態になります。VIN からの消費電流  $I_Q$  は  $3.6\mu\text{A}$  (標準値) になります。EN1 または EN2 電圧が  $0.6\text{V} \sim 1\text{V}$  の場合、LM25137 はスタンバイモードになります。VCC レギュレータはアクティブですが、コントローラはスイッチングしません。スタンバイモードの入力静止電流は  $260\mu\text{A}$  (標準値) です。

EN1/2 電圧が  $1\text{V}$  を上回ると LM25137 はイネーブルになります。ただし、多くのアプリケーションでは、図 7-2 に示すように抵抗分圧器  $R_{UV1}$  と  $R_{UV2}$  使用することで、高精度 UVLO レベルを確立できる利点があります。追加の電圧ヒステリシスを供給するため、 $R_{UV3}$  を直列に追加します。EN1 ピンと EN2 ピンをフローティングのままにしないでください。EN1/2 電圧を  $42\text{V}$  未満に維持します。

UVLO 抵抗を計算するには 式 1 を使用します。ここで、 $V_{IN(on)}$  および  $V_{IN(off)}$  は必要な入力電圧のターンオンおよびターンオフスレッショルドです。

$$R_{UV2} = \left[ \frac{V_{EN(off)} - (V_{IN(off)} / V_{IN(on)}) \cdot V_{EN(on)}}{I_{EN(hys)}} - R_{UV3} \right] \cdot \frac{V_{IN(on)}}{V_{IN(on)} - V_{EN(on)}} \quad (1)$$

$$R_{UV1} = R_{UV2} \cdot \left( \frac{V_{IN(on)}}{V_{EN(on)}} - 1 \right)$$

図 7-2. プログラマブル入力電圧 UVLO のオン、オフ

### 7.3.4 スイッチング周波数 (RT)

LM25137 発信機を RT から AGND の抵抗でプログラムし、フリーランニングスイッチング周波数を  $100\text{kHz} \sim 2.2\text{MHz}$  に設定します。式 2 を使用して、指定されたスイッチング周波数の RT 抵抗を計算します。

$$R_{RT} [\text{k}\Omega] = \frac{\frac{10^6}{F_{SW} [\text{kHz}]} - 15}{42.8} \quad (2)$$

### 7.3.5 パルス周波数変調および同期 (PFM/SYNC)

ダイオードの代わりにローサイドの MOSFET を実装した同期整流降圧レギュレータは、軽負荷、出力過電圧、プリバイアスのスタートアップ条件中は出力から負電流をシンクできます。LM25137 にはダイオード エミュレーション機能があり、ローサイド MOSFET の逆 (ドレインからソース) 電流を防止します。ダイオードエミュレーションモードに構成されている場合、ゼロクロスコンパレータを使用して SW 電圧を検出することによって逆電流が検出されると、ローサイド MOSFET はオフになります。この構成の利点は、軽負荷の状況で電力損失が小さいことです。ダイオードエミュレーションモードの欠点は、軽負荷時の過渡応答が遅くなることです。

ダイオードエミュレーションを構成するには、PFM/SYNC ピンを使用します。ダイオードエミュレーションをイネーブルにして、軽負荷時に高効率を実現するには、PFM/SYNC を VDDA に接続します。FPWM で連続導通モード (CCM) の動作が必要な場合は、PFM/SYNC を AGND に接続します。ダイオード エミュレーションは、プリバイアスのスタートアップ条件中に逆電流が流れることを防止するため、自動的に動作します。DCM から CCM 動作へと段階的に変化することで、単調なスタートアップ性能が実現します。

LM25137 を外部クロックソースと同期させるには、ロジックレベルの信号を PFM/SYNC に適用します。LM25137 は、最大 2.5MHz のプログラムされたフリーランニング周波数の ±20% に同期します。RT 抵抗と同期クロック信号がある場合、LM25137 は RT 抵抗を無視し、外部クロックと同期します。ただし、高デューティサイクル時に最小オフ時間に達すると、同期は無視され、スイッチング周波数を低下させて出力電圧レギュレーションを維持できます。

### 7.3.6 同期出力 (SYNCOUT)

SYNCOUT 電圧は、約 90° 遅れの HO2 (または 90° 早い HO1) の立ち上がりエッジを持つロジックレベル信号です。SYNCOUT 信号を使用して 2 つ目の LM25137 コントローラを同期すると、4 つの位相の位相差はすべて 90° になり、リップル電流キャンセレーションが最適化されます。

### 7.3.7 デュアルランダムスペクトラム拡散機能 (DRSS)

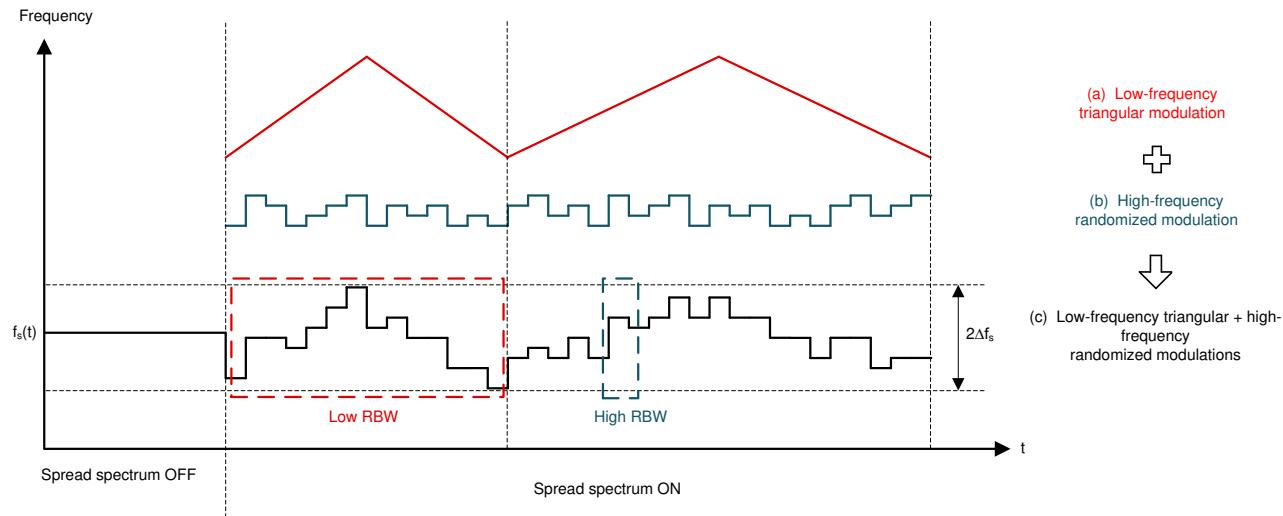

LM25137 にはデジタルスペクトラム拡散機能があり、広い周波数範囲にわたってスイッチングレギュレータの EMI シグネチャを低減します。図 7-3 に示すように、DRSS 機能は、低周波数の三角波変調プロファイルと、高周波数のサイクル単位のランダム変調プロファイルを組み合わせたものです。低周波数変調は低い無線周波数帯域で性能を向上させ、高周波のランダム変調は高い無線周波数帯域で性能を向上させます。

スペクトラム拡散は、狭帯域信号を広帯域信号に変換し、エネルギーを複数の周波数にわたって拡散することで機能します。業界規格では周波数帯域ごとに異なる EMI レシーバ解像度の帯域幅 (RBW) 設定を要求しているため、RBW はスペクトラム拡散の性能に影響を及ぼします。DRSS は、低周波数の三角波変調と高周波数のサイクル単位ランダム変調プロファイルにより、それぞれ低 RBW および高 RBW での EMI 性能を同時に向上できます。DRSS により、伝導エミッションを CISPR 25 の低周波数帯域 (150kHz ~ 30MHz) で 10dB $\mu$ V、高周波帯域 (30MHz ~ 108MHz) で 5dB $\mu$ V に低減できます。PFM/SYNC に外部クロック信号を印加すると、DRSS が無効になります。CNFG から AGND への抵抗を使用して LM25137 を構成する場合は、表 7-1 を参照してください。

図 7-3. DRSS の実装

表 7-1. CNFG 抵抗の構成

| R <sub>CNFG</sub> | 1 次側/2 次側 | DRSS   | 独立またはインターリープ |

|-------------------|-----------|--------|--------------|

| 10kΩ              | 1 次側      | ディセーブル | 個別           |

| 19.1kΩ            | 1 次側      | ±5%    | 個別           |

| 29.4kΩ            | 1 次側      | ±10%   | 個別           |

| 41.2kΩ            | 1 次側      | ディセーブル | インターリープ型     |

| 54.9kΩ            | 1 次側      | ±5%    | インターリープ型     |

| 71.5kΩ            | 1 次側      | ±10%   | インターリープ型     |

| 90.9kΩ            | セカンダリ     | 該当なし   | インターリープ型     |

### 7.3.8 構成可能なソフトスタート (RSS)

LM25137 のソフトスタート機能は、レギュレータを徐々に定常状態動作点へと到達させることで、起動時のストレスや突入電流を低減します。RSS と AGND の間に抵抗を使用して、ソフトスタート時間をプログラムします。RSS ピンが AGND に短絡する場合、ソフトスタート時間は 1.5ms です。RSS 抵抗が 500kΩ より大きい場合（またはピンが解放回路のままになっている場合）、LM25137 はデフォルトで 6.5ms のソフトスタート時間になります。

式 3 を使用して、指定されたソフトスタート時間の RSS 抵抗を計算します。

$$R_{SS} [\text{k}\Omega] = 4.38 \cdot t_{SS} [\text{ms}] \quad (3)$$

### 7.3.9 出力電圧の設定ポイント (FB1、FB2)

LM25137 は、3 つの固定出力電圧の設定ポイント 1 つに対して個別に構成することも、または外付けの抵抗分割器を使用して目的の出力電圧に調整することも可能です。表 7-2 に示すように、それぞれの FB ピンを 7.5kΩ、24.9kΩ、48.7kΩ で VDDA に接続することで、3.3V、5V、12V の電圧設定ポイントに V<sub>OUT1</sub> または V<sub>OUT2</sub> を構成します。

表 7-2. 帰還構成抵抗

| VDDA へのプルアップ抵抗 | V <sub>OUT</sub> 設定ポイント |

|----------------|-------------------------|

| 7.5kΩ          | 3.3V                    |

| 24.9kΩ         | 5V                      |

| 48.7kΩ         | 12V                     |

表 7-2. 帰還構成抵抗 (続き)

| VDDA へのプルアップ抵抗 | V <sub>out</sub> 設定ポイント |

|----------------|-------------------------|

| 設置されていません      | 外部 FB 分圧器の設定            |

LM25137 の VCC 電圧がその立ち下がり UVLO スレッショルド以下になるまで低下して電源がオフになり再びオンになります。VCC が 3.8V を超えるまで、構成の設定はラッチされ変更できません。

または、出力と AGND との間に外付けの抵抗分圧器を接続して出力電圧を設定します。FB レギュレーション電圧は 0.8V で、出力電圧設定ポイントの範囲は 0.8V ~ 36V です。式 4 を使用すると、それぞれ R<sub>FB1</sub> と R<sub>FB2</sub> と表される帰還抵抗の上限と下限を計算することができます。図 7-4 を参照してください。

$$R_{FB1} = \left( \frac{V_{OUT}}{V_{REF}} - 1 \right) \cdot R_{FB2} \quad (4)$$

R<sub>FB2</sub> の推奨開始値は 10kΩ ~ 20kΩ です。

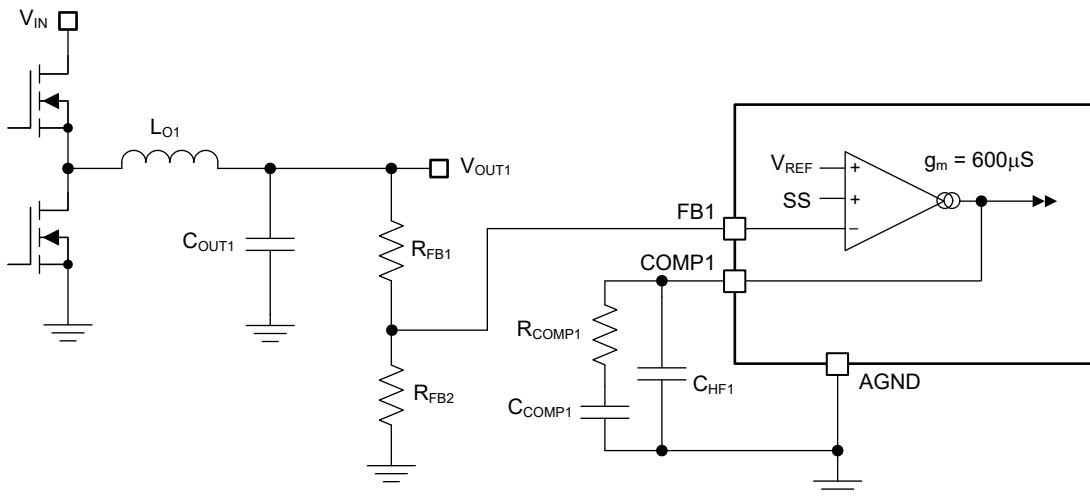

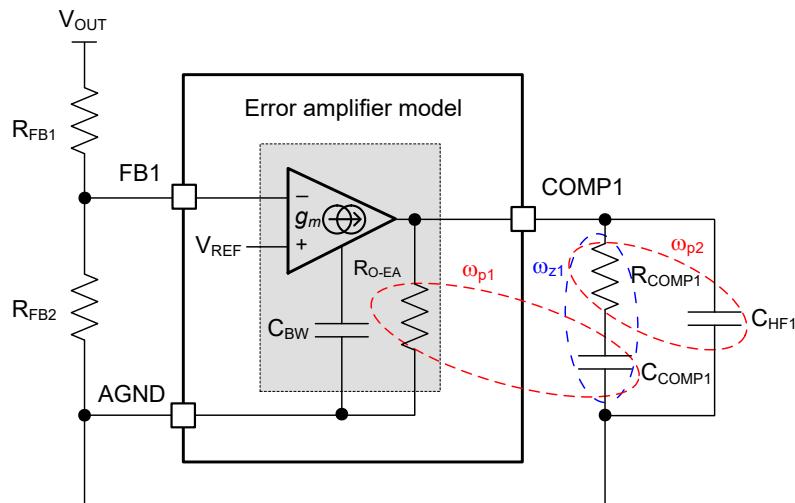

図 7-4. 可変出力設定による電圧ループ

軽負荷時の効率を向上させる必要がある場合は、外付け抵抗を注意深く選択してください。外付け分圧器の消費電流は、LM25137 のスリープ電流に加算されます。V<sub>IN</sub> に反映される分割電流は、V<sub>OUT</sub>/V<sub>IN</sub> の比で増減します。

### 7.3.10 エラー アンプと PWM コンパレータ (FB1, FB2, COMP1, COMP2)

LM25137 の各チャネルには独立した高ゲイン相互コンダクタンスアンプがあり、フィードバック電圧と内部高精度基準電圧 (0.8V) の間の差に比例した誤差電流を生成します。相互コンダクタンスアンプの出力は対応する COMP ピンに接続されるため、ユーザーが外部制御ループ補償を行うことができます。TI では一般的に、ピーク電流モード制御用の type-II 補償ネットワークをお勧めしています。COMP1/2 が 100mV 未満にプルされると、HO1/2 および LO1/2 のドライバ出力を無効化できます。

#### 7.3.10.1 スロープ補償

LM25137 には、ピーク電流モード制御と 50% を超えるデューティ サイクルで安定した動作を実現するスロープ補償が提供されています。式 5 を使用して降圧インダクタンスを計算し、スロープ補償の寄与がインダクタ電流のダウンスロープの 1 倍になるようにします。

$$L_{O(IDEAL)} [\mu H] = \frac{V_{OUT} [V] \cdot R_s [m\Omega]}{22 \cdot F_{SW} [\text{MHz}]} \quad (5)$$

- 一般に、インダクタンスの値が低いほど、ピークツーピークのインダクタリップル電流は増加します。これにより、サイズとコストは最小限に抑えられ、コア損失とピーク電流の増加によって軽負荷効率が下がる代わりに、過渡応答が向上します。

- 一般に、インダクタンスの値が大きいほどピークツーピークのインダクタリップル電流が低下し、スイッチピーカと RMS 電流が現象しますが、負荷過渡仕様を満たすためにより大容量の出力コンデンサが必要になります。

### 7.3.11 インダクタ電流センス (ISNS1+、BIAS1/VOUT1、ISNS2+、VOUT2)

降圧出力段のインダクタ電流を検出する方法には 2 種類あります。1 つ目は、インダクタと直列に電流センス抵抗 (シャントとも呼ばれます) を使用する方法、2 つ目はインダクタの DC 抵抗を利用する方法 (DCR 電流センシング) です。

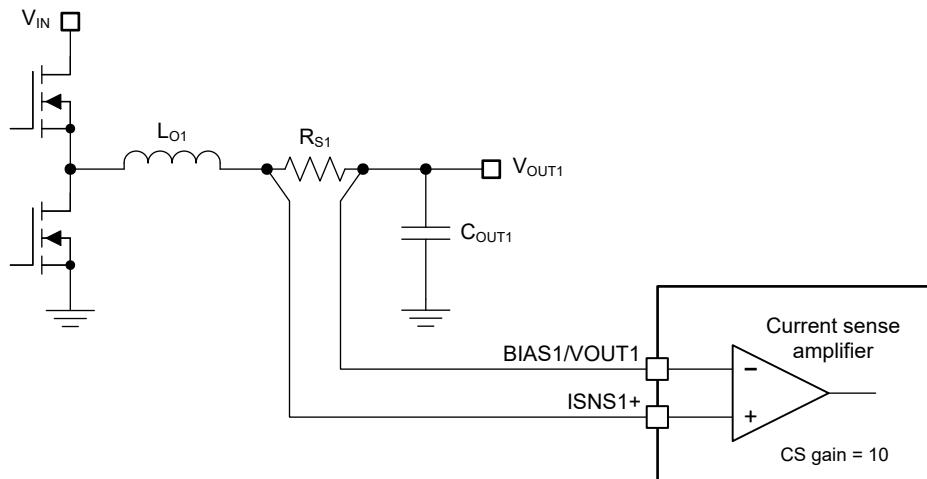

#### 7.3.11.1 シャント電流センシング

図 7-5 に、シャント抵抗を使用したインダクタ電流センシングを示します。この構成では、インダクタ電流を継続的に監視して、動作温度範囲全体での正確な過電流保護を実現します。最適な電流センス精度と過電流保護を実現するため、インダクタと出力の間に  $\pm 1\%$  の許容誤差の低寄生インダクタンスシャント抵抗を接続します。シャントでケルビンセンス接続を使用し、センスラインが LM25137 に差動で戻るよう配線します。

[ISNS1+、BIAS1/VOUT1] または [ISNS2+、VOUT2] で差動的に検出されたピーク電流が 60mV の電流制限スレッショルドを超えた場合、電流制限コンパレータは直ちにサイクルごとの電流制限のための各 HO 出力を停止します。式 6 を使用してシャント抵抗を計算します。

$$R_s = \frac{V_{CS-TH}}{I_{OUT(CL)} + \frac{\Delta I_L}{2}} \quad (6)$$

ここで、

- $V_{CS-TH}$  は、60mV の電流センススレッショルドです。

- $I_{OUT(CL)}$  は過電流設定ポイントで、最大負荷電流より大きな値を設定して、負荷過渡中の過電流コンパレータのトリッピングを防止します。

- $\Delta I_L$  は、ピークツーピークのインダクタリップル電流です。

図 7-5. シャント電流センシングの実装

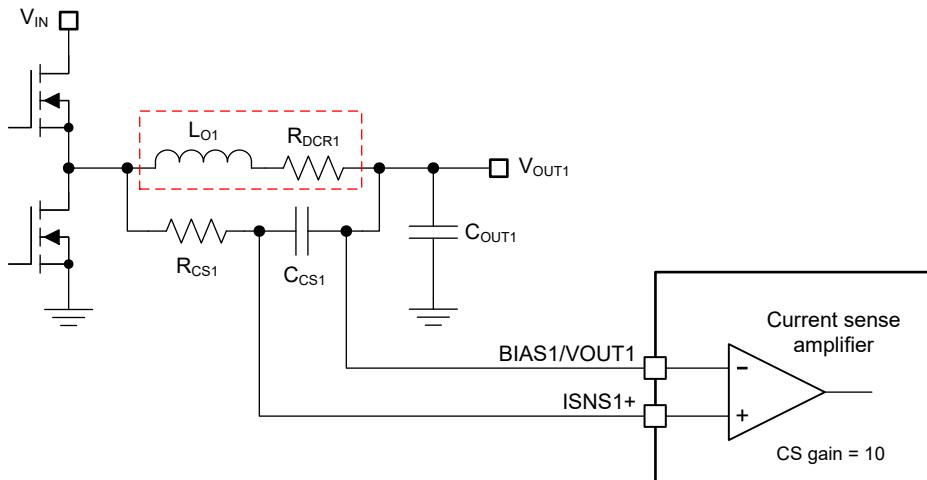

### 7.3.11.2 インダクタ DCR 電流センシング

精密な電流制限保護を必要としない大電力アプリケーションでは、インダクタ DCR 電流センシングが推奨されます。この手法では、インダクタと並列な RC センス ネットワークを利用して、ロスレスなインダクタ電流を実現して、これを連続監視することができます。室温で 10%~15% の範囲内での標準的な電流制限精度を得るには、DCR 許容誤差の小さなインダクタを選択します。[図 7-6](#) の部品  $R_{CS}$  と  $C_{CS}$  によりインダクタ間にローパス フィルタが作成され、インダクタ DCR 間の電圧降下の差動センシングが可能となります。

図 7-6. インダクタ DCR 電流センシングの実装

$s$  ドメインのセンスコンデンサ間の電圧降下を計算するには、[式 7](#) を使用します。 $R_{CS}C_{CS}$  時定数が  $L_O/R_{DCR}$  に等しい場合、センスコンデンサ  $C_{CS}$  間に発生する電圧はインダクタ DCR 電圧の複製であり、精密な電流センシングが可能となります。 $R_{CS}C_{CS}$  時定数が  $L_O/R_{DCR}$  時定数とは異なる場合、次のようなセンシング誤差が発生します。

- $R_{CS}C_{CS} > L_O/R_{DCR}$  の場合 → DC レベルは正しいが、AC 振幅は減衰する。

- $R_{CS}C_{CS} < L_O/R_{DCR}$  の場合 → DC レベルは正しいが、AC 振幅は増幅される。

$$V_{CS}(s) = \frac{1 + s \cdot \frac{L_O}{R_{DCR}}}{1 + s \cdot R_{CS} \cdot C_{CS}} \cdot R_{DCR} \cdot \left( I_{OUT(CL)} + \frac{\Delta I_L}{2} \right) \quad (7)$$

低インピーダンスセンシングネットワークを維持するために、100nF 以上の  $C_{CS}$  容量を選択してください。この結果、スイッチノードからのノイズピックアップの影響が低減されます。[セクション 8.4.1](#) をよく読み、ノイズと DC 誤差によってそれぞれ ISNS1/2+ ピンと VOUT1/2 ピンの間に印加される差動電流センス信号に誤りが発生しないように注意してください。

### 7.3.12 制御可能な最小オン時間

最小出力電圧の調整範囲には、LM25137 の 0.8V の電圧リファレンスと、制御可能なスイッチノードの最小パルス幅  $t_{ON(min)}$  という 2 つの制約があります。

$t_{ON(min)}$  は実質的に、指定されたスイッチング周波数における  $V_{OUT}/V_{IN}$  の電圧ステップダウン変換比を制限します。固定周波数の PWM 動作の場合、電圧の変換比は次の [式 8](#) を満たす必要があります。

$$\frac{V_{OUT}}{V_{IN}} > t_{ON(min)} \cdot F_{SW} \quad (8)$$

ここで、

- $t_{ON(min)}$  は 22ns (標準値) です

- $F_{SW}$  はスイッチング周波数です

目標とする電圧変換比が上記の条件を満たさない場合、LM25137 は固定スイッチング周波数動作からパルス スキッピング モードに遷移して、出力電圧のレギュレーションを維持します。たとえば、目標の出力電圧が 1.2V で、入力電圧 24V、スイッチング周波数 2.1MHz の場合、式 9 の電圧変換比の基準を満たしています。

$$\frac{1.2V}{24V} > 22ns \cdot 2.1MHz$$

$$0.05 > 0.046 \quad (9)$$

$V_{IN}$  の範囲が広いアプリケーションで低出力電圧の場合、式 8 の要件を満たすためのもう 1 つの方法は、LM25137 のスイッチング周波数を下げることです。

### 7.3.13 100% デューティ サイクル能力

内蔵 20μA チャージ ポンプは LM25137 では常にアクティブになっています。 $V_{IN}$  が  $V_{OUT}$  設定点に近づくと、デューティ サイクルは 100% に向かって延長されます。制御ループが  $t_{OFF(min)}$  より短いオフ時間を設定しようとすると、LM25137 その特定のスイッチング サイクルでオフ時間の間隔をスキップし、100% デューティ サイクル モードに移行します。これらの条件では、ローサイド MOSFET がオンにならないため、VCC からブートストラップ ダイオードを経由する通常のパスで  $C_{BOOT}$  を充電できません。代わりに、20μA チャージ ポンプは  $C_{BOOT}$  を充電し、ハイサイド MOSFET をオン状態に維持するので、真の 100% デューティ サイクルを達成できます。少なくとも制御ループが再度  $t_{OFF(min)}$  より長いオフ時間を要求するまでの間です。この動作により、入力から出力まで可能な限り低いドロップアウト電圧を実現できます。ハイサイド MOSFET にゲートソース間抵抗を追加すると、 $C_{BOOT}$  が放電され、100% デューティ サイクル動作に影響を及ぼす可能性があることに注意してください。

### 7.3.14 MOSFET ゲートドライバ(HO1, HO2, LO1, LO2)

LM25137 には、MOSFET ゲートドライバと、関連するハイサイドレベルシフタが搭載されており、外部の N チャネルパワー MOSFET を駆動します。ハイサイドゲートドライバは、内蔵ブートストラップダイオードおよび外付けブートストラップコンデンサ  $C_{BOOT}$  と連動して動作します。ローサイド MOSFET の導通時間内は、SW 電圧が約 0V で、 $C_{BOOT}$  はダイオードを経由して VCC から充電されます。

LM25137 は LO と HO 出力をアダプティブデッドタイム方式で制御するため、両方の出力 (LO と HO) が同時にイネーブルになることはなく、クロス導通を防止します。コントローラから LO をイネーブルにするようコマンドが送信されると、アダプティブデッドタイムロジックは最初に HO をディスエーブルにして、HO と GND 間の電圧が 2V (標準値) 以下に低下するまで待機します。次に、短い遅延 (HO 立ち上がりから LO 立ち上がりまでの遅延) の後に LO はイネーブルになります。同様に、LO 電圧が 2V を下回るまで、HO のターンオンは遅延されます。次に、短い遅延 (LO 立ち上がりから HO 立ち上がりまでの遅延) の後に HO はイネーブルになります。この方法により、任意のサイズの N チャネル MOSFET 部品や並列 MOSFET 構成に対して、適切なデッドタイムを確保することができます。直列ゲート抵抗を追加する場合は、直列ゲート抵抗のために実効デッドタイムが短くなる可能性があるため、注意が必要です。式 10 に従って、選択したハイサイドパワー MOSFET により、適切なブートストラップコンデンサの値  $C_{BOOT}$  が決まります。

$$C_{BOOT} = \frac{Q_G}{\Delta V_{CBOOT}} \quad (10)$$

ここで、

- $Q_G$  は、該当のゲートドライブ電圧 (通常 5V) におけるハイサイド MOSFET のゲート電荷の総量です

- $\Delta V_{CBOOT}$  は、ターンオン後のハイサイド MOSFET ドライバの電圧変動です

$C_{BOOT}$  を決定するには、利用可能なゲートドライブ電圧が大きな影響を受けないように  $\Delta V_{CBOOT}$  を選択します。 $\Delta V_{CBOOT}$  の許容範囲は 100mV~200mV です。ブートストラップコンデンサは、通常 0.1μF の低 ESR セラミックコンデ

ンサにする必要があります。公称 VCC 電圧が 5V の場合、 $V_{GS} = 4.5V$  で  $R_{DS(on)}$  が定格のロジック レベル パワー MOSFET を使用する必要があります。

### 7.3.15 出力構成(CNFG)

CNFG から AGND に接続した抵抗  $R_{CNFG}$  を使用して、LM25137 を 1 次コントローラ（独立したデュアル出力またはインターリープ単一出力）として、または大電流アプリケーションの並列位相用の 2 次コントローラとして構成します。

#### 7.3.15.1 独立したデュアル出力動作

LM25137 には独立して動作できる 2 つの出力があります。 $V_{OUT1}$  と  $V_{OUT2}$  はいずれも、必要に応じて VDDA から FB1 または FB2 に接続する 1 つの抵抗により、3.3V、5V、12V の固定出力設定ポイントに設定できます。または、式 4 に基づき、外部帰還抵抗を使用して、出力電圧を 0.8V ~ 36V の範囲に設定します。表 7-3 と図 7-7 を参照してください。

表 7-3. 独立したデュアル出力の構成モード

| $R_{CNFG}$ | 1 次側、2 次側 | DRSS  | 独立出力またはインターリープ出力 |

|------------|-----------|-------|------------------|

| 10kΩ       | 1 次側      | OFF   | 個別               |

| 19.1kΩ     | 1 次側      | DRSS1 | 個別               |

| 29.4kΩ     | 1 次側      | DRSS2 | 個別               |

図 7-7. LM25137 独立したデュアル出力用に構成されたレギュレータの回路図

#### 7.3.15.2 単一出力インターリープ動作

CNFG と AGND との間に接続された抵抗  $R_{CNFG}$  に基づき、LM25137 を单一出力インターリープ動作用に構成します。表 7-4 に示すように、41.2kΩ を使用して DRSS を無効化し、54.9kΩ または 71.5kΩ を使用してそれぞれ 5% または 10% の周波数拡散で DRSS を有効化します。これにより、チャネル 2 のエラーアンプは無効化され、エラーアンプはハイインピーダンス状態になります。その後、コントローラは 1 次側、2 次側の構成になり、SYNCOUT クロックは HO2 から 180° 遅れます（または HO1 より 180° 先行します）。

図 7-8 に示すように、COMP1 を COMP2 に接続し、FB1 を使用して出力電圧設定ポイントを設定します。必要に応じて PG1 を使用し、PG2 をオープンのままにするか、GND に接続します。

表 7-4. 単一出力インターリーブ動作の構成モード

| R <sub>CNFG</sub> | 1 次側/2 次側 | DRSS  | 独立出力またはインターリーブ出力 |

|-------------------|-----------|-------|------------------|

| 41.2kΩ            | 1 次側      | OFF   | インターリーブ型         |

| 54.9kΩ            | 1 次側      | DRSS1 | インターリーブ型         |

| 71.5kΩ            | 1 次側      | DRSS2 | インターリーブ型         |

図 7-8. LM25137 単一出力インターリーブ動作用に構成された 2 相レギュレータの回路図

### 7.3.15.3 単一出力多相動作

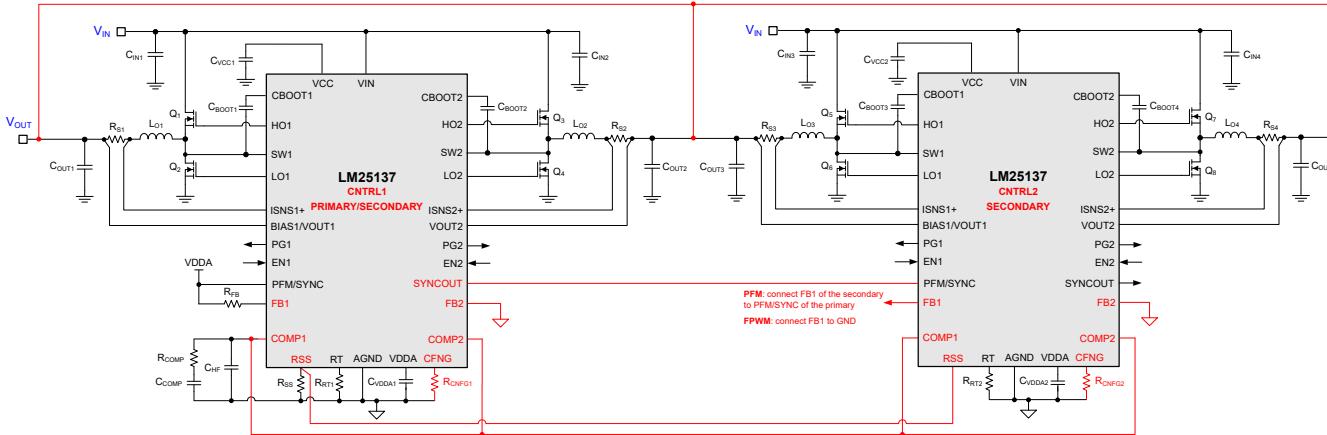

マルチフェーズ (3 相または 4 相) レギュレータには、図 7-9 に示すように、2 つの LM25137 コントローラが必要です。

1 つ目のコントローラ (CNTRL1) を 1 次コントローラ、2 つ目のコントローラを 2 次コントローラ (CNTRL2) として構成します。2 つ目のコントローラを構成する場合は、90kΩ 抵抗を CNFG から AGND に接続します。この接続により、2 次コントローラの帰還エラーアンプは両方ともディスエーブルになり、ハイインピーダンス状態になります。

- COMP1 ピンと COMP2 ピンを、1 次コントローラと 2 次コントローラの両方に互いに接続

- 1 次の SYNCOUT を 2 次コントローラの PFM/SYNC に接続

- 両方のコントローラの RSS ピンを接続

- すべての出力をまとめて接続

- FB2 (1 次側コントローラ) と FB2 (2 次側コントローラ) を GND に接続

- PFM モード動作が必要な場合は、2 次コントローラの FB1 を 1 次コントローラの PFM/SYNC に接続します。必要な場合は、FB1 を GND に接続します。

- 1 次の PG1 のみが該当します。2 次コントローラの PG1/2 と PG2 はオープンな状態を維持、または GND に接続できます。

1 次コントローラの SYNCOUT は位相差 90°で、インターリーブ動作を容易にします。LM25137 が 2 次モードの場合、RT は発振器に使用されず、代わりにスロープ補償に使用されます。そのため、1 次コントローラと同じ RT 抵抗を選択します。表 7-5 を参照してください。

詳細については、『多相降圧コンバータの利点』ホワイトペーパーと、『多相降圧設計のすべて』アプリケーションレポートを参照してください。

表 7-5. 単一出力マルチフェーズ動作の構成モード

| R <sub>CNFG</sub> | 1 次側、2 次側 | DRSS  | 独立出力またはインターリープ出力 |

|-------------------|-----------|-------|------------------|

| 41.2kΩ            | プライマリ     | OFF   | インターリープ型         |

| 54.9kΩ            | プライマリ     | DRSS1 | インターリープ型         |

| 71.5kΩ            | プライマリ     | DRSS2 | インターリープ型         |

| 90.9kΩ            | セカンダリ     | 該当なし  | インターリープ型         |

図 7-9. LM25137 単一出力インターリープ動作用に構成されたマルチフェーズレギュレータの回路図

## 7.4 デバイスの機能モード

### 7.4.1 スリープモード

LM25137 はピーク電流モード制御で動作するため、補償 (COMP) 電圧はピークインダクタ電流に比例します。無負荷または軽負荷状態では、出力コンデンサは非常にゆっくりと放電されます。その結果、COMP 電圧はサイクル単位でのドライバ出力パルスを要求しません。LM25137 のコントローラがスイッチングサイクルの検出に 16 回失敗すると、スリープモードに入り、低  $I_Q$  状態に切り替わって、入力から流れる電流を低減します。LM25137 をスリープモードにするには、ダイオードエミュレーション用にデバイスをプログラムする必要があります (PFM/SYNC を VDDA に接続)。

12V 入力時のスリープモードにおける標準的なコントローラ  $I_Q$  は、チャネル 1 および 2 を 5V および 3.3V 出力に設定した場合 1.5µA です。LM25137 がスリープ状態になると、PG1/2 は無効化されます。

### 7.4.2 PFM モード

ダイオードの代わりにローサイドの MOSFET を実装した同期整流降圧レギュレータは、軽負荷、過電圧、プリバイアスのスタートアップ条件中は出力から負電流をシンクできます。LM25137 にはダイオードエミュレーション機能があり、ローサイド MOSFET の逆 (ドレンからソース) 電流を防止します。ダイオードエミュレーション (DEM) 用に構成されている場合、ゼロクロスコンパレータを使用して印加可能な SW 電圧を検出することによって逆電流が検出されると、ローサイド MOSFET はオフになります。この構成の利点は、軽負荷条件時に電力損失が低減されることです。また、欠点は軽負荷時の過渡応答が遅くなることです。

表 7-6. PFM の設定

| PFM/SYNC | FPWM、PFM |

|----------|----------|

| VDDA     | PFM      |

| AGND     | FPWM     |

| 外部クロック   | FPWM     |

PFM/SYNC ピンを使用して、ダイオードエミュレーション機能を構成します。ダイオードエミュレーションをイネーブルにして、軽負荷時に不連続導通モード (DCM) の動作を実現するには、PFM/SYNC を VDDA に接続します。FPWM または

連続導通モード (CCM) の動作が必要な場合は、PFM/SYNC を AGND に接続します。表 7-6 を参照してください。ダイオードエミュレーションは、プリバイアスのスタートアップ中に逆電流が流れることを防止するため、自動的に動作します (PFM と FPWM モードの両方で)。DCM から CCM 動作へと段階的に変化することで、単調なスタートアップ性能が実現します。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

LM25137 は、高入力電圧を 2 つの低出力電圧に変換するために使用する、デュアルチャネルまたはデュアル位相の、同期整流、降圧コントローラです。以下のセクションではパワートレインと補償部品について検討し、シングルおよびデュアル出力を実装するための具体的な回路設計例を紹介しています。LM25137 ベースのレギュレータの設計プロセスを迅速化および効率化するため、包括的な LM25137 *Quickstart Calculator* クイックスタートカリキュレータをダウンロードして、特定のアプリケーションのコンポーネント選択を支援することができます。

#### 8.1.1 パワートレイン コンポーネント

同期整流降圧レギュレータの設計を効果的で信頼性の高いものにするには、降圧レギュレータのパワートレインコンポーネントを包括的に理解することが不可欠です。次のセクションでは、以下について説明します：

- パワー MOSFET

- 降圧インダクタ

- 入力と出力の各コンデンサ

- EMI 入力フィルタ

##### 8.1.1.1 パワー MOSFET

パワー MOSFET の選択は、DC/DC レギュレータの性能に並外れた影響を及ぼします。MOSFET は低オン抵抗  $R_{DS(on)}$  を内蔵しているため導通損失を低減し、同時に寄生容量が小さいため遷移時間が短くなり、スイッチング損失が低くなります。通常、MOSFET の  $R_{DS(on)}$  が低くなるほど、ゲートの電荷と出力の電荷 (それぞれ  $Q_G$  と  $Q_{OSS}$ ) は高くなり、逆もまた同じです。そのため、一般的に  $R_{DS(on)}$  と  $Q_G$  の積は MOSFET の性能指標として規定されます。使用されているパッケージの熱抵抗が低いため、MOSFET の消費電力によって MOSFET のダイ温度が過剰な高温になることはありません。

LM25137 アプリケーションでパワー MOSFET の選択に影響を与える主なパラメータは次のとおりです：

- $R_{DS(on)}$  ( $V_{GS} = 5V$  の場合)

- ドレン - ソース間電圧定格  $BV_{DSS}$  は、最大入力電圧に応じて、標準で 30V、40V、60V です。

- $V_{GS} = 5V$  におけるゲート電荷パラメータ

- 関連入力電圧における出力電荷  $Q_{OSS}$

- ボディダイオードの逆回復電荷  $Q_{RR}$

- ゲートスレッショルド電圧  $V_{GS(th)}$ 。MOSFET データシートの  $Q_G$  と  $V_{GS}$  のプロットにおけるミラー プラトーから算出されます。ミラープラトー電圧は通常 2.5V ~ 3.2V の範囲にあるため、LM25137 の 5V ゲートドライブの振幅によって、オン時には MOSFET は十分強化され、オフ時には  $C_{dV/dt}$  貫通に対するマージンが確保されます。

1 つのチャネルの MOSFET 関連の電力損失は、表 8-1 に示す式に集約されます。この式の添え字の 1 と 2 は、それぞれハイサイドとローサイド MOSFET のパラメータを表しています。インダクタのリップル電流の影響を考慮する場合でも、寄生インダクタンスやスイッチノード電圧のリンギングなどの 2 次損失モードは含まれません。LM25137 の製品フォルダから入手できる包括的な *クイックスタートカリキュレータ* では、 $R_{DS(on)}$  や  $Q_G$  などの、入力した MOSFET パラメータに基づいて電力損失を計算できます。

表 8-1. MOSFET の電力損失

| 電力損失モード                       | 下限側 MOSFET                                                                                                                                                                 | ローサイド MOSFET                                                                                                                                                              |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOSFET の導通 <sup>(2) (3)</sup> | $P_{cond1} = D \cdot \left( I_{OUT}^2 + \frac{\Delta I_L^2}{12} \right) \cdot R_{DS(on)1}$                                                                                 | $P_{cond2} = D' \cdot \left( I_{OUT}^2 + \frac{\Delta I_L^2}{12} \right) \cdot R_{DS(on)2}$                                                                               |

| MOSFET のスイッチング                | $P_{sw1} = \frac{V_{IN} \cdot F_{SW}}{2} \left[ \left( I_{OUT} - \frac{\Delta I_L}{2} \right) \cdot t_R + \left( I_{OUT} + \frac{\Delta I_L}{2} \right) \cdot t_F \right]$ | 無視できる範囲                                                                                                                                                                   |

| MOSFET ゲートドライブ <sup>(1)</sup> | $P_{Gate1} = V_{CC} \cdot F_{SW} \cdot Q_{G1}$                                                                                                                             | $P_{Gate2} = V_{CC} \cdot F_{SW} \cdot Q_{G2}$                                                                                                                            |

| MOSFET 出力電荷 <sup>(4)</sup>    | $P_{Coss} = F_{SW} \cdot (V_{IN} \cdot Q_{oss2} + E_{oss1} - E_{oss2})$                                                                                                    |                                                                                                                                                                           |

| ボディダイオード導通                    | 該当なし                                                                                                                                                                       | $P_{cond_BD} = V_F \cdot F_{SW} \left[ \left( I_{OUT} + \frac{\Delta I_L}{2} \right) \cdot t_{dt1} + \left( I_{OUT} - \frac{\Delta I_L}{2} \right) \cdot t_{dt2} \right]$ |

| ボディダイオードの逆回復 <sup>(5)</sup>   |                                                                                                                                                                            | $P_{RR} = V_{IN} \cdot F_{SW} \cdot Q_{RR2}$                                                                                                                              |

- (1) ゲートドライブ損失は、MOSFET の内部ゲート抵抗、外付けの直列ゲート抵抗、LM25137 の関連ドライバ抵抗に基づき分配されます。

- (2) MOSFET の  $R_{DS(on)}$  の正の温度係数は、約 4500ppm/°C です。MOSFET の接合部温度  $T_J$  と、周囲温度と比べて接合部温度がどれだけ上昇するかは、デバイスの総消費電力とその熱インピーダンスに依存します。最小入力電圧や、それに近い電圧で動作する時には、MOSFET の  $R_{DS(on)}$  は利用可能なゲートドライブ電圧の定格になります。

- (3)  $D' = 1-D$  は、デューティサイクルの補数です。

- (4) MOSFET の出力容量  $C_{oss1}$  と  $C_{oss2}$  は、電圧に対して高度な非線形形となります。これらの容量は、ハイサイド MOSFET ターンオフ時のインダクタ電流によりロスレスで充電されます。ただし、ターンオン時には電流は入力から流れため、ローサイド MOSFET の出力容量が充電されます。 $C_{oss1}$  のエネルギー  $E_{oss1}$  はターンオン時に消費されますが、この消費は  $C_{oss2}$  に保存されているエネルギー  $E_{oss2}$  で相殺されます。詳細については、『[GaN FET とシリコン MOSFET における DC-DC コンバータ性能のデッドタイム効果の比較](#)』 ECCE 2016 を参照してください。

- (5) MOSFET ボディダイオードの逆回復電荷  $Q_{RR}$  は、さまざまなパラメータ、特に順方向電流、電流遷移速度、温度に依存します。

ハイサイド (制御) MOSFET は、PWM のオン時間 (または D 間隔) 中にインダクタ電流を流し、通常はスイッチング損失のほとんどはここで発生します。そのため、導通損失とスイッチング損失への関与のバランスを取るハイサイド MOSFET を選択してください。ハイサイド MOSFET の総消費電力は、以下の合計になります。

- 導通による損失

- スイッチング (電圧と電流の重複)

- 出力電荷量

- 通常、ボディダイオードの逆回復に起因する正味の損失の 3 分の 2

ローサイド (同期) MOSFET は、ハイサイド MOSFET がオフ (または 1-D 間隔) のときにインダクタ電流を流します。ローサイド MOSFET はゼロ電圧でスイッチングするため、スイッチング損失は無視できます。電流はチャネルからボディダイオードへ流れますが、遷移デッドタイム中は逆方向にも流れます。LM25137 は適応型ゲートドライブタイミングを使用しているため、両方の MOSFET がオフのときに、ボディダイオードの導通損失を最小に抑えます。この損失は、スイッチング周波数に正比例します。

ステップダウン比の高いアプリケーションでは、スイッチング時間の大部分でローサイド MOSFET は電流を流します。そのため、高効率を実現するには、低  $R_{DS(on)}$  のときにローサイド MOSFET を最適化することが重要です。導通損失が大きすぎる場合、または目標とする  $R_{DS(on)}$  が単一の MOSFET で実現可能な値より低い場合は、2 つのローサイド MOSFET を並列に接続します。ローサイド MOSFET の総消費電力は、チャネル導通、ボディダイオード導通、ボディダイオードの逆回復に起因する正味の損失の通常 3 分の 1 の合計になります。LM25137 は、TI の [パワー MOSFET](#) の製品ラインを駆動するのに最適です。

### 8.1.1.2 降圧インダクタ

多くのアプリケーションでは、公称入力電圧におけるインダクタのリップル電流  $\Delta I_L$  が最大 DC 出力電流の 30% ~ 50% の間になるように降圧インダクタンスを選択します。式 12 に示されるピークインダクタ電流に基づき、式 11 を使用してインダクタンスを選択します。

$$L_O = \frac{V_{OUT}}{\Delta I_L \cdot F_{SW}} \cdot \left( 1 - \frac{V_{OUT}}{V_{IN}} \right) \quad (11)$$

$$I_{L(peak)} = I_{OUT} + \frac{\Delta I_L}{2} \quad (12)$$

インダクタのデータシートを参照し、飽和電流定格が特定の設計のピークインダクタ電流よりも十分に大きいことを確認します。フェライトコアのインダクタはコア損失が非常に低く、高スイッチング周波数で好まれます。そのため、設計の目標を銅損と飽和の防止に集中することができます。低インダクタのコア損失は、無負荷の入力電流の低下と軽負荷時の効率の向上により明らかです。ただし、フェライトのコア素材は飽和特性が高く、飽和電流を超過するとインダクタンスは急激に低下します。この動作の結果、インダクタのリップル電流には並外れた増加が生じ、出力電圧リップルも上昇するため、当然効率は低下し、信頼性も損なわれます。一般的に、インダクタの飽和電流定格はコア温度が上がるにつれて減少することに注意してください。もちろん、インダクタの飽和を防止するには正確な過電流保護が重要です。

### 8.1.1.3 出力コンデンサ

通常、出力コンデンサによるエネルギーの保存と制御ループ応答の組み合わせは、出力電圧の整合性を動的(過渡)許容誤差の仕様範囲内に保つために規定されます。電源管理アプリケーションで出力コンデンサを制限する通常の境界は、限られた中で利用可能なPCB面積、部品の取付面積とプロファイル、コストによって決まります。負荷ステップの振幅とスルーレートが増加するにつれて、コンデンサの寄生(等価直列抵抗(ESR)と等価直列インダクタンス(ESL))は、レギュレータの負荷過渡応答の形成において優先度がより高くなります。

出力コンデンサ  $C_{OUT}$  はインダクタのリップル電流をフィルタリングして、ステップ負荷過渡イベントのために電荷を蓄積します。一般的に、セラミックコンデンサの ESR は非常に低いため、出力電圧リップルとノイズスパイクは低減されますが、タンタルコンデンサとポリマー電解コンデンサは過渡負荷イベント用の比較的小さなフットプリントのものでも、バルク容量は非常に大きくなります。

$\Delta V_{OUT}$  で示されるピークツーピーク出力電圧リップルの静的仕様に基づき、式 13 で求められる値よりも高い出力容量を選択します。

$$C_{OUT} \geq \frac{\Delta I_L}{8 \cdot F_{SW} \sqrt{\Delta V_{OUT}^2 - (R_{ESR} \cdot \Delta I_L)^2}} \quad (13)$$

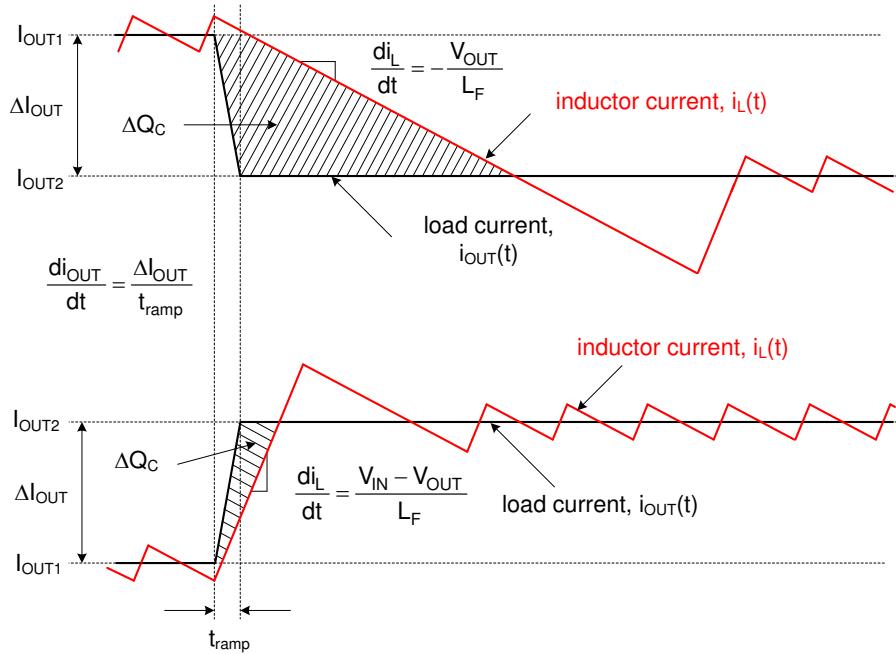

図 8-1 は、負荷の上昇遷移時と下降遷移時の関連電流の波形を概念的に表した図です。ここに示すように、インダクタ電流のスルーレートは、負荷過渡に伴い新しい負荷電流レベルに合うようにインダクタ電流が上昇する際の、大信号の制限を表しています。このスルーレートの制限により、出力コンデンサの電荷の損失はより大きくなります。そのため、負荷の上昇過渡時とその後はできる限り迅速に電荷を補充する必要があります。同様に、負荷の下降過渡時とその後は、インダクタ電流のスルーレートの制限により出力コンデンサの電荷が増大するため、できる限り早く放電する必要があります。

図 8-1.  $C_{OUT}$  の電荷の増大と損失を表す負荷過渡応答の図

低出力電圧 (3.3V など) への 12V 入力の標準的なレギュレータアプリケーションでは、負荷オフ時の過渡は出力電圧の過渡偏差という点でワーストケースになります。この電圧変換比では、定常状態のデューティサイクルは約 28% で、デューティサイクルがゼロに急減したときの大信号のインダクタ電流のスルーレートは約  $-V_{OUT}/L$  です。負荷オン過渡に比べると、インダクタ電流は必要なレベルに遷移するまでにかなり時間がかかります。出力コンデンサの電荷が過剰になると、出力電圧の深刻なオーバーシュートを引き起します。実際に、出力コンデンサからこの過剰な電荷をできるだけ早く放電するには、負荷ステップに従い、インダクタ電流が公称レベルを下回るようにする必要があります。このシナリオでは、出力容量が大きいほど有利に過剰な電荷を吸収して、電圧のオーバーシュートを最小限に抑えることができます。

このような負荷オフ過渡時に、出力電圧のオーバーシュート ( $\Delta V_{OVERSHOOT}$  と表記され、出力電流の段階的な減少は  $\Delta I_{OUT}$  で与えられます) の動的要件に合わせるように、式 13 で出力容量を計算します。

$$C_{OUT} \geq \frac{L_O \cdot \Delta I_{OUT}^2}{(V_{OUT} + \Delta V_{OVERSHOOT})^2 - V_{OUT}^2} \quad (14)$$

コンデンサメーカーのデータシートには、ESR と ESL が、仕様として明記、またはインピーダンスと周波数曲線の関係によって暗黙的に記載されています。種類、サイズ、構造に応じて、電解コンデンサには  $10m\Omega$  以上の非常に大きな ESR と  $10nH \sim 20nH$  の比較的高い ESL が内蔵されています。PCB パターンは寄生抵抗とインダクタンスにも寄与します。セラミック出力コンデンサはスイッチング周波数における ESR と ESL への寄与が小さく、容量性インピーダンスが優勢です。ただし、セラミックコンデンサのパッケージと電圧定格によっては、実効容量は印加された DC 電圧と動作温度で大幅に低下することがあります。

式 13 の ESR の項を無視すると、出力リップルの要件を満たすために必要な最小セラミック容量を簡単に見積もることができます。5V 出力の場合は、1210 のフットプリントで 4 つの  $47\mu F$ 、10V、X7R コンデンサを選ぶのが一般的です。負荷オフ過渡のオーバーシュート要件を満たすために追加容量が必要かどうかを決定するには、式 14 を使用します。

セラミックコンデンサと電解コンデンサを混在させて実装することは、化学的性質が異なっていても性能補完が可能なコンデンサを並列に接続する理由になります。各コンデンサの周波数応答は累積的で、各コンデンサは適用可能な周波数範囲の特定の部分で必要な性能を発揮します。セラミックは、低 ESR と ESL で優れた中域周波数と高周波数のデカップリング特性を実現し、スイッチング周波数の出力リップルを最小限に抑えます。一方、大きなバルク容量を持つ電解デバイスは低周波数でエネルギー保存を行うため、低周波数負荷過渡要求に対応します。

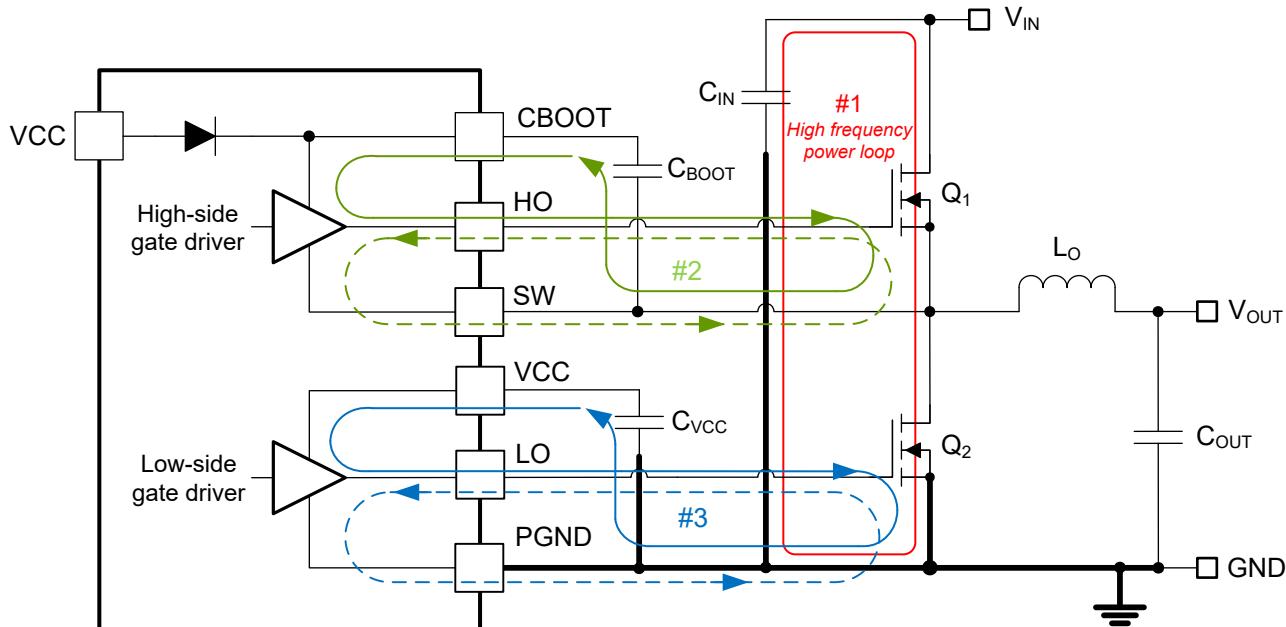

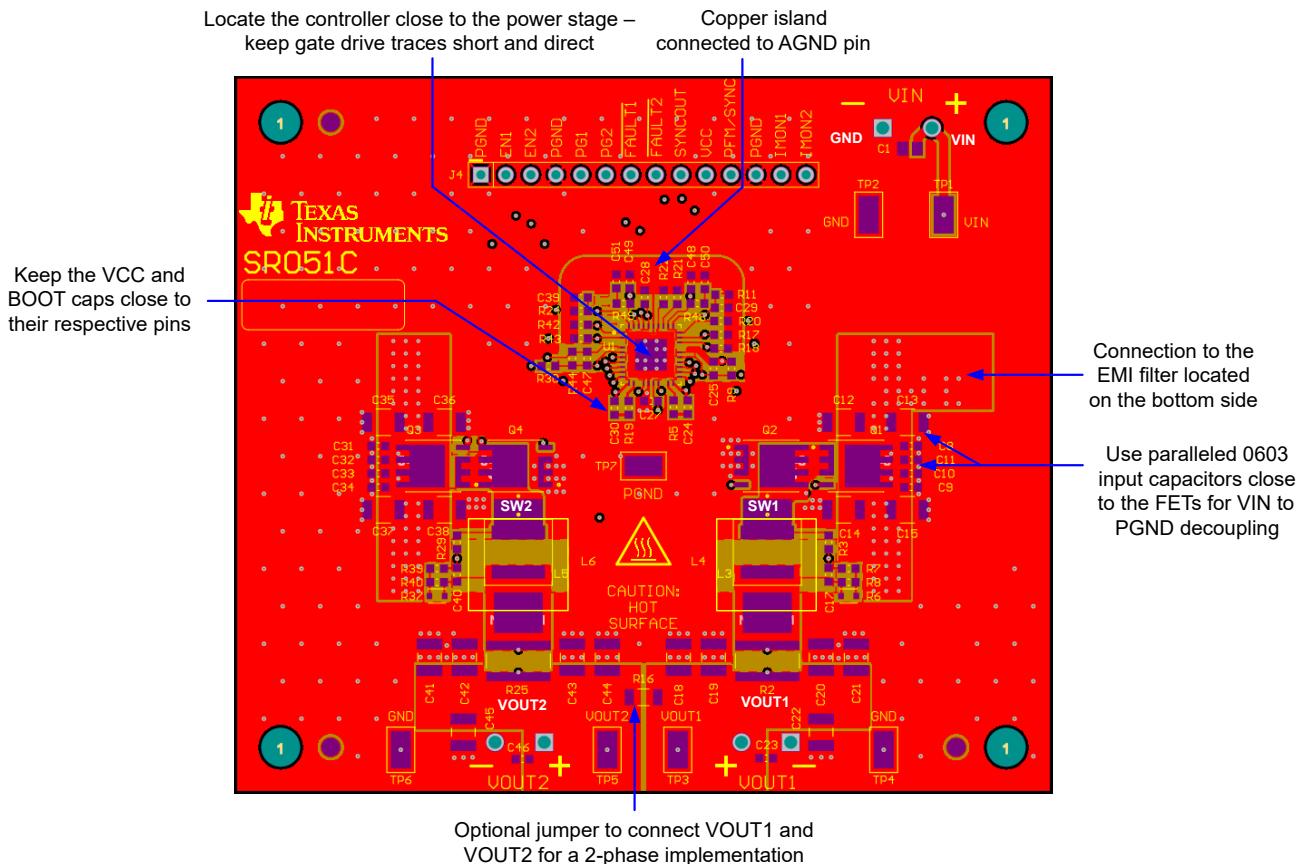

### 8.1.1.4 入力コンデンサ

入力コンデンサは、スイッチング周波数の AC 電流により、降圧出力段への入力リップル電圧を制限する必要があります。テキサス・インストゥルメンツは、幅広い温度範囲で低インピーダンスと高い RMS 電流定格を実現する X7S または X7R 誘電セラミックコンデンサの使用を推奨しています。スイッチングパワーループの寄生インダクタンスを最小化するためには、入力コンデンサをハイサイド MOSFET のドレイン側とローサイド MOSFET のソース側のできる限り近くに配置します。单一チャネル降圧レギュレータの入力コンデンサの RMS 電流を計算するには、式 15 を使用します。

$$I_{CIN,rms} = \sqrt{D \cdot \left( I_{OUT}^2 \cdot (1-D) + \frac{\Delta I_L^2}{12} \right)} \quad (15)$$

入力コンデンサの RMS 電流の最大値は  $D = 0.5$  のときに発生します。この時点で、入力コンデンサの RMS 電流定格は出力電流の約半分になります。

入力電流の DC 成分は入力電圧源と入力セラミックコンデンサによる AC 成分から供給されることが理想です。インダクタリップル電流を無視すると、入力コンデンサは、D 間隔の間に振幅 ( $I_{OUT} - I_{IN}$ ) の電流をソースし、1-D 間隔の間に  $I_{IN}$  をシンクします。そのため、入力コンデンサは、出力電流に等しいピークツーピーク振幅の方形波電流を導通します。その結果、AC リップル電圧の合成容量成分は三角波になります。ESR 関連のリップル成分だけでなく、ピークツーピークリップル電圧の振幅を計算するには、式 16 を使用します。

$$\Delta V_{IN} = \frac{I_{OUT} \cdot D \cdot (1-D)}{F_{SW} \cdot C_{IN}} + I_{OUT} \cdot R_{ESR} \quad (16)$$

$\Delta V_{IN}$  の入力電圧リップル仕様に基づいて、特定の負荷電流に必要な入力容量を計算するには、式 17 を使用します。

$$C_{IN} \geq \frac{D \cdot (1-D) \cdot I_{OUT}}{F_{SW} \cdot (\Delta V_{IN} - R_{ESR} \cdot I_{OUT})} \quad (17)$$

低 ESR のセラミックコンデンサは、より大きな値のバルク容量と並列に配置することで、レギュレータとダンピングの入力フィルタリングを最適化し、Q の高いセラミックと共振する入力寄生インダクタンスの影響を低減することができます。スイッチング周波数と負荷電流レベルにより異なりますが、通常 12V バッテリの車載用アプリケーションには、4 つの 10μF、50V、X7R のセラミックデカップリングコンデンサで十分です。セクション 8.1.1.5 で概説されているように、ディレーティングされたセラミック値の 3 ~ 4 倍に等しい入力バルクコンデンサを選択し、バルクコンデンサが全動作温度範囲で定格になるようにします。

もちろん、180°の位相差のあるインターリーブ スイッチング付き 2 チャネル降圧レギュレータは、入力リップル電流をキャンセルして、入力コンデンサの電流ストレスを低減することができます。上記の式は、1 つのチャネルがディスエーブルで他のチャネルが負荷状態のときに、計算結果が有効になります。

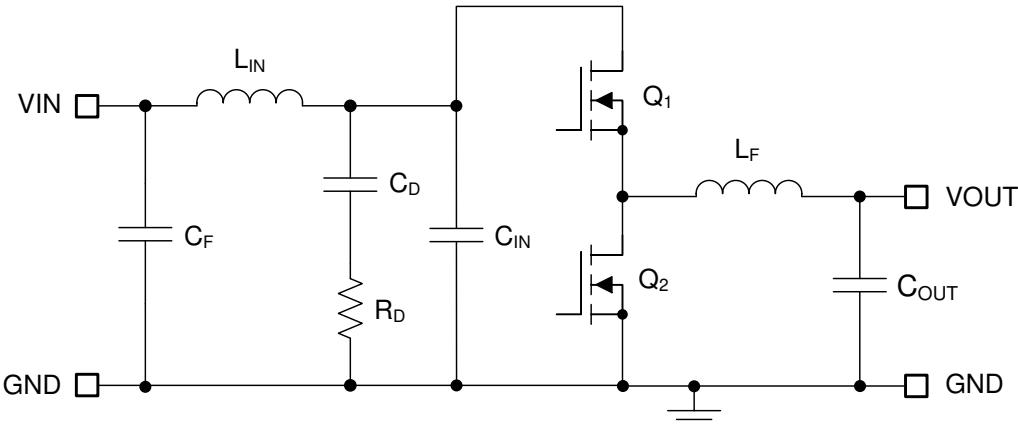

### 8.1.1.5 EMI フィルタ

スイッチングレギュレータは最小入力電圧および全負荷において最小となる負の入力インピーダンス特性を示します。LC フィルタの減衰不足は、フィルタの共振周波数に対して出力インピーダンスが高いことを示しています。安定性のため、LC 部品の特性インピーダンスで近似されるフィルタの出力インピーダンスは、レギュレータの入力インピーダンスの絶対値よりも小さくする必要があります。

$$Z_{IN} = \left| -\frac{V_{IN(min)}^2}{P_{IN}} \right| \quad (18)$$

EMI フィルタの設計手順は以下のとおりです。

- EMI フィルタに対して、スイッチング周波数で要求される減衰を計算します。ここで、 $C_{IN}$  はスイッチングレギュレータの入力における既存の容量を表しています。

- 通常、入力フィルタインダクタ  $L_{IN}$  は  $1\mu H \sim 6.8\mu H$  の間で選択されますが、大電流設計での損失を低減するためには、さらに小さい値にすることも可能です。

- 入力フィルタコンデンサ  $C_F$  を計算します。

図 8-2.  $\pi$  段 EMI フィルタ付き降圧レギュレータ

入力電流波形のフーリエ級数から最初に高調波電流を計算し、その値に入力インピーダンス（インピーダンスは既存の入力コンデンサ  $C_{IN}$  で定義）を乗算します。式 19 は必要な減衰を求める式を示します。

$$Attn = 20 \log \left( \frac{I_{L(Peak)}}{\pi^2 \cdot F_{SW} \cdot C_{IN}} \cdot \sin(\pi \cdot D_{MAX}) \cdot \frac{1}{1\mu V} \right) - V_{MAX} \quad (19)$$

ここで、

- $V_{MAX}$  は、適用可能な伝導 EMI仕様に許容される  $dB\mu V$  ノイズレベルです (CISPR 25 クラス 5 など)

- $C_{IN}$  は、降圧レギュレータの既存の入力容量です

- $D_{MAX}$  は最大動作デューティサイクルです (最小入力電圧時)

- $I_{L(Peak)}$  はピークインダクタ電流です

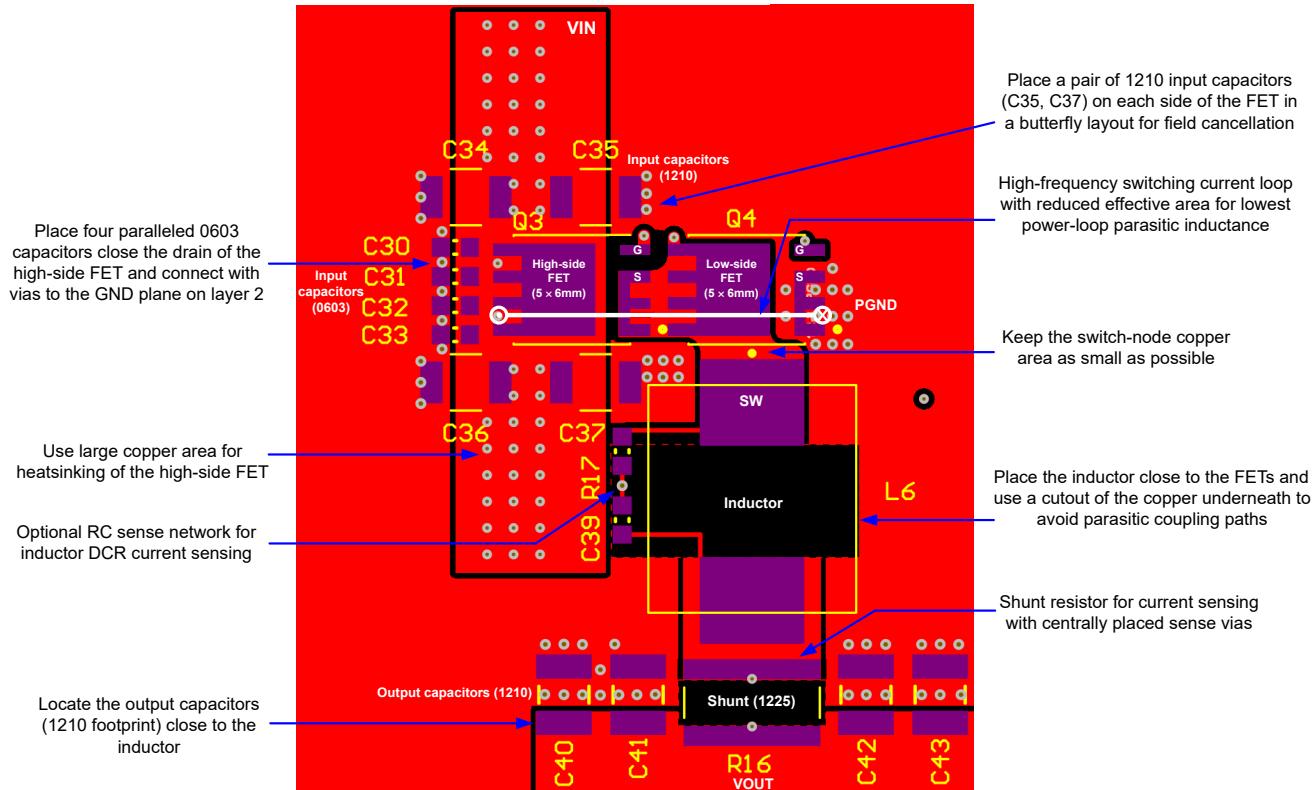

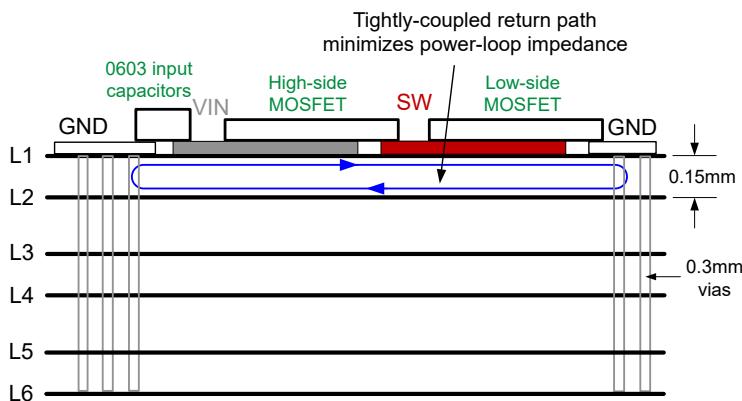

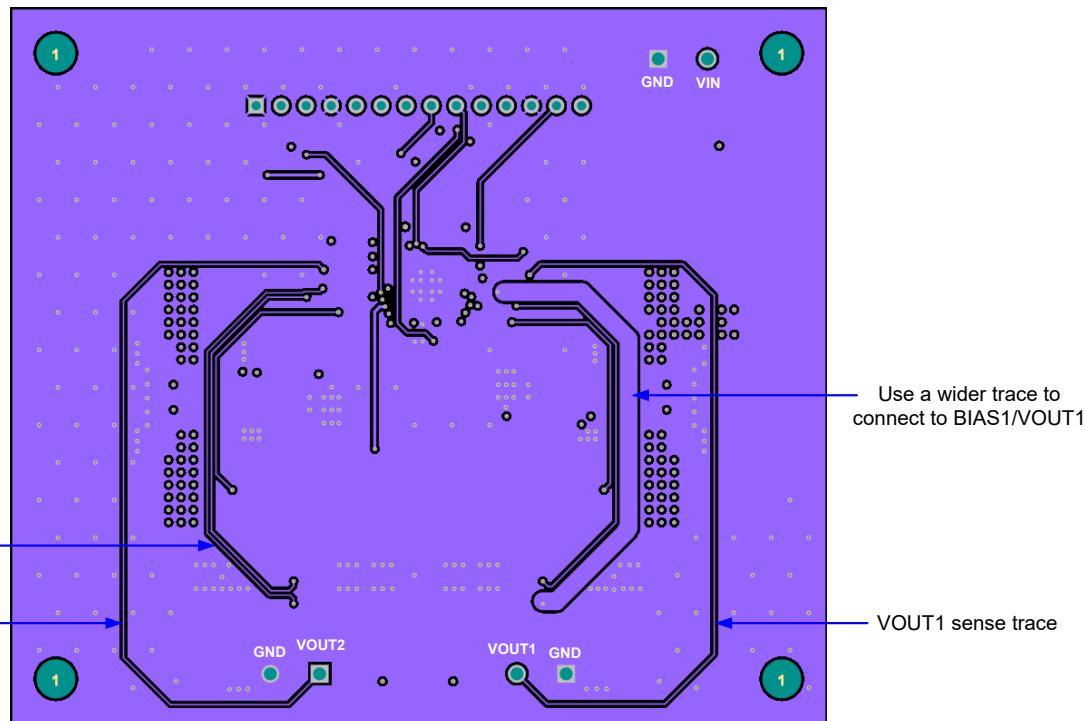

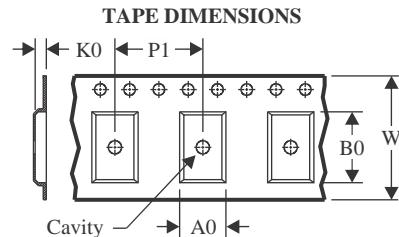

フィルタ設計の目的のため、入力時の電流を方形波でモデリングすることができます。式 20 から EMI フィルタ容量  $C_F$  を決定します。