## LMG365xR035 ドライバと保護機能を内蔵した 650V、35mΩ GaN FET

### 1 特長

- ゲートドライバ内蔵、650V、35mΩ の GaN 電力 FET

- >200V/ns の FET ホールド オフ

- 調整可能なスルーレートによるスイッチングパフォーマンスの最適化と EMI の軽減

- 10V/ns から 80V/ns の有効化スルーレート

- 10V/ns からフルスピードの有効化スルーレート

- 電源ピンと入力ロジックピンの 9V から 26V の電圧範囲で動作します

- 堅牢な保護

- サイクル単位の過電流保護と応答時間 300ns 未満のラッチ付き短絡保護

- のサージ耐性: 720V

- 内部過熱および UVLO 監視機能による自己保護

- 高度なパワー マネージメント

- LMG3656R035 は、ソフトスイッチング コンバータとを利用可能にするゼロ電圧検出機能 (ZVD) を備えています。

- LMG3657R035 は、ソフトスイッチング コンバータとを利用可能にするゼロ電流検出機能 (ZCD) を備えています。

- サーマル パッド付き 9.8mm × 11.6mm TOLL パッケージ

### 2 アプリケーション

- オープンラック サーバー PSU

- 商用テレコム整流器

- 一般的な冗長電源

- 無停電電源

- ソーラー インバータと産業用モーター ドライブ

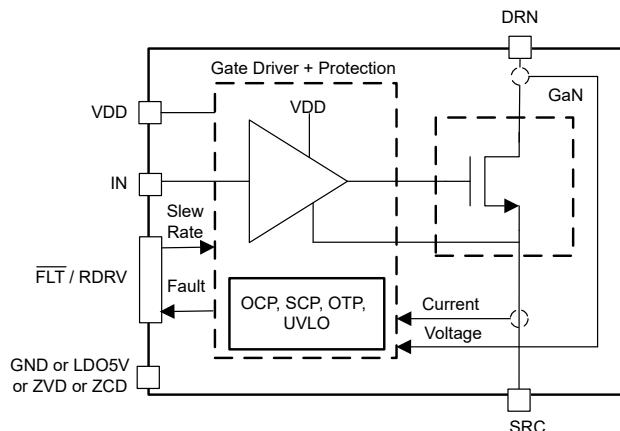

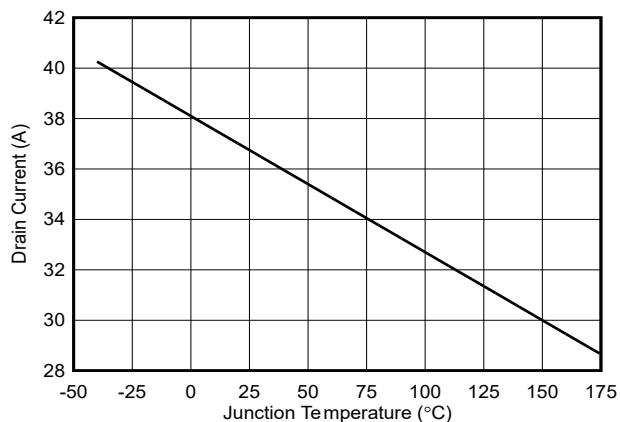

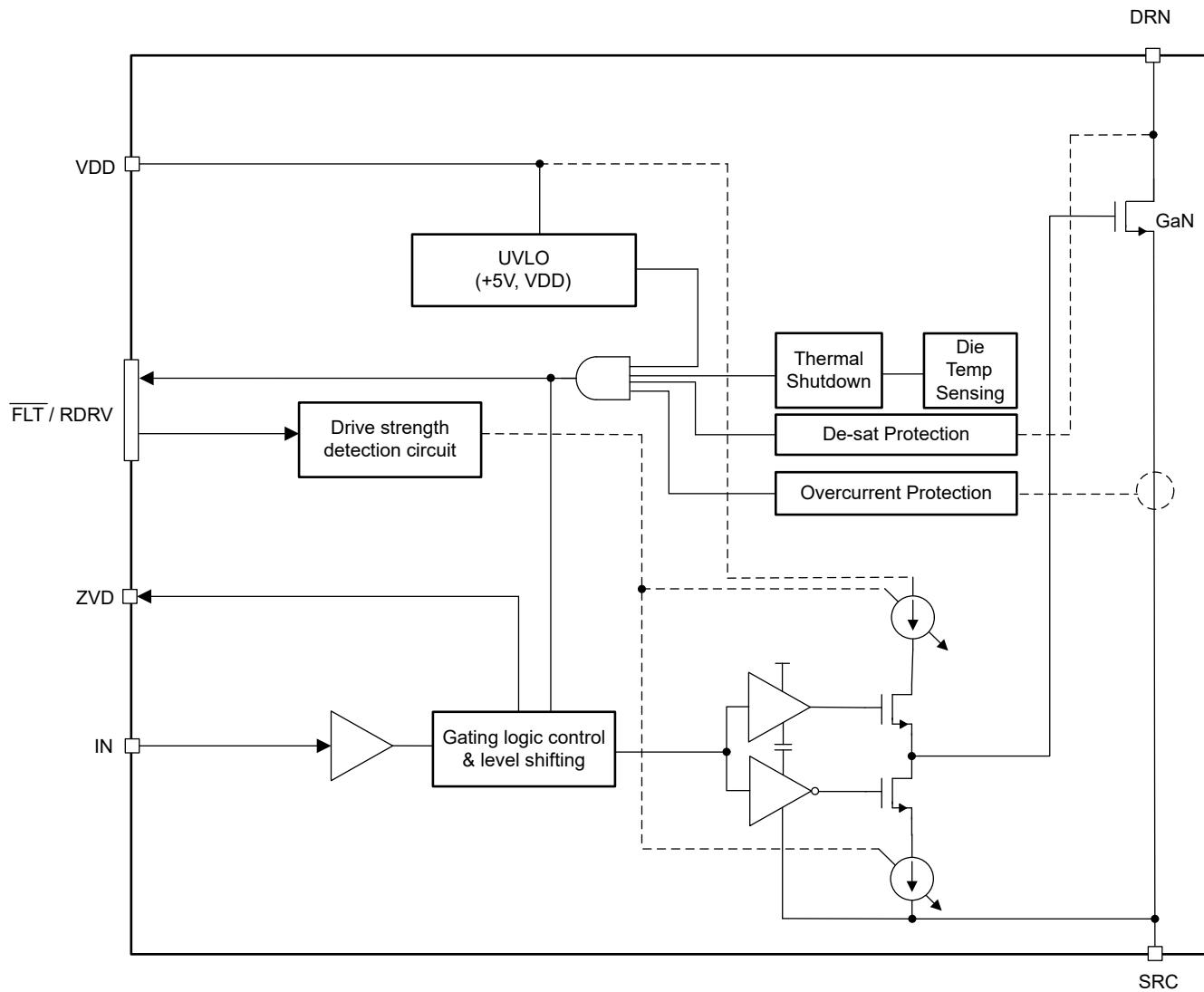

概略ブロック図

### 3 説明

統合型ドライバと保護機能を搭載した LMG365xR035 GaN FET は、スイッチ モード パワー コンバータを対象としています。このデバイスを使うと、設計者は新しいレベルの電力密度と効率を実現できます。

調整可能なゲート ドライブ強度により、独立な有効化と最大限無効化スルーレートの制御が可能で、EMI のアクティブ制御とスイッチング性能の最適化に使用できます。ターンオンのスルーレートは 10V/ns から 80V/ns まで変化しますが、ターンオフのスルーレート、負荷電流の大きさに応じて 10V/ns から最大値に制限することができます。保護機能として、低電圧ロックアウト (UVLO)、サイクル単位の電流制限、短絡保護、および過熱保護が搭載されています。LMG3651R035 は、外部デジタル アイソレータに電源を供給するための 5V LDO 出力を LDO5V ピンに備えています。LMG3656R035 は、ゼロ電圧検出 (ZVD) 機能を備えており、ゼロ電圧スイッチングが発生したとき ZVD ピンからパルスを出力します。LMG3657R035 は、ドレイン-ソース間電流が負であり、ゼロクロスポイント検出時に Low に遷移すると ZCD ピンを High に設定するゼロ電流検出 (ZCD) 機能を備えています。

#### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| LMG365xR035 | KLA (TOLL, 9)        | 9.8mm × 11.6mm           |

(1) 供給されているすべてのパッケージについては、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はビンも含まれます。

#### 製品情報

| 部品番号                       | LDO 5V 出力 | ゼロ電圧検出機能 | ゼロ電流検出機能 |

|----------------------------|-----------|----------|----------|

| LMG3650R035                | —         | —        | —        |

| LMG3651R035 <sup>(1)</sup> | あり        | —        | —        |

| LMG3656R035 <sup>(1)</sup> | —         | あり       | —        |

| LMG3657R035 <sup>(1)</sup> | —         | —        | あり       |

(1) 製品プレビュー

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                  |    |                        |    |

|------------------|----|------------------------|----|

| 1 特長             | 1  | 7.3 機能説明               | 17 |

| 2 アプリケーション       | 1  | 7.4 デバイスの機能モード         | 25 |

| 3 説明             | 1  | 8 アプリケーションと実装          | 26 |

| 4 ピン構成および機能      | 3  | 8.1 アプリケーション情報         | 26 |

| 5 仕様             | 4  | 8.2 代表的なアプリケーション       | 27 |

| 5.1 絶対最大定格       | 4  | 8.3 電源に関する推奨事項         | 33 |

| 5.2 ESD 定格       | 4  | 8.4 レイアウト              | 35 |

| 5.3 推奨動作条件       | 4  | 9 デバイスおよびドキュメントのサポート   | 42 |

| 5.4 熱に関する情報      | 5  | 9.1 ドキュメントの更新通知を受け取る方法 | 42 |

| 5.5 電気的特性        | 5  | 9.2 サポート・リソース          | 42 |

| 5.6 スイッチング特性     | 6  | 9.3 商標                 | 42 |

| 5.7 代表的特性        | 8  | 9.4 静電気放電に関する注意事項      | 42 |

| 6 パラメータ測定情報      | 10 | 9.5 用語集                | 42 |

| 6.1 スイッチング パラメータ | 10 | 10 改訂履歴                | 42 |

| 7 詳細説明           | 13 | 11 メカニカル、パッケージ、および注文情報 | 43 |

| 7.1 概要           | 13 | 11.1 テープおよびリール情報       | 45 |

| 7.2 機能ブロック図      | 14 |                        |    |

## 4 ピン構成および機能

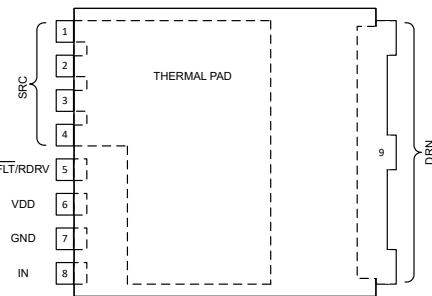

図 4-1. LMG3650R035、TOLL パッケージ (上面図)

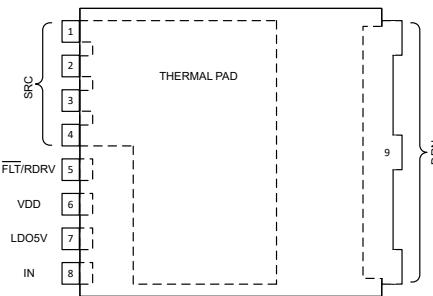

図 4-2. LMG3651R035、TOLL パッケージ (上面図)

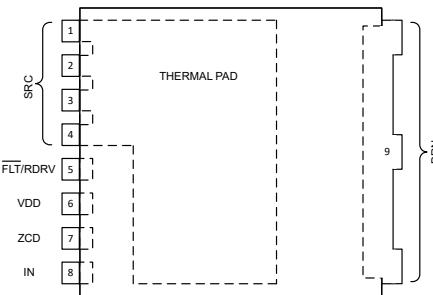

図 4-3. LMG3656R035、TOLL パッケージ (上面図)

図 4-4. LMG3657R035、TOLL パッケージ (上面図)

表 4-1. ピンの機能

| 名称       | ピン              |                 |                 |                 |      | タイプ<br>(1)                                                                                                                                               | 説明 |

|----------|-----------------|-----------------|-----------------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          | LMG3650<br>R035 | LMG3651<br>R035 | LMG3656<br>R035 | LMG3657<br>R035 |      |                                                                                                                                                          |    |

| SRC      | 1 ~ 4           | 1 ~ 4           | 1 ~ 4           | 1 ~ 4           | P    | GaN FET ソース。                                                                                                                                             |    |

| FLT/RDRV | 5               | 5               | 5               | 5               | O, I | 故障監視およびドライブ強度選択ピン。ターンオン時のドライブ強度を設定するために、このピンから GND へ抵抗を接続します。ターンオフ時のドライブ強度を設定するために、このピンから GND へ抵抗とコンデンサを直列で接続します。スルーレートは電源投入時に 1 回設定され、このピンは故障監視に使用されます。 |    |

| VDD      | 6               | 6               | 6               | 6               | P    | デバイス入力電源                                                                                                                                                 |    |

| GND      | 7               | —               | —               | —               | G    | 信号グランド。内部で SRC とサーマルパッドに接続。                                                                                                                              |    |

| LDO5V    | —               | 7               | —               | —               | P    | 外部デジタルアイソレーター用の 5V LDO 出力。                                                                                                                               |    |

| ZVD      | —               | —               | 7               | —               | O    | デバイスが電流スイッチング サイクルにおいてゼロ電圧スイッチングを達成しているかどうかを示す、ゼロ電圧検出信号を出力するプッシュプル デジタル出力。                                                                               |    |

| ZCD      | —               | —               | —               | 7               | O    | ドレイン ソース間の電流が負のときに ZCD ピンを high にし、ゼロを交差する点を検出すると low へ遷移するプッシュプルのデジタル出力。                                                                                |    |

| IN       | 8               | 8               | 8               | 8               | I    | FET のオン/オフ用に使用される CMOS 互換非反転入力                                                                                                                           |    |

| DRN      | 9               | 9               | 9               | 9               | P    | GaN FET のドレイン                                                                                                                                            |    |

| サーマル パッド | —               | —               | —               | —               | —    | サーマルパッド。                                                                                                                                                 |    |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 5 仕様

### 5.1 絶対最大定格

特に記述のない限り: 電圧は GND/SRC を基準にしています<sup>(1)</sup>

|                                   |                                                                                   |                                                    | 最小値               | 最大値 | 単位 |

|-----------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------|-------------------|-----|----|

| $V_{DS}$                          | ドレインソース間電圧、FET オフ                                                                 |                                                    |                   | 650 | V  |

| $V_{DS(\text{surge})}$            | ドレイン ソース間電圧、サージ条件、FET オフ                                                          |                                                    |                   | 720 | V  |

| $V_{DS(\text{tr})(\text{surge})}$ | ドレイン ソース間の過渡リギングのピーク電圧、サージ条件、FET オフ                                               |                                                    |                   | 800 | V  |

| ピン電圧                              |                                                                                   | VDD                                                | -0.5              | 26  | V  |

|                                   |                                                                                   | IN                                                 | -5 <sup>(2)</sup> | 28  | V  |

|                                   |                                                                                   | FLT/RDRV, ZVD<br>(LMG3656 のみ)、<br>ZCD (LMG3657 のみ) | -0.5              | 5.5 | V  |

|                                   |                                                                                   | LDO5V (LMG3651 のみ)                                 |                   | 5.5 | V  |

| $I_{D(\text{cnts})}$              | ドレイン (DRN から SRC) 連続電流、FET オン。 $T_j = 25^\circ\text{C}$ <sup>(3)</sup>            |                                                    | -40               | 40  | A  |

| $I_{D(\text{cnts})}$              | ドレイン (DRN から SRC) 連続電流、FET オン。 $T_j = 150^\circ\text{C}$ <sup>(3)</sup>           |                                                    | -33               | 33  | A  |

| $I_{D(\text{pulse})}$             | パルスドレイン電流、FET オン、 $t_p < 10\mu\text{s}$ 。 $T_j = 25^\circ\text{C}$ <sup>(3)</sup> |                                                    | -45               | 45  | A  |

| $I_{S(\text{cnts})}$              | ソース (SRC から DRN) 連続電流、FET オフ。 $T_j = 25^\circ\text{C}$                            |                                                    |                   | 40  | A  |

| $I_{S(\text{cnts})}$              | ソース (SRC から DRN) 連続電流、FET オフ。 $T_j = 150^\circ\text{C}$                           |                                                    |                   | 33  | A  |

| $T_j$                             | 動作時接合部温度 <sup>(4)</sup>                                                           |                                                    | -40               | 175 | °C |

| $T_{\text{stg}}$                  | 保存温度                                                                              |                                                    | -65               | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) IN ピン電圧は定常状態で最小 -0.5V に制限され、過渡的には 1μs 未満の期間で -5V まで許容されます。

- (3) 絶対最大定格は、デバイスの内部過電流保護機能によって制限されます。ただし、FET ドレインの固有の正方向パルス電流定格 ( $t_p < 10\mu\text{s}$ ) は接合温度によって変動します。25°C では典型値、150°C では典型値 68A です。FET が自動的にシャットオフされないように、正のパルス電流は過電流スレッショルドを下回る必要があります。

- (4) 接合部温度のテスト条件については、「電気的およびスイッチング特性」表を参照してください。

### 5.2 ESD 定格

|                    |      |                                                          | 値     | 単位 |

|--------------------|------|----------------------------------------------------------|-------|----|

| $V_{(\text{ESD})}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠 <sup>(1)</sup>    | ±2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±500  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

特に記述のない限り: 電圧は GND/SRC を基準にしています

|                      |                                                          |                    | 最小値 | 公称値 | 最大値 | 単位 |

|----------------------|----------------------------------------------------------|--------------------|-----|-----|-----|----|

|                      | 電源電圧                                                     | VDD                | 9   | 24  |     | V  |

|                      | 入力電圧                                                     | IN                 | 0   | 26  |     | V  |

| $I_{D(\text{cnts})}$ | ドレイン (DRN から SRC) 連続電流、FET オン。 $T_j = 25^\circ\text{C}$  |                    | -34 | 34  |     | A  |

| $I_{D(\text{cnts})}$ | ドレイン (DRN から SRC) 連続電流、FET オン。 $T_j = 150^\circ\text{C}$ |                    | -26 | 26  |     | A  |

|                      | 正のソース電流                                                  | LDO5V (LMG3651 のみ) |     |     | 25  | mA |

特に記述のない限り: 電圧は GND/SRC を基準にしています

|                     |                                                            | 最小値  | 公称値  | 最大値 | 単位 |

|---------------------|------------------------------------------------------------|------|------|-----|----|

| RDRV <sub>on</sub>  | FLT/RDRV と GND の間の外部ターンオン スルーレート制御抵抗からの抵抗                  | 29.4 | オープン |     | kΩ |

| RDRV <sub>off</sub> | 外部ターンオフ スルーレート制御用直列抵抗および FLT/RDRV と GND の間のコンデンサ構成からの抵抗と容量 | 2    | オープン |     | kΩ |

| CDRV <sub>off</sub> |                                                            | 0    | 1800 |     | pF |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     | KLA (TOLL) | 単位   |

|-----------------------------|---------------------|------------|------|

|                             |                     | 9 ピン       |      |

| R <sub>θJC</sub> (bot, avg) | 接合部からケース(底面)への平均熱抵抗 | 0.65       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

特に記載のない限り、電圧、抵抗、容量、インダクタンスは GND/SRC 基準で、 $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$ 、VDD = 12V、FLT/RDRV の抵抗 RDRV<sub>on</sub> と RDRV<sub>off</sub> はオープンです

| パラメータ                     |                        | テスト条件                                          | 最小値 | 標準値 | 最大値  | 単位 |

|---------------------------|------------------------|------------------------------------------------|-----|-----|------|----|

| <b>GaN パワー FET</b>        |                        |                                                |     |     |      |    |

| R <sub>DS(on)</sub>       | ドレインソース間オン抵抗           | T <sub>J</sub> = 25°C, I <sub>L</sub> = 16A    | 32  | 45  |      | mΩ |

|                           |                        | T <sub>J</sub> = 150°C, I <sub>L</sub> = 16A   | 65  |     |      | mΩ |

| V <sub>SD</sub>           | ソースドレイン間第 3 象限電圧       | T <sub>J</sub> = 25°C, I <sub>SD</sub> = 0.1A  | 1.1 |     |      | V  |

|                           |                        | T <sub>J</sub> = 150°C, I <sub>SD</sub> = 0.1A | 1.4 |     |      | V  |

|                           |                        | T <sub>J</sub> = 25°C, I <sub>SD</sub> = 20A   | 2.1 |     |      | V  |

|                           |                        | T <sub>J</sub> = 150°C, I <sub>SD</sub> = 20A  | 3.7 |     |      | V  |

| I <sub>DSS</sub>          | ドレインリーキ電流              | T <sub>J</sub> = 25°C, V <sub>DS</sub> = 650V  | 4   |     |      | μA |

|                           |                        | T <sub>J</sub> = 150°C, V <sub>DS</sub> = 650V | 7   |     |      | μA |

| C <sub>OSS</sub>          | 出力容量                   | V <sub>DS</sub> = 0V ~ 400V                    | 200 |     |      | pF |

| Q <sub>OSS</sub>          | 出力チャージ                 |                                                | 100 |     |      | nC |

| E <sub>OSS</sub>          | 蓄積された出力容量              |                                                | 15  |     |      | μJ |

| C <sub>OSS(tr)</sub>      | 時間に関連した実効出力容量          |                                                | 255 |     |      | pF |

| C <sub>OSS(er)</sub>      | エネルギーに関連する実効出力容量       |                                                | 200 |     |      | pF |

| Q <sub>RR</sub>           | 逆方向回復電荷                |                                                | 0   |     |      | nC |

| <b>過電流および短絡保護</b>         |                        |                                                |     |     |      |    |

| I <sub>T(OC)</sub>        | 過電流故障 – スレッショルド電流      | T <sub>J</sub> = -40°C                         | 38  | 42  | 46   | A  |

|                           |                        | T <sub>J</sub> = 25°C                          | 34  | 37  | 40   | A  |

|                           |                        | T <sub>J</sub> = 150°C                         | 26  | 29  | 33   | A  |

| V <sub>T(Idsat)</sub>     | 飽和電流検出 - スレッショルド電圧     |                                                | 8.5 | 9   | 9.6  | V  |

| <b>過熱保護</b>               |                        |                                                |     |     |      |    |

| T <sub>T+</sub>           | 温度故障 – 正方向のスレッショルド温度   |                                                |     | 190 |      | °C |

| T <sub>T(hyst)</sub>      | 温度故障 – スレッショルド温度ヒステリシス |                                                |     | 20  |      | °C |

| <b>IN</b>                 |                        |                                                |     |     |      |    |

| V <sub>IN, IT+</sub>      | 正方向入力スレッショルド電圧         |                                                | 1.6 | 2   | 2.45 | V  |

| V <sub>IN, IT-</sub>      | 負方向入力スレッショルド電圧         |                                                | 0.6 | 0.9 | 1.3  | V  |

| V <sub>IN, IT(hyst)</sub> | 入力スレッショルド電圧のヒステリシス     |                                                |     | 1   |      | V  |

| R <sub>PDN</sub>          | ブルダウン入力抵抗              |                                                | 115 | 150 | 185  | kΩ |

| <b>FLT/RDRV</b>           |                        |                                                |     |     |      |    |

特に記載のない限り、電圧、抵抗、容量、インダクタンスは GND/SRC 基準で、 $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$ 、 $V_{DD} = 12\text{V}$ 、 $\overline{FLT}/RDRV$  の抵抗  $RDRV_{on}$  と  $RDRV_{off}$  はオープンです

| パラメータ                |                        | テスト条件                                                                      | 最小値 | 標準値 | 最大値  | 単位 |

|----------------------|------------------------|----------------------------------------------------------------------------|-----|-----|------|----|

| $V_{OL}$             | Low レベル出力電圧            | 出力シンク 8mA                                                                  |     | 0.2 | 0.4  | V  |

| $V_{OH}$             | High レベル出力電圧           | 出力ソース 8mA                                                                  | 4.5 | 4.8 |      | V  |

| <b>VDD</b>           |                        |                                                                            |     |     |      |    |

| $I_{VDD(ON)}$        | パワ FET がオンの場合の静止電流     | $IN=1$                                                                     |     | 1.2 | 11.5 | mA |

| $I_{VDD(OFF)}$       | パワ FET がオフの場合の静止電流     | $IN=0$                                                                     |     | 0.7 | 1.1  | mA |

| $I_{CC\_op}$         | 140kHz での動作電流          | $f_{sw} = 140\text{kHz}$ 、 $V_{bus} = 0\text{V}$ 、ソフトスイッチング、デューティサイクル 50%。 |     | 3.2 | 4.8  | mA |

| $V_{VDD, T+ (UVLO)}$ | UVLO - 正方向のスレッショルド電圧   |                                                                            | 8.1 | 8.5 | 8.9  | V  |

| $V_{VDD, T- (UVLO)}$ | UVLO - 負方向のスレッショルド電圧   |                                                                            | 7.6 | 8   | 8.4  | V  |

| $V_{VDD, T(hyst)}$   | UVLO - スレッショルド電圧ヒステリシス |                                                                            |     | 0.5 |      | V  |

## 5.6 スイッチング特性

特に記載のない限り、電圧、抵抗、容量、インダクタンスは GND/SRC 基準で、 $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$ 、 $V_{DD} = 12\text{V}$ 、 $\overline{FLT}/RDRV$  の抵抗  $RDRV_{on}$  と  $RDRV_{off}$  はオープンです

| パラメータ            |                         | テスト条件                                                                                                                     | 最小値 | 標準値 | 最大値 | 単位   |

|------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| <b>スイッチング時間</b>  |                         |                                                                                                                           |     |     |     |      |

| $t_{d(on)}$      | ターンオン遅延時間               | $V_{IN} > V_{IN,IT+}$ から $V_{DS} < 320\text{V}$ まで、 $V_{BUS} = 400\text{V}$ 、 $L_{HB}$ 電流 = 0A、80V/ns                     |     | 50  | 60  | ns   |

|                  | ターンオン電流の立ち上がり時間 + 遅延時間  | $V_{IN} > V_{IN,IT+}$ から $V_{DS} < 320\text{V}$ まで、 $V_{BUS} = 400\text{V}$ 、 $L_{HB}$ 電流 = 10A、80V/ns                    |     | 50  | 60  | ns   |

| $t_{vf(on)}$     | ターンオン電圧の立ち下がり時間         | $V_{DS} < 320\text{V}$ から $V_{DS} < 80\text{V}$ まで、 $V_{BUS} = 400\text{V}$ 、 $L_{HB}$ 電流 = 10A、80V/ns                    | 3.4 | 4.3 | 5.2 | ns   |

|                  | ターンオンのスルーレート            | $V_{DS} = 200\text{V}$ のときの $dv/dt$ 、 $V_{BUS} = 400\text{V}$ 、 $L_{HB}$ 電流 = 10A、80V/ns                                  | 50  | 80  | 95  | V/ns |

|                  | パルス幅歪み                  | 80V/ns のスルーレート設定時の $IDS = 21\text{A}$ 。IN パルス幅と VSW パルス幅の差を測定                                                             |     | 16  | 24  | ns   |

|                  | 出力を L-H-L に変化させる最小入力パルス | SW が 200V を交差するように、スルーレートを 80V/ns に設定                                                                                     |     |     | 40  | ns   |

| $t_{d(off)}$     | 最高速度でのターンオフ遅延時間         | $V_{IN} < V_{IN,IT-}$ から $V_{DS} \geq 80\text{V}$ 。<br>$V_{BUS} = 400\text{V}$ 、 $I_L = 24\text{A}$ 、最高速またはフルターンオフ速度。     | 18  | 37  | 55  | ns   |

| $t_{vr(off)}$    | 最高速度時のターンオフ電圧立ち上がり時間    | $V_{DS} \geq 80\text{V}$ から $V_{DS} \geq 320\text{V}$ 。<br>$V_{BUS} = 400\text{V}$ 、 $I_L = 24\text{A}$ 、最高速またはフルターンオフ速度。 | 5   | 6   | 7   | ns   |

| <b>起動時間</b>      |                         |                                                                                                                           |     |     |     |      |

| $T_{DRV\_START}$ | ドライバ始動遅延                | ドライバ電源が UVLO を抜けてから、IN が high であればスイッチがオンになるまでの時間。                                                                        |     | 56  | 70  | μs   |

| <b>故障時間</b>      |                         |                                                                                                                           |     |     |     |      |

## 5.6 スイッチング特性 (続き)

特に記載のない限り、電圧、抵抗、容量、インダクタンスは GND/SRC 基準で、 $-40^\circ\text{C} \leq T_J \leq 150^\circ\text{C}$ 、 $V_{\text{DD}} = 12\text{V}$ 、 $\overline{\text{FLT}}/\text{RDRV}$  の抵抗  $\text{RDRV}_{\text{on}}$  と  $\text{RDRV}_{\text{off}}$  はオープンです

| パラメータ                                |  | テスト条件                              | 最小値                                                                                                                                                                      | 標準値 | 最大値 | 単位  |

|--------------------------------------|--|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|

| $t_{\text{off}}(\text{OC})$          |  | 過電流フォルト FET のターンオフ時間、過電流の前の FET オン | $I_D \geq I_{T(\text{OC})}$ から $V_{\text{ds}} > 10\text{V}$ 、 $\text{di}/\text{dt} = 100\text{A}/\mu\text{s}$ 、最高速のターンオフ速度                                               |     | 331 | 420 |

| $t_{\text{off}}(\text{OC\_ON})$      |  | 過電流の合計オン時間、過電流状態でのターンオン。           | $V_{\text{ds}} \leq 10\text{V}$ から $V_{\text{ds}} \geq 10\text{V}$ まで、OC レベルの 110% でターンオン、 $80\text{V}/\text{ns}$ のターンオンスルーレートで最高速のターンオフ速度。                              |     | 405 | 500 |

| $t_{\text{off\_cur}}(\text{SC\_ON})$ |  | ドレイン電流で測定された SC オン時間               | LS の $V_{\text{ds}}$ が $10\text{V}$ を超え、ハーフ ブリッジ構成で $80\text{V}/\text{ns}$ のターンオンスルーレート時に、LS の $I_{\text{ds}}$ が $50\text{A}$ 超から $I_{\text{ds}} 50\text{A}$ 未満になるまでを測定。 |     | 100 | 210 |

| $t_{\text{off\_cur}}(\text{SC})$     |  | ソース電流測定による SC 応答時間                 | ハーフ ブリッジ構成で $80\text{V}/\text{ns}$ のターンオンスルーレート時、LS の $V_{\text{ds}}$ が $9\text{V}$ 超から LS の $I_{\text{ds}}$ が $50\text{A}$ 未満になるまでの時間。。                                 |     | 155 | 300 |

|                                      |  | ラッチ故障リセット時間                        | ラッチされた故障を解除するためには、ゲートドライバ入力をローに保持しておく必要がある時間                                                                                                                             |     | 300 | 380 |

| <b>ゼロ電圧検出およびゼロ電流検出時間</b>             |  |                                    |                                                                                                                                                                          |     |     |     |

| $t_{\text{DL}}_{\text{ZVD}}$         |  | ZCD 遅延                             | 電流がゼロを下から上へ交差してから ZCD 出力パルスが出るまで: $\text{di}/\text{dt} = 0.03\text{A}/\text{ns}$                                                                                         |     | 22  | 38  |

| $t_{\text{WD}}_{\text{ZVD}}$         |  | ZVD 遅延                             | IN 立ち上がりから ZVD 出力パルスまで。 $80\text{V}/\text{ns}$ ターンオン速度。                                                                                                                  |     | 35  | 50  |

| $t_{\text{3rd\_zvd}}$                |  | ZVD パルス幅                           | $V_{\text{bus}} = 10\text{V}$ 、 $I_{\text{L}} = 5\text{A}$ 、ZVD パルス幅を測定                                                                                                  |     | 90  | 120 |

|                                      |  | ZVD パルスが出現し始めたときの第 3 象限導通時間        | $V_{\text{bus}} = 10\text{V}$ 、 $I_{\text{L}} = 5\text{A}$ のとき、ZVD パルスが出現したタイミングで $\text{fet}$ をオンにし、そのときの第 3 象限導通時間を測定 ( $80\text{V}/\text{ns}$ )。                      |     | 16  | 30  |

## 5.7 代表的特性

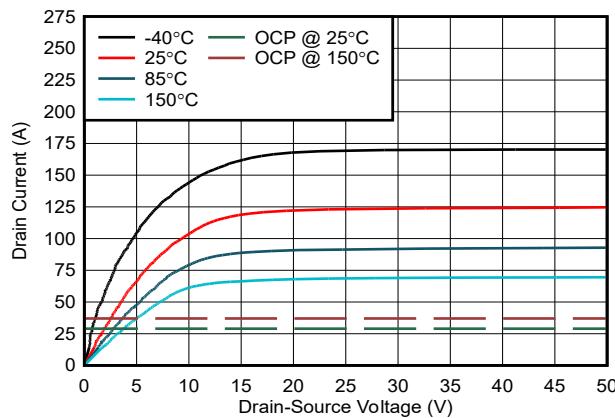

図 5-1. ドレイン電流とドレインソース間電圧との関係

IN = 0V

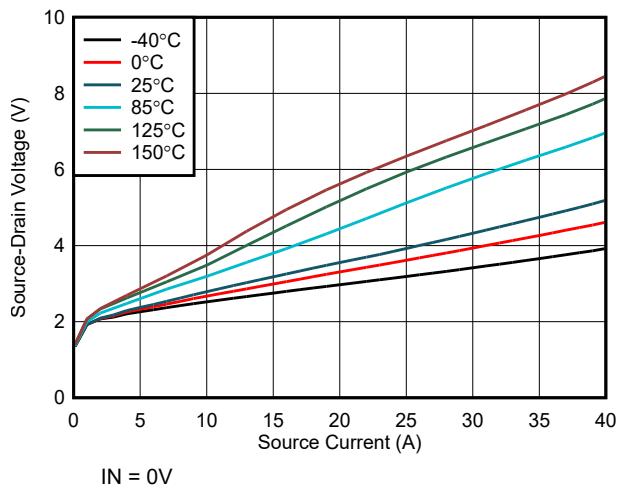

図 5-2. オフ状態のソースドレイン電圧とソース電流との関係

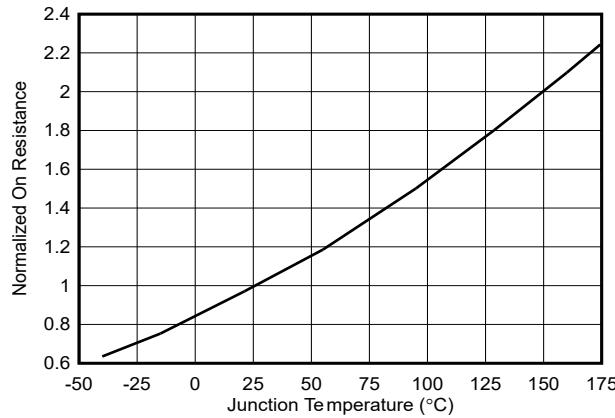

図 5-3. 接合部温度と正規化オン抵抗との関係

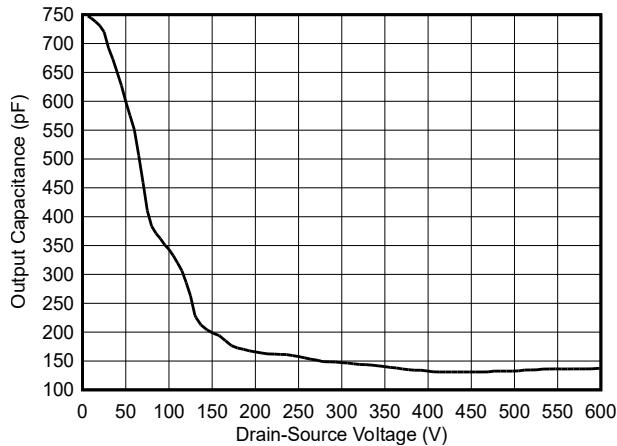

図 5-4. 出力キャパシタンスとドレインソース間電圧との関係

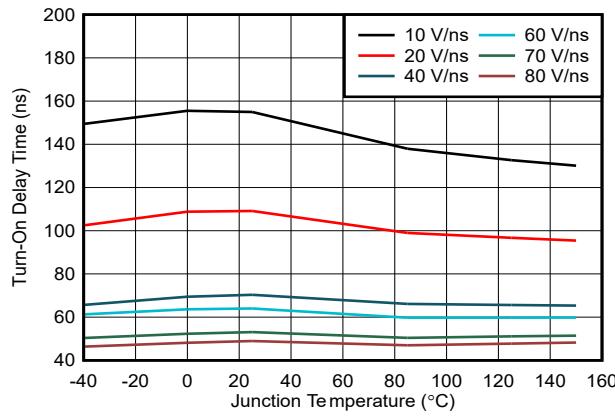

図 5-5. L ターンオン遅延時間と接合部温度との関係

図 5-6. ターンオン立ち上がり時間と接合部温度との関係

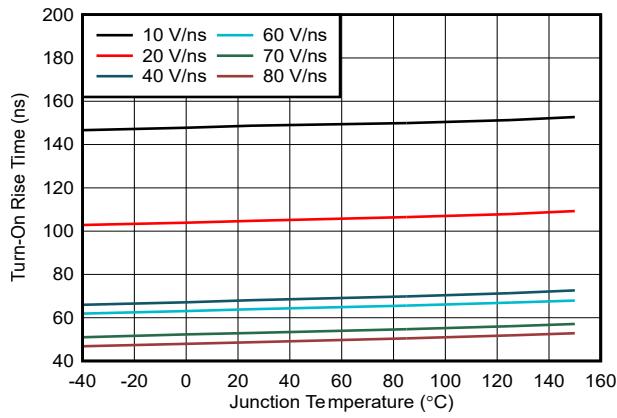

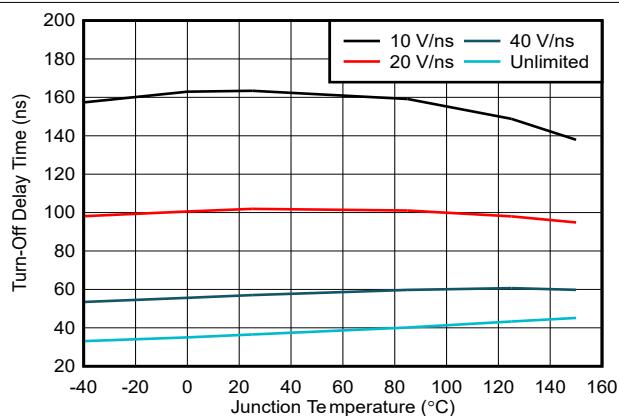

## 5.7 代表的特性 (続き)

図 5-7. ターンオフ遅延時間と接合部温度との関係

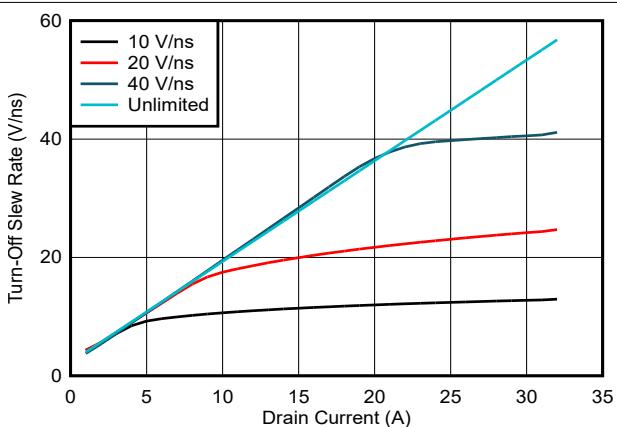

図 5-8. ターンオフのスルーレートとドレイン電流との関係

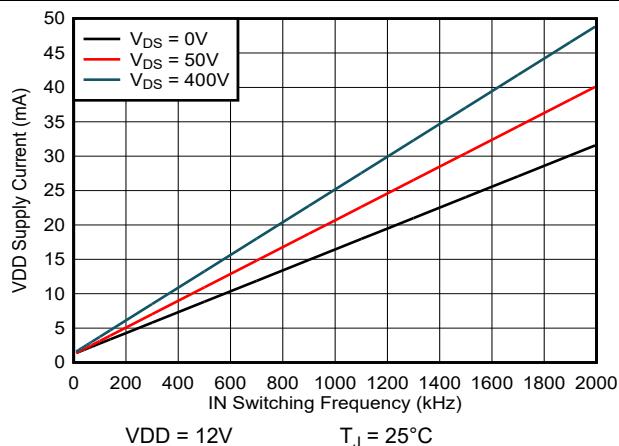

図 5-9. VDD 電源電流と入力スイッチング周波数との関係

図 5-10. VDD 電源電流と入力スイッチング周波数との関係

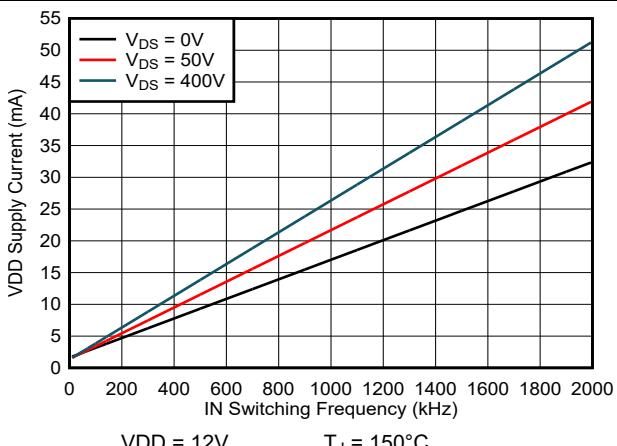

図 5-11. OCP と接合部温度との関係

## 6 パラメータ測定情報

### 6.1 スイッチング パラメータ

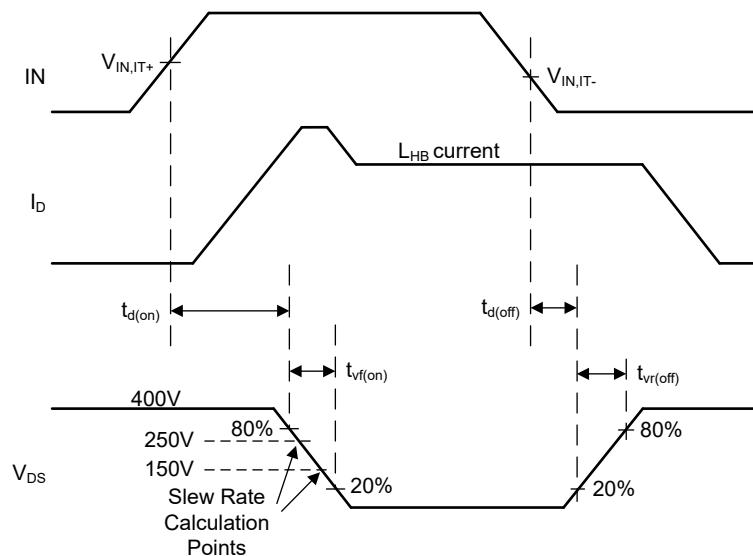

スイッチング パラメータの決定に使用する回路に、ほとんどのスイッチング パラメータの測定に使用する回路を示します。この回路の上部デバイスは、第3象限モードでのみインダクタ電流を再循環するために使用されます。下部デバイスはアクティブ・デバイスで、目的のテスト電流までインダクタ電流を増加させます。下側デバイスは、特定のインダクタ電流でスイッチング波形を生成するためにオフとオンを切り替えます。ドレイン電流(ソース側)とドレインソース間電圧の両方が測定されます。伝搬遅延とスルーレートを決定するための測定値に、具体的なタイミング測定値を示します。TIは、ハーフブリッジをダブル パルス テスターとして使用することを推奨しています。過剰な第3象限動作により、上部デバイスが過熱する可能性があります。

図 6-1. スイッチング・パラメータの決定に使用する回路

図 6-2. 伝搬遅延とスルーレートを決定するための測定値

### 6.1.1 ターンオン時間

ターンオン遷移には、ターンオン遅延時間とターンオン電圧降下時間という二つのタイミング要素があります。ターンオン遅延時間は、IN が High になってから、ドレインソース間電圧がバス電圧より 20% 低くなるまでの時間です。ターンオン電圧降下時間は、ドレインソース間電圧がバス電圧の 20% 低下に達してから、バス電圧の 80% 低下に達するまでの時間です。ターンオンのタイミング要素は、 $\overline{\text{FLT}}/\text{RDRV}$  ピンに接続されたターンオン駆動力用抵抗  $\text{RDRV}_{\text{on}}$  によって決まります。

### 6.1.2 ターンオフ時間

ターンオフ遷移には、ターンオフ遅延時間と、ターンオフの立ち下がり時間の 2 つのタイミング要素があります。ターンオフ遅延時間は、IN が Low になってから、ドレインソース間電圧がバス電圧の 20% まで上昇するまでの時間です。ターンオフ時の電圧立ち上がり時間は、ドレインソース電圧がバス電圧の 20% から 80% へ上昇するまでの時間を指します。ターンオフタイミング部品は  $\text{L}_{\text{HB}}$  負荷電流に依存しますが、LMG365xR035 にはターンオフの駆動強度を制限する機能もあります。ドレインソース間電流が十分高く、ターンオフ駆動強度が制限される場合、タイミング部品はプログラミング抵抗  $\text{RDRV}_{\text{on}}, \text{RDRV}_{\text{off}}$ 、および  $\overline{\text{FLT}}/\text{RDRV}$  ピンに接続された容量  $\text{CDRV}_{\text{off}}$  に依存します。

### 6.1.3 ドレインソース間のターンオンおよびターンオフスルーレート

ドレインソース間のターンオンとターンオフのスルーレートは、バス電圧の中間点付近で  $\text{V}_{\text{DS}}$  で測定します。単位はボルト/ナノ秒単位です。抵抗  $\text{RDRV}_{\text{on}}, \text{RDRV}_{\text{off}}$ 、および容量  $\text{CDRV}_{\text{off}}$  は  $\overline{\text{FLT}}/\text{RDRV}$  ピンに接続され、ターンオンスルーレートを設定し、ターンオフスルーレートを制限します。

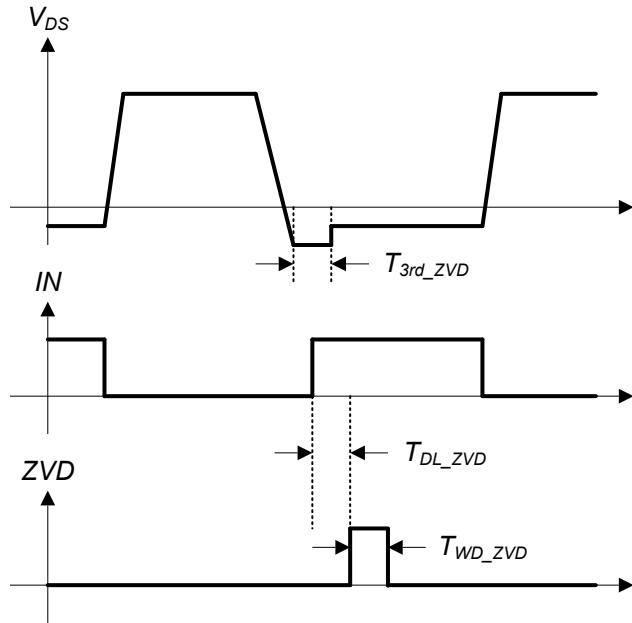

### 6.1.4 ゼロ電圧検出時間 (LMG3656R035 のみ)

**ZVD タイミング仕様**は、ゼロ電圧検出 (ZVD) ブロックに関するスイッチングタイミングを定義しており、デバイスのドレインソース間電圧、IN ピン信号、および ZVD 出力信号を示しています。デバイスがゼロ電圧スイッチング (ZVS) に達すると、ZVD ピンは幅  $\text{T}_{\text{WD}_ZVD}$  のパルス信号を出力し、IN ピンの立ち上がりエッジから ZVD パルスの立ち上がりエッジまでの遅延時間は  $\text{T}_{\text{DL}_ZVD}$  として定義されます。本デバイスがゼロ電圧スイッチングを検出できるようにするには、一定の第 3 象限導通時間が必要であり、 $\text{T}_{\text{3rd}_ZVD}$  はこのタイミングを示します。ZVD タイミング パラメータの詳細については、「ゼロ電圧検出 (ZVD) (LMG3656R070 のみ)」セクションを参照してください。

図 6-3. ZVD タイミング仕様

## 7 詳細説明

### 7.1 概要

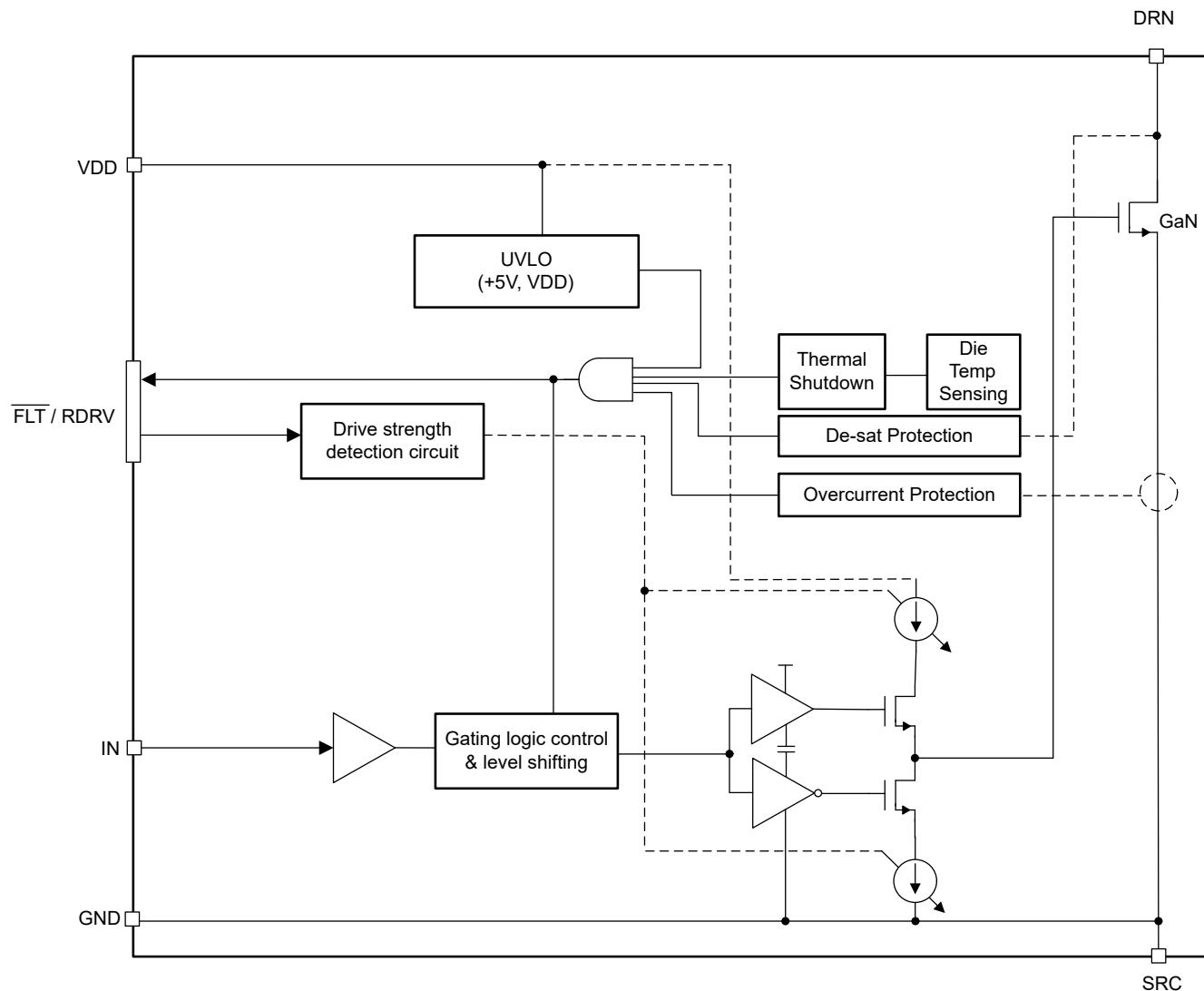

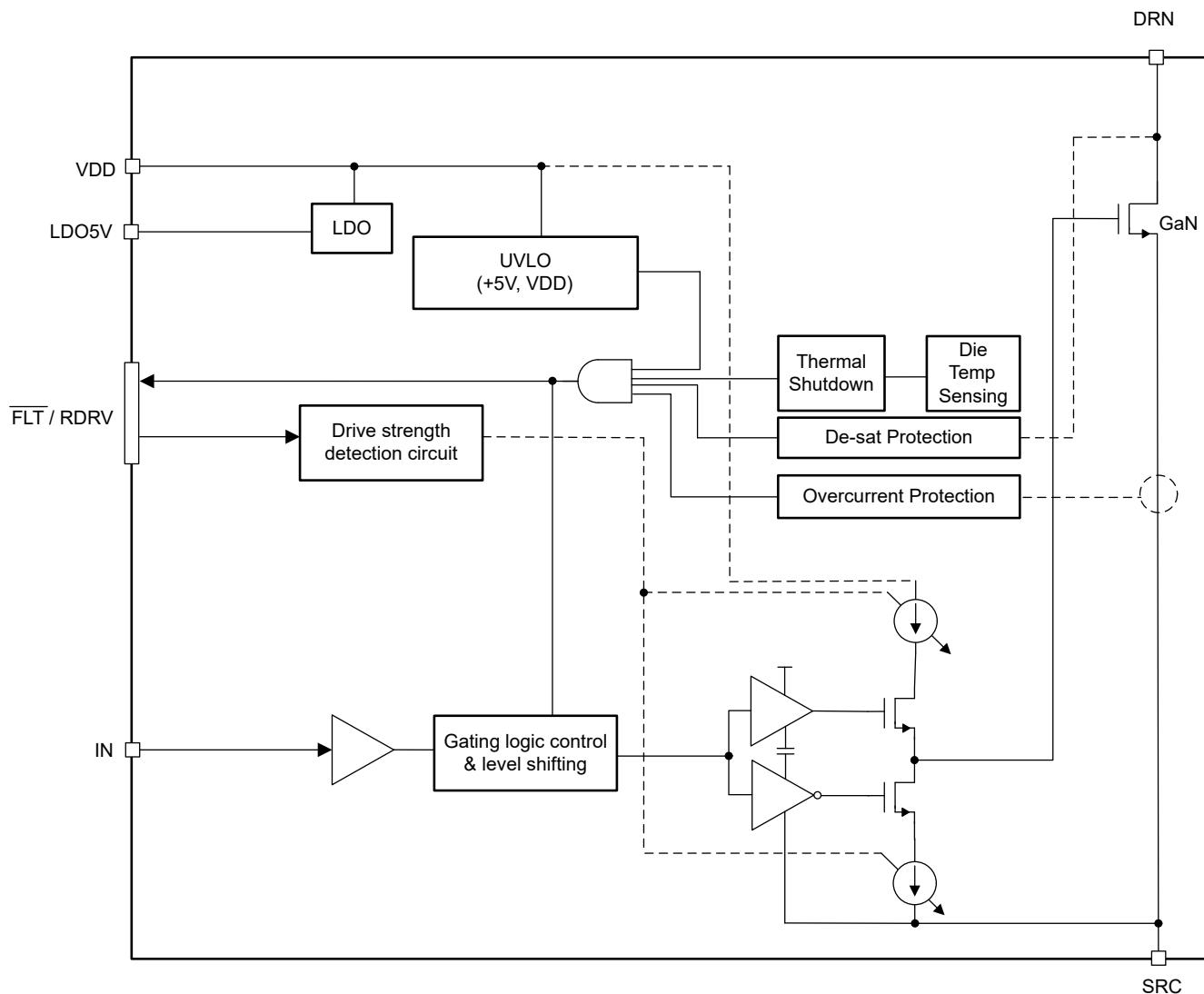

LMG365xR035 は、ゲートドライバが内蔵された高性能パワー GaN デバイスです。GaN デバイスはゼロ逆回復特性と超低出力容量を備えており、ブリッジベースのトポロジにおいて高効率を実現します。

内蔵ドライバにより、の高いドレイン スルーレートの場合にこのデバイスを確実にオフに維持できます。内蔵ドライバは、過電流、短絡、過温度、および VDD 低電圧から GaN デバイスを保護します。LMG3656R035 は、ゼロ電圧検出 (ZVD) 機能を備えており、ゼロ電圧スイッチング (ZVS) が発生したとき ZVD ピンからパルスを出力します。LMG3657R035 は、ドレイン ソース間電流が負であり、ゼロを交差するポイント検出時に Low に遷移すると ZCD ピンを high に設定するゼロ電流検出 (ZCD) 機能を備えています。

Si MOSFET とは異なり、GaN デバイスにはソースからドレインへの p-n 接合がないため、逆方向回復電荷がありません。ただし、GaN デバイスは依然として、p-n 接合のボディ・ダイオードと同様にソースからドレインへ導通しますが、電圧降下が大きく、導通損失が大きくなります。したがって、LMG365xR035GaN FET がオフの間、ソース ドレイン間導通時間を最小限に抑える必要があります。

## 7.2 機能ブロック図

### 7.2.1 LMG3650R035 機能ブロック図

### 7.2.2 LMG3651R035 機能ブロック図

### 7.2.3 LMG3656R035 機能ブロック図

### 7.2.4 LMG3657R035 機能ブロック図

## 7.3 機能説明

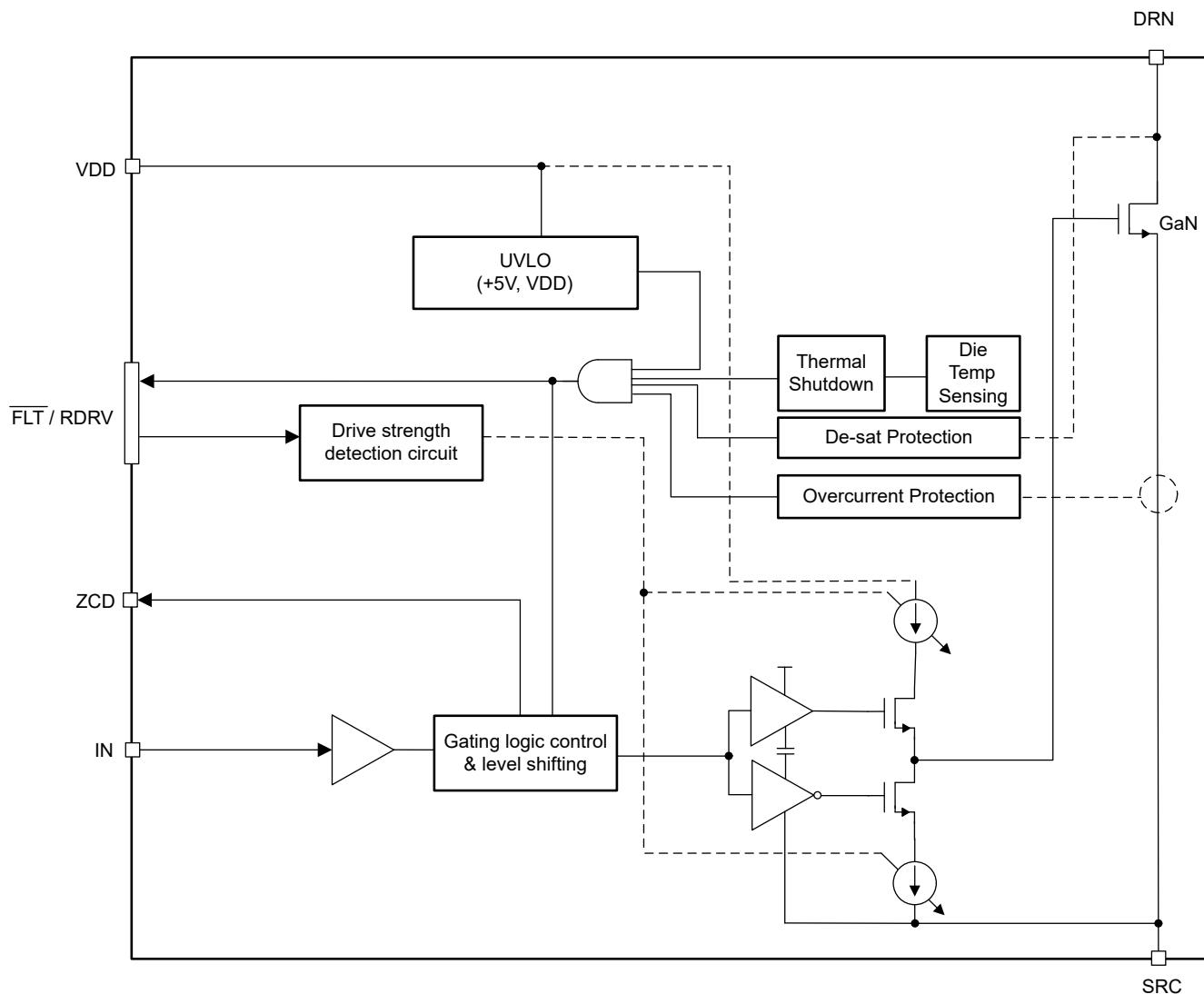

### 7.3.1 ドライブ強度調整

LMG365xR035 は、ユーザーがデバイスのドライブ強度を調整して望ましいスルーレートを得られるようにし、スイッチング損失の最適化や EMI の低減を行う際の柔軟性を提供します。ドライブ強度調整回路に示すように抵抗とコンデンサを接続することで、ターンオン スルーレートの典型値と、ターンオフ スルーレートの最大値を独立して制御できます。FLT/RDRV ピンの抵抗と容量は、電源投入時に 1 回検出されます。そのために、デバイスは外付けの RDRV<sub>on</sub>-RDRV<sub>off</sub>-CDRV<sub>off</sub> ネットワークに 0V から 1.2V へのステップ関数を印加し、その結果得られる電流波形を測定します。DC 測定値 ( $I_{up}$ ) によって、ターンオンのスルーレートの設定が決まり、抵抗 RDRV<sub>on</sub> によってプログラムされます。RDRV<sub>on</sub> - RDRV<sub>off</sub> - CDRV<sub>off</sub> に依存する AC 測定によってターンオフ スルーレート設定が決まり、その値は出力容量を充電するドレインソース間の電流の大きさに左右されます。ただし、その最大値は、RDRV<sub>on</sub> に並列接続された抵抗 RDRV<sub>off</sub> と容量 CDRV<sub>off</sub> によって設定された上限までに制限できます。

$$I_{up} = \frac{1.2}{RDRV_{on}} A \quad (1)$$

ターンオン スルーレート制御表とターンオフ スルーレート制御表に、各スルーレート設定における推奨される標準的な抵抗値と容量のプログラミング値を示します。表に記載されている  $RDRV_{on}$  値は、 $\overline{FLT}/RDRV$  ピンの寄生抵抗がないものと想定しています。ただし、実際のアプリケーションでは、このピンは故障監視のためにアイソレータ入力に接続されることがあります。アイソレータの内部構成には、プルアップ抵抗またはプルダウン抵抗が含まれる可能性があり、測定値とプログラムされたスルーレートとの間にミスマッチが生じます。これは、故障監視と駆動強度の調整の両方が同じピン  $\overline{FLT}/RDRV$  を共有するためです。内部プルアップは推奨されません。というのも、 $\overline{FLT}/RDRV$  ピンの電圧が、アイソレータの電源、 $R_{pull-up}$ 、そして  $RDRV_{on}$  との分圧によって変化し、その結果  $I_{up}$  を制御しにくくなるためです。内部プルダウン抵抗を備えたアイソレータを使用することが推奨されます。これは  $RDRV_{on}$  と並列経路を形成し、その場合の  $I_{up}$  は  $(R_{pull-down} \parallel RDRV_{on})$  で決まるためです。プログラムされたターンオン スルーレート設定と一致するように、 $RDRV_{on}$  を調整して、新しい  $I_{up}$  がプログラムされた値と一貫した状態を維持します。

$$I_{up} = \frac{1.2}{(R_{pull-down} \parallel RDRV_{on})} A \quad (2)$$

スルーレート設定は電源オン時に一度決定され、[障害通知](#)で説明されているように、 $\overline{FLT}/RDRV$  ピンは故障監視用のプッシュプル 5V デジタル出力として使用されます。 $RDRV_{off}$  および  $CDRV_{off}$  を使用しない場合、デバイスはフルスピードでオフになり、ターンオフのスルーレートは  $C_{oss}$  と負荷電流によって厳密に決定されます。 $RDRV_{on}$  を使用しない場合、このデバイスはデフォルトで 80V/ns のスルーレート設定になります。ターンオン設定が遅いと、 $E_{on}$  損失が大きくなり、ターンオフ設定が遅くなると  $E_{off}$  損失が大きくなります。

図 7-1. ドライブ強度調整回路

表 7-1. ターンオン スルーレート調整用推奨典型プログラミング抵抗値(kΩ)

| 標準ターンオン スルーレート (V/ns) | $RDRV_{on}(k\Omega)$ <sup>(1)</sup> |

|-----------------------|-------------------------------------|

| 10                    | 29.4                                |

| 20                    | 35.7                                |

| 40                    | 43.2                                |

| 60                    | 53.6                                |

| 70                    | 69.8                                |

| 80                    | > 400 <sup>(2)</sup>                |

(1) 出力容量を充電するドレイン ソース間電流の大きさに完全に依存します。

(2) プログラミング抵抗の開回路接続は許容されます。

表 7-2. ターンオフ スルーレート制限調整用推奨典型プログラミング抵抗値 (kΩ) および容量値 (pF)

| 最大ターンオフ スルーレート (V/ns) | $RDRV_{off}(k\Omega)$ <sup>(1)</sup> | $CDRV_{off}(pF)$ <sup>(2)</sup> |

|-----------------------|--------------------------------------|---------------------------------|

| 10                    | 2                                    | 1800                            |

| 20                    | 3.57                                 | 1000                            |

| 40                    | 7.68                                 | 470                             |

表 7-2. ターンオフ スルーレート制限調整用推奨典型プログラミング抵抗値 (kΩ) および容量値 (pF) (続き)

| 最大ターンオフ スルーレート (V/ns) | RDRV <sub>off</sub> (kΩ) <sup>(1)</sup> | CDRV <sub>off</sub> (pF) <sup>(2)</sup> |

|-----------------------|-----------------------------------------|-----------------------------------------|

| 制限なし <sup>(1)</sup>   | ハイインピーダンス                               | ハイインピーダンス                               |

(1) 抵抗値の許容誤差は  $\pm 1\%$  です。

(2) 静電容量の値に関して  $\pm 10\%$  の公差を維持しています。

例えば、 $RDRV_{on} = 53.6\text{k}\Omega$ 、 $RDRV_{off} = 3.57\text{k}\Omega$ 、 $CDRV_{off} = 1000\text{pF}$  と設定すると、ターンオン スルーレートは  $60\text{V/ns}$  となり、ターンオフ スルーレートは最大  $20\text{V/ns}$  に制限されます。

#### 注

寄生電力ループのインダクタンスは、 $V_{DS}$  スイッチング波形からの電圧スルーレートの読み出しに影響を与える可能性があります。電圧立ち下がりフェーズの前の立ち上がりフェーズで、インダクタンスにより  $V_{DS}$  の降下が生じます。この電圧降下が  $V_{DC}$  の  $20\%$  より大きい場合、電圧スルーレートの読み取り値が影響を受ける可能性があります。電力ループ設計ガイドラインと寄生電力ループインダクタンスの推定方法については、セクション 8.4.1.2 を参照してください。

### 7.3.2 GaN パワー FET のスイッチング機能

シリコン FET が長きにわたって支配的なパワースイッチ技術であったため、多くの設計者は、ドレンソース間電圧の銘板を、異なる技術のデバイスを比較する際の等価点として使用できることを知りません。シリコン FET の銘板のドレンソース間電圧は、アバランシェ ブレークダウン電圧によって設定されます。GaN FET の銘板のドレンソース間電圧は、データシートの仕様への長期的な準拠によって設定されます。

シリコン FET の銘板のドレンソース間電圧を超えると、即座に永続的な損傷を引き起こすことがあります。一方、GaN FET のブレークダウン電圧は銘板のドレンソース間の見出し電圧よりもはるかに高くなっています。たとえば、LMG365xR035 GaN パワー FET のブレークダウンドレンソース間電圧は  $800\text{V}$  を上回るため、LMG365xR035 は同じ銘板の定格を持つシリコン FET を超える条件下で動作できます。

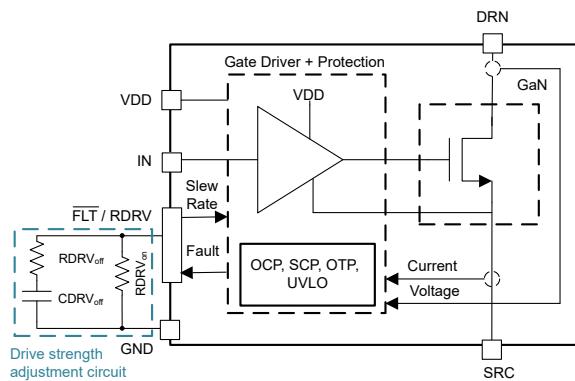

『GaN パワー FET のスイッチング機能』を使用して、LMG365xR035 GaN パワー FET のスイッチング機能を説明します。図に、スイッチング アプリケーション内の異なる 4 つのスイッチ サイクルについて、LMG365xR035 GaN パワー FET のドレンソース間電圧と時間との関係を示します。スイッチング周波数またはデューティ・サイクルに関する請求は行われません。最初の 2 サイクルは通常動作を示し、次の 2 サイクルはまれな入力電圧サージ時の動作を示します。LMG365xR035 GaN パワー FET は、ゼロ電圧スイッチング (ZVS) または不連続導通モード (DCM) のスイッチング条件でオンになるように設計されています。

図 7-2. GaN パワー FET のスイッチング機能

各サイクルは  $t_0$  より先に開始し、FET がオン状態になります。 $t_0$  の時点で GaN FET はターンオフし、寄生素子によってドレンソース間電圧に高周波でリングが生じます。高周波リングは、 $t_1$  だけ減衰しました。 $t_1$  と  $t_2$  の間の FET の

ドレインソース間電圧は、スイッチングアプリケーションの特性応答によって設定されます。特性はフラットライン（プラトー）として表示されますが、他の応答も可能です。 $t_2$  の時点では、GaN FET がオンになります。通常動作では、過渡リング電圧は 650V に制限され、プラトー電圧は 520V に制限されます。まれなサージ現象の場合、過渡リング電圧は 800V に制限され、プラトー電圧は 720V に制限されます。

### 7.3.3 VDD 電源

VDD は内部回路の入力電源です。VDD ピンは 9V から 24V までの広い電圧範囲に対応しています。

### 7.3.4 過電流および短絡保護

ドライバは、過電流と短絡という 2 種類の電流故障を検出します。

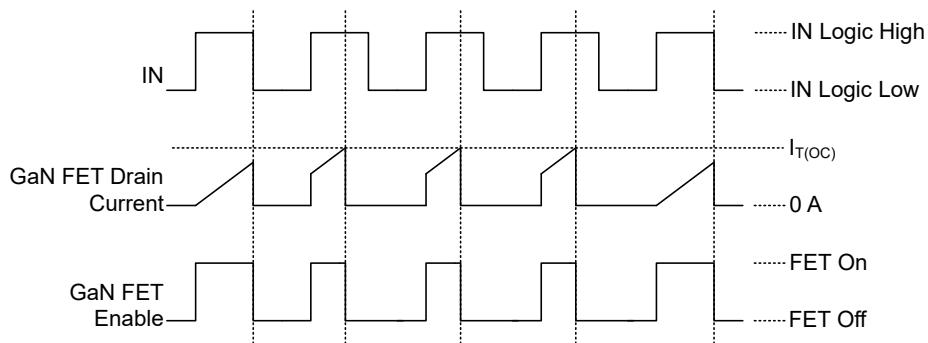

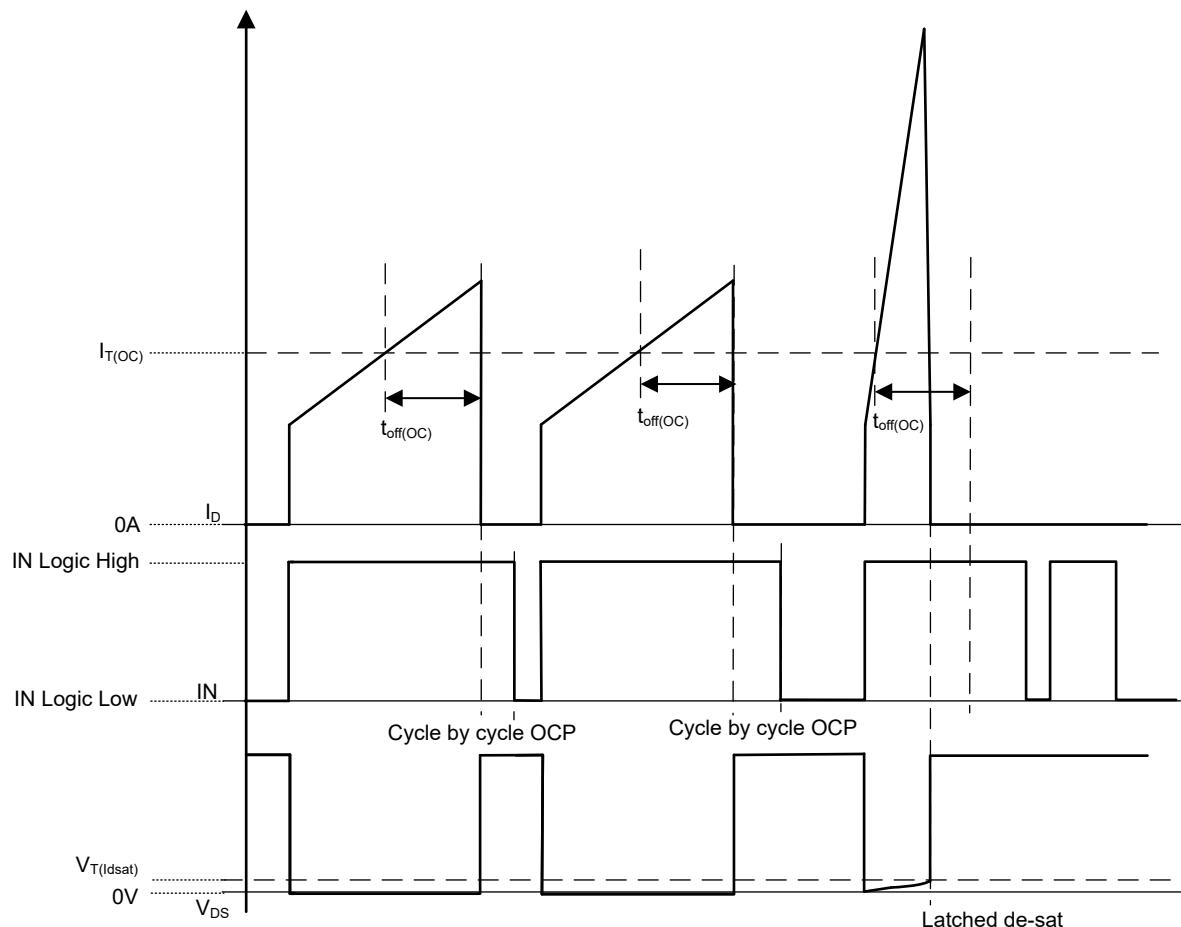

過電流保護（OCP）回路は、ドレイン電流を監視し、電流信号を内部で設定された制限値  $I_{T(OC)}$  と比較します。過電流を検出すると、LMG365xR035 は、サイクル単位の過電流保護動作に示すように、サイクル単位の保護を実行します。このモードでは、ドレイン電流が  $I_{T(OC)}$  に遅延  $t_{off(OC)}$  を加えた値を超えると、GaN デバイスがシャットオフされますが、IN ピン信号が LOW になると過電流信号はクリアされます。

次のサイクルで、GaN デバイスは通常どおりオンにすることができます。サイクル単位の機能は、定常状態の動作電流が OCP レベルを下回っているが、過渡応答が依然として電流制限に達する可能性があり、回路の動作を一時停止できない場合に使用します。このサイクルごとの機能は、過電流によって生じる導通損失から GaN デバイスが過熱するのを防ぎます。さらに、OCP レベルは接合温度に応じて動的に調整され、内部で設定された限界値  $I_{T(OC)}$  は低温では高く、温度が上昇するにつれて低下します。これは仕様に定義されており、式 3 に基づきます。動的調整により、より低い温度で大電流を流すことができます。

$$\frac{I_{T(OC)150^\circ\text{C}}}{I_{T(OC)25^\circ\text{C}}} = 77\% \quad (3)$$

短絡保護は飽和（de-sat）の検出に基づいています。この機能は、ドレインソース間電圧  $V_{DS}$  を監視し、内部で設定された制限値  $V_{T(Idsat)}$  と電圧を比較します。飽和は GaN に損傷を与える、その条件で動作を継続した場合に故障を引き起こす可能性があります。飽和が検出されると、GaN デバイスはラッチオフされます。高電流でデバイスをオフすると、大きな電圧オーバーシュートが発生します。そのため、飽和状態からオフにするときは、オフ動作時のオーバーシュート電圧やリングギングを低減するために、意図的に遅いドライバでデバイスをオフします。この高速応答回路により、急激な短絡状況が発生した場合でも GaN デバイスを保護できます。この保護では、GaN デバイスをシャットオフして、仕様に定義されている時間にわたって IN ピンを Low に保持するか、または VDD の電源をオフにすることによって、故障がリセットされるまで保持します。

安全面を考慮して、OCP はサイクルごとの動作を許可しますが、脱飽和はリセットされるまでデバイスをラッチオフします。どちらの障害も  $\overline{FLT}/\overline{RDRV}$  ピンで通知されます。

図 7-4 に、OC と脱飽和保護の動作を示します。最初の 2 サイクルでは、脱飽和が発動しないまま OC リミットがトリガされるため、サイクルごとの保護が働きます。3 番目のサイクルでは OC 制限がトリガされますが、 $t_{off(OC)}$  内に  $V_{DS}$  が  $V_{T(Idsat)}$  を上回ると、脱飽和保護がトリガされます。脱飽和保護がトリガされるため、ターンオフが遅くなり、ラッチ付き保護が発生します。

図 7-3. サイクル単位の過電流保護動作

図 7-4. 過電流検出と短飽和検出との関係

### 7.3.5 過熱保護

過温度保護は GaN FET の温度を監視し、温度が過温度保護スレッショルドを超えた場合に GaN デバイスをオフ状態に保持します。過熱保護ヒステリシスにより、誤った熱サイクルが防止されます。過熱保護がアサートされると、 $\overline{FLT}/\overline{RDRV}$  ピンで過熱故障が通知されます。デバイス温度が負方向のトリップ ポイントを下回ると、 $\overline{FLT}/\overline{RDRV}$  はデアサートされ、デバイスは自動的に通常動作に戻ります。

### 7.3.6 UVLO 保護

LMG365xR035 は広い  $V_{DD}$  電圧範囲に対応しています。しかし、 $V_{DD}$  電圧が  $V_{DD}$  UVLO スレッショルドを下回ると、GaN デバイスはスイッチングを停止し、オフ状態に保持されます。 $V_{DD}$  UVLO 電圧 ヒステリシスは、UVLO 電圧トリップポイント付近でのオン/オフのチャタリングを防止します。UVLO を示すために、 $\overline{FLT}/RDRV$  ピンは low にプルダウンされます。

### 7.3.7 障害通知

すべての故障は  $\overline{FLT}/RDRV$  ピンで通知され、入力ピンと出力ピンの両方として機能します。

ドライブ強度調整に示すように、 $\overline{FLT}/RDRV$  は、電源投入時に入力としてのみ構成され、ドライブ強度を調整できます。

$\overline{FLT}/RDRV$  はアクティブ Low のデジタル出力として使用され、その後の故障のステータスを示します。このピンはプッシュアップの 5V デジタル出力で、すべての故障がクリアされると high になります。つまり、このピンが high に強制されたとき、R1 を流れる静止電流が追加で発生することを意味します。

故障ピンに接続された外部デジタル受信器の入力スレッショルドのレベルによっては、電源投入時にこのピンへ強制される 1.2V のステップ閾数が、High として解釈される場合と Low として解釈される場合があります。このため、TI は受信側には CMOS 互換入力で一般的なような高いスレッショルドを持つものを使用し、TTL 互換入力は使用しないことを推奨しています。故障ピンに接続された外部デジタル レシーバの最小入力スレッショルドが 1.2V 以下の場合、LMG365xR035 がスイッチングを開始する前に、電源オン時の 1.2V ステップ機能を high と解釈できます。

### 7.3.8 補助 LDO (LMG3651R035 のみ)

LMG365xR035 内部の 5V 電圧レギュレータは、ハイサイド駆動信号用のデジタル アイソレータなど、外部負荷に電源を供給するために使用されます。LMG365xR035 のデジタル出力は、この 5V レールを電源電圧として使用します。安定性のためにコンデンサは必須ではありませんが、外付けコンデンサを入れない場合、過渡応答は劣化します。アプリケーションで LDO5V ピンを外部回路への電源として使用する場合、過渡応答を改善するために、TI は 0.1 $\mu$ F 以上のコンデンサを使用することを推奨しています。さらに過渡応答を改善するには、より大容量のコンデンサを使用します。デカップリング コンデンサが低 ESR のセラミックタイプであることを確認します。0.47 $\mu$ F を超える容量は、5V レールの立ち上がり時間により、LMG365xR035 の起動時間を遅くします。

### 7.3.9 ゼロ電圧検出 (ZVD) (LMG3656R035 のみ)

ゼロ電圧スイッチング (ZVS) コンバータは、パワーコンバータの効率を改善するために広く使用されています。ただし、LLC や三角波電流モード (TCM) トータムポール PFC などのソフトスイッチングトポロジでは、負荷条件、インダクタ、磁気パラメータ、制御手法によって ZVS が失われる可能性があり、システム効率に影響を及ぼします。ZVS を確実に実現するには、特定の設計マージンや追加回路が必要で、それによりコンバータの性能が低下し、部品が追加されます。

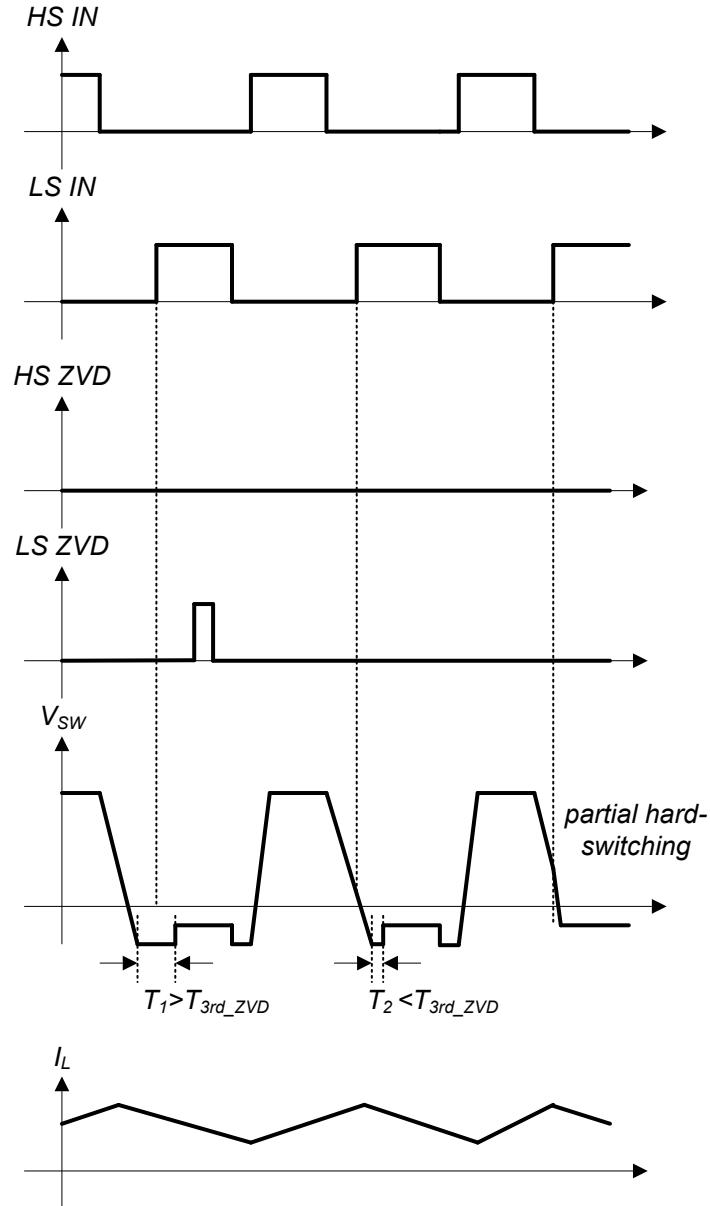

ソフトスイッチングコンバータのシステム設計を簡素化するため、LMG3656R035 部品には、ゼロ電圧検出 (ZVD) 回路が内蔵されており、電流スイッチングサイクル内で ZVS が達成されたかどうかを示すデジタル帰還信号を供給します。この回路図を、[ゼロ電圧検出回路のブロック図の回路図](#)に示します。IN ピン信号が high になると、ロジック回路はデバイスの  $V_{DS}$  が -1V を下回ったかどうかをチェックし、このスイッチング サイクルでデバイスがゼロ電圧スイッチングに成功したかどうかを判定します。ZVS が識別されると、[ZVD タイミング仕様](#)に示すように、 $T_{DL\_ZVD}$  の遅延時間後に  $T_{WD\_ZVD}$  幅のパルス出力が ZVD ピンから送信されます。本デバイスがゼロ電圧スイッチングを検出できるようにするには、一定の第 3 象限導通時間が必要であり、 $T_{3rd\_ZVD}$  はゲートドライバ強度の閾数を参照)。

図 7-5. ゼロ電圧検出回路のブロック図

CCM 降圧コンバータの ZVD 機能に、連続導通モード降圧コンバータに対する ZVD ピンの波形を示します。これらの波形は、ハード スイッチングとソフト スイッチングの両方において ZVD 機能がどのように動作するかを示しています。CCM 降圧コンバータ内の ZVD 機能の波形における  $I_L$  について、スイッチノードから外へ流れる負荷電流は正方向とみなされます。CCM 降圧動作では、ハイサイドのデバイスのハードスイッチング デバイスが動作し、ローサイドのデバイスは適切なデッドタイムの設定によりゼロ電圧スイッチングを実現できます。ローサイド デバイスの IN ピンが上昇する最初のスイッチング サイクルでは、スイッチ ノード電圧  $V_{DS}$  は 0 を下回り、 $T_1$  の期間にわたって第 3 象限導通を維持します。この第 3 象限導通時間  $T_1$  は、電気的特性に規定されている検出時間  $T_{3rd\_ZVD}$  より大きいため、ゼロ電圧遷移が識別され、ZVD ピンはパルス信号を出力します。ZVD パルスのパルス幅は、電気的特性表で  $T_{WD}$  として定義されます。2 番目のスイッチングサイクルでは、本デバイスがより早くオンになり、第 3 象限導通時間  $T_2$  は  $T_{3rd\_ZVD}$  より小さくなります。 $T_2$  は  $T_{3rd\_ZVD}$  未満であるため、デバイスが ZVS を達成していても、ZVD 信号は Low のままでです。3 番目のスイッチングサイクルでは、IN ピン信号がより早く進み、デバイスは部分的にハードスイッチングを行います。したがって、ZVS 遷移が発生しないときは、ZVD 出力は low のままでです。なお、この CCM 降圧動作では、ハイサイド デバイスが常にハードスイッチングでターンオンするため、ハイサイドの ZVD 出力はローレベルのままであります。

図 7-6. CCM 降圧コンバータでの ZVD 機能

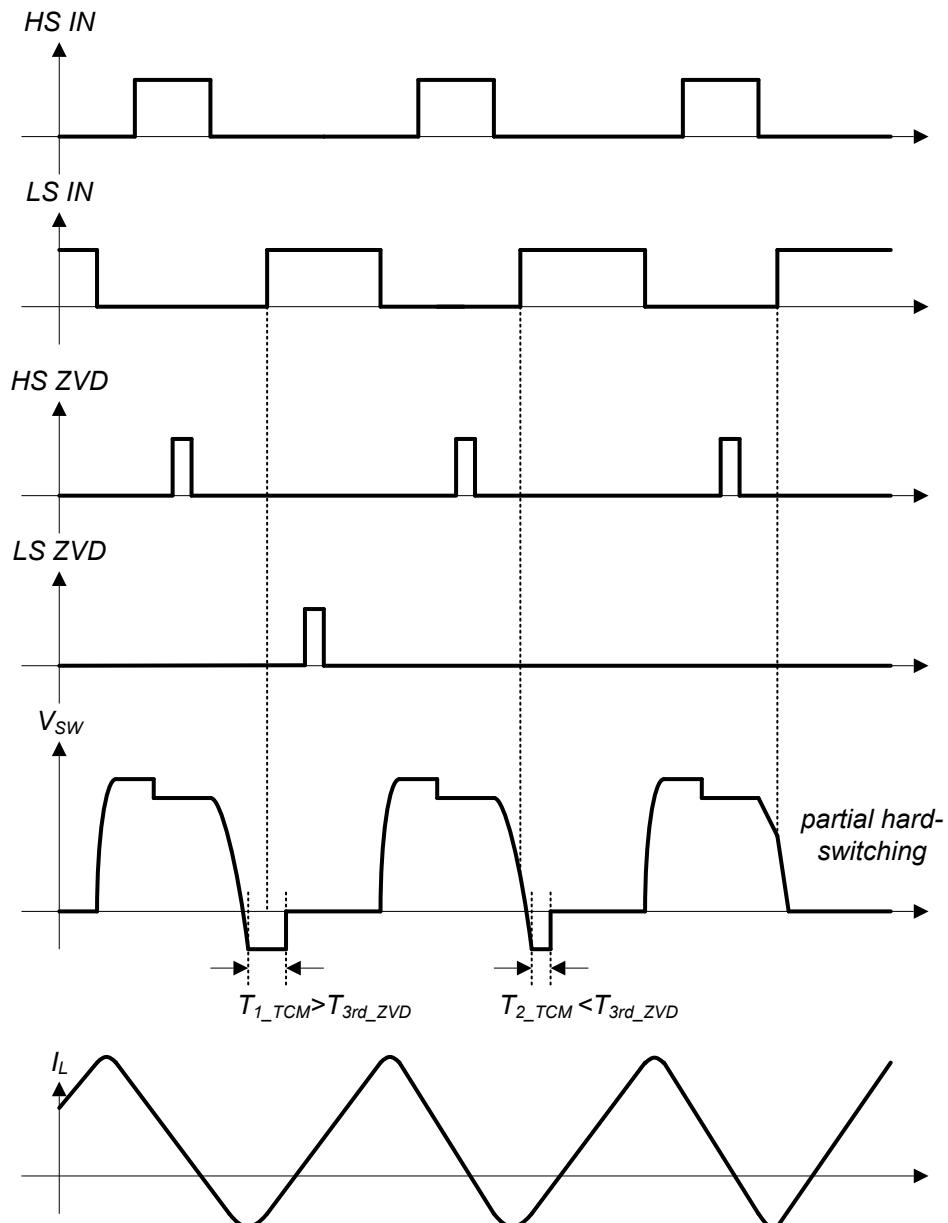

ZVD 機能により、ソフト スイッチング トポロジでの制御が容易になります。TCM TP PFC コンバータの ZVD 機能は、TCM トーテムポール PFC で ZVD 波形が容易になることを示しています。この図は、 $V_{IN}$  が  $V_{OUT}$  の半分を超えた場合の正のハーフ ラインサイクルを示しています。TCM TP PFC コンバータにおける ZVD 機能の負荷電流における波形の  $I_L$  は、スイッチ ノードに流入する電流は正と定義されます。最初のスイッチングサイクルでは、負荷電流によって十分な負電流が形成され、ローサイドデバイスは  $T_{3rd\_DET}$  を超える明確な第 3 象限導通時間で ZVS を実現します。そのため、ZVD ピンはパルス信号を出力します。次の 2 つのスイッチング サイクルでは ZVD パルスが出ないのは、第 2 サイクルで第 3 象限の導通時間が短くなり、第 3 サイクルではデバイスが ZVS を失うためです。

図 7-7. TCM TP PFC コンバータでの ZVD 機能

#### 7.4 デバイスの機能モード

このデバイスでは、[推奨動作条件](#)の範囲内では、適用される動作モードは一つだけです。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

LMG365xR035 は、最大 520V bus 電圧で動作するおよびソフトスイッチングを行うアプリケーションを対象としたパワー IC です。GaN デバイスは逆回復電荷がゼロであり、GaN デバイスの低い  $Q_{OSS}$  は、LLC や位相シフトフルブリッジ構成などのソフトスイッチング コンバータにも利点があります。ハーフブリッジ構成は、前述の 2 つのアプリケーションとその他多くのアプリケーションの基礎であるため、このセクションでは LMG365xR035 をハーフブリッジ構成で使用する方法について説明します。

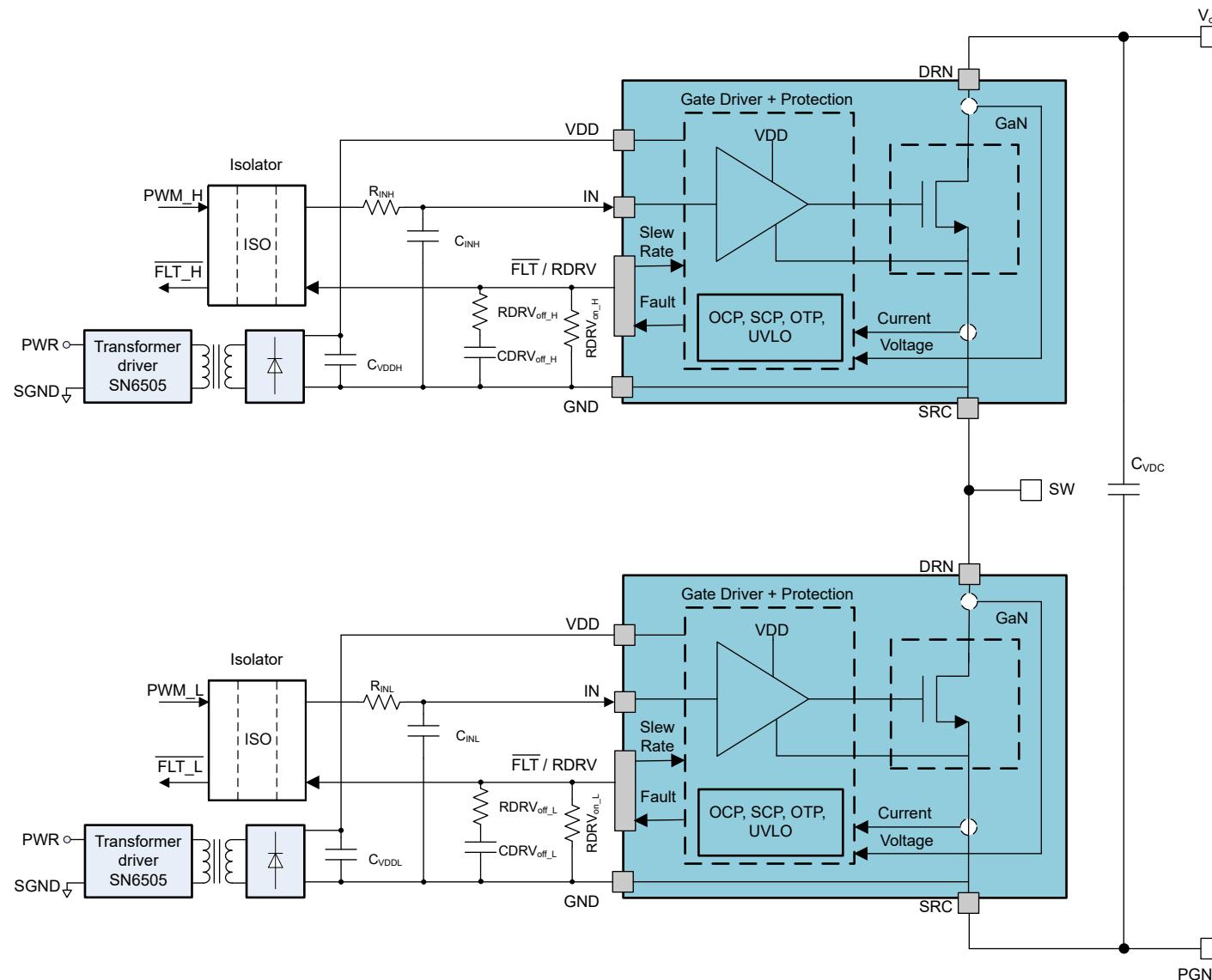

## 8.2 代表的なアプリケーション

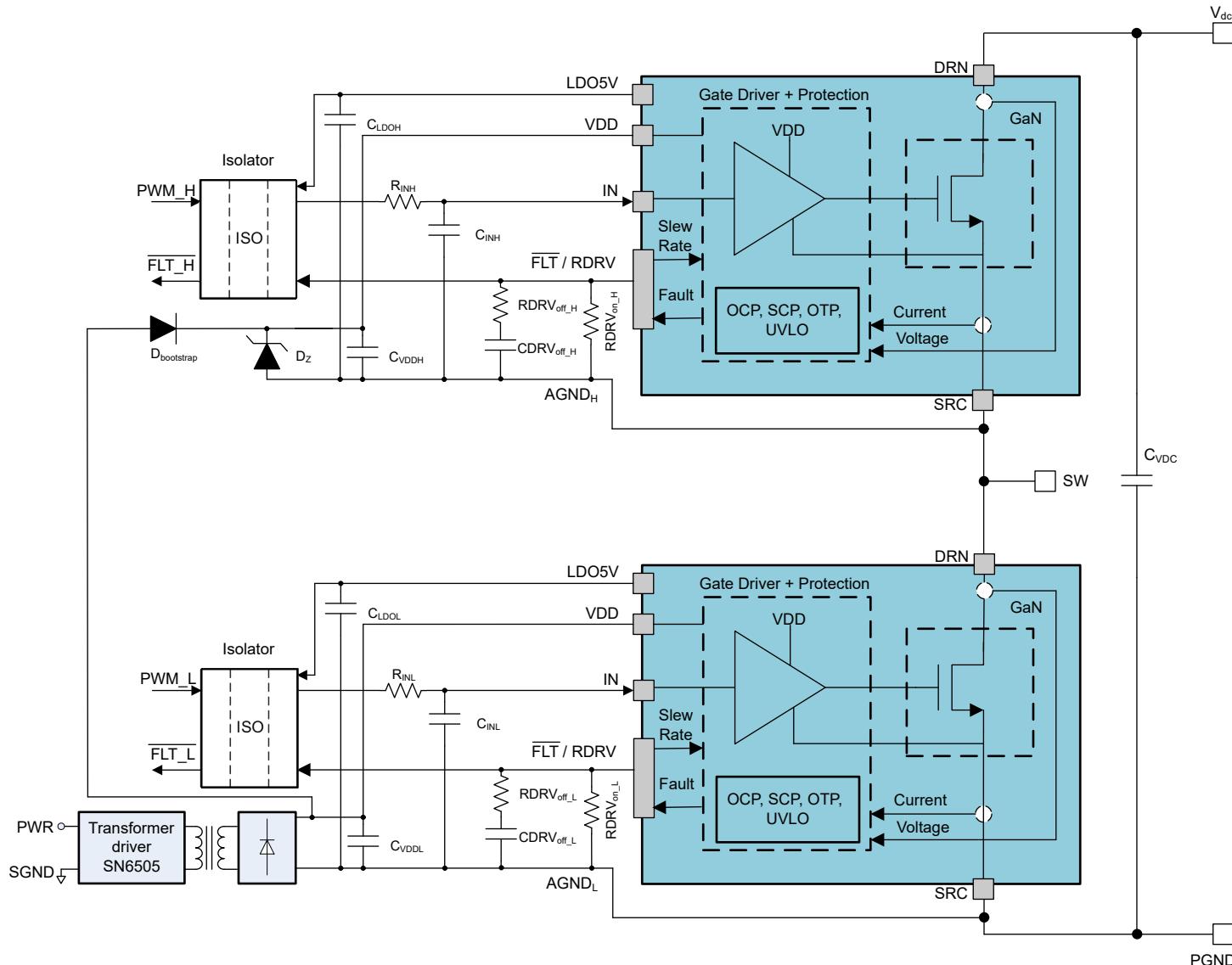

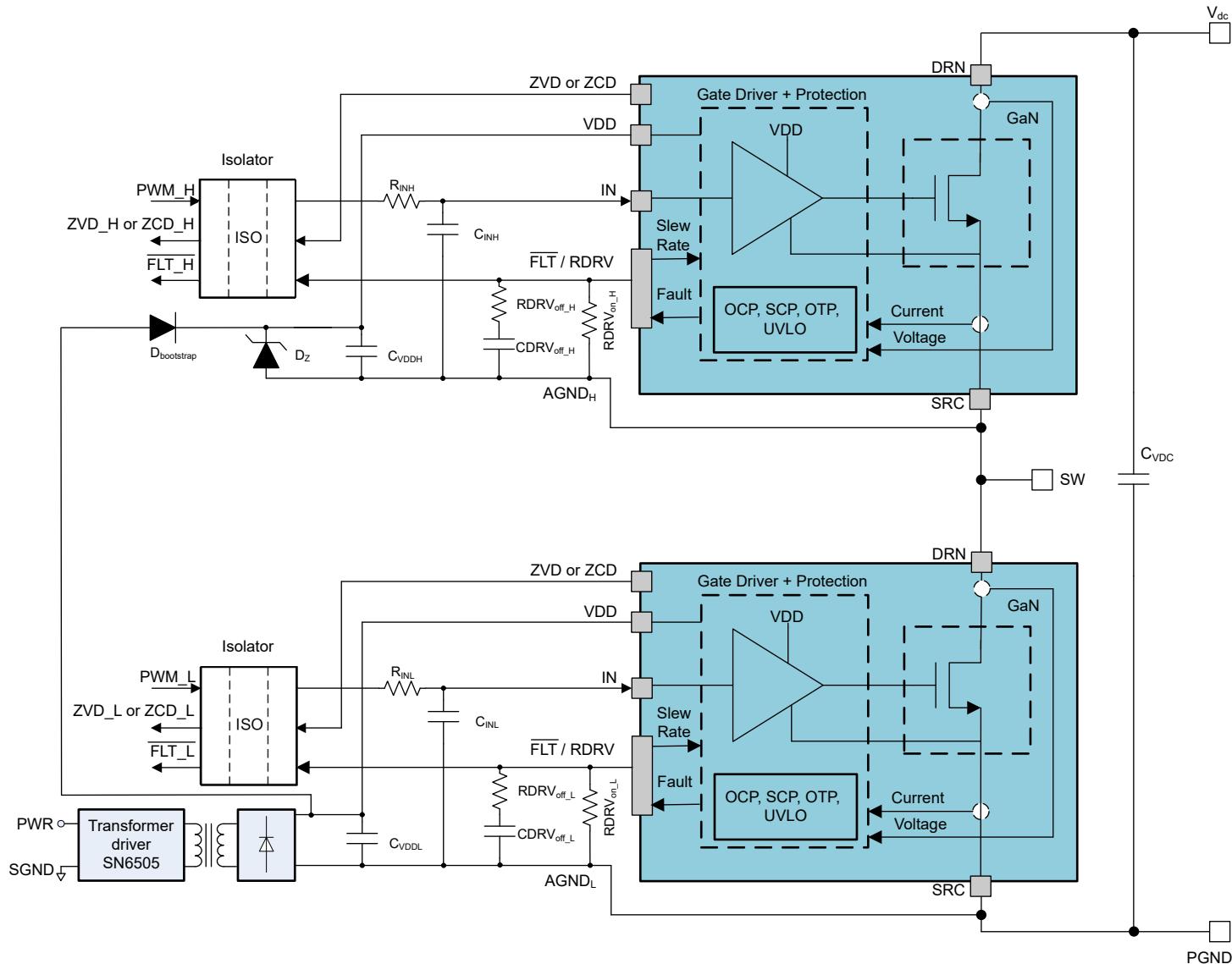

図 8-1. LMG3650R035 絶縁型電源を使用した標準的なハーフブリッジ アプリケーション

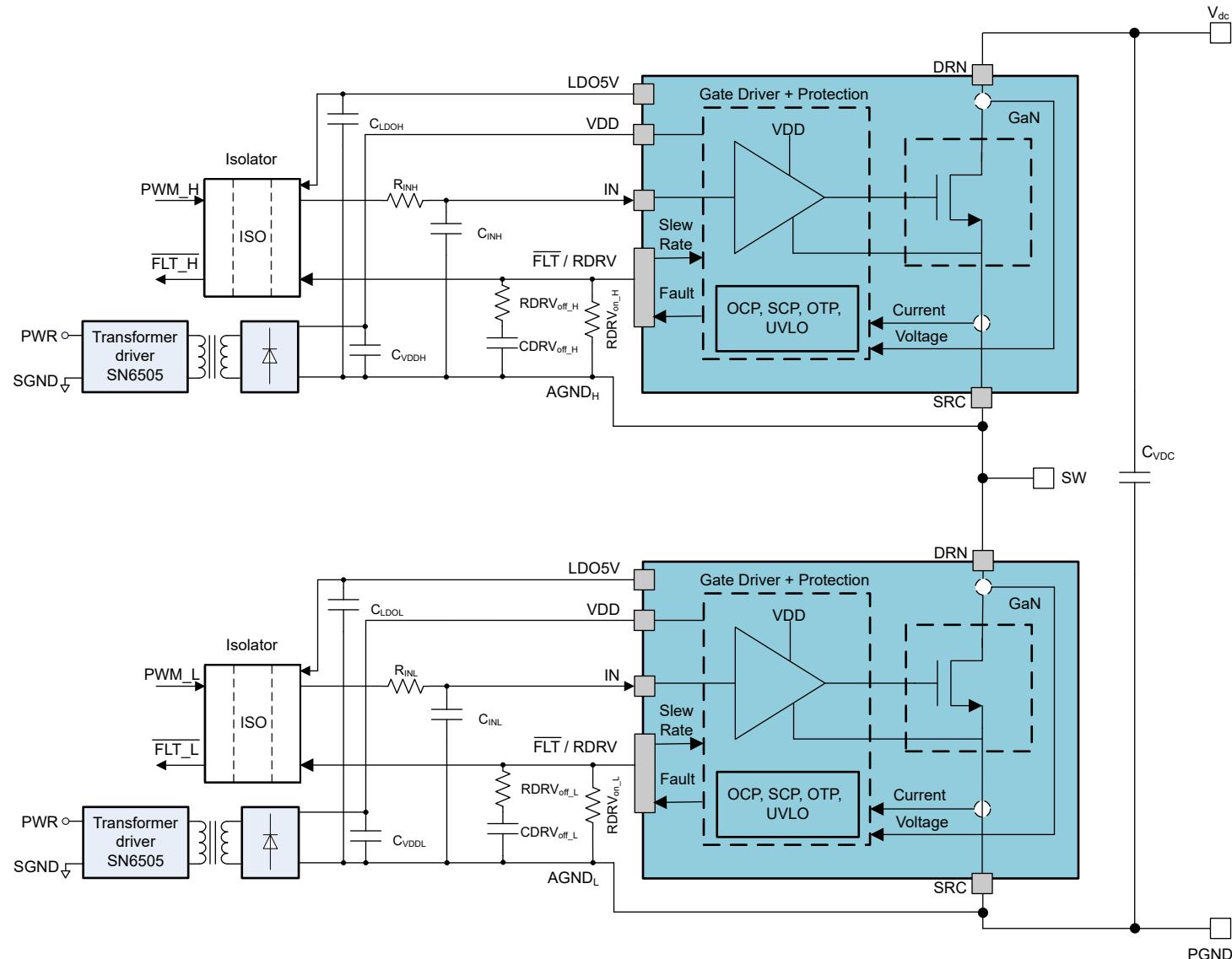

図 8-2. LMG3651R035 絶縁型電源を使用した標準的なハーフブリッジアプリケーション

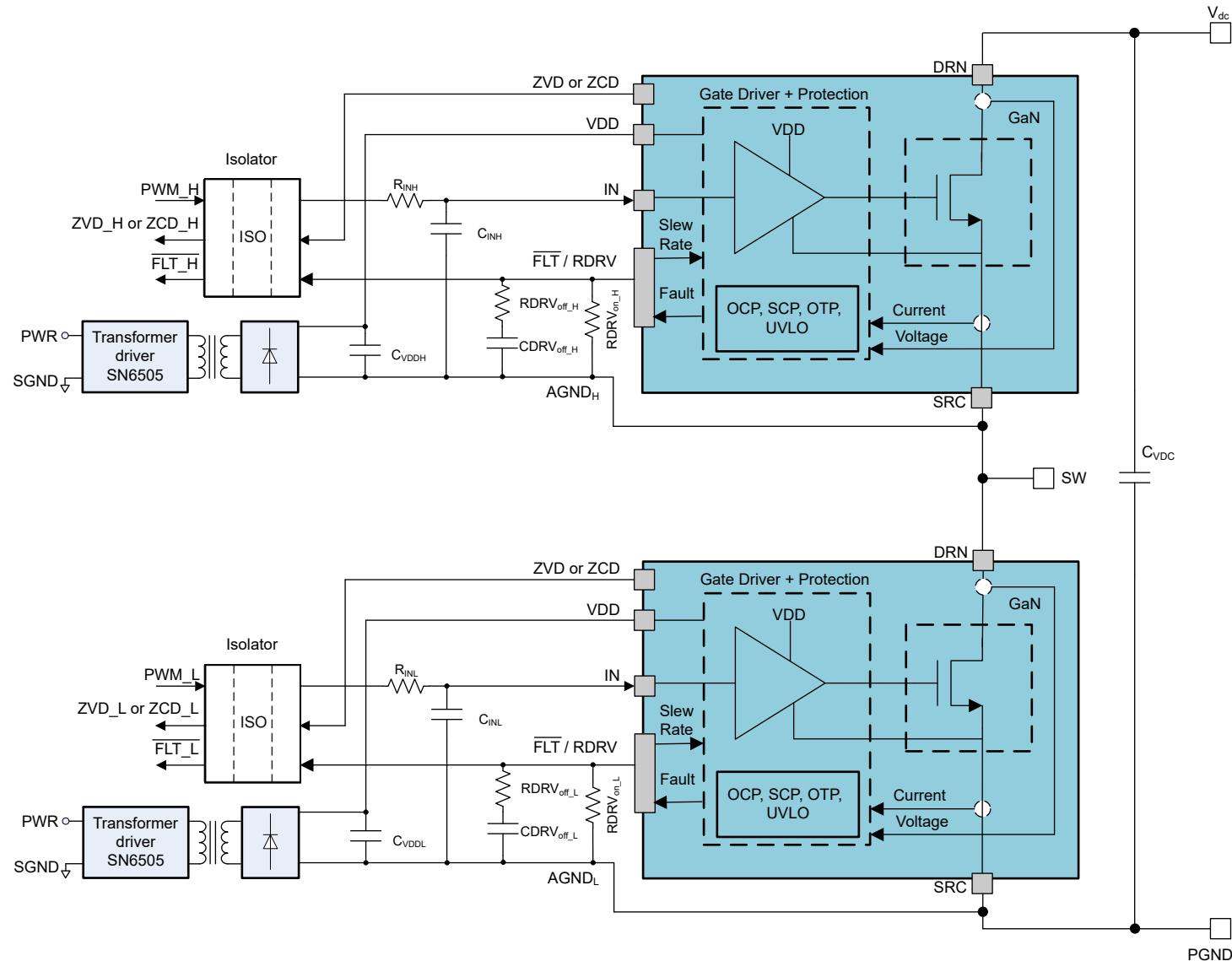

図 8-3. LMG3656R035 または LMG3657R035 絶縁型電源を使用した標準的なハーフブリッジ アプリケーション

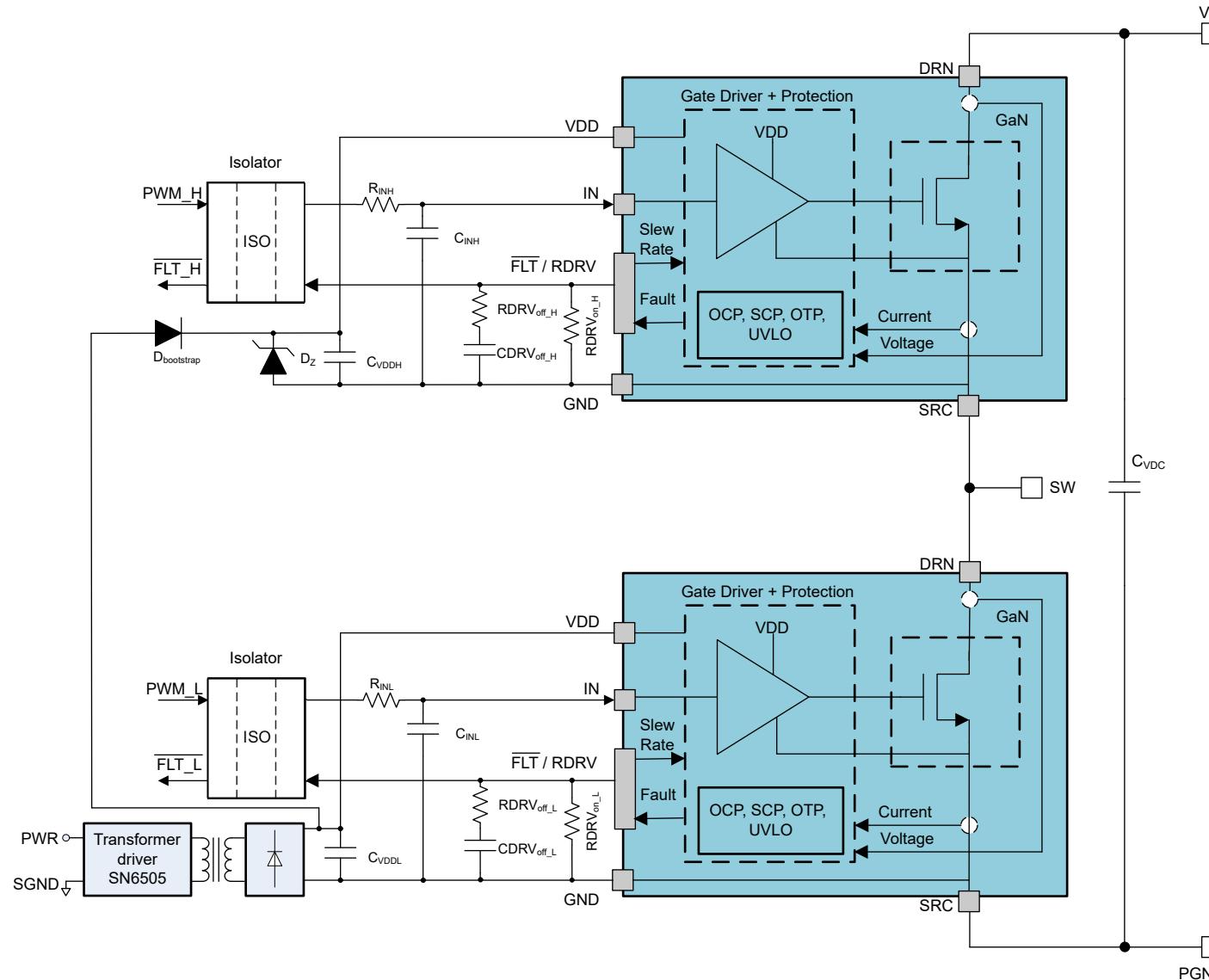

図 8-4. LMG3650R035 ブートストラップ付きの標準的なハーフブリッジ アプリケーション

図 8-5. LMG3651R035 ブートストラップ付きの標準的なハーフブリッジ アプリケーション

図 8-6. LMG3656R035 または LMG3657R035 ブートストラップ付きの標準的なハーフブリッジ アプリケーション

## 8.2.1 詳細な設計手順

高電圧パワーコンバータでは、高性能パワーコンバータには回路設計と PCB レイアウトが不可欠です。このデータシートでは、LMG365xR035 を使用するハーフブリッジの設計上の考慮事項を記載します。

### 8.2.1.1 スルーレートの選択

LMG365xR035 のターンオン スルーレートを約 10 V/ns から 80 V/ns に調整し、最大ターンオフ スルーレート制限を 10V/ns から無制限 ( $I_{ds}$  のみによって制御) に調整します。詳細については、[ドライブ強度の調整](#)を参照してください。

スルーレートは、GaN デバイスの性能に次の点で影響を及ぼします。

- スイッチング損失

- 電圧オーバーシュート

- ノイズ結合

- EMI(電磁干渉)放出

一般に、スルーレートが高いとスイッチング損失は小さくなりますが、高いスルーレートは電圧オーバーシュート、ノイズ結合、および EMI 放射を増加させる可能性もあります。高いスルーレートによって生じる課題を軽減するため、このデータシートの設計推奨事項に従います。LMG365xR035 を使用すると、回路設計者がアプリケーションの性能を最大限に引き出すために、適切なスルーレートを柔軟に選択できます。

### 8.2.1.2 信号レベル・シフト

ハーフブリッジでは、ハイサイド デバイスと制御回路の間の信号パスを絶縁するために、高電圧レベル シフタまたはデジタル アイソレータを使用します。ローサイドデバイスでは、アイソレータを使用することもオプションです。しかし、アイソレータを使用することで、ハイサイドとローサイドの信号パスの間の伝搬遅延を均等化し、GaN デバイスとコントローラに異なるグランドを使用することができます。ローサイド デバイスでアイソレータを使用しない場合、制御グランドと電源グランドはデバイスで接続し、基板上の他の場所には接続しないようにします。詳細については、[レイアウト ガイドライン](#)を参照してください。高速スイッチングデバイスでは、アイソレーターを使用しないと、コモン・グラウンド・インダクタンスがノイズ問題を引き起こす原因となりやすいです。

ノイズ耐性の向上には、レベル変換用のデジタルアイソレータの選択が重要です。GaN デバイスは、で 50V/ns を超える高い  $dv/dt$  を容易に実現できるため、同相過渡耐性 (CMTI) が高く、バリア容量が小さいアイソレータを使用することを TI は強くお勧めします。CMTI が小さいアイソレータは容易に誤信号を発生させ、貫通電流を引き起こす可能性があります。バリア容量は信号グランドと電源グランドとの間の絶縁容量の一部で、この容量はスイッチング中に発生する同相電流と EMI 放射に正比例します。さらに、TI はエッジトリガではないアイソレータを選択することを強く推奨しています。エッジトリガアイソレータでは、高  $dv/dt$  イベントが発生すると、アイソレータが動作状態を反転させ、回路の誤動作を引き起こす可能性があります。

一般的には、デフォルト出力が low の ON/OFF キー方式アイソレータが望まれます。デフォルトを low 状態にしておくことで、システムの立ち上げ時や故障復帰時にショートスルーが発生しないようにできます。高い CMTI イベントによって数ナノ秒程度の短い誤パルスが生じるため、TI はドライバ入力にローパス フィルタ (例えば 50Ω と 150pF の R-C) を配置して誤パルスを除去することを推奨しています。

## 8.3 電源に関する推奨事項

LMG365xR035 は、9V ~ 24V の非レギュレート VDD 電源のみが必要です。ローサイドの電源は、ローカルのコントローラ電源から取得します。ハイサイド デバイスの電源が、絶縁電源またはブートストラップ電源から供給されていることを確認します。

### 8.3.1 絶縁型電源の使用

ハイサイド デバイスを駆動するために絶縁型電源を使用する利点は、電力段のスイッチングやデューティサイクルがどうであっても動作する点にあります。絶縁型電源を使用すれば、電力段のスイッチングが始まる前にハイサイド デバイスへ電力を供給でき、スムーズな立ち上がりが可能になります

絶縁電源は、プッシュプルコンバータ、フライバックコンバータ、FlyBuck™コンバータ、または絶縁電源モジュールを用いて得ます。レギュレートされていない電源を使用する場合、LMG365xR035 の入力は最大電源電圧を超えないようにします。24V TVS ダイオードを使用して、LMG365xR035 の VDD 電圧をクランプし、保護を強化できます。

### 8.3.2 ブートストラップダイオードの使用

ハーフブリッジ構成では、ハイサイドデバイスにフローティング電源が必要になります。LMG365xR035 の性能を最大限に引き出すため、TI では、絶縁電源を使用することを強くお勧めします。ブートストラップ電源は、[ブートストラップダイオードの使用](#)の推奨事項に従って使用できます。

#### 8.3.2.1 ダイオードの選択

LMG365xR035 は逆方向回復電荷がなく、出力電荷が非常に制限されています。LMG365xR035 を使用した回路では、高い電圧スルーレートが生じる場合があります。適合するブートストラップダイオードが、高い出力電荷やリバースリカバリ電荷を生じさせないことを確認します。

リバースリカバリの影響を避けるため、GB01SLT06-214 のようなシリコンカーバイドダイオードを使用します。SiC ダイオードの出力電荷は 3nC です。その出力電荷には追加の損失がありますが、スイッチングステージの損失に支配されることはありません。

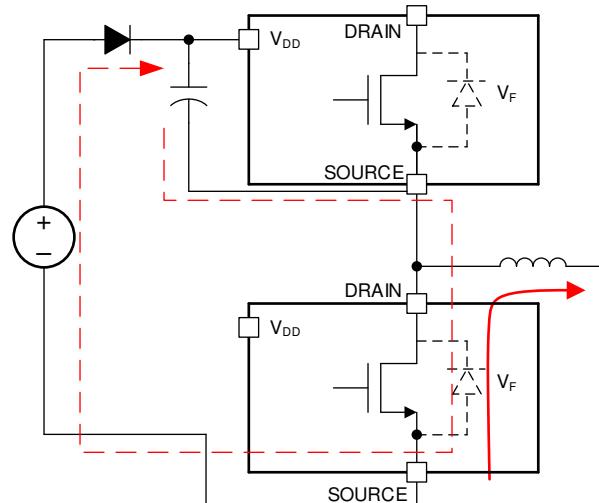

#### 8.3.2.2 ブートストラップ電圧の管理

同期整流型の降圧コンバータや、ローサイドスイッチがときどき第 3 象限で動作する他のコンバータでは、デッドタイム中にロー サイドの第 3 象限電圧ドロップ LMG365xR035 を含む経路を通じてブートストラップ電源が充電されます（[ブートストラップダイオードの充電経路](#)に記載）。この第 3 象限での電圧降下は大きくなることがあります。条件によってはブートストラップ電源を過充電してしまう可能性があります。LMG365xR035 の VDD 電源電圧が 26V 未満のままであることを確認します。

図 8-7. ブートストラップダイオードの充電パス

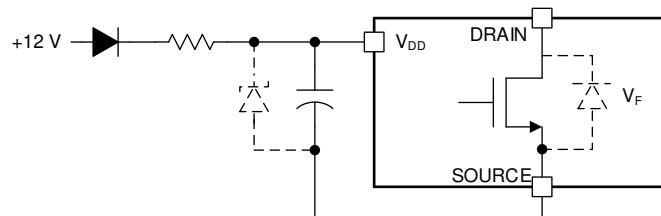

推奨ブートストラップ制御回路が示すように、推奨されるブートストラップ電源は、ブートストラップダイオード、直列抵抗、そして VDD バイパスコンデンサと並列に配置された 24V の TVS またはツェナーダイオードで構成されます。並列な配置により、ハイサイド LMG365xR035 への損傷を防止します。直列抵抗は、スタートアップ時とローサイドデバイスが第 3 象限モードで動作しているときの充電電流を制限します。この抵抗は、目的の動作周波数で LMG365xR035 を駆動するのに十分な電流が得られるよう選択します。100kHz で動作させる場合、TI は約 2Ω の値を推奨しています。より高い周波数では、十分な供給電流を確保するために、抵抗値を下げるか省略します。

図 8-8. 推奨されるブートストラップ・レギュレータ回路

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

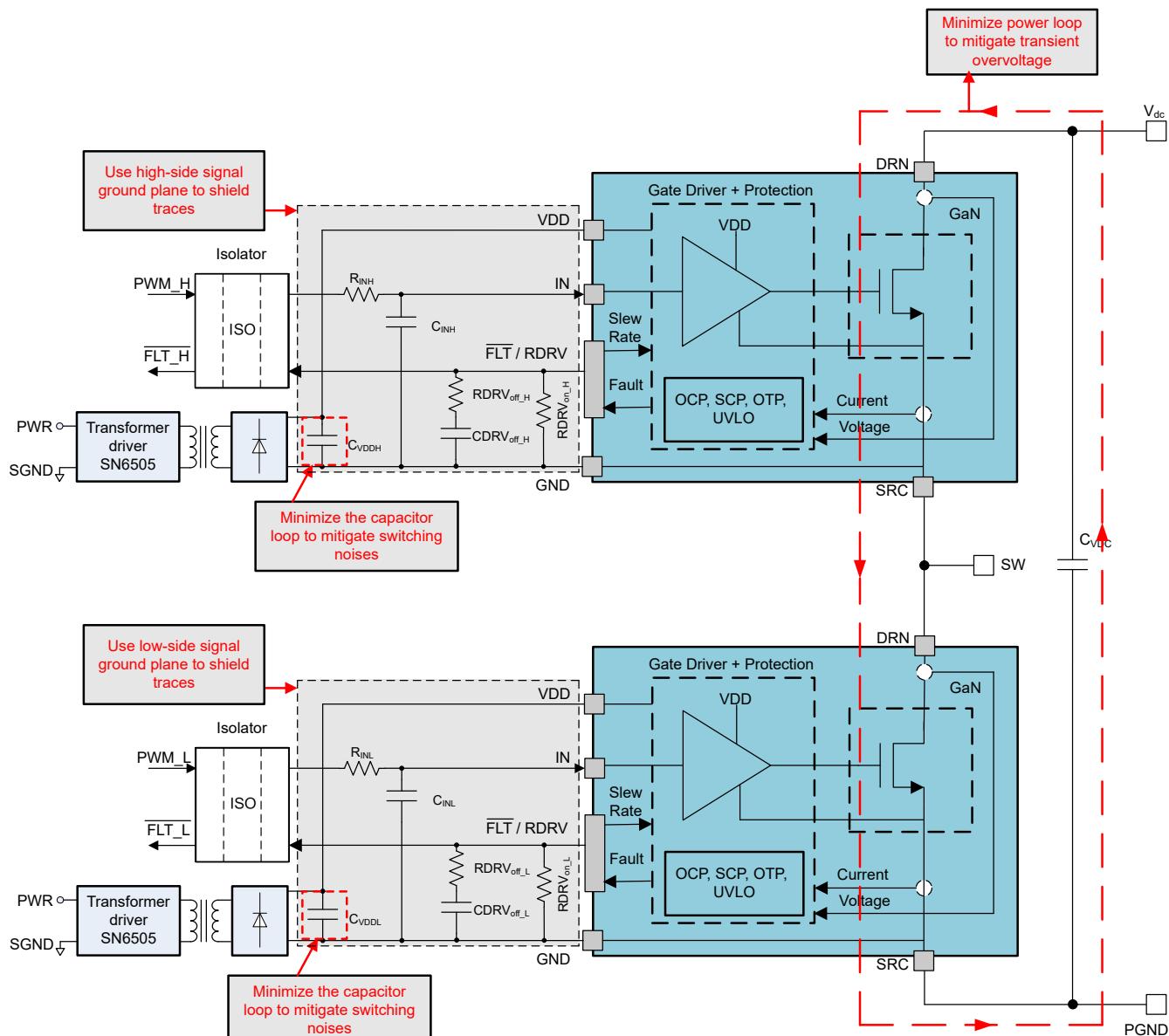

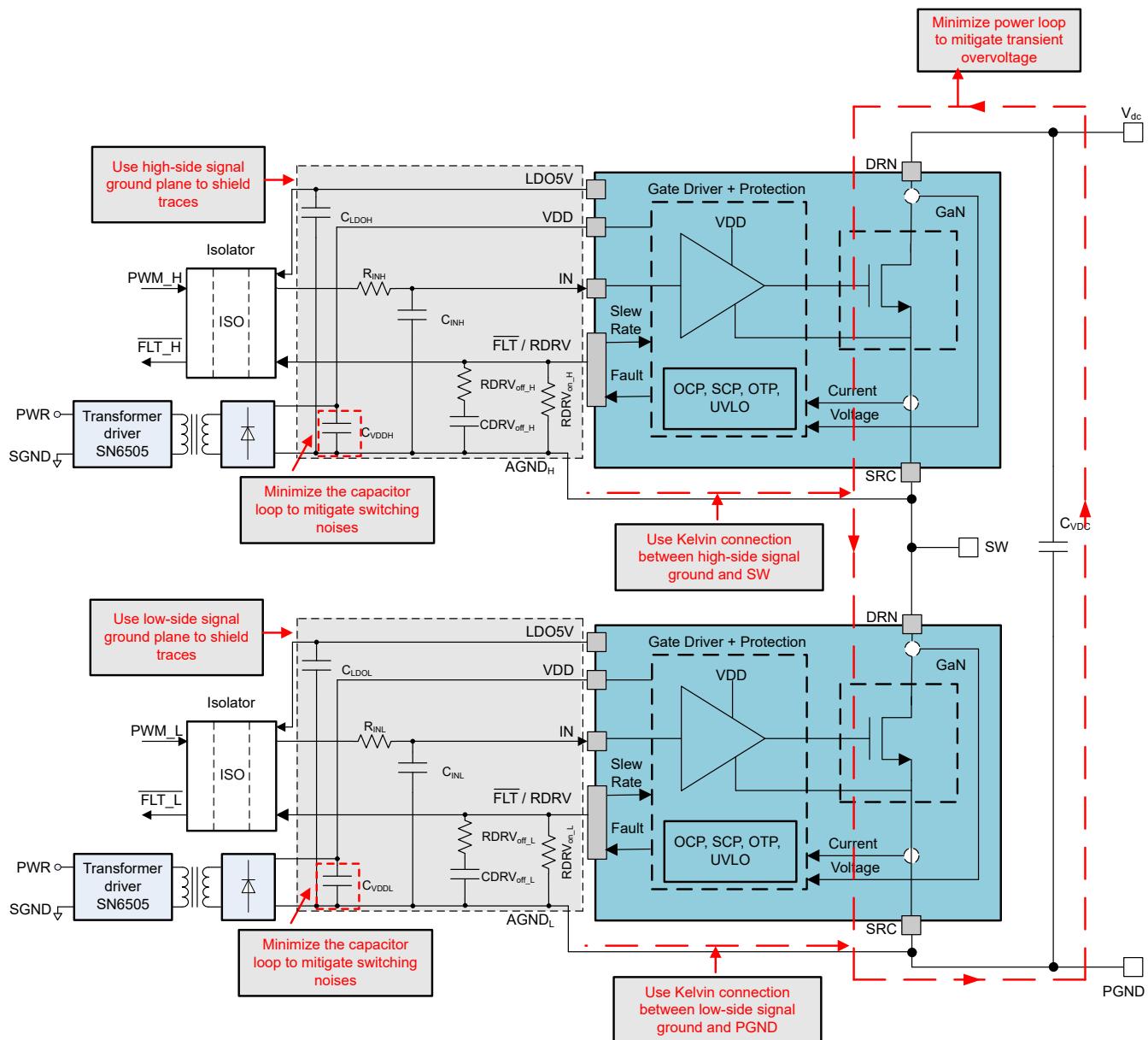

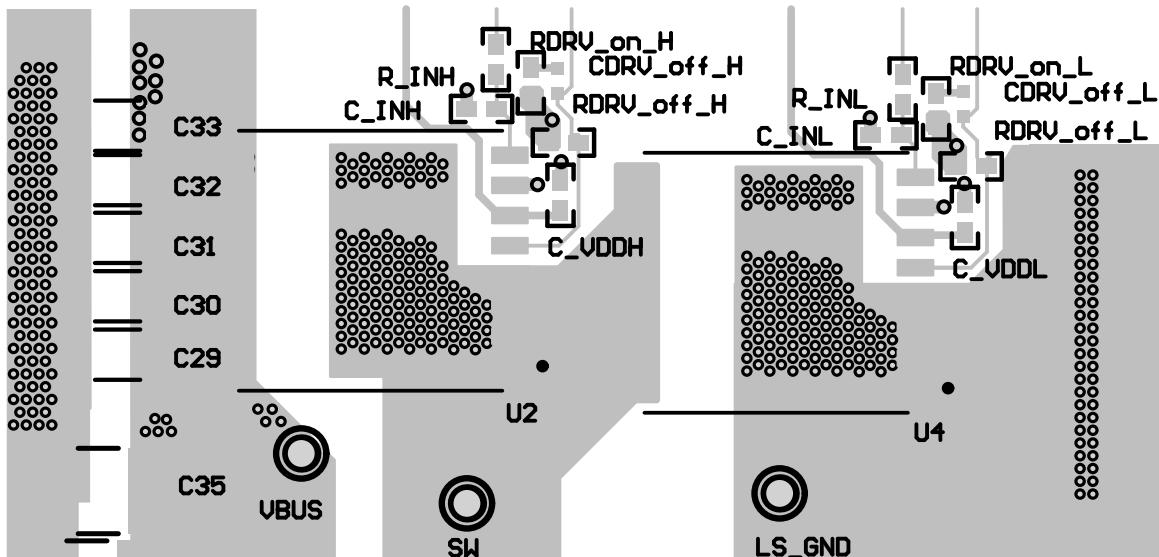

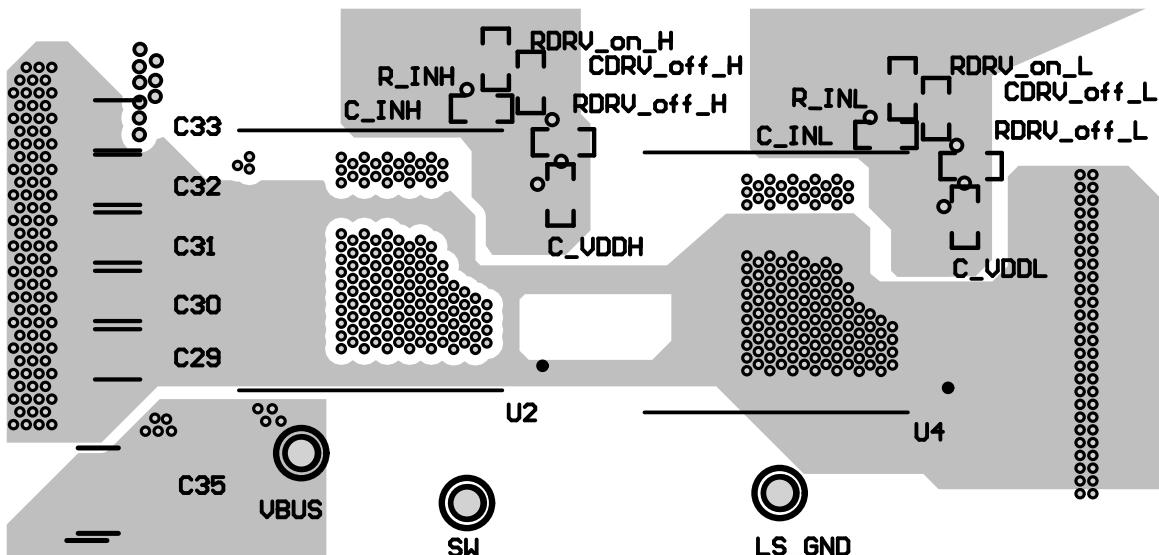

LMG365xR035 のレイアウトは、そのパフォーマンスと機能にとって重要です。通常、ハーフブリッジ構成はこれらの GaN デバイスで使用されるため、この構成ではレイアウトに関する推奨事項を考慮します。レイアウトの寄生インダクタンスを低減するため、4 層以上の基板を推奨します。以下の図は重要なレイアウト ガイドラインをまとめたもので、詳細については後続のセクションでさらに説明します。

図 8-9. LMG3650R035 レイアウトに関する考慮事項付きの代表的な回路図

図 8-10. LMG3651R035 レイアウトに関する考慮事項付きの代表的な回路図

図 8-11. LMG3656R035 または LMG3657R035 レイアウトに関する考慮事項付きの代表的な回路図

#### 8.4.1.1 半田接合に対する信頼

TOLL パッケージは一般的に大電流アプリケーションで使用されるため、SRC パッドと DRN パッドが半田マスク定義 (SMD) になっていることを確認します。実際のレイアウトでは、導電性を最大化するために、ソースパッドとトレインパッドはしばしば可能な限り PCB との大きな接触面積を確保できる銅プレーンに接続されます。メカニカル、パッケージ、および注文情報のランドパターンの例に示すように、電流が最小限で、主に信号接続に使用される他の半田パッドが非半田マスク定義 (NSMD) であることを確認します。最後に、NSMD パッドに接続する基板配線は、パッド側で配線が接続する位置において、パッド幅の 3 分の 2 未満であることを確認します。配線は、半田マスクで覆われていない限り、その区間においてパッド幅の 3 分の 2 という制限を維持する必要があります。トレースがハンダ・マスク下の場合、トレースの寸法に制限はありません。レイアウト例では、これらすべての記載されている推奨事項に従っています。

#### 8.4.1.2 電力ループのインダクタンス

ハーフ・ブリッジの 2 つのデバイスと高電圧バス容量で構成される電源ループは、スイッチング・イベント中に高い  $di/dt$  を印加します。パワー ループのインダクタンスを最小化することで、リングギングや電磁干渉 (EMI) を低減でき、デバイスにかかる電圧ストレスも減らせます。

電源ループのインダクタンスを最小限に抑えるため、電源デバイスをできるだけ近くに配置します。デカップリング コンデンサは、2 つのデバイスと並んで、両方のデバイスの近くに配置します。[セクション 8.4.2](#) では、デカップリング コンデンサはデバイスと同じ層に配置されています。帰路(この場合は PGND)は、最上層に近接した 2 番目の層に配置されています。下層ではなく内層を使用することで、ループの垂直寸法が小さくなり、インダクタンスが最小化されます。デバイスの端子とバス容量の両方に多数のビアを配置すると、インピーダンスを最小化しながら高周波スイッチング電流が内層に流れます。

電力ループ インダクタンスは、ドレイン ソース間電圧スイッチング波形のリングギング周波数  $f_{ring}$  に基づいて、次の式で推定できます:

$$L_{pl} = \frac{1}{4\pi^2 f_{ring}^2 C_{ring}} \quad (4)$$

**式 4**において、 $C_{ring}$  は、バス電圧での  $C_{oss}$  (標準値については[出力コンデンサとドレイン ソース電圧](#)を参照) と、基板および負荷インダクタまたはトランジスタからのドレイン ソース間寄生容量を加算した値に等しくなります。

負荷部品の寄生容量は特性評価が難しいため、パワー ループのインダクタンスを推定するには、負荷部品を取り外した状態で  $V_{DS}$  のスイッチング波形を取得することを TI は推奨しています。通常、[セクション 8.4.2](#) のパワーループ インダクタンスはおよそ 2.5nH です。

#### 8.4.1.3 信号-グランド接続

LMG365xR035 の SRC ピンは、電源 IC の GND ピン (信号グランド基準) に内部で接続されています。ローカルの信号グランド プレーンが、低インピーダンスのスター接続で GND ピンに接続されていることを確認します。さらに、ドライバに関連する受動部品 (バイパス コンデンサ) の帰路が GND ピンに接続されていることも確認します。[セクション 8.4.2](#) では、ローカルの信号グランド プレーンは、ローカル回路の帰路として機能させるため、2 層目に配置されています。ローカルの信号グランド プレーンは、GND ピンでのスター接続を除き、大電流の SRC ピンには接続しません。

#### 8.4.1.4 バイパス コンデンサ

VDD ピンのバイパス コンデンサ  $C_{VDDL}$  と  $C_{VDDH}$  は、低インピーダンスの配線で VDD ピンの近くに配置してください。

#### 8.4.1.5 スイッチ・ノードの静電容量

GaN デバイスは出力容量が非常に低く、高  $dv/dt$  で高速にスイッチングするため、スイッチング損失も非常に小さくなります。スイッチング損失の低さを維持するため、出力ノードに追加する容量は最小限にします。スイッチ ノードの PCB 容量を最小化するため、以下のガイドラインに従ってください:

- スイッチ・ノードのプレーンと他の電源プレーンおよびグランド・プレーンとの間のオーバーラップを最小限に抑えます。

- ハイサイドデバイスの下の GND リターンパスを細くしながら、低インダクタンスパスを維持します。

- ハイサイド・アイソレータ IC とブートストラップ・ダイオードは、静電容量の小さいものを選定します。

- パワーインダクタは、GaN デバイスにできるだけ近づけて配置してください。

- 巻線間静電容量を最小限に抑えるため、単層巻線を使用してパワー インダクタを構築します。

- 1 層インダクタを使用できない場合は、追加の静電容量から GaN デバイスを効果的にシールドするために、一次インダクタと GaN デバイスの間に小型インダクタを配置することを検討してください。

- 裏面のヒートシンクを使用する場合は、放熱性能を向上させるため、下層の銅層でスイッチ ノードの銅領域の面積が最小限のものを使用します。

#### 8.4.1.6 シグナルインテグリティ

LMG365xR035 への制御信号は、高速スイッチングによって発生する高  $dv/dt$  から保護します。制御信号とドレインの間の結合は、回路が不安定になり、破壊の可能性があります。制御信号 (IN, ZVD, ZCD,  $\overline{FLT}/RDRV$ ) は、隣接層に配置

したグランドプレーン上を配線します。[セクション 8.4.2](#)においては、たとえば、レイアウト例では、すべての信号がローカル信号グランドプレーンに近い層に配線されています。

ハイサイド デバイス用の配線と、PGND や HVBUS のような静的プレーンとの間の容量結合は、同相モード電流やグランドバウンスを引き起こす可能性があります。ハイサイド配線と静的プレーンとの重なりを減らすことで、容量結合を抑制できます。ハイサイド レベルシフタでは、入力側でも出力側でも、アイソレータの直下に銅が伸びないようにします。アイソレータの下に伸びている銅箔が、デバイスの CMTI を損なう可能性があります。

#### 8.4.1.7 高電圧間隔

LMG365xR035 を使用する回路は、最大 650V の高電圧を使用する可能性があります。LMG365xR035 を使用した回路をレイアウトする際は、アプリケーションに求められるクリープ距離および空間距離の要件と、その要件が GaN デバイスにどのように適用されるかを理解しておく必要があります。各トランジスタのソースとドレイン間、および高電圧電源とグランドの間で、機能的(または動作中)の絶縁が必要です。LMG365xR035 への入力回路と電源コントローラの間に機能絶縁、またはより強力な絶縁(強化絶縁など)が必要になることがあります。ユーザ特有の絶縁要件を満たす信号アイソレータと PCB 間隔(沿面距離と空間距離)を選定します。

LMG365xR035 の放熱を管理するためにヒートシンクを使用する場合は、ヒートシンクと PCB の間に必要な電気的絶縁と機械的間隔を確保します。

#### 8.4.1.8 基板に関する推奨事項

LMG365xR035 は Si 基板上に成長した横方向デバイスです。サーマル パッドは、電気的にも熱的にもデバイスのソースに接続されています。電力損失が大きいアプリケーションでは、PCB だけで冷却しようとしても、部品を適切な温度に保つには不十分な場合があります。部品の放熱を改善するために、TI は追加の熱を逃がせるよう PCB の背面にヒートシンクを取り付けることを推奨しています。電源プレーン、厚い銅層、そして多数のサーマル ビアを使用することで、LMG365xR035 で発生した熱を PCB 内に広く拡散させ、PCB の反対側へ効率的に逃がすことができます。トップ銅層とボトム層を接続することで、サーマルビアは熱の流れが熱伝導率の低い FR4 層をバイパスできるようにします。したがって、PCB の全体的な有効熱伝導率が向上します。サーマルビアは通常、機械的な穴あけによって形成されます。空気は熱伝導率が低いため、PCB を縦方向に熱を伝えるには、ビアの内側表面にめっきされた銅層を設けることが推奨されます。熱性能を向上させるには、より高いビア メッキの厚さを使用します。サーマルビアの効果をさらに高めるために、空隙を熱伝導率の高いエポキシや銅で充填します。また、デバイスのフットプリントに配置されているビアにも接続します。キヤップ処理をしないと、パッドの半田がビアに流れ込み、デバイス直下に半田ボイドが発生します。PCB 背面の露出部分に、熱伝導インターフェイス素材 (TIM) を介してヒートシンクを取り付けます。より効果的に熱を除去するために、ヒートシンクの下にあるボードの裏面から半田マスクを取り外します。

#### 8.4.2 レイアウト例

LMG365xR035 およびその周辺部品の正しいレイアウトは、正しい動作に不可欠です。ここに示すレイアウトは、[図 8-1](#) に示す GaN デバイスの回路図を反映しています。[図 8-1](#) のレイアウトは良好な結果が得られることが示されており、ガイドラインを意図しています。ただし、別のレイアウト方式でも許容できる性能を得ることは可能です。さらに、最新の推奨 PCB フットプリントについては、[セクション 11.2](#) 内のランド パターン例を参照してください。

最上層レイアウトと中間層レイアウトを示します。レイアウトは、LMG3650R035U2 および U4 コンポーネントの配置に拡大されます。中間層レイアウトには、ユーザーが最上層と中間層のレイアウトを整列できるように、最上層の部品のアウトラインが含まれています。

図 8-12. LMG3650R035 ハーフブリッジの最上層レイアウト

図 8-13. LMG3650R035 ハーフブリッジの中間層レイアウト

## 9 デバイスおよびドキュメントのサポート

テキサス・インスツルメンツでは、幅広い開発ツールを提供しています。デバイスの性能の評価、コードの生成、ソリューションの開発を行うためのツールとソフトウェアを以下で紹介します。

### 9.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 9.3 商標

FlyBuck™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.5 用語集

[テキサス・インスツルメンツ用語集](#)

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

### Changes from Revision \* (January 2025) to Revision A (December 2025)

Page

- |                            |   |

|----------------------------|---|

| • 「事前情報」から「量産ミックス」に更新..... | 1 |

|----------------------------|---|

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 付録 : パッケージ・オプション

### パッケージ情報

| 注文可能な型番         | ステータス<br><a href="#">(1)</a> | 資料の<br>タイプ<br><a href="#">(2)</a> | パッケージ   ピン数 | パッケージ数量   キ<br>ヤリア    | RoHS<br><a href="#">(3)</a> | リード端子の仕上げ/<br>ボールの原材料<br><a href="#">(4)</a> | MSL 定格/ピークリフロ<br>ー<br><a href="#">(5)</a> | 動作温度 (°C) | 部品マーキング<br><a href="#">(6)</a> |

|-----------------|------------------------------|-----------------------------------|-------------|-----------------------|-----------------------------|----------------------------------------------|-------------------------------------------|-----------|--------------------------------|

| LMG3650R035KLAR | アクティブ                        | 量産出荷中                             | KLA   9     | 2000   大口径のテー<br>プリール | RoHS<br>適用除外                | Sn                                           | Level-3-260C-168 HR                       | -40~175   | LMG3650 R035                   |

- (1) **ステータス:**ステータスの詳細については、TI の [製品ライフ サイクル](#) をご覧ください。

- (2) **資料のタイプ:**指定された量産開始前部品はプロトタイプ/検証用デバイスであり、実生産向けに承認またはリリースされたものではありません。テストおよび最終プロセス (品質保証、信頼性性能テスト、プロセス認証が含まれますが、これに限定されるものではありません) がまだ完了していない可能性があるほか、さらなる変更が加えられたり、中止される可能性もあります。注文可能になっている場合、その購入はチェックアウト時に新たな免責条項の対象となるものとします。また、これは早期内部評価のみを目的としたものです。これらの商品は、いかなる保証もなしで販売されています。

- (3) **RoHS 値:**はい、いいえ、RoHS 免除。詳細情報および値の定義については、[TI RoHS に関する声明](#) を参照してください。

- (4) **リード端子の仕上げ/ボールの原材料:**部品には複数の材料仕上げオプションがある場合があります。複数の仕上げオプションは、縦野線で区切られています。リード端子の仕上げ / ボールの原材料の値が最大列幅に収まらない場合は、2 行にまたがります。

- (5) **MSL 定格/ピークリフロー:**湿度感度レベルの定格、および半田付けのピーク (リフロー) 温度です。部品が複数の耐湿性定格を持つ場合、JEDEC 規格で最低レベルのみを示しています。プリント基板に部品を取り付けるために使用する実際のリフロー温度については、出荷ラベルをご確認ください。

- (6) **部品マーキング:**ロゴ、ロットトレースコード情報、または環境カテゴリに関する追加マークが部品に記載されることがあります。複数の部品マーキングが括弧の中に記載されています。括弧内で「～」で区切られた 1 つの部品マーキングのみが部品に表示されます。行がインデントされている場合は、前行の続きということです。2 行合わせたものが、そのデバイスの部品マーキング全体となります。

**重要なお知らせと免責事項:**このページに掲載されている情報は、発行日現在のテキサス・インスツルメンツの知識および見解を示すものです。テキサス・インスツルメンツの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。テキサス・インスツルメンツでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。テキサス・インスツルメンツおよびテキサス・インスツルメンツのサプライヤは、特定の情報を機密情報として扱っているため、CAS 番号やその他の制限された情報が公開されない場合があります。

いかなる場合においても、そのような情報から生じた TI の責任は、このドキュメント発行時点での TI 製品の価格に基づく TI からお客様への合計購入価格 (年次ベース) を超えることはありません。

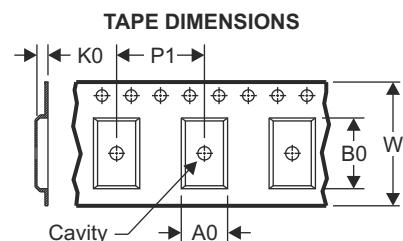

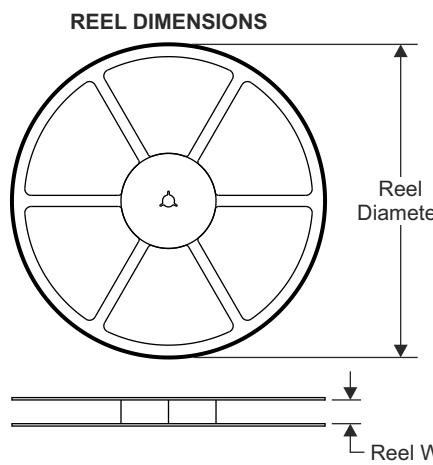

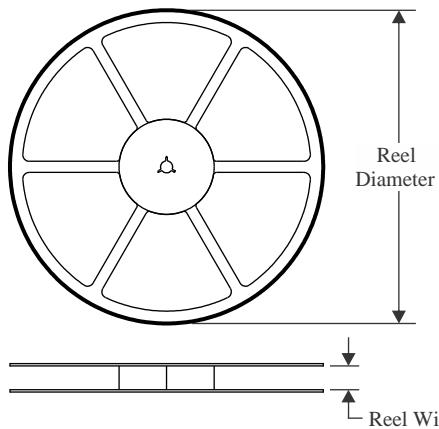

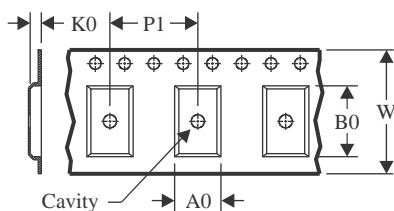

## 11.1 テープおよびリール情報

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

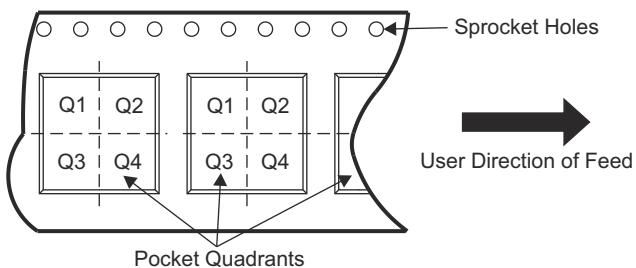

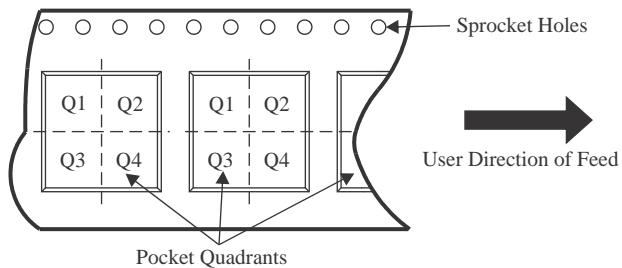

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| デバイス        | パッケージ<br>タイプ | パッケージ<br>図 | ピン | SPQ  | リール<br>直径 (mm) | リール<br>幅 W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | ピン 1 の<br>象限 |

|-------------|--------------|------------|----|------|----------------|------------------|------------|------------|------------|------------|-----------|--------------|

| LMG3650R035 | 送信先          | KLA        | 9  | 2000 | 330.0          | 24.4             | 10.20      | 11.98      | 2.6        | 12.0       | 21.0      | Q2           |

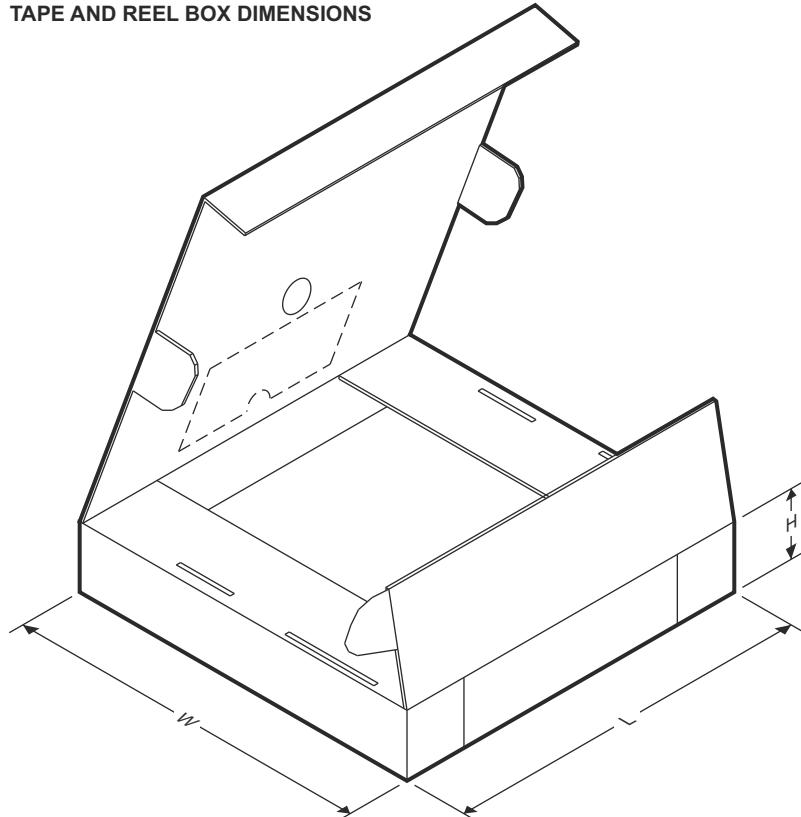

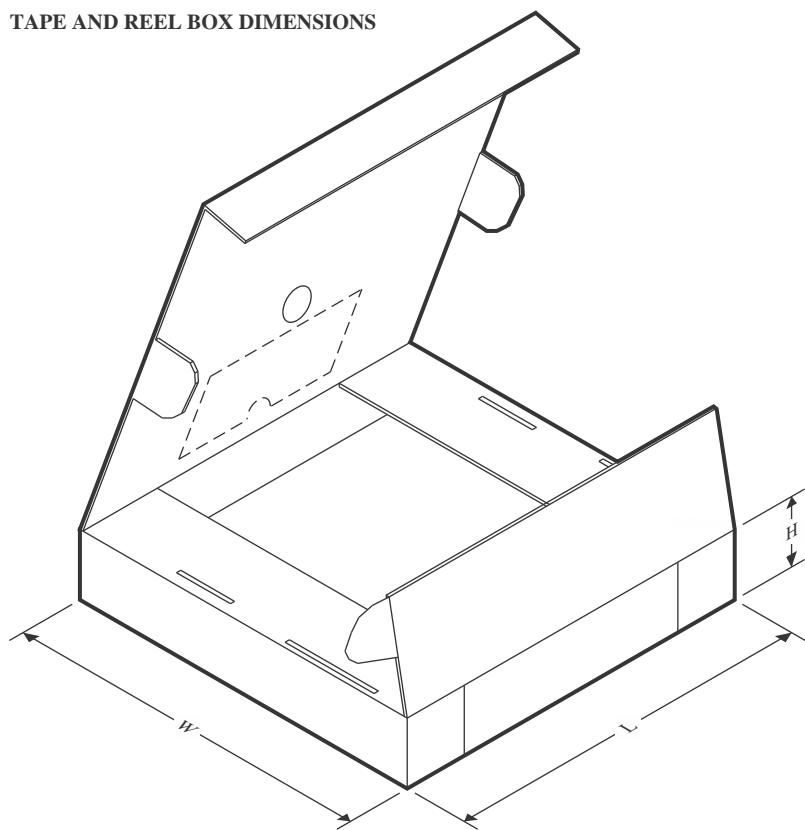

TAPE AND REEL BOX DIMENSIONS

| デバイス        | パッケージタイプ | パッケージ図 | ピン | SPQ  | 長さ (mm) | 幅 (mm) | 高さ (mm) |

|-------------|----------|--------|----|------|---------|--------|---------|

| LMG3650R035 | 送信先      | KLA    | 9  | 2000 | 356.0   | 356.0  | 45.0    |

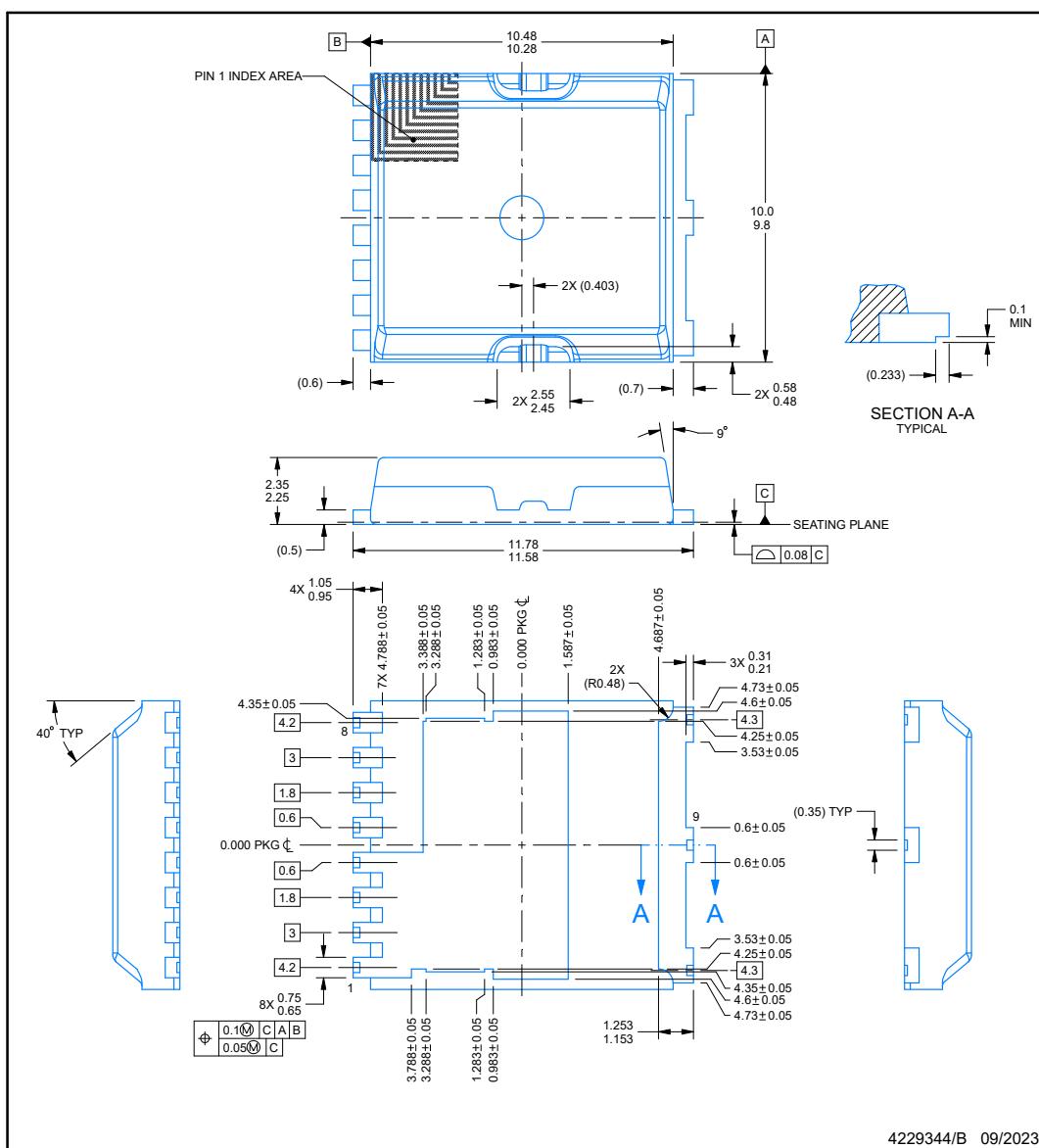

**KLA0009A**

**PACKAGE OUTLINE**

**TOLL - 2.35 mm max height**

TO LEADLESS

4229344/B 09/2023

**NOTES:**

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

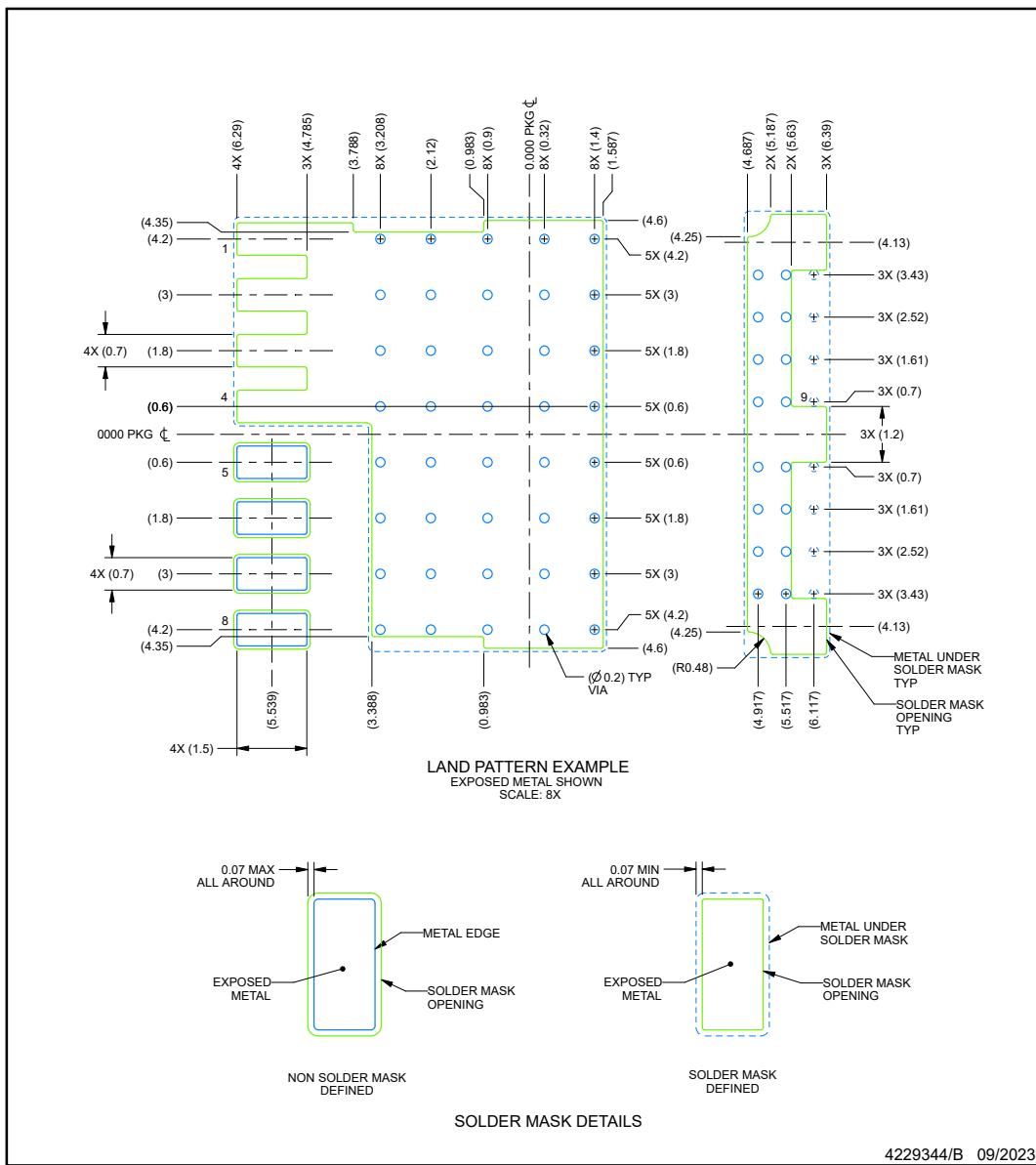

## EXAMPLE BOARD LAYOUT

KLA0009A

TOLL - 2.35 mm max height

TO LEADLESS

NOTES: (continued)

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

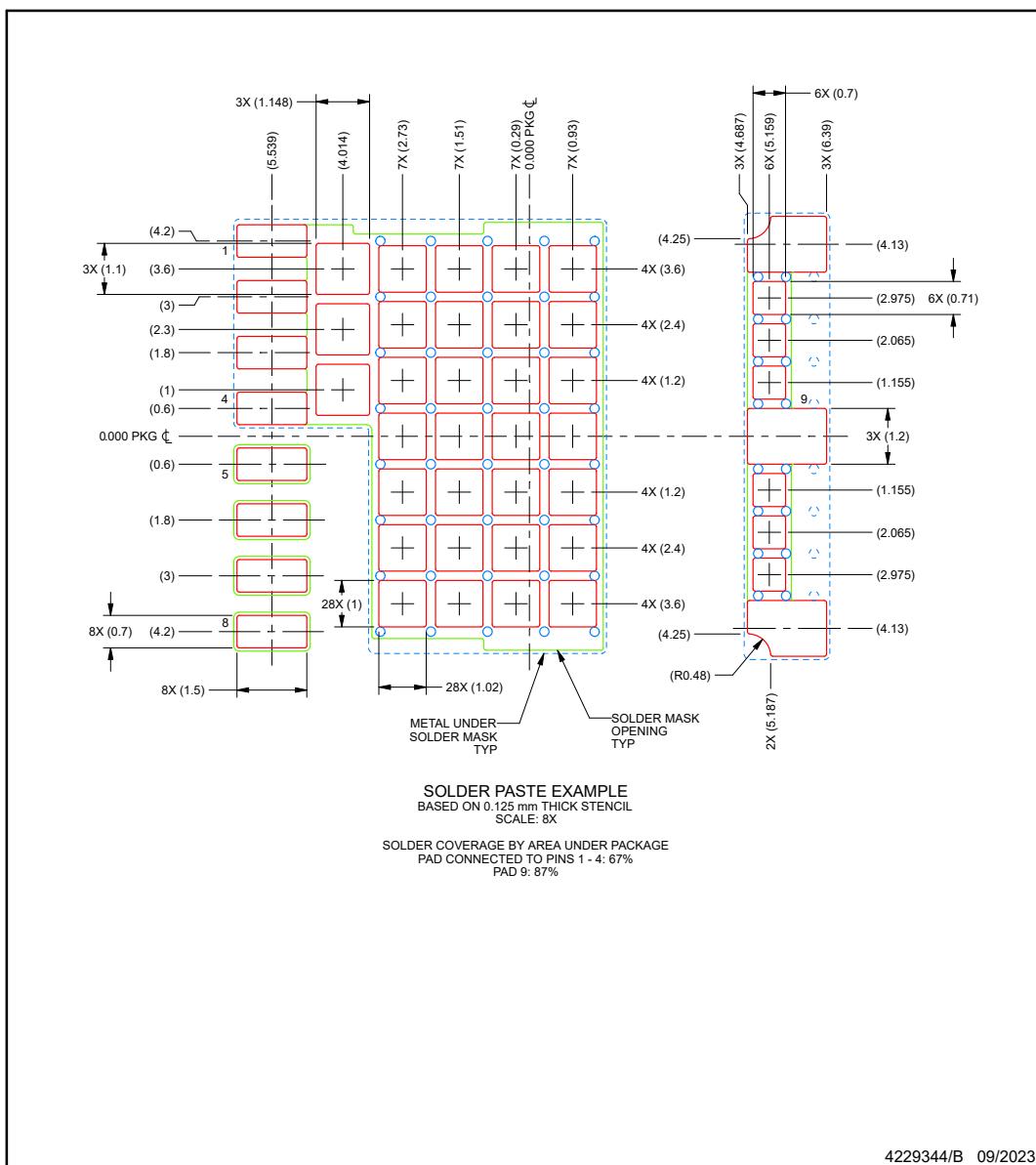

## EXAMPLE STENCIL DESIGN

KLA0009A

TOLL - 2.35 mm max height

TO LEADLESS

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LMG3650R035KLAR       | Active        | Production           | TO (KLA)   9   | 2000   LARGE T&R      | -           | SN                                   | Level-3-260C-168 HR               | -40 to 150   | LMG3650<br>R035     |

| XLMG3650R035KLAT      | Active        | Preproduction        | TO (KLA)   9   | 250   LARGE T&R       | -           | Call TI                              | Call TI                           | -40 to 150   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LMG3650R035KLAR | TO           | KLA             | 9    | 2000 | 330.0              | 24.4               | 10.2    | 11.98   | 2.6     | 12.0    | 24.0   | Q2            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMG3650R035KLAR | TO           | KLA             | 9    | 2000 | 356.0       | 356.0      | 45.0        |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月