# LMK00334 PCIe® Gen 1～Gen 7 向け 4 出力クロック バッファおよびレベル変換器

## 1 特長

- 3:1 入力マルチプレクサ

- 2つの汎用入力は最高 400MHz で動作し、LVPECL、LVDS、CML、SSTL、HSTL、HCSL、シングルエンド クロックに対応

- 1つの水晶振動子入力は、10MHz ~ 40MHz の水晶振動子またはシングルエンド クロックを受け入れます

- 2 バンクで、それぞれに 2 つの差動出力

- HCSL または Hi-Z (選択可能)

- PCIe® 仕様における加算 RMS 位相ジッタ

- Gen 5 で 7.2fs RMS (標準値)

- Gen 6 で 5fs RMS (標準値)

- Gen 7 で 3.5fs RMS (標準値)

- 高 PSRR: 156.25MHz で -72dBc

- 同期イネーブル入力付きの LVC MOS 出力

- 構成をピンで制御可能

- V<sub>CC</sub> コア電源: 3.3V ± 5%

- 3 つの独立した V<sub>CCO</sub> 出力電源: 3.3V, 2.5V ± 5%

- 産業用温度範囲: -40°C ~ +105°C

- 32 ピン WQFN (5mm × 5mm)

## 2 アプリケーション

- データセンター向けスイッチ

- コアルータ

- サーバー、コンピューティング、PCIe Gen 3.0～5.0

- リモート無線ユニットおよびベースバンド ユニット

## 3 説明

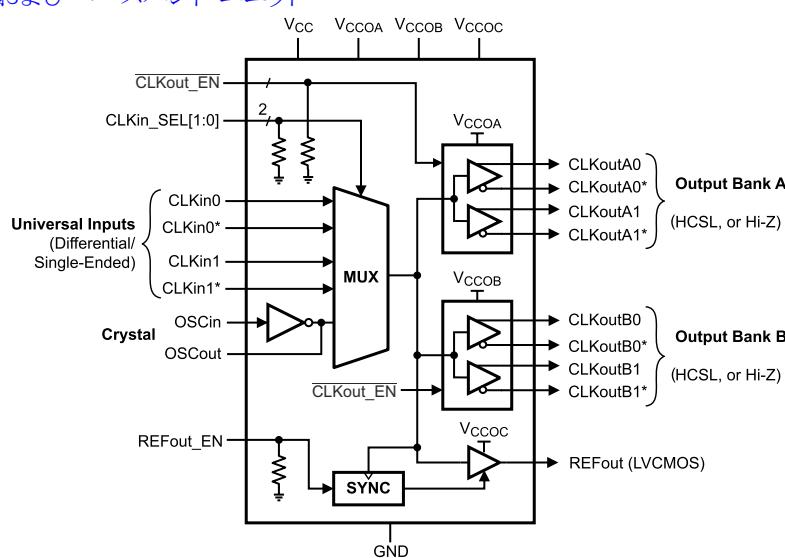

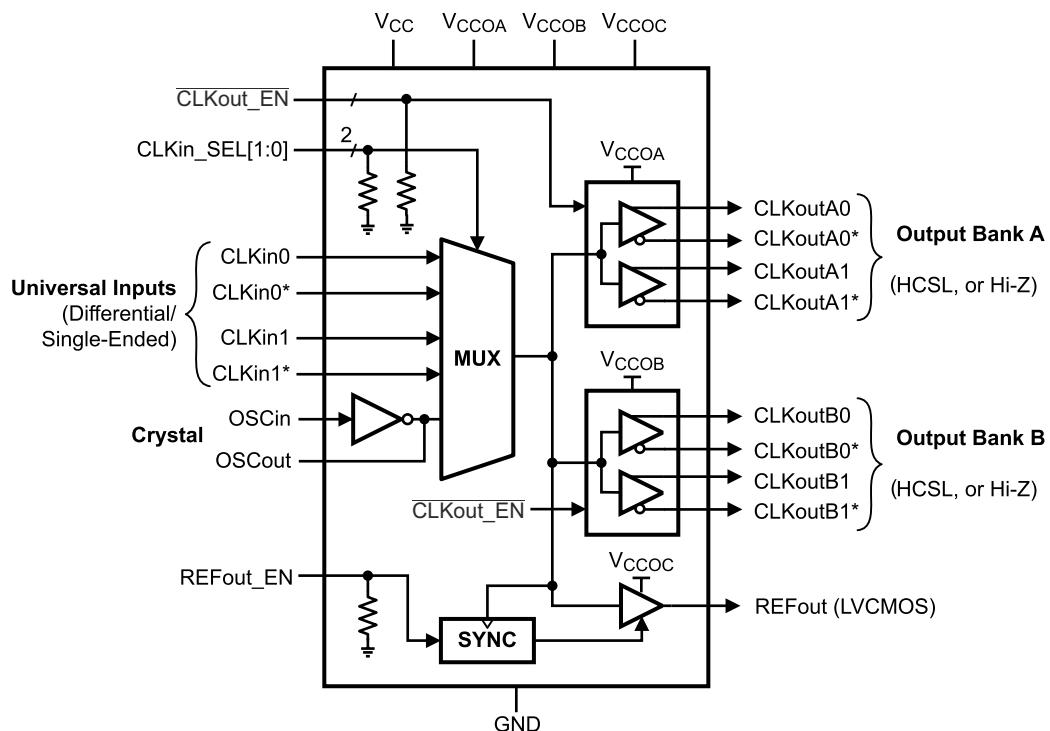

LMK00334 デバイスは 4 出力の HCSL ファンアウト バッファで、高周波数、低ジッタのクロック、データ分配、およびレベル変換を目的としています。このデバイスは、ADC、DAC、マルチ ギガビットイーサネット、XAUI、ファイバー チャネル、SATA/SAS、SONET/SDH、CPRI、高周波バックプレーンのリファレンス クロックを分配できます。

入力クロックは 2 つの汎用入力、または 1 つの水晶振動子入力から選択できます。選択された入力クロックは 2 つのバンクに分配され、それぞれのバンクには 2 つの HCSL 出力と 1 つの LVC MOS 出力があります。LVC MOS 出力には同期イネーブル入力があり、イネーブルまたはディスエーブル時にラント (微小) パルスなしの動作を実現できます。LMK00334 および 3.3V のコア電源と、3 系統の独立した 3.3V または 2.5V の出力電源で動作します。

LMK00334 は高性能、多用途性、省電力性を備えており、固定出力バッファ デバイスの代替として設計されると同時に、システムのタイミング マージンを向上させます。

### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| LMK00334 | RTV (WQFN, 32)       | 5.00mm × 5.00mm          |

(1) 詳細については、セクション 11 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

LMK00334 の機能ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                              |    |                             |    |

|------------------------------|----|-----------------------------|----|

| 1 特長.....                    | 1  | 7.3 機能説明.....               | 13 |

| 2 アプリケーション.....              | 1  | 7.4 デバイスの機能モード.....         | 15 |

| 3 説明.....                    | 1  | 8 アプリケーションと実装.....          | 16 |

| 4 ピン構成および機能.....             | 3  | 8.1 アプリケーション情報.....         | 16 |

| 5 仕様.....                    | 4  | 8.2 代表的なアプリケーション.....       | 16 |

| 5.1 絶対最大定格.....              | 4  | 8.3 電源に関する推奨事項.....         | 20 |

| 5.2 ESD 定格.....              | 4  | 8.4 レイアウト.....              | 24 |

| 5.3 推奨動作条件.....              | 5  | 9 デバイスおよびドキュメントのサポート.....   | 26 |

| 5.4 熱に関する情報.....             | 5  | 9.1 ドキュメントのサポート.....        | 26 |

| 5.5 電気的特性.....               | 5  | 9.2 ドキュメントの更新通知を受け取る方法..... | 26 |

| 5.6 タイミング要件、伝搬遅延、出力スキュー..... | 8  | 9.3 サポート・リソース.....          | 26 |

| 5.7 代表的特性.....               | 9  | 9.4 商標.....                 | 26 |

| 6 パラメータ測定情報.....             | 12 | 9.5 静電気放電に関する注意事項.....      | 26 |

| 6.1 差動電圧測定に関する用語.....        | 12 | 9.6 用語集.....                | 26 |

| 7 詳細説明.....                  | 13 | 10 改訂履歴.....                | 26 |

| 7.1 概要.....                  | 13 | 11 メカニカル、パッケージ、および注文情報..... | 27 |

| 7.2 機能ブロック図.....             | 13 |                             |    |

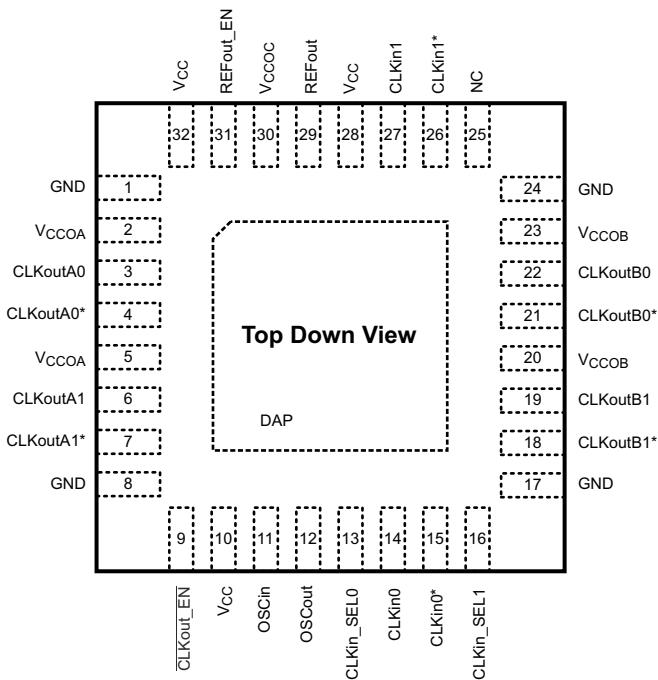

## 4 ピン構成および機能

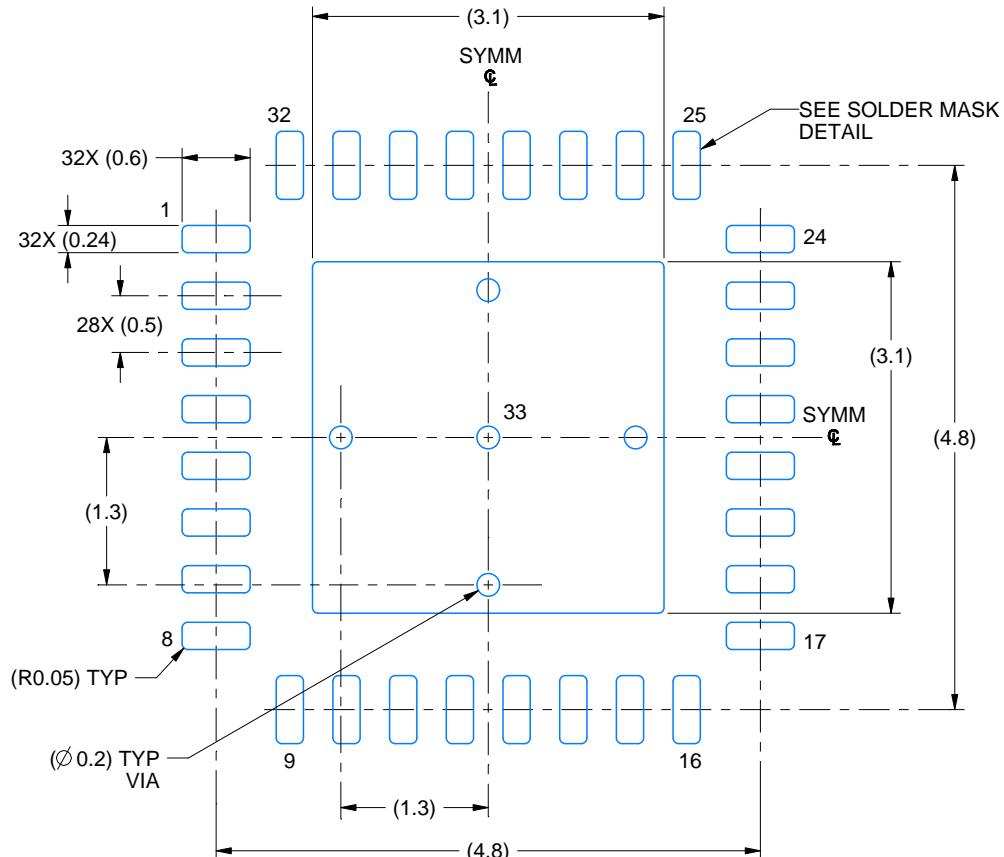

図 4-1. RTV パッケージ 32 ピン WQFN 上面図

表 4-1. ピンの機能

| ピン         |              | 種類 <sup>(1)</sup> <sup>(4)</sup> | 説明                                                                         |

|------------|--------------|----------------------------------|----------------------------------------------------------------------------|

| 名称         | 番号           |                                  |                                                                            |

| DAP        | DAP          | GND                              | ダイ取り付けパッド。放熱のため、PCB グランド プレーンに接続します。                                       |

| CLKin_SEL0 | 13           | I                                | クロック入力選択ピン <sup>(3)</sup>                                                  |

| CLKin_SEL1 | 16           | I                                | クロック入力選択ピン <sup>(3)</sup>                                                  |

| CLKin0     | 14           | I                                | ユニバーサル クロック入力 0 (差動/シングルエンド)                                               |

| CLKin0*    | 15           | I                                | ユニバーサル クロック入力 0 (差動/シングルエンド)                                               |

| CLKin1     | 27           | I                                | ユニバーサル クロック入力 1 (差動/シングルエンド)                                               |

| CLKin1*    | 26           | I                                | ユニバーサル クロック入力 1 (差動/シングルエンド)                                               |

| CLKout_EN  | 9            | I                                | バンク A とバンク B が Low、アクティブ出力バッファのイネーブル。 <sup>(3)</sup>                       |

| CLKoutA0   | 3            | O                                | 差動クロック出力 A0。                                                               |

| CLKoutA0*  | 4            | O                                | 差動クロック出力 A0。                                                               |

| CLKoutA1   | 6            | O                                | 差動クロック出力 A1。                                                               |

| CLKoutA1*  | 7            | O                                | 差動クロック出力 A1。                                                               |

| CLKoutB1   | 19           | O                                | 差動クロック出力 B1。                                                               |

| CLKoutB1*  | 18           | O                                | 差動クロック出力 B1。                                                               |

| CLKoutB0   | 22           | O                                | 差動クロック出力 B0。                                                               |

| CLKoutB0*  | 21           | O                                | 差動クロック出力 B0。                                                               |

| GND        | 1, 8, 17, 24 | GND                              | グランド                                                                       |

| NC         | 25           | —                                | 内部未接続。ピンは、 <b>絶対最大定格</b> に記載された電源電圧範囲内であれば、浮遊状態、グランド接続、またはその他任意の電位に接続できます。 |

| OSCin      | 11           | I                                | 水晶振動子の入力。XO、TCXO、または他の外部シングルエンド クロックから駆動することもできます。                         |

表 4-1. ピンの機能(続き)

| ピン                |            | 種類 <sup>(1) (4)</sup> | 説明                                                                                                                                                                |

|-------------------|------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                | 番号         |                       |                                                                                                                                                                   |

| OSCout            | 12         | O                     | 水晶振動子用出力。OSCin がシングルエンドクロックで駆動される場合、OSCout は未接続のままになります。                                                                                                          |

| REFout            | 29         | O                     | LVC MOS リファレンス出力。REFout_EN ピンを High にして出力を有効にします。                                                                                                                 |

| REFout_EN         | 31         | I                     | REFout イネーブル入力。イネーブル信号は、選択されたクロック入力と内部的に同期します。 <sup>(3)</sup>                                                                                                     |

| V <sub>CC</sub>   | 10, 28, 32 | PWR                   | コアおよび入力バッファブロック用の電源。V <sub>CC</sub> 電源は 3.3V で動作します。各 V <sub>CC</sub> ピンのすぐ近くに、0.1μF の低 ESR コンデンサを配置してバイパスします。                                                    |

| V <sub>CCOA</sub> | 2, 5       | PWR                   | バンク A 出力バッファ用電源。3.3V または 2.5V から V <sub>CCOA</sub> を動作。V <sub>CCOA</sub> ピンは内部で接続されています。各 V <sub>CC</sub> ピンのすぐ近くに、0.1μF の低 ESR コンデンサを配置してバイパスします。 <sup>(2)</sup> |

| V <sub>CCOB</sub> | 20, 23     | PWR                   | バンク B 出力バッファ用電源。3.3V または 2.5V から V <sub>CCOB</sub> を動作。V <sub>CCOB</sub> ピンは内部で接続されています。各 V <sub>CC</sub> ピンのすぐ近くに、0.1μF の低 ESR コンデンサを配置してバイパスします。 <sup>(2)</sup> |

| V <sub>CCOC</sub> | 30         | PWR                   | REFout バッファ用電源。3.3V または 2.5V から V <sub>CCOC</sub> を動作。各 V <sub>CC</sub> ピンのすぐ近くに、0.1μF の低 ESR コンデンサを配置してバイパスします。 <sup>(2)</sup>                                   |

(1) I = 入力、O = 出力、GND = グランド、PWR = 電源

(2) 出力電源電圧またはビン (V<sub>CCOA</sub>、V<sub>CCOB</sub>、V<sub>CCOC</sub>) は、区別が不要な場合や出力バンク / タイプから出力電源を推測できる場合、一般的に V<sub>CC</sub> と呼ばれます。

(3) 内部ブルダウン抵抗付きの CMOS 制御入力。

(4) 未使用の出力ビンは、最小限の銅配線長で浮遊状態にしておく必要があります (クロック出力内の注記を参照)。または、伝送ラインに接続されている場合は適切に終端するか、可能であれば無効化/Hi-Z にします。出力構成については クロック出力を、出力インターフェイスおよび終端技術については ターミネーションとクロックドライバの使用 を参照してください。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1) (2)</sup>

|                                  |                  | 最小値  | 最大値                     | 単位 |

|----------------------------------|------------------|------|-------------------------|----|

| V <sub>CC</sub> 、V <sub>CC</sub> | 電源電圧             | -0.3 | 3.6                     | V  |

| V <sub>IN</sub>                  | 入力電圧             | -0.3 | (V <sub>CC</sub> + 0.3) | V  |

| T <sub>L</sub>                   | リード温度 (半田付け、4 秒) |      | 260                     | °C |

| T <sub>J</sub>                   | 接合部温度            |      | 150                     | °C |

| T <sub>stg</sub>                 | 保存温度             | -65  | 150                     | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または推奨動作条件下に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の範囲内であっても推奨動作条件の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) 軍用/航空宇宙用仕様のデバイスをお求めの場合は、供給状況および仕様について テキサス・インスツルメンツの販売特約店または営業所にお問い合わせください。

### 5.2 ESD 定格

|                         |                                                         | 値     | 単位 |

|-------------------------|---------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | ±2000 | V  |

|                         | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | ±750  |    |

|                         | マシン モデル (MM)                                            | ±150  |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                  |                           | 最小値      | 標準値      | 最大値  | 単位       |

|------------------|---------------------------|----------|----------|------|----------|

| T <sub>A</sub>   | 周囲温度                      | -40      | 25       | 85   | °C       |

| T <sub>J</sub>   | 接合部温度                     |          |          | 125  | °C       |

| V <sub>CC</sub>  | コア電源電圧                    | 3.15     | 3.3      | 3.45 | V        |

| V <sub>CCO</sub> | 出力電源電圧 <sup>(1) (2)</sup> | 3.3V の範囲 | 3.3 – 5% | 3.3  | 3.3 + 5% |

|                  |                           | 2.5V の範囲 | 2.5 – 5% | 2.5  | 2.5 + 5% |

(1) 出力電源電圧またはピン (V<sub>CCOA</sub>、V<sub>CCOB</sub>、V<sub>CCOC</sub>) は、区別が不要な場合や出力バンク / タイプから出力電源を推測できる場合、一般的に V<sub>CCO</sub> と呼ばれます。

(2) 任意の出力バンクの V<sub>CCO</sub> は、V<sub>CC</sub> 以下でなければなりません (V<sub>CCO</sub> ≤ V<sub>CC</sub>)。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  | LMK00334 <sup>(2)</sup> | 単位        |

|-----------------------|-------------------------|-----------|

|                       | RTV (WQFN)              |           |

|                       | 32 ピン                   |           |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗            | 38.1 °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗     | 7.2 °C/W  |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗            | 12 °C/W   |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ        | 0.4 °C/W  |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ        | 11.9 °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗     | 4.5 °C/W  |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーション ノートを参照してください。

(2) この仕様は、5 本のサーマルビアでダイアタッチ パッド (DAP) を 4 層 JEDEC ボード上の内部銅プレーンに接続することを前提としています。これらのビアは、パッケージの放熱性能を向上させる上で重要な役割を果たします。TI は、基板レイアウトで可能な限り多くのビアを使用することを推奨しています。

## 5.5 電気的特性

特に記述のない限り: V<sub>CC</sub> = 3.3V ± 5%, V<sub>CCO</sub> = 3.3V ± 5%, 2.5V ± 5%, -40°C ≤ T<sub>A</sub> ≤ 85°C、CLKin は差動駆動、入力スルーレート ≥ 3V/ns。標準値は、V<sub>CC</sub> = 3.3V、V<sub>CCO</sub> = 3.3V、T<sub>A</sub> = 25°C の条件および製品特性評価時の推奨動作条件における、最も可能性が高いパラメトリック標準値を示します。このため、標準値は保証されません。<sup>(1)</sup>

| パラメータ                                                  | テスト条件                            | 最小値                                                             | 標準値                          | 最大値             | 単位   |

|--------------------------------------------------------|----------------------------------|-----------------------------------------------------------------|------------------------------|-----------------|------|

| <b>消費電流<sup>(1)</sup></b>                              |                                  |                                                                 |                              |                 |      |

| ICC_CORE                                               | コア電源電流、すべての出力がディスエーブル            | CLKinX を選択                                                      | 8.5                          | 10.5            | mA   |

|                                                        |                                  | OSCin を選択                                                       | 10                           | 13.5            | mA   |

| ICC_HCSL                                               |                                  |                                                                 | 50                           | 58.5            | mA   |

| ICC_CMOS                                               |                                  |                                                                 | 3.5                          | 5.5             | mA   |

| ICCO_HCSL                                              | 追加出力電源電流、HCSL バンクがイネーブル          | 両方のバンクに対する出力バンク バイアスおよび負荷電流を含み、すべての出力に R <sub>T</sub> = 50Ω を適用 | 65                           | 81.5            | mA   |

|                                                        |                                  |                                                                 | 9                            | 10              | mA   |

| ICCO_CMOS                                              | 追加出力消費電流、LVCMOS 出力がイネーブル         | 200MHz、C <sub>L</sub> = 5pF                                     | V <sub>CCO</sub> = 3.3V ± 5% | 7               | 8 mA |

|                                                        |                                  |                                                                 | V <sub>CCO</sub> = 2.5V ± 5% |                 |      |

| <b>電源リップル除去 (PSRR)</b>                                 |                                  |                                                                 |                              |                 |      |

| PSRR <sub>HCSL</sub>                                   | リップル誘起位相スプリアス レベル <sup>(2)</sup> | 156.25MHz                                                       | -72                          |                 | dBc  |

|                                                        | 差動 HCSL 出力                       | 312.5MHz                                                        | -63                          |                 |      |

| <b>CMOS 制御入力 (CLKin_SELn, CLKout_TYPEn, REFout_EN)</b> |                                  |                                                                 |                              |                 |      |

| V <sub>IH</sub>                                        | High レベル入力電圧                     |                                                                 | 1.6                          | V <sub>CC</sub> | V    |

特に記述のない限り:  $V_{CC} = 3.3V \pm 5\%$ ,  $V_{CCO} = 3.3V \pm 5\%$ ,  $2.5V \pm 5\%$ ,  $-40^\circ C \leq T_A \leq 85^\circ C$ , CLKin は差動駆動、入力スルーレート  $\geq 3V/ns$ 。標準値は、 $V_{CC} = 3.3V$ ,  $V_{CCO} = 3.3V$ ,  $T_A = 25^\circ C$  の条件および製品特性評価時の推奨動作条件における、最も可能性が高いパラメトリック標準値を示します。このため、標準値は保証されません。<sup>(1)</sup>

| パラメータ                                                         | テスト条件                                                                                     | 最小値                               | 標準値            | 最大値  | 単位       |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------|----------------|------|----------|

| $V_{IL}$<br>Low レベル入力電圧                                       |                                                                                           | GND                               |                | 0.4  | V        |

| $I_{IH}$<br>High レベル入力電流                                      | $V_{IH} = V_{CC}$ 、内部プルダウン抵抗                                                              |                                   |                | 50   | $\mu A$  |

| $I_{IL}$<br>Low レベル入力電流                                       | $V_{IL} = 0V$ 、内部プルダウン抵抗                                                                  | -5                                | 0.1            |      | $\mu A$  |

| <b>クロック入力 (CLKin0/CLKin0*, CLKin1/CLKin1*)</b>                |                                                                                           |                                   |                |      |          |

| $f_{CLKin}$<br>入力周波数範囲 <sup>(8)</sup>                         | 400MHz まで機能可能<br>出力周波数範囲およびタイミングは出力タイプごとに規定されています (LVC MOS 出力仕様を参照)                       | DC                                | 400            |      | MHz      |

| $V_{IHD}$<br>差動入力高レベル電圧                                       | CLKin は差動駆動                                                                               |                                   | $V_{CC}$       |      | V        |

| $V_{ILD}$<br>差動入力低電圧                                          |                                                                                           | GND                               |                |      | V        |

| $V_{ID}$<br>差動入力電圧スイング <sup>(3)</sup>                         |                                                                                           | 0.15                              | 1.3            |      | V        |

| $V_{CMD}$<br>差動入力 CMD 同相電圧                                    | $V_{ID} = 150mV$                                                                          | 0.25                              | $V_{CC} - 1.2$ |      |          |

|                                                               | $V_{ID} = 350mV$                                                                          | 0.25                              | $V_{CC} - 1.1$ |      | V        |

|                                                               | $V_{ID} = 800mV$                                                                          | 0.25                              | $V_{CC} - 0.9$ |      |          |

| $V_{IH}$<br>シングルエンド入力 IH 高電圧                                  | CLKinX はシングルエンド駆動 (AC または DC カップリング)、CLKinX* は GND への AC カップリング、または $V_{CM}$ 範囲内で外部バイアス   |                                   | $V_{CC}$       |      | V        |

| $V_{IL}$<br>シングルエンド入力 IL 低電圧                                  |                                                                                           | GND                               |                |      | V        |

| $V_{I\_SE}$<br>シングルエンド入力電圧スイング <sup>(8)</sup>                 |                                                                                           | 0.3                               | 2              |      | $V_{pp}$ |

| $V_{CM}$<br>シングルエンド入力 CM の同相電圧                                |                                                                                           | 0.25                              | $V_{CC} - 1.2$ |      | V        |

| ISO_MUX<br>Mux 絶縁、CLKin0 から CLKin1                            | $f_{OFFSET} > 50kHz$ , $P_{CLKinX} = 0dBm$                                                | $f_{CLKin0} = 100MHz$             | -84            |      |          |

|                                                               |                                                                                           | $f_{CLKin0} = 200MHz$             | -82            |      | dBc      |

|                                                               |                                                                                           | $f_{CLKin0} = 500MHz$             | -71            |      |          |

|                                                               |                                                                                           | $f_{CLKin0} = 1000MHz$            | -65            |      |          |

| <b>水晶振動子インターフェイス (OSCin, OSCout)</b>                          |                                                                                           |                                   |                |      |          |

| $F_{CLK}$<br>外部クロック周波数設定 <sup>(8)</sup>                       | OSCin 駆動シングルエンド、OSCout はフローティング                                                           |                                   |                | 250  | MHz      |

| $F_{XTAL}$<br>水晶振動子の周波数範囲                                     | 基本モード水晶振動子 $ESR \leq 200\Omega$ (10~30MHz) $ESR \leq 125\Omega$ (30~40MHz) <sup>(4)</sup> | 10                                | 40             |      | MHz      |

| $C_{IN}$<br>OSCin 入力容量                                        |                                                                                           |                                   | 1              |      | pF       |

| <b>HCSL 出力 (CLKoutAn/CLKoutAn*, CLKoutBn/CLKoutBn*)</b>       |                                                                                           |                                   |                |      |          |

| $f_{CLKout}$<br>出力周波数範囲 <sup>(8)</sup>                        | $R_L = 50\Omega$ を GND に接続、 $C_L \leq 5pF$                                                | DC                                | 400            |      | MHz      |

| ジッタ ADD_PCl e PCIe 7.0 の加算 RMS 位相ジッタ <sup>(8)</sup>           | PCIe Gen 7 フィルタ                                                                           | CLKin: 100MHz、スルーレート $\geq 3V/ns$ | 3.51           | 5.45 | fs       |

| ジッタ ADD_PCl e PCIe 6.0 の加算 RMS 位相ジッタ <sup>(8)</sup>           | PCIe Gen 6 フィルタ                                                                           | CLKin: 100MHz、スルーレート $\geq 3V/ns$ | 5.04           | 7.78 | fs       |

| ジッタ ADD_PCl e PCIe 5.0 の加算 RMS 位相ジッタ <sup>(8)</sup>           | PCIe Gen 5 フィルタ                                                                           | CLKin: 100MHz、スルーレート $\geq 3V/ns$ | 7.17           | 12.8 | fs       |

| ジッタ ADD_PCl e PCIe 4.0 の加算 RMS 位相ジッタ <sup>(8)</sup>           | PCIe Gen 4、PLL BW = 2~5MHz、CDR = 10MHz                                                    | CLKin: 100MHz、スルーレート $\geq 3V/ns$ | 20.3           | 30.5 | fs       |

| ジッタ ADD_PCl e PCIe 3.0 の加算 RMS 位相ジッタ <sup>(8)</sup>           | PCIe Gen 3、PLL BW = 2~5MHz、CDR = 10MHz                                                    | CLKin: 100MHz、スルーレート $\geq 3V/ns$ | 20.3           | 30.5 | fs       |

| JitterADD<br>加算 RMS ジッタの積分帯域幅<br>12MHz ~ 20MHz <sup>(5)</sup> | $V_{CCO} = 3.3V$ 、 $R_T = 50\Omega \sim GND$                                              | CLKin: 100MHz、スルーレート $\geq 3V/ns$ | 77             |      | fs       |

特に記述のない限り:  $V_{CC} = 3.3V \pm 5\%$ ,  $V_{CCO} = 3.3V \pm 5\%$ ,  $2.5V \pm 5\%$ ,  $-40^\circ C \leq T_A \leq 85^\circ C$ , CLKin は差動駆動、入力スルーレート  $\geq 3V/ns$ 。標準値は、 $V_{CC} = 3.3V$ ,  $V_{CCO} = 3.3V$ ,  $T_A = 25^\circ C$  の条件および製品特性評価時の推奨動作条件における、最も可能性が高いパラメトリック標準値を示します。このため、標準値は保証されません。<sup>(1)</sup>

| パラメータ                                                  | テスト条件                                                                                        |  | 最小値                                  | 標準値 | 最大値    | 単位     |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--------------------------------------|-----|--------|--------|

| ノイズ フロア ノイズ フロア $f_{OFFSET} \geq 10MHz^{(6)(7)}$       | $V_{CCO} = 3.3V$ 、<br>$R_T = 50\Omega \sim GND$                                              |  | $CLKin: 100MHz$ 、スルーレート $\geq 3V/ns$ |     | -161.3 | dBc/Hz |

| デューティ デューティ サイクル <sup>(8)</sup>                        | 50% 入力クロックデューティ サイクル                                                                         |  | 45%                                  |     | 55%    |        |

| $V_{OH}$ 出力 HIGH 電圧                                    | $T_A = 25^\circ C$ , DC 測定、<br>$R_T = 50\Omega \sim GND$                                     |  | 520                                  | 810 | 920    | mV     |

| $V_{OL}$ 出力 LOW 電圧                                     |                                                                                              |  | -150                                 | 0.5 | 150    | mV     |

| $V_{CROSS}$ 絶対交差点電圧 <sup>(8)(9)</sup>                  | $R_L = 50\Omega$ を GND に接続、 $C_L \leq 5pF$                                                   |  | 250                                  | 350 | 460    | mV     |

| $\Delta V_{CROSS}$ $V_{CROSS}$ <sup>(8)(9)</sup> の合計変動 |                                                                                              |  |                                      |     | 140    | mV     |

| $t_R$ 出力の立ち上がり時間 (20% から 80% へ) <sup>(9)(12)</sup>     | 250MHz、特性インピーダンス $50\Omega$ の最大 10 インチまでの均一な伝送ライン、 $R_L = 50\Omega$ から GND へ、 $C_L \leq 5pF$ |  | 225                                  | 400 | 400    | ps     |

| $t_F$ 出力の立ち下がり時間 (80% から 20% へ) <sup>(9)(12)</sup>     |                                                                                              |  | 225                                  | 400 | 400    | ps     |

#### LVC MOS 出力 (REFout)

|                                                     |                                                                                              |                                      |                           |        |      |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------|---------------------------|--------|------|

| $f_{CLKout}$                                        | 出力周波数範囲 <sup>(8)</sup>                                                                       | $C_L \leq 5pF$                       | DC                        | 250    | MHz  |

| Jitter <sub>ADD</sub>                               | 加算 RMS ジッタの積分帯域幅 1MHz ~ 20MHz <sup>(5)</sup>                                                 | $V_{CCO} = 3.3V$ 、<br>$C_L \leq 5pF$ | 100MHz、V 入力スルーレート = 3V/ns | 95     | fs   |

| ノイズ フロア ノイズ フロア $f_{OFFSET} \geq 10MHz^{(6)(7)}$    | $V_{CCO} = 3.3V$ 、<br>$C_L \leq 5pF$                                                         | 100MHz、V 入力スルーレート = 3V/ns            | -159.3                    | dBc/Hz |      |

| デューティ デューティ サイクル <sup>(8)</sup>                     | 50% 入力クロックデューティ サイクル                                                                         |                                      | 45%                       | 55%    |      |

| $V_{OH}$ 出力 HIGH 電圧                                 | 1mA 負荷                                                                                       | $V_{CCO} = 3.3V$                     | 28                        | mA     |      |

| $V_{OL}$ 出力 LOW 電圧                                  |                                                                                              |                                      | 20                        |        |      |

| $I_{OH}$ 出力高レベル電流 (ソース)                             | $V_O = V_{CCO} / 2$                                                                          | $V_{CCO} = 3.3V$                     | 28                        |        |      |

| $I_{OL}$ 出力低電流 (シンク)                                |                                                                                              | $V_{CCO} = 2.5V$                     | 20                        |        |      |

| $t_R$ 出力の立ち上がり時間 (20% から 80% へ) <sup>(9)(12)</sup>  | 250MHz、特性インピーダンス $50\Omega$ の最大 10 インチまでの均一な伝送ライン、 $R_L = 50\Omega$ から GND へ、 $C_L \leq 5pF$ |                                      | 225                       | 400    | ps   |

| $t_F$ 出力の立ち下がり時間 (80% から 20% へ) <sup>(10)(12)</sup> |                                                                                              |                                      | 225                       |        | 400  |

| $t_{EN}$ 出力イネーブル時間 <sup>(10)</sup>                  | $C_L \leq 5pF$                                                                               |                                      | 3                         | サイクル   |      |

| $t_{DIS}$ 出力ディスエーブル時間 <sup>(10)</sup>               |                                                                                              |                                      | 3                         |        | サイクル |

- (1) 消費電流と消費電力の計算の詳細については、および [熱管理](#) および [電源に関する推奨事項](#) を参照してください。

- (2) 電源リップル除去 (PSRR) は、シングルトーン正弦波信号 (リップル) が  $V_{CCO}$  電源に注入されたときに、クロック出力に変調される、シングルサイドバンドの位相スプリアス レベル (dBc 単位) として定義されます。振幅変調の影響がなく、かつ変調指数が小さいと仮定すると、ピークツーピークの決定性ジッタ (DJ) は、測定されたシングル サイドバンド位相スパー レベル (PSRR) を使用して次のように算出できます:  $DJ (ps pk-pk) = [(2 \times 10^{PSRR} / 20)] / (\pi \times f_{CLK}) \times 1E12$

- (3)  $V_{ID}$  および  $V_{OD}$  電圧の定義については、[差動電圧測定に関する用語](#) を参照してください。

- (4) 発振器回路に起動不良がないことを確認するためには、記載された ESR 要件を満たす必要があります。ただし、水晶振動子の最大消費電力 (ドライブ レベル) 仕様を下回るために、水晶振動子の ESR 値をより低くする必要があるとは限りません。水晶振動子の駆動レベルに関する考慮事項については、[水晶振動子インターフェイス](#) を参照してください。

- (5) 100MHz および 156.25MHz のクロック入力条件については、方法 #1 を使用して加算 RMS ジッタ ( $J_{ADD}$ ) を計算します:  $J_{ADD} = \sqrt{J_{OUT}^2 - J_{SOURCE}^2}$ 。ここで、 $J_{OUT}$  は、出力ドライバで測定された合計 RMS ジッタ、 $J_{source}$  は、CLKin に印加されるクロックソースの RMS ジッタです。625MHz クロック入力条件では、付加 RMS ジッタは、方法 #2 を使用して近似されます:  $J_{ADD} = \sqrt{2 \times 10^{dBc/10}} / (2 \times \pi \times f_{CLK})$  で、dBc は、出力ノイズ フロアの位相ノイズの電力を  $12kHz \sim 20MHz$  の帯域幅で積分した値です。位相ノイズ電力は次のように計算できます:  $dBc = Noise Floor + 10 \times \log_{10}(20MHz - 12kHz)$ 。

- (6) 出力バッファのノイズ フロアは、バッファの外位相ノイズとして測定されます。このオフセットは通常  $\geq 10MHz$  ですが、周波数が低い場合、測定機器の制限によりこの測定オフセットは最小で  $5MHz$  になることがあります。

- (7) クロックの入力スルーレートが小さくなると、位相ノイズ フロアは低下します。シングルエンド クロックと比べて、差動クロック入力 (LVPECL、LVDS) は、同相モードノイズ除去により、スルーレートが低い場合でもノイズ フロアの劣化を受けにくくなります。ただし、TI はデバイス出力で最高のノイズ フロア性能を実現するために、差動クロックに可能な限り高い入力スルーレートを使用することを推奨しています。

- (8) この仕様は特性評価によって検証されており、生産時には試験されません。

- (9) HCSL または CMOS の AC タイミング パラメータは、出力容量性負荷に依存します。

- (10) 出力イネーブル時間は、REFout\_EN が High になった後、出力がイネーブルになるために必要な入力クロック サイクル数です。同様に、出力ディセーブル時間は、REFout\_EN が Low になった後、出力がディセーブルされるために必要な入力クロック サイクル数です。正確に測定するため、REFout\_EN 信号は、入力クロック周期よりもはるかに速くエッジ遷移する必要があります。

- (11) 出力スキューは、同一の出力バッファ タイプおよび同一負荷を持ち、同一の電源電圧と温度条件で動作している任意の 2 つの出力間の伝搬遅延差です。

- (12) このパラメータは設計によって規定されており、生産時には試験されません。

## 5.6 タイミング要件、伝搬遅延、出力スキュー

|                |                                            |                                         | 最小値               | 標準値  | 最大値  | 単位   |

|----------------|--------------------------------------------|-----------------------------------------|-------------------|------|------|------|

| $t_{PD\_HCSL}$ | CLKin から HCSL までの伝搬遅延時間 <sup>(1) (2)</sup> | $R_T = 50\Omega \sim GND, C_L \leq 5pF$ | 295               | 590  | 885  | ps   |

| $t_{PD\_CMOS}$ | CLKin から LVCMOS への伝搬遅延 <sup>(1) (2)</sup>  | $C_L \leq 5pF$                          | $V_{CCO} = 3.3V$  | 900  | 1475 | 2300 |

|                |                                            |                                         | $V_{CCO} = 2.5 V$ | 1000 | 1550 | 2700 |

| $t_{SK(O)}$    | 出力スキュー <sup>(1) (9) (4)</sup>              | 任意の 2 つの CLKout 間のスキューの規定。              |                   | 30   | 50   | ps   |

| $t_{SK(PP)}$   | 部品間の遅延スキュー <sup>(1) (2) (3)</sup>          | 負荷条件は、伝搬遅延の仕様と同じです。                     |                   | 80   | 120  | ps   |

- (1) HCSL または CMOS の AC タイミング パラメータは、出力容量性負荷に依存します。

- (2) このパラメータは設計によって規定されており、生産時には試験されません。

- (3) 出力スキューは、同一の出力バッファ タイプおよび同一負荷を持ち、同一の電源電圧と温度条件で動作している任意の 2 つの出力間の伝搬遅延差です。

- (4) この仕様は特性評価によって検証されており、生産時には試験されません。

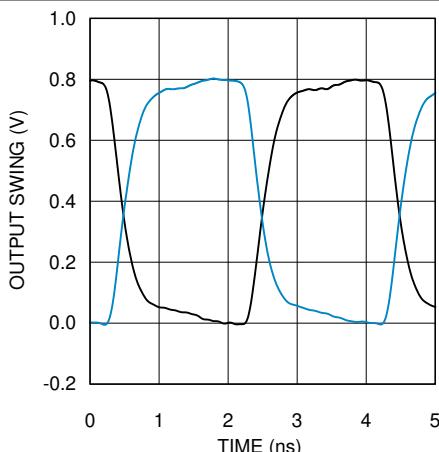

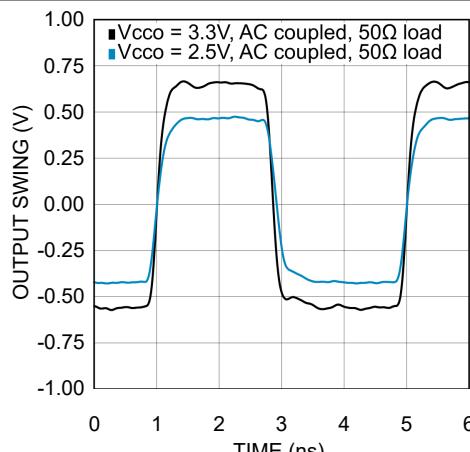

## 5.7 代表的特性

特に記述のない限り:  $V_{CC} = 3.3V$ ,  $V_{CCO} = 3.3V$ ,  $T_A = 25^\circ C$ , CLKin は差動駆動、入力スルーレート  $\geq 3V/ns$ 。

図 5-1. 250MHz での HCSL 出力スイング

図 5-2. 250MHz での LVCMS 出力スイング

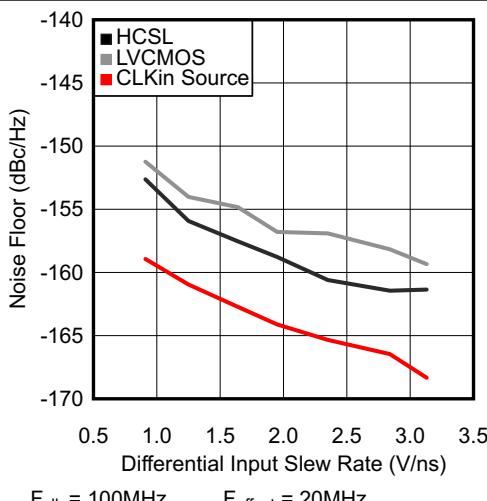

$F_{clk} = 100MHz \quad F_{offset} = 20MHz$

図 5-3. 100MHz におけるノイズフロアと CLKin スルーレートとの関係

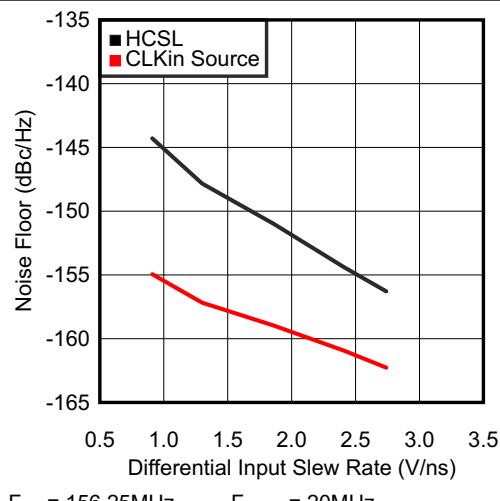

$F_{clk} = 156.25MHz \quad F_{offset} = 20MHz$

図 5-4. 156.25MHz におけるノイズフロアと CLKin スルーレートとの関係

## 5.7 代表的特性 (続き)

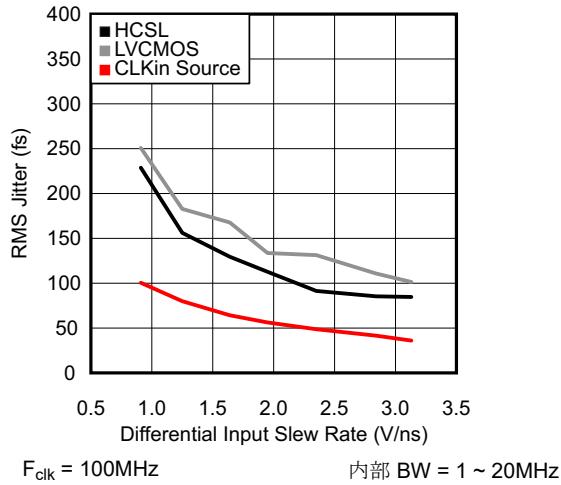

特に記述のない限り:  $V_{CC} = 3.3V$ ,  $V_{CCO} = 3.3V$ ,  $T_A = 25^\circ C$ , CLKin は差動駆動、入力スルーレート  $\geq 3V/ns$ 。

図 5-5. 100MHz での RMS ジッタと CLKin スルーレートとの関係

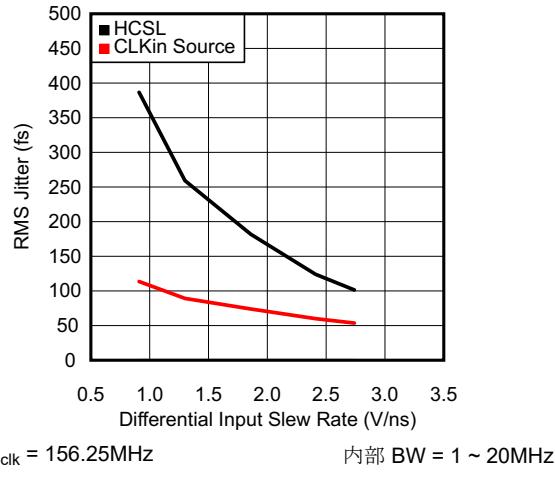

図 5-6. 156.25MHz での RMS ジッタと CLKin スルーレートとの関係

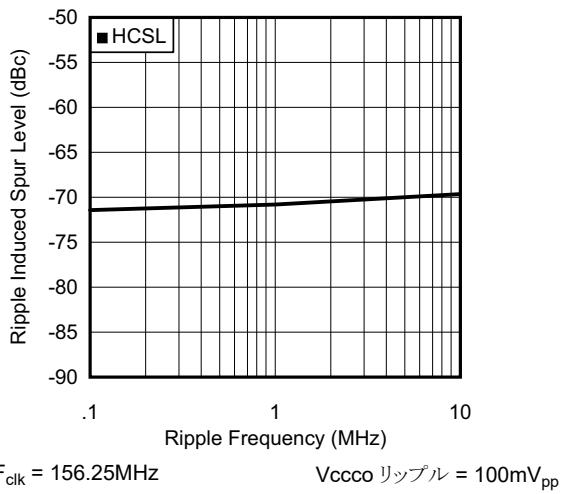

図 5-7. 156.25MHz での PSRR とリップル周波数との関係

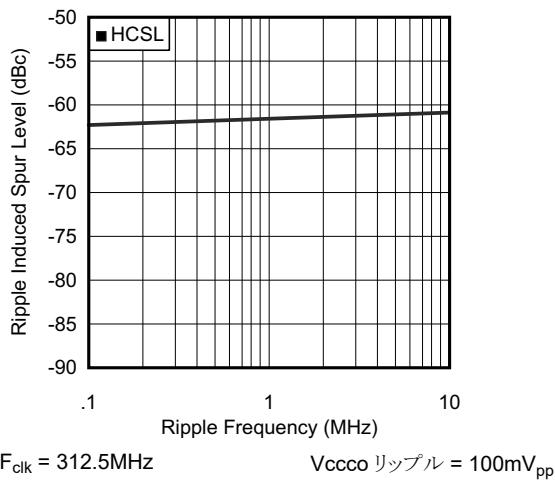

図 5-8. 312.5MHz での PSRR とリップル周波数との関係

## 5.7 代表的特性 (続き)

特に記述のない限り:  $V_{CC} = 3.3V$ ,  $V_{CCO} = 3.3V$ ,  $T_A = 25^\circ C$ , CLKin は差動駆動、入力スルーレート  $\geq 3V/ns$ 。

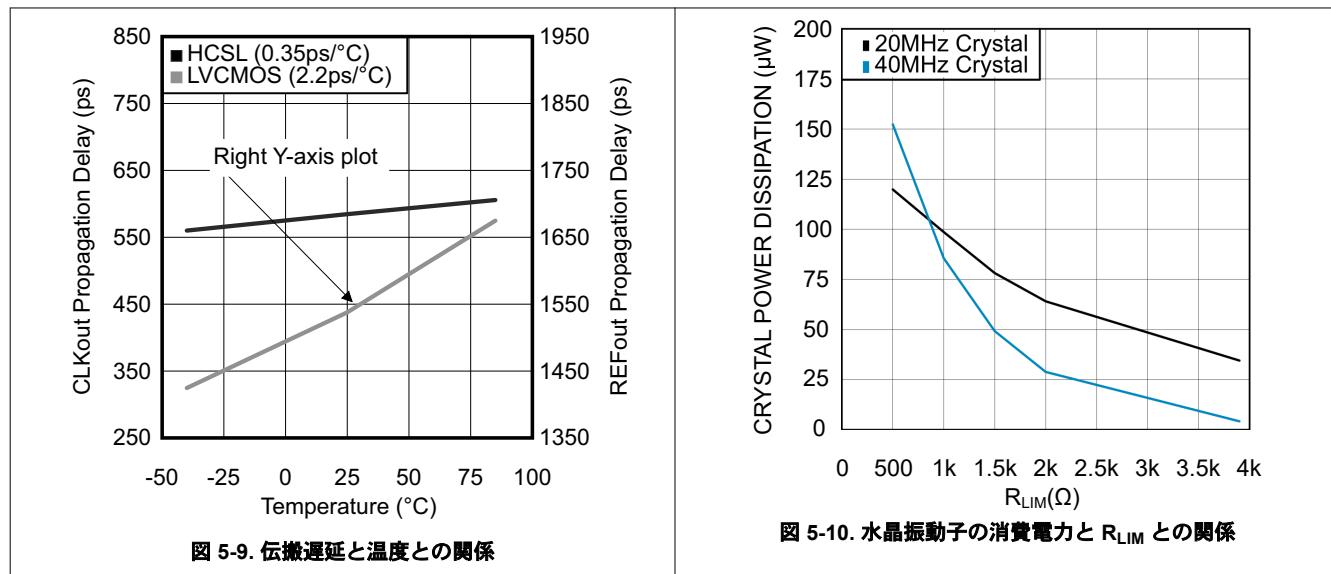

図 5-9. 伝搬遅延と温度との関係

図 5-10. 水晶振動子の消費電力と  $R_{LIM}$  との関係

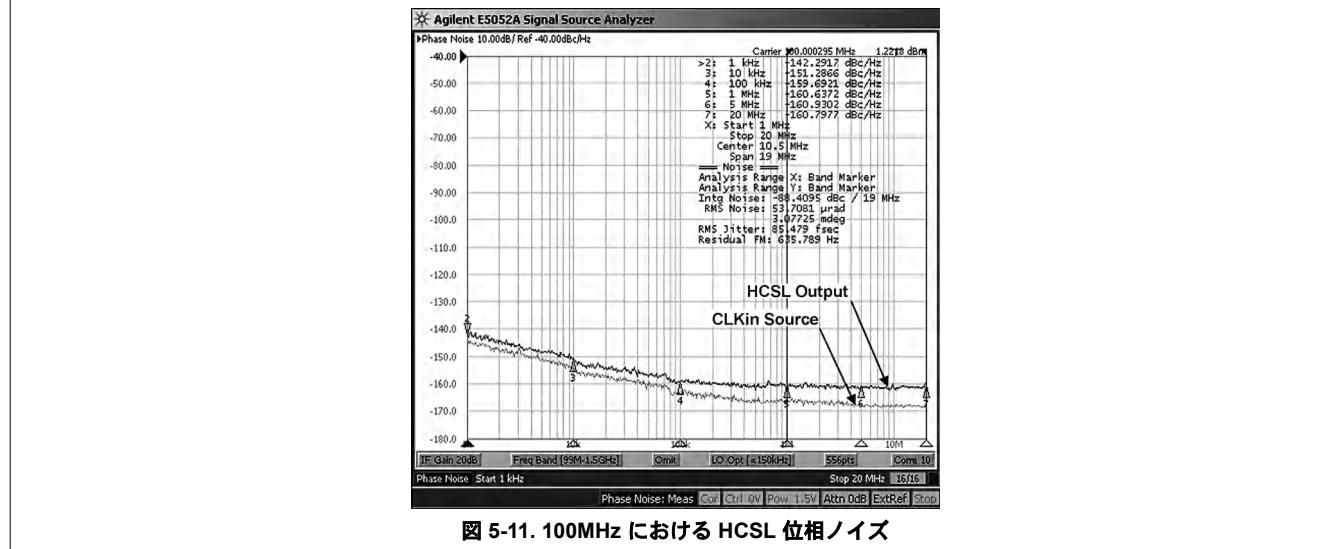

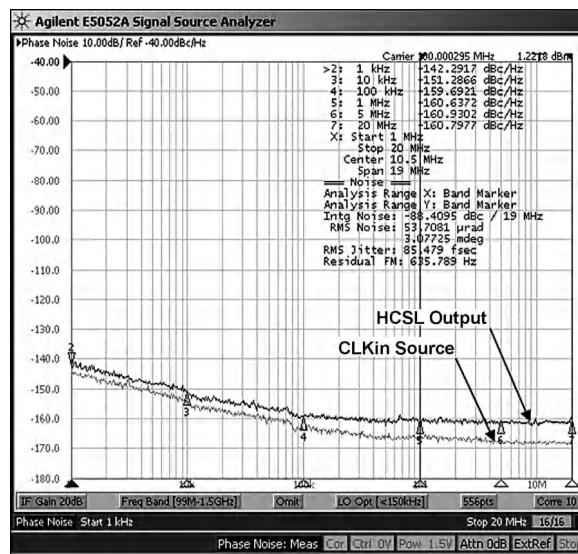

図 5-11. 100MHz における HCSL 位相ノイズ

## 6 パラメータ測定情報

### 6.1 差動電圧測定に関する用語

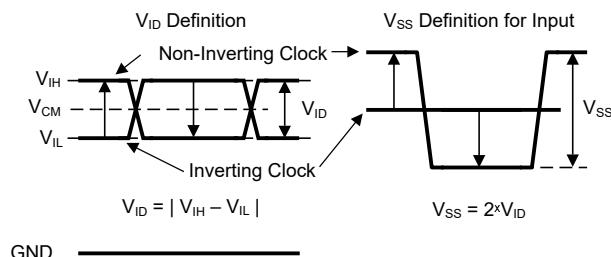

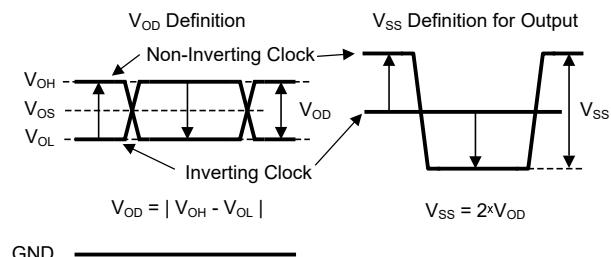

差動信号の差動電圧は 2 つの異なる定義で説明されるため、データシートを読んだり、他のエンジニアとコミュニケーションを取ったりする際に混乱を招くことがあります。このセクションでは、差動信号の測定と説明について取り上げており、この 2 つの異なる定義を理解し、使用時に区別できるようにします。

差動信号の説明における 1 つ目の定義は、反転信号と非反転信号との間の電圧電位の絶対値です。この 1 つ目の測定の記号は、入力電圧または出力電圧を表すかによって、通常は  $V_{ID}$  または  $V_{OD}$  となります。

差動信号の説明における 2 つ目の定義は、反転信号に対する非反転信号の電位を測定することです。この 2 つ目の測定の記号は  $V_{SS}$  であり、算出されたパラメータです。この信号は IC 内のどの場所でもグランドに対して存在せず、常に差動ペア基準でのみ存在しています。 $V_{SS}$  は、フローティングリファレンスを備えたオシロスコープで直接測定できます。それ以外の場合は、最初の説明で述べたように、 $V_{OD}$  の 2 倍の値として計算できます。

図 6-1 は入力信号の 2 つの異なる定義を並べて示し、図 6-2 は出力信号の 2 つの異なる定義を並べて示しています。 $V_{ID}$  (または  $V_{OD}$ ) の定義は、非反転信号および反転信号がグランドに対して遷移する DC レベル、 $V_{IH}$  と  $V_{OL}$  (または  $V_{OH}$  と  $V_{OL}$ ) を示します。 $V_{SS}$  の入力と出力の定義から、反転信号を電圧電位リファレンスとして考えると、非反転信号の電圧電位は非反転リファレンスを上下に推移しながら増加と減少を繰り返すことがわかります。これにより、差動信号のピークツーピーク電圧を測定できます。

$V_{ID}$  と  $V_{OD}$  は多くの場合ボルト (V) と定義され、 $V_{SS}$  はボルトのピークツーピーク ( $V_{PP}$ ) と定義されます。

図 6-1. 差動入力信号の 2 つの異なる定義

図 6-2. 差動出力信号の 2 つの異なる定義

詳細については、一般的なデータ伝送パラメータとその定義アプリケーションノートを参照してください。

## 7 詳細説明

### 7.1 概要

LMK00334 は、最高 400MHz で動作できる追加ジッタの小さい 4 出力の HCSL クロック ファンアウト バッファです。このデバイスは、オプションの水晶発振器入力を備えた 3:1 入力マルチプレクサ、2 つの HCSL 出力を持つ 2 系統のバンク、1 つの LVC MOS 出力、および 3 系統の独立した出力バッファ電源を備えています。入力選択および出力バッファ モードは、ピン ストラップにより制御されます。このデバイスは 32 ピン WQFN パッケージで提供され、LMK04800 ファミリのクロック コンディショナに採用されている高速かつ低ノイズの回路設計の多くを活用しています。

### 7.2 機能ブロック図

### 7.3 機能説明

#### 7.3.1 水晶振動子の消費電力と $R_{LIM}$ との関係

図 5-10 の場合、以下が適用されます:

- プロット内の代表的な RMS ジッタ一値は、各出力バッファ タイプにおける総出力 RMS ジッタ ( $J_{OUT}$ ) と、ソース クロックの RMS ジッタ ( $J_{SOURCE}$ ) を示しています。これらの値から、加算 RMS ジッタは次のように計算できます:  $J_{ADD} = \sqrt{J_{OUT}^2 - J_{SOURCE}^2}$ 。

- 20MHz 水晶振動子の特性: Abracan ABL シリーズ、AT カット、 $C_L = 18\text{pF}$ 、 $C_0 = 4.4\text{pF}$  測定値 (最大 7pF)、 $ESR = 8.5\Omega$  測定値 (最大 40Ω)、ドライブ レベル = 最大 1mW (標準値 100μW)。

- 40MHz 水晶振動子の特性 Abracan ABLS2 シリーズ、AT カット、 $C_L = 18\text{pF}$ 、 $C_0 = 5\text{pF}$  測定値 (最大 7pF)、 $ESR = 5\Omega$  測定値 (最大 40Ω)、ドライブ レベル = 最大 1mW (標準値 100μW)。

### 7.3.2 クロック入力

入力クロックは、CLKin0/CLKin0\*、CLKin1/CLKin1\*、または OSCin から選択できます。クロック入力の選択は、表 7-1 に示すように、CLKin\_SEL[1:0] 入力を使って制御されます。クロック入力要件については、[クロック入力の駆動](#)を参照してください。CLKin0 または CLKin1 が選択されると、水晶振動子回路はパワーダウンします。OSCin が選択されると、水晶発振器回路が起動し、クロックがすべての出力に分配されます。詳細については、[水晶振動子インターフェイス](#)をご覧ください。または、OSCin は水晶振動子ではなくシングルエンド クロック (最大 250MHz) で駆動することもできます。

表 7-1. 入力の選択

| CLKin_SEL1 | CLKin_SEL0 | 選択した入力         |

|------------|------------|----------------|

| 0          | 0          | CLKin0、CLKin0* |

| 0          | 1          | CLKin1、CLKin1* |

| 1          | X          | OSCin          |

表 7-2 に、CLKin0/CLKin0\* または CLKin1/CLKin1\* が選択されている場合の、入力状態に対する出力論理状態を示します。OSCin を選択すると、出力状態は OSCin 入力状態の反転コピーになります。

表 7-2. CLKin 入力と出力状態との関係

| 選択された CLKin の状態               | 有効化された 出力の状態 |

|-------------------------------|--------------|

| CLKinX および CLKinX* 入力はフローティング | ロジック Low     |

| CLKinX および CLKinX* 入力を短絡接続    | ロジック Low     |

| CLKin ロジック Low                | ロジック Low     |

| CLKin ロジック High               | ロジック High    |

### 7.3.3 クロック出力

バンク A および B の両方の HCSL 出力バッファは、表 7-3 に示すように CLKout\_EN [1:0] を使用して Hi-Z に無効化できます。すべての差動出力が必要ないアプリケーションでは、未使用的出力ピンは最小限の銅配線長で浮遊状態にしておく必要があります (次の注記を参照)。これにより、容量や不要な結合を最小限に抑え、消費電力を削減できます。すべての差動出力を使用しない場合、TI はバンクを無効化 (Hi-Z) して消費電力を削減することを推奨しています。出力インターフェイスおよび終端方法の詳細については、[ターミネーションとクロックドライバの使用](#)を参照してください。

#### 注

最適なはんだ付けを行うため、未使用ピンのパターン長は、ピンの半田マスキングを含むように最低限延長する必要があります。こうすることで、リフロー時に接続されているピンと同じ銅面積で、半田が適用されます。これにより、リフロー時に IC を水平に保つのに役立つ、良好で均一なフィレットはんだ接合が得られます。

表 7-3. 差動出力バッファ タイプの選択

| CLKout_EN | CLKoutX バッファ タイプ<br>(バンク A および B) |

|-----------|-----------------------------------|

| 0         | HCSL                              |

| 1         | 無効 (高インピーダンス)                     |

### 7.3.3.1 リファレンス出力

リファレンス出力 (REFout) は、選択された入力クロックの LVC MOS コピーを出力します。LVC MOS 出力 High レベルは、 $V_{CCO}$  電圧を基準としています。REFout は、表 7-4 に示すように、イネーブル入力ピン REFout\_EN を使用してイネーブルまたはディセーブルできます。

**表 7-4. リファレンス出力イネーブル**

| REFout_EN | REFout 状態     |

|-----------|---------------|

| 0         | 無効 (高インピーダンス) |

| 1         | イネーブル         |

REFout\_EN 入力は、SYNC ブロックによって選択された入力クロックと内部的に同期されます。この同期機能により、REFout クロックを有効化または無効化する際に、グリッチやラン パルスが発生するのを防ぎます。REFout は、REFout\_EN が High に切り替えられてから入力クロックの 3 サイクル以内 ( $t_{EN}$ ) に有効化されます。REFout は、REFout\_EN が Low に切り替えられてから入力クロックの 3 サイクル以内 ( $t_{DIS}$ ) に無効化されます。

REFout がディセーブルのとき、抵抗性負荷を使用して、出力をあらかじめ決められたレベルに設定できます。例えば、REFout が  $1k\Omega$  の負荷でグランドに接続されている場合、無効化時には出力が Low に引き下げられます。

## 7.4 デバイスの機能モード

### 7.4.1 $V_{CC}$ および $V_{CCO}$ 電源

LMK00334 および は、3.3V のコア電源 ( $V_{CC}$ ) と、3 系統の独立した 3.3V または 2.5V 出力電源 ( $V_{CCOA}$ 、 $V_{CCOB}$ 、 $V_{CCOC}$ ) を備えています。出力電源を 2.5V で動作させることで、消費電力を低減し、2.5V 受信デバイスとの出力レベル互換性を実現できます。HCSL の出力レベルは、規定された  $V_{CCO}$  範囲にわたって比較的一定です。消費電力、電源バイパス、電源リップル除去 (PSRR) など、電源関連のその他の考慮事項については、[電源に関する推奨事項](#)を参照してください。

---

#### 注

内部 ESD 保護回路がオンにならないように、 $V_{CCO}$  電圧が  $V_{CC}$  電圧を超えないように注意してください。

---

8 アプリケーションと実装

注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

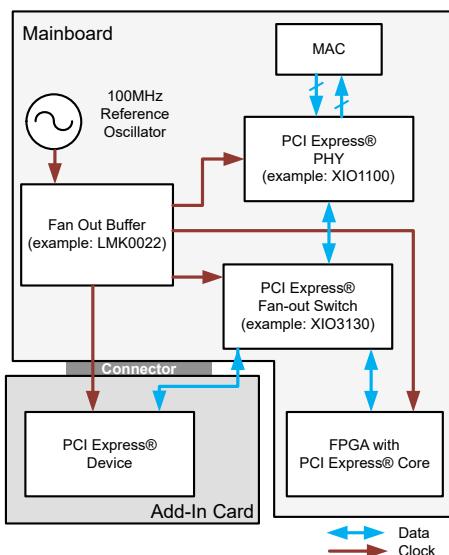

## 8.1 アプリケーション情報

サーバー カードなどの一般的な PCIe アプリケーションは、複数の構成要素で構成されており、それらすべてがリファレンス クロックを必要とします。最も一般的に使用される Common RefClk アーキテクチャでは、クロックは単一のソースから RX と TX の両方に分配されます。このためには、出力数の多いクロック生成器または LMK00334 などのバッファが必要になります。バッファによりクロック ツリーが簡素化され、コストとスペースが最適化された設計を実現できます。バッファを使用してクロックを分配するときは、付加ジッタを考慮する必要があります。LMK00334 は、追加ジッタの非常に低い PCIe クロック バッファで、現在および将来のすべての世代の PCIe に対応して設計されています。

## 8.2 代表的なアプリケーション

図 8-1. PCI Express アプリケーションの例

## 8.2.1 設計要件

### 8.2.1.1 クロック入力の駆動

LMK00334 は、2 つのユニバーサル入力(CLKin0/CLKin0\* および CLKin1/CLKin1\*)を備えており、DC カップリングの 3.3V または 2.5V LVPECL、LVDS、CML、SSTL、その他、[電気的特性](#) に規定された入力要件を満たす差動およびシングルエンド信号を受け入れることができます。このデバイスは、広い入力同相電圧範囲 ( $V_{CM}$ ) と入力電圧スイング ( $V_{ID}$ )/ ダイナミックレンジのため、広い範囲の信号を受け入れることができます。50% デューティサイクルと DC 平衡信号の場合、AC 結合を使用して入力信号を  $V_{CM}$  範囲内にシフトすることもできます。信号インターフェイスと終端テクニックについては、[ターミネーションとクロックドライバの使用](#)を参照してください。

可能な限り最良の位相ノイズおよびジッタ性能を得るために、入力のスルーレートが差動で 3V/ns 以上である必要があります。入力を低いスルーレートで駆動すると、ノイズ フロアとジッタが低下します。このため、シングルエンドよりも差動信号入力を推奨します。差動信号入力は、一般的により高いスルーレートと同相モード除去を提供するためです。ノイズ フロア対 CLKin スルーレートおよび RMS ジッタ対 CLKin スルーレートのプロットについては、[代表的特性](#) を参照してください。

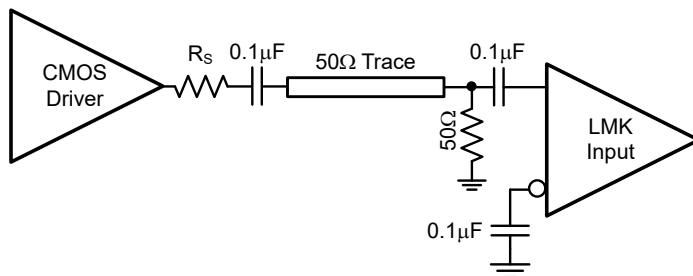

TI は、差動信号入力で CLKin/ CLKin\* ペアを駆動することを推奨していますが、クロックが [電気的特性](#) に示す CLKin ピンのシングルエンド入力仕様に準拠している場合、シングルエンド クロックでペアを駆動できます。3.3V または 2.5V LVC MOS のような大振幅のシングルエンド入力信号の場合、入力近くに 50Ω の負荷抵抗を配置し、信号の減衰によって入力のオーバードライブを防止するとともに、ライン終端によって反射を最小限に抑える必要があります。ここでも、性能の低下を最小限に抑えるため、シングルエンド入力スルーレートをできるだけ高くする必要があります。CLKin 入力の内部バイアス電圧は約 1.4V なので、図 8-2 に示すように、入力を AC 結合できます。LVC MOS ドライバの出力インピーダンスに  $R_s$  を加えた値は、伝送ラインおよび負荷終端の特性インピーダンスに一致させるため、およそ 50Ω にする必要があります。

図 8-2. シングルエンド LVC MOS 入力、AC カップリング

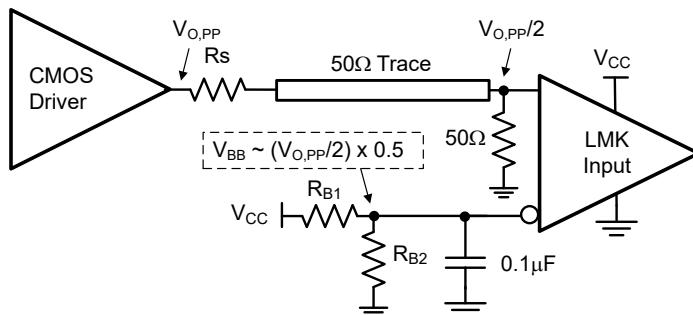

図 8-3 に示すように、シングルエンド クロックを CLKinX に DC 結合することもできます。信号の減衰とライン終端のため、CLKin 入力の近くに 50Ω の負荷抵抗を配置する必要があります。ドライバのシングルエンド振幅の半分 ( $V_{O,PP}/2$ ) が CLKinX を駆動するため、CLKinX\* は減衰後の入力振幅の中点電圧 ( $(V_{O,PP}/2) \times 0.5$ ) に外部バイアスする必要があります。外部バイアス電圧は、規定の入力同相電圧 ( $V_{CM}$ ) 範囲内である必要があります。これは、kΩ の範囲の外付けバイアス抵抗 ( $R_{B1}$  および  $R_{B2}$ ) またはその他の低ノイズ電圧リファレンスを使用して実現できます。これは、入力スイングが入力スルーレートが最大となる位置でしきい値電圧を横切ることを確認するものです。

図 8-3. シングルエンド LVC MOS 入力、DC 結合、同相バイアス付き

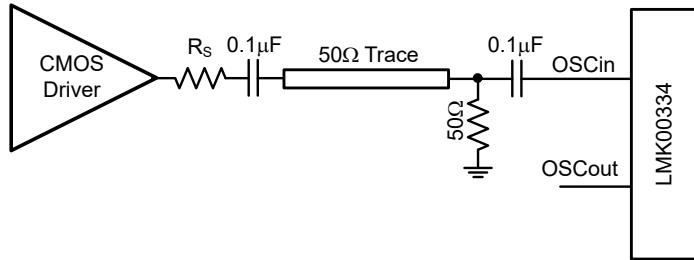

水晶発振器回路を使用しない場合は図 8-4、に示すように、シングルエンドの外部クロックで OSCin 入力を駆動できます。内部生成の入力バイアス電圧を持つ OSCin ピンには入力クロックを AC カップリングで接続し、OSCout ピンは未接続のままにする必要があります。OSCin は外部クロックを多重化する代替入力を提供しますが、TI ではユニバーサル入力 (CLKinX) のいずれかを使用することを推奨しています。これらの入力は、より高い動作周波数、優れた同相モードおよび電源雑音除去性能、そして電源電圧や温度変動に対する高い性能を備えているためです。

図 8-4. シングルエンド入力による OSCin ピンの駆動

### 8.2.1.2 水晶振動子インターフェイス

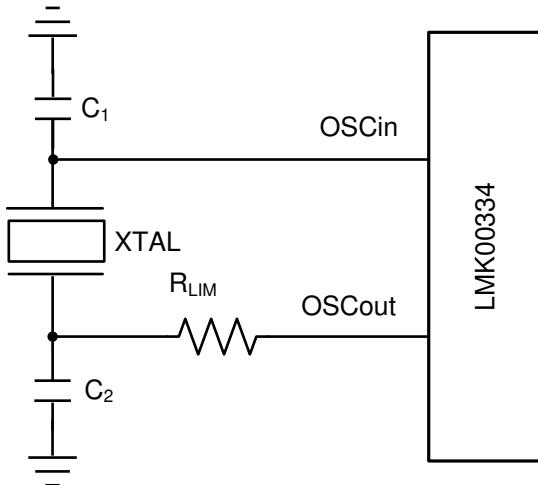

LMK00334 には、基本モードの AT カット水晶振動子をサポートする水晶発振器回路が内蔵されています。水晶振動子インターフェイスを 図 8-5 に示します。

図 8-5. 水晶振動子インターフェイス

負荷容量 ( $C_L$ ) は水晶振動子に固有であり、通常は 18pF~20pF 程度です。水晶振動子に対して  $C_L$  が規定されていますが、デバイスの OSCin 入力容量 ( $C_{IN} = 1\text{pF}$  標準値) や、PCB の寄生容量 ( $C_{STRAY}$  はおよそ 1pF ~ 3pF) が、個別の負荷容量値である  $C_1$  および  $C_2$  に影響を与える可能性があります。

並列共振回路では、ディスクリートコンデンサの値は次のように計算できます:

$$C_L = (C_1 \times C_2) / (C_1 + C_2) + C_{IN} + C_{STRAY} \quad (1)$$

通常、最適な対称性のため  $C_1 = C_2$  なので、式 1C<sub>1</sub>のみで次のように書き換えることができます:

$$C_L = C_1^2 / (2 \times C_1) + C_{IN} + C_{STRAY} \quad (2)$$

最後に、 $C_1$  を求めます:

$$C_1 = (C_L - C_{IN} - C_{STRAY}) \times 2 \quad (3)$$

**電気的特性**では、水晶振動子の起動を検証する条件について水晶振動子インターフェイスの仕様を提供していますが、電気的特性では水晶振動子の消費電力は規定されていません。設計者は、水晶振動子の消費電力が水晶メーカーが規定する最大ドライブ レベルを超えないことを確認する必要があります。水晶振動子をおーばドライブすると、早期劣化、周波数の変動、最終的な故障を引き起こす可能性があります。ドライブ レベルは、起動および定常動作の維持に必要な十分なレベルに保つ必要があります。

水晶振動子で消費される電力  $P_{XTAL}$  は、以下で計算できます:

$$P_{XTAL} = I_{RMS}^2 \times R_{ESR} \times (1 + C_0/C_L)^2 \quad (4)$$

ここで、

- $I_{RMS}$  は水晶振動子を流れる RMS 電流です。

- $R_{ESR}$  は、水晶振動子の実効等価直列抵抗です

- $C_{L(R)}$  は、水晶振動子に対して規定された負荷容量です

- $C_0$  は、水晶振動子に対して規定され最大シャント容量です

$I_{RMS}$  は、OSCSout に接続された水晶振動子のレッグに配置され、発振回路がアクティブな状態で電流プローブ (Tektronix CT-6 または同等品など) を使用して測定できます。

図 8-5 に示すように、必要に応じて、外付け抵抗  $R_{LIM}$  を使用して水晶振動子の駆動レベルを制限できます。選択した水晶振動子で消費される電力が、 $R_{LIM}$  を短絡した状態で水晶振動子に指定された励振レベルよりも高い場合、水晶振動子がオーバードライブされないようにするために、より大きな抵抗値が必要です。ただし、 $R_{LIM}$  を短絡した状態で、水晶振動子で消費される電力が駆動レベルよりも小さい場合、 $R_{LIM}$  にゼロ値を使用できます。出発点として、 $R_{LIM}$  の推奨値は  $1.5\text{k}\Omega$  です。

## 8.2.2 詳細な設計手順

### 8.2.2.1 ターミネーションとクロック ドライバの使用

クロック ドライバを終端する際は、位相ノイズおよびジッタ性能を最適化するために、次のガイドラインを考慮してください:

- 反射を防ぐため、良好なインピーダンス整合を実現するには伝送ラインの理論に従う必要があります。

- クロック ドライバには、適切な負荷が付属している必要があります。

- HCSL ドライバは電流出力が切り替えられ、 $50\Omega$  終端を介してグランドへの DC パスが必要です。

- 受信側が正しく動作するためには、指定された DC バイアスレベル (同相電圧) にバイアスされた信号を入力する必要があります。一部の受信回路には、適切な電圧レベルに自動的にバイアスするセルフ バイアス入力があります。この場合、信号は通常 AC カップリングとする必要があります。

### 8.2.2.2 DC 結合差動動作のターミネーション

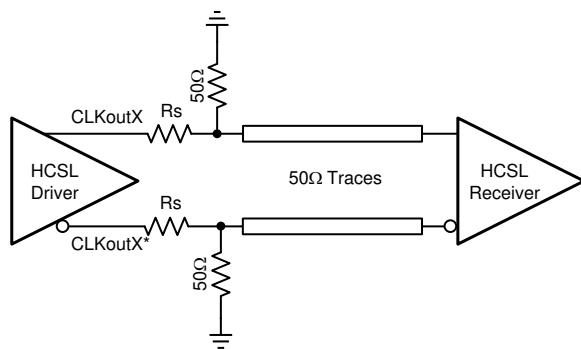

HCSL ドライバの DC 結合動作の場合、図 8-6 に示すように、ドライバ出力の近くのグランドに対して  $50\Omega$  で終端します。高速な過渡電流によるオーバーシュートを抑えるために、直列抵抗  $Rs$  を使用できます。HCSL ドライバはグランドへの DC パスを必要とするため、出力ドライバと  $50\Omega$  終端抵抗の間で AC カップリングを行うことはできません。

図 8-6. HCSL の動作、DC カップリング

### 8.2.2.3 AC 結合差動動作のターミネーション

AC カップリングは、異なる受信規格を駆動する際に DC バイアス レベル (同相モード電圧) をシフトさせることができます。AC カップリングでは、ドライバが受信側に DC バイアス電圧を供給できないため、受信側が最適な DC レベルにバイアスされていることを確認してください。

### 8.2.3 アプリケーション曲線

図 8-7. 100MHz における HCSL 位相ノイズ

## 8.3 電源に関する推奨事項

### 8.3.1 消費電流と消費電力の計算

電気的特性に規定されている消費電流値を使用して、任意のデバイス構成での合計消費電力と IC 消費電力を計算できます。総  $V_{CC}$  コア電源電流 ( $I_{CC\_TOTAL}$ ) は、式 5 を使って計算できます：

$$I_{CC\_TOTAL} = I_{CC\_CORE} + I_{CC\_BANKS} + I_{CC\_CMOS} \quad (5)$$

ここで、

- $I_{CC\_CORE}$  は、コア ロジックと入力ブロックの  $V_{CC}$  電流であり、選択した入力 (CLKinX または OSCin) に依存します。

- $I_{CC\_HCSL}$  は、バンク A および B の  $V_{CC}$  電流です

- $I_{CC\_CMOS}$  は、LVCMOS 出力の  $V_{CC}$  電流 (または REFout がディスエーブルの場合は 0mA) です。

出力電源 ( $V_{CCOA}$ 、 $V_{CCOB}$ 、 $V_{CCOC}$ ) は 3 系統の独立した電圧から給電できるため、それぞれの出力電源電流 ( $I_{CCO\_BANK\_A}$ 、 $I_{CCO\_BANK\_B}$ 、 $I_{CCO\_CMOS}$ ) は別々に算出する必要があります。

出力負荷が規定条件に一致する場合、バンク A またはバンク B の  $I_{CCO\_BANK}$  は、2 つのバンクに対して規定された対応する出力電源電流 ( $I_{CCO\_HCSL}$ ) の 50% として算出できます。それ以外の場合は、式 6 に示すように、 $I_{CCO\_BANK}$  をバンクごとに計算する必要があります。

$$I_{CCO\_BANK} = I_{BANK\_BIAS} + (N \times I_{OUT\_LOAD}) \quad (6)$$

ここで、

- $I_{BANK\_BIAS}$  は、出力バンクのバイアス電流 (固定値) です。

- $I_{OUT\_LOAD}$  は、負荷出力ペアごとの DC 負荷電流です。

- N は負荷のかかった出力ペアの数を表します (N = 0~2)。

表 8-1 に、HCSL の代表的な  $I_{BANK\_BIAS}$  値と  $I_{OUT\_LOAD}$  の式を示します。

**表 8-1. 代表的な出力バンクのバイアスと負荷電流**

| 現在のパラメータ         | HCSL         |

|------------------|--------------|

| $I_{BANK\_BIAS}$ | 2.4mA        |

| $I_{OUT\_LOAD}$  | $V_{OH}/R_T$ |

各電源ごとの消費電流が判明したら、総消費電力 ( $P_{TOTAL}$ ) は 式 7 によって算出できます:

$$P_{TOTAL} = (V_{CC} \times I_{CC\_TOTAL}) + (V_{CCOA} \times I_{CCO\_BANK}) + (V_{CCOB} \times I_{CCO\_BANK}) + (V_{CCOC} \times I_{CCO\_CMOS}) \quad (7)$$

デバイスが HCSL 出力で構成されている場合、終端抵抗で消費される電力 ( $P_{RT\_HCSL}$ ) も計算する必要があります。外部消費電力の値は、式 8 によって算出できます:

$$P_{RT\_HCSL} (\text{per HCSL pair}) = V_{OH}^2 / R_T \quad (8)$$

最後に、IC の消費電力 ( $P_{DEVICE}$ ) は、式 9 に示すように  $P_{TOTAL}$  から外部消費電力の値を差し引くことで算出できます:

$$P_{DEVICE} = P_{TOTAL} - N \times P_{RT\_HCSL} \quad (9)$$

ここで、

- $N$  は、GND に終端抵抗を接続した HCSL 出力ペアの数を表します。

### 8.3.1.1 消費電力の例: ワーストケース消費電力

この例では、ワーストケースの消費電力を推定するための構成の IC 消費電力を計算する方法を示します。この場合、[電気的特性](#)に規定されている電源電圧と電源電流の最大値を使用します：

- 最大  $V_{CC} = V_{CCO} = 3.465V$ 。 $I_{CC}$  および  $I_{CCO}$  の最大値。

- $CLKin0/CLKin0^*$  入力が選択されます。

- バンク A および B が有効化され、すべての出力が  $50\Omega$  で GND に終端されています。

- $REFout$  は、 $5pF$  負荷でイネーブルになります。

- $T_A = 85^\circ C$

前のセクションで得た電力の計算と最大電源電流の仕様を使用して、ユーザーは  $P_{TOTAL}$  と  $P_{DEVICE}$  を計算できます。

- [式 5](#) から:  $I_{CC\_TOTAL} = 10.5mA + 58.5mA + 5.5mA = 74.5mA$

- $I_{CCO\_HCSL}$  最大仕様から:  $I_{CCO\_BANK} = 50\%$  ( $I_{CCO\_HCSL} = 40.75mA$ )

- [式 7](#) から:  $P_{TOTAL} = (3.465V \times 74.5mA) + (3.465V \times 40.75mA) + (3.465V \times 40.75mA) + (3.465V \times 10mA) = 575.2mW$

- [式 8](#) から:  $P_{RT\_HCSL} = (0.92V)^2 / 50\Omega = 16.9mW$  (出力ペアごと)

- [式 9](#) から:  $P_{DEVICE} = 575.2mW - (4 \times 16.9mW) = 510.4mW$

このワーストケースの例では、IC デバイスは総消費電力 ( $575.2mW$ ) の約  $510.4mW$ 、すなわち  $88.7\%$  を消費し、残りの  $11.3\%$  は終端抵抗 (4 ペアで  $64.8mW$ ) で消費されます。 $38.1^\circ C / W$  の  $R_{ThetaJA}$  に基づき、ダイ接合部温度の推定値は周囲温度よりも約  $19.4^\circ C$  高く、 $T_A = 85^\circ C$  の場合は  $104.4^\circ C$  よりも高い値です。

### 8.3.2 電源バイパス

$V_{CC}$  および  $V_{CCO}$  電源には、 $0.1\mu F$  や  $0.01\mu F$  などの高周波バイパスコンデンサを各電源ピンのすぐ近くに配置する必要があります。 $1\mu F \sim 10\mu F$  のデカップリングコンデンサも、電源プレーンとグランドプレーンの間でデバイスの近くに配置する必要があります。すべてのバイパスコンデンサおよびデカップリングコンデンサは、直列インダクタンスを最小限に抑えるため、短い配線またはビアを介して電源プレーンおよびグランドプレーンに短く接続する必要があります。

#### 8.3.2.1 電源リップル除去

実際のシステム アプリケーションでは、スイッチング電源、デジタル ASIC や FPGA などから電源ノイズ(リップル)が発生することがあります。電源バイパスによってこのようなノイズの一部は除去できますが、電源リップルがデバイスの性能に与える影響を理解することが重要です。LMK00334 やなどのクロック分配デバイスの電源にシングルトーンの正弦波信号を印加すると、クロック出力(キャリア)に狭帯域の位相変調および振幅変調が生じる可能性があります。シングルサイドバンド位相ノイズスペクトルでは、リップルに起因する位相変調は、キャリアに対しての位相スプライアスレベルとして現れます(dBc で測定)。

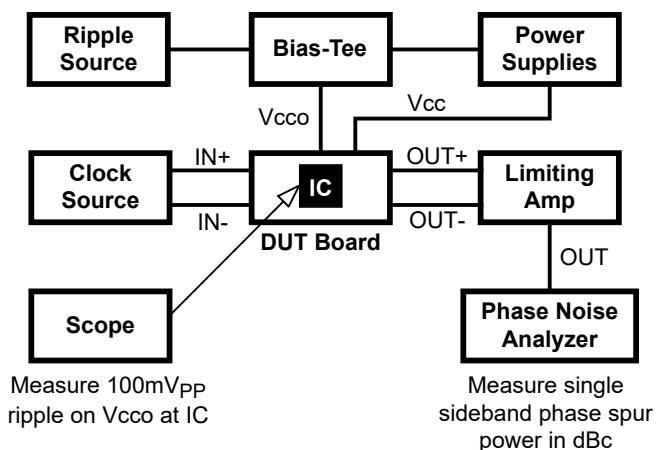

LMK00334 では、リップル信号が  $V_{CCO}$  電源に注入されたときに、電源リップル除去(PSRR)がクロック出力に変調されたシングルバンドの位相スプライアスレベル(dBc)として測定されます。PSRR の試験構成は 図 8-8 に示されます。

図 8-8. PSRR テスト設定

信号発生器を使用して、DUT ボードの  $V_{CCO}$  電源に正弦波信号を印加し、デバイスの  $V_{CCO}$  ピンでピークツーピークのリップル振幅を測定しました。リミティングアンプを使用して、差動出力クロックの振幅変調を除去し、位相ノイズアナライザ用に信号をシングルエンド信号へ変換します。位相スパー レベルの測定は、以下の電源リップル条件下で、156.25MHz および 312.5MHz のクロック周波数に対して行われます:

- リップル振幅: 100mVpp での  $V_{CCO} = 2.5V$

- リップル周波数: 100kHz, 1MHz, 10MHz

振幅変調の影響がなく、かつ変調指数が小さいと仮定すると、ピークツーピークの決定性ジッタ(DJ)は、測定されたシングルサイドバンド位相スパー レベル(PSRR)を使用して次のように算出できます:

$$DJ (\text{ps pk-pk}) = [(2 \times 10^{(\text{PSRR}/20)}) / (\pi \times f_{\text{CLK}})] \times 10^{12} \quad (10)$$

代表的特性に示されている PSRR 対リップル周波数プロットは、156.25MHz および 312.5MHz におけるリップルによる位相スパー レベルを示しています。LMK00334 は、リップル周波数範囲全体にわたり、非常に優れた安定した PSRR 特性を示します。HCSL の位相スパー レベルは、156.25MHz で  $-72\text{dBc}$  未満、312.5MHz で  $-63\text{dBc}$  未満です。式 10 を使用すると、これらの位相スプライアス レベルは決定論的ジッタ値である 156.25MHz で  $1.02\text{ps pk-pk}$ 、312.5MHz で  $1.44\text{ps pk-pk}$  に変換されます。テストでは、同じリップル振幅および周波数条件において、デバイスの PSRR 性能が  $V_{CCO} = 3.3V$  に対して向上することが示されています。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

このデバイスでは、次のガイドラインを考慮してください:

- HCSL ドライバの DC 結合動作の場合、図 8-9 に示すように、ドライバ出力の近くのグランドに対して  $50\Omega$  で終端します。

- バイパスコンデンサとデバイスの電源との間の接続はできる限り短くします。

- グランドプレーンへの低インピーダンス接続を使用して、コンデンサの反対側をグランドに接続します。

- コンデンサを裏面に実装する場合は、コンポーネント 0402 を使用できます。ただし、熱放散パッドへの半田付けは困難な場合があります。

- 部品側の実装には、0201 の本体サイズのコンデンサを使用して信号の配線を容易にします。

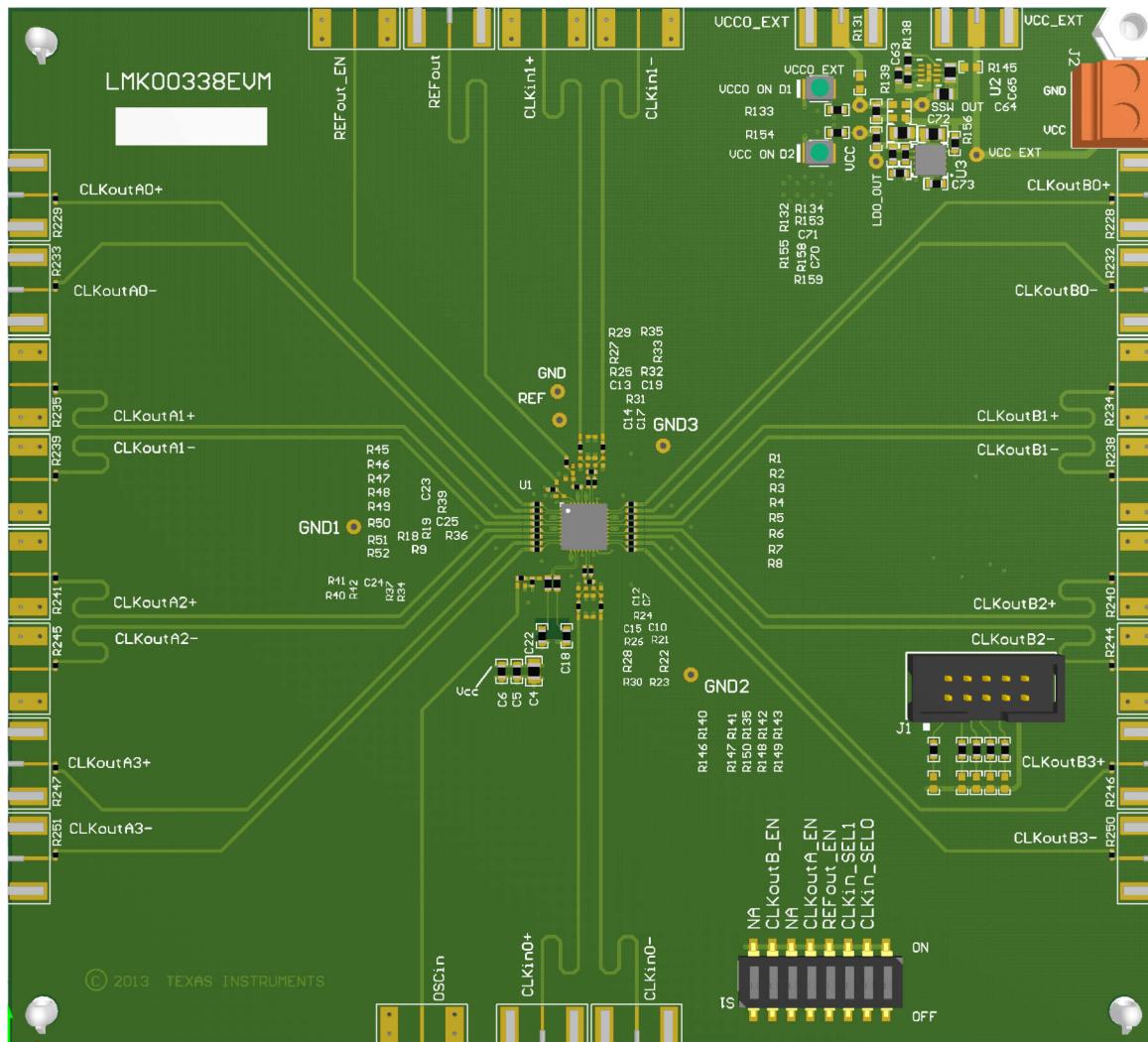

### 8.4.2 レイアウト例

図 8-9. LMK00334 レイアウトの例

#### 8.4.3 热管理

LMK00334 デバイスの消費電力は、熱管理に注意を要するほど大きくなる可能性があります。信頼性および性能の観点から、ダイ温度は最大  $125^{\circ}\text{C}$  に制限する必要があります。つまり、推定値として、 $T_A$  (周囲温度) にデバイスの消費電力と  $R_{\theta JA}$  を掛けた値を加えた合計が  $125^{\circ}\text{C}$  を超えないものとします。

このデバイスのパッケージには、主な放熱経路を提供するとともに、プリント基板への優れた電気グランドを実現する露出パッドがあります。パッケージからの放熱を最大化するため、PCB 上のパッケージのフットプリント内に、複数のビアでグラウンドプレーンへ接続するサーマル ランド パターンを設ける必要があります。露出したパッドは、パッケージから十分な熱伝導を提供するために半田付けする必要があります。

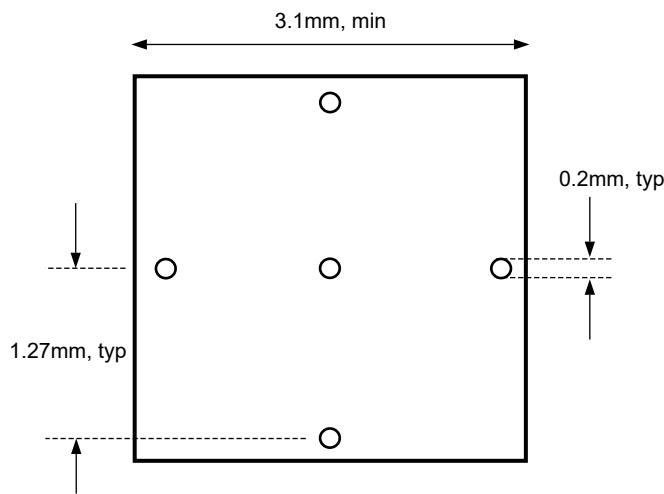

推奨されるランドおよびビア パターンを図 8-10 に示します。WQFN パッケージのハンダ付けの詳細については、<https://www.ti.com/packaging> を参照してください。

図 8-10. 推奨されるランドおよびビア パターン

接合部温度を最小限に抑えるため、グランド プレーン層が露出していない場合は、PCB に簡易ヒートシンクを組み込むことを TI は推奨しています。これは、デバイスからの PCB の反対側にある約 2 平方インチの銅領域を含めることで実現されます。この銅面は、防錆のためにめっきやはんだコーティングを施すことはできますが、可能であれば熱絶縁となるコンフォーマル コーティングは施さないでください。図 8-10 に示すビアは、これらの最上層と最下層の銅層とグランド層に接続する必要があります。これらのビアはヒートパイプとして機能し、熱エネルギーを基板のデバイス側から遠ざけることで、熱エネルギーをより効果的に放散できます。

## 9 デバイスおよびドキュメントのサポート

### 9.1 ドキュメントのサポート

#### 9.1.1 関連資料

関連資料については、以下を参照してください：

- テキサス・インスツルメンツ、[ハンダ付けの絶対最大定格アプリケーションノート](#)

- テキサス・インスツルメンツ、[一般的なデータ伝送パラメータと定義アプリケーションノート](#)

- テキサス・インスツルメンツ、テキサス・インスツルメンツのE2Eコミュニティフォーラムの[PCIeアプリケーションのクロック分配の最適化方法](#)

- テキサス・インスツルメンツ、『[LMK00338EVMユーザーガイド](#)』

- テキサス・インスツルメンツ、『[半導体およびICパッケージの熱評価基準](#)』アプリケーションノート

### 9.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 9.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

PCIe® is a registered trademark of PCI-SIG.

すべての商標は、それぞれの所有者に帰属します。

### 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.6 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision E (January 2022) to Revision F (August 2025) | Page |

|--------------------------------------------------------------------|------|

| 特長セクションに PCIe Gen 6 および Gen 7 の追加ジッタ仕様を追加.....                     | 1    |

| 特長セクションの PCIe Gen 3 から Gen 5 への追加ジッタ仕様を更新.....                     | 1    |

| 電気的特性セクションに、PCIe Gen 6 および Gen 7 の加算ジッタ仕様を追加.....                  | 5    |

| 電気的特性セクション内の PCIe Gen 3 から Gen 5 の加算ジッタ仕様を更新.....                  | 5    |

| <b>Changes from Revision D (July 2021) to Revision E (January 2022)</b> | <b>Page</b> |

|-------------------------------------------------------------------------|-------------|

| • データシートのタイトルを変更.....                                                   | 1           |

| • アプリケーションセクションにリンクを追加.....                                             | 1           |

| • 「説明」セクションにテキストを追加.....                                                | 1           |

| • パッケージ情報セクションに基板レイアウト例を追加。.....                                        | 27          |

| <b>Changes from Revision C (July 2017) to Revision D (July 2021)</b> | <b>Page</b> |

|----------------------------------------------------------------------|-------------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                 | 1           |

| • データシートに PCIe Gen 5.0 を追加.....                                      | 1           |

| • 図 8-4 および 図 8-5 の PN を LMK00334 に修正。.....                          | 18          |

| <b>Changes from Revision B (May 2017) to Revision C (July 2017)</b> | <b>Page</b> |

|---------------------------------------------------------------------|-------------|

| • PCIe 4.0 準拠データを追加.....                                            | 5           |

| <b>Changes from Revision A (October 2014) to Revision B (May 2017)</b> | <b>Page</b> |

|------------------------------------------------------------------------|-------------|

| • データシート全体を通して CLKout_EN ピンを CLKout_EN に変更.....                        | 1           |

| • ピン機能表に注 28 と注 32 を追加.....                                            | 3           |

| • 保管温度を「絶対最大定格」表に移動.....                                               | 4           |

| • 推奨動作条件表の出力電源電圧パラメータに試験条件を追加.....                                     | 5           |

| <b>Changes from Revision * (December 2013) to Revision A (October 2014)</b>                                                                  | <b>Page</b> |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • 以下のセクションを追加、更新、または名称変更:「製品情報」表、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクション..... | 1           |

| • 「電気的特性」の 1MHz を 12kHz に変更.....                                                                                                             | 5           |

| • 「付加ジッタは、加算 RMS ジッタに近似し...」を削除...".....                                                                                                     | 5           |

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LMK00334RTVR          | Active        | Production           | WQFN (RTV)   32 | 1000   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 85    | K00334              |

| LMK00334RTVR.A        | Active        | Production           | WQFN (RTV)   32 | 1000   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 85    | K00334              |

| LMK00334RTVT          | Active        | Production           | WQFN (RTV)   32 | 250   SMALL T&R       | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 85    | K00334              |

| LMK00334RTVT.A        | Active        | Production           | WQFN (RTV)   32 | 250   SMALL T&R       | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 85    | K00334              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF LMK00334 :**

- Automotive : [LMK00334-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

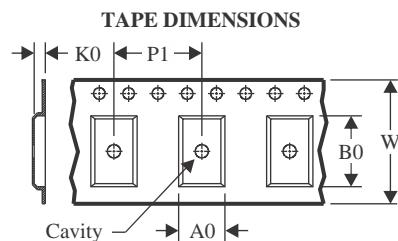

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

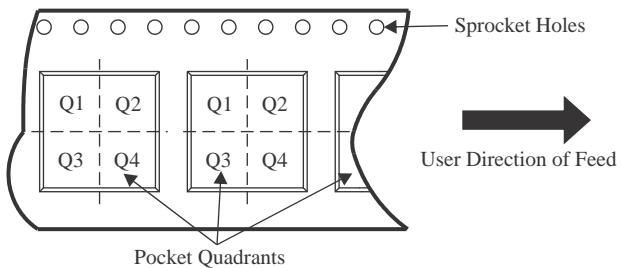

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LMK00334RTVR | WQFN         | RTV             | 32   | 1000 | 177.8              | 12.4               | 5.3     | 5.3     | 1.3     | 8.0     | 12.0   | Q1            |

| LMK00334RTVT | WQFN         | RTV             | 32   | 250  | 177.8              | 12.4               | 5.3     | 5.3     | 1.3     | 8.0     | 12.0   | Q1            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMK00334RTVR | WQFN         | RTV             | 32   | 1000 | 208.0       | 191.0      | 35.0        |

| LMK00334RTVT | WQFN         | RTV             | 32   | 250  | 208.0       | 191.0      | 35.0        |

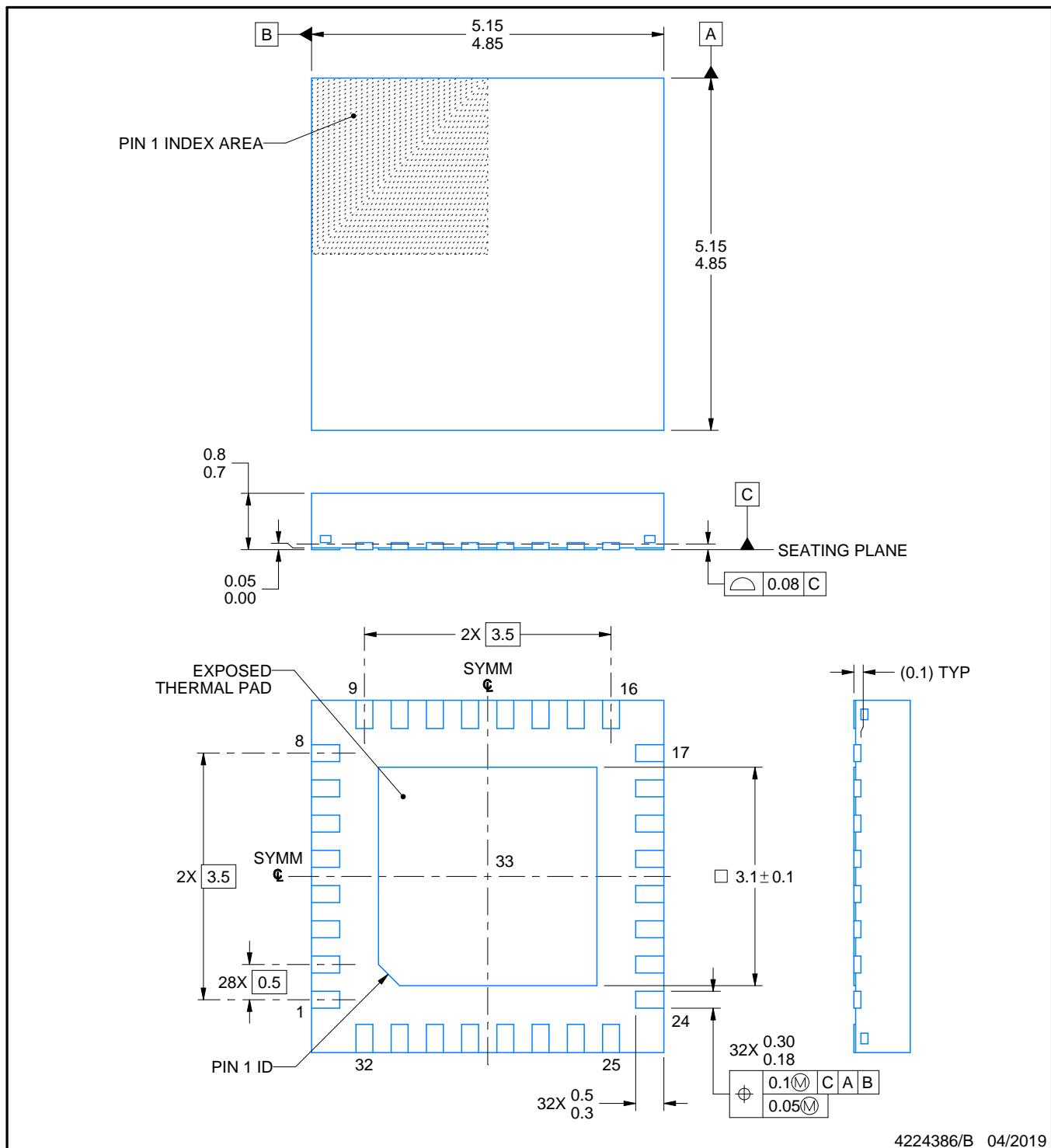

# PACKAGE OUTLINE

**RTV0032A**

**WQFN - 0.8 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

4224386/B 04/2019

**NOTES:**

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

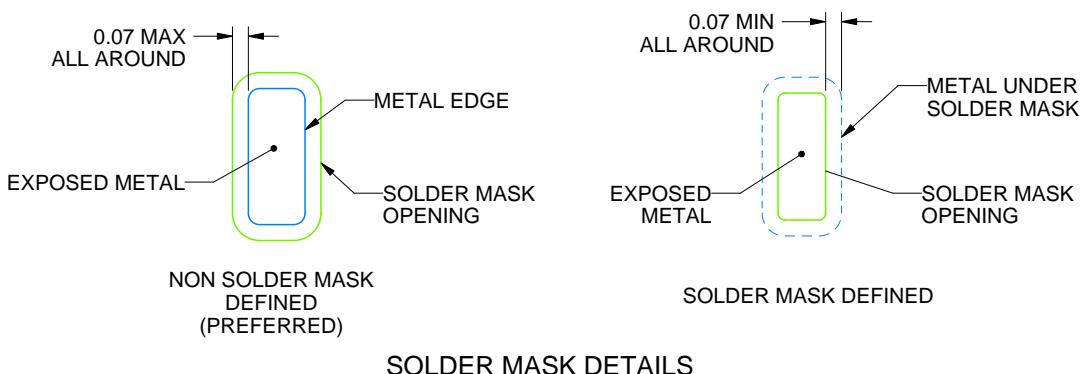

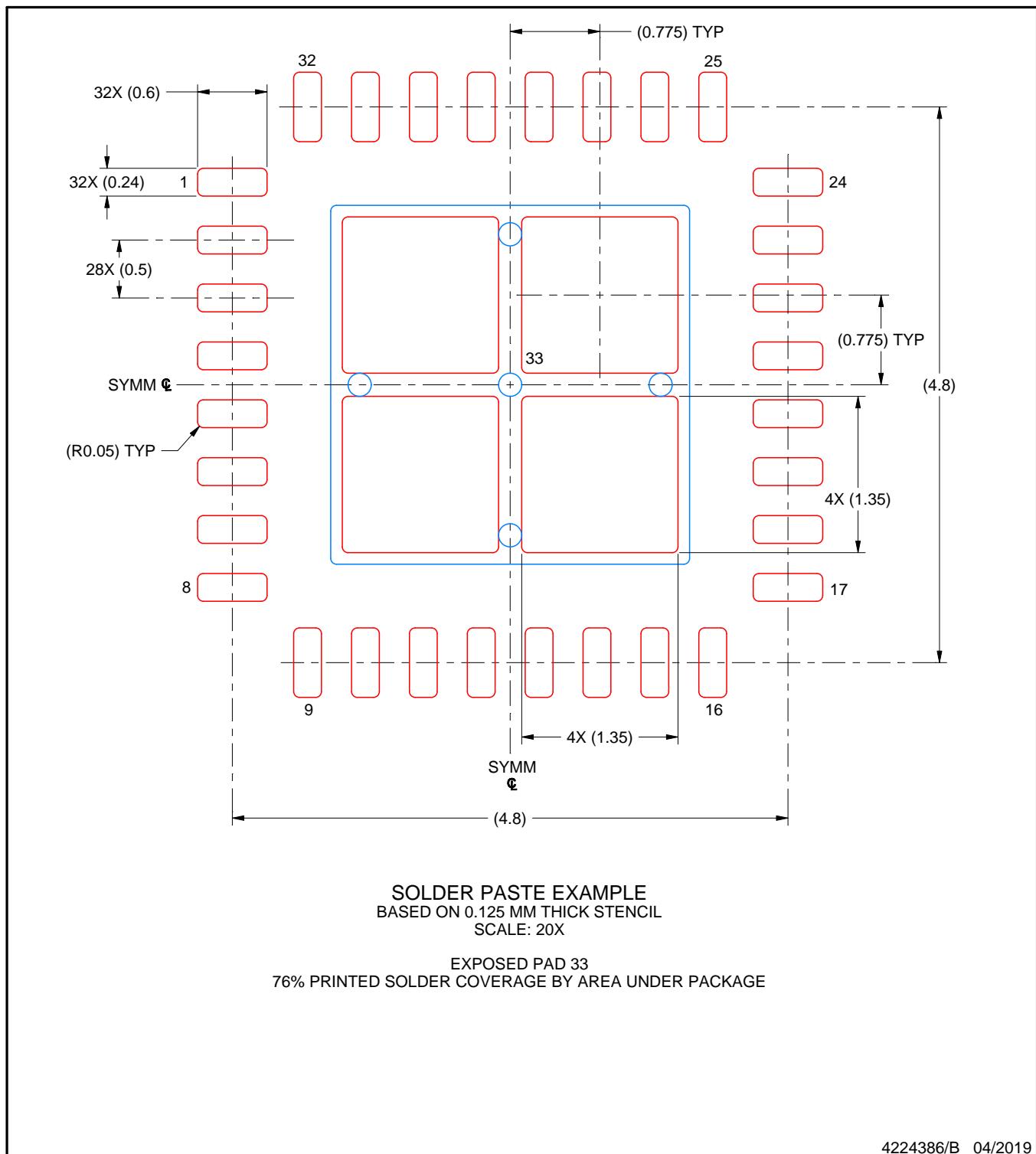

# EXAMPLE BOARD LAYOUT

RTV0032A

WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

4224386/B 04/2019

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# EXAMPLE STENCIL DESIGN

RTV0032A

WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月