# LMK05318B-Q1、車載および産業用途向け BAW VCO を搭載した 1 DPLL、2 APLL、2 入力、8 出力 () のネットワーク同期デバイス

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- $-40^{\circ}\text{C} \sim +105^{\circ}\text{C}$  の動作温度 (グレード 2)

- 超低ジッタ BAW VCO ベースのイーサネットクロック

- 4MHz の 1 次ハイパスフィルタ (HPF) を適用した場合、312.5MHz における標準 RMS ジッタは 32fs

- 4MHz の 1 次 HPF を適用した場合、156.25 MHz における標準 RMS ジッタは 44 fs

- 312.5MHz での RMS ジッタ 50fs (標準値) / 80fs (最大値)

- 156.25MHz での RMS ジッタ 60fs (標準値) / 90fs (最大値)

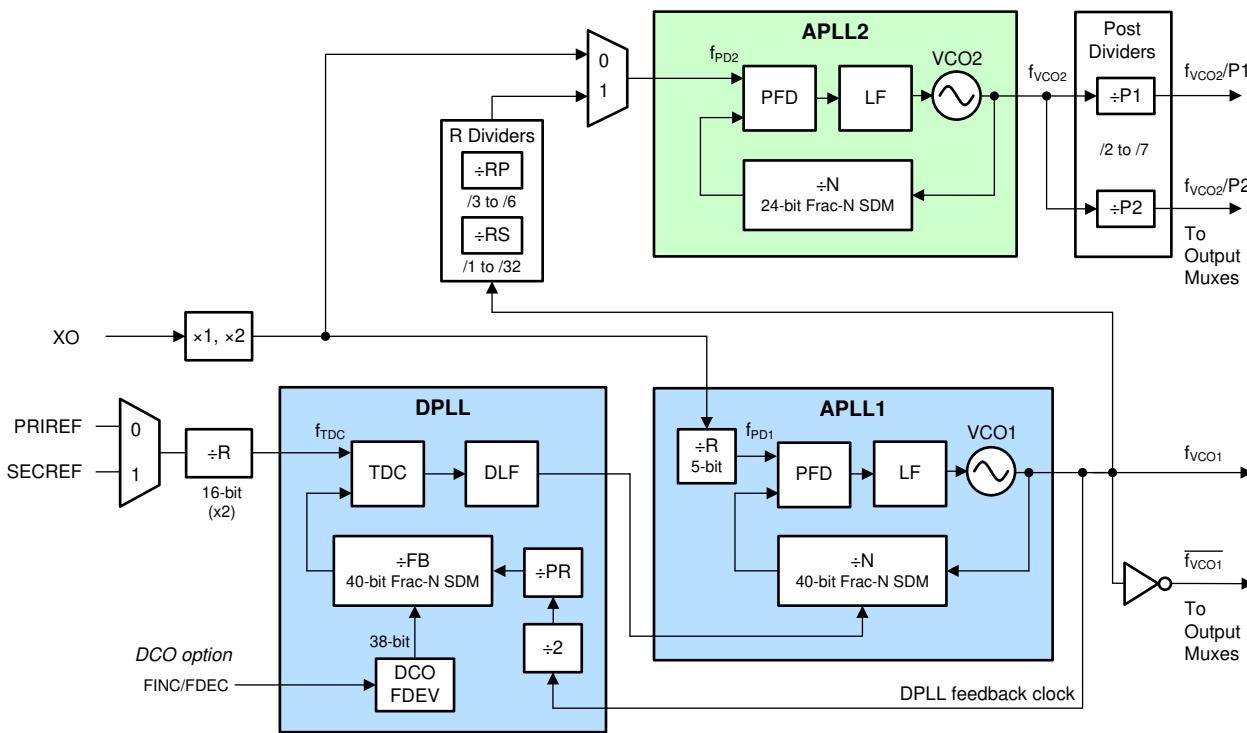

- 2 つのアナログ位相ロックループ (APLL) と対になつた 1 つの高性能デジタルフェーズロックループ (DPLL):

- 1mHz ~ 4kHz の範囲でプログラム可能な DPLL ループ帯域幅

- IEEE 1588PTP クロックステアリング向けに、1 ステップあたり 1ppt 未満の DCO 調整が可能

- 2 つの差動またはシングルエンド DPLL 入力

- 入力周波数: 1Hz (1PPS) ~ 800MHz

- デジタルホールドオーバーおよびヒットレススイッチング

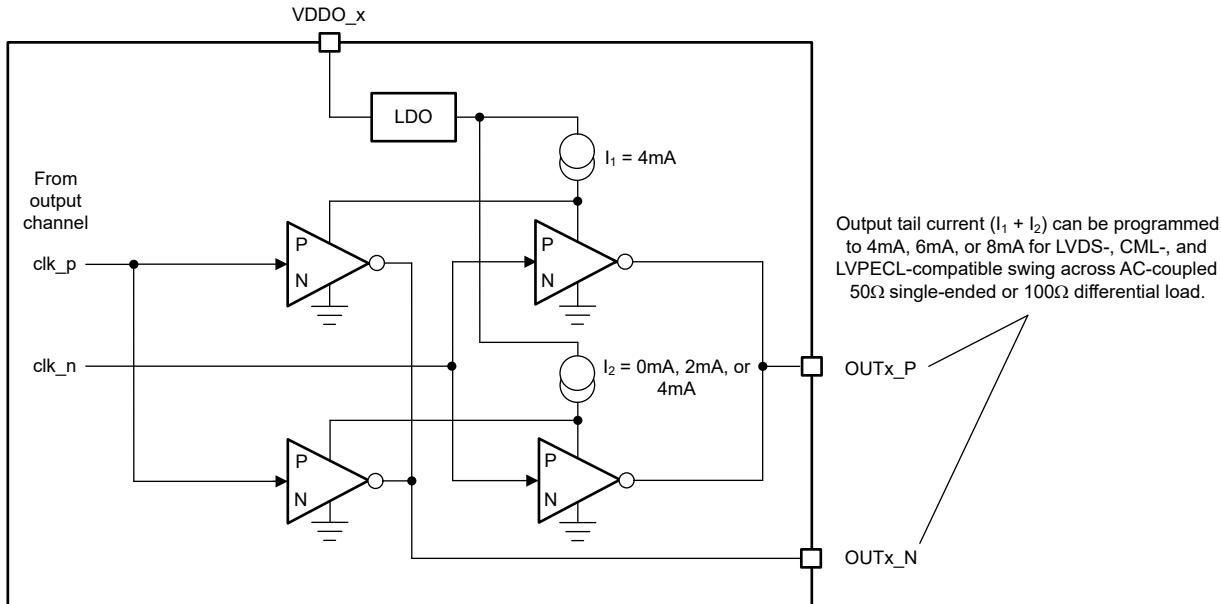

- 8 つのプログラム可能な AC-LVPECL、AC-CML、AC-LVDS、HSCL、および 1.8V LVC MOS の出力フォーマットに対応した差動出力。

- 1Hz (1PPS) ~ 1250MHz の出力周波数

- PCIe Gen 1~6 準拠

- I<sup>2</sup>C、3 線式 SPI、または 4 線式 SPI

- 3.3V のコア電源と、1.8V、2.5V、または 3.3V の出力電源

- $-40^{\circ}\text{C} \sim +105^{\circ}\text{C}$  の動作温度範囲

## 2 アプリケーション

- SyncE (G.8262)、SONET/SDH (Stratum 3/3E、G.813、GR-1244、GR-253)、IEEE 1588 PTP センダリクロック

- 56G/112G PAM4 SerDes 用ジッタクリーニング、ワンダ減衰、基準クロック生成

- 先進運転支援システム (ADAS)

- ADAS ドメインコントローラ

- インフォテインメントおよびクラスタ

- 車載対応、クラスタディスプレイ

- テレマティクス制御ユニット (TCU)

- 自動車向けインストルメントクラスター

- デジタルコックピット処理装置

- ボディエレクトロニクス / ライティング

- ザーンコントローラとボディドメインコントローラ

- 産業用

- 試験および測定機器

- 医療用画像処理

## 3 説明

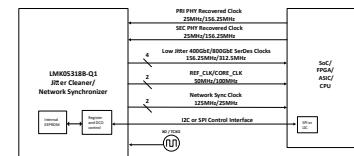

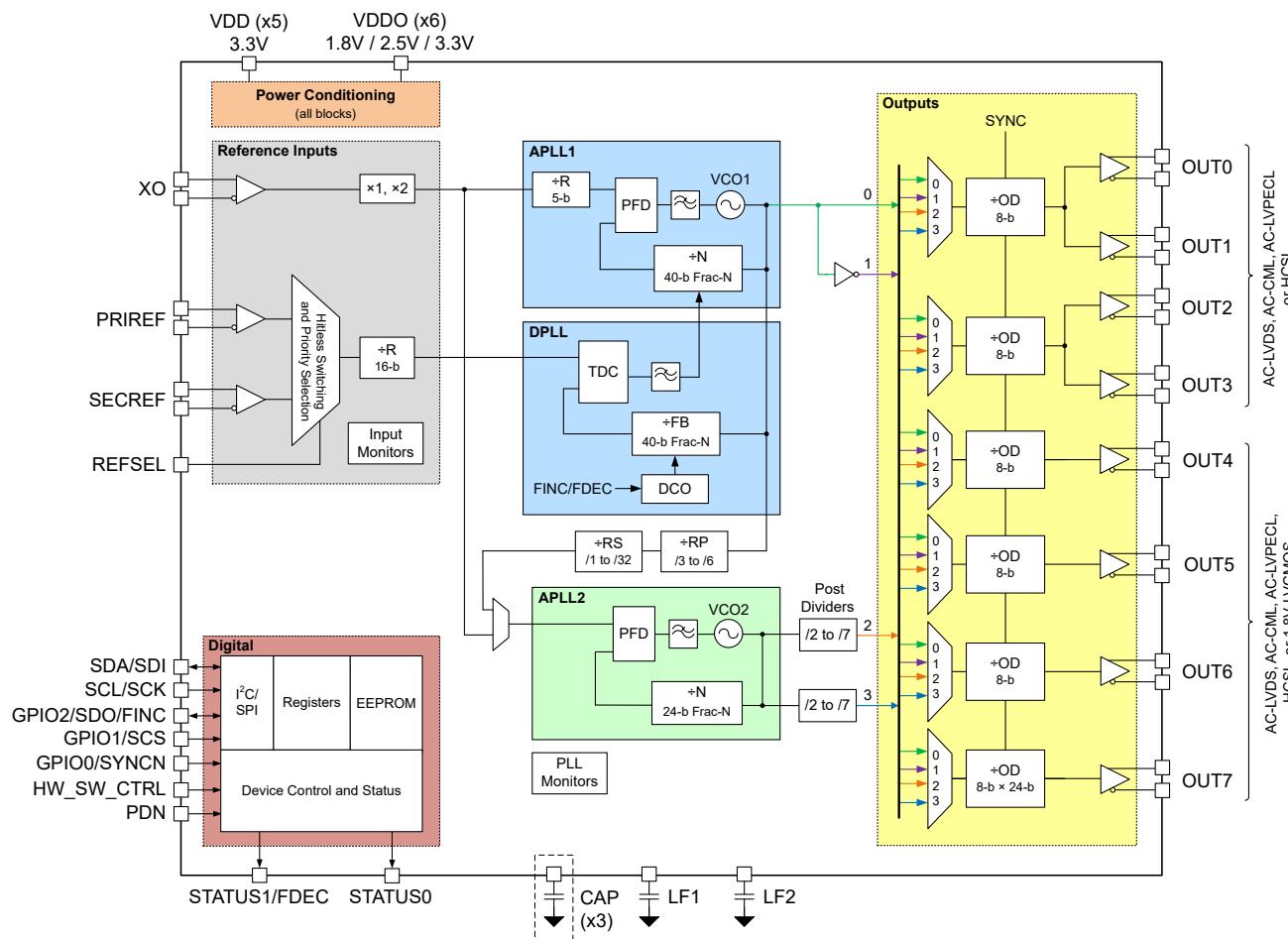

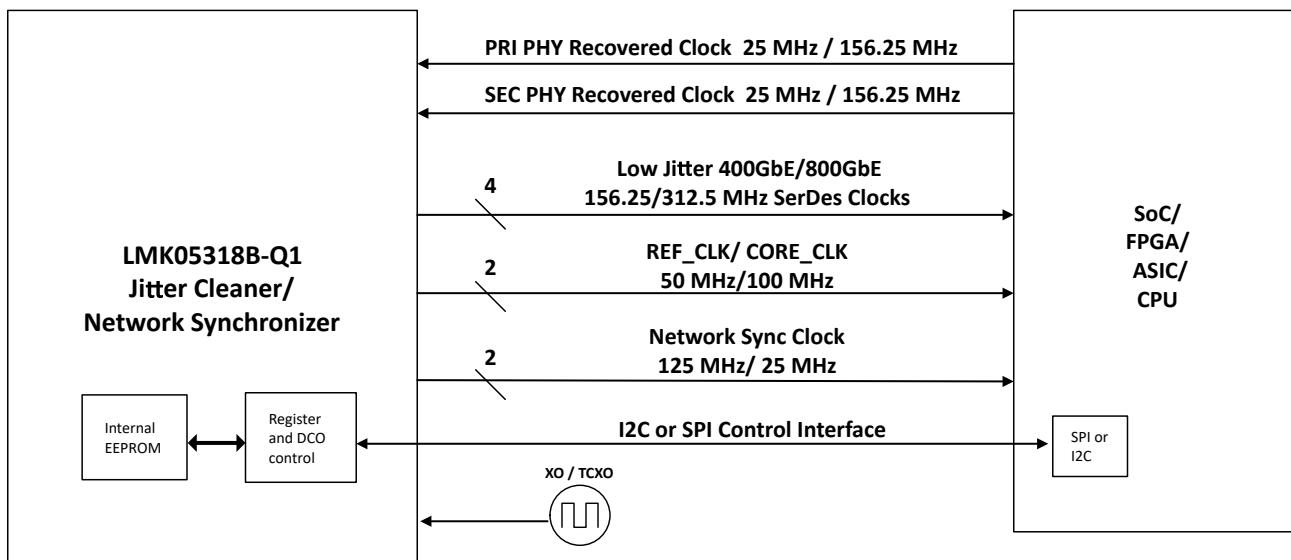

LMK05318B-Q1 は、イーサネットベースのネットワーキングアプリケーションの厳しい要件を満たすように設計された高性能ネットワークシンクロナイザおよびジッタクリーナです。

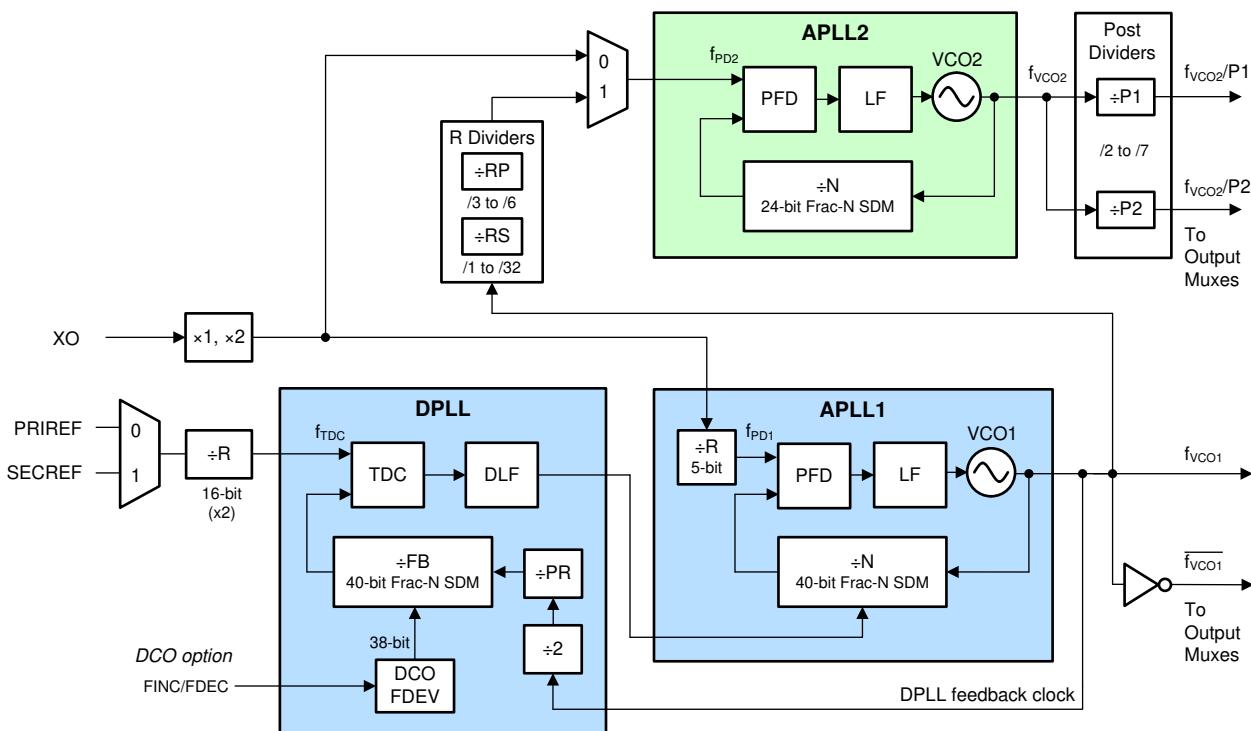

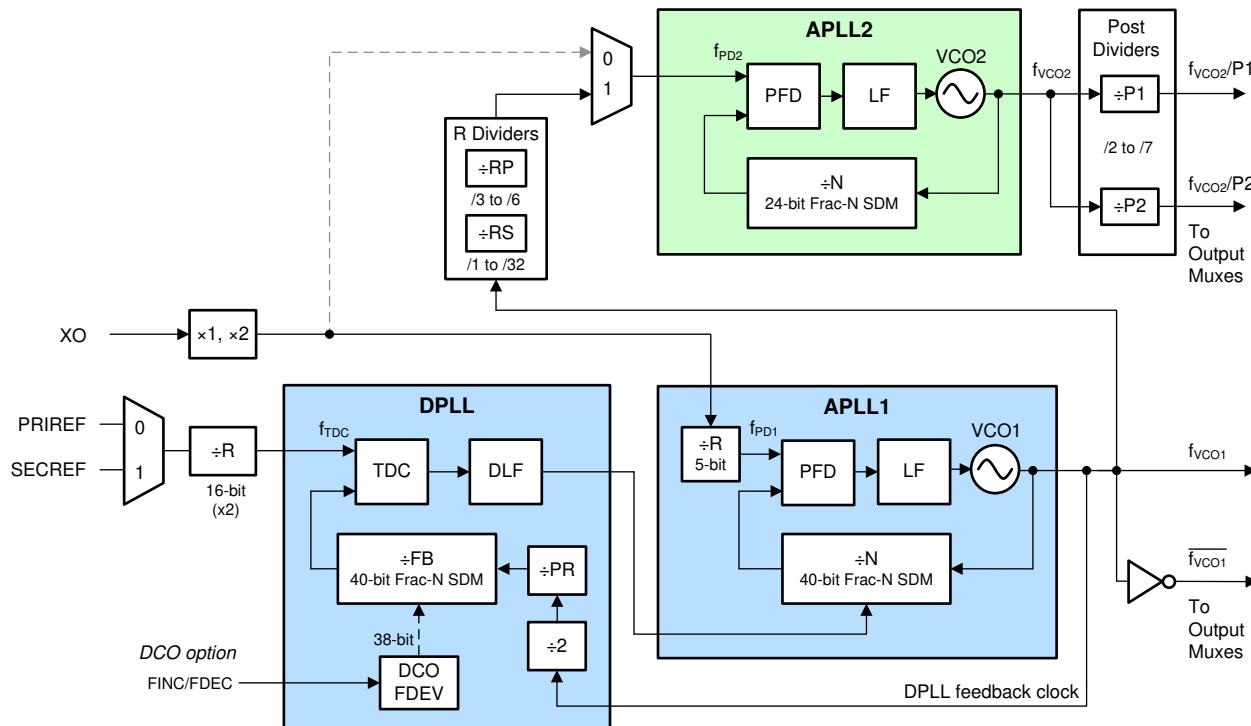

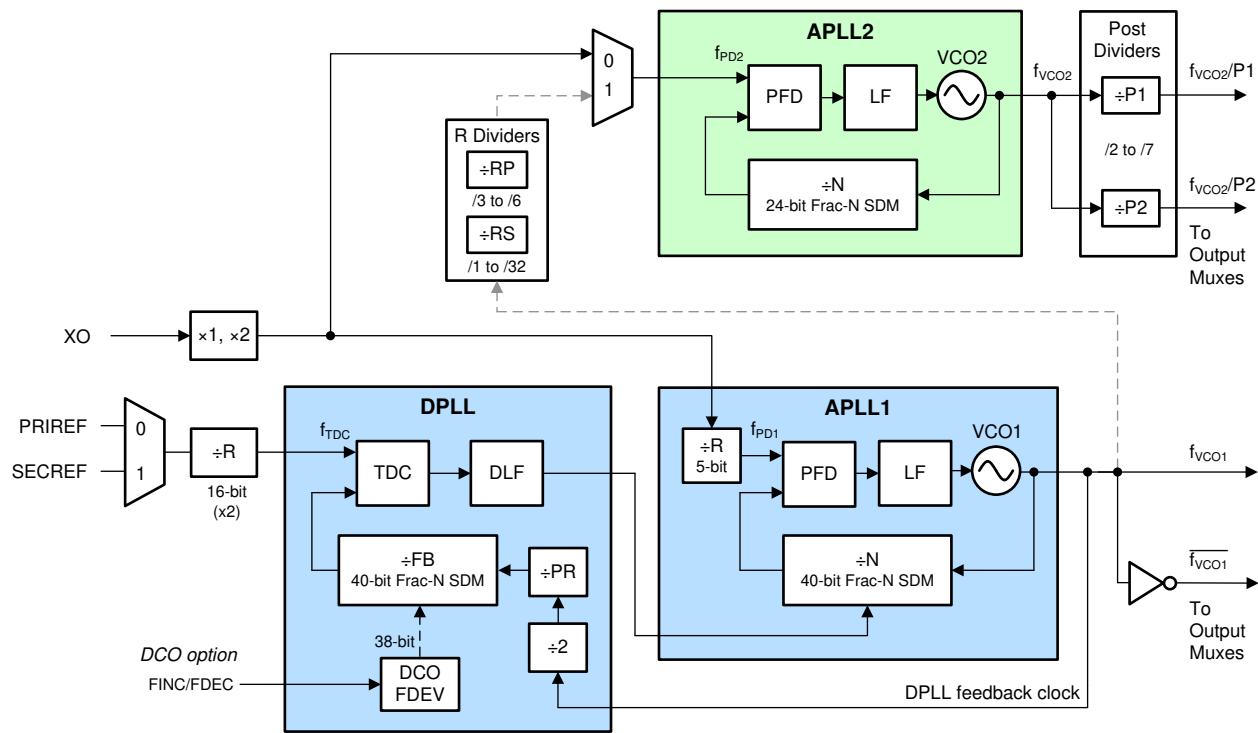

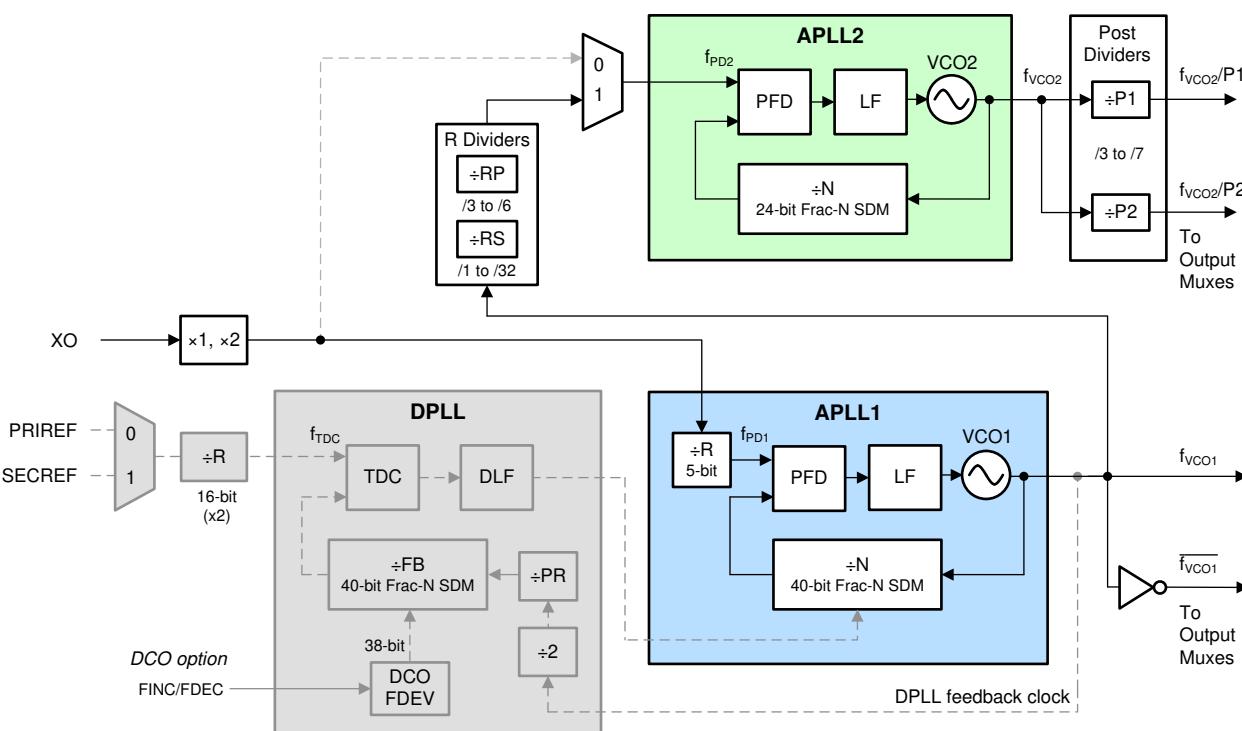

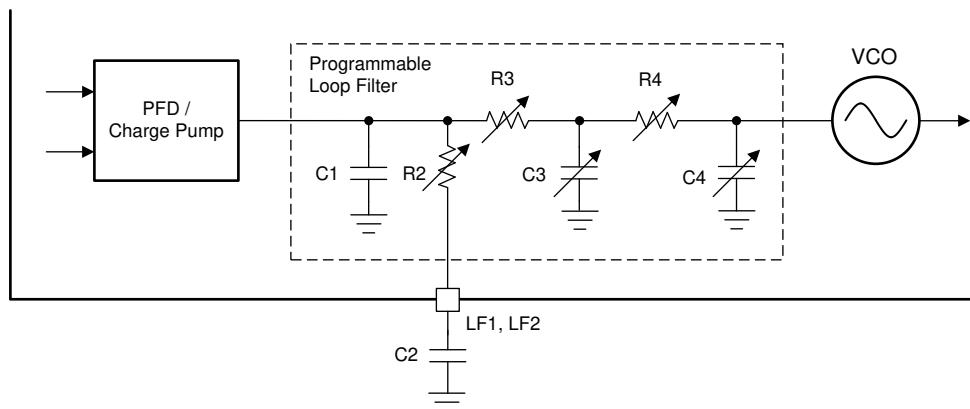

本デバイスは 1 つの DPLL と 2 つの APLL を内蔵しており、プログラマブルなループ帯域幅 (LBW) を用いることで、ヒットレススイッチングおよびジッタ低減を実現します。また、外付けのループフィルタコンデンサは 1 個のみとすることで、柔軟性と使いやすさを最大化しています。

APLL1 は、VCO1 に TI 独自のバルク音響波 (BAW) 技術を用いた超高性能 PLL を備えており、DPLL のリファレンス入力周波数やジッタ特性に依存することなく、12kHz ~ 20MHz の積分帯域で標準 50fs RMS ジッタの 312.5MHz 出力クロックを生成できます。APLL2 は、従来型の LC VCO を備えており、第 2 の周波数ドメインおよび / または同期ドメインのための選択肢を提供します。

内蔵 EEPROM は、起動時のカスタムシステム構成に使用できます。内蔵 LDO レギュレータは優れた電源ノイズ除去比 (PSNR) を提供し、電源供給ネットワークのコストと複雑さを低減します。

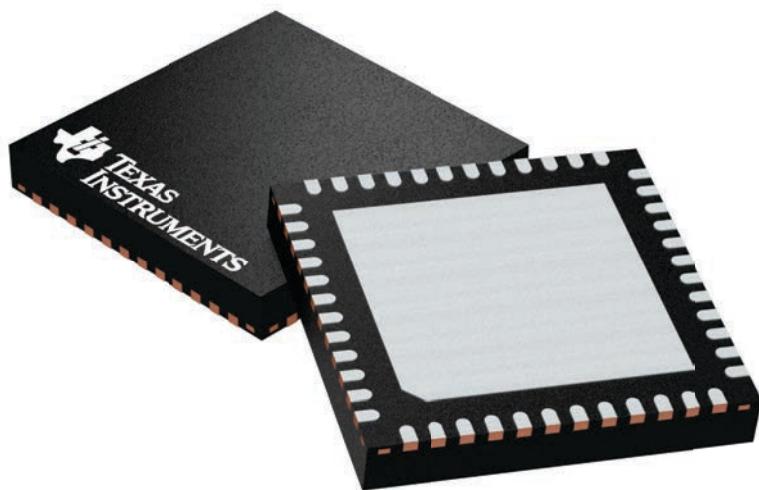

### パッケージ情報

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|--------------|----------------------|-------------------------|

| LMK05318B-Q1 | RGZ (QFN, 48)        | 7mm × 7mm               |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージサイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

代表的なシステムブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                  |           |                                     |    |

|----------------------------------|-----------|-------------------------------------|----|

| <b>1 特長</b>                      | <b>1</b>  | 8.3 機能説明.....                       | 30 |

| <b>2 アプリケーション</b>                | <b>1</b>  | 8.4 デバイスの機能モード.....                 | 57 |

| <b>3 説明</b>                      | <b>1</b>  | 8.5 プログラミング.....                    | 64 |

| <b>4 デバイスの比較</b>                 | <b>3</b>  | <b>9 アプリケーションと実装</b> .....          | 73 |

| <b>5 ピン構成および機能</b>               | <b>4</b>  | 9.1 アプリケーション情報.....                 | 73 |

| <b>6 仕様</b>                      | <b>8</b>  | 9.2 代表的なアプリケーション.....               | 76 |

| 6.1 絶対最大定格.....                  | 8         | 9.3 設計のベスト プラクティス.....              | 81 |

| 6.2 ESD 定格.....                  | 8         | 9.4 電源に関する推奨事項.....                 | 82 |

| 6.3 推奨動作条件.....                  | 8         | 9.5 レイアウト.....                      | 83 |

| 6.4 熱に関する情報:4層 JEDEC 標準 PCB..... | 9         | <b>10 デバイスおよびドキュメントのサポート</b> .....  | 87 |

| 6.5 熱に関する情報:10層カスタム PCB.....     | 9         | 10.1 デバイス サポート.....                 | 87 |

| 6.6 電気的特性.....                   | 9         | 10.2 ドキュメントのサポート.....               | 87 |

| 6.7 タイミング図.....                  | 17        | 10.3 ドキュメントの更新通知を受け取る方法.....        | 87 |

| 6.8 代表的特性.....                   | 19        | 10.4 サポート・リソース.....                 | 87 |

| <b>7 パラメータ測定情報</b> .....         | <b>22</b> | 10.5 商標.....                        | 87 |

| 7.1 出力クロックのテスト構成.....            | 22        | 10.6 静電気放電に関する注意事項.....             | 87 |

| <b>8 詳細説明</b> .....              | <b>24</b> | 10.7 用語集.....                       | 87 |

| 8.1 概要.....                      | 24        | <b>11 改訂履歴</b> .....                | 87 |

| 8.2 機能ブロック図.....                 | 25        | <b>12 メカニカル、パッケージ、および注文情報</b> ..... | 88 |

## 4 デバイスの比較

**表 4-1. デバイス比較表**

| 部品番号         | IN | OUT | DPLL | APLL | VCBO 周波数 [MHz] | LVC MOS 出力数量。 | 1PPS OUTPUT | 動作温度°C        |

|--------------|----|-----|------|------|----------------|---------------|-------------|---------------|

| LMK05318B-Q1 | 2  | 8   | 1    | 2    | 2500           | 4             | OUT7 のみ     | -40°C ~ 105°C |

| LMK05318B    | 2  | 8   | 1    | 2    | 2500           | 4             | OUT7 のみ     | -40°C ~ 85°C  |

| LMK5B12204   | 2  | 4   | 1    | 2    | 2500           | 2             | なし          | -40°C ~ 85°C  |

## 5 ピン構成および機能

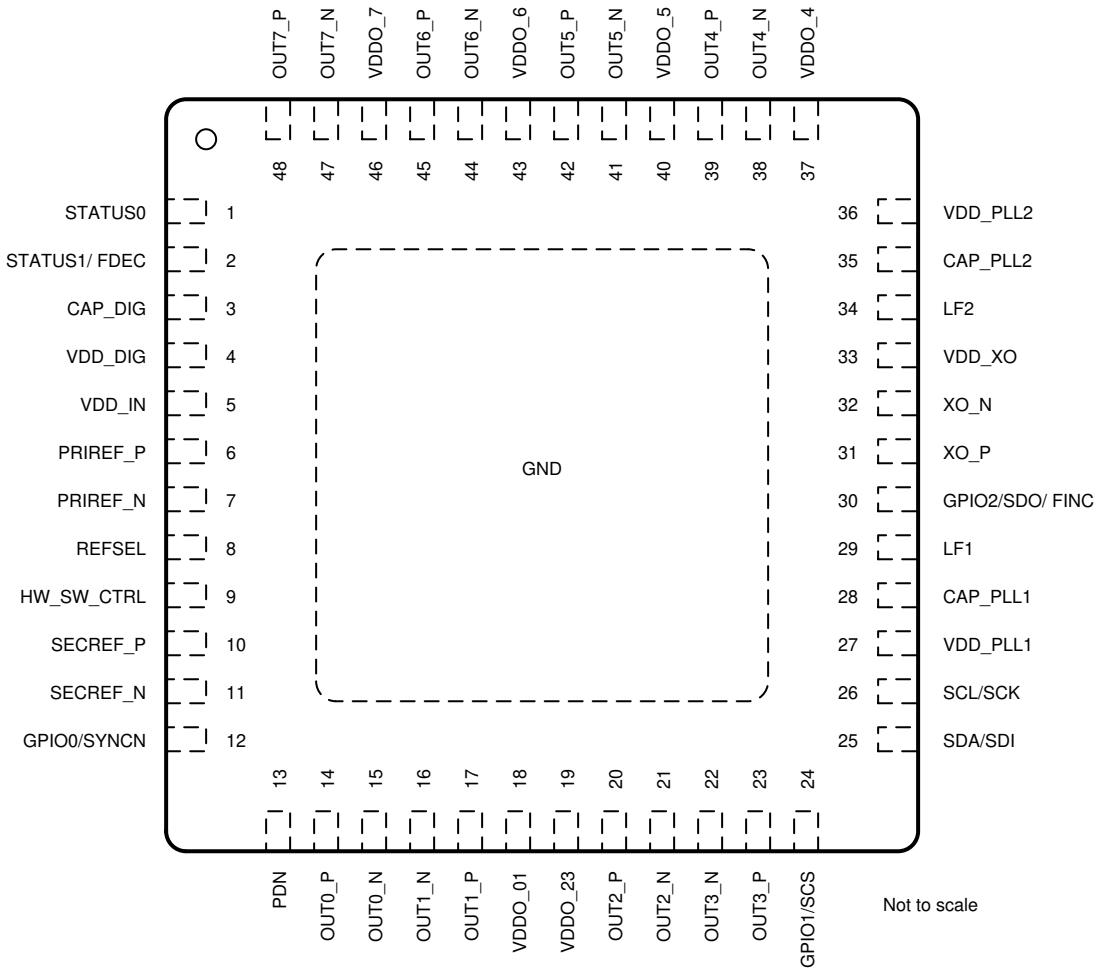

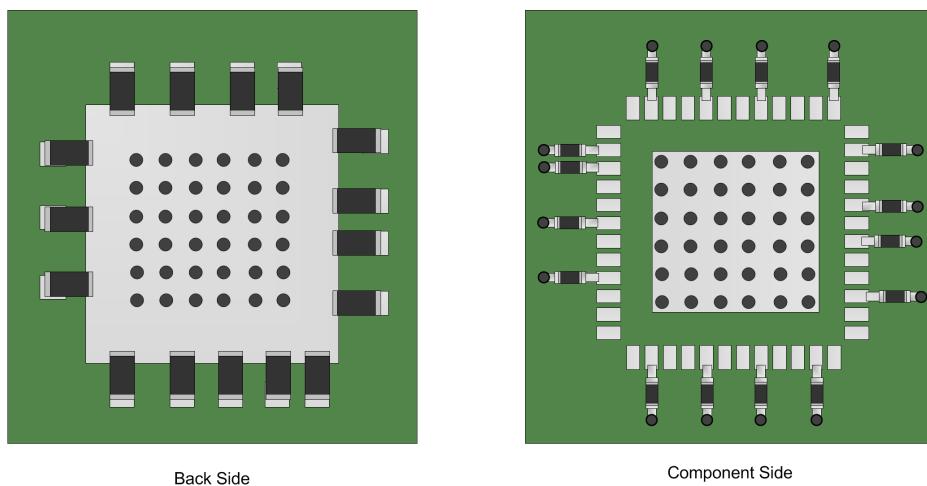

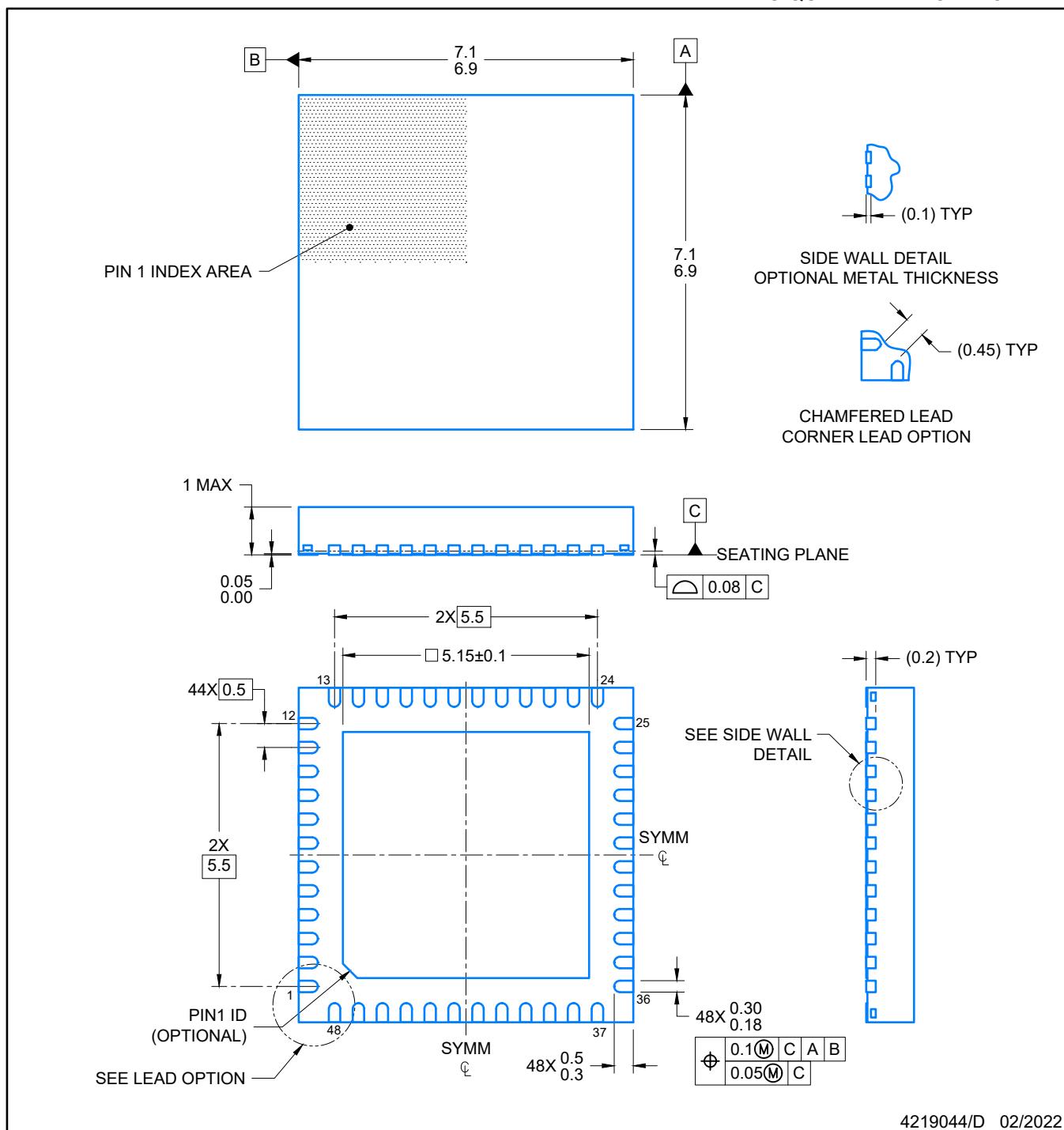

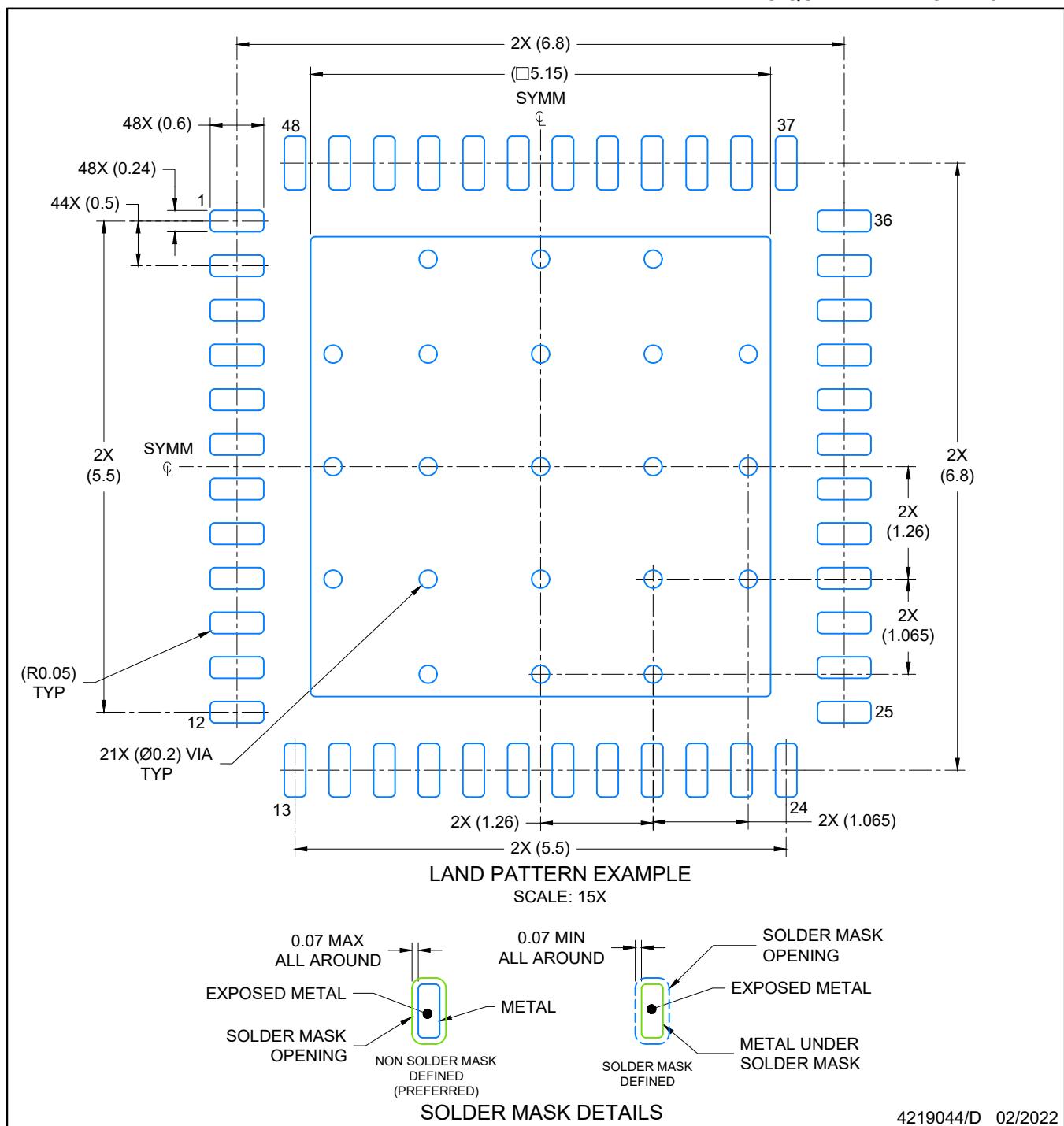

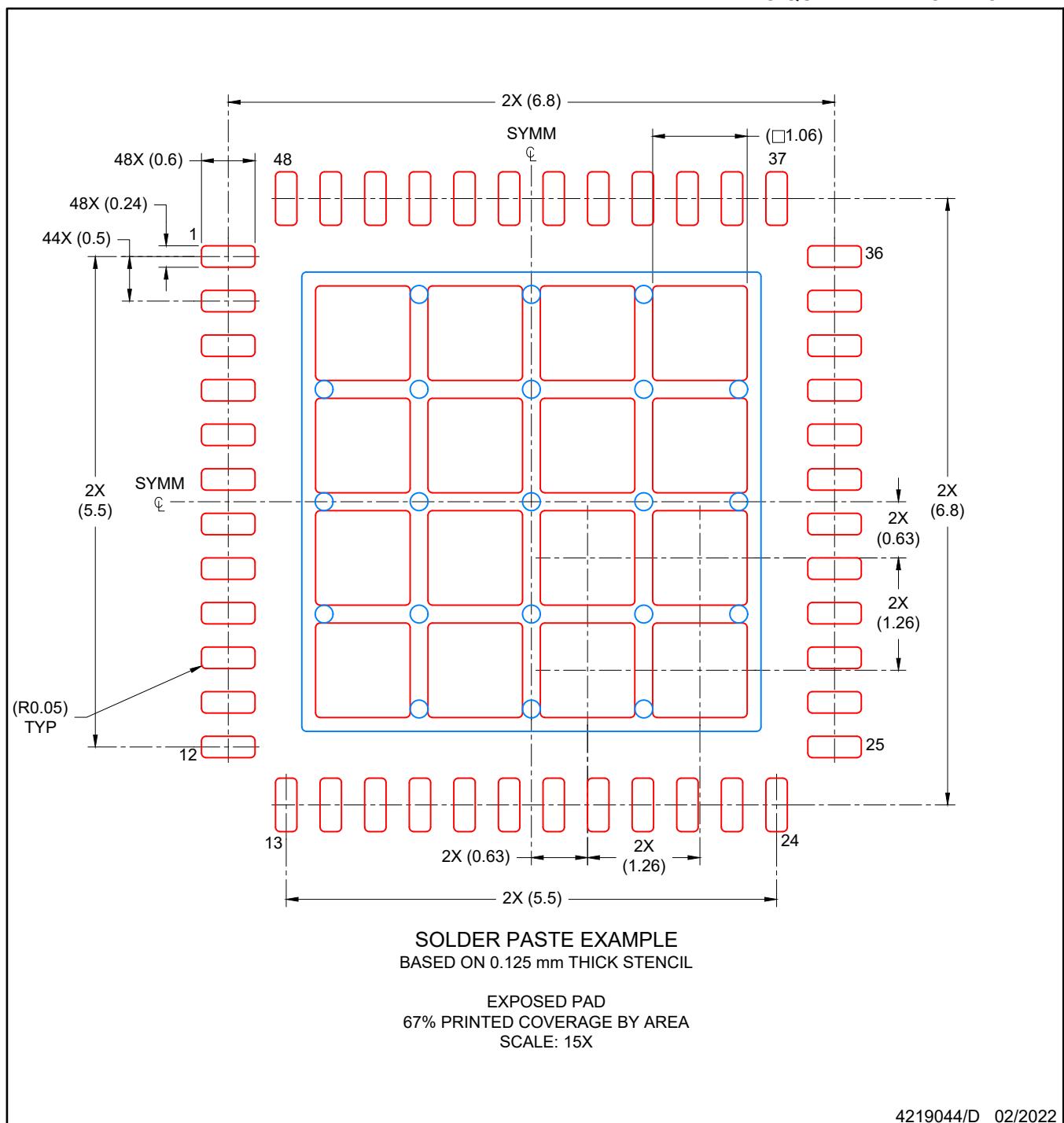

図 5-1. RGZ パッケージ 48 ピン VQFN 上面図

表 5-1. ピンの機能

| ピン       |     | タイプ <sup>(1)</sup> | 説明                                                                                                                               |

|----------|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号  |                    |                                                                                                                                  |

| 電源       |     |                    |                                                                                                                                  |

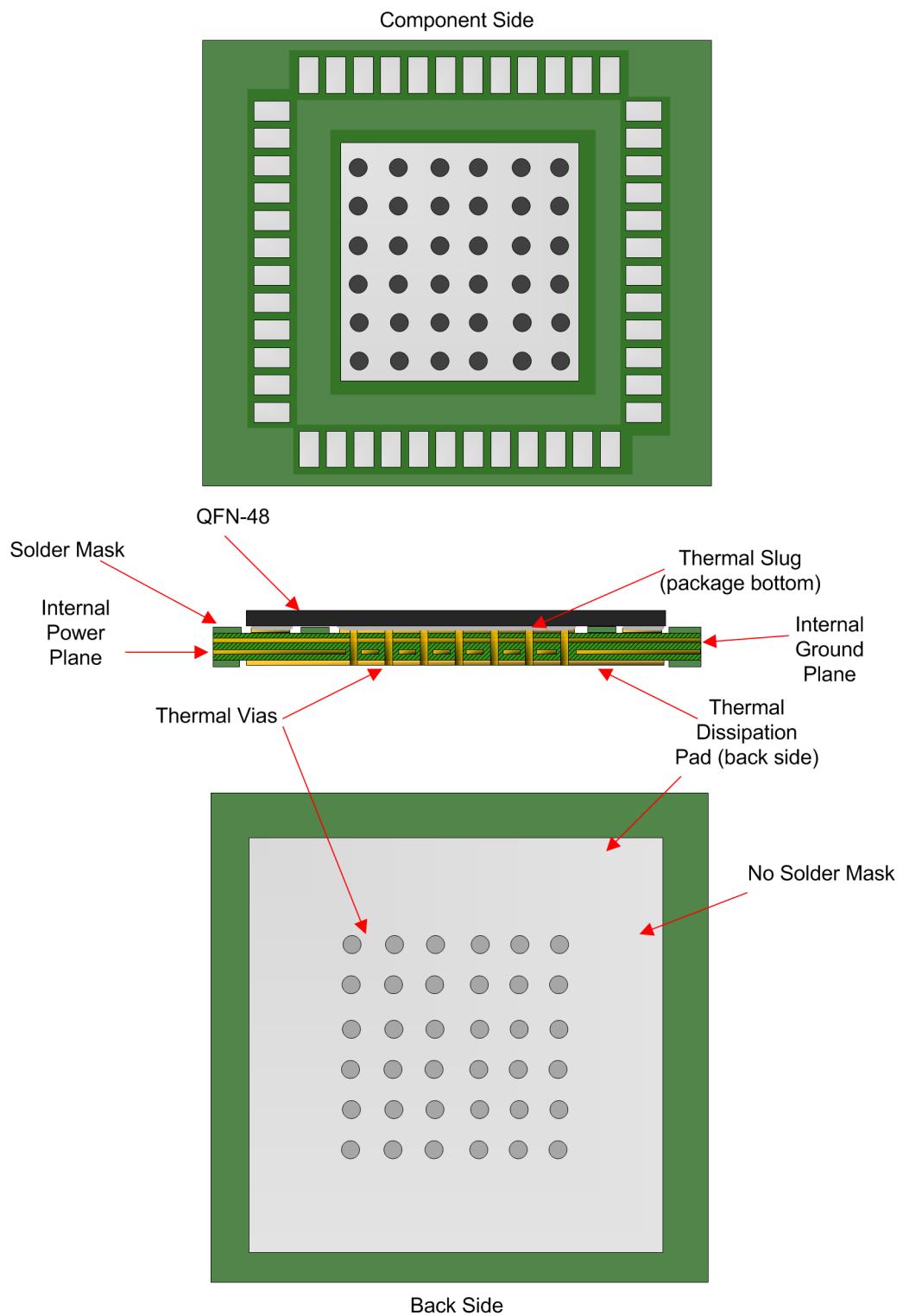

| GND      | PAD | G                  | グラウンド / サーマルパッド。<br>適切な電気的性能と熱性能を得るために、露出したパッドを PCB グラウンドに接続します。IC のグラウンド パッドを PCB のグラウンド層に接続するために、5×5 のビア パターンを使用することが推奨されています。 |

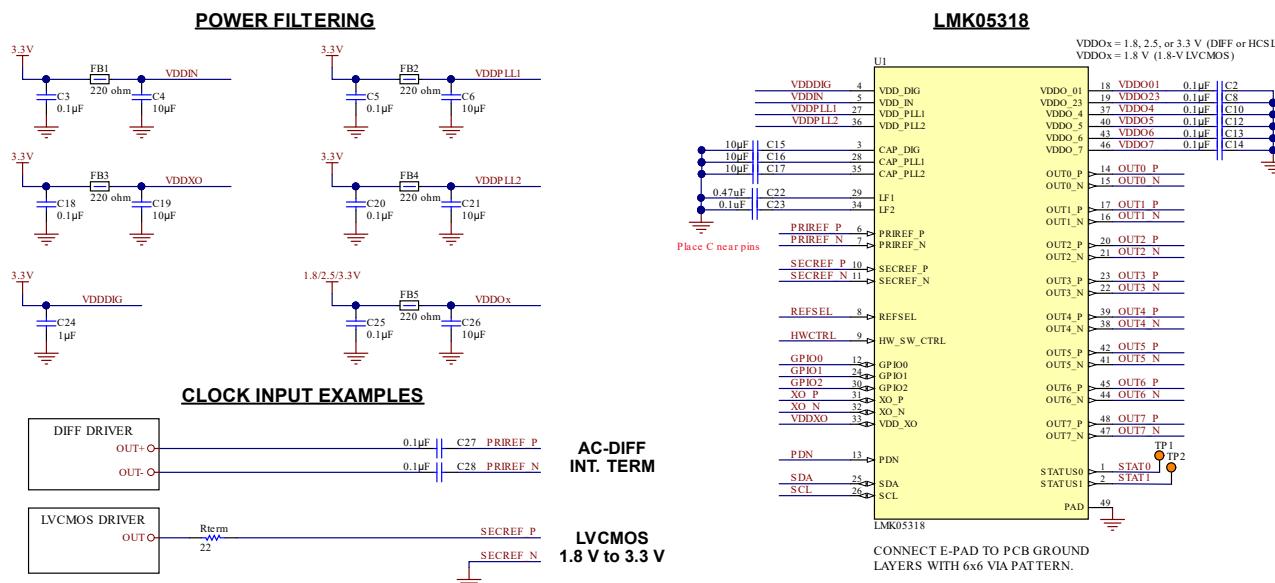

| VDD_IN   | 5   | P                  | プライマリ リファレンス (PRIREF) およびセカンダリ リファレンス (SECREF) 入力のコア電源 (3.3V)。<br>コンデンサをピンのできるだけ近くに配置します。推奨値は 0.1uF です。                          |

| VDD_XO   | 33  | P                  | XO 入力用のコア電源 (3.3V)。<br>コンデンサをピンのできるだけ近くに配置します。推奨値は 0.1uF です。                                                                     |

| VDD_PLL1 | 27  | P                  | PLL1、PLL2、デジタル ブロックのコア電源 (3.3V)。                                                                                                 |

| VDD_PLL2 | 36  | P                  | コンデンサは、できるだけピンの近くに配置します。推奨値は 0.1uF です。                                                                                           |

| VDD_DIG  | 4   | P                  |                                                                                                                                  |

**表 5-1. ピンの機能 (続き)**

| ピン       |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                   |

|----------|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号 |                    |                                                                                                                                                                                                                                                                                      |

| VDDO_01  | 18 | P                  | 出力クロック (OUT0~OUT7) 用の出力電源(1.8 V、2.5 V、または 3.3 V)。<br>コンデンサをピンのできるだけ近くに配置します。推奨値は 0.1 $\mu$ F です。対応する出力クロックを使用しない場合は、電源ピンをフローティング (接続なし) のままにできます。ピンの出力電源電圧レベルは、VDDO_x ピン間で混在させることも、同じにすることもできます。 <a href="#">電源の混在</a> を参照してください。                                                    |

| VDDO_23  | 19 | P                  |                                                                                                                                                                                                                                                                                      |

| VDDO_4   | 37 | P                  |                                                                                                                                                                                                                                                                                      |

| VDDO_5   | 40 | P                  |                                                                                                                                                                                                                                                                                      |

| VDDO_6   | 43 | P                  |                                                                                                                                                                                                                                                                                      |

| VDDO_7   | 46 | P                  |                                                                                                                                                                                                                                                                                      |

| コア ブロック  |    |                    |                                                                                                                                                                                                                                                                                      |

| LF1      | 29 | A                  | APLL1 用の外部ループ フィルタ コンデンサ。<br>各ピンに近くにコンデンサを配置します。推奨値は 0.47 $\mu$ F です (APLL LBW = 1.0kHz)。                                                                                                                                                                                            |

| LF2      | 34 | A                  | APLL2 用の外部ループ フィルタ コンデンサ。<br>各ピンに近くにコンデンサを配置します。推奨値は 0.1 $\mu$ F です (APLL LBW = 500kHz)。                                                                                                                                                                                             |

| CAP_PLL1 | 28 | A                  | APLL1 用の外部 LDO バイパス コンデンサ。コンデンサは、できるだけピンの近くに配置します。推奨値は 10 $\mu$ F です。                                                                                                                                                                                                                |

| CAP_PLL2 | 35 | A                  | APLL2 用の外部 LDO バイパス コンデンサ。コンデンサは、できるだけピンの近くに配置します。推奨値は 10 $\mu$ F です。                                                                                                                                                                                                                |

| CAP_DIG  | 3  | A                  | デジタル コア ロジック用外付け LDO バイパス コンデンサ。コンデンサは、できるだけピンの近くに配置します。推奨値は 10 $\mu$ F です。                                                                                                                                                                                                          |

| 入力ブロック   |    |                    |                                                                                                                                                                                                                                                                                      |

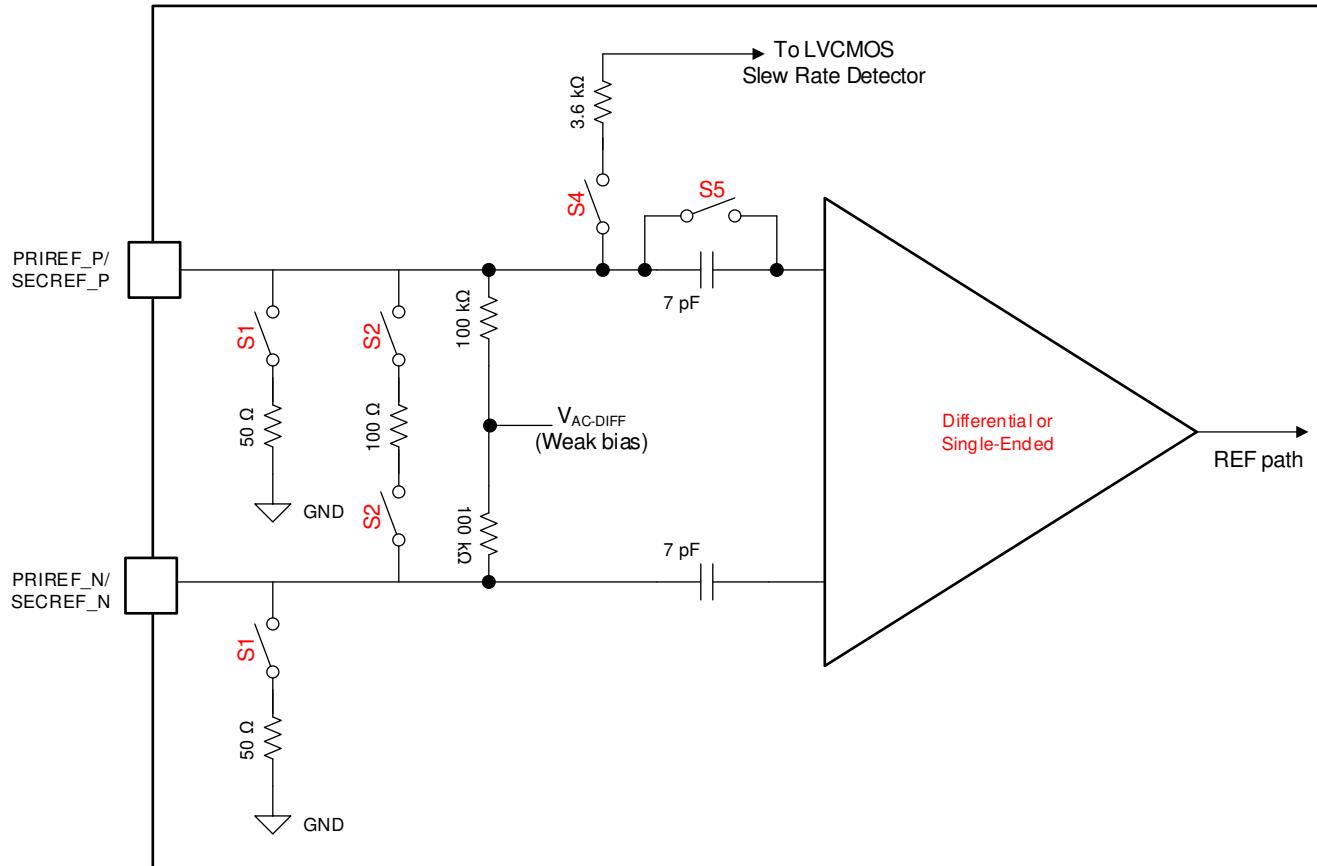

| PRIREF_P | 6  | I                  | DPLL プライマリおよびセカンダリ リファレンスクロック入力。                                                                                                                                                                                                                                                     |

| PRIREF_N | 7  | I                  | 各入力ペアは、DPLL 用リファレンスとして、差動入力およびシングル エンド入力の両方に対応しています。各入力ペアには内部終端を備えたプログラマブルな入力タイプがあり、AC 結合および DC 結合クロックの両方をサポートします。N 入力をグランドにプルダウンして、シングル エンドの LVCMOS クロックを P 入力に印加できます。未使用的入力ペアはフローティングのままにすることが可能。                                                                                  |

| SECREF_P | 10 | I                  | 低周波入力 (2kHz 未満) の場合、ノイズ耐性を向上させるために、内部 AC 結合コンデンサを無効にしてください。差動入力および LVCMOS 入力は、レシーバに対して DC 結合で接続できます。                                                                                                                                                                                 |

| SECREF_N | 11 | I                  | プログラマブル入力タイプについては、 <a href="#">リファレンス入力 (PRIREF_P/N と SECREF_P/N)</a> に詳述します。                                                                                                                                                                                                        |

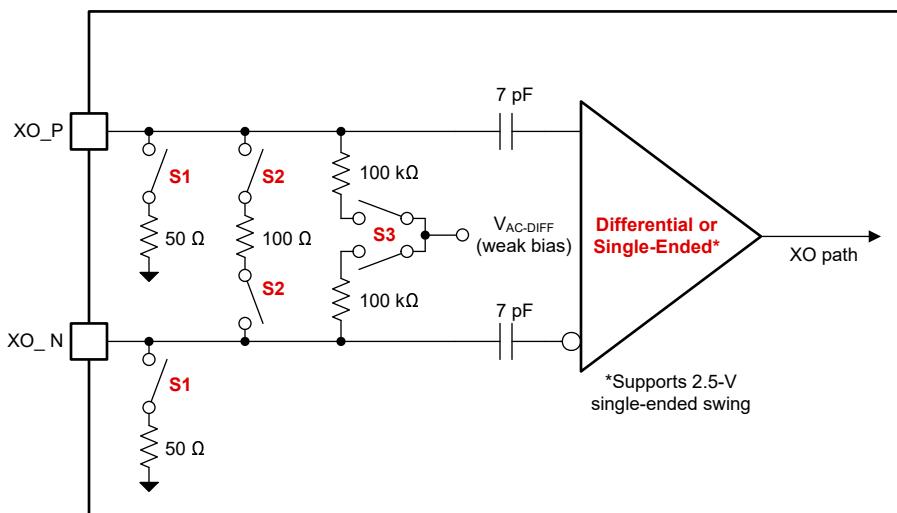

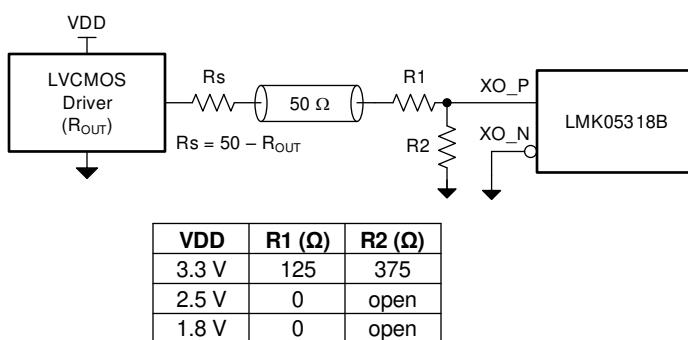

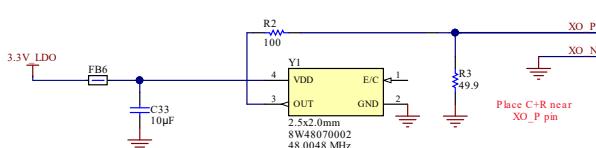

| XO_P     | 31 | I                  | XO/TCXO/OCXO 入力。                                                                                                                                                                                                                                                                     |

| XO_N     | 32 | I                  | この入力ペアは、APLL 用のリファレンスとして、低ジッタのローカル発信器からの差動クロック信号またはシングル エンドクロック信号を入力できます。この入力には内部終端を備えたプログラマブルな入力タイプがあり、AC 結合および DC 結合クロックの両方をサポートします。シングルエンドの LVCMOS クロック(最大 2.5 V)は、N 入力をグランドにプルダウンした状態で、P 入力に印加できます。低周波数の TCXO または OCXO を使用して、フリーラン / ホールドオーバー モード時にクロック出力周波数の精度と安定性を設定することができます。 |

|          |    |                    | DPLL がイネーブルなら、XO 周波数は VCO1 周波数と整数以外の関係を持つ必要があるため、APLL1 は分数モードで動作できます (DPLL を適切に動作させるために必要)。DPLL が無効化されている場合、XO の周波数は VCO1 の周波数に対して、整数比または非整数比のいずれの関係でも構いません。                                                                                                                         |

|          |    |                    | プログラマブルな入力タイプと周波数オプションについては、 <a href="#">発振器入力 (XO_P/N)</a> に詳細を示しています。                                                                                                                                                                                                              |

| 出力ブロック   |    |                    |                                                                                                                                                                                                                                                                                      |

| OUT0_P   | 14 | O                  | クロック出力 0 ~ 3 バンク。<br>プログラム可能なそれぞれの出力ドライバペアは、AC-LVDS、AC-CML、AC-LVPECL、HCSL をサポートできます。<br>未使用の差動出力は、有効なまま使用する場合は終端する必要があります、フローティングのままにする場合はレジスタで無効化する必要があります。<br>出力クロストークを最小限に抑えるため、PLL1 のクロックには OUT[0:3] バンクを使用することが推奨されます。                                                          |

| OUT0_N   | 15 | O                  |                                                                                                                                                                                                                                                                                      |

| OUT1_P   | 17 | O                  |                                                                                                                                                                                                                                                                                      |

| OUT1_N   | 16 | O                  |                                                                                                                                                                                                                                                                                      |

| OUT2_P   | 20 | O                  |                                                                                                                                                                                                                                                                                      |

| OUT2_N   | 21 | O                  |                                                                                                                                                                                                                                                                                      |

| OUT3_P   | 23 | O                  |                                                                                                                                                                                                                                                                                      |

| OUT3_N   | 22 | O                  |                                                                                                                                                                                                                                                                                      |

**表 5-1. ピンの機能 (続き)**

| ピン     |    | タイプ <sup>(1)</sup> | 説明 |

|--------|----|--------------------|----|

| 名称     | 番号 |                    |    |

| OUT4_P | 39 | O                  |    |

| OUT4_N | 38 | O                  |    |

| OUT5_P | 42 | O                  |    |

| OUT5_N | 41 | O                  |    |

| OUT6_P | 45 | O                  |    |

| OUT6_N | 44 | O                  |    |

| OUT7_P | 48 | O                  |    |

| OUT7_N | 47 | O                  |    |

クロック出力 4 ~ 7 パンク。

プログラム可能な出力ドライバペアは、AC-LVDS、AC-CML、AC-LVPECL、HCSL、1.8V の LVCMOS クロック (ペアごとに 1 または 2) をサポートしています。

未使用の差動出力は、有効なまま使用する場合は終端する必要があり、フローティングのままにする場合はレジスタで無効化する必要があります。

出力クロストークを最小限に抑えるため、PLL2 のクロックには OUT[4:7] パンクを使用することが推奨されます。PLL2 を使用しない場合、PLL2 からのクロスカッピングの影響を受けることなく、OUT[4:7] パンクを PLL1 クロックに使用できます。

**表 5-1. ピンの機能 (続き)**

| ピン                            |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                            | 番号 |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>ロジック制御 / ステータス (2) (3)</b> |    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

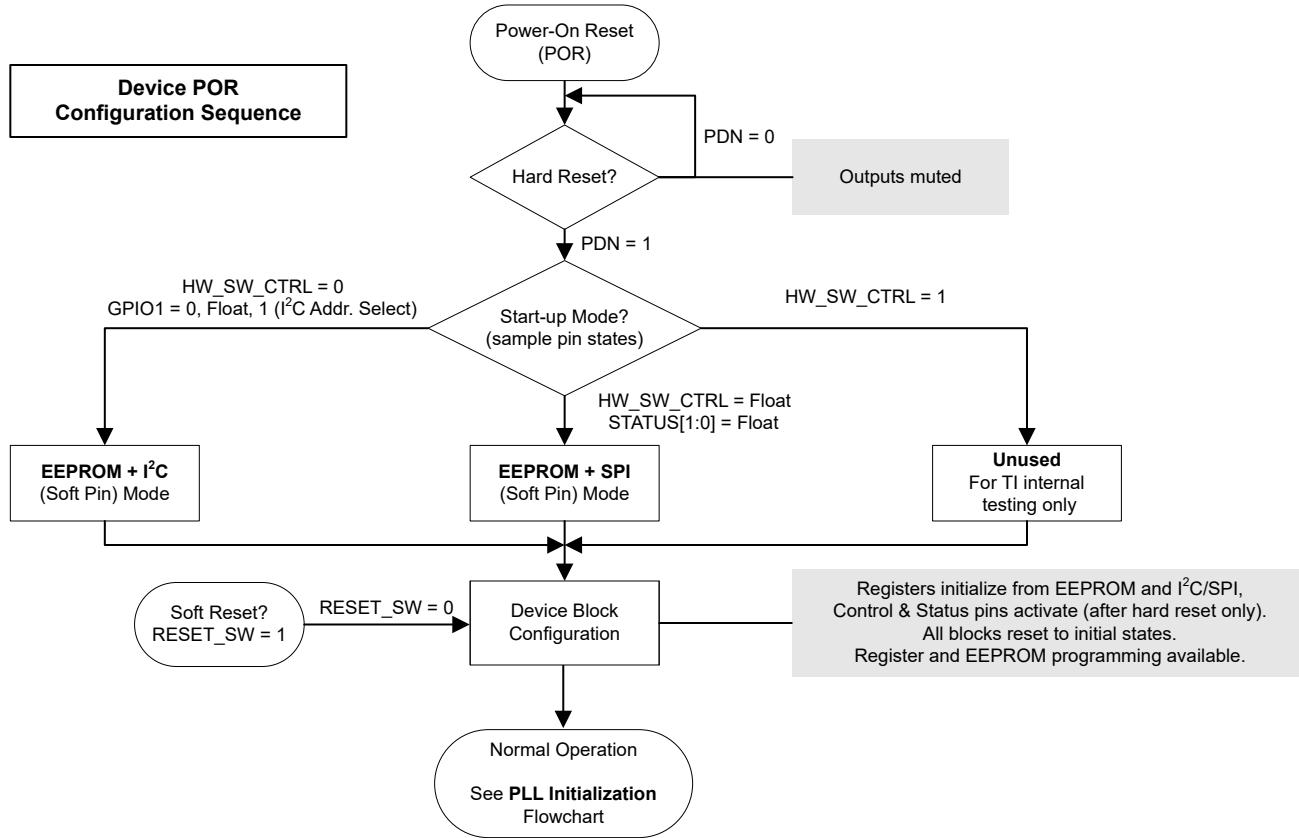

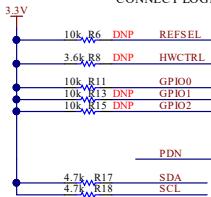

| HW_SW_CTRL                    | 9  | I                  | <b>デバイススタートアップ モード選択 (3 レベル、1.8V 互換)。</b><br>この入力はデバイスのスタートアップ モードを選択し、レジスタ、シリアル インターフェイス、およびロジック ピン機能の初期化に使用されるメモリ ページを決定します。入力レベルは、デバイスのパワーオンリセット (POR) 時にのみサンプリングされます。<br>スタートアップ モードの説明とロジック ピンの機能については、 <a href="#">表 8-10</a> を参照してください。                                                                                                                                                                                                                                                                                       |

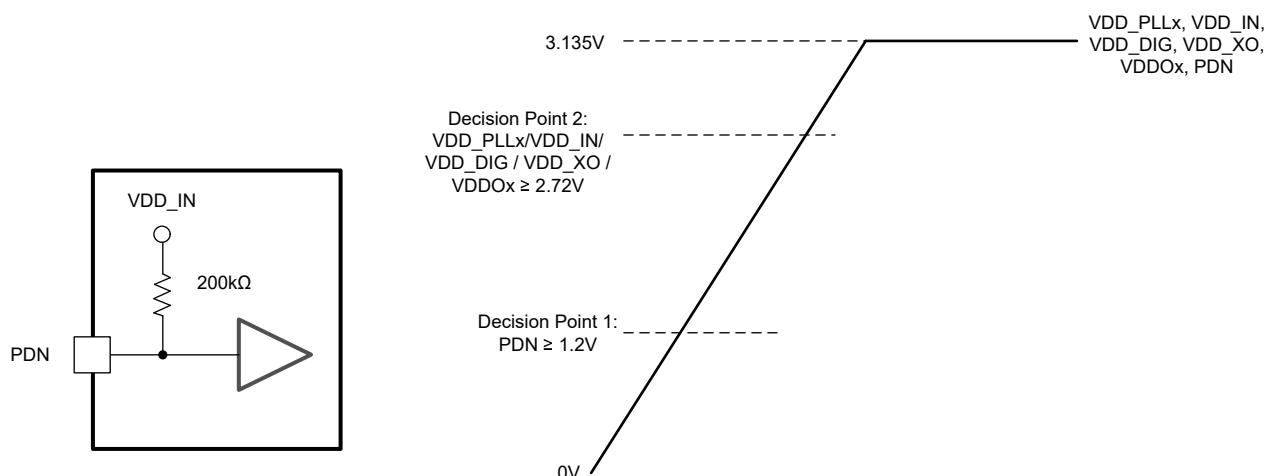

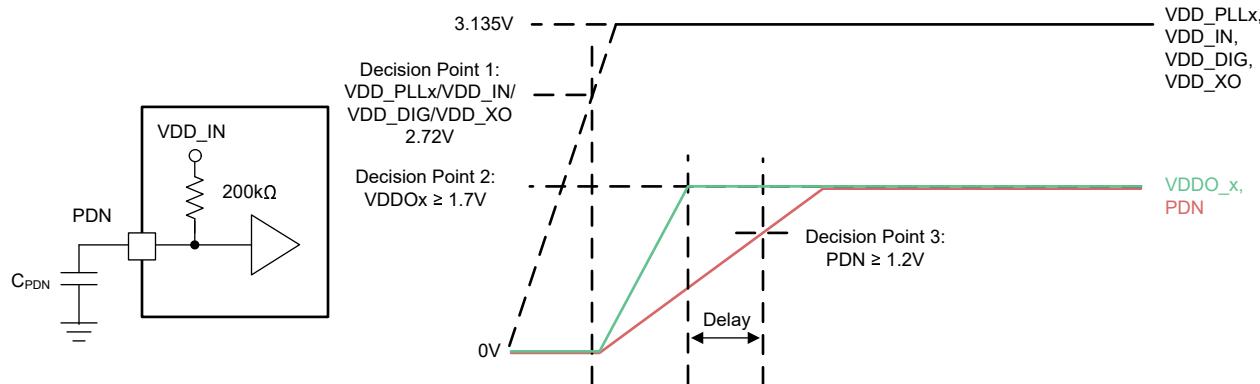

| PDN                           | 13 | I                  | <b>デバイスパワーダウン (アクティブ Low)。</b><br>PDN が Low に引き下げられると、デバイスはハードリセット状態となり、シリアル インターフェイスを含むすべてのブロックがパワーダウンします。PDN が High に引き上げられると、HW_SW_CTRL で選択されたデバイス モードに従ってデバイスが起動し、すべての内部回路が初期状態にリセットされたうえで通常動作を開始します。                                                                                                                                                                                                                                                                                                                            |

| SDA/SDI                       | 25 | I/O                | <b>I<sup>2</sup>C シリアルデータ I/O (SDA) または SPI シリアルデータ入力 (SDI)。</b> 表 8-10 を参照してください。<br>HW_SW_CTRL が 0 または 1 の場合、シリアルインターフェイスは I <sup>2</sup> C です。SDA および SCL ピン (オープンドレイン) には、外付けの I <sup>2</sup> C プルアップ抵抗が必要です。デフォルトの 7 ビットの I <sup>2</sup> C アドレスは 11001xxb で、MSB ビット (11001b) はオンチップ EEPROM から初期化され、 LSB ビット (xxb) はロジック入力ピンによって決定されます。HW_SW_CTRL が 0 の場合、LSB は POR 時の GPIO1 入力状態 (3 レベル) によって決定されます。HW_SW_CTRL が 1 の場合、LSB は 00b に固定されます。<br>HW_SW_CTRL がフローティングの場合、シリアルインターフェイスは SDI、SCK、SCS、SDO 各ピンを使用する SPI (4 線式、モード 0) です。 |

| SCL/SCK                       | 26 | I                  | <b>I<sup>2</sup>C シリアルクロック入力 (SCL) または SPI シリアルクロック入力 (SCK)。</b> 表 8-10 を参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GPIO0/SYNCN                   | 12 | I                  | <b>マルチファンクション入力または出力。</b><br><a href="#">表 8-10</a> を参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GPIO1/SCS                     | 24 | I                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GPIO2/SDO/FINC                | 30 | I/O                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| STATUS0                       | 1  | I/O                | <b>ステータス出力 0 および 1。</b><br>各出力は、プログラム可能なステータス信号選択、ドライバの種類 (3.3V LVC MOS またはオープンドレイン)、ステータス極性を備えています。オープンドレインには外付けプルアップ抵抗が必要です。使このピンをフローティングのままにします。                                                                                                                                                                                                                                                                                                                                                                                  |

| STATUS1/FDEC                  | 2  | I/O                | I <sup>2</sup> C モードでは、STATUS1/FDEC ピンは DCO モード制御入力ピンとして機能できます。表 8-10 を参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| REFSEL                        | 8  | I                  | <b>手動 DPLL リファレンスクロック入力選択 (3 レベル、1.8V 互換)。</b><br>REFSEL = 0 (PRIREF)、1 (SECREF)、または浮動小数点または V <sub>IM</sub> (自動選択)。この制御ピンは、レジスタのデフォルトまたはプログラムでイネーブルにする必要があります。使このピンをフローティングのままにします。                                                                                                                                                                                                                                                                                                                                                 |

- (1) G = グランド、P = 電源、I = 入力、O = 出力、I/O = 入出力、A = アナログ。

(2) 内部抵抗: PDN ピンには、V<sub>D</sub>INへの 200kΩ のプルアップ抵抗が内蔵されています。HW\_SW\_CTRL、GPIO、REFSEL、STATUS ピンには、PDN = 0 の場合は V<sub>IM</sub> (約 0.8V) への 150kΩ バイアス、または PDN = 1 の場合は 400kΩ ブルダウンがあります。

(3) 特に記述のない限り以下のとおり: ロジック入力は 2 レベル、1.8V 互換入力です。ロジック出力は 3.3V LVC MOS レベルです。

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                        |                      | 最小値  | 最大値      | 単位 |

|------------------------|----------------------|------|----------|----|

| VDD <sup>(2)</sup>     | コア電源電圧               | -0.3 | 3.6      | V  |

| VDDO <sup>(3)</sup>    | 出力電源電圧               | -0.3 | 3.6      | V  |

| V <sub>IN</sub>        | クロックおよびロジック入力の入力電圧範囲 | -0.3 | VDD+0.3  | V  |

| V <sub>OUT_LOGIC</sub> | ロジック出力の出力電圧範囲        | -0.3 | VDD+0.3  | V  |

| V <sub>OUT</sub>       | クロック出力の出力電圧範囲        | -0.3 | VDDO+0.3 | V  |

| T <sub>J</sub>         | 接合部温度                |      | 150      | °C |

| T <sub>stg</sub>       | 保管温度範囲               | -65  | 150      | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) VDD はすべてのコア電源ピンまたは電圧を指します。内部パワーオンリセット (POR) をトリガするために PDN を High に引き上げる前に、すべての VDD コア電源を投入しておく必要があります。

- (3) VDDO はすべての出力電源ピンまたは電圧を指します。VDDO\_X は、特定の出力チャネルの出力電源を表します。ここで、X はチャネル インデックスを表します。

### 6.2 ESD 定格

|                    |      | 値                                                                | 単位    |

|--------------------|------|------------------------------------------------------------------|-------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | ±2000 |

|                    |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | ±750  |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                       |                                           | 最小値   | 公称値 | 最大値   | 単位   |

|-----------------------|-------------------------------------------|-------|-----|-------|------|

| VDD <sup>(1)</sup>    | コア電源電圧                                    | 3.135 | 3.3 | 3.465 | V    |

| VDDO_X <sup>(2)</sup> | AC-LVDS、AC-CML、AC-LVPECL、HCSL ドライバの出力電源電圧 | 1.71  | 1.8 | 1.89  | V    |

|                       |                                           | 2.375 | 2.5 | 2.625 | V    |

|                       |                                           | 3.135 | 3.3 | 3.465 | V    |

|                       |                                           | 1.71  | 1.8 | 1.89  | V    |

| V <sub>IN</sub>       | クロックおよびロジック入力の入力電圧範囲                      | 0     |     | 3.465 | V    |

| T <sub>A</sub>        | 周囲温度または動作温度                               | -40   |     | 105   | °C   |

| T <sub>J</sub>        | 接合部温度                                     |       |     | 125   | °C   |

| t <sub>VDD</sub>      | 電源ランプ時間 <sup>(4)</sup>                    | 0.01  |     | 100   | ms   |

| n <sub>EEcyc</sub>    | EEPROM プログラミング サイクル <sup>(5)</sup>        |       |     | 100   | サイクル |

- (1) VDD はすべてのコア電源ピンまたは電圧を指します。内部パワーオンリセット (POR) が発生する前に、すべての VDD コア電源を投入しておく必要があります。

- (2) VDDO はすべての出力電源ピンまたは電圧を指します。VDDO\_X は、特定の出力チャネルの出力電源を表します。ここで、X はチャネル インデックスを表します。

- (3) LVC MOS ドライバは、VDDO\_X が 1.8 V ±5% の場合にフル レール ツー レールの振幅をサポートします。VDDO\_X が 2.5V または 3.3V の場合、出力チャネル内蔵の LDO レギュレータのドロップアウト電圧の影響により、LVC MOS ドライバは正側レールまで完全にはスイングしません。

- (4) 内部パワーオンリセットが適切に行われるために、VDD が 2.7V を超えて単調に上昇するのにかかる時間。より遅い、または単調ではない VDD ランプの場合は、VDD 電圧が有効になるまで PDN を低く維持します。

- (5)  $n_{EEcyc}$  は、顧客側のプログラミングに許可される最大 EEPROM プログラム サイクルを指定します。工場でプログラムされたサイクルの初期カウントは製造テストのためゼロではありませんが、工場でプログラムされたサイクルは  $n_{EEcyc}$  制限から除外されます。EEPROM プログラム サイクルの合計数は、8 ビットの NVM カウントステータスレジスタ (NVMCNT) から読み取ることができます。このレジスタは、プログラミング サイクルが成功するたびに自動的に 1 ずつインクリメントされます。TI は、顧客が  $n_{EEcyc}$  制限を超えた場合、EEPROM の耐久性を保証しません。

## 6.4 熱に関する情報：4 層 JEDEC 標準 PCB

| 熱評価基準 <sup>(1) (2) (3)</sup> |                     | LMK05318B -Q1 |      | 単位   |  |

|------------------------------|---------------------|---------------|------|------|--|

|                              |                     | RGZ (VQFN)    |      |      |  |

|                              |                     | 48 ピン         |      |      |  |

| R <sub>θJA</sub>             | 接合部から周囲への熱抵抗        |               | 23.3 | °C/W |  |

| R <sub>θJC(top)</sub>        | 接合部からケース (上面) への熱抵抗 |               | 13.2 | °C/W |  |

| R <sub>θJB</sub>             | 接合部から基板への熱抵抗        |               | 7.4  | °C/W |  |

| R <sub>θJC(bot)</sub>        | 接合部からケース (底面) への熱抵抗 |               | 1.4  | °C/W |  |

| Ψ <sub>JT</sub>              | 接合部から上面への特性パラメータ    |               | 0.2  | °C/W |  |

| Ψ <sub>JB</sub>              | 接合部から基板への特性パラメータ    |               | 7.3  | °C/W |  |

- (1) 従来および最新の熱評価基準の詳細については TI のアプリケーション ノート、[半導体および IC パッケージの熱評価基準](#) を参照してください。

- (2) 熱特性情報は、25 本のサーマルビア ( $5 \times 5$  配列、穴径 0.3 mm) を備えた 4 層の JEDEC 標準基板に基づいています。

- (3)  $\Psi_{JB}$  を使用すると、システム設計者はファインゲージ熱電対を使用してボード温度 ( $T_{PCB}$ ) を測定し、デバイスの接合部温度  $T_J = T_{PCB} + (\Psi_{JB} \times$  電力) を逆計算できます。 $\Psi_{JB}$  の測定は JESD51-6 で定義されています。

## 6.5 熱に関する情報：10 層カスタム PCB

| 熱評価基準 <sup>(1) (2) (3)</sup> |                  | LMK05318B -Q1 |     | 単位   |  |

|------------------------------|------------------|---------------|-----|------|--|

|                              |                  | RGZ (VQFN)    |     |      |  |

|                              |                  | 48 ピン         |     |      |  |

| R <sub>θJA</sub>             | 接合部から周囲への熱抵抗     |               | 9.1 | °C/W |  |

| R <sub>θJB</sub>             | 接合部から基板への熱抵抗     |               | 4.4 | °C/W |  |

| Ψ <sub>JT</sub>              | 接合部から上面への特性パラメータ |               | 0.2 | °C/W |  |

| Ψ <sub>JB</sub>              | 接合部から基板への特性パラメータ |               | 4.4 | °C/W |  |

- (1) 従来および最新の熱評価基準の詳細については TI のアプリケーション ノート、[半導体および IC パッケージの熱評価基準](#) を参照してください。

- (2) 熱特性情報は、25 本のサーマルビア ( $5 \times 5$  配列、穴径 0.3 mm) を備えた、10 層・200 mm × 250 mm × 1.6 mm の基板に基づいています。

- (3)  $\Psi_{JB}$  を使用すると、システム設計者はファインゲージ熱電対を使用してボード温度 ( $T_{PCB}$ ) を測定し、デバイスの接合部温度  $T_J = T_{PCB} + (\Psi_{JB} \times$  電力) を逆計算できます。 $\Psi_{JB}$  の測定は JESD51-6 で定義されています。

## 6.6 電気的特性

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ       | テスト条件             | 最小値                   | 標準値  | 最大値 | 単位 |

|-------------|-------------------|-----------------------|------|-----|----|

| <b>電源特性</b> |                   |                       |      |     |    |

| IDD_DIG     | コア消費電流 (VDD_DIG)  |                       | 21   |     | mA |

| IDD_IN      | コア消費電流 (VDD_IN)   |                       | 43   |     | mA |

| IDD_PLL1    | コア消費電流 (VDD_PLL1) | DPLL および APLL1 はイネーブル | 110  |     | mA |

| IDD_XO      | コア消費電流 (VDD_XO)   |                       | 20   |     | mA |

| IDD_PLL2    | コア消費電流 (VDD_PLL2) | APLL2 無効              | 18.5 |     | mA |

|             |                   | APLL2 イネーブル           | 120  |     | mA |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ                             |                                          | テスト条件                                             | 最小値                  | 標準値  | 最大値     | 単位   |

|-----------------------------------|------------------------------------------|---------------------------------------------------|----------------------|------|---------|------|

| IDDO_X                            | チャネルごとの出力消費電流 <sup>(3)</sup><br>(VDDO_X) | 出力 mux とディバイダは有効、ドライバは除外<br>ディバイダ値 = 2~6          |                      | 65   |         | mA   |

|                                   |                                          | 出力 mux とディバイダは有効。ドライバは除外<br>ディバイダ値 > 6            |                      | 70   |         | mA   |

|                                   |                                          | AC-LVDS                                           |                      | 11   |         | mA   |

|                                   |                                          | AC-CML                                            |                      | 16   |         | mA   |

|                                   |                                          | AC-LVPECL                                         |                      | 18   |         | mA   |

|                                   |                                          | HCSL、GND への 50 Ω 負荷                               |                      | 25   |         | mA   |

|                                   |                                          | 1.8V LVC MOS (x2)、100MHz                          |                      | 4.7  |         | mA   |

| IDD_PDN                           | 合計消費電流 (すべての VDD および VDDO ピン、3.3V)       | デバイスの電源オフ (PDN ピンを Low に保持)                       |                      | 56   | 75      | mA   |

| <b>XO 入力特性 (XO)</b>               |                                          |                                                   |                      |      |         |      |

| f <sub>IN</sub>                   | 入力周波数範囲                                  |                                                   | 10                   | 100  |         | MHz  |

| V <sub>IN-SE</sub>                | シングルエンド入力電圧スイング                          | シングル エンド入力、内部 AC カップリング                           | 0.4                  | 2.6  |         | Vpp  |

| V <sub>IN-DIFF</sub>              | 差動入力のピークツーピーク電圧スイング <sup>(16)</sup>      | 差動入力                                              | 0.4                  | 2    |         | Vpp  |

| V <sub>ID</sub>                   | 差動入力電圧スイング <sup>(12)</sup>               | 差動入力                                              | 0.2                  | 1    |         | V    |

| dV/dt                             | 入力スルーレート <sup>(14)</sup>                 |                                                   | 0.2                  | 0.5  |         | V/ns |

| IDC                               | 入力デューティサイクル                              |                                                   | 40                   | 60   |         | %    |

| I <sub>IN</sub>                   | 入力リーケージ                                  | 50Ω および 100Ω の内部終端は無効                             | -350                 | 350  |         | μA   |

| <b>リファレンス入力特性 (PRIREF、SECREF)</b> |                                          |                                                   |                      |      |         |      |

| f <sub>IN</sub>                   | 入力周波数範囲                                  | 差動入力 <sup>(4)</sup>                               | 5                    | 800  |         | MHz  |

|                                   |                                          | LVC MOS 入力                                        | 1E-6 <sup>(16)</sup> | 250  |         | MHz  |

| V <sub>IH</sub>                   | 入力 High 電圧                               | DC 結合入力                                           | 1.8                  |      |         | V    |

| V <sub>IL</sub>                   | 入力 Low 電圧                                | DC 結合入力                                           |                      | 0.6  |         | V    |

| V <sub>IN-SE</sub>                | シングルエンド入力電圧スイング                          | AC 結合入力                                           | 0.4                  | 2.6  |         | Vpp  |

| V <sub>IN-DIFF</sub>              | 差動入力ピークツーピーク電圧スイング <sup>(12)</sup>       | 差動入力、V <sub>HYST</sub> = 50mV                     | 0.4                  | 2    |         | Vpp  |

|                                   |                                          | 差動入力、V <sub>HYST</sub> = 200mV                    | 0.7                  | 2    |         | Vpp  |

| V <sub>ID</sub>                   | 差動入力電圧スイング <sup>(12)</sup>               | 差動入力、V <sub>HYST</sub> = 50mV                     | 0.2                  | 1    |         | V    |

|                                   |                                          | 差動入力、V <sub>HYST</sub> = 200mV                    | 0.35                 | 1    |         | V    |

| dV/dt                             | 入力スルーレート <sup>(14)</sup>                 |                                                   | 0.2                  | 0.5  |         | V/ns |

| I <sub>IN</sub>                   | 入力リーケージ                                  | 50Ω および 100Ω の内部終端は無効                             | -350                 | 350  |         | μA   |

| <b>VCO の特性</b>                    |                                          |                                                   |                      |      |         |      |

| f <sub>VCO1</sub>                 | VCO1 周波数範囲                               |                                                   | 2499.75              | 2500 | 2500.25 | MHz  |

| f <sub>VCO2</sub>                 | VCO2 周波数範囲                               |                                                   | 5500                 |      | 6250    | MHz  |

| ΔT <sub>CLL</sub>                 | 連続ロックで許容される温度ドリフト                        | ロック用にプログラムした後は、連続したロック状態を維持するため、出力設定を変更することはできません |                      | 125  |         | °C   |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ                      |                                   | テスト条件                                                                                                            | 最小値  | 標準値               | 最大値 | 単位     |

|----------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------|------|-------------------|-----|--------|

| <b>APLL の特性</b>            |                                   |                                                                                                                  |      |                   |     |        |

| f <sub>PD1</sub>           | APLL1 位相検出器周波数                    |                                                                                                                  | 1    | 100               | MHz |        |

| f <sub>PD2</sub>           | APLL2 位相検出器周波数                    |                                                                                                                  | 12   | 150               | MHz |        |

| t <sub>APLL1-LOCK</sub>    | APLL1 ロック時間 <sup>(13)</sup>       | ソフトリセットまたはハードリセットと APPLL1 出力が $\pm 25\text{ppm}$ $f_{XO} = 48\text{MHz}$ 以内、 $f_{PD1} = f_{XO}/2$ 以内の時間          | 1.0  |                   | ms  |        |

| t <sub>APLL2-LOCK</sub>    | APLL2 ロック時間 <sup>(13)</sup>       | ソフトリセットまたはハードリセットと APPLL2 出力が $\pm 25\text{ppm}$ 以内に安定するまでの時間、 $f_{XO} = 48\text{MHz}$ 、 $f_{PD2} = f_{XO}/2$    | 2.5  |                   | ms  |        |

|                            |                                   | ソフトリセットまたはハードリセットと APPLL2 出力が $\pm 25\text{ppm}$ 以内に安定するまでの時間、 $f_{XO} = 48\text{MHz}$ 、 $f_{PD2} = f_{VCO1}/18$ | 2.5  |                   | ms  |        |

| <b>AC-LVDS 出力特性 (OUTx)</b> |                                   |                                                                                                                  |      |                   |     |        |

| f <sub>OUT</sub>           | 出力周波数 <sup>(5)</sup>              |                                                                                                                  |      | 1250              | MHz |        |

| V <sub>OD</sub>            | 出力電圧スイング ( $V_{OH} - V_{OL}$ )    | 25MHz $\leq f_{OUT} \leq 800\text{MHz}$ (156.25MHz の標準値)                                                         | 250  | 390               | 450 | mV     |

|                            |                                   | $f_{OUT} = 50\text{MHz}$                                                                                         | 285  | 400               | 450 | mV     |

|                            |                                   | 100MHz $\leq f_{OUT} \leq 200\text{MHz}$                                                                         | 275  | 390               | 450 | mV     |

|                            |                                   | $f_{OUT} = 312.5\text{MHz}$                                                                                      | 270  | 385               | 450 | mV     |

|                            |                                   | $f_{OUT} = 625\text{MHz}$                                                                                        | 250  | 310               | 450 | mV     |

|                            |                                   | $f_{OUT} = 1250\text{MHz}$                                                                                       | 280  |                   |     | mV     |

| V <sub>OUT-DIFF</sub>      | 差動出力電圧スイング、ピーク ツー ピーク             |                                                                                                                  |      | $2 \times V_{OD}$ |     | Vpp    |

| V <sub>OS</sub>            | 出力同相モード                           |                                                                                                                  | 100  | 430               |     | mV     |

| t <sub>SK</sub>            | 出力間スキュー                           | 同じポスト デバイダ、出力分周値、出力タイプ                                                                                           |      | 100               |     | ps     |

| t <sub>R/f</sub>           | 出力立ち上がり / 立ち下がり時間 <sup>(13)</sup> | 20% ~ 80%、< 300MHz                                                                                               | 225  | 350               |     | ps     |

|                            |                                   | 中心点の周囲 $\pm 100\text{mV}$ 、300MHz $\leq f_{OUT} \leq 800\text{MHz}$                                              | 85   | 250               |     | ps     |

| PN <sub>FLOOR</sub>        | 出力位相ノイズ フロア                       | $f_{OUT} = 156.25\text{MHz}$ 、 $f_{OFFSET} > 10\text{MHz}$                                                       | -160 |                   |     | dBc/Hz |

| ODC                        | 出力デューティ サイクル <sup>(10)</sup>      |                                                                                                                  | 45   | 55                |     | %      |

| <b>AC-CML 出力特性 (OUTx)</b>  |                                   |                                                                                                                  |      |                   |     |        |

| f <sub>OUT</sub>           | 出力周波数 <sup>(5)</sup>              |                                                                                                                  |      | 1250              | MHz |        |

| V <sub>OD</sub>            | 出力電圧スイング ( $V_{OH} - V_{OL}$ )    | 25MHz $\leq f_{OUT} \leq 800\text{MHz}$ 、 $f_{OUT} = 156.25\text{MHz}$ での標準値                                     | 400  | 600               | 800 | mV     |

|                            |                                   | $f_{OUT} = 50\text{MHz}$                                                                                         | 500  | 620               | 700 | mV     |

|                            |                                   | 100MHz $\leq f_{OUT} \leq 200\text{MHz}$                                                                         | 490  | 600               | 690 | mV     |

|                            |                                   | $f_{OUT} = 312.5\text{MHz}$                                                                                      | 480  | 580               | 680 | mV     |

|                            |                                   | $f_{OUT} = 625\text{MHz}$                                                                                        | 350  | 460               | 600 | mV     |

|                            |                                   | $f_{OUT} = 1250\text{MHz}$                                                                                       | 400  |                   |     | mV     |

| V <sub>OUT-DIFF</sub>      | 差動出力電圧スイング、ピーク ツー ピーク             |                                                                                                                  |      | $2 \times V_{OD}$ |     | Vpp    |

| V <sub>OS</sub>            | 出力同相モード                           |                                                                                                                  | 150  | 550               |     | mV     |

| t <sub>SK</sub>            | 出力間スキュー                           | 同じポスト デバイダ、出力分周値、出力タイプ                                                                                           |      | 100               |     | ps     |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ                        |                                      | テスト条件                                                       | 最小値  | 標準値               | 最大値  | 単位     |

|------------------------------|--------------------------------------|-------------------------------------------------------------|------|-------------------|------|--------|

| $t_R/t_F$                    | 出力立ち上がり / 立ち下がり時間<br>(13)            | 20% ~ 80%、< 300MHz                                          |      | 225               | 300  | ps     |

|                              |                                      | 中心点の周囲 ±100mV、300MHz<br>$\leq f_{OUT} \leq 800MHz$          |      | 50                | 150  | ps     |

| $PN_{FLOOR}$                 | 出力位相ノイズ フロア                          | $f_{OUT} = 156.25MHz$ 、 $f_{OFFSET} > 10MHz$                |      | -160              |      | dBc/Hz |

| ODC                          | 出力デューティ サイクル(10)                     |                                                             |      | 45                | 55   | %      |

| <b>AC-LVPECL 出力特性 (OUTx)</b> |                                      |                                                             |      |                   |      |        |

| $f_{OUT}$                    | 出力周波数 <sup>(5)</sup>                 |                                                             |      | 1250              |      | MHz    |

| $V_{OD}$                     | 出力電圧スイング ( $V_{OH} - V_{OL}$ )       | 25MHz ≤ $f_{OUT} \leq 800MHz$ 、 $f_{OUT} = 156.25MHz$ での標準値 | 450  | 780               | 1000 | mV     |

|                              |                                      | $f_{OUT} = 50MHz$                                           | 660  | 810               | 920  | mV     |

|                              |                                      | 100MHz ≤ $f_{OUT} \leq 200MHz$                              | 640  | 780               | 900  | mV     |

|                              |                                      | $f_{OUT} = 312.5MHz$                                        | 620  | 740               | 880  | mV     |

|                              |                                      | $f_{OUT} = 625MHz$                                          | 500  | 620               | 760  | mV     |

|                              |                                      | $f_{OUT} = 1250MHz$                                         |      | 510               |      | mV     |

| $V_{OUT-DIFF}$               | 差動出力電圧スイング、ピーク ツー ピーク                |                                                             |      | $2 \times V_{OD}$ |      | Vpp    |

| $V_{os}$                     | 出力同相モード                              |                                                             | 300  |                   | 700  | mV     |

| $t_{SK}$                     | 出力間スキュー                              | 同じポスト デバイダ、出力分周値、出力タイプ                                      |      |                   | 100  | ps     |

| $t_R/t_F$                    | 出力立ち上がり / 立ち下がり時間<br>(13)            | 20% ~ 80%、< 300MHz                                          | 200  | 300               |      | ps     |

|                              |                                      | 中心点の周囲 ±100mV、300MHz<br>$\leq f_{OUT} \leq 800MHz$          |      | 35                | 100  | ps     |

| $PN_{FLOOR}$                 | 出力位相ノイズ フロア                          | $f_{OUT} = 156.25MHz$ 、 $f_{OFFSET} > 10MHz$                |      | -162              |      | dBc/Hz |

| ODC                          | 出力デューティ サイクル(10)                     |                                                             |      | 45                | 55   | %      |

| <b>HCSL 出力特性 (OUTx)</b>      |                                      |                                                             |      |                   |      |        |

| $f_{OUT}$                    | 出力周波数 <sup>(5)</sup>                 |                                                             |      | 625               |      | MHz    |

| $V_{OH}$                     | 出力 HIGH 電圧                           | $f_{OUT} \leq 400MHz$                                       | 600  | 880               |      | mV     |

|                              |                                      | $f_{OUT} = 625MHz$                                          | 500  | 800               |      | mV     |

| $V_{OL}$                     | 出力 LOW 電圧                            |                                                             | -150 | 150               |      | mV     |

| $t_{SK}$                     | 出力間スキュー                              | 同じポスト デバイダ、出力分周値、出力タイプ                                      |      | 100               |      | ps     |

| $dV/dt$                      | 出力スルーレート <sup>(13)</sup>             | 中心点の周囲 ±150mV、 $f_{OUT} \leq 400MHz$                        | 1.6  |                   | 4    | V/ns   |

| $PN_{FLOOR}$                 | 出力位相ノイズ フロア ( $f_{OFFSET} > 10MHz$ ) | 100MHz                                                      |      | -160              |      | dBc/Hz |

| ODC                          | 出力デューティ サイクル <sup>(10)</sup>         |                                                             |      | 45                | 55   | %      |

| <b>1.8V LVC MOS 出力特性</b>     |                                      |                                                             |      |                   |      |        |

| $f_{OUT}$                    | 出力周波数                                | OUT4、OUT5、OUT6 または OUT7                                     | 1E-6 | 200               |      | MHz    |

| $V_{OH}$                     | 出力 HIGH 電圧                           | $I_{OH} = 1mA$                                              | 1.2  |                   |      | V      |

| $V_{OL}$                     | 出力 LOW 電圧                            | $I_{OL} = 1mA$                                              |      |                   | 0.4  | V      |

| $I_{OH}$                     | 出力 HIGH 電流                           |                                                             |      | -23               |      | mA     |

| $I_{OL}$                     | 出力 LOW 電流                            |                                                             |      | 20                |      | mA     |

| $t_R/t_F$                    | 出力立ち上がり / 立ち下がり時間                    | 20% ~ 80%                                                   |      | 250               |      | ps     |

| $t_{SK}$                     | 出力間スキュー                              | 同じポスト デバイダ、出力分周値、出力タイプ                                      |      | 100               |      | ps     |

|                              | 出力間スキュー                              | 同じポスト デバイダ、出力分周値、<br>LVC MOS から DIFF                        |      |                   | 1.5  | ns     |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ               |                              | テスト条件                                                    | 最小値 | 標準値  | 最大値 | 単位     |

|---------------------|------------------------------|----------------------------------------------------------|-----|------|-----|--------|

| PN <sub>FLOOR</sub> | 出力位相ノイズ フロア                  | f <sub>OUT</sub> = 66.66MHz, f <sub>OFFSET</sub> > 10MHz |     | -160 |     | dBc/Hz |

| ODC                 | 出力デューティ サイクル <sup>(10)</sup> |                                                          | 45  |      | 55  | %      |

| R <sub>OUT</sub>    | 出力インピーダンス                    |                                                          |     | 50   |     | Ω      |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ                                                           | テスト条件                      | 最小値                               | 標準値 | 最大値 | 単位  |

|-----------------------------------------------------------------|----------------------------|-----------------------------------|-----|-----|-----|

| <b>3 レベルのロジック入力特性 (HW_SW_CTRL, GPIO1, REFSEL, STATUS [1:0])</b> |                            |                                   |     |     |     |

| V <sub>IH</sub>                                                 | 入力 High 電圧                 |                                   | 1.4 |     | V   |

| V <sub>IM</sub>                                                 | 入力 MID 電圧                  | 内部バイアスと PDN が Low にプルされた入力フローディング | 0.7 | 0.9 | V   |

| V <sub>IL</sub>                                                 | 入力 Low 電圧                  |                                   |     | 0.4 | V   |

| I <sub>IH</sub>                                                 | 高入力電流                      | V <sub>IH</sub> = VDD             | -40 | 40  | μA  |

| I <sub>IL</sub>                                                 | 入力 Low 電流                  | V <sub>IL</sub> = GND             | -40 | 40  | μA  |

| <b>2 レベル ロジック入力特性 (PDN, GPIO[2:0], SDI, SCK, SCS)</b>           |                            |                                   |     |     |     |

| V <sub>IH</sub>                                                 | 入力 High 電圧                 |                                   | 1.2 |     | V   |

| V <sub>IL</sub>                                                 | 入力 Low 電圧                  |                                   |     | 0.6 | V   |

| I <sub>IH</sub>                                                 | 高入力電流                      | V <sub>IH</sub> = VDD             | -40 | 40  | μA  |

| I <sub>IL</sub>                                                 | 入力 Low 電流                  | V <sub>IL</sub> = GND             | -40 | 40  | μA  |

| <b>ロジック出力特性 (STATUS[1:0], SDO)</b>                              |                            |                                   |     |     |     |

| V <sub>OH</sub>                                                 | 出力 HIGH 電圧                 | I <sub>OH</sub> = 1mA             | 2.4 |     | V   |

| V <sub>OL</sub>                                                 | 出力 LOW 電圧                  | I <sub>OL</sub> = 1mA             |     | 0.4 | V   |

| t <sub>R/t<sub>F</sub></sub>                                    | 出力立ち上がり / 立ち下がり時間          | 20% ~ 80%、LVCMOS モード、1kΩ から GND へ |     | 500 | ps  |

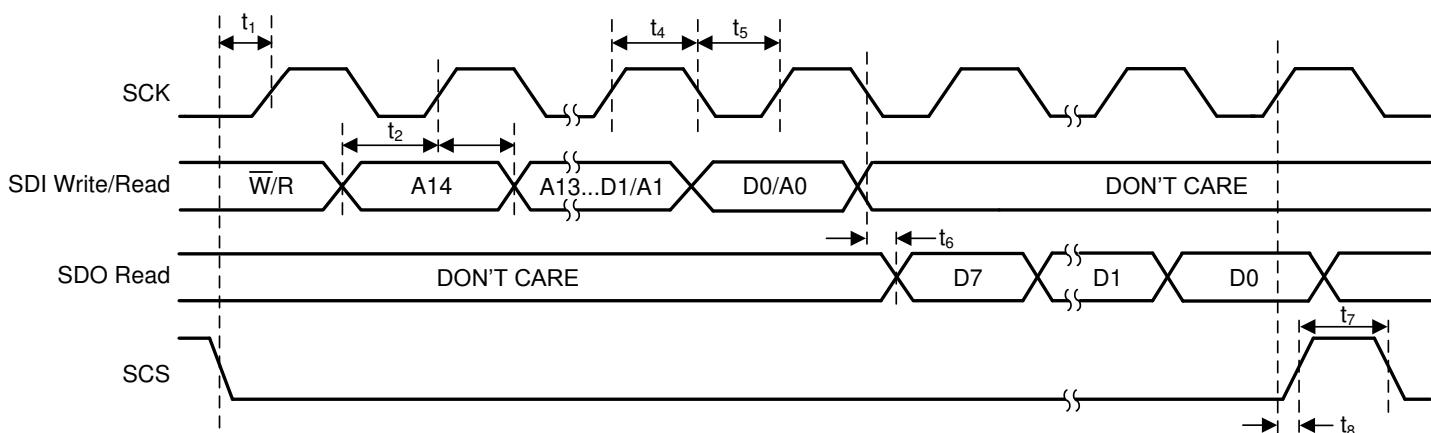

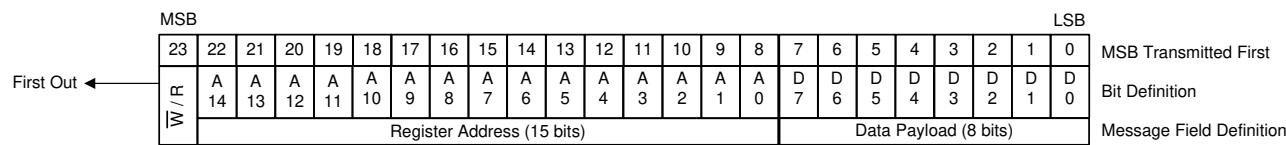

| <b>SPI タイミング要件 (SDI, SCK, SCS, SDO)</b>                         |                            |                                   |     |     |     |

| f <sub>SCK</sub>                                                | SPI クロック レート               |                                   |     | 20  | MHz |

|                                                                 | SPI クロック レート、NVM 書き込み      |                                   |     | 5   | MHz |

| t <sub>1</sub>                                                  | SCS から SCK までのセットアップ時間     |                                   | 10  |     | ns  |

| t <sub>2</sub>                                                  | SDI から SCK までのセットアップ時間     |                                   | 10  |     | ns  |

| t <sub>3</sub>                                                  | SDI から SCK までのホールド時間       |                                   | 10  |     | ns  |

| t <sub>4</sub>                                                  | SCK High 時間                |                                   | 25  |     | ns  |

| t <sub>5</sub>                                                  | SCK Low 時間                 |                                   | 25  |     | ns  |

| t <sub>6</sub>                                                  | SCK から SDO への有効なリードバック データ |                                   |     | 20  | ns  |

| t <sub>7</sub>                                                  | SCS パルス幅                   |                                   | 20  |     | ns  |

| t <sub>8</sub>                                                  | SDI から SCK までのホールド時間       |                                   | 10  |     | ns  |

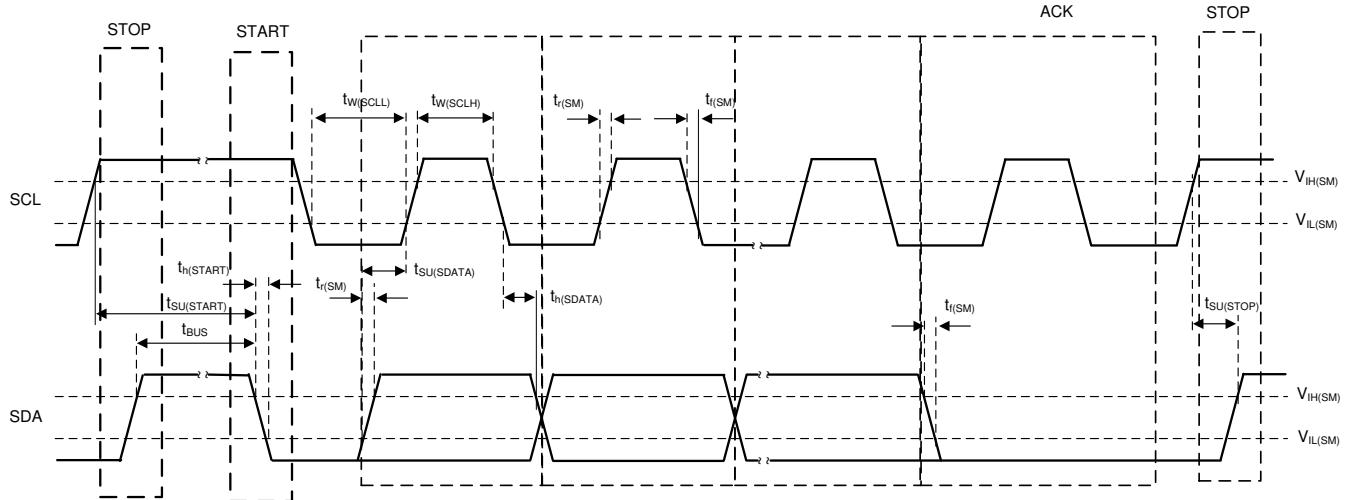

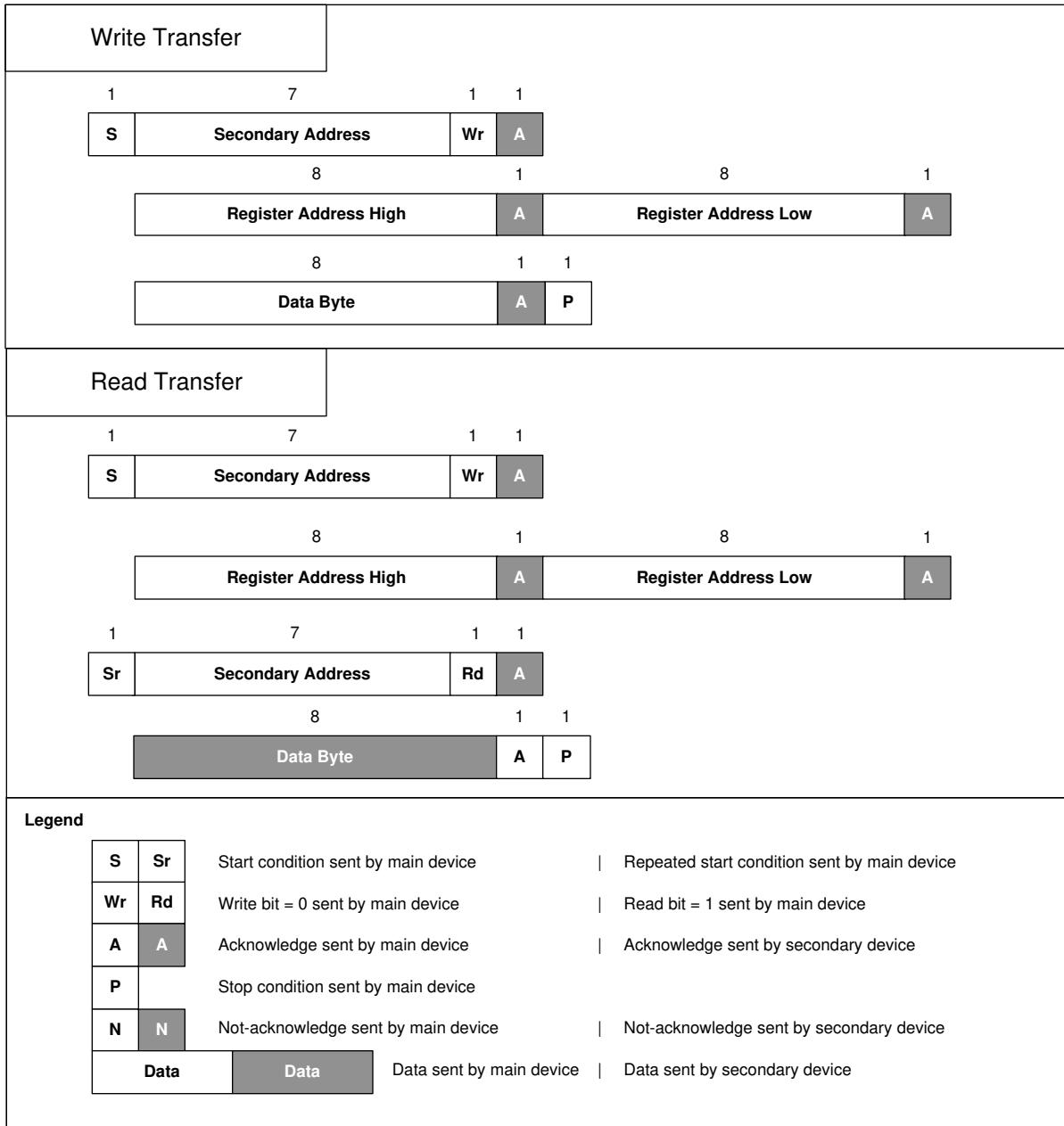

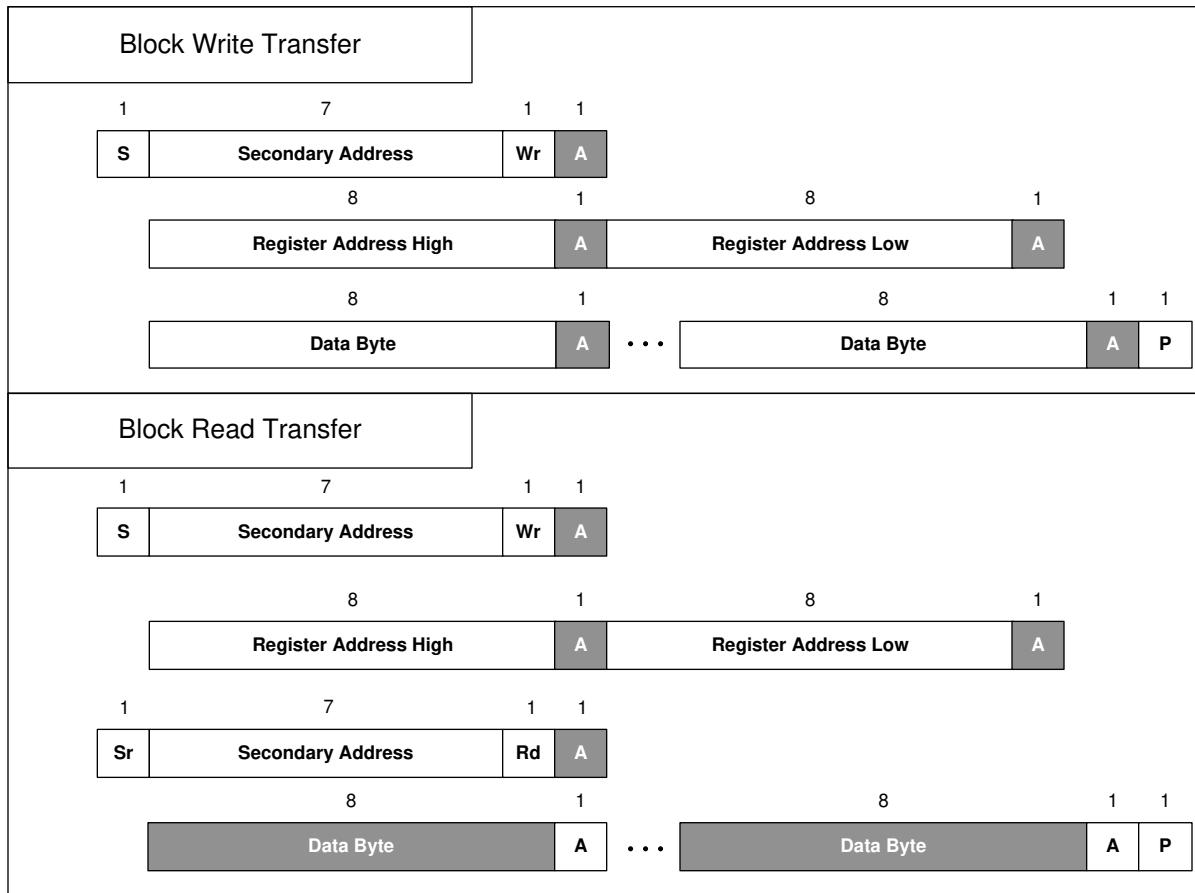

| <b>I<sup>2</sup>C 互換インターフェイス特性 (SDA, SCL)</b>                   |                            |                                   |     |     |     |

| V <sub>IH</sub>                                                 | 入力 High 電圧                 |                                   | 1.2 |     | V   |

| V <sub>IL</sub>                                                 | 入力 Low 電圧                  |                                   |     | 0.6 | V   |

| I <sub>IH</sub>                                                 | 入力リーケージ                    |                                   | -15 | 15  | μA  |

| V <sub>OL</sub>                                                 | 出力 LOW 電圧                  | I <sub>OL</sub> = 3mA             |     | 0.3 | V   |

| f <sub>SCL</sub>                                                | I <sup>2</sup> C クロック レート  | 標準                                |     | 100 | kHz |

|                                                                 |                            | ファスト モード                          |     | 400 |     |

| t <sub>SU(START)</sub>                                          | START 条件のセットアップ時間          | SCl が High になってから SDA が Low になる   | 0.6 |     | μs  |

| t <sub>H(START)</sub>                                           | START 条件のホールド時間            | SDA が Low になってから SDA が High になる   | 0.6 |     | μs  |

| t <sub>W(SCLH)</sub>                                            | SCL パルス幅 High              |                                   | 0.6 |     | μs  |

| t <sub>W(SCLL)</sub>                                            | SCL パルス幅 Low               |                                   | 1.3 |     | μs  |

| t <sub>SU(SDA)</sub>                                            | SDA のセットアップ時間              |                                   | 100 |     | ns  |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ          |                       | テスト条件                       | 最小値 | 標準値 | 最大値 | 単位 |

|----------------|-----------------------|-----------------------------|-----|-----|-----|----|

| $t_{H(SDA)}$   | SDA のホールド時間           | SCL が Low になってから SDA が有効になる | 0   |     |     | μs |

| $t_{R(IN)}$    | SDA/SCL 入力立ち上がり時間     |                             |     | 300 |     | ns |

| $t_{F(IN)}$    | SDA/SCL 入力立ち下がり時間     |                             |     | 300 |     | ns |

| $t_{F(OUT)}$   | SDA 出力立ち下がり時間         | $C_{BUS} \leq 400\text{pF}$ |     | 300 |     | ns |

| $t_{SU(STOP)}$ | ストップ条件のセットアップ時間       |                             | 0.6 |     |     | μs |

| $t_{BUS}$      | STOP と START 間のバス解放時間 |                             | 1.3 |     |     | μs |

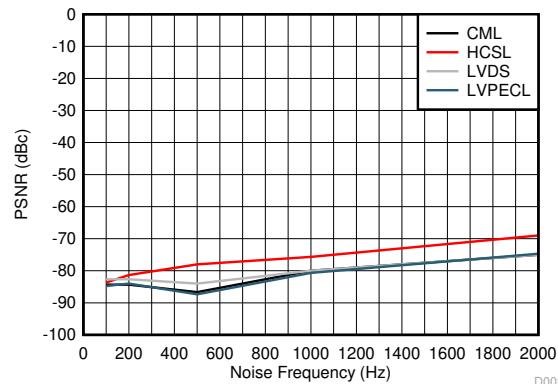

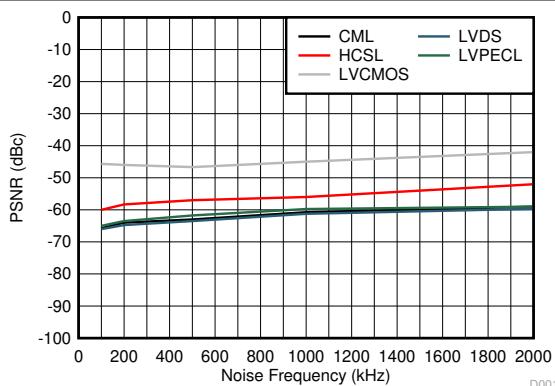

#### 電源ノイズ除去 (PSNR)/ クロストークによるスプリアス

|                              |                                                                |                                                                                        |     |  |     |

|------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|--|-----|

| $\text{PSNR}_{50\text{mV}}$  | 電源ノイズにより誘導されるスプリアス ( $V_N = 50\text{mVpp}$ ) <sup>(6)(7)</sup> | $V_{DD} = 3.3\text{V}, V_{DDO\_x} = 3.3\text{V}, 156.25\text{MHz}, \text{AC-DIFF 出力、}$ | -83 |  | dBc |

|                              |                                                                | $V_{DD} = 3.3\text{V}, V_{DDO\_x} = 3.3\text{V}, 156.25\text{MHz}, \text{HCSL 出力、}$    | -78 |  | dBc |

|                              |                                                                | $V_{DD} = 3.3\text{V}, V_{DDO\_x} = 2.5\text{V}, 156.25\text{MHz}, \text{AC-DIFF 出力}$  | -73 |  | dBc |

|                              |                                                                | $V_{DD} = 3.3\text{V}, V_{DDO\_x} = 2.5\text{V}, 156.25\text{MHz}, \text{HCSL 出力}$     | -68 |  | dBc |

| $\text{PSNR}_{25\text{mV}}$  | 電源ノイズにより誘導されるスプリアス ( $V_N = 25\text{mVpp}$ ) <sup>(6)(7)</sup> | $V_{DD} = 3.3\text{V}, V_{DDO\_x} = 1.8\text{V}, 156.25\text{MHz}, \text{AC-DIFF 出力}$  | -63 |  | dBc |

|                              |                                                                | $V_{DD} = 3.3\text{V}, V_{DDO\_x} = 1.8\text{V}, 156.25\text{MHz}, \text{HCSL 出力}$     | -58 |  | dBc |

|                              |                                                                | $V_{DD} = 3.3\text{V}, V_{DDO\_x} = 1.8\text{V}, 156.25\text{MHz}, \text{LVCMOS 出力、}$  | -45 |  | dBc |

| $\text{SPUR}_{\text{XTALK}}$ | 出力間クロストーク (隣接チャネル) によるスプリアス レベル <sup>(7)</sup>                 | $f_{\text{OUT}_X} = 156.25\text{MHz}, f_{\text{OUT}_Y} = 155.52\text{MHz}, \text{AC}$  | -75 |  | dBc |

#### PLL クロック出力の性能特性

|    |                                           |                                                                                                                                                                                                                               |    |     |        |

|----|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|--------|

| RJ | RMS 位相ジッタ (12kHz ~ 20MHz)                 | APLL1 から 625MHz AC-DIFF 出力, $f_{XO} = 48\text{MHz}, f_{PD1} = f_{XO}/2, f_{VCO1} = 2.5\text{GHz}$                                                                                                                             | 50 | 80  | fs RMS |

| RJ | RMS 位相ジッタ (12kHz ~ 20MHz)                 | APLL1 から 625MHz AC-DIFF 出力, $f_{XO} = 48\text{MHz}, f_{PD1} = f_{XO}/2, f_{VCO1} = 2.5\text{GHz}, f_{VCO1} = 2.5\text{GHz}, V_{DDO} = 3.3\text{V}$ 、電源リップル $V_N \leq 50\text{mV}, 100\text{kHz} \leq F_N \leq 10\text{MHz}$   | 55 | 100 | fs RMS |

| RJ | RMS 位相ジッタ (12kHz ~ 20MHz) <sup>(15)</sup> | APLL1 からの 625MHz AC-LVPECL、AC-CML、または AC-LVDS 出力。 $f_{XO} = f_{PD1} = 48\text{MHz}, f_{VCO1} = 2.5\text{GHz}, V_{DDO} = 3.3\text{V}, 4\text{MHz}$ の HPF フィルタ適用                                                                | 25 |     | fs RMS |

| RJ | RMS 位相ジッタ (12kHz ~ 20MHz)                 | APLL1 から 312.5MHz AC-LVPECL 出力, $f_{XO} = 48\text{MHz}, f_{PD1} = f_{XO}/2, f_{VCO1} = 2.5\text{GHz}$                                                                                                                         | 50 | 80  | fs RMS |

| RJ | RMS 位相ジッタ (12kHz ~ 20MHz)                 | APLL1 から 312.5MHz AC-DIFF 出力, $f_{XO} = 48\text{MHz}, f_{PD1} = f_{XO}/2, f_{VCO1} = 2.5\text{GHz}, f_{VCO1} = 2.5\text{GHz}, V_{DDO} = 3.3\text{V}$ 、電源リップル $V_N \leq 50\text{mV}, 100\text{kHz} \leq F_N \leq 10\text{MHz}$ | 55 | 110 | fs RMS |

| RJ | RMS 位相ジッタ (12kHz ~ 20MHz) <sup>(15)</sup> | APLL1 からの 312.5MHz AC-LVPECL 出力, $f_{XO} = f_{PD1} = 48\text{MHz}, f_{VCO1} = 2.5\text{GHz}, V_{DDO} = 3.3\text{V}, 4\text{MHz}$ の HPF フィルタ適用                                                                                 | 32 |     | fs RMS |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ            |                                           | テスト条件                                                                                                                                                                                                                           | 最小値  | 標準値  | 最大値 | 単位     |

|------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|--------|

| RJ               | RMS 位相ジッタ (12kHz ~ 20MHz) <sup>(15)</sup> | APLL1 からの 312.5MHz AC-CML 出力、 $f_{XO} = f_{PD1} = 48\text{MHz}$ 、 $f_{VCO1} = 2.5\text{GHz}$ 、 $VDDO = 3.3\text{V}$ 、4MHz の HPF フィルタ適用。                                                                                         |      | 34   |     | fs RMS |

| RJ               | RMS 位相ジッタ (12kHz ~ 20MHz) <sup>(15)</sup> | APLL1 からの 312.5MHz AC-LVDS 出力、 $f_{XO} = f_{PD1} = 48\text{MHz}$ 、 $f_{VCO1} = 2.5\text{GHz}$ 、 $VDDO = 3.3\text{V}$ 、4 MHz の HPF フィルタ適用。                                                                                       |      | 38   |     | fs RMS |

| RJ               | RMS 位相ジッタ (12kHz ~ 20MHz)                 | APLL1 から 156.25MHz AC-LVPECL 出力、 $f_{XO} = 48\text{MHz}$ 、 $f_{PD1} = f_{XO}/2$ 、 $f_{VCO1} = 2.5\text{GHz}$                                                                                                                    |      | 60   | 90  | fs RMS |

| RJ               | RMS 位相ジッタ (12kHz ~ 20MHz)                 | 156.25MHz APLL1 からの AC-LVPECL 出力、 $f_{XO} = 48\text{MHz}$ 、 $f_{PD1} = f_{XO}/2$ 、 $f_{VCO1} = 2.5\text{GHz}$ 、 $VDDO = 3.3\text{V}$ 、電源リップル $\leq 50\text{mV}$ 、 $100\text{kHz} \leq F_N \leq 10\text{MHz}$                    |      | 65   | 135 | fs RMS |

| RJ               | RMS 位相ジッタ (12kHz ~ 20MHz) <sup>(15)</sup> | APLL1 からの 156.25 MHz AC-LVPECL 出力、 $f_{XO} = f_{PD1} = 48\text{MHz}$ 、 $f_{VCO1} = 2.5\text{GHz}$ 、 $VDDO = 3.3\text{V}$ 、4MHz の HPF フィルタ適用。                                                                                    |      | 44   |     | fs RMS |

| RJ               | RMS 位相ジッタ (12kHz ~ 20MHz) <sup>(15)</sup> | APLL1 からの 156.25MHz AC-CML 出力、 $f_{XO} = f_{PD1} = 48\text{MHz}$ 、 $f_{VCO1} = 2.5\text{GHz}$ 、 $VDDO = 3.3\text{V}$ 、4 MHz の HPF フィルタ適用。                                                                                       |      | 51   |     | fs RMS |

| RJ               | RMS 位相ジッタ (12kHz ~ 20MHz) <sup>(15)</sup> | APLL1 からの 156.25MHz AC-LVDS 出力、 $f_{XO} = f_{PD1} = 48\text{MHz}$ 、 $f_{VCO1} = 2.5\text{GHz}$ 、 $VDDO = 3.3\text{V}$ 、4MHz の HPF フィルタ適用。                                                                                       |      | 63   |     | fs RMS |

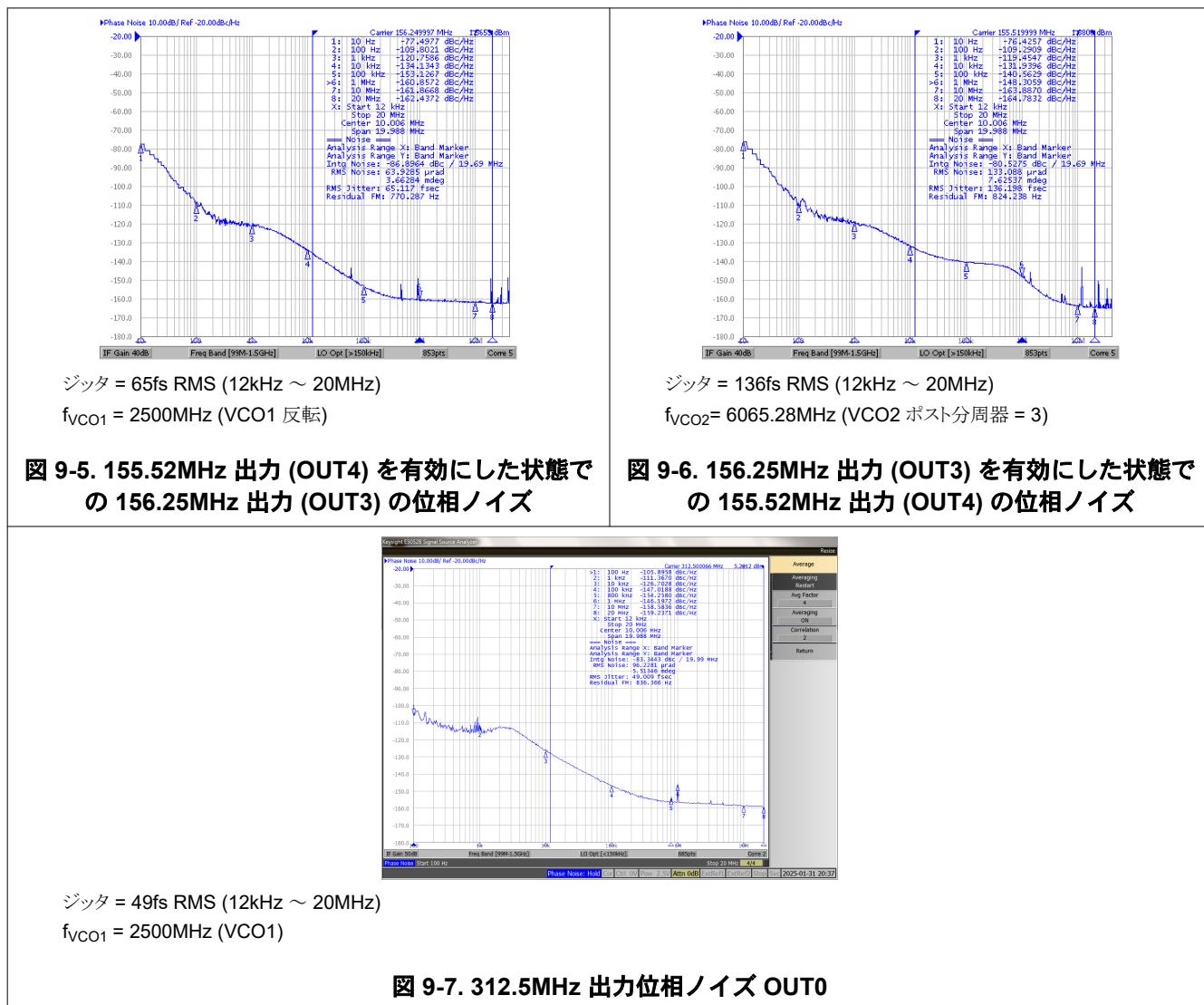

| RJ               | RMS 位相ジッタ (12kHz~20MHz)、出力クロストーク スピアスを除く  | OUT4、OUT5、OUT6、OUT7 の APLL2 からの 155.52MHz AC-LVPECL 出力。APLL1 からの 156.25MHz (その他のすべての出力)。 $f_{XO} = 48\text{MHz}$ 、 $f_{PD1} = f_{XO}/2$ 、 $f_{VCO1} = 2.5\text{GHz}$ 、 $f_{PD2} = f_{VCO1}/18$ 、 $f_{VCO2} = 5.59872\text{GHz}$ |      | 125  | 200 | fs RMS |

| RJ               | RMS 位相ジッタ (12kHz ~ 20MHz)                 | OUT4、OUT5、OUT6、OUT7 の APLL2 からの 155.52MHz AC-LVPECL 出力。APLL1 からの 156.25MHz (その他のすべての出力)。 $f_{XO} = 48\text{MHz}$ 、 $f_{PD1} = f_{XO}/2$ 、 $f_{VCO1} = 2.5\text{GHz}$ 、 $f_{PD2} = f_{VCO1}/18$ 、 $f_{VCO2} = 5.59872\text{GHz}$ |      | 145  |     | fs RMS |

| RJ               | RMS 位相ジッタ (12kHz~20MHz)、出力クロストーク スピアスを除く  | OUT4、OUT5、OUT6、OUT7 の APLL2 からの 153.6MHz AC-LVPECL 出力。APLL1 からの 156.25MHz (その他のすべての出力)。 $f_{XO} = 48\text{MHz}$ 、 $f_{PD1} = f_{XO}/2$ 、 $f_{VCO1} = 2.5\text{GHz}$ 、 $f_{PD2} = f_{VCO1}/18$ 、 $f_{VCO2} = 5.5296\text{GHz}$   |      | 125  | 200 | fs RMS |

| RJ               | RMS 位相ジッタ (12kHz ~ 20MHz)                 | OUT4、OUT5、OUT6、OUT7 の APLL2 からの 153.6MHz AC-LVPECL 出力。APLL1 からの 156.25MHz (その他のすべての出力)。 $f_{XO} = 48\text{MHz}$ 、 $f_{PD1} = f_{XO}/2$ 、 $f_{VCO1} = 2.5\text{GHz}$ 、 $f_{PD2} = f_{VCO1}/18$ 、 $f_{VCO2} = 5.5296\text{GHz}$   |      | 150  |     | fs RMS |

| BW               | DPLL 帯域幅範囲 <sup>(8)</sup>                 | プログラムされた帯域幅設定                                                                                                                                                                                                                   | 0.01 | 4000 |     | Hz     |

| J <sub>PK</sub>  | DPLL 閉ループ ジッタのピーク <sup>(11)</sup>         | $f_{REF} = 25\text{MHz}$ 、 $f_{OUT} = 10\text{MHz}$ 、DPLL BW = 0.1Hz または 10Hz                                                                                                                                                   |      | 0.1  |     | dB     |

| J <sub>TOL</sub> | ジッタの許容範囲                                  | ジッタ変調 = 10Hz、25.78125Gbps                                                                                                                                                                                                       |      | 6455 |     | UI p-p |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ         |                              | テスト条件                                  | 最小値 | 標準値      | 最大値 | 単位  |

|---------------|------------------------------|----------------------------------------|-----|----------|-----|-----|

| $t_{HITLESS}$ | 2つのリファレンス入力間の位相変動 (0ppm 誤差時) | 同一周波数の 2つのクロック入力間で、1回のスイッチオーバー動作に対して有効 |     | $\pm 50$ |     | ps  |

| $f_{HITLESS}$ | 無瞬断切り替え時の周波数過渡応答             | 同一周波数の 2つのクロック入力間で、1回のスイッチオーバー動作に対して有効 |     | $\pm 10$ |     | ppb |

- (1) デバイスの総消費電流は、特定の構成で有効になっているすべてのブロックについて、各ピンごとの  $IDD_x$  と  $IDDO_x$  を合算することで見積もることができます。

- (2) 構成 A (APLL2 を除くすべての PLL ブロックがディスエーブル) :  $f_{REF} = 25\text{MHz}$ ,  $f_{XO} = 48\text{MHz}$ ,  $f_{VCO1} = 2.5\text{GHz}$ 。

- (3) 動作出力の  $IDDO_x$  電流は、マルチプレクサ、分周器、出力形式の合計です。

- (4) 差動入力クロックが 5 MHz 未満の場合、TI は差動入力振幅モニタを無効化し、入力クロックの妥当性確認のために、周波数モニタやウンドウディテクタなどの別のモニタを少なくとも 1つ有効にすることを推奨します。それ以外の場合は、5MHz より低い入力に LVC MOS クロックを使用することを検討します。

- (5) 出力周波数は  $f_{OUT}$  の max 仕様を上回ることも可能ですが、出力スイングは  $V_{OD}$  min の仕様を下回ることがあります。

- (6) PSNR は、振幅  $V_N$  と周波数  $f_N$  (100kHz と 1MHz の間) の正弦波ノイズを VDD ピンと  $VDDO_x$  ピンに注入した際に測定された单側バンドスペクトラムレベル (dBc) です。

- (7)  $DJ_{SPUR} (\text{ps pk-pk}) = [2 \times 10^{(dBc/20)} / (\pi \times f_{OUT})] \times 1E6$ , ここで、dBc は PSNR レベル (dBc)、 $f_{OUT}$  は出力周波数 (MHz) です。

- (8) 実際のループ帯域幅を小さくすることもできます。有効なループ帯域幅範囲は、特定の構成で使用される DPLL TDC 周波数によって制限できます。

- (9) 本条件は、PDN の立ち上がりエッジ前に VDD および  $VDDO_x$  電源がランプアップ完了しており、XO 入力クロックの周波数および振幅が安定していることを前提としています。PLLs はシリアル キャリブレーション モードで起動し (PLL1 が PLL2 より先)、VCO 待機タイマは 0.4 ms、PLL ウェイトタイマは 3 ms に設定されています。また、出力は APLL ロック中のみ オートミュートが有効で、DPLL の オートミュート オプションは無効化されています。

- (10) パラメータは、いずれかの VCO ドメインから分周された PLL 出力について規定されます。

- (11) 0.1dB 以下の DPLL 閉ループ ジッタのピークは、TICS Pro ソフトウェアツールで構成されている DPLL の帯域幅設定に基づいています。

- (12) 最小制限は、差動入力振幅モニタの最小設定 ( $xREF\_LVL\_SEL = 0$ ) に適用されます。

- (13) 差動出力波形 ( $OUTx_P$ - $OUTx_N$ ) を測定します。2pF 負荷での出力。

- (14) 本データシートの後続セクションに示されるジッタ性能を満足するためには、すべての入力クロックにおいて最小 0.5 V/ns のスルーレートが推奨されます。クロック入力のスルーレートが低下すると、位相ノイズ性能は劣化し始めます。ただし、このデバイスは記載されている最小値までスルーレートで機能します。シングルエンド クロックと比較すると、差動クロック (LVDS, LVPECL) は、同相モード ノイズ除去の効果により、低スルーレート時における位相ノイズ性能の劣化を受けにくくなります。TI は、デバイス出力において最適な位相ノイズ性能を得るため、差動クロックには可能な限り高いスルーレートを使用することを推奨しています。

- (15) RMS ジッタは、RMS ジッタデータにハイパス ベッセル フィルタを適用する後処理によって算出されます。

- (16) 1Hz (1PPS) 入力は、PRIREF でのみサポートされ、SECREF ではサポートされていません。

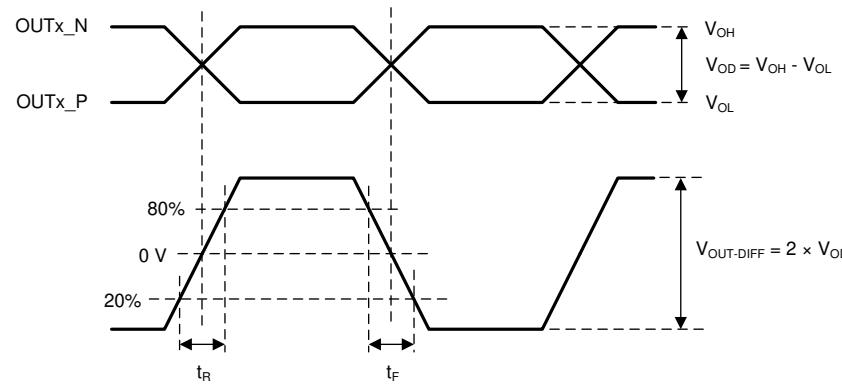

## 6.7 タイミング図

図 6-1. SPI タイミング パラメータ

図 6-2. I<sup>2</sup>C のタイミング図

図 6-3. 差動出力電圧と立ち上がり / 立ち下がり時間

図 6-4. シングルエンド出力電圧と立ち上がり / 立ち下がり時間

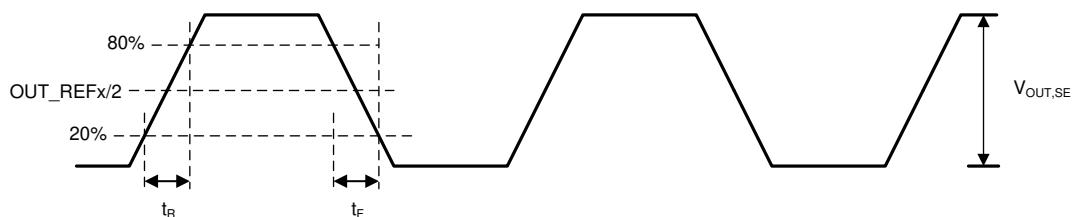

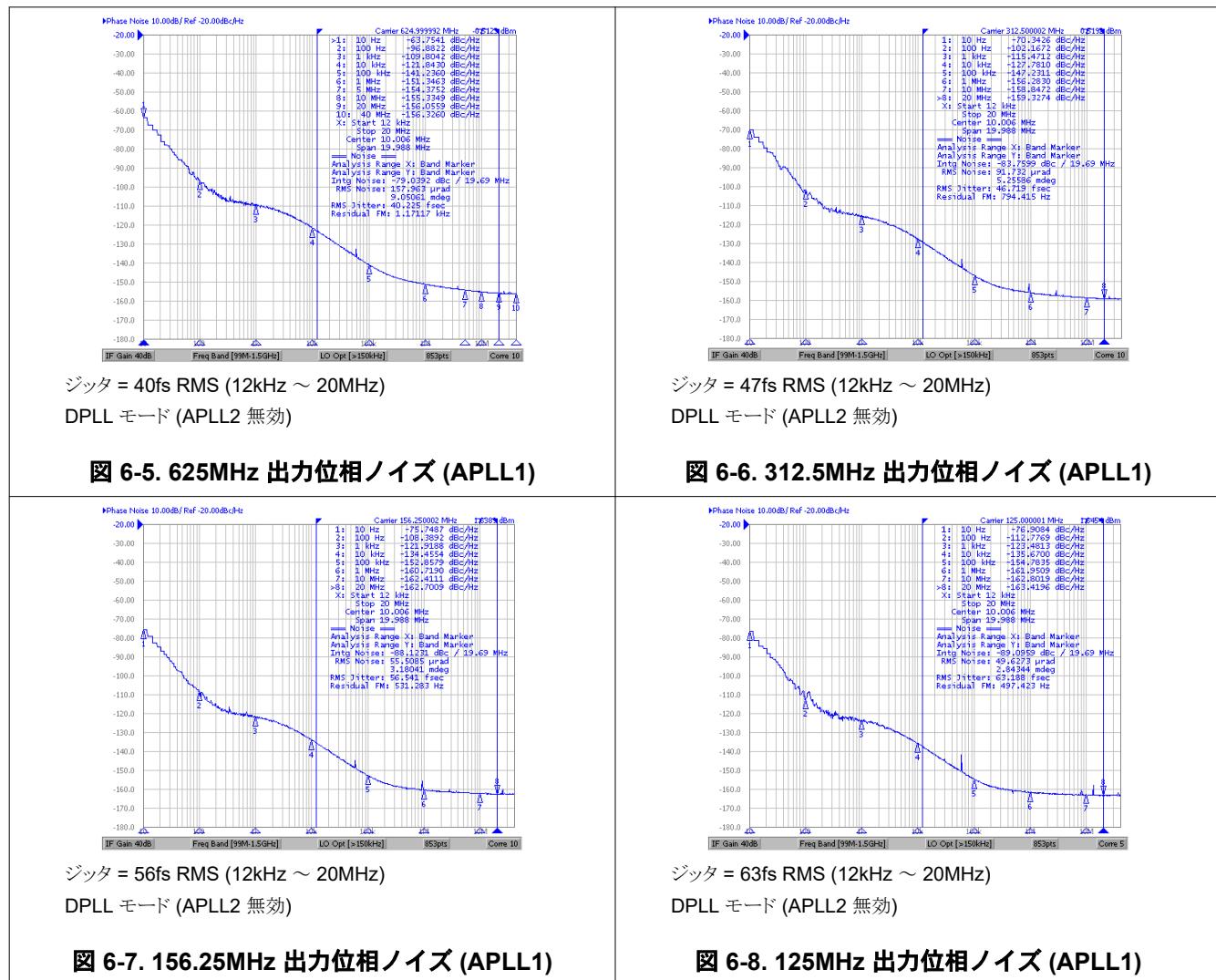

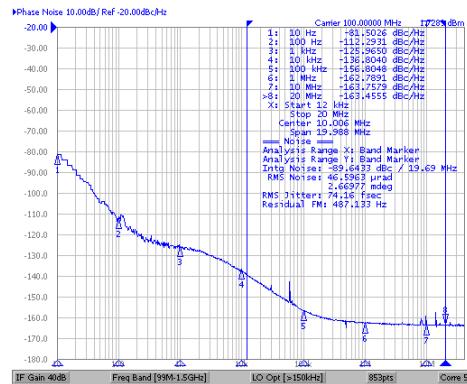

## 6.8 代表的特性

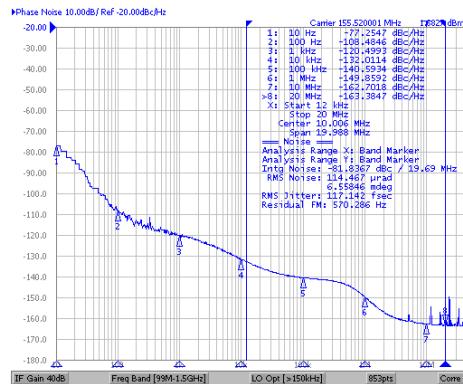

特に記述のない限り以下のとおり: VDD = 3.3V、VDDO = 1.8V、TA = 25°C、AC-LVPECL 出力測定値。DPLL:fREF = 25MHz、fTDC = 25MHz、BW DPLL = 10Hz、DPLL はリファレンスにロック。APLL1:fXO = 48MHz、fPD1 = 24MHz (fXO÷2)、fVCO1 = 2500MHz、BW APLL1 = 2.5kHz、DPLL モード。APLL2:fPD2 = 138.8MHz (fVCO1÷18)、BW APLL2 = 500kHz、APLL2 のカスケード モードは図 6-10 および図 6-11 です。さまざまな周波数オフセットでの PLL 出力クロックの位相ノイズは、外部クロック入力源 (REF IN、OCXO、XO)、内部ノイズ源 (PLL、VCO)、および構成済みの PLL ループ帯域幅 (BW REF-DPLL、BW TCXO-DPLL、BW APLL) など、さまざまなノイズの寄与要因によって決定されます。各外部クロック ソース (fSOURCE) に示される位相ノイズ プロファイルは、ソースで測定された位相ノイズに  $20 \times \log_{10} (f_{\text{OUT}} / f_{\text{SOURCE}})$  を追加し、PLL 出力周波数 (fOUT) によって正規化されます。

ジッタ = 74fs RMS (12kHz ~ 20MHz)

DPLL モード (APLL2 無効)

図 6-9. 100MHz 出力位相ノイズ (APLL1)

ジッタ = 117fs RMS (12kHz ~ 20MHz)

カスケード接続 APLL2 による DPLL モード

$$f_{VCO2} = 5598.72 \text{MHz}$$

図 6-10. 155.52MHz 出力位相ノイズ (APLL2)

ジッタ = 120fs RMS (12kHz ~ 20MHz)

カスケード接続 APLL2 による DPLL モード

$$f_{VCO2} = 5737.5 \text{MHz}$$

図 6-11. 212.5MHz 出力位相ノイズ (APLL2)

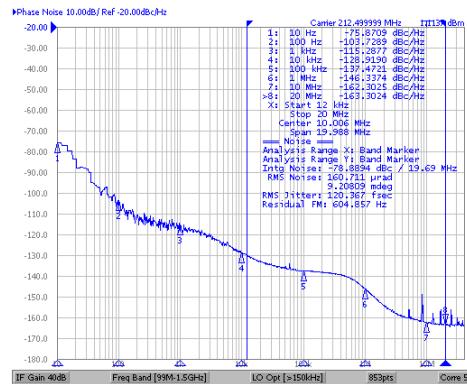

電源に注入される 50mVpp のノイズ (VDD = 3.3V, VDDO = 3.3V)

図 6-12. 156.25MHz 出力での PSNR とノイズ周波数 (50mVpp) との関係

電源に注入される 25mVpp のノイズ (VDD = 3.3V、VDDO = 1.8V)

$D_{SPUR} (\text{ps pk-pk}) = 2 \times 10^{(\text{dBc}/20)} / (\pi \times f_{\text{OUT}}) \times 1E6$ 。ここで、dBc は PSNR スプリアスレベル (dBc)、 $f_{\text{OUT}}$  は出力周波数 (MHz) です

図 6-13. 156.25MHz 出力での PSNR とノイズ周波数 (25mVpp) との関係

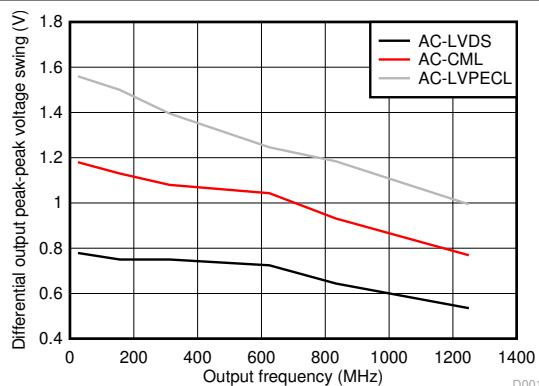

図 6-14. 出力スイングと周波数との関係

## 7 パラメータ測定情報

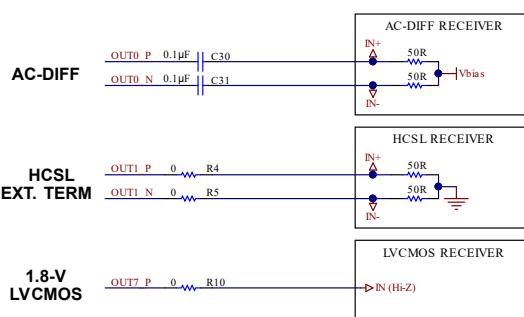

### 7.1 出力クロックのテスト構成

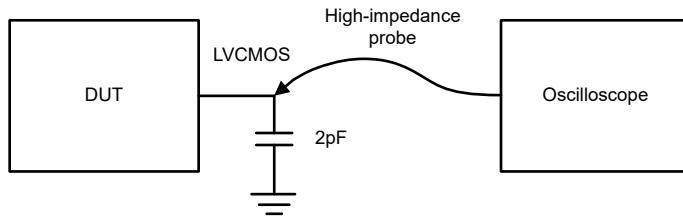

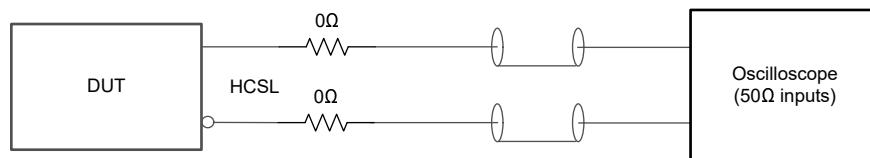

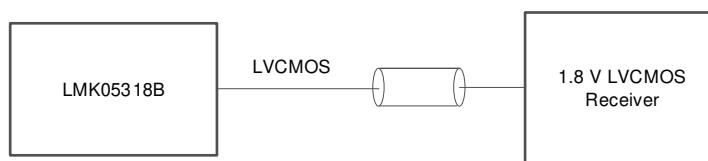

図 7-1. LVC MOS 出力テスト構成

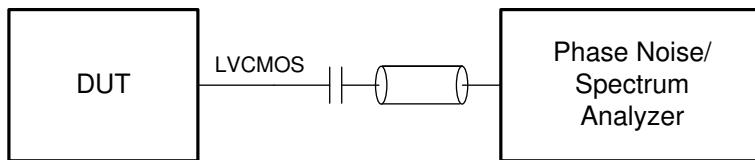

図 7-2. LVC MOS 出力位相ノイズテスト構成

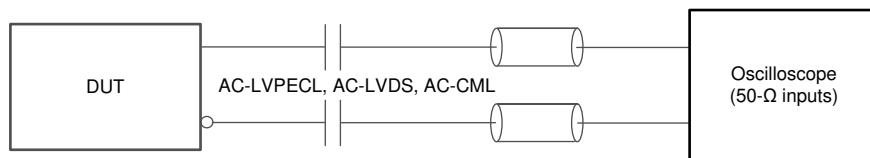

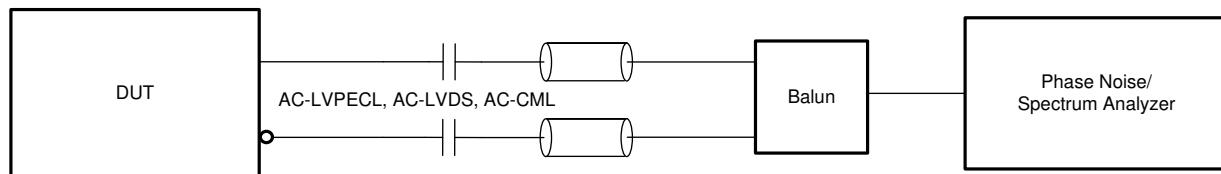

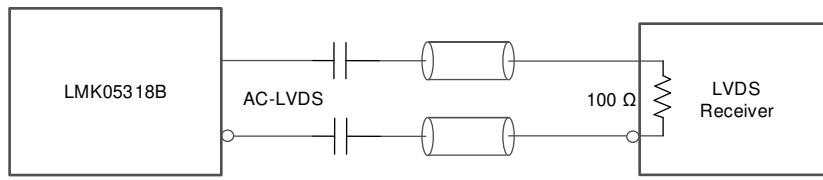

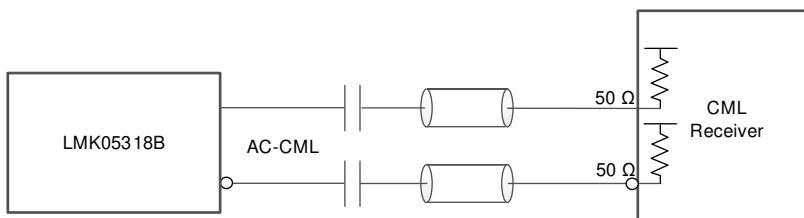

図 7-3. AC-LVPECL、AC-LVDS、AC-CML 出力 AC テスト構成

図 7-4. AC-LVPECL、AC-LVDS、AC-CML 出力位相ノイズ テスト構成

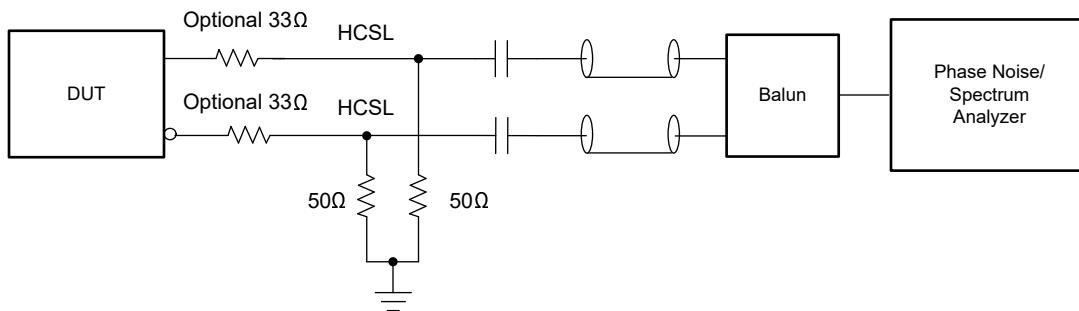

図 7-5. HCSL 出力テスト構成

図 7-6. HCSL 出力位相ノイズテスト構成

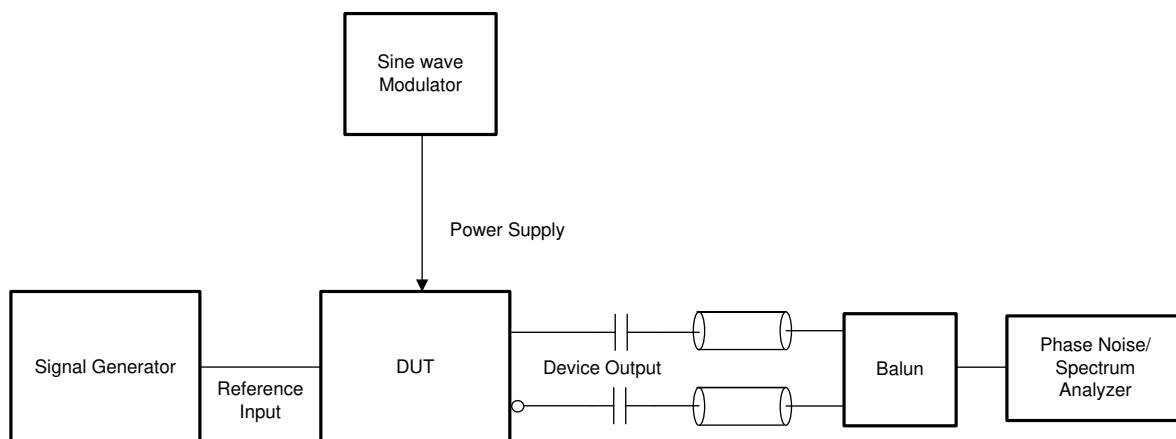

デバイスの電源に注入された既知のノイズ振幅と周波数で dBc 単位で測定されたシングル サイドバンド スピアス レベル。

図 7-7. 電源ノイズ除去 (PSNR) テスト構成

## 8 詳細説明

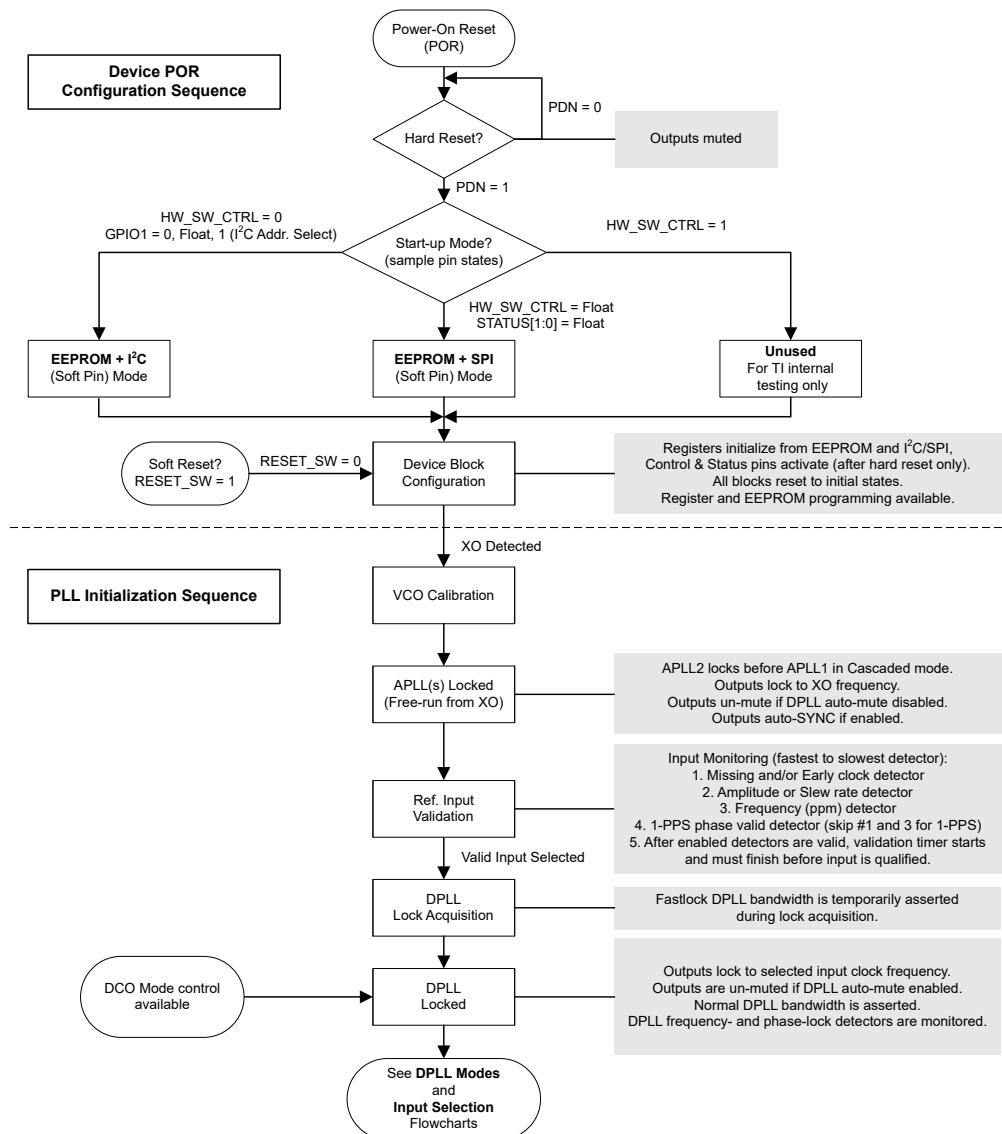

### 8.1 概要

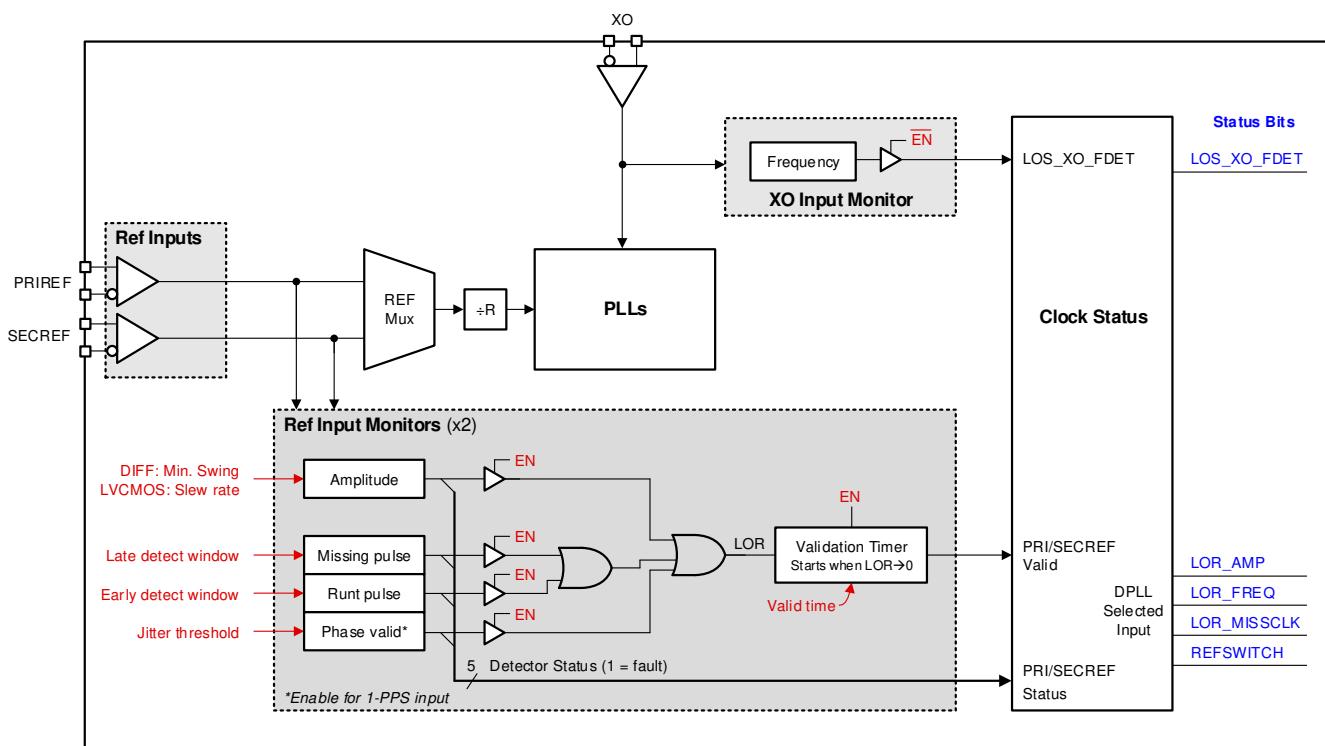

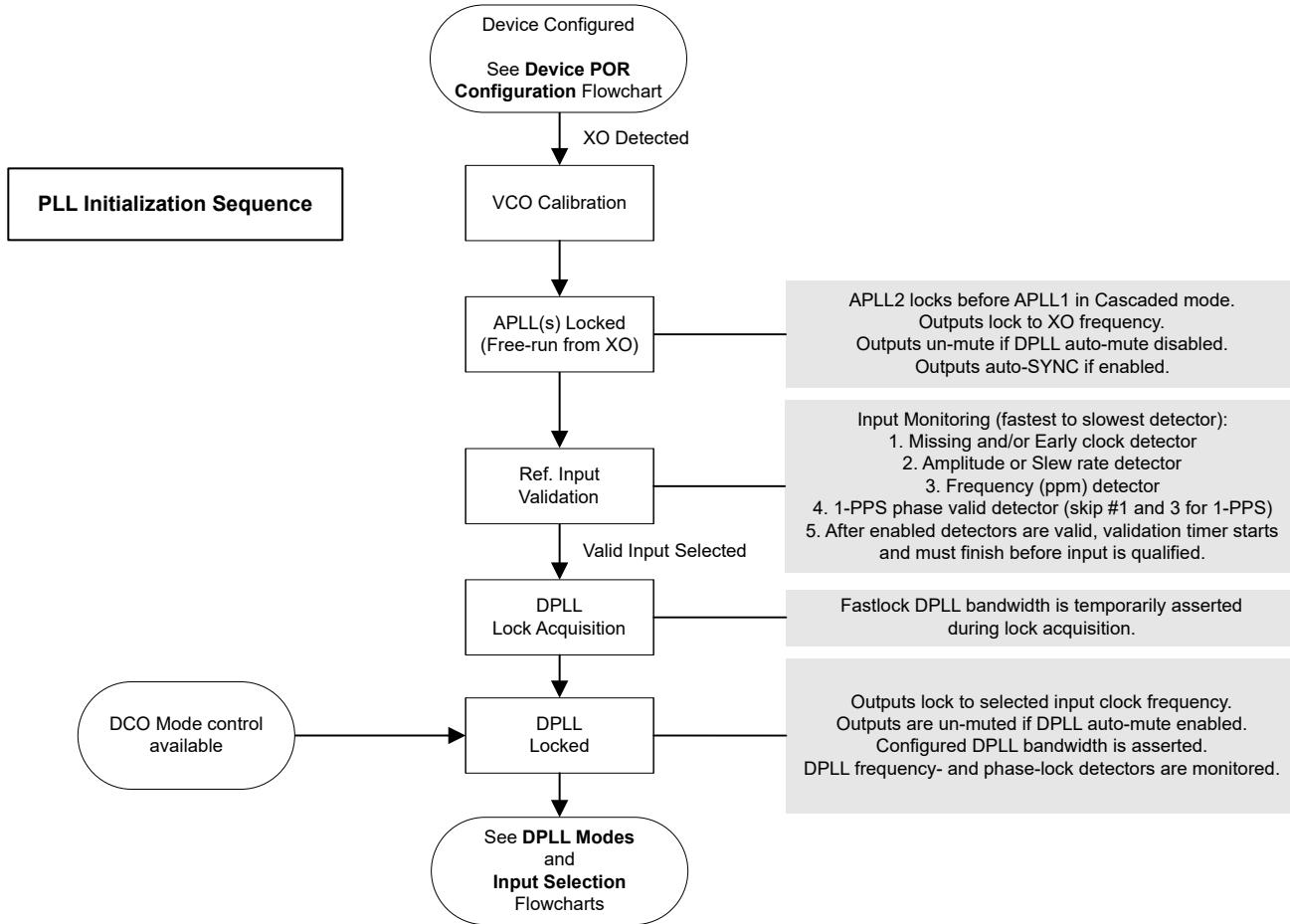

LMK05318B-Q1 には 2 つのリファレンス入力、1 つのデジタル PLL (DPLL)、VCO を内蔵した 2 つのアナログ PLL (APLL)、8 の出力クロックがあり、RMS 位相ジッタが APLL1 から標準値 50fs、APLL2 から標準値 125fs です。このデバイスの超低ジッタおよび高い PSNR により、高速シリアルリンクにおけるビット誤り率 (BER) を低減できます。

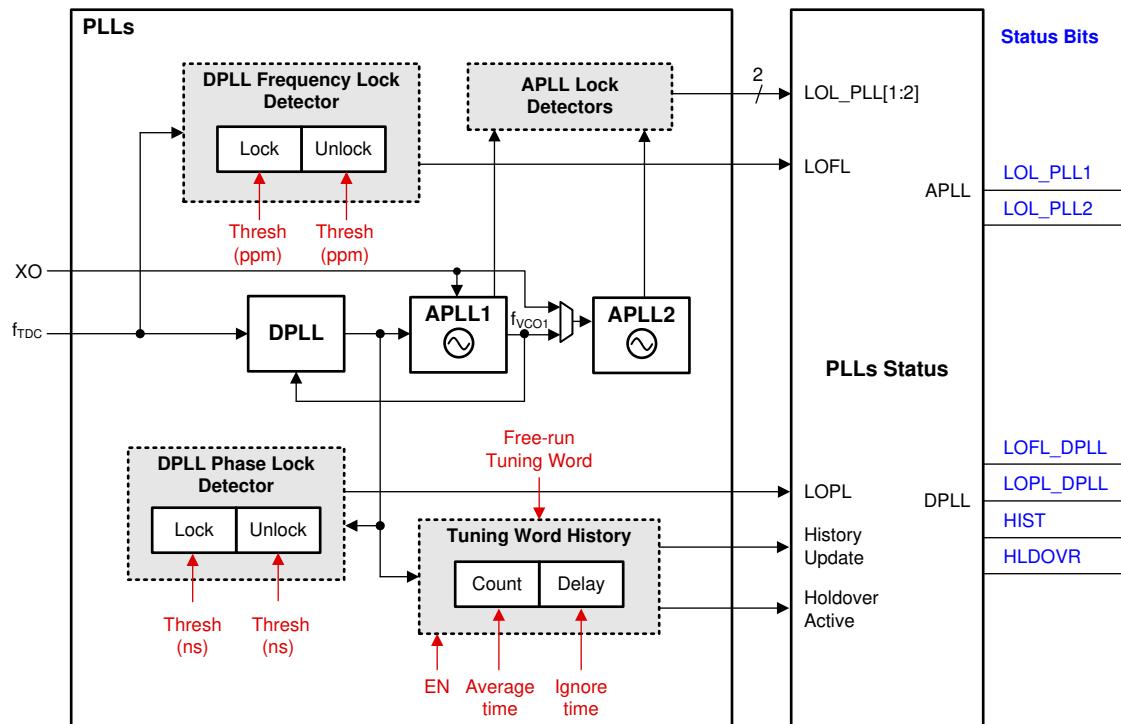

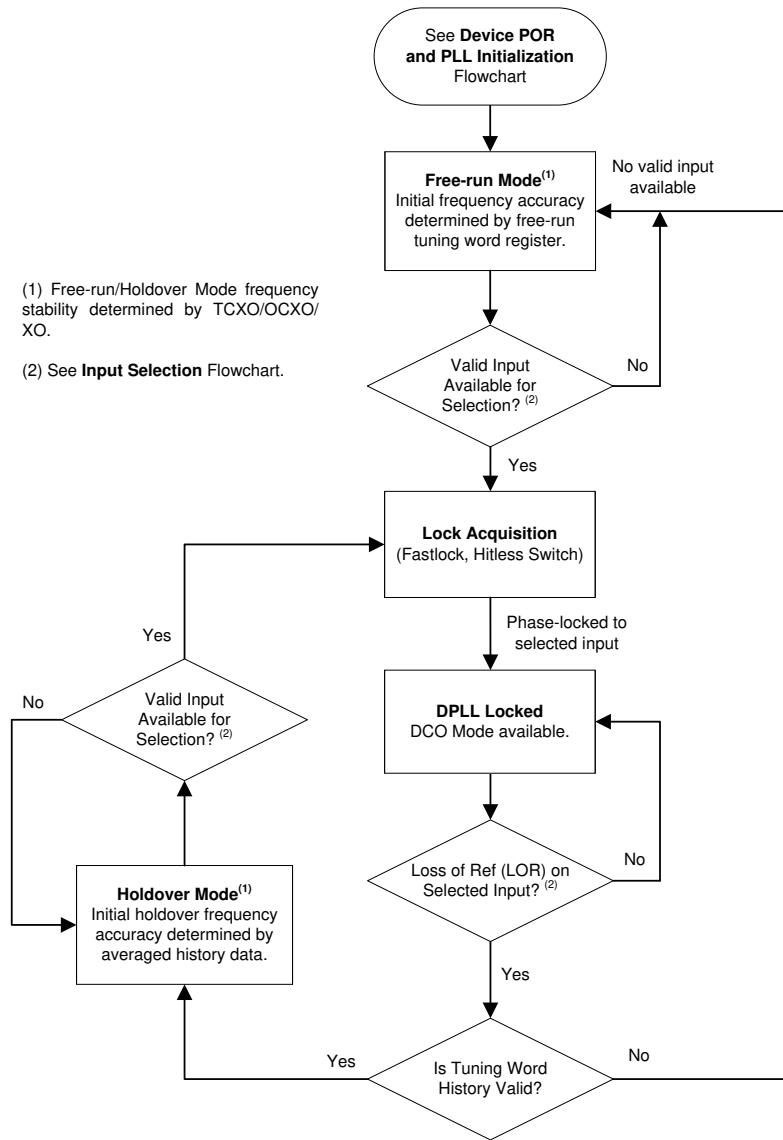

APLL1 は、非常に高い選択度を持つ超高性能 BAW VCO (VCBO)を使用しており、そのため外部発信器 (XO) 入力クロックの位相ノイズや周波数に依存しません。これにより全体の設計コストが最小化され、アプリケーションのフリーランおよびホールドオーバー時の周波数安定度要件を満たす、市販の XO、TCXO、または OCXO を使用することが可能になります。APLL1 は DPLL とカスケード接続されており、DPLL のリファレンス入力に APLL1 ドメインをロックすることで、同期クロック生成を可能にします。APLL2 は、APLL1 ドメインにロックした状態、またはフリーランの XO 入力にロックした状態のいずれかで、互いに無関係なクロック周波数を生成するために使用できます。

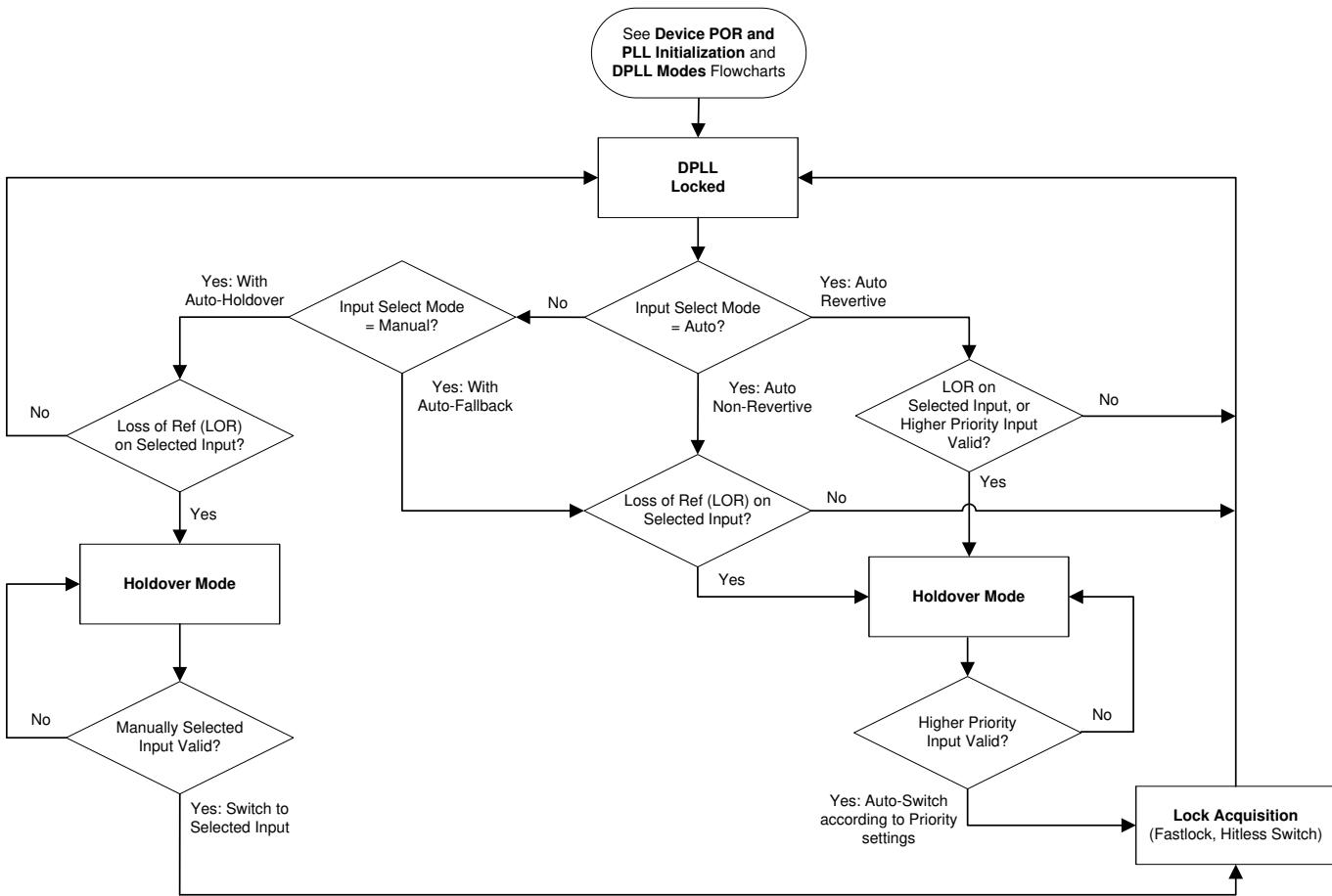

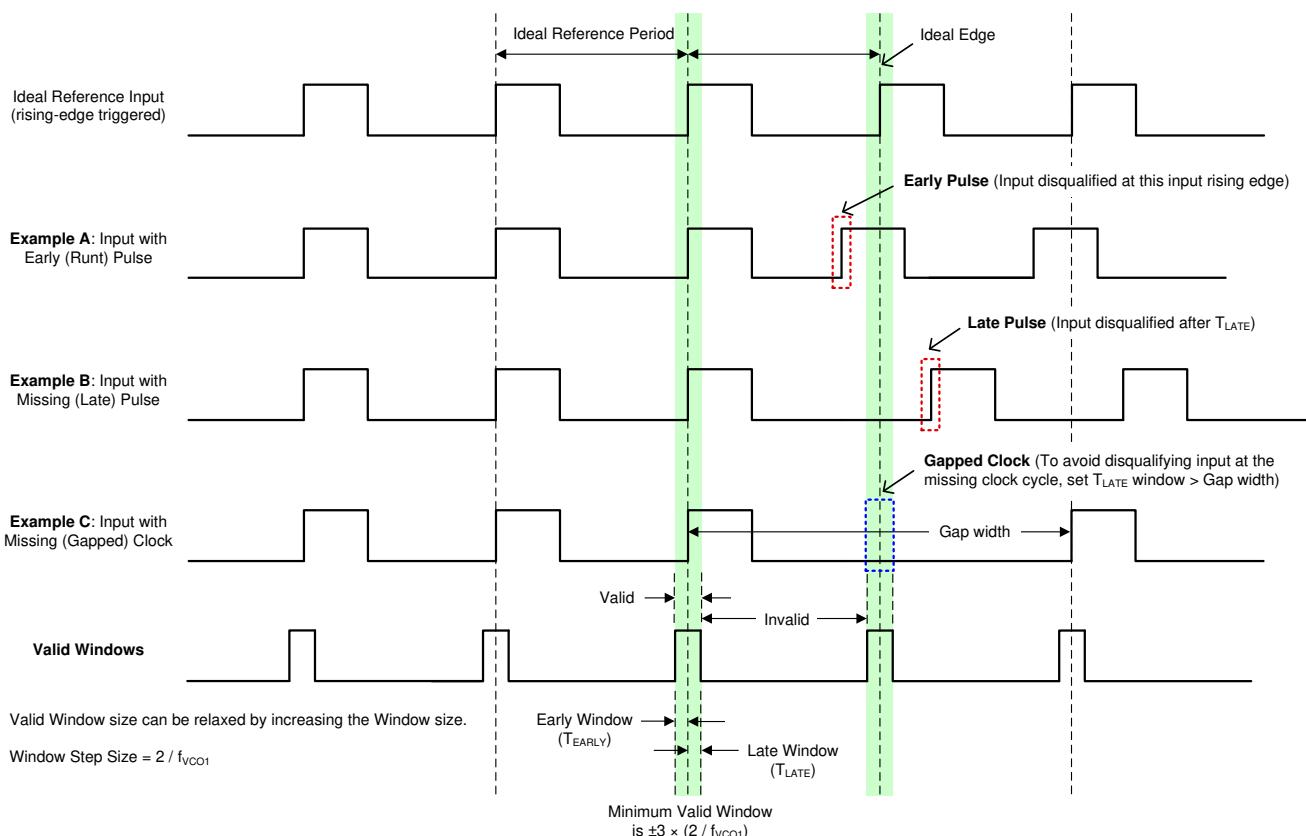

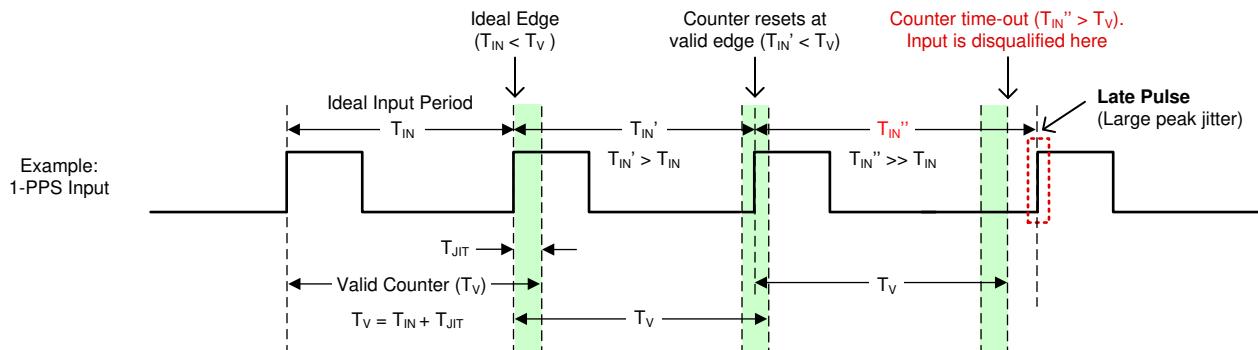

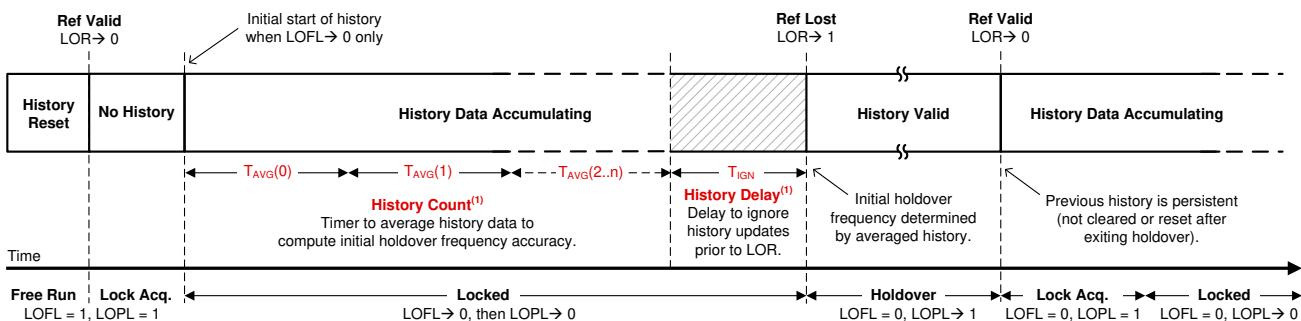

DPLL リファレンス入力マルチプレクサは、ソフトウェアまたはピン制御による、自動入力選択または手動入力選択をサポートしています。このデバイスは、独自の位相キャンセレーションによりヒットレス スイッチングを実現し、位相過渡性能を向上します (標準値 $\pm 50\text{ps}$ )。リファレンスクロック入力モニタリング ブロックはクロック入力を監視し、基準喪失(LOR)が検出された場合に、ヒットレス切り替えまたはホールドオーバーを実行します。LOR(基準喪失)状態は、入力モニタに設定されたしきい値制限のいずれかに違反した場合に検出されます。これには、振幅、、パルス欠落、ラントパルス、および 1PPS (1 秒パルス) 検出が含まれます。各入力検出器のスレッショルド制限は、クロック入力ごとに設定および有効化できます。チューニング ワード履歴モニタ機能により、ホールドオーバーへ移行した際の初期出力周波数精度は、ロック中の履歴平均周波数によって決定され、LOR 時の周波数および位相の乱れを最小限に抑えることができます。

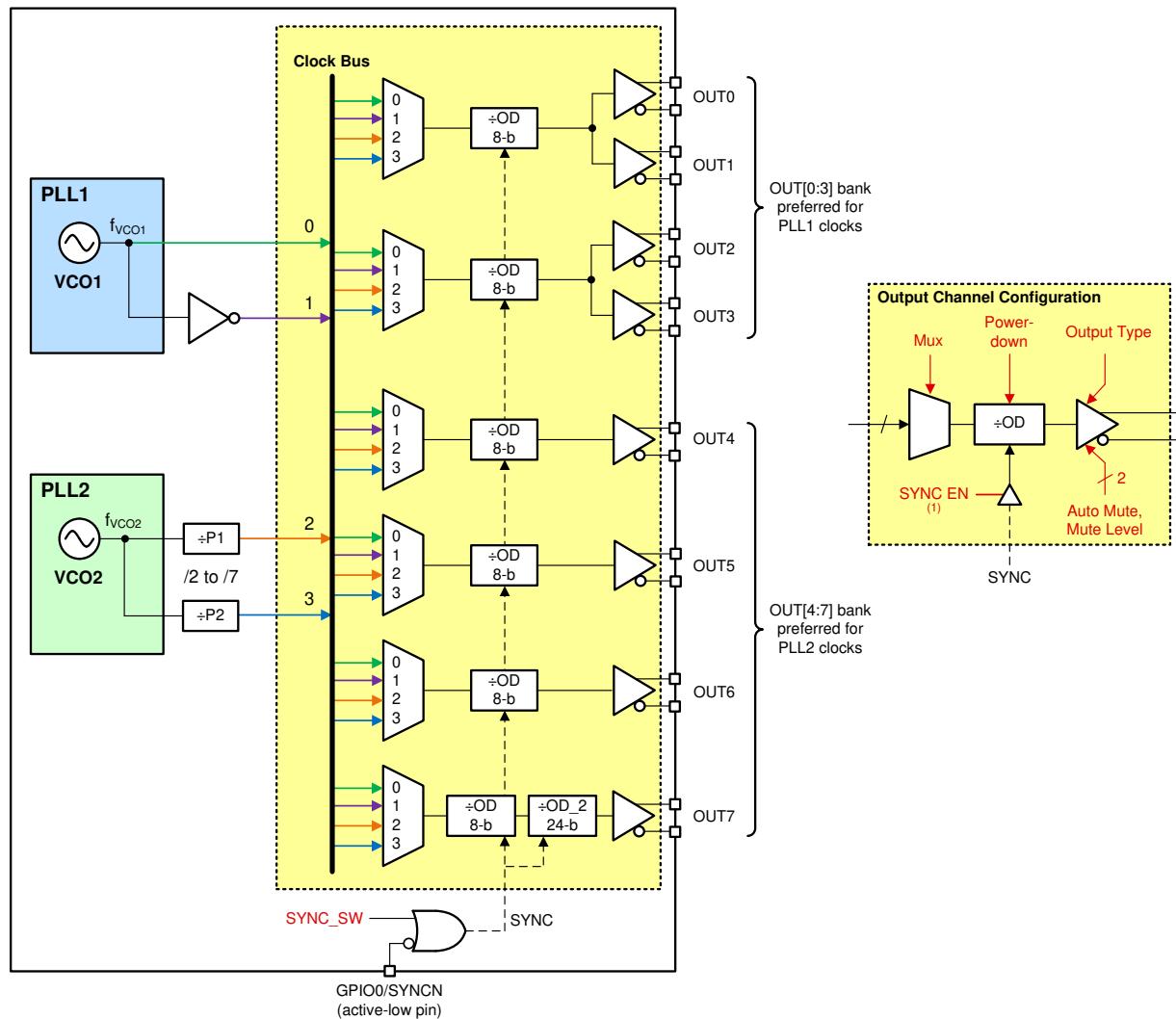

プログラマブル ドライバにより 8 の出力に対応しているため、最大 8 の差動クロック、または差動クロックと最大 4 つの 1.8V LVC MOS ペア (ペアごとに 2 つの出力) を使用できます。出力クロックは、出力チャネル マルチプレクサにより APLL/VCO 領域から生成できます。出力デバイダには SYNC 機能があり、複数の出力を位相整列できます。1PPS 出力は、出力 7 (OUT7) でサポートされています。

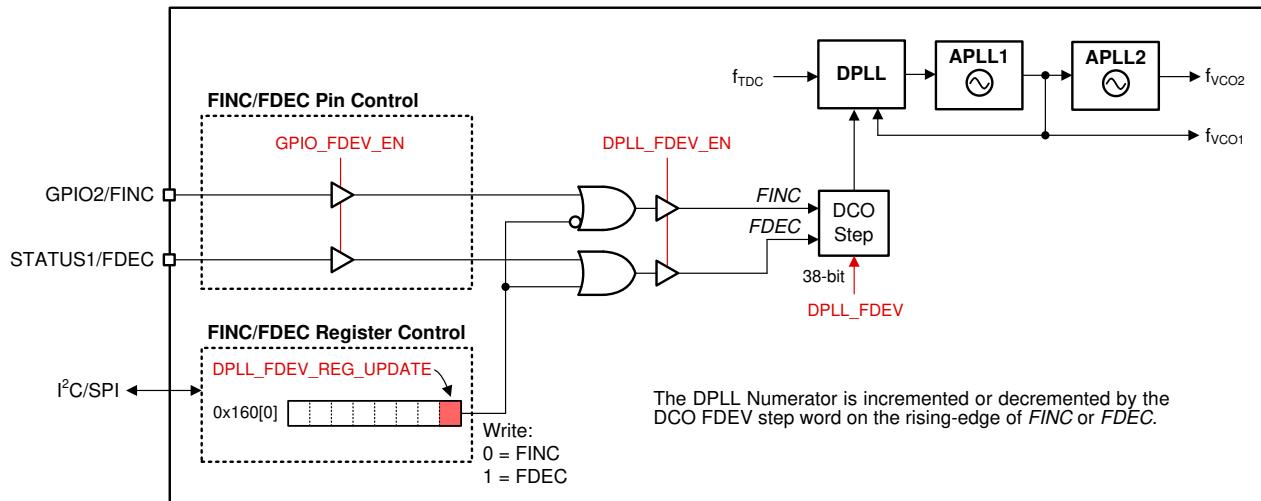

IEEE 1588PTP のペリフェラルクロックや他のクロック ステアリング用途をサポートするため、DPLL は DCO モードもサポートしており、外部ソフトウェアまたはピン制御によって、0.001ppb (10 億分の 1) 未満の周波数分解能で周波数および位相を高精度に調整できます。

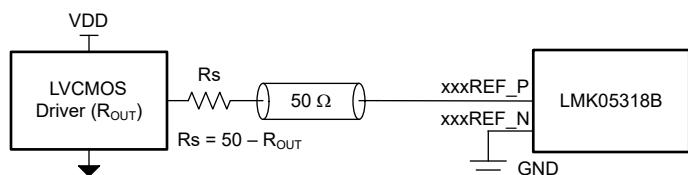

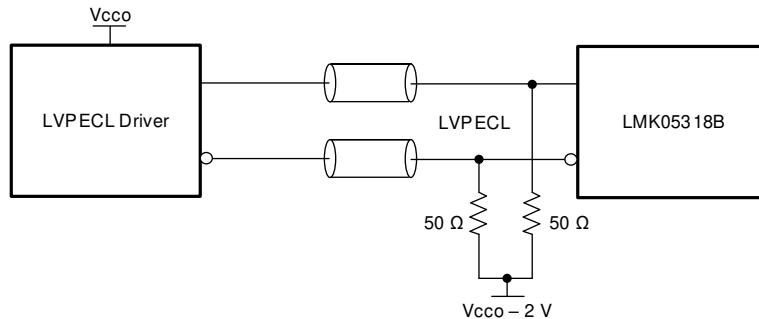

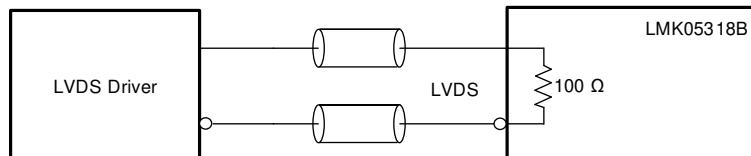

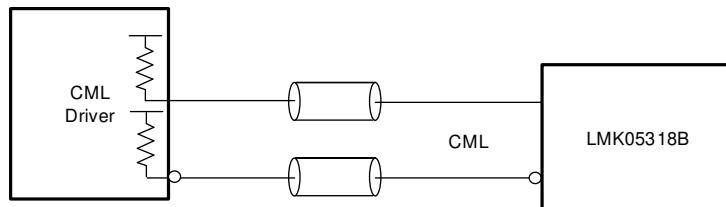

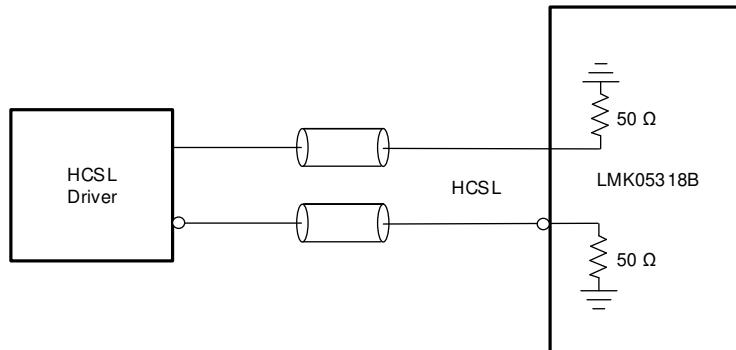

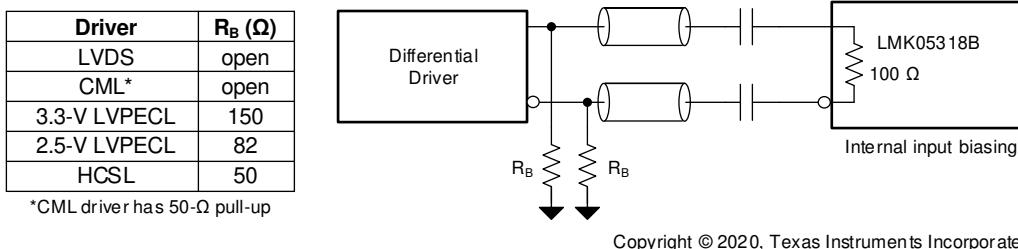

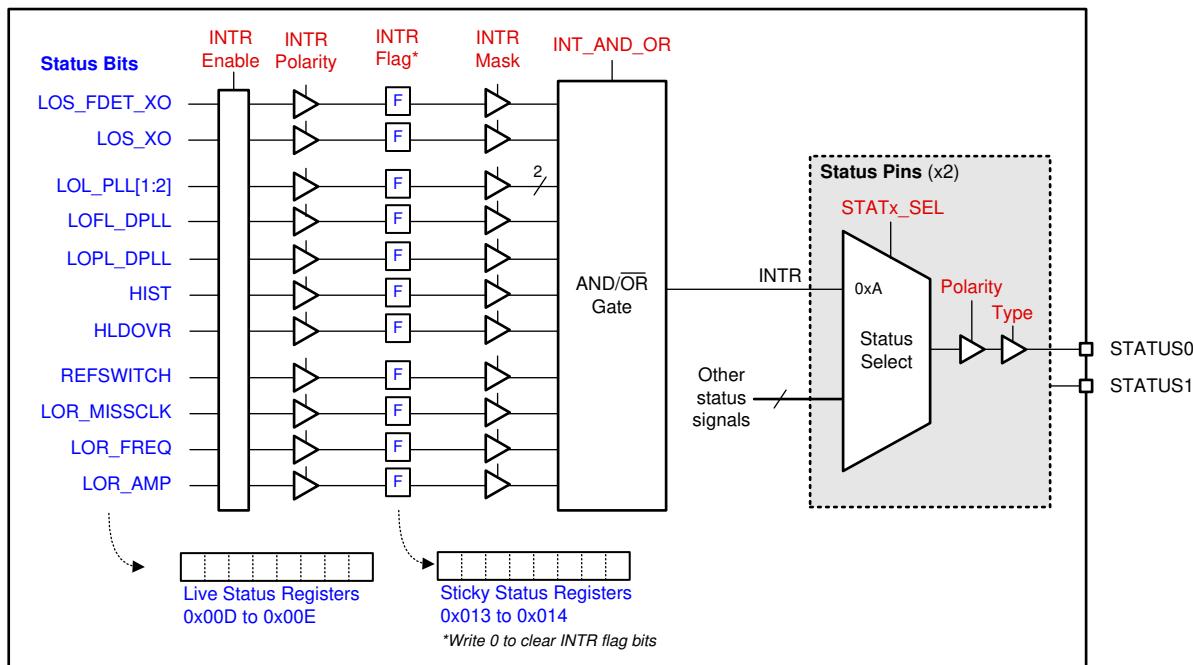

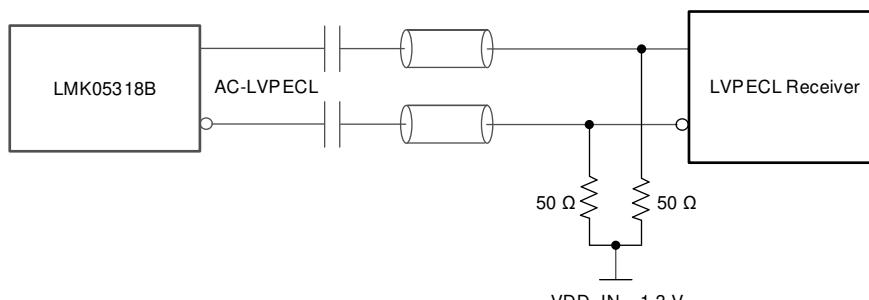

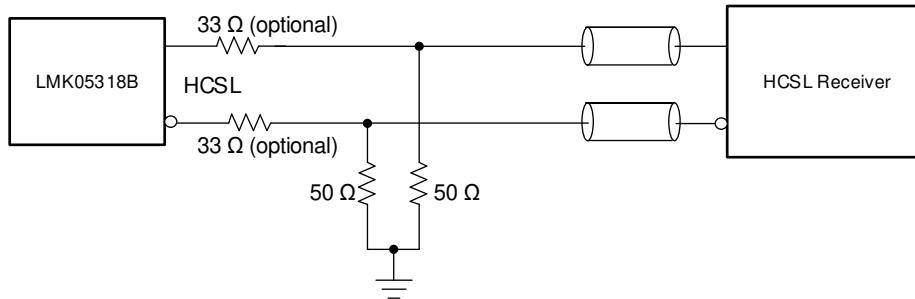

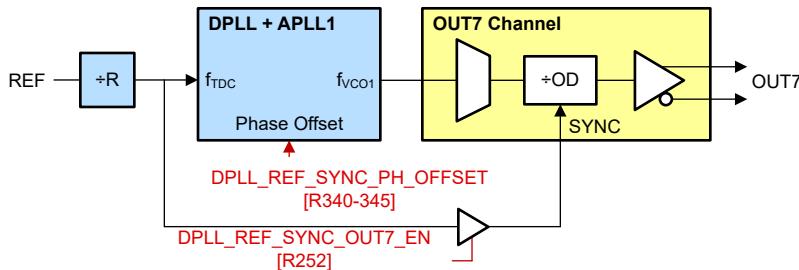

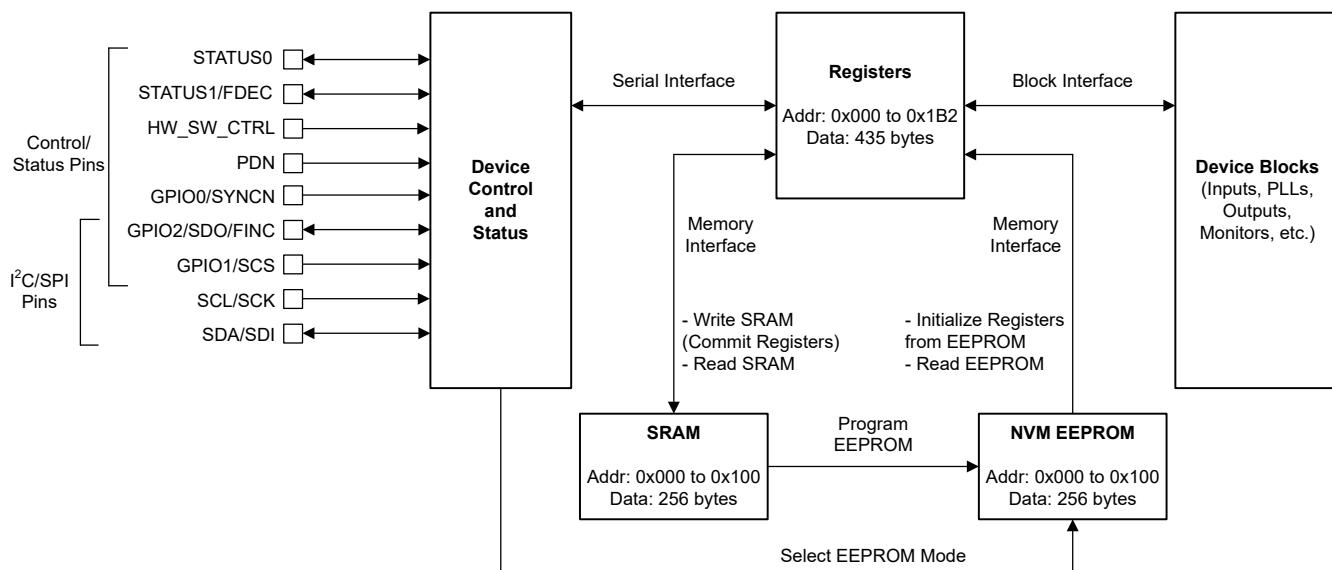

このデバイスは I<sup>2</sup>C または SPI を介して完全にプログラム可能であり、工場出荷時に事前プログラムされ、必要に応じてシステム内書き換えが可能な内部 EEPROM を用いて、カスタムの起動周波数設定をサポートします。クロック入力および PLL のモニタリング状態は、ステータス ピンや割り込みレジスタを通じて確認でき、完全な診断機能を提供します。