# LMK3H0102 リファレンスレス 2 差動または 5 シングルエンド出力 PCIe Gen 1 ~7 準拠 プログラマブル BAW クロック ジェネレータ

## 1 特長

- BAW 共振器を内蔵、外部リファレンスは不要

- フレキシブルな周波数生成:

- 2 チャネル分圧器: 2.5MHz ~ 400MHz の範囲で

最大 3 つの異なる出力周波数

- 最大 200MHz までの LVCMOS 出力をサポート:

1.8V、2.5V、または 3.3V

- OUT0 ピンおよび OUT1 ピン上で AC-LVDS、

DC-LVDS、LP-HCSL、LVCMOS の組み合わせ

- 追加の LVCMOS 出力により最大 5 つの

LVCMOS クロックを生成可能

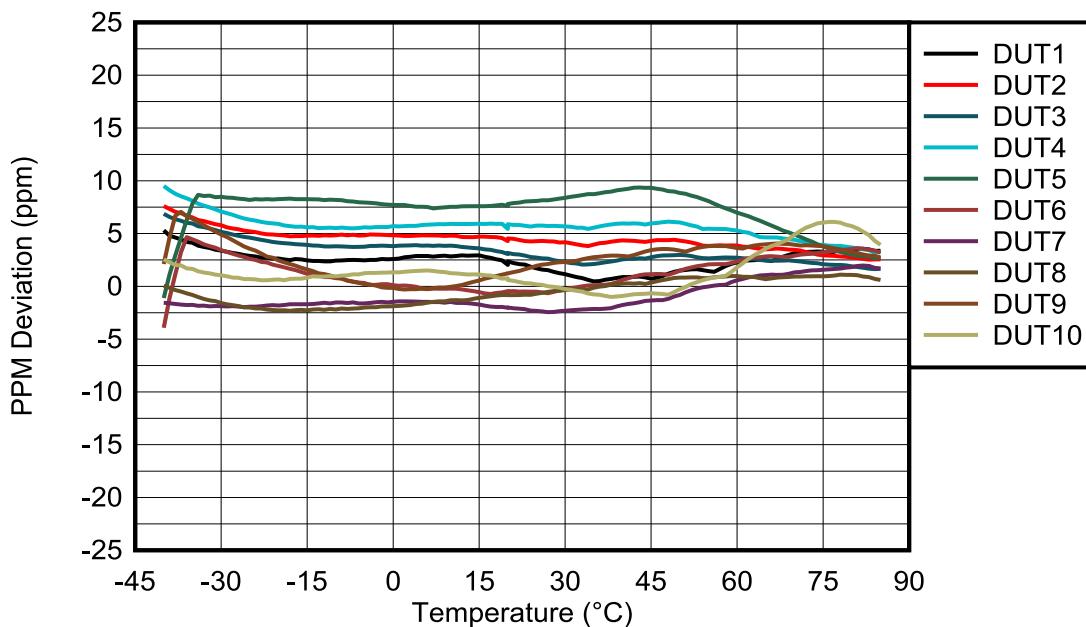

- 総出力周波数安定性:  $\pm 25\text{ppm}$

- 2 つの機能モード:  $\text{I}^2\text{C}$  または事前にプログラムされた

**OTP**

- 完全に構成可能な  $\text{I}^2\text{C}$  アドレス

- PCIe Gen 1 ~ Gen 7 準拠: 共通クロック (SSC、

SRNS、SRIS あり / なし)

- 非常に小さい PCIe ジッタ (SSC あり):

- PCIe Gen 3 の共通クロックのジッタ: 135.3fs 以下

(PCIe の上限は 1ps)

- PCIe Gen 4 の共通クロックのジッタ: 135.3fs 以下

(PCIe の上限は 500fs)

- PCIe Gen 5 の共通クロックのジッタ: 57.5fs 以下

(PCIe の上限は 150fs)

- PCIe Gen 6 の共通クロックのジッタ: 34.5fs 以下

(PCIe の上限は 100fs)

- PCIe Gen 7 の共通クロックのジッタ: 29.6fs 以下

(PCIe の上限は 67fs)

- プログラム可能な SSC 変調深度

- 事前プログラム済み: -0.1%、-0.25%、-0.3%

、および -0.5% のダウンスプレッド (200MHz FOD

周波数)

- 抵抗によるプログラミングが可能: -0.1% ~ -3% の

ダウンスプレッド、または  $\pm 0.05\%$  ~  $\pm 1.5\%$  のセン

ター スプレッド

- 電源電圧: 1.8V ~ 3.3V

- LP-HCSL 出力において、500kHz のスイッチング ノイ

ズで -93.1dBc の PSNR を提供する内蔵 LDO

- スタートアップ時間: <1.5ms

- 出力間スキュー: <50ps

- フェイルセーフ デジタル入力ピン

## 2 アプリケーション

- PCIe Gen 1 ~ Gen 7 のクロック生成

- サーバー マザーボード

- NIC、SmartNIC

- ハードウェア アクセラレータ

- マルチファンクション プリンタ

- PCIe SSD

- アドインカード、PCIe 拡張カード

## 3 説明

LMK3H0102 は、スペクトラム拡散クロック (SSC) をサポートする、2 出力 PCIe Gen 1 ~ Gen 7 準拠のリファレンスレス クロック ジェネレータです。このデバイスは、テキサス・インスツルメンツ独自のバルク弾性波 (BAW) 技術に基づいており、水晶振動子や外部クロックリファレンスを用いることなく、 $\pm 25\text{ppm}$  のクロック出力を供給します。このデバイスは、2 つの SSC クロック、2 つの非 SSC クロック、または 1 つの SSC クロックと 1 つの非 SSC クロックを同時に供給できます。このデバイスは、SSC ありまたは SSC なしの共通クロック、SRNS (Separate Reference No Spread)、SRIS (Separate Reference Independent Spread) など、Gen 1 から Gen 7 までの PCIe に完全準拠しています。

このデバイスは、ピンや  $\text{I}^2\text{C}$  インターフェイスを介して簡単に構成できます。デバイスへの電力供給には、外付けの DC/DC 回路を使用できます。電源のフィルタ処理と DC/DC 回路からの電源供給に関する詳細なガイドラインについては、「[電源に関する推奨事項](#)」を参照してください。

それぞれの LMK3H0102Axxx 構成の OTP のデフォルト設定については、『[LMK3H0102 構成ガイド](#)』を参照してください。

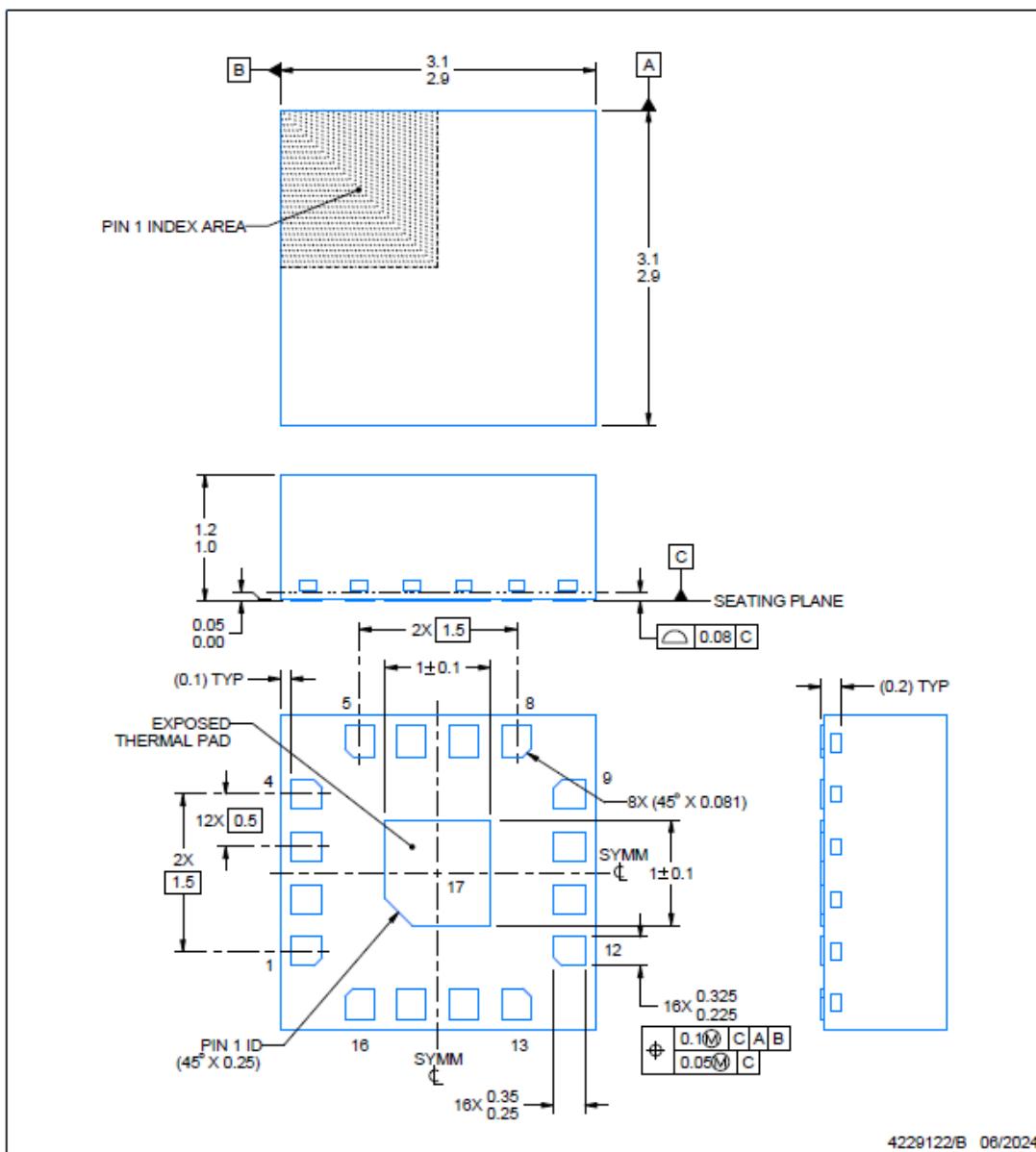

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------|----------------------|--------------------------|

| LMK3H0102 | RER (TQFN, 16)       | 3.0mm × 3.0mm            |

- (1) 利用可能なすべてのパッケージについては、「[メカニカル、パッケージ、および注文情報](#)」を参照してください。

(2) パッケージサイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

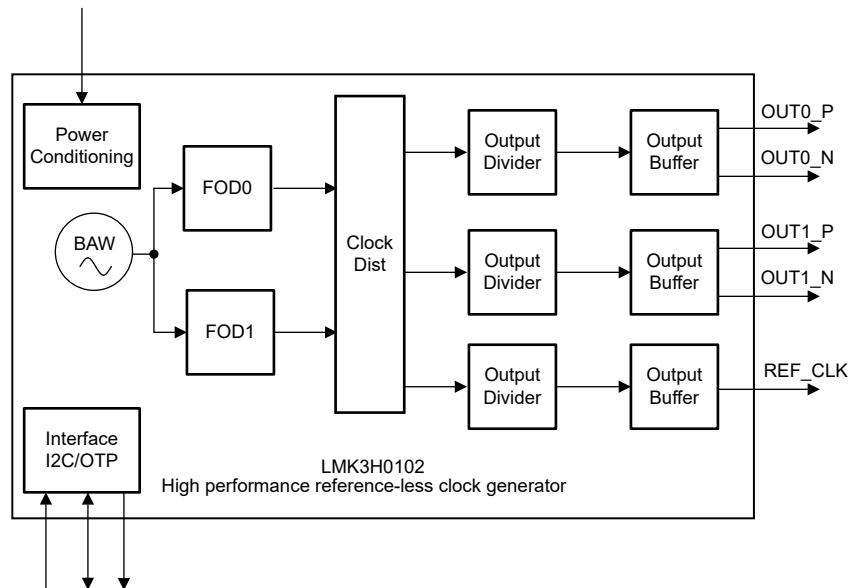

概略ブロック図

## 目次

|                                 |           |                               |           |

|---------------------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>                     | <b>1</b>  | 7.4 デバイスの機能モード                | <b>23</b> |

| <b>2 アプリケーション</b>               | <b>1</b>  | 7.5 プログラミング                   | <b>31</b> |

| <b>3 説明</b>                     | <b>1</b>  | <b>8 デバイスのレジスタ</b>            | <b>34</b> |

| <b>4 ピン構成および機能</b>              | <b>4</b>  | 8.1 レジスタ マップ                  | <b>34</b> |

| <b>5 仕様</b>                     | <b>6</b>  | <b>9 アプリケーションと実装</b>          | <b>45</b> |

| 5.1 絶対最大定格                      | 6         | 9.1 アプリケーション情報                | 45        |

| 5.2 ESD 定格                      | 6         | 9.2 代表的なアプリケーション              | 45        |

| 5.3 推奨動作条件                      | 6         | 9.3 電源に関する推奨事項                | 55        |

| 5.4 熱に関する情報                     | 7         | 9.4 レイアウト                     | 56        |

| 5.5 電気的特性                       | 7         | <b>10 デバイスおよびドキュメントのサポート</b>  | <b>57</b> |

| 5.6 I <sup>2</sup> C インターフェイス仕様 | 13        | 10.1 ドキュメントのサポート              | 57        |

| <b>6 パラメータ測定情報</b>              | <b>15</b> | 10.2 ドキュメントの更新通知を受け取る方法       | 57        |

| 6.1 出力フォーマットの構成                 | 15        | 10.3 サポート・リソース                | 57        |

| 6.2 差動電圧測定に関する用語                | 16        | 10.4 商標                       | 57        |

| <b>7 詳細説明</b>                   | <b>17</b> | 10.5 静電気放電に関する注意事項            | 57        |

| 7.1 概要                          | 17        | 10.6 用語集                      | 57        |

| 7.2 機能ブロック図                     | 18        | <b>11 改訂履歴</b>                | <b>57</b> |

| 7.3 機能説明                        | 18        | <b>12 メカニカル、パッケージ、および注文情報</b> | <b>59</b> |

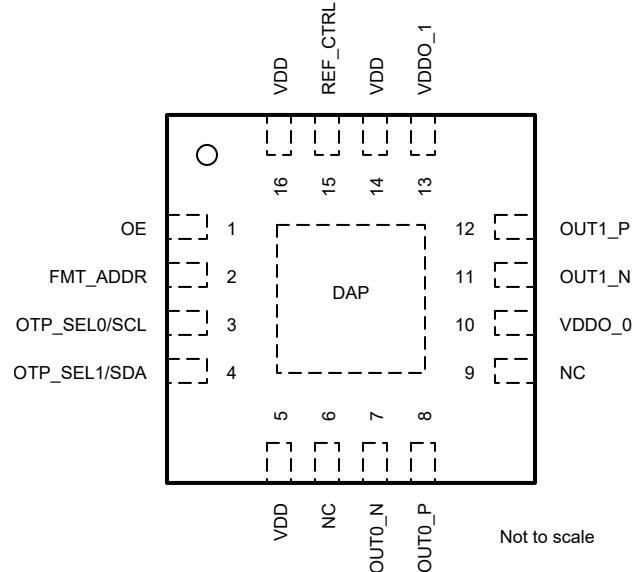

## 4 ピン構成および機能

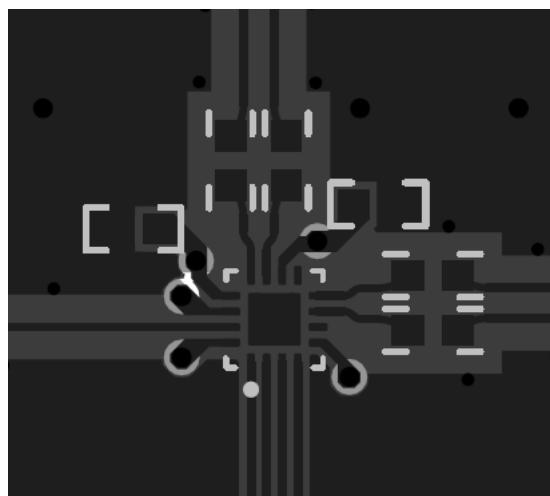

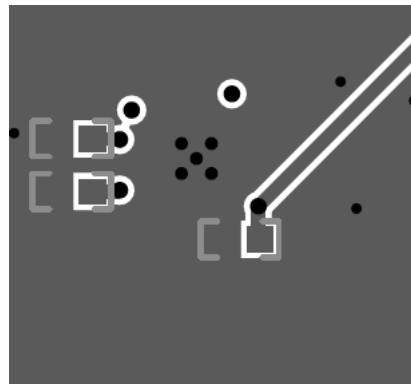

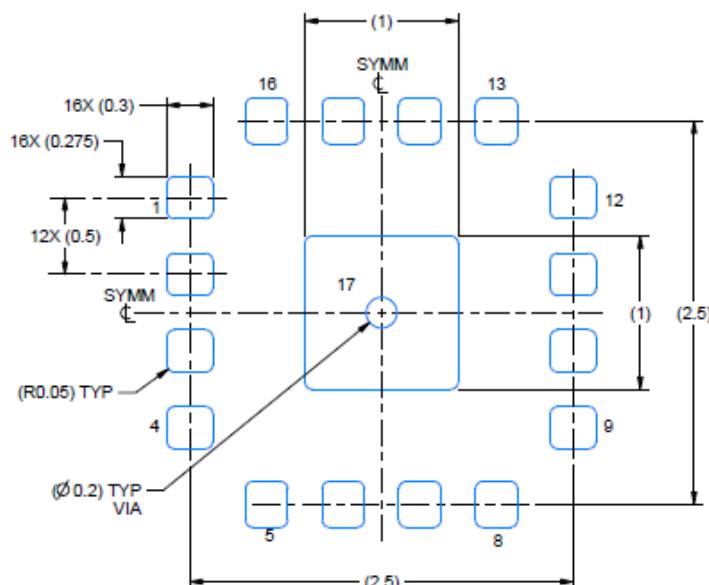

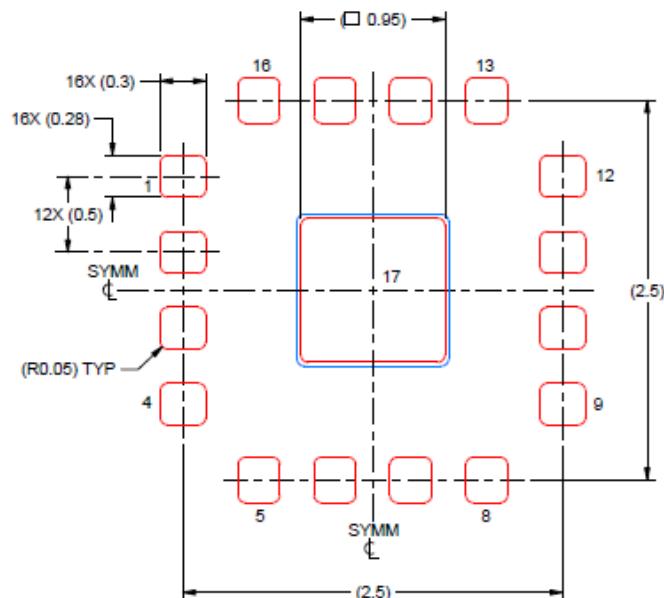

図 4-1. LMK3H0102 16 ピン TQFN (上面図)

表 4-1. ピンの機能

| ピン                    |       | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                |

|-----------------------|-------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                    | 番号    |                    |                                                                                                                                                                                                                                                                                                                   |

| OUT0_P、OUT0_N         | 8、7   | O                  | クロック出力 0。LP-HCSL (85Ω または 100Ω)、LVDS または 1.8V、2.5V、または 3.3V LVCMOS をサポートしています。                                                                                                                                                                                                                                    |

| OUT1_P、OUT1_N         | 12、11 | O                  | クロック出力 1。LP-HCSL (85Ω または 100Ω)、LVDS または 1.8V、2.5V、または 3.3V LVCMOS をサポートしています。                                                                                                                                                                                                                                    |

| REF_CTRL<br>(REF_CLK) | 15    | I/O                | <p>多機能ピン。パワーアップ時、このピンの状態がラッチされて、ピン 2、ピン 3、ピン 4 の機能が選択されます。パワーアップ前、I2C モードの場合は Low またはフローティングのままにし、OTP モードの場合は High にします。パワーアップ後、このピンは、追加の LVCMOS 出力 (REF_CLK)、アクティブ High の CLK_READY 信号、または ディスエーブルとしてプログラムできます。</p> <p>詳細については、「<a href="#">REF_CTRL の動作</a>」を参照してください。</p> <p>このピンには、880kΩ の内部プルダウン抵抗があります。</p> |

| OE                    | 1     | I                  | <p>出力イネーブル。アクティブ Low。2 ステートロジック入力ピン。</p> <p>このピンには 75kΩ の内部プルダウン抵抗があります。</p> <p>このピンは、OUT0 のみ、または OUT0 と OUT1 の両方を制御できます。詳細については、「<a href="#">出力イネーブル</a>」を参照してください。</p> <ul style="list-style-type: none"> <li>Low / フローティング: OUT0 および OUT1 はイネーブル</li> <li>High: OUT0 および OUT1 はディスエーブル</li> </ul>              |

**表 4-1. ピンの機能 (続き)**

| ピン                            |           | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------|-----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                            | 番号        |                    |                                                                                                                                                                                                                                                                                                                                                                       |

| FMT_ADDR                      | 2         | I                  | <p>多機能ピン。機能は、パワーアップ時に REF_CTRL (ピン 15) によって決定されます。詳細については、「<a href="#">OTP モード</a>」と「<a href="#">I2C モード</a>」を参照してください。このピンには、880kΩ の内部プルダウン抵抗があります。</p> <ul style="list-style-type: none"> <li><b>I2C モード:</b>このピンでは、I2C アドレス、OUT1 の出力イネーブルとしての機能、または機能なしの、いずれかが選択可能です。</li> <li><b>OTP モード:</b>このピンでは、出力フォーマット、OUT1 の出力イネーブルとしての機能、または機能なしの、いずれかが設定可能です。</li> </ul> |

| OTP_SEL0/SCL、<br>OTP_SEL1/SDA | 3, 4      | I, I/O             | <p>多機能ピン。機能は、パワーアップ時に REF_CTRL (ピン 15) によって決定されます。詳細については、「<a href="#">OTP モード</a>」と「<a href="#">I2C モード</a>」を参照してください。これらのピンには、880kΩ の内部プルダウン抵抗があります。</p> <ul style="list-style-type: none"> <li><b>I2C モード:</b>これらのピンは、I2C クロックとデータの接続です。</li> <li><b>OTP モード:</b>これらのピンは OTP ページを選択します。</li> </ul>                                                                 |

| VDD                           | 5, 14, 16 | P                  | 1.8V、2.5V、または 3.3V のデバイス電源。0.1μF コンデンサは、このピンのできるだけ近くに配置する必要があります。LMK3H0102V18 の場合、このピンには 1.8V のみを供給します。                                                                                                                                                                                                                                                               |

| VDDO_0、VDDO_1                 | 10, 13    | P                  | 1.8V、2.5V、または 3.3V の OUT0 と OUT1 電源。VDD が 1.8V または 2.5V の場合、VDDO ピンは VDD と同じ電圧でなければなりません。0.1μF コンデンサは、このピンのできるだけ近くに配置する必要があります。分割電源を使用する場合の適切な実装については、 <a href="#">パワーアップシーケンシング</a> を参照してください。                                                                                                                                                                       |

| NC                            | 6, 9      | 該当なし               | 接続なし。ピンは GND または VDD に接続するか、「 <a href="#">絶対最大定格</a> 」に記載されている電源電圧範囲内で任意の電位に接続することができます。                                                                                                                                                                                                                                                                              |

| DAP                           | 17        | G                  | GND                                                                                                                                                                                                                                                                                                                                                                   |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|           |                                                                | 最小値  | 最大値                | 単位 |

|-----------|----------------------------------------------------------------|------|--------------------|----|

| $V_{DD}$  | デバイス電源電圧                                                       | -0.3 | 3.9                | V  |

| $V_{DDO}$ | 出力電源電圧                                                         | -0.3 | 3.9                | V  |

| $V_{IN}$  | ロジック入力電圧 ( $V_{DD} = V_{DDO} = -0.3V \sim -3.9V$ )             | -0.3 | 3.9                | V  |

| $V_{OUT}$ | OUTx_P ピンと OUTx_N ピンに印加される電圧 (出力が High または Low の場合)            | -0.3 | $V_{DDO\_x} + 0.3$ | V  |

|           | OUTx_P ピンと OUTx_N ピンに印加される電圧 (出力が LVCMOS トライステートの場合)           | -0.3 | 1.89               | V  |

|           | OUTx_P ピンと OUTx_N ピンに印加される電圧 (出力が LP-HCSL または LVDS トライステートの場合) | -0.3 | 1.5                | V  |

| $T_J$     | 接合部温度                                                          |      | 105                | °C |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      |                                                              | 値          | 単位 |

|-------------|------|--------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup> | $\pm 2000$ | V  |

|             |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JS-002 に準拠、すべてのピン <sup>(2)</sup>    | $\pm 500$  |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

$V_{DD} = V_{DDO} = 1.8V, 2.5V, \text{または } 3.3V \pm 5\%$ 、 $T_A = T_{A,min} \sim T_{A,max}$

|            |                                     | 最小値   | 公称値 | 最大値   | 単位 |

|------------|-------------------------------------|-------|-----|-------|----|

| $V_{DD}$   | デバイス電源電圧                            | 1.71  | 1.8 | 1.89  | V  |

|            |                                     | 2.375 | 2.5 | 2.625 | V  |

|            |                                     | 3.135 | 3.3 | 3.465 | V  |

| $V_{DDO}$  | 出力電源電圧                              | 1.71  | 1.8 | 1.89  | V  |

|            |                                     | 2.375 | 2.5 | 2.625 | V  |

|            |                                     | 3.135 | 3.3 | 3.465 | V  |

| $T_A$      | 周囲温度                                | -40   |     | 85    | °C |

| $T_J$      | 接合部温度                               | -40   |     | 105   | °C |

| $t_{ramp}$ | 電源ランプ時間。 $V_{DD} = 1.8V$            | 0.05  |     | 5     | ms |

| $t_{ramp}$ | 電源ランプ時間。 $V_{DD} = 2.5V$ または $3.3V$ | 0.05  |     | 5     | ms |

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup>        |                   | LMK3H0102 | 単位   |

|-----------------------------|-------------------|-----------|------|

|                             |                   | RER (QFN) |      |

|                             |                   | 16 ピン     |      |

| $R_{\theta JA}$             | 接合部から周囲への热抵抗      | 69.8      | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への热抵抗 | 56.5      | °C/W |

| $R_{\theta JB}$             | 接合部から基板への热抵抗      | 38.6      | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 2.1       | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 38.5      | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース(底面)への热抵抗 | 10.3      | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体および IC の热評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

$V_{DD} = V_{DD0} = 1.8V$ 、 $2.5V$ 、または  $3.3V \pm 5\%$ 、 $T_A = T_{A,\text{min}} \sim T_{A,\text{max}}$

| パラメータ                     | テスト条件                                        | 最小値                                                                          | 標準値 | 最大値 | 単位      |

|---------------------------|----------------------------------------------|------------------------------------------------------------------------------|-----|-----|---------|

| <b>周波数安定性</b>             |                                              |                                                                              |     |     |         |

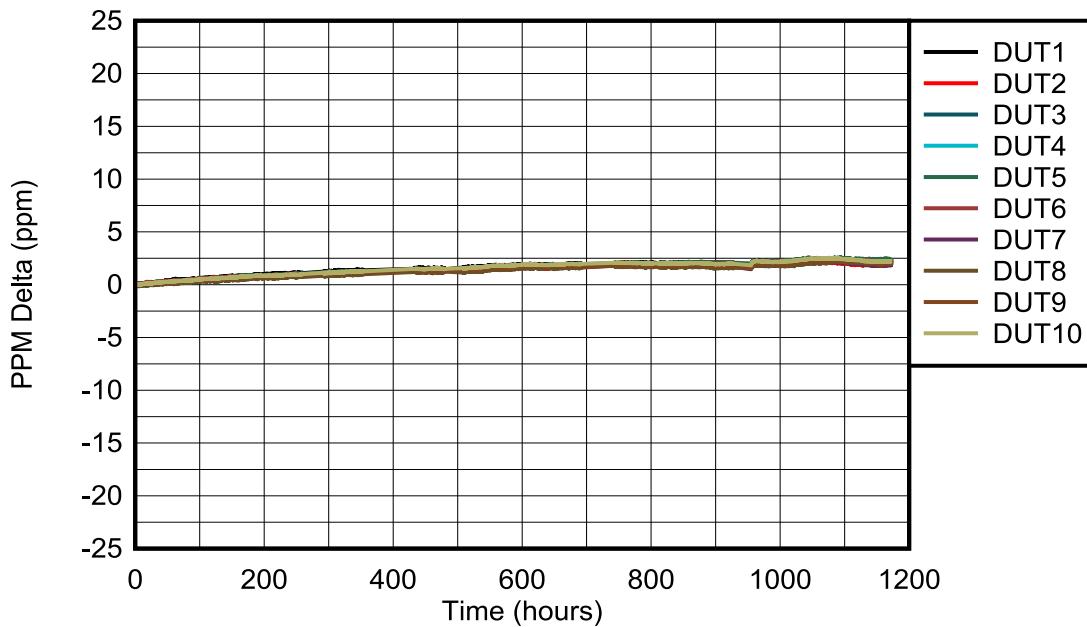

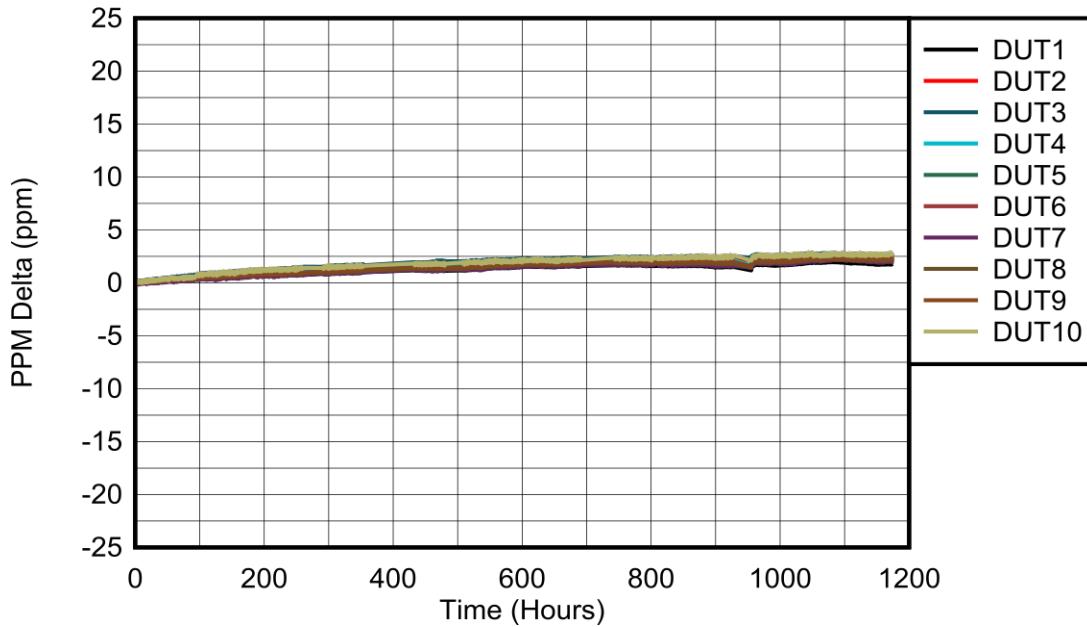

| $\Delta f_{\text{total}}$ | 総合的な周波数安定性                                   | 温度変化、 $25^{\circ}\text{C}$ での 10 年の経年劣化、半田付けによる変動、ヒステリシス、初期周波数精度など、すべての要因を含む | -25 | 25  | ppm     |

| <b>LP-HCSL クロック出力特性</b>   |                                              |                                                                              |     |     |         |

| $f_{\text{out}}$          | 出力周波数                                        |                                                                              | 2.5 | 400 | MHz     |

| $V_{\text{min}}$          | 出力 Low 電圧 (アンダーシュートを含む)                      |                                                                              | -60 | 25  | mV      |

| $V_{\text{overshoot}}$    | オーバーシュート電圧。 $V_{\text{max}} - V_{\text{OH}}$ |                                                                              |     | 150 | mV      |

| $V_{\text{OH},2.5/3.3}$   | 出力 High 電圧 $V_{DD} = 2.5V$ または $3.3V$        | コード = 0                                                                      | 563 | 625 | 688 mV  |

|                           |                                              | コード = 1                                                                      | 582 | 647 | 712 mV  |

|                           |                                              | コード = 2                                                                      | 601 | 668 | 735 mV  |

|                           |                                              | コード = 3                                                                      | 621 | 690 | 759 mV  |

|                           |                                              | コード = 4                                                                      | 641 | 712 | 783 mV  |

|                           |                                              | コード = 5                                                                      | 660 | 733 | 806 mV  |

|                           |                                              | コード = 6 (デフォルト)                                                              | 680 | 755 | 831 mV  |

|                           |                                              | コード = 7                                                                      | 699 | 777 | 855 mV  |

|                           |                                              | コード = 8                                                                      | 718 | 798 | 878 mV  |

|                           |                                              | コード = 9                                                                      | 738 | 820 | 902 mV  |

|                           |                                              | コード = 10                                                                     | 758 | 842 | 926 mV  |

|                           |                                              | コード = 11                                                                     | 777 | 863 | 949 mV  |

|                           |                                              | コード = 12                                                                     | 797 | 885 | 974 mV  |

|                           |                                              | コード = 13                                                                     | 816 | 907 | 998 mV  |

|                           |                                              | コード = 14                                                                     | 835 | 928 | 1021 mV |

|                           |                                              | コード = 15                                                                     | 855 | 950 | 1045 mV |

$V_{DD} = V_{DDO} = 1.8V, 2.5V, \text{または } 3.3V \pm 5\%, T_A = T_{A,min} \sim T_{A,max}$

| パラメータ                |                                | テスト条件                                                                       | 最小値   | 標準値 | 最大値   | 単位       |

|----------------------|--------------------------------|-----------------------------------------------------------------------------|-------|-----|-------|----------|

| $V_{OH,1.8}$         | 出力 High 電圧 $VDD = 1.8V$        | コード = 0                                                                     | 563   | 625 | 688   | mV       |

|                      |                                | コード = 1                                                                     | 582   | 647 | 712   | mV       |

|                      |                                | コード = 2                                                                     | 601   | 668 | 735   | mV       |

|                      |                                | コード = 3                                                                     | 621   | 690 | 759   | mV       |

|                      |                                | コード = 4                                                                     | 641   | 712 | 783   | mV       |

|                      |                                | コード = 5                                                                     | 660   | 733 | 806   | mV       |

|                      |                                | コード = 6 (デフォルト)                                                             | 680   | 755 | 831   | mV       |

|                      |                                | コード = 7                                                                     | 699   | 777 | 855   | mV       |

|                      |                                | コード = 8                                                                     | 718   | 798 | 878   | mV       |

|                      |                                | コード = 9                                                                     | 738   | 820 | 902   | mV       |

|                      |                                | コード = 10                                                                    | 758   | 842 | 926   | mV       |

|                      |                                | コード = 11                                                                    | 777   | 863 | 949   | mV       |

|                      |                                | コード = 12                                                                    | 797   | 885 | 974   | mV       |

|                      |                                | コード = 13                                                                    | 816   | 907 | 998   | mV       |

|                      |                                | コード = 14                                                                    | 835   | 928 | 1021  | mV       |

|                      |                                | コード = 15                                                                    | 855   | 950 | 1045  | mV       |

| $Z_{diff}$           | LP-HCSL 静的差動インピーダンス            |                                                                             | 80.75 | 85  | 91.25 | $\Omega$ |

|                      |                                |                                                                             | 95    | 100 | 105   | $\Omega$ |

| $dV/dt$              | 出力スルーレート (立ち上がりおよび立ち下がりエッジ)    | ゼロ交差点を中心に、差動波形の $-150mV \sim +150mV$ で測定されます。<br>$OUTx\_SLEW\_RATE = 0$ (1) | 2.1   | 3.1 |       | V/ns     |

|                      |                                | ゼロ交差点を中心に、差動波形の $-150mV \sim +150mV$ で測定されます。<br>$OUTx\_SLEW\_RATE = 0$     | 2.3   | 3.5 |       | V/ns     |

|                      |                                | ゼロ交差点を中心に、差動波形の $-150mV \sim +150mV$ で測定されます。<br>$OUTx\_SLEW\_RATE = 1$     | 2     | 3.2 |       | V/ns     |

|                      |                                | ゼロ交差点を中心に、差動波形の $-150mV \sim +150mV$ で測定されます。<br>$OUTx\_SLEW\_RATE = 2$     | 1.7   | 2.8 |       | V/ns     |

|                      |                                | ゼロ交差点を中心に、差動波形の $-150mV \sim +150mV$ で測定されます。<br>$OUTx\_SLEW\_RATE = 3$     | 1.4   | 2.7 |       | V/ns     |

| $\Delta dV/dt$       | 立ち上がりエッジレートと立ち下がりエッジレートの一一致    | (1) を参照                                                                     |       | 3   |       | %        |

| ODC                  | 出力デューティ サイクル                   | (1) を参照                                                                     | 47    | 53  |       | %        |

|                      |                                | $f_{out} \leq 325MHz$                                                       | 47    | 53  |       | %        |

|                      |                                | $325MHz < f_{out} \leq 400MHz$                                              | 47    | 53  |       | %        |

| $t_{skew}$           | 出力間スキュー                        | 同じ FOD、LP-HCSL 出力                                                           |       | 50  |       | ps       |

| $V_{cross}$          | 絶対交差点電圧                        | (1) を参照                                                                     | 280   | 480 |       | mV       |

| $\Delta V_{cross}$   | クロック エッジ全体における $V_{cross}$ の変動 | (1) を参照                                                                     |       | 30  |       | mV       |

| $ V_{RB} $           | リング バック電圧の絶対値                  | (1) を参照                                                                     | 100   |     |       | mV       |

| $t_{stable}$         | $V_{RB}$ が許容されるまでの時間           | (1) を参照                                                                     | 500   |     |       | ps       |

| $J_{cycle-to-cycle}$ | サイクル間ジッタ、共通クロック、SSC なし         | (1) を参照                                                                     |       | 20  |       | ps       |

| $J_{cycle-to-cycle}$ | サイクル間ジッタ、共通クロック、-0.5% SSC      | (1) を参照                                                                     |       | 25  |       | ps       |

$V_{DD} = V_{DDO} = 1.8V, 2.5V, \text{または } 3.3V \pm 5\%, T_A = T_{A,min} \sim T_{A,max}$

| パラメータ                   |                   | テスト条件   | 最小値   | 標準値  | 最大値    | 単位 |

|-------------------------|-------------------|---------|-------|------|--------|----|

| $t_{period\_abs}$       | ジッタと SSC を含む絶対周期  | (1) を参照 | 9.949 | 10   | 10.101 | ns |

| $t_{period\_avg\_CC}$   | 平均クロック周期精度、共通クロック | (1) を参照 | -100  | 2600 | ppm    |    |

| $t_{period\_avg\_SRIS}$ | 平均クロック周期精度、SRIS   | (1) を参照 | -100  | 1600 | ppm    |    |

**LVDS クロック出力特性**

|                      |                                              |                                  |      |      |       |    |

|----------------------|----------------------------------------------|----------------------------------|------|------|-------|----|

| $f_{out}$            | 出力周波数                                        |                                  | 2.5  | 400  | MHz   |    |

| $ V_{ODI} $          | 差動出力電圧の定常状態の振幅 $ V_{OUTP} - V_{OUTN} $       | 100Ω 外部終端                        | 250  | 350  | 450   | mV |

| $\Delta V_{pp-diff}$ | 相補出力状態間の差動出力電圧スイングの変化                        | 100Ω 外部終端                        |      | 50   | mV    |    |

| $V_{os}$             | 出力オフセット電圧 (同相電圧)                             | $V_{DDO} = 3.3V, 100\Omega$ 外部終端 | 1.12 | 1.2  | 1.365 | V  |

|                      |                                              | $V_{DDO} = 2.5V, 100\Omega$ 外部終端 | 1.1  | 1.2  | 1.345 | V  |

|                      |                                              | $V_{DDO} = 1.8V, 100\Omega$ 外部終端 | 0.8  | 0.97 | 1.365 | V  |

| $\Delta V_{os}$      | 相補出力状態間の $V_{os}$ の変化                        |                                  |      | 50   | mV    |    |

| $I_{SA}, I_{SB}$     | 短絡電流。ジェネレータ出力端子がジェネレータ回路の共通端子に短絡されたときの電流の大きさ |                                  | -24  | 24   | mA    |    |

| $I_{SAB}$            | 短絡電流。ジェネレータ出力端子が互いに短絡されたときの電流の大きさ            |                                  | -12  | 12   | mA    |    |

| $t_R, t_F$           | 20%~80% の差動立ち上がり / 立ち下がり時間                   | $OUTx\_SLEW\_RATE = 0$           | 195  | 323  | ps    |    |

|                      |                                              | $OUTx\_SLEW\_RATE = 1$           | 250  | 454  | ps    |    |

|                      |                                              | $OUTx\_SLEW\_RATE = 2$           | 270  | 635  | ps    |    |

|                      |                                              | $OUTx\_SLEW\_RATE = 3$           | 280  | 792  | ps    |    |

| $t_{skew}$           | 出力間スキュー                                      | 同じ FOD、LVDS 出力                   |      | 50   | ps    |    |

| ODC                  | 出力デューティ サイクル                                 |                                  | 47   | 53   | %     |    |

**LVC MOS クロック 出力特性**

|            |              |                                                         |                      |     |      |          |

|------------|--------------|---------------------------------------------------------|----------------------|-----|------|----------|

| $f_{out}$  | 出力周波数        |                                                         | 2.5                  | 200 | MHz  |          |

| $dV/dt$    | 出力スルーレート     | $V_{DDO} = 3.3V \pm 5\%, 20\% \sim 80\%$ で測定、負荷 $4.7pF$ | 2.6                  | 4.7 | V/ns |          |

|            |              | $V_{DDO} = 2.5V \pm 5\%, 20\% \sim 80\%$ で測定、負荷 $4.7pF$ | 2.6                  | 3.7 | V/ns |          |

|            |              | $V_{DDO} = 1.8V \pm 5\%, 20\% \sim 80\%$ で測定、負荷 $4.7pF$ | 1.5                  | 3.2 | V/ns |          |

| $V_{OH}$   | 出力 HIGH 電圧   | $I_{OH} = -15mA, 3.3V$ 時                                | $0.8 \times V_{DDO}$ | V   |      |          |

|            |              | $I_{OH} = -12mA, 2.5V$ 時                                |                      |     |      |          |

|            |              | $I_{OH} = -8mA, 1.8V$ 時                                 |                      |     |      |          |

| $V_{OL}$   | 出力 LOW 電圧    | $I_{OL} = 15mA, 3.3V$ 時                                 | 0.4                  | V   |      |          |

|            |              | $I_{OL} = 12mA, 2.5V$ 時                                 |                      |     |      |          |

|            |              | $I_{OL} = 8mA, 1.8V$ 時                                  |                      |     |      |          |

| $I_{leak}$ | 出力リーキ電流      | トライステート出力。 $V_{DD} = V_{DDO} = 3.465V$                  | -5                   | 0   | 5    | $\mu A$  |

| $R_{out}$  | 出力インピーダンス    |                                                         |                      | 17  |      | $\Omega$ |

| ODC        | 出力デューティ サイクル | $f_{out} \leq 156.25MHz$                                | 45                   | 55  | %    |          |

|            |              | $f_{out} > 156.25MHz$                                   | 40                   | 60  | %    |          |

| $t_{skew}$ | 出力間スキュー      | 同じ FOD、LVC MOS 出力                                       |                      | 50  | ps   |          |

| $C_{load}$ | 最大負荷容量       |                                                         |                      | 15  | pF   |          |

$V_{DD} = V_{DDO} = 1.8V, 2.5V, \text{または } 3.3V \pm 5\%, T_A = T_{A,min} \sim T_{A,max}$

| パラメータ                        |                                                               | テスト条件                                                                | 最小値                 | 標準値       | 最大値          | 単位  |

|------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------|---------------------|-----------|--------------|-----|

| <b>LVC MOS REFCLK 特性</b>     |                                                               |                                                                      |                     |           |              |     |

| $f_{out}$                    | 出力周波数                                                         | (2) を参照                                                              | 12.5 <sup>(3)</sup> | 200       | MHz          |     |

| dV/dt                        | 出力スルーレート                                                      | $V_{DDO} = 3.3V \pm 5\%, 20\% \sim 80\%$ で測定、負荷 4.7pF <sup>(2)</sup> | 2.6                 | 6.7       | V/ns         |     |

|                              |                                                               | $V_{DDO} = 2.5V \pm 5\%, 20\% \sim 80\%$ で測定、負荷 4.7pF <sup>(2)</sup> | 1.8                 | 4.5       | V/ns         |     |

|                              |                                                               | $V_{DDO} = 1.8V \pm 5\%, 20\% \sim 80\%$ で測定、負荷 4.7pF <sup>(2)</sup> | 1                   | 3.2       | V/ns         |     |

| $I_{leak}$                   | 出力リーク電流                                                       | トライステート条件時の出力。 $V_{DD} = V_{DDO} = 3.465V$ <sup>(2)</sup>            | -5                  | 5         | $\mu A$      |     |

| $R_{out}$                    | 出力インピーダンス                                                     |                                                                      | 17                  |           | $\Omega$     |     |

| ODC                          | 出力デューティ サイクル                                                  | $f_{out} \leq 156.25MHz$ <sup>(2)</sup>                              | 45                  | 55        | %            |     |

| ODC                          | 出力デューティ サイクル                                                  | $f_{out} > 156.25MHz$ <sup>(2)</sup>                                 | 40                  | 60        | %            |     |

| $C_{load}$                   | 最大負荷容量                                                        | (2) を参照                                                              |                     | 15        | pF           |     |

| RJ                           | ランダム ジッタ                                                      | 50MHz での 12kHz~20MHz の総合ジッタ <sup>(2)</sup>                           |                     | 0.5       | ps           |     |

| <b>SSC 特性</b>                |                                                               |                                                                      |                     |           |              |     |

| $f_{out}$                    | SSC をサポートする出力周波数範囲 (任意の出力フォーマット)                              |                                                                      | 2.5                 | 200       | MHz          |     |

| $f_{SSC}$                    | SSC 変調周波数                                                     |                                                                      | 30                  | 31.5      | 33           | kHz |

| $f_{SSC-deviation}$          | SSC 偏差 (変調深度)                                                 | ダウン スプレッド (プログラマブル)                                                  | -3                  | -0.1      | %            |     |

|                              |                                                               | センター スプレッド (プログラマブル)                                                 | $\pm 0.05$          | $\pm 1.5$ | %            |     |

| $f_{SSC-deviation-accuracy}$ | SSC 偏差精度                                                      | $f_{out} \leq 100MHz$ 、ダウン スプレッド                                     | 0                   | 0.01      | %            |     |

|                              |                                                               | $100MHz < f_{out} \leq 200MHz$ 、ダウン スプレッド                            | 0                   | 0.05      | %            |     |

|                              |                                                               | $f_{out} \leq 100MHz$ 、センター スプレッド                                    | 0                   | 0.01      | %            |     |

|                              |                                                               | $100MHz < f_{out} \leq 200MHz$ 、センター スプレッド                           | 0                   | 0.05      | %            |     |

| $df/dt$                      | SSC 最大周波数スルーレート                                               | $0 < f_{SSC-deviation} \leq -0.5\%$                                  |                     | 1250      | ppm/ $\mu s$ |     |

| <b>ジッタ特性</b>                 |                                                               |                                                                      |                     |           |              |     |

| $J_{PCle1-cc-SSC\_off}$      | PCIe Gen 1 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 86ps)                  | 両方の出力で SSC ディスエーブル                                                   |                     | 0.8       | ps           |     |

| $J_{PCle1-cc-SSC\_on}$       | PCIe Gen 1 共通クロックのジッタ、 $-0.5\% \leq SSC < 0\%$ (ジッタ制限 = 86ps) | 両方の出力で SSC イネーブル                                                     |                     | 1.4       | ps           |     |

| $J_{PCle2-cc-SSC\_off}$      | PCIe Gen 2 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 3ps)                   | 両方の出力で SSC ディスエーブル                                                   |                     | 0.2       | 0.3          | ps  |

| $J_{PCle2-cc-SSC\_on}$       | PCIe Gen 2 共通クロックのジッタ、 $-0.5\% \leq SSC < 0\%$ (ジッタ制限 = 3ps)  | 両方の出力で SSC イネーブル                                                     |                     | 0.3       | 0.5          | ps  |

| $J_{PCle2-SRNS}$             | PCIe Gen 2 の SRNS ジッタ                                         | 両方の出力で SSC ディスエーブル                                                   |                     | 0.2       | 0.3          | ps  |

| $J_{PCle2-SRIS}$             | PCIe Gen 2 の SRIS ジッタ、 $-0.3\% \leq SSC < 0\%$                | 両方の出力で SSC イネーブル                                                     |                     | 0.3       | 0.5          | ps  |

| $J_{PCle3-cc-SSC\_off}$      | PCIe Gen 3 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 1ps)                   | 両方の出力で SSC ディスエーブル                                                   |                     | 42.8      | 84.2         | fs  |

| $J_{PCle3-cc-SSC\_on}$       | PCIe Gen 3 共通クロックのジッタ、 $-0.5\% \leq SSC < 0\%$ (ジッタ制限 = 1ps)  | 両方の出力で SSC イネーブル                                                     |                     | 63.1      | 135.3        | fs  |

| $J_{PCle3-SRNS}$             | PCIe Gen 3 の SRNS ジッタ                                         | 両方の出力で SSC ディスエーブル                                                   |                     | 48.8      | 97.5         | fs  |

$V_{DD} = V_{DDO} = 1.8V, 2.5V, \text{または } 3.3V \pm 5\%, T_A = T_{A,min} \sim T_{A,max}$

| パラメータ                   |                                                                       | テスト条件                 | 最小値   | 標準値   | 最大値 | 単位 |

|-------------------------|-----------------------------------------------------------------------|-----------------------|-------|-------|-----|----|

| $J_{PCle3-SRIS}$        | PCIe Gen 3 の SRIS ジッタ、 $-0.3\% \leq \text{SSC} < 0\%$                 | 両方の出力で SSC イネーブル      | 194.1 | 418.5 |     | fs |

| $J_{PCle4-cc-SSC\_off}$ | PCIe Gen 4 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 500fs)                         | 両方の出力で SSC ディスエーブル    | 42.8  | 84.2  |     | fs |

| $J_{PCle4-cc-SSC\_on}$  | PCIe Gen 4 共通クロックのジッタ、 $-0.5\% \leq \text{SSC} < 0\%$ (ジッタ制限 = 500fs) | 両方の出力で SSC イネーブル      | 63.1  | 135.3 |     | fs |

| $J_{PCle4-SRNS}$        | PCIe Gen 4 の SRNS ジッタ                                                 | 両方の出力で SSC ディスエーブル    | 48.8  | 97.5  |     | fs |

| $J_{PCle4-SRIS}$        | PCIe Gen 4 の SRIS ジッタ、 $-0.3\% \leq \text{SSC} < 0\%$                 | 両方の出力で SSC イネーブル      | 98.5  | 205.4 |     | fs |

| $J_{PCle5-cc-SSC\_off}$ | PCIe Gen 5 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 150fs)                         | 両方の出力で SSC ディスエーブル    | 17.8  | 35.6  |     | fs |

| $J_{PCle5-cc-SSC\_on}$  | PCIe Gen 5 共通クロックのジッタ、 $-0.5\% \leq \text{SSC} < 0\%$ (ジッタ制限 = 150fs) | 両方の出力で SSC イネーブル      | 26.4  | 57.5  |     | fs |

| $J_{PCle5-SRNS}$        | PCIe Gen 5 の SRNS ジッタ                                                 | 両方の出力で SSC ディスエーブル    | 19.8  | 39    |     | fs |

| $J_{PCle5-SRIS}$        | PCIe Gen 5 の SRIS ジッタ、 $-0.3\% \leq \text{SSC} < 0\%$                 | 両方の出力で SSC イネーブル      | 30.2  | 63.9  |     | fs |

| $J_{PCle6-cc-SSC\_off}$ | PCIe Gen 6 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 100fs)                         | 両方の出力で SSC ディスエーブル    | 11    | 22    |     | fs |

| $J_{PCle6-cc-SSC\_on}$  | PCIe Gen 6 共通クロックのジッタ、 $-0.5\% \leq \text{SSC} < 0\%$ (ジッタ制限 = 100fs) | 両方の出力で SSC イネーブル      | 16    | 34.5  |     | fs |

| $J_{PCle6-SRNS}$        | PCIe Gen 6 の SRNS ジッタ                                                 | 両方の出力で SSC ディスエーブル    | 14.8  | 27.9  |     | fs |

| $J_{PCle6-SRIS}$        | PCIe Gen 6 の SRIS ジッタ、 $-0.3\% \leq \text{SSC} < 0\%$                 | 両方の出力で SSC イネーブル      | 22.2  | 45.9  |     | fs |

| $J_{PCle7-cc-SSC\_off}$ | PCIe Gen 7 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 67fs)                          | 両方の出力で SSC ディスエーブル    | 7.7   | 15.4  |     | fs |

| $J_{PCle7-cc-SSC\_on}$  | PCIe Gen 7 共通クロックのジッタ、 $-0.5\% \leq \text{SSC} < 0\%$ (ジッタ制限 = 67fs)  | 両方の出力で SSC イネーブル      | 12.1  | 29.6  |     | fs |

| $J_{PCle7-SRNS}$        | PCIe Gen 7 の SRNS ジッタ                                                 | 両方の出力で SSC ディスエーブル    | 10.4  | 19.6  |     | fs |

| $J_{PCle7-SRIS}$        | PCIe Gen 7 の SRIS ジッタ、 $-0.1\% \leq \text{SSC} < 0\%$                 | 両方の出力で SSC イネーブル      | 12.2  | 25.5  |     | fs |

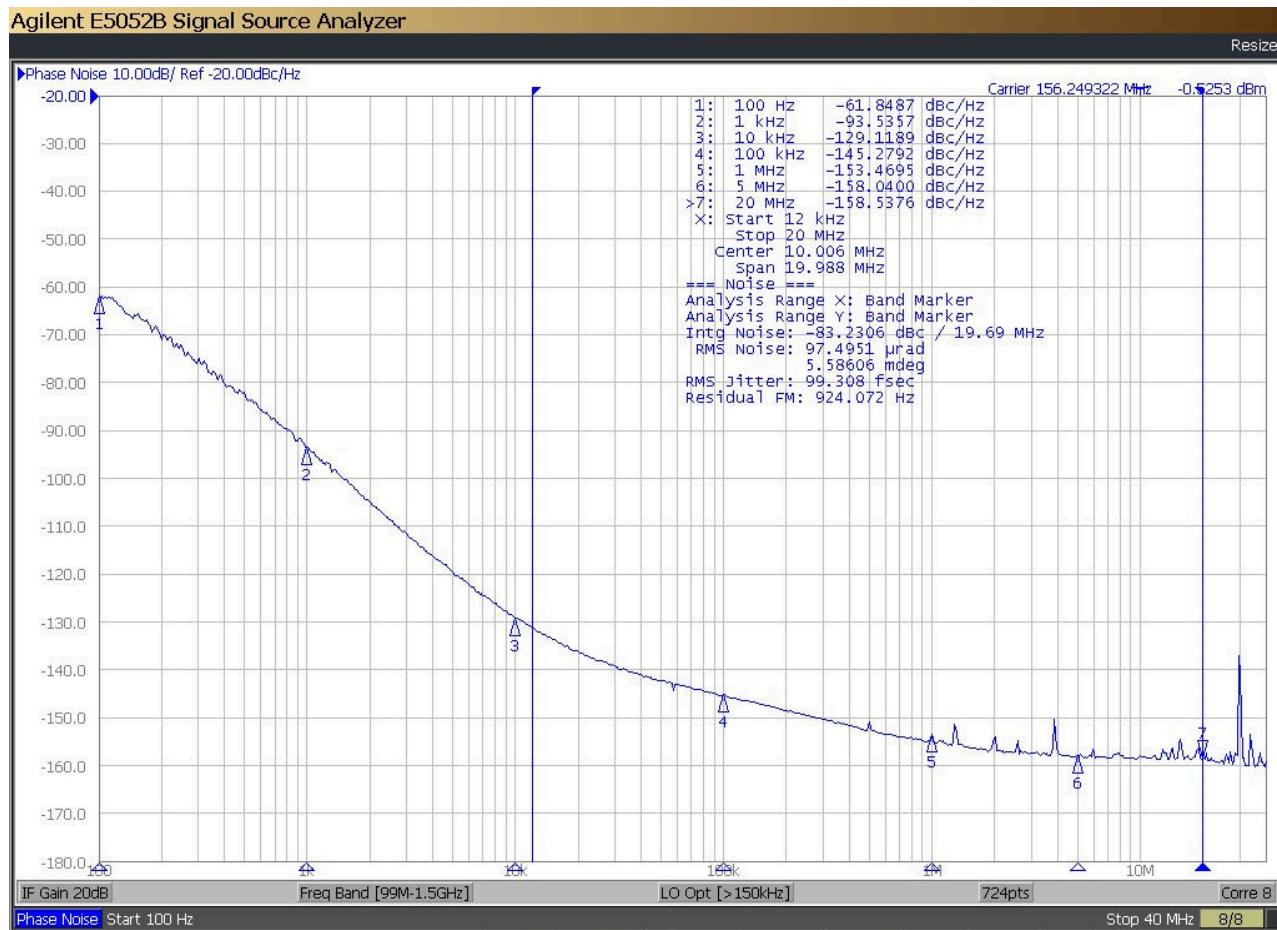

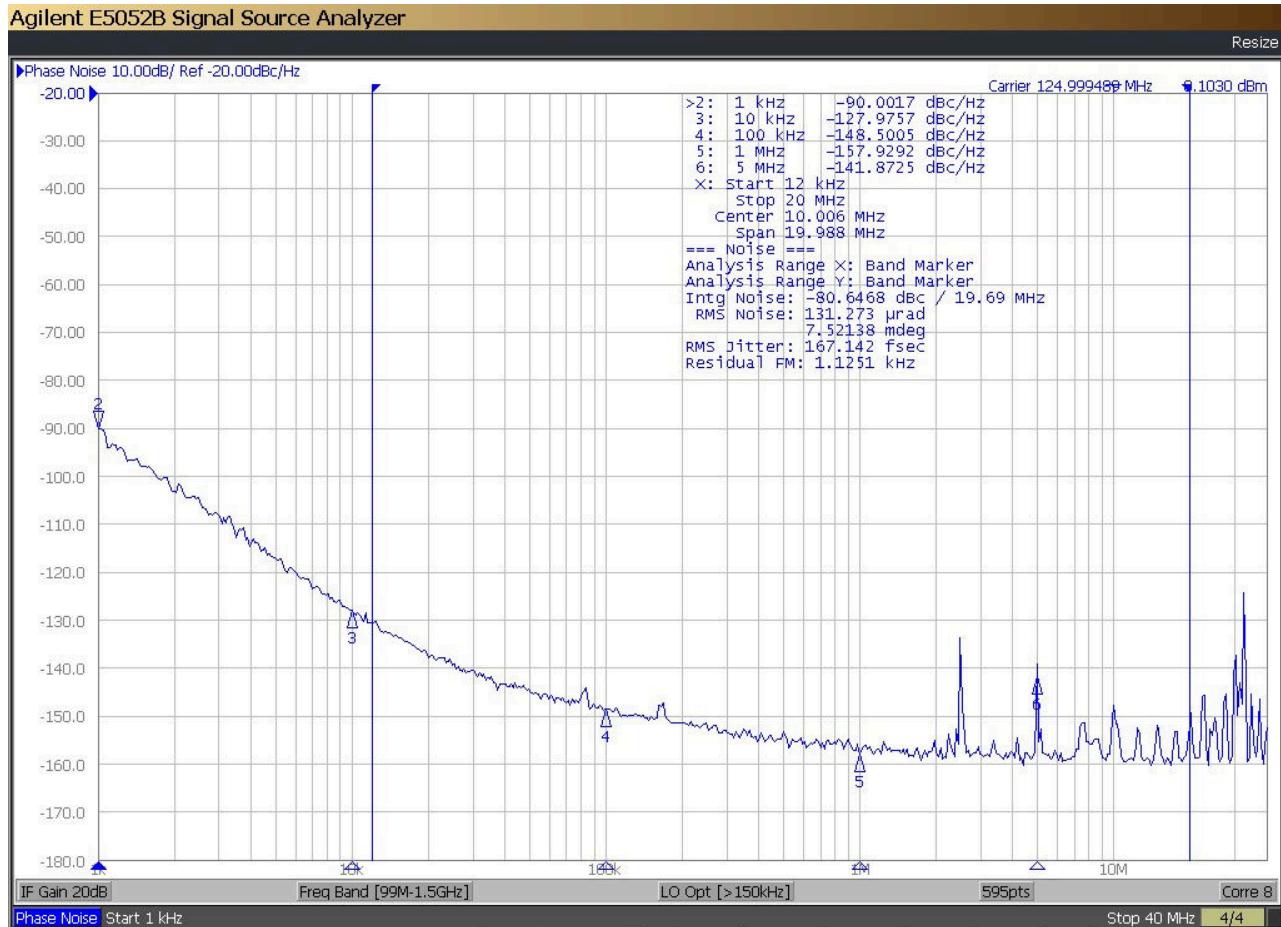

| $RJ_{RMS}$              | 12kHz ~ 20MHz RMS ジッタ                                                 | $f_{out} = 156.25MHz$ | 105   | 144   |     | fs |

**タイミング特性**

|               |             |                                                                                                         |   |             |

|---------------|-------------|---------------------------------------------------------------------------------------------------------|---|-------------|

| $t_{startup}$ | 起動時間        | $V_{DD} = 2.5V$ または $3.3V$ 。すべての $V_{DD}$ ピンが $2.1V$ に達してから最初の出力クロックの立ち上がりエッジまでの経過時間。出力クロックは常に仕様の範囲内です。 | 1 | ms          |

|               |             | $V_{DD} = 1.8V$ 。すべての $V_{DD}$ ピンが $1.6V$ に達してから最初の出力クロックの立ち上がりエッジまでの経過時間。出力クロックは常に仕様の範囲内です。            |   |             |

| $t_{OE}$      | 出力イネーブル時間   | $CLOCK\_READY$ ステータスが 1 になった後、OE アサートから最初の出力クロックの立ち上がりエッジまでの経過時間。ディスエーブル時には出力はトライステートされません。             | 7 | 出力クロック サイクル |

| $t_{OD}$      | 出力ディスエーブル時間 | OE デアサートから最後の出力クロックの立ち下がりエッジまでの経過時間。                                                                    | 7 | 出力クロック サイクル |

**消費電力特性**

$V_{DD} = V_{DDO} = 1.8V, 2.5V, \text{または } 3.3V \pm 5\%, T_A = T_{A,min} \sim T_{A,max}$

| パラメータ               |                                  | テスト条件                                           | 最小値    | 標準値    | 最大値 | 単位  |

|---------------------|----------------------------------|-------------------------------------------------|--------|--------|-----|-----|

| $I_{DD}$            | コア電源電流、出力ドライバは含まない               | 1つのFODがイネーブル、 $100MHz \leq f_{FOD} \leq 200MHz$ | 57.5   | 79.9   |     | mA  |

|                     |                                  | 1つのFODがイネーブル、 $200MHz < f_{FOD} \leq 400MHz$    | 67     | 90.7   |     | mA  |

|                     |                                  | 2つのFODがイネーブル、 $100MHz \leq f_{FOD} \leq 200MHz$ | 81.1   | 105.8  |     | mA  |

|                     |                                  | 2つのFODがイネーブル、 $200MHz < f_{FOD} \leq 400MHz$    | 97.8   | 125.8  |     | mA  |

| $I_{DDO}$           | 出力チャネルごとの出力電源電流                  | LP-HCSL。 $f_{out} \leq 100MHz$                  | 10.1   | 10.8   |     | mA  |

|                     |                                  | LP-HCSL。 $100MHz < f_{out} \leq 200MHz$         | 13.2   | 14.1   |     | mA  |

|                     |                                  | LP-HCSL。 $200MHz < f_{out} \leq 300MHz$         | 13.7   | 15.1   |     | mA  |

|                     |                                  | LP-HCSL。 $300MHz < f_{out} \leq 400MHz$         | 14.4   | 16.4   |     | mA  |

|                     |                                  | LVDS。 $f_{out} \leq 100MHz$                     | 6      | 8      |     | mA  |

|                     |                                  | LVDS。 $100MHz < f_{out} \leq 200MHz$            | 6.8    | 9.2    |     | mA  |

|                     |                                  | LVDS。 $200MHz < f_{out} \leq 300MHz$            | 7.6    | 10.2   |     | mA  |

|                     |                                  | LVDS。 $300MHz < f_{out} \leq 400MHz$            | 8.4    | 11.3   |     | mA  |

|                     |                                  | 1.8V LVCMOS。 $f_{out} = 50MHz^{(4)}$            | 4.2    | 5      |     | mA  |

|                     |                                  | 1.8V LVCMOS。 $f_{out} = 200MHz^{(4)}$           | 11.7   | 13.4   |     | mA  |

|                     |                                  | 2.5V LVCMOS。 $f_{out} = 50MHz^{(4)}$            | 5.6    | 6.4    |     | mA  |

|                     |                                  | 2.5V LVCMOS。 $f_{out} = 200MHz^{(4)}$           | 15.3   | 17.3   |     | mA  |

|                     |                                  | 3.3V LVCMOS。 $f_{out} = 50MHz^{(4)}$            | 6.8    | 7.7    |     | mA  |

|                     |                                  | 3.3V LVCMOS。 $f_{out} = 200MHz^{(4)}$           | 19.2   | 21.7   |     | mA  |

| $I_{DDREF}$         | REFCLK 電源電流                      | 1.8V LVCMOS。 $f_{out} = 50MHz^{(4)}$            | 3.4    | 3.9    |     | mA  |

|                     |                                  | 1.8V LVCMOS。 $f_{out} = 200MHz^{(4)}$           | 9.5    | 11.7   |     | mA  |

|                     |                                  | 2.5V LVCMOS。 $f_{out} = 50MHz^{(4)}$            | 4.7    | 5.3    |     | mA  |

|                     |                                  | 2.5V LVCMOS。 $f_{out} = 200MHz^{(4)}$           | 12.8   | 15.8   |     | mA  |

|                     |                                  | 3.3V LVCMOS。 $f_{out} = 50MHz^{(4)}$            | 5.9    | 6.6    |     | mA  |

|                     |                                  | 3.3V LVCMOS。 $f_{out} = 200MHz^{(4)}$           | 16.6   | 20.2   |     | mA  |

| PSNR 特性             |                                  |                                                 |        |        |     |     |

| $PSNR_{LVC}$<br>MOS | LVCMOS 出力の電源ノイズ除去 <sup>(5)</sup> | 10kHz                                           | -76.7  | -58.1  |     | dBc |

|                     |                                  | 50kHz                                           | -80.9  | -57.9  |     | dBc |

|                     |                                  | 100kHz                                          | -81.8  | -57    |     | dBc |

|                     |                                  | 500kHz                                          | -84.3  | -61.7  |     | dBc |

|                     |                                  | 1MHz                                            | -97.6  | -78.1  |     | dBc |

|                     |                                  | 5MHz                                            | -104.3 | -79    |     | dBc |

|                     |                                  | 10MHz                                           | -108.7 | -89.5  |     | dBc |

| $PSNR_{LVD}$<br>S   | LVDS 出力の電源ノイズ除去 <sup>(5)</sup>   | 10kHz                                           | -79.5  | -70.9  |     | dBc |

|                     |                                  | 50kHz                                           | -83.5  | -73.2  |     | dBc |

|                     |                                  | 100kHz                                          | -83    | -71.6  |     | dBc |

|                     |                                  | 500kHz                                          | -88.3  | -79    |     | dBc |

|                     |                                  | 1MHz                                            | -123.4 | -101.4 |     | dBc |

|                     |                                  | 5MHz                                            | -115   | -87.7  |     | dBc |

|                     |                                  | 10MHz                                           | -123.7 | -103.5 |     | dBc |

$V_{DD} = V_{DDO} = 1.8V, 2.5V, \text{または } 3.3V \pm 5\%, T_A = T_{A,min} \sim T_{A,max}$

| パラメータ                   |                        | テスト条件  | 最小値 | 標準値    | 最大値    | 単位  |

|-------------------------|------------------------|--------|-----|--------|--------|-----|

| PSNR <sub>LP-HCSL</sub> | LP-HCSL 出力の電源ノイズ除去 (5) | 10kHz  |     | -80.1  | -70.8  | dBc |

|                         |                        | 50kHz  |     | -84.7  | -72.9  | dBc |

|                         |                        | 100kHz |     | -84.6  | -70.1  | dBc |

|                         |                        | 500kHz |     | -93.1  | -78.8  | dBc |

|                         |                        | 1MHz   |     | -124.6 | -101.5 | dBc |

|                         |                        | 5MHz   |     | -114.3 | -88.3  | dBc |

|                         |                        | 10MHz  |     | -123   | -103.7 | dBc |

## 2ステートロジック入力特性

|                             |                                  |  |                      |                     |    |    |

|-----------------------------|----------------------------------|--|----------------------|---------------------|----|----|

| $V_{IH-Pin2}$               | ピン 2 の入力 High 電圧                 |  | $0.7 \times V_{DD}$  | $V_{DD} + 0.3$      | V  |    |

| $V_{IL-Pin2}$               | ピン 2 の入力 Low 電圧                  |  | GND - 0.3            | $0.3 \times V_{DD}$ | V  |    |

| $V_{IH-Pin1}$               | ピン 1 の入力 High 電圧                 |  | 1.15                 | $V_{DD} + 0.3$      | V  |    |

| $V_{IL-Pin1}$               | ピン 1 の入力 Low 電圧                  |  | -0.3                 | 0.65                | V  |    |

| $V_{IH-Pin3,4}$             | OTP_SEL[1:0] の入力 High 電圧         |  | $0.7 \times V_{DD}$  | $V_{DD} + 0.3$      | V  |    |

| $V_{IL-Pin3,4}$             | OTP_SEL[1:0] の入力 Low 電圧          |  | GND - 0.3            | 0.8                 | V  |    |

| $V_{IH-Pin15}$              | ピン 15 の入力 High 電圧                |  | $0.65 \times V_{DD}$ | $V_{DD} + 0.3$      | V  |    |

| $V_{IL-Pin15}$              | ピン 15 の入力 Low 電圧                 |  | -0.3                 | 0.4                 | V  |    |

| $R_{ext-up/down-Pin1,2}$    | ピン 1、2 の推奨外部プルアップ抵抗またはプルダウン抵抗    |  | 0                    | 1                   | 10 | kΩ |

| $R_{ext-up/down-Pin3,4,15}$ | ピン 3、4、15 の推奨外部プルアップ抵抗またはプルダウン抵抗 |  | 0                    | 10                  | 60 | kΩ |

| $t_R/t_F$                   | OE 信号の立ち上がり時間または立ち下がり時間          |  |                      | 10                  | ns |    |

| $C_{in}$                    | 入力容量                             |  |                      | 3                   | pF |    |

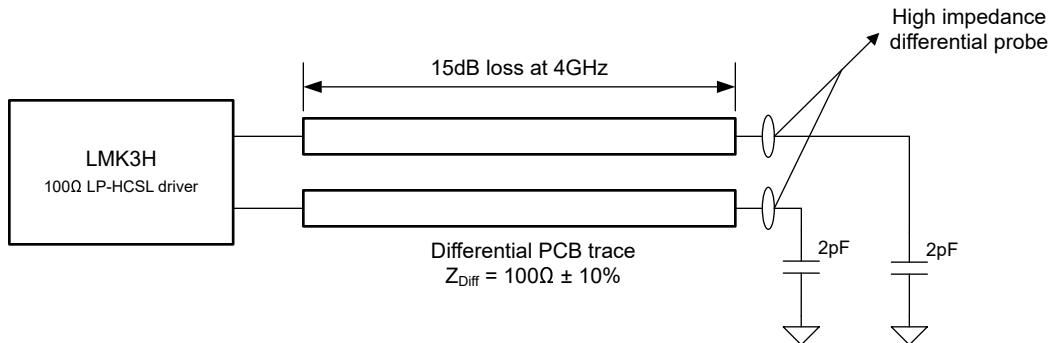

(1) PCIe テスト負荷、4GHz で 15dB 損失、 $f_{out} = 100MHz$ 、 $Z_{diff} = 100\Omega$

(2) 10kΩ 外部プルアップ抵抗またはプルダウン抵抗でテスト

(3) REFCLK は FOD0 または FOD1 のどちらからでも /2、/4、/8 に設定できます。どちらの FOD も 100~400MHz をサポートしています。

(4) 5インチのパターンで 4.7pF の容量性負荷

(5) 電源ピンはすべて接続されています。0.1μF コンデンサは各電源ピンの近くに配置されています。50mVpp のリップルを印加し、クロック出力でスペアリスレベルを測定します。

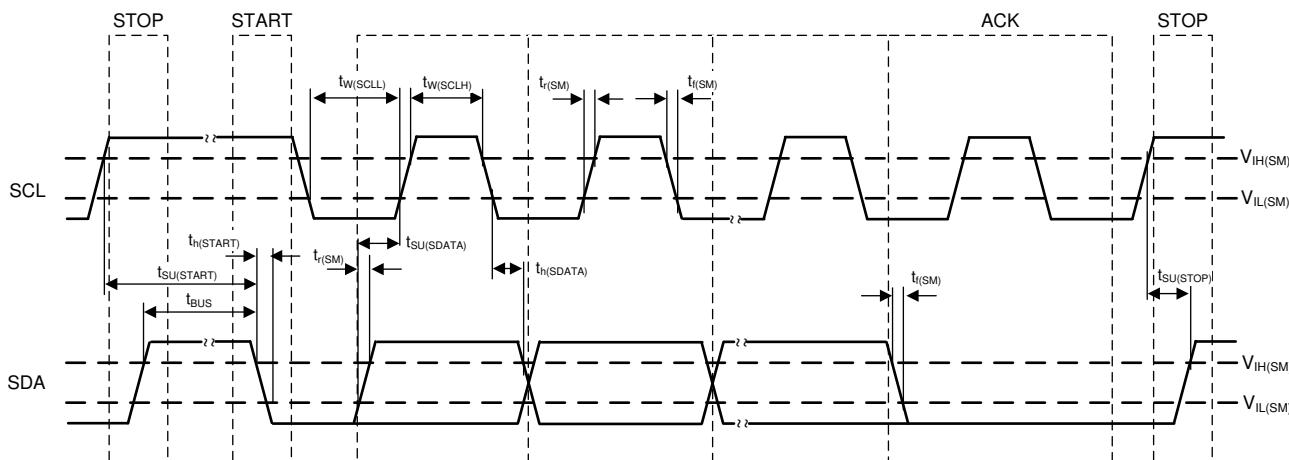

## 5.6 I<sup>2</sup>C インターフェイス仕様

すべてのタイミング要件は、 $V_{IH-min}$  と  $V_{IL-max}$  を基準としています。チップの  $V_{DD} = I^2C V_{DD}$  となります。

| パラメータ     |                   | テスト条件                          | スタンダード モード          |                     | ファスト モード             |                     | 単位 |

|-----------|-------------------|--------------------------------|---------------------|---------------------|----------------------|---------------------|----|

|           |                   |                                | 最小値                 | 最大値                 | 最小値                  | 最大値                 |    |

| $V_{IL}$  | 入力 Low 電圧         |                                | -0.3                | $0.3 \times V_{DD}$ | -0.3                 | $0.3 \times V_{DD}$ | V  |

| $V_{IH}$  | 入力 High 電圧        |                                | $0.7 \times V_{DD}$ | $0.3 \times V_{DD}$ | $0.7 \times V_{DD}$  | $0.3 \times V_{DD}$ | V  |

| $V_{hys}$ | シュミットトリガ入力のヒステリシス |                                |                     |                     | $0.05 \times V_{DD}$ |                     | V  |

| $V_{OL1}$ | Low レベル出力電圧 1     | 3mA のシンク電流の場合 $V_{DD} > 2V$    | 0                   | 0.4                 | 0                    | 0.4                 | V  |

| $V_{OL2}$ | Low レベル出力電圧 2     | 2mA のシンク電流の場合 $V_{DD} \leq 2V$ |                     |                     | 0                    | $0.2 \times V_{DD}$ | V  |

すべてのタイミング要件は、 $V_{IH-min}$  と  $V_{IL-max}$  を基準としています。チップの  $V_{DD} = I^2C V_{DD}$  となります。

| パラメータ        |                                          | テスト条件                                               | スタンダード モード          |     | ファスト モード                             |     | 単位            |

|--------------|------------------------------------------|-----------------------------------------------------|---------------------|-----|--------------------------------------|-----|---------------|

|              |                                          |                                                     | 最小値                 | 最大値 | 最小値                                  | 最大値 |               |

| $I_{OL}$     | Low レベル出力電流                              | $V_{OL} = 0.4 \text{ V}$                            | 3                   |     | 3                                    |     | mA            |

|              |                                          | $V_{OL} = 0.6 \text{ V}$                            |                     |     | 6                                    |     | mA            |

| $t_{OF}$     | $V_{IHmin}$ から $V_{ILmax}$ への出力立ち下がり時間   |                                                     |                     | 250 | $20 \times (V_{DD} / 5.5 \text{ V})$ | 250 | ns            |

| $t_{SP}$     | 入力フィルタにより抑制されるスパイクのパルス幅                  |                                                     |                     |     | 0                                    | 50  | ns            |

| $I_i$        | 各 I/O ピンの入力電流                            | $0.1 \times V_{DD} < V_{IN} < 0.9 \times V_{DDmax}$ | -10                 | 10  | -10                                  | 10  | $\mu\text{A}$ |

| $C_i$        | 各 I/O ピンの静電容量                            |                                                     |                     | 10  |                                      | 10  | $\text{pF}$   |

| $f_{SCL}$    | SCL クロック周波数                              |                                                     | 0                   | 100 | 0                                    | 400 | $\text{kHz}$  |

| $t_{HD-STA}$ | (繰り返し) START 条件のホールド時間                   | この時間が経過すると、最初のクロックパルスが生成されます                        | 4                   |     | 0.6                                  |     | $\mu\text{s}$ |

| $t_{low}$    | SCL クロックの Low 期間                         |                                                     | 4.7                 |     | 1.3                                  |     | $\mu\text{s}$ |

| $t_{high}$   | SCL クロックの High 期間                        |                                                     | 4                   |     | 0.6                                  |     | $\mu\text{s}$ |

| $t_{SU-STA}$ | 繰り返し START 条件のセットアップ時間                   |                                                     | 4.7                 |     | 0.6                                  |     | $\mu\text{s}$ |

| $t_{HD-DAT}$ | データホールド時間                                | $I^2C$ バス デバイス                                      | 0                   |     | 0                                    |     | $\mu\text{s}$ |

| $t_{SU-DAT}$ | データセットアップ時間                              |                                                     | 0.25                |     | 0.1                                  |     | $\mu\text{s}$ |

| $t_R$        | SDA 信号と SCL 信号の両方の立ち上がり時間 <sup>(1)</sup> |                                                     |                     | 300 | 20                                   | 300 | ns            |

| $t_F$        | SDA 信号と SCL 信号の両方の立ち下がり時間 <sup>(1)</sup> |                                                     |                     | 300 | $20 \times (V_{DD} / 5.5 \text{ V})$ | 300 | ns            |

| $t_{SU-STO}$ | STOP 条件のセットアップ時間                         |                                                     | 4                   |     | 0.6                                  |     | $\mu\text{s}$ |

| $t_{BUF}$    | STOP 条件と START 条件の間のバスフリー時間              |                                                     | 4.7                 |     | 1.3                                  |     | $\mu\text{s}$ |

| $C_B$        | 各バスラインの容量性負荷                             |                                                     | 400                 |     | 400                                  |     | $\text{pF}$   |

| $t_{VD-DAT}$ | データ有効時間                                  |                                                     | 3.45                |     | 0.9                                  |     | $\mu\text{s}$ |

| $t_{VD-ACK}$ | データ有効アクリッジ時間                             |                                                     | 3.45                |     | 0.9                                  |     | $\mu\text{s}$ |

| $V_{NL}$     | Low レベルでのノイズ マージン                        | ヒステリシスを含む、接続された各デバイスについて                            | $0.1 \times V_{DD}$ |     | $0.1 \times V_{DD}$                  |     | V             |

| $V_{NH}$     | High レベルでのノイズ マージン                       | ヒステリシスを含む、接続された各デバイスについて                            | $0.2 \times V_{DD}$ |     | $0.2 \times V_{DD}$                  |     | V             |

(1) 立ち上がり時間と立ち下がり時間のパラメータは、IO ドライバの特性、プルアップ抵抗値、パターンの総容量によって異なります。

## 6 パラメータ測定情報

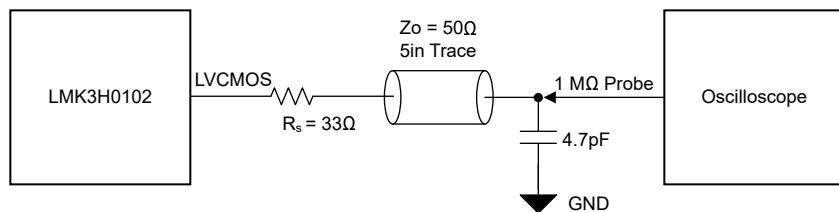

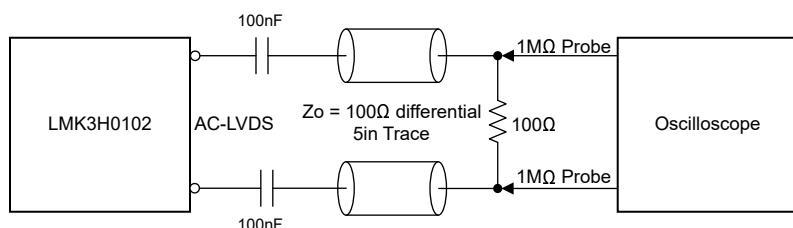

### 6.1 出力フォーマットの構成

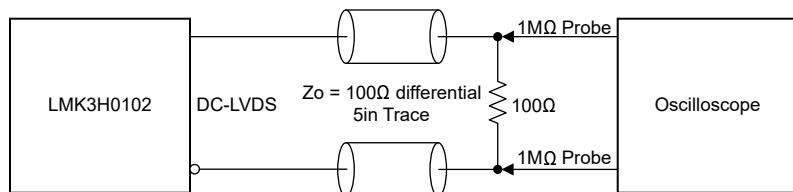

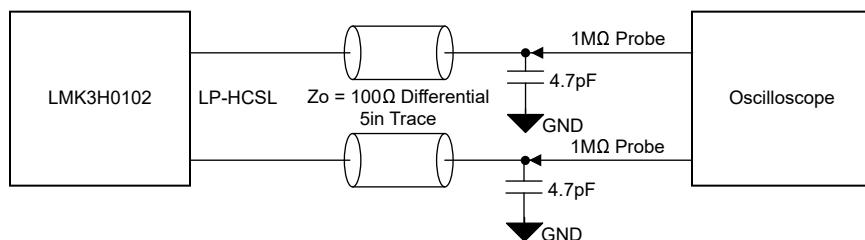

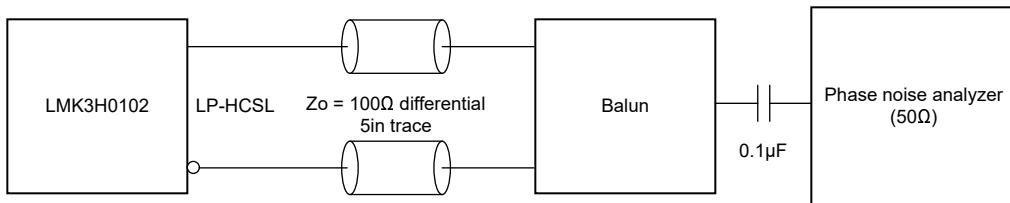

このセクションでは、LMK3H0102 の各出力フォーマット オプションの特性テストの設定について説明します。

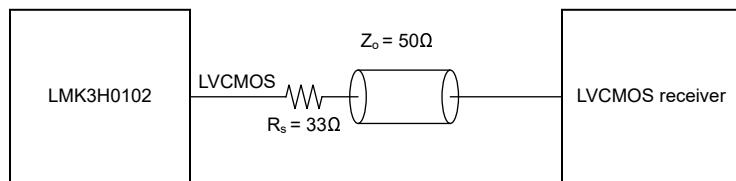

図 6-1. デバイス テスト時の LVC MOS 出力の構成

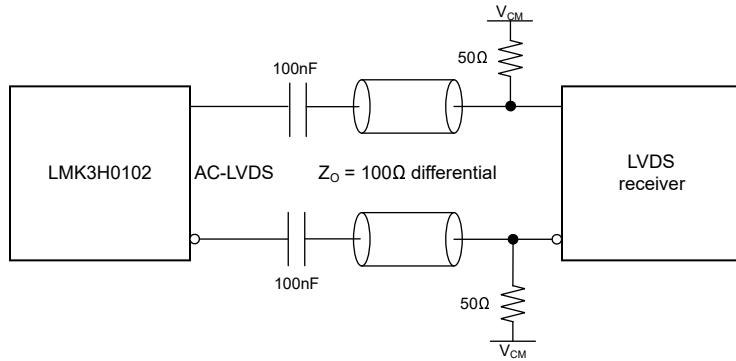

図 6-2. デバイス テスト時の AC-LVDS 出力の構成

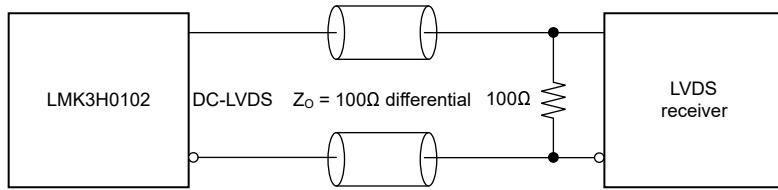

図 6-3. デバイス テスト時の DC-LVDS 出力の構成

図 6-4. 非 PCIe デバイス テスト時の LP-HCSL 出力の構成

図 6-5. PCIe デバイス テスト時の LP-HCSL 出力の構成

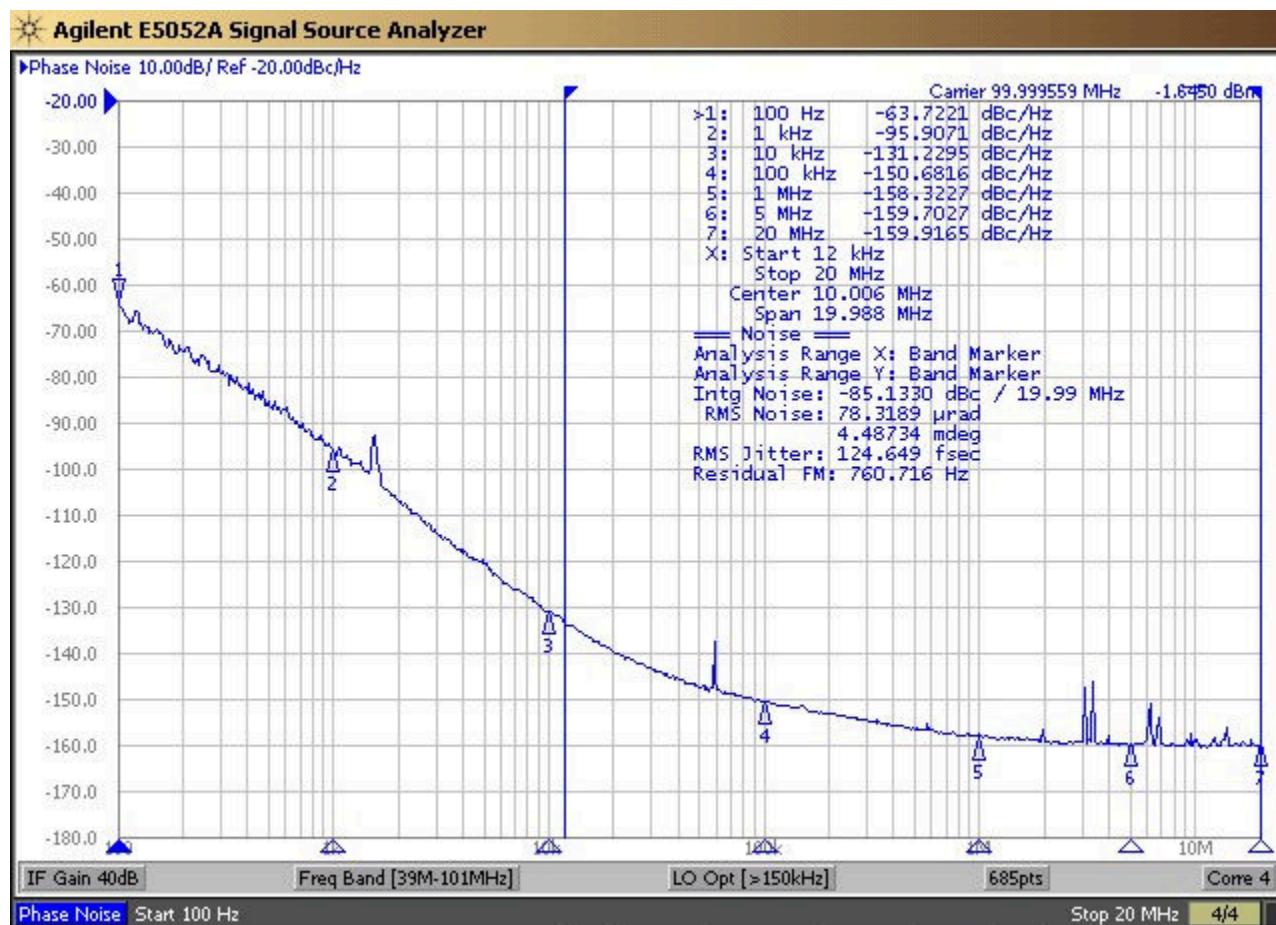

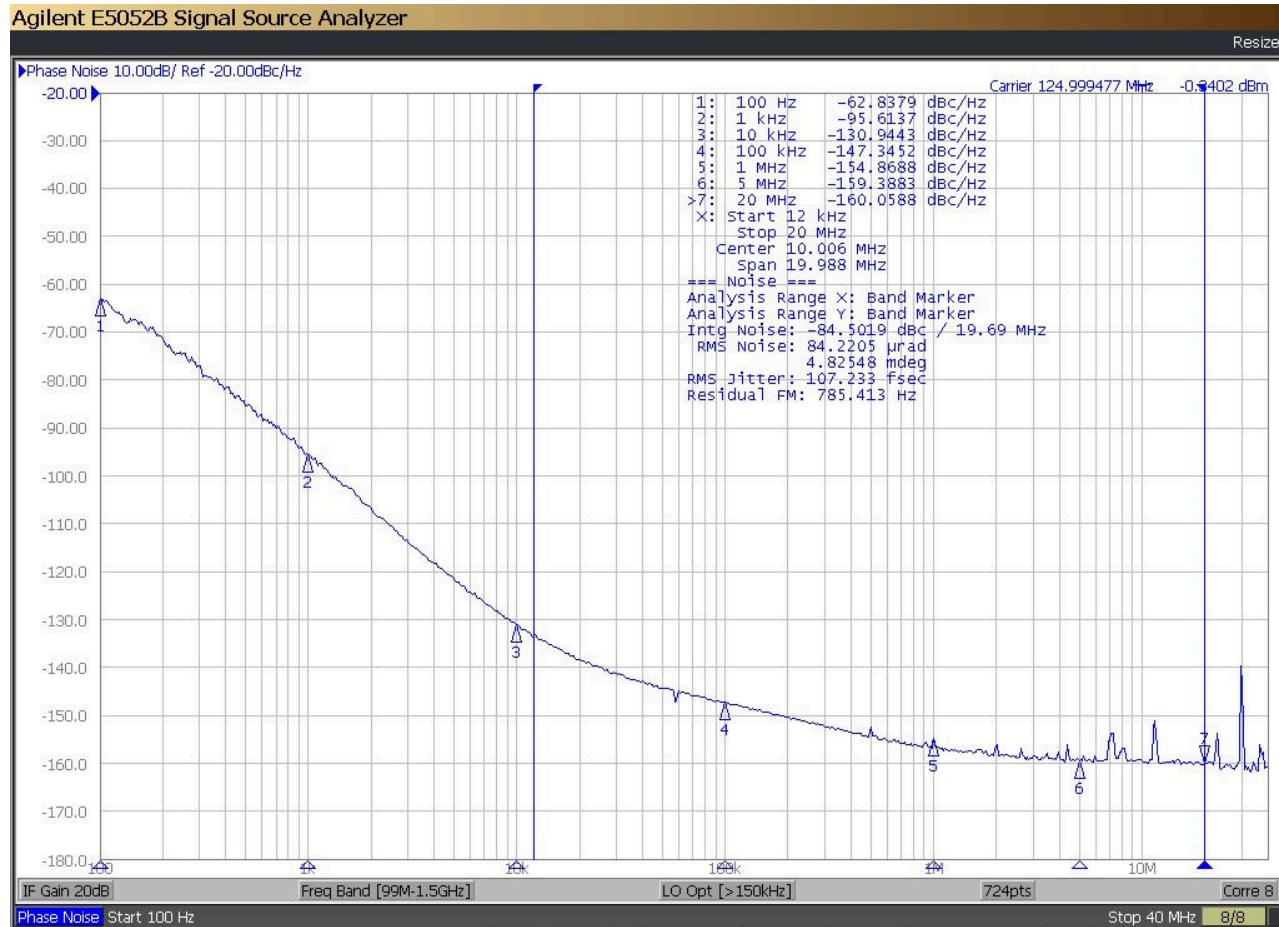

図 6-6. 位相ノイズ アナライザを使用した PCIe テストの構成

## 6.2 差動電圧測定に関する用語

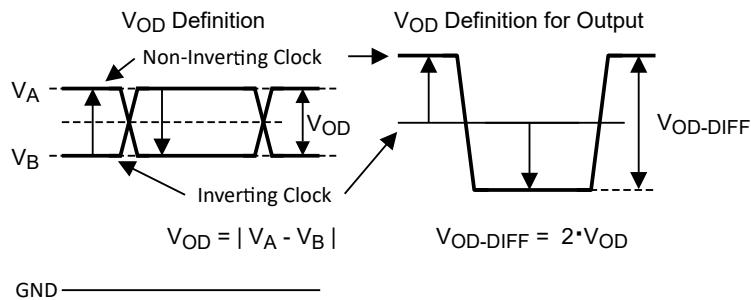

差動信号の差動電圧は 2 つの異なる定義で説明されるため、データシートを読んだり、他のエンジニアとコミュニケーションを取ったりする際に混乱を招くことがあります。このセクションでは、差動信号の測定と説明について取り上げており、この 2 つの異なる定義を理解し、使用時に区別できるようにします。

差動信号の説明における 1 つ目の定義は、反転信号と非反転信号との間の電圧電位の絶対値です。この 1 つ目の測定の記号は、入力電圧または出力電圧を表すかによって、通常は  $V_{ID}$  または  $V_{OD}$  となります。

差動信号の説明における 2 つ目の定義は、反転信号に対する非反転信号の電位を測定することです。この 2 つ目の測定の記号は  $V_{SS}$  であり、算出されたパラメータです。この信号は IC 内のどの場所でもグランドに対して存在せず、常に差動ペア基準でのみ存在しています。 $V_{SS}$  は、フローティングリファレンスを備えたオシロスコープで直接測定できます。それ以外の場合は、最初の説明で述べたように、 $V_{OD}$  の 2 倍の値として計算できます。

図 6-7 は入力信号の 2 つの異なる定義を並べて示し、図 6-8 は出力信号の 2 つの異なる定義を並べて示しています。 $V_{ID}$  と  $V_{OD}$  の定義では、非反転信号と反転信号がグランドに対して切り替わる  $V_A$  と  $V_B$  の DC レベルを示しています。 $V_{SS}$  の入力と出力の定義から、反転信号を電圧電位リファレンスとして考えると、非反転信号の電圧電位は非反転リファレンスを上下に推移しながら増加と減少を繰り返すことがわかります。これにより、差動信号のピークツーピーク電圧を測定できます。

$V_{ID}$  と  $V_{OD}$  は多くの場合ボルト (V) と定義され、 $V_{SS}$  はボルトのピークツーピーク ( $V_{PP}$ ) と定義されます。

図 6-7. 差動入力信号の 2 つの異なる定義

図 6-8. 差動出力信号の 2 つの異なる定義

## 7 詳細説明

### 7.1 概要

LMK3H0102 は、主に PCIe Gen 1～Gen 7 のクロック生成に使用されるデュアルチャネル クロック ジェネレータで、拡散スペクトラム クロック処理 (SSC) を用いる場合でも用いない場合でも対応できます。このデバイスにはバルク弾性波 (BAW) 共振器が内蔵されており、外部水晶振動子やクロックリファレンスは必要ありません。このデバイスには、OTP ページと呼ばれる 4 つの選択可能なメモリ ページがあります。メモリ内にあるこれらのページの集合は EFUSE と呼ばれます。

デフォルトの出力構成は、それぞれ  $100\Omega$  の LP-HCSL 出力フォーマットである 2 つの  $100\text{MHz}$  クロックで、起動時にはどちらもディスエーブルになっています。LMK3H0102 は、 $100\Omega$  LP-HCSL、 $85\Omega$  LP-HCSL、LVDS、および  $1.8\text{V}$ 、 $2.5\text{V}$ 、 $3.3\text{V}$  の LVCMSL 出力フォーマットをサポートしており、シングルエンド出力の場合は最大  $200\text{MHz}$ 、差動出力の場合は最大  $400\text{MHz}$  のプログラマブル出力周波数に対応しています。The LMK3H0102V33 は、 $3.3\text{V}$  の電源電圧のデフォルト構成の型番です。The LMK3H0102LMK3H0102V18 は、 $1.8\text{V}$  の電源電圧のデフォルト構成の型番です。追加の構成の型番は LMK3H0102Axxxx (xxxx は構成番号を示します) とです。『[LMK3H0102 構成ガイド](#)』には、LMK3H0102Axxxx OTP の構成ごとに、重要なデバイス設定とデフォルトのレジスタ設定の詳細が記載されています。

LMK3H0102 は、パワーアップ時に REF\_CTRL ピンで決定される 2 つの機能モードをサポートしています。ワンタイムプログラミング (OTP) モードと I<sup>2</sup>C モードです。

1. OTP モードでは、OTP\_SEL0 ピンと OTP\_SEL1 ピンによって、4 つの OTP ページのうちの 1 つが選択されます。すべての OTP ページのデフォルトの出力周波数は  $100\text{MHz}$  です。

2. I<sup>2</sup>C モードでは、アクティブなレジスタを変更することで LMK3H0102 が構成されます。デフォルト動作以外の構成が求められる場合は、起動時に毎回レジスタの書き込みが必要です。

デバイスピンの詳細な説明については、「[ピン構成および機能](#)」を参照してください。

LMK3H0102 には、次のような柔軟な SSC 構成が備えられています。

1. 両方の出力で SSC ディスエーブル

2. 両方の出力で SSC イネーブル

3. 単一出力で SSC がイネーブル

SSC 仕様とジッタ性能は、PCIe Gen 1～Gen 7 に完全準拠しています。SSC とジッタ性能の詳細については、「[拡散スペクトラム クロック処理](#)」を参照してください。

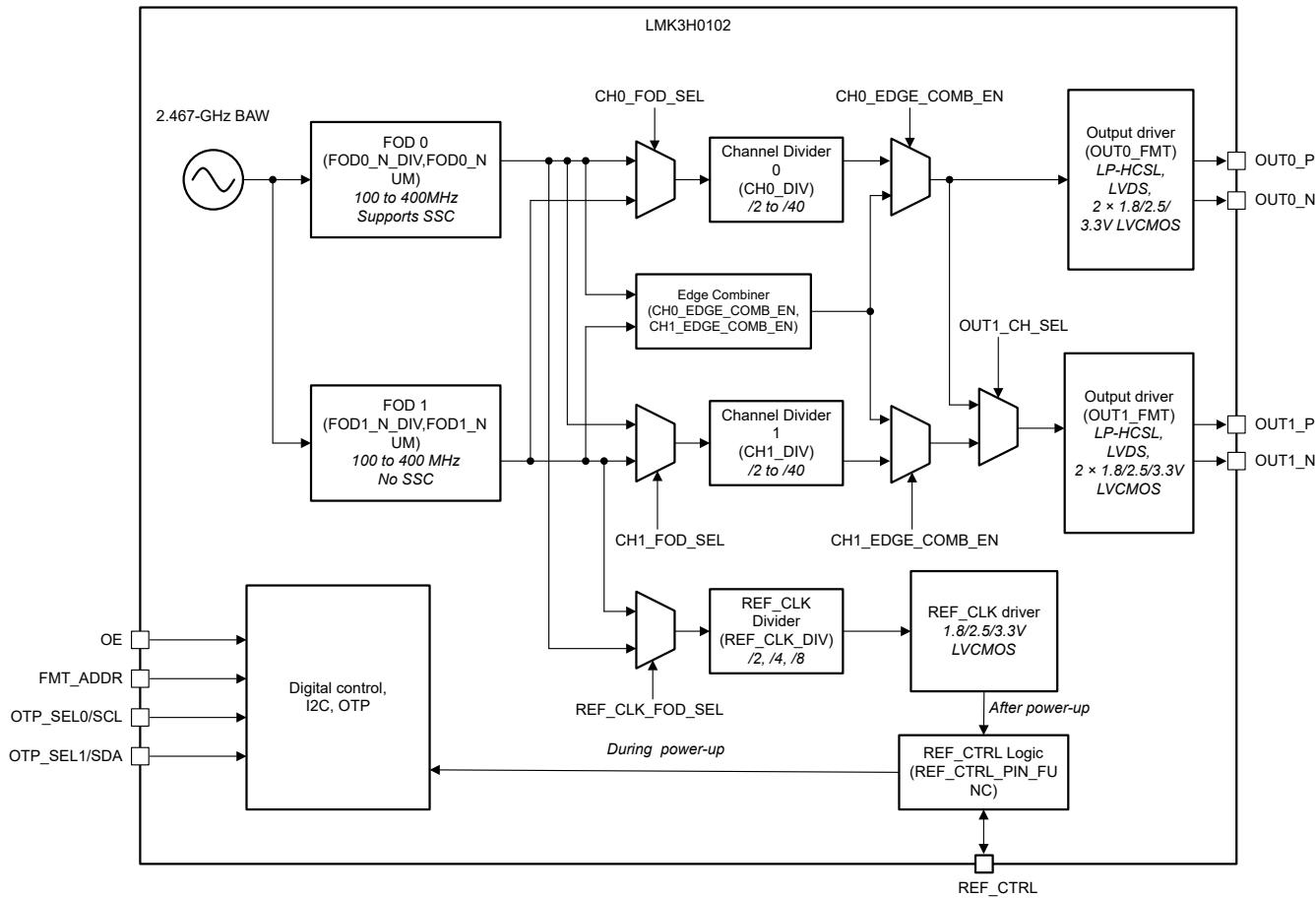

## 7.2 機能ブロック図

図 7-1. LMK3H0102 の機能ブロック図

## 7.3 機能説明

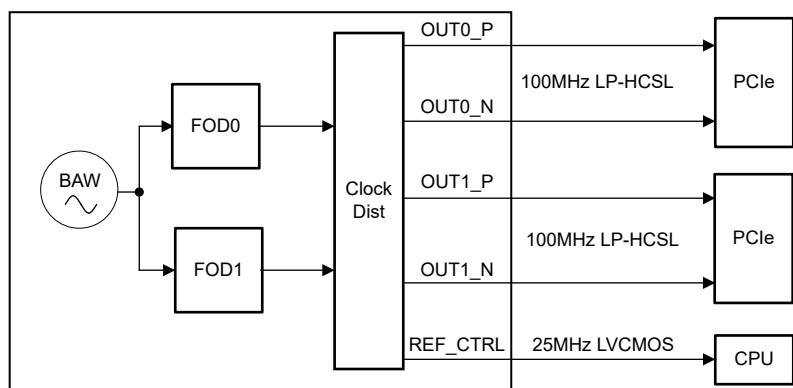

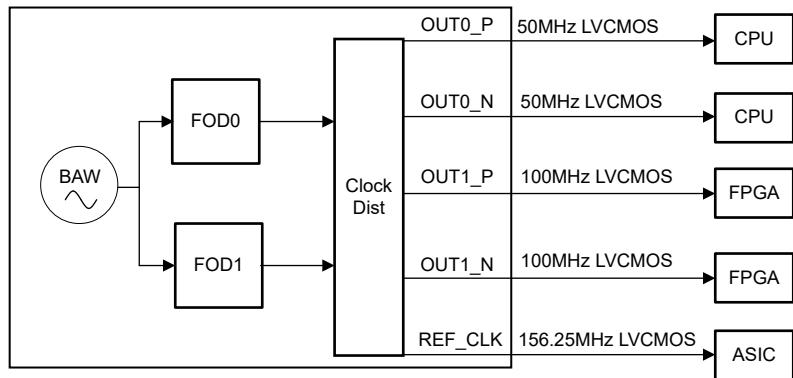

### 7.3.1 デバイス ブロック レベルの説明

LMK3H0102 は、BAW 発振器を内蔵したリファレンスレス クロック ジェネレータです。BAW 周波数 (公称 2467MHz) は 2 つの分数出力分周器 (FOD) によって分周され、それぞれ 100MHz~400MHz の周波数を生成できます。各 FOD は 2 つのチャネル分周器のいずれかに配線でき、これによって FOD 周波数を分周して、2.5MHz~200MHz の周波数を生成します。200MHz より高い周波数を生成するには、両方の FOD を利用するエッジ コンバイナを使用する必要があります。この場合、チャネル分周器はバイパスされて、200MHz~400MHz の周波数が生成されます。VDD に対応する電圧の追加の LVCMOS クロックは、オプションとして REF\_CTRL ピンで生成できます。

### 7.3.2 デバイス構成の制御

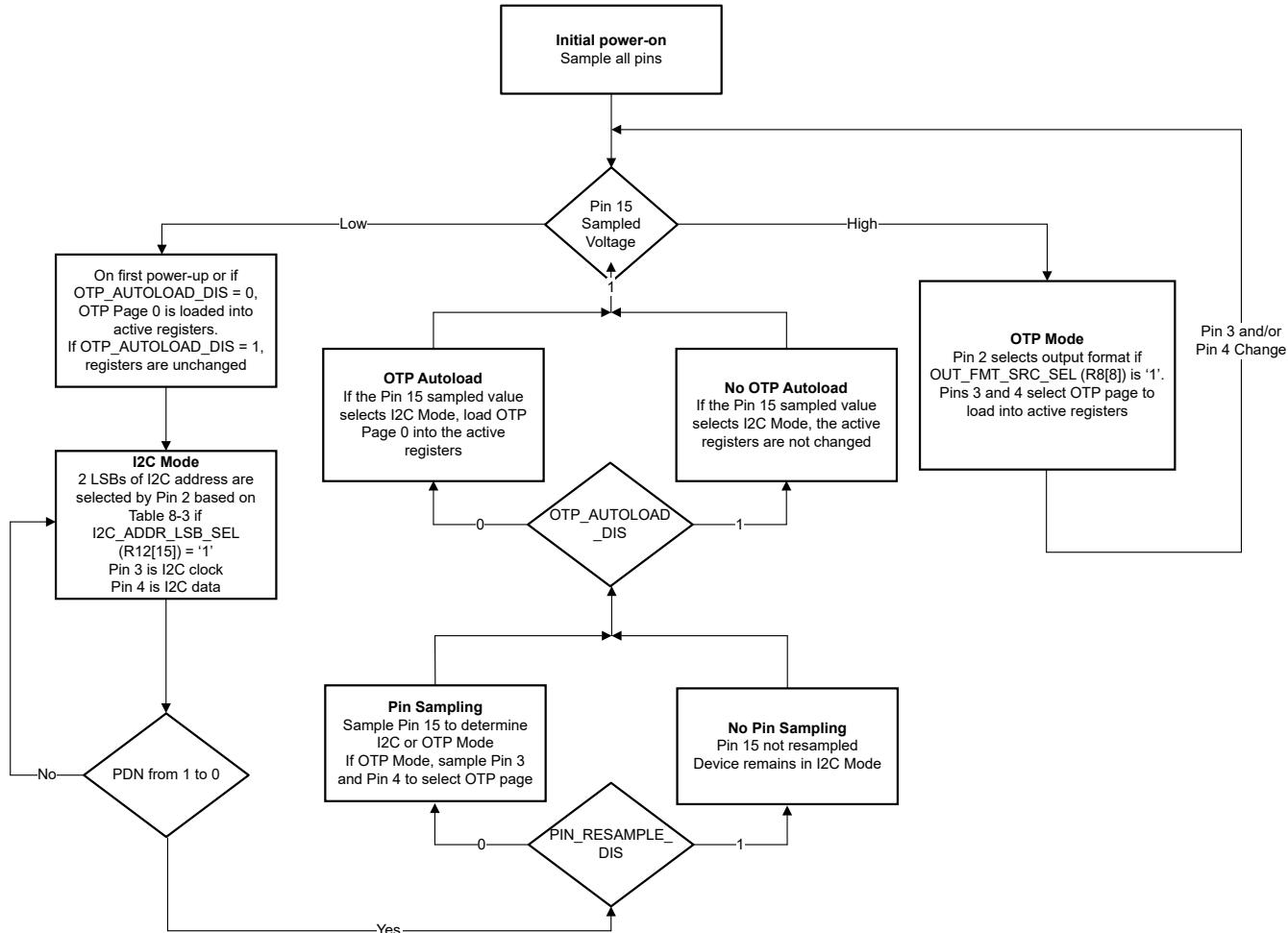

図 7-2 に、デバイスの状態、構成ピン、デバイスの初期化、デバイスの動作モードの関係を示します。OTP モードは、起動時に REF\_CTRL ピンが High になると開始されます。I<sup>2</sup>C モードは、起動時に REF\_CTRL ピンが Low になると開始されます。OTP モードでは、OTP\_SEL0/SCL ピンと OTP\_SEL1/SDA ピンの状態によって、アクティブ レジスタにロードされる OTP ページが決まります。このデバイスはワンタイム プログラマブルであり、内部 EFUSE に保存されているレジスタ設定は変更できません。REF\_CTRL ピンの状態を変更して、VDD をいったん Low にしてから再度 High にしてデバイスのパワー サイクルをトリガすると、デバイスは OTP モードから I<sup>2</sup>C モード、またはその逆に移行できます。OTP モードでは、REF\_CTRL ピンを High に保持した状態で、OTP\_SEL0 ピンまたは OTP\_SEL1 ピンのレベルを変更すると、ア

クティブな OTP ページが動的に変化します。デバイスは、新しい OTP ページをロードする前に、OTP\_SEL0 ピンと OTP\_SEL1 ピンが安定するまで 350 $\mu$ s 間待機します。

I<sup>2</sup>C モードでは、FMT\_ADDR ピンの状態によってデバイスの I<sup>2</sup>C アドレスが判定され、OTP\_SEL0/SCL ピンと OTP\_SEL1/SDA ピンはそれぞれ I<sup>2</sup>C クロックピンとデータピンとして転用されます。I<sup>2</sup>C モードでは、ホストはアクティブなデバイス レジスタを更新できます。プログラムされた構成とは異なる構成を使用する場合、各パワー サイクルの後にレジスタを書き込む必要があります。

PDN ビット (R10[1]) を 1 に設定すると、デバイスを低消費電力状態にできます。PDN ビットをクリアすると、デバイスは低消費電力状態から復帰します。DEV\_IDLE\_STATE\_SEL ビット (R10[4]) が 0 で、出力がディスエーブルの場合、デバイスは低消費電力状態に移行します。低消費電力状態への移行は、チャネル 0 で使用される FOD の周波数の変更、SSC 構成の変更、出力フォーマットの変更を行うために必要です。テキサス・インスツルメンツでは、この低消費電力状態でのレジスタへの書き込みを推奨しています。OTP\_AUTOLOAD\_DIS (R10[2]) ビットを 1 に設定し、PDN を 0 に設定する前に OTP ページ 0 が自動的にロードされないようにします。

低消費電力状態から復帰したときのデバイスの状態を判定するフィールドは 2 つあります。PIN\_RESAMPLE\_DIS (R10[3]) は、低消費電力状態から復帰したときに FMT\_ADDR ピン、OTP\_SEL0/SCL ピン、OTP\_SEL1/SDA ピン、REF\_CTRL ピンが再サンプリングされるかどうかを制御します。これらのピンが再サンプリングされる場合、REF\_CTRL ピンが High になるとデバイスは OTP モードに移行できます。このビットを 1 に設定すると、この機能がディスエーブルになります。OTP\_AUTOLOAD\_DIS は、低消費電力状態から復帰するときに OTP ページ 0 の内容がデバイス レジスタにロードされるかどうかを制御します。OTP\_AUTOLOAD\_DIS ビットが 1 で PIN\_RESAMPLE\_DIS が 1 の場合、レジスタの内容は変更されません。OTP\_AUTOLOAD\_DIS ビットが 0 で PIN\_RESAMPLE\_DIS が 1 の場合、OTP ページ 0 の内容がレジスタにロードされます。PIN\_RESAMPLE\_DIS が 0 で、REF\_CTRL が High になると、デバイスは OTP モードに移行します。この場合、OTP\_SEL0/SCL および OTP\_SEL1/SDA が、デバイス レジスタにロードされた OTP ページを制御します。

図 7-2. LMK3H0102 デバイスのモード図

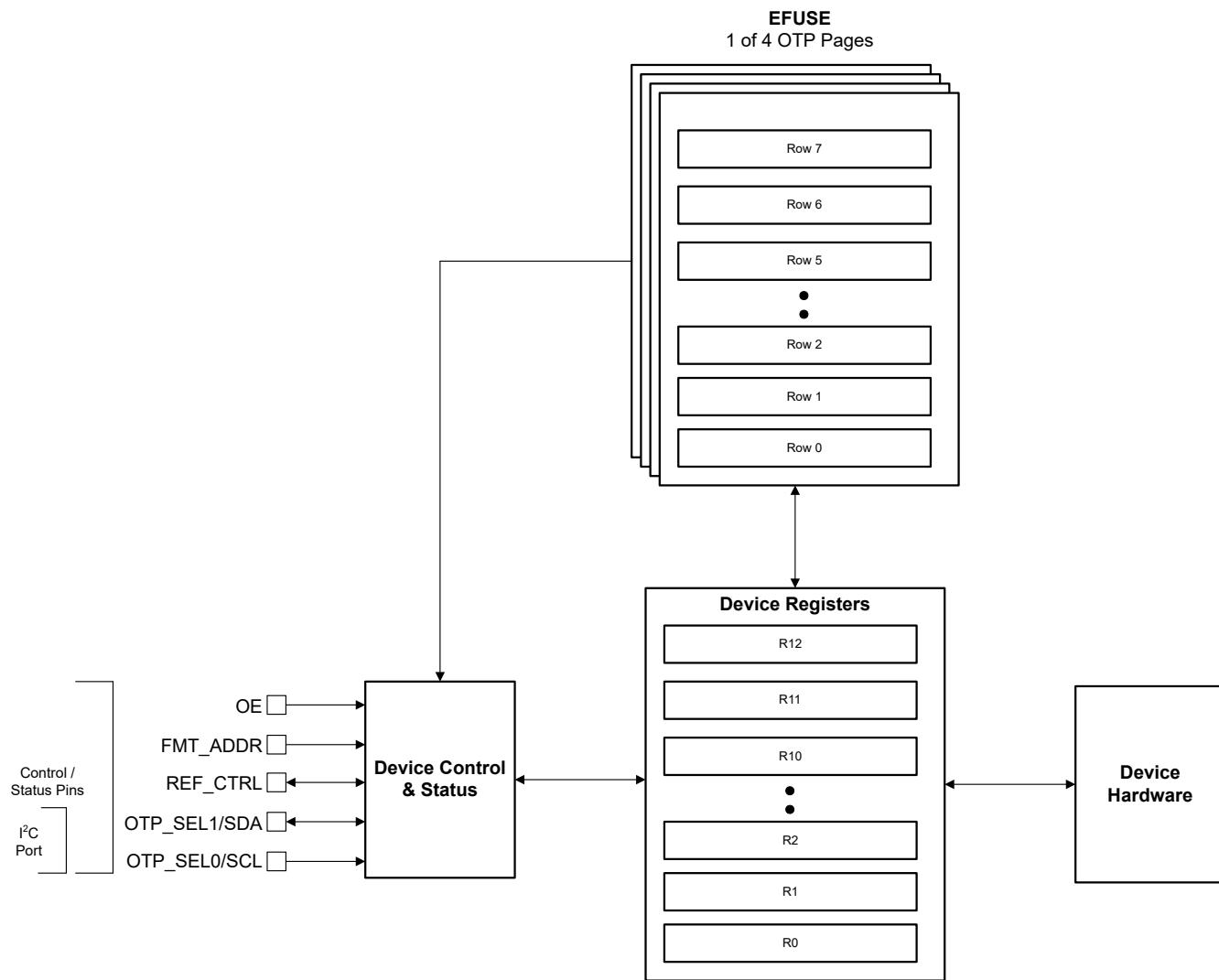

I<sup>2</sup>C モードでは、デバイス レジスタは OTP ページ 0 の内容で構成されます。OTP モードでは、これらの値は 4 つの OTP ページのいずれかから供給され、起動時の OTP\_SELx ピンの状態に基づいて選択できます。図 7-3 に、LMK3H0102 内のインターフェイスと制御ブロックを示しており、矢印はさまざまな組込みメモリからの読み取りおよび書き込みアクセスを示しています。

図 7-3. LMK3H0102 のインターフェイスと制御ブロック

### 7.3.3 OTP モード

このモードでは、構成ピンで 4 つのワンタイム プログラマブル (OTP) ページのいずれかを選択したり、出力フォーマットを選択したりできます。このモードでは、I<sup>2</sup>C ピンが OTP ページ選択に転用されるため、I<sup>2</sup>C はイネーブルになりません。[表 7-1](#) に、OTP\_SEL0 ピンと OTP\_SEL1 ピンの状態に基づいて選択された OTP ページを示します。

表 7-1. OTP モードにおける OTP ページ選択

| OTP_SEL1 ピン | OTP_SEL0 ピン | OTP ページ |

|-------------|-------------|---------|

| Low         | Low         | 0       |

| Low         | High        | 1       |

| High        | Low         | 2       |

| High        | High        | 3       |

デバイスの EFUSE は永続的にプログラムされており、OTP\_BURNT(R0[0]) = 1 です。新しい構成が必要な場合、各起動時に I<sup>2</sup>C を介して構成をロードする必要があります。OTP 構成は、TICS Pro のウィザードを使用して作成できます。カスタムの OTP 構成の注文可能な型番については、テキサス・インスツルメンツまでお問い合わせください。

以下のフィールドは、4つのOTPページで一意にすることができます。他のすべてのレジスタ設定は、OTPページで共有されます。

- **SSC\_EN:SSC** のイネーブルまたはディスエーブル。

- **OE\_0:OUT0** のイネーブルまたはディスエーブル。

- **OE\_1:OUT1** のイネーブルまたはディスエーブル。

- **OP\_TYPE\_CH0:OUT0** 出力フォーマットタイプ。「**出力フォーマットタイプ**」を参照してください。

- **OP\_TYPE\_CH1:OUT1** 出力フォーマットタイプ。「**出力フォーマットタイプ**」を参照してください。

- **SSC\_SETTING:SSC** 変調タイプ。「**拡散スペクトラムクロック処理**」を参照してください。

**OTP\_SEL1** ピンまたは **OTP\_SEL0** ピンの状態が変化すると、デバイスは自動的にパワー サイクルを行い、新しいOTPページをリロードします。新しいOTPにおいて、ピン3とピン4が安定状態に移行するまでの時間は 1.5ms 以内です。

### 7.3.4 I<sup>2</sup>C モード

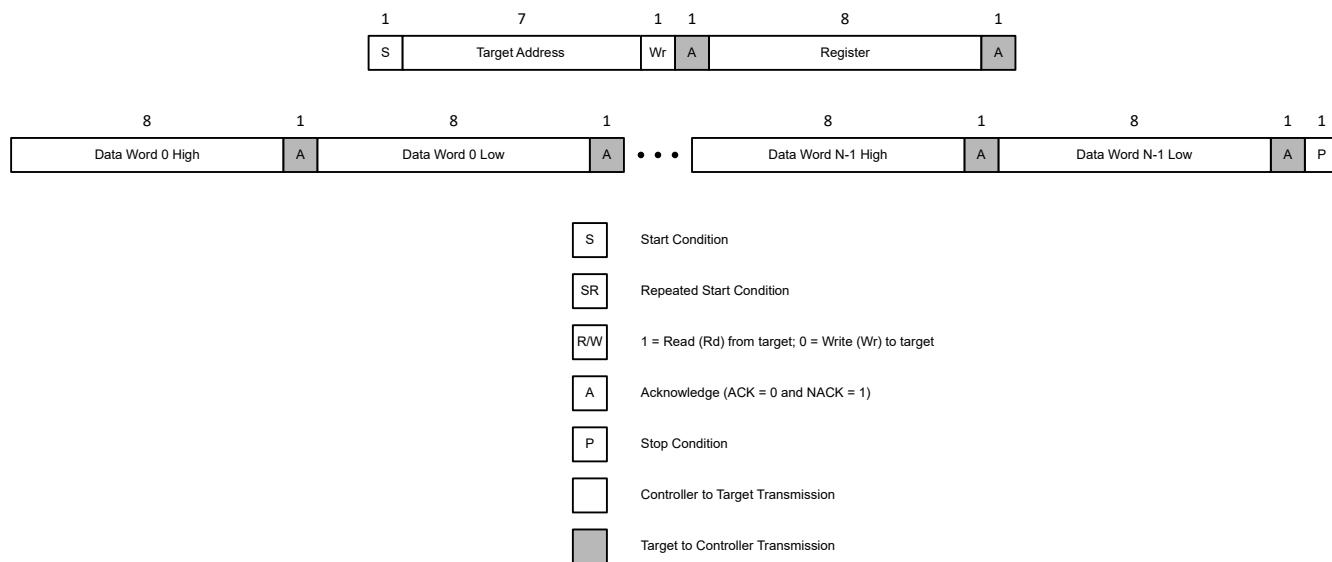

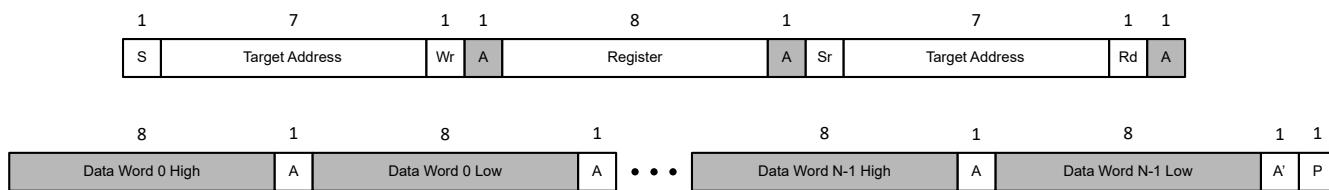

このモードでは、I<sup>2</sup>C がイネーブルで、SCA ピンと SDL ピンはそれぞれ I<sup>2</sup>C クロック ピンと I<sup>2</sup>C データ ピンとして機能します。表 7-2 に、FMT\_ADDR ピンで選択可能な 4 つのデフォルト I<sup>2</sup>C アドレスを示します。I<sup>2</sup>C アドレスの最上位 5 ビットは、I2C\_ADDR (R12[14:8]) の上位 5 ビットに設定されます。

I2C\_ADDR\_LSB\_SEL (R12[15]) = 0 の場合、FMT\_ADDR ピンは無視されて、I<sup>2</sup>C アドレスは I2C\_ADDR によってのみ決定されます。FMT\_ADDR ピンを I<sup>2</sup>C LSB 選択に使用する場合、このピンは個別の出力イネーブル制御用に構成することはできません。

表 7-2. I<sup>2</sup>C アドレスの選択

| REF_CTRL ピン <sup>(1)</sup> | FMT_ADDR ピン | I <sup>2</sup> C アドレス <sup>(2)</sup> |

|----------------------------|-------------|--------------------------------------|

| High                       | X           | 該当なし<br>(I <sup>2</sup> C ディスエーブル)   |

| Low                        | 0           | 0x68 / 0xD0                          |

| Low                        | 1           | 0x69 / 0xD2                          |

| Low                        | SDA に接続     | 0x6A / 0xD4                          |

| Low                        | SCL に接続     | 0x6B / 0xD8                          |

(1) これは、パワーアップ時の REF\_CTRL ピンの状態であり、実際に動作しているときのピンの状態ではありません。

(2) 0xD0、0xD2、0xD4、0xD8 の各アドレスは、R/W ビットが 0 に設定されています。

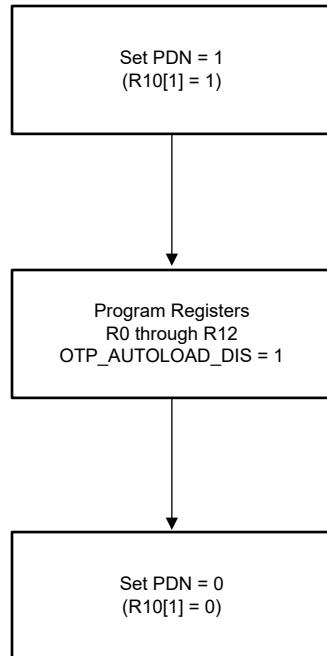

デバイスのレジスタを変更するときは、まず **PDN** を 1 に設定し、デバイスのレジスタに書き込んだ後で、**PDN** を 0 に設定します。図 7-4 にこのプロセスを示します。

図 7-4. LMK3H0102 のプログラミング シーケンス

## 7.4 デバイスの機能モード

### 7.4.1 フェイルセーフ入力

LMK3H0102 のデジタル入力ピンは、REF\_CTRL ピンを除き、フェイルセーフ入力動作をサポートするように設計されています。この機能により、VDD が印加される前に、デバイスを損傷することなくデジタル入力を駆動できます。デバイスでサポートされている最大入力電圧の詳細については、[絶対最大定格](#) を参照してください。

### 7.4.2 分数出力分周器

LMK3H0102 には、2 つの分数出力分周器が搭載されています。単一の FOD すべての出力が生成可能な場合、テキサス・インスツルメンツでは、消費電力を節約し性能を向上させるために、FOD1 をディスエーブルにすることを推奨しています。FOD1 を選択している出力チャネルがない場合、FOD1 はディスエーブルになります。

#### 7.4.2.1 FOD 動作

内部 BAW 共振器は、1 つまたは 2 つの分数出力分周器 (FOD) によって分周されます。FOD0 には SSC ジェネレータが搭載されていますが、FOD1 には SSC ジェネレータがありません。OUT0 と OUT1 の両方を SSC クロックにする必要がある場合、この 2 つのクロックは FOD0 をソースとしている必要があります。1 つの SSC クロックと 1 つの非 SSC クロックが同時に必要である場合、SSC クロック用に FOD0 がイネーブルに、非 SSC クロック用に FOD1 がイネーブルにされます。どちらの出力クロックも SSC を必要としない場合、どちらの FOD も使用できます。

#### 注

テキサス・インスツルメンツでは、アプリケーションで FOD が 1 つだけ必要な場合は、FOD0 をデフォルトの FOD として使用することを推奨しています。両方の FOD が使用されている場合は、テキサス・インスツルメンツは OUT0 を FOD0 に、OUT1 を FOD1 に使用することを推奨します。

最小チャネル分周器値が 2 であるため、単一の FOD によってクロック出力で生成可能な最大周波数は 200MHz です。200MHz を超える出力を生成するには、チャネル分周器をバイパスして、エッジコンバーナを使用します。これには、両方の FOD がイネーブルで、同じ整数分周器値と分数分子値、さらには同じゲイン較正値を持っている必要があります。一方の出力が 200MHz を超えると、もう一方の出力は、チャネル分周器値のいずれかで共有 FOD 周波数を分周したも

の、または FOD 周波数そのものを選択することしかできません。200MHz 未満では、OUT0 と OUT1 に異なる周波数を設定できるように、2 つの FOD を個別に構成できます。テキサス・インスツルメンツでは、OUT0 と OUT1 に決定論的な位相関係を持たせるために、可能な限り単一の FOD をソースとすることを推奨しています。

LMK3H0102 の FOD は、I<sup>2</sup>C プログラミング、またはプログラミングが行われない場合にはワンタイム プログラミング (OTP) 設定により、さまざまな出力周波数に対応するように構成できます。FOD は、整数 (FODx\_N\_DIV) と分数 (FODx\_NUM) の分周値を設定することで構成できます。表 7-3 に、各 FOD のこれらのフィールドのレジスタ位置を示します。

**表 7-3. FOD の整数分周および分子分周の位置**

| フィールド           | 登録       |

|-----------------|----------|

| FOD0_N_DIV      | R0[9:3]  |

| FOD0_NUM[23:16] | R1[15:8] |

| FOD0_NUM[15:0]  | R2[15:0] |

| FOD1_N_DIV      | R3[15:9] |

| FOD1_NUM[23:16] | R6[12:5] |

| FOD1_NUM[15:0]  | R8[15:0] |

整数分周値と分子分周値の設定方法の例を、式 1 と式 2 に示します。

$$FODx\_N\_DIV = \text{floor}\left(\frac{F_{BAW}}{F_{FOD}}\right) \quad (1)$$

ここで

- FODx\_N\_DIV: FOD 分周値の整数部分 (7 ビット、6~24)

- F<sub>BAW</sub>: BAW 周波数、2467MHz + オフセット、詳細は以下参照

- F<sub>FOD</sub>: 目標とする FOD 周波数 (100MHz~400MHz)

$$FODx\_NUM = \text{int}\left(\left(\left(\frac{F_{BAW}}{F_{FOD}}\right) - FODx\_N\_DIV\right) \times 2^{24}\right) \quad (2)$$

ここで、FODx\_NUM は FOD 分周値の分数部分 (24 ビット、0~16777215) です。

出力周波数 (F<sub>OUT</sub>) は、式 3 で示されているように、FOD 周波数に関連しており、エッジ コンバイナがイネーブルである場合は FOD 周波数に等しくなります。OUTDIV は 2、4、6、8、10、20、40 のいずれかです。

$$F_{OUT} = \frac{F_{FOD}}{\text{OUTDIV}} \quad (3)$$

式 4 を使用して、デバイスの BAW 周波数の実際の値を計算します。BAWFREQ\_OFFSET\_FIXEDLUT の値は、符号付き 16 ビット値である R238 を読み取ることで求めることができます。

$$F_{BAW} = 2467\text{MHz} \times (1 + (\text{BAWFREQ\_OFFSET\_FIXEDLUT} \times 128E - 9)) \quad (4)$$

#### 7.4.2.2 エッジ コンバイナ

エッジ コンバイナを使用して、200MHz を超える出力周波数を生成します。エッジ コンバイナを使用するには、CH0\_EDGE\_COMB\_EN (R3[3]) または CH1\_EDGE\_COMB\_EN (R3[7]) を 1 に設定します。エッジ コンバイナを使用する場合、両方の FOD が同じ周波数で動作する必要があります (つまり、分周値が一致している必要があります)。いずれかの CHx\_EDGE\_COMB\_EN ビットが 1 に設定されているときに、デバイスでは、FOD0 から FOD1 に分周器値を自動的にロードすることで、これに対応しています。エッジ コンバイナを使用している場合は FOD0 の SSC はサポートされないため、イネーブルにしないでください。いずれの FOD も引き続き LVCMOS REF\_CLK 出力を生成できます。

エッジ コンバイナを適切に動作させるためには、以下の条件を満たす必要があります。

- 両方の FOD のゲイン キャリブレーションコードを平均化する必要があります。たとえば、**DTC1\_GAIN\_RT = 200**、**DTC2\_GAIN\_RT = 220** の場合、両方のフィールドには 210 を書き込む必要があります。ゲイン キャリブレーションコードは、保護されたレジスタ領域にあります。R12[7:0] = 0x5B を使用して保護されたレジスタをロック解除し、平均化されたゲイン キャリブレーションコードのみを書き込み、R12[7:0] = 0x00 に設定することによって保護されたレジスタをロックします。詳細については、[R146](#)、[R147](#)、および [R148](#) を参照してください。

- エッジコンバイナが OUT1 のみに使用される場合、OUT0 のディスエーブル状態にかかわらず、**CH0\_FOD\_SEL (R3[4])** は常に 0 (FOD0) に設定する必要があります。

#### 7.4.2.3 デジタルステートマシン

LMK3H0102 のデジタルステートマシンには、FOD のいずれかに基づくクロックが搭載されています。**CH0\_FOD\_SEL (R3[4])** で選択された FOD は、ステートマシンのクロック分周器への入力を供給します。総合的な分周値は、**DIG\_CLK\_N\_DIV (R0[9:3])** フィールドに 2 を加算した値になります。**DIG\_CLK\_N\_DIV** を設定して、FOD 周波数をステートマシンの総合的なクロック分周値で除算した値が 40MHz～50MHz になるようにします。このクロックの設定に使用される分周器値は、保存されている値と等しくなります。たとえば、FOD0 の周波数が 200MHz で、**CH0\_FOD\_SEL** が 0 の場合、200MHz を 4 で分周すると 50MHz になるため、**DIG\_CLK\_N\_DIV** は 2 に設定する必要があります。

#### 7.4.2.4 拡散スペクトラムクロック処理

FOD0 は、拡散スペクトラムクロック処理 (SSC) をサポートしています。SSC は、出力周波数を変調することで、放射エミッションのピークを抑制するために使用できます。**SSC\_EN (R4[0])** = 1 のとき、FOD0 がソースのすべての出力には SSC が適用されます。**SSC\_MOD\_TYPE (R4[1])** は、ダウンスプレッド変調 (**SSC\_MOD\_TYPE** = 0) またはセンタースプレッド変調 (**SSC\_MOD\_TYPE** = 1) のいずれかを選択します。LMK3H0102 には、4 つのダウンスプレッド SSC オプションと 1 つのカスタム SSC オプションが内蔵されています。**SSC\_CONFIG\_SEL (R9[11:9])** は、カスタムオプションまたは事前設定済みオプションを選択します。事前設定済みオプションは、FOD0 からの 200MHz 出力用に最適化されます。[表 7-4](#) に、事前設定済み SSC オプションのレジスタ設定の詳細を示します。事前設定済み SSC オプションは、FOD0 からの 200MHz 出力用に最適化されます。エッジコンバイナを使用する場合、スペクトラム拡散クロック処理をディスエーブルにする必要があります。

表 7-4. 事前設定済み SSC の構成

| SSC_CONFIG_SEL | ダウンスプレッド SSC 深度                                    |

|----------------|----------------------------------------------------|

| 0x0            | カスタム、 <b>SSC_STEPS</b> と <b>SSC_STEP_SIZE</b> に基づく |

| 0x1            | -0.10%                                             |

| 0x2            | -0.25%                                             |

| 0x3            | -0.30%                                             |

| 0x4            | -0.50%                                             |

| その他すべての値       | 予約済み                                               |

カスタム SSC が選択された場合、**SSC\_STEPS (R4[14:2])** と **SSC\_STEP\_SIZE (R5)** を構成して、変調深度を設定する必要があります。[式 5](#) と [式 6](#) を使用して **SSC\_STEPS (R4[14:2])** レジスタの設定を決定し、[式 7](#) または [式 8](#) を使用して **SSC\_STEP\_SIZE (R5)** の設定を決定します。[式 7](#) はダウンスプレッド SSC 用で、[式 8](#) はセンタースプレッド SSC 用です。

$$\text{Down-spread: } \text{SSC_STEPS} = \text{int}\left(\left(\frac{F_{FOD0}}{F_{MOD}}\right) \div 2\right) \quad (5)$$

$$\text{Center-spread: } \text{SSC_STEPS} = \text{int}\left(\left(\frac{F_{FOD0}}{F_{MOD}}\right) \div 4\right) \quad (6)$$

ここで

- $F_{FOD0}$ : FOD0 周波数

- $F_{MOD}$ : 変調周波数。PCIe アプリケーションでは 31.5kHz を使用してください。

$$SSC\_STEP\_SIZE = \text{floor} \left( \frac{\left( \left( \frac{F_{BAW}}{F_{FOD0}} \right) \times \left( \frac{1}{1 - SSC\_DEPTH} \right) - 1 \right)}{SSC\_STEPS \times DEN} \right) \quad (7)$$

$$SSC\_STEP\_SIZE = \text{floor} \left( \frac{\left( \left( \frac{F_{BAW}}{F_{FOD}} \right) \times \left( \frac{1}{1 - SSC\_DEPTH} \right) - \left( \frac{1}{1 + SSC\_DEPTH} \right) \right)}{2 \times SSC\_STEPS \times DEN} \right) \quad (8)$$

ここで

- $SSC\_STEP\_SIZE$ : SSC のステップごとの分子インクリメント値

- $F_{BAW}$ : BAW 周波数、2467MHz。 $F_{BAW}$  値はデバイスごとに異なります。

- $SSC\_DEPTH$ : 変調深度、正の値で表されます。深度  $-0.5\%$  を使用する場合、この値は  $0.005$  になります。

- $SSC\_STEPS$ : ダウンスプレッドの場合は式 5、センター スプレッドの場合は式 6 から求めた結果

- $DEN$ : 分数分母、 $2^{24}$

SSC を使用する出力と使用しない出力が混在する場合、2 つの出力間にクロストークが発生する可能性があります。SSC を单一出力にのみ適用するよう構成する場合、テキサス・インスツルメンツに特定の構成の測定データをリクエストしてください。

SSC 設定を変更するときは、他の SSC 設定が構成されるまで、 $SSC\_EN$  を 1 に設定しないでください。SSC を構成する際は、次の手順を実行します。

1. PDN を 1 に設定します。

2. OTP\_AUTOLOAD\_DIS を 1 に設定します。

3. 必要に応じて、 $SSC\_MOD\_TYPE$ 、 $SSC\_STEP\_SIZE$ 、 $SSC\_STEPS$  を変更します。

4.  $SSC\_EN$  を 1 に設定します。

5. PDN を 0 に設定します。

#### 7.4.2.5 整数境界スプリアス

FOD の分周値の小数部分が整数境界に近い場合、整数境界スプリアスが発生することがあります。一般的に、この「整数境界」とは、小数部分が  $0.9 \sim 1$  または  $0 \sim 0.1$  である場合です。たとえば、BAW 周波数が 2467MHz、出力が 122.88MHz である場合、FOD は 245.76MHz で動作する必要があります。2467MHz を 245.76MHz で割った値は約 10.038 になります。分周値の小数部分は 0.038 で、 $0 \sim 0.1$  の範囲です。これは、122.88MHz 出力が生成されると、出力クロックに 12kHz~20MHz 帯域のスプリアスが発生する可能性があることを意味します。場合によっては、適切な周波数プランニングを行うことで、FOD 周波数とチャネル分周器値を増加させ、この点に対処できます。特定の周波数計画における整数境界スプリアスについてご不明な点がありましたら、テキサス・インスツルメンツにお問い合わせください。

#### 7.4.3 出力動作

##### 7.4.3.1 出力フォーマットの選択

このデバイスは、LP-HCSL ( $85\Omega$  と  $100\Omega$  の両方の内部終端)、LVDS、LVC MOS をサポートしています。LVC MOS 出力では、VDD が 3.3V の場合、VDDO は 1.8V、2.5V、または 3.3V にすることができます。それ以外の場合は、VDDO は VDD と同じ電圧でなければなりません。OUT0 と OUT1 が異なるフォーマットを使用する場合、DC-LVDS と差動 LVC MOS は、他のすべてのフォーマットと  $180^\circ$  の位相差があります。

表 7-5. レジスタを使用した出力フォーマット

| OUT0_FMT /<br>OUT1_FMT | 説明                       |

|------------------------|--------------------------|

| 0x0                    | LP-HCSL の $100\Omega$ 終端 |

| 0x1                    | LP-HCSL の $85\Omega$ 終端  |

**表 7-5. レジスタを使用した出力フォーマット (続き)**

| OUT0_FMT /<br>OUT1_FMT | 説明                                                                     |

|------------------------|------------------------------------------------------------------------|

| 0x2                    | AC 結合 LVDS                                                             |

| 0x3                    | DC 結合 LVDS                                                             |

| 0x4                    | OUTx_P で LVC MOS イネーブル<br>OUTx_N で LVC MOS ディスエーブル                     |

| 0x5                    | OUTx_P で LVC MOS ディスエーブル<br>OUTx_N で LVC MOS イネーブル                     |

| 0x6                    | OUTx_P で LVC MOS イネーブル<br>OUTx_N で LVC MOS イネーブル<br>位相差 180°<br>(1)    |

| 0x7                    | OUTx_P で LVC MOS イネーブル<br>OUTx_N で LVC MOS イネーブル<br>OUTx_P と OUTx_N 同相 |

(1) 最高の出力性能を得るには、テキサス・インストルメンツでは、OUTx\_P と OUTx\_N の両方のパターンが必要な場合は、位相差 180° の LVC MOS を使用することを推奨しています。

OTP モードでは、FMT\_ADDR ピンの機能は OUT\_FMT\_SRC\_SEL (R9[8]) によって決定できます。表 7-6 に、OUT\_FMT\_SRC\_SEL フィールドで使用できる出力フォーマットの設定を示します。出力フォーマットの選択に FMT\_ADDR ピンを使用する場合、このピンを個別の出力イネーブルに構成することはできません。

**表 7-6. FMT\_ADDR の出力フォーマット オプション**

| OUT_FMT_SR<br>C_SEL | FMT_ADDR ピン | 出力フォーマット                                               |

|---------------------|-------------|--------------------------------------------------------|

| 0                   | X           | OUT0_FMT (R6[2:0]) /<br>OUT1_FMT (R7[4:2]) で設定しま<br>す。 |

| 1                   | GND         | LP-HCSL の 100Ω 終端                                      |

| 1                   | VDD         | LP-HCSL の 85Ω 終端                                       |

#### 7.4.3.1.1 出力フォーマットのタイプ

図 7-5～図 7-8 に、選択された出力フォーマットに基づいた LMK3H0102 出力の接続方法を示します。

**図 7-5. LMK3H0102 の LVC MOS 出力と LVC MOS レシーバのインターフェイス**

図 7-6. LMK3H0102 の LVCMOS 出力と AC-LVDS レシーバのインターフェイス

図 7-7. LMK3H0102 の LVCMOS 出力と DC-LVDS レシーバのインターフェイス

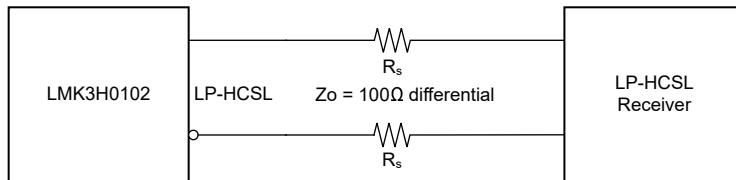

図 7-8. LMK3H0102 の LVCMOS 出力と LP-HCSL レシーバのインターフェイス

#### 7.4.3.1.1.1 LP-HCSL の終端

LP-HCSL 出力の場合、LMK3H0102 は内部の 50Ω 終端抵抗を使用して GND への終端を行います。外部の終端抵抗は必要ありません。

#### 7.4.3.2 出力スルーレート制御

すべての LVDS 出力と LP-HCSL 出力について、スルーレートを構成できます。OUT0\_SLEW\_RATE (R6[4:3]) と OUT1\_SLEW\_RATE (R7[6:5]) を使用すると、出力スルーレートを遅くして、OUT0 と OUT1 の EMI をそれぞれ低減することができます。表 7-7 に、使用可能なスルーレートのオプションを示します。

表 7-7. スルーレートの設定

| OUT0_SLEW_RATE<br>OUT1_SLEW_RATE | スルーレート            |

|----------------------------------|-------------------|

| 0x0                              | 2.3V/ns ~ 3.5V/ns |

| 0x1                              | 2.0V/ns ~ 3.2V/ns |

| 0x2                              | 1.7V/ns ~ 2.8V/ns |

| 0x3                              | 1.4V/ns ~ 2.7V/ns |

#### 7.4.3.3 REF\_CTRL の動作

起動時、REF\_CTRL ピンは、Low のときは I<sup>2</sup>C モードを選択し、High のときは OTP モードを選択します。起動後、LVCMOS REF\_CLK を出力するように REF\_CTRL をプログラムできます。これは、FOD0 または FOD1 のいずれかから生成され、その後整数分周器 (1/2, 1/4, 1/8) によって分周されます。または、このピンをディスエーブルしたり、「クロックレ

「デイ」信号として機能させたりすることもできます。REF\_CTRL\_PIN\_FUNC (R7[14:13]) は REF\_CTRL ピンの機能を制御します。表 7-8 に、これらのオプションを示します。

**表 7-8. 起動後の REF\_CTRL の機能**

| REF_CTRL_PIN_FUNC | REF_CTRL の機能       |

|-------------------|--------------------|

| 0x0               | ディスエーブル、強制的に Low   |

| 0x1               | ディスエーブル、トライステート    |

| 0x2               | REF_CLK LVC MOS 出力 |

| 0x3               | CLK_READY 出力       |

#### 7.4.4 出力イネーブル

##### 7.4.4.1 出力イネーブルの制御

このデバイスは、同期出力イネーブル (OE) をサポートしています。同期 OE とは、OE 信号がアサートまたはデアサートされたときに、出力にグリッチが発生しないことです。