# LMV551-Q1 3MHz、車載用Micropower PROアンプ

## 1 特長

- 車載アプリケーションに対応

- 以下のAEC-Q100試験ガイダンス

- デバイス温度範囲グレード1: 動作時周囲温度 $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$

- デバイスHBM ESD分類レベル2

- デバイスCDM ESD分類レベルC7

- 3Vおよび5Vでの性能を規定

- 高いユニティ・ゲイン帯域幅: 3MHz

- 消費電流:  $37\mu\text{A}$  (標準値)

- CMRR: 93dB

- PSRR: 90dB

- スルーレート:  $1\text{V}/\mu\text{s}$

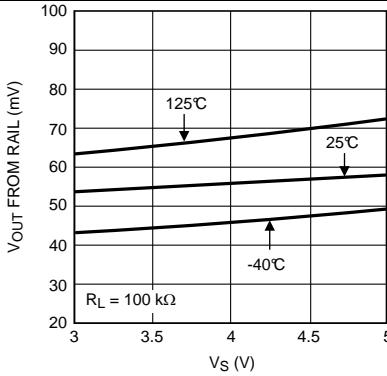

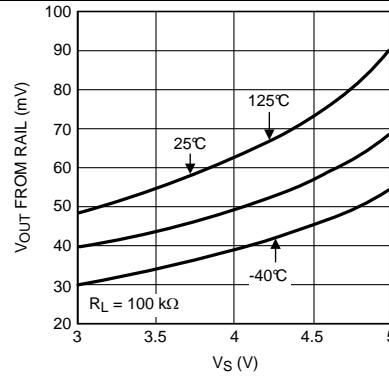

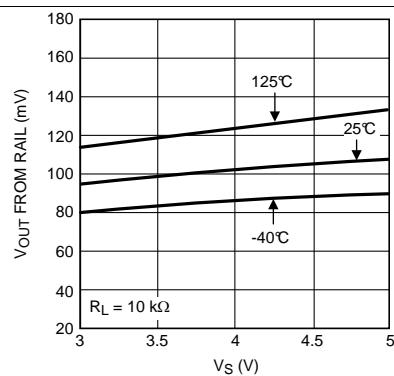

- 100k $\Omega$ 負荷での出力スイング: レールから70mV

- 全高調波歪み: 1kHz、2k $\Omega$ において0.003%

## 2 アプリケーション

- 車載サブシステム

- 携帯用およびバッテリ駆動のシステム

- ロボティクスおよび自動化

- センサおよび計測機器

- アクティブ・フィルタ

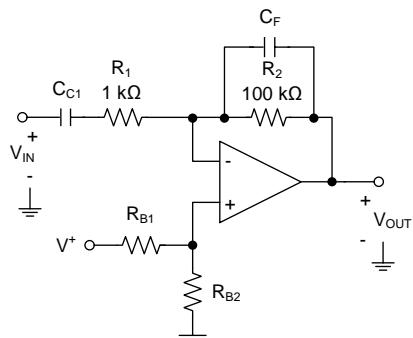

### 単一電源の反転アンプ

Copyright © 2016, Texas Instruments Incorporated

## 3 概要

LMV551-Q1は高性能、低消費電力のオペアンプで、TIの高度なVIP50プロセスで実装されています。LMV551-Q1は3MHzの帯域幅があり、消費電流がわずか $37\mu\text{A}$ で、このクラスのオペアンプとして非常に優れた帯域幅/電力比を実現しています。これらのアンプはユニティ・ゲイン安定で、広い帯域幅を必要とする低消費電力アンプ向けの非常に優れたソリューションです。

LMV551-Q1にはレール・ツー・レール出力段があり、同相入力範囲がグランドより低い電圧まで拡張されています。

LMV551-Q1の動作電源電圧範囲は2.7V～5.5Vです。このアンプは広い温度範囲( $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ )で動作でき、車載用アプリケーション、センサ・アプリケーション、および携帯型計測機器アプリケーション用の優れた選択肢です。

LMV551-Q1は、超小型の5ピンSC70パッケージで供給されます。

### 製品情報<sup>(1)</sup>

| 型番       | パッケージ    | 本体サイズ(公称)     |

|----------|----------|---------------|

| LM551-Q1 | SC70 (5) | 2.00mm×1.25mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

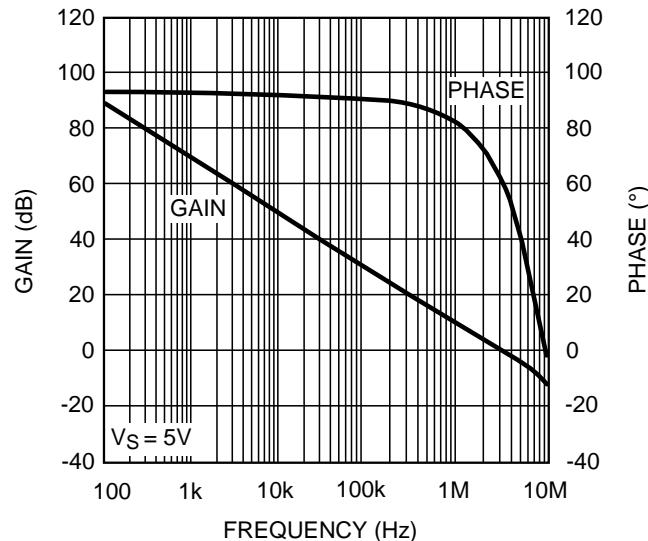

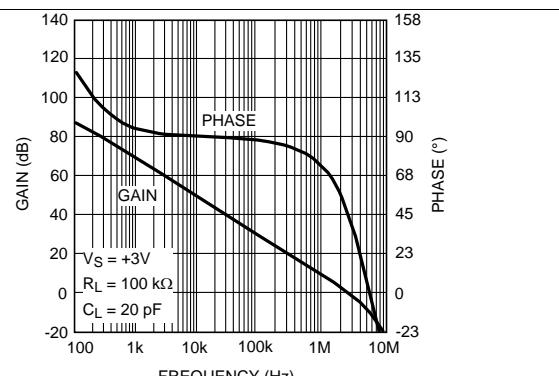

### オープン・ループ・ゲインおよび位相と周波数との関係

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、[www.ti.com](http://www.ti.com)で閲覧でき、その内容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SNOSD24

## 目次

|          |                                              |    |           |                                             |    |

|----------|----------------------------------------------|----|-----------|---------------------------------------------|----|

| <b>1</b> | 特長 .....                                     | 1  | <b>8</b>  | <b>Application and Implementation .....</b> | 16 |

| <b>2</b> | アプリケーション .....                               | 1  | 8.1       | Application Information.....                | 16 |

| <b>3</b> | 概要 .....                                     | 1  | 8.2       | Typical Application .....                   | 16 |

| <b>4</b> | 改訂履歴.....                                    | 2  | 8.3       | Dos and Don'ts .....                        | 18 |

| <b>5</b> | <b>Pin Configuration and Functions .....</b> | 3  | <b>9</b>  | <b>Power Supply Recommendations .....</b>   | 19 |

| <b>6</b> | <b>Specifications.....</b>                   | 4  | <b>10</b> | <b>Layout.....</b>                          | 19 |

| 6.1      | Absolute Maximum Ratings .....               | 4  | 10.1      | Layout Guidelines .....                     | 19 |

| 6.2      | ESD Ratings.....                             | 4  | 10.2      | Layout Example .....                        | 19 |

| 6.3      | Recommended Operating Conditions .....       | 4  | <b>11</b> | デバイスおよびドキュメントのサポート .....                    | 20 |

| 6.4      | Thermal Information .....                    | 4  | 11.1      | デバイス・サポート .....                             | 20 |

| 6.5      | Electrical Characteristics: 3 V .....        | 5  | 11.2      | ドキュメントのサポート .....                           | 20 |

| 6.6      | Electrical Characteristics: 5 V .....        | 6  | 11.3      | ドキュメントの更新通知を受け取る方法.....                     | 20 |

| 6.7      | Typical Characteristics .....                | 7  | 11.4      | コミュニティ・リソース .....                           | 20 |

| <b>7</b> | <b>Detailed Description .....</b>            | 12 | 11.5      | 商標 .....                                    | 20 |

| 7.1      | Overview .....                               | 12 | 11.6      | 静電気放電に関する注意事項 .....                         | 20 |

| 7.2      | Functional Block Diagram .....               | 12 | 11.7      | Glossary .....                              | 20 |

| 7.3      | Feature Description.....                     | 12 | <b>12</b> | メカニカル、パッケージ、および注文情報 .....                   | 20 |

| 7.4      | Device Functional Modes.....                 | 13 |           |                                             |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 目付      | 改訂内容 | 注  |

|---------|------|----|

| 2017年2月 | *    | 初版 |

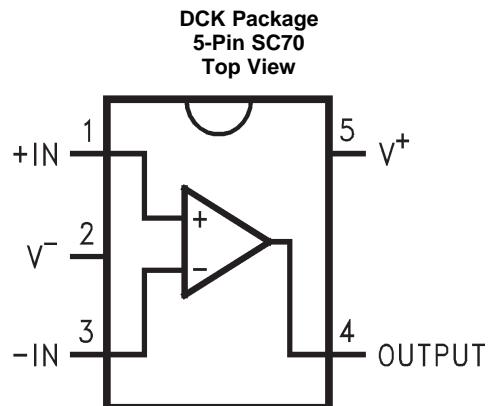

## 5 Pin Configuration and Functions

**Pin Functions: LMV551-Q1**

| PIN  |     | I/O | DESCRIPTION         |

|------|-----|-----|---------------------|

| NAME | NO. |     |                     |

| +IN  | 1   | I   | Non-inverting input |

| -IN  | 3   | I   | Inverting input     |

| OUT  | 4   | O   | Output              |

| V-   | 2   | P   | Negative supply     |

| V+   | 5   | P   | Positive supply     |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                                     | MIN                  | MAX                  | UNIT |

|-----------------------------------------------------|----------------------|----------------------|------|

| V <sub>IN</sub> Differential ( V <sup>+</sup> = 5V) |                      | ±2.5                 | V    |

| Supply voltage (V <sup>+</sup> - V <sup>-</sup> )   |                      | 6                    | V    |

| Voltage at input/output pins                        | V <sup>-</sup> - 0.3 | V <sup>+</sup> + 0.3 | V    |

| Junction temperature, T <sub>J</sub> <sup>(3)</sup> |                      | 150                  | °C   |

| Storage temperature, T <sub>stg</sub>               | -65                  | 150                  | °C   |

- (1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office / Distributors for availability and specifications.

- (3) The maximum power dissipation is a function of T<sub>J(MAX)</sub>, θ<sub>JA</sub>. The maximum allowable power dissipation at any ambient temperature is PD = (T<sub>J(MAX)</sub> - TA)/ θ<sub>JA</sub>. All numbers apply for packages soldered directly onto a PC board.

### 6.2 ESD Ratings

|                                            | VALUE                                                   | UNIT  |

|--------------------------------------------|---------------------------------------------------------|-------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 |

|                                            | Charged-device model (CDM), per AEC Q100-011            |       |

- (1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                                                   | MIN | NOM | MAX | UNIT |

|---------------------------------------------------|-----|-----|-----|------|

| Temperature range, T <sub>A</sub> <sup>(1)</sup>  | -40 |     | 125 | °C   |

| Supply voltage (V <sup>+</sup> - V <sup>-</sup> ) | 2.7 |     | 5.5 | V    |

- (1) The maximum power dissipation is a function of T<sub>J(MAX)</sub>, θ<sub>JA</sub>. The maximum allowable power dissipation at any ambient temperature is PD = (T<sub>J(MAX)</sub> - TA)/ θ<sub>JA</sub>. All numbers apply for packages soldered directly onto a PC board.

### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup>                                      | LMV551-Q1  | UNIT |

|--------------------------------------------------------------------|------------|------|

|                                                                    | DCK (SC70) |      |

|                                                                    | 5 PINS     |      |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance            | 303.5      | °C/W |

| R <sub>θJC(top)</sub> Junction-to-case (top) thermal resistance    | 135.5      | °C/W |

| R <sub>θJB</sub> Junction-to-board thermal resistance              | 81.1       | °C/W |

| Ψ <sub>JT</sub> Junction-to-top characterization parameter         | 8.4        | °C/W |

| Ψ <sub>JB</sub> Junction-to-board characterization parameter       | 80.4       | °C/W |

| R <sub>θJC(bot)</sub> Junction-to-case (bottom) thermal resistance | n/a        | °C/W |

- (1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 6.5 Electrical Characteristics: 3 V

Unless otherwise specified, all limits are specified for  $T_A = 25^\circ\text{C}$ ,  $V^+ = 3\text{V}$ ,  $V^- = 0\text{V}$ ,  $V_{CM} = V^+/2 = V_O$ . <sup>(1)</sup>

| PARAMETER          |                                   | TEST CONDITIONS                                                             | MIN <sup>(2)</sup>                                | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT                         |

|--------------------|-----------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------|--------------------|--------------------|------------------------------|

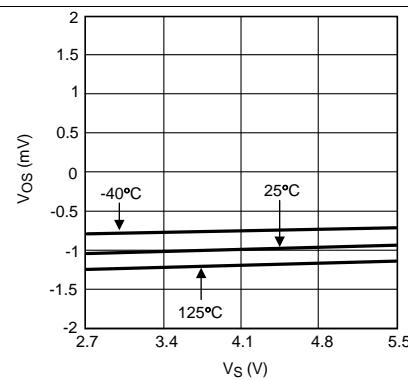

| V <sub>OS</sub>    | Input offset voltage              | $T_A = 25^\circ\text{C}$                                                    | -4.5                                              | 1                  | 3                  | mV                           |

|                    |                                   | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$                           | -8                                                |                    | 4.5                |                              |

| TC V <sub>OS</sub> | Input offset average drift        | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$                           |                                                   | 3.3                |                    | $\mu\text{V}/^\circ\text{C}$ |

| I <sub>B</sub>     | Input bias current <sup>(4)</sup> | $T_A = 25^\circ\text{C}$                                                    |                                                   | 20                 | 38                 | nA                           |

| I <sub>OS</sub>    | Input offset current              | $T_A = 25^\circ\text{C}$                                                    |                                                   | 1                  | 20                 | nA                           |

| CMRR               | Common mode rejection ratio       | $0\text{V} \leq V_{CM} \leq 2\text{V}$                                      | $T_A = 25^\circ\text{C}$                          | 74                 | 92                 | dB                           |

|                    |                                   |                                                                             | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 72                 |                    |                              |

| PSRR               | Power supply rejection ratio      | 3 V $\leq V^+ \leq 5\text{V}$ ,<br>$V_{CM} = 0.5\text{V}$                   | $T_A = 25^\circ\text{C}$                          | 80                 | 92                 | dB                           |

|                    |                                   |                                                                             | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 78                 |                    |                              |

|                    |                                   | 2.7 V $\leq V^+ \leq 5.5\text{V}$ ,<br>$V_{CM} = 0.5\text{V}$               | $T_A = 25^\circ\text{C}$                          | 80                 | 92                 |                              |

|                    |                                   |                                                                             | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 78                 |                    |                              |

| CMVR               | Input common-mode voltage         | CMRR $\geq 68\text{ dB}$                                                    | $T_A = 25^\circ\text{C}$                          | 0                  | 2.1                | V                            |

|                    |                                   | CMRR $\geq 60\text{ dB}$                                                    | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 0                  | 2.1                |                              |

| A <sub>VOL</sub>   | Large signal voltage gain         | 0.4 V $\leq V_O \leq 2.6\text{V}$ ,<br>$R_L = 100\text{k}\Omega$ to $V^+/2$ | $T_A = 25^\circ\text{C}$                          | 81                 | 90                 | dB                           |

|                    |                                   |                                                                             | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 78                 |                    |                              |

|                    |                                   | 0.4 V $\leq V_O \leq 2.6\text{V}$ ,<br>$R_L = 10\text{k}\Omega$ to $V^+/2$  | $T_A = 25^\circ\text{C}$                          | 71                 | 80                 |                              |

|                    |                                   |                                                                             | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 68                 |                    |                              |

| V <sub>O</sub>     | Output swing high                 | $R_L = 100\text{k}\Omega$ to $V^+/2$                                        | $T_A = 25^\circ\text{C}$                          | 40                 | 48                 | mV from rail                 |

|                    |                                   |                                                                             | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 58                 |                    |                              |

|                    |                                   | $R_L = 10\text{k}\Omega$ to $V^+/2$                                         | $T_A = 25^\circ\text{C}$                          | 85                 | 100                |                              |

|                    |                                   |                                                                             | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 120                |                    |                              |

|                    | Output swing low                  | $R_L = 100\text{k}\Omega$ to $V^+/2$                                        | $T_A = 25^\circ\text{C}$                          | 50                 | 65                 |                              |

|                    |                                   |                                                                             | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 77                 |                    |                              |

| I <sub>SC</sub>    | Output short circuit current      | Sourcing <sup>(5)</sup>                                                     |                                                   | 10                 |                    | mA                           |

|                    |                                   |                                                                             |                                                   | 25                 |                    |                              |

| I <sub>S</sub>     | Supply current                    | $T_A = 25^\circ\text{C}$                                                    |                                                   | 34                 | 42                 | $\mu\text{A}$                |

|                    |                                   | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$                           |                                                   | 52                 |                    |                              |

| SR                 | Slew rate                         | $A_V = +1, 10\%$ to $90\%$ <sup>(6)</sup>                                   |                                                   | 1                  |                    | $\text{V}/\mu\text{s}$       |

| $\Phi\text{m}$     | Phase margin                      | $R_L = 10\text{k}\Omega, C_L = 20\text{pF}$                                 |                                                   | 75                 |                    | °                            |

| GBW                | Gain bandwidth product            |                                                                             |                                                   | 3                  |                    | MHz                          |

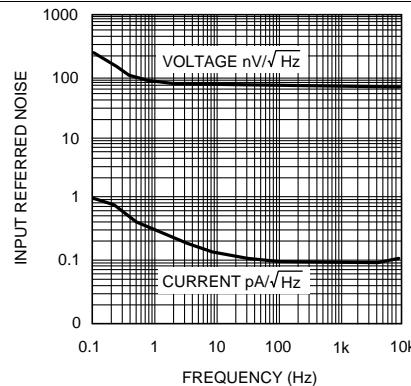

| e <sub>n</sub>     | Input-referred voltage noise      | f = 100 kHz                                                                 |                                                   | 70                 |                    | nV $\sqrt{\text{Hz}}$        |

|                    |                                   | f = 1 kHz                                                                   |                                                   | 70                 |                    |                              |

| i <sub>n</sub>     | Input-referred current noise      | f = 100 kHz                                                                 |                                                   | 0.1                |                    | pA $\sqrt{\text{Hz}}$        |

|                    |                                   | f = 1 kHz                                                                   |                                                   | 0.15               |                    |                              |

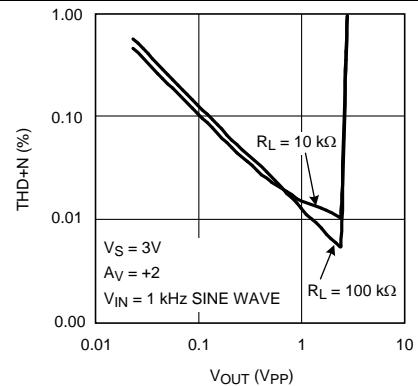

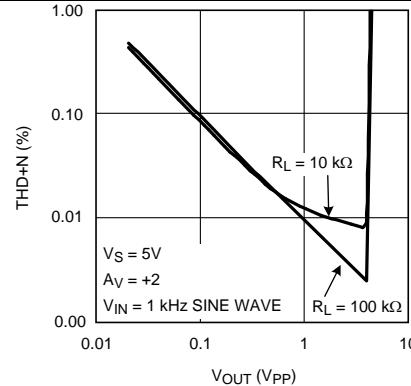

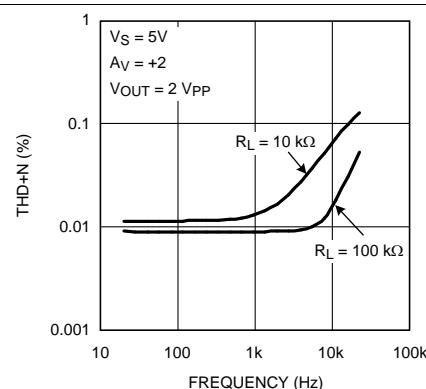

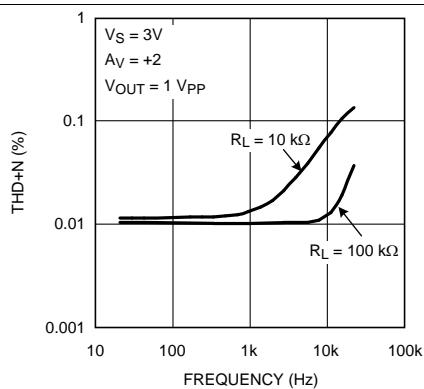

| THD                | Total harmonic distortion         | f = 1 kHz, $A_V = 2, R_L = 2\text{k}\Omega$                                 |                                                   | 0.003%             |                    |                              |

- (1) Electrical Table values apply only for factor testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No specify of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J = T_A$ .

- (2) Limits are 100% production tested at  $25^\circ\text{C}$ . Limits over the operating temperature range are specified through correlations using statistical quality control (SQC) method.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

- (4) Positive current corresponds to current flowing into the device.

- (5) The part is not short circuit protected and is not recommended for operation with heavy resistive loads.

- (6) Slew rate is the average of the rising and falling slew rates.

## 6.6 Electrical Characteristics: 5 V

Unless otherwise specified, all limits are specified for  $T_A = 25^\circ\text{C}$ ,  $V^+ = 5\text{V}$ ,  $V^- = 0\text{V}$ ,  $V_{CM} = V^+/2 = V_O$ . <sup>(1)</sup>

| PARAMETER          |                                   | TEST CONDITIONS                                                                   | MIN <sup>(2)</sup>                                | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT                         |

|--------------------|-----------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------|--------------------|--------------------|------------------------------|

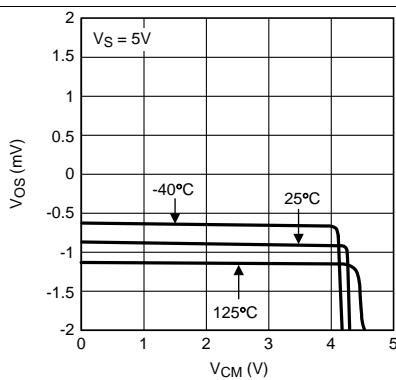

| V <sub>OS</sub>    | Input offset voltage              | $T_A = 25^\circ\text{C}$                                                          | -4.5                                              | 1                  | 3                  | mV                           |

|                    |                                   | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$                                 | -8                                                |                    | 4.5                |                              |

| TC V <sub>OS</sub> | Input offset average drift        | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$                                 |                                                   | 3.3                |                    | $\mu\text{V}/^\circ\text{C}$ |

| I <sub>B</sub>     | Input bias current <sup>(4)</sup> | $T_A = 25^\circ\text{C}$                                                          |                                                   | 20                 | 38                 | nA                           |

| I <sub>os</sub>    | Input offset current              | $T_A = 25^\circ\text{C}$                                                          |                                                   | 1                  | 20                 | nA                           |

| CMRR               | Common mode rejection ratio       | $0\text{V} \leq V_{CM} \leq 4\text{V}$                                            | $T_A = 25^\circ\text{C}$                          | 76                 | 93                 | dB                           |

|                    |                                   |                                                                                   | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 74                 |                    |                              |

| PSRR               | Power supply rejection ratio      | $3\text{V} \leq V^+ \leq 5\text{V}$ ,<br>$V_{CM} = 0.5\text{V}$                   | $T_A = 25^\circ\text{C}$                          | 78                 | 90                 | dB                           |

|                    |                                   | $2.7\text{V} \leq V^+ \leq 5.5\text{V}$ ,<br>$V_{CM} = 0.5\text{V}$               | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 75                 |                    |                              |

|                    |                                   |                                                                                   | $T_A = 25^\circ\text{C}$                          | 78                 | 90                 |                              |

|                    |                                   |                                                                                   | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 75                 |                    |                              |

| CMVR               | Input common-mode voltage         | $\text{CMRR} \geq 68\text{ dB}$                                                   | $T_A = 25^\circ\text{C}$                          | 0                  | 4.1                | V                            |

|                    |                                   | $\text{CMRR} \geq 60\text{ dB}$                                                   | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 0                  | 4.1                |                              |

| A <sub>VOL</sub>   | Large signal voltage gain         | $0.4\text{V} \leq V_O \leq 4.6\text{V}$ ,<br>$R_L = 100\text{k}\Omega$ to $V^+/2$ | $T_A = 25^\circ\text{C}$                          | 78                 | 90                 | dB                           |

|                    |                                   |                                                                                   | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 75                 |                    |                              |

|                    |                                   | $0.4\text{V} \leq V_O \leq 4.6\text{V}$ ,<br>$R_L = 10\text{k}\Omega$ to $V^+/2$  | $T_A = 25^\circ\text{C}$                          | 75                 | 80                 |                              |

|                    |                                   |                                                                                   | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 72                 |                    |                              |

| V <sub>O</sub>     | Output swing high                 | $R_L = 100\text{k}\Omega$ to $V^+/2$                                              | $T_A = 25^\circ\text{C}$                          | 70                 | 92                 | mV<br>from rail              |

|                    |                                   |                                                                                   | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ |                    | 122                |                              |

|                    |                                   | $R_L = 10\text{k}\Omega$ to $V^+/2$                                               | $T_A = 25^\circ\text{C}$                          | 125                | 155                |                              |

|                    | Output swing low                  | $R_L = 100\text{k}\Omega$ to $V^+/2$                                              | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ |                    | 210                |                              |

|                    |                                   |                                                                                   | $T_A = 25^\circ\text{C}$                          | 60                 | 70                 |                              |

|                    |                                   | $R_L = 10\text{k}\Omega$ to $V^+/2$                                               | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | 82                 |                    |                              |

| I <sub>sc</sub>    | Output short circuit current      | Sourcing <sup>(5)</sup>                                                           |                                                   | 10                 |                    | mA                           |

|                    |                                   | Sinking <sup>(5)</sup>                                                            |                                                   | 25                 |                    |                              |

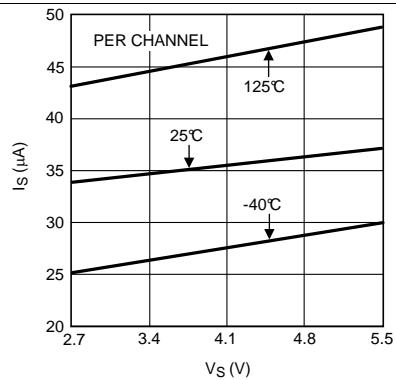

| I <sub>s</sub>     | Supply current                    | $T_A = 25^\circ\text{C}$                                                          |                                                   | 37                 | 46                 | $\mu\text{A}$                |

|                    |                                   | $T_A = -40^\circ\text{C}$ to $+125^\circ\text{C}$                                 |                                                   |                    | 54                 |                              |

| SR                 | Slew rate                         | $A_V = +1$ , $V_O = 1\text{V}_{PP}$ , 10% to 90% <sup>(6)</sup>                   |                                                   | 1                  |                    | $\text{V}/\mu\text{s}$       |

| $\Phi\text{m}$     | Phase margin                      | $R_L = 10\text{k}\Omega$ , $C_L = 20\text{pF}$                                    |                                                   | 75                 |                    | °                            |

| GBW                | Gain bandwidth product            |                                                                                   |                                                   | 3                  |                    | MHz                          |

| e <sub>n</sub>     | Input-referred voltage noise      | $f = 100\text{kHz}$                                                               |                                                   | 70                 |                    | $\text{nV}/\text{Hz}$        |

|                    |                                   | $f = 1\text{kHz}$                                                                 |                                                   | 70                 |                    |                              |

| i <sub>n</sub>     | Input-referred current noise      | $f = 100\text{kHz}$                                                               |                                                   | 0.1                |                    | $\text{pA}/\text{Hz}$        |

|                    |                                   | $f = 1\text{kHz}$                                                                 |                                                   | 0.15               |                    |                              |

| THD                | Total harmonic distortion         | $f = 1\text{kHz}$ , $A_V = 2$ , $R_L = 2\text{k}\Omega$                           |                                                   | 0.003%             |                    |                              |

- (1) Electrical Table values apply only for factor testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No specify of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J = T_A$ .

- (2) Limits are 100% production tested at  $25^\circ\text{C}$ . Limits over the operating temperature range are specified through correlations using statistical quality control (SQC) method.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

- (4) Positive current corresponds to current flowing into the device.

- (5) The part is not short circuit protected and is not recommended for operation with heavy resistive loads.

- (6) Slew rate is the average of the rising and falling slew rates.

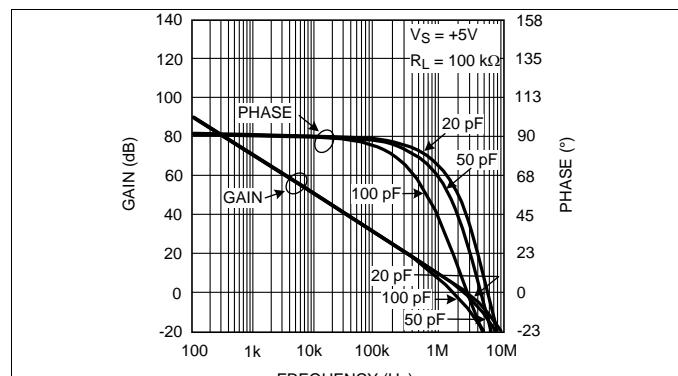

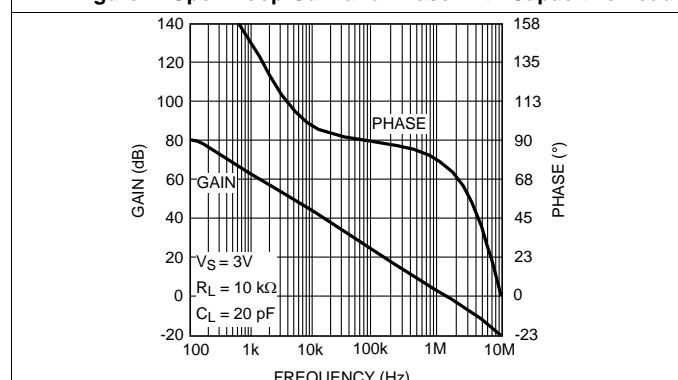

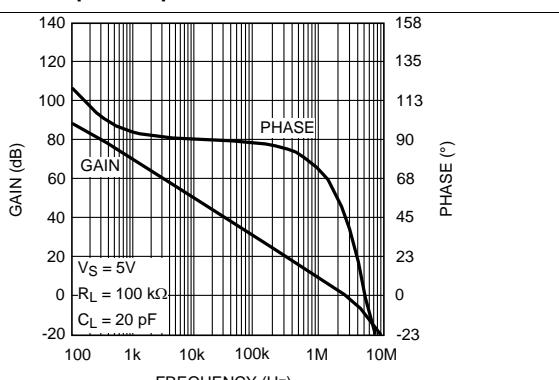

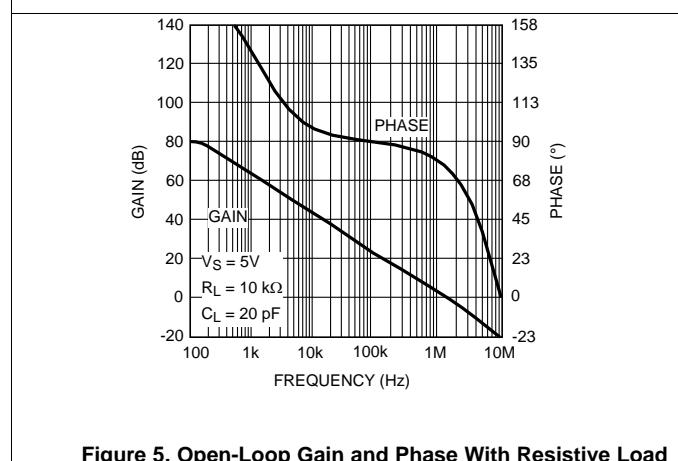

## 6.7 Typical Characteristics

Figure 1. Open-Loop Gain and Phase With Capacitive Load

Figure 2. Open-Loop Gain and Phase With Resistive Load

Figure 3. Open-Loop Gain and Phase With Resistive Load

Figure 4. Open-Loop Gain and Phase With Resistive Load

Figure 5. Open-Loop Gain and Phase With Resistive Load

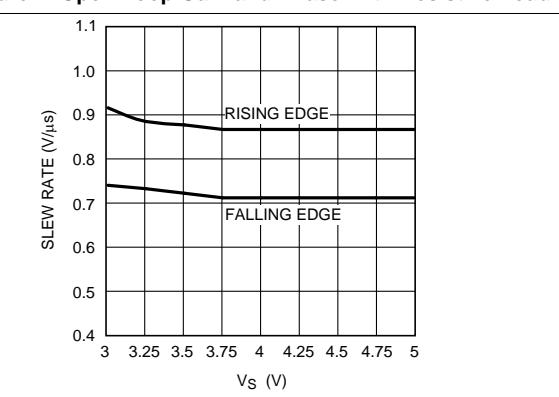

Figure 6. Slew Rate vs Supply voltage

## Typical Characteristics (continued)

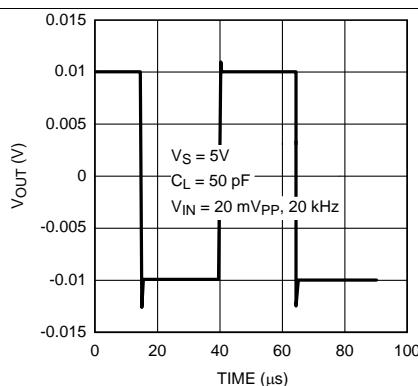

**Figure 7. Small-Signal Transient Response**

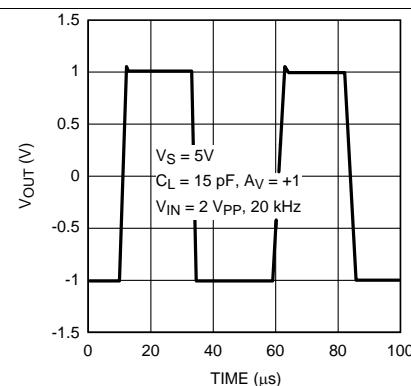

**Figure 8. Large-Signal Transient Response**

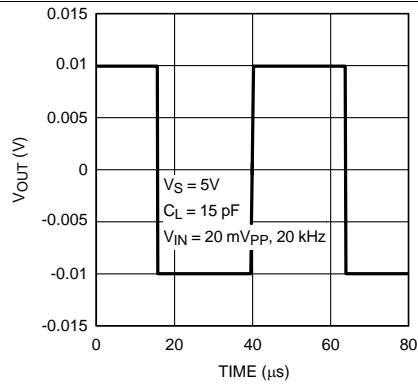

**Figure 9. Small-Signal Transient Response**

**Figure 10. Input Referred Noise vs Frequency**

**Figure 11. THD+N vs Amplitude at 3 V**

**Figure 12. THD+N vs Amplitude at 5 V**

## Typical Characteristics (continued)

**Typical Characteristics (continued)**

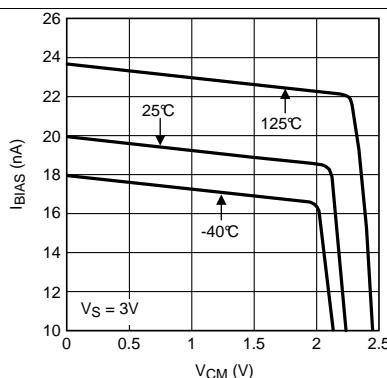

**Figure 19.  $I_{BIAS}$  vs  $V_{CM}$**

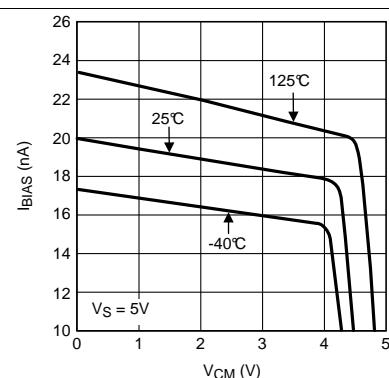

**Figure 20.  $I_{BIAS}$  vs  $V_{CM}$**

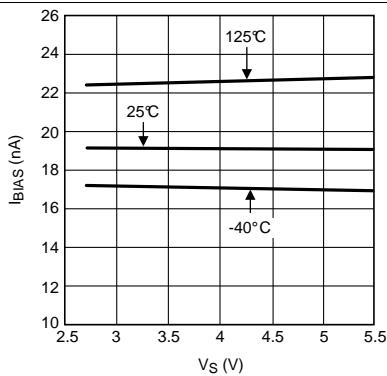

**Figure 21.  $I_{BIAS}$  vs Supply Voltage**

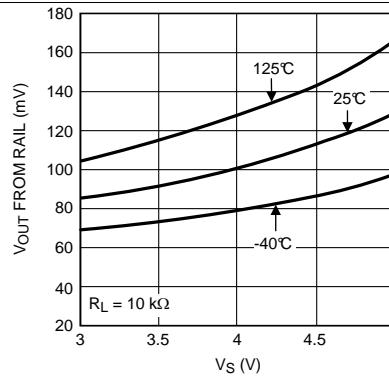

**Figure 22. Positive Output Swing vs Supply Voltage**

**Figure 23. Negative Output Swing vs Supply Voltage**

**Figure 24. Positive Output Swing vs Supply Voltage**

## Typical Characteristics (continued)

Figure 25. Negative Output Swing vs Supply Voltage

## 7 Detailed Description

### 7.1 Overview

The LMV551-Q1 is a high performance, low power operational amplifiers implemented with TI's advanced VIP50 process. The LMV551-Q1 features 3 MHz of bandwidth while consuming only 37  $\mu$ A of current, which is an exceptional bandwidth to power ratio in this op amp class. This amplifier is unity gain stable and provide an excellent solution for low power applications requiring a wide bandwidth.

### 7.2 Functional Block Diagram

Copyright © 2016,

Texas Instruments Incorporated

### 7.3 Feature Description

The differential inputs of the amplifier consist of a noninverting input (+IN) and an inverting input (-IN). The amplifier amplifies only the difference in voltage between the two inputs, which is called the differential input voltage. The output voltage of the op-amp  $V_{OUT}$  is given by [Equation 1](#):

$$V_{OUT} = A_{OL} (IN^+ - IN^-)$$

where

- $A_{OL}$  is the open-loop gain of the amplifier, typically around 100 dB (100,000x, or 10  $\mu$ V per volt). (1)

#### 7.3.1 Low Voltage and Low Power Operation

The LMV551-Q1 has performance ensured at supply voltages of 3 V and 5 V and are ensured to be operational at all supply voltages from 2.7 V to 5.5 V. For this supply voltage range, the LMV551-Q1 draw the extremely low supply current of less than 37  $\mu$ A.

#### 7.3.2 Wide Bandwidth

The bandwidth to power ratio of 3 MHz to 37  $\mu$ A per amplifier is one of the best bandwidth to power ratios ever achieved. This makes these devices ideal for low power signal processing applications such as portable media players and instrumentation.

#### 7.3.3 Low Input Referred Noise

The LMV551-Q1 provides a flatband input referred voltage noise density of 70 nV/ $\sqrt{\text{Hz}}$ , which is significantly better than the noise performance expected from an ultra low power op amp. They also feature the exceptionally low 1/f noise corner frequency of 4 Hz. This noise specification makes the LMV551-Q1 ideal for low power applications such as mobile devices and portable sensors.

#### 7.3.4 Ground Sensing and Rail-to-Rail Output

The LMV551-Q1 has a rail-to-rail output stage, which provides the maximum possible output dynamic range. This is especially important for applications requiring a large output swing. The input common mode range includes the negative supply rail which allows direct sensing at ground in a single supply operation.

## Feature Description (continued)

### 7.3.5 Small Size

The small footprint of the DCK (SC-70) package saves space on printed circuit boards, and enable the design of smaller and more compact electronic products. Long traces between the signal source and the op amp make the signal path susceptible to noise. By using a physically smaller package, the amplifier can be placed closer to the signal source, reducing noise pickup and enhancing signal integrity.

## 7.4 Device Functional Modes

### 7.4.1 Stability Of Op Amp Circuits

#### 7.4.1.1 Stability and Capacitive Loading

As seen in [Figure 26](#), the phase margin reduces significantly for  $C_L$  greater than 100 pF. This is because the op amp is designed to provide the maximum bandwidth possible for a low supply current. Stabilizing the amplifier for higher capacitive loads would have required either a drastic increase in supply current, or a large internal compensation capacitance, which would have reduced the bandwidth of the op amp. When the LMV551-Q1 is to be used for driving higher capacitive loads, it must be externally compensated.

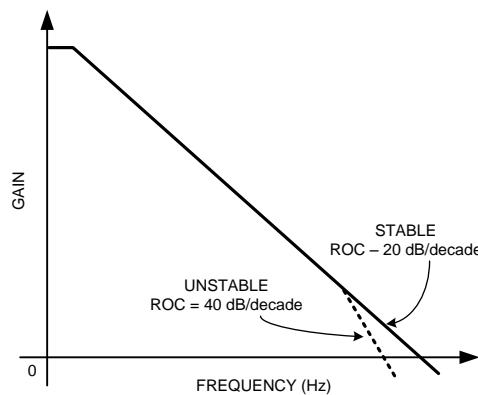

**Figure 26. Gain vs Frequency for an Op Amp**

An op amp, ideally, has a dominant pole close to DC, which causes its gain to decay at the rate of 20 dB/decade with respect to frequency. If this rate of decay, also known as the rate of closure (ROC), remains the same until the op amp's unity gain bandwidth crosses zero, the op amp is stable. If, however, a large capacitance is added to the output of the op amp, it combines with the output impedance of the op amp to create another pole in its frequency response before its unity gain frequency ([Figure 26](#)). This increases the ROC to 40 dB/ decade and causes instability.

In such a case a number of techniques can be used to restore stability to the circuit. The idea behind all these schemes is to modify the frequency response such that it can be restored to an ROC of 20 dB/decade, which ensures stability.

#### 7.4.1.1.1 In the Loop Compensation

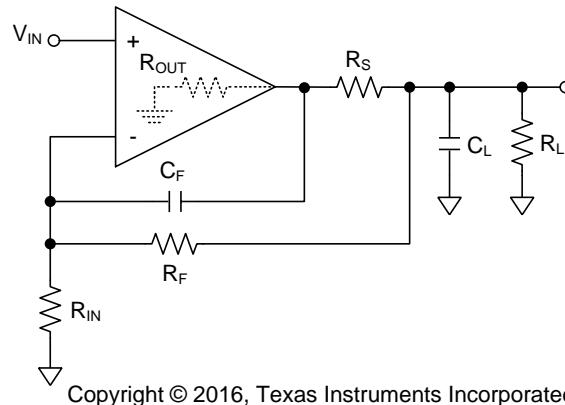

[Figure 27](#) illustrates a compensation technique, known as *in the loop* compensation, that employs an RC feedback circuit within the feedback loop to stabilize a non-inverting amplifier configuration. A small series resistance,  $R_S$ , is used to isolate the amplifier output from the load capacitance,  $C_L$ , and a small capacitance,  $C_F$ , is inserted across the feedback resistor to bypass  $C_L$  at higher frequencies.

## Device Functional Modes (continued)

Copyright © 2016, Texas Instruments Incorporated

**Figure 27. In the Loop Compensation**

The values for  $R_S$  and  $C_F$  are decided by ensuring that the zero attributed to  $C_F$  lies at the same frequency as the pole attributed to  $C_L$ . This ensures that the effect of the second pole on the transfer function is compensated for by the presence of the zero, and that the ROC is maintained at 20 dB/decade. For the circuit shown in Figure 27 the values of  $R_S$  and  $C_F$  are given by Equation 3. Values of  $R_S$  and  $C_F$  required for maintaining stability for different values of  $C_L$ , as well as the phase margins obtained, are shown in Table 1.  $R_F$ ,  $R_{IN}$ , and  $R_L$  are to be 10 kΩ, while  $R_{OUT}$  is 340 Ω.

$$R_S = \left( \frac{R_{OUT} \times R_{IN}}{R_F} \right) \quad (2)$$

$$C_F = \left( 1 + \frac{1}{A_{CL}} \right) \times \left( \frac{R_F + 2R_{IN}}{R_F^2} \right) \times C_L \times R_{OUT} \quad (3)$$

**Table 1. Phase Margins**

| $C_L$ (pF) | $R_S$ (Ω) | $C_F$ (pF) | PHASE MARGIN (°) |

|------------|-----------|------------|------------------|

| 50         | 340       | 8          | 47               |

| 100        | 340       | 15         | 42               |

| 150        | 340       | 22         | 40               |

Although this methodology provides circuit stability for any load capacitance, it does so at the price of bandwidth. The closed loop bandwidth of the circuit is now limited by  $R_F$  and  $C_F$ .

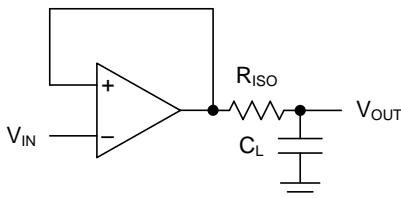

### 7.4.1.1.2 Compensation by External Resistor

In some applications it is essential to drive a capacitive load without sacrificing bandwidth. In such a case, in the loop compensation is not viable. A simpler scheme for compensation is shown in Figure 28. A resistor,  $R_{ISO}$ , is placed in series between the load capacitance and the output. This introduces a zero in the circuit transfer function, which counteracts the effect of the pole formed by the load capacitance and ensures stability. Consider the size of  $C_L$  and the level of performance desired to determine the value of  $R_{ISO}$ . Values ranging from 5 Ω to 50 Ω are usually sufficient to ensure stability. A larger value of  $R_{ISO}$  results in a system with less ringing and overshoot, but also limits the output swing and the short-circuit current of the circuit.

Copyright © 2016, Texas Instruments Incorporated

**Figure 28. Compensation by Isolation Resistor**

## 8 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The LVM551-Q1 has an operating supply voltage range from 2.7 V to 5.5 V. This amplifier can operate over a wide temperature range ( $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ ), making it a great choice for automotive applications, sensor applications as well as portable instrumentation applications.

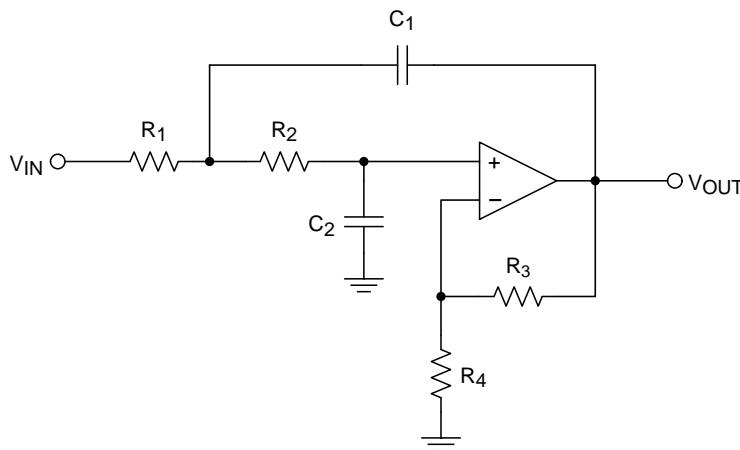

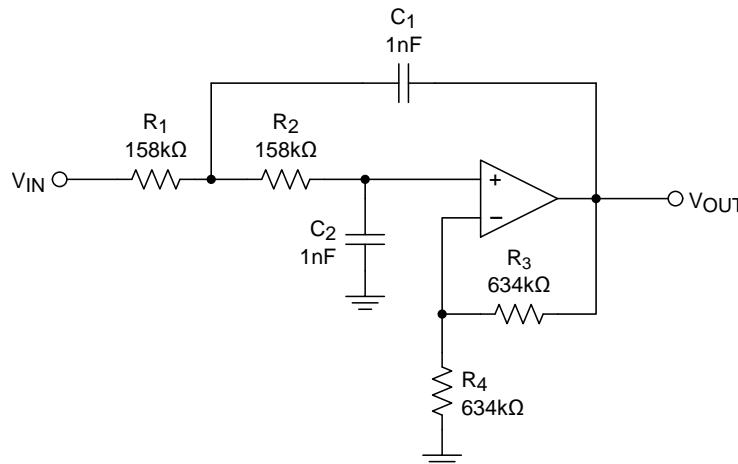

With a wide unity gain bandwidth of 3 MHz, low input referred noise density and an excellent BW to supply current ratio, the LVM551-Q1 is well suited for low-power filtering applications. Active filter topologies, such as the Sallen-Key low pass filter shown in [Figure 29](#), are very versatile, and can be used to design a wide variety of filters (Chebyshev, Butterworth or Bessel). For best results, the amplifier must have a bandwidth that is eight to ten times the filter frequency bandwidth. Failure to follow this guideline can result in phase shift of the amplifier and premature roll-off. The Sallen-Key topology, in particular, can be used to attain a wide range of Q, by using positive feedback to reject the undesired frequency range.

### 8.2 Typical Application

Figure 29. Two Pole Sallen-Key Low Pass Filter

#### 8.2.1 Design Requirements

As a design example:

Require:  $A_{LP} = 10$ , less than 1dB passband ripple, and a cutoff frequency of 1kHz.

#### 8.2.2 Detailed Design Procedure

There are many resources discussing the Sallen-Key lowpass filter topology.

Texas Instruments has made filter design easy by creating on-line and stand alone design tools, such as Webench Filter Designer and Filter Pro Desktop.

For this design, the stand-alone Filter Pro Desktop is used.

For the design, the following parameters are entered into the Filterpro software:

- Filter Type = Lowpass

- Gain = 10 V/V (20dB)

- Passband Frequency = 1 kHz

## Typical Application (continued)

- Allowable Ripple = 1 dB

- Filter Order = Checked and set to 2

- Response Type = Butterworth

- Filter Topology = Sallen-Key

- Component Tolerance - Resistor = E96 1%

- Component Tolerance - Capacitor = E6 20%

After entering these values, FilterPro returns the following recommended values:

- $R1 = 44.2 \text{ k}\Omega$

- $R2 = 38.3 \text{ k}\Omega$

- $R3 = 2.49 \text{ k}\Omega$

- $R4 = 22.6 \text{ k}\Omega$

- $C1 = 10 \text{ nF}$

- $C2 = 1.5 \text{ nF}$

The LMV551-Q1 is targeted for low power operation. The above resistor values are assumed for a *standard* power application. To save both quiescent and dynamic power, increase the value of the resistors.

The largest consumer of power is the gain setting feedback resistors R3 and R4, as these are DC coupled and represent a constant DC load to the amplifier. If the output is biased at 2.5 V, then  $2.5 \text{ V} / (22.6 \text{ k}\Omega + 2.49 \text{ k}\Omega) = 99.6 \mu\text{A}$  is flowing through the feedback network. This is significantly more than the 37uA quiescent current of the amplifier alone! Increasing the size of the feedback resistors by a decade from 22.6kΩ to 226kΩ, the current in the feedback network can be reduced down to 9.9μA.

Increasing the resistor values requires a proportional decrease in the values of the capacitors. If a resistor value is increased 10x, then the corresponding capacitor value must be decreased 10x. However, note that increasing the resistor values increases the contributed noise, and decreasing the capacitors to small values increases the sensitivity to stray capacitance.

There is a decision to be made about also scaling the filter components (R1, R2, C1 & C2). R1 and R2 are AC coupled to the output, so the only DC current flowing through these resistors is the input bias current of the LMV551-Q1 (typically 20 nA). However, large AC currents can flow through C2 and C1 during large signal swings. Scaling the filter components also reduces the peak AC signal currents. If the AC signals are expected to be large (several Vpp) and frequent, then scaling the filter values may be beneficial to overall power consumption. If the expected AC signals are small, it may not be worth the noise tradeoff to scale these values.

Because the LMV551-Q1 has a bipolar input, to maintain DC accuracy, the equivalent resistance seen by each amplifier input should be equal to cancel the bias current effects.

To maintain DC accuracy through bias current cancelling, the following relationship should be maintained:

$$(R1 + R2) = (R3 \parallel R4) \quad (4)$$

Fortunately, the filter Pro software makes changing and recalculating the values easy. By changing the value of any of the filter components (R1, R2, C1 & C2) in the schematic tab, the program automatically recalculates and scales these components. Conversely, changing the gain feedback components (R3 or R4) also causes the other feedback resistor to scale. However, Filter Pro does NOT maintain the relationship between the feedback and filter elements as described in [Equation 4](#) above. The feedback resistor values can be 'seeded' and scaled appropriately, as long as the original feedback resistor ratio is maintained.

## Typical Application (continued)

Figure 30. 1-kHz Sallen-Key Low Pass Filter with Values

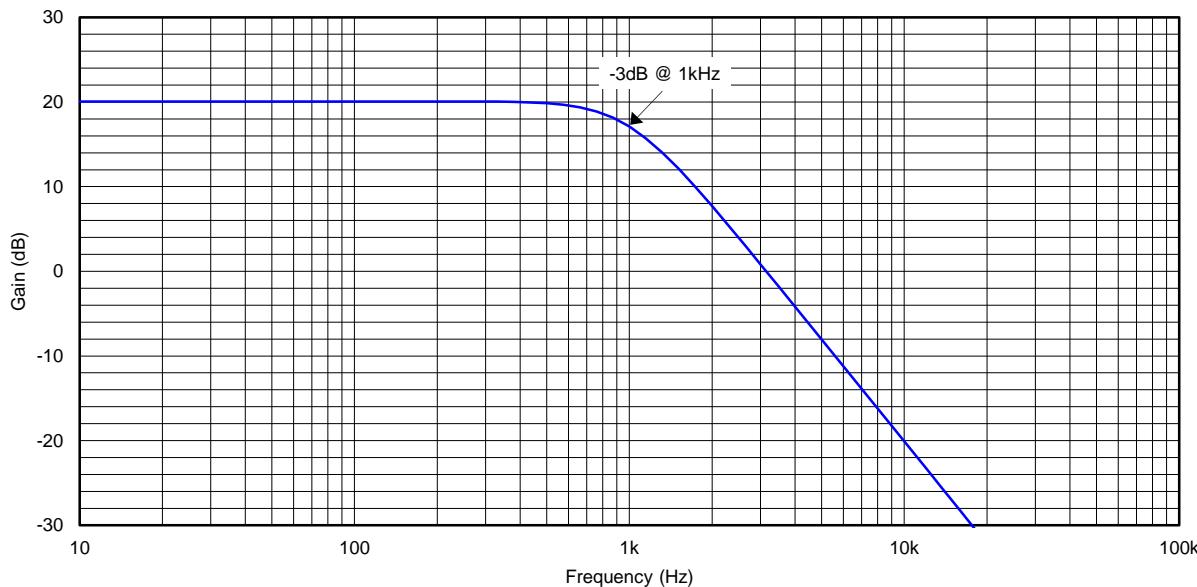

### 8.2.3 Application Curve

Figure 31 shows the simulated results of the example 1-KHz Sallen-Key Low Pass Filter.

Figure 31. 1KHz, 2-Pole Sallen-Key Low Pass Filter Results

## 8.3 Dos and Don'ts

Do properly bypass the power supplies.

Do add series resistance to the output when driving capacitive loads, particularly cables, Multiplexers and ADC inputs.

Do add series current limiting resistors and external Schottky clamp diodes if input voltage is expected to exceed the supplies. Limit the current to 1 mA or less (1 kΩ per V).

## 9 Power Supply Recommendations

For proper operation, the power supplies must be properly decoupled. For decoupling the supply lines, TI recommends that 10-nF capacitors be placed as close as possible to the op amp power supply pins. For single-supply, place a capacitor between  $V^+$  and  $V^-$  supply pins. For dual supplies, place one capacitor between  $V^+$  and ground, and one capacitor between  $V^-$  and ground.

## 10 Layout

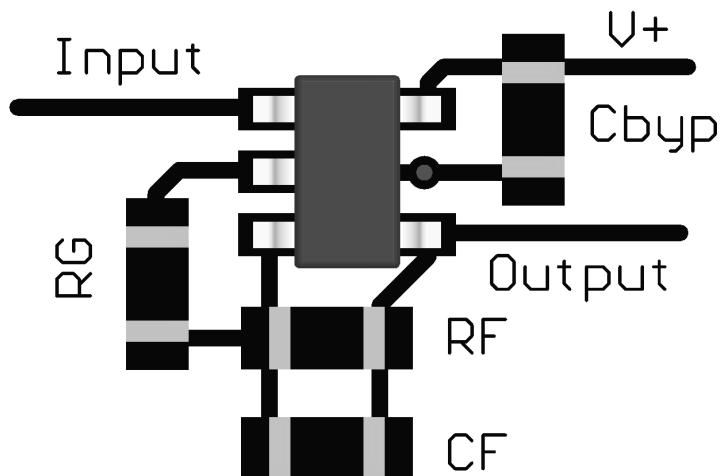

### 10.1 Layout Guidelines

The  $V^+$  pin should be bypassed to ground with a low-ESR capacitor.

The optimum placement is closest to the  $V^+$  and ground pins.

Ensure to minimize the loop area formed by the bypass capacitor connection between  $V^+$  and ground.

Connect the ground pin to the PCB ground plane at the pin of the device.

Place the feedback components as close to the device as possible and minimizing stray trace capacitance.

### 10.2 Layout Example

Figure 32. SC-70 Layout Example

## 11 デバイスおよびドキュメントのサポート

### 11.1 デバイス・サポート

#### 11.1.1 開発サポート

[LMV551 PSPICEモデル](#)(LMV551-Q1と互換)

[TINA-TI SPICE](#)ベースのアナログ・シミュレーション・プログラム

[DIP アダプタ評価モジュール](#)

[TIユニバーサル・オペアンプ評価モジュール](#)

[TI Filterpro](#)ソフトウェア

### 11.2 ドキュメントのサポート

#### 11.2.1 関連資料

追加アプリケーションについては、[『AN-31 オペアンプ回路コレクション』\(SNLA140\)](#)を参照してください。

### 11.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](#)のデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.4 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's [Terms of Use](#).

[TI E2E™オンライン・コミュニティ](#) [TIのE2E \( Engineer-to-Engineer \) コミュニティ](#)。エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立することができます。

[設計サポート](#) [TIの設計サポート](#) 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

### 11.5 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 11.6 静電気放電に関する注意事項

これらのデバイスは、限定期的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

### 11.7 Glossary

[SLYZ022 — TI Glossary](#).

This glossary lists and explains terms, acronyms, and definitions.

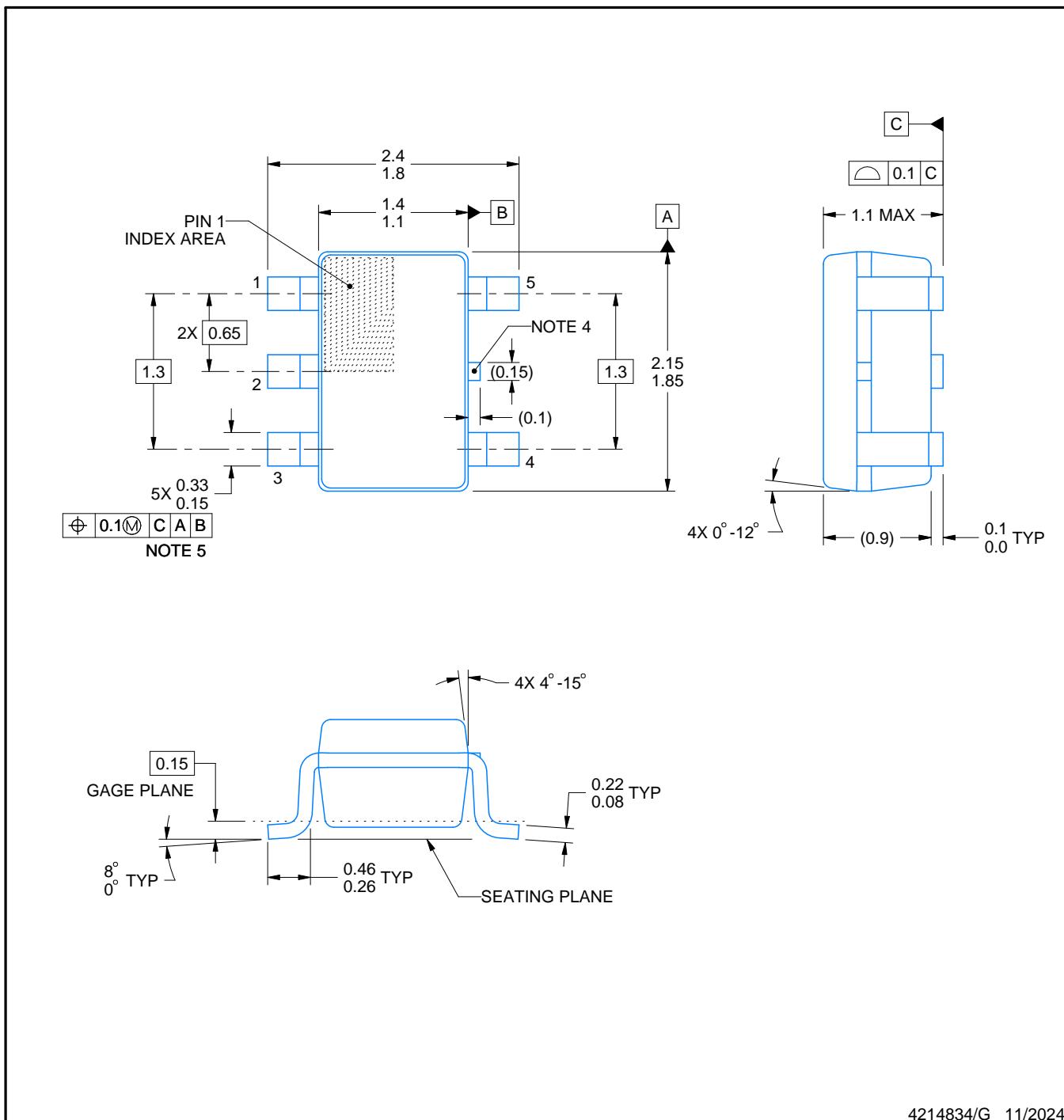

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LMV551QDCKRQ1         | Active        | Production           | SC70 (DCK)   5 | 3000   LARGE T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | 14U                 |

| LMV551QDCKRQ1.A       | Active        | Production           | SC70 (DCK)   5 | 3000   LARGE T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | 14U                 |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF LMV551-Q1 :**

- Catalog : [LMV551](#)

---

NOTE: Qualified Version Definitions:

- Catalog - TI's standard catalog product

# PACKAGE OUTLINE

DCK0005A

SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-203.

4. Support pin may differ or may not be present.

5. Lead width does not comply with JEDEC.

6. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25mm per side.

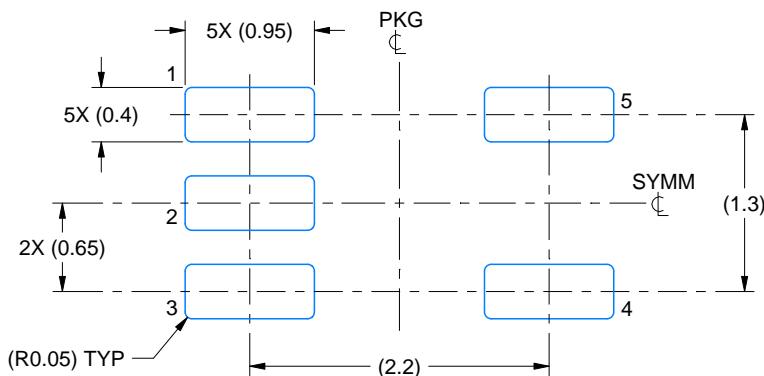

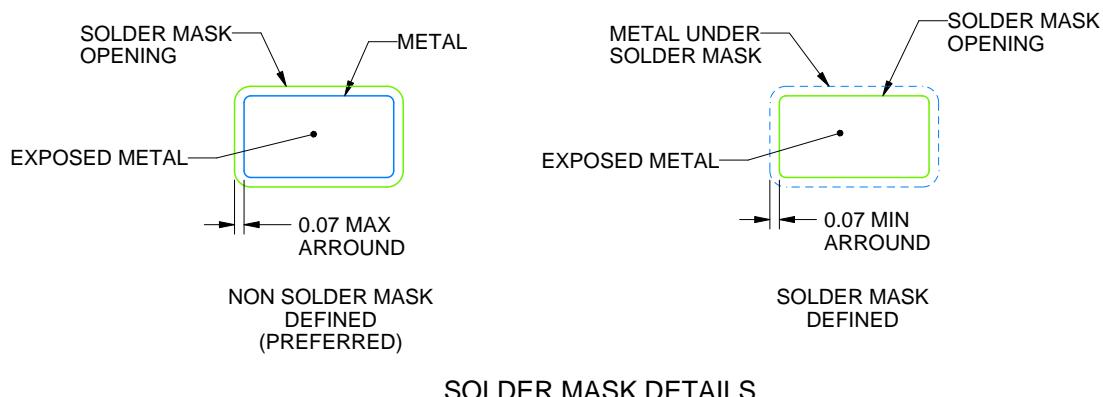

# EXAMPLE BOARD LAYOUT

DCK0005A

SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:18X

4214834/G 11/2024

NOTES: (continued)

7. Publication IPC-7351 may have alternate designs.

8. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

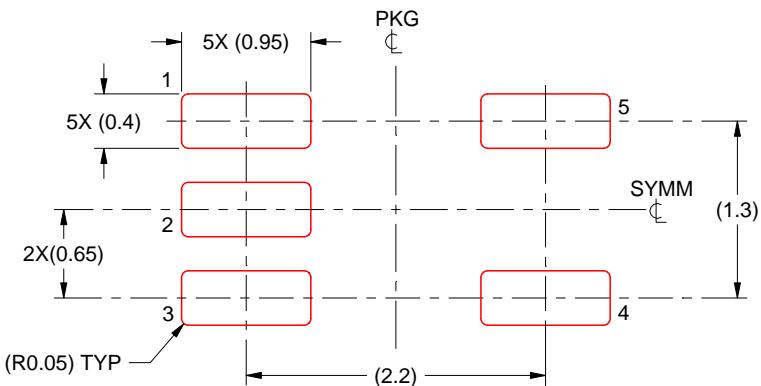

# EXAMPLE STENCIL DESIGN

DCK0005A

SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

SOLDER PASTE EXAMPLE

BASED ON 0.125 THICK STENCIL

SCALE:18X

4214834/G 11/2024

NOTES: (continued)

9. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

10. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月