## MC111、25V、単相 BLDC ドライバ

### 1 特長

- ホールセンサ内蔵、N チャネル H ブリッジ ドライバ

- $R_{DS(ON)}: 850\text{m}\Omega$  (HS + LS)

- 電流定格

- 設定可能な電流制限最大 1.21A

- 0.6A rms ( $T_A = 85^\circ\text{C}$ ,  $R_{θJA} = 100\text{ }^\circ\text{C/W}$ )

- 内蔵電源 (VM) クランプ

- 速度曲線と開始デューティサイクルを設定可能

- 整流方式: 方形波またはソフト (最大 90°)

- 方形波: 最大トルク / 速度

- ソフト: 速度と音響の最適化

- 設定可能な速度リファレンス入力: PWM または DC

- 入力 PWM 周波数範囲: 20Hz ~ 90kHz

- 入力 DC 電圧範囲: (0-3)V

- 出力 PWM 周波数: 25 または 50kHz

- 閉ループ速度制御精度: ±3%

- PWM ディザリングにより EMI を低減

- 設定可能なソフトスタート時間

- ホールオフセット角度および時間を設定可能

- 速度出力 0.5 倍、1 倍、2/3 倍、2 倍

- 回転子ロック検出出力 (RD)

- 設定可能な PWM モード

- 同期、非同期、ハイブリッド

- 高速全域での高効率を実現する自動消磁

- I<sup>2</sup>C を介したワンタイムプログラミング (2 ページ)

- 保護機能

- VM/GND と OUTx 間の短絡に対する過電流保護

- 自動再起動付き回転子ロック保護 (LRP)

- VM 低電圧誤動作防止 (UVLO)

- VM 過電圧保護 (OVP)

- サーマルシャットダウン (TSD)

- 構成可能な故障時のリトライ時間

- 機能的特徴 (動作継続)

- FG/RD と GND が短絡している場合

- PWM/DC と VM の間の短絡時の 100% 入力

### 2 アプリケーション

- 家電製品用冷却ファン

- CPU 冷却ファン

- GPU およびコンソール冷却ファン

- プロワ ファン

### 3 説明

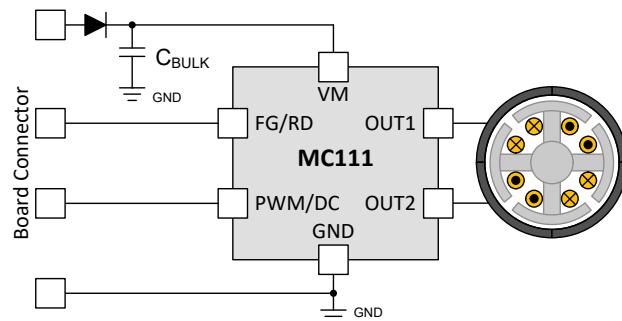

MC111 は、25V、850mΩ 定格のモーター ドライバで、単相ブラシレス DC モーター向けに、N チャネル フルブリッジ、チャージポンプ、ホールセンサ、整流制御ロジック、保護回路を内蔵しています。ホールセンサは、回転子の位置情報を整流ロジックに提供し、連続的な回転子の動作を維持します。整流ロジックは、方形波とソフト PWM 波形に設定して、音響ノイズを低減したり、速度 / 効率を最大化したりできます。

PWM/DC ピンのパルス幅変調信号のデューティサイクル、または (0 ~ 3)V の DC 電圧により、モーター速度が制御されます。FG/RD ピンは、モーター速度または回転子ロック状態を外部コントローラに通知するように設定できます。PWM/DC ピンと FG/RD ピンは、製造時に OTP を構成するためのプログラミング (OTP) モードをサポートする I<sup>2</sup>C インターフェイスとして一時的に構成できます。

MC111 は、モーターとデバイスの保護機能を内蔵しています。主な保護機能として、電源低電圧誤動作防止、過電圧保護、出力過電流保護、デバイス過熱シャットダウン、回転子ロック保護などがあります。

MC111 は、6 ピンの SOT23-FL パッケージで構成されています。SOT23-FL は、最大高さ 1.1mm のフラットリードパッケージです。

#### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | 本体サイズ (公称)       |

|-----------|----------------------|------------------|

| MC111DYMR | SOT23 (6)            | 3.80 mm × 2.90mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                               |           |                               |           |

|-------------------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>                   | <b>1</b>  | <b>7 レジスタ マップ</b>             | <b>34</b> |

| <b>2 アプリケーション</b>             | <b>1</b>  | <b>7.1 USR OTP レジスタ</b>       | <b>35</b> |

| <b>3 説明</b>                   | <b>1</b>  | <b>7.2 USR TM レジスタ</b>        | <b>49</b> |

| <b>4 ピン構成および機能</b>            | <b>3</b>  | <b>8 アプリケーションと実装</b>          | <b>53</b> |

| <b>5 仕様</b>                   | <b>4</b>  | <b>8.1 アプリケーション情報</b>         | <b>53</b> |

| 5.1 絶対最大定格                    | 4         | <b>8.2 代表的なアプリケーション</b>       | <b>55</b> |

| 5.2 ESD 定格 (通信機器)             | 4         | <b>8.3 電源に関する推奨事項</b>         | <b>57</b> |

| 5.3 推奨動作条件                    | 4         | <b>8.4 レイアウト</b>              | <b>58</b> |

| 5.4 熱に関する情報                   | 4         | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>60</b> |

| 5.5 電気的特性                     | 5         | <b>9.1 デバイス サポート</b>          | <b>60</b> |

| 5.6 I <sup>2</sup> C のタイミング要件 | 9         | <b>9.2 ドキュメントのサポート</b>        | <b>60</b> |

| 5.7 タイミング図                    | 10        | <b>9.3 ドキュメントの更新通知を受け取る方法</b> | <b>60</b> |

| <b>6 詳細説明</b>                 | <b>11</b> | <b>9.4 サポート・リソース</b>          | <b>60</b> |

| 6.1 概要                        | 11        | <b>9.5 商標</b>                 | <b>60</b> |

| 6.2 機能ブロック図                   | 11        | <b>9.6 静電気放電に関する注意事項</b>      | <b>60</b> |

| 6.3 機能説明                      | 11        | <b>9.7 用語集</b>                | <b>60</b> |

| 6.4 デバイスの機能モード                | 30        | <b>10 改訂履歴</b>                | <b>60</b> |

| 6.5 プログラミング                   | 32        |                               |           |

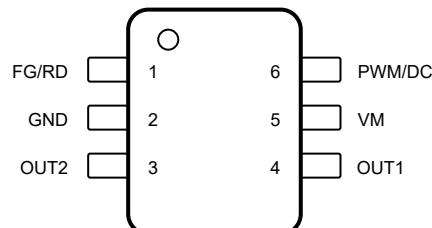

## 4 ピン構成および機能

図 4-1. MC111、6 ピン SOT-23、上面図

表 4-1. ピンの機能

| ピン<br>名称 | パッケージ<br>SOT23 | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                    |

|----------|----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FG/RD    | 1              | O                  | モーター速度または回転子ロック インジケータ出力。オープンドレイン出力には、所定のロジック High 電圧への外部プルアップ抵抗が必要です。テスト / プログラミング モードでは、このピンは I <sup>2</sup> C インターフェイスの SDA ピンになります。                                               |

| GND      | 2              | G                  | デバイスのグランド。システム グランドに接続。                                                                                                                                                               |

| OUT1     | 4              | O                  | ハーフブリッジ出力。モーターの巻線に接続します。                                                                                                                                                              |

| OUT2     | 3              | O                  | ハーフブリッジ出力。モーターの巻線に接続します。                                                                                                                                                              |

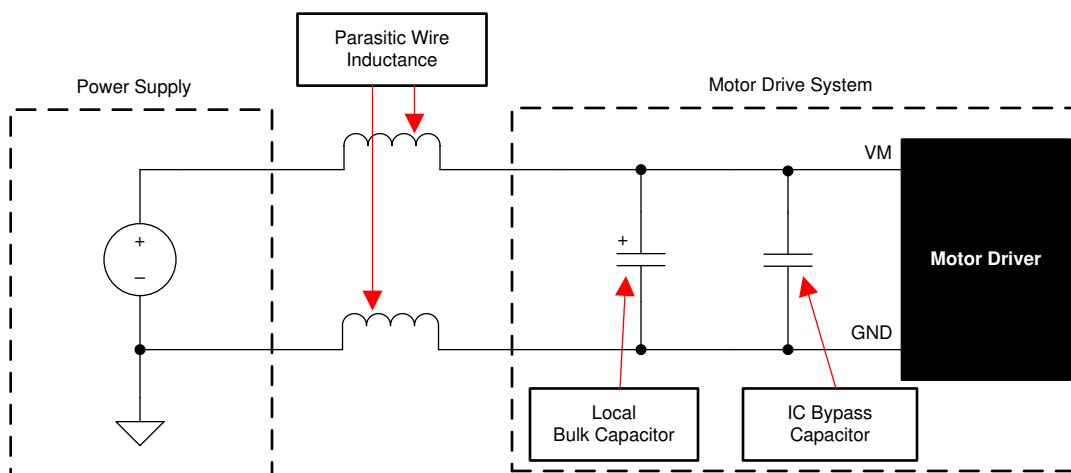

| VM       | 5              | P                  | デバイスおよびモーターの電源。モーター電源電圧に接続し、1 つの 0.1μF コンデンサおよび 1 つのパルク コンデンサを使用して GND にバイパスします。コンデンサの電圧定格は、デバイスの通常動作電圧の 2 倍以上とすることを推奨します。                                                            |

| PWM/DC   | 6              | I                  | モーター速度制御ピン - PWM または DC 信号を使用できます。PWM 入力モード (PWMDC_MODE = 0x0) でフローティングのままになると、このピンは内部で 100% デューティ サイクル入力にプルアップされます。テスト / プログラミング モードでは、このピンは I <sup>2</sup> C インターフェイスの SCL ピンになります。 |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源、NC = 未接続

## 5 仕様

### 5.1 絶対最大定格

動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                       |        |  | 最小値  | 最大値                 | 単位         |

|-----------------------|--------|--|------|---------------------|------------|

| 電源ピン電圧                | VM     |  | -0.5 | VM <sub>CLAMP</sub> | V          |

| 電源過渡電圧ランプ             | VM     |  | 0    | 2                   | V/ $\mu$ s |

| ロジックピン電圧              | PWM/DC |  | -0.5 | VM + 0.5            | V          |

| オーブンドレインピン電圧          | FG/RD  |  | -0.5 | VM + 0.5            | V          |

| 出力ピン電圧                | OUTx   |  | -1   | VM + 1              | V          |

| ピーク出力電流 (OUTx)        | OUTx   |  |      | 1.44                | A          |

| オーブンドレイン出力電流          | FG/RD  |  |      | 25                  | mA         |

| 周囲温度、T <sub>A</sub>   |        |  | -40  | 125                 | °C         |

| 接合部温度、T <sub>J</sub>  |        |  | -40  | 150                 | °C         |

| 保管温度、T <sub>stg</sub> |        |  | -65  | 150                 | °C         |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格 (通信機器)

|                    |      |                                                          | 値     | 単位 |

|--------------------|------|----------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | ±6000 | V  |

|                    |      | 荷電デバイスモデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±1000 |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|                     |                 |                            | 最小値  | 公称値 | 最大値 | 単位  |

|---------------------|-----------------|----------------------------|------|-----|-----|-----|

| V <sub>VM</sub>     | 電源電圧            | VM                         | 3.2  | 19  |     | V   |

| V <sub>IN</sub>     | ロジック入力電圧        | PWM/DC (PWM モードで構成されている場合) | 0    | VM  |     | V   |

| V <sub>IN</sub>     | アナログ入力電圧        | PWM/DC (DC モードで構成されている場合)  | 0    | 3.2 |     | V   |

| f <sub>PWM_IN</sub> | PWM 周波数         | PWM                        | 0.02 | 90  |     | kHz |

| V <sub>OD</sub>     | オーブンドレインブルアップ電圧 | FG/RD                      | 0    | VM  |     | V   |

| I <sub>OD</sub>     | オーブンドレイン出力電流    | FG/RD                      |      | 20  |     | mA  |

| T <sub>A</sub>      | 動作時周囲温度         |                            | -40  | 125 |     | °C  |

| T <sub>J</sub>      | 動作時接合部温度        |                            | -40  | 150 |     | °C  |

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup> |              | MC111       | 単位   |

|----------------------|--------------|-------------|------|

|                      |              | SOT23 (DYM) |      |

|                      |              | ピン          |      |

| R <sub>θJA</sub>     | 接合部から周囲への熱抵抗 | 156.1       | °C/W |

| 熱評価基準 <sup>(1)</sup>        |                   | MC111       | 単位   |

|-----------------------------|-------------------|-------------|------|

|                             |                   | SOT23 (DYM) |      |

|                             |                   | ピン          |      |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 | 63.1        | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗      | 25.6        | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 10.1        | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 25.5        | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース(底面)への熱抵抗 | 該当なし        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーションレポートを参照してください。

## 5.5 電気的特性

MC111:  $3.2V \leq V_{VM} \leq 19V$ ,  $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$  (特に記述のない限り)

標準値は  $T_J = 25^{\circ}\text{C}$  および  $V_{VM} = 12V$  での値です。

| パラメータ                            |                                             | テスト条件                                                                                                                 | 最小値  | 標準値  | 最大値  | 単位 |

|----------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|----|

| <b>電源 (VM)</b>                   |                                             |                                                                                                                       |      |      |      |    |

| $I_{VMQ}$                        | VM スリープ モード電流                               | $V_{PWM/DC} = 0V$ , SLEEP_EN = 0x1                                                                                    | 0.08 | 0.14 | mA   |    |

| $I_{VM}$                         | VM アクティブ モード電流                              | $V_{PWM/DC} = 3V$ (PWMDC_MODE = 0x1)<br>またはフローティング (PWM_DC = 0x0)、<br>OUTx 間は無負荷                                      | 3.9  | 5    | mA   |    |

| $t_{WAKE}$                       | スタンバイ / スリープ モードからのターンオン時間                  | PWM デューティ = 0% ~ 100% から<br>OUTx スイッチングまでに要する時間。<br>PWM 入力 (PWMDC_MODE = 0x0),<br>PWM_IN_RANGE = 0x0                  | 16   | ms   |      |    |

|                                  |                                             | PWM デューティ = 0% ~ 100% から<br>OUTx スイッチングまでに要する時間。<br>PWM 入力 (PWMDC_MODE = 0x0),<br>PWM_IN_RANGE = 0x1                  | 64   | ms   |      |    |

|                                  | スタンバイ / スリープ モードからのターンオン時間                  | DC 入力 = 0V ~ 3V から OUTx スイッチングまでに要する時間。DC 入力<br>(PWMDC_MODE = 0x1)                                                    | 1    | ms   |      |    |

| $t_{STOP_DET}$                   | DIN = 0% の検出に要する時間                          | PWM デューティ = 100% ~ 0% から、<br>RAMP_ON_STOP_DIS に従ってモーター停止を開始するのに要する時間。PWM 入力<br>(PWMDC_MODE = 0x0, PWM_IN_RANGE = 0x0) | 16   | ms   |      |    |

|                                  |                                             | PWM デューティ = 100% ~ 0% から<br>RAMP_ON_STOP_DIS に従ってモーター停止を開始するのに要する時間。PWM 入力<br>(PWMDC_MODE = 0x0, PWM_IN_RANGE = 0x1)  | 64   | ms   |      |    |

|                                  | DIN = 0% の検出に要する時間                          | DC 入力 = 3V ~ 0V から<br>RAMP_ON_STOP_DIS に従ってモーター停止を開始するのに要する時間。DC 入力<br>(PWMDC_MODE = 0x1)                             | 1.3  | ms   |      |    |

| <b>PWM/DC (SCL) および FG (SDA)</b> |                                             |                                                                                                                       |      |      |      |    |

| $V_{IL}$                         | 入力ロジック Low 電圧                               | アクティブまたはスタンバイ状態、あるいは<br>SCL モード時、PWM/DC ピンは PWM 入力モード (PWMDC_MODE = 0x0)、FG ピンは SDA モード                               | 0.8  | V    |      |    |

| $V_{IH}$                         | 入力ロジック High 電圧                              |                                                                                                                       | 2    | V    |      |    |

| $V_{HYS}$                        | 入力ヒステリシス                                    |                                                                                                                       | 0.15 | 0.2  | 0.26 | V  |

| $V_{SLEEP_DC}$                   | DC 入力モードでのスリープ移行のための<br>PWM/DC ピンの電圧スレッショルド | PWM/DC ピンに印加される電圧、<br>SLEEP_EN = 0x1, PWMDC_MODE = 0x1                                                                | 0    | 0.1  | 0.1  | V  |

MC111:  $3.2V \leq V_{VM} \leq 19V$ ,  $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  (特に記述のない限り)

標準値は  $T_J = 25^{\circ}C$  および  $V_{VM} = 12V$  での値です。

| パラメータ                 | テスト条件                                             | 最小値                                                                                                              | 標準値        | 最大値        | 単位       |

|-----------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------|------------|----------|

| $I_{IL}$<br>(PWM/DC)  | 入力ロジック Low 電流                                     | $V_I = 0V$ , SLEEP_EN = 0x0, PWM/DC ピンは PWM 入力モード (PWMDC_MODE = 0x0) または SCL モード                                 | 225        | 245        | 265      |

|                       |                                                   | $V_I = 0V$ , SLEEP_EN = 0x0, PWM/DC ピンは DC 入力モード (PWMDC_MODE = 0x1)                                              |            | 1          | $\mu A$  |

|                       |                                                   | $V_I = 0V$ , SLEEP_EN = 0x1, PWM/DC ピンは PWM 入力モード (PWMDC_MODE = 0x0) または DC 入力モード (PWMDC_MODE = 0x1) または SCL モード | 20         | 50         | 70       |

| $I_{IH}$<br>(PWM/DC)  | 入力ロジック High 電流                                    | $V_I = 3.3V$ , PWM/DC ピンは PWM 入力モード (PWMDC_MODE = 0x0) または DC 入力モード (PWMDC_MODE = 0x1) または SCL モード               | -1         | 0          | $\mu A$  |

|                       |                                                   | $V_I = V_{VM}$ , PWM/DC ピンは PWM 入力モード (PWMDC_MODE = 0x0) または DC 入力モード (PWMDC_MODE = 0x1) または SCL モード             | -1         | 0          | $\mu A$  |

| $V_{PU}$<br>(PWM/DC)  | 内部プルアップ電圧                                         | PWM 入力モード (PWMDC_MODE = 0x0), $VM \geq 3.6V$                                                                     | 2.7        | 2.9        | 3.2      |

|                       |                                                   | PWM 入力モード (PWMDC_MODE = 0x0), $VM < 3.6V$                                                                        | 2.55       | $VM$       | V        |

| $f_{PWM\_IN}$         | デューティ / 速度リファレンスの入力 PWM 周波数範囲                     | PWM 入力 (PWMDC_MODE = 0x0), PWM_IN_RANGE = 0x0                                                                    | 0.08       | 90         | kHz      |

|                       |                                                   | PWM 入力 (PWMDC_MODE = 0x0), PWM_IN_RANGE = 0x1                                                                    | 0.02       | 22         | kHz      |

| $V_{PWM\_ACC}$        | PWM 入力からのデューティ / 速度リファレンス精度                       | $20Hz \leq f_{PWM\_IN} \leq 45kHz$                                                                               |            | 0.4        | %        |

|                       |                                                   | $45kHz < f_{PWM\_IN} \leq 90kHz$                                                                                 |            | 0.8        | %        |

| $V_{DC}$              | デューティ / 速度リファレンスの DC 入力範囲                         | DC 入力 (PWMDC_MODE = 0x1), $3.2V \leq VM < 4.5V$                                                                  | 0          | $VM - 1.4$ | V        |

|                       |                                                   | DC 入力 (PWMDC_MODE = 0x1), $4.5V \leq VM \leq 35V$                                                                | 0          | 3.1        | V        |

| $V_{DC\_DIN\_0\%}$    | 0% デューティ / 速度リファレンス (DIN = 0%) の DC 入力スレッショルド     | DC 入力 (PWMDC_MODE = 0x1)                                                                                         |            | 0.1        | V        |

| $V_{DC\_DIN\_100\%}$  | 100% デューティ / 速度リファレンス (DIN = 100%) の DC 入力スレッショルド | DC 入力 (PWMDC_MODE = 0x1), $3.2V \leq VM < 4.5V$                                                                  | $VM - 1.4$ | 3.2        | V        |

|                       |                                                   | DC 入力 (PWMDC_MODE = 0x1), $4.5V \leq VM \leq 35V$                                                                | 2.9        | 3          | 3.2      |

| $V_{DC\_ACC}$         | DC 入力からのデューティ / 速度リファレンス精度                        | DC 入力 (PWMDC_MODE = 0x1), $4.5V \leq VM \leq 35V$                                                                |            | 3          | %        |

| $V_{OL}$ (FG)         | 出力ロジック Low 電圧                                     | $I_{OD} = 20mA$                                                                                                  |            | 0.4        | V        |

| $I_{OZ}$ (FG)         | 出力ロジック High 電流                                    | $V_{OD} = 3.3V$                                                                                                  | -1         | 1          | $\mu A$  |

| $I_{OZ}$ (FG)         | 出力ロジック High 電流                                    | $V_{OD} = VM$                                                                                                    | -1         | 1          | $\mu A$  |

| ドライバ出力 (OUTx)         |                                                   |                                                                                                                  |            |            |          |

| $R_{DS(on)}$<br>(H+L) | ハイサイドおよびローサイド MOSFET のオン抵抗                        | $V_{VM} = 3.2V$ , $I_O = 500mA$ , $T_A = 25^{\circ}C$                                                            | 0.85       | 1.02       | $\Omega$ |

| $R_{DS(on)}$<br>(H+L) | ハイサイドおよびローサイド MOSFET のオン抵抗                        | $V_{VM} = 12V$ , $I_O = 500mA$ , $T_A = 25^{\circ}C$                                                             | 0.8        | 0.95       | $\Omega$ |

MC111:  $3.2V \leq V_{VM} \leq 19V$ ,  $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  (特に記述のない限り)

標準値は  $T_J = 25^{\circ}C$  および  $V_{VM} = 12V$  での値です。

| パラメータ                           |                                           | テスト条件                                                                                                 | 最小値    | 標準値  | 最大値    | 単位       |

|---------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------|--------|------|--------|----------|

| $R_{DS(on)}$<br>(H+L)           | ハイサイドおよびローサイド MOSFET のオシ抵抗                | $V_{VM} = 12V$ , $I_O = 500mA$ , $T_A = 150^{\circ}C$                                                 |        | 1.3  | 1.5    | $\Omega$ |

| $f_{PWM\_OUT}$                  | PWM 出力周波数                                 | $PWM\_OUT\_FREQ = 0x0$ , DITHER_EN = 0x0                                                              | 23.5   | 25   | 26.25  | kHz      |

| $f_{PWM\_OUT}$                  | PWM 出力周波数                                 | $PWM\_OUT\_FREQ = 0x1$ , DITHER_EN = 0x0                                                              | 45     | 50   | 55     | kHz      |

| <b>デジタルラッチ ホール エフェクト センサ</b>    |                                           |                                                                                                       |        |      |        |          |

| $B_{OP}$                        | 動作ポイント                                    |                                                                                                       | 0.4    | 0.8  | 1.6    | mT       |

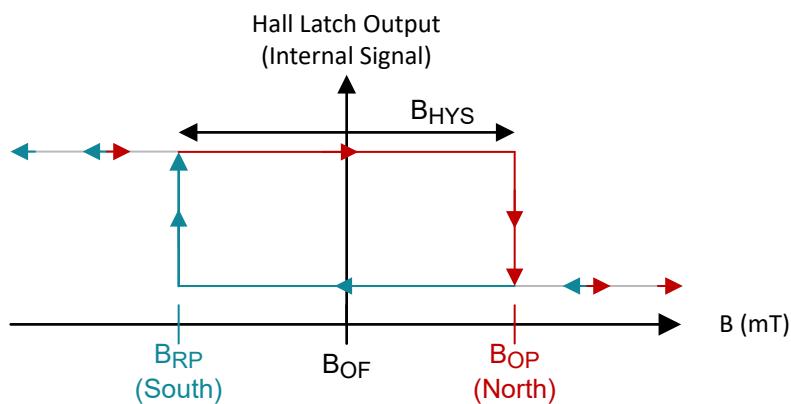

| $B_{RP}$                        | リリース ポイント                                 |                                                                                                       | -1.6   | -0.7 | -0.4   | mT       |

| $B_{HYS}$                       | ヒステリシス、 $B_{HYS} = (B_{OP} - B_{RP})$     |                                                                                                       | 1.2    | 1.6  | 3.2    | mT       |

| $B_{OF}$                        | 磁気オフセット、 $B_{OF} = (B_{OP} + B_{RP}) / 2$ |                                                                                                       | -1     | 0    | 1      | mT       |

| <b>発振器</b>                      |                                           |                                                                                                       |        |      |        |          |

| $f_{osc}$                       | 内部発振器の周波数                                 | $V_{VM} = 12V$ , $T_J = 25^{\circ}C$                                                                  | 24.625 | 25   | 25.375 | MHz      |

| $f_{osc}$                       | 内部発振器の周波数                                 |                                                                                                       | 24.25  | 25   | 25.75  | MHz      |

| <b>デューティ曲線</b>                  |                                           |                                                                                                       |        |      |        |          |

| $D_{OUT\_RES}$                  | LSBあたりの出力デューティ サイクル分解能                    | 50% 電圧レベル、0.4% $\leq DOUT \leq 99.6\%$ で測定                                                            |        | 0.4  |        | %        |

| $D_{HYS}$                       | $D_{IN}$ 立ち上がりの速度曲線ヒステリシス                 | DIN_HYS = 0x0。DIN を 0% から DIN0 + DIN_HYS までスイープします。出力 DOUT は DOUT0 からターゲット デューティ サイクルに変化します。          |        | 0    |        | %        |

|                                 |                                           | DIN_HYS = 0x1。DIN を 0% から DIN0 + DIN_HYS までスイープします。出力 DOUT は DOUT0 からターゲット デューティ サイクルに変化します。          |        | 1.2  |        | %        |

|                                 |                                           | DIN_HYS = 0x2。DIN を 0% から DIN0 + DIN_HYS までスイープします。出力 DOUT は DOUT0 からターゲット デューティ サイクルに変化します。          |        | 2.4  |        | %        |

|                                 |                                           | DIN_HYS = 0x3。DIN を 0% から DIN0 + DIN_HYS までスイープします。出力 DOUT は DOUT0 からターゲット デューティ サイクルに変化します。          |        | 4.8  |        | %        |

| $SPEED_{ERR}$                   | 閉ループ速度精度                                  | $T_J = 25^{\circ}C$ , SPEED_LOOP_EN = 0x1, $12.5\% \times MAX\_SPEED \leq SPEED\_REF \leq MAX\_SPEED$ |        | -1   | 1      | %        |

|                                 |                                           | SPEED_LOOP_EN = 0x1, $12.5\% \times MAX\_SPEED \leq SPEED\_REF \leq MAX\_SPEED$                       |        | -3   | 3      | %        |

| <b>整流</b>                       |                                           |                                                                                                       |        |      |        |          |

| $\theta_{HALL\_OS\_ANGLE}$      | 最小ホール オフセット角度                             | HALL_OS_ANGLE = 0x00                                                                                  |        | 0    |        | 度        |

|                                 | 最大ホール オフセット角度                             | HALL_OS_ANGLE = 0x1F                                                                                  |        | 43.8 |        | 度        |

| $\theta_{HALL\_OS\_ANGLE\_LSB}$ | LSBあたりのホール オフセット角度分解能                     | HALL_OS_ANGLE LSB                                                                                     |        | 1.4  |        | 度        |

| $T_{HALL\_OS}$                  | 最小ホール オフセット信号のリード / ラグ時間                  | HALL_OS_TIME = 0x00                                                                                   |        | 0    |        | $\mu s$  |

|                                 | 最大ホール オフセット信号リード / ラグ時間                   | HALL_OS_TIME = 0xFF                                                                                   |        | 2.55 |        | ms       |

| $T_{HALL\_OS\_LSB}$             | LSBごとのホール オフセット信号リード / ラグ時間分解能            | HALL_OS_TIME LSB                                                                                      |        | 10   |        | $\mu s$  |

MC111:  $3.2V \leq V_{VM} \leq 19V$ ,  $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  (特に記述のない限り)

標準値は  $T_J = 25^{\circ}C$  および  $V_{VM} = 12V$  での値です。

| パラメータ                 |                             | テスト条件                | 最小値               | 標準値   | 最大値 | 単位      |

|-----------------------|-----------------------------|----------------------|-------------------|-------|-----|---------|

| $t_{DEMAG}$           | 消磁期間の最小時間                   | $DEMAG\_TIME = 0x00$ |                   | 0     |     | $\mu s$ |

|                       | 消磁期間の最大時間                   | $DEMAG\_TIME = 0x20$ |                   | 1.29  |     | ms      |

| $t_{DEMAG\_LSB}$      | LSB ごとの $DEMAG\_TIME$ 時間分解能 |                      | $DEMAG\_TIME$ LSB | 10.24 |     | $\mu s$ |

| $\theta_{SRISE}$      | ソフト立ち上がりの最小角度               | $SRISE = 0x00$       |                   | 2.8   |     | 度       |

|                       | ソフト立ち上がりの最大角度               | $SRISE = 0x10$       |                   | 90    |     | 度       |

| $\theta_{SRISE\_LSB}$ | LSBあたりの $SRISE$ の角度分解能      |                      | $SRISE$ LSB       | 2.8   |     | 度       |

| $\theta_{SFALL}$      | ソフト立ち下がりの最小角度               | $SFALL = 0x00$       |                   | 2.8   |     | 度       |

|                       | ソフト立ち下がりの最大角度               | $SFALL = 0x1F$       |                   | 90    |     | 度       |

| $\theta_{SFALL\_LSB}$ | LSBあたりの $SFALL$ の角度分解能      |                      | $SRISE$ LSB       | 2.8   |     | 度       |

#### プレスタートと PWM ランプ / ソフトスタート

|                 |                                     |                                         |      |     |

|-----------------|-------------------------------------|-----------------------------------------|------|-----|

| PWM_RAMP_P_RATE | ソフトスタートおよび速度変化に対する出力デューティサイクルランプレート | PWM_RAMP_SEL = 0x0 (0 ~ 100% の場合 1.3s)  | 77   | %/s |

|                 |                                     | PWM_RAMP_SEL = 0x1 (0 ~ 100% の場合 2.6s)  | 38.5 | %/s |

|                 |                                     | PWM_RAMP_SEL = 0x2 (0 ~ 100% の場合 5.2s)  | 19.2 | %/s |

|                 |                                     | PWM_RAMP_SEL = 0x3 (0 ~ 100% の場合 10.4s) | 9.6  | %/s |

#### 保護回路

|                 |                                       |                                              |      |      |      |   |

|-----------------|---------------------------------------|----------------------------------------------|------|------|------|---|

| $V_{MCLAMP}$    | $VM$ クランプ電圧                           | $I_{clamp} = 20mA$                           | 19.5 | 25   | V    |   |

| $V_{MPOR}$      | デバイスの電源投入に必要な $VM$ パワーオンリセットのスレッショルド  | 電源立ち上がり                                      | 2.3  | 2.55 | 2.7  | V |

| $V_{MPOR\_HYS}$ | $VM$ パワーON リセット スレッショルド ヒステリシス        | 立ち上がりから立ち下がりへのスレッショルド                        | 0.04 | 0.09 | 0.13 | V |

| $V_{UVLO}$      | モーターの駆動を開始 / 停止するための電源低電圧誤動作防止スレッショルド | 電源立ち上がり ( $UVLO\_SEL = 0x0$ )                | 2.85 | 3    | 3.15 | V |

|                 |                                       | 電源立ち下がり ( $UVLO\_SEL = 0x0$ )                | 2.55 | 2.7  | 2.85 | V |

| $V_{UVLO\_HYS}$ | 電源 UVLO ヒステリシス                        | 立ち上がりから立ち下がりまでのスレッショルド ( $UVLO\_SEL = 0x0$ ) |      | 0.3  |      | V |

| $V_{UVLO}$      | モーターの駆動を開始 / 停止するための電源低電圧誤動作防止スレッショルド | 電源立ち上がり ( $UVLO\_SEL = 0x1$ )                | 3.97 | 4.2  | 4.5  | V |

|                 |                                       | 電源立ち下がり ( $UVLO\_SEL = 0x1$ )                | 2.55 | 2.7  | 2.85 | V |

| $V_{UVLO\_HYS}$ | 電源 UVLO ヒステリシス                        | 立ち上がりから立ち下がりまでのスレッショルド ( $UVLO\_SEL = 0x1$ ) |      | 1.5  |      | V |

| $V_{UVLO}$      | モーターの駆動を開始 / 停止するための電源低電圧誤動作防止スレッショルド | 電源立ち上がり ( $UVLO\_SEL = 0x2$ )                | 5.42 | 5.7  | 6    | V |

|                 |                                       | 電源立ち下がり ( $UVLO\_SEL = 0x2$ )                | 2.55 | 2.7  | 2.85 | V |

| $V_{UVLO\_HYS}$ | 電源 UVLO ヒステリシス                        | 立ち上がりから立ち下がりまでのスレッショルド ( $UVLO\_SEL = 0x2$ ) |      | 3    |      | V |

| $V_{UVLO}$      | モーターの駆動を開始 / 停止するための電源低電圧誤動作防止スレッショルド | 電源立ち上がり ( $UVLO\_SEL = 0x3$ )                | 7.2  | 7.6  | 8    | V |

|                 |                                       | 電源立ち下がり ( $UVLO\_SEL = 0x3$ )                | 2.55 | 2.7  | 2.85 | V |

| $V_{UVLO\_HYS}$ | 電源 UVLO ヒステリシス                        | 立ち上がりから立ち下がりまでのスレッショルド ( $UVLO\_SEL = 0x3$ ) |      | 4.9  |      | V |

| $V_{OVP}$       | 電源過電圧誤動作防止 (OVP)                      | 電源立ち上がり ( $OVP\_SEL = 0x1$ )                 | 21.5 | 22.7 | 23.9 | V |

| $V_{OVP}$       | 電源過電圧誤動作防止 (OVP)                      | 電源立ち下がり ( $OVP\_SEL = 0x1$ )                 | 20.1 | 21.2 | 22.3 | V |

| $V_{OVP}$       | 電源過電圧誤動作防止 (OVP)                      | 電源立ち上がり ( $OVP\_SEL = 0x2$ )                 | 17.5 | 18.4 | 19.3 | V |

| $V_{OVP}$       | 電源過電圧誤動作防止 (OVP)                      | 電源立ち下がり ( $OVP\_SEL = 0x2$ )                 | 15.9 | 16.9 | 17.9 | V |

| $V_{OVP\_HYS}$  | 電源過電圧ヒステリシス                           |                                              |      | 1.5  |      | V |

MC111:  $3.2V \leq V_{VM} \leq 19V$ ,  $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  (特に記述のない限り)

標準値は  $T_J = 25^{\circ}C$  および  $V_{VM} = 12V$  での値です。

| パラメータ               |                                                                            | テスト条件                                       | 最小値                  | 標準値                  | 最大値                   | 単位          |

|---------------------|----------------------------------------------------------------------------|---------------------------------------------|----------------------|----------------------|-----------------------|-------------|

| $t_{OVP\_DEG}$      | 電源過電圧グリッチ除去時間                                                              |                                             | 70                   | 80                   | 90                    | $\mu s$     |

| $t_{OVP\_BLANK}$    | 電源過電圧プランギング時間                                                              | OVP_BLANK_EN = 0x1、<br>OVP_BLANK_TIME = 0x0 |                      | 1                    |                       | ms          |

|                     |                                                                            | OVP_BLANK_EN = 0x1、<br>OVP_BLANK_TIME = 0x1 |                      | 4                    |                       | ms          |

| $I_{LIMIT}$         | Current limit threshold                                                    | ILIMIT_SEL = 0x0                            | 0.29                 | 0.32                 | 0.37                  | A           |

|                     |                                                                            | ILIMIT_SEL = 0x1                            | 0.38                 | 0.43                 | 0.49                  | A           |

|                     |                                                                            | ILIMIT_SEL = 0x2                            | 0.48                 | 0.53                 | 0.61                  | A           |

|                     |                                                                            | ILIMIT_SEL = 0x3                            | 0.58                 | 0.63                 | 0.73                  | A           |

|                     |                                                                            | ILIMIT_SEL = 0x4                            | 0.67                 | 0.73                 | 0.85                  | A           |

|                     |                                                                            | ILIMIT_SEL = 0x5                            | 0.76                 | 0.83                 | 0.97                  | A           |

|                     |                                                                            | ILIMIT_SEL = 0x6                            | 0.85                 | 0.94                 | 1.09                  | A           |

|                     |                                                                            | ILIMIT_SEL = 0x7                            | 0.94                 | 1.03                 | 1.21                  | A           |

|                     |                                                                            | ILIMIT_SEL = 0x8                            | 1.03                 | 1.12                 | 1.33                  | A           |

|                     |                                                                            | ILIMIT_SEL = 0x9                            | 1.11                 | 1.21                 | 1.44                  | A           |

| $t_{ILIMIT\_BLANK}$ | 電流制限プランギング時間 (最新の立ち上がりエッジ PWM (FET) 信号から適用)                                | ILIM_BLANK_SEL = 0x0                        |                      | 0.5                  |                       | $\mu s$     |

|                     |                                                                            | ILIM_BLANK_SEL = 0x1                        |                      | 1                    |                       | $\mu s$     |

| $t_{ILIMIT\_DEG}$   | 電流制限のグリッチ除去時間                                                              | ILIM_DEGLITCH_SEL = 0x0                     |                      | 0.6                  |                       | $\mu s$     |

|                     | 電流制限のグリッチ除去時間                                                              | ILIM_DEGLITCH_SEL = 0x1                     |                      | 1.1                  |                       | $\mu s$     |

| $I_{OCP}$           | 過電流保護トリップ ポイント (HS_FET)                                                    |                                             | 1.3 *<br>$I_{LIMIT}$ | 1.7 *<br>$I_{LIMIT}$ | 2.2 *<br>$I_{LIMIT}$  | A           |

| $I_{OCP}$           | 過電流保護トリップ ポイント (LS_FET)                                                    |                                             | 1.5 *<br>$I_{LIMIT}$ | 1.7 *<br>$I_{LIMIT}$ | 1.85 *<br>$I_{LIMIT}$ | A           |

| $t_{OCP\_DEG}$      | 過電流保護グリッチ除去時間                                                              |                                             |                      | 0.6                  |                       | $\mu s$     |

| $t_{LRD\_START}$    | 起動時の回転子ロック検出時間                                                             | LRD_TIME_STARTUP = 0x0                      | 0.31                 | 0.32                 | 0.34                  | s           |

|                     |                                                                            | LRD_TIME_STARTUP = 0x1                      | 0.42                 | 0.44                 | 0.46                  | s           |

|                     |                                                                            | LRD_TIME_STARTUP = 0x2                      | 0.5                  | 0.52                 | 0.55                  | s           |

|                     |                                                                            | LRD_TIME_STARTUP = 0x3                      | 1                    | 1.05                 | 1.1                   | s           |

| $N_{RETRY}$         | 回転子ロックと過電流に対するロング リトライ時間の比率。ロング リトライ時間 = $N_{RETRY} \times t_{LRD\_START}$ | LRD_LONG_RETRY_SEL = 0x0                    |                      | 2                    |                       |             |

|                     |                                                                            | LRD_LONG_RETRY_SEL = 0x1                    |                      | 4                    |                       |             |

|                     |                                                                            | LRD_LONG_RETRY_SEL = 0x2                    |                      | 8                    |                       |             |

|                     |                                                                            | LRD_LONG_RETRY_SEL = 0x3                    |                      | 10                   |                       |             |

|                     |                                                                            | LRD_LONG_RETRY_SEL = 0x4                    |                      | 12                   |                       |             |

|                     |                                                                            | LRD_LONG_RETRY_SEL = 0x5                    |                      | 16                   |                       |             |

|                     |                                                                            | LRD_LONG_RETRY_SEL = 0x6                    |                      | 24                   |                       |             |

|                     |                                                                            | LRD_LONG_RETRY_SEL = 0x7                    |                      | 28                   |                       |             |

| $t_{LRD\_RUN}$      | 起動時の回転子ロック検出時間                                                             | モーター動作中の回転子ロック                              | 0.29                 | 0.32                 | 0.35                  | s           |

| $T_{TSD}$           | サーマル シャットダウン温度                                                             |                                             | 155                  | 170                  | 185                   | $^{\circ}C$ |

| $T_{HYS}$           | サーマル シャットダウンヒステリシス                                                         |                                             |                      | 24                   |                       | $^{\circ}C$ |

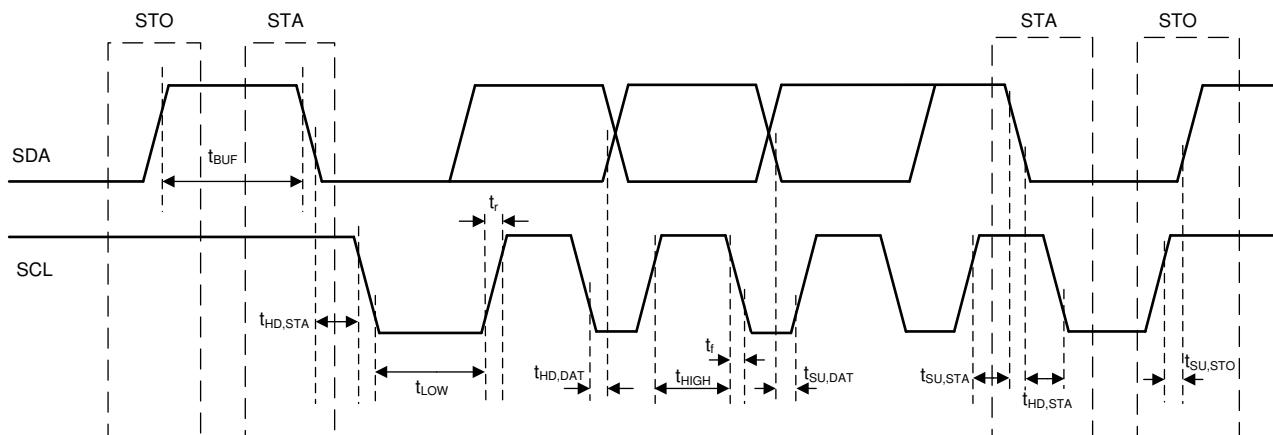

## 5.6 I<sup>2</sup>C のタイミング要件

|            |             | 最小値 | 公称値 | 最大値 | 単位  |

|------------|-------------|-----|-----|-----|-----|

| スタンダード モード |             |     |     |     |     |

| $f_{SCL}$  | SCL クロック周波数 | 0   | 100 |     | kHz |

|              |                                                 | 最小値  | 公称値  | 最大値  | 単位  |

|--------------|-------------------------------------------------|------|------|------|-----|

| $t_{HD,STA}$ | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック パルスが生成されます  | 4    |      |      | μs  |

| $t_{LOW}$    | SCL クロック Low 期間                                 | 4.7  |      |      | μs  |

| $t_{HIGH}$   | SCL クロックの High の時間                              | 4    |      |      | μs  |

| $t_{SU,STA}$ | 反復開始条件のセットアップ時間                                 | 4.7  |      |      | μs  |

| $t_{HD,DAT}$ | データ ホールド時間:I2C バス デバイスの場合                       | 0.01 | 3.45 |      | μs  |

| $t_{SU,DAT}$ | データ セットアップ時間                                    | 250  |      |      | ns  |

| $t_R$        | SDA と SCL の立ち上がり時間                              |      |      | 1000 | ns  |

| $t_F$        | SDA と SCL の立ち下がり時間                              |      |      | 300  | ns  |

| $t_{SU,STO}$ | STOP 条件のセットアップ時間                                | 4    |      |      | μs  |

| $t_{BUF}$    | STOP 条件と START 条件の間のバスフリー時間                     | 4.7  |      |      | μs  |

| ファストモード      |                                                 |      |      |      |     |

| $f_{SCL}$    | SCL クロック周波数                                     | 0    | 400  |      | kHz |

| $t_{HD,STA}$ | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック パルスが生成されます。 | 0.6  |      |      | μs  |

| $t_{LOW}$    | SCL クロック Low 期間                                 | 1.3  |      |      | μs  |

| $t_{HIGH}$   | SCL クロックの High の時間                              | 0.6  |      |      | μs  |

| $t_{SU,STA}$ | 反復開始条件のセットアップ時間                                 | 0.6  |      |      | μs  |

| $t_{HD,DAT}$ | データ ホールド時間:I2C バス デバイスの場合                       | 0.01 | 0.9  |      | μs  |

| $t_{SU,DAT}$ | データ セットアップ時間                                    | 50   |      |      | ns  |

| $t_R$        | SDA と SCL の立ち上がり時間                              |      |      | 300  | ns  |

| $t_F$        | SDA と SCL の立ち下がり時間                              |      |      | 300  | ns  |

| $t_{SU,STO}$ | STOP 条件のセットアップ時間                                | 0.6  |      |      | μs  |

| $t_{BUF}$    | STOP 条件と START 条件の間のバスフリー時間                     | 1.3  |      |      | μs  |

| $t_{SP}$     | 入力ノイズ フィルタにより抑制されるスパイクのパルス幅                     |      | 50   |      | ns  |

## 5.7 タイミング図

図 5-1. I<sup>2</sup>C のタイミング図

## 6 詳細説明

### 6.1 概要

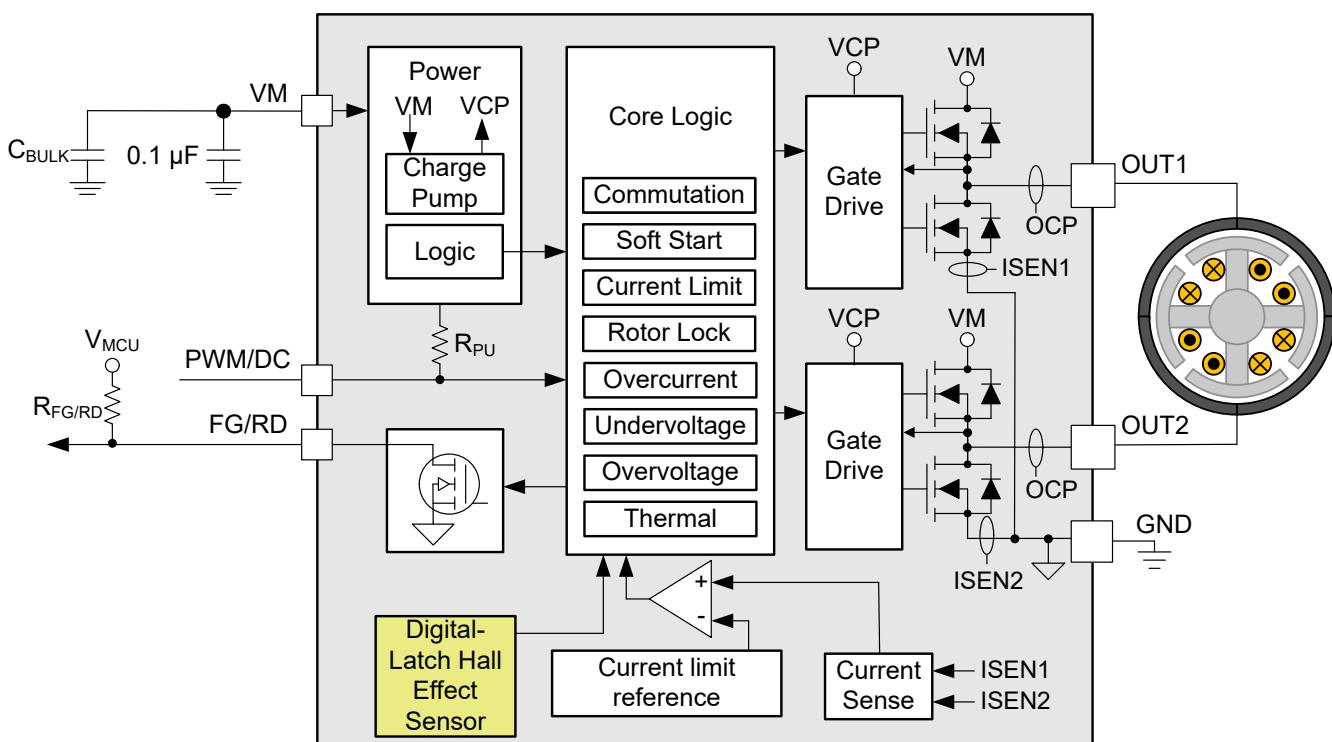

MC111 は、25V、850mΩ 定格、1.25A ピークの単相 BLDC モーター ドライバで、N チャネル フルブリッジ FET、チャージ ポンプ、ホール センサ、整流制御ロジック、保護回路を内蔵しています。ホール センサは、回転子の位置情報を整流ロジックに提供し、連続的な回転子の動作を維持します。整流ロジックは、方形波とソフト PWM 波形に設定して、音響ノイズを低減したり、速度 / 効率を最大化したりできます。

### 6.2 機能ブロック図

図 6-1. MC111 機能ブロック図

### 6.3 機能説明

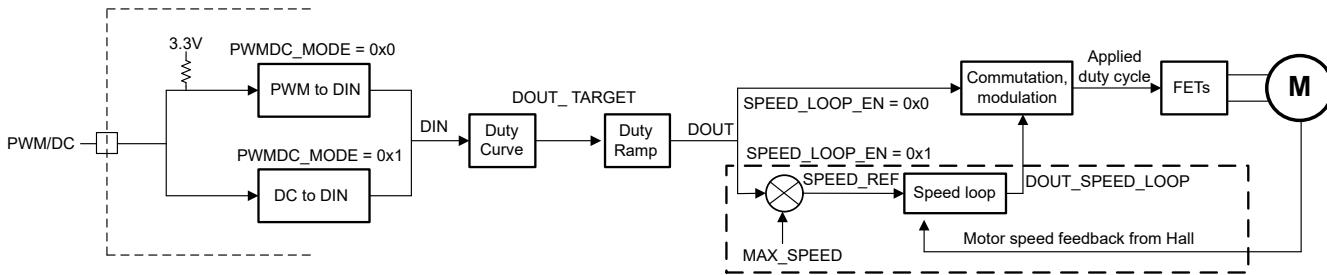

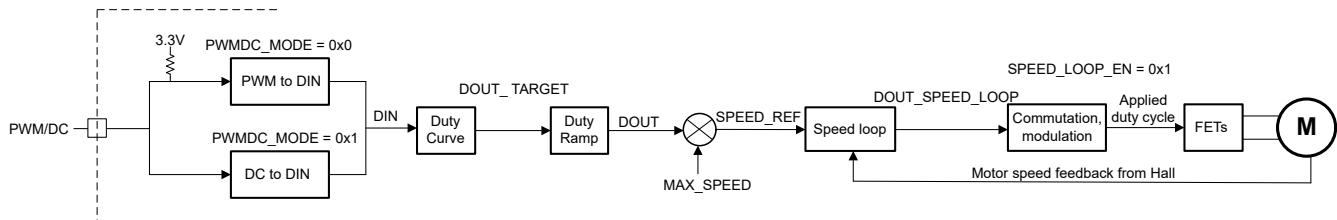

#### 6.3.1 モーター制御

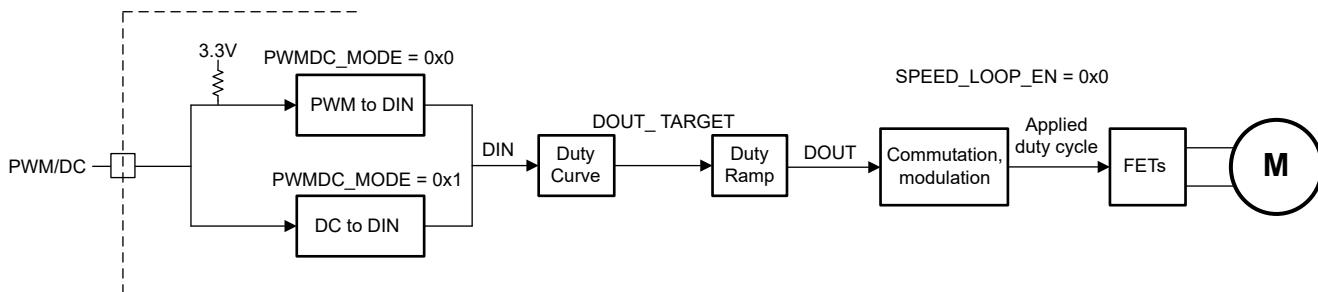

MC111 は、PWM/DC ピンにパルス幅変調 (PWM) または DC (アナログ) 入力を受けてモーター速度を制御します。MC111 は、入力デューティ (図 6-2 の DIN) をユーザー設定のターゲット出力デューティ サイクル (図 6-2 の DOUT\_TARGET) にマッピングするため、設定可能なデューティ曲線を提供します。MC111 は、出力デューティ サイクル (図 6-2 の DOUT) をスムーズに増減させて DOUT\_TARGET に到達させるため、ユーザーが設定可能なデューティランプも提供します。MC111 は、開ループ (デューティ サイクル) 制御と閉ループ (速度) 制御の両方をサポートしています。開ループ (デューティ サイクル) 制御では、印加されるデューティ サイクルは DOUT によって直接設定されます。閉ループ (速度) 制御では、印加されるデューティ サイクルは速度ループによって設定されます。内蔵のデジタルラッチ ホール センサは、整流アルゴリズムに対して回転子の位置とタイミングの情報を提供します。MC111 は、効率 / モーター速度と音響ノイズの間で最適化するために、方形波 および 出力 PWM 波形整形方式をサポートしています。MC111 は、H ブリッジで同期、非同期、およびハイブリッド出力 PWM 変調モードを提供します。設定可能なホール リード / ラグ角度と時間調整により、低速および高速の両方で効率を向上させることができます。さらに、MC111 は、整流前にモーター一巻線電流をゼロにまで低減するために、設定可能な消磁機能 (自動または手動) を備えており、DC バス (VM) 電圧スパイクや音響ノイズを最小化し、効率を向上させることができます。

図 6-2 に、MC111 のモーター制御ブロック図を示します。

図 6-2. MC111 モーター制御のブロック図

### 6.3.1.1 デューティ入力

MC111 は、PWM/DC ピンからデューティ入力 (DIN) を受け取ります。PWM/DC 入力は PWM 信号と DC (アナログ) 信号のどちらかにでき、PWMDC\_MODE ビットによって選択されます。入力 PWM 周波数の範囲は 20Hz ~ 90kHz (PWM\_IN\_RANGE ビットで設定された入力 PWM 周波数範囲) で、DC 入力の範囲は (0 ~ 3)V です。PWM/DC ピンにはプルアップ機能が内蔵されており、オン / オフ制御のみを必要とするアプリケーションで、ピンがフローティング / 未接続のままのとき、デューティ入力 (DIN) を 100% に設定できます。

#### 注

PWRUP\_PWMDC\_MASK が 0x1 に設定されている場合、MC111 はパワーアップ後、1 秒間待機してから、PWM/DC ピンからのデューティ入力に反応します。PWRUP\_PWMDC\_MASK が 0x0 に設定されている場合、パワーアップ時の待機時間はありません。

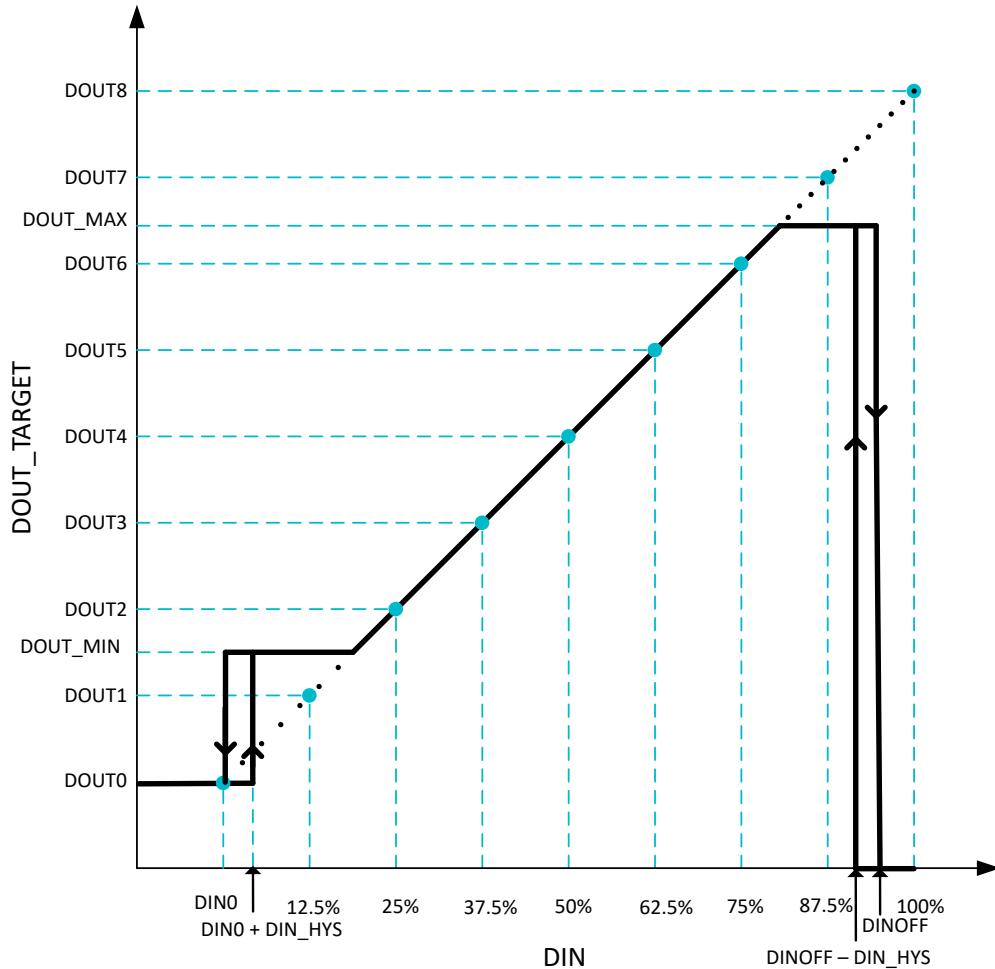

### 6.3.1.2 デューティ曲線

MC111 は、図 6-3 に示すように、構成可能なデューティ曲線をサポートしています。これにより、特定の使用事例に応じてターゲット出力デューティサイクル (DOUT\_TARGET) を入力デューティ (DIN) の関数として設定でき、単一プラットフォーム (MC111) でさまざまな最終アプリケーションに対応する BLDC ドライバ設計を実現できます。

図 6-3. デューティ曲線

デューティ曲線上の構成可能なポイントは次のとおりです。

- **DIN0、DOUT0:** DIN0 は、モーターの駆動を開始するための最小入力(開始) デューティサイクルを設定するために使用できます。STBY\_EN = 0x1 の場合、 $DIN \geq (DIN0 + DIN_{HYS})$  になるまでモーターは駆動されません。

$DIN_{HYS}$  は、DIN0 付近のヒステリシスを設定し、モーターの駆動を開始 / 停止します。MC111 は、STBY\_EN を 0x0 に、DOUT0 をゼロでない値に設定することで、 $DIN < DIN0$  の場合でもモーターを駆動する機能も備えています。

$DIN = 0\%$  のときのデバイスの状態は、表 6-5 に示すように、SLEEP\_EN ビットと STBY\_EN ビットによって設定されます。

- **DINOFF:** DINOFF は最大入力デューティサイクル(DIN)を設定し、それを上回るとモーターの駆動を停止するためのターゲット出力デューティサイクル(DOUT\_TARGET)が 0 に設定され、 $DIN \geq DINOFF$  のとき  $DOUT\_TARGET = 0\%$  になります。 $DIN < (DINOFF - DIN_{HYS})$  になると、モーター駆動が再開されます。

- **DOUT\_MIN:** DOUT\_MIN は、 $DIN0 < DIN < DINOFF$  のときの最小ターゲット出力デューティサイクル(DOUT\_TARGET)を設定します。

- **DOUT\_MAX:** DOUT\_MAX は、 $DIN < DINOFF$  のときの最大ターゲット出力デューティサイクル(DOUT\_TARGET)を設定します。

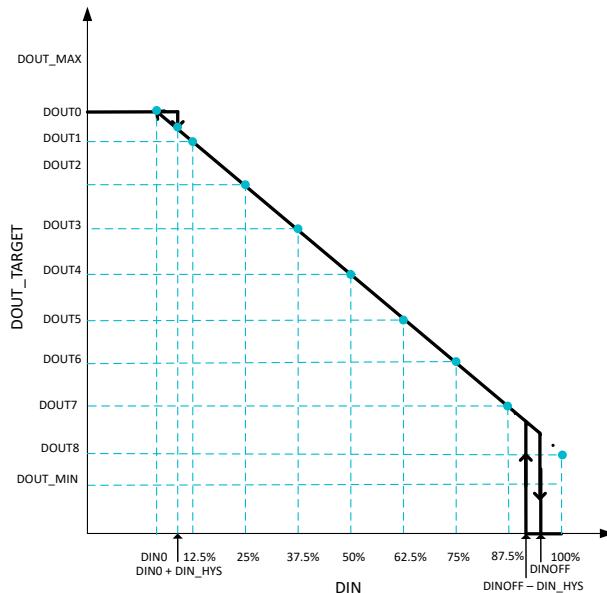

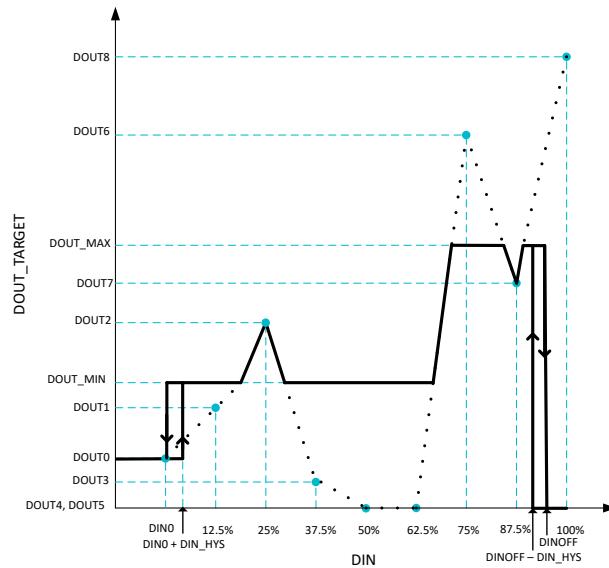

- **DOUTx:** DOUTx は、入力デューティの固定の間隔で出力デューティを設定します。DOUT1 は  $DIN = 12.5\%$  のときのターゲット出力デューティを設定し、DOUT2 は  $DIN = 25\%$  のときのターゲット出力デューティを設定します。以降同様に、DOUT8 は  $DIN = 100\%$  のときのターゲット出力デューティを設定します。DOUTx を使用して、正のスロープデューティ曲線を設定できます(デューティ曲線を参照)。DOUTx は、負のスロープを設定するためにも使用でき

ます(図 6-4 を参照)。また、DOUTx を使用して、混合スロープ(正、負、ゼロ)を設定することもできます(図 6-5 を参考)。

図 6-4. デューティ曲線 - 負のスロープ

図 6-5. デューティ曲線 - 混合スロープ

### 6.3.1.3 モーターの起動、速度変更、停止

#### モーター起動

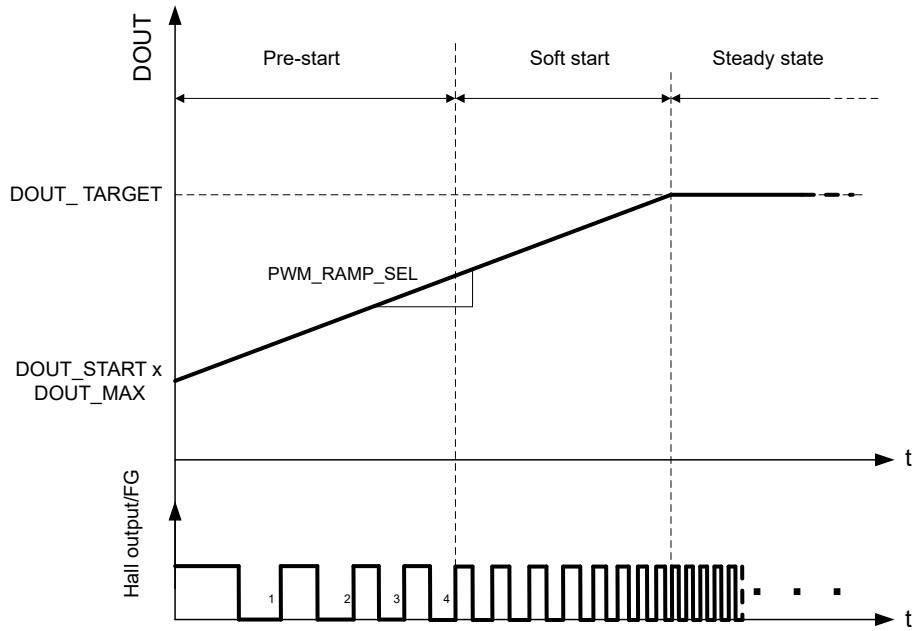

MC111 は図 6-6 に示すように、モーター起動時に目標出力デューティサイクル(図 6-2 の DOUT\_TARGET)に到達するまで、ユーザーが設定した 2 つのスロープランプを実装しています。この 2 段階ランプ(プリスタート、その後にソフトスタート)によって、信頼性の高い起動とモーター ノイズの低減が可能になります。

MC111 は、スタンバイモード、スリープモード、または故障モードを抜けると、プリスタートフェーズに移行します。プリスタートフェーズ中、MC111 は常に方形波整流方式でモーターを駆動します。PWM\_RAMP\_EN が 0x1 に設定されている場合、出力デューティサイクル(図 6-2 の DOUT)は PWM\_RAMP\_SEL で設定されたレートで次の値から直線的に増加します(速度ループが無効の場合 DOUT\_START × DOUT\_MAX、速度ループが有効の場合 DOUT\_START)。PWM\_RAMP\_EN が 0x0 に設定されている場合、DOUT は DOUT\_TARGET によって直接更新されます。プリスタートフェーズは、4 電気サイクル(8 ホールエッジ)が観測されるまで続きます。4 番目の電気サイクルが完了すると、デバイスはソフトスタートフェーズへ移行し、DOUT を DOUT\_TARGET まで上昇させます。なお、プリスタートフェーズ終了時点で DOUT がすでに DOUT\_TARGET に達している場合、ソフトスタートフェーズはスキップされ、デバイスは直接定常状態に入ります。MC111 が  $t_{LRD}$  内にホール信号の遷移を検出しなかった場合、デバイスは回転子ロック保護フォールト状態に移行します。起動シーケンス中の回転子ロック検出時間( $t_{LRD\_START}$ )は、LRD\_TIME\_STARTUP によって設定されます。定常状態では、回転子ロック検出時間( $t_{LRD\_RUN}$ )は 320ms に固定されています。プリスタートフェーズ中、ホールオフセット(角度および時間)は無効化されます。

図 6-6. モーター起動時の出力デューティ サイクル

ソフトスタートフェーズ中、DOUT は PWM\_RAMP\_SEL で設定されたレートで上昇します。このフェーズではホールオフセットと消磁が適用され、MC111 は COMMUTATION\_MODE、SRISE、SFALL ビットで設定された整流方式を使用します。DOUT が出力デューティまたは速度目標値に到達すると、ソフトスタートフェーズは終了します。

#### 速度変更

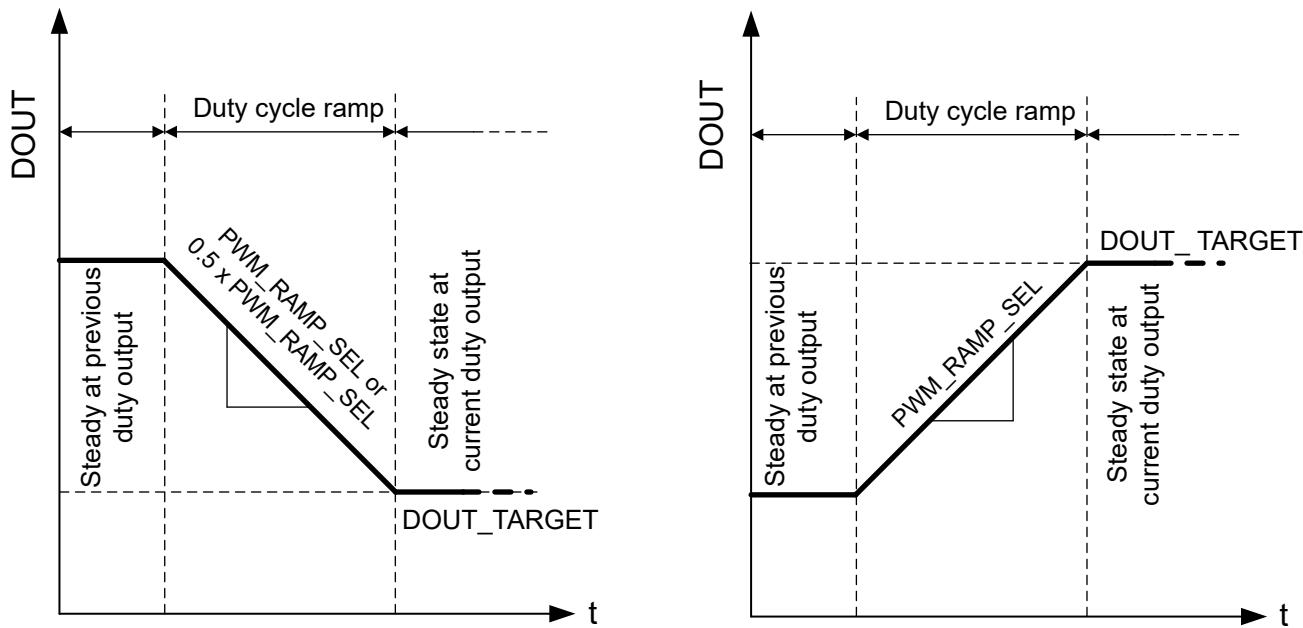

モーター動作中、DIN が変化すると、MC111 はユーザーが設定したランプ レートを使用して、出力デューティ サイクル(図 6-2 の DOUT)を前の目標デューティ サイクル(DOUT\_TARGET\_PREV)から新しい目標デューティ サイクル(DOUT\_TARGET)までスムーズに変化させます。加速中(DOUT\_TARGET > DOUT\_TARGET\_PREV)は、ランプ レートは PWM\_RAMP\_SEL によって設定され、減速中(DOUT\_TARGET < DOUT\_TARGET\_PREV)は、ランプ レートは PWM\_RAMP\_SEL (PWM\_DECEL\_SEL = 0x0 の場合) または  $0.5 \times PWM\_RAMP\_SEL$  (PWM\_DECEL\_SEL = 0x1 の場合) になります。PWM\_DECEL\_SEL = 0x1 は、モーターからの回生エネルギーのプッシュバックによる DC バススパイクを回避するため、減速中にランプを遅くします。図 6-7 に、PWM\_RAMP\_SEL に従う DOUT の増加および減少の例を示します。

図 6-7. デューティ サイクルのランプ

### ストップ

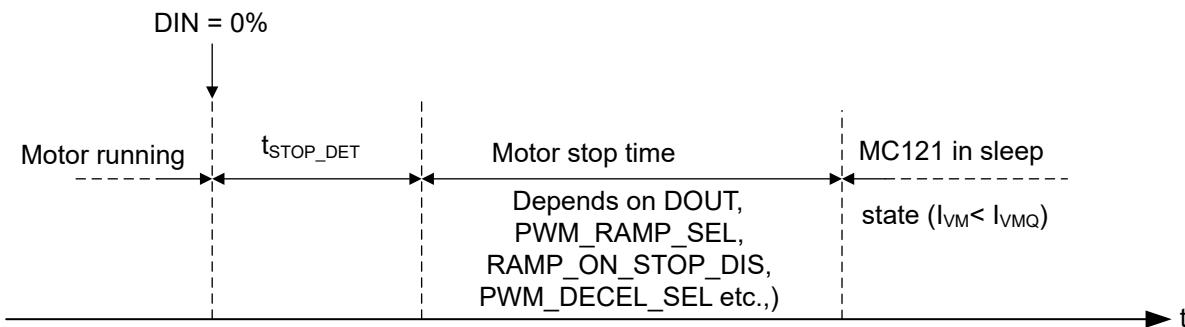

モーター停止 ( $DOUT\_TARGET = 0\%$ ) を受信すると、MC111 は  $RAMP\_ON\_STOP\_DIS$  の設定に基づいてモーターを停止します。 $RAMP\_ON\_STOP\_DIS$  が  $0x1$  に設定されている場合、モーター停止が検出されると ( $t_{STOP\_DET}$  以内に)、すべての FET がハイインピーダンスになります。 $RAMP\_ON\_STOP\_DIS$  が  $0x0$  に設定されている場合、デバイスは  $DOUT$  を  $PWM\_DECEL\_SEL$  で設定されたレートでゼロまでランプダウンし、その後すべての FET をハイインピーダンスにします。FET がハイインピーダンスになると、 $STBY\_EN$  および  $SLEEP\_EN$  ビットに応じて、MC111 はスタンバイ状態を継続するか、低消費電力スリープ状態に移行します。図 6-8 に、 $DIN$  が  $0\%$  に設定されている場合にスリープ状態へ移行するモーター停止シーケンスを示します。

図 6-8. DIN が 0% に設定されている場合のスリープ移行シーケンス

### 注

$PWM\_RAMP\_EN$  ビットを  $0x0$  に設定すると、デューティ サイクルのランプは無効化されます。デューティ サイクルのランプを無効にすると、 $DOUT$  にステップ変化が生じ ( $DIN$  変化時)、モーターの位相電流や DC バス電圧スパイクが大きくなる可能性があります。電流または電圧スパイクを回避するため、 $PWM\_RAMP\_EN$  を  $0x1$  に設定することを推奨します。

### 6.3.1.4 開ループ(デューティ サイクル)制御

開ループ制御モード (SPEED\_LOOP\_EN を 0x0 に設定) では、PWM/DC ピンからの入力デューティ (DIN) とデューティ曲線によって、整流波形のピーク出力デューティ サイクル (OUTx ピンに印加されるモーター位相電圧) DOUT が決まります (図 6-9 を参照)。H ブリッジ FET に印加されるデューティ サイクルは、整流モード (COMMUTATION\_MODE) と変調モード (PWM\_MODE) の設定で決まります。

図 6-9. 開(デューティ)ループ制御

### 6.3.1.5 閉ループ(速度)制御

図 6-10 に示す通り、MC111 には閉ループ(速度)制御モードがあり、各種動作条件 (VM、負荷) で一定の速度を維持するために使用できます。速度ループは、SPEED\_LOOP\_EN を 0x1 に設定し、速度リファレンス / 目標 (SPEED\_REF) を ( $DOUT \times MAX\_SPEED$ ) によって設定することで有効化されます。内蔵ホールセンサからのモーター速度フィードバックが SPEED\_REF と比較され、誤差は PI ループに供給されます。PI ループ Kp および Ki 係数は、KP\_RATIO と KI\_RATIO によって設定されます。速度ループの出力 (DOUT\_SPEED\_LOOP) は、印加されるピーク デューティ サイクルを設定します。速度ループの出力 (DOUT\_SPEED\_LOOP) が飽和すると、積分ワインドアップを防止するため、積分器が無効化されます。

図 6-10. 閉ループ(速度)制御

### 6.3.1.6 整流

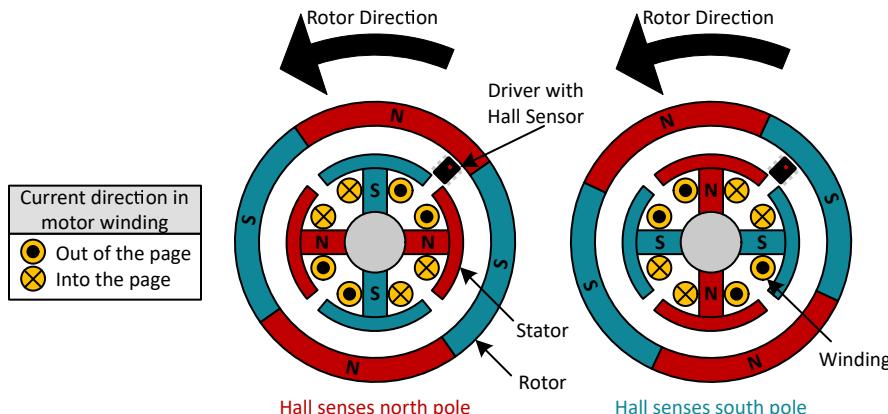

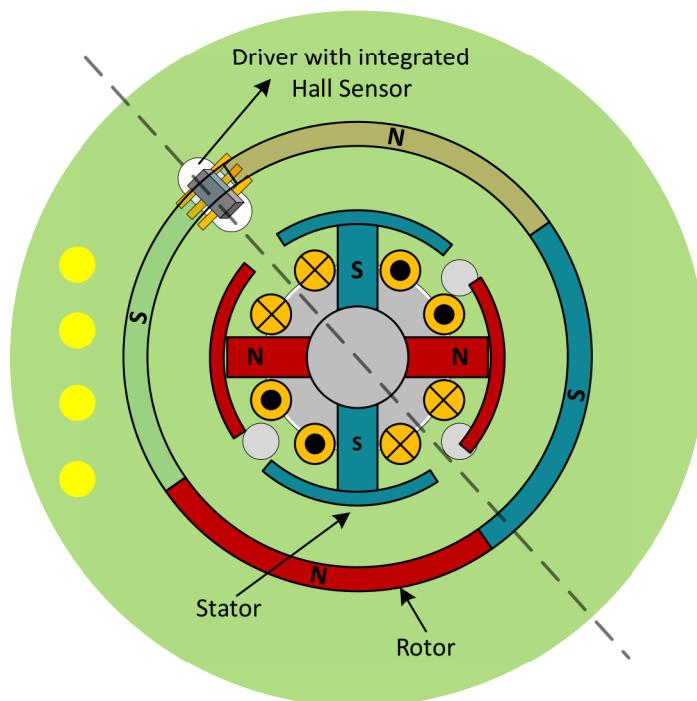

モーターにおける整流とは、固定子と回転子の磁場の向きを設定し、連続的な回転子の動作を維持するプロセスです。単相 BLDC モーターの回転子には、N 極と S 極が交互に切り替わる永久磁石が含まれています。固定子には 1 相の巻線があり、通電時に回転子の磁極を引き付けたり反発させたりします。MC111 に内蔵されたホールセンサは、モーターの整流のために固定子巻線に流す電流の方向を決定します。MC111 を使用した単相モーター整流の例を、図 6-11 に示します。適切なモーターの整流には、MC111 を 2 つの固定子極の間に配置し、ホール素子が回転子磁石の直下に位置するようにする必要があります。

図 6-11. 単相モーター整流の例

MC111 ドライバは、単相 BLDC モーター整流のために以下の機能を内蔵しています。

- 回転子の位置センシング用のデジタルラッチホールセンサ

- HALL\_OS\_ANGLE ビットと HALL\_ANGLE\_MODE ビットを使用した、リードまたはラグ角度を調整するためのホールセンサオフセット角度の設定

- HALL\_OS\_TIME ビットと HALL\_TIME\_MODE ビットを使用した、リードまたはラグ時間を調整するためのホールセンサ遅延の設定。

- HALL\_INVERT ビットによるホールオフセット信号の反転により、モーター回転方向の変更やホールセンサの各種の向きに対応

- COMMUTATION\_MODE ビットで、方形波とソフトの PWM デューティサイクル波形の選択

#### 6.3.1.6.1 ホールセンサ

MC111 はデジタルラッチホールセンサを内蔵しており、回転子の位置情報を整流アルゴリズムに提供します。以下のセクションでは、整流アルゴリズムに対するデバイスの向きと内部ホール信号の詳細を説明します。

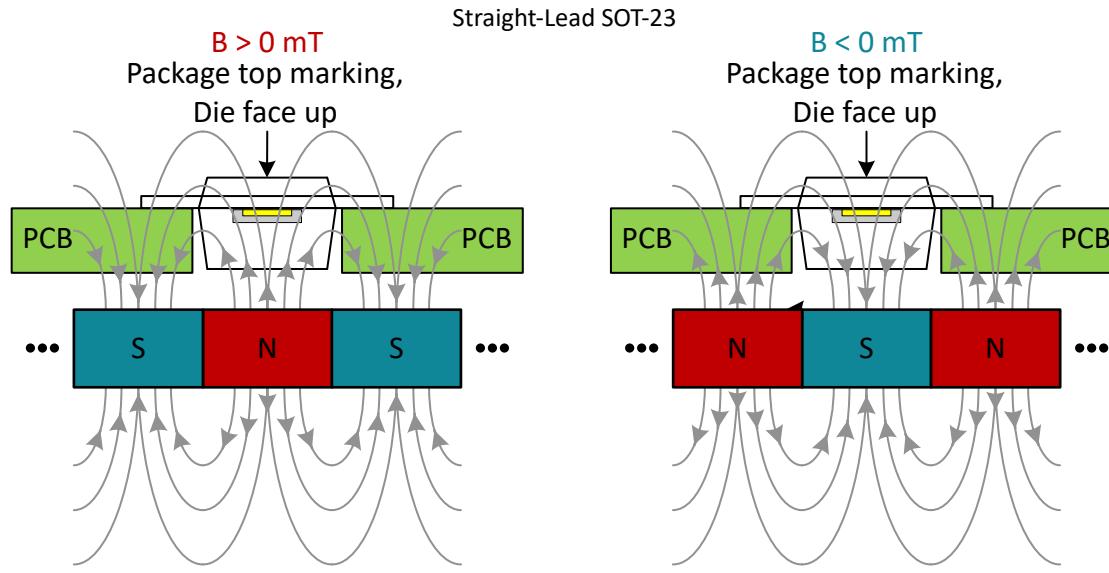

##### 6.3.1.6.1.1 磁界方向の定義

ホールセンサは、図 6-12 に黄色で示されたホールセンサの表面から磁束が外側へ向かう場合に、正の磁界 ( $B > 0\text{mT}$ ) を検出します。SOT パッケージはフリップチップオンリード構造を採用しているため、ホールセンサの表面は磁気回転子とは反対方向を向きます。この方向では、パッケージの下を N 極が通過すると、ホールセンサは正の磁界を検出します。

図 6-12. 回転子磁石とドライバを基準とした磁界方向の定義

#### 6.3.1.6.1.2 内部ホール ラッチ センサ出力

$B_{RP}$  と  $B_{OP}$  の間の磁界強度で本デバイスを電源オンすると、内部ホール ラッチ出力信号は不定となります。磁界強度が  $B_{OP}$  を上回ると、内部ホール ラッチ出力信号は Low になります。磁界強度が  $B_{RP}$  を下回ると、内部ホール ラッチ出力信号は High になります。

図 6-13. 内部ホール出力信号

#### 6.3.1.6.2 ホールオフセット

MC111 には、BEMF ゼロ交差に対するホール センサ (MC111) の相対位置によるホール センサと BEMF ゼロ交差間のオフセットを補償するためのオプションがあります。HALL\_OS\_ANGLE を使用すると、 $0^\circ$  から  $43.6^\circ$  までの範囲で、 $1.4^\circ$  刻みでホール オフセット角度の大きさを設定できます。ゼロ交差に対するこのオフセットの極性 (リードまたはラグ) は、HALL\_ANGLE\_MODE を使用して設定できます。

モーター位相電流を BEMF に合わせることで、さまざまな速度でモーター効率を最大化するには、ホール センサ出力に対してリード時間またはラグ時間を設定する必要があります。リード / ラグ時間 ( $t_{HALL\_OS\_TIME}$ ) は、HALL\_OS\_TIME の 0 から  $2.55\text{ms}$  まで ( $10\mu\text{s}$  単位) で設定できます。この時間の極性 (リードまたはラグ) は、HALL\_TIME\_MODE を使用して設定できます。

MC111 は、**HALL\_OS\_ANGLE**、**HALL\_ANGLE\_MODE**、**HALL\_OS\_TIME**、**HALL\_TIME\_MODE**に基づいて適用する必要があるリード時間またはラグ時間の合計を算出し、計算されたリード時間またはラグ時間を整流領域で適用します。たとえば、**HALL\_OS\_ANGLE** が  $-15.4^\circ$ 、**HALL\_OS\_TIME** が  $150\mu\text{s}$  に設定されており、モーターが  $500\text{Hz}$  で動作している場合、印加されるリードタイムは約  $64\mu\text{s}$  です。 $500\text{Hz}$  のとき、 $15.4^\circ$  は  $85.5\mu\text{s}$  に相当するので、実効リード / ラグ時間は  $(150 - 85.5)\mu\text{s} =$  約  $64\mu\text{s}$  です。

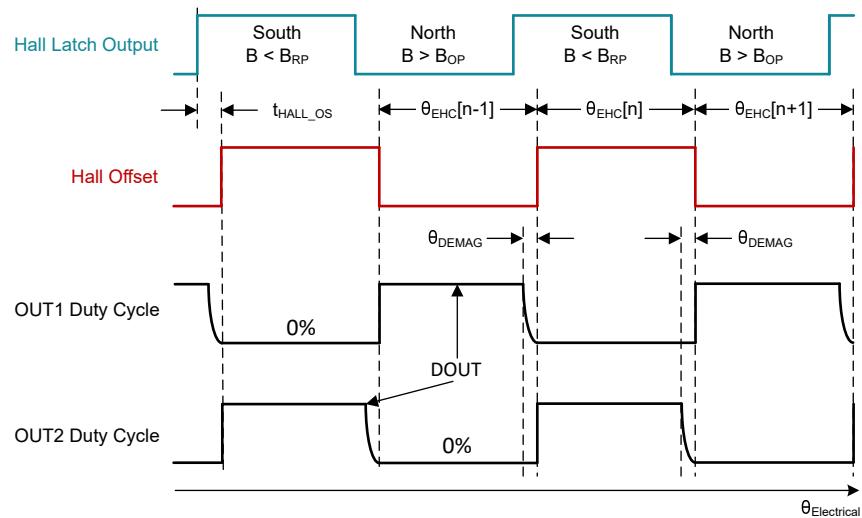

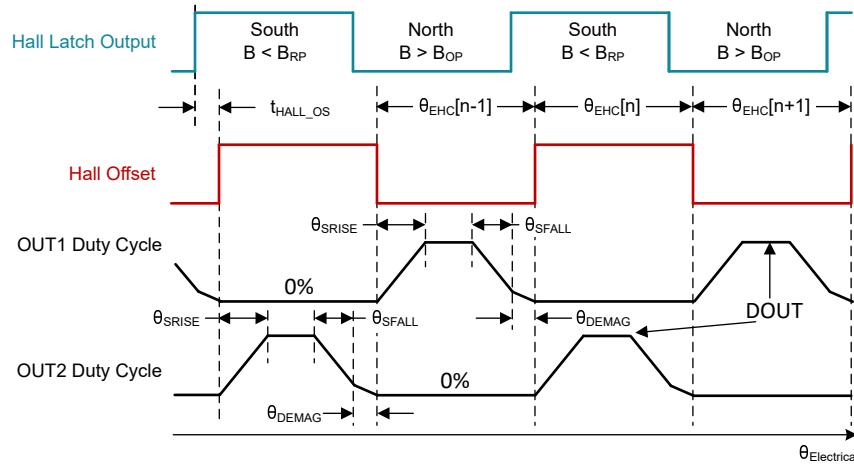

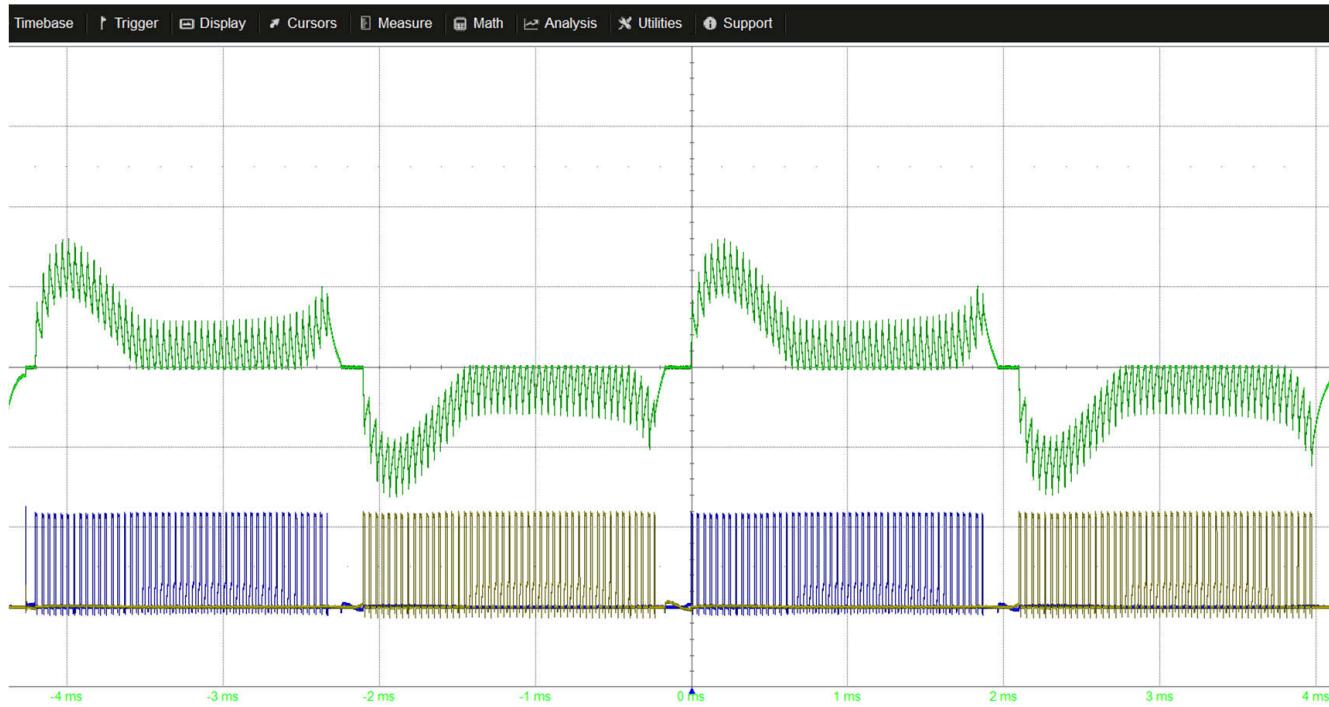

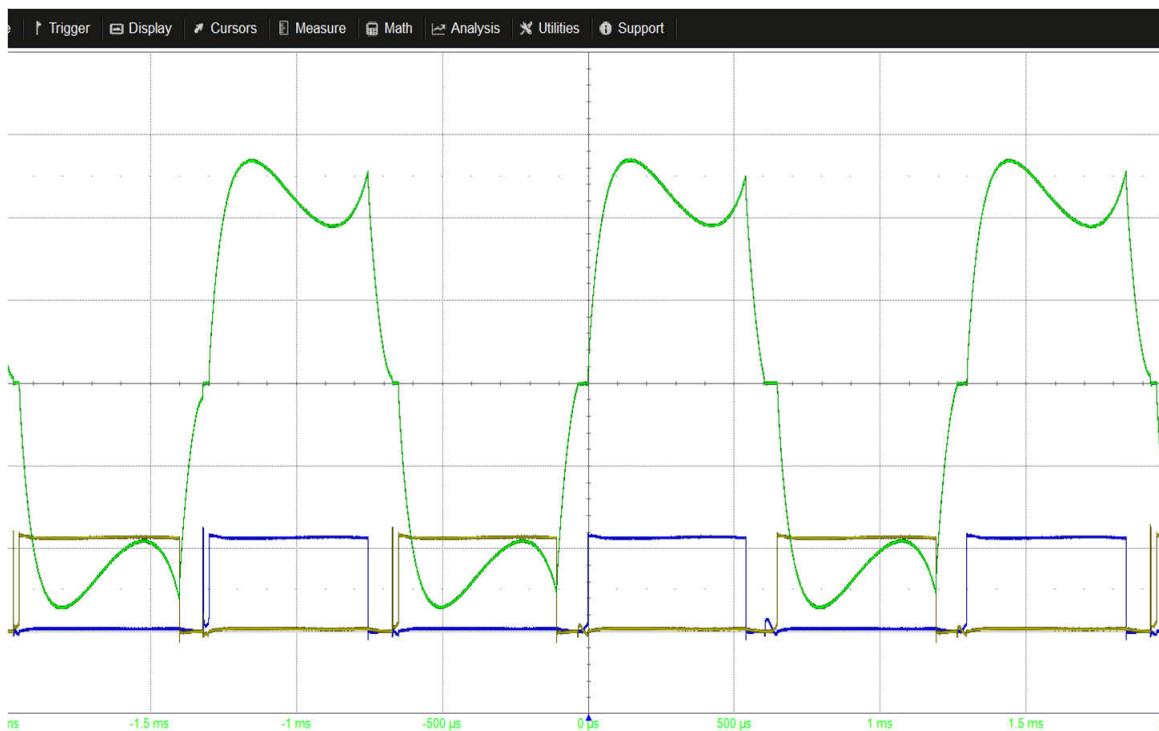

### 6.3.1.6.3 方形波整流

方形波整流は、MC111 によって実現されるシンプルな整流方式で、最大のトルク / 速度動作を可能にします。図 6-14 に、方形波整流におけるホールセンサ信号に対するドライバ出力電圧を示します。

図 6-14. 方形波整流のタイミング波形

方形波整流では、出力デューティサイクルは、電気的角度 ( $\theta_{\text{Electrical}}$ ) に対して  $DOUT$  で一定に維持されます。ホールセンサと **HALL\_INVERT** ビットからの信号によって、指令されたデューティサイクルでスイッチングする **OUTx** 端子と、 $180^\circ$  電気的半サイクル ( $\theta_{\text{EHC}}$ ) の間に GND にプルダウンされる **OUTx** 端子が決定されます。

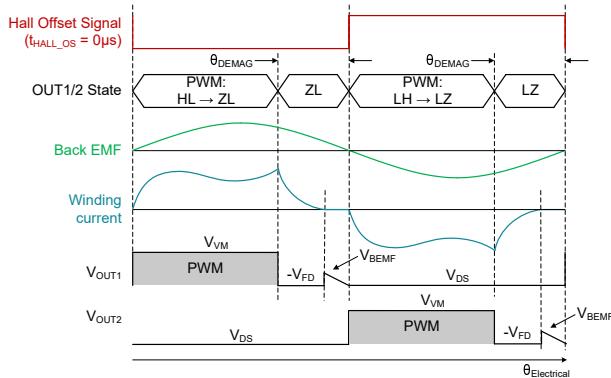

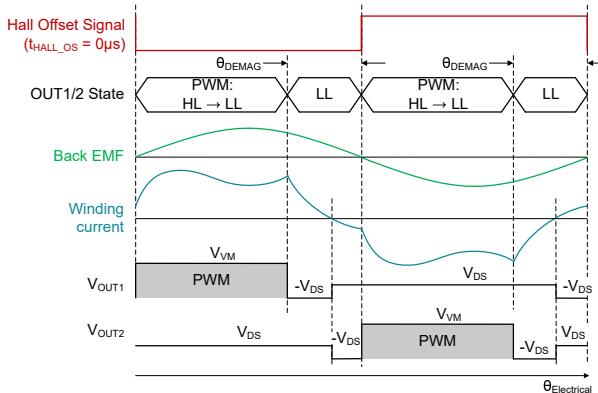

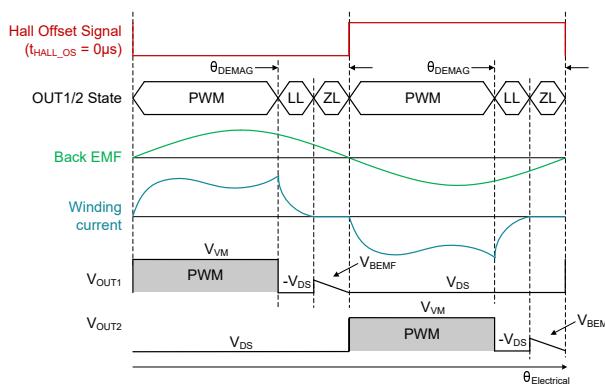

消磁状態  $\theta_{\text{DEMAG}}$  は、電気的半サイクルの終了時に発生し、**DEMAG\_TIME** ビットによって決定されます。消磁の目的は、整流イベントにより **OUTx** 電圧の極性を反転させる前に、モーター電流をゼロに低減し、固定子巻線を消磁することです。消磁により、整流中の VM 電源と **OUTx** の電圧スパイクが最小限に抑えられます。消磁は、back-EMF が最小となる整流領域周辺でのモーター電流スパイクを低減することで、効率も向上させます。**PWM\_MODE** は、セクション 6.3.1.7 で説明されているように、**PWM** オフ時間および  $\theta_{\text{DEMAG}}$  時間中のモーター電流の同期、非同期、またはハイブリッド変調を設定します。図 6-15、図 6-16、図 6-17 は、それぞれ  $\theta_{\text{DEMAG}}$  中の非同期、同期、およびハイブリッド再循環状態のタイミング図を示します。

図 6-15.  $\theta_{DEMAG}$  における非同期モードを使用した方波整流の詳細なタイミング図

図 6-16.  $\theta_{DEMAG}$  における同期モードを使用した方波整流の詳細なタイミング図

図 6-17.  $\theta_{DEMAG}$  におけるハイブリッド モードを使用した方波整流の詳細なタイミング図

消磁時間 (DEMAG\_TIME) は固定時間に設定することも、自動的に決定することもできます。AUTO\_DEMAG\_EN が 0x0 に設定されている場合、消磁時間は動作条件全体にわたって一定であり、DEMAG\_TIME ビットによって、モーターの速度に基づいて  $\theta_{DEMAG}$  が決定されます。AUTO\_DEMAG\_EN が 0x1 に設定されている場合、ドライバは  $\theta_{DEMAG}$  角度を自動的に調整し、モーターの速度に基づいて消磁時間を最適化します。

#### 6.3.1.6.4 ソフト整流

ソフト整流方式では、整流イベント後、 $\theta_{SRISE}$  中、PWM デューティサイクルは  $D_{OUT}$  まで上昇し、 $\theta_{SFALL}$  中は 0% に戻ります (図 6-18 を参照)。ソフト整流の目的は、方形波整流に比べて音響ノイズを低減することです。ホールセンサ信号遷移のタイミングによって、電気的半サイクル中の  $\theta_{SRISE}$  および  $\theta_{SFALL}$  の角度のタイミングが決定されます。 $\theta_{SRISE}$  および  $\theta_{SFALL}$  の角度は、SRISE および SFALL ビットを使用してプログラムできます。

図 6-18. ソフト整流のタイミング波形

SRISE、SFALL、DEMAG\_TIME ビットをプログラミングする際、 $\theta_{SRISE}$ 、 $\theta_{SFALL}$ 、 $\theta_{DEMAG}$  の合計が  $180^\circ$  を超えると、 $\theta_{SRISE}$  の角度が減少します。

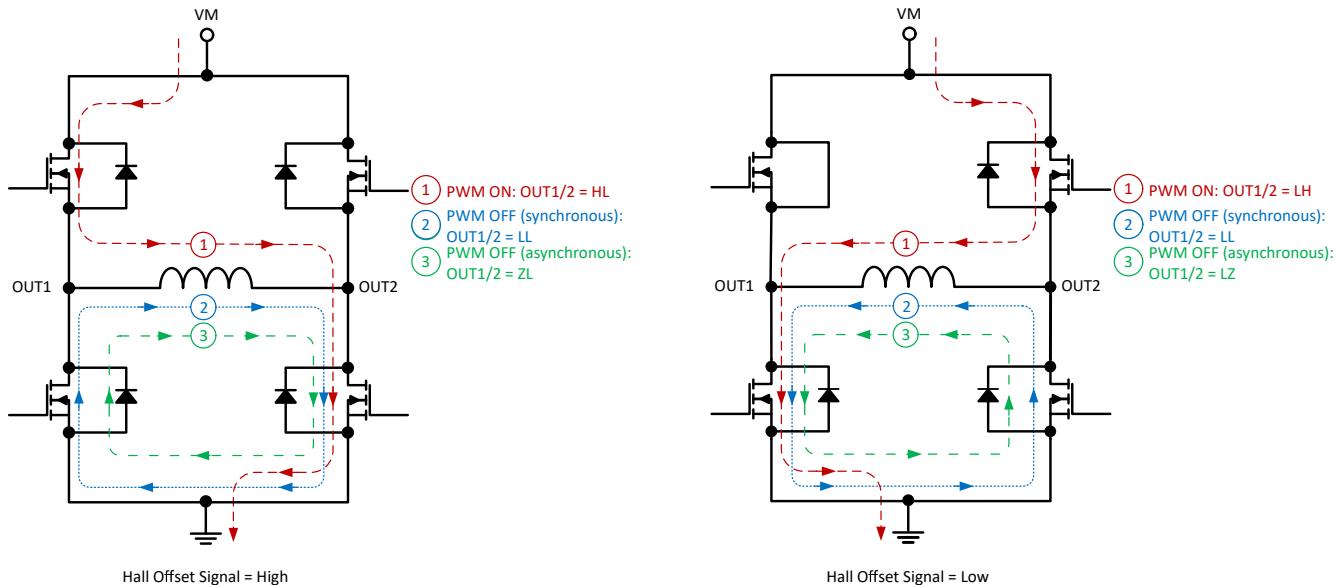

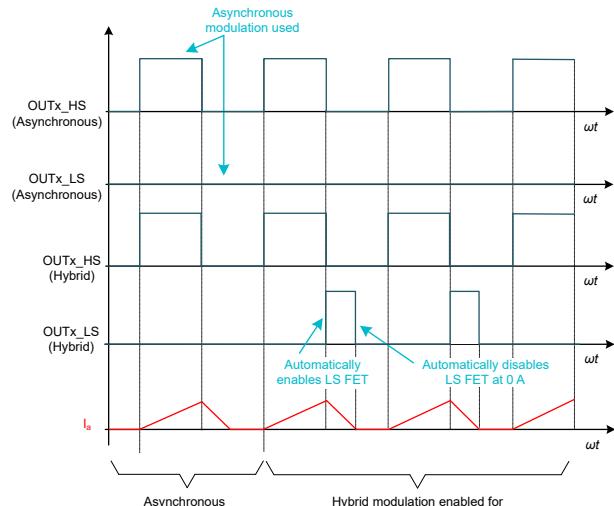

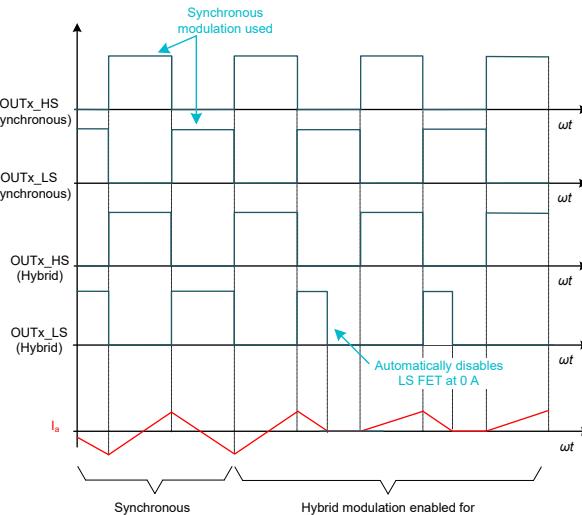

### 6.3.1.7 PWM 変調モード

MC111 には、同期、非同期、ハイブリッドの 3 種類の PWM 変調モードがあります。PWM\_MODE ビットによって、PWM 変調モードを設定します。同期モードでは、PWM オフ時間中に両方のローサイド FET がオンになります。また、フリーホール電流をボディダイオードではなく FET を通して導通することで、電力損失を低減します。ただし、ターンオフ電流やモーター巻線インダクタンスによっては、同期変調中に逆電流が流れ、負トルクが発生してモーター速度が低下する場合があります。非同期モードでは、PWM オフ時間中に 1 つのローサイド FET だけがオンに維持され、他の FET は無効化されます。フリーホール電流は、LS FET のボディダイオードを通して導通されます。非同期モードでは、PWM オフ時間中に逆電流は流れませんが、ボディダイオード導通により、電力損失が大きくなる可能性があります。ハイブリッドモードは、これら両方を組み合わせたものです。フリーホール電流が  $13\text{mA}$  未満に低下するまでは同期モードで動作し、その後は逆電流を防止するため非同期モードに切り替わります。

表 6-1 は、出力 PWM の H ブリッジ状態を示します。H は該当 OUTx レッグのハイサイド FET がオン、L はローサイド FET がオン。Z はその OUTx レッグの両方の FET がハイインピーダンスです。ホールオフセット信号は、ホールセンサの状態およびデバイス設定から決定される内部信号です。ホールオフセット信号によって、整流アルゴリズムのステートマシン内での出力スイッチング状態が決定されます。入力 PWM のデューティサイクルと、整流モード(方形波またはソフト)によって、出力 PWM の瞬時デューティサイクル  $D_{OUT}$  が決まります。

表 6-1. 出力状態の表

| ドライバ状態                          | 説明                                                        | PWM_MODE によって設定される変調モード | ホールオフセット信号 | OUT1 | OUT2 |

|---------------------------------|-----------------------------------------------------------|-------------------------|------------|------|------|

| DOUT                            | デューティサイクルあたりの PWM オン時間                                    | X                       | L          | L    | H    |

|                                 |                                                           | X                       | H          | H    | L    |

| (1-DOUT)、電流制限、 $\theta_{DEMAG}$ | PWM オフ時間(デューティ)中、電流制限オフ時間中、または整流イベント前の位相消磁中におけるモーター電流の再循環 | 非同期モード                  | L          | L    | Z    |

|                                 |                                                           |                         | H          | Z    | L    |

|                                 |                                                           |                         | 同期モード      | X    | L    |

図 6-19 は、PWM オン時間、PWM オフ時間、および消磁状態における H ブリッジを流れるモーター電流を示しています。消磁状態の詳細については、セクション 6.3.1.6.3 を参照ください。

図 6-19. モーター電流と出力状態

ハイブリッド PWM モードでは、PWM オフ時間中（同期モードと同様）に両方のローサイド FET を有効にすることで、ボディダイオードを通したモーター電流の再循環を防止します。モーター電流が 13mA 未満になると、ゼロ電流検出器が該当するローサイド FET を無効化し、H ブリッジを非同期モードに切り替えます。MC111 は同期モードと非同期モードを自動的に切り替えることで、デバイスの電力損失を低減するとともに、逆起電力による意図しない負電流がモーター巻線に流れることを防ぎます。

図 6-20. 非同期変調とハイブリッド変調

図 6-21. 同期変調とハイブリッド変調

表 6-2 は、PWM 変調モードを構成するための PWM\_MODE ビットフィールドの設定を示しています。

表 6-2. PWM\_MODE による変調モード

| PWM_MODE ビット | PWM および電流制限オフ時間 | 消磁状態 |

|--------------|-----------------|------|

| 000b         | 非同期             | 非同期  |

| 001b         | 非同期             | 同期   |

| 010b         | 同期              | 非同期  |

表 6-2. PWM\_MODE による変調モード (続き)

| PWM_MODE ビット | PWM および電流制限オフ時間 | 消磁状態   |

|--------------|-----------------|--------|

| 011b         | 同期              | 同期     |

| 100b         | 同期              | ハイブリッド |

| 101b         | 非同期             | ハイブリッド |

| 110b         | ハイブリッド          | 非同期    |

| 111b         | ハイブリッド          | ハイブリッド |

### 6.3.2 保護

MC111 は、回転子ロック、電流制限、過電流、VM 低電圧、VM 過電圧、過熱イベントに対する保護機能を内蔵しています。表 6-3 に、故障モードの開始とアクティブ モードへの復帰を示します。

表 6-3. デバイスの故障時の動作および応答

| 故障           | 条件                                                                          | H ブリッジ                                              | デバイス ロジック                     | FG/RD 表示 | 復帰                                                               |  |  |

|--------------|-----------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------|----------|------------------------------------------------------------------|--|--|

| 回転子ロックの保護    | $t_{LRD}$ の間ホール遷移が検出されず、<br>$LRD\_RETRY\_DIS = 0x0$                         | すべての FET が無効化<br>(ハイインピーダンス)                        | あり                            |          | $t_{lock\_long\_retry}$ または<br>$t_{lock\_quick\_retry}$ 後に自動リトライ |  |  |

|              | モーター ストール: 5 回連続の起動試行で、 $t_{LRD}$ の間ホール遷移が検出されず、<br>$LRD\_RETRY\_DIS = 0x1$ | すべての FET が無効化<br>(ハイインピーダンス)                        |                               |          | ラッチされる (ラッチされた故障は電源リセットまたはウェークアップによってのみクリアされる)                   |  |  |

| 電流制限         | $I_{OUTx,LS} > I_{LIMIT}$                                                   | PWM_MODE に基づいて HS FET を無効化し、<br>LS FET を介した電流再循環を行う | 有効                            | なし       | 次の出力 PWM デューティ サイクルの開始時に $I_{OUTx,LS} < I_{LIMIT}$               |  |  |

| 過電圧保護        | $V_{VM} > V_{OVP}$ (立ち上がり)、 $OVP\_EN = 0x1$                                 | すべての FET が無効化<br>(ハイインピーダンス)                        | あり (FGRD_FAULT_SEL = 0x1 の場合) |          | $V_{VM} < V_{OVP}$ (立ち下がり)                                       |  |  |

| 過電流保護        | $I_{OUTx} > I_{OCP}$ および<br>$OCP\_MODE = 0x0$                               | すべての FET が無効化<br>(ハイインピーダンス)                        |                               |          | $t_{lock\_long\_retry}$ 後に自動リトライ                                 |  |  |

|              | $I_{OUTx} > I_{OCP}$ および<br>$OCP\_RETRY\_MODE = 0x1$                        |                                                     |                               |          | 3 回連続の OCP イベント後にラッチされる (ラッチされた故障は電源リセットまたはウェークアップによってのみクリアされる)  |  |  |

| サーマル シャットダウン | $T_J > T_{TSD}$                                                             | すべての FET が無効化<br>(ハイインピーダンス)                        | 無効                            |          | $T_J < T_{TSD} - T_{HYS}$                                        |  |  |

| 低電圧保護        | $V_{VM} < V_{UVLO}$ (立ち下がり)                                                 | すべての FET が無効化<br>(ハイインピーダンス)                        |                               |          | $V_{VM} > V_{UVLO}$ (立ち上がり)                                      |  |  |

| 内蔵電源クランプ     | $V_{VM} > VM_{CLAMP}$ および<br>$VM_{CLAMP\_DIS} = 0x0$                        | HS FET 無効化 (ハイインピーダンス)                              | 有効                            | なし       | $V_{VM} < VM_{CLAMP}$                                            |  |  |

FG/RD ピンは、モーター速度または回転子ロックを検出するために、ファン コントローラへのフィードバックをサポートしています。FGRD\_MODE ビットを 0x0 に設定すると、周波数ジェネレータ (FG) 出力の FG/RD ピンが設定されます。内部ホールセンサ信号の遷移によって、FG 信号の周波数が決まります。FG\_MULTIPLIER ビットを設定することで、FG ピンは内部ホールセンサ周波数の 1/2、1、2/3、または 2 倍の係数でトグルします。FG\_MULTIPLIER ビットは、異なる数の磁極ペアを持つモーターをスワップする際に、システム設計とファームウェアの変更を最小限に抑えるのに役立ちます。FG\_HALL\_RAW\_EN が 0x0 に設定されている場合、FG ピンの信号はホールオフセット信号に対応します。FG\_HALL\_RAW\_EN = 0x1 の場合、FG ピンの信号はホールセンサ信号に直接対応します。FG\_HALL\_RAW\_EN = 0x1 の場合、本デバイスは 2/3 FG\_MULTIPLIER 設定をサポートしません。

FG/RD ピンは、表 6-4 に従って、デバイスの故障モード、回転子ロックの状態、アクティブ モードステータスを示します。モーターが停止 / アイドル状態 (DIN = 0% または DOUT\_TARGET = 0% によって停止) のときの FG ピンの状態は、回転子ロックまたはデバイスの故障状態を示すために使用される状態とは常に逆になります。たとえば、FGRD\_MODE、FGRD\_INVERT、FGRD\_FAULT\_SEL ビットの組み合わせにより、回転子ロックが FG ピンのアクティブ Low 信号で示される場合、モーターが停止 / アイドル状態のときの FG ピンの状態は (外部プルアップによって) High になります。

表 6-4. FG/RD ピンの動作

| FGRD_MODE ビット | FGRD_INVERT ビット | FGRD_FAULT_SEL ビット | アクティブ モード表示      | 回転子ロック表示         | 故障モード表示          |

|---------------|-----------------|--------------------|------------------|------------------|------------------|

| 0x0           | 0x0             | 0x0                | FG = トグル         | FG = Low にアサート   | FG = 直前の状態       |

|               | 0x0             | 0x1                |                  |                  | FG = Low にアサート   |

|               | 0x1             | 0x0                |                  | FG = High にプルアップ | FG = 直前の状態       |

|               | 0x1             | 0x1                |                  |                  | FG = High にプルアップ |

| 0x1           | 0x0             | 0x0                | RD = High にプルアップ | RD = Low にアサート   | RD = 直前の状態       |

|               |                 | 0x1                |                  |                  | RD = Low にアサート   |

|               | 0x1             | 0x0                | RD = Low にアサート   | RD = High にプルアップ | RD = 直前の状態       |

|               |                 | 0x1                |                  |                  | RD = High にプルアップ |

### 6.3.2.1 回転子ロックの保護

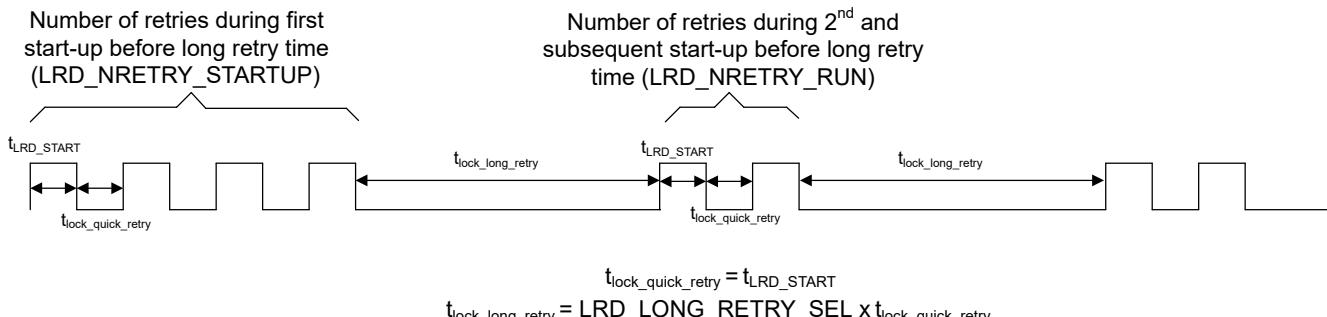

MC111 が回転子ロック検出時間 ( $t_{LRD}$ ) よりも長い時間ホール遷移を検出しない場合、回転子ロックの故障が認識され、すべての FET が無効化されます (ハイインピーダンス)。FG/RD ピンは、表 6-4 に従って回転子ロックの故障を示します。起動シーケンス中は、 $t_{LRD}$  は  $t_{LRD\_START}$  によって設定され、モーター動作 (定常状態) 中は、 $t_{LRD}$  は  $t_{LRD\_RUN}$  によって設定されます。起動中の回転子ロックリトライシーケンス ( $LRD\_RETRY\_DIS = 0x0$  の場合) を、図 6-22 に示します。パワーアップ / ウエークアップ後の最初の起動中、クイックリトライ試行回数は  $LRD\_NRETRY\_STARTUP$  によって設定されます。クイックリトライ時間はロックさ回転子検出時間 ( $t_{LRD\_START}$ ) と同じです。 $LRD\_NRETRY\_START$  試行が完了しても回転子ロックの状態が続くと、MC111 はロングリトライ時間 ( $t_{lock\_long\_retry}$ ) ( $LRD\_LONG\_RETRY\_SEL \times t_{LRD\_START}$ ) に入ります。ロングリトライ時間が経過すると、MC111 はモーターを再度回転させようします。パワーアップ / ウエークアップ後の 2 回目の起動試行では、クイックリトライ試行回数は  $LRD\_NRETRY\_RUN$  によって設定されますが、回転子ロック検出時間 ( $t_{LRD\_START}$ ) とクイックリトライ時間は同じままです。 $LRD\_NRETRY\_RUN$  試行が完了しても回転子ロック状態が続くと、MC111 はロングリトライ時間 ( $t_{lock\_long\_retry}$ ) に再び入ります。その後のモーター起動シーケンスでは、2 番目の起動サイクルと同じリトライパターンが使用されます (図 6-22 を参照)。リトライ時間が経過した後の各モーター起動の試行 (クイックまたはロングリトライ) は、プレスタート位相から開始されます (図 6-6 を参照)。

図 6-22. 起動中の回転子ロックリトライシーケンスおよびタイミング ( $LRD\_RETRY\_DIS = 0x0$  の場合)

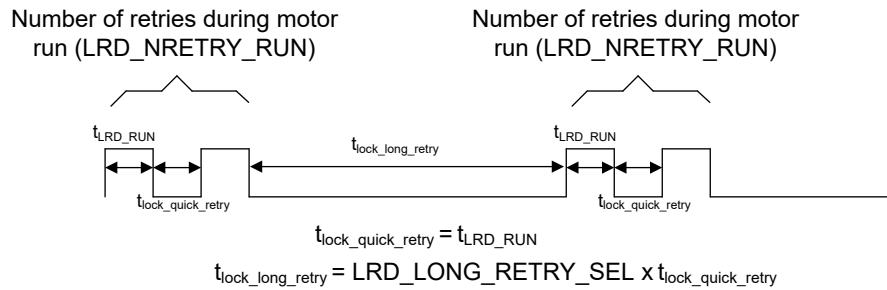

モーター動作中に回転子ロック状態が検出された場合 ( $t_{LRD\_RUN}$  の間ホール遷移がない場合)、すべての FET は無効化され (ハイインピーダンス)、FG/RD ピンは、表 6-4 に従って回転子ロックの故障を示します。MC111 は、回転子ロックのリトライシーケンスを開始する前に、ロングリトライ時間の 1 回分を待機します (図 6-23 を参照)。

図 6-23. 実行中の回転子ロック リトライ シーケンスおよびタイミング (LRD\_RETRY\_DIS = 0x0 の場合)

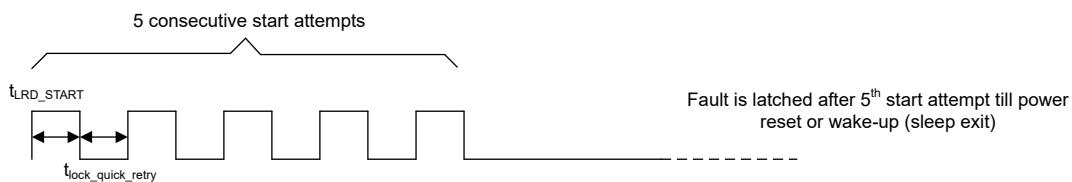

MC111 は、図 6-24 に示すように、LRD\_RETRY\_DIS = 0x1 を設定することで、5 回連続の起動試行が回転子ロックとなった際に、回転子ロックの故障をラッチする動作を選択できます。モーター動作は、電源リセットまたはウェークアップ(スリープ終了)によって再開できます。

図 6-24. 回転子ロック リトライ シーケンスおよびタイミング (LRD\_RETRY\_DIS = 0x1 の場合)

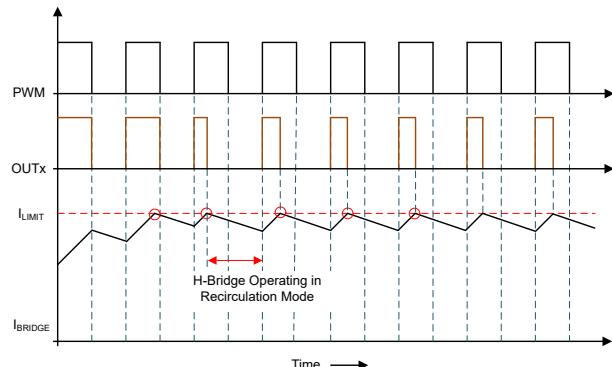

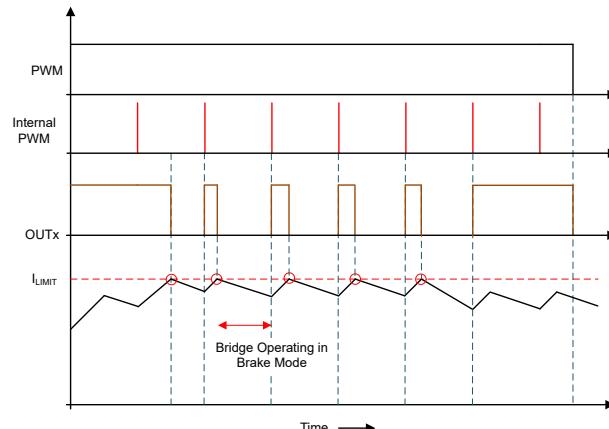

### 6.3.2.2 電流制限

電流制限機能は、起動時、過負荷、ストール時の過電流動作からモーターを保護します。モーター位相電流が  $I_{LIMIT}$  スレッショルドを超えると、MC111 はハイサイド FET をオフにすることで、サイクル単位の電流制限方式を適用します。 $ILIMIT\_SEL$  は電流制限スレッショルドを設定します。PWM\_MODE ビットは、セクション 6.3.1.7 に記載されている PWM オフ時間と同様に、電流制限オフ時間中のモーター電流の同期、非同期、またはハイブリッド再循環状態を設定します。

次の PWM 周期の開始時点でもモーター電流が  $I_{LIMIT}$  スレッショルドを上回っている場合、ローサイド FET は別の PWM 周期にわたり有効状態が維持されます。次の PWM 周期の開始までにモーター電流が  $I_{LIMIT}$  を下回ると、出力は、表 6-1 に示すように、整流アルゴリズムステートマシンによって決定される駆動状態に戻ります。

電流制限は、モーター電流が  $I_{LIMIT}$  スレッショルドを上回った場合に出力 PWM デューティサイクルを下げることで、モータートルクの上限を設定します。この電流制限機能は、整流ステートマシンによって決定される PWM デューティサイクルよりも優先されます。モーター電流が  $I_{LIMIT}$  スレッショルドを下回ると、整流ステートマシンが出力デューティサイクルを完全に制御します。図 6-25 および図 6-26 に、サイクル単位の電流制限方式の波形例を示します。

図 6-25. サイクル単位の電流制限動作

図 6-26. 100% PWM デューティ サイクルでのサイクル単位の電流制限動作

### 6.3.2.3 過電流保護 (OCP)

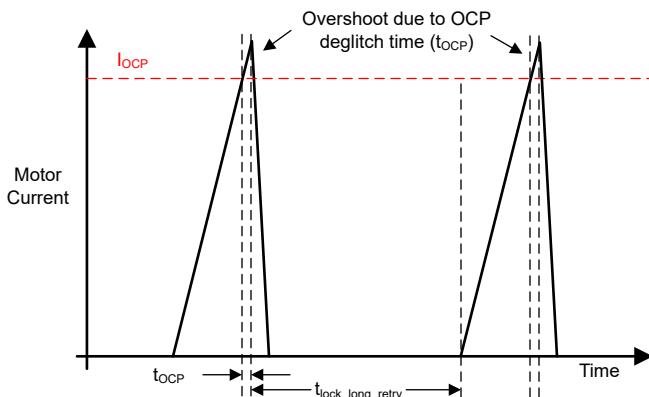

過電流保護 (OCP) 機能は、OUTx ピンの内蔵パワー FET を電源 (VM)、グランド、OUTx ピン間の短絡から保護します。図 6-27 に示すように、FET に流れる電流が OCP スレッショルド ( $I_{OCP}$ ) を上回る状態が OCP グリッチ除去時間 ( $t_{OCP}$ ) を超えて続くと、H ブリッジ内のすべての FET が無効化 (ハイインピーダンス) され、FG/RD ピンは 表 6-4 に示すように回転子ロックの故障を示します。OCP 故障の復帰は、OCP\_RETRY\_MODE によって設定されます。

図 6-27. OCP 動作

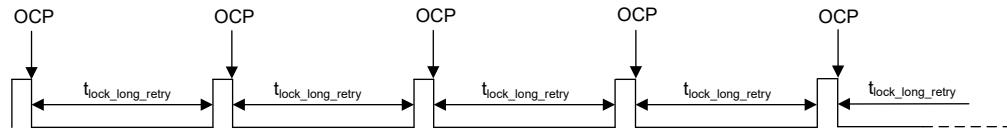

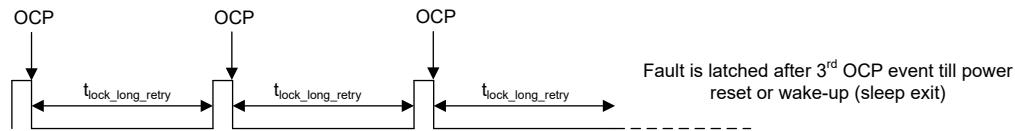

OCP\_RETRY\_MODE が 0x0 に設定されている場合、図 6-28 に示すように、 $t_{lock\_long\_retry}$  が経過すると MC111 は (開始前位相から) モーターの駆動を開始します。 $t_{lock\_long\_retry}$  は、( $LRD\_LONG\_RETRY\_SEL \times t_{LRD\_START}$ ) によって設定されます。OCP\_RETRY\_MODE が 0x1 に設定されている場合、MC111 は 3 回のリトライ後に故障をラッチします (リトライ時間は  $t_{lock\_long\_retry}$  によって設定)。以後のモーターの駆動は、故障状態をクリアするために以後のパワーリセットまたはウェークアップ (スリープ解除) の後にのみ可能です。

OCP\_RETRY\_MODE = 0x0

OCP\_RETRY\_MODE = 0x1

図 6-28. OCP リトライ モード

#### 6.3.2.4 VM 低電圧誤動作防止 (UVLO)

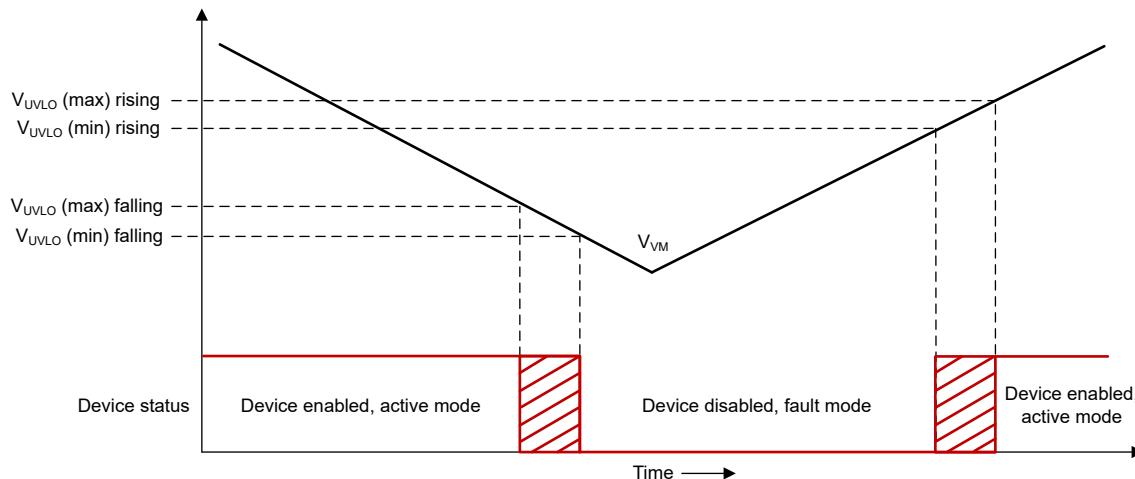

VM ピンの電圧が UVLO の立ち下がりスレッショルド電圧  $V_{UVLO}$  を下回ると、デバイスのすべての回路が無効化され、内部ロジックがリセットされます。UVLO\_SEL = 0x0 の場合、図 6-29 に示すように、 $V_{VM}$  電圧が UVLO の立ち上がりスレッショルドを上回ると、デバイスがパワーアップしてモーター動作が再開します。UVLO\_SEL ≠ 0x0 の場合、デバイスは常に UV\_P\_SEL = 0x0 に対応する UVLO 立ち上がりスレッショルドでパワーアップしますが、モーター動作は、VM が UVLO\_SEL で設定された UVLO 立ち上がりスレッショルドを上回った場合にのみ開始されます。UVLO\_SEL ≠ 0x0 および  $3.15 < VM < V_{UVLO}$  (立ち上がり) (UVLO\_SEL の設定に対応) の場合、VM UVLO の故障がアクティブになります。すべての FET が無効化され、FG/RD ピンは表 6-4 に従って回転子ロックの故障を示します。

図 6-29. VM UVLO の動作

#### 6.3.2.5 VM 過電圧保護 (OVP)

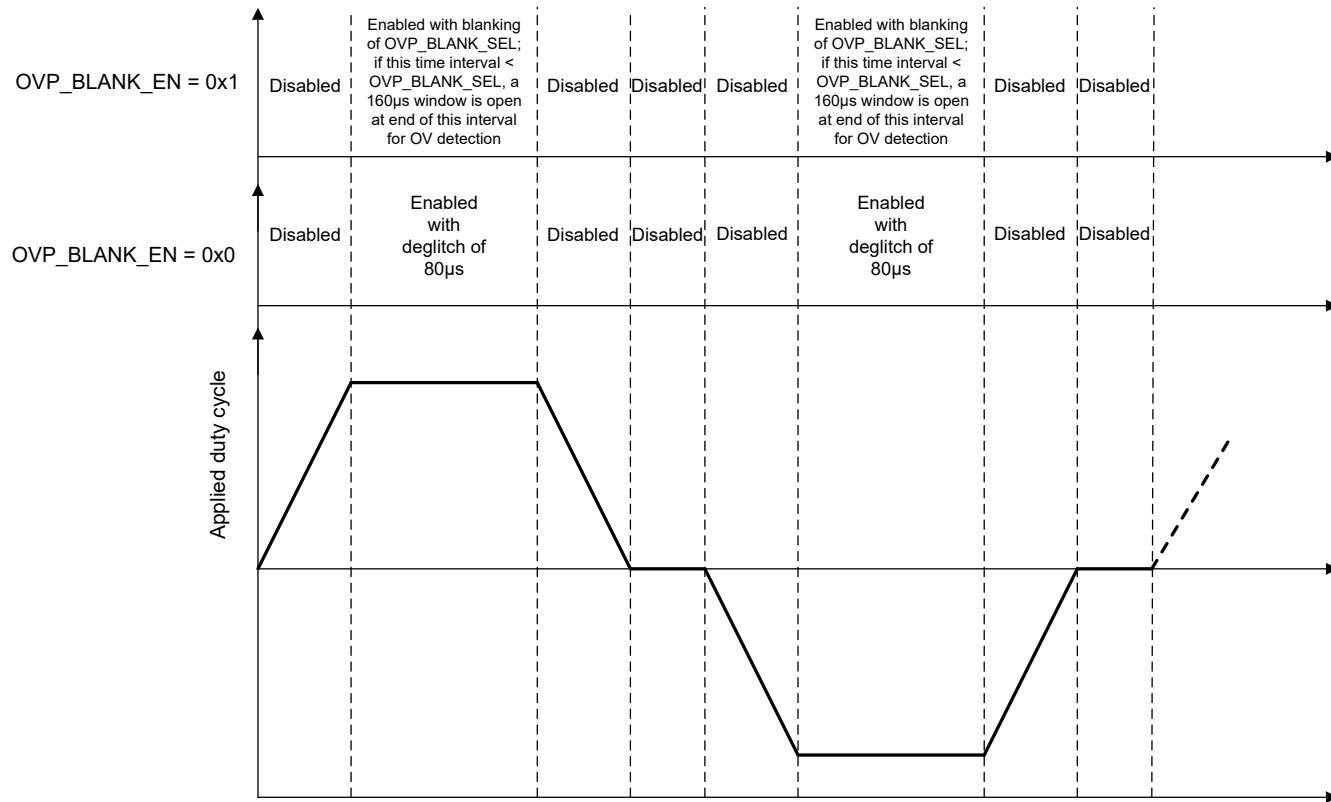

VM 電圧が  $V_{OVP}$  立ち上がりスレッショルドを上回ると、すべての FET がハイインピーダンスになります。FG/RD ピンは表 6-4 に従って回転子ロック故障を示します。VM 電圧が  $V_{OVP}$  立ち下がりスレッショルドを下回ると、デバイスは通常動作を再開します。OVP スレッショルドは OVP\_SEL で設定され、OVP\_EN を 0x0 に設定することで無効化できます。過電圧保護には  $80\mu\text{s}$  の固定グリッチ除去時間があり、スプリアス OVP トリガを防止します。通常のモーター動作時の過渡的な VM スパイクによる OVP の誤検出を避けるため、ソフト整流の立ち上がりおよび立ち下がり区間では過電圧保護が無効化されています。また、消磁区間中は OVP が常に無効化されています。さらに、ピーク デューティ サイクル区間では、OVP\_BLANK\_EN を 0x1 に設定して有効化できるブランкиング時間が OVP\_BLANK\_SEL (1ms または 4ms) によって提供され、OVP 検出の堅牢性が向上します。図 6-30 に、ソフト整流の各区間における OVP 検出動作を示します。方

形波整流では立ち上がり、立ち下がりの区間ではなく、ブランディング時間が有効化されている場合、整流インスタントから適用されます。

図 6-30. OVP 検出

### 6.3.2.6 サーマル シャットダウン (TSD)

ダイ温度がサーマル シャットダウン限界値 ( $T_{TSD}$ ) を超えると、H ブリッジ内のすべての FET が無効化されます。ダイ温度が安全なレベル ( $T_{TSD} - T_{HYS}$ ) まで低下すると、デバイスの動作は自動的に再開されます。

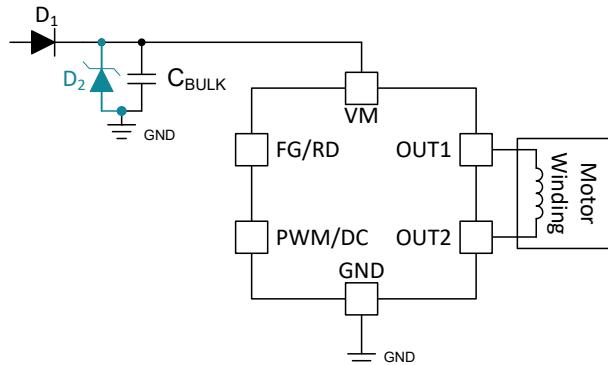

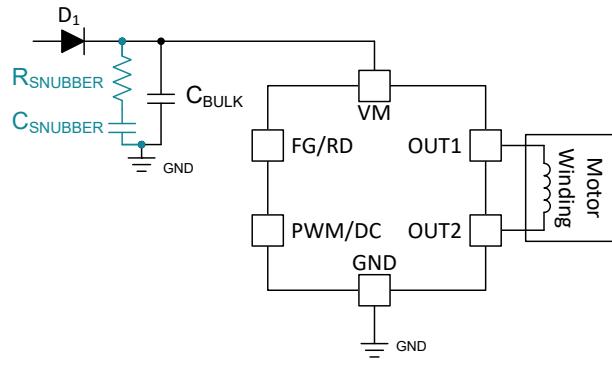

### 6.3.2.7 内蔵電源 (VM) クランプ

MC111 は、モーターからの回生エネルギーのバッファによる VM ピンの電圧スパイクを制限するために、電源 (VM) ピンにクランプを内蔵しています。VM\_CLAMP\_DIS が 0x1 に設定されている場合、クランプは無効化されます。VM 電圧が VM\_CLAMP レベルに達すると、デバイスはクランプを有効にして VM 電圧を制限します。クランプが作動すると、HS FET はハイインピーダンスになり、モーター駆動が停止します。クランプ回路は、クランプ回路が安全動作領域で規定された制限に達するまでエネルギーを吸収できます。SOA の制限値を超えると、クランプは無効化されます。(SOA で規定されたよりも) 高いエネルギーをクランプする必要がある場合、許容可能な外部 TVS ダイオードを追加します。

#### 注

クランプ動作中に、過電流保護 (OCP) または過熱 (TSD) などの障害が発生した場合、クランプは無効になります。

## 6.4 デバイスの機能モード

### 6.4.1 アクティブ モード

$V_{VM}$  電圧が  $V_{UVLO}$  電圧より大きく、 $D_{IN}$  が 0% を超えると、デバイスはアクティブ モードに移行します。 $t_{WAKE}$  時間が経過すると、デバイスは入力に応答可能になります。

#### 6.4.2 スリープモードとスタンバイモード

SLEEP は、スリープ(低消費電力)モードを有効にするために使用されます。スリープモード ( $SLEEP\_EN = 0x1$  および  $D_{IN} = 0\%$ ) では、デバイスは VM ピンから非常に低い静止電流 ( $I_{VMO}$ ) を引き込みます。これは、FET、ホールセンサ、電流センス、デジタルコア、内部レギュレータ、チャージポンプを含む内部回路を無効にすることで行われます。 $t_{WAKE}$  の間、 $D_{IN} > 0\%$  になると、デバイスはウェークアップしてアクティブ ( $STBY\_EN = 0x0$ ) またはスタンバイ ( $STBY\_EN = 0x1$ ) モードに移行します。

スリープモードが無効化されている ( $SLEEP = 0x0$ ) の場合、 $STBY\_EN$  によって  $D_{IN}$  に対するデバイスの動作が決定されます。 $D_{IN} < D_{IN0}$ かつ  $STBY\_EN = 0x0$  の場合、MC111 は DOUT0 に対応するデューティまたは速度でモーターを駆動します。 $D_{IN} < D_{IN0}$  および  $STBY\_EN = 0x1$  の場合、MC111 はモーター動作を停止 ( $DOUT = 0\%$ ) し、スタンバイ状態になります。

$SLEEP\_EN$  と  $STBY\_EN$  の値に関係なく、 $D_{IN} \geq (D_{IN0} + DHYS)$  の場合、MC111 はデューティ曲線で設定されたデューティまたは速度でモーターを駆動します。[表 6-5](#) に、スリープおよびスタンバイモードの動作を示します。

注

$D_{IN} = 0\%$  は、PWM 入力モード ( $PWM\_DC = 0x0$ ) ではデューティサイクル 0% に対応し、DC(アナログ)入力モード ( $PWM\_DC = 0x1$ ) では DC 電圧 < 100mV に対応します。

**表 6-5. スリープ/スタンバイモードの動作の概要**

| <b>SLEEP_EN</b> | <b>STBY_EN</b> | デバイスステータス変更の条件                             | デバイスステータス | <b>D<sub>OUT</sub></b>   | <b>Hプリッジ</b> |

|-----------------|----------------|--------------------------------------------|-----------|--------------------------|--------------|

| 0x0             | 0x0            | $D_{IN} < D_{IN0}$                         | アクティブモード  | DOUT0                    | PWM          |

|                 | 0x1            |                                            | スタンバイモード  | 0%                       | ハイインピーダンス    |

| X               | X              | $D_{INOFF} > D_{IN} \geq (D_{IN0} + DHYS)$ | アクティブモード  | デューティ曲線に従って $D_{IN}$ で設定 | PWM          |

| 0x1             | X              | $D_{IN} = 0\%$ 、 <a href="#">図 6-8</a> を参照 | スリープモード   | 0%                       | ハイインピーダンス    |

| 0x1             | 0x0            | $0\% < D_{IN} < D_{IN0}$                   | アクティブモード  | DOUT0                    | PWM          |

|                 | 0x1            |                                            | スタンバイモード  | 0%                       | ハイインピーダンス    |

#### 6.4.3 フォルトモード

MC111 は、[セクション 6.3.2](#) に記載されているシステム異常から保護されています。場合によっては、整流アルゴリズムが中断され、デバイスがモーターを再起動する必要があります。

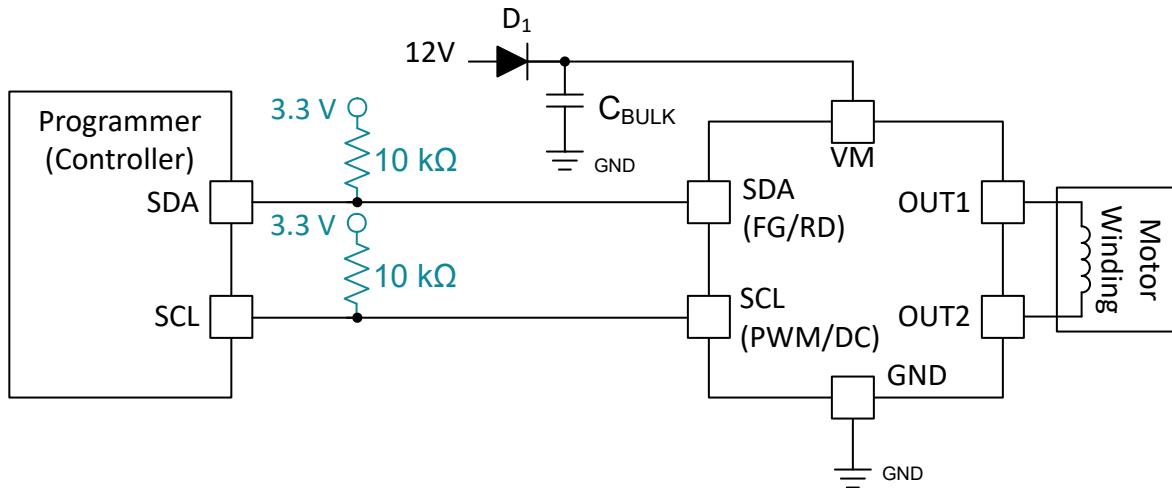

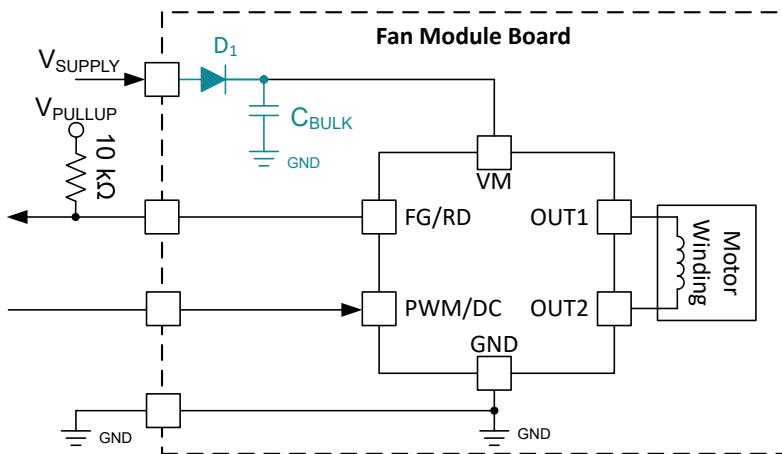

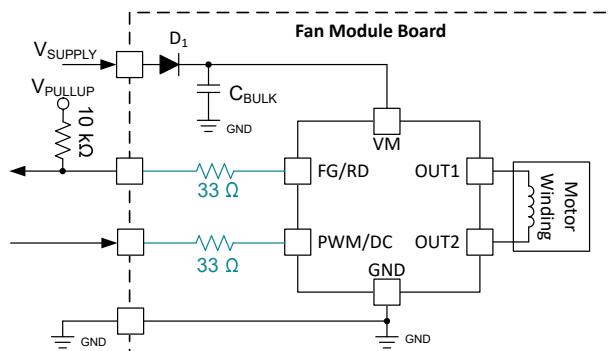

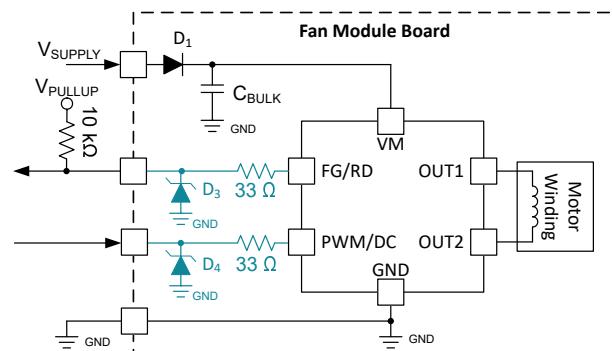

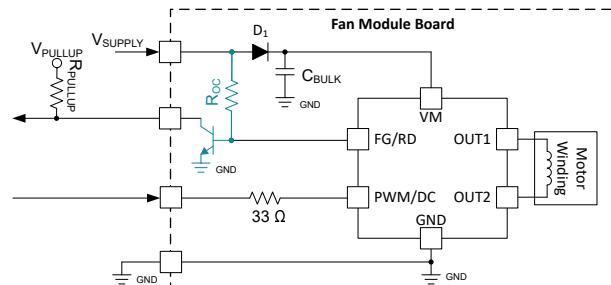

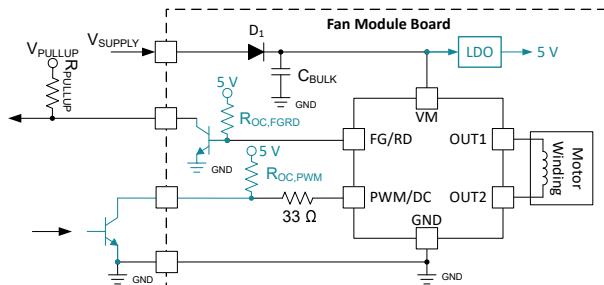

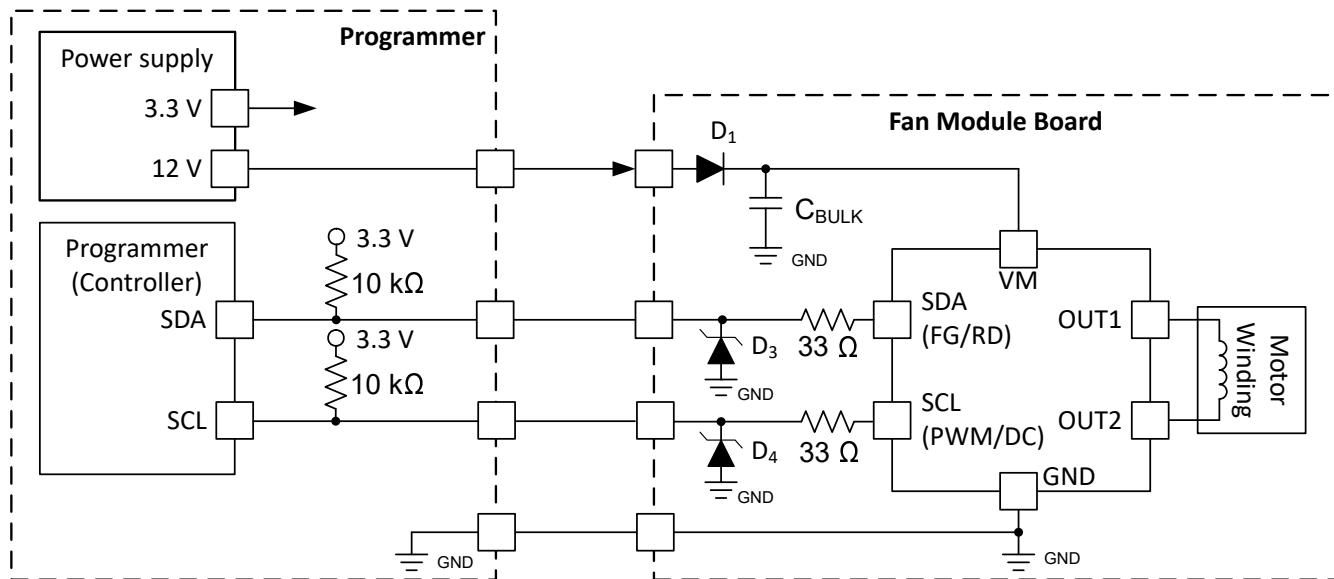

#### 6.4.4 テストモードとワンタイムプログラマブルメモリ

MC111 にはテストおよびプログラミングモードが統合されており、**PWM/DC** ピンと **FG/RD** ピンがデバイス構成とテストのための I<sup>2</sup>C インターフェイスをサポートしています。I<sup>2</sup>C インターフェイスにより、ワンタイムプログラマブル(OTP)メモリへのアクセスも可能になります。レジスタのプログラムにより、前のセクションで説明したデバイス構成が選択されます。[図 6-31](#) に、MC111 の構成とプログラミングのための基本的なハードウェア構成を示します。

図 6-31. I<sup>2</sup>C プログラマおよびファン モジュール

MC111 は、以下の手順でテストモードおよび OTP モードに移行します。

1. FG/RD ピンを Low にし、(20 ~ 80)% の範囲の任意のデューティで (416 ~ 833) kHz の範囲の高周波信号を 15 ~ 20 サイクルにわたって PWM/DC ピンに印加して、テストモードに入ります。I<sup>2</sup>C インターフェイスは、テストモードでアクティブです。

2. I<sup>2</sup>C 経由で MC111 と通信し、セクション 7 のレジスタの読み取りと書き込みを行い、レジスタを構成します。

3. I<sup>2</sup>C 通信による信頼性の高い OTP メモリプログラミングを維持するため、通信時間全体にわたって MC111 の電源ピン電圧 (VM) を 8V 以上に維持してください。

4. OTP モードのロックを解除するには、連続した書き込みフレームで、OTP モードのエントリキー 02h, 01h, 04h を USR\_OTP\_PRG\_UNLOCK レジスタに書き込みます。

5. OTP メモリを書き込むには、USR\_OTP\_CFG レジスタの USR\_OTP\_PROG\_ALL ビットに 1b を書き込みます。

## 6.5 プログラミング

MC111 は、テストモードでの I<sup>2</sup>C プログラミングをサポートしています。セクション 6.4.4 には、システムのプロトタイプ製作時や生産時にテストモードに移行し、レジスタの読み取りと書き込みを行い、OTP メモリをプログラムする方法を説明しています。外部プログラミング ハードウェアまたはオンボードのマイコンは、I<sup>2</sup>C インターフェイス経由で MC111 と接続できます。以下のセクションでは、I<sup>2</sup>C 通信プロトコルの詳細について説明します。

### 6.5.1 I<sup>2</sup>C 通信

I<sup>2</sup>C バスはデータライン (SDA) とクロックライン (SCL) で構成され、オフチップ プルアップ抵抗を備えています。バスがアイドルのときは、SDA ラインと SCL ラインの両方が High にプルされます。

通常はマイクロコントローラまたはデジタル信号プロセッサである制御装置がバスを制御します。制御装置は、SCL 信号とデバイス アドレスを生成する役割を担っています。コントローラは、データ転送の開始と停止を示す特定の条件も生成します。ペリフェラル デバイスは、コントローラ デバイスの制御下でバス上のデータを受信したり送信したりします。MC111 は、この文脈において I<sup>2</sup>C バス上のペリフェラル デバイスです。

MC111 のデバイスアドレスは 0x65 です。

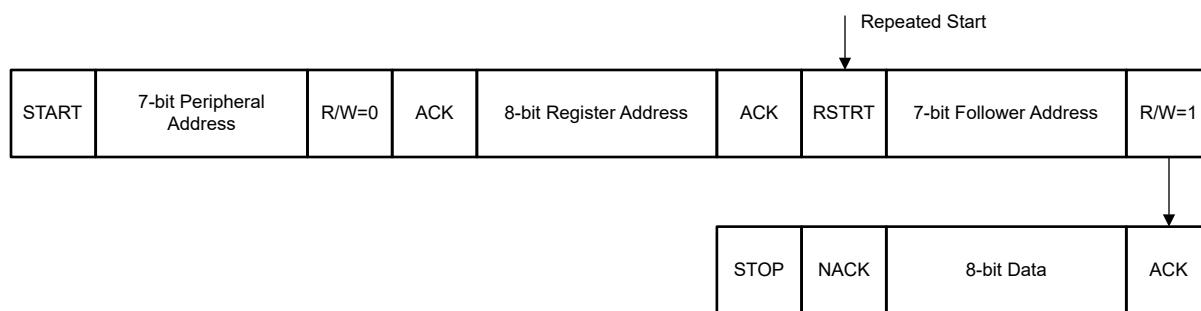

#### 6.5.1.1 I<sup>2</sup>C 読み出し

I<sup>2</sup>C 読み出し動作は、書き込み動作と同様に開始されます。コントローラ デバイスは、ペリフェラル デバイスの 7 ビットアドレスと R/W ビットを 0b に設定して、バス上に START 条件を送信します。ペリフェラル デバイスがアクノリッジ信号 (ACK) で応答した後、コントローラ デバイスは読み出し対象のレジスタの 8 ビットアドレスを送信します。ペリフェラル デ

バスが再び ACK で応答すると、コントローラ デバイスは START コマンド「RSTRT」を再送し、続いて R/W ビットを 1b としたペリフェラル アドレスを送信して読み出し動作であることを示します。コントローラ デバイスは SDA ラインを解放して、ペリフェラル デバイスからレジスタ データを読み出します。ペリフェラル デバイスは ACK 信号で応答し、レジスタ データの送信準備ができたことを示します。

コントローラ デバイスは、引き続きペリフェラル デバイスにクロック信号を供給します。ペリフェラル デバイスは、各クロックサイクルで SDA ラインに 8 ビットのレジスタ データを送信します。バイトの終わりに、コントローラ デバイスはネガティブ アクノリッジ (NACK) 信号を送信し、ペリフェラル デバイスに通信停止とバス解放を指示します。続いて、コントローラ デバイスは STOP 条件を送信します。

図 6-32. I<sup>2</sup>C 読み出しシーケンス

#### 6.5.1.2 I<sup>2</sup>C 書き込み

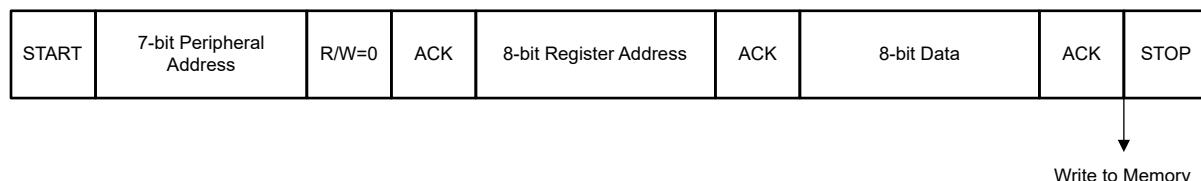

I<sup>2</sup>C バスに書き込むとき、コントローラ デバイスは、ペリフェラル デバイスの 7 ビット アドレスで START 条件をバスに送信し、R/W ビットを 0b に設定して、書き込み動作にあることを示します。ペリフェラル デバイスがアクノリッジ ビット (ACK) で応答した後、コントローラ デバイスはデータを受信するレジスタの 8 ビット アドレスを送信します。ペリフェラル デバイスが ACK ビットで再度応答した後、コントローラ デバイスは 8 ビット データを送信します。ペリフェラル デバイスは最後の ACK ビットで応答し、コントローラ は STOP 条件で転送を終了します。

図 6-33. I<sup>2</sup>C 書き込みシーケンス

## 7 レジスタ マップ

表 7-1 は、MC111 の I<sup>2</sup>C テスト モードでアクセス可能なワンタイム プログラマブル メモリ (OTP) およびテスト モードのレジスタ マップを示します。USER OTP マップ (アドレス 0x00 ~ 0x1B) には、エンド システム製造時のデバイス プログラミングで使用できる OTP レジスタが含まれています。USR TM レジスタ マップ (アドレス 0x20 ~ 0x26) では、システム設計者がシステムのプロトタイプ製作や開発中にデバイス設定を試せるよう、テスト モード構成を提供しています。書き込み済み OTP レジスタは、パワー サイクル後も書き込まれたデータを保持します。OTP 書き込み後、レジスタはテスト モードで新しいデータを受信できますが、デバイスのパワー サイクル時には、書き込まれた OTP 値がデフォルトとして使用されます。テスト モード レジスタ USR TM は OTP メモリ レジスタではなく、パワー サイクル時にリセットされます。

## 7.1 USR\_OTP レジスタ

表 7-1 に、USR\_OTP レジスタのメモリ マップト レジスタを示します。表 7-1 にないレジスタ オフセット アドレスはすべて予約済みと見なして、レジスタの内容は変更しないでください。

**表 7-1. USR\_OTP レジスタ**

| オフセット | 略称                  | レジスタ名                                                 | セクション        |

|-------|---------------------|-------------------------------------------------------|--------------|

| 0h    | INTERFACE_CONFIG0   | インターフェイス構成レジスタ 0                                      | セクション 7.1.1  |

| 1h    | INTERFACE_CONFIG1   | インターフェイス構成レジスタ 1                                      | セクション 7.1.2  |

| 2h    | START_STOP_CONFIG   | 開始および停止構成レジスタ                                         | セクション 7.1.3  |

| 3h    | DINO                | DINO の設定                                              | セクション 7.1.4  |

| 4h    | DOUT0               | DOUT0 の設定                                             | セクション 7.1.5  |

| 5h    | DOUT1               | DOUT1 の設定                                             | セクション 7.1.6  |

| 6h    | DOUT2               | DOUT2 の設定                                             | セクション 7.1.7  |

| 7h    | DOUT3               | DOUT3 の設定                                             | セクション 7.1.8  |

| 8h    | DOUT4               | DOUT4 の設定                                             | セクション 7.1.9  |

| 9h    | DOUT5               | DOUT5 の設定                                             | セクション 7.1.10 |

| Ah    | DOUT6               | DOUT6 の設定                                             | セクション 7.1.11 |

| Bh    | DOUT7               | DOUT7 の設定                                             | セクション 7.1.12 |

| Ch    | DOUT8               | DOUT8 の設定                                             | セクション 7.1.13 |

| Dh    | HALL_TIME_CONFIG    | ホール オフセット時間の構成レジスタ                                    | セクション 7.1.14 |

| Eh    | COMMUTATION_CONFIG0 | 整流構成レジスタ 0                                            | セクション 7.1.15 |

| Fh    | COMMUTATION_CONFIG1 | 整流構成レジスタ 1                                            | セクション 7.1.16 |

| 10h   | COMMUTATION_CONFIG2 | 整流構成レジスタ 2                                            | セクション 7.1.17 |

| 11h   | COMMUTATION_CONFIG3 | 整流構成レジスタ 3                                            | セクション 7.1.18 |

| 12h   | PROTECTION_CONFIG0  | 保護設定の構成レジスタ                                           | セクション 7.1.19 |

| 13h   | CLOSED_LOOP_CONFIG0 | MAX_SPEED の最下位バイト                                     | セクション 7.1.20 |

| 14h   | CLOSED_LOOP_CONFIG1 | 閉ループでの MAX_SPEED の KI_RATIO と MSN、および 開ループでの DOUT_MAX | セクション 7.1.21 |

| 15h   | CLOSED_LOOP_CONFIG2 | 閉ループでの KP_RATIO と LRD 設定                              | セクション 7.1.22 |

| 16h   | PROTECTION_CONFIG1  | 保護および PWM ディザリング用レジスタ                                 | セクション 7.1.23 |

| 17h   | GENERAL_CONFIG1     | ILIM_SEL、ホール、LRD 設定用レジスタ                              | セクション 7.1.24 |

| 18h   | GENERAL_CONFIG2     | VM クランプ、プリスタートランプ、ホール設定用レジスタ                          | セクション 7.1.25 |

| 19h   | GENERAL_CONFIG3     | サイレンス、極ペア、LRD 設定用レジスタ                                 | セクション 7.1.26 |

| 1Ah   | GENERAL_CONFIG4     | DEMAG およびサイレンス設定用構成レジスタ                               | セクション 7.1.27 |

| 1Bh   | USR_OTP_CRC         | USR_OTP に対して計算された CRC 用レジスタ                           | セクション 7.1.28 |

表の小さなセルに収まるように、複雑なビット アクセス タイプを記号で表記しています。表 7-2 に、このセクションでアクセス タイプに使用しているコードを示します。

**表 7-2. USR\_OTP アクセス タイプ コード**

| アクセス タイプ      | コード | 説明   |

|---------------|-----|------|

| 読み取りタイプ       |     |      |

| R             | R   | 読み出し |

| 書き込みタイプ       |     |      |

| W             | W   | 書き込み |

| リセットまたはデフォルト値 |     |      |

表 7-2. USR\_OTP アクセス タイプ コード (続き)

| アクセス タイプ | コード | 説明               |

|----------|-----|------------------|

| -n       |     | リセット後の値またはデフォルト値 |

### 7.1.1 INTERFACE\_CONFIG0 レジスタ (オフセット = 0h) [リセット = 00h]

INTERFACE\_CONFIG0 を表 7-3 に示します。

概略表に戻ります。

表 7-3. INTERFACE\_CONFIG0 レジスタのフィールドの説明

| ピット | フィールド             | タイプ | リセット | 説明                                                                                                                                                                                                      |

|-----|-------------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | HALL_DEGLITCH_EN  | R/W | 0h   | ホール センサからのホール信号のグリッチ除去を有効化します<br>0h = ホール グリッチ除去の無効化<br>1h = ホール グリッチ除去の有効化                                                                                                                             |

| 6   | PWM_IN_RANGE      | R/W | 0h   | 入力 PWM 信号の周波数検出範囲を選択します<br>0h = 80Hz~90kHz<br>1h = 20Hz~22kHz                                                                                                                                           |

| 5   | PWM_OUT_FREQ      | R/W | 0h   | OUTx の PWM スイッチング周波数を選択します<br>0h = 出力 PWM 周波数 25kHz<br>1h = 出力 PWM 周波数 50kHz                                                                                                                            |

| 4-3 | ILIM_BLANK_SEL    | R/W | 0h   | デッドタイムとデフォルトのブランкиングに加えて、電流制限 (ILIM) の追加のブランкиング時間を選択します<br>0h = 追加のブランкиングなし<br>1h = 160ns (公称) の追加ブランкиング<br>2h = 320ns の追加 ILIM ブランкиング<br>3h = 640ns の追加 ILIM ブランкиング                               |

| 2   | ILIM_DEGLITCH_SEL | R/W | 0h   | サイクル単位の電流制限 (ILIMIT) のグリッチ除去時間を選択します。<br>0h = 481ns ~ 732ns のグリッチ除去時間<br>1h = 925ns ~ 1.419us のグリッチ除去時間                                                                                                 |

| 1-0 | UVLO_SEL          | R/W | 0h   | UVLO がトリガされるスレッショルドを選択します<br>0h = 立ち上がりスレッショルド 3V、立ち下がりスレッショルド 2.7V<br>1h = 立ち上がりスレッショルド 4.2V、立ち下がりスレッショルド 2.7V<br>2h = 立ち上がりスレッショルド 5.7V、立ち下がりスレッショルド 2.7V<br>3h = 立ち上がりスレッショルド 7.6V、立ち下がりスレッショルド 2.7V |

### 7.1.2 INTERFACE\_CONFIG1 レジスタ (オフセット = 1h) [リセット = 60h]

INTERFACE\_CONFIG1 を表 7-4 に示します。

概略表に戻ります。