## OPA818 2.7GHz 高電圧、FET 入力、低ノイズオペアンプ

### 1 特長

- ・ 高速度:

- ゲイン帯域幅積 (GBWP): 2.7GHz

- 帯域幅 ( $G = 7V/V$ ): 765MHz

- 大信号帯域幅 ( $2V_{PP}$ ): 400MHz

- スルーレート: 1400V/ $\mu$ s

- ・ 非補償型ゲイン: 7V/V で安定

- ・ 低ノイズ:

- 入力電圧ノイズ: 2.2nV/ $\sqrt{Hz}$

- 入力電流ノイズ: 3fA/ $\sqrt{Hz}$  ( $f = 10kHz$ )

- ・ 入力バイアス電流: 4pA (標準値)

- ・ 低入力容量:

- 同相: 1.9pF

- 差動モード: 0.5pF

- ・ 低歪み ( $G = 7V/V$ ,  $R_L = 1k\Omega$ ,  $V_O = 2V_{PP}$ ):

- 1MHz での HD2, HD3: -104dBc, -108dBc

- 50MHz での HD2, HD3: -57dBc, -72dBc

- ・ 幅広い電源電圧範囲: 6V ~ 13V

- ・ 出力スイング: 8V<sub>PP</sub> ( $V_S = 10V$ )

- ・ 消費電流: 27.7mA

- ・ シャットダウン時の電源電流: 27 $\mu$ A

- ・ **OPA657** の性能アップグレード版

### 2 アプリケーション

- ・ 広帯域のトランシンピーダンスアンプ (TIA)

- ・ ウエハー スキャン機器

- ・ 光通信モジュール

- ・ 高速データ アクイジション (DAQ)

- ・ アクティブ プローブ

- ・ 光時間領域反射測定法 (OTDR)

- ・ テストおよび測定機器のフロントエンド

- ・ 医療用および化学用分析器

### 3 説明

OPA818 は、高速、高精度、広いダイナミック レンジのアプリケーションに適した非補償型電圧帰還オペアンプで

す。OPA818 は、広いゲイン帯域幅と 6V ~ 13V の広い電源電圧範囲を兼ね備えた低ノイズの JFET 入力段を備えています。高速スルーレート (1400V/ $\mu$ s) により、高い大信号帯域幅と低歪みを実現できます。このアンプは、TI 独自の高速、シリコン ゲルマニウム (SiGe) プロセスで製造されており、他の高速 FET 入力アンプと比較して大幅な性能向上を達成しています。

OPA818 は非常に多用途で広帯域 TIA フォトダイオードアンプで、光テストおよび通信機器、さらに多くの医療用、科学用、産業用機器に使用されています。OPA818 に、2.7GHz GBWP、2.4pF の低い合計入力容量、2.2nV/ $\sqrt{Hz}$  の入力ノイズを示します。OPA818 は、出力スイングが広い 20k $\Omega$  TIA ゲイン ( $R_F$ ) および 0.5pF のフォトダイオード容量 ( $C_D$ ) により、TIA 構成で 85MHz 信号帯域幅以上を実現します。入力バイアス電流がピコアンペア単位の低ノイズ アーキテクチャは、テストおよび測定アプリケーションにも最適です。通常は 7V/V 以上のゲインで安定しますが、OPA818 はノイズ ゲイン シェーピング手法を適用することで、より低いゲインのアプリケーションでも使用できるように設計されています。

OPA818 は、放熱用の露出サーマル パッドが付いた 5 ピン SOT-23 パッケージおよび 8 リードの WSON パッケージで供給されます。このデバイスは、産業用温度範囲の -40°C ~ +85°C で動作が規定されています。

#### パッケージ情報

| 部品番号 <sup>(1)</sup> | パッケージ <sup>(2)</sup> | パッケージ サイズ <sup>(3)</sup> |

|---------------------|----------------------|--------------------------|

| OPA818              | DRG (WSON, 8)        | 3mm × 3mm                |

|                     | DBV (SOT-23, 5)      | 2.9mm × 2.8mm            |

(1) [セクション 4](#) を参照してください。

(2) 詳細については、[セクション 11](#) を参照してください。

(3) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

## 高速光フロント エンド

## 目次

|                           |           |                               |           |

|---------------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>               | <b>1</b>  | 7.4 デバイスの機能モード                | <b>21</b> |

| <b>2 アプリケーション</b>         | <b>1</b>  | <b>8 アプリケーションと実装</b>          | <b>22</b> |

| <b>3 説明</b>               | <b>1</b>  | 8.1 アプリケーション情報                | <b>22</b> |

| <b>4 デバイス比較表</b>          | <b>3</b>  | 8.2 代表的なアプリケーション              | <b>24</b> |

| <b>5 ピン構成および機能</b>        | <b>4</b>  | 8.3 電源に関する推奨事項                | <b>27</b> |

| <b>6 仕様</b>               | <b>5</b>  | 8.4 レイアウト                     | <b>27</b> |

| 6.1 絶対最大定格                | <b>5</b>  | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>30</b> |

| 6.2 ESD 定格                | <b>5</b>  | 9.1 デバイス サポート                 | <b>30</b> |

| 6.3 推奨動作条件                | <b>5</b>  | 9.2 ドキュメントのサポート               | <b>30</b> |

| 6.4 熱に関する情報               | <b>5</b>  | 9.3 ドキュメントの更新通知を受け取る方法        | <b>30</b> |

| 6.5 電気的特性                 | <b>7</b>  | 9.4 サポート・リソース                 | <b>30</b> |

| 6.6 代表的特性: $V_S = \pm 5V$ | <b>10</b> | 9.5 商標                        | <b>30</b> |

| 6.7 代表的特性: $V_S = 6V$     | <b>17</b> | 9.6 静電気放電に関する注意事項             | <b>30</b> |

| <b>7 詳細説明</b>             | <b>18</b> | 9.7 用語集                       | <b>30</b> |

| 7.1 概要                    | <b>18</b> | <b>10 改訂履歴</b>                | <b>30</b> |

| 7.2 機能ブロック図               | <b>18</b> | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>31</b> |

| 7.3 機能説明                  | <b>18</b> |                               |           |

## 4 デバイス比較表

| デバイス                   | $V_S$ (V) | 帯域幅 (MHz)    | 入力   | スルーレート (V/μs) | 電圧ノイズ (nV/√Hz) | 最小安定ゲイン (V/V) |

|------------------------|-----------|--------------|------|---------------|----------------|---------------|

| OPA818                 | $\pm 6.5$ | 2700         | FET  | 1400          | 2.2            | 7             |

| OPA657                 | $\pm 5$   | 1600         | FET  | 700           | 4.8            | 7             |

| OPA656                 | $\pm 5$   | 230          | FET  | 290           | 7              | 1             |

| OPA659                 | $\pm 6$   | 350          | FET  | 2550          | 8.9            | 1             |

| LMH6629 <sup>(1)</sup> | $\pm 2.5$ | 800 または 4000 | BJT  | 530 または 1600  | 0.69           | 4 または 10      |

| OPA858                 | $\pm 2.5$ | 5500         | CMOS | 2000          | 2.5            | 7             |

| THS4631                | $\pm 15$  | 210          | FET  | 1000          | 7              | 1             |

(1) ピンで選択可能な補償。

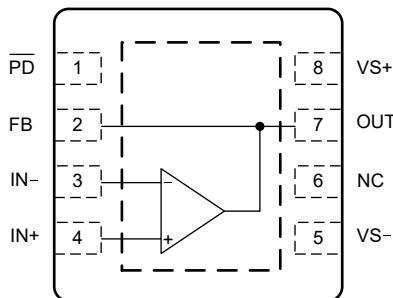

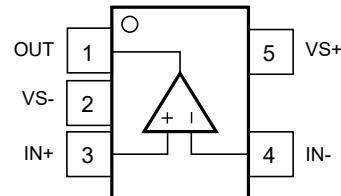

## 5 ピン構成および機能

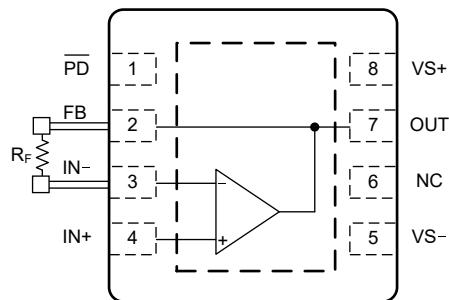

図 5-1. DRG パッケージ、8 ピン WSON (サーマル パッド付き) (上面図)

図 5-2. DBV パッケージ、5 ピン SOT-23 (上面図)

表 5-1. ピンの機能

| 名称       | ピン            |                 | タイプ | 説明                                                                                            |

|----------|---------------|-----------------|-----|-----------------------------------------------------------------------------------------------|

|          | DRG<br>(WSON) | DBV<br>(SOT-23) |     |                                                                                               |

| FB       | 2             | —               | 出力  | 帰還抵抗接続 (オプション)                                                                                |

| IN-      | 3             | 4               | 入力  | 反転入力                                                                                          |

| IN+      | 4             | 3               | 入力  | 非反転入力                                                                                         |

| NC       | 6             | —               | —   | 未接続 (ダイへの内部接続なし)                                                                              |

| OUT      | 7             | 1               | 出力  | アンプの出力                                                                                        |

| PD       | 1             | —               | 入力  | パワーダウン (Low = イネーブル、High = ディスエーブル)。内部 $1M\Omega$ プルアップにより、このピンをフローティングにできます。                 |

| VS-      | 5             | 2               | 電源  | 負電源                                                                                           |

| VS+      | 8             | 5               | 電源  | 正電源                                                                                           |

| サーマル パッド | サーマル パッド      | —               | —   | ダイのサブストレートから電気的に絶縁されていますが、ESD ダイオードはサーマル パッドにダウンボンディングされています。熱拡散プレーン (通常はグランド) に接続することを推奨します。 |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                |                                  | 最小値            | 最大値            | 単位 |

|----------------|----------------------------------|----------------|----------------|----|

| $V_S$          | 電源電圧、( $V_{S+}$ ) – ( $V_{S-}$ ) |                | 13.5           | V  |

| $V_{IN, Diff}$ | 差動入力電圧                           |                | $\pm 5$        | V  |

| $V_{CM}$       | 同相入力電圧                           | $V_{S-} - 0.5$ | $V_{S-} + 10$  | V  |

| $V_O$          | 出力電圧                             | $V_{S-} - 0.5$ | $V_{S+} + 0.5$ | V  |

| $I_I$          | 連続入力電流                           |                | $\pm 10$       | mA |

| $I_O$          | 連続出力電流 <sup>(2)</sup>            |                | 25             | mA |

|                | フィードバックピンの連続電流 <sup>(2)</sup>    |                | 13             | mA |

| $T_J$          | 接合部温度                            |                | 125            | °C |

| $T_A$          | 外気温度での動作時                        | -40            | 85             | °C |

| $T_{stg}$      | 保存温度                             | -65            | 150            | °C |

- (1) 「絶対最大定格」の範囲を超える動作は、デバイスに永続的な損傷を与える可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内で、一時的に「推奨動作条件」の範囲を超えた動作をさせる場合、必ずしもデバイスが損傷を受けるものではありませんが、完全には機能しない可能性があります。この方法でデバイスを動作させると、デバイスの信頼性、機能性、性能に影響を及ぼし、デバイスの寿命が短くなります。

- (2) エレクトロマイグレーションを制限するための長期的な連続電流。

### 6.2 ESD 定格

|             |      |                                                                  | 値          | 単位 |

|-------------|------|------------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | $\pm 2500$ | V  |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | $\pm 1000$ |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|       |        | 最小値 | 公称値 | 最大値 | 単位 |

|-------|--------|-----|-----|-----|----|

| $V_S$ | 単一電源電圧 | 6   | 10  | 13  | V  |

| $T_A$ | 周囲温度   | -40 | 25  | 85  | °C |

### 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     | OPA818       |      | 単位   |  |

|-----------------------------|---------------------|--------------|------|------|--|

|                             |                     | DBV (SOT-23) |      |      |  |

|                             |                     | 5 ピン         | 8 ピン |      |  |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 172          | 54.6 | °C/W |  |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 | 71.1         | 56.0 | °C/W |  |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        | 42.0         | 27.2 | °C/W |  |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 11.5         | 1.8  | °C/W |  |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 41.6         | 27.2 | °C/W |  |

| 熱評価基準 <sup>(1)</sup> |                | OPA818       |           | 単位   |

|----------------------|----------------|--------------|-----------|------|

|                      |                | DBV (SOT-23) | DRG (SON) |      |

|                      |                | 5 ピン         | 8 ピン      |      |

| 接合部からケース (底面) への熱抵抗  | $R_{θJC(bot)}$ | 該当なし         | 11.1      | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 6.5 電気的特性

$T_A \approx 25^\circ\text{C}$  の場合、 $V_{S+} = +5\text{V}$ 、 $V_{S-} = -5\text{V}$ 、閉ループゲイン ( $G$ ) = 7V/V、同相電圧 ( $V_{CM}$ ) = 中電圧、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧へ (特に記述のない限り)

| パラメータ        |                              | テスト条件                                                                              | 最小値                                       | 標準値        | 最大値        | 単位                           |

|--------------|------------------------------|------------------------------------------------------------------------------------|-------------------------------------------|------------|------------|------------------------------|

| <b>AC 特性</b> |                              |                                                                                    |                                           |            |            |                              |

| SSBW         | 小信号帯域幅                       | $V_O = 100\text{mV}_{PP}$                                                          | 765                                       | MHz        | 430        |                              |

|              |                              | $G = 10, V_O = 100\text{ mV}_{PP}$                                                 |                                           |            |            |                              |

|              | 周波数応答ピーク                     |                                                                                    | 1.4                                       |            |            | dB                           |

| LSBW         | 大信号帯域幅                       | $V_O = 2\text{V}_{PP}$                                                             | 400                                       |            |            | MHz                          |

| GBWP         | ゲイン帯域幅積                      | $G = 101\text{V/V}, V_O = 100\text{mV}_{PP}, R_F = 3.01\text{k}\Omega$             | 2700                                      |            |            | MHz                          |

|              | 0.1dB の平坦度に対する帯域幅            | $V_O = 100\text{mV}_{PP}$                                                          | 100                                       |            |            | MHz                          |

| SR           | スルーレート (20%-80%)             | $V_O = 4\text{V}$ ステップ、立ち上がりおよび立ち下がり                                               | 1400                                      | V/μs       | 1340       |                              |

|              |                              | $V_O = 4\text{V}$ ステップ、立ち上がりおよび立ち下がり、 $G = 10$                                     |                                           |            |            |                              |

| $t_r/t_f$    | 立ち上がり / 立ち下がり時間 (10% ~ 90%)  | $V_O = 100\text{mV}$ ステップ                                                          | 0.52                                      |            |            | ns                           |

| $t_S$        | セトリングタイム                     | $V_O = 2\text{V}$ ステップ、0.1% ~                                                      | 5.7                                       |            |            | ns                           |

|              | オーバーシュートとアンダーシュート            | $V_O = 2\text{V}$ ステップ                                                             | 7                                         |            |            | %                            |

|              | オーバードライブの復帰時間                | $V_O = (V_{S-} - 1\text{V}) \sim (V_{S+} + 1\text{V})$                             | 25                                        |            |            | ns                           |

| HD2          | 2 次高調波歪                      | $V_O = 2\text{V}_{PP}$                                                             | $f = 1\text{MHz}$                         | -84        | dBc        |                              |

|              |                              |                                                                                    | $f = 10\text{MHz}$                        | -64        |            |                              |

|              |                              |                                                                                    | $f = 50\text{MHz}$                        | -52        |            |                              |

|              |                              |                                                                                    | $f = 10\text{MHz}, R_L = 1\text{k}\Omega$ | -71        |            |                              |

| HD3          | 3 次高調波歪                      | $V_O = 2\text{V}_{PP}$                                                             | $f = 1\text{MHz}$                         | -106       | dBc        |                              |

|              |                              |                                                                                    | $f = 10\text{MHz}, \text{DRG パッケージ}$      | -99        |            |                              |

|              |                              |                                                                                    | $f = 10\text{MHz}, \text{DBV パッケージ}$      | -95        |            |                              |

|              |                              |                                                                                    | $f = 50\text{MHz}$                        | -74        |            |                              |

|              |                              |                                                                                    | $f = 10\text{MHz}, R_L = 1\text{k}\Omega$ | -82        |            |                              |

| $e_n$        | 入力電圧ノイズ                      | $f \geq 150\text{kHz}$                                                             | 2.2                                       |            |            | $\text{nV}/\sqrt{\text{Hz}}$ |

|              |                              | 1/f コーナー                                                                           | 15                                        |            |            | kHz                          |

| $i_n$        | 入力電流ノイズ                      | $f = 10\text{kHz}$                                                                 | 3                                         |            |            | $\text{fA}/\sqrt{\text{Hz}}$ |

|              |                              | $f = 1\text{MHz}$                                                                  | 145                                       |            |            |                              |

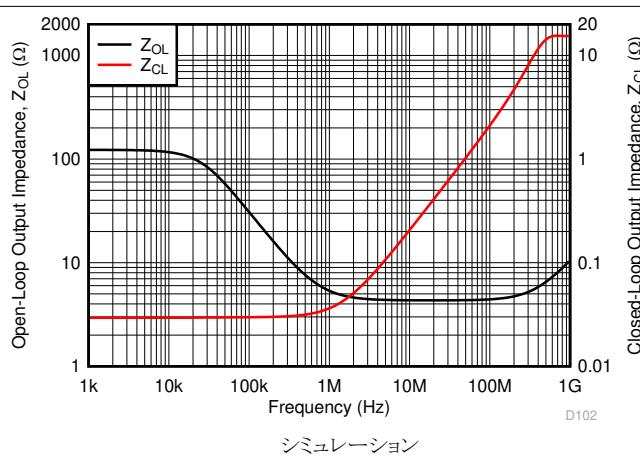

| $Z_{CL}$     | 閉ループ出力インピーダンス                | $f = 10\text{MHz}$                                                                 | 0.2                                       |            |            | $\Omega$                     |

| <b>DC 特性</b> |                              |                                                                                    |                                           |            |            |                              |

| $A_{OL}$     | 開ループ電圧ゲイン                    | $f = dc, V_O = \pm 2\text{V}$                                                      | 85                                        | 92         |            | dB                           |

| $V_{OS}$     | 入力オフセット電圧                    |                                                                                    |                                           | $\pm 0.35$ | $\pm 1.25$ | mV                           |

|              |                              | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                   |                                           |            | $\pm 1.8$  |                              |

|              | 入力オフセット電圧ドリフト <sup>(1)</sup> | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                   |                                           | $\pm 3$    | $\pm 20$   | $\mu\text{V}/^\circ\text{C}$ |

| $I_B$        | 入力バイアス電流 <sup>(2)</sup>      |                                                                                    |                                           | $\pm 4$    | $\pm 25$   | pA                           |

|              |                              | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                   |                                           |            | 700        |                              |

| $I_{OS}$     | 入力オフセット電流 <sup>(2)</sup>     |                                                                                    |                                           | $\pm 1$    | $\pm 25$   | pA                           |

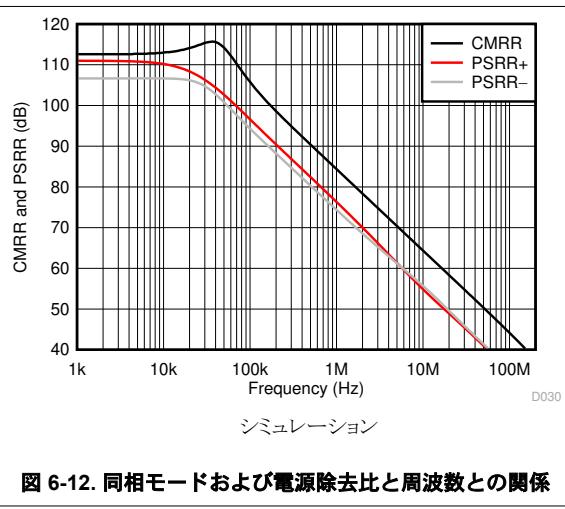

| CMRR         | 同相除去比                        | $f = dc, V_{CM} = \pm 0.5\text{V}$                                                 | 73                                        | 90         |            | dB                           |

|              |                              | $f = dc, V_{CM} = \pm 0.5\text{V}, T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$ | 70                                        |            |            |                              |

## 6.5 電気的特性 (続き)

$T_A \approx 25^\circ\text{C}$  の場合、 $V_{S+} = +5\text{V}$ 、 $V_{S-} = -5\text{V}$ 、閉ループゲイン ( $G$ ) = 7V/V、同相電圧 ( $V_{CM}$ ) = 中電圧、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧へ (特に記述のない限り)

| パラメータ         |                                           | テスト条件                                                                                                                                                                | 最小値                                | 標準値            | 最大値                                  | 単位       |  |

|---------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|--------------------------------------|----------|--|

|               | 内部帰還パターン抵抗                                | DRG パッケージのみ、デバイスはオフ、OUT から FB ピンへの抵抗                                                                                                                                 | 0.8                                | 1.2            | 1.7                                  | $\Omega$ |  |

| <b>入力</b>     |                                           |                                                                                                                                                                      |                                    |                |                                      |          |  |

|               | 同相入力インピーダンス                               |                                                                                                                                                                      | $500 \parallel 1.9$                |                | $\text{G}\Omega \parallel \text{pF}$ |          |  |

|               | 差動入力インピーダンス                               |                                                                                                                                                                      | $500 \parallel 0.5$                |                | $\text{G}\Omega \parallel \text{pF}$ |          |  |

|               | 最も正の入力電圧 <sup>(3)</sup>                   |                                                                                                                                                                      | $V_{S+} - 3.6$                     | $V_{S+} - 3.2$ | V                                    |          |  |

|               | 最大の負入力電圧 <sup>(3)</sup>                   |                                                                                                                                                                      | $V_{S-} - V_{S+} + 0.25$           |                | V                                    |          |  |

|               | 最大の正入力電圧での $\Delta V_{OS}$ <sup>(4)</sup> | $V_{CM} = V_{S+} - 3.6\text{V}$                                                                                                                                      | $\pm 0.03$                         |                | $\pm 1$                              | mV       |  |

|               |                                           | $V_{CM} = V_{S+} - 3.6\text{V}, T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                      | $\pm 1.5$                          |                |                                      |          |  |

|               | 最大の負入力電圧での $\Delta V_{OS}$ <sup>(4)</sup> | $V_{CM} = V_{S-} + 0.25\text{V}$                                                                                                                                     | $\pm 0.23$                         |                | $\pm 1$                              | mV       |  |

|               |                                           | $V_{CM} = V_{S-} + 0.25\text{V}, T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                     | $\pm 1.5$                          |                |                                      |          |  |

| <b>出力</b>     |                                           |                                                                                                                                                                      |                                    |                |                                      |          |  |

| $V_{OH}$      | 出力電圧スイング High                             |                                                                                                                                                                      | $V_{S+} - 1.2$                     | $V_{S+} - 1$   | V                                    |          |  |

|               |                                           | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                                                     | $V_{S+} - 1.3$                     |                |                                      |          |  |

|               |                                           | $R_L = 1\text{k}\Omega$                                                                                                                                              | $V_{S+} - 1$                       | $V_{S+} - 0.9$ |                                      |          |  |

|               |                                           | $R_L = 1\text{k}\Omega, T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                              | $V_{S+} - 1.2$                     |                |                                      |          |  |

| $V_{OL}$      | 出力電圧スイング Low                              |                                                                                                                                                                      | $V_{S-} + 1.2 \quad V_{S-} + 1.33$ |                | V                                    |          |  |

|               |                                           | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                                                     | $V_{S-} + 1.4$                     |                |                                      |          |  |

|               |                                           | $R_L = 1\text{k}\Omega$                                                                                                                                              | $V_{S-} + 1.1$                     | $V_{S-} + 1.2$ |                                      |          |  |

|               |                                           | $R_L = 1\text{k}\Omega, T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                              | $V_{S-} + 1.3$                     |                |                                      |          |  |

| $I_{O\_MAX}$  | リニア出力駆動                                   | $V_O = \pm 2.75\text{V}, R_L$ から中電圧 = $50\Omega$ 、<br>[無負荷 $V_{OS}$ からの $\Delta V_{OS}$ ] $\leq \pm 1\text{mV}$                                                      | $\pm 55$                           |                | mA                                   |          |  |

|               |                                           | $V_O = \pm 2.5\text{V}, R_L$ から中電圧 = $50\Omega$ 、<br>[無負荷 $V_{OS}$ からの $\Delta V_{OS}$ ] $\leq \pm 1\text{mV}$ 、<br>$T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$ | $\pm 50$                           |                |                                      |          |  |

| $I_{SC}$      | 出力短絡電流                                    |                                                                                                                                                                      | $\pm 110$                          |                | mA                                   |          |  |

| <b>電源</b>     |                                           |                                                                                                                                                                      |                                    |                |                                      |          |  |

| $V_S$         | 単一電源動作範囲                                  |                                                                                                                                                                      | 6                                  | 10             | 13                                   | V        |  |

| $I_Q$         | 静止電流 (チャネルあたり)                            | 無負荷                                                                                                                                                                  | 26.5                               | 27.7           | 29                                   | mA       |  |

|               |                                           | 無負荷、 $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                                                | 23                                 | $31.5$         |                                      |          |  |

| $I_Q$         | ドリフト                                      | 無負荷、 $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                                                | $42$                               |                | $\mu\text{V}/^\circ\text{C}$         |          |  |

| $PSRR+$       | 正の電源除去比                                   | $\Delta V_{S+} = \pm 0.25\text{V}$                                                                                                                                   | 75                                 | 95             | dB                                   |          |  |

|               |                                           | $\Delta V_{S+} = \pm 0.25\text{V}, T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                   | 70                                 |                |                                      |          |  |

| $PSRR-$       | 負の電源除去比                                   | $\Delta V_{S-} = \pm 0.25\text{V}$                                                                                                                                   | 80                                 | 94             | dB                                   |          |  |

|               |                                           | $\Delta V_{S-} = \pm 0.25\text{V}, T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                   | 74                                 |                |                                      |          |  |

| <b>パワーダウン</b> |                                           |                                                                                                                                                                      |                                    |                |                                      |          |  |

| $V_{TH\_EN}$  | 電圧スレッショルド有効化                              | $\overline{PD} > V_{TH\_EN}$ 時にパワーオン、無負荷                                                                                                                             | $V_{S+} - 1$                       | V              |                                      |          |  |

| $V_{TH\_DIS}$ | 電圧スレッショルド無効化                              | $\overline{PD} < V_{TH\_DIS}$ 時にパワーダウン、無負荷                                                                                                                           | $V_{S+} - 3$                       |                | V                                    |          |  |

|               | パワーダウン $I_Q (V_{S+})$                     | 無負荷                                                                                                                                                                  | $27 \quad 40$                      |                | $\mu\text{A}$                        |          |  |

|               | $\overline{PD}$ ピンのバイアス電流 <sup>(2)</sup>  | 無負荷、 $\overline{PD} = V_{S+}$                                                                                                                                        | -3                                 | -2             | $\mu\text{A}$                        |          |  |

|               |                                           | 無負荷、 $\overline{PD} = V_{S-}$                                                                                                                                        | $13 \quad 20$                      |                |                                      |          |  |

|               | ターンオン時間の遅延                                |                                                                                                                                                                      | $125$                              |                | ns                                   |          |  |

## 6.5 電気的特性 (続き)

$T_A \approx 25^\circ\text{C}$  の場合、 $V_{S+} = +5\text{V}$ 、 $V_{S-} = -5\text{V}$ 、閉ループ ゲイン ( $G$ ) = 7V/V、同相電圧 ( $V_{CM}$ ) = 中電圧、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧へ (特に記述のない限り)

| パラメータ      | テスト条件 | 最小値 | 標準値 | 最大値 | 単位 |

|------------|-------|-----|-----|-----|----|

| ターンオフ時間の遅延 |       |     | 170 |     | ns |

(1) 入力オフセット電圧ドリフト、入力バイアス電流ドリフトは、エンドポイントでデータを取得し、差動を計算し、温度範囲で割って計算されます。

(2) ピンから流れ出す方向の電流を正とみなします。 $I_{OS} = I_{B+} - I_{B-}$ 。

(3) 最大正 / 負入力電圧仕様での  $\Delta V_{OS}$  による定義

(4) 0V  $|V_{CM}|$  での規定  $V_{CM} - V_{OS}$  での  $\Delta V_{OS} = |V_{OS}|$

## 6.6 代表的特性 : $V_S = \pm 5V$

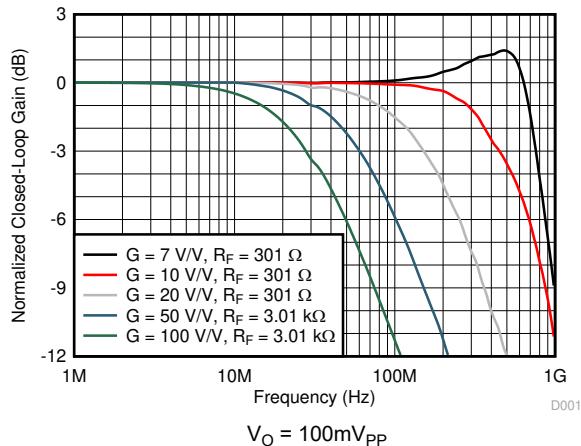

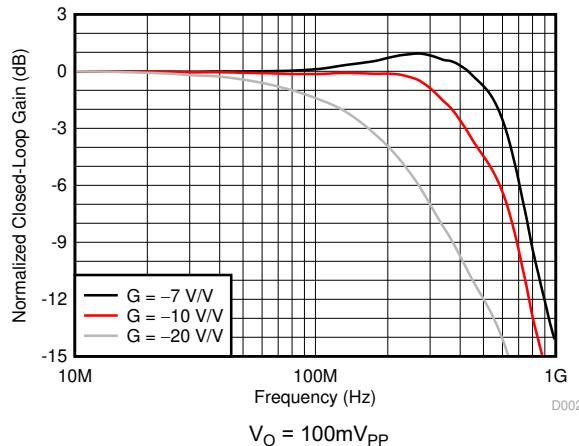

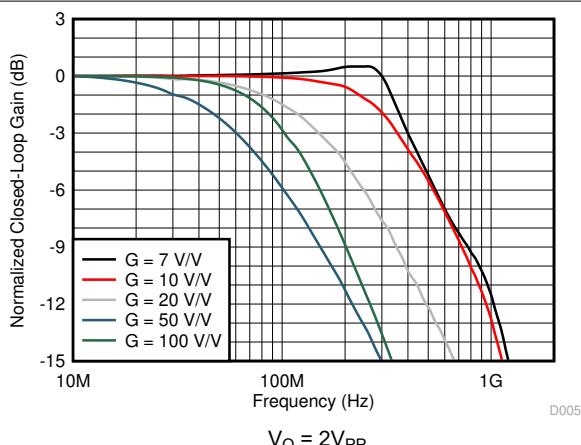

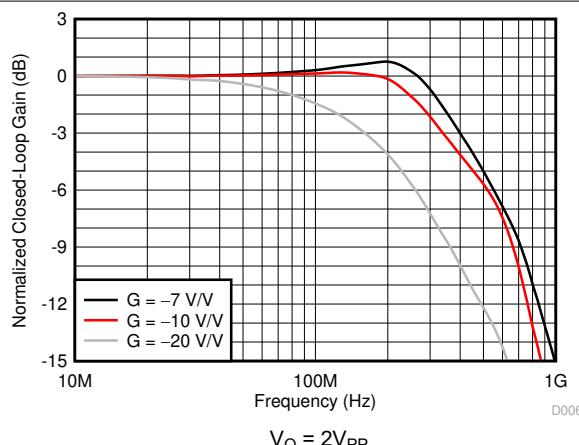

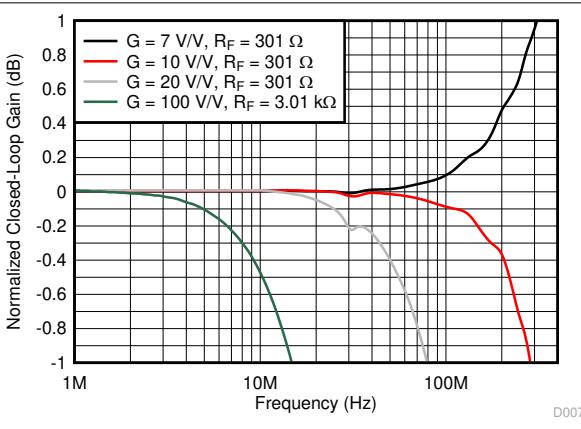

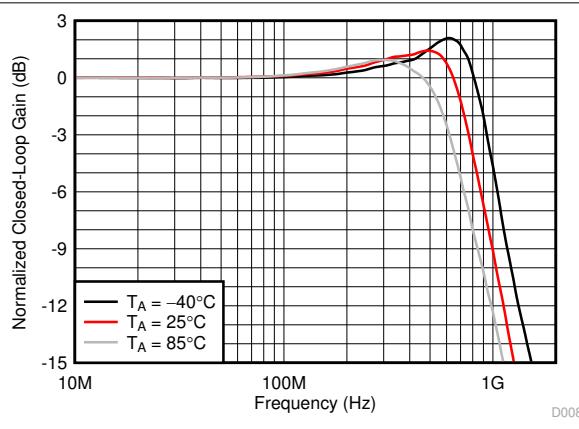

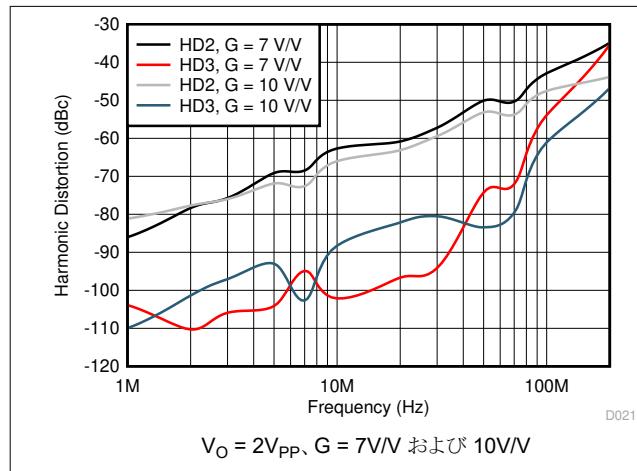

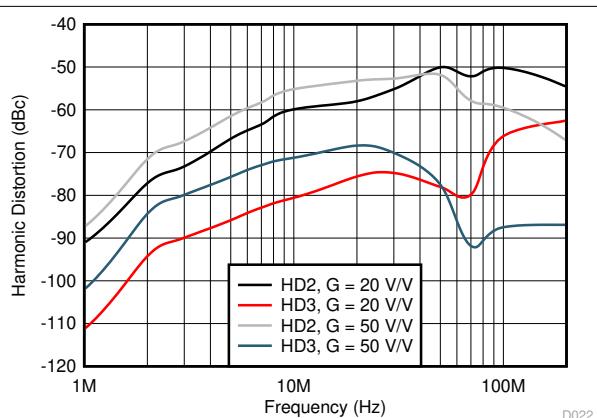

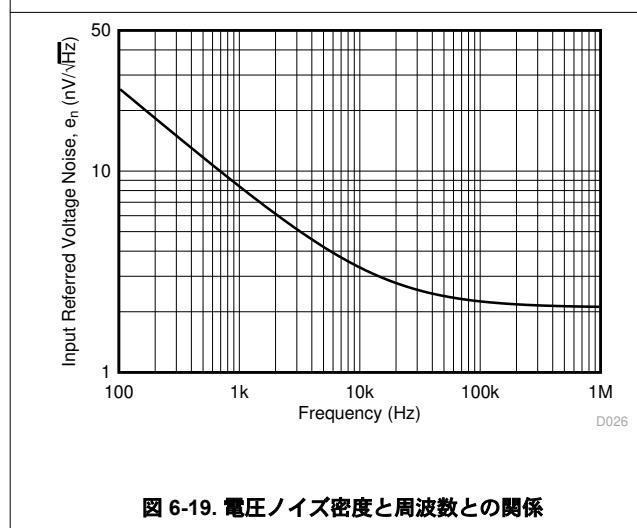

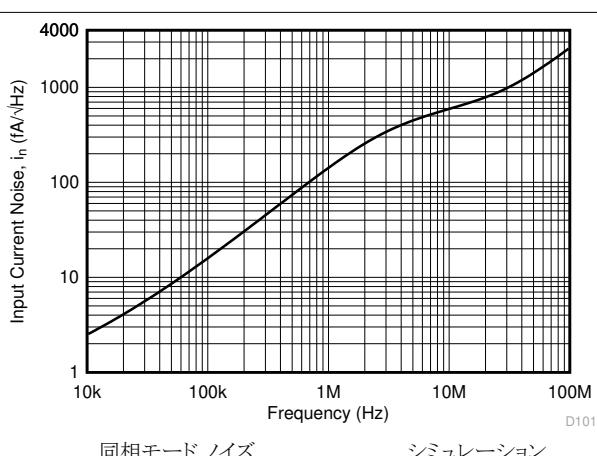

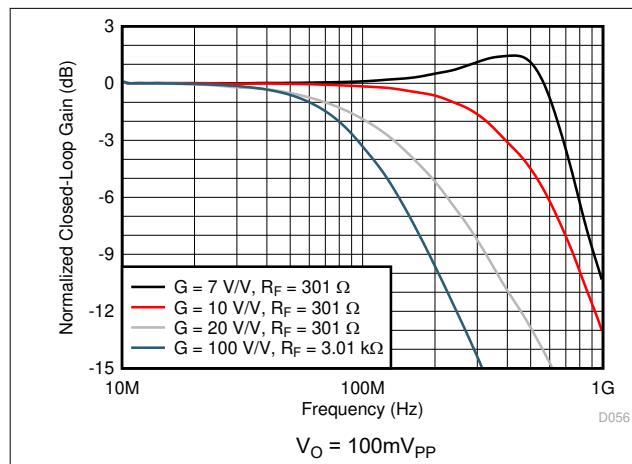

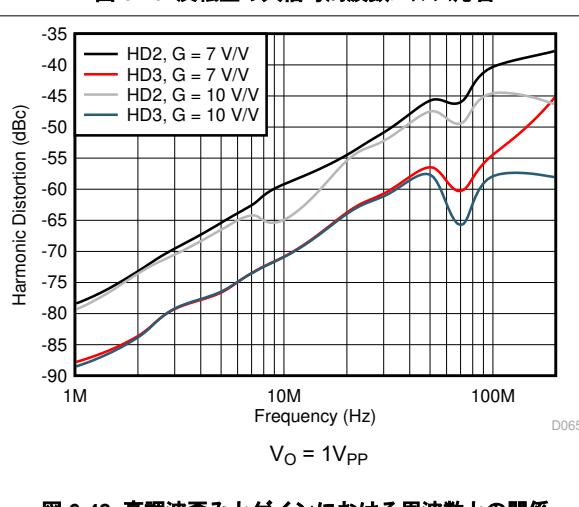

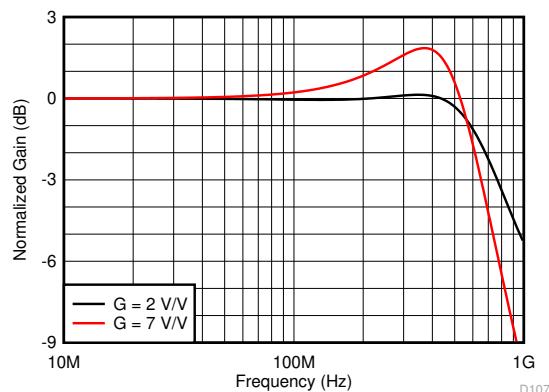

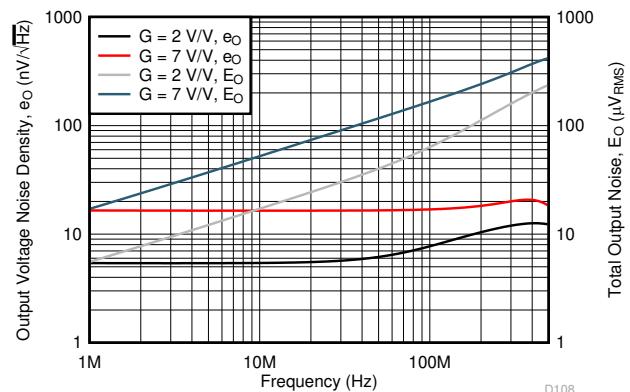

$T_A \approx 25^\circ C$  の場合、 $V_{S+} = +5V$ 、 $V_{S-} = -5V$ 、閉ループゲイン ( $G$ ) = 7V/V、 $V_{CM}$  = 中電圧、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧に接続、小信号  $V_O = 100mV_{PP}$ 、大信号  $V_O = 2V_{PP}$  (特に記述のない限り)

図 6-1. 非反転型の小信号周波数パルス応答

図 6-2. 反転型の小信号周波数パルス応答

図 6-3. 非反転型の大信号周波数パルス応答

図 6-4. 反転型の大信号周波数パルス応答

図 6-5. ゲイン平坦性と周波数との関係

図 6-6. 温度範囲全体における非反転小信号周波数応答

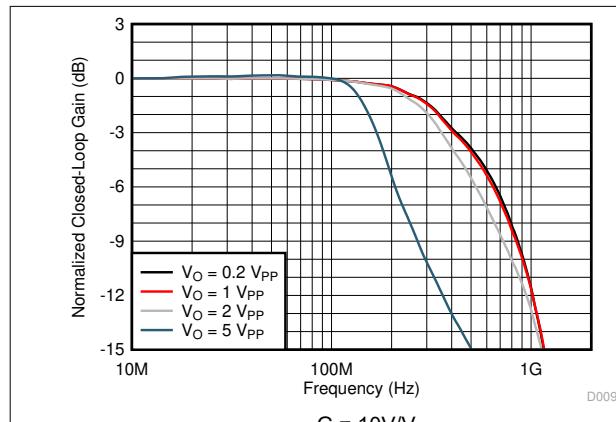

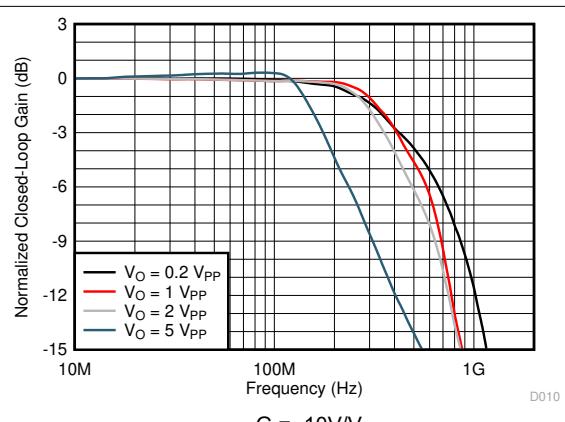

## 6.6 代表的特性 : $V_S = \pm 5V$ (続き)

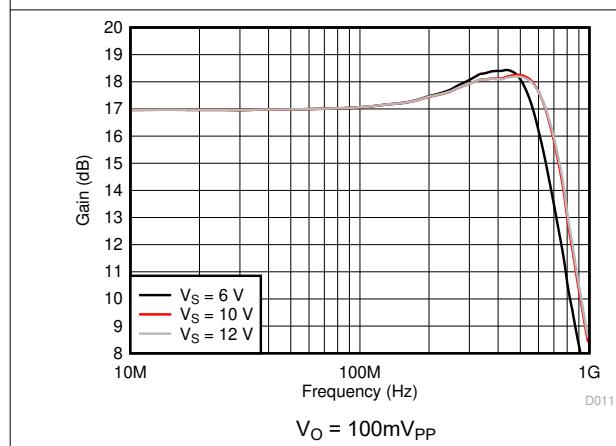

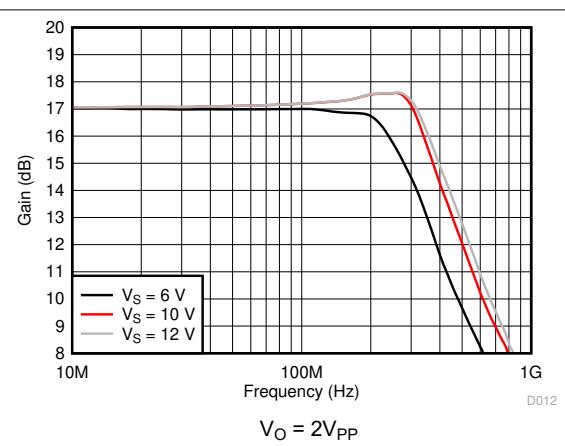

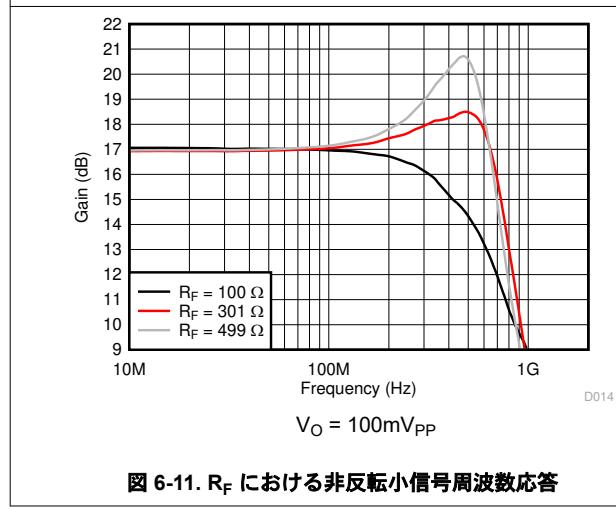

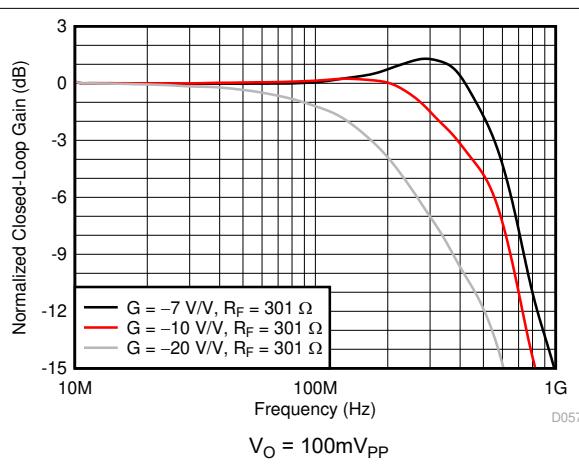

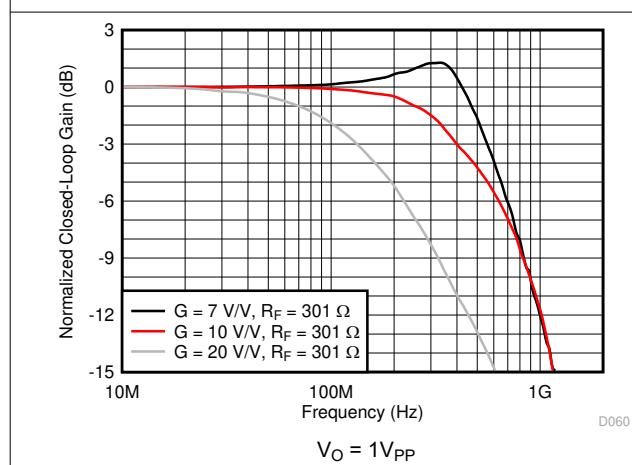

$T_A \approx 25^\circ C$  の場合、 $V_{S+} = +5V$ 、 $V_{S-} = -5V$ 、閉ループゲイン ( $G$ ) = 7V/V、 $V_{CM}$  = 中電圧、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧に接続、小信号  $V_O = 100mV_{PP}$ 、大信号  $V_O = 2V_{PP}$  (特に記述のない限り)

図 6-7. 出力スイングにおける非反転周波数応答

図 6-8. 出力スイングにおける反転周波数応答

図 6-9. 電源電圧における非反転小信号周波数応答

図 6-10. 電源電圧における非反転大信号周波数応答

図 6-11.  $R_F$  における非反転小信号周波数応答

図 6-12. 同相モードおよび電源除去比と周波数との関係

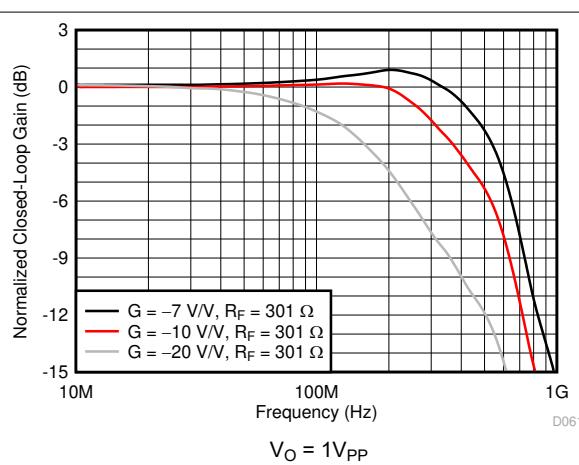

## 6.6 代表的特性 : $V_S = \pm 5V$ (続き)

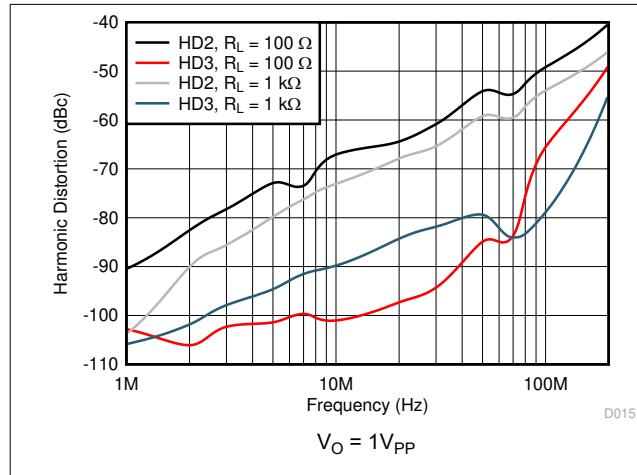

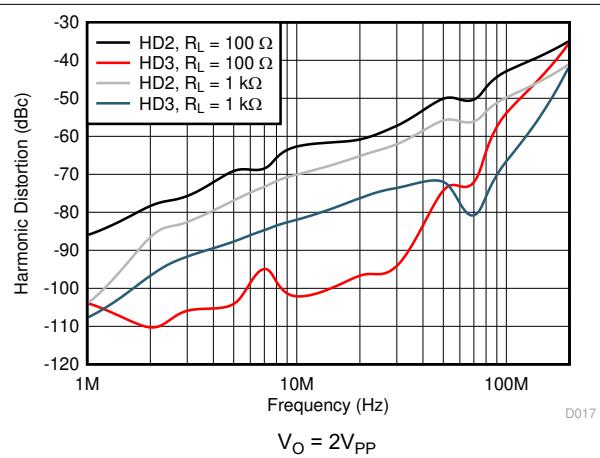

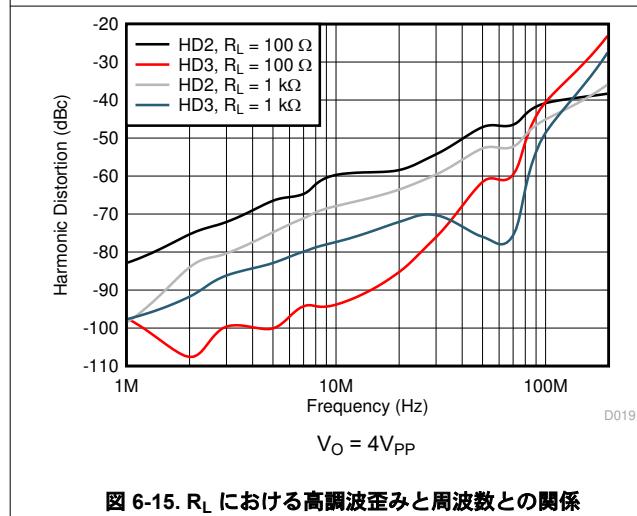

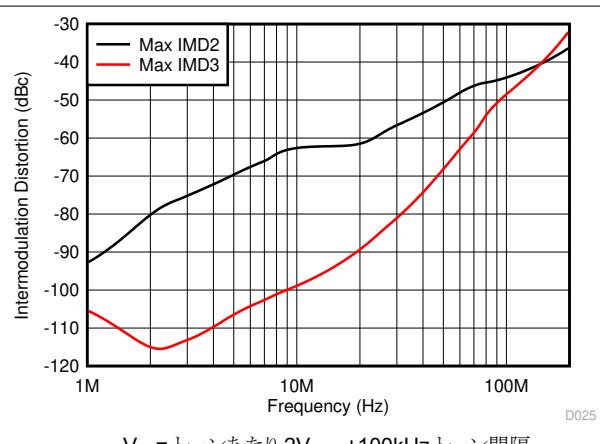

$T_A \approx 25^\circ C$  の場合、 $V_{S+} = +5V$ 、 $V_{S-} = -5V$ 、閉ループゲイン ( $G$ ) = 7V/V、 $V_{CM}$  = 中電圧、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧に接続、小信号  $V_O = 100mV_{PP}$ 、大信号  $V_O = 2V_{PP}$  (特に記述のない限り)

図 6-13.  $R_L$  における高調波歪みと周波数との関係

図 6-14.  $R_L$  における高調波歪みと周波数との関係

図 6-15.  $R_L$  における高調波歪みと周波数との関係

図 6-16. 相互変調歪みと周波数との関係

## 6.6 代表的特性 : $V_S = \pm 5V$ (続き)

$T_A \approx 25^\circ C$  の場合、 $V_{S+} = +5V$ 、 $V_{S-} = -5V$ 、閉ループゲイン ( $G$ ) = 7V/V、 $V_{CM}$  = 中電圧、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧に接続、小信号  $V_O = 100mV_{PP}$ 、大信号  $V_O = 2V_{PP}$  (特に記述のない限り)

図 6-17. 高調波歪みとゲインにおける周波数との関係

図 6-18. 高調波歪みとゲインにおける周波数との関係

図 6-19. 電圧ノイズ密度と周波数との関係

図 6-20. 電流ノイズ密度と周波数との関係

## 6.6 代表的特性 : $V_S = \pm 5V$ (続き)

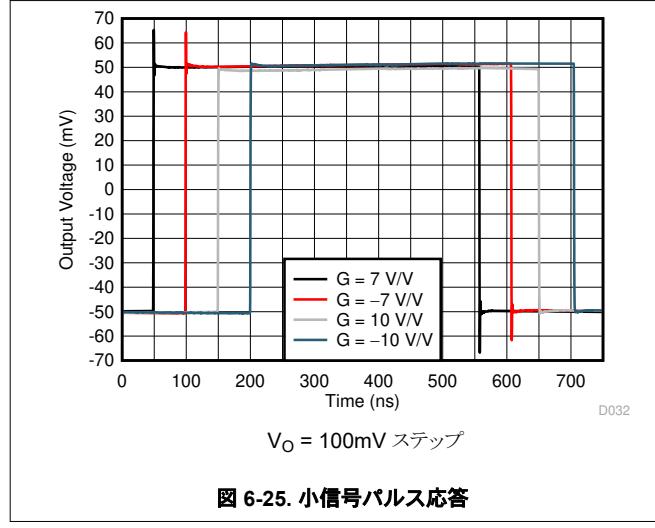

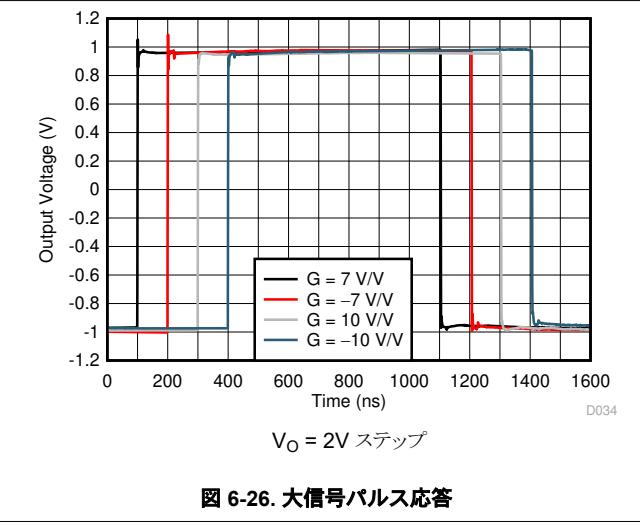

$T_A \approx 25^\circ\text{C}$  の場合、 $V_{S+} = +5V$ 、 $V_{S-} = -5V$ 、閉ループゲイン ( $G$ ) = 7V/V、 $V_{CM}$  = 中電圧、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧に接続、小信号  $V_O = 100\text{mV}_{PP}$ 、大信号  $V_O = 2V_{PP}$  (特に記述のない限り)

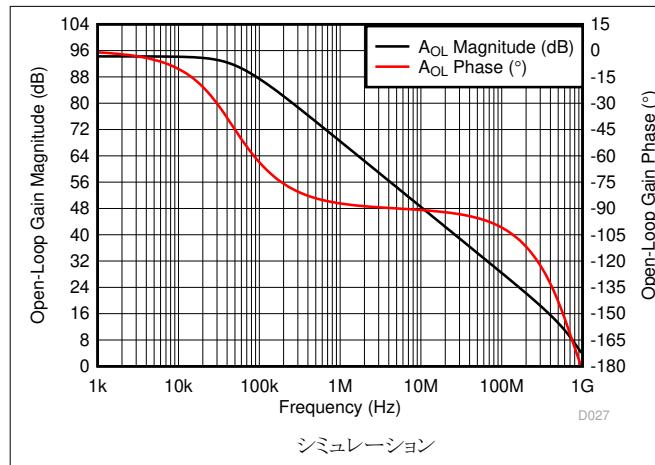

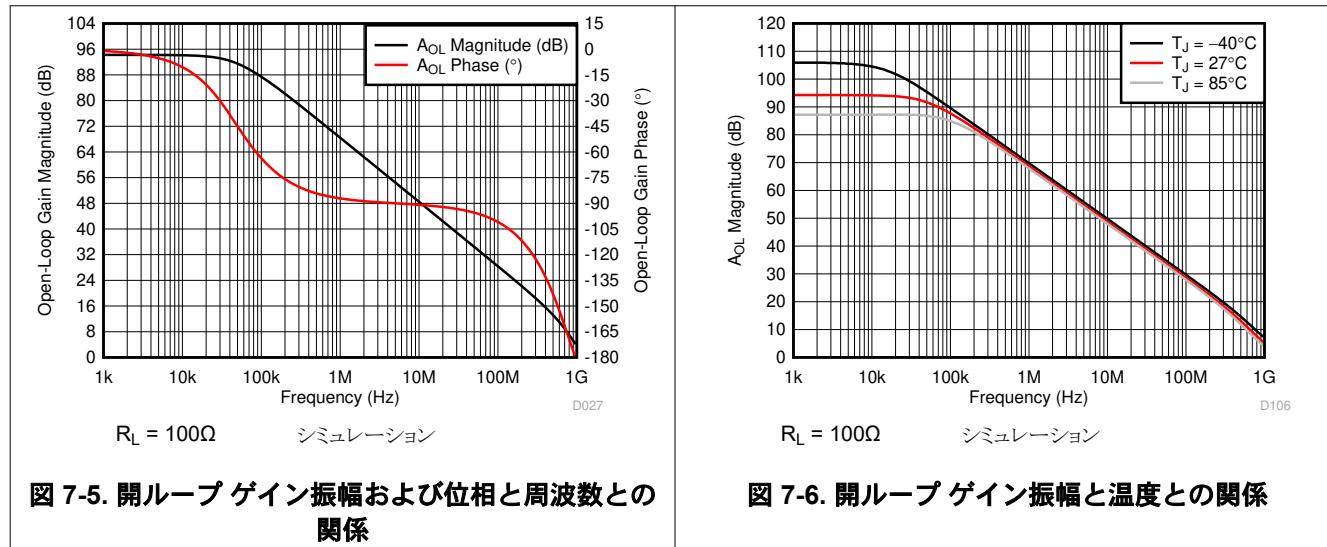

図 6-21. 開ループゲイン振幅および位相と周波数との関係

図 6-22. 開ループおよび閉ループの出力インピーダンスと周波数との関係

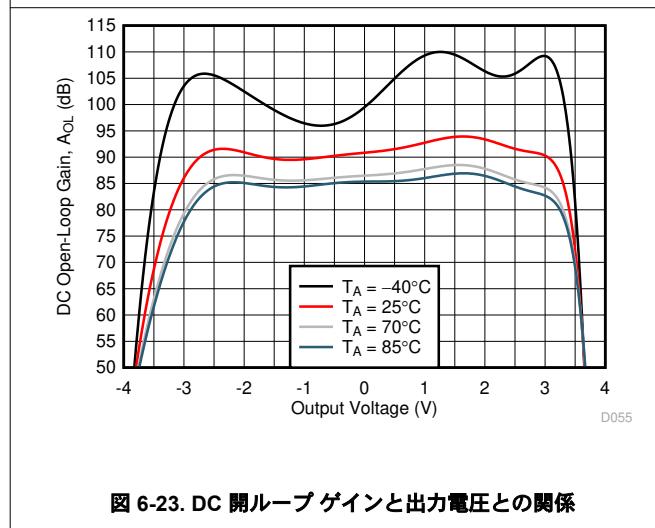

図 6-23. DC 開ループゲインと出力電圧との関係

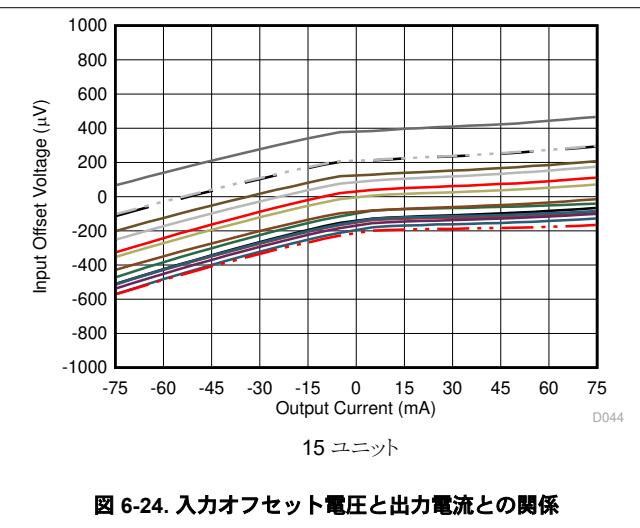

図 6-24. 入力オフセット電圧と出力電流との関係

図 6-25. 小信号パルス応答

図 6-26. 大信号パルス応答

## 6.6 代表的特性 : $V_S = \pm 5V$ (続き)

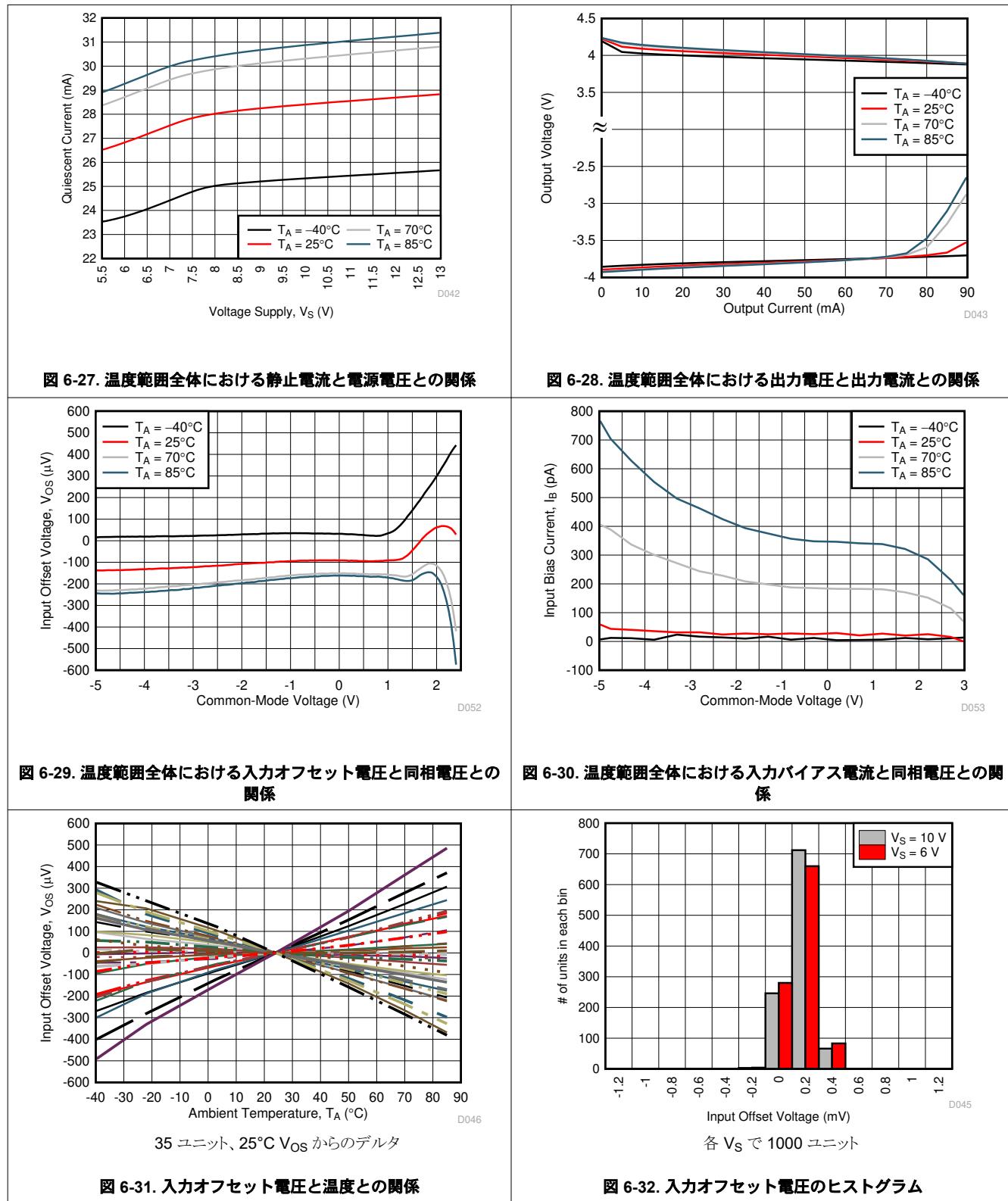

$T_A \approx 25^\circ\text{C}$  の場合、 $V_{S+} = +5V$ 、 $V_{S-} = -5V$ 、閉ループゲイン ( $G$ ) = 7V/V、 $V_{CM}$  = 中電圧、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧に接続、小信号  $V_O = 100\text{mV}_{PP}$ 、大信号  $V_O = 2\text{V}_{PP}$  (特に記述のない限り)

## 6.6 代表的特性 : $V_S = \pm 5V$ (続き)

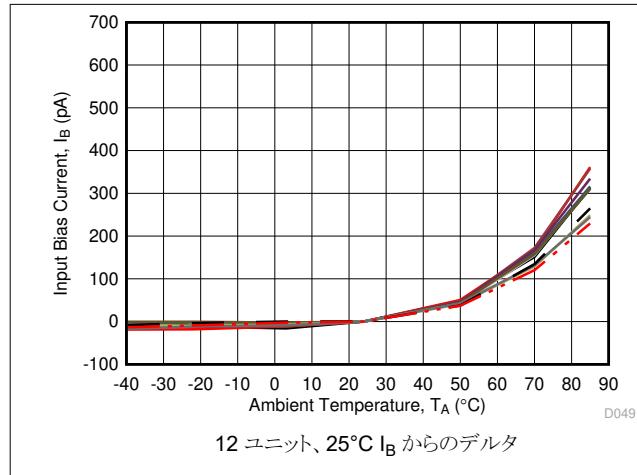

$T_A \approx 25^\circ\text{C}$  の場合、 $V_{S+} = +5V$ 、 $V_{S-} = -5V$ 、閉ループゲイン ( $G = 7\text{V/V}$ )、 $V_{CM} = \text{中電圧}$ 、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧に接続、小信号  $V_O = 100\text{mV}_{\text{PP}}$ 、大信号  $V_O = 2\text{V}_{\text{PP}}$  (特に記述のない限り)

図 6-33. 入力バイアス電流と温度との関係

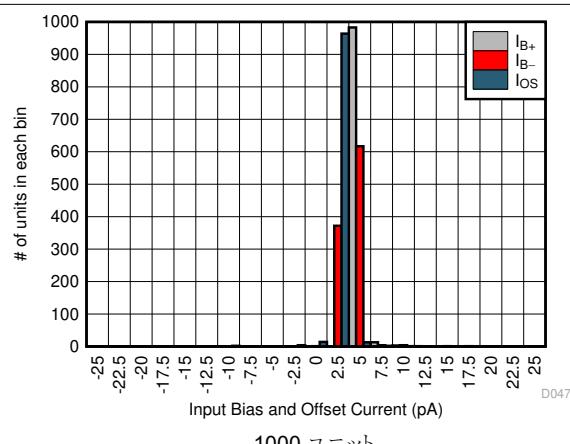

図 6-34. 入力バイアスおよびオフセット電流のヒストグラム

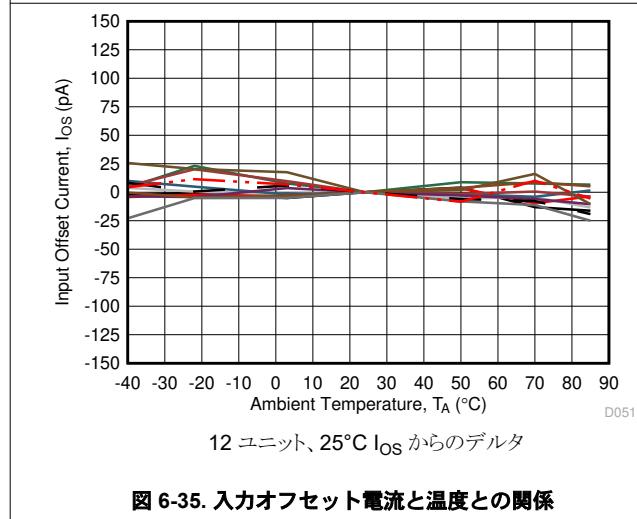

図 6-35. 入力オフセット電流と温度との関係

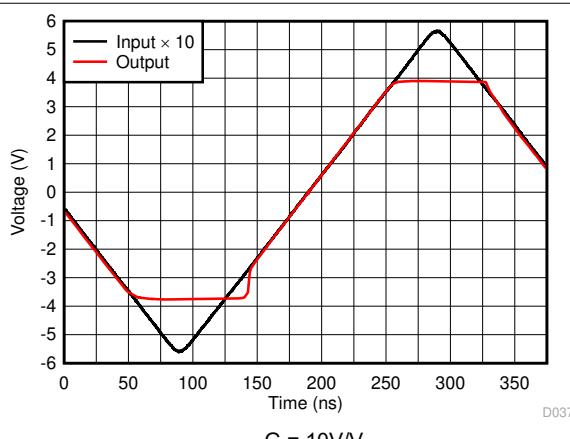

図 6-36. 出力オーバードライブ回復

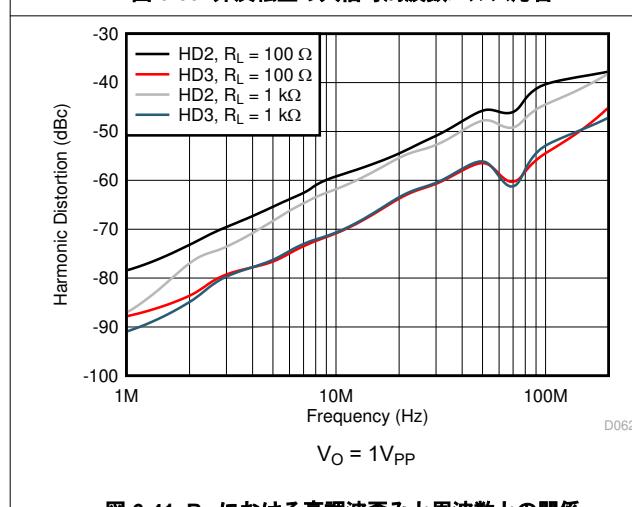

## 6.7 代表的特性 : $V_S = 6V$

$T_A \approx 25^\circ C$  の場合、 $V_{S+} = +4V$ 、 $V_{S-} = -2V$ 、閉ループゲイン ( $G$ ) = 7V/V、 $V_{CM}$  = 中電圧、 $R_F = 301\Omega$ 、 $R_L = 100\Omega$  を中電圧に接続、小信号  $V_O = 100mV_{PP}$ 、大信号  $V_O = 1V_{PP}$  (特に記述のない限り)

図 6-37. 非反転型の小信号周波数パルス応答

図 6-38. 反転型の小信号周波数パルス応答

図 6-39. 非反転型の大信号周波数パルス応答

図 6-40. 反転型の大信号周波数パルス応答

図 6-41.  $R_L$  における高調波歪みと周波数との関係

図 6-42. 高調波歪みとゲインにおける周波数との関係

## 7 詳細説明

### 7.1 概要

OPA818 は、13V 電源、2.7GHz ゲイン帯域幅積 (GBWP)、電圧帰還型オペアンプで、 $2.2\text{nV}/\sqrt{\text{Hz}}$  の低ノイズ JFET 入力段を備えています。OPA818 は、通常、7V/V 以上のゲインで安定するように非補償型になっています。非補償型アーキテクチャにより、高ゲイン アプリケーションで非常に高い GBWP と低歪み性能を実現しながら、静止電流を低く抑えるという有利なトレードオフが可能になります。高電圧機能と  $1400\text{V}/\mu\text{s}$  のスルーレートを組み合わせることで、高周波信号に対して広い出力振幅 ( $V_S = 12\text{V}$  で  $10\text{V}_{\text{PP}}$ ) を必要とするアプリケーションが可能になります。このようなアプリケーションとして、光フロントエンド、テストと測定、医療用システムなどが挙げられます。バイアス電流がピコアンペア単位の低ノイズ JFET 入力により、このデバイスは高 TIA ゲイン アプリケーションやテストや測定フロントエンドに特に最適です。また、OPA818 はパワーダウン モードを備えており、コアアンプを無効にして消費電力を削減できます。

OPA818 は、TI 独自の高電圧、高速、相補型バイポーラ SiGe プロセスで製造されています。

### 7.2 機能ブロック図

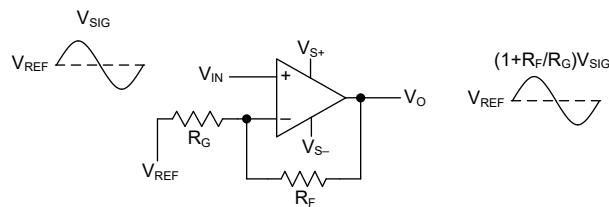

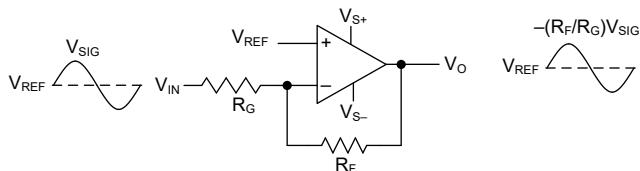

OPA818 は、2 つのハイインピーダンス入力と低インピーダンス出力を備えた従来型の電圧帰還オペアンプです。標準的なアンプ構成をサポートしています。図 7-1 および 図 7-2 に、2 つの基本的な構成を示します。各構成の dc 動作点は基準電圧 ( $V_{\text{REF}}$ ) によってレベル シフトされます。この電圧は通常、単一電源動作時の中間電圧に設定されます。 $V_{\text{REF}}$  は通常、分割電源アプリケーションではグランドに接続されます。

図 7-1. 非反転アンプ

図 7-2. 反転アンプ

### 7.3 機能説明

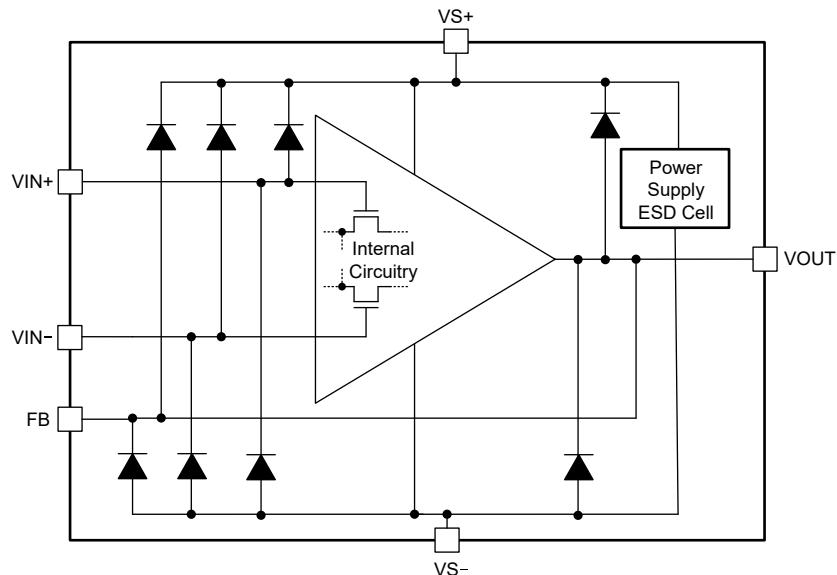

#### 7.3.1 入力およびESD 保護

OPA818 は、非常に高速な相補型バイポーラ プロセスを使って製造されています。これらの非常に小さな形状のデバイスでは、内部接合部ブレーク ダウン電圧は比較的低くなります。これらのブレークダウンは、セクション 6.1 に反映されています。図 7-3 に、すべてのデバイスピンが内部 ESD 保護ダイオードによってどのように保護されているかを示します。

これらのダイオードは、電源電圧を上回る入力オーバードライブ電圧に対してある程度の保護を提供します。これらの保護ダイオードは  $10\text{mA}$  (標準値) の連続電流に耐えます。より高い電流が流れる可能性がある場合 (たとえば、OPA818 を駆動する  $\pm 12\text{V}$  電源部品を含むシステムなど)、2 つの入力に直列に電流制限直列抵抗を追加して電流を制限します。値が大きい場合はノイズ性能と周波数応答の両方が低下するため、これらの抵抗値をできるだけ小さくします。 $V_{\text{IN}+}$  と  $V_{\text{IN}-}$  の間には双方 **ESD** ダイオードはありません。その結果、 $V_{\text{IN}+}$  と  $V_{\text{IN}-}$  の間の差動入力電圧は、入力 JFET 差動ペアの  $V_{\text{GS}}$  によって完全に吸収されます。セクション 6.1 の電圧定格は超えません。

図 7-3. 内部 ESD 保護

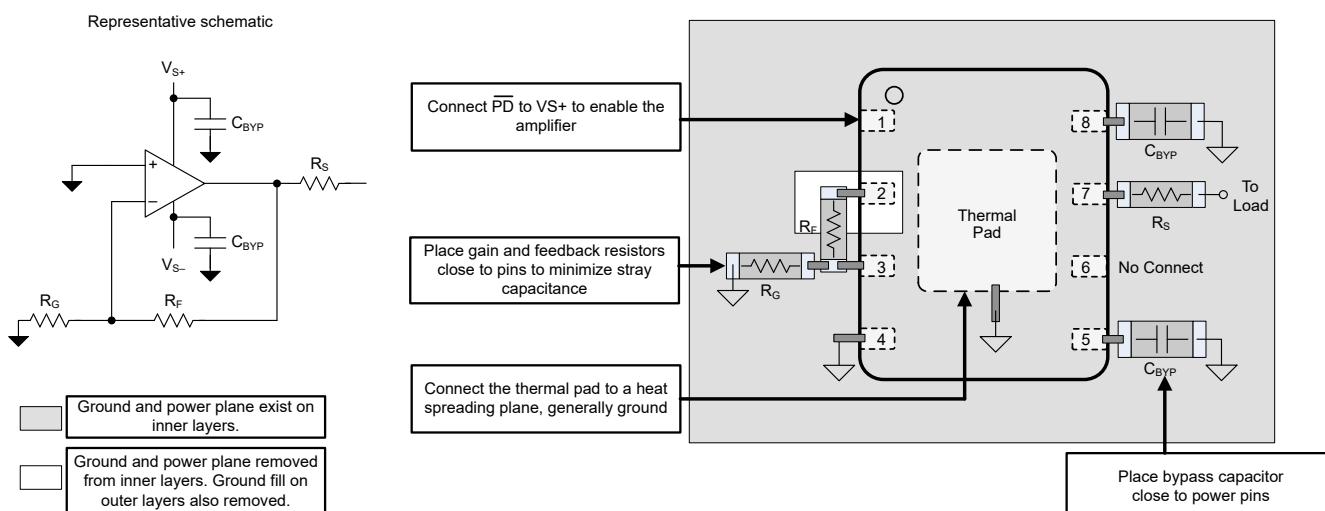

### 7.3.2 フィードバック ピン

高速アナログ設計では、OPA818 などの高速アンプから最高の性能を引き出すために、寄生容量とインダクタンスを最小限に抑えることが重要です。寄生成分は、フィードバック パスと反転入力に特に悪影響を及ぼします。寄生成分は、帰還に望ましくない極とゼロをもたらし、位相マージンを減少させる可能性、または不安定性を引き起こす可能性があります。この位相マージンの削減を補正するために使用される手法は、多くの場合、アプリケーション帯域幅を狭くします。システムエンジニアがこれらのトレードオフの選択をせずに済むように、またプリント基板 (PCB) のレイアウトを簡素化できるように、OPA818 ではフィードバック (FB) ピンを反転入力ピン (IN-) と同じ側に配置しています。図 7-4 に、この構成により、FB と IN- ピンとの間に非常に短い帰還抵抗 ( $R_F$ ) を接続し、PCB の設計労力を最小限に抑えて寄生成分を最小化する方法を示します。内部では、FB ピンは、シリコン上の金属配線を経由して VOUT に接続されています。この接続は固定の金属のサイズ設定により、FB ピンには電流許容能力が制限されるため、セクション 6.1 は連続動作に準拠します。

図 7-4. FB ピンと IN- ピンの間の  $R_F$  接続

### 7.3.3 広いゲイン帯域幅積の非補償型アーキテクチャ

図 7-5 に、OPA818 の開ループ ゲインと位相応答を示します。オペアンプの GBWP は、 $A_{OL}$  振幅プロットの 20dB/dec の一定のスロープ領域で測定されます。OPA818 の開ループ ゲインは 60dB で、この 20dB/dec のスロープに沿っており、対応する周波数インターーセプトは 2.7MHz です。60dB をリニア ユニット (1000V/V) に変換し、2.7MHz の周波数インターーセプトを乗算することで、OPA818 の GBWP は 2.7GHz となります。 $A_{OL}$  ボード線図は、 $A_{OL}$  振幅が 0dB (1V/V) 未満に低下する前に、 $A_{OL}$  応答の 2 番目の極が発生していることを示しています。この結果から、0dB  $A_{OL}$  で 180°を超える位相変化が現れ、アンプは 1V/V のゲインで安定できないことを示しています。OPA818 などのユニティ ゲインで安定していないアンプを、非補償型アーキテクチャにより、通常、等価な静止電流を持つユニティ

ゲインで安定しているアンプに比べて、より高い GBWP、高いスルーレート、より低いノイズを実現できます。非補償型アンプのもう 1 つの利点は、ユニティゲインで安定しているアンプに匹敵する静止電流の高ゲインアプリケーションで、より高い周波数で歪み性能を改善できることです。

OPA818 は、従来のゲイン回路で 7V/V (16.9dB) 以上のノイズゲインで安定しています (図 7-1 および 図 7-2 を参照)。ノイズゲインが 7V/V では、OPA818 には約 50° の位相マージンを持つ SSBW の 790MHz があります。

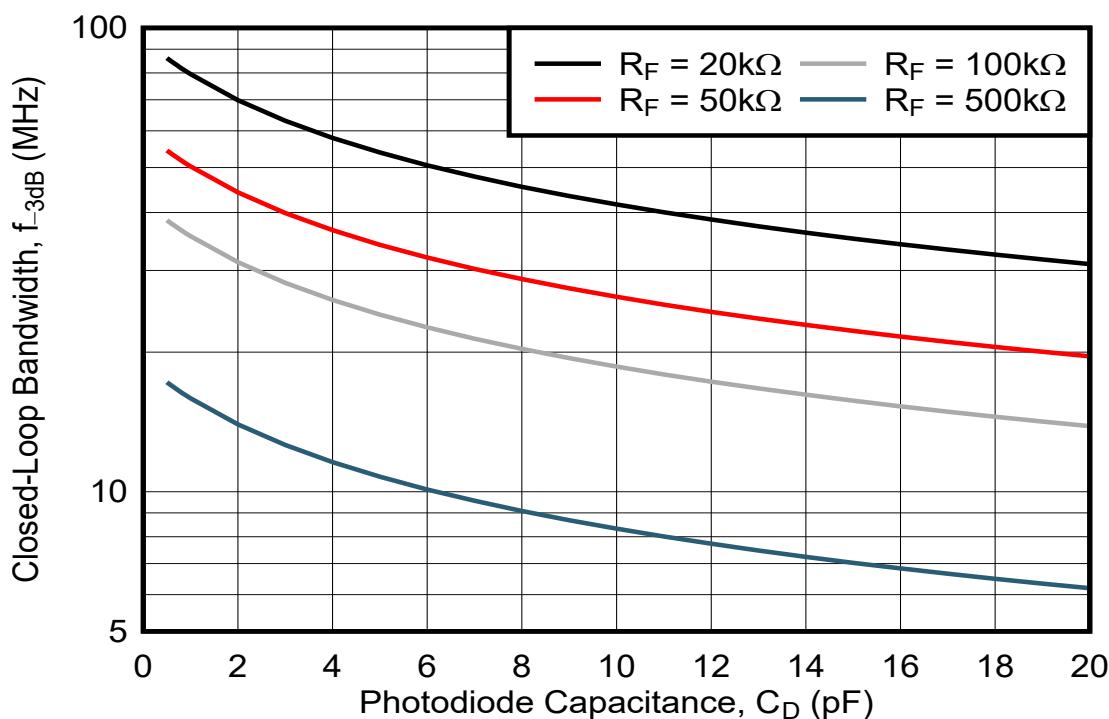

OPA818 は、GBWP が高く、電圧および電流ノイズが低いため、広帯域の中程度から高トランシスインピーダンスゲインのアプリケーションに最適なアンプです。低電流ノイズの JFET 入力は、50kΩ 以上のトランシスインピーダンスゲインを活用します。標準的なトランシスインピーダンスアンプ (TIA) 回路 (図 8-2 も参照) では、ユニティゲインで安定しているアンプは必要ありません。低周波数では、TIA のノイズゲインは 0dB (1V/V) であり、高い周波数では、ノイズゲインは合計入力容量 ( $C_{TOT}$ ) と帰還容量 ( $C_F$ ) の比によって設定されます。TIA の閉ループ帯域幅を最大化するため、帰還容量は通常、合計入力容量よりも小さくなります。この構成では、合計入力容量と帰還容量の比率が 1 より大きくなり、最終的に高い周波数での TIA のノイズゲインになります。ブログシリーズ『トランシスインピーダンスアンプについて知っておくべきこと - 第 1 部』および『トランシスインピーダンスアンプについて知っておくべきこと - 第 2 部』に、TIA 補償手法に関する詳細な説明が記載されています。

### 7.3.4 低入力容量

多くの場合、TIA アプリケーションの主な検討事項は、TIA の閉ループ帯域幅を最大化し、合計出力ノイズを最小化して信号対雑音比 (SNR) を最大化することです。TIA 回路の合計入力容量 ( $C_{TOT}$ ) により、周波数  $1/(2\pi R_F C_{TOT})$  でのトランシスインピーダンスゲイン (帰還抵抗  $R_F$ ) と組み合せたノイズゲインがゼロになります。固定  $R_F$  の場合、このゼロは低い周波数での  $C_{TOT}$  が高くなると、低い周波数でのノイズゲインは増加します。この構成では、 $C_{TOT}$  が低いほど、より低い等価閉ループ帯域幅と合計出力ノイズが大きくなります。OPA818 は、低い入力容量が特徴です (同相モードと差動を合わせて 2.4pF)。また、OPA818 は、低い総出力ノイズで高い閉ループ帯域幅も提供し、TIA アプリケーションで比較的高い静電容量のフォトダイオードを柔軟に選択できます。 $C_{TOT}$  には、アンプの入力容量、フォトダイオード容量、反転入力における PCB 寄生容量が含まれます。

## 7.4 デバイスの機能モード

### 7.4.1 分割電源動作 ( $+4V$ ~ $\pm 6.5V$ )

代表的な分割電源動作では、電源レールの間の中間点はグランドです。分割電源構成におけるグランドの中間点は、 $\pm 4V$  以上の対称電源電圧を使用する場合、OPA818 の有効な動作条件です。この構成により、信号ジェネレータ、ネットワーク アナライザ、オシロスコープ、スペクトル アナライザなど、グランドを基準とする入力と出力を持つ一般的なラボ機器と OPA818 を容易にインターフェイス接続できるようになります。しかし、 $\pm 4V$  未満の分割電源電圧を使用する場合は、同相入力範囲に非準拠とならないようとしてください。OPA818 の標準同相入力範囲には  $V_{S-}$  が含まれ、 $V_{S+}$  から  $3.2V$  まで拡張されていることに注意してください。たとえば、 $\pm 3V$  電源を使用する場合は、仕様の最大同相入力範囲に従って、信号の同相入力電圧が通常  $V_{S+}$  から  $3.2V$ 、 $V_{S+}$  から  $3.6V$  であることを確認してください。 $\pm 3V$  電源を使用する場合、グランドが同相入力範囲に含まれていないため、入力信号が中間点としてグランドがある場合、誤って動作してしまいます。この問題を防止するため、 $+4V$  ~  $\pm 6.5V$  電源を使用してください。

### 7.4.2 単一電源動作 (6V ~ 13V)

新しいシステムの多くは単一電源を使用して効率を向上させ、追加電源のコストを削減しています。OPA818 は分割電源構成で使用するように設計されています。しかし、入力と出力がデバイスのリニア動作内にバイアスされている限り、性能は単一電源で使用できます。回路を分割電源から単一電源に変更するには、 $V_{REF}$  を使用してすべての電圧を中電圧にレベルシフトします。 $8V$  未満の電源で動作する場合は、要件に非準拠とならないように、同相入力範囲をさらに考慮してください。アンプを単電源動作用に構成する利点の 1 つは、低電源レールが接地されるため、-PSRR の影響が最小限に抑えられることです。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

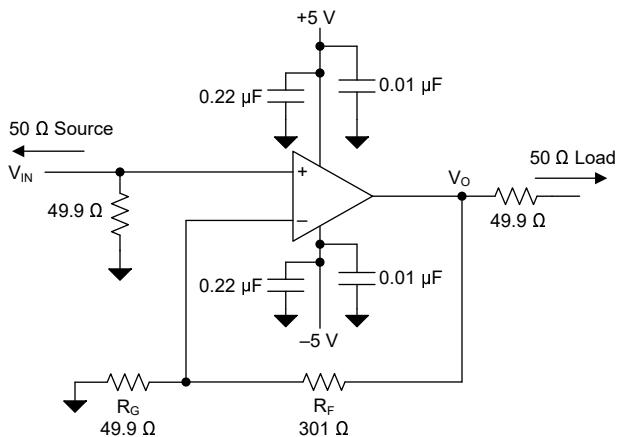

#### 8.1.1 広帯域、非反転動作

OPA818 は、調整された JFET 入力段の高い GBWP、低い入力電圧ノイズ、dc 精度という独自の組み合わせにより、電圧帰還アンプで非常に高い入力インピーダンスを実現します。2.7GHz の高い GBWP を使用して、高ゲインで高信号帯域幅を実現するか、フォトダイオードトランジスインピーダンス アプリケーションで実現可能な帯域幅やゲインを拡張します。OPA818 の性能を最大限に引き出すには、プリント基板 (PCB) のレイアウトと部品の選択に十分な注意を払ってください。このデータシートの以下のセクションも参照してください。

図 8-1 に、ほとんどの「[代表的特性:  \$V\_S = \pm 5V\$](#) 」の基礎として使用される反転ゲインが  $+7V/V$  の回路を示します。ほとんどの曲線は、駆動インピーダンスが  $50\Omega$  の信号ソースと、負荷インピーダンスが  $50\Omega$  の測定機器を使用して特徴付けられています。図 8-1 では、 $V_{IN}$  端子の  $49.9\Omega$  のシャント抵抗がテスト ジェネレータのソースインピーダンスと一致し、 $V_O$  端子の  $49.9\Omega$  直列抵抗が測定機器の負荷にマッチング抵抗を提供します。一般的に、データシートの電圧スイング仕様は出力ピン (図 8-1 の  $V_O$ ) での値、出力電力仕様は整合された  $50\Omega$  負荷での値に基づいています。出力における合計  $100\Omega$  の負荷と、 $350\Omega$  の合計帰還回路負荷を組み合わせると、図 8-1 の回路において、OPA818 には実質的に  $78\Omega$  の出力負荷がかかることになります。

図 8-1. 非反転  $G = +7V/V$  構成とテスト回路

電圧帰還オペアンプは、電流帰還製品とは異なり、幅広い抵抗値を使用してゲインを設定します。図 8-1 の非反転電圧アンプで制御された周波数応答を維持するため、 $R_F \parallel R_G$  の並列組み合わせが  $50\Omega$  未満であることを確認してください。非反転構成では、 $R_F \parallel R_G$  の並列組み合わせが、OPA818 の反転ノード (レイアウトの寄生容量を含む) の寄生入力容量と極を形成します。最高の性能を得るには、この極を OPA818 の閉ループ帯域幅よりも高い周波数に設定します。

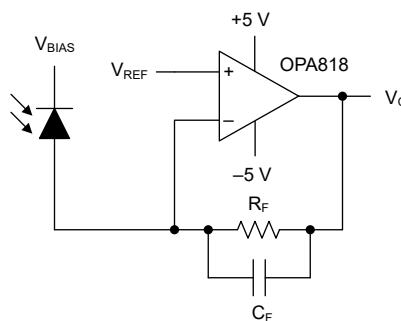

### 8.1.2 OPA818 を使用した広帯域トランスインピーダンスの設計

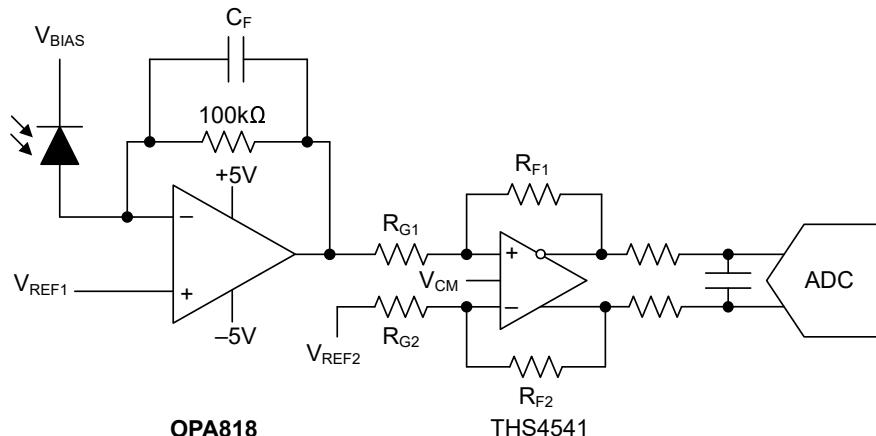

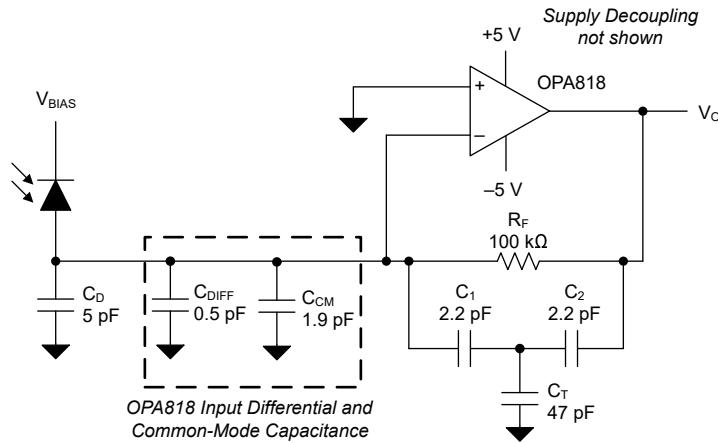

OPA818 は GBWP が高く、入力電圧ノイズと電流ノイズが低く、入力容量が小さいため、広帯域、低ノイズのトランスインピーダンス アプリケーションに最適化されています。高電圧対応能力により、電源電圧の柔軟性が向上し、出力電圧スイッチングが拡大します。図 8-2 に、代表的なフォトダイオードアンプ回路の回路例を示します。一般的に、TIA アプリケーションではフォトダイオードが逆バイアスされるため、図 8-2 の回路におけるフォトダイオード電流がオペアンプの帰還ループに流れ込み、フォトダイオード電流が増加するにつれて  $V_{REF}$  から出力電圧が減少するという結果になります。このタイプの構成では、アプリケーションの要求に応じて、 $V_{REF}$  を  $V_{S+}$  の近くにバイアスして、目的の出力スイッチングを実現できます。 $V_{REF}$  バイアスを使用するときは、同相入力範囲の要件に非準拠とならないようにしてください。

回路の閉ループ帯域幅  $f_{-3dB}$  を決定する主な設計要素は次のとおりです。

1. オペアンプの GBWP

2. トランスインピーダンスゲイン  $R_F$

3. フォトダイオード容量、アンプの入力容量 (同相容量と差動容量)、PCB 寄生容量を含む合計入力容量  $C_{TOT}$

図 8-2. 広帯域かつ低ノイズのトランスインピーダンスアンプ

式 1 に、バターワース応答に関する前述の 3 つの素子の関係を示します。

$$f_{-3dB} = \sqrt{\frac{GBWP}{2\pi R_F C_{TOT}}} \quad (1)$$

帰還抵抗  $R_F$  と合計入力容量  $C_{TOT}$  は、ノイズゲインにゼロをもたらし、補償されないまま放置すると不安定性が生じます。ゼロの影響を打ち消すため、帰還コンデンサ  $C_F$  を追加して、ノイズゲインに極を挿入します。『[高速アンプのトランスインピーダンスに関する考慮事項アプリケーションレポート](#)』では、特定のゲインと入力容量についてトランスインピーダンスアンプを補償する方法を示す理論と式について説明しています。アプリケーションレポートに掲載されている帯域幅と補償の式は、Excel™ カリキュレータで利用できます。『[トランスインピーダンスアンプについて知っておくべきこと—第1部](#)』では、カリキュレータへのリンクを提供しています。電圧  $V_{REF1}$  と  $V_{REF2}$  を使用する TIA フロントエンドのダイナミックレンジを最大化する方法の詳細については (『[高速光フロントエンドを参照](#)』)、『[アナログ TIA フロントエンドのダイナミックレンジの最大化](#)』アプリケーションノートを参照してください。

## 8.2 代表的なアプリケーション

### 8.2.1 高帯域幅の 100kΩ ゲイン トランスインピーダンス設計

OPA818 は GBWP が高く、入力電圧および電流ノイズが低いため、このデバイスは中程度から高いトランスインピーダンスゲインに対する優れた広帯域トランスインピーダンスアンプと言えます。

図 8-3. 広帯域、高感度、トランスインピーダンスアンプ

#### 8.2.1.1 設計要件

表 8-1 に示す設計要件に従って、高帯域幅、高トランスインピーダンスゲインのアンプを設計します。

表 8-1. 設計要件

| ターゲット帯域幅 (MHz) | トランスインピーダンスゲイン (kΩ) | フォトダイオード容量 (pF) |

|----------------|---------------------|-----------------|

| 24             | 100                 | 5               |

#### 8.2.1.2 詳細な設計手順

トランスインピーダンスゲインが比較的高い大面積の検出器から高帯域幅を必要とする設計は、OPA818 の入力電圧ノイズが低下するという利点があります。この入力電圧ノイズは、ダイオードのソース容量により周波数全範囲でピークアップされ、多くの場合、入力感度の制限要因となる可能性があります。図 8-3 に、セクション 8.2.1.1 で定義されたパラメータを持つトランスインピーダンス回路を示します。『トランスインピーダンスアンプについて知つておくべきこと - 第 1 部』に記載されている Excel カリキュレータを使用して、コンポーネントの選択をサポートするには、合計入力容量  $C_{TOT}$  を決定します。カリキュレータでは、 $C_{TOT}$  は  $C_{IN}$  と呼ばれます。 $C_{TOT}$  は、 $C_D$ 、 $C_{DIFF}$ 、 $C_{CM}$  の和 (7.4pF) です。この  $C_{TOT}$  の値、目標とする 24MHz の閉ループ帯域幅 ( $f_{-3dB}$ )、100kΩ のトランスインピーダンスゲインを使用すると、約 2.68GHz GBWP、帰還容量 ( $C_F$ ) が 0.092pF のアンプが必要になります。表 8-2 に、計算結果を示します。これらの結果は、 $Q = 0.707$ 、位相マージンは約 65°でのバターワース応答であり、これは 4.3% のオーバーシュートに相当します。

表 8-2. TIA カリキュレータに設計パラメータを入力した結果

| カリキュレータ II                  |         |     |

|-----------------------------|---------|-----|

| 閉ループ TIA 帯域幅 ( $f_{-3dB}$ ) | 24.00   | MHz |

| 帰還抵抗 ( $R_F$ )              | 100     | kΩ  |

| 入力コンデンサ ( $C_{IN}$ )        | 7.40    | pF  |

| オペアンプのゲイン帯域幅積 (GBWP)        | 2678.14 | MHz |

| 帰還容量 ( $C_F$ )              | 0.092   | pF  |

OPA818 は 2.7GHz GBWP に対応しているため、設計要件に最適です。計算された部品結果で課題となるのは、実質的に 0.092pF のコンデンサを実現できることです。このような小さなコンデンサは、 $C_1$ 、 $C_2$ 、 $C_T$  によって形成される容量性 T 回路を使用して実現されます (図 8-3 を参照)。T 回路の等価容量  $C_{EQ}$  は、式 2 で計算できます。

$$C_{EQ} = \frac{C_1 \times C_2}{C_1 + C_2 + C_T} \quad (2)$$

T 回路は、 $C_1$  と  $C_T$  を使用して入力から出力まで、また  $C_2$  と  $C_T$  を使用して出力から入力までの容量性アッテネータを形成します。 $C_T$  の値が  $C_1$  または  $C_2$  を上回ると、出力信号の一部だけが  $C_1$  に観測されます。この回路では、 $C_1$  経由で入力に供給されるシャント電流がかなり小さくなります。このシャント電流の影響の減少は、はるかに小さいコンデンサの動作と同等です。固定周波数では、より小型のコンデンサを使用するとインピーダンスが高くなるので、電流は減少します。入力から出力へ、またはその逆に対する同じレベルの減衰を維持します。T 回路に適切なコンデンサ値を見つけるには、コンデンサ  $C_1$  と  $C_2$  に、任意に低いものの実際には実現可能で等しい値を選択し、 $C_{EQ} = C_{TOT}$  を設定し、式 3 を使用して調整可能なコンデンサ  $C_T$  の値を取得します。図 8-3 のコンデンサ  $C_1$ 、 $C_2$ 、 $C_T$  の値は、このプロセスを使用して決定されます。

$$C_{EQ} = \frac{C_1 \times C_2 - (C_1 + C_2) \times C_{EQ}}{C_{EQ}} \quad (3)$$

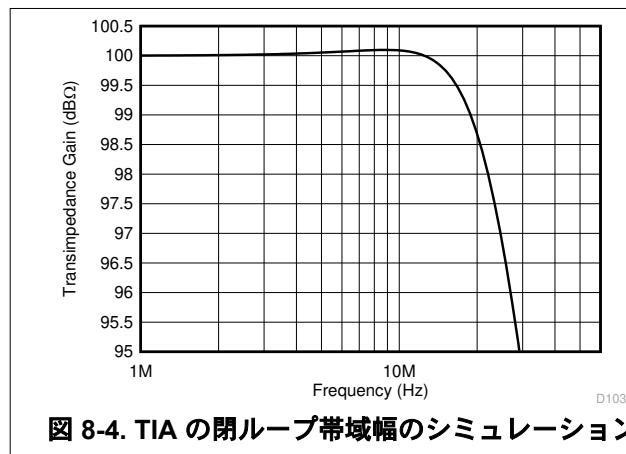

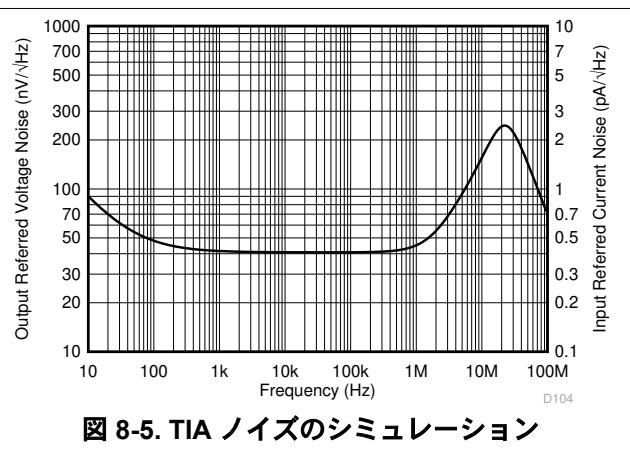

図 8-4 に、図 8-3 の TINA-TI™ シミュレーション ソフトウェアの閉ループ帯域幅応答を示します。この回路は  $f_{-3dB} = 24MHz$  用に設計されており、シミュレーションされた閉ループの 3dB 周波数は 24.6MHz で、ピークは約 0.1dB です。OPA818 TINA-TI ソフトウェア モデルは、TINA-TI ソフトウェアでシミュレーションするときに外部に追加されない入力同相モード コンデンサと差動コンデンサをモデル化しています。図 8-5 に、TIA 回路のノイズ シミュレーションを示します。出力換算電圧ノイズは、左側の Y 軸に示されています。入力換算電流ノイズは、基本的に、出力換算電圧ノイズをトランスインピーダンス ゲイン 100k で除算したもので、2 次側 Y 軸の右側に示されています。OPA818 TINA-TI ソフトウェア モデルはアンプの電圧および電流ノイズ性能を密接にモデル化しているため、シミュレーション結果はかなり高精度です。フラットバンド出力電圧ノイズは  $41nV/\sqrt{Hz}$  であり、入力換算電流ノイズの  $0.41pA/\sqrt{Hz}$  に相当します。アンプのノイズ ゲインが  $1V/V$  の比較的低周波数領域のノイズは、 $100k\Omega$  の抵抗の熱ノイズ ( $27^\circ C$  で  $40.7nV/\sqrt{Hz}$ ) によって支配されます。 $R_F$  と  $C_{TOT}$  で形成されるゼロを超える中周波数では、アンプのノイズ ゲインによってアンプの電圧ノイズが増幅されます。アンプのノイズは、この周波数以降で支配的なノイズの寄与要因になり始め、その後、3dB の閉ループ帯域幅を超える周波数で出力ノイズがロールオフし始めます。積分 RMS (二乗平均平方根) ノイズに注目すると、中周波数ノイズが重大な寄与になる可能性があります。そのため、システムの合計 RMS ノイズを最小限に抑えるため、OPA818 などの  $2.2nV/\sqrt{Hz}$  の低ノイズ アンプを使用してください。

### 8.2.1.3 アプリケーション曲線

図 8-4. TIA の閉ループ帯域幅のシミュレーション

図 8-5. TIA ノイズのシミュレーション

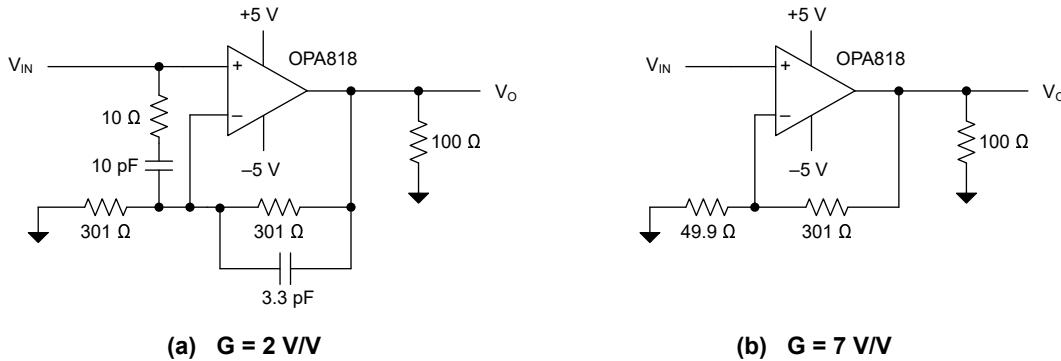

### 8.2.2 2V/V の非反転ゲイン

OPA818 は、従来型の帰還回路を使用する場合、通常、7V/V 以上のノイズ ゲイン構成で安定します。OPA818 は、フィードバック パスにコンデンサを使用し、入力間にコンデンサを使用することで、7V/V 未満のノイズ ゲインで構成できます。この構成により、低い周波数で目的のゲインが維持され、高い周波数でノイズ ゲインが増加して、アンプが安定するようになります。図 8-6 の構成 (a) は、コンデンサと抵抗を使用してノイズ ゲインを形成し、約 51°の位相マージンを実現することにより、2V/V のゲインで構成された OPA818 を示しています。これは、図 8-6 の従来型の 7V/V 構成 (b) で達成される位相マージンに非常に近いものです。

OPA818 のような非補償型アンプを最小安定ゲイン未満のゲインで使用する主な利点は、設計者が同等のユニティ ゲインで安定しているアキテクチャよりも低い電力レベルで低ノイズおよび低歪みの性能を活用できることです。図 8-6 の小信号周波数応答は、図 8-8 の 2V/V ゲイン構成 (a) で 100MHz を超える範囲で平坦な ac 性能を示しており、7V/V の最小安定ゲイン構成と比較して低いゲイン構成であるため、出力換算総ノイズも低くなっています (100MHz で 64nV/√Hz)。構成 (b) を 166nV/√Hz で比較した 図 8-8 も参照してください。10pF の入力コンデンサを小さくすると、システムはピークの増加や位相マージンの減少を犠牲にして、閉ループ帯域幅をより広くできます。パターン長を最小化し、反転入力に接続されているパターンや部品の下のプレーンを削除することで、寄生容量を最小化することが重要です (『レイアウトのガイドライン』を参照)。反転入力の寄生容量が 1pF ~ 2pF と小さい場合、フラットな周波数応答と必要な位相マージンを得るために、ノイズ形成部品の値を微調整する必要があります。図 8-6 の構成では、この寄生容量は考慮されていませんが、実用的な目的で考慮されています。45°の位相マージンは通常許容されますが、部品、PCB、およびプロセスの公差を許容するため、40°未満のものは推奨しません。非補償型アキテクチャの利点の詳細については、『性能向上のための非補償型オペアンプの使用』を参照してください。

図 8-6. 2V/V と 7V/V の非反転ゲイン構成

図 8-7. 図 8-6 のゲイン 2V/V と 7V/V 構成における小信号周波数応答

図 8-8. 図 8-6 のゲイン 2V/V と 7V/V 構成における出力ノイズ

## 8.3 電源に関する推奨事項

OPA818 は、6V (+4V–2V) ~ 12V (±6V) の電源電圧範囲で動作することが想定されています。OPA818 は、単一電源、分割、平衡および不平衡のバイポーラ電源をサポートしています。8V 未満の電源で動作している場合、中電圧はアンプの同相入力範囲外にすることができます。これらの電源条件の下で、リニア動作に向けて同相電圧を適切にバイアスします。そのため、低電源電圧での動作に対する制限は、JFET 入力段で使用可能な入力電圧範囲となります。12V の単一電源での動作には多くの利点があります。負電源をグラウンドに接続すると、-PSRR 項による dc 誤差が最小限に抑えられます。通常、ac 性能は、12V 動作時にわずかに改善し、電源電流の増加は最小限です。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

OPA818 などの高い周波数のアンプを使用して最適な性能を実現するには、基板レイアウトの寄生素子と外部部品の種類に細心の注意を払う必要があります。性能を最適化するための推奨事項として、以下が挙げられます。

- すべての信号 I/O ピンの ac グランドに対する寄生容量を最小化します。出力ピンと反転入力ピンの寄生容量が、不安定性の原因になる可能性があります。非反転入力では、寄生容量がソースインピーダンスに応答して、意図しない帯域制限を引き起こす可能性があります。グランドおよび電源金属のプレーンはコンデンサのプレートの 1 つとして機能し、信号トレースの金属は PCB 誘電体によって分離されたもう 1 つのプレートとして動作します。この不要な容量を減らすには、すべてのグランドプレーンと電源プレーンの信号 I/O ピンの周囲と下にプレーンカットアウトを設けることを推奨します。その他に、グランドおよび電源プレーンが基板上のその他の場所で決して途切れないようにします。アンプを TIA として構成する際には、必要な帰還コンデンサが 0.15pF 未満の場合は、抵抗からの寄生容量を最小化するために、2 つの直列抵抗を使うことを検討します。それぞれの値は、帰還ループ内で 1 つの抵抗の半分です。

- 電源ピンから高周波デカップリングコンデンサまでの距離を最小限 (0.25 インチ [0.635cm] 未満) にします。アンプの最大電源電圧の 3 倍以上の電圧定格を持つ、0.1- $\mu$ F、C0G、NPO タイプの高品質 pF デカップリングコンデンサを使用してください。この要件により、アンプのゲイン帯域幅仕様全体にわたってアンプの電源ピンへの低インピーダンスパスが実現します。デバイスのピンの配置では、グランドおよび電源プレーンのレイアウトを信号 I/O ピンの近くに配置しないようにしてください。ピンとデカップリングコンデンサ間のインダクタンスを最小にするため、電源パターンおよびグランドパターンは狭くならないようにします。常にこれらのコンデンサで、電源接続をデカップリングします。電源ピンに対して、低い周波数で効果のある、より大きな (2.2 $\mu$ F ~ 6.8 $\mu$ F) デカップリングコンデンサを使用します。こうしたより大型のコンデンサをデバイスから離れた場所に配置し、PCB と同じ領域にある複数のデバイス間でコンデンサを共有します。

- 外付け部品を慎重に選択および配置することで、OPA818 の高周波性能が維持されます。リアクタンスの小さい抵抗を使用します。最もよく機能するのは表面実装抵抗で、レイアウト全体をより厳密にすることができます。金属皮膜と炭素化合物を使ったアキシャルリード型抵抗を使うと、優れた高周波性能も実現できます。繰り返しになりますが、リードと PCB パターンの長さをできるだけ短くします。高周波アプリケーションでは、巻線抵抗を使用しないでください。出力ピンと反転入力ピンは寄生容量の影響を最も受けやすいので、帰還抵抗と直列出力抵抗 (ある場合) は、それぞれ反転入力ピンと出力ピンにできるだけ近づけて配置します。非反転入力終端抵抗といった他のネットワーク部品は、パッケージの近くに配置します。外部抵抗をシャントする寄生容量が少ない場合も、抵抗の値が過度に大きいと、時定数が大きくなり、性能が低下する可能性があります。OPA818 が従来型の電圧アンプとして構成されている場合、抵抗値は可能な限り低くし、負荷駆動に関する考慮事項と一致するようにしてください。抵抗値を小さくすると、寄生容量の影響が最小化され、抵抗のノイズ項は小さくなります。しかし、帰還回路 (非反転構成の場合は  $R_F + R_G$ 、反転構成の場合は  $R_F$ ) がアンプへの負荷として機能するため、抵抗値が小さいと動的消費電力と出力段の実効負荷が増加します。トランジンピーダンスアプリケーション (図 8-2 を参照) では、アプリケーションの必要性に応じて帰還抵抗を使用します。しかし、帰還補償コンデンサは反転ノード上のすべての寄生容量項を考慮して設定します。

- OPA818 などの高電圧デバイスでは、放熱が重要です。良好な熱放出を実現するために、サーマルパッドは、できれば OPA818 と同じ層にある熱拡散プレーンに接続するか、プレーンが異なる層にある場合はできるだけ多くのビアで接続します。周囲温度が高いときに良好な熱伝導を実現するために、OPA818 と同じ層に、幅広の金属でサーマルパッドに直接接続する熱拡散プレーンを少なくとも 1 つ配置します。熱拡散プレーンが複数利用可能な場合は、多数のビアで接続することで、熱伝導をさらに向上させてください。

5. OPA818 のような高速デバイスにはソケットを使用しないでください。ソケットによってリード長やピン間容量が増加することで、非常に厄介な寄生的回路が形成される可能性があり、スムーズで安定した周波数応答が妨げられる可能性があります。OPA818 を基板に半田付けすることで、最良の結果が得られます。

#### 8.4.1.1 熱に関する注意事項

OPA818 は、ほとんどの用途でヒートシンクや airflow を必要としません。許容される最大接合部温度から、許容される最大内部消費電力を設定します。これについては、次の段落で説明します。最大接合部温度は 105°C を超えないようにしてください。

動作時の接合部温度 ( $T_J$ ) は、 $T_A + P_D \times R_{\theta JA}$  で計算できます。合計内部消費電力 ( $P_D$ ) は、静止電力 ( $P_{DQ}$ ) と、負荷電力を供給するための出力段での追加消費電力 ( $P_{DL}$ ) の合計です。静止電力は、規定の無負荷時消費電流とデバイス全体の合計電源電圧の積です。 $P_{DL}$  は出力信号と負荷によって異なります。接地された抵抗負荷の場合、出力がいずれかの電源電圧の 1/2 に等しい電圧に固定されているときに  $P_{DL}$  は最大になります (バランス型バイポーラ電源の場合)。この条件で、 $P_{DL} = V_S^2 / (4 \times R_L)$  です。ここで、 $R_L$  には帰還ネットワーク負荷が含まれます。

出力段の電力と負荷に流入しない電力によって内部消費電力が決定されることに注意してください。

ワーストケースの例として、最大規定周囲温度 85°C で動作し、接地された 100Ω 負荷を駆動する 図 8-1 の回路の OPA818 を使用して最大  $T_J$  を計算します。

$$P_D = 10V \times 27.7mA + 5^2 / (4 \times (100\Omega \parallel 350.9\Omega)) \approx 357mW$$

$$\text{最大 } T_J = 85^\circ\text{C} + (0.357W \times 54.6^\circ\text{C/W}) = 104.5^\circ\text{C}.$$

図 8-1 の回路では、すべての実用的なシナリオは、より低い内部電力と接合部温度で動作できます。

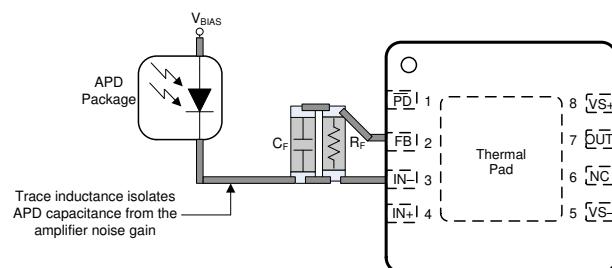

#### 8.4.2 レイアウト例

図 8-9. レイアウトに関する推奨事項

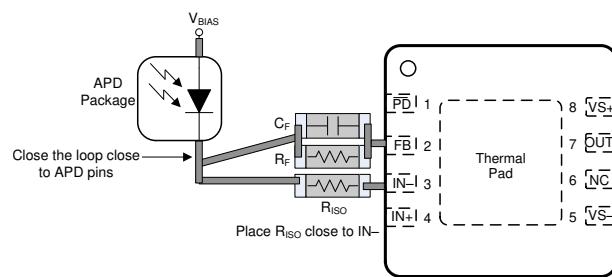

OPA818 をトランスインピーダンス アンプとして構成するときは、アバランシェ フォトダイオード (APD) とアンプの間のインダクタンスを最小限に抑えるよう十分に注意してください。フォトダイオードは、PCB 上でアンプと同じ面に必ず配置してください。アンプと APD を PCB の反対側に配置すると、ビアのインダクタンスによる寄生効果が増加します。APD パッケージは非常に大きくなる可能性があるため、APD を理想的なものよりも離れた場所に配置する必要があることがあります。2 つのデバイス間に距離を追加すると、APD とオペアンプの帰還回路の間のインダクタンスが増加します (式 4 も参照)。このアンプにより APD 容量がノイズ ゲイン伝達関数から分離されるため、非補償型アンプの安定性に悪影響を及ぼします。式 4 でノイズ ゲインを計算します。帰還回路間に追加された PCB 配線インダクタンスにより式 4 の分母が増加するため、ノイズ ゲインと位相マージンが低減されます。TO can のリード付き APD を使用する場合、TO can のリードを

できるだけ短くして、インダクタンスをさらに最小限に抑えます。また、アプリケーションで許可されている場合は、フォトダイオードを穴を通してではなく PCB のエッジにマウントすることを検討してください。

図 8-10 のレイアウトを改善するには、図 8-11 のいくつかのガイドラインに従ってください。従うべき主な 2 つのルールは次のとおりです。

- アンプの反転入力にできるだけ近い場所に、絶縁抵抗  $R_{ISO}$  を追加します。 $R_{ISO}$  の値は  $10\Omega \sim 20\Omega$  の範囲で選択します。この抵抗は、配線のインダクタンスとアンプの内部容量に起因する潜在的な共振を減衰させます。

- 帰還素子 ( $R_F$  と  $C_F$ ) と  $R_{ISO}$  間のループを、APD ピンにできるだけ近づけて配置します。この構成により、一段とバランスのとれたレイアウトが実現し、APD と帰還回路の間の誘導性絶縁が低減されます。

$$\text{Noise Gain} = \left(1 + \frac{Z_F}{Z_{IN}}\right) \quad (4)$$

ここで

- $Z_F$  は帰還回路の合計インピーダンスです

- $Z_{IN}$  は入力回路の合計インピーダンスです

図 8-10. 理想的ではない TIA レイアウト

図 8-11. TIA レイアウトの改善

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 開発サポート

- テキサス インスツルメンツ、『[広帯域の光フロントエンドリファレンス デザイン](#)』

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス インスツルメンツ、『[OPA817EVM ユーザーガイド](#)』

- テキサス・インスツルメンツ、『[高速アンプのトランスインピーダンスに関する考慮事項』アプリケーション レポート](#)

- テキサス インスツルメンツ、『[アナログ TIA フロントエンドのダイナミックレンジの最大化』技術概要](#)』

- テキサス インスツルメンツ、『[ブログ: トランスインピーダンス アンプについて知っておくべきこと—第1部](#)』

- テキサス インスツルメンツ、『[ブログ: トランスインピーダンス アンプについて知っておくべきこと—第2部](#)』

- テキサス インスツルメンツ、『[トレーニング ビデオ: トランスインピーダンス アンプ回路の設計方法](#)』

- テキサス インスツルメンツ、『[トレーニング ビデオ: 『高速トランスインピーダンス アンプの設計の流れ』](#)』

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 9.5 商標

、Excel™ is a trademark of Microsoft Corporation.

TINA-TI™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.7 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Changes from Revision A (March 2020) to Revision B (December 2025)

Page

- ドキュメント全体にわたって表、図、相互参照の採番方法を更新..... 1

---

|                                               |   |

|-----------------------------------------------|---|

| • DBV (SOT-23、5) パッケージと関連する内容を量産データとして追加..... | 1 |

| • DBV パッケージの高調波歪みを追加.....                     | 7 |

---

| Changes from Revision * (May 2019) to Revision A (March 2020) | Page |

|---------------------------------------------------------------|------|

| • ドキュメントのステータスを次のように変更:「事前情報」から:「量産データ」.....                  | 1    |

---

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins   | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| OPA818DBVR            | Active        | Production           | SOT-23 (DBV)   5 | 3000   LARGE T&R      | -           | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | O818                |

| OPA818DBVT            | Active        | Production           | SOT-23 (DBV)   5 | 250   SMALL T&R       | -           | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | O818                |

| OPA818IDRGR           | Active        | Production           | SON (DRG)   8    | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA818              |

| OPA818IDRGR.B         | Active        | Production           | SON (DRG)   8    | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA818              |

| OPA818IDRGRG4         | Active        | Production           | SON (DRG)   8    | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA818              |

| OPA818IDRGRG4.B       | Active        | Production           | SON (DRG)   8    | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA818              |

| OPA818IDRGT           | Active        | Production           | SON (DRG)   8    | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA818              |

| OPA818IDRGT.B         | Active        | Production           | SON (DRG)   8    | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA818              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

---

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

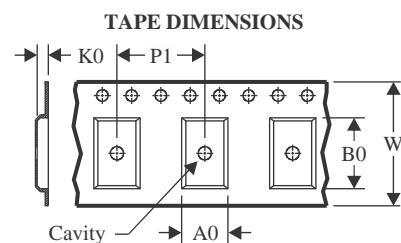

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

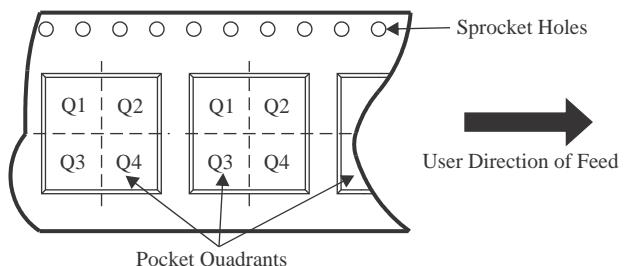

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| OPA818DBVR    | SOT-23       | DBV             | 5    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| OPA818DBVT    | SOT-23       | DBV             | 5    | 250  | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| OPA818IDRGR   | SON          | DRG             | 8    | 3000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| OPA818IDRGGR4 | SON          | DRG             | 8    | 3000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| OPA818IDRGRT  | SON          | DRG             | 8    | 250  | 180.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA818DBVR     | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| OPA818DBVT     | SOT-23       | DBV             | 5    | 250  | 210.0       | 185.0      | 35.0        |

| OPA818IDRGR    | SON          | DRG             | 8    | 3000 | 367.0       | 367.0      | 35.0        |

| OPA818IDRGGRG4 | SON          | DRG             | 8    | 3000 | 367.0       | 367.0      | 35.0        |

| OPA818IDRGRT   | SON          | DRG             | 8    | 250  | 210.0       | 185.0      | 35.0        |

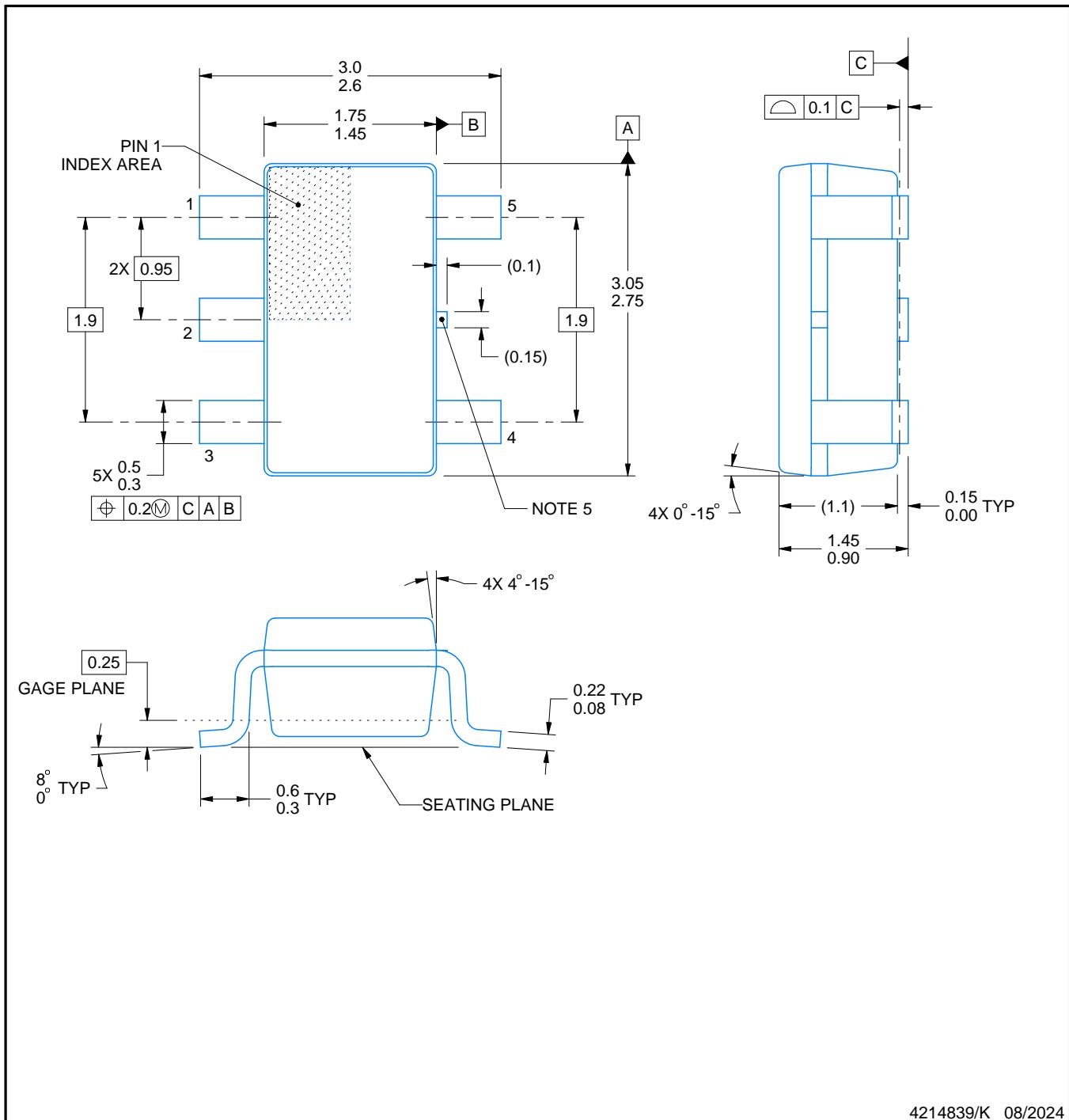

## PACKAGE OUTLINE

**DBV0005A**

## **SOT-23 - 1.45 mm max height**

## SMALL OUTLINE TRANSISTOR

4214839/K 08/2024

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

5. Support pin may differ or may not be present.

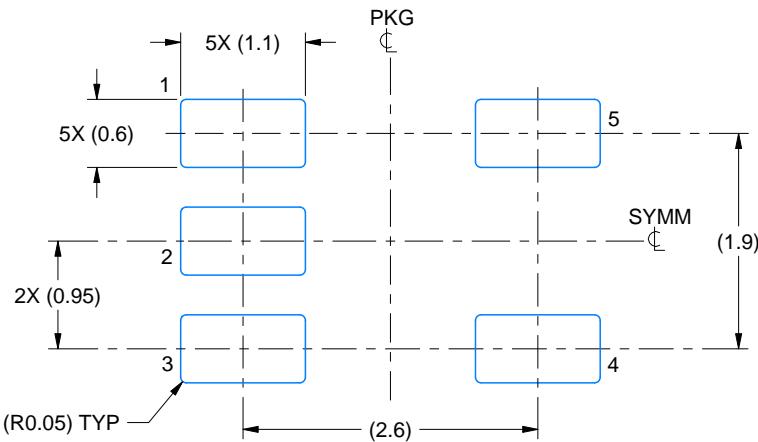

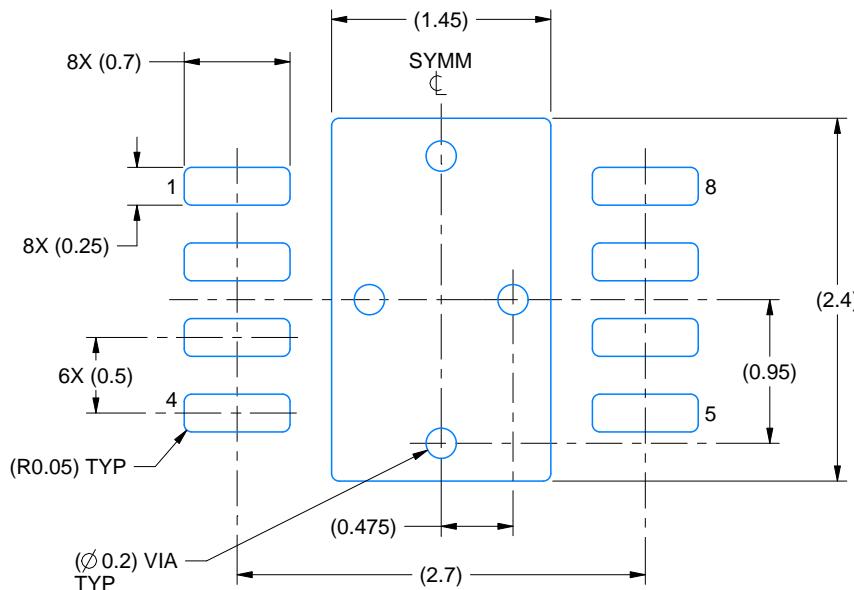

# EXAMPLE BOARD LAYOUT

DBV0005A

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:15X

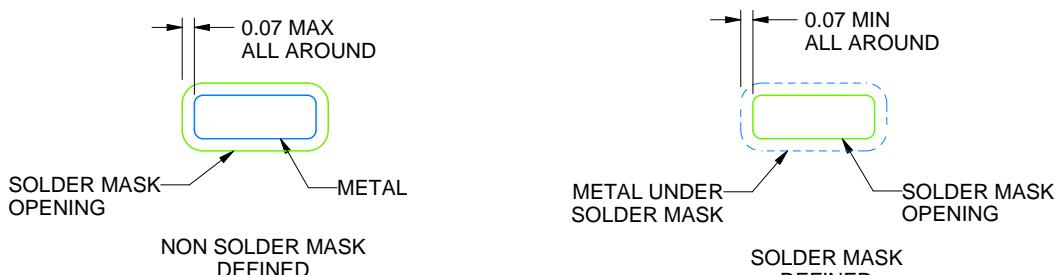

SOLDER MASK DETAILS

4214839/K 08/2024

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

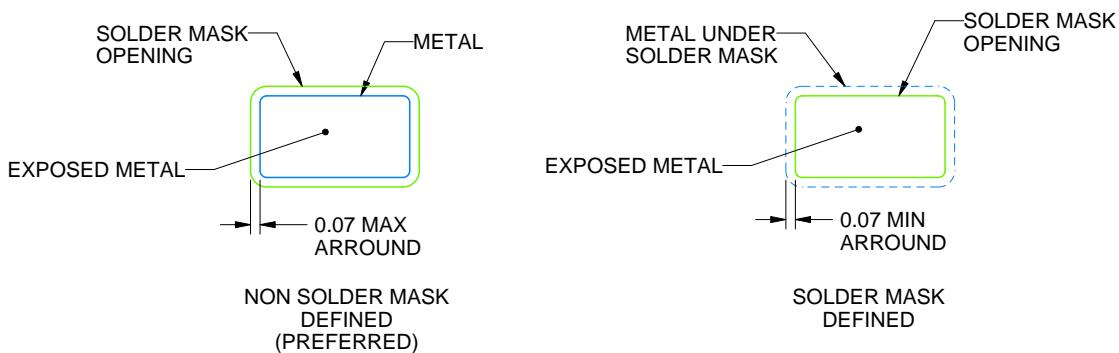

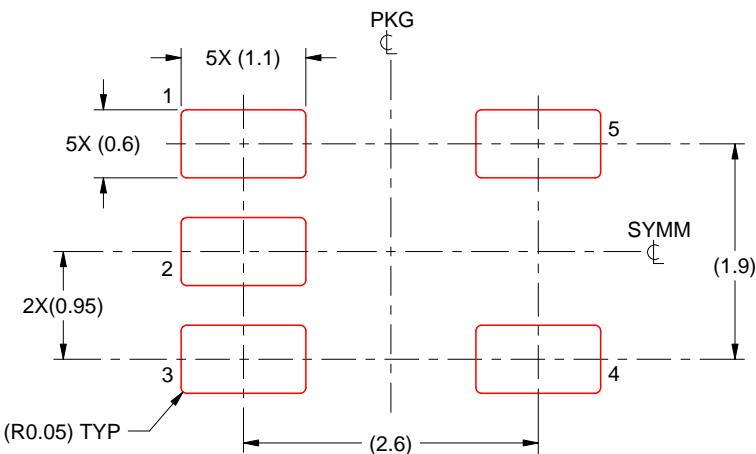

# EXAMPLE STENCIL DESIGN

DBV0005A

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE:15X

4214839/K 08/2024

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## GENERIC PACKAGE VIEW

### DRG 8

### WSON - 0.8 mm max height

3 x 3, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4225794/A

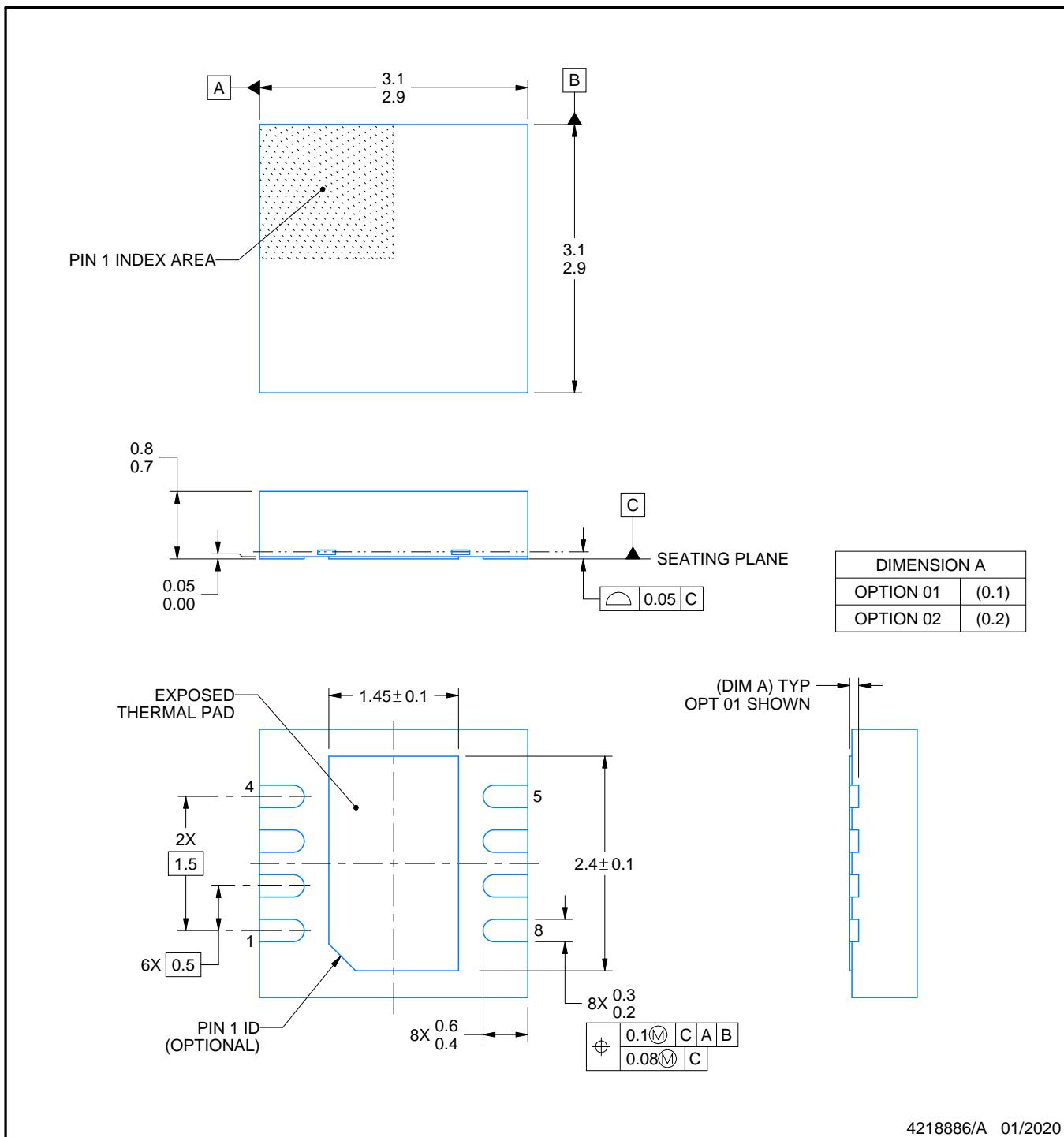

# PACKAGE OUTLINE

DRG0008B

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

4218886/A 01/2020

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

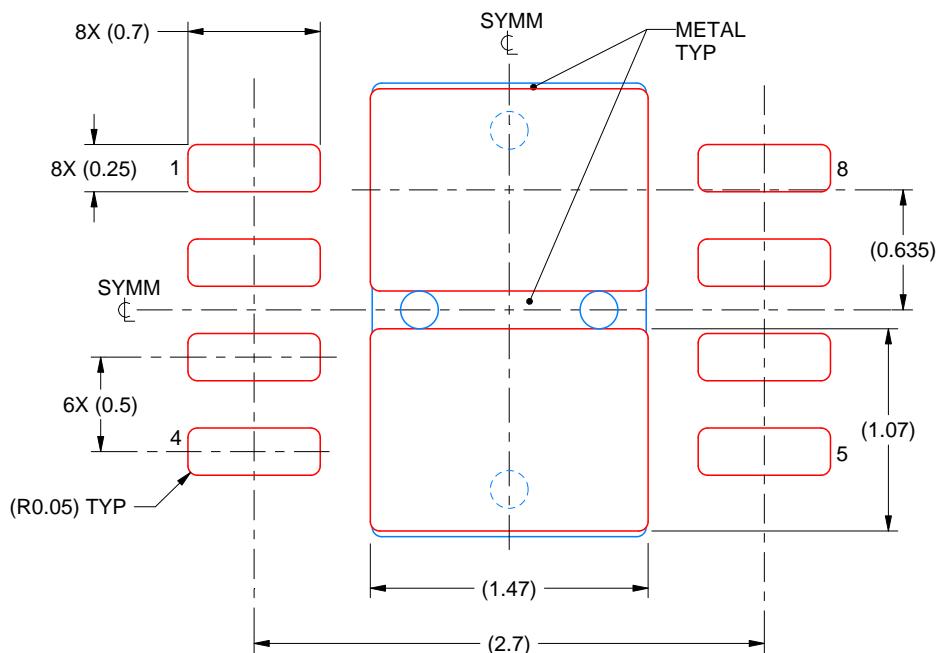

# EXAMPLE BOARD LAYOUT

DRG0008B

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

LAND PATTERN EXAMPLE

SCALE:20X

SOLDER MASK DETAILS

4218886/A 01/2020

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# EXAMPLE STENCIL DESIGN

DRG0008B

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD

82% PRINTED SOLDER COVERAGE BY AREA

SCALE:25X

4218886/A 01/2020

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月