## OPT3001-Q1 環境光センサ(ALS)

### 1 特長

- 車載デバイス用に AEC-Q100 認定済み

- 温度グレード 2 (USON パッケージ): -40°C ~ 105°C、T<sub>A</sub>

- 温度グレード 3 (USON パッケージ): -40°C ~ 85°C、T<sub>A</sub>

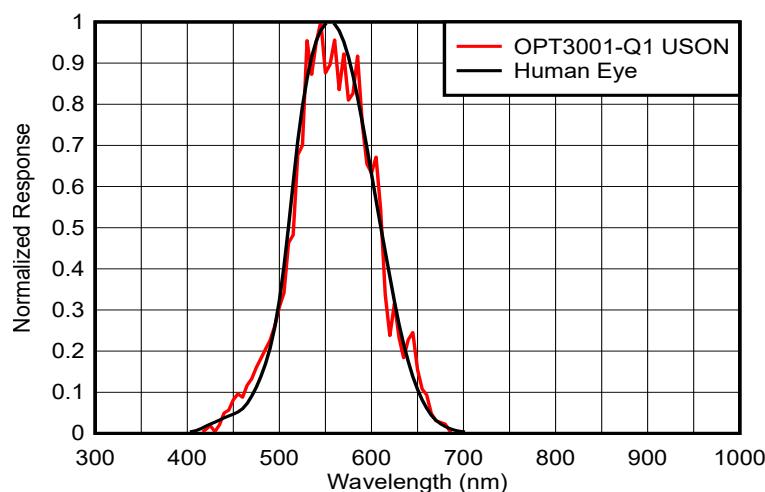

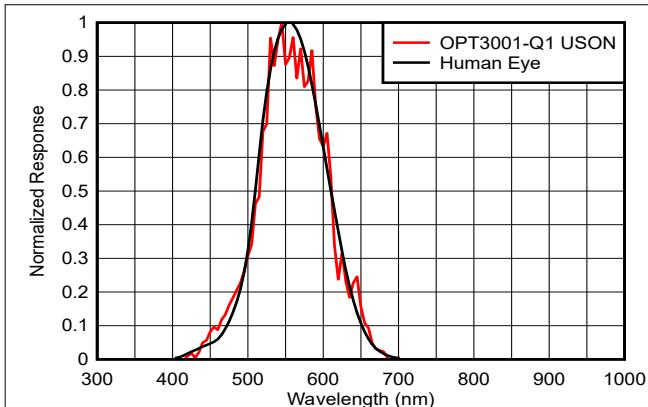

- 高精度の光フィルタリングにより人間の目に適合

- 99% 超 (標準値) の IR を除去 (USON パッケージ)

- 自動フルスケール設定機能により、ソフトウェアが簡素化され、適切な構成を実現

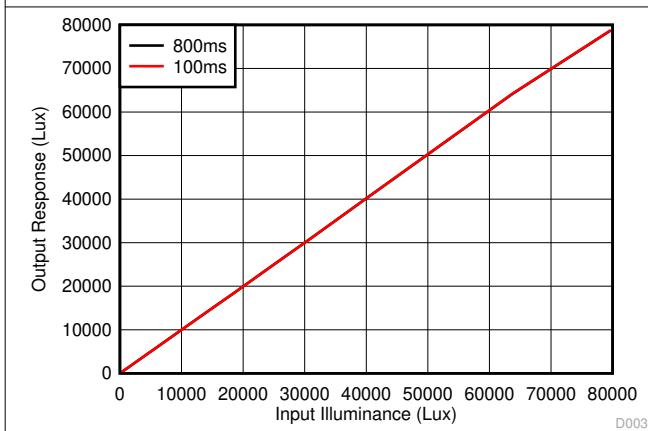

- 測定範囲: 0.01lux ~ 83klux

- 自動ゲイン範囲設定により、23 ビットの実効ダイナミックレンジを実現

- 12 個のバイナリ重み付けフルスケールレンジ設定: レンジ間のマッチング < 0.2% (標準値)

- 小さい動作電流: 1.8µA (標準値)

- 広い電源電圧範囲: 1.6V ~ 3.6V

- 5.5V 許容の I/O

- 柔軟な割り込みシステム

- 小さなフォームファクタ

- 2mm × 2mm × 0.65mm の USON パッケージ

### 2 アプリケーション

- 車載用車内および車外 照明

- インフォテインメントおよびクラスタ ディスプレイ

- エレクトロクロマティックミラーとスマートミラー

- ワイパー モジュール

- ヘッド アップ ディスプレイ (HUD) システム

- 車載用カメラ システム

#### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------|----------------------|--------------------------|

| OPT3001-Q1 | DNP (USON、6)         | 2.00mm × 2.00mm          |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SBOS853](#)

### 3 説明

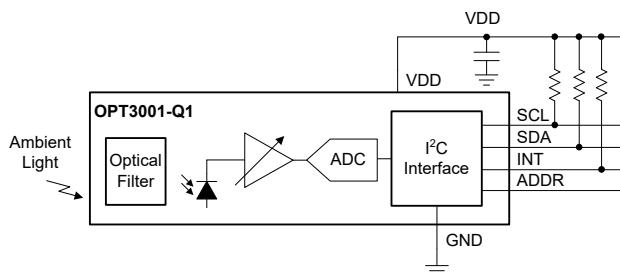

OPT3001-Q1 は、可視光の強度を測定する光センサです。このセンサの分光応答は、人間の目の明所視応答に非常に近く、一方で赤外線に対する高い遮断特性も備えています。

OPT3001-Q1 は、人間の目と同じように光の強度を測定するシングル チップの lux メーターです。OPT3001-Q1 デバイスは、高精度のスペクトル応答と強力な IR 除去により、光源にかかわらず人間の目の感覚に一致する照度を正確に測定できます。また、強力な IR 除去機能があるため、産業用のデザインで美観上の理由から暗色のガラス下にセンサを設置する必要がある場合でも、高い精度を維持できます。OPT3001-Q1 デバイスは、人間の目が感じる光環境を実現するシステム向けに開発された製品です。人間の目との一致度が低く、IR 除去も弱いフォトダイオード、フォトレジスタ、その他の環境光センサの代替品として理想的です。

柔軟なデジタル動作により、システムの統合が可能です。連続的な測定も、1 回のみの測定も実行できます。制御および割り込みシステムは自律的に動作するため、プロセッサがスリープ中でもセンサが適切なウェイクアップ イベントを調べ、割り込みピンで通知します。デジタル出力は、I<sup>2</sup>C および SMBus 互換の 2 線式シリアル インターフェイスで通知されます。

OPT3001-Q1 デバイスは消費電力が低く、電源電圧も低いため、バッテリ駆動のシステムで長時間動作可能です。

内蔵のフル lux 設定機能により、手動でフルスケール範囲を選択することなく、0.01 ルクスから 83k ルクスの測定に対応できます。この機能により、23 ビットの実効ダイナミック レンジにわたって光の測定が可能です。

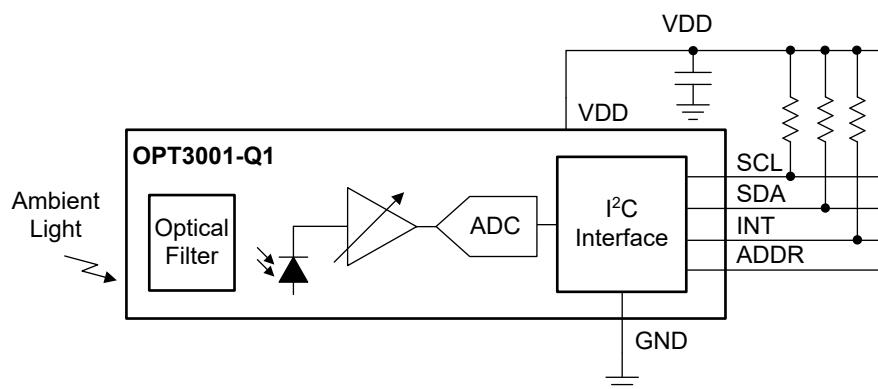

ブロック図

スペクトル応答：OPT3001-Q1 と人間の目の比較

## 目次

|                 |    |                           |    |

|-----------------|----|---------------------------|----|

| 1 特長            | 1  | 7.1 内部レジスタ                | 21 |

| 2 アプリケーション      | 1  | 8 アプリケーションと実装             | 28 |

| 3 説明            | 2  | 8.1 アプリケーション情報            | 28 |

| 4 ピン構成および機能     | 3  | 8.2 代表的なアプリケーション          | 29 |

| 5 仕様            | 4  | 8.3 設計のベスト プラクティス         | 32 |

| 5.1 絶対最大定格      | 4  | 8.4 電源に関する推奨事項            | 33 |

| 5.2 ESD 定格      | 4  | 8.5 レイアウト                 | 33 |

| 5.3 推奨動作条件      | 4  | 9 デバイスおよびドキュメントのサポート      | 33 |

| 5.4 熱に関する情報     | 4  | 9.1 ドキュメントのサポート           | 33 |

| 5.5 電気的特性       | 5  | 9.2 ドキュメントの更新通知を受け取る方法    | 34 |

| 5.6 タイミング要件 (1) | 6  | 9.3 サポート・リソース             | 34 |

| 5.7 代表的特性       | 8  | 9.4 商標                    | 34 |

| 6 詳細説明          | 12 | 9.5 静電気放電に関する注意事項         | 34 |

| 6.1 概要          | 12 | 9.6 用語集                   | 34 |

| 6.2 機能ブロック図     | 12 | 10 改訂履歴                   | 34 |

| 6.3 機能説明        | 13 | 11 メカニカル、パッケージ、および注文情報    | 36 |

| 6.4 デバイスの機能モード  | 15 | 11.1 ハンダ付けと取り扱いについての推奨事項  | 36 |

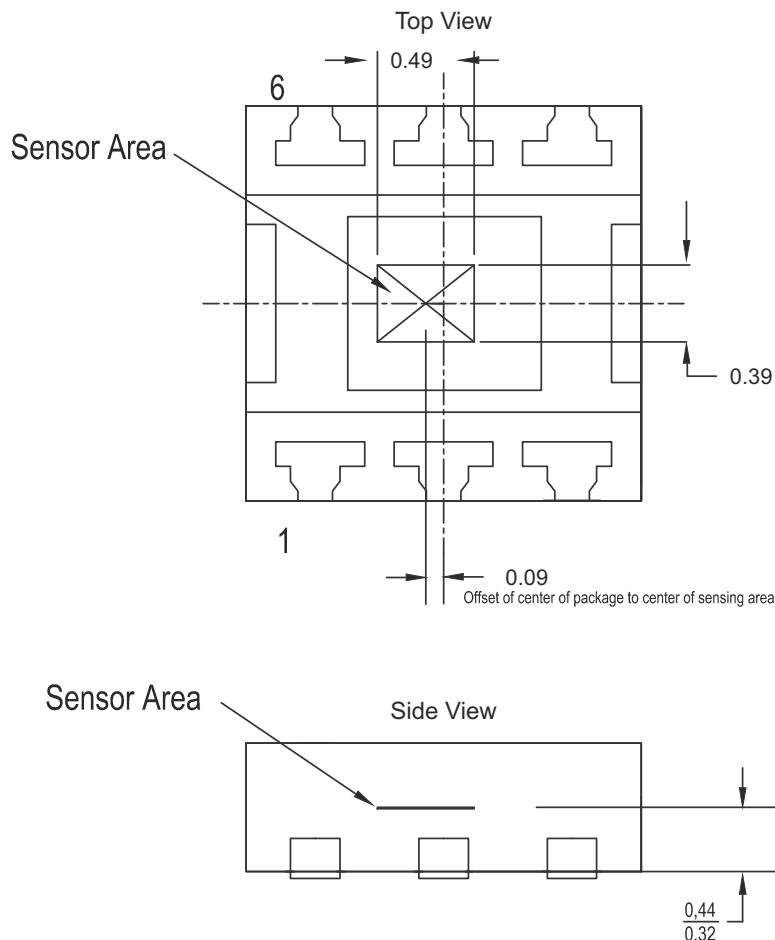

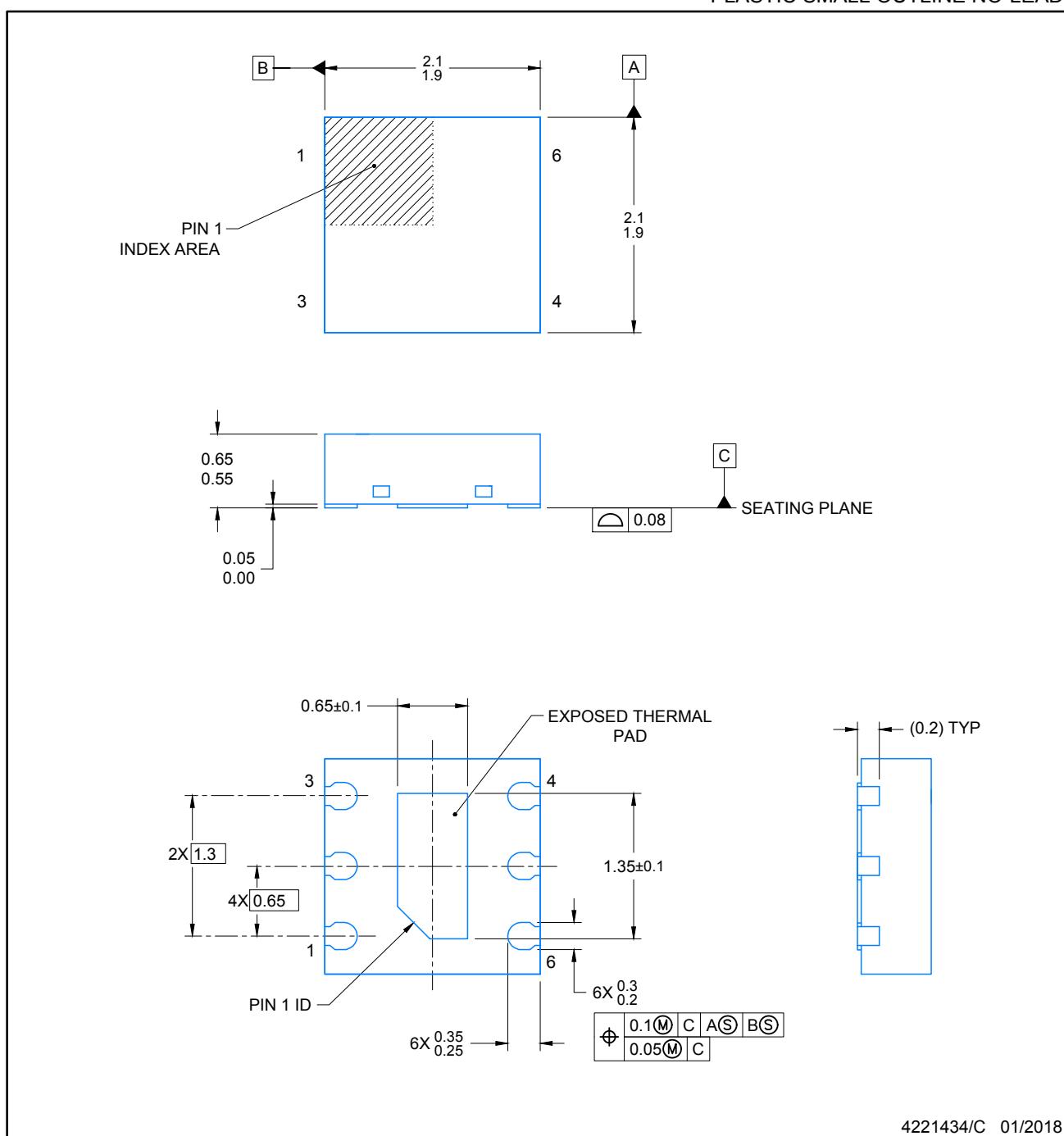

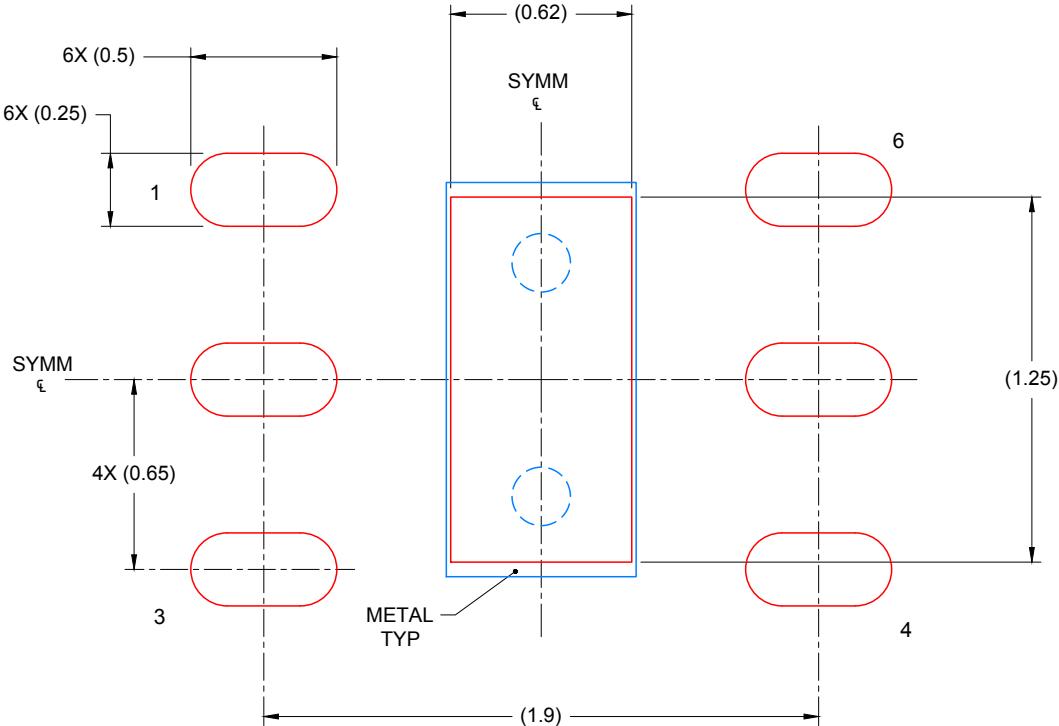

| 6.5 プログラミング     | 18 | 11.2 DNP (S-PDSO-N6) 機械図面 | 36 |

| 7 レジスタ マップ      | 21 |                           |    |

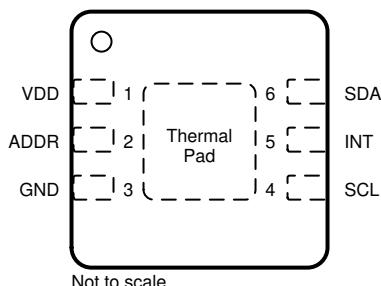

## 4 ピン構成および機能

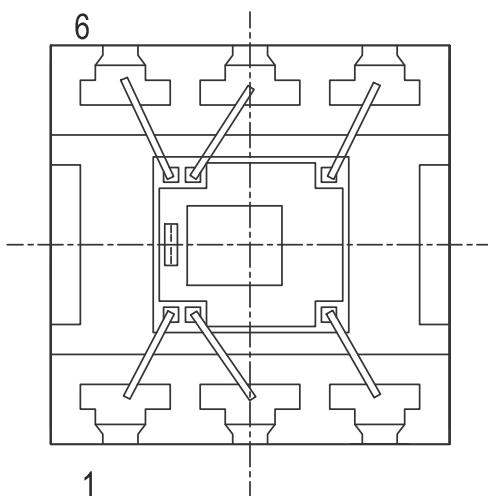

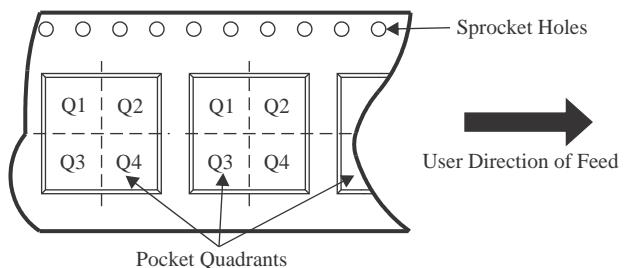

図 4-1. DNP パッケージ 6 ピン USON 上面図

表 4-1. ピンの機能

| ピン |                 | タイプ <sup>(1)</sup> | 説明                                                            |

|----|-----------------|--------------------|---------------------------------------------------------------|

| 番号 | 名称              |                    |                                                               |

| 1  | V <sub>DD</sub> | I                  | デバイス パワー。1.6V から 3.6V 電源へ接続します。                               |

| 2  | ADDR            | I                  | アドレスピン。このピンは I <sup>2</sup> C アドレスの LSB を設定します。               |

| 3  | GND             | P                  | グランド                                                          |

| 4  | SCL             | I                  | I <sup>2</sup> C クロック。10kΩ 抵抗を使用して 1.6V 電源と 5.5V 電源との間に接続します。 |

| 5  | INT             | O                  | 割り込み出力、オープンドレイン。10kΩ 抵抗を使用して 1.6V 電源と 5.5V 電源との間に接続します。       |

| 6  | SDA             | I/O                | I <sup>2</sup> C データ。10kΩ 抵抗を使用して 1.6V 電源と 5.5V 電源との間に接続します。  |

(1) I = 入力、O = 出力、I/O = 入力または出力、P = 電源

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                  |                         | 最小値  | 最大値                | 単位 |

|------------------|-------------------------|------|--------------------|----|

| 電圧               | VDD から GND              | -0.5 | 6                  | V  |

|                  | SDA、SCL、INT、ADDR から GND | -0.5 | 6                  | V  |

| 任意のピンへの電流        |                         | 10   |                    | mA |

| T <sub>J</sub>   | 接合部温度                   | 150  |                    | °C |

| T <sub>stg</sub> | 保存温度                    | -65  | 150 <sup>(2)</sup> | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) 105°C を超える温度に長時間さらされると、パッケージの変色、分光特性の歪み、測定精度の低下を引き起こす可能性があります。

### 5.2 ESD 定格

|                    |      |                                                                | 値     | 単位 |

|--------------------|------|----------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>   | ±2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup> | ±500  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                              |  | 最小値 | 公称値 | 最大値 | 単位 |

|------------------------------|--|-----|-----|-----|----|

| 電源電圧                         |  | 1.6 | 3.6 | 3.6 | V  |

| 動作温度 (グレード 2: OPT3001DNPQ1)  |  | -40 | 105 | 105 | °C |

| 動作温度 (グレード 3: OPT3001IDNPQ1) |  | -40 | 85  | 85  | °C |

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | OPT3001-Q1 | 単位   |

|-----------------------|---------------------|------------|------|

|                       |                     | DNP (USON) |      |

|                       |                     | 6 ピン       |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 71.2       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 45.7       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 42.2       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 2.4        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 42.8       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 17.0       | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

特に指定がない限り、すべての仕様は  $TA = 25^\circ\text{C}$ 、 $VDD = 3.3\text{V}$ 、変換時間 800ms ( $CT = 1$ )<sup>(1)</sup>、全自動フルスケール レンジ ( $RN[3:0] = 1100\text{b}$ )<sup>(1)</sup>、白色 LED、通常角度での入射光の条件において適用されます。

| パラメータ                        | テスト条件                                                                                               | 最小値                                           | 標準値                                                        | 最大値                 | 単位                 |

|------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------|---------------------|--------------------|

| <b>光</b>                     |                                                                                                     |                                               |                                                            |                     |                    |

| <b>USON バリエント</b>            |                                                                                                     |                                               |                                                            |                     |                    |

|                              | ピーク放射照度スペクトル応答性                                                                                     |                                               | 550                                                        |                     | nm                 |

| 測定出力結果                       | ADC コードあたり 0.64lux、フルスケール 2620.8 ルクス ( $RN[3:0] = 0110$ ) <sup>(1)</sup> 、2000 ルクス入力 <sup>(2)</sup> | 2812                                          | 3125                                                       | 3437                | ADC コード            |

|                              |                                                                                                     | 1800                                          | 2000                                                       | 2200                | lux                |

| 温度範囲全体での測定ドリフト               | 入力照度 = 2000lux                                                                                      |                                               | 0.02                                                       |                     | %/°C               |

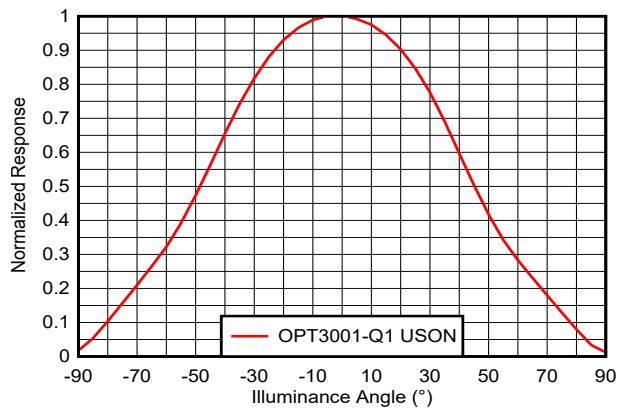

| 半値角                          | 最大出力値の 50%                                                                                          |                                               | 57                                                         |                     | 度                  |

| <b>共通仕様</b>                  |                                                                                                     |                                               |                                                            |                     |                    |

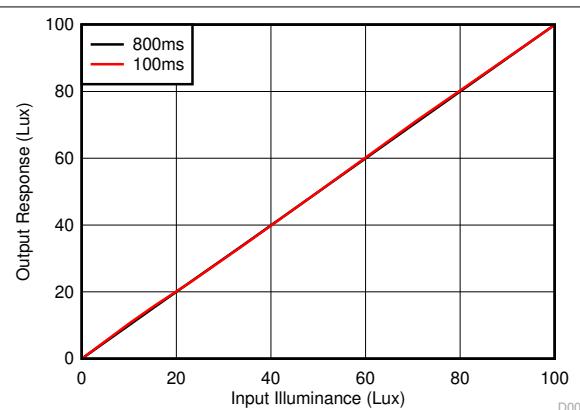

| 分解能 (LSB)                    | 最小フルスケール範囲 ( $RN[3:0] = 0000\text{b}$ ) <sup>(1)</sup> 、変換時間 800ms 時                                |                                               | 0.01                                                       |                     | lux                |

|                              | 最小フルスケール範囲 ( $RN[3:0] = 0000\text{b}$ ) <sup>(1)</sup> 、変換時間 100ms 時                                |                                               | 0.08                                                       |                     |                    |

| フルスケール照度                     |                                                                                                     | 83865.6                                       |                                                            |                     | lux                |

| ゲイン範囲間の相対精度 <sup>(3)</sup>   |                                                                                                     | 0.2                                           |                                                            |                     | %                  |

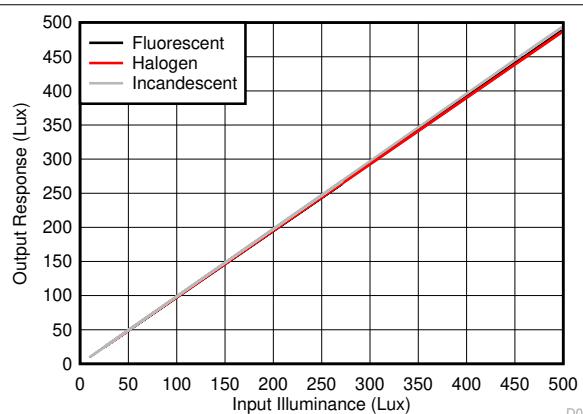

| 光源のバリエーション (白熱灯、ハロゲンランプ、蛍光灯) | 裸のデバイス、カバー ガラスなし                                                                                    | 4                                             |                                                            |                     | %                  |

| 直線性                          | 入力照度 > 40lux                                                                                        | 2                                             |                                                            |                     | %                  |

|                              | 入力照度は 40lux 未満                                                                                      | 5                                             |                                                            |                     | %                  |

| ダーク条件 ADC 出力                 | ADC コードごとに 0.01lux                                                                                  | 0                                             | 3                                                          |                     | ADC コード            |

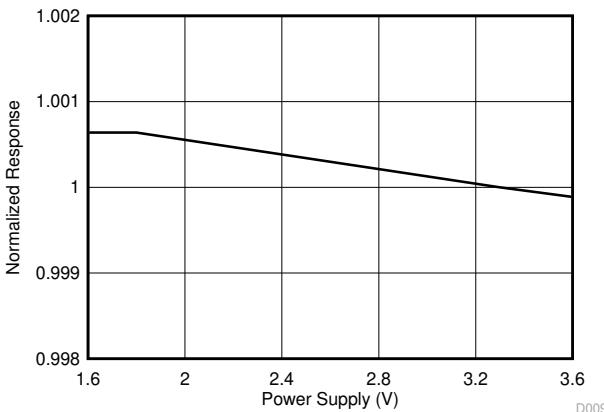

| PSRR                         | 電源除去比 <sup>(4)</sup>                                                                                | 3.6V および 1.6V での $VDD$                        | 0.1                                                        |                     | %/V <sup>(3)</sup> |

| <b>電源</b>                    |                                                                                                     |                                               |                                                            |                     |                    |

| $V_{DD}$                     | 動作範囲                                                                                                |                                               | 1.6                                                        | 3.6                 | V                  |

| $V_{I2C}$                    | $I^2C$ プルアップ抵抗の動作範囲                                                                                 | $I^2C$ プルアップ抵抗、 $V_{DD} \leq V_{I2C}$         | 1.6                                                        | 5.5                 | V                  |

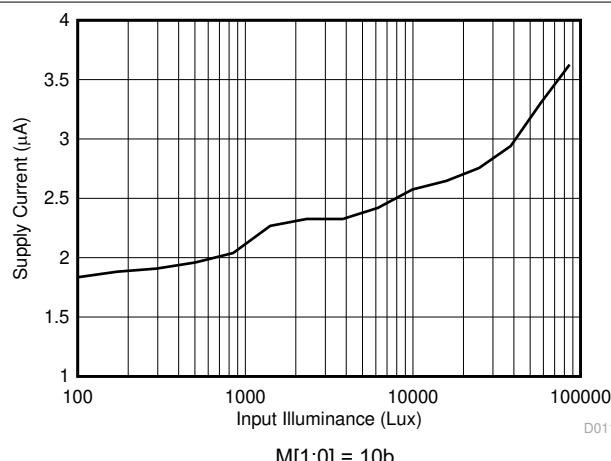

| $I_Q$                        | 静止時電流                                                                                               | 暗闇                                            | アクティブ、 $V_{DD} = 3.6V$                                     | 1.8                 | 2.5 $\mu\text{A}$  |

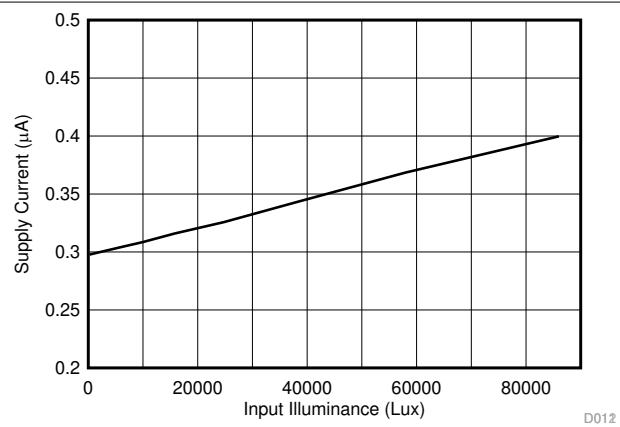

|                              |                                                                                                     |                                               | シャットダウン ( $M[1:0] = 00$ ) <sup>(1)</sup> 、 $V_{DD} = 3.6V$ | 0.3                 | 0.47 $\mu\text{A}$ |

|                              | フルスケール lux                                                                                          |                                               | アクティブ、 $V_{DD} = 3.6V$                                     | 3.7                 |                    |

|                              |                                                                                                     |                                               | シャットダウン ( $M[1:0] = 00$ ) <sup>(1)</sup>                   | 0.4                 |                    |

| POR                          | Power-on-reset threshold                                                                            |                                               |                                                            | 0.8                 | V                  |

| <b>デジタル</b>                  |                                                                                                     |                                               |                                                            |                     |                    |

| $C_{IO}$                     | I/O ピン容量                                                                                            |                                               | 3                                                          |                     | pF                 |

|                              | 総積分時間 <sup>(5)</sup>                                                                                | ( $CT=1$ ) <sup>(1)</sup> 、800ms モード、lux 範囲固定 | 720                                                        | 800                 | 880 ms             |

|                              |                                                                                                     | ( $CT=0$ ) <sup>(1)</sup> 、100ms モード、lux 範囲固定 | 90                                                         | 100                 | 110 ms             |

| $V_{IL}$                     | Low レベル入力電圧 (SDA、SCL、ADDR)                                                                          |                                               | 0                                                          | $0.3 \times V_{DD}$ | V                  |

| $V_{IH}$                     | High レベル入力電圧 (SDA、SCL、ADDR)                                                                         |                                               | $0.7 \times V_{DD}$                                        | 5.5                 | V                  |

| $I_{IL}$                     | Low レベル入力電流 (SDA、SCL、ADDR)                                                                          |                                               | 0.01                                                       | 0.25 <sup>(6)</sup> | $\mu\text{A}$      |

特に指定がない限り、すべての仕様は  $TA = 25^\circ\text{C}$ 、 $VDD = 3.3\text{V}$ 、変換時間 800ms ( $CT = 1$ )<sup>(1)</sup>、全自動フルスケール レンジ ( $RN[3:0] = 1100\text{b}$ )<sup>(1)</sup>、白色 LED、通常角度での入射光の条件において適用されます。

| パラメータ                                       |        | テスト条件               | 最小値 | 標準値 | 最大値                      | 単位            |

|---------------------------------------------|--------|---------------------|-----|-----|--------------------------|---------------|

| $V_{OL}$ 低レベル出力電流 (SDA および INT)             |        | $I_{OL}=3\text{mA}$ |     |     | 0.32                     | V             |

| $I_{ZH}$ 出力ロジック High、High-Z リーク電流 (SDA、INT) |        | $V_{DD}$ ピンで測定      |     |     | 0.01 0.25 <sup>(6)</sup> | $\mu\text{A}$ |

| 温度                                          |        |                     |     |     |                          |               |

| 仕様温度範囲                                      | 仕様温度範囲 | グレード 3 (USON パリアント) | -40 | 85  | 85                       | °C            |

- (1) 構成レジスタ内の制御フィールドを指します

- (2) 2,000lux に較正された白色 LED および 850nm LED でテスト済み

- (3) 隣接する上位のフルスケール レンジ設定で、固定されたほぼフルスケールの照度レベルを測定することにより特性評価を実施します。

- (4) PSRR とは、現在の測定値に対する lux 出力の変化率を、電源電圧の変化量で割ったものです。ここでは、3.6V および 1.6V の電源を使用した測定結果に基づいて特性評価されています。

- (5) 変換時間は、変換の開始からデータの読み出しが可能になるまでの時間であり、積分時間に 3ms を加えたものです。

- (6) 規定されているリーク電流は、主に生産試験装置の限界によるものです。代表的な値は、これよりかなり低くなります

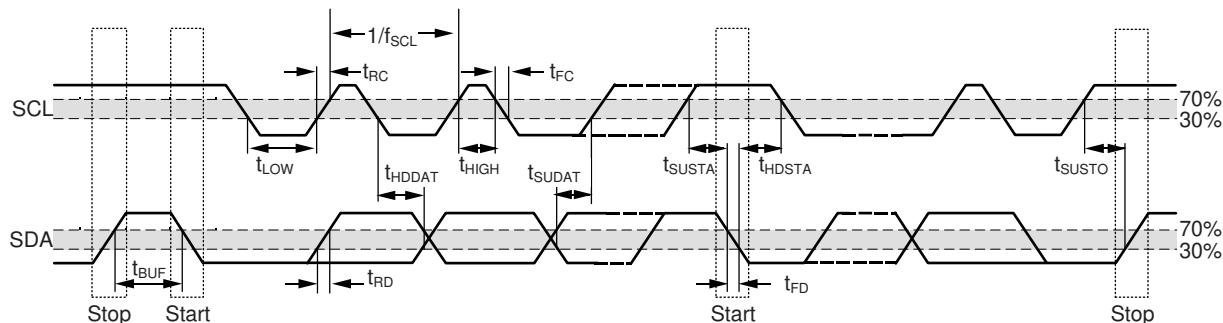

## 5.6 タイミング要件 <sup>(1)</sup>

|                                    |                                                            | 最小値  | 標準値 | 最大値 | 単位  |

|------------------------------------|------------------------------------------------------------|------|-----|-----|-----|

| <b>I<sup>2</sup>C フアスト モード</b>     |                                                            |      |     |     |     |

| $f_{SCL}$                          | SCL 動作周波数                                                  | 0.01 | 0.4 | 0.4 | MHz |

| $t_{BUF}$                          | STOP と START 間のバスフリー時間                                     | 1300 |     |     | ns  |

| $t_{HDSTA}$                        | リピート スタート後のホールド時間                                          | 600  |     |     | ns  |

| $t_{SUSTA}$                        | リピート スタート セットアップ時間                                         | 600  |     |     | ns  |

| $t_{SUSTO}$                        | ストップ セットアップ時間                                              | 600  |     |     | ns  |

| $t_{HDDAT}$                        | データ ホールド時間                                                 | 20   | 900 | 900 | ns  |

| $t_{SUDAT}$                        | データ セットアップ時間                                               | 100  |     |     | ns  |

| $t_{LOW}$                          | SCL クロックの Low 期間                                           | 1300 |     |     | ns  |

| $t_{HIGH}$                         | SCL クロックの High 期間                                          | 600  |     |     | ns  |

| $t_{RC}$ および $t_{FC}$              | クロックの立ち上がりおよび立ち下がり時間                                       |      | 300 | 300 | ns  |

| $t_{RD}$ および $t_{FD}$              | データ立ち上がり時間および立ち下がり時間                                       |      | 300 | 300 | ns  |

| $t_{TIMEO}$                        | バスのタイムアウト期間。SCL ラインがこの時間 Low に保持されると、バス ステート マシンはリセットされます。 | 28   |     |     | ms  |

| <b>I<sup>2</sup>C (ハイスピード モード)</b> |                                                            |      |     |     |     |

| $f_{SCL}$                          | SCL 動作周波数                                                  | 0.01 | 2.6 | 2.6 | MHz |

| $t_{BUF}$                          | STOP と START 間のバスフリー時間                                     | 160  |     |     | ns  |

| $t_{HDSTA}$                        | リピート スタート後のホールド時間                                          | 160  |     |     | ns  |

| $t_{SUSTA}$                        | リピート スタート セットアップ時間                                         | 160  |     |     | ns  |

| $t_{SUSTO}$                        | ストップ セットアップ時間                                              | 160  |     |     | ns  |

| $t_{HDDAT}$                        | データ ホールド時間                                                 | 20   | 140 | 140 | ns  |

| $t_{SUDAT}$                        | データ セットアップ時間                                               | 20   |     |     | ns  |

| $t_{LOW}$                          | SCL クロックの Low 期間                                           | 240  |     |     | ns  |

| $t_{HIGH}$                         | SCL クロックの High 期間                                          | 60   |     |     | ns  |

| $t_{RC}$ および $t_{FC}$              | クロックの立ち上がりおよび立ち下がり時間                                       |      | 40  | 40  | ns  |

| $t_{RD}$ および $t_{FD}$              | データ立ち上がり時間および立ち下がり時間                                       |      | 80  | 80  | ns  |

|             |                                                          | 最小値 | 標準値 | 最大値 | 単位 |

|-------------|----------------------------------------------------------|-----|-----|-----|----|

| $t_{TIMEO}$ | バスのタイムアウト期間。SCL ラインがこの時間 Low に保持されると、バスステートマシンはリセットされます。 |     | 28  |     | ms |

(1) すべてのタイミングパラメータは、最終的な安定電圧値に対して、Low 側は 30%、High 側は 70% のスレッショルドを基準としています。

図 5-1. I<sup>2</sup>C の詳細なタイミング図

## 5.7 代表的特性

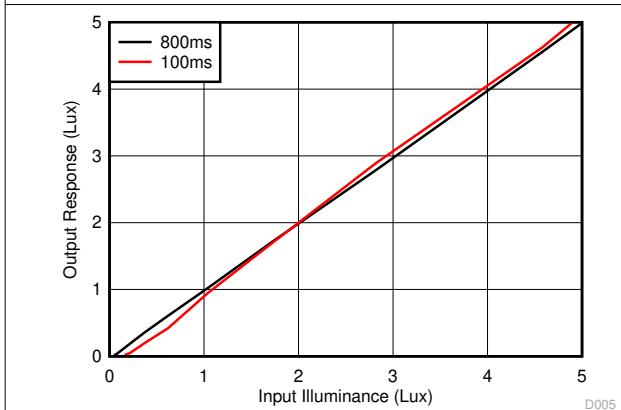

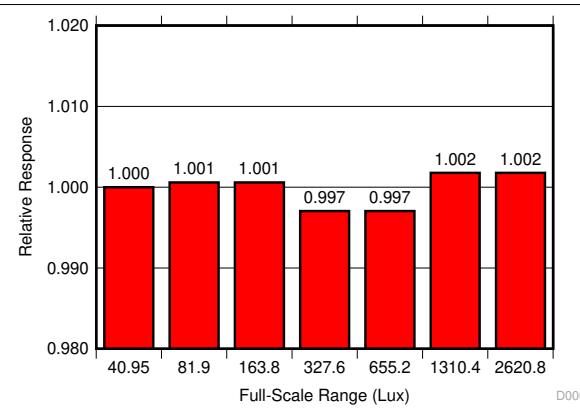

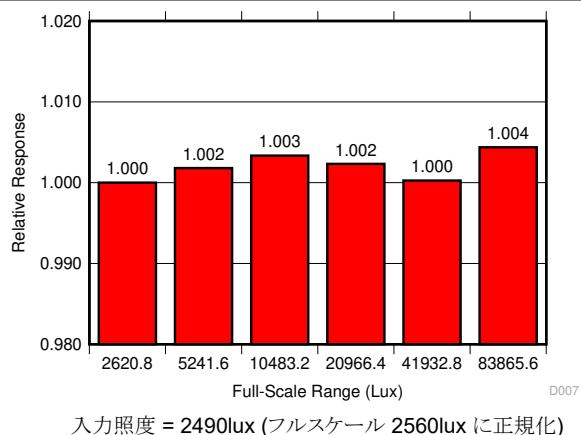

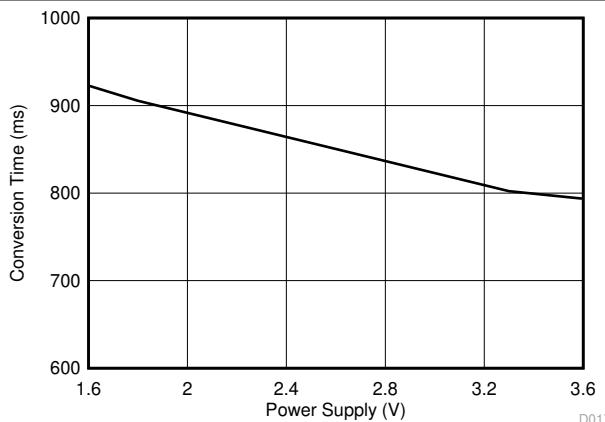

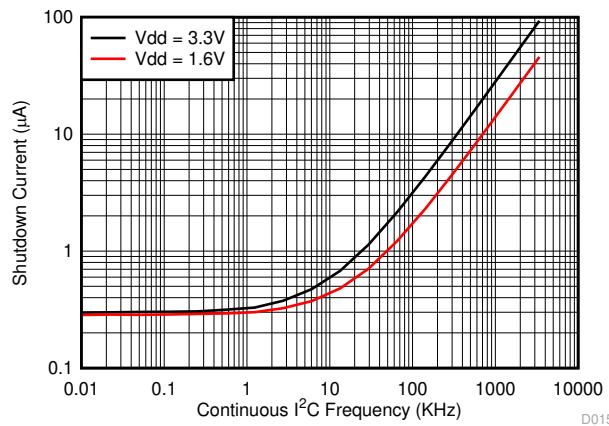

特に記述のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 3.3\text{V}$ 、800ms の変換時間 (CT = 1)、自動フルスケール範囲 (RN[3:0]=1100b)、白色 LED、光の通常角の入射角。

図 5-2. スペクトル応答と波長の関係

図 5-3. 出力応答と入力輝度との関係、複数の光源：蛍光、ハロゲン、白熱

D002

図 5-4. 出力応答と入力照度の関係：全範囲 = 0lux ~ 83klux

D003

図 5-5. 出力応答と入力照度の関係：中照度範囲 = 0lux ~ 100lux

D004

図 5-6. 出力応答と入力照度の関係：低範囲 = 0lux ~ 5lux

D005

図 5-7. フルスケール レンジのマッチング：最下位の 7 つの範囲

D006

入力照度 = 33lux (フルスケール 40.95lux に正規化)

図 5-8. フルスケール範囲の一致 (上位 6 つの範囲)

図 5-9. 変換時間と電源電圧との関係

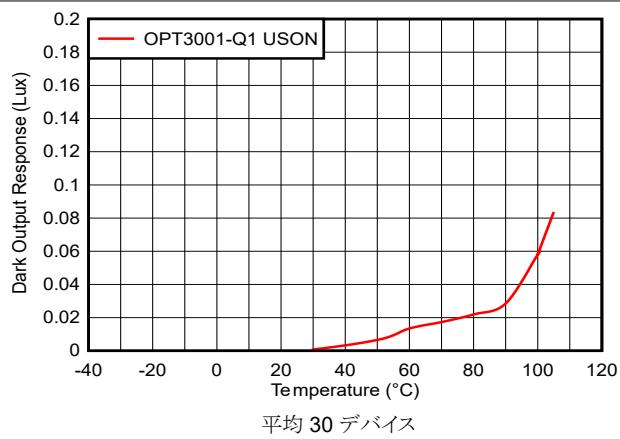

図 5-10. 暗応答と温度との関係 (グレード 2)

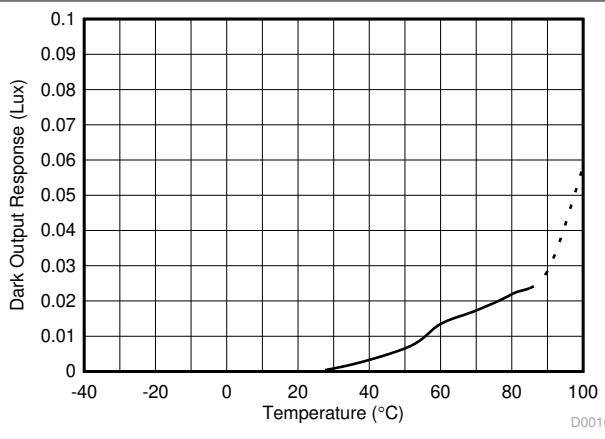

図 5-11. 暗応答と温度との関係 (グレード 3)

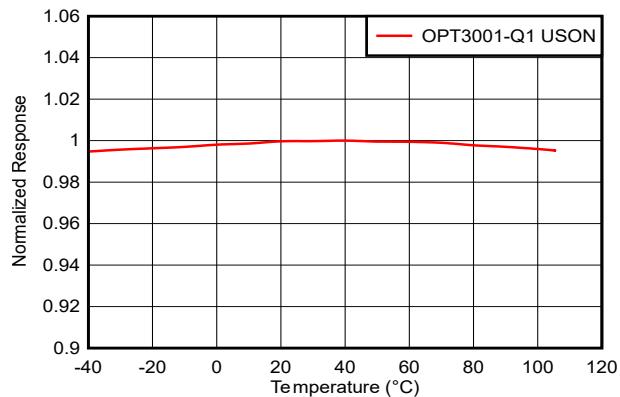

図 5-12. 正規化された応答と温度との関係 (グレード 2)

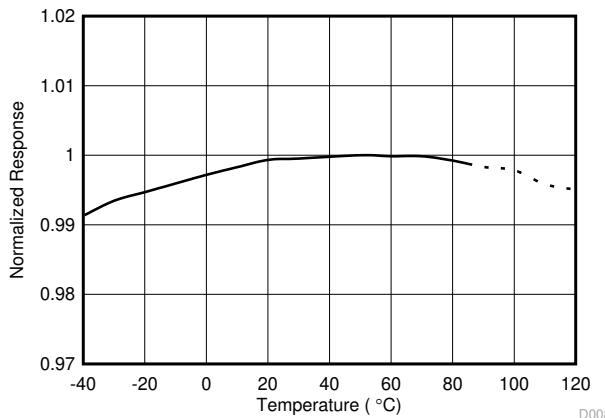

図 5-13. 正規化された応答と温度との関係 (グレード 3)

図 5-14. 正規化応答と電源電圧との関係

図 5-15. 正規化された応答と照度角度との関係

図 5-16. 消費電流と入力照度の関係

図 5-17. シャットダウン電流と入力照度の関係

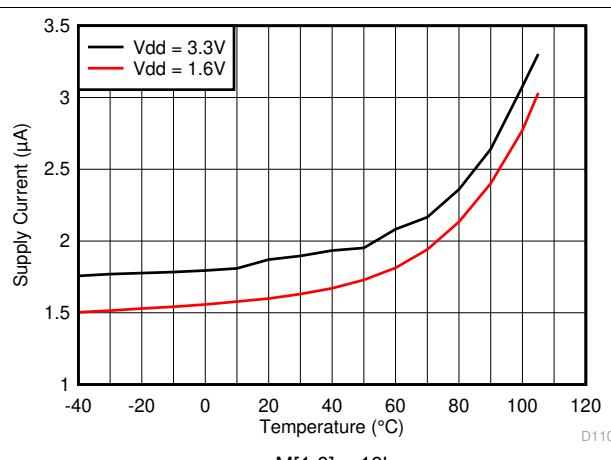

図 5-18. 消費電流と温度との関係 (グレード 2)

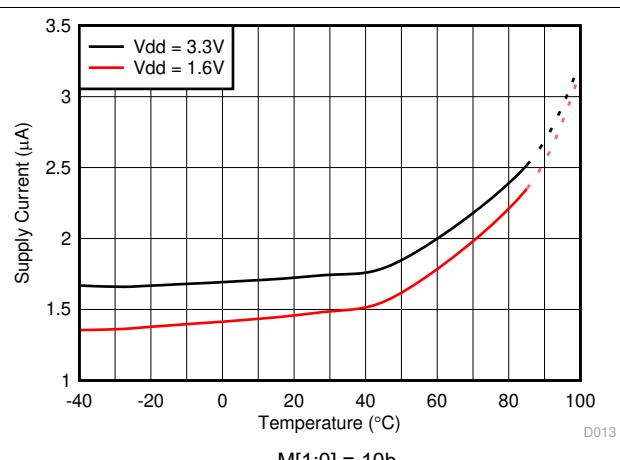

図 5-19. 消費電流と温度との関係 (グレード 3)

M[1:0] = 00b、入力照度 = 0lux

D111

M[1:0] = 00b、入力照度 = 0lux

D014

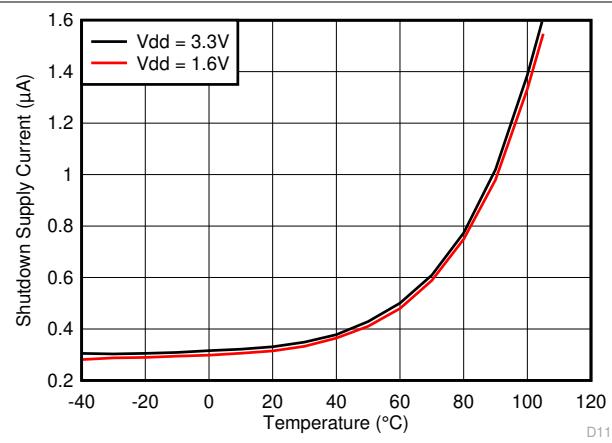

図 5-20. シャットダウン電流と温度との関係 (グレード 2)

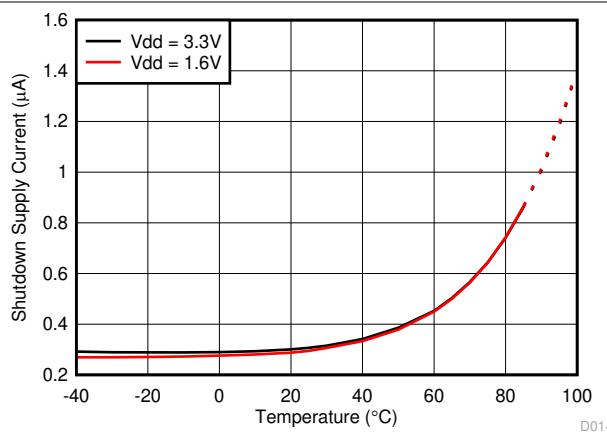

図 5-21. シャットダウン電流と温度との関係 (グレード 3)

D015

入力照度 = 80lux、SCL = SDA、I<sup>2</sup>C 周波数で連続的にトグル 注:一般的なアプリケーションでは、デューティサイクルが低いため、消費電流も少なくなります。

図 5-22. 電源電流と連続 I<sup>2</sup>C 周波数との関係

## 6 詳細説明

### 6.1 概要

OPT3001-Q1 デバイスは、デバイスを照らす周囲光を測定します。このデバイスは、人間の目に非常に近いスペクトル応答を持ち、かつ優れた赤外線除去機能を備えています。

センサのスペクトル応答を人間の目の応答に合わせることは非常に重要です。なぜなら、周囲光センサーは理想的な人間の照明環境を測定し、実現するために使用されるからです。人間が認識しない赤外線の強力な除去は、このマッチングの重要な要素です。このマッチングにより、OPT3001-Q1 デバイスは、目に見えて暗いものの、赤外線は透過するウィンドウの下での動作に特に適しています。

OPT3001-Q1 デバイスは、周囲光を測定し、その結果を lux 単位でデジタル信号として I<sup>2</sup>C バス経由で報告する完全な自己完結型デバイスです。測定結果はシステムに通知するためや、INT ピンを使ってプロセッサに割り込みをかけるためにも利用できます。その結果は、プログラム可能なウィンドウ比較を使用して要約し、INT ピンと通信することもできます。

OPT3001-Q1 デバイスは、自動的に最適なフルスケール範囲設定を選択するオートレンジモードに設定することができます。このモードでは、照明条件に応じて常に最適なフルスケール範囲が自動的に選択されます。このモードを使用すると、任意の測定に最適になるまで、ユーザーはソフトウェアをプログラムして、フルスケール範囲の測定と再調整を繰り返し実行する必要がなくなります。このデバイスは、連続動作またはシングルショット測定モードで動作するように命令できます。

このデバイスは結果を 100 ミリ秒または 800 ミリ秒のいずれかで積分するため、一般的な電球から発生する 50Hz および 60Hz のノイズの影響を最小限に抑えることができます。

このデバイスは、低消費電力のシャットダウン状態で起動し、OPT3001-Q1 デバイスはアクティブな状態にプログラムされて初めて動作時の消費電力を消費します。

OPT3001-Q1 の光学フィルタリングシステムは、光学表面上の非理想的な粒子や微小な影に対して過度に敏感ではありません。この感度の低減は、赤外線除去のためにセンサ領域の均一な光学照明の密度に対するデバイスの依存度が比較的小さいことによるものです。すべての光学機器において、最良の結果を得るために、光学表面の適切な清掃が常に推奨されます。

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 人間の目に類似

OPT3001-Q1 のスペクトル応答は人間の目とほぼ一致しています。周囲光センサの測定結果を、人にとって快適な環境づくりや、最適な光条件の実現に活用する場合、センサは人間の目が感じる光のスペクトルと同じ範囲を測定する必要があります。

また、このデバイスは赤外線 (IR) 除去にも優れています。この IR の除去は、実際の多くの光源には、人間が目にしない大量の赤外線成分が含まれているので、特に重要です。センサが人間の目に見えない赤外線を測定してしまうと、人が実際に感じる視覚体験を正確に再現することはできません。

さらに、周囲光センサーが暗いウインドウの下に隠されており(最終製品のユーザーからセンサが見えないようになっていいる場合)、OPT3001-Q1 デバイスの赤外線除去性能は非常に重要になります。これは、多くのダーク ウインドウが可視光を減衰させる一方で、赤外線を透過する性質を持つためです。可視光が減衰し、赤外線 (IR) が減衰しないことで、センサに届く光のうち赤外線の割合が相対的に高くなります。このような条件下でも、OPT3001-Q1 デバイスの高い赤外線除去性能により、測定結果は人間の目の感覚に非常によく一致します。

### 6.3.2 自動フルスケール レンジ設定

OPT3001-Q1 デバイスには、自動フルスケール レンジ設定機能が備わっており、最適なレンジを事前に予測して設定する必要がありません。このモードでは、OPT3001-Q1 デバイスは特定の照明条件に最適なフルスケール範囲を自動的に選択します。OPT3001-Q1 デバイスには、フルスケール レンジ設定間での測定結果の一致性が高いという特長があります。この一致により、異なるフルスケール レンジを選択した際に結果がばらつく問題や、レンジごとにユーザーがゲイン補正を行う必要がなくなります。詳細については、[セクション 6.4.1](#) セクションを参照してください。

### 6.3.3 割り込み動作、INT ピン、割り込み通知メカニズム

このデバイスには割り込み通知システムがあり、I<sup>2</sup>C バスに接続されているプロセッサがスリープに移行したり、その他の方法で、可能なアクションを必要とするユーザー定義のイベントが発生するまで、デバイスの結果を無視したりできます。あるいは、この同じ仕組みは、光の強度が関心のあるレベルを超えているかどうかを示す単一のデジタル信号を活用できる任意のシステムでも使用可能です。

割り込みイベントの条件は、高限界レジスタと低限界レジスタ、さらに構成レジスタのラッチおよびフォールト カウント フィールドによって制御されます。結果レジスタを上限レジスタおよび下限レジスタと比較した結果を、フォールト イベントと呼びます。フォールト カウント レジスタは、割り込みイベントを発生させるために必要な連続した同一結果のフォールト イベントの回数を決定し、その後、割り込み報告機構 (INT ピン、フラグ High フィールド、フラグ Low フィールド) の状態を変更します。ラッチ フィールドは、ラッチ付きウインドウスタイル比較と透過的ヒステリシス スタイル比較のどちらかを選択できるようになります。

INT ピンにはオープン ドレイン出力があるため、プルアップ抵抗を使用する必要があります。このオープン ドレイン出力により、オープン ドレインの INT ピンを持つ複数のデバイスを同じラインに接続することができ、デバイス間に論理 NOR または AND 機能を作成できます。INT ピンの極性は、構成レジスタ内の割り込み極性フィールドによって制御できます。POL フィールドが 0 に設定されると、ピンはアクティブ Low の動作で動作し、INT ピンがアクティブになるとピンが Low になります。POL フィールドが 1 に設定されると、ピンはアクティブ High の動作で動作し、高インピーダンスになるため、INT ピンがアクティブになったときにピンが High になります。

割り込み報告レジスタの詳細については、[セクション 7.1](#) セクションと[セクション 6.4.2](#) セクションを参照してください。

### 6.3.4 I<sup>2</sup>C バスの概要

OPT3001-Q1 は、I<sup>2</sup>C および SMBus インターフェイスと互換性があります。I<sup>2</sup>C および SMBus プロトコルは、本質的に互いに互換性があります。このドキュメントを通して、主な例として I<sup>2</sup>C インターフェイスを使用し、2 つのプロトコルの相違点について説明するときのみ SMBus プロトコルが指定されています。

OPT3001-Q1 デバイスは、2 本のピンでバスに接続されます。1 つはクロック入力用の SCL ピン、もう 1 つはオープンドレインの双方向データピンである SDA ピンです。コントローラ デバイスは、シリアルクロック (SCL) を生成し、バスアクセスを制御して、スタート条件およびストップ条件を生成します。特定のデバイスにアドレス指定を行うために、コントローラは、SCL が High のときにデータ信号ライン (SDA) をロジック High から Low レベルにプルし、スタート条件を開始します。バス上のすべてのターゲットデバイスは、SCL の立ち上がりエッジでターゲットアドレス バイトをソフトインし、最下位ビットによって読み取りか書き込みかの操作が指定されます。アドレス指定されたターゲットは、9 番目のクロック パルスのときアクノリッジ ビットを生成し、SDA を Low にプルして、コントローラに応答します。

その後でデータ転送が開始され、8 ビットのデータが送信されてから、アクノリッジ ビットが送信されます。データ転送中、SCL が High の間、SDA は安定した状態を維持する必要があります。SCL が High のとき SDA が変化すると、スタートまたはストップの条件と解釈されます。すべてのデータの転送が完了すると、コントローラはストップ条件を生成します。これは、SCL が High の状態で SDA を Low から High に引き上げることによって示されます。OPT3001-Q1 デバイスは、バスのロックアップを防止するため、I<sup>2</sup>C インターフェイスで 28ms のタイムアウトを備えています。SCL ラインがこの期間 Low に保持されると、バスステートマシンがリセットされます。

#### 6.3.4.1 シリアルバスアドレス

OPT3001-Q1 デバイスとの通信を行うには、最初にコントローラが I<sup>2</sup>C Start コマンドを開始する必要があります。その後、コントローラはターゲットアドレス バイトを使用して対象デバイスにアドレス指定を行う必要があります。ターゲットアドレス バイトは、7 つのアドレスビットと、動作が読み出しか書き込みかを示す 1 つの方向ビットで構成されます。

ADDR ピンを 4 つのピンのいずれかに接続すると、4 つの I<sup>2</sup>C アドレスが可能になります: GND、VDD、SDA、SCL。表 6-1 は、ADDR ピンの設定に対応する可能なアドレスをまとめたものです。ADDR ピンの状態は、すべてのバス通信時にサンプリングされるため、インターフェイス上で何らかの動作が行われる前に、所望のレベルに駆動または接続されている必要があります。

表 6-1. 可能な I<sup>2</sup>C アドレスと対応する ADDR 構成

| デバイスの I <sup>2</sup> C アドレス | ADDR ピン |

|-----------------------------|---------|

| 1000 100                    | GND     |

| 1000 101                    | VDD     |

| 1000 110                    | SDA     |

| 1000 111                    | SCL     |

#### 6.3.4.2 シリアルインターフェイス

OPT3001-Q1 デバイスは、I<sup>2</sup>C バスと SMBus バスの両方でターゲットデバイスとして動作します。バスへの接続は、SCL クロック入力ラインと SDA オープンドレインの入出力ラインを使用して行われます。OPT3001-Q1 デバイスは、スタンダード モード (最大 100kHz)、ファースト モード (最大 400kHz)、およびハイスピード モード (最大 2.6MHz) の通信プロトコルに対応しています。すべてのデータ バイトは、最上位ビットから先に送信されます。

SDA ピンおよび SCL ピンは、内蔵のスパイク抑制フィルタとシュミットトリガを備えており、入力スパイクとバスノイズの影響を最小限に抑えます。I<sup>2</sup>C バスのノイズ耐性の詳細については、セクション 8.1.1 セクションを参照してください。

## 6.4 デバイスの機能モード

### 6.4.1 自動フルスケール設定モード

OPT3001-Q1 デバイスには、自動フルスケール レンジ設定モードが搭載されており、ユーザーが最適なレンジを予測して設定する必要がありません。このモードは、構成レジスタ範囲番号フィールド (RN[3:0]) が **1100b** に設定されると開始します。

自動レンジ モードにおいて、デバイスが最初に行う測定は、**10ms** のレンジ評価測定です。その後、デバイスは、最初のフルスケール測定を行うために適切なフルスケール範囲を決定します。

その後の測定では、フルスケール範囲は前回の測定結果によって設定されます。測定値がフルスケールの下限寄りの場合、次回の測定ではフルスケール範囲が **1** 段階または **2** 段階低く設定されます。測定がフルスケールの上側に向かっている場合、次の測定では、フルスケール範囲が **1** つの設定だけ増加します。

急速に増加する光過渡事象が発生して、測定がフルスケール範囲を超えると、電流測定は終了します。この無効な測定値は報告されません。**10ms** の測定を行い、フルスケール範囲を評価し、適切にリセットします。次に、この適切なフルスケール範囲で新しい測定値を取得します。そのため、このモードで光が急激に増加する過渡現象が発生した場合、測定の完了および報告にかかる時間が、構成レジスタの変換時間フィールド (CT) で指定された時間より長くなる可能性があります。

### 6.4.2 割り込み通知メカニズムのモード

割り込み通知メカニズムのモードには、主に **2** つの種類があります。それは、ラッチ付きウインドウ比較モードと、透過型ヒステリシス比較モードです。構成レジスタラッチフィールド (L) (構成レジスタのビット 4 を参照) は、これら **2** つのモードのうち、使用するモードを制御します。各主要モードには、それぞれに対応する変換完了モードも存在します。変換完了モードは、スレッショルド下限レジスタの上位 **2** ビットが **11b** に設定されているときに有効になります。これらのメカニズムは、フラグ **High** フィールド、フラグ **Low** フィールド、変換完了フィールド、および **INT** ピンを通じて通知されます。

#### 6.4.2.1 ラッチ付きウインドウ スタイル比較モード

ラッチ型ウインドウ比較モードは、OPT3001-Q1 デバイスを使用して外部プロセッサに割り込みをかける場合によく選択されます。このモードでは、入力信号が上限レジスタを上回ったとき、または下限レジスタを下回ったとき、フォルトが認識されます。連続したフォルト イベントが割り込み報告メカニズムをトリガすると、それらのメカニズムはラッチされ、フォルトが **High** 側か **Low** 側の比較によるものかを報告します。これらのメカニズムは、構成レジスタが読み取られるまでラッチされたままであり、その際に **INT** ピンやフラグ **High**、フラグ **Low** のフィールドがクリアされます。セクション 6.5.1.3 セクションで詳細に説明する **SMBus** アラート応答プロトコルは、ピンをクリアしますが、フラグ **High** およびフラグ **Low** フィールドはクリアされません。このモードの動作と変換準備完了フラグを表 6-2 に示します。2 つのスレッショルド下限レジスタ MSB が **11b** に設定されている場合は、表 6-2 は適用されないことに注意します (MSB の説明については、セクション 6.4.2.2 を参照)。

**表 6-2. ラッチ付きウィンドウ スタイル比較モード：フラグ設定とクリアの概要**

| 動作                                                                                       | フラグ HIGH フィールド <sup>(2) (4)</sup> | フラグ LOW フィールド | INT ピン <sup>(1)</sup> | 変換準備完了 フィールド |

|------------------------------------------------------------------------------------------|-----------------------------------|---------------|-----------------------|--------------|

| 結果レジスタは、フォルト カウント時間にわたって上限レジスタを上回っています。詳細については、 <a href="#">結果レジスタと上限レジスタ</a> を参照してください。 | 1                                 | X             | アクティブ                 | 1            |

| フォルト カウント時間にわたって、結果レジスタは下限レジスタを下回っています。詳細については、 <a href="#">結果レジスタと下限レジスタ</a> を参照してください。 | X                                 | 1             | アクティブ                 | 1            |

| 変換は完了し、フォルト カウント基準が満たされていません                                                             | X                                 | X             | X                     | 1            |

| 構成レジスタ読み取り <sup>(3)</sup>                                                                | 0                                 | 0             | 非アクティブ                | 0            |

| 構成レジスタ書き込み、M[1:0] = 00b (シャットダウン)                                                        | X                                 | X             | X                     | X            |

| 構成レジスタ書き込み、M[1:0] > 00b (シャットダウンなし)                                                      | X                                 | X             | X                     | 0            |

| SMBus アラート応答プロトコル                                                                        | X                                 | X             | 非アクティブ                | X            |

(1) INT ピンは極性フィールド (POL) の設定によって異なります。INT ピンは、ピン状態がアクティブで  $POL = 0$  (アクティブ Low) の場合、またはピン状態が非アクティブで  $POL = 1$  (アクティブ High) の場合に Low になります。

(2) X = 前の状態から変化なし。

(3) 構成レジスタの読み取り直後に、デバイスは自動的に変換準備完了フィールドを 0 状態にリセットします。したがって、変換完了直後に構成レジスタを 2 回連続で読み取ると、1 回目は 1、2 回目は 0 が読み取られます。

(4) 上限レジスタは、下限レジスタより大きい値と想定されます。この仮定が正しくない場合、フラグの High フィールドとフラグの Low フィールドは異なる動作を取る可能性があります。

#### 6.4.2.2 透過ヒステリシス スタイル比較モード

透過ヒステリシス スタイル比較モードは、入力された光が関心のある光レベルより高いか低いかを示す单一のデジタル信号が必要な場合に、一般的に使用されます。結果レジスタの値が、フォルト カウント フィールドで設定された連続回数にわたって High リミット レジスタを上回った場合、INT ラインがアクティブになり、フラグ High フィールドが 1 に、フラグ Low フィールドが 0 に設定されます。結果レジスタの値が、フォルト カウント フィールドで設定された連続回数にわたって Low リミット レジスタを下回った場合、INT ラインは非アクティブになり、フラグ Low フィールドが 1 に、フラグ High フィールドが 0 に設定されます。INT ピン、フラグ High フィールドおよびフラグ Low フィールドは、構成の読み取りおよび書き込みで状態に変化しません。INT ピンおよびフラグ フィールドは、下限レジスタおよび上限レジスタに光の適切な比較を継続的に報告します。このデバイスは、いずれかの透過型比較モード中 (構成レジスタのラッチ フィールド = 0 の場合)、SMBus アラート応答プロトコルには応答しません。このモードの動作と変換準備完了を表 6-3 に示します。2 つのスレッショルド下限レジスタ MSB (表 7-6 の LE[3:2]) が 11 に設定されている場合は、この動作は表 6-3 に適用されないことに注意します。

**表 6-3. 透過ヒステリシス スタイル比較モード：フラグ設定とクリアの概要<sup>(2) (4)</sup>**

| 動作                                                                                       | フラグ HIGH フィールド | フラグ LOW フィールド | INT ピン <sup>(1)</sup> | 変換準備完了 フィールド |

|------------------------------------------------------------------------------------------|----------------|---------------|-----------------------|--------------|

| 結果レジスタは、フォルト カウント時間にわたって上限レジスタを上回っています。詳細については、 <a href="#">結果レジスタと上限レジスタ</a> を参照してください。 | 1              | 0             | アクティブ                 | 1            |

| フォルト カウント時間にわたって、結果レジスタは下限レジスタを下回っています。詳細については、 <a href="#">結果レジスタと下限レジスタ</a> を参照してください。 | 0              | 1             | 非アクティブ                | 1            |

| 変換は完了し、フォルト カウント基準が満たされていません                                                             | X              | X             | X                     | 1            |

| 構成レジスタ読み取り <sup>(3)</sup>                                                                | X              | X             | X                     | 0            |

| 構成レジスタ書き込み、M[1:0] = 00b (シャットダウン)                                                        | X              | X             | X                     | X            |

| 構成レジスタ書き込み、M[1:0] > 00b (シャットダウンなし)                                                      | X              | X             | X                     | 0            |

| SMBus アラート応答プロトコル                                                                        | X              | X             | X                     | X            |

#### 6.4.2.3 変換終了モード

変換完了インジケータ モードは、すべての測定結果をプロセッサで読み取る必要がある場合に使用できます。このモードでは、各測定の完了時に INT ピンがアクティブになることで、プロセッサに読み取りを促します。このモードに移行するには、下限レジスタの上位 2 ビット (下限レジスタの LE[3:2]) を 11b に設定します。この変換完了インジケータ モードは、ラッチ付きウィンドウ比較モードと併せて使用されるのが一般的です。INT ピンは、構成レジスタの読み取りが行われた場合、またはシャットダウン以外のパラメータで構成レジスタが書き換えられた場合、あるいは SMBus アラート応答に反応した場合に非アクティブになります。[表 6-4](#) に、各種動作の結果としての割り込み報告メカニズムを示します。

**表 6-4. ラッチ付きウィンドウ形式比較モードでの変換終了モード：

フラグ設定とクリアの概要 <sup>(2)</sup>**

| 動作                                                                                      | フラグ HIGH フィールド | フラグ LOW フィールド | INT ピン <sup>(1)</sup> | 変換準備完了 フィールド |

|-----------------------------------------------------------------------------------------|----------------|---------------|-----------------------|--------------|

| 結果レジスタは、フォルトカウント時間にわたって上限レジスタを上回っています。詳細については、 <a href="#">結果レジスタと上限レジスタ</a> を参照してください。 | 1              | X             | アクティブ                 | 1            |

| フォルトカウント時間にわたって、結果レジスタは下限レジスタを下回っています。詳細については、 <a href="#">結果レジスタと下限レジスタ</a> を参照してください。 | X              | 1             | アクティブ                 | 1            |

| 変換は完了し、フォルトカウント基準が満たされていません                                                             | X              | X             | アクティブ                 | 1            |

| 構成レジスタ読み取り <sup>(3)</sup>                                                               | 0              | 0             | 非アクティブ                | 0            |

| 構成レジスタ書き込み、M[1:0] = 00b (シャットダウン)                                                       | X              | X             | X                     | X            |

| 構成レジスタ書き込み、M[1:0] > 00b (シャットダウンなし)                                                     | X              | X             | X                     | 0            |

| SMBus アラート応答プロトコル                                                                       | X              | X             | 非アクティブ                | X            |

変換完了モードから標準の比較モードへ移行する際(つまり、LE[3:2] を 11b から 00b に設定変更する場合)には、構成レジスタのラッチ フィールド (L) が 1 のままだと INT ピンが正しくクリアされません。そのため、続けてラッチ フィールド (L) を 0 に書き込む必要があります。その後、必要に応じてラッチ フィールドを 1 に戻すことができます。

#### 6.4.2.4 変換終了および透過ヒステリシス スタイル比較モード

変換完了モードと透過型ヒステリシス比較モードは、同時に設定することも可能です。この組み合わせの動作は[表 6-5](#) に示します。

**表 6-5. 透過ヒステリシス比較モードにおける変換完了モードの動作：

フラグ設定とクリアの概要 <sup>(2)</sup>**

| 動作                                                                                      | フラグ HIGH フィールド | フラグ LOW フィールド | INT ピン <sup>(1)</sup> | 変換準備完了 フィールド |

|-----------------------------------------------------------------------------------------|----------------|---------------|-----------------------|--------------|

| 結果レジスタは、フォルトカウント時間にわたって上限レジスタを上回っています。詳細については、 <a href="#">結果レジスタと上限レジスタ</a> を参照してください。 | 1              | 0             | アクティブ                 | 1            |

| フォルトカウント時間にわたって、結果レジスタは下限レジスタを下回っています。詳細については、 <a href="#">結果レジスタと下限レジスタ</a> を参照してください。 | 0              | 1             | アクティブ                 | 1            |

| 変換は完了し、フォルトカウント基準が満たされていません                                                             | X              | X             | アクティブ                 | 1            |

| 構成レジスタ読み取り <sup>(3)</sup>                                                               | X              | X             | 非アクティブ                | 0            |

| 構成レジスタ書き込み、M[1:0] = 00b (シャットダウン)                                                       | X              | X             | X                     | X            |

| 構成レジスタ書き込み、M[1:0] > 00b (シャットダウンなし)                                                     | X              | X             | 非アクティブ                | 0            |

| SMBus アラート応答プロトコル                                                                       | X              | X             | X                     | X            |

## 6.5 プログラミング

OPT3001-Q1 デバイスは、スタンダード モード (最大 100kHz)、ファースト モード (最大 400kHz)、およびハイスピード モード (最大 2.6MHz) の通信プロトコルに対応しています。ファースト モードとスタンダード モードは、*F/S* と呼ばれるデフォルト プロトコルとして説明されています。ハイスピード モードについては、[セクション 6.5.1.1](#) セクションを参照してください。

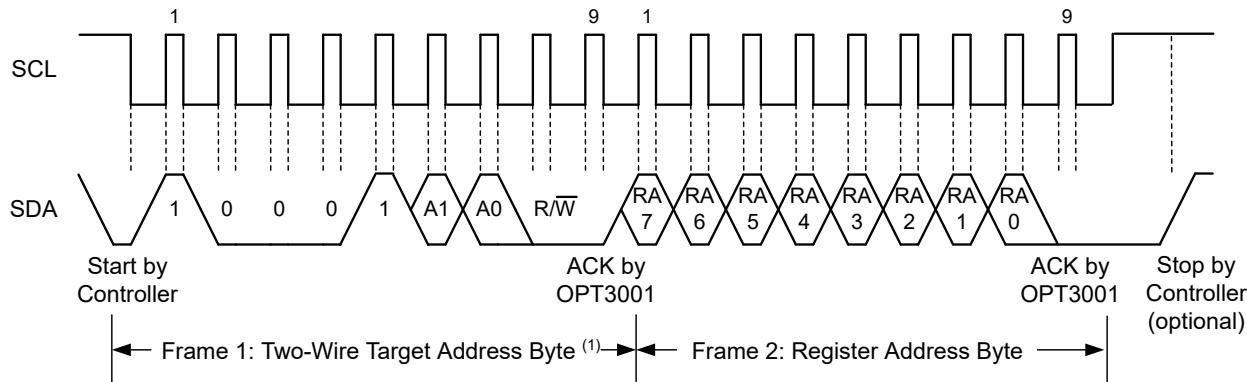

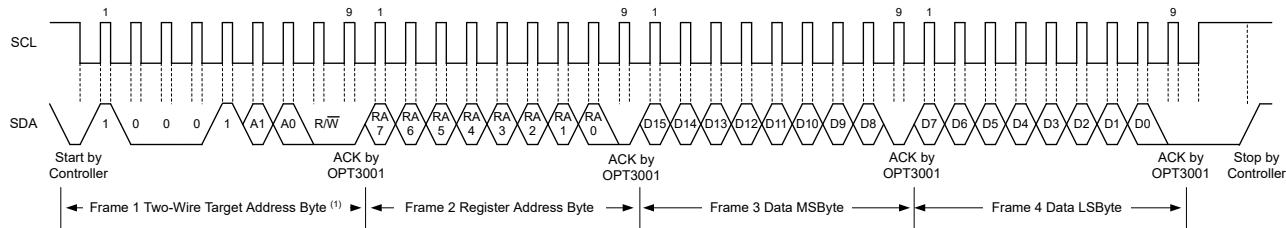

### 6.5.1 読み取りと書き込み

OPT3001-Q1 デバイスの特定のレジスタにアクセスするには、I<sup>2</sup>C 通信シーケンスの中で該当するレジスタ アドレスを書き込むことで行います。レジスタ、および対応のレジスタアドレスの一覧については、「[表 7-1](#)」を参照してください。レジスタアドレスの値 ([図 6-1](#) を参照) は、R/W ビットが **Low** になっているターゲット アドレス バイトの後に送信される最初のバイトです。

A. ターゲット アドレス バイトの値は、ADDR ピンの設定によって決まります。[表 6-1](#) を参照してください。

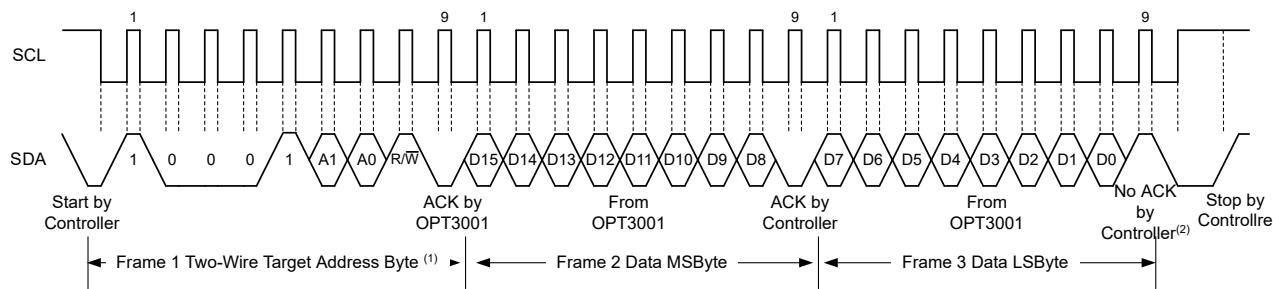

**図 6-1. I<sup>2</sup>C レジスタ アドレスの設定**

レジスタへの書き込みは、コントローラによって送信される最初のバイトから開始されます。このバイトはターゲット アドレスで、R/W ビットは **Low** です。その後で、OPT3001-Q1 デバイスは有効なアドレスの受信をアクノリッジします。コントローラから送信される次のバイトは、データが書き込まれるレジスタのアドレスです。次の 2 バイトは、レジスタのアドレスによってレジスタ アドレスに書き込まれます。OPT3001-Q1 デバイスは、データ バイトを受信するたびにアクノリッジします。コントローラは、開始条件または停止条件を生成することによりデータ転送を終了できます。

OPT3001-Q1 デバイスから読み出す場合、書き込み動作によってレジスタ ポインタに保存された最後の値が、読み出し動作中に読み出されるレジスタを決定します。読み出し動作のレジスタ アドレスを変更するには、新しい部分的な I<sup>2</sup>C 書き込みトランザクションを開始する必要があります。この部分書き込みは、R/W ビットが **Low** のターゲット アドレス バイトを送信し、その後にレジスタ アドレス バイトを送信し、ストップ コマンドを出すことで実行されます。その後、コントローラはスタート条件を生成し、R/W ビットを **High** に設定したターゲット アドレス バイトを送信して、読み取りコマンドを開始します。次のバイトはターゲットから送信され、レジスタのアドレスで指定されるレジスタの最上位バイトです。このバイトに続いて、コントローラからアクノリッジがあります。次に、ターゲットは最下位バイトを送信します。コントローラは、データ バイトの受信をアクノリッジします。コントローラは、任意のデータ バイトを受信した後にノン アクノリッジを生成するか、スタート条件またはストップ条件を生成することにより、データ転送を終了できます。同じレジスタから繰り返し読み取りを行いたい場合、毎回レジスタ アドレス バイトを送信する必要はありません。OPT3001-Q1 デバイスは、次の書き込み操作で番号が変更されるまで、レジスタ アドレスを保持します。

書き込みおよび読み取り動作のタイミング図を、それぞれ図 6-2 と図 6-3 に示します。レジスタのバイトは、最上位バイトが最初に、その後で最下位バイトが送信されることに注意してください。

- A. ターゲット アドレス バイトの値は、ADDR ピンの設定によって決まります。表 6-1 を参照してください。

**図 6-2. I<sup>2</sup>C 書き込み例**

- A. ターゲット アドレス バイトの値は、ADDR ピンの設定によって決まります。表 6-1 を参照してください。

B. コントローラからの ACK も送信できます。

**図 6-3. I<sup>2</sup>C 読み取り例**

### 6.5.1.1 高速 I<sup>2</sup>C モード

バスがアイドル状態のときは、SDA および SCL ラインの両方がプルアップ抵抗またはアクティブ プルアップ デバイスによって High に保持されます。マスターはスタート条件を生成した後、高速 (HS) マスター コード 0000 1XXXb を含む有効なシリアル バイトを送信します。この転送は、標準モードと高速モード (最大 400kHz) のどちらかで行われます。OPT3001-Q1 デバイスは HS マスター コードに対して アクノリッジしませんが、そのコードをアクノリッジし、内部フィルタを切り替えて 2.6MHz 動作に対応します。

次に、マスターは再スタート条件を生成します (再スタート条件のタイミングはスタート条件と同じです)。この再スタート条件の後、プロトコルは F/S モードと同じですが、許容転送速度は最高 2.6MHz になります。バスを HS モードで維持するには、終了条件を使用する代わりに、再スタート条件を使用します。終了条件を使用すると HS モードは終了し、OPT3001-Q1 デバイスのすべての内部フィルタは F/S モードをサポートするよう切り換わります。

### 6.5.1.2 ゼネラル コール リセット コマンド

I<sup>2</sup>C ゼネラル コール リセットを使用すると、ホスト コントローラは 1 つのコマンドで、バス上のすべての対応デバイスをリセットできます。ゼネラル コールは、I<sup>2</sup>C アドレス 0 (0000 0000b) に書き込むことによって開始されます。リセット コマンドは、続く 2 バイト目のアドレスが 06h (0000 0110b) のときに実行されます。このトランザクションでは、デバイスはアクノリッジ ビットを発行し、すべてのレジスタをパワーオン リセットのデフォルト状態に設定します。

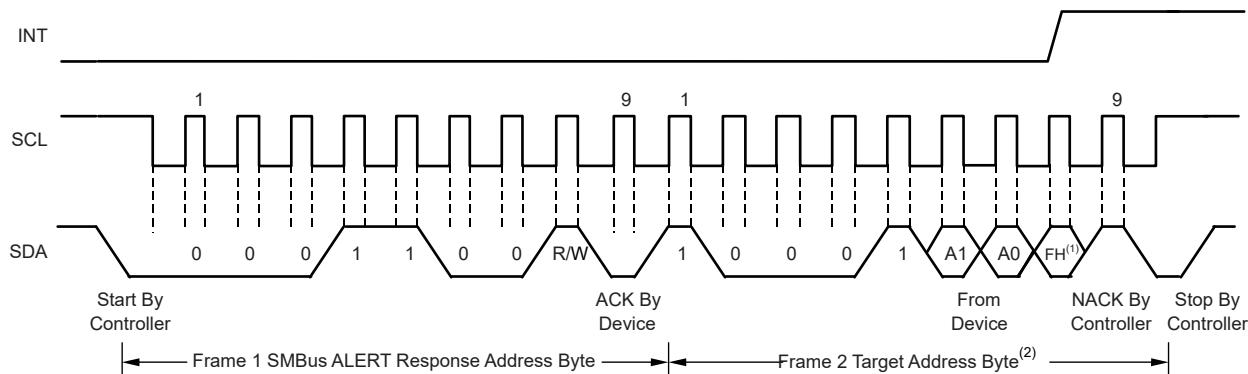

### 6.5.1.3 SMBus のアラート応答

SMBus のアラート応答により、どのデバイスが割り込みを発行したかをすばやく識別できます。このアラート応答機能がない場合、複数のターゲット デバイスが接続されている時に、どのデバイスが割り込みラインを引っ張ったのかプロセッサ側では判別できません。

OPT3001-Q1 デバイスは、ラッチ型ウインドウ比較モード (構成レジスタのラッチ フィールド = 1) のとき、SMBus アラート応答アドレスに応答するよう設計されています。OPT3001-Q1 デバイスは、透過モード (構成レジスタ、ラッチ フィールド=0) では、SMBus のアラート応答に応答しません。

OPT3001-Q1 デバイスから SMBus のアラート応答に対する応答動作を図 6-4 に示します。割り込みラインがプロセッサ側でアクティブに引かれると、コントローラはアラート応答ターゲット アドレス (0001 1001b) をブロードキャストすることができます。このアラート応答の後、アラートを発生させたターゲット デバイスは、アラート応答を認識して自身の I<sup>2</sup>C アドレスをバス上に送信することで識別されます。アラート応答は、複数のターゲット デバイスを同時にアクティブにすることもできます。複数のターゲットが応答を試みた場合、バス アービトレーション ルールが適用されます。最も低いアドレスを持つデバイスが調停で優先権を得ます。OPT3001-Q1 デバイスが調停に負けた場合、デバイスは I<sup>2</sup>C トランザクションを認識せず、INT ピンは認識状態のままで、I<sup>2</sup>C コントローラ プロセッサはそれに続く SMBus アラート応答を発行するよう要求されます。OPT3001-Q1 デバイスが調停に成功すると、デバイスはトランザクションを認識し、INT ピンを非アクティブに設定します。コントローラは、INT ピンをクリアするために、必要な回数だけ、同じコマンドを再度発行できます。フラグと INT ピンの制御方法の詳細については、セクション 6.4.2 セクションを参照してください。コントローラは、上記のアドレス ブロードキャストから OPT3001-Q1 割り込みのソースに関する情報を取得できます。フラグ High フィールド (構成レジスタ、ビット 6) は、アドレスの最終 LSB として送信され、OPT3001-Q1 の割り込み原因についてコントローラに追加情報を提供します。コントローラに追加情報が必要な場合は、結果レジスタまたは構成レジスタを照会できます。SMBus アラート応答があっても、フラグ High およびフラグ Low のフィールドはクリアされません。

- A. FH は、構成レジスタ内のフラグ High (FH) フィールドを指します (表 7-5 を参照してください)。

- B. A1 と A0 は ADDR ピンによって決定されます。表 6-1 を参照してください。

図 6-4. SMBus アラート応答のタイミング図

## 7 レジスタ マップ

### 7.1 内部レジスタ

デバイスは I<sup>2</sup>C バスで動作し、構成、ステータス、結果情報を含むレジスタにより動作します。すべてのレジスタは 16 ビット長です。

主に、結果、構成、下限、上限の 4 つのレジスタがあります。また、メーカー ID とデバイス ID の 2 つの ID レジスタも用意されています。表 7-1 に、各レジスタの一覧を示します。

**表 7-1. レジスタ マップ**

| レジスタ    | アドレス<br>(16 進) <sup>(1)</sup> | ビット<br>15 | ビット<br>14 | ビット<br>13 | ビット<br>12 | ビット<br>11 | ビット<br>10 | ビット<br>9 | ビット<br>8 | ビット<br>7 | ビット<br>6 | ビット<br>5 | ビット<br>4 | ビット<br>3 | ビット<br>2 | ビット<br>1 | ビット<br>0 |

|---------|-------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| 結果      | 00h                           | E3        | E2        | E1        | E0        | R11       | R10       | R9       | R8       | R7       | R6       | R5       | R4       | R3       | R2       | R1       | R0       |

| 構成      | 01h                           | RN3       | RN2       | RN1       | RN0       | CT        | M1        | M0       | OVF      | CRF      | FH       | FL       | L        | POL      | ME       | FC1      | FC0      |

| 下限      | 02h                           | LE3       | LE2       | LE1       | LE0       | TL11      | TL10      | TL9      | TL8      | TL7      | TL6      | TL5      | TL4      | TL3      | TL2      | TL1      | TL0      |

| 上限      | 03h                           | HE3       | HE2       | HE1       | HE0       | TH11      | TH10      | TH9      | TH8      | TH7      | TH6      | TH5      | TH4      | TH3      | TH2      | TH1      | TH0      |

| メーカー ID | 7Eh                           | ID15      | ID14      | ID13      | ID12      | ID11      | ID10      | ID9      | ID8      | ID7      | ID6      | ID5      | ID4      | ID3      | ID2      | ID1      | ID0      |

| デバイス ID | 7Fh                           | DID1<br>5 | DID1<br>4 | DID1<br>3 | DID1<br>2 | DID1<br>1 | DID1<br>0 | DID9     | DID8     | DID7     | DID6     | DID5     | DID4     | DID3     | DID2     | DID1     | DID0     |

(1) レジスタ オフセットとレジスタ アドレスは交互に使用されます。

#### 7.1.1 レジスタの説明

注

レジスタ オフセットとレジスタ アドレスは交互に使用されます。

##### 7.1.1.1 結果レジスタ (オフセット=00h)

このレジスタには、最新の光からデジタルへの変換結果が含まれています。この 16 ビットレジスタには、4 ビットの指数と 12 ビットの仮数部の 2 つのフィールドがあります。

**図 7-1. 結果レジスタ (読み取り専用)**

| 15 | 14 | 13 | 12 | 11  | 10  | 9  | 8  |

|----|----|----|----|-----|-----|----|----|

| E3 | E2 | E1 | E0 | R11 | R10 | R9 | R8 |

| R  | R  | R  | R  | R   | R   | R  | R  |

| 7  | 6  | 5  | 4  | 3   | 2   | 1  | 0  |

| R7 | R6 | R5 | R4 | R3  | R2  | R1 | R0 |

| R  | R  | R  | R  | R   | R   | R  | R  |

凡例: R = 読み取り専用

**表 7-2. 結果レジスタのフィールドの説明**

| ビット   | フィールド   | タイプ | リセット | 説明                                                            |

|-------|---------|-----|------|---------------------------------------------------------------|

| 15:12 | E[3:0]  | R   | 0h   | <b>指数。</b><br>これらのビットは指数ビットです。詳しくは、表 7-3 を参照してください。           |

| 11:0  | R[11:0] | R   | 000h | <b>分数結果。</b><br>これらのビットはストレート バイナリ コーディング (ゼロからフルスケール) の結果です。 |

**表 7-3. フルスケール範囲と LSB サイズを指數レベルの関数として表現**

| E3 | E2 | E1 | E0 | フルスケール レンジ (lux) | LSB サイズ ( LSBあたりの lux) |

|----|----|----|----|------------------|------------------------|

| 0  | 0  | 0  | 0  | 40.95            | 0.01                   |

表 7-3. フルスケール範囲と LSB サイズを指数レベルの関数として表現 (続き)

| E3 | E2 | E1 | E0 | フルスケールレンジ (lux) | LSB サイズ (LSBあたりの lux) |

|----|----|----|----|-----------------|-----------------------|

| 0  | 0  | 0  | 1  | 81.90           | 0.02                  |

| 0  | 0  | 1  | 0  | 163.80          | 0.04                  |

| 0  | 0  | 1  | 1  | 327.60          | 0.08                  |

| 0  | 1  | 0  | 0  | 655.20          | 0.16                  |

| 0  | 1  | 0  | 1  | 1310.40         | 0.32                  |

| 0  | 1  | 1  | 0  | 2620.80         | 0.64                  |

| 0  | 1  | 1  | 1  | 5241.60         | 1.28                  |

| 1  | 0  | 0  | 0  | 10483.20        | 2.56                  |

| 1  | 0  | 0  | 1  | 20966.40        | 5.12                  |

| 1  | 0  | 1  | 0  | 41932.80        | 10.24                 |

| 1  | 0  | 1  | 1  | 83865.60        | 20.48                 |

このレジスタの値を lux に変換するための計算式は、式 1 に示されています：

$$\text{lux} = \text{LSB\_Size} \times R[11:0] \quad (1)$$

ここで

$$\text{LSB\_Size} = 0.01 \times 2^{E[3:0]} \quad (2)$$

LSB\_Size は表 7-3 から取得することもできます。完全な lux 計算式は 式 3 に示されています：

$$\text{lux} = 0.01 \times (2^{E[3:0]}) \times R[11:0] \quad (3)$$

対応する LSB 重みとそれによる lux を持つ一連の結果レジスタ出力の例を、表 7-4 に示します。表 7-4 の例に示すように、指數 (E[3:0]) と分数結果 (R[11:0]) の多くの組み合わせは、同じ lux 結果にマッピングすることができます。

表 7-4. 結果レジスタを lux にデコードする例

| 結果レジスタ<br>(ビット 15:0、バイナリ) | 指數<br>(E[3:0]、16 進) | 分数の結果<br>(R[11:0]、16 進) | LSB の重み<br>(lux、10 進) | 結果の LUX (10 進数) |

|---------------------------|---------------------|-------------------------|-----------------------|-----------------|

| 0000 0000 0000 0001b      | 00h                 | 001h                    | 0.01                  | 0.01            |

| 0000 1111 1111 1111b      | 00h                 | FFFh                    | 0.01                  | 40.95           |

| 0011 0100 0101 0110b      | 03h                 | 456h                    | 0.08                  | 88.80           |

| 0111 1000 1001 1010b      | 07h                 | 89Ah                    | 1.28                  | 2818.56         |

| 1000 1000 0000 0000b      | 08h                 | 800h                    | 2.56                  | 5242.88         |

| 1001 0100 0000 0000b      | 09h                 | 400h                    | 5.12                  | 5242.88         |

| 1010 0010 0000 0000b      | 0Ah                 | 200h                    | 10.24                 | 5242.88         |

| 1011 0001 0000 0000b      | 0Bh                 | 100h                    | 20.48                 | 5242.88         |

| 1011 0000 0000 0001b      | 0Bh                 | 001h                    | 20.48                 | 20.48           |

| 1011 1111 1111 1111b      | 0Bh                 | FFFh                    | 20.48                 | 83865.60        |

指數フィールドは、指數マスクを有効にする (構成レジスタの ME フィールドを 1 に設定) ことで無効化 (ゼロに設定) できます。さらに、構成レジスタの RN[3:0] を 1100b (0Ch) 未満に設定してフルスケール レンジを手動で設定することで、手動設定のフルスケール モードにおけるより簡単な動作が可能になります。結果レジスタの内容から lux を計算するには、結果レジスタに、プログラムされたフルスケール範囲に関連する LSB の重み (ルクス単位) を乗算するだけです (表 7-3 を参照)。詳細については、下限レジスタを参照してください。

変換時間の関数としての lux 分解能の詳細については、構成レジスタ変換時間フィールド (CT、ビット 11) の説明を参照してください。

### 7.1.1.2 構成レジスタ (オフセット = 01h) [リセット = C810h]

このレジスタは、デバイスの主要な動作モードを制御します。このレジスタには 11 のフィールドがあるため、以下に説明します。構成レジスタに書き込んだときに測定変換が進行中の場合、アクティブな測定の変換はただちに中止されます。新しい構成レジスタが新たな変換を指示する場合、その変換が続いて開始されます。

デバイスの飽和状態を検出するため、常にオーバーフロー フラグ (OVF) を監視します。設定されたフルスケール範囲を大きく超える光レベルでは、結果レジスタの小数部 (R[11:0]) が 0xFFFF を示すとは限りません。オーバーフロー フラグが High (OVF = 1) を示している場合、設定されたフルスケール範囲で必ず飽和状態を示します。

**図 7-2. 構成レジスタ**

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| RN3 | RN2 | RN1 | RN0 | CT  | M1  | M0  | OVF |

| R/W | R   |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| CRF | FH  | FL  | L   | POL | ME  | FC1 | FC0 |

| R   | R   | R   | R/W | R/W | R/W | R/W | R/W |

凡例: R/W = 読み出し/書き込み、R = 読み出し専用

**表 7-5. 構成レジスタ フィールドの説明**

| ビット   | フィールド   | タイプ | リセット  | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|---------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | RN[3:0] | R/W | 1100b | <p><b>レンジ番号フィールド (読み取りまたは書き込み)。</b><br/> レンジ番号フィールドは、デバイスのフルスケールの lux 範囲を選択します。このフィールドの形式は、結果レジスタの指数フィールド (E[3:0]) と同じです。表 7-3 を参照してください。RN[3:0]を 1100b (0Ch) に設定すると、セクション 6.4.1 セクションに記載されているように、デバイスは自動フルスケール設定モードで動作します。このモードでは、自動的に選択された範囲が結果指数 (レジスタ 00h、E[3:0]) に通知されます。<br/> このデバイスは、電源投入時に自動フルスケール設定モードで「1100」として起動します。1101b、1110b、1111b (0Dh, 0Eh, 0Fh) のコードは将来の使用のために予約されています。</p>                                                                                                                                                                                            |

| 11    | CT      | R/W | 1b    | <p><b>変換時間フィールド (読み取りまたは書き込み)。</b><br/> 変換時間フィールドは、光からデジタルへの変換プロセスの長さを決定します。選択肢は 100ms と 800ms です。積分時間が長いほど、低ノイズ測定を行えます。<br/> 変換時間は、データ変換プロセスの有效分解能にも関係します。800Ms の変換時間により、lux 分解能を完全に規定することができます。結果レジスタおよび構成レジスタの E[3:0] が 0101b を超えるフルスケール範囲の場合、100ms の変換時間によって、規定された lux 分解能が得られます。結果レジスタおよび構成レジスタの E[3:0] が 0101b 以下のフルスケール範囲の場合、100ms の変換時間では選択されたフルスケール範囲によって最大 3 ビットまで有効な結果の分解能が低下する可能性があります。範囲は 0101b が 1 ビット減少しています。0100b、0011b、0010b、および 0001b の範囲では、分解能が 2 ビット低下します。0000b の範囲では、分解能が 3 ビット低下します。変換時間によって、結果レジスタのフォーマットや対応する LSB の重みは変わりません。<br/> 0 = 100ms<br/> 1 = 800ms</p> |

| 10:9  | M[1:0]  | R/W | 00b   | <p><b>変換動作フィールドのモード (読み取りまたは書き込み)。</b><br/> 変換動作モード フィールドは、デバイスが連続変換、シングルショット、または低消費電力シャットダウンモードのいずれで動作するかを制御します。デフォルトは 00b (シャットダウン モード) で、電源投入時には、適切にデバイスを設定してからのみ動作レベルの電力を消費します。<br/> このフィールドに 01b を書き込んでシングルショット モードを選択すると、デバイスが変換動作中はこのフィールドの読み値も 01b のままになります。シングルショット変換が完了すると、変換動作モード フィールドは自動的に 00b に設定され、デバイスはシャットダウンします。<br/> デバイスがシャットダウン モードに入るとき (シングルショット変換の完了、または構成レジスタへの手動書き込みによる場合のいずれでも)、報告フラグ (変換完了、フラグ High、フラグ Low) や INT ピンの状態には変化がありません。これらの信号は、デバイスがシャットダウン モードの間、以降の読み取り動作のために保持されます。<br/> 00 = シャットダウン (デフォルト)<br/> 01 = シングルショット<br/> 10, 11 = 連続変換</p>      |

表 7-5. 構成レジスタ フィールドの説明 (続き)

| ビット | フィールド | タイプ | リセット | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | OVF   | R   | 0b   | <p><b>オーバーフロー フラグ フィールド (読み取り専用)。</b><br/>         オーバーフロー フラグ フィールドは、データ変換処理中にオーバーフロー状態が発生したことを示します。これは通常、デバイスに当たる光が設定されたフルスケール範囲を超えた場合に発生します。この条件では、OVF は 1 に設定され、それ以外の場合、OVF は 0 のままで。このフィールドは、測定ごとに再評価されます。</p> <p>フルスケール範囲が手動で設定されている場合 (RN[3:0] フィールドが 1100b 未満)、結果レジスタがフルスケール未満の値を示していても、オーバーフロー フラグ フィールドが設定されることがあります。この現象は、入力光が一時的に大きくスパイクして積分型 ADC コンバータ回路を一時的に過負荷にしたもの、変換完了前に範囲内のレベルに戻った場合に発生します。そのため、オーバーフロー フラグ は変換プロセスで発生する可能性のあるエラーを報告します。この動作は、統合型コンバータに共通しています。</p> <p>フルスケール範囲が自動設定されている場合 (RN[3:0] フィールドが 1100b)、オーバーフロー フラグ フィールドが設定されるのは、入力光がデバイス全体のフルスケール レベルを超えた場合のみです。オーバーフロー状態が発生し、かつフルスケール範囲が最大でない場合、OPT3001-Q1 デバイスは現在の変換を中断し、フルスケール範囲をより高いレベルに設定して新しい変換を開始します。このフラグ はこの処理の最後に設定されます。このプロセスは、オーバーフロー状態が発生しないか、またはフルスケール範囲が最大範囲に設定されるまで繰り返されます。</p> |

| 7   | CRF   | R   | 0b   | <p><b>変換準備完了フィールド (読み取り専用)。</b><br/>         変換準備完了フィールドは、変換が完了したことを示します。このフィールドは変換の終了時に 1 に設定され、その後、構成レジスタがシャットダウン モード (動作モードフィールド M[1:0] = 00b) 以外の値で読み書きされると 0 にクリアされます。シャットダウン モードを書き込んでも、このフィールドの状態には影響しません。詳細については、<a href="#">セクション 6.4.2</a> セクションを参照してください。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6   | FH    | R   | 0b   | <p><b>フラグ High フィールド (読み取り専用)。</b><br/>         フラグ High フィールド (FH) は、変換結果が指定された閾値よりも大きいことを示します。FH は、結果が High リミット レジスタ (レジスタ アドレス 03h) に設定されたレベルを、フルカウント フィールド (FC[1:0]) で定義された連続回数分下回った場合に 1 に設定されます。このフィールドのクリアおよびその他の動作の詳細については、<a href="#">セクション 6.4.2</a> セクションを参照してください。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5   | FL    | R   | 0b   | <p><b>Low フィールドのフラグ (読み取り専用)。</b><br/>         フラグ Low (FL) フィールドは、変換結果が指定された注目レベルよりも小さい場合にそれを示します。FL は、結果が Low リミット レジスタ (レジスタ アドレス 02h) に設定されたレベルを、フルカウント フィールド (FC[1:0]) で定義された連続回数分下回った場合に 1 に設定されます。このフィールドのクリアおよびその他の動作の詳細については、<a href="#">セクション 6.4.2</a> セクションを参照してください。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4   | L     | R/W | 1b   | <p><b>ラッチ フィールド (読み取りまたは書き込み)。</b><br/>         ラッチ フィールドは、割り込み報告メカニズム (INT ピン、フラグ High フィールド (FH)、フラグ Low フィールド (FL)) の動作を制御します。このビットは、ラッチ型ウインドウ比較と透過的なヒステリシス形式の比較のいずれの報告スタイルを使用するかを選択します。</p> <p>0 の場合、デバイスは透過的なヒステリシス形式の比較動作で動作します。この場合、3 つの割り込み報告メカニズムは、結果レジスタと High リミット / Low リミット レジスタの比較結果を直接反映し、ユーザーによるクリア イベントはありません。詳細については、「<a href="#">セクション 6.3.3</a>」セクションを参照してください。</p> <p>1 = デバイスはラッチ型ウインドウ比較動作で動作し、ユーザーによるクリア イベントが発生するまで割り込み報告メカニズムをラッチします。</p>                                                                                                                                                                                                                                                                                                            |

| 3   | POL   | R/W | 0b   | <p><b>極性フィールド (読み取りまたは書き込み)。</b><br/>         極性フィールドは、INT ピンの極性を制御します。</p> <p>0 = INT ピンはアクティブ Low を通知し、割り込みイベント時にピンを Low にします。</p> <p>1 = INT ピンの動作は反転しており、割り込みイベント時に INT ピンはアクティブ High を報告し、高インピーダンス状態となって INT ピンがプルアップされることを可能にします。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2   | ME    | R/W | 0b   | <p><b>マスク指數フィールド (読み取りまたは書き込み)。</b><br/>         マスク指數フィールドは、フルスケール範囲が手動設定されている場合に、結果レジスタの指數フィールド (レジスタ 00h、ビット E[3:0]) を 0000b に固定します。これにより、フルスケール範囲を手動で設定した際の結果レジスタの処理が簡単になります。この動作は、マスク指數フィールドが 1 に設定され、かつレンジ番号フィールド (RN[3:0]) が 1100b 未満に設定されている場合に発生します。マスキングは結果レジスタに対してのみ実行されることに注意してください。割り込み通知メカニズムを使用している場合、下限レジスタおよび上限レジスタとの結果比較は、ME フィールドの影響を受けません。</p>                                                                                                                                                                                                                                                                                                                                                                                                             |

表 7-5. 構成レジスタ フィールドの説明 (続き)

| ビット | フィールド   | タイプ | リセット | 説明                                                                                                                                                                                                                                                                                                                                 |

|-----|---------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | FC[1:0] | R/W | 00b  | <p>フォルト カウント フィールド (読み取りまたは書き込み)。</p> <p>フォルト カウント フィールドは、割り込み報告メカニズム (INT ピン、フラグ High (FH)、フラグ Low (FL)) をトリガするのに必要な連続フォルト イベントの回数をデバイスに指示します。フォルト イベントについては、ラッチ フィールド (L)、フラグ High (FH)、フラグ Low (FL) の説明で記載されています。</p> <p>00 = 1 回のフォルト カウント (デフォルト)<br/> 01 = 2 回のフォルト カウント<br/> 10 = 4 回のフォルト カウント<br/> 11 = 8 回のフォルト カウント</p> |

### 7.1.1.3 下限レジスタ (オフセット = 02h) [リセット = C0000h]

このレジスタは、割り込み通知メカニズムの比較下限 (INT ピン、フラグ High フィールド (FH)、フラグ Low フィールド (FL)) を設定します (セクション 6.4.2 セクションを参照)。

図 7-3. 下限レジスタ

| 15  | 14  | 13  | 12  | 11   | 10   | 9   | 8   |

|-----|-----|-----|-----|------|------|-----|-----|

| LE3 | LE2 | LE1 | LE0 | TL11 | TL10 | TL9 | TL8 |

| R/W | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W |

| 7   | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

| TL7 | TL6 | TL5 | TL4 | TL3  | TL2  | TL1 | TL0 |

| R/W | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W |

凡例: R/W = 読み取り / 書き込み

表 7-6. 下限レジスタのフィールドの説明

| ビット   | フィールド    | タイプ | リセット | 説明                                                          |

|-------|----------|-----|------|-------------------------------------------------------------|

| 15:12 | LE[3:0]  | R/W | 0h   | <b>指數。</b><br>これらのビットは指數ビットです。詳しくは、表 7-7 を参照してください。         |

| 11:0  | TL[11:0] | R/W | 000h | <b>結果。</b><br>これらのビットはストレート バイナリ コーディング (ゼロからフルスケール) の結果です。 |

このレジスタの形式は、結果レジスタに記載されている結果レジスタの形式とほぼ同じです。下限レジスタ指數 (LE[3:0]) は、結果レジスタの指數 (E[3:0]) と類似しています。下限レジスタの結果 (TL[11:0]) は、結果レジスタの結果 (R[11:0]) と同様です。

このレジスタを lux スレッシュルドに変換するための式は式 4 に示されており、結果レジスタ用の式式 3 と類似しています。

$$\text{lux} = 0.01 \times (2^{\text{LE}[3:0]}) \times \text{TL}[11:0] \quad (4)$$

表 7-7 に、下限レジスタに適用される範囲とサイズからのフルスケール範囲と LSB サイズを示します。結果レジスタに示す詳細な説明と例は、下限レジスタにも適用されます。

表 7-7. フルスケール範囲と LSB サイズを指數レベルの関数として表現

| LE3 | LE2 | LE1 | LE0 | フルスケール レンジ (lux) | LSB サイズ ( LSB あたりの lux) |

|-----|-----|-----|-----|------------------|-------------------------|

| 0   | 0   | 0   | 0   | 40.95            | 0.01                    |

| 0   | 0   | 0   | 1   | 81.90            | 0.02                    |

| 0   | 0   | 1   | 0   | 163.80           | 0.04                    |

| 0   | 0   | 1   | 1   | 327.60           | 0.08                    |

| 0   | 1   | 0   | 0   | 655.20           | 0.16                    |

| 0   | 1   | 0   | 1   | 1310.40          | 0.32                    |

表 7-7. フルスケール範囲と LSB サイズを指数レベルの関数として表現 (続き)

| LE3 | LE2 | LE1 | LE0 | フルスケール レンジ (lux) | LSB サイズ ( LSB あたりの lux) |

|-----|-----|-----|-----|------------------|-------------------------|

| 0   | 1   | 1   | 0   | 2620.80          | 0.64                    |

| 0   | 1   | 1   | 1   | 5241.60          | 1.28                    |

| 1   | 0   | 0   | 0   | 10483.20         | 2.56                    |

| 1   | 0   | 0   | 1   | 20966.40         | 5.12                    |

| 1   | 0   | 1   | 0   | 41932.80         | 10.24                   |

| 1   | 0   | 1   | 1   | 83865.60         | 20.48                   |

## 注

結果レジスタと限界値レジスタは、比較のために内部で lux 値に変換されます。これらのレジスタは、異なる指數領域を持つことができます。ただし、手動で設定したフルスケール レンジ (構成レジスタで RN < 0Ch、かつマスク有効 (ME) がアクティブ) を使用する場合は、その値を LE[3:0] および HE[3:0] フィールドにプログラムすることで、レジスタ設定の選択が容易になります。この簡略化により、ユーザーは結果の指數部分を意識する必要がなく、小数部分のみを考慮すればよくなります。

## 7.1.1.4 上限レジスタ (オフセット = 03h) [リセット = BFFFh]

上限レジスタは、割り込み通知メカニズムの比較の上限 (INT ピン、フラグ High フィールド (FH)、フラグ Low フィールド (FL)) を設定します (詳細で [セクション 6.3.3 セクション](#) に説明されています)。このレジスタの形式は、下限レジスタ ([下限レジスタに記載](#)) と結果レジスタ ([結果レジスタに記載](#)) の形式とほぼ同じです。類似性をより詳細に説明するために、上限レジスタ指數 (HE[3:0]) は下限レジスタ指數 (LE[3:0]) および結果レジスタ指數 (E[3:0]) に似ています。上限レジスタの結果値 (TH[11:0]) は、下限レジスタの結果値 (TH[11:0]) および結果レジスタの結果値 (R[11:0]) と同様の構造になっています。上限レジスタと結果レジスタとの比較は、ME ビットの影響を受けないことに注意してください。

マスク有効 (ME) をアクティブにした状態で手動設定のフルスケール レンジを使用する場合、そのレンジを HE[3:0] ビットにプログラムすることで、このレジスタに設定すべき値の選定を簡素化できます。このレジスタを lux に変換する式は、[式 4](#) と同様です。フルスケールの値は [表 7-3](#) と同様です。

図 7-4. 上限レジスタ

| 15  | 14  | 13  | 12  | 11   | 10   | 9   | 8   |

|-----|-----|-----|-----|------|------|-----|-----|

| HE3 | HE2 | HE1 | HE0 | TH11 | TH10 | TH9 | TH8 |

| R/W | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W |

| 7   | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

| TH7 | TH6 | TH5 | TH4 | TH3  | TH2  | TH1 | TH0 |

| R/W | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W |

凡例: R/W = 読み取り / 書き込み

表 7-8. 上限レジスタのフィールドの説明

| ビット   | フィールド    | タイプ | リセット | 説明                                                         |

|-------|----------|-----|------|------------------------------------------------------------|

| 15:12 | HE[3:0]  | R/W | Bh   | <b>指數。</b><br>これらのビットは指數ビットです。                             |

| 11:0  | TH[11:0] | R/W | FFFh | <b>結果。</b><br>これらのビットはストレートバイナリ コーディング (ゼロからフルスケール) の結果です。 |

### 7.1.1.5 メーカー ID レジスタ (オフセット = 7Eh) [リセット = 5449h]

このレジスタは、デバイスを一意に識別するのに役立つことを目的としています。

**図 7-5. Manufacturer ID レジスタ**

| 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   |

|------|------|------|------|------|------|-----|-----|

| ID15 | ID14 | ID13 | ID12 | ID11 | ID10 | ID9 | ID8 |

| R    | R    | R    | R    | R    | R    | R   | R   |

| 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

| ID7  | ID6  | ID5  | ID4  | ID3  | ID2  | ID1 | ID0 |

| R    | R    | R    | R    | R    | R    | R   | R   |

凡例: R = 読み取り専用

**表 7-9. メーカー ID レジスタのフィールドの説明**

| ビット  | フィールド    | タイプ | リセット  | 説明                                                                    |

|------|----------|-----|-------|-----------------------------------------------------------------------|

| 15:0 | ID[15:0] | R   | 5449h | メーカー ID。<br>メーカー ID は 5449h です。ASCII コードでは、このレジスタは <i>TI</i> を読み出します。 |

### 7.1.1.6 デバイス ID レジスタ (オフセット = 7Fh) [リセット = 3001h]

このレジスタは、デバイスを一意に識別するのにも役立ちます。

**図 7-6. Device ID レジスタ**

| 15    | 14    | 13    | 12    | 11    | 10    | 9    | 8    |

|-------|-------|-------|-------|-------|-------|------|------|

| DID15 | DID14 | DID13 | DID12 | DID11 | DID10 | DID9 | DID8 |

| R     | R     | R     | R     | R     | R     | R    | R    |

| 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

| DID7  | DID6  | DID5  | DID4  | DID3  | DID2  | DID1 | DID0 |

| R     | R     | R     | R     | R     | R     | R    | R    |

凡例: R = 読み取り専用

**表 7-10. デバイス ID レジスタのフィールドの説明**

| ビット  | フィールド     | タイプ | リセット  | 説明                              |

|------|-----------|-----|-------|---------------------------------|

| 15:0 | DID[15:0] | R   | 3001h | デバイス ID。<br>デバイス ID は 3001h です。 |

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

周囲光センサは、周囲光の機能として制御を必要とする幅広いアプリケーションで使用されています。周囲光センサは、標準的に人間の目の分光感度特性に一致しているため、人間にとて快適な体験を提供することが目的である場合、フォトダイオードよりも優れています。非常に多くの用途としては、ディスプレイの明るさ制御や、産業用および家庭用の照明制御が挙げられます。

OPT3001-Q1 デバイスへのインターフェイスには、電気的および光学的という 2 つのカテゴリがあります。

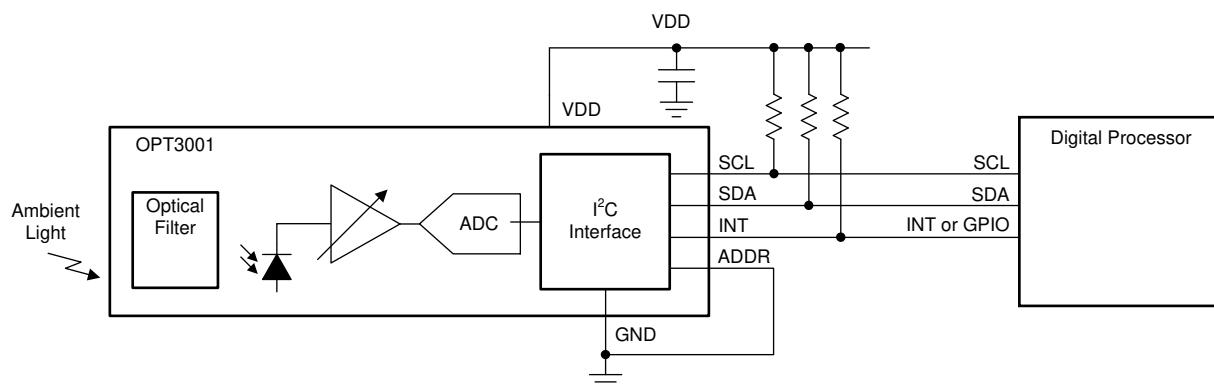

#### 8.1.1 電気的インターフェイス

電気的インターフェイスは、図 8-1 に示すように非常に簡単です。OPT3001-Q1 の I<sup>2</sup>C SDA ピンと SCL ピンを、アプリケーション プロセッサ、マイコン、他のデジタル プロセッサの同じピンに接続します。OPT3001-Q1 デバイスからの関心のあるイベントに基づく割り込みをデジタル プロセッサが必要とする場合は、INT ピンをプロセッサの割り込みピンまたは汎用 I/O ピンに接続します。この割り込みには複数の用途があり、たとえばシステムを低電力モードから復帰させるための信号として使用したり、関心のある周囲光イベントを待つ間に他の処理を行ったり、あるいはサンプルの読み出し準備が完了したことをプロセッサに通知したりすることができます。SDA および SCL ピンには、デジタル通信に適した電源とそれぞれのピンの間にプルアップ抵抗を接続します (これらのピンはオープンドレイン出力構造のためです)。INT ピンを使用する場合は、プルアップ抵抗を INT ピンに接続します。プルアップ抵抗の標準値は  $10k\Omega$  です。システムの速度、消費電力、ノイズ耐性などの要件のバランスを取るために、バスの容量と組み合わせて抵抗値を最適化できます。

電源とグランドに関する考慮事項については、セクション 8.4 セクションを参照してください。

SDA および SCL ピン回路にはスパイク抑制機能が組み込まれていますが、通信ラインへのノイズ結合を最小限に抑えるために、適切なレイアウト設計を行います。ノイズが発生する原因の一つとして、2 本の通信ライン間で信号の立ち上がりや立ち下がりが容量結合によって影響し合うことが挙げられます。もう一つのノイズ発生要因として、システム内に存在する他のスイッチング ノイズ源からの影響が挙げられます。特に通信ラインが長い場合には注意が必要です。ノイズの多い環境では、通信ラインをシールドすることで、デジタル I/O ラインに不要なノイズが結合し、誤って解釈される可能性を低減できます。

#### 8.1.2 光インターフェイス

光インターフェイスはパッケージ内で物理的に配置され、セクション 11 のセンサ領域で指定されているように、PCB から離れた向きに配置されています。

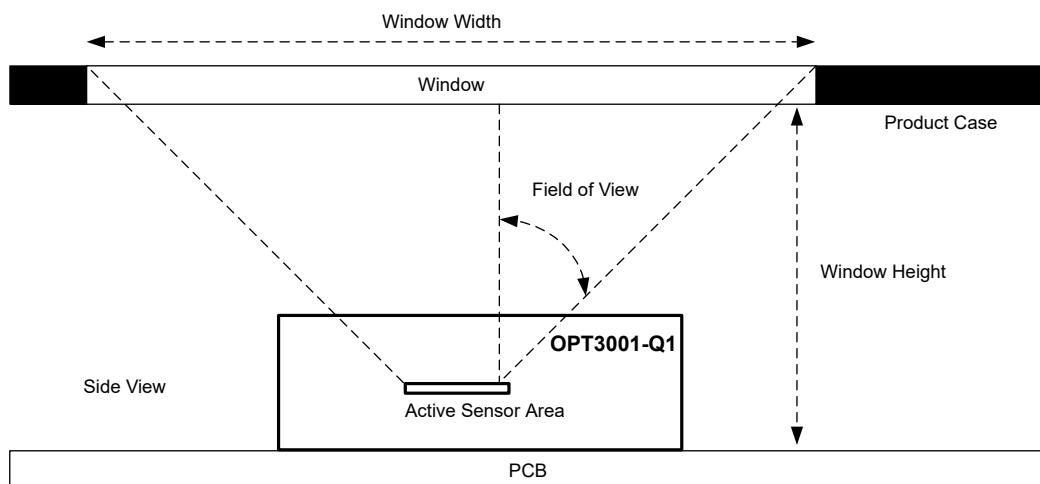

プラスチック製ハウジングや、外部からの光をセンサに当てるためのウインドウ (図 8-2 を参照) などの物理的な部品は、OPT3001-Q1 デバイスや周辺回路の保護に役立ちます。デザインの見た目をさらに良くするために、センサが見えないように暗色または不透明のウインドウを使用することもあります。このウインドウの素材には、通常、透明なプラスチックやガラスが使用されます。

光センサの検出エリアに当たる光に影響を与える物理的な部品は、すべて光センサの性能にも影響を与えます。そのため、最適な性能を得るには、これらの部品が与える影響をよく理解し、管理することが大切です。センサを照射するのに十分な視野から光を確保できるように、ウインドウの幅と高さを設計します。最高の性能を得るには、視野角を  $\pm 35^\circ$  以上、または理想的には  $\pm 45^\circ$  以上にします。視野角についての理解と設計については、OPT3001: 周辺光センサ アプリケーション ガイド アプリケーション ノートをご覧ください。

ダーク ウインドウの場合、可視光の透過率は通常 5% から 30% の範囲ですが、1% 未満の場合もあります。デザイン性を高めるために必要な範囲で、できるだけ低い可視光透過率を指定します。ただし、透過率を下げすぎるとセンサが測定できる光の量も減ってしまうため、必要以上に低くしないようにします。ウインドウを暗くする方法には、透明なウインドウ素

材にインクを塗布する方法や、ウインドウ素材自体に染料や他の光学物質を加える方法があります。ウインドウの可視光透過率を低くすることで、デザイン外部の光と OPT3001-Q1 デバイスで測定される光との間に比率が生じます。このデザイン外部の光を正確に測定するため、OPT3001-Q1 の測定値をこの比率で補償します。例を [セクション 8.2.2.2](#) に示します。

周囲光センサは、人間に最適な照明環境を作り出すのに役立ちます。そのため、人間の目の応答に合わせてセンサのスペクトル応答を一致させることが不可欠です。赤外線は人間の目には見えませんが、センサに赤外線除去機能がない場合、可視光の測定に干渉することがあります。したがって、干渉する赤外線に対する可視光の比率は、人間の目を表す実用的なシステムの精度に影響を与えます。OPT3001-Q1 デバイスは赤外線を強力に除去するため、白熱灯やハロゲンランプ、太陽光など赤外線の多い照明環境下でも、人間の感覚と一致した測定が可能です。

ダーク ウィンドウに使われるインクや染料は、主に可視光の透過を最小限に抑える目的で使われますが、中には赤外線を非常によく透過するものもあります。これらのインクと染料を使用すると、可視光と赤外線の比率がさらに低下し、センサの測定精度が低下します。しかし、OPT3001-Q1 デバイスは赤外線を優れた精度で除去できるため、この影響は最小限に抑えられます。そのため、[図 8-3](#) に示されているような分光応答特性を持つダーク ウィンドウの下でも良好な測定結果が得られます。

最良の精度を得るためにには、設計者が光学的な影響を十分に理解していない限り、格子状のウンドウ構造を避けます。格子状のウンドウ構造は、センサ上に不均一な照明パターンを作り出すため、光の入射角や設置位置の誤差によって測定結果が変動しやすくなります。もし格子状構造を採用したい場合でも、OPT3001-Q1 デバイスは、照明の均一性による測定への影響が非常に小さいため、優れたセンサの選択肢となります。

ライト パイプは、光をセンサに導くオプトメカニカル設計において魅力的に見える場合がありますが、システム設計者が設計全体や目的におけるライト パイプの光学的影響を十分に理解していない限り、周囲光センサではライト パイプの使用を避けてください。

## 8.2 代表的なアプリケーション

製品ケース内で、かつダーク ウィンドウの下に配置された状態で OPT3001-Q1 デバイスを用いて周囲光を測定する方法については、このセクションで説明します。この設計の回路図は、[図 8-1](#) に示します。

図 8-1. ダーク ウィンドウ越しの製品ケース内での周囲光の測定

## 8.2.1 設計要件

この設計の基本要件は次のとおりです:

- センサは目立たないように、ダーク ガラスの下に隠されています。この要件は、設計者の好みによって異なる主観的なものですのでご注意ください。

- 蛍光灯の測定精度は 15% です

- 蛍光灯、ハロゲンランプ、白熱灯といった光源間での測定値のばらつき（いわゆる光源バリエーション）は、可能な限り小さく抑えられています。

## 8.2.2 詳細な設計手順

### 8.2.2.1 光学機器的設計

電気設計が完了した後、次のタスクは光学機械設計です。図 8-2 に示すように、製品外部からセンサに光を送信するウィンドウを含む製品ケースを設計します。視野角を  $\pm 45^\circ$  にするために、ウィンドウの幅と高さを設計します。セクション 11 に示すように、視野角の厳密な設計では、センサ領域の位置を考慮しています。OPT3001-Q1 のアクティブ センサ領域は、パッケージの上面図における一方の軸には中心に配置されていますが、もう一方の軸にはわずかなオフセットがあります。ウィンドウのサイズ設定および配置について、より厳密な点については、[OPT3001: 周辺光センサ アプリケーションガイド](#) アプリケーション ノートをご覧ください。

図 8-2. OPT3001-Q1 デバイス上の製品ケースおよびウィンドウ

### 8.2.2.2 暗ウィンドウの選択と補償

ダーク ウィンドウの選定や補正には、いくつかの方法があります。このセクションで説明する方法は、多くのアプローチの 1 つです。

さまざまな濃さのウィンドウをいくつか試してみてください。デバイスの見た目とセンサ性能のバランスが最適になるよう、十分に暗いウィンドウを選んでください。なお、見た目の評価は設計者の主観によるものであるため、ウィンドウの透過率の仕様を参照するよりも、実際の製品にウィンドウを取り付けて観察することが望ましいです。選択したウィンドウが本当に必要な範囲以上に暗くなっていることを確認します。ウィンドウが暗すぎるとセンサに届く光が減り、センサの精度が低下してしまいます。

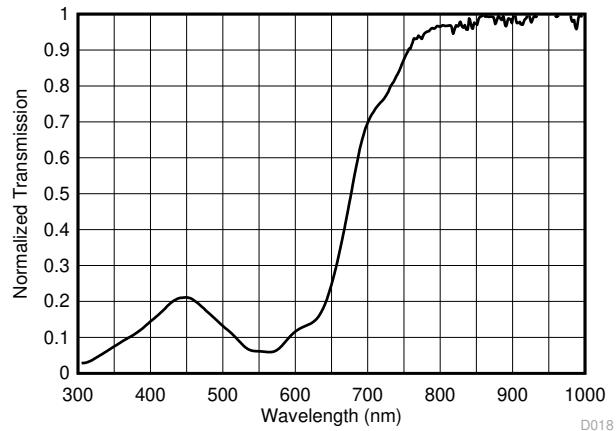

このアプリケーション例で選ばれたウィンドウはダーク タイプで、550nm における透過率は 7% 未満です。スペクトルの正規化された応答を、図 8-3 に示します。なお、透過スペクトルの測定に使用した機器では、ダーク ウィンドウ サンプルの絶対的な正確さ（非正規化値）は測定できず、相対的な正規化スペクトルのみが測定可能である点に注意してください。また、このウィンドウは、400nm から 650nm の可視光よりも、700nm を超える赤外線波長の方がはるかによく透過することにも注意してください。この赤外線と可視光の不均衡が、センサの可視光と赤外線の比率を減少させます。ウィンドウの

可視光透過率と赤外線透過率の比率ができるだけ近い(この比率の低下が最小限になる)ことが望ましいですが、図 8-6 に示されているように、OPT3001-Q1 デバイスはそのような条件下でも十分に良好な性能を発揮します。

図 8-3. 選択したダーク ウィンドウの正規化された透過スペクトル応答

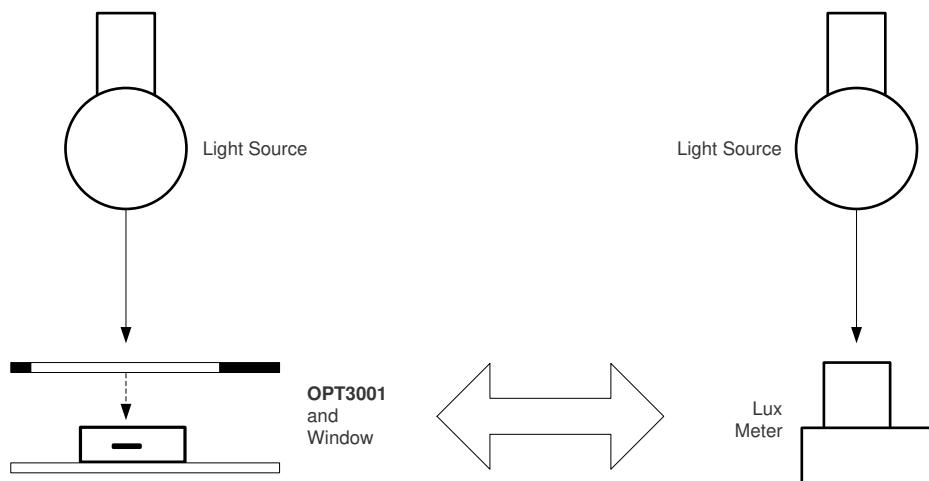

ダーク ウィンドウを選択した後で、後で補正するためにダーク ウィンドウの減衰効果を測定します。この減衰効果を測定するには、まず蛍光灯などの光源を lux メータで測定し、次に同じ光源をダーク ウィンドウ越しに OPT3001-Q1 デバイスで測定します。正確に測定するには、lux メータ、または OPT3001-Q1 デバイスとダーク ウィンドウを搭載した設計に対応できる治具を使用します。図 8-4 に示すように、各センシング領域の中心はまったく同じ X、Y、Z の位置にあります。この設計における Z 方向の位置(光源からの距離)は、OPT3001-Q1 デバイス本体ではなく、ウィンドウの上面となります。

図 8-4. 1 つの光源を使用し、lux メータまたは設計(ウィンドウおよび OPT3001-Q1 デバイス)を同じ X、Y、Z 位置に配置できる治具

この場所で蛍光灯の光を lux メータで測定すると 1000lux ですが、同じ場所でアプリケーション内のダーク ウィンドウ越しに OPT3001-Q1 デバイスで測定すると 73lux となります。そのため、蛍光灯の透過率は 7.3% です。この 7.3% は、lux メータ(またはフォトピック応答)の分光応答で重み付けされた、全スペクトルにわたる加重平均の減衰率です。

このダーク ウィンドウ越しのすべての OPT3001-Q1 測定値には、以下の式を適用します。

$$\text{Compensated Measurement} = \text{Uncompensated Measurement} / (7.3\%) \quad (5)$$

### 8.2.3 アプリケーション曲線

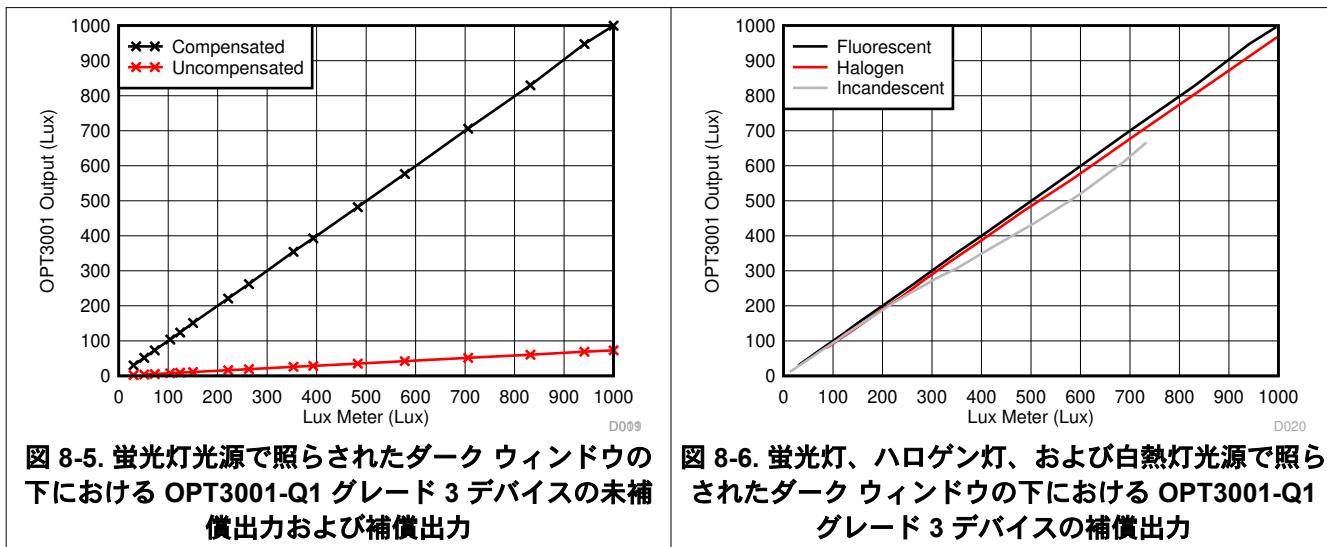

設計例が正しく測定されていることを検証するには、ニュートラル密度フィルタを使用して光を減衰させ、蛍光灯で連続した数の異なる光強度を作成します。光源と測定装置の距離を変えることでも、異なる光強度を作り出すことができます。しかしながら、光の強度を変えるこれら二つの方法には、わずかな精度のトレードオフがあり、本議論の範囲外となります。各輝度をウインドウの下にある lux メータと OPT3001-Q1 デバイスの両方で測定し、式 5 を使用して補償します。結果を図 8-5 に示します。これは、アプリケーションが lux メータと非常によく似た結果を正確に報告していることを示しています。

ウインドウの赤外線透過率と可視光透過率の比率が大きいにもかかわらず、設計がさまざまな光源を正しく測定することを検証するために、ハロゲン電球と白熱電球を用いてアプリケーションの測定を行います。蛍光灯に使用した物理的な位置と光の減衰手順を使用します。図 8-6 に、結果を示します。

ダーク ウインドウを追加すると、同じ測定結果をウインドウ (図 5-3) とウインドウ (図 8-6) なしで比較することで、結果が変化します。予想された変化の後でも、パフォーマンスはまだ良好です。いずれのデータも正解の 15% 以内で、他のバルブ測定値の 15% 以内です。

OPT3001-Q1 デバイスは、あらゆる角度の光で lux メータと一致しないため、結果は異なる角度の光で変化する可能性があります。

光源間の測定のばらつきが許容できない場合は、可視光の透過率が赤外線光の透過率に近い別のウインドウを選択します。

図 8-5. 蛍光灯光源で照らされたダーク ウィンドウの下における OPT3001-Q1 グレード 3 デバイスの未補償出力および補償出力

図 8-6. 蛍光灯、ハロゲン灯、および白熱灯光源で照らされたダーク ウィンドウの下における OPT3001-Q1 グレード 3 デバイスの補償出力

### 8.3 設計のベスト プラクティス

他の光学製品と同様に、OPT3001-Q1 デバイスを取り扱うときは特に注意を払う必要があります。OPT3001-Q1 デバイスはほこりや傷に対する感度が低い設計となっていますが、適切な光学デバイスの取り扱い手順を守ることが推奨されます。

デバイスの光学表面は、試作段階でも量産工程においても最適な性能を発揮させるために、常に清潔に保つ必要があります。光学表面に傷がつくるのを防ぐため、接触部分がプラスチックまたはゴム製のピンセットの使用が推奨されます。可能な限り金属製の工具での取り扱いは避けてください。光学表面は、指紋やほこり、その他の光学性能を妨げる汚れが付着しないよう清潔に保つ必要があります。

デバイスの光学表面を清掃する必要がある場合は、純水またはイソプロピル アルコールの使用が推奨されます。柔らかい綿棒でやさしく数回ブラッシングする程度で十分です。光学表面に傷をつけるおそれのある研磨性のある清掃用具や工具、過度な力の使用は避けてください。

OPT3001-Q1 デバイスの性能が十分に発揮されていない場合は、光学表面に汚れ、傷、またはその他の光学的な異常がないか確認してください。

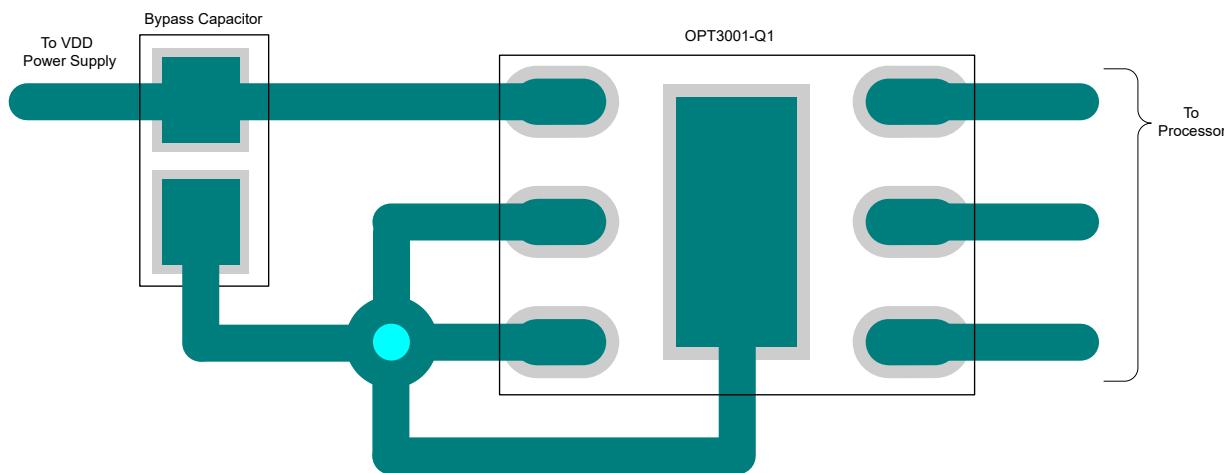

## 8.4 電源に関する推奨事項

OPT3001-Q1 デバイスは電源の影響を受けにくい設計となっていますが、常に適切な電源設計を行うことが推奨されます。最高の性能を得るには、OPT3001-Q1 の  $V_{DD}$  ピンには  $100\text{nF}$  のバイパスコンデンサをデバイスの近くに配置し、安定した低ノイズの電源が必要です。OPT3001-Q1 デバイスへの電力供給には多くのオプションがあります。本デバイスの消費電流レベルは非常に低いためです。

## 8.5 レイアウト

### 8.5.1 レイアウトのガイドライン

OPT3001-Q1 デバイスの PCB レイアウト設計には、いくつかの考慮事項が必要です。OPT3001-Q1 デバイスの近くにコンデンサを配置して、電源をバイパスします。光学的に反射性のある部品の表面も、設計の性能に影響を与えることに注意してください。センサ周囲のすべての構成部品および構造物の立体的な形状を考慮することで、副次的な光の反射による予期しない測定誤差を回避できます。通常は、コンデンサおよび部品を部品の高さの少なくとも 2 倍の距離に配置するだけで十分です。最も最適な光学レイアウトは、すべての近接部品を OPT3001-Q1 デバイスから PCB の反対側に配置することです。ただし、このアプローチは、すべての設計の制約に対して実用的ではありません。

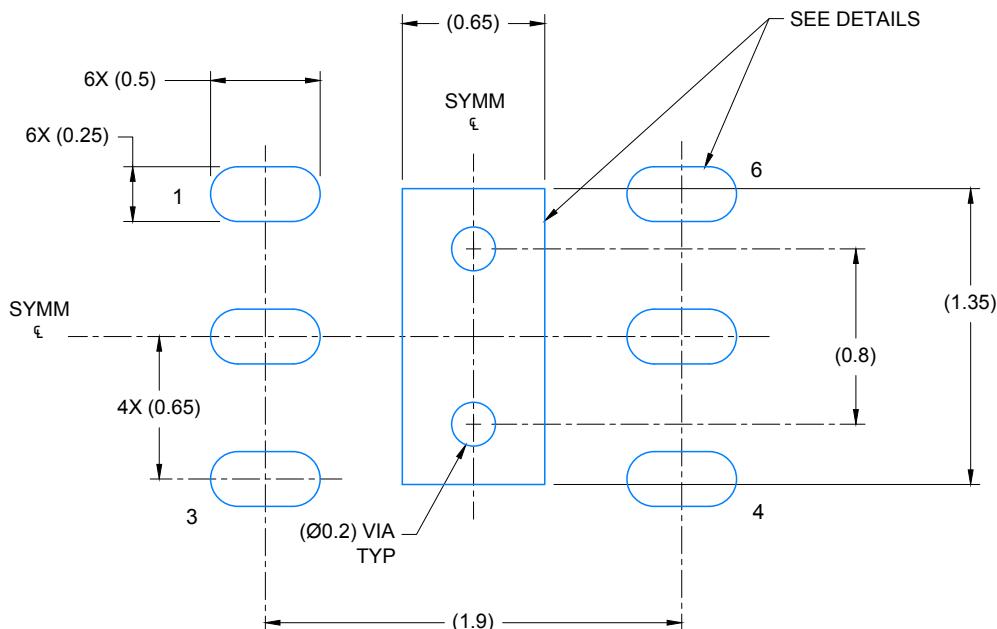

サーマル パッドは電気的にグランドに接続することが推奨されます。この接続は、PCB パターンによって行うか、またはサーマル パッド上にビアを設けて直接グランドに接続することで実現できます。サーマル パッドにビアを設ける場合は、はんだが適切な接合面から吸い取られるのを防ぐために、ビアの直径は  $0.2\text{mm}$  未満の小径にすることが推奨されます。

OPT3001-Q1 デバイスを使用した PCB の例が図 8-7 に示されています。

### 8.5.2 レイアウト例

図 8-7. OPT3001-Q1 の USON レイアウトの例

## 9 デバイスおよびドキュメントのサポート

### 9.1 ドキュメントのサポート

#### 9.1.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『OPT3001: 周辺光センサ アプリケーション ガイド』アプリケーション ノート

- テキサス・インスツルメンツ、『OPT3001EVM ユーザー ガイド』

- テキサス・インスツルメンツ、『[QFN/SON の PCB 実装](#)』アプリケーション ノート

## 9.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。右上の【アラートを受け取る】をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 9.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

## 9.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 9.6 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (December 2024) to Revision C (June 2025) | Page |

|-------------------------------------------------------------------|------|

| 文書全体から SOT-5X3 バリアントを削除.....                                      | 1    |

| ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                | 2    |

| Changes from Revision A (December 2018) to Revision B (December 2024) | Page |

|-----------------------------------------------------------------------|------|

| SOT-5X3 バリアントの動作温度とパッケージ サイズを追加.....                                  | 1    |

| ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                    | 2    |

| シリアル インターフェイスのセクションに、電気的インターフェイスのセクションへのリンクを追加.....                   | 14   |

| アプリケーション情報を <a href="#">セクション 8</a> セクションを追加.....                     | 28   |

| Changes from Revision * (March 2017) to Revision A (December 2018) | Page |

|--------------------------------------------------------------------|------|

| 以下を追加。デバイス温度グレード 2: -40°C ~ 105°C の動作時周囲温度範囲.....                  | 1    |

| 以下を追加。デバイス温度グレード 3: -40°C ~ 85°C の動作時周囲温度範囲.....                   | 1    |

| 以下を追加。動作時温度範囲 (グレード 2): -40°C ~ 105°C.....                         | 1    |

| ダーク応答と温度との関係 (グレード 2)を追加.....                                      | 8    |

|                                      |   |

|--------------------------------------|---|

| • 正規化された応答と温度との関係 (グレード 2) を追加.....  | 8 |

| • 電源電流と温度との関係 (グレード 2) を追加.....      | 8 |

| • シャットダウン電流と温度との関係 (グレード 2) を追加..... | 8 |

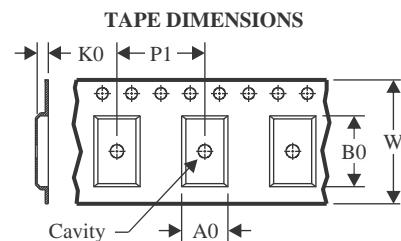

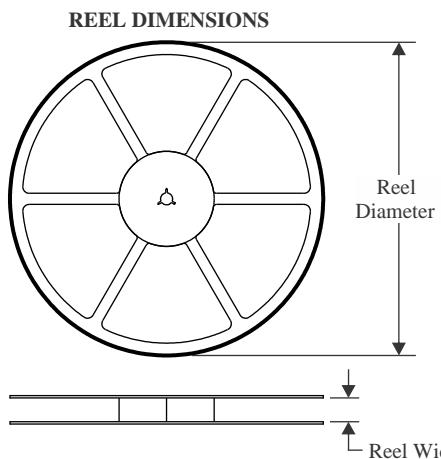

## 11 メカニカル、パッケージ、および注文情報