# TAS2320 19W モノラル デジタル入力 Class-D スピーカ アンプ 15V PVDD をサポート

## 1 特長

- パワフルな Class-D アンプ

- 19W 出力電力 (@1% THD+N)

- 15V 外部 PVDD 電源

- クラス最高の効率

- 1% TDH+N 電源で最大 93.2% の効率

- 14.7mW のアイドルチャネル電力 (ノイズゲートオフ)

- 5.3mW のアイドルチャネル電力 (ノイズゲートオン)

- 内蔵 1.8V VDD Y-ブリッジ

- 高性能オーディオチャネル

- 14.2μV の A 特性アイドルチャネルノイズ

- 114.4dB のダイナミックレンジ

- -90dB の THD+N

- ERC と SSM による低 EMI 特性

- <1μs のチップ間群遅延マッチング

- 先進の内蔵機能

- 信号検出高効率モード

- 高精度電源電圧モニタおよび温度センサ

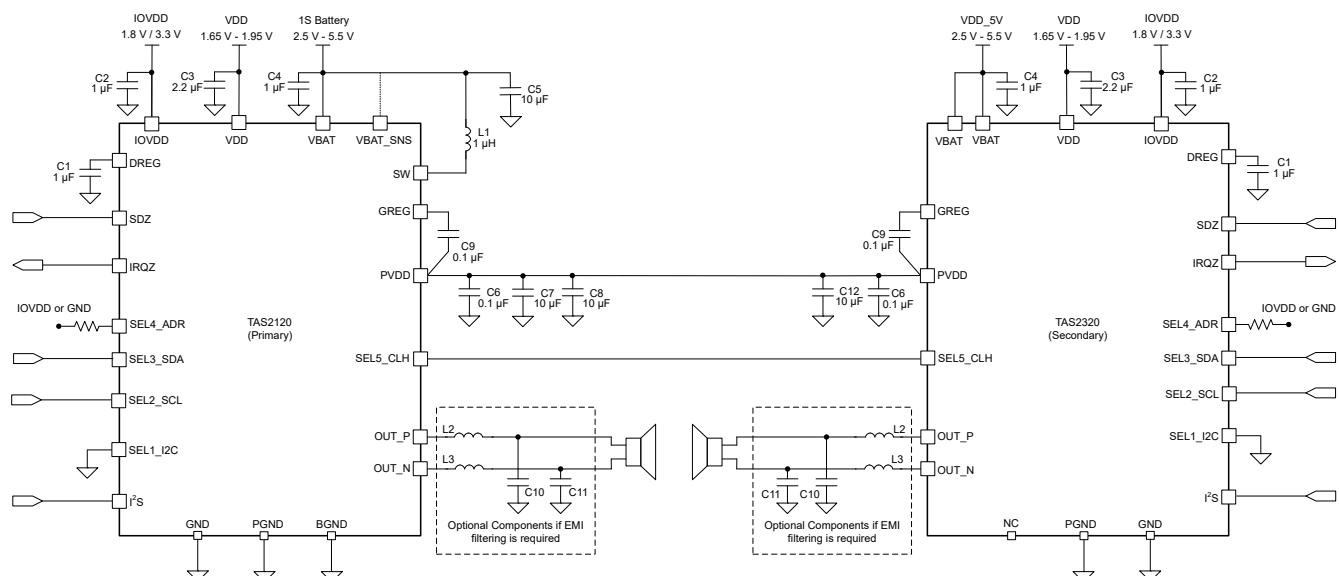

- ブースト共有セカンダリデバイスサポート

- 外部 Class-H 昇圧制御アルゴリズム

- 使いやすい機能

- HW ピン制御または I<sup>2</sup>C 制御

- クロックベースのパワーアップ / ダウン

- 自動クロックレート検出: 16~192kHz

- MCLK フリー動作

- 過熱および過電流保護

- 電源とユーザーインターフェイス

- VBAT: 2.5V ~ 5.5V

- VDD: 1.65V ~ 1.95V

- IOVDD: 1.8V または 3.3V

- PVDD: 2.5V ~ 15V

- I<sup>2</sup>S/TDM: 8 チャネル

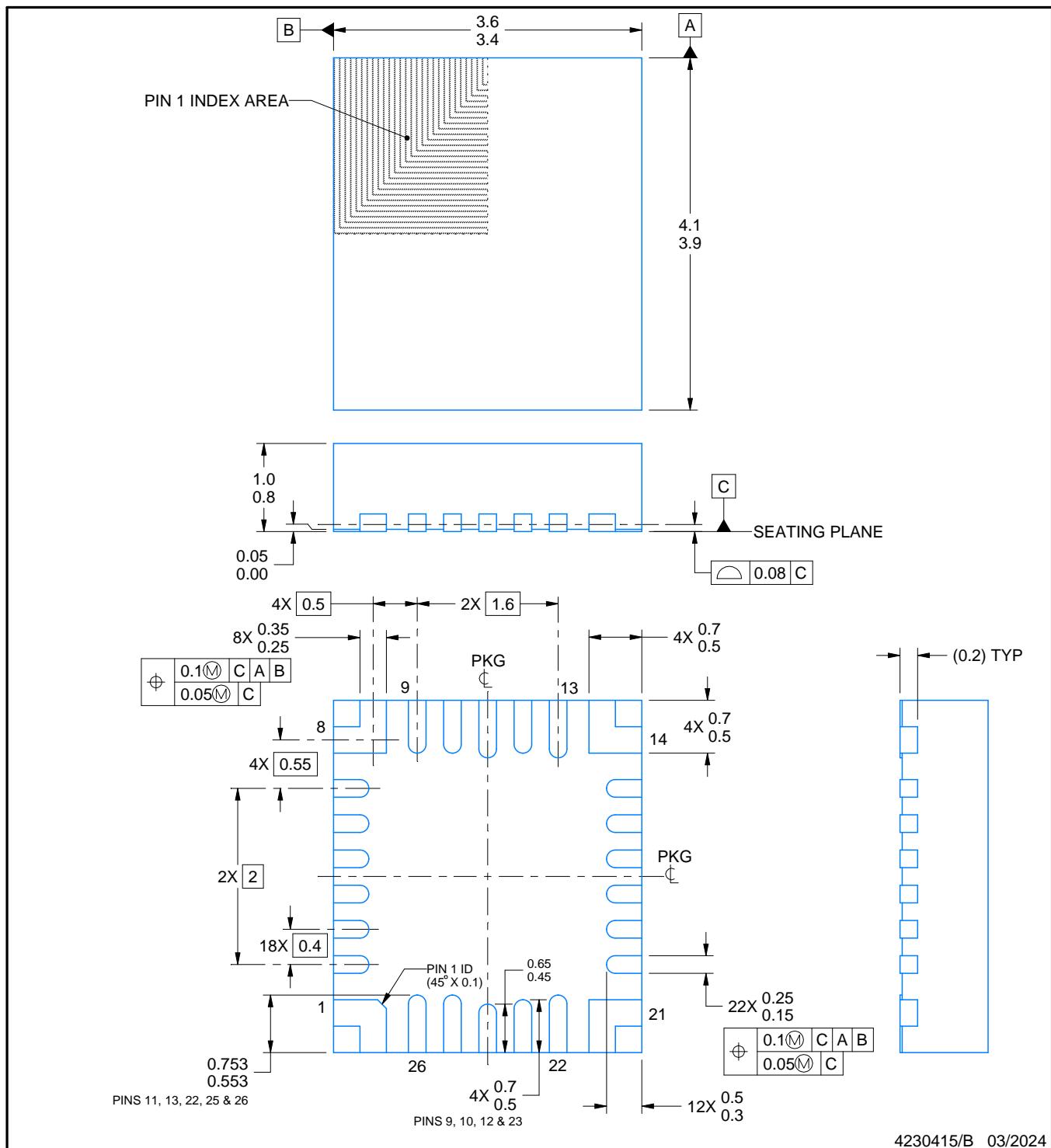

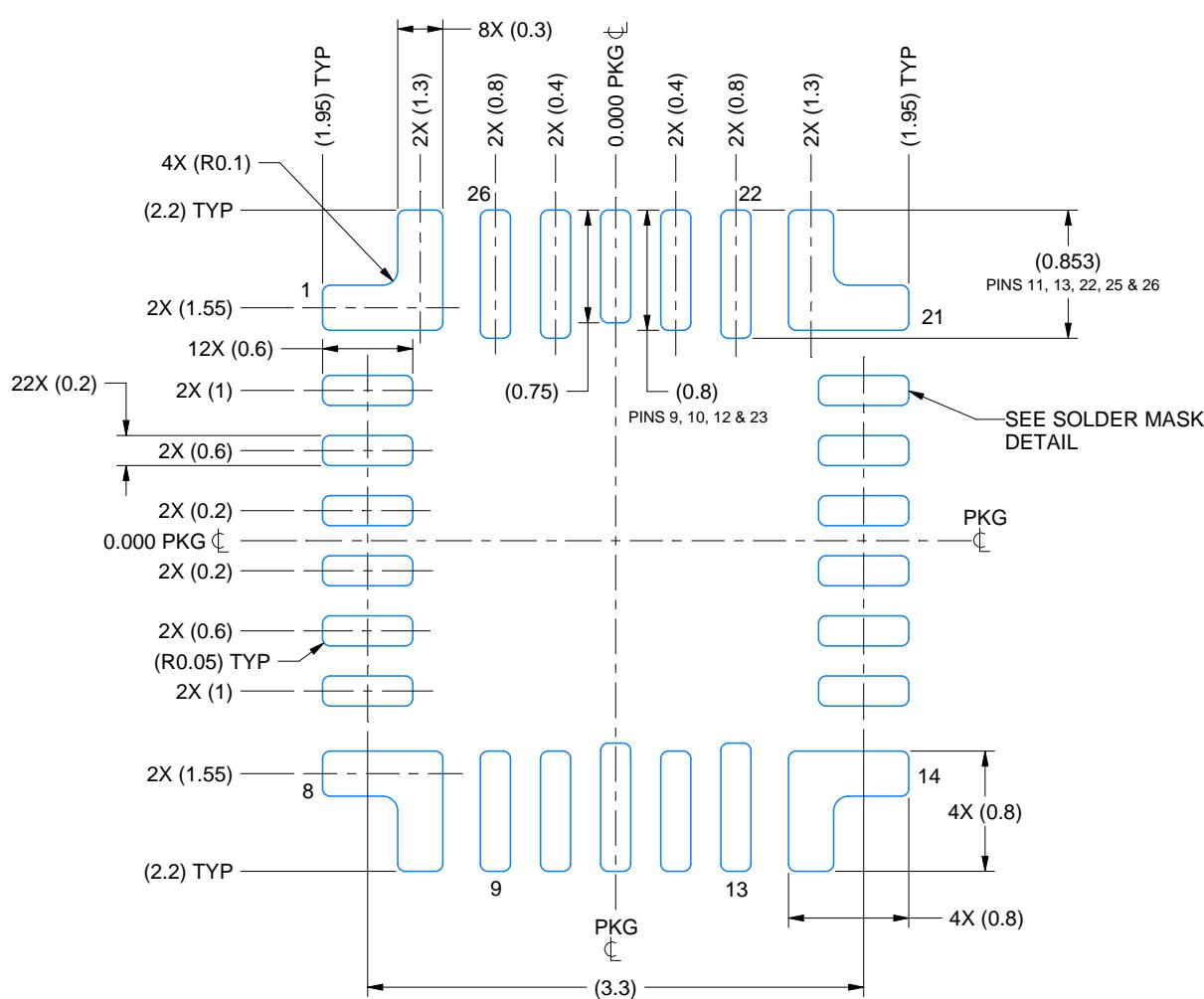

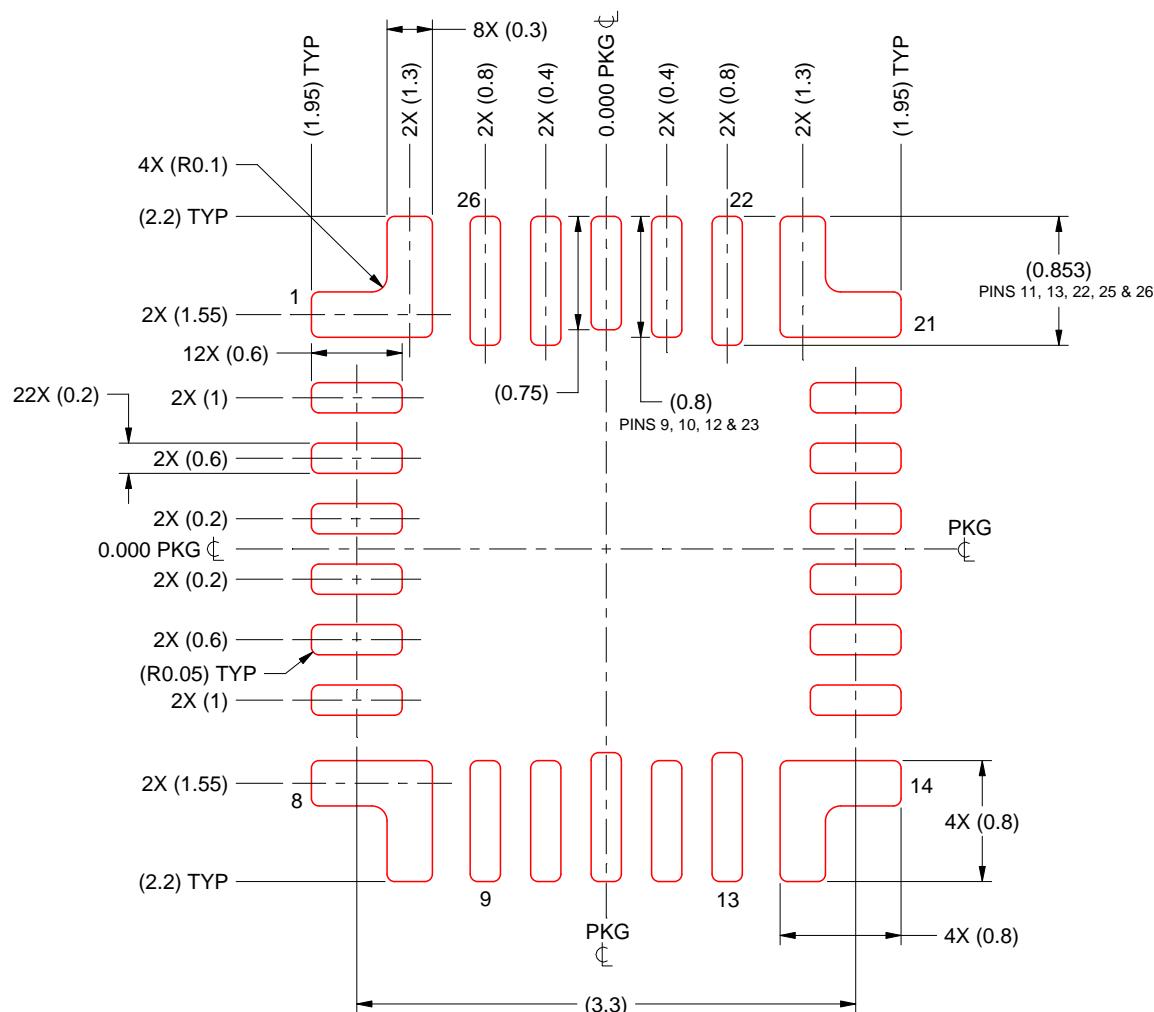

- 0.4mm ピッチの 26 ピン QFN パッケージ

## 2 アプリケーション

- スマートスピーカ (音声アシスタント)

- Bluetooth およびワイヤレススピーカ

- ビルオートメーション

- タブレット、ウェアラブル

- ラップトップ、デスクトップ PC

## 3 説明

TAS2320 は、大きなピーク電力でスピーカを効率的に駆動できるように設計された、モノラル、デジタル入力 Class-D オーディオアンプです。

TAS2320 は、音楽再生と音声通話の実際の使用事例で最長のバッテリ寿命を実現するように最適化されています。Y ブリッジ、アルゴリズムなどの先進の効率最適化機能により、本デバイスはすべての動作電力領域にわたってクラス最高の効率を達成できます。Class-D アンプは、ここで最大 19W の出力電力を供給可能であり、外部 PVDD 電源を使用する場合にも同様に動作します。

最大 4 つのデバイスが、I<sup>2</sup>S/TDM および I<sup>2</sup>C インターフェイス経由で共通のバスを共有できます。TAS2320 は、I<sup>2</sup>C 制御を必要とせずに所望の動作モードへデバイスを設定できる、HW ピンベースの事前定義済み制御にも対応しています。

### 製品情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|---------|----------------------|-------------------------|

| TAS2320 | QFN                  | 4mm × 3.5mm             |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージサイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

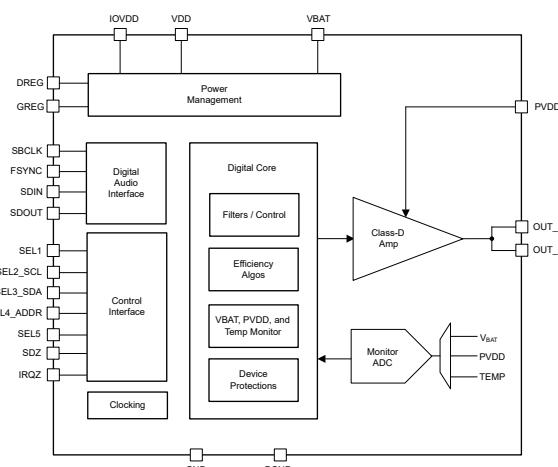

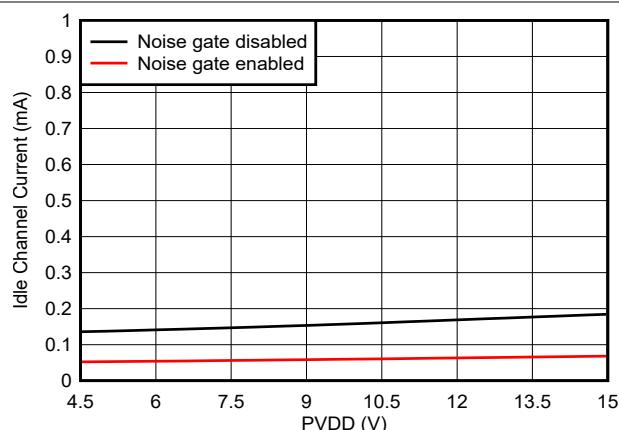

機能プロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLASFC5](#)

## 目次

|                    |           |                               |    |

|--------------------|-----------|-------------------------------|----|

| <b>1 特長</b>        | <b>1</b>  | 7.3 PAGE 2 レジスタ               | 61 |

| <b>2 アプリケーション</b>  | <b>1</b>  | 7.4 PAGE 4 レジスタ               | 65 |

| <b>3 説明</b>        | <b>1</b>  | 7.5 PAGE 5 レジスタ               | 70 |

| <b>4 ピン構成および機能</b> | <b>3</b>  | 7.6 PAGE 6 レジスタ               | 71 |

| <b>5 仕様</b>        | <b>5</b>  | 7.7 PAGE 7 レジスタ               | 75 |

| 5.1 絶対最大定格         | 5         | 7.8 PAGE 8 レジスタ               | 77 |

| 5.2 ESD 定格         | 5         | 7.9 BOOK100 PAGE9 レジスタ        | 79 |

| 5.3 推奨動作条件         | 5         | <b>8 アプリケーションと実装</b>          | 80 |

| 5.4 熱に関する情報        | 5         | 8.1 アプリケーション情報                | 80 |

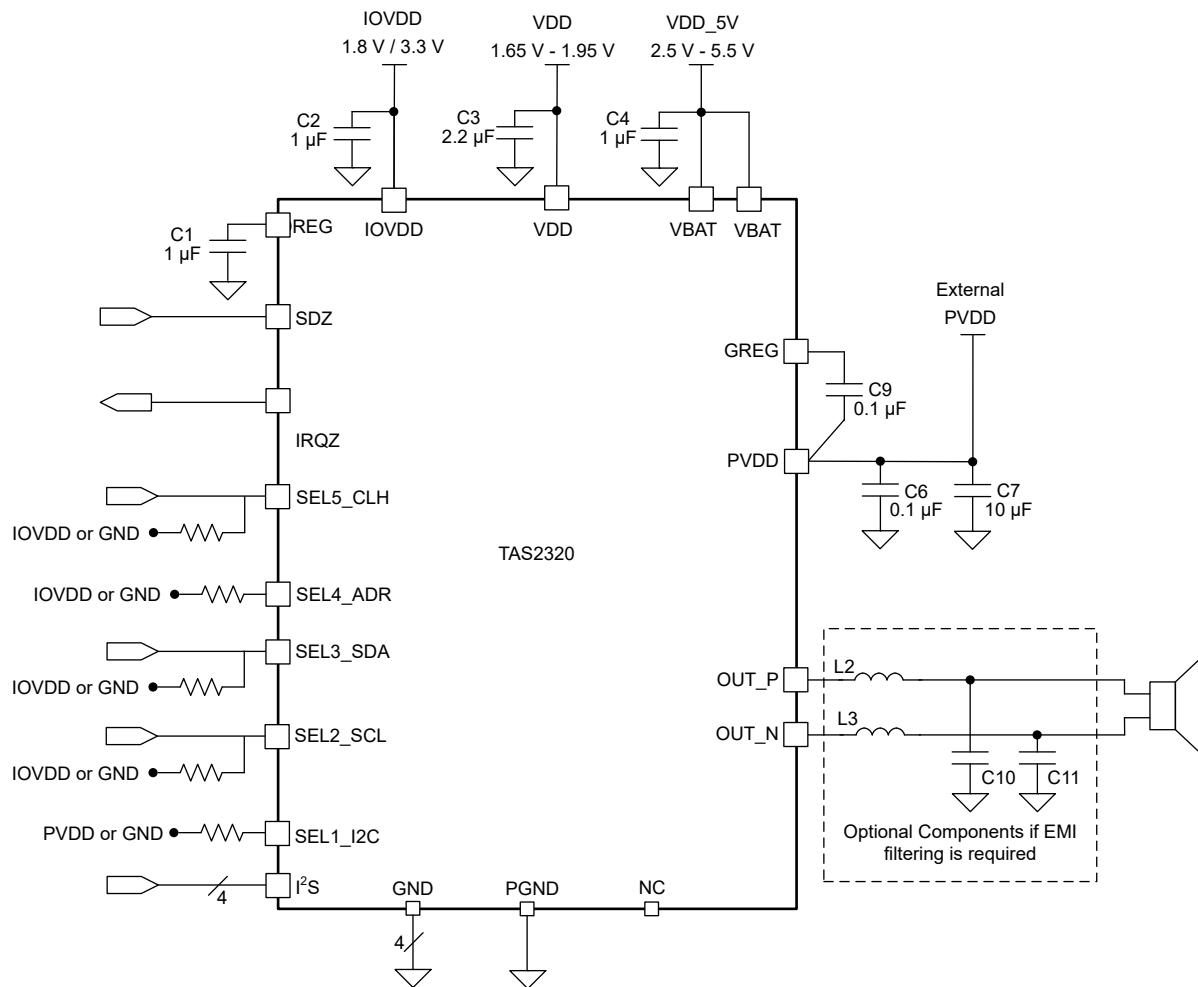

| 5.5 電気的特性          | 6         | 8.2 代表的なアプリケーション              | 80 |

| 5.6 タイミング要件        | 9         | 8.3 推奨事項および禁止事項               | 84 |

| 5.7 タイミング図         | 11        | 8.4 電源に関する推奨事項                | 84 |

| 5.8 代表的特性          | 11        | 8.5 レイアウト                     | 84 |

| <b>6 詳細説明</b>      | <b>16</b> | <b>9 デバイスおよびドキュメントのサポート</b>   | 86 |

| 6.1 概要             | 16        | 9.1 ドキュメントのサポート               | 86 |

| 6.2 機能ブロック図        | 16        | 9.2 ドキュメントの更新通知を受け取る方法        | 86 |

| 6.3 デバイスの機能モード     | 16        | 9.3 サポート・リソース                 | 86 |

| 6.4 機能説明           | 22        | 9.4 商標                        | 86 |

| 6.5 プログラミング        | 35        | 9.5 静電気放電に関する注意事項             | 87 |

| <b>7 レジスタ マップ</b>  | <b>40</b> | 9.6 用語集                       | 87 |

| 7.1 ページ 0 レジスタ     | 41        | <b>10 改訂履歴</b>                | 87 |

| 7.2 ページ 1 レジスタ     | 59        | <b>11 メカニカル、パッケージ、および注文情報</b> | 87 |

## 4 ピン構成および機能

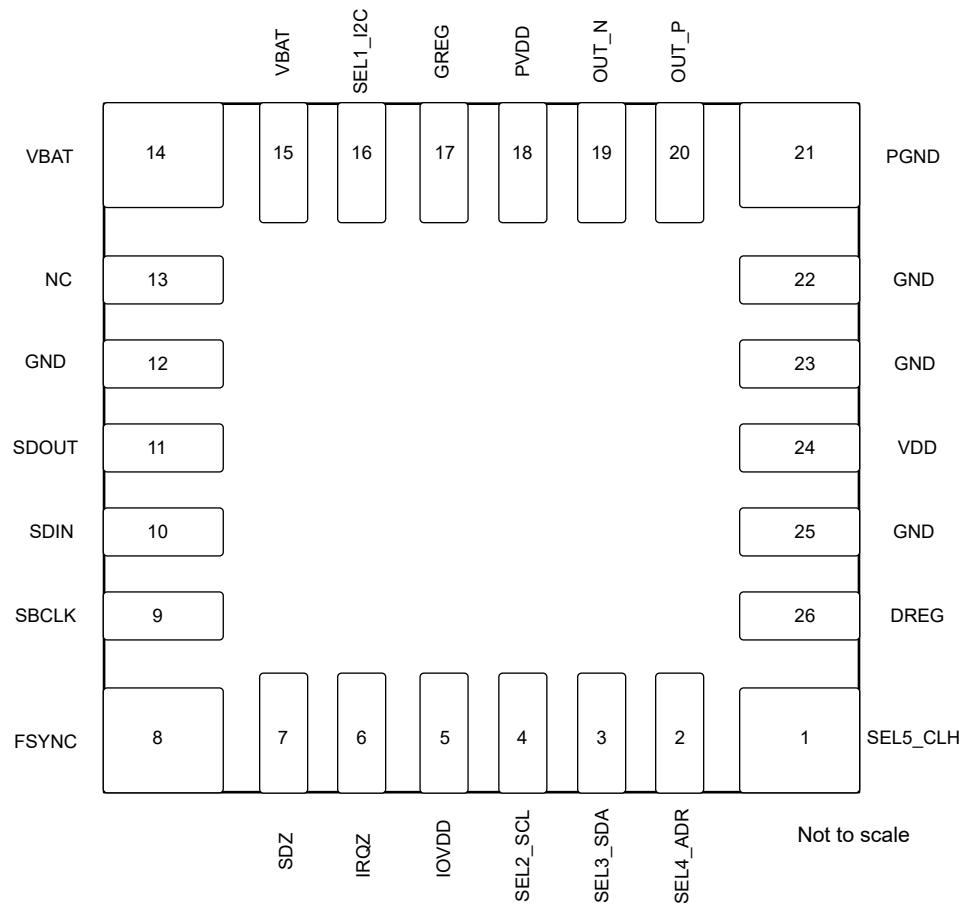

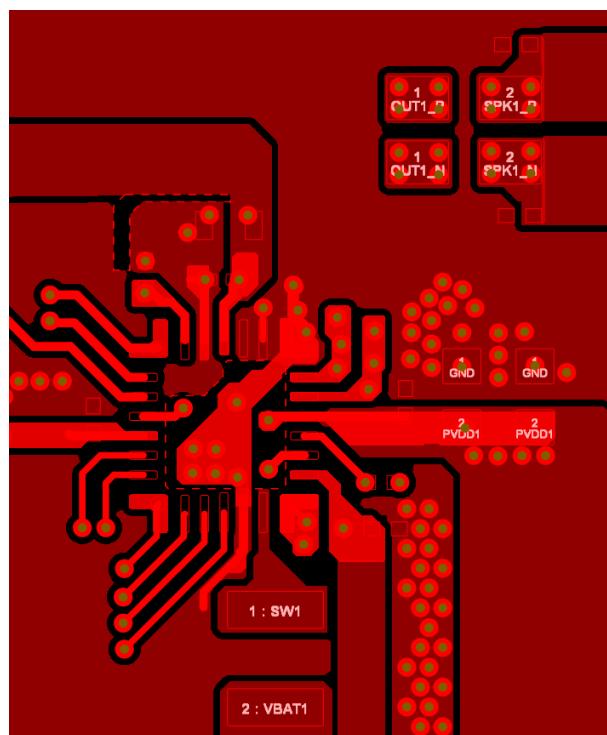

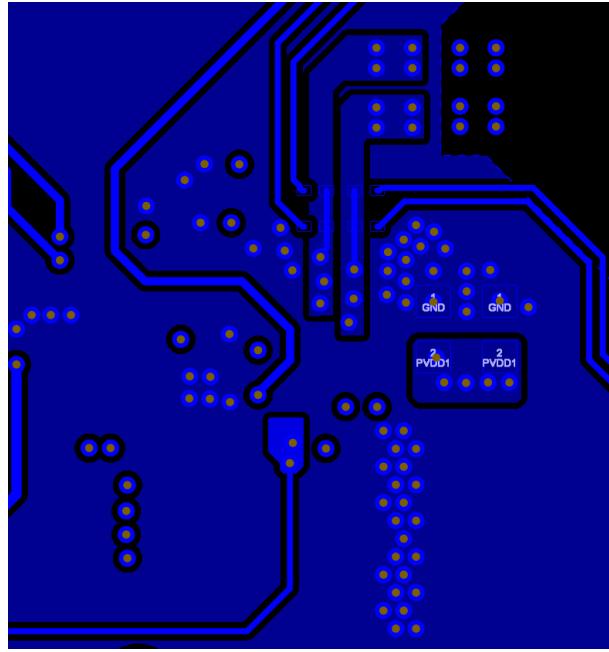

図 4-1. QFN パッケージ 底面図

### ピンの機能

| ピン       |                | 種類 <sup>(1)</sup> | 説明                                                                                                                                 |

|----------|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号             |                   |                                                                                                                                    |

| DREG     | 26             | P                 | デジタルコア電圧レギュレータ出力。コンデンサを使用して GND にバイパスします。外部負荷に接続しないでください。                                                                          |

| FSYNC    | 8              | I                 | I <sup>2</sup> S ワードクロックまたは TDM フレーム同期。                                                                                            |

| GREG     | 17             | P                 | ハイサイドゲート CP レギュレータ出力。外部負荷に接続しないでください。                                                                                              |

| GND      | 12, 22, 23, 25 | P                 | PCB グラウンドプレーンに接続します。複数のビアで必要とされるグラウンドプレーンへの強力な接続。                                                                                  |

| IOVDD    | 5              | P                 | 1.8V または 3.3V デジタル IO 電源。コンデンサを使用して GND にデカップリングします。                                                                               |

| IRQZ     | 6              | O                 | オープンドレイン、アクティブ Low 割り込みピン。オプションの内部ブルアップを使用しない場合は、抵抗を使用して IOVDD にブルアップします。                                                          |

| NC       | 13             | -                 | 接続なし。フローティングのままになります。                                                                                                              |

| OUT_N    | 19             | O                 | Class-D の負出力。                                                                                                                      |

| OUT_P    | 20             | O                 | Class-D の正出力。                                                                                                                      |

| PGND     | 21             | P                 | Class-D 電力段のグラウンド。複数のビアを使用して PCB GND プレーンに強力に接続します。                                                                                |

| PVDD     | 18             | P                 | Class-D 電力段の電源。コンデンサを使用して GND にデカップリングします。                                                                                         |

| SBCLK    | 9              | I                 | I <sup>2</sup> S または TDM シリアルビットクロック。                                                                                              |

| SDIN     | 10             | I                 | I <sup>2</sup> S または TDM シリアルデータ入力。                                                                                                |

| SDOUT    | 11             | I/O               | I <sup>2</sup> S または TDM シリアルデータ出力。                                                                                                |

| SDZ      | 7              | I                 | アクティブ Low のハードウェアシャットダウン。                                                                                                          |

| SEL1_I2C | 16             | I                 | HW モード: 1 ピンを選択します。アンプのゲインレベル選択に加えて、ボリュームランプのインペル/ディスエーブルを設定できます。<br>I <sup>2</sup> C モード: I <sup>2</sup> C モードを選択するには GND に短絡します。 |

| SEL2_SCL | 4              | I                 | HW モード: 2 ピンを選択します。I <sup>2</sup> S、TDM、左揃え選択。<br>I <sup>2</sup> C モード: クロックピン。抵抗を使用して IOVDD にブルアップします。                            |

| SEL3_SDA | 3              | I/O               | HW モード: 3 ピンを選択します。データ有効の立ち上がりエッジと立ち下がりエッジの選択。<br>I <sup>2</sup> C モード: データピン。抵抗を使用して IOVDD にブルアップします。                             |

| SEL4_ADR | 2              | I                 | HW モード: 4 ピン、Y ブリッジスレッショルド構成設定を選択します。<br>I <sup>2</sup> C モード: I <sup>2</sup> C アドレスピン。                                            |

| SEL5_CLH | 1              | I/O               | HW モード: 5 ピンを選択します。IOVDD に接続。<br>I <sup>2</sup> C モード: Class-H 制御。共有昇圧出力または外部昇圧 PWM の生成。共有昇圧機能または外部昇圧機能を使用していない場合、GND に短絡します。      |

| VBAT     | 15             | P                 | バッテリ電源入力。2.5V ~ 5.5V の電源に接続し、コンデンサでデカップリングします。                                                                                     |

|          | 14             | I                 | バッテリ電源入力。2.5V ~ 5.5V 電源に接続します。                                                                                                     |

| VDD      | 24             | P                 | 1.8V 電源に接続し、コンデンサで GND にデカップリングします。                                                                                                |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グラウンド、P = 電源。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                  |                      | 最小値  | 最大値      | 単位 |

|------------------|----------------------|------|----------|----|

| 電源電圧             | PVDD                 | -0.3 | 19       | V  |

| 電源電圧             | VBAT                 | -0.3 | 6        | V  |

| 電源電圧             | VDD                  | -0.3 | 2        | V  |

| 電源電圧             | IOVDD                | -0.3 | 6        | V  |

| Class-D 出力       | OUTP、OUTM            | -0.7 | 19       | V  |

| ハイサイド駆動レギュレータ    | GREG                 | -0.3 | PVDD + 6 | V  |

| デジタル電源レギュレータ     | DREG                 | -0.3 | 1.65     | V  |

| デジタル IO ピン       | IOVDD 電源を基準とするデジタルピン | -0.3 | 6        | V  |

| T <sub>stg</sub> | 保存温度                 | -65  | 150      | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                    |      | 値                                                                | 単位         |

|--------------------|------|------------------------------------------------------------------|------------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | ±2000<br>V |

|                    |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> |            |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                    |              | 最小値              | 公称値 | 最大値  | 単位 |

|--------------------|--------------|------------------|-----|------|----|

| V <sub>BAT</sub>   | バッテリ電源       | 2.5              | 3.6 | 5.5  | V  |

| V <sub>PVDD</sub>  | アンプ電源        | V <sub>BAT</sub> | 12  | 15   | V  |

| V <sub>VDD</sub>   | 電源電圧         | 1.65             | 1.8 | 1.95 | V  |

| V <sub>IOVDD</sub> | IO 電源電圧 1.8V | 1.62             | 1.8 | 1.98 | V  |

| V <sub>IOVDD</sub> | IO 電源電圧 3.3V | 3.0              | 3.3 | 3.6  | V  |

| R <sub>SPK</sub>   | スピーカの抵抗      | 3.2              | 8   | 38.4 | Ω  |

| L <sub>SPK</sub>   | スピーカのインダクタンス | 5                | 33  | 100  | μH |

| T <sub>A</sub>     | 周囲温度         | -40              |     | 85   | °C |

| T <sub>J</sub>     | 接合部温度        | -40              |     | 150  | °C |

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup> |              | 標準 JEDEC <sup>(2)</sup> | 単位   |

|----------------------|--------------|-------------------------|------|

|                      |              | HR-QFN                  |      |

|                      |              | 26 ピン                   |      |

| R <sub>θJA</sub>     | 接合部から周囲への熱抵抗 | 51.5                    | °C/W |

| 熱評価基準 <sup>(1)</sup>        |                   | 標準 JEDEC <sup>(2)</sup> | 単位   |

|-----------------------------|-------------------|-------------------------|------|

|                             |                   | HR-QFN                  |      |

|                             |                   | 26 ピン                   |      |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 | 28.5                    | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗      | 15.3                    | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 0.9                     | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 15.2                    | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

(2) JEDEC 規格 4 層 PCB

## 5.5 電気的特性

$T_A = 25^\circ\text{C}$ 、 $PVDD = 12\text{V}$ 、 $VDD = 1.8\text{V}$ 、 $IOVDD = 1.8\text{V}$ 、 $RL = 8\Omega + 33\mu\text{H}$ 、 $f_{in} = 1\text{kHz}$ 、 $f_s = 48\text{kHz}$ 、ゲイン =  $21\text{dBV}$ 、SDZ=1、ノイズ ゲート無効、Class-D エッジレートを  $2\text{V/ns}$  に設定、I<sub>2</sub>C モード動作、特に記載のない限り、 $22\text{Hz} \sim 20\text{kHz}$  の非加重帯域幅で Audio Precision でフィルタなしで測定。<sup>(1)</sup>

| パラメータ                           | テスト条件                      | 最小値                                                                                                                                        | 標準値   | 最大値 | 単位            |

|---------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|---------------|

| <b>アンプ性能</b>                    |                            |                                                                                                                                            |       |     |               |

| $P_{OUT\_EXT\_PVDD}$            | 最大出力電力 - 1% THD+N          | $R_L = 8\Omega + 33\mu\text{H}$                                                                                                            | 8.3   |     | W             |

|                                 |                            | $R_L = 4\Omega + 33\mu\text{H}$                                                                                                            | 14.6  |     | W             |

|                                 |                            | $R_L = 8\Omega + 33\mu\text{H}$ 、 $PVDD = 15\text{V}$                                                                                      | 11.2  |     | W             |

|                                 |                            | $R_L = 4\Omega + 33\mu\text{H}$ 、 $PVDD = 15\text{V}$                                                                                      | 19    |     | W             |

| $P_{OUT\_EXT\_PVDD}$            | 最大出力電力 - 10% THD+N         | $RL = 8\Omega + 33\mu\text{H}$                                                                                                             | 10.3  |     | W             |

|                                 |                            | $RL = 4\Omega + 33\mu\text{H}$                                                                                                             | 18.0  |     | W             |

| $\eta_{SYSTEM\_EXT\_1W}$        | $P_{OUT}$ でのシステム効率性 = 1.0W | $R_L = 8\Omega + 33\mu\text{H}$                                                                                                            | 88.5  |     | %             |

|                                 |                            | $R_L = 4\Omega + 33\mu\text{H}$                                                                                                            | 84.3  |     | %             |

| $\eta_{SYSTEM\_EXT\_MAX\_POUT}$ | 1% THD+N 電源レベルでのシステム効率性    | $R_L = 8\Omega + 33\mu\text{H}$                                                                                                            | 93.2  |     | %             |

|                                 |                            | $R_L = 4\Omega + 33\mu\text{H}$                                                                                                            | 88.5  |     | %             |

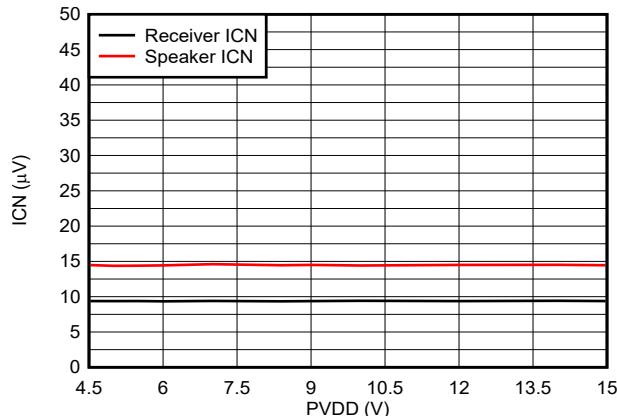

| $V_{N\_EXT}$                    | アイドル チャネル ノイズ              | A 特性重み付け、ゲイン = $21\text{dBV}$ (スピーカー モード)、DAC 動作中                                                                                          | 14.2  |     | $\mu\text{V}$ |

| $DNR\_EXT$                      | ダイナミック レンジ                 | A 特性重み付け、-60dBFS 方式、 $RL = 8\Omega + 33\mu\text{H}$                                                                                        | 114.4 |     | dB            |

| $THD+N\_EXT$                    | 全高調波歪み + ノイズ               | $P_{OUT} = 1\text{W}$ 、 $R_L = 8\Omega + 33\mu\text{H}$                                                                                    | 0.003 |     | %             |

|                                 |                            | $P_{OUT} = 1\text{W}$ 、 $R_L = 4\Omega + 33\mu\text{H}$                                                                                    | 0.004 |     | %             |

| $K_{CP\_EXT}$                   | クリックおよびポップ性能               | 障害を除く、オーディオ チャネルのすべての動的な電源オン/オフ、ミュートのオン/オフ、電源オン/オフ、ノイズ ゲート モードの出入りを含みます。ピーク A 特性重み付け電圧で測定。 $RL = 8\Omega + 33\mu\text{H}$ 、入力 = デジタル サイレンス | -68   |     | $\text{dBV}$  |

| $V_{os\_EXT}$                   | 出力オフセット電圧                  | アイドル チャネル                                                                                                                                  | -1    | 1   | $\text{mV}$   |

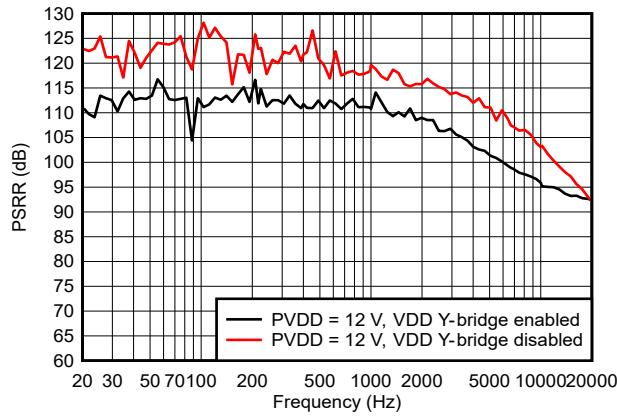

| $PSRR_{PVDD\_EXT}$              | PVDD 電源除去比                 | $PVDD + 200\text{mV}_{pp}$ 、リップル周波数 = $217\text{Hz}$                                                                                       | 119   |     | dB            |

|                                 |                            | $PVDD + 200\text{mV}_{pp}$ 、リップル周波数 = $1\text{kHz}$                                                                                        | 115   |     | dB            |

|                                 |                            | $PVDD + 200\text{mV}_{pp}$ 、リップル周波数 = $20\text{kHz}$                                                                                       | 91    |     | dB            |

| $PSRR_{VBAT\_EXT}$              | VBAT 電源除去比                 | $VBAT + 200\text{mV}_{pp}$ 、 $f_{ripple} = 217\text{Hz}$                                                                                   | 118   |     | dB            |

|                                 |                            | $VBAT + 200\text{mV}_{pp}$ 、 $f_{ripple} = 1\text{kHz}$                                                                                    | 116   |     | dB            |

|                                 |                            | $VBAT + 200\text{mV}_{pp}$ 、 $f_{ripple} = 20\text{kHz}$                                                                                   | 102   |     | dB            |

$T_A = 25^\circ\text{C}$ 、 $\text{PVDD} = 12\text{V}$ 、 $\text{VDD} = 1.8\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $\text{RL} = 8\Omega + 33\mu\text{H}$ 、 $\text{Fin} = 1\text{kHz}$ 、 $\text{Fs} = 48\text{kHz}$ 、ゲイン = 21dBV、SDZ=1、ノイズ ゲート無効、Class-D エッジ レートを 2V/ns に設定、I<sup>2</sup>C モード動作、特に記載のない限り、22Hz～20kHz の非加重帯域幅で Audio Precision でフィルタなしで測定。<sup>(1)</sup>

| パラメータ                                |           | テスト条件                                                                        | 最小値 | 標準値 | 最大値 | 単位 |

|--------------------------------------|-----------|------------------------------------------------------------------------------|-----|-----|-----|----|

| $\text{PSRR}_{\text{VD}_\text{EXT}}$ | VDD 電源除去比 | $\text{VDD} + 200\text{mV}_{\text{pp}}$ 、 $f_{\text{ripple}} = 21\text{Hz}$  | 113 |     |     | dB |

|                                      |           | $\text{VDD} + 200\text{mV}_{\text{pp}}$ 、 $f_{\text{ripple}} = 1\text{kHz}$  | 113 |     |     | dB |

|                                      |           | $\text{VDD} + 200\text{mV}_{\text{pp}}$ 、 $f_{\text{ripple}} = 20\text{kHz}$ | 91  |     |     | dB |

#### TDM シリアル ポート

|                                                        |                                 |       |       |      |

|--------------------------------------------------------|---------------------------------|-------|-------|------|

| 最 PCM サンプル レートと FSYNC 入力周波数                            |                                 | 16    | 192   | kHz  |

| 最 SBCLK 入力周波数                                          | I <sup>2</sup> S/TDM での動作       | 0.512 | 24.57 | MHz  |

| SBCLK の最大入力ジッタ                                         | 性能を低下させない許容範囲 40kHz 未満の RMS ジッタ |       | 0.5   | ns   |

|                                                        | 性能を低下させない許容範囲 40kHz 以上の RMS ジッタ |       | 5     | ns   |

| I <sup>2</sup> S および TDM モードにおける FSYNC 当たりの SBCLK サイクル | 値: 64、96、128、192、256、384、512    | 64    | 512   | サイクル |

#### PCM 再生特性 (fs ≤ 48kHz)

|                    |                           |                                                          |       |    |      |

|--------------------|---------------------------|----------------------------------------------------------|-------|----|------|

| fs                 | サンプル レート                  |                                                          | 16    | 48 | kHz  |

|                    | オーディオ チャネル パスバンド LPF コーナー | リップル < パス バンド リップル                                       | 0.454 |    | fs   |

|                    | オーディオ チャネル パス バンド リップル    | 20Hz ~ LPF のカットオフ                                        | ±0.1  |    | dB   |

|                    | オーディオ チャネル ストップ バンド 減衰    | ≥ 0.55fs                                                 | 60    |    | dB   |

|                    |                           | ≥ 1fs                                                    | 65    |    | dB   |

| オーディオ チャネル グループ 遅延 |                           | Fin = 1kHz、最低レイテンシ モード (Y ブリッジ、ノイズ ゲートはディスエーブル)          | 8.5   |    | 1/fs |

|                    |                           | fin = 1kHz、Class-H ディセーブル                                | 16.5  |    | 1/fs |

|                    |                           | DC ~ 20kHz、最低レイテンシ モード (HPF バイパス、Y ブリッジ、ノイズ ゲートはディスエーブル) | 13    |    | 1/fs |

|                    |                           | DC ~ 20kHz、HPF バイパス                                      | 21    |    | 1/fs |

#### PCM 再生特性 (fs > 48kHz)

|                    |                           |                                                                 |       |     |      |

|--------------------|---------------------------|-----------------------------------------------------------------|-------|-----|------|

| fs                 | サンプル レート                  |                                                                 | 88.2  | 192 | kHz  |

|                    | オーディオ チャネル パスバンド LPF コーナー | fs = 96kHz                                                      | 0.469 |     | fs   |

|                    |                           | fs = 192kHz                                                     | 0.234 |     | fs   |

|                    | オーディオ チャネル パス バンド リップル    | 20Hz ~ LPF のカットオフ                                               | ±0.2  |     | dB   |

|                    | オーディオ チャネル ストップ バンド 減衰    | Fs = 96kHz、fin ≥ 0.55fs                                         | 60    |     | dB   |

|                    |                           | fs = 96kHz、fin ≥ 1fs                                            | 65    |     | dB   |

|                    |                           | fs = 192kHz、0.55fs ≥ fin ≥ 0.275fs                              | 60    |     | dB   |

| オーディオ チャネル グループ 遅延 |                           | Fin = 1kHz、Fs = 96kHz、最低遅延モード (Y ブリッジ、ノイズ ゲートはディスエーブル)          | 11    |     | 1/fs |

|                    |                           | Fin = 1kHz、Fs = 96kHz、Class-H はディスエーブル                          | 6.7   |     | 1/fs |

|                    |                           | DC ~ 20kHz、Fs = 96kHz、最低遅延モード (HPF バイパス、Y ブリッジ、ノイズ ゲートはディスエーブル) | 11.5  |     | 1/fs |

|                    |                           | DC ~ 40kHz、Fs = 96kHz、HPF バイパス                                  | 28.6  |     | 1/fs |

#### 保護回路

$T_A = 25^\circ\text{C}$ 、 $\text{PVDD} = 12\text{V}$ 、 $\text{VDD} = 1.8\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $\text{RL} = 8\Omega + 33\mu\text{H}$ 、 $\text{Fin} = 1\text{kHz}$ 、 $\text{Fs} = 48\text{kHz}$ 、ゲイン = 21dBV、SDZ=1、ノイズ ゲート無効、Class-D エッジ レートを 2V/ns に設定、I<sub>2</sub>C モード動作、特に記載のない限り、22Hz～20kHz の非加重帯域幅で Audio Precision でフィルタなしで測定。<sup>(1)</sup>

| パラメータ                        | テスト条件                                       | 最小値 | 標準値 | 最大値 | 単位 |

|------------------------------|---------------------------------------------|-----|-----|-----|----|

| サーマル シャットダウン温度               |                                             | 140 |     |     | °C |

| サーマル シャットダウン再試行時間            |                                             | 1.5 |     |     | s  |

| VBAT 低電圧誤動作防止スレッショルド (UVLO)  | UVLO がアサートされている                             | 1.9 |     |     | V  |

|                              | UVLO が解除されます                                |     | 2.3 |     | V  |

| VDD 低電圧誤動作防止スレッショルド (UVLO)   | UVLO がアサートされている                             | 1.4 |     |     | V  |

|                              | UVLO が解除されます                                |     | 1.6 |     | V  |

| PVDD 低電圧誤動作防止スレッショルド (UVLO)  | UVLO がアサートされるのは                             | 2.6 |     |     | V  |

|                              | UVLO が解除されるのは                               |     | 2.8 |     | V  |

| PVDD の過電圧誤動作防止スレッショルド (OVLO) | OVLO がアサートされ、OVLO 保護がイネーブルになります。            |     | 16  |     | V  |

| 出力短絡保護                       | 出力間、出力 ~ GND、出力 ~ PVDD、出力 ~ VBAT、H ブリッジ モード | 5.3 |     |     | A  |

#### 電源オン/オフ時間

|                      |                                                             |                    |      |    |

|----------------------|-------------------------------------------------------------|--------------------|------|----|

| $T_{\text{STDBY}}$   | SDZ がアサートされてから I <sub>2</sub> C コマンドに対してデバイスが準備完了となるまでの起動時間 |                    | 300  | us |

| $T_{\text{ACTIVE}}$  | ソフトウェア シャットダウン解除からアンプ出力が有効になるまでの起動時間                        | ボリューム ランピング ディセーブル | 1.6  | ms |

|                      |                                                             | ボリューム ランピングがイネーブル  | 3.9  | ms |

| $T_{\text{TURNOFF}}$ | ソフトウェア シャットダウンがアサートされてからアンプ出力が High-Z になるまでのオフ時間            | ボリューム ランピング ディセーブル | 0.2  | ms |

|                      |                                                             | ボリューム ランピングがイネーブル  | 13.9 | ms |

#### 消費電流

|                         |                          |                                            |      |    |

|-------------------------|--------------------------|--------------------------------------------|------|----|

| $I_{Q_{\text{HW\_SD}}}$ | ハードウェア シャットダウン モードでの消費電流 | PVDD、SDZ = 0                               | 0.1  | μA |

|                         |                          | VBAT、SDZ = 0                               | 0.1  | μA |

|                         |                          | VDD、SDZ = 0                                | 0.2  | μA |

|                         |                          | IOVDD、SDZ = 0                              | 0.1  | μA |

| $I_{Q_{\text{SW\_SD}}}$ | ソフトウェア シャットダウン時の消費電流     | PVDD、すべてのクロックが停止                           | 0.1  | μA |

|                         |                          | VBAT、すべてのクロックが停止                           | 0.1  | μA |

|                         |                          | VDD、すべてのクロックが停止                            | 12   | μA |

|                         |                          | IOVDD、すべてのクロックが停止                          | 0.1  | μA |

| $I_{Q_{\text{NG}}}$     | アイドル チャネルでの消費電流          | PVDD、 $P_{\text{OUT}} = 0$ 、ノイズゲートがイネーブル   | 0.1  | mA |

|                         |                          | VBAT、 $P_{\text{OUT}} = 0$ 、ノイズ ゲートがイネーブル  | 0.15 | mA |

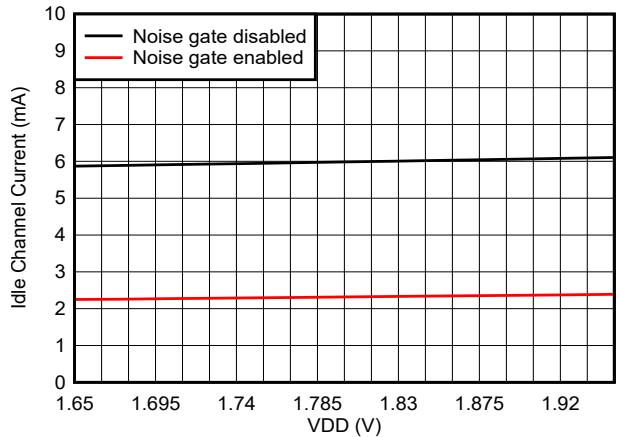

|                         |                          | VDD、 $P_{\text{OUT}} = 0$ 、ノイズ ゲートがイネーブル   | 2.2  | mA |

|                         |                          | IOVDD、 $P_{\text{OUT}} = 0$ 、ノイズ ゲートがイネーブル | 0.1  | mA |

|                         |                          | 合計電力、 $P_{\text{OUT}} = 0$ 、ノイズ ゲートがイネーブル  | 5.3  | mW |

$T_A = 25^\circ\text{C}$ 、 $\text{PVDD} = 12\text{V}$ 、 $\text{VDD} = 1.8\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $\text{RL} = 8\Omega + 33\mu\text{H}$ 、 $\text{Fin} = 1\text{kHz}$ 、 $\text{Fs} = 48\text{kHz}$ 、ゲイン = 21dBV、SDZ=1、ノイズ ゲート無効、Class-D エッジ レートを 2V/ns に設定、I<sup>2</sup>C モード動作、特に記載のない限り、22Hz～20kHz の非加重帯域幅で Audio Precision でフィルタなしで測定。<sup>(1)</sup>

| パラメータ         |                 | テスト条件                                | 最小値  | 標準値 | 最大値 | 単位 |

|---------------|-----------------|--------------------------------------|------|-----|-----|----|

| $I_{Q\_IDLE}$ | アイドル チャネルでの消費電流 | PVDD、 $P_{OUT} = 0$ 、ノイズ ゲートがディセーブル  | 0.2  |     |     | mA |

|               |                 | VBAT、 $P_{OUT} = 0$ 、ノイズ ゲートがディセーブル  | 0.5  |     |     | mA |

|               |                 | VDD、 $P_{OUT} = 0$ 、ノイズ ゲートがディセーブル   | 6    |     |     | mA |

|               |                 | IOVDD、 $P_{OUT} = 0$ 、ノイズ ゲートがディセーブル | 0.1  |     |     | mA |

|               |                 | 合計電力、 $P_{OUT} = 0$ 、ノイズ ゲートがディセーブル  | 14.7 |     |     | mW |

#### デジタル IO

|                         |                                  |                                                        |                                   |   |               |

|-------------------------|----------------------------------|--------------------------------------------------------|-----------------------------------|---|---------------|

| $V_{IH}$                | High レベル デジタル入力ロジック電圧スレッショルド     | すべてのデジタルピン                                             | $0.7 \times \text{IOVDD}$         |   | V             |

| $V_{IL}$                | Low レベル デジタル入力ロジック電圧スレッショルド      | すべてのデジタルピン                                             | $0.3 \times \text{IOVDD}$         |   | V             |

| $V_{OH}$                | High レベル デジタル出力電圧                | SDA、SCL、IRQZ を除くすべてのデジタルピン: $I_{OH} = 100\mu\text{A}$  | $\text{IOVDD}$<br>(正の温度係数) - 0.2V |   | V             |

| $V_{OL}$                | Low レベル デジタル出力電圧                 | SDA、SCL、IRQZ を除くすべてのデジタルピン: $I_{OL} = -100\mu\text{A}$ | 0.2                               |   | V             |

| $V_{OL(I^2C)}$          | Low レベル デジタル出力電圧                 | SDA および SCL: $I_{OL} = -1\text{mA}$                    | $0.2 \times \text{IOVDD}$         |   | V             |

| $V_{OL(IRQZ)}$          | オープンドレイン出力におけるローレベル デジタル出力電圧     | IRQZ ピン: $I_{OL} = -1\text{mA}$                        | 0.2                               |   | V             |

| $I_{IH}$ <sup>(1)</sup> | デジタル入力への入力ロジック High リーケージ        | すべてのデジタルピン。入力 = IOVDD。                                 | -1                                | 1 | $\mu\text{A}$ |

| $I_{IL}$ <sup>(1)</sup> | デジタル入力への入力ロジック Low リーケージ         | すべてのデジタルピン: 入力 = GND                                   | -1                                | 1 | $\mu\text{A}$ |

| $C_{IN}$                | デジタル入力の入力容量                      | すべてのデジタルピン                                             | 5                                 |   | pF            |

| $R_{PD}$                | デジタル入力 / IO ピンがアサートされたときのプルダウン抵抗 | すべてのデジタルピン。プルダウン抵抗オプションがイネーブル                          | 18                                |   | k $\Omega$    |

- (1) エラッタ: IRQZ 信号がプルアップされると、追加で 2mA ~ 3mA の電流消費が予想されます。詳細は「すべきこととすべきでないこと」セクションを参照してください。

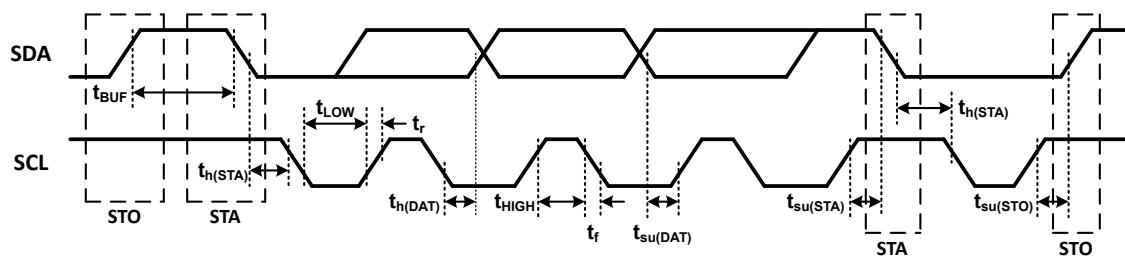

## 5.6 タイミング要件

$T_A = 25^\circ\text{C}$ 、 $\text{VDD} = \text{IOVDD} = 1.8\text{V}$  (特に記述のない限り)

|                               |                                                 | 最小値 | 公称値  | 最大値 | 単位            |

|-------------------------------|-------------------------------------------------|-----|------|-----|---------------|

| <b>I<sup>2</sup>C - 標準モード</b> |                                                 |     |      |     |               |

| $f_{SCL}$                     | SCL クロック周波数                                     | 0   | 100  |     | kHz           |

| $t_{HD;STA}$                  | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック パルスが生成されます。 | 4   |      |     | $\mu\text{s}$ |

| $t_{LOW}$                     | SCL クロック Low 期間                                 | 4.7 |      |     | $\mu\text{s}$ |

| $t_{HIGH}$                    | SCL クロックの High の時間                              | 4   |      |     | $\mu\text{s}$ |

| $t_{SU;STA}$                  | 反復開始条件のセットアップ時間                                 | 4.7 |      |     | $\mu\text{s}$ |

| $t_{HD;DAT}$                  | データ ホールド時間:I <sup>2</sup> C バス デバイスの場合          | 0   | 3.45 |     | $\mu\text{s}$ |

| $t_{SU;DAT}$                  | データ セットアップ時間                                    | 250 |      |     | ns            |

T<sub>A</sub> = 25°C、VDD = IOVDD = 1.8V (特に記述のない限り)

|                     |                             | 最小値 | 公称値 | 最大値  | 単位 |

|---------------------|-----------------------------|-----|-----|------|----|

| t <sub>r</sub>      | SDA と SCL の立ち上がり時間          |     |     | 1000 | ns |

| t <sub>f</sub>      | SDA と SCL の立ち下がり時間          |     |     | 300  | ns |

| t <sub>SU;STO</sub> | STOP 条件のセットアップ時間            | 4   |     |      | μs |

| t <sub>BUF</sub>    | STOP 条件と START 条件の間のバスフリー時間 | 4.7 |     |      | μs |

| C <sub>b</sub>      | 各バスラインの容量性負荷                |     |     | 400  | pF |

#### I<sup>2</sup>C - 高速モード

|                     |                                                 |                           |     |     |

|---------------------|-------------------------------------------------|---------------------------|-----|-----|

| f <sub>SCL</sub>    | SCL クロック周波数                                     | 0                         | 400 | kHz |

| t <sub>HD;STA</sub> | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック パルスが生成されます。 | 0.6                       |     | μs  |

| t <sub>LOW</sub>    | SCL クロック Low 期間                                 | 1.3                       |     | μs  |

| t <sub>HIGH</sub>   | SCL クロックの High の時間                              | 0.6                       |     | μs  |

| t <sub>SU;STA</sub> | 反復開始条件のセットアップ時間                                 | 0.6                       |     | μs  |

| t <sub>HD;DAT</sub> | データホールド時間:I <sup>2</sup> C バスデバイスの場合            | 0                         | 0.9 | μs  |

| t <sub>SU;DAT</sub> | データセットアップ時間                                     | 100                       |     | ns  |

| t <sub>r</sub>      | SDA と SCL の立ち上がり時間                              | 20 + 0.1 × C <sub>b</sub> | 300 | ns  |

| t <sub>f</sub>      | SDA と SCL の立ち下がり時間                              | 20 + 0.1 × C <sub>b</sub> | 300 | ns  |

| t <sub>SU;STO</sub> | STOP 条件のセットアップ時間                                | 0.6                       |     | μs  |

| t <sub>BUF</sub>    | STOP 条件と START 条件の間のバスフリー時間                     | 1.3                       |     | μs  |

| C <sub>b</sub>      | 各バスラインの容量性負荷                                    |                           | 400 | pF  |

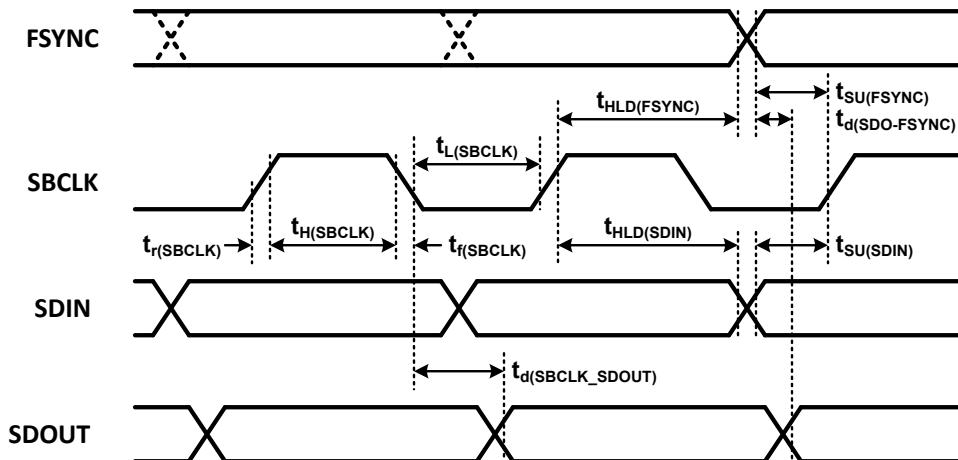

#### TDM ポート

|                             |                                                                                                  |                            |        |     |

|-----------------------------|--------------------------------------------------------------------------------------------------|----------------------------|--------|-----|

| f <sub>sbclk</sub>          | SBCLK 周波数範囲                                                                                      | 0.384                      | 24.576 | MHz |

| t <sub>H(SBCLK)</sub>       | SBCLK の High 期間                                                                                  | 0.35/f <sub>sbclk</sub>    |        | ns  |

| t <sub>L(SBCLK)</sub>       | SBCLK の Low 期間                                                                                   | 0.35/f <sub>sbclk</sub>    |        | ns  |

| t <sub>SU(FSYNC)</sub>      | FSYNC のセットアップ時間                                                                                  | 8                          |        | ns  |

| t <sub>HLD(FSYNC)</sub>     | FSYNC のホールド時間                                                                                    | 8                          |        | ns  |

| t <sub>SU(SDIN)</sub>       | SDIN のセットアップ時間                                                                                   | 8                          |        | ns  |

| t <sub>HLD(SDIN)</sub>      | SDIN のホールド時間                                                                                     | 8                          |        | ns  |

| t <sub>d(SBCLK-SDOUT)</sub> | SBCLK から SDOUT への遅延:SBCLK の立ち下がりエッジの 10% または SBCLK の立ち上がりエッジの 90% から SDOUT の 50%、IOVDD = 1.8V まで |                            | 30     | ns  |

| t <sub>d(SBCLK-SDOUT)</sub> | SBCLK から SDOUT への遅延:SBCLK の立ち下がりエッジの 10% または SBCLK の立ち上がりエッジの 90% から SDOUT の 50%、IOVDD = 3.3V まで |                            | 18.5   | ns  |

| t <sub>r(SBCLK)</sub>       | SBCLK の立ち上がり時間:10%~90% の立ち上がり時間                                                                  | 0.15 / f <sub>sbclk</sub>  |        | ns  |

| t <sub>f(SBCLK)</sub>       | SBCLK の立ち下がり時間:90%~10% の立ち上がり時間                                                                  | 0.15 / f <sub>sbclk</sub>  |        | ns  |

| t <sub>f(SBCLK-CLH)</sub>   | SBCLK から CLH への遅延:Boost 共有設定                                                                     | 1 / 2 * f <sub>sbclk</sub> |        | ns  |

## 5.7 タイミング図

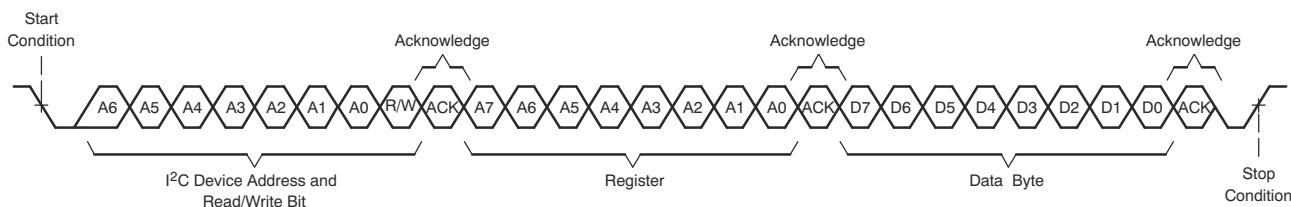

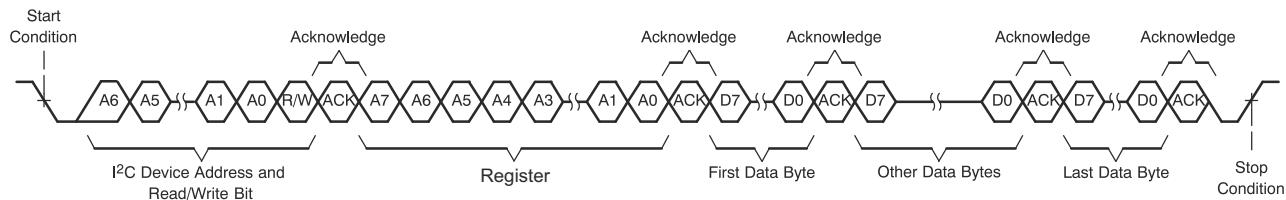

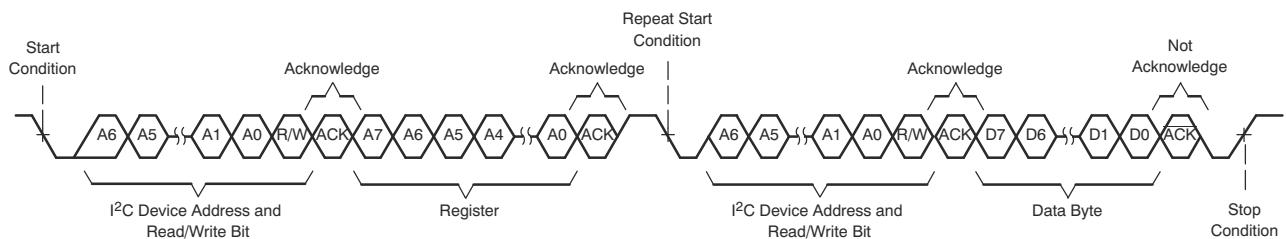

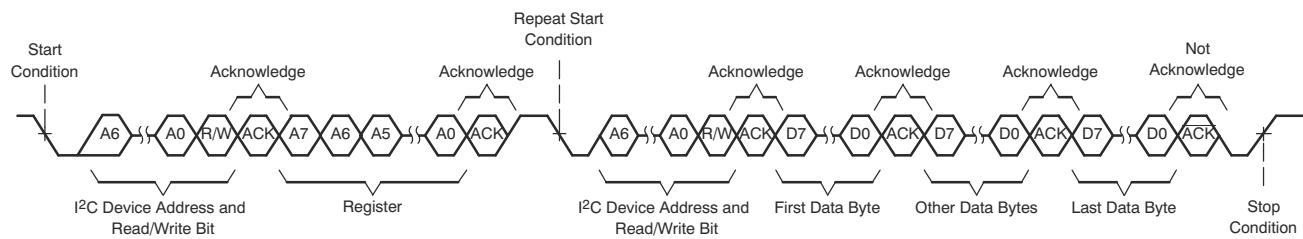

図 5-1. I<sup>2</sup>C のタイミング図

図 5-2. I<sup>2</sup>S/ TDM のタイミング図

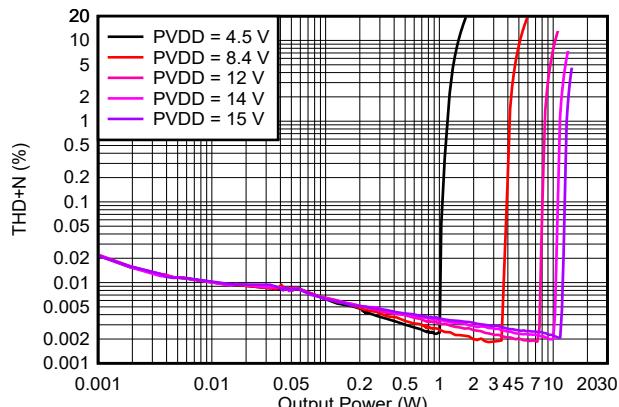

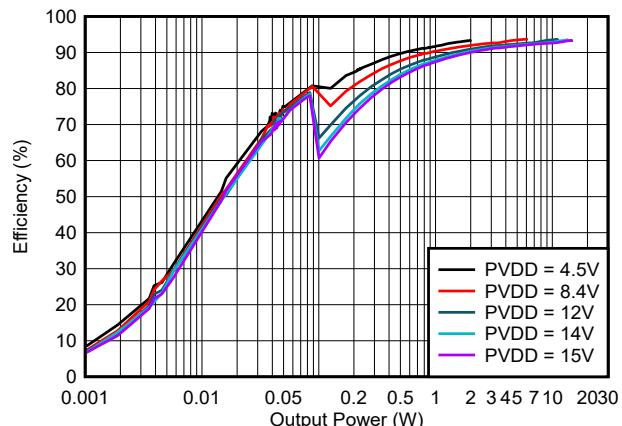

## 5.8 代表的特性

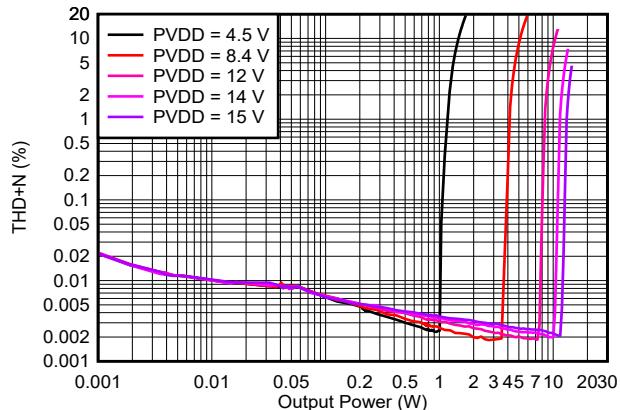

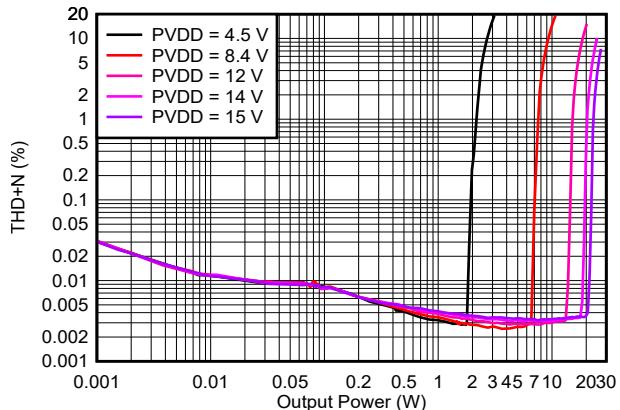

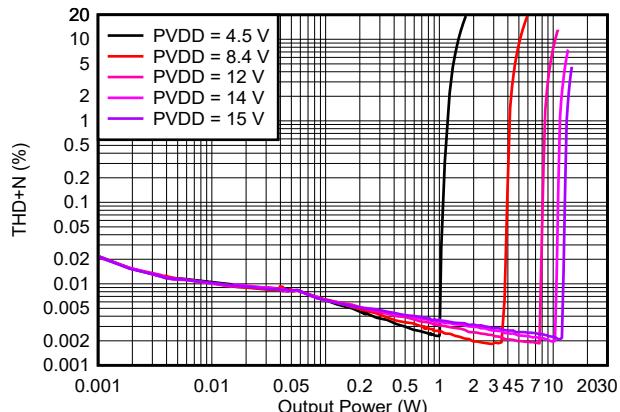

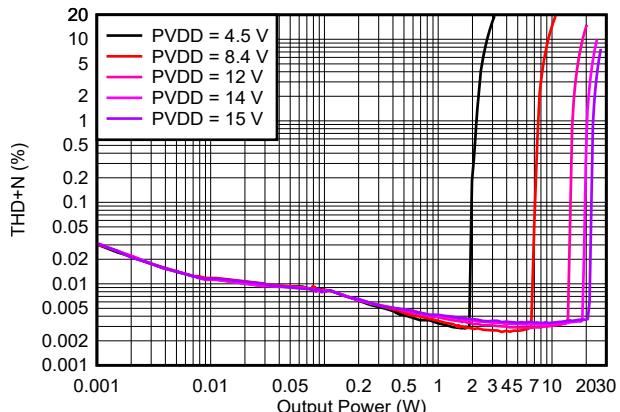

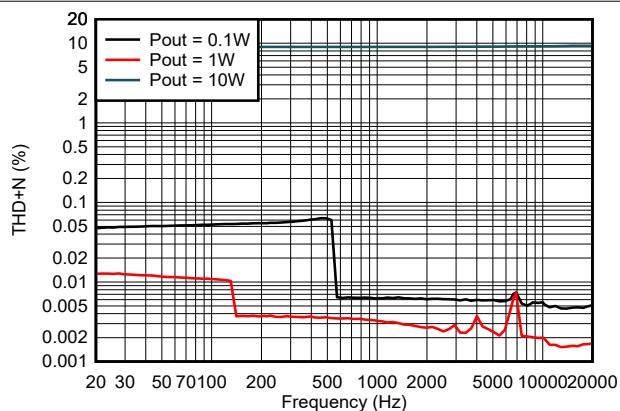

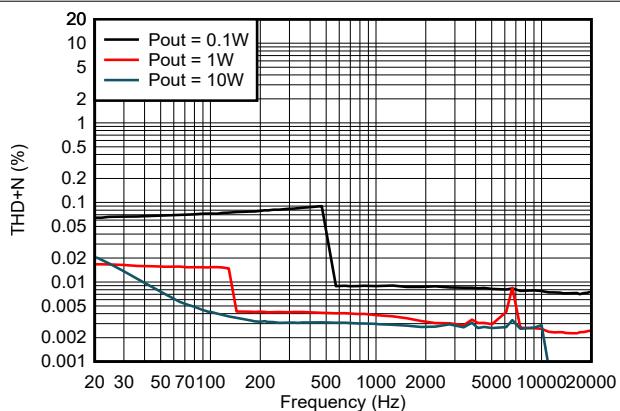

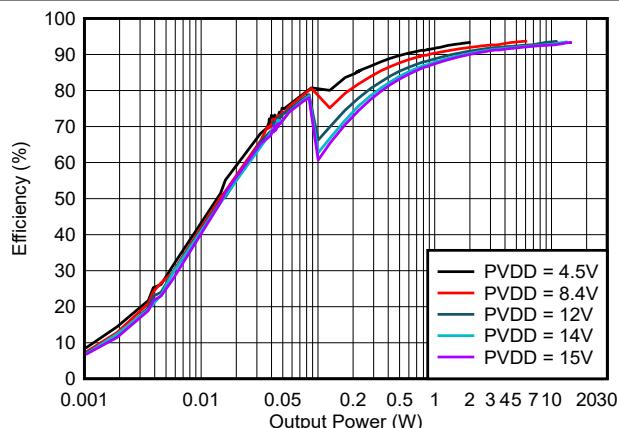

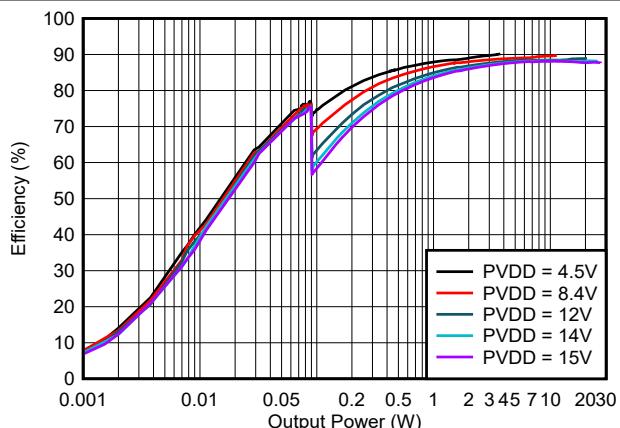

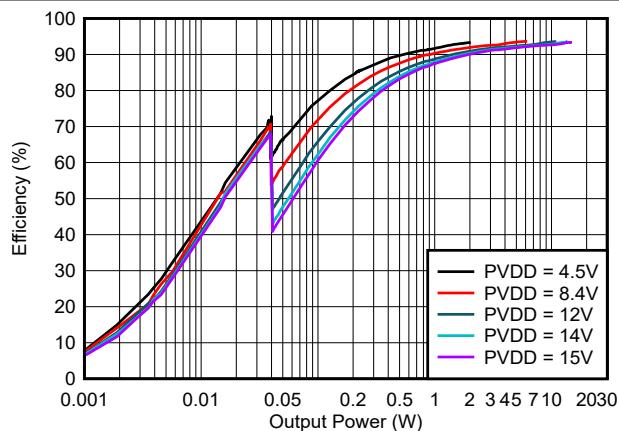

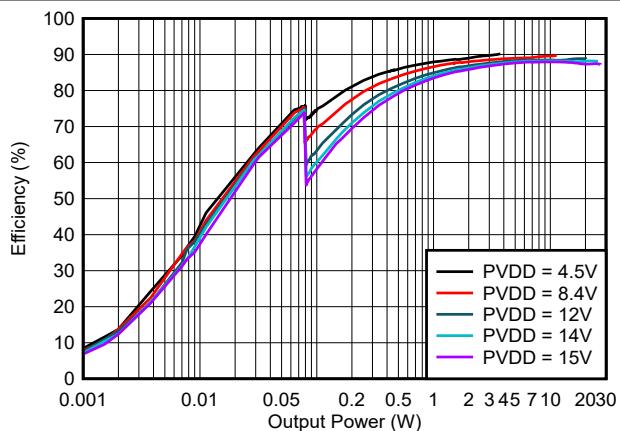

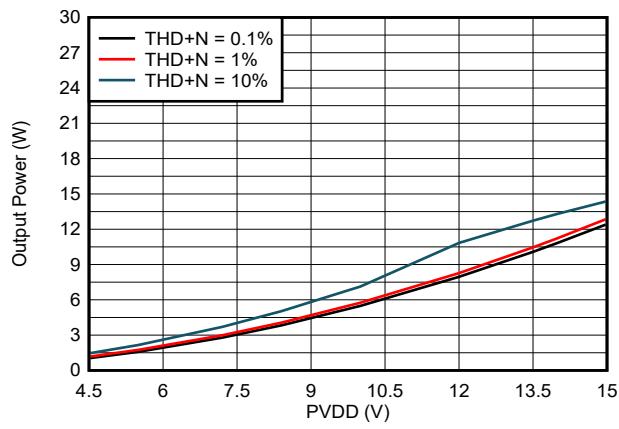

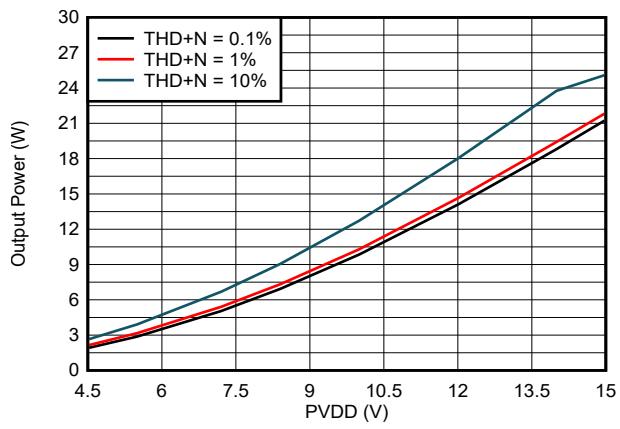

$T_A = 25^\circ\text{C}$ 、 $\text{VBAT} = 3.6\text{V}$ 、 $\text{PVDD} = 12\text{V}$ 、 $\text{VDD} = 1.8\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $\text{Fin} = 1\text{kHz}$ 、 $\text{Fs} = 48\text{kHz}$ 、ゲイン = 21dBV、 $\text{SDZ} = 1$ 、ノイズ ゲート ディセーブル、I<sup>2</sup>C 動作モード、22Hz~20kHz の重み付けなし帯域幅を使用してオーディオ精度で測定されたフィルタはフリー（特に記載のない限り）。

$R_L = 8\Omega$

図 5-3. THD+N と出力電力との関係

$R_L = 4\Omega$

図 5-4. THD+N と出力電力との関係

$R_L = 8\Omega$

HW ピン制御

図 5-5. THD+N と出力電力との関係

$R_L = 4\Omega$

HW ピン制御

図 5-6. THD+N と出力電力との関係

$R_L = 8\Omega$

図 5-7. THD+N と周波数との関係

$R_L = 4\Omega$

図 5-8. THD+N と周波数との関係

$R_L = 8\Omega$

図 5-9. 効率と出力電力との関係

$R_L = 4\Omega$

図 5-10. 効率と出力電力との関係

$R_L = 8\Omega$

HW ピン制御

図 5-11. 効率と出力電力との関係

$R_L = 4\Omega$

HW ピン制御

図 5-12. 効率と出力電力との関係

$R_L = 8\Omega$

図 5-13. 出力電力と PVDD 電圧との関係

$R_L = 4\Omega$

図 5-14. 出力電力と PVDD 電圧との関係

$R_L = 8\Omega$

図 5-15. アイドルチャネルノイズと PVDD 電圧との関係

$R_L = 8\Omega$

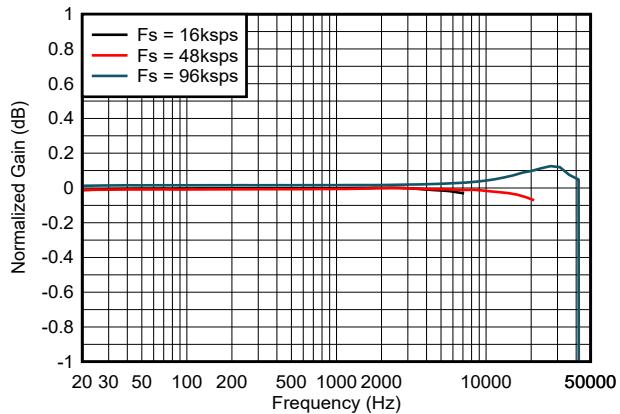

図 5-16. オーディオチャネル周波数応答

$R_L = 8\Omega$

図 5-17. PSRR と周波数との関係

$R_L = 8\Omega$

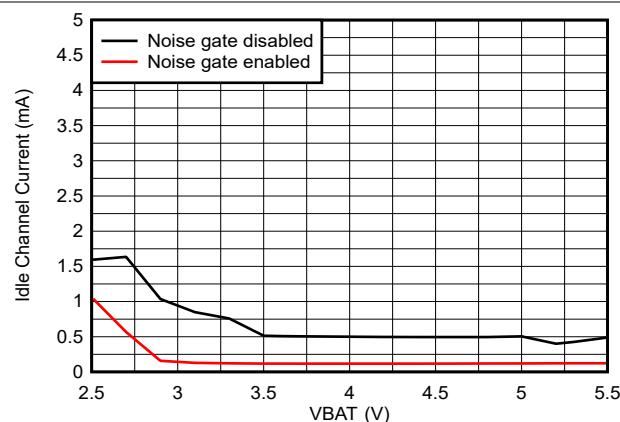

図 5-18. アイドルチャネル電流と VDD 電圧との関係

$R_L = 8\Omega$

図 5-19. アイドル チャネル電流と VBAT 電圧との関係

$R_L = 8\Omega$

図 5-20. アイドル チャネル電流と PVDD 電圧との関係

## 6 詳細説明

### 6.1 概要

TAS2320 は、すべての出力電力範囲で最高の効率を発揮し、バッテリ駆動時間を延長できるよう最適化されたモノラルデジタル入力対応 Class-D アンプです。基板スペースに制約のあるアプリケーション向けに、小型ソリューション サイズで提供されます。デバイスは、高精度なスピーカ電圧/電流センサ、さらにを統合しています。

### 6.2 機能ブロック図

図 6-1. 最上位機能ブロック図

### 6.3 デバイスの機能モード

#### 6.3.1 動作モード

##### 6.3.1.1 ハードウェア シャットダウン

デバイスは、SDZ ピンを Low にアサートすることでパワーダウンできます。SDZ ピンが Low にプルダウンされたときのデバイスのシャットダウン動作は、SDZ\_MODE レジスタの設定によって制御されます。

ハードウェア シャットダウン モード (SDZ\_MODE[1:0] = 00 または 01) では、SDZ ピンが Low にアサートされると、デバイスは電源から最小の静止電流を消費します。このモードではすべてのレジスタの状態が失われ、デフォルト設定に戻り、I<sup>2</sup>C 通信は無効になります。

**SDZ\_MODE[1:0] = 00** に設定されている場合、オーディオ再生中に **SDZ** ピンが **Low** にアサートされると、デバイスは通常のパワー ダウン シーケンスに従います。具体的には、オーディオのボリュームをランプ ダウン (有効な場合) し、**Class-D** スイッチングを停止し、アナログおよびデジタル ブロックの電源を落としてパワー ダウン時のポップ ノイズを防止し、最終的にデバイスをハードウェア シャットダウン モードに移行させます。このモードでは、**SDZ** ピンが **Low** にアサートされている間、**I<sup>2</sup>C** 通信が無効になります。

**SDZ\_MODE[1:0] = 01** に設定されている場合、**SDZ** ピンが **Low** にアサートされると、デバイスは即座にハードウェア シャットダウンに入り、パワー ダウン シーケンス処理は行われません。このモードでは、**SDZ** ピンを **Low** にアサートする前に、オーディオ入力信号をアイドル チャネルまでランプ ダウンさせることが推奨されます。これを実現するために、デバイスのソフトウェア ミュート モードを使用できます。このモードでは、**SDZ** ピンが **Low** にアサートされている間、**I<sup>2</sup>C** 通信が無効になります。

最後に、**SDZ\_MODE[1:0] = 10** に設定することで、デバイスをソフトウェア シャットダウン モードに構成できます。このモードでは、**SDZ** ピンが **Low** にプルダウンされると、デバイスは通常のパワー ダウン シーケンスに従い、ソフトウェア シャットダウン モードに入ります。すべてのデバイス レジスタ構成は、**SDZ** ピンが **Low** にプルダウンされる前のデバイスの状態から、そのまま保持されます。このモードでは、**SDZ** ピンが **Low** にアサートされている間、**I<sup>2</sup>C** 通信は引き続き利用可能です。

**表 6-1. シャットダウン制御**

| <b>SDZ_MODE[1:0]</b> | <b>構成</b>                         |

|----------------------|-----------------------------------|

| 00 (デフォルト)           | パワーダウン シーケンスによるハードウェア シャットダウン モード |

| 01                   | ハードウェア シャットダウン モード - 即時           |

| 10                   | ソフトウェア シャットダウン モード (すべてのレジスタ値は保持) |

| 11                   | 予約済み                              |

**SDZ\_MODE[1:0]** が 00 または 10 の場合、デバイスはシャットダウン シーケンスを実行し、シャットダウン時間の全期間にわたって **SDZ** ピンを **Low** に保持する必要があります。シャットダウン時間は、電気的特性セクションのパワーアップ/パワーダウン時間セクションで規定されています。**SDZ** がリリースされると、デバイスは関連する構成ピンおよびアドレス ピンをサンプリングし、その後ソフトウェア シャットダウン モードに入ります。

### 6.3.1.2 ハードウェア構成モード

この TAS2320 デバイスは、セレクト ピン 1 からセレクト ピン 5 に使用される抵抗終端に応じて、ピン制御ベースの HW モードで動作できます。本デバイスのピン制御に基づく HW モードの動作は、**I<sup>2</sup>C** 通信によるソフトウェア ベースの構成を使わなくともデバイス構成を簡素化できるよう設計されています。

**表 6-2. セレクト ピンの機能**

| <b>ピン名を選択します</b> | <b>機能</b>                        |

|------------------|----------------------------------|

| SEL1             | ボリューム ランプの有効/無効オプション付きアンプ ゲイン設定  |

| SEL2             | <b>I<sup>2</sup>S</b> 、TDM、左揃え選択 |

| SEL3             | データ有効の立ち上がり/立ち下がり エッジの選択         |

| SEL4             | Y ブリッジスレッショルド構成                  |

| SEL5             | 電源電圧モードの選択                       |

**表 6-3. SEL1 HW モード構成**

| <b>SEL1 の接続</b> | <b>アンプ ゲイン</b>              | <b>ボリューム ランプ</b>            |

|-----------------|-----------------------------|-----------------------------|

| GND への直接短絡      | <b>I<sup>2</sup>C</b> 経由で構成 | <b>I<sup>2</sup>C</b> 経由で構成 |

| 1.2kΩ から GND へ  | 6dBV                        | ディセーブル                      |

**表 6-3. SEL1 HW モード構成 (続き)**

| SEL1 の接続           | アンプ ゲイン | ボリューム ランプ |

|--------------------|---------|-----------|

| 1.2kΩ から VBAT へ    | 12dBV   | ディセーブル    |

| 5kΩ から GND へ       | 18dBV   | ディセーブル    |

| 330Ω を VBAT との間に接続 | 21dBV   | ディセーブル    |

| 5kΩ から VBAT へ      | 6dBV    | イネーブル     |

| 24kΩ から GND へ      | 12dBV   | イネーブル     |

| 24kΩ から VBAT へ     | 18dBV   | イネーブル     |

| VBAT への直接短絡        | 21dBV   | イネーブル     |

**表 6-4. SEL2 HW モード構成**

| SEL2 の接続       | 構成                                |

|----------------|-----------------------------------|

| GND への直接短絡     | I <sup>2</sup> S、L または TDM0       |

| 330Ω から IOVDD  | I <sup>2</sup> S R または TDM1       |

| IOVDD への直接短絡   | I <sup>2</sup> S (L+R)/2 または TDM2 |

| 1.2kΩ から GND へ | 左揃え L または TDM3                    |

| 1.2kΩ から IOVDD | 左揃えの R または TDM4                   |

| 5kΩ から GND へ   | 左揃え (L+R)/2 または TDM5              |

| 5kΩ から IOVDD   | I <sup>2</sup> S、L または TDM6       |

| 24kΩ から GND へ  | I <sup>2</sup> S R または TDM7       |

| 24kΩ から IOVDD  | 予約済み                              |

**表 6-5. SEL3 HW モード構成**

| SEL3 の接続     | 構成              |

|--------------|-----------------|

| GND への直接短絡   | 立ち上がりエッジでデータが有効 |

| IOVDD への直接短絡 | 立ち下がりエッジでデータが有効 |

**表 6-6. SEL4 HW モード構成**

| SEL4 の接続      | 構成                    |

|---------------|-----------------------|

| GND への直接短絡    | 80mW の Y ブリッジ スレッショルド |

| IOVDD への直接短絡  | 40mW の Y ブリッジ スレッショルド |

| 24kΩ から IOVDD | 1mW の Y ブリッジ スレッショルド  |

**表 6-7. SEL5 HW モード構成**

| SEL5 の接続     | 構成         |

|--------------|------------|

| IOVDD への直接短絡 | HW モード電源構成 |

### 6.3.1.3 ソフトウェア電力モード制御とソフトウェア リセット

SEL1 ピンが GND に短絡すると、TAS2320 は I<sup>2</sup>C モードに構成され、I<sup>2</sup>C インターフェイス経由で構成レジスタを変更することで構成できます。

TAS2320 の電力状態は、レジスタ MODE[1:0] を使用して制御できます。いずれかモード設定を変更しても、デバイスの既存の構成レジスタ設定が失われることはありません。

**表 6-8. ソフトウェア モード制御**

| MODE[1:0] | 構成              |

|-----------|-----------------|

| 00        | アクティブ動作モードのデバイス |

**表 6-8. ソフトウェア モード制御 (続き)**

| MODE[1:0]  | 構成                               |

|------------|----------------------------------|

| 01         | 予約済み                             |

| 10 (デフォルト) | ソフトウェア シャットダウン モードのデバイス          |

| 11         | クロックベースのアクティブおよびシャットダウン モードのデバイス |

**アクティブ状態:** MODE[1:0] が '00' に設定されると、デバイスはアクティブ動作モードに入り、が、クリック音やポップ音を最小限に抑えるための適切なパワーアップ シーケンスで起動します。

**ソフトウェア シャットダウン状態:** MODE[1:0] が「10」に設定されると、デバイスはソフトウェア シャットダウン モードに入ります。このモードは、オーディオ再生に必要なすべてのアナログ ブロックの電源を落としますが、デバイスのレジスタ状態が失われることはありません。ソフトウェア シャットダウンがアサートされたときにオーディオが再生中の場合、Class-D はボリュームをランプダウンしてからシャットダウンします。デアサートされると、Class-D アンプはスイッチングを再開し、ボリュームはプログラムされたデジタル ボリューム設定へ段階的に戻ります。

**クロック ベースのアクティブおよびシャットダウン状態:** MODE[1:0] が「11」に設定されている場合、デバイスは ASI 入力ピン (BCLK および FSYNC) に入力される有効な ASI クロック信号に基づいて、アクティブ状態とシャットダウン状態の間を切り替えます。クロックが印加されると、デバイスは自動的にクロック信号を検出し、パワーアップ時のクリック音やポップ音を回避するために適切なパワーアップ シーケンスに従います。オーディオ チャネルが起動中に ASI クロックが取り外されると、デバイスは自動的にパワーダウン シーケンスを開始し、クリック音やポップ音を回避します。クロックを停止する前に入力データ ストリームで音量をランプダウンすることが推奨されます。これによりポップ音やクリック音の影響を最小限にできます(この動作はデバイスのソフトウェア ミュート モードを使用して実現できます)。

TAS2320 は、SW\_RESET レジスタを 1 に設定することで、デフォルト構成にリセットできます。デバイスがパワーアップしているときに SW\_RESET ビットが High に設定されると、すべてのチャネルは即座にパワー ダウンされます。SW\_RESET が High にセットされると、すべてのレジスタがデフォルト状態に復元されます。このビットは自己クリアされ、リセットが完了すると「0」に戻ります。

また、デバイスのステータスがアクティブ動作モードに達したときに INT\_LTCH0[1] ビット ([セクション 6.3.2](#)) を使用して、ホストに信号を送信することもできます。このビットはライブ デバイスステータスピットであり、デバイスステータスをリアルタイムで反映します。このビットは、デバイスがアクティブ モードのときは High にセットされ、デバイスがシャットダウン モードのときは Low にセットされます。

#### 6.3.1.4 効率および省電力モード

TAS2320 は、すべての動作条件で最高のシステムレベルの効率を達成するように設計された複数の省電力モードを備えています。デバイスは、設定されたモードおよび信号条件に基づいて、あるモードから次のモードへと移行します。モード間の遷移は自動で行われ、遷移中も高性能なオーディオ レベルを確保できるよう設計されています。

##### 6.3.1.4.1 ノイズゲート

ノイズ ゲート機能がイネーブルになると、デバイスはアクティブ再生モード中の無音期間を自動的に検出し、アイドル チャネルの消費電力を大幅に削減してバッテリ寿命を延ばします。この機能は、長い無音期間を含む信号の再生、例えば音声通話や映画のトラックなどに有用です。

デバイスは、NG\_TH\_LVL[2:0] レジスタで構成されたプログラム済みノイズ ゲート スレッショルドに対して入力オーディオ信号レベルを監視します。オーディオ信号がスレッショルドを下回ると、内部ヒステリシス タイマがイネーブルになります。信号レベルが NG\_HYST\_TIMER[1:0] の全期間にわたって構成済みの NG\_TH\_LVL[2:0] 未満である場合、デバイスはノイズ ゲート モードに入り、アイドル チャネルの消費電力を低減します。ノイズ ゲート動作モードでは、Class-D PWM 出力のような高スイッチング ブロックは OFF にされ、出力は Low にプルダウンされます。Class-D の出力インピーダンスは、CLASSD\_HIZ\_MODE レジスタを使用してノイズ ゲートモードがアクティブのときに制御できます。ノイズ ゲート モードがアクティブの間、Class-D 出力はスイッチングせず、デバイスはオーディオ出力信号を生成しません。デバイスがノイ

ズゲートモードのとき、**NG\_STATUS**ビットは **high** に設定され、デバイスがノイズゲートモードを終了すると、ステータスビットは **low** にセットされます。

信号レベルが **NG\_TH\_LVL[1:0]** を超えると、デバイスは低 **I<sub>Q</sub>** モードでブロックを自動的にウェークアップし、オーディオ入力信号の再生を開始します。ノイズゲートからウェークアップでは、ノイズゲートモードからアクティブ再生モードへの遷移時間中に入力信号データをバッファリングすることで、信号の忠実度が維持されます。デバイスは、ノイズゲートからアクティブ再生への遷移中にオーディオ入力サンプルを失うことはありません。

ノイズゲートモードへの遷移およびノイズゲートモードからの復帰は、適切なシャットダウンおよびパワーアップシーケンスに従うことで、クリック音やポップノイズが発生しないように設計されています。

**表 6-9. ノイズゲートスレッショルド**

| <b>NG_TH_LVL[2:0]</b> | 構成       |

|-----------------------|----------|

| 000                   | -85dBFS  |

| 001                   | -90dBFS  |

| 010                   | -95dBFS  |

| 011                   | -100dBFS |

| 100 (デフォルト)           | -105dBFS |

| 101                   | -110dBFS |

| 110                   | -115dBFS |

| 111                   | -120dBFS |

**表 6-10. ノイズゲートヒステリシスタイマ**

| <b>NG_HYST_TIMER[1:0]</b> | 構成     |

|---------------------------|--------|

| 00                        | 10ms   |

| 01 (デフォルト)                | 50ms   |

| 10                        | 100ms  |

| 11                        | 1000ms |

#### 6.3.1.4.2 音楽用効率モード

音楽用効率モード機能が有効になると、デバイスはアクティブ再生モード中の低電力信号状態を自動的に検出し、全体の **I<sub>Q</sub>** 消費電力を低減してバッテリ寿命を延ばします。この機能は、音楽トラック、音声通話、映画のトラックなど、信号レベルが変動する動的なオーディオ信号に有用です。

このデバイスは、**MUSIC\_EFF\_MODE\_THR[23:0]** レジスタで設定されたプログラムされた音楽効率スレッショルドと比較して、入力オーディオ信号レベルを監視します。オーディオ信号がスレッショルドを下回ると、内部ヒステリシスタイマがイネーブルになります。信号レベルが **MUSIC\_EFF\_MODE\_TIMER[23:0]** の全期間にわたって構成済みの **MUSIC\_EFF\_MODE\_THR[23:0]** 未満である場合、デバイスは音楽用効率モードに入ります。デバイスが音楽用効率モードのとき、**MUSIC\_EFF\_STATUS**ビットは **high** に設定され、デバイスが音楽用効率モードを終了すると、ステータスビットは **low** に設定されます。

信号レベルが **MUSIC\_EFF\_MODE\_THR[23:0]** を上回ると、デバイスは自動的に低 **I<sub>Q</sub>** モードでブロックをウェークアップし、オーディオ入力信号の再生を継続します。音楽用効率モードから通常動作への移行は、最小限のクリックとポップで行われます。デバイスが音楽用効率モードである間、オーディオチャネルの性能は維持され、出力信号レベルやノイズには影響しません。

**MUSIC\_EFF\_MODE\_THR[23:0]** レジスタと **MUSIC\_EFF\_MODE\_TIMER[23:0]** レジスタは、PPC3 ソフトウェア [セクション 6.4.1](#) を使用して構成できます。

### 6.3.2 フォルトとステータス

パワー アップ シーケンス中、パワーオンリセット回路 (POR) は VDD ピンおよび IOVDD ピンを監視し、電源が有効になるまでデバイスをリセット状態 (すべての構成レジスタを含む) に保持します。VDD または IOVDD の電源電圧が UVLO 電圧スレッショルドを下回るデイップが発生すると、デバイスはすべてのレジスタ構成とともに即座にリセットされます。

動作モード中、デバイスは内部ステータスおよびフォルト状態を監視し、IRQZ 割り込みピンおよび内部 I<sup>2</sup>C ベースの割り込みレジスタを使用して、エラーやステータス状態をホストに通知できます。IRQZ ピンでの割り込み生成は、対応する割り込みマスク レジスタ ビットを構成することでマスクできます。

表 6-11 には、デバイスが監視するさまざまなフォルトと割り込み、および割り込み生成の有効化/無効化や I<sup>2</sup>C 割り込みステータスの読み取りに対応する構成ビットが一覧されています

**表 6-11. 障害と割り込み**

| カテゴリ                                           | 割り込み            | 割り込みマスク レジスタ ビット | デフォルトのマスク ステータス | 割り込みラッチ ステータスピット |

|------------------------------------------------|-----------------|------------------|-----------------|------------------|

| リミッタおよび電圧低下保護<br><a href="#">セクション 6.4.2.4</a> | 電圧低下検出          | INT_MASK0[3]     | マスクしない          | INT_LTCH0[3]     |

|                                                | BOP がアクティブ      | INT_MASK0[2]     | マスクしない          | INT_LTCH0[2]     |

|                                                | BOP 無限ホールド      | INT_MASK0[7]     | マスクしない          | INT_LTCH0[7]     |

|                                                | リミッタ アクティブ      | INT_MASK0[4]     | マスクしない          | INT_LTCH0[4]     |

|                                                | リミッタの減衰         | INT_MASK0[6]     | マスクしない          | INT_LTCH0[6]     |

|                                                | 変曲点以下に供給        | INT_MASK0[5]     | マスクしない          | INT_LTCH0[5]     |

| 電源電圧モニタ<br><a href="#">セクション 6.4.5</a>         | PVDD 過電圧        | INT_MASK3[2]     | マスクしない          | INT_LTCH3[2]     |

|                                                | PVDD 低電圧        | INT_MASK1[7]     | マスクしない          | INT_LTCH1[7]     |

| 過熱保護<br><a href="#">セクション 6.4.6</a>            | 過熱警告 135°C      | INT_MASK1[4]     | マスク付き           | INT_LTCH1[4]     |

|                                                | 過熱警告 125°C      | INT_MASK1[3]     | マスク付き           | INT_LTCH1[3]     |

|                                                | 過熱警告 115°C      | INT_MASK1[2]     | マスク付き           | INT_LTCH1[2]     |

|                                                | 過熱警告 105°C      | INT_MASK1[1]     | マスク付き           | INT_LTCH1[1]     |

|                                                | 過熱エラー           | INT_MASK3[7]     | マスクしない          | INT_LTCH3[7]     |

| クロック保護<br><a href="#">セクション 6.4.7.1</a>        | ウォッチドッグの有効期限    | INT_MASK2[7]     | マスクしない          | INT_LTCH2[7]     |

|                                                | フレームの同期外れ       | INT_MASK2[5]     | マスク付き           | INT_LTCH2[5]     |

|                                                | 内 PLL クロック エラー  | INT_MASK2[4]     | マスクしない          | INT_LTCH2[4]     |

|                                                | 内 TDM クロック エラー  | INT_MASK2[3]     | マスク付き           | INT_LTCH2[3]     |

|                                                | 電源投入前クロック エラー   | INT_MASK4[2]     | マスクしない          | INT_LTCH4[2]     |

|                                                | クロック比変化誤差       | INT_MASK2[2]     | マスク付き           | INT_LTCH2[2]     |

|                                                | Fs 変更誤差         | INT_MASK2[1]     | マスク付き           | INT_LTCH2[1]     |

|                                                | Fs の無効なエラー      | INT_MASK2[0]     | マスク付き           | INT_LTCH2[0]     |

|                                                | フレームの同期外れ       | INT_MASK2[5]     | マスク付き           | INT_LTCH2[5]     |

|                                                | 内部 PLL クロック エラー | INT_MASK2[4]     | マスクしない          | INT_LTCH2[4]     |

| その他の保護およびステータス                                 | デジタル ウォッチドッグ    | INT_MASK2[7]     | マスクしない          | INT_LTCH2[7]     |

|                                                | Class-D 過電流誤差   | INT_MASK3[3]     | マスクしない          | INT_LTCH3[3]     |

|                                                | デバイスはアクティブ      | INT_MASK0[1]     | マスク付き           | INT_LTCH0[1]     |

#### 6.3.2.1 割り込み生成およびクリア

IRQZ はオープン ドレイン出力であり、マスクされていないフォルト条件時に Low でアサートされるため、IOVDD に抵抗でプルアップする必要があります。デバイスには内部プルアップ抵抗 (18kΩ) が搭載されており、IRQZ\_PU レジスタ ビットを設定することで評価できます。

IRQZ ピンでの割り込み生成は、*IRQZ\_PIN\_CFG[1:0]* レジスタを使用して構成できます。自動再試行機能を備えた割り込みの場合、*RETRY\_WAIT\_TIME* レジスタを使用して再試行タイマを設定できます。割り込みピンの極性は、*IRQZ\_POL* レジスタビットを high にセットすることで、デフォルトのアクティブ Low からアクティブ High に変更できます。

ラッチされた割り込みは、*INT\_CLR\_LTCH* ビットを high にセットすることでクリアできます。これはセルフ クリア ビットで、割り込みがクリアされると自動的に low に更新されます。割り込みは、SDZ ピンを Low にプルダウンしてハードウェア シヤットダウンを行うか、*SW\_RESET* ビットを使用したソフトウェアリセットによってもクリアできます。

**表 6-12. IRQZ ピンの構成**

| <i>IRQZ_PIN_CFG[1:0]</i> | 構成                                                      |

|--------------------------|---------------------------------------------------------|

| 00                       | 予約済み                                                    |

| 01 (デフォルト)               | マスクされていないラッチ割り込みで生成される割り込み                              |

| 10                       | 予約済み                                                    |

| 11                       | マスクされていないラッチ割り込みが発生した場合、2 ~ 4ms の間隔で 4ms ごとに割り込みが生成されます |

**表 6-13. 再試行待機タイマ**

| <i>RETRY_WAIT_TIME</i> | 構成              |

|------------------------|-----------------|

| 0 (デフォルト)              | 1.5 ごとに再試行します   |

| 1                      | 100ms ごとに再試行します |

## 6.4 機能説明

### 6.4.1 PurePath™ Console 3 ソフトウェア

TAS2320 の高度な機能とデバイス構成は、PurePath Console 3 (PPC3) ソフトウェアを使用して実行できます。ベース PPC3 ソフトウェアは、[TI の Web サイト](#) からダウンロードしてインストールできます。TAS2320 アプリケーションをインストールした後、-in-base PPC3 ソフトウェアを使用してダウンロードできるようになります。TAS2320 PPC3 アプリケーションは、以下のセクションで説明される必要なレジスタ係数を計算するため、I<sup>2</sup>C モードで PPC3 を使用することが強く推奨されます。デバイスの構成は、PPC3 で選択されたオプションに基づくレジスタ更新によって最適化されます。これが、デバイスを最適な性能で構成するために推奨される方法です。TAS2320 PPC3 アプリケーションがデバイスの計算と更新を行った後、PPC3 の「End System Integration」(エンド システムの統合) タブを使用して、最終的なシステム統合用のファイルを生成できます。

### 6.4.2 再生信号パス

#### 6.4.2.1 デジタル ボリューム制御およびアンプ出力レベル

オーディオ入力からスピーカ端子までのゲインは、アンプのアナログ ゲイン レベル (*A<sub>AMP</sub>*) とデジタル ボリューム制御 (*A<sub>DVC</sub>*) を設定することで制御されます。[式 1](#) は、アンプの出力電圧を計算します。アンプのアナログ ゲイン設定は、再生チャネルを起動する前に設定する必要があり、チャネルがアクティブな間に変更すべきではありません。デジタル ボリューム制御は、チャネルがアクティブな状態でも変更可能であり、ソフトなボリューム ランプ アップ/ダウン機能によって出力電圧のあるレベルから別のレベルへ滑らかに移行させることができます。

$$V_{AMP} = \text{Input} + A_{dvc} + A_{AMP} \text{ dBV} \quad (1)$$

ここで、

- *V<sub>AMP</sub>* は、アンプ出力電圧 (dBV) です

- 入力は、0dBFS を基準とした dB 単位のデジタル入力振幅です

- *A<sub>DVC</sub>* はデジタル ボリューム制御設定で、6dB から -110dB までを 0.5dB 刻みで調整可能です

- *A<sub>AMP</sub>* はアンプ出力レベルの設定で、-0.071dBV から 21.0dBV まで 0.5017dBV 刻みです。

アンプの出力レベルの設定は **dBV** ( $1V_{rms}$  に対する **dB**) 単位で表記し、フルスケールのデジタル オーディオ入力 (0dBFS)、デジタル ボリューム制御を 0dB に設定しています。これらのレベルは、アンプ内でのアナログ クリッピングにより達成できない場合があるため、あくまでゲインを示す目的で使用すべきであることに注意してください。

以下の表に、**AMP\_LVL** レジスタを使用してプログラマブルなゲイン設定を示します。**AMP\_LVL** が 9dBV 未満に設定されている場合、再生チャネルは自動的に低ノイズ モードまたはレシーバ動作モードに構成されます。

**表 6-14. アンプ出力レベルの設定**

| <b>AMP_LVL[5:0]</b> | フルスケール出力   |                             |

|---------------------|------------|-----------------------------|

|                     | <b>dBV</b> | <b>V<sub>PEAK</sub> (V)</b> |

| 0x00                | 21.000     | 15.9                        |

| 0x01                | 20.498     | 15.0                        |

| 0x02                | 19.997     | 14.1                        |

| 0x03                | 19.495     | 13.3                        |

| 0x04                | 18.993     | 12.6                        |

| ...                 | ...        | ...                         |

| 0x27                | 1.434      | 1.7                         |

| 0x28                | 0.932      | 1.6                         |

| 0x29                | 0.430      | 1.5                         |

| 0x2A                | -0.071     | 1.4                         |

| 0x2B-0x3F           | 予約済み       | 予約済み                        |

デジタル ボリューム制御に変更が加えられると、デバイスは **DVC\_SLEW\_RATE** レジスタ ビットに基づいて音量を新しい設定値までランプ動作で移行させます。**DVC\_SLEW\_RATE** が 0xFFFFFFF に設定されている場合、ボリューム ランプはディセーブルされます。これは、システム ホストがボリューム ランプを制御する場合に、起動、シャットダウン、およびデジタル ボリュームの変更を高速化するために使用できます。ボリューム ランプが無効になっている場合、クリック音やポップノイズを防ぐために、デバイスのシャットダウンおよび起動時には入力オーディオ データ ストリームをデジタル無音状態に保つ必要があります。

デバイスは、**DVC\_LEVEL** を 0x000000 に設定することでソフトウェア ベースのミュート状態にすることができます。

デジタル電圧制御レジスタ **DVC\_LEVEL** および **DVC\_SLEW\_RATE** レジスタは、PPC3 ソフトウェア [セクション 6.4.1](#) を使用して設定できます。

**表 6-15. デジタル ボリューム制御**

| <b>DVC_LEVEL[23:0]</b> | ボリューム (dB)  |

|------------------------|-------------|

| 0x000000               | ソフトウェア ミュート |

| 0x00000D (MIN)         | -110        |

| ...                    | ...         |

| 0x400000               | 0 (デフォルト)   |

| ...                    | ...         |

| 0x7FB261 (MAX)         | 6           |

**表 6-16. デジタル ボリューム ランプレート**

| <b>DVC_SLEW_RATE[23:0]</b> | ランプレート@ 48kHz (s) |

|----------------------------|-------------------|

| 0x00036A                   | 1000ms            |

| ...                        | ...               |

| 0x034A51                   | 4ms (デフォルト)       |

| ...                        | ...               |

| 0x7FFFFF                   | 0 - ランプがディスエーブル   |

#### 6.4.2.2 ハイパス フィルタ

オーディオ再生信号に過度な DC と低周波数の内容が含まれていると、ラウドスピーカが損傷する可能性があります。再生パスは、この問題が発生することを防ぐハイパス フィルタ (HPF) を採用しています。HPF は 1 次フィルタであり、**AUDIO\_HPF\_N0**, **AUDIO\_HPF\_N1**, **AUDIO\_HPF\_D1** レジスタを使用して、48ksps fs の場合にデフォルトの 2Hz から変更できます。HPF のフィルタ周波数は FSYNC クロックの変化に応じてスケーリングされ、異なる FSYNC クロック周波数に対して所望のカットオフ周波数を得られるよう再設定することができます。HPF 係数を適切にディスエーブルするように、係数を変更することもできます。これらの係数は、PPC3 ソフトウェア [セクション 6.4.1](#) を使用して計算および設定する必要があります。

#### 6.4.2.3 Class-D アンプ

TAS2320 は、低アイドル チャネル ノイズ、低歪み、高 PSRR の高性能 Class-D アンプを内蔵しています。Class-D アンプは、SBCLK 周波数から生成されたクロック周波数でスイッチングし、常に入力クロック ソースに同期します。**SAMP\_RATE\_CFG** レジスタを使うと、44.1kHz の倍数と 48kHz の倍数の差に基づいて入力クロック ソースを選択できます。

**表 6-17. サンプル レート構成**

| <b>SAMP_RATE_CFG</b> | 構成                                 |

|----------------------|------------------------------------|

| 0 (デフォルト)            | オーディオ データレートは 48ksps の整数倍または約数です   |

| 1                    | オーディオ データレートは 44.1ksps の整数倍または約数です |

EMI 特性を改善するために、Class-D アンプはプログラマブルなエッジ レート制御 (ERC) と Class-D クロック スプレッド スペクトラム変調 (SSM) をサポートしています。

Class-D のエッジ レートは、**CLASSD\_OUTPUT\_EDGERATE\_CTRL[1:0]** レジスタを使用して制御できます。デフォルトでは、Class-D 出力のエッジ レートは最速設定に構成され、システムの高効率化を可能にしています。Class-D 出力のエッジ レートは、他の構成設定を使用して遅くすることができ、高周波数での EMI エネルギーを低減できますが、効率は低下します。出力エッジ レートの正確な変化速度は出力負荷条件によって異なり、以下の表に示す値はデフォルトの負荷条件におけるおよそのエッジ レートレベルです。

**表 6-18. Class-D 出力エッジ レート制御**

| <b>CLASSD_OUTPUT_EDGERATE_CTRL[1:0]</b> | 構成                         |

|-----------------------------------------|----------------------------|

| 00                                      | Class-D 出力エッジ レート: 0.5V/ns |

| 01                                      | Class-D 出力エッジ レート: 1.0V/ns |

| 10                                      | 予約済み                       |

| 11 (デフォルト)                              | Class-D 出力エッジ レート: 2V/ns   |

この Class-D アンプは、PVDD ハイサイド グランド パワー FET を含めて、各出力パワー FET に過電流保護機能を備えています。

Class-D アンプの出力インピーダンスは、**CLASSD\_HIZ\_MODE** 制御レジスタを使用してノイズ ゲート モード中に出力がスイッチングを停止するときに制御できます。

**表 6-19. Class-D high-Z モード制御**

| <b>CLASSD_HIZ_MODE</b> | 構成                   |

|------------------------|----------------------|

| 0 (デフォルト)              | 2.5kΩ で出力をブレダウン      |

| 1                      | 13kΩ を超える電圧で出力をブレダウン |

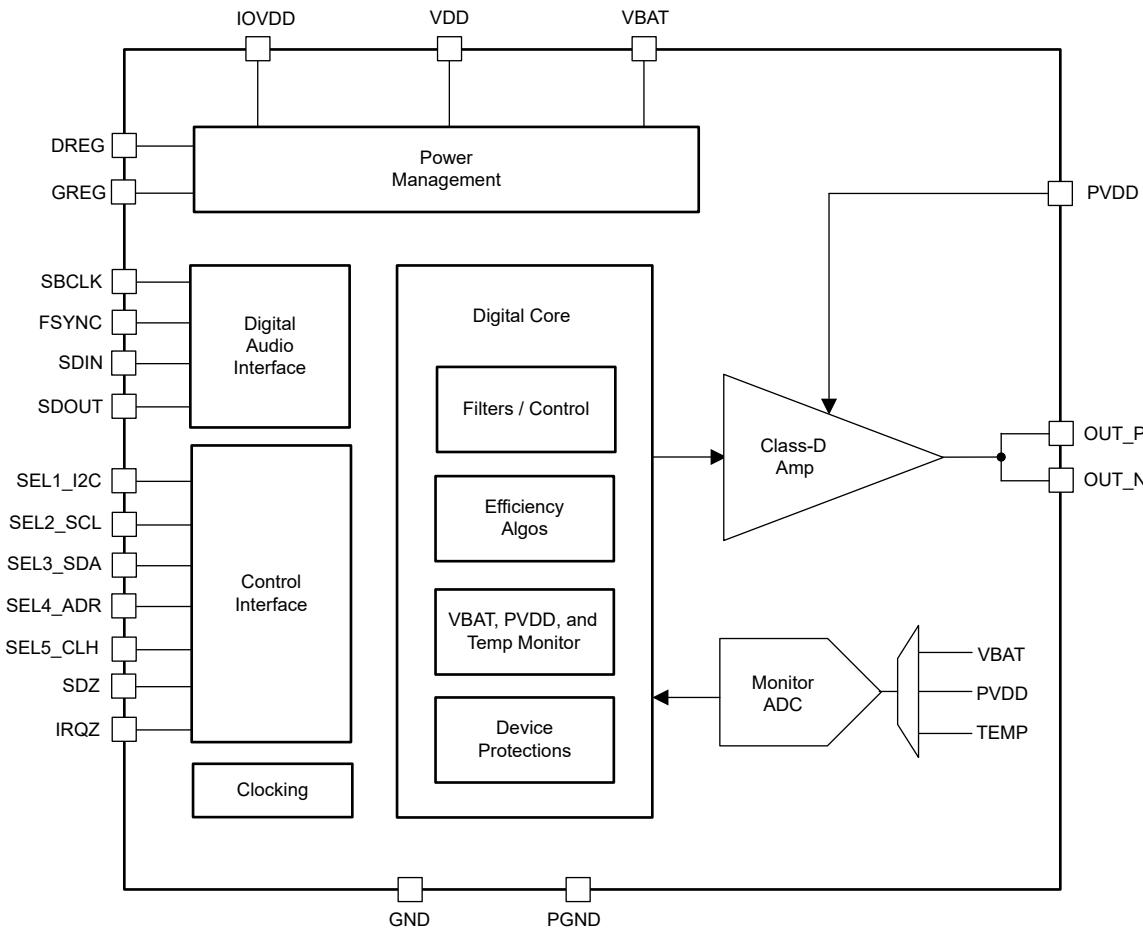

#### 6.4.2.4 ブラウンアウト防止機能付き電源トラッキング リミッタ

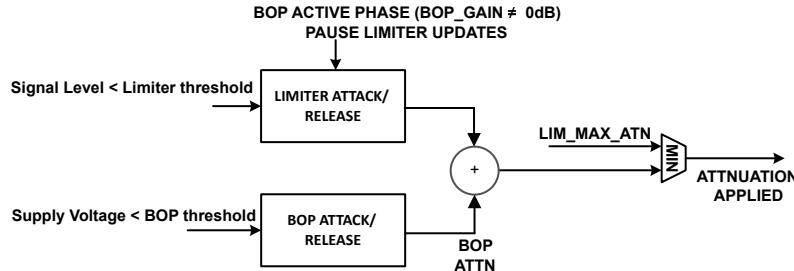

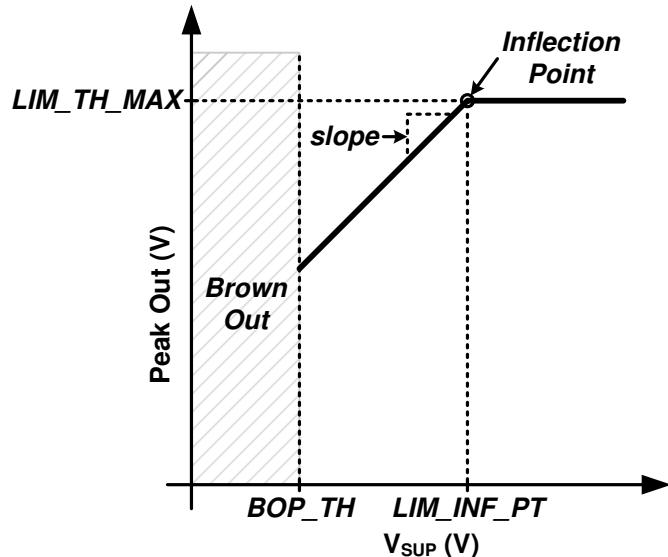

TAS2320 は、オーディオ信号とともに Class-D 電源電圧を監視し、オーディオ信号のピークがプログラム可能なスレッショルドを超えたときに、自動的にゲインを下げます。これにより、クリッピングを防止して、充電終了時のバッテリ条件で再生時間を延ばすことができます。リミッタ電圧低下とモジュールは、信号レベル、チャネル ゲイン、選択した電源電圧の状態に基づいて、必要な信号減衰を計算します。

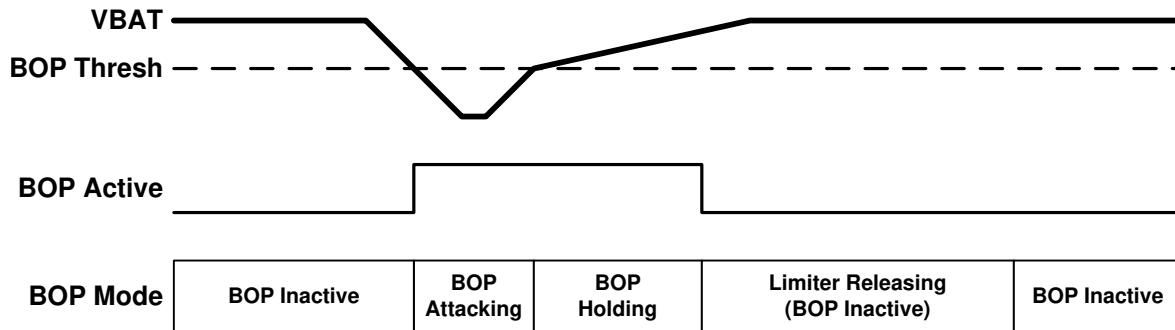

図 6-2. リミッタおよび電圧低下保護モジュール

電圧低下防止 (BOP) モジュールは、バッテリ電源の一時的な電圧低下に対して迅速に応答できるよう、優先入力を提供します。BOP 機能をイネーブルにするには、*BOP\_EN* レジスタ ビットを High にセットします。電圧低下条件を判定するために追跡される電源電圧は、*BOP\_SRC* レジスタ ビットを使用して、システム構成の必要性に応じて PVDD として構成できます。レジスタ *BOP\_THR\_LVL[23:0]* を設定することで構成された電圧低下スレッショルドを選択した電源が低下すると、BOP はゲインの低下を開始します。ゲイン低減率 (db/サンプル) は、*BOP\_ATK\_RATE[23:0]* レジスタの設定によって構成できます。電源電圧が電圧低下スレッショルドを上回ると、BOP はプログラムされたホールド タイマ *BOP\_HLD\_COUNT[23:0]* の経過後にゲインのリリースを開始します。BOP 機能では、*LIM\_RLS\_RATE[23:0]* レジスタ設定を使用して、電圧低下イベント後にリリースします。リリース レートとは、ゲインが増加する速度を表し、db/ サンプル比で示されます。BOP イベント中、リミッタの更新は一時停止されます。これは、BOP イベント中にリミッタが解放されないようにするためです。

図 6-3. 電圧低下防止イベント

レジスタ ビット *BOP\_INF\_HLD* を High に設定することで、BOP イベントが検出されたときにゲイン減衰を保持するようにデバイスを構成できます。ビットが high にプログラムされている場合、リミッタと BOP モジュールはゲイン減衰を解放せず、レジスタ ビット *BOP\_HLD\_CLR* を high に設定することにより無限ホールドがクリアされるまで、デバイスをプログラムされた最小ゲイン減衰レベルに保持します。ホールド クリア ビットはセルフ クリアされ、ホールドがクリアされると、自動的に low 状態にリセットされます。

ハード電圧低下レベルを設定することで、BOP のゲイン減衰によってバッテリ電圧低下を抑制できない場合に、デバイスをシャットダウンさせることができます。デバイスの電圧低下によるシャットダウンは、*BOPSD\_EN* ビットが high に設定されると有効になり、バッテリ電圧が *BOPSD\_THR\_LVL[23:0]* レジスタ ビットで設定された電圧スレッショルドを下回るとシャットダウンします。

リミッタおよび電圧低下防止機能によって適用される最大減衰レベルは、**LIM\_MAX\_ATN** レジスタで設定可能です。この減衰制限は、特長間で共有されます。例えば、最大減衰量が 6dB に設定されており、リミッタによって 4dB のゲイン低下が行われた場合、電圧低下防止機能はさらに 2dB だけゲインを下げることができます。リミッタあるいは電圧低下防止機能がアタック動作中に最大減衰値へ到達すると、それ以上のゲイン低減は行われません。

図 6-4. リミッタと電圧低下ゲインの減衰

#### 6.4.2.4.1 電圧リミッタおよびクリッピング保護

電源トラッキング リミッタは、**LIM\_MODE[1:0]** レジスタを使用して構成できます。VBAT 電圧モードでは、リミッタは電圧リミッタとして VBAT 電源電圧を追従し、PVDD 電圧モードでは、リミッタは PVDD 電圧を追従します。

表 6-20. リミッタ モードの選択

| <b>LIM_MODE[1:0]</b> | 構成              |

|----------------------|-----------------|

| 00 (デフォルト)           | ディセーブル          |

| 01                   | VBAT 電圧ベースのリミッタ |

| 10                   | PVDD 電圧ベースのリミッタ |

| 11                   | 予約済み            |

リミッタは、固定信号スレッショルド レベルに基づいて出力信号を低減するように構成するか、選択した電源電圧を追跡する動的スレッショルドに基づく信号を減衰するように構成できます。レジスタ ビット **SUPPLY\_HEADROOM\_LIM\_MODE** は、動的な電源トラッキングを可能にし、システムで電源電圧が変化したときのクリッピング歪みを制限するために使用できます。

表 6-21. リミッタの動的電源ヘッドルーム トラッキン

グ モード

| <b>SUPPLY_HEADROOM_LIM_MO<br/>DE</b> | 構成                                                     |

|--------------------------------------|--------------------------------------------------------|

| 0 (デフォルト)                            | ディセーブル                                                 |

| 1                                    | イネーブル。リミッタのスレッショルドは、監視対象の電源電圧の固定パーセンテージに基づいて動的に変更されます。 |

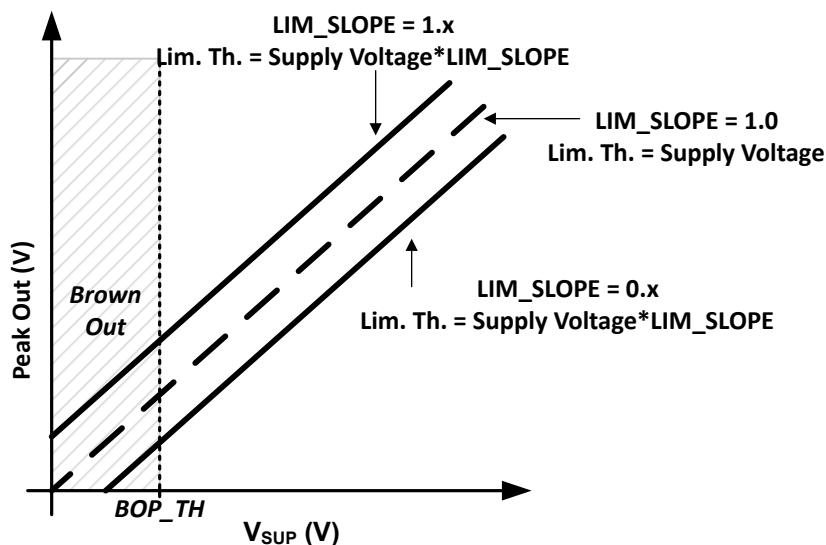

**SUPPLY\_HEADROOM\_LIM\_MODE** が high に設定されると、リミッタは監視対象の電源電圧に対する固定のパーセンテージとしてスレッショルドを設定します。リミッタは、出力信号レベルが設定されたスレッショルドを超えると、ゲインの低減を開始します。例えば、電圧リミットを電源電圧より 10% 低く設定する場合、**LIM\_SLOPE[23:0]** を 0.9 に設定し、スレッショルドは監視されている電源電圧に 1.1 を掛けて算出します。同様に、**LIM\_SLOPE[23:0]** を 1.0 より大きく設定すると、リミッタのスレッショルドは電源電圧より高く設定され、制御されたわずかなクリッピングが発生します。

図 6-5. ダイナミック電源ヘッドルームを持つリミッタ

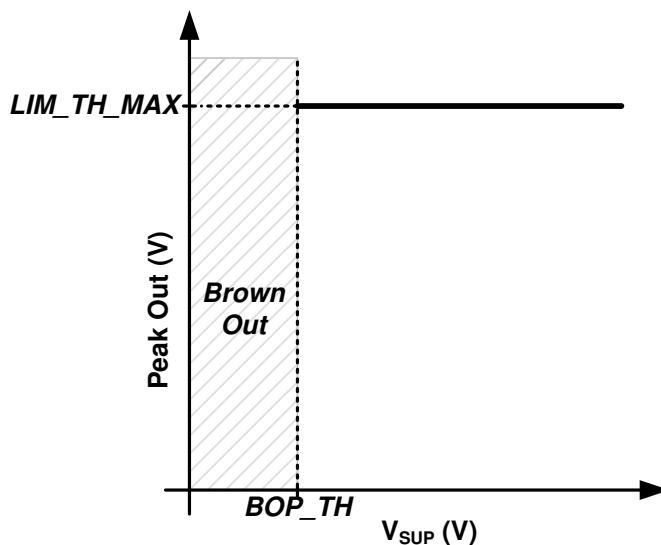

`SUPPLY_HEADROOM_LIM_MODE` が low に設定されている場合、リミッタは出力信号レベルがリミッタのスレッショルドを超えるとゲインの低減を開始します。リミッタは、プログラム可能な変曲点より下で選択された電源を追従し、最小スレッショルド値を持つように構成できます。図 6-6 は、選択された電源レベルに関係なく一定レベルに制限するよう構成されたリミッタを示しています。この動作を実現するには、リミッタの最大スレッショルドを `LIM_TH_MAX[23:0]` で目標レベルに設定します。`LIM_INF_PT[23:0]` を使用して、リミッタの変曲点を許容される最小電源設定より低く設定します。リミッタ最小スレッショルドレジスタ `LIM_TH_MIN[23:0]` は、この使用ケースにおいてリミッタの動作に影響を与えません。

図 6-6. 固定スレッショルドのリミッタ

図 6-7 は、最小スレッショルドなしでスレッショルド以下の選択された電源をリミッタが追従するように構成する方法を示しています。`LIM_TH_MAX[23:0]` レジスタを希望するスレッショルドに設定し、`LIM_INF_PT[23:0]` レジスタを、選択された電源に応じてリミッタがスレッショルドを低減し始める変曲点に設定します。`LIM_SLOPE[23:0]` レジスタビットを使用すると、電源電圧をトラッキングするリミッタのスロープを  $V/V$  単位で変更できます。例えば、スロープ値を  $1V/V$  にすると、電源電圧が  $1V$  低下するごとにリミッタのスレッショルドが  $1V$  低下します。選択された電源を追従するときにリミッタが最小スレッショルド低減を持たないようにするために、`LIM_TH_MIN[23:0]` を選択された電源の最小値より低く設定します。

図 6-7. 変曲点を持つリミッタ

スレッショルド以下で選択された電源を追従するリミッタを実現するには、前の例で説明した方法でリミッタを構成し、**LIM\_TH\_MIN[23:0]** レジスタを希望する最小スレッショルドに設定します。これを、以下の図 6-8 に示します。

図 6-8. 変曲点と最小スレッショルドを持つリミッタ

リミッタには構成可能なアタックレート (dB/Sample)、ホールド時間 (サンプル数)、リリースレート (db/サンプル) があり、これらは **LIM\_ATK\_RATE[23:0]**, **LIM\_HLD\_COUNT[23:0]**, **LIM\_RLS\_RATE[23:0]** のレジスタビットで設定できます。

#### 6.4.2.5 トーン ジェネレータ

TAS2320 は、内蔵トーン ジェネレータを使用して、内部で正弦トーンを生成できます。この機能は、レジスタビット **INTERNAL\_TONE\_GEN\_ENZ** を low に設定することで有効化できます。**INTERNAL\_TONE\_PLAYBACK\_EN** ビットを high に設定すると、トーン信号の再生を開始します。high に設定すると、デバイスは設定された **TONE\_GEN\_CTRL\_xx** レジスタに基づいて正弦トーンの生成を開始します。トーン ジェネレータは、16Hz から最大  $0.45 \times F_s$  までの任意の周波数を生成できます。ここで  $F_s$  は、入力デジタル クロックのサンプリング レートです。トーン信

号の振幅は、*TONE\_GEN\_CNTRL\_XX* レジスタを使用して制御することもできます。PPC3 ソフトウェアを使用して、トーンの周波数と振幅をプログラムすることをお勧めします。

内部で生成されるトーンは、受信オーディオ ストリームと混合することも、入力オーディオ ストリームを置き換えることもできますが、*INTERNAL\_TONE\_MIXING\_EN* レジスタで生成されるトーン信号のみが生成されます。

**表 6-22. 内部トーン ジェネレータの混合オプション**

| <i>INTERNAL_TONE_MIXING_EN</i> | 構成                                        |

|--------------------------------|-------------------------------------------|

| 0                              | 内部トーンのみが生成されます。                           |

| 1 (デフォルト)                      | 内部で生成されるトーンは、入力オーディオ データと混合されて、一緒に再生されます。 |

トーン ジェネレータは、BCLK などの外部クロック ソースを使用することも、*INTERNAL\_TONE\_CLK\_SEL* レジスタを使用して、外部クロック ソースなしでもトーン信号を生成するために内部発振器を使用して生成することもできます。

**表 6-23. 内部トーン クロック ソースの選択**

| <i>INTERNAL_TONE_CLK_SEL</i> | 構成                      |

|------------------------------|-------------------------|

| 0 (デフォルト)                    | トーン ジェネレータは外部クロックを使用します |

| 1                            | トーン ジェネレータは、内部発振器を使用します |

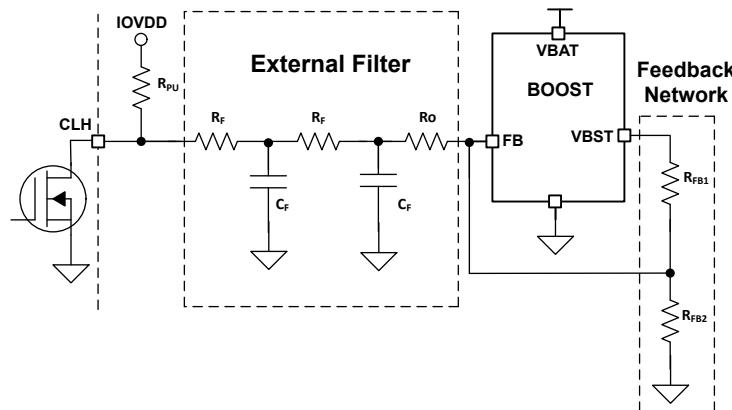

#### 6.4.3 デジタルオーディオシリアルインターフェイス

このデバイスは柔軟なオーディオシリアルインターフェース(ASI)ポートを提供します。このポートは、ステレオ I<sup>2</sup>S、左揃え、TDMなどさまざまなフォーマットに対応するように構成できます。モノラルオーディオ再生は、SDINピンから行うことが可能です。SDOUTピンは、Iセンス、Vセンス、PVDD電圧、VBAT電圧、ダイ温度、ステータス、およびエコーリファレンス用のオーディオを含むサンプルストリームを送信するために使用されます。

TDMシリアルオーディオポートは、44.1/48kHzでは最大16個の32ビットタイムスロット、88.2/96kHzでは8個の32ビットタイムスロット、176.4/192kHzでは4個の32ビットタイムスロットをサポートします。デバイスは、幅32ビットのタイムスロットを2個、または幅16、24、32ビットのタイムスロットを4個または8個サポートします。デバイスはタイムスロット数を自動検出できるため、プログラムする必要はありません。TDMバス上で検出されたPCMデータのサンプリングレートおよびSBCLKとFSYNCの比率は、それぞれ読み取り専用レジスタビット*FS\_RATE\_DETECTED[2:0]*および*FS\_RATIO\_DETECTED[3:0]*に報告されます。

**表 6-24. PCMデータサンプルレートが検出されました**

| <i>FS_RATE_DETECTED[2:0]</i><br>(読み出し専用) | 設定              |

|------------------------------------------|-----------------|

| 000                                      | 予約済み            |

| 001                                      | 14.7kHz/16kHz   |

| 010                                      | 22.05kHz/24kHz  |

| 011                                      | 29.4kHz/32kHz   |

| 100 (デフォルト)                              | 44.1kHz/48kHz   |

| 101                                      | 88.2kHz/96kHz   |

| 110                                      | 176.4kHz/192kHz |

| 111                                      | エラー状態           |

フレームは FSYNC が High から Low、または Low から High へのいずれかの遷移で開始します (FRAME\_START レジスタビットで設定)。FSYNC および SDIN は、SBCLK の立ち上がりエッジか立ち下がりエッジのいずれかを使用してサンプリングされます (RX\_EDGE レジスタビットで設定)。RX\_OFFSET[4:0] レジスタビットでは、FSYNC の遷移からタイ

ムスロット 0 の開始までの SBCLK のサイクル数を定義します。この値は通常、左揃えフォーマットの場合は 0、I<sup>2</sup>S フォーマットの場合は 1 に設定されます。

**RX\_SLEN[1:0]** レジスタビットは、RX タイムスロットの長さを 16、24、32 (デフォルト) ビットに設定します。タイムスロット内のオーディオサンプルのワード長は、**RX\_WLEN[1:0]** レジスタビットで設定します。デフォルトでは、RX ポートはタイムスロット内のオーディオサンプルを左揃えにしますが、**RX\_JUSTIFY** レジスタビットで右揃えに変更することも可能です。このデバイスは、モノラルとステレオのダウンミックス再生 ( $[L+R]/2$ ) に対応しています。デフォルトでは、デバイスは I<sup>2</sup>C ベースアドレスのオフセット (AD1 ピンと AD2 ピンで設定) と同じタイムスロットからモノラル再生を行います。**RX\_SCFG[1:0]** レジスタビットを使用すると、**RX\_SLOT\_R[3:0]** レジスタビットと **RX\_SLOT\_L[3:0]** レジスタビットの設定により、再生ソースを左側のタイムスロット、右側のタイムスロット、またはステレオダウンミックスにオーバーライドすることができます。

タイムスロットがフレーム境界を超えたときに部分的に受信するか、すべて受信するかのいずれかを選択した場合、レシーバはデジタル的にミュートされたサンプルと同等のヌルサンプルを返します。

TDM ポートは、**SDOUT** ピンを通じて複数のサンプルストリームを送信することができ、これにはスピーカ電圧センス、スピーカ電流センス、割り込みおよびステータス、**PVDD** 電圧、**VBAT** 電圧、ダイ温度が含まれます。

**SBCLK** の立ち上がりエッジか立ち下がりエッジのいずれかを使用して、**SDOUT** ピンでデータを送信することができます。この機能は、**TX\_EDGE** レジスタビットをセットして構成できます。**TX\_OFFSET[2:0]** レジスタビットは、フレーム開始時からタイムスロット 0 の開始時までの **SBCLK** のサイクル数を定義します。この値は、左揃えフォーマットの場合は 0、I<sup>2</sup>S フォーマットの場合は 1 にプログラムされます。TDM TX は、**TX\_FILL** レジスタビットの設定に応じて、ロジック 0 かハイインピーダンスのいずれかを送信できます。オプションのバスキーパーは、すべてのデバイスがハイインピーダンスで駆動している場合、**SDOUT** ピンの状態を弱く保持します。**SDOUT** で必要なバスキーパーは 1 つだけのため、この機能は **TX\_KEEPEN** レジスタビットでディセーブルにできます。バスキーパーは、**TX\_KEEPLN** レジスタビットを使用して、1LSB のみバスを保持するか、常時(永続的に)バスを保持するかを構成できます。さらに、**TX\_KEEPACY** レジスタビットを使用して、キーパーの LSB を 1 フルサイクルの間駆動するか、ハーフサイクルだけ駆動するかも設定できます。

電圧と電流のセンス値の TDM 送信は、それぞれ **VSNS\_TX** および **ISNS\_TX** レジスタビットを使用してイネーブルにできます。各センスストリームは、個別に有効化または無効化できます。これは、すべてのデバイスで全ストリームをバス上に送信する必要がない場合に、限られた TDM 帯域幅を管理するのに有用です。

各センスストリームに対する **VSNS\_SLOT[5:0]** および **ISNS\_SLOT[5:0]** は、MSB の送信が開始されるタイムスロット位置を定義します。例えば、**VSNS\_SLOT** が 2 に設定されている場合、上位 8 ビット (MSB) はタイムスロット 2 に、下位 8 ビット (LSB) はタイムスロット 3 に送信されます。

アクティブに送信されるサンプルストリームに割り当てるタイムスロットが競合しないようにすることが重要です。例えば、**VSNS\_SLOT** が 2 に、**ISNS\_SLOT** が 3 に設定されている場合、電圧センスの下位 8 ビット (LSB) は、電流センスの上位 8 ビット (MSB) と競合します。このような設定では、競合するビットスロットにおいて予測不可能な送信結果が生じます(例えば、どちらに優先順位があるかは定義されていません)。

電圧センスおよび電流センスの値は、デフォルトで測定された 16 ビットのフル値が送信されます。**IVMON\_SLEN[1:0]** ビットを使用すると、1 スロットで 8MSB ビットだけを送信するか、または複数のスロットにまたがって 12MSB ビットの値を送信することができます。ホストプロセッサで 24 ビットの I<sup>2</sup>S/TDM データのみを処理する場合は、特殊な 12 ビットモードを使用します。デバイスは、電圧センススロットと電流センススロットを 1 スロットずらして設定し、連続する 8 ビットスロットを 3 つ使用する必要があります。このモードでは、デバイスは最初の 12MSB ビットを送信し、次に前のスロットで指定された 2 番目の 12MSB ビットを送信します。

このデバイスは、入力電源電圧の監視および TDM 送信にも対応しています。PVDD スロットの有効化および長さの設定には、**PVDD\_SLOT[5:0]**、**PVDD\_TX**、および **PVDD\_SLEN** のレジスタビットを使用できます。同様に、VBAT スロットの有効化および長さの設定には、**VBAT\_SLOT[5:0]**、**VBAT\_TX**、および **VBAT\_SLEN** のレジスタビットを使用できます。ダイ温度は、同じ方法でデバイスから送信することもできます。ダイ温度のイネーブルとスロット設定は、**TEMP\_TX** および **TEMP\_SLOT[5:0]** レジスタビットを使用して行います。

スロットのステータス情報は **STATUS\_SLOT[5:0]** レジスタビットで確認できます。**STATUS\_TX** レジスタビットを High にセットすると、ステータス送信はイネーブルになります。タイムスロットがフレーム境界を超えて送信されるように選択した場合、トランシッタはフレーム境界で送信を切り捨てます。

#### 6.4.3.1 デジタルループバック

このデバイスはループバック機能をサポートしており、**SDIN** データを 2 つのレベルで **SDOUT** にループさせることができます。この機能を **TDM\_LOOPBACK** レジスタビットによってイネーブルにした場合、デバイス内で ASI データデコードを行わずに、ループバックが IO ピンレベルで実行されます。その他のオプションとして、**TDM\_DESER\_LOOPBACK** レジスタビットによってループバック機能をイネーブルにすることができます。この場合、**SDIN** データはまずデバイス内で ASI プロトコルデコードを経由してから、**SDOUT** を介して送り返されます。これらの **SDIN** から **SDOUT** へのループバックオプションは、オーディオシステムのボードレベルデバッグに有用です。

デバイスは、リミッタや **BOP** など内部信号処理ブロックの後段で、エコー リファレンス用のデジタルオーディオデータを **SDOUT** 信号経由でループバックすることもできます。これにより、オーディオシステムは、デバイスに接続されたホストプロセッサで、ノイズおよびエコー キャンセルアルゴリズムを実行できます。エコー リファレンスは、**AUDIO\_TX** レジスタビットの構成でイネーブルできます。スロットの長さとタイムスロットは、**AUDIO\_SLEN** および **AUDIO\_SLOT[5:0]** レジスタビットを使用して選択できます。

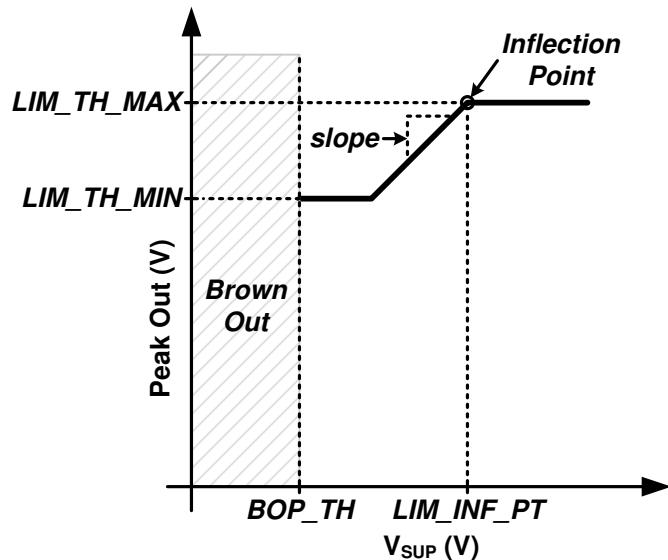

#### 6.4.4 外部 Class-H 昇圧コントローラ

TAS2320 には Class-H アルゴリズムが実装されており、ユーザーは外部電源を制御して、歪みをクリッピングすることなく高いダイナミックレンジを実現する十分なマージンを維持しながら、システム効率を最適化することができます。

イネーブルにすると、コントローラはデバイスの **CLH** ピンで PWM 信号を生成し、そのデューティサイクルはスピーカーのピーク電圧に比例します。外部 RC フィルタを使用しているため、信号はアナログ電圧に変換され、フィードバック入力を使用した昇圧コンバータの制御に使用することができます。

以下の図に、**CLH** ピンを外部昇圧コントローラの RC ネットワークに接続する方法を示します。

図 6-9. CLH ピンと外部コンポーネント

**CLH** ピンはデフォルトでオープンドレイン構成になっており、ワイヤード OR 構成により、1 つの RC 回路で簡単にマルチチャネル制御ループを構成できます。

#### 6.4.5 電源電圧モニタ

TAS2320 は、電源電圧ピンを監視するための SAR ADC を内蔵しています。検出された電圧は、デバイス内部の機能や保護に使用されるほか、デジタルデータバスを介してストリーミングしたり、I2C レジスタを通じて読み取ることもできます。

モニタ ADC は、**PVDD** ピン電圧と比較して **VBAT** ピンをより高いレートでサンプリングします。このサンプリング速度を、**VBAT** よりも **PVDD** ピンのサンプリングレートを優先させるために切り替えることができます。

**表 6-25. 電源モニタ サンプリング レート**

| SUPPLY_SAMPLING_RATE | 構成                             |

|----------------------|--------------------------------|

| 0 (デフォルト)            | VBAT サンプリング レートは PVDD より高くなります |

| 1                    | PVDD サンプリング レートは VBAT より高くなります |

監視された VBAT 電圧と PVDD 電圧は *VBAT\_CNV* レジスタおよび *PVDD\_CNV* レジスタに格納され、I<sup>2</sup>C コマンドを使用して読み取ることができます。

電源モニタは、VBAT 低電圧、PVDD 過電圧および低電圧、などの電圧保護にも使用されます。電圧保護機能は電源電圧を監視し、電圧が保護スレッショルドレベルを超えるとデバイスをシャットダウンします。また、デバイスは対応する�オルトレジスタも設定し、セクション 6.3.2 で説明されているように構成された割り込みマスクレジスタに基づいて IRQZ ピンで割り込みを生成できます。�オルト条件のためにデバイスがシャットダウンされると、*MODE[1:0]* レジスタ ビットを使用してデバイスを再電源オンすることができます。

PVDD 過電圧保護は、監視された PVDD 電圧をプログラム可能なスレッショルドと比較することで行われ、内部昇圧モードでは を使用して、では *PVDD\_OVLO\_TH\_SEL\_EXT* を使用して制御できます。PVDD 過電圧保護はデフォルトでイネーブルになっており、*PVDD\_OV\_DET\_DIS* ビットを high にセットすることでディスエーブルにすることもできます。

#### 6.4.6 過熱保護

TAS2320 は、デバイス接合部温度モニタを内蔵しており、過熱からデバイスを保護します。内部温度が過熱スレッショルドを超えると、デバイスは自動的にシャットダウンし、対応する割り込みレジスタに過熱フラグを設定します。*OTE\_RETRY* ビットが high にセットされていると、デバイスは自動的にパワーアップを再試行できます。high に設定すると、デバイスは *RETRY\_WAIT\_TIME* 設定 (デフォルトで 1.5 秒) のたびに再電源投入を試みます

過熱保護に加えて、デバイスには過熱警告スレッショルドがあり、接合部温度がシャットダウンに近づいた際にシステムが割り込みやフラグを発生させることができます。内部温度が 105°C、115°C、125°C、135°C では、4 つの過熱警告フラグが使用できます。各過熱警告フラグは個別に設定することにより、IRQZ パッドへの割り込み生成を制御できます。過熱警告フラグの最小温度およびステップ サイズは、*THERMAL\_WARN\_MIN\_TEMP[23:0]* レジスタと *THERMAL\_WARN\_TEMP\_STEP[23:0]* レジスタを使用してプログラムできます

リアルタイムの内部接合部温度を監視する方法はレジスタ *TMP\_CNV* に保存され、i<sup>2</sup>c コマンドを使用して読み取ることができます。

#### 6.4.7 クロックおよびPLL

TDM/I<sup>2</sup>S モードでは、デバイスは SBCLK で動作します。以下の 表 6-26 には、各サンプルレートおよび SBCLK と FSYNC の比に対する有効な SBCLK 周波数が示されています。44.1kHz ベースのクロッキングの場合でも、48ksps と 44.1ksps 間の対応する比率変更を適用することで、同じ表を使用できます。

192kHz のサンプリング レートはサポートされていますが、データは内部的に 96kHz にダウンサンプリングされます。したがって、エイリアシングを防ぐために 40kHz を超える音声信号を入力しないようにします。さらに、BOP やリミッターなどのすべての処理ブロックも影響を受け、192kHz のオーディオを受け取る際に 96kHz のサンプリング レートを使用する必要があります。

サンプル レートが *SAMPLE\_RATE\_CFG* ビット経由で適切に設定されている場合、SBCLK と FSYNC の比率が有効である限り、追加の設定は不要です。デバイスは、入力された PCM FSYNC および BCLK の周波数を自動的に検出し、オーディオ信号の再生用に自動設定します。検出されたクロック レートは、読み出し専用レジスタ *FS\_RATIO\_DETECTED* および *FS\_RATE\_DETECTED* を使用して読み出すことができます。デバイスは不適切な SBCLK 周波数や SBCLK 対 FSYNC 比を検出し、ボリュームは再生パスを低下させて、可聴アーティファクトを最小限に抑えます。

**表 6-26. サポートされる SBCLK 周波数 (MHz) (48kHz ベースのサンプル レート)**

| サンプルレート (kHz) | SBCLK 対 FSYNC 比 |       |       |       |        |        |        |        |        |        |        |     |      |      |

|---------------|-----------------|-------|-------|-------|--------|--------|--------|--------|--------|--------|--------|-----|------|------|

|               | 16              | 24    | 32    | 48    | 64     | 96     | 128    | 192    | 256    | 384    | 512    | 125 | 250  | 500  |

| 16kHz         | 該当なし            | 0.384 | 0.512 | 0.768 | 1.024  | 1.536  | 2.048  | 3.072  | 4.096  | 6.144  | 8.192  | 2   | 4    | 8    |

| 24kHz         | 0.384           | 0.576 | 0.768 | 1.152 | 1.536  | 2.304  | 3.072  | 4.608  | 6.144  | 9.216  | 12.288 | 3   | 6    | 12   |

| 32kHz         | 0.512           | 0.768 | 1.024 | 1.536 | 2.048  | 3.072  | 4.096  | 6.144  | 8.192  | 12.288 | 16.384 | 4   | 8    | 16   |

| 48kHz         | 0.768           | 1.152 | 1.536 | 2.304 | 3.072  | 4.608  | 6.144  | 9.216  | 12.288 | 18.432 | 24.576 | 6   | 12   | 24   |

| 96kHz         | 1.536           | 2.304 | 3.072 | 4.608 | 6.144  | 9.216  | 12.288 | 18.432 | 24.576 | 該当なし   | 該当なし   | 12  | 24   | 該当なし |

| 192kHz        | 3.027           | 4.608 | 6.144 | 9.216 | 12.288 | 18.432 | 24.576 | 該当なし   | 該当なし   | 該当なし   | 該当なし   | 24  | 該当なし | 該当なし |

#### 6.4.7.1 自動クロックに基づくウェークアップおよびクロック エラー

TAS2320 は、ASI クロック自動検出機能を使用して、アクティブからシャットダウン、またその逆への柔軟な動作モード遷移をサポートします。MODE[1:0] が「11」に設定されている場合、デバイスは ASI 入力ピン (BCLK および FSYNC) に入力される有効な ASI クロック信号に基づいて、アクティブ状態とソフトウェア シャットダウン状態の間を切り替えます。このモードで ASI クロックが検出されない場合、デバイスはソフトウェア シャットダウン状態にとどまり、VDD ピンはソフトウェア シャットダウン モード  $I_Q$  で、有効な BCLK および FSYNC クロックが検出されるまで保持されます。有効なクロックが検出されると、デバイスはアクティブ状態で起動し、クロックが有効である限りその状態を維持します。ソフトウェアまたはハードウェアのシャットダウンコマンドが使用されると、デバイスはシャットダウンされます。

本デバイスは、CLK\_ERR\_PWR\_EN のステータスに基づいて誤ったクロック構成を検出したときに、割り込みフラグを検出および上昇させることができます。このビットを High に設定すると、デバイスはクロックピンの動作を監視し、エラーが発生した場合はラッチ割り込みステータスレジスタにフラグを立てます。デバイスは、対応する割り込み MASK レジスタのステータスに基づいて、IRQZ ピンを使用して割り込みを発生させることもできます。エラー保護ビットがイネーブルのとき、クロック エラーが検出された場合、デバイスは適切なシャットダウン シーケンスによって自動的にシャットダウンし、無効なクロックによるクリック音やポップ音を最小限に抑えます。

デバイスがシャットダウン状態のとき、クロック エラー検出は遅延可能で、システムは入力クロックを安定させるのに必要な時間を確保できます。クロック エラー検出でのこのパワーアップ遅延は、CLK\_HALT\_TIMER によって構成された内部パワーアップ クロック エラー検出タイマを使用して制御されます。デバイスが CLK\_HALT\_TIMER の満了時に有効なクロックを検出しない場合、パワーアップ前クロック エラーが INT\_LTCH4[2] ビットにフラグされ、INT\_MASK4[2] ビットのステータスに基づいて IRQZ ピンに対応する割り込みが生成できます。MODE[1:0] が 11 (ASI モードでのウェークアップ) に構成されている場合、「000」の CLK\_HALT\_TIMER は推奨されず、デバイスがソフトウェア シャットダウンに移行しなくなり、デバイスがシャットダウンしている間に VDD  $I_Q$  が増加します。

デバイスの電源が投入されると、CLK\_ERR\_PWR\_EN ビットのステータスに基づいて、外部および内部で生成されるクロックが継続的に監視されます。有効化されている場合、外部または内部クロックのエラーが発生すると、クロック エラー ステータス レジスタ INT\_LTCH2[3] ビットによってフラグが設定され、INT\_MASK2[3] のステータスに基づいて IRQZ ピンに対応する割り込みが生成できます。

システムの柔軟性を高めるため、デバイスは検出されたクロック エラーのタイプにエラー ステータスも設定します。デバイスは、汎用クロック エラー割り込み生成を使用する代わりに、特定のタイプのクロック エラーに対して IRQZ ピンで割り込みを発生させるように構成することもできます。以下の 表 6-29 は、さまざまな種類のクロック エラーと、それに対応するステータス ビットおよび割り込み MASK レジスタ ビットを説明しています。検出されたクロック エラーのタイプに基づいて、以下の表に示す 1 つ以上のレジスタ ビットを設定できます。

いずれかの種類のクロック エラーが原因でデバイスがシャットダウンした場合、MODE[1:0] が「11」に設定されているときに、デバイスは自動的に電源の再投入を試みることができます。

**表 6-27. クロック エラー検出制御**

| CLK_ERR_PWR_EN | 設定            |

|----------------|---------------|

| 0              | ディセーブル        |

| 1              | イネーブル (デフォルト) |

**表 6-28. クロック停止タイマ**

| CLK_HALT_TIMER[2:0] | 設定             |

|---------------------|----------------|

| 000                 | ディセーブル (無限時間)。 |

| 001                 | 0.8ms (デフォルト)  |

| 010                 | 3.2ms          |

| 011                 | 34.1ms         |

| 100                 | 68.3ms         |

| 101                 | 256ms          |

| 110                 | 768ms          |