# TCAN1473A-Q1 車載対応、スリープモード搭載、信号改善対応 CAN FD トランシーバ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認定済み

- **機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- ISO 11898-2:2024 で定義されている信号改善機能 (SIC) を実装

- リングングを排除してビット対称性を強化し、バス信号をアクティブに改善

- Classic CAN ネットワークでの使用に対する下位互換性

- 広い動作入力電圧範囲

- 最大 8Mbps の classic CAN および CAN FD をサポート

- $V_{IO}$  レベル シフト対応: 1.7V ~ 5.5V

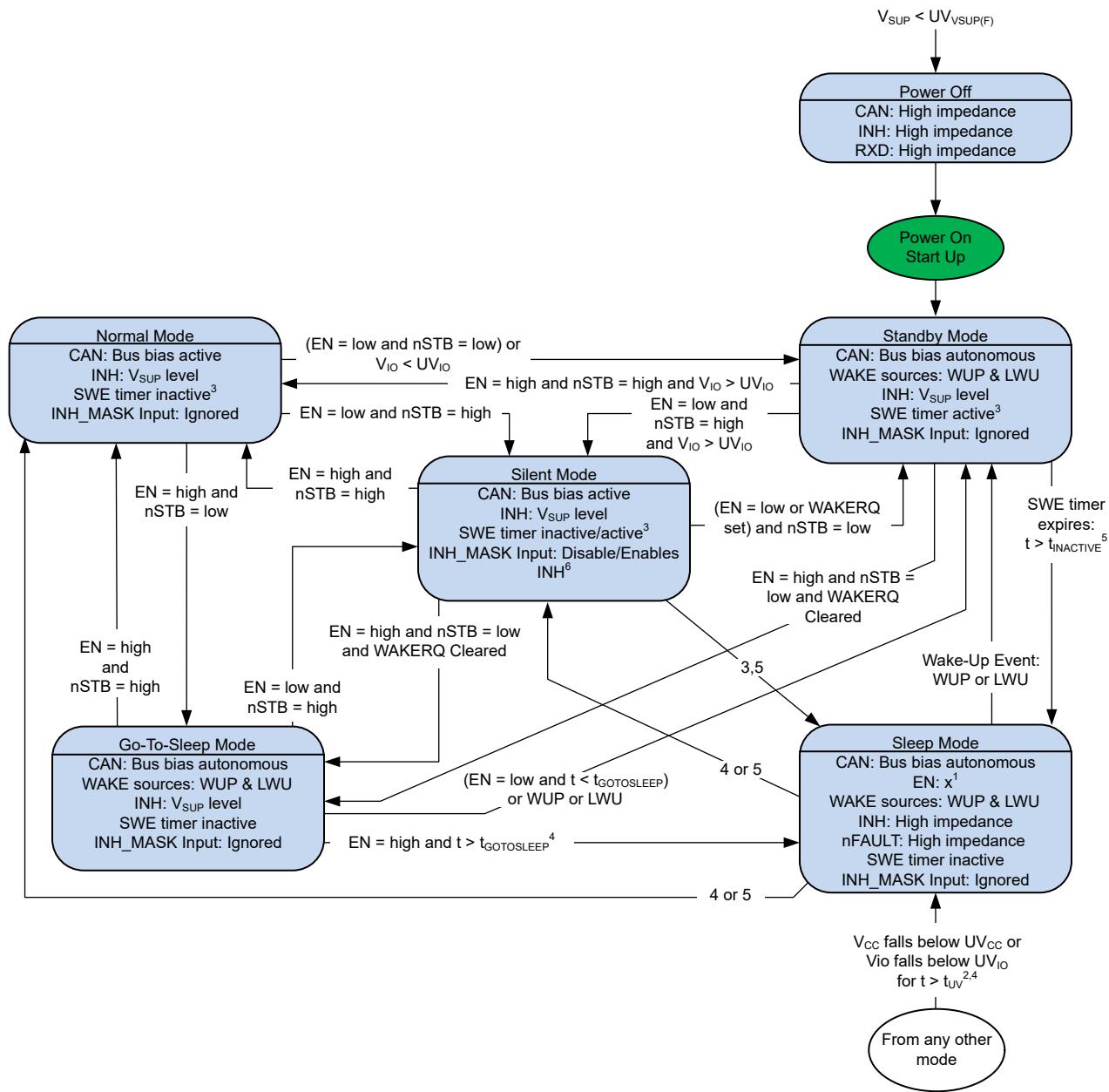

- 動作モード:

- 通常モード

- サイレントモード

- スタンバイモード

- リモートおよびローカルウェークアップをサポートする、低消費電力のスリープモード

- システム電源制御のための高電圧 INH 出力

- INH\_MASK ピンにより、スプリアスウェイクアップイベント時に INH をディセーブルに維持

- ウェークピンによるローカル WAKE アップのサポート

- スリープウェイクエラー (SWE) タイマにより、システム電源障害やソフトウェア障害が発生した場合でも、スタンバイモードからスリープモードへの安全な移行を実現

- パワーアップ時間延長に対応可能

- 電源非接続時の規定された挙動

- バスおよび IO 端子は高インピーダンス

- 保護機能:

- CAN バスの障害耐性: ±58V

- $V_{SUP}$  でのロードダンプのサポート

- IEC ESD 保護

- 低電圧保護

- サーマルシャットダウン保護機能

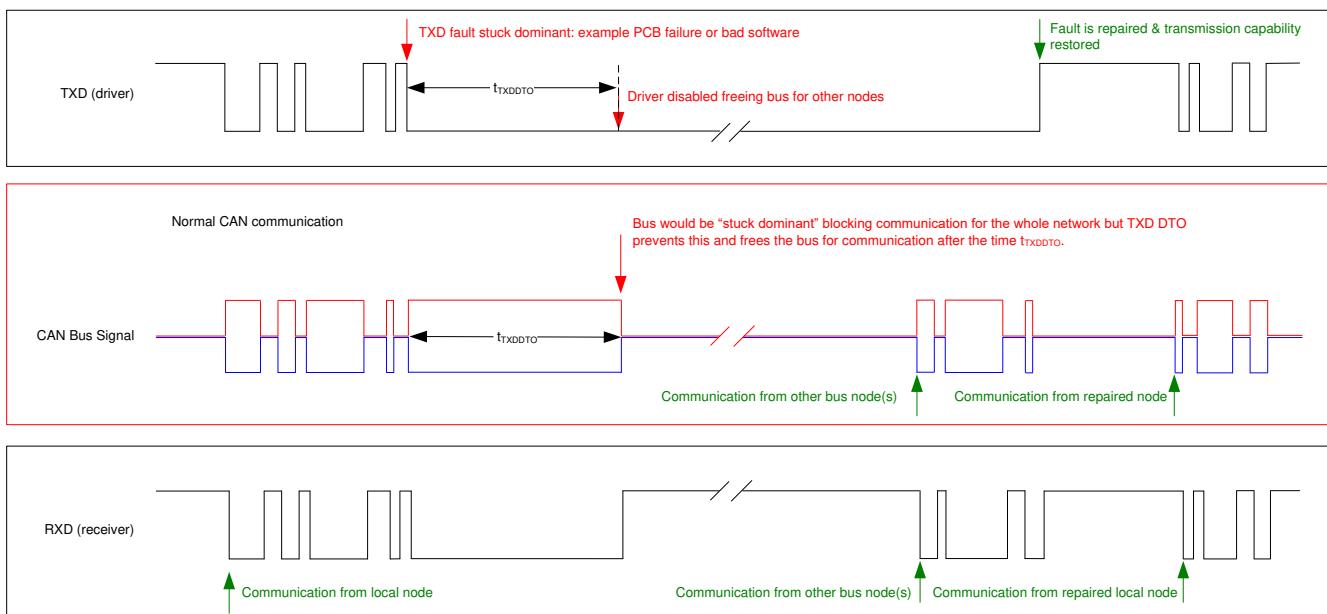

- TXD ドミナント状態タイムアウト (TXD DTO)

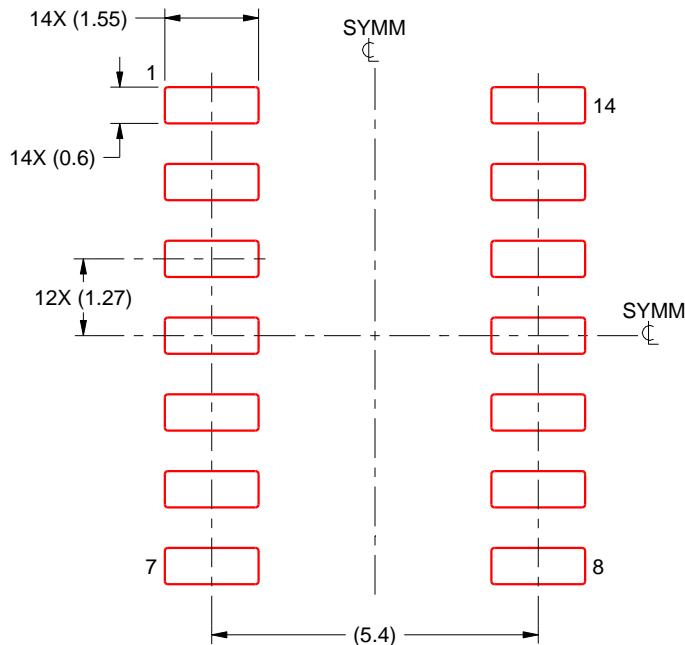

- 14 ピンのリード付き (SOT および SOIC) パッケージおよび自動光学検査 (AOI) 性能向上のためのウェッタブルフランク付きリードレス (VSON) パッケージで供給

## 2 アプリケーション

- ボディエレクトロニクスおよび照明

- 車載ゲートウェイ

- 先進運転支援システム (ADAS)

- インフォテインメントおよびクラスター

- ハイブリッド、電気、パワートレインシステム

- 個人用移動車両: 電動バイク

- 産業用輸送

## 3 説明

TCAN1473A-Q1 は、CAN (Controller Area Network) トランシーバであり、信号改善機能 (SIC) 仕様を含む ISO 11898-2:2024 CAN 仕様の物理層要件を満たしています。このデバイスは、ドミナントとリセッショナルのエッジで信号リングングを低減し、複雑なネットワークトポロジで高いスループットを実現します。SIC により、アプリケーションは複数の未終端のスタブを持つ大規模ネットワークで 2Mbps、5Mbps、および 8Mbps で動作できるため、CAN FD (CAN Flexible Datarate) の真のメリットが引き出されます。

TCAN1473A-Q1 を使用すると、システムに存在する各種電源供給の有効無効を INH 出力ピンで切り替えることにより、バッテリの消費電流をシステムレベルで低減できます。これにより、CAN バスを監視しながら、TCAN1473A-Q1 を除くすべてのシステムコンポーネントの電源が遮断される低電流スリープ状態を実現します。ウェークアップイベントを検出すると、TCAN1473A-Q1 が INH を High に駆動してシステム起動を開始します。

TCAN1473A-Q1 は、スタンバイモードでの 4 分間 ( $t_{INACTIVE}$ ) の非アクティブ状態の後でスリープモードへ安全に移行できるように SWE タイマを備えています。これにより、MCU がデバイスを通常モードに移行できなかった場合に、デバイスは必ず低消費電力のスリープモードに移行します。

INH\_MASK 機能を使用しない場合 (INH\_MASK ピンがフローティング状態、または GND に接続されている場合)、本デバイスは、TCAN1043A-Q1 や TCAN1043H-Q1 などの Classical CAN FD トランシーバとピン互換です。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

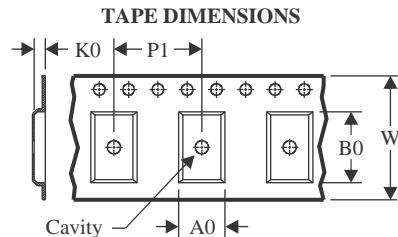

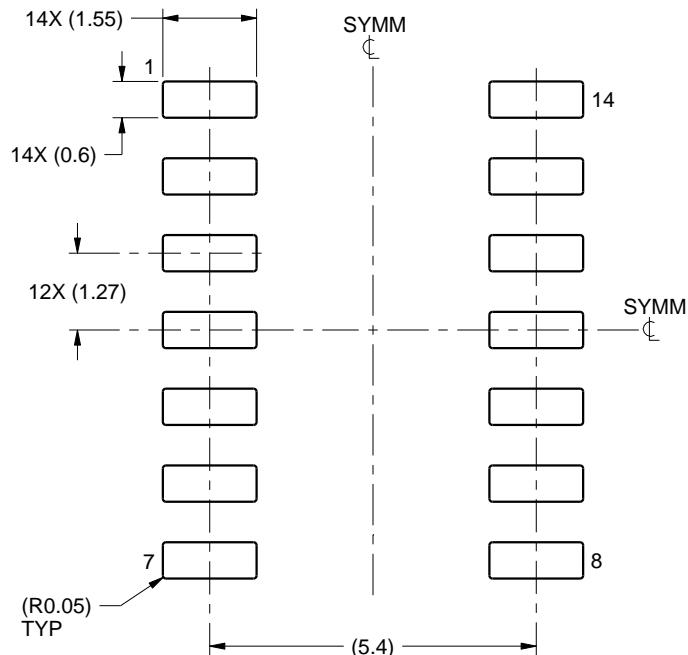

### パッケージ情報

| 部品番号          | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------------|----------------------|--------------------------|

| TCAN1473AC-Q1 | SOT (DYY)            | 4.2mm × 3.26mm           |

|               | SOIC (D)             | 8.65mm × 6mm             |

|               | VSON (DMT)           | 4.5mm × 3mm              |

- (1) 詳細については、[セクション 11](#)を参照してください。

(2) パッケージ サイズ(長さ × 幅)は公称値であり、該当する場合はピンも含まれます。

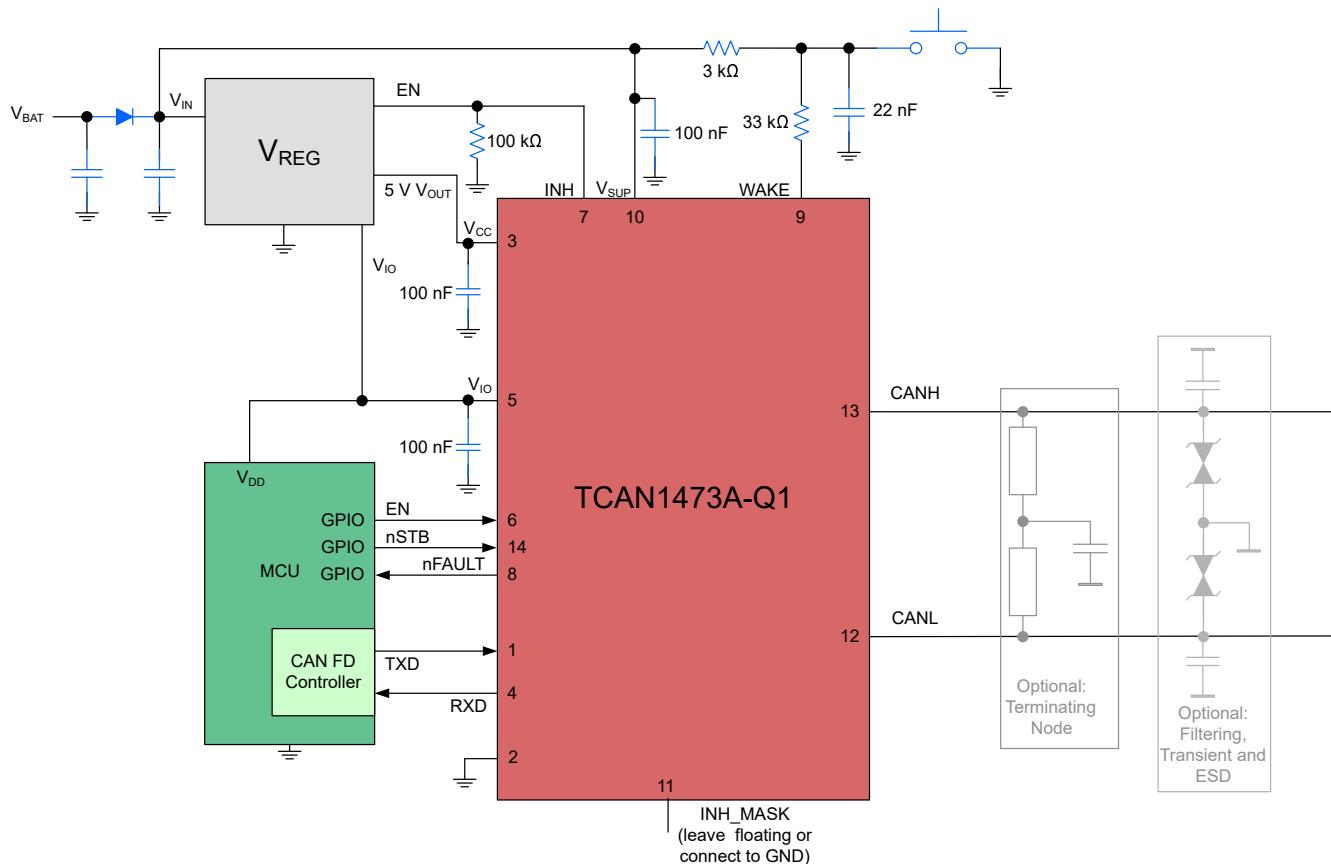

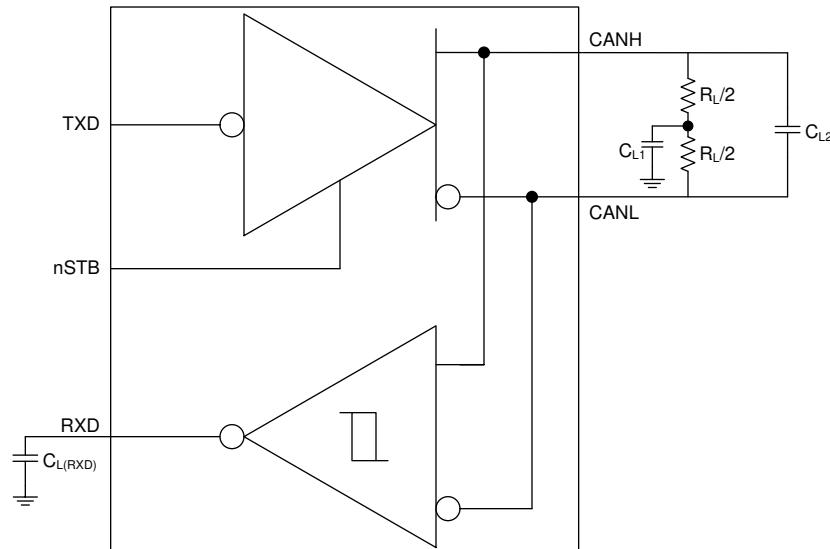

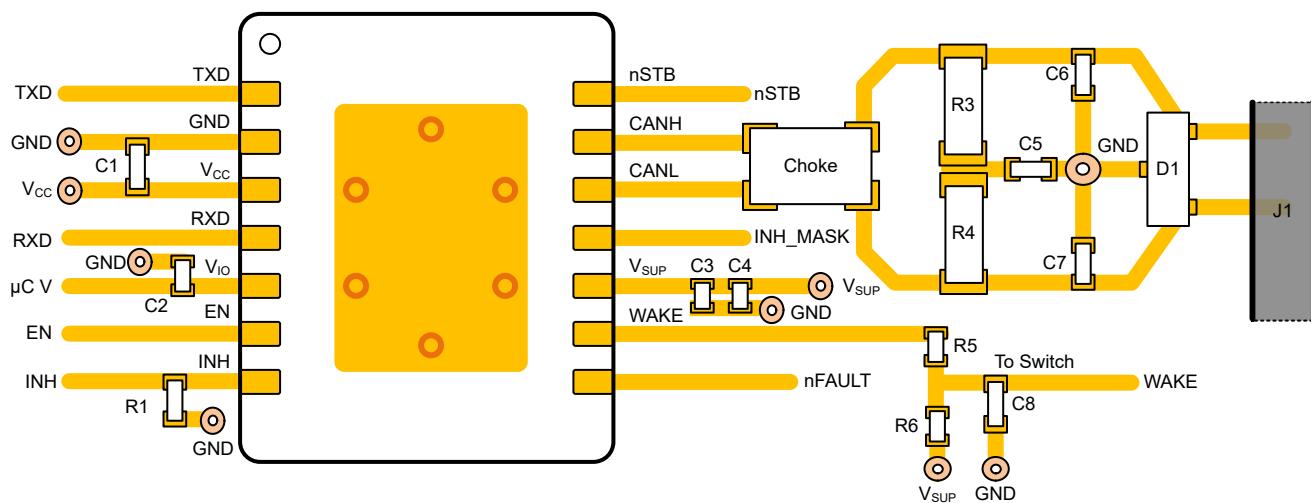

概略回路図

## 目次

|                          |    |                             |    |

|--------------------------|----|-----------------------------|----|

| 1 特長.....                | 1  | 7.1 概要.....                 | 19 |

| 2 アプリケーション.....          | 1  | 7.2 機能ブロック図.....            | 20 |

| 3 説明.....                | 1  | 7.3 機能説明.....               | 21 |

| 4 ピン構成および機能.....         | 4  | 7.4 デバイスの機能モード.....         | 28 |

| 5 仕様.....                | 5  | 8 アプリケーション情報に関する免責事項.....   | 39 |

| 5.1 絶対最大定格.....          | 5  | 8.1 アプリケーション情報.....         | 39 |

| 5.2 ESD 定格.....          | 5  | 8.2 電源に関する推奨事項.....         | 42 |

| 5.3 ESD 定格 - IEC 仕様..... | 5  | 8.3 レイアウト.....              | 42 |

| 5.4 推奨動作条件.....          | 6  | 9 デバイスおよびドキュメントのサポート.....   | 44 |

| 5.5 熱に関する情報.....         | 6  | 9.1 ドキュメントのサポート.....        | 44 |

| 5.6 消費電力定格.....          | 7  | 9.2 ドキュメントの更新通知を受け取る方法..... | 44 |

| 5.7 電源特性.....            | 7  | 9.3 サポート・リソース.....          | 44 |

| 5.8 電気的特性.....           | 8  | 9.4 商標.....                 | 44 |

| 5.9 タイミング要件.....         | 11 | 9.5 静電気放電に関する注意事項.....      | 44 |

| 5.10 スイッチング特性.....       | 11 | 9.6 用語集.....                | 44 |

| 5.11 代表的特性.....          | 13 | 10 改訂履歴.....                | 44 |

| 6 パラメータ測定情報.....         | 14 | 11 メカニカル、パッケージ、および注文情報..... | 44 |

| 7 詳細説明.....              | 19 |                             |    |

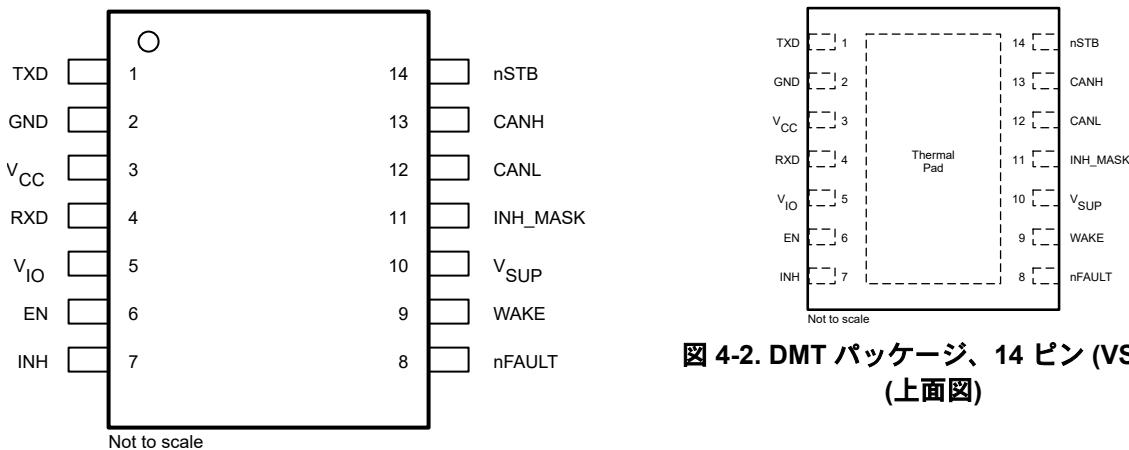

## 4 ピン構成および機能

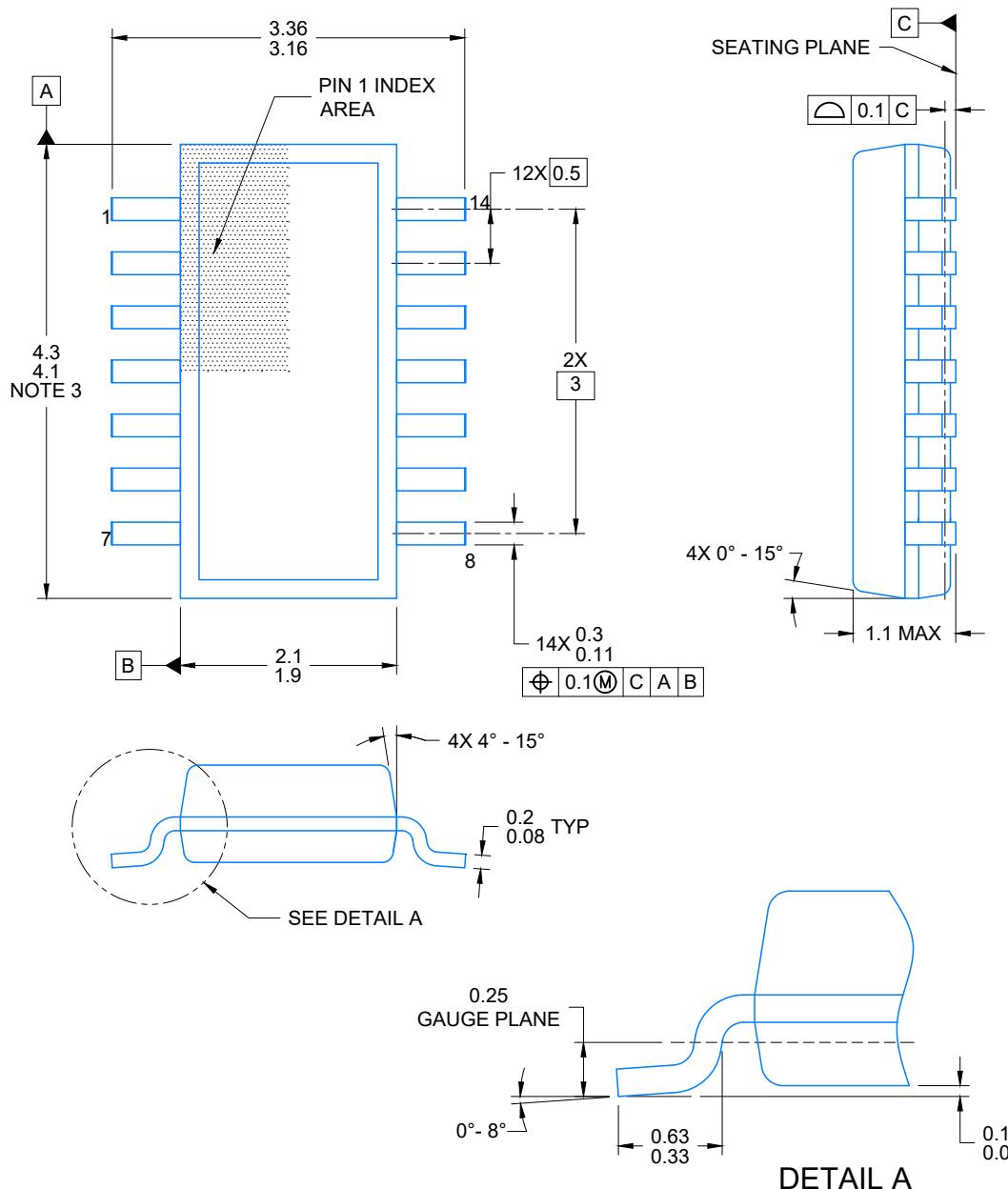

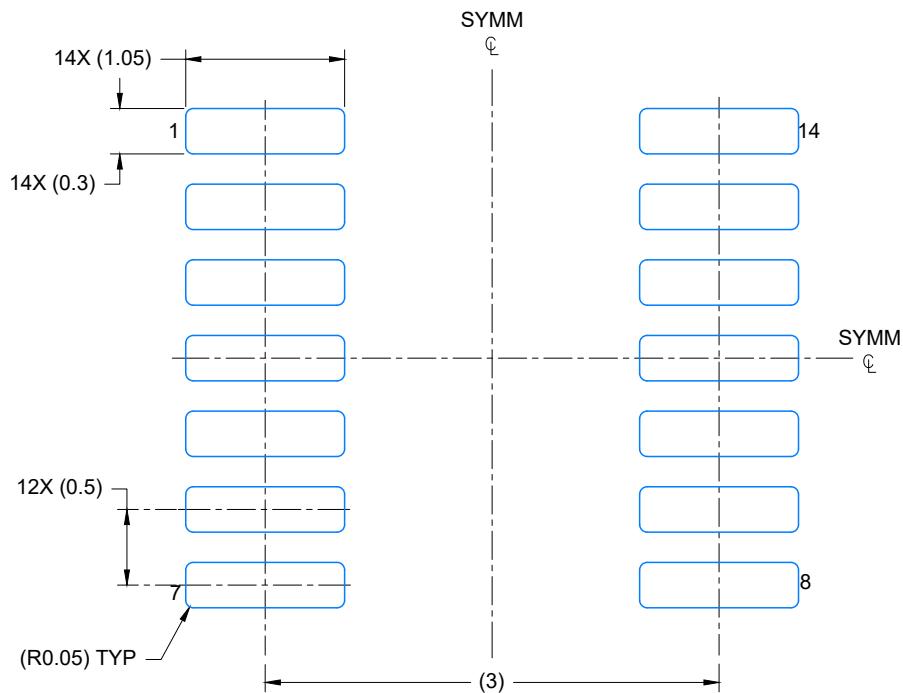

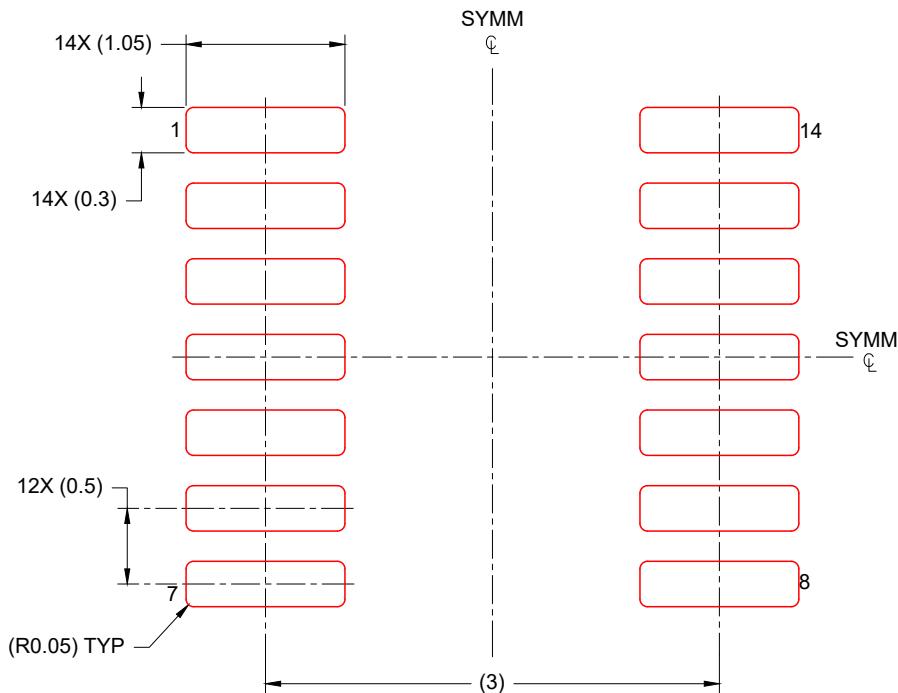

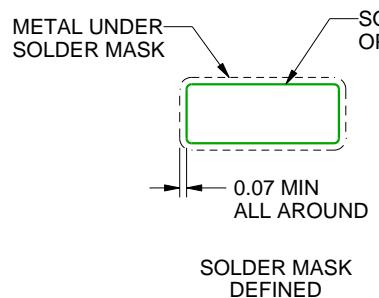

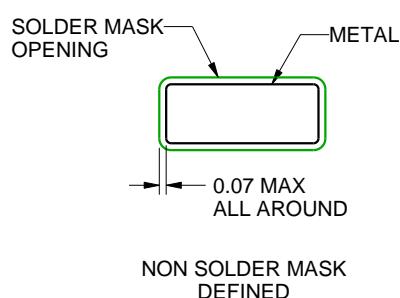

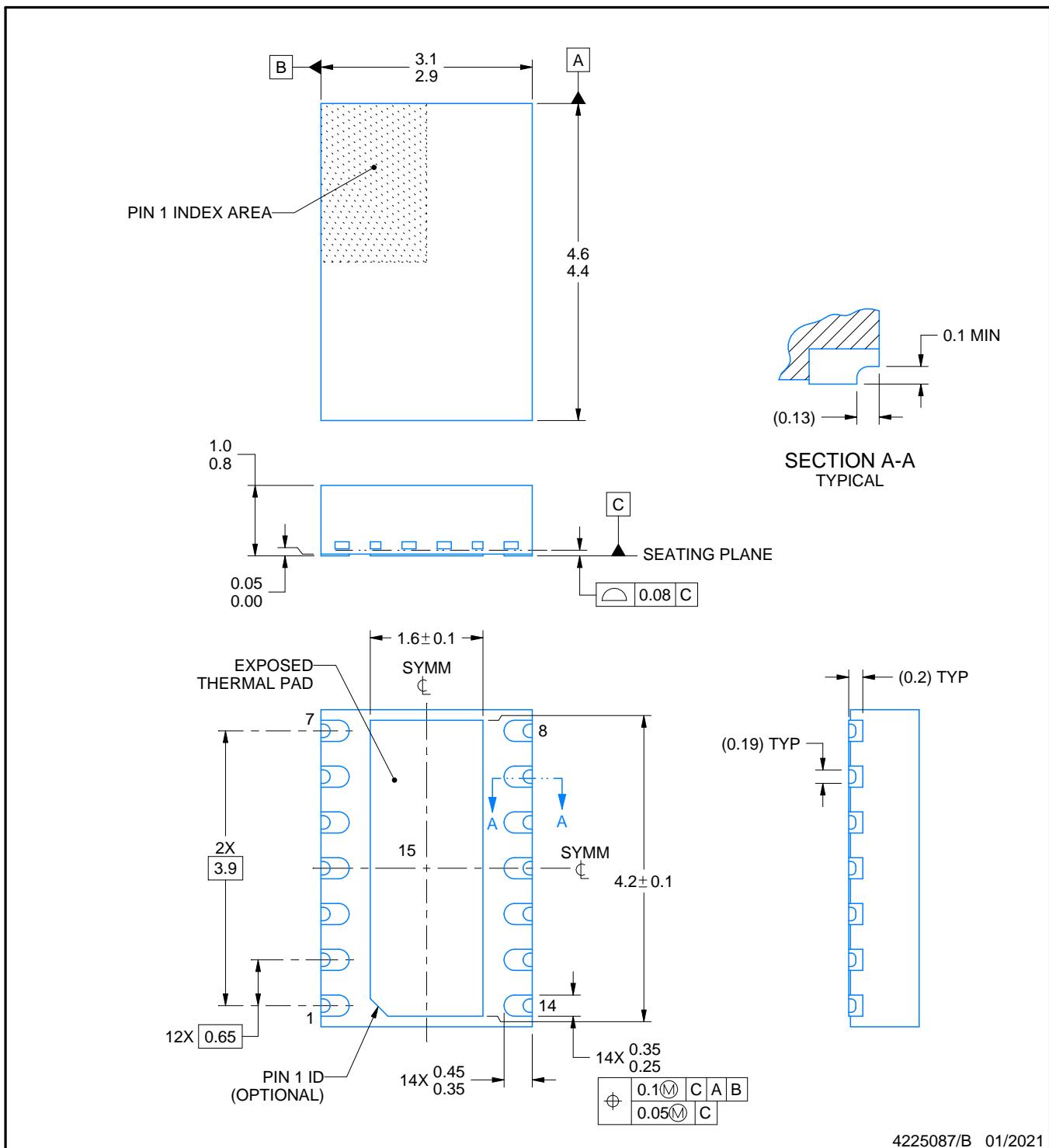

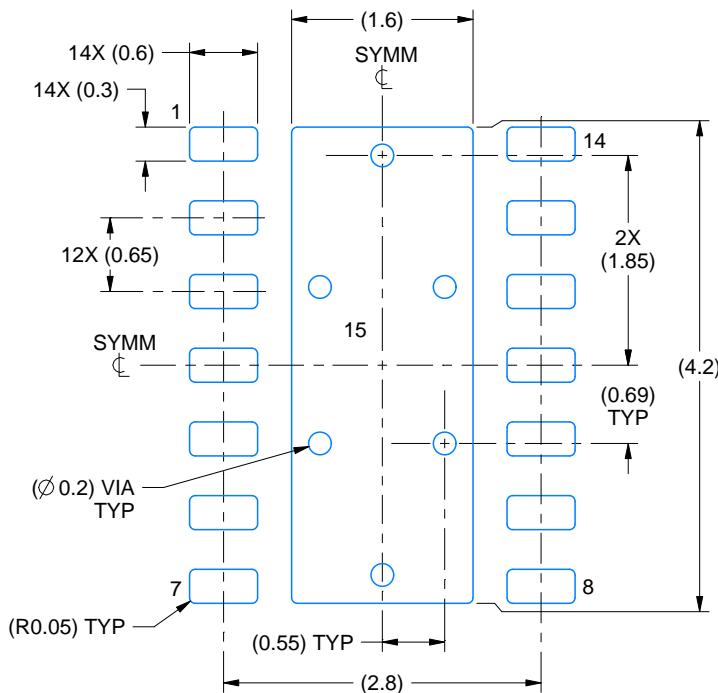

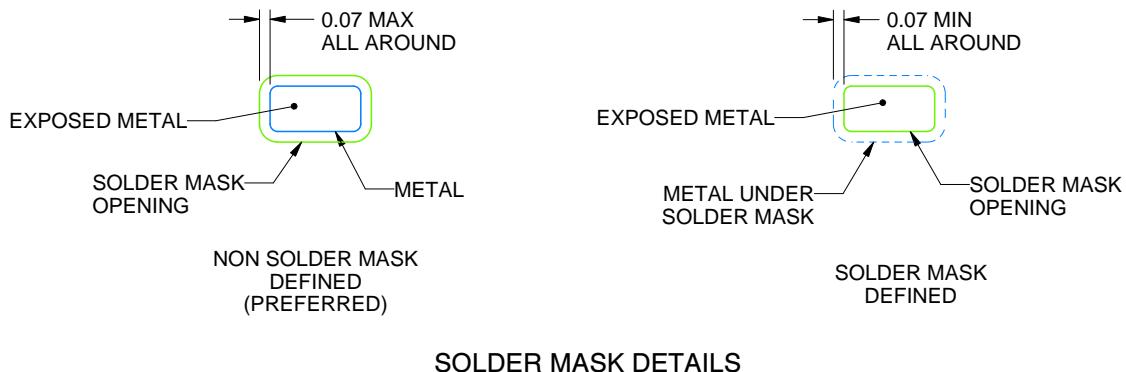

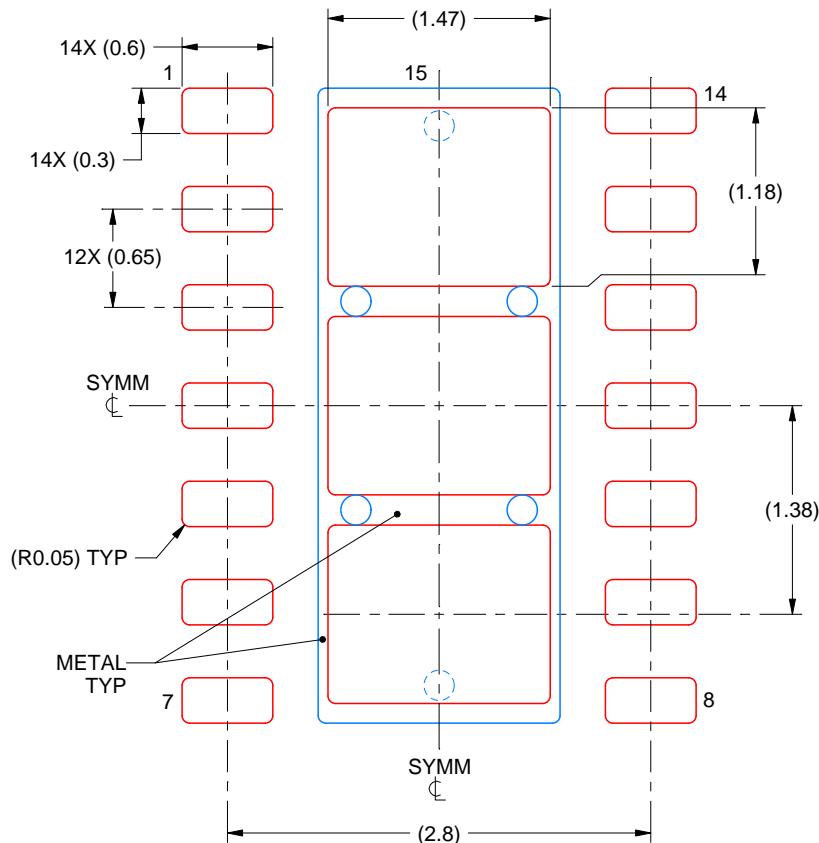

図 4-1. D および DYY パッケージ、14 ピン (SOIC)

および SOT(上面図)

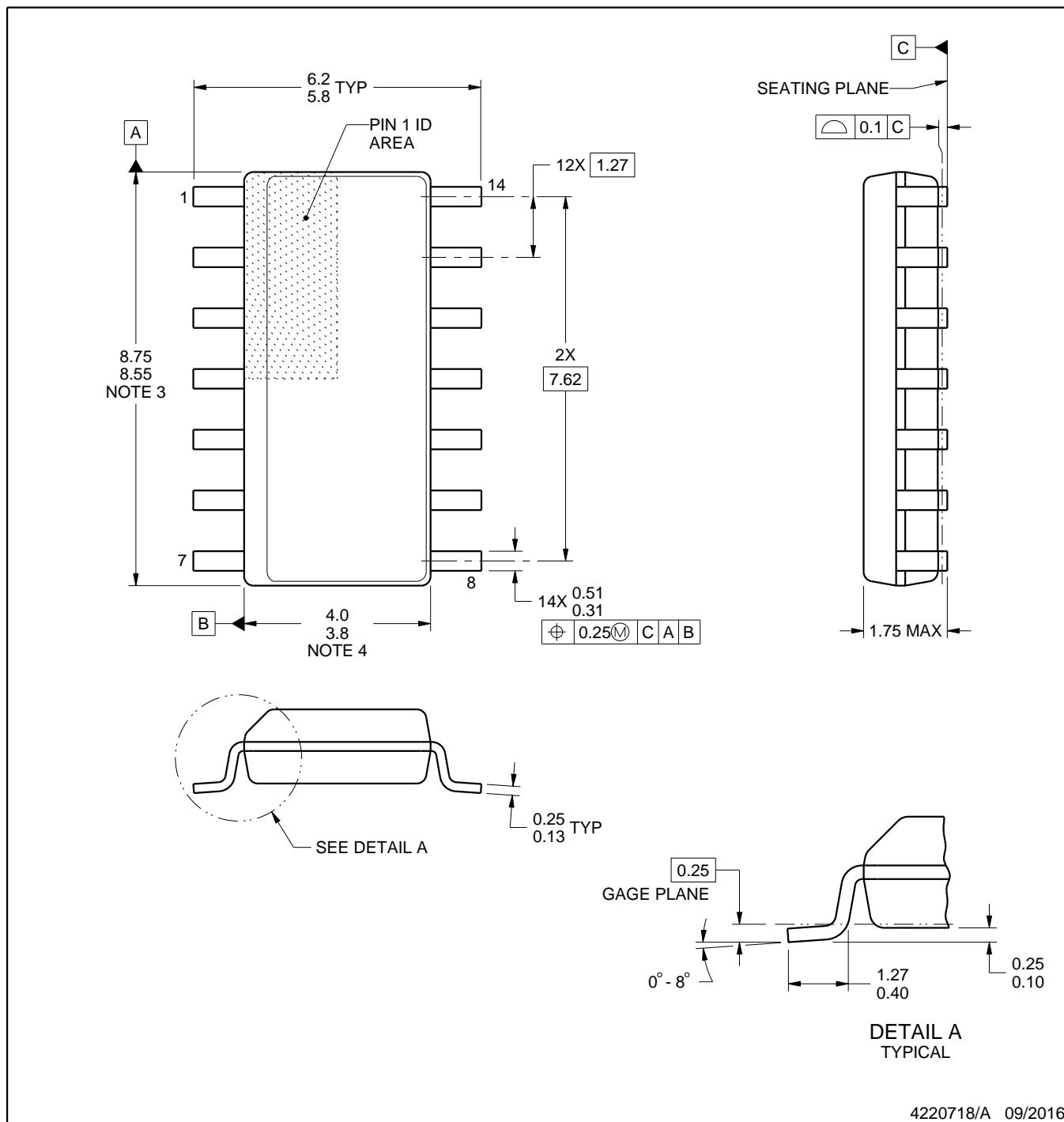

図 4-2. DMT パッケージ、14 ピン (VSON)

(上面図)

表 4-1. ピンの機能

| ピン               |    | タイプ <sup>(1)</sup> | 説明                                                                                                                             |

|------------------|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 名称               | 番号 |                    |                                                                                                                                |

| TXD              | 1  | I                  | CAN 送信データ入力、内蔵プルアップ                                                                                                            |

| GND              | 2  | GND                | グランド接続                                                                                                                         |

| V <sub>CC</sub>  | 3  | P                  | 5V トランシーバ電源                                                                                                                    |

| RXD              | 4  | O                  | CAN 受信データ出力、V <sub>IO</sub> < UV <sub>IO</sub>                                                                                 |

| V <sub>IO</sub>  | 5  | P                  | I/O 電源電圧                                                                                                                       |

| EN               | 6  | I                  | モード制御用のイネーブル入力、内蔵プルダウン                                                                                                         |

| INH              | 7  | O                  | システム電圧レギュレータと電源を制御するための INHIBIT ピン、高電圧                                                                                         |

| nFAULT           | 8  | O                  | フォルト出力、反転ロジック                                                                                                                  |

| WAKE             | 9  | I                  | ローカル WAKE 入力端子、高電圧                                                                                                             |

| V <sub>SUP</sub> | 10 | P                  | バッテリからの高電圧供給                                                                                                                   |

| INH_MASK         | 11 | I                  | INH_MASK ピンは、INH 機能をアクティブ/非アクティブにするために使用されます。GND を接続先とする内部プルダウン。INH_MASK 機能が必要ない場合は、フローティングのままにするか、GND に接続できます。電源には接続しないでください。 |

| CANL             | 12 | I/O                | Low レベル CAN バス入出力ライン                                                                                                           |

| CANH             | 13 | I/O                | High レベル CAN バス入出力ライン                                                                                                          |

| nSTB             | 14 | I                  | サイレントモード制御入力、内蔵プルアップ                                                                                                           |

| サーマル パッド         | —  | —                  | 熱解放のため、サーマルパッドはプリント基板 (PCB) のグランドプレーンに接続します                                                                                    |

(1) I = 入力、O = 出力、P = 電源、GND = グランド

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                       |                                                 | 最小値  | 最大値                             | 単位 |

|-----------------------|-------------------------------------------------|------|---------------------------------|----|

| V <sub>SUP</sub>      | 電源電圧 <sup>(2)</sup>                             | -0.3 | 45                              | V  |

| V <sub>CC</sub>       | 電源電圧                                            | -0.3 | 6                               | V  |

| V <sub>IO</sub>       | 電源電圧 I/O レベル シフタ                                | -0.3 | 6                               | V  |

| V <sub>BUS</sub>      | CAN バス I/O 電圧 (CANH、CANL)                       | -58  | 58                              | V  |

| V <sub>DIFF</sub>     | CAN バス差動電圧 ( $V_{DIFF} = V_{CANH} - V_{CANL}$ ) | -58  | 58                              | V  |

| V <sub>WAKE</sub>     | WAKE 入力電圧                                       | -45  | 45 および $V_I \leq V_{SUP} + 0.3$ | V  |

| V <sub>INH</sub>      | INH ピン電圧                                        | -0.3 | 45 および $V_O \leq V_{SUP} + 0.3$ | V  |

| V <sub>LOGIC</sub>    | ロジック ピン電圧                                       | -0.3 | 6                               | V  |

| I <sub>O(LOGIC)</sub> | ロジック ピン出力電流                                     |      | 8                               | mA |

| I <sub>O(INH)</sub>   | 禁止ピン出力電流                                        |      | 6                               | mA |

| I <sub>O(WAKE)</sub>  | WAKE ピン出力電流                                     |      | 3                               | mA |

| T <sub>J</sub>        | 接合部温度                                           | -40  | 165                             | °C |

| T <sub>STG</sub>      | 保存温度                                            | -65  | 150                             | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。推奨動作条件の範囲外ではあるが、絶対最大定格の範囲内で短時間動作している場合、デバイスは損傷を受けない可能性がありますが、完全には機能しない可能性があります。この方法でデバイスを動作させると、デバイスの信頼性、機能性、性能に影響を及ぼし、デバイスの寿命を短縮する可能性があります。

- (2) 300ms 間最大 45V のロード ダンプに耐えることが可能

### 5.2 ESD 定格

|                  |      |                                             | 値                                           | 単位    |   |

|------------------|------|---------------------------------------------|---------------------------------------------|-------|---|

| V <sub>ESD</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 に準拠 <sup>(1)</sup> | V <sub>SUP</sub> 、CANH、CANL、グランドを基準とした WAKE | ±8000 | V |

|                  |      |                                             | V <sub>SUP</sub> 、CANH、CANL、WAKE を除くすべてのピン。 | ±4000 | V |

|                  |      | 荷電デバイス モデル (CDM)、AEC Q100-011 準拠            | すべてのピン                                      | ±750  | V |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 ESD 定格 - IEC 仕様

|                  |      |                                             |                                                   | 値      | 単位 |

|------------------|------|---------------------------------------------|---------------------------------------------------|--------|----|

| V <sub>ESD</sub> | 静電放電 | CANH、CANL、V <sub>SUP</sub> 、WAKE 端子から GND へ | ISO 10605 準拠の電源なし接触放電 <sup>(1)</sup>              | ±8000  | V  |

| V <sub>ESD</sub> | 静電放電 | CANH および CANL 端子から GND へ                    | ISO 10605 電源接触放電に準拠した SAE J2962-2 <sup>(2)</sup>  | ±8000  | V  |

| V <sub>ESD</sub> | 静電放電 | CANH および CANL 端子から GND へ                    | ISO 10605 に準拠した SAE J2962-2 動力空中放電 <sup>(2)</sup> | ±15000 | V  |

## 5.3 ESD 定格 - IEC 仕様 (続き)

|            |                                    |                                 | 値                                              | 単位   |   |

|------------|------------------------------------|---------------------------------|------------------------------------------------|------|---|

| $V_{TRAN}$ | ISO-7637-2 準拠した過渡電圧 <sup>(1)</sup> | CAN、 $V_{SUP}$ 、WAKE 端子から GND へ | パルス 1                                          | -100 | V |

|            |                                    |                                 | パルス 2                                          | 75   | V |

|            |                                    |                                 | パルス 3a                                         | -150 | V |

|            |                                    |                                 | パルス 3b                                         | 100  | V |

|            | ISO-7637-3 準拠の過渡電圧 <sup>(2)</sup>  | CAN 端子から GND へ                  | 100nF のカッピングコンデンサを備えた直接カッピングコンデンサ「低速過渡パルス」- 電源 | ±30  | V |

(1) ここに示す結果は、IEC 62228-3 IC はトランシーバの EMC 評価のパート 3 に固有のものです。CAN トランシーバ。IBEE Zwickau によって実施されたテスト、ご要望に応じて EMC レポートを提供します。

(2) ここに示す結果は、SAE J2962-2 通信トランシーバの認定要件で CAN 固有のものです。OEM 承認の独立系サードパーティが実施したテストで、要求に応じて EMC レポートを入手できます。

## 5.4 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|               |                    | 最小値 | 公称値 | 最大値 | 単位 |

|---------------|--------------------|-----|-----|-----|----|

| $V_{SUP}$     | 電源電圧               | 4.5 | 40  |     | V  |

| $V_{IO}$      | I/O 電源電圧           | 1.7 | 5.5 |     | V  |

| $V_{CC}$      | CAN トランシーバ電源電圧     | 4.5 | 5.5 |     | V  |

| $I_{OH(DO)}$  | デジタル出力 High レベル電流  | -2  |     |     | mA |

| $I_{OL(DO)}$  | デジタル出力 Low レベル電流   |     | 2   |     | mA |

| $I_{O(INH)}$  | 禁止出力電流             |     | 4   |     | mA |

| $T_J$         | 動作時接合部温度           | -40 | 150 |     | °C |

| $T_{SDR}$     | サーマル シャットダウン       | 175 |     |     | °C |

| $T_{SDF}$     | サーマルシャットダウンリリース    | 160 |     |     | °C |

| $T_{SD(HYS)}$ | サーマル シャットダウンヒステリシス | 10  |     |     | °C |

## 5.5 热に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | TCAN1473A-Q1 |            |           | 単位   |

|----------------------|---------------------|--------------|------------|-----------|------|

|                      |                     | D (SOIC)     | DMT (VSON) | DYY (SOT) |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 87.1         | 39.7       | 91.0      | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 41.8         | 41.1       | 41.7      | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 43.7         | 15.9       | 25.6      | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 8.5          | 0.9        | 25.4      | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 43.3         | 15.9       | 1.1       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 該当なし         | 6.6        | 該当なし      | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.6 消費電力定格

| パラメータ |        | テスト条件                                                                                                                                                                                 | 消費電力 | 単位 |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|

| $P_D$ | 平均消費電力 | $V_{SUP} = 14V, V_{CC} = 5V, V_{IO} = 5V, T_J = 27^\circ C, R_L = 60\Omega, nSTB = 5V, EN = 5V, C_{L_RXD} = 15pF$ 。25% の送信 (ドミナント) レートで 500kbps の標準的な CAN 動作条件。                       | 62   | mW |

|       |        | $V_{SUP} = 14V, V_{CC} = 5.5V, V_{IO} = 5.5V, T_J = 150^\circ C, R_L = 50\Omega, nSTB = 5.5V, EN = 5.5V, C_{L_RXD} = 15pF$ 。50% の伝送 (支配的) 速度と負荷のかかったネットワークで 1Mbps での一般的な高負荷 CAN 動作条件。 | 135  | mW |

## 5.7 電源特性

特に記述がない限り、 $T_J = -40^\circ C \sim 150^\circ C$ 、 $V_{CC} = 4.75V \sim 5.25V$  での推奨動作条件です。すべての標準値は、 $25^\circ C, V_{SUP} = 12V, V_{IO} = 3.3V, V_{CC} = 5V, R_L = 60\Omega$  で測定されたものです

| パラメータ              |                                      | テスト条件                                                                                 | 最小値  | 標準値  | 最大値 | 単位      |

|--------------------|--------------------------------------|---------------------------------------------------------------------------------------|------|------|-----|---------|

| <b>電源電圧および電流特性</b> |                                      |                                                                                       |      |      |     |         |

| $I_{SUP\_NORMAL}$  | 電源電流<br>CAN アクティブ                    | 通常モード、サイレント モード、スリープ移行モード                                                             |      | 140  |     | $\mu A$ |

| $I_{SUP\_STBY}$    | 電源電流、スタンバイモード<br>CAN 自律:非アクティブ       | スタンバイ モード <sup>(2)</sup>                                                              |      | 65   |     | $\mu A$ |

| $I_{SUP\_SLEEP}$   | 電源電流<br>CAN 自律:非アクティブ                | スリープ モード                                                                              | 18   | 33   |     | $\mu A$ |

| $I_{SUP\_BIAS}$    | 電源電流<br>CAN 自律アクトティブ時の追加電流           | $5.5V < V_{SUP} \leq 28V^{(1)}$                                                       |      | 50   |     | $\mu A$ |

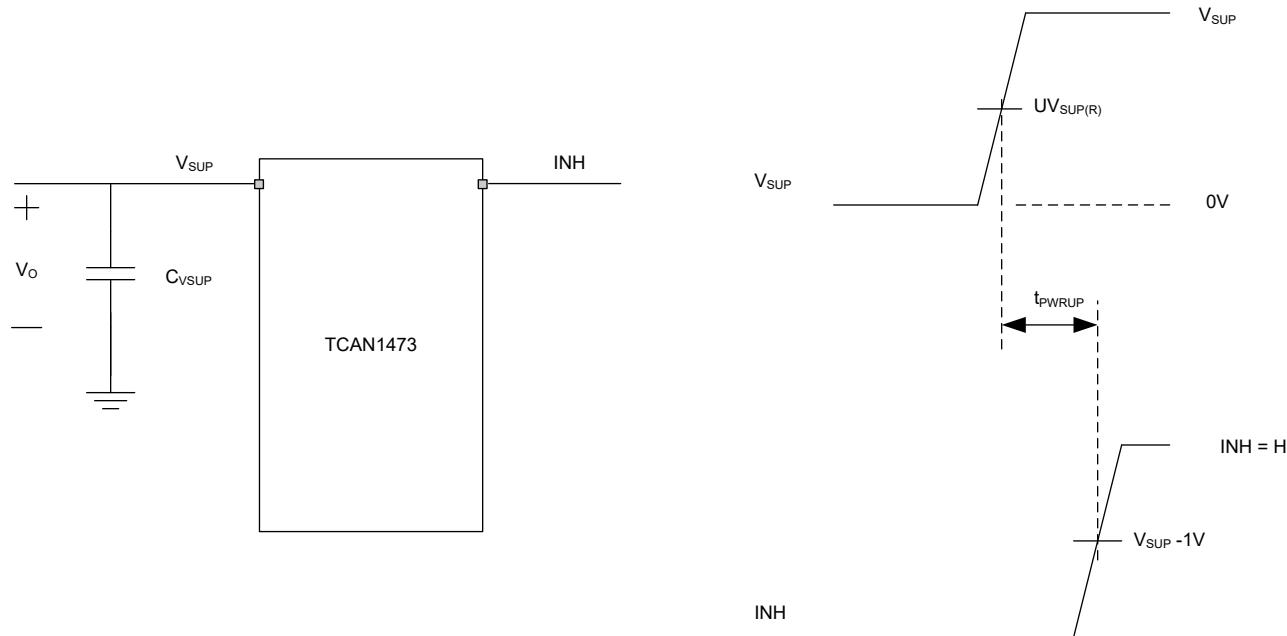

| $UV_{SUP(R)}$      | 低電圧 $V_{SUP}$ スレッショルド立ち上がり           | 増加                                                                                    | 3.85 | 4.4  |     | V       |

| $UV_{SUP(F)}$      | 低電圧 $V_{SUP}$ スレッショルド立ち下がり           | 減少                                                                                    | 3.5  | 4.25 |     | V       |

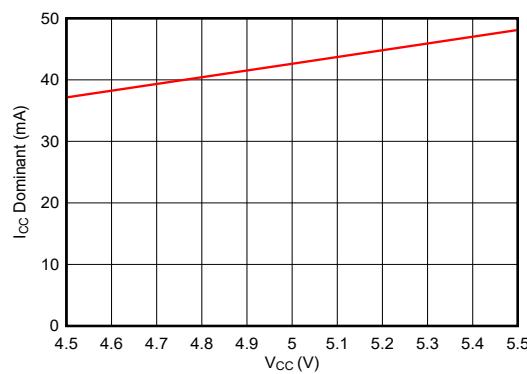

| $I_{CC\_NORMAL}$   | 電源電流<br>CAN アクティブ:ドミナント              | 通常モード<br>$TXD = 0V, R_L = 60\Omega, C_L = \text{オープン}$<br><a href="#">電源テスト回路</a> を参照 |      | 60   |     | $mA$    |

|                    | 電源電流<br>CAN アクティブ:ドミナント              | 通常モード<br>$TXD = 0V, R_L = 50\Omega, C_L = \text{オープン}$                                |      | 70   |     | $mA$    |

|                    | $V_{CC}$ 電源電流通常モード<br>バス フォルト時のドミナント | 通常モード<br>$TXD = 0V, R_L = \text{オープン}, C_L = \text{オープン}, CANH = -25V$                |      | 110  |     | $mA$    |

| $I_{CC\_NORMAL}$   | 電源電流<br>CAN アクティブ:リセシティブ             | 通常モード<br>$TXD = V_{IO}, R_L = 50\Omega, C_L = \text{オープン}$                            |      | 5    |     | $mA$    |

| $I_{CC\_STBY}$     | 電源電流<br>CAN 自律:非アクティブ                | スタンバイ モード、 $T_J = -40^\circ C \sim 85^\circ C$<br>$EN = nSTB = 0V$                    |      | 2    |     | $\mu A$ |

| $I_{CC\_STBY}$     | 電源電流<br>CAN 自律:非アクティブ                | スタンバイ モード<br>$EN = nSTB = 0V$                                                         |      | 5    |     | $\mu A$ |

| $I_{CC\_SILENT}$   | 電源電流                                 | サイレントおよびスリープ移行モード<br>$TXD = nSTB = V_{IO}, R_L = 50\Omega, C_L = \text{オープン}$         |      | 3    |     | $mA$    |

| $I_{CC\_SLEEP}$    | 電源電流<br>CAN 自律:非アクティブ                | スリープ モード、 $T_J = -40^\circ C \sim 85^\circ C$<br>$EN = 0V$ または $V_{IO}, nSTB = 0V$    |      | 2    |     | $\mu A$ |

|                    | 電源電流<br>CAN 自律:非アクティブ                | スリープ モード<br>$EN = 0V$ または $V_{IO}, nSTB = 0V$                                         |      | 5    |     | $\mu A$ |

| $UV_{CC(R)}$       | 低電圧 $V_{CC}$ スレッショルド立ち上がり            | 増加                                                                                    | 4.1  | 4.4  |     | V       |

| $UV_{CC(F)}$       | 低電圧 $V_{CC}$ スレッショルド立ち下がり            | 減少                                                                                    | 3.5  | 3.9  |     | V       |

| $V_{HYS(UVCC)}$    | $UV_{CC}$ のヒステリシス電圧                  |                                                                                       | 50   | 250  | 320 | $mV$    |

| $I_{IO\_NORMAL}$   | I/O 電源電流                             | 通常モード<br>$RXD$ フロー ティング、 $TXD = 0V$                                                   |      | 350  |     | $\mu A$ |

|                    | I/O 電源電流                             | 通常モード、スタンバイ モード、またはスリープ<br>移行モード<br>$RXD$ フロー ティング、 $TXD = V_{IO}$                    |      | 5    |     | $\mu A$ |

## 5.7 電源特性 (続き)

特に記述がない限り、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{CC} = 4.75\text{V} \sim 5.25\text{V}$  での推奨動作条件です。すべての標準値は、 $25^\circ\text{C}$ 、 $V_{SUP} = 12\text{V}$ 、 $V_{IO} = 3.3\text{V}$ 、 $V_{CC} = 5\text{V}$ 、 $R_L = 60\Omega$  で測定されたものです

| パラメータ           |                           | テスト条件                                                                           | 最小値 | 標準値           | 最大値  | 単位            |

|-----------------|---------------------------|---------------------------------------------------------------------------------|-----|---------------|------|---------------|

| $I_{IO\_SLEEP}$ | I/O 電源電流                  | スリープ モード、 $T_J = -40^\circ\text{C} \sim 85^\circ\text{C}$<br>$nSTB = 0\text{V}$ | 2.5 | $\mu\text{A}$ | 5    | $\mu\text{A}$ |

|                 | I/O 電源電流                  | スリープ モード<br>$nSTB = 0\text{V}$                                                  |     |               |      |               |

| $UV_{IO(R)}$    | $V_{IO}$ 低電圧スレッショルド立ち上がり  |                                                                                 | 増加  | 1.4           | 1.65 | V             |

| $UV_{IO(F)}$    | $V_{IO}$ 低電圧スレッショルドの立ち下がり |                                                                                 | 減少  | 1             | 1.25 | V             |

| $V_{HYS(UVIO)}$ | $UV_{IO}$ のヒステリシス電圧       |                                                                                 | 30  | 60            | 160  | mV            |

- (1)  $I_{SUP(BIAS)}$  は、CAN 自律アクティブ モードの総電源電流から、CAN 自律非アクティブ モードの電源電流を減算することで計算されます

- (2) 有効なウェークアップ後、CAN トランシーバは CAN 自律アクティブ モードに切り替わり、CAN 自律非アクティブ モードでは、指定された  $I_{SUP}$  電流に  $I_{SUP(BIAS)}$  電流を追加する必要があります。

## 5.8 電気的特性

特に記述がない限り、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{CC} = 4.75\text{V} \sim 5.25\text{V}$  での推奨動作条件です。すべての標準値は、 $25^\circ\text{C}$ 、 $V_{SUP} = 12\text{V}$ 、 $V_{IO} = 3.3\text{V}$ 、 $V_{CC} = 5\text{V}$ 、 $R_L = 60\Omega$  で測定されたものです

| パラメータ                          |                                                                                                                 | テスト条件                                                                                                                                                                                                                       | 最小値                                                                                                                                                          | 標準値   | 最大値   | 単位  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----|

| <b>CAN ドライバの特性</b>             |                                                                                                                 |                                                                                                                                                                                                                             |                                                                                                                                                              |       |       |     |

| $V_{CANH(D)}$                  | バス出力電圧 (ドミナント) CANH                                                                                             | $TXD = 0\text{V}, 45 \leq R_L \leq 65\Omega, C_L = \text{オープン}, R_{CM} = \text{オープン}$<br><a href="#">図 6-4</a> および <a href="#">図 6-1</a> を参照                                                                                | 3                                                                                                                                                            | 4.26  | 4.26  | V   |

| $V_{CANL(D)}$                  | バス出力電圧 (ドミナント) CANL                                                                                             | <a href="#">図 6-1</a> および <a href="#">図 6-4</a> を参照                                                                                                                                                                         | 0.75                                                                                                                                                         | 2.01  | 2.01  | V   |

| $V_{CANH(R)}$<br>$V_{CANL(R)}$ | リセッショル出力電圧<br>バスバイアスがアクティブ                                                                                      | $TXD = V_{IO}, R_L = \text{オープン}$ (無負荷)、 $R_{CM} = \text{オープン}$<br><a href="#">図 6-1</a> および <a href="#">図 6-4</a> を参照                                                                                                      | 2                                                                                                                                                            | 3     | 3     | V   |

| $V_{CANH(R)}$<br>$V_{CANL(R)}$ | リセッショル出力電圧<br>バスバイアスがアクティブ                                                                                      | $TXD = V_{IO}, 45 \leq R_L \leq 65\Omega, C_L = \text{オープン}, C_{SPLIT} = 4.7\text{nF}$<br><a href="#">図 6-1</a> および <a href="#">図 6-4</a> を参照                                                                               | 2.256                                                                                                                                                        | 2.756 | 2.756 | V   |

| $V_{SYM}$                      | ドライバ対称性<br>バスバイアスアクティブ<br>$(V_{O(CANH)} + V_{O(CANL)}) / V_{REC}$<br>ここで、 $V_{REC} = V_{CANH(R)} + V_{CANL(R)}$ | $nSTB = V_{IO}, R_L = 45 \leq R_L \leq 65\Omega, C_{SPLIT} = 4.7\text{nF}, C_L = \text{オープン}, R_{CM} = \text{オープン}, TXD = 250\text{kHz}, 1\text{MHz}, 2.5\text{MHz}$<br><a href="#">図 6-1</a> および <a href="#">図 6-4</a> を参照 | 0.95                                                                                                                                                         | 1.05  | 1.05  | V/V |

| $V_{SYM\_DC}$                  | DC ドライバ対称性<br>バスバイアスアクティブ<br>$V_{CC} - V_{O(CANH)} - V_{O(CANL)}$                                               | $nSTB = V_{IO}, R_L = 45 \leq R_L \leq 65\Omega, C_L = \text{オープン}$<br><a href="#">図 6-1</a> および <a href="#">図 6-4</a> を参照                                                                                                  | -300                                                                                                                                                         | 300   | 300   | mV  |

| $V_{DIFF(D)}$                  | 差動出力電圧<br>バスバイアスアクティブ<br>ドミナント                                                                                  | CANH - CANL                                                                                                                                                                                                                 | $nSTB = V_{IO}, TXD = 0\text{V}, 45 \leq R_L \leq 65\Omega, C_L = \text{オープン}$<br><a href="#">図 6-1</a> および <a href="#">図 6-4</a> を参照                        | 1.5   | 3     | V   |

|                                |                                                                                                                 | CANH - CANL                                                                                                                                                                                                                 | $nSTB = V_{IO}, TXD = 0\text{V}, 45\Omega \leq R_L \leq 70\Omega, CL = \text{オープン}$<br><a href="#">図 6-4</a> および <a href="#">図 6-1</a> を参照                   | 1.5   | 3.3   | V   |

|                                |                                                                                                                 | CANH - CANL                                                                                                                                                                                                                 | $nSTB = V_{IO}, TXD = 0\text{V}, R_L = 2240\Omega, C_L = \text{オープン}$<br><a href="#">図 6-4</a> および <a href="#">図 6-1</a> を参照                                 | 1.5   | 5     | V   |

| $V_{DIFF(R)}$                  | 差動出力電圧<br>バスバイアスアクティブ<br>リセッショル                                                                                 | CANH - CANL                                                                                                                                                                                                                 | $nSTB = V_{IO}, TXD = V_{IO}, 45 \leq R_L \leq 65\Omega, C_L = \text{オープン}, C_{SPLIT} = 4.7\text{nF}$<br><a href="#">図 6-1</a> および <a href="#">図 6-4</a> を参照 | -50   | 50    | mV  |

| $V_{DIFF(R)}$                  | 差動出力電圧<br>バスバイアスアクティブ<br>リセッショル                                                                                 | CANH - CANL                                                                                                                                                                                                                 | $nSTB = V_{IO}, TXD = V_{IO}, R_L = \text{オープン}\Omega, C_L = \text{オープン}$<br><a href="#">図 6-4</a> および <a href="#">図 6-1</a> を参照                             | -50   | 50    | mV  |

| $V_{CANH(INACT)}$              | バスバイアスが非アクティブの場合の CANH のバス出力電圧                                                                                  |                                                                                                                                                                                                                             | $nSTB = 0\text{V}, TXD = V_{IO}, R_L = \text{オープン}$ (無負荷)、 $C_L = \text{オープン}$<br><a href="#">図 6-1</a> および <a href="#">図 6-4</a> を参照                        | -0.1  | 0.1   | V   |

## 5.8 電気的特性 (続き)

特に記述がない限り、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{CC} = 4.75\text{V} \sim 5.25\text{V}$  での推奨動作条件です。すべての標準値は、 $25^\circ\text{C}$ 、 $V_{SUP} = 12\text{V}$ 、 $V_{IO} = 3.3\text{V}$ 、 $V_{CC} = 5\text{V}$ 、 $R_L = 60\Omega$  で測定されたものです

| パラメータ             | テスト条件                                                                                                                                       | 最小値                                                                                                                                             | 標準値  | 最大値  | 単位       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|

| $V_{CANL(INACT)}$ | $nSTB = 0\text{V}$ 、 $TXD = V_{IO}$ 、 $R_L = \text{オープン}$ (無負荷)、 $C_L = \text{オープン}$<br><a href="#">図 6-4</a> および <a href="#">図 6-1</a> を参照 | -0.1                                                                                                                                            | 0.1  | 0.1  | V        |

| $V_{DIFF(INACT)}$ | $nSTB = 0\text{V}$ 、 $TXD = V_{IO}$ 、 $R_L = \text{オープン}$ (無負荷)、 $C_L = \text{オープン}$<br><a href="#">図 6-4</a> および <a href="#">図 6-1</a> を参照 | -0.2                                                                                                                                            | 0.2  | 0.2  | V        |

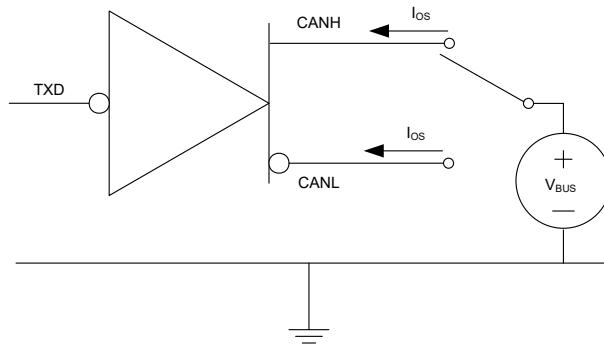

| $I_{CANH(OS)}$    | 短絡時の定常状態出力電流、ドミナント、CANH                                                                                                                     | $nSTB = V_{IO}$ 、 $TXD = 0\text{V}$<br>$\sim 15\text{V} \leq V_{(CANH)} \leq 40\text{V}$<br><a href="#">図 6-1</a> および <a href="#">図 6-8</a> を参照 | -100 |      | mA       |

| $I_{CANL(OS)}$    | 短絡時の定常状態出力電流、ドミナント、CANL                                                                                                                     | $nSTB = V_{IO}$ 、 $TXD = 0\text{V}$<br>$\sim 15\text{V} \leq V_{(CANL)} \leq 40\text{V}$<br><a href="#">図 6-1</a> および <a href="#">図 6-8</a> を参照 |      | 100  | mA       |

| $I_{OS(REC)}$     | 短絡時の定常状態出力電流<br>バスバイアス アクティブ<br>リセッショブ                                                                                                      | $nSTB = V_{IO}$ 、 $V_{BUS} = CANH = CANL$<br>$-27\text{V} \leq V_{BUS} \leq 42\text{V}$<br><a href="#">図 6-8</a> および <a href="#">図 6-1</a> を参照  | -3   | 3    | mA       |

| $R_{SE_ACT_REC}$  | アクティブ リセッショブ駆動位相時のシングル エン<br>ド SIC インピーダンス (CANH から同相バイアス、<br>CANL から同相バイアス)                                                                | $2\text{V} \leq V_{CANH,CANL} \leq VCC - 2\text{V}$<br>( $-12\text{V} \leq V_{O(D)} \leq 12\text{V}$ の場合)<br>( <a href="#">図 6-13</a> を参照)      | 37.5 | 66.5 | $\Omega$ |

| $R_{DIFF_ACT_RC}$ | アクティブ リセッショブ駆動位相の差動入力抵抗<br>(CANH から CANL)                                                                                                   | $2\text{V} \leq V_{CANH,CANL} \leq VCC - 2\text{V}$<br>( <a href="#">図 6-13</a> を参照)                                                            | 75   | 133  | $\Omega$ |

### CAN レシーバの特性

|                   |                                                                |                                                                                                                    |       |     |               |

|-------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------|-----|---------------|

| $V_{IT(DOM)}$     | レシーバがドミナント状態の入力電圧範囲<br>バスバイアス アクティブ                            | $nSTB = V_{IO}, -12\text{V} \leq V_{CM} \leq 12\text{V}$<br><a href="#">図 6-5</a> および <a href="#">表 7-6</a> を参照    | 0.9   | 8   | V             |

| $V_{IT(REC)}$     | レシーバリセッショブ状態の差動入力電圧範囲<br>バスバイアスが非アクティブ                         |                                                                                                                    | -3    | 0.5 | V             |

| $V_{HYS}$         | 入力スレッショルド ヒステリシス電圧<br>バスバイアス アクティブ                             | $nSTB = V_{IO}$<br><a href="#">図 6-5</a> および <a href="#">表 7-6</a> を参照                                             |       | 135 | mV            |

| $V_{DIFF(DOM)}$   | レシーバリセッショブ状態の差動入力電圧範囲<br>バスバイアスが非アクティブ                         | $nSTB = 0\text{V}, -12\text{V} \leq V_{CM} \leq 12\text{V}$<br><a href="#">図 6-5</a> および <a href="#">表 7-6</a> を参照 | 1.150 | 8   | V             |

| $V_{DIFF(REC)}$   | レシーバリセッショブ状態の差動入力電圧範囲<br>バスバイアスが非アクティブ                         |                                                                                                                    | -3    | 0.4 | V             |

| $V_{CM}$          | 同相範囲                                                           | $nSTB = V_{IO}$<br><a href="#">図 6-5</a> および <a href="#">表 7-6</a> を参照                                             | -12   | 12  | V             |

| $I_{OFF(LKG)}$    | パワーオフ (電源オフ) バス入力リーク電流                                         | $V_{SUP} = 0\text{V}$ 、 $CANH = CANL = 5\text{V}$                                                                  |       | 4.5 | $\mu\text{A}$ |

| $C_I$             | グランドに対する入力容量 (CANH または CANL)<br><sup>(1)</sup>                 | $TXD = V_{CC} = V_{IO}$                                                                                            |       | 40  | pF            |

| $C_{ID}$          | 差動入力容量 <sup>(1)</sup>                                          | $TXD = V_{CC} = V_{IO}$                                                                                            |       | 20  | pF            |

| $R_{DIFF_PAS_RC}$ | パッシブ リセッショブ<br>位相の差動入力抵抗                                       | $TXD = V_{CC} = V_{IO} = 5\text{V}$ , $nSTB = 5\text{V}$<br>$-12\text{V} \leq V_{CM} \leq 12\text{V}$              | 30    | 100 | k $\Omega$    |

| $R_{SE_PAS_REC}$  | パッシブ リセッショブ位相でのシングル エンド入力<br>抵抗 (CANH/CANL)                    |                                                                                                                    | 15    | 50  | k $\Omega$    |

| $R_{IN(M)}$       | 入力抵抗マッチング:<br>$[1 - R_{IN(CANH)} / R_{IN(CANL)}] \times 100\%$ | $V_{(CANH)} = V_{(CANL)} = 5\text{V}$                                                                              | -3    | 3   | %             |

| $R_{CBF}$         | バス フォルト回路の有効な差動負荷インピーダンス範囲                                     | $R_{CM} = R_L, C_L = \text{オープン}$                                                                                  | 45    | 70  | $\Omega$      |

### TXD の特性

|                |                    |                                                   |      |                    |

|----------------|--------------------|---------------------------------------------------|------|--------------------|

| $V_{IH}$       | High レベル入力電圧       |                                                   | 0.7  | $V_{IO}$           |

| $V_{IL}$       | Low レベル入力電圧        |                                                   |      | 0.3 $V_{IO}$       |

| $I_{IH}$       | High レベル入力リーク電流    | $TXD = V_{IO} = 5.5\text{V}$                      | -2.5 | 1 $\mu\text{A}$    |

| $I_{IL}$       | Low レベル入力リーク電流     | $TXD = 0\text{V}, V_{IO} = 5.5\text{V}$           | -137 | -2.5 $\mu\text{A}$ |

| $I_{LKG(OFF)}$ | 電源がない場合のリーク電流です    | $TXD = 5.5\text{V}, V_{SUP} = V_{IO} = 0\text{V}$ | -1   | 1 $\mu\text{A}$    |

| $R_{PU}$       | $V_{IO}$ へのプルアップ抵抗 |                                                   | 40   | 60 80 k $\Omega$   |

## 5.8 電気的特性 (続き)

特に記述がない限り、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{CC} = 4.75\text{V} \sim 5.25\text{V}$  での推奨動作条件です。すべての標準値は、 $25^\circ\text{C}$ 、 $V_{SUP} = 12\text{V}$ 、 $V_{IO} = 3.3\text{V}$ 、 $V_{CC} = 5\text{V}$ 、 $R_L = 60\Omega$  で測定されたものです

| パラメータ                 |                                                          | テスト条件                                                                                | 最小値  | 標準値             | 最大値               | 単位  |  |  |

|-----------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|------|-----------------|-------------------|-----|--|--|

| C <sub>I</sub>        | 入力容量                                                     | $V_{IN} = 0.4 \times \sin(2 \times \pi \times 2 \times 10^6 \times t) + 2.5\text{V}$ | 5    |                 | pF                |     |  |  |

| <b>RXD の特性</b>        |                                                          |                                                                                      |      |                 |                   |     |  |  |

| V <sub>OH</sub>       | High レベル出力電圧                                             | $I_O = -1.5\text{mA}$ 、 $V_{IO} = 1.7\text{V}$                                       | 0.8  |                 | $V_{IO}$          |     |  |  |

| V <sub>OH</sub>       | High レベル出力電圧                                             | $I_O = -2\text{mA}$ 、 $V_{IO} \geq 2.5\text{V}$                                      | 0.8  |                 | $V_{IO}$          |     |  |  |

| V <sub>OL</sub>       | Low レベル出力電圧                                              | $I_O = 2\text{mA}$                                                                   | 0.2  |                 | $V_{IO}$          |     |  |  |

| I <sub>LKG(OFF)</sub> | 電源がない場合のリーコンデンサー電流です                                     | RXD = 5.5V、 $V_{SUP} = V_{IO} = 0\text{V}$                                           | -1   |                 | 1 $\mu\text{A}$   |     |  |  |

| <b>nSTB の特性</b>       |                                                          |                                                                                      |      |                 |                   |     |  |  |

| V <sub>IH</sub>       | High レベル入力電圧                                             |                                                                                      |      |                 | 0.7               |     |  |  |

| V <sub>IL</sub>       | Low レベル入力電圧                                              |                                                                                      |      |                 | 0.3               |     |  |  |

| I <sub>IH</sub>       | High レベル入力リーコンデンサー電流                                     | nSTB = $V_{IO} = 5.5\text{V}$                                                        | 0.5  |                 | 137 $\mu\text{A}$ |     |  |  |

| I <sub>IL</sub>       | Low レベル入力リーコンデンサー電流                                      | nSTB = 0V、 $V_{IO} = 5.5\text{V}$                                                    | -1   |                 | 1 $\mu\text{A}$   |     |  |  |

| I <sub>LKG(OFF)</sub> | 電源がない場合のリーコンデンサー電流です                                     | nSTB = 5.5V、 $V_{IO} = 0\text{V}$                                                    | -1   |                 | 1 $\mu\text{A}$   |     |  |  |

| R <sub>PD</sub>       | プルダウン抵抗から GND                                            |                                                                                      |      |                 | 40                | 60  |  |  |

| <b>nFAULT の特性</b>     |                                                          |                                                                                      |      |                 |                   |     |  |  |

| V <sub>OH</sub>       | High レベル出力電圧                                             | $I_O = -2\text{mA}$                                                                  | 0.8  |                 | $V_{IO}$          |     |  |  |

| V <sub>OL</sub>       | Low レベル出力電圧                                              | $I_O = 2\text{mA}$                                                                   | 0.2  |                 | $V_{IO}$          |     |  |  |

| I <sub>LKG(OFF)</sub> | 電源がない場合のリーコンデンサー電流です                                     | nFAULT = 5.5V、 $V_{IO} = 0\text{V}$                                                  | -1   |                 | 1 $\mu\text{A}$   |     |  |  |

| <b>INH_MASK の特性</b>   |                                                          |                                                                                      |      |                 |                   |     |  |  |

| V <sub>IH</sub>       | High レベル入力電圧                                             |                                                                                      |      |                 | 0.7               |     |  |  |

| V <sub>IL</sub>       | Low レベル入力電圧                                              |                                                                                      |      |                 | 0.3               |     |  |  |

| I <sub>IH</sub>       | High レベル入力リーコンデンサー電流                                     | INH_MASK = $V_{CC} = V_{IO} = 5.5\text{V}$                                           | 0.5  |                 | 137 $\mu\text{A}$ |     |  |  |

| I <sub>IL</sub>       | Low レベル入力リーコンデンサー電流                                      | INH_MASK = 0V、 $V_{CC} = V_{IO} = 5.5\text{V}$                                       | -1   |                 | 1 $\mu\text{A}$   |     |  |  |

| I <sub>LKG(OFF)</sub> | 電源がない場合のリーコンデンサー電流です                                     | INH_MASK = 5.5V、 $V_{CC} = V_{IO} = 0\text{V}$                                       | -1   |                 | 1 $\mu\text{A}$   |     |  |  |

| R <sub>PD</sub>       | プルダウン抵抗から GND <sup>(1)</sup>                             |                                                                                      |      |                 | 40                | 60  |  |  |

| <b>EN の特性</b>         |                                                          |                                                                                      |      |                 |                   |     |  |  |

| V <sub>IH</sub>       | High レベル入力電圧                                             |                                                                                      |      |                 | 0.7               |     |  |  |

| V <sub>IL</sub>       | Low レベル入力電圧                                              |                                                                                      |      |                 | 0.3               |     |  |  |

| I <sub>IH</sub>       | High レベル入力リーコンデンサー電流                                     | EN = $V_{CC} = V_{IO} = 5.5\text{V}$                                                 | 0.5  |                 | 137 $\mu\text{A}$ |     |  |  |

| I <sub>IL</sub>       | Low レベル入力リーコンデンサー電流                                      | EN = 0V、 $V_{CC} = V_{IO} = 5.5\text{V}$                                             | -1   |                 | 1 $\mu\text{A}$   |     |  |  |

| I <sub>LKG(OFF)</sub> | 電源がない場合のリーコンデンサー電流です                                     | EN = 5.5V、 $V_{CC} = V_{IO} = 0\text{V}$                                             | -1   |                 | 1 $\mu\text{A}$   |     |  |  |

| R <sub>PD</sub>       | プルダウン抵抗から GND                                            |                                                                                      |      |                 | 40                | 60  |  |  |

| <b>WAKE の特性</b>       |                                                          |                                                                                      |      |                 |                   |     |  |  |

| V <sub>IH</sub>       | High レベル入力電圧                                             | スリープ モード                                                                             |      | $V_{SUP} - 2$   |                   | $V$ |  |  |

| V <sub>IL</sub>       | Low レベル入力電圧                                              |                                                                                      |      | $V_{SUP} - 3.5$ |                   | $V$ |  |  |

| I <sub>IH</sub>       | High レベル入力リーコンデンサー電流                                     | WAKE = $V_{SUP} - 1\text{V}$                                                         | -3   |                 | $\mu\text{A}$     |     |  |  |

| I <sub>IL</sub>       | Low レベル入力リーコンデンサー電流                                      | WAKE = 1V                                                                            | 3    |                 | $\mu\text{A}$     |     |  |  |

| <b>INH の特性</b>        |                                                          |                                                                                      |      |                 |                   |     |  |  |

| $\Delta V_H$          | $V_{SUP}$ から INH への High レベル電圧降下 ( $V_{SUP} - V_{INH}$ ) | $I_{INH} = -6\text{mA}$                                                              | 0.5  |                 | 1                 |     |  |  |

| I <sub>LKG(INH)</sub> | スリープ モードリーコンデンサー電流                                       | INH = 0V                                                                             | -0.5 |                 | 0.5 $\mu\text{A}$ |     |  |  |

| R <sub>PD</sub>       | プルダウン抵抗                                                  | スリープ モード                                                                             | 2.5  |                 | 4                 |     |  |  |

(1) 設計により規定され、ベンチ特性評価により検証されている

## 5.9 タイミング要件

特に記述がない限り、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{CC} = 4.75\text{V} \sim 5.25\text{V}$  での推奨動作条件です。すべての標準値は、 $25^\circ\text{C}$ 、 $V_{SUP} = 12\text{V}$ 、 $V_{IO} = 3.3\text{V}$ 、 $V_{CC} = 5\text{V}$ 、 $R_L = 60\Omega$  で測定されたものです

| パラメータ                | テスト条件                                                                       | 最小値                                                                                               | 標準値 | 最大値  | 単位            |

|----------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|------|---------------|

| <b>電源の特性</b>         |                                                                             |                                                                                                   |     |      |               |

| $t_{PWRUP}$          | $V_{SUP} \geq UV_{SUP(R)}$ 後、INH がアクティブになるために必要な時間                          |                                                                                                   | 500 |      | $\mu\text{s}$ |

| $t_{UV}$             | 低電圧フィルタ時間 $V_{CC}$ および $V_{IO}$ <sup>(1)</sup>                              | $V_{CC} \leq UV_{CC}$ または $V_{IO} \leq UV_{IO}$                                                   | 100 | 350  | ms            |

| $t_{UV(REF-ENABLE)}$ | 低電圧イベント後の再有効化時間 <sup>(1)</sup>                                              | $UV_{CC}$ または $UV_{IO}$ 低電圧イベントからデバイスが通常動作に戻るまでの時間                                                |     | 200  | $\mu\text{s}$ |

| <b>デバイス特性</b>        |                                                                             |                                                                                                   |     |      |               |

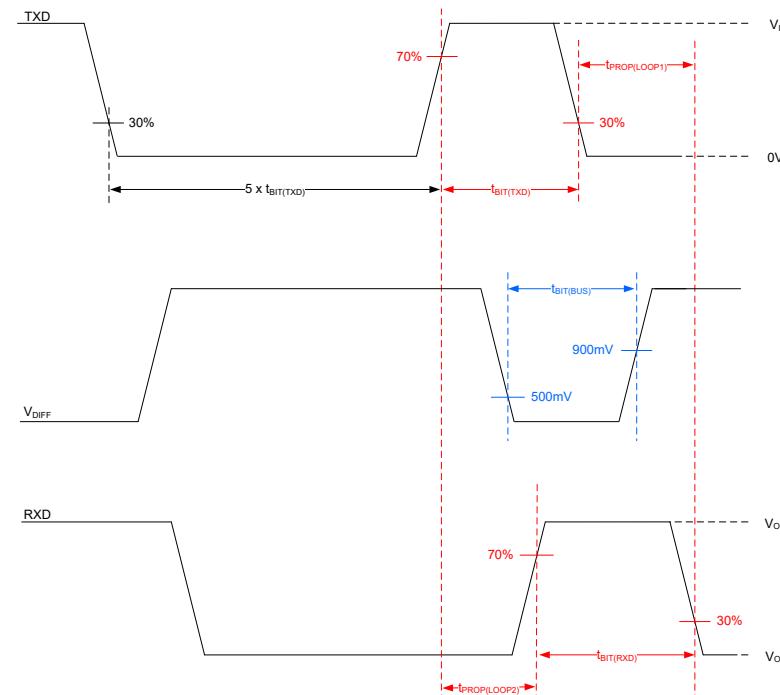

| $t_{PROP(LOOP1)}$    | 合計ループ遅延、ドライバ入力 (TXD) からレシーバ出力 (RXD) までリセッショナルドミナントまで                        | $R_L = 60\Omega$ 、 $C_L = 100\text{pF}$ 、 $C_{L(RXD)} = 15\text{pF}$<br><a href="#">図 6-6 を参照</a> | 100 | 190  | ns            |

| $t_{PROP(LOOP2)}$    | 合計ループ遅延、ドライバ入力 (TXD) からレシーバ出力 (RXD) までドミナントからリセッショナルドミナントまで                 | $R_L = 60\Omega$ 、 $C_L = 100\text{pF}$ 、 $C_{L(RXD)} = 15\text{pF}$<br><a href="#">図 6-6 を参照</a> | 110 | 190  | ns            |

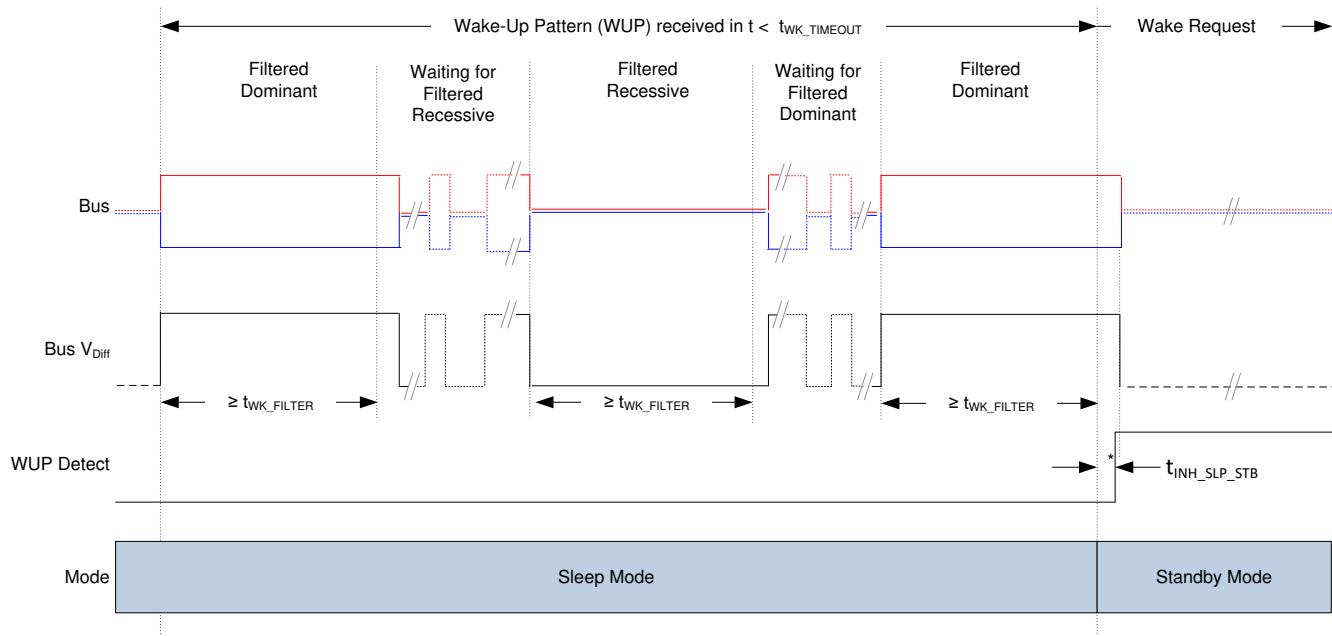

| $t_{WK(TIMEOUT)}$    | バス ウエーカーアップ タイムアウト値 <sup>(1)</sup>                                          |                                                                                                   | 0.8 | 2    | ms            |

| $t_{WK(FILTER)}$     | ウェーカーアップ リクエストのフィルタ処理されたバス要件を満たすバス時間 <sup>(1)</sup>                         |                                                                                                   | 0.5 | 0.95 | $\mu\text{s}$ |

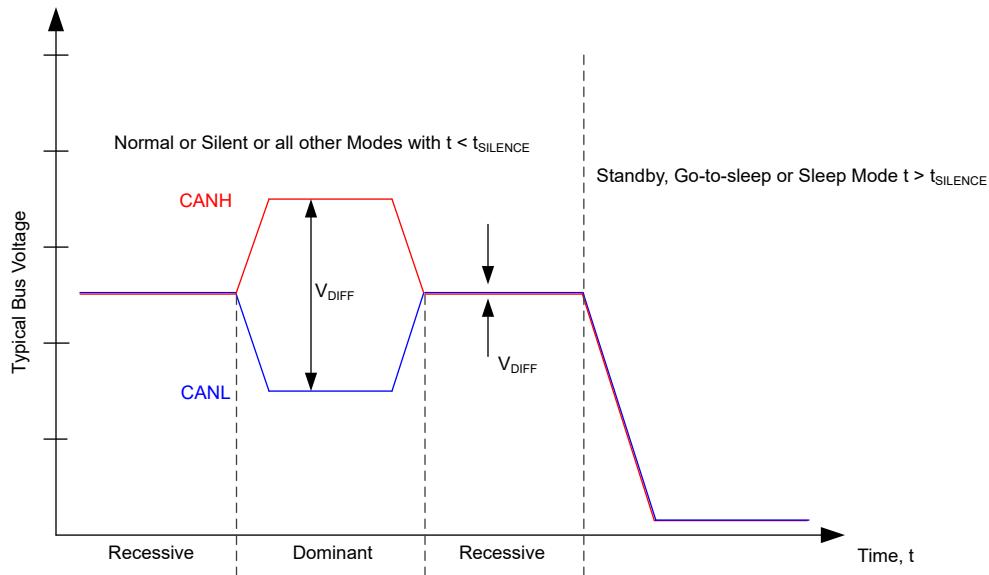

| $t_{SILENCE}$        | バス非アクティブのタイムアウト <sup>(1)</sup>                                              | バスがドミナントからリセッショナルドミナントに、またはリセッショナルドミナントに変化すると、タイマがリセットされ、再起動されます                                  | 0.6 | 1.2  | s             |

| $t_{INACTIVE}$       | 電源投入時の非アクティブ状態に対する、スタンバイモードのハードウェア タイマ                                      |                                                                                                   | 3   | 4    | 5             |

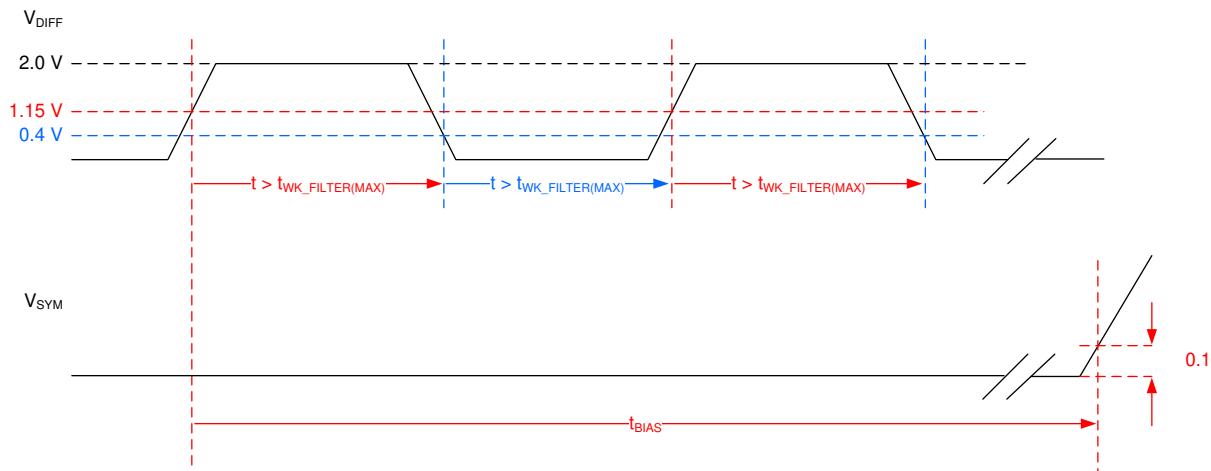

| $t_{BIAS}$           | バス バイアス応答時間 <sup>(1)</sup>                                                  | $nSTB = EN = 0V$ 、 $R_L = 60\Omega$ 、 $C_{SPLIT} = 4.7nF$<br><a href="#">図 6-9 および図 8-3 を参照</a>   |     | 200  | $\mu\text{s}$ |

| $t_{CBF}$            | バス故障検出時間                                                                    | $45 \leq R_{CM} \leq 70\Omega$<br>$C_L = \text{オープン}$                                             | 2.5 |      | $\mu\text{s}$ |

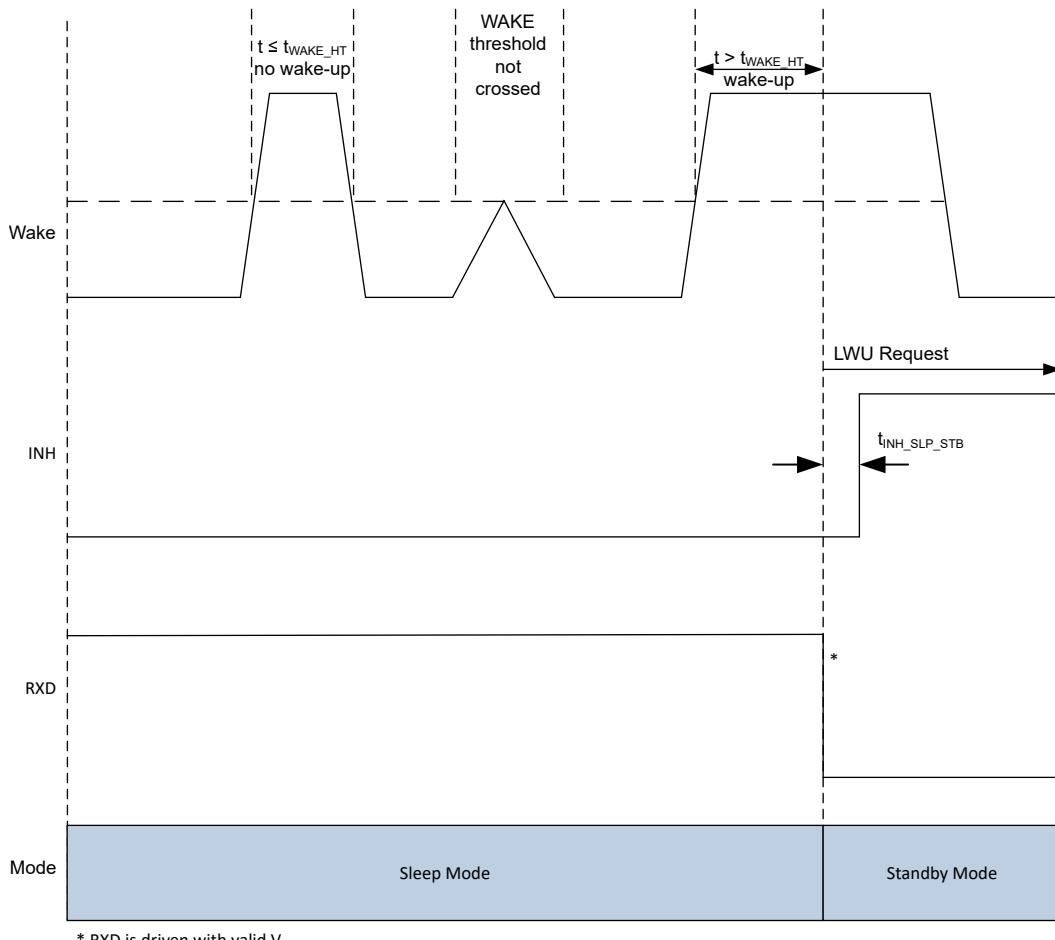

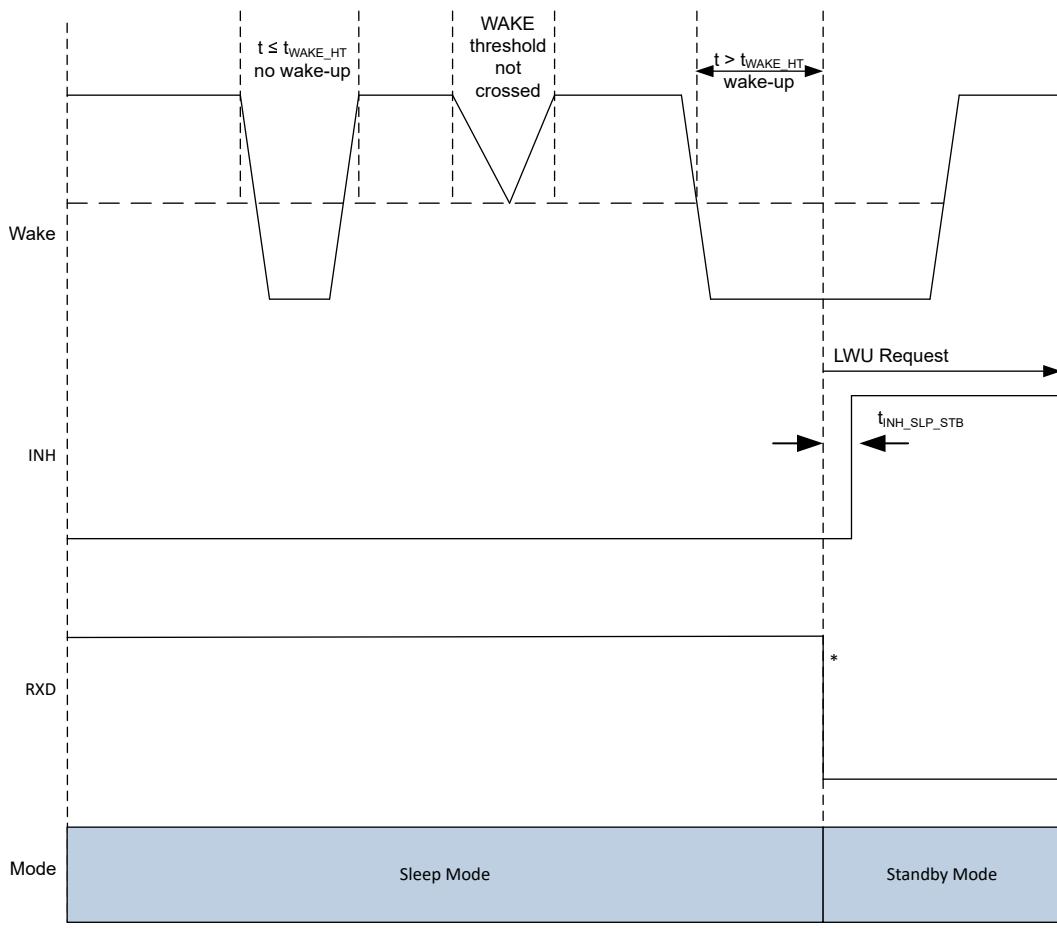

| $t_{WAKE\_HT}$       | LWU を認識するために、WAKE ピンの立ち上がりエッジまたは立ち下がりエッジの後に WAKE ピンの電圧が通常安定になるホールド時間        |                                                                                                   | 5   | 50   | $\mu\text{s}$ |

| <b>モード変更特性</b>       |                                                                             |                                                                                                   |     |      |               |

| $t_{INH\_SLP\_STB}$  | WUP または LWU イベント後に INH がアサートされるまでの時間 <sup>(1)</sup>                         |                                                                                                   | 100 |      | $\mu\text{s}$ |

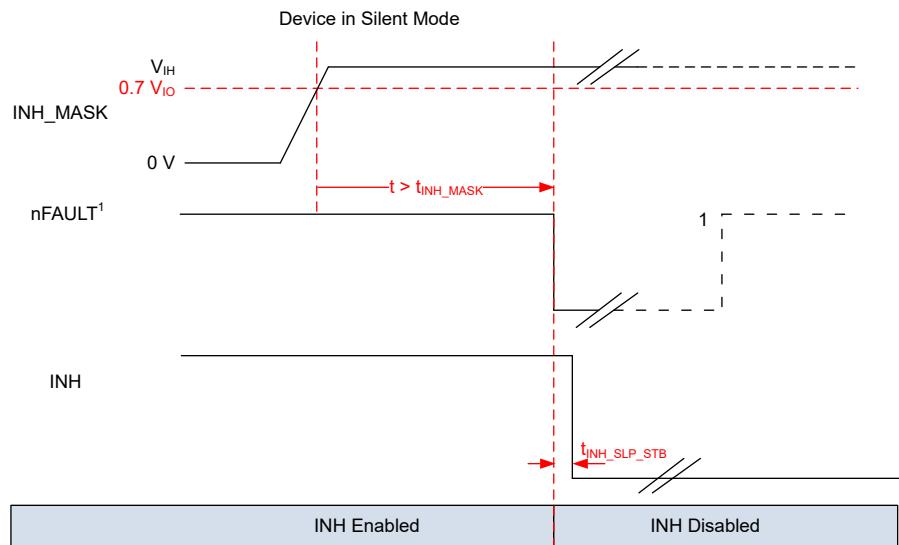

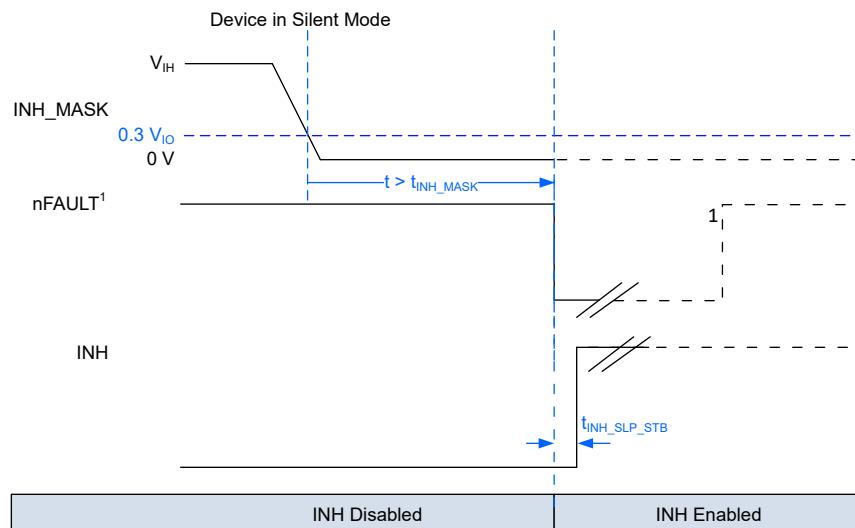

| $t_{INH\_MASK}$      | INH_MASK 機能を有効化 / 無効化するため、立ち上がりエッジまたは立ち下がりエッジ後に INH_MASK が安定している必要のあるホールド時間 | <a href="#">図 6-10 および 図 6-11 を参照してください</a>                                                       | 50  |      | $\mu\text{s}$ |

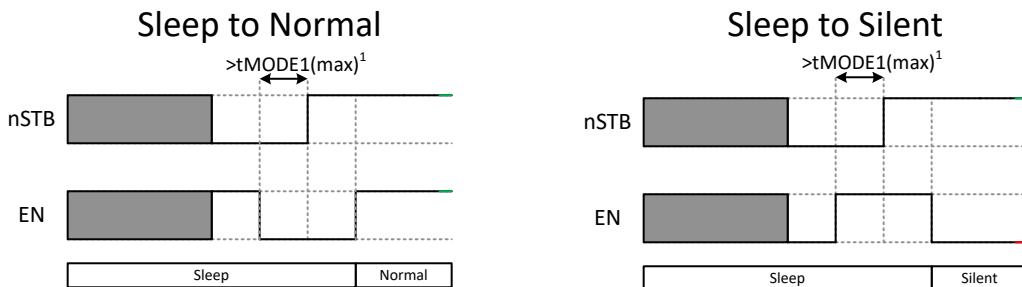

| $t_{MODE1}$          | スリープ モードから通常またはサイレント モードに移行するまでのモード変更時間 <sup>(1)</sup>                      | VCC および VIO が UV スレッショルドを超えてから通常またはサイレント モードに移行するまでの時間を測定。                                        |     | 20   | $\mu\text{s}$ |

| $t_{MODE2}$          | 通常モード、サイレント モード、スタンバイ モードとスリープ モードからスタンバイ モードへのモード変更時間 <sup>(1)</sup>       | 通常モード、サイレント モード、スタンバイ モードとスリープ モードからスタンバイ モードへのモード変更時間                                            |     | 10   | $\mu\text{s}$ |

| $t_{GOTOSLEEP}$      | スリープ モードへの遷移の最小ホールド時間 <sup>(1)</sup>                                        | $EN = H$ および $nSTB = L$                                                                           | 20  | 50   | $\mu\text{s}$ |

(1) 設計により規定され、ベンチ特性評価により検証されている

## 5.10 スイッチング特性

特に記述がない限り、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{CC} = 4.75\text{V} \sim 5.25\text{V}$  での推奨動作条件です。すべての標準値は、 $25^\circ\text{C}$ 、 $V_{SUP} = 12\text{V}$ 、 $V_{IO} = 3.3\text{V}$ 、 $V_{CC} = 5\text{V}$ 、 $R_L = 60\Omega$  で測定されたものです

| パラメータ                  | テスト条件                                                      | 最小値                                                                                           | 標準値 | 最大値 | 単位 |

|------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----|-----|----|

| <b>ドライバ特性</b>          |                                                            |                                                                                               |     |     |    |

| $t_{prop(TxD-busdom)}$ | 伝搬遅延時間、High から Low TXD エッジからバスドミナントまで (リセッショナルドミナントまで)     | $R_L = 60\Omega$ 、 $C_L = 100\text{pF}$ 、 $R_{CM} = \text{オープン}$<br><a href="#">図 6-4 を参照</a> | 80  |     | ns |

| $t_{prop(TxD-busrec)}$ | 伝搬遅延時間、Low から High TXD エッジからバスリセッショナルドミナントからリセッショナルドミナントまで |                                                                                               | 80  |     | ns |

## 5.10 スイッチング特性 (続き)

特に記述がない限り、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{CC} = 4.75\text{V} \sim 5.25\text{V}$  での推奨動作条件です。すべての標準値は、 $25^\circ\text{C}$ 、 $V_{SUP} = 12\text{V}$ 、 $V_{IO} = 3.3\text{V}$ 、 $V_{CC} = 5\text{V}$ 、 $R_L = 60\Omega$  で測定されたものです

| パラメータ                  |                                                                            | テスト条件                                                                                                                                                                                                                                                                                            | 最小値 | 標準値 | 最大値 | 単位 |

|------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| $t_{sk(p)}$            | パルス スキュー ( $ t_{prop(TxD\text{-busdom})} - t_{prop(TxD\text{-busrec})} $ ) | $R_L = 60\Omega$ 、 $C_L = 100\text{pF}$ 、 $R_{CM} = \text{オープン}$<br>$t_R$ 差動出力信号の立ち上がり時間<br>$t_F$ 差動出力信号の立ち下がり時間<br>(図 6-4 を参照)                                                                                                                                                                  | 3   |     | ns  |    |

| $t_R$                  | 差動出力信号の立ち上がり時間                                                             |                                                                                                                                                                                                                                                                                                  | 25  |     | ns  |    |

| $t_F$                  | 差動出力信号の立ち下がり時間                                                             |                                                                                                                                                                                                                                                                                                  | 25  |     | ns  |    |

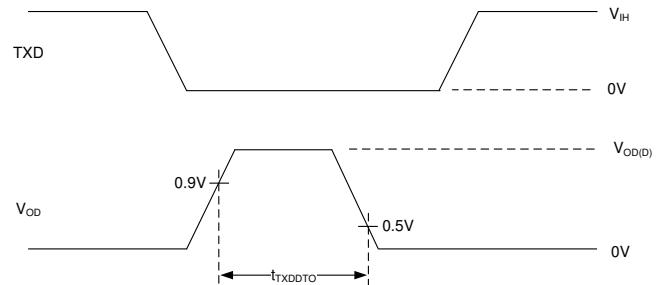

| $t_{TXDDTO}$           | ドミナント タイムアウト                                                               | $TxD = 0\text{V}$ 、 $R_L = 60\Omega$ 、 $C_L = \text{オープン}$<br>図 6-7 を参照                                                                                                                                                                                                                          | 1.2 |     | 3.8 | ms |

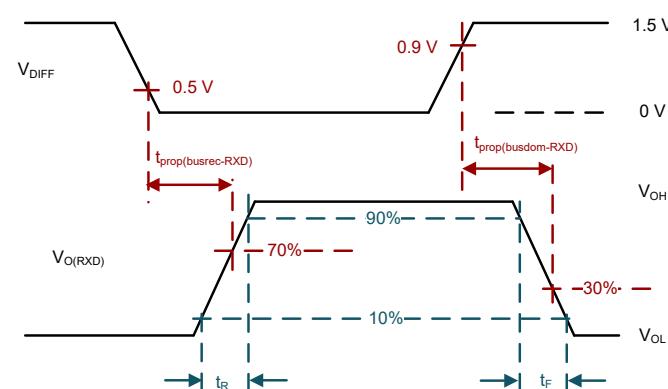

| レシーバの特性                |                                                                            |                                                                                                                                                                                                                                                                                                  |     |     |     |    |

| $t_{prop(busdom-RxD)}$ | 伝搬遅延時間、バス ドミナント入力から RxD Low 出力まで                                           | $C_{L(RxD)} = 15\text{pF}$<br>(図 6-5 を参照)                                                                                                                                                                                                                                                        |     | 110 |     | ns |

| $t_{prop(busrec-RxD)}$ | 伝搬遅延時間、バス からリセッショップ入力、リセッショップ入力から RxD High 出力まで                            |                                                                                                                                                                                                                                                                                                  |     | 110 |     | ns |

| $t_R$                  | 出力信号の立ち上がり時間 (RxD)                                                         | 図 6-5 を参照                                                                                                                                                                                                                                                                                        | 3   |     | ns  |    |

| $t_F$                  | 出力信号の立ち下がり時間 (RxD)                                                         |                                                                                                                                                                                                                                                                                                  | 3   |     | ns  |    |

| $t_{BUSDOM}$           | ドミナント タイムアウト                                                               | $R_L = 60\Omega$ 、 $C_L = \text{オープン}$<br>図 6-7 を参照                                                                                                                                                                                                                                              | 1.4 |     | 3.8 | ms |

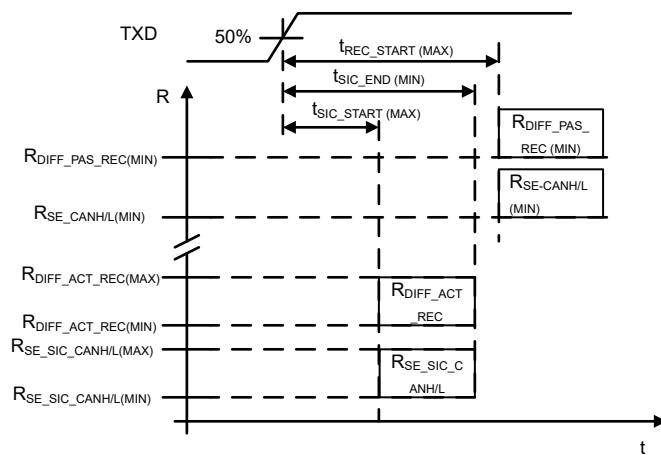

| CAN FD 信号改善特性          |                                                                            |                                                                                                                                                                                                                                                                                                  |     |     |     |    |

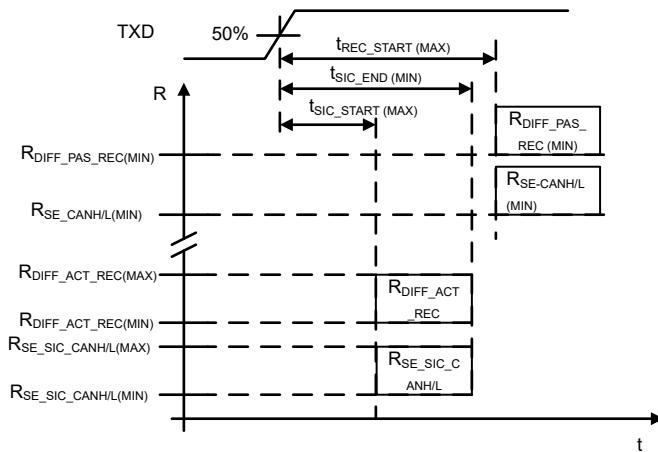

| $t_{PAS\_REC\_START}$  | パッシブ リセッショップ位相の開始時間                                                        | $R_L = 45\Omega \sim 65\Omega$ 、 $C_{L1} = \text{オープン}$ 、 $C_{L2} = 100\text{pF}$ 、 $C_{L(RxD)} = 15\text{pF}$<br>50% しきい値で 5ns 未満のスロープを持つ TXD 立ち上がりエッジから、信号改善位相の終了までの時間を測定:<br>$R_{DIFF\_PAS\_REC} \geq \text{MIN } R_{DIFF\_ACT\_REC}$ 、<br>$R_{SE\_CANH/L} \geq \text{MIN } R_{SE\_SIC\_REC}$ | 365 |     | 530 | ns |

| $t_{SIC\_START}$       | アクティブ 信号改善位相の開始時間                                                          | $R_L = 45\Omega \sim 65\Omega$ 、 $C_{L1} = \text{open}$ 、 $C_{L2} = 100\text{pF}$ 、 $C_{L(RxD)} = 15\text{pF}$<br>50% しきい値で 5ns 未満のスロープを持つ TXD 立ち上がりエッジから、信号改善位相の開始までの時間を測定                                                                                                                      |     | 120 |     | ns |

| $t_{SIC\_END}$         | アクティブ 信号改善位相の終了時間                                                          | $R_L = 45\Omega \sim 65\Omega$ 、 $C_{L1} = \text{オープン}$ 、 $C_{L2} = 100\text{pF}$ 、 $C_{L(RxD)} = 15\text{pF}$<br>50% しきい値で 5ns 未満のスロープを持つ TXD 立ち上がりエッジから、信号改善位相の終了までの時間を測定                                                                                                                      | 355 |     |     | ns |

| $t_{\Delta Bit(Bus)}$  | 送信されるビット幅変化                                                                | $R_L = 60\Omega$ 、 $C_{L1} = \text{オープン}$ 、 $C_{L2} = 100\text{pF}$ 、 $C_{L(RxD)} = 15\text{pF}$<br>TXD ビット長に対するバス リセッショップの変動 (図 6-6)<br>$t_{\Delta Bit(Bus)} = t_{Bit(Bus)} - t_{Bit(TxD)}$ 、 $t_{Bit(TxD)} \geq 125\text{ns}$ を参照)                                                             | -10 |     | 10  | ns |

| $t_{\Delta Bit(RxD)}$  | 受信したビット幅変化                                                                 | $R_L = 60\Omega$ 、 $C_{L1} = \text{オープン}$ 、 $C_{L2} = 100\text{pF}$ 、 $C_{L(RxD)} = 15\text{pF}$<br>RXD ビット長に対する TXD ビット長 の相対的なリセッショップ ビット長の変動 (図 6-6)<br>$t_{\Delta Bit(RxD)} = t_{Bit(RxD)} - t_{Bit(TxD)}$ 、 $t_{Bit(TxD)} \geq 125\text{ns}$ を参照)                                            | -30 |     | 20  | ns |

| $t_{\Delta REC}$       | レシーバのタイミングの対称性                                                             | $R_L = 60\Omega$ 、 $C_{L1} = \text{オープン}$ 、 $C_{L2} = 100\text{pF}$ 、 $C_{L(RxD)} = 15\text{pF}$<br>RXD パス ビット長に対するリセッショップ ビット長の変動 (図 6-6)<br>$t_{\Delta REC} = t_{Bit(RxD)} - t_{Bit(Bus)}$ 、 $t_{Bit(TxD)} \geq 125\text{ns}$ を参照)                                                             | -20 |     | 15  | ns |

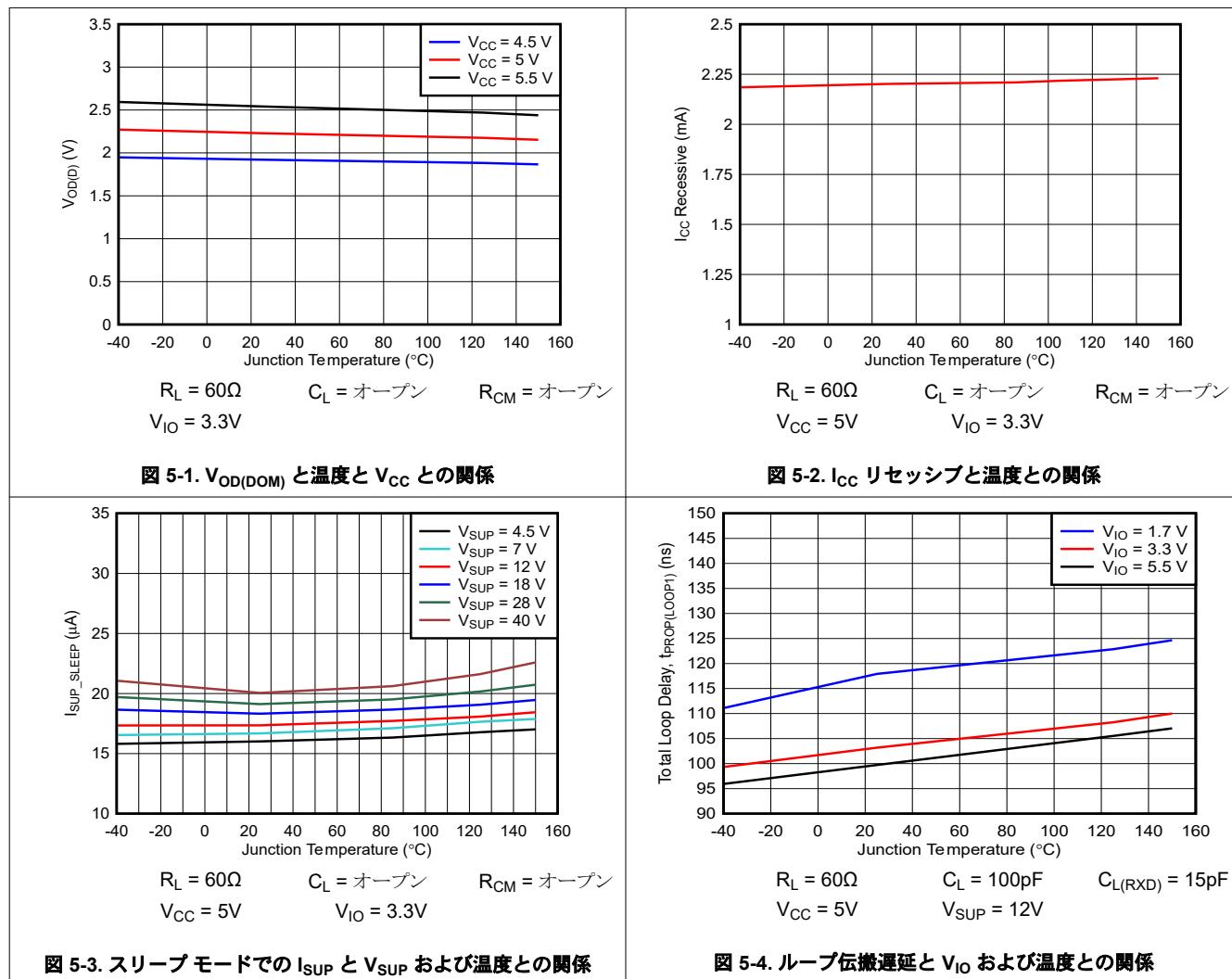

## 5.11 代表的特性

## 6 パラメータ測定情報

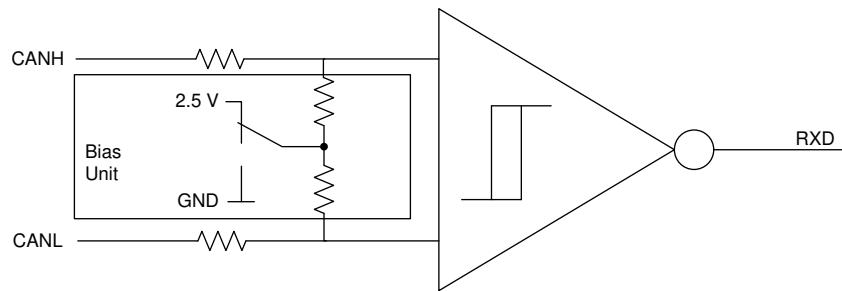

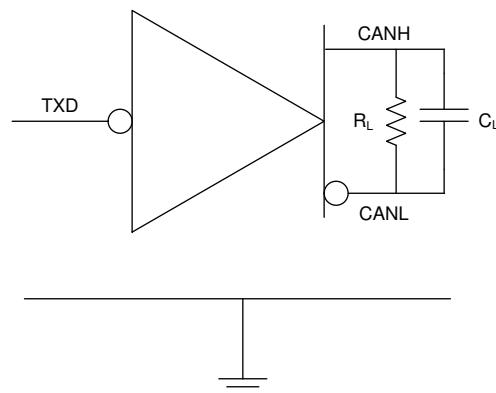

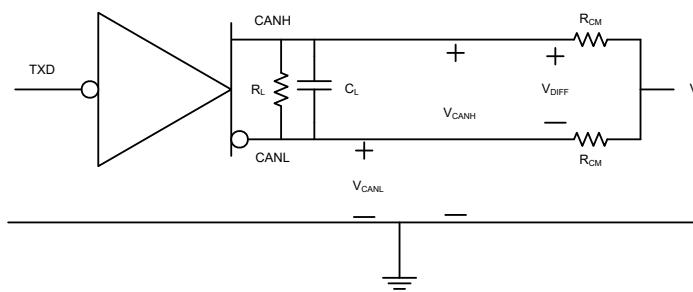

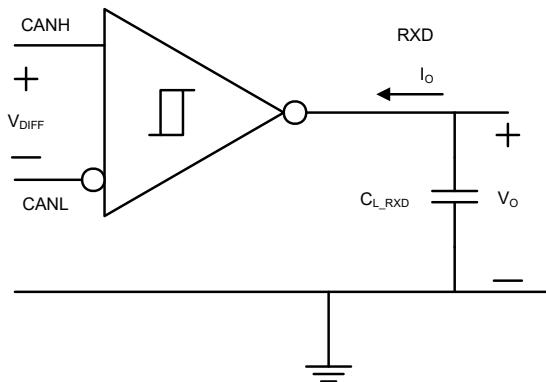

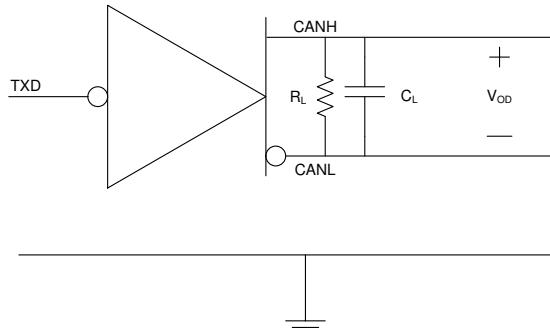

図 6-1. 同相バイアス ユニット / レシーバ

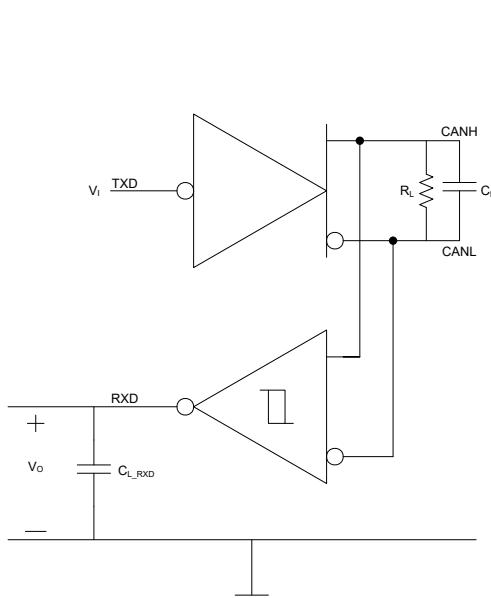

図 6-2. テスト回路

図 6-3. 電源テスト回路

図 6-4. ドライバテスト回路と測定

図 6-5. レシーバのテスト回路と測定

図 6-6. トランスマッタとレシーバのタイミング動作テスト回路と測定

図 6-7. TXD ドミナント タイムアウトのテスト回路と測定

図 6-8. ドライバ短絡電流テスト回路と測定

図 6-9. バイアス応答時間の測定

1. サイレント モードを終了すると、nFAULT<sup>1</sup> はクリアされます

図 6-10. INH ディセーブルのタイミング図

1. サイレント モードを終了すると、nFAULT<sup>1</sup> はクリアされます

図 6-11. INH イネーブルのタイミング図

図 6-12. パワーアップのタイミング

図 6-13. アクティブおよびパッシブリセッシブ位相時の SIC タイミングとインピーダンス

## 7 詳細説明

### 7.1 概要

TCAN1473A-Q1 デバイスは、ISO 11898-2:2024 コントローラエリアネットワーク物理層規格の信号改善機能 (SIC) の仕様を満たすか、それを上回っています。この TCAN1473A-Q1 はデータレートに依存しないため、デバイスは、従来の CAN アプリケーションをサポートするための下位互換性があり、同時に最大 8 メガビット/秒 (Mbps) の CAN FD ネットワークもサポートします。

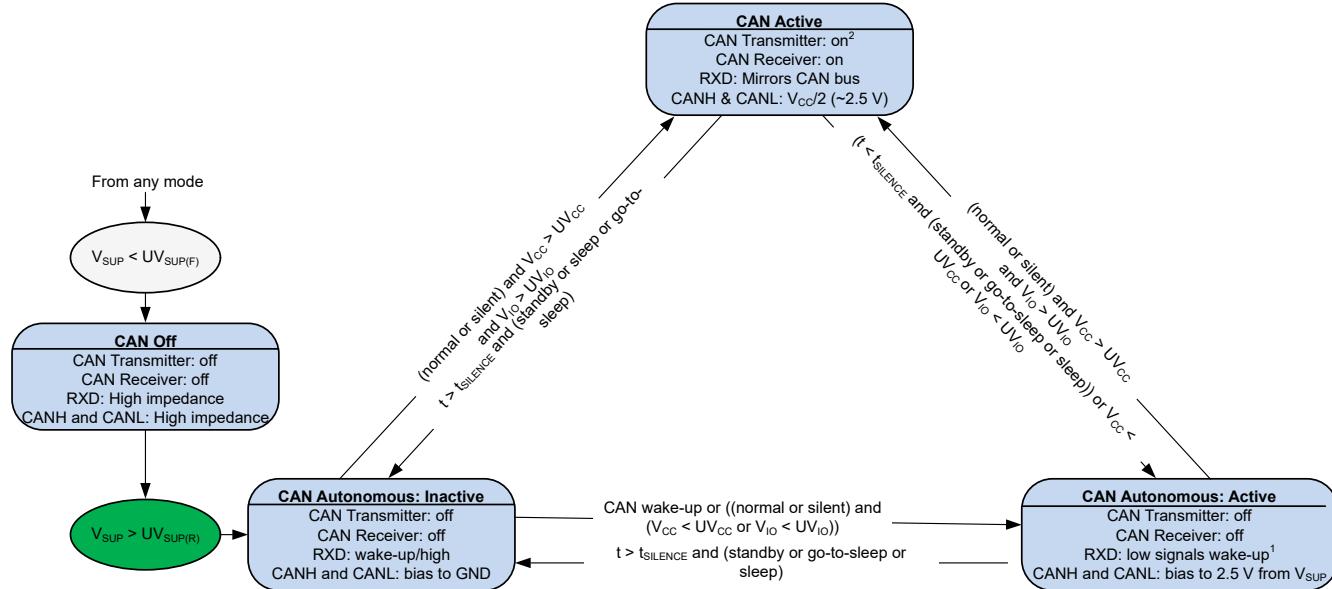

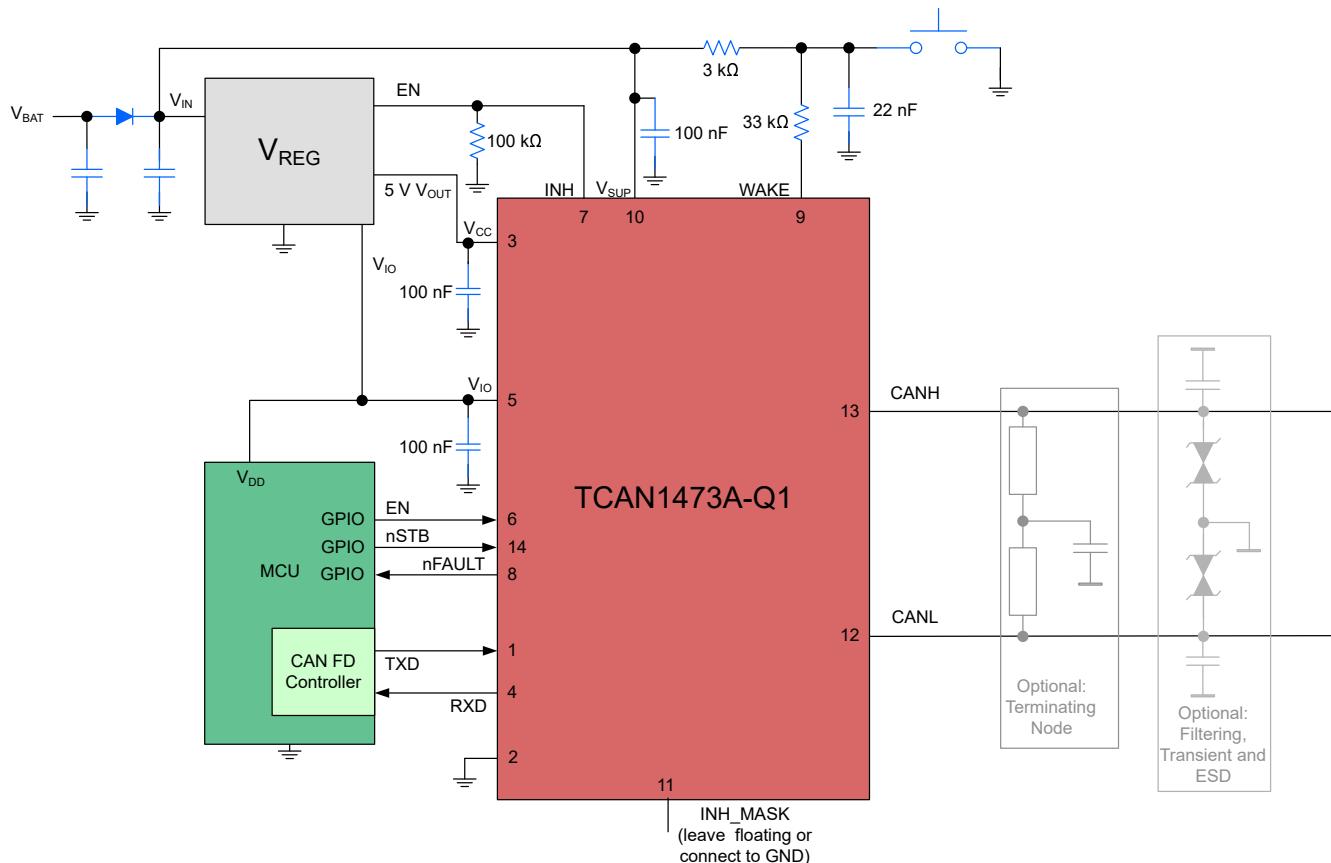

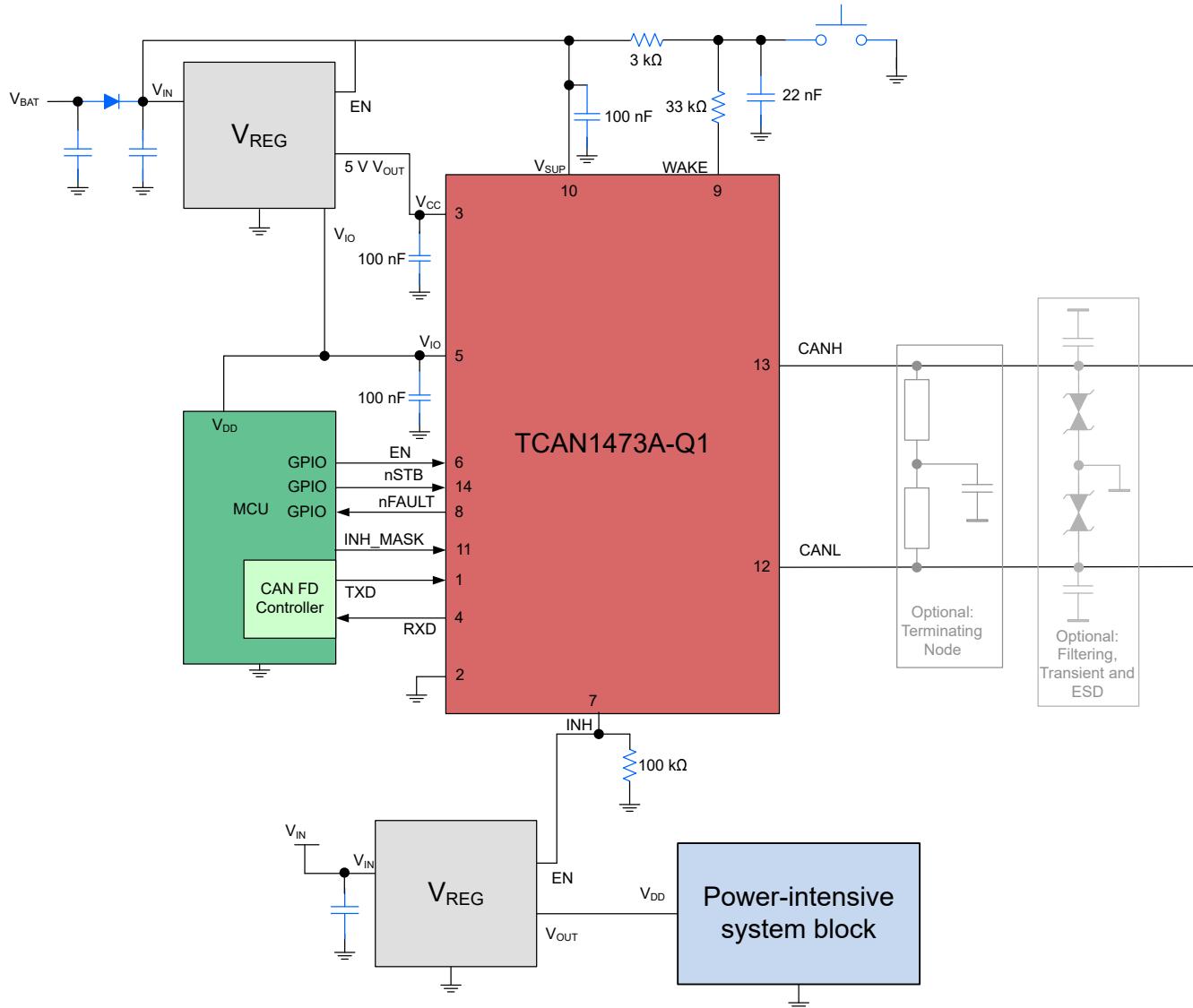

このトランシーバには、 $V_{SUP}$ 、 $V_{CC}$  および  $V_{IO}$  3 つの独立した電源入力があります。 $V_{IO}$  を使用することで、TCAN1473A-Q1 はレベル シフタを必要とせずに、1.8V、2.5V、3.3V、5V のコントローラと直接接続できます。TCAN1473A-Q1 を使用すると、システムに存在する各種電源供給の有効 / 無効を INH 出力ピンで切り替えることにより、バッテリの消費電流をシステム レベルで低減できます。これにより、TCAN1473A-Q1 を除くすべてのシステム コンポーネントに対して電力が遮断される超低電流スリープ状態を実現し、CAN バスを監視しながら低消費電力状態にすることができます。バス上でウェークアップ イベントが検出された場合、または WAKE 入力を介してローカル ウェーイクアップが要求された場合、デバイスが INH を HIGH に駆動してノードの起動を開始します。INH ピンの動作は、INH\_MASK 機能を使用して調整されます。

TCAN1473A-Q1 は、低電圧検出、CAN バス障害検出、SWE タイマー、バッテリ接続検出、サーマル シャットダウン (TSD)、ドライバ優先タイムアウト (TXD DTO)、最大  $\pm 58V$  のバス フォルト保護を含む多くの保護および診断機能を備えています。

#### 7.1.1 信号改善

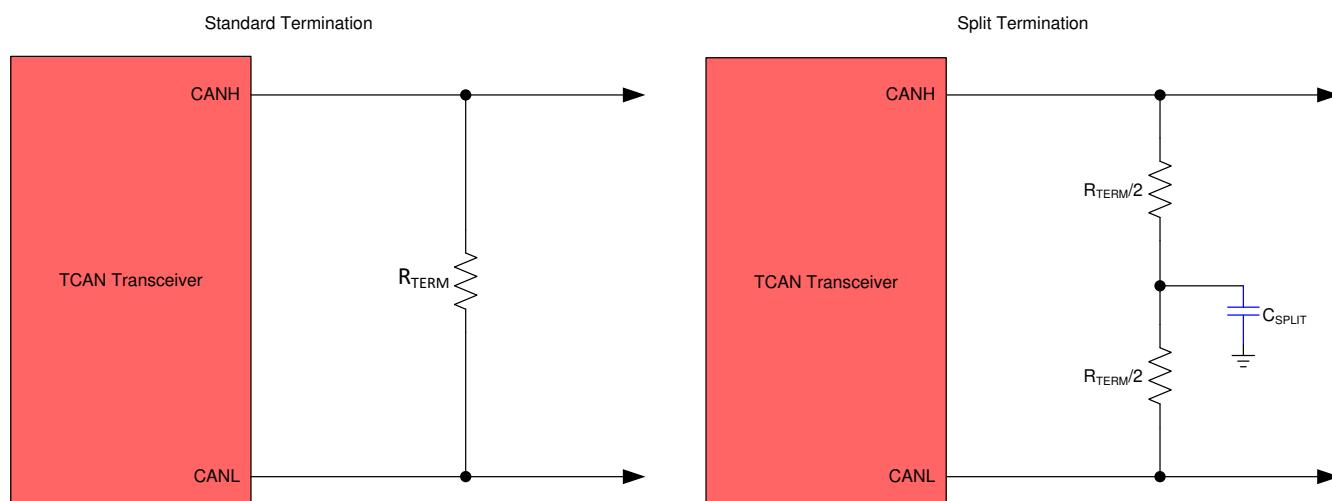

TCAN1473A-Q1 信号リングを最小限に抑えることで複雑なスタートポロジで達成可能な最大データレートを向上させる信号改善機能 (SIC) が含まれています。信号のリングは、複雑な CAN ネットワーク内のさまざまなポイントでのインピーダンスの不整合に起因する反射の結果です。

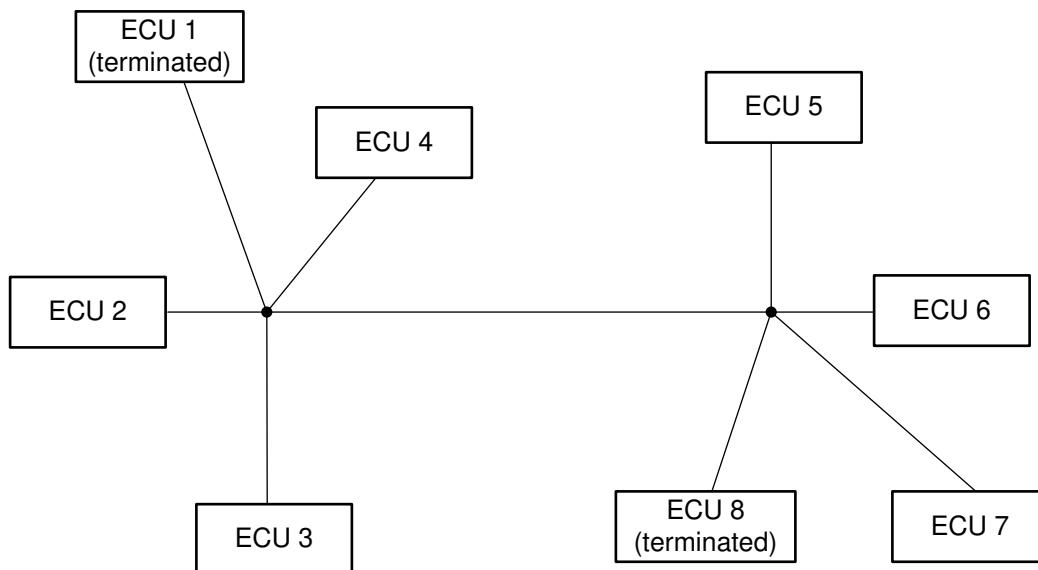

図 7-1 に、スター ネットワークの例を示します。

図 7-1. CAN ネットワーク : スター トポロジ

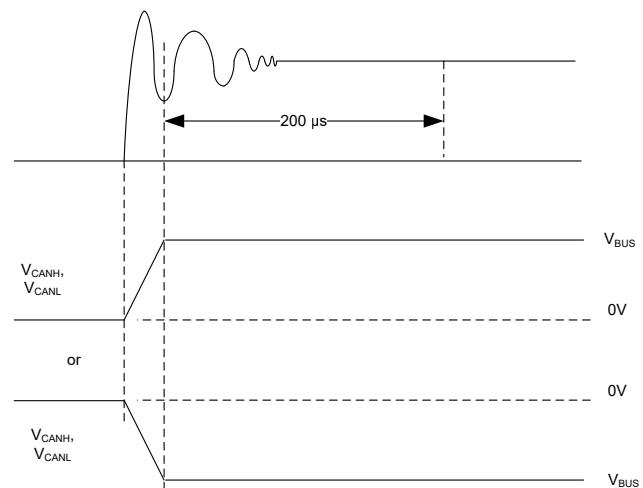

トランシッタによって駆動される場合、リセッショナルからドミナントへの信号のエッジは、通常はクリーンです。CAN トランシーバのトランシッタ出力インピーダンスは  $R_{ID(dom)}$  であり、ネットワーク特性インピーダンスと一致しています。通常の CAN FD トランシーバの場合、ドミナントからリセッショナルへのエッジの時に、ドライバの出力インピーダンスが約  $60k\Omega$  になることで反射された信号によるインピーダンスのミスマッチを引き起こし、リングが発生します。TCAN1473A-Q1 は、TX ベースの信号改善機能 (SIC) によってこの問題を解決します。TCAN1473A-Q1 は、反射を最小限に抑えるため、少なくして

も  $t_{SIC\_END}$  までバスを強くリセシブに駆動し続け、サンプリング ポイントではリセシブ ビットがクリーンになります。このアクティブ リセシブ位相では、トランスマッタの出力インピーダンスが低くなります ( $R_{DIFF\_ACT\_REC}$ )。このフェーズの後、デバイスはパッシブなリセシブフェーズに移行し、ドライバはハイ インピーダンス状態になります。この現象については、図 7-2 を使用して説明します。詳細については、[sicSIC を活用して CAN-FD トランシーバの真の可能性を引き出す方法](#)を解説したホワイトペーパーをご覧ください。

図 7-2. TX ベースの信号改善機能

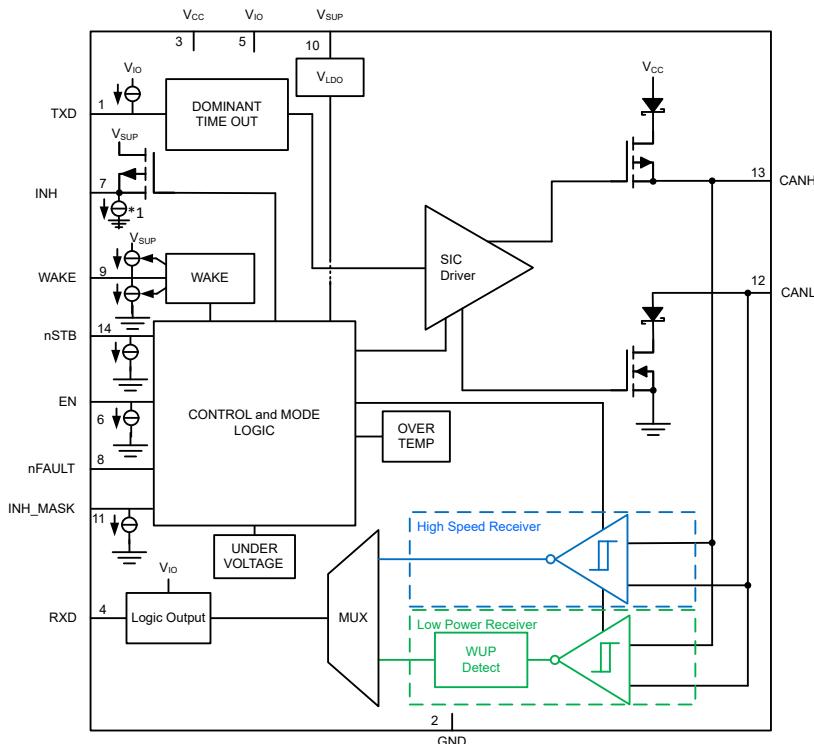

## 7.2 機能ブロック図

1. デバイスがスリープ モードのとき、INH ピンでは、4MΩ (標準値) のプルダウン抵抗がアクティブになります。

図 7-3. TCAN1473A-Q1 機能ブロック図

## 7.3 機能説明

### 7.3.1 電源ピン

TCAN1473A-Q1 はに、3 つの独立した電源入力が実装されており、デバイスの異なる部分をレギュレートします。

#### 7.3.1.1 $V_{SUP}$ ピン

このピンは、バッテリ電源に接続されます。この電源は、デジタル コアと低消費電力 CAN レシーバをサポートする内部レギュレータに電力を供給します。

#### 7.3.1.2 $V_{CC}$ ピン

このピンは、CAN トランシーバに 5V の電源電圧を供給します。

#### 7.3.1.3 $V_{IO}$ ピン

このピンは、CAN FD コントローラの I/O 電圧と一致するように、デジタル I/O 電圧を供給します。1.7V ~ 5.5V の I/O 電圧に対応し、幅広いコントローラをサポートしています。

### 7.3.2 デジタル入力および出力

#### 7.3.2.1 TXD ピン

TXD は、CAN FD コントローラから TCAN1473A-Q1 への、 $V_{IO}$  を基準とするロジック レベルの入力信号です。TXD は  $V_{IO}$  レベルにバイアスされ、ピンがフローティングの場合に強制的にリセッショブ入力になります。

#### 7.3.2.2 RXD ピン

RXD は、 $V_{IO}$  を基準とした、TCAN1473A-Q1 から CAN FD コントローラへのロジック レベル信号出力です。有効な  $V_{IO}$  が存在すると、RXD ピンはロジック High 出力として  $V_{IO}$  レベルに駆動されます。

電源オンまたはウェークアップ イベントが発生すると、RXD ピンは Low になります。

#### 7.3.2.3 nFAULT ピン

nFAULT は、 $V_{IO}$  を基準とする、TCAN1473A-Q1 から CAN FD コントローラへのロジック レベル出力信号です。nFAULT 出力は、ロジック High 出力として  $V_{IO}$  レベルに駆動されます。

nFAULT 出力は、TCAN1473A-Q1 ステータス インジケータ フラグを CAN FD コントローラに送信するために使用されます。nFAULT ピンにより外部から通知される特定のフォルトシナリオについては、表 7-1 を参照してください。スリープ モードで外部から通知されるフォルトシナリオがないため、TCAN1473A-Q1 は nFAULT ピンをスリープ モードでハイインピーダンス状態にして電力を節約します。

#### 7.3.2.4 EN ピン

EN は、CAN FD コントローラから TCAN1473A-Q1 への、 $V_{IO}$  を基準とするロジック レベルの入力信号です。EN 入力ピンは、nSTB ピンと組み合わせてモード選択に使用します。システム過剰な電力供給や誤ウェークアップ イベントを防止するために、EN は内部で low にプルされています。

#### 7.3.2.5 nSTB ピン

nSTB は、CAN FD コントローラから TCAN1473A-Q1 への  $V_{IO}$  を基準とするロジック レベル入力信号です。また、nSTB 入力ピンは EN ピンと組み合わせたモード選択用です。nSTB は内部的に low にプルされ、過剰なシステム電力と誤ウェークアップ イベントを防止します。

#### 7.3.2.6 INH\_MASK ピン

INH\_MASK は、CAN FD コントローラから TCAN1473A-Q1 への  $V_{IO}$  を基準とするロジック レベル入力信号です。サイレント モードのとき、INH\_MASK 入力ピンを使用して、INH 機能をディセーブルおよびイネーブルにできます。この機能を使用して、電力集約型の任意のシステム ブロックへの電源を制御し、スプリアス ウェイクアップ イベントによって低消費電力モードからシステム ブロックへの電源の投入を回避できます。INH がトランシーバまたはトランシーバ背後のコントローラへの電源を制御するために使用されている場合、INH\_MASK 機能は使用しないでください。このようなシナリオで

INH\_MASK を使用すると、デバイスがサイレントモードに移行し、INH 機能を有効にできなくなります。INH\_MASK 機能を使用するためのアプリケーション回路図例については、[図 8-2](#) を参照してください。

INH\_MASK には、コールド スタート時に INH 機能を強制的にイネーブル状態にするプルダウン抵抗があります。INH\_MASK をアクティブにするには、トランシーバがサイレントモードである必要があります。サイレントモードに移行すると、INH\_MASK ピンは  $t > t_{INH\_MASK}$  の間 high になり、INH が無効にする必要があります。TCAN1473A-Q1 はこの値をラッピングし、 $V_{CC}$  および  $V_{IO}$  のパワー サイクルと状態遷移を通じて保持します。 $V_{SUP}$  で低電圧フォルトに移行すると、ラッピングされた値は失われ TCAN1473A-Q1 です。INH 機能を再度イネーブルにするには、トランシーバがサイレントモードになっており、 $t > t_{INH\_MASK}$  ピンの間 low にプルする必要があります。INH\_MASK 機能の使用手順については、[図 6-10](#) および [図 6-11](#) を参照してください。

TCAN1473A-Q1 は、サイレントモード中に nFAULT を low に駆動することで、INH\_MASK の状態が変化したことをシステム コントローラに通知します。INH\_MASK 状態の変化に対するアクノリッジとして nFAULT = low を使用するには、INH\_MASK 状態の変化を開始する前に、nFAULT が high (すなわち、既存のフォルトがない) になっている必要があります。通常、スタンバイ、スリープ移行、またはスリープモードにモード遷移すると、nFAULT ピンはクリアされます。

### 7.3.3 GND

GND はトランシーバのグランドピンです。GND は、PCB グランドに接続する必要があります。

### 7.3.4 INH ピン

INH ピンは、外部レギュレータの制御に使用する高電圧出力です。これらのレギュレータは一般的に、マイクロプロセッサおよび  $V_{IO}$  ピンを駆動するために使用されます。INH 機能は、スリープモードを除くすべてのモードでオンになります。スリープモードでは、INH ピンはオフになり、高インピーダンス状態に移行します。これにより、スリープモード中はノードを最小消費電力状態にできます。INH 出力に  $100\text{k}\Omega$  負荷を追加することで、High 駆動状態から Low 状態への遷移時間を高速化し、フローティングのままにしたときにピンを強制的に Low にすることができます。

この端子は、電力出力ではなく、高電圧ロジック端子として扱う必要があります。INH ピンは電源管理デバイスの EN 端子を駆動するために使用し、電源供給のスイッチとしては使用しないでください。この端子は逆接バッテリ保護を備えていないため、システムモジュール外部へは接続しないでください。

INH 機能は、サイレントモードで INH\_MASK ピンを使用して無効化/イネーブルできます。詳細については、[INH\\_MASK ピン](#) を参照してください。

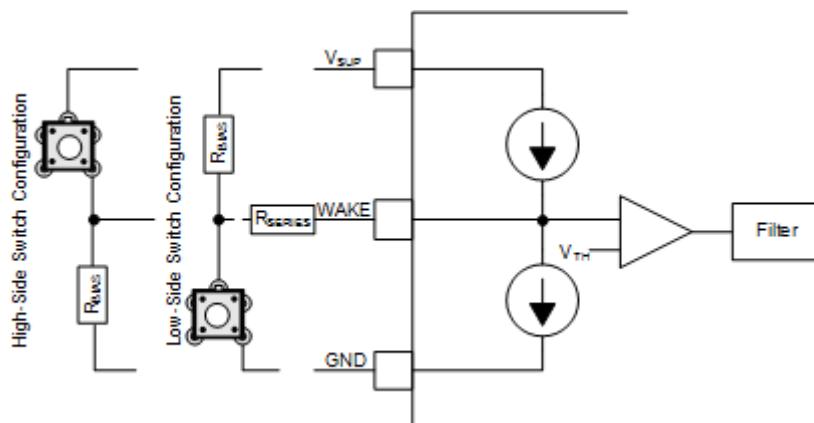

### 7.3.5 WAKE ピン

WAKE ピンは、ローカル ウェイクアップ (LWU) 機能に使用される高電圧逆ブロック入力です。WAKE ピンは双方向エッジトリガであり、WAKE ピン遷移の立ち上がりエッジまたは立ち下がりエッジでローカル ウェイクアップ (LWU) を認識します。LWU 機能については、「[WAKE 入力端子によるローカル ウェイクアップ \(LWU\)](#)」セクションで詳しく説明します。

### 7.3.6 CAN バス ピン

これらは CAN High と CAN Low、CANH と CANL の差動バスピンです。これらのピンは、CAN トランシーバおよび低電圧ウェークレシーバに内部接続されています。

### 7.3.7 フォルト

#### 7.3.7.1 内部および外部のフォルト インジケータ

次のデバイスステータス インジケータ フラグが実装されており、MCU がデバイスおよびシステムのステータスを判定できます。故障に加えて、nFAULT 故障端末は、 $V_{SUP}$  バッテリ端末でのウェイクアップリクエストと「コールド」電源投入シーケンスも通知するため、システムは必要な診断やコールド ブートシーケンスを実行できます。RXD 端子はウェイクアップリクエストを通知し、フォルトは nFAULT 出力に対して多重化(論理和)されます。

表 7-1. TCAN1473A-Q1 トランシーバステータス インジケータ

| EVENT                        | フラグ名                  | 原因                                                            | インディケータ <sup>(1)</sup>                                                                                                            | フラグがクリアされます                                                                                                             | 備考                                                                                                      |

|------------------------------|-----------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| パワーアップ                       | PWRON                 | $V_{SUP}$ の電源投入時および $UV_{SUP}$ を下回った後の $V_{SUP}$ の復帰時         | スタンバイまたはスリープ モードからサイレント モードに移行すると、nFAULT = Low                                                                                    | 通常モードへの遷移の後です                                                                                                           | コールド スタート条件により、ローカル ウエークアップ WAKERQ、WAKESR、および PWRON フラグが生成されます。                                         |

| ウェークアップ リクエスト                | WAKERQ <sup>(2)</sup> |                                                               | スタンバイ モードに移行したときにウェークアップ後、nFAULT = RXD = Low                                                                                      | 通常モードへの遷移後または $t \geq t_{UV}$ で、 $V_{CC} < UV_{CC(F)}$ または $V_{IO} < UV_{IO(F)}$ となります                                  | ウェークアップ リクエストは、スタンバイ、スリープ移行、またはスリープ モードのみセットできます。 $UV_{CC}$ または $UV_{IO}$ のタイマをリセットします。                 |

| ウェークアップ ソース認識 <sup>(3)</sup> | WAKESR                | CAN バスでのウェークアップ イベント、WAKE ピンでの状態遷移、または最初のパワーアップ               | 通常モードに移行するとき利用可能 <sup>(4)</sup><br>nFAULT = low WAKE ピンからのローカル ウェークアップ イベントを示します<br>nFAULT = high CAN バスからのリモート ウェークアップ イベントを示します | 通常モードで TXD に 4 回の劣勢から優勢へのエッジが発生した後、通常モードを終了するか、 $t \geq t_{UV}$ で $V_{CC} < UV_{CC(F)}$ または $V_{IO} < UV_{IO(F)}$ となります | コールド スタート条件により、ローカル ウエークアップ WAKERQ、WAKESR、および PWRON フラグが生成されます。                                         |

| INH_MASK の変更                 | INHMASK               | INH_MASK の値が変更されました                                           | サイレント モードに移行した後、nFAULT = low                                                                                                      | 通常モード、スタンバイ モード、スリープ モードへのモード遷移                                                                                         | nFAULT をフラグ インジケータとして使用するには、INH_MASK の状態の変化を開始する前に nFAULT が high になっている必要があります (つまり、既存のフォルトが存在してはなりません) |

| アンダーボルテージ                    | UV <sub>CC</sub>      | $V_{CC} < UV_{CC(F)}$                                         | 外部からは表示されません                                                                                                                      | $V_{CC} > UV_{CC(R)}$ ,<br>または、ウェークアップ リクエストが発生します                                                                      |                                                                                                         |

|                              | UV <sub>IO</sub>      | $V_{IO} < UV_{IO(F)}$                                         | 外部からは表示されません                                                                                                                      | $V_{IO} > UV_{IO(R)}$ ,<br>または、ウェークアップ リクエストが発生します                                                                      |                                                                                                         |

|                              | UV <sub>SUP</sub>     | $V_{SUP} < UV_{SUP(F)}$                                       | 外部からは表示されません                                                                                                                      | $V_{SUP} > UV_{SUP(R)}$                                                                                                 | $V_{SUP} > UV_{SUP(R)}$ になると、 $V_{SUP}$ 低電圧イベントによってコールドスタート条件が生成されます。                                   |

| CAN バスの不具合                   | CBF                   | CAN バス故障を参照                                                   | nFAULT = 通常モードでのみ low <sup>(5)</sup>                                                                                              | 通常モードを終了するとき、または通常モード時に TXD ピンが連続する、ドミナントからリセッショブへの 4 回遷移にわたって CAN バス フォルトが検出されない場合                                     | CAN バス フォルトは、ドミナントからリセッショブへの遷移を 4 回連続して持続する必要があります                                                      |

| ローカル フォルト                    | TXDCLP                | CAN アクティブ モードに移行すると、TXD は Low になります。                          |                                                                                                                                   |                                                                                                                         | TXDCLP がクリアされるまで、CAN ドライバはディスエーブルのまま維持されます。TXDCLP フォルト中、CAN レシーバはアクティブのままになります                          |

|                              | TXDDTO                | $T \geq t_{TXDDTO}$ の間の TXD ドミナント タイムアウト、ドミナント (Low) 信号       |                                                                                                                                   |                                                                                                                         | TXDDTO がクリアされるまで、CAN ドライバはディスエーブルのまま維持されます。TXDDTO フォルト中、CAN レシーバはアクティブのままになります                          |

|                              | TXDRXD                | $t \geq t_{TXDDTO}$ の間、TXD ピンと RXD ピンは互いに短絡しています              | nFAULT = 通常モードからサイレント モードに移行すると Low になります                                                                                         |                                                                                                                         | TXDRXD がクリアされるまで、CAN ドライバはディスエーブルのまま維持されます。TXDRXD フォルト中、CAN レシーバはアクティブのままになります                          |

|                              | CANDOM                | CAN バス ドミナント フォルト。 $t \geq t_{BUSDOM}$ にわたってドミナント バス信号を受信した場合 |                                                                                                                                   |                                                                                                                         | CANDOM フォルト中も CAN ドライバはイネーブルのままで                                                                        |

|                              | TSD                   | サーマル シャットダウン、 $T_J \geq T_{SDR}$                              |                                                                                                                                   |                                                                                                                         | $T_J < T_{SDP}$ および RXD = low および TXD = high、または通常モード、スタンバイ モード、スリープ移行、またはスリープ モードへの遷移                  |

- (1)  $V_{IO}$  と  $V_{SUP}$  が存在します。

- (2) スリープ移行モードへの遷移は、WAKERQ フラグがクリアされるまでブロックされます。

- (3) ウェークアップ ソース認識は、最初のウェークアップ ソースを反映します。追加のウェークアップ イベントが発生した場合でも、ソースは元のウェークアップ ソースを示します。

- (4) インジケータは、フラグがクリアされるまで、通常モードでのみ使用できます

- (5) CAN バス障害フラグは、TXD の 4 つのドミナントからリセッショブへのエッジの後に示されます

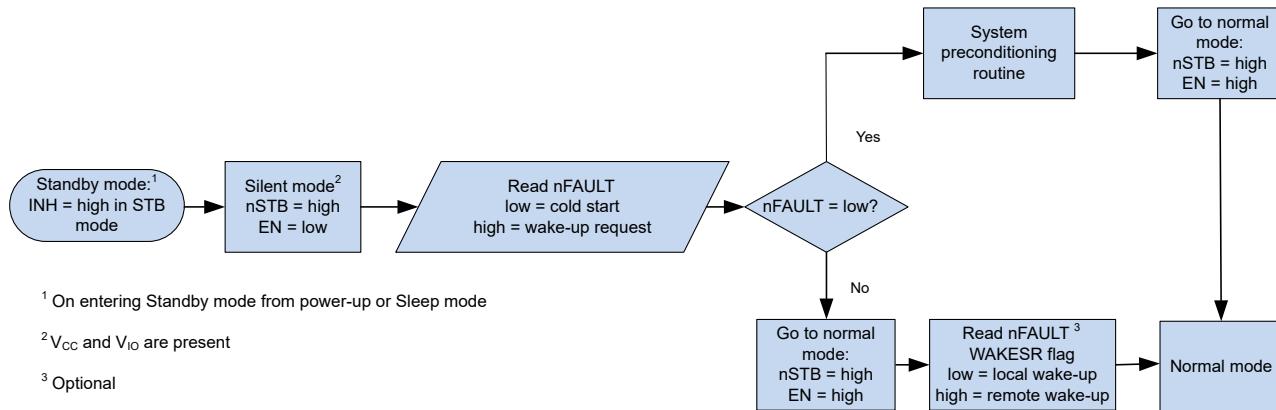

### 7.3.7.1.1 パワーアップ(PWRON フラグ)

これは、システムの電源オンシーケンスを制御するために使用できる内部および外部フラグです。トランシーバに新しいバッテリを接続すると、コールドスタート状態を示す **PWRON** フラグが設定されます。TCAN1473A-Q1 は、 $V_{SUP} < UV_{SUP(F)}$  のあらゆる低電圧条件をコールドスタートとして処理します。したがって、 $V_{SUP} > UV_{SUP(R)}$  条件が満たされると、TCAN1473A-Q1 は **PWRON** フラグを設定します。このフラグを使用して、コールドスタート状況でのみ呼び出されるルーチンにシステムが入ります。**PWRON** フラグは、スタンバイモードまたはスリープモードからサイレントモードに移行した後、nFAULT が low に駆動されて示されます。このフラグは、通常モードへの遷移後にクリアされます。

図 7-4. サイレントモードに移行して、PWRON とウェーク要求を区別

### 7.3.7.1.2 ウェイクアップ要求(WAKERQ フラグ)

これは、スタンバイ、スリープ移行、スリープモードで設定できる内部および外部フラグです。このフラグは、有効なローカルウェイクアップ(LWU)要求が発生する、有効なリモートウェイク要求が発生する、または  $V_{SUP}$  で電源投入時に設定されます。このフラグが設定されると、 $UV_{CC}$  または  $UV_{IO}$  フォルト検出の  $t_{UV}$  タイマがクリアされます。このフラグは、通常モードに移行するとき、または  $V_{CC}$  または  $V_{IO}$  の低電圧イベント中にクリアされます。

### 7.3.7.1.3 低電圧フォルト

この TCAN1473A-Q1 デバイスには、すべての電源端子に低電圧検出回路が実装されています。 $V_{SUP}$ 、 $V_{CC}$  および  $V_{IO}$ 。低電圧フラグは内部インジケータフラグであり、nFAULT 出力ピンには示されません。

#### 7.3.7.1.3.1 $V_{SUP}$ の低電圧

$UV_{SUP}$  は、 $V_{SUP}$  の電圧が低電圧検出電圧スレッショルド  $UV_{SUP}$  を下回ると設定されます。 $V_{SUP} > UV_{SUP(R)}$  になると、PWRON および WAKERQ フラグがセットされます。

#### 7.3.7.1.3.2 $V_{CC}$ の低電圧

$UV_{CC}$  は、 $V_{CC}$  の電圧が、 $t_{UV}$  低電圧フィルタ時間よりも長い間低電圧検出電圧スレッショルド  $UV_{CC}$  を下回ると設定されます。

#### 7.3.7.1.3.3 $V_{IO}$ の低電圧

$UV_{IO}$  は、 $V_{IO}$  の電圧が、 $t_{UV}$  低電圧フィルタ時間よりも長い間低電圧検出電圧スレッショルド  $UV_{IO}$  を下回ると設定されます。

### 7.3.7.1.4 CAN バス フォルト(CBF フラグ)

TCAN1473A-Q1 デバイスは、以下の 6 つのフォルト条件を検出し、nFAULT ピンを割り込みとして low に設定できるため、コントローラへの通知と CAN バス フォルトが発生した場合に動作できます。これらの障害は、CAN バスでドミナント信号を送信している間に検出されます。これらのフォルト条件のいずれかが 4 回連続してドミナントからリセッショブへのビット

遷移持続した場合、nFAULT は、nFAULT ピンを low に駆動することにより、通常モードで CAN バス障害フラグを示します。CAN バスドライバはアクティブのままでです。表 7-2 に、TCAN1473A-Q1 で検出できるフォルト条件を示します。

**表 7-2. バス フォルト ピンの状態および検出表**

| 故障 | 条件                   |

|----|----------------------|