# TCAN157x-Q1 車載用 CAN FD SIC トランシーバ、パーシャル ネットワーク対応

## 1 特長

- AEC-Q100 (グレード 1): 車載アプリケーション認定済み

- ISO 11898-2:2024 附属書 A に規定される信号改善機能を備えた CAN バスの 2Mbps および 5Mbps 通信の要件への適合

- 最高 8Mbps の CAN FD 通信レート

- エラー フリーの 従来 CAN または CAN FD データの送受信で選択的ウェークとパーシャル ネットワークをサポート

- **機能安全品質管理:**

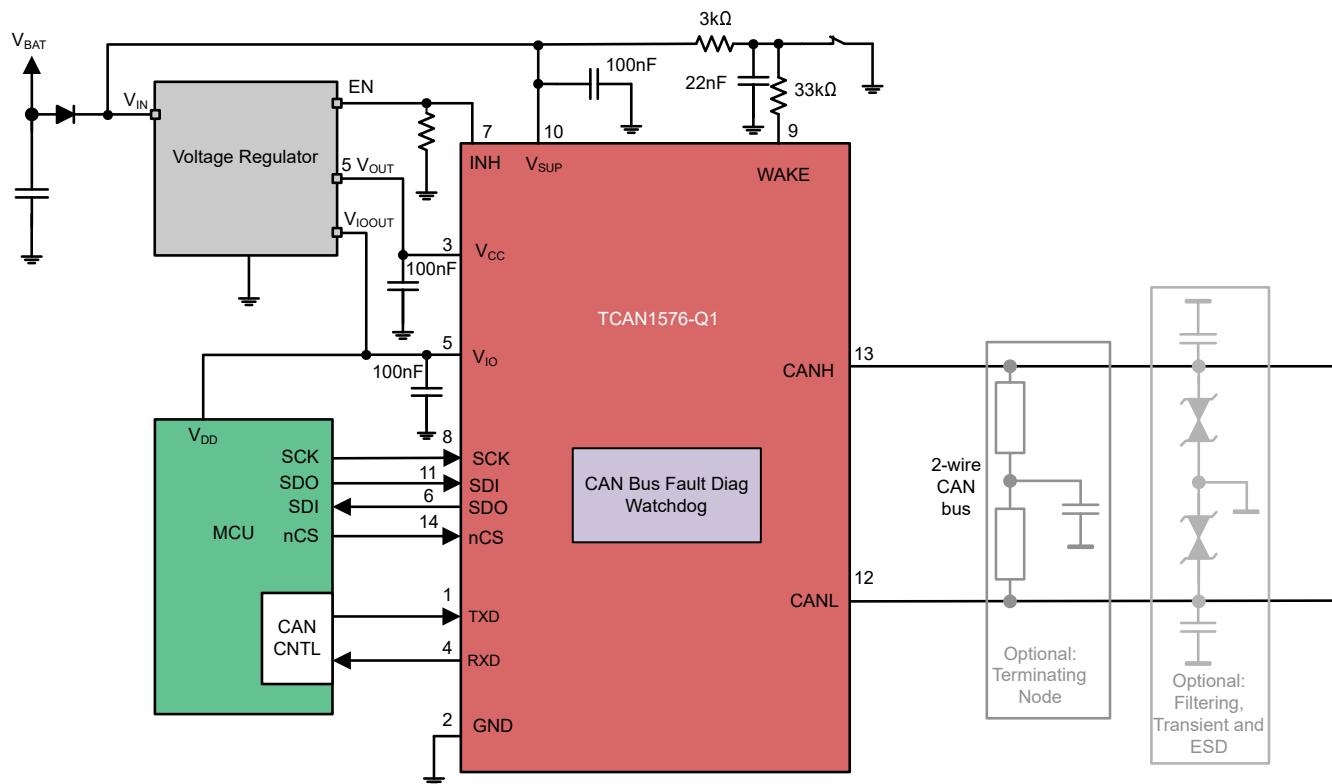

TCAN1576-Q1

- **機能安全対応:** TCAN1575-Q1

- TCAN157x-Q1 はプロセッサの IO 公称電圧 1.8V ~ 5V に対応

- 広い動作範囲:

- ±58V のバス フォルト保護

- ±12V 同相モード

- TCAN1576-Q1 は以下をサポート:

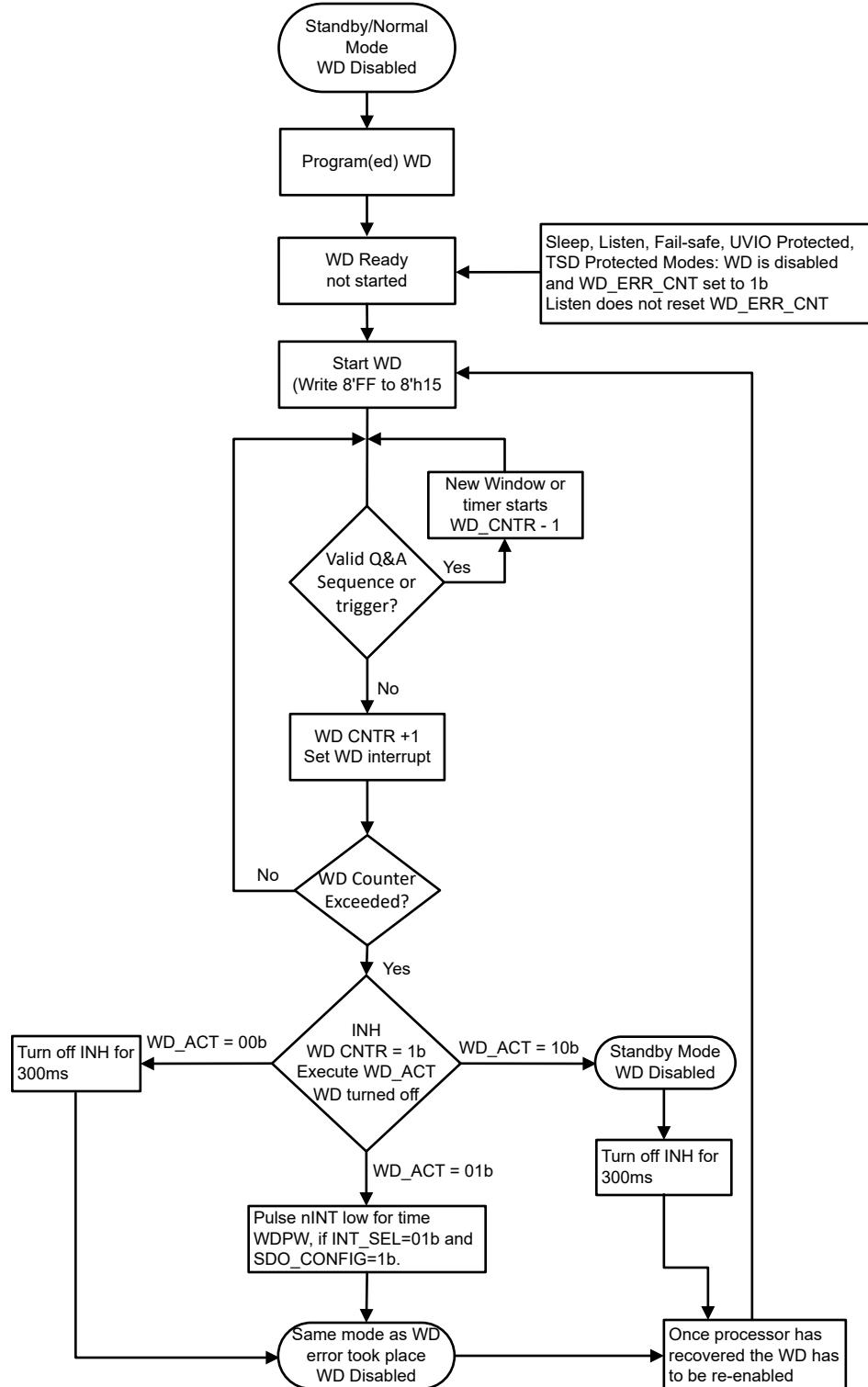

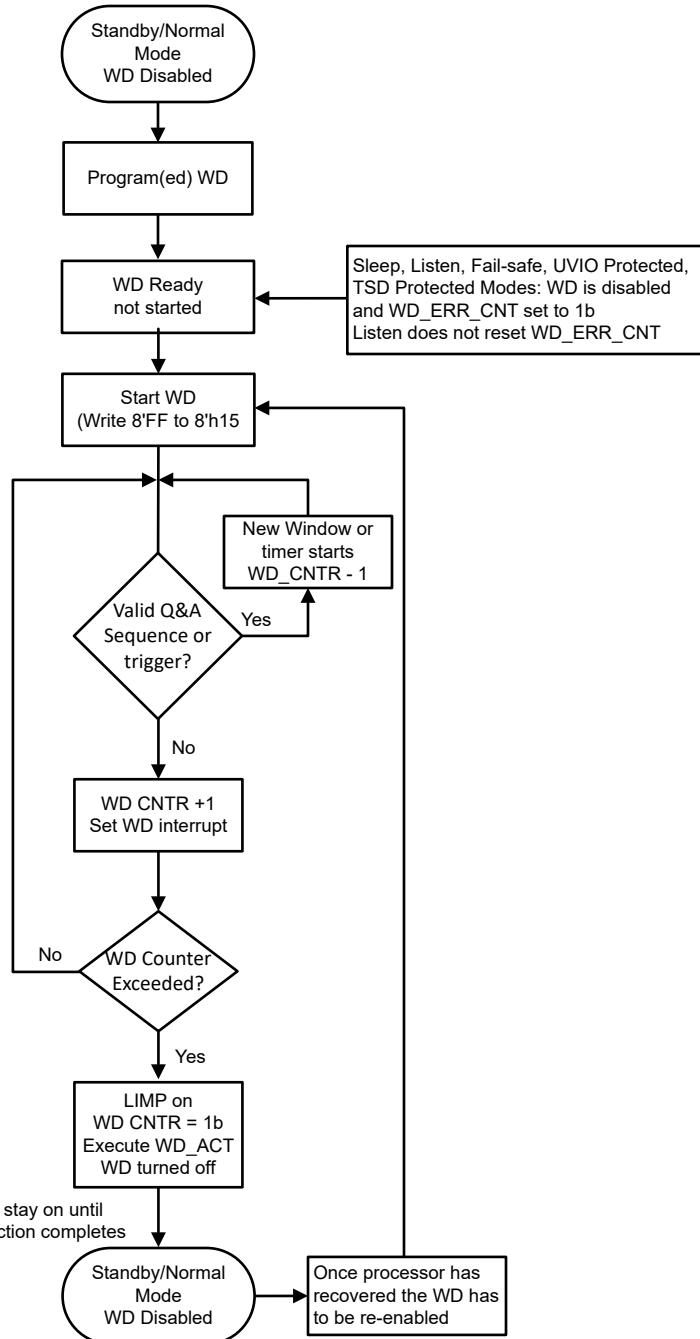

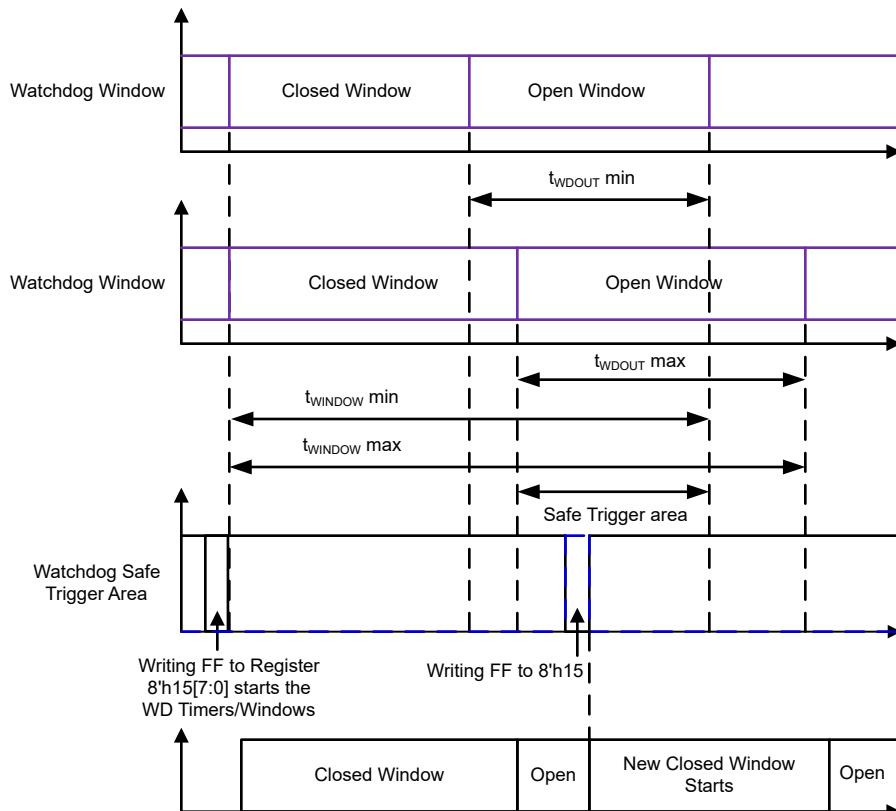

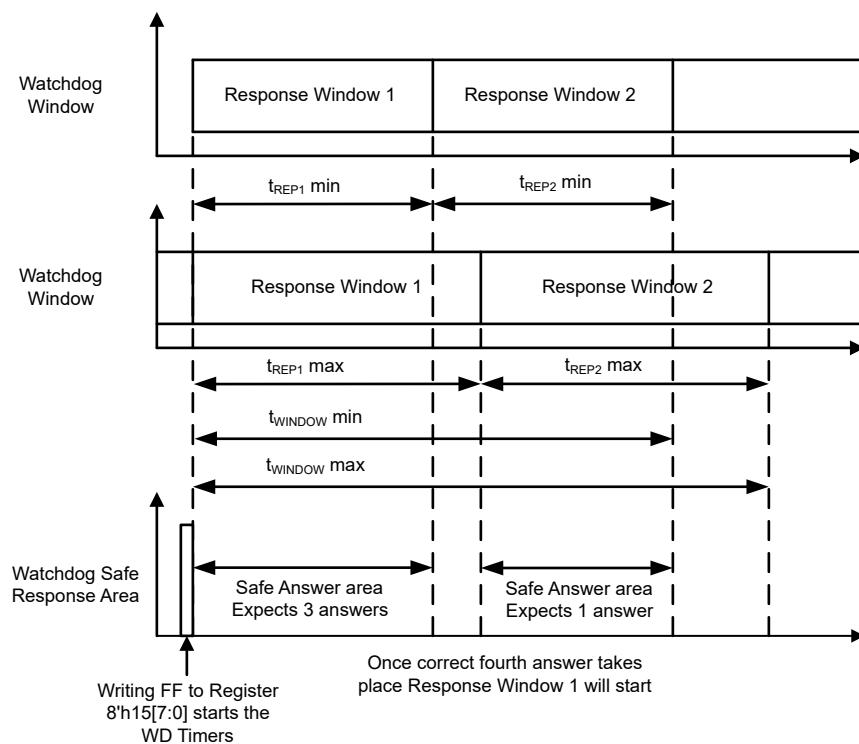

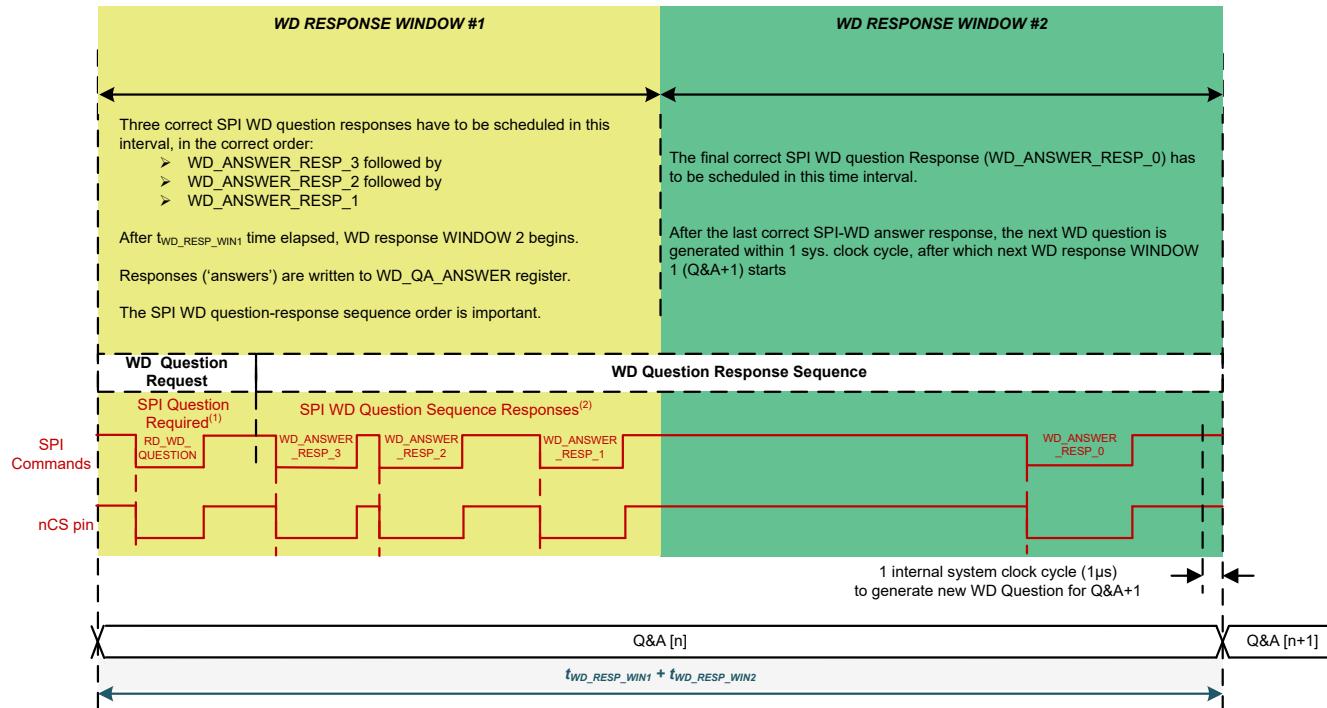

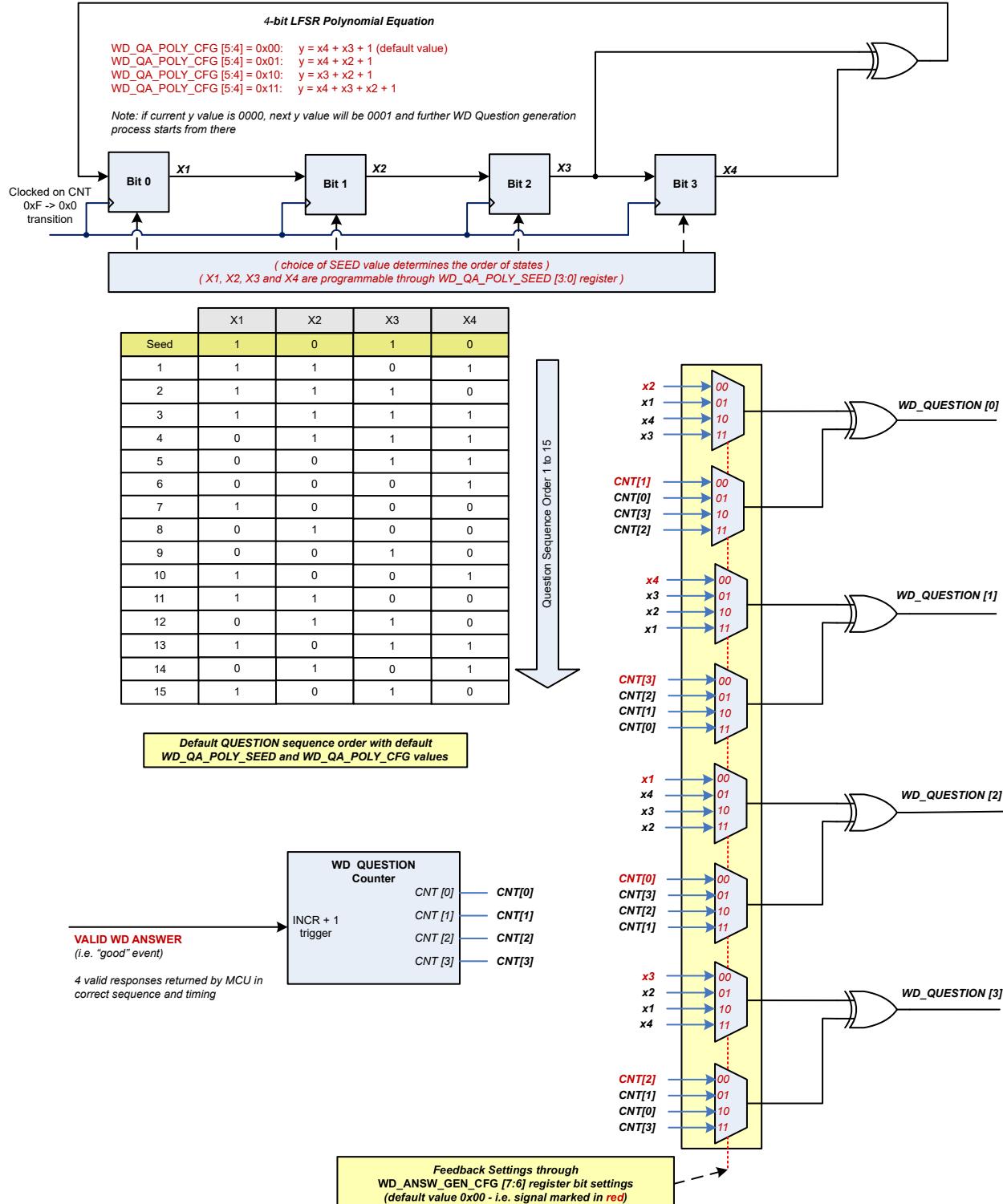

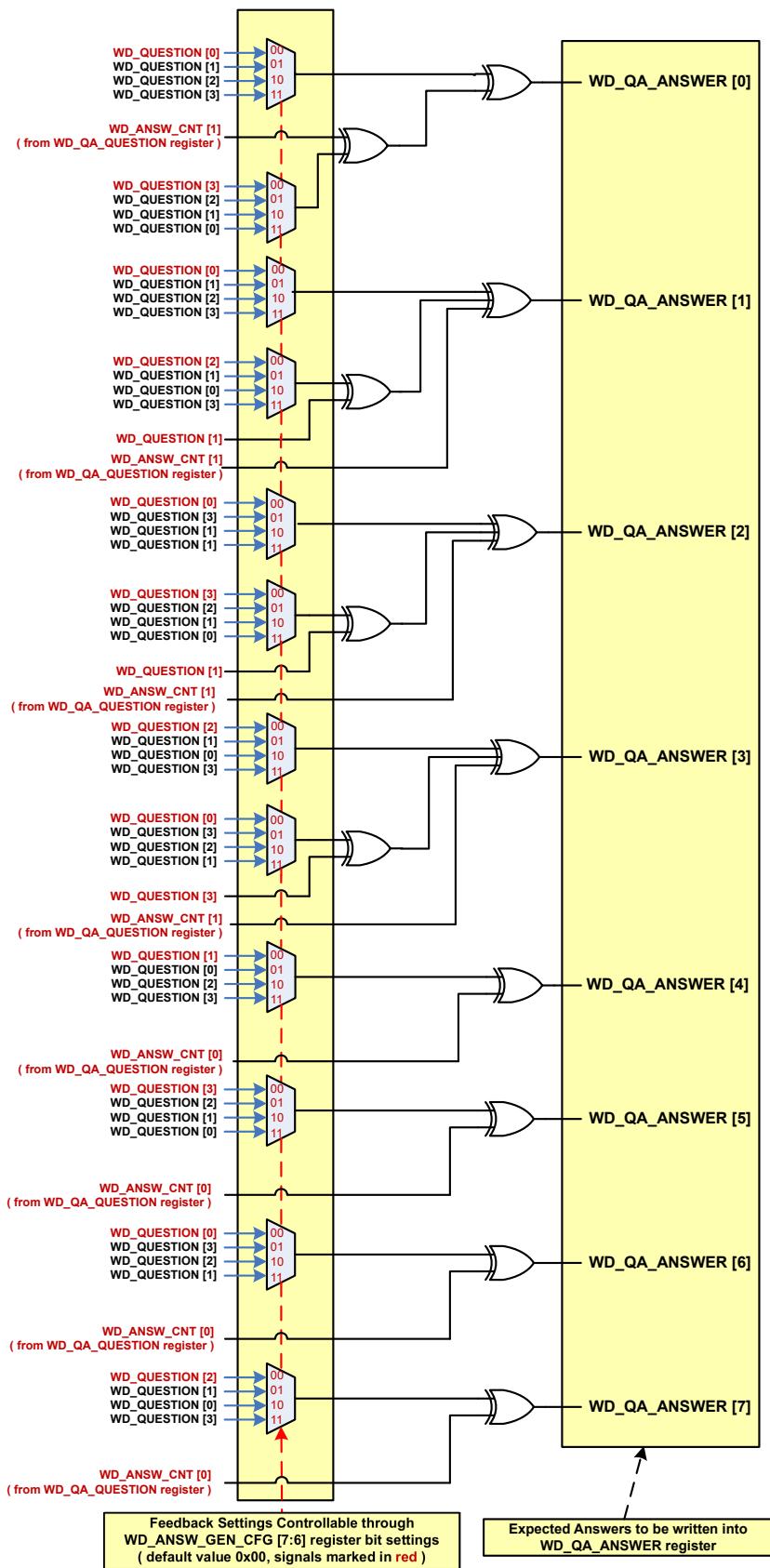

- ウオッチドッグ: タイムアウト、ウインドウ、Q&A

- バス フォルト診断および報告

- プログラマブルの INH/LIMP ピン

- 14 ピン SOIC、VSON、SOT23 パッケージ

- 自動光学検査 (AOI) 性能を向上させた VSON パッケージ

## 2 アプリケーション

- ボディ エレクトロニクス / 照明

- 車載用インフォテインメントおよびクラスタ

- ハイブリッド、電動、パワートレインシステム

- 産業用輸送

## 3 説明

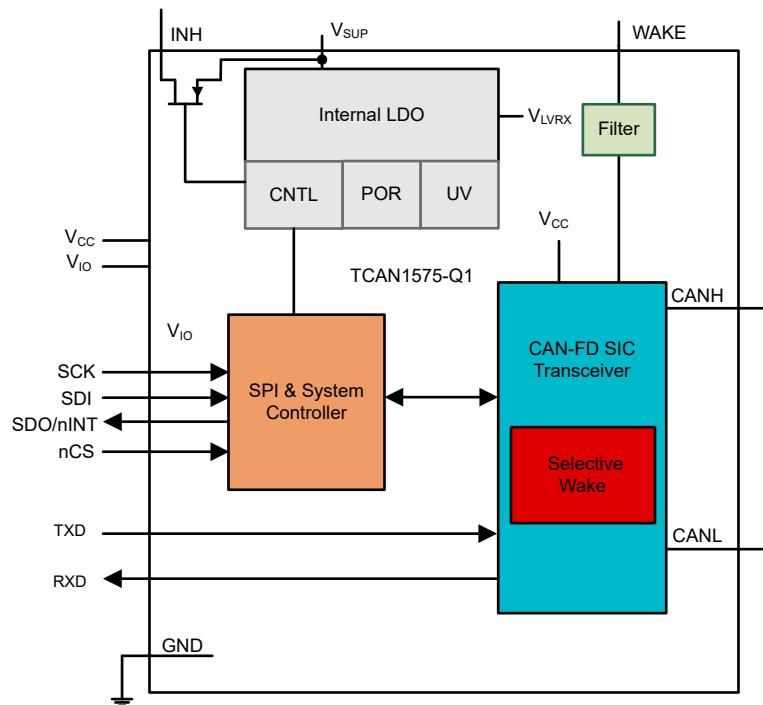

TCAN157x-Q1 は、拡張型の高速 CAN FD に対応した SIC トランシーバです。データレート最大 8Mbps をサポートする高速 CAN SIC 仕様について ISO 11898-2:2024 (付属書 A) の物理層要件に準拠します。これらのデバイスは SPI により設定を行い、全機能へアクセスできます。V<sub>IO</sub> 端子に印加する電圧に合わせて 1.8V ~ 5V のプロセッサ I/O 公称電圧をサポートし、低電力プロセッサの採用を可能にします。

これらのトランシーバは選択的ウェークをサポートしています (WUF 識別に基づいてウェークアップできます)。この機能により、システムにパーシャル ネットワークを実装し、アクティブ状態のノード数が少ない状態で動作させることができます (残りのノードは低消費電力スリープ モードに留まります)。選択的ウェーク付きトランシーバ機能は ISO 11898-2:2024 規格の仕様を満たしています。

TCAN1576-Q1 は、ウォッチドッグと先進バス診断をサポートするフル機能のデバイスです。デバッグを簡単にするため、先進バス フォルト診断および通信機能を使用して特定のバス フォルトを判定できます。

TCAN157x-Q1 は、ファミリ内および TCAN1145-Q1 と TCAN1146-Q1 CAN FD パーシャル ネットワーク対応トランシーバとレジスタ互換性があります。TCAN157x-Q1 は、ハードウェアの変更なし、かつ最小限のソフトウェア変更で機能を実装できる柔軟性をシステム設計者に提供します。TCAN1576-Q1 の inhibit ピン (INH) は、ノード電力を有効にするために使えます。または、ウォッチドッグ エラーが発生した際のリープ ホーム ピンとして構成できます。

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| TCAN1575-Q1 | SOIC (D) (14)        | 8.65 mm × 3.9mm          |

| TCAN1576-Q1 | VSON (DMT) (14)      | 4.5 mm × 3mm             |

|             | SOT23 (DYY) (14)     | 4.2 mm × 2mm             |

(1) 詳細については、[セクション 13](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

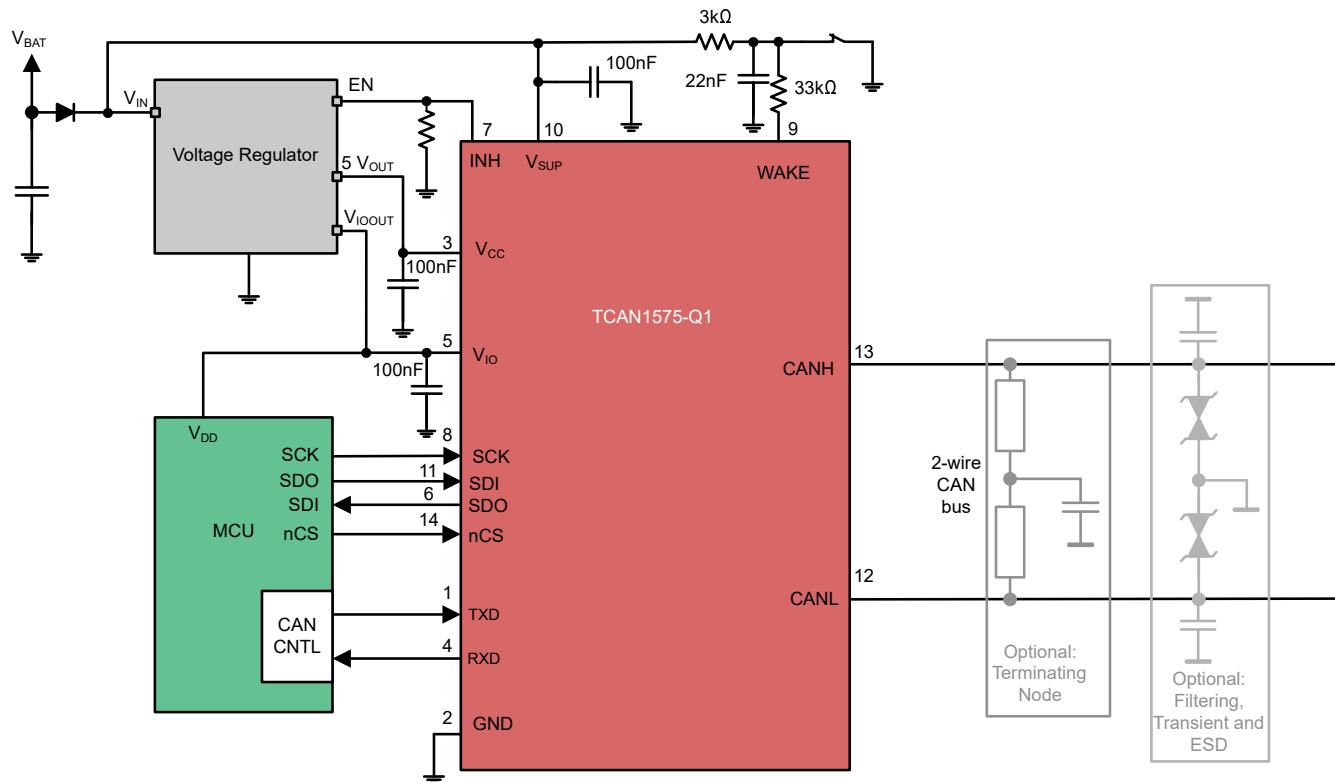

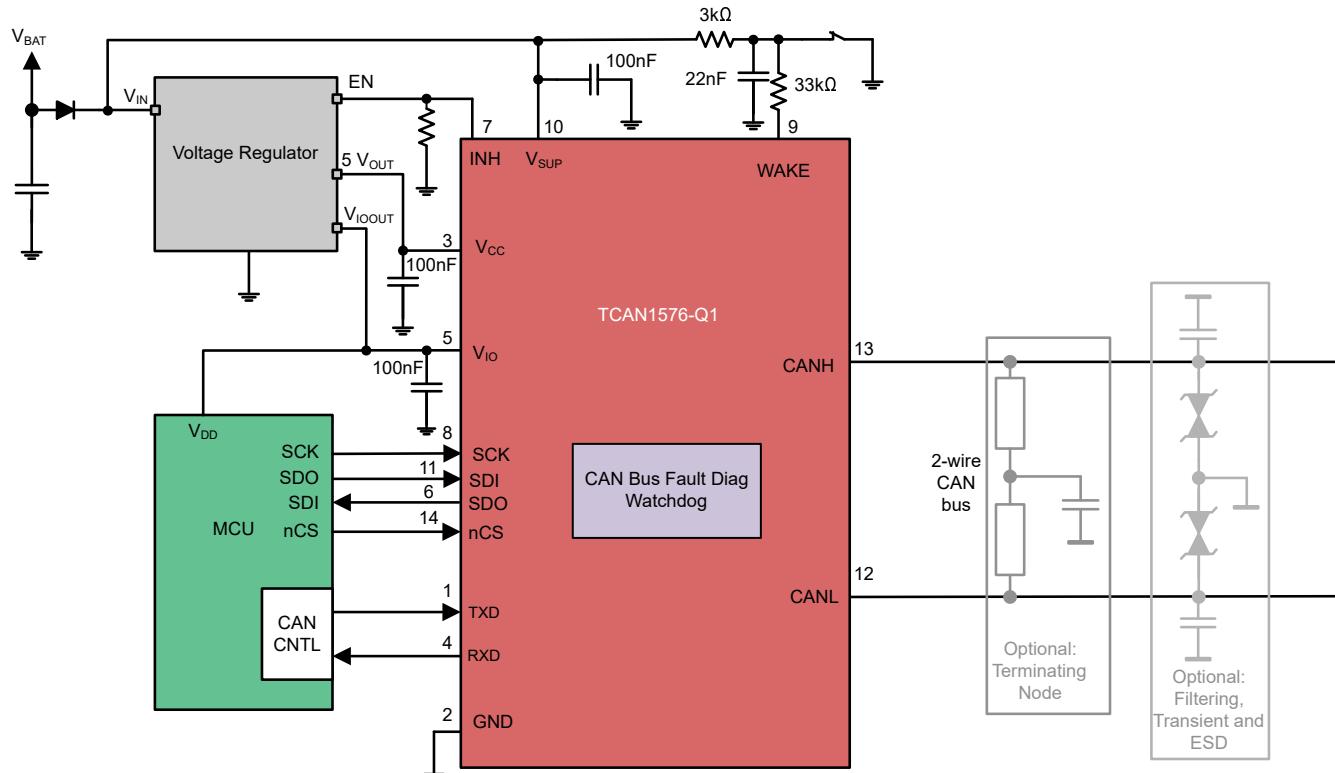

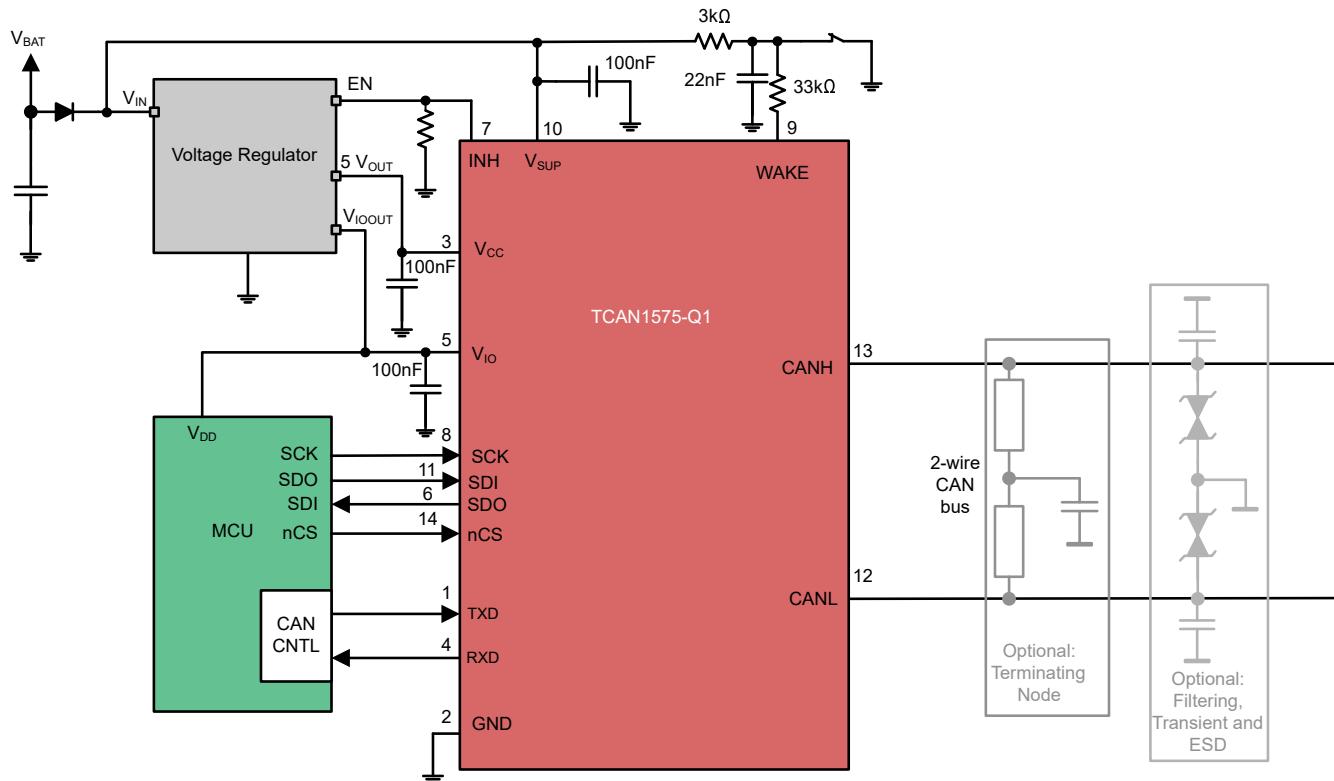

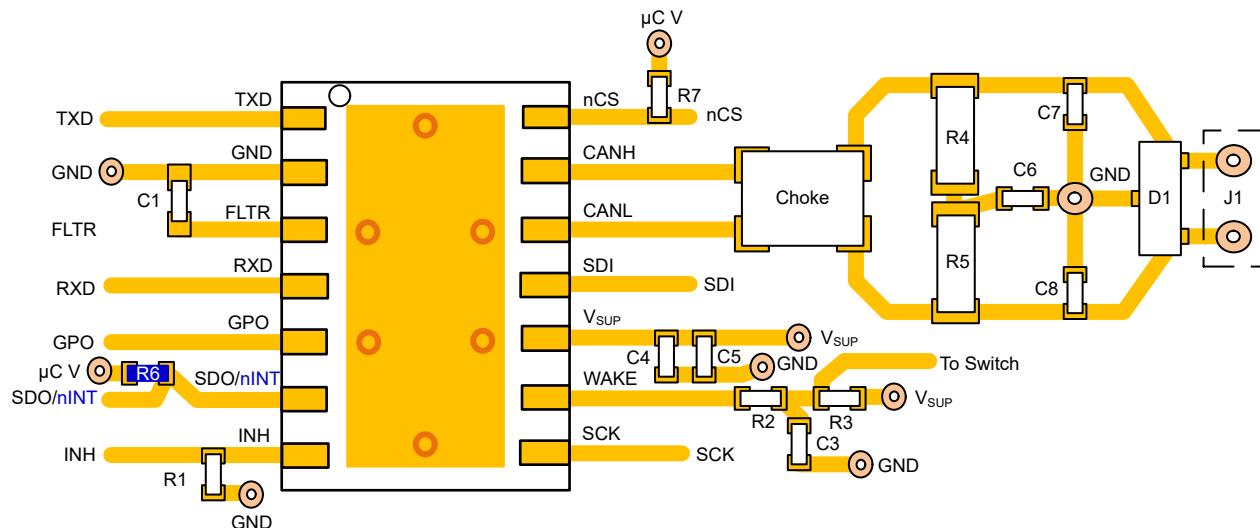

概略回路図

概略回路図

## 目次

|                    |           |                               |            |

|--------------------|-----------|-------------------------------|------------|

| <b>1 特長</b>        | <b>1</b>  | 8.3 機能説明                      | <b>26</b>  |

| <b>2 アプリケーション</b>  | <b>1</b>  | 8.4 デバイスの機能モード                | <b>31</b>  |

| <b>3 説明</b>        | <b>1</b>  | 8.5 プログラミング                   | <b>75</b>  |

| <b>4 デバイス比較表</b>   | <b>3</b>  | <b>9 アプリケーション情報に関する免責事項</b>   | <b>78</b>  |

| <b>5 ピン構成および機能</b> | <b>4</b>  | 9.1 アプリケーション情報                | <b>78</b>  |

| <b>6 仕様</b>        | <b>5</b>  | 9.2 代表的なアプリケーション              | <b>82</b>  |

| 6.1 絶対最大定格         | <b>5</b>  | 9.3 電源に関する推奨事項                | <b>85</b>  |

| 6.2 ESD 定格         | <b>5</b>  | 9.4 レイアウト                     | <b>85</b>  |

| 6.3 推奨動作条件         | <b>5</b>  | <b>10 レジスタ</b>                | <b>87</b>  |

| 6.4 熱に関する情報        | <b>6</b>  | 10.1 レジスタ マップ                 | <b>87</b>  |

| 6.5 電源の特性          | <b>6</b>  | <b>11 デバイスおよびドキュメントのサポート</b>  | <b>116</b> |

| 6.6 電気的特性          | <b>7</b>  | 11.1 ドキュメントのサポート              | <b>117</b> |

| 6.7 タイミング要件        | <b>9</b>  | 11.2 ドキュメントの更新通知を受け取る方法       | <b>117</b> |

| 6.8 スイッチング特性       | <b>10</b> | 11.3 サポート・リソース                | <b>117</b> |

| 6.9 代表的特性          | <b>13</b> | 11.4 商標                       | <b>117</b> |

| <b>7 パラメータ測定情報</b> | <b>15</b> | 11.5 静電気放電に関する注意事項            | <b>117</b> |

| <b>8 詳細説明</b>      | <b>22</b> | 11.6 用語集                      | <b>118</b> |

| 8.1 概要             | <b>22</b> | <b>12 改訂履歴</b>                | <b>119</b> |

| 8.2 機能ブロック図        | <b>23</b> | <b>13 メカニカル、パッケージ、および注文情報</b> | <b>119</b> |

## 4 デバイス比較表

| デバイス番号         | CAN FD SIC トランシーバ | 選択式ウェーブアップ機能 | ウォッチャドッグ | バス フォルト診断機能 | リープホーム対応 | SOIC | VSON | SOT |

|----------------|-------------------|--------------|----------|-------------|----------|------|------|-----|

| TCAN1575D-Q1   | X                 | X            |          |             |          | X    |      |     |

| TCAN1575DMT-Q1 | X                 | X            |          |             |          |      | X    |     |

| TCAN1575DYY-Q1 | X                 | X            |          |             |          |      |      | X   |

| TCAN1576D-Q1   | X                 | X            | X        | X           | X        | X    |      |     |

| TCAN1576DMT-Q1 | X                 | X            | X        | X           | X        |      | X    |     |

| TCAN1576DYY-Q1 | X                 | X            | X        | X           | X        |      |      | X   |

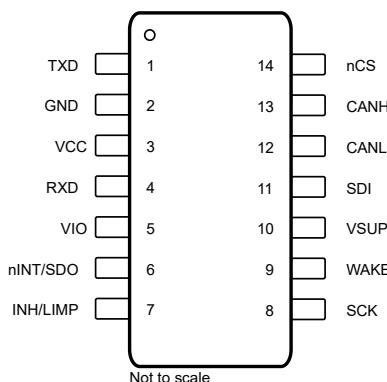

## 5 ピン構成および機能

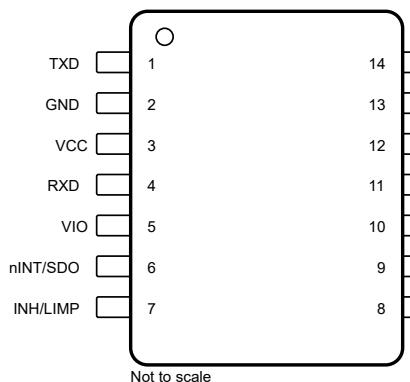

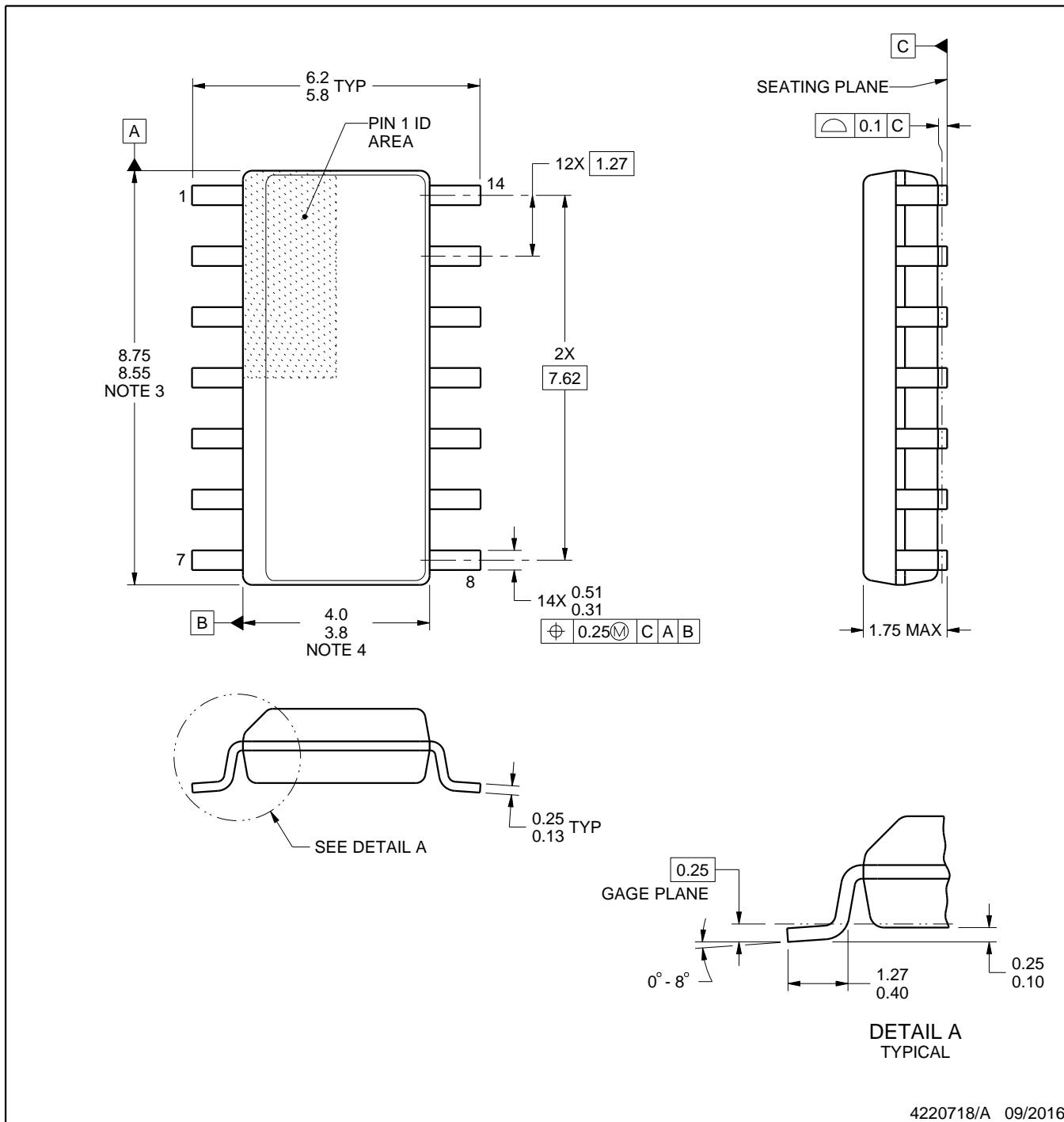

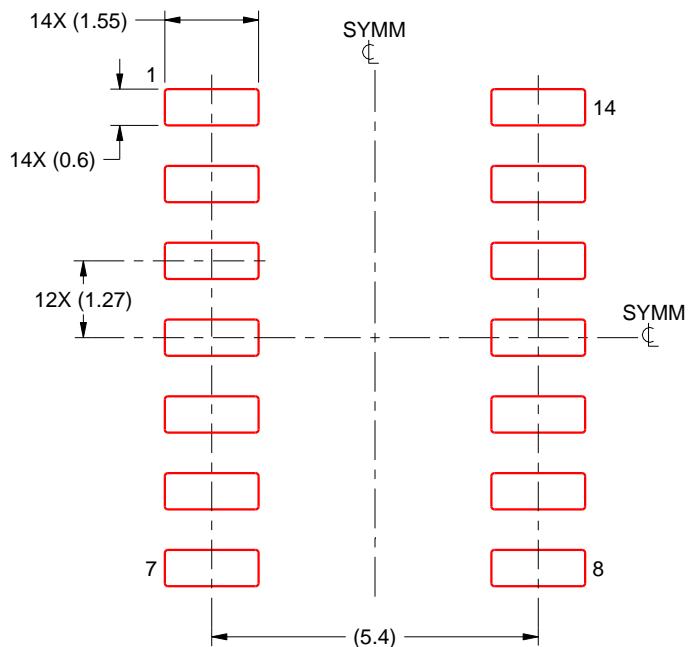

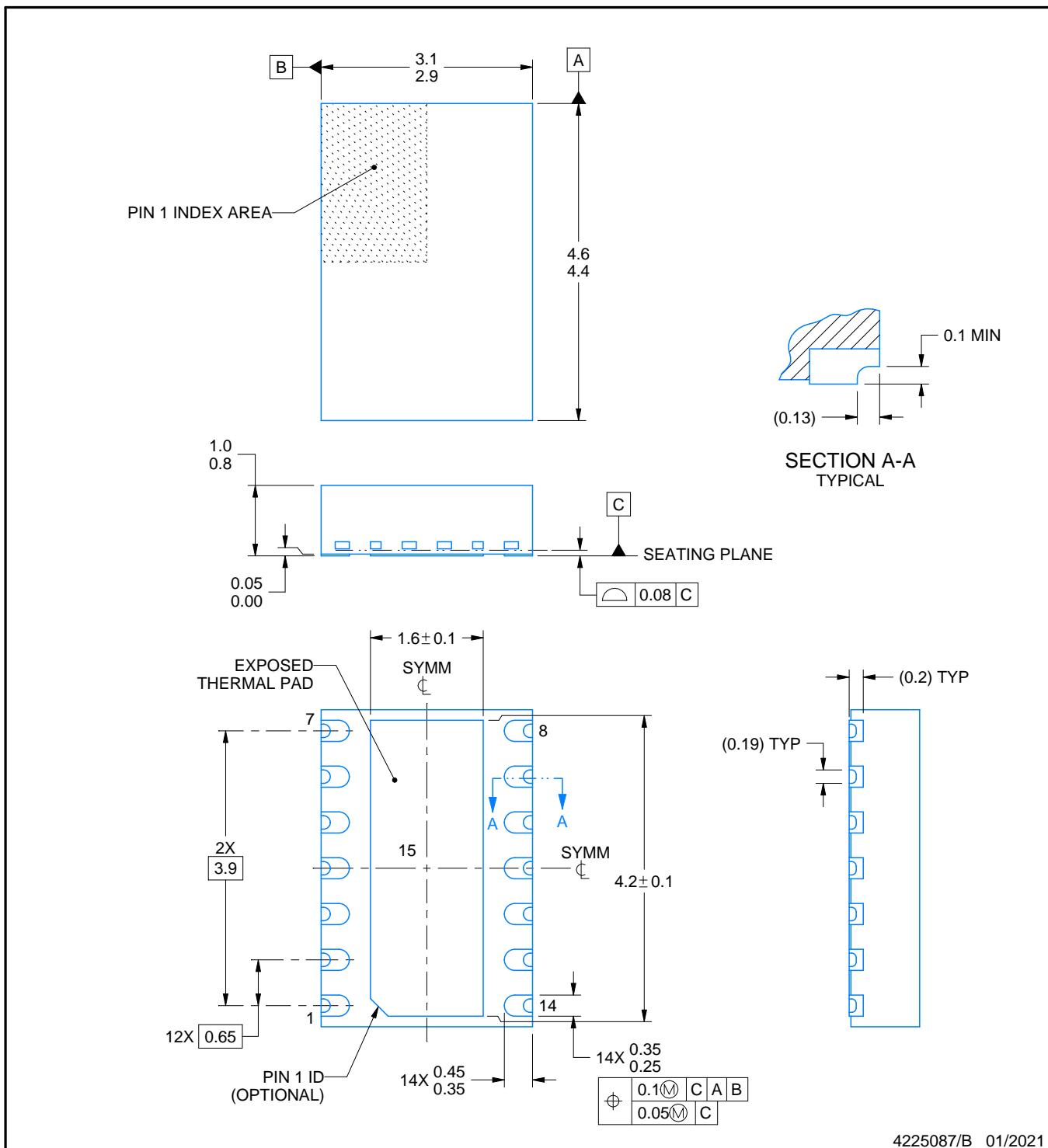

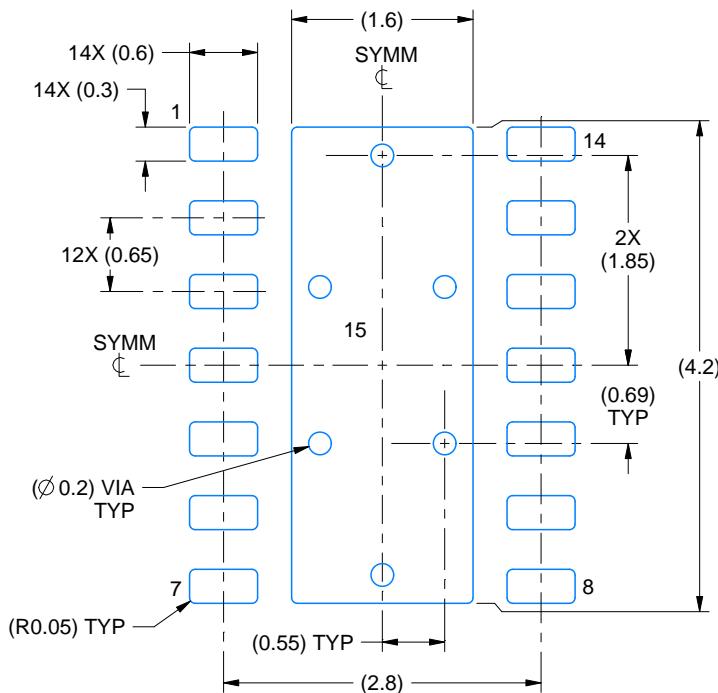

図 5-1. D パッケージ、14 ピン (SOIC)、上面図

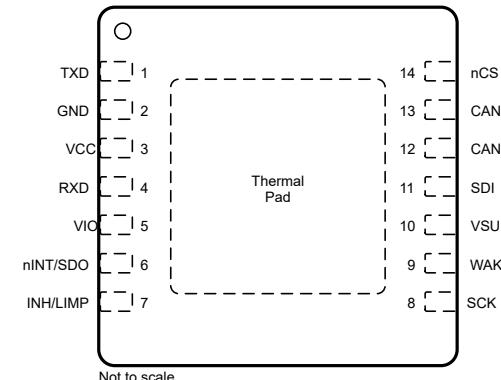

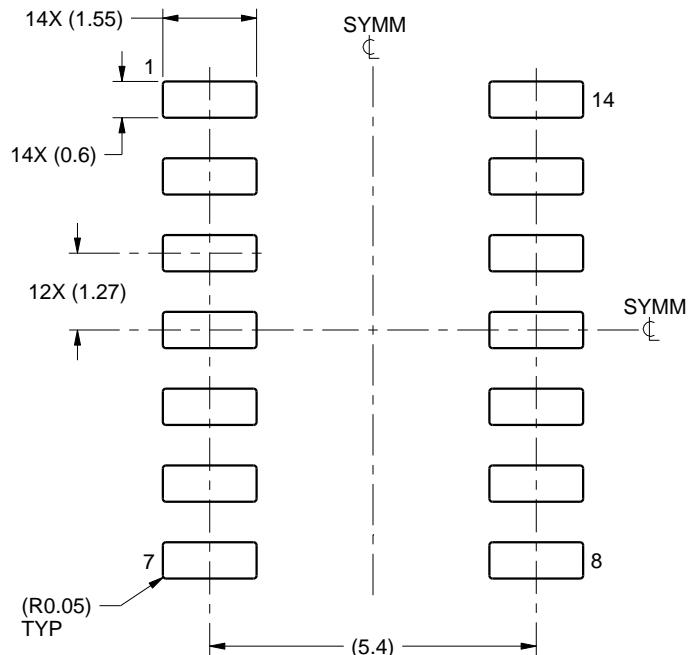

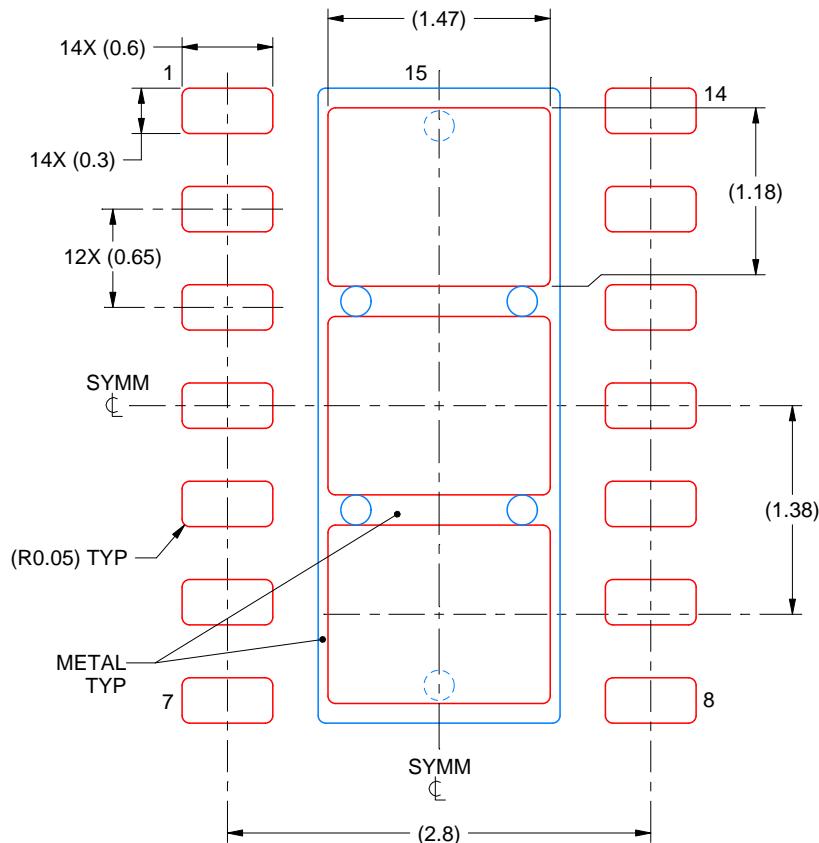

図 5-2. DMT パッケージ、14 ピン (VSON)、上面図

図 5-3. DYY パッケージ、14 ピン (SOT-23)、上面図

表 5-1. ピンの機能

| ピン<br>番号 | タイプ <sup>(2)</sup><br>名称 | 説明                                                                                          |

|----------|--------------------------|---------------------------------------------------------------------------------------------|

| 1        | TXD                      | DI CAN 送信データ入力 (ドミナントバス状態の場合は Low、リセッシブバス状態の場合は High)                                       |

| 2        | GND                      | グランド接続 <sup>(1)</sup>                                                                       |

| 3        | V <sub>cc</sub>          | 5V CAN バス電源電圧                                                                               |

| 4        | RXD                      | DO CAN 受信データ出力 (ドミナント・バス状態の場合は Low、リセッシブ・バス状態の場合は High)                                     |

| 5        | VIO                      | デジタル I/O 電源電圧                                                                               |

| 6        | nINT/SDO                 | DO nCS が Low のときはシリアルデータ出力、nCS が High のときは nINT                                             |

| 7        | INH/LIMP                 | HVO デフォルトでは、システム電圧レギュレータと電源を制御する Inhibit ピンとして動作します。TCAN1576-Q1 では、このピンを LIMP ホーム機能用に設定できます |

| 8        | SCK                      | DI SPI クロック入力。                                                                              |

| 9        | WAKE                     | HVI ローカル WAKE 入力端子                                                                          |

| 10       | VSUP                     | HVP バッテリからの高電圧供給                                                                            |

| 11       | SDI                      | シリアル データ入力                                                                                  |

| 12       | CANL                     | BI/O Low レベル CAN バス I/O ライン                                                                 |

| 13       | CANH                     | BI/O High レベル CAN バス I/O ライン                                                                |

| 14       | nCS                      | DI チップ セレクト (アクティブ "Low")                                                                   |

(1) GND ピンは GND に半田付けされています。DMT パッケージのパッドは、放熱性向上のため、グラウンドプレーンに半田付けすることを推奨します

(2) DI = デジタル入力、DO = デジタル出力、HVI = 高電圧入力、HVO = 高電圧出力、HVP = 高電圧電源、P = 電源、BI/O = バス入出力

## 6 仕様

### 6.1 絶対最大定格

動作周囲温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                   |                                                 | 最小値  | 最大値                            | 単位 |

|-------------------|-------------------------------------------------|------|--------------------------------|----|

| $V_{SUP}$         | デバイス電源電圧                                        | -0.3 | 42                             | V  |

| $V_{CC}$          | CAN 電源電圧                                        | -0.3 | 6                              | V  |

| $V_{IO}$          | 電源電圧 I/O レベル シフタ                                | -0.3 | 6                              | V  |

| $V_{BUS}$         | CAN バス I/O 電圧 (CANH、CANL)                       | -58  | 58                             | V  |

| $V_{DIFF}$        | CAN バス差動電圧 ( $V_{DIFF} = V_{CANH} - V_{CANL}$ ) | -58  | 58                             | V  |

| $V_{WAKE}$        | WAKE 入力電圧                                       | -18  | 42                             | V  |

| $V_{INH}$         | INH ピン電圧                                        | -0.3 | 42 および $VO \leq V_{SUP} + 0.3$ | V  |

| $V_{LOGIC}$       | ロジック ピン電圧 (RXD、TXD、SPI)                         | -0.3 | 6                              | V  |

| $I_{O(LOGIC)}$    | ロジック ピン出力電流 (RXD、SDO)                           |      | 4                              | mA |

| $I_{O(INH/LIMP)}$ | Inhibit/LIMP ピン出力電流                             |      | 6                              | mA |

| $I_{O(WAKE)}$     | WAKE ピン出力電流                                     |      | 3                              | mA |

| $T_J$             | 接合部温度                                           | -40  | 165                            | °C |

| $T_{stg}$         | 保存温度                                            | -65  | 150                            | °C |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|             |      |                                                                                | 値          | 単位 |

|-------------|------|--------------------------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM) 分類レベル H2、 $V_{SUP}$ 、CANL/H、WAKE ピン、AEC Q100-002 準拠 <sup>(1)</sup> | $\pm 8000$ | V  |

|             |      | 人体モデル (HBM) 分類レベル 3A、その他のすべてのピン、AEC Q100-002 に準拠 <sup>(1)</sup>                | $\pm 4000$ |    |

|             |      | 荷電デバイス モデル (CDM) 分類レベル C5、AEC Q100-011 準拠                                      | $\pm 750$  |    |

|             |      | コーナー ピン (1, 7, 8, 14)<br>その他のピン                                                | $\pm 750$  |    |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 6.3 推奨動作条件

|                   |                   | 最小値  | 公称値  | 最大値 | 単位 |

|-------------------|-------------------|------|------|-----|----|

| $V_{SUP}$         | 電源電圧              | 4.5  | 28   | V   |    |

| $V_{IO}$          | I/O 電源電圧          | 1.71 | 5.5  | V   |    |

| $V_{CC}$          | CAN トランシーバ電源電圧    | 4.75 | 5.25 | V   |    |

| $I_{OH(DO)}$      | デジタル出力 High レベル電流 | -2   |      | mA  |    |

| $I_{OL(DO)}$      | デジタル出力 Low レベル電流  |      | 2    | mA  |    |

| $I_{O(INH/LIMP)}$ | Inhibit/LIMP ピン電流 |      | 1    | mA  |    |

| $T_J$             | 接合部温度             | -40  | 150  | °C  |    |

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                     | TCAN157x-Q1 |            |             | 単位   |

|----------------------|---------------------|-------------|------------|-------------|------|

|                      |                     | D (SOIC)    | DMT (VSON) | DYY(SOT-23) |      |

|                      |                     | 14-PINS     | 14-PINS    | 14-PINS     |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 82.6        | 37.5       | 91.8        | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 37.3        | 37.8       | 33.8        | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 39.4        | 13.9       | 30.6        | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 6.6         | 0.7        | 0.8         | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 38.9        | 13.9       | 30.4        | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 該当なし        | 4.7        | 該当なし        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 6.5 電源の特性

パラメータは  $-40^{\circ}\text{C} \leq T_j \leq 150^{\circ}\text{C}$  で有効 (特に記述のない限り)

| パラメータ                   | テスト条件                                                                                                                                 | 最小値                                                                                           | 標準値  | 最大値  | 単位 |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|----|

| パッテリからの電源供給             |                                                                                                                                       |                                                                                               |      |      |    |

| $I_{\text{SUP}}$        | スリープ モード: 選択的ウェークオフ、 $4.5\text{V} \leq V_{\text{SUP}} \leq 28\text{V}$                                                                | 20                                                                                            | 35   | 40   | μA |

|                         | スタンバイ モード: 選択的ウェークオフ、 $4.5\text{V} \leq V_{\text{SUP}} \leq 28\text{V}$                                                               | 60                                                                                            | 95   | 120  | μA |

|                         | CAN バスのリスニング時、バイアスを $2.5\text{V}$ に接続した場合の追加電流。                                                                                       | 15                                                                                            | 40   | 55   | μA |

|                         | WAKE ピンからの追加電流                                                                                                                        | 1                                                                                             | 2    | 3    | μA |

|                         | 通常モード                                                                                                                                 | 1                                                                                             | 1.5  | 2    | mA |

|                         | 選択的ウェークアップ機能が有効でバスがアクティブのときの追加電流                                                                                                      | 400                                                                                           | 550  | 600  | μA |

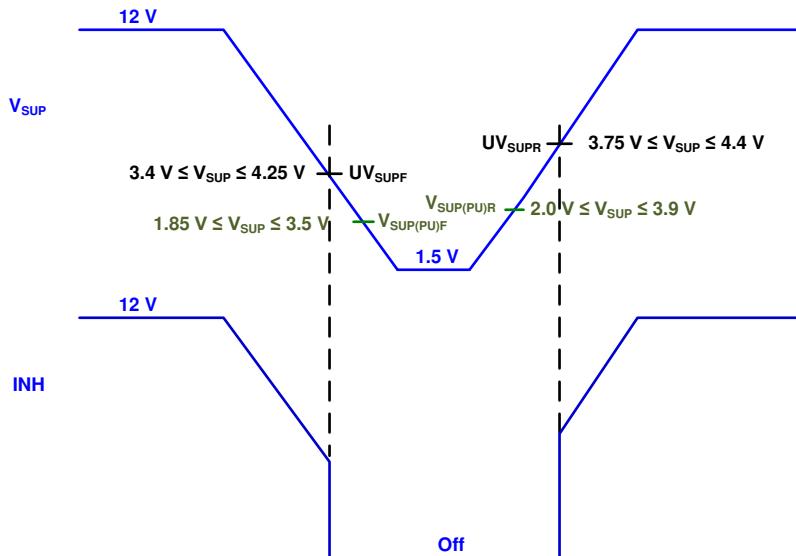

| $V_{\text{SUP(PU)R}}$   | 電源オン検出                                                                                                                                | $V_{\text{SUP}}$ 立ち上がり                                                                        | 1.9  | 3.9  | V  |

| $V_{\text{SUP(PU)F}}$   | 電源オフ検出                                                                                                                                | $V_{\text{SUP}}$ 立ち下がり                                                                        | 1.8  | 3.5  | V  |

| $UV_{\text{SUPR}}$      | 電源低電圧からの復帰                                                                                                                            | $V_{\text{SUP}}$ 立ち上がり                                                                        | 3.75 | 4.4  | V  |

| $UV_{\text{SUPF}}$      | 電源低電圧検出                                                                                                                               | $V_{\text{SUP}}$ 立ち下がり                                                                        | 3.4  | 4.25 | V  |

| $V_{\text{CC}}$ からの電源供給 |                                                                                                                                       |                                                                                               |      |      |    |

| $I_{\text{CC}}$         | 通常モード: リセッショブ、 $V_{\text{TXD}} = V_{\text{IO}}$                                                                                       | 3                                                                                             | 5    | 7    | mA |

|                         | 通常モード: ドミナント、 $V_{\text{TXD}} = 0\text{V}$ 、 $R_{\text{L}} = 60\Omega$ 、 $C_{\text{L}} = \text{開放}$ 、典型的なバス負荷                         | 60                                                                                            | 70   | 80   | mA |

|                         | 通常モード: ドミナント、 $V_{\text{TXD}} = 0\text{V}$ 、 $R_{\text{L}} = 50\Omega$ 、 $C_{\text{L}} = \text{開放}$ 、バス高負荷                            | 70                                                                                            | 80   | 90   | mA |

|                         | 通常モード: ドミナント (バスフォルト時)、 $V_{\text{TXD}} = 0\text{V}$ 、 $C_{\text{ANH}} = -25\text{V}$ 、 $R_{\text{L}}$ および $C_{\text{L}} = \text{開放}$ | 110                                                                                           | 120  | 130  | mA |

|                         | スタンバイ モード: 選択的ウェークオフ、 $V_{\text{TXD}} = V_{\text{IO}}$ 、 $R_{\text{L}} = 50\Omega$ 、 $C_{\text{L}} = \text{開放}$                       | 3.5                                                                                           | 8    | 12   | μA |

|                         | スリープ モード                                                                                                                              | 2.5                                                                                           | 5    | 7    | μA |

| $UV_{\text{CCR}}$       | 電源低電圧からの復帰                                                                                                                            | $V_{\text{CC}}$ 立ち上がり                                                                         | 4.2  | 4.5  | V  |

| $UV_{\text{CCF}}$       | 電源低電圧検出                                                                                                                               | $V_{\text{CC}}$ 立ち下がり                                                                         | 3.5  | 4    | V  |

| $V_{\text{IO}}$ からの電源供給 |                                                                                                                                       |                                                                                               |      |      |    |

| $I_{\text{IO}}$         | $V_{\text{IO}}$ からの I/O 電源電流                                                                                                          | スリープ モード: $V_{\text{TXD}} = V_{\text{IO}}$ 、 $1.71\text{V} < V_{\text{IO}} < 5.5\text{V}$ の条件 | 10   | 15   | μA |

| $I_{\text{IO}}$         | $V_{\text{IO}}$ からの I/O 電源電流                                                                                                          | スタンバイ モード: $V_{\text{TXD}} = V_{\text{IO}}$                                                   | 10   | 15   | μA |

|                         |                                                                                                                                       | 通常モード: リセッショブ                                                                                 | 10   | 15   | μA |

|                         |                                                                                                                                       | 通常モード: ドミナント                                                                                  | 40   | 50   | μA |

| $UV_{\text{IOR}}$       | 電源低電圧からの復帰                                                                                                                            | $V_{\text{IO}}$ 立ち上がり                                                                         | 1.4  | 1.65 | V  |

## 6.5 電源の特性 (続き)

パラメータは  $-40^{\circ}\text{C} \leq T_j \leq 150^{\circ}\text{C}$  で有効 (特に記述のない限り)

| パラメータ             | テスト条件                            | 最小値 | 標準値  | 最大値 | 単位 |

|-------------------|----------------------------------|-----|------|-----|----|

| $V_{\text{VIOF}}$ | 電源低電圧検出<br>$V_{\text{IO}}$ 立ち下がり | 1   | 1.25 |     | V  |

## 6.6 電気的特性

パラメータは  $-40^{\circ}\text{C} \leq T_j \leq 150^{\circ}\text{C}$ 、 $4.75\text{V} \leq V_{\text{CC}} \leq 5.25\text{V}$  で有効 (特に記述のない限り)

| パラメータ                 | テスト条件                                                                                                                                                    | 最小値                                                                                                                                                                                                                                                  | 標準値   | 最大値   | 単位  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----|

| <b>CAN ドライバの電気的特性</b> |                                                                                                                                                          |                                                                                                                                                                                                                                                      |       |       |     |

| $V_{\text{O(D)}}$     | バス出力電圧 (ドミナント) CANH                                                                                                                                      | レシーバのテスト回路と測定 を参照してください。<br>$V_{\text{TXD}} = 0\text{V}$ 、 $R_{\text{L}} = 45\Omega \sim 65\Omega$ 、 $C_{\text{L}} = \text{開放}$ 、 $R_{\text{CM}} = \text{開放}$                                                                                        | 3     | 4.26  | V   |

|                       | バス出力電圧 (ドミナント) CANL                                                                                                                                      |                                                                                                                                                                                                                                                      | 0.75  | 2.01  | V   |

| $V_{\text{O(R)}}$     | CANH、CANL のリセッショブ時のバス出力電圧                                                                                                                                | バスの状態 (物理的ビット表現) および レシーバのテスト回路と測定 を参照してください。 $V_{\text{TXD}} = V_{\text{IO}}$ 、 $R_{\text{L}} = \text{開放}$ (無負荷)、 $R_{\text{CM}} = \text{開放}$                                                                                                       | 2     | 2.5   | V   |

| $V_{\text{(DIFF)}}$   | 差動電圧                                                                                                                                                     |                                                                                                                                                                                                                                                      | -42   | 42    | V   |

| $V_{\text{OD(R)}}$    | CANH、CANL の終端済みバスにおける出力電圧 (リセッショブ)                                                                                                                       | $V_{\text{TXD}} = V_{\text{IO}}$ 、 $45\Omega \leq R_{\text{L}} \leq 65\Omega$ 、スプリット終端容量 $4.7\text{nF}$                                                                                                                                              | 2.256 | 2.756 | V   |

| $V_{\text{OD(D)}}$    | 差動出力電圧 (ドミナント)、拡張バス負荷                                                                                                                                    | バスの状態 (物理的ビット表現) および レシーバのテスト回路と測定 を参照してください。 $V_{\text{TXD}} = 0\text{V}$ 、 $45\Omega \leq R_{\text{L}} \leq 65\Omega$ 、 $C_{\text{L}} = \text{開放}$ 、 $R_{\text{CM}} = \text{開放}$                                                                   | 1.5   | 3     | V   |

|                       |                                                                                                                                                          | バスの状態 (物理的ビット表現) を レシーバのテスト回路と測定 を参照してください。 $V_{\text{TXD}} = 0\text{V}$ 、 $45\Omega \leq R_{\text{L}} = 70\Omega$ 、 $C_{\text{L}} = \text{開放}$ 、 $R_{\text{CM}} = \text{開放}$                                                                        | 1.5   | 3.3   | V   |

|                       |                                                                                                                                                          | バスの状態 (物理的ビット表現) および レシーバのテスト回路と測定 を参照してください。 $V_{\text{TXD}} = 0\text{V}$ 、 $R_{\text{L}} = 2.24\text{k}\Omega$ 、 $C_{\text{L}} = \text{開放}$ 、 $R_{\text{CM}} = \text{開放}$                                                                          | 1.5   | 5     | V   |

| $V_{\text{OD(R)}}$    | 差動出力電圧 (リセッショブ)                                                                                                                                          | バスの状態 (物理的ビット表現) および レシーバのテスト回路と測定 を参照してください。 $V_{\text{TXD}} = V_{\text{IO}}$ 、 $R_{\text{L}} = 60\Omega$ 、 $C_{\text{L}} = \text{開放}$ 、 $R_{\text{CM}} = \text{開放}$                                                                                | -120  | 12    | mV  |

|                       |                                                                                                                                                          | バスの状態 (物理的ビット表現) および レシーバのテスト回路と測定 を参照してください。 $V_{\text{TXD}} = V_{\text{IO}}$ 、 $R_{\text{L}} = \text{開放}$ (無負荷)、 $C_{\text{L}} = \text{開放}$ 、 $R_{\text{CM}} = \text{開放}$                                                                          | -50   | 50    | mV  |

| $V_{\text{O(INACT)}}$ | バスバイアス無効 (STBY) 時の CANH バス出力電圧<br>バスバイアス無効 (STBY) 時の CANL バス出力電圧<br>バスバイアス無効 (STBY) 時の CANH - CANL (リセッショブ) のバス出力電圧                                      | バスの状態 (物理的ビット表現) および レシーバのテスト回路と測定 を参照してください。 $V_{\text{TXD}} = V_{\text{IO}}$ 、 $R_{\text{L}} = \text{開放}$ 、 $C_{\text{L}} = \text{開放}$ 、 $R_{\text{CM}} = \text{開放}$                                                                               | -0.1  | 0.1   | V   |

|                       |                                                                                                                                                          |                                                                                                                                                                                                                                                      | -0.1  | 0.1   | V   |

|                       |                                                                                                                                                          |                                                                                                                                                                                                                                                      | -0.2  | 0.2   | V   |

| $V_{\text{SYM}}$      | 出力対称性 (ドミナントまたはリセッショブ)<br>( $V_{\text{O(CANH)}} + V_{\text{O(CANL)}}$ ) / $V_{\text{REC}}$                                                               | バスの状態 (物理的ビット表現) および レシーバのテスト回路と測定 を参照してください。 $45\Omega \leq R_{\text{L}} \leq 65\Omega$ 、 $C_{\text{L}} = \text{開放}$ 、 $R_{\text{CM}} = \text{開放}$ 、 $C_{\text{1}} = 4.7\text{nF}$ 、 $\text{TXD} = 250\text{kHz}$ 、 $1\text{MHz}$ 、 $2.5\text{MHz}$ | 0.95  | 1.05  | V/V |

| $V_{\text{SYM\_DC}}$  | 出力対称性 (ドミナントまたはリセッショブ) ( $V_{\text{CC}} - V_{\text{O(CANH)}} - V_{\text{O(CANL)}}$ )、HS-PMA 実装の想定最高ビットレートに対応する周波数 $< 1\text{MHz}$ または $< 2\text{Mbit/s}$ | バスの状態 (物理的ビット表現) および レシーバのテスト回路と測定 を参照してください。 $45\Omega \leq R_{\text{L}} \leq 65\Omega$ 、 $C_{\text{L}} = \text{オープン}$ 、 $R_{\text{CM}} = \text{オープン}$ 、 $C_{\text{1}} = 4.7\text{nF}$                                                              | -300  | 300   | mV  |

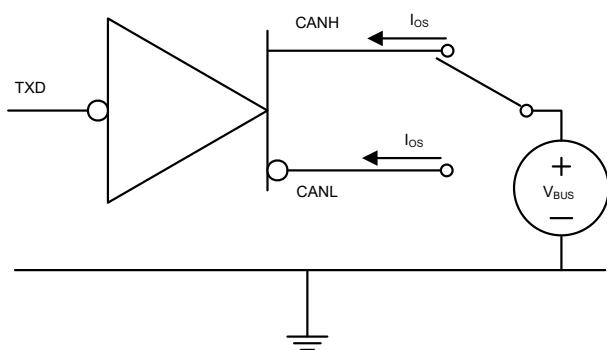

| $I_{\text{OS\_DOM}}$  | 短絡定常状態出力電流、ドミナント、図 9-1 および 図 9-8 を参照してください                                                                                                               | $-3.0\text{V} \leq V_{\text{CANH}} \leq +18.0\text{V}$ 、 $\text{CANL} = \text{開放}$ 、 $V_{\text{TXD}} = 0\text{V}$                                                                                                                                    | -115  |       | mA  |

|                       |                                                                                                                                                          | $-3.0\text{V} \leq V_{\text{CANL}} \leq +18.0\text{V}$ 、 $\text{CANH} = \text{開放}$ 、 $V_{\text{TXD}} = 0\text{V}$                                                                                                                                    |       | 115   | mA  |

| $I_{\text{OS\_REC}}$  | 短絡定常状態出力電流、リセッショブ。図 9-1 および 図 9-8 を参照してください                                                                                                              | $-27\text{V} \leq V_{\text{BUS}} \leq +42\text{V}$ 、 $V_{\text{BUS}} = \text{CANH} = \text{CANL}$                                                                                                                                                    | -5    | 5     | mA  |

## 6.6 電気的特性 (続き)

パラメータは  $-40^{\circ}\text{C} \leq T_j \leq 150^{\circ}\text{C}$ 、 $4.75\text{V} \leq V_{\text{CC}} \leq 5.25\text{V}$  で有効 (特に記述のない限り)

| パラメータ                       | テスト条件                                                                                                                                                                                                                                             | 最小値  | 標準値  | 最大値 | 単位       |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|----------|

| $R_{\text{SE\_ACT\_REC}}$   | TXD=0V、<br>$-12\text{V} \leq V_{\text{O(D)}} \leq 12\text{V}$<br>の条件下での $2\text{V} \leq V_{\text{O(D)}} \leq \text{VCC-2V}$ 、 $\Delta V/\Delta I$ 使<br>用 (RX セクションの $R_{\text{SE\_PAS\_REC}}$ /<br>$R_{\text{DIFF\_PAS\_REC}}$ と同様)、バス無負荷         | 37.5 | 66.5 |     | $\Omega$ |

| $R_{\text{DIFF\_ACT\_REC}}$ | $2\text{V} \leq V_{\text{O(D)}} \leq \text{VCC-2V}$<br>、<br>TXD の立ち上りエッジからアクティブリセッショップ駆<br>動期間 ( $t_{\text{REC\_START}}$ ) 経過までの継続時間、 $\Delta V/\Delta I$ 使<br>用 (RX セクションの $R_{\text{SE\_PAS\_REC}}$ /<br>$R_{\text{DIFF\_PAS\_REC}}$ と同様)、バス無負荷 | 75   | 133  |     | $\Omega$ |

### CAN レシーバの電気的特性

|                             |                                                                                                               |                                                                                                                                                                   |      |     |               |

|-----------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|---------------|

| $V_{\text{ITDOM}}$          | レシーバがドミナント状態の差動入力電圧範囲、<br>バスバイアスがアクティブ                                                                        | $-12\text{V} \leq V_{\text{CANL}} \leq +12\text{V}$<br>$-12\text{V} \leq V_{\text{CANH}} \leq +12\text{V}$ 、レシーバのテスト回路と<br>測定 および 通常およびサilent モードのレシ<br>ーバ機能表 を参照 | 0.9  | 8   | V             |

| $V_{\text{ITREC}}$          | レシーバリセッショップ状態の差動入力電圧範囲、バ<br>スバイアスがアクティブ                                                                       |                                                                                                                                                                   | -3   | 0.5 | V             |

| $V_{\text{HYS}}$            | 入力スレッショルドのヒステリシス電圧、通常モード<br>および選択的ウェイク モード                                                                    |                                                                                                                                                                   | 120  |     | mV            |

| $V_{\text{DIFF\_DOM}}$      | レシーバドミナント状態の差動入力電圧範囲、バ<br>スバイアスがアクティブ時                                                                        | $12\text{V} \leq V_{\text{CANL}} \leq +12\text{V}$<br>$-12\text{V} \leq V_{\text{CANH}} \leq +12\text{V}$ 、レシーバのテスト回路と<br>測定 および 通常およびサilent モードのレシ<br>ーバ機能表 を参照  | 1.15 | 8   | V             |

| $V_{\text{DIFF\_REC}}$      | レシーバリセッショップ状態の差動入力電圧範囲、バ<br>スバイアスがアクティブ中                                                                      |                                                                                                                                                                   | -3   | 0.4 | V             |

| $V_{\text{CM}}$             | 同相モードの範囲:通常モードおよびスタンバイ<br>モード                                                                                 |                                                                                                                                                                   | -12  | 12  | V             |

| $I_{\text{OFF(LKG)}}$       | パワーオフ (電源オフ) バス入力リーク電流                                                                                        | $\text{CANH} = \text{CANL} = 5\text{V}$ 、 $V_{\text{CC}} = V_{\text{IO}} = V_{\text{sup}}$ を $0\Omega$<br>および $47\text{k}\Omega$ の抵抗を介して GND に接続                  | -5   | 5   | $\mu\text{A}$ |

| $C_{\text{I}}$              | グランドに対する入力容量 (CANH または<br>CANL) <sup>(1)</sup>                                                                |                                                                                                                                                                   |      | 40  | pF            |

| $C_{\text{ID}}$             | 差動入力容量 <sup>(1)</sup>                                                                                         |                                                                                                                                                                   |      | 20  | pF            |

| $R_{\text{DIFF\_PAS\_REC}}$ | パッシブ・リセッショップ期間中の差動入力抵抗                                                                                        | $V_{\text{TXD}} = V_{\text{IO}}$ 、通常モード。 $-2\text{V} \leq V_{\text{CANH}} \leq +7\text{V}$ 、<br>$-2\text{V} \leq V_{\text{CANL}} \leq +7\text{V}$                 | 12   | 100 | k $\Omega$    |

| $R_{\text{SE\_CANH/L}}$     | パッシブ リセッショップ期間中のシングル エンド入力<br>抵抗 (CANH または CANL)                                                              | $-2\text{V} \leq V_{\text{CANH}} \leq +7\text{V}$<br>$-2\text{V} \leq V_{\text{CANL}} \leq +7\text{V}$                                                            | 6    | 50  | k $\Omega$    |

| $R_{\text{IN(M)}}$          | 入力抵抗マッチング: $[2 \times (R_{\text{IN(CANH}}} - R_{\text{IN(CANL)}}) / (R_{\text{CANH}} + R_{\text{IN(CANL)}})]$ | $V_{\text{CANH}} = V_{\text{CANL}} = 5\text{V}$                                                                                                                   | -1   | 1   | %             |

### INH 出力端子 (高電圧出力)

|                       |                                    |                                |     |    |                  |

|-----------------------|------------------------------------|--------------------------------|-----|----|------------------|

| $\Delta V_{\text{H}}$ | $V_{\text{SUP}}$ から INH への高レベル電圧降下 | $I_{\text{INH}} = -6\text{mA}$ | 0.5 | 1  | V                |

| $R_{\text{pd}}$       | プルダウン抵抗                            | スリープ モード                       | 7   | 10 | $\text{M}\Omega$ |

### WAKE 入力端子

|                 |              |                                      |   |   |               |

|-----------------|--------------|--------------------------------------|---|---|---------------|

| $V_{\text{IH}}$ | High レベル入力電圧 | 選択的ウェークアップまたはスタンバイ モード、<br>WAKE ピン有効 | 4 |   | V             |

| $V_{\text{IL}}$ | Low レベル入力電圧  | 選択的ウェークアップまたはスタンバイ モード、<br>WAKE ピン有効 |   | 2 | V             |

| $I_{\text{IL}}$ | Low レベル入力電流  | $\text{WAKE} = 1\text{V}$            | 1 | 2 | $\mu\text{A}$ |

### SDI、SCK、nCS、TXD 入力端子

|                       |                 |                                                                       |     |     |                     |

|-----------------------|-----------------|-----------------------------------------------------------------------|-----|-----|---------------------|

| $V_{\text{IH}}$       | High レベル入力電圧    |                                                                       | 0.7 |     | $V_{\text{IO}}$     |

| $V_{\text{IL}}$       | Low レベル入力電圧     |                                                                       |     |     | 0.3 $V_{\text{IO}}$ |

| $I_{\text{IH}}$       | High レベル入力リーク電流 | $1.71\text{V} \leq V_{\text{IO}} \leq 5.5\text{V}$                    | -1  | 1   | $\mu\text{A}$       |

| $I_{\text{IL}}$       | Low レベル入力リーク電流  | 入力 = $0\text{V}$ 、 $1.71\text{V} \leq V_{\text{IO}} \leq 5.5\text{V}$ | -30 | -2  | $\mu\text{A}$       |

| $C_{\text{IN}}$       | 入力容量            | 20MHz 時                                                               | 2   | 15  | pF                  |

| $I_{\text{LKG(OFF)}}$ | 電源がない場合のリーク電流です | 入力 = $5.5\text{V}$ 、 $V_{\text{IO}} = V_{\text{SUP}} = 0\text{V}$     | -1  | 0   | $\mu\text{A}$       |

| $R_{\text{pu}}$       | プルアップ抵抗         |                                                                       | 250 | 350 | 450                 |

| <b>RXD、SDO 出力端子</b>   |                 |                                                                       |     |     |                     |

## 6.6 電気的特性 (続き)

パラメータは  $-40^{\circ}\text{C} \leq T_j \leq 150^{\circ}\text{C}$ 、 $4.75\text{V} \leq V_{\text{CC}} \leq 5.25\text{V}$  で有効 (特に記述のない限り)

| パラメータ                 |                                                       | テスト条件                                                                            | 最小値  | 標準値             | 最大値 | 単位                 |

|-----------------------|-------------------------------------------------------|----------------------------------------------------------------------------------|------|-----------------|-----|--------------------|

| $V_{\text{OH}}$       | High レベル出力電圧                                          | $I_{\text{OH}} = -1.5\text{mA}$ , $V_{\text{IO}} = 1.71\text{V}$                 | 0.8  | $V_{\text{IO}}$ | 0.8 |                    |

|                       |                                                       | $I_{\text{OH}} = -2\text{mA}$ , $V_{\text{IO}} \geq 2.5\text{V}$                 |      |                 |     |                    |

| $V_{\text{OL}}$       | Low レベル出力電圧                                           | $I_{\text{OL}} = 2\text{mA}$                                                     |      | 0.2             |     | $V_{\text{IO}}$    |

| $I_{\text{LKG(OFF)}}$ | 無電源時リーク電流 - SDO ピン                                    | $V_{\text{nCS}} = V_{\text{IO}}$ , $V_{\text{O}} = 0\text{V} \sim V_{\text{IO}}$ | -5   | 5               |     | $\mu\text{A}$      |

| $R_{\text{RXD(PU)}}$  | RXD ピンのプルアップ抵抗                                        | UV <sub>SUP</sub> および POR 状態、ならびにスリープ モード時にアクティブ                                 | 40   | 60              | 80  | $\text{k}\Omega$   |

| $I_{\text{LKG(RXD)}}$ | $V_{\text{IO}}$ 印加時、 $R_{\text{RXD(PU)}}$ 有効時の RXD 電流 | $V_{\text{RXD}} = V_{\text{IO}}$ , $V_{\text{O}} = 0\text{V} \sim V_{\text{IO}}$ | -1   | 1               |     | $\mu\text{A}$      |

|                       |                                                       | $V_{\text{RXD}} = \text{GND}$ , UV <sub>SUP</sub> および POR 状態、ならびにスリープ モード時にアクティブ | -140 |                 | -20 | $\mu\text{A}$      |

| サーマル シャットダウン          |                                                       |                                                                                  |      |                 |     |                    |

| $T_{\text{SDR}}$      | サーマル シャットダウン                                          |                                                                                  | 175  |                 |     | $^{\circ}\text{C}$ |

| $T_{\text{SDF}}$      | サーマル シャットダウン解除                                        |                                                                                  | 160  |                 |     | $^{\circ}\text{C}$ |

| $T_{\text{SDW}}$      | サーマル シャットダウン警告                                        |                                                                                  | 150  |                 |     | $^{\circ}\text{C}$ |

| $T_{\text{SDHYS}}$    | サーマル シャットダウンヒステリシス                                    |                                                                                  | 10   |                 |     | $^{\circ}\text{C}$ |

(1) ISO 11898-2:2024 に準拠したテスト

## 6.7 タイミング要件

パラメータは  $-40^{\circ}\text{C} \leq T_j \leq 150^{\circ}\text{C}$  で有効 (特に記述のない限り)

|                            |                                                                                                                                                               | 最小値 | 公称値  | 最大値 | 単位            |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------------|

| 電源                         |                                                                                                                                                               |     |      |     |               |

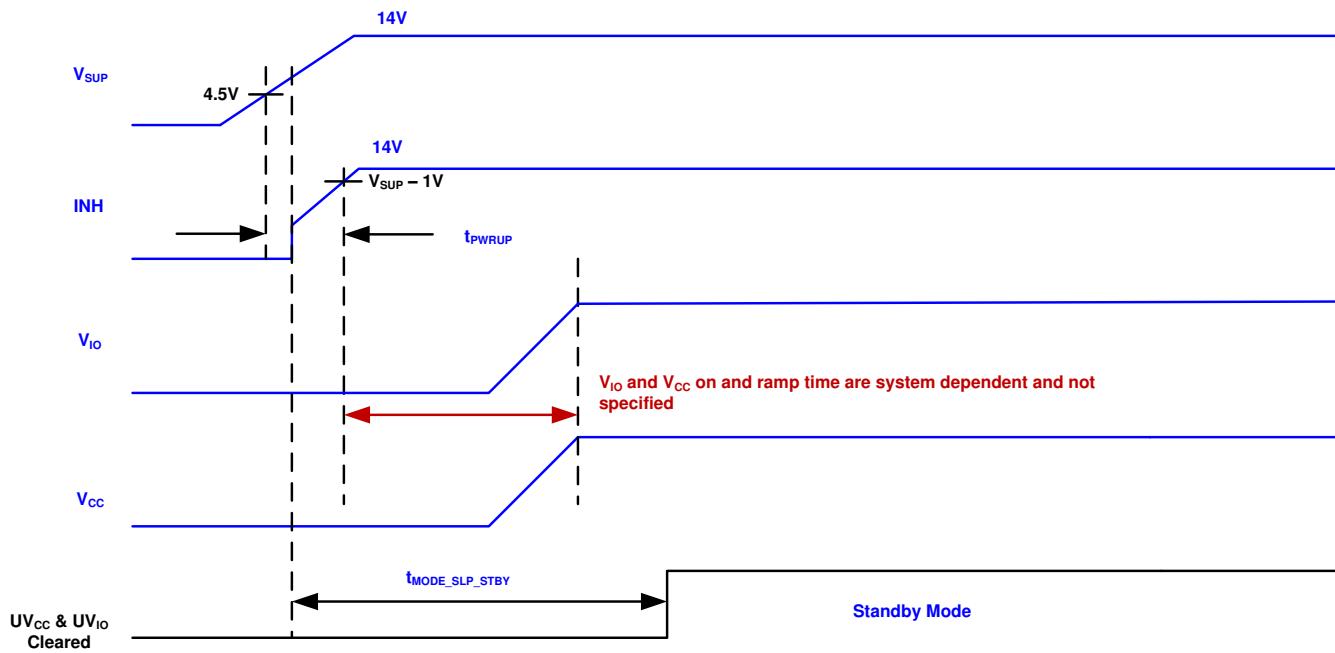

| $t_{\text{PWRUP}}$         | V <sub>SUP</sub> が 4.4V を超えてから INH がアクティブになるまでの時間、 <a href="#">起動タイミング</a> を参照                                                                                |     | 2    | 4   | ms            |

| $t_{\text{UVFLTR}}$        | 低電圧検出遅延時間                                                                                                                                                     | 3   | 50   |     | $\mu\text{s}$ |

| $t_{\text{UVSLP}}$         | UV <sub>CC</sub> や UV <sub>IO</sub> の低電圧状態が解除されてから、スリープ モードまたはフェイリセーフ モードへ移行するまでの時間                                                                           | 200 | 400  |     | ms            |

| モード変更                      |                                                                                                                                                               |     |      |     |               |

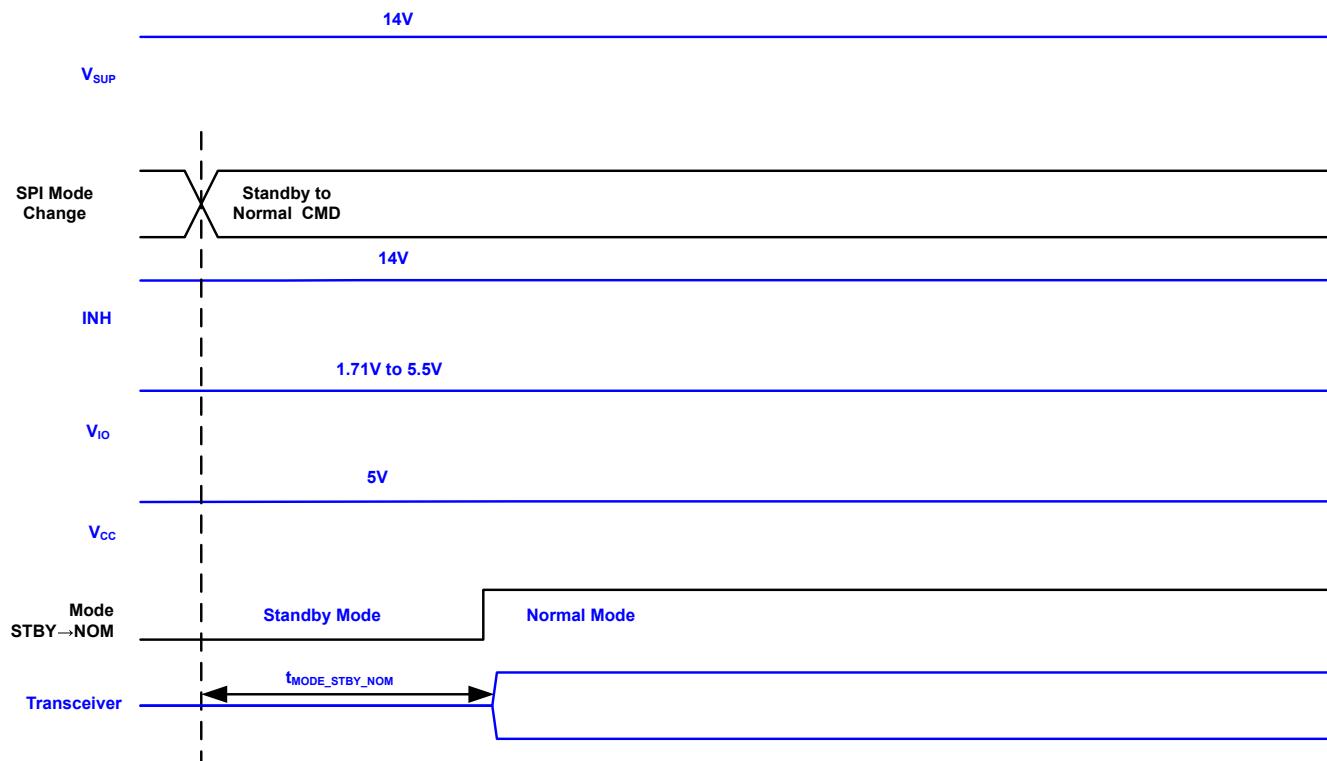

| $t_{\text{MODE_STBY_NOM}}$ | SPI を介してこのコマンドを受信した後、スタンバイ モードから通常モードに移行するのに要する時間、 <a href="#">セクション 7</a> を参照                                                                                |     | 70   |     | $\mu\text{s}$ |

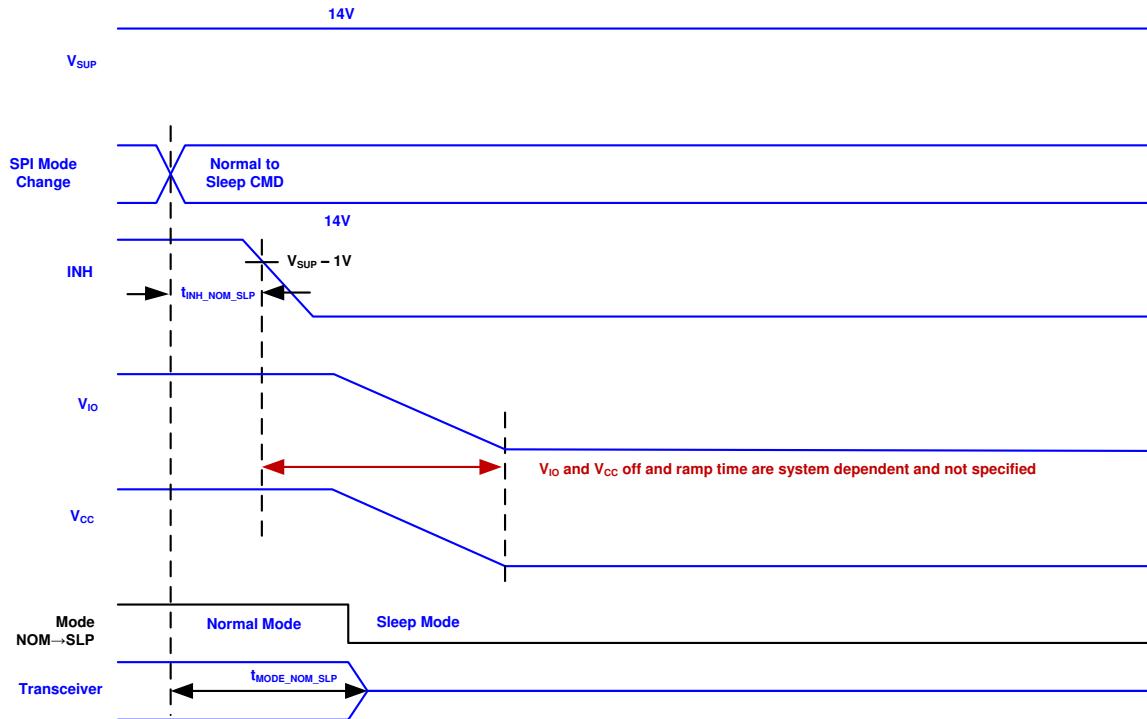

| $t_{\text{MODE_NOM_SLP}}$  | SPI を介してこのコマンドを受信した後、通常モードからスリープ モードに移行するのに要する時間、 <a href="#">通常からスリープへのタイミング</a> を参照                                                                         |     | 200  |     | $\mu\text{s}$ |

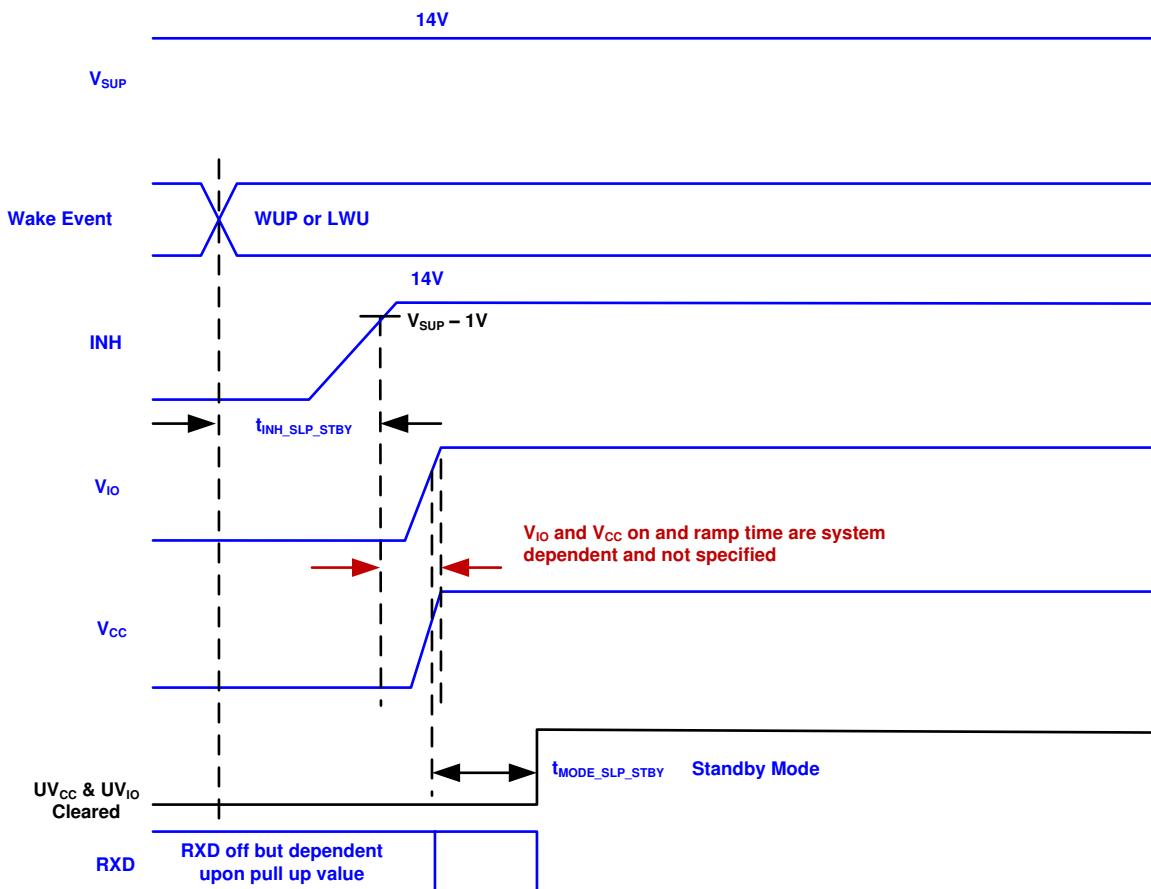

| $t_{\text{MODE_SLP_STBY}}$ | INH がオンになった後、UV <sub>CC</sub> および UV <sub>IO</sub> 解除から RXD ピンが Low にプルダウンされるまでの時間、 <a href="#">(3) スリープからスタンバイへのタイミング</a> を参照                                |     | 100  |     | $\mu\text{s}$ |

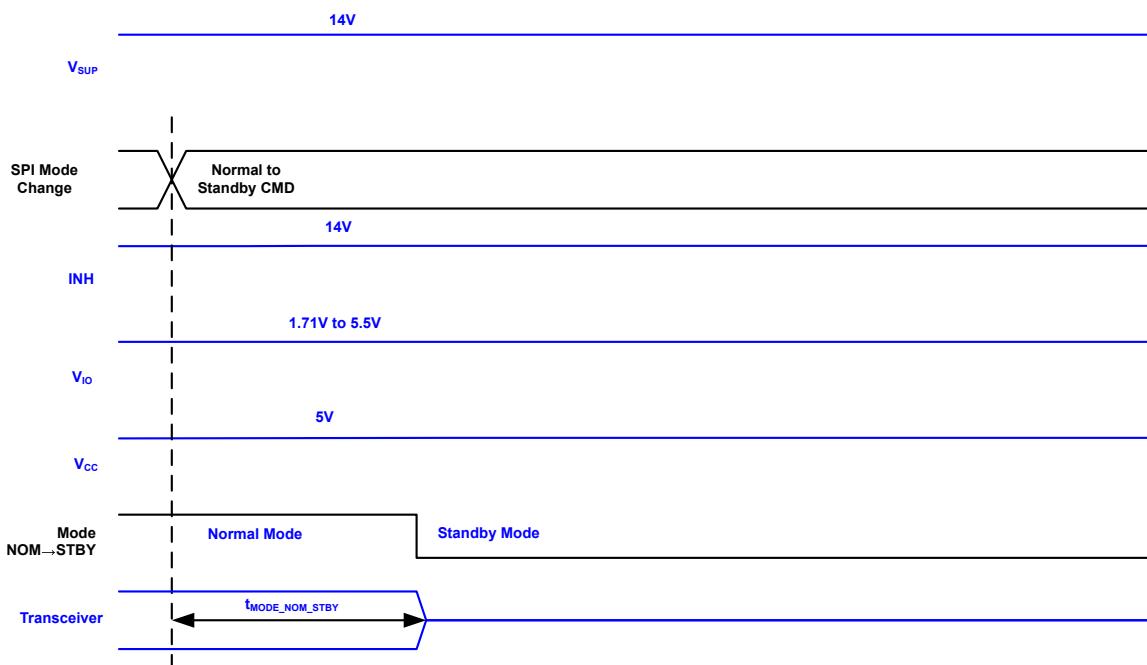

| $t_{\text{MODE_NOM_STBY}}$ | SPI を介してこのコマンドを受信した後、通常モードからスタンバイ モードに移行するのに要する時間、 <a href="#">通常からスタンバイへのタイミング</a> を参照                                                                       |     | 70   |     | $\mu\text{s}$ |

| $t_{\text{INH_SLP_STBY}}$  | WUP、LWU または WUF イベント後、INH アサートまでの時間、 <a href="#">スリープからスタンバイへのタイミング</a> を参照                                                                                   |     | 100  |     | $\mu\text{s}$ |

| $t_{\text{INH_NOM_SLP}}$   | 通常モードからスリープ モードへ移行するための SPI 書き込み実行から、INH がオフになるまでの時間、 <a href="#">通常からスリープへのタイミング</a> を参照                                                                     |     | 50   |     | $\mu\text{s}$ |

| デバイスタイミング                  |                                                                                                                                                               |     |      |     |               |

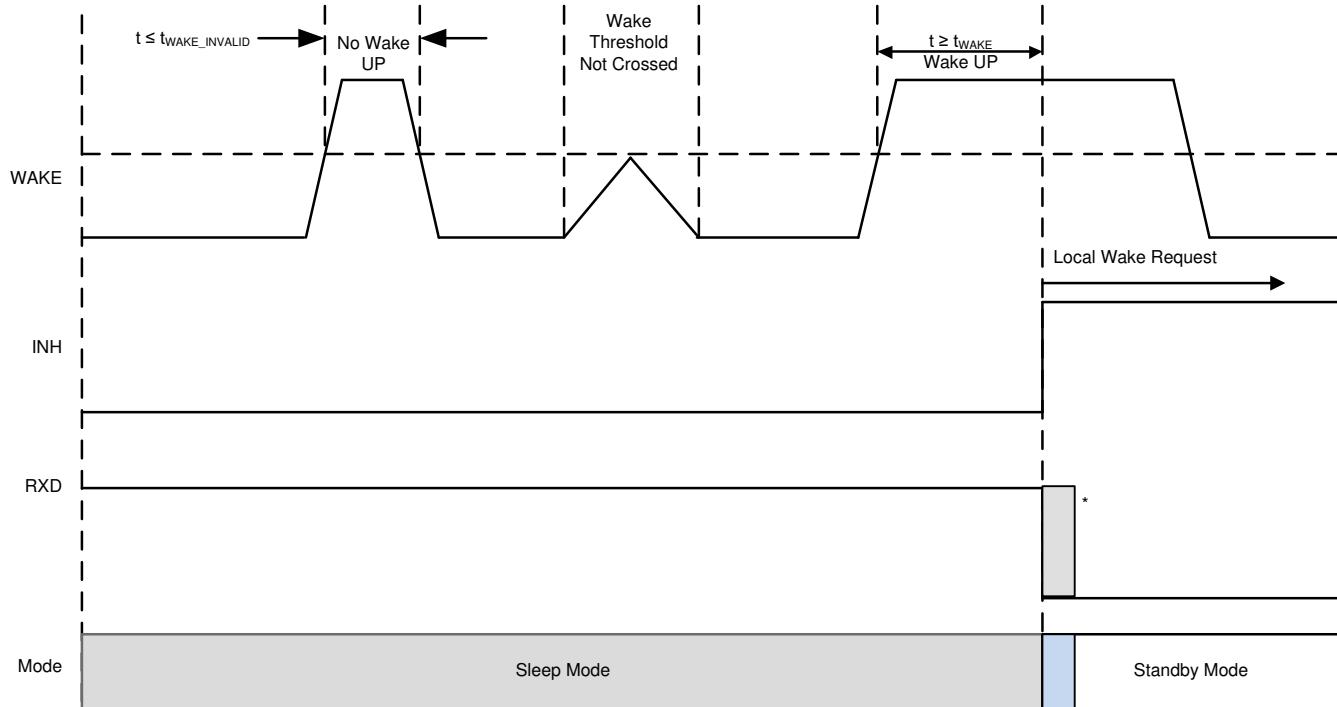

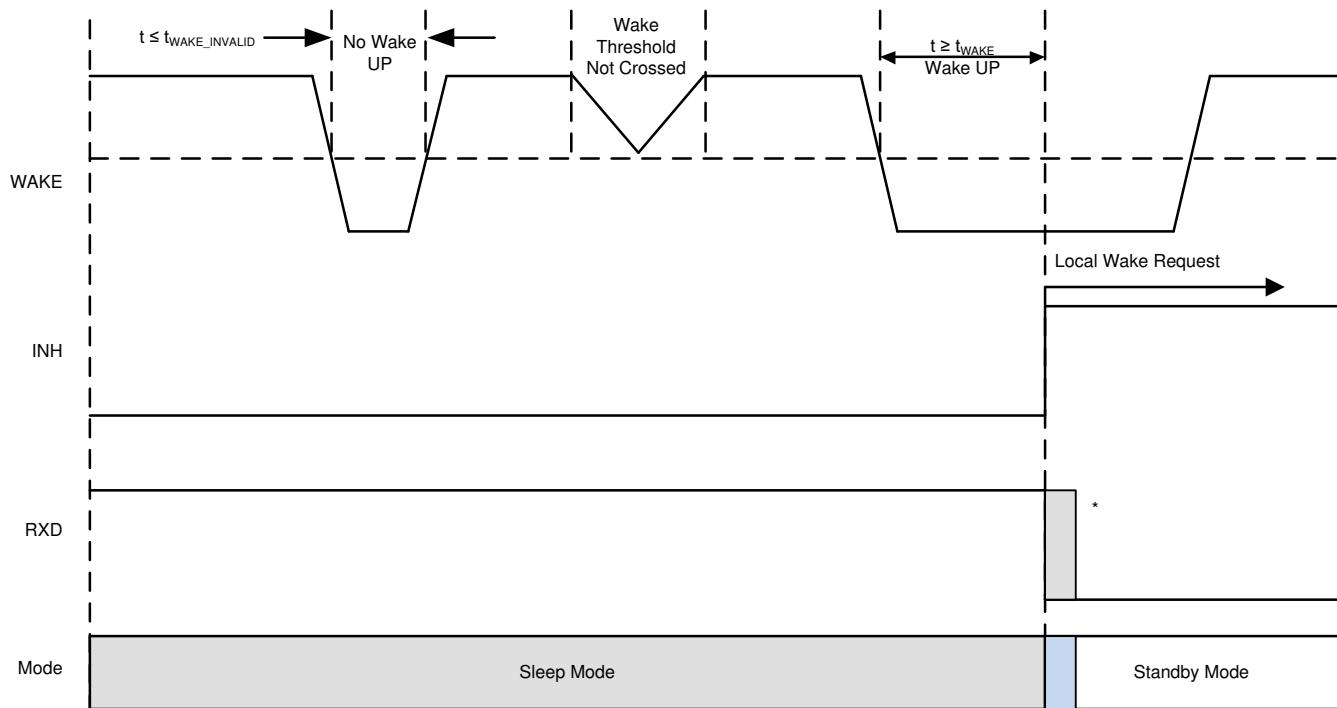

| $t_{\text{WAKE}}$          | WAKE 端子のエッジからのウェークアップ時間、スタンバイ、選択式ウェーク、スリープ モード、 <a href="#">ローカル ウェークアップ – 立ち上がりエッジ</a> および <a href="#">ローカル ウェークアップ – 立ち下がりエッジ</a> を参照                       |     | 40   |     | $\mu\text{s}$ |

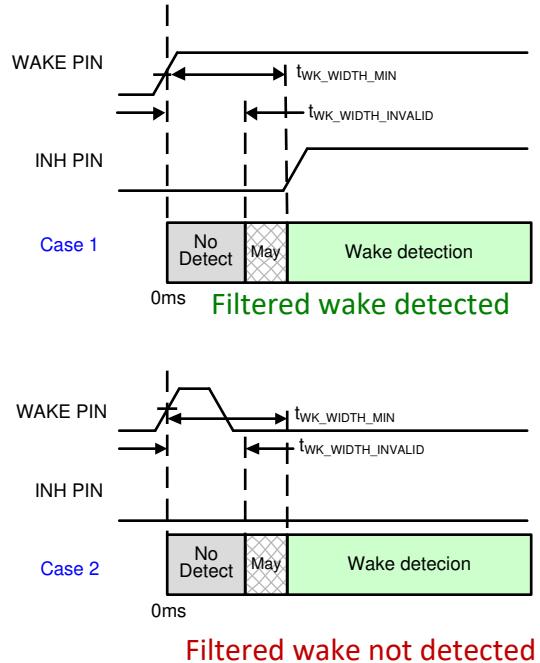

| $t_{\text{WAKE_INVALID}}$  | この値より短い WAKE 端子パルスはフィルタによって除去されます、 <a href="#">ローカル ウェークアップ – 立ち上がりエッジ</a> および <a href="#">ローカル ウェークアップ – 立ち下がりエッジ</a> を参照                                    |     | 10   |     | $\mu\text{s}$ |

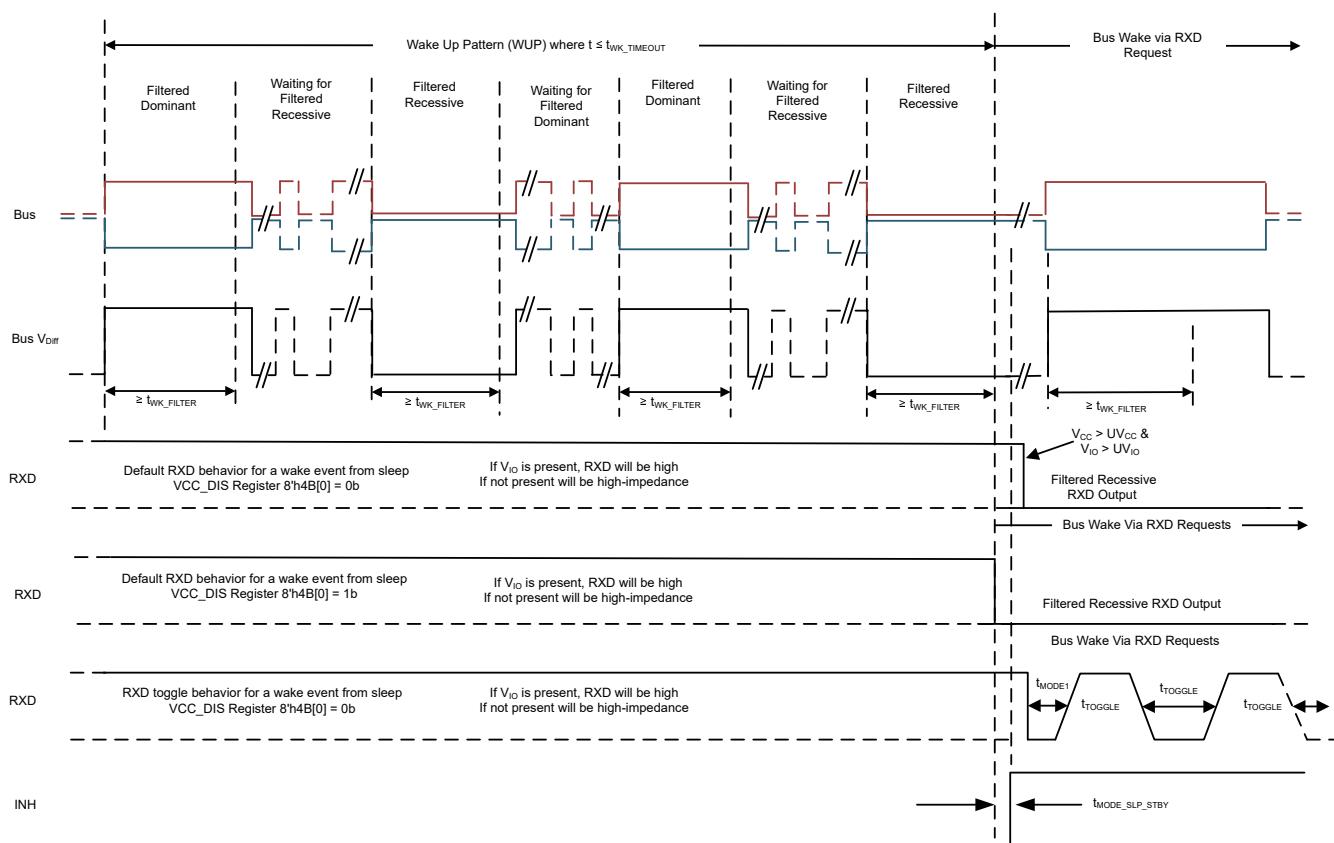

| $t_{\text{WK_TIMEOUT}}$    | バス ウェークアップ タイムアウト値、 <a href="#">ウェークアップ パターン (WUP)</a> と RXD 要求によるバス ウェーク (BWRR) を参照                                                                          | 0.5 | 2    |     | ms            |

| $t_{\text{WK_FILTER}}$     | ウェークアップ要求に対するフィルタ付きバス要件を満たすために必要なバス時間、 $4.75\text{V} \leq V_{\text{CC}} \leq 5.25\text{V}$ 、 <a href="#">ウェークアップ パターン (WUP)</a> と RXD 要求によるバス ウェーク (BWRR) を参照 | 0.5 | 0.95 |     | $\mu\text{s}$ |

## 6.7 タイミング要件 (続き)

パラメータは  $-40^{\circ}\text{C} \leq T_j \leq 150^{\circ}\text{C}$  で有効 (特に記述のない限り)

|                                     |                                                                                                          | 最小値  | 公称値  | 最大値 | 単位            |

|-------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|-----|---------------|

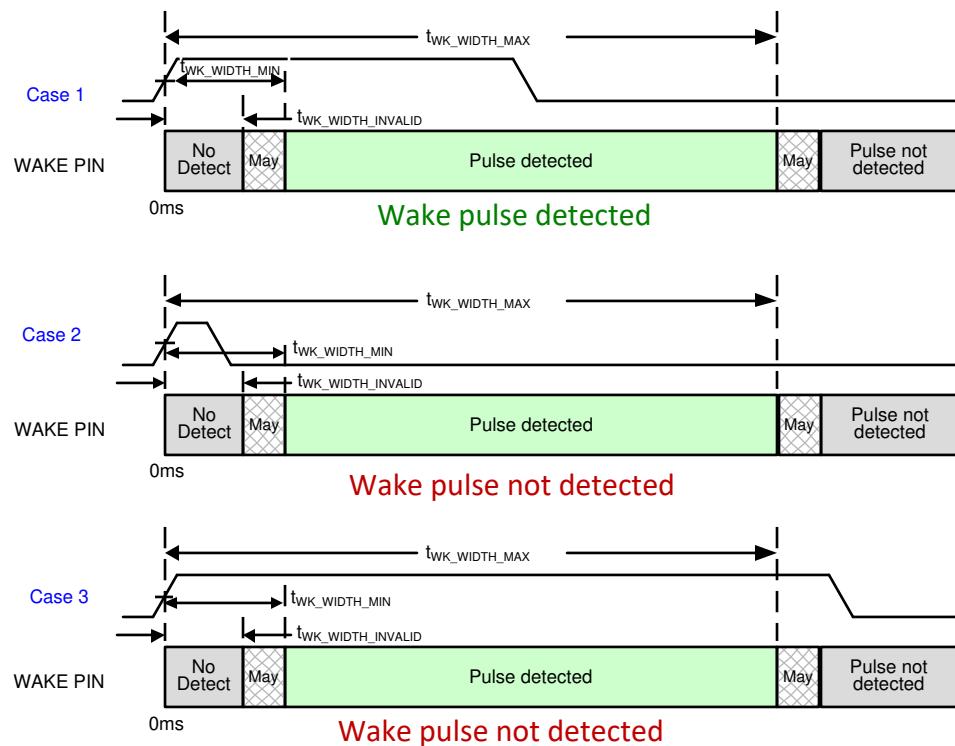

| $t_{WK\_WIDTH\_MIN}$ <sup>(4)</sup> | WAKE ピンの最小パルス幅 レジスタ <sup>(1)</sup> <sup>(2)</sup> 11h[3:2] = 00b、WAKE ピンのパルス動作 を参照                       | 10   |      |     | ms            |

|                                     | WAKE ピンの最小パルス幅 レジスタ <sup>(1)</sup> <sup>(2)</sup> 11h[3:2] = 01b、WAKE ピンのパルス動作 を参照                       | 20   |      |     | ms            |

|                                     | WAKE ピンの最小パルス幅 レジスタ <sup>(1)</sup> <sup>(2)</sup> 11h[3:2] = 10b、WAKE ピンのパルス動作 を参照                       | 40   |      |     | ms            |

|                                     | WAKE ピンの最小パルス幅 レジスタ <sup>(1)</sup> <sup>(2)</sup> 11h[3:2] = 11b、WAKE ピンのパルス動作 を参照                       | 80   |      |     | ms            |

| $t_{WK\_WIDTH\_INVALID}$            | 無効と見なされる最大 WAKE 端子パルス幅 <sup>(1)</sup> <sup>(2)</sup> レジスタ 11h[3:2] = 00b、WAKE ピンのパルス動作 を参照               |      | 5    |     | ms            |

|                                     | 無効と見なされる最大 WAKE 端子パルス幅 <sup>(1)</sup> <sup>(2)</sup> レジスタ 11h[3:2] = 01b、WAKE ピンのパルス動作 を参照               |      | 10   |     | ms            |

|                                     | 無効と見なされる最大 WAKE 端子パルス幅 <sup>(1)</sup> <sup>(2)</sup> レジスタ 11h[3:2] = 10b、WAKE ピンのパルス動作 を参照               |      | 20   |     | ms            |

|                                     | 無効と見なされる最大 WAKE 端子パルス幅 <sup>(1)</sup> <sup>(2)</sup> レジスタ 11h[3:2] = 11b、WAKE ピンのパルス動作 を参照               |      | 40   |     | ms            |

| $t_{WK\_WIDTH\_MAX}$                | 最大 WAKE 端子パルス ウィンドウ <sup>(1)</sup> レジスタ 11h[1:0] = 00b、WAKE ピンのパルス動作 を参照                                 | 750  | 950  |     | ms            |

|                                     | 最大 WAKE 端子パルス ウィンドウ <sup>(1)</sup> レジスタ 11h[1:0] = 01b、WAKE ピンのパルス動作 を参照                                 | 1000 | 1250 |     | ms            |

|                                     | 最大 WAKE 端子パルス ウィンドウ <sup>(1)</sup> レジスタ 11h[1:0] = 10b、WAKE ピンのパルス動作 を参照                                 | 1500 | 1875 |     | ms            |

|                                     | 最大 WAKE 端子パルス ウィンドウ <sup>(1)</sup> レジスタ 11h[1:0] = 11b、WAKE ピンのパルス動作 を参照                                 | 2000 | 2500 |     | ms            |

| $t_{SILENCE}$                       | バス非アクティビティ タイムアウト時間。バスがドミナントからリセッショブに、またはその逆に変化すると、タイマがリセットされ、再起動されます。                                   | 0.6  | 1.2  |     | s             |

| $t_{INACTIVE}$                      | スリープ ウェーク エラー (SWE) タイマ                                                                                  | 3.75 | 5    | 最小値 |               |

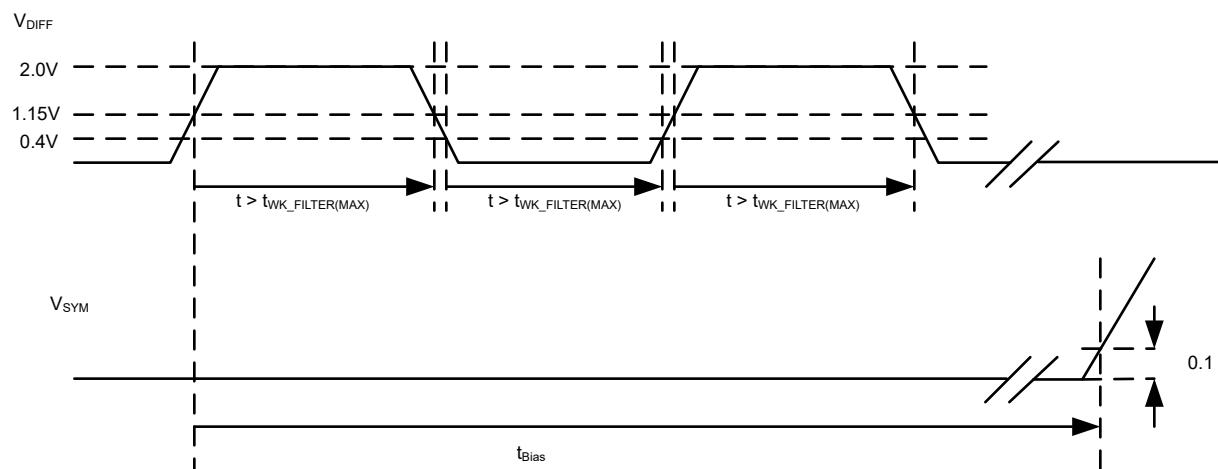

| $t_{Bias}$                          | ドミナント、リセッショブ、ドミナントのシーケンスが開始してからの経過時間です。Vsym $\geq 0.1$ までの各フェーズ 6 $\mu\text{s}$ 、バイアス応答時間測定のテスト信号の定義 を参照 |      | 250  |     | $\mu\text{s}$ |

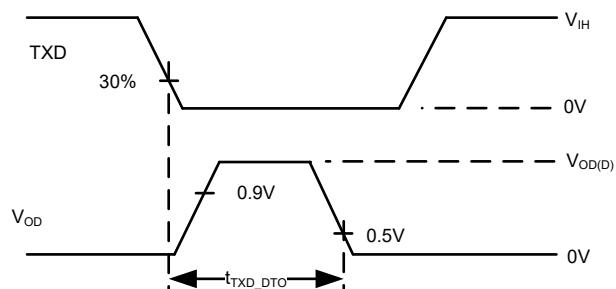

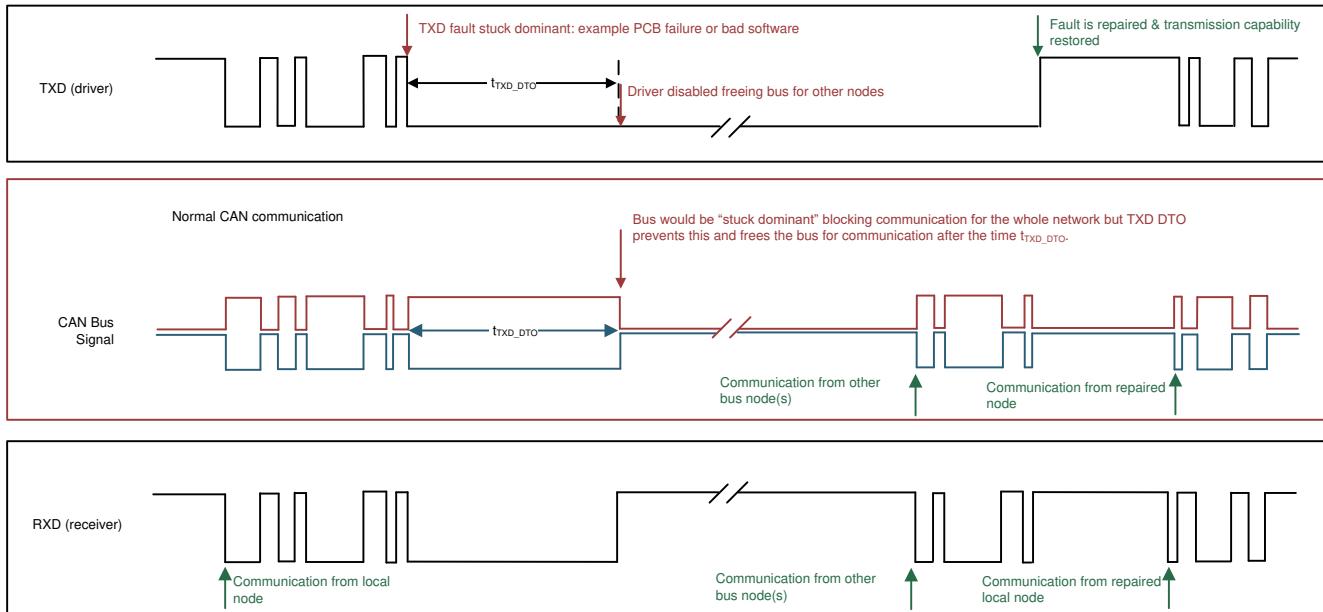

| $t_{TXD\_DTO}$                      | ドミナント タイムアウト、 $R_L = 60\Omega$ 、 $C_L = \text{開放}$ 、TXD ドミナント タイムアウトのテスト回路と測定 を参照                        | 1    | 5    |     | ms            |

| $t_{TOGGLE}$                        | WUP 後にプログラムされた場合の RXD ピンのトグルタイミング、ウェークアップ パターン (WUP) と RXD 要求によるバス ウェーク (BWRR) を参照                       | 5    | 10   | 15  | $\mu\text{s}$ |

- (1) このパラメータは、レジスタ 11h[7:6] = 11b の場合にのみ有効です

- (2) これは、デバイスがグッド パルスとして検出する WAKE ピン入力の最小パルス幅です。最小  $t_{WK\_WIDTH\_MIN}$  と最大  $t_{WK\_WIDTH\_INVALID}$  の間の値は不定であり、有効と見なされる場合と見なされない場合があります。このパラメータは、 $t_{WK\_WIDTH\_MIN}$  と組み合わせて WAKE 入力パルスが有効かどうかを判定します

- (3) INH がノード電力をオンにした後、 $V_{CC}$  および  $V_{IO}$  が  $UV_{CC}$  および  $UV_{IO}$  を上回っていることに依存します。

- (4)  $t_{WK\_WIDTH\_INVALID}$  は レジスタ 11h[3:2] を用いてこの値を設定します

## 6.8 スイッチング特性

パラメータは  $-40^{\circ}\text{C} \leq T_j \leq 150^{\circ}\text{C}$  で有効 (特に記述のない限り)

| パラメータ                      | テスト条件                                                    | 最小値 | 標準値 | 最大値 | 単位 |

|----------------------------|----------------------------------------------------------|-----|-----|-----|----|

| <b>CAN トランシーバのスイッチング特性</b> |                                                          |     |     |     |    |

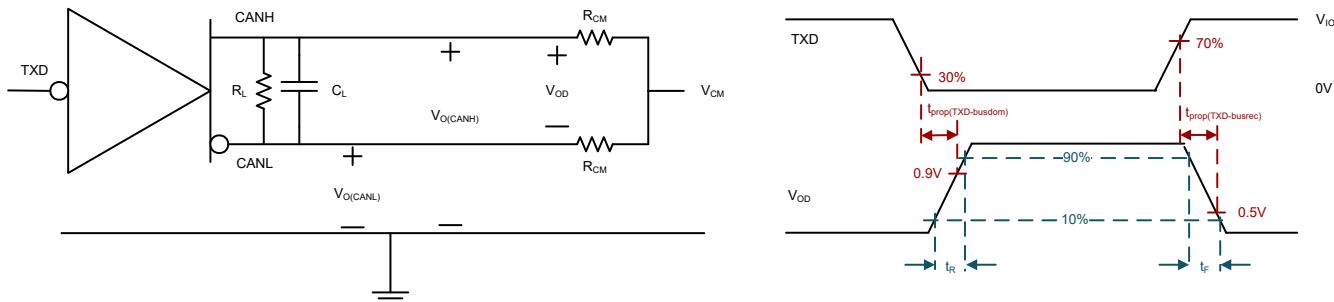

| $t_{prop(TxD-busdom)}$     | 伝搬遅延時間、High から Low TXD エッジからバス ドミナントまで (リセッショブからドミナントまで) |     | 80  |     | ns |

| $t_{prop(TxD-busrec)}$     | 伝搬遅延時間、Low から High TXD エッジからバス リセッショブまで (ドミナントからリセッショブ)  |     | 80  |     | ns |

| $t_{sk(p)}$                | パルス スキュー ( $t_{pHR} - t_{pLDI}$ )                        | 10  | 40  |     | ns |

| $t_{R/F}$                  | 差動出力信号の立ち上がり時間                                           | 5   | 55  | 75  | ns |

## 6.8 スイッチング特性 (続き)

パラメータは  $-40^{\circ}\text{C} \leq T_j \leq 150^{\circ}\text{C}$  で有効 (特に記述のない限り)

| パラメータ                                  | テスト条件                                                                                                                                             | 最小値                                                                                                                                                                                                                                             | 標準値 | 最大値 | 単位  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|

| $t_{\text{prop(busdom-RxD)}}$          | 測定条件は $C_{\text{L(RXD)}} = 15\text{pF}$ 、<br>レシーバのテスト回路と測定 を参照。TXD の入<br>力信号は立ち上り時間 (10% ~ 90%) および立<br>ち下り時間 (90% ~ 10%) が 10ns 未満である必<br>要があります | 110                                                                                                                                                                                                                                             | ns  | 110 | ns  |

| $t_{\text{prop(busrec-RxD)}}$          |                                                                                                                                                   |                                                                                                                                                                                                                                                 |     |     |     |

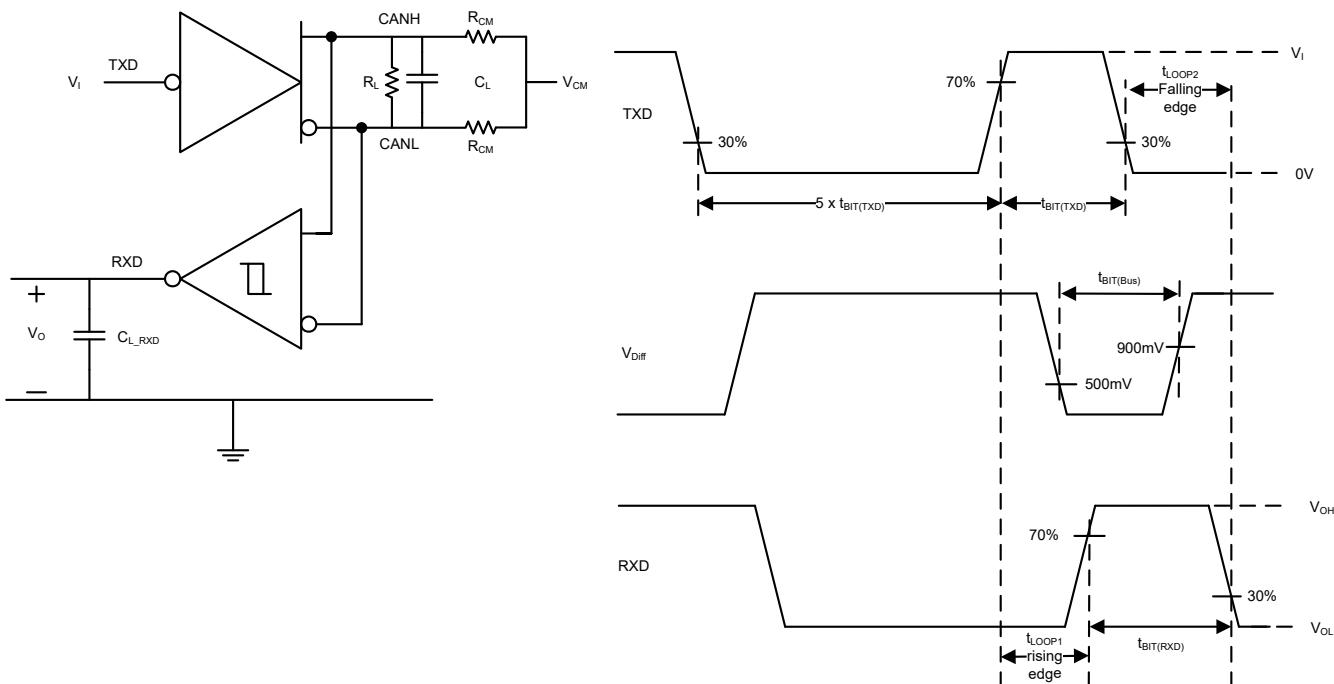

| $t_{\text{PROP(LOOP1)}}$               | 合計ループ遅延、ドライバ入力 (TXD) からレシ<br>バ出力 (RXD) までドミナントからリセシブまで                                                                                            | 45Ω ≤ $R_{\text{L}}$ ≤ 65Ω、 $C_{\text{L}} = 100\text{pF}$ 、 $C_{\text{L(RXD)}} = 15\text{pF}$<br>、トランシミッタとレシーバのタイミング動作テスト回<br>路と測定 を参照                                                                                                          | 100 | 190 | ns  |

| $t_{\text{PROP(LOOP2)}}$               | 合計ループ遅延、ドライバ入力 (TXD) からレシ<br>バ出力 (RXD) までリセシブからドミナントまで                                                                                            | 45Ω ≤ $R_{\text{L}}$ ≤ 65Ω、 $C_{\text{L}} = 100\text{pF}$ 、 $C_{\text{L(RXD)}} = 15\text{pF}$<br>、トランシミッタとレシーバのタイミング動作テスト回<br>路と測定 を参照                                                                                                          | 110 | 190 | ns  |

| <b>CAN FD ピットのタイミング</b>                |                                                                                                                                                   |                                                                                                                                                                                                                                                 |     |     |     |

| $t_{\text{BIT(BUS)}}$ <sup>(1)</sup>   | $t_{\text{BIT(TXD)}} = 500\text{ns}$ の CAN バス出力ピンの<br>2Mbps ピット時間                                                                                 | $45\Omega \leq R_{\text{L}} \leq 65\Omega$ 、 $C_{\text{L}} = 100\text{pF}$ 、 $C_{\text{L(RXD)}} = 15\text{pF}$<br>$\Delta t_{\text{REC}} = t_{\text{BIT(RXD)}} - t_{\text{BIT(BUS)}}$<br>トランシミッタとレシーバのタイミング動作テスト回<br>路と測定 を参照                   | 490 | 510 | ns  |

|                                        | $t_{\text{BIT(TXD)}} = 200\text{ns}$ の CAN バス出力ピンの<br>5Mbps ピット時間                                                                                 |                                                                                                                                                                                                                                                 | 190 | 210 |     |

| $t_{\text{BIT(BUS)}}$ <sup>(1)</sup>   | $t_{\text{BIT(TXD)}} = 125\text{ns}$ の CAN バス出力ピンの<br>8Mbps ピット時間 <sup>(2)</sup>                                                                  | $R_{\text{L}} = 60\Omega$ 、 $C_{\text{L}} = 100\text{pF}$ 、 $C_{\text{L(RXD)}} = 15\text{pF}$<br>$\Delta t_{\text{REC}} = t_{\text{BIT(RXD)}} - t_{\text{BIT(BUS)}}$<br>トランシミッタとレシーバのタイミング動作テスト回<br>路と測定 を参照                                    | 115 | 135 | ns  |

| $t_{\text{BIT(RXD)}}$ <sup>(1)</sup>   | $t_{\text{BIT(TXD)}} = 500\text{ns}$ の CAN バス出力ピンの<br>2Mbps ピット時間                                                                                 | $45\Omega \leq R_{\text{L}} \leq 65\Omega$ 、 $C_{\text{L}} = 100\text{pF}$ 、 $C_{\text{L(RXD)}} = 15\text{pF}$<br>$\Delta t_{\text{REC}} = t_{\text{BIT(RXD)}} - t_{\text{BIT(BUS)}}$<br>トランシミッタとレシーバのタイミング動作テスト回<br>路と測定 を参照                   | 470 | 520 | ns  |

|                                        | $t_{\text{BIT(TXD)}} = 200\text{ns}$ の CAN バス出力ピンの<br>5Mbps ピット時間                                                                                 |                                                                                                                                                                                                                                                 | 170 | 220 |     |

| $t_{\text{BIT(RXD)}}$ <sup>(1)</sup>   | $t_{\text{BIT(TXD)}} = 125\text{ns}$ の CAN バス出力ピンの<br>8Mbps ピット時間 <sup>(2)</sup>                                                                  | $R_{\text{L}} = 60\Omega$ 、 $C_{\text{L}} = 100\text{pF}$ 、 $C_{\text{L(RXD)}} = 15\text{pF}$<br>$\Delta t_{\text{REC}} = t_{\text{BIT(RXD)}} - t_{\text{BIT(BUS)}}$<br>トランシミッタとレシーバのタイミング動作テスト回<br>路と測定 を参照                                    | 95  | 145 | ns  |

| $\Delta t_{\text{REC}}$ <sup>(1)</sup> | $t_{\text{BIT(TXD)}} = 500\text{ns}$ の 2Mbps 受信タイミング対称<br>性                                                                                       | $45\Omega \leq R_{\text{L}} \leq 65\Omega$ 、 $C_{\text{L}} = 100\text{pF}$ 、 $C_{\text{L(RXD)}} = 15\text{pF}$<br>$\Delta t_{\text{REC}} = t_{\text{BIT(RXD)}} - t_{\text{BIT(BUS)}}$<br>トランシミッタとレシーバのタイミング動作テスト回<br>路と測定 を参照                   | -20 | 15  | ns  |

|                                        | $t_{\text{BIT(TXD)}} = 200\text{ns}$ の 5Mbps 受信タイミング対称<br>性                                                                                       |                                                                                                                                                                                                                                                 | -20 | 15  |     |

| $\Delta t_{\text{REC}}$ <sup>(1)</sup> | $t_{\text{BIT(TXD)}} = 125\text{ns}$ <sup>(2)</sup> の 8Mbps 受信タイミング対<br>称性                                                                        | $R_{\text{L}} = 60\Omega$ 、 $C_{\text{L}} = 100\text{pF}$ 、 $C_{\text{L(RXD)}} = 15\text{pF}$<br>$\Delta t_{\text{REC}} = t_{\text{BIT(RXD)}} - t_{\text{BIT(BUS)}}$<br>トランシミッタとレシーバのタイミング動作テスト回<br>路と測定 を参照                                    | -20 | 15  | ns  |

| <b>信号改善特性</b>                          |                                                                                                                                                   |                                                                                                                                                                                                                                                 |     |     |     |

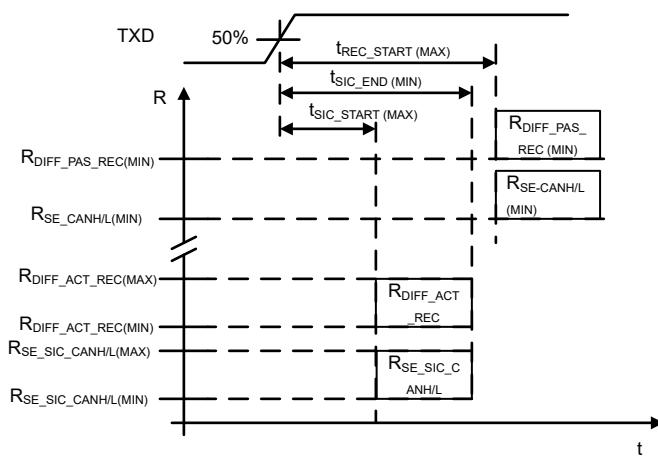

| $t_{\text{PAS_REC_START}}$             | パッシブ リセシブ位相の信号改善開始時間                                                                                                                              | 50% スレッショルドでスロープが 5ns 未満の<br>TXD 立ち上がりエッジから信号改善フェーズ終了<br>までの測定、<br>$R_{\text{DIFF_PAS_REC}} \geq \text{MIN } R_{\text{DIFF_ACT_REC}}$ 、<br>$R_{\text{SE_CANHL}} \geq \text{MIN } R_{\text{SE_SIC_REC}}$<br>トランシミッタとレシーバのタイミング動作テスト回<br>路と測定 を参照 |     | 530 | ns  |

| $t_{\text{ACT_REC_START}}$             | アクティブ信号改善位相の開始時間                                                                                                                                  | 50% スレッショルドでスロープが 5ns 未満の<br>TXD 立ち上がりエッジを測定、                                                                                                                                                                                                   |     | 120 | ns  |

| $t_{\text{ACT_REC_END}}$               | アクティブ信号改善位相の終了時間                                                                                                                                  | 50% スレッショルドでスロープが 5ns 未満の<br>TXD 立ち上がりエッジを測定、                                                                                                                                                                                                   | 355 |     | ns  |

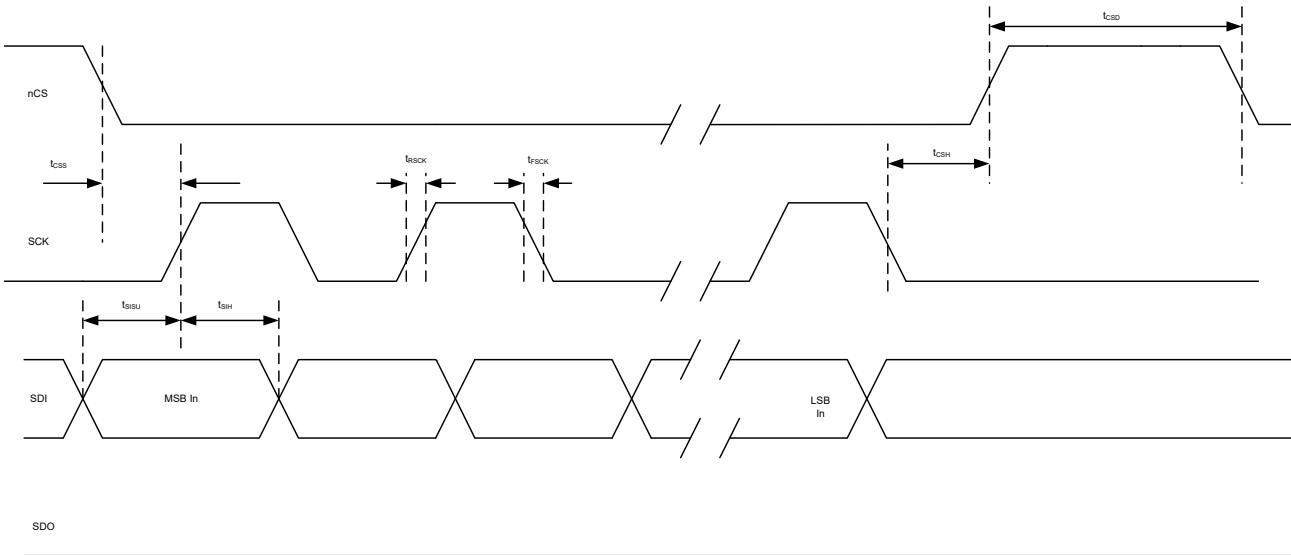

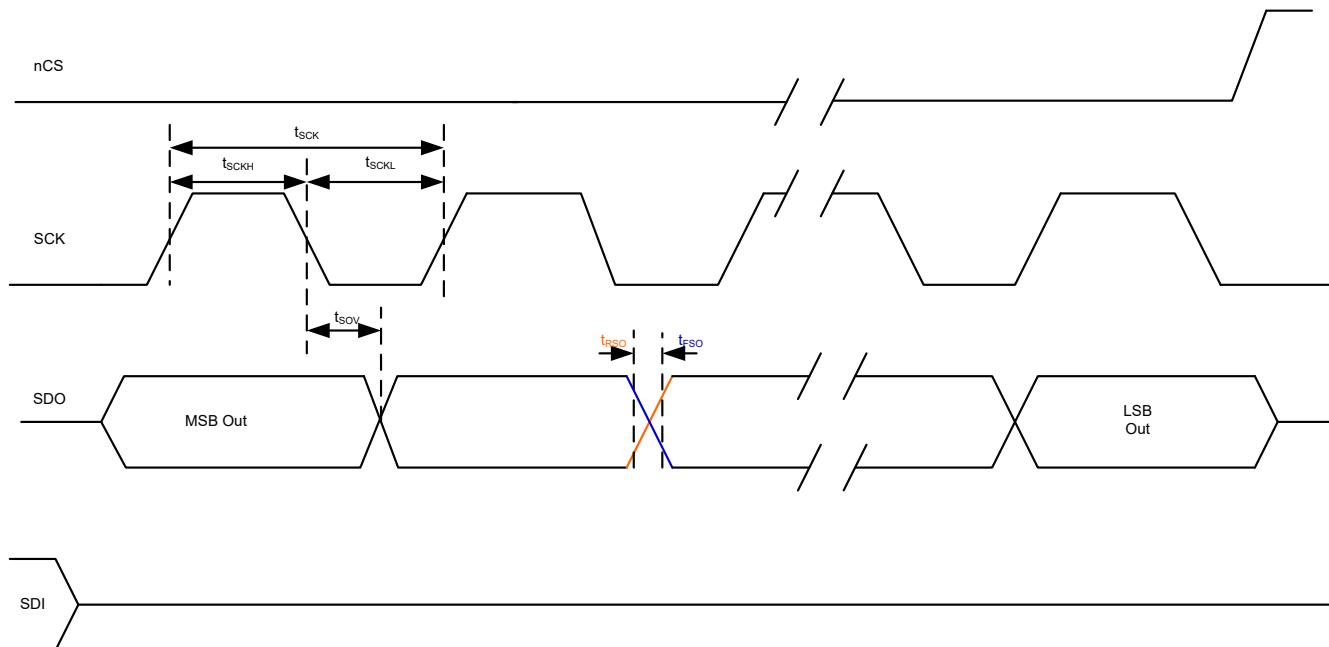

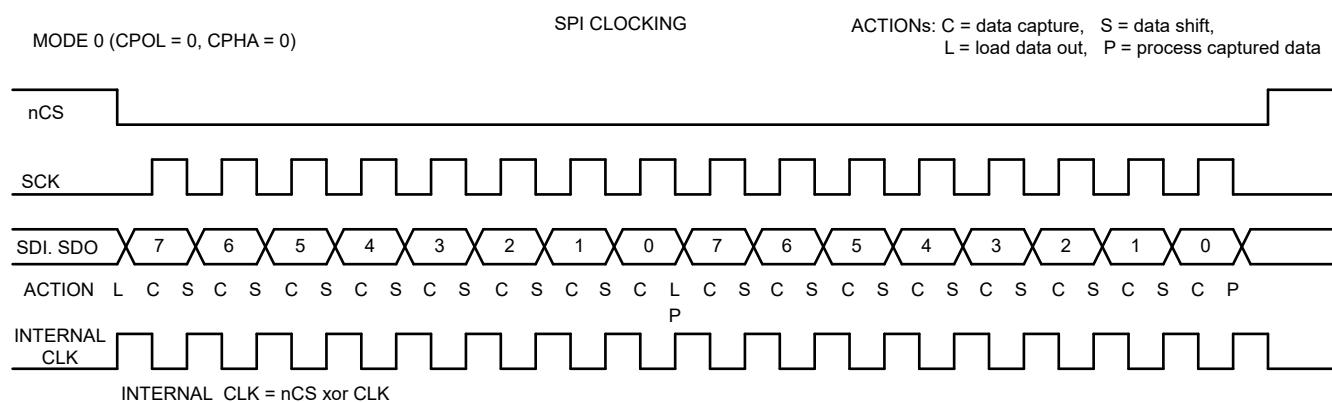

| <b>SPI スイッチング特性</b>                    |                                                                                                                                                   |                                                                                                                                                                                                                                                 |     |     |     |

| $f_{\text{SCK}}$                       | SCLK、SPI クロック周波数                                                                                                                                  | 通常モード、スタンバイ モード、リッスン モード、フ<br>エイルセーフ モード                                                                                                                                                                                                        |     | 4   | MHz |

|                                        |                                                                                                                                                   | スリープ モード: $V_{\text{IO}}$ が存在する場合                                                                                                                                                                                                               |     | 10  | kHz |

| $t_{\text{SCK}}$                       | SCLK、SPI クロック周期                                                                                                                                   | 通常モード、スタンバイ モード、リッスン モード、フ<br>エイルセーフ モード、SPI AC 特性読み取り を参<br>照                                                                                                                                                                                  | 250 |     | ns  |

|                                        |                                                                                                                                                   | スリープ モード: $V_{\text{IO}}$ が存在する場合、SPI AC 特<br>性読み取り を参照                                                                                                                                                                                         | 1   |     | μs  |

## 6.8 スイッチング特性 (続き)

パラメータは  $-40^{\circ}\text{C} \leq T_j \leq 150^{\circ}\text{C}$  で有効 (特に記述のない限り)

| パラメータ             |                    | テスト条件                                                                   | 最小値 | 標準値 | 最大値 | 単位 |

|-------------------|--------------------|-------------------------------------------------------------------------|-----|-----|-----|----|

| $t_{\text{RSCK}}$ | SCK の立ち上がり時間       | <a href="#">SPI AC 特性書き込み</a> を参照                                       |     | 40  |     | ns |

| $t_{\text{FSCK}}$ | SCK の立ち下がり時間       | <a href="#">SPI AC 特性書き込み</a> を参照                                       |     | 40  |     | ns |

| $t_{\text{SCKH}}$ | SCK, SPI クロック high | 通常モード、スタンバイ モード、リッスン モード、フェイリセーフ モード、 <a href="#">SPI AC 特性読み取り</a> を参照 | 125 |     |     | ns |

|                   |                    | スリープ モード: $V_{\text{IO}}$ が存在する場合、 <a href="#">SPI AC 特性読み取り</a> を参照    | 500 |     |     | ns |

| $t_{\text{SCKL}}$ | SCK, SPI クロック low  | 通常モード、スタンバイ モード、リッスン モード、フェイリセーフ モード、 <a href="#">SPI AC 特性読み取り</a> を参照 | 125 |     |     | ns |

|                   |                    | スリープ モード: $V_{\text{IO}}$ が存在する場合                                       | 500 |     |     | ns |

| $t_{\text{CSS}}$  | チップ セレクト セットアップ時間  | <a href="#">SPI AC 特性書き込み</a> を参照                                       | 100 |     |     | ns |

| $t_{\text{CSH}}$  | チップ セレクトのホールド時間    | <a href="#">SPI AC 特性書き込み</a> を参照                                       | 100 |     |     | ns |

| $t_{\text{CSD}}$  | チップ セレクトのディスエーブル時間 | <a href="#">SPI AC 特性書き込み</a> を参照                                       | 50  |     |     | ns |

| $t_{\text{SISU}}$ | セットアップ時間のデータ       | 通常モード、スタンバイ モード、リッスン モード、フェイリセーフ モード、 <a href="#">SPI AC 特性書き込み</a> を参照 | 50  |     |     | ns |

|                   |                    | スリープ モード: $V_{\text{IO}}$ が存在する場合、 <a href="#">SPI AC 特性書き込み</a> を参照    | 200 |     |     | ns |

| $t_{\text{SIH}}$  | ホールド時間のデータ         | 通常モード、スタンバイ モード、リッスン モード、フェイリセーフ モード、 <a href="#">SPI AC 特性書き込み</a> を参照 | 50  |     |     | ns |

|                   |                    | スリープ モード: $V_{\text{IO}}$ が存在する場合、 <a href="#">SPI AC 特性書き込み</a> を参照    | 200 |     |     | ns |

| $t_{\text{SOV}}$  | データ出力有効            | 通常モード、スタンバイ モード、リッスン モード、フェイリセーフ モード、 <a href="#">SPI AC 特性読み取り</a> を参照 |     | 80  |     | ns |

|                   |                    | スリープ モード: $V_{\text{IO}}$ が存在する場合、 <a href="#">SPI AC 特性読み取り</a> を参照    |     | 200 |     | ns |

| $t_{\text{RSO}}$  | データ出力の立ち上がり時間      | <a href="#">SPI AC 特性読み取り</a> を参照                                       |     | 40  |     | ns |

| $t_{\text{FSO}}$  | データ出力の立ち下がり時間      | <a href="#">SPI AC 特性読み取り</a> を参照                                       |     | 40  |     | ns |

(1) TXD の入力信号の立ち上がり時間と立ち下がり時間 (10% ~ 90%) は 10ns 未満とするものとします

(2) ISO 11898-2 パラメータ、ベンチ検証済み

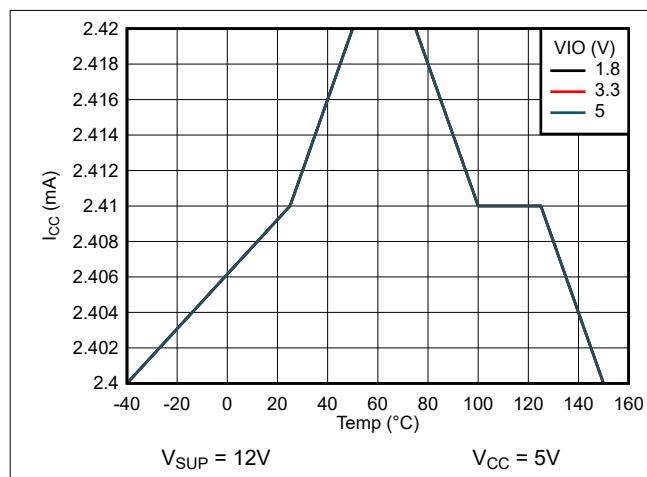

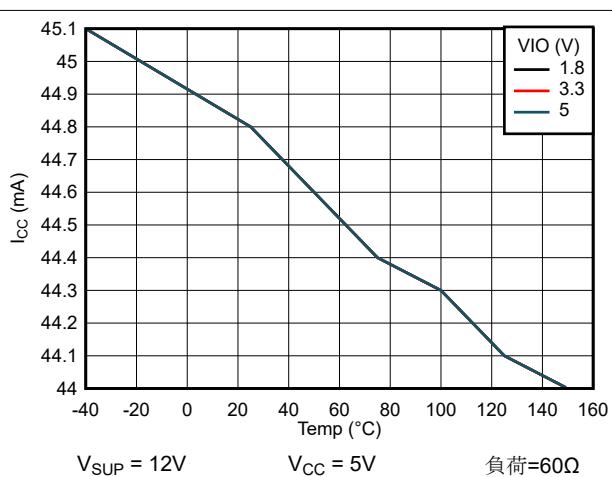

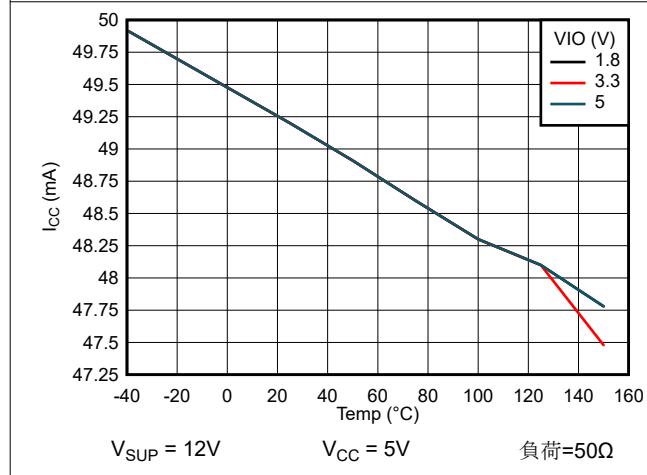

## 6.9 代表的特性

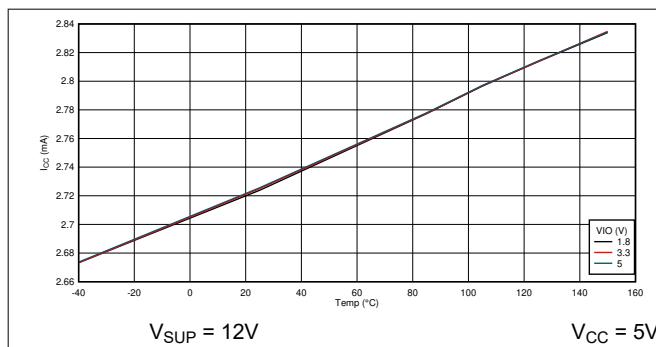

図 6-1. 通常モード リセッシブ  $I_{CC}$  と温度の関係

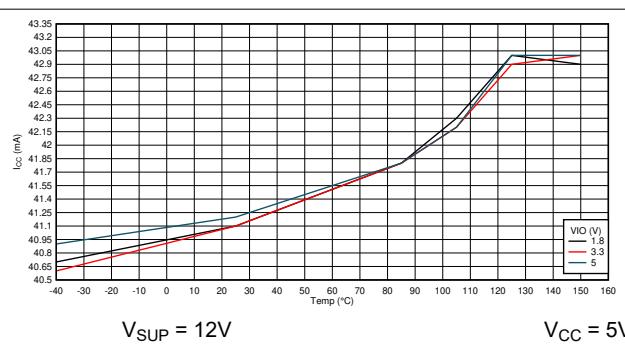

図 6-2. 通常モード ドミナント  $I_{CC}$  と温度の関係

図 6-3. 通常モード ドミナント  $I_{CC}$  と温度の関係

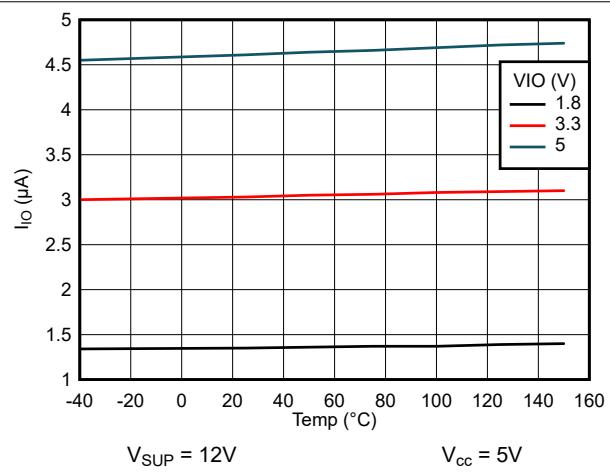

図 6-4. 通常モード リセッシブ  $I_{IO}$  と温度の関係

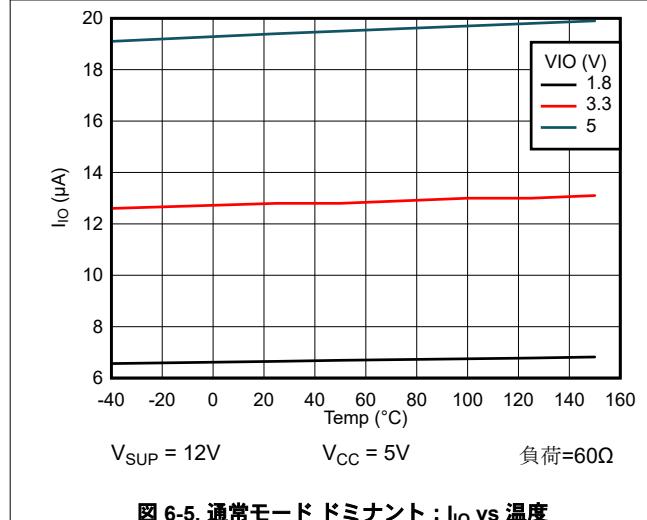

図 6-5. 通常モード ドミナント :  $I_{IO}$  vs 温度

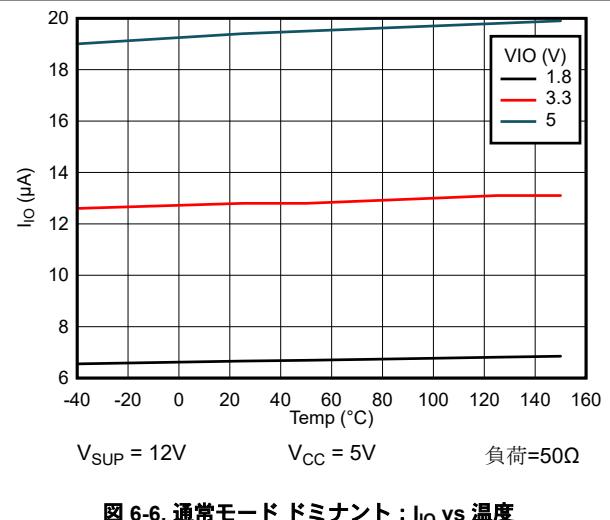

図 6-6. 通常モード ドミナント :  $I_{IO}$  vs 温度

## 6.9 代表的特性 (続き)

## 7 パラメータ測定情報

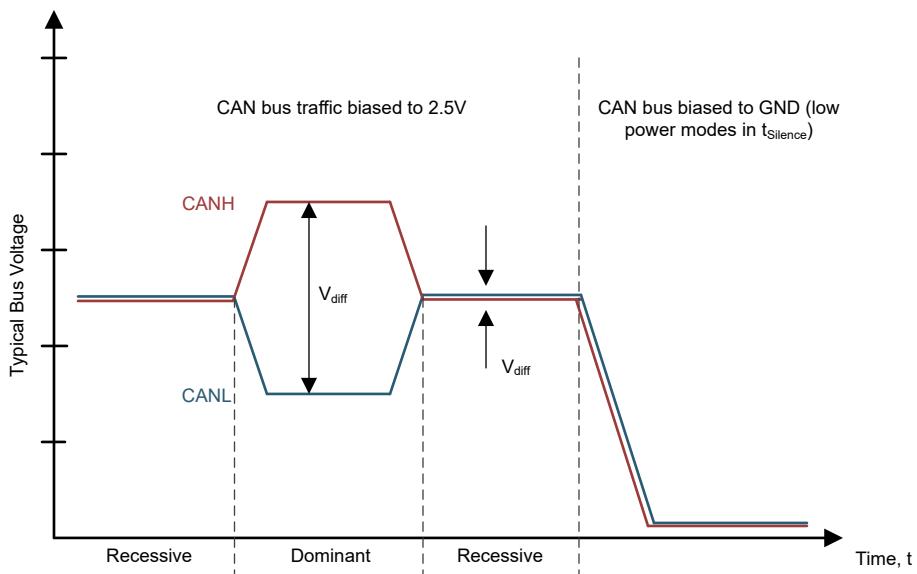

図 7-1. バスの状態 (物理的ビット表現)

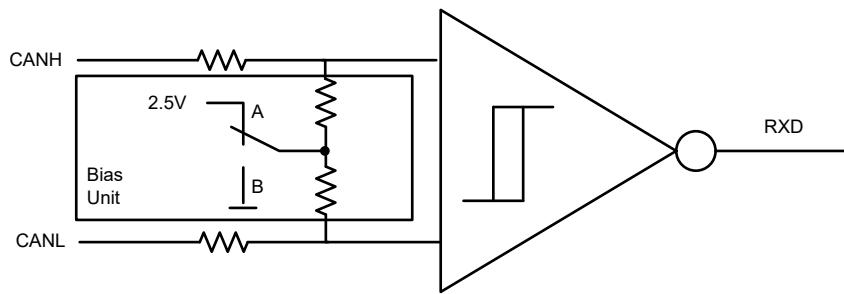

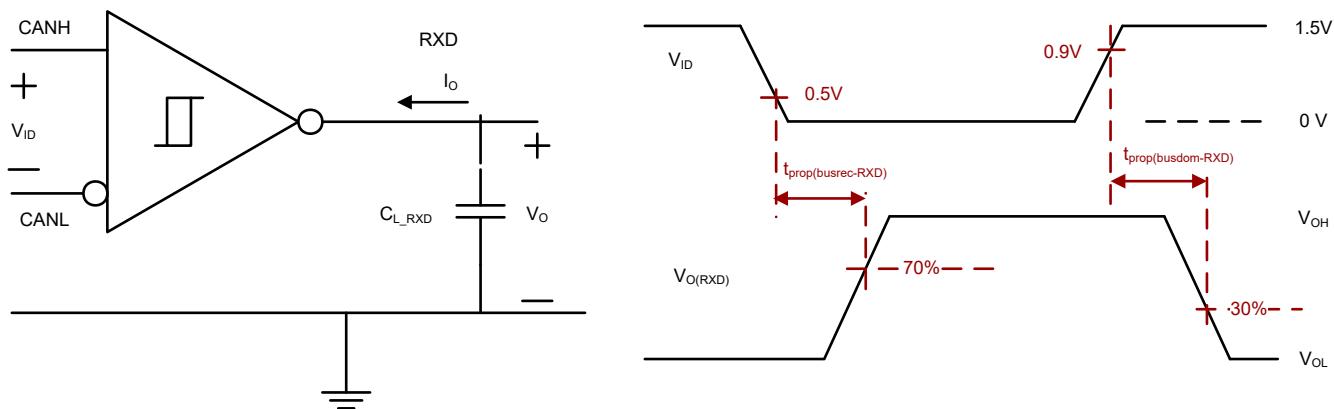

図 7-2. 簡略化されたリセシシブ同相バイアスユニットおよびレシーバ

### 注

A: 通常モードおよびリッスン モード、または  $t_{silence}$  状態にないその他のすべてのモード

B:  $t_{silence}$  状態にある通常モードおよびリッスン モード以外のすべてのモード

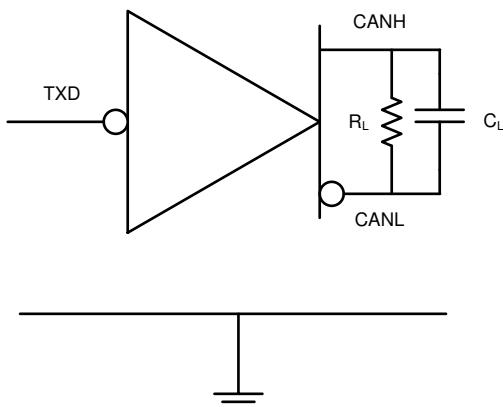

図 7-3. 電源テスト回路

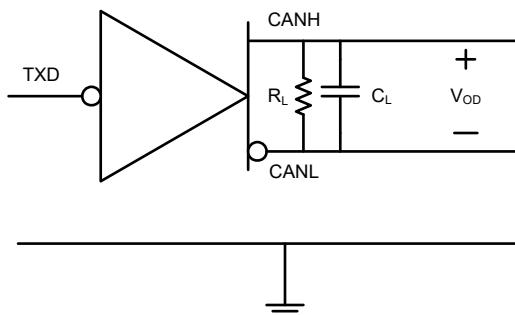

図 7-4. ドライバテスト回路と測定

図 7-5. レシーバのテスト回路と測定

図 7-6. トランシミッタとレシーバのタイミング動作テスト回路と測定

図 7-7. TXD ドミナント タイムアウトのテスト回路と測定

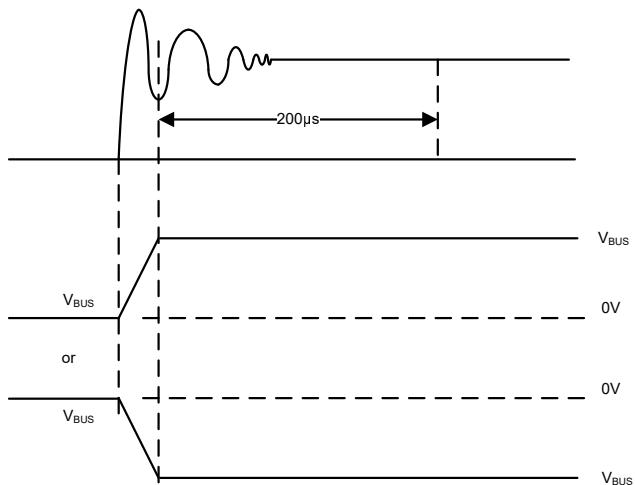

図 7-8. ドライバ短絡電流テスト回路と測定

図 7-9. バイアス応答時間測定のテスト信号の定義

図 7-10. SPI AC 特性書き込み

図 7-11. SPI AC 特性読み取り

図 7-12. 起動タイミング

図 7-13. スリープからスタンバイへのタイミング

図 7-14. 通常からスリープへのタイミング

図 7-15. 通常からスタンバイへのタイミング

図 7-16. スタンバイから通常へのタイミング

注

青色の信号は TCAN157x-Q1 の入力または出力信号です。黒の信号は TCAN157x-Q1 の内部にあります。タイミング図 図 7-12、図 7-13、図 7-14、図 7-15、図 7-16 には色分けがされています。

図 7-17. 信号改善機能におけるアクティブ リセッシブ フェーズ期間中の抵抗値

## 8 詳細説明

### 8.1 概要

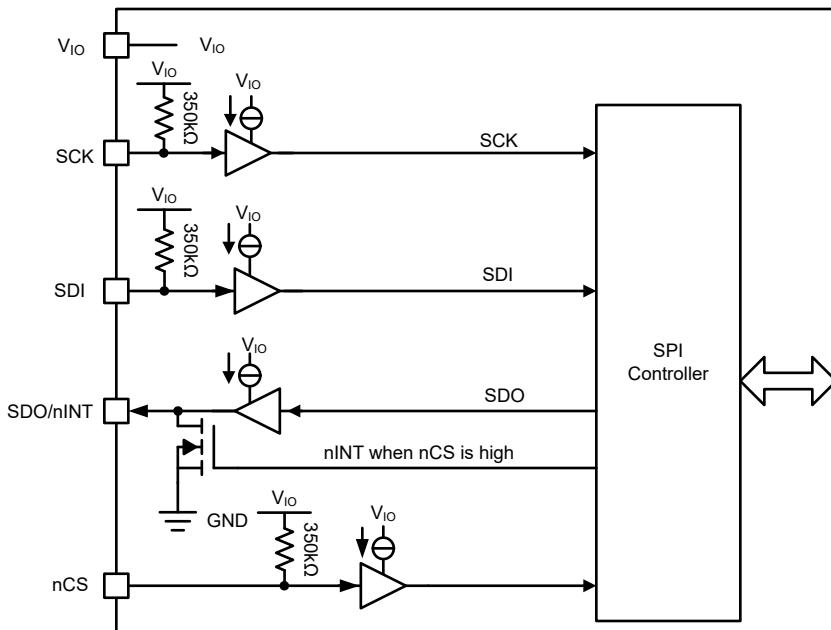

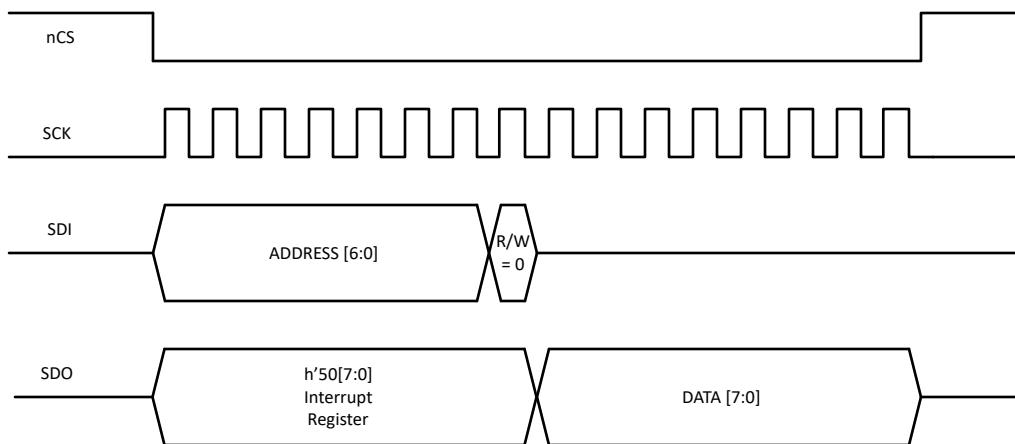

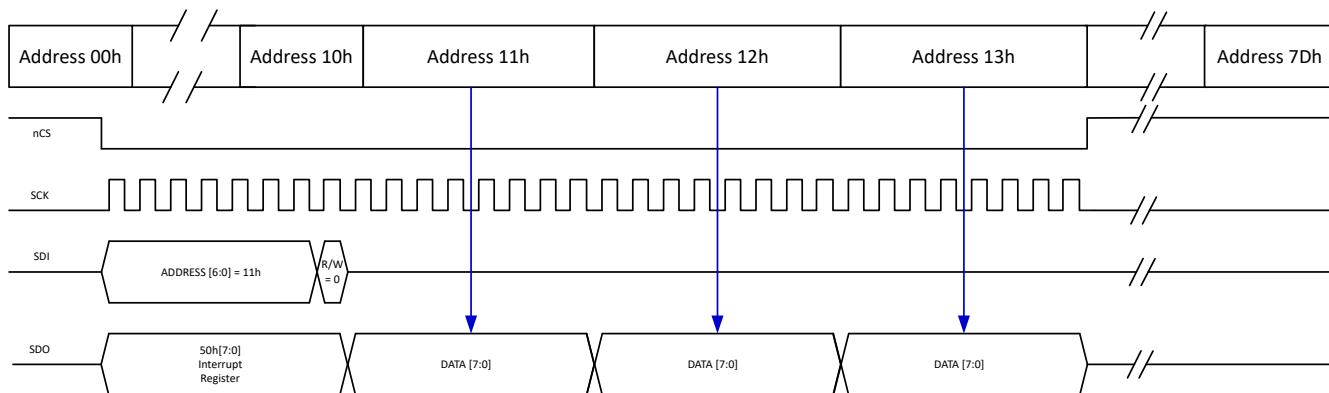

TCAN1576-Q1 は、最大 8Mbps のデータ レートに対応し、信号改善機能 (SIC) を備えた CAN FD トランシーバです。ISO 11898-2:2024 附属書 A に準拠した高速 CAN の物理層要件および最大 5Mbps までの信号改善 (SIC) 仕様を満たしています。このデバイスは、専用 CAN フレームでの選択的ウェークアップ機能をサポートしています。さらに、このデバイスは、ISO 11898-2:2024 付属書 A に定義された ウェークアップ パターン (WUP) を実装している CAN バス経由での遠隔ウェークアップも可能です。TCAN1576-Q1 は、 $V_{IO}$  ピンを使用して 1.8V、3.3V、5V のプロセッサをサポートしています。プロセッサ インターフェイスは、SPI、RXD、TXD 端子を経由して行います。このデバイスは、構成のためにローカル マイクロプロセッサに接続するシリアル ペリフェラル インターフェイス (SPI) を備えており、SPI は、最大 4MHz のクロック レートをサポートします。システム設計の柔軟性を高めるため、チップ セレクト ピンが High のときは、シリアルデータ出力 (SDO) ピンを割り込み出力ピンとして構成できます。

TCAN1576-Q1 は、CAN FD トランシーバ機能を提供しており、バスへの差動送信およびバスからの差動受信に対応します。さらに、さまざまな保護機能を備えており、デバイスおよび CAN ネットワークの堅牢性を高めています。

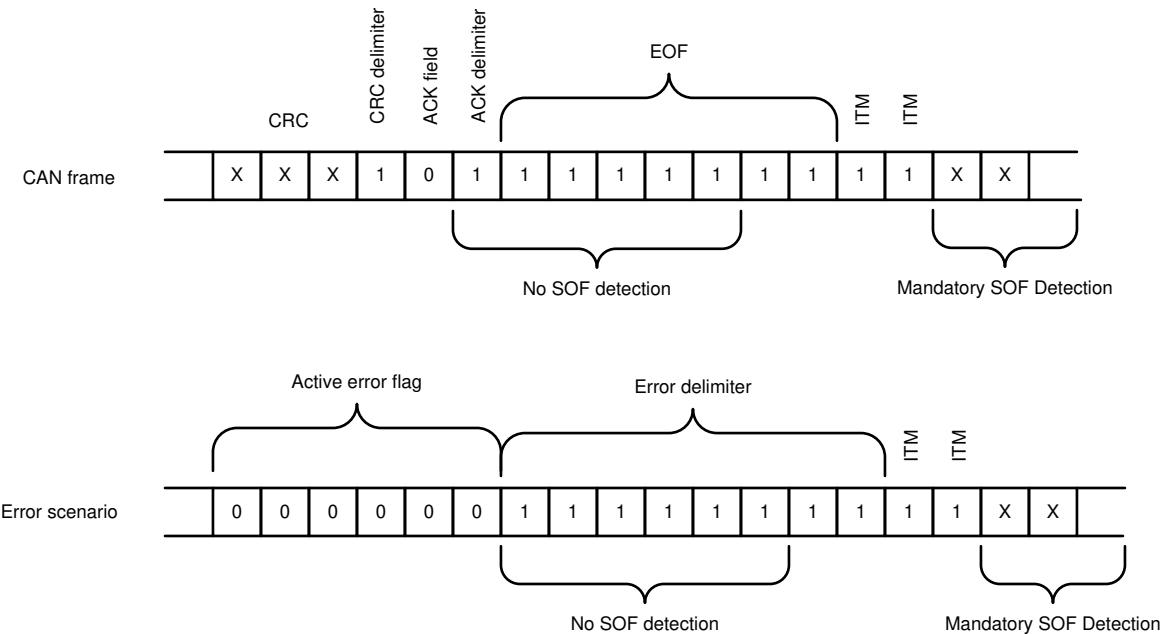

CAN バスは、動作中に 2 つの論理状態を持ちます (図 7-1 および 図 7-2 を参照)。

リセッショブ バス状態とは、各ノードのレシーバにある高抵抗の内部入力抵抗を介して、終端抵抗間でバスが約 2.5V の同相モード電圧にバイアスされている状態を指します。リセッショブはロジック High に相当し、通常はバス上の差動電圧がほぼ 0V です。リセッショブ状態もアイドル状態です。

ドミナント バス状態とは、1 つ以上のドライバによってバスが差動駆動される場合をいいます。電流が終端抵抗を流れることで、バス上に差動電圧が発生します。ドミナント状態はロジック Low に相当し、バス上の差動電圧が CAN ドミナントの最小スレッショルドを超える状態を指します。ドミナント状態はリセッショブ状態を上書きします。

アビトリエーション中は、複数の CAN ノードが同時に支配的なビットを送信することができます。この時のバスの差動電圧は、單一ドライバの差動電圧よりも大きくなります。

トランシーバには 3 つ目の状態として、バス端子が内部レシーバの高抵抗によってグランドに弱くバイアスされる状態もあります。図 7-1 と 図 7-2 を参照してください。

TCAN1576-Q1 は、『機能説明』に示されている多くの拡張機能を備えています。高度なバス フォルト検出、フェイルセーフ機能、ウォッチドッグなどの拡張機能は、プロセッサ割り込みが提供されます。これについては、各サブセクションで説明します。

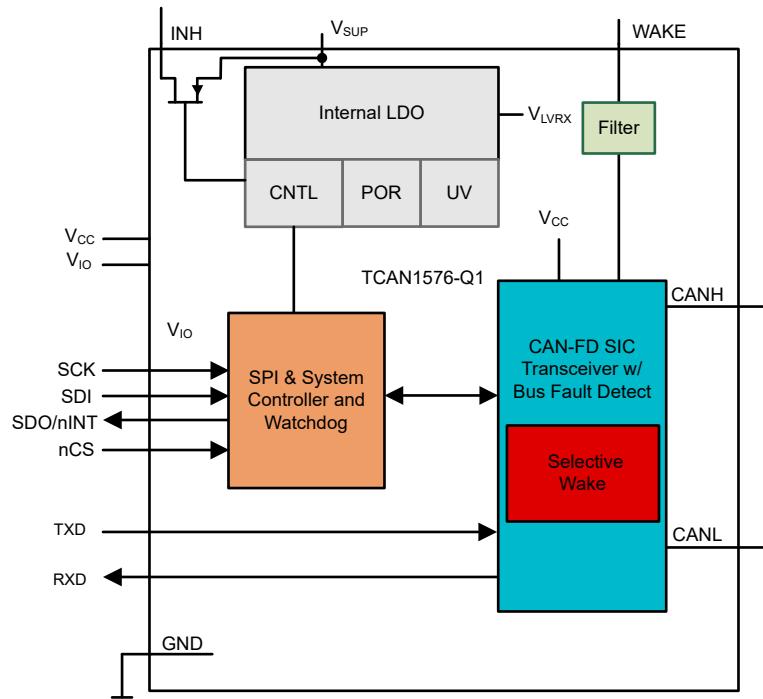

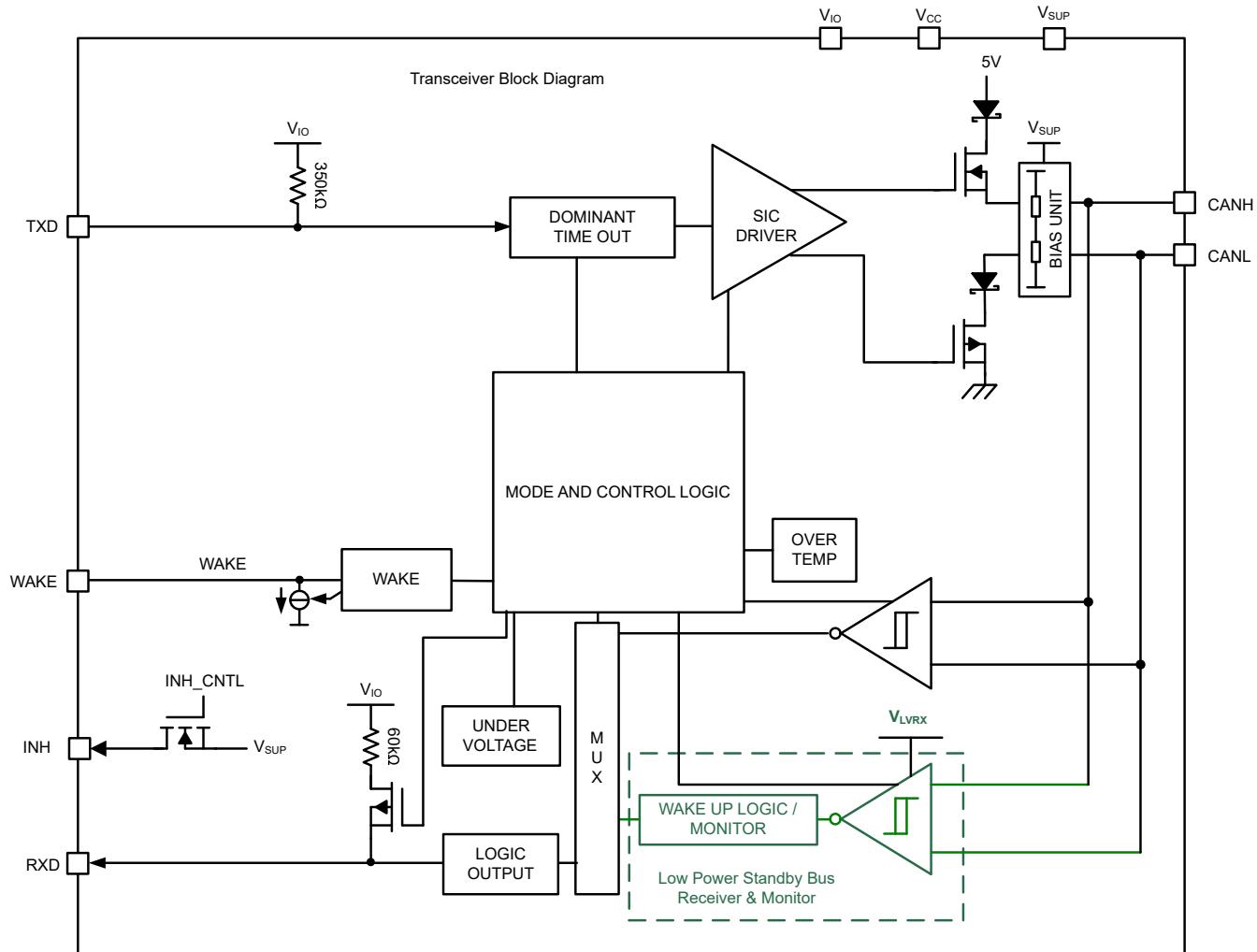

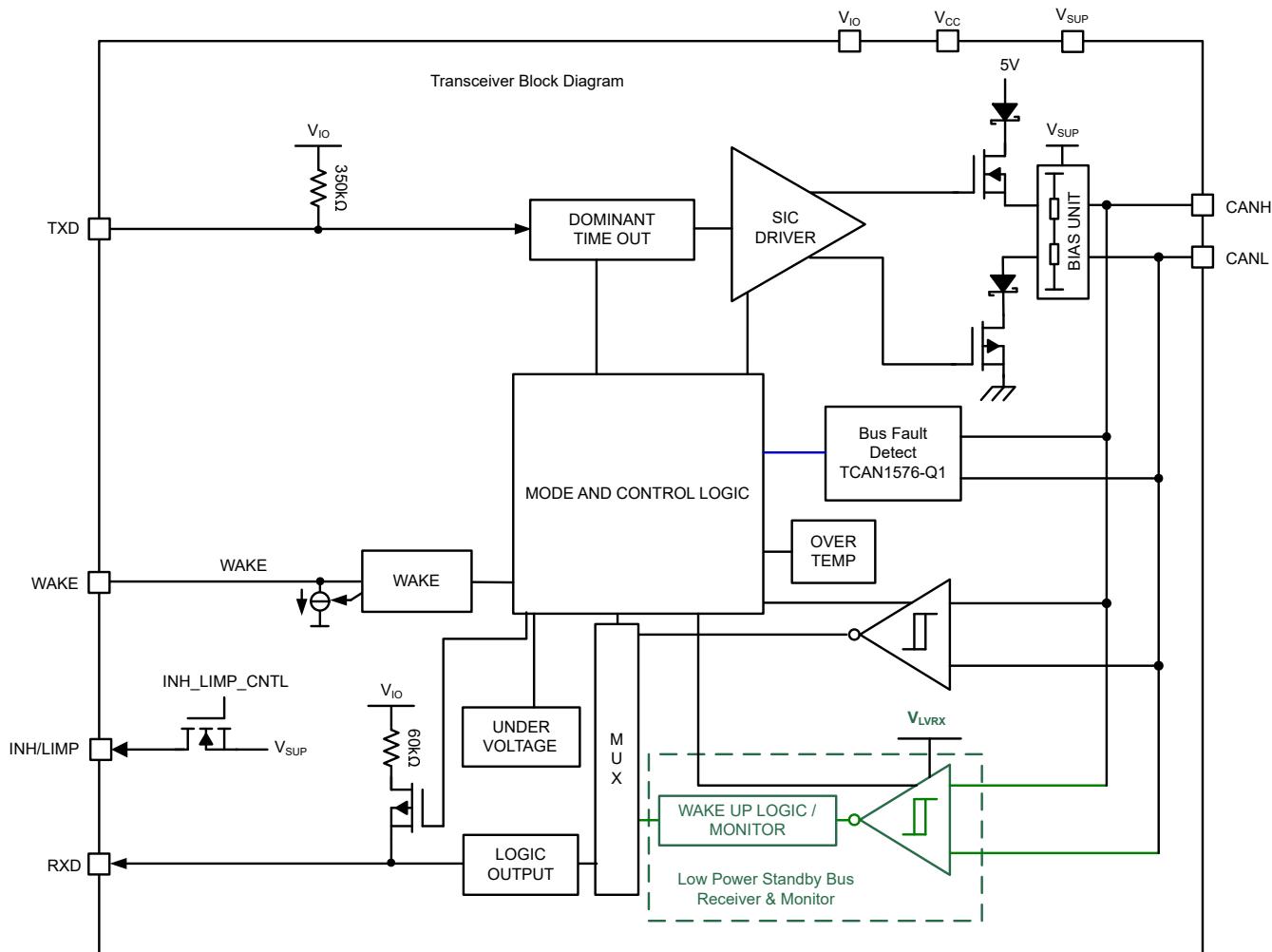

## 8.2 機能ブロック図

図 8-1. TCAN1575-Q1 機能ブロック図

図 8-2. TCAN1576-Q1 機能ブロック図

図 8-3. TCAN1575-Q1 トランシーバのブロック図

図 8-4. TCAN1576-Q1 トランシーバのブロック図

図 8-5. TCAN157x-Q1 およびデジタル IO のブロック図

## 8.3 機能説明

### 8.3.1 $V_{SUP}$ ピン

この  $V_{SUP}$  ピンは、バッテリ電源に接続されます。このピンは、デジタルコアと低電力 CAN レシーバーをサポートする内部レギュレータに電源を供給します。

### 8.3.2 $V_{IO}$ ピン

$V_{IO}$  ピンは、マイクロプロセッサの IO 電圧に合わせたデジタル IO 電圧を供給するため、レベルシフタを必要とせずに接続することができます。 $V_{IO}$  は SPI ピンをサポートしています。TCAN157x-Q1 ファミリは 1.8V、3.3V、5V の入出力電圧に対応したプロセッサをサポートしており、非常に広範なコントローラに対応できます。

### 8.3.3 $V_{CC}$ ピン

$V_{CC}$  ピンは、内部の CAN トランシーバに 5V を供給します。

### 8.3.4 GND ピン

GND ピンはグランド用です。放熱のために DMT パッケージのサーマル パッドを GND プレーンに接続することを推奨しますが、必須ではありません。

### 8.3.5 INH/LIMP ピン

INH ピンは高電圧出力ピンで、 $V_{SUP}$  からダイオード電圧降下分を差し引いた電圧を出力し、外部の高電圧レギュレータを有効にします。これらのレギュレータは通常、マイクロプロセッサおよび  $V_{IO}$  ピンをサポートするために使用されます。INH 機能は、スリープ モードを除くすべてのモードでオンになります。スリープ モードでは、INH ピンは無効となり、ハイインピーダンス状態に移行します。これにより、スリープ モード中はノードを最小消費電力状態にすることが可能です。INH 機能が不要な場合は、SPI インターフェイスを使用してレジスタ 8'h1A[6]=1b を設定し、この機能を無効にすることができます。TCAN1576-Q1 は、レジスタ 8'h1A[5]=1b を設定することで、このピンを LIMP ホーム ピンとして構成可能です。LIMP ピンとして構成した場合は、LIMP ホーム モードの外部回路に接続されます。ウォッチ ドッグ エラーが発生し、プログラムされたエラー カウンタを超えた場合、デバイスは LIMP ピンをオンにします。フェイルセーフ モードが有効な場合は、モード遷移時に LIMP ピンがオンになります。LIMP ピンが一度オンになると、LIMP\_SEL\_RESET のレジスタ 8'h1A[3:2] に従って、ウォッチドッグのエラーなし状態が所定期間継続されるまで、LIMP ピンはオンのままになります。LIMP\_RESET のレジスタ 8'h1A[1] に 1b を書き込むと、LIMP ピンがオフになります。

### 注

INH や LIMP ピンは「高電圧ロジック端子」として扱われ、電源出力端子ではありません。そのため、このピンは通常、システムの電源管理デバイスの EN ピンを駆動するために使用され、電源供給自体のスイッチ用途には使われません。この端子は逆バッテリ保護されていないため、システム モジュール外部に接続しないでください。

#### 8.3.6 WAKE ピン

WAKE ピンはローカル ウエークアップ (LWU) に使用されます。この機能については、[セクション 8.4.4.2](#) にて説明しています。このピンはデフォルトで双方向エッジトリガとして構成されており、WAKE ピンにおける立ち上がりまたは立ち下がりエッジのどちらかの遷移によってローカル ウエークアップ (LWU) が認識されます。このデフォルト値は SPI コマンドによって変更することができます。設定は、立ち上がりエッジのみ、立ち下がりエッジのみ、特定の幅とタイミングを持つパルス、またはフィルタ処理された立ち上がりまたは立ち下がりエッジのいずれかに構成できます。これらの設定は、レジスタ 8'h11[7:0] を使用して行います。このピンは、2 つの抵抗の間に接続された 22nF のコンデンサをグラウンドに対して接続する必要があります。

#### 8.3.7 TXD ピン

TXD ピンは、プロセッサから CAN バスへの入力です。

#### 8.3.8 RXD ピン

RXD ピンは CAN バスからプロセッサへの出力です。ウェーク イベントが発生すると、このピンはデフォルトで Low にプルダウンされます。レジスタ 8'h12[2]=1b、RXD\_WK\_CONFIG に設定することで、ウェークアップ動作をパルスに変更します。電源投入時、 $V_{IO} \geq UV_{IO}$ 、 $V_{CC} \geq UV_{CC}$  となると、デバイスはスタンバイ モードに入るため RXD ピンは Low にプルダウンされます。 $V_{CC} \geq UV_{CC}$  の要件を解除するには、VCC\_DIS レジスタ 8'h4B[0] に 1b を書き込みます。RXD ピンには  $V_{IO}$  に対する  $60\text{k}\Omega$  の内部プルアップがあり、 $V_{SUP} \leq UV_{SUP}$ 、POR またはデバイスがスリープ モードのときに有効になります。

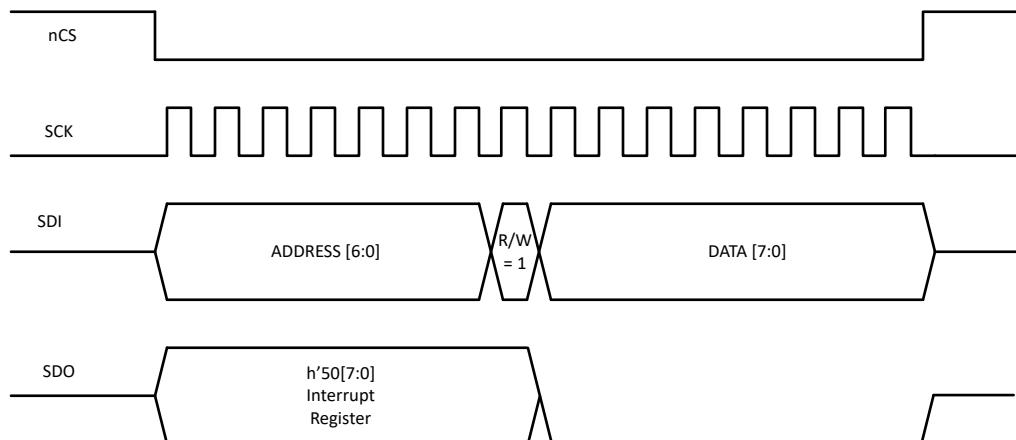

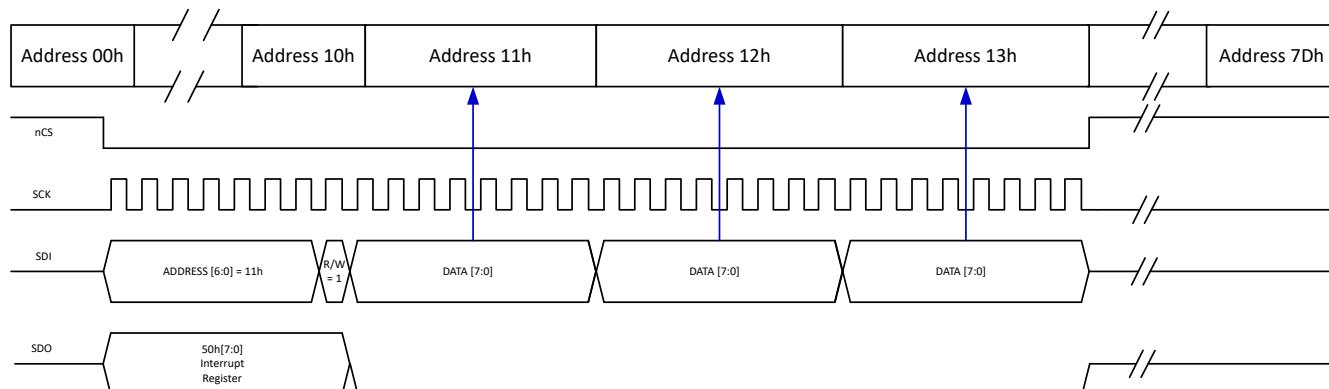

#### 8.3.9 SDO または nINT 割り込みピン

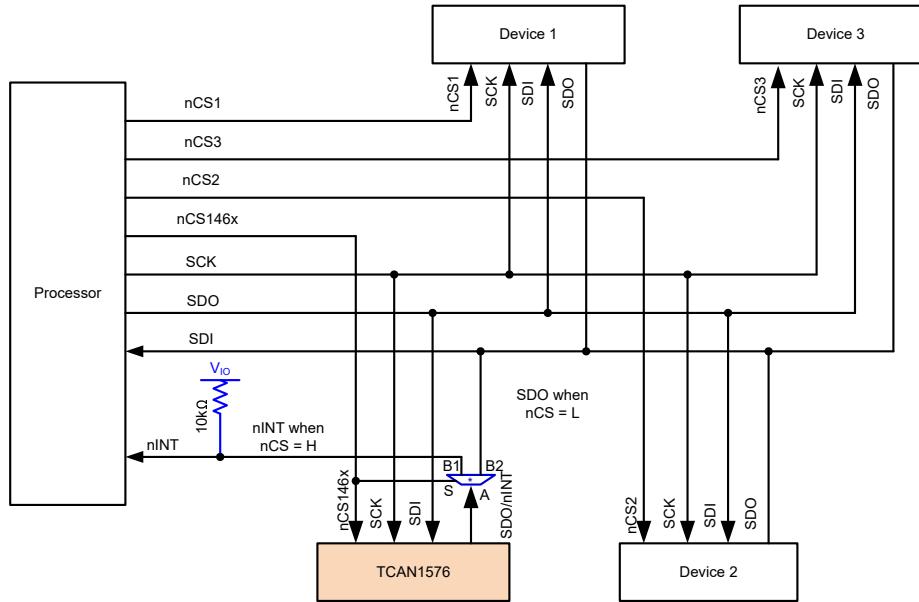

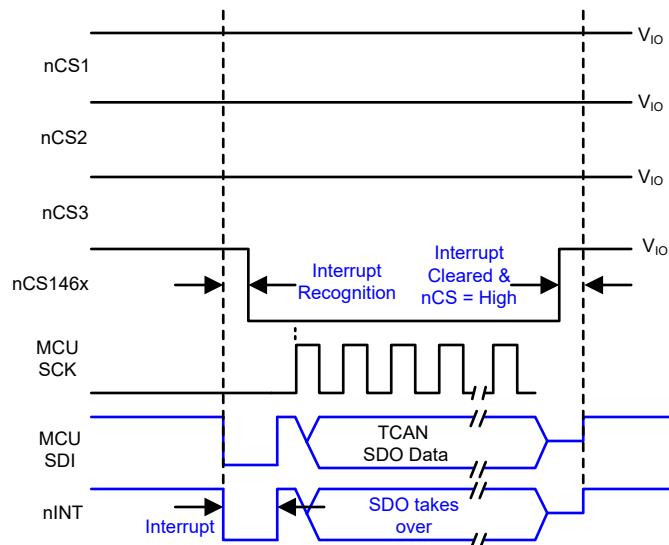

nINT は SPI シリアルデータ出力 (SDO) 機能とピンを共有し、デフォルトは SDO のみとなります。このピンを nINT として使用する場合、レジスタ 8'h29[0] SDO\_CONFIG を 1b に設定する必要があります。nINT をサポートするよう設定した場合、nCS ピンが High のとき、このピンは割り込み出力として機能します。デフォルトでは、グローバル割り込み 8'h50[7:0] に対して Low にプルされます。nCS が Low の場合、デバイスは SPI ポートを使用しており、このピンは TCAN1576-Q1 からのシリアル データ出力となります。[図 8-6](#) と [図 8-7](#) に、nINT 機能を使用した場合の高レベル システム例およびタイミング図を示しています。

図 8-6. nINT 機能を使用したシステム例

\* This shows an interrupt and how SDO would behave

\* Device recognizes nCS pulled low and releases nINT function for SDO

\* See SPI section for overall SPI bus timing

図 8-7. nINT のタイミング図

## 注

- nINT 機能を使用する場合、SPI バスはポイントツー ポイントアーキテクチャを推奨しますが、必須ではありません。

- マルチドロップ システムで nINT 機能を使用するときに、割り込みが SDO ラインを乱さないようにするには、まず別のデバイスと SPI 通信を行う前に nINT 機能を無効化し、通信終了後に再度有効化することを推奨します。

- nINT は、マスクされていないレジスタ 8'h50 ~ 8'h54 のすべてのフォルトのロジカル OR です。

### 8.3.10 nCS ピン

nCS ピンは、SPI チップ セレクト ピンです。クロックが存在し、このピンが **Low** にプルされると、デバイスの書き込みと読み取りが行われます。

### 8.3.11 SCK

SCK ピンは、TCAN1576-Q1 に対する SPI のシリアル入力クロックです。最大クロック レートは **4MHz** です。スリープ モード中でも VIO が供給されていれば、SPI アクセスは可能ですが、動作速度が制限されます。nCS を **Low** にしてから読み取りまたは書き込みを開始するまでに **10μs** 以上の遅延を設けた場合、最大 SPI クロック レートで通信することができます。

### 8.3.12 SDI

nCS が **low** のとき、このピンは、デバイスのプログラミングまたはデータの要求に使用される SPI シリアル データ入力ピンです。

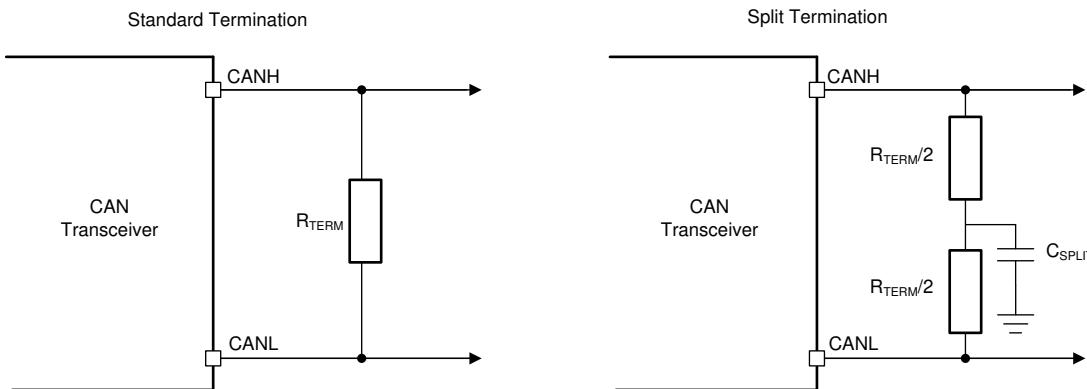

### 8.3.13 CANH および CANL バス ピン

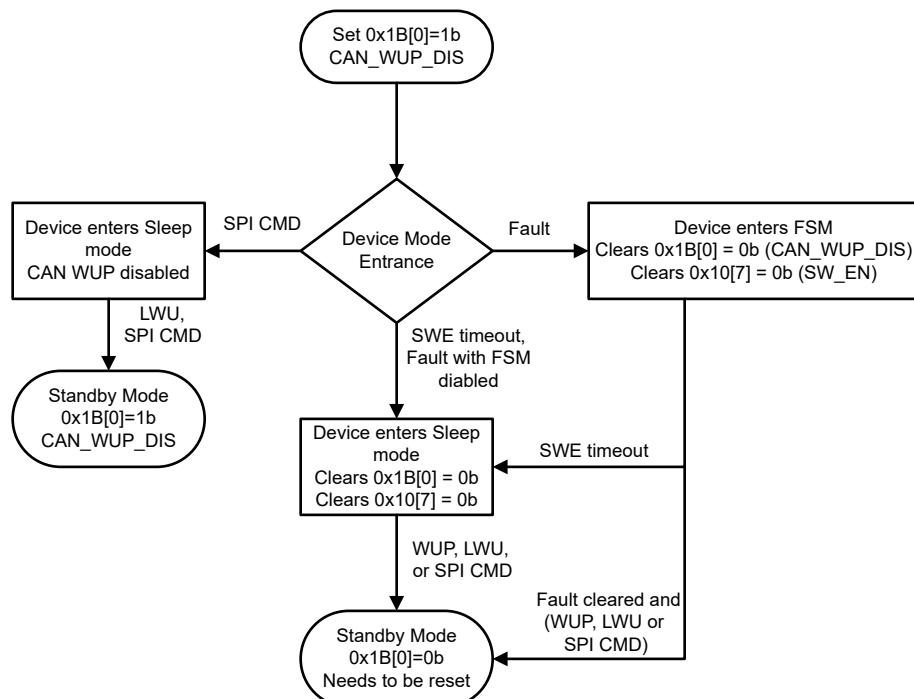

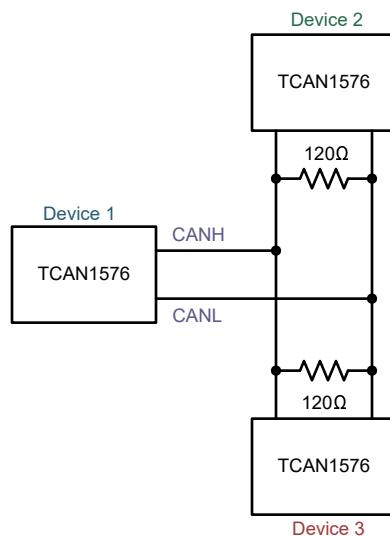

これらは CAN High と CAN Low の差動バスピンです。これらのピンは、CAN トランシーバおよび低電圧 WUP CAN レシーバに接続されています。バス ピンの機能については、本書全体で順次説明されています。CAN WUP レシーバは、CAN ウェークアップ パターンでデバイスをスリープ モードから起動するために使用します（[セクション 8.4.4.1](#) を参照）。システムが CAN バスからのウェークアップを必要としない場合は、レジスタ **8'h1B[0]** に **1b** を設定することで CAN ウェークアップを無効化できます（[図 8-8 を参照](#)）。CAN バスのバイアスは ISO 11898-2:2024 の要件に準拠しています（[『CAN バスのバイアス印加』](#)を参照）。

図 8-8. CAN バス ウェークアップ パターンの無効化

注

SWE のタイムアウト参照値は、**SWE\_EN = 1b** のときに有効となります

### 8.3.14 CAN FD SIC トランシーバ

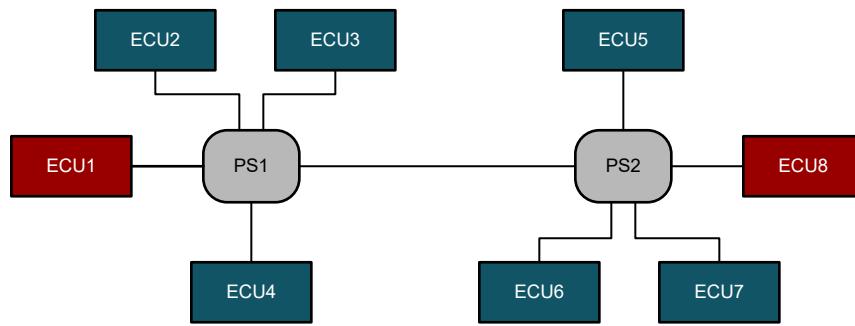

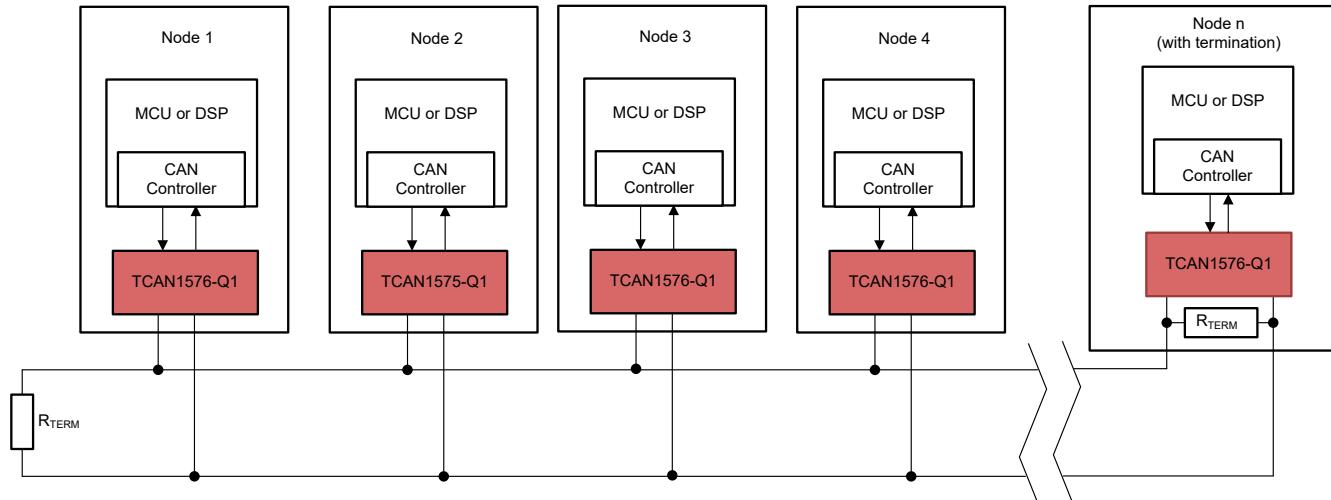

信号の改善は、CAN FD トランシーバに追加される付加的な機能であり、複雑なスタートポロジで信号のリンクを最小化し、実現可能な最大データレートを改善します。信号のリンクは、スタブとして機能するノードのために CAN ネットワーク内のさまざまなポイントでインピーダンスの不整合が発生することに起因する、反射の結果です。図 8-9 に、複雑なネットワークの例を示します。

図 8-9. CAN FD 信号改善トポロジ

リセシシブからドミナントへの信号エッジは、バスがトランスマッタによって強く駆動されるため、通常はクリーンです。CAN トランシーバのトランスマッタ出力インピーダンスは約  $50\Omega$  であり、ネットワーク特性インピーダンスと一致しています。通常の CAN FD トランシーバの場合、ドミナントからリセシシブへのエッジにおいて、ドライバの出力インピーダンスが約  $60\text{k}\Omega$  になり、信号は反射によるインピーダンス不整合の影響を受け、リンクが発生します。TCAN157x-Q1 は、この問題を TX ベースの信号改善機能 (SIC) によって解決します。TCAN157x-Q1 は、 $t_{REC\_START}$  までバスのリセシシブ状態を強く駆動し続けることで、反射を減衰させ、リセシシブ ビットがサンプリング ポイントでクリーンになります。アクティブなリセシシブ フェーズでは、トランスマッタの出力インピーダンスが低くなります (約  $100\Omega$ )。このフェーズが終了し、デバイスがパッシブ リセシシブ フェーズになると、ドライバの出力インピーダンスはハイ インピーダンスに移行します。この現象については、図 7-17 で説明しています。

## 8.4 デバイスの機能モード

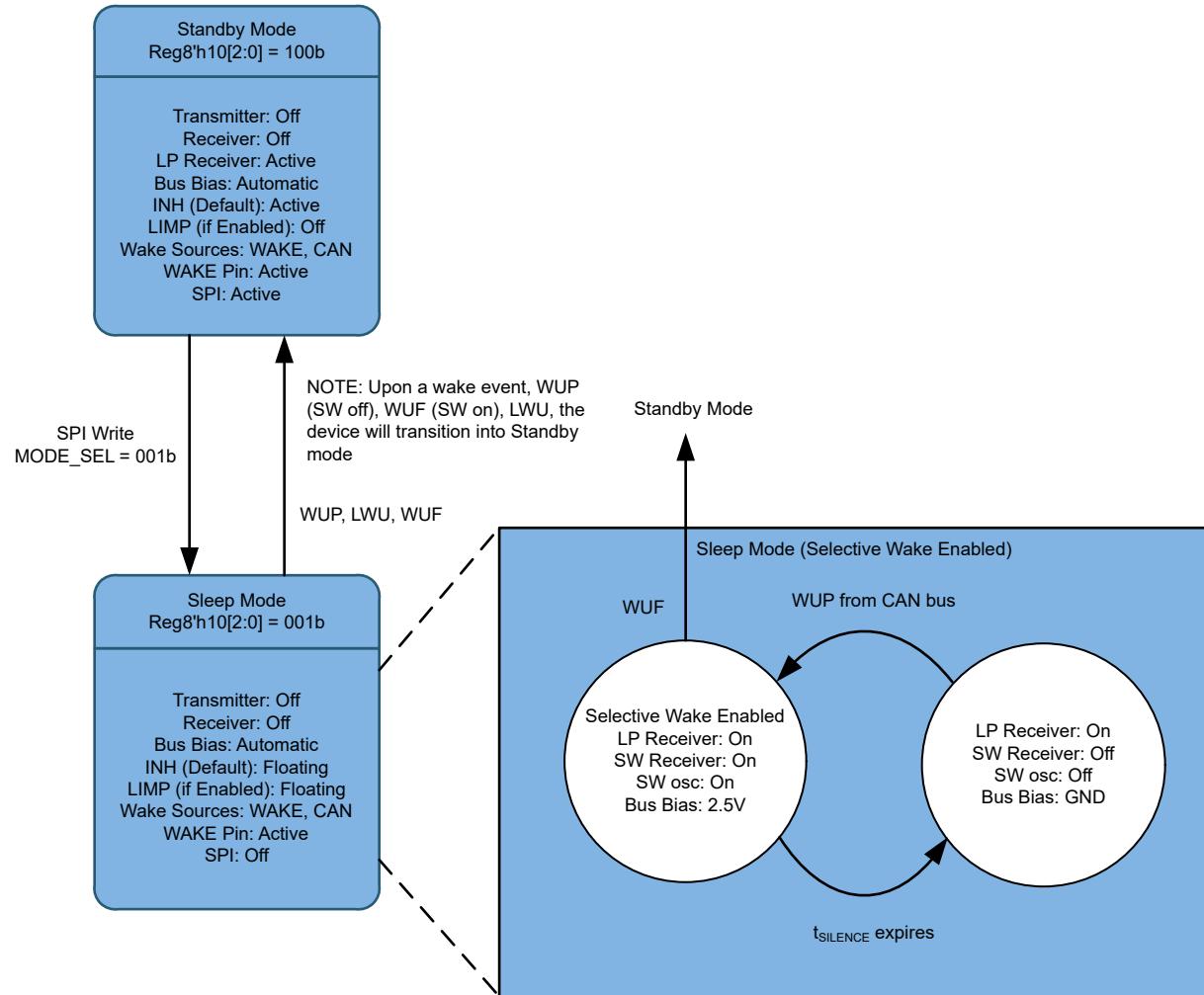

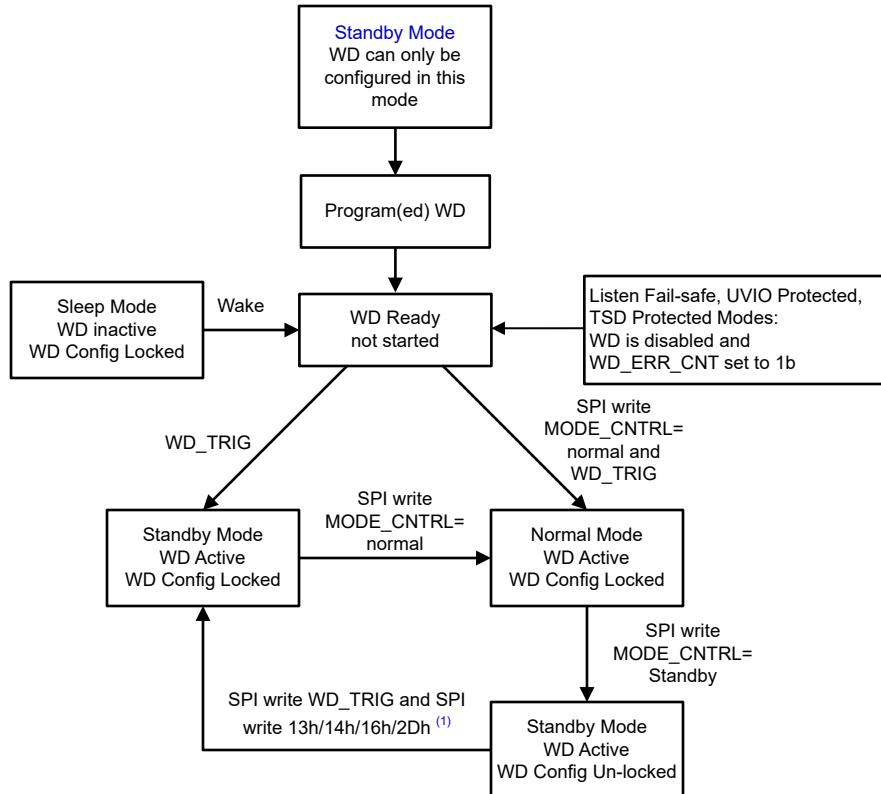

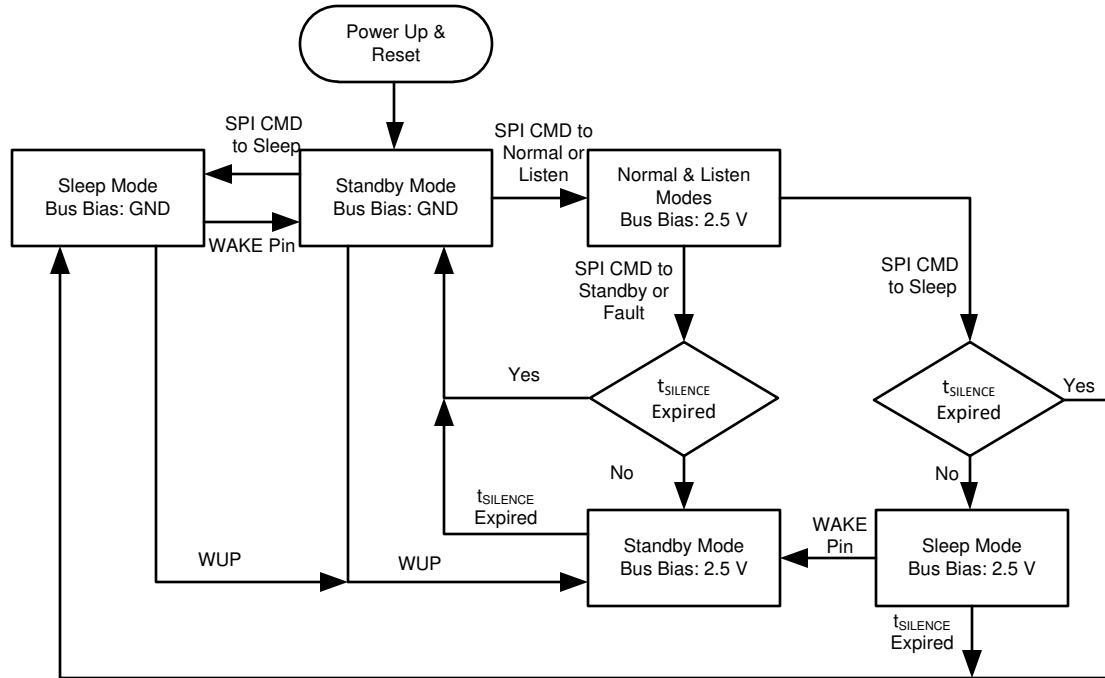

TCAN1576-Q1 には、通常、スタンバイ、リッスン、スリープ、フェイルセーフといった複数の機能モードがと、2 つの保護モードがあります。最初の 4 つのモードは、SPI レジスタ 8h10[2:0] によって設定されます。フェイルセーフ モードは、有効の場合、さまざまなフォルト条件によって遷移します。保護モードは、フェイルセーフ モードが無効の場合、デバイスまたはバスを保護するために使用される変更されたスタンバイ モードです。TCAN1576-Q1、WUP または LWU イベントを受信すると、自動的にスリープ モードからスタンバイ モードに移行します。選択的ウェークが有効な場合、デバイスは WUP を受信後にウェークアップ フレーム (WUF) を検出しようとします。WUF が検出されない場合、デバイスは再びスリープ モードに戻ります。各モードにおいて、デバイスのどの機能ブロックが動作しているかについては、表 8-1 を参照してください。

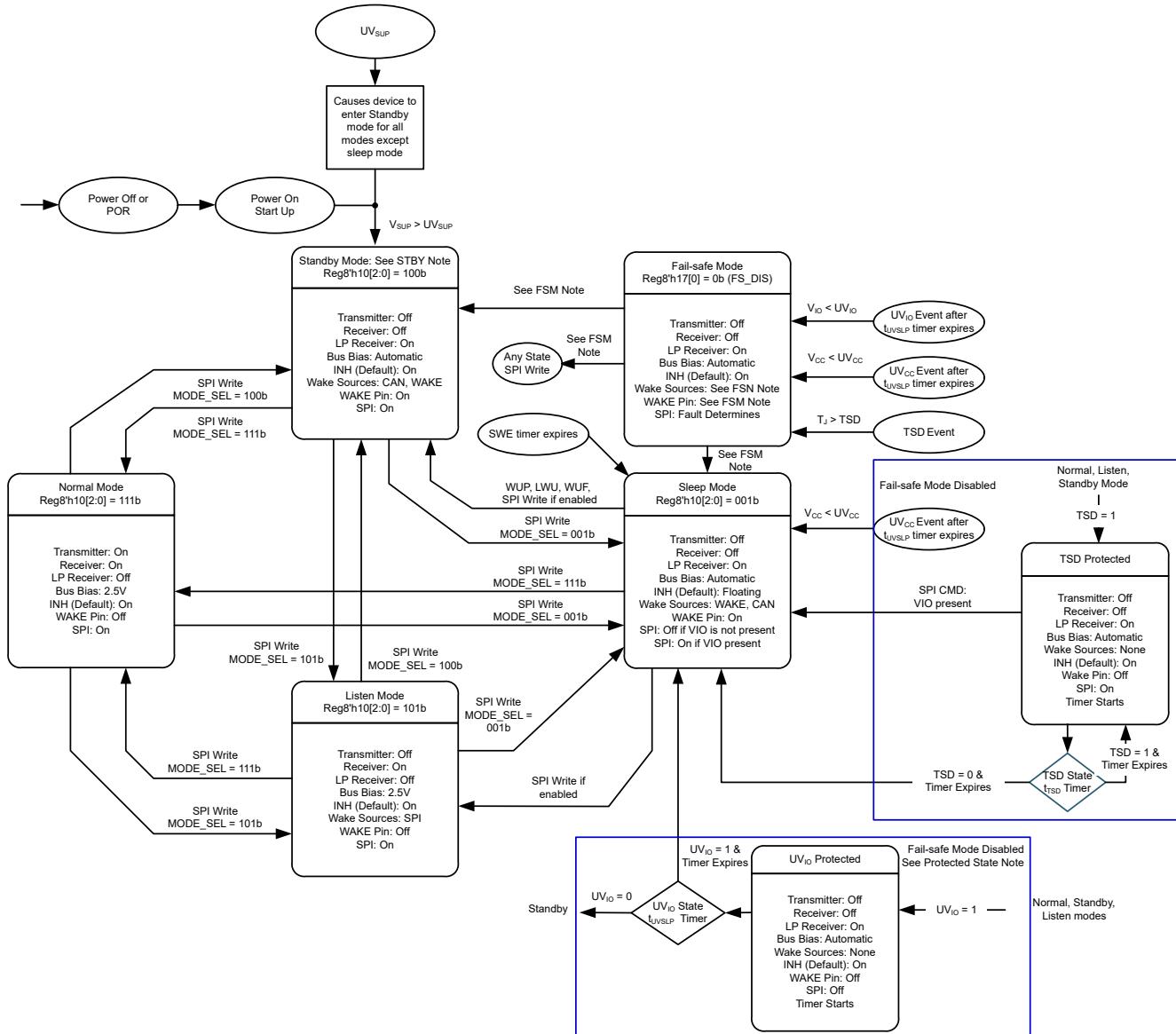

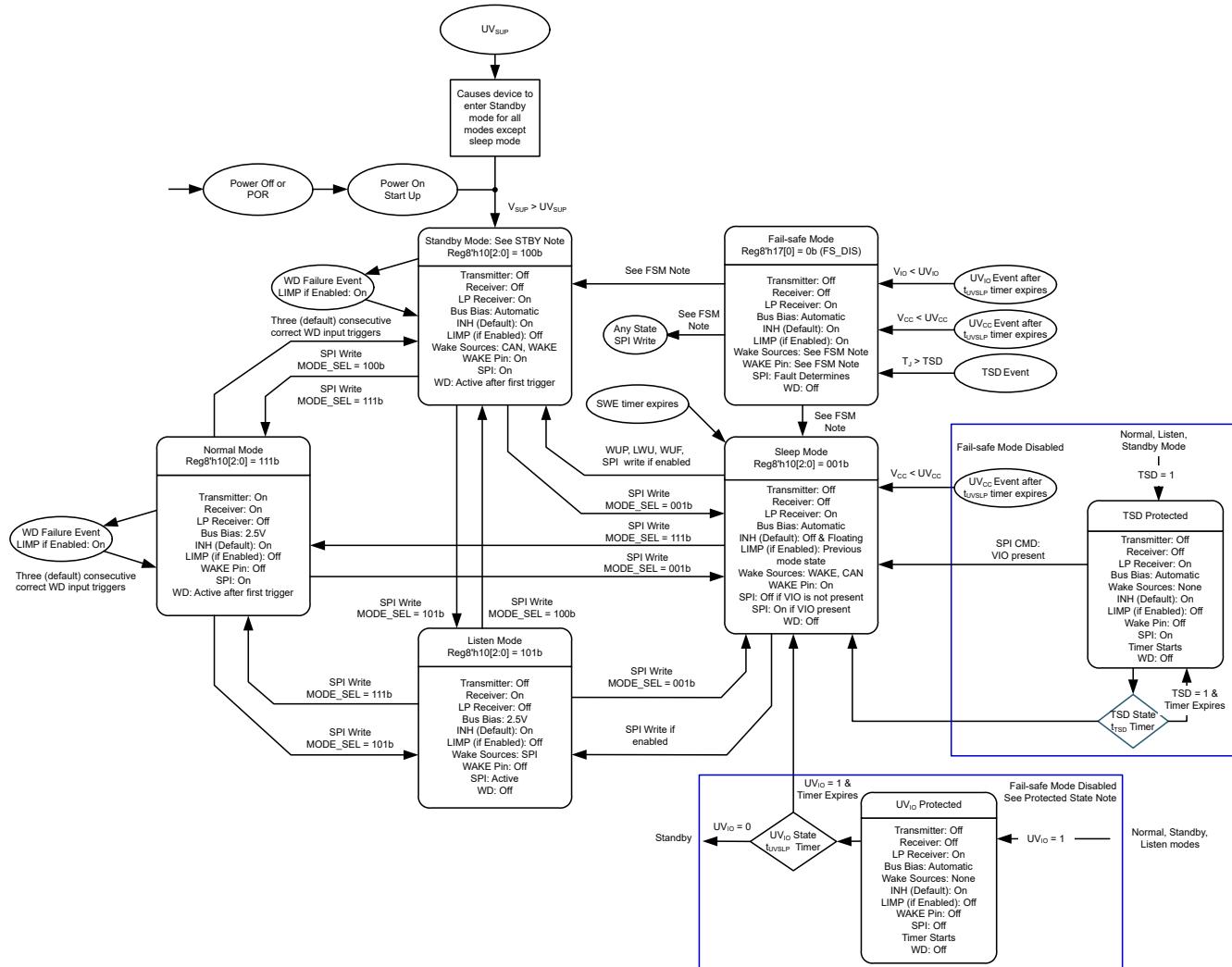

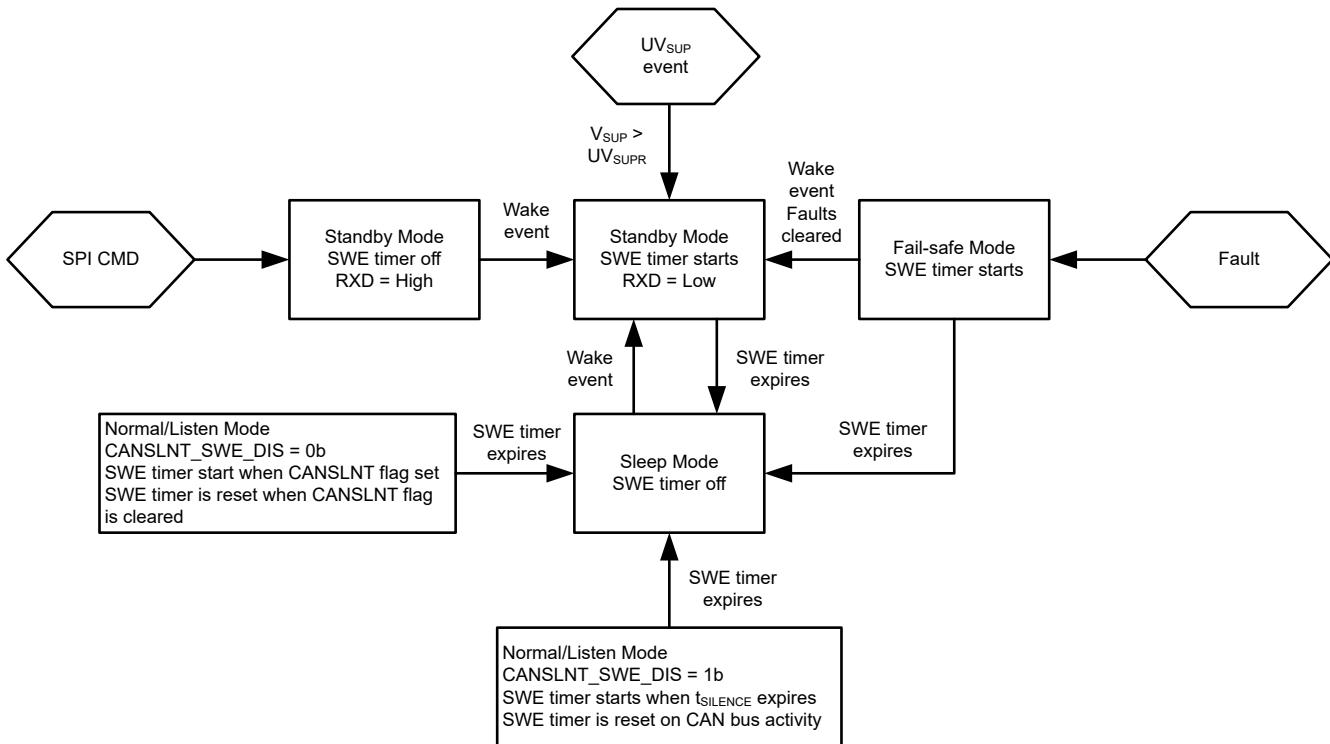

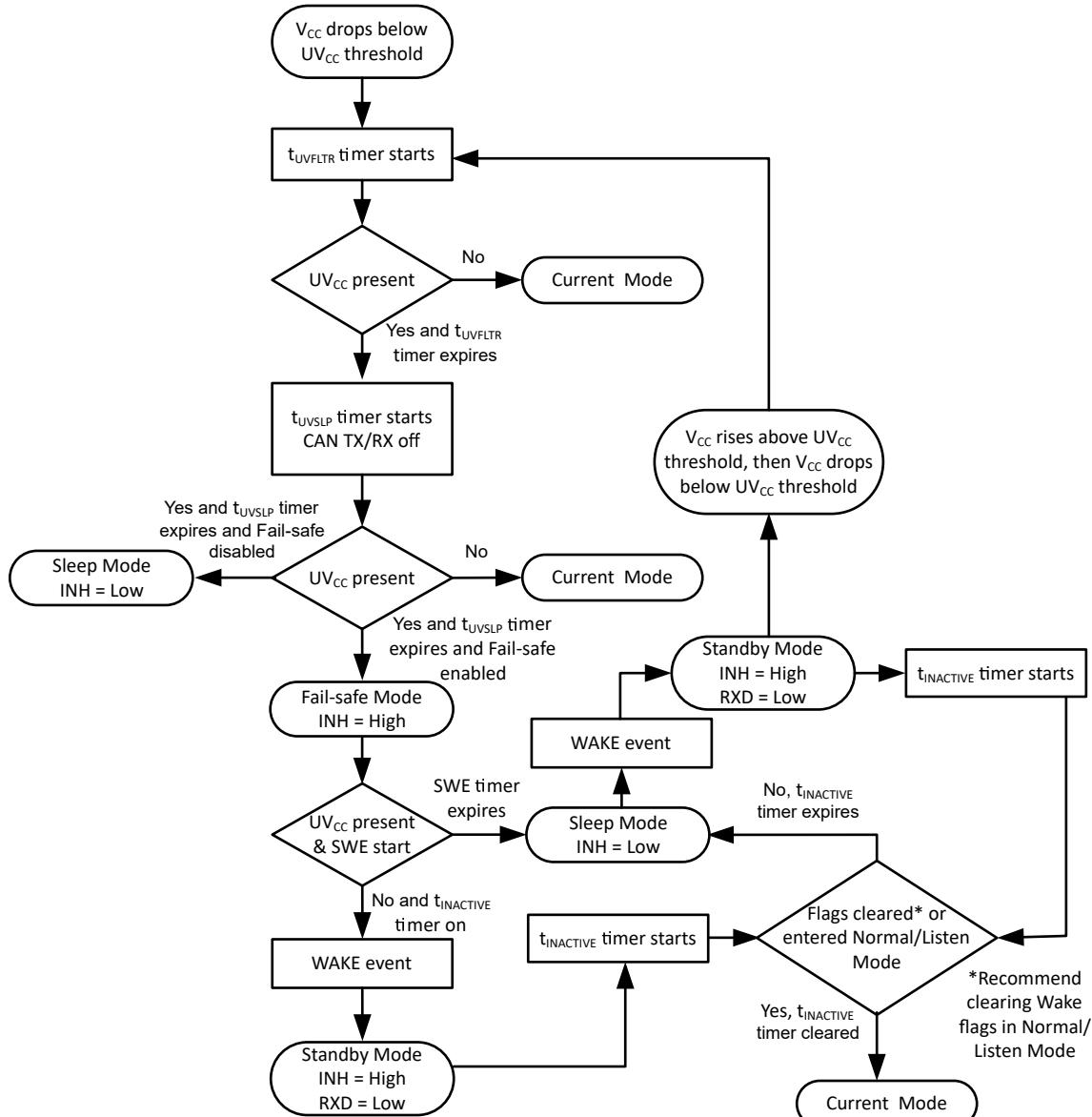

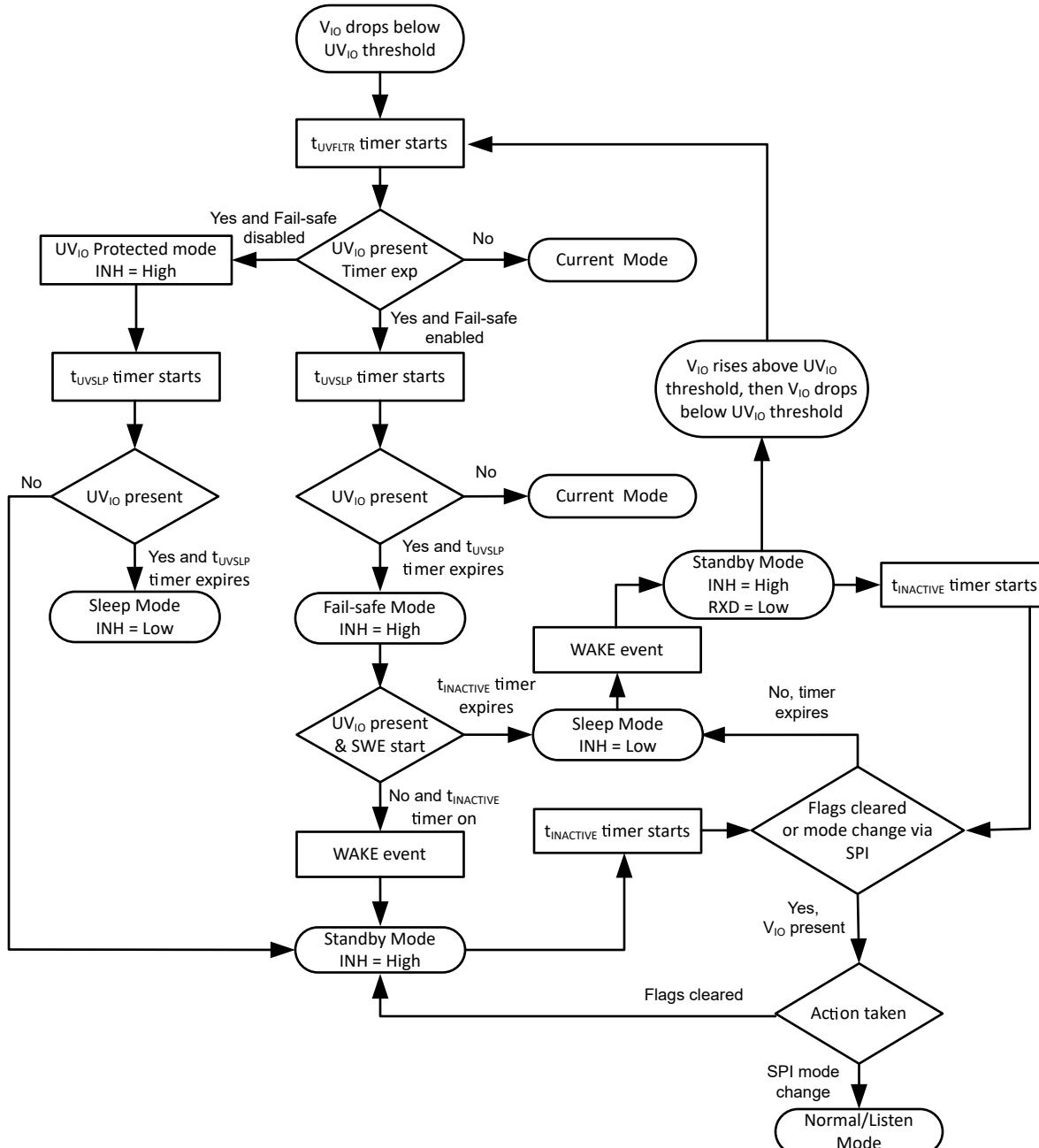

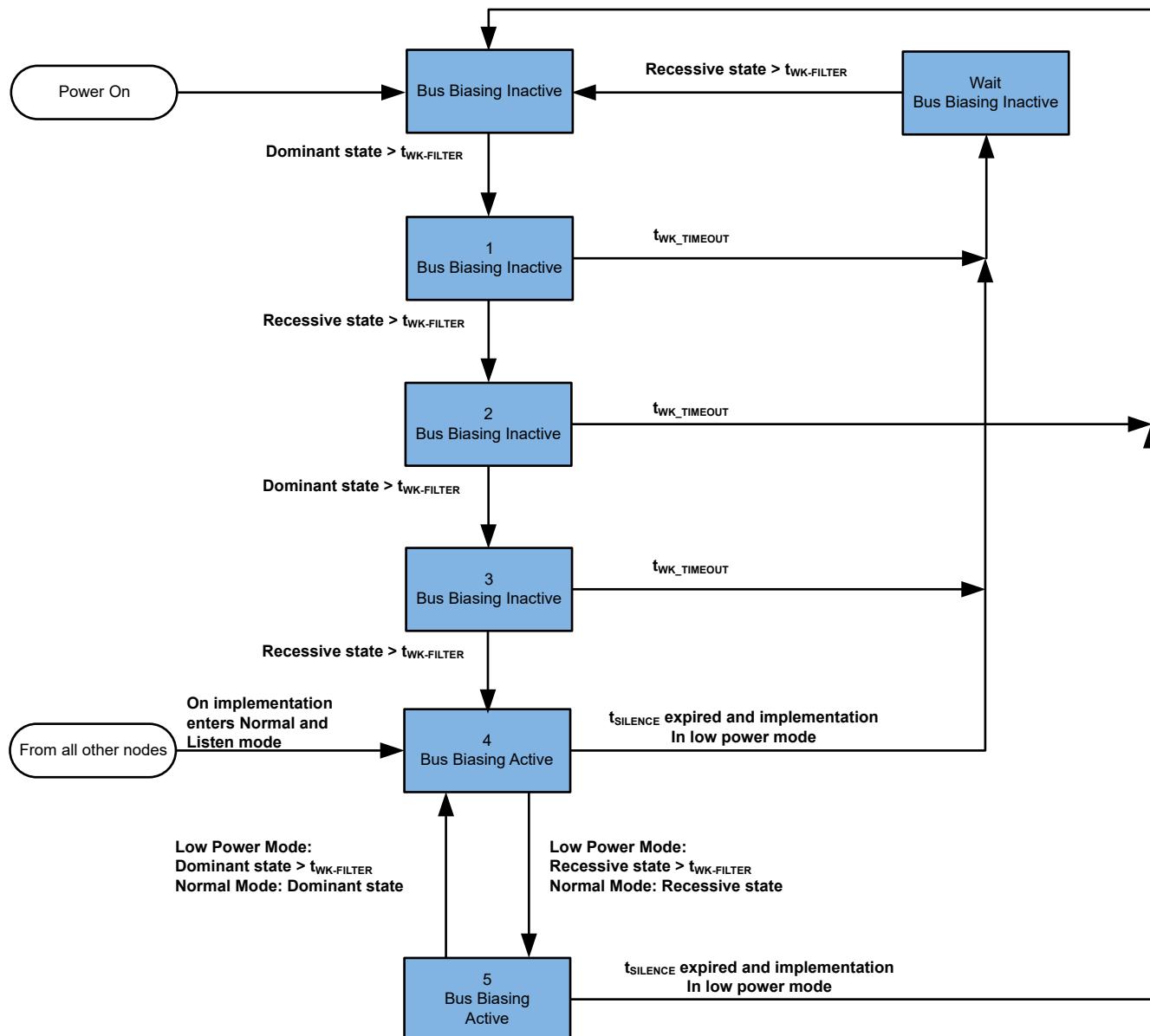

TCAN1576-Q1 の状態図および各機能モードにおける CAN バスのバイアス状態については、図 8-10、図 8-11

**表 8-1. モードの概要**

| ブロック                            | 通常                                  | スタンバイ                               | リッスン             | スリープ             | フェイルセーフ   | UV <sub>IO</sub> 保護 (フェイルセーフ無効) | TSD 保護 (フェイルセーフ無効) |

|---------------------------------|-------------------------------------|-------------------------------------|------------------|------------------|-----------|---------------------------------|--------------------|

| nINT (有効の場合)                    | オン                                  | オン                                  | オン               | オフ               | フォルトにより決定 | オフ                              | オン                 |

| INH                             | オン                                  | オン                                  | オン               | オフ               | オン        | オン                              | オン                 |

| LIMP (有効の場合):<br>TCAN1576-Q1    | WD エラーが発生した場合、または前モードの状態がクリアされるまでオン | WD エラーが発生した場合、または前モードの状態がクリアされるまでオン | 前モードの状態がクリアされるまで | 前モードの状態がクリアされるまで | オン        | 前モードの状態がクリアされるまで                | 前モードの状態がクリアされるまで   |

| WAKE                            | オフ                                  | オン                                  | オフ               | オン               | 注記を参照     | オフ                              | オフ                 |

| SPI                             | オン                                  | オン                                  | オン               | VIO が存在する場合はオン   | フォルトにより決定 | オフ                              | オン                 |

| ウォッチドッグ (有効の場合):<br>TCAN1576-Q1 | オン                                  | オン                                  | オフ               | オフ               | オフ        | オフ                              | オフ                 |

| 低消費電力 CAN RX                    | オフ                                  | オン                                  | オフ               | オン               | オン        | オン                              | オン                 |

| CAN トランスマッタ                     | オン                                  | オフ                                  | オフ               | オフ               | オフ        | オフ                              | オフ                 |

| CAN レシーバ                        | オン                                  | オフ                                  | オン               | オフ               | オフ        | オフ                              | オフ                 |

### 注

フェイルセーフ モードには、「フォルトにより決定」と記載されるブロックが複数あります。以下に説明を示します。

- フォルト条件が UV<sub>CC</sub> または TSD の場合、nINT および SPI はアクティブです。フォルト条件が UV<sub>IO</sub> 場合、これらのブロックはオフです。

- フェイルセーフモードの INH (デフォルト) はオンのため、プロセッサには電源が供給され、発生したフォルトを読み取ることができます。フェイルセーフ カウンタを使用している場合、指定回数のウェークアップとフェイルセーフ復帰のサイクルが発生すると、INH はいったんオフにされ、その後オンに設定されます。

- 低消費電力 CAN (WUP) レシーバは、V<sub>SUP</sub> から給電されます。UV<sub>SUP</sub> イベントが発生すると、このレシーバはオフになります。

- フェイルセーフ カウンタの上限に達し、かつレジスタ 8'h17[6:4] = 100b, FS\_CNTR\_ACT の場合、デバイスはスリープ モードに移行し、ウェーク要求に応答しません。デバイスを通常動作に戻すには、ハードリセット (パワーサイクル) が必要です。

- フェイルセーフ モードでは、SWE タイマ (有効な場合) が起動し、フォルトがクリアされるまでは WAKE イベントは無視されます。フォルトがクリアされると、WAKE ピンはアクティブになります。

- 有効化されており、SWE タイマがタイムアウトした場合、デバイスはスリープ モードに入ります。これは、たとえフォルトがクリアされていても、ウェイク イベントが発生していない、あるいはモード変更のような SPI 通信が行われていない場合に発生します。

- UV<sub>CC</sub> イベント中は、CAN トランスマッタとレシーバはオフで、低電力 CAN レシーバはオンです。

図 8-10. TCAN1575-Q1 デバイス状態図

図 8-11. TCAN1576-Q1 デバイス状態図

## 注

## 3 つのデバイス状態図すべてに関する注記

- スタンバイモードの注記 (STBY の注記)

- スリープモード、フェイルセーフモードからの移行、または電源投入時からスタンバイモードに移行する際、SWE タイマが開始します。

- SWE タイマが満了する前に、モード変更または割り込みクリアを行う必要があります。

- フェイルセーフモードの注記 (FSM 注記)

- フェイルセーフモードから復帰するには、�オルトがクリアされている必要があります。

- そのうえで、ウェイクイベントが発生しスタンバイに入るか、または

- もしくは、SPI 書き込みにより、(�オルトがクリアされていれば) 任意の状態へ移行できます。

- 有効化されている場合、フェイルセーフモードに移行すると SWE タイマが開始します。

- SWE タイマがタイムアウトすると、デバイスはスリープモードに移行します。

- SWE タイマがタイムアウトし、かつ�オルトがクリアされていても、ウェイクイベントがない場合には、デバイスはスリープモードに入ります。

- 保護状態の注記

- UVIO 保護ステータスは、デバイスに整合する IO 電圧レールが取り除かれたときに発生します。これによりデバイスとプロセッサ間に電圧の不整合が生じ、タイマがタイムアウトして  $UVIO = 1$  の場合、デバイスはスリープモードへ移行します。

- サーマルシャットダウンおよび UVIO イベントが同時に発生した場合、デバイスはスリープモードに移行します。

- $UV_{SUP}$  が発生すると  $UV_{SUP}$  モードに移行し、 $V_{SUP} > UV_{SUPR}$  になると、デバイスはスタンバイモードに移行します。ただしスリープモード中に発生した場合を除きます。スリープモード中の場合はスリープモードへ戻ります。

図 8-12. 選択的ウェーク有効時のスリープモード

### 注

状態図のデフォルトでは、スリープモード中 SPI はオフです。 $V_{IO}$  が存在する場合、SPI はスリープモードでも動作しますが、データレートは低下します。これには、図 8-12 に示すように、選択的ウェークのサブ状態が含まれます。

#### 8.4.1 通常モード

これは、本デバイスの通常の動作モードです。CAN ドライバとレシーバは完全に動作し、CAN 通信は双方向です。ドライバは、CAN FD コントローラの TXD 信号に入力されたデジタル信号を、CANH および CANL の差動出力へ変換します。レシーバは、CANH および CANL の差動信号を RXD 信号のデジタル出力へ変換し、CAN FD コントローラへ出力します。通常モードは、SPI を介して有効と無効を切り替えます。

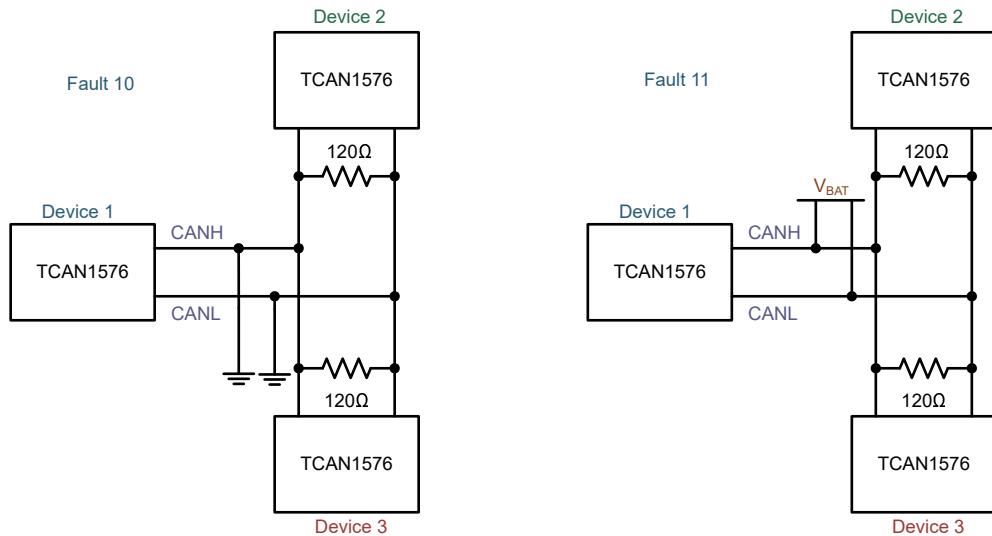

フェイルセーフモードおよび SWE タイマが有効な場合、通常モードへ移行する SPI コマンドを実行すると SWE タイマは停止します。スタンバイモード中には、割り込みをクリアすることを推奨します。通常モード中 (SWE タイマ有効時) に SWE タイマが開始されるケースは次の 2 つです。