# TCAN5102-Q1 SPI、UART、または I<sup>2</sup>C コントローラ付き自動車用 CAN FD ライトレスポンダ、プログラマブル PWM 搭載

## 1 特長

- AEC-Q100 : 車載アプリケーション認定済み

- CAN FD Light Responder は ISO 11898-1:202x に準拠

- TCAN4572-Q1 CAN FD Light Commander を使用する場合、最大 5Mbps の CAN FD Light データレートをサポートします

- 以下のような外部 CAN トランシーバを制御する能力 : TCAN1162x-Q1、TCAN1043A、TCAN1463A

- CAN バス経由でプログラム可能

- 電源電圧 : 3.3V ~ 5V

- 最大 8 つのチップ セレクトにより、最大 20MHz に対応する SPI コントローラをサポート

- 最大 2.5Mbaud をサポートする UART コントローラ

- I<sup>2</sup>C コントローラで高速モード プラス (1MHz) をサポート

- 他の機能と多重化可能な 13 の GPIO

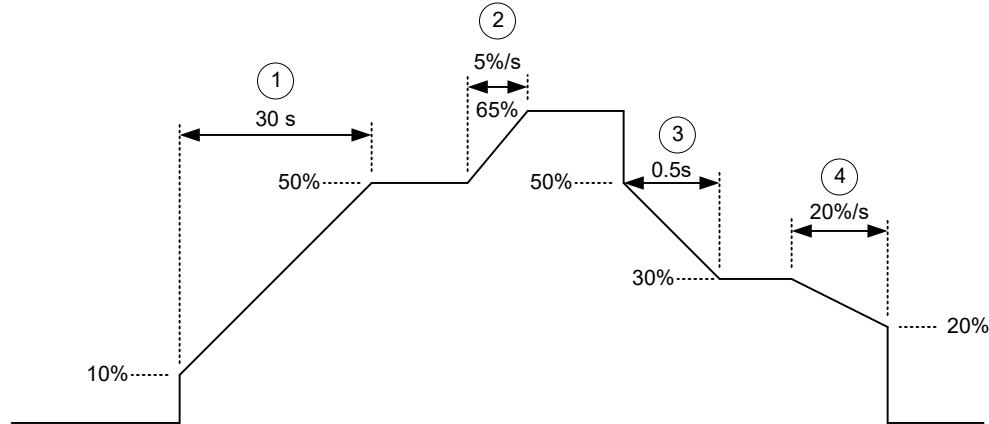

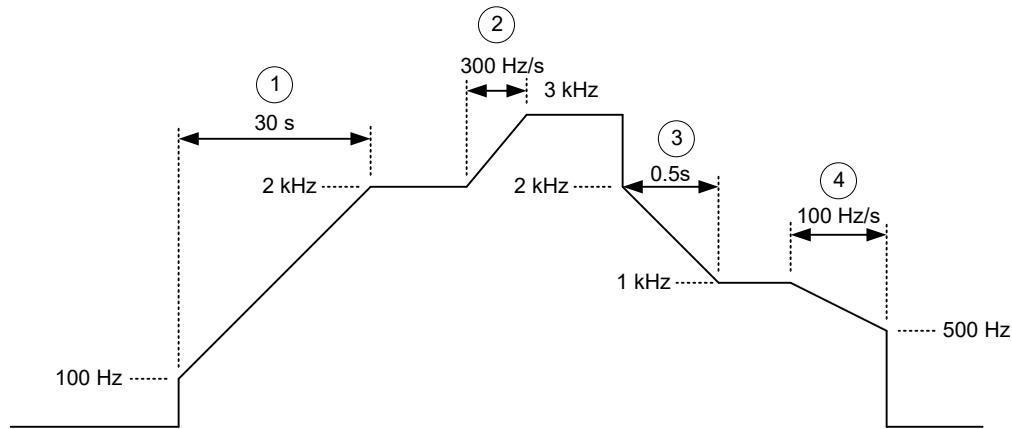

- モーター制御用の台形波ランプ プロファイルをサポートするプログラマブル PWM 出力

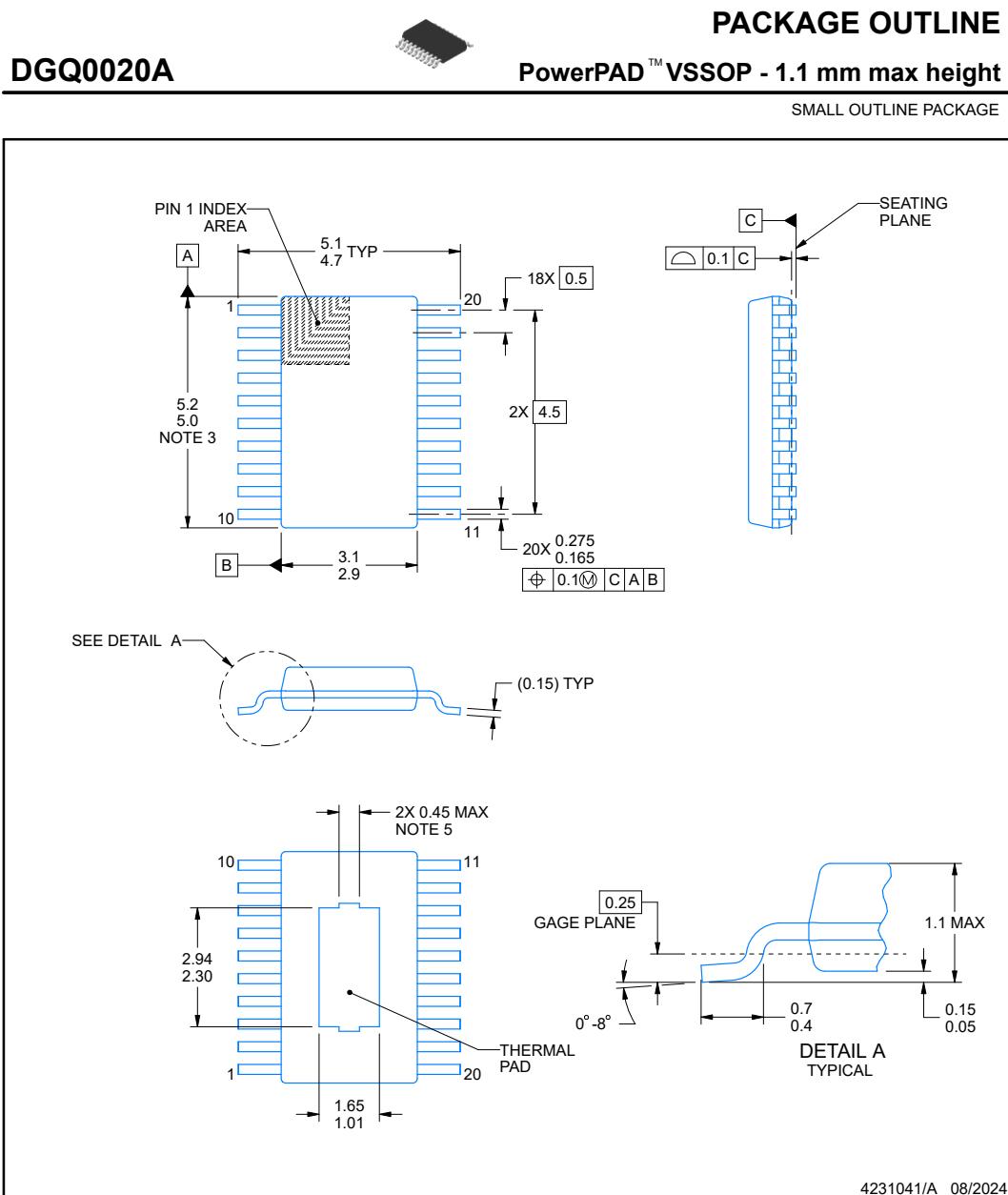

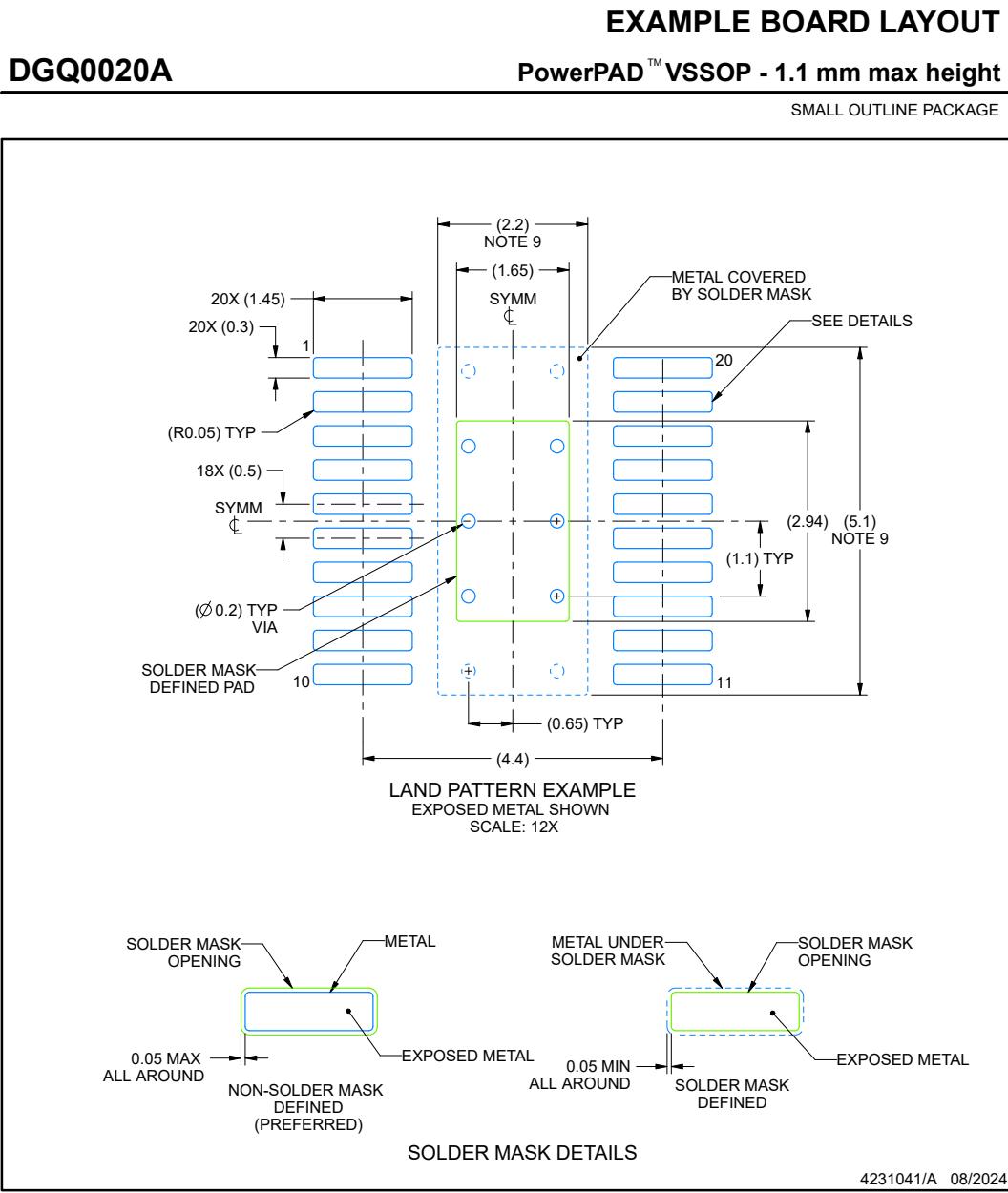

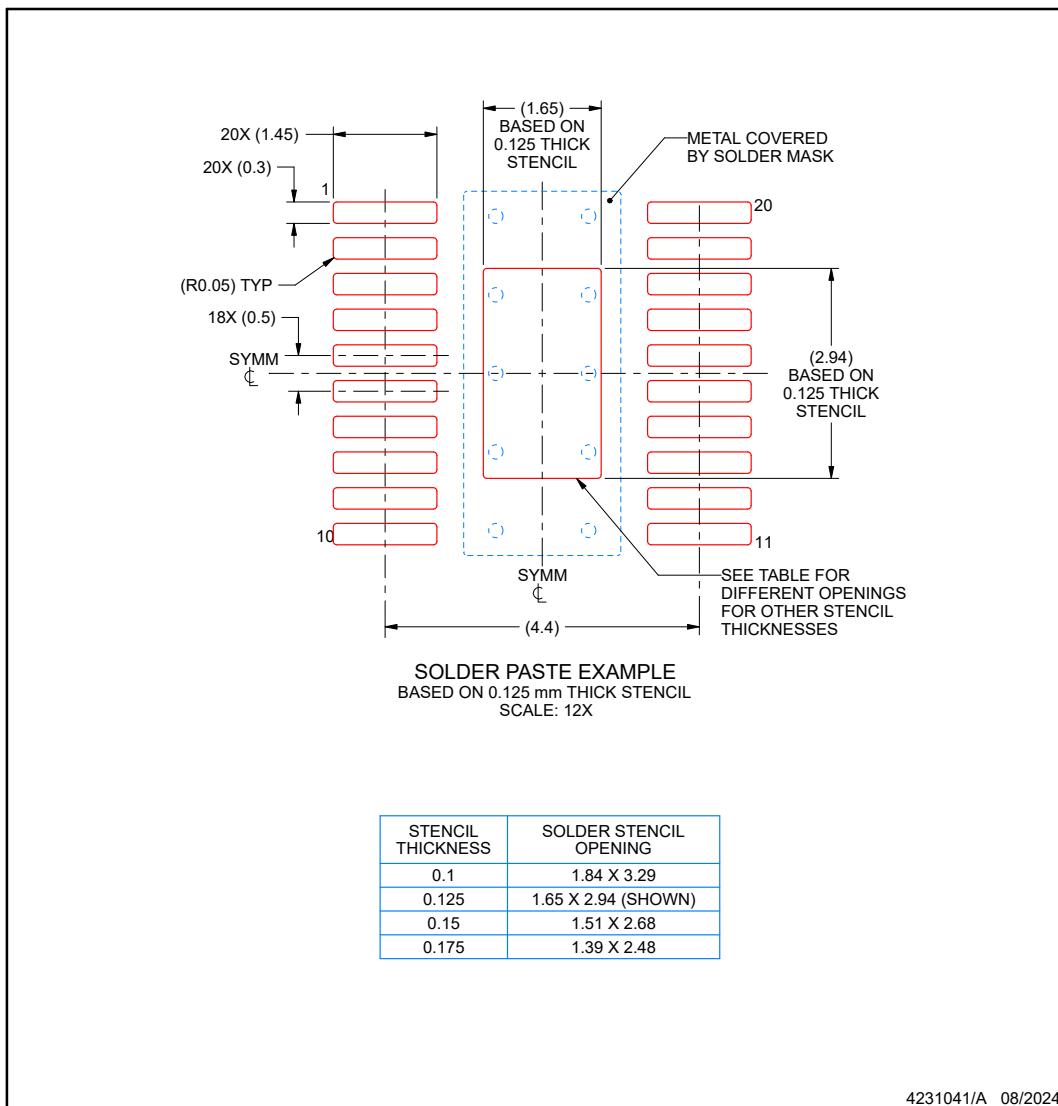

- 20 ピン VSSOP (DGQ) パッケージ

## 2 アプリケーション

- ボディ エレクトロニクスおよび照明

- ハイブリッド、電動、パワートレインシステム

- インフォテインメントおよびクラスター

- 電化製品

## 3 説明

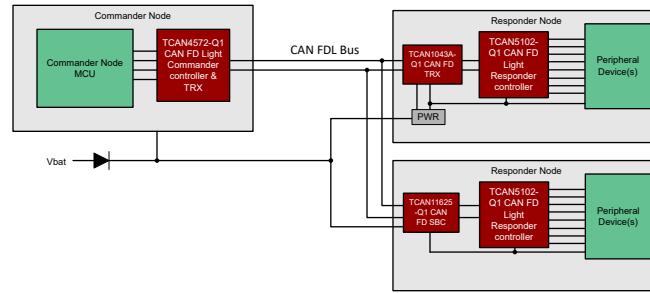

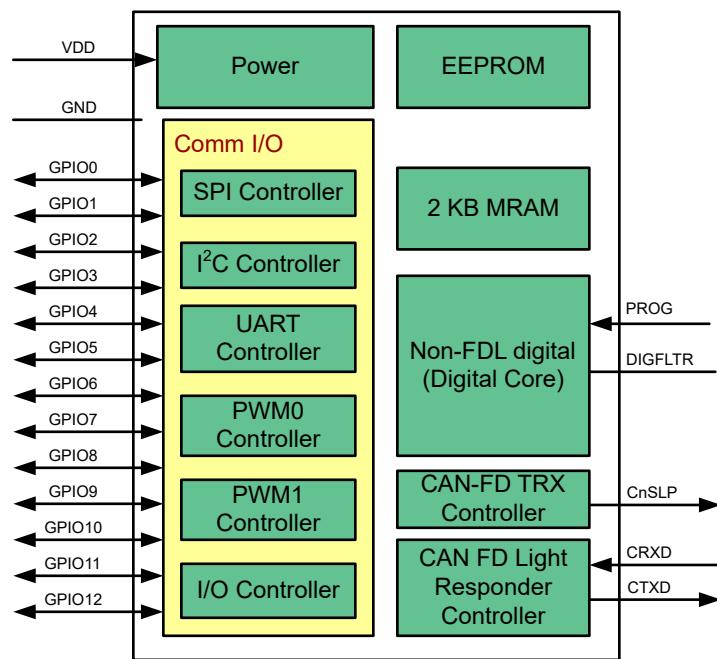

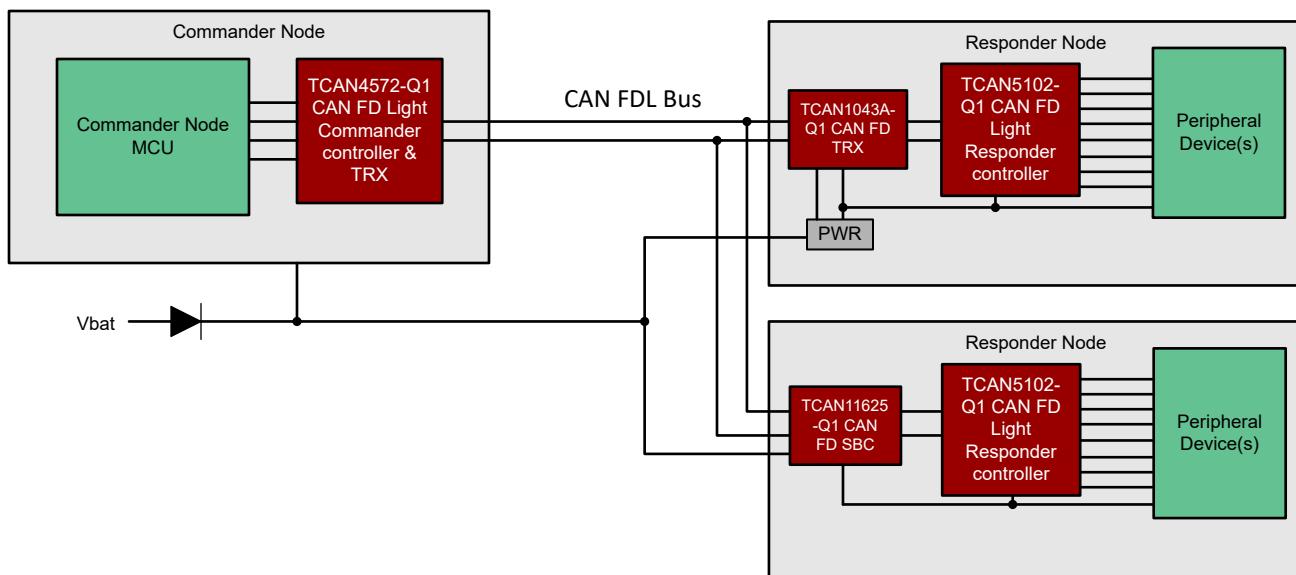

TCAN5102-Q1 は、CiA 604-1 および ISO 11898-1 : 2024 と互換性のあるコントロール エリア ネットワーク (CAN) フレキシブル データ (FD) ライトレスポンダ デバイスで、専用の CAN FD ライト コマンダを使用した場合、最大 5Mbps のデータ レートをサポートできます。このデバイスは、レスポンダ ノード プロセッサを必要としないコマンダ レスponsa アーキテクチャにおいて CAN FD ライト レスponsa ノード アプリケーションをサポートするように設計されています。レスponsa ノードへの制御はすべて、コマンダ ノード プロセッサからの CAN バスを介して行われるため、レスponsa ノード プロセッサやソフトウェアは不要です。

デバイスは CAN FD ライト コマンダ ノードからデータやコマンドを受信し、これらのコマンドをシリアルペリフェラル インターフェイス (SPI) コントローラ、UART コントローラ、I<sup>2</sup>C コントローラ、GPIO ピンのいずれかまたは両方に変換して、TCAN5102-Q1 が制御しているデバイスやペリフェラル デバイスと通信します。PWM 出力チャネルは、ステッパ モーターを制御するためのハードウェアで台形波ランプ プロファイルもサポートしています。デューティ サイクルまたは周波数を上昇させることができます。外部水晶振動子やクロックは不要です。このデバイスは、外部の TCAN1162x-Q1、TCAN1043A-Q1、TCAN1463A-Q1 CAN FD (SIC) トランシーバを制御し、システム レベルの柔軟性を確保します。このデバイスは、CAN FD トランシーバ / SBC を利用してノードの電力を制御し、CAN RXD (CRXD) ピンを Low にラッチすることでウェークアップ信号を TCAN5102-Q1 に伝達します。

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| TCAN5102-Q1 | 20 ピン (VSSOP、DGQ)    | 5.1mm × 4.9mm            |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

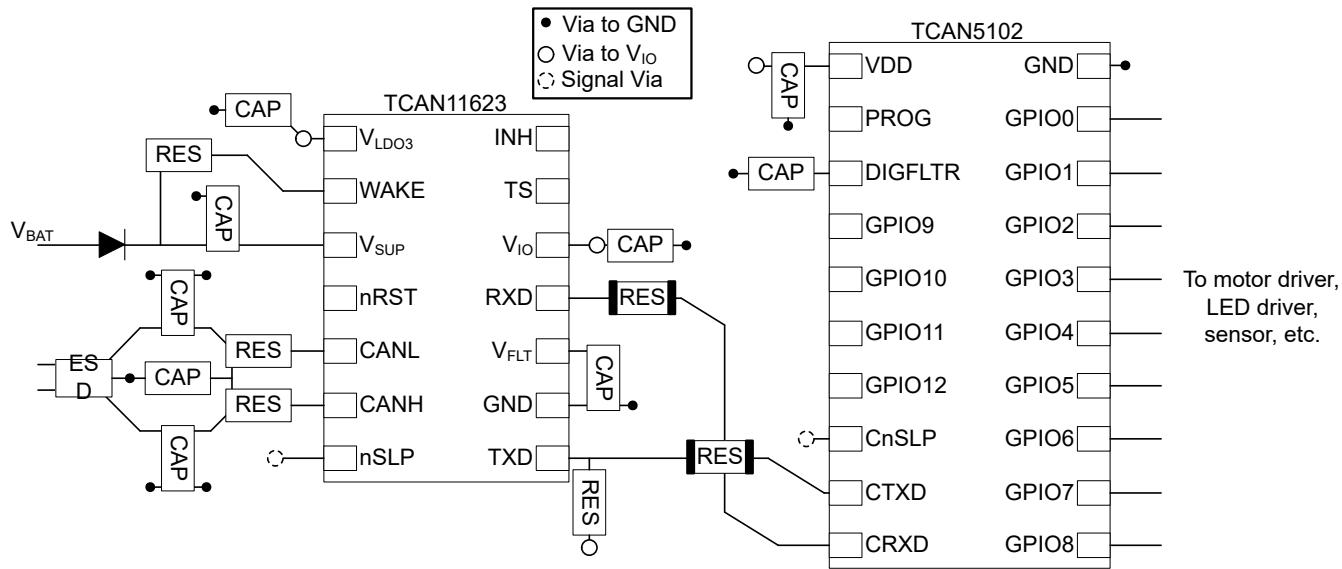

CAN FD ライトコマンダーレスポンダ アプリケーション

## ADVANCE INFORMATION

## 目次

|                                     |    |                             |     |

|-------------------------------------|----|-----------------------------|-----|

| 1 特長.....                           | 1  | 7.4 デバイスの機能モード.....         | 20  |

| 2 アプリケーション.....                     | 1  | 7.5 プログラミング.....            | 21  |

| 3 説明.....                           | 1  | 7.6 レジスタ マップ.....           | 58  |

| 4 ピン構成および機能.....                    | 4  | 8 アプリケーションと実装.....          | 228 |

| 5 仕様.....                           | 5  | 8.1 アプリケーション情報.....         | 228 |

| 5.1 絶対最大定格.....                     | 5  | 8.2 代表的なアプリケーション.....       | 228 |

| 5.2 ESD 定格.....                     | 5  | 8.3 電源に関する推奨事項.....         | 229 |

| 5.3 推奨動作条件.....                     | 5  | 8.4 レイアウト.....              | 229 |

| 5.4 熱に関する情報.....                    | 5  | 9 デバイスおよびドキュメントのサポート.....   | 231 |

| 5.5 電源の特性.....                      | 6  | 9.1 ドキュメントのサポート.....        | 231 |

| 5.6 電気的特性.....                      | 6  | 9.2 ドキュメントの更新通知を受け取る方法..... | 231 |

| 5.7 タイミング要件.....                    | 7  | 9.3 サポート・リソース.....          | 231 |

| 5.8 スイッチング特性.....                   | 8  | 9.4 商標.....                 | 231 |

| 5.9 I <sup>2</sup> C バスタイミング要件..... | 10 | 9.5 静電気放電に関する注意事項.....      | 231 |

| 6 パラメータ測定情報.....                    | 12 | 9.6 用語集.....                | 231 |

| 7 詳細説明.....                         | 15 | 10 改訂履歴.....                | 231 |

| 7.1 概要.....                         | 15 | 11 メカニカル、パッケージ、および注文情報..... | 232 |

| 7.2 機能ブロック図.....                    | 15 | 11.1 メカニカルデータ.....          | 233 |

| 7.3 機能説明.....                       | 17 |                             |     |

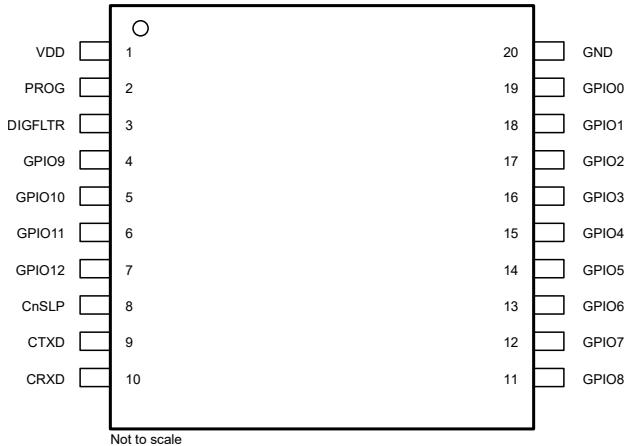

## 4 ピン構成および機能

図 4-1. DGQ 20-PIN (上面図)

表 4-1. ピンの機能

| ピン              |    | タイプ <sup>(1)</sup> | 説明                                                   |

|-----------------|----|--------------------|------------------------------------------------------|

| 名称              | 番号 |                    |                                                      |

| VDD             | 1  | P                  | デバイス電源入力、3.3V または 5V                                 |

| PROG            | 2  | I                  | デバイスの構成およびデバッグのための入力                                 |

| DIGFLTR         | 3  | P                  | デジタル電源フィルタピン                                         |

| GPIO9/CS4/SCL   | 4  | I/O                | 汎用入出力ピン、SPI チップセレクトチャネル 4 出力、I <sup>2</sup> C クロック出力 |

| GPIO10/CS5/SDA  | 5  | I/O                | 汎用入出力ピン、SPI チップセレクトチャネル 5 出力、I <sup>2</sup> C データピン  |

| GPIO11/CS6/PWM0 | 6  | I/O                | 汎用入出力ピン、SPI チップセレクトチャネル 6 出力、または PWM0 出力             |

| GPIO12/CS7/PWM1 | 7  | I/O                | 汎用入出力ピン、SPI チップセレクトチャネル 6 出力、または PWM1 出力             |

| CnSLP           | 8  | O                  | CAN トランシーバ制御出力ピン (nSLP)                              |

| CTXD            | 9  | O                  | CAN トランシーバ TXD 出力ピン (トランシーバの TXD 入力ピンに接続)            |

| CRXD            | 10 | I                  | CAN トランシーバ RXD 入力ピン (トランシーバの RXD 出力ピンに接続)            |

| GPIO8/URXD      | 11 | I/O                | 汎用入出力ピンまたは UART RXD 入力                               |

| GPIO7/UTXD      | 12 | I/O                | 汎用入出力ピンまたは UART TXD 出力                               |

| GPIO6/PICO      | 13 | I/O                | 汎用入出力ピンまたは SPI ベリフェラル入力、コントローラ出力                     |

| GPIO5/POCI      | 14 | I/O                | 汎用入出力ピンまたは SPI ベリフェラル出力、コントローラ入力                     |

| GPIO4/SCK       | 15 | I/O                | 汎用入出力ピンまたは SPI クロック出力                                |

| GPIO3/CS0       | 16 | I/O                | 汎用入出力ピンまたは SPI チップセレクトチャネル 0 出力                      |

| GPIO2/CS1       | 17 | I/O                | 汎用入出力ピンまたは SPI チップセレクトチャネル 1 出力                      |

| GPIO1/CS2       | 18 | I/O                | 汎用入出力ピンまたは SPI チップセレクトチャネル 2 出力                      |

| GPIO0/CS3       | 19 | I/O                | 汎用入出力ピンまたは SPI チップセレクトチャネル 3 出力                      |

| GND             | 20 | P                  | グラウンドピン                                              |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

### 注

複数の機能を持つピンについては、ピンを構成するために IO\_CFG レジスタを参照し、ピンの多重化の詳細については、[セクション 7.3.4](#) を参照してください。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                        |               | 最小値  | 最大値 | 単位 |

|------------------------|---------------|------|-----|----|

| VDD                    | 電源入力          | -0.3 | 6   | V  |

| DIGFLTR                | デジタルコアフィルタピン  | -0.3 | 1.8 | V  |

| V <sub>LOGIC_IN</sub>  | ロジックピン入力電圧範囲  | -0.3 | 6   | V  |

| V <sub>LOGIC_OUT</sub> | ロジック ピン出力電圧範囲 | -0.5 | 6   | V  |

| I <sub>O(LOGIC)</sub>  | ロジック ピン出力電流   |      | 12  | mA |

| T <sub>J</sub>         | 接合部温度         | -40  | 150 | °C |

| T <sub>stg</sub>       | 保存温度          | -65  | 150 | °C |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の範囲内であっても、推奨動作条件の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                    |      |                                                                 | 値     | 単位 |

|--------------------|------|-----------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM) 分類レベル 3A、その他のすべてのピン、AEC Q100-002 に準拠 <sup>(1)</sup> | ±2000 | V  |

|                    |      | 荷電デバイス モデル (CDM)、分類レベル C5、AEC Q100-011 に準拠                      | ±750  |    |

|                    |      | 角のピン<br>その他のピン                                                  | ±750  |    |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

外気温度範囲での動作時 (特に記述がない限り)

|                        |                         | 最小値   | 公称値 | 最大値 | 単位 |

|------------------------|-------------------------|-------|-----|-----|----|

| VDD                    | 電源電圧                    | 3.0   |     | 5.5 | V  |

| I <sub>OH(DO)</sub>    | デジタル出力 High レベル電流       |       | -12 |     | mA |

| I <sub>OL(DO)</sub>    | デジタル出力 Low レベル電流        |       |     | 12  | mA |

| C <sub>(VDD)</sub>     | VDD 電源容量                | 1     |     |     | μF |

| C <sub>(DIGFLTR)</sub> | デジタルコアフィルタのピン容量         | 0.33  | 1   |     | μF |

| ESR <sub>CO</sub>      | 電源ピンおよびフィルタピンの ESR 容量要件 | 0.001 |     | 1   | Ω  |

| T <sub>J</sub>         | 動作ジャンクション温度範囲           | -40   |     | 125 | °C |

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | TCAN5102-Q1 | 単位   |

|-----------------------|---------------------|-------------|------|

|                       |                     | RGY (QFN)   |      |

|                       |                     | 24-PINS     |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 31.8        | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 11.8        | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 21.4        | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 2.8         | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.3         | °C/W |

## 5.4 熱に関する情報 (続き)

| 熱評価基準 <sup>(1)</sup> |                  | TCAN5102-Q1 | 単位   |

|----------------------|------------------|-------------|------|

|                      |                  | RGY (QFN)   |      |

|                      |                  | 24-PINS     |      |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ | 11.8        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電源の特性

外気温度範囲での動作時 (特に記述がない限り)

| パラメータ               |                        | テスト条件                                                                                                 | 最小値  | 標準値  | 最大値           | 単位 |

|---------------------|------------------------|-------------------------------------------------------------------------------------------------------|------|------|---------------|----|

| <b>VDD</b>          |                        |                                                                                                       |      |      |               |    |

| IDD                 | VDD 供給電流デバイス(通常モード時)   | 通常モード、VDD = 5V<br>$I_I = 0, 0V$ または VDD<br>SPI、UART、I2C 無効化                                           | 1.4  | 1.8  | mA            |    |

|                     |                        | 通常モード、VDD = 3.3V<br>$I_I = 0, 0V$ または VDD<br>SPI、UART、I2C 無効化                                         | 1.4  | 1.8  | mA            |    |

| IDD                 | VDD 供給電流デバイス(スリープモード時) | スリープモード、VDD = 5V<br>$I_I = 0, 0V$ または VDD<br>$-40^{\circ}\text{C} \leq T_J \leq 85^{\circ}\text{C}$   | 10   | 20   | $\mu\text{A}$ |    |

|                     |                        | スリープモード、VDD = 5V<br>$I_I = 0, 0V$ または VDD<br>$T_J > 85^{\circ}\text{C}$                               | 20   | 60   | $\mu\text{A}$ |    |

|                     |                        | スリープモード、VDD = 3.3V<br>$I_I = 0, 0V$ または VDD<br>$-40^{\circ}\text{C} \leq T_J \leq 85^{\circ}\text{C}$ | 10   | 20   | $\mu\text{A}$ |    |

|                     |                        | スリープモード、VDD = 3.3V<br>$I_I = 0, 0V$ または VDD<br>$T_J > 85^{\circ}\text{C}$                             | 20   | 60   | $\mu\text{A}$ |    |

| UV <sub>DDR</sub>   | 電源低電圧立ち上がりリストップ        | VDD 立ち上がり                                                                                             | 2.35 | 2.95 | V             |    |

| UV <sub>DDF</sub>   | 電源低電圧立ち下がりリストップ        | VDD 立ち下がり                                                                                             | 2.1  | 2.7  | V             |    |

| UV <sub>DDHYS</sub> | 電源低電圧検出ヒステリシス          |                                                                                                       | 350  | 430  | mV            |    |

## 5.6 電気的特性

外気温度範囲での動作時 (特に記述がない限り)

| パラメータ            |              | テスト条件    | 最小値 | 標準値 | 最大値 | 単位 |

|------------------|--------------|----------|-----|-----|-----|----|

| <b>GPIO (入力)</b> |              |          |     |     |     |    |

| $V_{IH}$         | High レベル入力電圧 | GPIOx ピン | 0.7 | VDD |     |    |

|                  |              | CRXD ピン  | 0.7 |     |     |    |

|                  |              | PROG ピン  | 0.7 |     |     |    |

| $V_{IL}$         | Low レベル入力電圧  | GPIOx ピン | 0.3 | VDD |     |    |

|                  |              | CRXD ピン  | 0.3 |     |     |    |

|                  |              | PROG ピン  | 0.3 |     |     |    |

## 5.6 電気的特性(続き)

外気温度範囲での動作時(特に記述がない限り)

| パラメータ              |                   | テスト条件                                       | 最小値  | 標準値  | 最大値 | 単位          |

|--------------------|-------------------|---------------------------------------------|------|------|-----|-------------|

| $I_{IH}$           | High レベル入力リーク電流   | GPIOx ピン<br>入力 = VDD<br>VDD プルアップ/プルダウン抵抗無効 | -1   |      | 1   | $\mu A$     |

|                    |                   | CRXD ピン<br>入力 = VDD                         | -1   |      | 1   |             |

|                    |                   | PROG ピン<br>入力 = VDD                         |      | 90   | 140 |             |

| $I_{IL}$           | Low レベル入力リーク電流    | GPIOx ピン<br>入力 = 0V<br>プルアップ/プルダウン抵抗無効      | -1   |      | 1   | $\mu A$     |

|                    |                   | PROG ピン<br>入力 = 0V                          | -1   |      | 1   |             |

|                    |                   | CRXD<br>入力 = 0V                             | -140 |      | -90 |             |

| $C_{IN}$           | 入力容量              | 20 MHz、GPIOx ピン                             |      | 4    | 10  | $pF$        |

|                    |                   | 1 MHz、CRXD ピン                               |      | 4    | 10  |             |

|                    |                   | 1 MHz、PROG ピン                               |      | 4    | 10  |             |

| $I_{LKG(OFF)}$     | 電源がない場合のリーク電流です   | GPIOx ピン<br>入力 = 5.5V、VDD = 0V              | -1   | 0    | 1   | $\mu A$     |

| $R_{PD}$           | プルダウン抵抗           | GPIOx (有効の場合)                               | 40   | 60   | 80  | $k\Omega$   |

|                    |                   | PROG                                        | 40   | 60   | 80  |             |

| $R_{PU}$           | プルアップ抵抗           | GPIOx (有効の場合)                               | 40   | 60   | 80  | $k\Omega$   |

|                    |                   | CRXD                                        | 40   | 60   | 80  |             |

| <b>GPIOs(出力)</b>   |                   |                                             |      |      |     |             |

| $V_{OH}$           | High レベル出力電圧      | GPIOx、CTXD、CnSLP ピン $I_{OH} = 10mA$         | 0.7  | 0.85 |     | VDD         |

|                    |                   | GPIOx、CTXD、CnSLP ピン $I_{OH} = 2mA$          | 0.8  | 0.9  |     |             |

| $V_{OL}$           | Low レベル出力電圧       | GPIOx、CTXD、CnSLP ピン $I_{OL} = -10mA$        |      | 0.15 | 0.3 | VDD         |

|                    |                   | GPIOx、CTXD、CnSLP ピン $I_{OL} = -2mA$         |      | 0.1  | 0.2 |             |

| $I_{OH}$           | High レベル入力電流      | GPIOx、CTXD、CnSLP ピン<br>$V_O = 0.7 VDD$      | 10   | 12   |     | $mA$        |

| $I_{OL}$           | Low レベル出力電流       | GPIOx、CTXD、CnSLP ピン<br>$V_O = 0.3 VDD$      |      | -12  | -10 | $mA$        |

| $I_{LKG(OFF)}$     | 電源がない場合のリーク電流です   | CTXD、CnSLP ピン<br>$VPIN = 5.5 V$             | -5   |      | 5   | $\mu A$     |

| <b>サーマルシャットダウン</b> |                   |                                             |      |      |     |             |

| $TSD_F$            | サーマルシャットダウン下降     |                                             | 155  | 171  | 180 | $^{\circ}C$ |

| $TSD_R$            | サーマルシャットダウン上昇     |                                             | 160  | 176  | 190 | $^{\circ}C$ |

| $TSD_{HYS}$        | サーマルシャットダウンヒステリシス |                                             | 2    | 5    | 10  | $^{\circ}C$ |

## 5.7 タイミング要件

|              |                                 | 最小値 | 標準値 | 最大値 | 単位 |

|--------------|---------------------------------|-----|-----|-----|----|

| <b>電源</b>    |                                 |     |     |     |    |

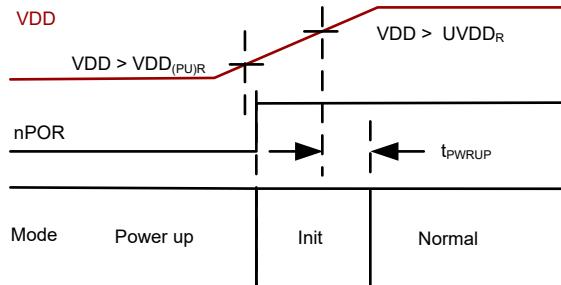

| $t_{PWRUP}$  | デバイスが起動するまでに、VDD が POR を超えた後の時間 |     | 2   |     | ms |

| <b>モード変更</b> |                                 |     |     |     |    |

## 5.7 タイミング要件 (続き)

|                      |                                                                             | 最小値  | 標準値 | 最大値  | 単位      |

|----------------------|-----------------------------------------------------------------------------|------|-----|------|---------|

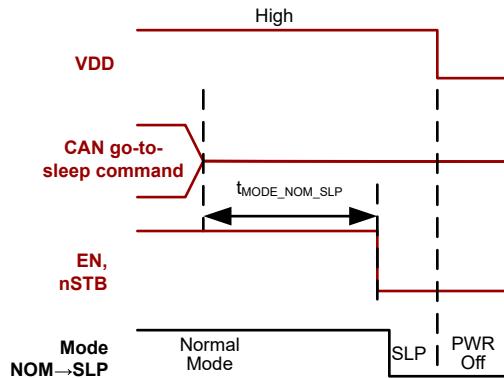

| $t_{MODE\_NOM\_SLP}$ | デバイスが CAN トランシーバをオフにする「Go-to-sleep」コマンドからの経過時間                              |      | 100 | 600  | $\mu s$ |

| <b>デバイスタイミング</b>     |                                                                             |      |     |      |         |

| $t_{MODE\_POR\_NOM}$ | POR から通常モードへの移行時間、CAN メッセージ受信準備完了                                           |      | 150 | 400  | $\mu s$ |

| <b>SPI のタイミング要件</b>  |                                                                             |      |     |      |         |

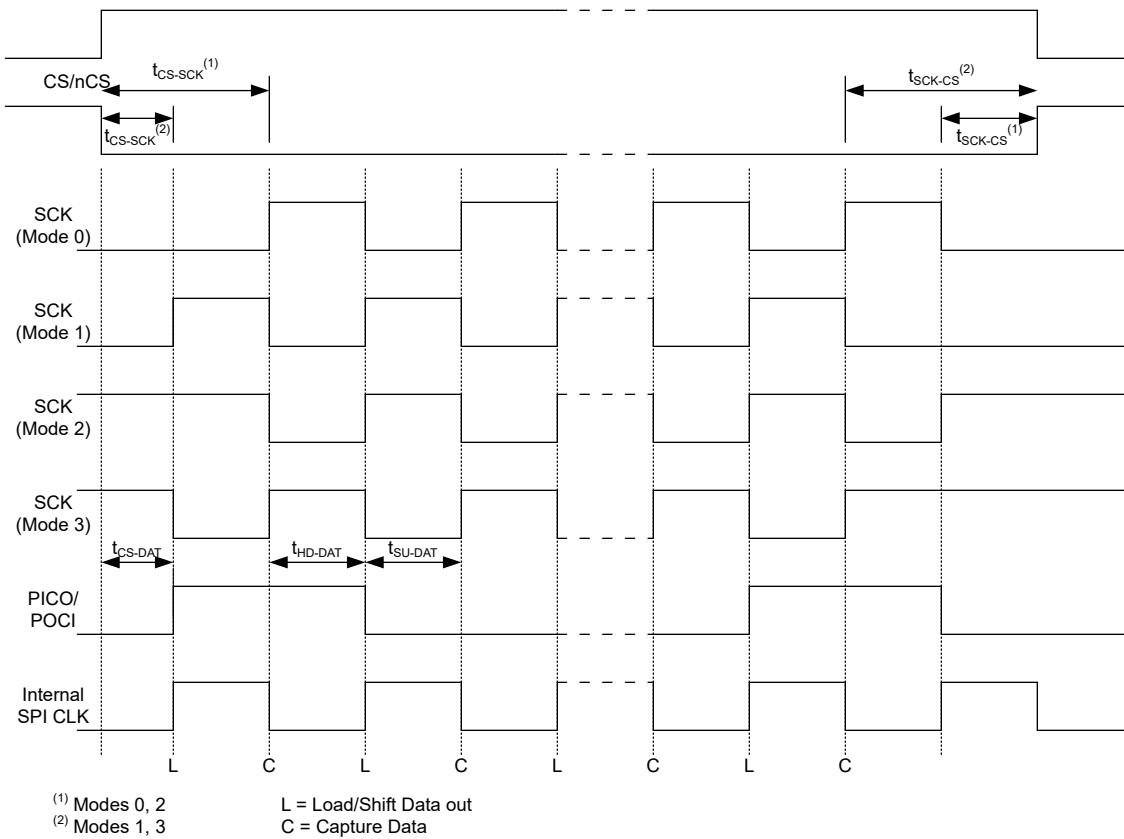

| $t_{HD-DAT}$         | アクティブ SCK エッジ後の POCI 入力ホールド時間要件<br><a href="#">SPI のタイミング特性</a> を参照してください   | 20   |     |      | ns      |

| $t_{SU-DAT}$         | アクティブ SCK エッジ前の POCI 入力セットアップ時間要件<br><a href="#">SPI のタイミング特性</a> を参照してください | 5    |     |      | ns      |

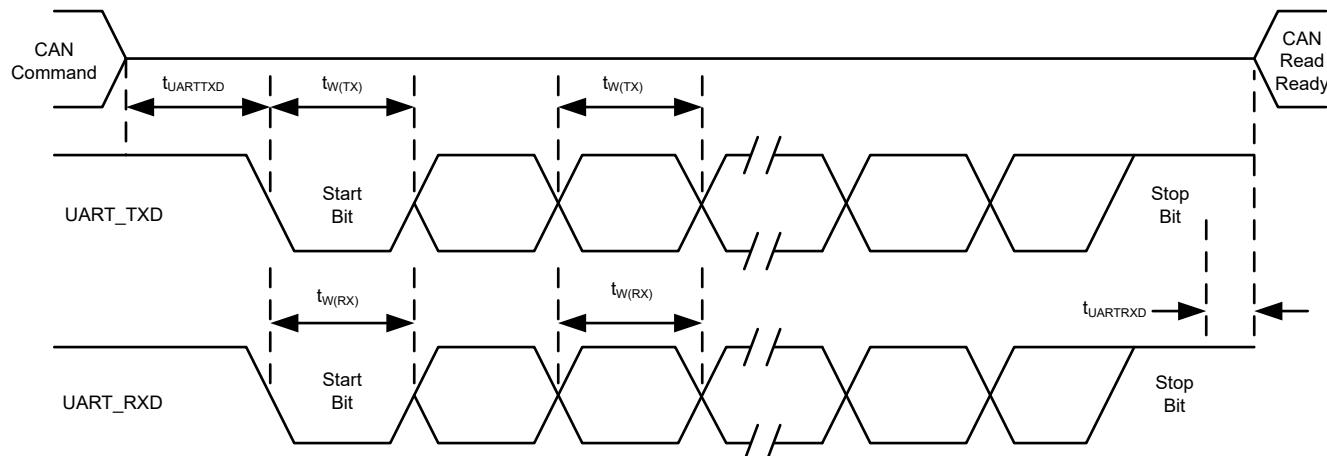

| <b>UART</b>          |                                                                             |      |     |      |         |

| $t_{W(RX)}$          | パルス幅、受信開始、停止、データビット <sup>(1)</sup>                                          | 0.97 | 1   | 1.04 | U       |

(1) U = UART のボーレート = 1/ プログラムされたボーレート

## 5.8 スイッチング特性

外気温度範囲での動作時 (特に記述がない限り)

| パラメータ                 | テスト条件                                                 | 最小値                                                              | 標準値  | 最大値  | 単位   |

|-----------------------|-------------------------------------------------------|------------------------------------------------------------------|------|------|------|

| <b>SPI スイッチング特性</b>   |                                                       |                                                                  |      |      |      |

| $f_{SCK-MAX}$         | SCK、最大 SPI クロック周波数 <sup>(1)</sup>                     | 通常モード、 $C_L = 20pF$                                              | 20   |      | MHz  |

| $t_{SCK-MIN}$         | SCK、最小 SPI クロック周期 <sup>(1)</sup>                      | 通常モード、 $C_L = 20pF$                                              | 50   |      | ns   |

| $t_{SCKR}$            | SCK の立ち上がり時間 <sup>(1)</sup>                           | 通常モード、 $C_L = 20pF$                                              | 4    | 10   | ns   |

| $t_{SCKF}$            | SCK の立ち下がり時間 <sup>(1)</sup>                           | 通常モード、 $C_L = 20pF$                                              | 4    | 8    | ns   |

| $t_{SCKH}$            | SCK、SPI クロック high <sup>(1)</sup>                      | 通常モード                                                            | 0.47 | 0.49 | 0.5  |

| $t_{SCKL}$            | SCK、SPI クロック low <sup>(1)</sup>                       | 通常モード                                                            | 0.5  | 0.51 | 0.53 |

| $t_{SCK-CS}$          | 最後の SCK エッジから CS 非アクティブ状態までの遅延時間 <sup>(1)</sup>       | 通常モード<br><a href="#">SPI のタイミング特性</a> を参照してください                  | 0.44 | 0.5  | 0.52 |

| $t_{CS-SCK}$          | CS アクティブから最初の SCK エッジまでの遅延時間 <sup>(1)</sup>           | 通常モード<br><a href="#">SPI のタイミング特性</a> を参照してください                  | 0.49 | 0.5  | 0.57 |

| $t_{HD-DAT}$          | キャプチャ SCK エッジから PICO データ変更までのデータホールド時間 <sup>(1)</sup> | 通常モード<br><a href="#">SPI のタイミング特性</a> を参照してください                  | 0.47 | 0.5  | 0.51 |

| $t_{CS-DV}$           | 遅延時間、チップセレクトのアクティブエッジから PICO データ有効まで <sup>(1)</sup>   | 通常モード<br>の SPI モード 0、2<br><a href="#">SPI のタイミング特性</a> を参照してください | 0    | 5    | ns   |

|                       |                                                       | 通常モード<br>の SPI モード 1、3<br><a href="#">SPI のタイミング特性</a> を参照してください |      | 0.5  | 0.57 |

| <b>I2C のスイッチング特性</b>  |                                                       |                                                                  |      |      |      |

| $t_{STUCKBUS\_I2C}$   | バスラインがデバイスがバスをスタッカ状態と見なすまで「スタッカ」状態を維持する時間。            |                                                                  | 25   | 40   | 65   |

| $f_{SB\_SCLOUT\_I2C}$ | I2C スタックバス回復パターンバスをスタッカ解除しようとした際に生成されるクロック周波数         |                                                                  | 5.5  | 8.5  | 14   |

| <b>UART</b>           |                                                       |                                                                  |      |      |      |

## 5.8 スイッチング特性(続き)

外気温度範囲での動作時(特に記述がない限り)

| パラメータ            |                                            | テスト条件                                                      | 最小値  | 標準値 | 最大値  | 単位  |

|------------------|--------------------------------------------|------------------------------------------------------------|------|-----|------|-----|

| $t_{baud}$       | 最大 UART ボーレート                              |                                                            |      |     | 2.5  | MHz |

| $t_{UARTTXD}$    | CAN コマンド完了から UART 送信開始までの時間                |                                                            |      | 1   | 2    | U   |

| $t_{UARTRXD}$    | UART 受信から CAN 読み取り準備完了までの時間 <sup>(1)</sup> | 最後のデータ / パリティビットの終了を UARTRXN ビットは、 $C_L = 20\text{pF}$ を設定 |      | 0.5 | 2    | U   |

| $t_W(\text{TX})$ | パルス幅、送信開始、停止、データビット <sup>(1) (2)</sup>     | $C_L = 20\text{pF}$                                        | 0.98 |     | 1.02 | U   |

- (1) 設計により規定されています。

- (2) U = UART のボーレート = 1/プログラムされたボーレート

- (3) S = SPI クロック周期 = 1/SPI クロック周波数

## 5.9 I<sup>2</sup>C バス タイミング要件

外気温度範囲での動作時 (特に記述がない限り)

|                                       |                                               |                                   | 最小値                           | 最大値  | 単位  |

|---------------------------------------|-----------------------------------------------|-----------------------------------|-------------------------------|------|-----|

| <b>I<sup>2</sup>C バス - スタンダード モード</b> |                                               |                                   |                               |      |     |

| f <sub>scl</sub>                      | I <sup>2</sup> C クロック周波数                      |                                   | 0                             | 100  | kHz |

| t <sub>sch</sub>                      | I <sup>2</sup> C クロックの High 時間 <sup>(1)</sup> |                                   | 4                             |      | μs  |

| t <sub>scl</sub>                      | I <sup>2</sup> C クロックの Low 時間 <sup>(1)</sup>  |                                   | 4.7                           |      | μs  |

| t <sub>sp</sub>                       | I <sup>2</sup> C スパイク時間                       |                                   |                               | 50   | ns  |

| t <sub>sds</sub>                      | I <sup>2</sup> C シリアル データ セットアップ時間            |                                   | 250                           |      | ns  |

| t <sub>sdh</sub>                      | I <sup>2</sup> C シリアル データ ホールド時間              |                                   | 0                             |      | ns  |

| t <sub>icr</sub>                      | I <sup>2</sup> C 入力の立ち上がり時間 <sup>(1)</sup>    |                                   |                               | 1000 | ns  |

| t <sub>icf</sub>                      | I <sup>2</sup> C 入力の立ち下がり時間                   |                                   |                               | 300  | ns  |

| t <sub>ocf</sub>                      | I <sup>2</sup> C 出力の立ち下がり時間                   | 10pF ~ 400pF バス                   |                               | 300  | ns  |

| t <sub>buf</sub>                      | STOP と START 間の I <sup>2</sup> C バスのフリー時間     |                                   | 4.7                           |      | μs  |

| t <sub>sts</sub>                      | I <sup>2</sup> C START または反復 START 条件の設定      |                                   | 4.7                           |      | μs  |

| t <sub>sth</sub>                      | I <sup>2</sup> C START または反復 START 条件ホールド     |                                   | 4                             |      | μs  |

| t <sub>sps</sub>                      | I <sup>2</sup> C STOP 条件の設定                   |                                   | 4                             |      | μs  |

| t <sub>vd(data)</sub>                 | 有効データ時間                                       | SCL Low から SDA 出力有効まで             |                               | 3.45 | μs  |

| t <sub>vd(ack)</sub>                  | ACK 条件の有効データ時間                                | SCL Low から SDA (出力) Low への ACK 信号 |                               | 3.45 | μs  |

| C <sub>b</sub>                        | I <sup>2</sup> C バスの容量性負荷                     |                                   |                               | 400  | pF  |

| <b>I<sup>2</sup>C バス - ファスト モード</b>   |                                               |                                   |                               |      |     |

| f <sub>scl</sub>                      | I <sup>2</sup> C クロック周波数                      |                                   | 0                             | 400  | kHz |

| t <sub>sch</sub>                      | I <sup>2</sup> C クロックの High 時間 <sup>(1)</sup> |                                   | 0.6                           |      | μs  |

| t <sub>scl</sub>                      | I <sup>2</sup> C クロックの Low 時間 <sup>(1)</sup>  |                                   | 1.3                           |      | μs  |

| t <sub>sp</sub>                       | I <sup>2</sup> C スパイク時間                       |                                   |                               | 50   | ns  |

| t <sub>sds</sub>                      | I <sup>2</sup> C シリアル データ セットアップ時間            |                                   | 100                           |      | ns  |

| t <sub>sdh</sub>                      | I <sup>2</sup> C シリアル データ ホールド時間              |                                   | 0                             |      | ns  |

| t <sub>icr</sub>                      | I <sup>2</sup> C 入力の立ち上がり時間 <sup>(1)</sup>    |                                   | 20                            | 300  | ns  |

| t <sub>icf</sub>                      | I <sup>2</sup> C 入力の立ち下がり時間                   | 20 × (V <sub>CC</sub> / 5.5V)     | 300                           |      | ns  |

| t <sub>ocf</sub>                      | I <sup>2</sup> C 出力の立ち下がり時間                   | 10pF ~ 400pF バス                   | 20 × (V <sub>CC</sub> / 5.5V) | 300  | ns  |

| t <sub>buf</sub>                      | STOP と START 間の I <sup>2</sup> C バスのフリー時間     |                                   | 1.3                           |      | μs  |

| t <sub>sts</sub>                      | I <sup>2</sup> C START または反復 START 条件の設定      |                                   | 0.6                           |      | μs  |

| t <sub>sth</sub>                      | I <sup>2</sup> C START または反復 START 条件ホールド     |                                   | 0.6                           |      | μs  |

| t <sub>sps</sub>                      | I <sup>2</sup> C STOP 条件の設定                   |                                   | 0.6                           |      | μs  |

| t <sub>vd(data)</sub>                 | 有効データ時間                                       | SCL Low から SDA 出力有効まで             |                               | 0.9  | μs  |

| t <sub>vd(ack)</sub>                  | ACK 条件の有効データ時間                                | SCL Low から SDA (出力) Low への ACK 信号 |                               | 0.9  | μs  |

| C <sub>b</sub>                        | I <sup>2</sup> C バスの容量性負荷                     |                                   |                               | 400  | pF  |

| <b>I<sup>2</sup>C バス - 高速モード プラス</b>  |                                               |                                   |                               |      |     |

| f <sub>scl</sub>                      | I <sup>2</sup> C クロック周波数                      |                                   | 0                             | 1000 | kHz |

| t <sub>sch</sub>                      | I <sup>2</sup> C クロックの High 時間 <sup>(1)</sup> |                                   | 0.26                          |      | μs  |

| t <sub>scl</sub>                      | I <sup>2</sup> C クロックの Low 時間 <sup>(1)</sup>  |                                   | 0.5                           |      | μs  |

| t <sub>sp</sub>                       | I <sup>2</sup> C スパイク時間                       |                                   |                               | 50   | ns  |

## 5.9 I<sup>2</sup>C バス タイミング要件 (続き)

外気温度範囲での動作時 (特に記述がない限り)

|                       |                                            |                                   | 最小値                           | 最大値  | 単位 |

|-----------------------|--------------------------------------------|-----------------------------------|-------------------------------|------|----|

| t <sub>sds</sub>      | I <sup>2</sup> C シリアル データ セットアップ時間         |                                   | 50                            |      | ns |

| t <sub>sdh</sub>      | I <sup>2</sup> C シリアル データ ホールド時間           |                                   | 0                             |      | ns |

| t <sub>icr</sub>      | I <sup>2</sup> C 入力の立ち上がり時間 <sup>(1)</sup> |                                   |                               | 120  | ns |

| t <sub>icf</sub>      | I <sup>2</sup> C 入力の立ち下がり時間                |                                   | 20 × (V <sub>CC</sub> / 5.5V) | 120  | ns |

| t <sub>ocf</sub>      | I <sup>2</sup> C 出力の立ち下がり時間                | 10pF ~ 550pF バス                   | 20 × (V <sub>CC</sub> / 5.5V) | 120  | ns |

| t <sub>buf</sub>      | STOP と START 間の I <sup>2</sup> C バスのフリー時間  |                                   | 0.5                           |      | μs |

| t <sub>sts</sub>      | I <sup>2</sup> C START または反復 START 条件の設定   |                                   | 0.26                          |      | μs |

| t <sub>sth</sub>      | I <sup>2</sup> C START または反復 START 条件ホールド  |                                   | 0.26                          |      | μs |

| t <sub>sps</sub>      | I <sup>2</sup> C STOP 条件の設定                |                                   | 0.26                          |      | μs |

| t <sub>vd(data)</sub> | 有効データ時間                                    | SCL Low から SDA 出力有効まで             |                               | 0.45 | μs |

| t <sub>vd(ack)</sub>  | ACK 条件の有効データ時間                             | SCL Low から SDA (出力) Low への ACK 信号 |                               | 0.45 | μs |

| C <sub>b</sub>        | I <sup>2</sup> C バスの容量性負荷                  |                                   |                               | 550  | pF |

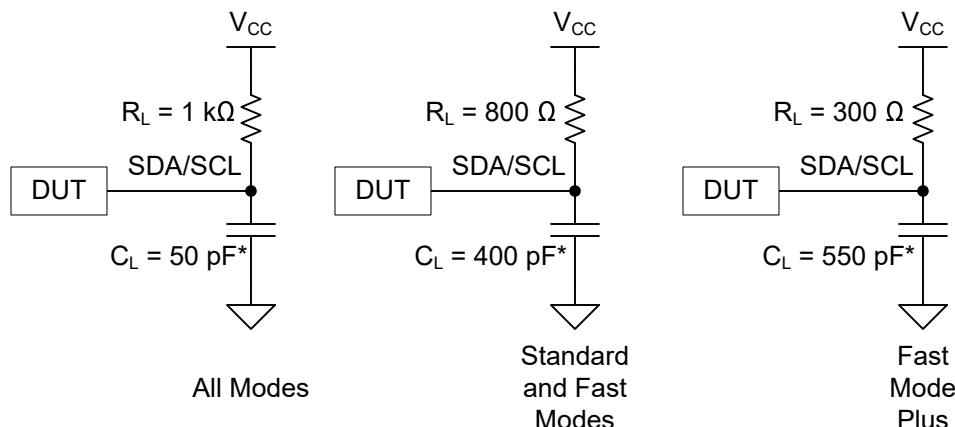

- (1) このパラメータが満たされていることを確認するのは、システム設計者の責任です。この値は、バスの負荷とプルアップ抵抗によって異なります。

## 6 パラメータ測定情報

図 6-1. 起動タイミング

図 6-2. 通常モードからスリープモードへのタイミング

図 6-3. SPI タイミング特性

図 6-4. UART タイミング特性

\* $C_L$  includes probe and jig capacitance

図 6-5. I2C バス負荷

## 7 詳細説明

### 7.1 概要

TCAN5102-Q1 は、CiA 604-1 および ISO 11898-1 : 2024 と互換性のあるコントロール エリア ネットワーク (CAN) フレキシブル データ (FD) ライトレスポンダ デバイスで、専用の CAN FD ライト コマンドを使用した場合、最大 5Mbps のデータ レートをサポートできます。このデバイスは、レスポンダ ノード プロセッサを必要としないコマンド レスponsa アーキテクチャにおいて CAN FD ライトレスポンダ ノード アプリケーションをサポートするように設計されています。レスポンダ ノードへの制御はすべて、コマンド ノード プロセッサからの CAN バスを介して行われるため、レスポンダ ノード プロセッサやソフトウェアは不要です。

デバイスは CAN FD ライト コマンド ノードからデータやコマンドを受信し、これらのコマンドをシリアル ペリフェラル インターフェイス (SPI) コントローラ、UART コントローラ、I<sup>2</sup>C コントローラ、GPIO ピンのいずれかまたは両方に変換して、TCAN5102-Q1 が制御しているデバイスやペリフェラル デバイスと通信します。PWM 出力チャネルは、ステッパ モーターを制御するためのハードウェアで台形波ランプ プロファイルもサポートしています。デューティ サイクルまたは周波数を上昇させることができます。外部水晶振動子やクロックは不要です。このデバイスは、外部の TCAN1162x-Q1、TCAN1043A-Q1、TCAN1463A-Q1 CAN FD (SIC) トランシーバーを制御し、システム レベルの柔軟性を確保します。このデバイスは、CAN FD トランシーバー / SBC を利用してノードの電力を制御し、CAN RXD (CRXD) ピンを Low にラッチすることでウェークアップ信号を TCAN5102-Q1 に伝達します。

### 7.2 機能ブロック図

図 7-1. ハイレベルブロック図

## ADVANCE INFORMATION

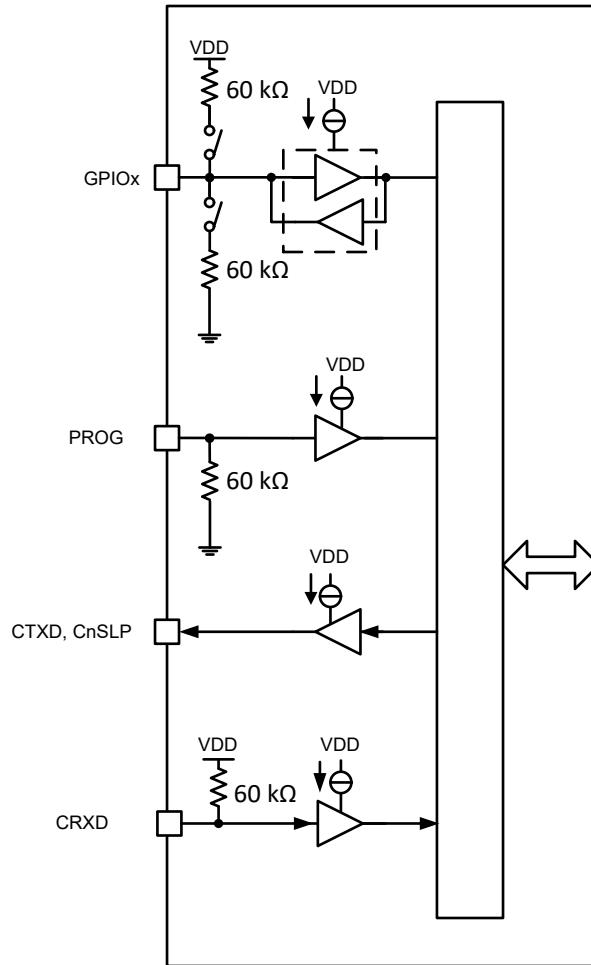

図 7-2. 入力および出力のブロック図

## 7.3 機能説明

### 7.3.1 VDD

VDD はデバイスの電源入力であり、デジタル入出力電圧レベルを 3.3V と 5V に設定します。

### 7.3.2 PROG ピン

PROG ピンは、ECU 開発フェーズで使用されます。電源投入時にこのピンを GND に設定すると、CAN バスを使用してライン終了プログラミング経由で TCAN5102-Q1 をプログラムできます。CAN バスのプログラミングデータ レートは、このプロセスでは 1Mbps に設定されています。

### 7.3.3 DIGFLTR ピン

このピンを使用して、内部デジタルコアレギュレータのフィルタリングを行います。フィルタ コンデンサの推奨値については、「推奨動作条件」表を参照してください。

### 7.3.4 GPIOx およびピンの多重化の特殊機能

TCAN5102-Q1 には 12 本の GPIO ピンがあり、複数の用途に構成できます。汎用 I/O として、このピンは入力、プッシュプル出力、またはオープン ドレイン出力に設定できます。また、これらのピンにはユーザーが有効なプルアップ / プルダウン抵抗も内蔵されています。

デバイス内のさまざまなシリアルインターフェイスと IP ブロックをサポートするために、複数のピンに GPIO と多重化するオプションがあります。追加機能はレジスタ設定内で「特殊機能」と呼ばれ、この場合ピンはもはや GPIO として動作せず、代わりに特殊な IP ブロックに接続されます。特殊機能用に構成している場合、このピンにはプルアップおよびプルダウン抵抗構成のみが使用されます。特殊機能を選択すると、出力 / 入力、プッシュプル / オープン ドレインなどのモードが自動的に設定されます。たとえば、SPI POCI 対応する GPIO が特殊機能として選択されている場合、その GPIO の設定が SPI IP によって上書きされ、その GPIO が入力になるように構成されます。必要に応じて、そのピンで内部プルアップまたはプルダウン抵抗を有効にすることで、既知のピン状態を実現できます。

#### 注

一部のピンには、2 つの特殊機能が割り当てられています。競合のイネーブルが発生した場合、プライオリティの高い IP が優先されます。たとえば、SPI IP ブロックが SPI チップセレクトチャネル 4 (CS4) をイネーブルにしており、I<sup>2</sup>C IP もイネーブルになっている場合、GPIO9 は I<sup>2</sup>C の SCL ピンに多重化されます。すべてのピンのデフォルトのプログラムされていない動作は、入力で高インピーダンスです。

GPIO のデフォルトのパワーオン状態を EEPROM に保存することで、パワーオン応答を行えます。電源オフ時、または POR スレッショルドを下回っているとき、これらのピンは高インピーダンス状態になります。デバイスの電源投入後、構成が EEPROM から GPIO レジスタにコピーされます。出力動作に影響を与える可能性のある構成レジスタのみが EEPROM に保存されます。保存されるレジスタは以下の通りです

1. IO\_OE\_0 および IO\_OE\_1

2. IO\_RE\_0 および IO\_RE\_1

3. IO\_PU\_0 および IO\_PU\_1

4. IO\_OUTPUT\_0 および IO\_OUTPUT\_1

表 7-1. 特殊機能向けのピンのマルチプレクシング

| ピン | 名称     | 低優先度     | 高優先度                 |

|----|--------|----------|----------------------|

| 4  | GPIO9  | SPI CS4  | I <sup>2</sup> C SCL |

| 5  | GPIO10 | SPI CS5  | I <sup>2</sup> C SDA |

| 6  | GPIO11 | SPI CS6  | PWM0                 |

| 7  | GPIO12 | SPI CS7  | PWM1                 |

| 11 | GPIO8  | UART RXD | -                    |

| 12 | GPIO7  | UART TXD | -                    |

| 13 | GPIO6  | SPI PICO | -                    |

表 7-1. 特殊機能向けのピンのマルチプレクシング (続き)

| ピン | 名称    | 低優先度     | 高優先度 |

|----|-------|----------|------|

| 14 | GPIO5 | SPI POCI | -    |

| 15 | GPIO4 | SPI SCK  | -    |

| 16 | GPIO3 | SPI CS0  | -    |

| 17 | GPIO2 | SPI CS1  | -    |

| 18 | GPIO1 | SPI CS2  | -    |

| 19 | GPIO0 | SPI CS3  | -    |

### 7.3.4.1 GPIO 同期

出力として構成された GPIO は、同時に更新をサポートします。この GPIO 出力の更新を行うには、2 つのモードがあります

1. デフォルト : IO\_OUTPUT\_x レジスタが更新されると、GPIO は直ちに更新されます (各バイト)

2. 同期 : 更新は IO\_OUTPUT\_1 への書き込み後にのみ行われます。すべてを同期するには、まず IO\_OUTPUT\_0 に書き込み、次に IO\_OUTPUT\_1 への書き込みが完了すると、すべてのビットが同時に更新されます

この機能は、GPIO\_OUT\_SYNC ビットを 1 にセットすることで、[MRAM\\_IP\\_CFG](#) レジスタで有効になります。

### 7.3.5 EEPROM

TCAN5102-Q1 は EEPROM を内蔵しており、電源オン構成時に以下の情報を保存するために使用されます :

1. CAN バスのデータレート

2. CAN ID

3. ブロードキャスト CAN ID およびマスク

4. 構成ロック (データレートおよび CAN ID)

5. パワーオンリセットピンの状態を設定するのに必要な GPIO 構成

- a. IO\_OE\_0 および IO\_OE\_1

- b. IO\_RE\_0 および IO\_RE\_1

- c. IO\_PU\_0 および IO\_PU\_1

- d. IO\_OUTPUT\_0 および IO\_OUTPUT\_1

---

#### 注

EEPROM には CRC フィールドがあり、CRC に故障が検出されると、デバイスは CAN インターフェイスを無効にし、GPIO を高インピーダンス状態に保持します

### 7.3.6 SPI コントローラ

TCAN5102-Q1 は SPI コントローラを搭載しており、8 つのチップセレクトと、SPI チャネル 0 ~ 3 に異なる SPI 設定を備えています。最後の 4 チャネルは、SPI チャネル 3 と構成を共有します。4 つの最初のチャネルはそれぞれ、独立した SPI 速度、SPI モードを持つことができます。別のチップセレクトを使用すると、共有の SPI POCI、PICO、SCK ラインとの通信を実行できます。チップセレクトは、アクティブ High とアクティブ Low のどちらかに構成できます。メッセージはメッセージ RAM (MRAM) に格納され、IP が機能するには MRAM 内の領域を割り当てる必要があります。詳細については「[セクション 7.5.3](#)」を参照。

SPI コントローラの構成と使用方法の詳細については、[セクション 7.5.4](#) を参照してください。

### 7.3.7 UART コントローラ

TCAN5102-Q1 は、UART コントローラを搭載しています。UART は、LIN、RS232、RS485、Flexwire など、さまざまなインターフェイスで使用される標準的なバイト指向プロトコルです。このコントローラは分数ボーレート分周器を備えており、多様なインターフェイスで使用できる幅広いボーレートに対応しています。

メッセージはメッセージ RAM (MRAM) に格納され、IP が機能するには MRAM 内の領域を割り当てる必要があります。詳細については「[セクション 7.5.3](#)」を参照。MRAM を使用せずに、UART IP をシングルバイト モードで実行できます。このモードには、UART 構成レジスタにイネーブル ビットがあります。

UART コントローラの構成と使用方法の詳細については、[セクション 7.5.5](#) を参照してください。

### 7.3.8 I<sup>2</sup>C コントローラ

TCAN5102-Q1 には I<sup>2</sup>C コントローラが搭載されており、標準、高速モード、高速モード プラスをサポートしています。標準のコントローラに加えて、スタック バス回復機能も内蔵されており、SDA ラインが Low に固着したことを検出し、バスを解除しようとする SCL ラインをトグルできます。また、クロック ストレッチ時間が  $t_{STUCKBUS\_I2C}$  時間より短い限り、クロック ストレッチもサポートされます。

メッセージはメッセージ RAM (MRAM) に格納され、IP が機能するには MRAM 内の領域を割り当てる必要があります。詳細については「[セクション 7.5.3](#)」を参照。

I<sup>2</sup>C コントローラの構成と使用方法の詳細については、[セクション 7.5.6](#) を参照してください。

#### 7.3.8.1 I<sup>2</sup>C スタック バス回復

I<sup>2</sup>C コントローラには、スタック バス回復 (SBR) と呼ばれるオプション機能があります。スタック バス回復は、SDA または SCL ラインが Low に固着した場合にバスを修正しようとします。これは、バス上にノイズがあり、I<sup>2</sup>C ペリフェラルが誤ったクロック数を認識するようになる場合に発生する可能性があります。スタック バス回復により、SCL ラインが最大 16 回トグルされ、問題の原因となるデバイスをバスの解放に試みます。詳細については、[セクション 7.5.6.2](#) を参照してください。

### 7.3.9 PWM コントローラ

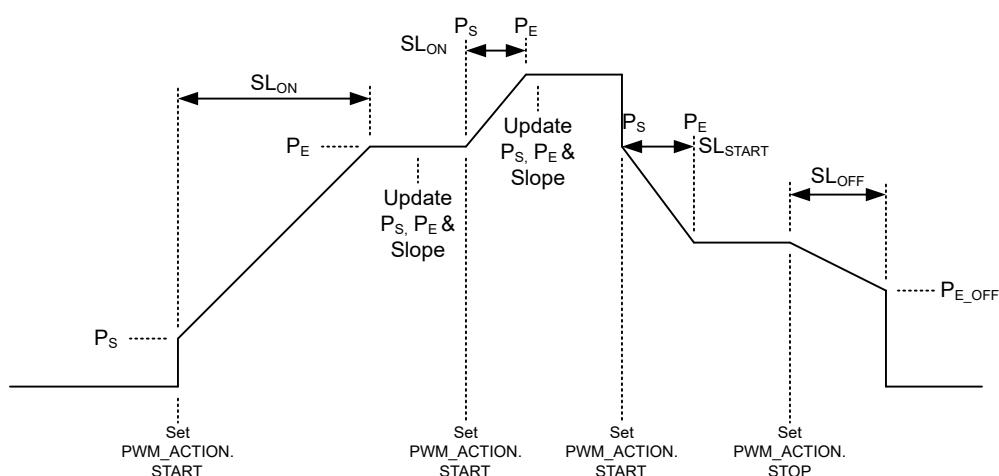

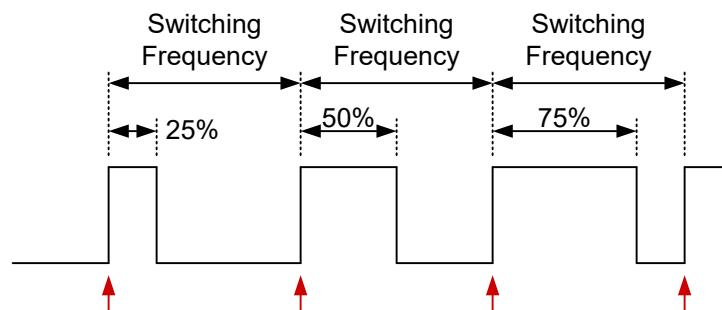

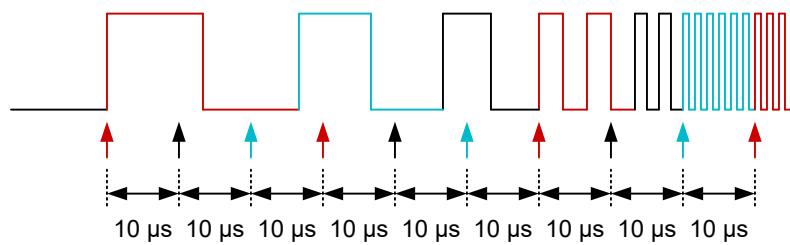

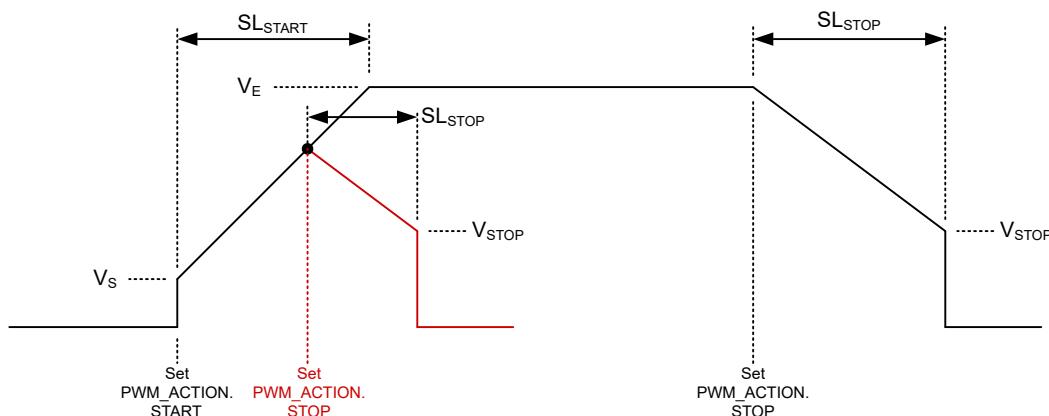

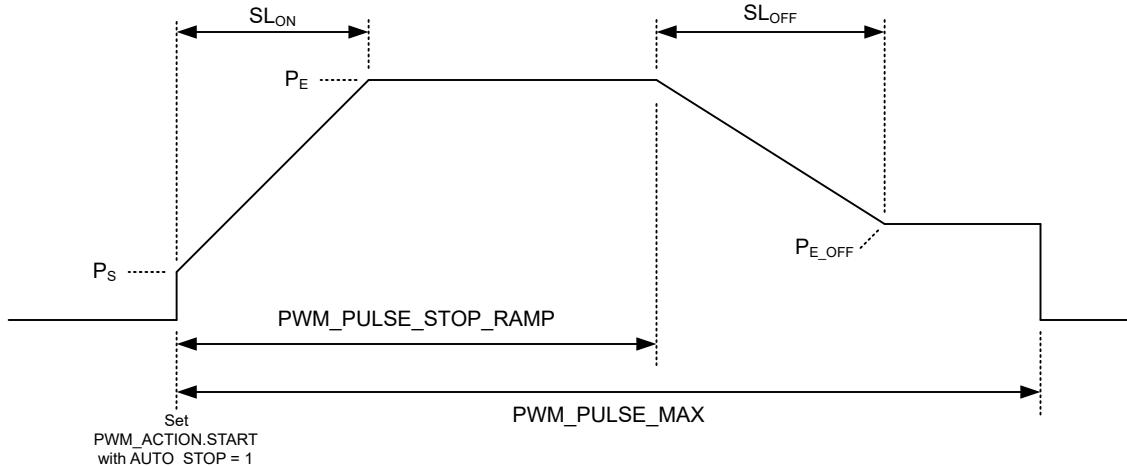

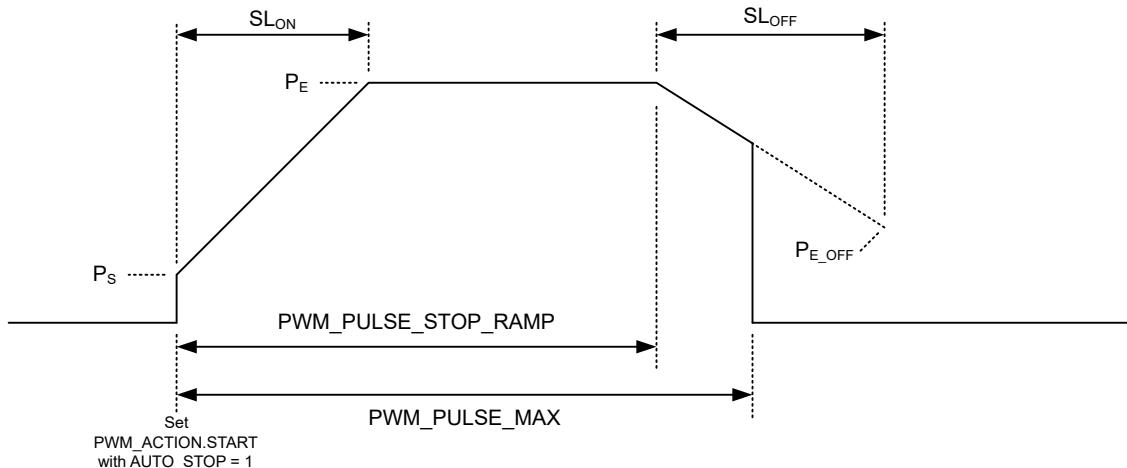

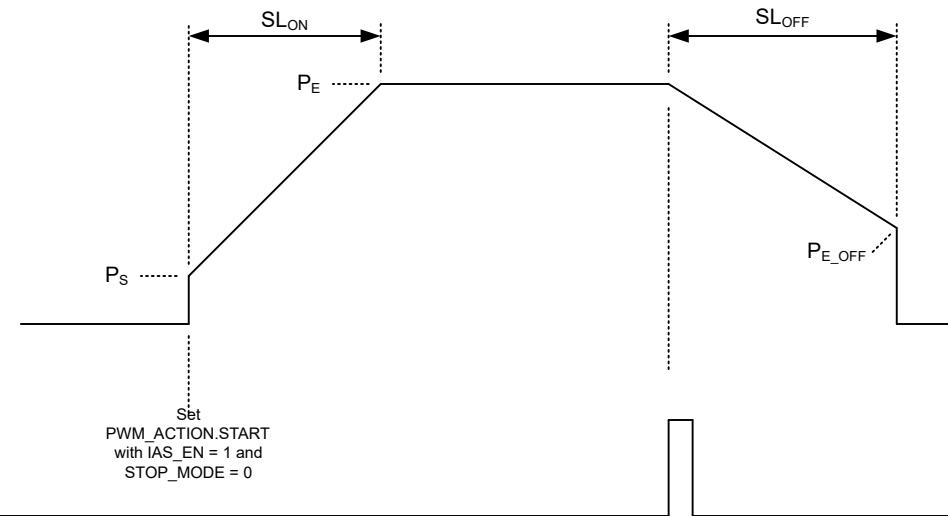

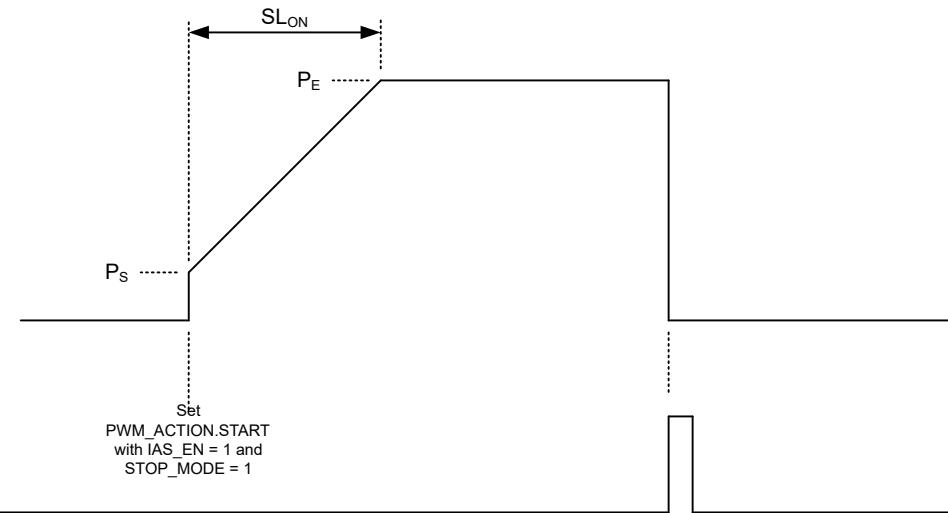

TCAN5102-Q1 は、ランプ機能を内蔵した PWM コントローラを備えています。PWM コントローラは、固定デューティ サイクルと周波数による静的 / 一般的な PWM 出力をサポートするだけでなく、デューティ サイクルまたは周波数をランプさせる高度な PWM 機能もサポートしており、基本的なモーター制御に対応できます。このコントローラはステッピング モーター制御を念頭に開発されており、ユーザーが加速および減速プロファイルをプログラムできるようになっています。コントローラがランプを開始するように指示されると、演算を行い、指定されたランプ プロファイルを PWM 出力で実行します。

PWM コントローラは、PWM パルス カウントなどの追加機能もサポートしており、ユーザーは PWM 出力を設定して加速および減速プロファイルを生成し、所定のパルス数 / ステップ数の後に自動的に停止することができます。シーケンスはレジスタにプログラムされ、ランプを開始するために指示される以外、アップストリーム コントローラからの介入は必要ありません。

追加機能として、GPIO 入力を使用して、減速ランプを開始するか、PWM 出力を直ちにオフにすることができます。これはリミット スイッチやモーターの故障検出に役立ちます。

PWM コントローラの構成と使用方法の詳細については、[セクション 7.5.7](#) を参照してください。

### 7.3.10 CAN トランシーバの制御ピン

TCAN5102-Q1 には CAN トランシーバが内蔵されておらず、外部トランシーバが必要です。この結果、ユーザーはサポートする CAN トランシーバを選択できます。このデバイスには、CAN TXD、RXD、nSLP ピンがあります。nSLP ピンを使用して、スリープ モードへの移行時に外部トランシーバのスリープ モードまたはスタンバイ モードを制御します。

### 7.3.11 低電圧ロックアウトおよび電源オフのデバイス

TCAN5102-Q1 は、デバイス (VDD) の電源レールを監視します。VDD の低電圧が監視されます。UVDD 故障が検出されると、デバイスに対応する状態変化があります。

表 7-2. VDD 故障とデバイス モード

| VDD    | デバイス モード      |

|--------|---------------|

| > UVDD | 正常            |

| < UVDD | パワーオン オン リセット |

## 7.4 デバイスの機能モード

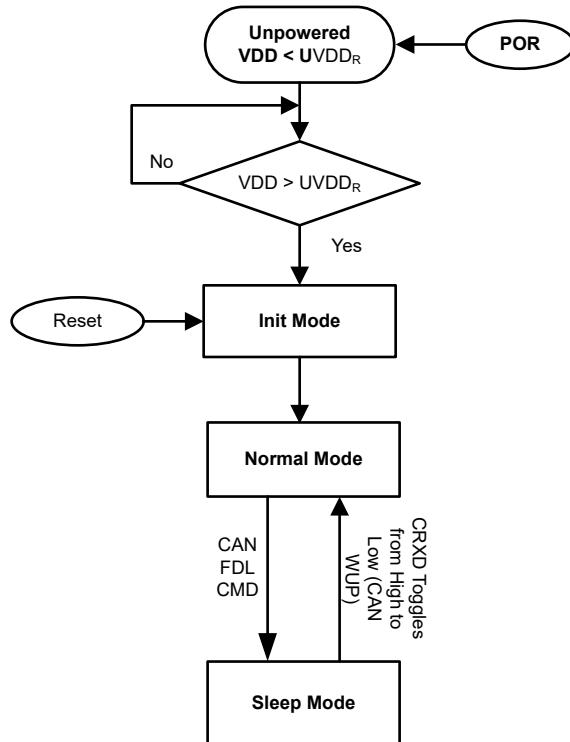

TCAN5102-Q1 には、電源オフ、初期化、スリープ、通常モードの 4 つの動作モードがあります。各モードでの各種デバイスブロックの動作については、表 7-3 を参照してください。全体の動作モードがどのように相互作用するかについては、図 7-3 を参照してください。

表 7-3. モードの概要

| ブロック             | init      | 正常              | スリープ      |

|------------------|-----------|-----------------|-----------|

| CAN トランシーバ制御     | オフ (Hi-Z) | オン              | オフ        |

| CAN nSLP         | オフ (Hi-Z) | High (VDD)      | Low (GND) |

| SPI              | オフ (Hi-Z) | プログラムされている場合はオン | オフ        |

| I <sup>2</sup> C | オフ (Hi-Z) | プログラムされている場合はオン | オフ        |

| UART             | オフ (Hi-Z) | プログラムされている場合はオン | オフ        |

| GPIOx            | オフ (Hi-Z) | プログラムによる        | プログラムによる  |

図 7-3. TCAN5102-Q1 動作モード

### 7.4.1 初期モード

これは、電源投入時の初期動作モードです。これは、VDD が  $UV_{DD}$  よりも大きくなり、保存されたデバイス構成がロードされると移行される遷移モードです。設定が読み込まれると、デバイスはノーマル モードに移行します。

init モードでは EEPROM が読み取られ、EEPROM が読み取られると、構成がレジスタにコピーされ、デバイスは通常モードに遷移します。保存する構成の詳細については、[セクション 7.3.5](#) を参照してください。

#### 7.4.2 スリープ モード

スリープ モードは、このデバイスにおける最も低消費電力の状態です。TCAN5102-Q1 は、CAN バスからスリープ移行コマンドを受信し、次の操作を実行します：

- 内部のハウス キーピング処理を実行します

- 外部 CAN トランシーバをスリープ モードにします

CAN トランシーバがスリープ モードに移行すると、VDD に電力は想定されません。デバイスは電源が供給されていない状態です。スリープ モード中でも VDD に給電し続けることが可能です。CAN トランシーバからの WUP 信号を受信するまで、このデバイスは低消費電力状態のまま維持されます。

#### 7.4.3 通常モード

INIT モードを終了すると、デバイスは通常モードに移行します。ノーマル モードではトランシーバがアクティブになり、デバイスはデータの受信または送信準備が整います。

### 7.5 プログラミング

デバイスは、構成に CAN FD Light インターフェイスを使用します。構成は、デバイス上のレジスタに書き込むことで行われます。デバイス レジスタへのアクセスに使用する特定の CAN FD メッセージ構造があります。このデバイスがデバイス レジスタへのアクセスのために、複数のフレーム形式をサポートします。

#### 7.5.1 SPI ペリフェラル モードによるデバイス プログラミング

構成プログラミングには 2 つのオプションがあります：

1. CAN FD ライトを使用したプログラム (PROG ピンを使用してボーレートを強制的に 1Mbps に設定)

2. SPI を使用する場合 (PROG ピンと RXD ピンでトグル シーケンスを行い、ローカルの SPI ペリフェラルを有効にして、プログラマが EEPROM に書き込みできるようにします)

CAN インターフェイスが使用できない場合、EEPROM をプログラムする手段として SPI ペリフェラル モード方式を使用できます。この方法では、ローカル SPI ペリフェラルをイネーブルにするために、特定のイベント シーケンスが必要です。デバイスが SPI ペリフェラルモードの場合、CAN インターフェイスはディスエーブルされ、電源を入れ直すまでディスエーブルのままになります。

#### 7.5.2 CAN FD Light プロトコル

TCAN5102-Q1 は、論理リンク制御 (LLC) と FD ベース フレーム フォーマット (FBFF) を使用することにより、CiA 604-1 および CiA 604-3 通信規格をサポートします。[表 7-4](#) を参照してください。

表 7-4. プロトコル CiA フォーマット

| フィールド   | サイズ        | 機能                                    |

|---------|------------|---------------------------------------|

| 識別子 :   | 11 ビット     | ベース識別子 (ターゲット ID またはブロードキャスト ID)      |

| DLC     | 4 ビット      | ISO 11898-1:2015 の表 5 に指定されているデータ長コード |

| LLC データ | 0 ~ 64 バイト | データ フレームのデータ コンテンツ                    |

送受信されるすべてのフレームが FBFF であり、かつビット ESI = 0 および BRS = 0 であるため、フォーマット フィールド内のすべてのビットは固定されています。そのため、フォーマット フィールドは省略されます。

デバイス プロトコルは要求と応答に分割されます。デバイス要求とは、このデバイスに対して特定のレジスタへの読み取りまたは書き込みを実行するよう求める要求のことです。要求には常に 3 つ以上のフィールドがあり、任意の操作をデコードするために必要です。これらのフィールドは常に、CAN フレーム データ セクションの開始位置にあります。

1. オペコード (Op Code) : これは、デバイスに対して、レジスタまたは FIFO に対する読み取りか書き込みが行われているのかを示します

2. 長さ : 転送されるデータの合計サイズ (バイト単位) を示します (デバイスのヘッダの後)

### 3. アドレス登録書き込みまたは読み取り中のレジスタまたは FIFO の 16 ビットアドレス

デバイスレスポンスは、リクエストを受信したことを要求元のデバイスに知らせ、そのリクエストが処理中であるか、あるいは無効であることを伝えるために送信されます。応答には、少なくとも 3 つのフィールドが含まれています

1. オペコード (Op Code) : 受信したオペコードを繰り返します

2. 長さ : ヘッダの後に返されるデータの合計サイズ (バイト単位) を示します。リクエストが書き込みの場合には、書き込まれたバイト数を反映しますが、実際のデータは送信されません。長さフィールドは、書き込まれたバイト数を確認するために使用されます

3. ステータス バイト : リクエストのステータスを示します。これには、OK/ 成功、または無効なアドレスや長さなどの何らかのエラーがあります。

デバイスで使用される識別子には 2 種類あります。ターゲット識別子は、個々のレスポンダに一意の特定のアドレスです。これにより、コマンダは個々のノードをアドレス指定 / 設定できます。ブロードキャスト識別子もサポートされており、ブロードキャスト ID およびマスクフィールドを使用して 1 つまたは複数の ID に一致します。ブロードキャスト ID からのリクエストは実行されますが、CAN FD Light ではアービトレイションがサポートされていないため、レスポンダからの応答はありません。ブロードキャストは、コマンダが一度に多数のノードを構成する場合や、複数のノードをスリープ状態にする場合に便利です。しかし、これはレスポンスフレームを破棄するため、レスポンダによって確認されることはありません。

#### 7.5.2.1 CAN フレーム形式

標準 CAN フレーム形式では、CAN ペイロードの 3 バイトをヘッダーとして使用し、オペコード (op code)、データ長、アドレスの 3 つのフィールドを含みます。

| CAN ID          | CTRL | Byte 0               | Byte 1     | Byte 2    | Byte 3 | • • • |

|-----------------|------|----------------------|------------|-----------|--------|-------|

| Device ID[10:0] |      | OP[7:6]/<br>LEN[5:0] | ADDR[15:8] | ADDR[7:0] | Data   |       |

図 7-4. 標準 CAN フレーム形式要求の例

表 7-5. 標準 CAN フレーム形式の要求ヘッダ フィールド

| バイト | ビット | フィールド      | 説明                                                                         |

|-----|-----|------------|----------------------------------------------------------------------------|

| 0   | 7:6 | OPCODE     | デバイスのオペコード<br>2'b00 = 書き込み<br>2'b01 = 読み出し<br>2'b10 = 予約済み<br>2'b11 = 予約済み |

|     | 5:0 | LEN        | このヘッダ有効値 (書き込み) 後に転送されるデータ バイト数<br>: 0 ~ 61<br>有効な値 (読み取り) : 0 ~ 62        |

| 1   | 7:0 | ADDR[15:8] | アドレスの上位バイト                                                                 |

| 2   | 7:0 | ADDR[7:0]  | アドレスの下位バイト                                                                 |

#### 注

複数バイトの読み出しの場合、開始アドレスがシリアル通信ブロック (I2C、SPI、UART) の RX FIFO の前である場合、FIFO は實際には読み出されません。代わりに、RX FIFO に対応するバイトは 0 を返し、読み取りが続行されます。これは、RX FIFO でバースト読み出しが「スタッカ」しないようにするためです。読み取りの開始アドレスが RX FIFO から始まる場合、読み取られるすべてのバイトは RX FIFO からのみ得られます。

| CAN ID          | CTRL | Byte 0               | Byte 1      | Byte 2 | • • • |

|-----------------|------|----------------------|-------------|--------|-------|

| Device ID[10:0] |      | OP[7:6]/<br>LEN[5:0] | STATUS_BYTE | Data   |       |

図 7-5. 標準 CAN フレーム形式応答の例

**表 7-6. 標準 CAN フレーム形式応答のヘッダ フィールド**

| バイト | ビット | フィールド  | 説明                                                                                                                     |

|-----|-----|--------|------------------------------------------------------------------------------------------------------------------------|

| 0   | 7:6 | OPCODE | デバイスのオペコード<br>2'b00 = 書き込み<br>2'b01 = 読み出し<br>2'b10 = 予約済み<br>2'b11 = 予約済み                                             |

|     | 5:0 | LEN    | 要求されたデータ バイト数が有効であれば、ヘッダの後にバイト数を工口送信します。                                                                               |

|     |     |        | <b>注</b><br>応答が書き込み要求に対するものである場合、長さ フィールドには要求されたバイト数が入りますが、ヘッダーの後にデータは送信されません。これにより、応答フレームが書き込み要求に対するものであるとの確認が可能になります |

| 1   | 7:5 | RSVD   | 予約済み                                                                                                                   |

| 1   | 4   | FE     | 前の要求のフレーミング エラー。要求は無視されます。通常、DLC が 3 バイト未満の場合に発生し、ヘッダには最低要件があります                                                       |

| 1   | 3   | IO     | 無効な操作です。要求は無視されます                                                                                                      |

| 1   | 2   | IL     | 無効な長さです。要求は無視されます                                                                                                      |

| 1   | 1   | IA     | アドレスが無効です。要求は無視されます                                                                                                    |

| 1   | 0   | OK     | OK リクエスト、リクエストの完了、または進行中です                                                                                             |

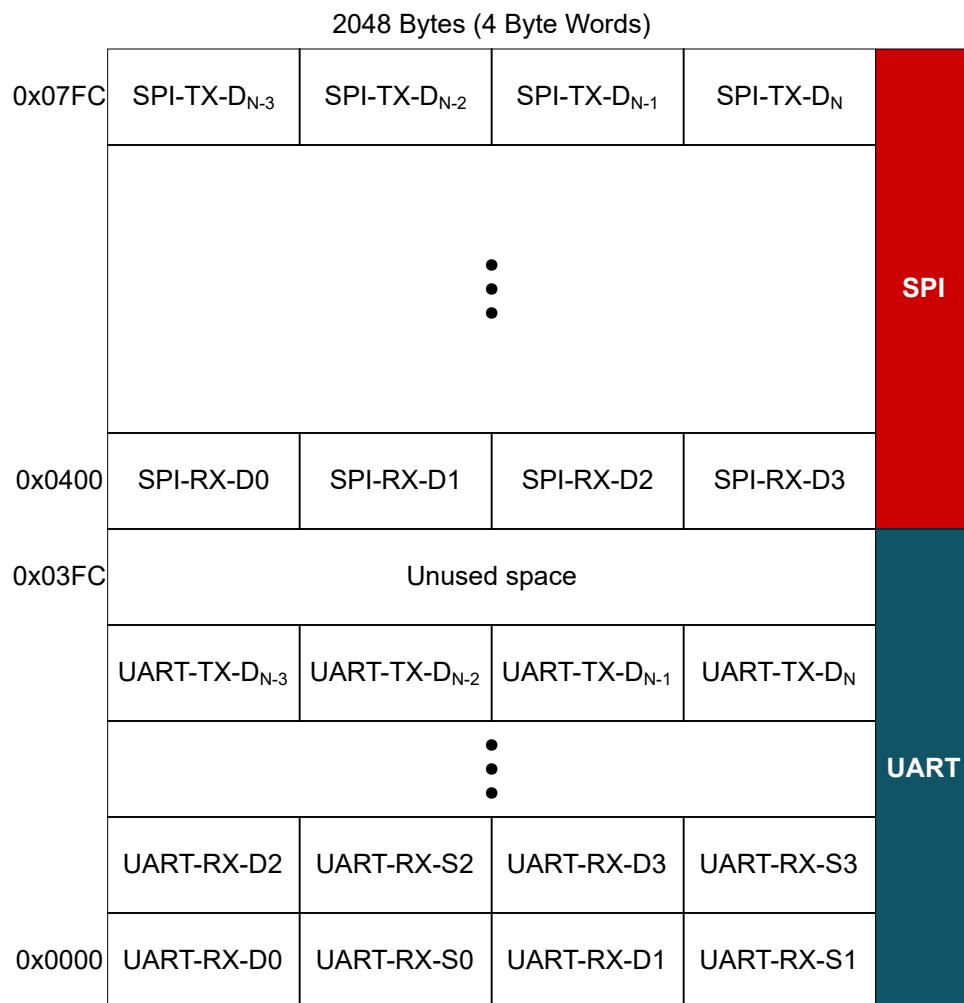

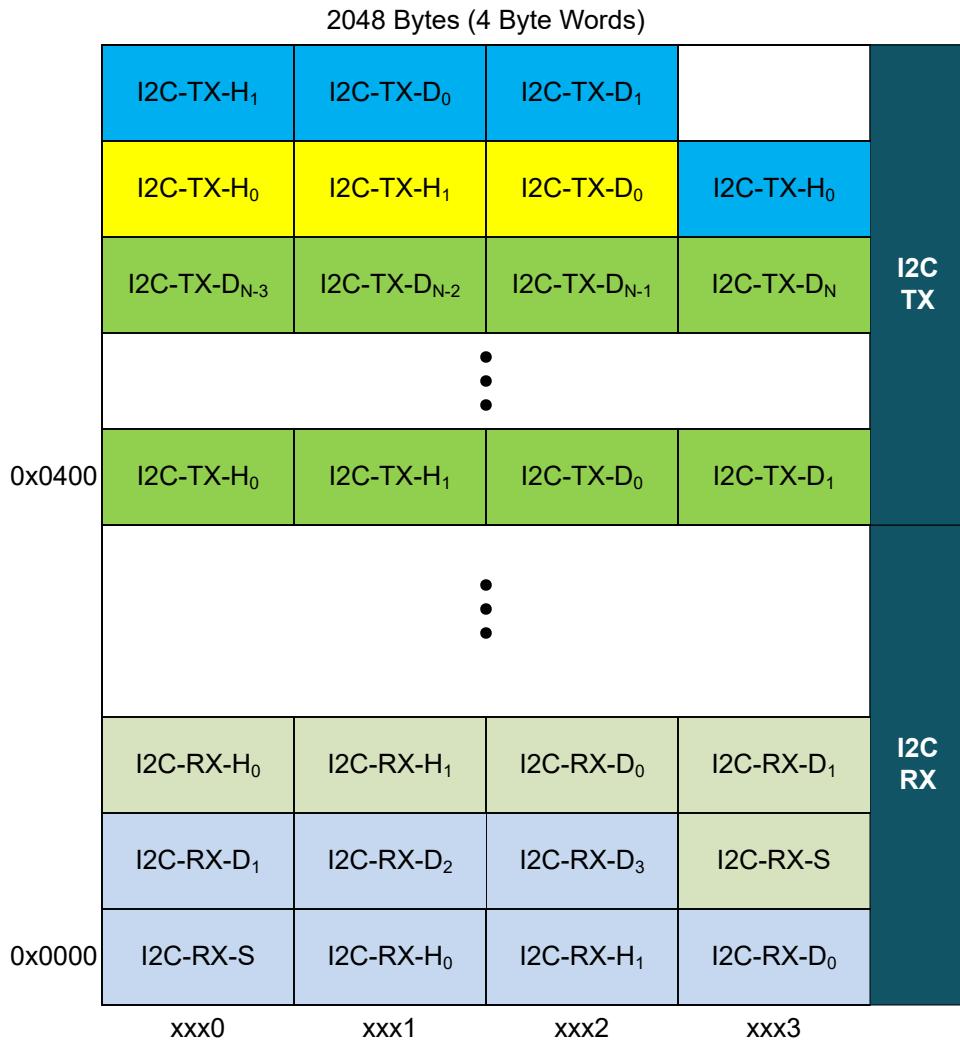

### 7.5.3 メッセージ RAM (MRAM) および IP イネーブル

TCAN5102-Q1 には 2kB のメッセージ RAM (MRAM) があり、SPI、I2C、UART 通信のメールボックスを格納するために使用されます。この RAM は、エンド アプリケーションのニーズに基づき、2 つの IP ブロックに割り当てられたメモリを任意の組み合わせで 25% 単位に分割できます。RX と TX の間の分割は調整できず、常に 50/50% です。RX および TX FIFO の処理は TCAN5102-Q1 によって行われるため、各 IP ブロックに割り当てる MRAM の量を選択しないでユーザーの設定は不要です。

SPI と I2C はメモリ使用に関して単純な分割を行い、割り当てられたメモリの 50% は TX データの格納に使用され、残りの 50% は指定されていれば RX データの格納に使用されます。

UART では、受信した各バイトのステータスを格納するために追加のバイトが必要です。つまり、UART で受信する各データ バイトごとに、そのバイトのステータスを格納するために 1 バイトが追加が必要になります。その結果、UART に割り当てられたメモリの 3 分の 2 だけが実際のデータ バイトの格納に使用されます。

表 7-7 に、各 IP ブロックの TX バッファまたは RX バッファに割り当てられるデータのバイト数を示します。表示されるサイズは TX バッファと RX バッファの両方で同じ値ですが、両者で共有される値ではありません。たとえば、MRAM 領域の 100% が SPI に割り当てられている場合、SPI TX サイズは 1024 バイト、SPI RX バッファは 1024 バイトです。TX バッファと RX バッファを合わせると合計で 2048 バイトとなり、これがメモリ全体に相当します。

MRAM の 50 % が SPI と UART に割り当てられた例では、SPI の RX と TX のサイズはそれぞれ 512 で、合計 1 kB となります。UART IP は、バッファごとにわずか 340 バイトです。UART RX では、受信した各バイトのステータスを格納するために追加のバイトが必要となるため、利用可能な 1024 バイトのうちデータ格納に使用されるのは 3 分の 2 だけです。内部では、TX バッファと RX バッファに保存できるバイト数は同一です。このため、残りの 4 バイトは 3 つの機能 (TX、RX、RX ステータス) に均等に分割できないため、4 バイトのデータは未使用のままになります。

#### 注

MRAM のアロケーション設定は、SPI および I2C 用の IP モジュールを有効化するために使用されます。モジュールにメモリがアロケーションされると、モジュールは有効化されます。ただし、モジュールで使用する GPIO は、GPIO 構成レジスタで手動で特殊機能に設定する必要があります。

**表 7-7. MRAM アロケーション**

| SPI へのアロケーション % | SPI TX または RX サイズ (バイト) | UART TX または RX サイズ (バイト) | 使用された合計バイト数 (合計に対する %) |

|-----------------|-------------------------|--------------------------|------------------------|

| 100%            | 1024                    | 0                        | 2048 (100%)            |

| 75%             | 768                     | 168                      | 2040 (99.6%)           |

| 50%             | 512                     | 340                      | 2044 (99.8%)           |

| 25%             | 256                     | 512                      | 2048 (100%)            |

| 0%              | 0                       | 680                      | 2040 (99.6%)           |

**表 7-8. MRAM アロケーション**

| MRAM_IP_EN (16 進) | SPI へのアロケーション % | UART へのアロケーション % | I2C へのアロケーション % | SPI TX および RX サイズ (バイト) | UART TX および RX サイズ (バイト) | I2C TX および RX サイズ (バイト) | 使用された合計バイト数 (合計に対する %) |

|-------------------|-----------------|------------------|-----------------|-------------------------|--------------------------|-------------------------|------------------------|

| 0h                | 0%              | 0%               | 0%              | 0                       | 0                        | 0                       | 0 (0%)                 |

| 1h                | 0%              | 100%             | 0%              | 0                       | 680                      | 0                       | 2040 (99.61%)          |

| 2h                | 25%             | 75%              | 0%              | 256                     | 512                      | 0                       | 2048 (100%)            |

| 3h                | 50%             | 50%              | 0%              | 512                     | 340                      | 0                       | 2044 (99.8%)           |

| 4h                | 75%             | 25%              | 0%              | 768                     | 168                      | 0                       | 2040 (99.61%)          |

| 5h                | 100%            | 0%               | 0%              | 1024                    | 0                        | 0                       | 2048 (100%)            |

| 6h                | 0%              | 0%               | 100%            | 0                       | 0                        | 1024                    | 2048 (100%)            |

| 7h                | 0%              | 25%              | 75%             | 0                       | 168                      | 768                     | 2040 (99.61%)          |

| 8h                | 0%              | 50%              | 50%             | 0                       | 340                      | 512                     | 2044 (99.8%)           |

| 9h                | 0%              | 75%              | 25%             | 0                       | 512                      | 256                     | 2048 (100%)            |

| Ah                | 25%             | 0%               | 75%             | 256                     | 0                        | 768                     | 2048 (100%)            |

| Bh                | 50%             | 0%               | 50%             | 512                     | 0                        | 512                     | 2048 (100%)            |

| Ch                | 75%             | 0%               | 25%             | 768                     | 0                        | 256                     | 2048 (100%)            |

図 7-6. MRAM レイアウト例 (SPI と UART を有効化し、50 % で分割した場合)

図 7-7. サンプル データ付き MRAM レイアウト例 (MRAM の 100 % を I2C に割り当てた場合)

上の図には、MRAM が I2C のデータを保持する方法の例が示されています。各 I2C フレーム / メッセージは異なる色で示され、各 RX または TX FIFO 内でメッセージが密にグループ化される様子を表しています。ユーザーは、FIFO 内でデータがどのように格納されるかを意識する必要はなく、FIFO の合計サイズと、ヘッダやステータス バイトもメモリに格納されるという事実だけを把握していれば十分です。

#### 7.5.4 SPI コントローラ

##### 注

モジュールを使用する前に、適切な GPIO を特殊機能に設定する必要があります ([セクション 7.3.4](#) および [セクション 7.6.1.18](#) を参照)、MRAM はアロケーション メモリによってモジュールをイネーブルにする必要があります ([セクション 7.5.3](#) および [セクション 7.6.1.17](#) を参照)。GPIO が特殊機能に設定され、メモリを割り当てる MRAM 構成を選択してモジュールが有効化されてはじめて、そのモジュールを使用できます。適切な SPI 構成レジスタを、[セクション 7.6.2](#) に示します。

##### 7.5.4.1 SPI ピン

SPI 通信では通常、他の SPI デバイスとの通信に 4 本のピンを使用します：クロック (SCLK)、データ入力 (PICO)、データ出力 (POCI)、およびチップ セレクト (CS または nCS)。

#### 7.5.4.1.1 SPI クロック (SCLK)

SPI クロック出力ピンは、ターゲット ペリフェラルとの間でデータの入出力を同期させるためのクロックを生成します。このピンは、4 つの SPI モード (2 種類のクロック極性) のいずれにも設定でき、下流ペリフェラルとの最大限の柔軟性と互換性を提供します。

#### 7.5.4.1.2 ペリフェラル入力とコントローラ出力 (PICO)

この出力ピンは、ペリフェラル デバイス (ダウンストリーム デバイス) にデータをシフトするために使用されます。チップ セレクト信号がアサートされると (設定により High または Low のいずれか)、PICO はターゲット / ペリフェラル デバイスにデータをシフト出力します。このピンは、ペリフェラル / ターゲット デバイスのシリアルデータ入力 (SDI) ピンに接続されます。

#### 7.5.4.1.3 ペリフェラル出力、コントローラ入力 (POCI)

この入力ピンは、ペリフェラル / 下流デバイスからデータをシフト出力し、このデバイス / コントローラに入力するために使用されます。POCI ピンは、通常ペリフェラル / ターゲット デバイスのシリアルデータ出力 (SDO) ピンに接続します。

#### 7.5.4.1.4 チップ セレクト (CS または nCS)

チップ セレクト出力ピンは、ターゲット ペリフェラルとの通信時にそのことを通知するために使用されます。このデバイスは、個別の極性選択機能を備えた最大 4 つの独立したチップ セレクト チャネルをサポートしています。

#### 7.5.4.2 SPI クロック ジェネレータ

TCAN5102-Q1 SPI モジュールには、8 ビットの除数を使用するプログラマブル クロック ジェネレータが内蔵されています。SPI\_DR レジスタは、SPI\_DR レジスタ内の値よりも 1 つ大きいと解釈され、半周期で使用されます。除数の式は次のとおりです：

$$\text{Divisor} = (\text{Clock Frequency} / (\text{Desired SPI clock frequency} \times 2)) - 1 \quad (1)$$

クロック周波数は 40MHz です。この式は、サポートされる最大 SPI 周波数が 20MHz で、最小周波数が 78,125Hz であることを示しています。

**表 7-9. 共通 SPI クロック**

| 必要な SPI クロック | クロックの生成に使用される除数 | SPI_DR 値 (HEX) |

|--------------|-----------------|----------------|

| 80kHz        | 249             | 0xF9           |

| 100kHz       | 199             | 0xC7           |

| 200kHz       | 99              | 0x63           |

| 250kHz       | 79              | 0x4F           |

| 500kHz       | 39              | 0x27           |

| 1MHz         | 19              | 0x13           |

| 2MHz         | 9               | 0x09           |

| 4MHz         | 4               | 0x04           |

| 5MHz         | 3               | 0x03           |

| 6.67MHz      | 2               | 0x02           |

| 10MHz        | 1               | 0x01           |

| 20MHz        | 0               | 0x00           |

#### 7.5.4.3 SPI 制御プロトコル

SPI の TX または RX FIFO を読み書きする際には、対象ペリフェラルへの読み書きをより堅牢にするために、追加の 2 バイトのヘッダが付加されます。2 つの形式があり、いずれも類似していますが、SPI の TX または RX FIFO への読み取りか書き込みかによって異なります。

RX FIFO を読み出す際、データ フィールドの先頭には常に 2 バイトのヘッダが付加されます。このヘッダーには、残りのバイト数や、読み出しが前回の読み出しの継続であるかどうかの情報が含まれています(単一の CAN フレームに収まりきらない大きな SPI メッセージに必要です)。

TX FIFO に書き込む場合、メッセージの最初の書き込みのみに 2 バイトのヘッダーが含まれます。

ヘッダ形式の詳細については、[SPI 受信 FIFO \(アドレス = h1010\)](#) および [SPI 送信 FIFO \(アドレス = h1010\)](#) を参照してください。

#### 7.5.4.3.1 SPI 書き込み例 1

これは、1 つの CAN フレームに収まる SPI 経由のバイト ストリーム送信の基本的な例です。デバイスが SPI フレームのすべてのバイト (SPI ヘッダで指定されたバイト数によって決定) を受信すると、SPI フレームの送信を開始します。

##### 注

モジュールを使用する前に、適切な GPIO を特殊機能に設定する必要があります ([セクション 7.3.4](#) および [セクション 7.6.1.18](#) を参照)、MRAM はアロケーション メモリによってモジュールをイネーブルにする必要があります ([セクション 7.5.3](#) および [セクション 7.6.1.17](#) を参照)。GPIO が特殊機能に設定され、メモリを割り当てる MRAM 構成を選択してモジュールが有効化されてはじめて、そのモジュールを使用できます。適切な SPI 構成レジスタを、[セクション 7.6.2](#) に示します。

表 7-10. 設計パラメータと前提条件

| パラメータ              | 値                                                 |

|--------------------|---------------------------------------------------|

| CAN フレーム フォーマット    | 標準フレーム フォーマット                                     |

| 転送するバイト数           | 10'B                                              |

| SPI チャネル           | チャネル 1                                            |

| 受信データを RX FIFO に保存 | なし                                                |

| SPI バイト ストリーム      | 0x11、0x22、0x33、0x44、0x55、0x66、0x77、0x88、0x99、0xAA |

次の表は、手順と CAN バス上で送信されるデータを示しています。バスの中央ゲートウェイ / コントローラは ECU と呼ばれ、TCAN デバイスは「レスポンダ」と呼ばれます。

- 太字で示された 16 進値は、CAN フレーム ヘッダのバイトを表します (この例では標準フレーム形式です)

- イタリック体で示された 16 進値は、SPI ヘッダ バイトを表します

- 書式なしで示された 16 進値は、SPI データ バイトです

表 7-11. CAN シーケンスの例 (シングル CAN フレーム)

| ステップ | トランスマッタ         | データ                                                                               | 説明                                                                                                                                                                                                                  |

|------|-----------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ECU (DLC = 16B) | <b>0x0C、0x10、0x10、0x01、0x0A、0x11、0x22、0x33、0x44、0x55、0x66、0x77、0x88、0x99、0xAA</b> | ECU は、レジスタ 0x1010 (SPI TX FIFO) に 10 バイトの書き込みを要求します。SPI ヘッダには、store = 0、SPI チャネル = 1、および 10 バイトの SPI フレームが含まれます。その後、10 バイトのデータはデバイスにシフトインされます。これら 15 バイトのデータを収めるため、CAN DLC は 16 バイトでなければならないため、末尾に 0x00 がパディングされます。 |

| 2    | レスポンダ           | <b>0x0C、0x01</b>                                                                  | レスポンダは OK を返信し、要求を受信したことをアクノリッジします。                                                                                                                                                                                 |

| 3    | SPI             | PICO: 0x11、0x22、0x33、0x44、0x55、0x66、0x77、0x88、0x99、0xAA                           | この時点で、レスポンダは SPI チャネル 1 で 10 バイトの SPI 転送を実行します。                                                                                                                                                                     |

**表 7-12. CAN シーケンス例 (ペイロードを転送する複数の CAN フレーム)**

| ステップ | トランスマッタ          | データ                                                                | 説明                                                                                                                                                                                 |

|------|------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ECU (DLC = 8B)   | <b>0x05、0x10、0x10、0x01、0x0A、0x11、0x22、0x33</b>                     | ECU は、レジスタ 0x1010 (SPI TX FIFO) に 5 バイトの書き込みを要求します。SPI ヘッダには、store = 0、SPI チャネル = 1、および 10 バイトの SPI フレームが含まれます。SPI フレームの最初の 3 バイトのデータだけが転送されました。                                   |

| 2    | レスポンダ            | <b>0x05、0x01</b>                                                   | レスポンダは OK を返信し、要求を受信したことをアクノリッジします。                                                                                                                                                |

| 3    | ECU (DLC = 3B)   | <b>0x42、0x10、0x12</b>                                              | ECU は、TX FIFO ステータスおよび TX s ステータス レジスタを読み取るために、2 バイトの読み出しを要求します。この手順はオプションですが、部分的な書き込みに役立つ情報がいくつか表示されます。                                                                           |

| 4    | レスポンダ (DLC = 4B) | <b>0x42、0x01、0x0C、0x87</b>                                         | SPI_TXFS によると、TX FIFO には 12 バイト分の空き領域があるため、オーバーフローの危険はありません。SPI_TXES は、予想どおり TXEIP (TX 素子が進行中) フラグがセットされており、現在の SPI フレームがメモリ内で未完成であり、さらに 7 バイトのデータ (TXEBP フィールド) を必要としていることを示しています |

| 5    | ECU (DLC = 12B)  | <b>0x07、0x10、0x10、0x44、0x55、0x66、0x77、0x88、0x99、0xAA、0x00、0x00</b> | ECU は、同じアドレスへの 7 バイトの書き込み要求を継続します。このフレームを格納できる CAN DLC は 12 バイトであるため、末尾に 2 バイトのパディングが追加されます。これらのパディング バイトの値は問題にならず、無視されます。                                                         |

| 6    | レスポンダ            | <b>0x07、0x01</b>                                                   | レスポンダは OK を返信し、要求を受信したことをアクノリッジします。                                                                                                                                                |

| 7    | SPI              | PICO: 0x11、0x22、0x33、0x44、0x55、0x66、0x77、0x88、0x99、0xAA            | この時点で、レスポンダは SPI チャネル 1 で 10 バイトの SPI 転送を実行します。POCI は無視されます。                                                                                                                       |

#### 7.5.4.3.2 SPI のバイト読み取り例 1

これは、SPI を介してバイトストリームを送受信する基本的な例です。デバイスが SPI フレームのすべてのバイト (SPI ヘッダで指定されたバイト数によって決定) を受信すると、SPI フレームの送信を開始します。この例では、受信した POCI データを格納し、後で読み戻すことができます。

#### 注

モジュールを使用する前に、適切な GPIO を特殊機能に設定する必要があります ([セクション 7.3.4](#) および [セクション 7.6.1.18](#) を参照)、MRAM はアロケーション メモリによってモジュールをイネーブルにする必要があります ([セクション 7.5.3](#) および [セクション 7.6.1.17](#) を参照)。GPIO が特殊機能に設定され、メモリを割り当てる MRAM 構成を選択してモジュールが有効化されてはじめて、そのモジュールを使用できます。適切な SPI 構成レジスタを、[セクション 7.6.2](#) に示します。

**表 7-13. 設計パラメータと前提条件**

| パラメータ              | 値                                                 |

|--------------------|---------------------------------------------------|

| CAN フレーム フォーマット    | 標準フレーム フォーマット                                     |

| 転送するバイト数           | 10B                                               |

| SPI チャネル           | チャネル 2                                            |

| 受信データを RX FIFO に保存 | あり                                                |

| SPI バイトストリーム       | 0x11、0x22、0x33、0x44、0x55、0x66、0x77、0x88、0x99、0xAA |

次の表は、手順と CAN バス上で送信されるデータを示しています。バスの中央ゲートウェイ / コントローラは ECU と呼ばれ、TCAN デバイスは「レスポンダ」と呼ばれます。

- 太字で示された 16 進値は、CAN フレームヘッダのバイトを表します (この例では標準フレーム形式です)

- イタリック体で示された 16 進値は、SPI ヘッダ バイトを表します

- 書式なしで示された 16 進値は、SPI データ バイトです

**表 7-14. CAN シーケンスの例 (シングル CAN フレーム)**

| ステップ | トランスマッタ           | データ                                                                                                                 | 説明                                                                                                                                                                                                                  |

|------|-------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ECU (DLC = 16B)   | <b>0x0C、0x10、0x10、0x82、0x0A、0x11、0x22、0x33、0x44、0x55、0x66、0x77、0x88、0x99、0xAA、0x00</b>                              | ECU は、レジスタ 0x1010 (SPI TX FIFO) に 10 バイトの書き込みを要求します。SPI ヘッダには、store = 1、SPI チャネル = 2、および 10 バイトの SPI フレームが含まれます。その後、10 バイトのデータはデバイスにシフトインされます。これら 15 バイトのデータを収めるため、CAN DLC は 16 バイトでなければならないため、末尾に 0x00 がパディングされます。 |

| 2    | レスポンダ             | <b>0x0C、0x01</b>                                                                                                    | レスポンダは OK を返信し、要求を受信したことをアクノリッジします。                                                                                                                                                                                 |

| 3    | SPI               | PICO: 0x11、0x22、0x33、0x44、0x55、0x66、0x77、0x88、0x99、0xAA<br>POCI : 0x01、0x02、0x03、0x04、0x05、0x06、0x07、0x08、0x09、0x0A | この時点では、レスポンダは SPI チャネル 2 で 10 バイトの SPI 転送を実行します。POCI データは RX FIFO に保存されます                                                                                                                                           |

| 4    | ECU               | <b>0x43、0x10、0x0F</b>                                                                                               | ECU は、レジスタ 0x100F~0x1011 (SPI_STATUS および SPI_RXFS) から 3 バイトの読み取りを要求します。バースト読み取りが 0x1010 (SPI_RX_FIFO) からではなく開始されたため、そのレジスタに対応するバイトはパディングとして 0 になります。FIFO から開始されないバースト読み取りでは、FIFO に対応するバイトは「0」として返されます。              |

| 5    | レスポンダ             | <b>0x43、0x01、0xCA、0x00、0x01</b>                                                                                     | レスポンダは、レジスタ 0x100F のデータ、0x1010 に対しては 0、0x1011 のデータを返します。結果のデータは、TX FIFO が空であり、RX FIFO に 1 つの SPI フレームが含まれ、次の RX FIFO エレメントに 10 バイトのデータがあることを示しています。この情報により、ECU はデバイスから 10 + 2 (SPI ヘッダ) バイトの読み取りを要求すべきことを認識します。     |

| 6    | ECU               | <b>0x4C、0x10、0x10</b>                                                                                               | ECU は、RX FIFO から 12 バイト (データ 10 バイト + ヘッダ 2 バイト) の読み取りを要求します                                                                                                                                                        |

| 7    | レスポンダ (DLC = 16B) | <b>0x4C、0x01、0x02、0x0A、0x01、0x02、0x03、0x04、0x05、0x06、0x07、0x08、0x09、0x0A、0x00、0x00</b>                              | レスポンダは要求された 12 バイトのデータを返します。SPI ヘッダ バイトは、これがフレーム読み出しの開始であること、SPI チャネル 2 が使用されたこと、そして 10 バイトの SPI データを読み出す必要があることを示しています (これは CAN フレーム全体に収まります)。このデータを格納できる最も近い CAN DLC サイズは 16 バイトであったため、末尾に 2 バイトのパディングが追加されました。   |

**表 7-15. CAN シーケンス例 (ペイロードを転送する複数の CAN フレーム)**

| ステップ | トランスマッタ          | データ                                                                                                                 | 説明                                                                                                                                                                                                     |

|------|------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ECU (DLC = 8B)   | <b>0x05、0x10、0x10、0x02、0x0A、0x11、0x22、0x33</b>                                                                      | ECU は、レジスタ 0x1010 (SPI TX FIFO) に 5 バイトの書き込みを要求します。SPI ヘッダには、store = 1、SPI チャネル = 2、および 10 バイトの SPI フレームが含まれます。SPI フレームの最初の 3 バイトのデータだけが転送されました。                                                       |

| 2    | レスポンダ (DLC = 2B) | <b>0x05、0x01</b>                                                                                                    | レスポンダは OK を返信し、要求を受信したことをアクノリッジします。                                                                                                                                                                    |

| 3    | ECU (DLC = 12B)  | <b>0x07、0x10、0x10、0x44、0x55、0x66、0x77、0x88、0x99、0xAA、0x00、0x00</b>                                                  | ECU は、同じアドレスへの 7 バイトの書き込み要求を継続します。このフレームを格納できる CAN DLC は 12 バイトであるため、末尾に 2 バイトのパディングが追加されます。これらのパディング バイトの値は問題にならず、無視されます。                                                                             |

| 4    | レスポンダ (DLC = 2B) | <b>0x07、0x01</b>                                                                                                    | レスポンダは OK を返信し、要求を受信したことをアクノリッジします。                                                                                                                                                                    |

| 3    | SPI              | PICO: 0x11、0x22、0x33、0x44、0x55、0x66、0x77、0x88、0x99、0xAA<br>POCI : 0x01、0x02、0x03、0x04、0x05、0x06、0x07、0x08、0x09、0x0A | この時点では、レスポンダは SPI チャネル 2 で 10 バイトの SPI 転送を実行します。POCI データは RX FIFO に保存されます                                                                                                                              |

| 4    | ECU (DLC = 3B)   | <b>0x43、0x10、0x0F</b>                                                                                               | ECU は、レジスタ 0x100F~0x1011 (SPI_STATUS および SPI_RXFS) から 3 バイトの読み取りを要求します。バースト読み取りが 0x1010 (SPI_RX_FIFO) からではなく開始されたため、そのレジスタに対応するバイトはパディングとして 0 になります。FIFO から開始されないバースト読み取りでは、FIFO に対応するバイトは「0」として返されます。 |

**表 7-15. CAN シーケンス例 (ペイロードを転送する複数の CAN フレーム) (続き)**

| ステップ | トランスマッタ           | データ                                                                           | 説明                                                                                                                                                                                                                                                                                                                                                                   |

|------|-------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5    | レスポンダ (DLC = 5B)  | <b>0x43, 0x01, 0xCA, 0x00, 0x01</b>                                           | レスポンダは、レジスタ 0x100F のデータ、0x1010 に対しては 0, 0x1011 のデータを返します。結果のデータは、TX FIFO が空であり、RX FIFO に 1 つの SPI フレームが含まれ、次の RX FIFO エレメントに 10 バイトのデータがあることを示しています。この情報により、ECU はデバイスから 10 + 2 (SPI ヘッダ) バイトの読み取りを要求すべきことを認識します。                                                                                                                                                     |

| 6    | ECU (DLC = 3B)    | <b>0x48, 0x10, 0x10</b>                                                       | ECU は、RX FIFO から 8 バイトの読み取りを要求します (ヘッダ 2 バイト + データ 6 バイトを含みます)                                                                                                                                                                                                                                                                                                       |

| 7    | レスポンダ (DLC = 12B) | <b>0x48, 0x01, 0x02, 0x0A, 0x01, 0x02, 0x03, 0x04, 0x05, 0x06, 0x00, 0x00</b> | レスポンダは要求された 8 バイトのデータを返します (DLC は 12 ですが、CAN レスponsヘッダの後の 8 バイトのデータのみが有効であり、0 はパディングであることが分かります)。SPI ヘッダ バイトは、これがフレーム読み出しの開始であること、SPI チャネル 2 が使用されたこと、そして残り 10 バイトの SPI データを読み出す必要があることを示しています。このデータを格納できる最も近い CAN DLC サイズは 12 バイトであったため、末尾に 2 バイトのパディングが追加されました。ECU には 10 バイトの SPI データを読み出す必要があると伝えられましたが、要求したのは 6 バイトだけでした。これは、読み取るべき SPI データが 4 バイト残っていることを意味します。 |

| 8    | ECU (DLC = 3B)    | <b>0x46, 0x10, 0x10</b>                                                       | ECU は、読み取りを完了するために RX FIFO から 6 バイト (データ 4 バイト + ヘッダ 2 バイト) の読み取りを要求します。                                                                                                                                                                                                                                                                                             |

| 9    | レスポンダ (DLC = 8B)  | <b>0x46, 0x01, 0x82, 0x04, 0x07, 0x08, 0x09, 0x0A</b>                         | レスポンダは要求された 6 バイトのデータを返します。SPI ヘッダ バイトは、これがフレーム読み出しの継続であること、SPI チャネル 2 が使用されたこと、そして残り 4 バイトの SPI データを読み出す必要があることを示しています (これはこのフレームに収まります)。送信データが CAN フレーム サイズに一致したため、パディング バイトは不要でした。                                                                                                                                                                                |

## 7.5.5 UART コントローラ

### 注

モジュールを使用する前に、適切な GPIO を特殊機能に設定する必要があります (セクション 7.3.4 およびセクション 7.6.1.18 を参照)、MRAM はアロケーション メモリによってモジュールをイネーブルにする必要があります (セクション 7.5.3 およびセクション 7.6.1.17 を参照)。GPIO が特殊機能に設定され、メモリを割り当てる MRAM 構成を選択してモジュールが有効化されはじめて、そのモジュールを使用できます。適切な UART 構成レジスタを、セクション 7.6.4 に示します。

### 7.5.5.1 UART ポーレート生成と分数除数

TCAN5102-Q1 UART にはプログラマブル ポーリュエレータが搭載されており、リファレンス クロックを 1 ~ ( $2^{16} - 1$ ) の範囲の除数で分周し、10 進分解能は 1/64 です。ポーレート ジェネレータの出力周波数は、ポーレートの 16 倍です。ポーレート ジェネレータへの入力クロックは常に 40MHz です。除数の式は次のとおりです：

$$\text{Divisor} = (40E6 / (\text{Desired baud rate} \times 16)) \quad (2)$$

レジスタに入力するためには必要な値を計算するには、以下の関数が必要です：

- TRUNC(X) : X を切り捨て、実数の整数部分だけを返します。例 : TRUNC (3.14) = 3

- ROUND(X) : X を最も近い整数に丸めます。例 : ROUND(3.1) = 3 および ROUND(3.6) = 4

- >> : 右方向へのビットシフト操作。例 : 0x1000 >> 8 = 0x0010。または 0b0001 0000 0000 0000 >> 8 = 0b0000 0000 0001 0000

- & : ビット単位の AND 関数。ビットをマスクするために使用されます。例 : 0x1234 & 0x00FF = 0x0034 および 0x8765 & 0xFF00 = 0x8700

必要な除数が見つかったら、以下からレジスタ値を計算できます：

$$\text{UART\_BR\_MSB} = \text{TRUNC}(\text{Divisor}) \gg 8 \quad (3)$$

$$\text{UART\_BR\_LSB} = \text{TRUNC}(\text{Divisor}) \& 0xFF \quad (4)$$

$$\text{UART\_BR\_FRAC} = \text{ROUND}([\text{Divisor} - \text{TRUNC}(\text{Divisor})] \times 64) \quad (5)$$

表 7-16. 16x ポーレート分周器 (40 MHz クロック) を使用したポーレート

| 希望するポーレート | 16x CLOCK の生成に使<br>用される除数 | 取得可能な最も近い<br>除数 | UART_BR_<br>MSB 値<br>(HEX) | UART_BR_<br>LSB 値<br>(HEX) | UART_BR_<br>FRAC 値<br>(HEX) | 希望値と実測値のパーセン<br>ト誤差 (%) |

|-----------|---------------------------|-----------------|----------------------------|----------------------------|-----------------------------|-------------------------|

| 400       | 6250.0000                 | 6250            | 0x18                       | 0x6A                       | 0x00                        | 0                       |

| 2400      | 1041.6667                 | 1041 43/64      | 0x04                       | 0x11                       | 0x2B                        | 0                       |

| 4800      | 520.8333                  | 520 53/64       | 0x02                       | 0x08                       | 0x35                        | 0.001                   |

| 9600      | 260.4167                  | 260 27/64       | 0x01                       | 0x04                       | 0x1B                        | 0.002                   |

| 10000     | 250.0000                  | 250             | 0x00                       | 0xFA                       | 0x00                        | 0                       |

| 19200     | 130.2083                  | 130 13/64       | 0x00                       | 0x82                       | 0x0D                        | 0.004                   |

| 25000     | 100.0000                  | 100             | 0x00                       | 0x64                       | 0x00                        | 0                       |

| 28800     | 86.8056                   | 86 52/64        | 0x00                       | 0x56                       | 0x34                        | 0.008                   |

| 38400     | 65.1042                   | 65 7/64         | 0x00                       | 0x41                       | 0x07                        | 0.008                   |

| 50000     | 50.0000                   | 50              | 0x00                       | 0x32                       | 0x00                        | 0                       |

| 57600     | 43.4028                   | 43 26/64        | 0x00                       | 0x2B                       | 0x1A                        | 0.008                   |

| 75000     | 33.3333                   | 33 21/64        | 0x00                       | 0x21                       | 0x15                        | 0.016                   |

| 100000    | 25.0000                   | 25              | 0x00                       | 0x19                       | 0x00                        | 0                       |

| 115200    | 21.7014                   | 21 45/64        | 0x00                       | 0x15                       | 0x2D                        | 0.008                   |

| 128000    | 19.5313                   | 19 34/64        | 0x00                       | 0x13                       | 0x22                        | 0                       |

| 153600    | 16.2760                   | 16 18/64        | 0x00                       | 0x10                       | 0x12                        | 0.032                   |

| 200000    | 12.5000                   | 12 32/64        | 0x00                       | 0x0C                       | 0x20                        | 0                       |

| 225000    | 11.1111                   | 11 7/64         | 0x00                       | 0x0B                       | 0x07                        | 0.016                   |

| 230400    | 10.8507                   | 10 54/64        | 0x00                       | 0x0A                       | 0x36                        | 0.064                   |

| 250000    | 10.0000                   | 10              | 0x00                       | 0x0A                       | 0x00                        | 0                       |

| 256000    | 9.7656                    | 9 49/64         | 0x00                       | 0x09                       | 0x31                        | 0                       |

| 300000    | 8.3333                    | 8 21/64         | 0x00                       | 0x08                       | 0x15                        | 0.063                   |

| 400000    | 6.2500                    | 6 16/64         | 0x00                       | 0x06                       | 0x10                        | 0                       |

| 460800    | 5.4253                    | 5 27/64         | 0x00                       | 0x05                       | 0x1B                        | 0.064                   |

| 500000    | 5.0000                    | 5               | 0x00                       | 0x05                       | 0x00                        | 0                       |

| 750000    | 3.3333                    | 3 21/64         | 0x00                       | 0x03                       | 0x15                        | 0.156                   |

| 921600    | 2.7127                    | 2 46/64         | 0x00                       | 0x02                       | 0x2E                        | 0.224                   |

| 1000000   | 2.5000                    | 2 32/64         | 0x00                       | 0x02                       | 0x20                        | 0                       |

### 7.5.5.2 UART 制御プロトコル

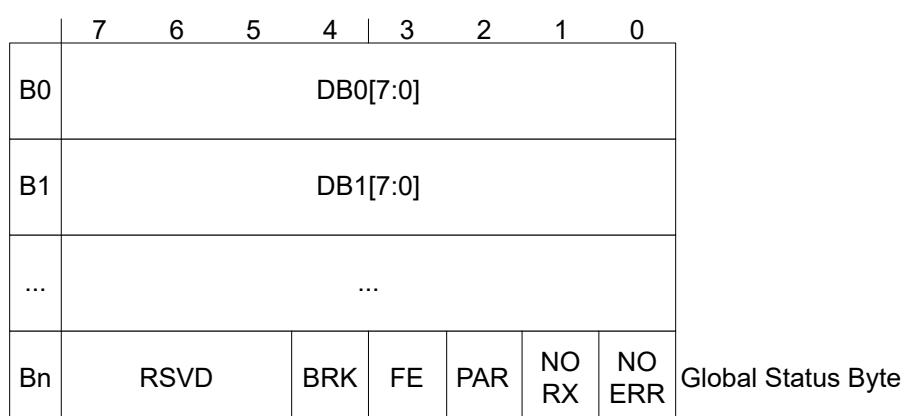

UART はバイトベースの転送であり、上位のプロトコルではないため、フレームの概念はありません。UART モジュールは、各バイトのエラーをチェックして、バイトをシフトイン / シフトアウトします。このため、受信される各バイトにはステータス バイトが関連付けられ、エラーが発生した場合に MCU にアラートを送信します。エラーが共通することは想定されないため、エラーが発生しない限り、各バイトのステータス バイトを読み取る必要はありません。スループットを節約するため、各 UART RX FIFO 読み取りの終了には、グローバル ステータス バイトが追加されます。このグローバル ステータス バイトは、読み出されたすべてのバイトのステータス バイトを論理和したものです。これにより、MCU は転送されたバイト ブロックに対してエラーが報告されたかどうかを判断できます。その場合は、読み取りを要求できます。どのバイトが故障しており、どのエラーを受信したかを判別するために、RX エラー ステータス レジスタを読み出します。

データの送受信時に使用される追加の UART 固有のヘッダではなく、RX FIFO の読み取り時のグローバル ステータス バイトのみです。

レジスタおよびデータ形式の詳細については、UART 送信 FIFO (アドレス = h2010)、UART 受信 FIFO (アドレス = h2010)、UART 受信エラーステータス (アドレス = h2011) を参照してください。

#### 7.5.5.2.1 UART 書き込み例 1

これは、UART を介してバイトストリームを送信する基本的な例です。デバイスが TX FIFO にバイトを受信すると、デバイスは UART バイトの送信を開始します。

##### 注