## 3チャネル低消費電力ビデオアンプ I<sup>2</sup>C制御、選択可能フィルタ、+6dBゲイン、SAG補正、 2:1入力マルチプレクサ、および選択可能入力バイアスモード付

### 特 長

- 3チャネル・ビデオアンプ CVBS, Sビデオ、EDTV, HDTV Y'P'B'P'R'およびG'B'R'(R'G'B')ビデオ対応

- I<sup>2</sup>Cによる各チャネルの全機能の制御

- ローパスフィルタ内蔵

- 5次のバタワース特性

- 8.5MHz, 16MHz, 34MHzのコーナー周波数およびバイパス(200MHz)を選択可能

- 選択可能な入力バイアスモード

- シンクチップ・クランプのAC結合

- バイアスのAC結合

- 入力を135mVシフトするDC結合

- DC結合

- 2:1入力マルチプレクサにより複数入力源が可能

- 固定の6dBゲイン(2V/V)

### SAG補正

- +2.7Vから+5Vの単電源動作

- 5mA/チャネル@3.3Vの低消費電流

- 独立したディスエーブル(0.1μA)およびミュート制御

- レール・ツー・レール出力：

- 入出力のACあるいはDC結合が可能な、両レールまで100mV以内の出力振幅

- 最大2ビデオライン(75Ω)をドライブ可能

- 0.25% / 0.75°の低差動ゲイン/位相

- QFNリードレス・パッケージあるいは小サイズのTSSOPパッケージで提供

### ア プ リ ケ シ ョ ン

- セットトップボックスの出力ビデオバッファ

- PVR/DVDR出力バッファ

- USB / ポータブルの低消費電力ビデオバッファ

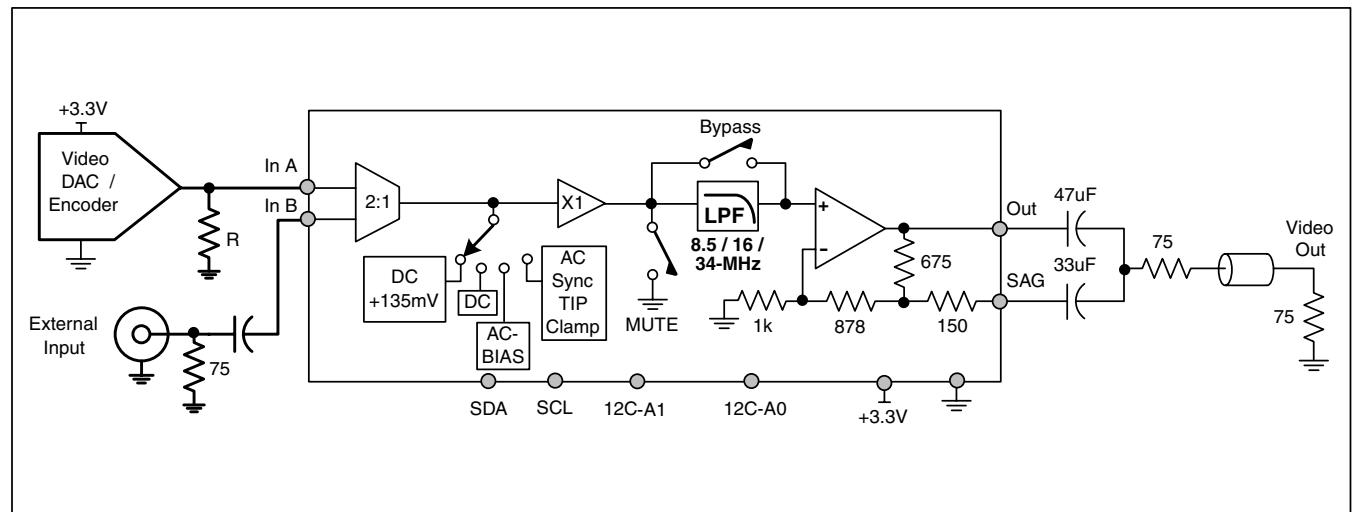

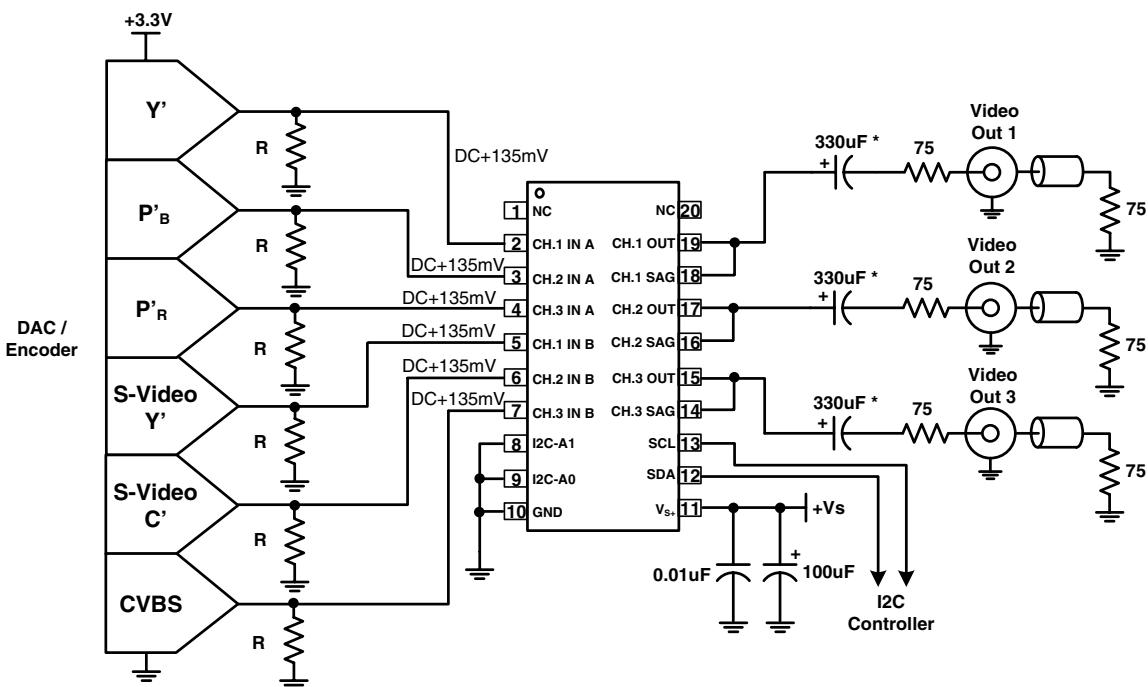

図 1. 3.3V单電源、DC入力/ACビデオ出力システム、w/SAG補正(3チャネルのうち1つを表示)

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 概要

革新的なシリコン-ゲルマニウム(SiGe)相補型のBiCom-3プロセスで製造されたTHS7303は、低消費電力の単電源2.7Vから5Vで動作する、3チャネルを集積したビデオバッファです。THS7303は選択可能な5次のバタワースフィルタを内蔵し、データコンバータのイメージノイズを除去します。その中の8.5MHzは、コンポジット、Sビデオ、および480i/576iを含むSDTVに最適な選択になります。また、16MHzフィルタはEDTV480p/576pに最適であり、34MHzフィルタはHDTV720p/1080i規格に有効です。1080pあるいはG'B'R' (RG'B')信号についてはフィルタをバイパスし、200MHz帯域幅、300V/ $\mu$ sのアンプで信号をバッファすることができます。

THS7303の各チャネルは個別にすべての機能についてI<sup>2</sup>C制御が可能であり、どのようなアプリケーションにも柔軟に対応します。そのレール・ツー・レールの出力段により、ACおよびDC結合の両方のアプリケーションが可能です。また、6dBゲインは内蔵のSAG補正とともに、出力ビデオバッファとしての最大限の柔軟性を提供します。

THS7303の柔軟性の一部として、2:1MUX入力はACあるいはDC結合入力を選択できます。そのAC結合モードには、CVBS/Y'/G'B'R'向けのシンクチップ・クランプと、C'/P'<sub>B</sub>/P'<sub>R</sub>

チャネル向けのシンクあるいは固定バイアスのオプションがあります。また、DC入力オプションにはDC入力あるいは、0V入力時に出力のシンク(sync、同期信号)のダイナミックレンジを最大にするDC+135mV入力オフセットシフトがあります。

THS7303は、すべての出力バッファのアプリケーションに最適な選択です。すなわち、5mA/チャネルの消費電流(合計消費電力50mW)により、USBによる電力供給やポータブルといったビデオ・アプリケーションに対して優れた選択となります。また、THS7303を完全にディスエーブルすると、わずかに0.1 $\mu$ Aしか消費しません。

THS7303は、省スペースのリードレスMSOPパッケージ(QFN)およびTSSOPパッケージで提供しております。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 絶対最大定格

Over operating free-air temperature (unless otherwise noted)<sup>(1)</sup>

|                                                                                                         | UNIT                         |

|---------------------------------------------------------------------------------------------------------|------------------------------|

| Supply voltage, V <sub>S+</sub> to GND                                                                  | 5.5 V                        |

| Input voltage, V <sub>I</sub>                                                                           | -0.4V to V <sub>S+</sub>     |

| Output current, I <sub>O</sub>                                                                          | $\pm$ 150 mA                 |

| Continuous power dissipation                                                                            | See Dissipation Rating Table |

| Maximum junction temperature, any condition <sup>(2)</sup> T <sub>J</sub>                               | 150 °C                       |

| Maximum junction temperature, continuous operation, long term reliability <sup>(3)</sup> T <sub>J</sub> | 125 °C                       |

| Storage temperature range, T <sub>stg</sub>                                                             | -65 °C to 150 °C             |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds                                            | 300 °C                       |

| ESD ratings                                                                                             | HBM                          |

|                                                                                                         | 2500 V                       |

|                                                                                                         | CDM                          |

|                                                                                                         | 750 V                        |

|                                                                                                         | MM                           |

|                                                                                                         | 200 V                        |

(1) 絶対最大定格に掲げた以上のストレスを加えると、デバイスの永久破壊が生じことがあります。また、これらはストレスの定格のみであり、これらの条件あるいは「推奨動作条件」で示すものを超える条件でのデバイスの機能動作は含まれません。絶対最大定格の条件下にデバイスを長期間置くと、その信頼性が低下することがあります。

(2) あらゆる条件下での絶対最大接合温度は、シリコンプロセスの制約により限定されます。

(3) 連続動作時の絶対最大接合温度は、パッケージの制約により限定されます。この温度以上で動作させると、デバイスの信頼性や寿命が低下することがあります。

## 推奨動作条件

|                                     | MIN | MAX | UNIT |

|-------------------------------------|-----|-----|------|

| Supply Voltage, V <sub>S+</sub>     | 2.7 | 5   | V    |

| Ambient Temperature, T <sub>A</sub> | -40 | 85  | °C   |

## 各パッケージの電力消費定格表

| PACKAGE         | $\theta_{JC}$<br>(°C/W) | $\theta_{JA}$<br>(°C/W) | POWER RATING <sup>(4)</sup><br>( $T_J = 125^\circ\text{C}$ ) |                          |

|-----------------|-------------------------|-------------------------|--------------------------------------------------------------|--------------------------|

|                 |                         |                         | $T_A = 25^\circ\text{C}$                                     | $T_A = 85^\circ\text{C}$ |

| QFN - 20 (RGP)  | 20.4                    | 46.2 <sup>(2,3)</sup>   | 2.16 W                                                       | 0.86 W                   |

| TSSOP - 20 (PW) | 32.3                    | 83.0 <sup>(1)</sup>     | 1.20 W                                                       | 0.48 W                   |

- (1) このデータはJEDECの高KテストPCBで採取しました。JEDECの低KテストPCBでは、 $\theta_{JA}$ は125.8°Cです。

(2) このデータは、4層の3"x3"のテストPCBにPowerPADを半田付けして採取しました。PowerPADは、熱的有利性とは別に機械的強度のためにPCBに半田付けする必要があります。さもないとデバイスがより熱的ストレス変動に敏感になり、機構的信頼性が低減することがあります。

(3) 高電力消費のアプリケーションでは、PowerPADをPCBに半田付けする必要があります。さもないと、デバイスの信頼性や寿命が低下することがあります。熱的に強化されたパッケージであるPowerPADの使用に関する詳細な資料は、TIテクニカル・ブリーフのSLMA002をご覧ください。

(4) 電力定格は接合温度125°Cで定まります。この温度は、ひずみが実質的に増加し始め、長期間の信頼性が低下し始める点になります。最終版PCBの熱的管理では、最善の特性と信頼性を得るために接合温度を125°C以下に保つように努力しなければなりません。

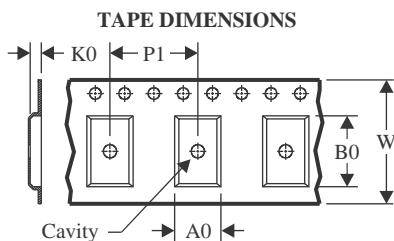

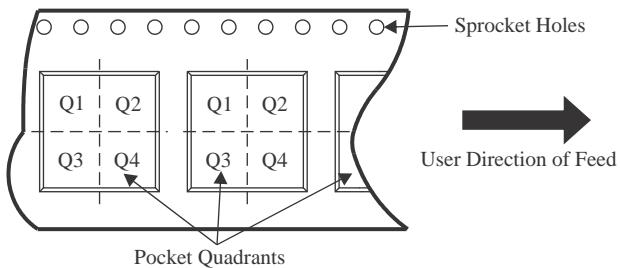

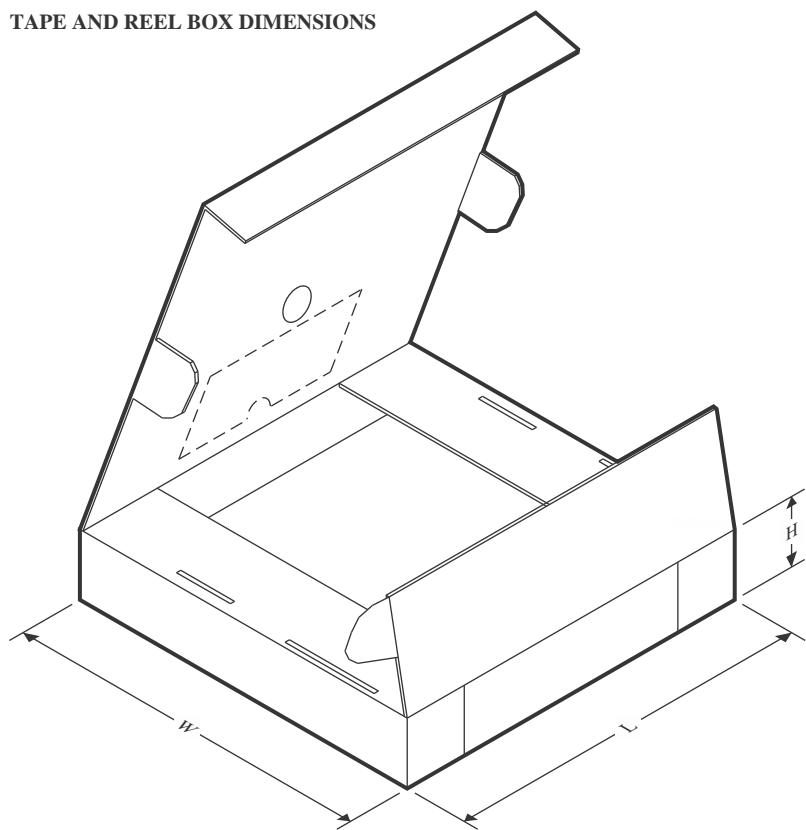

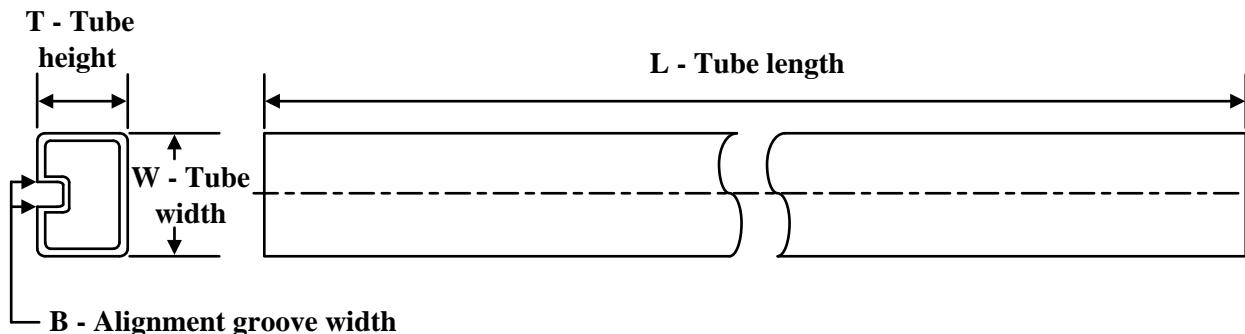

## パッケージ/発注に関する資料

注記：これらのパッケージは、鉛フリーおよびグリーン製造規格に準拠しています。

| PACKAGED DEVICES | PACKAGE TYPE              | TRANSPORT MEDIA,<br>QUANTITY | ECO STATUS <sup>(1)</sup> |

|------------------|---------------------------|------------------------------|---------------------------|

| THS7303RGPT      | QFN - Leadless<br>MSOP-20 | Tape and Reel, 250           | Pb-Free, Green            |

| THS7303RGPR      |                           | Tape and Reel, 3000          | Pb-Free, Green            |

| THS7303PW        |                           | Rails, 75                    | Pb-Free, Green            |

| THS7303PWR       | TSSOP-20                  | Tape and Reel, 2500          | Pb-Free, Green            |

- (1) エコ-ステータス資料。指定物質内容を含む詳細な別資料は、[www.ti.com/leadfree](http://www.ti.com/leadfree)でご覧になれます。

グリーン：弊社は「グリーン」の意味を、鉛フリー（リードフリー）だけでなく、臭素（Br）を含むハロゲン族や錫（Sb）が製品総重量の0.1%を超えないパッケージ材料を、より少なく使用することと定義します。

N/A：鉛フリー（リードフリー）がまだ入手できません。変換の予定は[www.ti.com/leadfree](http://www.ti.com/leadfree)でご覧ください。

鉛フリー：弊社は「鉛フリー（リードフリー）」の意味を、鉛集中が製品総重量の0.1%を超えないことを含むRoHSと互換性があり、半田付けを要する設計の場合、鉛フリー半田付け処理の指定に適合するものと定義します。

## ファンクション図

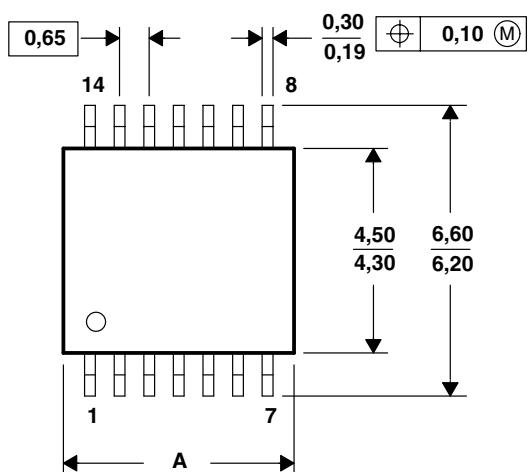

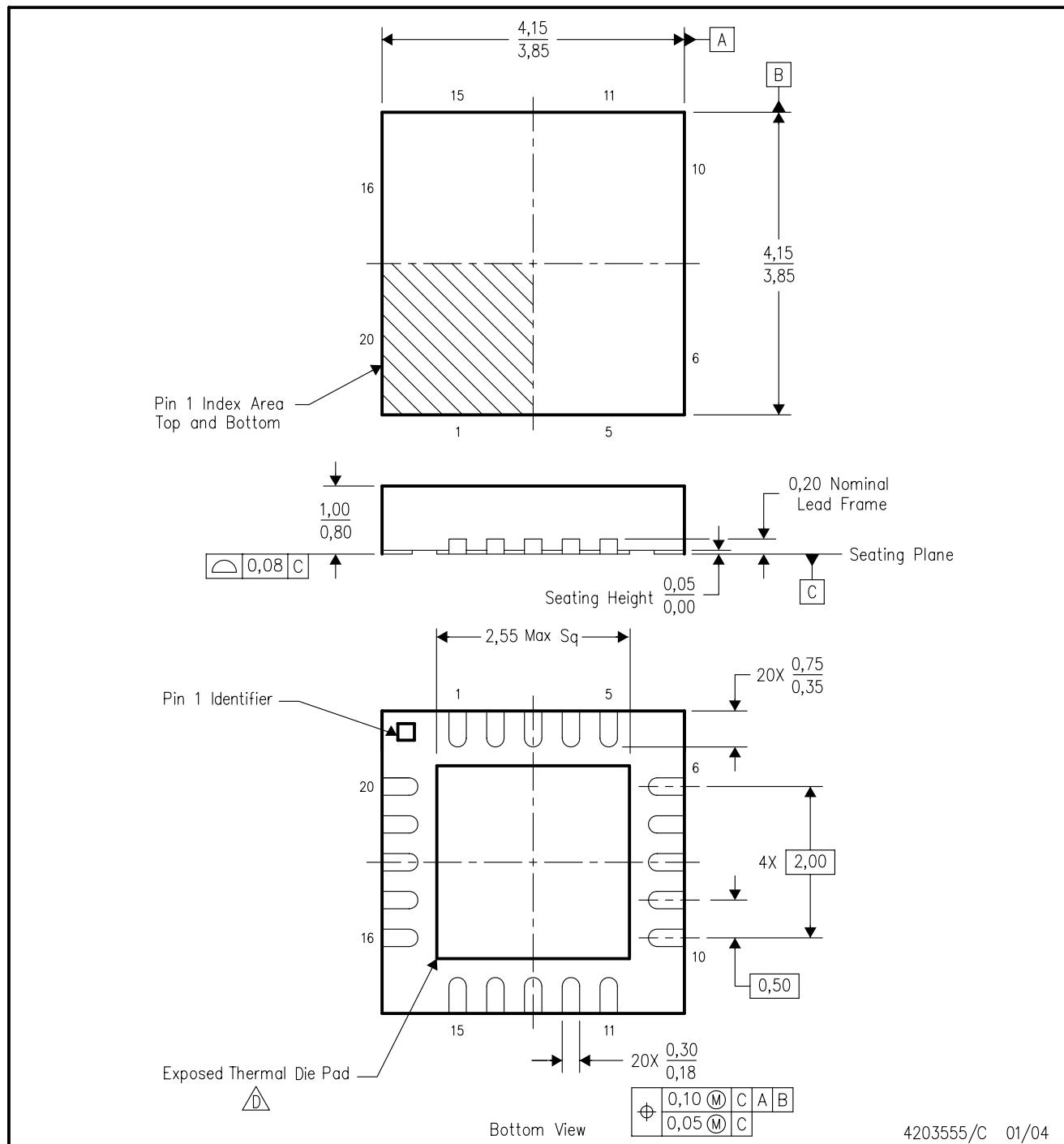

## 端子構成

| TOP VIEW |    | THS7303PW       | TOP VIEW        | THS7303RGP                   |

|----------|----|-----------------|-----------------|------------------------------|

|          |    | TSSOP-20 (PW)   |                 | QFN - Leadless MSOP-20 (RGP) |

| 1        | 20 | NC              | CH. 1 – INPUT A | CH. 1 – INPUT A              |

| 2        | 19 | CH. 1 – OUTPUT  | CH. 2 – INPUT A | NC                           |

| 3        | 18 | CH. 1 – SAG     | CH. 3 – INPUT A | NC                           |

| 4        | 17 | CH. 2 – OUTPUT  | CH. 1 – INPUT B | CH. 1 – OUTPUT               |

| 5        | 16 | CH. 2 – SAG     | CH. 2 – INPUT B | CH. 2 – SAG                  |

| 6        | 15 | CH. 3 – OUTPUT  | CH. 3 – INPUT B | CH. 3 – OUTPUT               |

| 7        | 14 | CH. 3 – SAG     | I2C-A1          | CH. 3 – SAG                  |

| 8        | 13 | SCL             | I2C-A1          | SCL                          |

| 9        | 12 | SDA             | I2C-A1          | GND                          |

| 10       | 11 | V <sub>s+</sub> | GND             | V <sub>s+</sub>              |

See Notes A and B

See Notes A, B, and C

注 A: NCは内部接続が無いピンを示します。

B: THS7303の電源が供給されたときのデフォルト状態はディスエーブルです。

C: PowerPADは他のすべてのピンと電気的に絶縁されており、GNDからV<sub>s+</sub>までのあらゆる範囲の電位と接続可能です。しかし、一般にPowerPADはGNDプレーンに接続します。GNDプレーンが物理的に最も大きく、最大の熱量を消費できるからです。

## 端子解説

| PIN NUMBER |        | PIN NAME            | DESCRIPTION                                                                                                                                                      |

|------------|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP-20   | QFN-20 |                     |                                                                                                                                                                  |

| 1, 20      | 18, 19 | N/C                 | No Internal Connection                                                                                                                                           |

| 2          | 20     | CH. 1 – INPUT A     | Video Input Channel 1 – Input A                                                                                                                                  |

| 3          | 1      | CH. 2 – INPUT A     | Video Input Channel 2 – Input A                                                                                                                                  |

| 4          | 2      | CH. 3 – INPUT A     | Video Input Channel 3 – Input A                                                                                                                                  |

| 5          | 3      | CH. 1 – INPUT B     | Video Input Channel 1 – Input B                                                                                                                                  |

| 6          | 4      | CH. 2 – INPUT B     | Video Input Channel 2 – Input B                                                                                                                                  |

| 7          | 5      | CH. 3 – INPUT B     | Video Input Channel 3 – Input B                                                                                                                                  |

| 8          | 6      | I <sup>2</sup> C-A1 | I <sup>2</sup> C Slave Address Control Bit A1 – Connect to Vs+ for a Logic 1 preset value or GND for a Logic 0 preset value.                                     |

| 9          | 7      | I <sup>2</sup> C-A0 | I <sup>2</sup> C Slave Address Control Bit A0 – Connect to Vs+ for a Logic 1 preset value or GND for a Logic 0 preset value.                                     |

| 10         | 8      | GND                 | Ground Reference Pin for All Internal Circuitry                                                                                                                  |

| 11         | 9      | Vs+                 | Positive Power Supply Input Pin – Connect to +2.7V to +5V                                                                                                        |

| 12         | 10     | SDA                 | Serial data line of the I <sup>2</sup> C bus. Pull-up resistor should have a minimum value = 2-kΩ and a maximum value = 19-kΩ. Pull up to Vs+                    |

| 13         | 11     | SCL                 | I <sup>2</sup> C bus Clock Line. Pull-up resistor should have a minimum value = 2-kΩ and a maximum value = 19-kΩ. Pull up to Vs+                                 |

| 14         | 12     | CH. 3 – SAG         | Video Output Channel 3 SAG Correction Pin. If SAG is not Utilized, Connect Directly to CH. 3 – OUTPUT Pin.                                                       |

| 15         | 13     | CH. 3 – OUTPUT      | Video Output Channel 3 From Either CH. 3 – INPUT A or CH. 3 – INPUT B                                                                                            |

| 16         | 14     | CH. 2 – SAG         | Video Output Channel 2 SAG Correction Pin. If SAG is not Utilized, Connect Directly to CH. 2 – OUTPUT Pin.                                                       |

| 17         | 15     | CH. 2 – OUTPUT      | Video Output Channel 2 From Either CH. 2 – INPUT A or CH. 2 – INPUT B                                                                                            |

| 18         | 16     | CH. 1 – SAG         | Video Output Channel 1 SAG Correction Pin. If SAG is not Utilized, Connect Directly to CH. 1 – OUTPUT Pin.                                                       |

| 19         | 17     | CH. 1 – OUTPUT      | Video Output Channel 1 From Either CH. 1 – INPUT A or CH. 1 – INPUT B                                                                                            |

| ---        | PAD    | Thermal Pad         | The thermal pad under the QFN package Must be soldered to the PCB for mechanical strength. This pad is electrically isolated from all active circuitry and pins. |

## 電氣的特性 3.3V

$R_L = 150 \Omega$  to GND, Filter Select = 8.5MHz, Input Bias = DC, SAG pin shorted to Output Pin, unless otherwise noted.

| PARAMETER                                                   | CONDITIONS                             | TYP       | OVER TEMPERATURE |                |                  |       | UNITS   | MIN/<br>MAX |

|-------------------------------------------------------------|----------------------------------------|-----------|------------------|----------------|------------------|-------|---------|-------------|

|                                                             |                                        | 25°C      | 25°C             | 0°C to<br>70°C | -40°C to<br>85°C |       |         |             |

| <b>AC PERFORMANCE</b>                                       |                                        |           |                  |                |                  |       |         |             |

| Small-Signal Bandwidth (-3dB)<br>Vo – 0.1Vpp                | Filter Select = 8.5-MHz (Note 1)       | 8.5       | 7.7 / 9.3        | 7.3 / 9.8      | 7.1 / 10         | MHz   | Min/Max |             |

|                                                             | Filter Select = 16-MHz (Note 1)        | 16        | 14.5 / 17.6      | 13.5 / 19      | 13.3 / 20        | MHz   | Min/Max |             |

|                                                             | Filter Select = 34-MHz (Note 1)        | 34        | 30.6 / 37.4      | 29.2 / 38.8    | 28.6 / 39.4      | MHz   | Min/Max |             |

|                                                             | Filter Select = Bypass                 | 180       |                  |                |                  | MHz   | Typ     |             |

| Large-Signal Bandwidth (-3dB)<br>Vo – 2Vpp                  | Filter Select = 8.5-MHz                | 8.5       |                  |                |                  | MHz   | Typ     |             |

|                                                             | Filter Select = 16-MHz                 | 16        |                  |                |                  | MHz   | Typ     |             |

|                                                             | Filter Select = 34-MHz                 | 34        |                  |                |                  | MHz   | Typ     |             |

|                                                             | Filter Select = Bypass                 | 55        |                  |                |                  | MHz   | Typ     |             |

| Slew Rate                                                   | Filter Select = Bypass                 | 270       |                  |                |                  | V/us  | Typ     |             |

| Group Delay at 100kHz                                       | Filter Select = 8.5-MHz                | 57        |                  |                |                  | ns    | Typ     |             |

|                                                             | Filter Select = 16-MHz                 | 33        |                  |                |                  | ns    | Typ     |             |

|                                                             | Filter Select = 34-MHz                 | 17.4      |                  |                |                  | ns    | Typ     |             |

|                                                             | Filter Select = Bypass                 | 3         |                  |                |                  | ns    | Typ     |             |

| Group Delay Variation<br>With Respect to 100kHz             | Filter Select = 8.5-MHz: @ 5.1-MHz     | 10.5      |                  |                |                  | ns    | Typ     |             |

|                                                             | Filter Select = 16-MHz: @ 11-MHz       | 8         |                  |                |                  | ns    | Typ     |             |

|                                                             | Filter Select = 34-MHz: @ 27-MHz       | 5         |                  |                |                  | ns    | Typ     |             |

| Attenuation<br>With Respect to 100kHz                       | Filter Select = 8.5-MHz: @ 5.75-MHz    | 0.4       | 0.2 / 0.7        | 0.1 / 1.2      | 0.1 / 1.4        | dB    | Min/Max |             |

|                                                             | Filter Select = 8.5-MHz: @ 27-MHz      | 42.5      | 38               | 36             | 35               | dB    | Min     |             |

|                                                             | Filter Select = 16-MHz: @ 11-MHz       | 0.5       | 0.2 / 0.8        | 0.1 / 1.2      | 0.1 / 1.4        | dB    | Min/Max |             |

|                                                             | Filter Select = 16-MHz: @ 54-MHz       | 44.5      | 39               | 37             | 36               | dB    | Min     |             |

|                                                             | Filter Select = 34-MHz: @ 27-MHz       | 0.7       | 0.3 / 1.1        | 0.2 / 1.5      | 0.2 / 1.7        | dB    | Min/Max |             |

|                                                             | Filter Select = 34-MHz: @ 74-MHz       | 28.5      | 24               | 22             | 20               | dB    | Min     |             |

| Mute Attenuation                                            | f = 1-MHz                              | 75        |                  |                |                  | dB    | Typ     |             |

| Differential Gain (NTSC / PAL)                              | Filter Select = 8.5-MHz: NTSC/PAL      | 0.25/0.4  |                  |                |                  | %     | Typ     |             |

| Differential Phase (NTSC / PAL)                             | Filter Select = 8.5-MHz: NTSC/PAL      | 0.65/0.75 |                  |                |                  | °     | Typ     |             |

| Total Harmonic Distortion<br>f = 1MHz, 2Vpp                 | Filter Select = 8.5-MHz                | -60       |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = 16-MHz                 | -60       |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = 34-MHz                 | -60       |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = Bypass                 | -70       |                  |                |                  | dB    | Typ     |             |

| Signal to Noise Ratio<br>(Unified Weighting per CCIR 576-2) | Filter Select = 8.5-MHz                | 81        |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = 16-MHz                 | 78        |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = 34-MHz                 | 76        |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = Bypass – Note 2        | 66        |                  |                |                  | dB    | Typ     |             |

| Channel-to-Channel Crosstalk<br>(Vo = 2Vpp)                 | Filter Select = 8.5-MHz: @ 1-MHz       | -63       |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = 16-MHz: @ 2-MHz        | -62       |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = 34-MHz: @ 5-MHz        | -60       |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = Bypass: @ 10-MHz       | -60       |                  |                |                  | dB    | Typ     |             |

| MUX Isolation                                               | Filter Select = 8.5-MHz: @ 5.5-MHz     | 94        |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = 16-MHz: @ 11-MHz       | 90        |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = 34-MHz: @ 27-MHz       | 83        |                  |                |                  | dB    | Typ     |             |

|                                                             | Filter Select = Bypass: @ 60-MHz       | 76        |                  |                |                  | dB    | Typ     |             |

| AC Gain – All Channels                                      | f = 100kHz                             | 6.0       | 5.7 / 6.3        | 5.6 / 6.4      | 5.6 / 6.4        | dB    | Min/Max |             |

| Output Impedance                                            | f = 5-MHz                              | 0.2       |                  |                |                  | Ω     | Typ     |             |

| <b>DC PERFORMANCE</b>                                       |                                        |           |                  |                |                  |       |         |             |

| Output Offset Voltage                                       | Bias = DC                              | 15        | 25               | 35             | 40               | mV    | Max     |             |

| Average Offset Voltage Drift                                | Bias = DC                              |           |                  |                | 20               | µV/°C | Typ     |             |

| Biased Output Voltage                                       | Bias = DC + 135mV, Vin = 0V            | 260       | 230 / 290        | 205 / 320      | 190 / 340        | mV    | Min/Max |             |

|                                                             | Bias = AC                              | 1.65      | 1.55 / 1.75      | 1.5 / 1.8      | 1.45 / 1.85      | V     | Min/Max |             |

| Sync Tip Clamp Voltage                                      | Bias = AC STC , Clamp Voltage          | 135       | 120 / 150        | 105 / 165      | 95 / 175         | mV    | Min/Max |             |

| Input Bias Current                                          | Bias = DC, - implies Ib out of the pin | -0.5      | -2               | -3             | -3               | µA    | Max     |             |

| Average Bias Current Drift                                  | Bias = DC                              |           |                  |                | 10               | nA/°C | Typ     |             |

| Sync Tip Clamp Bias Current                                 | Bias = AC STC, Low Bias                | 2.4       | 1.4 / 3.4        | 1.2 / 3.7      | 1.1 / 3.8        | uA    | Min/Max |             |

|                                                             | Bias = AC STC, Mid Bias                | 6.5       | 5.5 / 7.5        | 5.3 / 7.8      | 5.1 / 8          | uA    | Min/Max |             |

|                                                             | Bias = AC STC, High Bias               | 9         | 8 / 10           | 7.7 / 10.4     | 7.5 / 10.6       | uA    | Min/Max |             |

注 A : 上表の最小/最大値は設計保証のみです。

B : 最大帯域幅100MHz, 重みづけ無し、傾斜ゼロ

## 電気的特性 3.3V (続き)

$R_L = 150 \Omega$  to GND, Filter Select = 8.5MHz, Input Bias = DC, SAG pin shorted to Output Pin, unless otherwise noted.

| PARAMETER                         | CONDITIONS                                                                             | TYP     | OVER TEMPERATURE |               |               |       |          |

|-----------------------------------|----------------------------------------------------------------------------------------|---------|------------------|---------------|---------------|-------|----------|

|                                   |                                                                                        | 25 °C   | 25 °C            | 0 °C to 70 °C | -40°C to 85°C | UNITS | MIN/ MAX |

| <b>INPUT CHARACTERISTICS</b>      |                                                                                        |         |                  |               |               |       |          |

| Input Voltage Range               | Bias = DC – limited by output                                                          | 0 / 1.6 | 0 / 1.55         | 0 / 1.55      | 0 / 1.55      | V     | Min      |

| Input Resistance                  | Bias = AC bias mode                                                                    | 19      |                  |               |               | kΩ    | Typ      |

|                                   | Bias = DC, DC+135mV, AC STC                                                            | 3       |                  |               |               | MΩ    | Typ      |

| Input Capacitance                 |                                                                                        | 2       |                  |               |               | pF    | Typ      |

| <b>OUTPUT CHARACTERISTICS</b>     |                                                                                        |         |                  |               |               |       |          |

| High Output Voltage Swing         | $R_L = 150 \Omega$ to Midrail                                                          | 3.15    | 3.05             | 2.95          | 2.95          | V     | Min      |

|                                   | $R_L = 150 \Omega$ to GND                                                              | 3.05    | 2.95             | 2.85          | 2.85          | V     | Min      |

|                                   | $R_L = 75 \Omega$ to Midrail                                                           | 3.05    | 2.95             | 2.8           | 2.8           | V     | Min      |

|                                   | $R_L = 75 \Omega$ to GND                                                               | 2.9     | 2.8              | 2.7           | 2.7           | V     | Min      |

| Low Output Voltage Swing          | $R_L = 150 \Omega$ to Midrail                                                          | 0.15    | 0.25             | 0.3           | 0.3           | V     | Max      |

|                                   | $R_L = 150 \Omega$ to GND                                                              | 0.085   | 0.15             | 0.2           | 0.2           | V     | Max      |

|                                   | $R_L = 75 \Omega$ to Midrail                                                           | 0.24    | 0.33             | 0.4           | 0.4           | V     | Max      |

|                                   | $R_L = 75 \Omega$ to GND                                                               | 0.085   | 0.15             | 0.2           | 0.2           | V     | Max      |

| Output Current (Sourcing)         | $R_L = 10 \Omega$ to Midrail                                                           | 65      | 55               | 50            | 50            | mA    | Min      |

| Output Current (Sinking)          | $R_L = 10 \Omega$ to Midrail                                                           | 70      | 60               | 55            | 55            | mA    | Min      |

| <b>POWER SUPPLY</b>               |                                                                                        |         |                  |               |               |       |          |

| Maximum Operating Voltage         |                                                                                        | 3.3     | 5.5              | 5.5           | 5.5           | V     | Max      |

| Minimum Operating Voltage         |                                                                                        | 3.3     | 2.6              | 2.6           | 2.6           | V     | Min      |

| Maximum Quiescent Current         | Per Channel Vin =100mV                                                                 | 5       | 6                | 6.6           | 6.9           | mA    | Max      |

| Minimum Quiescent Current         | Per Channel Vin =100mV                                                                 | 5       | 4.2              | 4             | 3.9           | mA    | Min      |

| Power Supply Rejection (+PSRR)    | $V_{S+} = 3.5V$ to 3.1V                                                                | 48      | 42               | 40            | 40            | dB    | Min      |

| <b>DISABLE CHARACTERISTICS</b>    |                                                                                        |         |                  |               |               |       |          |

| Quiescent Current                 | All 3 Channels Disabled – Note 3                                                       | 0.1     | 0.2              | 0.3           | 0.3           | uA    | Max      |

| Turn-on time delay( $t_{ON}$ )    | Time for $I_S$ to reach 50% of final value after I <sup>2</sup> C control is initiated | 1       |                  |               |               | μs    | Typ      |

| Turn-off time delay ( $t_{off}$ ) |                                                                                        | 1       |                  |               |               | μs    | Typ      |

注 A: I<sup>2</sup>C回路はディスエーブルモードでもアクティブであることに注意。ここに示す電流は、THS7303のI<sup>2</sup>C回路がアクティブでないときの値です。

## 電気的特性 5V

$R_L = 150 \Omega$  to GND, Filter Select = 8.5MHz, Input Bias = DC, SAG pin shorted to Output Pin, unless otherwise noted.

| PARAMETER                                                   | CONDITIONS                             | OVER TEMPERATURE |             |             |               |       |         |

|-------------------------------------------------------------|----------------------------------------|------------------|-------------|-------------|---------------|-------|---------|

|                                                             |                                        | 25°C             | 25°C        | 0°C to 70°C | -40°C to 85°C | UNITS | MIN/MAX |

| <b>AC PERFORMANCE</b>                                       |                                        |                  |             |             |               |       |         |

| Small-Signal Bandwidth (-3dB)<br>Vo - 0.1Vpp                | Filter Select = 8.5-MHz (Note 1)       | 8.5              | 7.7 / 9.3   | 7.3 / 9.8   | 7.1 / 10      | MHz   | Typ     |

|                                                             | Filter Select = 16-MHz (Note 1)        | 16               | 14.5 / 17.6 | 13.5 / 19   | 13.3 / 20     | MHz   | Typ     |

|                                                             | Filter Select = 34-MHz (Note 1)        | 34               | 30.6 / 37.4 | 29.2 / 38.8 | 28.6 / 39.4   | MHz   | Typ     |

|                                                             | Filter Select = Bypass                 | 200              |             |             |               | MHz   | Typ     |

| Large-Signal Bandwidth (-3dB)<br>Vo - 2Vpp                  | Filter Select = 8.5-MHz                | 8.5              |             |             |               | MHz   | Typ     |

|                                                             | Filter Select = 16-MHz                 | 16               |             |             |               | MHz   | Typ     |

|                                                             | Filter Select = 34-MHz                 | 34               |             |             |               | MHz   | Typ     |

|                                                             | Filter Select = Bypass                 | 65               |             |             |               | MHz   | Typ     |

| Slew Rate                                                   | Filter Select = Bypass                 | 300              |             |             |               | V/us  | Typ     |

| Group Delay at 100kHz                                       | Filter Select = 8.5-MHz                | 56               |             |             |               | ns    | Typ     |

|                                                             | Filter Select = 16-MHz                 | 32.5             |             |             |               | ns    | Typ     |

|                                                             | Filter Select = 34-MHz                 | 17               |             |             |               | ns    | Typ     |

|                                                             | Filter Select = Bypass                 | 2.8              |             |             |               | ns    | Typ     |

| Group Delay Variance<br>With Respect to 100kHz              | Filter Select = 8.5-MHz: @ 5.1-MHz     | 10.5             |             |             |               | ns    | Typ     |

|                                                             | Filter Select = 16-MHz: @ 11-MHz       | 8                |             |             |               | ns    | Typ     |

|                                                             | Filter Select = 34-MHz: @ 27-MHz       | 5                |             |             |               | ns    | Typ     |

| Attenuation<br>With Respect to 100kHz                       | Filter Select = 8.5-MHz: @ 5.75-MHz    | 0.4              | 0.2 / 0.7   | 0.1 / 1.2   | 0.1 / 1.4     | dB    | Min/Max |

|                                                             | Filter Select = 8.5-MHz: @ 27-MHz      | 42.5             | 38          | 36          | 35            | dB    | Min     |

|                                                             | Filter Select = 16-MHz: @ 11-MHz       | 0.5              | 0.2 / 0.8   | 0.1 / 1.2   | 0.1 / 1.4     | dB    | Min/Max |

|                                                             | Filter Select = 16-MHz: @ 54-MHz       | 44.5             | 39          | 37          | 36            | dB    | Min     |

|                                                             | Filter Select = 34-MHz: @ 27-MHz       | 0.7              | 0.3 / 1.1   | 0.2 / 1.5   | 0.2 / 1.7     | dB    | Min/Max |

|                                                             | Filter Select = 34-MHz: @ 74-MHz       | 28.5             | 24          | 22          | 20            | dB    | Min     |

| Mute Attenuation                                            | f = 1-MHz                              | 75               |             |             |               | dB    | Typ     |

| Differential Gain (NTSC / PAL)                              | Filter Select = 8.5-MHz: NTSC/PAL      | 0.3/0.5          |             |             |               | %     | Typ     |

| Differential Phase (NTSC / PAL)                             | Filter Select = 8.5-MHz: NTSC/PAL      | 0.7/0.85         |             |             |               | °     | Typ     |

| Total Harmonic Distortion<br>f = 1MHz, 2Vpp                 | Filter Select = 8.5-MHz                | -60              |             |             |               | dB    | Typ     |

|                                                             | Filter Select = 16-MHz                 | -60              |             |             |               | dB    | Typ     |

|                                                             | Filter Select = 34-MHz                 | -60              |             |             |               | dB    | Typ     |

|                                                             | Filter Select = Bypass                 | -70              |             |             |               | dB    | Typ     |

| Signal to Noise Ratio<br>(Unified Weighting per CCIR 576-2) | Filter Select = 8.5-MHz                | 81               |             |             |               | dB    | Typ     |

|                                                             | Filter Select = 16-MHz                 | 78               |             |             |               | dB    | Typ     |

|                                                             | Filter Select = 34-MHz                 | 76               |             |             |               | dB    | Typ     |

|                                                             | Filter Select = Bypass – Note 2        | 66               |             |             |               | dB    | Typ     |

| Channel-to-Channel Crosstalk                                | Filter Select = 8.5-MHz: @ 1-MHz       | -63              |             |             |               | dB    | Typ     |

|                                                             | Filter Select = 16-MHz: @ 2-MHz        | -62              |             |             |               | dB    | Typ     |

|                                                             | Filter Select = 34-MHz: @ 5-MHz        | -60              |             |             |               | dB    | Typ     |

|                                                             | Filter Select = Bypass: @ 10-MHz       | -60              |             |             |               | dB    | Typ     |

| MUX Isolation                                               | Filter Select = 8.5-MHz: @ 5.5-MHz     | 94               |             |             |               | dB    | Typ     |

|                                                             | Filter Select = 16-MHz: @ 11-MHz       | 90               |             |             |               | dB    | Typ     |

|                                                             | Filter Select = 34-MHz: @ 27-MHz       | 83               |             |             |               | dB    | Typ     |

|                                                             | Filter Select = Bypass: @ 60-MHz       | 76               |             |             |               | dB    | Typ     |

| AC Gain – All Channels                                      | f = 100kHz                             | 6.0              | 5.7 / 6.3   | 5.6 / 6.4   | 5.6 / 6.4     | dB    | Min/Max |

| Output Impedance                                            | f = 5-MHz                              | 0.2              |             |             |               | Ω     | Typ     |

| <b>DC PERFORMANCE</b>                                       |                                        |                  |             |             |               |       |         |

| Output Offset Voltage                                       | Bias = DC                              | 15               | 25          | 35          | 40            | mV    | Max     |

| Average Offset Voltage Drift                                | Bias = DC                              |                  |             |             | 20            | µV/°C | Typ     |

| Biased Output Voltage                                       | Bias = DC + 135mV, Vin = 0V            | 270              | 240 / 300   | 215 / 325   | 200 / 340     | mV    | Min/Max |

|                                                             | Bias = AC                              | 2.5              | 2.35 / 2.65 | 2.3 / 2.7   | 2.25/2.75     | V     | Min/Max |

| Sync Tip Clamp Voltage                                      | Bias = AC STC , Clamp Voltage          | 135              | 120 / 150   | 105 / 165   | 95 / 175      | mV    | Min/Max |

| Input Bias Current                                          | Bias = DC, - implies Ib out of the pin | -0.5             | -2          | -3          | -3            | µA    | Max     |

| Average Bias Current Drift                                  | Bias = DC                              |                  |             |             | 10            | nA/°C | Typ     |

| Sync Tip Clamp Bias Current                                 | Bias = AC STC, Low Bias                | 2.4              | 1.4 / 3.4   | 1.2 / 3.7   | 1.1 / 3.8     | uA    | Min/Max |

|                                                             | Bias = AC STC, Mid Bias                | 6.5              | 5.5 / 7.5   | 5.3 / 7.8   | 5.1 / 8       | uA    | Min/Max |

|                                                             | Bias = AC STC, High Bias               | 9                | 8 / 10      | 7.7 / 10.4  | 7.5 / 10.6    | uA    | Min/Max |

注 A : 上表の最小/最大値は設計保証のみです。

B : 最大帯域幅100MHz, 重みづけ無し、傾斜ゼロ

## 電気的特性 5V (続き)

$R_L = 150 \Omega$  to GND, Filter Select = 8.5MHz, Input Bias = DC, SAG pin shorted to Output Pin, unless otherwise noted.

| PARAMETER                           | CONDITIONS                                                                             | TYP      | OVER TEMPERATURE |               |                 |       |     |

|-------------------------------------|----------------------------------------------------------------------------------------|----------|------------------|---------------|-----------------|-------|-----|

|                                     |                                                                                        | 25 °C    | 25 °C            | 0 °C to 70 °C | -40 °C to 85 °C | UNITS |     |

| <b>INPUT CHARACTERISTICS</b>        |                                                                                        |          |                  |               |                 |       |     |

| Input Voltage Range                 | Bias = DC – limited by output                                                          | 0 / 2.45 | 0 / 2.4          | 0 / 2.35      | 0 / 2.35        | V     | Min |

|                                     | Bias = AC bias mode                                                                    | 19       |                  |               |                 | kΩ    | Typ |

| Input Resistance                    | Bias = DC, DC+135mV, AC STC                                                            | 3        |                  |               |                 | MΩ    | Typ |

| Input Capacitance                   |                                                                                        | 2        |                  |               |                 | pF    | Typ |

| <b>OUTPUT CHARACTERISTICS</b>       |                                                                                        |          |                  |               |                 |       |     |

| High Output Voltage Swing           | $R_L = 150 \Omega$ to Midrail                                                          | 4.8      | 4.7              | 4.6           | 4.6             | V     | Min |

|                                     | $R_L = 150 \Omega$ to GND                                                              | 4.65     | 4.5              | 4.4           | 4.4             | V     | Min |

|                                     | $R_L = 75 \Omega$ to Midrail                                                           | 4.7      | 4.6              | 4.5           | 4.5             | V     | Min |

|                                     | $R_L = 75 \Omega$ to GND                                                               | 4.4      | 4.2              | 4.1           | 4.1             | V     | Min |

| Low Output Voltage Swing            | $R_L = 150 \Omega$ to Midrail                                                          | 0.2      | 0.25             | 0.3           | 0.3             | V     | Max |

|                                     | $R_L = 150 \Omega$ to GND                                                              | 0.1      | 0.15             | 0.2           | 0.2             | V     | Max |

|                                     | $R_L = 75 \Omega$ to Midrail                                                           | 0.3      | 0.4              | 0.5           | 0.5             | V     | Max |

|                                     | $R_L = 75 \Omega$ to GND                                                               | 0.1      | 0.15             | 0.2           | 0.2             | V     | Max |

| Output Current (Sourcing)           | $R_L = 10 \Omega$ to Midrail                                                           | 80       | 70               | 65            | 60              | mA    | Min |

| Output Current (Sinking)            | $R_L = 10 \Omega$ to Midrail                                                           | 85       | 75               | 70            | 65              | mA    | Min |

| <b>POWER SUPPLY</b>                 |                                                                                        |          |                  |               |                 |       |     |

| Maximum Operating Voltage           |                                                                                        | 5        | 5.5              | 5.5           | 5.5             | V     | Max |

| Minimum Operating Voltage           |                                                                                        | 5        | 2.6              | 2.6           | 2.6             | V     | Min |

| Maximum Quiescent Current           | Per Channel Vin=100mV                                                                  | 6        | 7.2              | 7.8           | 8.1             | mA    | Max |

| Minimum Quiescent Current           | Per Channel Vin=100mV                                                                  | 6        | 5.1              | 4.9           | 4.7             | mA    | Min |

| Power Supply Rejection (+PSRR)      | $V_{S+} = 5.2V$ to 4.8V                                                                | 48       | 42               | 40            | 40              | dB    | Min |

| <b>DISABLE CHARACTERISTICS</b>      |                                                                                        |          |                  |               |                 |       |     |

| Quiescent Current                   | All 3 Channels Disabled – Note 3                                                       | 0.1      | 0.2              | 0.3           | 0.3             | uA    | Max |

| Turn-on time delay( $t_{(ON)}$ )    | Time for $I_S$ to reach 50% of final value after I <sup>2</sup> C control is initiated | 1        |                  |               |                 | μs    | Typ |

| Turn-off time delay ( $t_{(off)}$ ) |                                                                                        | 1        |                  |               |                 | μs    | Typ |

注 A: I<sup>2</sup>C回路はディスエーブルモードでもアクティブであることに注意。ここに示す電流は、THS7303のI<sup>2</sup>C回路がアクティブでないときの値です。

## I<sup>2</sup>Cインターフェイスのタイミング特性

V<sub>S+</sub> = 3V to 5V

| PARAMETER                                                         | STANDARD MODE |      | FAST MODE |     | UNITS |

|-------------------------------------------------------------------|---------------|------|-----------|-----|-------|

|                                                                   | MIN           | MAX  | MIN       | MAX |       |

| f <sub>SCL</sub> Clock frequency, SCL                             | 0             | 100  | 0         | 400 | kHz   |

| t <sub>w(H)</sub> Pulse duration, SCL high                        | 4             |      | 0.6       |     | μs    |

| t <sub>w(L)</sub> Pulse duration, SCL low                         | 4.7           |      | 1.3       |     | μs    |

| t <sub>r</sub> Rise time, SCL and SDA                             |               | 1000 |           | 300 | ns    |

| t <sub>f</sub> Fall time, SCL and SDA                             |               | 300  |           | 300 | ns    |

| t <sub>su(1)</sub> Setup time, SDA to SCL                         | 250           |      | 100       |     | ns    |

| t <sub>h(1)</sub> Hold time, SCL to SDA                           | 0             |      | 0         |     | ns    |

| t <sub>(buf)</sub> Bus free time between stop and start condition | 4.7           |      | 1.3       |     | μs    |

| t <sub>su(2)</sub> Setup time, SCL to start condition             | 4.7           |      | 0.6       |     | μs    |

| t <sub>h(2)</sub> Hold time, start condition to SCL               | 4             |      | 0.6       |     | μs    |

| t <sub>su(3)</sub> Setup time, SCL to stop condition              | 4             |      | 0.6       |     | μs    |

| C <sub>b</sub> Capacitive load for each bus line                  |               | 400  |           | 400 | pF    |

## アプリケーション資料

THS7303はビデオ出力バッファのアプリケーションを目標にしています。他の多くのアプリケーションにも使用できますが、ビデオ信号のニーズと要求事項がTHS7303の最も重要な設計パラメータでした。革新的なシリコン・ゲルマニウム(SiGe)相補型のBiCom-3プロセスで製造されるTHS7303は、非常に低消費電力にもかかわらず、ビデオ用集積回路に一般的に見られない多くの特長を備えています。各チャネル構成は、他のチャネルに対して完全に独立しています。これにより、構成がどうあるべきか指定するデバイスよりも、THS7303はエンドユーザにより指定されるあらゆる構成が各チャネルについて可能です。その結果、高度に柔軟なシステムが得られます。THS7303には以下の特長があります。

- システムへのインターフェイスが容易なI<sup>2</sup>Cインターフェイス。

- 単電源による2.7Vから5V動作。それぞれ15mAおよび18mAという低静的消費電流。

- 2:1入力MUX(マルチプレクサ)

- DC, DC+135mVシフト、ACバイアス、あるいはACシンクチップクランプを選択可能な入力構成。

- DACリコンストラクションあるいはADCイメージノイズ除去のための、選択可能な5次のローパスフィルタ。

- SDTV NTSCと480i, PAL/SECAMと576i, およびSビデオ信号用の8.5MHz

- EDTV 480pと576p YP<sub>B</sub>P<sub>R</sub>信号、およびG'B'R'(R'G'B') VGA信号用の16MHz

- HDTV 720pと1080i YP<sub>B</sub>P<sub>R</sub>信号、およびG'B'R'SVGAとXGA信号用の34MHz

- G'B'R' SXGAとUXGA信号とともにHDTV 1080p YP<sub>B</sub>P<sub>R</sub>信号を通過するバイパスモード

- 2V/V(+6dB)の内部固定ゲインのバッファが、DC結合、従来のAC結合、あるいはSAG補正のAC結合で2ビデオラインをドライブ可能。

- 消費電流を0.1uAまで低減するディスエーブルモード。あるいはTHS7303に電源を印加したまま信号を通過させないミュート機能。

### 動作電圧

THS7303は、-40°Cから+85°Cの温度範囲において2.7Vから5Vの電源電圧で動作するように設計されています。全温度範囲における特性へ及ぼす影響は、薄膜抵抗および高品質の低温度係数コンデンサの組込みにより小さくできます。

電源ピンには、0.1uFから0.01uFのコンデンサをできるだけ近く配置します。さらに、100uFのような大容量コンデンサを電源ラインに配置し、50/60Hzのライン周波数に関わる問題を最小にします。

### 入力電圧

THS7303の入力範囲は、グランドから(V<sub>S+</sub> - 1.4V)までの入力信号が可能です。しかし、2V/V(+6dB)の内部固定ゲインのため、一般に出力が許容リニア入力範囲の制約要素になります。例えば5V電源の場合、リニア入力範囲はグランドから3.6Vまでです。しかしこの+6dBゲインにより、リニア出力範囲が許容リニア入力範囲をGND(後に説明するように、実際は約50mV)から2.5Vまでに制限します。

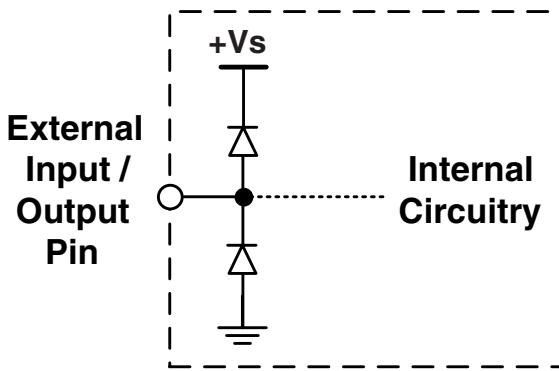

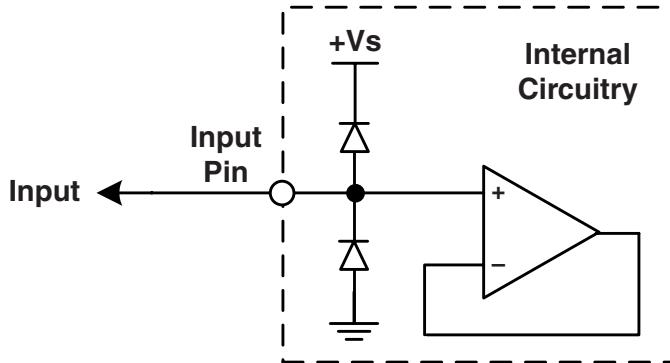

図4. 内部ESD保護

## 入力過電圧保護

THS7303は、非常に高速な相補型バイポーラCMOSプロセスで製造されています。これらは非常に微細なデバイスのため、その内部接合ブレークダウン電圧が比較的低いです。この低ブレークダウン電圧は絶対最大定格表に反映されています。また、デバイスのすべての入出力ピンは、図4に示すように、電源とグランドに接続した内部ESD保護ダイオードで保護されています。

これらのダイオードは、電源電圧以上およびグランドレベル以下の入力過電圧に対して同様に適度に保護しています。また保護ダイオードは、一般に30mAの連続電流をオーバードライブ時に流せます。

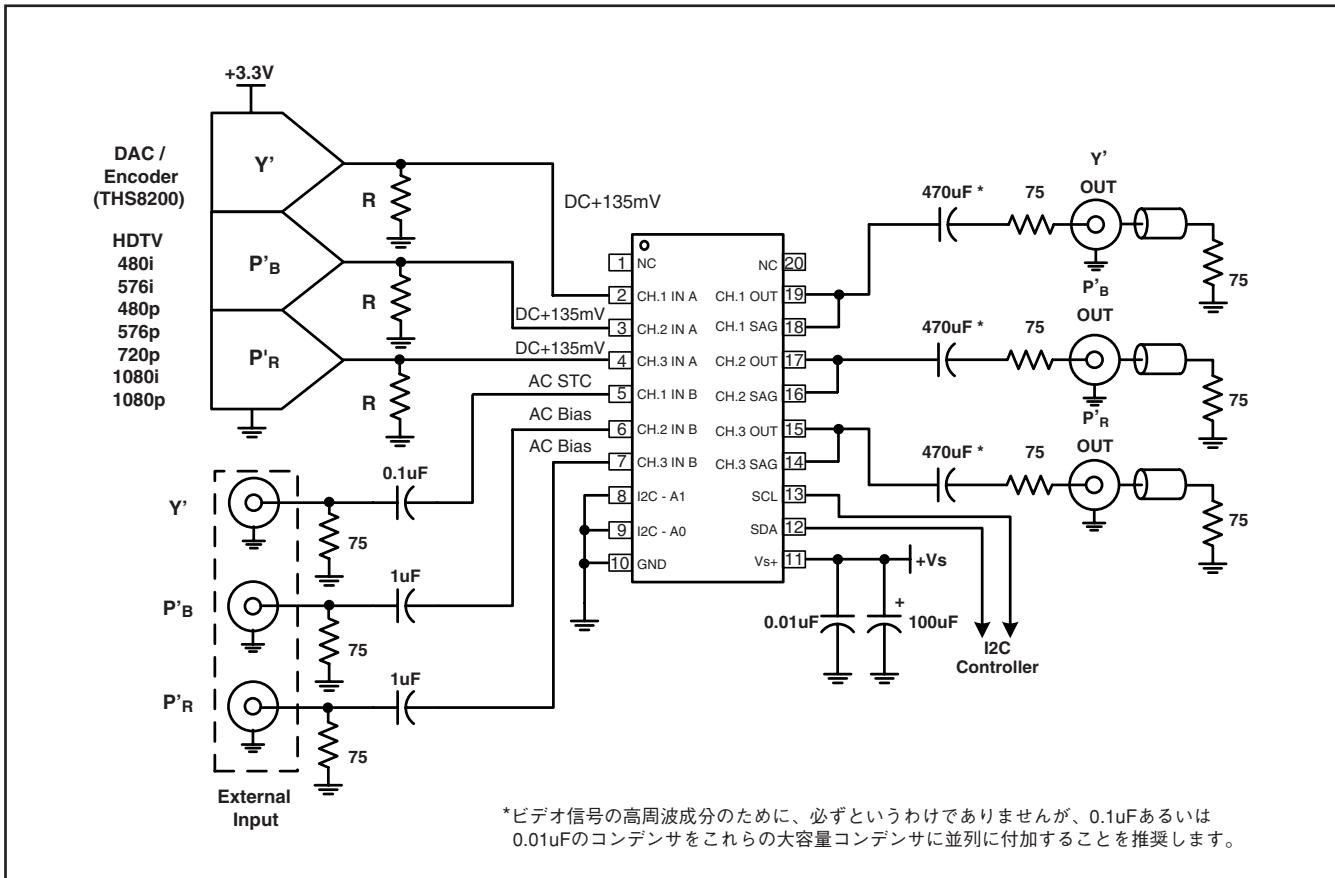

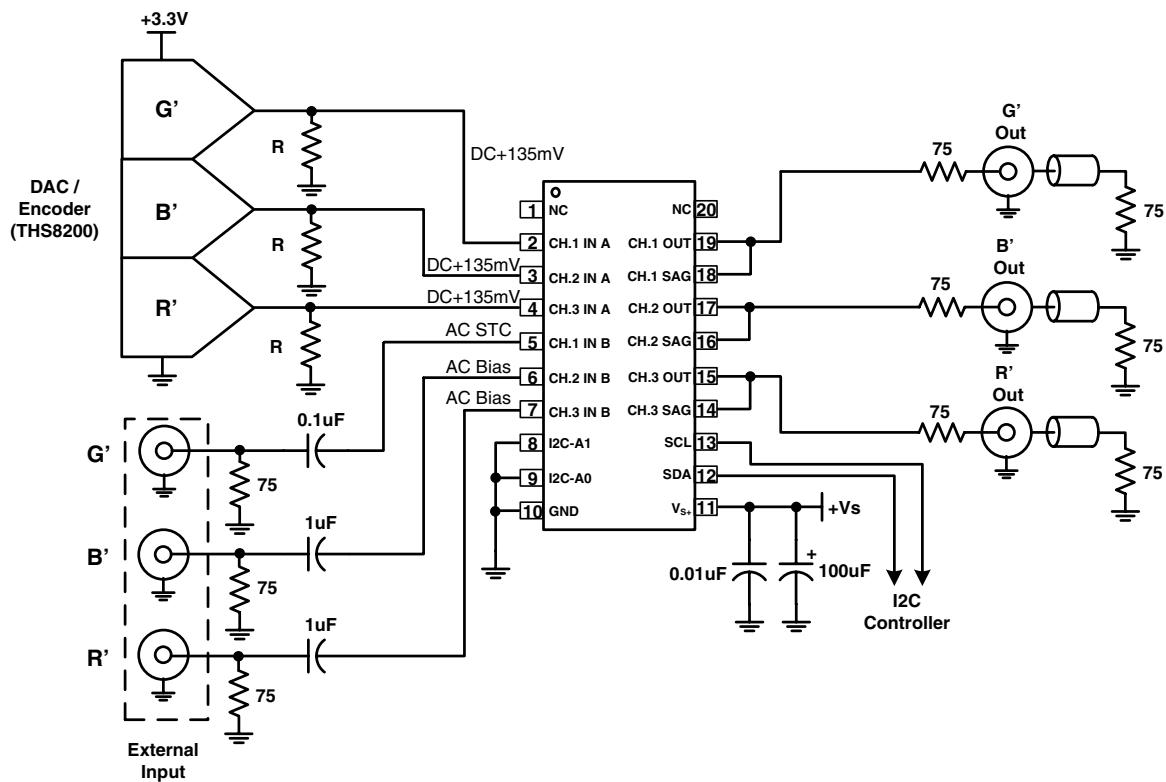

## 代表的な構成

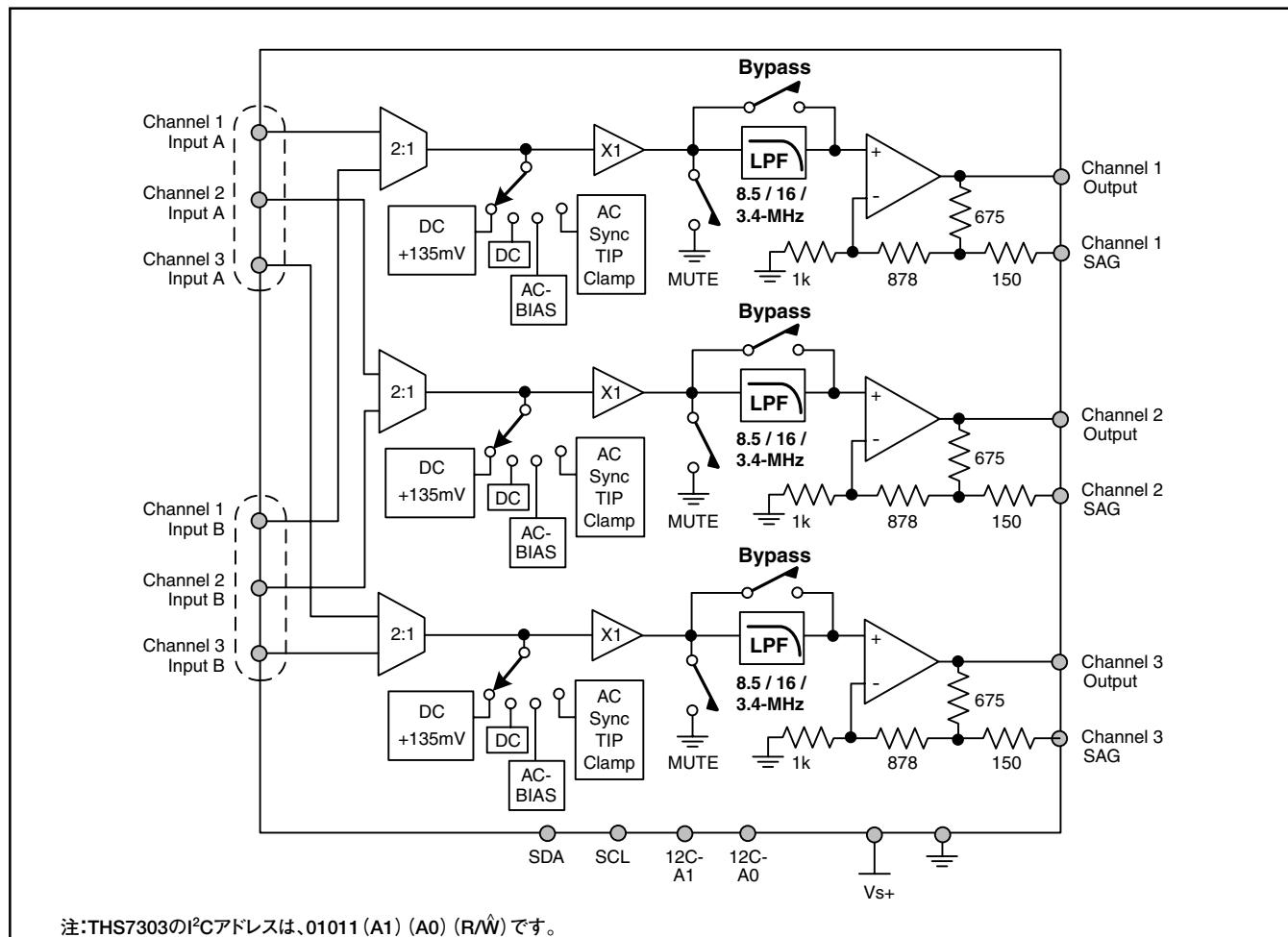

THS7303をビデオバッファとして使用する代表的なアプリケーション回路を図5に示します。この図は、THS7303の3入力チャネルをドライブするDAC（あるいはTHS8200のようなエンコーダ）を示します。高品位ビデオ（HD）あるいはエンハンスト・デフィニション（ED） $YP'_B P'_R$ （ときには $Y'UV'$ 、あるいは誤って $YC'_B C'_R$ と記される）チャネルが図示されていますが、これらはSビデオ $Y/C'$ チャネル、および標準品位ビデオ（SD）システムのコンポジット・ビデオ・ベースバンド信号（CVBS）にも容易に置き換えられます。またこれらの信号は、 $G'B'R'$ （aka  $R'G'B'$ ）あるいは、シンク信号の配置によって一般に $R'G'sB'$ （シンク・オン・グリーン）や $R'SG'sB's$ （シンク・オン・オール・シグナル）と呼ばれる他の種類にも置き換えられます。

図中の2番目の入力セット（Bチャネル）は、一般にバス・スルー機能として使用される外部入力でドライブされています。これらのチャネルもまた、HD、ED、SD、あるいは $G'B'R'$ ビデ

オ信号に置き換えることができます。このようにTHS7303の柔軟性により、他の入力セットに関係なく、実際のあらゆる入力信号をTHS7303にドライブすることができます。例えば、THS7303はチャネル1を入力Aに接続し、その一方でチャネル2、3を入力Bに接続するように構成できます。これらのオプションの構成方法については、本文献の後半でI<sup>2</sup>Cインターフェイスについて述べている複数のアプリケーション・ノート節をご覧ください。

本文献中では $Y'$ をより一般的な輝度（Y）ではなく、ルーマ・チャネルとして使用していることに注意願います。その理由は、輝度の本来の定義をCIE（国際照明委員会）により規定されたように説明するためです。ビデオは、非線形項のガンマがGBR信号に加えられて $G'B'R'$ 信号を形成するので、本来の輝度の意味合いから外れています。これらの $G'B'R'$ 信号は、数学的にルーマ（Y')を生成するのに使用されます。このように本来の輝度（Y）は取り扱われず、したがって専門用語に違いがあります。

この基本的な論拠はクロマ（C'）項（彩度項）にも適用されます。クロマは非線形の $G'B'R'$ 項から派生するので非線形です。本来のクロミナンス（C）（色信号）は線形のGBRから派生し、したがってクロマ（C'）とクロミナンス（C）には違いがあります。色差信号（ $P'_B/P'_R/U'/V'$ ）もまたこのように記述され、非線形（ガンマ補正）信号であることを示します。

最後に、 $R'G'B'$ （一般に誤ってRGBとされる）は、グリーン信号が緑の色情報とともに一般にシンク信号を含むことを考慮して、ときに $G'B'R'$ （ここでも一般に誤ってGBRとされる）と呼ばれます。これは、ルーマ信号もシンク情報を載せていることに似ています。したがって、R'よりもG'を最初に配置する順番になります。さらに、 $YP'_B P'_R$ において $P'_B$ が2番目に呼ばれるのも同様で、B'が2番目で次にR'になります。

図5. エンコーダ/DACおよびAC結合ラインドライブの外部入力からの、代表的な $Y'P'B P'_R$ 入力

## 入力モード動作 - DC

THS7303への入力はAC結合とDC結合の両方が可能です。多くのDACやビデオ・エンコーダがTHS7303にDC接続できます。しかし、DC結合のひとつのがたは、THS7303の入力に0Vを印加した場合です。THS7303の入力には0V信号を問題なく印加できますが、そのTHS7303の出力レベルが0V信号になりません。これは出力トランジスタの制限によるため、あらゆる单電源アンプにあてはまることです。CMOSおよびバイポーラのトランジスタは、かなりの量の電流をシンク(sink 吸い込み)する場合、両方とも0Vにななりません。このトランジスタの特質は、かなりの量の電流をソースする場合に最大出力電圧が常に電源電圧より低い理由と同じです。

THS7303の構成にかかわらず内部ゲインは+6dB (2V/V) に固定であり、このゲインがクリッピング問題を生じない線形な入力電圧の許容範囲を指定します。例えば、電源電圧を3Vに設定すると、かなりの電流をドライブする場合の最大出力は約2.9Vになります。したがって、クリッピングを防止するには、許容入力は $2.9V/2 = 1.45V$ になります。このことは推奨最大電源電圧の5Vまであてはまり、その場合に出力のクリッピングを防止すると、約 $4.9V/2 = 2.45V$ の入力範囲が可能になります。

この動作モードにおけるTHS7303の入力インピーダンスは $> 1M\Omega$ です。これは図6に示すように、単一利得アンプとして構成される入力バッファによるものです。

THS7303の入力段はPNPバイポーラトランジスタで設計されています。したがって、有限量のバイアス電流がTHS7303の入力ピンから流れ出しています。このバイアス電流は代表値で約 $1.5\mu A$ であり、その流路を必要とし、それがないと、入力段の電圧が上昇します。例えば、入力ノードでグランドに対して $1M\Omega$ の抵抗があれば、その結果入力ノードに表れる電圧は $1.5\mu A \times 1M\Omega = 1.5V$ になります。しかし、ほとんどの現行のDACは信号源電圧を生成するための抵抗をグランド間に要するので、一般にこのバイアス電流は問題になりません。この信号生成用の抵抗は一般に $300\Omega$ 以下であり、DACに出力がないときの電圧はおよそ $1.5\mu A \times 300\Omega = 0.45mV$ となり、たいした問題になりません。

図 6. 等価DC入力モード回路

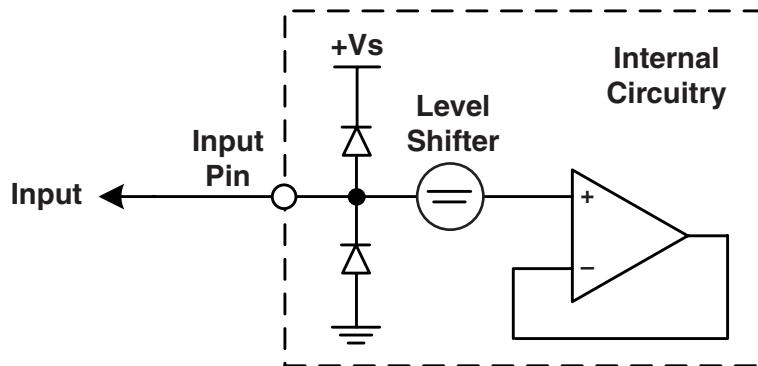

### 入力モード動作 - DC + 135mVシフト

入力モードをDCに設定した場合、0Vの入力信号を印加するとクリッピングが発生します。このクリッピングは、ビデオ信号上のシンクの振幅(水平と垂直の両方のシンク振幅)を減衰します。この減衰は、このビデオ信号のレシーバが伝送ラインにおける損失を補償するAGCループを使用している場合に問題となります。ビデオAGC回路の中には、水平シンクの振幅でゲインを設定するものもあります。したがって、シンクの振幅でクリッピングが発生すると、AGC回路はゲインを過大に設定し、そのためルーマやクロマのゲイン補正が過大になることがあります。この過大な設定の結果、過剰な輝度の表示と過剰な色の飽和の画像になります。

他のAGC回路はクロマ・バーストの振幅をレベル制御に使用しており、シンク信号の減衰は適正なゲイン設定に影響しません。しかし、飽和やクリッピングが発生しないようにするのが、一般的に優れた設計技術となります。トランジスタは飽和から回復するのに有限の時間を必ず要します。したがって、この飽和は信号のタイミング遅れやその他の原因になります。

飽和やクリッピング問題を防止するために、THS7303にはDC+135mVシフトの入力モードがあります。このモードは入力電圧を取り入れて、内部で+135mVを加算して信号をシフトします。また、THS7303には+6dB (2V/V) のゲインがあるため、0Vの入力信号を印加したときの出力信号は270mVになります。THS7303のレール・ツー・レール出力段は、一般的なビデオ負荷の接続時にこのレベルを生成できます。このようにして、シンク信号の飽和やクリッピングが発生しないように保証しています。このシフト量は入力信号に関係なく一定です。例えば1V入力が印加されると、出力は2.27Vになります。

DC入力モードとまったく同様に、このモードでのTHS4509の入力インピーダンスは $>1M\Omega$ です。さらに、DC入力モードと同じ約1.5uAの入力バイアス電流が入力に流れ出します。しかし、先にDC入力モードで述べたものと同じ予防策に従えば、あらゆる入力バイアス電流による潜在的な問題を最小限にします。図7にDC+135mVシフトモード動作時の等価入力回路を示します。

図 7. DC+135mV入力モードの等価回路

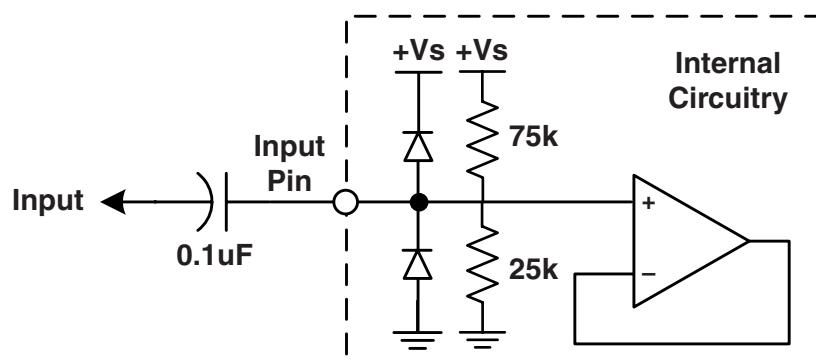

### 入力モード動作 - ACバイアス

他の多くのアプリケーションはAC結合入力を必要とします。AC結合は、DC入力レベルがその対応する出力ビデオ信号を、変化あるいはクリッピングさせないことを保証します。最初に説明するAC結合モードはACバイアスモードです。これは、外付けの1uF結合コンデンサのTHS7303側で、単純に内部DCバイアス電圧を入力信号に印加するものです。

印加されるDCバイアス電圧は、図8に示すように単純な抵抗分圧回路で内部的に設定されます。このDCバイアス電圧は  $V_{s+}/4$  に設定しています。3.3V電源では入力バイアス電圧は名目値で0.825Vになり、5V電源では名目値で1.25Vになります。

このモードにおける入力インピーダンスはおよそ  $19k\Omega$  です。このインピーダンスは1uFの入力コンデンサとともに、ハイパスフィルタのコーナー周波数を8.5Hzに設定します。これより低い周波数が必要な場合は、単純にコンデンサの容量を増加すると、コーナー周波数は反比例して低下します。例えば、4.7uFのコンデンサを使用すると1.8Hzのハイパスのコーナー周波数になります。ドループ(傾斜)が小さくなります。この動作モードでは、あらゆる容量値が使用できます。

この動作モードには、クロマ( $C'$ )、 $P'_B$ 、 $P'_R$ 、 $U'$ 、 $V'$ 、およびシンクのない $B'$ と $R'$ 信号の使用を推奨します。

図 8. ACバイアス入力モードの等価回路

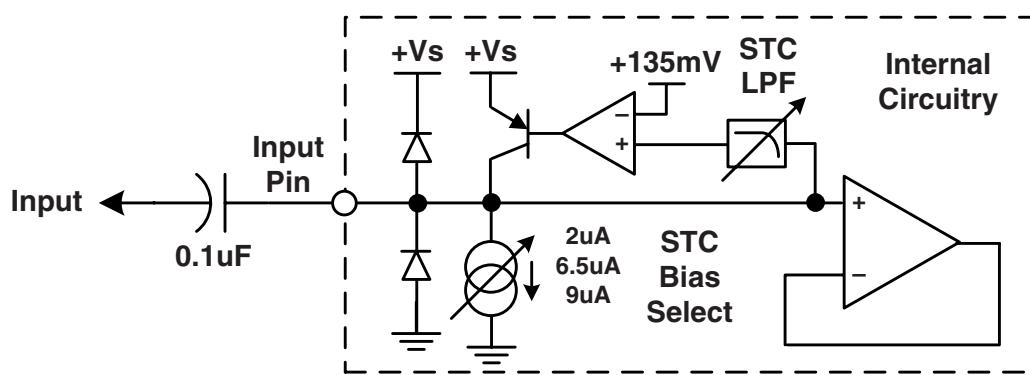

## 入力モード動作 - ACシンクチップ・クランプ

最後に説明する入力モード動作は、シンクチップ・クランプ(STC)を用いたAC結合です。これも入力に直列に結合コンデンサを必要とします。本文献ではシンクチップ・クランプという用語を使用することに注意願います。その一方で、THS7303はこのモード機能の実行に基づいたDC復元回路であると称する方が、よりふさわしいことにも注意願います。この回路は能動クランプ回路であり、受動的なダイオードクランプ機能ではありません。また、CVBS, Y, およびG'信号のようにシンクがある信号に必要なAC結合の場合に、この機能を使用します。

THS7303の入力には内部制御ループがあり、印加される入力電圧の最小値を約135mVにクランプします。このとき、DC+135mV入力シフトの場合とまったく同様に、出力電圧の最小値は270mVになります。入力信号が135mVを下回ろうとすると、THS7303の内部制御ループが最大10mAまでの電流を供給して、結合コンデンサのTHS7303の入力側における電位を高めます。その電位が135mVを超えると同時に、制御ループは電流の供給を停止します。

シンクチップ・クランプのレベルに関する問題のひとつは、VCR信号や貧弱なPCBレイアウトに見られる反射にありがちな、オーバーシュートのあるシンクエッジに対してどのように反応するかということです。理想的には、STCは入力信号のオーバーシュート電圧に対して反応すべきでありません。さもなくとも、この反応がバイアス電圧を過大に引き上げ、ビデオ信号の他の部分でクリッピングを生じることになります。

この入力信号のオーバーシュート問題を最小にするため、THS7303の特許申請中の内部STC制御ループには、図9に示すI<sup>2</sup>Cで選択可能なローパスフィルタがあります。このフィルタは、

約500kHz, 2.5MHz, あるいは5MHzが選択できます。500kHzフィルタは、THS7303の5次のローパスフィルタが8.5MHz動作に選定されたときに有効です。このフィルタの効果は、制御ループの反応を遅くして、入力のオーバーシュート電圧でクランプせず、シンク信号の平坦な部分でクランプするようにします。2.5MHzフィルタは、より高レートのビデオ信号に関連するより短いシンク時間に対応するため、16MHzの信号LPFとともに使用するのが最適です。HDTVおよびG'B'R'信号については、5MHzのSTCフィルタを選択して、高速なシンクレートで適切なクランプができるようにします。この遅延の結果、シンクにはSTCのLPFに依存して150nsから2usの間に発生する電圧シフトが明らかにあります。このシフト量は、入力コンデンサと選択したSTC入力バイアス電流で定まる信号のドリップ量に依存します。しかし、シンクの主たる目的はシンク信号のエッジで生じる同期をとるタイミングなので、このシフトはほとんどのシステムにおいて意識する必要がありません。

本当にひどいオーバーシュートやリンギングの場合、この機能は入力信号のオーバーシュート問題を十分に排除できませんが、STCシステムは不適切なクランプレベルを最小限度にするのにかなり役立ちます。また、この問題を小さくするのに役立つ別の方法として、外付けコンデンサ(例えば、10pFから47pF)を終端抵抗に並列にグランドに接続すると、オーバーシュート問題を排除するのに役立ちます。

図 9. ACシンクチップ・クランプ入力モードの等価回路

ACシンクチップ・クランプ(STC)動作を使用する場合、ある有限量の放電バイアス電流も必ず発生します。先に述べたように、入力信号が135mVのクランプレベルを下回ると、THS7303の内部ループが最大10mAまでの電流を供給してバイアス電圧を高めます。しかし、入力信号が135mVの入力レベルを上回ると何が起こるでしょうか？問題は、ビデオ信号が常にこのレベルを上回り、どうしてもそれを変えられないことです。しかし、入力信号のシンクのレベルがこの135mVを超える場合、内部の放電電流がAC結合のバイアス信号を適正な135mVまで低下させます。

この放電電流はビデオ信号を大幅に変えるほど大きいものであってはならず、さもないと画像品質問題が発生します。この変化は、印加される一定のルーマ信号の傾斜(akaドループ)を見るか、またその結果である出力信号を見ると分かることがよくあります。ビデオラインの最初から最後におけるルーマレベルの変化が、ライン傾斜(ドループ)の量になります。この傾斜量は、一般的な公式であるにより容易に分かります。ここで、 $i$ は放電電流であり、 $C$ は一般に0.1uFの外付けの結合コンデンサです。電流( $i$ )とコンデンサ( $C$ )が一定であれば、傾斜は  $i/C = dV/dt$ で定まります。

放電電流が非常に微小の場合、傾斜の量は非常に小さく、これは一般的に好ましいことです。しかし、システムがシンク信号をとらえる時間は非常に長くなります。このシンク信号をとらえることをハム・リジェクション(ハム除去)とも呼びます。ハムはAC電圧周波数の50Hzあるいは60Hzにより発生します。放電電流とAC結合コンデンサの値は、ハム・リジェクションおよびライン傾斜の量を定めます。

ハム・リジェクションとライン傾斜の適切な量については、多くの人々が異なる考えを持っているため、THS7303はI2Cインターフェイスで選択可能な可変シンク(sink, 吸い込み)バイアス電流を組み込んでいます。その中の低バイアスモードは、非常に小さなライン傾斜のための約2uAのDCシンクバイアス電流を選択します。しかし、より多くのハム・リジェクションが必要な場合は、中間バイアスモードを選択すると、DCシンクバイアス電流を約6.5uAに増加します。厳しい環境には、高バイアスモードにすると約9uAのDCシンクバイアス電流があります。これらの高い方のバイアスモードによりハム・リジェクションは増加しますが、ライン傾斜も増加することが欠点です。ハム・リジェクションとライン傾斜を変えるその他の方法は、使用して

いる入力コンデンサを変更することです。コンデンサを0.1uFから0.22uFに大きくすると、ハム・リジェクションとライン傾斜が2.2の割合で低減します。また、この入力コンデンサを小さくすると、反対の効果を実現します。

THS7303のAC STCモード時における入力インピーダンスは一般に $>1M\Omega$ です。STC制御ループが電流を供給してバイアス電圧を100mVまで増加する必要がある場合、インピーダンスは明らかに変化します。しかし、この変化は一般に瞬時かつシンク信号のみについて発生し、ビデオ信号時にインピーダンスが大幅に変わることはありません。

AC STC制御ループの安定性を適正に保つには、適正な入力コンデンサを使用して、信号源インピーダンスが $1k\Omega$ 以下である必要があります。さもないと、制御ループがリンギングを発生する可能性があり、このリンギングはTHS7303の出力に現われます。DCモード動作の場合と同様に、多くのDACおよびエンコーダは抵抗を使用してその出力電圧を生成しています。これらの抵抗は一般に $300\Omega$ 以下です。したがって、AC STC制御ループの安定性は保証されます。しかし、THS7303の入力から見た信号源インピーダンスが非常に高いかオープンの場合、単純に $1k\Omega$ の抵抗をGND間に付加すると、THS7303の適正な動作が保証されます。

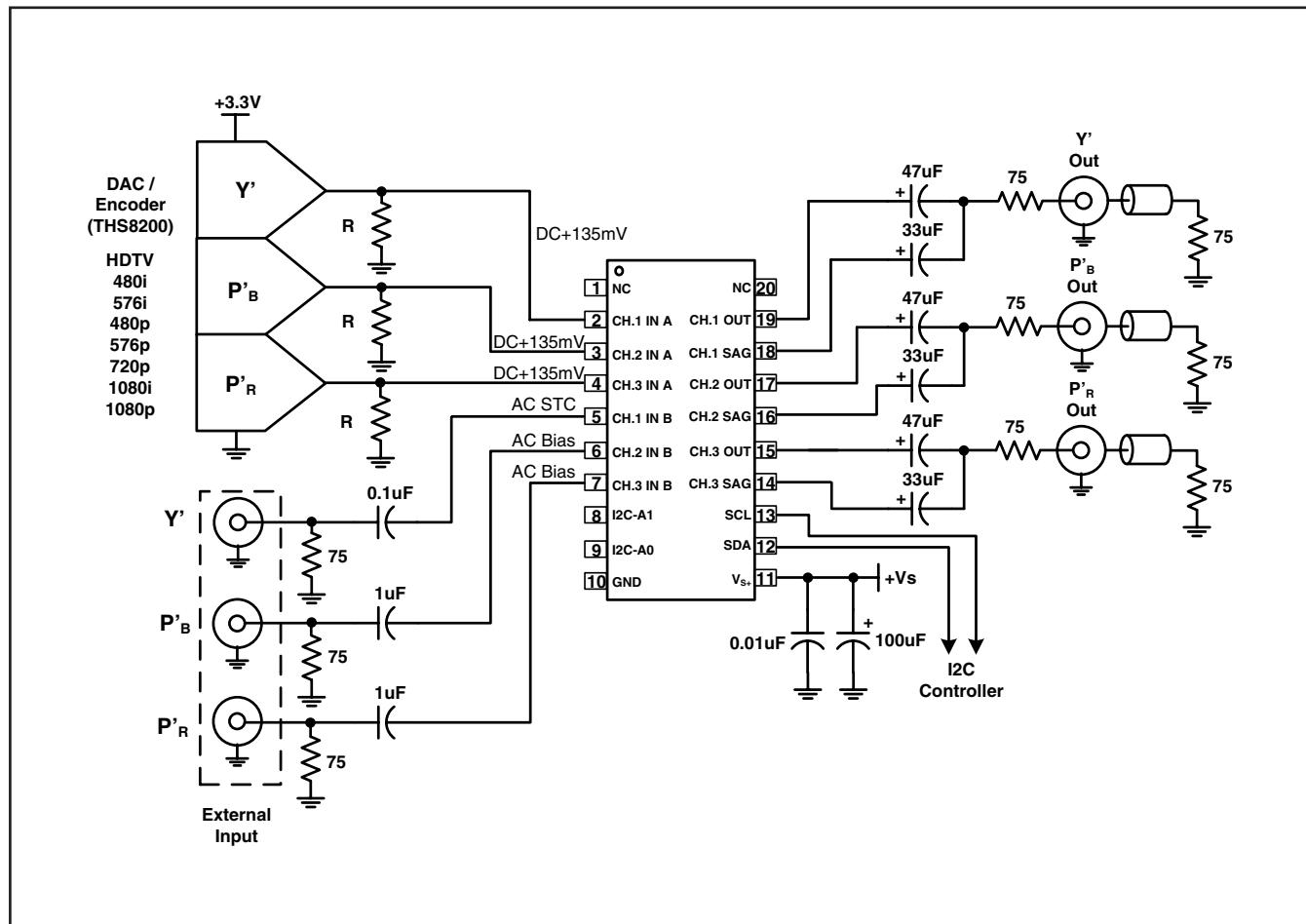

## 出力モード動作 - DC結合

THS7303はレール・ツー・レールの出力段を組み込んでおり、大容量のAC結合コンデンサなしでラインの直接ドライブに使用できます。このドライブは、各チャネルの出力ピンをそれに対応するチャネルのSAG出力ピンに、図10のように単に接続するだけでなれます。このドライブ方法はAC結合でないので、最適なライン傾斜およびフィールド傾斜(ドループ)特性を提供します。ただし入力がAC結合の場合、それによって生ずる傾斜が出力の結合状態に関係なく出力に見られることは留意してください。THS7303の80mAの出力電流ドライブ能力は、出力のダイナミックレンジをできるだけ広く保つつつ、2つのビデオライン(基本的に $75\Omega$ 負荷)を同時にドライブできるように設計されました。

しかし、DC結合に関するひとつの問題は、ラインがグランドに終端している場合です。ACバイアスモードが選択されていると、THS7303の出力は中間レール( $V_{S+}$ とGNDの中間)になります。2ラインがグランドに終端しているとDC電流パスが形成され、高出力電圧振幅がわずかに低下し、THS7303の消費電力が増加します。THS7303は最高125°Cまでの接合温度で動作するよう設計されていますが、接合温度がそれを超えないように注意する必要があります。さもないと、長期間の信頼性が低下することがあります。リードレスQFNパッケージを使用して、

サーマルパッドをPCBのグランドプレーンに接続すると、サーマルパッドが提供する低熱抵抗により、このリスクは小さくなります。このグランド終端構成ではチャネル当たりわずかに10mW以下の消費電力が増加するだけですが、THS7303全体の低消費電力設計により、TSSOPパッケージを高周囲温度で使用する場合でも、潜在的な熱問題を最小限度にとどめております。

THS7303は入力モード動作にかかわらず、DC結合でラインをドライブできることに注意願います。DC結合で唯一必要なことは、ビデオラインを出力ピンと直列に適切に終端(一般に $75\Omega$ )することだけです。この終端は、THS7303の出力における容量性負荷効果を分離するのに役立ちます。容量性負荷を分離しないと、出力バッファのリングングや発振を発生する潜在的な要因のために不安定になります。したがって、THS7303の出力に直接見える寄生容量は、最適特性を得るために25pF以下に抑えます。2つのビデオラインをドライブする場合、各ラインにそれぞれ $75\Omega$ のソース終端(信号源終端)抵抗を接続し、ラインを相互に分離することに注意願います。

図 10. DC結合ラインドライブの代表的なG'B'R'(R'G'B')システム

## 出力モード動作 - AC結合

おそらく、最も一般的なビデオ信号とラインを結合する方法は、大容量コンデンサを使用することです。このコンデンサは一般に220uFから1000uFであり、470uFが最も一般的です。この容量値は、本文献で先述したAC結合によるライン傾斜(ドリープ)やフィールド傾斜を最小限にするために、このように大きなものである必要があります。DC結合構成とまったく同様に、各チャネルの出力ピンを対応チャネルのSAG出力ピンと直接に、できるだけTHS7303の近くで接続します。

AC結合はいくつかの理由でなされますが、最も一般的な理由は受信側のビデオシステムの操作性を十分に保証することです。AC結合になると、グランドループの発生が排除されます。また、送信側で使用される基準DC電圧に関係なく、受信側がその必要に応じてDC基準電圧を設定することも保証します。

先述したDC出力モード動作とまったく同様に、各ラインにAC結合コンデンサと直列に75Ωソース終端抵抗を接続します。2つのラインをドライブする場合は、図11に示すようにコンデンサと抵抗を共有するより、各ラインで個別にコンデンサと抵抗を接続する方が最善です。この個別接続は、ライン間のDC絶縁と先述の潜在的問題を保証するのに役立ちます。2つのラインが1個の1000uFを共有することができますが、グランドループお

よび2つのレシーバ間の干渉が発生する可能性があります。

最後に、エッジレートおよび動作周波数により、必ずというわけではありませんが、0.01uFから0.1uFのコンデンサを220uFから1000uFの大コンデンサに並列に配置することを推奨します。これらの大コンデンサは、ほとんどの場合アルミ電界です。このアルミ電界コンデンサには非常に大きなESR(等価直列抵抗)があり、その構造上含まれるインダクタンスのために、高周波時のインピーダンスがかなり大きくなります。そこで、小容量の0.01uFから0.1uFのコンデンサは、大コンデンサよりも低いインピーダンスで、これらの高周波(>1MHz)信号を通過させるのに役立ちます。これは特にED、HD、およびG'B'R'信号の使用時にあてはまります。これらの信号のエッジレートおよび周波数成分は、HD信号で30MHz以上に達し、G'B'R'信号で100MHzを超えます。これらの周波数は、一般的なアルミ電界コンデンサだけでは効果的に通過させることができません。

すべてのビデオラインでは同じ容量値を使用するのが普通ですが、Sビデオシステムにおけるクロマ信号の周波数帯域幅は、ルーマチャネルと同程度の低周波あるいは高周波にする必要はありません。したがって、クロマラインの容量は0.1uFのような小さい値にできます。

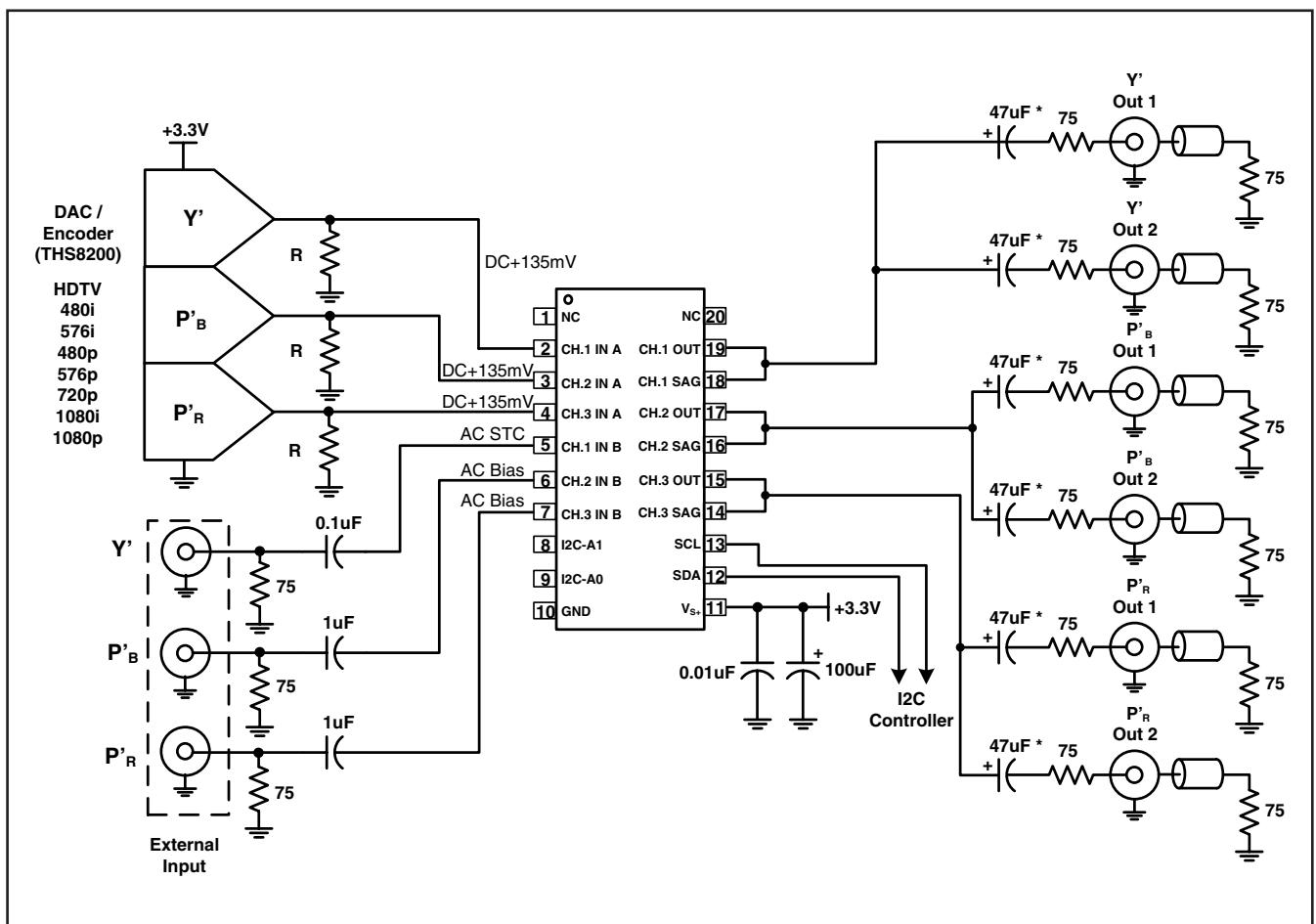

図 11. 2つのAC結合ビデオラインをドライブする代表的なYP'\_BP'\_Rシステム

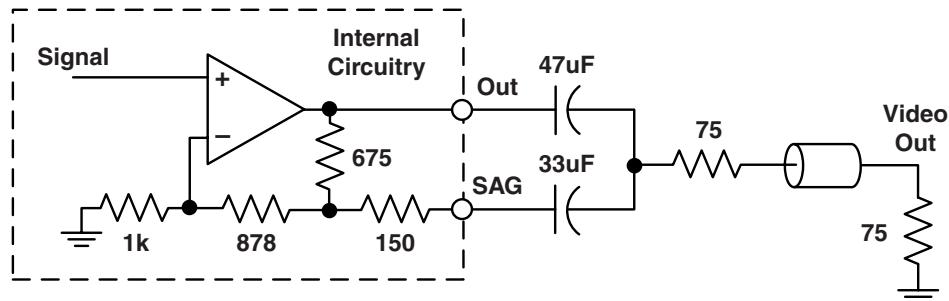

## 出力モード動作 - SAG補正のAC結合

AC結合はラインドループ問題の他に、もうひとつの潜在的な問題を抱えています。すなわち、サイズとコストです。330uFから1000uFのコンデンサは一般に非常に大きく、システム内でもとても高くなります。これをチャネル数倍すると、そのサイズとコストは著しいものになります。しかし、それでもAC結合を使用してグランドループ問題を排除し、ビデオ機器間相互の操作性を保つのは非常に重要です。

SAG補正是、より小さなコンデンサでビデオ信号をAC結合するのに使用できる方法です。SAGという名称が何を意味するか正確に述べている公的な文献はありませんが、それは『信号振幅ゲイン補正』(Signal Amplitude Gain correction)の意味だと信じられています。SAG補正是出力バッファの帰還網を操作してなされます。THS7303は、所要の外付け部品点数を最小化しつつ、この補正手法を利用するように設計されました。図12は、1つのビデオラインをドライブするSAG構成とともに、出力バッファ段の基本的な構成を示します。

SAG補正是低周波動作および高周波動作を観察して解析できます。低周波ではコンデンサのインピーダンスが非常に高く、そのときのアンプのゲインは $1 + ((675 + 878) / 1k) = 2.55V/V$ すな

わち (+8.1dB) になります。しかし、高周波ではコンデンサのインピーダンスが非常に低く、アンプのゲインは $1 + ((675 || 150) + 878) / 1k = 1 + (1k/1k) = 2V/V$ すなわち (+6.0dB) となります。このゲインは、2重に終端された75Ω分圧回路 (-6dB) の作用を打ち消し、その結果、ビデオ出力信号を入力信号の振幅と等しくするのに必要な値そのものです。

SAG出力ピンがアンプ出力に直接接続される場合、DC結合およびAC結合で見られるように、ゲインは適正に2V/V (+6dB) になることが容易に分かります。また、SAGピンが負帰還網の一部であることも分かります。したがって、コンデンサと配線はTHS7303にできるだけ接近させ、寄生問題を最小限にします。さもないと、ビデオ信号にリングングが発生することがあります。

SAG補正を使用すると、低周波のゲインは高周波のゲインよりも大きいです (8.1dB対6.0dB)。このゲインは、47uFコンデンサのインピーダンスの増加による信号の減衰を打ち消します。このアンプのゲイン増加は33uFコンデンサ（および関連の内部抵抗値）で定まり、低周波（一般に約15Hz）でのQ値を高めます。これら2個のコンデンサの比は、このQ値の向上の周波数と振幅を決定します。

図 12. SAG補正のAC結合を使用したTHS7303の出力バッファ.

内部抵抗値は、47uFおよび33uFのコンデンサを使う場合にシステムを最適化し、かつ330uFコンデンサ1個のときの特性に近くなるように選定しました。これらのコンデンサの値は必要であれば変えることができますが、システムの特性もそれに応じて変わります。例えば、22uFのコンデンサを両方に使用すると、ライン傾斜とフィールド傾斜が増加します。しかし、システムの中には、アプリケーション次第でこの組み合わせでも良いと考えられるものもあります。また、それぞれ68uFおよび47uFのような、より大きな値を使用するとフィールドタイム歪みが低減し、1個の470uFコンデンサの特性に近づきます。

DCゲインがおよそ2.55V/Vあることに注意する必要があります。したがって、入力にDCバイアスがあると、出力DCバイアスは入力の2.55倍になります。例えば、入力が DC+135mVシフトの場合には、出力のバイアス点は 345mVになります。さらに、ACバイアス入力モードが選択されている場合、DC動作点は3.3V電源でVs/4×2.55すなわち2.1V、また5V電源で3.2Vになります。しかし、DC動作点と出力のレール・ツー・レール能力の間にまだ十分な余裕があるため、この追加のオフセットによりTHS7303の特性は劣化しません。

この構成に関して考えられる問題のひとつは、3.0Vのような低電源電圧を使用する場合、低周波での高ゲインにより信号の飽和が発生し得ることです。したがって、起こり得る飽和を最小限にすべく、内部抵抗は低周波ゲインを小さくするよう選定されました。他のSAG補正用部品では低周波ゲインがより高くなり(10dBかそれ以上)、低電源電圧時にはダイナミック波形とDCの両方で、容易にアンプ出力にクリッピングが発生します。ここで言う他のSAG補正用部品は、SAGピンに直列の抵抗を使用していません。この直列抵抗を使用しないと非常に大きなQ値の増加になり、飽和問題を発生します。これらのシステムでは、この問題を小さくするのに非常に非常に大きな帰還コンデンサを要しますが、それがSAG補正の利点を極めて小さなものにしてしまいます。

図13はTHS7303のSAG補正の構成を示します。ここで、Sビデオクロマのチャネルが設定される場合、結合コンデンサが一般に0.1uFと非常に小さいので、SAG補正を行う意味が無いことに注意願います。したがって、OUTPUTピンを直接SAGピンに接続することを、この0.1uFコンデンサの使用とともにお奨めします。

図 13. AC結合ビデオラインをドライブする代表的なYP'BP'Rシステム

## ローパスフィルタモードおよびバイパスモード

THS7303の各チャネルには5次のローパスフィルタが組み込まれています。これらのビデオ復元フィルタは、ビデオ信号のレシーバへ通過するDACイメージノイズを小さくします。レシーバの設計によっては、このDACイメージノイズを除去しないと、ADCのエイリアシングのために画像品質問題が発生します。フィルタのまた別の利点は、信号の収差を除去することです。DACの中には、それ自身の内部フィルタリングが優れていないと、この収差を出力するものもあります。この収差の除去は、画像品質および信号がビデオ帯域幅条件を確実に満足することの両方に役立ちます。

各フィルタのバタワース特性は修正されています。すなわち各フィルタのQが、従来のバタワース応答の0.707よりもわずかに低く修正されています。バタワース応答の利点は、コーナー周波数における最初の減衰がかなり急峻で、かつ周波数応答が非常に平坦なことです。この特性の問題は、コーナー周波数付近において群遅延が著しく生じることです。群遅延は、位相変化(ラジアン/秒)を振幅変化で割ったものとして定義されます。群遅延の増加は、時間領域のパルス応答のオーバーシュートとそれによるリンギングに相当します。したがって、ベッセルやチェビシェフのような他のタイプは、ビデオ・アプリケーションに一般に奨められません。それらのタイプのフィルタには非常に大きい群遅延変動がコーナー周波数付近にあり、著しいオーバーシュートとリンギングを生ずるからです。

THS7303のフィルタはQが低く、したがってコーナー周波数付近の群遅延変動は小さいです。その結果、時間領域のパルス応答には少しオーバーシュートがありますが、真正のバタワースフィルタほど多くはありません。さらに、周波数応答の最初の減衰レートは真正のバタワース応答ほど高速ではありませんが、パルスおよび群遅延特性の利点を考慮して、許容できる減衰レートであるとみなされます。

集積回路内のアクティブフィルタについての関心事のひとつに、周囲温度およびそれによるチップ温度が変化したときのフィルタ特性の変動があります。この温度の影響を最小限度にするために、THS7303はBiCom-3プロセスによる薄膜金属抵抗および高品質で小温度係数のコンデンサを使用しています。そのためTHS7303のフィルタは、プロセス変動および温度変化に対して適正なフィルタ特性を保つことが設計保証されています。この特性により、チャネル間の遅延時間差を非常に小さくしています。これは適正なビデオ信号特性に要求されるものです。

THS7303には、バイパスモードとともに選択可能な名目値が8.5MHz、16MHz、および34MHzのコーナー(-3dB)周波数のフィルタがあります。8.5MHzフィルタは、標準品位(SD)NTSC、PAL、およびSECAMコンポジットビデオ信号(CVBS)

に最適です。また、Sビデオ信号(Y' C')、480i/576i YP'BP'R'、およびY'UV'ビデオ信号にも最適です。その-3dBコーナー周波数は、27MHzで40dBの減衰を得て、かつビデオ信号を最大限に平坦にするために8.5MHzに設計されました。この27MHzは、多くのビデオレシーバにおいて見られるADCの2次と3次のナイキスト領域間の一般的な周波数です。このようにフィルタ特性を設計したことは重要なことです。さもないと、レシーバに見られるADCのエイリアシング効果により、27MHz付近のあらゆる信号がベースバンドにも現れるからです。

16MHzフィルタは、480pおよび576p YP'BP'R'ビデオ信号(エンハンスト・デフィニション、EDとも呼ばれる)を通過させるために設計されました。また、このフィルタはビデオ・スペクトラムで非常に平坦な周波数応答であり、G'B'R'(R'G'B') VGA信号の通過にも使用できます。34MHzフィルタは、高品位(HD)720pおよび1080i YP'BP'R'ビデオ信号と、G'B'R'(R'G'B') SVGAおよびXGA信号を通過させるために設計されました。4:2:2システムを使用すると、P'BP'R'チャネルはY'チャネルに要する帯域をフルで必要としません。しかし、Y'チャネルと同じフィルタ周波数を使用して、3信号すべての群遅延とタイミングの整合をとることを推奨します。さもないと、タイミング変動を最小限度にするための余分な遅延補償が必要になりそうです。

THS7303のバイパスモードには200MHz帯域幅(-3dB)および300V/usスルーレートがあり、G'B'R'(R'G'B') SXGAおよびUXGA信号をわずかな減衰で通過させます。このバイパスモードは、60MHzビデオ信号帯域幅を要するHDTV1080p信号にも使用できます。

THS7303のI<sup>2</sup>Cインターフェイスにより、各チャネルを相互に完全独立した構成にできます。この構成の利点のひとつは、信号にかかわらず適正な入力構成および必要なローパスフィルタを設定した1個のTHS7303経由で、複数の出力エンコーダ(あるいはDAC)を転送できるということです。これはポータブルシステムや、システム出力が1セットのみ(あるいは2セット並列)を要する非常な低価格システムに使用できます。I<sup>2</sup>Cコマンドの単純な更新により、THS7303のチャネルは即座かつ苦労なく変更できます。このひとつの例を図14に示します。そこでは、入力MUXにより1セットのHDTV信号がTHS7303に入力され、次にI<sup>2</sup>Cコマンドの更新で、1セットのSDTV信号が適切な入力モードとローパスフィルタのTHS7303を通して転送されます。

\*ビデオ信号の高周波成分のために、必ずというわけではありませんが、0.1uFあるいは0.01uFのコンデンサをこれらの大容量コンデンサに並列に付加することを推奨します。

図14. 1個のTHS7303をドライブする、代表的なEDTV/HDTVおよびSDTVエンコーダDAC

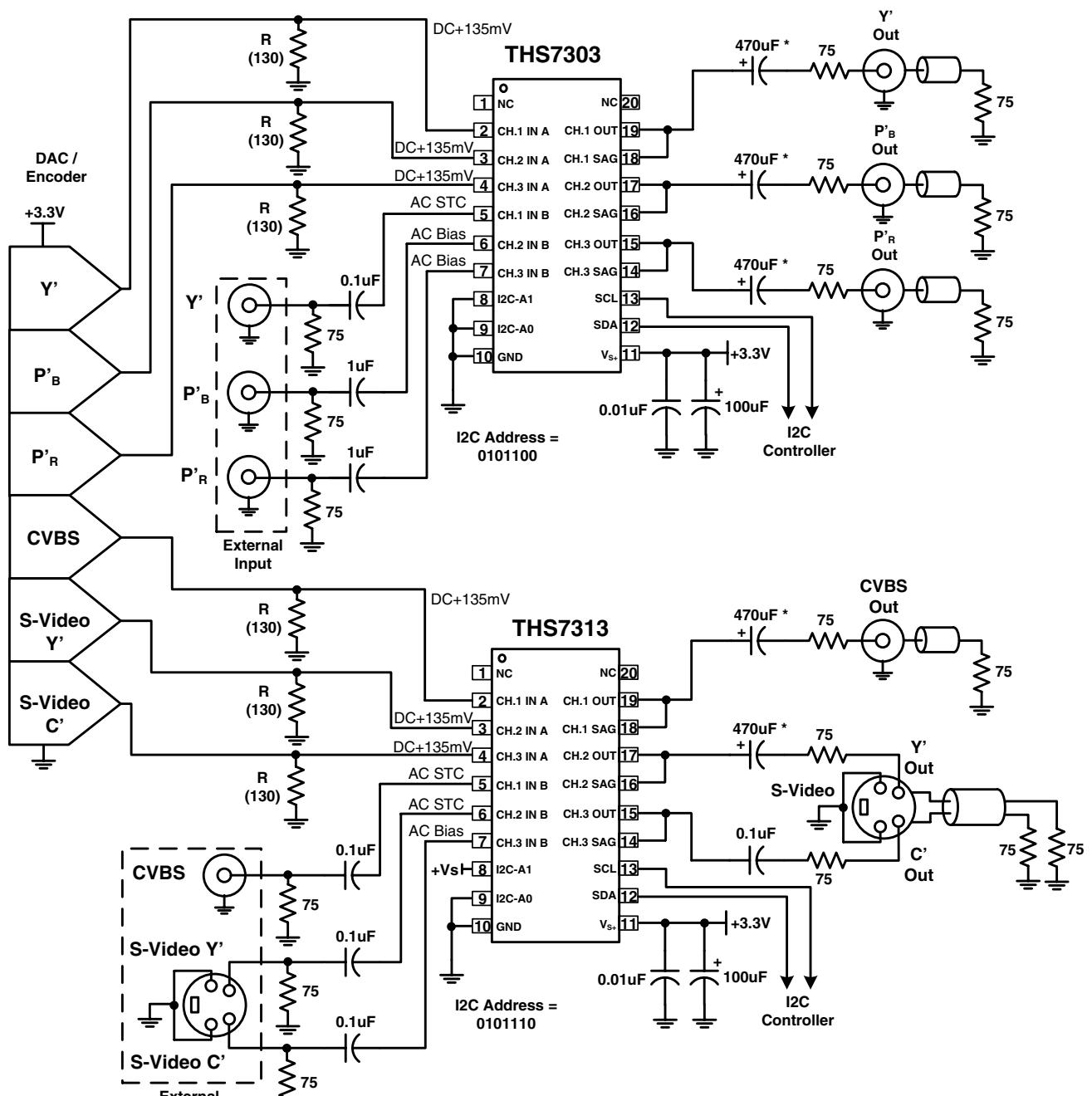

図14の回路はスペースとコストを節約できますが、出力接続を兼用するのは最善のソリューションではないかもしれません。完璧な6チャネルシステムには、THS7303とTHS7313 (THS7313データシートを参照) を図15のように同時に使用する方が確実に良策です。THS7313はSDTV信号用であり、フィルタが

8.5MHzだけです。また、I<sup>2</sup>C節で述べますが、I<sup>2</sup>C - A1およびI<sup>2</sup>C - A0ラインのロジックによって、各デバイスのI<sup>2</sup>Cアドレスは個別の4アドレスの1個にできるので、両デバイスを同一システム内で使用するのは非常に簡単です。

図 15. THS7303およびTHS7313にインターフェイスする、代表的な6チャネルSDTV/EDTV/HDTVエンコーダ

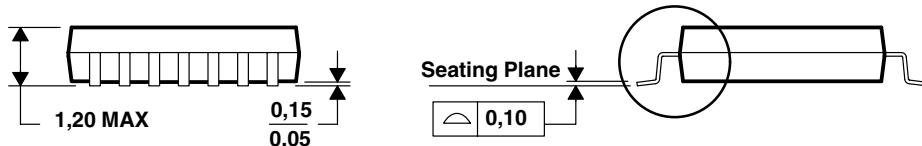

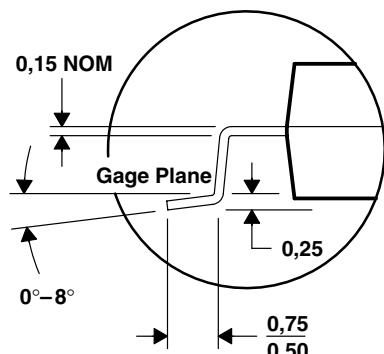

## パッケージ・オプション

THS7303は、簡便な信号フロー・スルー構成(入力と出力が両側に分離)の20ピンTSSOPパッケージと、サーマルパッド付きの20ピン・リードレスパッケージ(RGP)で提供されています。両パッケージとともに、最新の鉛フリー(RoHSと互換)およびグリーン製造条件に適合しています。リードレスRGPパッケージは、非常に小さなPCB面積しか占有せず、1mm(最大)以下の非常に低いパッケージ高さです。しかし、この新パッケージの欠点のひとつは、リードがサーマルパッドとともにすべてパッケージの底面にあることです。したがって、このパッケージのPCBでの配置および修正を適切に行うには、組み立ておよび修正用の適当な工具が必要です。テキサス・インスツルメンツは、いくつかのアプリケーション・ノートによって、RGP(および他のQFN)パッケージの利点の使用を望まれるカスタマをサポートしております。これについてはアプリケーション・ノート『QFN/SONのPCBへの取り付け(SLUA271)』およびアプリケーション・レポート『クゥアド・フラットパック・ノーリード・ロジックパッケージ(SCBA017)』をご覧ください。両者ともにwww.ti.comからダウンロードして入手できます。

RGPパッケージのサーマルパッドは、シリコンチップで発生してPCBに伝わる熱に対して非常に低い熱抵抗パスを与えま

す。これによってアンプは、シリコンチップ温度を許容温度に保ちながら相当な熱量を消費できます。この許容温度に維持すると長期信頼性が改善されます。

PCBの銅プレーンに接続するサーマルパッドの別の目的は、サーマル・ショック、温度サイクリング、キー・プッシュ、パッケージせん断力、および他の基板レベルの試験を受けたときのパッケージの機械的強度を改善することです。サーマルパッドをPCBの銅プレーンに接続しないと、半田付け不良を発生することがあります。

THS7303は、シリコン・オン・インシュレータ(SOI)プロセスであるBiCom-3プロセスで製造されています。サーマルパッド自体は、すべてのpinおよびすべての能動回路から電気的に絶縁されています。この絶縁によって、サーマルパッドは基本的にGNDからVs+までのどの電位にも接続できます。しかし、サーマルパッドはPCBのグランドプレーンに接続することを推奨します。グランドプレーンは一般にPCB中で最大の銅面積を占めるため、熱的特性および機械的強度が改善されます。また、グランドプレーンは一般にPCB上で最も静的な銅プレーンであり、シリコンチップ上の能動回路に結合する高周波ノイズを低減します。

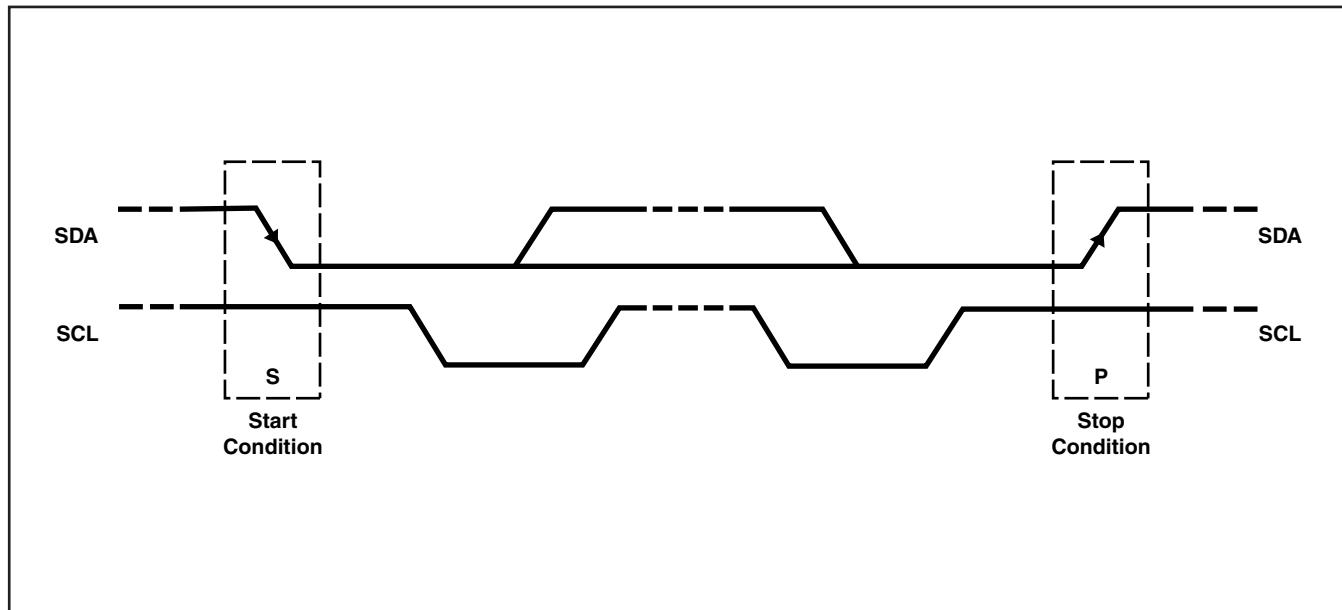

図 16. I<sup>2</sup>Cスタートおよびストップ条件

## I<sup>2</sup>Cインターフェイス・ノート

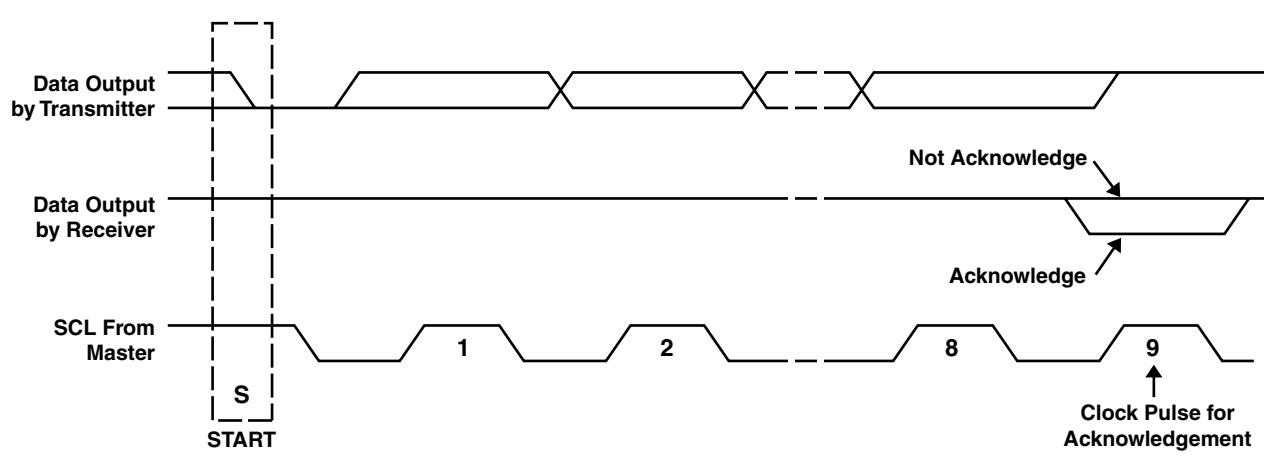

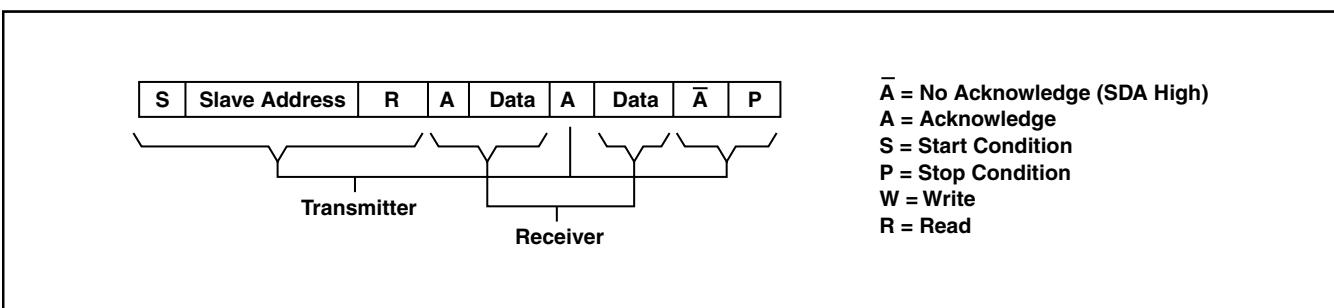

I<sup>2</sup>Cインターフェイスは、THS7303の内部レジスタへのアクセスに使用されます。I<sup>2</sup>Cは2線式シリアル・インターフェイスであり、フィリップス・セミコンダクタによって開発されました(I<sup>2</sup>C仕様、バージョン2.1、2000年1月を参照)。このバスは、プルアップ構造のデータライン(SDA)とクロックライン(SCL)からなります。バスがアイドル状態の場合、SDAとSCLの両ラインはハイレベルに吊り上げられます。すべてのI<sup>2</sup>C互換デバイスは、オープンドレインのI/OピンであるSDAとSCL経由でI<sup>2</sup>Cバスに接続します。マスターデバイスは普通の場合マイクロコントローラかデジタル・シグナル・プロセッサであり、これらがバスを制御します。マスターにはSCL信号およびデバイス・アドレスを生成する役割があります。またマスターには、データ転送のSTARTおよびSTOPを示す特定の条件を生成する役割もあります。THS7303はスレーブとして働き、I<sup>2</sup>Cバス仕様に定義されるように標準モード転送(100kbps)および高速モード転送(400kbps)に対応します。THS7303は高速モード(3.4Mbps)で全機能が試験されていますが、高速モードについての保証はされていません。

基本的なI<sup>2</sup>Cスタートおよびストップのアクセスサイクルを図16に示します。

基本アクセスサイクルは以下の構成です。

- スタート条件

- スレーブアドレス・サイクル

- あらゆるデータサイクル数

- ストップ条件

## 一般的なI<sup>2</sup>Cプロトコル

- マスターがスタート条件を生成してデータ転送を始めます。スタート条件は図16に示すように、SCLがハイのときにSDAラインでハイからローへの遷移が発生する場合です。すべてのI<sup>2</sup>C互換のデバイスがスタート条件を認識します。

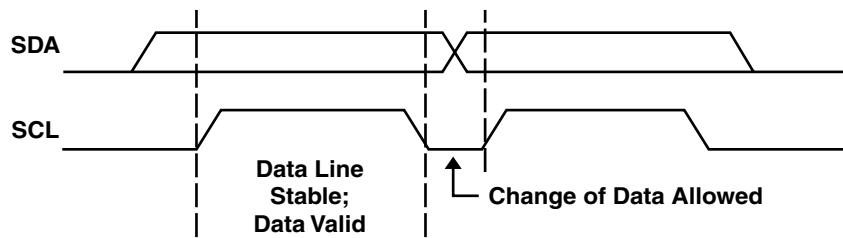

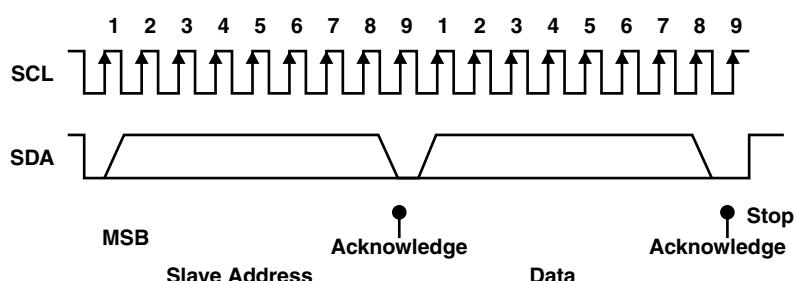

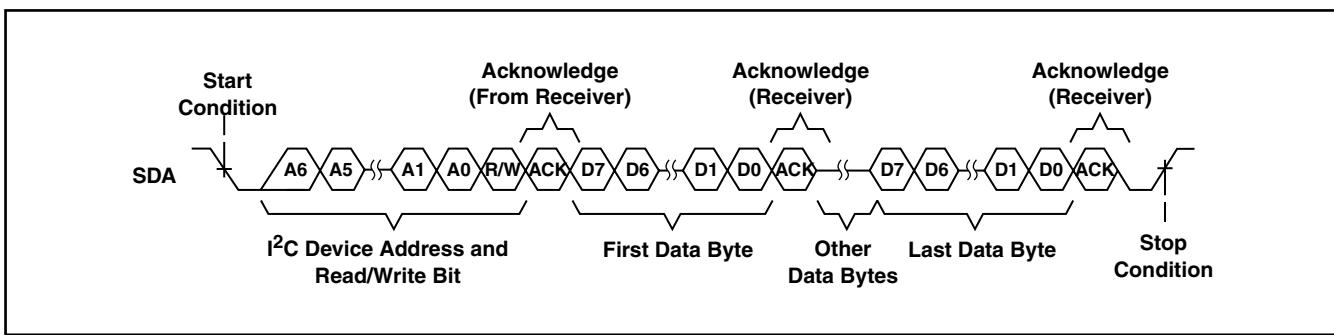

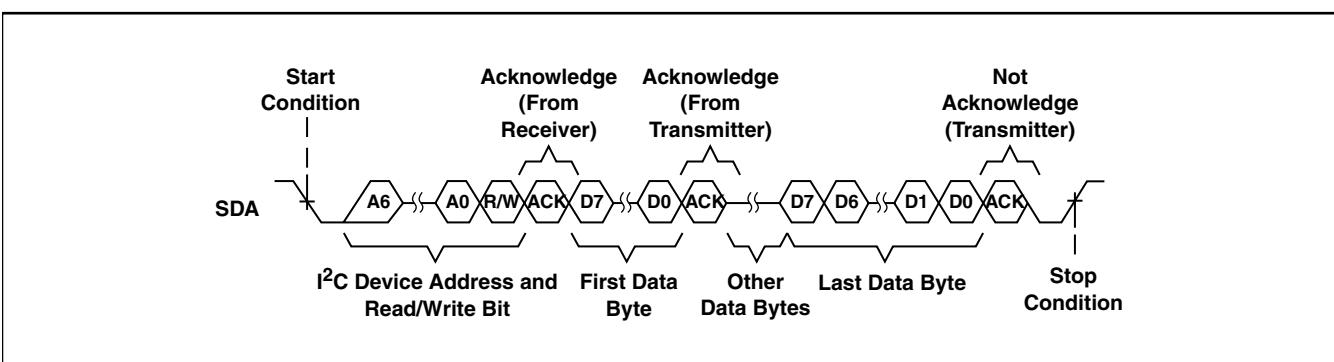

- 次にマスターはSCLパルスを発生し、7ビットのアドレスおよびリード・ライト方向ビットR/WをSDAラインに転送します。転送の間、マスターはデータが有効であることを保証します。有効データ条件には、クロックパルスのハイレベル区間全体でSDAラインが安定であることが必要です(図17参照)。すべてのデバイスは、マスターが送ったアドレスを認識し、それを内部の固定アドレスと比較します。アドレスが一致したスレーブデバイスだけが、9番目のSCLサイクルのハイ区間にSDAラインをローに下げてアクノリッジを発生します(図18参照)。このアクノリッジを検出して、マスターはスレーブとのコミュニケーション・リンクが確立したことを見知します。

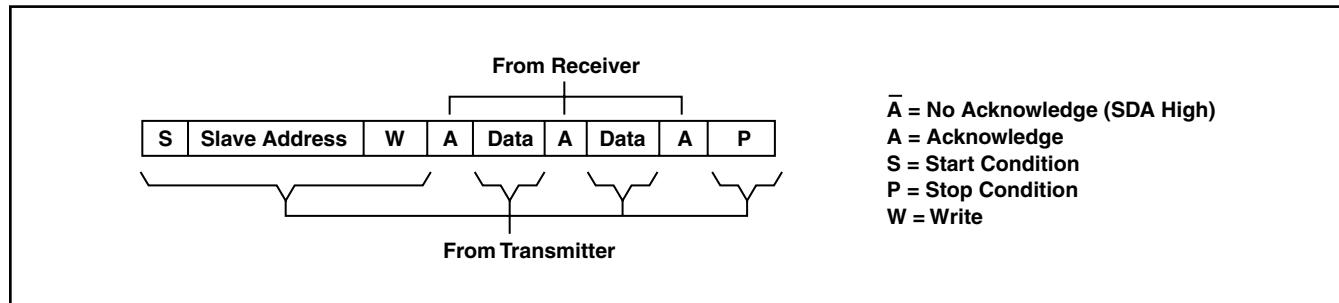

- マスターはさらなるSCLサイクルを発生して、スレーブへのデータ転送(R/Wビットが1)あるいはスレーブからのデータの受け取り(R/Wビットが0)を行います。いずれの場合でも、レシーバ(受け手)はトランスマッタ(送り手)が送るデータを承認する必要があります。したがって、アクノリッジ信号はどちらがレシーバになるかによって、マスターあるいはスレーブのいずれも発生できます。8ビットのデータと1ビットのアクノリッジからなる9ビットの有効データのシーケンスは、必要なだけ続けることができます(図19参照)。

- データ転送の終了を知らせるために、マスターはストップ条件を生成します。これはSCLラインがハイのときに、SDAラインをローからハイに吊り上げて行います(図16参照)。こうしてバスを開放し、アドレス指定したスレーブとのコミュニケーション・リンクを停止します。すべてのI<sup>2</sup>C互換のデバイスが、ストップ条件を認識する必要があります。ストップ条件の受け取りにより、すべてのデバイスがバスの開放を知り、スタート条件を待ち、さらにアドレスの一致が続きます。

図 17. I<sup>2</sup>C ビット転送

図 18. I<sup>2</sup>C アクノリッジ

図 19. I<sup>2</sup>C アドレスおよびデータサイクル

ライトサイクルでは、受け側のデバイスがSDA信号をローにドライブできるように、転送側デバイスはアクノリッジサイクルの間だけSDA信号ラインをドライブしてはなりません。アドレスバイトに続く各バイト転送の後で、受け側のデバイスは1SCLクロックサイクルだけSDAラインをローに下げます。最

後のバイトが転送された後、ストップ条件が転送側デバイスによって生成されます。ライトサイクルの例は、図20および図21で見ることができます。THS7303は複数のライト転送の発生を禁止していることに注意願います。より詳細は『例—THS7303へのライト』の節をご覧ください。

リードサイクルでは、スレーブであるレシーバは最初のアドレスバイトがそのレシーバのアドレスであると解読したら、それを承認します。スレーブによるこの最初の承認に引き続いて、マスターデバイスはレシーバになり、スレーブによって送られたデータバイトを承認します。マスターがスレーブに要求されたデータバイトをすべて受け取ると、ノット・アクノリッジ

(Abar) 条件がマスターによって生成されます。このノット・アクノリッジは、ストップ条件(P)になる直前にSDA信号をハイにして生成します。このシーケンスは、図22および図23に示すようにリードサイクルを終了します。THS7303は複数のリード転送の発生を禁止していることに注意願います。より詳細は『例—THS7303からのリード』の節をご覧ください。

図 20. I<sup>2</sup>Cライトサイクル

図 21. 複数バイトのライト転送

図 22. I<sup>2</sup>Cリードサイクル

図 23. 複数バイトのリード転送

| Fixed Address |       |       |       |       | Selectable With Address Pins |            | Read/Write Bit |

|---------------|-------|-------|-------|-------|------------------------------|------------|----------------|

| Bit 7 (MSB)   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 (A1)                   | Bit 1 (A0) | Bit 0 (R/W)    |

| 0             | 1     | 0     | 1     | 1     | 0                            | 0          | 0              |

| 0             | 1     | 0     | 1     | 1     | 0                            | 0          | 1              |

| 0             | 1     | 0     | 1     | 1     | 0                            | 1          | 0              |

| 0             | 1     | 0     | 1     | 1     | 0                            | 1          | 1              |

| 0             | 1     | 0     | 1     | 1     | 1                            | 0          | 0              |

| 0             | 1     | 0     | 1     | 1     | 1                            | 0          | 1              |

| 0             | 1     | 0     | 1     | 1     | 1                            | 1          | 0              |

| 0             | 1     | 0     | 1     | 1     | 1                            | 1          | 1              |

表1. THS7303スレーブアドレス

## スレーブアドレス

SDAおよびSCLは、ともにプルアップ抵抗で正電源に接続する必要があります。これらの抵抗は $2\text{k}\Omega$ から $19\text{k}\Omega$ の範囲というI<sup>2</sup>C仕様に従います。バスが空いている場合、両ラインはハイレベルです。アドレスバイトは、マスターデバイスからのスタート条件の後に最初に受け取るバイトです。そのアドレスの上位5ビット(MSB)は、製造時に01011にプリセットされています。THS7303アドレスのその次の2ビットは、I<sup>2</sup>C-A1およびI<sup>2</sup>C-A0ピンのロジックレベルにより制御されます。I<sup>2</sup>C-A1およびI<sup>2</sup>C-A0アドレス入力は、Vs+に接続してロジック1に、GNDに接続してロジック0にできます。あるいは、TTL/CMOSロジックレベルで能動的にドライブして設定できます。デバイスアドレスはこの2ピンの状態で設定され、ラッチされません。したがって、ダイナミックなアドレス制御システムを使用して、同一システム内にいくつかのデバイスを組み込みます。同一のI<sup>2</sup>Cバスについて、ロジックを追加せずに最大4個までのTHS7303を接続できます。表1にTHS7303の取り得るアドレスを記載します。

## チャネル選択レジスタの種類(サブ・アドレス)

THS7303は、図20および22のような単バイト転送プロトコルのみを使用して動作します。その各内部アドレスレジスタとその

機能を表2および3に示します。デバイスへのライトには、チャネルに相当する内部サブ・アドレスへ1バイトのデータを送る必要があります。3チャネルをすべて制御する必要がある場合は、マスターはすべてのサブ・アドレス(すべてのチャネル)を一度に繰り返さなければなりません。この繰り返しは、本文献の『例—THS7303へのライト』節に示すTHS7303への適正なライト手順のように行います。

リードサイクルでは、THS7303はその選択されたサブ・アドレス(すなわちチャネル)のデータを1回の転送で、情報を要求しているマスターデバイスに送ります。THS7303からの適正なリード手順については、本文献の『例—THS7303からのリード』節をご覧ください。

パワーアップ(電源立ち上げ)時のTHS7303のレジスタは、ランダムな状態です。このランダム状態は、適正なライトシーケンスがTHS7303になされるまで続きます。合計で9バイトのデータにより、THS7303のすべてのチャネルを完全に構成します。THS7303への構成自体は非常に速くかつ簡単であり、システムのパワーアップ時に行います。

| REGISTER NAME | BIT ADDRESS<br>(b <sub>7</sub> b <sub>6</sub> b <sub>5</sub> ...b <sub>0</sub> ) |

|---------------|----------------------------------------------------------------------------------|

| Channel 1     | 0000 0001                                                                        |

| Channel 2     | 0000 0010                                                                        |

| Channel 3     | 0000 0011                                                                        |

表2. THS7303チャネル選択レジスタのビット割り当て

## チャネルレジスタ・ビットの種類

先述したように、サブ・アドレス(チャネル選択)制御レジスタの各ビットにより、ユーザは個々にTHS7303の機能を制御できます。この処理の利点により、ユーザは各チャネルを他のチャネルとは独立して制御できます。ビットの種類は下の表3に解説します。

ビット7(MSB)および6-ACシンクチップ・クランプ・モード時のローパスフィルタ機能の制御。AC-STCモードが使用されていない場合、この機能は無視されます。

ビット5—THS7303の入力MUXの制御

ビット4および3—5次ローパスフィルタの-3dBコーナー周波数またはバイパスモード動作の制御。

ビット2, 1, および0(LSB)—THS7303の入力バイアスおよび省電力機能の選択。シンクチップ・クランプが選択されている場合、DC入力シンクバイアス電流も選択可能です。低バイアスモードは、ライン傾斜を非常に小さくするために約2uAのDCシンクバイアス電流です。しかし、よりハム・リジェクションが必要ならば、中間バイアスモードを選択すると、DCシンクバイアス電流が約6.5uAに増加します。厳しい環境下については、高バイアスモードの約9uAのDCシンクバイアス電流があります。高い方のバイアスモードの欠点はライン傾斜が増加することですが、ハム・リジェクションは改善されます。

| BIT              | FUNCTION                                      | BIT VALUE(S) | RESULT                                            |

|------------------|-----------------------------------------------|--------------|---------------------------------------------------|

| (MSB)<br>7, 6    | STC Low Pass Filter Selection                 | 0 0          | 500-kHz Filter – Useful for 8.5-MHz Video LPF     |

|                  |                                               | 0 1          | 2.5-MHz Filter – Useful for 16-MHz Video LPF      |

|                  |                                               | 1 0          | 5-MHz Filter – Useful for 34-MHz/Bypass Video LPF |

|                  |                                               | 1 1          | 5-MHz Filter – Useful for 34-MHz/Bypass Video LPF |

| 5                | Input MUX Selection                           | 0            | Input A Select                                    |

|                  |                                               | 1            | Input B Select                                    |

| 4, 3             | Low-Pass Filter Frequency Selection           | 0 0          | 8.5-MHz LPF – Useful for SDTV, S-Video, 480i      |

|                  |                                               | 0 1          | 16-MHz LPF – Useful for EDTV 480p and VGA         |

|                  |                                               | 1 0          | 34-MHz LPF – Useful for 720p, 1080i, and XGA      |

|                  |                                               | 1 1          | Bypass LPF – Useful for G'B'R' and 1080p          |

| 2, 1, 0<br>(LSB) | Input Bias Mode Selection and Disable Control | 0 0 0        | Disable Channel – Conserves Power                 |