**THVD4421**

JAJSOM2 - APRIL 2024

# THVD4421 120Ω の切り替え可能終端抵抗と IEC-ESD 保護機能を内蔵したマル チプロトコル (RS-232、RS-422、RS485) トランシーバ

### 1 特長

- TIA/EIA-485A および TIA/EIA-232F 規格の要件に 適合またはそれを上回る性能

- RS-232 仕様のトランスミッタ 2 個とレシーバ 2 個

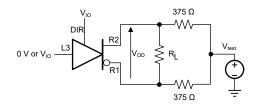

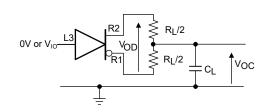

- RS-485 仕様のトランスミッタ 1 個とレシーバ 1 個

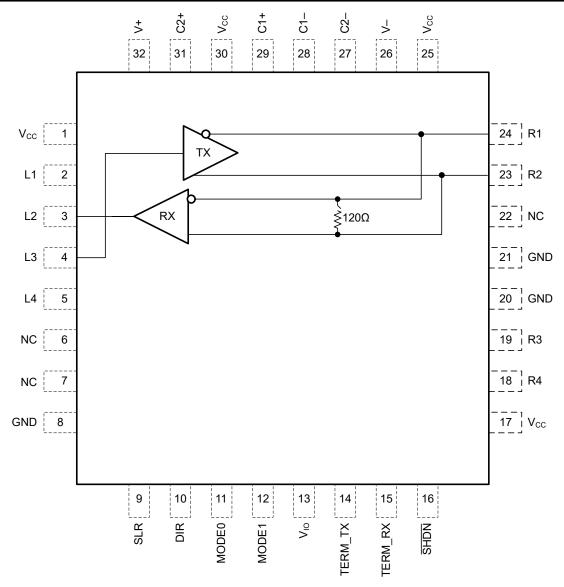

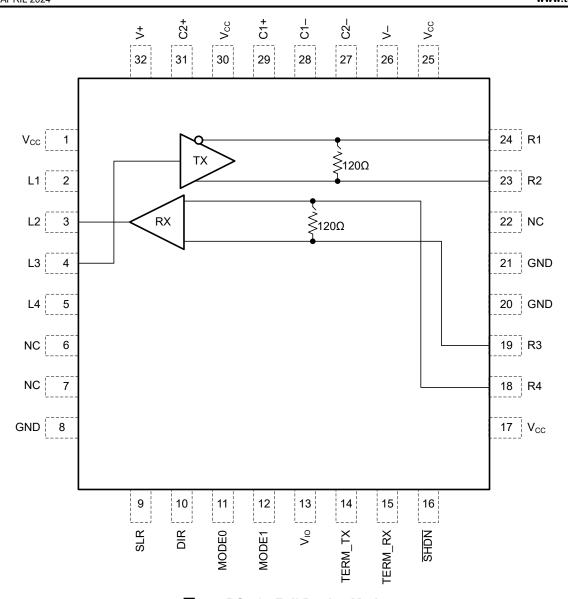

- RS-485 モード用のオンチップの切り替え可能な 120Ω 終端抵抗

- RS-232 信号伝送用チャージ ポンプを内蔵

- 電源電圧:3V~5.5V

- ロジック データおよび制御信号用の 1.65V~5.5V 電

- 5V 電源で 2.1V を超える RS-485 差動出力により PROFIBUS に準拠

- RS-232 モードでの大きな出力スイング (代表値 ±9V)

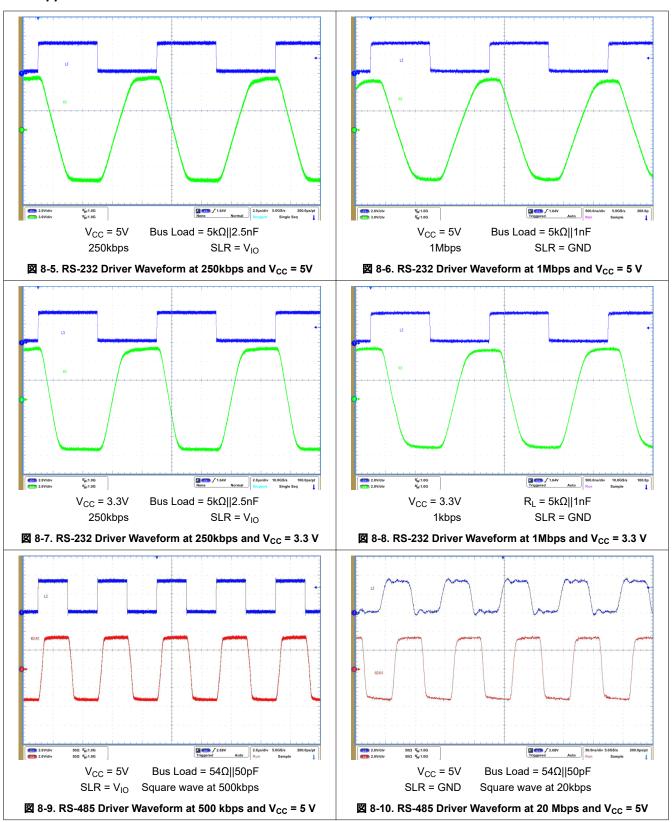

- SLR ピンで選択可能なデータレート:

- RS-232 3T5R モード: 250kbps、1Mbps

- RS-485 の半二重および全二重モード:500kbps、 20Mbps

- バス I/O 保護

- ±16kV HBM ESD

- ±8kV IEC 61000-4-2 接触および ±15kV 気中放

- ±4kV IEC 61000-4-4 高速過渡バースト

- RS-232 モードに対する診断ループバック

- ディセーブル状態でシャットダウンピン使用により大幅 に消費電流を低減 (標準値 10µA)

- グリッチのない電源投入/切断によるホットプラグイン

- RS-485 仕様の 1/8 単位負荷 (最大 256 個のバスノ

- RS-485 レシーバに対する開放、短絡、アイドル バス のフェイルセーフ

- バス短絡保護、サーマル シャットダウン

- 拡張周囲温度範囲:-40℃~125℃

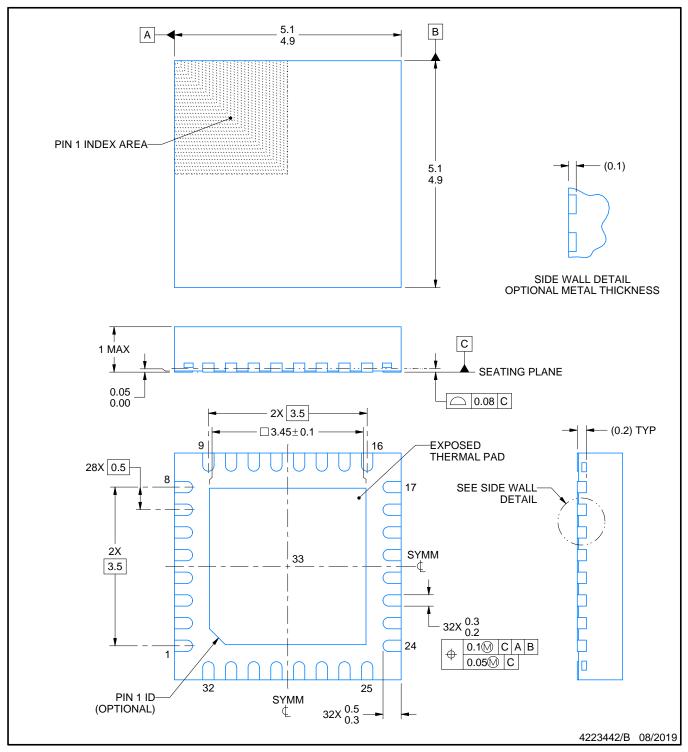

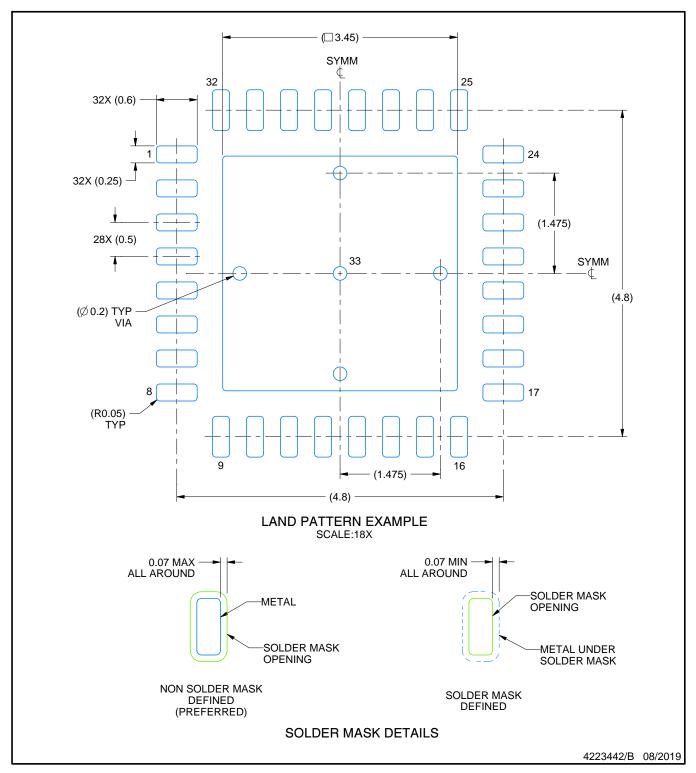

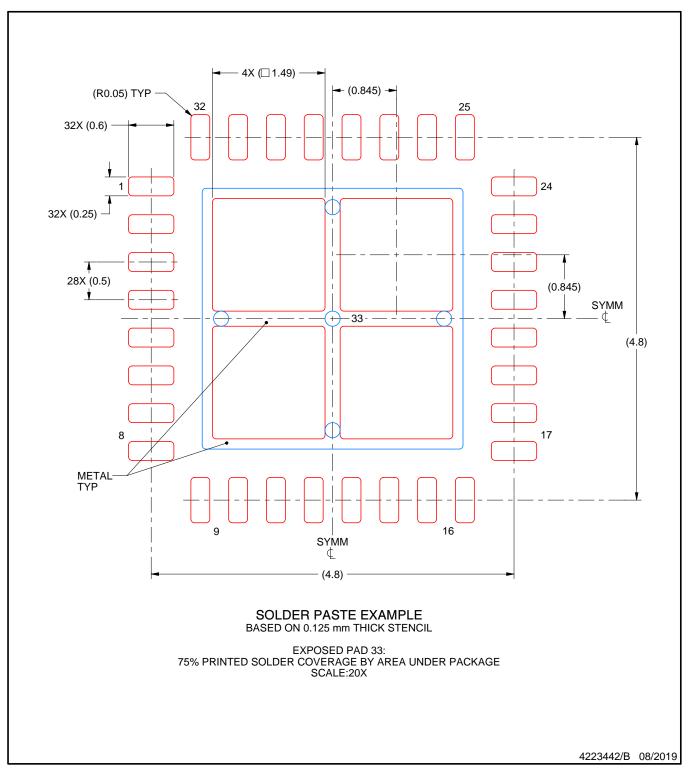

- 省スペースで熱効率の高い 5mm × 5mm VQFN-32 パッケージ

# 2 アプリケーション

- 産業用 PC

- ファクトリ オートメーション / 制御

- HVAC システム

- ビルオートメーション

- POS 端末

- グリッド インフラ

- 産業用輸送

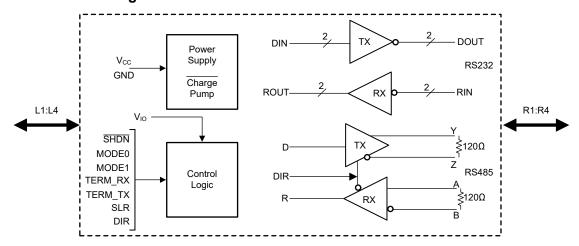

#### 3 概要

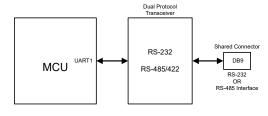

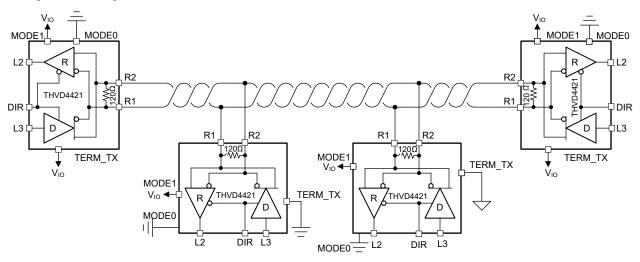

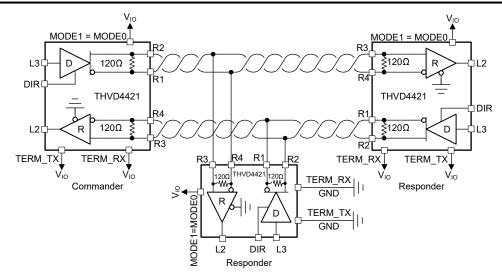

THVD4421 は、RS-232、RS-422、RS-485 の各物理層 をサポートする、高集積で堅牢なマルチプロトコルトランシ ーバです。このデバイスは、2 つのトランスミッタと2 つの レシーバを搭載しており、2T2R RS-232 ポートを実現しま す。また、このデバイスには 1 つのトランスミッタと 1 つの レシーバが内蔵されており、半二重と全二重の RS-485 ポートを実現できます。モード選択ピンにより、プロトコルの 共有バスおよびロジックピンが共通の単一のコネクタを共 有できるようになります。RS-485 バス ピンと RS-232 レシ ーバ入力の終端が内蔵されているため、外付け部品なし で完全な機能を持つ通信ポートを実現できます。これらの デバイスはスルーレート選択機能を備えています。このス ルーレート選択機能を使うと、SLRピンの設定に基づいて 2 つの最大速度でこれらのデバイスを使うことができます。

レベル 4 IEC ESD 保護機能を内蔵しているため、システ ムレベルの外部保護部品は不要です。RS-232 には、ロ ジックからバスへ、およびバスからロジックパスへの機能の 完全性をチェックし、また、ケーブルとコネクタの短絡をチ ェックする、診断ループバック モードが搭載されていま す。さらに、RS-485 レシーバのフェイルセーフ機能は、バ ス入力が開放または短絡しているとき、またはバスがアイド ル状態のときに、受信したロジック出力をロジック High に 駆動します。シャットダウンモードの消費電流は非常に小 さく (代表値 10µA)、消費電力の制約が厳しいアプリケー ションに最適です。このデバイスには、RS-232 用のチャ ージ ポンプ、および RS-232 と RS-485 の両方のドライ バ / レシーバに電力を供給する 3V~5.5V の電源が必要 です。独立したロジック電源  $V_{IO}$  (1.65V $\sim$ 5.5V) により、 低レベルのマイクロコントローラとのインターフェイスが可 能です。

#### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| THVD4421 | VQFN (32)            | 5mm × 5mm                |

- 詳細については、セクション 11 を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

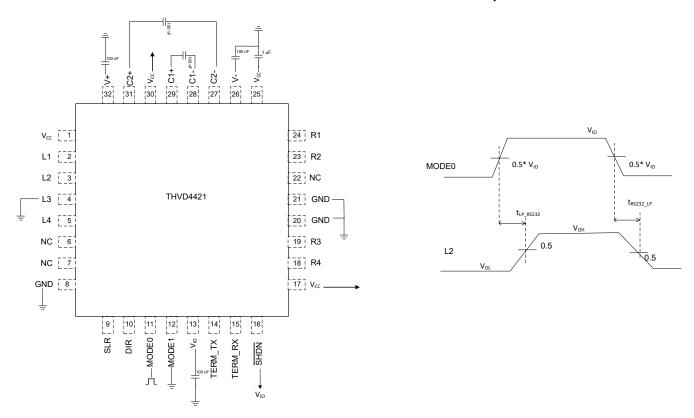

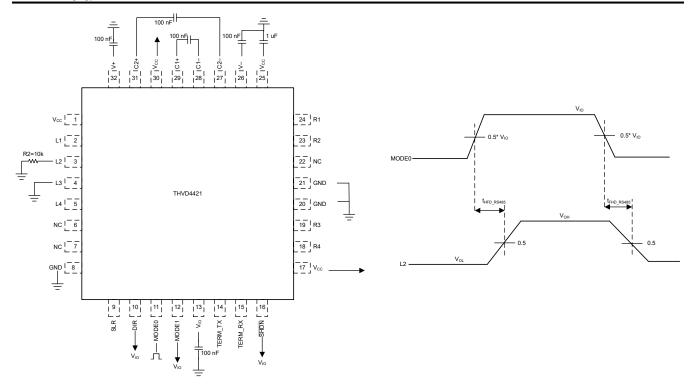

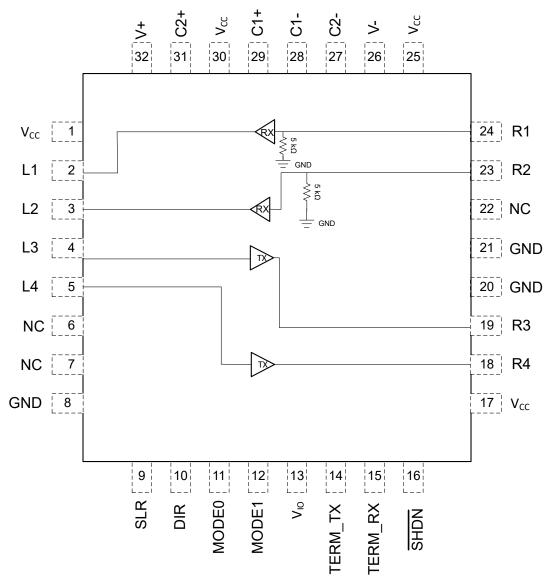

THVD4421 の概略回路図

### **Table of Contents**

| 1 | 特長                                                | 1              | ( |

|---|---------------------------------------------------|----------------|---|

| 2 | アプリケーション                                          | 1              | 7 |

| 3 | 概要                                                | 1              |   |

| 4 | Pin Configuration and Functions                   | 3              |   |

| 5 | Specifications                                    |                |   |

|   | 5.1 Absolute Maximum Ratings                      | <mark>5</mark> |   |

|   | 5.2 ESD Ratings                                   |                | 8 |

|   | 5.3 ESD Ratings [IEC]                             | <u>5</u>       |   |

|   | 5.4 Recommended Operating Conditions              |                |   |

|   | 5.5 Thermal Information                           | 6              |   |

|   | 5.6 Power Dissipation                             |                |   |

|   | 5.7 Electrical Characteristics                    |                | , |

|   | 5.8 Switching Characteristics_RS-485_500kbps      | 10             |   |

|   | 5.9 Switching Characteristics_RS-485_20Mbps       | 10             |   |

|   | 5.10 Switching Characteristics, Driver_RS232      | 11             |   |

|   | 5.11 Switching Characteristics, Receiver_RS232    | 11             |   |

|   | 5.12 Switching Characteristics_MODE switching     | 12             |   |

|   | 5.13 Switching Characteristics_RS-485_Termination |                |   |

|   | resistor                                          | 13             | • |

|   | 5.14 Switching Characteristics_Loopback mode      |                | • |

|   | 5.15 Typical Characteristics                      | 14             |   |

|   |                                                   |                |   |

| o Parameter Measurement information     | 17 |

|-----------------------------------------|----|

| 7 Detailed Description                  | 23 |

| 7.1 Overview                            | 23 |

| 7.2 Functional Block Diagrams           | 23 |

| 7.3 Feature Description                 | 24 |

| 7.4 Device Functional Modes             |    |

| 8 Application and Implementation        | 33 |

| 8.1 Application Information             | 33 |

| 8.2 Typical Application                 |    |

| 8.3 Power Supply Recommendations        | 38 |

| 8.4 Layout                              | 39 |

| 9 Device and Documentation Support      | 41 |

| 9.1 Device Support                      | 41 |

| 9.2ドキュメントの更新通知を受け取る方法                   | 41 |

| 9.3 サポート・リソース                           | 41 |

| 9.4 Trademarks                          | 41 |

| 9.5 静電気放電に関する注意事項                       |    |

| 9.6 用語集                                 | 41 |

| 10 Revision History                     | 41 |

| 11 Mechanical, Packaging, and Orderable |    |

| Information                             | 41 |

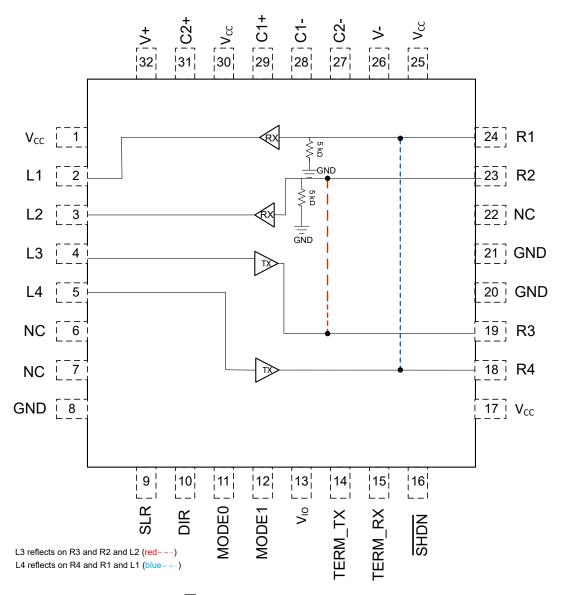

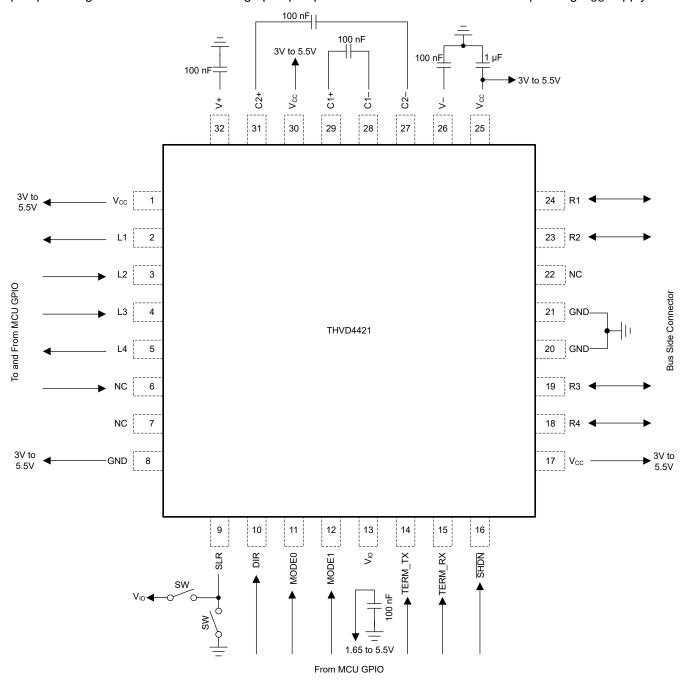

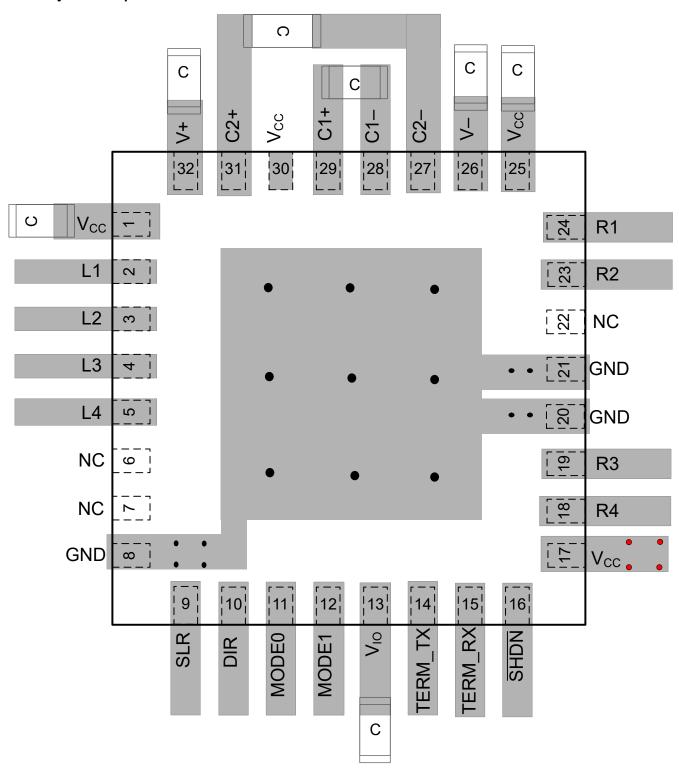

# 4 Pin Configuration and Functions

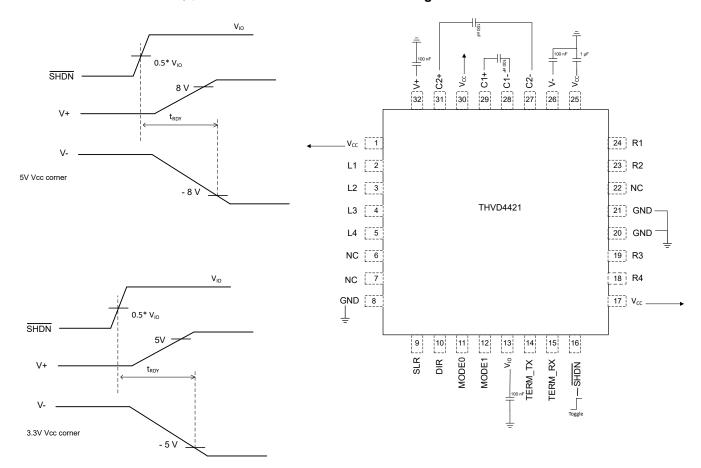

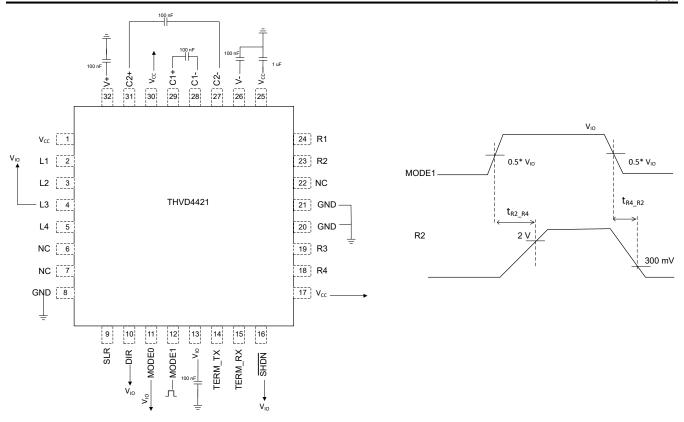

図 4-1. THVD4421 32-Pin VQFN Package (RHB) Top View

表 4-1. Pin Functions

| NAME               | NO. | TYPE | DESCRIPTION                                                                                              |

|--------------------|-----|------|----------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>    | 1   | Р    | 3V to 5.5V supply voltage                                                                                |

| L1                 | 2   | 0    | Logic output                                                                                             |

| L2                 | 3   | 0    | Logic output (RS-232/RS-485)                                                                             |

| L3                 | 4   | I    | Logic input (RS-232/RS-485)                                                                              |

| L4                 | 5   | I    | Logic input                                                                                              |

| NC                 | 6   |      | Not connected internally. Can be left open or Grounded on PCB.                                           |

| V <sub>CC</sub>    | 7   | Р    | 3V to 5.5V supply voltage                                                                                |

| GND <sup>(1)</sup> | 8   | G    | Ground                                                                                                   |

| SLR                | 9   | I    | Slew rate control, internal pull-down. SLR=H enables slow speed (250kbps for RS-232, 500kbps for RS-485) |

| DIR                | 10  | 1    | RS-485 TX/RX enable/disable. Internal pull-down                                                          |

| MODE0              | 11  | 1    | MODE control nine                                                                                        |

| MODE1              | 12  | 1    | MODE control pins                                                                                        |

| V <sub>IO</sub>    | 13  | Р    | 1.65V to 5.5V logic supply voltage                                                                       |

| TERM_TX            | 14  | 1    | 120Ω Termination enable/disable across R1/R2 terminals. Internal Pull down                               |

| TERM_RX            | 15  | I    | 120Ω Termination enable/disable across R3/R4 terminals. Internal Pull down                               |

| SHDN               | 16  | 1    | Device enable/disable. Internal pull-down                                                                |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

### 表 4-1. Pin Functions (続き)

| NAME               | NO.    | TYPE | DESCRIPTION                                                     |  |

|--------------------|--------|------|-----------------------------------------------------------------|--|

| V <sub>CC</sub>    | 17     | Р    | 3V to 5.5V supply voltage                                       |  |

| R4                 | 18     | I/O  | RS-232 driver output or RS-485 inverting receiver input (B)     |  |

| R3                 | 19     | I/O  | RS-232 driver output or RS-485 non-inverting receiver input (A) |  |

| GND <sup>(1)</sup> | 20, 21 | G    | Ground                                                          |  |

| NC                 | 22     |      | Not connected internally. Can be left open or Grounded on PCB.  |  |

| R2                 | 23     | I/O  | RS-232 receiver input or RS-485 bus pin (Y or A)                |  |

| R1                 | 24     | I/O  | RS-232 receiver input or RS-485 bus pin (Z or B)                |  |

| V <sub>CC</sub>    | 25     | Р    | 3V to 5.5V supply voltage                                       |  |

| V-                 | 26     |      | Negative charge pump rail                                       |  |

| C2-                | 27     |      | Negative terminal of charge pump capacitor                      |  |

| C1-                | 28     |      | Negative terminal of charge pump capacitor                      |  |

| C1+                | 29     |      | Positive terminal of charge pump capacitor                      |  |

| V <sub>CC</sub>    | 30     | Р    | 3V to 5.5V supply voltage                                       |  |

| C2+                | 31     |      | Positive terminal of charge pump capacitor                      |  |

| V+                 | 32     |      | Positive charge pump rail                                       |  |

<sup>(1)</sup> GND pins 8, 20, 21 all must be grounded on PCB.

Copyright © 2024 Texas Instruments Incorporated

1

Product Folder Links: THVD4421

### 5 Specifications

### 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                            |                                                                                 | MIN                   | MAX                   | UNIT |

|--------------------------------------------|---------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| Bus supply voltage                         | V <sub>CC</sub> to GND                                                          | -0.5                  | 6                     | V    |

| Logic supply voltage                       | V <sub>IO</sub> to GND                                                          | -0.5                  | V <sub>CC</sub> + 0.2 | V    |

| Charge pump positive-output supply voltage | V+ to GND                                                                       | -0.3                  | 14                    | V    |

| Charge pump negative-output supply voltage | V- to GND                                                                       | 0.3                   | -14                   | V    |

| Charge pump capacitor terminals            | C1+ to GND                                                                      | V <sub>CC</sub> - 0.3 | V+                    | V    |

| Charge pump capacitor terminals            | C2+ to GND                                                                      | -0.3                  | V+                    | V    |

| Charge pump capacitor terminals            | C1- to GND                                                                      | -0.3                  | V <sub>CC</sub>       | V    |

| Charge pump capacitor terminals            | C2- to GND                                                                      | V-                    | -0.3                  | V    |

| Bus voltage                                | Voltage at any bus pin (R1, R2, R3, R4) with respect to GND                     | -16                   | 16                    | V    |

| Differential bus voltage                   | (R1-R2) or (R2-R1), (R3-R4) or (R4-R3) with termination disabled                | -22                   | 22                    | V    |

| Differential bus voltage RS485 mode        | (R1-R2) or (R2-R1), (R3-R4) or (R4-R3) with termination enabled                 | -6                    | 6                     | V    |

| Input voltage                              | Range at any logic pin (L3, L4, SLR, SHDN, TERM_TX, TERM_RX, MODE0, MODE1, DIR) | -0.3                  | V <sub>IO</sub> + 0.2 | V    |

| Receiver output current                    | I <sub>O</sub> (L1, L2)                                                         | -8                    | 8                     | mA   |

| Storage temperature                        | T <sub>stg</sub>                                                                | -65                   | 150                   | °C   |

| Junction temperature                       | TJ                                                                              | -40                   | 170                   | °C   |

<sup>1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings

|                                            |                         |                                                                                |                                        | VALUE   | UNIT |

|--------------------------------------------|-------------------------|--------------------------------------------------------------------------------|----------------------------------------|---------|------|

| V <sub>(ESD)</sub> Electrostatic discharge |                         | Human-body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001 <sup>(1)</sup>          | Bus terminals (R1, R2, R3, R4) and GND | ±16,000 | V    |

|                                            | Liectrostatic discharge |                                                                                | All pins except bus terminals and GND  | ±4,000  | V    |

|                                            |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> |                                        | ±1,500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 5.3 ESD Ratings [IEC]

|                    |                                                                                                                                                         |                                      |                                        | VALUE   | UNIT |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------|---------|------|

|                    | 0 /                                                                                                                                                     | Contact discharge, per IEC 61000-4-2 |                                        | ±8,000  |      |

| V <sub>(ESD)</sub> | powered or unpowered state, In<br>powered condition- either<br>shutdown or RS232 or RS485<br>mode, on chip termination ON or<br>OFF, loopback ON or OFF | Air-gap discharge, per IEC 61000-4-2 | Bus terminals (R1, R2, R3, R4) and GND | ±15,000 | V    |

| V <sub>(EFT)</sub> | Electrical fast transient in RS485<br>HD or FD mode                                                                                                     | Per IEC 61000-4-4                    | Bus terminals (R1, R2, R3, R4)         | ±4,000  | V    |

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

## **5.4 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                              |                                                         |                                                | MIN                 | NOM | MAX                 | UNIT |

|------------------------------|---------------------------------------------------------|------------------------------------------------|---------------------|-----|---------------------|------|

| V <sub>CC</sub>              | Supply voltage                                          |                                                | 3                   |     | 5.5                 | V    |

| V <sub>IO</sub>              | I/O supply voltage                                      |                                                | 1.65                |     | V <sub>CC</sub>     | V    |

| V <sub>I (RS-485)</sub>      | Input voltage at any bus terminal (I                    | R1, R2, R3, R4) in RS-485 mode <sup>(1)</sup>  | -7                  |     | 12                  | V    |

| V <sub>ID</sub>              | Differential input voltage in RS-485 R3) ]              | mode [ (R1-R2) or (R2-R1), (R3-R4) or (R4-     | -12                 |     | 12                  | V    |

| V <sub>I (RS-232)</sub>      | Receiver input voltage in RS-232 r                      | node                                           | -15                 |     | 15                  | V    |

| V <sub>IH</sub>              | High-level input voltage (L3, L4, SI MODE1, DIR inputs) | _R, <del>SHDN</del> , TERM_TX, TERM_RX, MODE0, | 0.7*V <sub>IO</sub> |     | V <sub>IO</sub>     | V    |

| V <sub>IL</sub>              | Low-level input voltage (L3, L4, SL MODE1, DIR inputs)  | R, SHDN, TERM_TX, TERM_RX, MODE0,              | 0                   |     | 0.3*V <sub>IO</sub> | V    |

| Io                           | Output current, driver in RS-485 m                      | ode                                            | -60                 |     | 60                  | mA   |

| I <sub>OR</sub>              | Output current, receiver                                | V <sub>IO</sub> = 1.8 V or 2.5 V               | -2                  |     | 2                   | mA   |

| I <sub>OR</sub>              | Output current, receiver                                | V <sub>IO</sub> = 3.3 V or 5 V                 | -4                  |     | 4                   | mA   |

| R <sub>L</sub>               | Differential load resistance in RS-4                    | 85 mode                                        | 54                  | 60  |                     | Ω    |

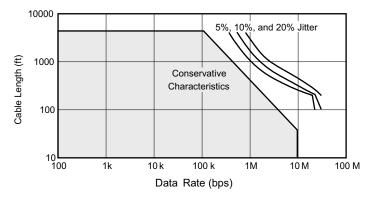

|                              | Signaling rate in DS 495 mode                           | SLR = V <sub>IO</sub>                          |                     |     | 500                 | kbps |

| 4 /4                         | Signaling rate in RS-485 mode                           | SLR = GND or floating                          |                     |     | 20                  | Mbps |

| 1/t <sub>UI</sub>            | Cianalina rata in DC 222 made                           | SLR = V <sub>IO</sub>                          |                     |     | 250                 | kbps |

| 1710                         | Signaling rate in RS-232 mode                           | SLR = GND or floating                          |                     |     | 1                   | Mbps |

| 1/t <sub>UI (loopback)</sub> | Signaling rate in RS-232 loopback                       | mode                                           |                     |     | 1                   | Mbps |

| T <sub>A</sub> (2)           | Operating ambient temperature                           |                                                | -40                 |     | 125                 | °C   |

<sup>(1)</sup> The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

#### 5.5 Thermal Information

|                       |                                              | THVD4421  |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RHB (QFN) | UNIT |

|                       |                                              | 32 PINS   |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 31.0      | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 22.1      | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 11.8      | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.3       | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 11.7      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.5       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the yes application report.

### 5.6 Power Dissipation

| PARAMETER                                                                |                            | TEST CONDITIONS                     |          |          | Typical | Max | UNIT  |

|--------------------------------------------------------------------------|----------------------------|-------------------------------------|----------|----------|---------|-----|-------|

| Driver outputs externally shorted to receiver inputs, MODE1, MODE0 = 11, | Unterminated, TERM_TX = L, | SLR = H                             | 500 kbps | 160      | 200     | 10/ |       |

|                                                                          |                            | TERM_RX = L                         | SLR = L  | 20Mbps   | 390     | 450 | mW    |

| D (NO-403)                                                               |                            | TERM_RX = TERM_TX = V <sub>IO</sub> | SLR = H  | 500 kbps | 430     | 500 | mW    |

|                                                                          |                            |                                     | SLR = L  | 20Mbps   | 500     | 575 | 11100 |

資料に関するフィードバック(ご意見やお問い合わせ) を送信

<sup>2)</sup> Operation is specified for internal (junction) temperatures up to 150°C. Self-heating due to internal power dissipation should be considered for each application. Maximum junction temperature is internally limited by the thermal shut-down (TSD) circuit which disables the driver and receiver when the junction temperature reaches 170°C.

### 5.6 Power Dissipation (続き)

| PARAMETER               |                                 | TEST CONDITIONS                                                                                            |         |          | Typical | Max | UNIT |

|-------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------|---------|----------|---------|-----|------|

| D                       | RS-232 mode with MODE1, MODE0 = |                                                                                                            | SLR = L | 1 Mbps   | 310     | 490 | mW   |

| P <sub>D (RS-232)</sub> | 01                              | $V_{CC}$ = $V_{IO}$ = 5.5V, R3, R4 bus lines loaded with 3 k $\Omega$ , R3 load cap = 2500 pF, L3 toggling | SLR = H | 250 kbps | 180     | 200 | mW   |

### 5.7 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted). All typical values are at 25°C and supply voltage of  $V_{CC}$  = 5 V,  $V_{IO}$  = 3.3 V, unless otherwise noted.

|                     | PARAMETER                                                   | TEST CONDITIONS                                                                           |                                                                                        | MIN                   | TYP                   | MAX  | UNIT     |

|---------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------|-----------------------|------|----------|

| Driver_R            | S-485                                                       |                                                                                           |                                                                                        |                       |                       | ·    |          |

|                     |                                                             | R <sub>L</sub> = 60 Ω, −7 V ≤ V <sub>test</sub> ≤ 12 V (See ⊠ 6-1 )                       |                                                                                        | 1.5                   | 2                     |      | V        |

|                     |                                                             | $R_L$ = 60 Ω, -7 V ≤ $V_{test}$ ≤ 12 V, 4.5 V ≤ $V_{CC}$ ≤ 5.5 V (S                       | ee 🗵 6-1 )                                                                             | 2.1                   | 3                     |      | V        |

| $ V_{OD} $          | Driver differential output voltage magnitude                | R <sub>L</sub> = 100 Ω (See 🗵 6-2 )                                                       |                                                                                        | 2                     | 2.5                   |      | V        |

|                     | voitago magnitado                                           | R <sub>L</sub> = 54 Ω, 4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V (See ⊠ 6-2 )                       |                                                                                        | 2.1                   | 3.3                   |      | V        |

|                     |                                                             | R <sub>L</sub> = 54 Ω (See 🗵 6-2 )                                                        |                                                                                        | 1.5                   | 3.3                   |      | V        |

| $\Delta  V_{OD} $   | Change in magnitude of differential output voltage          | $R_L$ = 54 $\Omega$ or 100 $\Omega$ (See $\boxtimes$ 6-2 )                                |                                                                                        | -50                   |                       | 50   | mV       |

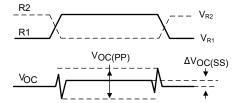

| V <sub>oc</sub>     | Common-mode output voltage                                  | $R_L$ = 54 $\Omega$ or 100 $\Omega$ (See $\boxtimes$ 6-2 )                                |                                                                                        |                       | V <sub>CC</sub> /2    | 3    | V        |

| $\Delta V_{OC(SS)}$ | Change in steady-state common-mode output voltage           | $R_L$ = 54 $\Omega$ or 100 $\Omega$ (See $\boxtimes$ 6-2 )                                |                                                                                        | -50                   |                       | 50   | mV       |

| I <sub>os</sub>     | Short-circuit output current (bus terminals)                | DIR = $V_{IO}$ , -7 V $\leq$ ( $V_{R2}$ or $V_{R1}$ ) $\leq$ 12 V, or R1 shorted t        | $VIR = V_{IO}$ , -7 V $\leq$ ( $V_{R2}$ or $V_{R1}$ ) $\leq$ 12 V, or R1 shorted to R2 |                       |                       | 250  | mA       |

|                     | Driver High impedance output leakage current on             | MODE1, MODE0 = 11, TERM_TX = GND, DIR = GN<br>V <sub>O</sub> = -7V, +12V                  |                                                                                        |                       |                       | 125  | μΑ       |

| l <sub>OZD</sub>    | R1 and R2 in Full duplex mode                               | MODE1, MODE0 = 11, TERM_TX = V <sub>IO</sub> , DIR = GND, +12V                            | $V_{CC} = 5.5V, V_{O} = -7V,$                                                          | - 325                 |                       | 350  | μΑ       |

| Receiver            | RS-485                                                      |                                                                                           |                                                                                        |                       |                       | ,    |          |

| I <sub>I</sub>      | Bus input current (termination disabled)                    | Half and full duplex modes, DIR = 0 V, V <sub>CC</sub> and V <sub>IO</sub> = 0 V or 5.5 V | V <sub>I</sub> = 12 V<br>V <sub>I</sub> = -7 V                                         | -125                  | 75<br>–70             | 125  | μA<br>μA |

| I <sub>RXT</sub>    | Receiver bus input leakage current with termination enabled | Full duplex mode, $V_{CC}$ and $V_{IO}$ = 5.5 V, TERM_RX = $V_{IO}$                       | VI = - 7 to 12 V                                                                       | -325                  |                       | 325  | μA       |

| V <sub>TH+</sub>    | Positive-going input threshold voltage <sup>(1)</sup>       |                                                                                           | I.                                                                                     |                       | - 70                  | - 40 | mV       |

| V <sub>TH-</sub>    | Negative-going input threshold voltage <sup>(1)</sup>       | Over common-mode range of - 7 V to 12 V                                                   |                                                                                        | -200                  | -150                  |      | mV       |

| V <sub>HYS</sub>    | Input hysteresis                                            |                                                                                           |                                                                                        | 25                    | 80                    |      | mV       |

| C <sub>A,B</sub>    | Input differential capacitance                              | Measured between R3 and R4, f = 1 MHz                                                     |                                                                                        |                       | 45                    |      | pF       |

| V <sub>OH</sub>     | Output high voltage, L2 pin                                 | I <sub>OH</sub> = -4 mA, V <sub>IO</sub> = 3 to 3.6 V or 4.5 V to 5.5 V                   |                                                                                        | V <sub>IO</sub> - 0.4 | V <sub>IO</sub> – 0.2 |      | V        |

| V <sub>OL</sub>     | Output low voltage, L2 pin                                  | I <sub>OL</sub> = 4 mA, V <sub>IO</sub> = 3 to 3.6 V or 4.5 V to 5.5 V                    |                                                                                        |                       | 0.2                   | 0.4  | V        |

| V <sub>OH</sub>     | Output high voltage, L2 pin                                 | $I_{OH}$ = -2 mA, $V_{IO}$ = 1.65 to 1.95 V or 2.25 V to 2.75 V                           |                                                                                        | V <sub>IO</sub> - 0.4 | V <sub>IO</sub> – 0.2 |      | V        |

| V <sub>OL</sub>     | Output low voltage, L2 pin                                  | I <sub>OL</sub> = 2 mA, V <sub>IO</sub> = 1.65 to 1.95 V or 2.25 V to 2.75 V              |                                                                                        |                       | 0.2                   | 0.4  | V        |

| I <sub>OZ</sub>     | Output high-impedance current, L2 pin                       | V <sub>O</sub> = 0 V or V <sub>IO</sub> , DIR = VIO, MODE1, MODE0= 10 (ha                 | alf duplex mode)                                                                       | -2                    |                       | 2    | μΑ       |

| Driver_R            | S-232                                                       |                                                                                           |                                                                                        |                       |                       |      |          |

| V <sub>OH</sub>     | High-level output voltage                                   | All DOUT (R3, R4) at R <sub>L</sub> = 3 k $\Omega$ to GND, DIN (L3, L4) 3.6 V             |                                                                                        | 5                     | 5.5                   | 7    | V        |

| V <sub>OL</sub>     | Low-level output voltage                                    | All DOUT (R3, R4) at R <sub>L</sub> = 3 k $\Omega$ to GND, DIN (L3, L4) 3.6 V             | $= V_{IO}; V_{CC} = 3 V to$                                                            | -7                    | -5.5                  | -5   | V        |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

### 5.7 Electrical Characteristics (続き)

over operating free-air temperature range (unless otherwise noted). All typical values are at 25°C and supply voltage of  $V_{CC}$  = 5 V,  $V_{IO}$  = 3.3 V, unless otherwise noted.

|                                | PARAMETER                                                                  | TE                                                                            | EST CONDITIONS                                                            |                                                                                    | MIN                   | TYP                   | MAX          | UNIT     |

|--------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------|-----------------------|--------------|----------|

| V <sub>OH</sub>                | High-level output voltage                                                  | All DOUT (R3, R4) at $R_L = 3 \text{ k}$ to 5.5 V                             | Ω to GND, DIN (L3                                                         | $(L4) = GND; V_{CC} = 4.5 V$                                                       | 7.8                   | 9                     | 11           | V        |

| V <sub>OL</sub>                | Low-level output voltage                                                   | All DOUT (R3, R4) at $R_L = 3 \text{ k}$ 5.5 V                                | Ω to GND, DIN (L3                                                         | , L4) = $V_{IO}$ ; $V_{CC}$ = 4.5 V t                                              | O –11                 | -9                    | -7.7         | V        |

| I <sub>OS</sub>                | Short-circuit output current                                               | V <sub>CC</sub> = 3.6 V                                                       | V <sub>O</sub> = 0 V                                                      |                                                                                    |                       | ±35                   | ±60          | mA       |

| ios                            | (2)                                                                        | V <sub>CC</sub> = 5.5 V                                                       | V <sub>O</sub> = 0 V                                                      |                                                                                    |                       |                       | 100          | ША       |

| r <sub>o</sub>                 | Output resistance on R3, R4                                                | $V_{CC} = 0 \text{ V}, V_{+} = 0 \text{ V}, \text{ and } V_{-} = 0 \text{ V}$ | V <sub>O</sub> = ±2 V                                                     |                                                                                    | 300                   | 10M                   |              | Ω        |

| I <sub>off</sub>               | Output leakage current on R3, R4                                           | SHDN = GND                                                                    | $V_O = \pm 12 \text{ V}$ $V_O = \pm 10 \text{ V}$                         | $V_{CC} = 3 \text{ to } 3.6 \text{ V}$<br>$V_{CC} = 4.5 \text{ to } 5.5 \text{ V}$ |                       |                       | ±125<br>±125 | μA<br>μA |

| Receiver                       | RS-232                                                                     |                                                                               | 10 =101                                                                   | 100 110 10 1                                                                       |                       |                       |              |          |

|                                |                                                                            | I <sub>OH</sub> = -4 mA, V <sub>IO</sub> = 3 to 3.6 V o                       | or 4.5 V to 5.5 V                                                         |                                                                                    | V <sub>IO</sub> - 0.5 | V <sub>IO</sub> – 0.2 |              | V        |

| V <sub>OH</sub>                | High-level output voltage L1/L2                                            | $I_{OH} = -2 \text{ mA}, V_{IO} = 1.65 \text{ to } 1.9$                       |                                                                           | 75 V                                                                               |                       | V <sub>IO</sub> – 0.2 |              | V        |

|                                | Low-level output                                                           | I <sub>OL</sub> = 4 mA, V <sub>IO</sub> = 3 to 3.6 V or                       | 4.5 V to 5.5 V                                                            |                                                                                    |                       |                       | 0.4          | V        |

| V <sub>OL</sub>                | voltage L1/L2                                                              | I <sub>OL</sub> = 2 mA, V <sub>IO</sub> = 1.65 to 1.95                        | <sub>L</sub> = 2 mA, V <sub>IO</sub> = 1.65 to 1.95 V or 2.25 V to 2.75 V |                                                                                    |                       |                       | 0.4          | V        |

|                                | Positive-going input                                                       | V <sub>CC</sub> = 3.3 V                                                       |                                                                           |                                                                                    |                       | 1.6                   | 2.4          | V        |

| V <sub>IT+</sub>               | threshold voltage on<br>RS-232 receiver inputs (R1,<br>R2)                 | V <sub>CC</sub> = 5 V                                                         |                                                                           |                                                                                    |                       | 1.9                   | 2.4          | V        |

|                                | Negative-going input                                                       | / <sub>CC</sub> = 3.3 V                                                       |                                                                           |                                                                                    |                       | 1.1                   |              | V        |

| $V_{IT-}$                      | threshold voltage on<br>RS-232 receiver inputs (R1,<br>R2)                 | V <sub>CC</sub> = 5 V                                                         |                                                                           |                                                                                    | 0.8                   | 1.4                   |              | ٧        |

| V <sub>hys</sub>               | Input hysteresis on receiver inputs (V <sub>IT+</sub> – V <sub>IT-</sub> ) |                                                                               |                                                                           |                                                                                    | 0.4                   | 0.5                   |              | ٧        |

| I <sub>off</sub>               | Output leakage current on receiver output pins L1/L2                       | SHDN = 0 V                                                                    |                                                                           |                                                                                    |                       | ±0.05                 | ±10          | μΑ       |

| rı                             | Input resistance on receiver input pins                                    | -15 V ≤ V <sub>I</sub> ≤ 15 V                                                 |                                                                           |                                                                                    | 3                     | 5                     | 7            | kΩ       |

| Thermal F                      | Protection                                                                 |                                                                               |                                                                           |                                                                                    | ·                     |                       |              |          |

| T <sub>SHDN</sub>              | Thermal shutdown threshold                                                 | Temperature rising                                                            |                                                                           |                                                                                    | 150                   | 170                   |              | °C       |

| T <sub>HYS</sub>               | Thermal shutdown hysteresis                                                |                                                                               |                                                                           |                                                                                    |                       | 15                    |              | °C       |

| Supply                         |                                                                            |                                                                               |                                                                           |                                                                                    |                       |                       |              |          |

| UV <sub>VCC</sub> (rising)     | Rising under-voltage threshold on V <sub>CC</sub>                          |                                                                               |                                                                           |                                                                                    |                       | 2.5                   | 2.7          | V        |

| UV <sub>VCC</sub><br>(falling) | Falling under-voltage threshold on V <sub>CC</sub>                         |                                                                               |                                                                           |                                                                                    | 1.9                   | 2.1                   |              | V        |

| UV <sub>VCC(hys</sub>          | Hysteresis on under-voltage of $V_{\rm CC}$                                |                                                                               |                                                                           |                                                                                    | 100                   | 400                   |              | mV       |

| UV <sub>VIO</sub> (rising)     | Rising under-voltage threshold on V <sub>IO</sub>                          |                                                                               |                                                                           |                                                                                    |                       | 1.5                   | 1.6          | V        |

| UV <sub>VIO</sub><br>(falling) | Falling under-voltage threshold on V <sub>IO</sub>                         |                                                                               |                                                                           |                                                                                    | 1.2                   | 1.4                   |              | V        |

| UV <sub>VIO(hys)</sub>         | Hysteresis on under-voltage of V <sub>IO</sub>                             |                                                                               |                                                                           |                                                                                    | 85                    | 100                   |              | mV       |

### 5.7 Electrical Characteristics (続き)

over operating free-air temperature range (unless otherwise noted). All typical values are at 25°C and supply voltage of  $V_{CC}$  = 5 V,  $V_{IO}$  = 3.3 V, unless otherwise noted.

|                              | PARAMETER                                                                         | TEST CONDITIONS                                                                                                                              |                                                          | MIN                 | TYP                 | MAX                 | UNIT |

|------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------|---------------------|---------------------|------|

|                              |                                                                                   | $V_{CC}$ = 4.5 V to 5.5 V, $\overline{SHDN}$ = GND, all other logic inpload on bus, $T_A \le 125$ °C                                         | out pins floating, no                                    |                     | 5                   | 20                  | μA   |

|                              | Supply current in shutdown                                                        | $V_{CC}$ = 3 V to 3.6 V, $\overline{SHDN}$ = GND, all other logic input on bus, $T_A \le$ 125 $^{\circ}C$                                    | pins floating, no load                                   |                     | 3                   | 15                  | μA   |

| ICC_SHDN                     | mode                                                                              | $V_{CC}$ = 4.5 V to 5.5 V, $\overline{SHDN}$ = GND, all other logic inpload on bus, $T_A \le 105$ °C                                         | out pins floating, no                                    |                     | 5                   | 15                  | μA   |

|                              |                                                                                   | $V_{CC}$ = 3 V to 3.6 V, $\overline{SHDN}$ = GND, all other logic input on bus, $T_A \le$ 105 $^{\circ}C$                                    | pins floating, no load                                   |                     | 3                   | 10                  | μA   |

| I <sub>IO_SHDN</sub>         | Logic supply current in shutdown mode                                             | V <sub>IO</sub> = 1.65 V to 5.5 V, SHDN = GND, all other logic inp                                                                           | out pins floating                                        |                     |                     | 2                   | μΑ   |

|                              | Supply current (quiescent),                                                       | Driver and receiver enabled, DIR = V <sub>IO</sub> , MODE1, MODE0 = 11 (Full duplex)                                                         | No load                                                  |                     | 1.7                 | 3.4                 | mA   |

| I <sub>CC_485</sub>          | V <sub>CC</sub> = 4.5 V to 5.5 V<br>TERM_RX, TERM_TX=<br>Floating or low, SLR = X | Driver enabled, receiver disabled, DIR = V <sub>IO</sub> ,<br>MODE1, MODE0 = 10 (Half duplex)                                                | No load                                                  |                     | 1.3                 | 2.8                 | mA   |

| ricating of low, out ( - X   | Driver disabled, receiver enabled, DIR = GND, MODE1, MODE0 = 10 (Half duplex)     | No load                                                                                                                                      |                                                          | 0.8                 | 1.5                 | mA                  |      |

|                              | Supply current (quiescent),                                                       | Driver and receiver enabled, DIR = V <sub>IO</sub> , MODE1, MODE0 = 11 (Full duplex)                                                         | No load                                                  |                     | 1.5                 | 2.8                 | mA   |

| I <sub>CC_485</sub>          | V <sub>CC</sub> = 3 V to 3.6 V<br>TERM_RX, TERM_TX=                               | Driver enabled, receiver disabled, DIR = V <sub>IO</sub> , MODE1, MODE0 = 10 (Half duplex)                                                   | No load                                                  |                     | 1                   | 2.3                 | mA   |

|                              | Floating or low, SLR = X                                                          | Driver disabled, receiver enabled, DIR = GND, MODE1, MODE0 = 10 (Half duplex)                                                                | No load                                                  |                     | 0.7                 | 1.3                 | mA   |

|                              | Logic supply current (quiescent), V <sub>IO</sub> = 3 to 3.6 V                    | Driver disabled, Receiver enabled, SLR = GND, DIR = GND; MODE1, MODE0 = 10 (half duplex)                                                     | No load                                                  |                     | 7                   | 17                  | μA   |

| I <sub>IO_485</sub>          | TERM_RX, TERM_TX= Floating                                                        | Driver disabled, Receiver enabled, SLR = V <sub>IO</sub> ; DIR = GND; MODE1, MODE0 = 10 (half duplex)                                        | No load                                                  |                     | 8                   | 21                  | μΑ   |

| I <sub>CCDT_485</sub>        | Supply current in RS-485 driver termination mode                                  | Driver enabled with termination ON; MODE1, MODE0 = 11 (full duplex)                                                                          | DIR= V <sub>IO</sub> , TERM_TX<br>= V <sub>IO</sub>      |                     | 38                  | 50                  | mA   |

| I <sub>CCRT_485</sub>        | Supply current in RS-485 receiver termination mode                                | Receiver enabled with termination ON; MODE1, MODE0 = 11 (full duplex)                                                                        | DIR = GND,<br>TERM_RX = V <sub>IO</sub>                  |                     | 1                   | 1.5                 | mA   |

| I <sub>CC_RS232</sub>        | Supply current in RS-232 mode                                                     | MODE1, MODE0 = 01, SHDN = V <sub>IO</sub> ; other logic inputs floating                                                                      | No load                                                  |                     | 3.2                 | 4                   | mA   |

| I <sub>CC_RS232</sub><br>_LB | Supply current in RS-232 loopback mode                                            | MODE1 = 0, MODE0 = 0; L3 = L4 = static logic high, -40 °C $\leq$ T <sub>A</sub> $\leq$ 85 °C                                                 | No extra load on<br>RS-232 drivers or on<br>logic output |                     | 12                  | 14                  | mA   |

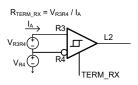

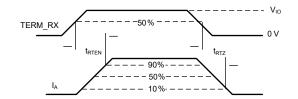

| On-Chip to                   | ermination resistor_RS-485                                                        |                                                                                                                                              |                                                          |                     |                     |                     |      |

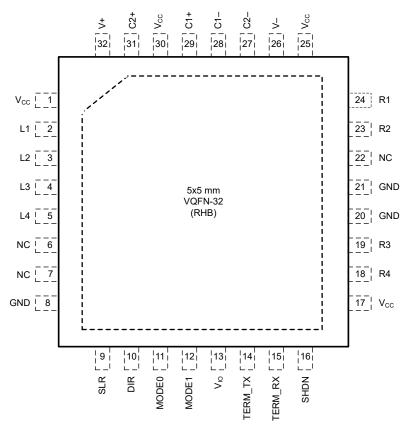

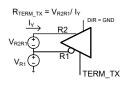

| R <sub>TERM_TX</sub>         | 120 Ω termination across<br>Driver output R1/R2<br>terminals                      | MODE1, MODE0 = 11 (Full duplex) or 10 (half duplex TERM_TX = V <sub>IO</sub> , V <sub>R2R1</sub> = 2 V, V <sub>R1</sub> = -7 V, 0 V, 10 V, S | •                                                        | 102                 | 120                 | 138                 | Ω    |

| R <sub>TERM_RX</sub>         | 120 Ω termination across receiver output R3/R4 terminals                          | MODE1, MODE0 = 11 (Full duplex); TERM_RX = V <sub>IO</sub> V, 0 V, 10 V, See ☑ 6-9                                                           | , V <sub>R3R4</sub> = 2 V, V <sub>R4</sub> = -7          | 102                 | 120                 | 138                 | Ω    |

| Logic                        | I                                                                                 |                                                                                                                                              |                                                          |                     |                     |                     |      |

| I <sub>IN</sub>              | Input current (L3, L4, DIR, SHDN, SLR, TERM_TX, TERM_RX, MODE1, MODE0)            | 1.65 V ≤ V <sub>IO</sub> ≤ 5.5 V, 0 V ≤ V <sub>IN</sub> ≤ V <sub>IO</sub>                                                                    |                                                          | -20                 |                     | 5                   | μA   |

| V <sub>IT+(IN)</sub>         | Rising threshold: logic inputs                                                    |                                                                                                                                              |                                                          |                     | 0.6*V <sub>IO</sub> | 0.7*V <sub>IO</sub> | V    |

| V <sub>IT-(IN)</sub>         | Falling threshold: logic inputs                                                   | 1.65 V ≤ V <sub>IO</sub> ≤ 5.5 V                                                                                                             |                                                          | 0.3*V <sub>IO</sub> | 0.4*V <sub>IO</sub> |                     | V    |

| V <sub>IN(HYS)</sub>         | Input threshold: logic inputs                                                     |                                                                                                                                              |                                                          | 0.1*V <sub>IO</sub> | 0.2*V <sub>IO</sub> |                     | V    |

<sup>(1)</sup> Under any specific conditions,  $V_{TH+}$  is assured to be at least  $V_{HYS}$  higher than  $V_{TH-}$ .

<sup>(2)</sup> Short-circuit durations should be controlled to prevent exceeding the device absolute power dissipation ratings, and not more than one output should be shorted at a time.

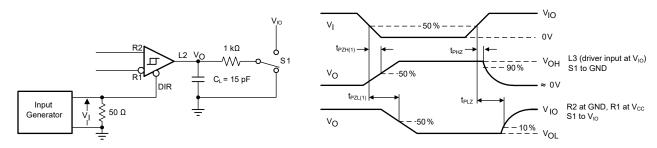

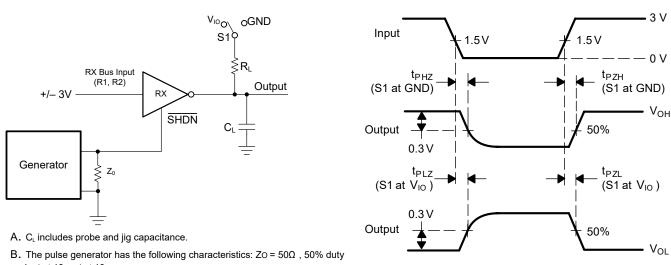

### 5.8 Switching Characteristics\_RS-485\_500kbps

500-kbps (with SLR =  $V_{IO}$ ) over recommended operating conditions. All typical values are at 25°C and supply voltage of  $V_{CC}$  = 5 V,  $V_{IO}$  = 3.3 V, unless otherwise noted. (1)

|                                              | PARAMETER                                                           | TEST CONDI                                          | TIONS                                             | MIN | TYP | MAX  | UNIT |

|----------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------|-----|-----|------|------|

| Driver                                       |                                                                     |                                                     |                                                   |     |     | -    |      |

|                                              | Differential output vice/fell time                                  |                                                     | V <sub>CC</sub> = 3 to 3.6 V, Typical at 3.3V     | 210 | 300 | 600  | ns   |

| t <sub>r</sub> , t <sub>f</sub>              | Differential output rise/fall time                                  |                                                     | V <sub>CC</sub> = 4.5 to 5.5 V,<br>Typical at 5 V | 250 | 300 | 600  | ns   |

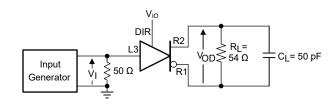

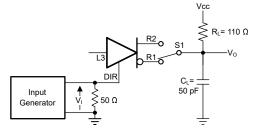

|                                              | Drangation delay                                                    | $R_L = 54 \Omega, C_L = 50 pF$                      | V <sub>CC</sub> = 3 to 3.6 V, Typical at 3.3V     |     | 250 | 450  | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub>          | Propagation delay                                                   | See ☑ 6-3                                           | V <sub>CC</sub> = 4.5 to 5.5 V,<br>Typical at 5 V |     | 250 | 450  | ns   |

|                                              | t <sub>SK(P)</sub> Pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub> |                                                     | V <sub>CC</sub> = 3 to 3.6 V, Typical at 3.3V     |     | 2   | 15   | ns   |

| <sup>L</sup> SK(P)                           |                                                                     |                                                     | V <sub>CC</sub> = 4.5 to 5.5 V,<br>Typical at 5 V |     | 2   | 15   | ns   |

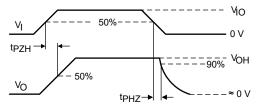

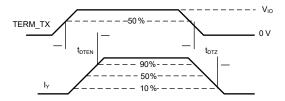

| t <sub>PHZ</sub> , t <sub>PLZ</sub>          | Disable time                                                        | MODE1, MODE0 = 10 (half duplex) or 11 (full duplex) | See ☒ 6-4 and ☒ 6-5                               |     | 80  | 150  | ns   |

| t <sub>PZH</sub> , t <sub>PZL</sub>          | Enable time                                                         | MODE1, MODE0 = 11 (full duplex): receiver enabled   |                                                   |     | 200 | 650  | ns   |

| Receiver                                     |                                                                     |                                                     |                                                   |     |     |      |      |

| t <sub>r</sub> , t <sub>f</sub>              | Output rise/fall time                                               |                                                     |                                                   |     | 13  | 20   | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub>          | Propagation delay                                                   | C <sub>L</sub> = 15 pF                              | See 図 6-6                                         |     | 700 | 1200 | ns   |

| t <sub>SK(P)</sub>                           | Pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub>                    |                                                     |                                                   |     | 10  | 45   | ns   |

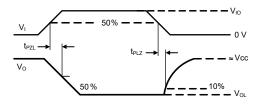

| t <sub>PHZ</sub> , t <sub>PLZ</sub>          | Disable time in half duplex mode                                    |                                                     |                                                   |     | 30  | 80   | ns   |

| t <sub>PZH(1)</sub>                          | Funda dina dina balkahara                                           | MODE1, MODE0 = 10, TERM_TX<br>= V <sub>IO</sub>     | See 図 6-7                                         |     | 60  | 155  | ns   |

| t <sub>PZL(1)</sub>                          | Enable time in half duplex mode                                     | * IU                                                |                                                   |     | 450 | 1250 | ns   |

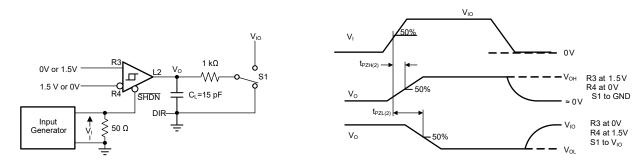

| t <sub>PZH(2)</sub> ,<br>t <sub>PZL(2)</sub> | Enable time from shutdown with TX disabled in full duplex mode      | DIR = 0 V; MODE1, MODE0 = 11                        | See 図 6-8                                         |     | 7   | 16   | μs   |

<sup>(1)</sup> A, B are RX input, Y/Z are driver output terminals in Full duplex mode

### 5.9 Switching Characteristics\_RS-485\_20Mbps

20-Mbps (SLR = GND) over recommended operating conditions. All typical values are at 25°C and supply voltage of  $V_{CC}$  = 5 V,  $V_{IO}$  = 3.3 V. (1)

|                                                                     | PARAMETER                                        | TEST CON                                            | IDITIONS                                          | MIN | TYP | MAX | UNIT |

|---------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|---------------------------------------------------|-----|-----|-----|------|

| Driver                                                              |                                                  |                                                     |                                                   |     |     | '   |      |

|                                                                     | Differential output via /fall time               |                                                     | V <sub>CC</sub> = 3 to 3.6 V, Typical at 3.3 V    | 5   | 10  | 15  | ns   |

| t <sub>r</sub> , t <sub>f</sub>                                     | Differential output rise/fall time               |                                                     | V <sub>CC</sub> = 4.5 to 5.5 V,<br>Typical at 5 V | 5   | 10  | 15  | ns   |

|                                                                     | Dranagation dalay                                | $R_L = 54 \Omega, C_L = 50 pF$                      | V <sub>IO</sub> = 1.65 V to 1.95V                 | 14  | 25  | 58  | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub>                                 | Propagation delay                                | See 図 6-3                                           | V <sub>IO</sub> = 3 V to 3.6 V                    | 9   | 20  | 46  | ns   |

| t <sub>SK(P)</sub> Pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub> |                                                  | V <sub>CC</sub> = 3 to 3.6 V, Typical at 3.3 V      |                                                   | 1   | 3.5 | ns  |      |

|                                                                     | Pulse skew,  tpHL - tpLH                         |                                                     | V <sub>CC</sub> = 4.5 to 5.5 V,<br>Typical at 5 V |     | 1   | 3.5 | ns   |

| t <sub>PHZ</sub> , t <sub>PLZ</sub>                                 | Disable time                                     | MODE1, MODE0 = 10 (half duplex) or 11 (full duplex) | See ⊠ 6-4 and ⊠ 6-5                               |     | 11  | 65  | ns   |

| t <sub>PZH</sub> , t <sub>PZL</sub>                                 | Enable time                                      | MODE1, MODE0 = 11 (full duplex): receiver enabled   |                                                   |     | 8   | 80  | ns   |

| Receiver                                                            |                                                  |                                                     |                                                   |     |     |     |      |

| t <sub>r</sub> , t <sub>f</sub>                                     | Output rise/fall time                            |                                                     |                                                   |     | 5   | 10  | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub>                                 | Propagation delay                                | C <sub>L</sub> = 15 pF                              | See 🗵 6-6                                         |     | 40  | 70  | ns   |

| t <sub>SK(P)</sub>                                                  | Pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub> |                                                     |                                                   |     |     | 10  | ns   |

### 5.9 Switching Characteristics\_RS-485\_20Mbps (続き)

20-Mbps (SLR = GND) over recommended operating conditions. All typical values are at 25°C and supply voltage of V<sub>CC</sub> = 5  $V_{10} = 3.3 V_{.}$  (1)

| PARAMETER                                    |                                                                | TEST CONDITIONS                                 |           | MIN | TYP | MAX | UNIT |

|----------------------------------------------|----------------------------------------------------------------|-------------------------------------------------|-----------|-----|-----|-----|------|

| t <sub>PHZ</sub> , t <sub>PLZ</sub>          | Disable time in half duplex mode                               | MODE1, MODE0 = 10, TERM_TX                      |           |     | 20  | 80  | ns   |

| t <sub>PZH(1)</sub> ,<br>t <sub>PZL(1)</sub> | Enable time in half duplex mode                                | WODE1, MODE0 = 10, TERM_TX<br>= V <sub>IO</sub> | See 図 6-7 |     | 50  | 160 | ns   |

| t <sub>PZH(2)</sub> ,<br>t <sub>PZL(2)</sub> | Enable time from shutdown with TX disabled in full duplex mode | DIR = 0 V; MODE1, MODE0 = 11                    | See 図 6-8 |     | 4   | 15  | μs   |

A, B are RX input, Y/Z are driver output terminals in Full duplex mode.

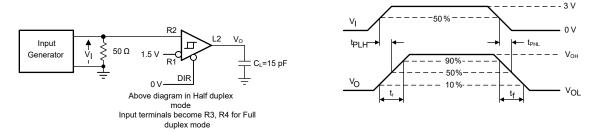

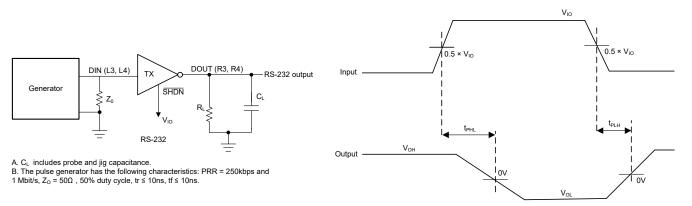

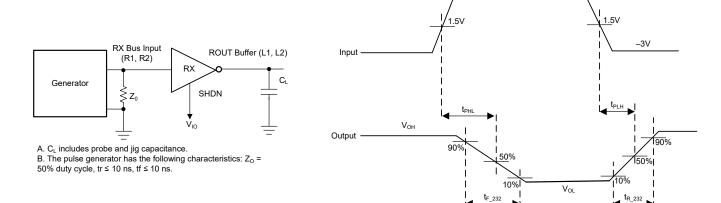

### 5.10 Switching Characteristics, Driver\_RS232

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)(1)

|                                        | PARAMETER                             | TEST C                                                                      | ONDITIONS                                                | MIN  | TYP <sup>(2)</sup> | MAX  | UNIT |

|----------------------------------------|---------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------|------|--------------------|------|------|

| 250 kbp                                | os                                    |                                                                             |                                                          |      |                    | '    |      |

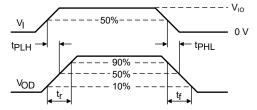

|                                        | Maximum data rate                     | $R_L = 3 \text{ k}\Omega$<br>One DOUT switching                             | C <sub>L</sub> = 2500 pF<br>See ⊠ 6-15                   | 250  | 500                |      | kbps |

| t <sub>PHL</sub> ,<br>t <sub>PHL</sub> | Transmitter propagation delay         | $R_L = 3 \text{ k}\Omega \text{ to } 7 \text{ k}\Omega$                     | C <sub>L</sub> = 150 pF to 2500 pF<br>See ☑ 6-15         |      | 0.8                | 2    | μs   |

| t <sub>sk(p)</sub>                     | Transmitter Pulse skew <sup>(3)</sup> |                                                                             | See 🗵 0-15                                               |      | 220                | 600  | ns   |

| CD(+r)                                 | Class rate transition region          | $V_{CC} = 3.3 \text{ V} \pm 10\%, 5 \text{ V} \pm 10\%,$                    | C <sub>L</sub> = 150 pF to 1000 pF                       | 6    |                    | 30   | \//a |

| SR(tr)                                 | Slew rate, transition region          | $R_L$ = 3 kΩ to 7 kΩ, See $\boxtimes$ 6-16                                  | C <sub>L</sub> = 150 pF to 2500 pF                       | 4    |                    | 30   | V/µs |

| 1 Mbps                                 |                                       |                                                                             |                                                          |      |                    | '    |      |

|                                        |                                       | $R_L = 3 k\Omega$                                                           | C <sub>L</sub> = 250 pF, V <sub>CC</sub> = 3 to 3.6 V    | 1000 |                    |      | kbps |

|                                        | Maximum data rate                     | One DOUT switching, See ⊠ 6-15                                              | C <sub>L</sub> = 1000 pF, V <sub>CC</sub> = 4.5 to 5.5 V | 1000 |                    |      | kbps |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Transmitter propagation delay         | $R_1 = 3k \text{ to } 7 \text{ k}\Omega$ , See $\boxtimes 6-15$             | C <sub>L</sub> = 150 pF to 1000 pF                       |      | 300                | 800  | ns   |

| t <sub>sk(p)</sub>                     | Pulse skew <sup>(3)</sup>             |                                                                             |                                                          |      | 25                 | 150  | ns   |

| SD/tr)                                 | Slow rate transition region           | $R_L$ = 3k to 7 kΩ, VCC = 4.5 V to $C_L$ = 150 pF to 1000 pF, See $\square$ | 18                                                       |      | 150                | V/µs |      |

| SR(tr)                                 | Slew rate, transition region          | $R_L$ = 3k to 7 k $\Omega$ , VCC = 3 V to 3.6 V                             | 6-16                                                     | 15   |                    | 150  | V/µs |

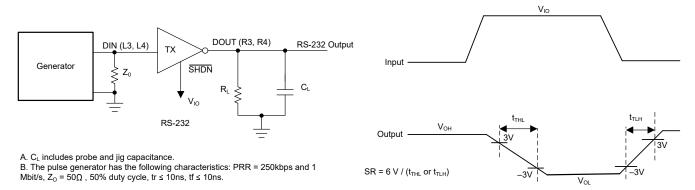

- Test conditions are C1–C4 = 0.1  $\mu$ F at V<sub>CC</sub> = 3.3 V + 0.3 V; V<sub>CC</sub> = 5 V  $\pm$  0.5 V. All typical values are at V<sub>CC</sub> = 3.3 V or V<sub>CC</sub> = 5 V, and T<sub>A</sub> = 25°C. Pulse skew is defined as  $|t_{PLH}-t_{PHL}|$  of each channel of the same device.

### 5.11 Switching Characteristics, Receiver\_RS232

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)(1)

|                      | PARAMETER                                                             | TEST CONDITIONS                                            | MIN TYP <sup>(2)</sup> | MAX | UNIT |

|----------------------|-----------------------------------------------------------------------|------------------------------------------------------------|------------------------|-----|------|

| 250 kbp              | s                                                                     |                                                            |                        |     |      |

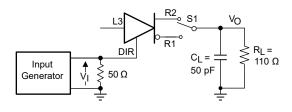

| t <sub>PLH</sub>     | Propagation delay time, low- to high-level output                     | C = 450 pF See W 6 47                                      | 150                    | 550 | ns   |

| t <sub>PHL</sub>     | Propagation delay time, high- to low-level output                     | - C <sub>L</sub> = 150 pF, See ⊠ 6-17                      | 150                    | 550 | ns   |

| t <sub>PLH</sub>     | Propagation delay time, low- to high-level output                     | C = 45 pF Coo   W C 47                                     | 130                    | 520 | ns   |

| t <sub>PHL</sub>     | Propagation delay time, high- to low-level output                     | C <sub>L</sub> = 15 pF, See 図 6-17                         | 130                    | 520 | ns   |

|                      | Rise/fall time (receiver buffer output), V <sub>IO</sub> = 3 to 5.5 V | C <sub>L</sub> = 150 pF, See ⊠ 6-17                        | 20                     | 50  | ns   |

| t <sub>R_232</sub> , |                                                                       | C <sub>L</sub> = 15 pF, See ⊠ 6-17                         | 5                      | 10  | ns   |

| t <sub>F_232</sub>   | Rise/fall time (receiver buffer output), V <sub>IO</sub> = 1.65 to    | C <sub>L</sub> = 150 pF, See ⊠ 6-17                        | 40                     | 90  | ns   |

|                      | 2.75 V                                                                | C <sub>L</sub> = 15 pF, See ⊠ 6-17                         | 10                     | 20  | ns   |

| t <sub>en</sub>      | Output enable time                                                    | C - 450 pF D - 2 kO Coo W 6 40                             | 6                      | 14  | us   |

| t <sub>dis</sub>     | Output disable time                                                   | C <sub>L</sub> = 150 pF, R <sub>L</sub> = 3 kΩ, See ⊠ 6-18 | 100                    | 200 | ns   |

|                      | Pulse skew <sup>(3)</sup>                                             | C <sub>L</sub> = 150 pF, See ⊠ 6-17                        | 50                     | 135 | ns   |

| t <sub>sk(p)</sub>   | Fuise Skew(-)                                                         | C <sub>L</sub> = 15 pF, See ⊠ 6-17                         | 50                     | 135 | ns   |

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

### 5.11 Switching Characteristics, Receiver\_RS232 (続き)

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)(1)

|                      | PARAMETER                                                             | TEST CONDITIONS                                            | MIN TYP <sup>(2)</sup> | MAX | UNIT |

|----------------------|-----------------------------------------------------------------------|------------------------------------------------------------|------------------------|-----|------|

| 1 Mbps               |                                                                       |                                                            |                        |     |      |

| t <sub>PLH</sub>     | Propagation delay time, low- to high-level output                     | C <sub>I</sub> = 150 pF, See ⊠ 6-17                        | 150                    | 550 | ns   |

| t <sub>PHL</sub>     | Propagation delay time, high- to low-level output                     | - C <sub>L</sub> = 130 μr, See ⊠ 0-17                      | 150                    | 550 | ns   |

| t <sub>PLH</sub>     | Propagation delay time, low- to high-level output                     | C = 45 pF Sec   W C 47                                     | 130                    | 520 | ns   |

| t <sub>PHL</sub>     | Propagation delay time, high- to low-level output                     | C <sub>L</sub> = 15 pF, See 図 6-17                         | 130                    | 520 | ns   |

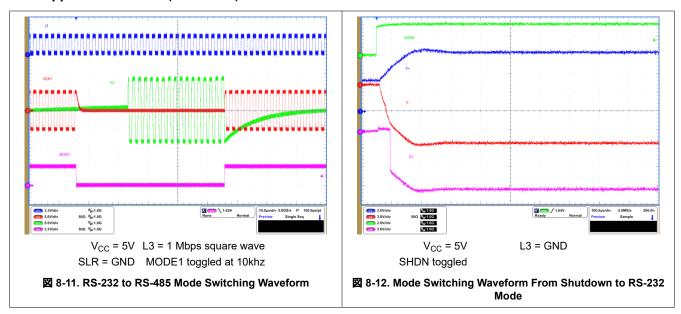

|                      | Rise/fall time (receiver buffer output), V <sub>IO</sub> = 3 to 5.5 V | C <sub>L</sub> = 150 pF, See ⊠ 6-17                        | 20                     | 50  | ns   |