# TPS22810 2.7~18V、79mΩオン抵抗、熱保護付き負荷スイッチ

## 1 特長

- シングル・チャネル負荷スイッチを内蔵

- 動作時周囲温度: -40°C~+105°C

- SOT23-6 (DBV): 最大連続電流2A<sup>1</sup>

- WSON (DRV): 最大連続電流3A<sup>1</sup>

- 入力電圧範囲: 2.7V~18V

- 絶対最大入力電圧: 20V

- オン抵抗( $R_{ON}$ )

- $V_{IN} = 12V$ で $R_{ON} = 79m\Omega$  (標準値)

- 静止電流

- $V_{IN} = 12V$ において62μA (標準値)

- シャットダウン電流

- $V_{IN} = 12V$ において500nA (標準値)

- サーマル・シャットダウン

- 低電圧誤動作防止(UVLO)

- 可変クイック出力放電(QOD)

- CTピンで立ち上がり時間を設定可能

- SOT23-6パッケージ

- 2.9mm×2.8mm、0.95mmピッチ、

高さ1.45mm (DBV)

- WSONパッケージ

- 2mm×2mm、0.65mmピッチ、

高さ0.75mm (DRV)

- ESD性能はJESD 22に準拠しテスト済み

- HBM  $\pm 2kV$ 、CDM  $\pm 1kV$

(1) 熱性能を考慮する必要があります

## 2 アプリケーション

- HDTV

- 産業用システム

- セットトップ・ボックス

- 監視システム

## 3 概要

TPS22810はシングル・チャネルの負荷スイッチで、立ち上がり時間を設定可能、クイック出力放電(QOD)が内蔵されています。さらに、このデバイスには接合部温度の上昇からデバイスを保護するため、サーマル・シャットダウン機能が搭載されています。これらの機能により、デバイスの安全な動作が本質的に保証されています。このデバイスにはNチャネルMOSFETが搭載され、2.7V~18Vの入力電圧範囲で動作できます。SOT23-5 (DBV)パッケージは最大で2Aの電流をサポートできます。WSON (DRV)パッケージは最大で3Aの電流をサポートできます。スイッチはオン/オフ入力により制御され、低電圧の制御信号と直接接続が可能です。

デバイスの立ち上がり時間を設定可能なため、大きな負荷容量により発生する突入電流が大幅に減少し、電源ドループが低減、または生じなくなります。低電圧誤動作防止機能は、VIN電圧がスレッショルド値よりも低下した場合にデバイスの電源をオフにし、想定よりも低い電圧の供給によって下流の回路が損害を受けることを防止します。QODピンは設定可能で、デバイスの立ち下がり時間を制御し、電源オフ時の設計を柔軟に行えるようにします。

TPS22810はリード付きのSOT-23パッケージ(DBV)で供給され、ハンダ付け結合部を目視で検査できるほか、WSONパッケージ(DRV)でも供給されます。このデバイスは、-40°C~+105°Cの周囲温度範囲で動作するよう規定されています。

### 製品情報<sup>(1)</sup>

| 型番       | パッケージ      | 本体サイズ(公称)     |

|----------|------------|---------------|

| TPS22810 | SOT-23 (6) | 2.90mm×2.80mm |

|          | WSON (6)   | 2.00mm×2.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

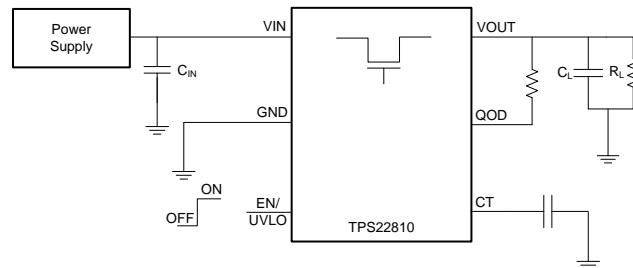

### 概略回路図

Copyright © 2016, Texas Instruments Incorporated

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SLVSDH0

## 目次

|     |                                                |    |      |                                            |    |

|-----|------------------------------------------------|----|------|--------------------------------------------|----|

| 1   | 特長 .....                                       | 1  | 9.4  | Device Functional Modes.....               | 17 |

| 2   | アプリケーション .....                                 | 1  | 10   | <b>Application and Implementation.....</b> | 18 |

| 3   | 概要 .....                                       | 1  | 10.1 | Application Information.....               | 18 |

| 4   | 改訂履歴.....                                      | 2  | 10.2 | ON and OFF Control.....                    | 18 |

| 5   | <b>Device Comparison Table .....</b>           | 3  | 10.3 | Input Capacitor (Optional).....            | 18 |

| 6   | <b>Pin Configuration and Functions .....</b>   | 3  | 10.4 | Output Capacitor (Optional).....           | 18 |

| 7   | <b>Specifications.....</b>                     | 4  | 10.5 | Typical Application .....                  | 18 |

| 7.1 | Absolute Maximum Ratings .....                 | 4  | 11   | <b>Power Supply Recommendations .....</b>  | 23 |

| 7.2 | ESD Ratings .....                              | 4  | 12   | <b>Layout.....</b>                         | 24 |

| 7.3 | Recommended Operating Conditions .....         | 4  | 12.1 | Layout Guidelines .....                    | 24 |

| 7.4 | Thermal Information .....                      | 4  | 12.2 | Layout Example .....                       | 24 |

| 7.5 | Electrical Characteristics.....                | 5  | 12.3 | Thermal Considerations .....               | 24 |

| 7.6 | Switching Characteristics.....                 | 7  | 13   | デバイスおよびドキュメントのサポート .....                   | 25 |

| 7.7 | Typical DC Characteristics .....               | 8  | 13.1 | デバイス・サポート .....                            | 25 |

| 7.8 | Typical AC Characteristics.....                | 9  | 13.2 | ドキュメントのサポート .....                          | 25 |

| 8   | <b>Parameter Measurement Information .....</b> | 11 | 13.3 | ドキュメントの更新通知を受け取る方法.....                    | 25 |

| 9   | <b>Detailed Description .....</b>              | 12 | 13.4 | コミュニティ・リソース .....                          | 25 |

| 9.1 | Overview .....                                 | 12 | 13.5 | 商標 .....                                   | 25 |

| 9.2 | Functional Block Diagram .....                 | 13 | 13.6 | 静電気放電に関する注意事項 .....                        | 25 |

| 9.3 | Feature Description.....                       | 13 | 13.7 | Glossary .....                             | 25 |

| 14  | メカニカル、パッケージ、および注文情報 .....                      | 25 |      |                                            |    |

## 4 改訂履歴

| Revision B (May 2017) から Revision C に変更                                                                                                                                                | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • Changed Rise time can be calculated by multiplying to Rise time can be calculated by dividing in the <i>Feature Description</i> Section 9.3.4 <i>Adjustable Rise Time (CT)</i> ..... | 17   |

| Revision A (December2016) から Revision B に変更         | Page |

|-----------------------------------------------------|------|

| • 「特長」、「概要」セクション、「推奨動作条件」表にWSON (DRV)電流の情報を追加 ..... | 1    |

| • WSON (DRV)パッケージ 追加 .....                          | 1    |

| 2016年12月発行のものから更新                                                                                                                                   | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • $I_{MAX}$ および $I_{PLS}$ を「絶対最大定格」表から削除 .....                                                                                                      | 1    |

| • Deleted $I_{MAX}$ and $I_{PLS}$ from the <i>Absolute Maximum Ratings</i> table .....                                                              | 4    |

| • Changed the Quiescent current MAX value From: 70 $\mu$ A To: 80 $\mu$ A in the <i>Electrical Characteristics</i> table .....                      | 5    |

| • Changed the Quiescent current MAX value for $V_{IN} = 2.7$ V From: 60 $\mu$ A To: 70 $\mu$ A in the <i>Electrical Characteristics</i> table ..... | 5    |

| • Changed the Shutdown current MAX value From: 2.25 $\mu$ A To: 2.3 $\mu$ A in the <i>Electrical Characteristics</i> table .....                    | 5    |

## 5 Device Comparison Table

| DEVICE   | R <sub>ON</sub> at 12 V | Package | QUICK OUTPUT DISCHARGE | T <sub>A</sub> | MAXIMUM OUTPUT CURRENT | ENABLE      |

|----------|-------------------------|---------|------------------------|----------------|------------------------|-------------|

| TPS22810 | 79 mΩ                   | DBV     | Configurable           | 105°C          | 2 A                    | Active High |

| TPS22810 | 79 mΩ                   | DRV     | Configurable           | 105°C          | 3 A                    | Active High |

## 6 Pin Configuration and Functions

### Pin Functions

| NAME    | PIN   |      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|---------|-------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         | NO,   |      |     |                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|         | SOT23 | WSON |     |                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| CT      | 4     | 3    | O   | Switch slew rate control. Can be left floating                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| EN/UVLO | 3     | 5    | I   | Active high switch control input and UVLO adjustment. Do not leave floating                                                                                                                                                                                                                                                                                                                                               |  |  |

| GND     | 2     | 4    | —   | Device ground                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| QOD     | 5     | 2    | O   | Quick Output Discharge pin. This functionality can be enabled in one of three ways.<br><ul style="list-style-type: none"> <li>• Placing an external resistor between VOUT and QOD</li> <li>• Tying QOD directly to VOUT and using the internal resistor value (<math>R_{PD}</math>)</li> <li>• Disabling QOD by leaving pin floating</li> </ul> See the <a href="#">Quick Output Discharge (QOD)</a> for more information |  |  |

| VIN     | 1     | 6    | I   | Switch input. Place ceramic bypass capacitor(s) between this pin and GND                                                                                                                                                                                                                                                                                                                                                  |  |  |

| VOUT    | 6     | 1    | O   | Switch output                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup> <sup>(2)</sup>

|               |                              | MIN  | MAX                       | UNIT |

|---------------|------------------------------|------|---------------------------|------|

| $V_{IN}$      | Input voltage                | -0.3 | 20                        | V    |

| $V_{OUT}$     | Output voltage               | -0.3 | min( $V_{IN} + 0.3$ , 20) | V    |

| $V_{EN/UVLO}$ | EN/UVLO voltage              | -0.3 | 20                        | V    |

| $T_J$         | Maximum junction temperature |      | 150                       | °C   |

| $T_{stg}$     | Storage temperature          | -65  | 150                       | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

### 7.2 ESD Ratings

|             |                         | VALUE                                                                          | UNIT       |

|-------------|-------------------------|--------------------------------------------------------------------------------|------------|

| $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | $\pm 2000$ |

|             |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> |            |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

### 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|               |                                                                   | MIN              | MAX      | UNIT |

|---------------|-------------------------------------------------------------------|------------------|----------|------|

| $V_{IN}$      | Input voltage                                                     | 2.7              | 18       | V    |

| $V_{EN/UVLO}$ | EN/UVLO voltage                                                   | 0                | 18       | V    |

| $V_{OUT}$     | Output voltage                                                    |                  | $V_{IN}$ | V    |

| IMAX          | Maximum continuous switch current, $T_A = 65^\circ\text{C}$ (DBV) |                  | 2        | A    |

|               | Maximum continuous switch current, $T_A = 65^\circ\text{C}$ (DRV) |                  | 3        |      |

| $T_A$         | Operating free-air temperature <sup>(1)</sup>                     | -40              | 105      | °C   |

| $C_{IN}$      | Input capacitor                                                   | 1 <sup>(2)</sup> |          | μF   |

(1) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature [ $T_{A(max)}$ ] is dependent on the maximum operating junction temperature [ $T_{J(MAX)}$ ], the maximum power dissipation of the device in the application [ $P_{D(MAX)}$ ], and the junction-to-ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the following equation:  $T_{A(MAX)} = T_{J(MAX)} - (\theta_{JA} \times P_{D(MAX)})$ .

(2) See the [Detailed Description](#) section.

### 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> | TPS22810                                     |            | UNIT |

|-------------------------------|----------------------------------------------|------------|------|

|                               | DBV (SOT23)                                  | DRV (WSON) |      |

|                               | 6 PINS                                       | 6 PINS     |      |

| $R_{0JA}$                     | Junction-to-ambient thermal resistance       | 182        | °C/W |

| $R_{0JC(top)}$                | Junction-to-case (top) thermal resistance    | 127.2      | °C/W |

| $R_{0JB}$                     | Junction-to-board thermal resistance         | 16.9       | °C/W |

| $\psi_{JT}$                   | Junction-to-top characterization parameter   | 26.4       | °C/W |

| $\psi_{JB}$                   | Junction-to-board characterization parameter | 36.3       | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 7.5 Electrical Characteristics

Unless otherwise noted, the specification in the following table applies over the following ambient operating temperature  $-40^{\circ}\text{C} \leq T_A \leq +105^{\circ}\text{C}$ . Typical values are for  $T_A = 25^{\circ}\text{C}$ .

| PARAMETER                                               | TEST CONDITIONS                                | TA                                              | MIN                                             | TYP  | MAX  | UNIT          |

|---------------------------------------------------------|------------------------------------------------|-------------------------------------------------|-------------------------------------------------|------|------|---------------|

| $I_Q, V_{IN}$<br>Quiescent current                      | $V = 18 \text{ V}, I = 0 \text{ A}$            | $V_{IN} = 18 \text{ V}$                         | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  | 62   | 80   | $\mu\text{A}$ |

|                                                         |                                                | $V_{IN} = 18 \text{ V}$                         | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |      | 85   |               |

|                                                         |                                                | $V_{IN} = 12 \text{ V}$                         | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  | 62   | 80   |               |

|                                                         |                                                | $V_{IN} = 12 \text{ V}$                         | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |      | 85   |               |

|                                                         |                                                | $V_{IN} = 5 \text{ V}$                          | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  | 59   | 80   |               |

|                                                         |                                                | $V_{IN} = 5 \text{ V}$                          | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |      | 85   |               |

|                                                         |                                                | $V_{IN} = 3.3 \text{ V}$                        | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  | 53   | 80   |               |

|                                                         |                                                | $V_{IN} = 3.3 \text{ V}$                        | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |      | 85   |               |

|                                                         |                                                | $V_{IN} = 2.7 \text{ V}$                        | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  | 49   | 70   |               |

|                                                         |                                                | $V_{IN} = 2.7 \text{ V}$                        | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |      | 85   |               |

| $I_{SD}, V_{IN}$<br>Shutdown current                    | $V_{ON} = 0 \text{ V}, V_{OUT} = 0 \text{ V}$  | $V_{IN} = 18 \text{ V}$                         | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  | 0.5  | 2.3  | $\mu\text{A}$ |

|                                                         |                                                | $V_{IN} = 18 \text{ V}$                         | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |      | 3.8  |               |

|                                                         |                                                | $V_{IN} = 12 \text{ V}$                         | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  | 0.5  | 2.3  |               |

|                                                         |                                                | $V_{IN} = 12 \text{ V}$                         | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |      | 3.8  |               |

|                                                         |                                                | $V_{IN} = 5 \text{ V}$                          | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  | 0.5  | 2.3  |               |

|                                                         |                                                | $V_{IN} = 5 \text{ V}$                          | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |      | 3.8  |               |

|                                                         |                                                | $V_{IN} = 3.3 \text{ V}$                        | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  | 0.5  | 2.3  |               |

|                                                         |                                                | $V_{IN} = 3.3 \text{ V}$                        | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |      | 3.8  |               |

|                                                         |                                                | $V_{IN} = 2.7 \text{ V}$                        | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  | 0.5  | 2.3  |               |

|                                                         |                                                | $V_{IN} = 2.7 \text{ V}$                        | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |      | 3.8  |               |

| $I_{EN/UVLO}$<br>EN/UVLO input leakage current          | $V_{IN} = 18 \text{ V}, I_{OUT} = 0 \text{ A}$ | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |                                                 |      | 0.1  | $\mu\text{A}$ |

| $V_{UVR}$<br>VIN UVLO threshold, rising                 |                                                | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ | 2                                               | 2.54 | 2.62 | V             |

| $V_{UVhyst}$<br>VIN UVLO hysteresis                     |                                                | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |                                                 | 5%   |      |               |

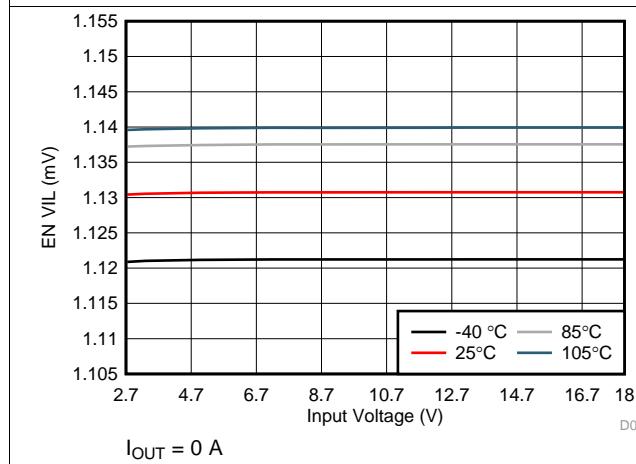

| $V_{ENR}$<br>EN threshold voltage, rising               |                                                | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ | 1.13                                            | 1.23 | 1.3  | V             |

| $V_{ENF}$<br>EN threshold voltage, falling              |                                                | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ | 1.08                                            | 1.13 | 1.18 | V             |

| $V_{SHUTF}$<br>EN threshold voltage for low IQ shutdown |                                                | $-40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ | 0.5                                             | 0.75 | 0.9  | V             |

## Electrical Characteristics (continued)

Unless otherwise noted, the specification in the following table applies over the following ambient operating temperature  $-40^{\circ}\text{C} \leq T_{\text{A}} \leq +105^{\circ}\text{C}$ . Typical values are for  $T_{\text{A}} = 25^{\circ}\text{C}$ .

| PARAMETER       | TEST CONDITIONS                                                    | $T_{\text{A}}$                                                                     | MIN             | TYP | MAX | UNIT             |

|-----------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|-----|-----|------------------|

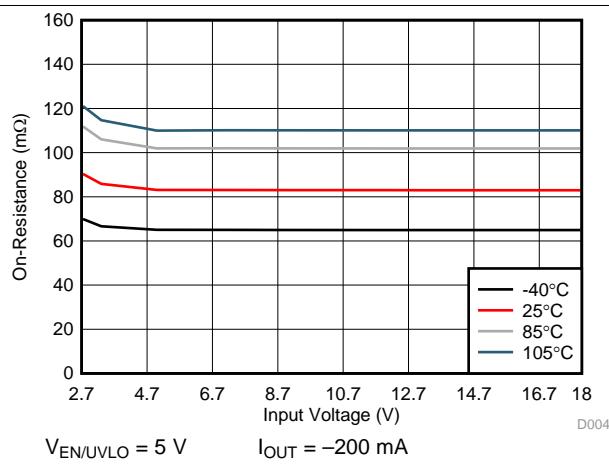

| $R_{\text{ON}}$ | $V_{\text{IN}} = 18\text{ V}$ , $I_{\text{OUT}} = -200\text{ mA}$  | 25°C                                                                               |                 | 79  | 86  | $\text{m}\Omega$ |

|                 |                                                                    | -40°C to +85°C                                                                     |                 |     | 105 |                  |

|                 |                                                                    | -40°C to +105°C                                                                    |                 |     | 115 |                  |

|                 | $V_{\text{IN}} = 12\text{ V}$ , $I_{\text{OUT}} = -200\text{ mA}$  | 25°C                                                                               |                 | 79  | 86  |                  |

|                 |                                                                    | -40°C to +85°C                                                                     |                 |     | 105 |                  |

|                 |                                                                    | -40°C to +105°C                                                                    |                 |     | 115 |                  |

|                 | $V_{\text{IN}} = 9\text{ V}$ , $I_{\text{OUT}} = -200\text{ mA}$   | 25°C                                                                               |                 | 79  | 86  |                  |

|                 |                                                                    | -40°C to +85°C                                                                     |                 |     | 105 |                  |

|                 |                                                                    | -40°C to +105°C                                                                    |                 |     | 115 |                  |

|                 | $V_{\text{IN}} = 5\text{ V}$ , $I_{\text{OUT}} = -200\text{ mA}$   | 25°C                                                                               |                 | 79  | 86  |                  |

|                 |                                                                    | -40°C to +85°C                                                                     |                 |     | 105 |                  |

|                 |                                                                    | -40°C to +105°C                                                                    |                 |     | 115 |                  |

| $R_{\text{PD}}$ | $V_{\text{IN}} = 3.3\text{ V}$ , $I_{\text{OUT}} = -200\text{ mA}$ | 25°C                                                                               |                 | 83  | 92  | $\Omega$         |

|                 |                                                                    | -40°C to +85°C                                                                     |                 |     | 115 |                  |

|                 |                                                                    | -40°C to +105°C                                                                    |                 |     | 125 |                  |

|                 | $V_{\text{IN}} = 2.7\text{ V}$ , $I_{\text{OUT}} = -200\text{ mA}$ | 25°C                                                                               |                 | 86  | 95  |                  |

|                 |                                                                    | -40°C to +85°C                                                                     |                 |     | 120 |                  |

|                 |                                                                    | -40°C to +105°C                                                                    |                 |     | 130 |                  |

| TS              | Thermal shutdown                                                   | $V_{\text{IN}} = V_{\text{OUT}} = 18\text{ V}$ , $V_{\text{EN/UVLO}} = 0\text{ V}$ | -40°C to +105°C |     | 290 | 350              |

|                 |                                                                    | $V_{\text{IN}} = V_{\text{OUT}} = 12\text{ V}$ , $V_{\text{EN/UVLO}} = 0\text{ V}$ | -40°C to +105°C |     | 265 | 350              |

|                 |                                                                    | $V_{\text{IN}} = V_{\text{OUT}} = 5\text{ V}$ , $V_{\text{EN/UVLO}} = 0\text{ V}$  | -40°C to +105°C |     | 250 | 400              |

| TSHDN Hyst      | Thermal shutdown hysteresis                                        | TSD hysteresis, $V_{\text{IN}} = 18\text{ V}$                                      | -40°C to +105°C |     | 30  | °C               |

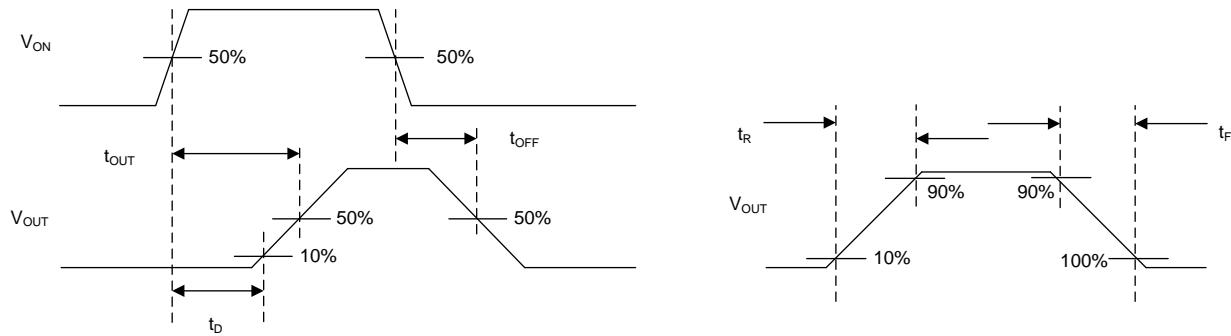

## 7.6 Switching Characteristics

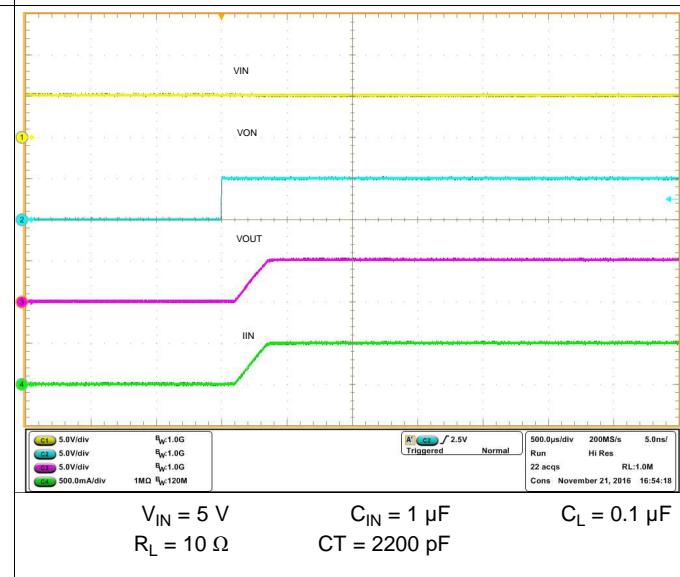

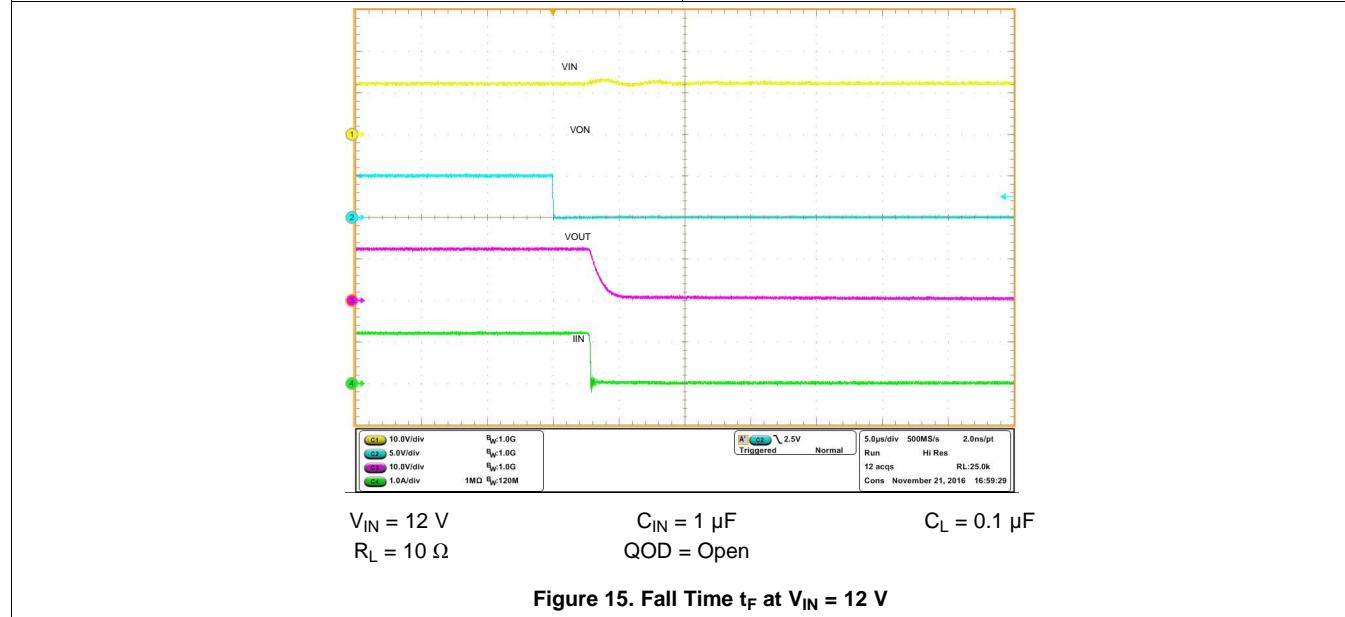

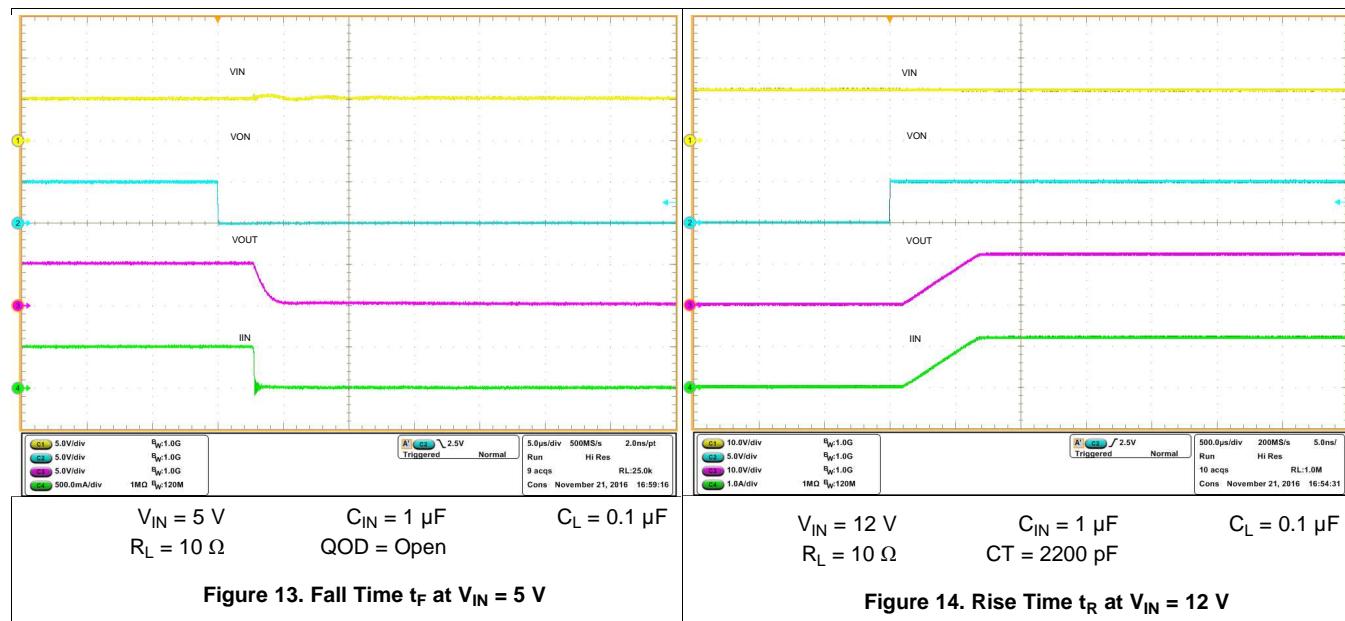

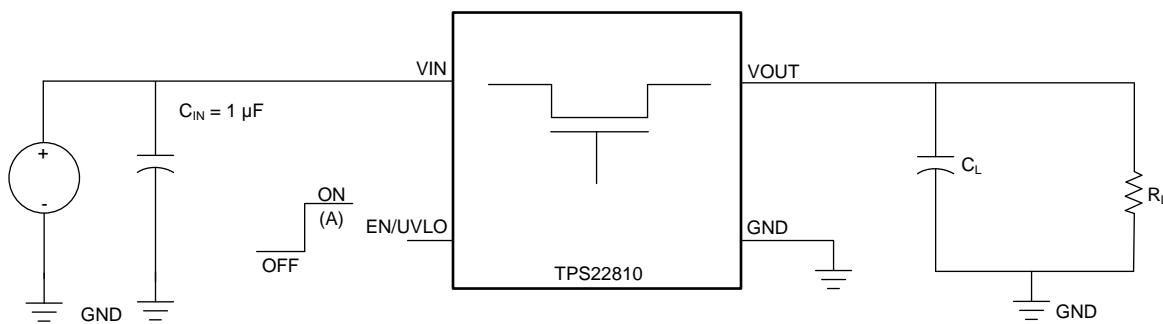

Refer to the timing test circuit in [Figure 16](#) (unless otherwise noted) for references to external components used for the test condition in the switching characteristics table. Switching characteristics shown below are only valid for the power-up sequence where VIN is already in steady state condition before the EN/UVLO pin is asserted high.

| PARAMETER                                                                                                                                        | TEST CONDITIONS     | MIN                                                                                             | TYP | MAX           | UNIT |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------|-----|---------------|------|

| <b><math>V_{IN} = 18 \text{ V}</math>, <math>V_{EN/UVLO} = 5 \text{ V}</math>, <math>T_A = 25^\circ\text{C}</math> (unless otherwise noted)</b>  |                     |                                                                                                 |     |               |      |

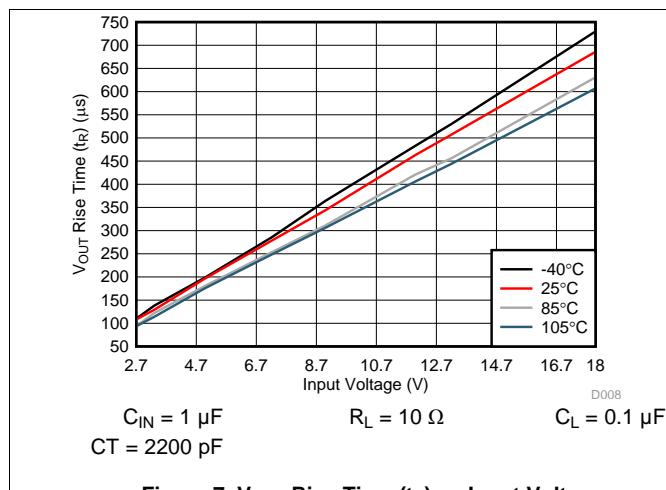

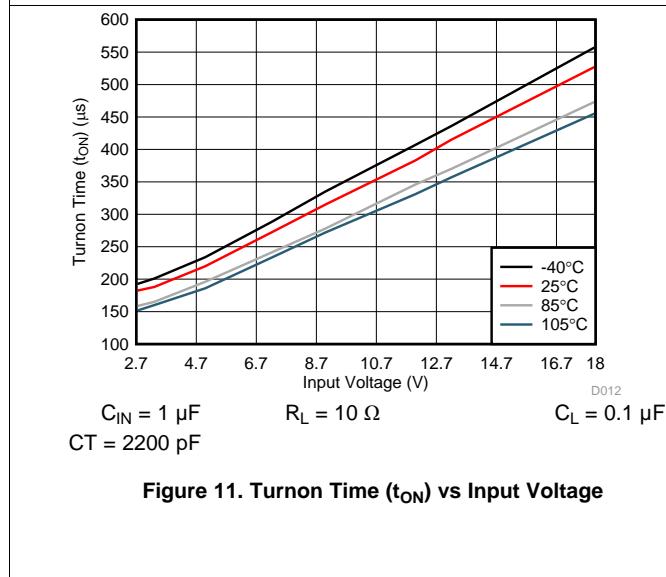

| $t_{ON}$                                                                                                                                         | Turnon time         | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 520 | $\mu\text{s}$ |      |

| $t_{OFF}$                                                                                                                                        | Turnoff time        | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 3.3 |               |      |

| $t_R$                                                                                                                                            | $V_{OUT}$ rise time | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 700 |               |      |

| $t_F$                                                                                                                                            | $V_{OUT}$ fall time | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 2   |               |      |

| $t_D$                                                                                                                                            | Delay time          | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 180 |               |      |

| <b><math>V_{IN} = 12 \text{ V}</math>, <math>V_{EN/UVLO} = 5 \text{ V}</math>, <math>T_A = 25^\circ\text{C}</math> (unless otherwise noted)</b>  |                     |                                                                                                 |     |               |      |

| $t_{ON}$                                                                                                                                         | Turnon time         | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 380 | $\mu\text{s}$ |      |

| $t_{OFF}$                                                                                                                                        | Turnoff time        | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 3.3 |               |      |

| $t_R$                                                                                                                                            | $V_{OUT}$ rise time | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 460 |               |      |

| $t_F$                                                                                                                                            | $V_{OUT}$ fall time | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 2   |               |      |

| $t_D$                                                                                                                                            | ON delay time       | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 150 |               |      |

| <b><math>V_{IN} = 3.3 \text{ V}</math>, <math>V_{EN/UVLO} = 5 \text{ V}</math>, <math>T_A = 25^\circ\text{C}</math> (unless otherwise noted)</b> |                     |                                                                                                 |     |               |      |

| $t_{ON}$                                                                                                                                         | Turnon time         | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 185 | $\mu\text{s}$ |      |

| $t_{OFF}$                                                                                                                                        | Turnoff time        | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 3.3 |               |      |

| $t_R$                                                                                                                                            | $V_{OUT}$ rise time | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 120 |               |      |

| $t_F$                                                                                                                                            | $V_{OUT}$ fall time | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 2   |               |      |

| $t_D$                                                                                                                                            | ON delay time       | $R_L = 10 \Omega$ , $C_{IN} = 1 \mu\text{F}$ , $C_L = 0.1 \mu\text{F}$ , $CT = 2200 \text{ pF}$ | 130 |               |      |

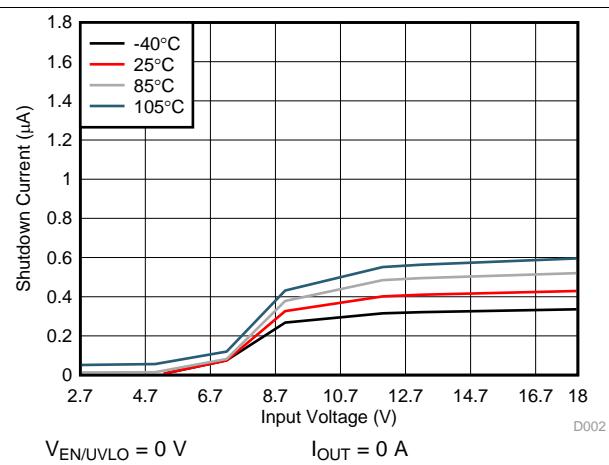

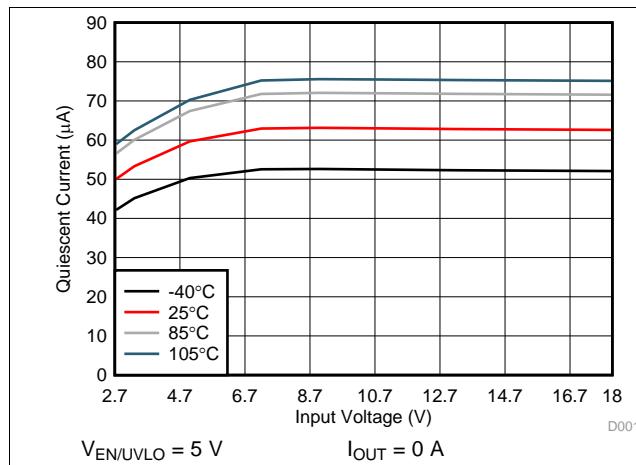

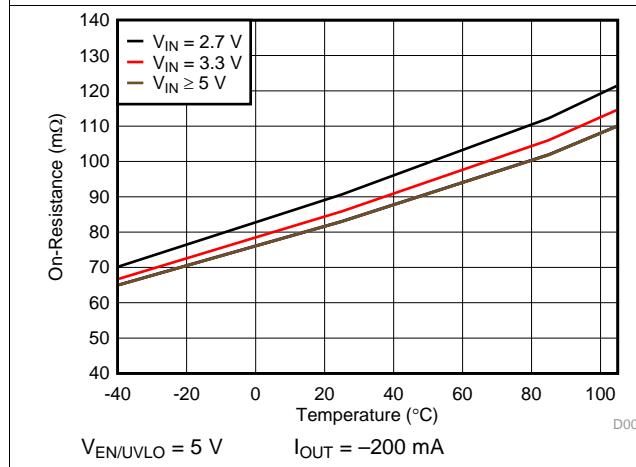

## 7.7 Typical DC Characteristics

**Figure 1. Quiescent Current vs Input Voltage**

**Figure 2. Shutdown Current vs Input Voltage**

**Figure 3. On-Resistance vs Temperature**

**Figure 4. On-Resistance vs Input Voltage**

**Figure 5. EN VIL vs Input Voltage**

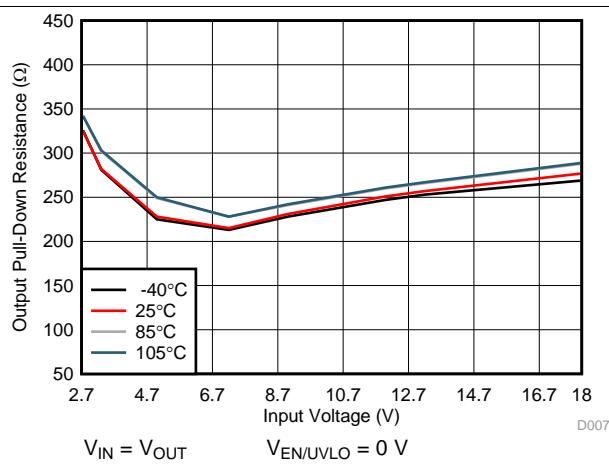

**Figure 6. Output Pull-Down Resistance vs Input Voltage**

## 7.8 Typical AC Characteristics

**Figure 7.  $V_{OUT}$  Rise Time ( $t_R$ ) vs Input Voltage**

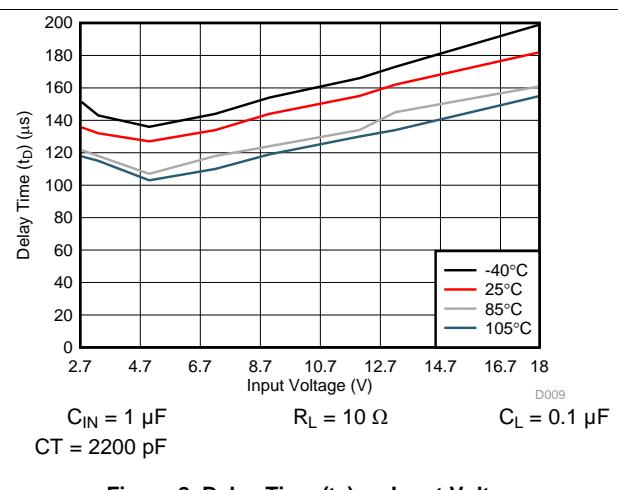

**Figure 8. Delay Time ( $t_D$ ) vs Input Voltage**

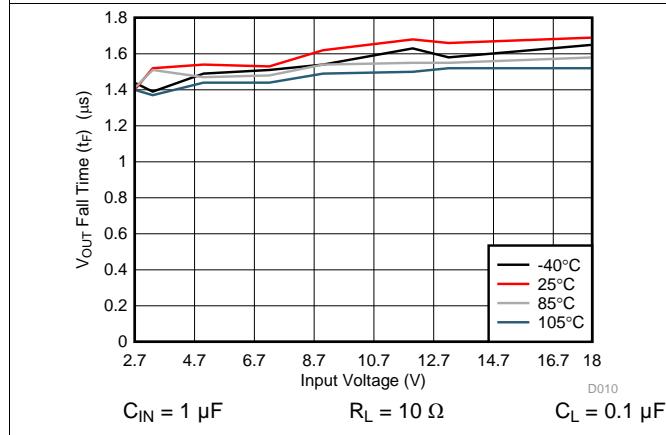

**Figure 9.  $V_{OUT}$  Fall Time ( $t_F$ ) vs Input Voltage**

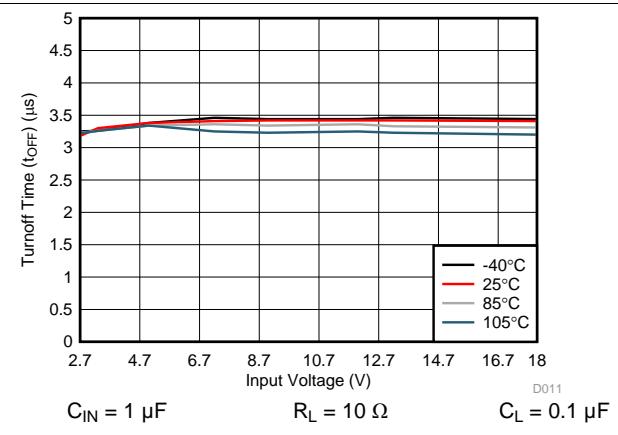

**Figure 10. Turnoff Time ( $t_{OFF}$ ) vs Input Voltage**

**Figure 11. Turnon Time ( $t_{ON}$ ) vs Input Voltage**

**Figure 12. Rise Time  $t_R$  at  $V_{IN} = 5 \text{ V}$**

## Typical AC Characteristics (continued)

## 8 Parameter Measurement Information

A. Rise and fall times of the control signal are 100 ns

**Figure 16. Test Circuit**

**Figure 17. Timing Waveforms**

## 9 Detailed Description

### 9.1 Overview

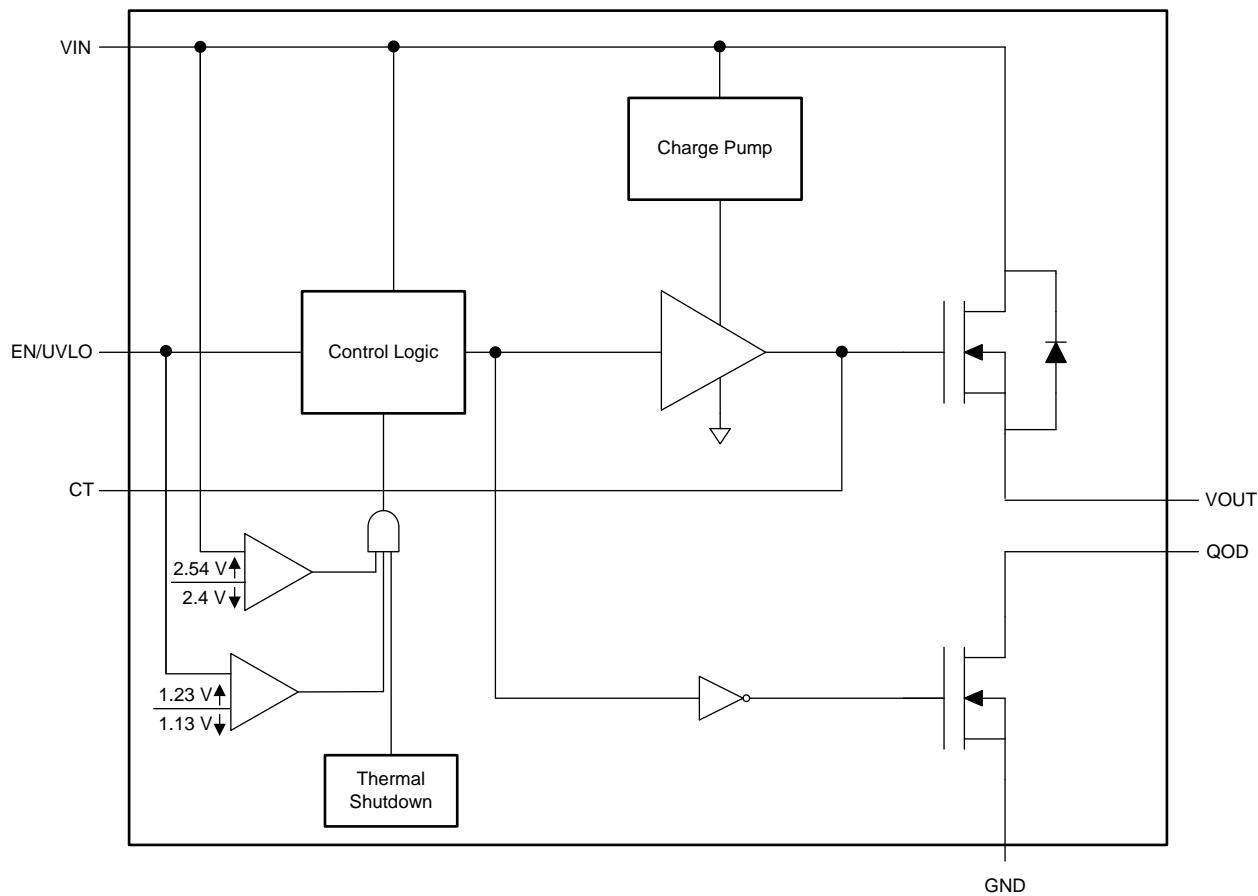

The TPS22810 is a 6-pin, 2.7-18-V load switch with thermal protection in two separate package options. To reduce voltage drop for low voltage and high current rails, the device implements a low resistance N-channel MOSFET which reduces the drop out voltage across the device.

The device starts its operation by monitoring the VIN bus. When VIN exceeds the undervoltage-lockout threshold (UVVR), the device samples the EN/UVLO pin. A high level on this pin enables the internal MOSFET. As VIN rises, the internal MOSFET of the device starts conducting and allow current to flow from VIN to VOUT. When EN/UVLO is held low (below VENF), internal MOSFET is turned off.

A voltage  $V(EN/UVLO) < V(ENF)$  on this pin turns off the internal FET, thus disconnecting VIN from VOUT, while voltage below  $V(SHUTF)$  takes the device into shutdown mode, with IQ less than 1  $\mu$ A to ensure minimal power loss.

The device has a configurable slew rate which helps reduce or eliminate power supply droop because of large inrush currents. The device also features an internal RPD resistor, which discharges VOUT once the switch is disabled.

During shutdown, the device has very low leakage currents, thereby reducing unnecessary leakages for downstream modules during standby. Integrated control logic, driver, charge pump, and output discharge FET eliminates the need for any external components which reduces solution size and bill of materials (BOM) count.

The device also features a QOD pin, which allows the configuration of the discharge rate of VOUT once the switch is disabled.

The device has a thermal protection feature. Due to this device protects itself against thermal damage due to over-temperature and over-current conditions. Safe Operating Area (SoA) requirements are thus inherently met without any special design consideration by the board designer.

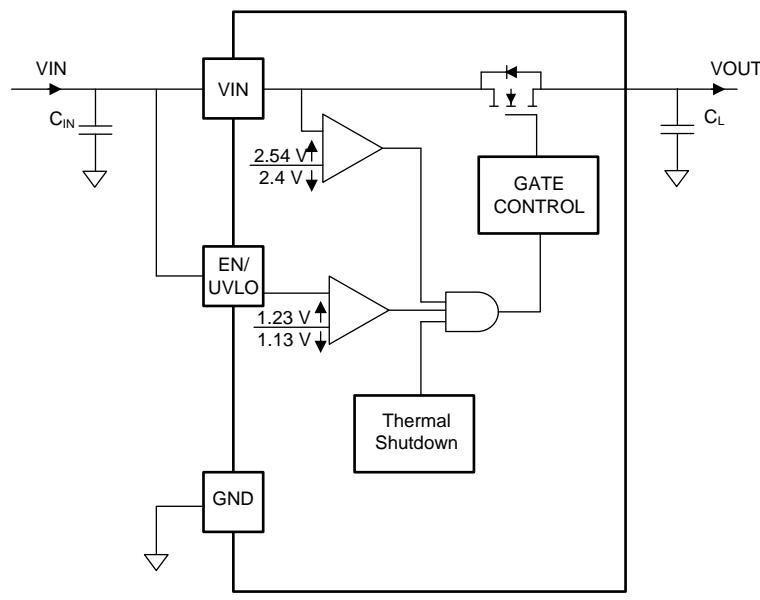

## 9.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

## 9.3 Feature Description

### 9.3.1 On and Off Control

The EN/UVLO pin controls the state of the switch. EN/UVLO is active high and has a low threshold, making it capable of interfacing with low-voltage signals. The EN/UVLO pin is compatible with standard GPIO logic threshold. It can be used with any microcontroller with 1.2 V or higher GPIO voltage. This pin cannot be left floating and must be driven either high or low for proper functionality.

### 9.3.2 Quick Output Discharge (QOD)

The TPS22810 includes a QOD feature. The QOD pin can be configured in one of three ways:

- QOD pin shorted to VOUT pin. Using this method, the discharge rate after the switch becomes disabled is controlled with the value of the internal resistance  $R_{PD}$ . The value of this resistance is listed in the [Electrical Characteristics](#) table.

- QOD pin connected to VOUT pin using an external resistor  $R_{EXT}$ . After the switch becomes disabled, the discharge rate is controlled by the value of the total resistance of the QOD. To adjust the total QOD resistance, [Equation 1](#) can be used.

$$R_{QOD} = R_{PD} + R_{EXT}$$

where

- $R_{QOD}$  is the total output discharge resistance

- $R_{PD}$  is the internal pulldown resistance

- $R_{EXT}$  is the external resistance placed between the VOUT and QOD pin.

(1)

## Feature Description (continued)

- QOD pin is unused and left floating. Using this method, there is no quick output discharge functionality, and the output remains floating after the switch is disabled.

Note that during thermal shutdown, the QOD functionality is not available. The device does not discharge the load as RPD does not become engaged.

The fall times of the device depend on many factors including the total resistance of the QOD,  $V_{IN}$ , and the output capacitance. When QOD is connected to VOUT, the fall time changes over  $V_{IN}$  as the internal  $R_{PD}$  varies over  $V_{IN}$ . To calculate the approximate fall time of  $V_{OUT}$  for a given  $R_{QOD}$ , use [Equation 2](#) and [Table 1](#).

$$V_{CAP} = V_{IN} \times e^{-t/\tau}$$

where

- $V_{CAP}$  is the voltage across the capacitor (V)

- $t$  is the time since power supply removal (s)

- $\tau$  is the time constant equal to  $R_{QOD} \times C_L$

(2)

The fall times' dependency on  $V_{IN}$  becomes minimal as the QOD value increases with additional external resistance. See [Table 1](#) for QOD fall times.

**Table 1. QOD Fall Times**

| $V_{IN}$ (V) | FALL TIME (μs) 90% - 10%, $C_{IN} = 1 \mu F$ , $I_{OUT} = 0 A$ , $V_{IN} = 0 V$ , $ON = 0 V$ <sup>(1)</sup> |                  |                   |                    |                  |                   |

|--------------|-------------------------------------------------------------------------------------------------------------|------------------|-------------------|--------------------|------------------|-------------------|

|              | $T_A = 25^\circ C$                                                                                          |                  |                   | $T_A = 85^\circ C$ |                  |                   |

|              | $C_L = 1 \mu F$                                                                                             | $C_L = 10 \mu F$ | $C_L = 100 \mu F$ | $C_L = 1 \mu F$    | $C_L = 10 \mu F$ | $C_L = 100 \mu F$ |

| 18           | 470                                                                                                         | 4700             | 47000             | 470                | 4700             | 47000             |

| 12           | 450                                                                                                         | 4500             | 45000             | 450                | 4500             | 45000             |

| 9            | 440                                                                                                         | 4400             | 44000             | 440                | 4400             | 44000             |

| 5            | 500                                                                                                         | 5000             | 50000             | 480                | 4800             | 48000             |

| 3.3          | 600                                                                                                         | 6000             | 60000             | 570                | 5700             | 57000             |

(1) TYPICAL VALUES WITH QOD SHORTED TO VOUT

### 9.3.2.1 QOD when System Power is Removed

The adjustable QOD can be used to control the power down sequencing of a system even when the system power supply is removed. When the power is removed, the input capacitor,  $C_{IN}$ , discharges at  $V_{IN}$ . Past the set UVLO level, the pull-down resistance RPD becomes disabled and the output no longer becomes discharged. If there is still remaining charge on the output capacitor, this results in longer fall times. Care must be taken such that  $C_{IN}$  is large enough to meet the device UVLO settings.

### 9.3.2.2 Internal QOD Considerations

Special considerations must be taken when using the internal  $R_{PD}$  by shorting the QOD pin to the VOUT pin. The internal  $R_{PD}$  is a pulldown resistance designed to quickly discharge a load after the switch has been disabled. Care must be used to ensure that excessive current does not flow through  $R_{PD}$  during discharge so that the maximum  $T_J$  of  $125^\circ C$  is not exceeded. When using only the internal  $R_{PD}$  to discharge a load, the total capacitive load must not exceed  $200 \mu F$ . Otherwise, an external resistor,  $R_{EXT}$ , must be used to ensure the amount of current flowing through  $R_{PD}$  is properly limited and the maximum  $T_J$  is not exceeded. To ensure the device is not damaged, the remaining charge from  $C_L$  needs to decay naturally through the internal QOD resistance and must not be driven.

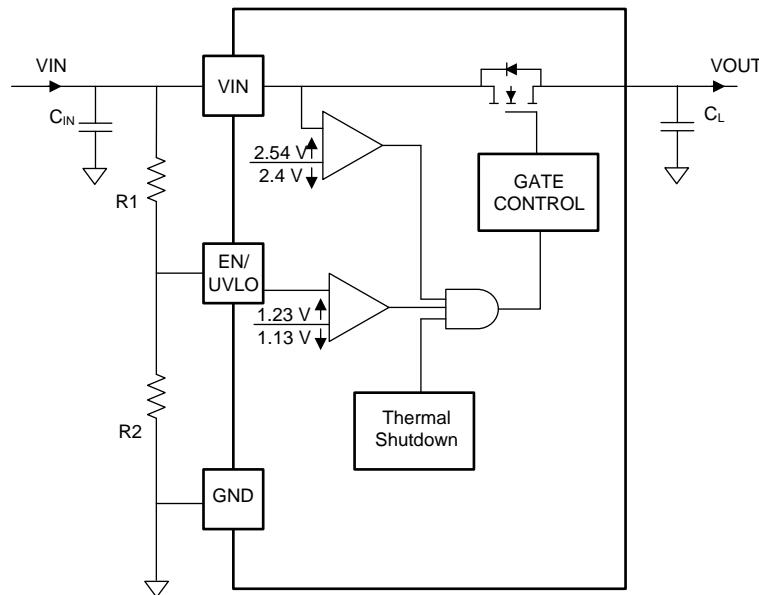

### 9.3.3 EN/UVLO

As an input pin, EN/UVLO controls the ON and OFF state of the internal MOSFET. In its high state, the internal MOSFET is enabled. A low on this pin turns off the internal MOSFET. High and Low levels are specified in the parametric table of the datasheet

A voltage  $V(EN/UVLO) < V(ENF)$  on this pin turns off the internal FET, thus disconnecting  $V_{IN}$  from  $V_{OUT}$ , while voltage below  $V(SHUTF)$  takes the device into shutdown mode, with  $I_Q$  less than  $1 \mu A$  to ensure minimal power loss.

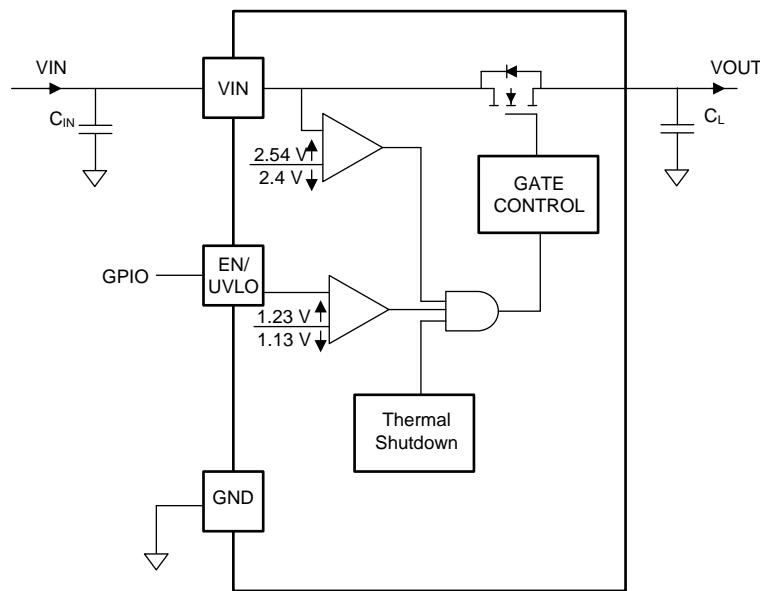

The EN/UVLO pin can be directly driven by a 1.8 V, 3.3 V or 5 V general purpose output pin.

The internal de-glitch delay on EN/UVLO falling edge is intentionally kept low (2.5  $\mu$ s typical) for quick detection of power failure. For applications where a higher de-glitch delay on EN/UVLO is desired, or when the supply is particularly noisy, it is recommended to use an external bypass capacitor from EN/UVLO to GND.

The undervoltage lock out can be programmed by using an external resistor divider from supply VIN terminal to EN/UVLO terminal to GND as shown in [Figure 18](#). When an undervoltage or input power fail event is detected, the internal FET is quickly turned off. If the Under-Voltage Lock-Out function is not needed, the EN/UVLO terminal must be connected to the VIN terminal. EN/UVLO terminal must not be left floating.

The device also implements internal undervoltage-lockout (UVLO) circuitry on the VIN terminal. The device disables when the VIN terminal voltage falls below internal UVLO Threshold V(UVF). The internal UVLO threshold has a hysteresis of 125 mV (5% of V(UVR)). See [Figure 19](#) and [Figure 20](#).

Copyright © 2016, Texas Instruments Incorporated

**Figure 18. Configuring UVLO with External Resistor Network**

Copyright © 2016, Texas Instruments Incorporated

Figure 19. Using 1.8 V/3.3 V GPIO Signal Directly from Processor

Copyright © 2016, Texas Instruments Incorporated

Figure 20. Default UVLO Threshold V(UVR) Using No Additional External Components

#### 9.3.4 Adjustable Rise Time (CT)

A capacitor to GND on the CT pin sets the slew rate. The voltage on the CT pin can be as high as 2.5 V. An approximate formula for the relationship between CT and slew rate is shown in [Equation 3](#). This equation accounts for 10% to 90% measurement on VOUT and does NOT apply for  $CT < 1 \text{ nF}$ .

Use [Table 2](#) to determine rise times for when  $C_t \geq 1 \text{ nF}$ .

$$SR = 46.62 / C_t$$

where

- SR is the slew rate (in  $\text{V}/\mu\text{s}$ )

- CT is the the capacitance value on the CT pin (in pF)

- The units for the constant a are  $\mu\text{s}/\text{V}$ . The units for the constant b are  $\mu\text{s}/(\text{V} \times \text{pF})$ . (3)

Rise time can be calculated by dividing the input voltage by the slew rate. [Table 2](#) contains rise time values measured on a typical device. Rise times shown below are only valid for the power-up sequence where VIN is already in steady state condition before the EN/UVLO pin is asserted high.

**Table 2. Rise Time Table**

| CT (pF) | RISE TIME (μs) 10% - 90%, $C_L = 0.1 \mu\text{F}$ , $C_{IN} = 1 \mu\text{F}$ , $R_L = 10 \Omega$ |            |           |           |             |

|---------|--------------------------------------------------------------------------------------------------|------------|-----------|-----------|-------------|

|         | VIN = 18 V                                                                                       | VIN = 12 V | VIN = 9 V | VIN = 5 V | VIN = 3.3 V |

| 0       | 115                                                                                              | 91         | 78        | 60        | 98          |

| 470     | 136                                                                                              | 94         | 80        | 63        | 98          |

| 1000    | 310                                                                                              | 209        | 158       | 91        | 102         |

| 2200    | 688                                                                                              | 464        | 345       | 198       | 135         |

| 4700    | 1430                                                                                             | 957        | 704       | 397       | 265         |

| 10000   | 3115                                                                                             | 2085       | 1540      | 864       | 550         |

| 27000   | 8230                                                                                             | 5460       | 4010      | 2245      | 1430        |

### 9.3.5 Thermal Shutdown

The switch disables when the junction temperature ( $T_J$ ) rises above the thermal shutdown threshold,  $T_{SD}$ . The switch re-enables once the temperature drops below the  $T_{SD} - T_{SD,HYS}$  value.

## 9.4 Device Functional Modes

The features of the TPS22810 depend on the operating mode. [Table 3](#) summarizes the Device Functional Modes.

**Table 3. Function Table**

| EN/UVLO | Device State |

|---------|--------------|

| L       | Disabled     |

| H       | Enabled      |

## 10 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 10.1 Application Information

This section highlights some of the design considerations when implementing this device in various applications. A PSPICE model for this device is also available in the product page of this device on [www.ti.com](http://www.ti.com) (See the [デバイス・サポート](#) section for more information).

### 10.2 ON and OFF Control

The EN/UVLO pin controls the state of the switch. Asserting EN/UVLO high enables the switch. EN/UVLO is active high and has a low threshold, making it capable of interfacing with low-voltage signals. The EN/UVLO pin is compatible with standard GPIO logic thresholds. It can be used with any microcontroller with 1.2 V or higher GPIO voltage. This pin cannot be left floating and must be driven either high or low for proper functionality.

### 10.3 Input Capacitor (Optional)

To limit the voltage drop on the input supply caused by transient inrush currents when the switch turns on into a discharged load capacitor, a capacitor needs to be placed between VIN and GND. A 1- $\mu$ F ceramic capacitor,  $C_{IN}$ , placed close to the pins, is usually sufficient. Higher values of  $C_{IN}$  can be used to further reduce the voltage drop during high current applications. When switching heavy loads, it is recommended to have an input capacitor about 10 times higher than the output capacitor to avoid excessive voltage drop.

### 10.4 Output Capacitor (Optional)

Due to the integrated body diode in the NMOS switch, a  $C_{IN}$  greater than  $C_L$  is highly recommended. A  $C_L$  greater than  $C_{IN}$  can cause VOUT to exceed VIN when the system supply is removed. This can result in current flow through the body diode from VOUT to VIN. A  $C_{IN}$  to  $C_L$  ratio of 10 to 1 is recommended for minimizing VIN dip caused by inrush currents during startup; however, a 10 to 1 ratio for capacitance is not required for proper functionality of the device. A ratio smaller than 10 to 1 (such as 1 to 1) can cause slightly more VIN dip upon turnon due to inrush currents.

This can be mitigated by increasing the capacitance on the CT pin for a longer rise time.

### 10.5 Typical Application

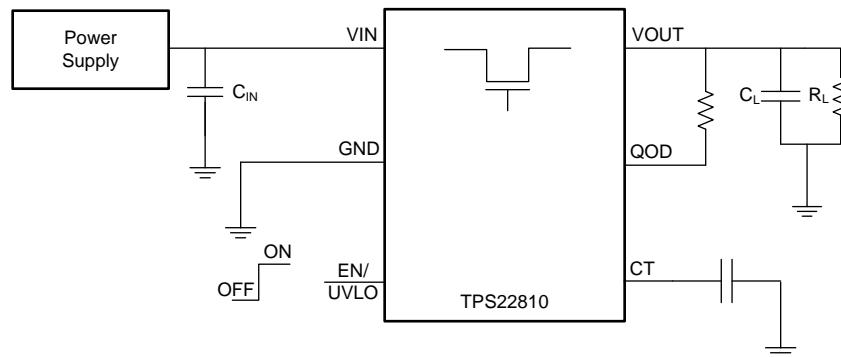

This typical application demonstrates how the TPS22810 can be used to power downstream modules.

Copyright © 2016, Texas Instruments Incorporated

Figure 21. Typical Application Schematic

## Typical Application (continued)

### 10.5.1 Design Requirements

For this design example, use the values listed in [Table 4](#) as the design parameters:

**Table 4. Design Parameters**

| DESIGN PARAMETER                  | EXAMPLE VALUE |

|-----------------------------------|---------------|

| $V_{IN}$                          | 12 V          |

| Load current                      | 2 A           |

| $C_L$                             | 22 $\mu$ F    |

| Desired fall time                 | 20 ms         |

| Maximum acceptable inrush current | 400 mA        |

### 10.5.2 Detailed Design Procedure

#### 10.5.2.1 Shutdown Sequencing During Unexpected Power Loss

Using the adjustable Quick Output Discharge function of the TPS22810, adding a load switch to each power rail can be used to manage the power down sequencing in the event of an unexpected power loss (that is battery removal). To determine the QOD values for each load switch, first confirm the power down order of the device you wish to power sequence. Be sure to check if there are voltage or timing margins that must be maintained during power down. Next, consult [Table 1](#) to determine appropriate  $C_L$  and  $R_{QOD}$  values for each power rail's load switch so that the load switches' fall times correspond to the order in which they need to be powered down. In the above example, we must have this power rail's fall time to be 4 ms. Using [Equation 2](#), we can determine the appropriate  $R_{QOD}$  to achieve our desired fall time.

Since fall times are measured from 90% of  $V_{OUT}$  to 10% of  $V_{OUT}$ , using [Equation 2](#), we get [Equation 4](#) and [Equation 5](#).

$$1.2V = 10.8V \times e^{-(20ms)/(R_{QOD} \times (22\mu F))} \quad (4)$$

$$R_{QOD} = 413.7 \Omega \quad (5)$$

Consulting [Figure 6](#),  $R_{PD}$  at  $V_{IN} = 12$  V is approximately 250  $\Omega$ . Using [Equation 1](#), the required external QOD resistance can be calculated as shown in [Equation 6](#) and [Equation 7](#).

$$413.7 \Omega = 250 \Omega + R_{EXT} \quad (6)$$

$$R_{EXT} = 163.7 \Omega \quad (7)$$

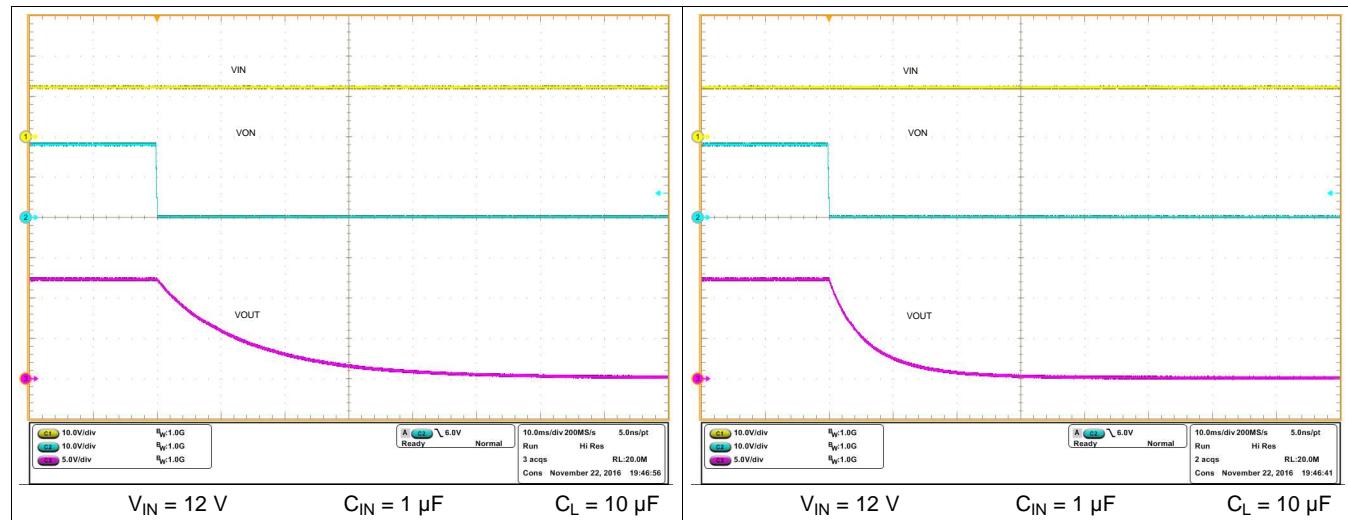

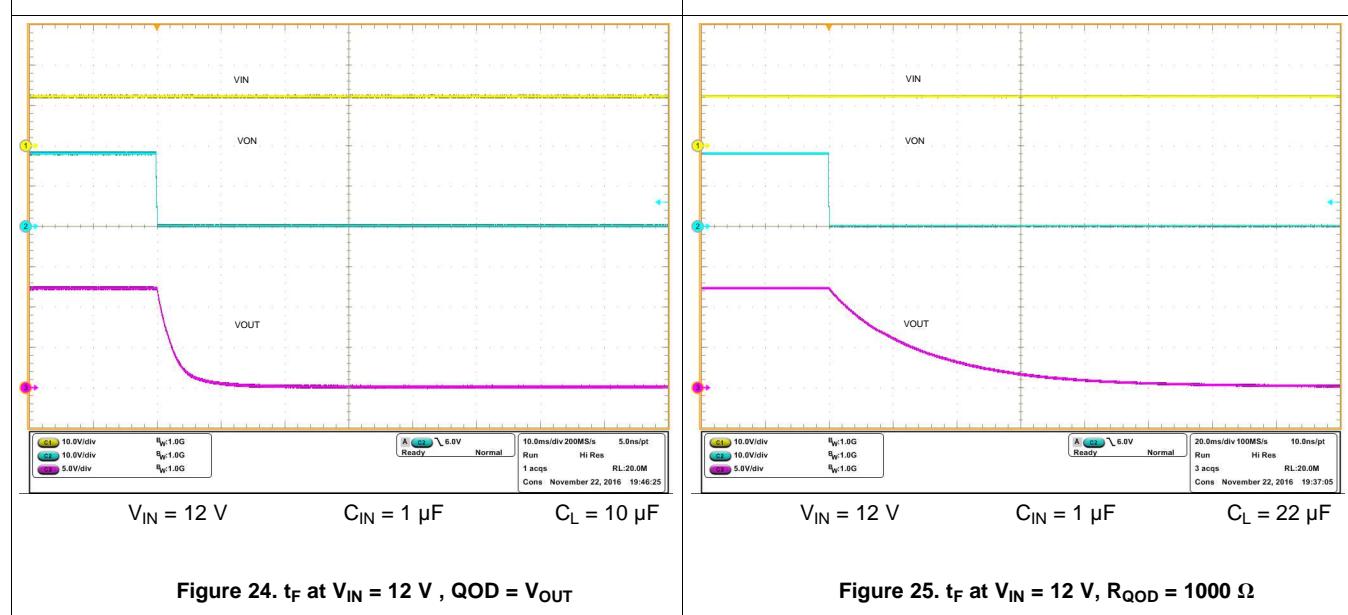

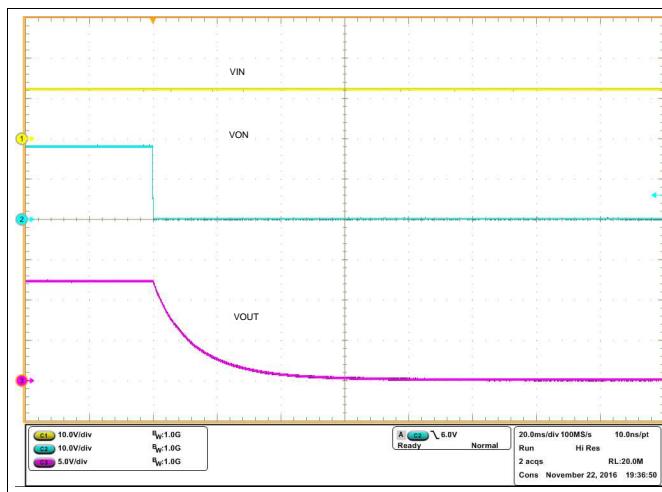

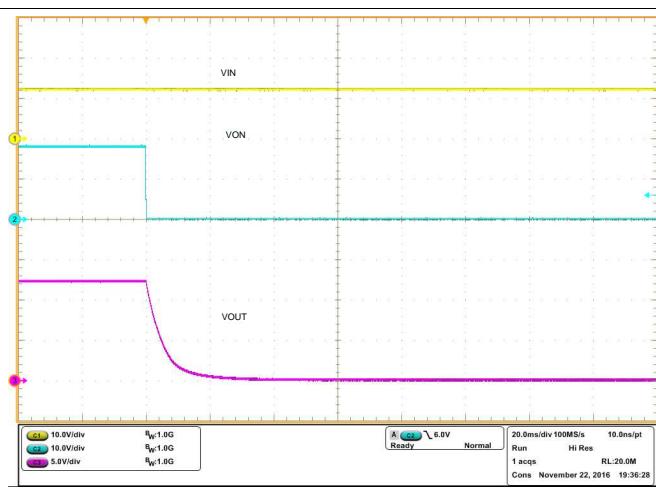

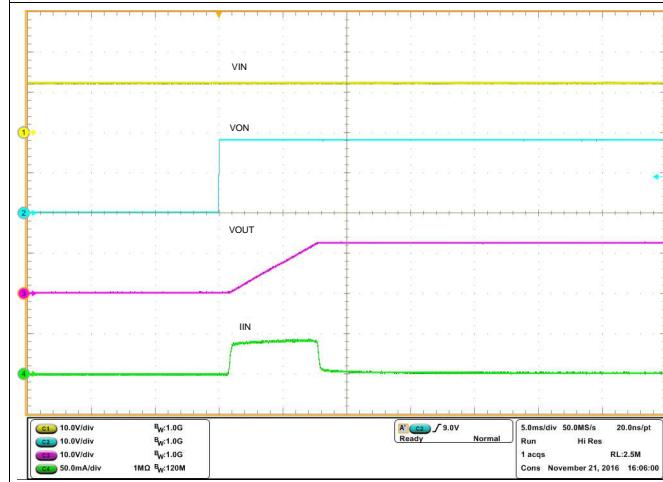

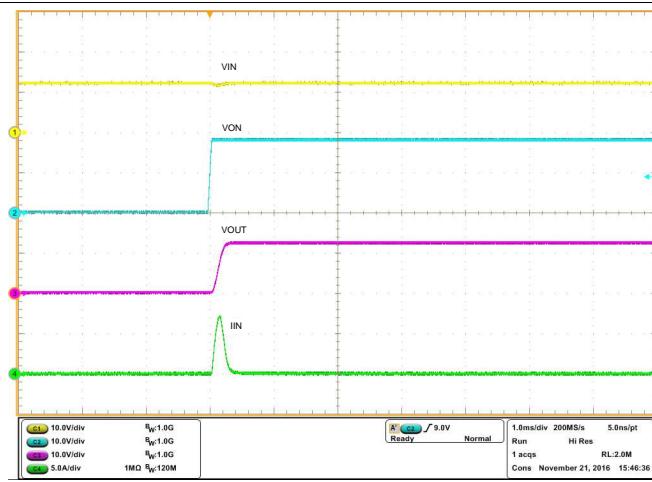

[Figure 22](#) through [Figure 25](#) are scope shots demonstrating an example of the QOD functionality when power is removed from the device (both ON and VIN are disconnected simultaneously). In the scope shots, the  $V_{IN} = 12$  V and correspond to when  $R_{QOD} = 1000 \Omega$ ,  $R_{QOD} = 500 \Omega$ , and QOD =  $V_{OUT}$  with two values of  $C_L = 10 \mu F$  and  $22 \mu F$ .

**Figure 23. Fall Time  $t_F$  at  $V_{IN} = 12$  V,  $R_{QOD} = 500 \Omega$**

**Figure 26.  $t_F$  at  $V_{IN} = 12$  V,  $R_{QOD} = 500$   $\Omega$**

**Figure 27.  $t_F$  at  $V_{IN} = 12$  V,  $QOD = V_{OUT}$**

### 10.5.2.2 VIN to VOUT Voltage Drop

The VIN to VOUT voltage drop in the device is determined by the  $R_{ON}$  of the device and the load current. The  $R_{ON}$  of the device depends upon the VIN conditions of the device. Refer to the  $R_{ON}$  specification of the device in the [Electrical Characteristics](#) table of this datasheet. Once the  $R_{ON}$  of the device is determined based upon the VIN conditions, use [Equation 8](#) to calculate the VIN to VOUT voltage drop.

$$\Delta V = I_{LOAD} \times R_{ON}$$

where

- $\Delta V$  is the voltage drop from VIN to VOUT

- $I_{LOAD}$  is the load current

- $R_{ON}$  is the On-resistance of the device for a specific  $V_{IN}$

(8)

An appropriate  $I_{LOAD}$  must be chosen such that the  $I_{MAX}$  specification of the device is not violated.

### 10.5.2.3 Inrush Current

To determine how much inrush current is caused by the  $C_L$  capacitor, use [Equation 9](#).

$$I_{INRUSH} = C_L \times \frac{dV_{OUT}}{dt}$$

where

- $I_{INRUSH}$  is the amount of inrush caused by  $C_L$

- $C_L$  is the capacitance on VOUT

- $dt$  is the Output Voltage rise time during the ramp up of VOUT when the device is enabled

- $dV_{OUT}$  is the change in  $V_{OUT}$  during the ramp up of VOUT when the device is enabled

(9)

The appropriate rise time can be calculated using the design requirements and the inrush current equation. As we calculate the rise time (measured from 10% to 90% of  $V_{OUT}$ ), we account for this in our  $d_{VOUT}$  parameter (80% of  $V_{OUT} = 9.6$  V) as shown in [Equation 10](#) and [Equation 11](#).

$$400 \text{ mA} = 22 \mu\text{F} \times 9.6 \text{ V}/dt \quad (10)$$

$$dt = 528 \mu\text{s} \quad (11)$$

To ensure an inrush current of less than 400 mA, choose a CT value that yields a rise time of more than 528  $\mu$ s. Consulting [Table 2](#) at  $V_{IN} = 12$  V,  $CT = 4700$  pF provides a typical rise time of 957  $\mu$ s. Using this rise time and voltage into [Equation 9](#), yields [Equation 12](#) and [Equation 13](#).

$$I_{INRUSH} = 22 \mu\text{F} \times 9.6 \text{ V}/957 \mu\text{s} \quad (12)$$

$$I_{INRUSH} = 220 \text{ mA} \quad (13)$$

An appropriate  $C_L$  value must be placed on VOUT such that the  $I_{MAX}$  and  $I_{PLS}$  specifications of the device are not violated.

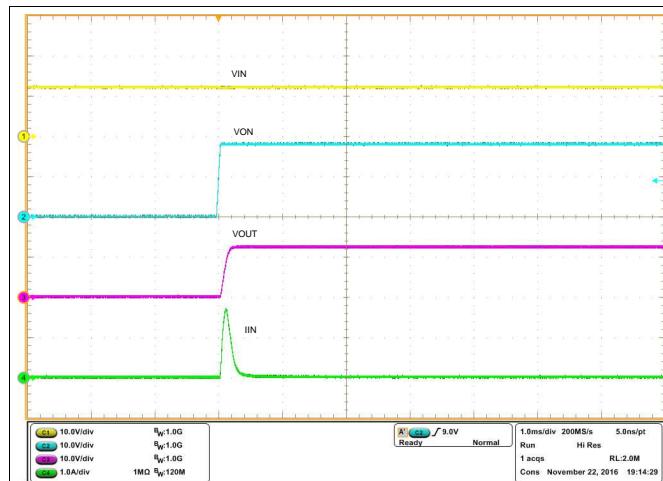

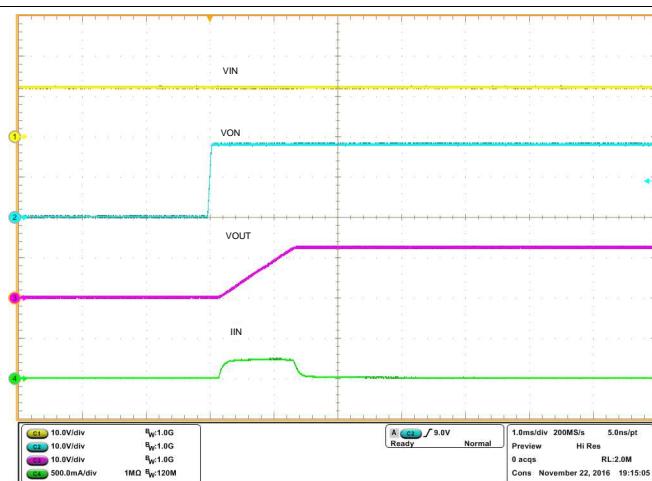

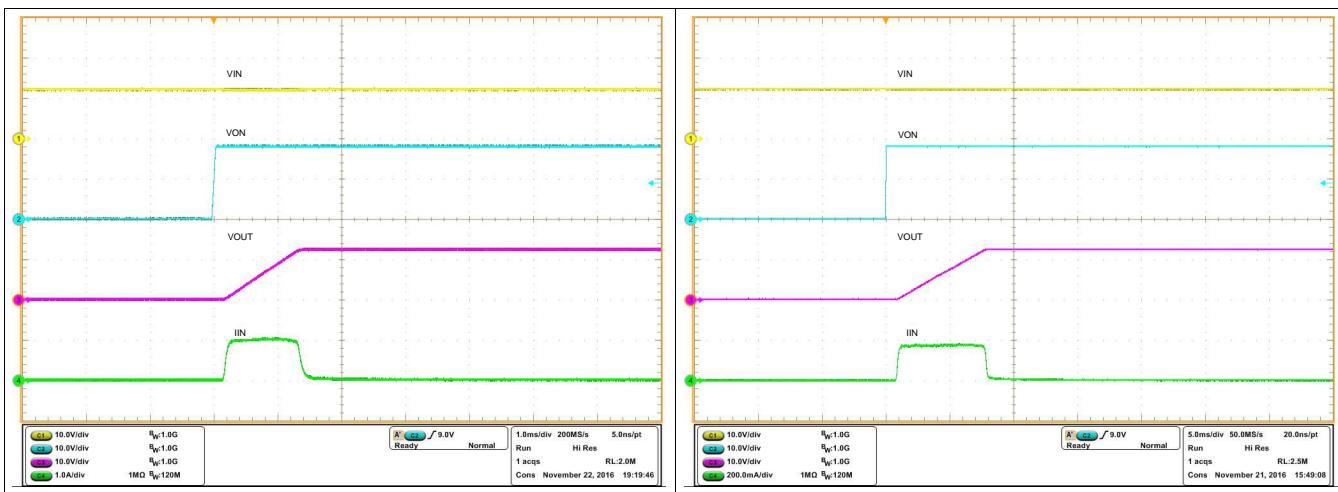

### 10.5.3 Application Curves

See the oscilloscope captures below for an example of how the CT capacitor can be used to reduce inrush current for  $V_{IN} = 12$  V. See the *Adjustable Rise Time (CT)* section for rise times for corresponding CT values.

**Figure 28. TPS22810 Inrush Current With  $C_L = 22 \mu\text{F}$ , CT = 0 pF**

**Figure 29. TPS22810 Inrush Current with  $C_L = 22 \mu\text{F}$ , CT = 4700 pF**

**Figure 30. TPS22810 Inrush Current With  $C_L = 22 \mu\text{F}$ , CT = 27000 pF**

**Figure 31. TPS22810 Inrush Current With  $C_L = 100 \mu\text{F}$ , CT = 0 pF**

**Figure 32. TPS22810 Inrush Current

With  $C_L = 100 \mu\text{F}$ ,  $CT = 4700 \text{ pF}$**

**Figure 33. TPS22810 Inrush Current

With  $C_L = 100 \mu\text{F}$ ,  $CT = 27000 \text{ pF}$**

## 11 Power Supply Recommendations

The device is designed to operate from a  $V_{IN}$  range of 2.7 V to 18 V. This supply must be well regulated and placed as close to the device terminal as possible with the recommended 1- $\mu\text{F}$  bypass capacitor. If the supply is located more than a few inches from the device terminals, additional bulk capacitance may be required in addition to the ceramic bypass capacitors. If additional bulk capacitance is required, an electrolytic, tantalum, or ceramic capacitor of 1  $\mu\text{F}$  may be sufficient.

The TPS22810 operates regardless of power sequencing order. The order in which voltages are applied to  $V_{IN}$  and  $ON$  does not damage the device as long as the voltages do not exceed the absolute maximum operating conditions.

## 12 Layout

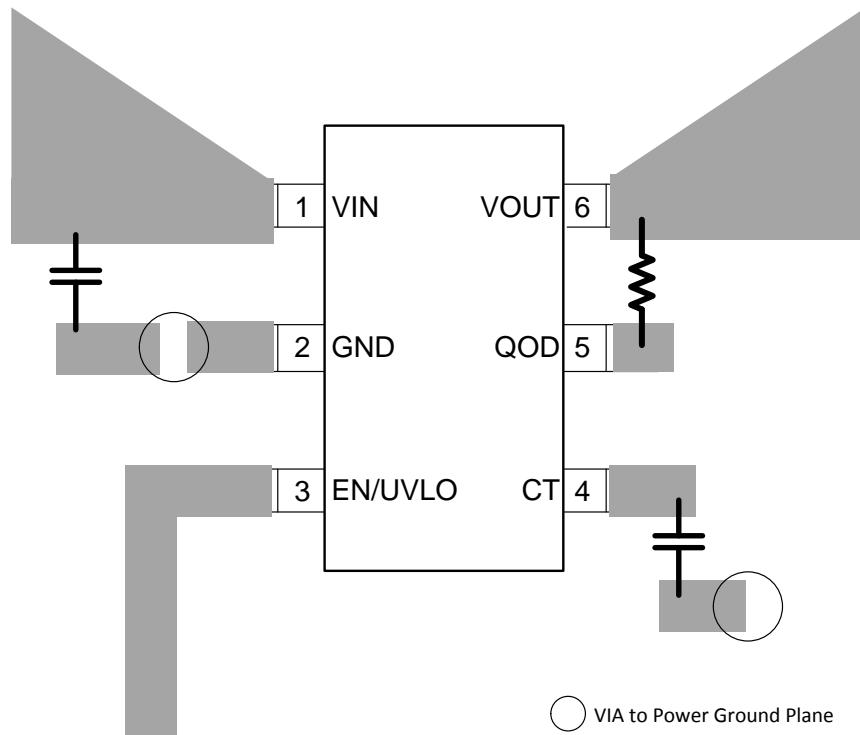

### 12.1 Layout Guidelines

1. VIN and VOUT traces must be as short and wide as possible to accommodate for high current.

2. The VIN pin must be bypassed to ground with low ESR ceramic bypass capacitors. The typical recommended bypass capacitance is 1- $\mu$ F ceramic with X5R or X7R dielectric. This capacitor must be placed as close to the device pins as possible.

### 12.2 Layout Example

Figure 34. Recommended Board Layout

### 12.3 Thermal Considerations

For best performance, all traces must be as short as possible. To be most effective, the input and output capacitors must be placed close to the device to minimize the effects that parasitic trace inductances may have on normal and short-circuit operation. Using wide traces for VIN, VOUT, and GND helps minimize the parasitic electrical effects along with minimizing the case to ambient thermal impedance.

The maximum IC junction temperature must be restricted to 150°C under normal operating conditions. To calculate the maximum allowable dissipation,  $P_{D(\max)}$  for a given output current and ambient temperature, use Equation 14.

$$P_{D(\max)} = \frac{T_{J(\max)} - T_A}{\theta_{JA}}$$

where

- $P_{D(\max)}$  is the maximum allowable power dissipation

- $T_{J(\max)}$  is the maximum allowable junction temperature (150°C for the TPS22810)

- $T_A$  is the ambient temperature of the device

- $\theta_{JA}$  is the junction to air thermal impedance. Refer to the *Thermal Information* table. This parameter is highly dependent upon board layout.

## 13 デバイスおよびドキュメントのサポート

### 13.1 デバイス・サポート

#### 13.1.1 開発サポート

TPS22810 PSpiceトランジエント・モデルについては、『[TPS22810 PSpiceトランジエント・モデル](#)』を参照してください。

### 13.2 ドキュメントのサポート

#### 13.2.1 関連資料

関連資料については、以下を参照してください。

- 『[TPS22810 負荷スイッチ評価モジュール](#)』

- 『[ディスクリート・ソリューションに置き換わる負荷スイッチの選択](#)』

- 『[負荷スイッチのタイミング](#)』

### 13.3 ドキュメントの更新通知を受け取る方法

ドキュメント更新の通知を、シリコンの正誤表も含めて受け取るには、[ti.com](http://ti.com)でお使いの製品のフォルダへ移動します。右上の隅にある「通知を受け取る」ボタンをクリックします。これによって登録が行われ、変更された製品情報の概要を毎週受け取ることができます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 13.4 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's [Terms of Use](#).

**TI E2E™オンライン・コミュニティ** [TIのE2E \( Engineer-to-Engineer \) コミュニティ](#)。エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立てることができます。

**設計サポート** [TIの設計サポート](#) 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

### 13.5 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 13.6 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

### 13.7 Glossary

[SLYZ022](#) — [TI Glossary](#).

This glossary lists and explains terms, acronyms, and definitions.

## 14 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあります、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins   | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS22810DBVR          | Active        | Production           | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes         | NIPDAU   SN                          | Level-1-260C-UNLIM                | -40 to 105   | 19HF                |

| TPS22810DBVR.A        | Active        | Production           | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 19HF                |

| TPS22810DBVRG4        | Active        | Production           | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 19HF                |

| TPS22810DBVRG4.A      | Active        | Production           | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 19HF                |

| TPS22810DBVT          | Active        | Production           | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes         | NIPDAU   SN                          | Level-1-260C-UNLIM                | -40 to 105   | 19HF                |

| TPS22810DBVT.A        | Active        | Production           | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 19HF                |

| TPS22810DRV           | Active        | Production           | WSON (DRV)   6   | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 1CRH                |

| TPS22810DRV.A         | Active        | Production           | WSON (DRV)   6   | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 1CRH                |

| TPS22810DRVRG4        | Active        | Production           | WSON (DRV)   6   | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 1CRH                |

| TPS22810DRVRG4.A      | Active        | Production           | WSON (DRV)   6   | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 1CRH                |

| TPS22810DRV           | Active        | Production           | WSON (DRV)   6   | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 1CRH                |

| TPS22810DRV.A         | Active        | Production           | WSON (DRV)   6   | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 1CRH                |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

---

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPS22810 :**

- Automotive : [TPS22810-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

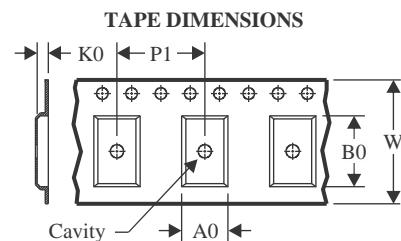

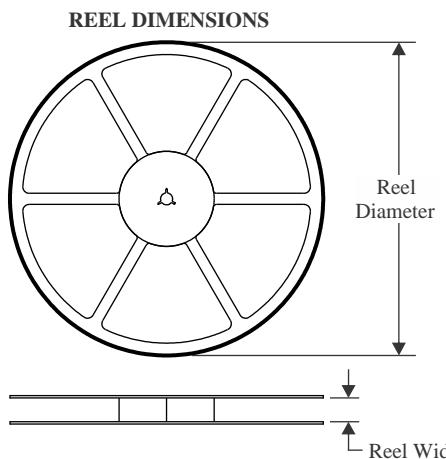

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

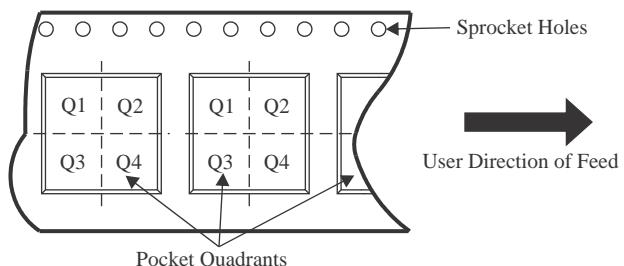

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS22810DBVR   | SOT-23       | DBV             | 6    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TPS22810DBVRG4 | SOT-23       | DBV             | 6    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TPS22810DBVT   | SOT-23       | DBV             | 6    | 250  | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TPS22810DRV    | WSON         | DRV             | 6    | 3000 | 178.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

| TPS22810DRVRG4 | WSON         | DRV             | 6    | 3000 | 180.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

| TPS22810DRV    | WSON         | DRV             | 6    | 250  | 180.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

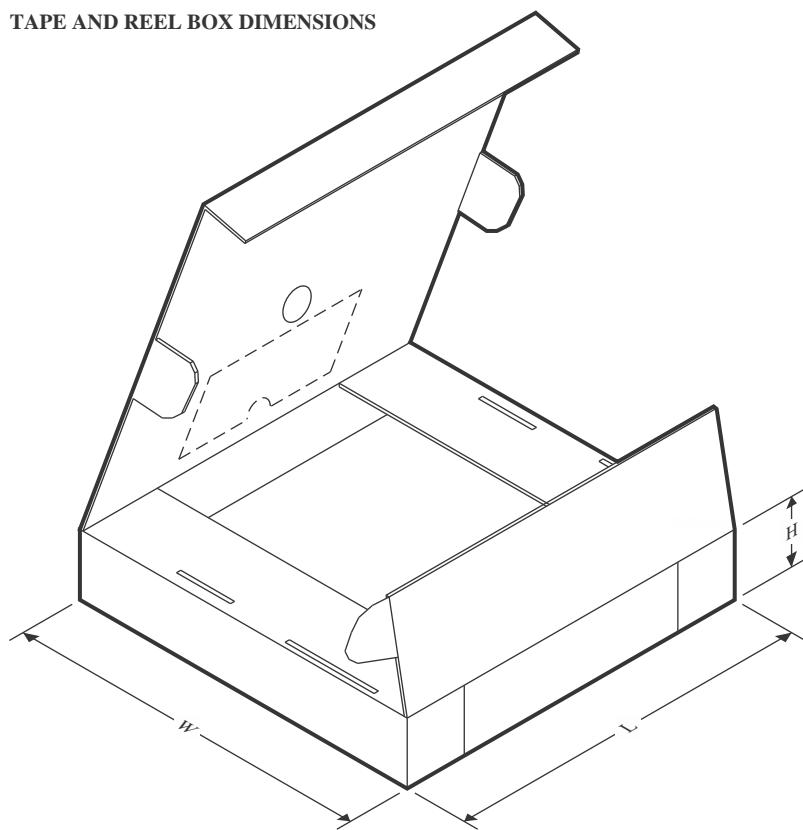

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS22810DBVR    | SOT-23       | DBV             | 6    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS22810DBVRG4  | SOT-23       | DBV             | 6    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS22810DBVT    | SOT-23       | DBV             | 6    | 250  | 210.0       | 185.0      | 35.0        |

| TPS22810DRVVR   | WSON         | DRV             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

| TPS22810DRVVRG4 | WSON         | DRV             | 6    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS22810DRVVT   | WSON         | DRV             | 6    | 250  | 210.0       | 185.0      | 35.0        |

**DRV 6**

**GENERIC PACKAGE VIEW**

**WSON - 0.8 mm max height**

PLASTIC SMALL OUTLINE - NO LEAD

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4206925/F

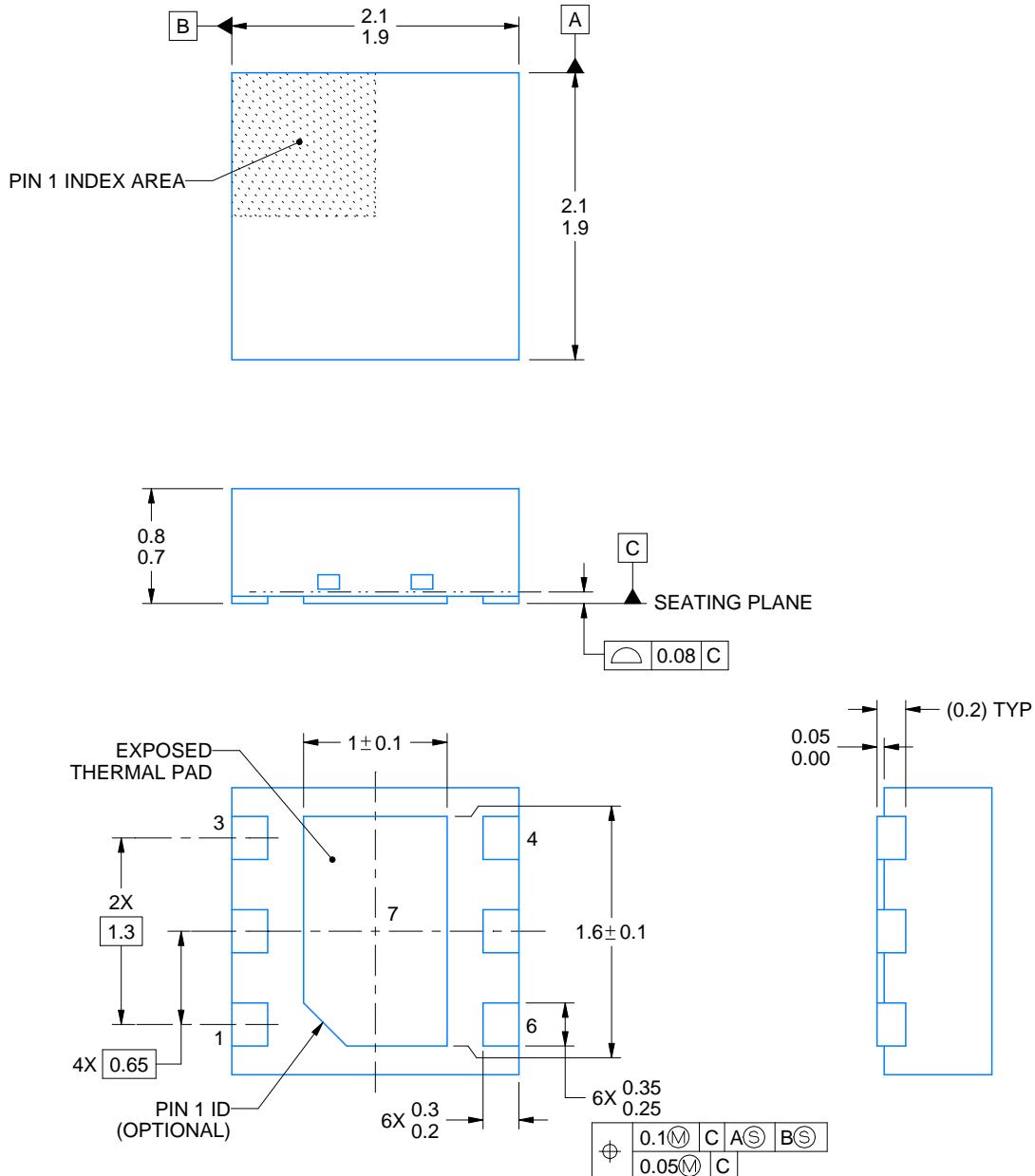

## PACKAGE OUTLINE

**DRV0006A**

## WSON - 0.8 mm max height

## PLASTIC SMALL OUTLINE - NO LEAD

4222173/B 04/2018

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

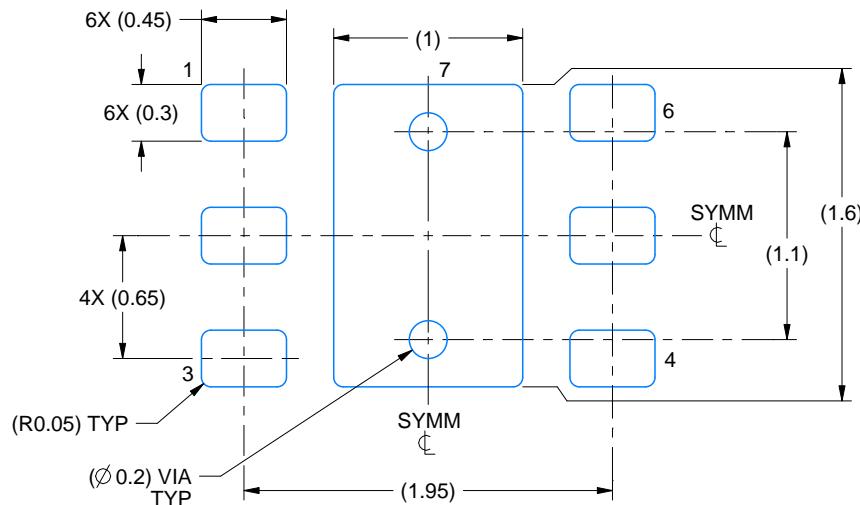

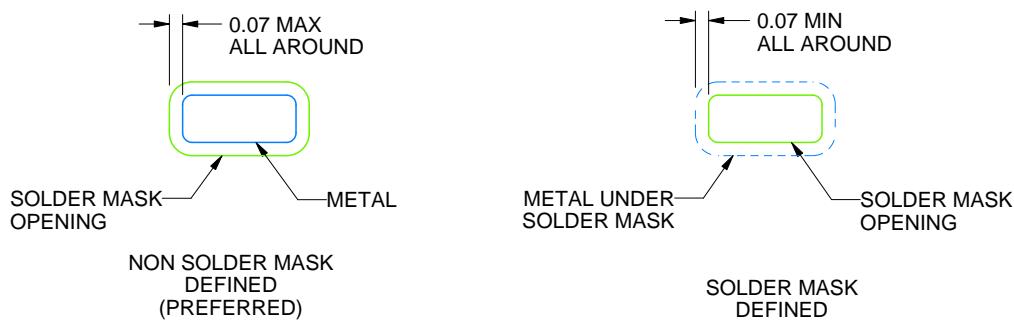

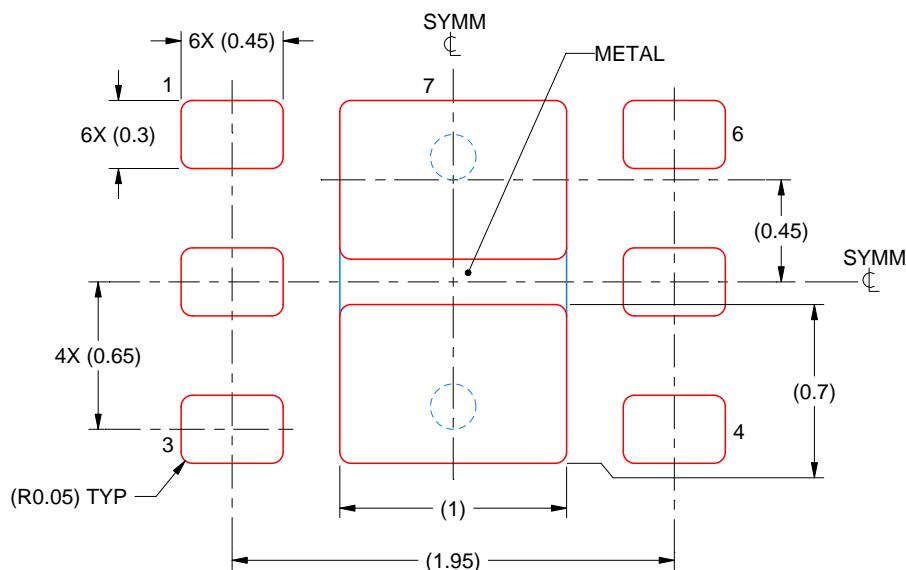

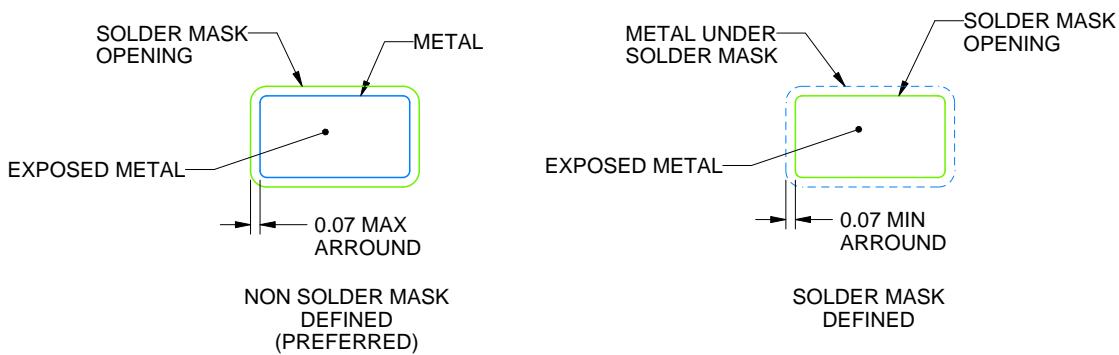

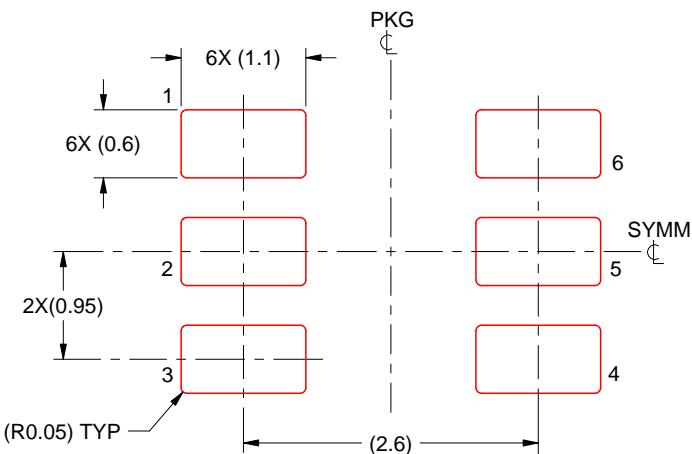

# EXAMPLE BOARD LAYOUT

DRV0006A

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

LAND PATTERN EXAMPLE

SCALE:25X

SOLDER MASK DETAILS

4222173/B 04/2018

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If some or all are implemented, recommended via locations are shown.

# EXAMPLE STENCIL DESIGN

DRV0006A

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD #7

88% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

SCALE:30X

4222173/B 04/2018

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

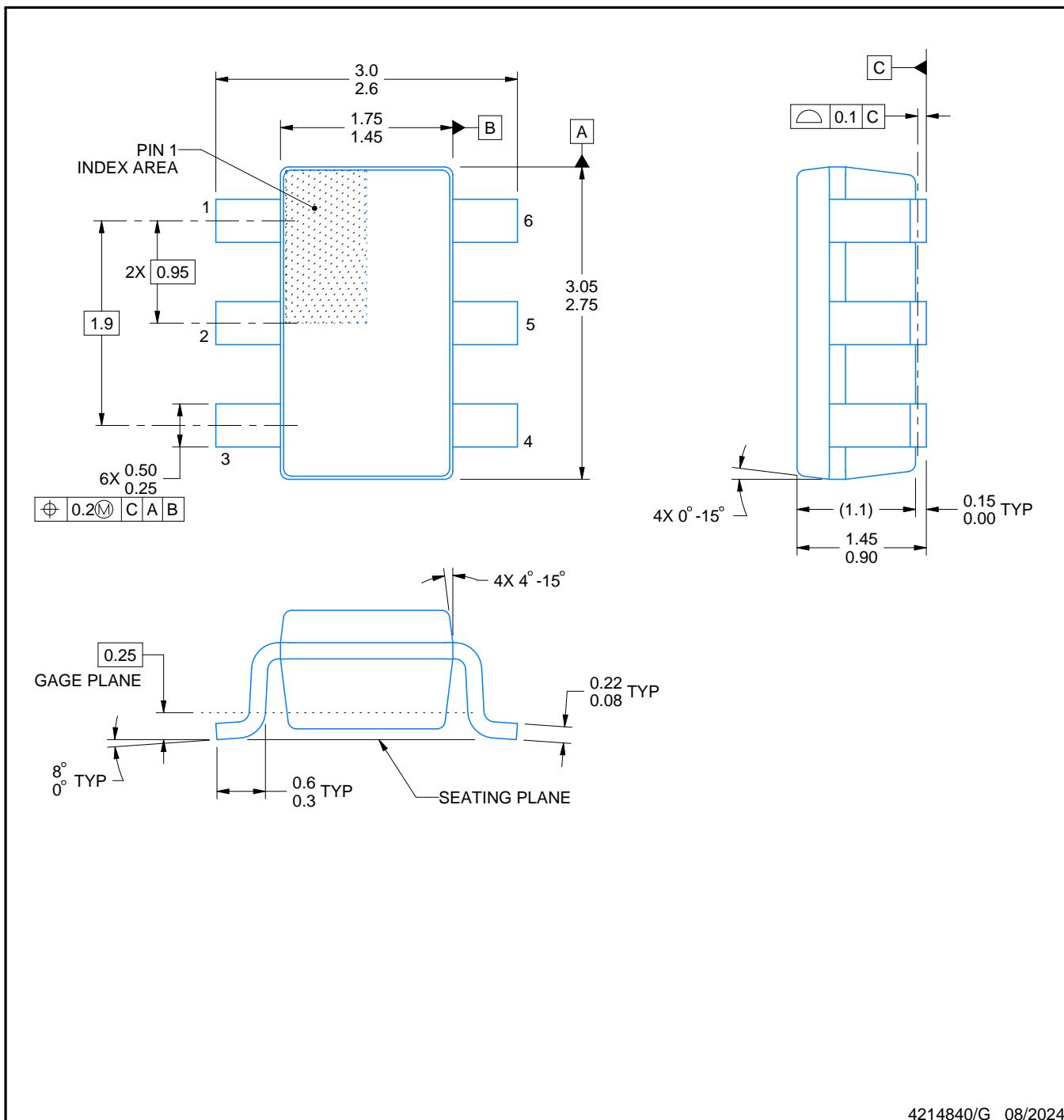

# PACKAGE OUTLINE

DBV0006A

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.25 per side.

4. Leads 1,2,3 may be wider than leads 4,5,6 for package orientation.

5. Reference JEDEC MO-178.

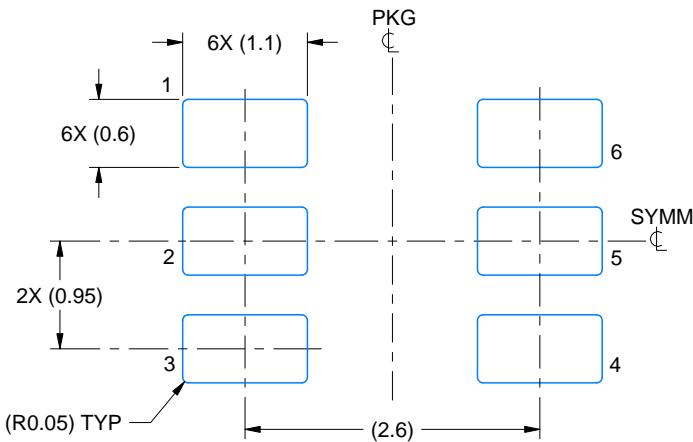

# EXAMPLE BOARD LAYOUT

DBV0006A

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:15X

SOLDER MASK DETAILS

4214840/G 08/2024

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

DBV0006A

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE:15X

4214840/G 08/2024

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月