# TPS2HCS10-Q1 11.3mΩ、車載用デュアルチャネル、SPI制御ハイサイドスイッチ、I<sub>2</sub>Tワイヤ保護低消費電力モード搭載

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード 1: -40°C ~ 125°C

- 36V の負荷ダンプへの耐性

- nFET を内蔵した SPI 制御のデュアルチャネルスマートハイサイドスイッチ。

- MCU を介さないワイヤハーネス保護機能と SPI でプログラム可能なヒューズ曲線を内蔵

- 持続的な過負荷状態からの保護

- SPI でプログラム可能な可変過電流保護によりシステムレベルの信頼性を向上

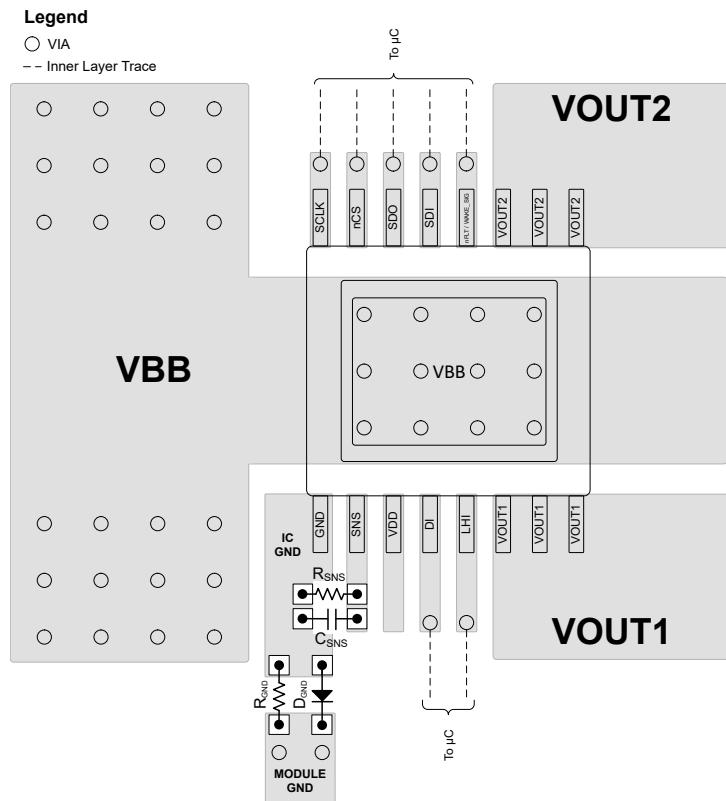

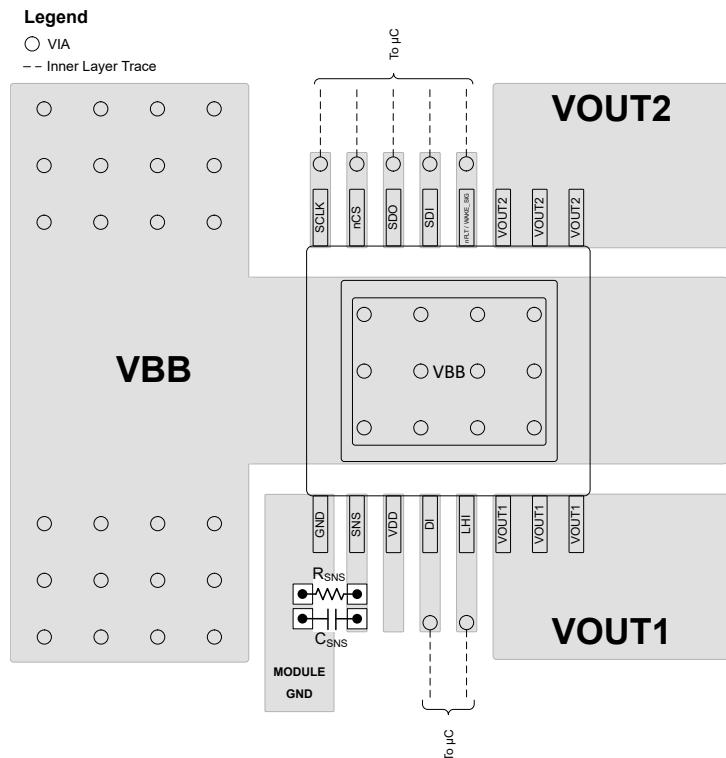

- 幅広い容量性入力 ECU の負荷電流ニーズに対応する SPI で構成可能な容量性充電モード

- 低静止電流 / 低消費電力オノン状態で常時オンの負荷に電力を供給、MCU に対するウェーク信号によりウェイクオン時の負荷電流を自動的に供給

- 堅牢な出力保護機能を内蔵:

- サーマル保護内蔵

- グランド短絡からの保護

- 逆電源電圧による FET の自動スイッチオンを含むバッテリ逆接続からの保護

- バッテリまたはグランドの喪失時に使用できる自動シャットオフ機能

- 誘導性負荷の逆起電圧の発生を防止する出力クランプを内蔵

- SPI によるデジタルセンス出力で以下を測定するように構成可能:

- 負荷電流 (内蔵 ADC による高精度の測定)

- 出力または電源電圧、FET 温度

- SPI インターフェイスによる完全なフォルト診断と FLT ピンによるフォルト表示

- 開放負荷およびバッテリへの短絡の検出

## 2 アプリケーション

- 車載ゾーン ECU

- パワー ディストリビューション モジュール

- 車体制御モジュール

## 3 説明

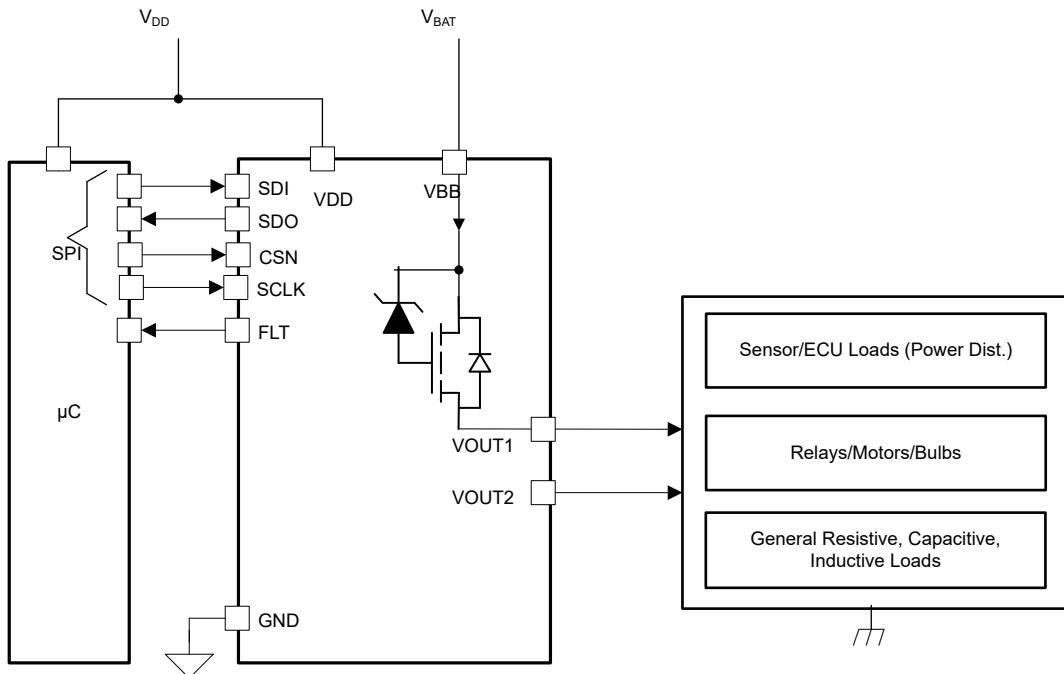

TPS2HCS10-Q1 デバイスは、シリアル ペリフェラル インターフェイス (SPI) を介して制御されるデュアルチャネルのスマートハイサイドスイッチであり、電源分配やアクチュエータ駆動用途を目的としています。このデバイスには堅牢な保護機能が内蔵されており、短絡や過負荷の状態から出力ワイヤと負荷を確実に保護できます。このデバイスは SPI 経由で構成できる過電流保護機能を搭載しており、大きな突入電流を必要とする負荷に対応できる十分な柔軟性と強化された保護機能を実現します。このデバイスには、過負荷状態が持続した場合にスイッチをオフにする、電流と時間の関係を設定可能なヒューズ特性 (プログラムブルヒューズ プロファイル) も組み込まれています。これらの 2 つの機能を組み合わせた完全な保護機能により、あらゆる負荷プロファイルに対してワイヤハーネスを最適化できます。

このデバイスは、パワー ディストリビューション スイッチ アプリケーションの ECU 負荷用に、SPI で構成可能な容量性充電モードをサポートしています。このデバイスには、低消費電力モード (LPM) が 2 種類あり、自動エントリモードと手動エントリモードを備えています。これにより、デバイス自身の消費電流を約 10 ~ 20µA に抑えつつ、負荷側の ECU に電流を供給することができます。

TPS2HCS10-Q1 デバイスは SPI による高精度のデジタル電流検出も備えているため、負荷の診断も強化されます。負荷電流、チャネル出力電圧、出力 FET 温度をシステムの MCU に報告することで、スイッチや負荷の障害を診断することができます。

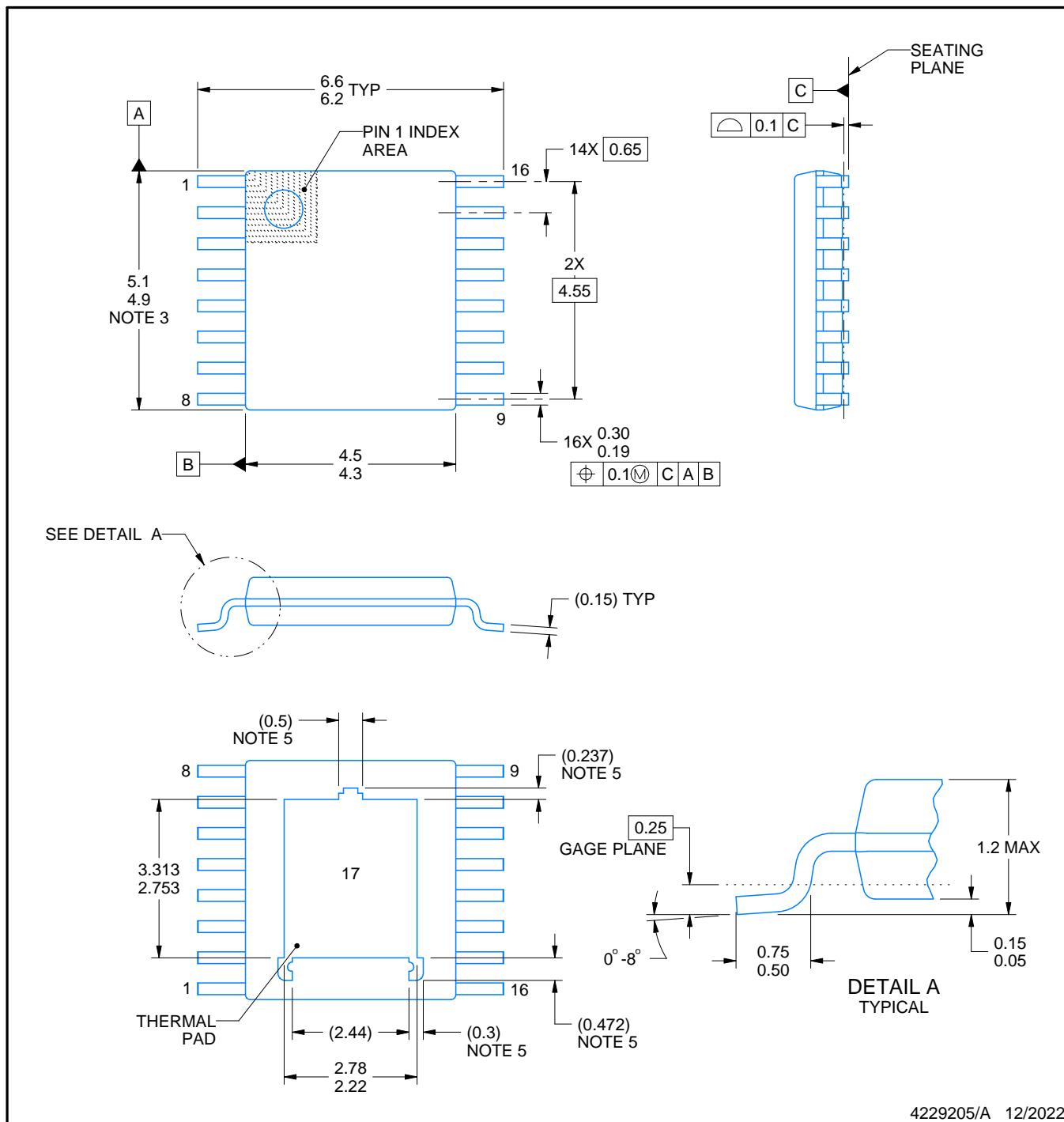

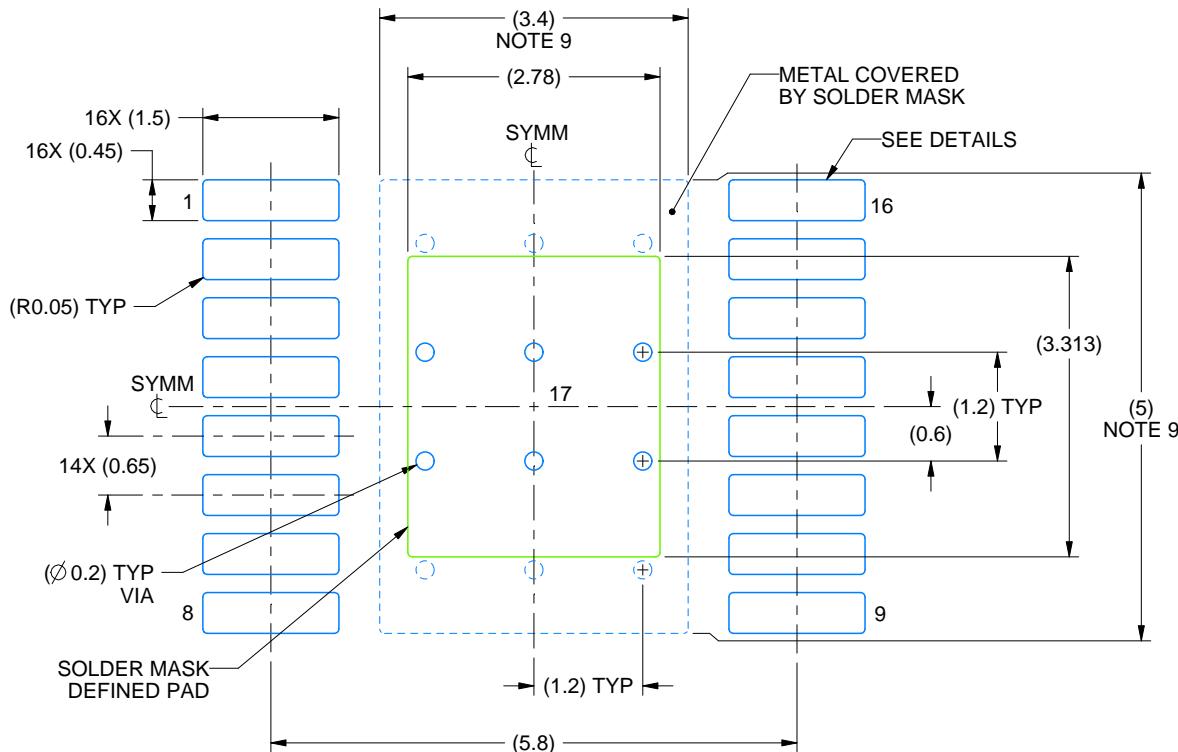

TPS2HCS10-Q1 は、PCB の実装面積を削減できる HTSSOP パッケージで提供されています。

### パッケージ情報

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|--------------|----------------------|--------------------------|

| TPS2HCS10-Q1 | PWP (HTSSOP、16)      | 5mm x 6.4mm              |

(1) 供給されているすべてのパッケージについては、セクション 12 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

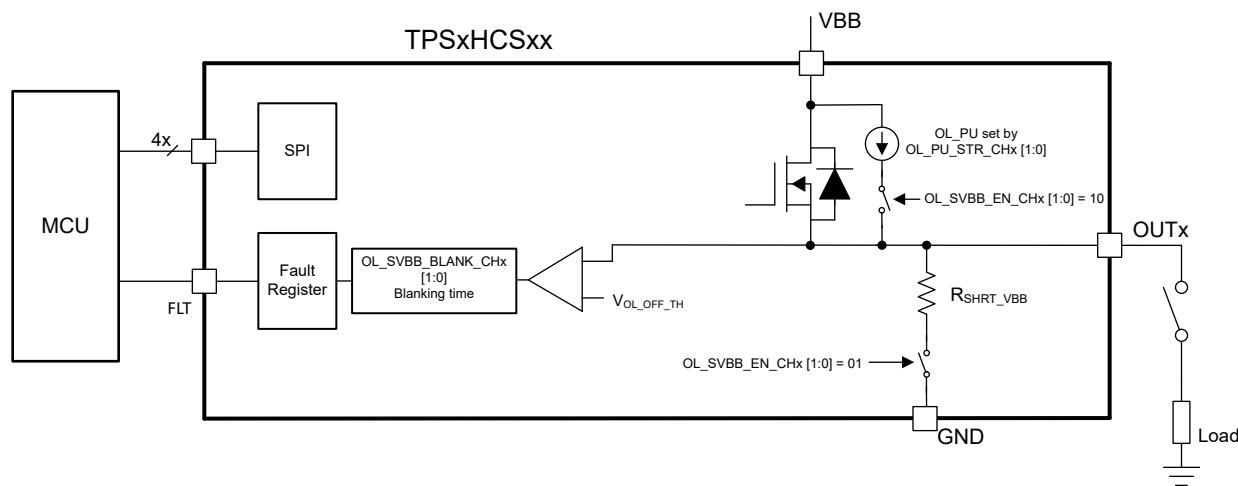

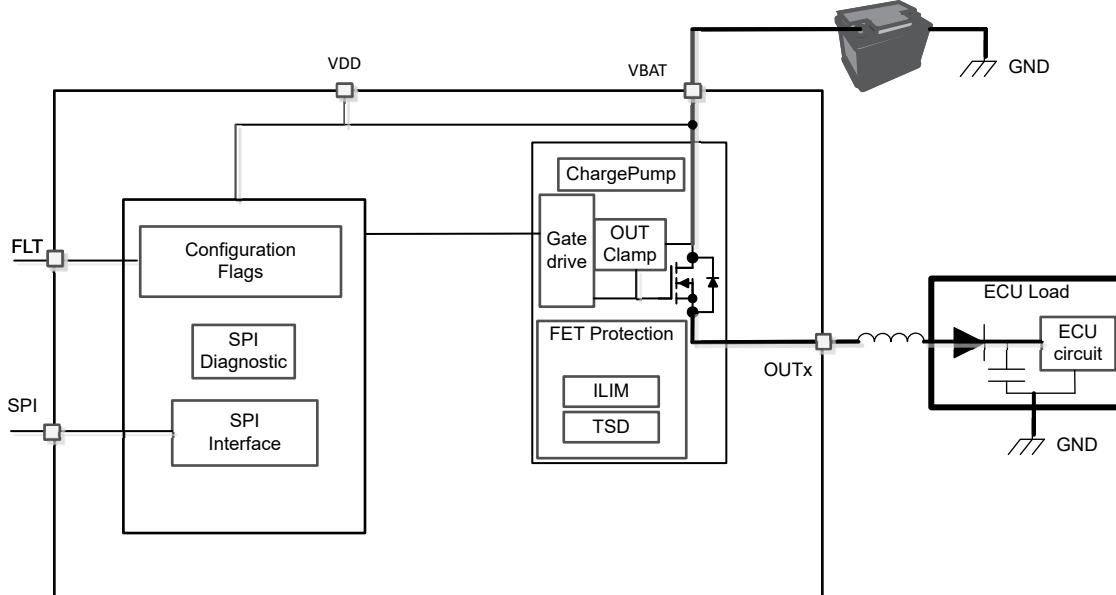

概略回路図

## 目次

|                    |    |                         |     |

|--------------------|----|-------------------------|-----|

| 1 特長               | 1  | 8.1 概要                  | 20  |

| 2 アプリケーション         | 1  | 8.2 機能ブロック図             | 21  |

| 3 説明               | 1  | 8.3 機能説明                | 21  |

| 4 デバイス比較表          | 4  | 8.4 デバイスの機能モード          | 42  |

| 5 ピン構成および機能        | 5  | 8.5 TPS2HCS10-Q1 のレジスタ  | 66  |

| 5.1 バージョン A パッケージ  | 5  | 9 アプリケーションと実装           | 108 |

| 5.2 ピン配置 - バージョン A | 5  | 9.1 アプリケーション情報          | 108 |

| 5.3 バージョン B パッケージ  | 6  | 9.2 代表的なアプリケーション        | 110 |

| 5.4 ピン配置 - バージョン B | 6  | 9.3 電源に関する推奨事項          | 111 |

| 6 仕様               | 7  | 9.4 レイアウト               | 112 |

| 6.1 絶対最大定格         | 7  | 10 デバイスおよびドキュメントのサポート   | 114 |

| 6.2 ESD 定格         | 7  | 10.1 サード・パーティ製品に関する免責事項 | 114 |

| 6.3 推奨動作条件         | 7  | 10.2 ドキュメントの更新通知を受け取る方法 | 114 |

| 6.4 熱に関する情報        | 8  | 10.3 サポート・リソース          | 114 |

| 6.5 電気的特性          | 8  | 10.4 商標                 | 114 |

| 6.6 SPI のタイミング要件   | 14 | 10.5 静電気放電に関する注意事項      | 114 |

| 6.7 スイッチング特性       | 14 | 10.6 用語集                | 114 |

| 6.8 代表的特性          | 16 | 11 改訂履歴                 | 114 |

| 7 パラメータ測定情報        | 19 | 12 メカニカル、パッケージ、および注文情報  | 115 |

| 8 詳細説明             | 20 |                         |     |

## 4 デバイス比較表

表 4-1. デバイスのオプション

| デバイスバージョン | 部品番号          | アクティブ状態での出力制御 | $R_{SNS} = 700\Omega$ に基づく I <sub>2</sub> T 範囲 | 過電流保護 (I <sub>OCP</sub> ) 範囲 | LIMP HOME 状態 |

|-----------|---------------|---------------|------------------------------------------------|------------------------------|--------------|

| A         | TPS2HCS10A-Q1 | SPI で設定       | $8.8A^2s \sim 350A^2s$                         | 10A~25A                      | あり           |

| B         | TPS2HCS10B-Q1 | DIX ピンでのみ設定   |                                                |                              | なし           |

## 5 ピン構成および機能

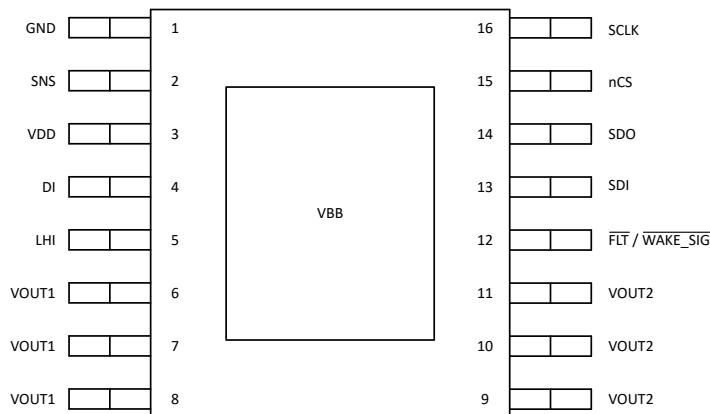

### 5.1 バージョン A パッケージ

図 5-1. TPS2HCS10A-Q1 PWP パッケージ、16 ピン HTSSOP (上面図)

### 5.2 ピン配置 - バージョン A

| ピン           |                   | タイプ | 説明                                                                                                                        |

|--------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------|

| 番号           | 名称                |     |                                                                                                                           |

| 1            | GND               | GND | デバイスのグランド                                                                                                                 |

| 2            | SNS               | O   | SNS 電流出力 - IC の GND ピンに対して並列 RC ネットワークを使用します。                                                                             |

| 3            | VDD               | 電源  | ロジック電源入力 - セラミックコンデンサを使用して、IC の GND ピンに近づけてデカッピングします。                                                                     |

| 4            | DI                | I   | LIMP HOME モードで構成している場合、このモードでの出力動作を設定します。このピンは、10K 抵抗の tor 保護を使用して MCU または他の HI/LO ソースに接続し、逆極性 FET のターンオン機能を有効にする必要があります。 |

| 5            | LHI               | I   | LIMP HOME モードを有効にするための外部入力 (アクティブ High)。                                                                                  |

| 6、7、8        | VOUT1             | O   | チャネル 1 の出力                                                                                                                |

| 9、10、11      | VOUT2             | O   | チャネル 2 の出力                                                                                                                |

| 12           | FLT /<br>WAKE_SIG | O   | フォルト出力 - 任意の (1 つまたは複数) チャネルのオープンドレイン、VDD ピンへの 4.7K 抵抗によってプルアップ。また、キオフ モードでの負荷電流要求時に MCU へのウェイク信号として機能します。                |

| 13           | SDI               | I   | SPI デバイス (2 次側) データ入力                                                                                                     |

| 14           | SDO               | O   | デバイスからの SPI データ出力。VDD への内部プルアップ。                                                                                          |

| 15           | CSN               | I   | チップセレクト。VDD への内部プルアップ                                                                                                     |

| 16           | SCLK              | I   | SPI クロック入力                                                                                                                |

| サーマル パッ<br>ド | VBB               | 電源  | 電源                                                                                                                        |

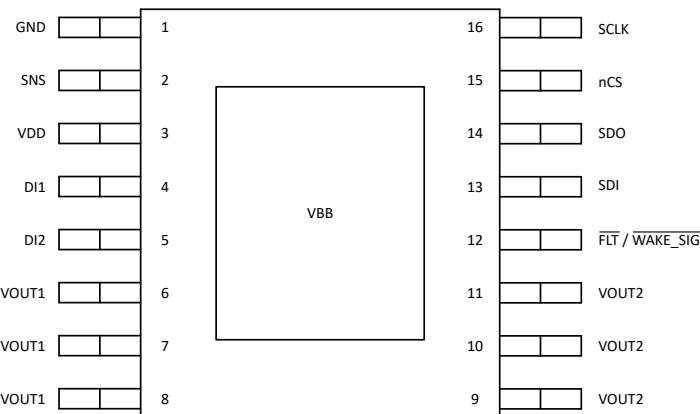

### 5.3 バージョン B パッケージ

図 5-2. PWP パッケージ、16 ピン HTSSOP (上面図) - TPS2HCS10B-Q1

### 5.4 ピン配置 - バージョン B

| ピン           |                   | タイプ | 説明                                                                                                        |

|--------------|-------------------|-----|-----------------------------------------------------------------------------------------------------------|

| 番号           | 名称                |     |                                                                                                           |

| 1            | GND               | GND | デバイスのグランド                                                                                                 |

| 2            | SNS               | O   | SNS 電流出力 - GND との間に抵抗を使用します。                                                                              |

| 3            | VDD               | 電源  | ロジック電源入力 - セラミックの 1 $\mu$ F コンデンサを使用して、IC の GND ピンに近づけてデカップリングします。                                        |

| 4            | DI1               | I   | チャネル 1 の出力をオンにするため有効にします。このピンは、10K 抵抗の tor 保護を使用して MCU または他の HI/LO ソースに接続し、逆極性 FET のターンオン機能を有効にする必要があります。 |

| 5            | DI2               | I   | チャネル 2 の出力をオンにするため有効にします。                                                                                 |

| 6、7、8        | VOUT1             | O   | チャネル 1 の出力                                                                                                |

| 9、10、11      | VOUT2             | O   | チャネル 2 の出力                                                                                                |

| 12           | FLT /<br>WAKE_SIG | O   | フォルト出力 - 任意の(1つまたは複数の)チャネルのオープンドレイン、VDD ピンへの 4.7K 抵抗によってプルアップ。また、キーオフ モードでの負荷電流要求時に MCU へのウェイク信号として機能します。 |

| 13           | SDI               | I   | SPI デバイス(2次側)データ入力                                                                                        |

| 14           | SDO               | O   | デバイスからの SPI データ出力。VDD への内部プルアップ。                                                                          |

| 15           | CSN               | I   | チップセレクト。VDD への内部プルアップ                                                                                     |

| 16           | SCLK              | I   | SPI クロック入力                                                                                                |

| サーマル パッ<br>ド | VBB               | 電源  | 電源                                                                                                        |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                                      |                                                                                          | 最小値  | 最大値          | 単位 |

|------------------------------------------------------|------------------------------------------------------------------------------------------|------|--------------|----|

| 最大連続電源電圧 $V_{VBB}$                                   |                                                                                          |      | 28           | V  |

| 負荷ダンプ電圧                                              | ISO16750-2:2010(E)                                                                       |      | 36           | V  |

| $V_{BB}$ ピンの最大過渡電圧 (ISO 7637 パルス 2a 過渡時の例) $V_{BBt}$ |                                                                                          |      | 54           | V  |

| 電源電圧への短絡対応能力                                         | $I_{OCP} = 25A, L_{OUT} = 5\mu H, t_{SHORT} = 300ms, T_A = 125^\circ C$                  |      | 24           | V  |

| 短絡電源電圧耐性、並列モード                                       | PARALLEL_12 = 1, $I_{OCP} = 20A, L_{OUT} = 5\mu H, t_{SHORT} = 300ms, T_A = 125^\circ C$ |      | 24           | V  |

| $V_{OUT}$ 電圧                                         |                                                                                          | -30  | $V_{VS}+0.3$ | V  |

| 逆極性電圧、 $V_{BB}$ ピンで連続動作                              |                                                                                          | -18  |              | V  |

| 低電源ピン電圧、 $V_{DD}$                                    |                                                                                          | -0.3 | 7            | V  |

| デジタル入力ピン電圧範囲、 $V_{DIG}$                              | SDI, SDO, SCLK, $\overline{CS}$                                                          | -0.3 | 7            | V  |

| センス・ピン電圧、 $V_{SNS}$                                  |                                                                                          | -0.3 | 7            | V  |

| $FLT$ ピン電圧、 $V_{FLT}$                                |                                                                                          | -0.3 | 7            | V  |

| Limp home アクティブ化ピン電圧、 $V_{LHI}$                      |                                                                                          |      | $V_{BB}$     | V  |

| Limp home 直接入力ピン電圧、 $V_{DI}$                         |                                                                                          | -0.3 | 7            | V  |

| 逆グランド電流、 $I_{GND}$                                   | $V_{BB} < 0V$                                                                            |      | -50          | mA |

| 最大接合部温度、 $T_J$                                       |                                                                                          |      | 150          | °C |

| 保管温度、 $T_{stg}$                                      |                                                                                          | -65  | 150          | °C |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。

「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しなくなる可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|             |                     |                                                      | 値                               | 単位         |

|-------------|---------------------|------------------------------------------------------|---------------------------------|------------|

| $V_{(ESD)}$ | 静電放電 <sup>(1)</sup> | 人体モデル (HBM)、AEC Q100-002 分類レベル H2 準拠                 | $V_{BB}$ と $V_{OUTx}$ を含むすべてのピン | $\pm 2000$ |

|             |                     | 人体モデル (HBM)、AEC Q100-002 分類レベル H3A 準拠 <sup>(2)</sup> | $V_{BB}$ と $V_{OUTx}$           | $\pm 4000$ |

|             |                     | 荷電デバイス モデル (CDM)、AEC Q100-011 分類レベル C5 準拠            | すべてのピン                          | $\pm 750$  |

(1) AEC-Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

(2) すべての ESD 衝撃は、GND に接続されたピンの基準電圧によるものです

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|               |         | 最小値                | 最大値 | 単位 |

|---------------|---------|--------------------|-----|----|

| $V_{BB\_NOM}$ | 公称電源電圧  | 6                  | 18  | V  |

| $V_{BB\_EXT}$ | 拡大電源電圧  | 動作電圧範囲の条件を参照してください | 3   | V  |

| $V_{DD}$      | 低電圧電源電圧 | 3.0                | 5.5 | V  |

## 6.3 推奨動作条件 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

|           |                          | 最小値  | 最大値      | 単位 |

|-----------|--------------------------|------|----------|----|

| $V_{DIG}$ | すべてのデジタル入力ピンの電圧          | -0.3 | 5.5      | V  |

| $V_{FLT}$ | FLT ピン電圧                 | -0.3 | 5.5      | V  |

| $V_{LHI}$ | Limp home アクティブ化ピン電圧、LHI |      | $V_{BB}$ | V  |

| $V_{DI}$  | Limp home 直接ピン入力電圧、DI    | -0.3 | 5.5      | V  |

| $T_A$     | 外気温度での動作時                | -40  | 125      | °C |

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1) (2)</sup> |                     | TPS2HCS10-Q1 | 単位   |

|--------------------------|---------------------|--------------|------|

|                          |                     | PWP          |      |

|                          |                     | 16 ピン        |      |

| $R_{\theta JA}$          | 接合部から周囲への熱抵抗        | 33.0         | °C/W |

| $R_{\theta JC(top)}$     | 接合部からケース (上面) への熱抵抗 | 26.2         | °C/W |

| $R_{\theta JB}$          | 接合部から基板への熱抵抗        | 9.4          | °C/W |

| $\Psi_{JT}$              | 接合部から上面への特性パラメータ    | 3.0          | °C/W |

| $\Psi_{JB}$              | 接合部から基板への特性パラメータ    | 9.3          | °C/W |

| $R_{\theta JC(bot)}$     | 接合部からケース (底面) への熱抵抗 | 1.1          | °C/W |

(1) 従来および最新の熱評価基準の詳細については、<https://www.ti.com/lit/an/spra953c/spra953c.pdf> アプリケーション レポートを参照してください。

(2) 熱パラメータは、JESD51-5 および JESD51-7 に準拠した 4 層 PCB に基づいています。

## 6.5 電気的特性

$V_{BB} = 6V \sim 18V$ 、 $V_{DD} = 3.0V \sim 5.5V$ 、 $T_J = -40^{\circ}C \sim 150^{\circ}C$  (特に記述のない限り)

| パラメータ                | テスト条件                                    | 最小値                                              | 標準値                 | 最大値  | 単位      |

|----------------------|------------------------------------------|--------------------------------------------------|---------------------|------|---------|

| 入力電圧および電流            |                                          |                                                  |                     |      |         |

| $V_{Clamp}$          | $I_{OUT} = 10mA$ $V_{BB} > 28V$          | $T_J = 25^{\circ}C \sim 150^{\circ}C$            | 35                  | 40   | 45      |

|                      | $I_{OUT} = 10mA$ $12V < V_{BB} < 28V$    | $T_J = -40^{\circ}C \sim 150^{\circ}C$           | 30                  | 34   | 38      |

|                      | $I_{OUT} = 10mA$ $V_{BB} = 3V$           | $T_J = -40^{\circ}C \sim 150^{\circ}C$           | 27.5                | 36.5 | V       |

| $V_{VBB\_UVLOR}$     | $V_{BB}$ 低電圧誤動作防止の立ち上がり電圧                | デバイスの GND ピンを基準に測定。                              | 3.0                 | 3.5  | 4.0     |

| $V_{VBB\_UVLOF}$     | $V_{BB}$ 低電圧誤動作防止の立ち下がり電圧                |                                                  | 2.6                 | 2.8  | 3.0     |

| $V_{BB\_UV\_WRN\_R}$ | $V_{BB}$ 電圧 UV_WRN 立ち上がりスレッショルド          | デバイスの GND ピンに関する測定。                              | 4.9                 |      | V       |

| $V_{BB\_UV\_WRN\_F}$ | $V_{BB}$ 電圧 UV_WRN 立ち下がりスレッショルド          |                                                  | 4.5                 |      | V       |

| $V_{VDD\_UVLOR}$     | $V_{VDD}$ 低電圧誤動作防止の立ち上がり電圧               | デバイスの GND ピンを基準に測定されます                           | 1.94                | 2.2  | V       |

| $V_{VDD\_UVLOF}$     | $V_{VDD}$ 低電圧誤動作防止の立ち下がり                 |                                                  | 1.86                | 2.07 | V       |

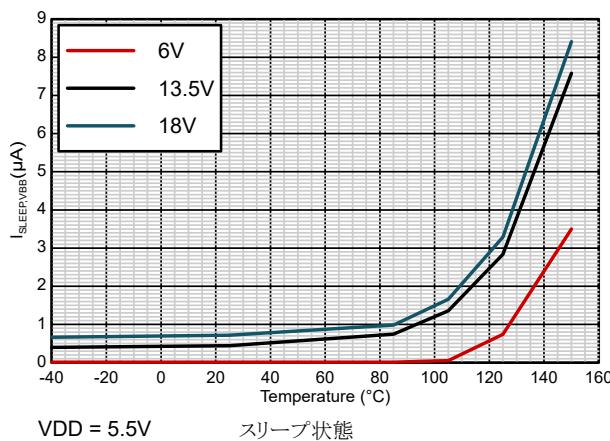

| $I_{SLEEP, VBB}$     | スリープ電流 (すべての MOSFET チャネルを含むデバイス全体のリーク電流) | $V_{BB} \leq 18V$ 、デバイスはスリープ モード、 $V_{OUT} = 0V$ | $T_J = 25^{\circ}C$ | 0.5  | $\mu A$ |

|                      |                                          |                                                  | $T_J = 85^{\circ}C$ | 2.2  | $\mu A$ |

## 6.5 電気的特性 (続き)

$V_{BB} = 6V \sim 18V$ 、 $V_{DD} = 3.0V \sim 5.5V$ 、 $T_J = -40^{\circ}C \sim 150^{\circ}C$  (特に記述のない限り)

| パラメータ            |                    | テスト条件                                                     | 最小値                           | 標準値  | 最大値 | 単位      |

|------------------|--------------------|-----------------------------------------------------------|-------------------------------|------|-----|---------|

| $I_{SLEEP, VDD}$ | VDD ピンからのスリープ電流    | $V_{VDD} \leq 5.5V$ 、デバイスはスリープモード、 $V_{OUT} = 0V$         | $T_J = 25^{\circ}C$           |      | 0.3 | $\mu A$ |

|                  |                    |                                                           | $T_J = 85^{\circ}C$           |      | 0.5 | $\mu A$ |

| $I_{OUT(OFF)}$   | (チャネルあたりの) 出力リーケ電流 | $V_{OUT} = 0V$ 、チャネル無効、アクティブ / 構成状態                       | $T_J = -40 \sim 125^{\circ}C$ | 1    | 12  | $\mu A$ |

| $I_Q, VDD$       | VDD 静止時電流          | アクティブ状態、SCLK オフ                                           | $V_{DD} = 5.5V$               | 1.4  | 1.6 | mA      |

|                  |                    | アクティブ状態、SCLK ON                                           |                               |      | 2.2 | mA      |

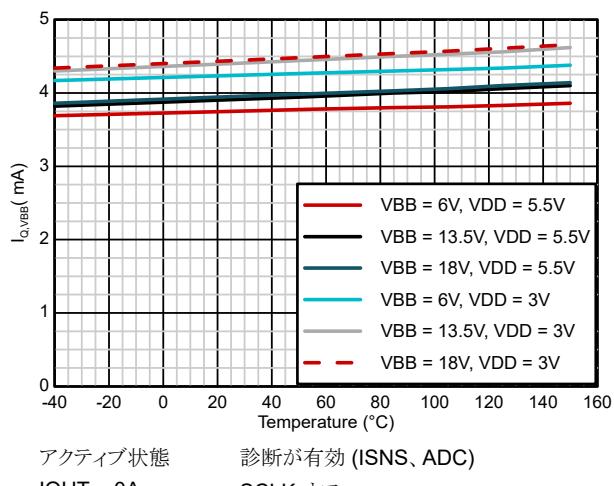

| $V_{BB} I_Q$     | $V_{BB}$ 静止電流      | すべてのチャネルが有効、 $I_{OUTx} = 0A$ 、SCLK オフ、診断は無効               | $V_{DD} = 5.5V$               | 3.8  | 4.3 | mA      |

|                  |                    |                                                           | $V_{DD} = 3.0V$               | 4.25 | 5.2 | mA      |

|                  |                    | すべてのチャネルがイネーブル、 $I_{OUTx} = 0A$ 、SCLK オフ、診断が有効 (ISNS、ADC) | $V_{DD} = 5.5V$               | 3.9  | 4.5 | mA      |

|                  |                    |                                                           | $V_{DD} = 0V$                 | 4.4  | 5.5 | mA      |

| $I_{L, CONT}$    | チャネルごとの連続負荷電流      | すべてのチャネルが有効、 $T_{AMB} = 85^{\circ}C$                      |                               | 7    |     | A       |

|                  |                    | 1 つのチャネルが有効、 $T_{AMB} = 85^{\circ}C$                      |                               | 12   |     | A       |

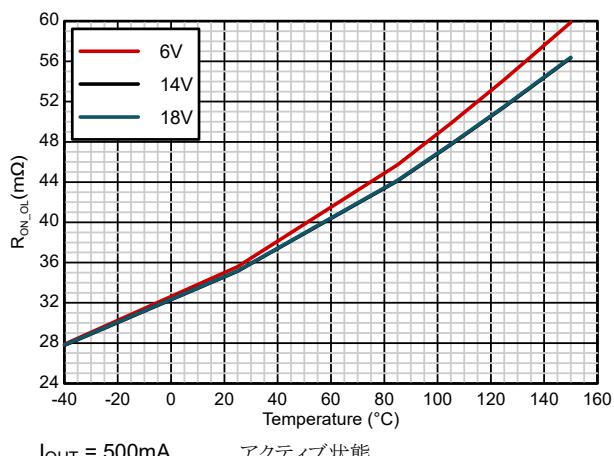

### Ron の特性

|                 |                                                     |                                                                       |                      |      |           |   |

|-----------------|-----------------------------------------------------|-----------------------------------------------------------------------|----------------------|------|-----------|---|

| $R_{ON}$        | オン抵抗                                                | $6V \leq V_{BB} \leq 28V$ 、 $I_{OUTx} = 1A$ 、 $OL\_ON\_EN\_CH1 = 0$   | $T_J = 25^{\circ}C$  | 11.3 | $m\Omega$ |   |

|                 |                                                     |                                                                       | $T_J = 150^{\circ}C$ | 22   | $m\Omega$ |   |

| $R_{ON\_OL}$    | オン抵抗、 $OL\_ON$ モード                                  | $6V \leq V_{BB} \leq 28V$ 、 $I_{OUTx} = 0.3A$ 、 $OL\_ON\_EN\_CHx = 1$ | $T_J = 25^{\circ}C$  | 36   | $m\Omega$ |   |

|                 |                                                     |                                                                       | $T_J = 150^{\circ}C$ | 70   | $m\Omega$ |   |

| $R_{ON(REV)}$   | 逆極性時のオン抵抗                                           | $-18V \leq V_{BB} \leq -7V$ 、                                         | $T_J = 25^{\circ}C$  | 13   | $m\Omega$ |   |

|                 |                                                     |                                                                       | $T_J = 150^{\circ}C$ | 26   | $m\Omega$ |   |

| $\Delta R_{ON}$ | チャネル間のオン抵抗差のパーセンテージ ( $R_{ON, CHx} - R_{ON, CHy}$ ) | $V_{BB} \geq 6V$ 、 $T_J = 25^{\circ}C$                                |                      | 0.5  | 7         | % |

### 電流センス特性

|                |                                |                                                             |                    |      |      |

|----------------|--------------------------------|-------------------------------------------------------------|--------------------|------|------|

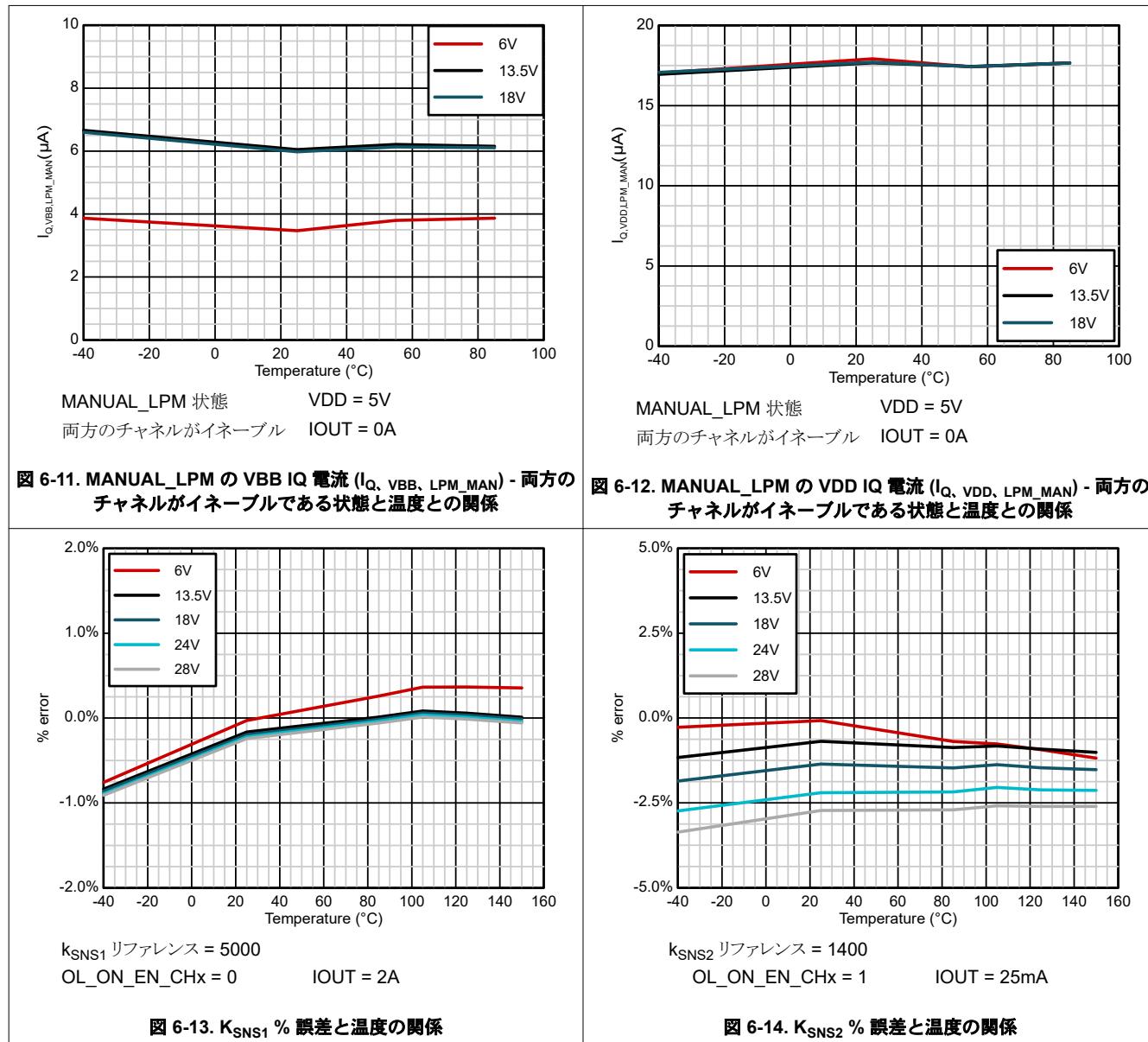

| $K_{SNS}$      | 電流センス比<br>$I_{OUTx} / i_{SNS}$ | $I_{OUT} = 1.0A$ 、 $OL\_ON\_EN\_CHx = 0$                    |                    | 5000 |      |

| $K_{SNS}$      | 電流センス比<br>$I_{OUTx} / i_{SNS}$ | $I_{OUT} = 50mA$ 、 $OL\_ON\_EN\_CHx = 1$                    |                    | 1400 |      |

| $I_{SNS\_SAT}$ | 飽和検出電流                         | $V_{BB} > 6V$ 、 $RSNS = 374\Omega$<br>$OL\_ON\_EN\_CHx = 0$ | $I_{OUT} \geq 30A$ | 6    | $mA$ |

## 6.5 電気的特性 (続き)

$V_{BB} = 6V \sim 18V$ 、 $V_{DD} = 3.0V \sim 5.5V$ 、 $T_J = -40^{\circ}C \sim 150^{\circ}C$  (特に記述のない限り)

| パラメータ                    |                                                          | テスト条件                                             |                    | 最小値   | 標準値  | 最大値         | 単位  |         |  |

|--------------------------|----------------------------------------------------------|---------------------------------------------------|--------------------|-------|------|-------------|-----|---------|--|

| K <sub>SNS1</sub>        | $I_{OUT}$ 全体にわたって $K_{SNS1}$<br>比 $I_{OUT} / I_{SNS1}$   | $RSNS = 374\Omega$<br>$OL\_ON\_EN\_CHx = 0$       | $I_{OUT} = 20A$    | 5000  |      |             |     |         |  |

|                          |                                                          |                                                   |                    | -3    | 3    | %           |     |         |  |

|                          |                                                          |                                                   | $I_{OUT} = 10A$    | 5000  |      |             |     |         |  |

|                          |                                                          |                                                   |                    | -5    | 5    | %           |     |         |  |

|                          |                                                          |                                                   |                    | 5000  |      |             |     |         |  |

|                          |                                                          | $RSNS = 698\Omega$<br>$OL\_ON\_EN\_CHx = 0$       | $I_{OUT} = 5A$     | -5    | 5    | %           |     |         |  |

|                          |                                                          |                                                   |                    | 5000  |      |             |     |         |  |

|                          |                                                          |                                                   | $I_{OUT} = 2.5A$   | -5    | 5    | %           |     |         |  |

|                          |                                                          |                                                   |                    | 5000  |      |             |     |         |  |

|                          |                                                          |                                                   |                    | -5    | 5    | %           |     |         |  |

| K <sub>SNS2</sub>        | $I_{OUT}$ 全体にわたって $K_{SNS2}$<br>比 $I_{OUT} / I_{SNS2}$   | $RSNS = 698\Omega$<br>$OL\_ON\_EN\_CHx = 1$       | $I_{OUT} = 1A$     | 5000  |      |             |     |         |  |

|                          |                                                          |                                                   |                    | -5    | 5    | %           |     |         |  |

|                          |                                                          |                                                   | $I_{OUT} = 500mA$  | 5000  |      |             |     |         |  |

|                          |                                                          |                                                   |                    | -7    | 7    | %           |     |         |  |

|                          |                                                          |                                                   |                    | 5000  |      |             |     |         |  |

|                          |                                                          | $RSNS = 698\Omega$<br>$OL\_ON\_EN\_CHx = 1$       | $I_{OUT} = 250mA$  | -10   | 10   | %           |     |         |  |

|                          |                                                          |                                                   |                    | 5000  |      |             |     |         |  |

|                          |                                                          |                                                   | $I_{OUT} = 100mA$  | -20   | 20   | %           |     |         |  |

|                          |                                                          |                                                   |                    | 5000  |      |             |     |         |  |

|                          |                                                          |                                                   |                    | -20   | 20   | %           |     |         |  |

| $I_{ENTRY\_OL\_ON}$      | OL_ON モードに移行するための $I_{OUT}$ 電流 ( $OL\_ON\_EN\_CHx = 1$ ) |                                                   |                    | 0.5   |      |             | A   |         |  |

| $I_{EXIT\_OL\_ON}$       | OL_ON モードを終了するための $I_{OUT}$ 電流 ( $OL\_ON\_EN\_CHx = 1$ ) |                                                   |                    |       | 1.7  |             | A   |         |  |

| <b>ADC の特性</b>           |                                                          |                                                   |                    |       |      |             |     |         |  |

| $V_{ADCEFHI}$            | ADC リファレンス電圧                                             |                                                   |                    |       | 2.76 | 2.81        | 2.9 | V       |  |

| $I_{sample}$             | 電流センス サンプリング時間                                           | マルチブレクサ タイミングと ADC 変換時間を含みます                      |                    |       | 50   |             |     | $\mu s$ |  |

| $I_{ADC}$                | ADC 消費電流                                                 |                                                   |                    |       |      | 0.5         |     | mA      |  |

| <b>SNS 特性</b>            |                                                          |                                                   |                    |       |      |             |     |         |  |

| ISNS <sub>ADC, ACC</sub> | ISNS ADC の精度                                             | $OL\_ON\_EN\_CHx = 0$ 、<br>$ISNS\_SCALE\_CHx = 0$ | $SNS$ ピン電圧 = 2.7V  | -3    | 3    | %           |     |         |  |

|                          |                                                          |                                                   | $SNS$ ピン電圧 = 1.4V  | -3.25 | 3.25 | %           |     |         |  |

|                          |                                                          |                                                   | $SNS$ ピン電圧 = 0.7V  | -4    | 4    | %           |     |         |  |

|                          |                                                          |                                                   | $SNS$ ピン電圧 = 0.1V  | -15   | 15   | %           |     |         |  |

|                          |                                                          | $OL\_ON\_EN\_CHx = 1$ 、<br>$ISNS\_SCALE\_CHx = 1$ | $SNS$ ピン電圧 = 0.04V | -10.5 | 10.5 | %           |     |         |  |

|                          |                                                          |                                                   | $SNS$ ピン電圧 = 0.01V | -37.5 | 37.5 | %           |     |         |  |

| $ADC_{TSNS}$             | $T_{SNS}$ ADC 出力コード                                      | $T_J = 25^{\circ}C$                               | バッファ ゲインを含みます      |       | 474  |             |     |         |  |

| $TSNS_{ACC}$             | $T_{SNS}$ の測定精度                                          |                                                   |                    | -17   | 17   | $^{\circ}C$ |     |         |  |

| $ADC_{VSNS}$             | 出力電圧測定の ADC コード                                          | $VOUTx = 13.5V$ 、デバイスの GND を基準                    | バッファ ゲインを含みます      |       | 459  |             |     |         |  |

## 6.5 電気的特性 (続き)

$V_{BB} = 6V \sim 18V$ 、 $V_{DD} = 3.0V \sim 5.5V$ 、 $T_J = -40^{\circ}C \sim 150^{\circ}C$  (特に記述のない限り)

| パラメータ                      |                                    | テスト条件                                                        |                                                                                             | 最小値   | 標準値  | 最大値  | 単位      |

|----------------------------|------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------|------|------|---------|

| $V_{SNS\_ACC}$             | $V_{OUT\_SNS}$ ( $V_{SNS}$ ) の測定精度 |                                                              |                                                                                             | -5    | 5    | 5    | %       |

| $ADC_{VBBNS}$              | $V_{BB}$ 電圧測定の ADC コード             | $V_{BB} = 13.5V$ 、デバイスの GND を基準                              | バッファ ゲインを含みます                                                                               | 452   |      |      |         |

| $V_{BBSNS\_ACC}$           | $V_{BB}$ ( $V_{BBSNS}$ ) の測定精度     |                                                              |                                                                                             | -5    | 5    | 5    | %       |

| <b>過電流保護特性</b>             |                                    |                                                              |                                                                                             |       |      |      |         |

| $I_{OCP\_RANGE}$           | 過電流保護スレッショルド、即時シャットダウン範囲           | $di/dt = 2A/\mu s$                                           |                                                                                             | 10    | 25   | 25   | A       |

| $I_{OCP}$                  | 過電流保護スレッショルド、即時シャットダウン             | $di/dt = 2A/\mu s$<br>$T_J = -40^{\circ}C \sim 150^{\circ}C$ | $ILIMIT\_SET\_CHx = 0x0$                                                                    | 10    | 10   | 10   | A       |

|                            |                                    |                                                              | $ILIMIT\_SET\_CHx = 0x1$                                                                    | 12.5  | 12.5 | 12.5 | A       |

|                            |                                    |                                                              | $ILIMIT\_SET\_CHx = 0x2$                                                                    | 15    | 15   | 15   | A       |

|                            |                                    |                                                              | $ILIMIT\_SET\_CHx = 0x3$                                                                    | 17.5  | 17.5 | 17.5 | A       |

|                            |                                    |                                                              | $ILIMIT\_SET\_CHx = 0x4$                                                                    | 20    | 20   | 20   | A       |

|                            |                                    |                                                              | $ILIMIT\_SET\_CHx = 0x5$                                                                    | 22.5  | 22.5 | 22.5 | A       |

|                            |                                    |                                                              | $ILIMIT\_SET\_CHx = 0x6$                                                                    | 25    | 25   | 25   | A       |

| $I_{OCP\_RANGE, PARALLEL}$ | 過電流保護スレッショルド、即時シャットダウン - 並列モードでの範囲 | $di/dt = 2A/\mu s$<br>$PARALLEL\_12 = 1$                     |                                                                                             | 10    | 20   | 20   | A       |

| $t_{OCP\_DETECT}$          | 即時シャットダウン検出時間                      | $T_J = -40^{\circ}C \sim 150^{\circ}C$                       | $I_{OUT} = I_{OCP}$ から $I_{OCP}$ 検出まで、 $R_{OUT} = I_{OCP}$ の 150%、 $L_{IN} = L_{OUT} = 0nH$ | 0.3   | 0.3  | 1.5  | $\mu s$ |

| $t_{OCP\_TOFF}$            | 即時シャットダウン ターンオフ時間                  | $T_J = -40^{\circ}C \sim 150^{\circ}C$                       | $I_{OCP}$ 検出から $V_{OUTx}$ の 10% まで、 $R_{OUT} = I_{OCP}$ の 150%、 $L_{IN} = L_{OUT} = 0nH$    |       | 7.5  | 7.5  | $\mu s$ |

| <b>コンデンサ充電電流の制限</b>        |                                    |                                                              |                                                                                             |       |      |      |         |

| $I_{CL\_Reg}$              | 突入電流期間内の電流レギュレーション モード電流           | $T_J = -40^{\circ}C \sim 150^{\circ}C$<br>$di/dt < 0.01A/ms$ | $INRUSH\_LIMIT\_CHx = 0$                                                                    | 0.82  | 1.5  | 2.18 | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = 1$                                                                    |       | 1.85 | 1.85 | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = 2$                                                                    |       | 2.25 | 2.25 | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = 3$                                                                    |       | 2.6  | 2.6  | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = 4$                                                                    | 1.8   | 3    | 4.2  | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = 5$                                                                    |       | 3.4  | 3.4  | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = 6$                                                                    |       | 3.8  | 3.8  | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = 7$                                                                    |       | 5    | 5    | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = 8$                                                                    |       | 6.25 | 6.25 | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = 9$                                                                    |       | 7.5  | 7.5  | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = A$                                                                    |       | 8.7  | 8.7  | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = B$                                                                    |       | 10.1 | 10.1 | A       |

|                            |                                    |                                                              | $INRUSH\_LIMIT\_CHx = C$                                                                    |       | 11.3 | 11.3 | A       |

| $t_{INRUSH\_RANGE}$        | 突入時間の設定範囲                          | $INRUSH\_DURATION\_CHx$ の範囲                                  |                                                                                             | 0     | 0    | 100  | ms      |

| <b>フォルト特性</b>              |                                    |                                                              |                                                                                             |       |      |      |         |

| $I_{OL\_OFF}$              | オフ状態でのオープン負荷 (OL) 検出における内部プルアップ電流  | スイッチ ディスエーブル、<br>$OL\_OFF\_EN\_CHx = イネーブル$                  | $OL\_PULLUP\_STR = 00$                                                                      | 20.1  | 26.5 | 100  | $\mu A$ |

|                            |                                    |                                                              | $OL\_PULLUP\_STR = 01$                                                                      | 48.1  | 60   | 126  | $\mu A$ |

|                            |                                    |                                                              | $OL\_PULLUP\_STR = 10$                                                                      | 103.2 | 127  | 208  | $\mu A$ |

|                            |                                    |                                                              | $OL\_PULLUP\_STR = 11$                                                                      | 213   | 260  | 348  | $\mu A$ |

## 6.5 電気的特性 (続き)

$V_{BB} = 6V \sim 18V$ 、 $V_{DD} = 3.0V \sim 5.5V$ 、 $T_J = -40^{\circ}C \sim 150^{\circ}C$  (特に記述のない限り)

| パラメータ                  | テスト条件                                  |                                                                      |                                        | 最小値  | 標準値 | 最大値  | 単位         |

|------------------------|----------------------------------------|----------------------------------------------------------------------|----------------------------------------|------|-----|------|------------|

| $R_{SHRT\_VBB}$        | オフ状態での $V_{BB}$ への短絡検出におけるブルダウン抵抗      | チャネル無効、オフ状態での $V_{BB}$ 短絡診断機能が有効化されている状態                             |                                        | 5.5  | 6.8 | 8    | k $\Omega$ |

| $V_{OL\_OFF\_TH}$      | オフ状態でのオーブン負荷 (OL) 検出電圧                 | チャネル無効化、オフ状態での開放負荷診断イネーブル、 $V_{OUTx}$                                |                                        | 1.9  | 2.5 | 2.95 | V          |

| $T_{ABS}$              | サーマル シャットダウン                           |                                                                      |                                        | 155  | 180 | 205  | °C         |

| $T_{OTW}$              | サーマル シャットダウン警告                         |                                                                      |                                        | 130  | 150 | 170  | °C         |

| $T_{REL}$              | 相対的なサーマル シャットダウンの温度                    |                                                                      |                                        |      | 60  |      | °C         |

| $T_{HYS}$              | サーマル シャットダウン ヒステリシス                    |                                                                      |                                        | 20   | 25  | 30   | °C         |

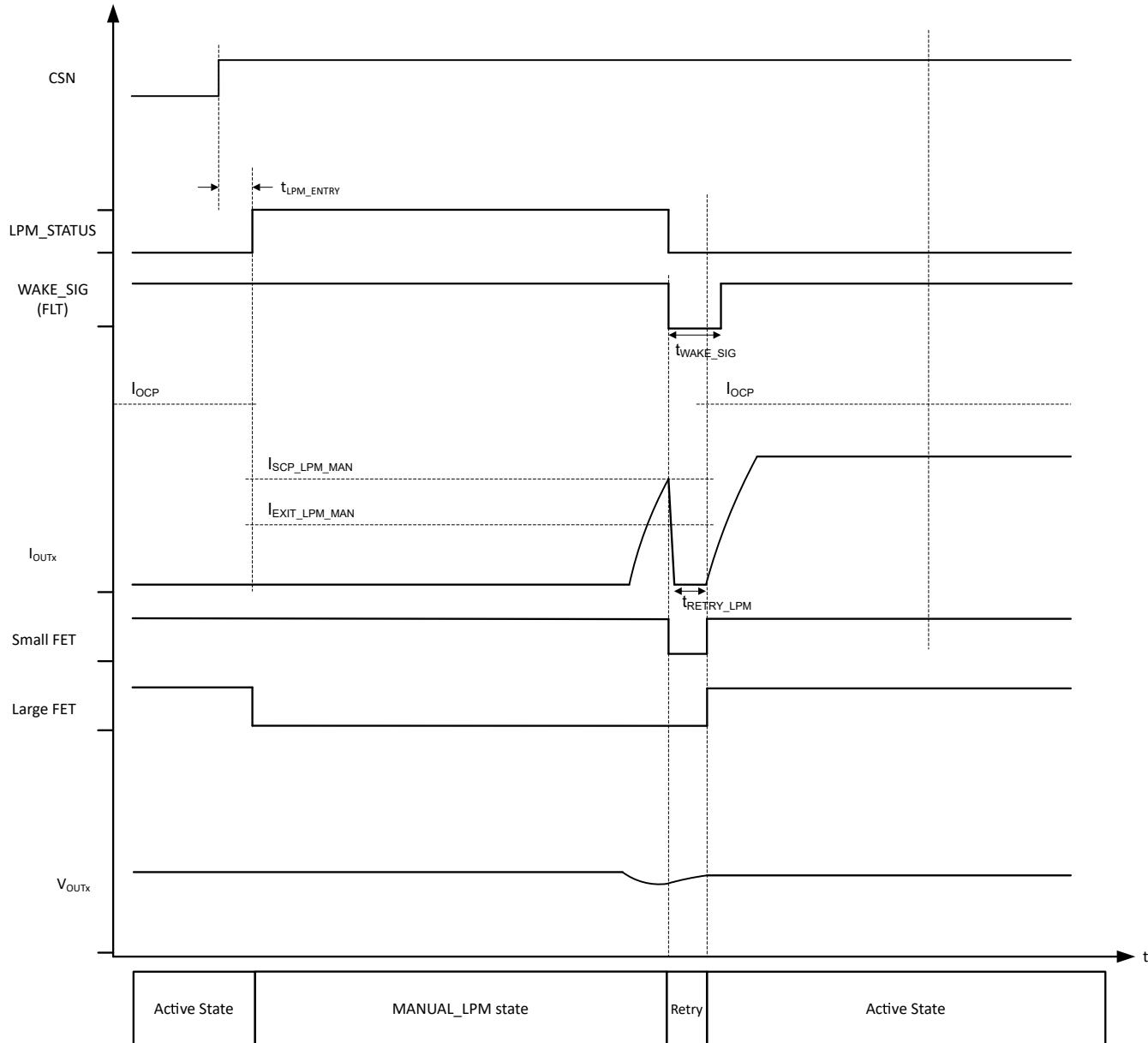

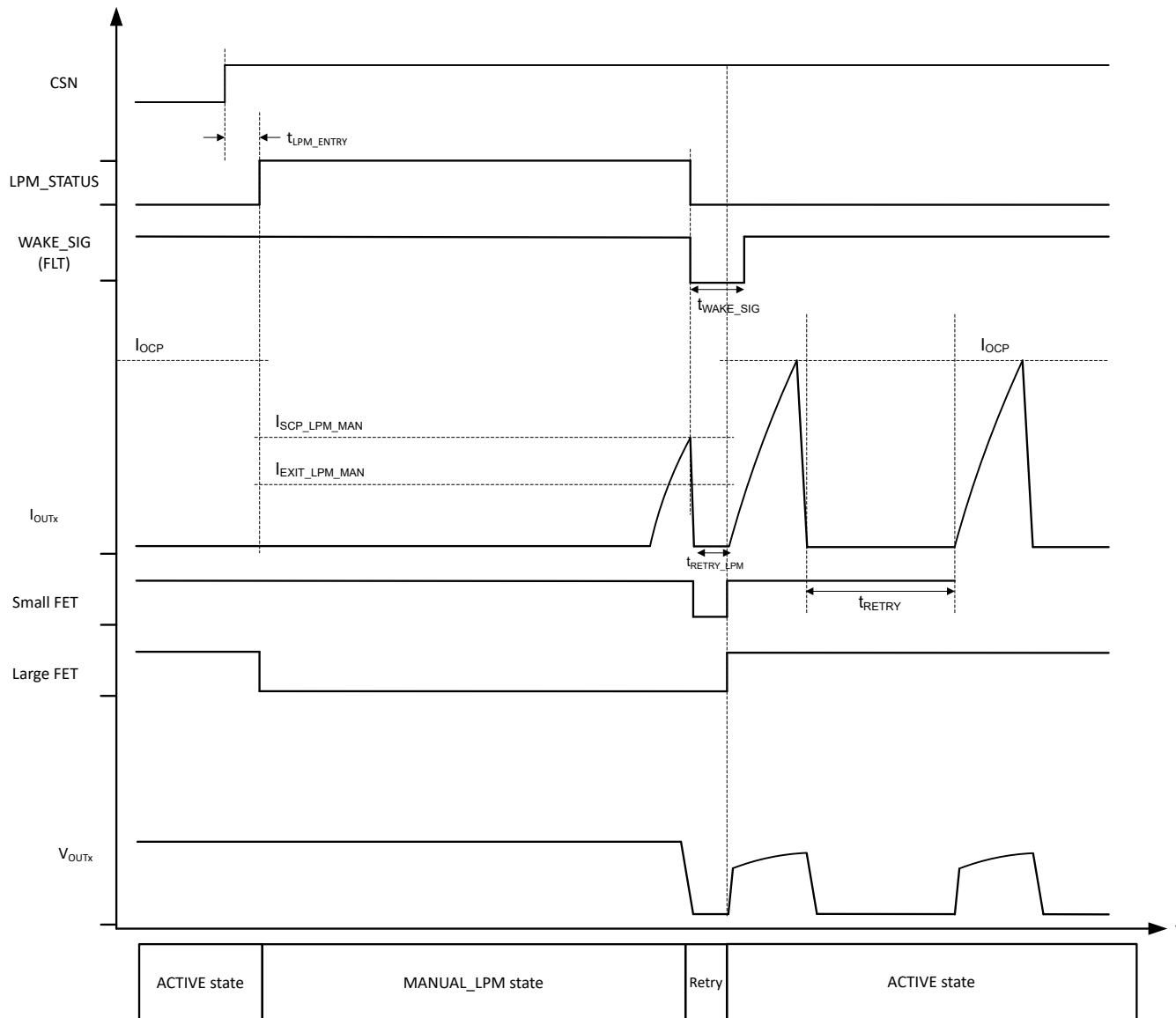

| $t_{RETRY}$            | 再試行時間                                  | 故障シャットダウンからスイッチ再有効化までの時間(サーマル シャットダウンまたは過電流)。PWM は次のサイクルまで待機してから再びオン |                                        |      | 2   |      | ms         |

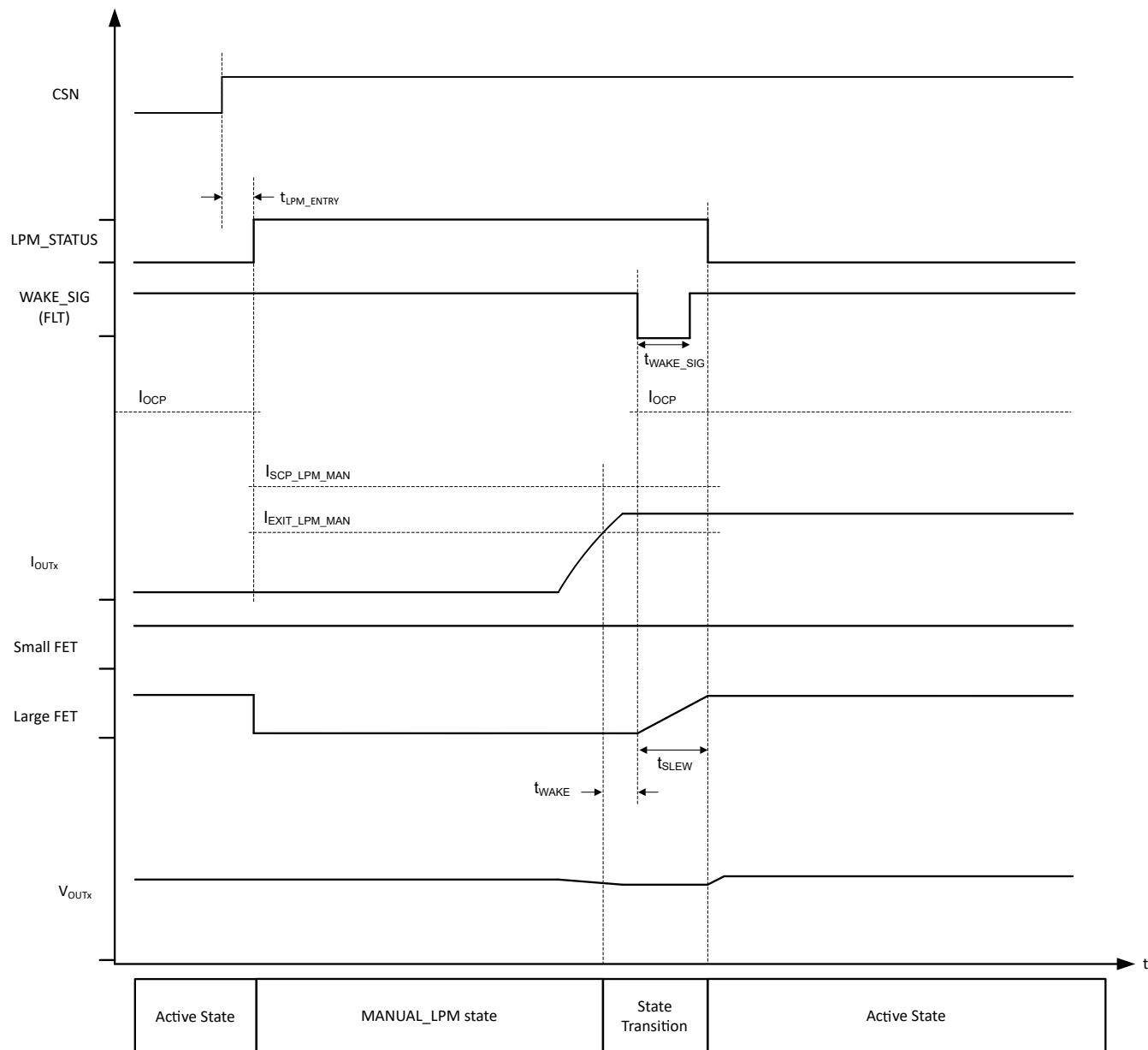

| $t_{WAKE\_SIG}$        | LPM 終了を示す WAKE_SIG / FLT ピンのインジケータ     |                                                                      |                                        |      | 100 |      | μs         |

| タイミング特性                |                                        |                                                                      |                                        |      |     |      |            |

| $OSC_{ACC}$            | 発振回路の精度                                |                                                                      |                                        | -10  | 10  |      | %          |

| $PWM_{FREQ}$           | PWM 周波数                                | PWM_EN = 1                                                           | PWM_FREQ_CHx = 101                     | 372  | 425 | 478  | Hz         |

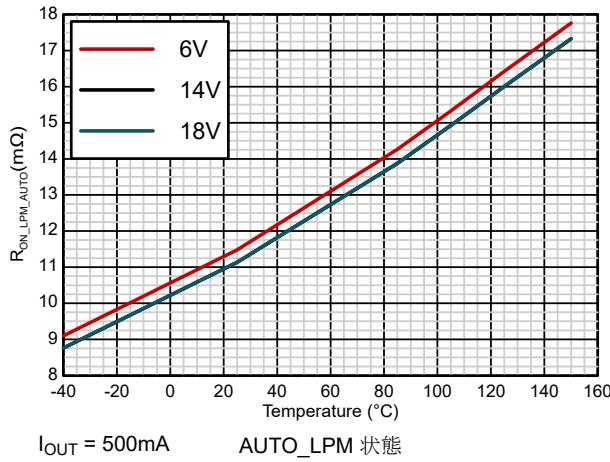

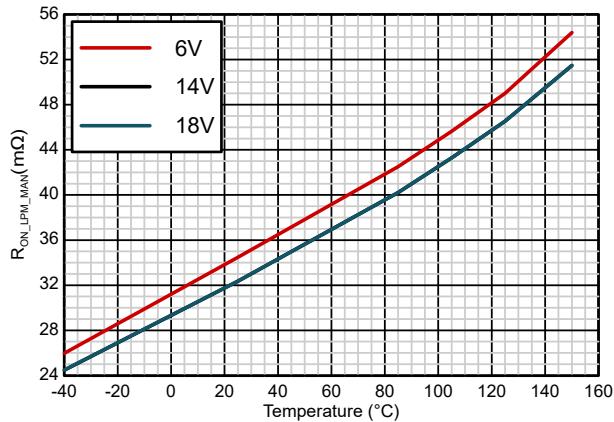

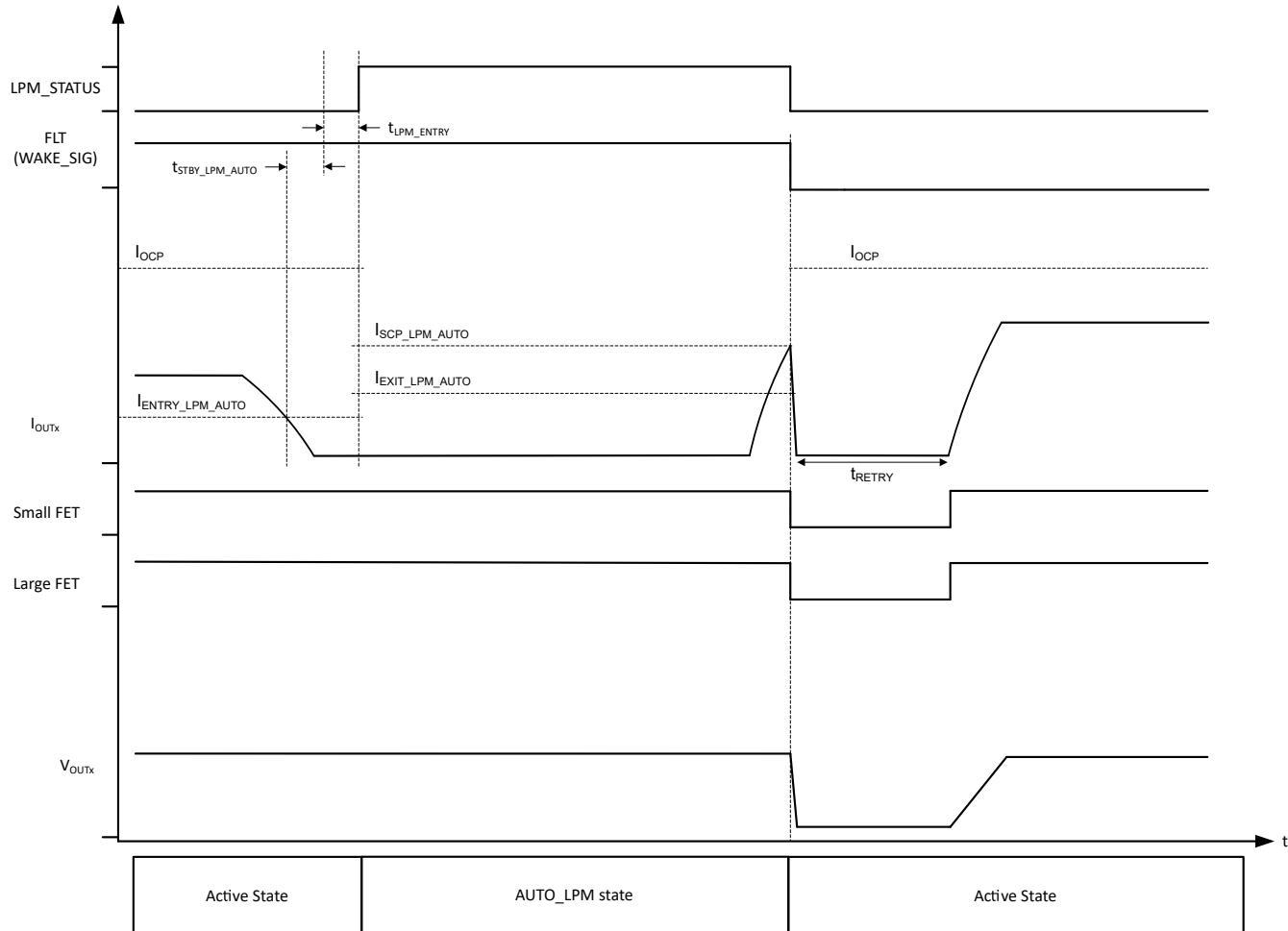

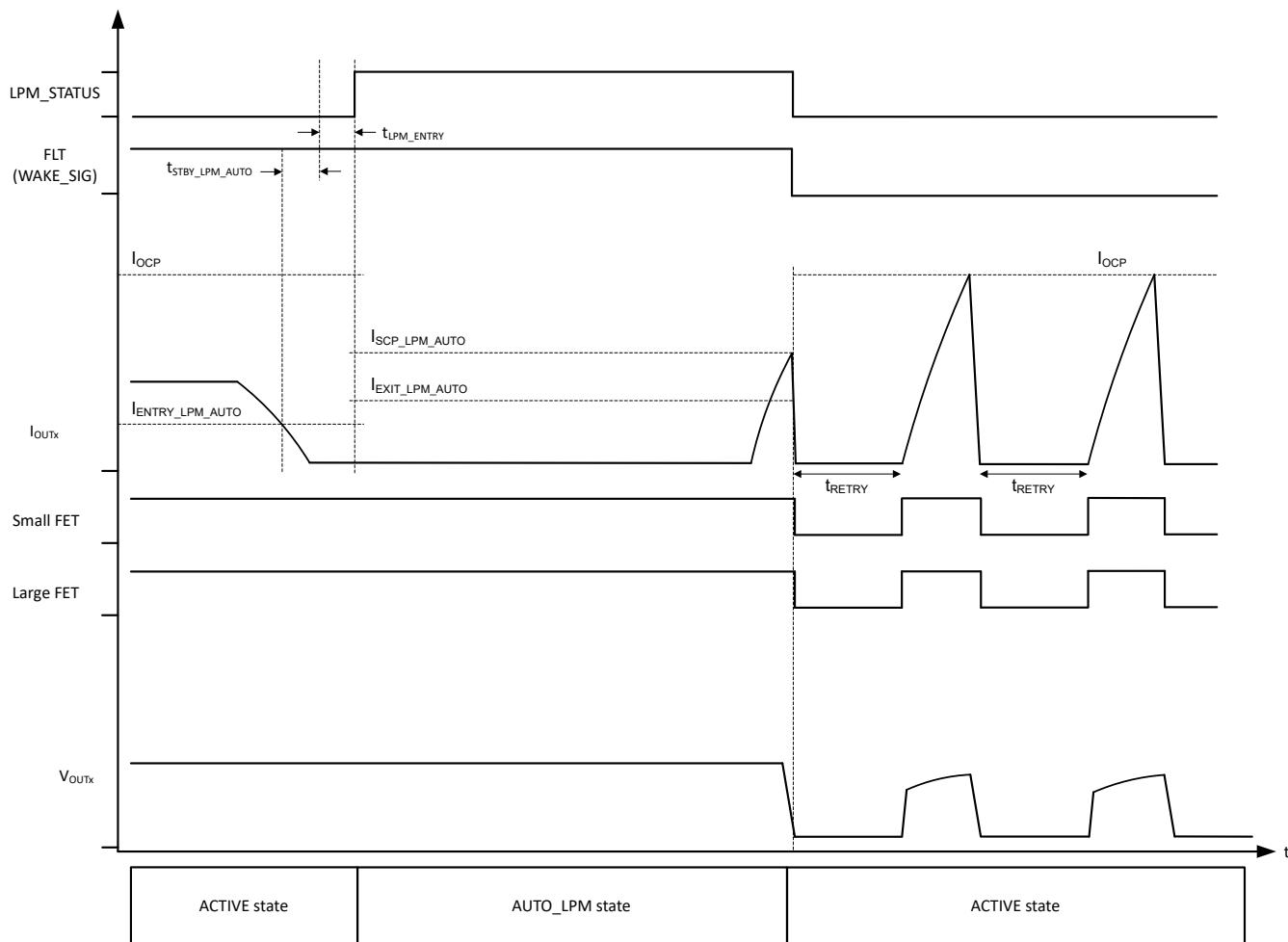

| 低電力モードの特性              |                                        |                                                                      |                                        |      |     |      |            |

| $R_{ON, LPM\_AUTO}$    | AUTO_LPM モードでの $R_{ON}$                |                                                                      | $T_J = -40^{\circ}C \sim 105^{\circ}C$ | 11.3 | 22  |      | m $\Omega$ |

| $R_{ON, LPM\_MAN}$     | MANUAL_LPM モードの $R_{ON}$               |                                                                      | $T_J = -40^{\circ}C \sim 105^{\circ}C$ | 36   | 70  |      | m $\Omega$ |

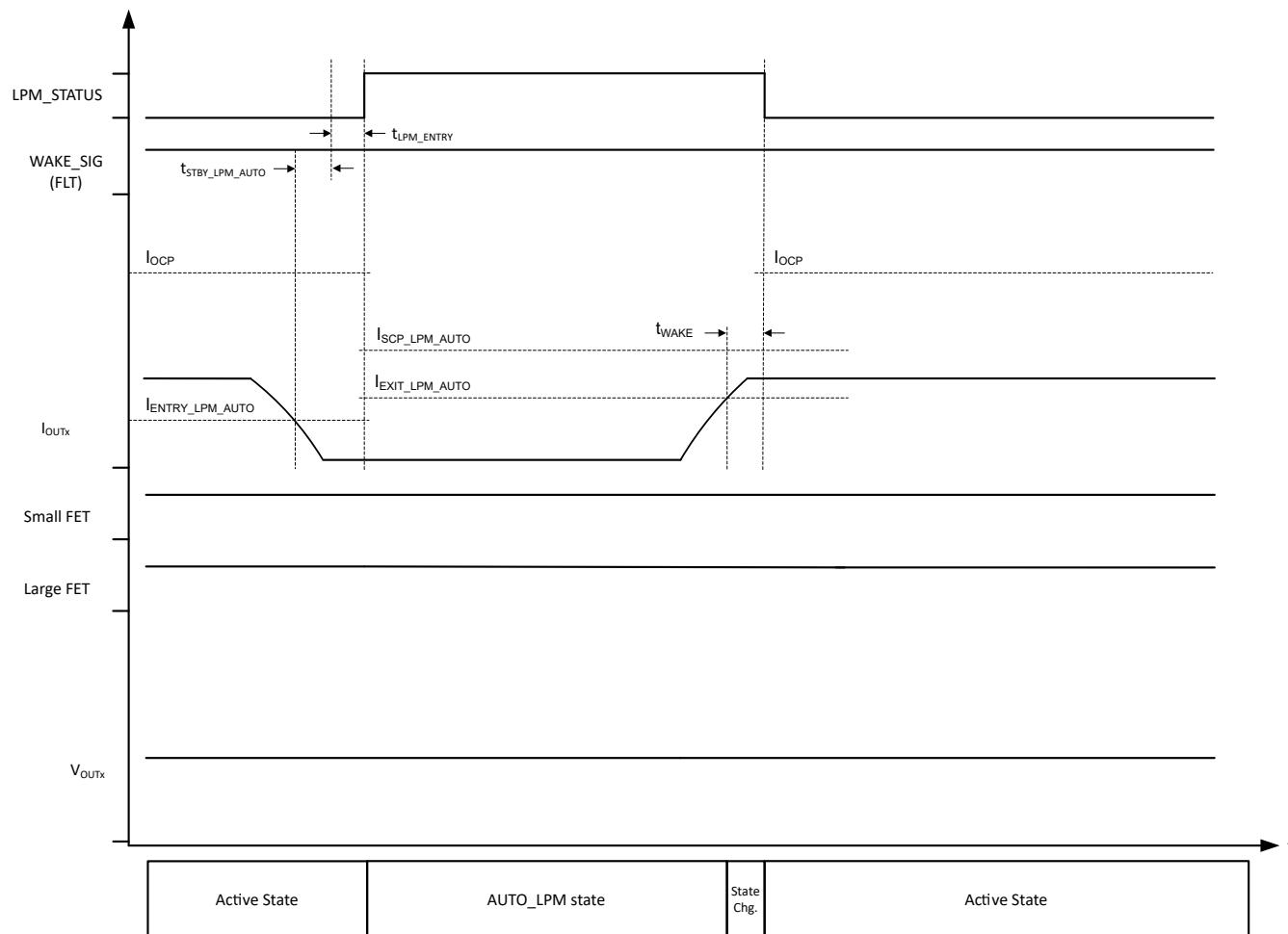

| $I_{ENTRY\_LPM\_AUTO}$ | AUTO_LPM 状態に移行するための $I_{OUT}$ 電流       |                                                                      | $T_J = -40^{\circ}C \sim 105^{\circ}C$ | 0.95 |     |      | A          |

| $I_{EXIT\_LPM\_AUTO}$  | AUTO_LPM 状態を終了するための $I_{OUT}$ 電流       |                                                                      | $T_J = -40^{\circ}C \sim 105^{\circ}C$ | 1.05 |     |      | A          |

| $I_{SCP\_LPM\_AUTO}$   | AUTO_LPM 状態の短絡検出スレッショルド                |                                                                      | $T_J = -40^{\circ}C \sim 105^{\circ}C$ | 13.7 |     |      | A          |

| $I_{EXIT\_LPM\_MAN}$   | MANUAL_LPM 終了の $I_{OUTx}$ スレッショルド      | $1mA/\mu s$ における電流ランプ<br>$T_J = -40^{\circ}C \sim 85^{\circ}C$       | MAN_LPM_EXIT_CURR_CHx = 00             | 330  | 500 | 670  | mA         |

|                        |                                        |                                                                      | MAN_LPM_EXIT_CURR_CHx = 01             | 450  | 625 | 900  | mA         |

|                        |                                        |                                                                      | MAN_LPM_EXIT_CURR_CHx = 10             | 100  | 150 | 225  | mA         |

|                        |                                        |                                                                      | MAN_LPM_EXIT_CURR_CHx = 11             | 220  | 325 | 450  | mA         |

| $I_{SCP\_LPM\_MAN}$    | チャネルが短絡を検出したときの負荷電流                    | $di/dt = 5mA/\mu s$                                                  |                                        |      | 4.0 |      | A          |

| $t_{RETRY\_LPM}$       | LPM 状態の再試行時間                           |                                                                      |                                        |      | 5   |      | μs         |

| $t_{STBY\_LPM\_AUTO}$  | AUTO_LPM 状態に移行するまでのスタンバイ時間             | $I_{OUTx} \leq I_{ENTRY\_LPM\_AUTO}$                                 |                                        |      | 20  |      | ms         |

| $t_{LPM\_ENTRY}$       | LPM 状態に移行する時間                          |                                                                      |                                        |      | 200 |      | μs         |

| $t_{WAKE}$             | $I_{EXIT\_LPM\_MAN}$ 検出時間              |                                                                      |                                        |      | 5   |      | μs         |

| $t_{SLEW}$             | $I_{EXIT\_LPM\_MAN}$ の後、メイン FET のスルーハイ |                                                                      |                                        |      | 200 |      | μs         |

## 6.5 電気的特性 (続き)

$V_{BB} = 6V \sim 18V$ 、 $V_{DD} = 3.0V \sim 5.5V$ 、 $T_J = -40^{\circ}C \sim 150^{\circ}C$  (特に記述のない限り)

| パラメータ                 |                           | テスト条件                                                               | 最小値        | 標準値  | 最大値  | 単位      |

|-----------------------|---------------------------|---------------------------------------------------------------------|------------|------|------|---------|

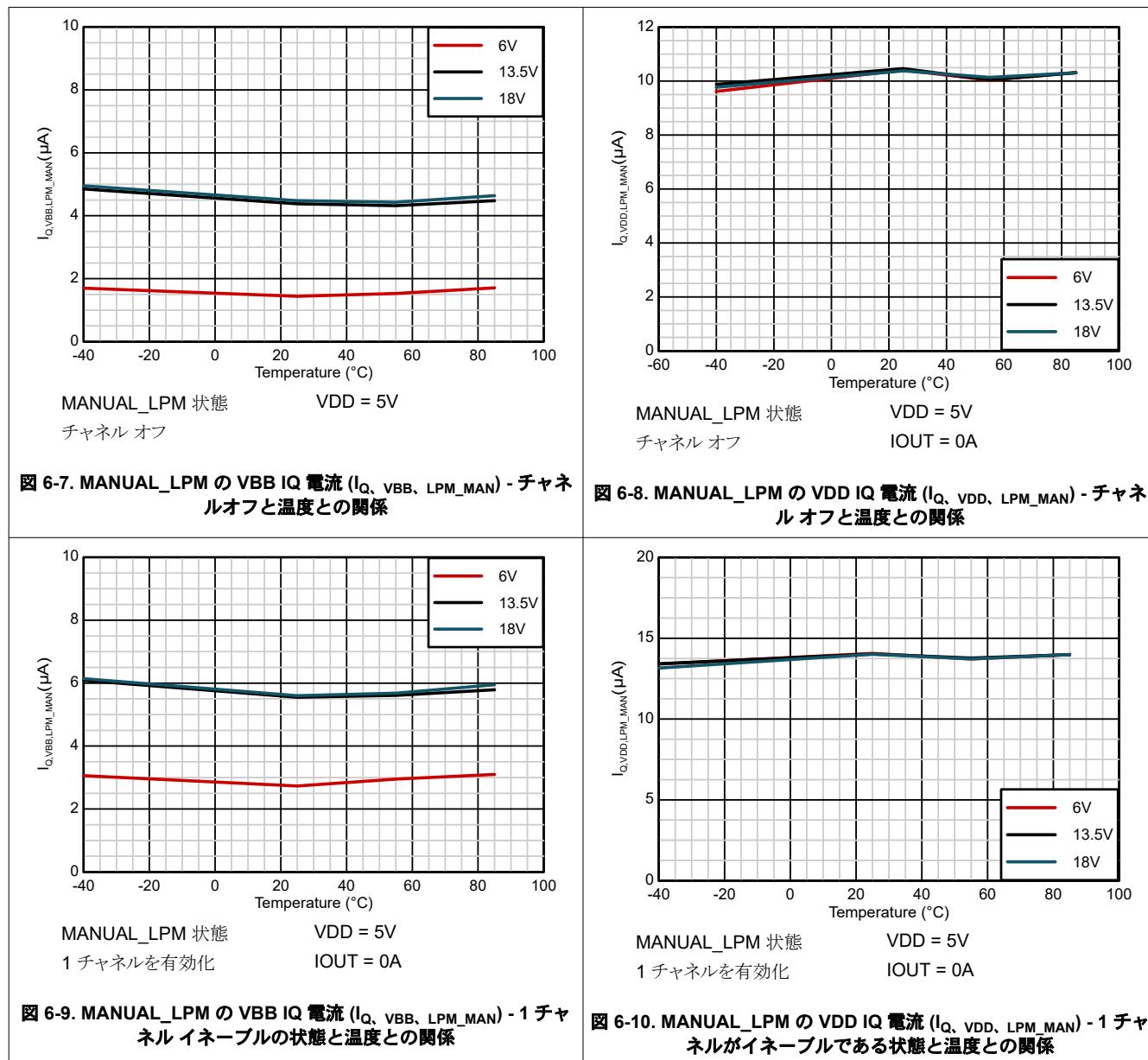

| $I_Q, VDD, LPM\_MAN$  | MANUAL_LPM モードでの VDD 静止電流 | $V_{DD} = 5.0V, I_{OUTx} = 0A, T_J = -40^{\circ}C \sim 85^{\circ}C$ | 両方のチャネルがオフ | 9    | 18   | $\mu A$ |

|                       |                           |                                                                     | 1つのチャネルがオン | 12.3 | 21.6 | $\mu A$ |

|                       |                           |                                                                     | 両方のチャネルがオン | 15.6 | 23   | $\mu A$ |

| $I_Q, VDD, LPM\_AUTO$ | AUTO_LPM の VDD 静止電流       | $V_{DD} = 5.0V, I_{OUTx} = 0A, T_J = -40^{\circ}C \sim 85^{\circ}C$ | 両方のチャネルがオフ | 9    | 18   | $\mu A$ |

|                       |                           |                                                                     | 1つのチャネルがオン | 12.3 | 21.6 | $\mu A$ |

|                       |                           |                                                                     | 両方のチャネルがオン | 15.6 | 23   | $\mu A$ |

| $I_Q, VBB, LPM\_MAN$  | MANUAL_LPM モードでの VBB 静止電流 | $V_{DD} = 5.0V, I_{OUTx} = 0A, T_J = -40^{\circ}C \sim 85^{\circ}C$ | 両方のチャネルがオフ | 3.72 | 7    | $\mu A$ |

|                       |                           |                                                                     | 1つのチャネルがオン | 5.1  | 9.1  | $\mu A$ |

|                       |                           |                                                                     | 両方のチャネルがオン | 6.42 | 9.5  | $\mu A$ |

| $I_Q, VBB, LPM\_AUTO$ | AUTO_LPM の VBB 静止電流       | $V_{DD} = 5.0V, I_{OUTx} = 0A, T_J = -40^{\circ}C \sim 85^{\circ}C$ | 両方のチャネルがオフ | 10.4 | 15.5 | $\mu A$ |

|                       |                           |                                                                     | 1つのチャネルがオン | 11   | 15.8 | $\mu A$ |

|                       |                           |                                                                     | 両方のチャネルがオン | 11.6 | 16.1 | $\mu A$ |

### デジタル入力ピンの特性

|                |                                |                             |                      |                      |                        |

|----------------|--------------------------------|-----------------------------|----------------------|----------------------|------------------------|

| $V_{IH, SPI}$  | 入力電圧 high レベル (SCLK, SDI, CSN) | $3.0V \leq VDD \leq 5.5V$   | $0.7 \times V_{VDD}$ |                      | $V$                    |

| $V_{IL, SPI}$  | 入力電圧 low レベル (SCLK, SDI, CSN)  | $3.0V \leq VDD \leq 5.5V$   |                      | $0.3 \times V_{VDD}$ | $V$                    |

| $R_{PD, SCLK}$ | SCLK 内部プルダウン抵抗                 |                             |                      | 1.80                 | $2.26 \text{ M}\Omega$ |

| $I_{IH, SCLK}$ | 高レベルの入力電流                      | SCLK                        | $V_{SCLK} = 5V$      |                      | $\mu A$                |

| $R_{PD, SDI}$  | SDI 内部プルダウン抵抗                  |                             |                      | 1.80                 | $2.26 \text{ M}\Omega$ |

| $I_{IH, SDI}$  | 高レベルの入力電流                      | SDI                         | $V_{SDI} = 5V$       |                      | $\mu A$                |

| $R_{PU, CSN}$  | CSN 内部プルアップ抵抗                  |                             |                      | 85                   | $90 \text{ k}\Omega$   |

| $V_{IH, DI}$   | 高レベルの入力電圧                      | DI (バージョン A)                |                      | 1.65                 | $V$                    |

| $V_{IL, DI}$   | 低レベルの入力電圧                      |                             |                      | 0.8                  | $V$                    |

| $R_{PD, DI}$   | 内部プルダウン抵抗。                     |                             |                      | 772                  | $850 \text{ k}\Omega$  |

| $I_{IH, DI}$   | 高レベルの入力電流                      |                             | $V_{DI} = 5V$        | 6                    | $\mu A$                |

| $V_{IH, DI1}$  | 高レベルの入力電圧                      | DI1 (バージョン B)               |                      | 1.65                 | $V$                    |

| $V_{IL, DI1}$  | 低レベルの入力電圧                      |                             |                      | 0.8                  | $V$                    |

| $R_{PD, DI1}$  | 内部プルダウン抵抗。                     |                             |                      | 772                  | $850 \text{ k}\Omega$  |

| $I_{IH, DI1}$  | 高レベルの入力電流                      |                             | $V_{DI1} = 5V$       | 6                    | $\mu A$                |

| $V_{IH, LHI}$  | 高レベルの入力電圧                      | LHI (バージョン A)               |                      | 1.65                 | $V$                    |

| $V_{IL, LHI}$  | 低レベルの入力電圧                      |                             |                      | 0.8                  | $V$                    |

| $R_{PD, LHI}$  | 内部プルダウン抵抗。                     |                             |                      | 772                  | $850 \text{ k}\Omega$  |

| $I_{IH, LHI}$  | 高レベルの入力電流                      |                             | $V_{LHI} = 5V$       | 6                    | $\mu A$                |

| $V_{IH, DI2}$  | 高レベルの入力電圧                      | DI2 (バージョン B)               |                      | 1.65                 | $V$                    |

| $V_{IL, DI2}$  | 低レベルの入力電圧                      |                             |                      | 0.8                  | $V$                    |

| $R_{PD, DI2}$  | 内部プルダウン抵抗。                     |                             |                      | 772                  | $850 \text{ k}\Omega$  |

| $I_{IH, DI2}$  | 高レベルの入力電流                      |                             | $V_{DI2} = 5V$       | 6                    | $\mu A$                |

| デジタル出力ピンの特性    |                                |                             |                      |                      |                        |

| $V_{OH, SDO}$  | 出力ロジック高電圧ドロップ                  | SDO ピン電流 = -2mA             |                      | 0.2                  | $V$                    |

| $V_{OL, SDO}$  | 出力ロジック Low 電圧                  | SDO ピン電流 = 2mA              |                      | 0.2                  | $V$                    |

| $V_{OL\_FLT}$  | 出力ロジック low 電圧ドロップ              | $\overline{FLT}$ ピン電流 = 4mA |                      | 0.55                 | $V$                    |

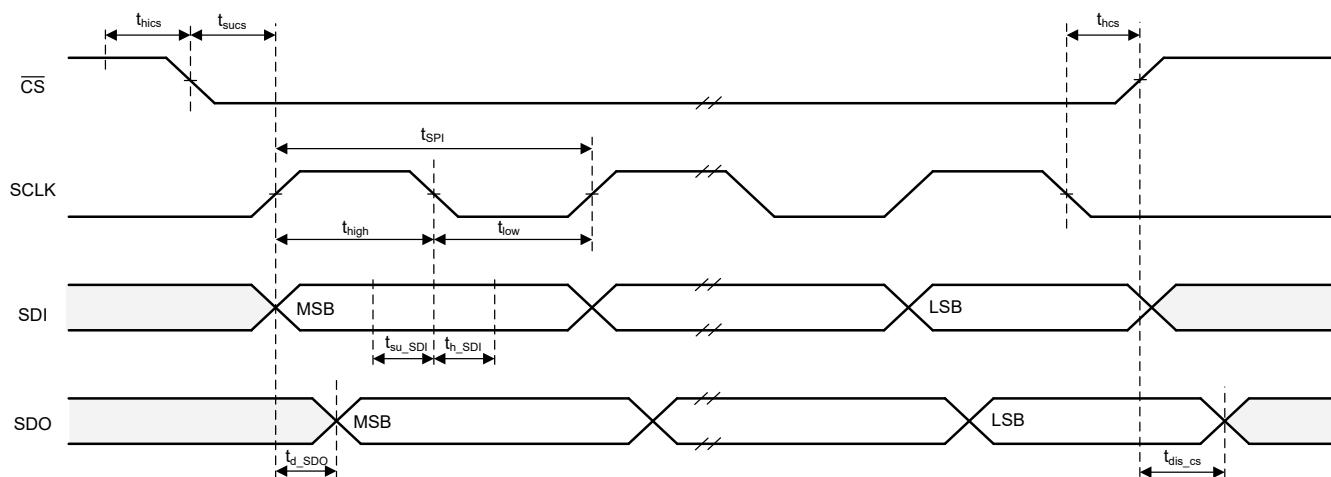

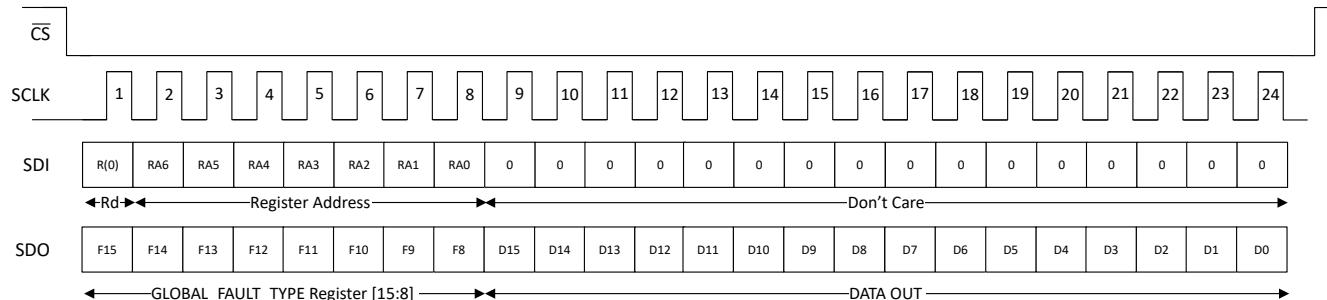

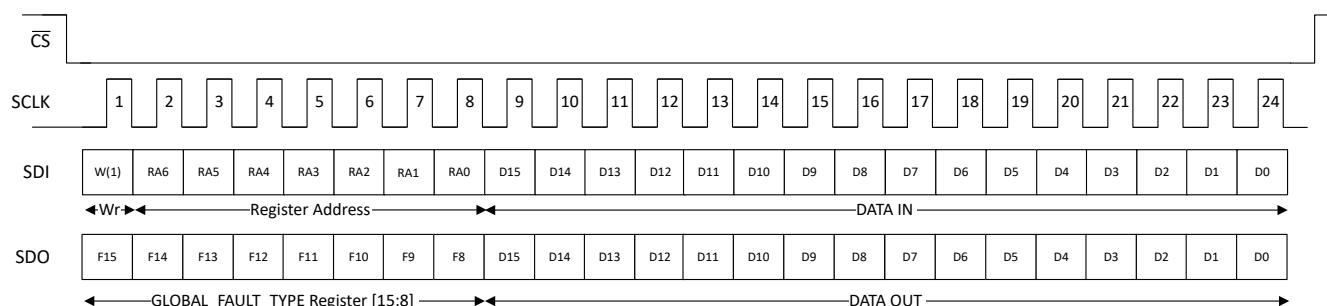

## 6.6 SPI のタイミング要件

動作時接合部温度範囲全体  $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ 、 $V_{DD} = 3.0\text{V} \sim 5.5\text{V}$  (デバイスの GND ピン基準で測定)

| パラメータ                |                                                 | テスト条件                                                        | 最小値 | 公称値 | 最大値 | 単位  |

|----------------------|-------------------------------------------------|--------------------------------------------------------------|-----|-----|-----|-----|

| $f_{\text{SPI}}$     | SPI クロック (SCLK) 周波数                             | $C_{\text{SDO}} = 30\text{pF}$ 、IO 保護抵抗 $0.47\text{k}\Omega$ |     | 8   |     | MHz |

| $t_{\text{High}}$    | High 時間: SCLK ロジック High の時間                     |                                                              | 45  |     |     | ns  |

| $t_{\text{Low}}$     | ロータイム: SCLK ロジック Low の期間                        |                                                              | 45  |     |     | ns  |

| $t_{\text{suCS}}$    | CS セットアップ時間: CS の立ち下がりエッジと SCLK の立ち上がりエッジ間の時間遅延 |                                                              | 45  |     |     | ns  |

| $t_{\text{SU\_SDI}}$ | SDI のセットアップ時間: SCLK 立ち下がりエッジ前の SDI のセットアップ時間    |                                                              | 15  |     |     | ns  |

| $t_{\text{H\_SDI}}$  | SDI ホールド時間: SCLK の立ち下がりエッジ前の SDI のホールド時間        |                                                              | 30  |     |     | ns  |

| $t_{\text{D\_SDO}}$  | 遅延時間: SCLK の立ち上がりエッジから SDO の有効データまでの時間遅延        |                                                              |     | 30  |     | ns  |

| $t_{\text{hcs}}$     | ホールド時間: SCLK の立ち下がりエッジと CS の立ち上がりエッジとの間の時間      |                                                              | 45  |     |     | ns  |

| $t_{\text{dis\_cs}}$ | CS ディセーブル時間、CS 高から SDO 高インピーダンスまで               |                                                              |     | 10  |     | ns  |

| $t_{\text{hics}}$    | CS が High でなければならない SPI 転送非アクティブ時間 (二回の転送間の時間)  |                                                              | 500 |     |     | ns  |

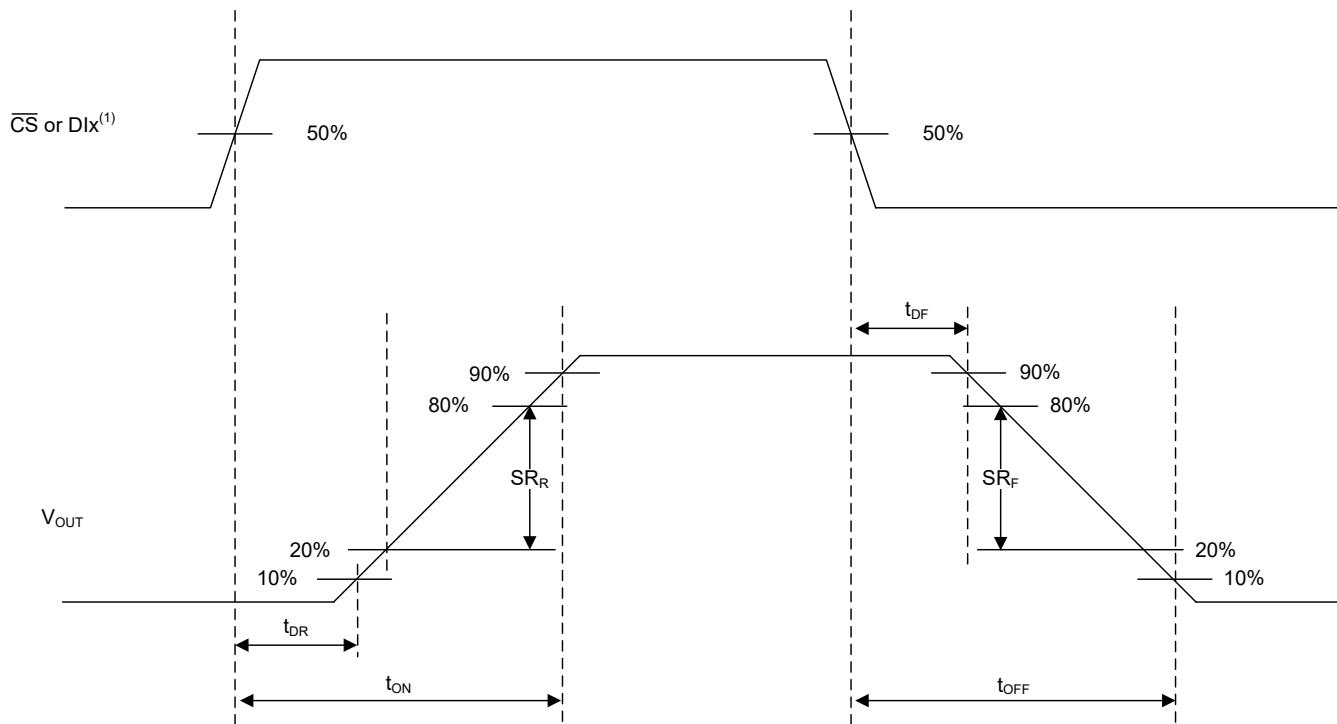

## 6.7 スイッチング特性

$V_{BB} = 13.5\text{V}$ 、 $R_L = 2\Omega$ 、 $T_J = -40 \sim 150^{\circ}\text{C}$  (特に記述のない限り)

| パラメータ            |                                                        | テスト条件                 | 最小値 | 標準値  | 最大値 | 単位   |

|------------------|--------------------------------------------------------|-----------------------|-----|------|-----|------|

| $t_{\text{DR}}$  | チャネル ターンオン遅延時間<br>(CS または Dlx の 50% ~ $V_{OUT}$ の 10%) | SLRT_CHx = 00         |     | 45   |     | μs   |

|                  |                                                        | SLRT_CHx = 01         |     | 35   |     | μs   |

|                  |                                                        | SLRT_CHx = 10 (デフォルト) |     | 30   |     | μs   |

|                  |                                                        | SLRT_CHx = 11         |     | 23   |     | μs   |

| $t_{\text{DF}}$  | チャネルターンオフ遅延時間<br>(CS または Dlx の 50% ~ $V_{OUT}$ の 90%)  | SLRT_CHx = 00         |     | 35   |     | μs   |

|                  |                                                        | SLRT_CHx = 01         |     | 25   |     | μs   |

|                  |                                                        | SLRT_CHx = 10 (デフォルト) |     | 20   |     | μs   |

|                  |                                                        | SLRT_CHx = 11         |     | 16   |     | μs   |

| $SR_R$           | $V_{OUT}$ の立ち上がりスルーレート<br>( $V_{OUT}$ の 20% ~ 80%)     | SLRT_CHx = 00         |     | 0.14 |     | V/μs |

|                  |                                                        | SLRT_CHx = 01         |     | 0.2  |     | V/μs |

|                  |                                                        | SLRT_CHx = 10 (デフォルト) |     | 0.25 |     | V/μs |

|                  |                                                        | SLRT_CHx = 11         |     | 0.32 |     | V/μs |

| $SR_F$           | $V_{OUT}$ 立ち下がりスルーレート<br>( $V_{OUT}$ の 80% ~ 20%)      | SLRT_CHx = 00         |     | 0.13 |     | V/μs |

|                  |                                                        | SLRT_CHx = 01         |     | 0.2  |     | V/μs |

|                  |                                                        | SLRT_CHx = 10 (デフォルト) |     | 0.26 |     | V/μs |

|                  |                                                        | SLRT_CHx = 11         |     | 0.33 |     | V/μs |

| $t_{\text{ON}}$  | チャネルターンオン時間<br>(CS または Dlx の 50% ~ $V_{OUT}$ の 90%)    | SLRT_CHx = 00         |     | 130  |     | μs   |

|                  |                                                        | SLRT_CHx = 01         |     | 95   |     | μs   |

|                  |                                                        | SLRT_CHx = 10 (デフォルト) |     | 75   |     | μs   |

|                  |                                                        | SLRT_CHx = 11         |     | 60   |     | μs   |

| $t_{\text{OFF}}$ | チャネル ターンオフ時間<br>(CS または Dlx の 50% ~ $V_{OUT}$ の 10%)   | SLRT_CHx = 00         |     | 115  |     | μs   |

|                  |                                                        | SLRT_CHx = 01         |     | 75   |     | μs   |

|                  |                                                        | SLRT_CHx = 10 (デフォルト) |     | 60   |     | μs   |

|                  |                                                        | SLRT_CHx = 11         |     | 50   |     | μs   |

## 6.7 スイッチング特性 (続き)

$V_{BB} = 13.5V$ 、 $R_L = 2\Omega$ 、 $T_J = -40 \sim 150^\circ C$  (特に記述のない限り)

| パラメータ     |                                                     | テスト条件                 | 最小値 | 標準値  | 最大値 | 単位 |

|-----------|-----------------------------------------------------|-----------------------|-----|------|-----|----|

| $E_{ON}$  | ターンオン時のスイッチングエネルギー損失<br>(10% ~ 90% からの $V_{OUT}$ )  | SLRT_CHx = 00         |     | 1.43 |     | mJ |

|           |                                                     | SLRT_CHx = 01         |     | 1.03 |     | mJ |

|           |                                                     | SLRT_CHx = 10 (デフォルト) |     | 0.77 |     | mJ |

|           |                                                     | SLRT_CHx = 11         |     | 0.64 |     | mJ |

| $E_{OFF}$ | ターンオフ時のスイッチング エネルギー損失<br>(90% ~ 10% からの $V_{OUT}$ ) | SLRT_CHx = 00         |     | 1.48 |     | mJ |

|           |                                                     | SLRT_CHx = 01         |     | 0.95 |     | mJ |

|           |                                                     | SLRT_CHx = 10 (デフォルト) |     | 0.68 |     | mJ |

|           |                                                     | SLRT_CHx = 11         |     | 0.54 |     | mJ |

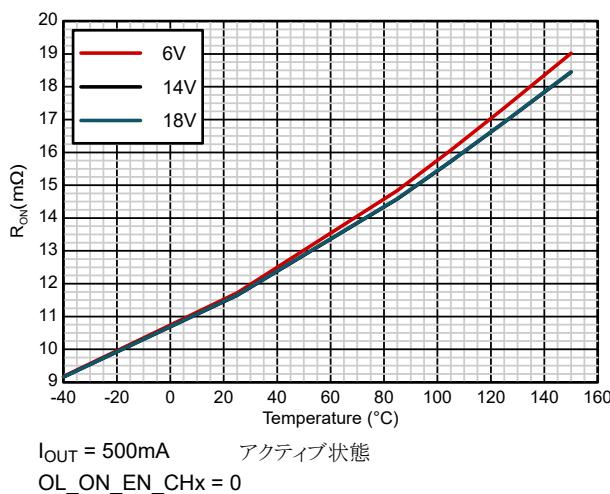

## 6.8 代表的特性

図 6-1. オン抵抗 ( $R_{ON}$ ) と温度との関係

図 6-2. オン抵抗、OL\_ON モード ( $R_{ON\_OL}$ ) と温度との関係

図 6-3. AUTO\_LPM のオン抵抗 ( $R_{ON\_LPM\_AUTO}$ ) と温度との関係

図 6-4. MANUAL\_LPM のオン抵抗 ( $R_{ON\_LPM\_MAN}$ ) と温度との関係

図 6-5. VBB スリープ電流 ( $I_{SLEEP}$ ,  $V_{BB}$ ) と温度との関係

図 6-6. VBB IQ 電流 ( $I_Q$ ,  $V_{BB}$ ) と温度との関係

## 6.8 代表的特性 (続き)

## 6.8 代表的特性 (続き)

## 7 パラメータ測定情報

<sup>(1)</sup> Rise and fall time of  $\overline{CS}$  or  $Dlx$  is 100 ns.

図 7-1. スイッチング特性の定義

図 7-2. SPI のタイミング特性の定義

## 8 詳細説明

### 8.1 概要

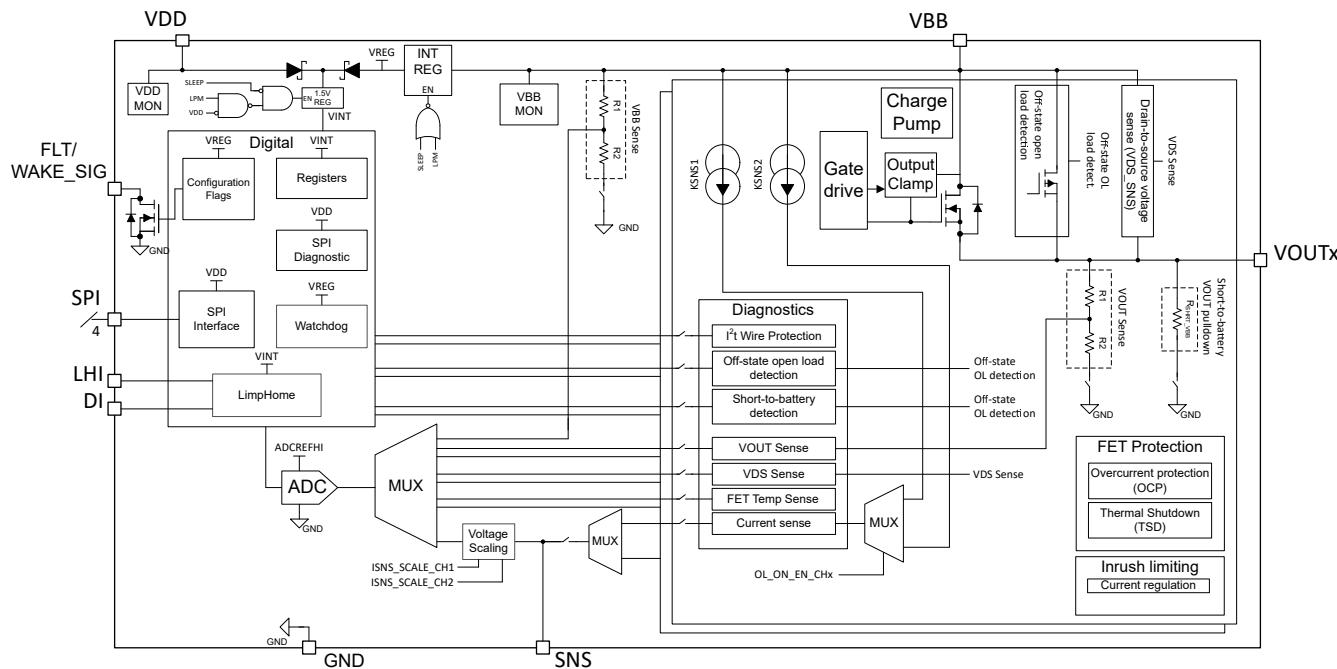

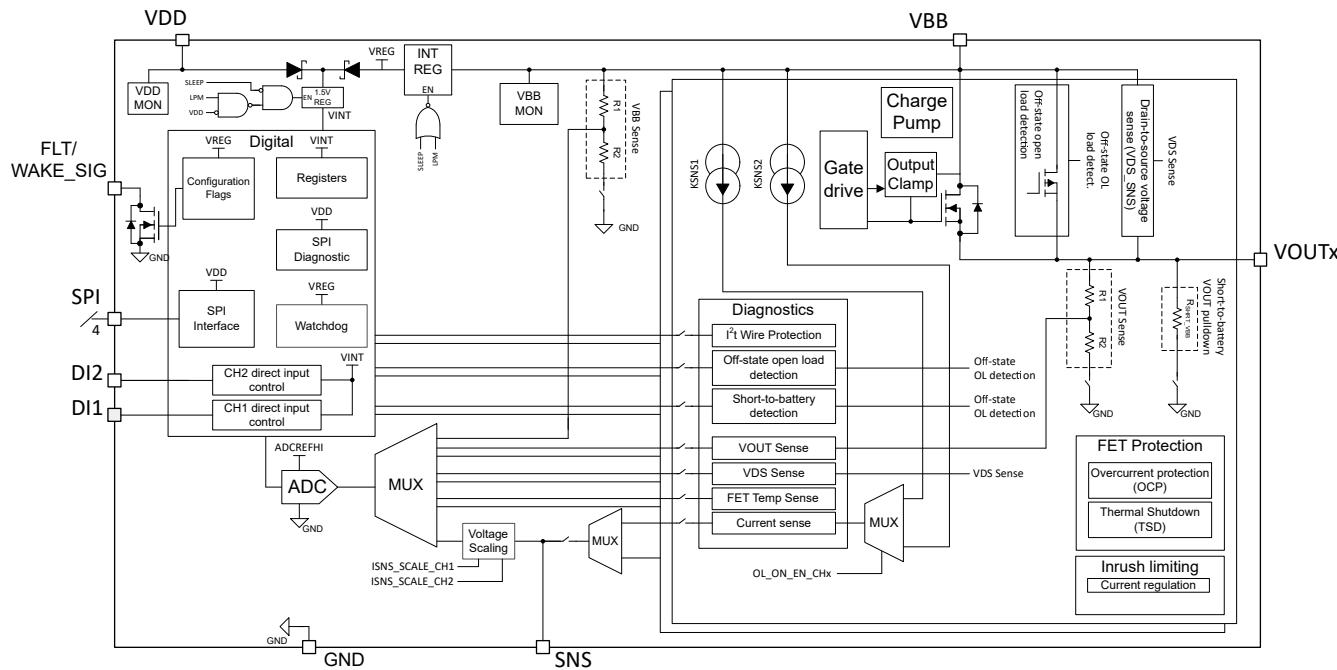

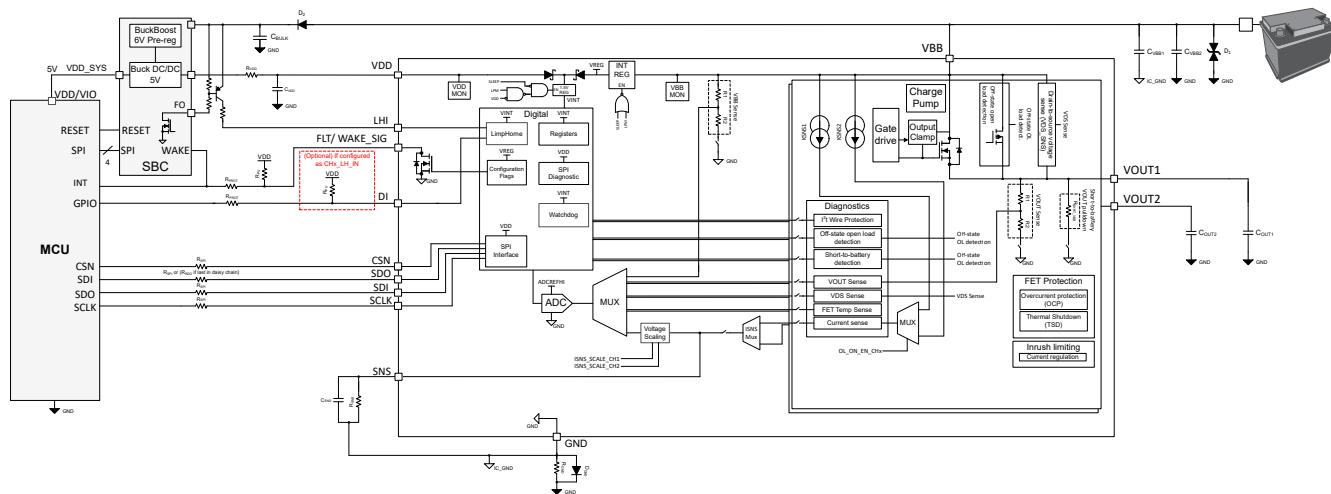

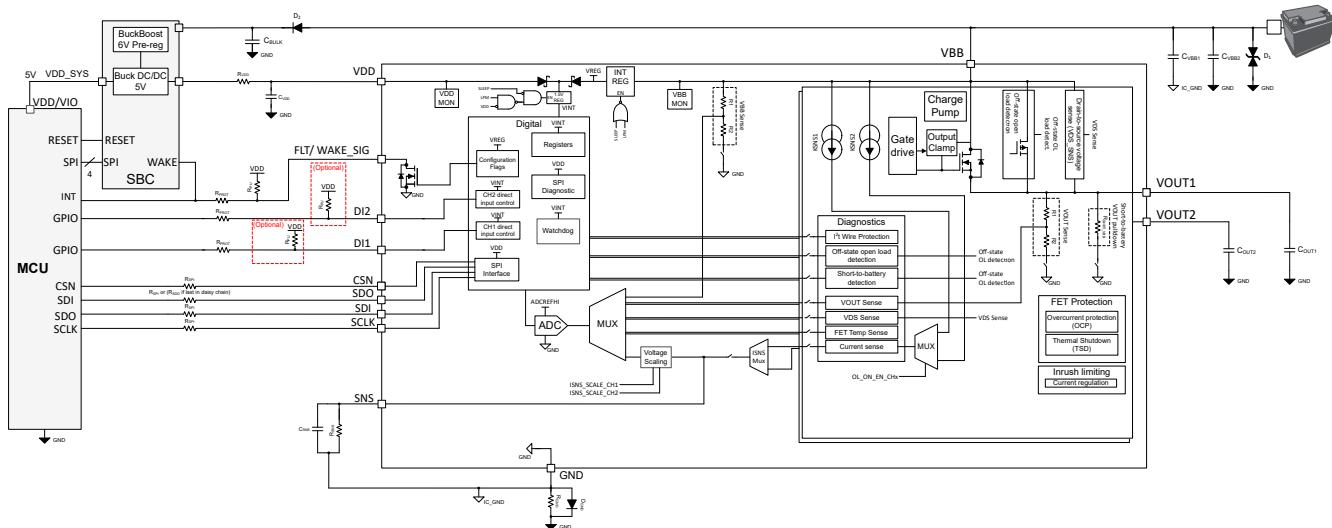

TPS2HCS10-Q1 デバイスはデュアル チャネルのスマート ハイサイド スイッチで、12V の車載用バッテリで使用するよう設計されています。TPS2HCS10-Q1 デバイスは、SPI 制御および構成、また主要デバイスの ADC と負荷診断を備えたデジタル読み出し機能を備えています。このデバイスは、パワー ディストリビューション スイッチに必要な特定の機能に加えて、アクチュエータ駆動アプリケーション用のハイサイド スイッチで見られる従来の保護およびデジタル化機能も備えています。

診断機能として、デジタル電流、出力電圧、FET 温度センス出力を備えており、SPI シリアル インターフェイス経由で読み取ることができます。高精度の負荷電流センスにより、複雑な負荷を診断できます。デバイスの出力電圧センスと FET 温度センスの機能により、スイッチや負荷障害を診断できます。

このデバイスには、サーマル シャットダウン、過電流保護、過渡耐性、バッテリ逆接続動作による保護機能が搭載されています。さらに、このデバイスには、定義済みのヒューズまたは時間電流曲線による、SPI で構成可能なワイヤ ハーネス保護機能も搭載されています。この保護機能は、SPI で構成可能なスレッショルドを持つ即時のスイッチオフ過電流保護機能と組み合わせて動作し、過負荷および短絡フォルトに対する完全な保護を提供します。

また、TPS2HCS10-Q1 デバイスには、数百 mA の範囲の電流を供給できる低静止電流モードも内蔵されていますが、 $\mu$ A 単位の電流しか消費しません。このデバイスは、負荷電流が増加すると自動的に大電流モードに切り替わり、マイコンにウェーク信号を供給します。さらに、このデバイスには容量性充電モードが搭載されており、電源のピーク電流負荷を低減できます。この 2 つの機能を組み合わせることで、オフボード ECU アプリケーションへのパワー ディストリビューション スイッチをサポートできます。

診断、パワー ディストリビューション、保護機能の詳細については、ドキュメントの「[機能説明](#)」および「[アプリケーション情報](#)」セクションを参照してください。

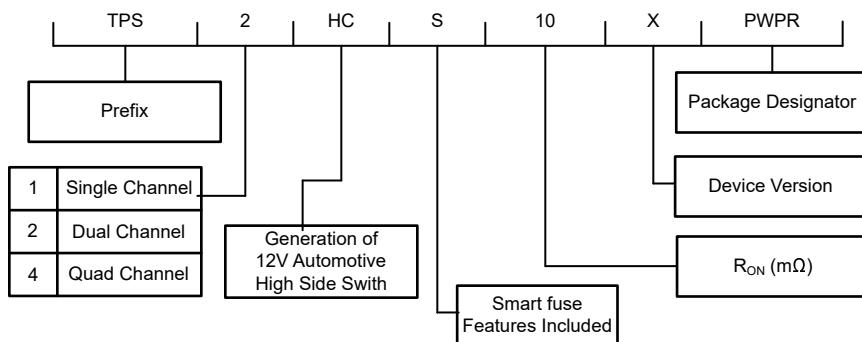

TPS2HCS10-Q1 は、TI ハイサイド スイッチ ファミリ デバイスの 1 つです。各デバイスの型番はデバイスの動作要素を示します。図 8-1 に、デバイスの命名規則の例を示します。

図 8-1. 命名規則

## 8.2 機能ブロック図

図 8-2. TPS2HCS10A-Q1 機能ブロック図

図 8-3. TPS2HCS10B-Q1 機能ブロック図

## 8.3 機能説明

### 8.3.1 保護メカニズム

#### 8.3.1.1 過電流保護

TPS2HCS10-Q1 デバイスには、さまざまな過電流イベントからデバイスを保護するため、以下の機能があります：

- 突入期間中の容量性負荷充電

- 即時シャットダウン過電流保護 (I<sub>OCP</sub>)

- プログラム可能なヒューズ保護 (または I<sub>2T</sub> 保護) (有効な場合)

- サーマル シャットダウン ( $T_{REL}$  および  $T_{ABS}$ )

- LPM 状態での短絡保護 ( $I_{SCP\_LPM\_MAN}$  または  $I_{SCP\_LPM\_AUTO}$ )

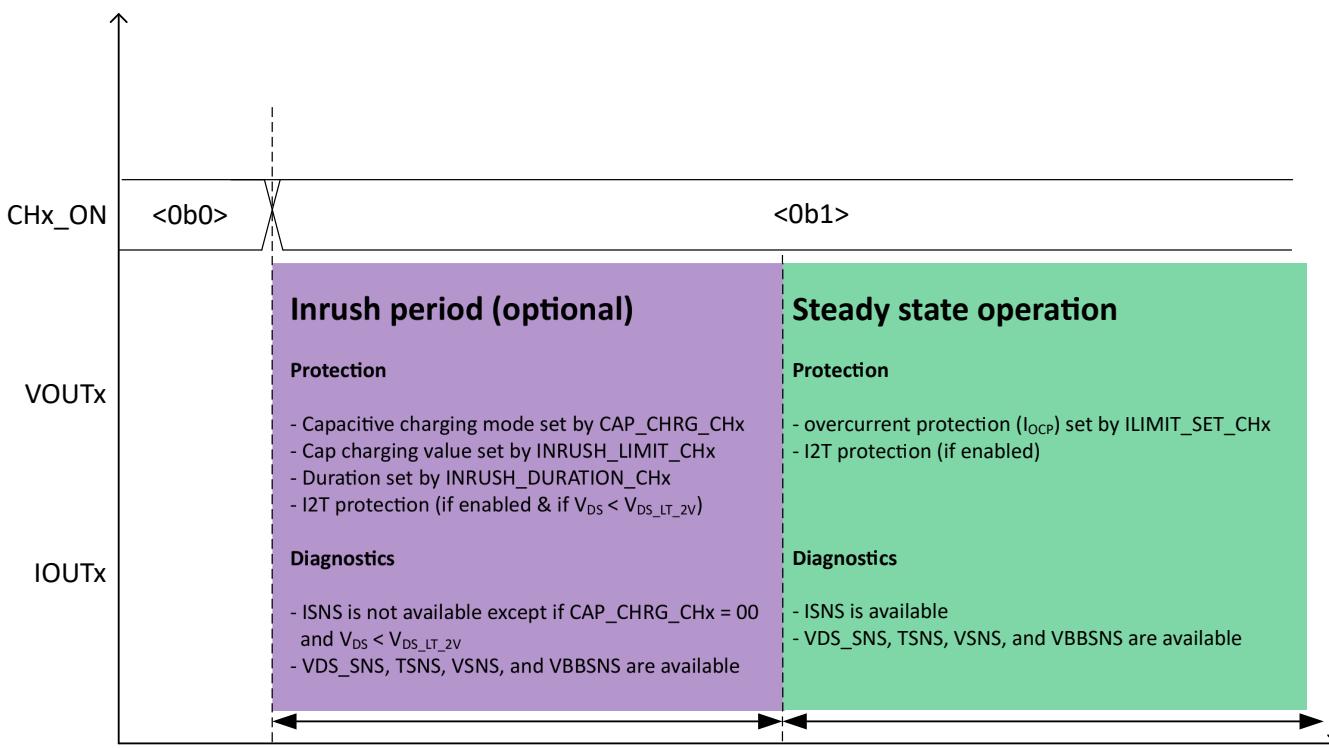

過電流保護に関して、このデバイスには 2 つの動作モードがあります。1 つはチャネル起動時のオプションの突入電流期間、もう 1 つは定常動作中のモードです。オプションの突入電流期間は、チャネルの初期オン時にバルブ、モータの停止電流、または容量性負荷など、さまざまな突入電流を扱えるように設定できます。ILIM\_CONFIG\_CHx レジスタ内の CAP\_CHRG\_CHx、INRUSH\_DURATION\_CHx、および INRUSH\_LIMIT\_CHx ビットは、突入期間中のデバイスの動作を制御します。I<sub>2T</sub> 保護 (有効な場合) は、CAP\_CHRG\_CHx = 00 の場合、および  $V_{DS} < V_{DS\_LT\_2V}$  の場合に突入期間中にのみアクティブです。突入期間の完了後、定常状態動作が引き継ぎます。定常状態動作中、過電流保護 (I<sub>OCP</sub>) はアクティブで、I<sub>2T</sub> 保護はアクティブ (イネーブルの場合) です。

突入期間中、有効になっている場合、すべての電圧検出 (V<sub>B</sub>、V<sub>OUT</sub>、V<sub>DS</sub>) および FET 温度検出を使用できます。電流センスは、 $V_{DS} < V_{DS\_LT\_2V}$  の場合、または突入期間の完了してデバイスが定常状態動作している後でのみ CAP\_CHRG\_CHx = 00 でのみ利用できます。定常動作中は、電圧検出、FET 温度検出、および電流検出のすべてが利用可能です。

図 8-4 に、オプションの突入期間と定常状態動作における過電流保護の概要を示します。

突入期間および定常動作中に利用できる各種保護機能の詳細については、以下のセクションを参照してください。LPM 状態での過電流保護については、LPM セクションで説明します。

図 8-4. 過電流保護モードの概要

#### 8.3.1.1.1 突入時間 – 過電流保護

突入時間はデバイスのオプション モードであり、チャネルの初期オン時に発生する電球、モータの停止電流、または容量負荷など、さまざまな立ち上がり電流を処理できるように構成することができます。突入期間は、ILIM\_CONFIG\_CHx レジスタ内の CAP\_CHRG\_CHx、INRUSH\_DURATION\_CHx、および INRUSH\_LIMIT\_CHx ビットによって設定できます。

突入時間が有効化されている場合、これらの状態のいずれかでチャネルが有効になっている場合、アクティブ状態および LIMP\_HOME 状態の両方で有効になります。

このデバイスには、突入期間中に 2 種類のオフセット電流保護設定があり、CAP\_CHRG\_CHx ビットを使用して設定できます：

- 容量性充電なし、即時シャットダウン過電流保護 (I<sub>OCP</sub>) のみ

- 電流制限レギュレーション (I<sub>CL\_REG</sub>)

容量性充電設定を使用しない場合、定常状態と比較して突入期間中に異なる過電流保護 (I<sub>OCP</sub>) 値を持つことができ、電球電流による突入やモーターストール電流が可能です。さらに、容量性充電なし設定では、V<sub>DS</sub> < V<sub>DS\_LT\_2V</sub> のとき、I<sub>2T</sub> 保護 (イネーブルの場合) がアクティブになります。電流制限レギュレーション モードにより、デバイスはダウンストリームの ECU の入力コンデンサなどの大きな容量を充電できます。CAP\_CHRG\_CHx ビットの設定によっては、INRUSH\_LIMIT\_CHx の値が変化します。各チャネルの過電流保護は独立しており、チャネルごとに設定できます。[表 8-1](#) に、突入期間における 2 つの過電流保護の概要を示します。

**表 8-1. 突入電流期間における静電容量性充電モードの概要**

| 容量性充電モード<br>(CAP_CHRG_CHx) | 過電流タイプ                                 | 範囲         | 期間の設定方法                   | 値の設定方法                 | I <sub>2T</sub> のサポート                          |

|----------------------------|----------------------------------------|------------|---------------------------|------------------------|------------------------------------------------|

| 00                         | 即時シャットダウン (I <sub>OCP</sub> )          | 10A～25A    | INRUSH_DURATION_CHx [2:0] | INRUSH_LIMIT_CHx [3:0] | はい、V <sub>DS</sub> < V <sub>DS_LT_2V</sub> の場合 |

| 01                         |                                        |            | 非対応                       |                        |                                                |

| 10                         | 電流制限レギュレーション<br>(I <sub>CL_REG</sub> ) | 1.5A～11.3A | INRUSH_DURATION_CHx [2:0] | INRUSH_LIMIT_CHx [3:0] | なし                                             |

| 11                         |                                        |            | 非対応                       |                        |                                                |

INRUSH\_DURATION\_CHx ビットでは、突入期間の持続時間を設定します。0ms から 100ms まで設定できます。INRUSH\_DURATION\_CHx = 0 の場合、突入期間は 0ms に設定され、チャネルが最初にイネーブルになったとき突入期間は開始されません。突入期間中に過電流またはサーマル シャットダウンの障害が原因で再試行が行われた場合、再試行するたびに突入期間を終了するためのタイマがリセットされます。

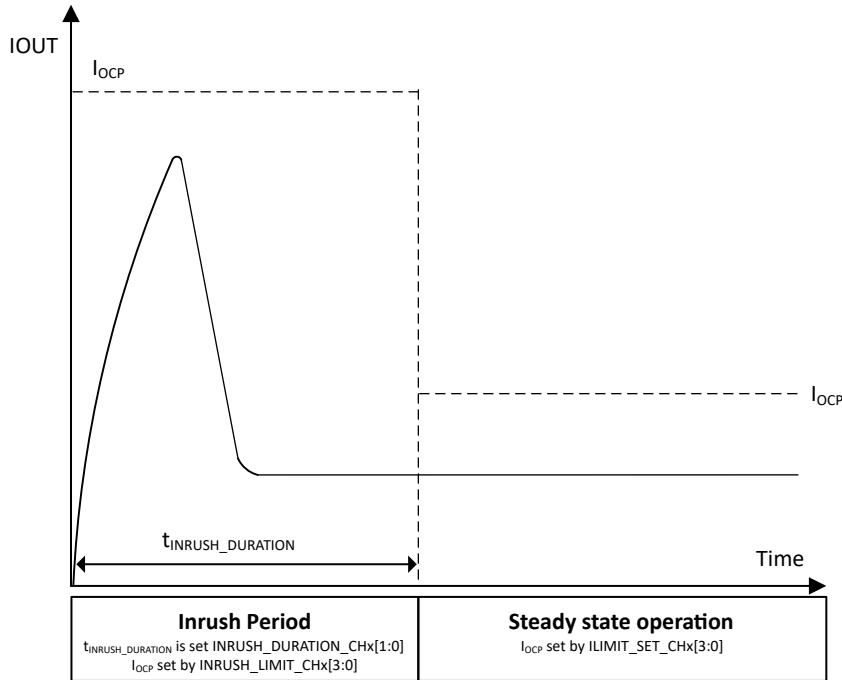

### 容量性充電なし — CAP\_CHRG\_CHx [1:0] = 00

容量性充電設定がないため、デバイスは定常状態動作と比較して、突入期間中に異なる即時シャットダウン過電流保護 (I<sub>OCP</sub>) 値を得ることができます。電球電流突入やモーターストール電流など、起動時の各種の突入電流イベントを可能にします。

CAP\_CHRG\_CHx [1:0] = 00 の場合、立ち上がり期間中の即時シャットダウン過電流保護 (I<sub>OCP</sub>) の値は INRUSH\_LIMIT\_CHx [3:0] ビットで設定され、期間は INRUSH\_DURATION\_CHx [2:0] ビットで設定されます。立ち上がり期間のタイマが終了すると、定常動作時の即時シャットダウン過電流保護 (I<sub>OCP</sub>) の値は ILIMIT\_SET\_CHx [3:0] ビットによって設定されます。

CAP\_CHRG\_CHx [1:0] = 00 の場合、V<sub>DS</sub> < V<sub>DS\_LT\_2V</sub> のときに I<sub>2T</sub> 保護 (有効な場合) および電流検出が利用可能です。

[図 8-5](#) にこの例を示します。

図 8-5. 容量性充電なし ( $CAP\_CHRG\_CHx[1:0] = 00$ ) - 電球駆動例

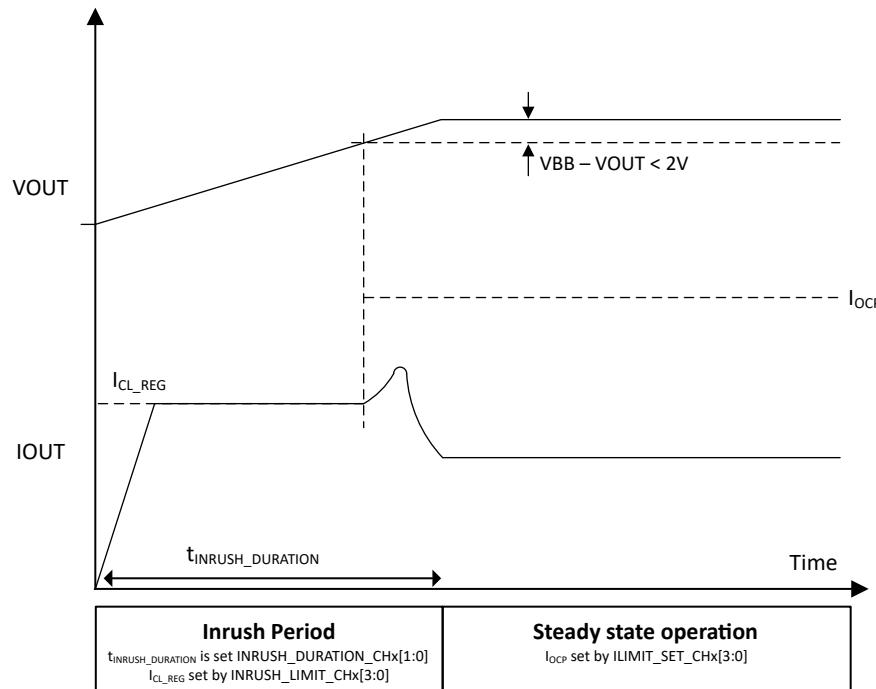

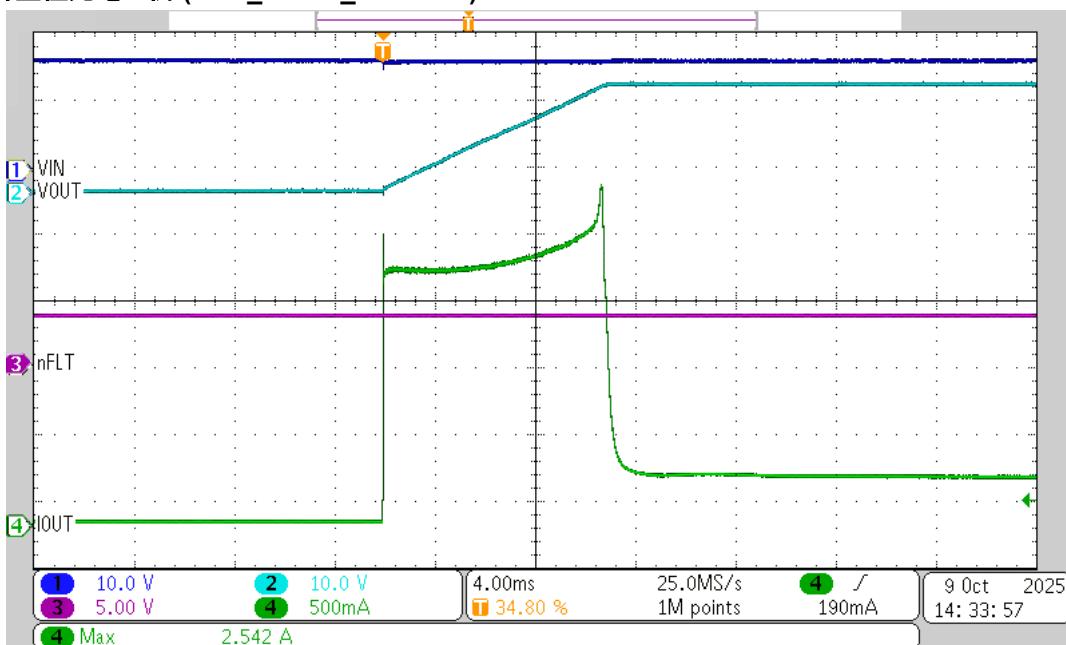

#### 電流制限レギュレーション容量性充電モード — $CAP\_CHRG\_CHx[1:0] = 10$

デバイスは、大容量の下流キャパシタ負荷 (ECU のバルク入力キャパシタなど) を充電するために、電流制限レギュレーション付き容量性充電モードを提供します。 $CAP\_CHRG\_CHx[1:0] = 10$  の場合、チャネルが初期に有効化された際、電流制限レギュレーション モードは  $INRUSH\_LIMIT\_CHx[3:0]$  で設定された値で出力電流をクランプします。デバイスは、キャパシタ負荷の充電が完了するか、立ち上がり期間が終了するか、またはサーマル シャットダウンが発生するまで、電流を継続的に制限します。 $INRUSH\_LIMIT\_CHx[3:0]$  ビットで設定可能な範囲は 1.5A から 11.3A であり、電気的特性表では  $I_{CL\_REG}$  として規定されています。 $VOUT$  電圧が  $V_{BB} - 2V$  を超え、突入時間タイマがタイムアウトしていない場合、デバイスは大きなスパイクなしに、電流制限レギュレーションをゆっくりと終了できます。図 8-6 に、電流制限レギュレーション容量性充電モードと、突入期間タイマが満了する前のスロー終了の例を示します。

図 8-6. 電流制限レギュレーションの容量性充電 (CAP\_CHRG\_CHx [ECU] 1:0 = 10) - ECU 入力バルク容量駆動例

#### 8.3.1.1.2 過電流保護—定常状態動作

デバイスがオプションの突入期間 (有効化されている場合) を完了すると、デバイスは安定動作に移行します。この動作では、即時シャットダウン過電流保護 ( $I_{OCP}$ ) と I2T 保護 (イネーブルの場合) によって過電流保護が実現されます。 $I_{OCP}$  は過電流保護機能であり、出力電流が ILIMIT\_SET\_CHx [3:0] ビットで設定された  $I_{OCP}$  スレッショルドを超えた場合、チャネルを即座にオフにします。 $I_{OCP}$  機能はディスエーブルにすることはできず、デバイスがイネーブルの間、定常状態の動作で常にアクティブになります。I2T 保護は、定義された時間電流曲線に基づいて、プログラム可能なヒューズ保護を提供します。I2T 保護の意図は、溶断しているヒューズの動作と一致していることです。I2T 保護の時間電流曲線は、NOM\_CUR\_CHx [2:0] ビットと I2T\_TRIP\_CHx [3:0] ビットで設定できます。ISWCL\_CHx [1:0] ビットおよび  $I_{OCP}$  は、I2T 保護における時間-電流特性曲線を定義する際にも役立ちます。 $I_{OCP}$  および I2T 保護 (イネーブルの場合) はアクティブ状態でアクティブになり、突入期間後にチャネルが定常状態で動作している場合は LIMP\_HOME 状態です。

次のセクションでは、I2T 保護と  $I_{OCP}$  保護について説明します。

#### 8.3.1.1.3 プログラマブルヒューズ保護

デバイスには、チャネルごとにプログラム可能なヒューズ保護が内蔵されています。この保護機能は定義された時間電流曲線に基づいており、溶断ヒューズ データシートでは一般に I<sub>2t</sub> 保護と呼ばれます。この目的は、溶断型ヒューズのスイッチのターンオフ動作を一致させることです。NOM\_CUR\_CHx [2:0] ビットと I2T\_TRIP\_CHx [3:0] ビットは時間電流曲線を設定しますが、本デバイスは固定遅延シャットダウン ( $I_{SWCL}$ ) および即時シャットダウン保護 ( $I_{OCP}$ ) も使用して、デバイスの完全な I2T 保護を実現しています。TPS2HCS10-Q1 の I2T 保護は、次の 4 つの領域で構成されています。

1. 公称電流

2. ヒューズシャットダウン

3. 固定遅延シャットダウン

4. 即時シャットダウン保護 ( $I_{OCP}$ )

公称電流領域 (1) では、デバイスをオフにすることなく無制限に電流を供給できる領域が定義されています。これは、溶断式ヒューズのヒューズ電流定格とほぼ等しくなります。この領域は NOM\_CUR\_CHx [2:0] ビットによって設定されます。

出力電流が **NOM\_CUR\_CHx** 設定より小さい場合、デバイスは前述のように無期限に電流を供給でき、**I2T** の蓄積が開始されることはありません。出力電流が **NOM\_CUR\_CHx** の設定以上の場合、デバイスは **I2T** 累積ループに入り、**I2T\_TRIP\_CHx [3:0]** スレッショルドが満たされるまで累積を開始します。出力電流が **I2T\_TRIP\_CHx** 値に達する前に **NOM\_CUR\_CHx** を下回ると、デバイスは **I2T** 蓄積を停止しますが、デバイスに電力が供給されている限り、累積エネルギーの追跡を継続します。

公称電流領域の上は、**I2T\_TRIP\_CHx [3:0]** ビットによって設定されるヒューズ シャットダウン領域 (2) です。この領域は、時間電流曲線の曲率と、デバイスの **I2T** の蓄積がアクティブである領域を定義します。出力電流レベルと **NOM\_CUR\_CHx** の設定に基づき、デバイスは設定された **I2T\_TRIP** 値をベースに異なる時間間隔でトリップします。デバイスの時間電流曲線は [式 1](#) で定義されます。

$$I2T_{TRIP} = \left( I_{OUT}^2 - NOM_{CUR\_CHx}^2 \right) \times t \quad (1)$$

累積エネルギーが **I2T\_TRIP** 値を超えず、電流が **NOM\_CUR\_CH** を下回ると、式 1 を使用して、累積エネルギーがゼロになるまで、**ISNS** の値に基づいて累積エネルギーをデクリメントします。デバイスがデクリメントして 0 まで減少し続ける間、**I2T\_MOD** ビットは累積エネルギーが 0 に戻るまで 1 のまま保持されます。その後、**I2T\_MOD** ビットはゼロに戻ります。チャネルが **I2T** ループに入っていたために変換が無効になっていた場合、**I2T\_MOD = 0** になると変換は再度有効になります。

ヒューズ シャットダウン領域の上は、デバイスが固定遅延シャットダウンを提供する固定遅延シャットダウン領域 (3) です。これは **ISWCL\_CHx [1:0]** および **SWCL\_DLY\_TMR\_CHx [1:0]** ビットで設定されます。**ISWCL\_CHx [1:0]** は出力電流値を設定し、**SWCL\_DLY\_TMR\_CHx** は時間を設定します。出力電流が **SWCL\_DLY\_TMR\_CHx** に対して連続的に **ISWCL\_CHx** レベルを超えると、チャネルはただちにオフになります。

**I2T\_TRIP\_CHx** の値を超えたため、または **ISWCL\_CHx** の機能が原因でシャットダウンが発生した場合、デバイスは **TCLDN\_CHx [1:0]** で設定された期間オフのままになります。**TCLDN\_CHx [1:0] = 00** の場合、デバイスはオフのままでです。再試行は行いません。この設定で再試行するには、**TCLDN\_CHx [1:0]** ビットを別の設定に変更する必要があります。設定を変更すると、新しい設定で定義されたクールダウン時間の経過後、デバイスは再試行します。チャネルが **I2T** シャットダウン状態に入ると、アキュムレータの値は 0 にリセットされるため、再試行時間を調整して、ワイヤ ハーネスが冷却するのに十分な時間が確保されるようにする必要があります。また、チャネルが **I2T** シャットダウン状態に移行すると、**NOM\_CUR\_CHx**、**I2T\_TRIP\_CHx**、**ISWCL\_CHx** の値は変更できないことに注意してください。

固定遅延シャットダウン領域の上は、即時シャットダウン過電流保護 ( $I_{OCP}$ ) 領域 (4) です。この領域は **ILIMIT\_SET\_CHx [3:0]** ビットで設定されます。出力電流が  $I_{OCP}$  レベルを超えると、デバイスは直ちにオフになります。 $I_{OCP}$  の再試行またはラッチオフの動作は **LATCH\_CHx** ビットで設定されます。これは次のセクションで説明します。

**I2T** 保護のこれらの動作領域を [図 8-7](#) に示します。

図 8-7. ヒューズベースのシャットダウンの動作領域

レジスタマップの `NOM_CUR_CHx`、`I2T_TRIP_CHx`、`ISWCL_CHx` の値は、 $R_{SNS}$  値 700Ω に基づきます。このデバイスは、異なる  $R_{SNS}$  値に基づいてこれらの値をスケーリングできる柔軟性を備えています。`NOM_CUR_CHx`、`I2T_TRIP_CHx`、`ISWCL_CHx` をスケーリングする式を以下に定義します。

$$NOM_{CUR,ADJ,TYP} = \frac{NOM_{CUR700} \times 700}{R_{SNS,ADJ,TYP}} \quad (2)$$

$$I_{SWCL,ADJ,TYP} = \frac{I_{SWCL,700} \times 700}{R_{SNS,ADJ,TYP}} \quad (3)$$

$$I2T_{ADJ,TYP} = I2T_{700} \times \left( \frac{700}{R_{SNS,ADJ,TYP}} \right)^2 \quad (4)$$

ここで、

$$NOM_{CUR700} = NOM_{CUR\_CHx} \text{ value in the datasheet based on } R_{SNS} \text{ of } 700\Omega \quad (5)$$

$$I_{SWCL,700} = I_{SWCL} \text{ value in the datasheet based on } R_{SNS} \text{ of } 700\Omega \quad (6)$$

$$I2T_{700} = I2T \text{ trip value in the datasheet based on } R_{SNS} \text{ of } 700\Omega \quad (7)$$

#### 8.3.1.1.4 即時シャットダウン過電流保護 (OCP)

定常動作時、デバイスは即時シャットダウン型の過電流保護 ( $I_{OCP}$ ) を備えています。この保護機能は、出力電流が `ILIMIT_SET_CHx [3:0]` ビットで設定された  $I_{OCP}$  スレッショルドを超えた場合に、チャネルを即座にオフにします。

$I_{LIMIT\_SET\_CHx}$  [3:0] ビットにより、 $I_{OCP}$  機能をチャネルごとに設定できます。 $I_{OCP}$  機能はディスエーブルにすることはできず、デバイスがイネーブルの間、定常状態の動作で常にアクティブになります。

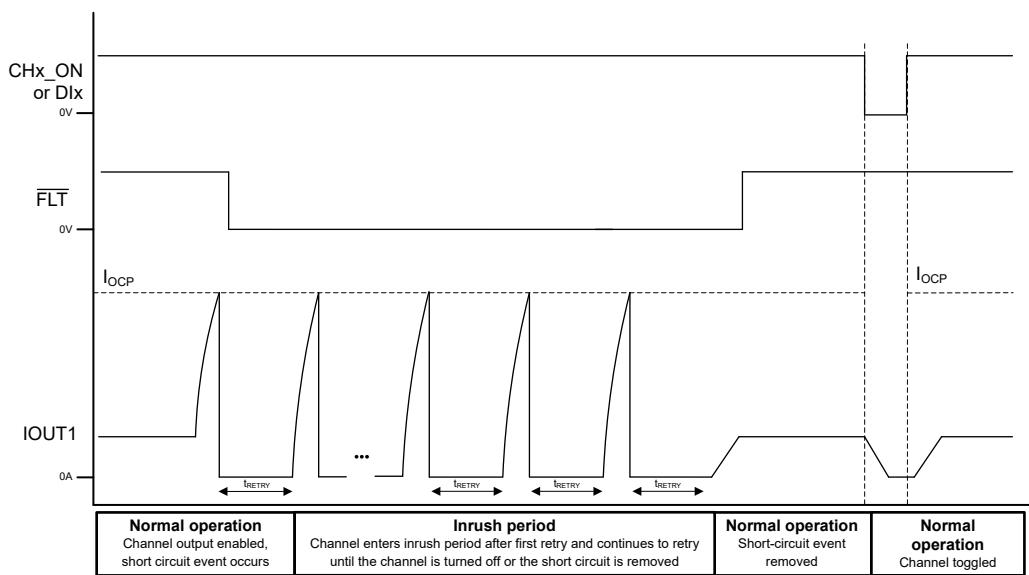

$I_{OCP}$  レベルを超えた場合、チャネルは直ちにオフになり、 $LATCH\_CHx$  ビットの設定に基づいて再試行またはラッチオフのいずれかを行います。 $LATCH\_CHx = 0$  の場合、デバイスは  $t_{RETRY}$  後に再試行します。再試行時間が経過した後、構成されている場合、デバイスは突入期間内に起動します。 $LATCH\_CHx = 1$  かつ  $I_{OCP}$  レベルを超えた場合、デバイスはラッチオフし、 $CHx\_ON$  ビット (バージョン A) がトグルされるか、 $Dlx$  ピン (バージョン B) がトグルされるか、 $LATCH\_CHx$  ビットがトグルされるまで再試行しません。デバイスがアクティブ状態の後、MCU は LPM ビットをクリアして、各種デバイス設定における再試行とラッチオフの動作の詳細については、以下の「再試行とラッチオフの動作」セクションを参照してください。

$LIMP\_HOME$  状態では、 $CHx\_LH\_IN$  ビットでチャネルが  $LIMP\_HOME$  状態で ON に設定されている場合、 $LATCH\_CHx$  設定に関係なく、デバイスは連続的に再試行を行うことに注意します。

#### 8.3.1.1.5 自動再試行とラッチオフ動作

サーマルシャットダウンまたは過電流保護故障が発生した場合、 $CHx\_CONFIG$  レジスタ内の  $LATCH\_CHx$  ビット設定に基づいて、故障が発生したチャネルは自動で再試行するか、またはラッチオフします。 $CAP\_CHRG\_CHx$  の設定によっては、自動再試行の応答は異なる動作をします。

$LIMP\_HOME$  状態では、 $CHx\_LH\_IN$  ビットでチャネルが  $LIMP\_HOME$  状態で ON に設定されている場合、 $LATCH\_CHx$  設定に関係なく、デバイスは連続的に再試行を行うことに注意します。 $LIMP\_HOME$  状態での再試行動作は、 $CAP\_CHRG\_CHx$  ビットの設定方法に応じて、以下のセクションに示す動作に従います。

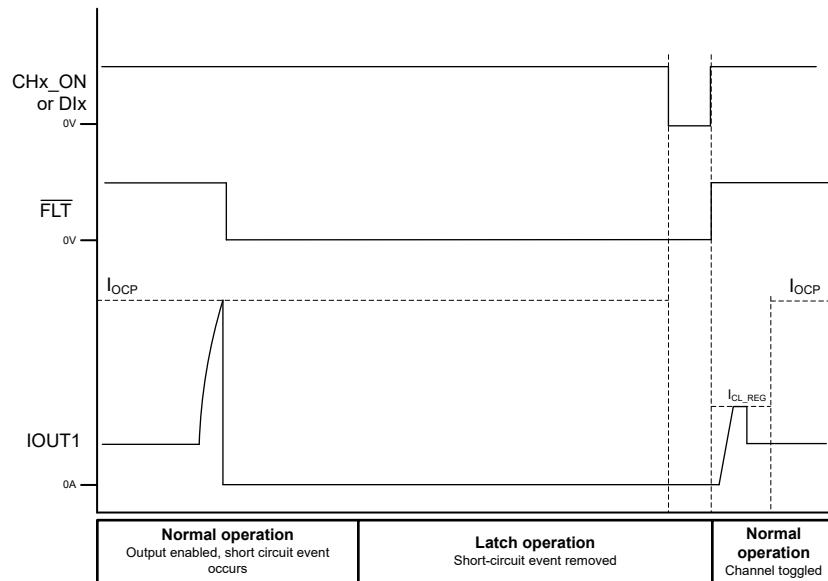

#### 自動再試行動作 — 容量性充電モードなし ( $CAP\_CHRG\_CHx = 00$ )

$CAP\_CHRG\_CHx = 00$ 、 $LATCH\_CHx = 0$  の状態で短絡イベントが発生した場合、チャネルがオフになり  $t_{RETRY}$  が経過すると、デバイスは  $INRUSH\_LIMIT\_CHx$  [3:0] ビットで設定された  $I_{OCP}$  レベルを用いて、立ち上がり期間中に再試行を行います。 $INRUSH\_DURATION\_CHx$  [2:0] は引き続き、突入期間の持続時間を設定します。定常状態動作で発生するホットショートケースを図 8-8 に示します。突入期間中に短絡状態で起動した場合、定常状態でのホットショート時と同じ試行動作になります。ただし、最初の過電流シャットダウンレベルは、 $INRUSH\_LIMIT\_CHx$  [3:0] によって決まります。

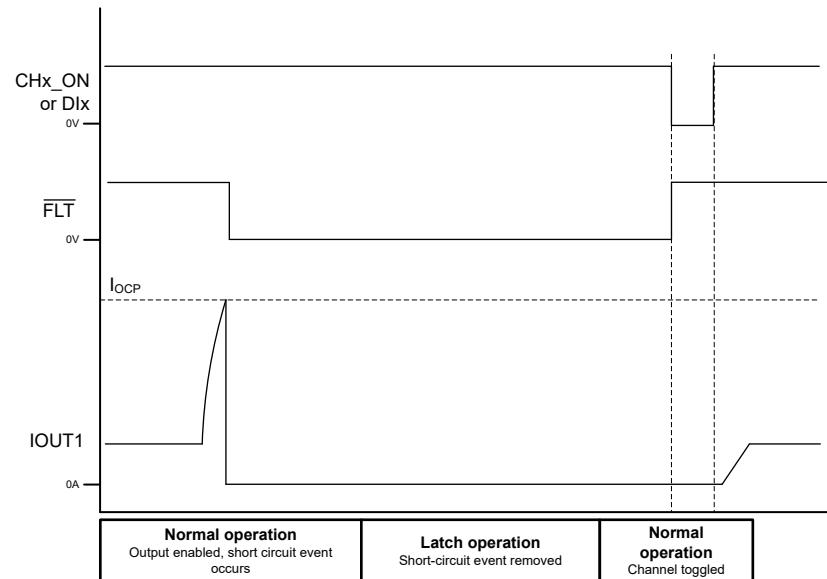

図 8-8. 定常動作中のホットショート ( $CAP\_CHRG\_CHx = 00$ 、自動再試行動作 :  $LATCH\_CHx = 0$  の場合)

### ラッチオフ動作 — 容量性充電モードなし (CAP\_CHRG\_CHx = 00)

$LATCH_{CHx} = 1$  かつ  $CAP_{CHRG_{CHx}} = 00$  で、 $I_{OCP}$  レベルを超えた場合、デバイスはラッチオフになり、 $CH_{x\_ON}$  ビット (バージョン A) がトグルされるか、 $D_{lx}$  ピン (バージョン B) がトグルされるか、 $LATCH_{CHx}$  ビットがトグルされるまで再試行しません。出力トグルまたは  $LATCH_{CHx}$  ビットトグルによってラッチをリセットすると、構成されている場合、チャネルは突入期間に起動します。次の 図 8-9 に、 $LATCH_{CHx} = 1$  で定常状態動作中にホットショートが発生した場合のラッチ動作を示します。図 8-10 に、突入期間中にチャネルが短絡イベントを開始した場合のラッチ動作を示します。

図 8-9. 定常状態動作時のホットショート、 $CAP_{CHRG_{CHx}} = 00$ 、ラッチオフ ( $LATCH_{CHx} = 1$ )

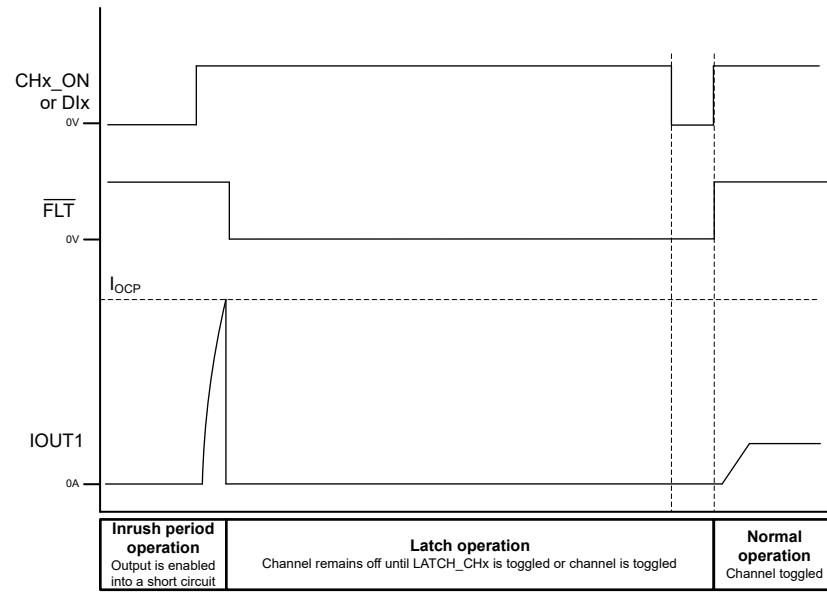

図 8-10.  $CAP_{CHRG_{CHx}} = 00$ 、ラッチオフ ( $LATCH_{CHx} = 1$ ) の状態で短絡イベントを開始

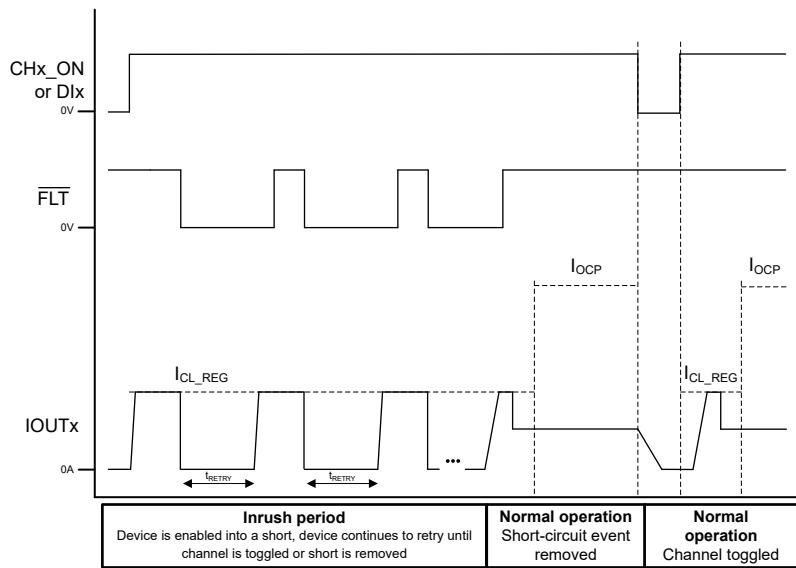

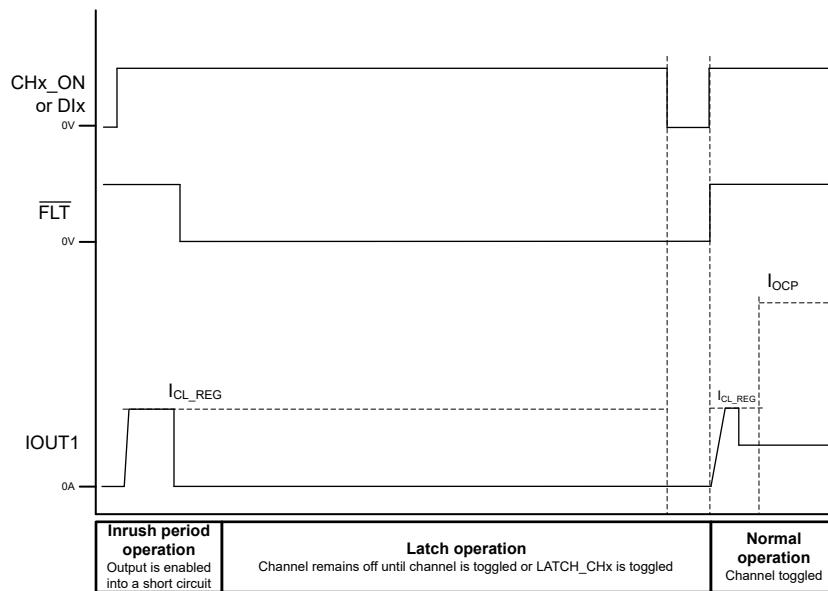

### 自動再試行動作 — 電流制限レギュレーション充電モード (CAP\_CHRG\_CHx = 10)

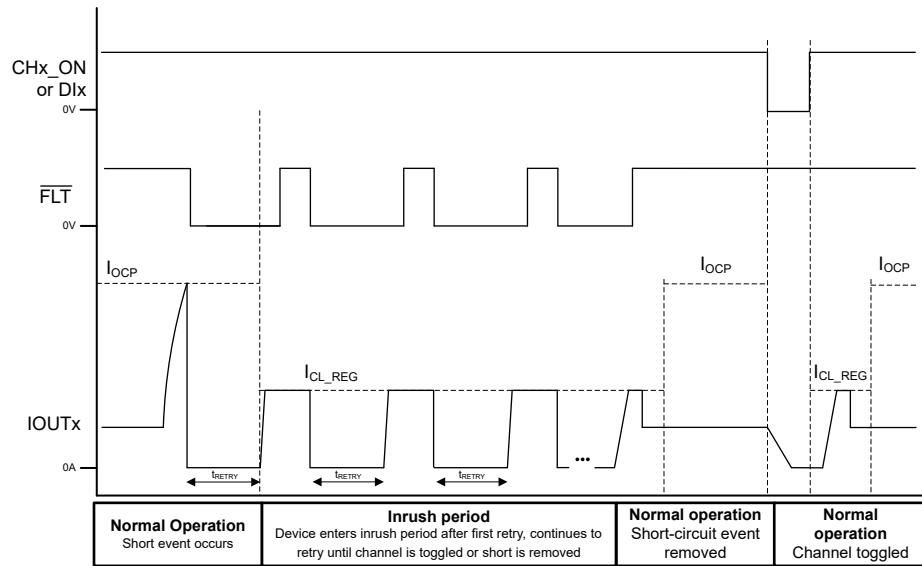

定常動作中に短絡イベントが発生し、 $CAP_{CHRG_{CHx}} = 10$  かつ  $LATCH_{CHx} = 0$  の場合、チャネルがオフになり  $t_{RETRY}$  が経過すると、デバイスは  $INRUSH\_LIMIT_{CHx}$  [3:0] ビットで設定された電流制限レギュレーション ( $I_{CL\_REG}$ ) を

用いて、立ち上がり期間中に再試行を行います。図 8-11 に、定常状態動作で  $CAP\_CHRG\_CHx = 10$ 、 $LATCH\_CHx = 0$  のとき発生するホットショートイベントを示します。図 8-12 に、突入期間中にチャネルが短絡イベントを開始した場合の自動再試行動作を示します。

図 8-11. 定常動作中のホットショート ( $CAP\_CHRG\_CHx = 10$ 、自動再試行動作 :  $LATCH\_CHx = 0$  の場合)

図 8-12.  $CAP\_CHRG\_CHx = 10$  および自動再試行 ( $LATCH\_CHx = 0$ ) で短絡イベントを開始

### ラッチオフ動作 — 電流制限による容量充電モード ( $CAP\_CHRG\_CHx = 10$ )

$LATCH\_CHx = 1$  かつ  $CAP\_CHRG\_CHx = 10$  で、 $I_{OCP}$  レベルを超えた場合、デバイスはラッチオフになり、 $CHx\_ON$  ビット (バージョン A) がトグルされるか、 $Dlx$  ピン (バージョン B) がトグルされるか、 $LATCH\_CHx$  ビットがトグルされるまで再試行しません。出力トグルまたは  $LATCH\_CHx$  ビットトグルによってラッチをリセットすると、構成されている場合、チャネルは突入期間に起動します。次の 図 8-13 に、 $LATCH\_CHx = 1$  で定常状態動作中にホットショートが発生した場合のラッチ動作を示します。図 8-14 に、突入期間中にチャネルが短絡イベントを開始した場合のラッチ動作を示します。

図 8-13. 定常状態動作時のホットショート、 $CAP\_CHRG\_CHx = 10$ 、ラッチオフ ( $LATCH\_CHx = 1$ )

図 8-14.  $CAP\_CHRG\_CHx = 10$ 、ラッチオフ ( $LATCH\_CHx = 1$ ) の状態で短絡イベントを開始

### 8.3.1.2 サーマルシャットダウン

デバイスには、各パワー FET に温度センサが搭載されており、デバイスのコントローラ部分には、各 FET の温度 ( $T_{J,FET}$ ) およびコントローラの温度 ( $T_{J,CONTROLLER}$ ) を監視します。デバイスがサーマル・シャットダウン障害と見なされる場合は 2 つあります。

- 相対サーマルシャットダウン ( $T_{REL}$ ):  $T_{J,FET} - T_{J,CONTROLLER} > T_{REL}$

- 絶対サーマルシャットダウン ( $T_{ABS}$ ):  $T_{J,FET} > T_{ABS}$

上記のいずれかの故障が発生すると、該当するスイッチがオフになります。該当するチャネルの温度センサの測定値に基づいて、各チャネルがオフになります。その結果、一方のチャネルのみで過熱フォルトが検出された場合、もう一方のチャネルは動作を継続します。

## 相対サーマル シャットダウン ( $T_{REL}$ )

相対的なサーマル・シャットダウンイベントは、グランドへの短絡イベントなど、コントローラ温度 ( $T_{J, FET}$ ) に対して FET 温度 ( $T_{J, CONTROLLER}$ ) が急速に上昇する、大きなピーク電力イベントが発生する場合に発生することがあります。相対温度 ( $T_{J, FET} - T_{J, CONTROLLER}$ ) が  $T_{REL}$  を超えると、関連するチャネルがオフになります。

## 絶対サーマル シャットダウン ( $T_{ABS}$ )

絶対的サーマル・シャットダウンは、FET 温度 ( $T_{J, FET}$ ) が  $T_{ABS}$  を上回ると発生します。これは、チャネルが永続的な短絡使用事例など、長い期間にわたって過電流にさらされた場合に発生する可能性があります。FET 温度 ( $T_{J, FET}$ ) が  $T_{ABS}$  を超えると、関連するチャネルがオフになります。

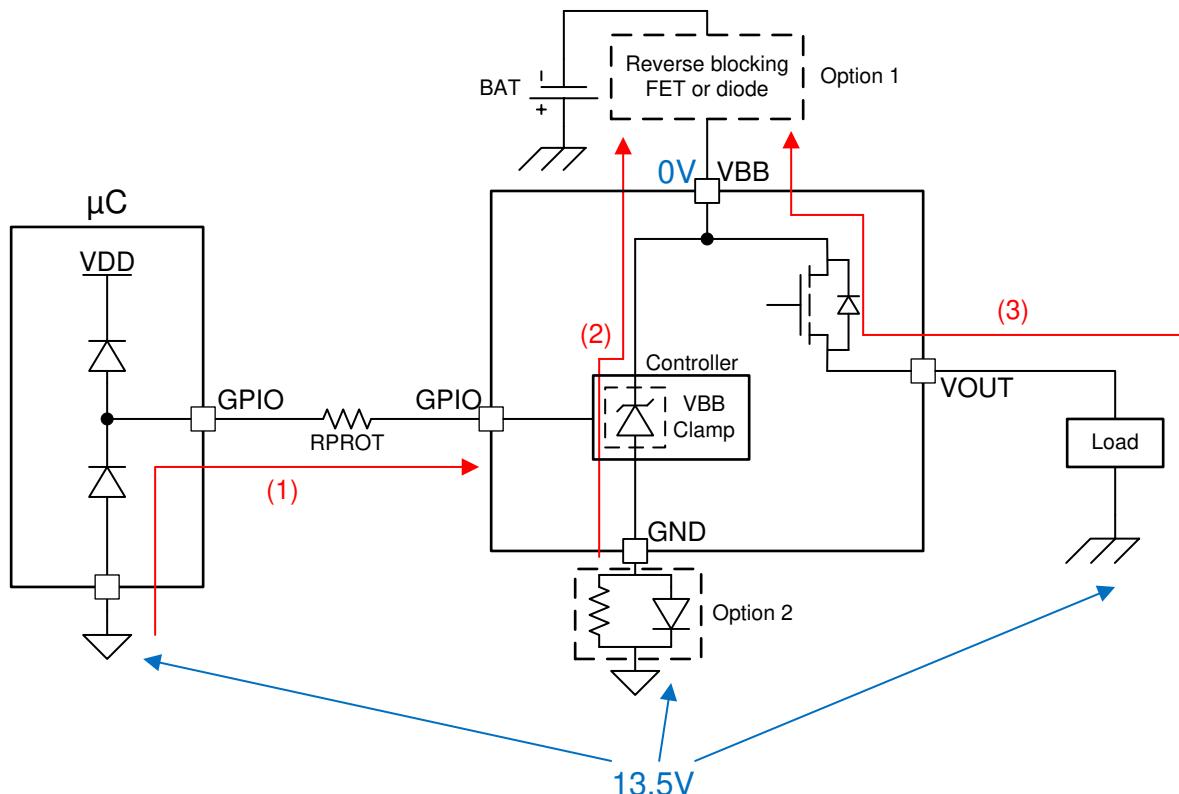

### 8.3.1.3 逆極性バッテリ

逆接続状態では、MOSFET のボディダイオード内で過剰な電力損失が発生するのを防ぐため、出力の状態 (SW\_STATE レジスタで設定) に関係なく、スイッチは自動的に有効になります。多くのアプリケーション (抵抗性負荷など) では、バッテリ逆接続時に全負荷電流が存在する可能性があります。自動スイッチオン機能を有効にするには、DI ピン (バージョン A) または DI1 (バージョン B) に MCU からグランドへのパスが必要です。または、未使用の場合は  $R_{PROT}$  を介してグランドに接続する必要があります。

システムの逆極性バッテリを処理するには 2 つのオプションがあります。最初のオプションは、ブロッキング デバイス (FET またはダイオード) をバッテリ電源と直列に配置し、すべての電流パスをブロックすることです。2 つ目のオプションは、ハイサイド スイッチの GND ノードの抵抗と並列にブロッキング ダイオードを配置することです。この方法では、内部回路を流れる電流を制限することで、スイッチのコントローラ部分 (パス 2) を保護します。さらに、2 番目の方法では、デバイスの自動スイッチオン機能により、デバイスを低  $R_{ON}$  状態に移行させ、スイッチを効率的に流れ、負荷 (パス 3) を通過させることができます。2 番目のオプションで使用するダイオードは、複数のハイサイドスイッチ間で共有できます。

図 8-15. バッテリ逆接続時の電流パス

逆バッテリ保護の詳細については、TI の [ハイサイド スイッチの逆バッテリ保護](#) アプリケーション ノートを参照してください。

### 8.3.2 診断機能

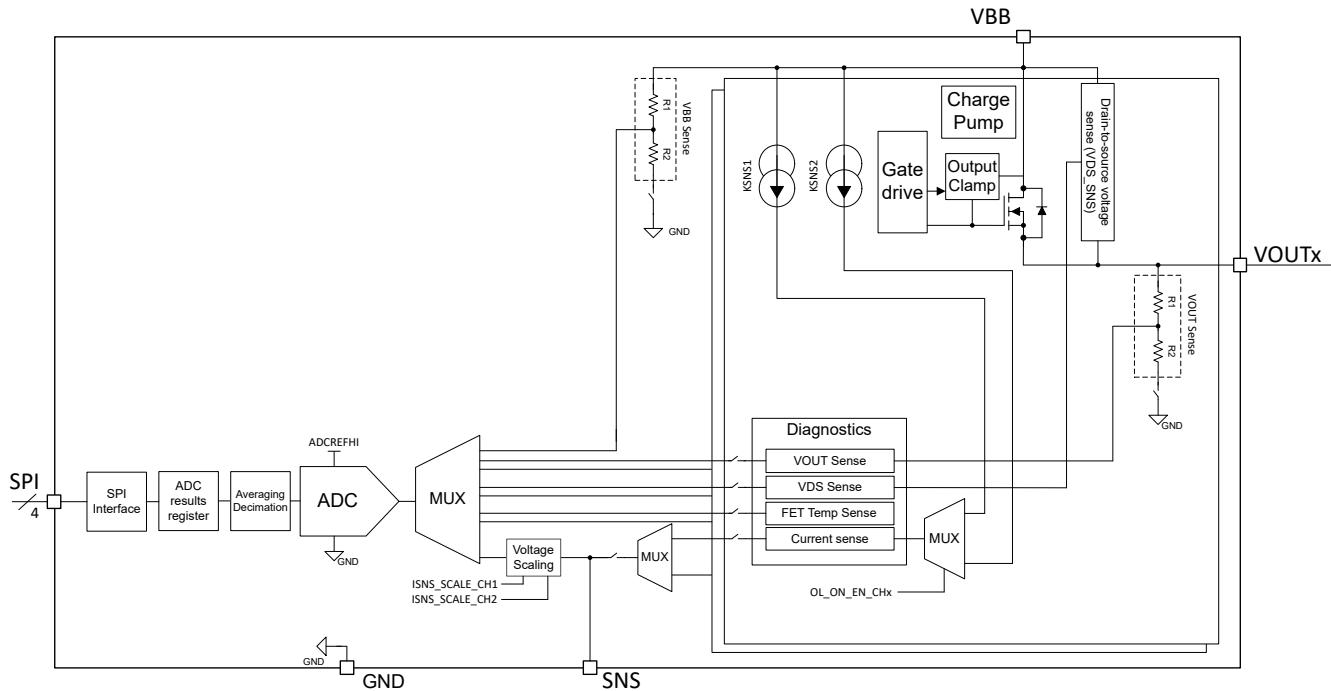

#### 8.3.2.1 ADC 内蔵

TPS2HCS10-Q1 は内蔵の逐次比較 10 ビット ADC を備えており、さまざまなアナログ信号をデジタル信号に変換し、SPI 経由で読み取ることができます。ADC は、以下に示すアナログ信号を変換できます。

- CH1 および CH2 電流検出 (ISNS1/2)

- CH1 および CH2 MOSFET 温度検出 (TSNS1/2)

- VBB 電圧検出 (VBB\_SNS)

- CH1 および CH2 VOUT 電圧検出 (VSNS1/2)

- CH1 および CH2 MOSFET ドレイン - ソース間電圧 (VDS) 検出 (VDS\_SNS1/2)

図 8-18 に、内蔵 ADC の機能ブロック図と ADC へのアナログ信号入力を示します。

アナログ信号の変換では、温度検出を除くすべてのアナログ信号の変換を、ADC\_CONFIG レジスタを介してグローバルに無効化するか、CHx\_CONFIG レジスタを介してチャネルごとに無効化できます。温度センシングはチャネルごとの無効化はできません。ADC\_TSNS\_DIS ビットでのみグローバルに無効化できます。

静止電流を低減するため、デバイスは ADC が ISNSx 信号のいずれかを変換しているときのみ電流検出回路を有効化し、他のすべての信号変換中は無効化します。また、デバイスには遅延の設定が可能なので、ADC のサンプリング レートを下げることで、デバイスの静止電流をさらに低減できます。遅延は、ADC\_CONFIG レジスタの ADC\_ISNS\_SAMPLE\_CONFIG [1:0] ビットで設定します。

I2T 保護が有効 (I2T\_EN\_CHx = 1) で、いずれかのチャネルが I2T モードではない (I2T\_MOD\_CHx = 0) 場合、デバイスは各アナログ信号を、設定可能な遅延で、ラウンド ロビン シーケンスを使用して変換します。次の 図 8-16 に、チャネルが I2T モード (I2T\_MOD\_CHx = 0) で、すべてのアナログ信号変換が有効である場合の ADC スケジューリングを示します。I2T 保護が無効の場合、以下のラウンド ロビン シーケンスも適用されます。

|             | ISNS1 | ISNS2 | TSNS1 | TSNS2 | VBB_SNS | VSNS1 | VSNS2 | VDS_SNS1 | VDS_SNS2 | Configurable delay<br>ADC_ISNS_SAMPLE_CONFIG [1:0] |

|-------------|-------|-------|-------|-------|---------|-------|-------|----------|----------|----------------------------------------------------|

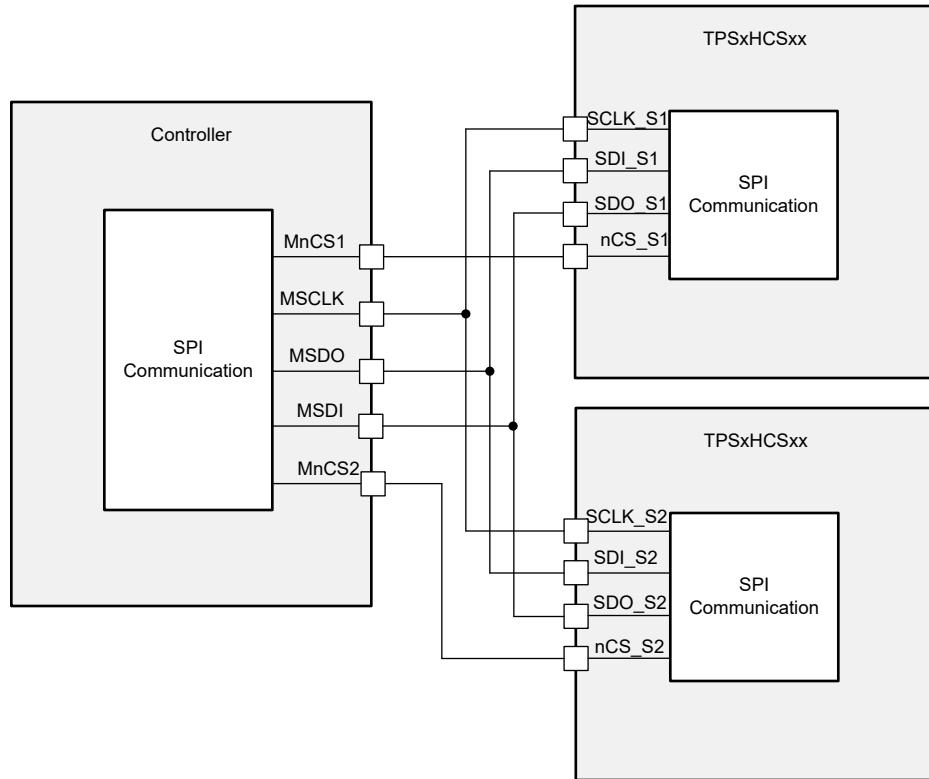

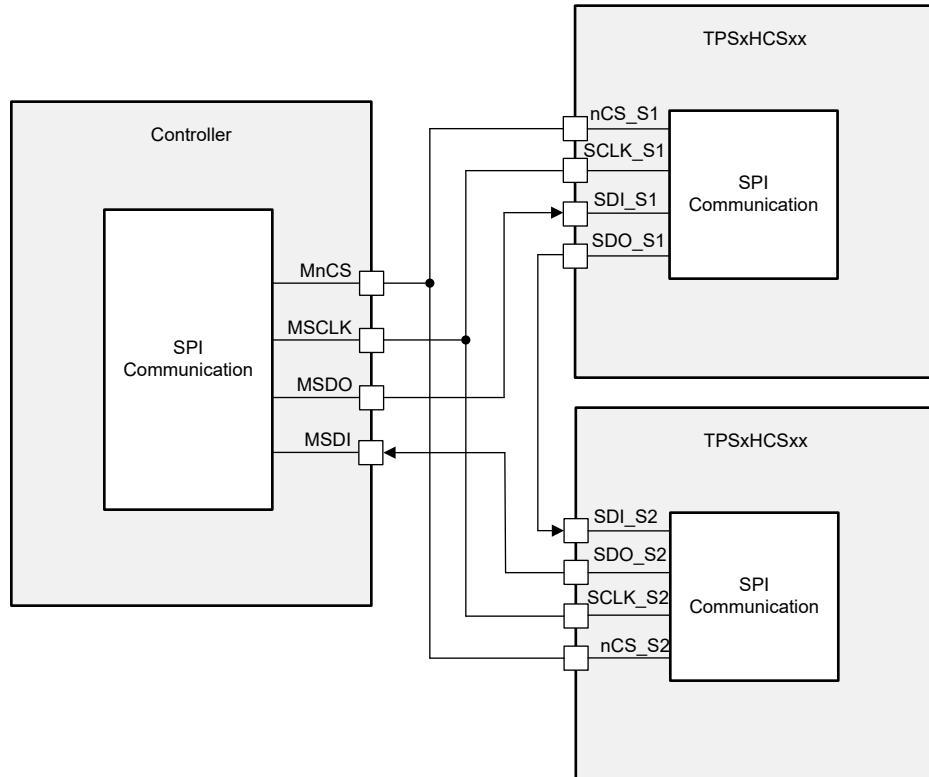

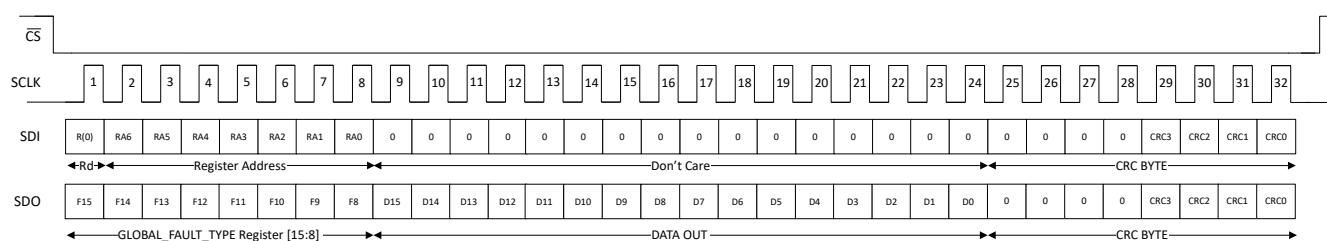

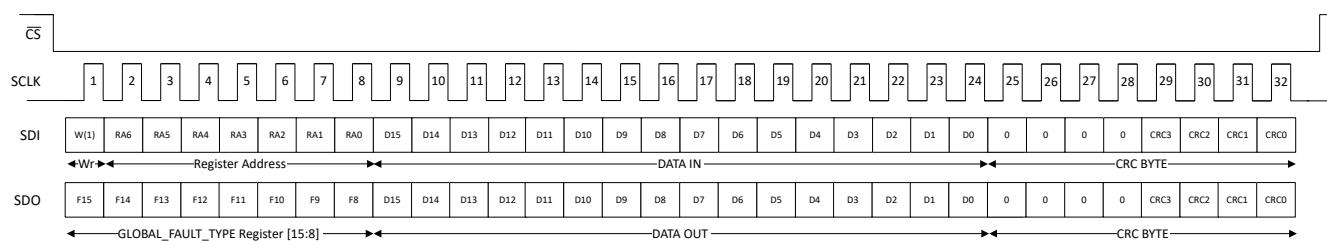

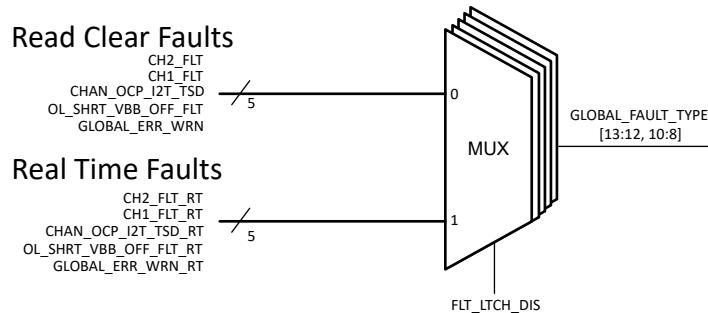

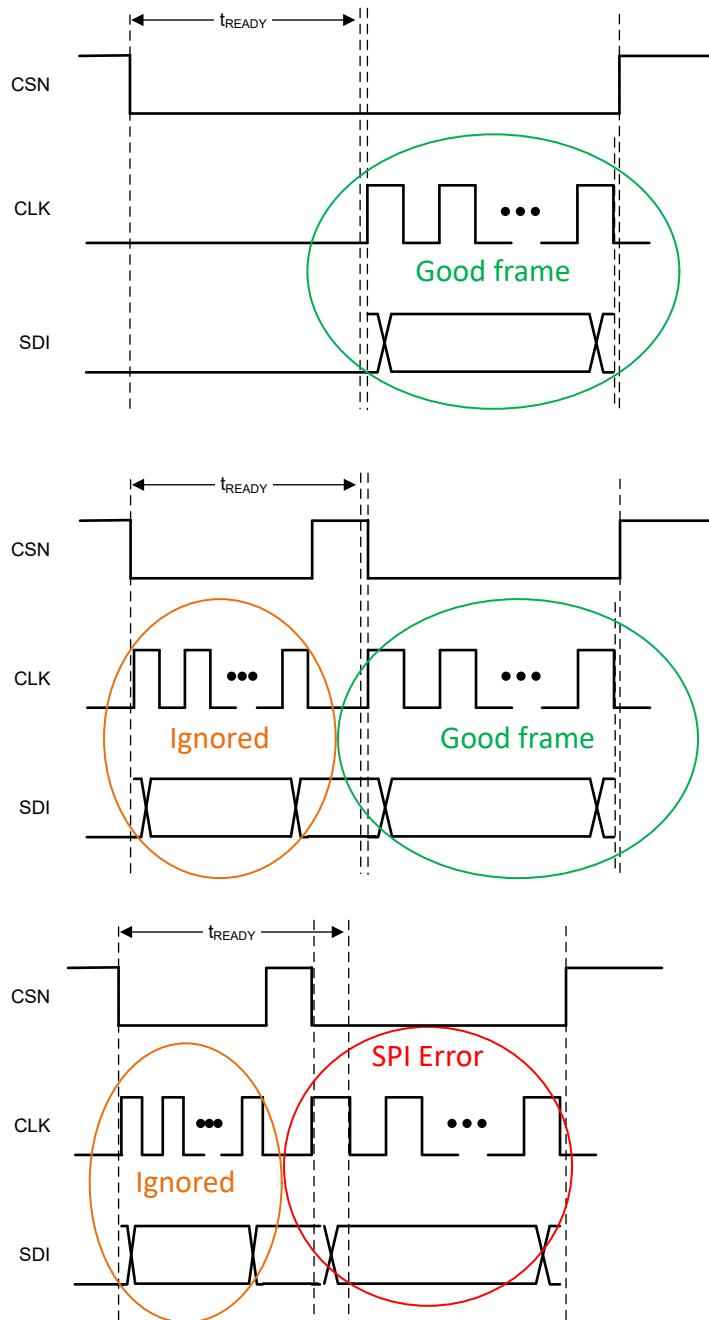

| ISNS_EN     | 1     |       |       |       |         |       |       |          | 0        |                                                    |